#### Power optimization strategies within a H.264 encoding system-on-chip

Ngoc-Mai Nguyen

#### ► To cite this version:

Ngoc-Mai Nguyen. Power optimization strategies within a H.264 encoding system-on-chip. Electronics. Université Grenoble Alpes; Trường Đại học Quốc Gia Hà Nội, 2015. English. NNT: 2015GREAT049. tel-01218637

#### HAL Id: tel-01218637 https://theses.hal.science/tel-01218637

Submitted on 21 Oct 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ GRENOBLE ALPES

#### THÈSE

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

préparée dans le cadre d'une cotutelle entre l'*Université Grenoble Alpes* et l'*Université Nationale du Vietnam, Hanoi*

Spécialité : **Automatique - Productique** Arrêté ministériel : le 6 janvier 2005 - 7 août 2006

Présentée par

#### Ngoc-Mai NGUYEN

Thèse dirigée par Xuan-Tu TRAN et Suzanne LESECQ codirigée par Edith BEIGNÉ

préparée au sein des Laboratoire d'Electronique et des Technologies de l'Information, CEA Grenoble et Laboratoire SIS, VNU-UET, Hanoi

dans l'École Doctorale d'Electronique, Electrotechnique, Automatique et Traitement du Signal (EEATS) et l'UET du VNU

# Stratégies d'optimisation de la consommation pour un système sur puce encodeur H.264

Thèse soutenue publiquement le **29/06/2015**, devant le jury composé de :

**M. Nicolas MARCHAND** Laboratoire GIPSA-Lab, Président M. Alain MERIGOT Université Paris XI, Rapporteur Mme. Nadine AZEMARD LIRMM, Rapporteur M. Xuan-Tu TRAN Université Nationale du Vietnam, Directeur de thèse M. Amara AMARA ISEP, Membre M. Huu-Duc NGUYEN Université Nationale du Vietnam, Membre Mme. Edith BEIGNÉ CEA, Invité Mme. Suzanne LESECQ CEA, Co-directeur de thèse, Invité

## Contents

| C  | onter | $\mathbf{nts}$ |                                                        | i            |

|----|-------|----------------|--------------------------------------------------------|--------------|

| Li | st of | Abbre          | eviations                                              | $\mathbf{V}$ |

| Li | st of | Figure         | es                                                     | viii         |

| Li | st of | Tables         | 5                                                      | xiii         |

| In | trod  | uction         |                                                        | 1            |

|    | Cont  | text of        | video coding                                           | 1            |

|    | Mot   | ivations       | and objectives                                         | 2            |

|    | Cont  | tributio       | ns of the work                                         | 3            |

|    | Expl  | lanatior       | n for the different CMOS technologies and operating    |              |

|    |       | freque         | ncy in the results presented in the thesis             | 5            |

|    | Orga  | anizatio       | n of the manuscript                                    | 7            |

| 1  | The   | e H.264        | AVC video coding standard and its implemen-            |              |

|    | tati  | ons            |                                                        | 9            |

|    | 1.1   | H.264          | video coding standard in the history of video coding   |              |

|    |       | standa         | urds                                                   | 10           |

|    |       | 1.1.1          | The video coding standards before the $H.264/AVC$ .    | 10           |

|    |       | 1.1.2          | The H.264 Advanced Video Coding standard               | 12           |

|    |       | 1.1.3          | Video coding standards from other organizations, H.265 | /HEVC        |

|    |       |                | standard and the consideration of standard selection   | 13           |

|    | 1.2   | Overvi         | iew of H.264 video coding standard                     | 14           |

|    |       | 1.2.1          | Video coding basic concepts                            | 14           |

|    |       | 1.2.2          | H.264/AVC basic concepts                               | 17           |

|    | 1.3   | H.264/         | AVC implementation solutions                           | 20           |

|    |       |                |                                                        |              |

|          |     | 1.3.1  | Software  | e implementations                                                 | 20 |

|----------|-----|--------|-----------|-------------------------------------------------------------------|----|

|          |     | 1.3.2  | Challeng  | ges in implementing the H.264/AVC and so-                         |    |

|          |     |        |           |                                                                   | 21 |

|          |     | 1.3.3  | Trends i  | n hardware implementation of the $H.264/AVC$                      |    |

|          |     |        | coding    |                                                                   | 24 |

|          | 1.4 | Overv  | iew of H. | 264/AVC hardware encoder implementations                          | 26 |

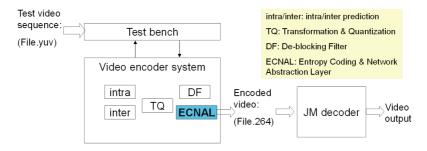

|          |     | 1.4.1  | Basic pi  | pelining design                                                   | 27 |

|          |     | 1.4.2  | Design i  | mprovements for specific purposes                                 | 29 |

|          | 1.5 | Power  | -oriented | design for H.264/AVC hardware encoders $\ .$ .                    | 32 |

|          |     | 1.5.1  | Low-pov   | ver design techniques                                             | 32 |

|          |     | 1.5.2  | Low-pov   | ver techniques for H.264/AVC encoder hard-                        |    |

|          |     |        | ware im   | plementation                                                      | 34 |

|          |     | 1.5.3  | Discussi  | on                                                                | 38 |

|          | 1.6 | Conclu | usion     |                                                                   | 40 |

|          |     |        |           |                                                                   |    |

| <b>2</b> | The |        |           | atform and its EC-NAL module                                      | 43 |

|          | 2.1 | The V  | ENGME     | platform                                                          | 45 |

|          |     | 2.1.1  | Introdue  | ction to the VENGME platform                                      | 45 |

|          |     | 2.1.2  |           | re architecture of the VENGME $H.264/AVC$                         |    |

|          |     |        | video en  | coder                                                             | 47 |

|          |     | 2.1.3  | Dataflov  | v control                                                         | 52 |

|          |     | 2.1.4  | Verificat | tion and implementation results                                   | 54 |

|          |     | 2.1.5  | Power s   | imulation for VENGME platform                                     | 57 |

|          | 2.2 | Ŭ      |           | tropy coder and bytestream NAL data packer                        |    |

|          |     | for H. |           | video encoder                                                     | 60 |

|          |     | 2.2.1  |           | ation for the entropy coding and data packing                     |    |

|          |     |        |           | $1.264/\text{AVC}$ standard $\dots \dots \dots \dots \dots \dots$ | 61 |

|          |     |        | 2.2.1.1   | Byte stream encoded video                                         | 61 |

|          |     |        | 2.2.1.2   | Zigzag scan and CAVLC                                             | 63 |

|          |     |        | 2.2.1.3   | Exp-Golomb coding                                                 | 67 |

|          |     | 2.2.2  | Analysis  | s of previous works                                               | 69 |

|          |     |        | 2.2.2.1   | Implementations related to processing speed                       | 69 |

|          |     |        | 2.2.2.2   | Implementations focusing on area cost $\ldots$                    | 70 |

|          |     |        | 2.2.2.3   | Implementations focusing on power consump-                        |    |

|          |     |        |           | tion                                                              | 71 |

|          |     |        | 2.2.2.4   | Lessons learned from the previous works                           | 72 |

|   | 2.3        | The E   | Entropy C    | oder and data packer (EC-NAL) module de-       |           |

|---|------------|---------|--------------|------------------------------------------------|-----------|

|   |            | sign fo | or the VE    | NGME platform                                  | 73        |

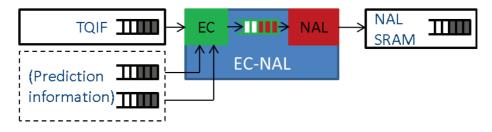

|   |            | 2.3.1   | EC-NAI       | architecture and main engines                  | 74        |

|   |            | 2.3.2   | CAVLC        | encoder                                        | 75        |

|   |            | 2.3.3   | Exp-Gol      | omb encoder                                    | 82        |

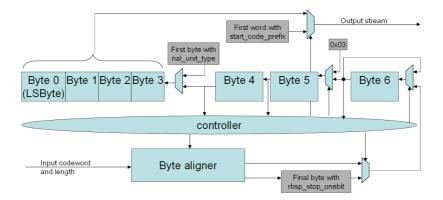

|   |            | 2.3.4   | BSNAL        | data packer                                    | 83        |

|   | 2.4        | The V   | <b>ENGME</b> | EC-NAL module implementation results and       |           |

|   |            | compa   | arison .     |                                                | 85        |

|   |            | 2.4.1   | Results :    | for CAVLC encoder                              | 85        |

|   |            | 2.4.2   | Results :    | for EC-NAL module                              | 88        |

|   | 2.5        | Power   | · simulatio  | on for the VENGME EC-NAL module                | 89        |

|   | 2.6        | Concl   | usion        |                                                | 91        |

| 3 | FIF        | 'O-leve | el control   | power management method and its ap-            |           |

|   |            | ation   |              | I                                              | 95        |

|   | 3.1        |         | · managen    | nent using the FIFO/buffer-level control: an   |           |

|   | -          |         | _            |                                                | 97        |

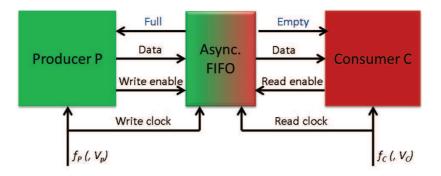

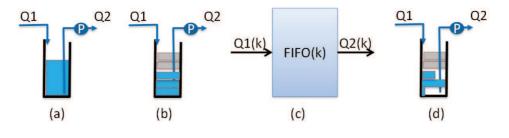

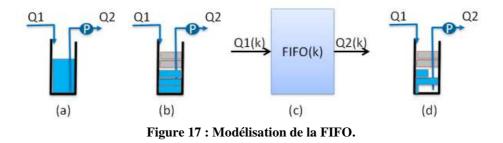

|   |            | 3.1.1   |              | ncepts                                         | 98        |

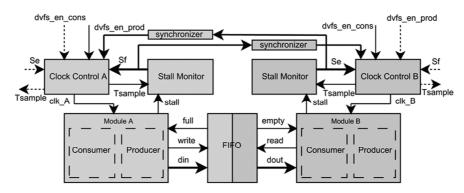

|   |            |         | 3.1.1.1      | FIFO-based systems                             | 98        |

|   |            |         | 3.1.1.2      | FIFO-level based DFS method                    | 99        |

|   |            |         | 3.1.1.3      | Case-study                                     | 99        |

|   |            | 3.1.2   |              | s works                                        | 101       |

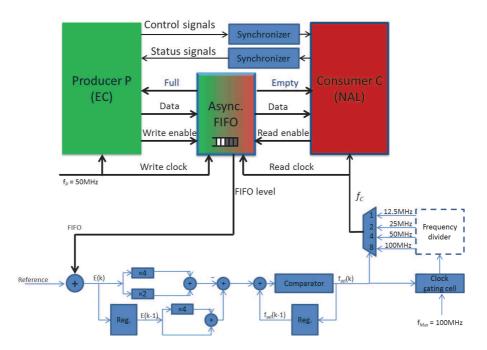

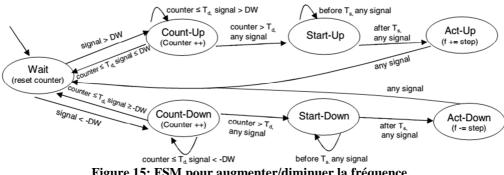

|   | 3.2        | -       |              | ed DFS control                                 | 108       |

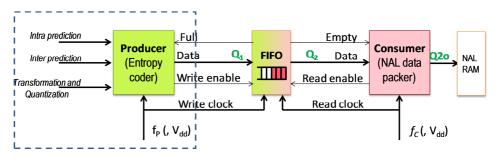

|   | 0.2        | 3.2.1   |              | k modeling                                     | 109       |

|   |            | 3.2.2   |              | er design                                      | 111       |

|   |            | 3.2.3   |              | entation constraints and remarks               | 113       |

|   |            | 3.2.4   | -            | $\gamma$ analysis                              |           |

|   |            | 0.2.1   | 3.2.4.1      | Nyquist stability criterion: summary           |           |

|   |            |         | 3.2.4.2      | Application of the Nyquist criterion approach  | 111       |

|   |            |         | 0.2.1.2      | to our system                                  | 122       |

|   |            |         | 3.2.4.3      | Topological separation condition: summary      | 122       |

|   |            |         | 3.2.4.4      | Application of the topological separation con- | 120       |

|   |            |         | 0.4.4.4      | dition to our system                           | 133       |

|   | 3.3        | MATT    | AR simu      | lation results                                 | 133 $138$ |

|   | э.э<br>3.4 |         |              |                                                |           |

|   | 0.4        | Concr   | usion        |                                                | 140       |

| 4 | Imp        | olemen  | tation a     | nd validation of the FIFO-level based          |           |

DFS method

141

| 4.1     | Hardw   | vare design and implementation                          | 142  |

|---------|---------|---------------------------------------------------------|------|

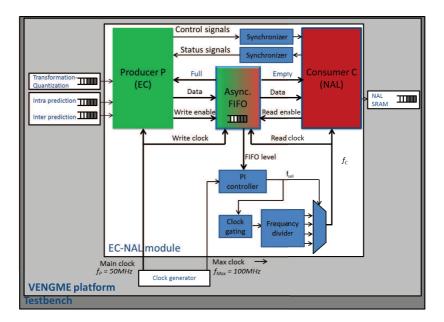

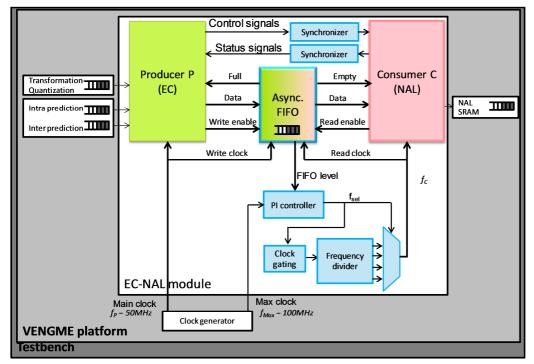

|         | 4.1.1   | CDC interface implementation in EC-NAL module .         | 143  |

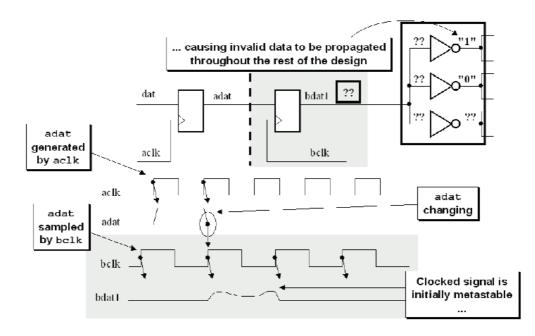

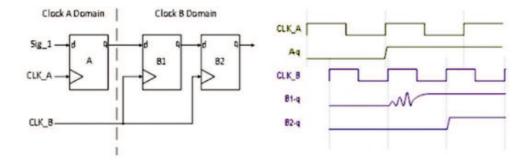

|         |         | 4.1.1.1 Metastability and synchronization techniques    | 144  |

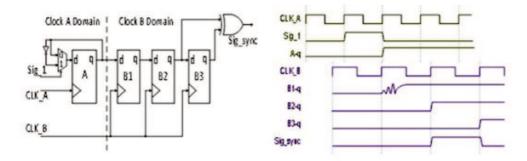

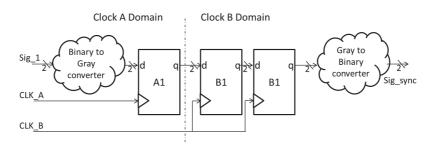

|         |         | 4.1.1.2 Implementation of the synchronizer              | 147  |

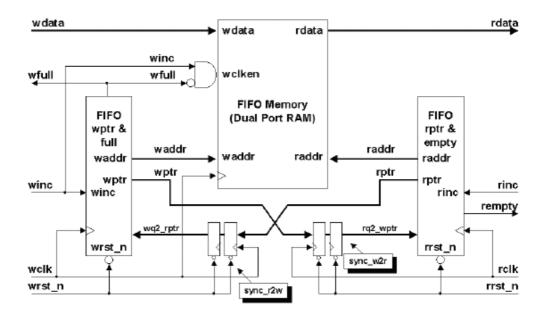

|         |         | 4.1.1.3 Implementation of an asynchronous FIFO .        | 147  |

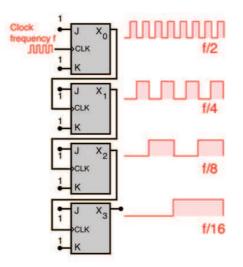

|         | 4.1.2   | Implementation of a frequency divider                   | 148  |

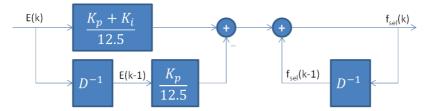

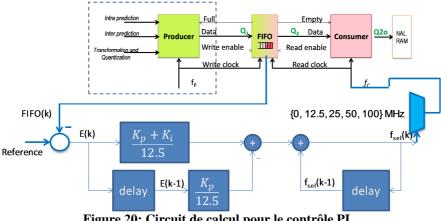

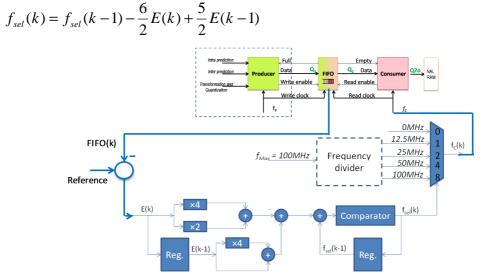

|         | 4.1.3   | Implementation of the PI controller                     | 149  |

|         |         | 4.1.3.1 Implementation of the PI controller             | 149  |

|         |         | 4.1.3.2 Controller coefficients requirements and se-    |      |

|         |         | lection                                                 | 150  |

| 4.2     | Verific | ation of the FIFO-level-based DFS method                | 151  |

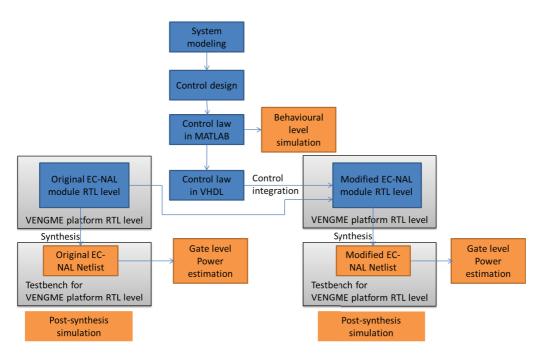

|         | 4.2.1   | Verification methodology                                | 152  |

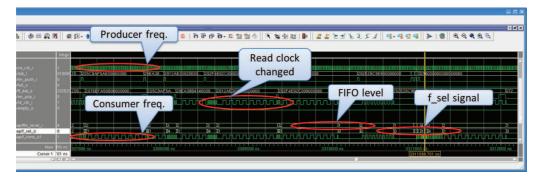

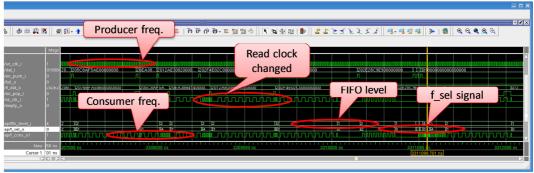

|         | 4.2.2   | Simulation demonstration                                | 153  |

| 4.3     | Valida  | tion of the control of the FIFO occupancy level for DFS | 5154 |

|         | 4.3.1   | Validation methodology                                  | 154  |

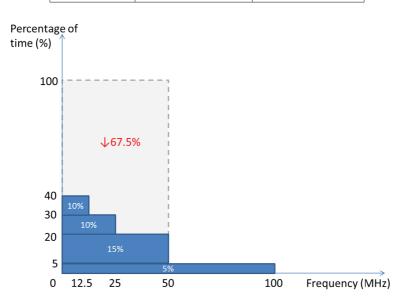

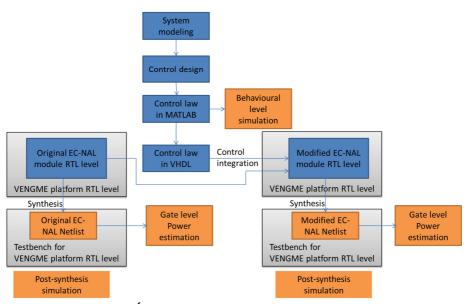

|         | 4.3.2   | Power gain estimation at behavioural model level        | 154  |

|         | 4.3.3   | Power gain estimation at gate level                     | 156  |

|         |         | 4.3.3.1 Synthesis results                               | 156  |

|         |         | 4.3.3.2 Post-synthesis simulation results               | 157  |

|         |         | 4.3.3.3 Power estimation results at gate level          | 159  |

|         | 4.3.4   | Discussion                                              | 163  |

| 4.4     | Conclu  | usion                                                   | 165  |

| Conclu  | sion    |                                                         | 167  |

| Bibliog | graphy  |                                                         | 171  |

## **List of Abbreviations**

| Abbreviation | Description                                                     |

|--------------|-----------------------------------------------------------------|

| AHB          | Advanced High-performance Bus                                   |

| AMBA         | Advanced Microcontroller Bus Architecture                       |

| APB          | Advanced Peripheral Bus                                         |

| ASIC         | Application-Specific Integrated Circuit                         |

| AVS          | Audio Video coding Standard                                     |

| ATSC         | Advanced Television Systems Committee                           |

| AVC          | Advanced Video Coding                                           |

| BBC R&D      | British Broadcasting Corporation Research and Development       |

| CABAC        | Context Adaptive Binary Arithmetic Coding                       |

| CAVLC        | Context Adaptive Variable Length Coding                         |

| CCITT        | Comité Consultatif International Téléphonique et Télégraphique  |

|              | (International Telegraph and Telephone Consultative Committee), |

|              | renamed ITU-T in 1993                                           |

| CD           | Compact Disc                                                    |

| CIF          | Common Intermediate Format                                      |

| DCSS         | Dynamic Clock Supply Stop                                       |

| DF           | De-blocking Filter                                              |

| DFS          | Dynamic Frequency Scaling                                       |

| DPM          | Dynamic Power Management                                        |

| DVD          | Digital Video Disc                                              |

| DVFS         | Dynamic Frequency and Voltage Scaling                           |

| DVS          | Dynamic Voltage Scaling                                         |

| Exp-Golomb   | Expotential Golomb (coding)                                     |

| FIFO         | First In, First Out                                             |

| FME          | Fractional Motion Estimation                                    |

| FPGA         | Field-Programmable Gate Array                                   |

| Abbreviation         | Description                                        |

|----------------------|----------------------------------------------------|

| fps                  | frame per second                                   |

| HD                   | High Definition                                    |

| HDL                  | Hardware Description Language                      |

| HEVC                 | High Efficiency Video Coding                       |

| HTML                 | HyperText Markup Language                          |

| IC                   | Integrated Circuit                                 |

| IEC                  | International Electrotechnical Commission          |

| IME                  | Integer Motion Estimation                          |

| IP                   | Intellectual Property                              |

| ISDN                 | Integrated Services for Digital Network            |

| ISO                  | International Organization for Standardization     |

| ITU                  | International Telecommunication Union              |

| ITU-T                | ITU Telecommunication Standardization Sector       |

| JVT                  | Joint Video Team                                   |

| kbps                 | kilobits per second                                |

| LUT                  | Look-Up Table                                      |

| MAU                  | Memory Access Unit                                 |

| Mbps                 | Mega-bits per second                               |

| MC                   | Motion Compensation                                |

| ME                   | Motion Estimation                                  |

| MPEG                 | Moving Picture Experts Group                       |

| NCC                  | Normalized Cross Correlation                       |

| NTSC                 | National Television System Committee               |

| P2P                  | Point-to-Point                                     |

| PAL                  | Phase Alternating Line                             |

| PMRME                | Parallel Multi-Resolution Motion Estimation        |

| PSNR                 | Peak Signal-to-Noise Ratio                         |

| QCIF                 | Quarter Common Intermediate Format                 |

| QoS                  | Quality of Service                                 |

| RAM                  | Random-Access Memory                               |

| ROM                  | Read-Only Memory                                   |

| RTL                  | Register Transfer Level                            |

| SAD                  | Sum of Absolute Differences                        |

| SATD                 | Absolute Transformed Differences                   |

| SD                   | Standard Definition                                |

| SHD                  | Sum of Hamming Distances                           |

| SMPTE                | Society of Motion Picture and Television Engineers |

| $\operatorname{SoC}$ | System-on-Chip                                     |

\_

| Abbreviation  | Description                                                |

|---------------|------------------------------------------------------------|

| SSD           | Sum of Squared Differences                                 |

| SW            | Search Window                                              |

| $\mathrm{TV}$ | Television                                                 |

| UHDT          | Ultra High Definition Television                           |

| VCD           | Video Compact Disc                                         |

| VCEG          | Video Coding Experts Group                                 |

| VENGME        | Video Encoder for the Next Generation Multimedia Equipment |

| VHDL          | VHSIC Hardware Description Language                        |

| VHSIC         | Very High Speed Integrated Circuit                         |

| VLC           | Variable Length Coding                                     |

| VLSI          | Very-Large-Scale Integration                               |

## **List of Figures**

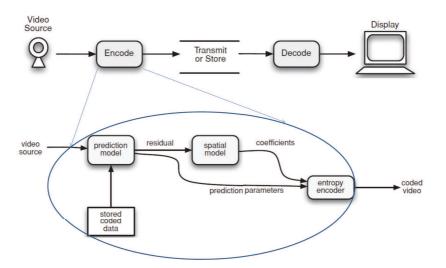

| 1.1     | Fundamentals of video coding, modified from [Rich10T]                 | 16   |

|---------|-----------------------------------------------------------------------|------|

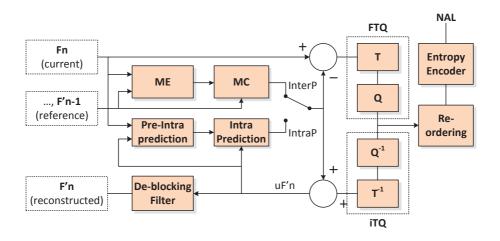

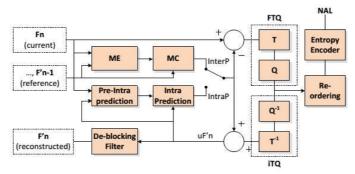

| 1.2     | Functional diagram of the H.264/AVC encoder [Nguy14A]. $\therefore$   | 19   |

| 1.3     | Intra prediciton, mode 4 pixels, for pixels $a - p$ of a block using  |      |

|         | the samples $A - Q$ from the neighbour blocks [Khan08T]               | 22   |

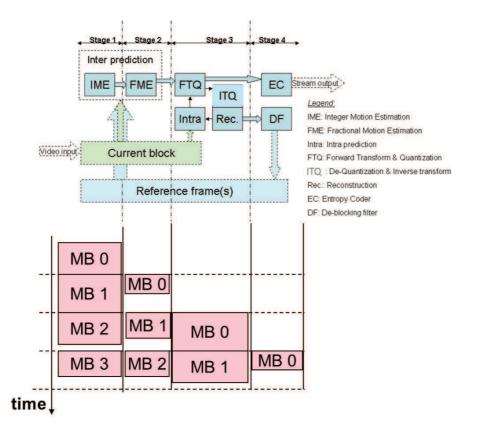

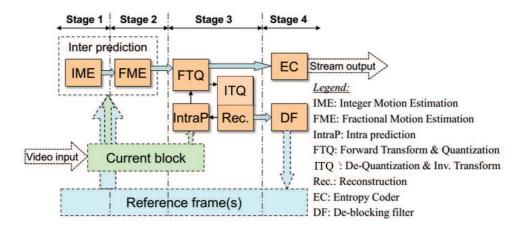

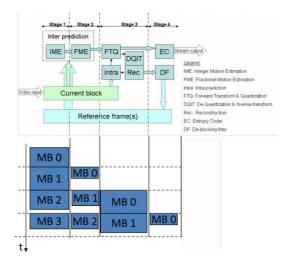

| 1.4     | An example of pipelining solution for video encoding                  | 24   |

| 1.5     | Program method for fine-grained Asynchronous Array of simple          |      |

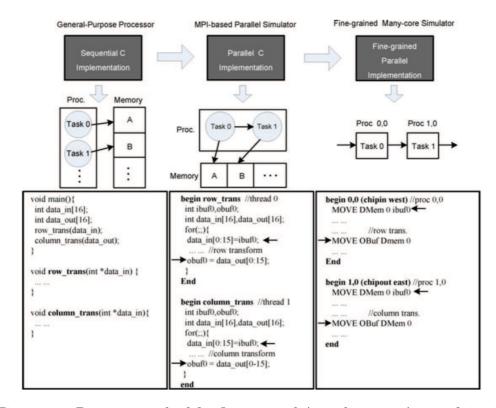

|         | Processors (AsAP) system [Xiao11A]                                    | 25   |

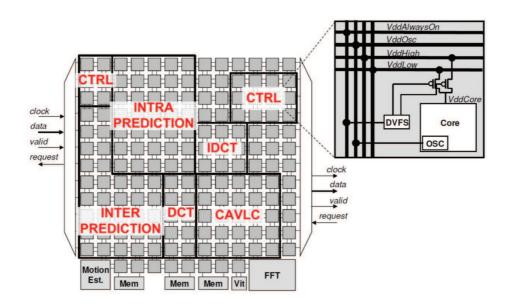

| 1.6     | H.264 encoder mapped onto a AsAP chip $[Le07A]$                       | 25   |

| 1.7     | A conventional four-stage pipelining architecture for H.264 hard-     |      |

|         | ware encoder                                                          | 27   |

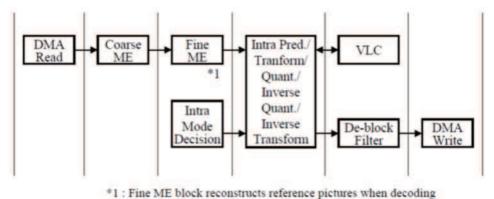

| 1.8     | An pipelining architecture of H.264/AVC hardware encoder closed       |      |

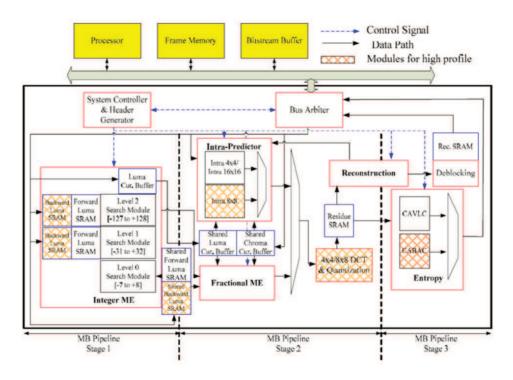

|         | to the clasical pipeline [Moch07A]                                    | 28   |

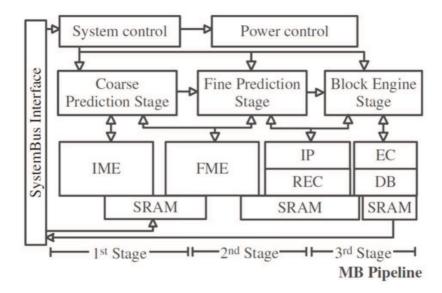

| 1.9     | A 3-stage pipelining architecture of H.264/AVC hardware en-           |      |

|         | coder proposed in [Chen09A]                                           | 29   |

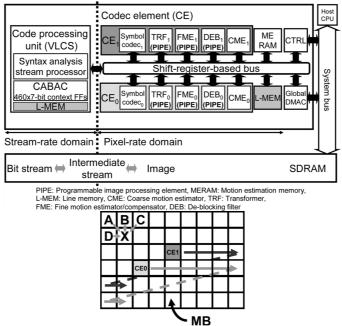

| 1.10    | High speed pipelining architecture for H.264 hardware encoder,        |      |

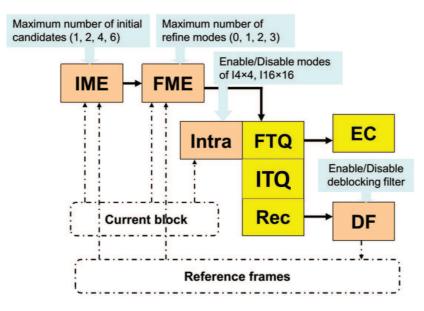

|         | proposed in [Iwat09A]                                                 | 31   |

| 1.11    | Two-stage frame pipelining H.264 encoder architecture, adapted        |      |

|         | from [Chen08A]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 32   |

| 1.12    | Power estimation and optimization based on abstraction levels,        |      |

|         | modified from [LecNENTS1]                                             | 33   |

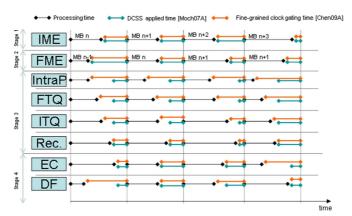

| 1.13    | DCSS and fine-grained clock gating exploit schedule of H.264          | ~~   |

|         | encoder                                                               | 35   |

| 1.14    | Low-power H.264/AVC hardware encoder architecture proposed            | 9.0  |

| 1 1 1 1 | in [Lin08A1].                                                         | 36   |

| 1.15    | Parameterized H.264/AVC video encoder, modified from [Chen09A]        | . 37 |

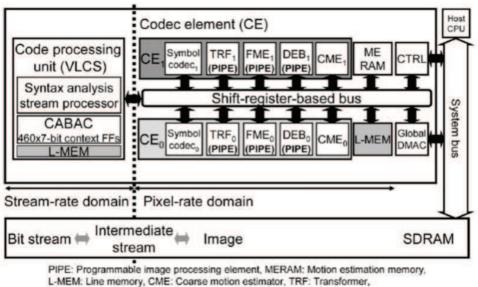

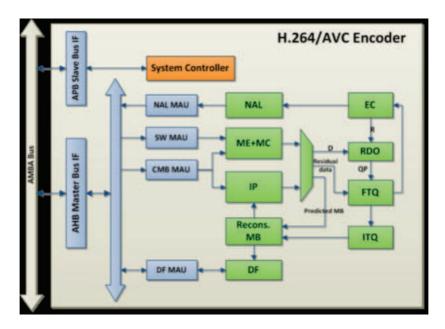

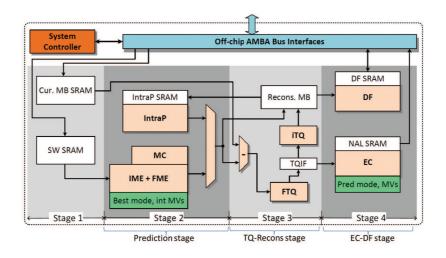

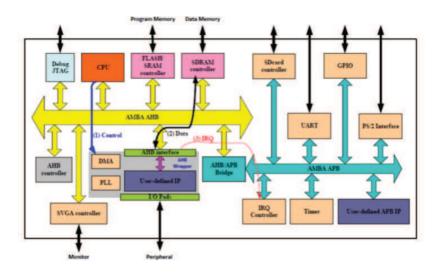

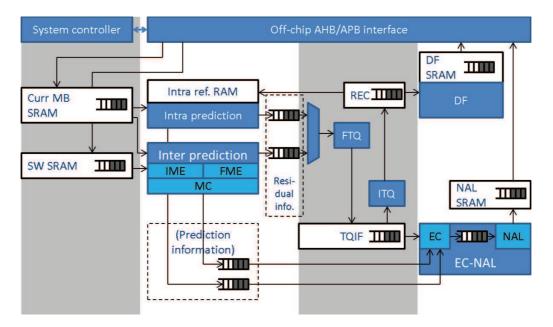

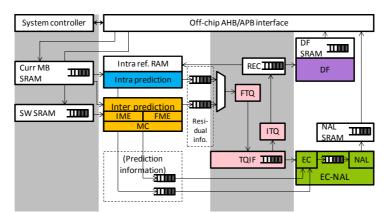

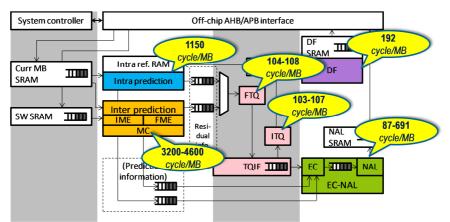

| 2.1  | The VENGME H.264/AVC video encoder architecture                                       | 48 |

|------|---------------------------------------------------------------------------------------|----|

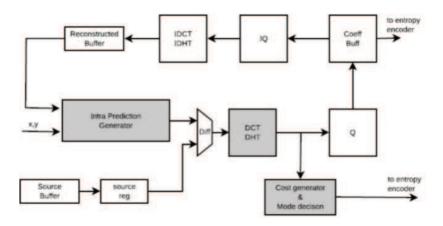

| 2.2  | Dataflow of the Intra prediction module                                               | 49 |

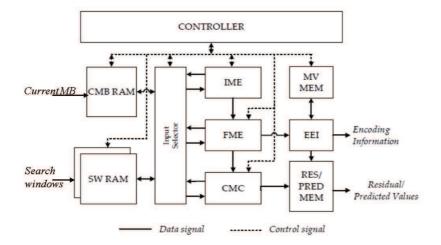

| 2.3  | The architecture of Inter prediction module [Tran13B]                                 | 50 |

| 2.4  | Architecture of the Transformation and Quantization module                            |    |

|      | [Tran13B]                                                                             | 51 |

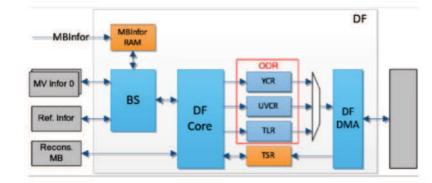

| 2.5  | The architecture of De-blocking filter module [Tran13B]                               | 52 |

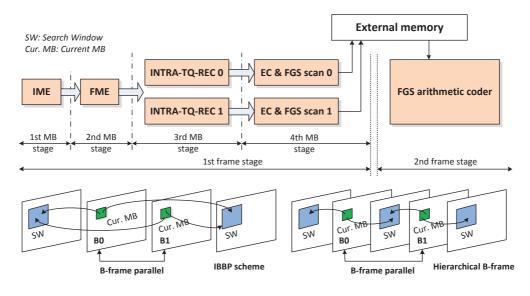

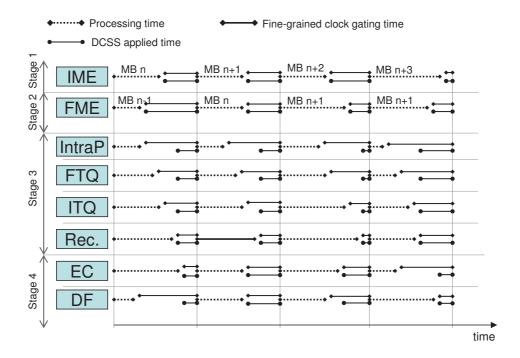

| 2.6  | VENGME pipelining schedule                                                            | 53 |

| 2.7  | The VENGME verification method [Tran13B].                                             | 54 |

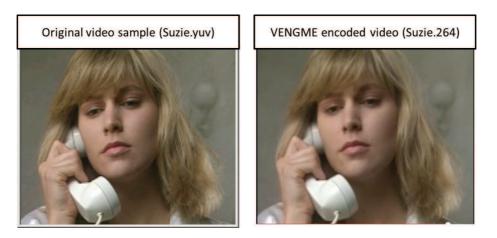

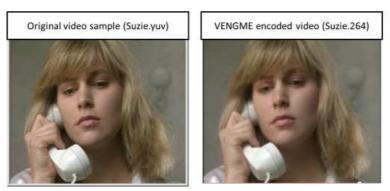

| 2.8  | Video frames in the original and the VENGME encoded video                             |    |

|      | streams.                                                                              | 55 |

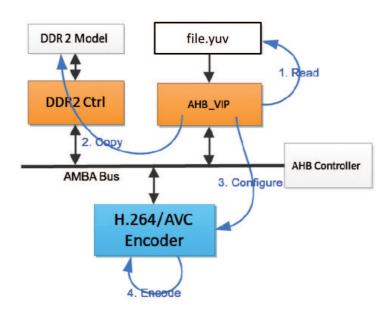

| 2.9  | System-on-Chip for VENGME validation [Tran13B]                                        | 55 |

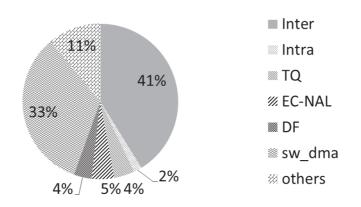

| 2.10 | Power consumption composition of VENGME system                                        | 59 |

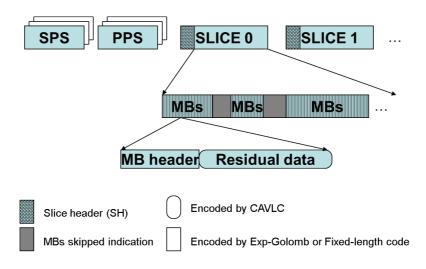

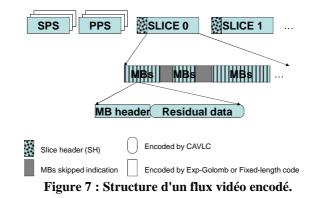

| 2.11 | Encoded video data structure                                                          | 62 |

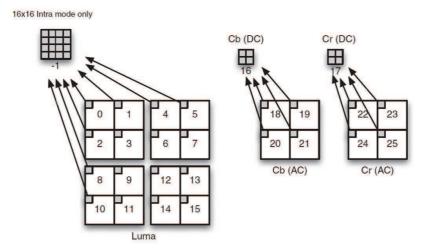

| 2.12 | Block scanning order in one MB [Rich03H]                                              | 63 |

| 2.13 | Zigzag scan order in one block [Nguy12A]                                              | 64 |

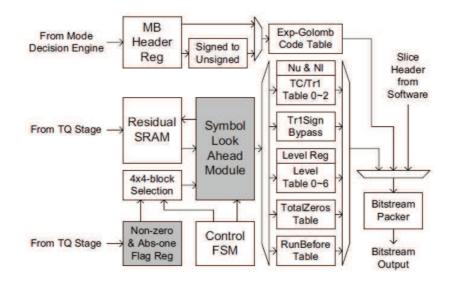

| 2.14 | Architecture of a low-power Entropy Coder [Tsai06L]                                   | 71 |

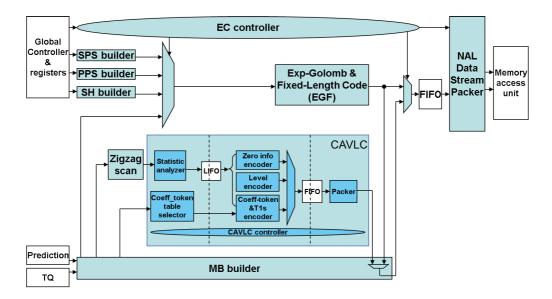

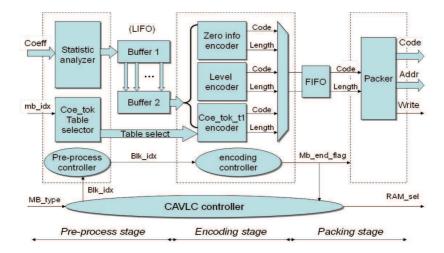

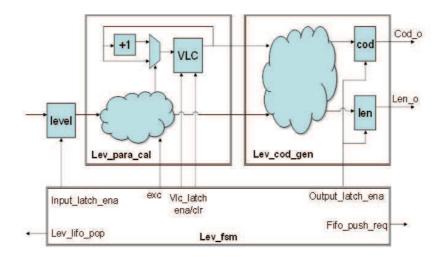

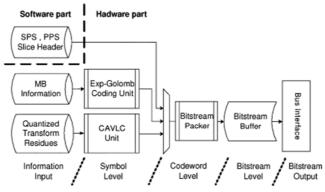

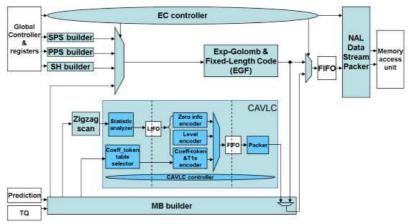

| 2.15 | Entropy coder and data packer architecture overview                                   | 74 |

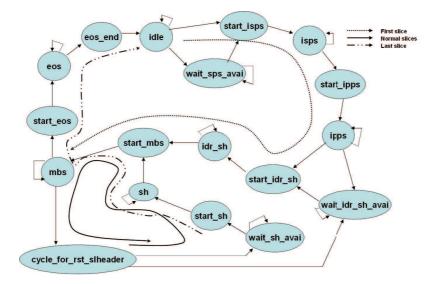

| 2.16 | Finite state machine of the the entropy coder                                         | 75 |

| 2.17 | Three-stage pipeline architecture of the VENGME CAVLC en-                             |    |

|      | coder                                                                                 | 75 |

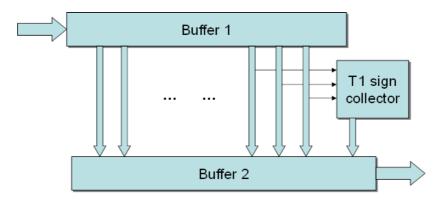

| 2.18 | Trailing one signs $(T1s)$ extraction during buffer copy                              | 77 |

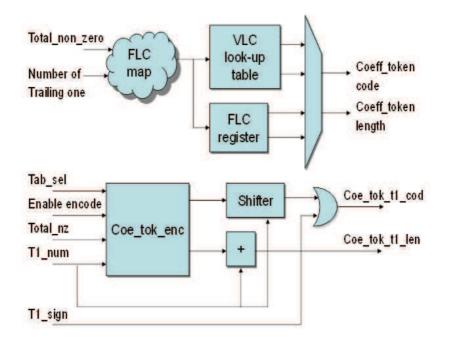

| 2.19 | $\operatorname{Coeff\_token}$ and $\operatorname{T1}$ signs encoded into one codeword | 78 |

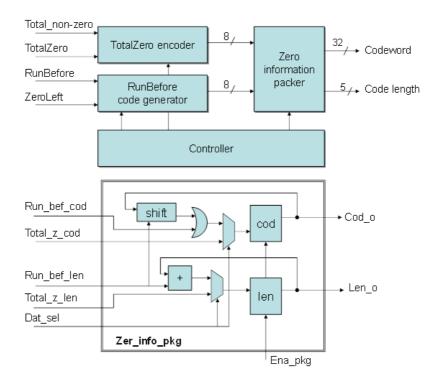

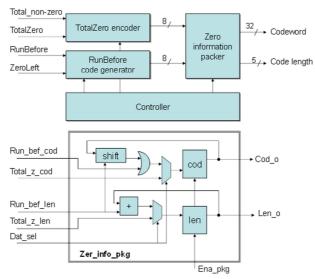

| 2.20 | Position and architecture of the zero information packer (Zer_info_pk                 | (g |

|      | in the zero information encoder                                                       | 79 |

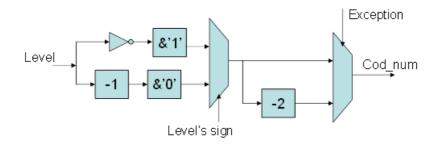

| 2.21 | Architecture of the <b>level</b> encoder                                              | 81 |

| 2.22 | Code - number arithmetic expression with optimization                                 | 81 |

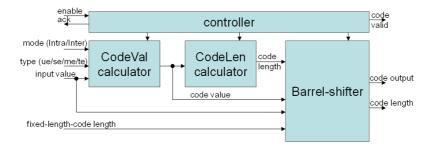

| 2.23 | Architecture of the Exp-Golomb and Fixed-length coder (EGF).                          | 83 |

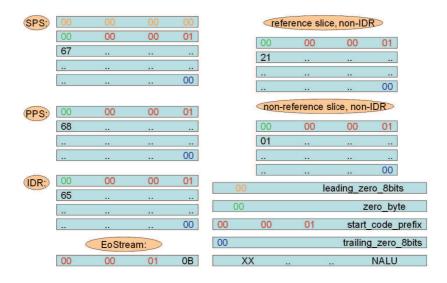

| 2.24 | Proposed syntax of BSNALU.                                                            | 84 |

| 2.25 | Architecture of the NAL packing engine                                                | 84 |

| 2.26 | Power consumption and area at targeted frequencies of CAVLC                           |    |

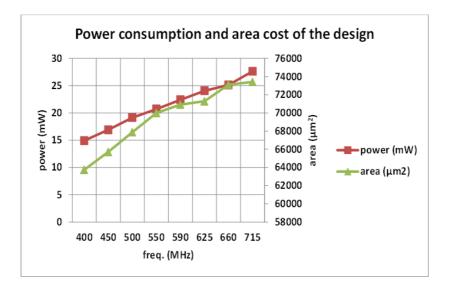

|      | implementation                                                                        | 86 |

| 2.27 | Verification method for EC                                                            | 88 |

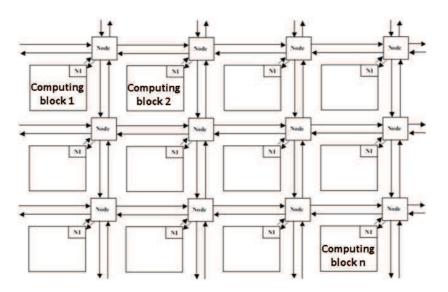

| 3.1  | General figure of multi-computing architecture, modified from                         |    |

|      | [Beig05A].                                                                            | 96 |

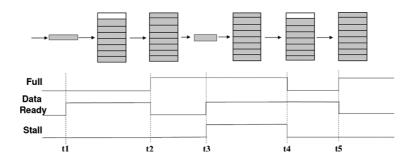

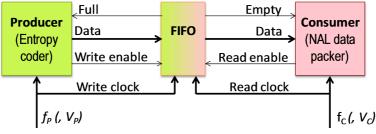

| 3.2  | FIFO communication between producer and consumer modules.                             | 98 |

| 3.3  | The VENGME H.264/AVC encoder platform with FIFO links                         |      |

|------|-------------------------------------------------------------------------------|------|

|      | between modules                                                               | 100  |

| 3.4  | EC module and its FIFO link between entropy coder and NAL                     |      |

|      | sub-modules.                                                                  | 101  |

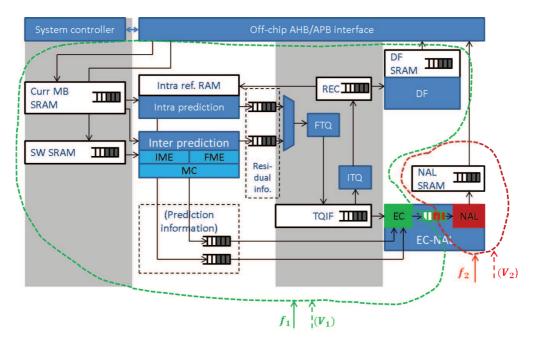

| 3.5  | The VENGME H.264/AVC encoder platform with 2 power do-                        |      |

|      | mains                                                                         | 102  |

| 3.6  | Stall state on producer side [Chou09P]                                        | 104  |

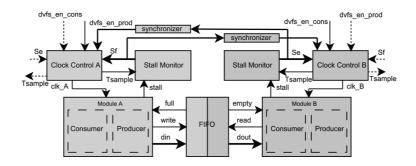

| 3.7  | Hardware implementation of the method presented in [Chou09P]                  | .104 |

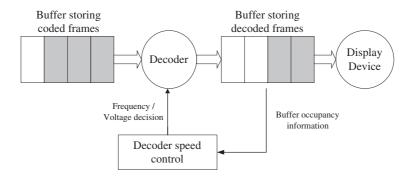

| 3.8  | Voltage and/or frequency scaling method on a multimedia de-                   |      |

|      | code and display system [Lu03R]                                               | 106  |

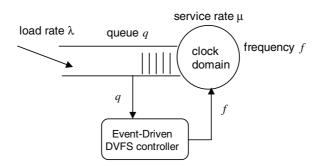

| 3.9  | Queue-Domain model [Wu05V].                                                   | 106  |

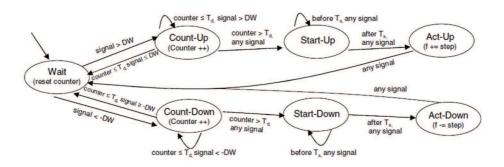

| 3.10 | Finite State Machine (FSM) implementation for each queue sig-                 |      |

|      | nal [Wu05V]                                                                   | 107  |

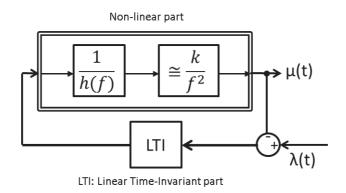

| 3.11 | Closed-loop system with non-linearities in $[Wu05V]$                          | 107  |

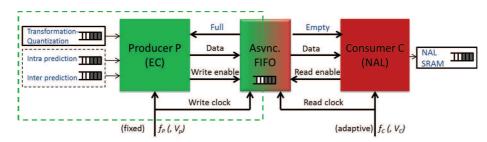

| 3.12 | Entropy coder - Bytestream NAL data packer (EC-NAL) mod-                      |      |

|      | ule where power management method based on FIFO-occupancy                     |      |

|      | level is applied.                                                             | 109  |

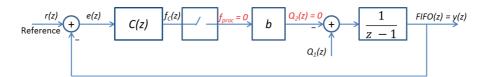

| 3.13 | FIFO model.                                                                   | 109  |

| 3.14 | Information recorded. It contains the consumer stall $(Cwait)$                |      |

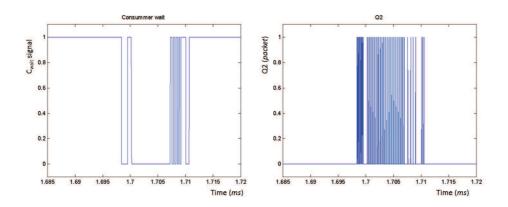

|      | signal and the $Q^2$ value                                                    | 111  |

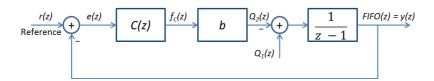

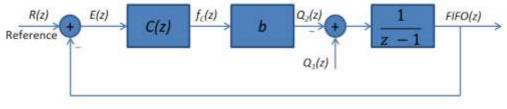

| 3.15 | Closed-loop control scheme of the FIFO level                                  | 112  |

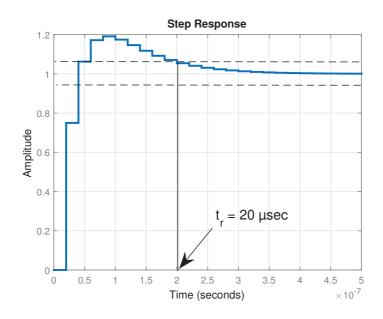

| 3.16 | Step response of the linear closed-loop system. The poles in                  |      |

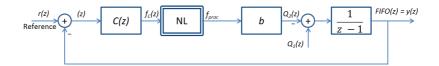

|      | closed-loop are equal to $0.75$ and $0.5$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 114  |

| 3.17 | Closed-loop control scheme of the FIFO level with non-linearity               |      |

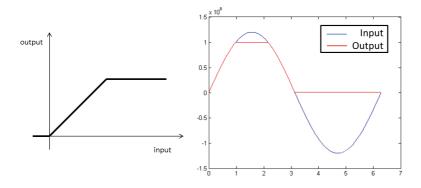

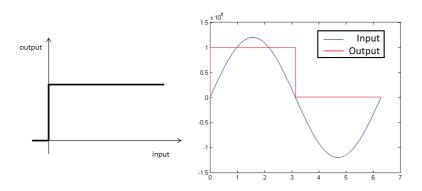

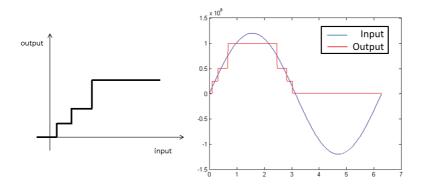

|      | (NL) added                                                                    | 114  |

| 3.18 | Input and output of a saturation block                                        | 114  |

| 3.19 | Input and output of a relay block                                             | 115  |

| 3.20 | Input and output of a quantizer block.                                        | 115  |

| 3.21 | Anti-windup scheme in the controller using a saturation                       | 116  |

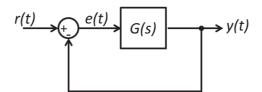

| 3.22 | Closed-loop system with the open-loop transfer function $G(s)$ .              | 118  |

| 3.23 | Closed-loop system with a proportional gain $K$                               | 118  |

| 3.24 | Closed-loop stability criteria using the open loop transfer func-             |      |

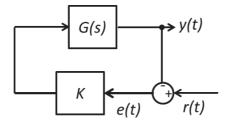

|      | tion $G(s)$ and the critical point $-1/K$ .                                   | 119  |

| 3.25 | An example of mapping the Nyquist plot when the open-loop                     |      |

|      | system has poles on the imaginary axis [lpsa]                                 | 119  |

| 3.26 | Closed-loop with a non-linearity $N$ .                                        | 121  |

х

| 3.27 | Closed-loop system with the controller, the system and a non-                            |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | uniform quantizer.                                                                       | 122 |

| 3.28 | General odd quantizer                                                                    | 123 |

| 3.29 | Admissible applied frequencies.                                                          | 124 |

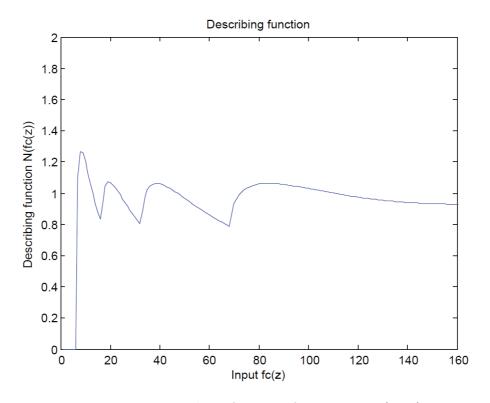

| 3.30 | Describing function for Equation (3.19).                                                 | 125 |

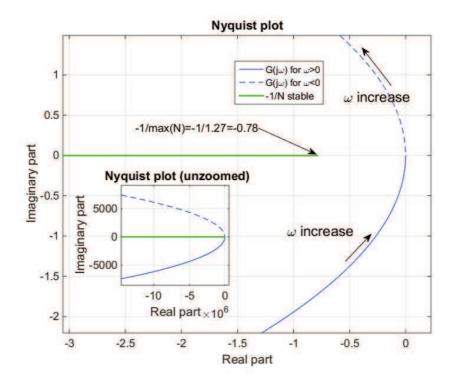

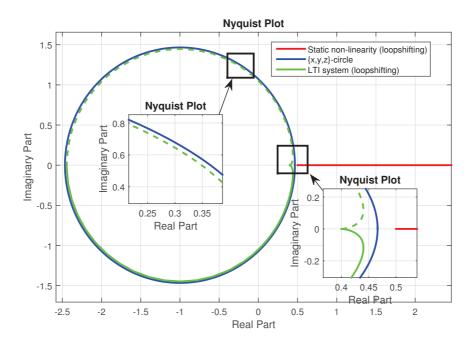

| 3.31 | Nyquist stability criterion considering the describing function                          |     |

|      | (3.19)                                                                                   | 126 |

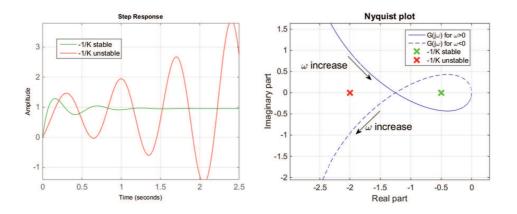

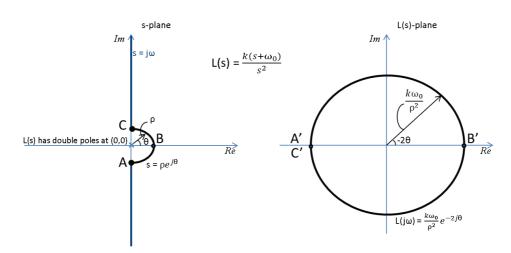

| 3.32 | Nyquist plot of $L(s) = \frac{k(s+\omega_0)}{s^2}$ for the detour $s = \rho e^{j\theta}$ | 127 |

| 3.33 | Open-loop system when the calculated $f_C < 6.25.$                                       | 128 |

| 3.34 | The closed-loop system contains a LTI plant $G(j\omega)$ and a nega-                     |     |

|      | tive feedback $\mathcal{D}(\bullet)$                                                     | 129 |

| 3.35 | The closed-loop system with loop shifting. $\ldots$ $\ldots$ $\ldots$                    | 130 |

| 3.36 | System to which the topological separation stability condition is                        |     |

|      | applied                                                                                  | 133 |

| 3.37 | Input $f_C$ and output $f_{prac}$ of the non-linear block which is a                     |     |

|      | quantizer                                                                                | 135 |

| 3.38 | Nyquist plot with the semiplane separation. $\ldots$ $\ldots$ $\ldots$                   | 135 |

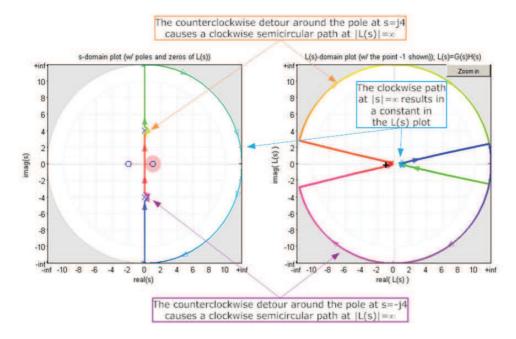

| 3.39 | Nyquist plot with the circle separation                                                  | 137 |

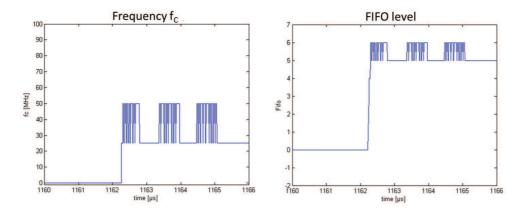

| 3.40 | Simulation results for closed-loop poles $z_{1,2} = 0.5 \pm 0.2i$ (left:                 |     |

|      | clock frequency $f_C$ , right: FIFO level)                                               | 138 |

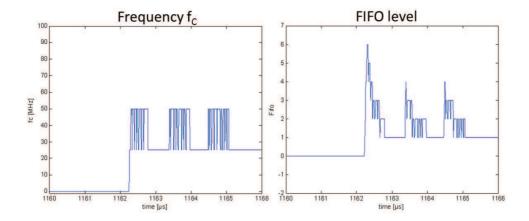

| 3.41 | Simulation results for closed-loop poles $z_{1,2} = 0.9$ (left: clock                    |     |

|      | frequency $f_C$ , right: FIFO level)                                                     | 139 |

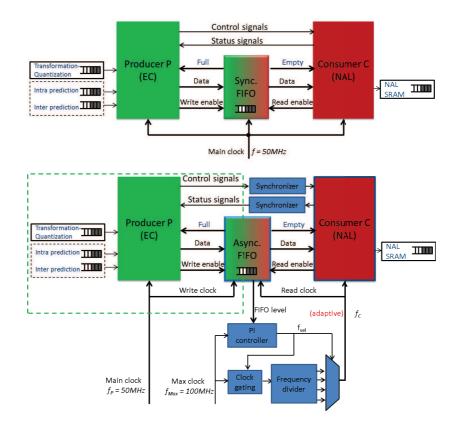

| 4.1  | Architecture of the original and modified EC-NAL modules to                              |     |

| 1.1  | apply the FIFO-level-based DFS method                                                    | 143 |

| 4.2  | Metastable state of CDC signal and the propagation of the signal                         | -   |

|      | in the design $[Cumm08C]$ .                                                              | 144 |

| 4.3  | Conventional synchronizer with two flip-flops [Jain14S]                                  |     |

| 4.4  | Toggle synchronizer for pulse synchronization [Jain14S]                                  |     |

| 4.5  | Gray encoding used for multi-bit signals [Jain14S].                                      |     |

| 4.6  | Architecture of an asynchronous FIFO [Cumm02S]                                           |     |

| 4.7  | A four-bit binary counter used as frequency divider [HyPh]                               |     |

| 4.8  | Calculating circuit to be implemented.                                                   |     |

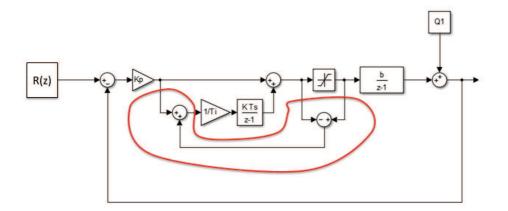

| 4.9  | The controller with $z_1 = 0.75$ and $z_2 = 0.5$ is integrated into the                  |     |

|      | EC-NAL module.                                                                           | 151 |

| 4.10 | Integration of the DFS controller in the H.264 encoder                                   | 152 |

| 4.11 | Waveform of the selected PI controller applied on the EC-NAL            |

|------|-------------------------------------------------------------------------|

|      | module                                                                  |

| 4.12 | Validation flow of the DFS control based on FIFO occupancy level. $155$ |

| 4.13 | DFS control method: estimated power reduction from post-                |

|      | synthesis simulation results                                            |

## **List of Tables**

| 0.2  | Different CMOS technologies used during the thesis              | 6   |

|------|-----------------------------------------------------------------|-----|

| 1.1  | Chronology of video coding formats and standards                | 11  |

| 1.2  | A survey of H.264 hardware video encoders                       | 39  |

| 2.1  | Targeted features and parameters of the VENGME design           | 47  |

| 2.2  | VENGME implementation results for the $130nm$ CMOS tech-        |     |

|      | nology                                                          | 56  |

| 2.3  | Power composition of the VENGME H.264 encoder, obtained         |     |

|      | using SpyGlass, with $32nm$ CMOS technology                     | 58  |

| 2.4  | Syntax of a byte stream NAL unit                                | 63  |

| 2.5  | Thresholds to increase the VLC number                           | 66  |

| 2.6  | Examples of Exp-Golomb coding                                   | 68  |

| 2.7  | Comparison of EC designs from the state-of-the-art              | 72  |

| 2.8  | An example of a 8-bit word in VLC tables                        | 82  |

| 2.9  | Hardware cost comparison                                        | 87  |

| 2.10 | Comparison of CAVLC results                                     | 87  |

|      | Implementation results of the EC module                         | 89  |

| 2.12 | Power composition of the EC-NAL module using synchronous        |     |

|      | FIFO with technology CMOS $32nm$ , at $50MHz$ and voltage $1V$  | 90  |

| 2.13 | Power composition of the EC-NAL module using asynchronous       |     |

|      | FIFO with technology CMOS $32nm$                                | 91  |

| 4.1  | Synthesis results of the original NAL submodule and of the syn- |     |

|      | chronous FIFO                                                   | 156 |

| 4.2  | Synthesis results of the modified NAL submodule and the asyn-   |     |

|      | chronous FIFO                                                   | 157 |

| 4.3  | Frequency for the NAL submodule during simulation time og        |     |

|------|------------------------------------------------------------------|-----|

|      | VENGME test video                                                | 158 |

| 4.4  | Power results of the synchronous FIFO and of the origininal NAL  |     |

|      | submodules                                                       | 159 |

| 4.5  | Power results of the controller, frequency divider, asynchronous |     |

|      | FIFO and modified NAL submodules                                 | 159 |

| 4.6  | Power results of the modified version when the NAL frequency     |     |

|      | is equal to $100MHz$                                             | 161 |

| 4.7  | Power results of the modified version when the NAL frequency     |     |

|      | is equal to $50MHz$                                              | 162 |

| 4.8  | Power results of the modified version when the NAL frequency     |     |

|      | is equal to $25MHz$                                              | 162 |

| 4.9  | Power results of the modified version when the NAL frequency     |     |

|      | is equal to $12.5MHz$                                            | 163 |

| 4.10 | Power results of the modified version when the NAL frequency     |     |

|      | is equal to $0Hz$                                                | 163 |

## Acknowledgements

I would like to express my deepest gratitude to my PhD supervisors, Dr. Suzanne Lesecq, senior scientist at CEA-LETI and Dr. Xuan-Tu Tran, professor, Head of the Department of Science, Technology and International Relations, Deputy Head of the UET-Key Laboratory for Smart Integrated Systems, at Vietnam National University, Hanoi for their excellent guidance, caring, patiently correcting my writing and helping me to improve my French.

I am also grateful to my adviser, Mrs. Edith Beigne, senior scientist at CEA-LETI, for sharing expertise, and sincere and valuable guidance and encouragement to me.

I would like to thank Prof. Nicolas Marchand, Head of Control Systems Department, Deputy director of GIPSA-lab, Directeur de Recherche CNRS, for doing me great honour by presiding the jury.

I would like to thank Prof. Alain Merigot, professor at University Paris XI and Dr. Nadine Azemard, professor at LIRMM, for accepting to be reporters.

I would also like to thank Prof. Huu-Duc Nguyen, Deputy Director of the Vietnam National University, Hanoi and Prof. Amara Amara, Deputy Managing Director Research and International Cooperation at ISEP, for their participation in the jury.

This PhD work was conducted in the collaboration between the Vietnam National University, Hanoi and CEA-LETI. I would like to thank both organizations, many thank to Mr. Hervé Fanet, for the supports that permit me to do this thesis.

I take this opportunity to express gratitude to Mr. Fabien Clermidy and Mr. Vincent Olive for their welcome and for providing me excellent atmosphere for doing research.

Special thanks goes to my colleagues, Van-Huan Tran, Duy-Hieu Bui, Nam-

Khanh Dang, Pascal Vivet, David Coriat, Sebatien Thuries, Warody Lombardy and Mikhailo Zarudniev, who shared to me their advices and supports during my PhD work. I also place on record, my sense of gratitude to all the dear colleagues, students in the three laboratories, the UET-Key Laboratory for Smart Integrated Systems (SIS), at Vietnam National University, Hanoi, the Laboratory of Silicon Integration and Digital Architecture (LISAN) and the Laboratory of Infrastructure and Software Tools for Chip (LIALP) at CEA-LETI, France, for warm and friendly working environment.

I would never have been able to finish my PhD thesis without the help from friends, and support from my family. Many thanks go to my friends who always support me and encourage me with their best wishes. I also thank my parents and my elder sister for the unceasing encouragement, support and attention. I would like to thank my husband. He is always there cheering me up and stood by me through the good times and bad. Finally, a special thank to my little son, Trung-Kien, Tony Vu, for coming into my life in September 2014.

Grenoble, June 2015.

#### Bonne lecture !

## List of publications

This is the list of my publications during my thesis:

N.-M. Nguyen, E. Beigne, D.-H. Bui, N.-K. Dang, S. Lesecq, P. Vivet and X.-T. Tran. An Overview of H.264 Hardware Encoder Architectures including Low-Power Features. In *REV Journal on Electronics and Communications (JEC)*, pp. 8-17, Vol. 4, No. 1-2, January - June, 2014, ISSN: 1859 – 387X.

N.-M. Nguyen, E. Beigne, S. Lesecq, D.-H. Bui, N.-K. Dang and X.-T. Tran. H.264/AVC Hardware Encoders and Low-Power Features. In *Proceeding of the IEEE Asia Pacific Conference on Circuits And Systems*, APCCAS 2014, pp. 77-80, Okinawa, Japan, November 2014.

N.-M. Nguyen, W. Lombardi, E. Beigne, S. Lesecq, and X.-T. Tran. FIFO-levelbased Power Management and its Application to a H.264 Encoder. In *Proceeding* of the IEEE Industrial Electronics Conference, IECON14, pp. 158-163, Dallas, TX, USA, October 2014.(Best Presentation Award)

N.-M. Nguyen, E. Beigne, S. Lesecq, P. Vivet, D.-H. Bui, and X.-T. Tran. Hardware implementation for entropy coding and byte stream packing engine in H.264/AVC. In *Proceeding of the International Conference on Advanced Technologies for Communications*, ATC 2013, pp. 360-365, Ho Chi Minh city, Vietnam, October 2013.

N.-M. Nguyen, X.-T. Tran, P. Vivet, and S. Lesecq. An efficient Context Adaptive Variable Length coding architecture for H.264/AVC video encoders. In *Proceeding of the International Conference on Advanced Technologies for Communications*, ATC 2012, pp. 158-164, Hanoi, Vietnam, October 2012. (Best Student

$\mathbf{Paper} \ \mathbf{Award})$

## Introduction

#### Context of video encoding

Video codec (compression-decompression) chips have been recently used in various applications, for instance video conferencing, security and monitoring systems, entertaining applications. To meet the need of mobile applications, video codec is preferred to be implemented in hardware than in software, due to better power efficiency and real-time capacities. One of the latest and most efficient standards for video applications is the H.264 Advanced Video Coding (H.264/AVC) [H.264] which provides better video quality at a lower bit-rate than the previous ones [Joch02P]. It has been specified in the co-operation between the ITU-T Video Coding Experts Group and the ISO/IEC Moving Picture Experts Group. The H.264/AVC specification adopts many advanced methods and algorithms for video compressing and also improves them. This makes the standard more efficient but requires more complex hardware implementation and consumes a huge amount of power.

Recently, the H.264 successor, namely the H.265/High Effciency Video Coding (HEVC) has been released. The H.265/HEVC recommendation [H.265] has been formally published in 2013, two years after this PhD thesis was started. It was jointly developed by the ITU-T and ISO/IEC organizations. It is promisingly bandwidth saving with 40-52% of bit rate reduction in comparison to the H.264/AVC [Rodr13P]. This enables Ultra High Definition Television (UHTV). However, this new standard also exhibits high computing complexity, much more intensive than the H.264 standard, which leads to shortened battery lifespan and higher power consumption. With these higher costs, the switch to the new standard has to be carefully thought and the H.264/AVC video codecs are still under use.

INTRODUCTION

The "Video Encoder for the Next Generation Multimedia Equipments" (VENGME) project, a research project granted by Vietnam National University, Hanoi (VNU), aims at designing and implementing a hardware H.264/AVC encoder targeting mobile platforms. The current design is optimized for CIF video. However, the VENGME architecture can be extended for larger resolutions by enlarging the reference memory and the search window.

To bring the H.264/AVC standard into commercial products, especially for hand-held devices, designers need to apply low-power techniques when designing the video codec. Targeting mobile applications, the VENGME platform was designed using low-power design features. Some blocks in the platform present nice power figures and performances, similar to state-ofthe-art designs. However, the whole platform power results are not outstanding in comparison to state-of-the-art hardware video encoders. To improve the platform power results, its imbalance workload can be exploited via different power control techniques. This includes applying Dynamic Power Management (DPM) methods, for instance, Dynamic Voltage and Frequency Scaling (DVFS) approaches [Yada12A].

#### Motivations and objectives

Many research efforts have been made to produce electronic circuits and systems that can perform more tasks with limited resources while consuming less energy. Technology evolution has increased significantly the operating speed and integration density. Meantime, energy and power consumption have become a tremendous problem because of their effects on the system reliability, cooling cost, and battery lifetime, especially for mobile devices, along with environmental considerations. Therefore, power consumption reduction is strongly required when designing complex system-on-chips.

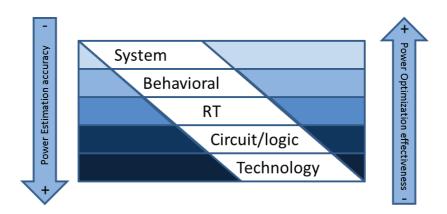

Static and dynamic techniques have been proposed in order to decrease the power consumption. Static techniques are applied at design time while dynamic ones adapt the circuit functioning during the operating time [Lu01C].

For System-on-Chips, power consumption is influenced by four main factors, namely the supply voltage, the switching activity in the circuit, the switching capacity load, and the clock frequency. Techniques to reduce the power consumption are based on the fact that the chip never works at its maximum power capacity and that there are always some idle or lower speed operating parts of the chip during the operating time. There are numerous existing low-power optimization mechanisms ranging from circuit level (power gating [Chio06T], clock gating [Khan99A], etc.) up to system (DVFS [Sylv07A, Ma10E, Vive10O]) and software level (idle mode programming, automatic wake up, etc.) [Deva95A]. Recent study, [Choi05F, Qu07P, Sula08U, Herb12E, Yada12D, Stan13E, Zhur13S] provide new solutions and improvements for these techniques.

The objective of this PhD thesis is firstly to design the EC-NAL module of the VENGME video encoder. Secondly, the VENGME architecture is analyzed to extract the power properties. Thirdly, we propose new mechanisms to control power consumption for a fully hardware H.264 encoder system-on-chip, the VENGME platform. Then, a low-level hardware control solution is proposed to reduce the power consumption of the system. Finally, hardware implementation and validation are realized to prove nice features and performances of the hardware control solution and evaluate the proposed mechanism.

#### Contributions of the work

To answer the objectives, this thesis proposes the following three contributions for both module and platform levels:

#### • Design of the entropy coder and data packer (EC-NAL) module

This contribution requires a full understanding of the H.264 encoder techniques. The H.264 implementations are reviewed and the available implementations on hardware are classified and analyzed.

The entropy coder and data packer (EC-NAL) is the final module in the encoding path of a video encoder. Its role is to eliminate the static redundancy in the video data. It receives data from most of the modules in the platform (all modules in the encoding path) and compresses this data using some entropy coding techniques. There are three main entropy coding techniques possible for H.264, namely, Exp-Golomb, CAVLC and CABAC [H.264]. In our entropy coder, the techniques applied are Exp-Golomb and CAVLC, equivalent to the Baseline or the Main profile of the H.264 standard. To understand the H.264 encoding process and the operation of the VENGME H.264 video encoder, we have proposed, designed and implemented the EC-NAL module in the VENGME H.264 video coding platform. The module has been integrated and validated into the complete platform.

This contribution has been published in:

- "An efficient Context Adaptive Variable Length coding architecture for H.264/AVC video encoders" [Nguy12A] presents the CAVLC encoder, one of the main engines of the Entropy Coder (EC);

- "Hardware implementation for entropy coding and byte stream packing engine in H.264/AVC" [Nguy13A] presents the design and implementation of the whole VENGME EC-NAL module.

## • Power estimation at RTL level for the VENGME H.264 encoder platform

An early power estimation is performed on the full VENGME platform to obtain a first evaluation of the power composition and the needs for applying power management methods (e.g. is there any chance to decrease the power consumption).

This power estimation result are presented in the publication: "H.264/AVC Hardware Encoders and Low-Power Features" [Nguy14H].

#### • Propose a method to the reduce the power consumption based on the FIFO occupancy level

Methods to manage and optimize power consumption aim at changing some of the four factor influencing the power consumption of digital CMOS circuits, given a means to monitor the workload status of the circuit. Some techniques based on controlling the status of a memory buffer were studied and analyzed.

The method proposed in our work is based on automatics control theory. The control decision is made according to the FIFO occupancy level in the communication link between two calculating submodules. The method was modeled and verified using Matlab. The controlled system is also proved to be stable. The proposed method is modeled, implemented, validated and applied onto the FIFO embedded in the EC-NAL module of the VENGME platform.

The controller was then modeled in VHDL, implemented in hardware. Its operation is verified via the integration into the EC-NAL module of the VENGME platform. The method was also validated with power estimation before and after applying it.

This work is presented in the publication "FIFO-levelbased Power Management and its Application to a H.264 Encoder" [Nguy14F].

#### Explanation for the different CMOS technologies and operating frequencies in the results presented in the thesis

This thesis work is conducted in three laboratories, namely the Smart Integrated Systems (SIS) laboratory in Vietnam National University, Hanoi (VNU), Vietnam, the Laboratory of Silicon Integration and Digital Architecture (LISAN) and the Laboratory of Infrastructure and Software Tools for Chip (LIALP) in CEA-LETI, France. The VENGME platform architecture is designed in the SIS laboratory. Low-power techniques, e.g. DFS techniques, are acquired from the LISAN laboratory. The automatic control is studied with the LIALP laboratory.

As a consequence, the author had the opportunity to work with largenode technologies and with more advanced ones. Table 0.2 shows the different CMOS technologies and operating frequencies used during the thesis. As can be seen, many technology changes have been done. These changes are imposed by the tools available in the laboratories at the time the developments have been done.

In the beginning phase of the thesis, the Entropy Coder and Network Abstraction Layer data packer (EC-NAL) module was designed. The CAVLC encoder, an important engine in the Entropy Coder (EC) submodule, was designed firstly, in 2012, in Vietnam. The engine was then synthesized in CEA-LETI, France, on the 65nm CMOS technology from STM. At the moment, to explore the operating capability of the design, the CAVLC encoder was synthesized with a wide range of frequencies, from 400MHz to 715MHz.

INTRODUCTION

| Year | Design             | Task                                              | Tool                                             | Place              | Technology                               | $\begin{array}{c} {\rm Frequency} \\ ({\it MHz}) \end{array}$ |

|------|--------------------|---------------------------------------------------|--------------------------------------------------|--------------------|------------------------------------------|---------------------------------------------------------------|

| 2012 | CAVLC<br>encoder   | synthesis                                         | Design Compiler<br>from Synopsys                 | CEA-LETI<br>France | CMOS 65nm<br>from STM                    | 400-715                                                       |

| 2013 | EC-NAL<br>module   | synthesis                                         | Design Compiler<br>from Synopsys                 | VNU<br>Vietnam     | CMOS 180 <i>nm</i><br>from AMS           | 100                                                           |

| 2013 | VENGME<br>platform | Power<br>simulation<br>@ RTL level                | SpyGlass<br>from Atrenta                         | CEA-LETI<br>France | CMOS 32nm<br>from STM                    | 50                                                            |

| 2013 | EC-NAL<br>module   | Power<br>simulation<br>@ RTL level                | SpyGlass<br>from Atrenta                         | CEA-LETI<br>France | CMOS 32nm<br>from STM                    | 50                                                            |

| 2014 | VENGME<br>platform | synthesis                                         | Design Compiler<br>from Synopsys                 | VNU<br>Vietnam     | CMOS 130nm<br>from<br>Global<br>Foundary | 100                                                           |

| 2014 | EC-NAL<br>module   | Synthesis,<br>Power<br>estimation<br>@ gate level | RC from<br>Cadence<br>PrimeTime<br>from Synopsys | CEA-LETI<br>France | FDSOI 28 <i>nm</i><br>from STM           | 50 & 100                                                      |

Table 0.2: Different CMOS technologies used during the thesis

Then, the EC-NAL module was designed in France and was sent to VNU, Vietnam, at RTL level, to be integrated in the platform. Thus, the module synthesis was performed, in Vietnam, in 2013, using the technology at hand, which is the 180nm CMOS technology from AMS. The operating frequency was decided to be 100MHz according to the VENGME project specification.

Simultaneously, the VENGME platform, at RTL level, was sent to France, for the low-power strategy sake. In this platform, the defined operating frequency was 50MHz. During this phase of the thesis, the power simulation at RTL level using SpyGlass from Atrenta was performed in CEA-LETI, with the 32nm CMOS technology from STM. The power simulation results at platform level allow to analyze the power distribution over the various modules of the platform and to seek for extra power optimization.

The FIFO/buffer-level-based DFS method was, then, proposed and the EC-NAL module was selected for the method to be firstly implemented in. To enable DFS, the FIFO within the EC-NAL module was modified from a synchronous FIFO to an asynchronous one. Power simulations, for the EC-NAL module, at RTL level using SpyGlass were performed with the

same technology and operating frequency. The power results shows that the modification of the FIFO in the EC-NAL module increases the module power consumption. However, this increase seems to be small enough in comparison to the expected power gain from applying the DFS method.

In 2014, the whole VENGME platform was synthesized on the 130nm CMOS technology from Global Foundary, with the operating frequency of 100MHz. All the synthesis and power simulation at RTL level results will be presented in Chapter 2.

The proposed DFS method proposed was modeled in VHDL and implemented in hardware. To evaluate the power gain, synthesis and gate level power estimation were performed in CEA-LETI, on the 28nm FDSOI technology from STM. The main operating frequency is 50MHz and for the DFS part, the maximum frequency is 100MHz. The power estimation at gate level and DFS method evaluation will be presented in Chapter 4.

This explains the different CMOS technologies and frequencies that have been used during this PhD thesis.

#### Organization of the manuscript

Apart from this introduction, the document contains four chapters and a conclusion. The first chapter introduces the H.264 video coding standard in relation with other video coding standards in use. Some basic concepts of video coding in general and of H.264 video coding in particular are also presented. Moreover, at the end of the chapter, a state-of-art of H.264 encoding hardware implementations is provided and analyzed. This contents firstly shows some issues in implementing the H.264 video coding standards and lastly review the available hardware implementations of H.264 video encoder.

The second chapter introduces the VENGME platform. This is a hardware of H.264/AVC video encoder targeting mobile applications. The VENGME platform has been designed by the research group in Vietnam in the framework of the VENGME project. The architecture, modeling and validation of the EC-NAL module, one of the main contributions, is also presented in this chapter. The results of the power simulations at RTL level for the whole VENGME platform and for the EC-NAL module help in seeking a power optimization solution for the VENGME platform. In the third chapter, FIFO-based power management and optimization methods are reviewed and analyzed. Then, a FIFO-level-based method to control the power consumption is proposed and applied to the FIFO embedded in the EC-NAL module. All the steps from system modeling, control design, stability analysis and MATLAB simulation results are in turn presented.

The fourth chapter presents the hardware implementation of the FIFOlevel-based method proposed in the previous chapter. Simulation and power estimation results enable verifying the control operation and validating the method.

Finally, the conclusion summarizes the works performed during this thesis and it also draws some future works perspectives.

#### Chapter 1

## The H.264/AVC video coding standard and its implementations

Thanks to technology evolution, video application, even for basic applications such as television, has become one of the most used technology applications nowadays. It is more and more popular in daylife applications, for instance, in television broadcast over cable or satellite; in many storage medias as DVD, Blu-ray disc, in video on internet, video chat, video telephone, video conferencing, etc. High video quality, large video size are increasingly required for these applications. Moreover, storage space and bandwidth are limited and expensive. Thus, video compression technology that reduces the video data size is obviously essential. To allow international video exchange and make video data formats world-wide-accepted leading to video codecs (compressing and decompressing) cheaper, international standardization is mandatory.

The objectives of this chapter are to firstly review video coding formats and standards from the past to present, and their application range. Then, the basic concepts of video coding techniques and the H.264 Advanced Video Coding (H.264/AVC) standard will be presented. Lastly, the main difficulties and trends in implementing the H.264/AVC will be discussed with an overview and analysis of different implementations.

## 1.1 H.264 video coding standard in the history of video coding standards

This section provides a brief review of video coding standards and their applications. The details on coding techniques are not in the scope of the present document. The reader interested in such details can consult [Scha95D, Joch02P, Jaco07A]. Table 1.1 presents a chronology of some popular video coding formats and standards. As can be seen, the first standard considered, H.120, has been standardized in the 1980s while the latest evolution of the H.264, named H.265, has been published in 2013, after the beginning of the present work.

#### 1.1.1 The video coding standards before the H.264/AVC

The first digital video coding standard is the H.120 recommendation [H.120], standardized by the ITU-T<sup>1</sup> in 1984. Its target was to transmit video over dedicated point-to-point (P2P) data communication lines, NTSC (National Television System Committee) at 1544*kbps*, or PAL (Phase Alternating Line) at 2048*kbps* [Jaco07A]. The H.120 was superseded [itu] and it is essentially not in use today.

In 1988, the H.261 recommendation [H.261] was approved by the ITU-T Video Coding Experts Group (VCEG). It was the first successful practical digital video coding standard, operating at 64 - 2048kbps [Sull05O]. The recommendation H.261 designed the coding algorithm to support the transmission of colour video over Integrated Services for Digital Network (ISDN) at  $p \times 64kbps$  with low delay, where p is between 1 and 30. The targeting resolutions were Common Intermediate Format (CIF)  $352 \times 288$  pixels and Quarter CIF (QCIF)  $176 \times 144$  pixels [Scha95D].

The International Electrotechnical Commission of the International Organization for Standardization [iso] (ISO/IEC) [iec] also developed a video coding standard for the coding of moving pictures and associated audio at up to about 1.5Mbps (the MPEG-1) [mpeg-1]. The MPEG-1 was in use more frequently than the H.261, especially in Video CD (VCD) in Asia [Sull05O]. However, the lack of interlaced features [Jaco07A] has limited its applications.

10

$<sup>^1{\</sup>rm The}$  Telecommunication Standardization Sector of the International Telecommunication Union

| Year | Video coding<br>formats/standards | Developed/<br>Standardized by                          | Application range                                                                                                                           |

|------|-----------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1984 | H.120                             | CCITT (ITU-T now)                                      | Video transmission (NTSC or PAL)<br>over P2P data communication lines                                                                       |

| 1988 | H.261                             | CCITT (ITU-T now)                                      | Video transmission<br>over ISDN lines                                                                                                       |

| 1993 | MPEG-1                            | ISO/IEC                                                | Digital satellite/cable TV;<br>Video CD;                                                                                                    |

| 1994 | H.262/MPEG-2                      | (joint)<br>ITU-T & ISO/IEC                             | DVD players;<br>camcorders; video recorders;<br>distribution networks                                                                       |

| 1995 | H.263                             | ITU-T                                                  | Video conferencing; cellphone codec;<br>World Wide Web-distributed video                                                                    |

| 1998 | MPEG-4 Visual                     | ISO/IEC                                                | DVD; mobile multimedia;<br>internet multimedia; broadcast TV;<br>videophone; [MP4Apps]                                                      |

| 2000 | VP3                               | On2 Tech.                                              | Released into the open source community<br>in 2001 by On2 Tech.                                                                             |

| 2001 | VP4                               | On2 Tech.                                              |                                                                                                                                             |

| 2002 | VP5                               | On2 Tech.                                              |                                                                                                                                             |

| 2003 | H.264/MPEG-4 AVC                  | (joint)<br>ITU-T & ISO/IEC                             | HD video like Blu-ray Disc;<br>HDTV broadcast over terrestrial, cable<br>and satellite; video streaming<br>(Vimeo, YouTube, iTunes Store,); |

| 2003 | VP6                               | On2 Tech.                                              | Adobe's Flash video; YouTube video;<br>video conference over IP;<br>satellite broadcasts                                                    |

| 2005 | VP7                               | On2 Tech.                                              | Adobe's Flash video; video streaming;                                                                                                       |

| 2005 | AVS                               | The government of<br>the People's Republic<br>of China | within mainland China                                                                                                                       |

| 2006 | SMPTE $421M/VC-1$                 | Microsoft - SMPTE                                      | Blu-ray Disc; Window media; HD DVD;                                                                                                         |

| 2008 | VP8                               | On2 Tech Google                                        | Adobe's Flash video; YouTube<br>video; (open source by Google)                                                                              |

| 2010 | Dirac/VC-2                        | BBC Research - SMPTE                                   | Ultra HDTV; used by BBC<br>to transmit HDTV                                                                                                 |

| 2013 | VP9                               | Google                                                 | HTML5 video; some smart TVs;<br>YouTube for 4K resolution;                                                                                  |

| 2013 | H.265/HEVC                        | (joint)<br>ITU-T & ISO/IEC                             | Ultra HDTV;<br>used by ATSC, DVB & Blu-ray disc                                                                                             |

#### Table 1.1: Chronology of video coding formats and standards

The H.262/MPEG2 video coding standard [H.262] was developed jointly by the ITU-T VCEG and the ISO/IEC Moving Picture Experts Group (MPEG) in 1994 as the successor of the MPEG-1 (in 1993). It is compatible with the MPEG-1 standard and widely used. It was designed for a bit rate from 3 to 10Mbps and supports both standard-definition (SD,  $720 \times 480/576$ pixels) and high-definition (HD,  $1920 \times 1080$  pixels) [Jaco07A].

In 1995, the ITU-T provided the H.263 video coding standard [H.263]. The H.263 successfully dominated video conferencing and cell phone video applications. Then, different versions (H.263+, H.263++, ...) and several annexes were published.

The ISO/IEC MPEG has developed the MPEG-4 Visual video compression format, the second part of the MPEG-4 standard [mpeg-4]. The standard was finalized in 1998. It is applied in several means of video storage and video transmission, such as mobile multimedia, Digital Video Disc (DVD), video streaming on internet, broadcasting, digital television (TV) box,... [MP4Apps]. During its enhancement, many functionalities have been added. For instance, interactive graphics, object and shape coding, face modeling, scalable coding, 3D graphics,... are the novel coding concepts added to the MPEG-4 standard. However, few of these techniques have been successfully used in commercial applications due to their complexities [Jaco07A].

#### 1.1.2 The H.264 Advanced Video Coding standard

The H.264/AVC video coding standard [H.264], the successor of the H.263, is one of the most widely used video compression standard. It was recommended by the Joint Video Team (JVT), that was formed by the ITU-T VCEG and the ISO/IEC MPEG groups in 2001. Using block-based coding, it was a step "back to basics" in comparison to MPEG-4 Visual coding techniques [Jaco07A]. Its primary technical objectives are to improve significantly the coding efficiency; to have high loss/error robustness; to exhibit low latency capability and to enable "network friendliness" i.e. flexibility for user over various systems and networks [Wieg03O]. The first recommendation was finalized in 2003.

The H.264/AVC contains a wide set of video coding tools to support a variety of applications ranging from mobile services, video conferencing, digital broadcast for IPTV, HDTV and digital storage media. Compared to previous standards such as MPEG-4, H.263, MPEG-2, the H.264/AVC standard achieves respectively 39%, 49%, and 64% of bit-rate reduction [Joch02P]. The H.264/AVC standard will be discussed in more details in Section 1.2.

#### 1.1.3 Video coding standards from other organizations, H.265/HEVC standard and the consideration of standard selection

After the H.264/AVC standard was introduced, video coding standards have not been given by a unique standardization group, e.g. ITU-T or ISO/IEC. Several companies and/or organizations have developed their own video compression formats [Jaco07A]. For instance:

- the Audio Video coding Standard (AVS) was developed in 2005 by the government of the People's Republic of China to avoid paying royalties for the patents on international standards. Some semiconductor companies support the standard, but it is mainly used within mainland China [Jaco07A];

- the TrueMotion video codec series, known as VP3 to VP7, were developed by the On2 Technologies company [Jaco07A]. In 2001, On2 has released the VP3 codec implementation as open-source. The VP6 was applied in the Adobe Flash video codec. With the acquisition of On2 Technologies in 2010, the Google Inc. [Goog] has obtained the rights on the VP8 video codec. It has been announced as a royalty-free alternative to the H.264/AVC video codec. Several tests have been performed to compare both codecs [Fell11T]. They have shown that, up to a compression ratio of six, the H.264/AVC (the reference software implementations x264 and JM) shows better quality than the VP8 codec by means of Peak Signal-To-Noise ratio (PSNR). Then, at a higher compression ratio, the quality of both codecs is comparable. Moreover, the x264 codec encoding speed is 350% higher than the VP8 one [Fell11T];

- the Windows Media Video video codec version 9 was developed by Microsoft [Micr]. This video format was then standardized by the Society of Motion Picture and Television Engineers (SMPTE) [smpte]

as the SMPTE 421M (or VC-1) video coding standard. The standard does not provide cost-saving by avoiding the use of patented technologies from third parties. Moreover, it compresses less well than the H.264 [Jaco07A]. The Dirac video compression format was developed by the BBC Research and Developement (BBC R&D) [bbcrd]. Its I-frame-only subset, Dirac Pro, was standardized by the SMPTE and known as VC-2.

Recently, the H.264 successor, H.265/High Efficiency Video Coding (HEVC), and its royalty-free alternative VP9 by Google, have been released. The H.265/HEVC recommendation [H.265] has been formally published in 2013. It was jointly developed by the ITU-T and ISO/IEC organizations. It is promisingly bandwidth saving with 40-52% of bit rate reduction in comparison to the H.264/AVC [Rodr13P]. This enables Ultra High Definition Television (UHTV). However, this new standard also requires computing complexity much more intensive than the H.264 standard, which leads to shortened battery lifespan and higher power consumption. With these higher costs, the switch to the new standard has to be carefully thought.

#### 1.2 Overview of H.264 video coding standard

This section provides readers with some basic concepts of video coding techniques in general. It also summarizes advanced techniques used in the H.264 video coding standard.

#### 1.2.1 Video coding basic concepts

Video coding techniques are applied during the *encoding process* to compress an original video data to a lower bit rate one. The reduced data is then stored or transmitted via a communication channel. To display the video, the *decoding process* is performed to decompress the video data into the original format, see Figure 1.1. As in other data compression techniques, lossy video coding techniques can be used: the decoded and the original videos are different. For lossless video coding techniques, the decoding process produces the same video as the original one (i.e. without loss).

A digital video signal is the result of sampling the natural visual scene [Rich03H]. Thus the video signal contains a sequence of *video frames*, i.e.

image samples at points in time. Temporal sampling is usually performed at the intervals of 1/25 or 1/30 second. A frame might be composed of two fields containing odd- and even- numbered lines of spatial sampling. *Progressive sampling* samples the complete frame at once. *Interlaced sampling* gives the interlaced fields which are sampled at two different temporal points. Each spatial sample, i.e. a *pixel*, is a square picture element where the image information is supposed identical. The size of the video frame in pixels (width dimension  $\times$  height dimension) is called the display resolution. During the encoding process, a frame may be divided into blocks of  $m \times n$  pixels, or into slices (i.e. specific groups of pixels).

If the video picture is monochrome, it requires only the brightness to represent image information. A colour video contains both luminance (luma), i.e. brightness, and colour information. In RGB colour space, the image is represented with three additive primary colours of light (Red, Green, and Blue). A given colour is created by a particular combination of Red, Green and Blue. Because the human visual system is less sensitive to colour than to luminance, if we separate the colour information into luma and colour, we can store the colour information with a lower resolution than the one of the luma information. The YCbCr (or YUV) colour space is one of the ways to represent a colour image in luma and colour separately. Y is the luma component which is calculated as:

$$Y = k_r R + k_a G + k_b B \tag{1.1}$$

where  $k_r, k_g, k_b$  are the weighting factors. The colour information is represented with colour differences, named chrominance (chroma):

$$Cr = R - Y$$

$$Cg = G - Y$$

$$Cb = B - Y$$

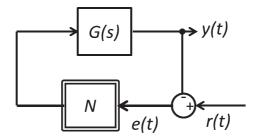

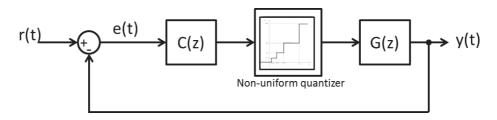

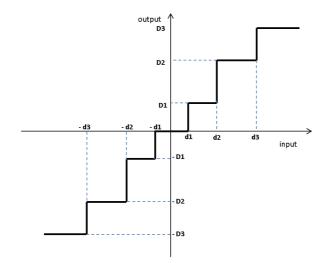

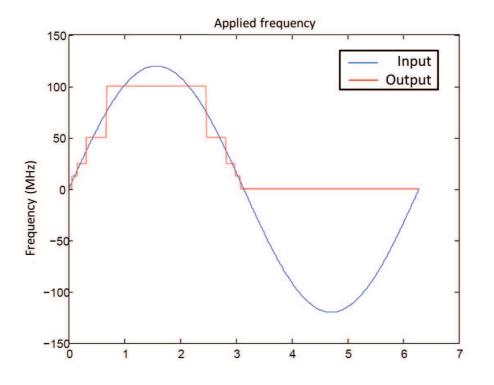

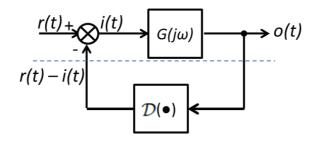

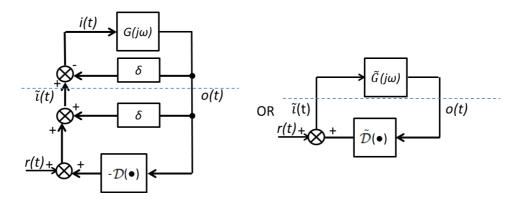

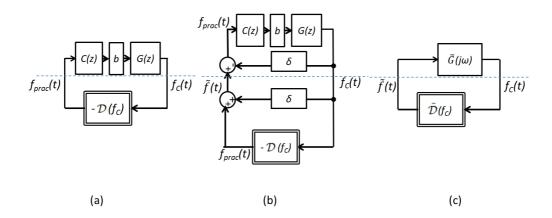

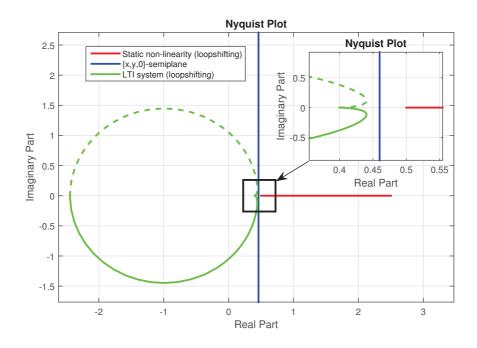

(1.2)