# Conception et évaluation des systèmes logiciels de classifications de paquets haute-performance

Peng He

#### ▶ To cite this version:

Peng He. Conception et évaluation des systèmes logiciels de classifications de paquets haute-performance. Génie logiciel [cs.SE]. Université Grenoble Alpes; Institute of Computing Technologies (Pekin, Chine), 2015. Français. NNT: 2015GREAA007. tel-01221162

# HAL Id: tel-01221162 https://theses.hal.science/tel-01221162

Submitted on 27 Oct 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

### **DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES**

préparée dans le cadre d'une cotutelle entre l'*Université Grenoble Alpes* et L'académie des Sciences de Chine

Spécialité : Informatique

Arrêté ministériel : le 6 janvier 2005 - 7 août 2006

Présentée par

## Peng HE

Thèse dirigée par Kavé Salamatian et Gaogang Xie

préparée au sein des Laboratoires LISTIC et Institut des technologies Informatique de l'académie des sciences de Chine

dans l'École Doctorale SISEO

# Conception et évaluation des systèmes logiciels de classifications de paquets haute-performance

Thèse soutenue publiquement le **02 MAI 2015**, devant le jury composé de :

#### Mr Thierry TURLETTI

Directeur de Recherche à l'INRIA Sophia-Antipolis, Président et Rapporteur **Mr Serge FDIDA**

Professeur à l'université Pierre et Marie Curie, Rapporteur

#### Mr Laurent Mathy

Professeur à l'université de Liège, Membre

#### Mr Steve Uhlig

Professeur à l'université Queen Mary de Londres, Membre

#### Mr Kavé Salamatian

Professeur à l'université de Savoie , directeur de thèse

#### Mr Gaogang Xie

Professeur à l'académie des sciences de Chine, directeur de thèse

#### 1. Motivations

La classification de paquets est à la base de nombreux services avancées dans les réseaux tels que les pare-feux, la détection et la prévention d'intrusion, l'équilibrage de charge, la gestion de la Qualité de service, *etc.* Cette opération consiste généralement en la comparison de champs d'entête des paquets par rapport à un ensemble de règles prédéfinies et à l'application des actions associées à ces règles aux paquets validant celles-ci. Au vu de son importance, la classification haute performance de paquets a été extensivement étudié durant les dix dernières années. Les approches classiques de classification sont généralement fondées sur des solutions matérielles dédiées. Mais, récemment les systèmes de classification logiciels ont attiré un intérêt croissant [1,2,3]. Dans la suite nous décrirons les raisons de cet intérêt.

#### L'émergence des SDNs

Les réseaux logiciels, défini par le sigle SDN (Software defined Network) sont des réseaux où les plans de contrôle et de données sont physiquement séparés. Des switches installés dans le cœur du réseau transfèrent les paquets en fonction de règles définies dans le plan de contrôle qui peut être distant. Cette séparation simplifie la gestion de réseaux étendus et complexes, et la définition de politiques de traitement dans ces réseaux. Néanmoins, pour que de telle solutions soient possible, il est nécessaire d'avoir un plan de données suffisamment flexible afin de transférer le plus rapidement possible ses différentes taches. L'architecture OpenFlow [4] est aujourd'hui le standard de facto qui donne les abstractions des fonctionnalités du plan de données. En suivant la spécification OpenFlow, un switch doit pouvoir appliquer une classification sur au moins 10 champs. Mais les matériels informatiques actuels ne peuvent pas gérer plus de quelques milliers de telles règles, e.g., la taille de la mémoire TCAM du commutateur HP ProCurve 5406zl ne permet pas de stocker plus de 1500 règles. Cette limitation du nombre de règles, réduit sérieusement le déploiement des réseaux SDN. De plus la version 1.3 de l'architecture OpenFlow recommande jusqu'à 30 champs optionnels pour la classification. Cette multitude de champs impose un challenge technique important sur la conception des matériels pour SDN.

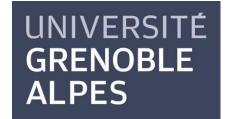

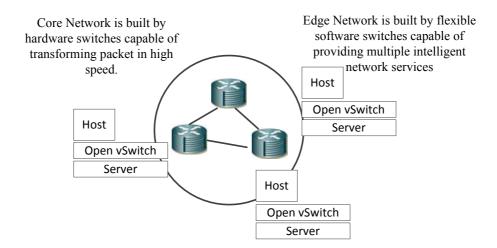

Dans [5] Martin Casado et ces co-auteurs proposent une solution pragmatique pour l'évolution des SDNs qui suggère de traiter le cœur du réseau et de l'accès de façon séparés. Le réseau d'accès se positionne à l'interface entre le réseau et les serveurs et clients terminaux et fourni des services réseaux comme la virtualisation, l'ingénierie de trafic, la qualité de service, etc. Le cœur de réseau, pour sa part ne transmet que des paquets à haute vitesse. Les auteurs de [5] proposent que le cœur et l'accès du réseau soient gérer par des contrôleurs indépendants. Similairement à MPLS, les routeurs du réseau d'accès ajoutent des étiquettes (tags) aux paquets qui sont transmis au cœur de réseau. Ces étiquettes sont utilisées dans le cœur de réseau pour simplifier la classification des paquets. Cette architecture est présentée dans la Figure 1.

Le volume de trafic dans le réseau d'accès est relativement plus faible, mais les besoins en classification de paquets y sont aussi les plus importants. C'est donc à ce niveau qu'il faut concentrer le déploiement de solutions flexibles de classification logicielle qui se fondent sur plusieurs champs d'entête. L'exemple typique de ceci est donnée par les « Open vSwitch » [6] qui échangent les paquets entrants entre plusieurs machines virtuelles en utilisant une classification fondée sur des règles OpenFlow. Ainsi la classification de paquets est un des éléments principaux des SDN et la performance des ces algorithmes conditionne la

performance de ces réseaux.

Figure 1- architecture de réseaux SDN

#### L'externalisation des services réseaux.

L'informatique dans le nuage (*Cloud computing*) a permis la séparation de la propriété de l'infrastructure matérielle et des applications s'exécutant sur ceux-ci. Les services réseaux sont parmi les services de bases fournis par l'infrastructure informatique. Il est donc pertinent d'explorer la possibilité d'externaliser les services réseaux et les fonctionnalités ci-rattachant dans le nuage. Ceci permettrait de faire bénéficier aux services réseaux les bienfait de la virtualisation dans le nuage. Il y'a déjà plusieurs entreprises pionnière, comme AT&T, qui proposent déjà pare-feux dans le nuage, réduisant de cette façon le CAPEX/OPEX des petites entreprises. Cisco a aussi produit une image de machine virtuelle implantant un pare-feu filtrant.

La classification de paquet est une composante essentielle de ces systèmes virtualisés, et elle doit être implanté de façon logicielle afin de pouvoir être déployé sur des matériels quelconque.

#### Le besoin de la virtualisation réseau

De plus en plus dans la pratique, ont observe des centres de données partagés entre plusieurs acteurs ayant chacun leur propre plan d'adressage. Dans le cadre du nuage et la virtualisation, le matériel exécutant un service n'est pas déterminé et fixé à l'avance et il peut changer d'emplacement. On peut donc dans ce genre de scénario avoir une architecture réseau par acteur dans le centre de données et il convient de virtualiser le réseau afin de pouvoir exécuter sur un seul support matérielle plusieurs routeurs relatifs aux divers acteurs du réseau. Dans [7], les auteurs montrent que dans ces scénarios, l'opérateur réseau a besoin de règles avec une granularité très fine afin de séparer le trafic réseaux entre les différentes propriétaires. Ces règles à grains fin consomment beaucoup de ressources matérielles et aboutissent même parfois à des pannes réseaux de grande ampleur [8]. Le débit d'addition de nouvelle règle peut atteindre 3000 changement par seconde et le nombre de règle à traiter dans ces scénarios peut facilement atteindre 60 K règles. Ceci aboutit à une consommation des ressources importantes et un besoin de mise à jour fréquentes de règles de classification qui n'est compatible qu'avec une implantation logicielle de la classification de paquets.

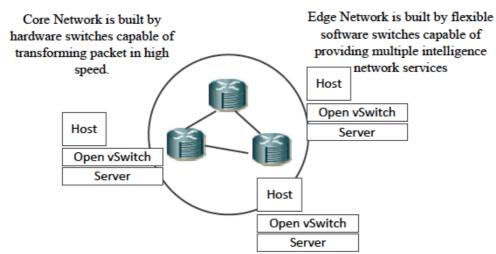

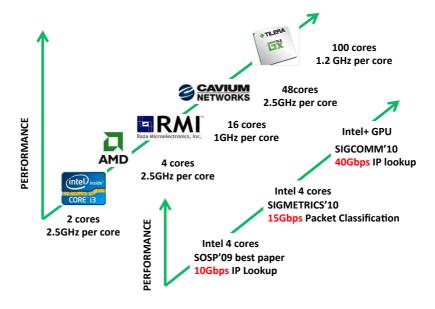

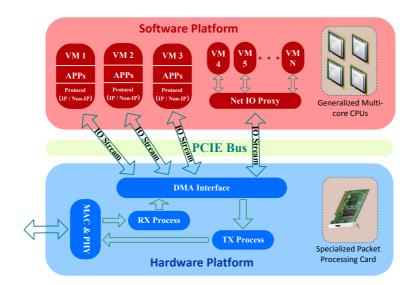

Figure 2 : Architecture Multi-cœurs et performances des routeurs logiciel

#### Les avancées dans les architectures multi-cœurs et dans le parallélisme à grain fin

Ainsi que je le montre dans la figure 2, le développement des processeurs multi-cœurs permet aujourd'hui d'atteindre des performances comparables aux routeurs commerciaux, mais avec un coût largement inférieur. Ceci s'est traduit depuis quelques années par plusieurs travaux de recherche visant à l'implantation de routeurs sur des architectures de serveurs communs [9,10,11]. Le system STORM de classification de paquets par logiciel [12] ainsi que le routeur logiciel accéléré à l'aide de GPU PacketShader [14] démontrent que la flexibilité et la performance élevée ne sont pas mutuellement exclusive sur les plateformes logicielles. Le projet PEARL décrit dans [13] est important puisque j'y ai contribué et développement l'architecture de ce système.

Alors que les librairies de capture et de traitement de paquets telle que Netmap [15], DPDK (Data Plane Development Kit) réduisent le goulot d'étranglement des entrées/sorties dans le système d'exploitation et réduisent la complexité du développement d'application haute performance. Ainsi le goulot d'étranglement se transfère maintenant sur la classification efficace de paquets.

# 2. Problématiques de recherche

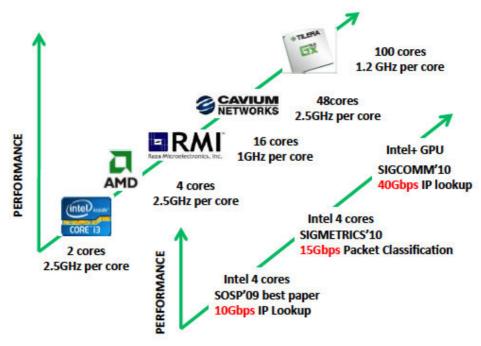

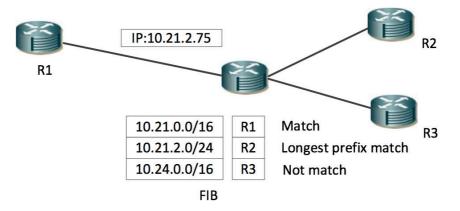

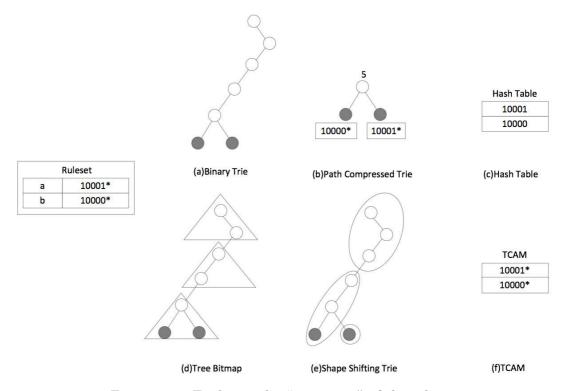

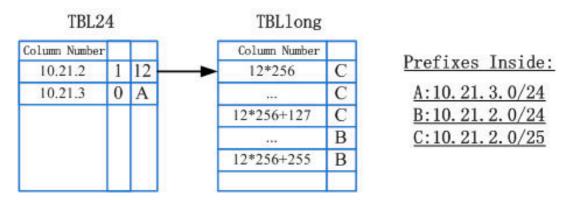

Dans cette thèse, je discuterai principalement de deux problèmes: un problème de classification en une seule dimension, le routage IP, et un problème de classification multidimensionnel fondés sur des arbres de décision. Le problème du routage IP consiste en la recherche du plus long préfixe correspondant à une adresse IP donnée. Je présente ce problème dans la figure 3 ci-dessous.

Le routage IP est fondamentalement un problème de recherche plus long préfixe commun dans une table de routage contenant jusqu'à 500 K préfixes. Au vue de

Figure 3- Routage IP par recherche de plus long préfixes communs

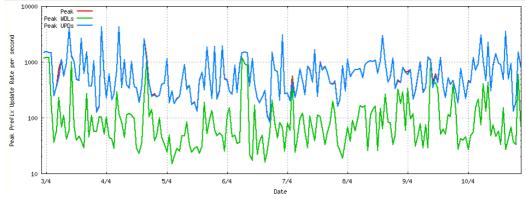

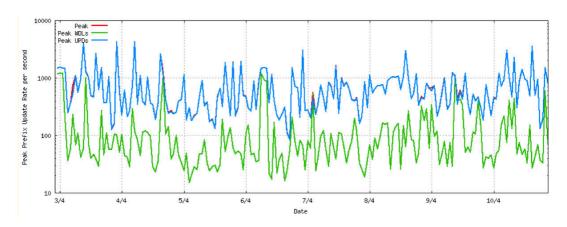

l'augmentation constante des débits sur les liens réseaux, le temps qui reste pour faire une recherche de plus long préfixe se réduit de façon régulière. Ainsi sur un lien à 100 Gbps le temps restant pour la recherche de préfixes, est de l'ordre que quelques dizaines de nanosecondes. En plus de la vitesse de recherche, il faut aussi intégrer les changements dans les tables de routage. Nous montrons dans la figure 4 une courbe de variation du nombre de mises à jours dans les tables de routages IP qui montre un débit de changement de l'ordre de 1000 mise à jour par seconde.

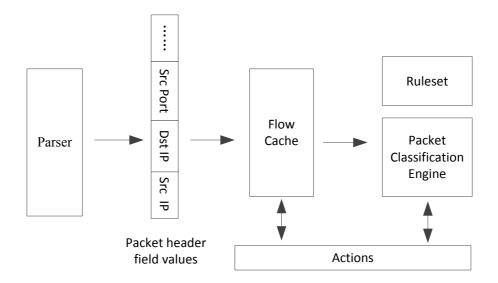

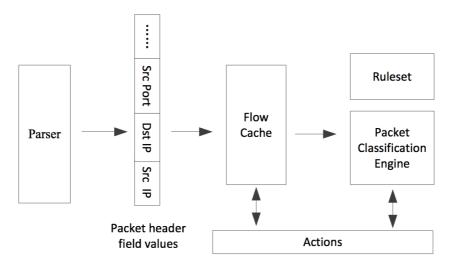

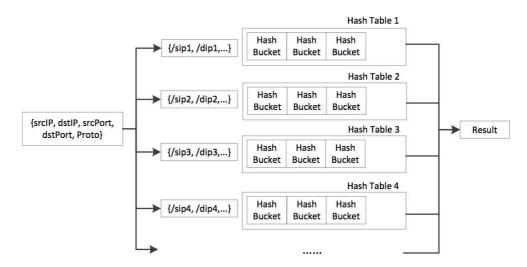

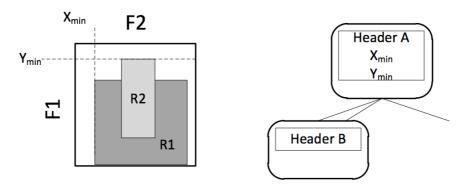

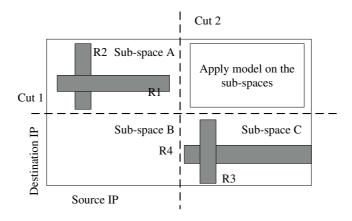

Le second thème de ma recherche a porté sur les ensembles de règles multidimensionnelles. Dans la Figure 5 nous montrons un système de classification typique et dans la Table 1 un ensemble de règles typique. Un ensemble de règles multidimensionnelles consiste en un ensemble d'intervalles définis sur plusieurs champs et une action à appliquer à un paquet qui vérifierait la règle.

|    | SIP         | DIP             | SP      | DP          | L4 protocol | Act.   |

|----|-------------|-----------------|---------|-------------|-------------|--------|

| R1 | 10.1.0.0/16 | 191.243.60.0/24 | 0:65535 | 1521:1521   | TCP         | DROP   |

| R2 | 10.1.0.0/16 | 58.62.126.0/24  | 0:65535 | 1724:1724   | TCP         | DROP   |

| R3 | 10.3.7.0/24 | 58.62.126.0/24  | 0:65535 | 1521:1521   | TCP         | PERMIT |

| R4 | 23.3.7.0/24 | 58.49.16.0/24   | 0:65535 | 14753:14753 | TCP         | PERMIT |

| R5 | 23.5.7.0/24 | 58.49.16.0/24   | 0:65535 | 5631:5631   | UDP         | RESET  |

Table 1- exemple de règles multi-dimensionnelles typique

Figure 4: Fréquence de mises à jours des tables de routages.

Figure 5- Architecture de classification de paquets

### 3. Contributions principales de la thèse

#### Conception d'algorithme

L'objectif principal de cette thèse, a été la conception d'algorithmes de classification de paquets rapide et efficace. A la différence des travaux précédents qui ont tenté de proposer un nouvel algorithme sans faire une analyse rétrospective afin de comprendre pourquoi les performances des algorithmes précédents étaient mauvaise, ma démarche dans cette thèse a été de commencer par une étude approfondie des algorithmes classiques de classification de paquets. Cette analyse m'a permis de lier les les propriétés intrinsèques des ensembles de règles à la performance des algorithmes de classification. Je me suis appuyé sur cette analyse pour proposer un cadre permettant aux ingénieurs de choisir, en fonction des propriétés des ensembles de règles, les briques algorithmes nécessaires à l'implantation d'algorithme de classification rapide et efficace.

Dans la suite je commencerai pas décrire les observations sur les propriétés des ensembles de règles.

#### Propriétés des règles d'apprentissage

Un ensemble de règles de classification de paquets peut être considérée comme une collection d'intervalles définis sur plusieurs champs. Nous présentons dans la table 2 un ensemble de règles contenant 6 règles définies sur 2 champs de 4 bits, où « \* » signifie n'importe quelle

| Rule # | Field 1 | Field 2 | Action |

|--------|---------|---------|--------|

| R1     | 111*    | *       | DROP   |

| R2     | 110*    | *       | PERMIT |

| R3     | *       | 010*    | DROP   |

| R4     | *       | 011*    | PERMIT |

| R5     | 01**    | 10**    | DROP   |

| R6     | *       | *       | PERMIT |

Table 2- ensemble de règles de test

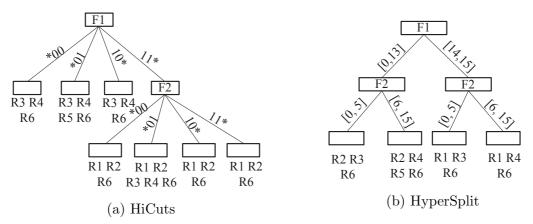

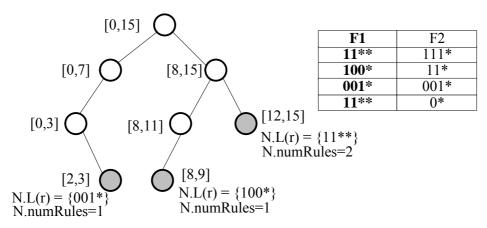

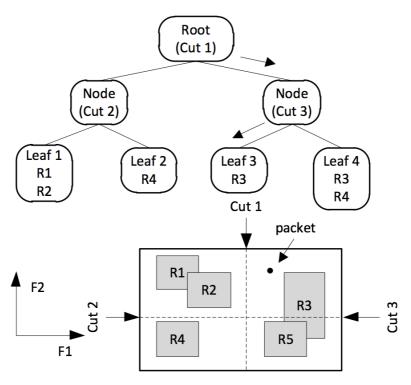

Figure 6- Classification par arbre de décision

valeur. Cet ensemble de règles peut être transformé en 4 intervalles distinct sur le champ 1 (R1 : [14,15], R2: [12,13] ; R5: [4,7] ; autre règles :[0,15]), et 4 sur le champ 2 (R3 :[4, 5] ; R4 : [6, 7] ; R5 : [8, 11] autres règles : [0, 15]). Une règle de classification de paquets peut être interprétée de façon géométrique : une règle définie sur k champs peut être considérée comme un k-orthotope, i.e., un hyper-rectangle dans l'espace de dimension k. Par exemple, la règle R1 dans la table 2, définie dans l'espace des champs, une bande rectangulaire bi-dimensionnelle, où la largeur est 2 unités (de 14 à 15) dans le sens de l'axe du champ 1, et la longueur balaie la totalité de la portée du champ 2 où il y'a un symbole « \* ». Similairement, la règle 3 définie une autre région rectangulaire, mais dont la largeur est dans le sens de l'axe du champ 2. Les différentes règles définissent chacune un k-orthotope qui peuvent se couper et définir des formes imbriqués et complexes. Un algorithme de classification est un algorithme auquel on donne les coordonnées d'un point dans l'espace et qui retourne l'identifiant du plus petit rectangle recouvrant ce point.

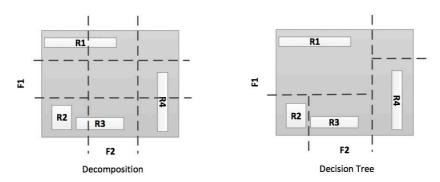

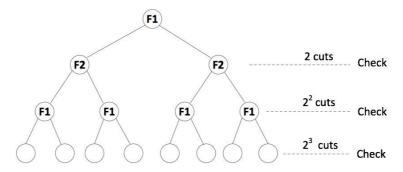

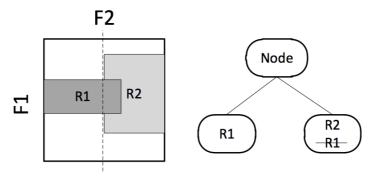

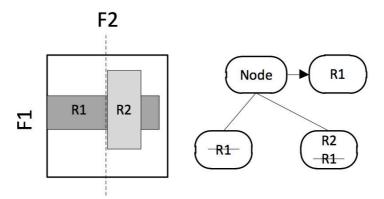

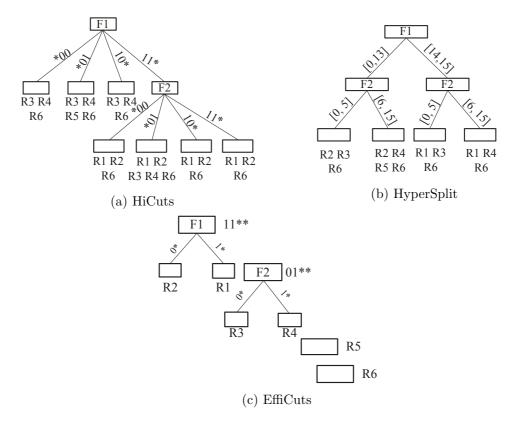

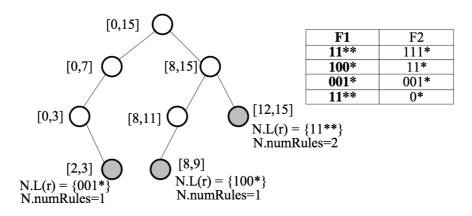

Maintenant étudions ce que fait un algorithme de classification utilisant un arbre de décision. Nous présentons dans la figure 6-b, un arbre de décision implantant la classification suivant les règles de la table 2. A la racine de l'arbre, une coupe est appliquée au champ 1 qui est divisé en deux parties [0,13] et [14,15]. Au second niveau, une coupe est appliquée au champ 2 qui est divisé en deux parties [0,5] et [6,15]. Ainsi chaque nœud dans l'arbre de décision peut être considéré comme une coupe appliquée dans une l'espace des champs. En appliquant ces coupes en suivant un chemin dans un arbre de décision, l'espace est partitionné en régions de plus plus en petites et ayant une intersection avec de moins en moins de k-orthotopes.

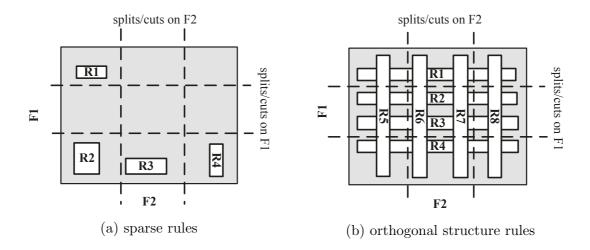

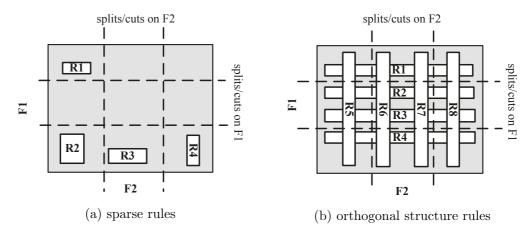

Finalement, la classification est efficace si à la fin il n'y a qu'une règle dans la région définie par la feuille du l'arbre de décision. La description précédente permet de comprendre les propriétés de l'ensemble de règle ayant un impact important sur la performance de la classification. Quand les règles sont clairsemées comme dans la figure 7-a, les coupes peuvent de façon efficaces séparer les différentes règles nécessitant que peu d'empreinte mémoire. Néanmoins, on observe fréquemment dans les ensembles de règles observées en pratique des structures orthogonales comme celles présentées dans la figure 7-b. Dans l'ensemble des règles définies dans la table 2, les règles R1, R2, R3 et R4 sont orthogonales. Quand de telles structures existent dans l'ensemble des règles, aucune coupe ne permet de séparer l'espace en régions ne contenant qu'une seule règle. Au mieux peut on avoir  $O(N^K)$  régions contenant K

Figure 7- Structures orthogonales et règles clairsemées

règles orthogonales, où K est la dimension de l'espace et N le nombre de règles orthogonales. Quand ceci arrive, chaque règle orthogonale doit être dupliquée dans toutes feuilles de l'arbre de décision, ce qui aboutit à un gaspillage de mémoire et une empreinte mémoire très importante.

Une seconde propriété importante de l'ensemble de règles résulte de la comparaison entre les deux arbres de décision dans la Figure 6. L'arbre dans la Figure 6-a est un arbre obtenu en appliquant des coupes de tailles égales à chacune des dimensions, alors que celui dans la figure 6-b utilise des coupes de tailles inégales. L'utilisation de coupes à tailles égales, quand cela est possible, réduit l'empreinte mémoire pour le stockage ainsi que le nombre d'opérations nécessaire pour le parcours de l'arbre. Par contre les coupes à tailles égales peuvent résulter en des duplications de règles quand une règle coupe plusieurs intervalles, ou du gaspillage quand aucune règle n'existe dans un intervalle. Plus la taille des intervalles est uniforme, plus l'utilisation de coupes à tailles égales est efficace. Par contre les coupes à tailles inégales sont plus efficaces, quand la taille des intervalles est non-uniforme. Il est ainsi nécessaire d'évaluer par le biais de métriques l'uniformité de la taille des intervalles afin de décider de la bonne stratégie de coupes à appliquer.

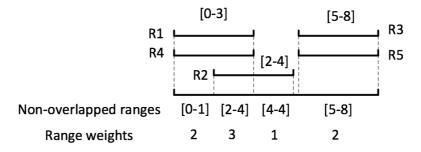

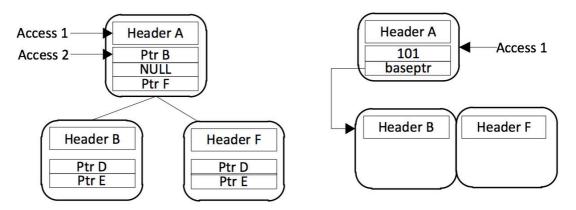

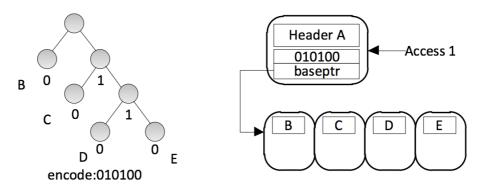

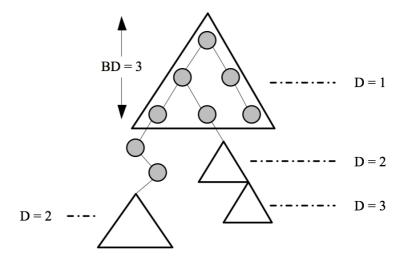

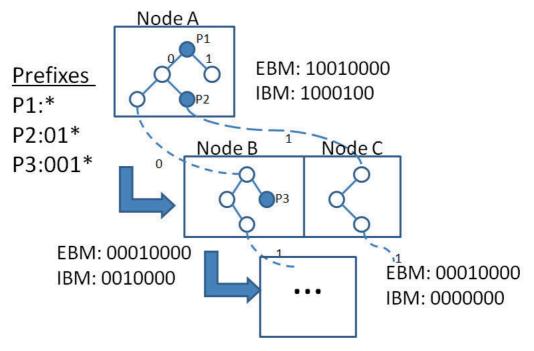

A cette fin j'ai développé durant ma thèse une méthodologie d'évaluation de l'uniformité des intervalles, par le biais d'arbres d'intervalles. L'arbre d'intervalles centrée est un arbre binaire permettant de représenter un ensemble d'intervalle. Chaque nœud de l'arbre d'intervalle contient des intervalles de règles et est représenté par un point x, le point médian de tous les intervalles contenus dans le nœud. La construction de l'arbre se fait en partitionnant l'ensemble des intervalles de règles contenus dans le nœud en trois sous-ensembles : le premier sous-ensemble contient toutes les règles qui contiennent le point x, le second sous-ensemble, nommé le sous-ensemble de droite, contient toutes les règles qui sont complètement à droite du point x, et le sous-ensemble de gauche, contient toutes les règles complètement à gauche du point x. On construit le fils de droite du nœud en utilisant les intervalles dans le sous-ensemble de droite et le fils de gauche avec le sous-ensemble de gauche. Je présente dans la figure 8 un exemple d'arbre d'intervalle centré. La structure de l'arbre d'intervalles centrés construit sur chaque dimension de l'ensemble de règle donne une indication importante sur l'uniformité des règles. Les règles avec des intervalles larges sont généralement absorbées par les nœuds proches de la racine de l'arbre, alors que les intervalles

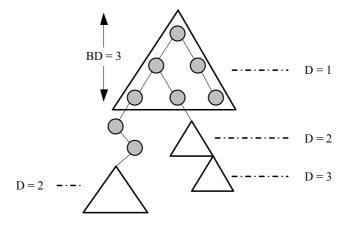

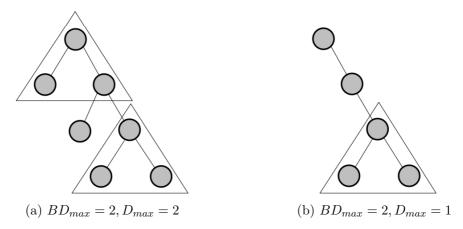

Figure 8- Arbre d'intervalle centrés

courts sont généralement associés aux feuilles de l'arbre. Un arbre totalement équilibré signifie que tout l'intervalle rattaché à toutes règles est de même taille, et ainsi qu'une coupe en intervalles de tailles égale sera parfaite. Par contre un arbre non-équilibré privilégie une coupe en intervalles de tailles inégales. En pratique, les arbres d'intervalles construits sur des ensembles de règles réalistes sont non équilibrés. Ils contiennent des nœuds ayant un seul fils, et des feuilles à divers niveaux de l'arbre. En fait ont peut analyser un arbre comme plusieurs sous-arbres quasi-équilibrés de tailles différents (voir figure 9). Afin de caractériser ces arbres, j'ai défini deux métriques pour les arbres d'intervalles. Je défini pour chaque nœud, sa profondeur d'équilibre BD comme la hauteur de l'arbre quasi-équilibré auquel le nœud appartient, et la distance d'équilibre D comme le nombre d'arbre quasi-équilibrés entre la racine de l'arbre et le nœud. La totalité de l'arbre est caractérisée par  $D_{\max}$  et  $BD_{\max}$ , respectivement la valeur maximale de D et de BD pour tous les nœuds de l'arbre. Une grande valeur de  $D_{\max}$  signifie que l'arbre contient beaucoup de sous-arbres de petites tailles et que les intervalles dans l'ensemble de règles ne sont pas uniformes. Par contre, une petite valeur de  $D_{\max}$  signifie une couverture plus uniforme.

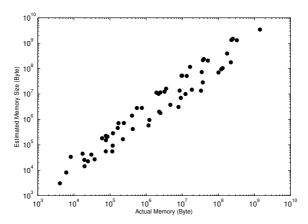

Les observations précédentes sur les propriétés des ensembles de règles m'ont permis de développer un estimateur de la taille de l'empreinte mémoire nécessaire pour implanter un arbre de décision en utilisant les principaux algorithmes existants dans la littérature : *hypercut* [16, 17] et *hypersplit* [18].

Figure 9- structure de l'arbre d'intervalles centrés

Figure 10- Estimation de l'empreinte mémoire

Cet estimateur qui n'utilise pas les détails d'implantation de chaque algorithme permet de prédire avec une bonne précision l'empreinte mémoire. Les résultats de cette estimation sont présentés dans la figure 10.

L'estimateur d'empreinte mémoire ainsi que la connaissance obtenue sur la structure des ensembles de règles m'a permet d'obtenir une compréhension fine des mécanismes contrôlant la complexité des algorithmes de classification de paquets. Dans la suite, je m'appuie sur cette compréhension afin de concevoir de nouveaux algorithmes ou d'améliorer ceux existant.

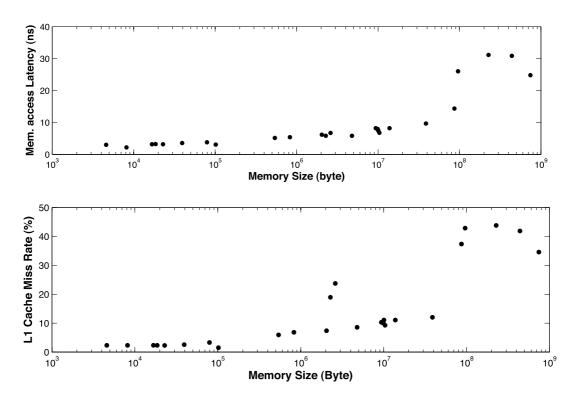

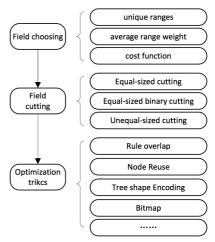

#### Cadre décisionnel pour concevoir des algorithmes de classification

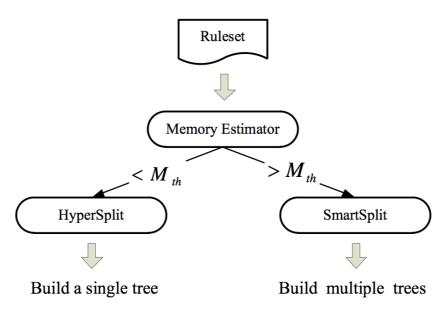

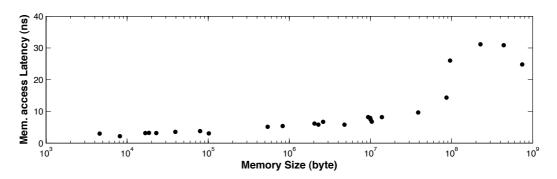

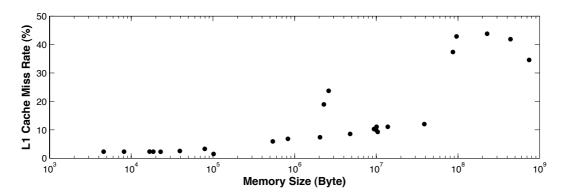

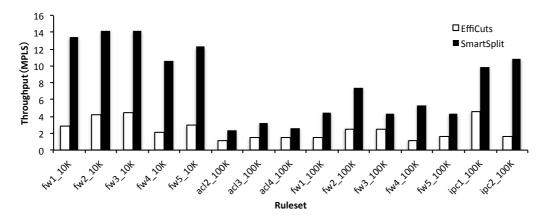

Afin de comprendre quels sont les paramètres qui jouent réellement sur la performance réelle des classificateurs de paquets logiciels, nous mesuré la performance de l'algorithme de classification HyperSplit sur 25 ensembles de règles. Les paramètres mesurés sont les taux de défaut de mémoire cache, la latence moyenne d'accès à la mémoire et la taille de l'empreinte mémoire. Je présente dans la figure 11 la relation de la taille de l'empreinte mémoire avec la latence moyenne d'accès à la mémoire et au taux de défaut de mémoire cache.

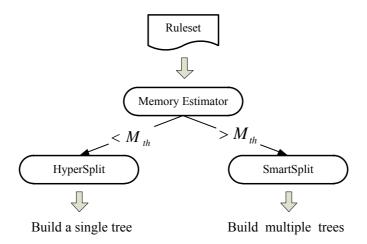

La figure 11 montre que la latence moyenne d'accès à ma mémoire augmente lentement quand la taille de la mémoire croît de 10 Ko à 10 Mo. A partir de 10 Mo la latence explose. Cette augmentation notable peut être expliqué en regardant la courbe du taux de défaut de mémoire cache et en prenant en compte la taille de la mémoire cache des processeurs de notre plateforme d'évaluation (4Mo de cache L3). La figure 11 montre que le taux de défaut de mémoire cache reste inférieur à 10% quand l'empreinte mémoire est inférieure à 10 Mo, mais elle augmente brutalement à plus de 50% pour des tailles de mémoires plus grandes. Il apparaît ainsi que dès que la taille de l'empreinte mémoire dépasse la taille de la mémoire cache des processeurs le taux de défaut de mémoire augmente. Il est ainsi important de s'assurer que l'empreinte mémoire ne dépasse pas les 10 Mo. J'ai utilisé ce critère en combinaison avec l'estimateur de taille d'empreinte mémoire afin de construire un outil d'aide à la décision permettant de choisir l'algorithme le plus efficace pour un ensemble de règles données. Cet outil d'aide à la décision est appelé « smartsplit ».

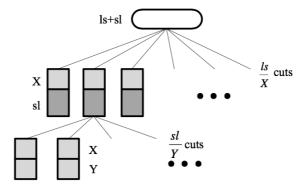

SmartSplit traite de deux décisions. Une première décision est liée à l'uniformité des intervalles de règles et est relative à la décision du type de la coupe a appliquée, et au choix de

Figure 11- Latence moyenne d'accès à la mémoire et taux de défaut de mémoire cache en fonction de l'empreinte mémoire des algorithmes de classifications de paquets

la dimension à laquelle il faut l'appliquer. La seconde décision est liée à l'existence des structures orthogonales dans l'ensemble des règles et à la pertinence de découper l'ensemble en sous-ensembles sans règles orthogonales.

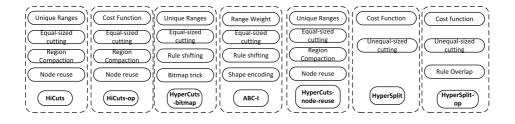

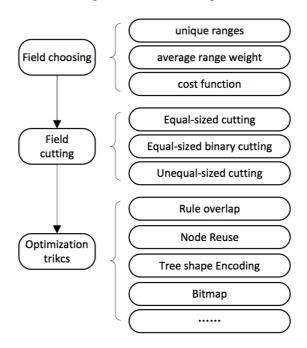

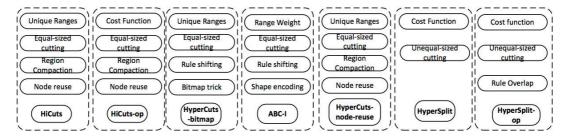

La première décision est relative aux deux problèmes suivants: 1) comment choisir la dimension sur laquelle il convient de faire une coupe, et 2) comment choisir le type de coupe à appliquer: coupe à taille égale, ou coupe inégales. Je décris dans la figure 12 les éléments qui caractérisent cette première décision. En combinant les différents éléments et en particulier les différentes astuces d'implémentation, j'ai développé plusieurs variantes des algorithmes existants que j'appelle méta-méthodes. Celles-ci sont listés dans la table 3 ci-dessous. L'étape

Figure 12- Décision sur le type de coupe

suivante a été de comparer la performance atteinte par ces différentes méta-méthodes.

Table 3-meta-méthodes de classification

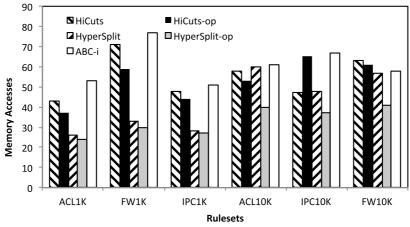

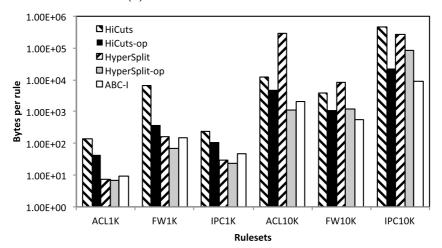

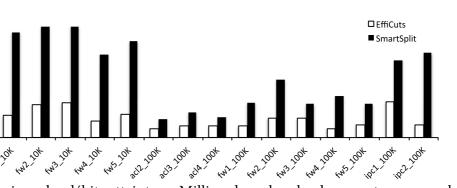

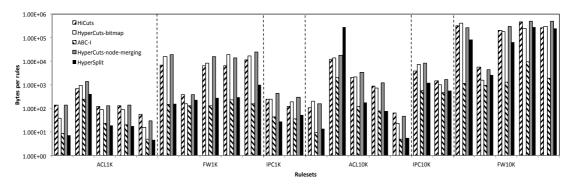

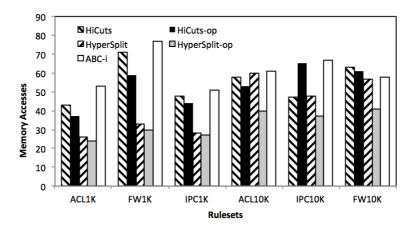

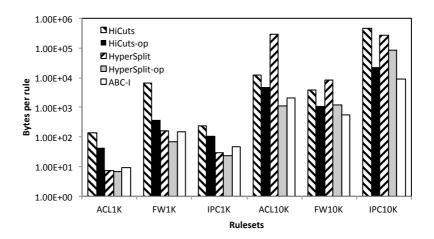

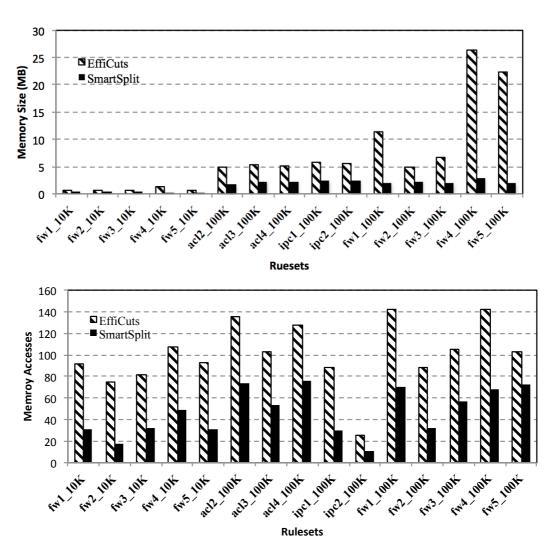

(a) nombre d'accès mémoire

(b) empreinte mémoire (octets/règles)

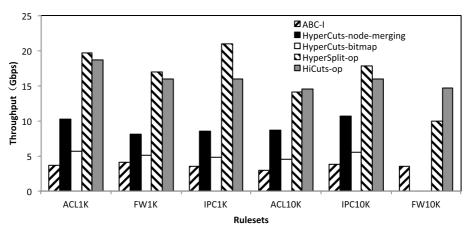

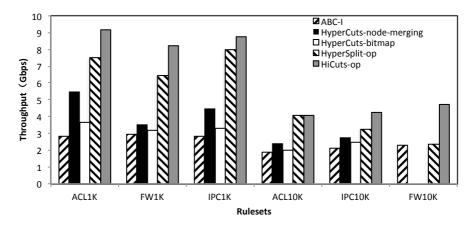

(c) débit mesuré avec des paquets de 64 o en utilisant un seul cœur de calcul Figure 13- performance des méta-algorithmes

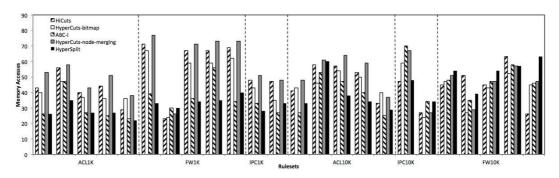

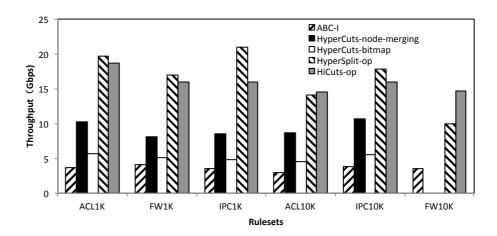

Je présente dans la figure 13 les performances obtenues par les différentes méta-méthodes comparées à celle obtenue par l'état de l'art des algorithmes de classifications. La plateforme d'évaluation était un serveur Intel avec un processeur 3.3GHz, avec une cache L1 de 256 Ko, une cache L2 de 1 Mo, une cache L3 de 4 Mo. Toutes les expérimentations ont été effectuées en utilisant un seul cœur de calcul. Nous avons utilisé ClassBench pour générer 24 ensembles de règles de différents types. La figure 13 montre que les optimisations HiCuts-op que j'ai

Figure 14- Cadre de décision liée à décision de découper l'ensemble de règles en sous-règles

proposées permettent de réduite l'empreinte mémoire de l'algorithme HiCuts de 2 ~20 avec 10% d'accès mémoire en moins. Similairement HyperSplit-op atteint une réduction d'empreinte mémoire 2~200 et 10 à 30% d'accès mémoire en moins. La dernière figure présente le débit mesuré en terme de volume de trafic traité par seconde. Nous observons que sur un lien saturé avec des paquets de 64 octets, nous obtenons un débit supérieur à 20 Go par secondes sur la plupart des configuration en utilisant un seul cœur de calcul. En comparaison, les résultats présentés dans [12] qui définissent l'état de l'art ne dépassent pas 16 Go par seconde en utilisant 8 cœurs de calculs avec des paquets de 128 o. Ceci montre le gain important de performance que j'ai obtenu par rapport à l'état de l'art.

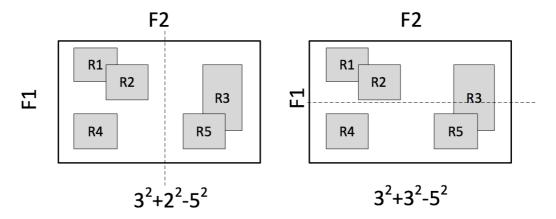

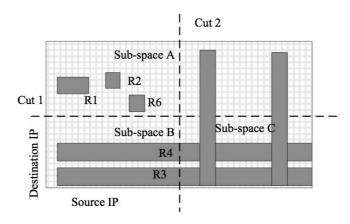

Un second cadre de décision que j'ai développé durant cette thèse, a été la décision liée à l'existence des structures orthogonales dans l'ensemble des règles et à la pertinence de découper l'ensemble en sous-ensembles sans règles orthogonales. Je commencerais par décrire la méthodologie de découpage de l'ensemble de règles. L'objectif de ce découpage est de se débarrasser des structures orthogonales qui aboutissent à une duplication importante des règles et une large empreinte mémoire. La méthodologie de découpage consiste initialement à construire pour chacun des champs IP source et destination, l'arbre des intervalles centrés et à calculer leur valeur du paramètre  $D_{\text{max}}$ . Ensuite, nous trouvons les règles qui sont définies par un intervalle large sur chacune des adresses IP source et destination. Une règle est définie comme large sur une dimension si l'intervalle qui défini cette règle recouvre plus de la moitié de l'intervalle possible. Ainsi on peut définir sur l'adresse IP source et destination 4 catégories : (large, large), (large, small), (small, large), (small, small). Les ensembles (large, large), (large, small), (small, large) définissent chacun un arbre de décision dans lequel il n'y a plus de règles orthogonales. L'ensemble des règles (small, small) est ajoutée à l'ensemble des règles (large, small) si  $D_{\text{max}}$  (srcIP)<  $D_{\text{max}}$  (dstIP), et aux règles (small, large) sinon. Ensuite sur chacun de ces arbres nous appliquons le cadre défini précédemment pour le choix de la méthode de coupe à appliquer : de taille égale ou de taille inégale.

La décision sur la pertinence d'appliquer un découpage est décrite dans la figure 14. J'ai utilisé l'estimateur de taille de mémoire décrit précédemment pour calculer pour un ensemble de règles donnée la taille de l'empreinte mémoire sans découper en sous-ensembles

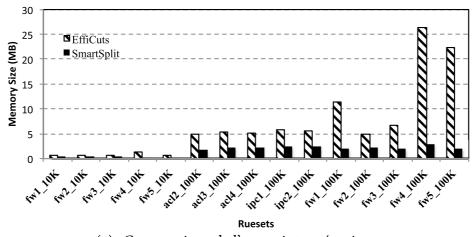

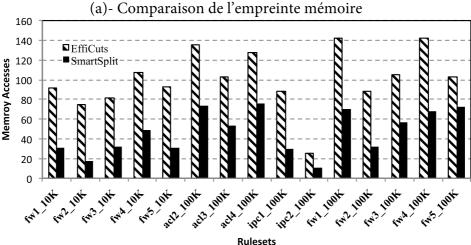

(b)-Comparaison du nombre d'accès mémoire

16

14

12 10

> 6 4

Throughput (MPLS)

(c)- Comparaison des débits atteints en Million de recherche de paquet par seconde Figure 15- Comparaison des performances atteintes par EffiCuts et SmartSplit

et en découpant en sous-ensemble de la façon décrite précédemment. Si la taille de l'empreinte mémoire sans découpage dépasse le seuil de 10 Mo, je découpe l'ensemble des règles. Ceci aboutit à un cadre décisionnel que j'appelle SmartSplit. Une autre approche de découpage d'ensemble de règles en sous règles est aussi proposée dans la littérature [20]. Cette approche qui est appelé Efficuts, défini un état de l'art dans les méthodes découpant l'ensemble de règles.

| Type   | Size     | AutoPC(MLPS) | EffiCuts(MLPS) | speedup |

|--------|----------|--------------|----------------|---------|

|        | 1K       | 11.3*        | 4.5            | 2.4     |

| ACL    | 10K      | 6.9*         | 3.1            | 2.2     |

|        | 100K     | 8.6*         | 2.2            | 3.9     |

|        | 1K       | 9.8*         | 2.4            | 4.1     |

| FW     | 10K      | 10.7         | 2.1            | 5.1     |

|        | 100K     | 7.4          | 2.5            | 3.0     |

|        | 1K       | 12.6*        | 3.0            | 4.25    |

| IPC    | 10K      | 5.3*         | 1.48           | 3.6     |

|        | 100K     | 9.91         | 1.63           | 6.1     |

| Averag | ge Speed | dup: 3.8     | ·              |         |

Table 4- Comparaison des débits atteint par Efficut et SmartSplit en millions de recherche par seconde

Je présente dans la figure 15 la comparaison des performances atteintes par EffiCuts et SmartSplit. On peut observer que SmartSplit a largement de meilleures performances qu'EffiCuts aussi bien en terme d'empreingte mémoire qu'en terme d'accès mémoire, e.g., pour l'ensemble de règle fw5 contenant 100K règles, EffiCuts consomme 22.46 Mo de mémoire, alors que SmartSplit a seulement besoin de 1.98 Mo, un réduction de 11.3. De plus en comparant l'empreinte mémoire après découpage de l'ensemble de règles avec celle-ci avant on observe que pour un même ensemble de règle l'empreinte mémoire passe de plusieurs Go à moins de 2 Mo. Autre point notable est que SmartSplit ne découpe l'ensemble de règles qu'en trois sous-ensembles alors qu'Efficuts peut découper en 9 sous-ensembles et avoir a gérer ainsi 9 sous arbres. Je présente dans la table 4 la comparaison des débits atteints par Efficuts et SmartSplit montre que SmartSplit atteint en moyenne un débit 3.8 supérieur.

Ceci termine la description résumée d'une partie des contributions de ma thèse. C'est travaux ont aboutit a deux publications [20, 21].

#### PEARL: un prototype pour le SDN/NFV

Déployer, expérimenter et tester de nouveaux protocoles et systèmes sur l'Internet a toujours été un défi important. La simulation n'a jamais remplacé le déploiement en réel de système et l'expérimentation *in vivo*. Ainsi l'accès à une plateforme programmable et flexible pouvant implanter du traitement de paquet a haut débit, et quo permettrait ainsi le déploiement et l'expérimentation des concepts développés en recherche en très importante. De plus, avec l'avancée graduelle vers les architecture de l'Internet du futur qui sera plus polymorphique que l'Internet monolithique actuel, il faudrait pouvoir permettre à plusieurs paradigme architecturaux de coexister, par exemple un routeur pourra avoir a gérer en même temps un réseau NDN [22] et un réseau IP classique. Ainsi, les plateformes pour l'Internet du futur devront permettre l'exécution en parallèle, de plusieurs routeurs virtuels tout en assurant une indépendance entre ces instances virtuelles.

Malheureusement, les architectures classiques de traitement de paquet ne sont pas adaptées à la flexibilité que j'ai décrite plus haut. Ceci m'a motivé pour concevoir et construire une plateforme de routeur virtuel programmable, PEARL (ProgrammablE virtuAl Router pLatform), qui permet de garantir une très haute performance tout en validant des contraintes d'indépendance. Les défis de la conception de PEARL étaient multiples. Il fallait tout d'abord gérer la balance flexibilité *vs.* performance qui se traduit généralement par la volonté de

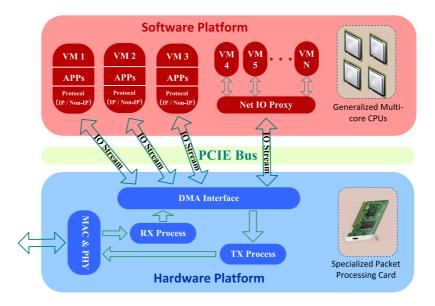

Figure 16- Architecture PEARL

pousser des fonctionnalités dans le matériel, plutôt que de les implanter en logiciel ce qui garantirait la flexibilité. Le second défi était d'assurer l'isolation entre les instances de routeurs virtuels s'exécutant sur la plateforme en utilisant le moins de ressources possibles. Je décris dans cette partie l'architecture de PEARL, ces composants principaux et la performance atteinte par cette plateforme innovante.

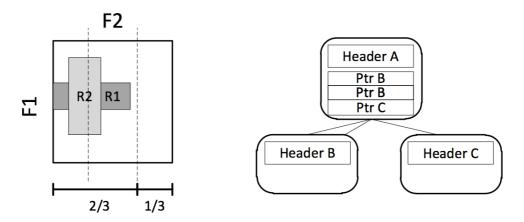

#### Description de la plateforme PEARL

La Plateforme PEARL utilise une plateforme hybride combinant des processeurs multi-cœurs Intel qui exécute du code classique, et des cartes de traitements de paquets spécialisé qui implantent le traitement haut-débit de paquets. La plateforme est présenté dans la Figure 16. L'environnement de virtualisation utilisé est fondée sur LXC, une environnement à base de Linux [22]. Cet environnement autorise l'exécution en parallèle de plusieurs instances de routeurs virtuels, et chaque instance peut être considéré comme une machine totalement séparée.

Les cartes spécialisées dédiées contiennent des éléments de traitement de paquets FPGA ainsi que des mémoires TCAM et SRAM. Cette carte permet le traitement rapide des paquets tout en garantissant une isolation forte entre instances s'exécutant. Ainsi PEARL peut implanter plusieurs plans de données virtuels en allouant à chaque plan des ressources matérielles séparées. Ceci facilite l'isolation au niveau matériel.

L'isolation au niveau logiciel est gérée par LXC. La liaison entre le matériel et le logiciel est faite par le biais d'un bus PCI Express à haut débit et une DMA multi-flot. Chaque flot d'entrée sortie peut être ou dédiés à un routeur virtuel unique ou partagé entre plusieurs routeurs virtuels grâce à un proxy d'entrées/sorties. La flexibilité est atteinte par l'utilisation de ressources TAP/TUN comme interface réseau pour chaque machine virtuelle. Ainsi chaque machine virtuelle peut être considérée comme une machine Linux standard contenant

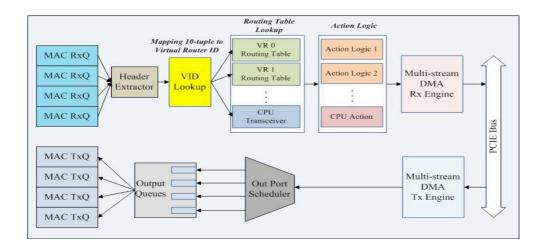

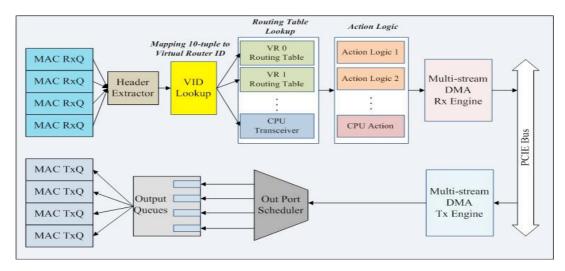

Figure 17-Architecture du plan de données de PEARL

plusieurs ports réseaux. Ainsi une pile protocolaire IPv4, IPv6, OpenFlow peuvent être facilement déployé sur ces instances virtuelles.

L'architecture du plan de données de PEARL dans la carte de traitement matérielle, décrite dans la figure 17, permet de transférer l'étape de distribution de paquets aux différentes machines virtuelles qui est généralement le goulot d'étranglement de performance au niveau matériel ce qui permet une vitesse de transfert de paquet importante. Le plan de données est fondés sur un pipeline contenant deux chemins séparés : un chemin d'envoi et un chemin de réception. De plus, la virtualisation LXC est suffisamment légère pour ne pas avoir d'impact important sur la performance. Ainsi la plateforme atteint un niveau de performance élevé.

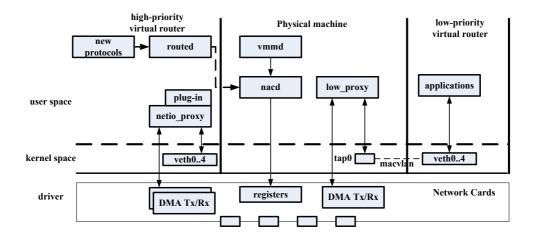

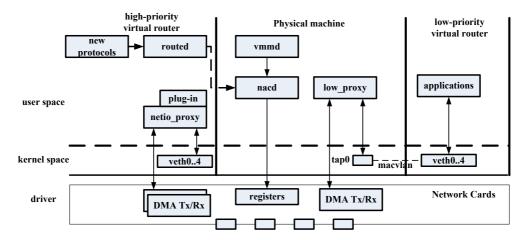

La plateforme logicielle de PEARL consiste en plusieurs composants présentés dans la figure 18. Le composant *vmmd* fournit les fonctions de gestion de base nécessaire au routeur virtuel, et aux cartes de traitement de paquets. Le composant *nacd* fournit à toutes les cartes de traitement une interface uniforme vers l'extérieur de l'environnement virtualisé; Le composant *routed* s'occupe du routage et transforme les règles de transfert définies par le noyau ou l'application utilisateur en format uniforme pour chaque routeur virtuel afin de les implanter dans la TCAM. Le composant *netio* permet le transfert de paquets entre les interfaces physique et les interfaces virtuelles.

J'ai défini deux types de routeur virtuel dans PEARL: routeur virtuel de haute et basse priorités. Chaque instance de routeur virtuel haute priorité est lié à une paire de mémoire tampon Rx/Tx de la DMA et à un espace indépendant dans la mémoire TCAM. Grace à la capacité de recherche rapide de la TCAM, et des entrées/sorties rapides fournies par la carte matérielle, le routeur virtuel haute priorité peut atteindre un débit de transfert très important. Les routeurs virtuels basse priorité partagent tous ensembles une paire de mémoire tampons Rx/Tx, et n'utilisent pas la TCAM pour la recherche dans la table de routage.

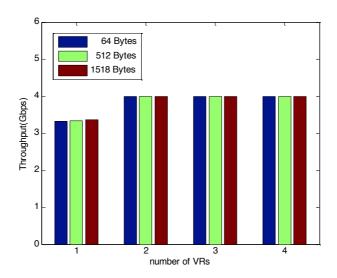

Dans la suite, je présente les performances obtenues par la plateforme PEARL. La plateforme PEARL a été implanté sur un serveur équipé d'un processeur Xeon 2.5 GHz avec 16 Go de RAM DDR2. Une carte matérielle spécialisée contenant des FPGAs ainsi qu'une TCAM a été ajouté à cette plateforme. Afin de montrer la flexibilité de la plateforme PEARL, j'ai évalué trois configuration : routeur IPv4 virtuel de haute performance, un routeur virtuel

Figure 18- Architecture logicielle de PEARL

virtuel IPv4/IPv6 au niveau noyau et un routeur IPv4 implanté en tant que routeur virtuel basse priorité. J'ai mesuré pour chaque scenario avec des tailles de paquets (64, 512, 1518 octets pour les paquets IPv4 et 78, 512 et 1518 pour les paquets IPv6).

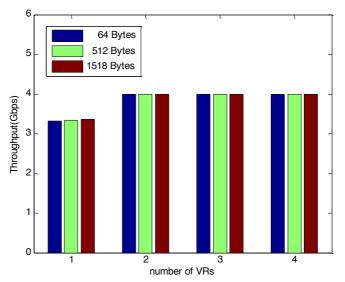

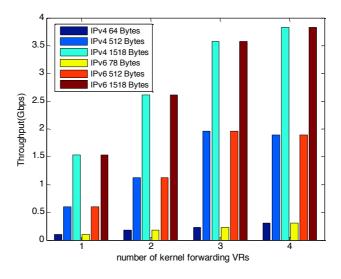

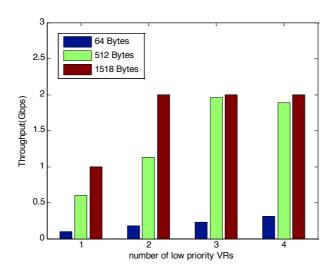

La figure 19-a montre le débit atteint dans le premier scenarios en fonction du nombre du routeurs virtuels. Chacun des routeurs virtuels est implanté comme un routeur haute priorité. Nous observons que dès que le nombre d'instance de routeur virtuel atteint 2, nous atteignons la limite théorique de notre conception qui est de 4 Gbps.

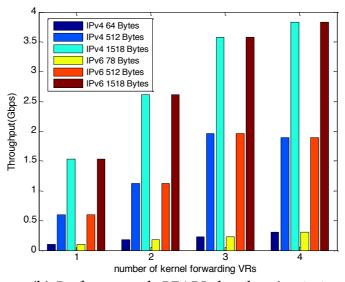

La figure 19-b illustre le débit en fonction du nombre d'instance de routeur virtuel IPv4/IPv6. Ici aussi les routeurs sont à haute priorité sauf qu'aucun routeur n'a d'espace dédiés dans TCAM, et d'autre terme l'espace des tables de routage est partagé dans la TCAM. On observe ici que le débit s'approche des 4 Go avec 4 instances de routeurs virtuels.

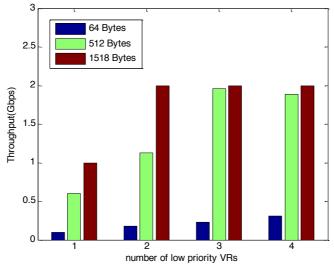

La figure 19-c montre le débit atteint dans le troisième scénario, ou on ajoute des routeurs virtuels de basses priorités. Tous ces routeurs virtuels se partagent une paire de canal entrées/sorties Tx/Rx de la DMA. On peut observer que le débit global dans ce scénario ne dépasse pas les 2 Gbps et que le goulot d'étranglement reste principalement le partage des paquets entre les différents routeurs virtuels.

La plateforme PEARL a été le sujet d'une publication [23] qui a obtenu une grande visibilité car elle a été publiée dans un numéro spécial visant l'architecture de l'Internet du futur.

(a)- performance du scenario 1 de PEARL, routeur virtuel implanté en haute priorité en function du nombre d'instance de routeurs virtuels

(b)-Performance de PEARL dans le scénario 2

(c)- Performance de PEARL dans le scénario 3.

Figure 19- Performance de la plateforme PEARL pour différents scénarios d'utilisation

## Bibliographie

- [1]-Martin Casado, Michael J Freedman, Justin Pettit, Jianying Luo, Nick McKeown, and Scott Shenker. Ethane: Taking control of the enterprise. ACM SIGCOMM Computer Communication Review, 37(4):1-12, 2007.

- [2]- Dilip A Joseph, Arsalan Tavakoli, and Ion Stoica. A policy-aware switching layer for data centers. In ACM SIGCOMM Computer Communication Review, volume 38, pages 51-62. ACM, 2008.

- [3]-Lucian Popa, Norbert Egi, Sylvia Ratnasamy, and Ion Stoica. Building extensible networks with rule-based forwarding. In OSDI, pages 379-392, 2010.

- [4]- N. McKeown, T. Anderson, H. Balakrishnan, G. Parulkar, L. Peterson, J. Rexford, S. Shenker, and J. Turner. Openow: enabling innovation in campus networks. ACM SIGCOMM Computer Communication Review, 38(2):69-74, 2008.

- [5]-Martin Casado, Teemu Koponen, Scott Shenker, and Amin Tootoonchian. Fabric: a retrospective on evolving sdn. In Proceedings of the first workshop on Hot topics in software de\_ned networks, pages 85-90. ACM, 2012.

- [6]-Ben Pfaff, Justin Pettit, Keith Amidon, Martin Casado, Teemu Koponen, and Scott Shenker. Extending networking into the virtualization layer. In Hotnets, 2009

- [7]- Stefan Nilsson and Gunnar Karlsson. Ip-address lookup using lc-tries. Selected Areas in Communications, IEEE Journal on, 17(6):1083{1092, 1999.

- [8]-The amazon ec2 outage no one noticed. <a href="http://www.praxicom.com/2008/04/the-amazon-ec2.html">http://www.praxicom.com/2008/04/the-amazon-ec2.html</a>.

- [9]-B. Chen and R. Morris. Flexible control of parallelism in a multiprocessor pc router. In Proceedings of the 2001 USENIX Annual Technical Conference, pages 333-346, 2001.

- [10]-M. Dobrescu, N. Egi, K. Argyraki, B.G. Chun, K. Fall, G. Iannaccone, A. Knies, M. Manesh, and S. Ratnasamy. Routebricks: Exploiting parallelism to scale software routers. In ACM SOSP, volume 9. Citeseer, 2009.

- [11]-Dong Zhou, Bin Fan, Hyeontaek Lim, Michael Kaminsky, and David G Andersen. Scalable, high performance ethernet forwarding with cuckooswitch. In Proceedings of the ninth ACM conference on Emerging networking experiments and technologies, pages 97-108. ACM, 2013.

- [12]-Y. Ma, S. Banerjee, S. Lu, and C. Estan. Leveraging parallelism for multi-dimensional packetclassi\_cation on software routers. In ACM SIGMETRICS Performance Evaluation Review, volume 38, pages 227{238. ACM, 2010.

- [13]-Gaogang Xie, Peng He, Hongtao Guan, Zhenyu Li, Layong Luo, Jianhua Zhang, Yonggong Wang, and K Salamatian. Pearl: a programmable virtual router platform. Communications

- Magazine, IEEE, 49(7):71-77, 2011.

- [14]-S. Han, K. Jang, K.S. Park, and S. Moon. Packetshader: a gpu-accelerated software router. In ACM SIGCOMM Computer Communication Review, volume 40 pages 195-206. ACM, 2010.

- [15]-Luigi Rizzo. netmap: a novel framework for fast packet i/o. In Proceedings of the 2012 USENIX conference on Annual Technical Conference, pages 9–9. USENIX Association, 2012.

- [16]- P. Gupta and N. McKeown. Packet classification using hierarchical intelligent cuttings. In Hot Interconnects VII, pages 34–41, 1999.

- [17]-S. Singh, F. Baboescu, G. Varghese, and J. Wang. Packet classification using multidimensional cutting. In Proceedings of the 2003 conference on Applications, technologies, architectures, and protocols for computer communications, pages 213–224. ACM, 2003.

- [18]- Y. Qi, L. Xu, B. Yang, Y. Xue, and J. Li. Packet classification algorithms: From theory to practice. In INFOCOM 2009, IEEE, pages 648–656. IEEE, 2009.

- [19]–B. Vamanan, G. Voskuilen, and TN Vijaykumar. Efficuts: optimizing packet classification for memory and throughput. In ACM SIGCOMM Computer Communication Review, volume 40, pages 207–218. ACM, 2010.

- [20]- Peng He, Gaogang Xie, Hongtao Guan, Laurent Mathy, Salamatian Kavé. Toward predictable performance in decision tree based packet classification algorithms. *19th IEEE Workshop on Local & Metropolitan Area Networks (LANMAN)*, *2013*, Apr 2013, Belgium. pp.1-6, 2013

- [21]- Peng He; Gaogang Xie; Salamatian, K.; Mathy, L., "Meta-algorithms for Software-Based Packet Classification," *Network Protocols (ICNP), 2014 IEEE 22nd International Conference on*, vol., no., pp.308,319, 21-24 Oct. 2014

- [22]-Van Jacobson, Diana K Smetters, James D Thornton, Michael F Plass, Nicholas H Briggs, and Rebecca L Braynard. Networking named content. In Proceedings of the 5th international conference on Emerging networking experi- ments and technologies, pages 1–12. ACM, 2009.

- [23]-Linux container. https://linuxcontainers.org.

- [24]-Gaogang Xie, Peng He, Hongtao Guan, Zhenyu Li, Layong Luo, Jianhua Zhang, Yonggong Wang, and K Salamatian. Pearl: a programmable virtual router plat- form. Communications Magazine, IEEE, 49(7):71–77, 2011.

# DESIGN AND EVALUATION OF HIGH PERFORMANCE SOFTWARE BASED PACKET CLASSIFICATION SYSTEMS

Peng He

A DISSERTATION

PRESENTED TO THE FACULTY

OF GRENOBLE UNIVERSITY

IN CANDIDACY FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY

BY THE DEPARTMENT OF

ELECTRICAL ENGINEERING

ADVISER: KAVÉ SALAMATIAN, GAOGANG XIE

September 2014

© Copyright by Peng He, 2014.

All rights reserved.

#### Abstract

Packet classification consists of matching packet headers against a set of pre-defined rules, and performing the action(s) associated with the matched rule(s). As a key technology in the data-plane of network devices, packet classification has been widely deployed in many network applications and services, such as firewalling, load balancing, VPNs etc. Packet classification has been extensively studied in the past two decades. Traditional packet classification methods are usually based on specific hardware. With the development of data center networking, software-defined networking, and application-aware networking technology, packet classification methods based on multi/many processor platform are becoming a new research interest. In this dissertation, packet classification has been studied mainly in three aspects: algorithm design framework, rule-set features analysis and algorithm implementation and optimization.

In the dissertation, we review multiple proposed algorithms and present a decision tree based algorithm design framework. The framework decomposes various existing packet classification algorithms into a combination of different types of "meta-methods", revealing the connection between different algorithms. Based on this framework, we combine different "meta-methods" from different algorithms, and propose two new algorithms, HyperSplit-op and HiCuts-op. The experiment results show that HiCuts-op achieves  $2 \sim 20 \times$  less memory size, and 10% less memory accesses than HiCuts, while HyperSplit-op achieves  $2 \sim 200 \times$  less memory size, and  $10\% \sim 30\%$  less memory accesses than HyperSplit.

In the dissertation, we also explore the connections between the rule-set features and the performance of various algorithms. We find that the "coverage uniformity" of the rule-set has a significant impact on the classification speed, and the size of "orthogonal structure" rules usually determines the memory size of algorithms. Based on these two observations, we propose a memory consumption model and a quantified method for coverage uniformity. Using the two tools, we propose a new multi-decision

tree algorithm — SmartSplit and a algorithm policy framework — AutoPC. Compared to EffiCuts algorithm, SmartSplit achieves around  $2.9\times$  speedup and up to  $10\times$  memory size reduction. For a given rule-set, AutoPC can automatically recommend a "right" algorithm for the rule-set. Compared to using a single algorithm on all the rulesets, AutoPC achieves in average 3.8 times faster.

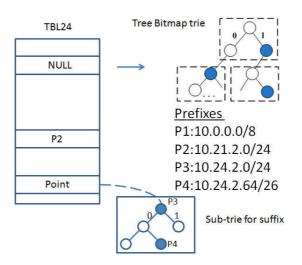

We also analyze the connection between prefix length and the update overhead for IP lookup algorithms. We observe that long prefixes will always result in more memory accesses using Tree Bitmap algorithm while short prefixes will always result in large update overhead in DIR-24-8. Through combining two algorithms, a hybrid algorithm SplitLookup is proposed to reduce the update overhead. Experimental results show that, the hybrid algorithm achieves 2 orders of magnitudes less in memory accesses when performing short prefixes updating, but its lookup speed with DIR-24-8 is close.

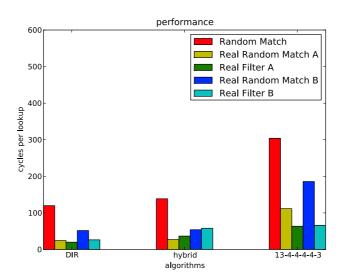

In the dissertation, we implement and optimize multiple algorithms on the multi/many core platform. For IP lookup, we implement two typical algorithms — DIR-24-8 and Tree Bitmap, and present several optimization tricks for these two algorithms. For multi-dimensional packet classification, we have implemented HyperCuts/HiCuts and the variants of these two algorithms, Adaptive Binary Cuttings, EffiCuts, HiCuts-op and HyperSplit-op. The SplitLookup algorithm has achieved up to 40Gbps throughput on TILEPro64 many-core processor. The HiCuts-op and HyperSplit-op have achieved up to 10 to 20Gbps throughput on a single core of Intel processors.

In general, we study the packet classification algorithms from both the perspectives of algorithm and rule-set features. We reveal the connections between the algorithmic tricks and rule-set features and therefore develop an adaptive framework for rule-sets with different features. We also implement various algorithms and compare the real performance of all these algorithms. Results in this dissertation provide insight for new algorithm design and the guidelines for efficient algorithm implementation.

# Acknowledgements

To my parents.

# Contents

|   | Abs  | tract .          |                                                                  | iii  |  |

|---|------|------------------|------------------------------------------------------------------|------|--|

|   | Ack  | Acknowledgements |                                                                  |      |  |

|   | List | of Tab           | les                                                              | xiii |  |

|   | List | of Figu          | ires                                                             | XV   |  |

| 1 | Intr | oduct            | ion                                                              | 1    |  |

|   | 1.1  | Motiv            | ation                                                            | 1    |  |

|   |      | 1.1.1            | The needs of SDN<br>(Software Defined Networking) evolution $$ . | 1    |  |

|   |      | 1.1.2            | The needs of outsourcing network services                        | 3    |  |

|   |      | 1.1.3            | The needs of network virtualization                              | 4    |  |

|   |      | 1.1.4            | The advance of multi-core and commodity hardware                 | 4    |  |

|   | 1.2  | Resea            | rch problems in this thesis                                      | 6    |  |

|   | 1.3  | Main             | contributions                                                    | 9    |  |

|   |      | 1.3.1            | The algorithm design framework                                   | 9    |  |

|   |      | 1.3.2            | Modeling the ruleset features                                    | 9    |  |

|   |      | 1.3.3            | Evaluating multiple packet classification algorithms             | 10   |  |

|   |      | 1.3.4            | PEARL: A prototype for SDN/NFV                                   | 11   |  |

|   | 1.4  | Paper            | organization                                                     | 11   |  |

| 2 | Stat | te of a          | rt in packet classification algorithms                           | 12   |  |

|   | 2.1  | Packe            | t classification problems                                        | 12   |  |

|   | 2.2        | тургса                                                                 | al packet classification solutions                                                                     | 14                                     |

|---|------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------|

|   | 2.3        | IP loo                                                                 | kup algorithms                                                                                         | 16                                     |

|   |            | 2.3.1                                                                  | A basic algorithm                                                                                      | 17                                     |

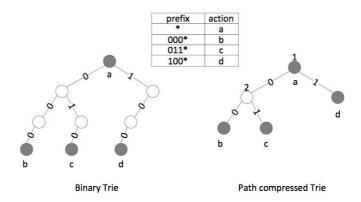

|   |            | 2.3.2                                                                  | Typical trie-based algorithms                                                                          | 17                                     |

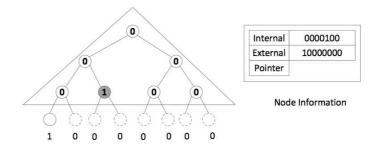

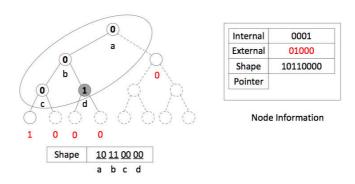

|   |            | 2.3.3                                                                  | Shape Shifting                                                                                         | 20                                     |

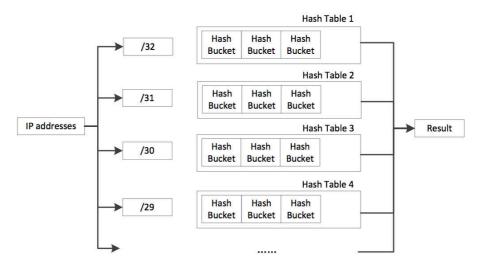

|   |            | 2.3.4                                                                  | Hash-based IP lookup Algorithms                                                                        | 22                                     |

|   |            | 2.3.5                                                                  | Conclusion                                                                                             | 26                                     |

|   | 2.4        | Multi-                                                                 | dimensional Packet Classification Algorithms                                                           | 26                                     |

|   |            | 2.4.1                                                                  | Complexity of the basic problem                                                                        | 26                                     |

|   |            | 2.4.2                                                                  | Decomposition based algorithms                                                                         | 28                                     |

|   |            | 2.4.3                                                                  | Hash-based algorithms                                                                                  | 30                                     |

|   |            | 2.4.4                                                                  | Decision tree based algorithms                                                                         | 30                                     |

|   |            | 2.4.5                                                                  | Conclusion                                                                                             | 32                                     |

|   | 2.5        | Key id                                                                 | lea: exploit the "sparseness" of rulesets                                                              | 32                                     |

| 3 | Ana        | atomy                                                                  | of Decision Tree Algorithms: Framework and Evaluation                                                  | 35                                     |

|   | 3.1        | N. f                                                                   |                                                                                                        | 36                                     |

|   |            | Motiva                                                                 | ation                                                                                                  |                                        |

|   |            | 3.1.1                                                                  | Studying the performance variation of existing algorithms                                              | 36                                     |

|   |            |                                                                        |                                                                                                        | 36<br>37                               |

|   | 3.2        | 3.1.1<br>3.1.2                                                         | Studying the performance variation of existing algorithms                                              |                                        |

|   | 3.2<br>3.3 | 3.1.1<br>3.1.2<br>Backgr                                               | Studying the performance variation of existing algorithms Evaluating and analyzing existing algorithms | 37                                     |

|   |            | 3.1.1<br>3.1.2<br>Backgr                                               | Studying the performance variation of existing algorithms Evaluating and analyzing existing algorithms | 37<br>37                               |

|   |            | 3.1.1<br>3.1.2<br>Backg<br>The D                                       | Studying the performance variation of existing algorithms Evaluating and analyzing existing algorithms | 37<br>37<br>40                         |

|   |            | 3.1.1<br>3.1.2<br>Backg<br>The D<br>3.3.1                              | Studying the performance variation of existing algorithms Evaluating and analyzing existing algorithms | 37<br>37<br>40<br>41                   |

|   |            | 3.1.1<br>3.1.2<br>Backg:<br>The D<br>3.3.1<br>3.3.2<br>3.3.3           | Studying the performance variation of existing algorithms Evaluating and analyzing existing algorithms | 37<br>37<br>40<br>41<br>46             |

|   | 3.3        | 3.1.1<br>3.1.2<br>Backg:<br>The D<br>3.3.1<br>3.3.2<br>3.3.3           | Studying the performance variation of existing algorithms Evaluating and analyzing existing algorithms | 37<br>37<br>40<br>41<br>46<br>53       |

|   | 3.3        | 3.1.1<br>3.1.2<br>Backg:<br>The D<br>3.3.1<br>3.3.2<br>3.3.3<br>Experi | Studying the performance variation of existing algorithms Evaluating and analyzing existing algorithms | 37<br>37<br>40<br>41<br>46<br>53<br>54 |

|   | 3.5 | Exper   | iment Results                                          | 57 |

|---|-----|---------|--------------------------------------------------------|----|

|   |     | 3.5.1   | Comparing memory size and memory accesses              | 57 |

|   |     | 3.5.2   | Real throughput                                        | 60 |

|   | 3.6 | Concl   | usion                                                  | 61 |

| 4 | Met | ta algo | orithms for software-based Packet Classification       | 63 |

|   | 4.1 | Motiv   | ation                                                  | 63 |

|   | 4.2 | Backg   | ground and Observations                                | 66 |

|   |     | 4.2.1   | Influence on temporal performance                      | 67 |

|   |     | 4.2.2   | Influence on spatial performance                       | 68 |

|   |     | 4.2.3   | Application to existing algorithms                     | 69 |

|   |     | 4.2.4   | Discussions                                            | 71 |

|   | 4.3 | Memo    | ory footprint estimation                               | 72 |

|   |     | 4.3.1   | Improving memory size estimation                       | 75 |

|   |     | 4.3.2   | The bound of memory consumption                        | 76 |

|   |     | 4.3.3   | Limitations                                            | 78 |

|   | 4.4 | Chara   | acterizing range distribution uniformity               | 79 |

|   |     | 4.4.1   | Interval tree                                          | 79 |

|   |     | 4.4.2   | Characterizing the shape of interval trees             | 83 |

|   |     | 4.4.3   | Algorithm decision framework                           | 85 |

|   |     | 4.4.4   | SmartSplit algorithm                                   | 86 |

|   | 4.5 | The A   | AutoPC framework                                       | 88 |

|   | 4.6 | Exper   | imental Methodology                                    | 88 |

|   | 4.7 | Exper   | iment Results                                          | 90 |

|   |     | 4.7.1   | Memory Size and Real Performance                       | 90 |

|   |     | 4.7.2   | Memory estimation under different number of partitions | 92 |

|   |     | 4.7.3   | Estimated and Actual Memory                            | 92 |

|   |     | 4.7.4   | Study the error of the memory estimation               | 95 |

|   |     | 4.7.5   | Comparing SmartSplit and EffiCuts                 | 99  |

|---|-----|---------|---------------------------------------------------|-----|

|   |     | 4.7.6   | Real Performance Evaluation                       | 102 |

|   | 4.8 | CONC    | CLUSION                                           | 103 |

| 5 | Eva | luating | g and Optimizing IP lookup on Manycore Processors | 105 |

|   | 5.1 | Introd  | luction                                           | 105 |

|   | 5.2 | Backg   | round                                             | 107 |

|   |     | 5.2.1   | The Tree bitmap algorithm                         | 107 |

|   |     | 5.2.2   | The DIR-24-8-BASIC algorithm                      | 109 |

|   |     | 5.2.3   | The TILEPro64 architecture                        | 110 |

|   | 5.3 | IP Loc  | okup on TILEPro64                                 | 111 |

|   |     | 5.3.1   | Implementation                                    | 111 |

|   |     | 5.3.2   | Optimization tricks                               | 112 |

|   | 5.4 | Perfor  | mance Evaluation                                  | 114 |

|   |     | 5.4.1   | Evaluation Traces                                 | 114 |

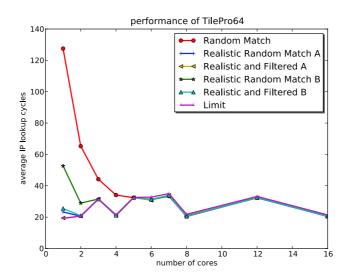

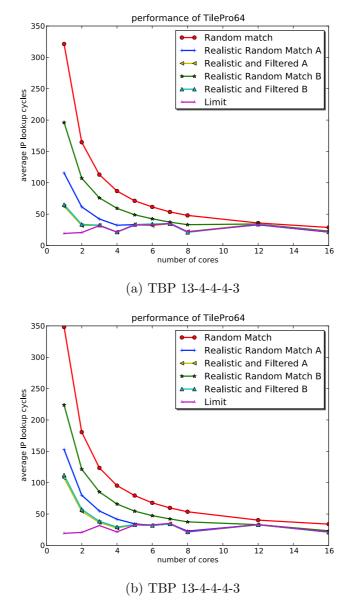

|   |     | 5.4.2   | Single-core Performance Evaluations               | 117 |

|   |     | 5.4.3   | Parallel Performance Evaluations                  | 118 |

|   | 5.5 | A Hyb   | orid IP Lookup Scheme: SplitLookup                | 121 |

|   | 5.6 | Conclu  | usion                                             | 124 |

| 6 | PEA | ARL: A  | A Programmable Virtual Router Platform            | 126 |

|   | 6.1 | Introd  | luction                                           | 126 |

|   | 6.2 | Design  | n Goals                                           | 128 |

|   | 6.3 | Platfo  | rm design and Implementation                      | 129 |

|   |     | 6.3.1   | System Overview                                   | 129 |

|   |     | 6.3.2   | Software Platform                                 | 134 |

|   |     | 6.3.3   | Evaluation and Discussion                         | 137 |

|   | 6.4 | Relate  | ed Work                                           | 139 |

|                  | 6.5 Conclusion | . 141 |

|------------------|----------------|-------|

| 7                | Conclusion     | 142   |

| $\mathbf{B}^{i}$ | ibliography    | 146   |

# List of Tables

| 1.1  | A toy ruleset                                                 | 7   |

|------|---------------------------------------------------------------|-----|

| 2.1  | a 3-dimensional ruleset                                       | 29  |

| 3.1  | The performance results of different algorithms               | 36  |

| 3.2  | An example ruleset                                            | 38  |

| 3.3  | The cons and pros of all the optimization tricks              | 52  |

| 3.4  | The meta methods of different algorithms                      | 53  |

| 3.5  | The setup of the experimental platform                        | 54  |

| 3.6  | The node information and size of different algorithms         | 56  |

| 4.1  | Performance comparison on different rulesets                  | 63  |

| 4.2  | An example ruleset                                            | 67  |

| 4.3  | Ruleset with a lot of distinct $small$ ranges on Field 1      | 72  |

| 4.4  | the number of unique IP small ranges in large rulesets        | 80  |

| 4.5  | Node data structure size in bytes                             | 89  |

| 4.6  | Estimated and Actual Memory size of Large rulesets            | 95  |

| 4.7  | split distribution of each fields                             | 96  |

| 4.8  | estimate errors after restricting the split fields, $n = 16.$ | 97  |

| 4.9  | estimate errors after restring split field, $n=256$           | 98  |

| 4.10 | Detailed Information of Large rulesets                        | 101 |

| 4.11 | Real Performance Evaluation of AutoPC and EffiCuts            | 103 |

| 5.1 | frequency and cache size            | 110 |

|-----|-------------------------------------|-----|

| 5.2 | cache system and cache miss penalty | 110 |

| 5.3 | Evaluation Traces                   | 117 |

| 5.4 | update overhead of two algorithms   | 123 |

# List of Figures

| 1.1  | The core and edge of SDN                                                  | 3  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | Multi-core and the performance of software-based router scaling $\ . \ .$ | 5  |

| 1.3  | IP lookup                                                                 | 6  |

| 1.4  | The update frequency peak in backbone network [72]                        | 7  |

| 1.5  | The packet classification system                                          | 7  |

| 2.1  | Path Compressed Trie                                                      | 18 |

| 2.2  | Tree Bitmap encoding                                                      | 19 |

| 2.3  | The Shape Shifting Encoding Scheme                                        | 20 |

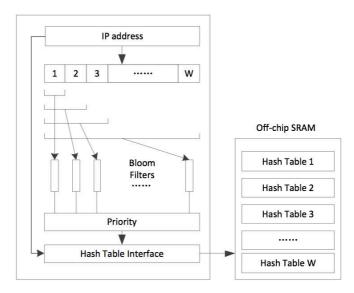

| 2.4  | Hash based IP lookup                                                      | 22 |

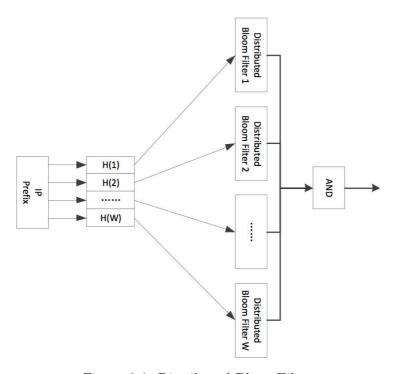

| 2.5  | Bloom-Filter based IP lookup algorithm                                    | 24 |

| 2.6  | Distributed BloomFilter                                                   | 25 |

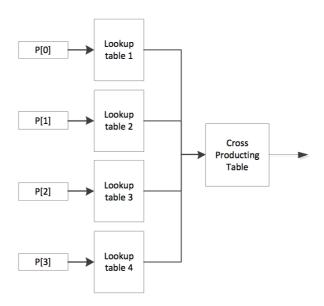

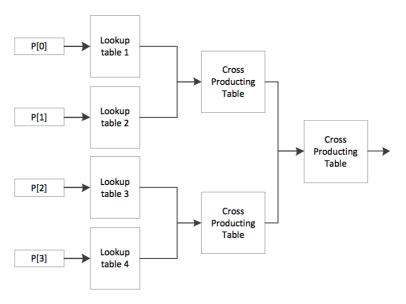

| 2.7  | the Crossproducting algorithm                                             | 28 |

| 2.8  | The RFC algorithm                                                         | 29 |

| 2.9  | The Tuple Space Search algorithm                                          | 31 |

| 2.10 | The Decision Tree based algorithm and the Decomposition algorithms        | 31 |

| 2.11 | Exploring the "sparseness" of the rulesets                                | 33 |

| 3.1  | Decision tree algorithms                                                  | 39 |

| 3.2  | The decision tree design framework                                        | 40 |

| 3.3  | The cutting process of HyperCuts                                          | 43 |

| 3.4  | Calculating the range weight                                                        |    |  |  |

|------|-------------------------------------------------------------------------------------|----|--|--|

| 3.5  | Minimal cost function                                                               |    |  |  |

| 3.6  | Rule Overlap                                                                        |    |  |  |

| 3.7  | Using Bitmap to reduce the memory accesses and memory size                          | 48 |  |  |

| 3.8  | Rule shifting                                                                       | 48 |  |  |

| 3.9  | Node reuse                                                                          | 49 |  |  |

| 3.10 | Region Compaction                                                                   | 50 |  |  |

| 3.11 | Shape encoding                                                                      | 50 |  |  |

| 3.12 | Meta methods of different algorithms                                                | 55 |  |  |

| 3.13 | The memory access of different algorithms                                           | 57 |  |  |

| 3.14 | The memory size of different algorithms (bytes/rule) $\ \ldots \ \ldots \ \ldots$   | 57 |  |  |

| 3.15 | The memory accesses of optimized algorithms                                         | 59 |  |  |

| 3.16 | The memory footprint of optimized algorithms<br>(Byte/rule) $\ \ \ldots \ \ \ldots$ | 59 |  |  |

| 3.17 | The throughput of different algorithms under the low locality traffic . 6           |    |  |  |

| 3.18 | The thoughput of different algorithms under the high locality traffic $.$           | 61 |  |  |

| 4.1  | Decision trees built by different algorithms                                        | 65 |  |  |

| 4.2  | Geometric View of Packet Classification Rules                                       | 69 |  |  |

| 4.3  | The distribution of $(small, small)$ rules is skewed                                | 75 |  |  |

| 4.4  | Improved Memory Size model                                                          | 76 |  |  |

| 4.5  | The rule splitting process in the proof                                             | 78 |  |  |

| 4.6  | The interval tree data structure                                                    | 81 |  |  |

| 4.7  | Balanced Tree Distance and Balanced Tree Depth                                      | 83 |  |  |

| 4.8  | Measuring algorithm                                                                 | 84 |  |  |

| 4.9  | the measurement results of two interval trees                                       | 84 |  |  |

| 4.10 |                                                                                     |    |  |  |

| 4.11 | Average Memory Access Latency and Memory Size                                       |    |  |  |

|      | Cache Misses Rate and Memory size                                                   | 91 |  |  |

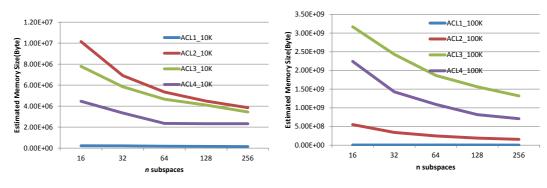

| 4.13 | $acl10k \ldots \ldots \ldots \ldots \ldots \ldots \ldots$               | 92  |  |  |

|------|-------------------------------------------------------------------------|-----|--|--|

| 4.14 | acl100k                                                                 | 92  |  |  |

| 4.15 | fw10k                                                                   | 93  |  |  |

| 4.16 | fw100k                                                                  | 93  |  |  |

| 4.17 | ipc10k                                                                  | 93  |  |  |

| 4.18 | ipc100k                                                                 | 93  |  |  |

| 4.19 | Estimated and Actual memory size with $binth=16$                        | 93  |  |  |

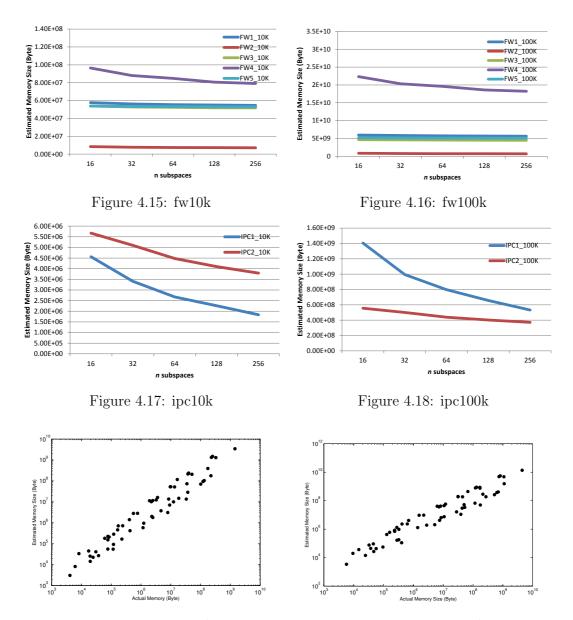

| 4.20 | Estimated and Actual memory size with $binth=8$                         | 93  |  |  |

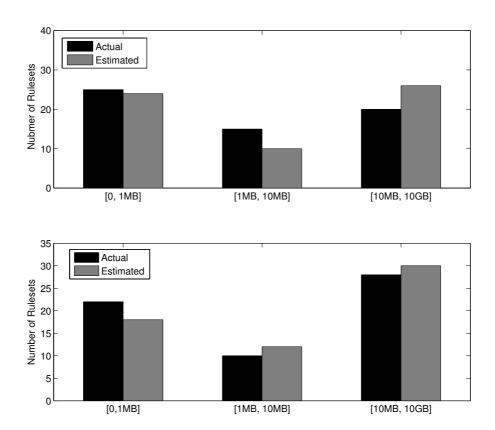

| 4.21 | The estimated and actual number of rule<br>sets for $binth=16(top)$ and |     |  |  |

|      | binth = 8(bottom)                                                       | 94  |  |  |

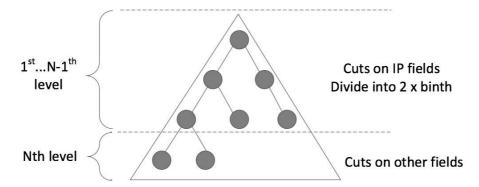

| 4.22 | A decision tree model                                                   | 99  |  |  |

| 4.23 | Memory and Accesses for EffiCuts and SmartSplit                         | 100 |  |  |

| 4.24 | Comparing the measured performance of SmartSplit and EffiCuts $$        | 102 |  |  |

| 5.1  | The Tree Bitmap Algorithm                                               | 108 |  |  |

| 5.2  | The DIR-24-8-BASIC Algorithm                                            | 109 |  |  |

| 5.3  | Fast internal bitmap checking                                           | 114 |  |  |

| 5.4  | Random Match Trace Generation                                           | 116 |  |  |

| 5.5  | Single core Performance Results                                         | 118 |  |  |

| 5.6  | Pipeline Parallel Performance of Tree Bitmap                            | 119 |  |  |

| 5.7  | Run-to-complete Parallel Performance of DIR-24-8-BASIC                  | 120 |  |  |

| 5.8  | Run-to-complete Parallel Performance of Tree Bitmap                     |     |  |  |

| 5.9  | Data Structure of the hybrid algorithm                                  | 123 |  |  |

| 5.10 | Performance of our hybrid IP lookup scheme                              | 124 |  |  |

| 6.1  | Overview of PEARL architecture                                          | 130 |  |  |

| 6.2  | PEARL hardware data plane architectural                                 | 131 |  |  |

| 6.3  | Packet Processing Path in software                                      | 134 |  |  |

| 6.4 | Throughput of high performance IPv4 virtual routers | 138 |

|-----|-----------------------------------------------------|-----|

| 6.5 | Throughput of high performance IPv4 virtual routers | 138 |

| 6.6 | Throughput of high performance IPv4 virtual routers | 139 |

# Chapter 1

# Introduction

# 1.1 Motivation

Packet classification enables advanced services in various network applications, such as firewalling, network intrusion detection/prevention, load balancing and QoS etc. In general, packet classification consists of matching packet headers against a set of pre-defined rules, and performing the action(s) associated to the matched rule(s).

As one of the key technologies in many network devices, high performance packet classification methods have been extensively studied in the past decade. Traditional packet classification systems are usually based on dedicated hardware. However, recently software based packet classification systems have attracted a lot of research interests [7, 29, 47]. We will list the reason why software based packet classification systems become important.

# 1.1.1 The needs of SDN(Software Defined Networking) evolution

In Software Defined networks, the control plane and the data plane are physically separated. The switches inside the network forward the packets based on the rules installed by the control plane. This physical separation eases both the management of large and complex networks and programming network policies. To implement such an architecture, however, a general packet forwarding plane is needed to execute various dataplane lookup tasks. In the current development of SDN, the OpenFlow [38] protocol is the *de facto* standard for the abstraction of data plane function. According to the OpenFlow specification, OpenFlow switches need to provide at least flexible packet classification on 10 fields. However, the hardware resources of current commercial switches can only support a few thousands of 10 tuple rules – the TCAM volume of HP ProCurve 5406zl switch is only capable of storing 1.5 thousands rules. Such limited hardware resources severely hinder the deployment of SDN. Moreover, with the development of SDN, more and more packet header fields have been added in the specification. By the version 1.3, there are more than 30 optional fields in the OpenFlow specification. These multiple matching fields impose technical challenges to SDN development.

Martin Casado etc. proposed in [8] a pragmatic solution for SDN evolution. In their paper, Martin suggests to treat Core Network and Edge Network separately. The Edge Network provides interfaces between the network and the hosts, and also provides network services such as virtualization, traffic engineering and QoS etc. The Core Network only transfers the packets in high speed. Similar to MPLS, the edge switches add different tags into different types of packets, and deliver these packets into the network core. The network core and edge is managed by logical separated controller. Figure 1.1 shows this network architecture.

The required packet processing performance at the edge of the network is not high because of the low traffic volume of each host, but the Edge Network requires flexible packet processing. Since current network switches use specific hardware for packet forwarding, in the short term, it is difficult to provide programmability based on the specific hardware.

Figure 1.1: The core and edge of SDN

Therefore, Edge Network devices will be built using mainly the software-based systems on commodity hardware. Using efficient algorithms, these systems are capable of forwarding packets according to the flexible rules that specify multiple packet header fields [75]. As a typical example, Open vSwitch [46] transforms packets based on OpenFlow rules between multiple virtual machines.

The packet classification algorithm is one of the key algorithms in the above software-based systems. The study on the adaption and performance of these algorithms on software-based systems is therefore required for SDN evolution.

# 1.1.2 The needs of outsourcing network services

Cloud computing enables the separation of the ownership of the infrastructure and of the applications. Since the network service is one of the basic services provided by the IT infrastructure, researchers begin to explore the possibility of outsourcing network functionality to the cloud, providing network services for multiple tenants. There are already a lot of pioneers in the industry which aims to provide cloud-based network services, such as AT&T that provides cloud firewalls, reducing the CAPEX/OPEX of small enterprises.

Cisco releases a software image [66] that can be deployed directly in mainstream virtual machines as a firewall filtering packets. Many startups begin to provide cloud-based systems, such as WAN optimizer provided by Aryaka [65], cloud-based IDS (Intrusion Detection System) provided by ZScaler [76], and a middle-box architecture offered by Embrance [67].

Packet classification is an important component in the above systems. Since these systems are also built mostly on commodity hardware, the study on software-based packet classification therefore meets the needs of outsourcing network services.

# 1.1.3 The needs of network virtualization

The paper [43] shows that in multi-tenants data centers, the network operators need fine-grained rules to separate the network traffic between different tenants. These fine-grained rules consume a lot of hardware resources for packet processing, and even lead to network crash [64]. Experiments [43] show that when the number of newly added flows grows at 3K/s, and the number of rules reaches to 60K, Open vSwitch will consume 25% of one single CPU. Also, when the number of prefix combination increases, Open vSwitch consumes more processing resources.

Therefore efficient packet classification algorithms are needed to process more fine-grained rules and reduce resource consumption.

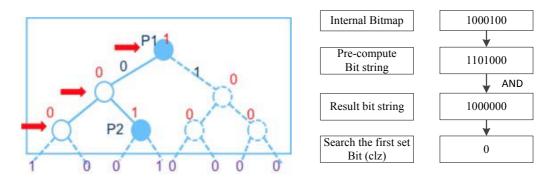

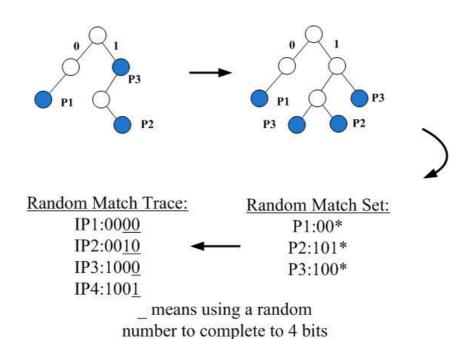

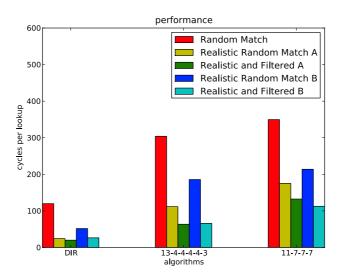

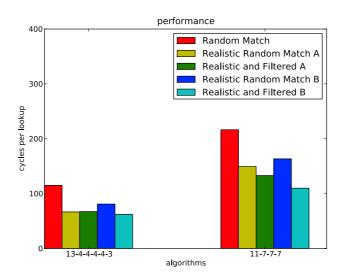

# 1.1.4 The advance of multi-core and commodity hardware