## Development of CMOS sensor with digital pixels for ILD vertex detector

Wei Zhao

#### ▶ To cite this version:

Wei Zhao. Development of CMOS sensor with digital pixels for ILD vertex detector. Other. Université de Strasbourg, 2015. English. NNT: 2015STRAE004. tel-01223460

#### HAL Id: tel-01223460 https://theses.hal.science/tel-01223460

Submitted on 2 Nov 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE STRASBOURG

## ÉCOLE DOCTORALE DE PHYSIQUE ET CHIMIE PHYSIQUE Institut Pluridisciplinaire Hubert Curien (IPHC)

## THÈSE présentée par :

#### Wei ZHAO

soutenue le : 25 Mars 2015

pour obtenir le grade de : Docteur de l'Université de Strasbourg

Discipline : Électronique, Électrotechnique et Automatique

Spécialité : Instrumentation et Microélectronique

## Development of CMOS sensors with digital pixels for the ILD vertex detector

#### Composition du jury:

Directeur de thèse : M. Yann HU Professeur, Université de Strasbourg

Rapporteurs externes: M. Hans KRUGER Professeur, Universität Bonn

M. Michel PAINDAVOINE Professeur, Université de Bourgogne Examinateurs: M. Christophe de LA TAILLE Professeur, École Polytechnique Professeur, Université de Strasbourg

## **Contents**

| ıa | bie o | t conte | nts              |              |         |        |      |      |      |      |   | 1    |

|----|-------|---------|------------------|--------------|---------|--------|------|------|------|------|---|------|

| Li | st of | Figures |                  |              |         |        |      |      |      |      |   | v    |

| Li | st of | Tables  |                  |              |         |        |      |      |      |      |   | ix   |

| Ac | knov  | wledge  | nents            |              |         |        |      |      |      |      |   | xi   |

| Ré | ésum  | é en Fr | ançais           |              |         |        |      |      |      |      |   | xiii |

| In | trodu | ction   |                  |              |         |        |      |      |      |      | : | xxv  |

| 1  | The   | ILC an  | d ILD            |              |         |        |      |      |      |      |   | 1    |

|    | 1.1   | The In  | ernational Line  | ear Collider |         |        | <br> | <br> | <br> | <br> |   | 2    |

|    |       | 1.1.1   | Physics progra   | m            |         |        | <br> | <br> | <br> | <br> |   | 2    |

|    |       | 1.1.2   | Machine overv    |              |         |        |      |      |      |      |   | 3    |

|    | 1.2   | ILD .   |                  |              |         |        | <br> | <br> | <br> | <br> |   | 5    |

|    |       | 1.2.1   | ILD concept ov   | erview       |         |        | <br> | <br> | <br> | <br> |   | 6    |

|    |       | 1.2.2   | ILD vertex dete  |              |         |        |      |      |      |      |   | 6    |

|    |       | 1.2.3   | Time Projection  |              |         |        |      |      |      |      |   | 8    |

|    |       | 1.2.4   | Silicon tracking |              |         |        |      |      |      |      |   | 9    |

|    |       | 1.2.5   | Calorimeter sy   |              |         |        |      |      |      |      |   | 10   |

|    |       | 1.2.6   | ILD outer dete   |              |         |        |      |      |      |      |   | 11   |

|    | 1.3   | Summ    | ary              |              |         |        | <br> | <br> | <br> | <br> |   | 11   |

|    | Bibl  |         | ,                |              |         |        |      |      |      |      |   | 12   |

| 2  | СМО   | OS Pixe | l Sensors for l  | LD Vertex    | Detec   | tor    |      |      |      |      |   | 13   |

|    | 2.1   | The de  | tection principl | e of silicon | detect  | ors    | <br> | <br> | <br> | <br> |   | 13   |

|    |       | 2.1.1   | Energy deposit   | ion by char  | rge par | ticles | <br> | <br> | <br> | <br> |   | 13   |

|    |       | 2.1.2   | Silicon detecto  | r physics .  |         |        | <br> | <br> | <br> | <br> |   | 14   |

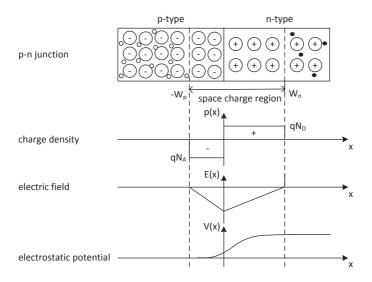

|    |       |         | 2.1.2.1 P-N j    | unction .    |         |        | <br> | <br> | <br> | <br> |   | 14   |

|    |       |         | 2.1.2.2 Char     | ge collectic | on      |        | <br> | <br> | <br> | <br> |   | 16   |

|    |       |         | 2.1.2.3 Signa    | al current   |         |        | <br> | <br> | <br> | <br> |   | 18   |

|    |       | 2.1.3   | Radiation dam    | age          |         |        | <br> | <br> | <br> | <br> |   | 18   |

ii CONTENTS

|   |       |           | 2.1.3.1      | Bulk damage                                         |    | 18 |

|---|-------|-----------|--------------|-----------------------------------------------------|----|----|

|   |       |           | 2.1.3.2      | Surface damage                                      |    | 19 |

|   |       |           | 2.1.3.3      | Radiation-tolerant design                           |    | 20 |

|   | 2.2   | Candid    | late pixel   | technologies for ILD-VTX                            |    | 21 |

|   |       | 2.2.1     | Fine Pixe    | el CCD (FPCCD)                                      |    | 22 |

|   |       | 2.2.2     | DEPFET       | sensors                                             |    | 23 |

|   |       | 2.2.3     | CMOS p       | xel sensors (CPS)                                   |    | 24 |

|   |       |           | 2.2.3.1      | Detection principle                                 |    | 24 |

|   |       |           | 2.2.3.2      | Pros and cons of CPS                                |    | 25 |

|   |       |           | 2.2.3.3      | Basic architectures of CPS                          |    | 26 |

|   |       |           | 2.2.3.4      | Development status of CPS                           |    | 29 |

|   | 2.3   | Conce     | ptual con    | siderations for the ILD-VTX based on C              | PS | 31 |

|   |       | 2.3.1     | Overviev     | v of the VTX configuration $\ldots \ldots$          |    | 32 |

|   |       | 2.3.2     | Innermo      | st layer                                            |    | 33 |

|   |       | 2.3.3     | Outer la     | yers                                                |    | 35 |

|   | 2.4   | Conclu    | ision        |                                                     |    | 36 |

|   | Bibli | iograph   | y            |                                                     |    | 38 |

| 3 | Stu   | ty of C   | DS with I    | Pixel-level ADCs                                    |    | 41 |

| • |       | -         |              | trics of ADCs                                       |    | _  |

|   | 3.2   |           |              | es                                                  |    |    |

|   | 5.2   | 3.2.1     |              | nverter                                             |    |    |

|   |       | 3.2.2     |              | converter                                           |    |    |

|   |       | 3.2.3     | -            | elta ( $\Sigma$ - $\Delta$ ) converter              |    |    |

|   |       | 3.2.4     |              | nverter                                             |    |    |

|   |       | 3.2.5     | -            | ve approximation register converter                 |    |    |

|   | 3.3   |           |              | of pixel-level ADC technology                       |    |    |

|   |       | 3.3.1     |              | fered by pixel-level digitization                   |    | 48 |

|   |       |           | 3.3.1.1      | Chip-level digitalization                           |    |    |

|   |       |           | 3.3.1.2      | Column-level digitalization                         |    |    |

|   |       |           | 3.3.1.3      | Pixel-level digitalization                          |    | 49 |

|   |       | 3.3.2     | Requirer     | nents of process                                    |    | 50 |

|   |       | 3.3.3     | -            | the-art                                             |    | 52 |

|   | 3.4   | Conclu    | ısion        |                                                     |    | 55 |

|   |       |           |              |                                                     |    | 56 |

| 4 | Doc   | ian of (  | DC with      | pixel-level SAR ADCs                                |    | 61 |

| 7 | 4.1   | _         |              | design                                              |    | 61 |

|   | 4.2   |           |              | ure                                                 |    |    |

|   | 7∙⊿   | 4.2.1     |              | strategy                                            |    |    |

|   |       |           |              | Strategy                                            |    |    |

|   |       | 1 • 4 • 4 | 14111A11 7TA | , <i>o</i> , ,, c, |    |    |

CONTENTS

|   |       |          | 4.2.2.1 Conventional SAR ADC architecture         |

|---|-------|----------|---------------------------------------------------|

|   |       |          | 4.2.2.2 Proposed CPS with pixel-level SAR ADCs 67 |

|   | 4.3   | Design   | of building blocks                                |

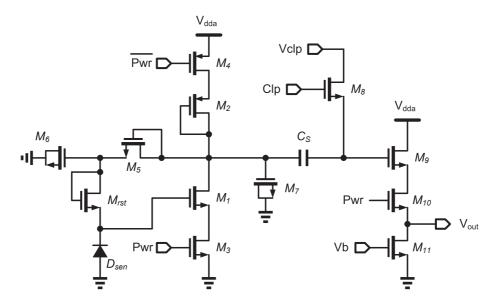

|   |       | 4.3.1    | Sensing diode with in-pixel amplifier             |

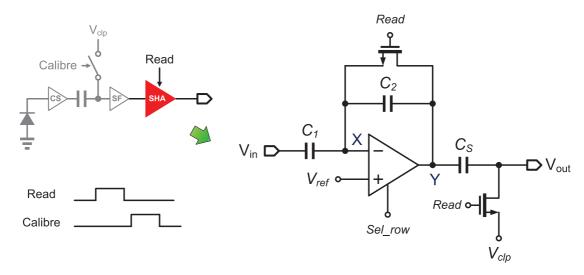

|   |       | 4.3.2    | Sample-and-hold amplifier                         |

|   |       |          | 4.3.2.1 Specifications                            |

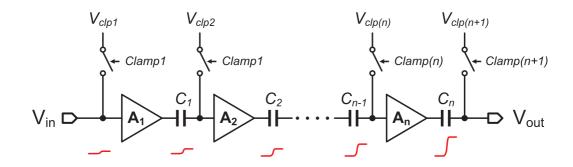

|   |       |          | 4.3.2.2 Architecture selection                    |

|   |       |          | 4.3.2.3 Circuit implementation                    |

|   |       |          | 4.3.2.4 Noise analysis                            |

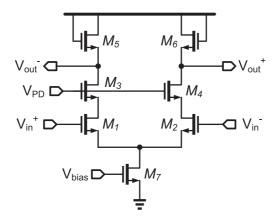

|   |       | 4.3.3    | Pre-amplifier in comparator                       |

|   |       |          | 4.3.3.1 Specifications                            |

|   |       |          | 4.3.3.2 Architecture selection                    |

|   |       |          | 4.3.3.3 Circuit implementation                    |

|   |       |          | 4.3.3.4 Simulation results                        |

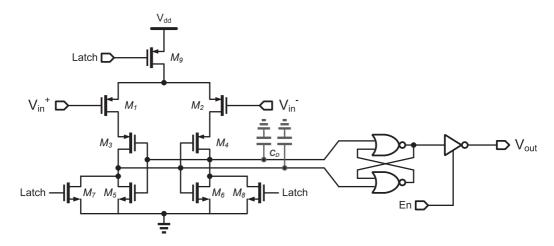

|   |       | 4.3.4    | Latch                                             |

|   |       |          | 4.3.4.1 Architecture selection                    |

|   |       |          | 4.3.4.2 Circuit implementation                    |

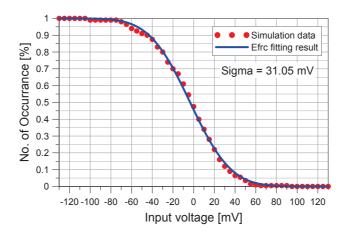

|   |       |          | 4.3.4.3 Simulation results                        |

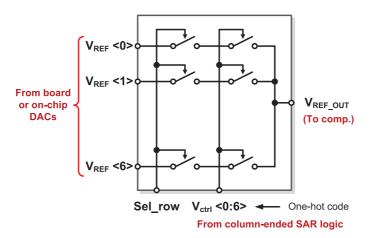

|   |       | 4.3.5    | Multiplexer DAC                                   |

|   |       | 4.3.6    | SAR control logic                                 |

|   | 4.4   | Layou    | t implementation                                  |

|   |       | 4.4.1    | Signal routing plan                               |

|   |       | 4.4.2    | Power routing plan                                |

|   | 4.5   | Conclu   | ısion                                             |

|   | Bibli | ograph   | y                                                 |

| 5 | Des   | ian of s | a CPS with pixel-level single-slope ADCs          |

| • |       | •        | evel SS ADC with column-ended memory              |

|   | 0.1   | 5.1.1    | Architecture                                      |

|   |       | 5.1.2    | Circuit implementation                            |

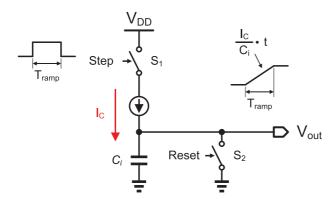

|   |       | 0.1.1    | 5.1.2.1 Adaptive ramp generator                   |

|   |       |          | 5.1.2.2 Buffer                                    |

|   |       |          | 5.1.2.3 Column-ended memory                       |

|   |       | 5.1.3    | Layout                                            |

|   |       |          | 5.1.3.1 Pixel matrix                              |

|   |       |          | 5.1.3.2 Peripheral                                |

|   | 5.2   | Pixel-l  | evel SS ADC with in-pixel memory                  |

|   |       | 5.2.1    | Architecture                                      |

|   |       | 5.2.2    | Circuit implementation                            |

|   |       |          | 5.2.2.1 Open-loop S/H amplifier                   |

|   |       |          |                                                   |

V TABLE OF CONTENTS

|    |              |          | 5.2.2.2    | Comparator    |             |          |       | <br> | <br> | <br>. 122 |

|----|--------------|----------|------------|---------------|-------------|----------|-------|------|------|-----------|

|    |              |          | 5.2.2.3    | In-pixel mer  | nory        |          |       | <br> | <br> | <br>. 123 |

|    |              | 5.2.3    | Layout     |               |             |          |       | <br> | <br> | <br>. 124 |

|    | 5.3          | Conclu   | ısion      |               |             |          |       | <br> | <br> | <br>. 125 |

|    | Bibli        | iograph  | у          |               |             |          |       | <br> | <br> | <br>. 126 |

| 6  | Cha          | racteria | zation of  | MIMADC chi    | ip          |          |       |      |      | 127       |

|    | 6.1          | Measu    | rement sy  | stem          |             |          |       | <br> | <br> | <br>. 128 |

|    | 6.2          | Test re  | sults of S | AR-ADC matr   | ix          |          |       | <br> | <br> | <br>. 129 |

|    |              | 6.2.1    | Noise pe   | rformance .   |             |          |       | <br> | <br> | <br>. 130 |

|    |              | 6.2.2    | Linearity  | measuremen    | nt          |          |       | <br> | <br> | <br>. 133 |

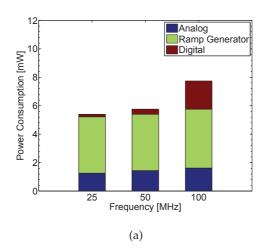

|    |              | 6.2.3    | Power co   | nsumption m   | ieasuremer  | nt       |       | <br> | <br> | <br>. 135 |

|    | 6.3          | Test re  | sults of S | S-ADC matrix  | with colur  | nn memo  | ories | <br> | <br> | <br>. 135 |

|    |              | 6.3.1    | Noise pe   | rformance .   |             |          |       | <br> | <br> | <br>. 136 |

|    |              | 6.3.2    | Linearity  | measuremen    | ıt          |          |       | <br> | <br> | <br>. 137 |

|    |              | 6.3.3    | Power co   | nsumption m   | ieasuremer  | nt       |       | <br> | <br> | <br>. 139 |

|    | 6.4          | Test re  | sults of S | S-ADC matrix  | with in-pix | xel memo | ories | <br> | <br> | <br>. 140 |

|    |              | 6.4.1    | -          | rformance .   |             |          |       |      |      |           |

|    |              | 6.4.2    | Linearity  | measuremen    | ıt          |          |       | <br> | <br> | <br>. 144 |

|    |              | 6.4.3    |            | nsumption m   |             |          |       |      |      |           |

|    | 6.5          | Conclu   | ısion      |               |             |          |       | <br> | <br> | <br>. 146 |

|    | Bibli        | iograph  | у          |               |             |          |       | <br> | <br> | <br>. 149 |

| Co | nclu         | sions a  | and persp  | ectives       |             |          |       |      |      | 151       |

| A  | Sch          | ematic   | s of the t | est boards fo | or MIMAD    | C chip   |       |      |      | 155       |

| В  | Calc         | culation | n of offse | t in pre-amp  | lifier      |          |       |      |      | 161       |

| С  | Hist         | ogram    | measure    | ment of ADC   | Clinearity  |          |       |      |      | 165       |

| Αb | Abstract 167 |          |            |               |             |          |       |      |      |           |

## **List of Figures**

| R.1  | Architecture de l'expérience ILD                                  | iv   |

|------|-------------------------------------------------------------------|------|

| R.2  | Géométrie d'un détecteur de vertex                                | ΧV   |

| R.3  | Architecture du MIMADC-SAR                                        | vii  |

| R.4  | Synoptique d'un pixel du MIMADC-SS1                               | viii |

| R.5  | Schéma de un pixel du MIMADC-SS2                                  | ix   |

| R.6  | Photographie du prototype MIMADC bondé sur la carte de test       | XX   |

| R.7  | Photo de la carte de test du MIMADC                               |      |

| 1.1  | Schematic layout of the ILC                                       | 4    |

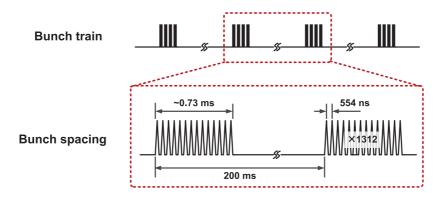

| 1.2  | Bunch structure of the ILC                                        | 5    |

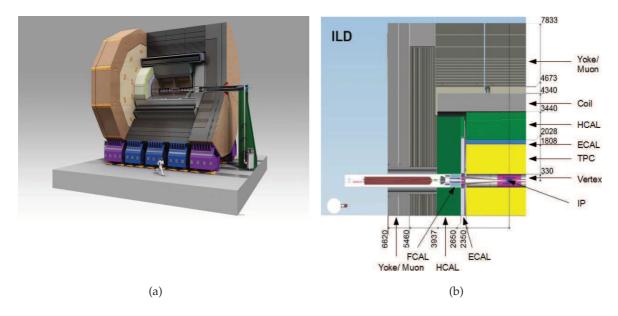

| 1.3  | Cut-away view and quadrant view of the ILD                        | 6    |

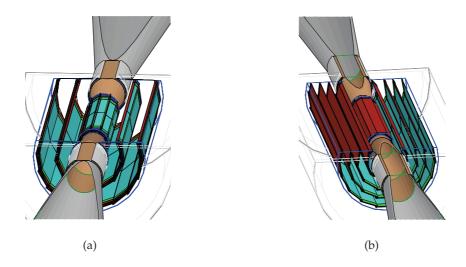

| 1.4  | Two options for the ILD vertex detector geometries                | 8    |

| 2.1  | Approximation of an abrupt p-n junction                           | 15   |

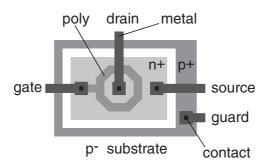

| 2.2  | Radiation tolerant layout of an NMOS tansistor                    | 21   |

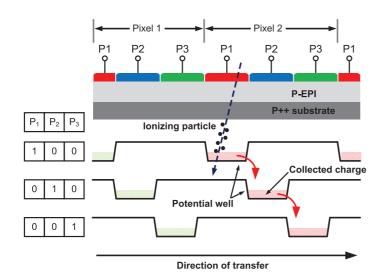

| 2.3  | Principle of a typical CCD                                        | 22   |

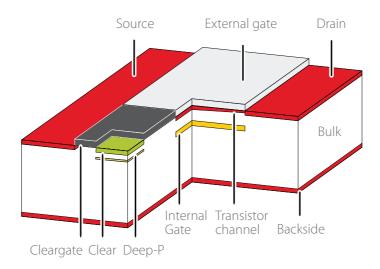

| 2.4  | Cross-sectional view of DEPFET pixel                              | 24   |

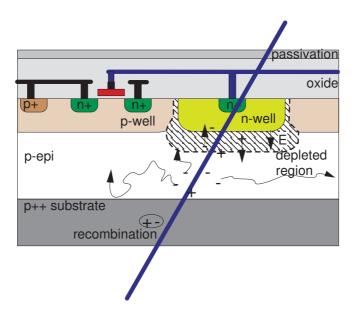

| 2.5  | Cross-sectional view and operation principle of a typical CPS     | 25   |

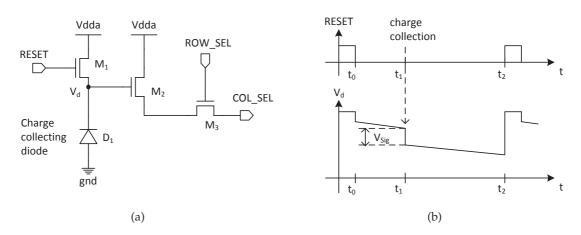

| 2.6  | 3-T pixel cell – architecture and time diagram                    | 26   |

| 2.7  | Self-biased pixel cell (SB-pixel) – architecture and time diagram | 27   |

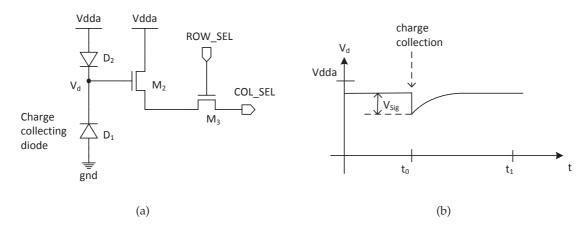

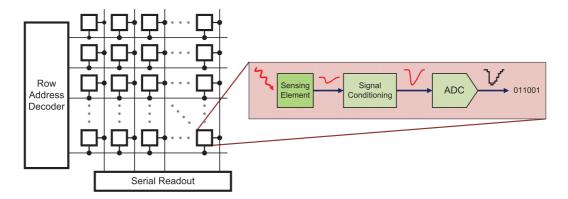

| 2.8  | Block diagram of a typical CMOS pixel sensor with analog outputs  | 28   |

| 2.9  | Schematic diagram of a pixel cell and column-ended discriminator  | 28   |

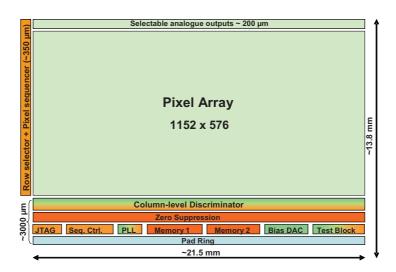

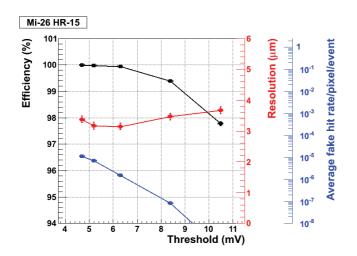

| 2.10 | Floorplan of MIMOSA-26                                            | 30   |

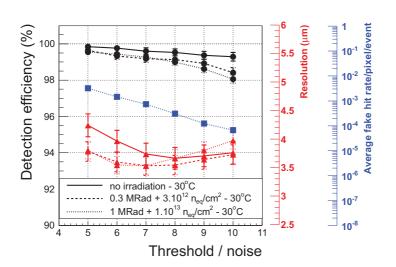

| 2.11 | Beam test results of MIMOSA-26                                    | 31   |

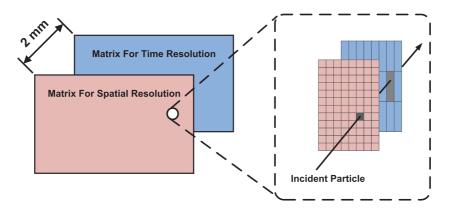

| 2.12 | Structure of the double-sided ladder for the innermost layer      | 33   |

| 3.1  |                                                                   | 42   |

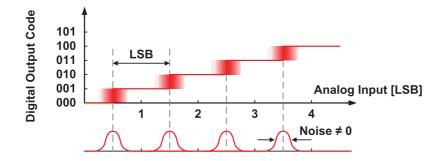

| 3.2  | Effect of temporal noise on the ADC transfer curve                | 43   |

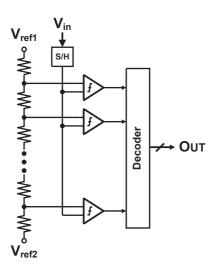

| 3.3  | Topology of a typical flash ADC                                   | 44   |

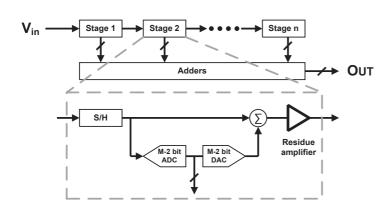

| 3.4  | Topology of a typical pipeline ADC                                | 45   |

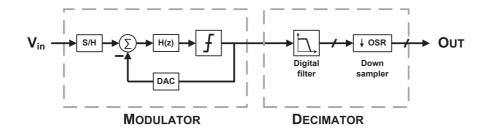

| 3.5  | Topology of a typical $\Sigma$ - $\Delta$ ADC                     | 45   |

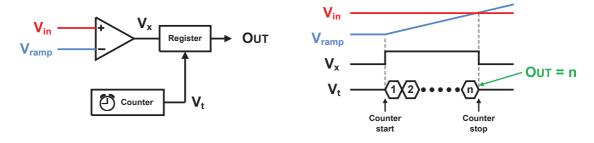

| 3.6  | Principle of single-slope ADCs                                    | 46   |

| 3.7  | 1                                                                 | 47   |

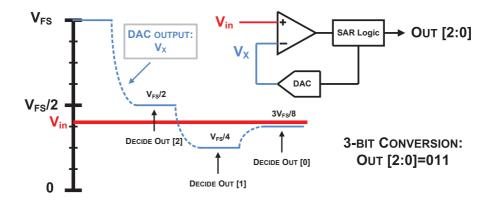

| 3.8  | Integration structures of on-chip ADCs                            | 48   |

vi LIST OF FIGURES

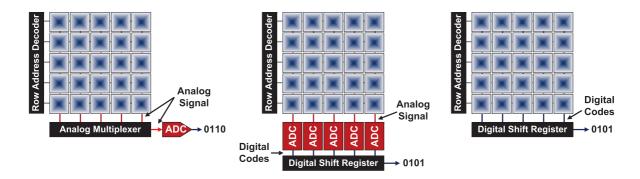

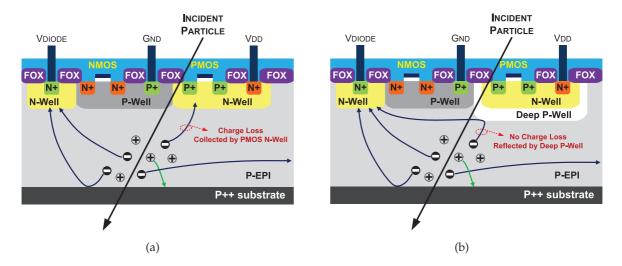

| 3.9  | Charge collection principle in dual-well and DNW processes                               | 51  |

|------|------------------------------------------------------------------------------------------|-----|

| 3.10 | Measurement results of MIMOSA-32 fabricated in Towerjazz 0.18 $\mu m$ process $$ .       | 52  |

| 4.1  | Generic architecture of a CPS integrated with pixel-level ADCs                           | 62  |

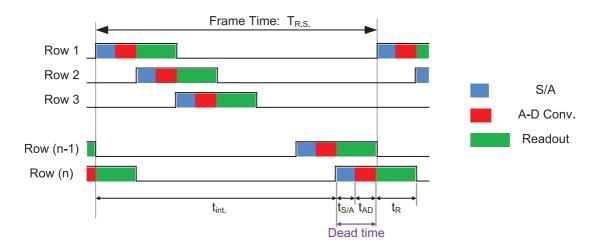

| 4.2  | Principe of the rolling shutter readout                                                  | 63  |

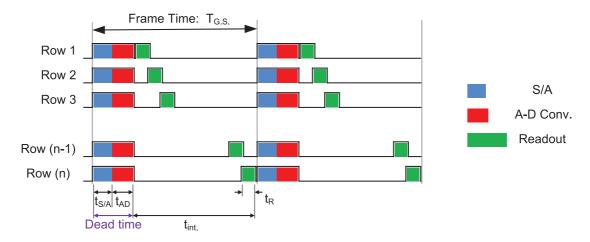

| 4.3  | Principe of the global shutter readout                                                   | 64  |

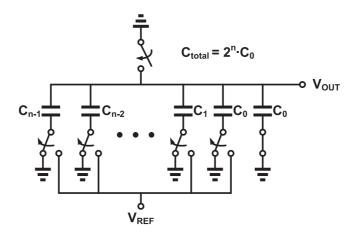

| 4.4  | A typical scheme of binary weighted charge-distribution DAC                              | 67  |

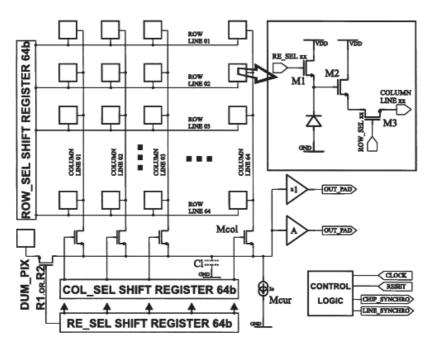

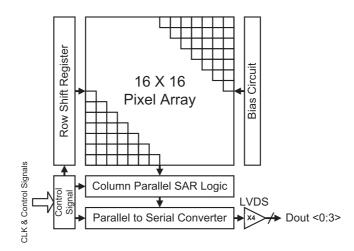

| 4.5  | Architecture of the MIMADC-SAR pixel matrix                                              | 68  |

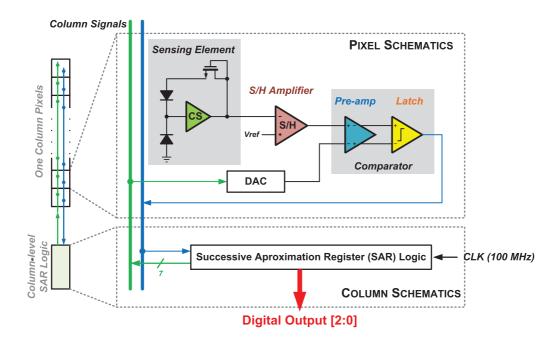

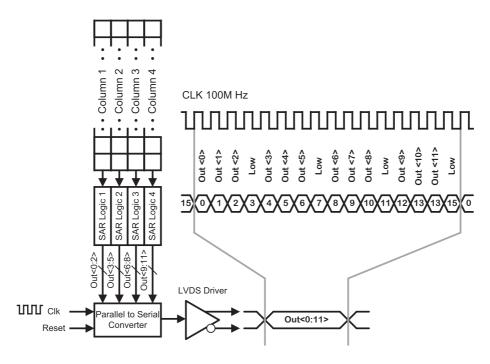

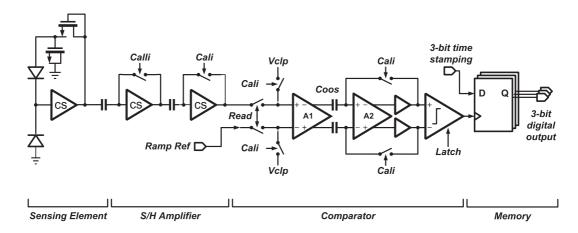

| 4.6  | Block diagram of MIMADC-SAR circuits                                                     | 69  |

| 4.7  | The output sequence from a LVDS link                                                     | 69  |

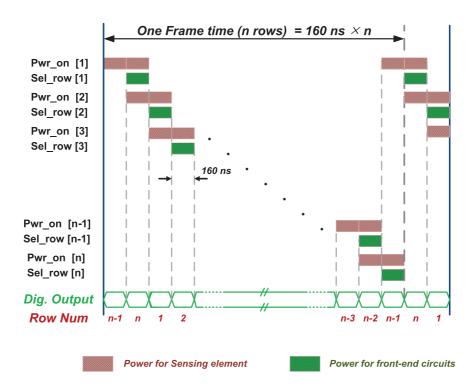

| 4.8  | The timing of the rolling shutter mode in MIMADC-SAR                                     | 70  |

| 4.9  | Schematic of the sensing diode together with the in-pixel amplifier                      | 71  |

| 4.10 | Architecture of a typical open-loop S/H amplifier                                        | 74  |

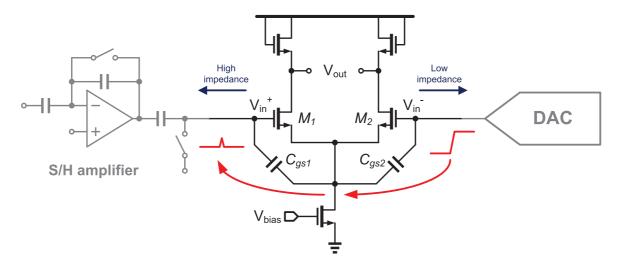

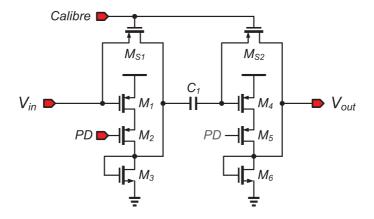

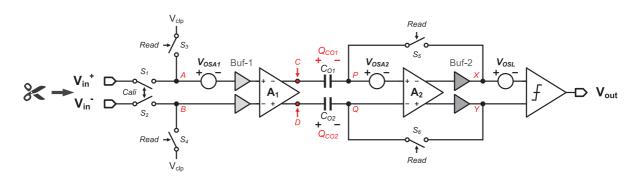

| 4.11 | Architecture diagram of the S/H amplifier used in MIMADC-SAR                             | 75  |

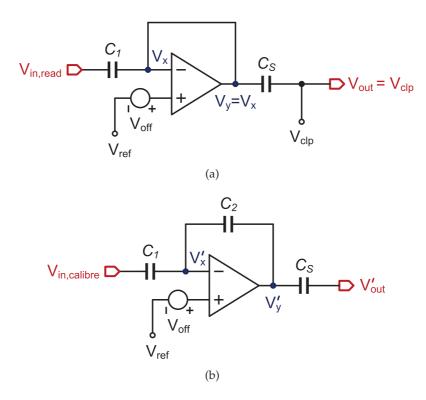

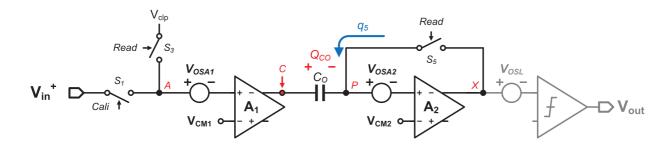

| 4.12 | Equivalent circuits of the S/H amplifier in "Read" phase and "Calibre" phase .           | 76  |

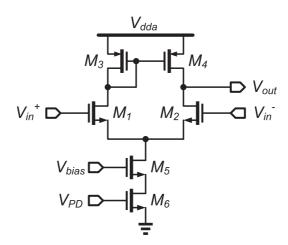

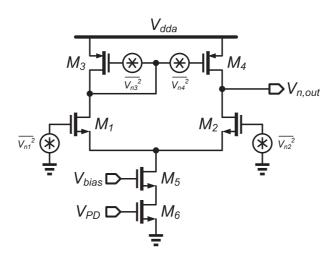

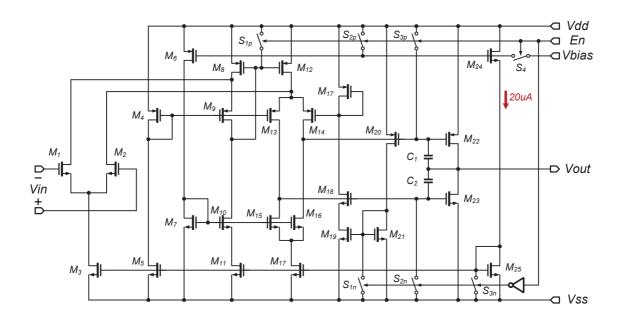

| 4.13 | Schematic of the operational amplifier in the S/H amplifier                              | 77  |

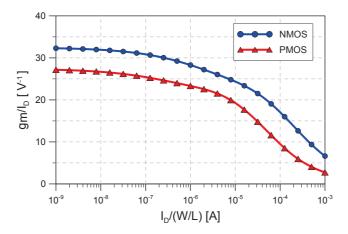

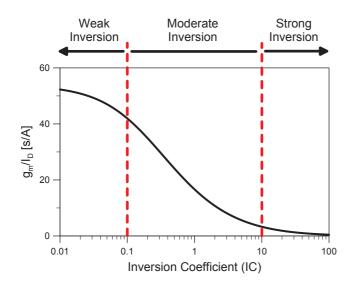

| 4.14 | Ratio $g_m/I_D$ at the different bias current for NMOS and PMOS respectively             | 78  |

| 4.15 | $g_m/I_d$ versus the inversion coefficient (IC)                                          | 79  |

| 4.16 | Noise equivalent model for the operational amplifier in the S/H amplifier. $\ \ . \ \ .$ | 80  |

| 4.17 | Simulation results of the noise of the op-amp in the S/H amplifier                       | 82  |

| 4.18 | A typical comparator architecture                                                        | 83  |

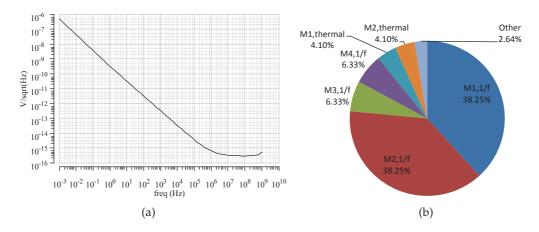

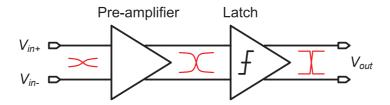

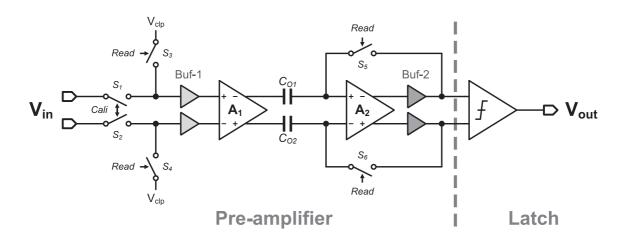

| 4.19 | Block diagram of the comparator                                                          | 84  |

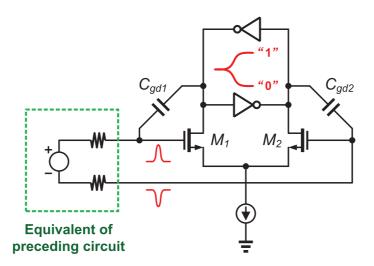

| 4.20 | Principle of the input feedthrough                                                       | 86  |

| 4.21 | Principle of the kickback noise                                                          | 87  |

| 4.22 | Schematics of the source-follower in the "Buf-1" and "Buf-2"                             | 88  |

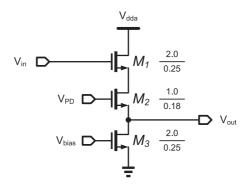

| 4.23 | Schematics of the amplifier in the pre-amplifier                                         | 89  |

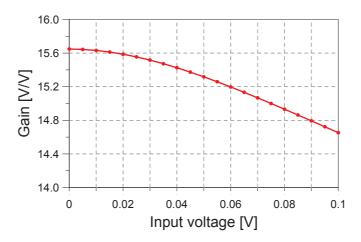

| 4.24 | Simulated gain of the pre-amplifier with a input voltage swept from 0 to 100 $\mbox{mV}$ | 90  |

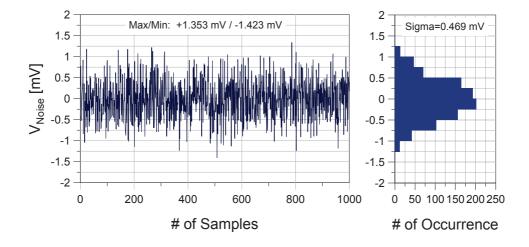

| 4.25 | Equivalent input noise of the preamplifier by 1000 times transient noise simulation      | 91  |

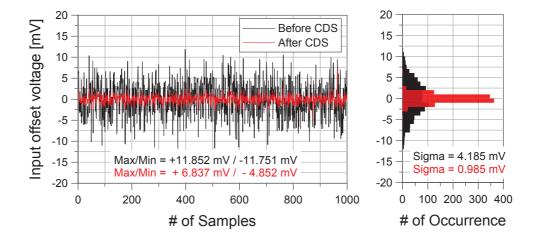

| 4.26 | Equivalent input offset of the preamplifier in case of w/o CDS by 1000 times             |     |

|      | Monte-carlo simulation                                                                   | 91  |

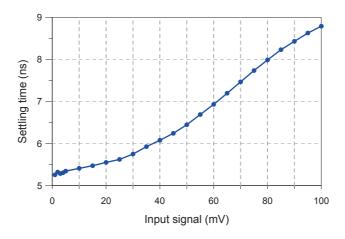

| 4.27 | Settling time of the pre-amplifier versus input signal                                   | 92  |

| 4.28 | Schematic of the latch                                                                   | 93  |

| 4.29 | Simulation result of the normalized response of the latch                                | 95  |

| 4.30 | Schematics of the multiplexer DAC                                                        | 96  |

| 4.31 | Layout of the column-ended SAR logic                                                     | 97  |

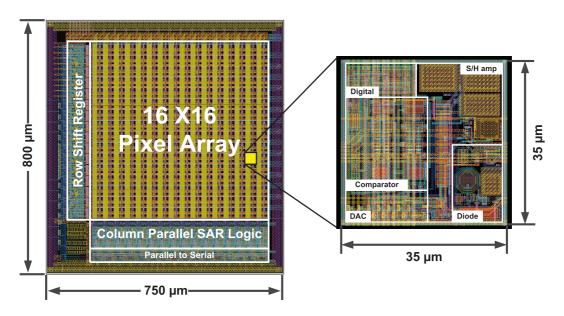

| 4.32 | Layout of the MIMADC-SAR pixel matrix combining with a zoomed view of                    |     |

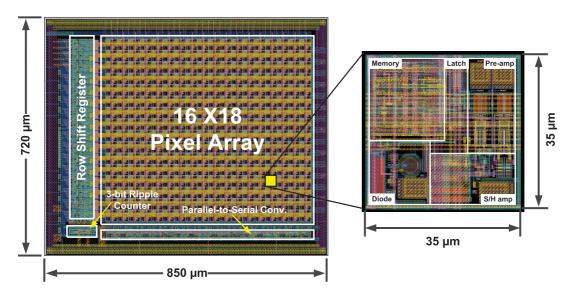

|      | the pixel                                                                                | 98  |

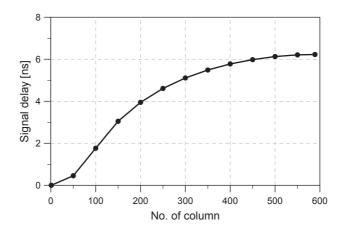

| 4.33 | Delay of a signal wire within a full scale sensor of 590 column                          | 99  |

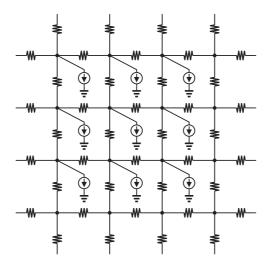

| 4.34 | DC equivalent model of the power grid for the static analysis                            | 100 |

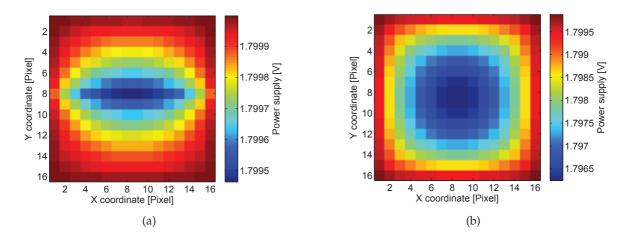

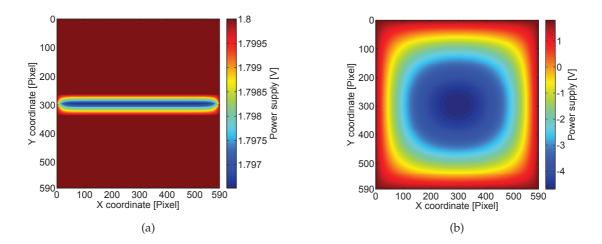

| 4 35 | Simulation result of the IR drop in a 16×16 pixel matrix                                 | 101 |

LIST OF FIGURES vii

| 4.36 | Simulation result of the IR drop in a fully-scaled 590×590 pixel matrix            | 102 |

|------|------------------------------------------------------------------------------------|-----|

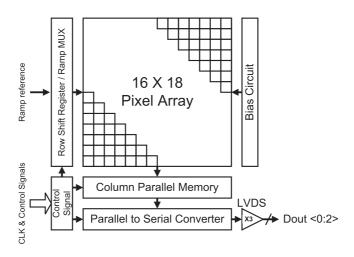

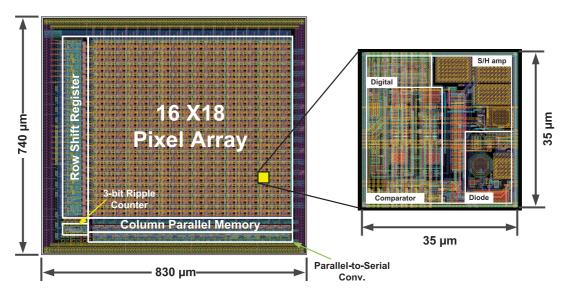

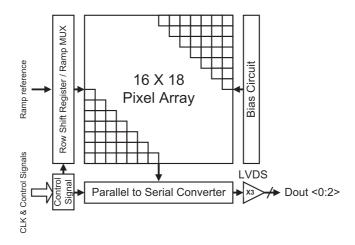

| 5.1  | Architecture of MIMADC-SS1 pixel matrix                                            | 106 |

| 5.2  | Block diagram of MIMADC-SS1 circuits                                               | 107 |

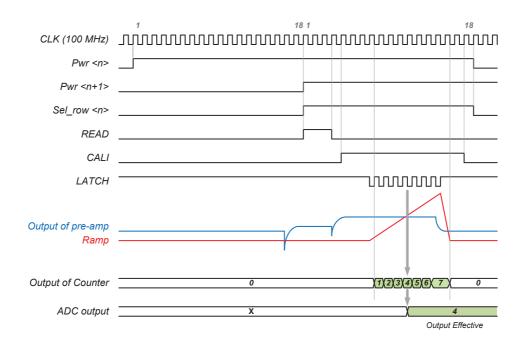

| 5.3  | Timing of the pixel in MIMADC-SS1                                                  | 107 |

| 5.4  | Principle of a typical ramp generator                                              | 108 |

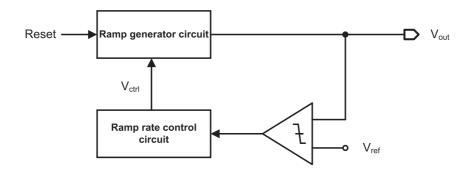

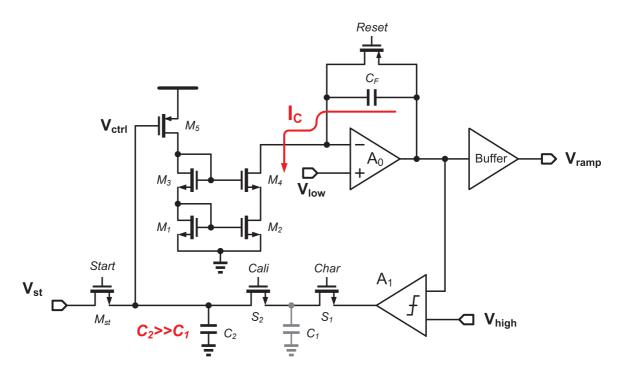

| 5.5  | Block diagram of the adaptive ramp generator                                       | 109 |

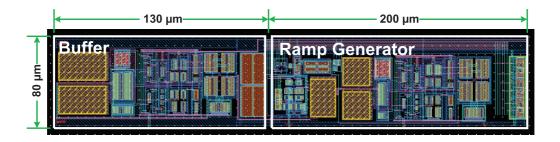

| 5.6  | Schematic of the adaptive ramp generator                                           |     |

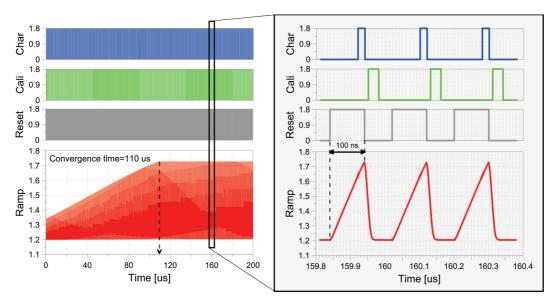

| 5.7  | Transient simulation results of adaptive ramp generator                            |     |

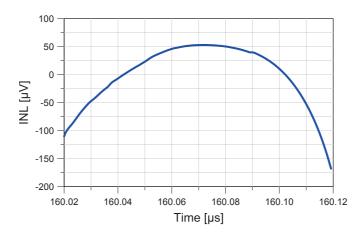

| 5.8  | Transient simulation results of INL for the adaptive ramp generator                |     |

| 5.9  | Schematic of the op-amp with rail-to-rail AB-class output                          |     |

| 5.10 | Layout of the MIMADC-SS1 pixel matrix combining with a zoomed view of the          |     |

|      | pixel                                                                              | 115 |

| 5.11 | Layout of the ramp generator and buffer                                            | 116 |

|      | Architecture of MIMADC-SS2 pixel matrix                                            |     |

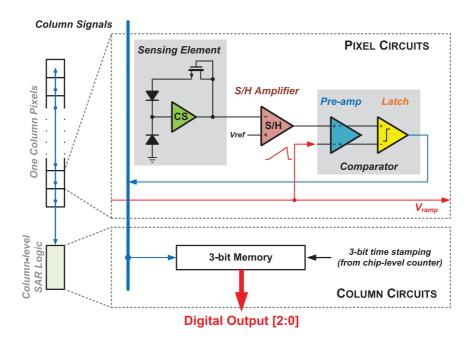

|      | Schematic of the pixel in MIMADC-SS2                                               |     |

|      | Schematic of the open-loop S/H amplifier                                           |     |

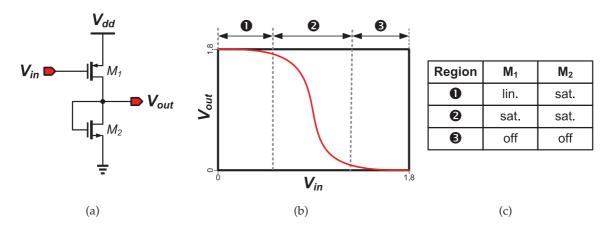

|      | Input/output transfer characteristic of a CS amplifier                             |     |

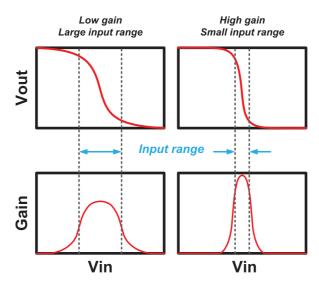

| 5.16 | The relation of input range and gain in an open-loop amplifier                     | 121 |

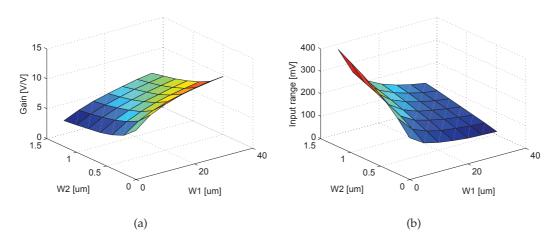

| 5.17 | (a) Gain, and (b) input range of a CS amplifier with various transistor aspect     |     |

|      | ratios                                                                             | 121 |

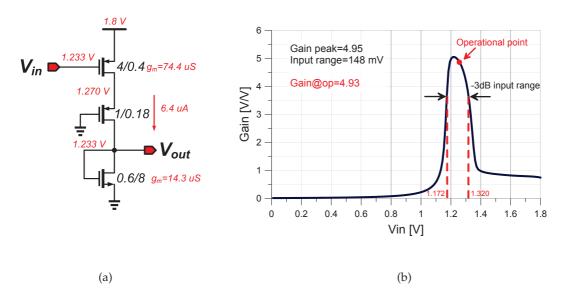

| 5.18 | (a) Schematic of the CS amplifier with the transistor aspect ratio and operational |     |

|      | point, and (b) the simulated transfer curve                                        | 122 |

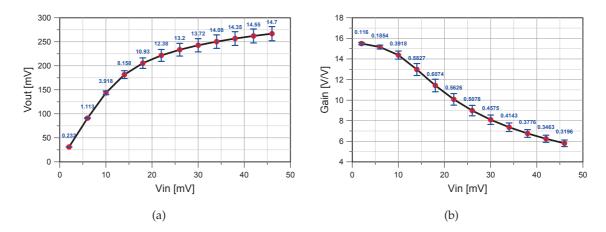

| 5.19 | Simulation results of transfer function and gain in terms of the S/H amplifier .   | 123 |

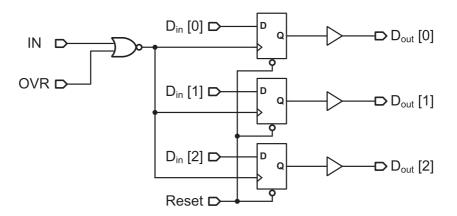

| 5.20 | Schematic of the in-pixel memory used in MIMADC-SS2                                | 124 |

| 5.21 | Layout of the MIMADC-SS2 pixel matrix combining with a zoomed view of the          |     |

|      | pixel                                                                              | 124 |

|      |                                                                                    |     |

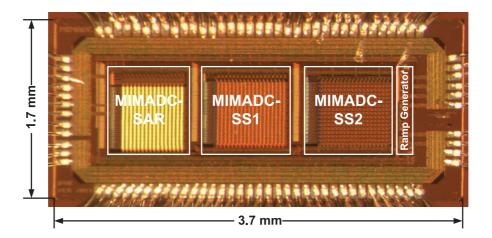

|      | Microphotograph of the MIMADC chip                                                 |     |

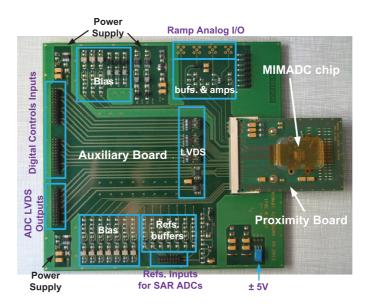

| 6.2  | Photo of the test boards                                                           |     |

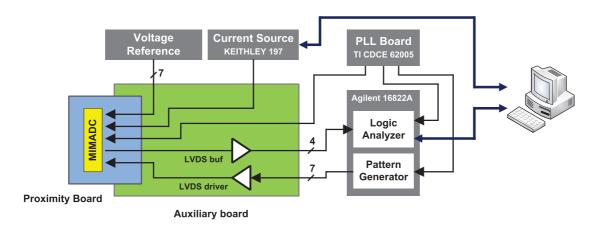

| 6.3  | Diagram of the acquisition system                                                  |     |

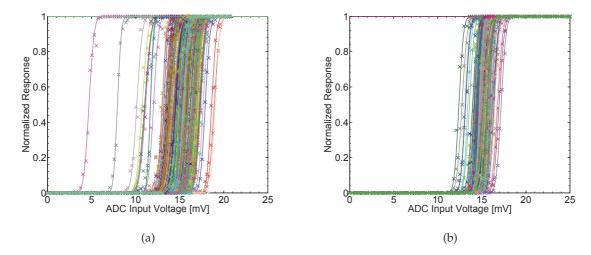

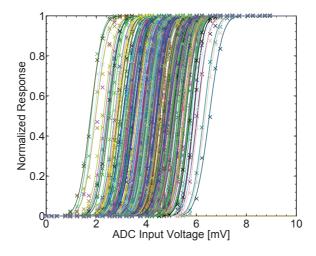

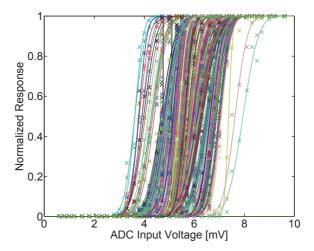

| 6.4  | Normalized response of the 256 pixel-level SAR ADCs                                |     |

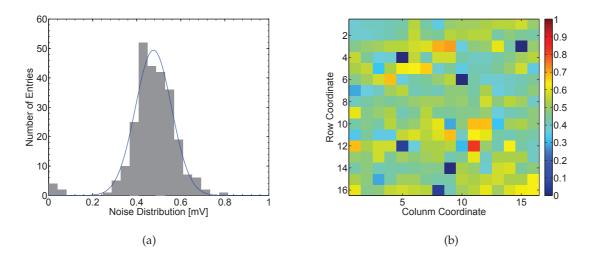

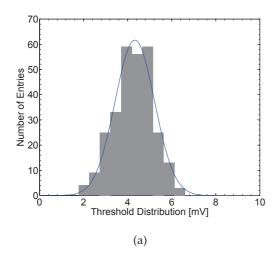

| 6.5  | Temporal noise distribution of the 256 pixel-level SAR ADCs                        |     |

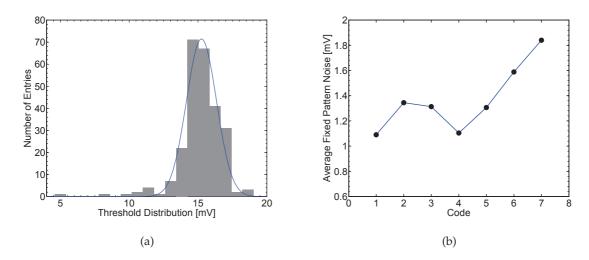

| 6.6  | Distribution of the fixed pattern noise (FPN) of 256 pixel-level SS ADCs           |     |

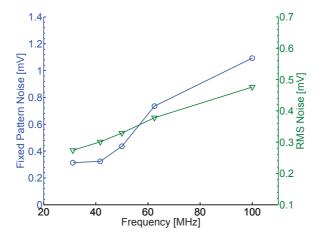

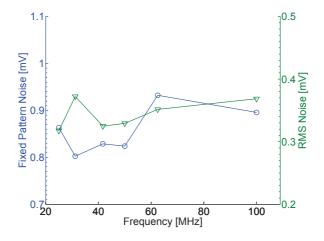

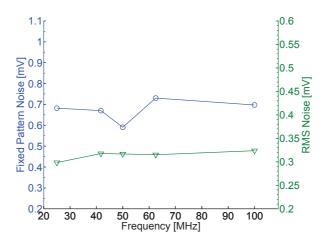

| 6.7  | Average FPN and rms TN of the SAR ADCs measured at various frequencies             |     |

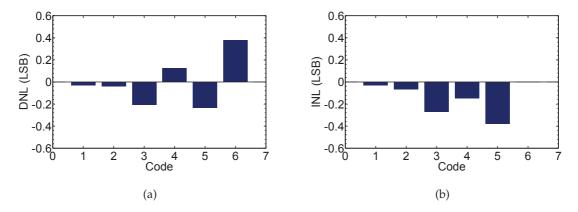

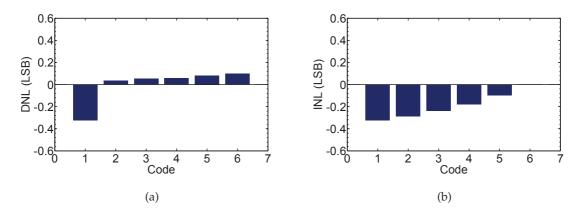

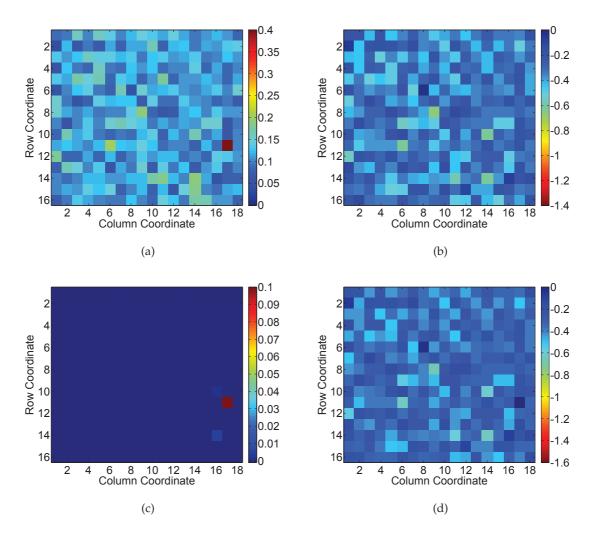

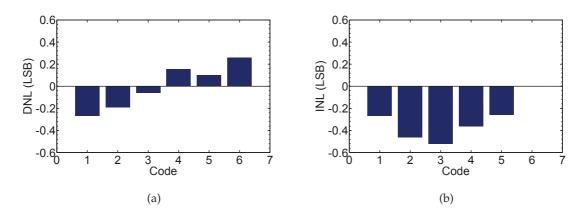

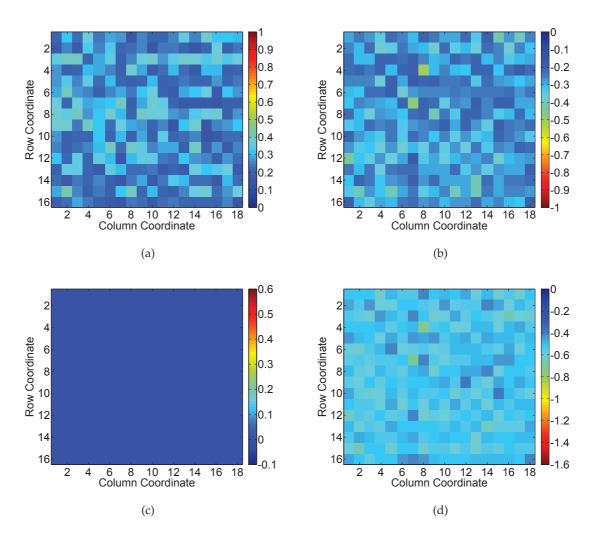

| 6.8  | Measured DNL and INL over the 256 SAR ADCs                                         | 133 |

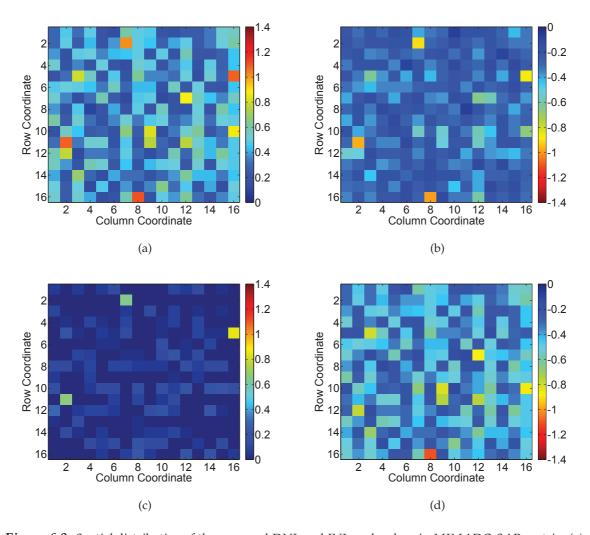

| 6.9  | Spatial distribution of the measured DNL and INL peak values in the MIMADC-        | 104 |

| (10  | SAR matrix.                                                                        |     |

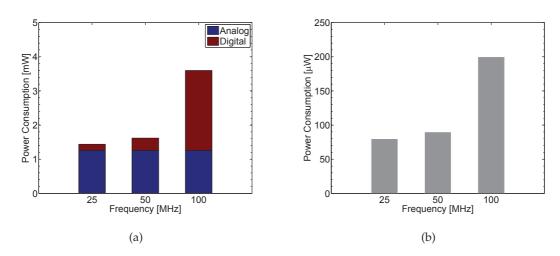

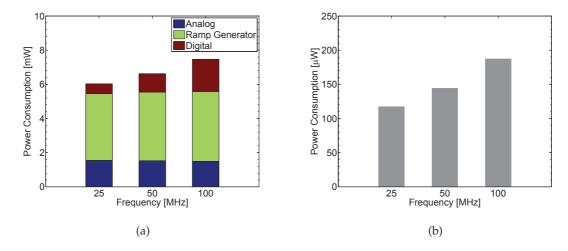

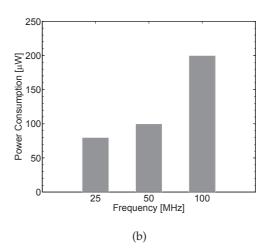

|      | Power consumption of the MIMADC-SAR matrix                                         |     |

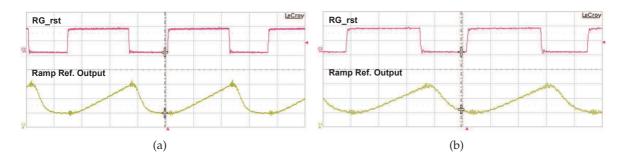

|      | Measured ramp reference at the clock frequency of 50 MHz and 100 MHz               |     |

| 0.12 | Responses of the 288 SS ADCs in the MIMADC-SS1 matrix                              | 136 |

viii List of Figures

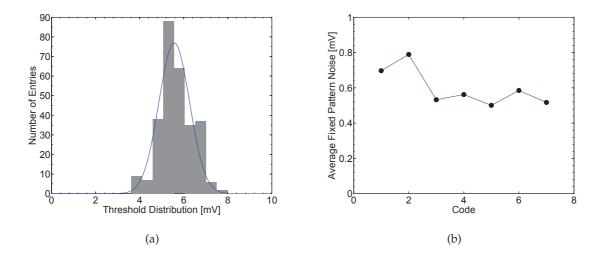

| 6.13 | Distribution of the fixed pattern noise of 288 SS ADCs in the MIMADC-SS1         |     |

|------|----------------------------------------------------------------------------------|-----|

|      | matrix                                                                           | 137 |

| 6.14 | Distribution of the temporal noise of the 288 SS ADCs in the MIMADC-SS1          |     |

|      | matrix                                                                           | 138 |

| 6.15 | Average FPN and rms TN of the SS ADCs in the MIMADC-SS1 matrix mea-              |     |

|      | sured at various frequencies                                                     | 138 |

| 6.16 | Average DNL and INL over the 288 SS ADCs in the MIMADC-SS1 matrix                | 139 |

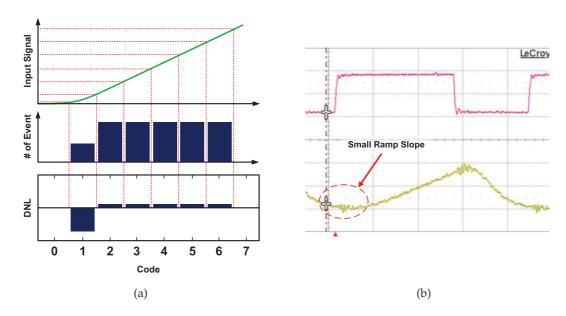

|      | Influence of the nonlinearity of ramp signal on DNL of ADCs                      |     |

| 6.18 | Spatial distribution of the measured DNL and INL peak values in the MIMADC-      |     |

|      | SS1 matrix                                                                       | 141 |

| 6.19 | Power consumption of the MIMADC-SS1 matrix                                       | 142 |

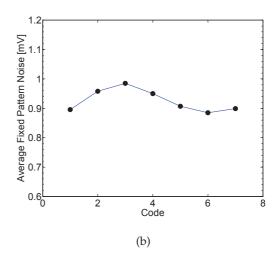

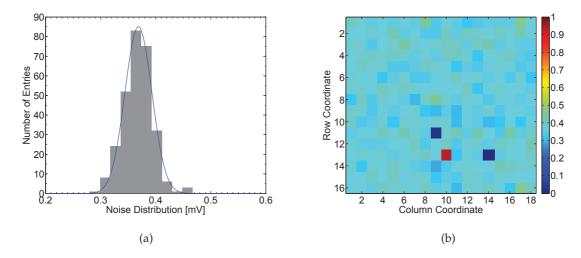

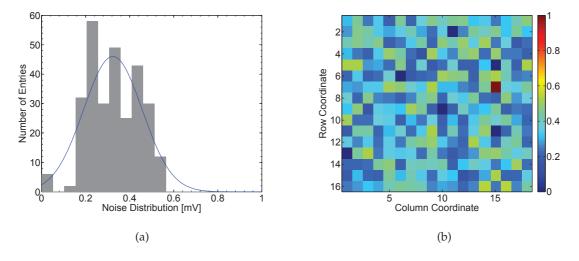

| 6.20 | Response of the 288 pixel-level SS ADCs in the MIMADC-SS2 matrix                 | 142 |

| 6.21 | Distribution of the fixed pattern noise of the 288 pixel-level SS ADCs in the    |     |

|      | MIMADC-SS2                                                                       | 143 |

| 6.22 | Distribution of the temporal noise of the 256 pixel-level SS ADCs in the MIMADC- |     |

|      | SS2 matrix                                                                       | 143 |

| 6.23 | Average FPN and rms TN of the SS ADCs in the MIMADC-SS2 matrix mea-              |     |

|      | sured at various frequencies                                                     | 144 |

| 6.24 | Average DNL and INL over the 288 SS ADCs in the MIMADC-SS2 matrix                | 144 |

| 6.25 | Spatial distributions of the measured DNL and INL peak values in the MIMADC-     |     |

|      | SS2 matrix                                                                       | 145 |

| 6.26 | Power consumption of the MIMADC-SS2 matrix                                       | 146 |

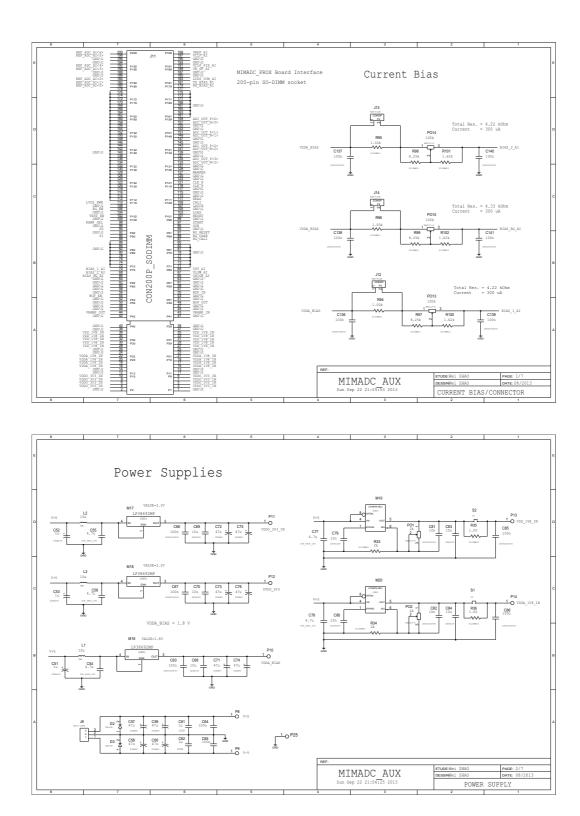

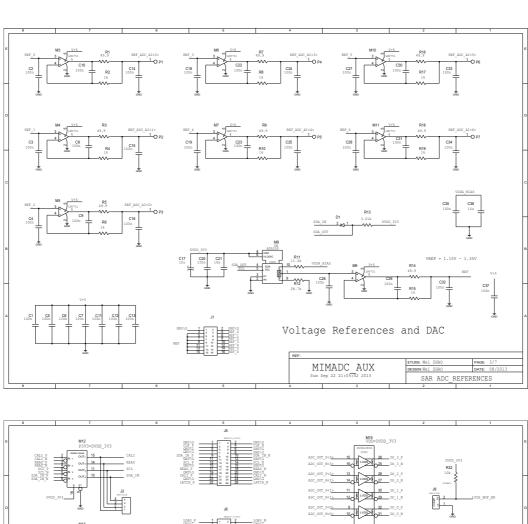

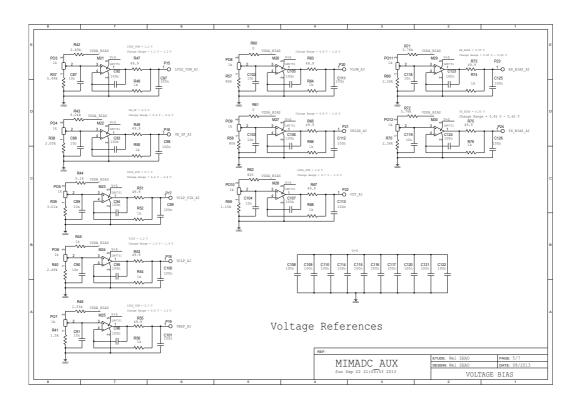

| A.1  | First and second page of the schematic of the MIMADC auxiliary test board        | 156 |

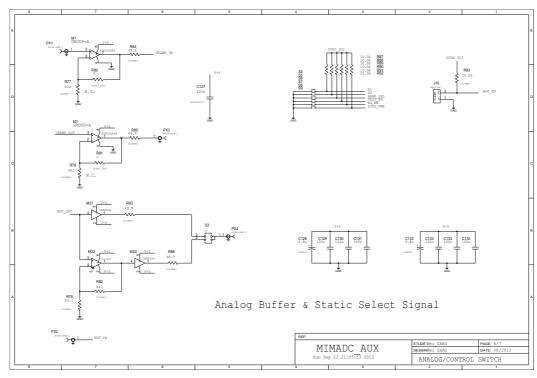

| A.2  | Third and fourth page of the schematic of the MIMADC auxiliary test board        | 157 |

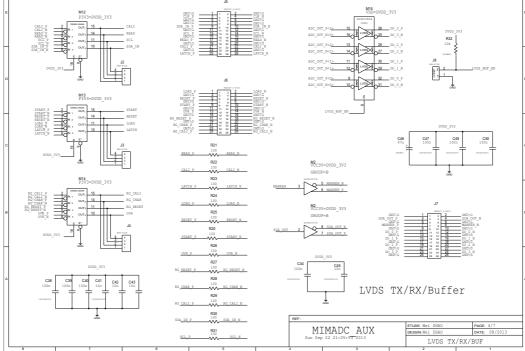

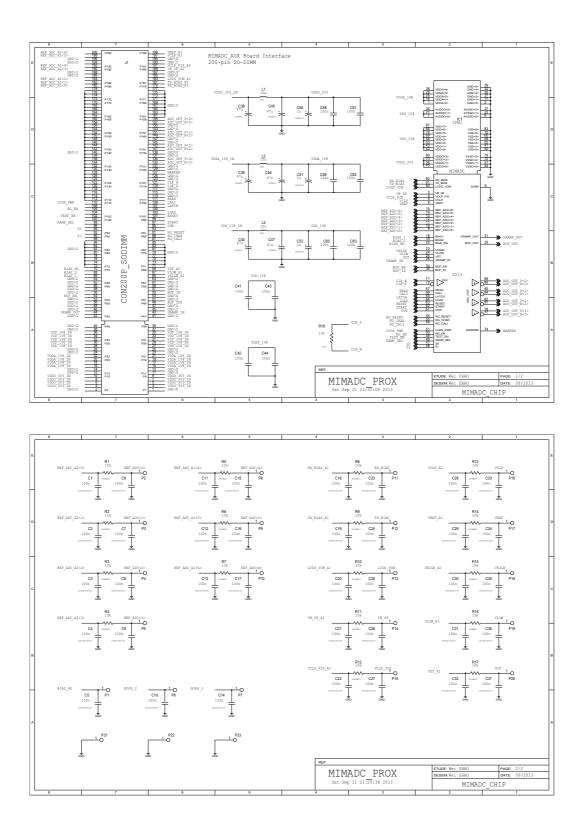

| A.3  | Fifth and sixth page of the schematic of the MIMADC auxiliary test board         | 158 |

| A.4  | First and second page of the schematic of the MIMADC proximity test board        | 159 |

| B.1  | Architecture of the pre-amplifier including the input offset sources             | 161 |

| B.2  | Half circuit of Fig. B.1                                                         | 162 |

## **List of Tables**

| R.1               | Résumé des performances du microcircuit MIMADC                                                              | хi             |

|-------------------|-------------------------------------------------------------------------------------------------------------|----------------|

| 1.1<br>1.2<br>1.3 | Major physics processes to be studied by the ILC                                                            | 3<br>4<br>8    |

| 2.1               | Measured and calculated single point resolution as a function of pixel pitch,                               | 33             |

|                   | ADC resolution and resistivity of the epitaxial layer                                                       | 36             |

| 3.1               | Performance survey of the pixel-level ADCs published in the literature related to pixel sensor applications | 54             |

| 4.1               | Transistor aspect ratios and operational points of the op-amp used in the S/H                               |                |

|                   | amplifier                                                                                                   | 79             |

| 4.2               | Summary of the simulation results for the op-amp in S/H amplifier 8                                         | 30             |

| 4.3               | Summary of the simulation results of the source-follower                                                    | 38             |

| 4.4               | Summary of the simulation results of the amplifier                                                          | 39             |

| 4.5               | Comparison of the typical latch architectures                                                               | 93             |

| 5.1<br>5.2        | Summary of the simulation results of the adaptive ramp generator                                            | 12             |

|                   | gain. (10 pF capacitance load)                                                                              | 14             |

| 6.1               | Performance summary of the MIMADC prototype                                                                 | <del>1</del> 7 |

| 6.2               | Comparison of the column-level ADCs and with the pixel-level ADCs in this                                   |                |

|                   | work                                                                                                        | 18             |

LIST OF TABLES

## **Acknowledgements**

I would like to express my thanks to all the people who have accompanied me through the years over which the work described in this thesis has been performed.

First of all, I would like to express my gratitude to my supervisor Prof. Yann Hu for giving me the opportunity to conduct such exciting research. I would also like to thank Dr. Christine Hu-Guo, the leader of microelectronics group, who was always willing to support me with interesting discussions and valuable suggestion, broadening my view and keeping me up to date about the sensor design. I would like to thank Dr. Marc Winter, the leader of the CMOS-ILC research group for his guidance during my thesis.

I would like to thank the members of my jury, Prof. Wilfried Uhring from the CNRS-ICUBE for his leadership during the defense, Dr. Hans Krüger from the University of Bonn, Germany, Prof. Michel Paindavoine from the University of Bourgogne, and prof. Christophe de La Taille from the CNRS-Omega, for reviewing my thesis and for their comments and suggestions.

I owe my gratitude to Kimmo Jaaskelainen for his help during the sensor measurement. I am also grateful to Thê-Duc Le for his suggestions in the test board design. I extend my gratitude to Yunan Fu for his comments in the circuit design.

I am sincerely grateful to all the other colleagues in PICSEL group: Abdelkader Himmi, Andrei Dorokhov, Auguste Besson, Christian Illinger, Claude Colledani, Frederic Morel, Gilles Claus, Gregory Bertolone, Guy Doziere, Hung Pham, Isabelle Valin, Jerome Baudot, Liang Zhang, Maciej Kachel, Mathieu Goffe, Mathieu Specht, Michal Szelezniak, Qingyuan Liu, Sylviane Molinet, Tianyang Wang, Wojciech Dulinski, Xiaochao Fang, Yang Zhou, and Zhan Shi for their kind help, suggestions, and technical support during this thesis.

I would also like to thank China Scholarship Council (CSC) for their financial support.

Last but not least, I am grateful for my parents for their love and support throughout my life.

xii Acknowledgements

## Résumé en Français

#### **R.1 Introduction**

Afin d'étendre notre compréhension des mystères de l'univers, des expériences de physique subatomique ont été menées. Ces expériences nécessitent des détecteurs fiables pour mesurer le produit de la collision. L'énergie des particules est mesurée avec des calorimètres, et les impulsions sont fournies par le trajectomètre. Parce les quarks lourds ont une durée de vie courte de l'ordre de picoseconde, ils ne peuvent être reconnus que par les trajectoires provenant des vertex de la désintégration secondaire. Cette tâche est accomplie avec le détecteur de vertex (VTX) avec une grande précision pour être placé très près du point d'interaction. Cette thèse vise à contribuer au développement d'un type prometteur de capteur de pixels de silicium — CMOS Pixel Sensor (CPS) — utilisé pour équiper le détecteur de vertex pour le Collisionneur Linéaire International (International Linear Collider, ILC).

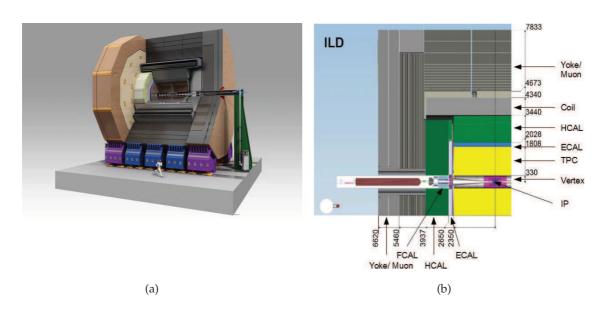

L'ILC est la prochaine grande installation expérimentale en physique des hautes énergies, en complément pour le LHC (Large Hadron Collider au CERN). Les caractéristiques proéminentes de l'ILC y compris l'énergie du faisceau bien défini, des faisceaux polarisés, un background de fonctionnement propre, permettre une mesure précise pour vérifier et étendre les découvertes réalisée au LHC. Par exemple, deux deux expériences — ATLAS et CMS appartenant au LHC ont confirmé l'existence du boson de Higgs à ∼125 GeV/c². L'ILC peut mesurer ses propriétés avec précision, y compris la masse, le spin, les canaux de désintégration pour vérifier l'identité davantage. Le fonctionnement de l'ILC commencera à partir d'une énergie de centre-de-masse de 500 GeV et une luminosité de 1,8×10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>, par la suite monter finalement à  $\sim$ 1 TeV [1]. La longueur totale de l'installation de l'ILC est l'ILC 31 km. Le seul point d'interaction est entouré par un parmi deux détecteurs — International Grand Detector (ILD) et Silicon Detector (SiD) fonctionnant dans un schéma push-pull à partager une même luminosité. Tous les deux détecteurs suivent l'algorithme de flux de particules (Particle Flow Algorithm, FPA) pour séparer et mesurer les particules neutres dans le calorimètre et les particules chargées dans le trajectomètre. Leur différence principale entre est que le trajectomètre dans l'ILD est hybridée par TPC et de silicium, tandis que le SiD est réalisé par tout-silicium. La figure R.1(a) montre une vue artistique complète de l'expérience ILD. Le détecteur est composé de plusieurs sous-détecteurs, qui sont illustrés sur la figure R.1(b).

xiv Résumé

Figure R.1: Architecture de l'expérience ILD. (a) Vue en perspective de l'expérience ILD, (b) vue du détecteur en coupe.

La capacité de reconstruire les vertex de la désintégration de la particule de courte durée de vie s'appuie sur le fait que le VTX dispose une mesure de haute précision des trajectoires des particules chargées dans le voisinage du point d'interaction. Afin d'atteindre une résolution spatiale de point extraordinaire, le VTX est composé d'une structure cylindrique concentrique multi-couche et chaque couche présente une forte résolution spatiale. En plus, un budget de matière comprimé est imposé pour chaque couche. La condition opérationnelle de rigueur impose aussi des exigences sur la vitesse de lecture et la tolérance au rayonnement. Malheureusement, les exigences mentionnées sont généralement en contradiction, ce qui résulte en un défi pour la R&D du VTX.

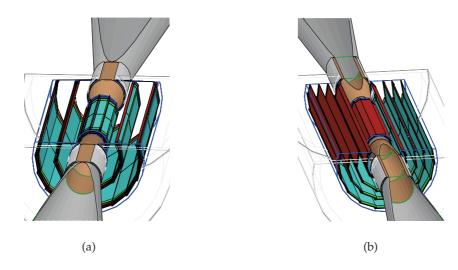

Deux géométries candidates existent pour l'ILD-VTX, comme l'illustre la figure R.2: une avec 5 couches simple-face ce qui signifie qu'un seul côté de chaque couche est équipé des capteurs, et l'autre avec 3 couches double-face où tous les deux côtés de chaque couche sont montés avec des capteurs indépendants [2]. Plusieurs techniques de capteurs sont activement développées pour satisfaire les exigences du détecteur de vertex de l'ILD. Parmi eux, les capteurs à pixels CMOS (CPS) est un candidat prometteur. Une série de prototypes CPS développée à l'IPHC (Institut Pluridisciplinaire Hubert Curien, Strasbourg, France), appelé MIMOSA, a été vérifiée en performances par les tests de faisceau. Le volume sensible constitué par la couche épitaxiale de haute résistance peut être implémenté en même temps que les circuits de traitement du signal sur le même substrat de silicium par le procédé CMOS du commerce. Une structure de grande densité en pixel assure la résolution spatiale suffisante. Le CPS permet que l'amincissement soit adéquat pour l'application de faible masse. Le sujet de cette thèse est le développement des prototypes CPS dédiés aux couches externes du détecteur de

Résumé

Figure R.2: Géométrie d'un détecteur de vertex: (a) 3 couches doubles (VTX-DL); (b) 5 couches simples (VTX-SL).

vertex de l'ILD.

La R&D des capteurs pour le VTX dans l'ILD est motivée par les contraintes de fonctionnement. Il exist une différence significative dans les contraintes de fonctionnement entre la couche la plus interne et les couches extérieures, en raison de la variation du gradient de la densité des impacts en rapport avec le rayon de la couche. Dans la couche la plus intérieure, l'accent dans la conception est mis sur la vitesse de lecture et la granularité. Le CPS peut bénéficier de la géométrie des couches à double face puisque une face est montée par le capteur de segmentation élevée pour la haute résolution spatiale, et l'autre côté est muni des capteurs composés de pixels allongés pour la vitesse de lecture élevée [3]. La priorité des capteurs montés sur les couches externes est une faible consommation d'énergie en raison du rapport élevé de couverture de la surface sensible (~90 %) dans le VTX. Entre temps, la faible densité des impacts s'accommode de pixels des plus grandes dimensions, ainsi que dans la vitesse de lecture. Un pixel relativement grand de  $35 \times 35 \,\mu\text{m}^2$  est adopté de manière à réduire le nombre de colonnes, et en outre la consommation d'énergie. La perte en résolution spatiale est compensée par l'encodage du signal sur 3-4 bits de CAN (Convertisseurs Analogiques Numériques) pour parvenir à une résolution spatiale estimée à ~3-4 μm. Les prototypes précédents ont permis de vérifier que le bruit du pixel est d'environ 1 mV. Afin diminuer la résolution sur la position de reconstruction de la particule, le bit le moins significatif (least significant bit, LSB) est fixé au niveau du bruit du pixel. Le premier capteur prototype qui cible les couches externes de l'ILD-VTX, appelé MIMOSA-31, avait été conçu avant cette thèse. Il est composé de 48×64 pixels avec un pas de 35 μm, et du CAN 4-bits de colonnes parallèles qui numérise les sorties de chaque colonne.

CAN dans le CPS fournissent une relation de correspondance un-à-un entre la quantité de la charge recueillie et les codes numériques nécessaires pour positionner les particules in-

xvi Résumé

cidentes. Dans les capteurs à pixel, les CAN peuvent être implémentés à des niveaux divers, entre autre au niveau de la puce, de la colonne et du pixel. En comparaison des CAN au niveau de la puce, ceux au niveau de la colonne présentent l'avantage d'un temps de relaxation élevé à la fréquence de conversion, présentant ainsi une réduction de la consommation d'énergie. Cependant, le rapport signal sur bruit (Signal-to-Noise Ratio, SNR) est considérablement dégradé parce que les signaux analogiques faibles qui sortent des pixels doivent traverser le long bus de colonne, et cela devient encore pire pour un capteur de grande échelle. En outre, les tampons analogiques, avec la capacité de conduite forte pour entraîner les grandes capacités parasites réparties sur les fils de colonnes, résultent une consommation d'énergie significative.

La cause des problèmes mentionnés ci-dessus réside en ce que les sorties analogiques des capteurs ne sont pas seulement sensibles au bruit, mais aussi difficiles d'être traitées davantage. Le concept du capteur numérique de pixel (Digital Pixel Sensor, DPS) est proposé qui comporte la sortie tout-numérique directement à partir du pixel. La sortie numérisée a le mérite de l'immunité au bruit et est facile d'être dirigée, ce qui fournit une performance supérieure sur le SNR et la consommation d'énergie. Dans le DPS, les circuits complexes de traitement du signal sont intégrés dans les pixels afin d'obtenir des fonctions plus intelligentes. La numérisation de pixel permet également l'opération parallèle de pixel pour atteindre une vitesse de lecture élevée. En plus, des circuits en plus petit nombre de colonnes conduisent à moins de zones mortes existant dans le capteur. Le CAN au niveau du pixel est la clé essentielle dans la construction du DPS. Le principal défi dans la conception est comment intégrer un CAN complète au sein d'un pixel de zone limitée. Le circuit de pixel complexe aussi demande un agencement sophistiqué pour réduire la diaphonie entre les blocs voisins. Ceux défis seront étudiés dans ce travail.

#### **R.2 Travail Doctoral**

Les capteurs équipant les couches externes du VTX ont la priorité sur le SNR et la consommation d'énergie, ce qui offre une opportunité de remplacer les CAN de colonnes parallèles par ceux au niveau du pixel. Entre temps, la grande taille du pixel est également en faveur de la disposition complexe. Dans cette thèse, un prototype de capteur, appelé MIMADC, est mis implémenté par un processus de 0,18  $\mu$ m CIS, visant à l'application de la couche extérieure VTX dans l'ILD. L'objectif de ce capteur est de vérifier la faisabilité du CPS intégré avec les CAN au niveau des pixels à fonctionner dans un contexte de fréquence élevée. Trois matrices sont incluses dans ce prototype, mais avec deux types de CAN au niveau de pixel différents: une matrice, appelé MIMADC-SAR, avec des CAN à registre à approximations successives (SAR); les deux autres, appelé MIMADC-SS1 et -SS2, avec des CAN à une seule pente (Single-Slope, SS) CAN. Toutes les trois sont dotées de pixels de la même taille de  $35\times35~\mu\text{m}^2$  et une résolution de 3-bit, réduisant ainsi la consommation d'énergie tout en gardant la résolution spatiale nécessaire.

Résumé xvii

#### R.2.1 Conception de CAN SAR de niveau de pixels

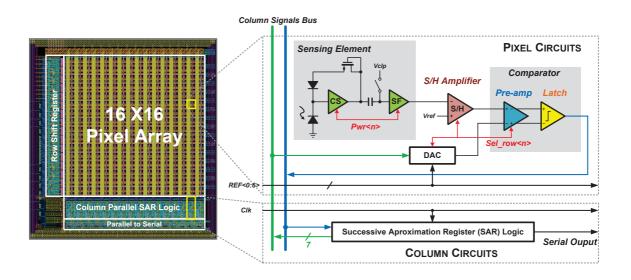

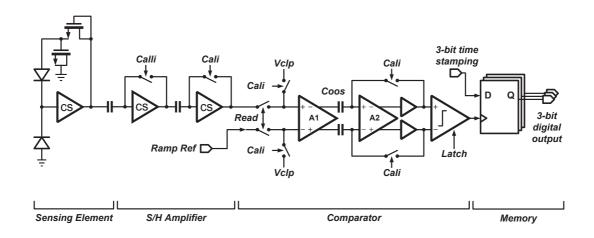

*Figure R.3:* Architecture du MIMADC-SAR.

La figure R.3 présente le schéma fonctionnel d'un convertisseur SAR qui contient une matrice de  $16 \times 16$  pixels. La matrice de pixels est lue en mode volet roulant qui pilote via un sélecteur de ligne et un séquenceur de pixels situés sur le côté gauche. En mode volet roulant où la matrice est lue, une seule ligne est sous tension et contribue ainsi à la consommation d'énergie de la matrice. Chaque pixel inclut un élément de détection et un CAN SAR. L'élément de détection combine amplification au sein des pixels et opération d'échantillonnage double liée. Afin de maximiser le rapport signal sur bruit, un amplificateur de source commune avec un gain et une rétroaction améliorés a été utilisé.

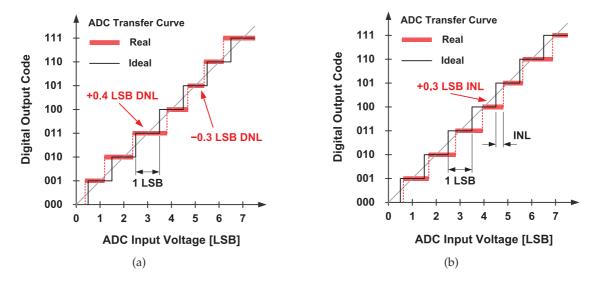

Le CAN SAR se compose d'un amplificateur d'échantillonnage-mise en attente (sampling-and-hold, S/H), d'un convertisseur numérique-analogique (CNA), d'un comparateur et d'un circuit logique SAR. Pour améliorer la précision de conversion et réduire le bruit à motif fixe (fixed pattern noise, FPN), un amplificateur à boucle fermée est utilisé. Le gain de cet amplificateur est défini par le rapport de deux condensateurs, menant ainsi à une dispersion minimisée du processus. Le comparateur comprend un préamplificateur et une bascule dynamique. Les influences du décalage du verrou, du bruit de «kickback» et de la traversée d'entrée sont nettement atténuées dans la conception. Dans un CAN SAR typique, le CNA mis en place par un ensemble de condensateurs à poids binaire occupe un vaste espace et nécessite une grande quantité de courant pour piloter. Dans cette configuration, une structure multiplexe de commutateurs est utilisée pour respecter les exigences relatives à l'intégration au sein des pixels et à une faible consommation d'énergie. Pour le processus CMOS de 0,18 µm

xviii Résumé

employé, la zone de pixels limitée ne peut pas intégrer le circuit logique SAR. Le mode volet roulant où la matrice est lue nous permet de localiser le circuit logique SAR à l'extrémité de la colonne. Chaque circuit logique SAR au niveau de la colonne est partagé par les pixels dans la colonne correspondante. Malgré la présence de circuits au niveau de la colonne, la numérisation au sein des pixels permet de garantir de bonnes performances en termes de bruit, de vitesse et de consommation d'énergie. En outre, la contribution du circuit logique à la zone insensible est négligeable.

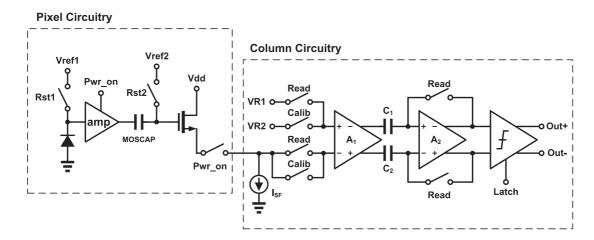

#### R.2.2 Conception de CAN SS de niveau de pixels

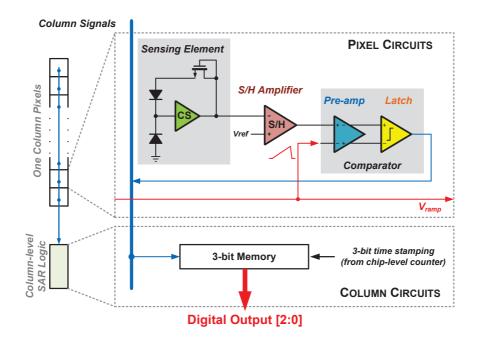

Nous proposons deux matrices de pixels avec des CAN de niveau de pixels basés sur des architectures SS. Chacune d'entre elles contient  $16 \times 18$  pixels. La principale différence entre elles est la disposition des mémoires numériques : dans la matrice MIMADC-SS1, les mémoires sont placées à l'extrémité des colonnes, de la même façon que le circuit logique SAR du modèle MIMADC-SAR; dans la matrice MIMADC-SS2, les mémoires sont intégrées dans chaque pixel. De plus, la différence réside également dans la conception de l'amplificateur S/H.

*Figure R.4:* Synoptique d'un pixel du MIMADC-SS1.

Le schéma fonctionnel de la matrice MIMADC-SS1 est illustré dans la figure R.4. Les circuits de pixels sont les mêmes que ceux de la matrice MIMADC-SAR. Les mémoires du CAN

Résumé xix

se trouvent à l'extrémité des colonnes et sont partagées par les pixels dans la colonne correspondante. Cette architecture assouplit la limitation de la zone de pixels et permet de mettre en place les mémoires par les bascules «flip-flop» fournies par la bibliothèque de cellules standard.

Figure R.5: Schéma de un pixel du MIMADC-SS2.

Dans les deux matrices précédentes (MIMADC-SAR et MIMADC-SS1), le circuit au niveau de la colonne limite l'extension d'une lecture de volet roulant à ligne unique vers une approche à plusieurs lignes. Afin d'atteindre une vitesse de lecture supérieure adaptée à l'énergie de collision de l'ILC allant jusqu'à 1 TeV, une architecture différente (MIMADC-SS2) a été conçue. Comme illustré sur la figure R.5, dans la matrice MIMADC-SS2 le pixel est intégré à une chaîne de signal complète qui couvre la détection de particules, l'amplification, la conversion analogique-numérique et le stockage de données. Cette architecture permet d'utiliser une méthode de lecture flexible pour un taux de trame élevé et/ou une consommation d'énergie basse. Pour économiser la zone de pixels pour les mémoires, un amplificateur S/H à deux étages et à boucle ouverte est employé.

Afin de générer une référence de rampe pour les CAN SS, un générateur de rampe sur puce a été conçu. Pour être différente du générateur de rampe traditionnel basé sur le chargement d'un condensateur avec un courant constant, notre conception utilise une architecture adaptative. Les principaux paramètres du signal de rampe (par ex. le temps de montée) peuvent être régulés sur la carte. La rétroaction assure une haute linéarité et une bonne tolérance aux variations de processus.

#### R.2.3 Caractérisation de la puce MIMADC

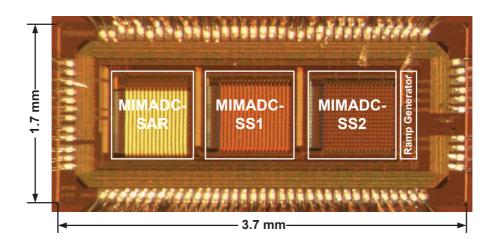

La microphotographie de la matrice MIMADC est montrée sur la figure R.6. La taille de

XX RÉSUMÉ

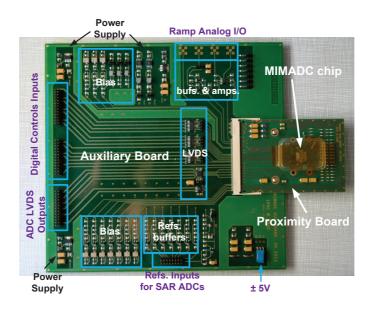

Figure R.6: Photographie du prototype MIMADC bondé sur la carte de test.

la puce est de 1,7×3,7 mm². Les résultats du CAN en série sont transmis par quatre paires de dispositifs de signalisation différentielle à basse tension (Low-Voltage Differential Signaling, LVDS), qui sont multiplexés par trois matrices. Les trois différents types de CAN peuvent être caractérisés indépendamment. Deux cartes de test ont été conçues et fabriquées. Comme illustré sur la figure R.7, la puce est microcâblée à la carte de proximité, laquelle peut être branchée dans la carte auxiliaire. Un stimulus analogique d'amplitude variable est injecté dans les entrées du CAN. Les résultats de la mesure vérifient les performances de base, notamment le bruit temporal, le bruit à motif fixe, la non-linéarité et la consommation d'énergie. Le prototype a été mesuré en utilisant une horloge externe de 100 MHz pour générer la séquence du temps de fonctionnement. Le temps de conversion correspondant des CAN SAR et des CAN SS est respectivement de 160 ns et de 180 ns. En outre, la puce a également été mesurée avec une fréquence d'horloge inférieure pour explorer l'influence de la diaphonie, qui est généralement fonction de la fréquence. Les caractéristiques mesurées des trois matrices sont résumées dans le tableau R.1.

#### **R.3 Conclusion**

Dans ce thèse, nous présentons des études faites sur les capteurs de pixels CMOS pour aux couches externes de l'ILD-VTX. Le premier prototype de capteur CMOS intégré à des CAN de niveau de pixels à 3 bits a été conçu en ayant pour objectif de réduire la consommation d'énergie sans perdre de résolution spatiale. Diverses architectures de CAN et topologies de puce ont été explorées pour vérifier la faisabilité de la mise en place de CAN dans une

Résumé xxi

Figure R.7: Photo de la carte de test du MIMADC

| Charactéristiques           | SAR                        | SS-1              | SS-2     |  |  |

|-----------------------------|----------------------------|-------------------|----------|--|--|

| Technologie                 | То                         | werjazz 0,18 µm ( | CIS      |  |  |

| Résolution                  |                            | 3 bits            |          |  |  |

| Fréquence d'échantillonnage | 6,25 MS/s                  | 5,55              | MS/s     |  |  |

| DNL                         | 0,38 LSB                   | 0,32 LSB          | 0,27 LSB |  |  |

| INL                         | 0,38 LSB                   | 0,32 LSB          | 0,46 LSB |  |  |

| TN (rms)                    | 0,48 mV                    | 0,37 mV           | 0,32 mV  |  |  |

| FPN (rms)                   | 1,10 mV                    | 0,90 mV           | 0,70 mV  |  |  |

| Taille des pixels           | $35\times35~\mu\text{m}^2$ |                   |          |  |  |

| Tension d'alimentation      | 1,8 V                      |                   |          |  |  |

| Dissipation de puissance    | 200 μW                     | 188 μW            | 200 μW   |  |  |

Table R.1: Résumé des performances du microcircuit MIMADC

xxii Résumé

zone de pixels limitée avec une consommation d'énergie très basse. Les résultats des tests ont démontré une bonne puissance ainsi que l'efficacité de la zone. Par conséquent, le CPS intégré avec les CAN au niveau des pixels est un choix potentiel pour les conceptions aux couches externes du détecteur de vertex de l'ILD.

Résumé xxiii

#### **Bibliographie**

[1] C. Adolphsen, M. Barone, B. Barish, K. Buesser, P. Burrows, J. Carwardine, J. Clark, H. M. Durand, G. Dugan, E. Elsen, A. Enomoto, B. Foster, S. Fukuda, W. Gai, M. Gastal, R. Geng, C. Ginsburg, S. Guiducci, M. Harrison, H. Hayano, K. Kershaw, K. Kubo, V. Kuchler, B. List, W. Liu, S. Michizono, C. Nantista, J. Osborne, M. Palmer, J. M. Paterson, T. Peterson, N. Phinney, P. Pierini, M. Ross, D. Rubin, A. Seryi, J. Sheppard, N. Solyak, S. Stapnes, T. Tauchi, N. Toge, N. Walker, A. Yamamoto, and K. Yokoya, "The International Linear Collider Technical Design Report – Volume 3.II: Accelerator Baseline Design," Jun. 2013.

- [2] J. E. Brau, J. Fuster, L. Hesla, M. Illenseer, P. Royole-Degieux, R. Takahashi, B. Warmbein, S. Yamada, H. Yamamoto, M. Zhang, "International Linear Collider Physics and Detectors: 2011 Status Report," Aug. 2012.

- [3] Y. Voutsinas, "Optimization of a vertex detector for the ILC and study of Higgs Boson couplings," Ph.D. dissertation, Université de Strasbourg, 2012.

xxiv Résumé

### Introduction

In order to extend our understanding of the mysteries of universe, dedicated subatomic physics experiments are built. These experiments require reliable detectors to measure the products of the collision. The energy of the particles is measured by the calorimeters, and the momenta is provided by the tracking detector. Because the heavy quarks have a short lifetime of the order of picosecond, they can only be recognized by the tracks originating from the secondary decay vertices. This task is taken by the vertex detector (VTX) with high precision to be placed very close to the interaction point. This thesis aims to contribute to the development of a promising type of silicon pixel sensor—CMOS Pixel Sensor (CPS) —used to equip the vertex detector for the International Linear Collider (ILC).

The ILC is the next large experimental facility in high-energy physics, as a complement to the LHC (Large Hadron Collider at CERN). The prominent features of the ILC including the well-defined beam energy, polarised beams, clean operational background, enable a precise measurement to verify and extend the discoveries from the LHC. For instance, two experiments—ATLAS and CMS—belonging to the LHC have confirmed the existence of the Higgs boson at  $\sim$ 125 GeV/ $c^2$ . ILC can measure its properties precisely including the mass, spin, decay channels to further verify the identity. The functioning of the ILC will start from a centre-of-mass energy of 500 GeV together with a luminosity of  $1.8\times10^{34}~\rm cm^{-2}s^{-1}$ , and then finally upgrade to  $\sim$ 1 TeV. The total length of the ILC facility is  $\sim$ 31 km. The only interaction point is surrounded by one out of two detectors—International Large Detector (ILD) and Silicon Detector (SiD)—operated in a push-pull scheme to share the same luminosity. Both two detectors follow the Particle Flow Algorithm (FPA) to separate and measure the neutral particles in the calorimeter and the charged particles in the tracker. The main difference between them are that the tracker in the ILD is hybridized by a TPC and a silicon structure, but the SiD is realized by an all-silicon approach.

The ability of reconstructing the decay vertices of the short living particle relies on that the VTX has a highly precise measurement of the tracks of the charged particles in the vicinity of the interaction point. In order to reach an extraordinary spatial point resolution, the VTX is composed of a cylindrical concentric multi-layer structure and each layer exhibits a high spatial resolution. In addition, a low material budget is mandatory for each layer. The stringent operational condition also imposes requirements on the readout speed and radiation toler-

XXVI

ance. Unfortunately, the requirements mentioned are generally in contradiction, which results in a challenge for the R&D of the VTX.

Two candidate geometries exist for the ILD-VTX: one with 5 single-sided layers meaning that only one side of each layer is equipped with the sensors, and the other one with 3 double-sided layers where both sides of each layer are mounted with independent sensors. Several sensor techniques are actively developed to adapt the requirements of ILD vertex detector. Among them, the CMOS pixel sensor (CPS) is a promising candidate. A series of CPS prototypes developed at the IPHC (Institut Pluridisciplinaire Hubert Curien, Strasbourg, France), called MIMOSA, has been verified in performances by the beam tests. The sensitive volume can be implemented together with the signal processing circuits on the same silicon substrate by the commercial CMOS process. A high density pixel structure ensures the sufficient spatial resolution. The CPS allows thinning to be suit for the low-mass application. The subject of this thesis is the development of CPS prototype dedicated to the outer layers of the ILD vertex detector.

The R&D of the sensors for the ILD-VTX is driven by the running constraints. There is a significant difference in the running constraints between the innermost layer and the outer layers, because of the gradient variation of the hit density related to the layer radius. In the innermost layer, the emphasis of design is given on the fast readout speed and high granularity. The CPS can benefit from the geometry of double-sided layers since one side is mounted by the high-segmented sensors for the high spatial resolution, and the other side is equipped with the sensors composed of the elongated pixels for the high readout speed. The priority of the sensors mounted on the outer layers is low power consumption due to the large coverage ratio of the sensitive area (~90%) in the VTX. Meanwhile, the low hit density allows for the use of larger dimension pixels and the slower readout speed. A relatively large pixel of  $35\times35 \,\mu\text{m}^2$  is adopted to reduce the number of the columns, and further the power consumption. The loss of the spatial resolution is compensated by the signal being quantized by the 3-4 bits ADCs (Analog to Digital Converters) to reach an estimated spatial resolution of  $\sim$ 3-4 µm. The first prototype sensor that targets the outer layers of ILD-VTX, called MIMOSA-31, had been designed before this thesis. It is composed of  $48\times64$  pixels with a pitch of 35 µm, and the 4-bit column-parallel ADCs digitalizing the outputs from each column.

ADCs in the CPS provide an one-to-one corresponding relation between the collected charge quantity and the digital codes needed for positioning the incident particles. In the pixel sensors, the ADCs can be implemented at various levels including the chip-, column-and pixel-level. In comparison to the chip-level ADCs, the column-level ones present the advantage of a great relaxation in the conversion speed. However, the signal-to-noise ratio (SNR) is dramatically degraded because the weak analog outputs from the pixels have to drive the long column-bus, and this becomes even worse for a large scale sensor. Moreover, the analog buffers with the strong driving ability for driving the large parasitic capacitances distributed on the column wires result in a significant power consumption.

Introduction xxvii

The reason of the aforementioned problems lies in that the analog outputs of sensors are not only sensitive to noise, but also difficult to be further processed. The concept of digital pixel sensor (DPS) that features all-digital output directly from pixels was proposed. The digitalized outputs are immune to noise and easy to be driven, which provide superior performances on SNR and power consumption. In DPS, complex signal processing circuits are integrated within pixels to realize more smart functions. The in-pixel digitalization also allows the parallel pixel operation to reach a high readout speed. In addition, less column circuits lead to less insensitive area existing in the sensor. The pixel-level ADC is the key block in building the DPS. The main challenge in design is to integrate a complete ADC within an area-limited pixel. The complex pixel circuit also asks for a sophisticated layout to reduce the crosstalk among the neighboring blocks. Those challenges will be studied in this work.

The sensors for the outer layers of VTX have the priorities on SNR and power consumption, which will benefit from the approach of integrating CPS with pixel-level ADC. Meanwhile, the large pixel size is also in favour of the complex layout. In this thesis, a prototype sensor, called MIMADC, has been implemented by a 0.18  $\mu m$  CIS process, aiming to the application of the outer layer VTX in the ILD. The target of this sensor is to verify the feasibility of the CPS integrated with pixel-level ADCs. Three matrices are included in this prototype but with two different types of pixel-level ADCs: one with successive approximation register (SAR) ADCs, and the other two with single-slope (SS) ADCs. All of them feature a same pixel size of  $35\times35~\mu m^2$ , a resolution of 3-bit, and a power consumption of  $\sim\!200~\mu W/pixel$ . The matrix with the SAR ADCs has the scale of  $16\times16$ , and is read out in the rolling shutter method with the conversion time of 160 ns. The matrices integrated with SS ADCs include  $16\times18$  pixels, but with a little longer conversion time of 180 ns.

In this thesis, we study the feasibility of employing pixel-level ADCs within CPS to meet the requirements of the outer layer VTX in the ILD. A prototype sensor has been implemented to verify the concept of using SAR ADCs and SS ADCs for the in-pixel integration.

This thesis is organized as follows:

- In chapter 1, the physics motivation of the ILC is introduced. Then the ILC project and required detectors are briefly presented. As an important subdetector, ILD, its structure and specification are reviewed in order to better understand the requirements of the ILD vertex detector.

- In chapter 2, the detector techniques dedicated to the ILD-VTX are discussed. In the beginning, the basic physics of charge generation and collection are explained. The issue about the silicon damage due to the particle irradiation is discussed. In the second part, several detector techniques are presented as the candidates to the VTX. The discussion focuses on the knowledge of the CPS including the principle, basic architecture and development status. Then, a detailed discussion on a typical CPS—MIMOSA-26 is presented. Lastly, we address the conceptual considerations for the ILD-VTX based on the CPS.

xxviii Introduction

• In chapter 3, we study the ADCs used in the CPS at the system-level. The basic performances and the typical structures of ADCs are briefly introduced. The pros and cons of chip-, column- and pixel-level ADCs are analyzed. The results show that pixel-level ADCs features some merits that are attractive for the sensors used in the outer layers of VTX. The selection of the process and the ADC type are also studied. Finally, a report on the state-of-the-art of the pixel-level ADCs in pixel sensors is provided.

- In chapter 4 and 5, the design of the prototype sensor MIMADC is discussed in detail. Chapter 4 focuses on the studies about the implementation of the pixel-level SAR ADCs within a small size pixel. The discussion starts from the sensor architecture, circuit design, to the layout implementation, and focuses especially on the compactness of the circuit and the noise analysis. Chapter 5 addresses the design with the SS ADCs. Besides the pixel design, some peripheral circuits including the adaptive ramp generator and bandgap are also covered.

- In chapter 6, the detailed experiments for the MIMADC prototype are presented. A comparison of the pixel-level ADCs characteristics with the previous column-level ADCs is provided.

- In the conclusion, the results obtained in this thesis will be summarized and the main conclusions will be presented. At the end, the perspectives for the CPS integrated with pixel-level ADCs are addressed.

# 1

#### The ILC and ILD

The goal of high-energy physics is to understand the fundamental constituents of matter and the forces between them. The laws governing the particles and their interactions were summed up in a quantum gauge field theory, called the Standard Model. This model describes matter made of six types of quarks and six types of leptons, interacting with each other through strong, weak and electromagnetic interactions. Quarks are grouped in pairs, up (u) and down (*d*), charm (*c*) and strange (*s*), and top (*t*) and bottom (*b*). Leptons are also grouped in pairs, electron and electron neutrino, muon and muon neutrino, and tau and tau neutrino. The forces carriers, including photon, Z boson, W boson and gluon, make up the third section of the Standard Model. They transmit three of the four fundamental forces through which matter interacts. The Standard Model has been verified by numerous high-precision experiments over a wide range of energies. Nevertheless, it is not yet a complete theory, for example it does not describe "dark matter" that makes up 80% of the mass in the universe, and it does not include gravitation. In the Standard Model, the quarks, leptons, and bosons acquire their mass from the spontaneous symmetry breaking of the electroweak symmetry through a hypothetical field, called the Higgs field. The problem of the Higgs field is likely to be connected to the questions about the matter content of the universe. A way to prove the existence of the Higgs field and to study its interactions is to find and study the quantum of this field, called the Higgs boson. In 2012, the LHC (Large Hadron Collider) at CERN announced the discovery of the "Higgs-like particle" near 125 GeV. After the discovery of the Higgs boson, it becomes natural to study its properties with great precision. The International Linear Collider (ILC) was designed to study in detail the Higgs boson and search for new discoveries beyond the Standard Model.

The ILC is a proposed electron-positron linear collider, which will produce collisions at a centre-of-mass energy ranging up to 1 TeV and cover a wide range of physics programs. To facilitate its physics goal, it is essential to develop efficient collider detectors. And one of the most important ingredients of such complex is to construct a fine pitch, low-mass, high precision pixel vertex detector as close to the interaction point as possible. Such a vertex detector is motivated by the identification of the flavour of the particles containing heavy (*b* and *c*) quarks which originate from the electron-positron collisions, and decay very close to

2 1. The ILC and ILD

the interaction point. The development of the vertex detector for the ILC is the main topic of this thesis.

This chapter is intended to provide an introductory overview of the ILC, including its major physical programs and the baseline accelerator parameters. The main features of the ILD (International Linear Detector), one of the proposed detectors for the ILC, are reviewed.

#### 1.1 The International Linear Collider

After the Higgs discovery, many more years of follow-up research will be needed to measure the properties of the Higgs particle with unprecedented precision. While the LHC and its high luminosity upgrade will certainly improve its precision on Higgs property measurements, it has been appreciated that an electron-positron collider operating at the centre-ofmass energy range of 250 GeV to 1 TeV would be an ideal instrument for the precise study of the Higgs particle. The ILC, a high luminosity linear electron-positron collider, will be an ideal candidate. As a lepton collider, the ILC will provide much cleaner events than a hadron collider. At the ILC, each bunch crossing produces a few hadrons in the final state and a large number of secondary electron-positron pairs, but these are mainly confined to small volume within 1 cm of the beam. Because of the much more benign environment at the ILC than at the LHC, the tracking detectors of the ILC can be made as thin as technically feasible. At the ILC, both the vertex detector and the calorimeter can be placed much closer to the interaction point, leading to excellent b, charm and  $\tau$  tagging capabilities. In addition, the reduced pileup from multiple collisions in each beam crossing much facilitates the event reconstruction at the ILC. The electron-positron environment thus provides a setting in which the basic high-energy collision can be measured with high precision.

#### 1.1.1 Physics program

One of the advantages of a linear collider is its ability to operate, with only minor modification, at any energy within its range that might give the greatest physics potential. This flexibility allows the designers of the ILC to envision experimental programs at a series of energies well adapted to individual physics goal.

Table 1.1 lists the major physics processed to be studied at the ILC in the various stages of its program, and the full detail can be found in the Physics Volume of the ILC Technical Design Report [1]. The table indicates the various Standard Model reactions that will be accessed at increasing collider energies, from 90 GeV to 1000 GeV, and their physic motivations. For any new particle in the ILC energy range, the ILC offers a rich program to address its properties. The ILC experiments have the capability to measure the masses with high precision, determine the electroweak quantum numbers and measure any associated mixing angles and the decay branching ratios in a model-independent way.

| Energy       | Reaction                                                                                                                                                                                                                     | Physics Goal                                                                                                                   |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 91 GeV       | $e^+e^- 	o Z$                                                                                                                                                                                                                | ultra-precision electroweak                                                                                                    |

| 160 GeV      | $e^+e^- 	o WW$                                                                                                                                                                                                               | ultra-precision W mass                                                                                                         |

| 250 GeV      | $e^+e^- 	o Zh$                                                                                                                                                                                                               | precision Higgs coupling                                                                                                       |

| 350-400 GeV  | $e^{+}e^{-} \rightarrow t\bar{t}$<br>$e^{+}e^{-} \rightarrow WW$<br>$e^{+}e^{-} \rightarrow \nu\bar{\nu}h$                                                                                                                   | top quark mass and couplings precision W couplings precision Higgs couplings                                                   |

| 500 GeV      | $\begin{array}{c} e^{+}e^{-} \rightarrow f\bar{f} \\ e^{+}e^{-} \rightarrow t\bar{t}h \\ e^{+}e^{-} \rightarrow Zhh \\ e^{+}e^{-} \rightarrow \tilde{\chi}\tilde{\chi} \\ e^{+}e^{-} \rightarrow AH, H^{+}H^{-} \end{array}$ | precision search for $Z'$ Higgs couplings to top Higgs self-coupling search for supersymmetry search for extended Higgs states |

| 700-1000 GeV | $\begin{array}{c} e^{+}e^{-} \rightarrow \nu \bar{\nu} h h \\ e^{+}e^{-} \rightarrow \nu \bar{\nu} V V \\ e^{+}e^{-} \rightarrow \nu \bar{\nu} t \bar{t} \\ e^{+}e^{-} \rightarrow \tilde{t} \tilde{t}^{*} \end{array}$      | Higgs self-couplings<br>composite Higgs sector<br>composite Higgs and top<br>search for supersymmetry                          |

**Table 1.1:** Major physics processes to be studied by the ILC, together with the lowest centre-of-mass energy at which they can be studied, from [1].

#### 1.1.2 Machine overview

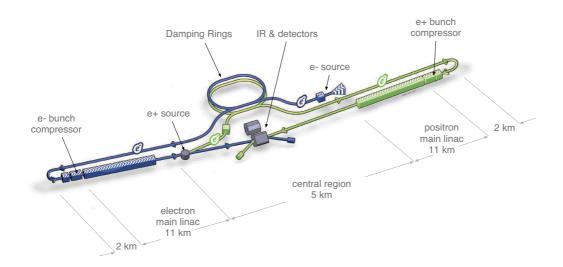

The ILC, based on the 1.3 GHz superconducting radio-frequency (SCRF) accelerating technology, is designed to reach 200-500 GeV (extendable to 1 TeV) centre-of-mass energy with high luminosity. The collider design is the result of nearly twenty years of research and development. Figure 1.1 shows a schematic view of the overall layout of the ILC, indicating the location of the major sub-systems [1]:

- **electron source** the polarised electron source is produced by a laser illuminating a strained GaAs photocathode in a DC gun;

- **positron source** positrons are obtained from a beam of electron-positron pairs, which is generated by the high-energy photons transporting the high-energy electron beam through a helical undulator;

- **damping rings (DR)** one electron ring and one positron ring, operating at a beam energy of 5 GeV in the baseline design, are housed in a common tunnel at the center of the ILC complex, with a circumference of 3.2 km;

- main linacs two 11 km long main linacs are for electrons and positrons, utilising 1.3 GHz SCRF cavities; they are operating at an average gradient of 31.5 MV/m, with a pulse length of 1.65 ms;

- ring to main linac (RTML) the layout of the RTML systems are identical for both electrons and positrons, consisting of a 5 GeV transport line, betatron- and energy-

4 1. The ILC and ILD

Figure 1.1: Schematic layout of the ILC, indicating all the major subsystems [2].

collimation systems, spin rotators, and a two stage bunch compressor system prior to injection into the main linac;

• **beam delivery system (BDS)** — it is responsible for bringing the two beams into collision with a 14 mrad crossing angle, at a single interaction point which can be shared by two detectors (in a so-called "push-pull" configuration).

The top-level parameters for the baseline design have been optimized to provide the maximum achievable physics performances with a relatively low risk and minimum cost [3]. Some of the ILC baseline parameters are summarized in Table 1.2.

| Centre-of-mass energy            | GeV                                           | 250  | 350  | 500  |

|----------------------------------|-----------------------------------------------|------|------|------|

| Luminosity                       | $\times 10^{34} \text{cm}^{-2} \text{s}^{-1}$ | 0.75 | 1.0  | 1.8  |

| Luminosity pulse repetition rate | Hz                                            | 5    | 5    | 5    |

| Bunch population                 | $\times 10^{10}$                              | 2    | 2    | 2    |

| Number of bunches                |                                               | 1312 | 1312 | 1312 |

| Linac bunch interval             | ns                                            | 554  | 554  | 554  |

| RMS bunch length                 | μm                                            | 300  | 300  | 300  |

| RMS horizontal beam size at IP   | nm                                            | 729  | 684  | 474  |

| RMS vertical beam size at IP     | nm                                            | 7.7  | 5.9  | 5.9  |

*Table 1.2:* ILC 250-500 GeV baseline parameters, form [3].

**Beam-induced backgrounds** The rate for the events from the high-energy electron-positron interactions are low, therefore the unwanted interactions are crucial in the ILC. The most important sources are machine-induced backgrounds, in which a major contribution is electron-positron pairs created by scattering of beamstrahlung photons.

1.2. ILD 5