# Study and design of CMOS RF power circuits and modulation capabilities for communication applications

Heider Marconi Guedes Madureira

#### ▶ To cite this version:

Heider Marconi Guedes Madureira. Study and design of CMOS RF power circuits and modulation capabilities for communication applications. Micro and nanotechnologies/Microelectronics. Université de Bordeaux, 2015. English. NNT: 2015BORD0093. tel-01228512

## HAL Id: tel-01228512 https://theses.hal.science/tel-01228512

Submitted on 13 Nov 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE EN COTUTELLE PRÉSENTÉE POUR OBTENIR LE GRADE DE

### **DOCTEUR DE**

## L'UNIVERSITÉ DE BORDEAUX

## ET DE L'UNIVERSITÉ DE BRASILIA

ÉCOLE DOCTORALE UBX

DEPARTAMENTO DE ENGENHARIA ELÉTRICA – UNIVERSIDADE DE BRASÍLIA

SPÉCIALITÉ MICROELECTRONIQUE

Par Heider Marconi Guedes MADUREIRA

# Study and Design of CMOS RF Power Circuits and Modulation Capabilities for Communication Applications

Sous la direction de Eric KERHERVÉ, Nathalie DELTIMPLE et de Sandro HADDAD

Soutenue le 15 Juin 2015

#### Membres du jury :

| M. CARVALHO, Paulo | Professeur | UnB, Brésil         | Président          |

|--------------------|------------|---------------------|--------------------|

| M. de LIMA, Robson | Professeur | UFBA, Brésil        | Rapporteur         |

| M. MARIANO, André  | Professeur | UFPR, Brésil        | Rapporteur         |

| M. KERHERVÉ, Eric  | Professeur | IPB ENSEIRB-MATMECA | Directeur de Thèse |

| M. HADDAD, Sandro  | Professeur | UnB, Brésil         | Directeur de Thèse |

| M. SOUZA, Antônio  | Professeur | UFPB, Brésil        | Examinateur        |

**Titre:** Étude et conception des circuits de puissance CMOS RF et nouvelles fonctionnalités de modulation pour des applications de communication

#### Résumé:

La consommation d'énergie est devenue un aspect clé dans l'électronique moderne. Dans les produits tels que les téléphones cellulaires et les tablettes, la complexité est d'offrir des interfaces de communication multistandard et des capacités de calcul élevées. La technologie CMOS moderne a évolué de telle sorte que le hardware est devenu très efficace, permettant une capacité de calcul dans les appareils portables d'être comparable à des ordinateurs. Dans le contexte des communications mobiles, l'utilisation d'un circuit optimisé pour chaque standard de communication augmente la durée de vie de la batterie, mais augmente également la complexité des PCB (Printed Circuit Board), avec plus de composant à placer et à connecter à l'antenne (ou aux antennes). Les simulations RF et électromagnétiques à l'aide de logiciels spécialisés sont souvent nécessaires pour s'assurer que les caractéristiques à haute fréquence du PCB sont correctes, augmentant ainsi le temps de développement et les coûts.

Afin de répondre à cette problématique, des efforts ont été faits pour fusionner les fonctions essentielles en RF. Par exemple, des solutions où la fonction mélangeur est fusionnée avec la fonction oscillateur ou la fonction amplificateur à faible bruit avec la fonction mélangeur peuvent être trouvée dans la littérature. Dans ce travail, nous développons l'idée de fusionner la fonction amplificateur de puissance avec la fonction oscillateur pour créer un circuit appelé oscillateur de puissance.

L'oscillateur de puissance pourrait idéalement être utilisé dans un émetteur RF. Dans cette architecture, les signaux en bande de base analogiques ou numériques sont utilisées pour moduler l'oscillateur de puissance menant à un émetteur RF efficace, flexible et simple. Comme tous les signaux de commande sont en bande de base, peu de circuits RF seraient nécessaires pour mettre en œuvre l'architecture proposée, ce qui facilité les problèmes de reconfiguration qui sont présents dans les circuits RF traditionnels.

Les communications mobiles à haut débit sont déjà une réalité dans de nombreux pays. Le LTE (Long Term Evolution) est devenu une référence mondiale pour les applications mobiles. Géré par le *3rd Generation Partnership Project (3GPP)*, cette norme exige fonctionnalités qui repoussent les limites technologiques de conception de circuits intégrés tels que:

- 1) adaptation la largeur de bande de canal de 1,4 MHz à 20 MHz;

- 2) fréquences centrales de 700 MHz (dans la bande 12) à 3500 MHz (dans la bande 22);

- 3) compatibilité avec les systèmes mis en place;

- 4) différents schémas de modulation, à partir du QPSK jusqu'au 64-QAM.

Les spécifications sont très contraignantes et un émetteur traditionnel ne peut pas répondre à toutes ces caractéristiques à la fois. Aussi, la nécessité de reconfiguration dans le hardware est évidente.

Ce travail porte sur l'étude d'un émetteur RF reconfigurable basée sur une architecture innovante. Au centre de cette architecture, se trouve un oscillateur de puissance. L'utilisation d'un circuit qui peut être directement modulé par un signal en bande de base et être reliée directement à l'antenne conduit à une architecture plus simple de émetteur, dans lequel moins

de circuits RF sont utilisés. Nous nous fixons une spécification, le Brésil et l'Europe partageant une bande de fréquence identique autour de 2,5 GHz, tous les circuits RF développées dans cette thèse seront conçus autour de cette fréquence centrale.

Dans cette étude, le problème de reconfiguration est séparé en deux problèmes plus simples: (i) générer le signal d'entrée correct, qui peut être obtenu par traitement de bande de base numérique ou analogique et (ii) la conception d'un oscillateur de puissance qui peut respecter les spécifications. Notez que le problème de la conception de nombreux blocs de construction RF est maintenant réduit à un circuit.

Vu que le thème central de ce travail comporte des amplificateurs de puissance, une discussion sur ces circuits doit être faite. Dans la chaîne de transmission, la fonction de l'amplificateur de puissance est de fournir à l'antenne un signal modulé avec des paramètres de qualité à des niveaux de puissance suffisants pour être reçues avec une qualité raisonnable après l'atténuation et de la distorsion du canal. Dans ce contexte, une qualité suffisante et raisonnable sont définis par la norme de communication souhaité.

Compte tenu de la conception de l'amplificateur de puissance, afin de pouvoir contrôler le compromis en fonction des caractéristiques souhaitées, il est possible de modifier la polarisation du dispositif actif conduisant à des différentes classes de fonctionnement. Les amplificateurs de puissance peuvent être classés en deux grandes catégories:

- 1) "sinusoïdale": dans cette catégorie, le dispositif actif est utilisé comme une source de courant commandée. Des exemples sont des classes A, AB, B et C. La différence entre ces classes sont les conditions de polarisation du dispositif actif, ce qui modifie l'angle de conduction.

- 2) commuté: dans cette catégorie, le dispositif actif est utilisé comme un interrupteur. Les exemples sont les classes D, E et F. La différence entre ces classes est la forme generée. Idéalement, les amplificateurs de puissance commutés en classe E peuvent atteindre 100% d'efficacité et, pour cette raison, ils sont utilisés dans ce travail.

Les circuits de Classe E profitent de composants réactifs afin d'obtenir un rendement élevé. Dans le principe de fonctionnement théorique, ils sont composés d'un interrupteur et d'un réseau passif. Le transistor est utilisé en tant que commutateur et, par conséquent, lors du fonctionnement du signal large. La charge de sortie, dans ce travail a été faite 50 ohms en raison de les caracteristiques de mesure est le seul composant qui dissipe de la puissance dans ce circuit.

En Classe E, la forme d'onde de tension est conçu pour répondre à des conditions de commutation au zéro de tension (ZVS) et zéro commutation de la pente de tension (ZdVS). ZVS établit que l'interrupteur se ferme lorsque la tension de forme d'onde atteint une tension nulle au tant que ZdVS demande que la dérivée de la tension doit également être égal à zéro lorsque le commutateur se ferme. La condition ZVS est essentiel pour les formes d'onde non se chevauchent tout en ZdVS est utilisé pour réduire le chevauchement en cas de paramètres ou de variations de fréquence. Comme la définition de circuits en classe E est faite par des équations du domaine temporel, la méthodologie de conception est essentiellement fait en utilisant des approches dans le domaine temporel.

Par ailleurs, les circuits en Classe E trouvent une grande utilité dans la conception RF en raison de ses caractéristiques à utiliser la capacité parasite afin d'obtenir un rendement élevé. Malheureusement, il se fait au détriment de haute tension sur le transistor.

Dans les technologies CMOS modernes, la tension de claquage des dispositifs ont tendance à devenir plus petit après chaque noeud de la technologie. Au lieu d'ajouter transistors supplémentaires pour faire face à la contrainte de tension intrinsèque à la classe E, l'ingénierie de forme d'onde peut être utilisé pour créer un amplificateur avec certaines caractéristiques intéressantes, telles que faible contrainte de tension ou une plus grande capacité d'alimentation, par exemple.

Comme une solution possible au problème de la contrainte de tension, une modification à la classe E est apportée grâce à l'ingéniérie de forme d'onde, qui conduit à la classe EF2. Le nom de la classe définit la mise en œuvre. Dans le cas de EF2, conditions ZVS et ZdVS sont héritées de la classe E et un court-circuit à la deuxième harmonique de la tension est utilisé. Présenter ouvre (haute impédance) et un short (basse impédance) est typique des amplificateurs de puissance de classe F.

Après une recherche dans la littérature, la classe EF2 présente la contrainte de tension moins forte que la classe E et, d'autre part, le courant est le plus élevé. Visant des transistors basse tension de claquage, la classe EF2 est la solution la plus adaptée en raison des faibles tensions de claquage des transistors de la technologie. La principale différence entre la classe E et la classe EF2, du point de vue de la mise en œuvre, est un circuit LC série à travers le commutateur conçu pour court-circuiter la deuxieme harmonique de la tension aux bornes de l'interrupteur.

Dans les circuits de classe E ordinaires, le rapport cyclique de la tension d'entrée est de 50%. Dans le cas de la classe EF2, le rapport cyclique optimal est de 35%. Sous cette condition, non seulement le stress de tension à travers le commutateur est inférieure à la classe E avec un rapport cyclique de 50% (qui est choisi à l'optimum), mais aussi la capacité de manipulation de puissance est 43% plus élevé.

Une autre caractéristique intéressante du circuit de EF2 de classe est dans le spectre de sortie: la deuxième harmonique du signal RF générée a moins de puissance que la classe E en raison du court circuit présenté à une telle harmonique. Le concepteur peut utiliser cette caractéristique dans chaque circuit, par exemple, en abaissant les spécifications sur le filtre de sortie.

L'amplificateur de puissance classe EF2 ainsi réalisé est l'élément de base de l'oscillateur de puissance. Considérant les opérations en boîte noire, un oscillateur de puissance peut être faite d'un VCO ordinaire dont le signal de sortie est amplifié pour être livré à l'antenne. De cette manière, l'oscillateur et l'amplificateur de puissance sont encore nettement séparées. Le circuit présenté dans ce travail utilise une stratégie différente en essayant de fusionner vraiment les deux circuits. Il est connu que chaque oscillateur est basé sur un amplificateur avec une sorte de rétroaction. Par consequence, pour accomplir un oscillateur de puissance, un amplificateur de puissance peut avoir sa sortie renvoyé à l'entrée afin de soutenir auto-oscillation.

Dans ce travail, la technologie 130 nm CMOS HCMOS9GP de STMicroelectronics a été utilisé. La technologie standard dispose de 6 couches métalliques, des transistors de 1,2 V avec de multiples options (faible fuite ou dispositifs à grande vitesse). La technologie fournit

aussi des condensateurs MOM et des inductances planaires modélisées avec facteur de qualité autour de 10.

Le flux de conception a été réalisé en utilisant Cadence IC 5 avec STMicroelectronics 130 nm CMOS standard. Les verifications RDC (Design Rule Check) et LVS (Disposition contre schématiques) ont été faits en utilisant Calibre de Mentor Graphics.

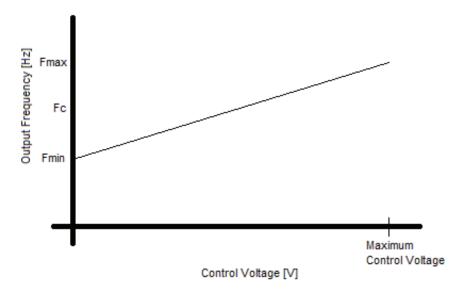

Au préalable, une étude théorique sur les performances réalisables de modulation directe sur un oscillateur est faite. Cette analyse est basée sur quelques définitions importantes, telles que le gain de l'oscillateur compte tenu de la tension de commande de l'oscillateur comme étant limitée, ce qui est le cas dans les implémentations réelles. La conclusion de cette analyse est qu'il existe une limite supérieure à la vitesse de modulation de phase à cause de la forme d'onde générée est continu. Ceci est un résultat général et cette limitation est intrinsèque à la modulation directe d'oscillateurs et ne précise pas la puissance de sortie.

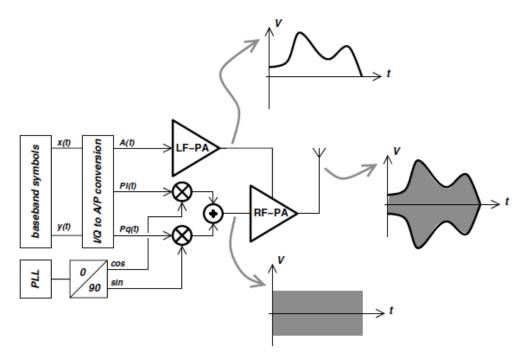

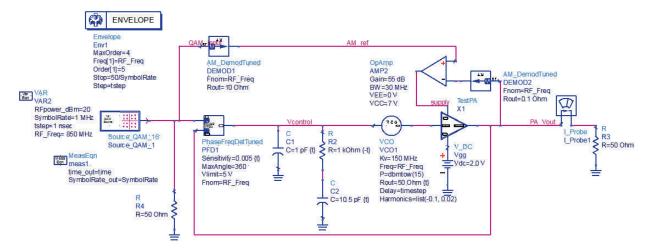

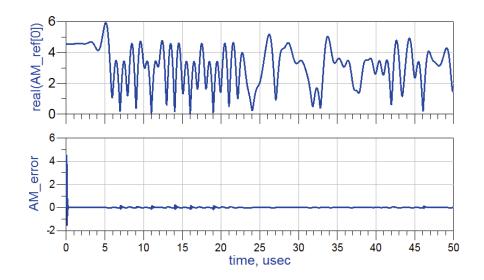

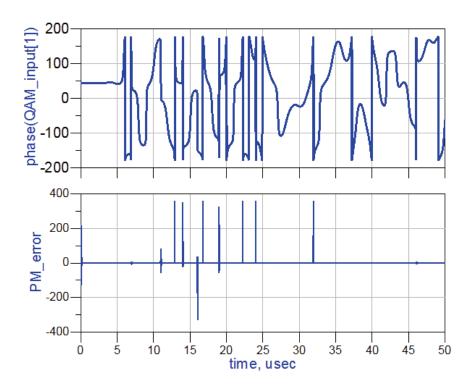

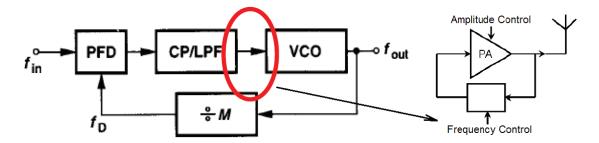

Suite à l'analyse mathématique, une modélisation de haut niveau de l'architecture d'émetteur a été faite dans Agilent ADS. Un modèle de l'architecture complète contenant un amplificateur de puissance au niveau du transistor est réalisé afin de montrer la viabilité de l'architecture. La principale motivation pour la construction de ce modèle est d'obtenir un aperçu de la performance avec peu d'effort de conception. L'architecture est constituée par une boucle de contre-réaction de phase et une boucle de contre-réaction d'amplitude.

La boucle de phase est mis en œuvre par un PLL de type III et les blocs de construction, tels que le détecteur de phase-fréquence et pompe de charge, ont été prises à partir de la bibliothèque Agilent ADS. La boucle d'amplitude est mis en oeuvre avec des démodulateurs d'amplitude, qui déplacent les informations d'amplitude de RF en bande de base, et un amplificateur de contre-réaction qui compare la sortie générée et l'entrée de référence, tout en générant un signal d'erreur.

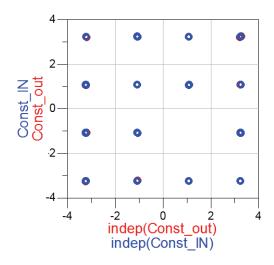

Ces simulations montrent la viabilité technique de la solution et de l'information de la performance. L'architecture est capable de générer une modulation complexe tel que 16-QAM tandis que la boucle de phase impose un autre limiteur de vitesse en tant que filtre passe-bas de la PLL a un grand temps de mise en oeuvre. Ce résultat démontre les limitations d'utilisation de cette architecture pour les standards de communication à hauts débit telles que le LTE.

L'étude préalable a néanmoins permis de démontrer la pertinence de cette architecture pour un émetteur RF, le travail suivant porte sur la conception du circuit. Comme l'oscillateur de puissance est principalement composé d'un amplificateur de puissance, le travail a commencé par la conception d'un amplificateur de puissance qui pourrait être utilisé pour prouver la stratégie d'utilisation de la classe EF2 pour réduire le stress de tension.

L'amplificateur a été conçu en utilisant 50 ohm impédance d'entrée en raison de la configuration de mesure qui sera utilisé. Un driver de classe C a été utilisé pour fournir du gain de puissance et contrôler le rapport cyclique du signal qui conduira l'étage de puissance principal. L'étage de puissance principal a été conçu pour répondre aux exigences de classe EF2 l'aide d'un commutateur en cascade pour réduire le stress de tension sur chaque dispositif. A la connaissance de l'auteur, il s'agit de la première implantation d'un amplificateur de puissance classe EF2 aux fréquences RF. Tous les inductances ont été conçues pour avoir un facteur de qualité élevé de la fréquence d'intérêt. Des condensateurs de découplage ont été

ajoutés pour augmenter la stabilité de l'amplificateur. Un plan de masse a été ajouté afin de réduire l'influence de l'impédance de masse.

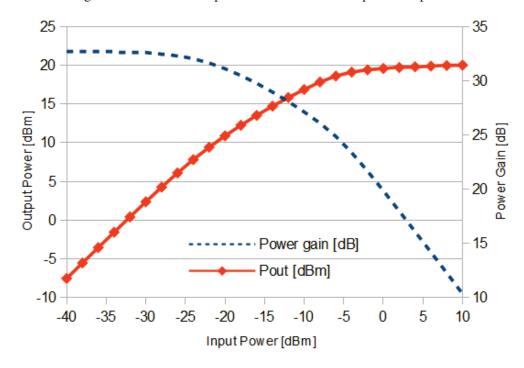

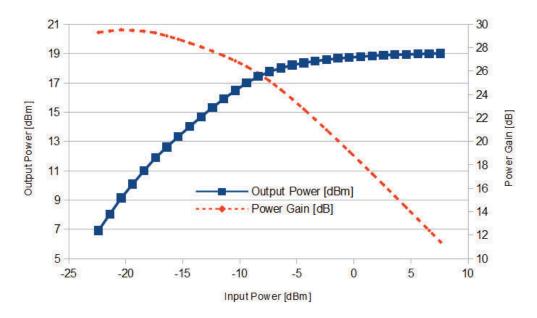

Les résultats de simulation montre que le circuit atteint 20 dBm puissance de sortie avec une puissance d'entrée de 0 dBm et consomme 192,6 mW pour fournir 55% d'efficacité de drain et 50% de PAE (Power Added Efficiency). Cet amplificateur de puissance a également été conçu pour conserver ses caractéristiques sur une large bande passante. En fait, il est capable de travailler à partir de 1,5 GHz à 3 GHz (bande passante à -3dB). Les mesures effectuées confirment la bonne fonctionnalité du circuit avec une puissance de sortie maximum de 15.9 dBm, un rendement de drain de 36% et une PAE de 34%. Une réduction du rendement a été observée entre simulations et mesures. La puissance de sortie a chuté et, par conséquent, l'efficacité. Les observations des donnés expérimentales indiquent des problemes dans le découplage du circuit et de nouvelles mesures sur un PCB sont en cours de développement.

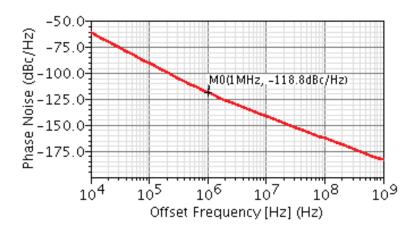

L'oscillateur de puissance quant à lui utilise l'amplificateur de puissance précédent plus l'ajout d'un réseau de rétroaction passif pour mettre en oeuvre une réaction de tension. En simulation, comme en mesures, l'oscillateur de puissance délivre un signal de sortie sinusoidal. En simulation, la puissance de sortie est égale à 20 dBm avec une efficacité de 40% DC-RF. Le circuit montre un bruit de phase de -118 dBc /Hz @ 1 MHz d'offset et 300 MHz de bande de couverture. Comme pour l'amplificateur de puissance, une dégradation des performances a été observée dans les mesures, un circuit imprimé est également en cours de conception de ce circuit.

Afin de permettre de longues simulations, un modèle VerilogA de l'oscillateur de puissance a été effectué. Ce modèle avait pour but de réduire l'effort de calcul nécessaire pour simuler le comportement de l'oscillateur de puissance lors de la connexion dans l'architecture de l'émetteur. Le modèle a été construit sur la base d'une table et les données ont été obtenues à partir des simulations post-layout.

L'architecture de l'émetteur a été simulé par le modèle de l'amplificateur de puissance. La même architecture qui avait été prouvé dans ADS a été utilisé, mais cette fois, l'information au niveau transistor a été utilisé et, pour cette raison, cette dernière simulation est plus précis que le premier présenté. La capacité de générer de modulation de l'amplitude, la fréquence et de phase est représenté sans la nécessité de modifier le hardware. Ce résultat indique la flexibilité de l'architecture proposée.

Les travaux futurs incluent la caractérisation complète des circuits mis en œuvre, un test de robustesse pour les circuits de classe EF2 et la mise en œuvre complète de l'architecture proposée dans le silicium.

Mots clés: Oscillateur de puissance, amplificateur de puissance, CMOS, RF

**Title:** Study and Design of CMOS RF Power Circuits and Modulation Capabilities for Communication Applications

#### Abstract:

This work presents the study, design and measurement of RF circuits aiming communication applications. The need for flexible and reconfigurable RF hardware leads to the need of alternative transmitter architectures. In the center of this innovative architecture, there is the power oscillator. This circuit is composed of a power amplifier in a positive feedback loop so it oscillates. As the circuit under study is mainly composed of a power amplifier, a study on power amplifier is mandatory. Modern CMOS technologies impose difficulties in the efficient RF generation due to low breakdown voltages. In order to reduce the voltage stress on the transistors, waveform-engineering techniques are used leading to the use of class EF2. The design and measurement of a class EF2 power amplifier and power oscillator are shown. The circuits were implemented in standard STMicroelectronics 0.13um CMOS. Correct behavior for the circuits was obtained in measurement, leading to a first implementation of class EF2 in RF frequencies. From a system perspective, the proposed architecture is shown to be flexible and able to generate different modulations without change in the hardware. Reconfigurability is shown not only in modulation but also in output power level. The limitations of this architecture are discussed and some mathematical modeling is presented.

**Keywords:** Power oscillator, power amplifier, CMOS, RF

#### Unité de recherche

[Laboratoire IMS, UMR 5218, 351 Cours de la Liberation, 33405 Talence Cedex, France]

#### Acknowledgements

I would like to thank my supervisors Sandro Haddad, Nathalie Deltimple e Eric Kerhervé for the work and dedication. To Professors José Camargo da Costa e Paulo Henrique Portela for the opportunity that was given me of being part of the team and have the experience of living in Europe.

To all my friends of the support and help in moments of hard work and sometimes not so much. I would like to thank the friends Marcos Carneiro, Dean Karolak, Rosário Desposito, Mario Weiss, Oskar Holstensson e Dwight Cabrera for sharing the experience and work.

To the team of DFchip, specially my friend Rafael Ferreira for being there when I could not. To the old team of LPCI, José Edil, Gilmar Beserra, Genival Araújo, Daniel Café, Pedro Aurélio for the seed of would become this work.

To my friend Ana Régia Neves for all the endeless.

Finally, I would like to thank my mother, Wany de Cassia de Carvalho Guedes, and my father, Marco Aurélio Madureira Ribeiro, for absolutely everything. This work is only a tiny fraction of all I would never accomplish if it were not for your support.

Heider Marcôni Guedes Madureira

# **SUMMARY**

| 1 | INTRO | DUCTION                                              | -  |

|---|-------|------------------------------------------------------|----|

|   | 1.1   | CONTEXTUALIZATION                                    | 1  |

|   | 1.2   | Goals of This Work                                   | 3  |

|   | 1.3   | Main Contributions                                   | 3  |

|   | 1.4   | ORGANIZATION OF THE DOCUMENT                         | 3  |

| 2 | BIBLI | OGRAPHICAL RESEARCH                                  | 4  |

|   | 2.1   | COMMUNICATIONS STANDARDS                             |    |

|   | 2.2   | Architecture of RF transmitters                      |    |

|   | 2.2.1 | HOMODYNE                                             |    |

|   | 2.2.2 | HETERODYNE                                           |    |

|   | 2.2.3 | Towards a Simpler Architecture                       |    |

|   | 2.3   | Power Amplifiers                                     |    |

|   | 2.3.1 | KEY PARAMETERS OF POWER AMPLIFIERS                   |    |

|   | 2.3.2 | COMBINANTION OF STAGES                               |    |

|   | 2.3.3 | CLASSICAL TRADE-OFF IN POWER AMPLIFIER DESIGN        |    |

|   | 2.3.4 | SINUSOIDAL CLASSES                                   |    |

|   | 2.3.5 | SWITCHED CLASSES                                     |    |

|   | 2.4   | Voltage Stress in Power Amplifiers                   |    |

|   | 2.5   | Power Oscillators                                    |    |

|   | 2.6   | Power Amplifier Linearization Techniques             |    |

|   | 2.6.1 | OPEN LOOP STRATEGIES.                                |    |

|   | 2.6.2 | CLOSED LOOP STRATEGIES                               |    |

|   | 2.7   | Technology issues                                    |    |

|   | 2.7.1 | INTEGRATED CAPACITORS                                |    |

|   | 2.7.2 | INTEGRATED INDUCTORS                                 |    |

| 3 | METH  | ODOLOGY                                              | 32 |

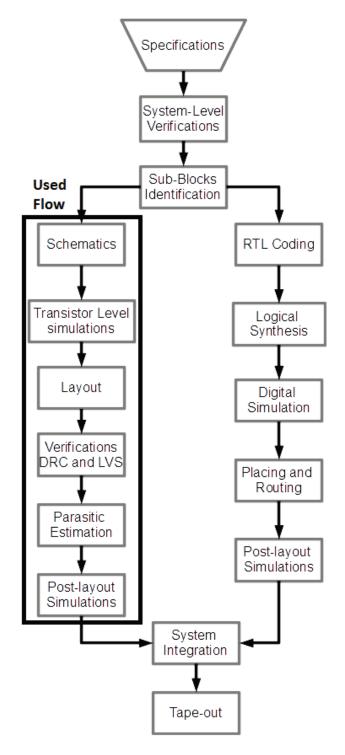

| • | 3.1   | Analog Integrated Circuit Design Methodology         | _  |

|   | 3.1.1 | Design Methodology for a Power Amplifier             |    |

|   | 3.1.2 | Design Methodology for a Power Oscillator            |    |

|   | 3.2   | MEASUREMENT PROCEDURES                               |    |

|   | 3.2.1 | MEASUREMENT OF THE POWER AMPLIFIER                   |    |

|   | 3.2.2 | MEASUREMENT OF THE POWER OSCILLATOR                  |    |

|   |       |                                                      |    |

| 4 |       | AND RESULTS                                          | _  |

|   | 4.1   | HIGH LEVEL MODELING OF THE RF TRANSMITTER            |    |

|   | 4.2   | POWER AMPLIFIER DESIGN AND RESULTS                   |    |

|   | 4.2.1 | INPUT MATCHING NETWORK AND DRIVER STAGE              |    |

|   | 4.2.2 | Main Power Stage                                     |    |

|   | 4.2.3 | Power Amplifier Simulation and Measurement Results   |    |

|   | 4.3   | Power Oscillator Design                              |    |

|   | 4.3.1 | POWER OSCILLATOR SIMULATIONS AND MEASUREMENT RESULTS |    |

|   | 4.4   | HIGH LEVEL MODELING OF THE POWER OSCILLATOR          |    |

|   | 4.5   | RF Transmitter Architecture                          |    |

|   | 4.5.1 | PLI LOCK ACQUISITION                                 | 71 |

|    |        | AMPLITUDE MODULATIONFREQUENCY AND PHASE MODULATION |    |

|----|--------|----------------------------------------------------|----|

|    |        | LUSIONList of Publications                         |    |

| RI | EFEREI | NCES                                               | 82 |

# LIST OF FIGURES

| 1.1  | Heterodyne transmitter architecture. [4]                                                                   | 1  |

|------|------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Direct modulation architecture [4]                                                                         | 2  |

| 1.3  | Transmitter based on Power Oscillator [4]                                                                  | 2  |

| 2.1  | Direct conversion transmitter [9]                                                                          | 5  |

| 2.2  | Two-step conversion transmitter [9]                                                                        | 6  |

| 2.3  | Transmitter based on Power Oscillator [4]                                                                  | 7  |

| 2.4  | Important definitions of a power amplifier [17].                                                           | 8  |

| 2.5  | Fictional AM/AM characteristics[20].                                                                       | 9  |

| 2.6  | Typical AM/PM characteristics [21].                                                                        | 10 |

| 2.7  | Circuit topology for sinusoidal PA [24].                                                                   | 11 |

| 2.8  | Class A waveforms: (a) voltage and (b) current                                                             | 12 |

| 2.9  | Class B waveforms: (a) voltage and (b) current                                                             | 13 |

| 2.10 | Class C waveforms: (a) voltage and (b) current                                                             | 13 |

| 2.11 | Representation of biasing scheme and conduction angle.                                                     | 14 |

| 2.12 | Efficiency and output power as a function of the operating class [19]                                      | 14 |

| 2.13 | Harmonic generation as a function of the operating class [25]                                              | 15 |

| 2.14 | Class D amplifier                                                                                          | 16 |

| 2.15 | Ideal class E circuit                                                                                      | 17 |

| 2.16 | Ideal class E waveforms: (a)voltage and (b)current [27]                                                    | 18 |

| 2.17 | Waveforms for optimum operation. (a) Class E at $D = 0.5$ . (b) Class EF2 at $D = 0.35$ . (c)              |    |

|      | Class E/F3 at D = $0.55.[37]$                                                                              | 20 |

| 2.18 | Ideal class EF2 circuit.                                                                                   | 21 |

|      | Output power capability versus duty cycle [37]                                                             | 21 |

| 2.20 | Normalized transistor voltage and current waveforms of (a) class E, (b) class EF2 and (c) class E/F3. [37] | 22 |

| 2 21 | Normalized output spectrum for class E and class EF2 ideal power amplifier                                 |    |

|      | Block diagram of an arbitrary control system.                                                              | 24 |

|      | Power oscillator block diagram                                                                             |    |

|      | Principle of predistortion [17].                                                                           |    |

|      | Polar loop architecture [56].                                                                              |    |

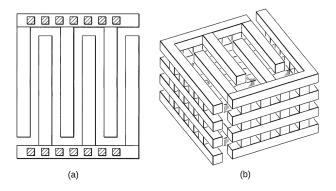

|      | Finger capacitor: (a) top view and (b) 3D structure.                                                       | 29 |

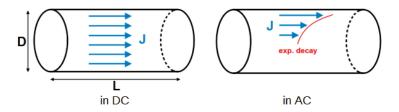

|      | Skin Effect                                                                                                | 30 |

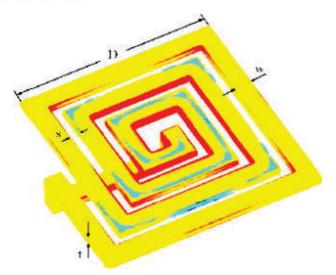

|      | Skin Effect in planar inductors [63].                                                                      | 30 |

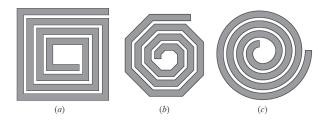

|      | Planar inductor shapes.                                                                                    |    |

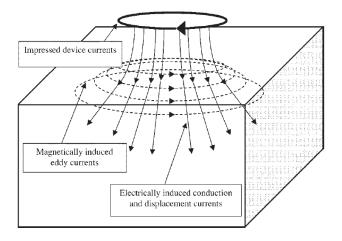

|      | Electrically and magnetically induced currents [68].                                                       |    |

| 3.1  | Mixed signal circuit design flow.                                                                          | 33 |

| 3.2  | Ideal class E schematics                                                                                   | 34 |

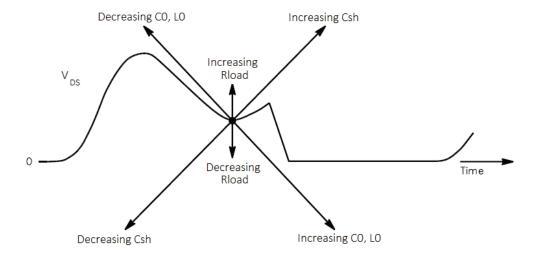

| 3.3  | Effects of adjusting the load network [70]                                                                 | 35 |

| 3.4  | Class EF2 ideal schematic.                                                                                 | 35 |

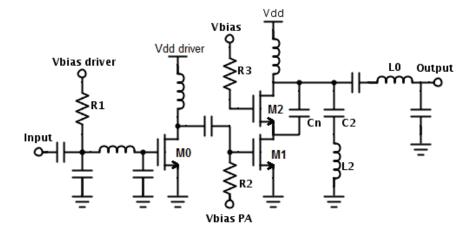

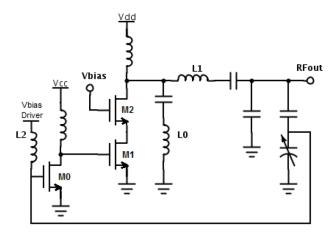

| 3.5  | Schematic of the power amplifier                                                                           | 37 |

| 3.6  | Schematic of the power amplifier                                                                           | 39 |

| 4.1  | Transfer function of a linear VCO with limited tuning range                                                | 41 |

| 4.2  | Schematic of the high level model of a polar transmitter                                                   |    |

| 4.3  | Simulation results for amplitude modulation.                                                               | 45 |

| 4.4  | Simulation results for phase modulation.                                                 | 46 |

|------|------------------------------------------------------------------------------------------|----|

| 4.5  | Simulated constellation.                                                                 | 47 |

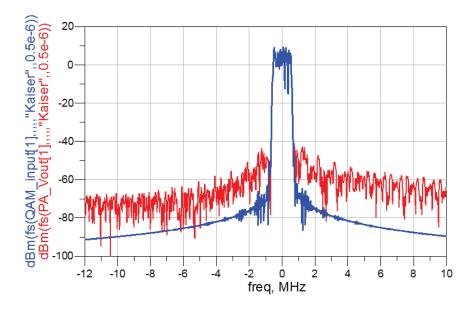

| 4.6  | Simulated input and output spectrum.                                                     | 47 |

| 4.7  | Schematic of the power amplifier                                                         | 48 |

| 4.8  | Negative capacitance implementation[35]                                                  |    |

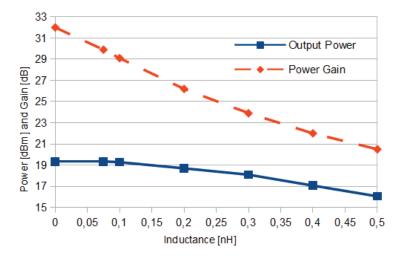

| 4.9  | Dependence of output power and power gain over source degenerating parasitic inductance. | 50 |

| 4.10 | Ground plane cell from polysilicon to metal 6.                                           | 51 |

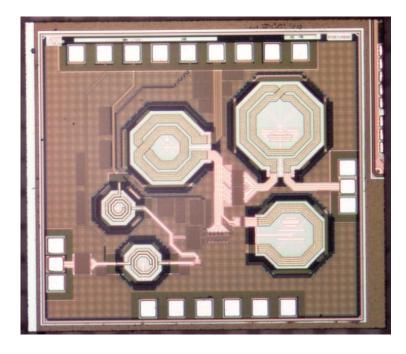

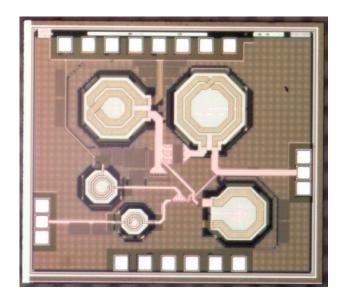

| 4.11 | Micrograph of the prototyped class EF2 power amplifier                                   | 51 |

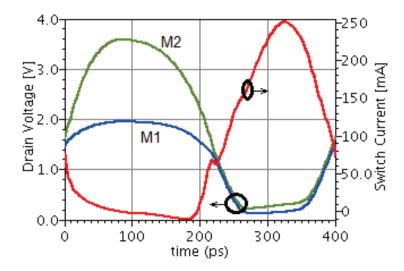

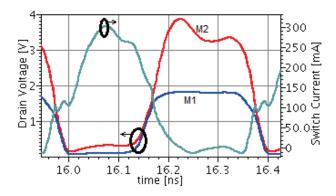

| 4.12 | Simulated current and voltage waveforms in the class EF2 power amplifier                 | 52 |

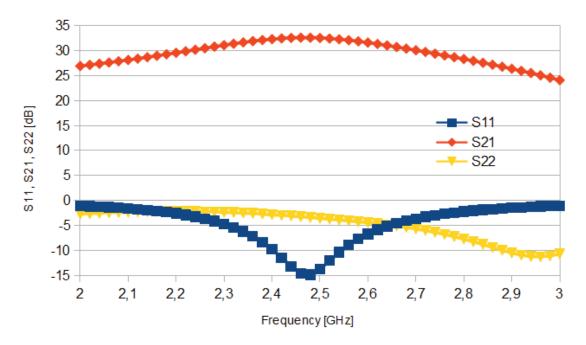

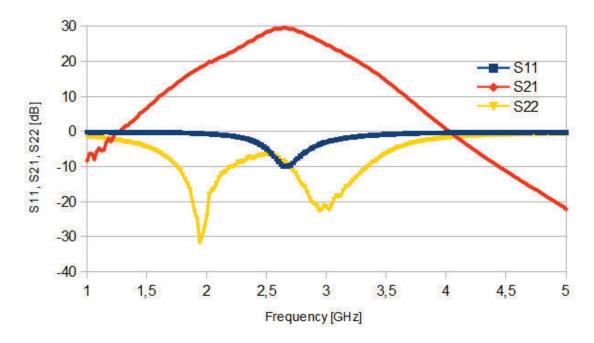

|      | Simulated small signal S parameters                                                      |    |

| 4.14 | Measured small signal S parameters                                                       | 53 |

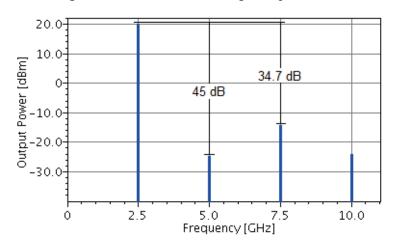

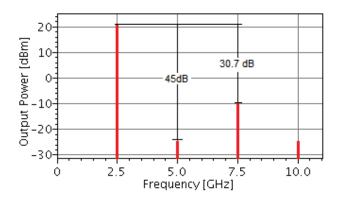

| 4.15 | Simulated spectrum for the class EF2 power amplifier.                                    | 53 |

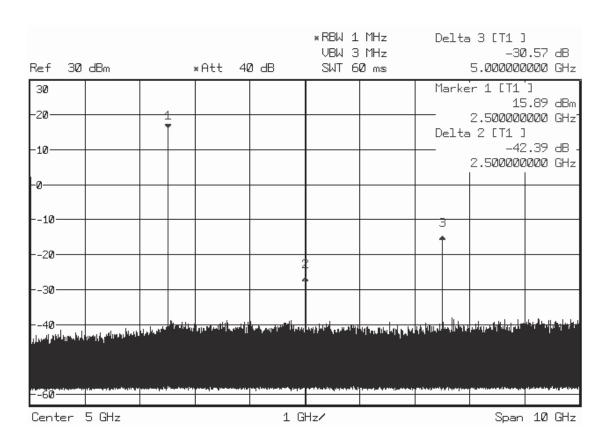

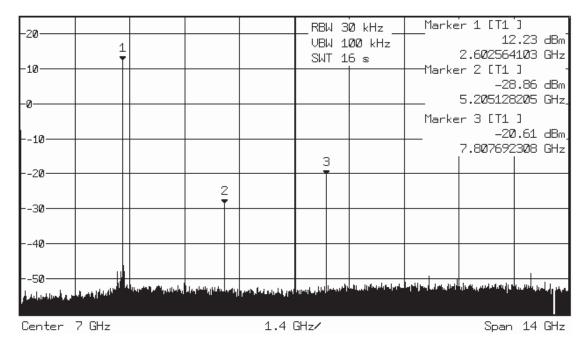

|      | Measured spectrum of the class EF2 power amplifier.                                      |    |

| 4.17 | Simulated output power and gain versus input power.                                      | 55 |

|      | Measured output power and gain versus input power.                                       |    |

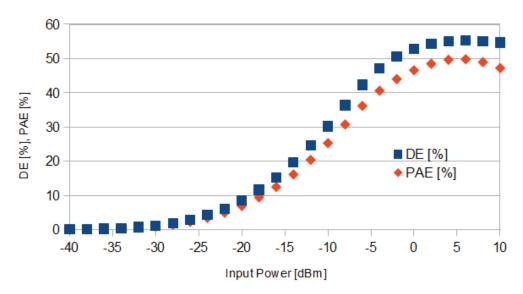

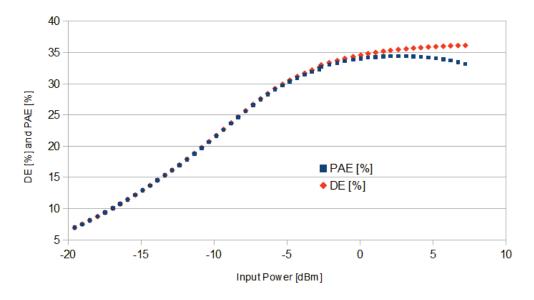

| 4.19 | Simulated efficiencies: DE and PAE                                                       | 56 |

| 4.20 | Measured efficiencies: DE and PAE                                                        | 56 |

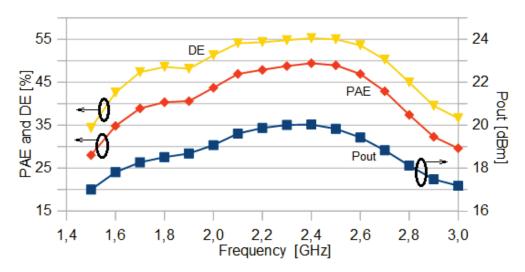

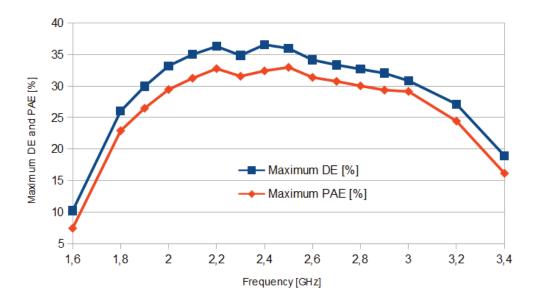

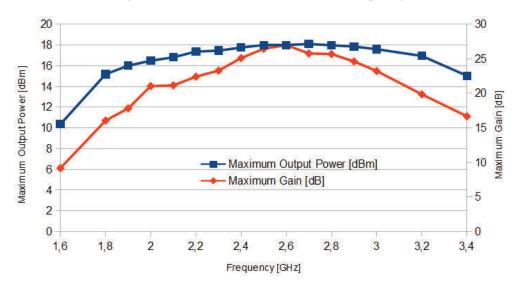

| 4.21 | Simulated performance over frequency                                                     | 57 |

|      | Measured efficiencies over frequency                                                     |    |

| 4.23 | Measured output power and gain over frequency                                            | 58 |

|      | Schematic of the implemented power oscillator                                            |    |

| 4.25 | Micrograph of the prototyped class EF2 power oscillator                                  | 60 |

| 4.26 | Simulated current and voltage waveforms in the class EF2 power oscillator                | 61 |

| 4.27 | Simulated spectrum generated by the power oscillator.                                    | 61 |

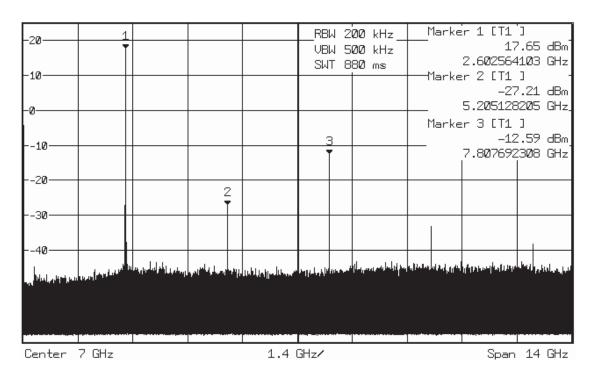

| 4.28 | Measured spectrum generated by the power oscillator at nominal biasing                   | 62 |

| 4.29 | Measured spectrum generated by the power oscillator at 2.5 V supply voltage              | 63 |

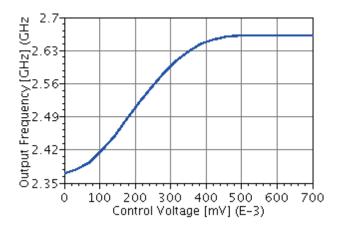

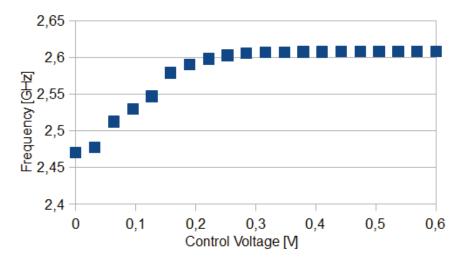

| 4.30 | Simulated voltage to frequency transfer function.                                        | 64 |

| 4.31 | Measured voltage to frequency transfer function.                                         | 64 |

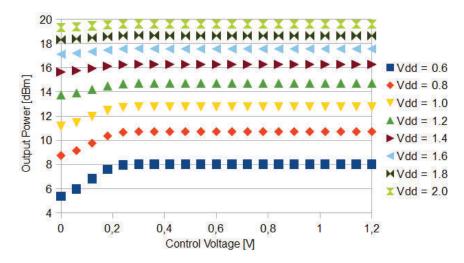

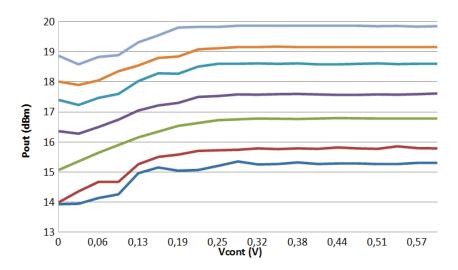

| 4.32 | Simulated dependence between output power and control voltage.                           | 65 |

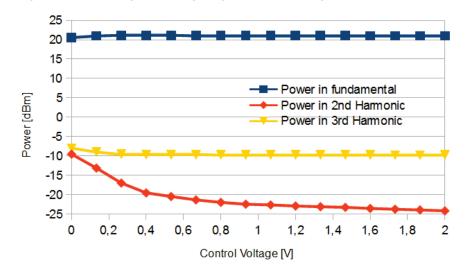

| 4.33 | Measured dependence between output power and control voltage.                            | 65 |

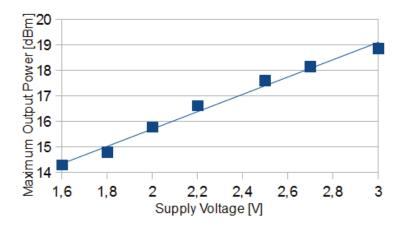

| 4.34 | Measured transfer function from supply voltage to output power.                          | 66 |

| 4.35 | Simulated power in each harmonic along control voltage.                                  | 66 |

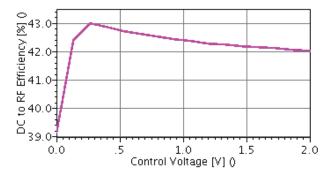

|      | Simulated DC-RF efficiency.                                                              | 66 |

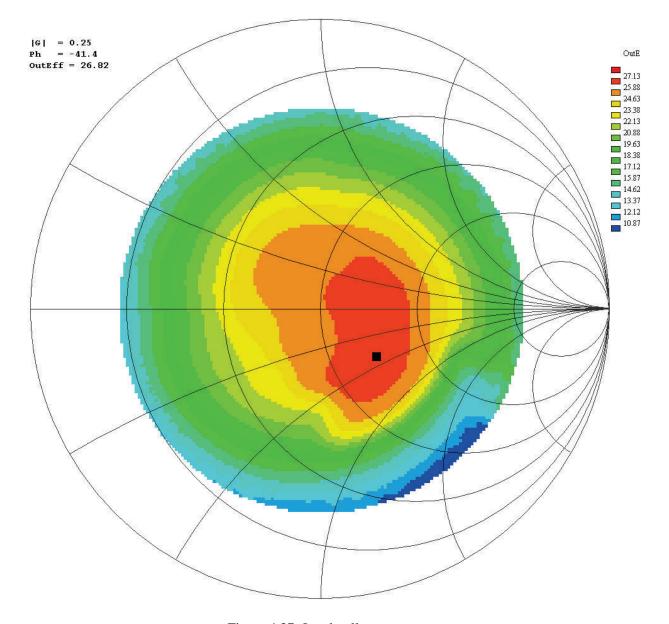

| 4.37 | Load pull measurement.                                                                   | 67 |

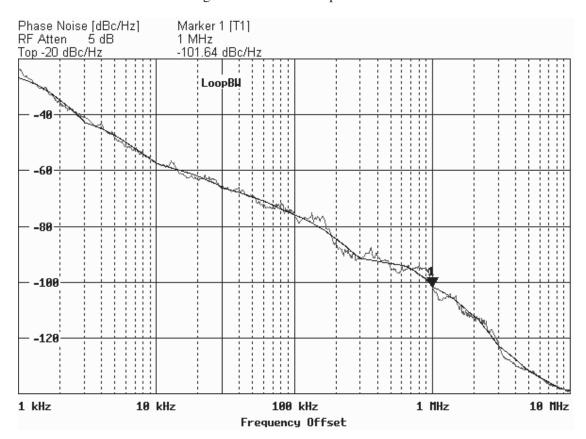

| 4.38 | Simulated phase noise.                                                                   | 68 |

| 4.39 | Measured phase noise.                                                                    | 68 |

| 4.40 | Simulated RF transmitter based on a power oscillator.                                    | 70 |

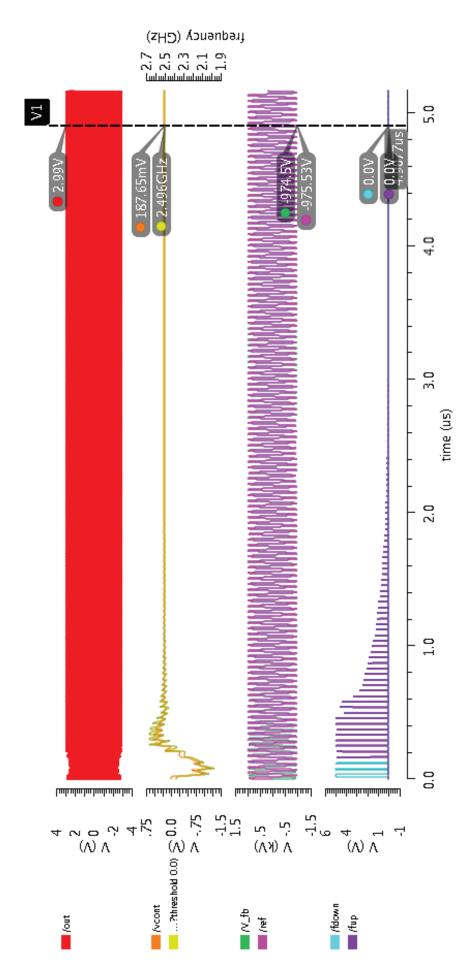

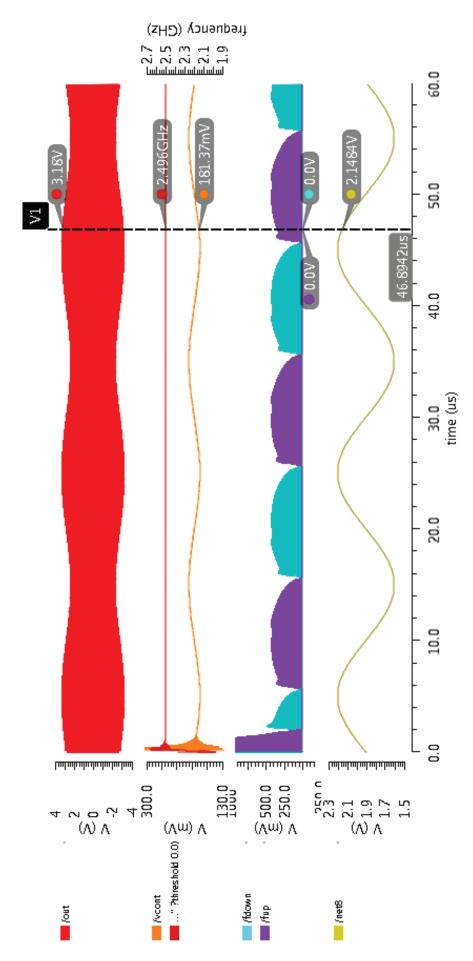

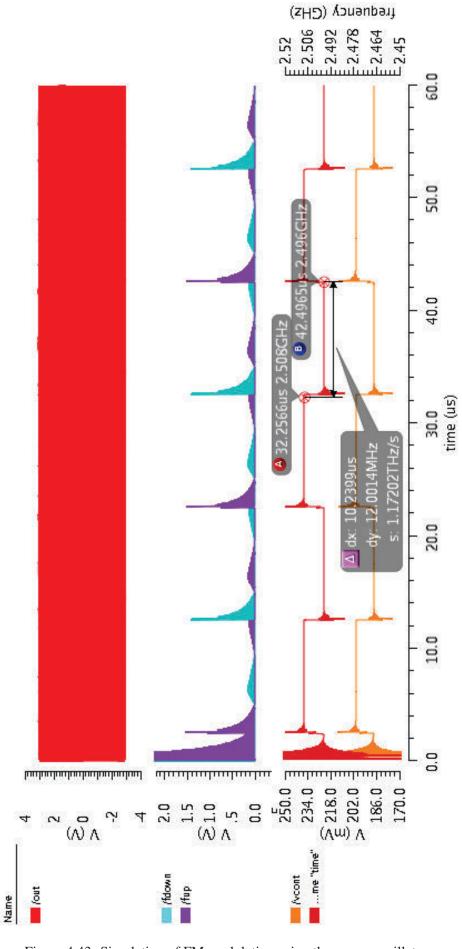

| 4.41 | Simulation of the PLL using the power oscillator.                                        | 74 |

| 4.42 | Simulation of AM modulation using the power oscillator.                                  | 75 |

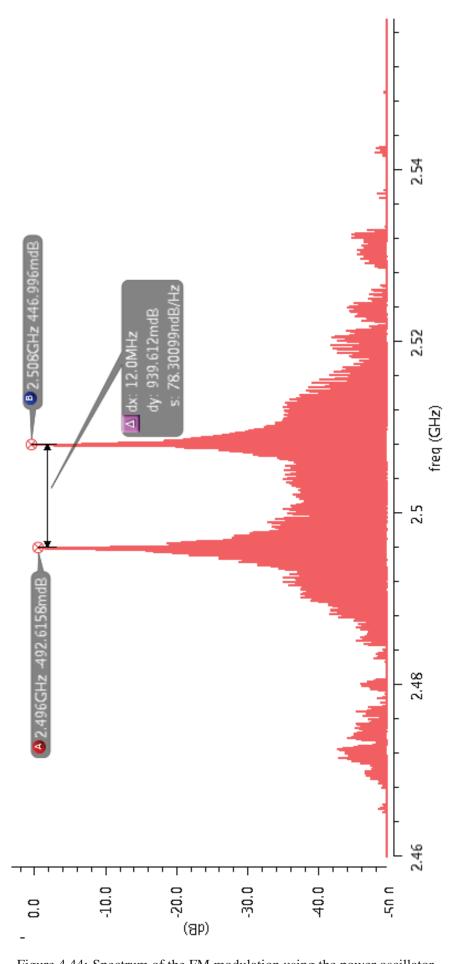

|      | Simulation of FM modulation using the power oscillator                                   | 76 |

| 4.44 | Spectrum of the FM modulation using the power oscillator                                 | 77 |

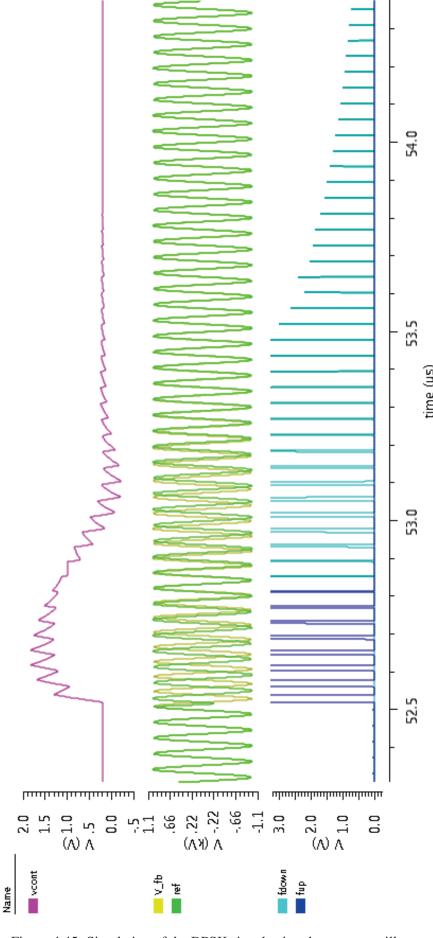

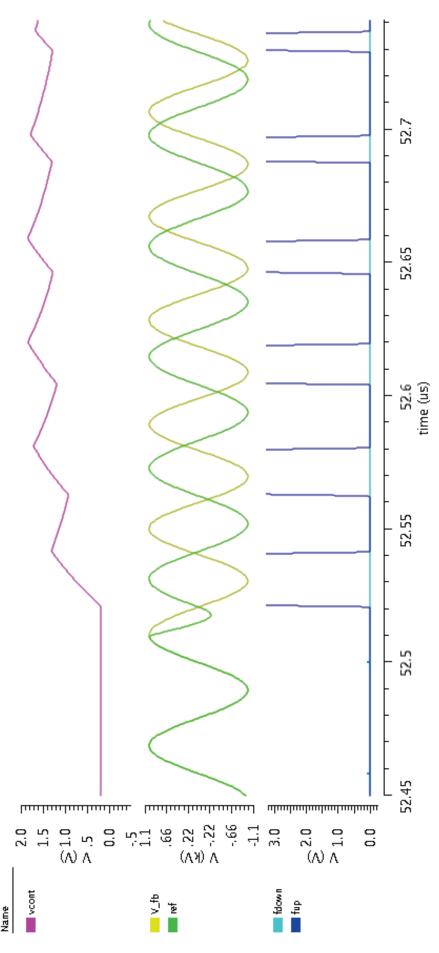

| 4.45 | Simulation of the BPSK signal using the power oscillator.                                | 78 |

| 4.46 | Detail of the simulation showing the switching moment                                    | 79 |

# LIST OF TABLES

| 4.1 | Comparison among other PA found in the literature      | 58 |

|-----|--------------------------------------------------------|----|

| 4.2 | Comparison among power oscillator from the literature. | 69 |

### LIST OF SYMBOLS

#### **Symbols**

$\mathcal{L}\{\Delta\omega\}$  Phase noise dBc/Hz

#### **Abbreviations**

AM Amplitude Modulation FM Frequency Modulation PM Phase Modulation

CAD Computer Assisted Design CCO Current Controlled Oscillator

CMOS Complementary Metal-Oxide Semiconductor

DRC Design Rule Check

PCB Printed Circuit Board

PLL Phase Locked Loop

DE Drain Efficiency

PAE Power Added Efficiency

LNA Low Noise Amplifier

LVS Layout versus Schematic

MIM Metal-Insulator-Metal cap

MIM Metal-Insulator-Metal capacitor MOM Metal-Oxide-Metal capacitor

ng Number of gates

PA Power Amplifier

PVCO Power VCO

PD Phase Detector

PLL Phase Locked Loop

PNOISE Periodic Noise

PSS Periodic Steady State

Q Quality Factor RF Radio Frequency SoC System on Chip

VCO Voltage Controlled Oscillator

VHDL VHSIC Hardware Description Language

#### 1 INTRODUCTION

#### 1.1 CONTEXTUALIZATION

Energy consumption has become a key aspect in modern electronics. In consumer products such as cell phones and tablets the raising complexity has the goal to offer high computational power and multistandard communication interfaces. Modern CMOS technology have evolved such that the hardware is very power efficient enabling computational power in portable devices to be comparable to computers. In the context of communication, the use of an optimized circuit for each communication standard increases the battery lifetime but increases the complexity of the PCB as more chips must be placed and connected to the antenna or antennas. RF simulations are often needed to ensure the correct high frequency characteristics of the PCB, increasing development time and cost.

Another application where energy consumption is a key aspect are wireless sensor networks. It is well known that energy is the strongest limitation of these engineering solutions and much work has been presented in order to address this issue, from hardware design [1], efficient communication protocols [2], high level modeling for energy optimization [3] among many others. In this type of application, the communication is also responsible for the largest part of the consumption.

Observing these engineering solutions, it is possible to conclude that, in order to increase the battery lifetime, special care must be taken with the RF transceivers, from hardware to software. In hardware level, the most power hungry circuit inside the transceiver is the power amplifier that is often narrow band and optimized for a given communication standard offering reasonable efficiency. These considerations are made assuming that typical transmitter architectures are used.

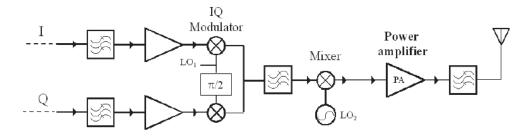

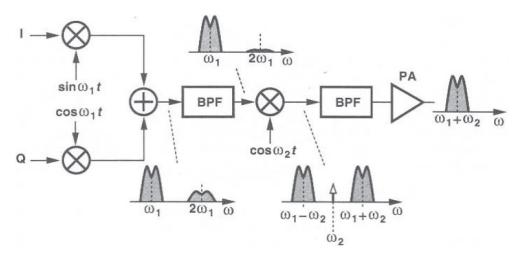

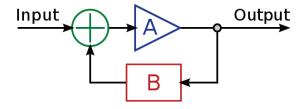

The most common architectures are homodyne and heterodyne, discussed in Chapter 2. These systems are based on large number of RF blocks such as filters, mixers and tuned amplifiers. A typical heterodyne transmitter is shown in Figure 1.1.

Figure 1.1: Heterodyne transmitter architecture. [4]

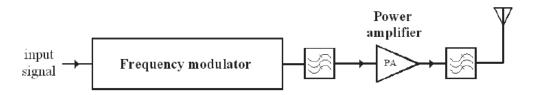

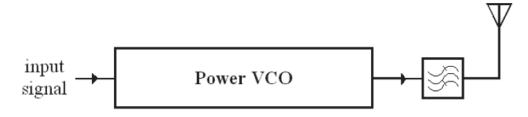

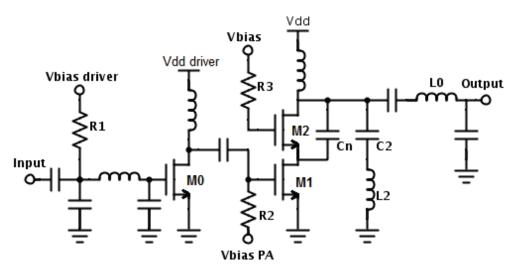

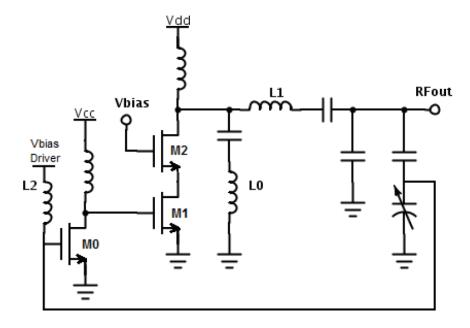

Efforts have been made to merge essential RF functions and examples of this trend is shown in [5] [6]. In all these works, the power amplifier is clearly separate from the other circuits. One other trend in architectural level is to simplify the RF part of the transmitter towards digital circuits and the up-conversion as close as possible from the antenna. A simplified RF transmitter is shown in Figure 1.2.

Figure 1.2: Direct modulation architecture [4]

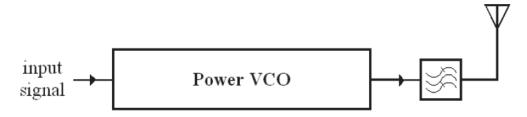

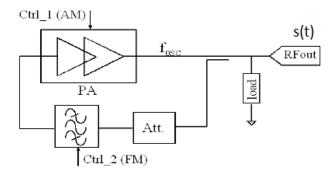

Taking both trends into account, circuit level and architecture level, it is possible to think of a transmitter composed basically by a power oscillator. The modulation of this transmitter is composed of digital or baseband signals that are used to modulate signal generated by the circuit. The proposed architecture is shown in Figure 1.3. The idea is that the input signal modulates the RF carrier. In this way, being able to reconfigure the input signal would lead to a reconfigurable RF transmitter reducing the problems already described for classical architectures.

Figure 1.3: Transmitter based on Power Oscillator [4]

Being the center of the whole transmitter it is important to fully understand the characteristics of the power oscillator as well advantages, limitations and difficulties in its design. This work is aimed at this target.

This work is part of a cooperation between University of Brasília and University of Bordeaux implemented in 2010 by a Capes-Cofecub Program coordinated by Professor Paulo Henrique Portela. Two thesis in co-supervision have been supported by the program:

- The research about the implementation of Doherty power amplifiers in submicron CMOS technologies developed by Marcos Lajovic Carneiro supervised by Professor Paulo Henrique Portela from University of Brasilia, Professor Eric Kerhervé and Associate Professor Nathalie Deltimple from University of Bordeaux and defended in December 2013.

- This work on the study of power oscillators supervised by Professor Sandro Augusto Pavlik Haddad from University of Brasilia, Professor Eric Kerhervé and Associate Professor Nathalie Deltimple from University of Bordeaux.

Both students spent 18 months in France and were able to design and prototype CMOS circuits connected to the research topic.

#### 1.2 GOALS OF THIS WORK

As part of the discussed cooperation, this work had the main goal to study, design and measure an RF power oscillator dedicated to communication standards. Further results include the study of the technical viability of direct modulation of the oscillator in order to obtain a system closer to the one depicted in Figure 1.3.

#### 1.3 MAIN CONTRIBUTIONS

The main contributions of this work are listed and commented in the list below.

- The study of waveform engineering to address the problem of voltage stress in switched power amplifiers;

- The use of class EF2 circuits in RF, which will be presented in Chapter 2;

- The design and measurement of class EF2 power amplifier;

- The design and measurement of class EF2 power oscillator;

- Study of the direct modulation of a power amplifier and the presentation of theoretical limits;

#### 1.4 ORGANIZATION OF THE DOCUMENT

In order to provide an overview on the research topics made in this work, related work on RF amplifiers, oscillators, some waveform engineering techniques and reconfigurable RF transmitters are presented in Chapter 2.

The design methodology for analog integrated circuit design and the measurement procedures are presented in Chapter 3. The used methodology for the design of the power amplifier and power oscillator are also shown. Specific comments are made about the measurement of each prototyped circuit.

Simulation and measurement results are presented in Chapter 4. The results include some theoretical analysis on direct modulation of oscillators, design and measurement of the designed power amplifier and power oscillator, a discussion on simulation issues and the proposed RF transmitter architecture.

The conclusions, future work and list of publications are presented on Chapter 5.

### 2 BIBLIOGRAPHICAL RESEARCH

This Chapter describes the theoretical background needed to evaluate this work. Among the different subjects covered in this text, special attention will be given to the following topics: (i) power amplifiers (with a special discussion about class E switched power amplifier), (ii) voltage stress in power amplifiers in modern CMOS technology, (iii) oscillators and power oscillators, (iv) common RF transmitter architectures and (v) issues on the used technology.

#### 2.1 COMMUNICATIONS STANDARDS

High throughput mobile communication is already reality in many countries. The LTE (Long Term Evolution) has come up as a solution as a world wide standard for mobile applications. Managed by 3rd Generation Partnership Project (3GPP), this standard requires features that push the technological limits of IC design such as [7]:

- scalable channel bandwidth from 1.4 MHz up to 20 MHz;

- center frequencies from 700 MHz (in band 12) to 3500 MHz (in band 22);

- compatibility to the implemented systems;

- different modulation schemes, from QPSK to 64-QAM.

The standard also defines several criteria for ACPR (Adjacent Channel Power Ratio), output power levels and transmission quality, to name a few. All these specifications have a direct impact on the circuit performance and the document [7] concerns only the user equipment. Other parts of the network hardware are specified in similar documents.

Both Brazil and Europe share the specification of use of the band around 2.5 GHz. For this reason, all this work is made in this band. The viability of the solutions shown here do not depend on frequency and a redesign would be necessary to address other frequencies.

The items shown above present the the need of a very flexible hardware, that is able to be reconfigured depending on the situation of use. This work studies a reconfigurable RF transmitter based on an innovative architecture.

Futher information about LTE can be found in 3GPP website or in [8].

#### 2.2 ARCHITECTURE OF RF TRANSMITTERS

This section presents an analysis on basic transmitter architectures: homodyne and heterodyne. A brief discussion is made about the advantages and limitations. The goal is to understand why these architectures are difficult to be made reconfigurable and flexible in order to address the multistandard requirements discussed earlier.

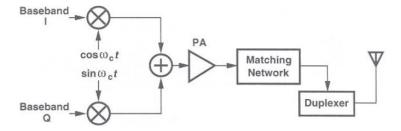

#### 2.2.1 Homodyne

Homodyne transmitters are characterized by direct frequency conversion from baseband to the desired RF frequency. The block diagram is shown in Figure 2.1. In this Figure, the orthogonal components I and Q are considered to be already modulated either by analog or digital means. The mixers are responsible for frequency conversion. The carrier frequency is generated by a PLL that is omitted. Notice that the RF power contained in the carrier frequency generated by the PLL is often very low, only enough to create a voltage to drive the LO input of the mixers. It is also important to notice that, as components I and Q are orthogonal, the RF carrier must also be composed of two orthogonal components. The adder is responsible for building the modulated RF signal that must be power amplified by the PA. The matching network is responsible for presenting the correct impedance to the output of the PA and the duplexer makes the connection among the antenna and the transmit and receive paths.

Figure 2.1: Direct conversion transmitter [9]

In real world implementations, all circuits are optimized to a given frequency band with linearity and frequency characteristics defined by the desired modulation scheme. Changing these parameters would demand alterations in the hardware which are often not possible. In Figure 2.1 filters for spurious attenuation are also omitted. These highly selective filters are also hard to tune.

Despite the difficulty in turning the transmitter in a multistandard system, this architecture suffers from serious drawbacks. One of them is the disturbance of the carrier generator by the PA. A fraction of the powerful modulated signal generated by the PA reaches the VCO through the substrate creating a "noisy" carrier due to injection pulling or locking. This effect is very common in modern technologies that use a highly doped, low impedance, substrate and which makes it difficult to be solved by shielding [10].

Another problem that may occur is the so called I/Q mismatch. Difficulties in generating carrier signals exactly 90° apart generate component signals that are not orthogonal in the carrier frequency causing intersymbol distortion, increasing EVM (Error Vector Magnitude). In the modulation constellation this can be observed by a moving or rotating the ideal constellation [11]. In some part because of these two

problems direct conversion architectures are less common than multiple conversion counterparts.

#### 2.2.2 Heterodyne

In order to address these two serious problems, the heterodyne architecture (with multiple frequency conversions) have been proposed [12] and a typical block diagram is shown in Figure 2.2. Because of the different frequencies among the modulated RF signal generated by the PA and all the oscillators in the system, the problem of leakage is mitigated. The signal still leaks but it causes negligible (if any) effects. The generation of the modulated signal is made in an intermediate frequency where the phase imbalance is better controlled.

Figure 2.2: Two-step conversion transmitter [9]

The solution for the leakage and I/Q imbalance comes at the expense of a larger complexity and power consumption as more blocks are needed. The reconfigurability problem then is increased as more blocks needs to be reconfigurable.

The trend towards reconfigurability and integration are present in RF architectures as digital interfaces are pushed further and further towards the RF circuitry. Some examples of this trend are shown in [13]. Being configurable by software, the digital circuitry around the RF circuits could lead more flexibility. Rethinking the RF part, then, becomes necessary to replace the several separate circuits and reduce the need for filtering.

#### 2.2.3 Towards a Simpler Architecture

The classical transmitter architectures present one characteristic in common: both deal with frequency translation using mixers. Being RF circuits, mixers tend to be tuned circuits. In addition, when the filtering provided by the mixer itself is not sufficient to fulfill the specifications, filters banks are included.

Even though work on reconfigurable RF circuits can be found, maintaining the efficiency and performance is very hard [14][15][16]. This fact leads to the use of specialized transceivers for each communication standard instead of one reconfigurable transceiver. The use of one reconfigurable transceiver could

simplify the PCB on which the final product is mounted, reducing design costs and increasing robustness.

The use of a circuit that can be directly modulated by a baseband signal and be directly connected to the antenna leads to a much simpler transmitter architecture, in which fewer RF circuits are used. The proposed architecture is presented in Figure 1.3 and repeated here for convenience.

Figure 2.3: Transmitter based on Power Oscillator [4]

In this way, the problem of reconfigurability is separate in two simpler problems: (i) generate the correct input signal, which can be achieved by digital or analog base band processing and (ii) designing a power oscillator that can fullfil the specifications. Notice that the problem of designing many RF building blocks is now reduced to one circuit.

#### 2.3 POWER AMPLIFIERS

Being the center topic of this work, a discussion on power amplifiers must be made. In the transmit chain, the function of the power amplifier is to deliver to the antenna a modulated signal with some quality parameters in sufficient power levels to be received with reasonable quality after the channel's attenuation and distortion. In this context, sufficient and reasonable quality are defined by the desired communication standard.

The specifications of the PA will be strongly dependent on the desired modulated signal, due to an intrinsic trade-off between linearity and efficiency that will be discussed in later sections of this Chapter.

In modern portable devices, the end user's satisfaction is very dependent on the battery lifetime. As the power amplifier is normally the most power hungry circuit of the transmit chain, a well designed power amplifier can have significant impact on the such experience. In order to maintain the usage time, an efficient power amplifier can lead to smaller, lighter and cheaper batteries affecting the whole product.

#### 2.3.1 Key Parameters of Power Amplifiers

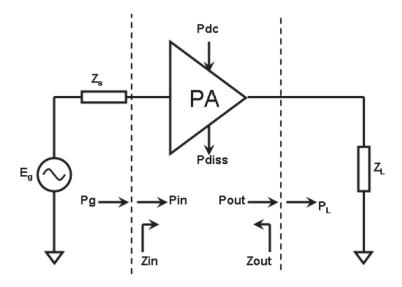

In order to be able to compare different power amplifiers, well defined figures of merit are needed. Important definitions are made with the help of Figure 2.4.

In Figure 2.4, a power amplifier is driven by a power source  $E_g$  that presents output impedance of  $Z_s$ . The load connected to its output is  $Z_L$ . The input and output impedances of the power amplifier are  $Z_{in}$  and  $Z_{out}$ , respectively. The input and output power are  $P_{in}$  and  $P_{out}$ , respectively.  $P_g$  is the power available from the source and  $P_L$  is the power delivered to the load. The DC input power is  $P_{DC}$  and  $P_{diss}$

Figure 2.4: Important definitions of a power amplifier [17].

is the power dissipated by the amplifier.

Considering that the input and output impedances are matched,  $P_g = P_{in}$  and  $P_{out} = P_L$ . This situation is common and desired, since no power reflection is desired. Considering the impedances are matched, the power gain is defined as:

$$G = \frac{P_{out}}{P_{in}} \tag{2.1}$$

It is also important to define efficiency for a power amplifier. In this context there are two widely used definitions [18]:

1. Drain efficiency ( $\eta$ ): in this text the acronym DE will be used for this parameter. It quantifies the efficiency of the DC power into RF power. It is calculated as follows:

$$\eta = \frac{P_L}{P_{DC}} \tag{2.2}$$

2. Power Added Efficiency: in this text the acronym PAE will be used for this parameter. It also quantifies the efficiency of the DC power into RF power but takes into account the power needed to drive the amplifier. It is important to notice that the PAE will tend to DE when the power gain is large, because lower input power is needed to generate the same output power. It is calculated as follows:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} = \eta \left( 1 - \frac{1}{G} \right) \tag{2.3}$$

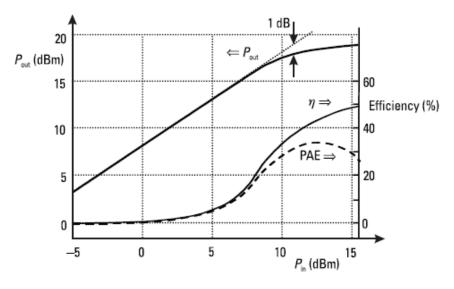

As power amplifiers must often be able to deal with large signal swing, this type of circuit is frequently under operating conditions that lead to signal distortion, specially when operating close to the maximum output power. It is important to be able to understand the notion of gain compression. The AM/AM

characteristic depicts how output power, and consequently power gain, behaves as a function of input power. The typical AM/AM characteristic of a PA is shown in Figure 2.5. In this Figure, typical curve shapes are shown for output power, PAE and Drain Efficiency ( $\eta$ ). Also depicted in Figure 2.5 is the so called "1 dB output power compression point" (OCP1) and this parameter is defined as a 1dB output power deviation from the ideal linear curve. Under high input power levels it is possible to observe that the output characteristics deviate from the ideal linear response. When the PA operates above OCP1, the amplifier is said to be compressed. A complete description and analysis of these distortions are not in the scope of this work and further information can be found in [19].

Figure 2.5: Fictional AM/AM characteristics[20].

It is in the compression region that the amplifier's efficiency reaches its maximum, because the output power is maximum. For that reason, from the efficiency point of view it is interesting to work at that region most of the time.

Along with the efficient (but non-linear) operation, distortion becomes an issue. Parameters such as ACPR (adjacent channel power ration) [18] quantifies the amount of harmonic content generated by the amplifier in amplitude domain. This parameter is specified for each communication standard and has the goal to protect the adjacent channel from interference. One way to estimate this parameter in simulation is to apply two tones to the input of the amplifier and study the output spectrum. Even order intermodulation will fall inside the communication band raising the power in the adjacent channel.

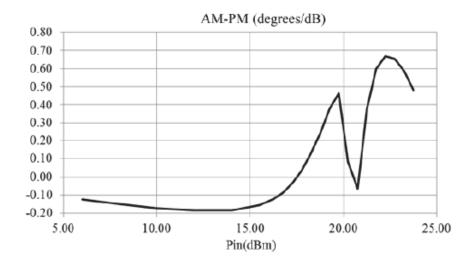

It is important to notice that no information is given about phase distortion. The existence of uncompensated phase distortion may cause symbol error in phase modulated signals such as PSK or QAM and increase EVM measurements. Typical AM/PM characteristics are shown in Figure 2.6.

This type of non-linearity is a direct result of current clipping and overdrive and often demands linearization. Linearization schemes will be treated later in the text.

Figure 2.6: Typical AM/PM characteristics [21].

#### 2.3.2 Combinantion of Stages

In order to obtain larger power gain, a power amplifier may be composed of more than one stage. In the case of having a power amplifier composed by 2 stages, the total gain, in dB, is given by:

$$G_T = G_1 + G_2 (2.4)$$

In Equation 2.4,  $G_1$  and  $G_2$  represents the gain of first and second stage, respectively, while  $G_T$  is the total gain of the power amplifier.

The PAE of the composite amplifier is given by [22]:

$$PAE_T = \frac{\eta_2}{1 + \frac{\eta_2}{\eta_1 \cdot G_1 \cdot G_2}} \tag{2.5}$$

Equation 2.5 states that the overall efficiency is dominated by the efficiency of the 2nd stage if the gain of the power amplifier is large. Bearing this result in mind, it is feasible to use a driver to increase the power gain and still obtain an efficient power amplifier.

#### 2.3.3 Classical trade-off in Power Amplifier Design

As shown in Figure 2.5, linear operation is frequently obtained at high backoff. In this situation, the output power is far from the maximum power and, thus, the efficiency is low. This fact exemplifies a strong trade off in power amplifier desing: linearity x efficiency.

Techniques have been proposed to increase the efficiency at high backoff at the expense of circuit complexity such as Doherty technique [23] but these issues are beyond the scope of this text.

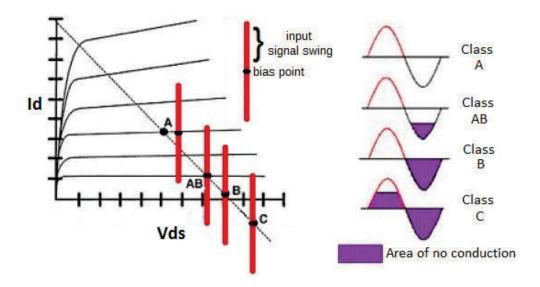

In order to be able to control the trade off as a function of the desired specifications, it is possible to alter the biasing of the active device leading to different operating classes. Power amplifiers can be classified in two broad categories:

- "Sinusoidal": in this category, the active device is used as a controlled current source. Examples are classes A, AB, B and C. The difference among these classes is the biasing conditions of the active device, which changes the conduction angle.

- Switched: in this category, the active device is used as a switch. Examples are classes D, E and F. The difference among these classes is the waveform the switch deals with.

A complete analysis on the design of each class is made in [19]. In this text a small description about the operating classes is made for comparison purposes.

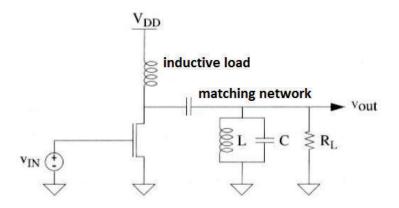

#### 2.3.4 Sinusoidal Classes

All "sinusoidal" amplifiers could be built using a common-source amplifier with an inductive load and an output matching network as shown in Figure 2.7. Changes in the class of operation come from a change in the bias voltage of source  $V_{in}$ .

Figure 2.7: Circuit topology for sinusoidal PA [24].

#### 2.3.4.1 Class A Power Amplifiers

Class A is defined when the DC bias voltage of the transistor is such that it is able to conduct current the whole time. An other way of stating this is saying the conduction angle is 360°, which means the transistor conducts current the whole cycle. Considering a first order transistor model for simplicity, in class A, the transistor must be always on. Which leads to:

$$V_{IN} \ge V_{th} \tag{2.6}$$

There are two ways of obtaining such a behavior: (i) maintaining the input voltage swing and increasing the DC biasing or (ii) maintaining the DC biasing and reducing the input voltage swing. The first approach increases the DC current, increasing the power consumption to make the amplifier achieve larger maximim

output power in class A. The second approach has the exact opposite behavior, reducing the output power to maintain the transistor biased in class A. It can also be shown that these changes in the signal do not alter the theoretical efficiency [19].

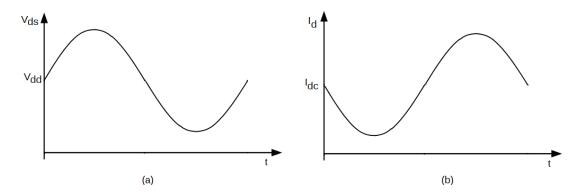

In this class, as the transistor is always carrying current, the transistor voltage-to-current characteristics are never chopped leading to higher linearity. This linear behavior is achieved at the expense of efficiency as much DC power is used to bias the transistor. The voltage and current waveforms are shown in Figure 2.8.

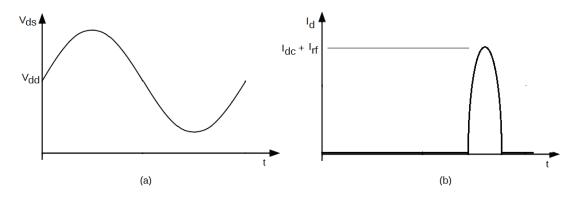

Figure 2.8: Class A waveforms: (a) voltage and (b) current.

Assuming all devices are lossless and that the transistor is an ideal transconductor ( $v_{ds_{sat}}=0$ ), the theoretical maximum efficiency can be shown to be 50% [25]. This value of efficiency leads to heating problems and low usage time in battery powered devices. This is obviously a very optimistic limit and its assumptions also lead to an important discussion on the voltage stress the transistor must be able to sustain. When operating at the maximum theoretical output power, the transistor must be able to sustain voltages up to  $2V_{dd}$ . This becomes a serious issue assuming that device scaling forces reductions in breakdown voltage [24].

As a conclusion, class A power amplifiers delivers linearity at the cost of low efficiency and relatively large device stress. For these reasons, class A amplifiers are rare in RF applications [24].

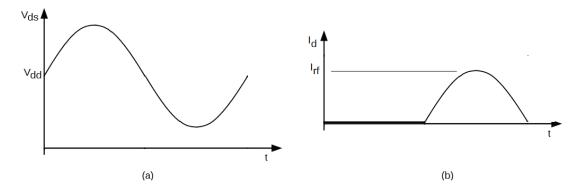

#### 2.3.4.2 Class B Power Amplifiers

Still considering the first order transistor model, biasing the transistor exactly at the threshold voltage, leads to 180° conduction angle, meaning that the transistor would conduct current for exactly half a cycle. As in reality the device does not turn on abruptly, class B is an idealization but serves well for categorization purposes.

Reducing the conduction angle, reduces the DC power dissipation, potentially leading higher efficiency. As the current would be chopped in 50% of the duty cycle, the output power is non-sinusoidal and harmonics are generated, polluting side bands if proper care is not taken. On the other hand, the circuit is able to deliver proportional input-output power characteristics, addressing the problem of power amplification.

At maximum output power, it can also be shown that the theoretical maximum efficiency is 78,5% maintaining the voltage stress up to  $2V_{dd}$ . In class B, efficiency is traded for linearity, exemplifying this

common design decision. The ideal class B voltage and current waveforms are shown in Figure 2.9.

Figure 2.9: Class B waveforms: (a) voltage and (b) current.

It is important to comment class AB power amplifiers. This class is obtained when the conduction angle is kept any value between  $180^{\circ}$  and  $360^{\circ}$ . The efficiency increases as the operation leaves class A towards class B and voltage stress issues are kept constant when operating at maximum power.

#### 2.3.4.3 Class C Power Amplifiers

Keeping the tendency of reducing the DC bias voltage of the transistor, reduces the conduction angle to values lower than 180°, leading the transistor to conduct less than half of the period. The drain current consists of a periodic train of pulses. The non-linearity is stronger than in class B as the current leaves the sinusoidal-like shape and tends to train of pulses. The harmonic content is also increased. The fictional class C voltage and current waveforms are shown in Figure 2.9.

Figure 2.10: Class C waveforms: (a) voltage and (b) current.

The biasing conditions with a fictional input swing, a representation of the conduction angles is shown in Figure 2.11

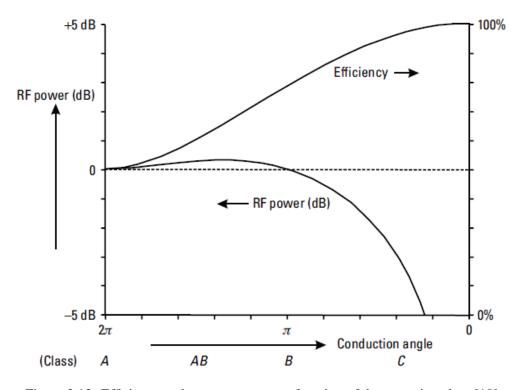

Considering  $2\Phi$  the total conduction angle, Equation 2.7 [25] describes how the theoretical efficiency varies once the conduction angle is changed.

$$\eta_{max} = \frac{2\Phi - \sin(2\Phi)}{4(\sin\Phi - \Phi\cos\phi)} \tag{2.7}$$

Figure 2.11: Representation of biasing scheme and conduction angle.

In fact, Equation 2.7 is general and can be used for any conduction angle, from class A to deep class C. The evolution of efficiency and normalized output power with the operation class is shown in Figure 2.12.

Figure 2.12: Efficiency and output power as a function of the operating class [19]

Some interesenting aspects can be observed in Figure 2.12. First of all, the manner the efficiency depends on the conduction angle is shown. When operating near class A, a reduction in the conduction angle leads to marginal increase in efficiency. The same asymptotic behavior is observed in deep class C.

Regarding the power handling capability (normalized with respect to class A operation) also displays important characteristics. In ideal class B, the circuit is capable of dealing with as much power as its class

A counterpart. The difference would be the efficiency and harmonic content generation. As the conduction angle is reduced, the power handling capability is also strongly reduced leading to the paradoxical 100% efficiency but no output power. This effect can be explained by the fact that the current pulses become narrower as the conduction angle is reduced, ultimately not allowing any current to flow.

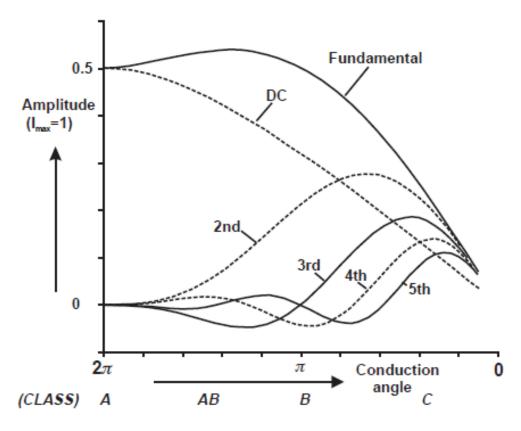

The increase in power handling capability observed in class AB can be explained by an increase in the current flowing in the fundamental frequency. As a consequence of the non-linearity, harmonic content is generated. It is shown in Figure 2.13.

Figure 2.13: Harmonic generation as a function of the operating class [25]

A reduction in the DC component is explained by the reduction in the quiescent current flowing through the transistor. Power in the 2nd harmonic grows rapidly affecting the power leakage to adjacent channels. It can be observed that as the conduction angle is reduced, stronger non-linearity is obtained as expected. The combination of Figures 2.12 and 2.13 clearly show how the linearity versus efficiency trade off is present in power amplifier design.

As the transistor is used as a current source in sinusoidal classes, in order to obtain maximum power, full voltage swing is needed. In this sense, all sinusoidal classes present similar voltage stress across the transistor, ideally  $2V_{dd}$ .

#### 2.3.5 Switched Classes

In this section, switched classes are discussed. Treating the transistor like a switch, instead of a current source, can, ideally, lead to 100% efficiency. The discussion starts with class D and follows on to class E.

#### 2.3.5.1 Class D

A class D amplifier is shown in Figure 2.14. Observing the biasing of the transistor, it is normally off as  $V_{gs}=0$ . Considering  $V_{th}=0$  for simplicity, each transistor of Figure 2.14 is biased in class B. They share one side of a transformer that serves as DC feed.

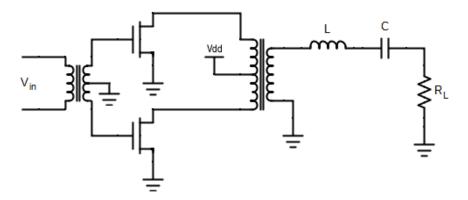

Figure 2.14: Class D amplifier

Considering that inductor L and capacitor C form a high quality factor series LC tank tuned to the fundamental, the only frequency allowed to flow through  $R_L$  is the fundamental. The basic difference between a class B and a class D amplifier is how the transistors are driven. In class D power amplifier, the transistor are driven hard enough to make them behave as switches, either off or in deep triode region, with a low  $R_{on}$ .

The voltage on the drains of the transitors vary between 0, due to switching, and  $2V_{dd}$ , due to reaction from the transformer and, if the switch is considered ideal, theoretical efficiency of 100% is achieved [24]. As the transistor is operated as a switch, it is ideally, impossible to control the output power with respect to the input power, i.e., the amplifier operates in compression. A reduction in the input power, may lead the transistor not to operate as a switch. This would lead to a not correct class D operation, thus, reducing the overall efficiency.

As the efficiency depends on non overlapping voltage and current waveforms, very sharp switching is necessary of the correct operation in class D and, consequently, high efficiency. Often the transistor sizes are made very big in order to reduce  $R_{on}$ , reducing the switching speed due to parasitic capacitance. This characteristic limits the use of class D amplifiers in many applications but works using this class have been reported [26].

#### 2.3.5.2 Class E

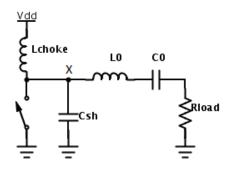

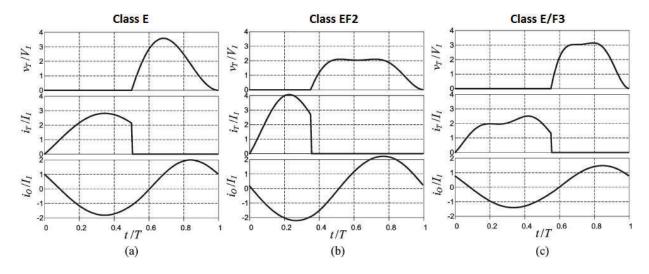

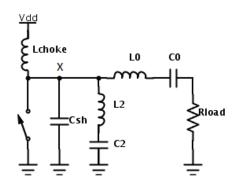

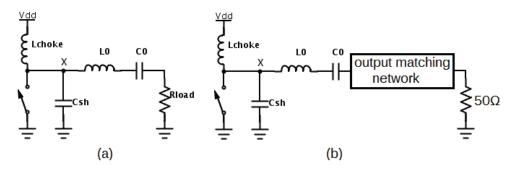

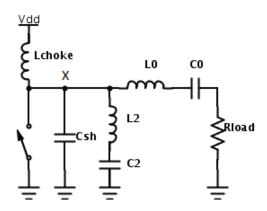

Class E circuits take advantage of reactive components in order to obtain high efficiency. The ideal class E circuit is shown in Figure 2.15. The transistor is used as a switch and, hence, in large signal operation. The passive components used are  $L_{choke}$ ,  $C_{sh}$ ,  $L_0$  and  $C_0$ . The resistor  $R_{load}$  represents the load seen at the terminal of  $C_0$ .

The idea behind switching-mode PA, such as class E, is designing the time domain voltage and current

Figure 2.15: Ideal class E circuit

waveforms in a way they never overlap. Notice here that the mentioned voltage is at point X (across the switch) and the current through the switch. If there is no overlap between these two waveforms, the transient power dissipation on the switch is always zero, leading to high efficiency. The ideal time-domain waveforms are shown in Figure 2.16 and the ideal output power is given by Equation 2.8, where k is a constant dependent on the class and  $V_{dd}$  is the supply voltage.

$$P_{out} = k \cdot \frac{V_{dd}^2}{R_{load}} \tag{2.8}$$

Mathematically, class E operation is obtained if Equations 2.9 and 2.10 are simultaneously solved.

$$v_x(t_1) = 0 (2.9)$$

$$\frac{\delta v_x(t_1)}{\delta t} = 0 \tag{2.10}$$

It can be shown that the output power is related to the discontinuity in the current waveform as the switch opens [27]. The voltage waveform is designed to meet zero voltage switching (ZVS) and zero voltage slope switching (ZdVS) conditions. ZVS establishes that the switch closes when voltage waveform achieves zero voltage while ZdVS estates that the derivative of the voltage should also be zero when the switch closes. The ZVS condition is essential for the non overlapping waveforms while ZdVS is used to minimize overlap in case of parameters or frequency variations.

In high frequencies, at the moment of the switch commutation, some overlap between voltage and current occur and, as the curret is often high at this moment, losses are not negligible. One way to address this issue is to use the called class  $E_m$ : This class fulfils conditions presented in Equations 2.9 and 2.10 also for the current across the switch. In its name, "m" stands for microwave. This higher efficiency is obtained at the cost of complexity as two power amplifiers are put to work in parallel. More discussion about this class is made in [28].

As the definition of class E circuits is made by time domain equations, the design methodology is basically made using time domain approaches. It is important to mention that Figure 2.16 is obtained for a normalized voltage and load class E circuit, i.e.,  $V_{dd} = 1$  and  $R_L = 1$ .

Figure 2.16: Ideal class E waveforms: (a)voltage and (b)current [27]

Despite the apparent simplicity of the schematic shown in Figure 2.15, the use of class E circuits is attractive in RF frequency due to the existence of capacitor  $C_{sh}$ . This capacitance is necessary for the correct operation in class E and can be implemented by the parasitic capacitance of the transistor. In this sense, the parasitic capacitance becomes necessary instead of a burden as it was shown to be in class D.

Assuming an ideal switch, the simultaneous solution of Equations 2.9 and 2.10 is obtained by the correct design of the passive network. The LC tank formed by  $C_0$  and  $L_0$  play two roles in the design. The capacitor  $C_0$  and part of the inductor  $L_0$  are dimensioned to be a filter tuned to the switching frequency. Supposing this filter has a high quality factor, a sinusoidal current flows through the load resistor, despite the non-linear behavior. The rest of inductance present in  $L_0$ , called excess inductance in [29], is used, along with  $C_{sh}$  to shape the voltage and current waveforms. This assumption is valid if  $L_{choke}$  is considered a real RF choke. In this way, it does not participate in the waveform engineering [27]. Ideal design equations are derived in [29].

Another issue is to design the switch. Assuming the transistor is being driven by sufficent power to set it to triode when it is ON,  $R_{on}$  can be estimated as shown in Equation 2.11:

$$R_{on} = \frac{1}{\mu_n C_{ox} W / L(V_{gs} - V_{th} - V_{ds}/2)} \approx \frac{1}{W}$$

(2.11)

It is clear that using large device width reduces the parasitic resistance and, therefore, it should be maximized to increase efficiency. Nevertheless, once  $R_{on}$  becomes smaller than the resistive losses in the passives, further increase in W does not affect the efficiency. On the other hand, the size of the device is limited by the parasitic capacitance needed to implement the passive network around the transistor. If the device width is increased beyond this point, correct class E cannot be obtained.

Concerning robustness of the solution, the presence of high voltages and high currents create the so called *hot carries*. They are very energetic carriers that can be injected in the oxide causing a shift in the transistor parameters and, in the long term, cause breakdown of the oxide. This problem is alleviated in class E amplifiers as voltage and current are non-overlapping [27].

Many works present the ideal waveforms expected for this kind of circuit, for instance [30]. This kind of circuit was proposed in [29] back in 1975. In [29], the time domain waveforms are presented as well as a design methodology based on closed form equations with idealized assumptions. In the ideal class E, a large impedance inductance is used as a choke, not allowing the AC current to vary along the time since this current is supplied by a large impedance in a similar way as DC current sources work. When the choke impedance is made high enough, its value does not affect the sizing of the other passive devices. A very extensive review about the class E power amplifier has been made in [27], including ideal equations, non-idealities and design guide lines. Special attention should be given to the methods of solving the class E equations in the presence of non-idealities as it leads to a optimized circuit that does not entirely fulfill class E definition in order to achieve highest efficiency.

Other works aimed at better understanding of the class E circuits and the literature on the subject is large. One work that summarizes the history of class E circuits is [27]. The authors also analyze the effect of a finite inductance instead of a choke, presenting the advantages and drawbacks. It is shown that the power capability of the amplifier is increased if a finite inductance is used, at the expense of a time varying AC current drained from the power supply. As the supply is often not capable of delivering high AC currents, large decoupling capacitors are needed to provide such current. One other drawback is the more complex design since the equations presented by Sokal [29] no longer apply and the value of the inductance affects all other device values.

A study on different passive networks able to deliver class E waveforms is made in [31]. This work uses the finite DC-feed inductance to present a class E power amplifier that presents no series resonating tank ( $L_0$  and  $C_0$  in Figure 2.15). As a consequence, upper harmonics are higher and narrow band operation is achieved. Other passive networks, such as the "parallel network circuit", capable of wideband operation, are studied in [31].

Several issues arise when implementing a class E circuit in modern CMOS technologies. In IC design, large inductances are hard to implement on chip and tend to be lossy. Thus, the implementation of on chip  $L_{choke}$  is not feasible. As the DC-feed inductance is comparable with  $L_0$ , it also has effect on the shape of the waveforms. Also the quality factor of  $L_0$  leads to non-sinusoidal currents flowing through the resistor.

Class E PA also suffers from a well known drawback: the voltage stress across the switch is high, 3.56 times the supply voltage in the ideal case [29], depicted in Figure 2.16. As the output power is a strong function of the supply voltage, it is desirable to be able to work with higher supply voltages since reducing the load ( $R_{load}$  in Figure 2.15), leads to ohmic losses in the transformation network. On the other hand, modern CMOS technologies present lower breakdown voltage after each generation. These two facts pose a serious problem in designing high power CMOS class E PA.

One possibility is to use cascoded transistors in order to split the voltage stress among many devices. This approach is commonly used and can be found in [32], [33] and [34]. Although this approach adds the  $R_{ON}$  of another device, it allows an increase in the supply voltage. Roughly, if n transistors are stacked, the supply voltage can be increased by n and the load resistor made  $n^2$  times smaller for the same output power. In this scenario, if the output power is kept constant, the current flowing through the switch is reduced by n, reducing the losses in the passives and in the switch.

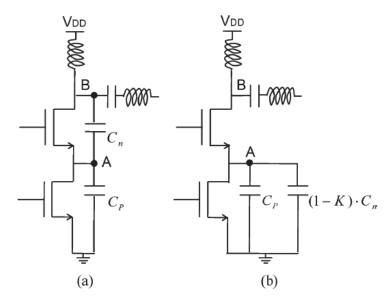

Also using cascode switches, the works [35] and [36] deal with the parasitic capacitance added between the transistors. It is shown to be an important source of efficiency loss. Tuning this capacitance out with an inductor [32] [34] demands large area and is a narrow band approach. Instead of using inductors, a capacitor is used to implement a negative capacitance that subtracts the parasitics leading to higher efficiencies. Increases of around 2% to 3% were observed in the present work.

#### 2.4 VOLTAGE STRESS IN POWER AMPLIFIERS

Class E circuits find great use in RF design due to its characteristics to use the parasitic capacitance in order to obtain high efficiency. Unfortunately, it comes at the expense of high voltage stress.

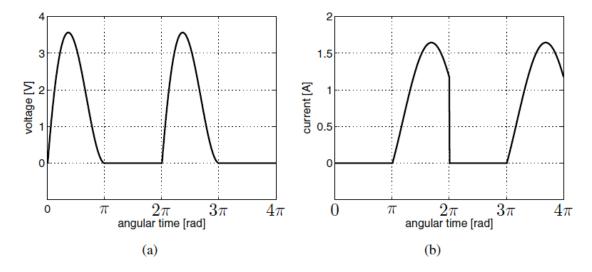

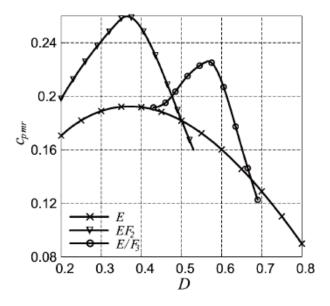

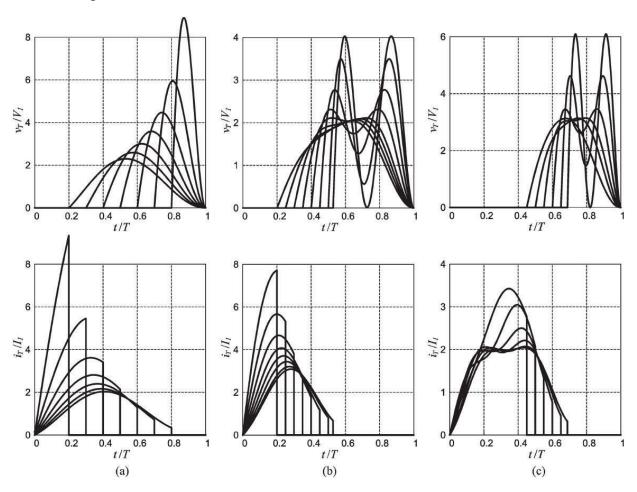

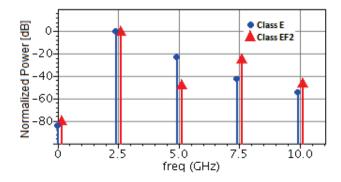

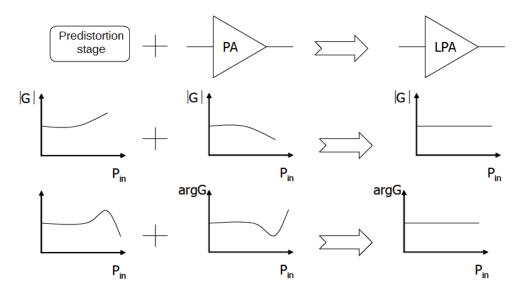

Instead of adding extra transistors to deal with the voltage stress intrinsic to class E, waveform engineering can be used to create an amplifier with certain interesting characteristics, such as lower voltage stress or greater power capability, for example.