# Distributed clock generator for globally and locally synchronous chips with a large size

Chuan Shan

#### ▶ To cite this version:

Chuan Shan. Distributed clock generator for globally and locally synchronous chips with a large size. Operating Systems [cs.OS]. Université Pierre et Marie Curie - Paris VI, 2014. English. NNT: 2014PA066623. tel-01230550

## HAL Id: tel-01230550 https://theses.hal.science/tel-01230550

Submitted on 18 Nov 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE l'UNIVERSITÉ PIERRE ET MARIE CURIE

École Doctorale Informatique, Télécommunications et Électronique (EDITE)

Présentée par :

Chuan SHAN

# Pour obtenir le grade de : DOCTEUR de l'UNIVERSITÉ PIERRE ET MARIE CURIE

Sujet de la thèse :

## GÉNÉRATEUR DISTRIBUÉ D'HORLOGE POUR PUCES GLOBALEMENT ET LOCALEMENT SYNCHRONES DE GRANDE TAILLE

Présentée le :

14.11.2014

Le jury est composé de :

| M. Patrick GIRARD  | LIRMM Montpellier         | Rapporteur            |

|--------------------|---------------------------|-----------------------|

| M. Laurent FESQUET | TIMA Grenoble             | Rapporteur            |

| M. Gérard BERRY    | Collège de France         | Examinateur           |

| M. Daniel ETIEMBLE | Université Paris Sud, LRI | Examinateur           |

| M. Alain GREINER   | UPMC, LIP6                | Examinateur           |

| M. François ANCEAU | CNAM                      | Directeur de Thèse    |

| M. Dimitri GALAYKO | UPMC, LIP6                | Co-directeur de Thèse |

## DOCTORAL DISSERTATION PIERRE AND MARIE CURIE UNIVERSITY

Doctoral School of Informatics, Telecommunications and Electronics (EDITE)

Presented by:

Chuan SHAN

# To obtain the degree of : DOCTOR OF PHILOSOPHY AT UNIVERSITY OF PIERRE AND MARIE CURIE

Thesis title:

## DISTRIBUTED CLOCK GENERATOR FOR GLOBALLY AND LOCALLY SYNCHRONOUS CHIPS WITH A LARGE SIZE

Presented on:

11.14.2014

Members of jury:

| M. Patrick GIRARD  | LIRMM Montpellier         | Reviewer      |

|--------------------|---------------------------|---------------|

| M. Laurent FESQUET | TIMA Grenoble             | Reviewer      |

| M. Gérard BERRY    | Collège de France         | Examinator    |

| M. Daniel ETIEMBLE | Université Paris Sud, LRI | Examinator    |

| M. Alain GREINER   | UPMC, LIP6                | Examinator    |

| M. François ANCEAU | CNAM                      | Supervisor    |

| M. Dimitri GALAYKO | UPMC, LIP6                | Co-Supervisor |

## **Abstract**

This thesis addresses the problem of global synchronization of large system on chip (SoC) in the context of deep submicron technologies.

With the development of the silicon microtechnology and with the increase of density of integration, conventional clock distribution systems become more and more difficult to be implemented in modern chips. Some designers turn toward the asynchronous communications protocols, in order to remove the need of a global clock, however, the cost of this choice is a lower verification level and a high complexity of design. This research focuses on the study of an alternative clock generation technique, allowing implementation of highly reliable synchronous digital circuit in deep submicron CMOS technologies.

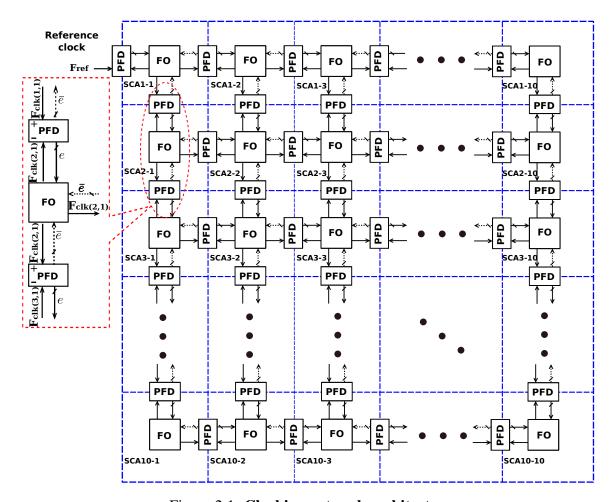

My PhD work is subsequent to the project HODISS funded by ANR, in which a distributed network of all digital phase-locked loop (ADPLL) was presented for the first time. The basic idea of this approach consists in generating clock signals locally by oscillators in each synchronous clocking area (SCA), and making these oscillators coupled with their neighboring ones in phase by using ADPLL technique. If well designed, all the locally generated clock signals should be synchronized with the reference clock both in frequency and in phase.

My PhD project aims study and implementation on silicon of a large network of ADPLLs  $(10\times10)$ , containing 100 nodes generating each a clock for the local digital circuitry. Comparing to the study curried out previously in the HODISS project, the design of blocks composing the network was adapted to the constraints related to the network scale. For instance, the resolution of the phase measurement has been increased (20 ps), the power consumption was reduced (1 mW per node). The modeling of the ADPLL networks at several abstraction levels and by different tools (VHDL, Spice, FPGA) allowed a response to study the quality of the global synchronization between the oscillators in function of different parameters of the network, and in particular, on the network size.

During my PhD project, the prototype  $10\times10$  was implemented on silicon generating clocks in the range 903-1161 MHz. It highlights a maximum phase error of less than 40 ps between two clocks in any neighboring zones. The implemented prototype is under fabrication at the period of editing of this manuscript.

Another important result of this study is the analysis of phase error between two non-neighboring oscillators in distance. By studying an FPGA prototype of the network, we obtained that maximum phase error at steady state between any observed clock signal and the reference signal is less than three steps of the PFD quantification steps.

In order to validate the performances of the clock synchronization in the implemented ASIC, we designed an on-chip clocking error measurement circuit, whose operation is based

on a measure of the integrity of a periodic sequence transmitted between two clocking domains. This circuit has a low rate for the off-chip readout (several MHz), and a high resolution ( $\pm 2.5$  ps).

Reconfigurability is another attractive feature of the distributed network of ADPLLs. In this research, we have explored this feature and proposed a novel topology with different configurations for nodes on the border and in the kernel of the network. This topology has an advantage in prohibiting phase error propagation and reflection.

**Thesis title:** Distributed clocking for synchronous SoC

**Key words:** synchronous clocking, multioscillator architecture, all-digital phase locked loop, on-chip clock error characterization

**Thesis Supervisor:** François ANCEAU, Professor at Conservatoire national des arts et métiers

**Thesis Co-Supervisor:** Dimitri GALAYKO, Associate Professor at Pierre and Marie Curie University (Paris VI)

## Acknowledgements

I would like to take this opportunity to express my sincere thanks to all those who participated directly or indirectly to the success of my thesis. I would never have been able to finish my dissertation without the guidance of my committee members, help from friends, and support from my family.

I would like to express my special appreciation and thanks to my supervisor Dr. Dimitri Galayko, for his excellent guidance, patience, giving my this opportunity and providing me with an excellent atmosphere for doing research. I would also like to thank my supervisor Dr. François Anceau for his brilliant ideas and suggestions, which inspired me a lot. Without their supervision and constant help this dissertation would not have been possible.

I would like to thank our collaborators Olivier Billoint and Sylvain Féruglio for their effort spent on this project. Their great experience and competence make our research team more complete.

I would like also to thank all my colleagues at SoC-LIP6. They created a warm environment in the SoC department. A special thanks to Eldar Zianbetov and Mohammad Javidan. They were always willing to help and give their best suggestions. Without their help, I might spend much more time on the chip implementation.

Many thank to my parents for all of the sacrifices that they have made on my behalf. They were always supporting me and encouraging me with their best wishes.

Finally I would like to thank all my friends in France and in China. I am grateful for their constant support and encouragement.

Chuan SHAN

## **Contents**

|   | Intro | oduction  | : motivation de l'étude                                           | XX111  |

|---|-------|-----------|-------------------------------------------------------------------|--------|

|   |       | Défis d   | le génération d'une horloge globale dans les SoCs                 | xxiii  |

|   |       | Défis d   | le caractériser l'erreur de phase entre deux signaux d'horloge    | XXV    |

|   | Rése  | eau de Pl | LLs tout numériques pour la génération d'horloge                  | xxvi   |

|   | Résu  | ımé de c  | contribution                                                      | xxviii |

|   | Con   | ception o | des composants                                                    | XXX    |

|   |       | Conver    | tisseur temps-numérique (TDC)                                     | XXX    |

|   |       | Filtre n  | numérique                                                         | XXX    |

|   | Le re | éseau d'. | ADPLLs tour numériques réalisé                                    | xxxii  |

|   | Cara  | ctérisati | on sur puce de l'erreur de phase entre deux signaux d'horloge     | XXXV   |

|   | Con   | clusion   |                                                                   | xxxvii |

|   | Pers  | pectives  | et travail futur                                                  | xli    |

|   |       | Modéli    | isation d'ADPLL pour l'étude de l'erreur de phase résiduelle dans |        |

|   |       |           | l'état d'équilibre                                                | xli    |

|   |       | Explor    | ation de la propriété de tolérance de faute                       | xli    |

|   |       | La dist   | ribution d'horloge pour les circuits en 3-D                       | xlii   |

| 1 | Intr  | oductio   | n                                                                 | 1      |

|   | 1.1   | Area o    | f focus                                                           | 1      |

|   |       | 1.1.1     | Problem of clocking in large digital circuits                     | 2      |

|   | 1.2   | Enviro    | nment of the PhD project: the starting point and motivations      | 5      |

|   |       | 1.2.1     | Network of coupled PLLs for clocking: history of the concept      | 5      |

|   |       | 1.2.2     | Digital phase synthesis                                           | 7      |

|   |       | 1.2.3     | Presentation of an ADPLL network prototype designed at LIP6 prior |        |

|   |       |           | to my PhD thesis                                                  | 9      |

|   |       | 1.2.4     | Phase frequency detector (PFD)                                    | 9      |

|   |       | 1.2.5     | Digital loop control of ADPLL network node                        | 16     |

|   |       | 1.2.6     | Digitally controlled oscillator (DCO)                             | 17     |

|   |       | 1.2.7     | Modeling of ADPLL and of ADPLL network                            | 21     |

|   |       | 1.2.8     | Stability of the PLL networks                                     | 23     |

|   |       | 1.2.9     | Multiplicity of synchronization modes                             | 24     |

|   |       | 1.2.10    | Discussion of test results of the implemented prototype           | 26     |

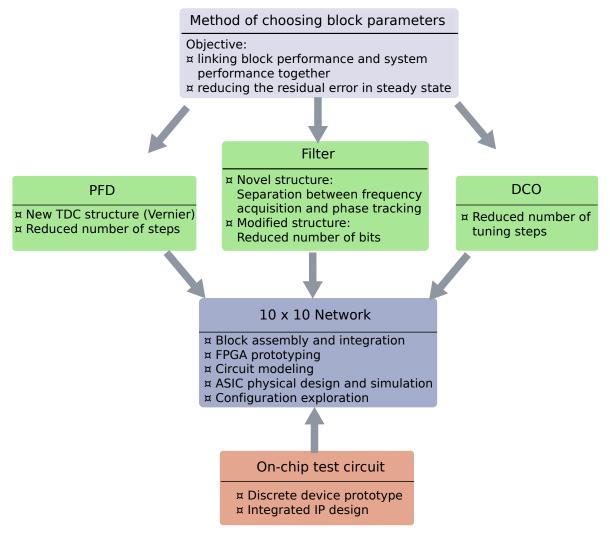

|   | 1.3   | Origina   | al contribution of my PhD project                                 | 29     |

|   | 1.4   | Thesis    | outline                                                           | 31     |

xii Contents

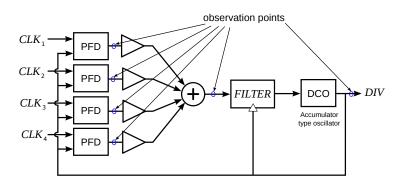

| 2 | Net  | work of  | distributed ADPLLs                                                                     |

|---|------|----------|----------------------------------------------------------------------------------------|

|   | 2.1  | Introdu  | uction                                                                                 |

|   | 2.2  | The ar   | chitecture of clocking network proposed in this PhD project                            |

|   | 2.3  | Impact   | t of quantization in ADPLL on its operation in steady state                            |

|   |      | 2.3.1    | Step 1: Impact of PFD and DCO quantization steps on the residual                       |

|   |      |          | error                                                                                  |

|   |      | 2.3.2    | Step 2: impact of rounding in digital filter on the correction of residual phase error |

|   |      | 2.3.3    | Step 3: validation of block parameters by transient simulations                        |

|   | 2.4  |          | ication of the network                                                                 |

|   | 2.5  | •        | asion                                                                                  |

| 3 | ADI  | PLL blo  | ocks design                                                                            |

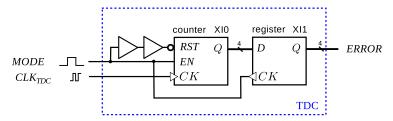

|   | 3.1  | Phase    | frequency detector (PFD)                                                               |

|   |      | 3.1.1    | The digital PFD architecture                                                           |

|   |      | 3.1.2    | Improvement of time-to-digital converter                                               |

|   |      | 3.1.3    | Implementation of PFD                                                                  |

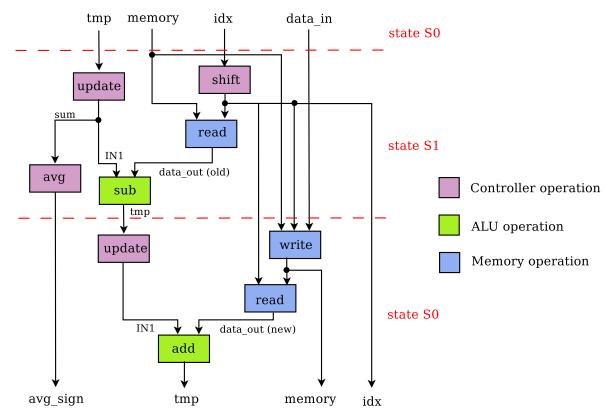

|   | 3.2  | Digital  | I filter in the ADPLL network                                                          |

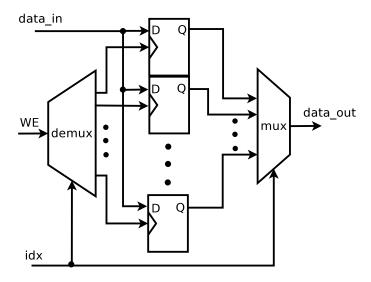

|   |      | 3.2.1    | Architecture of digital filter                                                         |

|   |      | 3.2.2    | Implementation of the filter                                                           |

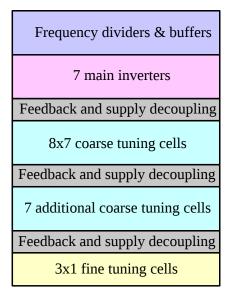

|   | 3.3  | Digital  | lly controlled oscillator (DCO)                                                        |

|   |      | 3.3.1    | DCO Architecture                                                                       |

|   |      | 3.3.2    | Control algorithm                                                                      |

|   |      | 3.3.3    | Implementation                                                                         |

|   |      | 3.3.4    | Serial programming interface (SPI)                                                     |

|   |      | 3.3.5    | Simulation results                                                                     |

|   | 3.4  | Conclu   | asion                                                                                  |

| 4 | Buil | t-In Clo | ock Error Characterization Circuit                                                     |

|   | 4.1  | Introdu  | uction                                                                                 |

|   | 4.2  | State o  | of art                                                                                 |

|   | 4.3  | Test m   | ethodology                                                                             |

|   |      | 4.3.1    | Measurement theory                                                                     |

|   |      | 4.3.2    | Architecture of measurement circuit                                                    |

|   | 4.4  | Low fr   | requency discrete circuit prototype                                                    |

|   | 4.5  | High f   | requency on-chip prototype                                                             |

|   |      | 4.5.1    | Voltage-controlled delay (VCD)                                                         |

|   |      | 4.5.2    | Physical design of test circuit on silicon                                             |

|   |      | 4.5.3    | Modeling of clock generator for system verification                                    |

|   |      | 4.5.4    | Simulation results                                                                     |

|   | 4.6  | Proced   | lure of measurement                                                                    |

|   | 4.7  | Conclu   | ısion                                                                                  |

Contents

| 5 | Clo | ck network FPGA prototyping                                         | 107 |

|---|-----|---------------------------------------------------------------------|-----|

|   | 5.1 | Introduction                                                        | 107 |

|   | 5.2 | Implementation of FPGA based blocks                                 | 110 |

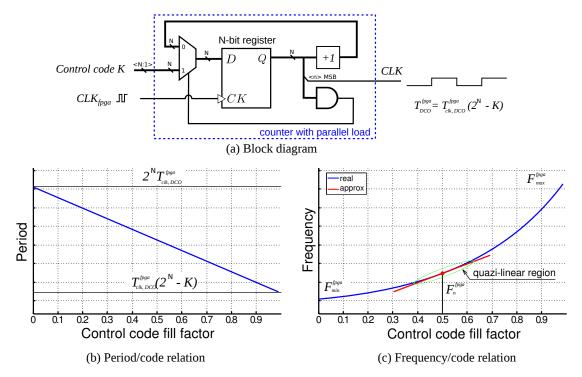

|   |     | 5.2.1 Synthesizable DCO                                             | 110 |

|   |     | 5.2.2 Synthesizable TDC                                             | 113 |

|   | 5.3 | Experimental results                                                | 116 |

|   |     | 5.3.1 Stability and prevention of mode-lock                         | 116 |

|   |     | 5.3.2 Phase error between two remote local clocks                   | 122 |

|   | 5.4 | Conclusion                                                          | 128 |

| 6 | Clo | ck network silicon implementation                                   | 129 |

|   | 6.1 | Introduction                                                        | 129 |

|   | 6.2 | Methodology of chip design                                          | 130 |

|   | 6.3 | Implementation of local clock generator (NODE)                      | 134 |

|   | 6.4 | Floorplan of the chip                                               | 138 |

|   | 6.5 | Design for test(DFT)                                                | 139 |

|   |     | 6.5.1 Chip programming                                              | 140 |

|   |     | 6.5.2 Built-in test circuits placement                              | 140 |

|   |     | 6.5.3 Definition of the input/outputs of the chip                   | 141 |

|   | 6.6 | Chip layout                                                         | 145 |

|   | 6.7 | Simulation results                                                  | 146 |

|   | 6.8 | Conclusion                                                          | 148 |

| 7 | "Sw | imming pool"-like distributed architecture                          | 149 |

|   | 7.1 | Introduction                                                        | 149 |

|   | 7.2 | Modeling of infinite ADPLL network by a continuous wave propagation |     |

|   |     | medium                                                              | 150 |

|   |     | 7.2.1 From a discrete network to a continuous medium                | 151 |

|   |     | 7.2.2 An analogy with damped wave equation                          | 153 |

|   | 7.3 | ADPLL network with limited surface                                  | 154 |

|   | 7.4 | Simulation results                                                  | 156 |

|   | 7.5 | Conclusion                                                          | 160 |

| 8 | ADI | PLL with sliding-window for wide range frequency tracking           | 161 |

|   | 8.1 | Introduction                                                        | 161 |

|   | 8.2 | State of art                                                        | 163 |

|   | 8.3 | "Sliding window" architecture                                       | 166 |

|   |     | 8.3.1 Reference frequency indicator (RFI)                           | 166 |

|   |     | 8.3.2 Coarse frequency adjustment                                   | 167 |

|   |     | 8.3.3 Phase error correction                                        | 172 |

|   | 8.4 | Comparison with conventional PLL                                    | 174 |

|   |     | 8.4.1 Functional Simulation results                                 | 174 |

xiv

|    |        | 8.4.2     | Power consumption comparison                                       | 175 |

|----|--------|-----------|--------------------------------------------------------------------|-----|

|    | 8.5    | Clock     | distribution network using "sliding window" ADPLL                  | 176 |

|    |        | 8.5.1     | Network structure                                                  | 176 |

|    |        | 8.5.2     | Evaluation of functional performance of system                     | 177 |

|    | 8.6    | Conclu    | asion                                                              | 182 |

| 9  | Con    | clusion   | and Perspectives                                                   | 183 |

|    | 9.1    | Thesis    | summary and conclusions                                            | 183 |

|    | 9.2    | Future    | work                                                               | 186 |

|    |        | 9.2.1     | Modelling of ADPLL for the study of residual phase error in steady |     |

|    |        |           | state                                                              | 186 |

|    |        | 9.2.2     | Exploration of fault-tolerance property                            | 187 |

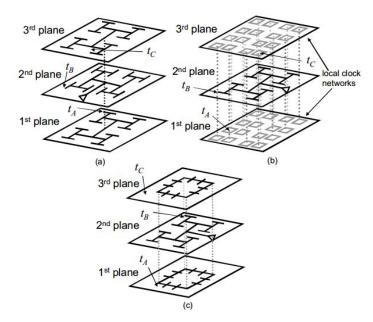

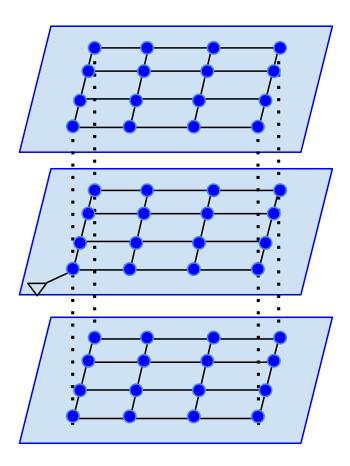

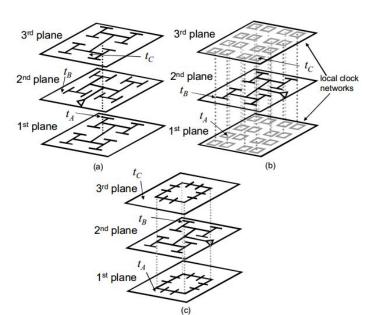

|    |        | 9.2.3     | Clock distribution for 3-D chip                                    | 187 |

| Aŗ | pend   | ices      |                                                                    | 191 |

| A  | VHI    | OL mod    | els of the ADPLL blocks                                            | 193 |

| В  | VHI    | OL mod    | els for built-in test circuit                                      | 219 |

| C  | Mat    | lab scri  | pts                                                                | 225 |

| D  | FPG    | A prote   | otyping of the clocking network                                    | 233 |

| E  | Tcl s  | script fo | or automatic floorplan of network                                  | 239 |

| Bi | bliogr | aphy      |                                                                    | 247 |

## **List of Figures**

| 1    | Synchronisation des circuits numériques complexes                                      | xxiv    |

|------|----------------------------------------------------------------------------------------|---------|

| 2    | <b>Definition d'erreur d'horloge</b> $\Delta t_i$                                      | xxvi    |

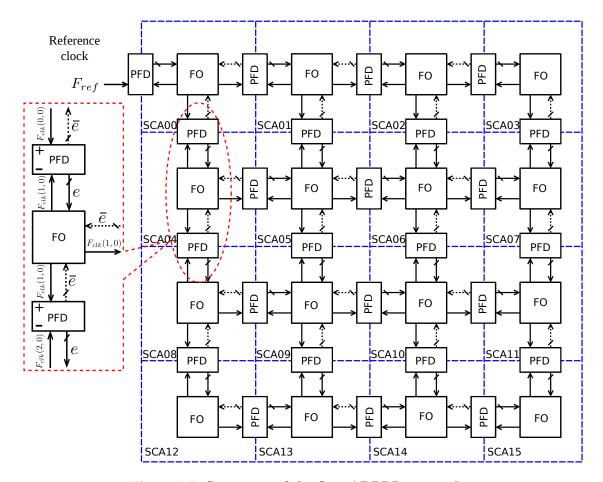

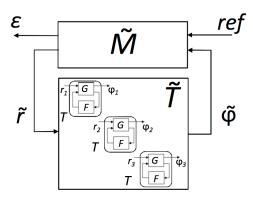

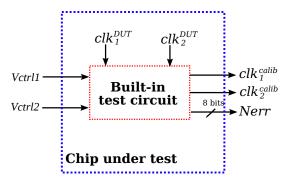

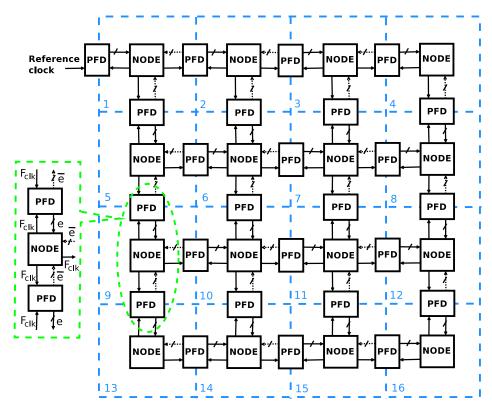

| 3    | Topology of the proposed clock network and architecture of the network node .          | xxvii   |

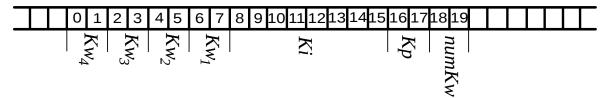

| 4    | Block diagram of proposed time-to-digital converter                                    | XXX     |

| 5    | Filtre de boucle pour le traitement du signal d'erreur: quatre contrôleurs de          |         |

|      | gain d'entrée suivi par l'addition à quatre entrées, filtre PI et trois décodeurs B2T. | xxxi    |

| 6    | Proposed architecture for PLL                                                          | xxxii   |

| 7    | Clocking network architecture                                                          | xxxiii  |

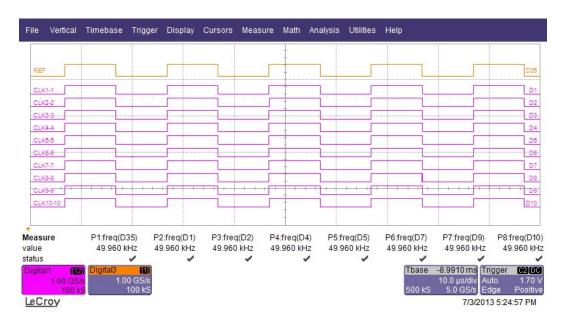

| 8    | Local clock signals together with reference                                            | xxxiv   |

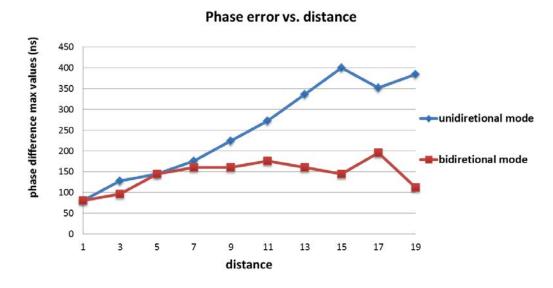

| 9    | Maximal value of phase error in function of distance to the reference clock            | XXXV    |

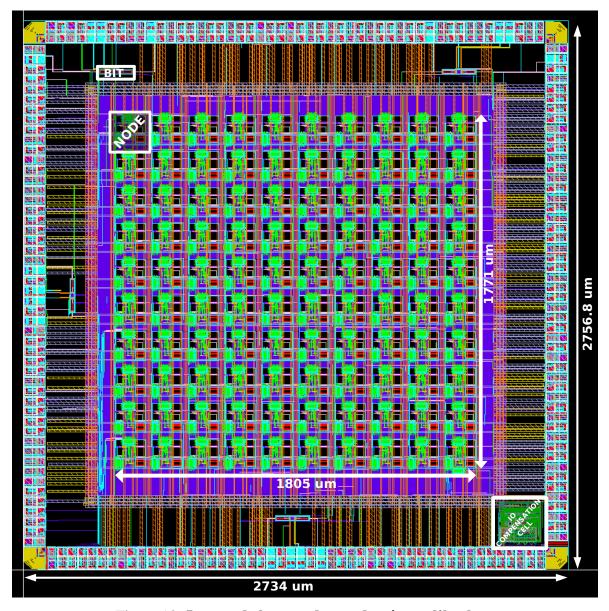

| 10   | Layout of the test chip of the clock network                                           | xxxvi   |

| 11   | Analyse théorique: (a) PDF d'origine de l'incertitude d'horloge; (b) PDF avec          |         |

|      | un décalage $\Delta = \Delta_x$ ; (c) $a$ vs. $\Delta$ ; (d) ER vs. $\Delta$           | xxxvii  |

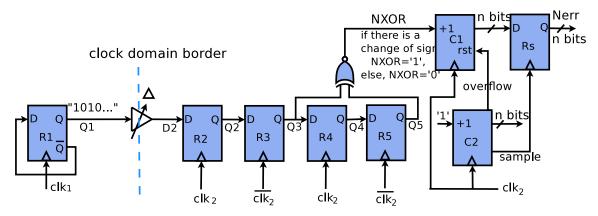

| 12   | Architecture of test circuit                                                           | xxxviii |

| 13   | Différents réseaux de distribution d'horloge 3-D au sein du circuit de test de         |         |

|      | [38]: (a) H-arbres, (b) H-arbre et anneaux/mailles locales, (c) H-arbre et anneaux     |         |

|      | globaux                                                                                | xliii   |

| 14   | L'approche proposée de distribution d'horloge 3-D en utilisant le réseau               |         |

|      | d'ADPLL                                                                                | xliv    |

| 1.1  | Clock domains in a SoC                                                                 | 1       |

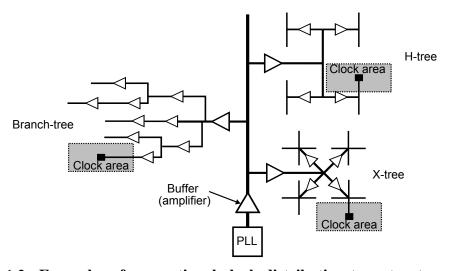

| 1.2  | Examples of conventional clock distribution tree structures                            | 2       |

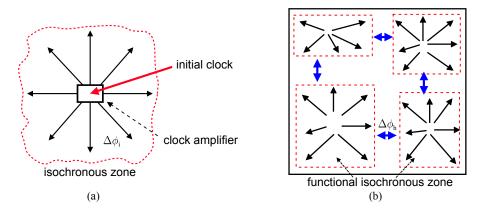

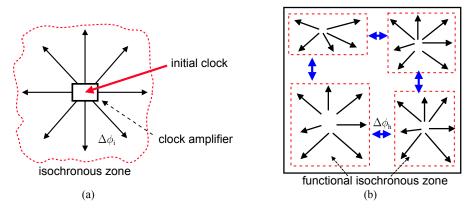

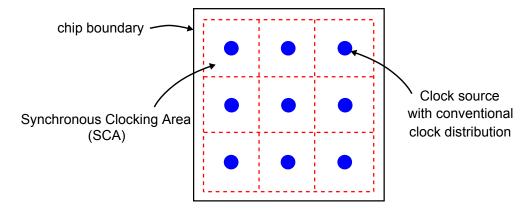

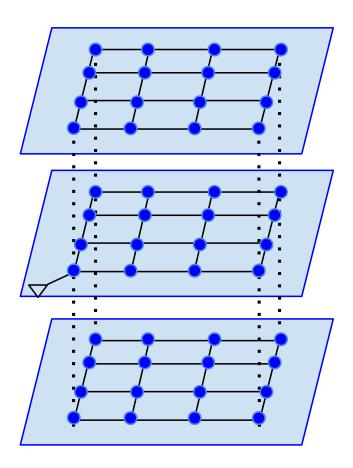

| 1.3  | Basic idea of multioscillator clocking approach                                        | 5       |

| 1.4  | Topology of the proposed clock network and architecture of the network node .          | 6       |

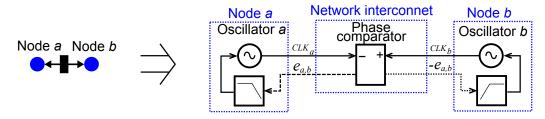

| 1.5  | Phase coupling between two oscillators                                                 | 7       |

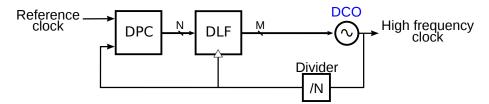

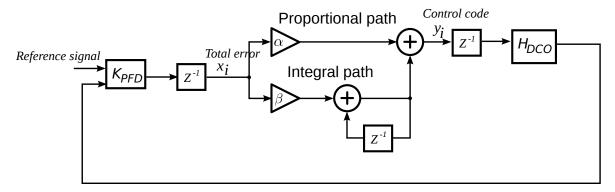

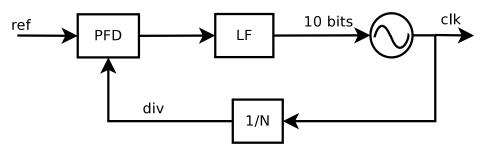

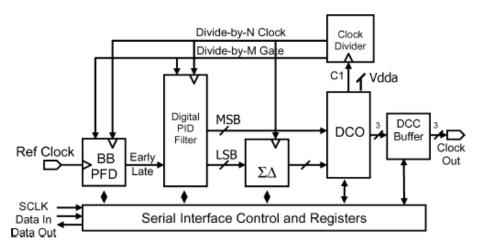

| 1.6  | Block diagram of the ADPLL                                                             | 8       |

| 1.7  | Structure of the first ADPLL network                                                   | 10      |

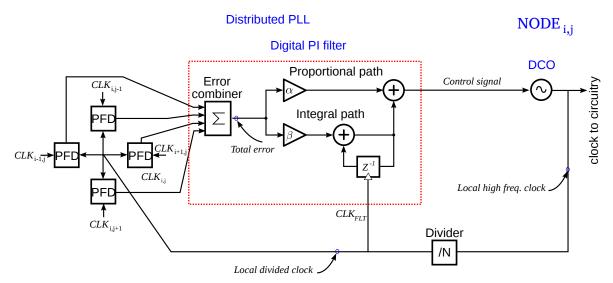

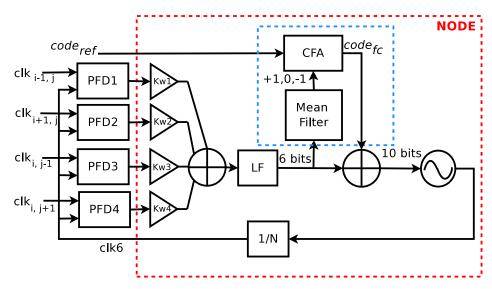

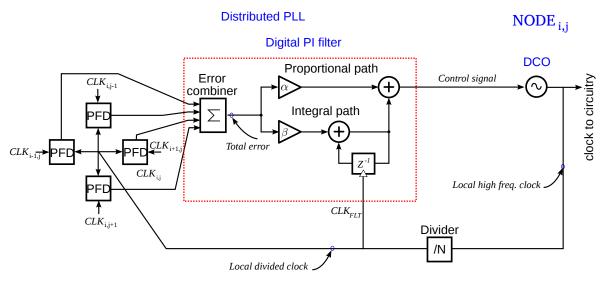

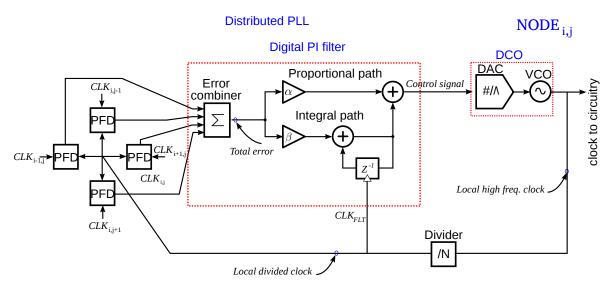

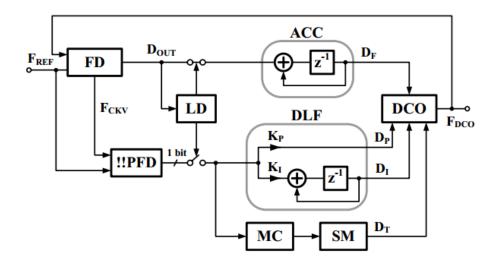

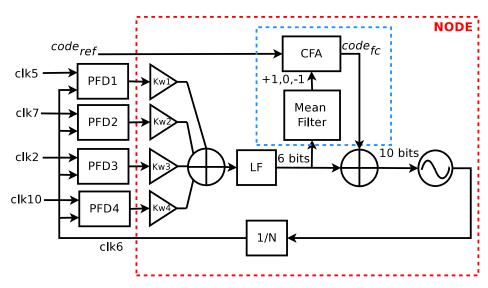

| 1.8  | Structure of a node in ADPLL network                                                   | 10      |

| 1.9  | The phase/frequency detector                                                           | 11      |

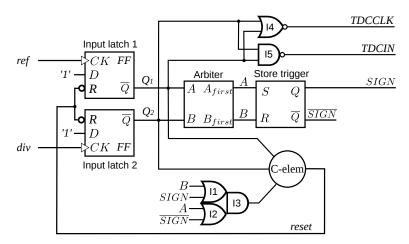

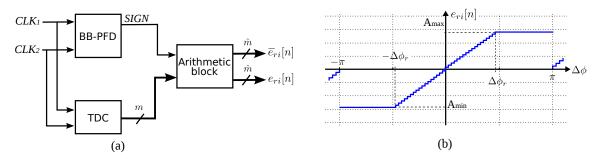

| 1.10 | Proposed phase/frequency detector for clock network                                    | 11      |

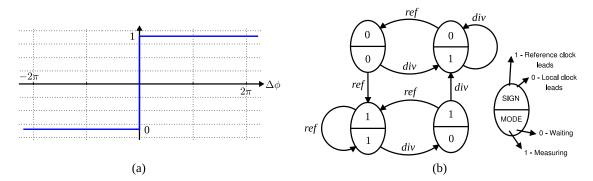

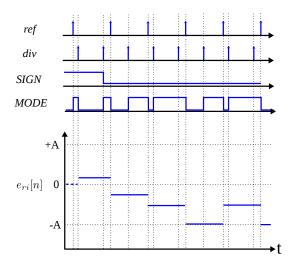

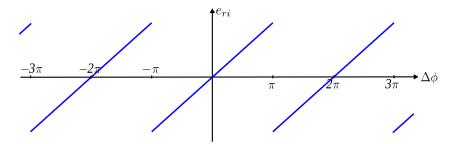

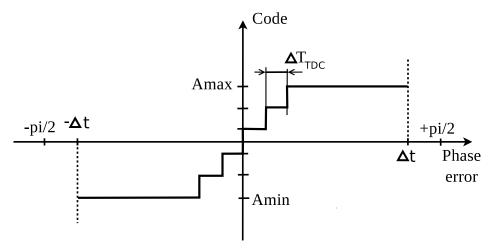

| 1.11 | Principle of operation of proposed PFD                                                 | 12      |

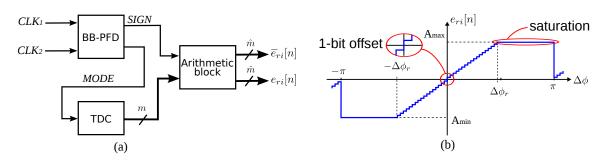

| 1.12 | Schematic diagram of the bang-bang phase/frequency detector                            | 13      |

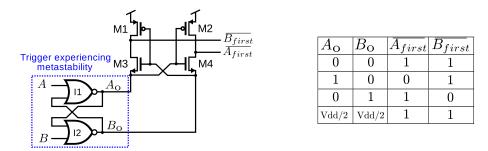

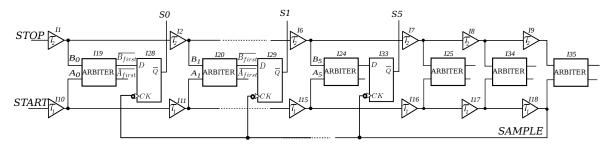

| 1.13 | Proposed in [59] arbiter circuit                                                       | 13      |

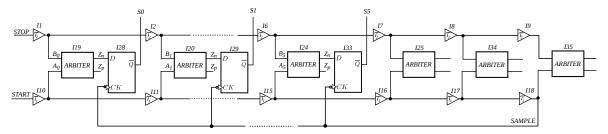

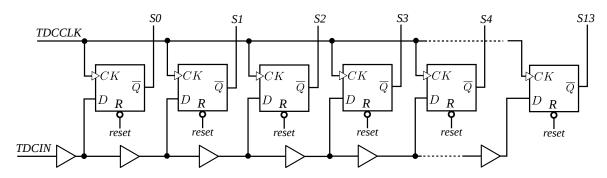

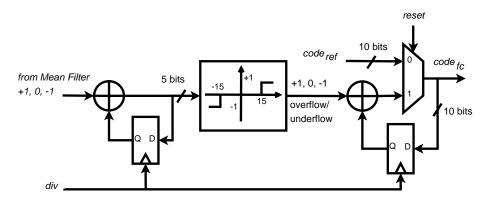

| 1.14 | Block diagram of proposed time-to-digital converter                                    | 15      |

xvi List of Figures

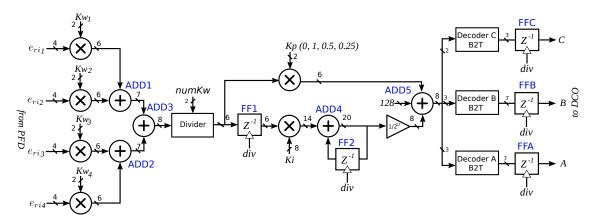

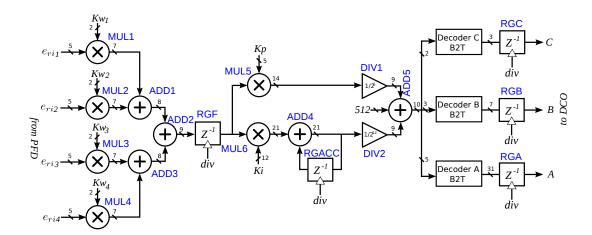

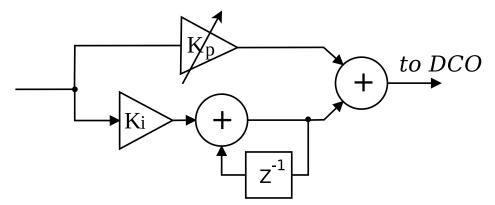

| 1.15 | Error signal processing block                                                                     | 16 |

|------|---------------------------------------------------------------------------------------------------|----|

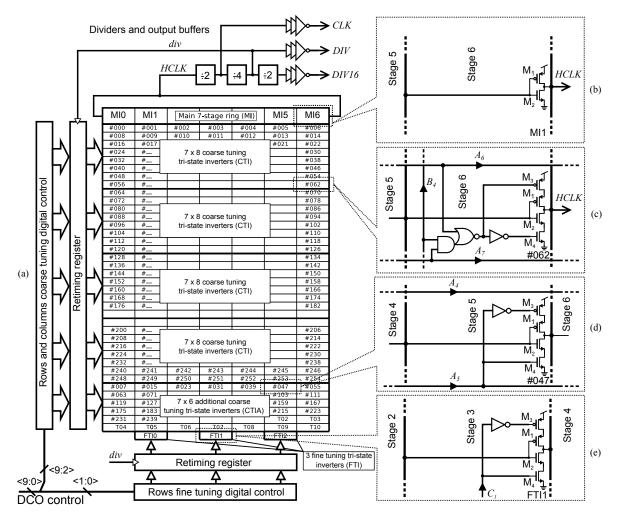

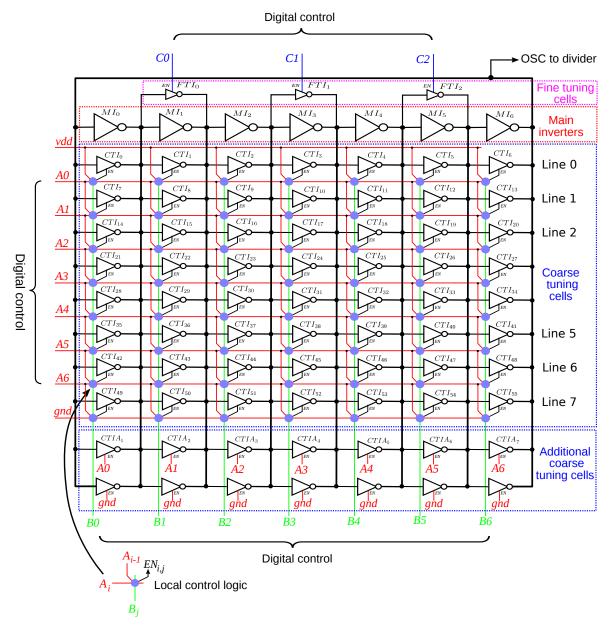

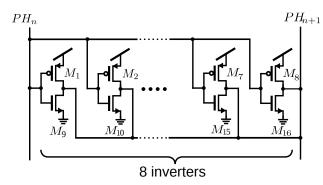

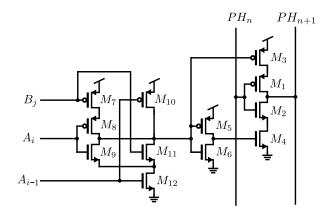

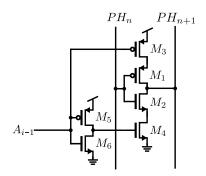

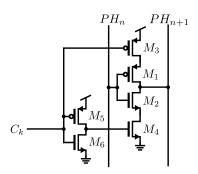

| 1.16 | DCO architecture: (a) structure, (b) main inverters, (c) circuit diagram of the                   |    |

|      | coarse tuning cell, (d) circuit diagram of the additional coarse tuning cell, (e)                 |    |

|      | circuit diagram of the fine tuning tuning cell                                                    | 19 |

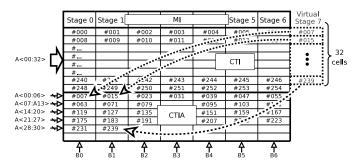

| 1.17 | Virtual extension of the 8 <sup>th</sup> stage of the oscillator principle                        | 19 |

| 1.18 | LTI model of ADPLL for Z-domain transfer function calculation                                     | 23 |

| 1.19 | Representation of the PLL network for stability study in [47]                                     | 24 |

| 1.20 | Cyclic nature of the conventional analog linear phase comparator                                  | 25 |

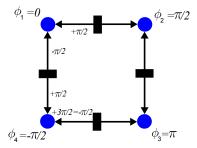

| 1.21 | Illustration of the mode-locking phenomenon in a $2\times 2$ mesh network                         | 25 |

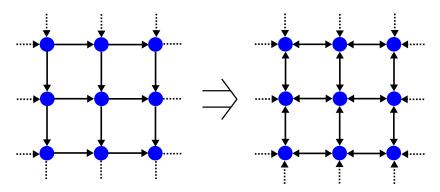

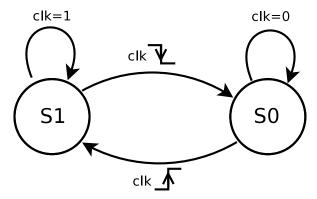

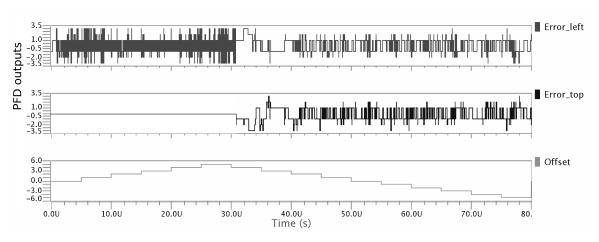

| 1.22 | Dynamic reconfiguration of the network from uni- to bidirectional                                 | 20 |

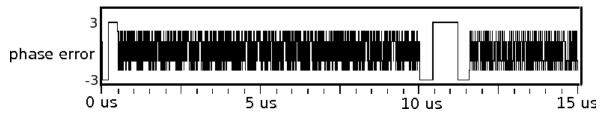

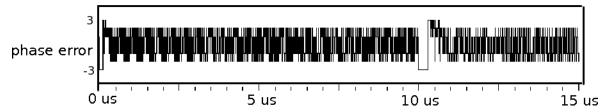

| 1.23 | Synchronous clocks in the bidirectional configuration                                             | 2  |

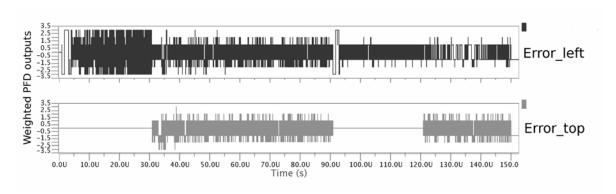

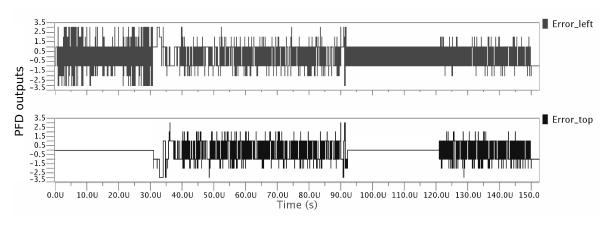

| 1.24 | Outputs of the PFDs in bidirectional configuration                                                | 2  |

| 1.25 | Structure of work contribution                                                                    | 30 |

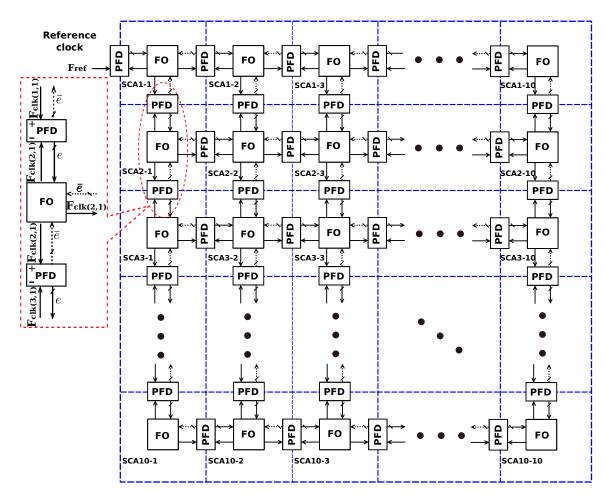

| 2.1  | Clocking network architecture                                                                     | 3. |

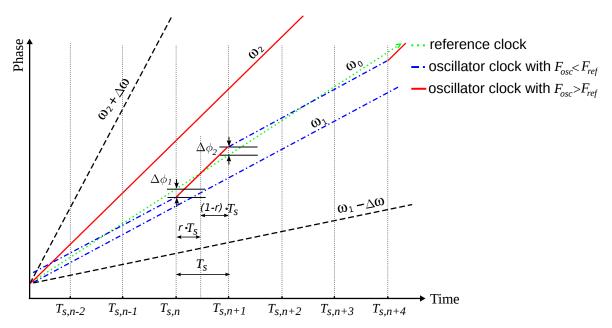

| 2.2  | Phase evolution of reference clock and divided oscillator clock: $\omega_1 < \omega_0 < \omega_2$ | 38 |

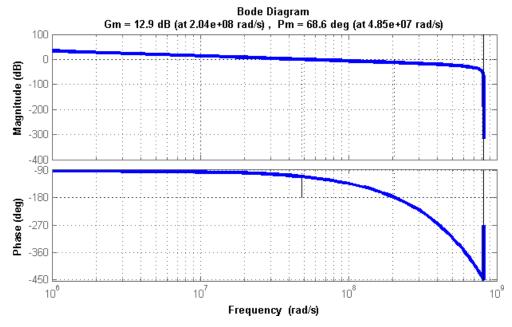

| 2.3  | <b>Bode diagram of the LTI model of the system (Fig. 1.18)</b> : $K = 1.2e7$ rad/s and            |    |

|      | $\beta/\alpha = 0.012$                                                                            | 42 |

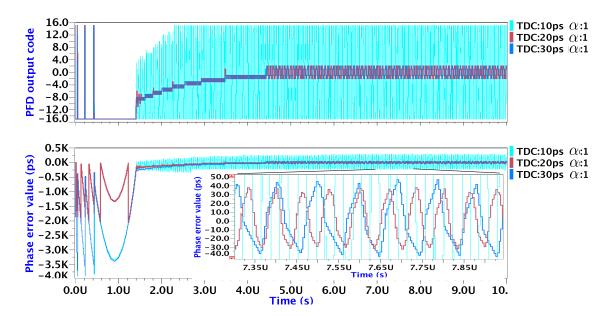

| 2.4  | Time simulations with different TDC resolution and same filter/DCO pa-                            |    |

|      | rameters (VHDL model): reference clock frequency: 249.5 MHz, DCO 3 in                             |    |

|      | Tab. 2.1 used                                                                                     | 4  |

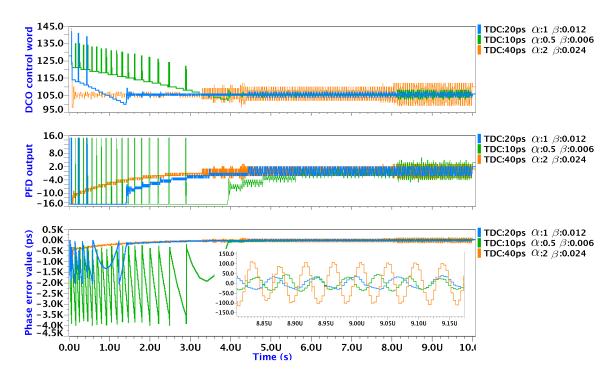

| 2.5  | Time simulations with the same loop gain and $\beta/\alpha$ ratio (VHDL model):                   |    |

|      | reference clock frequency: 249.5 MHz, DCO 3 in Tab. 2.1 used                                      | 4. |

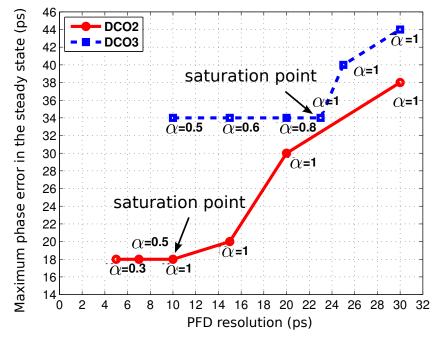

| 2.6  | The maximum values of residual phase errors of an ADPLL in the steady                             |    |

|      | state with different PFD and filter coefficients (VHDL model)                                     | 4. |

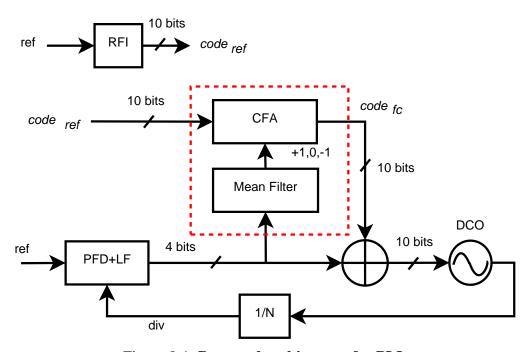

| 3.1  | Proposed phase/frequency detector for clock network                                               | 50 |

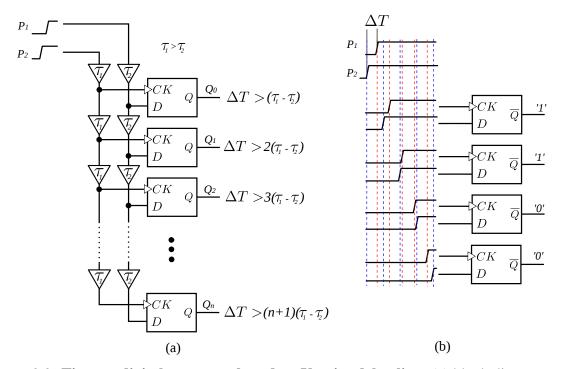

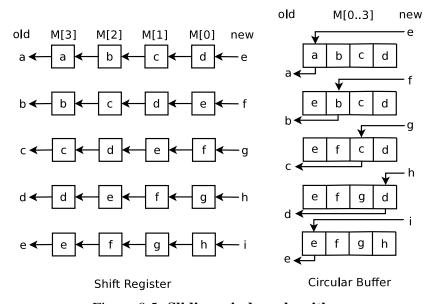

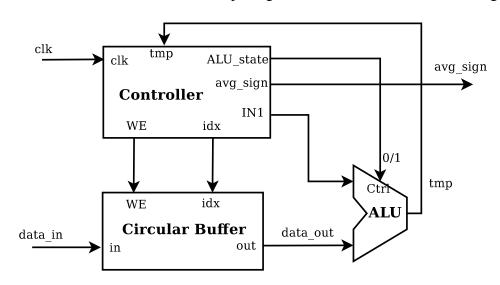

| 3.2  | Time-to-digital converter                                                                         | 5  |

| 3.3  | Block diagram of proposed time-to-digital converter                                               | 52 |

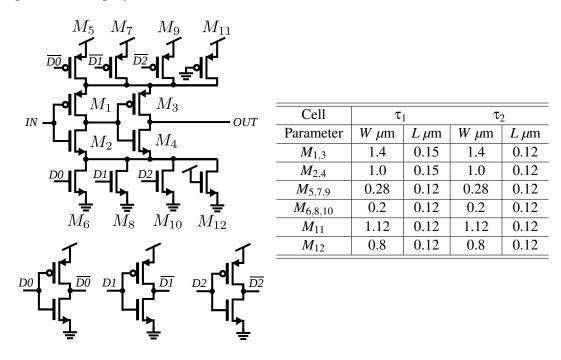

| 3.4  | Schematic diagram of the delay cells in Vernier TDC                                               | 53 |

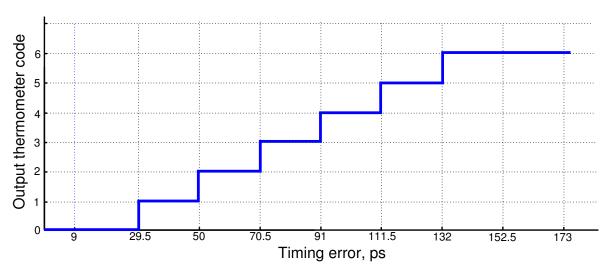

| 3.5  | Simulated transfer function of the designed flash time-to-digital converter                       | 54 |

| 3.6  | Layout of the proposed PFD                                                                        | 5  |

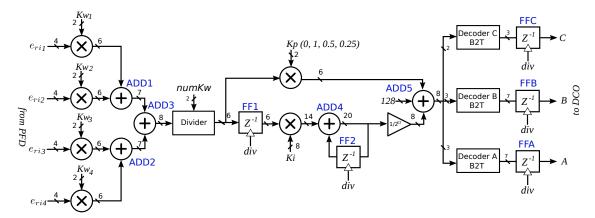

| 3.7  | <b>Loop filter for error signal processing</b> : four input gain controllers followed by          |    |

|      | the four-input adder, PI filter and three B2T decoders                                            | 5  |

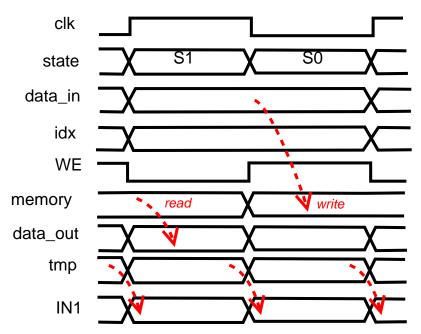

| 3.8  | Programming sequence of parameters                                                                | 59 |

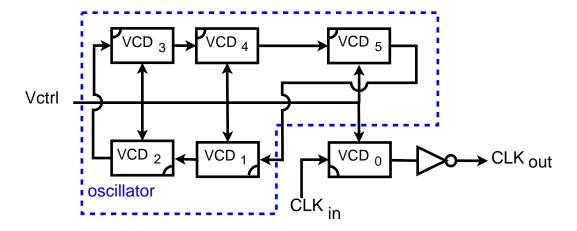

| 3.9  | Core of the proposed oscillator                                                                   | 6  |

| 3.10 | Ring oscillator cell control table                                                                | 6  |

| 3.11 | Schematic of a main inverter of oscillator                                                        | 6  |

| 3.12 | Schematic diagram of the coarse tuning cells                                                      | 6  |

| 3.13 | Schematic diagram of the additional coarse tuning cells                                           | 6  |

| 3.14 | Schematic diagram of the fine tuning cells                                                        | 6  |

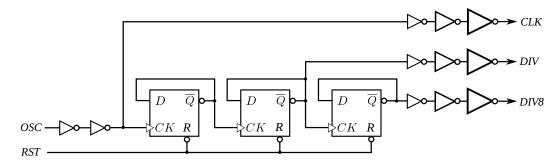

| 3.15 | Schematic diagram of the feedback frequency divider                                               | 6: |

List of Figures xvii

| 3.16 | Floorplan of the designed oscillator                                                | 66 |

|------|-------------------------------------------------------------------------------------|----|

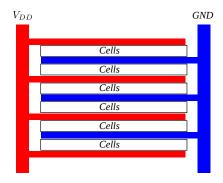

|      | Interdigital multi-finger power routing                                             | 67 |

|      | Layout of the designed oscillator                                                   | 67 |

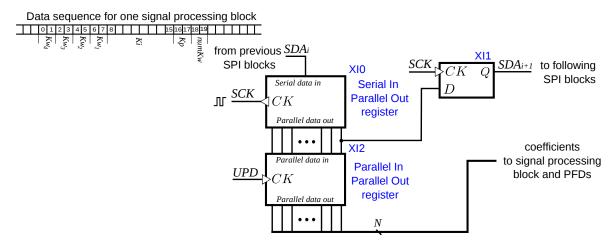

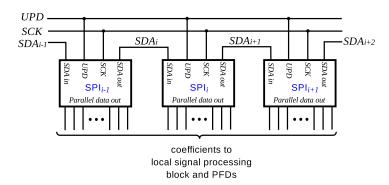

|      | Schematic of the programming interface                                              | 69 |

|      | Cascading the programming interfaces of several blocks                              | 69 |

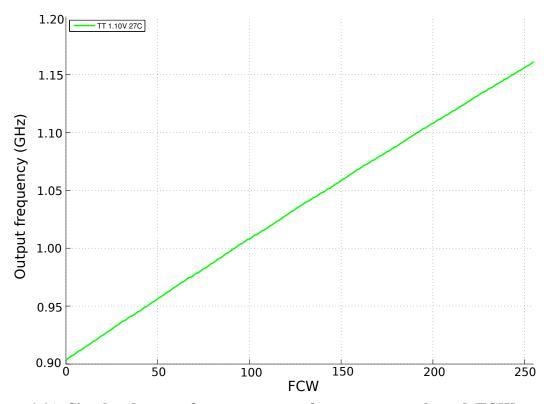

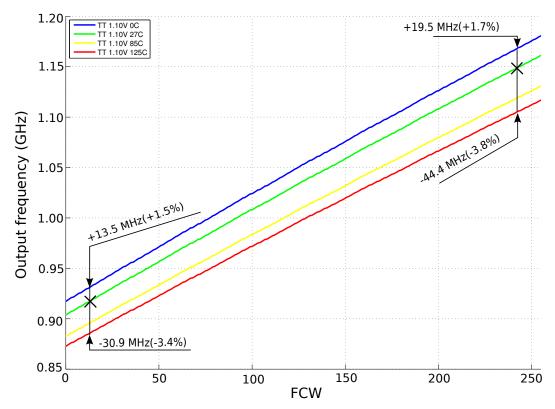

|      | Simulated output frequency versus frequency control word (FCW): typical             |    |

|      | condition                                                                           | 70 |

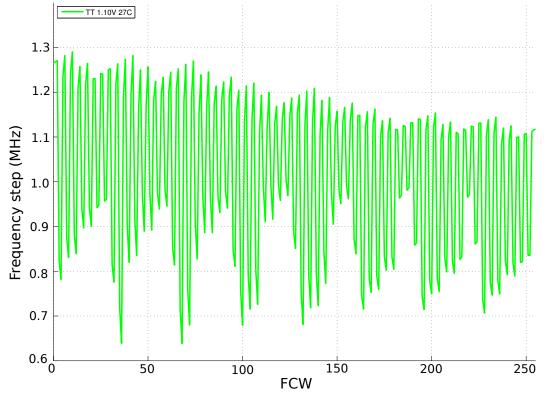

| 3.22 | Frequency step vs. FCW: typical condition                                           | 70 |

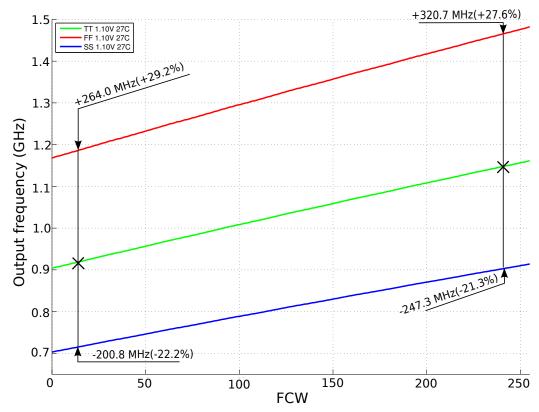

|      | Simulated output frequency versus frequency control word (FCW) in dif-              |    |

|      | <b>ferent process corners</b> : process variations: TT, FF and SS                   | 71 |

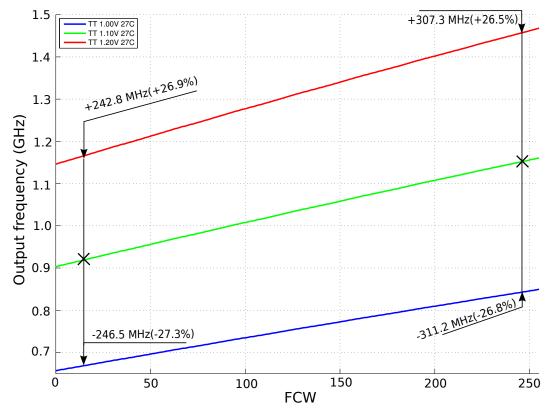

| 3.24 | Simulated output frequency versus frequency control word (FCW) with dif-            |    |

|      | <b>ferent supply voltages</b> : 1 V, 1.1 V and 1.2 V                                | 72 |

| 3.25 | Simulated output frequency versus frequency control word (FCW) at dif-              |    |

|      | <b>ferent temperatures</b> : 0°C, 27°C, 85°C and 125°C                              | 73 |

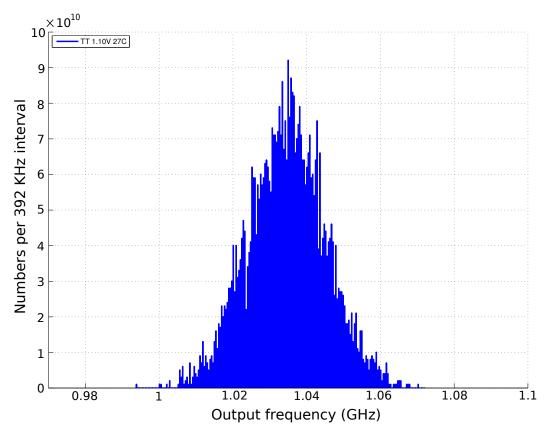

| 3.26 | Monte-Carlo simulation at center frequency                                          | 73 |

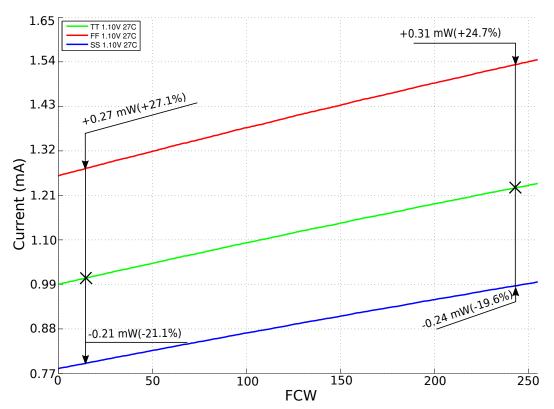

| 3.27 | <b>Power consumption vs. FCW in different process corners</b> : process variations: |    |

|      | TT, FF and SS                                                                       | 74 |

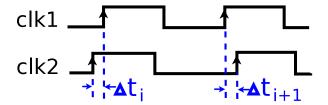

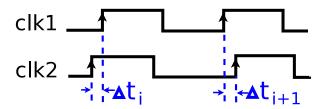

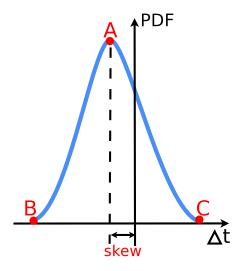

| 4.1  | <b>Definition of the clock error</b> $\Delta t_i$                                   | 79 |

| 4.2  | Gaussian distribution of clock phase error                                          | 80 |

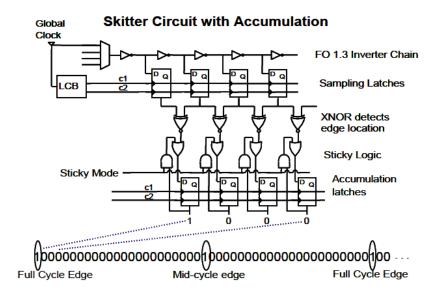

| 4.3  | Delay chain based "Skitter" circuit proposed in [13]                                | 81 |

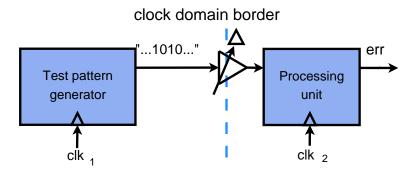

| 4.4  | Basic architecture of measurement circuit                                           | 82 |

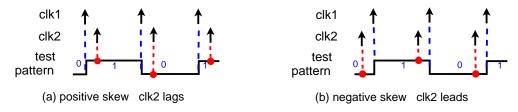

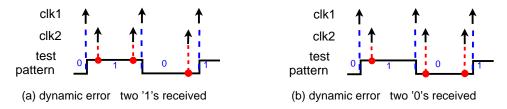

| 4.5  | Received data integrity: fixed static error                                         | 83 |

| 4.6  | Received data integrity: dynamic error                                              | 83 |

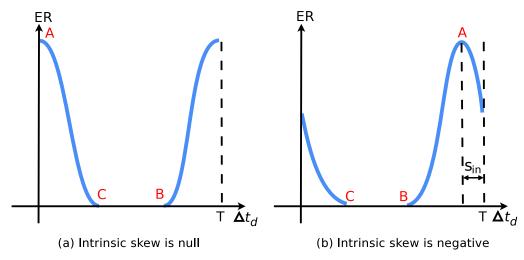

| 4.7  | Theory analysis: (a) Original PDF of clock uncertainty; (b) PDF with a shift        |    |

|      | $\Delta = \Delta_x$ ; (c) a vs. $\Delta$ ; (d) ER vs. $\Delta$                      | 85 |

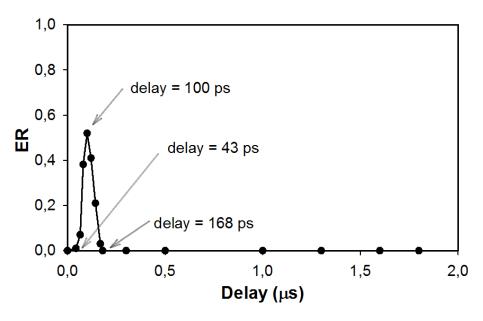

| 4.8  | ER distribution with respect to single positive delay                               | 86 |

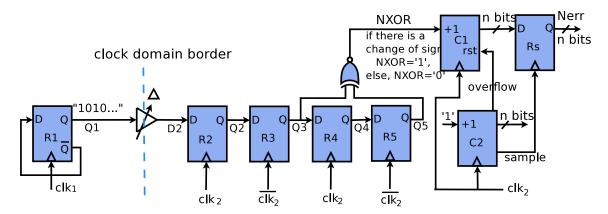

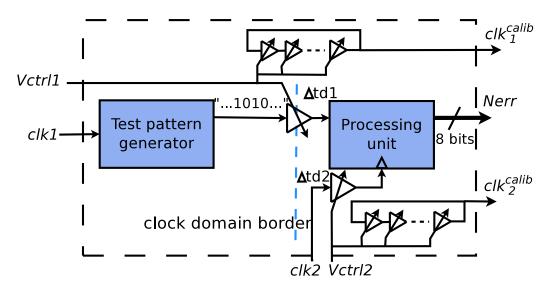

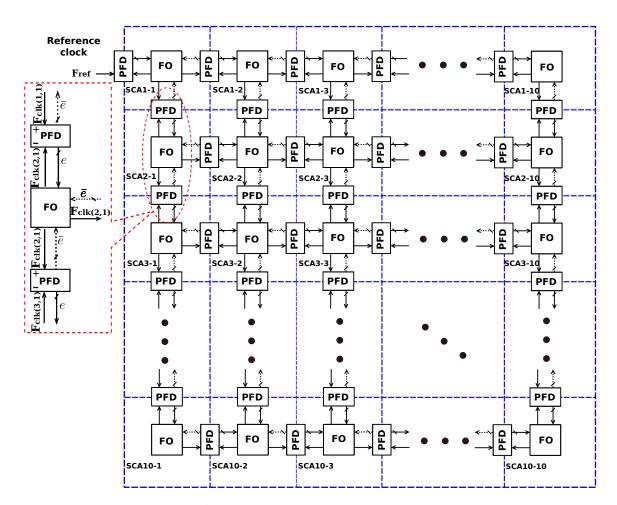

| 4.9  | Architecture of test circuit                                                        | 86 |

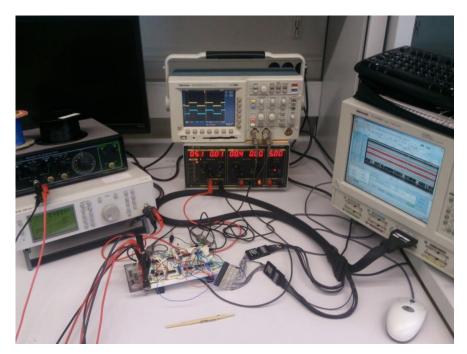

| 4.10 | Measurement environment of prototype                                                | 87 |

| 4.11 | Generation of clk2 with static and dynamic errors                                   | 87 |

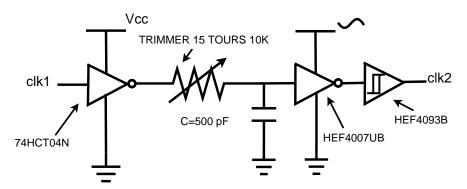

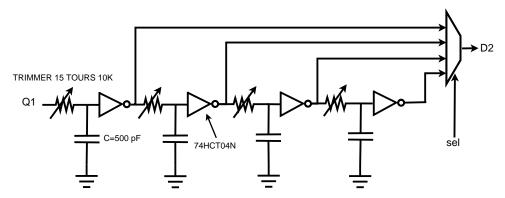

| 4.12 | Variable delay circuit in discrete circuit prototype                                | 88 |

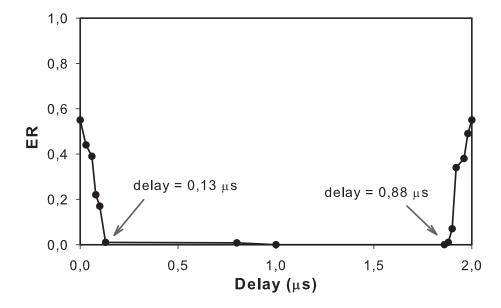

| 4.13 | Test of prototype without skew                                                      | 88 |

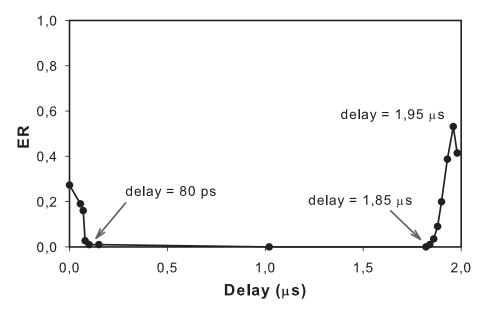

| 4.14 | Test of prototype with a skew of -40 ns                                             | 89 |

| 4.15 | Test of prototype with a skew of -40 ns                                             | 89 |

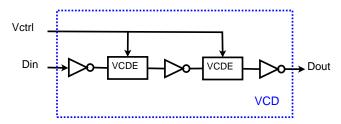

| 4.16 | ASIC prototype architecture                                                         | 90 |

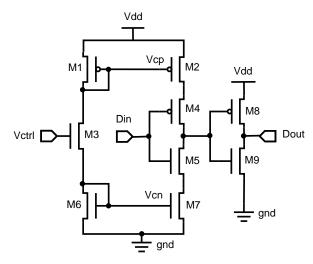

| 4.17 | Voltage-controlled delay element[24]                                                | 91 |

| 4.18 | Voltage-controlled delay with 2 stages                                              | 91 |

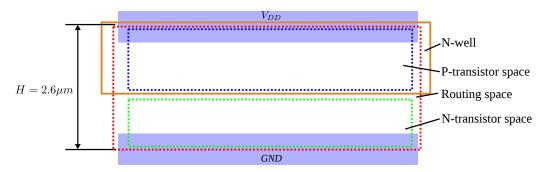

| 4.19 | Cell layout template                                                                | 92 |

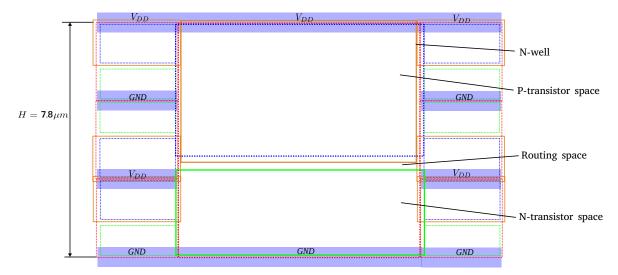

| 4.20 | Delay element layout template                                                       | 93 |

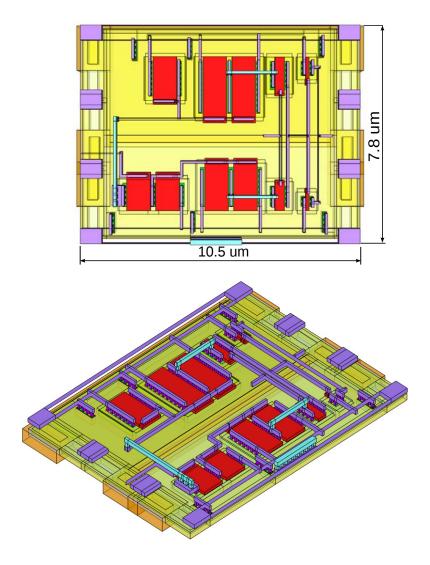

| 4.21 | layout of VCD and calibration oscillator                                            | 94 |

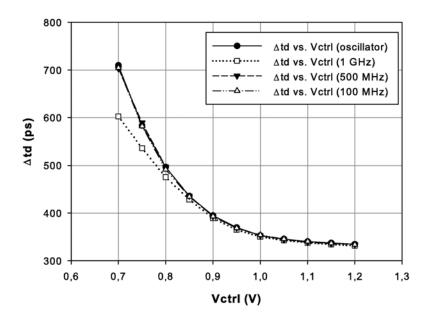

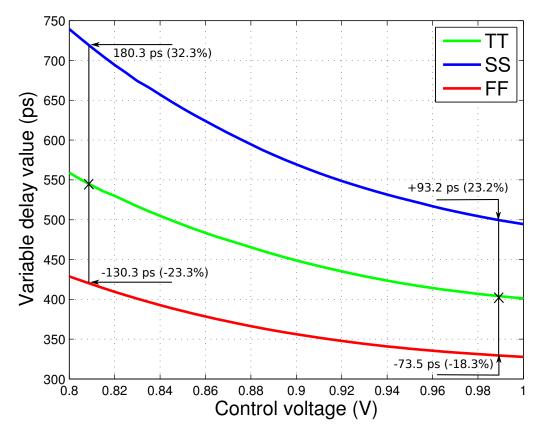

| 4.22 | Variable delay in function of control voltage                                       | 95 |

| 4.23 | Place of VCD and calibration oscillator                                             | 95 |

xviii List of Figures

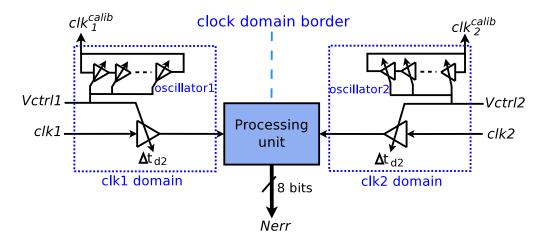

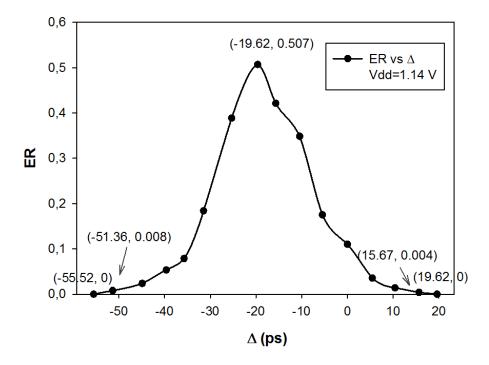

| 4.24 | Architecture of implemented built-in test circuit                                   | 95  |

|------|-------------------------------------------------------------------------------------|-----|

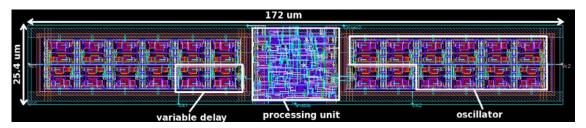

| 4.25 | Layout of built-in test circuit                                                     | 96  |

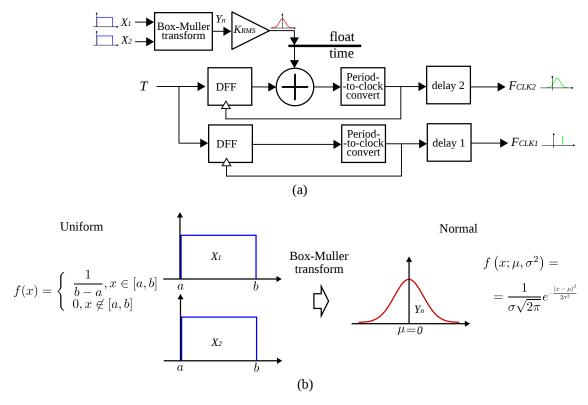

| 4.26 | VHDL model for clock generation: (a) block diagram and (b) generation of a          |     |

|      | random variable with normal distribution using Box-Muller transform                 | 96  |

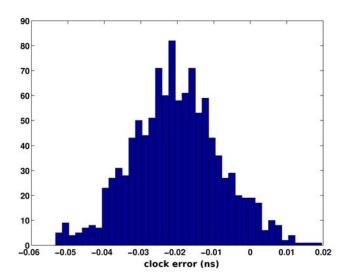

| 4.27 | Histogram of clock errors between clk1 and clk2                                     | 97  |

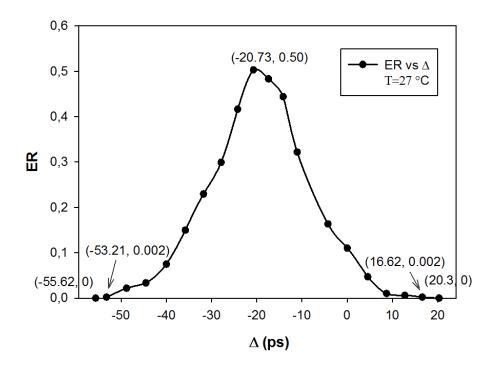

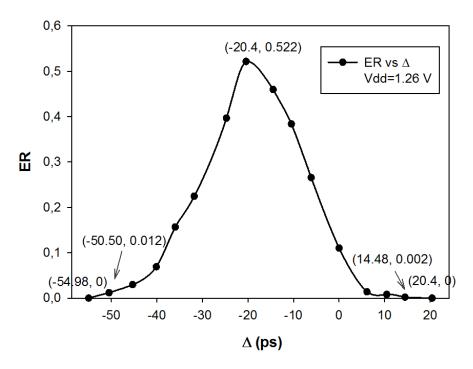

| 4.28 | ASIC prototype error rate (T = $27$ °C)                                             | 98  |

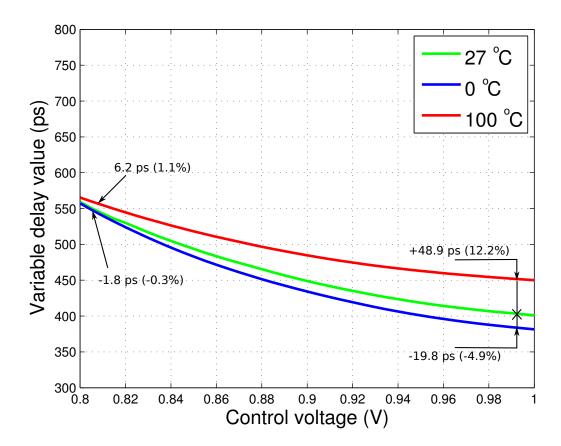

| 4.29 | Simulated variable delay value versus control voltage at different temperatures:    | 99  |

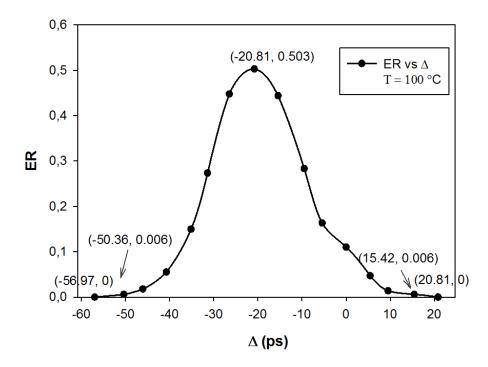

| 4.30 | ASIC prototype error rate measurement (T = $100 ^{\circ}$ C)                        | 100 |

| 4.31 | Simulated variable delay value versus control voltage in different process corners: | 100 |

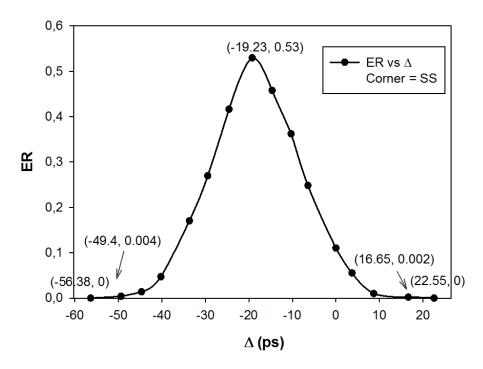

| 4.32 | ASIC prototype error rate measurement (Corner SS)                                   | 101 |

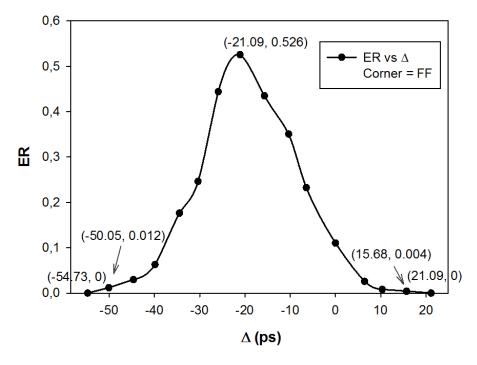

| 4.33 | ASIC prototype error rate measurement (Corner FF)                                   | 101 |

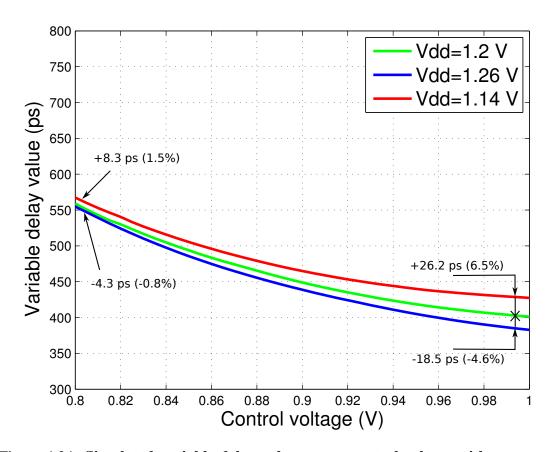

| 4.34 | Simulated variable delay value versus control voltage with power supply variation:  | 102 |

| 4.35 | ASIC prototype error rate measurement (Vdd=1.2 V + 5%)                              | 103 |

| 4.36 | ASIC prototype error rate measurement (Vdd=1.2 V - 5%)                              | 103 |

| 4.37 | The integration of proposed test circuit on the chip                                | 104 |

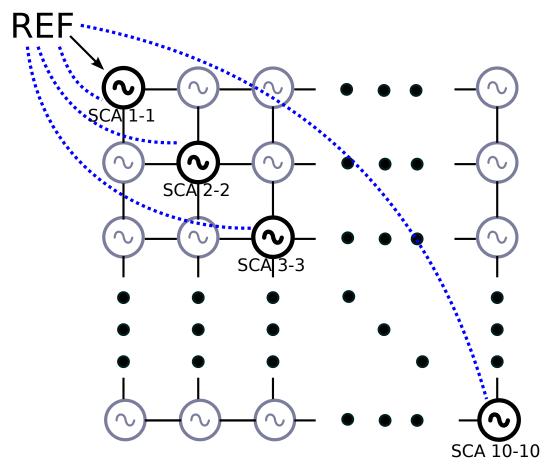

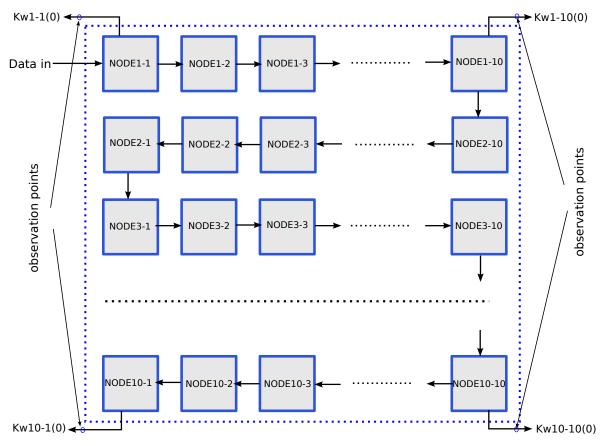

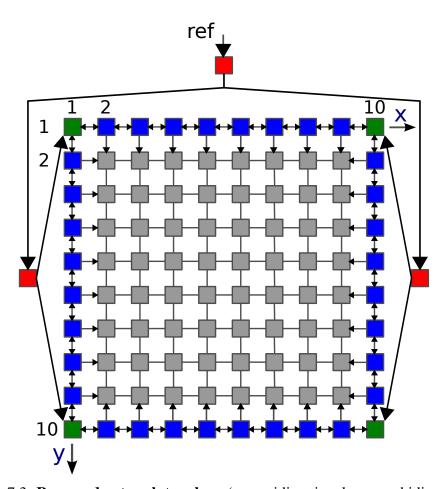

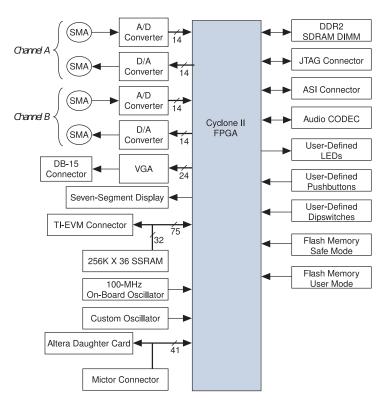

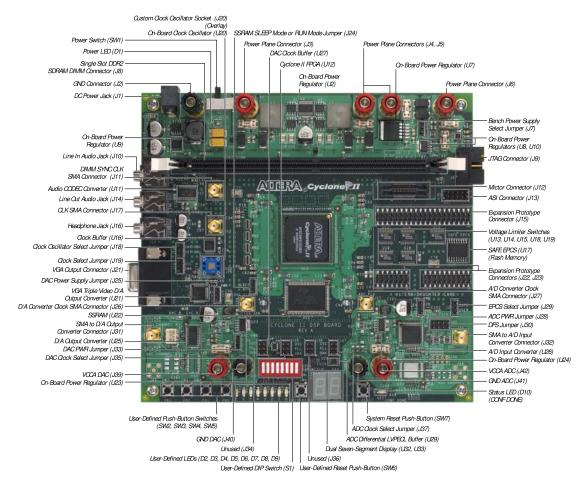

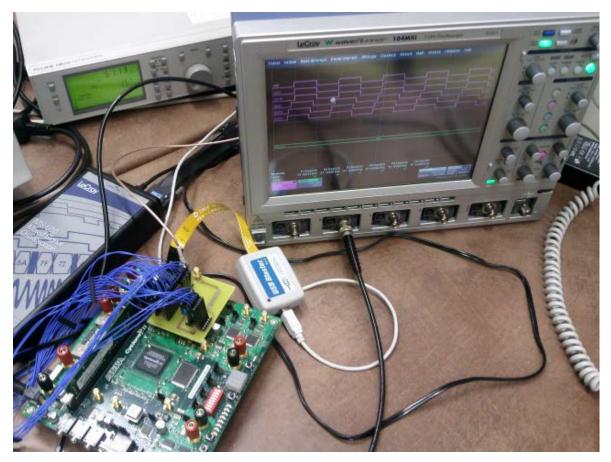

| 5.1  | Structure of the implemented clock network                                          | 109 |

| 5.2  | Repeating discrete ramp function in the DDFS                                        | 111 |

| 5.3  | Schematic diagram of the proposed FPGA implementation of the oscillator             | 112 |

| 5.4  | Conventional phase detector                                                         | 114 |

| 5.5  | Block diagram of the node in a FPGA prototype with observation points               | 116 |

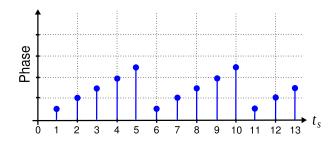

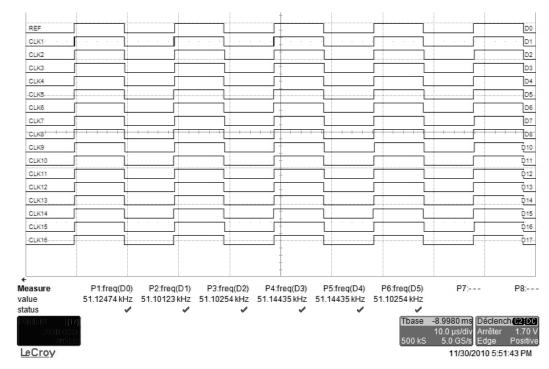

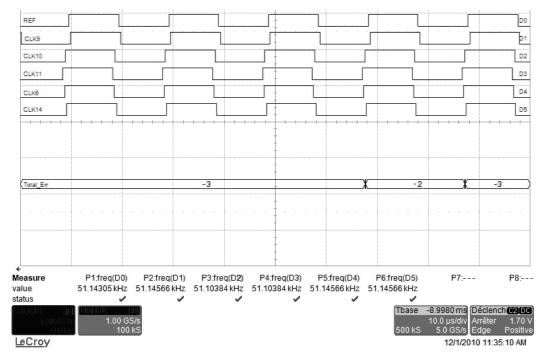

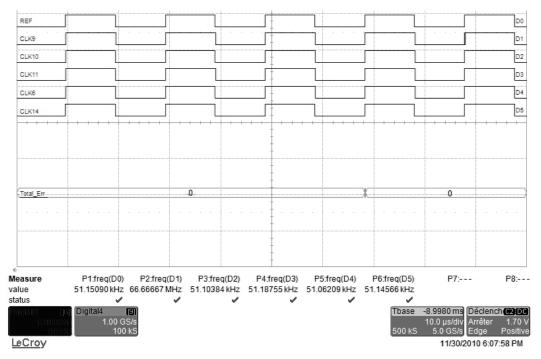

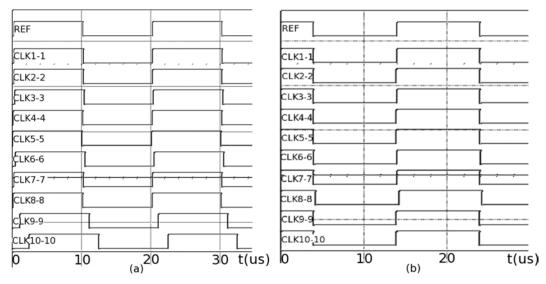

| 5.6  | Local clock signals together with reference                                         | 117 |

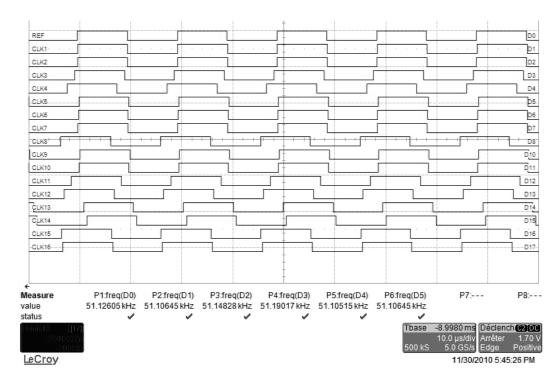

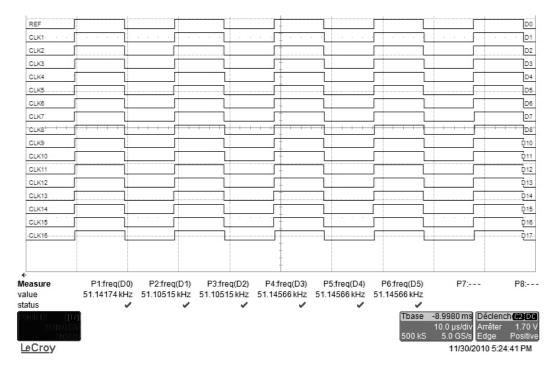

| 5.7  | Local clock signals together with reference                                         | 118 |

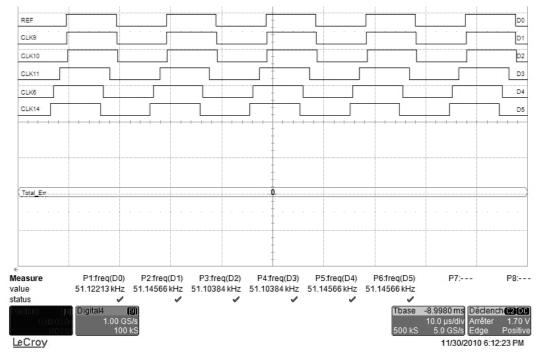

| 5.8  | Local clock signals around Node 10 together with reference and integer sum of       |     |

|      | the node errors (Total_Err)                                                         | 118 |

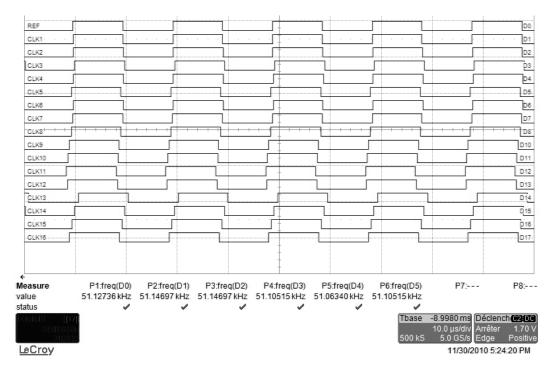

| 5.9  | Local clock signals together with reference                                         | 119 |

| 5.10 | Local clock signals around Node 10 together with reference and integer sum of       |     |

|      | the node errors (Total_Err)                                                         | 119 |

| 5.11 | Local clock signals together with reference                                         | 120 |

| 5.12 | Local clock signals around Node 10 together with reference and integer sum of       |     |

|      | the errors                                                                          | 120 |

| 5.13 | Local clock signals together with reference                                         | 121 |

| 5.14 | Unidirectional mode topology                                                        | 122 |

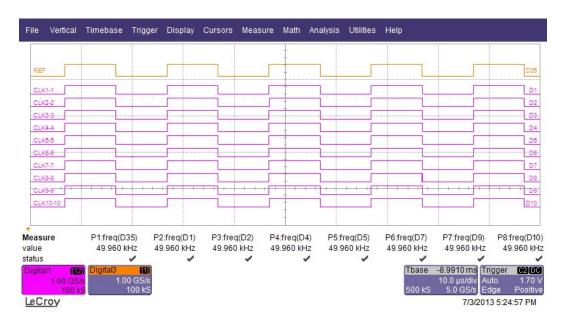

| 5.15 | Clocks in unidirectional mode at steady state                                       | 122 |

| 5.16 | Experiment principle diagram (Prototype-2): bidirectional configuration, ini-       |     |

|      | tial frequencies of nodes are different                                             | 123 |

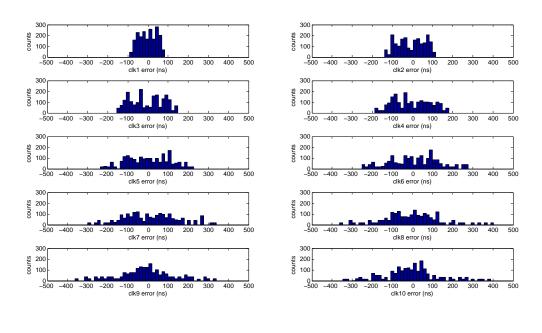

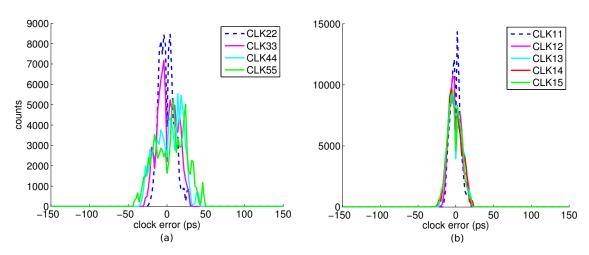

| 5.17 | Histogram of phase errors between local clock signals and the reference in          |     |

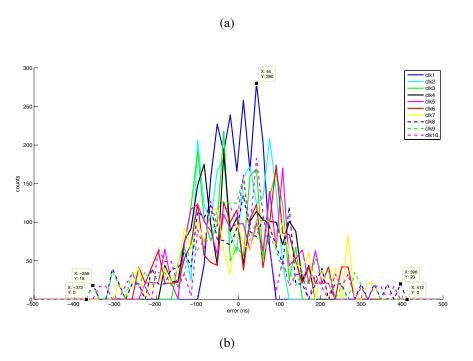

|      | $10 \times 10$ <b>prototype</b> : unidirectional                                    | 124 |

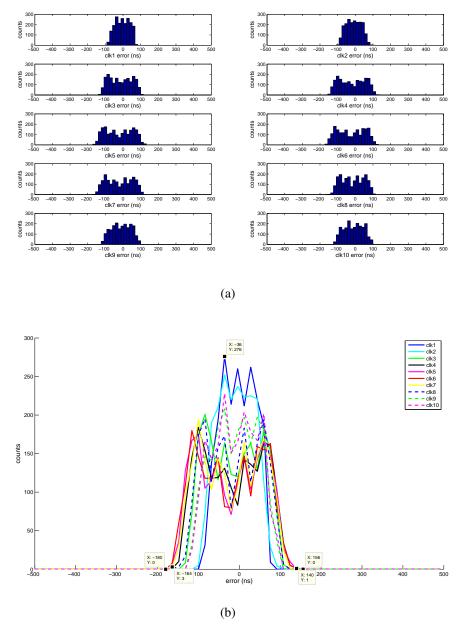

| 5.18 | Histogram of phase errors between local clock signals and the reference in          |     |

|      | $10 \times 10$ <b>prototype</b> : bidirectional                                     | 125 |

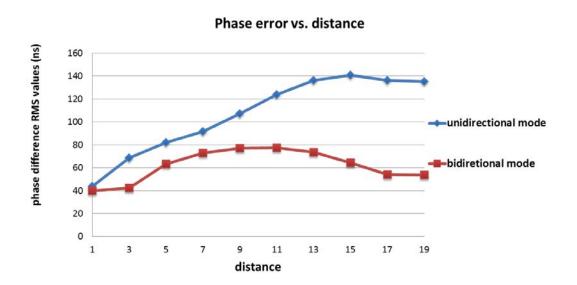

| 5.19 | Maximal value of phase error in function of distance to the reference clock         | 126 |

| 5.20 | RMS value of phase error in function of distance to the reference clock             | 127 |

List of Figures xix

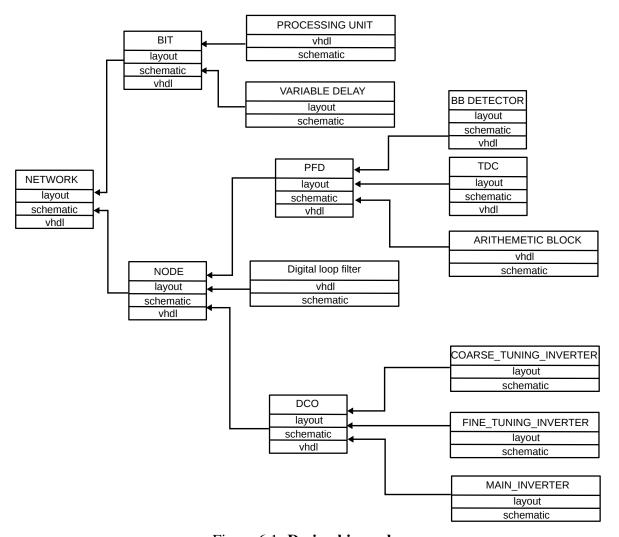

| 6.1        | Design hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 130   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

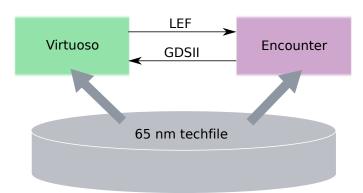

| 6.2        | Design environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 131   |

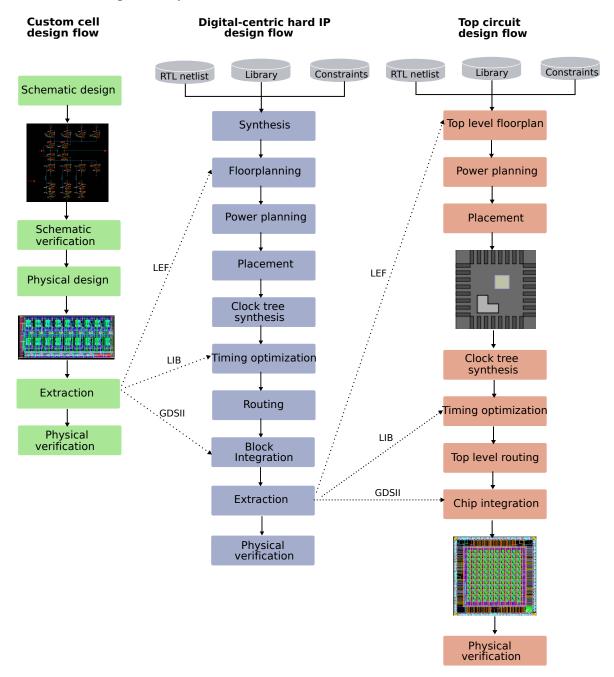

| 6.3        | Top-down design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 132   |

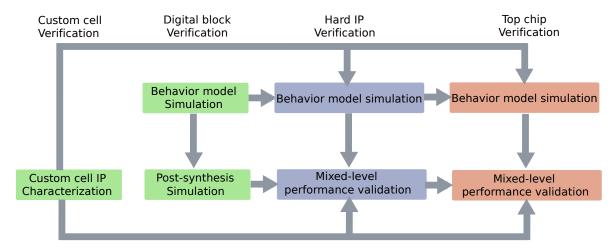

| 6.4        | Top-down verification flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 133   |

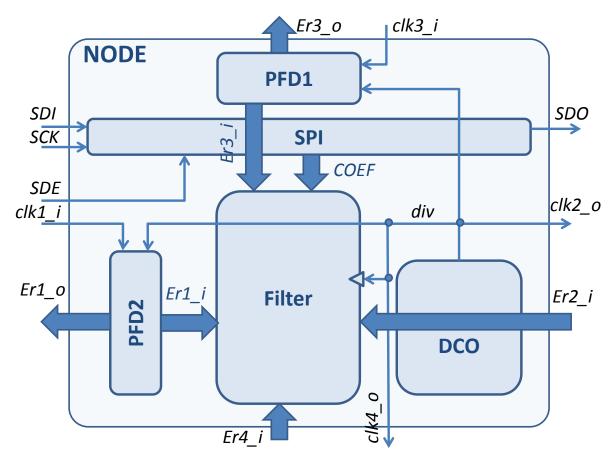

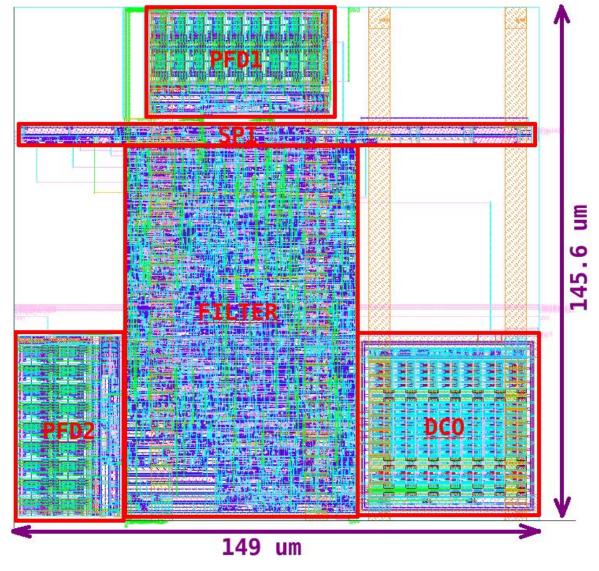

| 6.5        | Structure of a NODE: one DCO, two PFDs and digital processing block (SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|            | and loop filter)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 134   |

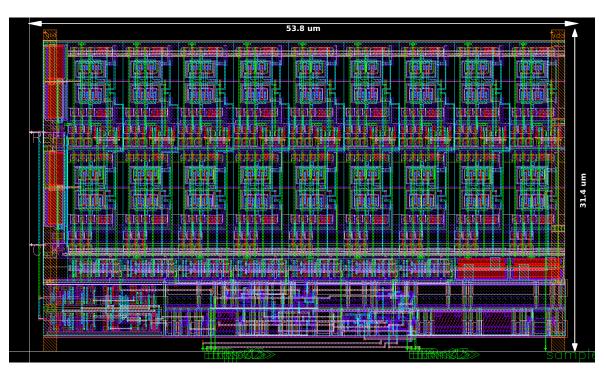

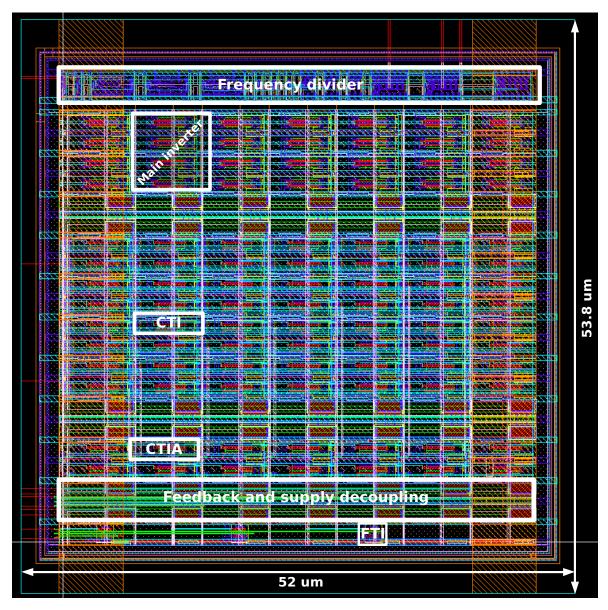

| 6.6        | Layout of the block NODE: one DCO, two PFDs and digital processing block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|            | (SPI and loop filter)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 135   |

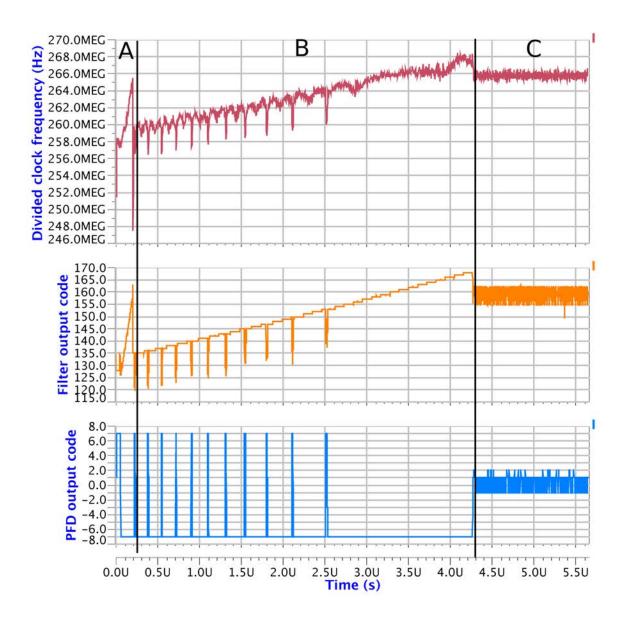

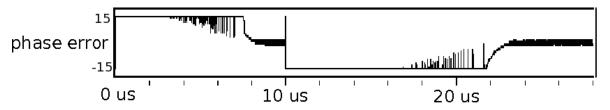

| 6.7        | Post-layout simulation of one NODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 137   |

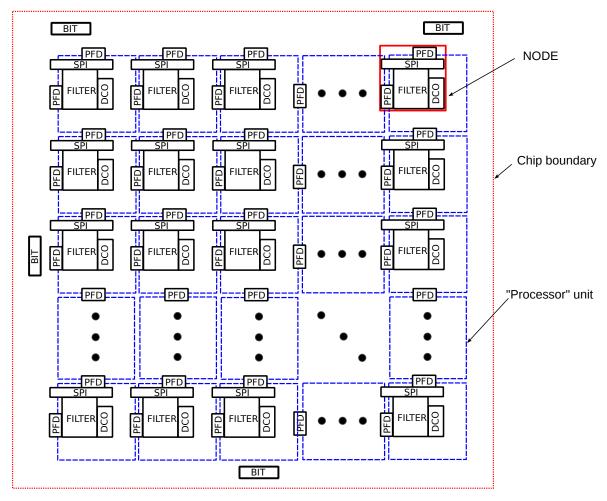

| 6.8        | Preliminary floorplan of the test chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 139   |

| 6.9        | The connection sequence of the programmable blocks of the network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 141   |

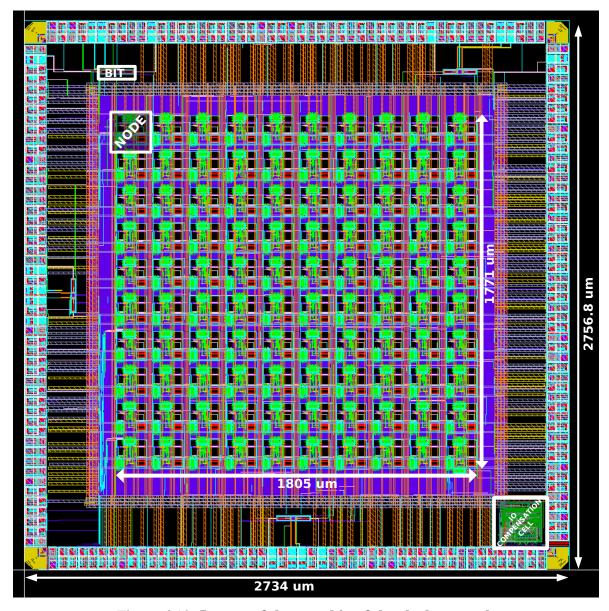

| 6.10       | Layout of the test chip of the clock network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 145   |

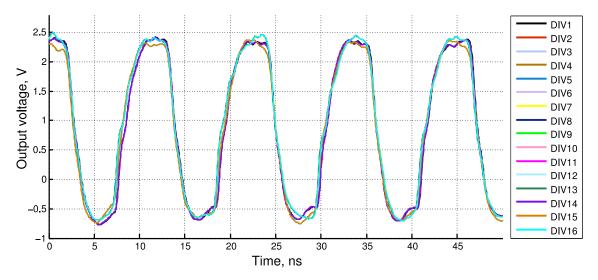

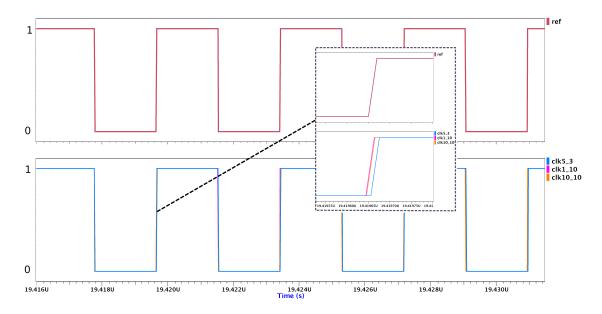

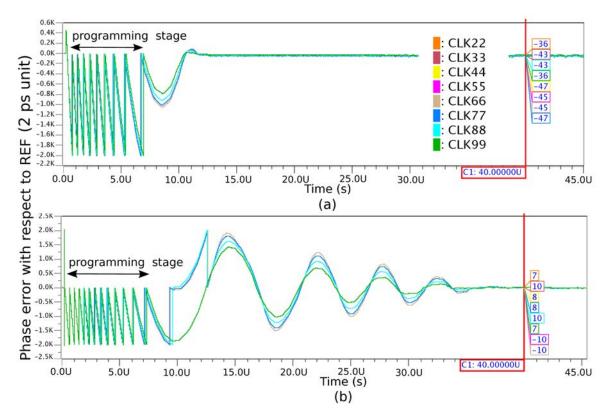

| 6.11       | Clock signals in the network in steady mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 146   |

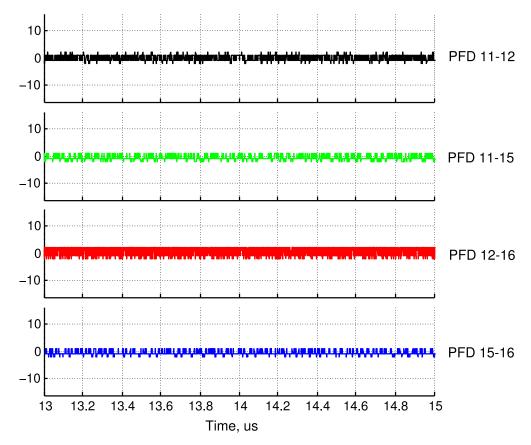

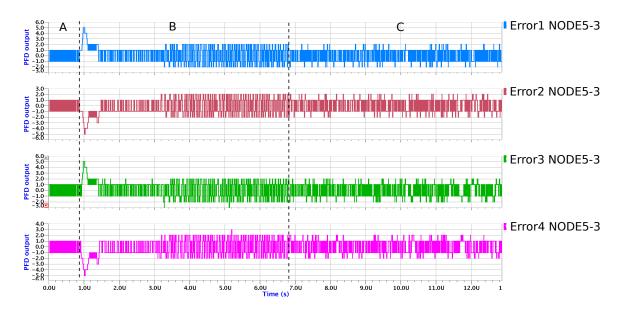

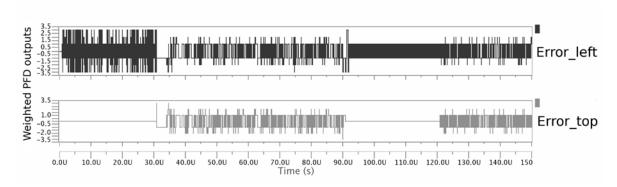

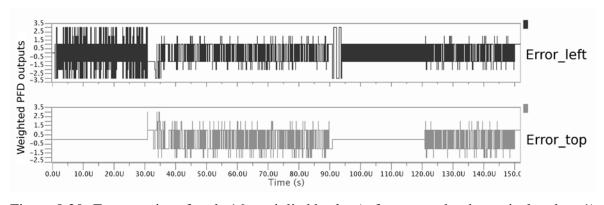

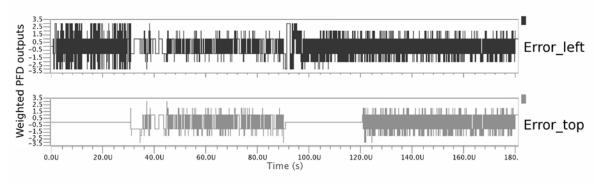

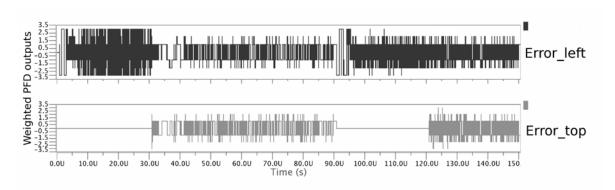

| 6.12       | <b>PFD outputs between NODE5-3 and its neighboring nodes:</b> A) programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

|            | mode; B) unidirectional mode; C) bidirectional mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 147   |

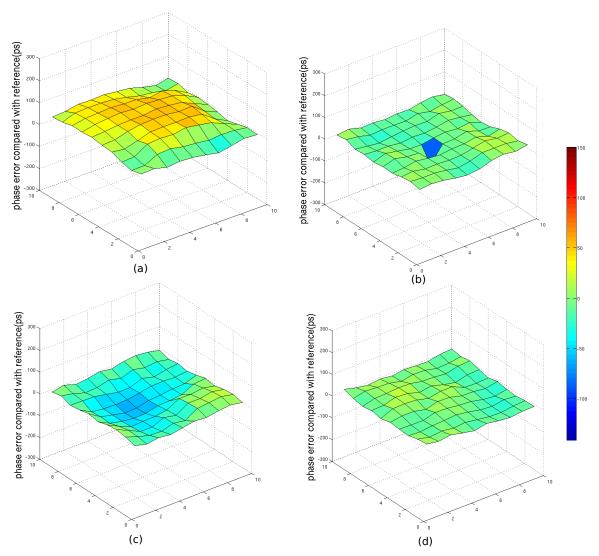

| <b>7</b> 1 | The state of the s | 1.50  |

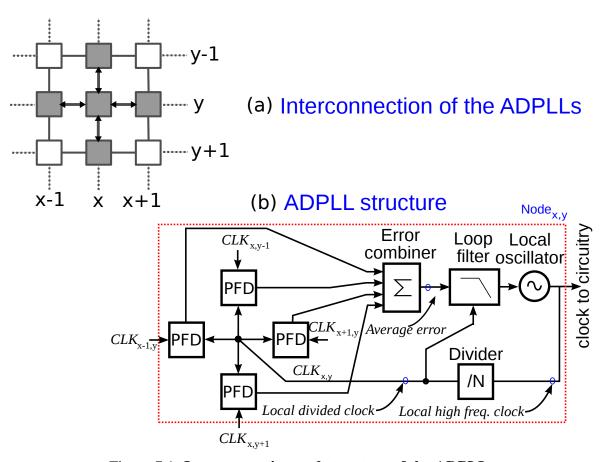

| 7.1        | Interconnection and structure of the ADPLLs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 150   |

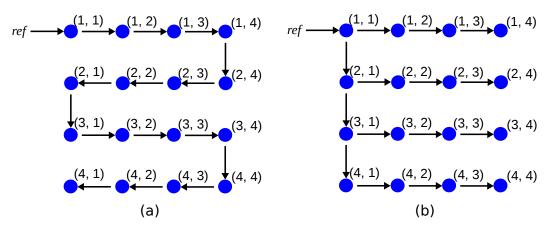

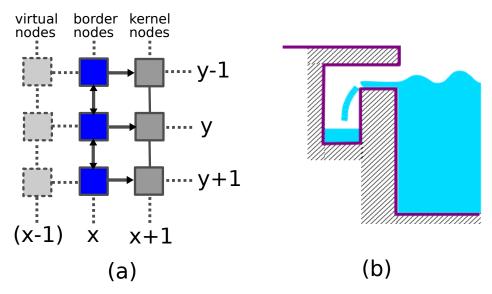

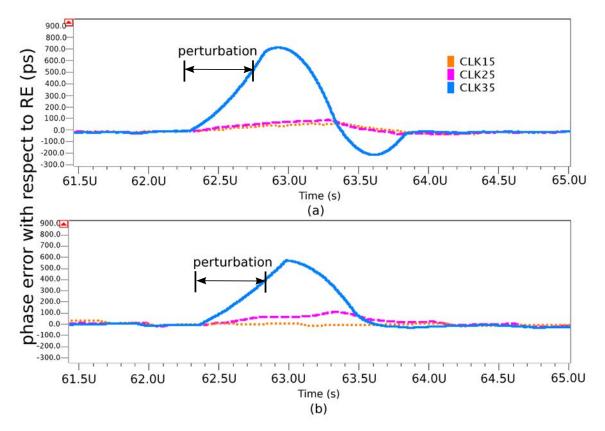

| 7.2        | (a) Interconnection of nodes at the border of network: (→: unidirectional;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.7.4 |