# Compact modeling and circuit design based on ferroelectric tunnel junction and spin-Hall-assisted spin-transfer torque

Zhaohao Wang

## ► To cite this version:

Zhaohao Wang. Compact modeling and circuit design based on ferroelectric tunnel junction and spin-Hall-assisted spin-transfer torque. Micro and nanotechnologies/Microelectronics. Université Paris Saclay (COmUE), 2015. English. NNT: 2015SACLS036. tel-01231506

## HAL Id: tel-01231506 https://theses.hal.science/tel-01231506

Submitted on 20 Nov 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

NNT: 2015SACLS036

# THESE DE DOCTORAT DE L'UNIVERSITE PARIS-SACLAY, préparée à l'Université Paris-Sud

ÉCOLE DOCTORALE N° 575 Electrical, Optical, Bio-physics and Engineering (EOBE)

Spécialité de doctorat PHYSIQUE

Par

# Zhaohao WANG

## Modélisation compacte et conception de circuit à base de jonction tunnel ferroélectrique et de jonction tunnel magnétique exploitant le transfert de spin assisté par effet Hall de spin

(Compact modeling and circuit design based on ferroelectric tunnel junction and spin-Hall-assisted spin-transfer torque)

## Thèse présentée et soutenue à Orsay, le 14 Octobre 2015 :

**Composition du Jury :**

| M Ian O'CONNOR          | Professeur,                                                            | Président          |

|-------------------------|------------------------------------------------------------------------|--------------------|

| Mme Julie GROLLIER      | École Centrale de Lyon<br>Chargé de recherche, HDR,<br>CNRS/Thales Lab | Rapporteur         |

| M Lionel TORRES         | Professeur,<br>Université Montpellier 2                                | Rapporteur         |

| M Jöerg WUNDERLICH      | Research Scientist,<br>Hitachi Cambridge Laboratory                    | Examinateur        |

| M Weisheng ZHAO         | Chargé de recherche,<br>CNRS/IEF                                       | Examinateur        |

| M Jacques-Olivier KLEIN | Professeur,<br>Université Paris-Sud                                    | Directeur de thèse |

## Acknowledgements

My PhD study began in September 2012. I would like to thank all the peoples who helped and supported me in the research and the life during the past three years.

I sincerely appreciate my supervisor Prof. Jacques-Olivier Klein, professor in Univ. Paris Sud, and my co-supervisor Mr Weisheng Zhao, researcher in CNRS, for giving me the opportunity to come to France and pursue a PhD in physics, and more importantly, for their guidance, patience, and understanding over the past three years. Prof. Jacques-Olivier Klein provided me with continuous support throughout my entire PhD study. Especially, he carefully went through the manuscript of my thesis and kindly helped me to revise my "summary in French", despite of his busy schedule. Mr Weisheng Zhao always provided me with enlightening instructions and encouragement, especially when I fell into a depression due to the research difficulties. I had a really wonderful and memorable learning experience with Prof. Jacques-Olivier Klein and Mr Weisheng Zhao.

I wish to express my deep gratitude to the members of the jury for their efforts to review my thesis. Special thanks to the rapporteurs, Mme Julie Grollier and Prof. Lionel Torres, for writing reports for the manuscript of my thesis. Also thanks to the examiner and the president, Mr Jöerg Wunderlich and Prof. Ian O'Connor, for reading and evaluating my manuscript.

I would like to thank my teachers and my colleagues in NANOARCHI and NOMADE groups of IEF: Damien Querlioz, Djaafar Chabi, Christopher Bennett, Joseph S. Friedman, Nicolas Locatelli, Nesrine Ben Romdhane, Adrien Vincent, Alice Mizrahi, Ivanka Barisic, Nicolas Vernier, Dafiné Ravelosona, Sylvain Eimer, Thibaut Devolder, Joo-Von Kim, Jean-Paul Adam, Liza Herrera-Diez, Yuting Liu, Karin Garcia, Felipe Garcia-Sanchez, Rémy Soucaille, Adrien Le Goff...

I am especially grateful to my three main collaborators: Mr Anes Bouchenak-Khelladi, who provided me with great help and useful advices during the early stage of my PhD study. Dr. Djaafar Chabi, who taught me lots of knowledge about neuromorphic systems. Ms Erya Deng, who helped me a lot in the design and simulation of non-volatile circuits.

I also thank Dr. André Chanthbouala (CNRS/Thales Lab), Prof. Alexei Gruverman (Univ. Nebraska-Lincoln), and Mr Soren Boyn (CNRS/Thales Lab). I have asked them some questions about the FTJ by e-mail. They always replied to me with patient and valuable answers.

I want to thank administrators in IEF: Mme Marie-Pierre Caron, Mme Sylvie Lamour, Mme Lydia Pactole ... Their kind help makes my daily life in IEF go very well. Also thanks to Prof. Eric Cassan and Mme Laurence Stephen from Doctoral School, for their assistance in my registration and thesis defense.

A special gratitude goes to my Chinese friends: Yue Zhang, Wang Kang, Weiwei Lin, Erya Deng, Chenxing Deng, Hezhi Zhang, Yida Wen, Wei Xu, You Wang, Xiaoyang Lin, Li Su, Yu Zhang, Gefei Wang, Qi An, Jingfang Hao, Men Su, Yanpei Liu, Yuan Shen, Ping Che, Xusheng Wang, Jianjia Yi, Xin Xu, Prof. Jianchang Yan, Nan Guan, Lu Lu, Xing Dai, Jihua Zhang, Yameng Xu, Weiwei Zhang, Ji Xiao, Juanjuan Jia, Prof. Junlin Bao, Yichen Li, Menghao Li, Yunyu Lu, Shihui Shi, Huaxiang Zhu, Ke Wang, Zukun Qu, Jiang Xu ... I cannot write all the names. I will always treasure the happy life I shared with them in France.

I wish to express my heartfelt gratitude to my family, especially to my parents Mr Xuanguang Wang and Mme Shulian Wang. Their selfless love and encouragement enable me to finish my study. This thesis is dedicated to them.

Finally, I would like to thank China Scholarship Council (CSC) for the financial support.

Zhaohao WANG

09 October 2015, Orsay

# Contents

| Acknowledgements                                                | I   |

|-----------------------------------------------------------------|-----|

| Abstract                                                        | VII |

| Résumé                                                          | IX  |

| Chapter 1 General introduction                                  | 1   |

| Chapter 2 State-of-the-art                                      | 7   |

| 2.0 Preface                                                     |     |

| 2.1 Ferroelectric tunnel junctions (FTJs)                       | 8   |

| 2.1.1 Structure and working principle                           |     |

| 2.1.2 Proposal and implementation of FTJs                       |     |

| 2.1.2.1 Critical thickness for ferroelectricity                 |     |

| 2.1.2.2 General FTJs                                            |     |

| 2.1.2.3 Special FTJs                                            |     |

| 2.1.3 FTJs towards memristive device                            |     |

| 2.1.3.1 Memristors                                              |     |

| 2.1.3.2 Memristive effect of FTJs                               |     |

| 2.2 Magnetic tunnel junctions (MTJs)                            |     |

| 2.2.1 Structure and working principle                           |     |

| 2.2.2 Main milestones in the MTJ development                    |     |

| 2.2.2.1 Enhanced TMR effect                                     |     |

| 2.2.2.2 Efficient write approaches                              |     |

| 2.2.2.3 Perpendicular magnetic anisotropy                       |     |

| 2.2.3 Magnetization switching induced by spin-orbit interaction |     |

| 2.3 Related non-volatile memories and logic circuits            |     |

| 2.4 Summary                                                     |     |

| Chapter 3 Compact modeling of the FTJ                           | 37  |

| 3.0 Preface                                                     |     |

| 3.1 Physical models of the FTJ                                  |     |

| 3.1.1 Tunneling resistance model                                |     |

| 3.1.2 TER ratio model                                           |     |

| 3.1.3 Dynamic switching model                                        |         |

|----------------------------------------------------------------------|---------|

| 3.1.4 Memristive model                                               |         |

| 3.1.5 Discussion on the static switching model                       |         |

| 3.2 Electrical model of the FTJ for the circuit simulation           |         |

| 3.2.1 Modeling language                                              |         |

| 3.2.2 Model parameters                                               |         |

| 3.2.3 Model hierarchy                                                |         |

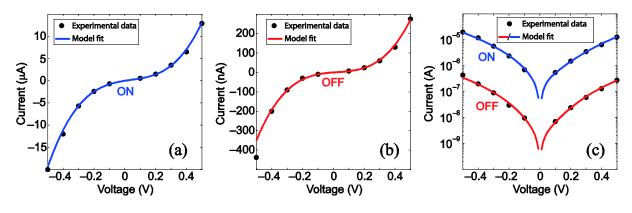

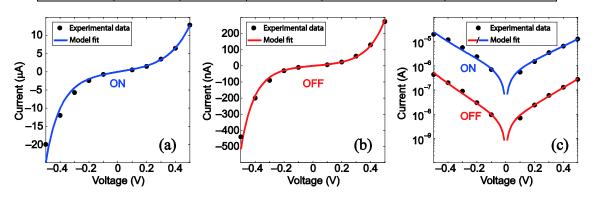

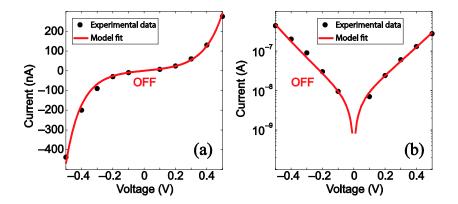

| 3.2.4 Validation of the electrical model                             | 59      |

| 3.3 Conclusion                                                       | 61      |

| Chapter 4 Circuit design and simulation based on the FTJ             | 63      |

| 4.0 Preface                                                          |         |

| 4.1 FTJ-based random access memory                                   |         |

| 4.1.1 Memory architecture                                            |         |

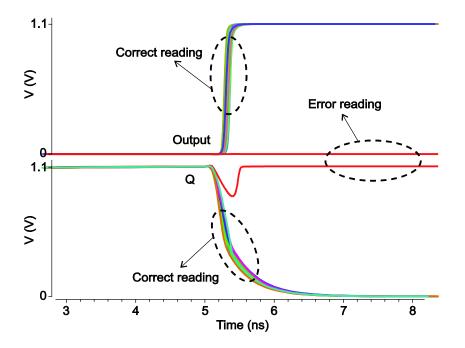

| 4.1.2 Simulation and validation                                      |         |

| 4.1.3 Read performance                                               |         |

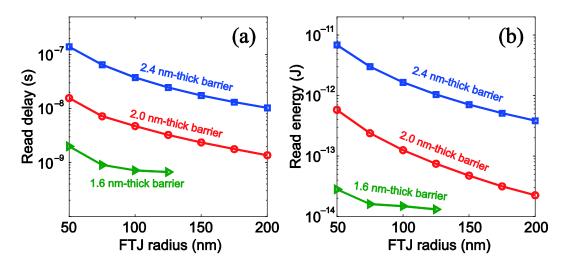

| 4.1.3.1 Dependence on the FTJ size                                   |         |

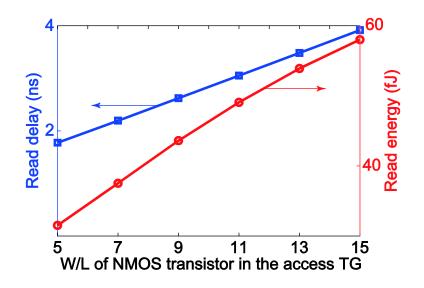

| 4.1.3.2 Dependence on the access transistor size                     |         |

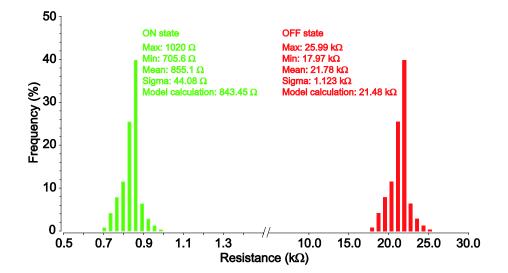

| 4.1.3.3 Reliability analysis                                         |         |

| 4.1.4 Write performance                                              |         |

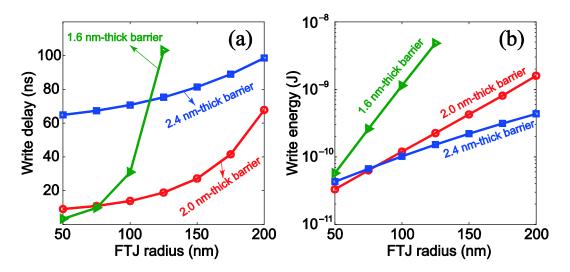

| 4.1.4.1 Dependence on the FTJ size                                   |         |

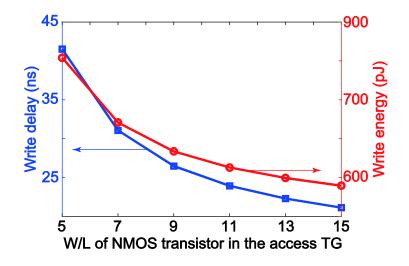

| 4.1.4.2 Dependence on the access transistor size                     | 77      |

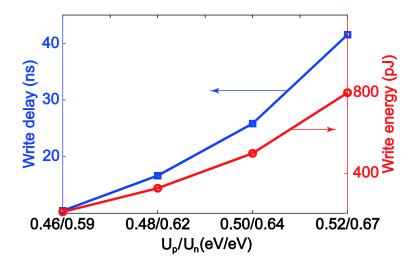

| 4.1.4.3 Dependence on the creep energy barrier                       |         |

| 4.1.5 Summary                                                        |         |

| 4.2 FTJ-based neuromorphic systems                                   |         |

| 4.2.1 Preliminary knowledge on the neuromorphic systems              |         |

| 4.2.2 Spike-timing dependent plasticity (STDP) implemented by the FT | J-based |

| synapse array                                                        |         |

| 4.2.2.1 General introduction of STDP                                 |         |

| 4.2.2.2 Architecture and operation                                   |         |

| 4.2.2.3 Simulation and validation                                    |         |

| 4.2.2.4 Performance analysis                                         |         |

| 4.2.3 Supervised learning implemented with the FTJ-based crossbar                   |                |

|-------------------------------------------------------------------------------------|----------------|

| 4.2.3.1 Architecture and operation                                                  |                |

| 4.2.3.2 Simulation and validation                                                   |                |

| 4.2.3.3 Fault-tolerance analysis                                                    | 100            |

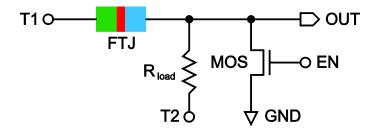

| 4.3 An idea: logic is implemented inside a single FTJ                               | 101            |

| 4.3.1 Working principle                                                             | 102            |

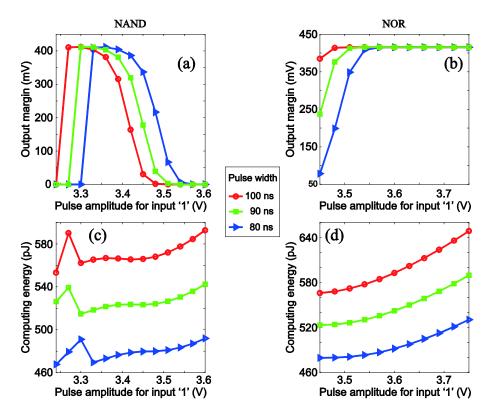

| 4.3.2 Performance optimization                                                      | 106            |

| 4.4 Conclusion                                                                      | 108            |

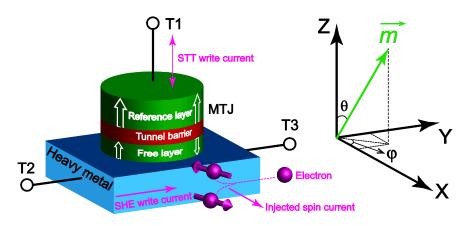

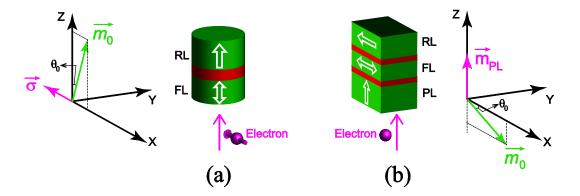

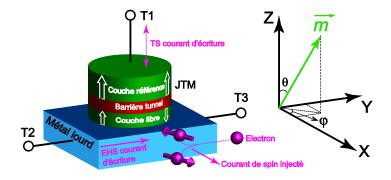

| Chapter 5 Spin-Hall-assisted spin-transfer torque                                   | 111            |

| 5.0 Preface                                                                         | 112            |

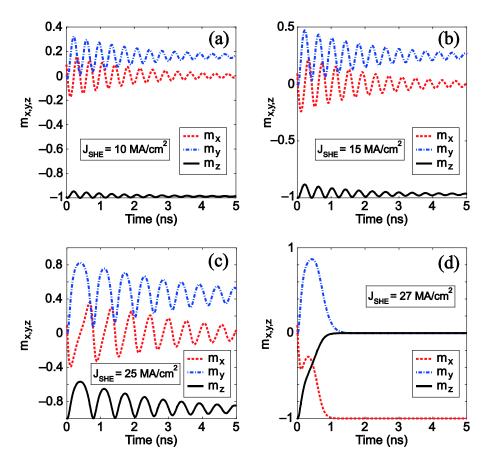

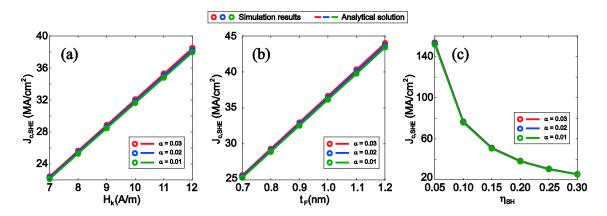

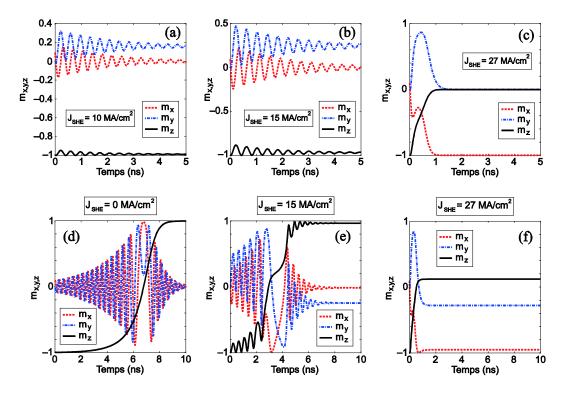

| 5.1 Simulation and discussion on the spin-Hall-assisted STT                         | 112            |

| 5.1.1 Model and assumptions                                                         | 112            |

| 5.1.2 Magnetization dynamics in the absence of STT                                  | 115            |

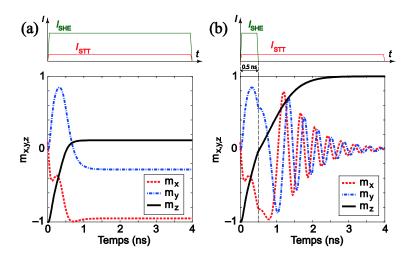

| 5.1.3 Magnetization dynamics driven by the combination of STT and SH                | ( <b>T</b> 119 |

| 5.1.4 Influences of the initial azimuthal angle and the SHE write current direction |                |

| 5.1.5 The influence of field-like torques                                           | 123            |

| 5.2 Compact electrical model of the spin-Hall-assisted MTJ                          | 126            |

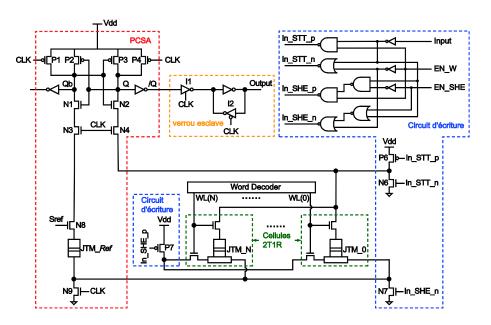

| 5.3 Magnetic flip-flop array with spin Hall assistance                              | 129            |

| 5.3.1 Circuit design                                                                | 130            |

| 5.3.2 Simulation and validation                                                     | 131            |

| 5.3.3 Performance analysis                                                          | 133            |

| 5.4 Magnetic full-adder with spin Hall assistance                                   | 136            |

| 5.5 Conclusion                                                                      | 138            |

| Chapter 6 Conclusions and perspectives                                              | 141            |

| References                                                                          | 147            |

| Appendix A: Source code of the FTJ electrical model                                 |                |

| Appendix B: Source code of the spin-Hall-assisted STT MTJ elect                     | trical         |

| model                                                                               | 177            |

| Appendix C: List of Figures                                                         | 181            |

| Appendix D: List of Tables            |     |

|---------------------------------------|-----|

| Appendix E: List of Abbreviations     |     |

| Appendix F: List of Universal Symbols |     |

| Appendix G: List of Publications      |     |

| Appendix H : Synthèse en Français     | 199 |

### Abstract

Non-volatile memory (NVM) devices have been attracting intensive research interest since they promise to solve the increasing static power issue caused by CMOS technology scaling. This thesis focuses on two fields related to NVM: one is the ferroelectric tunnel junction (FTJ), which is a recent emerging NVM device. The other one is the spin-Hall-assisted spin-transfer torque (STT), which is a recent proposed write approach for the magnetic tunnel junction (MTJ). Our objective is to develop the compact models for these two technologies and to explore their application in the non-volatile circuits through simulation.

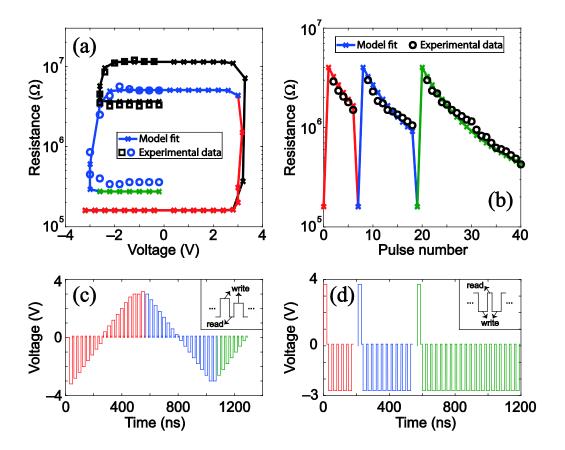

First, we investigated physical models describing the electrical behaviors of the FTJ such as tunneling resistance, dynamic ferroelectric switching and memristive response. The accuracy of these physical models is validated by a good agreement with experimental results. In order to develop an electrical model available for the circuit simulation, we programmed the aforementioned physical models with Verilog-A language and integrated them together. The developed electrical model can run on Cadence platform (a standard circuit simulation tool) and faithfully reproduce the behaviors of the FTJ.

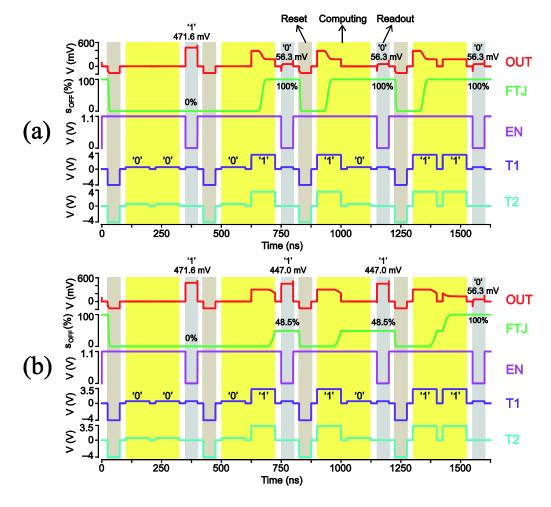

Then, by using the developed FTJ model and STMicroelectronics CMOS design kit, we designed and simulated three types of circuits: i) an FTJ-based random access memory (FTRAM), ii) two FTJ-based neuromorphic systems, one of which emulates spike-timing dependent plasticity (STDP) learning rule, the other implements supervised learning of logic functions, iii) an FTJ-based Boolean logic block, by which NAND and NOR logic are demonstrated. The influences of the FTJ parameters on the performance of these circuits were analyzed based on simulation results.

Finally, we focused on the reversal of the perpendicular magnetization driven by spin-Hallassisted STT in a three-terminal MTJ. In this scheme, two write currents are applied to generate spin-Hall effect (SHE) and STT. Numerical simulation based on Landau-Lifshitz-Gilbert (LLG) equation demonstrates that the incubation delay of the STT can be eliminated by the strong SHE, resulting in ultrafast magnetization switching without the need to strengthen the STT. We applied this novel write approach to the design of the magnetic flip-flop and full-adder. Performance comparison between the spin-Hall-assisted and the conventional STT magnetic circuits were discussed based on simulation results and theoretical models.

**Keywords**: Ferroelectric tunnel junction, magnetic tunnel junction, Spin-Hall effect, Spin-transfer torque, compact model, non-volatile circuits.

### Résumé

Les mémoires non-volatiles (MNV) sont l'objet d'un effort de recherche croissant du fait de leur capacité à limiter la consommation statique, qui obère habituellement la réduction des dimensions dans la technologie CMOS. Dans ce contexte, cette thèse aborde plus spécifiquement deux technologies de mémoires non volatiles : d'une part les jonctions tunnel ferroélectriques (JTF), dispositif non volatil émergent, et d'autre part les dispositifs à transfert de spin (TS) assisté par effet Hall de spin (EHS), approche alternative proposée récemment pour écrire les jonctions tunnel magnétiques (JTM). Mon objectif est de développer des modèles compacts pour ces deux technologies et d'explorer, par simulation, leur intégration dans les circuits non-volatiles.

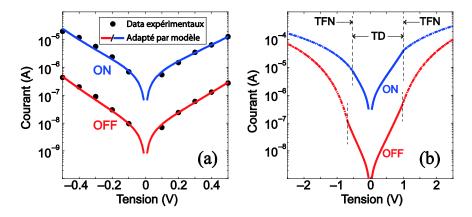

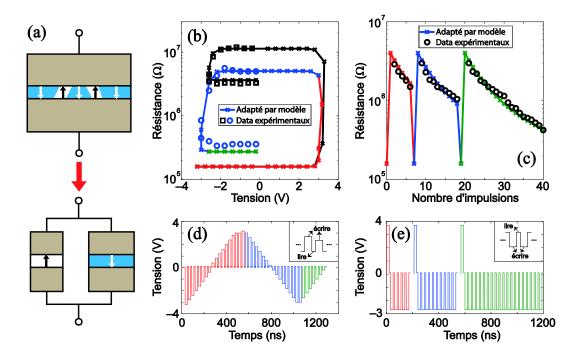

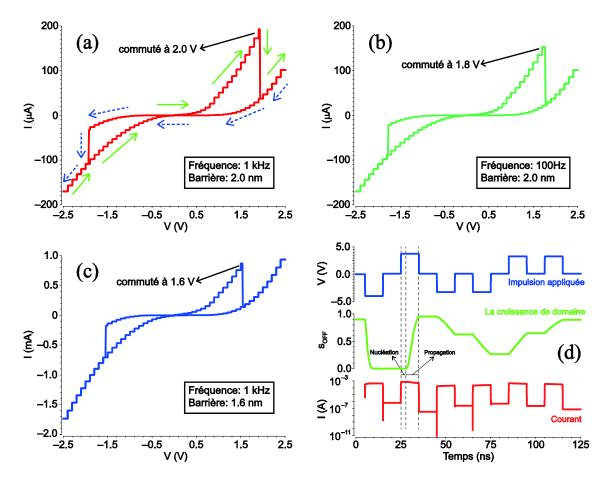

J'ai d'abord étudié les modèles physiques qui décrivent les comportements électriques des JTF : la résistance tunnel, la dynamique de la commutation ferroélectrique et leur comportement memristif. La précision de ces modèles physiques est validée par leur bonne adéquation avec les résultats expérimentaux. Afin de proposer un modèle compatible avec les simulateurs électriques standards, nous j'ai développé les modèles physiques mentionnés ci-dessus en langue Verilog-A, puis je les ai intégrés ensemble. Le modèle électrique que j'ai conçu peut être exploité sur la plate-forme Cadence (un outil standard pour la simulation de circuit). Il reproduit fidèlement les comportements de JTF.

Ensuite, en utilisant ce modèle de JTF et le design-kit CMOS de STMicroelectronics, j'ai conçu et simulé trois types de circuits: i) une mémoire vive (RAM) basée sur les JTF, ii) deux systèmes neuromorphiques basés sur les JTF, l'un qui émule la règle d'apprentissage de la plasticité synaptique basée sur le décalage temporel des impulsions neuronale (STDP), l'autre mettant en œuvre l'apprentissage supervisé de fonctions logiques, iii) un bloc logique booléen basé sur les JTF, y compris la démonstration des fonctions logiques NAND et NOR. L'influence des paramètres de la JTF sur les performances de ces circuits a été analysée par simulation.

Finalement, nous avons modélisé la dynamique de renversement de l'aimantation dans les dispositifs à anisotropie perpendiculaire à transfert de spin assisté par effet Hall de spin dans un JTM à trois terminaux. Dans ce schéma, deux courants d'écriture sont appliqués pour générer l'EHS et le TS. La simulation numérique basée sur l'équation de Landau-Lifshitz-Gilbert (LLG) démontre que le délai d'incubation de TS peut être éliminé par un fort EHS, conduisant à la commutation ultra-rapide de l'aimantation, sans pour autant requérir une augmentation excessive du TS. Nous avons appliqué cette nouvelle méthode d'écriture à la conception d'une bascule magnétique et d'un additionneur 1 bit magnétique. Les performances des circuits magnétiques

assistés par l'EHS ont été comparés à ceux écrits par transfert de spin, par simulation et par une analyse fondée sur le modèle théorique.

**Mots clés** : jonction tunnel ferroélectrique, jonction tunnel magnétique, Effet Hall de spin, transfert de spin, modèle compacte, circuits non-volatiles.

# **Chapter 1 General introduction**

### **Background**

According to the recent prediction by International Technology Roadmap for Semiconductors (ITRS) [1], the static power consumption of System-on-chip (SoC) Consumer Portable chips will dramatically increase in the next decade. For instance, it was predicted that the memory static power in 2026 will be triple that in 2016 (3 W versus 1 W, see Figure *SYSD6* in Ref. [1]). Such a trend is attributed to the fact that leakage current of transistors makes an increasing contribution to the total power consumption with the shrinking feature size of complementary metal-oxide-semiconductor (CMOS) process [2], especially below 90 nm technology node. The growth of static power limits the application prospect of the CMOS circuits, and it urgently needs to be addressed with alternative design.

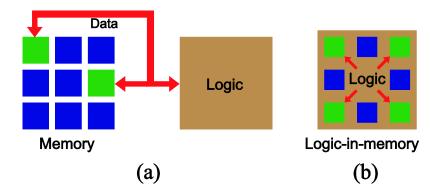

In the modern CMOS-based digital systems (e.g. microprocessors), memories are the main sources of static power consumption since they store a large number of data which must be maintained by an ongoing power supply. Accordingly, this type of memories is called volatile memories. In contrast, non-volatile memories (NVMs) can retain the stored information without the need of an activated power supply. Therefore, a promising approach for reducing the static power consumption is to replace volatile memories with NVMs. In this background, the present thesis focuses on the study of two types of NVM devices: ferroelectric tunnel junctions (FTJs) and magnetic tunnel junctions (MTJs).

### **Motivation**

The FTJ is an emerging NVM device which utilizes the ferroelectric polarization to store the information [3]–[4]. Actually the concept of the FTJ is not an emerging idea, which has been proposed by *L. Esaki* early in 1971 [5]. However, the experimental demonstration was not implemented until the 2000s [6]–[10] due to the difficulty in fabricating ultrathin ferroelectric films. Since 2000s, FTJs have attracted more and more research interests due to its promising performance. For instance, fast switching of 10 ns and high OFF/ON resistance ratio up to the order of 100 have been demonstrated in a recent FTJ prototype [10]. In 2011, the FTJ was listed as one of "emerging research devices" by ITRS report [11]. More attractively, it was recently found that some FTJs are essentially memristors [12]–[15], a kind of nonlinear circuit elements whose resistance can be continuously adjusted according to their current or voltage history [16]–[18]. Thanks to the memristor-like characteristic, the FTJ can be used as a synapse in neuromorphic systems [19] and thus prompts the research of another emerging field: memristor-based neuromorphic systems.

Nevertheless, the FTJ research is still in its infancy. In particular, the application of FTJs in memories and logic circuits has not been sufficiently studied. Currently most effort is devoted to the performance improvement of the single FTJ nanopillar. Therefore, it is necessary to expand the FTJ research from device level to circuit level. The application potential of FTJs in various circuits and systems (e.g. memories and neuromorphic systems) needs to be assessed. Such a situation prompts us to develop an electrical model for the FTJ and to explore its potential applications in NVMs and NV logic circuits (NVLs).

The MTJ is another promising NVM device which stores the data with magnetization state [20]–[21]. The concept of the MTJ was proposed almost as early as that of the FTJ, which can be traced back to 1975 when *Jullière* reported the first tunnel magnetoresistance effect (TMR effect, will be detailed in Chapter 2) at low temperature (4.2 K) [20]. But the research on the MTJ bloomed earlier than the FTJ, since the room-temperature TMR effect was demonstrated for the first time in 1995 [22]–[23], earlier than the first experimental demonstration of the FTJ in the 2000s. So far, the application of MTJs has been extended to magnetoresistive random access memory (MRAM) [24] and magnetic logic circuits [25]. Various demonstrators and even commercial products [26] have been developed.

One ambitious goal of MRAM development is to substitute for volatile dynamic or static random access memories (SRAMs or DRAMs). But current technologies still have a gap compared with this goal. In particular, the write technology of MTJs desires further breakthrough. Currently, mainstream write approach for the MTJ is spin-transfer torque (STT, will be detailed in Chapter 2) [27]–[29], but it suffers from a large incubation delay and a high risk of barrier breakdown. Recently strong spin-orbit interaction in the heavy metal was experimentally [30]–[33] and theoretically [34] studied to provide novel methods of magnetization switching and to overcome the drawbacks of the STT. These progresses drive us to focus on a promising write approach called spin-Hall-assisted STT for the perpendicular-anisotropy MTJ (p-MTJ), which was originally proposed in Ref. [34]. We expect that spin-Hall-assisted STT can improve the write performance of MRAM or magnetic logic circuits compared with the conventional STT.

### **Objectives and methods**

The above-mentioned motivation sets three objectives for the present thesis:

First, an electrical model of the FTJ needs to be developed in order to bridge the gap between physical behaviors and electrical properties. This model is also indispensable to design and analyze the FTJ-based circuits and systems.

Second, we aim to apply the FTJ to three fields: random access memory (RAM), neuromorphic systems and NV Boolean logic block, where FTJs serve various roles. The influence of FTJ parameters on the performance of these systems should be discussed and analyzed.

Finally, spin-Hall-assisted STT needs to be studied from the viewpoint of magnetization dynamics. Performance improvement over the conventional STT should be validated in some NV applications such as magnetic flip-flop (MFF) and magnetic full-adder (MFA).

These objectives were achieved through the simulation research based on computer-aided design (CAD) software. In the FTJ modeling terms, the experimental results to be fit were extracted from the published literatures. The electrical model was programmed with *Verilog-A* language [35], which is compatible with standard circuit simulation tools. The magnetization dynamics driven by spin-Hall-assisted STT was studied by the numerical simulation based on a modified Landau-Lifshitz-Gilbert (LLG) equation (an equation describing magnetization dynamics, will be detailed in Chapter 2) [36]. An electrical model of spin-Hall-assisted STT-MTJ was developed also with *Verilog-A* language. Hybrid CMOS/FTJ and CMOS/MTJ circuits were designed on *Cadence* platform by using *STMicroelectronics* CMOS 40 nm and 28 nm design kits [37]–[38] in combination with the developed FTJ or MTJ models. Circuit simulation was performed with *Spectre* simulator.

### **Organization of the present thesis**

The present thesis is divided into six chapters as follows.

This chapter presented the background, motivation, objectives and methods.

In Chapter 2, the state-of-the-art of FTJs and MTJs will be reviewed. The basic principle and key technologies related to our work will also be introduced.

In Chapter 3, we will develop a compact electrical model of the FTJ based on related physical theories. The developed model can be well fit to the experimental results extracted from Refs. [10] and [12]. Finally, we will perform single-cell simulation to validate the accuracy and applicability of our developed model.

In Chapter 4, we will design, simulate and analyze hybrid FTJ/CMOS circuits with the developed FTJ model and *STMicroelectronics* CMOS 40 nm design kit. Four circuits or systems will be studied including an FTJ-based random access memory (FTRAM), two FTJ-based neuromorphic systems and an FTJ-based Boolean logic block. Performance analysis for these circuits and systems will be presented as well.

In Chapter 5, based on a modified LLG equation, we will perform numerical simulation to analyze the magnetization dynamics driven by spin-Hall-assisted STT in a p-MTJ. Then we will

develop an electrical model of the spin-Hall-assisted STT-MTJ for the further circuit simulation. By using the developed model and *STMicroelectronics* CMOS 28 nm design kit, we will design and simulate an MFF and an MFA with spin-Hall assistance. Performance comparison between these spin-Hall-assisted magnetic circuits and the conventional STT ones will be discussed based on simulation results.

In Chapter 6, we will summarize the present thesis with conclusions and perspectives.

# **Chapter 2 State-of-the-art**

| 2.0 Preface                                                      | 8  |

|------------------------------------------------------------------|----|

| 2.1 Ferroelectric tunnel junctions (FTJs)                        | 8  |

| 2.1.1 Structure and working principle                            | 8  |

| 2.1.2 Proposal and implementation of FTJs                        | 12 |

| 2.1.2.1 Critical thickness for ferroelectricity                  | 12 |

| 2.1.2.2 General FTJs                                             | 13 |

| 2.1.2.3 Special FTJs                                             | 15 |

| 2.1.3 FTJs towards memristive device                             | 16 |

| 2.1.3.1 Memristors                                               | 16 |

| 2.1.3.2 Memristive effect of FTJs                                | 18 |

| 2.2 Magnetic tunnel junctions (MTJs)                             | 20 |

| 2.2.1 Structure and working principle                            | 20 |

| 2.2.2 Main milestones in the MTJ development                     | 23 |

| 2.2.2.1 Enhanced TMR effect                                      | 24 |

| 2.2.2.2 Efficient write approaches                               | 24 |

| 2.2.2.3 Perpendicular magnetic anisotropy                        | 27 |

| 2.2.3 Magnetization switching induced by spin-orbit interaction. | 28 |

| 2.3 Related non-volatile memories and logic circuits             | 32 |

| 2.4 Summary                                                      | 36 |

### 2.0 Preface

This chapter reviews the history and current status of FTJs and MTJs. The preliminary knowledge for understanding the basics of these two devices is presented as well. In addition, some key technologies involved in the device application are discussed.

### 2.1 Ferroelectric tunnel junctions (FTJs)

### 2.1.1 Structure and working principle

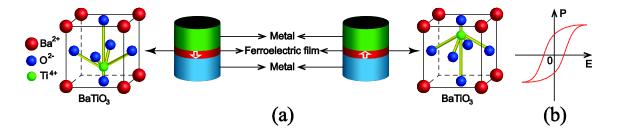

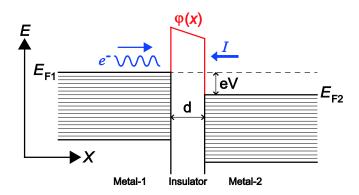

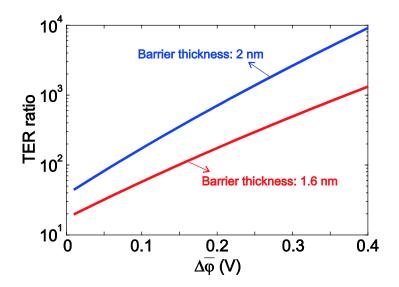

Generally, the core structure of an FTJ is composed of ferroelectric ultrathin film sandwiched between two metals (M/FE/M structure) [3], as shown in Figure 2.1(a). The ferroelectric film acts as a barrier through which electrons can flow by means of tunneling effect. The ferroelectric barrier has a spontaneous polarization arising from the displacement of cation with respect to its centrosymmetric position (see Figure 2.1(a) showing an example of barium titanate  $BaTiO_3$ ). This spontaneous polarization can be switched between two directions, as shown in Figure 2.1(b). The polarization switching can be achieved by applying an external voltage or mechanical stress. In the present thesis, mechanical properties are not discussed and thus the switching of an FTJ is voltagedriven. The polarization switching induces the modulation of the barrier potential profile so that the probabilities of electron tunneling are different for the opposite polarization orientations. As a consequence, the tunneling resistance of an FTJ can be switched between ON (low-resistance) and OFF (high-resistance) states by applying an external voltage, which is so-called tunnelelectroresistance (TER) effect [39]. Accordingly, OFF/ON resistance ratio is defined as TER ratio. TER effect enables the FTJ to store 1-bit binary information. Moreover, the storage is non-volatile as the spontaneous polarization can remain in the absence of the external voltage, which allows the FTJ to be applied in the NVMs and NVLs.

Figure 2.1 (a) Core structure of a typical FTJ. In the left and right sides, BaTiO<sub>3</sub> is taken as example to show the lattice of the polarized ferroelectric barrier. (b) Polarization-electric field (P-E) hysteresis loop of the ferroelectric barrier.

To fabricate an FTJ, two requirements are obligatory: first, the ferroelectric film must be thin enough to make electron tunneling feasible. Second, two barrier/metal interfaces must be asymmetric to generate unequal potential barrier heights for the opposite polarization orientations. The detailed working principle will be described below.

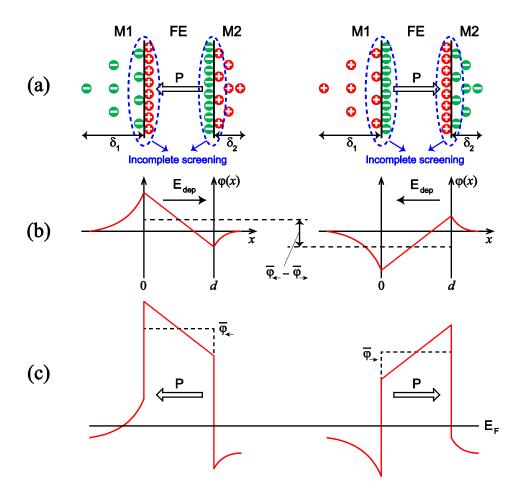

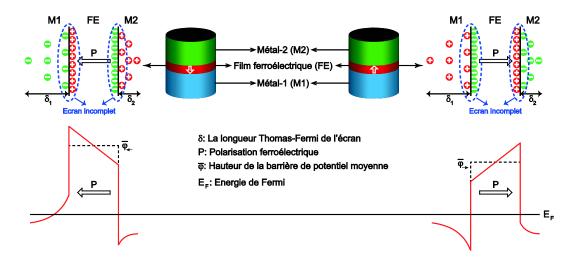

Figure 2.2 illustrates the potential profile of an FTJ for the opposite polarization orientations in the absence of the applied voltage. Here two metals (M1 and M2) are designed with different materials to produce asymmetric interfaces. As mentioned above, the potential profile varies when ferroelectric polarization is reversed. The factors modulating the potential profile include, but not limited to [3], [39]–[40]: i) the polarization reversal; ii) the barrier thickness variation caused by converse piezoelectric effect; iii) the change of barrier/electrode interfaces induced by imperfect screening of polarization charges. Among them, the third one is considered to be a dominant factor responsible for TER effect, as discussed below.

Figure 2.2 (a) Distribution of polarization charges and screening charges at two barrier/metal interfaces, (b) electrostatic potential induced by asymmetric charge screening, (c) Overall potential profile of the FTJ [39].

As shown in Figure 2.2(a), the ferroelectric polarization induces surface charges at the barrier/metal interfaces. These surface charges have to be screened by the charges from the metals. However, the screening is incomplete because the screening charges in one metal usually distributes over a finite distance from the interface, which is called screening length ( $\delta_1$  and  $\delta_2$  in Figure 2.2(a)). We assumed that there is no other interface effect influencing the distribution of charges. In this case, the incomplete charge screening at barrier/metal interfaces gives rise to a depolarization field [41] opposing the ferroelectric polarization ( $E_{dep}$  in Figure 2.2(b)). We also assumed that the depolarization field is the only origin of the tilting of electrostatic potential inside the ferroelectric film. Then, since the screening lengths are unequal for the two metals M1 and M2, electrostatic potential at two barrier/metal interfaces is asymmetric, as shown in Figure 2.2(b). Under these conditions, if the FTJ is short circuited, the electrostatic potential profile ( $\varphi(x)$ ) can be given by a simple Thomas-Fermi model [39], as

$$\varphi(x) = \begin{cases} \pm \frac{\sigma_s \delta_1}{\varepsilon_0} \exp\left(\frac{x}{\delta_1}\right), & x \le 0 \\ \mp \frac{\sigma_s}{\varepsilon_0 d} \left[x(\delta_1 + \delta_2) - \delta_1 d\right], & 0 < x < d \\ \mp \frac{\sigma_s \delta_2}{\varepsilon_0} \exp\left(-\frac{x - d}{\delta_2}\right), & x \ge d \end{cases}$$

(2.1)

where  $\delta_1$  and  $\delta_2$  are the Thomas-Fermi screening lengths in M1 and M2,  $\sigma_s$  is the screening charge per unit area,  $\varepsilon_0$  is the vacuum permittivity, *d* is the FE film thickness. The upper and lower signs ( $\pm$  or  $\mp$ ) correspond to the cases where polarization towards M1 and M2, respectively.

The overall potential profile is shown in Figure 2.2(c), which is the superposition of the potential barrier created by the FE film, the difference of Fermi energy between two metals, and  $\varphi(x)$ . With Eq. (2.1), the average potential barrier heights for the opposite polarization orientations ( $\bar{\varphi}_{\leftarrow}$  and  $\bar{\varphi}_{\rightarrow}$ , see Figure 2.2(c)) are calculated by

$$\begin{cases} \overline{\varphi}_{\leftarrow} = U + \frac{\sigma_s}{2\varepsilon_0} (\delta_1 - \delta_2), & \text{polarization towards M1} \\ \\ \overline{\varphi}_{\rightarrow} = U + \frac{\sigma_s}{2\varepsilon_0} (\delta_2 - \delta_1), & \text{polarization towards M2} \end{cases}$$

(2.2)

where U is the sum of other contributions to potential profile except for  $\varphi(x)$ .

Since  $\delta_1 \neq \delta_2$ , the average potential barrier heights are different for the opposite polarization orientations (i.e.  $\bar{\varphi}_{\leftarrow} \neq \bar{\varphi}_{\rightarrow}$ , see Figure 2.2 (b)–(c)). Accordingly, tunneling resistances are also different due to the exponential dependence of the tunneling current on the square root of the

potential barrier height [42]. This is the source of TER effect in an FTJ. Conversely, if two metals are identical and corresponding barrier/metal interfaces are symmetric,  $\delta_1 = \delta_2$  and  $\bar{\varphi}_{\leftarrow} = \bar{\varphi}_{\rightarrow}$ , the tunneling resistances are identical for the opposite polarization orientations and thus there is no TER effect. In reality, the interfacial condition is more complicated than the ideal assumptions, thus the unequal potential barrier is not always from the use of different metal materials [4]. In one word, asymmetric barrier/metal interface plays a dominant role in generating the TER effect.

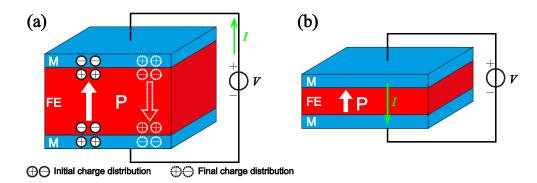

Note that although both the conventional ferroelectric capacitor (FeCap) and FTJ store nonvolatile information through the ferroelectric polarization, yet their readout operations are totally different [43]–[44]. The ferroelectric film of the FeCap is thicker (typically 100 nm) than that of the FTJ, it is thus impossible that electron tunneling occurs through such a thick barrier in the FeCap. For reading the information stored in a FeCap, a voltage larger than coercive voltage is applied across the ferroelectric barrier, resulting in a transient current flowing through the external circuit (see Figure 2.3(a)). During this process, the transferred charges (Q) are given by [44]

$$Q = \frac{\varepsilon VA}{d} + (\Delta P)A \tag{2.3}$$

where the first item is the charges for the dielectric response, the second item is the charges for the switching current.  $\varepsilon$  is the absolute permittivity of the ferroelectric film, *V* is the applied voltage, *A* is the FeCap area,  $\Delta P$  is the polarization change. Depending on the relative orientation between the applied voltage and the initial polarization, the ferroelectric polarization is reversed or remains unchanged, accordingly  $\Delta P = 2P_s$  or  $\Delta P = 0$  ( $P_s$  is the spontaneous polarization). As a consequence, the transient currents are different for the opposite initial polarization orientations. The stored information can be read by comparing the transient currents.

Figure 2.3 Comparison of the readout operation between the FeCap (a) and FTJ (b) [43].

The readout operation of the FeCap brings two drawbacks: first, since the polarization is possibly reversed during the readout, the stored information is destroyed (destructive readout),

which requires an additional reset operation to restore the initial polarization after the readout operation. Second, since the readout is performed by sensing the charges, the cell area must be large enough to provide detectable charges, which limits the scaling of the FeCap. The FTJ can overcome these drawbacks because: the information stored in an FTJ is read by measuring the tunneling resistance (see Figure 2.3(b)) and therefore the read voltage can be small to avoid destabilizing the polarization, achieving non-destructive readout. Moreover the FTJ has better scaling capability than the FeCap thanks to its larger readout current density.

### 2.1.2 Proposal and implementation of FTJs

#### 2.1.2.1 Critical thickness for ferroelectricity

As mentioned in Chapter 1, the concept of the FTJ appeared early in 1971, when *L. Esaki* proposed a tunnel device whose resistance states can be switched by reversing the polarization of the ferroelectric barrier. This device was named "polar switch" and was considered the prototype of the FTJ [5]. But in the subsequent 30 years, the fabrication of the FTJ was not realized due to a technological paradox: on the one hand, the FTJ requires a thin enough barrier to enable the electron tunnel effect; on the other hand, as the ferroelectricity is a cooperative phenomenon, the polarization in a thin ferroelectric film is apt to collapse due to depolarization field and finite-size effects [45]. The minimal thickness for holding stable polarization is called critical thickness. In 1972, *Batra* and *Silverman*'s theoretical calculation suggested that the critical thickness of triglycine sulphate (a ferroelectric material) is 400 nm [46]. Such a large thickness predetermined the unfeasibility of the FTJ. Therefore little effort was devoted to the FTJ research until the critical thickness was experimentally decreased to several nanometers in the 2000s.

Table 2.1 summarizes some important achievements in reducing the critical thickness of the ferroelectric film. These technical progresses made it feasible to keep the ferroelectricity in a film with a thickness of only a few unit cells. In this context, the FTJ research revived from theoretical prediction [3], [39]–[40], [56] to experimental demonstration [6]–[10], [12]–[15], [57]–[77].

| Year | Group                     | Material                                               | Thickness | Reference |

|------|---------------------------|--------------------------------------------------------|-----------|-----------|

| 1996 | J. Karasawa et al.        | PbTiO <sub>3</sub>                                     | 10 nm     | [47]      |

| 1998 | <i>T. Maruyama</i> et al. | PbZr <sub>0.25</sub> Ti <sub>0.75</sub> O <sub>3</sub> | 10 nm     | [48]      |

| 1999 | N. Yanase et al.          | BaTiO <sub>3</sub>                                     | 12 nm     | [49]      |

| 1999 | <i>T. Tybell</i> et al.   | $Pb(Zr_{0.2}Ti_{0.8})O_3$                              | 4 nm      | [50]      |

| 2003 | J. Junquera et al.        | BaTiO <sub>3</sub>                                     | 2.4 nm    | [51]*     |

Table 2.1 Demonstrated critical thickness of the ferroelectric film

| 2004 | D. D. Fong et al.  | PbTiO <sub>3</sub>                     | 1.2 nm | [52]  |

|------|--------------------|----------------------------------------|--------|-------|

| 2005 | N. Sai et al.      | PbTiO <sub>3</sub> /BaTiO <sub>3</sub> | 1 nm   | [53]* |

| 2006 | L. Despont et al.  | PbTiO <sub>3</sub>                     | 1.2 nm | [54]  |

| 2006 | D. A. Tenne et al. | BaTiO <sub>3</sub>                     | 0.4 nm | [55]  |

\* Based on the theoretical calculation.

### 2.1.2.2 General FTJs

In 2003, the authors of Ref. [6] claimed the first experimental demonstration of the FTJ, which was fabricated with a  $Pb(Zr_{0.52}Ti_{0.48})O_3$  barrier and achieved an OFF/ON resistance ratio of 400% at room temperature. However, in 2008 the same group suggested that the origin of resistive switching of their first FTJ is possibly not ferroelectricity due to the insufficient evidence [57]. They pointed out that it is necessary to monitor simultaneously the current-voltage (I-V) characteristic and polarization hysteresis loop to confirm the correlation between the resistive switching and ferroelectricity.

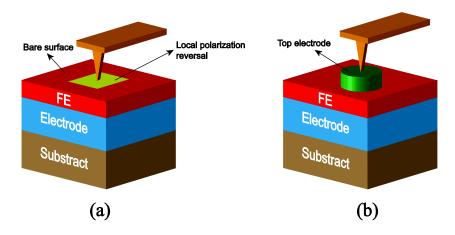

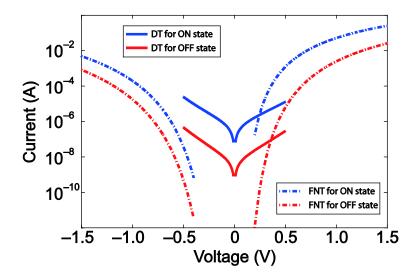

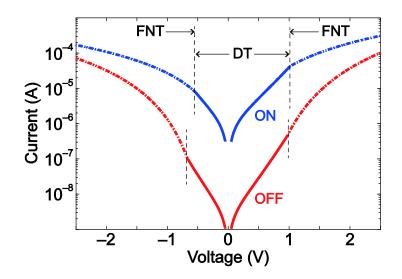

In 2009, the direct evidence for polarization-induced resistive switching was experimentally demonstrated by three groups [7]–[9]. In Ref. [7] a sharp metal tip was placed above 30 nm-thick  $Pb(Zr_{0.2}Ti_{0.8})O_3$  (PZT) film so that electrons were injected from the tip into PZT by means of Fowler-Nordheim tunneling (FNT) [58]. The polarization reversal induced a 500-fold change in tunneling current. In Ref. [8] the conductive-tip was contacted to BaTiO<sub>3</sub> (BTO) films of various thicknesses (1~3 nm). By applying a voltage across the tip and substrate, electrons flowed through BTO by direct tunneling (DT). OFF/ON ratio as high as 750 was reached in a 3 nm-thick film. The authors of Ref. [9] also independently observed TER effect and obtained an OFF/ON ratio of 80 with a 4.8 nm-thick BTO barrier. In 2010, an OFF/ON ratio of 500 was achieved through a 3.6 nm-thick PbTiO<sub>3</sub> (PTO) barrier [59] by the same group as Ref. [8]. All these experiments provided the comparison of the results between ferroelectric polarization and tunneling current to prove the dominant role of ferroelectricity in the observed resistive switching. Nevertheless, these results were obtained at the material level instead of device level. That is to say, resistive switching occurred at the local region (near the tip) of a bare ferroelectric film, as shown in Figure 2.4(a). There was no solid-state FTJ with well-defined electrodes demonstrated (see Figure 2.4(b)).

Figure 2.4 TER effect is observed in two experimental environments: (a) a bare FE material is contacted with a measuring tip, (b) FE film is sandwiched between two electrodes to form an authentic solid-state FTJ.

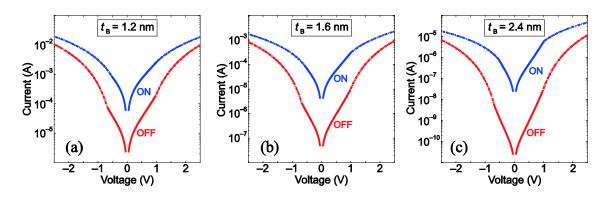

In 2011, resistive switching was demonstrated with a Cu/BTO/La<sub>0.7</sub>Sr<sub>0.3</sub>MnO<sub>3</sub> (LSMO) structure [60], but it was attributed to thermionic injection instead of electron tunneling due to the relative thick barrier (9 nm). Until 2012, the first solid-state FTJ intended to the memory application was reported in Ref. [10]. It used a Co/BTO(2 nm-thick)/LSMO structure and exhibited a large OFF/ON ratio (~100), high switching speed (~10 ns under 4 V bias) and low write current density (~10<sup>4</sup> A/cm<sup>2</sup>). Since then, more solid-state FTJs have been demonstrated by different groups [12]–[14], [61]–[72]. Some of them are summarized in Table 2.2. Although so rapid progresses have been made, some crucial performance metrics of FTJs are still far away from the requirements of the integrated circuits. For instance, FTJs suffer from the polarization relaxation which results in poor data retention [65]. Their endurance is also inferior to other NV memories (e.g. ~10<sup>6</sup> cycles in Ref. [66], which are the best results so far). Hence, fabricating high-performance FTJ nanopillars remains the top priority for this field.

| Year | Structure    | Barrier<br>thickness | Diameter<br>or area  | R.A* product for<br>ON state                       | TER<br>ratio | Ref. |

|------|--------------|----------------------|----------------------|----------------------------------------------------|--------------|------|

| 2012 | Co/BTO/LSMO  | 2 nm                 | 0.5 μm               | $\sim 20 \text{ k}\Omega \cdot \mu m^2$            | ~100         | [10] |

| 2012 | Co/PZT/LSMO  | 1.2–1.6 nm           | 0.04 μm <sup>2</sup> | $\sim 6 M\Omega \cdot \mu m^2$                     | ~300         | [61] |

| 2012 | Ag/BTO/SRO*  | 3 nm                 | 20 nm                | -                                                  | ~100         | [62] |

| 2012 | Co/BTO/LSMO  | 1.6–3.2 nm           | 5 µm                 | $20 \sim 100 \text{ M}\Omega \cdot \mu \text{m}^2$ | ~1000        | [13] |

| 2013 | Co/BFO/CCMO* | 4.6 nm               | 0.18 µm              | $\sim 2 \ k\Omega \cdot \mu m^2$                   | ~10000       | [14] |

| 2013 | Cr/BTO/Pt    | 3 nm                 | 0.8 µm               | $\sim 300 \text{ M}\Omega \cdot \mu m^2$           | ~30          | [64] |

Table 2.2 Solid-state FTJs developed by several groups

\*Some abbreviations: R.A-Resistance-area, SRO-SrRuO<sub>3</sub>, BFO-BiFeO<sub>3</sub>, CCMO-Ca<sub>0.96</sub>Ce<sub>0.04</sub>MnO<sub>3</sub>

#### 2.1.2.3 Special FTJs

For those FTJs mentioned in Section 2.1.2.2, TER effect originates from the modulation of potential barrier height in response to the polarization reversal. This mechanism exactly follows the original theoretical description of TER effect mentioned in Section 2.1.1 [3], [39]–[40]. This is the reason why we call them "general FTJs". Actually, ferroelectric polarization can also be used for tuning the other properties to generate TER effect in FTJs, which we call "special FTJs".

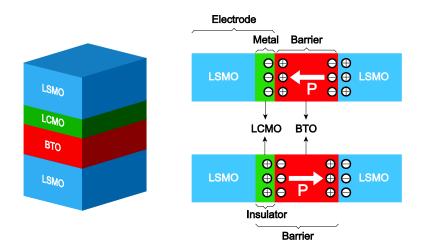

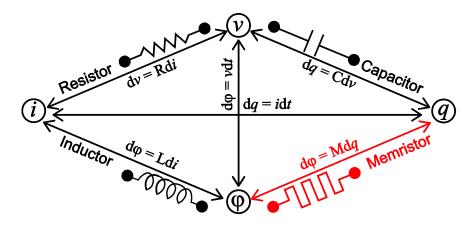

In Ref. [67], a layer of La<sub>0.5</sub>Ca<sub>0.5</sub>MnO<sub>3</sub> (LCMO) was inserted between the ferroelectric barrier (BTO) and an electrode (LSMO) to form a structure shown in Figure 2.5. The LCMO layer was deliberately designed at the transition state between the ferromagnetic-metallic phase and antiferromagnetic-insulating phase. When the ferroelectric polarization points towards the LCMO layer, the charge screening leads to the electron accumulation or hole depletion in the LCMO layer, which drives the LCMO layer to ferromagnetic-metallic phase. In this case, the LCMO layer is considered a part of the electrode. Conversely, the LCMO layer becomes antiferromagnetic-insulating phase and acts as a part of the barrier. As a consequence, the barrier thickness can be changed by switching the polarization. Since the tunneling resistance is exponentially dependent on the barrier thickness [42], TER effect can be produced in this FTJ. Experimentally, an enhanced TER ratio up to 100 was obtained with 3 nm-thick BTO and 0.8 nm-thick LCMO.

Figure 2.5 FTJ based on polarization-induced metal-insulator transition [67].

In Ref. [68], one of the electrodes in the FTJ was fabricated with Nb-doped SrTiO<sub>3</sub> (Nb:STO), which is a n-type semiconductor, as shown in Figure 2.6. Depending on the polarization directions, majority carriers (electrons) deplete or accumulate in the semiconductor layer. If deplete, the space charge region of the semiconductor layer creates an additional Schottky barrier added into the barrier. Conversely, the majority carriers accumulate within a thin region to eliminate the space

charge region and therefore only the ferroelectric layer is included into the barrier. As a result, TER ratio can be enhanced due to the polarization-induced change in barrier thickness, similar to aforementioned Ref. [67]. TER ratio as high as  $10^4$  was experimentally observed in this FTJ.

Figure 2.6 FTJ based on polarization-induced modulation of space charge region [68].

Besides the above-mentioned examples, there has been also other special FTJs demonstrated [15], [73]–[77]. Their common feature is that interface property is sensitive to the polarization reversal, which contributes to TER effect. These special FTJs extend the family of NV devices and enrich the ferroelectrics-based physics.

### 2.1.3 FTJs towards memristive device

In the previous sections, those FTJs are regarded as binary devices. Actually, many of them have the ability of multilevel storage. More exactly speaking, some FTJs are naturally memristors. To describe this issue, below we introduce briefly the concept of the memristor and then explain the memristive effect of FTJs.

### 2.1.3.1 Memristors

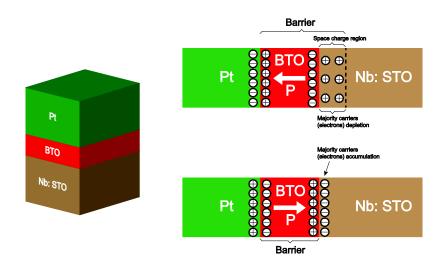

In 1971, the memristor was theoretically discovered by *L. Chua* as a nonlinear circuit element in addition to three basic linear ones: the resistor, the capacitor and the inductor [16]. Chua's theory is illustrated in Figure 2.7, where four basic circuit variables are defined: current *i*, voltage *v*, charge *q*, and magnetic flux  $\varphi$ . Each pair of variables is linked together by an equation. Hence six equations can be derived from different combinations. Among them, Eq. (2.4) describes an unknown circuit element at that time, which was named "memristor" by *Chua*.

$$\mathrm{d}\varphi = M\mathrm{d}q \tag{2.4}$$

where M is the memristance, it has the same unit (Ohm) as the resistance. But unlike the resistance, memristance is defined as a charge-dependent variable instead of a constant. Based on this definition, Eq. (2.4) is written as

$$d\varphi = M(q)dq \Rightarrow vdt = M[q(t)]idt \Rightarrow \begin{cases} v(t) = M[q(t)]i(t) \\ \frac{dq(t)}{dt} = i(t) \end{cases}$$

(2.5)

where *t* is the time.

Figure 2.7 Six equations link four circuit variables and define four circuit elements.

Thus the memristor is considered a nonlinear device whose resistance is dependent on the current history. In 1976, *Chua* expanded the concept of the memristor to broader memristive systems [78], where charge q was replaced with an internal state variable w, as

$$\begin{cases} v(t) = R \left[ w(t), i \right] i(t) \\ \frac{dw(t)}{dt} = f(w, i) \end{cases} \quad \text{or} \quad \begin{cases} v(t) = R \left[ w(t), v \right] i(t) \\ \frac{dw(t)}{dt} = f(w, v) \end{cases}$$

(2.6)

where two groups of equations describe the current-controlled and voltage-controlled memristive systems, respectively.  $f(\cdot)$  is a system-dependent function. Here we substitute *R* for *M*. Eq. (2.6) is a mathematical criterion for judging whether a device is a memristor or not. Recently, *Chua* provided a more intuitive definition: most resistive switching devices can be classified as memristors if their I-V pinched hysteresis loops can be adjusted by frequency or amplitude of applied pulses [17].

The memristor research is a similar story to that of FTJs. More than 30 years passed from the proposal of the memristor to the physical realization of the first passive memristor. In 2008, the scientists from *Hewlett-Packard* (*HP*) Labs claimed that they have fabricated the passive

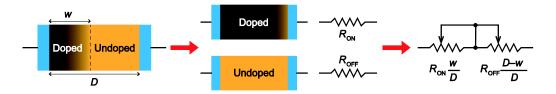

memristor for the first time [18]. Their device modeling is illustrated in Figure 2.8, where a semiconductor film with a thickness of D was sandwiched between two metal electrodes. The semiconductor film includes two regions, one of which has a high concentration of dopants and the other has a low one. These two regions are possessed of high resistance and low resistance, respectively. When an external voltage is applied to the device, the boundary between two regions can be moved due to the drift of the charged dopants. Therefore this device is equivalent to two variable resistors connected in series. Based on the above analysis, *HP* scientists gave a group of equations to describe the I-V relationship, as

$$\begin{cases} v(t) = \left[ R_{ON} \frac{w(t)}{D} + R_{OFF} \left( 1 - \frac{w(t)}{D} \right) \right] i(t) \\ \frac{dw(t)}{dt} = \mu_V \frac{R_{ON}}{D} i(t) \end{cases}$$

(2.7)

where  $R_{ON}$  and  $R_{OFF}$  are the resistances corresponding to the fully-doped and fully-undoped states, respectively.  $\mu_V$  is the average ion mobility, w is the width of the doped region. Eq. (2.7) has the same form as Eq. (2.6), proving that the proposed device is indeed a memristor with a state variable of w.

Figure 2.8 The model of the memristor developed by HP lab [18].

The finding of the memristor drives the development of many emerging fields. The fascinating one is in the high-density synapse array of neuromorphic systems [19]. More details about memristor-based neuromorphic system will be presented in Section 4.2. Here we just emphasize a fact that more and more types of memristors have sprung up and attracted much research interest from industry and academia [79] due to the great application potential. In this context, the memristive effect of FTJs was experimentally observed, as detailed below.

### 2.1.3.2 Memristive effect of FTJs

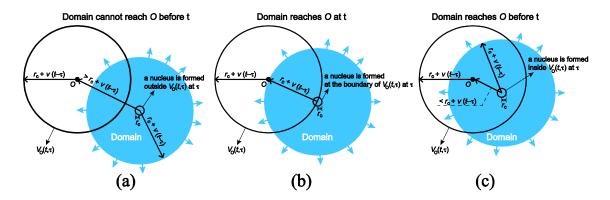

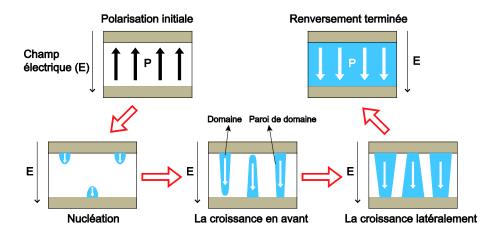

First of all, the switching process of ferroelectric polarization needs to be introduced since it is closely related to the memristive effect of FTJs. In a ferroelectric material, ferroelectric domain is a region in which dipoles have the same polarization direction. The boundary between neighboring

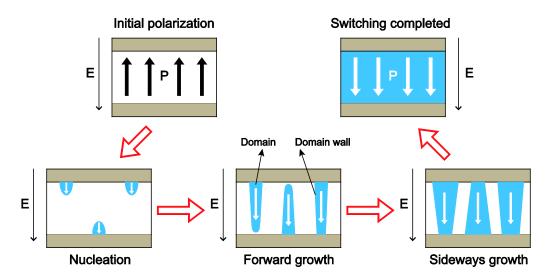

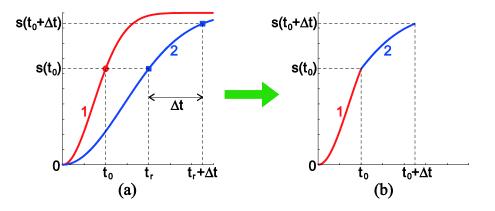

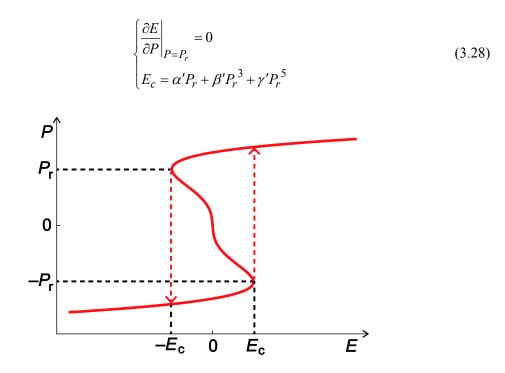

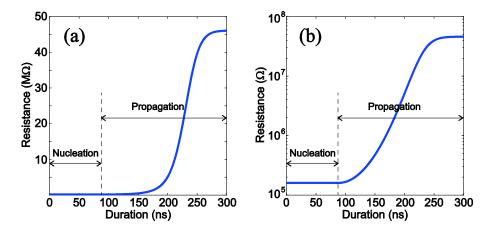

domains is called domain wall (see Figure 2.9). Experiment measurements demonstrate that polarization reversal is associated with the evolution of switched ferroelectric domain, including the nucleation, forward growth and sideways growth [45], [80]–[82], as shown in Figure 2.9. Since the FTJs use ultrathin films (< 5 nm), the delay of the forward growth can be neglected. Therefore the switching of the FTJ is mainly dominated by the domain nucleation and domain wall propagation. It is seen from Figure 2.9 that the opposite domains possibly coexist in the same film during the polarization reversal. In other words, the polarization is reversed continuously rather than abruptly under the action of an external voltage. Recall the above description that the electrical properties of some FTJs are directly controlled by the ferroelectric polarization, it is feasible that the FTJ resistance varies continuously with the gradual polarization-controlled state variable.

Figure 2.9 Polarization reversal driven by an external electric field (or voltage).

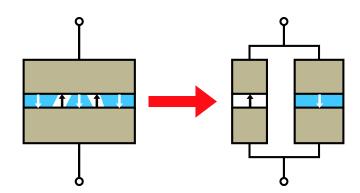

In Refs. [12] and [14], the FTJ was modeled as two resistors connected in parallel, as shown in Figure 2.10. Each resistor is represented by an FTJ full of ON-state or OFF-state domain. Under the action of an external voltage, the total resistance of the FTJ varies with the change in volume fraction of ferroelectric domain, as

$$\frac{1}{R} = \frac{1 - s_{OFF}}{R_{ON}} + \frac{s_{OFF}}{R_{OFF}}$$

(2.8)

where  $s_{OFF}$  are the volume fraction of the domain corresponding to OFF state.  $R_{ON}$  ( $R_{OFF}$ ) is the resistance when FTJ is in fully-ON (fully-OFF) state. Hence  $s_{OFF}$  is regarded as the state variable for this memristor-like FTJ.

Figure 2.10 Schematic model for the memristive effect of FTJs in Refs. [12] and [14].

In Refs. [13] and [65], the memristive behavior of the FTJ was attributed to the charge migration and accumulation at barrier/metal interface. Depending on the polarity of the applied voltage, the charges/oxygen vacancies accumulate or dissipate at the interface, leading to a tunable barrier height and adjustable resistance.

In Ref. [15], the FTJ has the same structure as Figure 2.6. Since the width of the space charge region is determined by the amount of the polarization charges to be screened, the barrier thickness can be continuously tuned during the polarization reversal. Accordingly, the FTJ resistance also continuously varies with the polarization change, and the memristive behavior can be observed.

In summary, the continuously-adjustability of ferroelectric polarization enables the FTJ to work as a memristor. The application field of FTJs is extended thanks to the memristive effect.

### **2.2 Magnetic tunnel junctions (MTJs)**

### 2.2.1 Structure and working principle

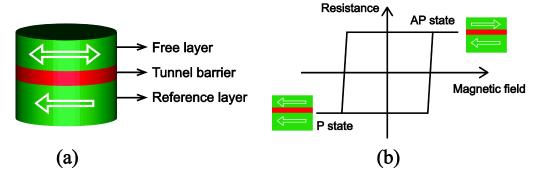

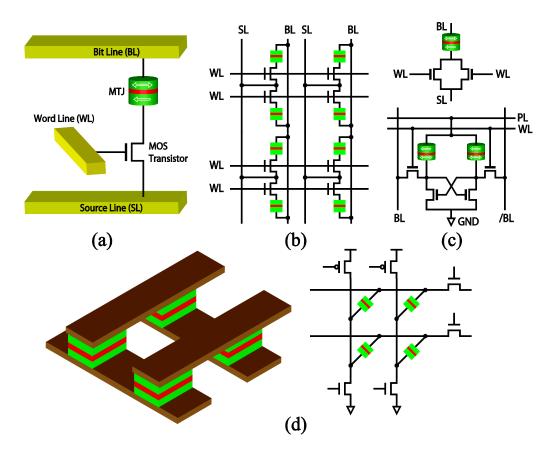

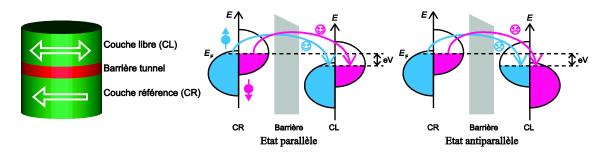

The core structure of an MTJ is shown in Figure 2.11(a), where an insulating barrier is sandwiched between two ferromagnetic (FM) layers [20]. The barrier is enough thin to enable the electron tunneling effect. Each FM layer has a magnetization which can be switched by a magnetic field between two stable directions along the anisotropy axis. In real electronic application, the magnetization of one FM layer is fixed and the other is switchable. The former is named the reference layer (RL, or pinned layer) while the latter is the free layer (FL). The magnetization of the FL can be switched to be parallel (P) or anti-parallel (AP) to that of the RL, which gives a low or high tunneling resistance (see Figure 2.11(b)). This resistance is specially called tunneling magnetoresistance (TMR). TMR ratio is the primary performance for an MTJ. It is defined as

$$TMR = \frac{\Delta R}{R_P} = \frac{R_{AP} - R_P}{R_P}$$

(2.9)

where  $R_P$  and  $R_{AP}$  are the resistances for P and AP states, respectively. TMR effect qualifies the MTJ as a binary non-volatile memory cell.

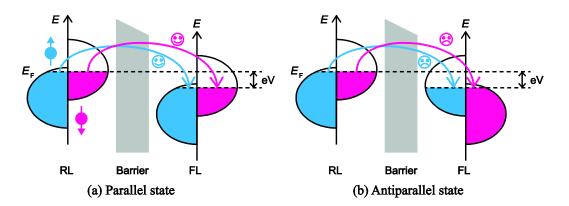

Figure 2.11 (a) Core structure of a typical MTJ, (b) TMR effect of the MTJ.

The mechanisms behind TMR effect is spin-dependent tunneling, which can be explained from the viewpoint of band structure, as illustrated in Figure 2.12. For an FM material, there is an imbalance between the populations of spin-up and spin-down at the Fermi level [21], [83]. The density of states available for spin-up is unequal to those for spin-down, resulting in a net magnetic moment and contributing to the magnetization of the FM material. The electrons near the Fermi level act as the carriers during the transport. Since the barrier is thin enough, the electron conserves its spin while it travels from one FM layer to the other one by tunneling effect. In other words, a spin-up electron can flow through the barrier if and only if it can find a spin-up state to occupy at the Fermi level of the other FM layer, so does spin-down electron. For the P state, the band structures of two FM layers are nearly identical, thereby all the spin-up or spin-down electrons from one FM layer can easily find an available state in the other FM layer. Conversely, in the AP state, only partial electrons can act as carriers for the tunneling current. As a consequence, the TMR for the P state is lower than that for the AP state.

Figure 2.12 Spin-dependent tunneling in an MTJ.

The extent of band imbalance in an FM layer can be evaluated by the spin-polarization P, which is defined as

$$P = \frac{\left|n_{\uparrow} - n_{\downarrow}\right|}{n_{\uparrow} + n_{\downarrow}} \tag{2.10}$$

where  $n_{\uparrow}$  and  $n_{\downarrow}$  are the numbers of spin-up and spin-down carriers, respectively.

Analysis based on Figure 2.12 indicates that TMR effect is strongly dependent on the spinpolarization. *Jullière* developed a model to describe this dependence [20], as

$$\begin{cases} R_P = \frac{2}{1 + P_1 P_2} \\ R_{AP} = \frac{2}{1 - P_1 P_2} \end{cases} \Rightarrow TMR = \frac{2P_1 P_2}{1 - P_1 P_2} \end{cases}$$

(2.11)

where  $P_1$  and  $P_2$  are spin-polarization in two FM layers. It is seen that the TMR ratio increases with the spin-polarization.

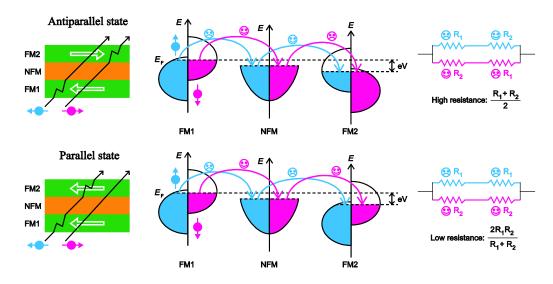

In addition, it is necessary to distinguish the TMR effect from giant magnetoresistance (GMR) effect, which is generated in metal multilayer films [84]–[86]. In the following text, this metal multilayer film is called GMR device. Similar to the MTJ, a typical GMR device has also two FM layers whose relative magnetization orientation (P or AP) determines the resistance state (low or high resistance). But there are mainly three differences between GMR devices and MTJs, as follows:

First, the GMR device uses a non-ferromagnetic (NFM) metal to separate two FM layers. Thus, electron passes through the device by *spin-dependent scattering*, as shown in Figure 2.13. But in an MTJ, the non-ferromagnetic metal is replaced with an insulator, and the electronic transportation mechanism is *spin-dependent tunneling*.

Second, in a GMR device, current can flow "in the layer plane" (CIP) or "perpendicular to plane" (CPP) [87], as shown in Figure 2.14. But for an MTJ, current passes through the device only perpendicularly.

Third, since each layer of the GMR device is conductor, it generally carries larger current than the MTJ. The GMR device is used for spin-valve read head in hard disk drive (HDD) [88]–[89]. The MTJ preferably acts as the memory cell in non-volatile MRAM [24].

Figure 2.13 GMR effect induced by spin-dependent scattering.

Figure 2.14 Two arrangements for GMR devices: (a) CIP and (b) CPP.

### 2.2.2 Main milestones in the MTJ development

MTJs and GMR devices flourish an emerging research field called "Spintronics", in which the spin plays a more dominant role than the charge in electron transport. Spintronics can be traced to the first experiment of measuring TMR effect by *Jullière* in 1975 [20], but its rise benefited from the observation of spin-injection by *M. Johnson* [90] and the discovery of GMR effect (2007 Nobel Prize in Physics) by *A. Fert* [84] and *P. Grunberg* [85] in the 1980s. These pioneering works made it possible to control the spin freedom in electronics. Up to nowadays, spintronics has a wide range of subjects and topics [91]–[93], and it is unnecessary to include all aspects in the present thesis. This section will focus on some crucial progresses in MTJ development, which are related to the topic of the present thesis.

#### 2.2.2.1 Enhanced TMR effect

In 1975, for the first time, *Jullière* observed a TMR ratio of 16.3% (as the definition of Eq. (2.9)) in Fe/Ge/Co MTJ at low temperature (4.2 K) [20]. But it cannot be applied to real electronic devices which operate at room temperature (RT) and even higher. Moreover, the observed TMR ratio was much smaller than the predicted value by Jullière model (see Eq. (2.11)). The loss of TMR ratio was attributed to the small tunneling spin-polarization induced by non-ideal fabrication process [94]. In the subsequent years, much effort was devoted to the pursuit of larger TMR ratio at RT.

Significant progress was made in 1994 when large TMR ratio was obtained at RT (18% at 300 K [22] and 11.8% at 295 K [23]) by using amorphous Al<sub>2</sub>O<sub>3</sub> insulating barrier. These results opened up the research of room-temperature TMR effect and attracted research interests to Al<sub>2</sub>O<sub>3</sub>-based MTJ. During that period, observed TMR ratio reached up to 70% in a CoFeB/Al<sub>2</sub>O<sub>3</sub>/CoFeB MTJ [95].

To further enhance the TMR effect, it was suggested that crystalline MgO should be used for the tunneling barrier to replace amorphous Al<sub>2</sub>O<sub>3</sub>. Theoretical calculation indicated that TMR ratio can reach the order of 100% even 1000% in a Fe/MgO/Fe MTJ [96]–[97]. The increase in TMR ratio is attributed to the filteration effect of the crystalline MgO: the electrons whose wave functions are symmetrical to the lattice have larger tunneling probabilities than those electrons without this symmetry. Such a symmetry difference makes an additional contribution to TMR ratio. But amorphous Al<sub>2</sub>O<sub>3</sub> does not have the ability of filtering the symmetry of wave function, resulting in a smaller TMR ratio. These theoretical works prompted the first experimental demonstrations of giant TMR ratio using Fe/MgO/Fe (180% at RT) [98] and CoFe/MgO/CoFe (220% at RT) [99] in 2004. Since then, MgO has worked as the mainstream material for the MTJ barrier to keep large TMR ratio. So far, TMR ratio as high as 604% has been reported in a CoFeB/MgO/CoFeB MTJ [100].

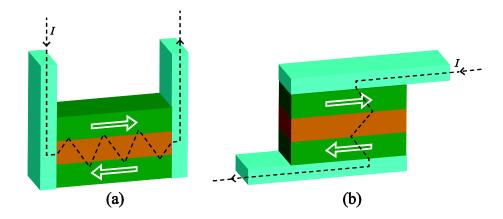

#### 2.2.2.2 Efficient write approaches

As mentioned in Section 2.2.1, the write operation of an MTJ is achieved by switching the FL magnetization. In the first-generation write approach called field-induced magnetic switching (FIMS), the magnetization switching is driven by an external magnetic field, which is induced by the currents flowing through two orthogonal write lines (digit and bit lines) [101], as illustrated in Figure 2.15(a). To switch an MTJ, two currents are applied to digit and bit lines in order to generate the hard-axis and easy-axis switching fields, respectively. The written state is determined by the polarity of the current flowing through the bit line. This write approach suffers from the

narrow operating window induced by half-selectivity disturbance. Researchers from *Freescale* improved this approach by using a synthetic antiferromagnet FL and proposed a novel toggle switching mode [102]. Based on this technology, *Freescale* launched the first commercial 4-Mbit MRAM product (No. MR2A16A). Nevertheless, FIMS requires large write current (~10 mA), resulting in the poor scalability due to the limit of electromigration.

Figure 2.15 Write approaches for the MTJ: (a) FIMS and (b) TAS.

Thermal assisted switching (TAS) [103] is an improved write approach compared with the FIMS. Its procedure is shown in Figure 2.15(b), where one current flowing through the MTJ heats the FL and reduces the write field. In this way, one write line is enough to generate the switching magnetic field. TAS has lower write power than FIMS, but it still cannot overcome the scalability issue. In addition, TAS has lower write speed since it requires a cooling down after the heating.

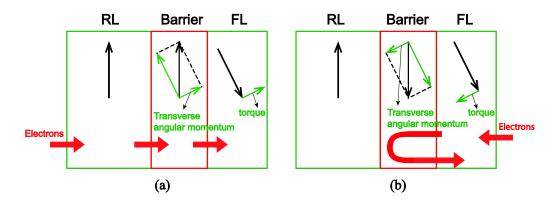

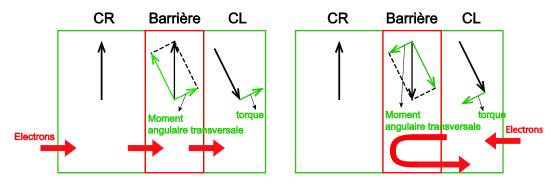

For eliminating the drawbacks of FIMS and TAS, an alternative write approach without the need of magnetic field is desired. This idea was fulfilled by *Berger* and *Slonczewski*'s theoretical prediction [27]–[28], whose principle is illustrated in Figure 2.16. While electrons flow from the RL to FL, they are spin-polarized by the RL and acquire a spin angular momentum nearly aligned to the RL magnetization. After these spin-polarized electrons pass into the FL, their transverse angular momentum must be transferred to the FL magnetization due to the conservation of angular momentum. This transfer induces a torque to force the FL magnetization to be parallel to the RL one, and then the P state is written. Such a current-induced torque is named spin-transfer torque (STT). If the electrons flow along the opposite direction, they will be spin-polarized against the RL magnetization by the reflection from the RL (see Figure 2.16(b)). In this case the MTJ is switched to AP state by the STT.

Figure 2.16 Principle of the spin-transfer torque. (a) If electrons flow from the RL to FL, the MTJ is switched to P state. (b) If electrons flow from the FL to RL, the MTJ is switched to AP state.

To understand the STT-induced magnetization switching, the FL magnetization is abstracted to a unit magnetic moment  $\vec{m}$  under the macrospin approximation. Then the dynamics of magnetization switching can be described by a Landau-Lifshitz-Gilbert (LLG) equation [36] including the STT, as

$$\frac{\partial \vec{m}}{\partial t} = -\gamma \mu_0 \vec{m} \times \vec{H}_{\text{eff}} + \alpha \vec{m} \times \frac{\partial \vec{m}}{\partial t} - \frac{\gamma \cdot h J P}{2 e t_F M_s} \vec{m} \times \left( \vec{m} \times \vec{m}_r \right)$$

(2.12)

where  $\vec{H}_{eff}$  is the effective magnetic field, which is the sum of different magnetic fields, such as the external magnetic field, the demagnetization field and the anisotropy field.  $\gamma$  is the gyromagnetic ratio.  $\mu_0$  is the vacuum permeability.  $\alpha$  is the Gilbert damping constant.  $\hbar$  is the reduced Planck constant, *P* is the spin-polarization, *e* is the elementary charge,  $t_F$  is the FL thickness,  $M_s$  is the saturation magnetization,  $\vec{m}_r$  is the unit vector along the RL magnetization. *J* is the write current density.

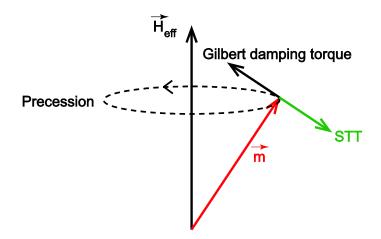

There are three torques in the right side of Eq. (2.12). Their roles are illustrated by Figure 2.17 [29], [104]. The first item is the field-induced torque which causes the magnetic moment to precess around the effective magnetic field. The second item is the Gilbert damping torque which leads to the relaxation of the precession. The third item is the STT, which is proportional to the write current density. The STT resists or assists the Gilbert damping torque depending on the polarity of the current. For the resisting case, if the current density is larger than a threshold value, the STT is strong enough to overwhelm the Gilbert damping torque and to reverse the magnetization. Accordingly, the current-induced magnetization switching occurs.

Figure 2.17 Magnetization dynamics described by Eq. (2.12).

Following the above theoretical works, STT switching was experimentally demonstrated in GMR devices [105]–[106] and MTJs [107]–[108] successively. Recently commercial STT-MRAM products have also been launched [109]. The STT switching has lower process complexity than FIMS and TAS since it requires only a bidirectional current. More importantly, the write current density for the STT switching is lower (1–10 MA/cm<sup>2</sup>) and the scalability is more promising. Currently, the STT has become the mainstream write technology for the MRAM, which will be detailed in Section 2.3.

#### 2.2.2.3 Perpendicular magnetic anisotropy

Another important advance in the MTJ development is the implementation of perpendicular magnetic anisotropy (PMA). In earlier studies, MTJs had in-plane magnetic anisotropy, which is inferior to PMA due to two reasons as follows.

First, magnetic anisotropy of the MTJ is directly related to the thermal stability and data retention. In-plane anisotropy mainly originates from the shape anisotropy. Thereby an elongated cell surface and a thin thickness are required to provide enough thermal stability. With the shrinking of the MTJ size, the in-plane-anisotropy MTJ (i-MTJ) has difficulty in maintaining the satisfying thermal stability. The perpendicular-anisotropy MTJ (p-MTJ) has no requirement for the elongated shape and thus can overcome this issue.

Second, the p-MTJ is more suitable for the STT switching than the i-MTJ. It is explained as follows. The critical current ( $I_{c0}$ ) for the STT switching can be derived from LLG equation (see Eq. (2.12)). For the i-MTJ, it is expressed as

$$I_{c0||} \simeq \alpha \frac{\gamma \mu_0 e}{\mu_B P} M_s V_F \left( H_{k||} + \frac{M_s}{2} \right)$$

(2.13)

where  $\mu_B$  is the Bohr magneton,  $V_F$  is the FL volume,  $H_{k\parallel}$  is the uniaxial in-plane anisotropy field. Other possible fields (e.g. the dipole field) are neglected. The energy barrier of thermal stability (*E*) of the i-MTJ is given by

$$E_{||} = \frac{\mu_0 M_s H_{k||} V_F}{2} \tag{2.14}$$

The comparison between Eqs. (2.13) and (2.14) indicates that the STT must overcome additional field  $M_s/2$  which makes no contribution to the thermal stability. But in a p-MTJ, the critical current is proportional to the thermal stability, as

$$I_{c0\perp} \simeq \alpha \frac{\gamma \mu_0 e}{\mu_B P} M_s V_F H_{k\perp} = 2\alpha \frac{\gamma e}{\mu_B P} E_{\perp}$$

(2.15)

Therefore p-MTJ requires lower write current than i-MTJ given the same thermal stability.

Motivated by the above advantages, researchers made much effort to obtain the PMA in the MTJ. In 2002, p-MTJ was experimentally demonstrated for the first time with a TbFeCo/CoFe/Al<sub>2</sub>O<sub>3</sub>/CoFe/GdFeCo structure, where the PMA is caused by the exchange coupling of TbFeCo/CoFe and CoFe/GdFeCo [110]. In 2006, the STT switching and the PMA were simultaneously implemented in Co/Ni multilayers [111]. Shortly afterwards, in 2007, the same task was achieved in a CoFeB/MgO/CoFeB MTJ [112]. But the TMR ratio of this MTJ was not satisfying (only 15%) due to non-fully crystallized MgO barrier and the insufficient annealing. High-performance CoFeB/MgO-based STT-PMA-MTJs were obtained in 2010 [113]–[114]. Typically, high TMR ratio (120%), small area (40 nm in diameter), high thermal stability factor (40), and low write current (49  $\mu$ A) can be achieved [113].

#### 2.2.3 Magnetization switching induced by spin-orbit interaction

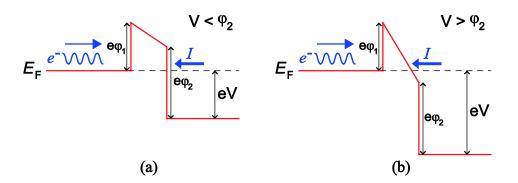

Recently, lots of progresses have been made in the study of high-performance MTJs. For instance, sub-volume p-MTJ ( $\leq 40$  nm in diameter) has been invested much research effort to accomplish low write current while keeping high thermal stability [115]–[121]. In the aspect of write approach, electric field-assisted mechanism was proposed to achieve ultrafast switching speed (sub-nanosecond) and low write energy by modulating the interfacial perpendicular anisotropy [122]–[123]. This section will introduce another newfound write approach using spin-orbit interaction, which is also the basis for the work of Chapter 5. Before beginning, two main bottlenecks limiting the switching performance of the STT are presented.

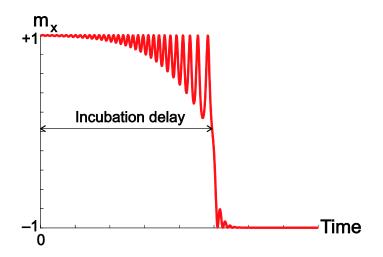

First, the STT switching needs an undesirable incubation delay, which is explained as follows. According to Eq. (2.12), initial STT is zero if the magnetizations of the FL and RL ( $\vec{m}$  and  $\vec{m}_r$ ) are exactly collinear. It is thermal fluctuation that causes a little misalignment of the magnetizations and provides a small STT to trigger the switching process. An example of time-resolved STT switching is shown in Figure 2.18, where the magnetic anisotropy is in-plane (X-axis) and an initial angle of 6.5° is assumed. It is seen that the magnetization evolves slowly during a long initial stage, which is so-called incubation delay. Such a delay hinders the STT from achieving ultrafast switching.

Figure 2.18 Time-resolved X-component of the normalized FL magnetization in an i-MTJ.

Second, faster STT switching requires a larger write current (or write voltage), which adds the risk of barrier breakdown as the write current directly flow through the MTJ.

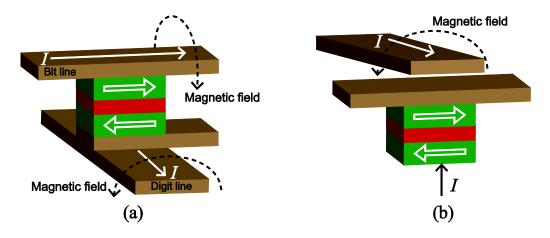

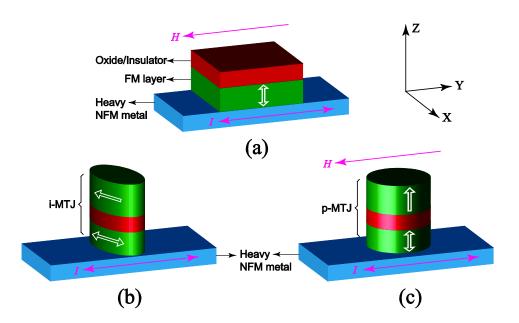

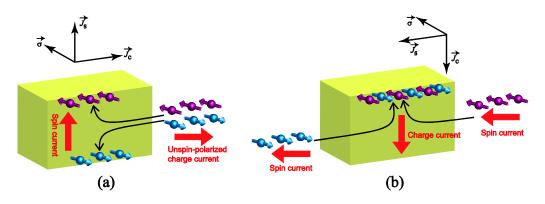

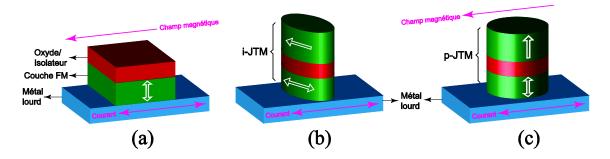

To overcome the above bottlenecks, spin-orbit interaction was recently investigated to provide an alternative write approach. Spin-orbit interaction means that the electron's spin angular momentum interacts with its orbital angular momentum. In some materials, spin-orbit interaction can be strong enough to generate significant spin accumulation from an unpolarized charge current. The spin accumulation induces a torque (called spin-orbit torque, SOT) to switch the magnetization [124]. Such an SOT-induced magnetization switching has been experimentally demonstrated in three device geometries shown in Figure 2.19. In Figure 2.19(a), an FM layer with perpendicular magnetization is sandwiched between an oxide-insulator and an NFM heavy metal strip (e.g. Pt, Ta) [30]–[33], [125]–[128]. In Figure 2.19(b)–(c), the heavy metal strip is contacted to the FL of the overlying i-MTJ [33], [129]–[130] and p-MTJ [131], respectively. The key idea of these designs is that an in-plane charge current flowing through the heavy metal (Y-axis) can generate the SOT for the magnetization switching. The origin of this SOT is still under the debate, possibly Rashba effect [30]–[31], spin Hall effect (SHE) [32]–[33], [127]–[130] or both [126]. These two effects are explained below.

Figure 2.19 Three device geometries used in the experiments of spin-orbit torque-induced magnetization switching.

Rashba effect originates from the breaking of structural inversion symmetry [132]–[133]. It can occur in those devices shown in Figure 2.19 since the FM layer or FL is sandwiched between two different materials to break the vertical inversion symmetry. Rashba effect results in an effective magnetic field  $(\vec{H}_R)$  as

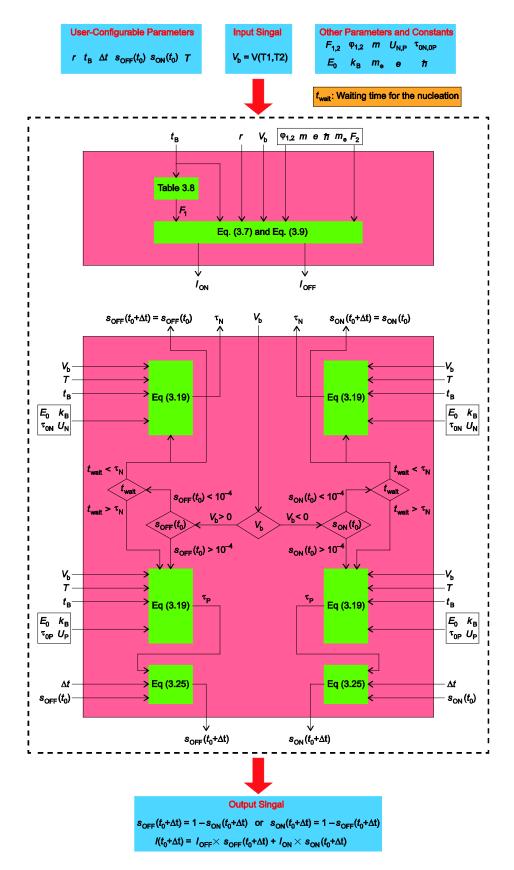

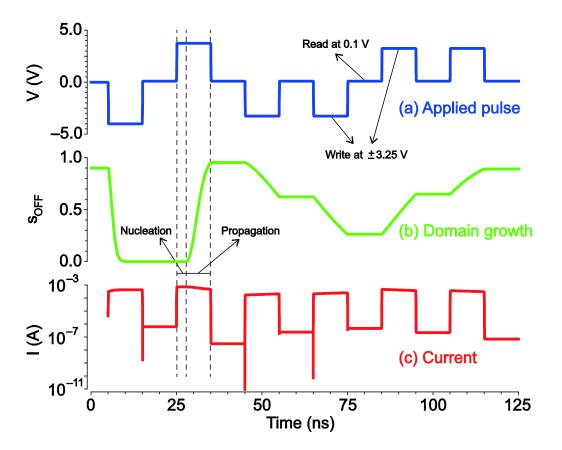

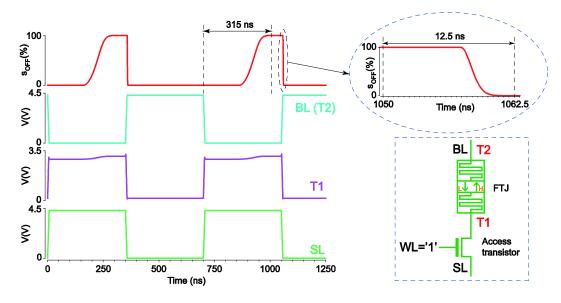

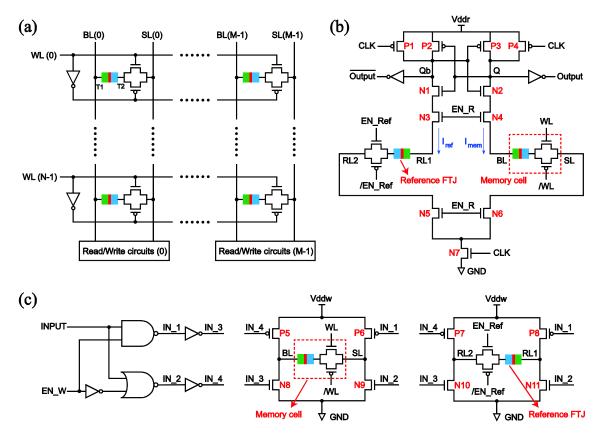

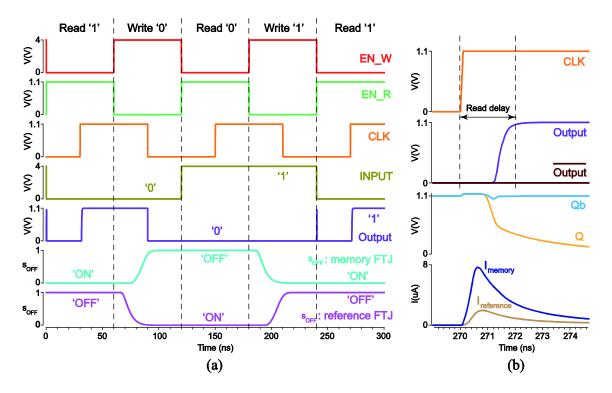

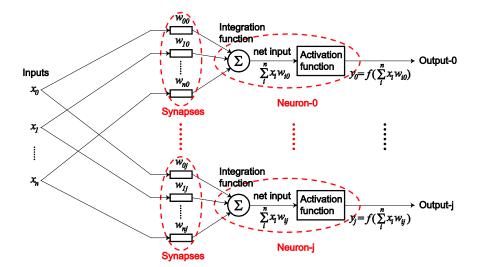

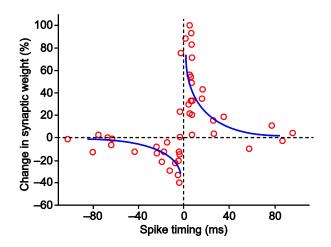

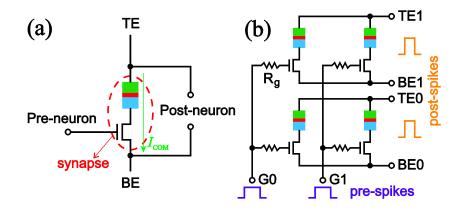

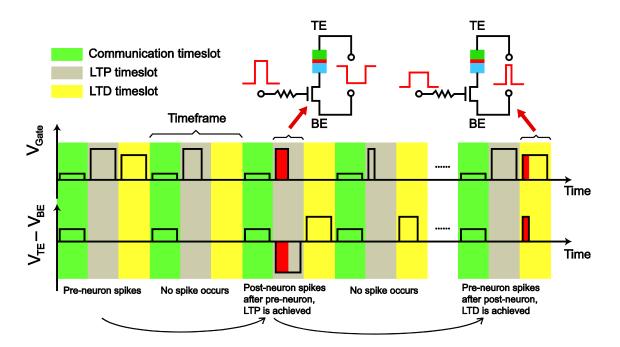

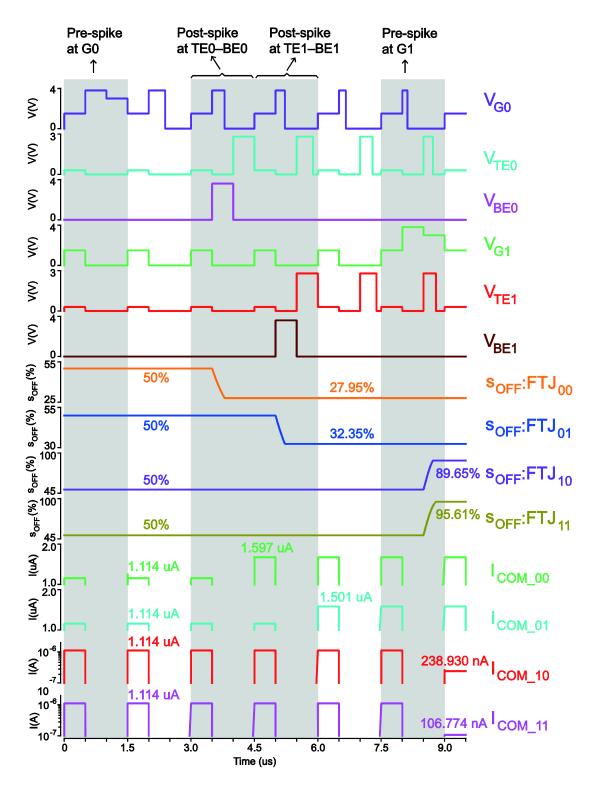

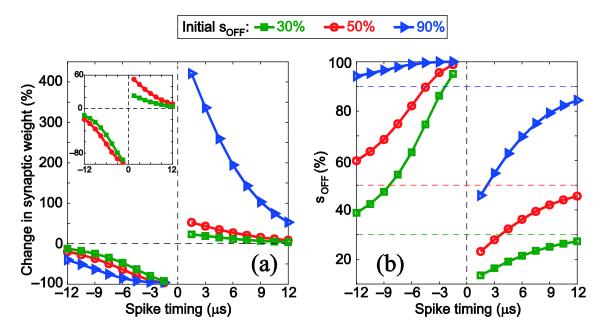

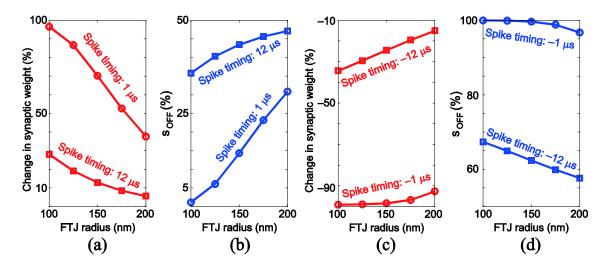

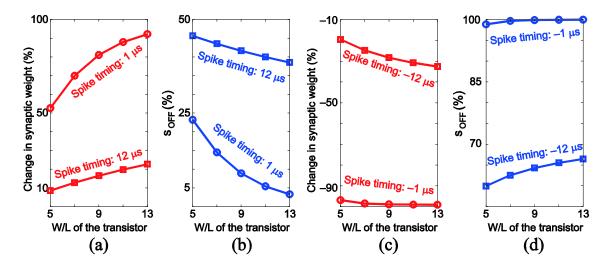

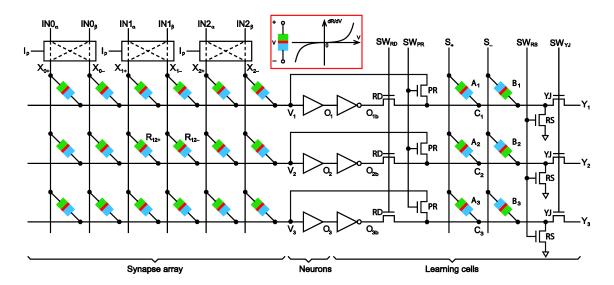

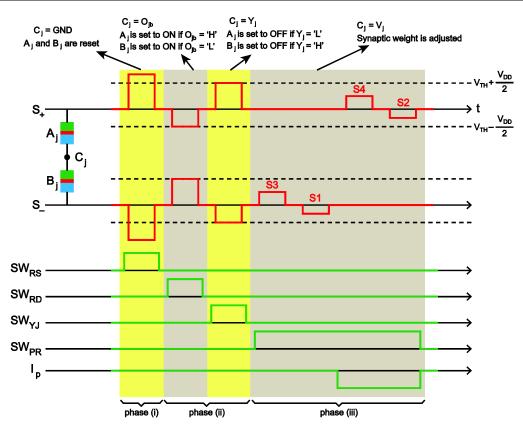

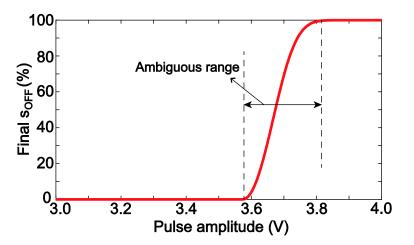

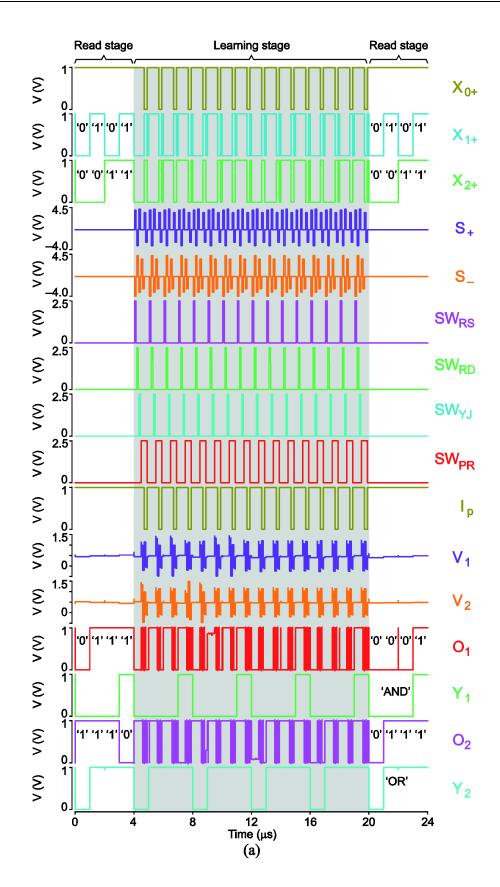

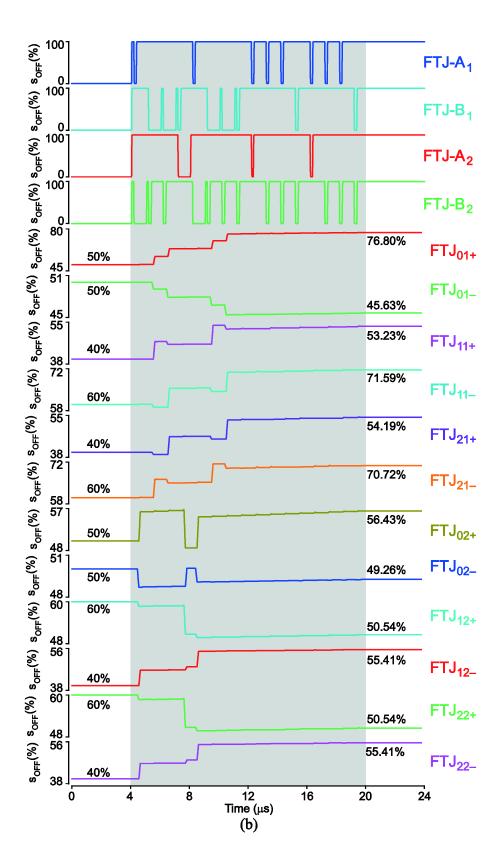

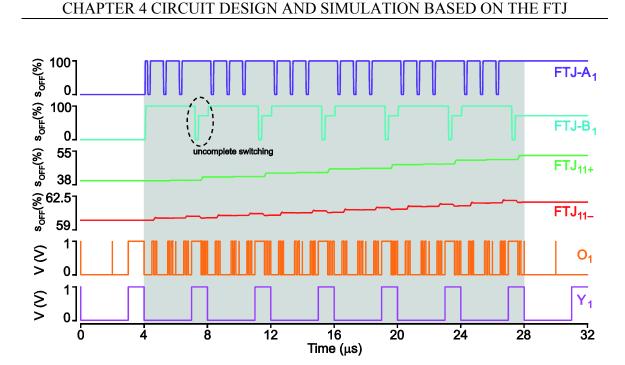

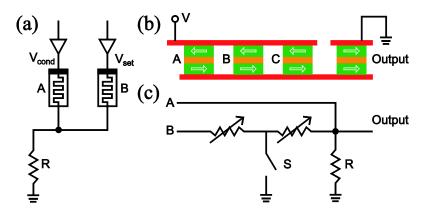

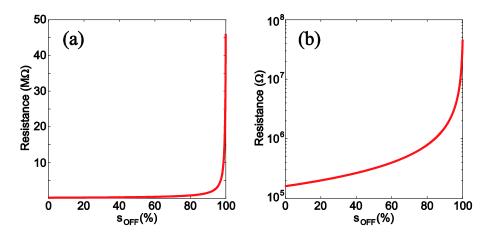

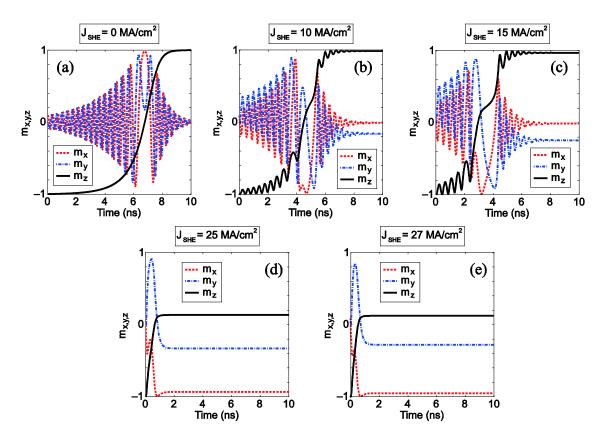

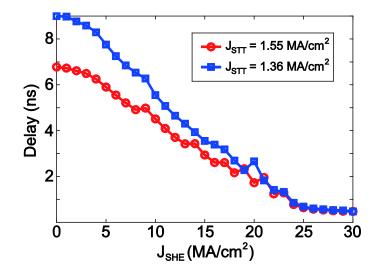

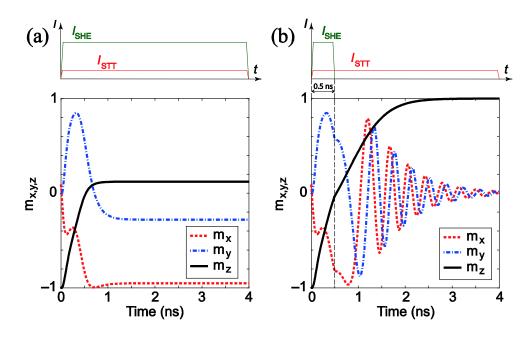

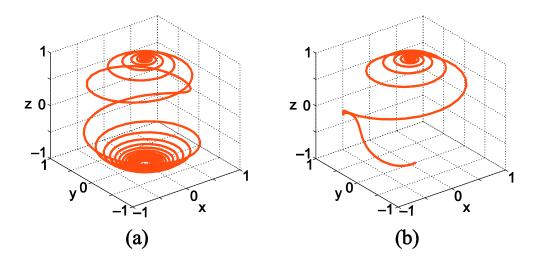

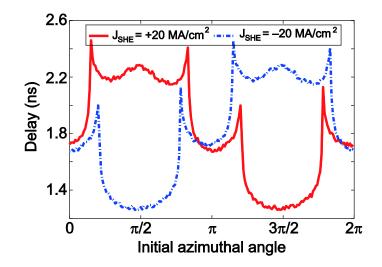

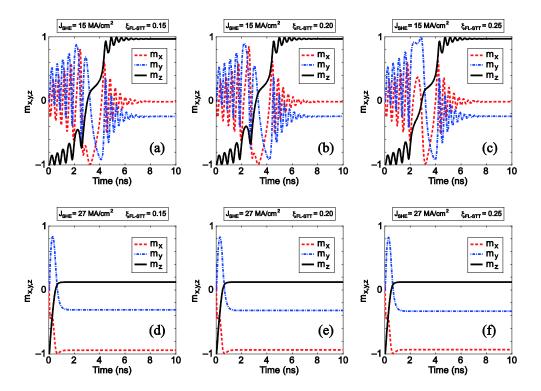

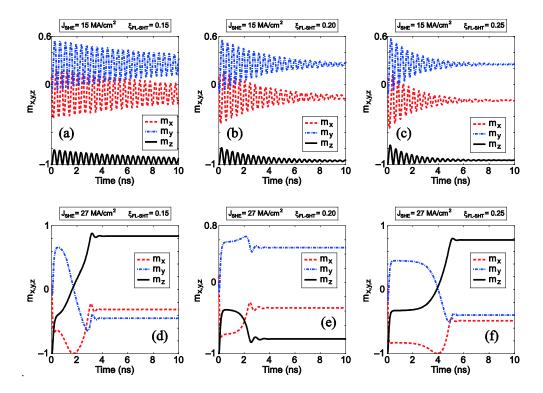

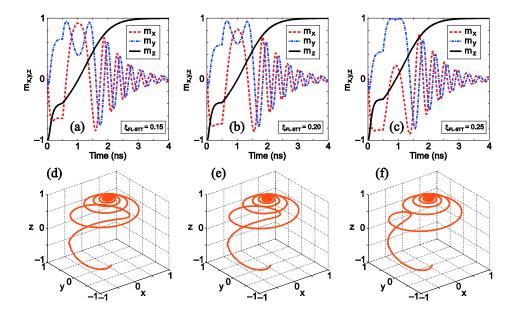

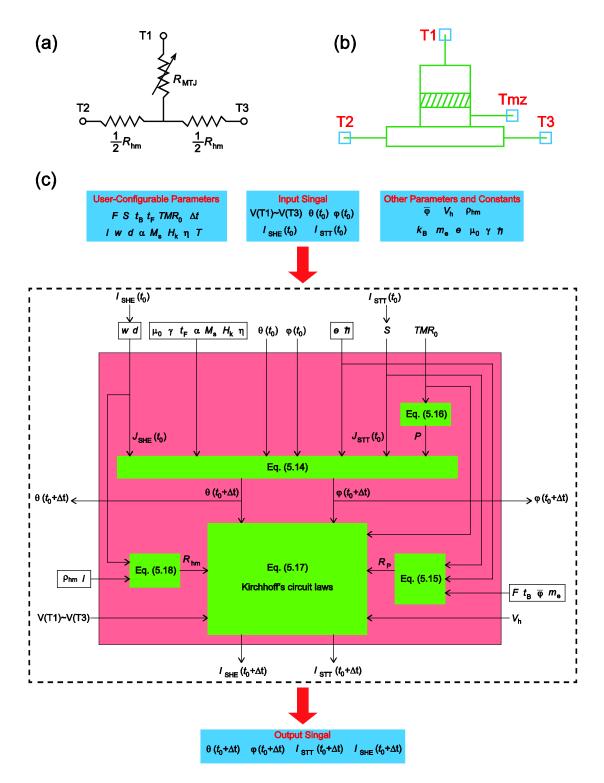

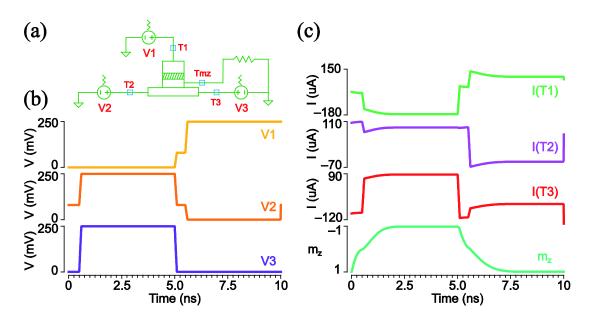

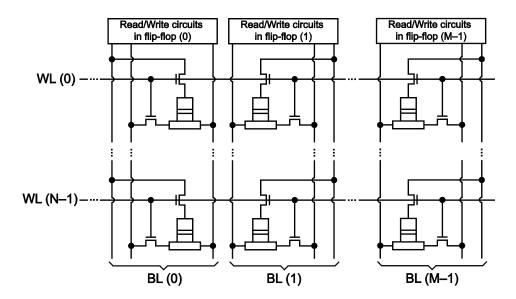

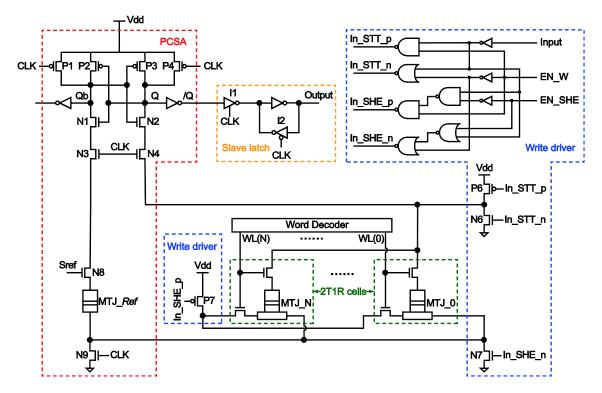

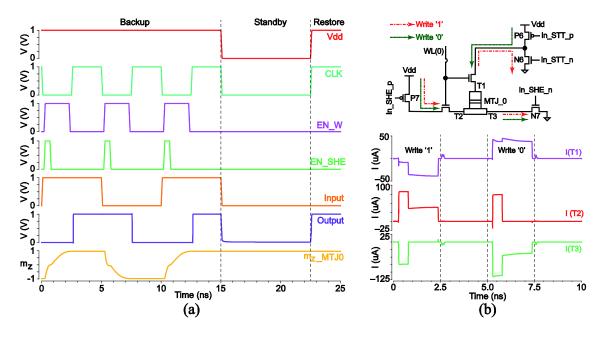

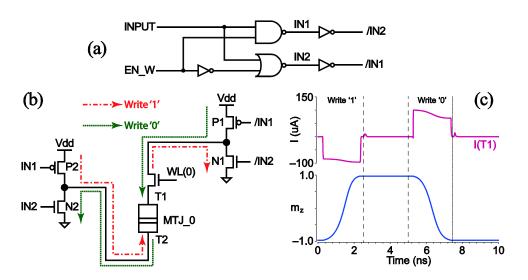

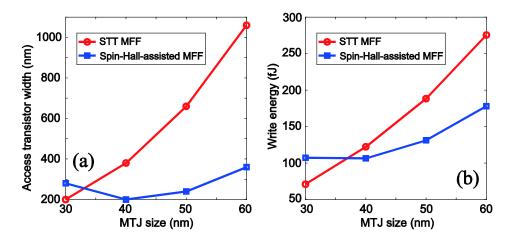

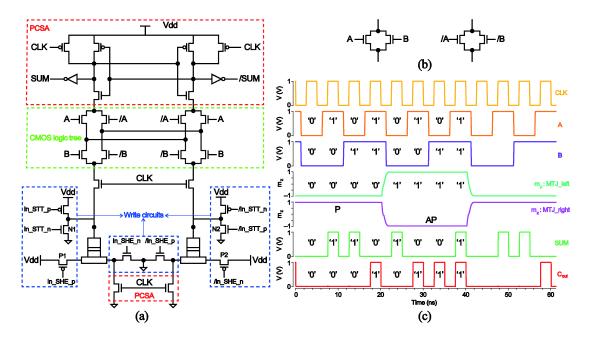

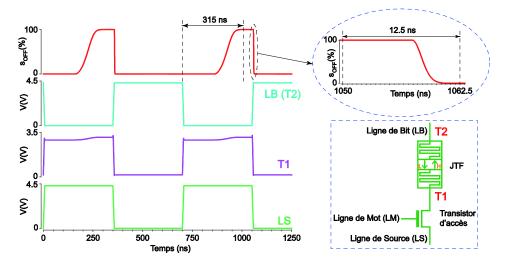

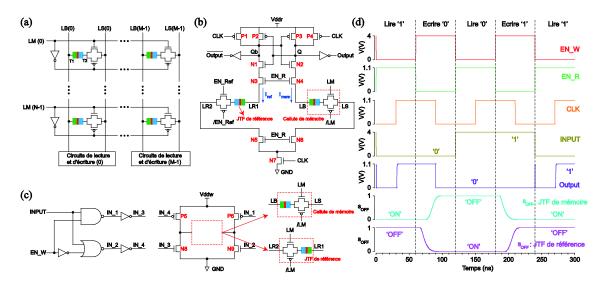

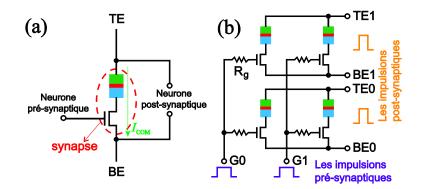

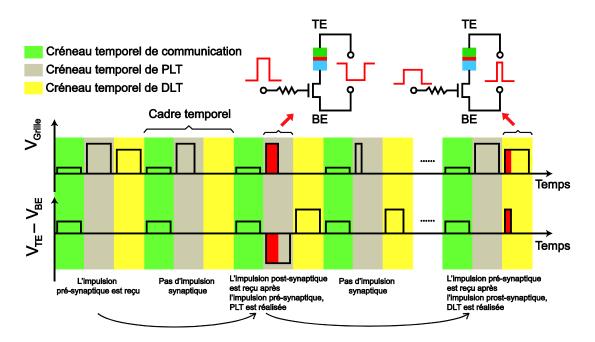

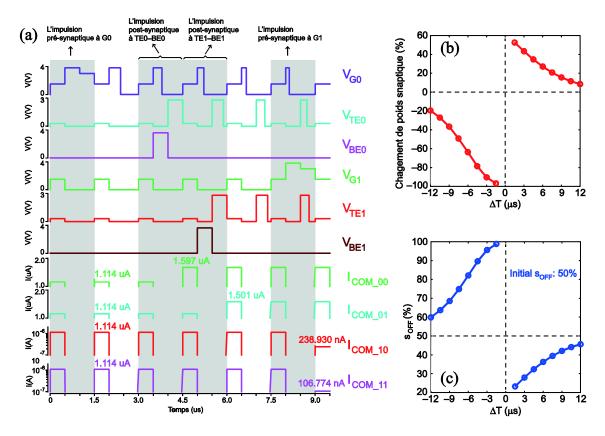

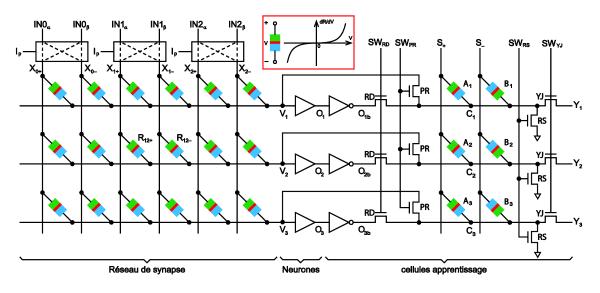

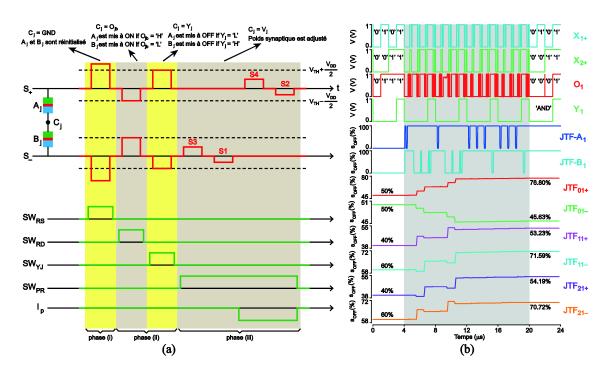

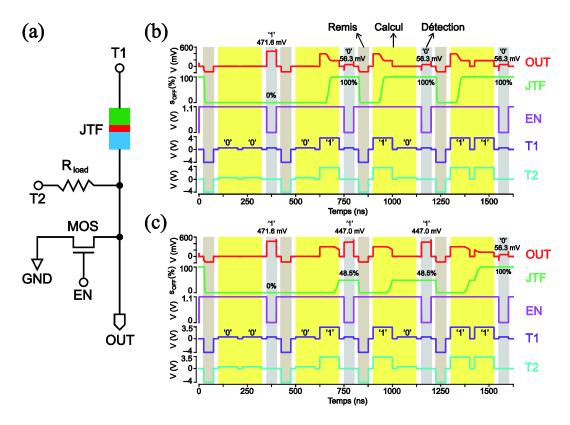

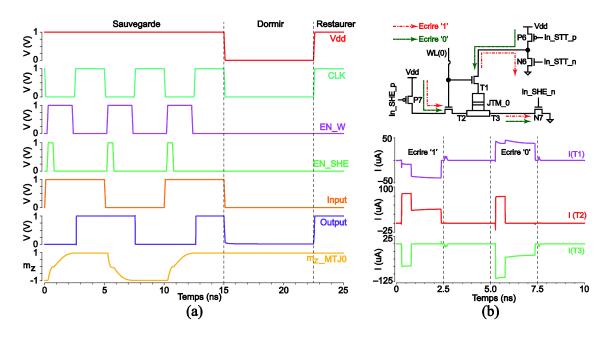

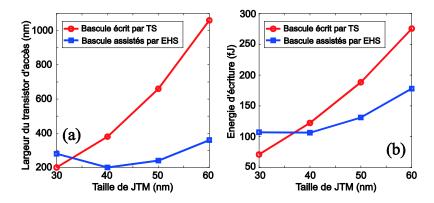

$$\vec{H}_R = \alpha_R \vec{e}_z \times \vec{J} \tag{2.16}$$