## Linéarisation à base de réseaux de neurones pour amplificateurs de puissance

Blaise Mulliez

#### ▶ To cite this version:

Blaise Mulliez. Linéarisation à base de réseaux de neurones pour amplificateurs de puissance. Micro et nanotechnologies/Microélectronique. INP Toulouse, 2015. Français. NNT: . tel-01241354

## HAL Id: tel-01241354 https://theses.hal.science/tel-01241354

Submitted on 15 Dec 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

En vue de l'obtention du

## DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par : l'Institut National Polytechnique de Toulouse (INP Toulouse)

Présentée et soutenue le 30 juin 2015 par :

BLAISE MULLIEZ

Linéarisation à base de réseaux de neurones pour amplificateurs de puissance

#### **JURY**

Professeur à l'Université JEAN-DIDIER LEGAT Examinateur catholique de Louvain Maître de conférences à OLIVIER BERNAL Examinateur l'Université de Toulouse LAURENT GATET Ingénieur CNES Invité Ingénieur Freescale PHILIPPE LANCE Invité Ingénieur DGA Francis DOUKHAN Invité JEAN-BAPTISTE Professeur à l'Université Rapporteur BEGUERET de Bordeaux Professeur à l'Université PASCAL NOUET Rapporteur Montpellier II Professeur à l'Université

de Toulouse

Directrice de thèse

#### École doctorale et spécialité :

GEET : Micro et Nanosystèmes

Unité de Recherche:

HÉLÈNE TAP

Laboratoire d'Analyse et d'Architecture des Systèmes

$\grave{A}$  Maman

### RÉSUMÉ

L'essor des télécommunications spatiales au cours des deux dernières décennies impose de transmettre les données à des débits toujours plus importants et avec une qualité de service irréprochable. Néanmoins, afin d'obtenir un bilan de liaison et une efficacité spectrale optimaux, l'amplificateur de puissance embarqué doit être utilisé près de sa zone de saturation, ce qui entraîne de fortes non-linéarités des signaux émis. Afin de contourner ce problème, les amplificateurs sont souvent précédés d'un linéariseur.

Les dispositifs de linéarisation embarqués actuellement sont toutefois incapables de s'adapter à différents amplificateurs ou de prendre en compte les dérives des caractéristiques des amplificateurs au cours du temps et en fonction de la température : ils ne sont pas adaptatifs. L'objectif de cette thèse est de concevoir une architecture innovante capable de linéariser différentes caractéristiques de transfert d'amplificateurs de puissance. Les réseaux de neurones analogiques offrent des performances intéressantes d'approximation de fonctions non-linéaires et sont reconfigurables. Ils représentent donc une solution pertinente pour répondre à cette problématique.

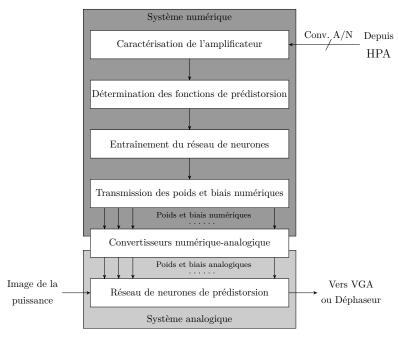

Tout d'abord, une technique innovante, générique, rapide et précise d'extraction des fonctions de prédistorsion, ayant fait l'objet d'un brevet, est présentée et appliquée aux caractéristiques de trois amplificateurs fournies par le CNES. La modélisation de ces fonctions de prédistorsion par des réseaux de neurones valide ensuite, grâce à des simulations comportementales statiques et dynamiques, le concept de prédistorsion analogique adaptative par réseaux de neurones. Enfin, un ASIC analogique de prédistorsion, développé en technologie CMOS  $0,35\mu m$ , comprenant un réseau de neurones et un circuit de déphasage réglable novateur est présenté. Le circuit, capable de générer les différentes fonctions de prédistorsion avec une grande précision, pourra par la suite être intégré dans un banc de test permettant de linéariser de manière adaptative divers amplificateurs de puissance afin d'en évaluer les performances réelles.

Mots-clés: Linéarisation, Prédistorsion, Amplificateur de puissance, Réseau de neurones, CMOS, ASIC

#### **ABSTRACT**

The spectacular growth of space telecommunications during the last two decades requires an always higher data transmission speed and a flawless service quality. Nevertheless, in order to optimize the link budget and the spectral efficiency, the embedded High Power Amplifiers (HPA) are used close to their saturation point, which leads to strongly non-linear emitted signals. To circumvent this issue, a linearizer is often implemented before the amplifier.

However, the linearization devices used today are not able adapt to different amplifiers or to HPA characteristics drift under the influence of aging and temperature variations: they are not adaptive. The objective of the work presented in this dissertation is the design of an innovating architecture capable of linearizing several HPA transfer characteristics. Analog Neural Networks (ANN) provide attractive performances for non-linear functions modelling and are reconfigurable. They are therefore a relevant choice to respond to this specific issue.

First, a patented, innovating, generic, fast and accurate technique to determine the predistortion functions is detailed and used with the characteristics of three HPA provided by the French Space Agency (CNES). Then, the modelling of these predistortion functions with neural networks and behavioral static and dynamic simulations of these networks validate the concept of adaptive analog predistortion based on neural networks. Eventually, an analog predistortion ASIC, designed in a CMOS  $0.35\mu m$  technology, including a neural network and an innovative configurable phase-shifting circuit, is described. The integrated circuit is able to generate the different predistortion functions and will be later embedded in a test-bench to demonstrate its ability to adaptively linearize several High Power Amplifiers.

Keywords: Linearization, Predistortion, Power Amplifier, Neural Network, CMOS, ASIC

## REMERCIEMENTS

Je souhaite remercier tous ceux qui ont été à mes côtés et m'ont aidé, soutenu et supporté pendant toute la durée de ce cette thèse.

En premier lieu, je tiens évidemment à remercier très chaleureusement ma directrice de thèse, Hélène TAP. Elle m'a fait confiance et m'a toujours apporté son soutien et ses (bons) conseils au cours de l'élaboration de cette thèse. Si son rôle de directrice s'arrête à la fin de ce doctorat, je sais qu'elle sera toujours là pour m'aider, me guider et me soutenir, sur un plan professionnel comme sur un plan personnel.

MM. Jean-Baptiste BEGUERET et Pascal NOUET m'ont fait l'honneur d'être les rapporteurs de ma thèse. Ils ont pris le temps de lire scrupuleusement et d'évaluer avec soin mon tapuscrit. Je les en remercie.

Je souhaite également remercier MM. Jean-Didier LEGAT, Olivier BERNAL, Philippe LANCE et Laurent GATET qui ont accepté de participer à mon jury de thèse. En particulier, j'exprime toute ma gratitude à Laurent, porteur du projet, pour la rigueur qu'il m'a instillée, pour avoir su m'aiguiller et m'encourager dans mes moments de doute et pour ses (très longs) mails, très riches et très pédagogiques et qui m'ont, plus d'une fois, maintenu éveillé une bonne partie de la nuit!

Au cours de mes travaux, j'ai été accueilli au sein du groupe de recherches OSE du LAAS. Les discussions que j'ai pu avoir avec tous les membres du laboratoire, en réunion ou autour d'un café, m'ont énormément apportées. Je ne citerai personne, pour ne pas risquer d'oublier du monde et de faire un impair, mais j'ai réellement apprécié le temps passé en leur compagnie et je leur en suis extrêmement reconnaissant. En particulier, je remercie tous les thésards que j'ai côtoyés pour m'avoir supporté tous les jours, pendant plusieurs années pour certains. Ils m'ont beaucoup aidé et je leur souhaite tout le courage qu'ils m'ont apporté.

Durant ma thèse, j'ai effectué de nombreux enseignements à l'ENSEIHT, avec Francis BONY, Julien PERCHOUX, Adam QUOTB et Emmanuelle PEUCH. Merci à eux de m'avoir sorti de mes simulations et de mes circuits pour encadrer des TPs! Paradoxalement, ça fait du bien!

Ce travail n'aurait pu être mené à bien sans l'aide du CNES et de la DGA, cofinanceurs de mes travaux, qui, au travers de leur soutien matériel, ont reconnu mon travail et m'ont fait confiance.

Passons à présent à des remerciements plus personnels.

Je remercie mon Papou.net qui est venu assister à la soutenance de son Petit Lapin, mes sœurs, toute ma famille et ma belle-famille qui, avec cette question récurrente et lancinante, "quand est-ce que tu la soutiens, cette thèse?", m'ont permis de ne jamais dévier de mon objectif final.

Merci à tous les amis qui, de près ou de loin, m'ont encouragé et ont cru en moi. Merci aux "gros" en général qui m'ont supporté pendant ces longues années. Mes derniers remerciements vont à Laurie, ma chère petite femme, pour son soutien quotidien indéfectible. Elle a su appréhender un sujet qui lui était jusque-là quasiment inconnu et son regard de néophyte sur le thème m'a été d'une grande aide pour préciser et affiner mon propos. Elle aussi m'a supporté, m'a soutenu, m'a poussé, m'a critiqué, m'a encouragé, m'a félicité, m'a bichonné. Et je ne saurais lui exprimer assez la joie que j'éprouve à me lancer avec elle dans ce nouveau projet qu'elle porte dans son ventre!

Encore un immense merci à tous pour m'avoir aidé à mener à bien cette belle thèse!

| Re       | ésumé                                                                                                                                                                                                                                       | i                          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Re       | emerciements                                                                                                                                                                                                                                | iii                        |

| Ta       | able des matières                                                                                                                                                                                                                           | viii                       |

| Ta       | able des figures                                                                                                                                                                                                                            | xiv                        |

| Li       | ste des tableaux                                                                                                                                                                                                                            | $\mathbf{x}\mathbf{v}$     |

| N        | otations                                                                                                                                                                                                                                    | xvii                       |

| In       | ntroduction                                                                                                                                                                                                                                 | 1                          |

| Ι        | Contexte des travaux                                                                                                                                                                                                                        | 5                          |

| 1        | Les familles d'amplificateurs de puissance  1.1 Les familles d'amplificateurs de puissance                                                                                                                                                  | 7<br>8<br>11<br>12         |

| 2        | Le potentiel besoin de linéarisation  2.1 Codage d'une donnée numérique en un signal exploitable par l'amplificateur  2.2 Le diagramme de constellation d'une modulation de signal mono-fréquence  2.3 Modulations de signaux monoporteuses | 15<br>15<br>16<br>18<br>21 |

| 3        | Les solutions pour prévenir ou corriger les non-linéarités         3.1 L'utilisation de l'amplificateur en recul          3.2 L'égalisation ou la post-distorsion          3.3 La linéarisation          3.4 Discussion                     | 23<br>23<br>24<br>24<br>28 |

| II<br>de | Architecture innovante de linéariseur paramétrable à base<br>e réseaux de neurones                                                                                                                                                          | 31                         |

| 1        | Caractéristiques de transfert AM/AM et AM/PM mono-fréquences d'un linéariseur par prédistorsion  1.1 Techniques de détermination des caractéristiques de prédistorsion                                                                      | <b>33</b>                  |

|          | 1.2               | Procédé innovant de détermination des caractéristiques AM/AM et AM/PM       |                          |

|----------|-------------------|-----------------------------------------------------------------------------|--------------------------|

|          |                   | d'un linéariseur par prédistorsion                                          | 34                       |

|          | 1.3               | Caractéristiques idéales de transfert du système "Linéariseur + Amplifica-  |                          |

|          |                   | teur"                                                                       | 39                       |

|          | 1.4               | Mise en application                                                         | 43                       |

|          | 1.5               | Conclusion                                                                  | 43                       |

| 2        | Arc               | chitectures de linéariseur par prédistorsion                                | 45                       |

|          | 2.1               | Les différentes architectures de linéariseur envisageables                  | 45                       |

|          | 2.2               | Architecture détaillée d'un linéariseur à prédistorsions série              | 46                       |

|          | 2.3               | Simulation comportementale du linéariseur proposé                           | 51                       |

|          | 2.4               | Conclusion                                                                  | 56                       |

| 3        | Mo                | délisation des caractéristiques de prédistorsion par réseaux de neu-        |                          |

|          | ron               | es                                                                          | 57                       |

|          | 3.1               | Introduction aux réseaux de neurones                                        | 57                       |

|          | 3.2               | Le choix d'une architecture de réseaux de neurones dans le cadre de la      |                          |

|          |                   | linéarisation par prédistorsion                                             | 60                       |

|          | 3.3               | Exploitation des réseaux de neurones pour la linéarisation d'amplificateurs |                          |

|          |                   | de puissance                                                                | 63                       |

|          | 3.4               | Conclusion                                                                  | 65                       |

|          |                   |                                                                             |                          |

|          |                   | Conception d'un démonstrateur de linéariseur par pré-<br>csion              | 67                       |

|          |                   |                                                                             |                          |

| 1        |                   | sentation du circuit électronique de prédistorsion                          | 69                       |

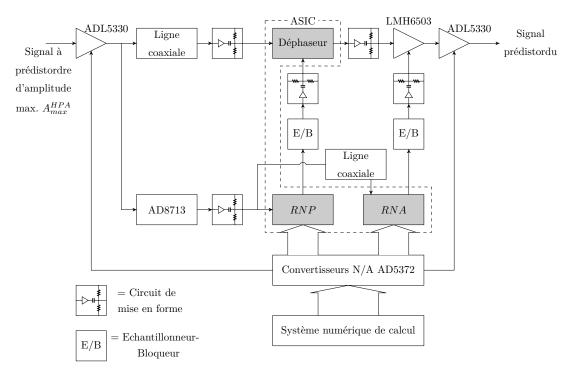

|          | 1.1               | Propriétés du signal à prédistordre                                         | 69                       |

|          | 1.2               | Choix des circuits électroniques                                            | 71                       |

|          | 1.3               | Mise en forme des signaux internes au linéariseur                           | 76                       |

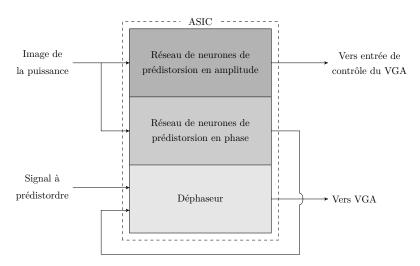

|          | 1.4               | Architecture haut niveau de l'ASIC                                          | 76                       |

|          | 1.5               | Synthèse                                                                    | 77                       |

| <b>2</b> | Gér               | néralités sur le circuit intégré de prédistorsion                           | <b>7</b> 9               |

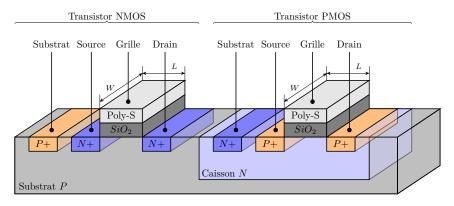

|          | 2.1               | Le choix technologique                                                      | 79                       |

|          | 2.2               | Caractéristiques électriques du transistor MOS                              | 80                       |

|          | 2.3               | Analyse de structures élémentaires                                          | 84                       |

|          | 2.4               | Considérations générales sur le circuit intégré de prédistorsion            | 95                       |

|          | 2.5               | Conclusion                                                                  | 97                       |

| 3        | Le                | réseau de neurones analogique                                               | 99                       |

|          |                   |                                                                             |                          |

|          | 3.1               | Considérations générales                                                    | 99                       |

|          | 3.1               | Considérations générales                                                    |                          |

|          |                   |                                                                             | 102                      |

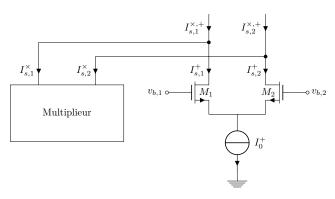

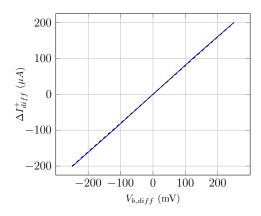

|          | 3.2               | Le multiplieur                                                              | 102<br>106               |

|          | 3.2<br>3.3        | Le multiplieur                                                              | 102<br>106<br>109        |

|          | 3.2<br>3.3<br>3.4 | Le multiplieur                                                              | 102<br>106<br>109<br>112 |

| 4            | Le o       | circuit déphaseur                                                          | 121          |

|--------------|------------|----------------------------------------------------------------------------|--------------|

|              | 4.1        | Cahier des charges                                                         | . 121        |

|              | 4.2        | Etat de l'art                                                              | . 122        |

|              | 4.3        | Architecture du circuit déphaseur                                          | . 123        |

|              | 4.4        | Implantation du DDCC                                                       | . 125        |

|              | 4.5        | Implantation des composants passifs configurables                          |              |

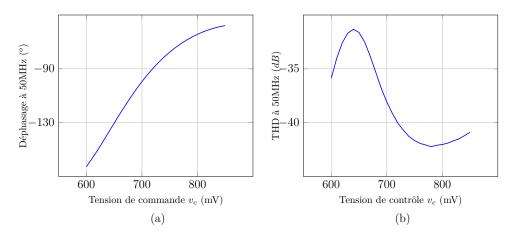

|              | 4.6        | Simulation du circuit déphaseur                                            |              |

|              | 4.7        | Conclusion                                                                 | . 144        |

| 5            | Exp        | loitation de l'ASIC dans le contexte de la prédistorsion                   | 145          |

|              | 5.1        | Linéarisation en amplitude par l'intermédiaire du réseau de neurones inté- |              |

|              | <b>-</b> - | gré dans l'ASIC                                                            | . 145        |

|              | 5.2        | Linéarisation en phase par l'intermédiaire du réseau de neurones intégré   | 1 47         |

|              | r 9        | dans l'ASIC                                                                |              |

|              | 5.3        | Discussion                                                                 |              |

|              | 5.4        | Conclusion                                                                 | . 150        |

| $\mathbf{C}$ | oncl       | usion                                                                      | <b>153</b>   |

|              |            |                                                                            |              |

| Α            | nne        | xes                                                                        | 157          |

| Pι           | ublica     | ation                                                                      | 159          |

| $\mathbf{A}$ | Tec        | hniques de représentation des non-linéarités d'un amplificateur de         |              |

|              |            | ssance                                                                     | 161          |

|              |            | Le rapport C/I                                                             |              |

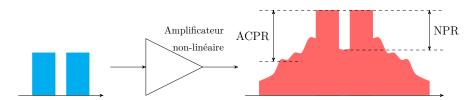

|              |            | L'ACPR                                                                     |              |

|              |            | Le NPR                                                                     |              |

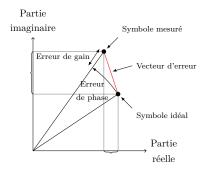

|              |            | L'EVM                                                                      |              |

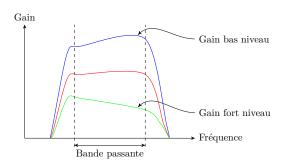

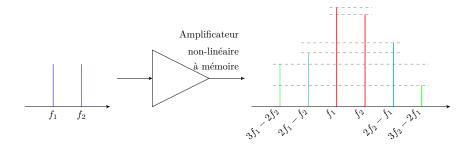

|              | A.5        | Les effets mémoire                                                         | . 164        |

| В            |            | hniques de modélisation et implantation des non-linéarités d'un            | 4 A <b>-</b> |

|              | -          | ollificateur de puissance                                                  | 167          |

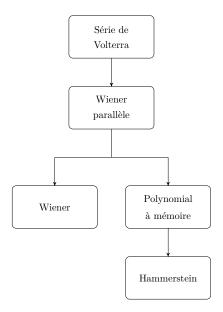

|              |            | Modèles sans prise en compte des effets mémoire                            |              |

|              | B.2        | Modèles avec prise en compte des effets mémoire                            |              |

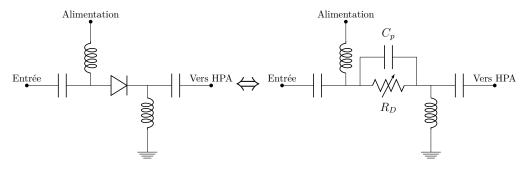

|              | В.3        | Implantations existantes de fonctions de prédistorsion                     | . 176        |

| $\mathbf{C}$ | App        | prentissage des réseaux de neurones                                        | 183          |

|              | C.1        | Ensembles d'apprentissage, de validation et calculs d'erreurs              | . 183        |

|              | C.2        | Calibrage et phénomène de surajustement                                    | . 184        |

|              | C.3        | Différents algorithmes d'apprentissage                                     | . 185        |

| D            | Con        | apléments de résultats de simulations                                      | 189          |

|              | D.1        | Simulations de modules de prédistorsion idéaux                             | . 189        |

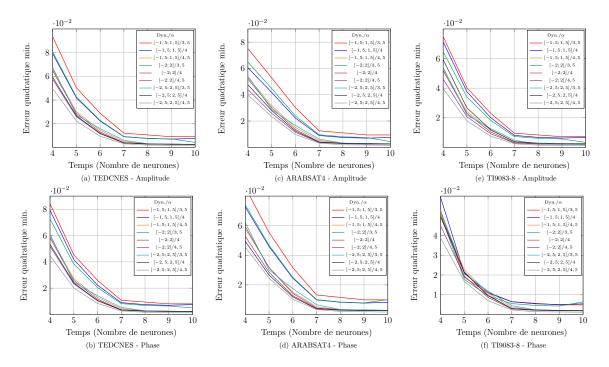

|              | D.2        | Etude statistique de calibrage des réseaux de neurones                     |              |

|              | D.3        | Simulations des modules de commande à base de réseaux de neurones          |              |

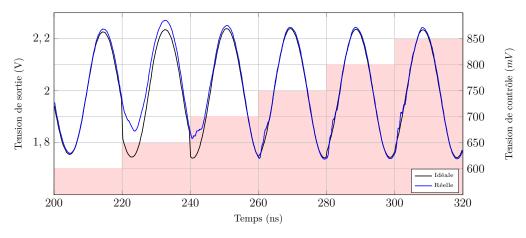

|              | D.4        | Simulations comportementales du DDCC                                       | . 193        |

| D.5 Exploitation de l'ASIC dans le cadre de la linéarisation par prédistorsion |       |

|--------------------------------------------------------------------------------|-------|

| d'amplificateurs de puissance                                                  | . 194 |

| Bibliographie                                                                  | 199   |

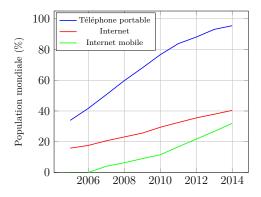

| Figure 1 -       | Accès aux services de télécommunications de 2005 à aujourd'hui                  | 1  |

|------------------|---------------------------------------------------------------------------------|----|

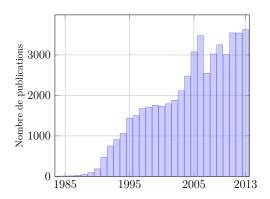

| Figure 2 -       | Nombre de publications contenant les mots-clé "Neural Network" (Source :        |    |

| ISI Web          | Of Science)                                                                     | 2  |

| D                |                                                                                 |    |

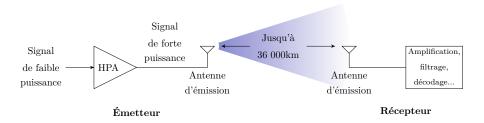

| FIGURE I.1.1 –   | •                                                                               | _  |

|                  | en évidence du rôle de l'amplificateur de puissance                             | 7  |

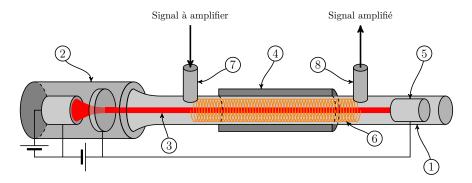

|                  | Vue en coupe d'un Amplificateur à Tube à Ondes Progressives                     | 8  |

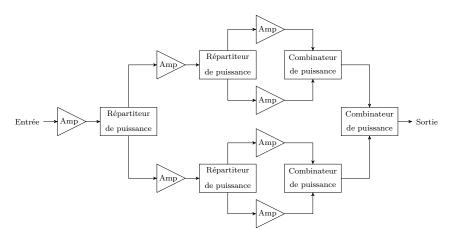

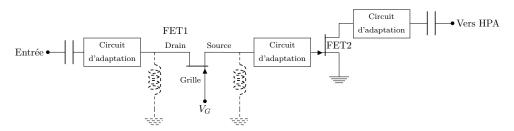

| Figure I.1.3 –   | Architecture typique d'un amplificateur de puissance à état solide              | 9  |

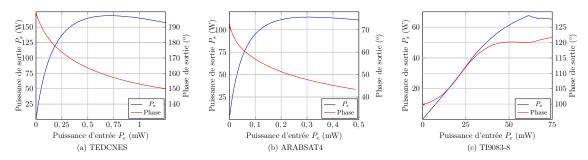

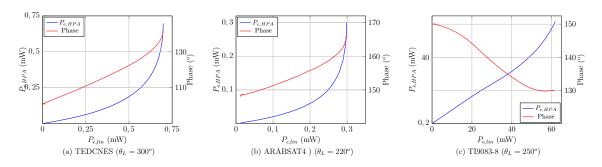

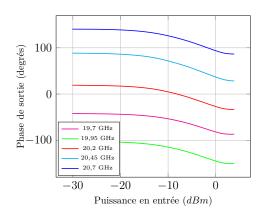

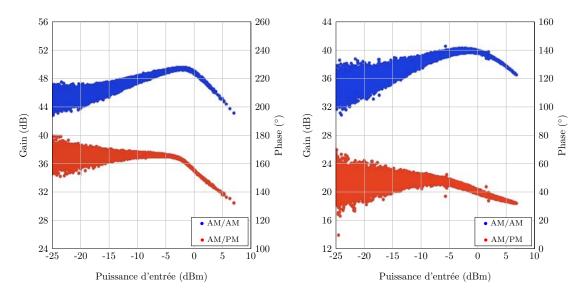

|                  | Caractéristiques AM/AM et AM/PM des amplificateurs TEDCNES, ARAB-               |    |

|                  | TI9083-8                                                                        | 11 |

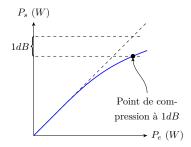

| FIGURE I.1.5 –   | Détermination du point de compression à 1db                                     | 12 |

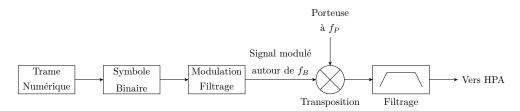

| FIGURE I.2.1 -   | Chaîne de codage d'une donnée numérique                                         | 16 |

| FIGURE I.2.2 -   | Exemple de transmission mono-porteuse                                           | 17 |

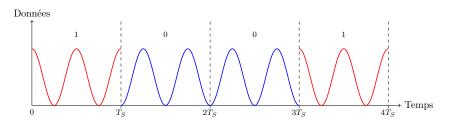

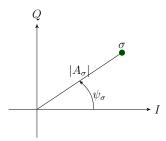

| FIGURE I.2.3 -   | Représentation d'un symbole binaire sur un diagramme de constellation           | 18 |

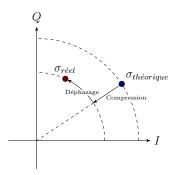

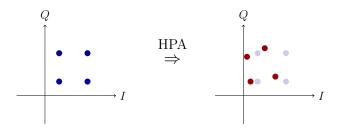

| Figure I.2.4 -   | Impact des non-linéarités d'un amplificateur de puissance sur la position des   |    |

|                  | s binaires sur le diagramme de constellation                                    | 18 |

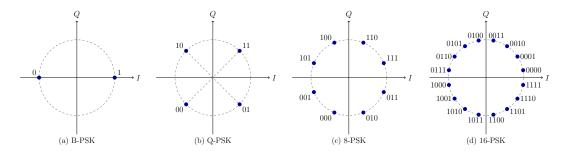

|                  | Diagrammes de constellation des modulations BPSK, QPSK, 8-PSK et 16-PSK         | 19 |

| FIGURE I.2.6 -   | Diagrammes de constellation des modulations 16-QAM, 64-QAM, 16-APSK             |    |

| et 32-Al         |                                                                                 | 20 |

|                  | Exemple de déformation d'un diagramme de constellation d'une modulation         |    |

|                  | litude et en phase sous l'influence des non-linéarités d'un amplificateur de    |    |

| _                |                                                                                 | 21 |

| F                |                                                                                 |    |

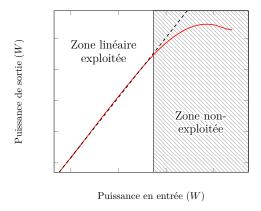

| Figure I.3.1 -   | Utilisation d'un amplificateur en $\mathit{back}\text{-}\mathit{off}$           | 23 |

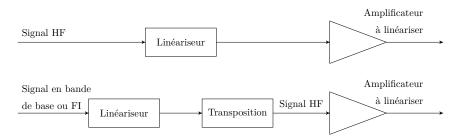

| Figure I.3.2 -   | Les deux familles de linéariseur en fonction de sa position dans la chaine      |    |

| d'émissi         | on                                                                              | 25 |

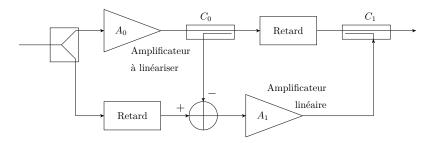

| Figure I.3.3 -   | Synoptique d'un système de linéarisation utilisant la technique Feedforward     | 26 |

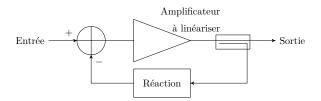

| Figure I.3.4 $-$ | Synoptique d'un système de linéarisation utilisant la technique à contre-       |    |

| réaction         |                                                                                 | 26 |

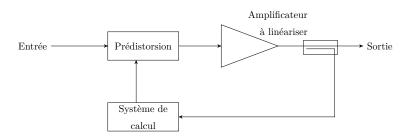

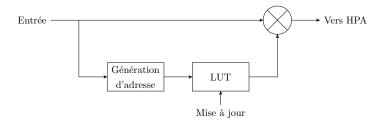

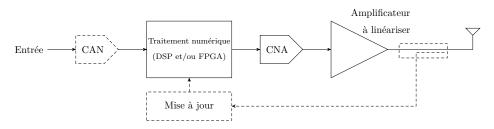

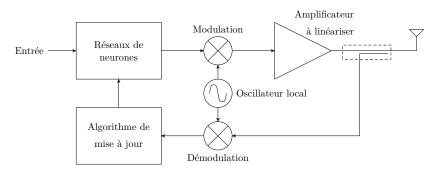

| Figure I.3.5 $-$ | Synoptique d'un système de linéarisation utilisant une prédistorsion adaptative | 27 |

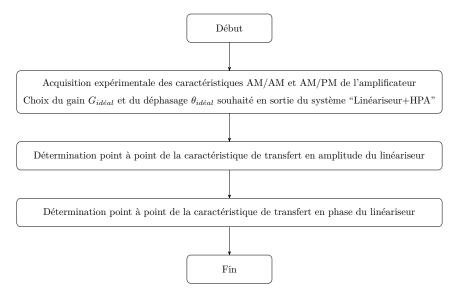

| FIGURE II 1 1 _  | Procédé de détermination des caractéristiques de transfert d'un linéariseur     |    |

|                  | listorsion                                                                      | 35 |

|                  | Système "Linéariseur+HPA" et fonctions de transfert associées                   | 35 |

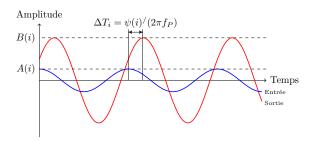

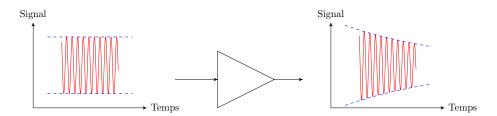

|                  | Représentation temporelle des signaux d'entrée et de sortie d'un amplifica-     | 30 |

|                  | puissance                                                                       | 36 |

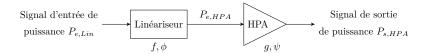

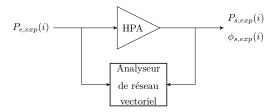

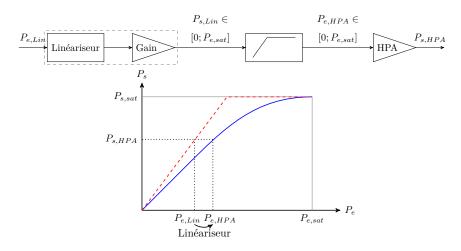

|                  | Synopsis d'un système de prédistorsion                                          | 37 |

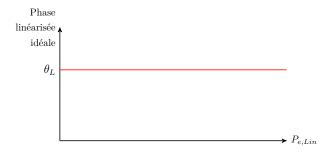

|                  | Caractéristique AM/PM linéarisée                                                | 40 |

|                  | - ,                                                                             |    |

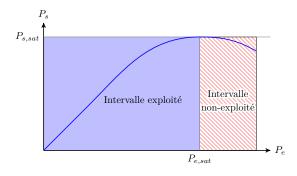

|                  | Réduction de l'intervalle de puissance moyenne d'excitation de l'amplificateur  | 40 |

|                  | Système "Linéariseur + HPA" et intervalles de puissances d'entrée et de         | 11 |

|                  | optimaux                                                                        | 41 |

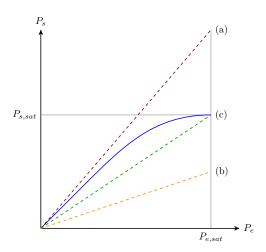

| FIGURE II.1.8 -  | Trois caractéristiques linéarisées possibles                                    | 41 |

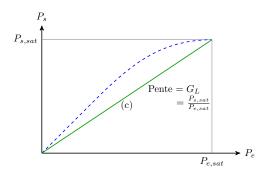

| FIGURE II.1.9 — Architecture de la chaîne de transmission permettant de générer des caractéristiques de même pente que (a) jusqu'à atteindre $P_{s,sat}$ et mise en évidence du besoin de gain dans le linéariseur |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| FIGURE II.1.10 — Caractéristique AM/AM linéarisée idéale                                                                                                                                                           | . 43 |

| FIGURE II.1.11 — Caractéristiques AM/AM et AM/PM des linéariseurs idéaux définis pour les aux amplificateurs TEDCNE, ARABSAT4 et TI9083-8                                                                          |      |

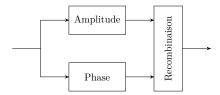

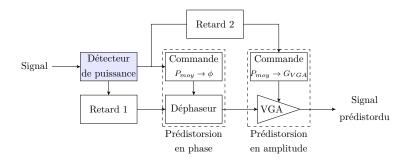

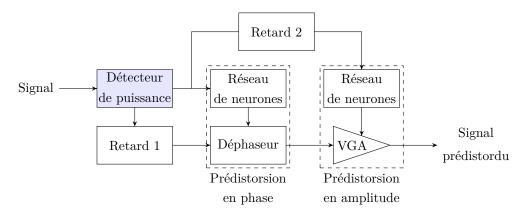

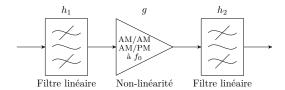

| FIGURE II.2.1 – Architecture de linéarisation à prédistorsions parallèles                                                                                                                                          | . 46 |

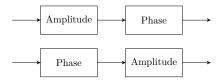

| FIGURE II.2.2 – Deux architectures de linéariseur à prédistorsions série $\dots \dots \dots$                                                                                                                       | . 46 |

| FIGURE II.2.3 – Exemple de modules permettant d'obtenir une grandeur proportionnelle à l'amplitude ou à la puissance moyenne d'un signal $\dots \dots \dots \dots \dots$                                           |      |

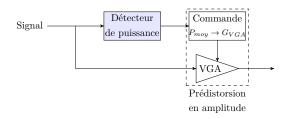

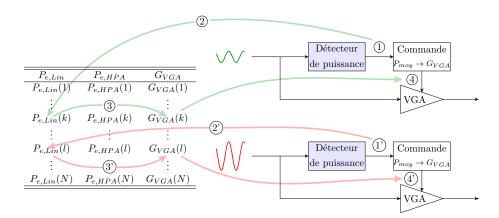

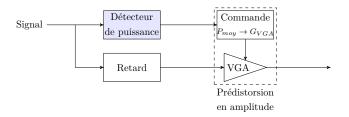

| FIGURE II.2.4 – Module de prédistorsion en amplitude                                                                                                                                                               | . 48 |

| FIGURE II.2.5 — Etapes de la prédistorsion en amplitude permettant d'appliquer au VGA le facteur d'atténuation correcte                                                                                            |      |

| FIGURE II.2.6 — Module de prédistorsion en amplitude avec retard                                                                                                                                                   |      |

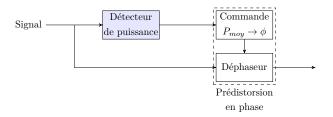

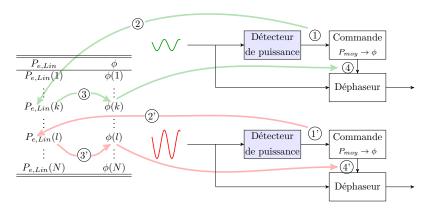

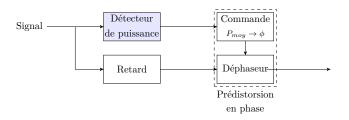

| FIGURE II.2.7 — Module de prédistorsion en phase                                                                                                                                                                   |      |

| ${\tt FIGURE~II.2.8~-~Etapes~de~la~pr\'edistorsion~en~phase~permettant~d'appliquer~au~d\'ephaseur~la}$                                                                                                             |      |

| consigne de déphasage correcte                                                                                                                                                                                     |      |

| FIGURE II.2.9 — Module de prédistorsion en phase avec retard                                                                                                                                                       |      |

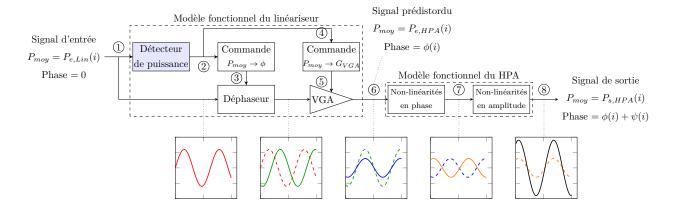

| FIGURE II.2.10 – Architecture détaillée du linéariseur à prédistorsion proposé dans ce tapusci<br>FIGURE II.2.11 – Topologie du système simulé représentant l'architecture de la figure II.2.10                    |      |

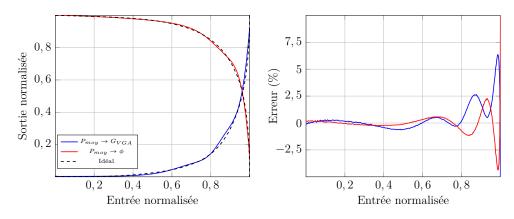

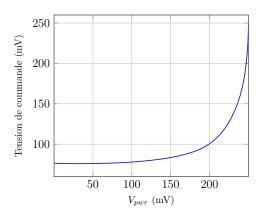

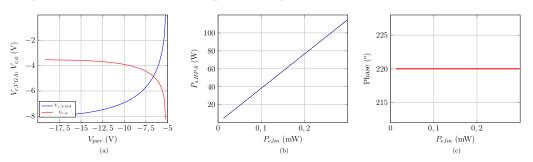

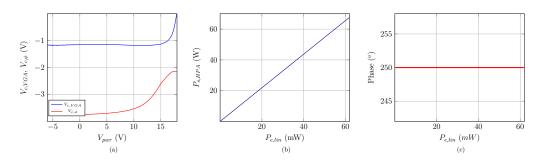

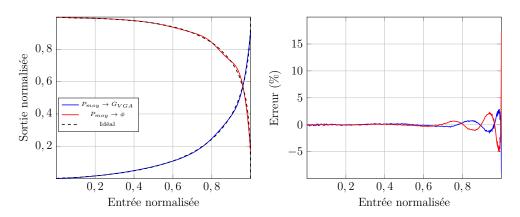

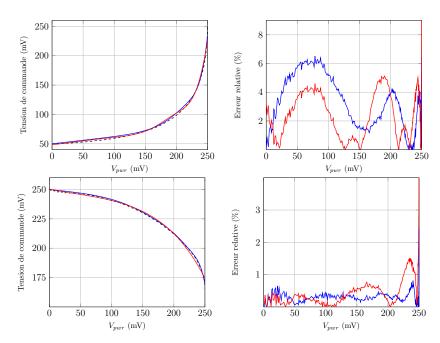

| FIGURE II.2.11 – Topologie du système simule représentant l'architecture de la figure II.2.10<br>FIGURE II.2.12 – Caractéristiques de transfert des modules de commande $P_{mov} \to G_{VGA}$ et                   |      |

| Proof. II.2.12 — Caracteristiques de transfert des modules de commande $T_{moy} \to GVGA$ et $P_{moy} \to \phi$ de l'amplificateur TEDCNES                                                                         |      |

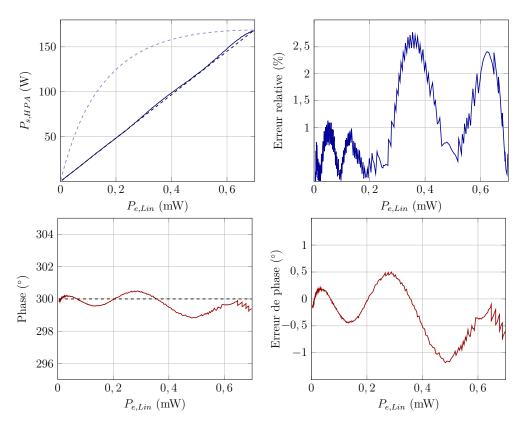

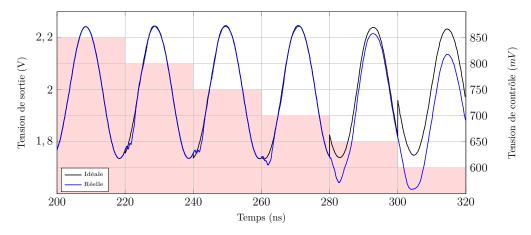

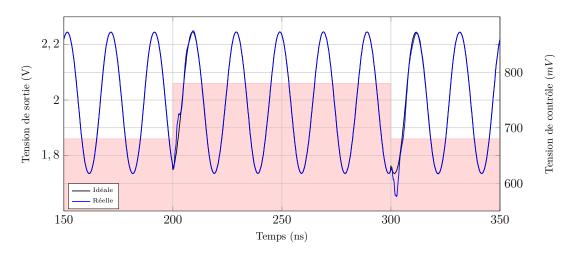

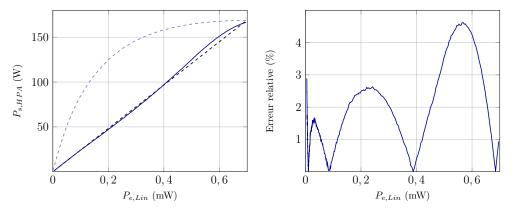

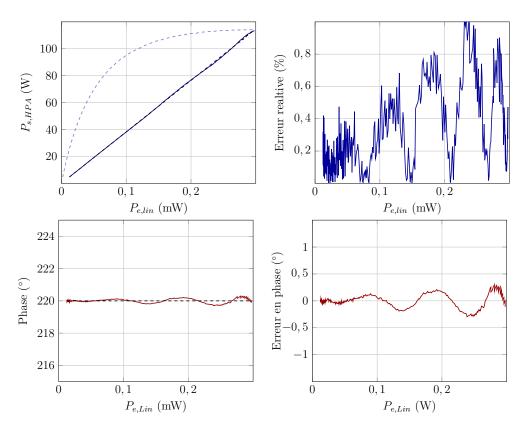

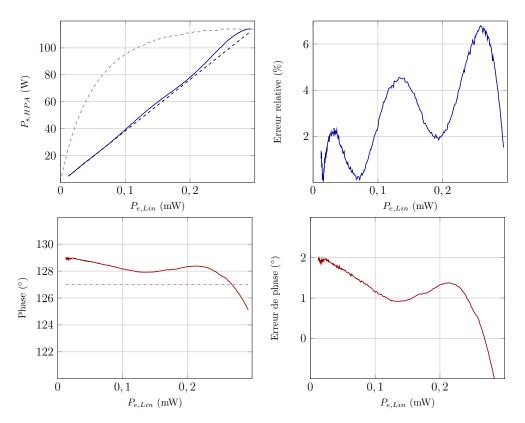

| FIGURE II.2.13 – Simulation de l'architecture de la figure II.2.10 et linéarisation de l'amplificateur de puissance TEDCNES                                                                                        |      |

| cateur de puissance l'EDONES                                                                                                                                                                                       | . 90 |

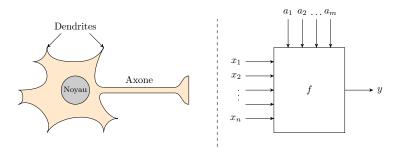

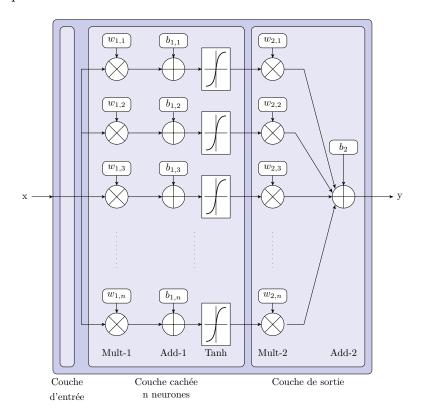

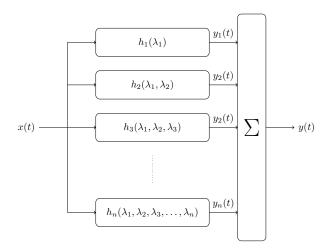

| FIGURE II.3.1 – Représentation de neurones biologique et formel                                                                                                                                                    | . 58 |

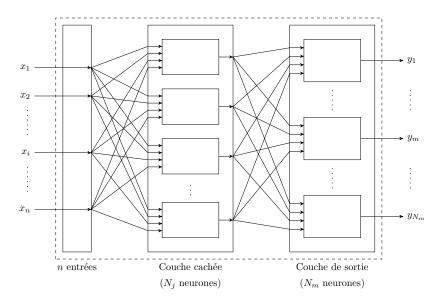

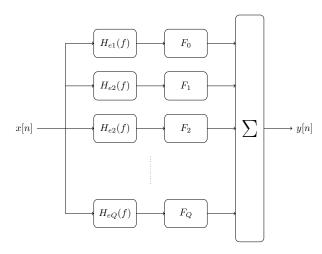

| FIGURE II.3.2 — Représentation d'un réseau de neurones non-bouclé à $n$ entrées, une couche cachée de $N_i$ neurones et $N_m$ neurones de sortie                                                                   |      |

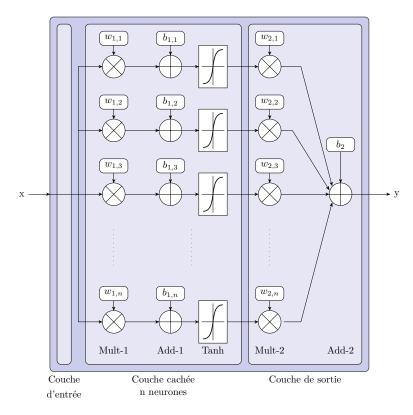

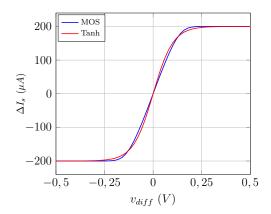

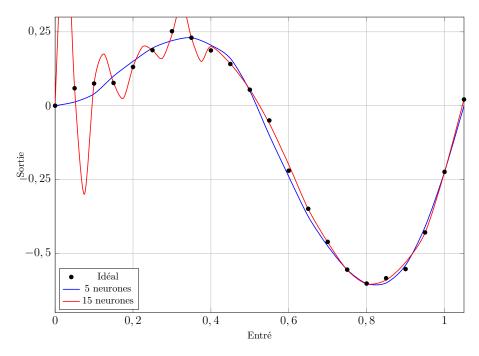

| FIGURE II.3.3 – Structure d'un Perceptron Multi-Couches à fonction d'activation sigmoïdale                                                                                                                         |      |

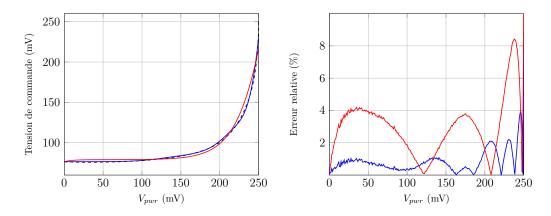

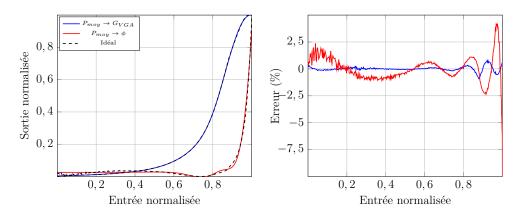

| FIGURE II.3.4 – Modélisation par réseaux de neurones des caractéristiques des modules de commande $P_{moy} \to G_{VGA}$ et $P_{moy} \to \phi$ associé à l'amplificateur TEDNCES                                    |      |

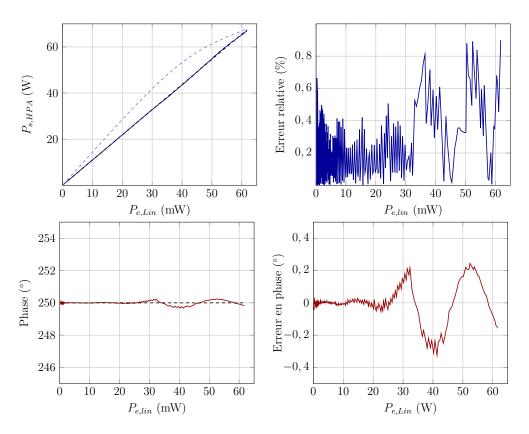

| FIGURE II.3.5 — Simulation de l'architecture de la figure II.2.10 et linéarisation de l'amplifi-                                                                                                                   | . 01 |

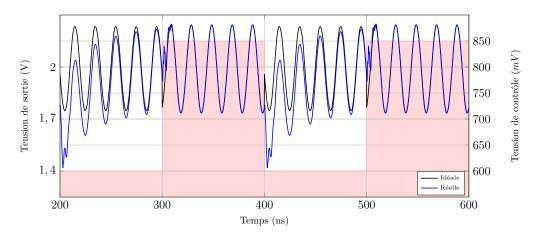

| cateur de puissance TEDCNES à l'aide de réseaux de neurones                                                                                                                                                        | . 65 |

| FIGURE III.1.1 – Architecture du linéariseur à concevoir                                                                                                                                                           | . 69 |

| ${\it Figure~III.1.2~-Implantation~propos\'ee~permettant~de~fixer~l'amplitude~maximale~du~signal}$                                                                                                                 |      |

| dans le circuit de linéarisation                                                                                                                                                                                   | . 71 |

| FIGURE III.1.3 – Fonctionnement du linéariseur                                                                                                                                                                     | . 75 |

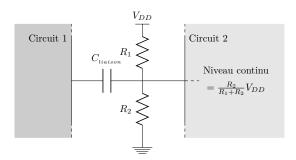

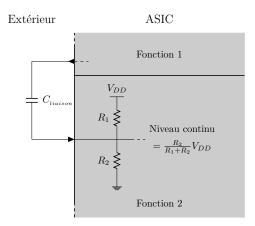

| Figure III.1.4 – Circuit permettant d'adapater le niveau continu d'un signal                                                                                                                                       | . 77 |

| Figure III.1.5 – Interconnexions entre les fonctions de l'ASIC                                                                                                                                                     | . 77 |

| Figure III.<br>1.6 – Représentation haut niveau du circuit électronique du linéariseur<br>$\   .$                                                                                                                  | . 78 |

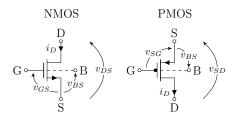

| FIGURE III.2.1 – Vues en coupe des transistors NMOS et PMOS dans un caisson $N\text{-}Well$ .                                                                                                                      | . 81 |

| FIGURE III.2.2 – Symboles des transistors NMOS et PMOS                                                                                                                                                             | . 81 |

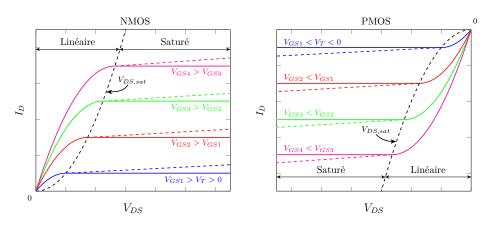

| FIGURE III.2.3 – Caractéristiques statiques des transistors NMOS et PMOS $$                                                                                                                                        | . 82 |

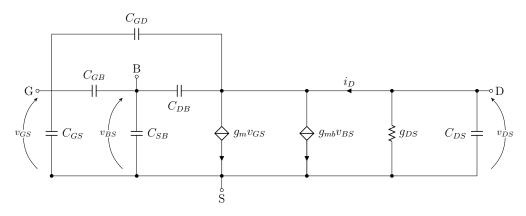

| FIGURE III.<br>2.4 – Modèle petit signal haute fréquence d'un transistor MOS en zone saturée                                                                                                                       | . 83 |

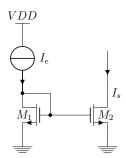

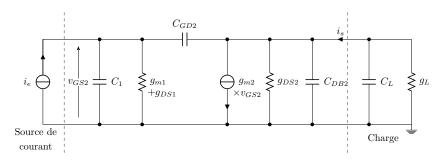

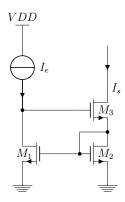

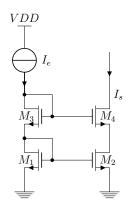

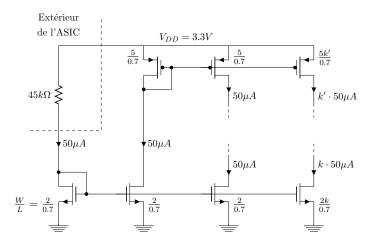

| Figure III.2.5 – Implantation d'un miroir de courant simple                                                                                                                                                        | . 85 |

| FIGURE III.2.6 – Schéma équivalent petit signal d'un miroir de courant simple                                                                                                                                      | . 86 |

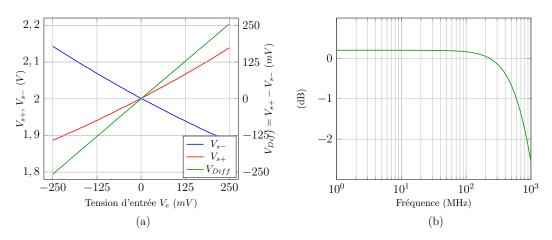

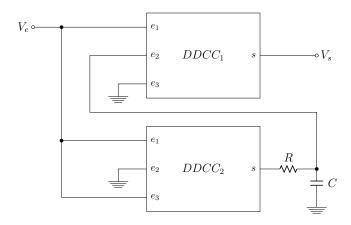

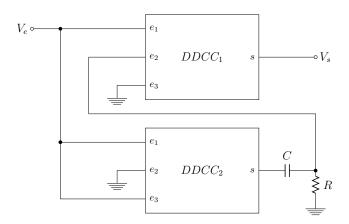

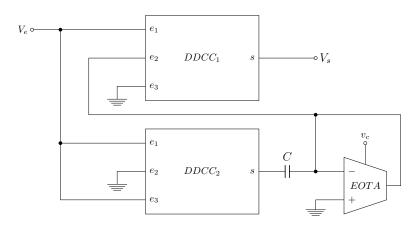

| Figure III.4.3 – Schéma du circuit déphaseur développé durant cette thèse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 124   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

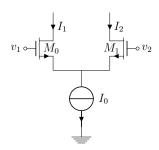

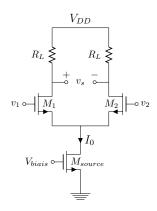

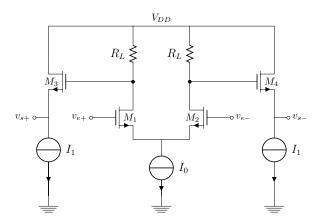

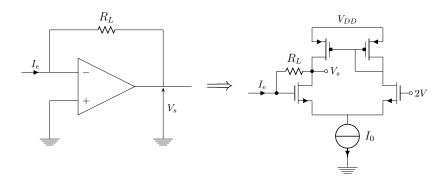

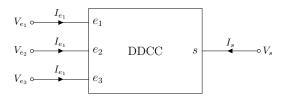

| Figure III.4.4 – Implantation d'un amplificateur différentiel de différences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 125   |

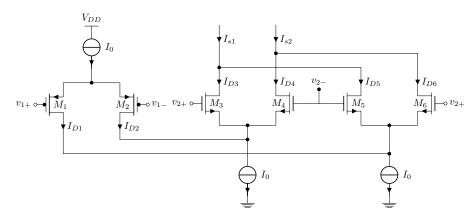

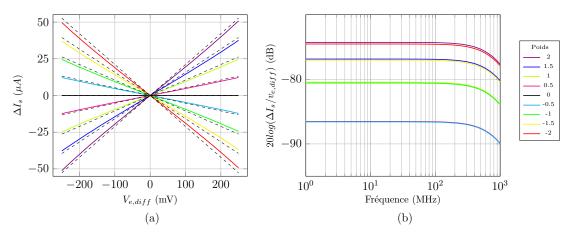

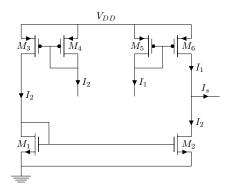

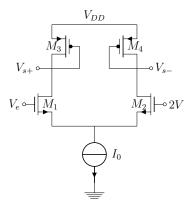

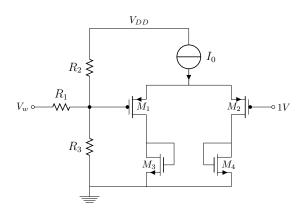

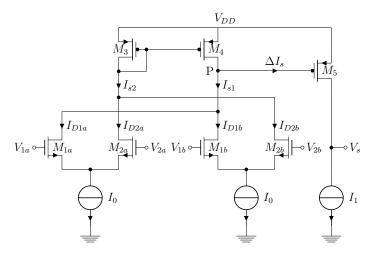

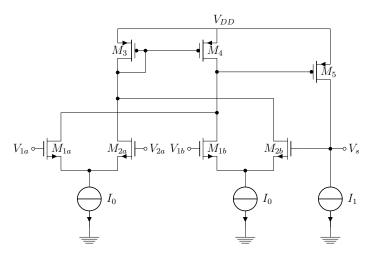

| FIGURE III.4.5 – Implantation d'un convoyeur différentiel de différences de courant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 127   |

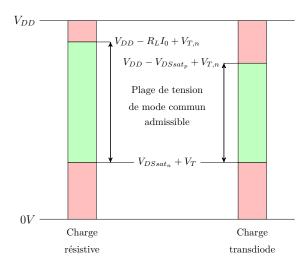

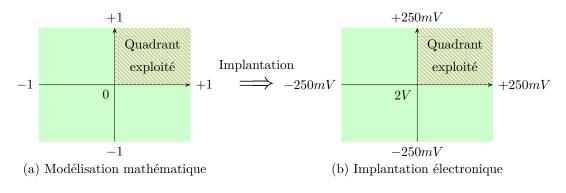

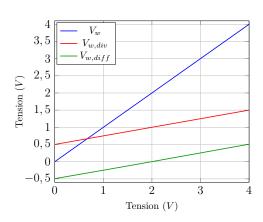

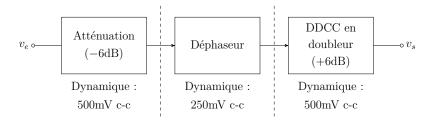

| Figure III.4.6 – Modification de la dynamique de travail du circuit déphaseur $\dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 128   |

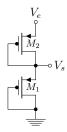

| FIGURE III.4.7 – Implantation d'un atténuateur par 2 à l'aide de transistors PMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 128   |

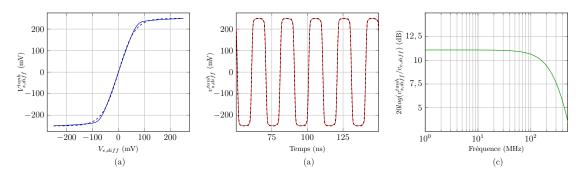

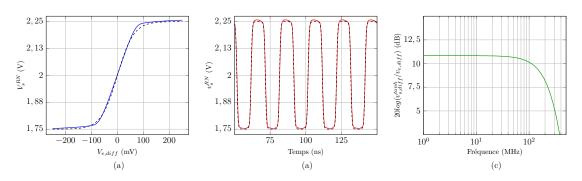

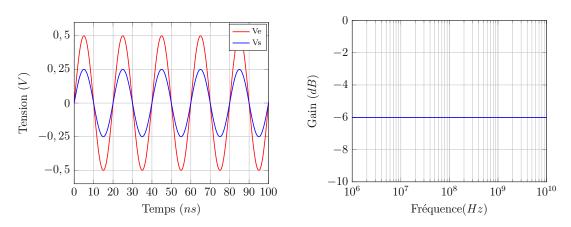

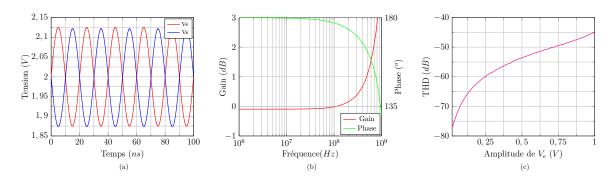

| ${\it Figure~III.4.8~-Simulations~temporelle~et~fréquentielle~de~l'atténuateur~de~la~figure~III.4.7~.}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 128   |

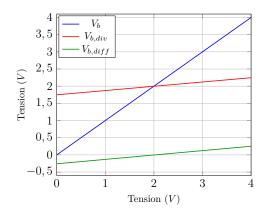

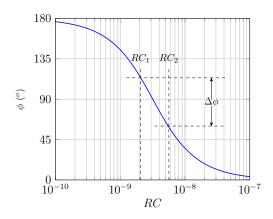

| Figure III.4.9 – Phase du circuit déphaseur en fonction de $RC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 131   |

| Figure III.4.10 –<br>Etude des variations du produit $RC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 131   |

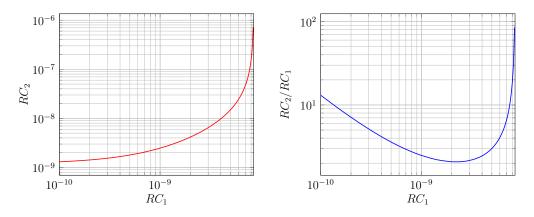

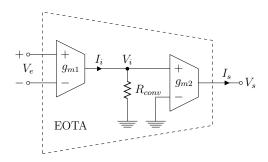

| ${\it Figure~III.4.11~-Mod\'elisation~d'une~r\'esistance~\`a~la~masse~par~un~amplificateur~transconductance}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 133   |

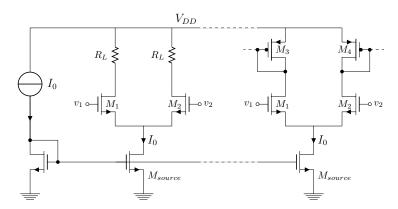

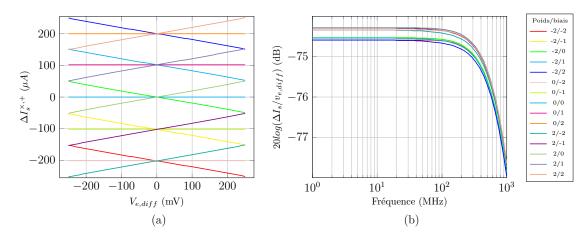

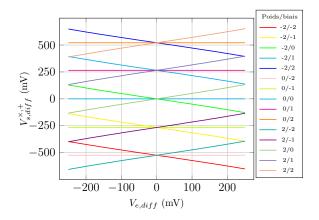

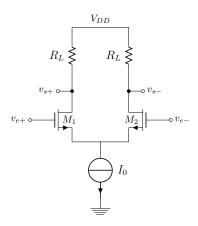

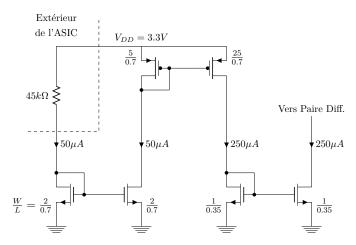

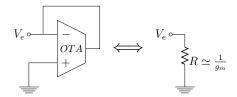

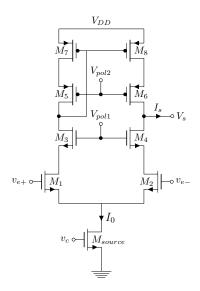

| $ FIGURE~III.4.12~-OTA~r\'ealis\'e~\`a~partir~d'une~paire~diff\'erentielle~charg\'ee~par~un~miroir~de~courant au paire~diff\'erentielle~charg\'ee~par~un~miroir~de~courant au paire~diff\'erentielle~charg\'ee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~miroir~de~chargee~par~un~de~chargee~par~un~de~chargee~par~un~de~chargee~par~un~de~chargee~par~un~de~chargee~par~un~de~chargee~par~un~de~chargee~par~un~de~cha$ | 134   |

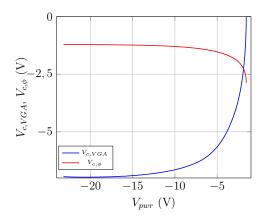

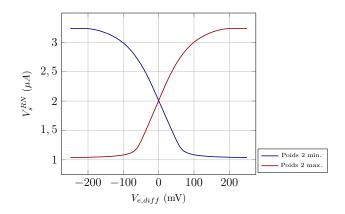

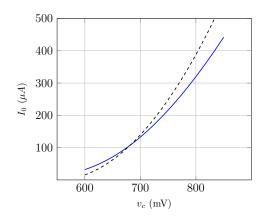

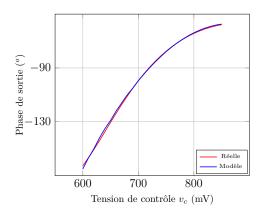

| FIGURE III.4.13 –<br>Courant simulé généré par ${\cal M}_{source}$ en fonction de la tension de contrôle<br>$v_c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| pour $V_{DS,source} = 1V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 135   |

| FIGURE III.4.14 – Amplificateur transconductance téléscopique cascode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 135   |

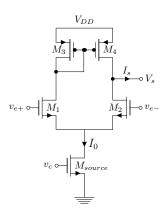

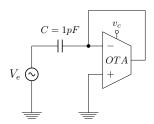

| FIGURE III.4.15 –Filtre passe-haut du premier ordre configurable avec un OTA en tant que                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| résistance variable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 136   |

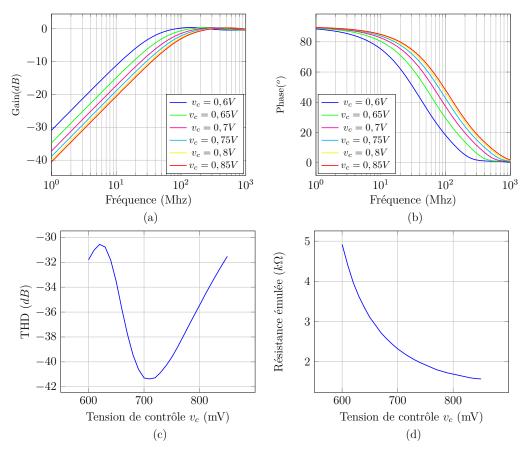

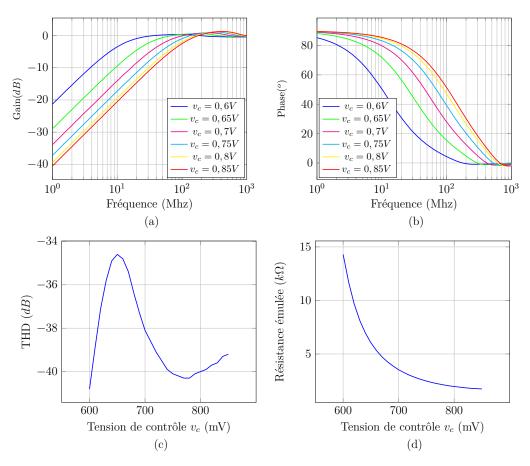

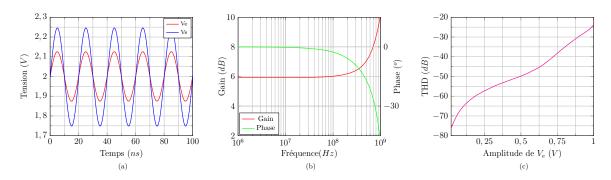

| FIGURE III.4.16 –Simulation du filtre passe-haut du premier ordre configurable avec un OTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

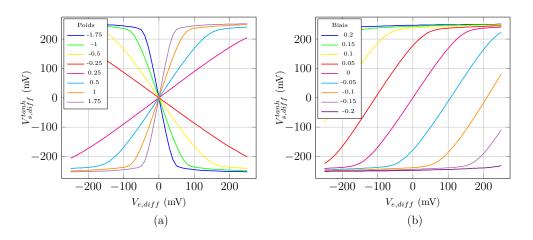

| en tant que résistance variable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 137   |

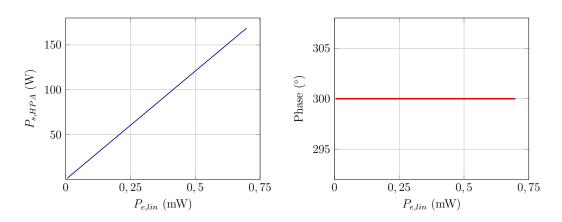

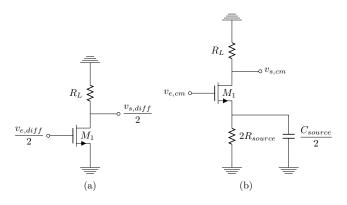

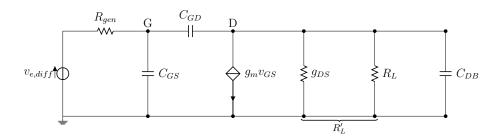

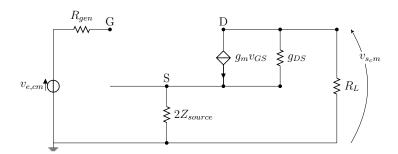

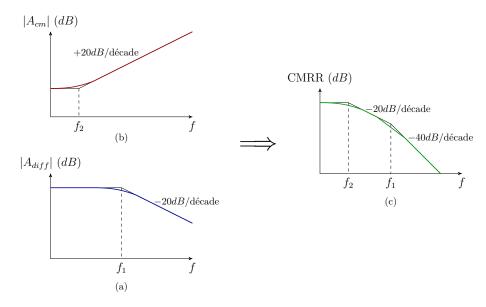

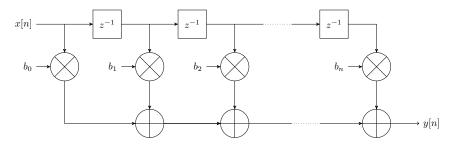

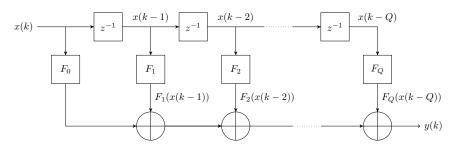

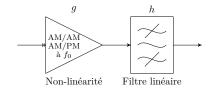

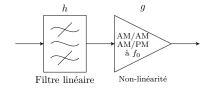

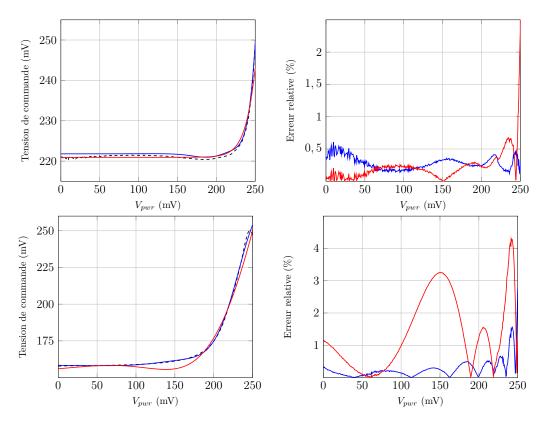

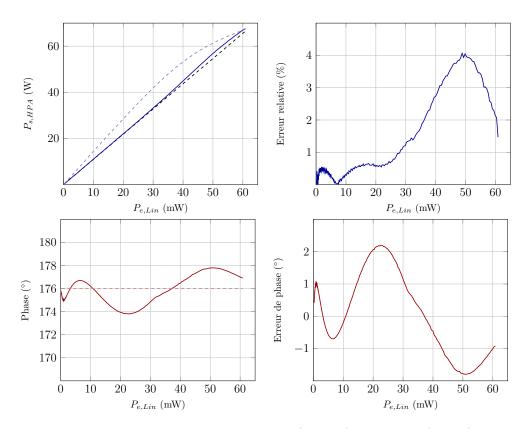

| Figure III.4.17 –<br>Amplificateur à transconductance à paramétrage étendu $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 138   |