# A Reproducible Research Methodology for Designing and Conducting Faithful Simulations of Dynamic HPC Applications

Luka Stanisic

#### ▶ To cite this version:

Luka Stanisic. A Reproducible Research Methodology for Designing and Conducting Faithful Simulations of Dynamic HPC Applications. Distributed, Parallel, and Cluster Computing [cs.DC]. Université Grenoble Alpes, 2015. English. NNT: 2015GREAM035. tel-01248109v2

# HAL Id: tel-01248109 https://theses.hal.science/tel-01248109v2

Submitted on 21 Jan 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ DE GRENOBLE

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique

Présentée par

#### Luka STANISIC

Thèse dirigée par **Jean-François MÉHAUT** et codirigée par **Arnaud LEGRAND**

Préparée au sein du LIG, Laboratoire d'Informatique de Grenoble et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# A Reproducible Research Methodology for Designing and Conducting Faithful Simulations of Dynamic Task-based Scientific Applications

Thèse soutenue publiquement le **30 octobre 2015**, devant le jury composé de :

#### M. Martin QUINSON

Full Professor, École Normale Supérieure de Rennes, Président

#### Mrs. Sherry X. LI

Senior Scientist, Lawrence Berkeley National Laboratory, Rapporteur

#### M. Raymond NAMYST

Full Professor, Université de Bordeaux/Laboratoire Bordelais de Recherche en Informatique, Rapporteur

#### M. Grigori FURSIN

Research Scientist, Inria Saclay, Examinateur

#### M. Jean-François MÉHAUT

Full Professor, Université de Grenoble/Laboratoire d'Informatique de Grenoble, Directeur de thèse

#### M. Arnaud LEGRAND

Research scientist, CNRS/Laboratoire d'Informatique de Grenoble, Co-Directeur de thèse

# Acknowledgements

First I would like to thank the members of the jury for accepting to be the part of this committee. They provided me with very useful remarks, questions and suggestions for the future directions of this work.

I would like to thank my family and friends who supported me and who came to the thesis defense from far away. I also thank my friends from Grenoble, especially Ben and Nata, who made this 3 years of PhD one of the most wonderful periods of my life.

I will never forget the incredibly pleasant and motivating surrounding, created by all members and former members of MESCAL, MOAIS, NANOSIM/CORSE teams that I worked with. I would particularly like to thank Brice VIDEAU, who though me many technical and research related things and who was regularly encouraging me. A special thanks goes to Jean-François MÉHAUT, who was always there when needed the most and whose advises helped me to always stay on the right track.

Finally and foremost, I would like to thank Arnaud LEGRAND whose incredible energy, character and knowledge inspired and guided me from the beginning until the end of the thesis. I feel extremely privileged to get so much of his time and to work beside him throughout these years.

# **Abstract**

The evolution of High-Performance Computing systems has taken a sharp turn in the last decade. Due to the enormous energy consumption of modern platforms, miniaturization and frequency scaling of processors have reached a limit. The energy constraints has forced hardware manufacturers to develop alternative computer architecture solutions in order to manage answering the ever-growing need of performance imposed by the scientists and the society. However, efficiently programming such diversity of platforms and fully exploiting the potentials of the numerous different resources they offer is extremely challenging. The previously dominant trend for designing high performance applications, which was based on large monolithic codes offering many optimization opportunities, has thus become more and more difficult to apply since implementing and maintaining such complex codes is very difficult. Therefore, application developers increasingly consider modular approaches and dynamic application executions. A popular approach is to implement the application at a high level independently of the hardware architecture as Directed Acyclic Graphs of tasks, each task corresponding to carefully optimized computation kernels for each architecture. A runtime system can then be used to dynamically schedule those tasks on the different computing resources.

Developing such solutions and ensuring their good performance on a wide range of setups is however very challenging. Due to the high complexity of the hardware, to the duration variability of the operations performed on a machine and to the dynamic scheduling of the tasks, the application executions are non-deterministic and the performance evaluation of such systems is extremely difficult. Therefore, there is a definite need for systematic and reproducible methods for conducting such research as well as reliable performance evaluation techniques for studying these complex systems.

In this thesis, we show that it is possible to perform a clean, coherent, reproducible study, using simulation, of dynamic HPC applications. We propose a unique workflow based on two well-known and widely-used tools, Git and Org-mode, for conducting a reproducible experimental research. This simple workflow allows for pragmatically addressing issues such as provenance tracking and data analysis replication. Our contribution to the performance evaluation of dynamic HPC applications consists in the design and validation of a coarse-grain hybrid simulation/emulation of StarPU, a dynamic task-based runtime for hybrid architectures, over SimGrid, a versatile simulator for distributed systems. We present how this tool can achieve faithful performance predictions of native executions on a wide range of heterogeneous machines and for two different classes of programs, dense and sparse linear algebra applications, that are a good representative of the real scientific applications.

# Résumé

Le calcul à hautes performances s'est vu contraint d'évoluer de façon radicalement différente durant la dernière décennie. La miniaturisation et l'augmentation de la fréquence des processeurs a atteint ses limites en raison des consommations d'énergies déraisonnables induites. Cette contrainte énergétique a conduit les fabricants de matériel à développer de nombreuses architectures alternatives afin de répondre aux besoins toujours croissants de puissance de calcul de la communauté scientifique. Cependant, programmer efficacement des plates-formes aussi diverses et exploiter l'intégralité des ressources qu'elles offrent s'avère extrêmement difficile. L'approche classique de conception d'application haute performance consistant à se reposer sur des codes monolithiques offrant de nombreuses opportunités d'optimisation est ainsi devenue de plus en plus difficile à appliquer en raison de difficulté d'implémentation, de portabilité et de maintenance. Par conséquent, les développeurs de telles applications considèrent de plus en plus couramment des approches modulaires et une exécution dynamique des différents composants. Une approche populaire consiste à implémenter ces applications à relativement haut niveau, indépendamment de l'architecture matérielle, en se reposant sur un paradigme basé sur la notion de graphe de tâches où chaque tâche correspond à un noyau de calcul soigneusement optimisé pour chaque architecture cible. Un système de runtime peut alors ensuite être utilisé pour ordonnancer dynamiquement ces tâches sur les différentes ressources de calcul à disposition.

Garantir l'efficacité de telles applications sur un large spectre de configurations reste néanmoins un défi majeur. En effet, en raison de la grande complexité du matériel, de la variabilité des temps d'exécution des calculs et de la dynamicité d'ordonnancement des tâches, l'exécution des applications n'est pas déterministe et l'évaluation de la performance de ces systèmes est très délicate. Par conséquent, il est nécessaire de disposer d'une méthodologie systématique, rigoureuse et reproductible pour conduire de telles études et évaluer la performance de tels systèmes.

Dans cette thèse, nous montrons qu'il est possible d'étudier les performances de telles applications dynamiques à l'aide de simulations, et ce de façon fiable, cohérente et reproductible. Nous proposons dans un premier temps une méthode de travail originale basée sur deux outils couramment utilisés dans notre communauté, Git et Org-mode, et permettant de mettre en oeuvre une recherche expérimentale reproductible. Cette approche simple permet de résoudre de façon pragmatique des problèmes tels que le suivi de la provenance des expériences ou la réplication de l'analyse des données expérimentales. Dans un second temps, nous contribuons à l'évaluation de performance d'applications dynamiques en concevant et en validant une simulation/émulation hybride à gros grains de StarPU, un runtime dynamique utilisant le paradigme de graphes de tâches et particulièrement adapté à l'exploitation d'architecture hybrides. Cette simulation est réalisée à l'aide de SimGrid, un simulateur polyvalent de systèmes distribués. Nous présentons comment notre approche permet d'obtenir des prédictions de performances d'exécutions réelles fiables sur un large panel de machines hétérogènes. Nous appliquons notre approche à deux classes de programmes différentes, les applications d'algèbre linéaire dense et creuse, qui sont représentatives d'un grand nombre d'applications scientifiques.

# Contents

| 1 | Intr | oducti |                                                   |

|---|------|--------|---------------------------------------------------|

|   | 1.1  | Contri | butions                                           |

|   |      | 1.1.1  | Methodology for conducting reproducible research  |

|   |      | 1.1.2  | Simulating dynamic HPC applications               |

|   | 1.2  | Thesis | organization                                      |

| 2 | Bac  | kgroui | $_{ m nd}$                                        |

|   | 2.1  | _      | amming challenges for HPC application developers  |

|   |      | 2.1.1  | HPC applications                                  |

|   |      | 2.1.2  | Different architectures used in HPC               |

|   |      | 2.1.3  | Exploiting machine resources                      |

|   |      | 2.1.4  | Dynamic task-based runtimes                       |

|   |      | 2.1.5  | Linear algebra applications                       |

|   |      |        | Dense linear algebra                              |

|   |      |        | Sparse linear algebra                             |

|   | 2.2  | Exper  | imental challenges for HPC application developers |

|   | 2.3  | Concl  |                                                   |

|   |      |        |                                                   |

| 3 |      | ated V |                                                   |

|   | 3.1  | Repro  | ducible research                                  |

|   |      |        | Code and data accessibility                       |

|   |      |        | Platform accessibility                            |

|   |      |        | Setting up environments                           |

|   |      |        | Conducting experiments                            |

|   |      |        | Provenance tracking                               |

|   |      |        | Documenting                                       |

|   |      |        | Extendability                                     |

|   |      |        | Replicable analysis                               |

|   |      |        | Conclusion                                        |

|   | 3.2  |        | mance evaluation and simulation                   |

|   |      | 3.2.1  | Different simulation approaches                   |

|   |      |        | Emulation                                         |

|   |      |        | Cycle-accurate simulation                         |

|   |      |        | Coarse-grain simulation                           |

|   |      |        | Hybrid approaches                                 |

|   |      | 3.2.2  | Simulating resources                              |

|   |      |        | Modeling communications                           |

|   |      |        | Modeling CPU                                      |

|   |      |        | Modeling GPU                                      |

|   |      | 3.2.3  | Simulating applications                           |

|   |      |        | Simulating MPI applications                       |

|   |      |        | Simulating task-based runtimes                    |

CONTENTS

|   |     | 3.2.4  | SimGrid: a toolkit for Simulating Large Heterogeneous Systems |

|---|-----|--------|---------------------------------------------------------------|

| 4 | Met | hodolo | ogy 31                                                        |

|   | 4.1 |        | and Org-mode based workflow                                   |

|   |     | 4.1.1  | Git branching structure                                       |

|   |     | 4.1.2  | Using Org-mode for improving reproducible research            |

|   |     |        | Environment capture                                           |

|   |     |        | Laboratory notebook                                           |

|   |     |        | Using literate programming for conducting experiments         |

|   |     | 4.1.3  | Git workflow in action                                        |

|   |     | 4.1.5  | Managing experiments with Git                                 |

|   |     |        |                                                               |

|   |     |        | Reproducing experiments                                       |

|   |     |        | Fixing code                                                   |

|   |     |        | Making transversal analysis                                   |

|   |     |        | Writing reproducible articles                                 |

|   | 4.2 |        | hing results                                                  |

|   |     | 4.2.1  | The partially opened approach with figshare hosting           |

|   |     | 4.2.2  | The completely open approach with public Git hosting          |

|   | 4.3 | Conclu | asion                                                         |

| _ | ъ   |        | DII G. C. I                                                   |

| 5 | 5.1 |        | tarPU over SimGrid 45 ing a runtime candidate for simulation  |

|   | -   |        |                                                               |

|   | 5.2 |        | g StarPU over SimGrid                                         |

|   | 5.3 |        | ing the StarPU runtime                                        |

|   |     | 5.3.1  | Synchronization                                               |

|   |     | 5.3.2  | Memory allocations                                            |

|   |     | 5.3.3  | Submission of data transfers                                  |

|   |     | 5.3.4  | Scheduling overhead                                           |

|   |     | 5.3.5  | Duration of runtime operations                                |

|   | 5.4 | Model  | ing communication                                             |

|   |     | 5.4.1  | Different PCI bus models                                      |

|   |     |        | Fatpipe model                                                 |

|   |     |        | Complete graph model                                          |

|   |     |        | Treelike model                                                |

|   |     | 5.4.2  | Model based on calibration                                    |

|   | 5.5 | Model  | ing computation                                               |

|   |     |        | Modeling parameter dependent kernels                          |

|   |     |        | Modeling kernels with complex codes                           |

|   |     |        | Limitations due to the simplistic machine models              |

|   | 5.6 | Conclu | sion                                                          |

|   |     |        |                                                               |

| 6 | Per |        | ice Prediction of Dense Linear Algebra Applications 57        |

|   | 6.1 | Experi | mental settings                                               |

|   |     | 6.1.1  | Applications                                                  |

|   |     | 6.1.2  | Machines                                                      |

|   | 6.2 | Model  | ing kernel variability                                        |

|   |     | 6.2.1  | Analyzing kernel duration distributions                       |

|   |     | 6.2.2  | Using histograms to approximate distributions                 |

|   | 6.3 | Evalua | ation methodology                                             |

|   | 6.4 |        | the model needs to be carefully adapted                       |

|   |     | 6.4.1  | GPU memory limit                                              |

|   |     | 6.4.2  | Specific GPUs/CUDA version                                    |

|   |     | 6.4.3  | Elaborated communication model for complex machines           |

|   | 6.5 |        | ate performance predictions for hybrid machines               |

CONTENTS

| A  | A.1          | A.1.1<br>A.1.2<br>A.1.3<br>A.1.4           | Controlling the simulation quality Opening new horizons  1  Seations International peer reviewed journals International peer reviewed conference proceedings Short communications in conferences and workshops Master Thesis | 101<br>102<br>102<br><b>05</b><br>105<br>105<br>105<br>105 |

|----|--------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| A  | A.1          | Public<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4 | Controlling the simulation quality Opening new horizons  1  Sections                                                                                                                                                         | 102<br>102<br>105<br>105<br>105<br>105                     |

| A  |              | Public<br>A.1.1<br>A.1.2                   | Controlling the simulation quality Opening new horizons  S  International peer reviewed journals International peer reviewed conference proceedings                                                                          | 102<br>102<br><b>05</b><br>105<br>105                      |

| A  |              | Public<br>A.1.1                            | Controlling the simulation quality Opening new horizons  S International peer reviewed journals                                                                                                                              | 102<br>102<br>. <b>05</b><br>105<br>105                    |

| A  |              | Public                                     | Controlling the simulation quality                                                                                                                                                                                           | 102<br>102<br><b>05</b><br>105                             |

| A  |              |                                            | Controlling the simulation quality                                                                                                                                                                                           | 102<br>102<br>. <b>05</b>                                  |

| Λ. | Det          | onon a se                                  | Controlling the simulation quality                                                                                                                                                                                           | 102<br>102                                                 |

|    |              |                                            | Controlling the simulation quality                                                                                                                                                                                           | 102                                                        |

|    |              |                                            |                                                                                                                                                                                                                              |                                                            |

|    |              |                                            | Scaling to larger platforms                                                                                                                                                                                                  | 101                                                        |

|    |              |                                            |                                                                                                                                                                                                                              |                                                            |

|    |              | 8.2.2                                      | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                        | 101                                                        |

|    |              |                                            | Model universality                                                                                                                                                                                                           | 99                                                         |

|    |              |                                            | Simulation of sub-optimal native executions                                                                                                                                                                                  | 99                                                         |

|    |              |                                            | Modeling contention                                                                                                                                                                                                          | 98                                                         |

|    |              |                                            | Modeling memory distance                                                                                                                                                                                                     | 98                                                         |

|    |              | 8.2.1                                      | Current limitations                                                                                                                                                                                                          | 98                                                         |

|    | 8.2          | Simula                                     | ating dynamic HPC applications                                                                                                                                                                                               | 97                                                         |

|    |              |                                            | Current limitations and future work                                                                                                                                                                                          | 96                                                         |

|    | 8.1          | Metho                                      | odology for conducting reproducible research                                                                                                                                                                                 | 95                                                         |

| 8  | Con          |                                            |                                                                                                                                                                                                                              | 95                                                         |

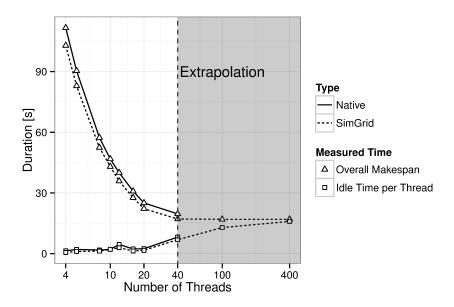

|    |              | 7.7.2                                      | Extrapolation                                                                                                                                                                                                                | 93                                                         |

|    |              | 7.7.1                                      | Memory consumption                                                                                                                                                                                                           | 92                                                         |

|    | 7.7          |                                            | al studies enabled by such approach                                                                                                                                                                                          | 92                                                         |

|    |              | 7.6.2                                      | Evaluation on the Riri machine                                                                                                                                                                                               | 90                                                         |

|    |              | 7.6.1                                      | Evaluation on the Fourmi machine                                                                                                                                                                                             | 88                                                         |

|    | 7.6          |                                            | ation quality evaluation                                                                                                                                                                                                     | 88                                                         |

|    | 7.5          |                                            | ation methodology                                                                                                                                                                                                            | 86                                                         |

|    | _            | 7.4.4                                      | Accounting for kernels variability                                                                                                                                                                                           | 86                                                         |

|    |              | 7.4.3                                      | Matrix dependent kernels                                                                                                                                                                                                     | 85                                                         |

|    |              |                                            | Simulation                                                                                                                                                                                                                   | 85                                                         |

|    |              | 7.4.2                                      | Parameter dependent kernels                                                                                                                                                                                                  | 82                                                         |

|    |              | 7.4.1                                      | Simple negligible kernels                                                                                                                                                                                                    | 82                                                         |

|    | 7.4          |                                            | ing qr_mumps kernels                                                                                                                                                                                                         | 80                                                         |

|    | 7.3          |                                            | imental settings                                                                                                                                                                                                             | 80                                                         |

|    | 7.2          |                                            | g qr_mumps on top of SimGrid                                                                                                                                                                                                 | 79                                                         |

|    | 7.1          |                                            | ps, a task-based multifrontal solver                                                                                                                                                                                         | 77                                                         |

| 7  |              |                                            | nce Prediction of Sparse Linear Algebra Applications                                                                                                                                                                         | 77                                                         |

|    |              | 0.0.2                                      | studying hypothetical platforms                                                                                                                                                                                              | 10                                                         |

|    |              | 6.8.2                                      | Studying hypothetical platforms                                                                                                                                                                                              | 75                                                         |

|    | 0.0          | 6.8.1                                      | al studies enabled by such approach                                                                                                                                                                                          | 74<br>74                                                   |

|    | 6.8          |                                            | e the model breaks and is harder to adapt: NUMA machines                                                                                                                                                                     | 74                                                         |

|    |              |                                            | the model breeks and is harden to adent. NIIMA machines                                                                                                                                                                      | 72                                                         |

|    | $6.6 \\ 6.7$ | Osing                                      | both CPUs and GPUs for computation                                                                                                                                                                                           | 69                                                         |

CONTENTS

# List of Figures

| 1.1               | Diagram illustrating contributions (in gray) of our work that are related to methodology and performance evaluation. In this thesis, for the simulation aspect of our work we consider solely the case where applications rely on a runtime. Our workflow for doing reproducible research is however completely general           | 3               |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

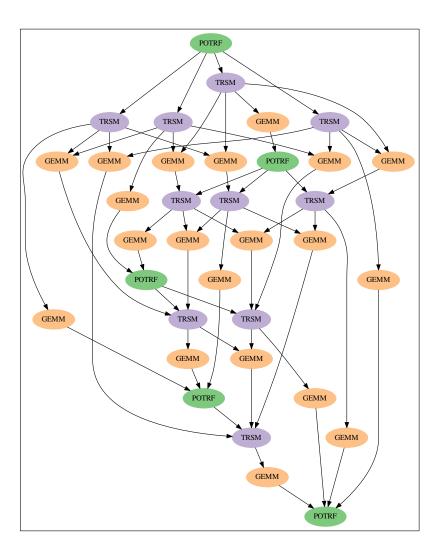

| 2.1               | An example of DAG: task graph of the tiled Cholesky factorization of $5 \times 5$ matrix with the block dimension 960, implemented in StarPU                                                                                                                                                                                      | 10              |

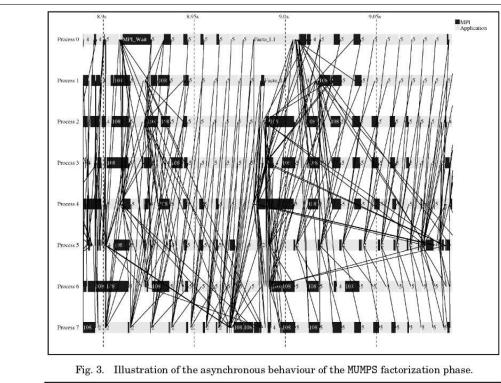

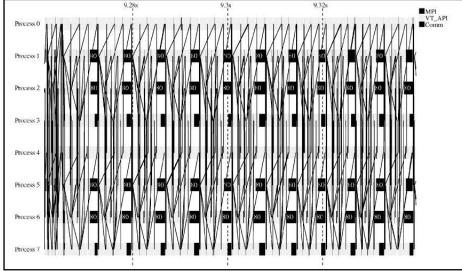

|                   | solvers as done by Amestoy et al. in [ADLL01]. MUMPS has very irregular patterns, which makes it a good candidate for using dynamic task-based runtime systems. $$ .                                                                                                                                                              | 14              |

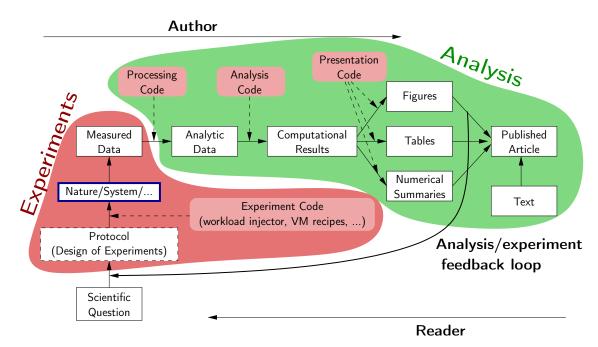

| 3.1               | Ideally, the experimenter would keep track of the whole set of decisions taken to conduct its research as well as all the code used to both conduct experiments and perform the analysis. Figure inspired by Roger D. Peng et al. [Rog09]                                                                                         | 18              |

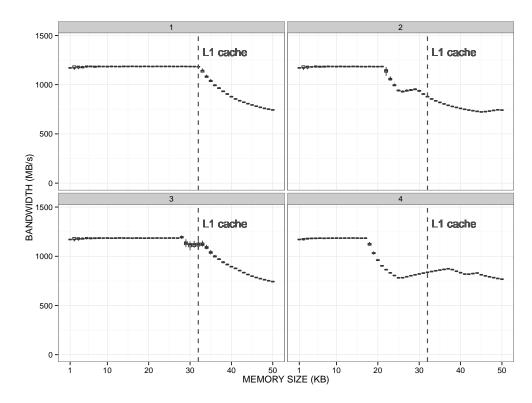

| 4.1               | Reproducibility issue on ARM Snowball: 4 consecutive experiments with identical input parameters behaving differently; 42 repetitions for each array size depicted by boxplots show no noise within each single experiment.                                                                                                       | 32              |

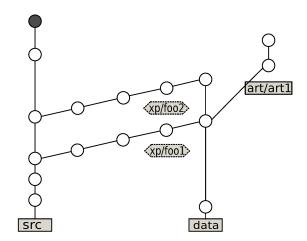

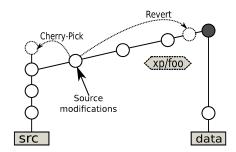

| $4.2 \\ 4.3$      | Proposed Git branching scheme with 4 different types of branches                                                                                                                                                                                                                                                                  | $\frac{34}{39}$ |

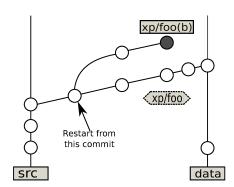

| $\frac{4.3}{4.4}$ | Restart or reproduce experiments starting from a certain commit                                                                                                                                                                                                                                                                   | 40              |

| 4.5               | Handling source modifications that occurred during the experimentation                                                                                                                                                                                                                                                            | 41              |

| 5.1               | Implementing the simulation mode requires some code modifications of StarPU. This simple example illustrates the SimGrid (lines 2-14) and Native (lines 16-25) modes for executing StarPU's conditional wait                                                                                                                      | 48              |

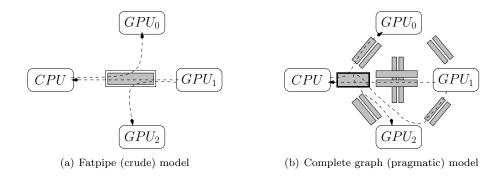

| 5.2               | Communication and topology modeling alternatives. In the crude modeling, a single link is used and communications do not interfere with each others. The pragmatic complete graph modeling allows for accounting for both the heterogeneity of communications and the global bandwidth limitation imposed by the PCI bus. Complex |                 |

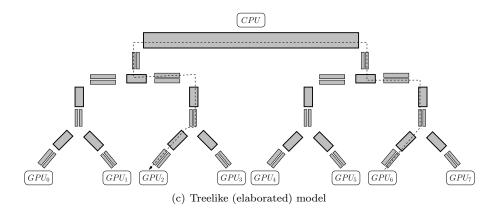

| 5.3               | machine architecture demand for even more elaborated models                                                                                                                                                                                                                                                                       | 50              |

| 5.4               | GPU2 using CUDA                                                                                                                                                                                                                                                                                                                   | 52              |

| 0.1               | GPUs and their interconnect                                                                                                                                                                                                                                                                                                       | 53              |

| 6.1               | Tiled Cholesky factorization.                                                                                                                                                                                                                                                                                                     | 58              |

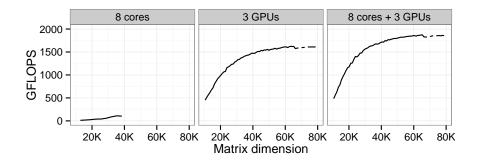

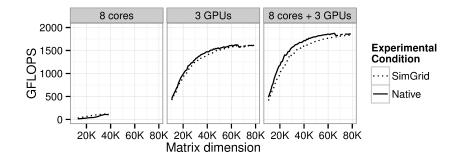

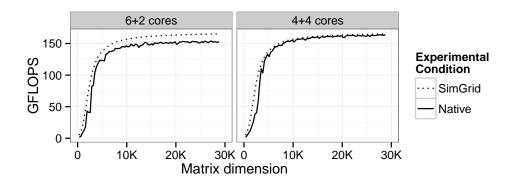

| 6.2               | For dense linear algebra applications, most of the processing power is provided by GPUs. These plots depict the performance of the Cholesky application on the Mirage machine (see Table $6.1$ ). A clearer view of these performance when restricting                                                                            |                 |

|                   | to CPU resources (8 cores) is provided in Figure 6.17 (4+4 cores)                                                                                                                                                                                                                                                                 | 59              |

LIST OF FIGURES

LIST OF FIGURES

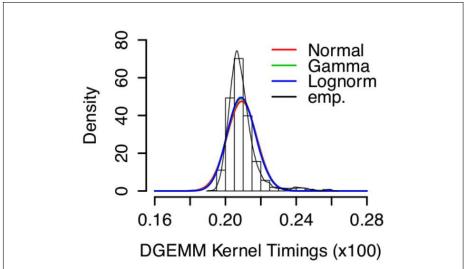

| 6.3         | Analysis of the kernel duration distribution as done by Haugen et al. in [HKY <sup>+</sup> 14]. A normal law approximates the sample distribution very accurately. However we believe this is valid only for simple multi-core CPUs                                                                                            | 60          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

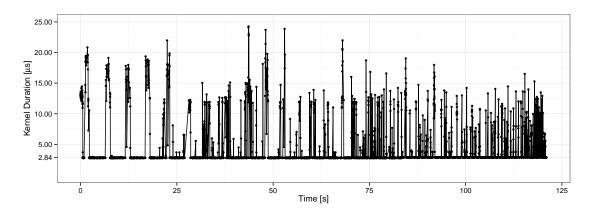

| 6.4         | GEMM kernel durations on a GPU in a single $72,000 \times 72,000$ Cholesky factorization, presented as a time sequence. Most of the values are around 2.84 microseconds, but there is a significant number of higher durations as well                                                                                         | 61          |

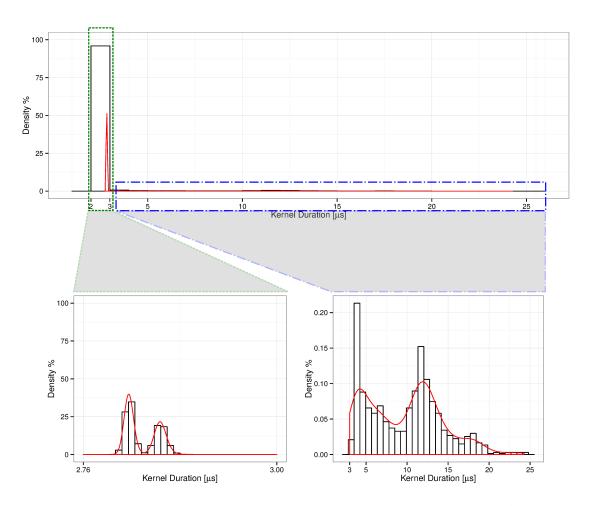

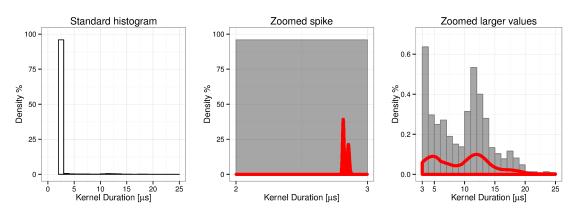

| 6.5         | Distribution of GEMM kernel durations on a GPU in a single 72,000 × 72,000 Cholesky factorization. Top plot presents the distribution constructed for all observations, while bottom ones are reconstructed for two separate groups of observation depending on their duration value.                                          | 62          |

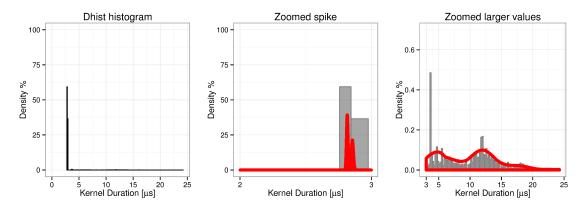

| 6.6         | Approximating GEMM duration with two types of histograms                                                                                                                                                                                                                                                                       | 63          |

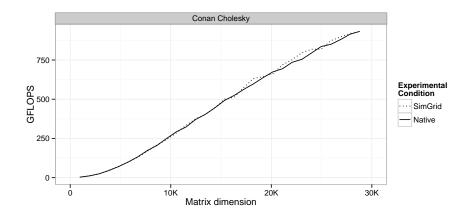

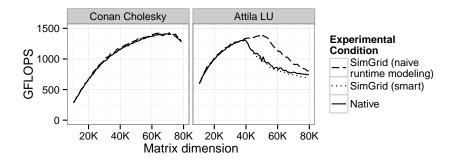

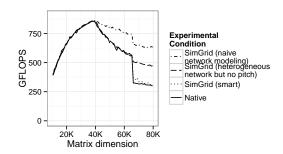

| 6.6<br>6.7  | Initial results of StarPU simulation for the simplistic use cases were already very accurate. More complex scenarious required more sophisticated models                                                                                                                                                                       | 67          |

| 6.8         | Illustrating the influence of modeling runtime. Careless modeling of runtime may be perfectly harmless in some cases, it turns out to be misleading in others                                                                                                                                                                  | 67          |

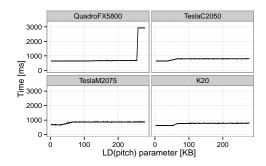

| 6.9         | Transfer time of 3,600 KB using cudaMemcpy2D depending on the pitch of the matrix.                                                                                                                                                                                                                                             | 68          |

| 6.10        | Performance of the LU application on Hannibal (QuadroFX5800 GPUs) using different modeling assumptions                                                                                                                                                                                                                         | 68          |

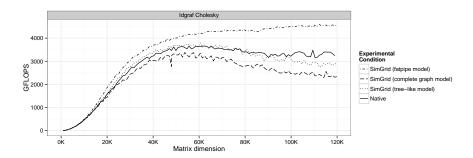

|             | Simulating machines with complex architectures such as Idgraf (see Figure $5.4$ ) require more elaborated models                                                                                                                                                                                                               | 69          |

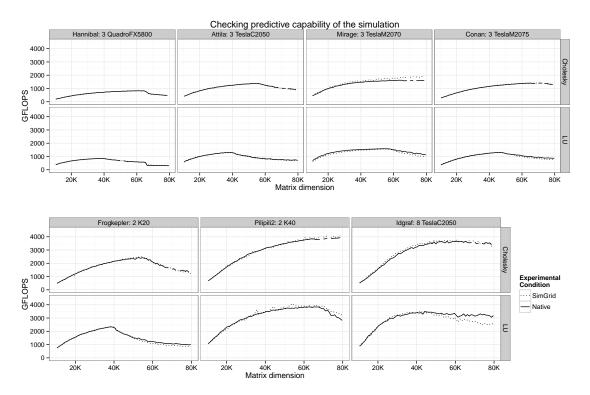

|             | Checking predictive capability of our simulator in a wide range of settings                                                                                                                                                                                                                                                    | 70          |

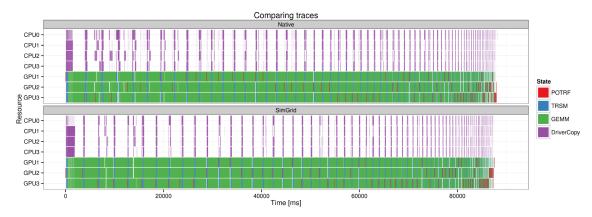

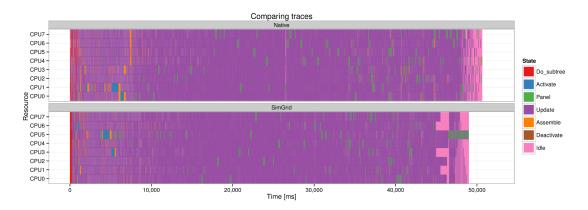

| 6.13        | Comparing execution traces (native execution on top vs. simulated execution at the bottom) of the Cholesky application with a $72,000 \times 72,000$ matrix on the Conan                                                                                                                                                       | <b>—</b> 1  |

| 0.14        | machine but using only GPU resources for processing the application                                                                                                                                                                                                                                                            | 71          |

|             | Illustrating simulation accuracy for Cholesky application using different resources of the Mirage machine                                                                                                                                                                                                                      | 71          |

| 6.15        | Comparing execution traces (native execution on top vs. simulated execution at the bottom) of the Cholesky application with a $72,000 \times 72,000$ matrix on the Mirage machine using 8 cores and 3 GPUs as workers. Adding 8 cores, improved the performance by approximatelly 20% compared to the performances obtained in | <b>7</b>    |

| c 1c        | Figure 6.13                                                                                                                                                                                                                                                                                                                    | 71          |

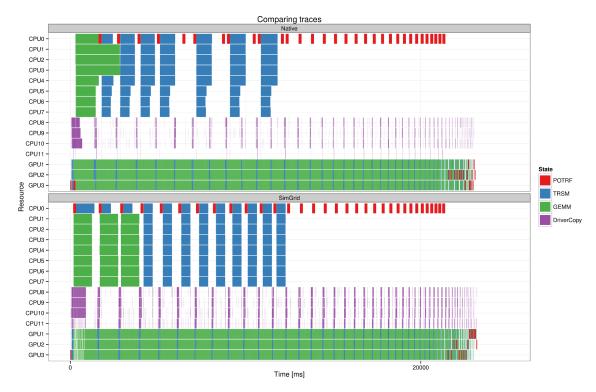

| 0.10        | bottom) of the Cholesky application with a $48,000 \times 48,000$ matrix on the Mirage machine using 8 cores and 3 GPUs as workers. Executing kernels on CPUs is much longer since Intel MKL libraries were not used, however simulation predictions are                                                                       |             |

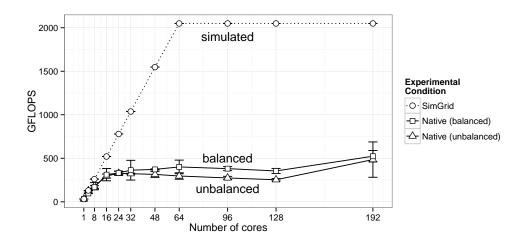

| 6.17        | still very precise                                                                                                                                                                                                                                                                                                             | 72<br>73    |

| 6 18        | Simulation predictions of Cholesky application with a 32,000×32,000 matrix (block                                                                                                                                                                                                                                              | 1.          |

| 0.10        | size $320 \times 320$ ) on large NUMA Idchire machine are precise for a small number of                                                                                                                                                                                                                                        |             |

|             | cores, but scale badly. The reason is that the memory is shared, while models are                                                                                                                                                                                                                                              | <del></del> |

| <i>c</i> 10 | not taking into account various NUMA effects                                                                                                                                                                                                                                                                                   | 73          |

| 6.19        | Cholesky on Attila: studying the impact of different schedulers                                                                                                                                                                                                                                                                | 75          |

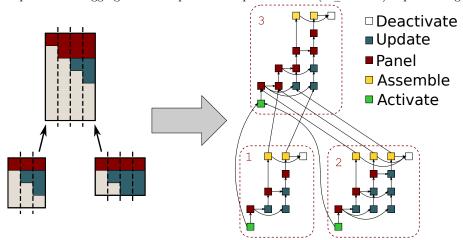

| 7.1         | Sequential version (left) and corresponding STF version from [ABGL14] (right) of                                                                                                                                                                                                                                               |             |

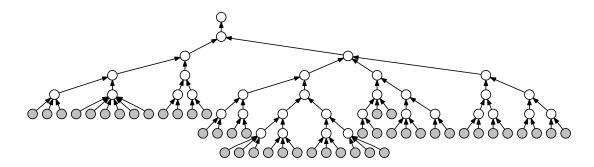

| 7.2         | the multifrontal $QR$ factorization with 1D partitioning of frontal matrices Typical elimination tree: each node corresponds to a front and the resulting tree                                                                                                                                                                 | 78          |

|             | is traversed from the bottom to the top. To reduce the overhead incurred by managing a large number of fronts, subtrees are proposed and aggregated into entimized                                                                                                                                                             |             |

|             | aging a large number of fronts, subtrees are pruned and aggregated into optimized sequential tasks (Do_subtree) depicted in gray                                                                                                                                                                                               | 78          |

| 7.3         | Processing a front requires a complexe series of Panel and Update tasks induced by the staircase structure. The dependencies between these operations expressed by                                                                                                                                                             | 10          |

|             | the Starcase structure. The dependencies between these operations expressed by the STF code leads to a fine-grain DAG dynamically scheduled by the runtime system.                                                                                                                                                             | 78          |

LIST OF FIGURES

LIST OF FIGURES

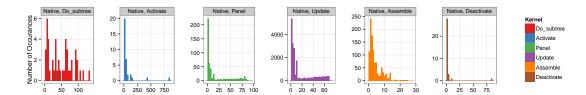

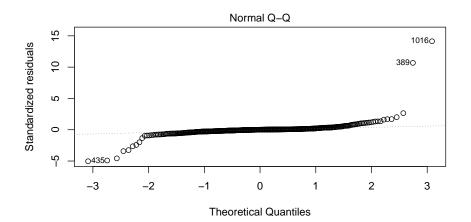

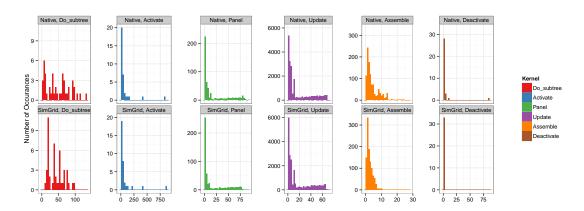

| 7.4  | Distribution of the qr_mumps kernel duration when factorizing the e18 matrix (see      |                   |

|------|----------------------------------------------------------------------------------------|-------------------|

|      | Table 7.2). The distribution shapes is similar for other matrices. Most kernels        |                   |

|      | have a (difficult to model) multi-modal distribution                                   | 81                |

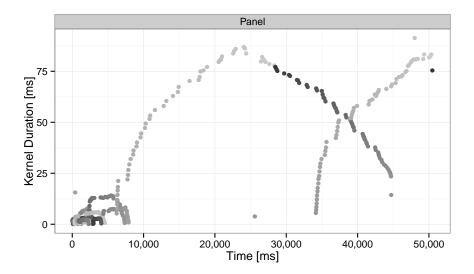

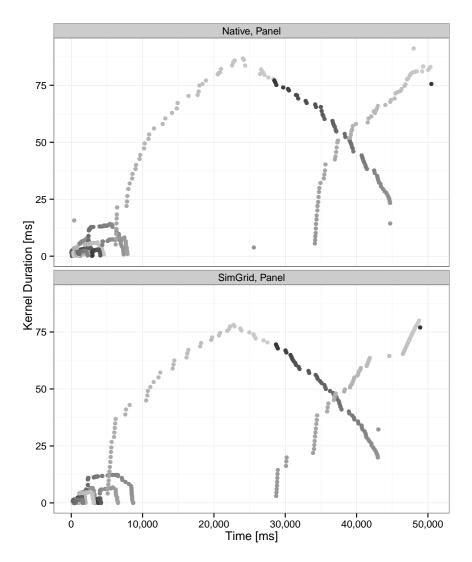

| 7.5  | Duration of the Panel kernel as a time sequence for the e18 matrix. The patterns       |                   |

|      | suggest that this duration depends on specific parameters that evolve throughout       |                   |

|      | the execution of the application                                                       | 81                |

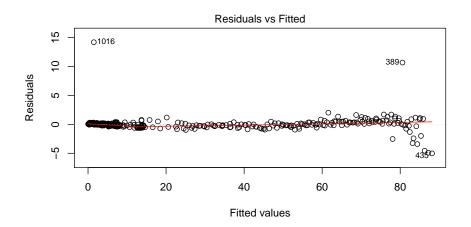

| 7.6  | Analysing linear model for Panel kernel                                                | 84                |

| 7.7  | Automatically generated code for computing the duration of Panel and Update kernels.   | 85                |

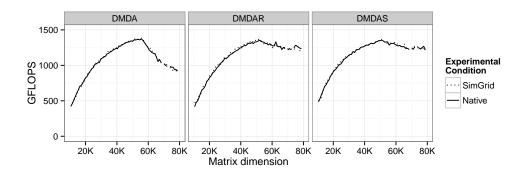

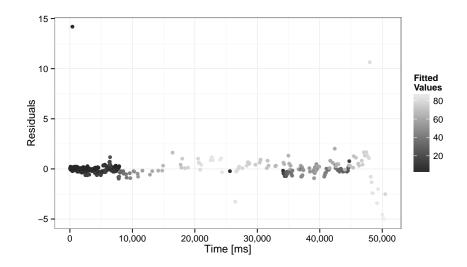

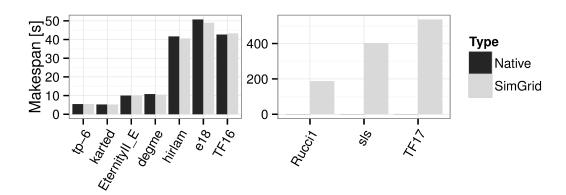

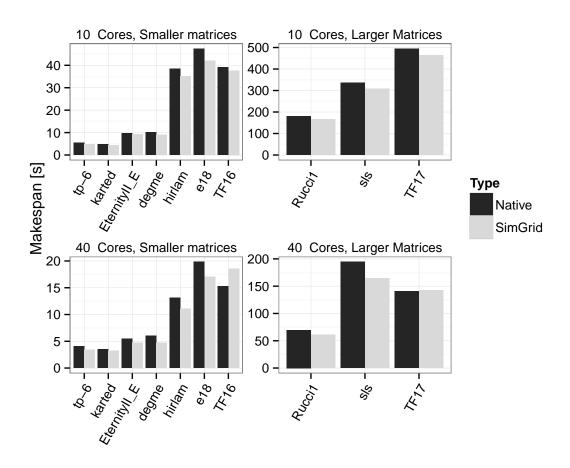

| 7.8  | Makespans on the 8 CPU cores Fourmi machine for 10 different matrices. Native          |                   |

|      | results on 3 largest matrices are not presented, because they are too long, since the  |                   |

|      | factorization exceeds RAM memory capacities of the Fourmi machine                      | 88                |

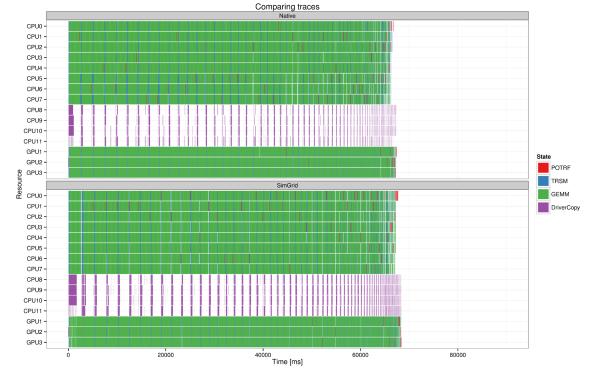

| 7.9  | Gantt chart comparison on the 8 CPU cores Fourmi machine                               | 88                |

| 7.10 | Comparing kernel distribution duration on 8 CPU cores Fourmi machine                   | 89                |

| 7.11 | Comparing Panel as a time sequence on 8 CPU cores Fourmi machine. Color is             |                   |

|      | related to the task id                                                                 | 90                |

| 7.12 | Results on the Riri machine using 10 or 40 CPU cores. When using a single node         |                   |

|      | (10 cores), the results match relatively well although not as well as for the Fourmi   |                   |

|      | machine due to a more complex and packed processor architecture. When using 4          |                   |

|      | nodes (40 cores), the results are still within a reasonnable bound despite the NUMA    |                   |

|      | effects                                                                                | 91                |

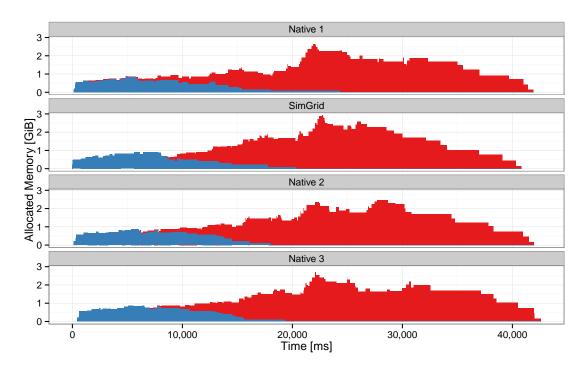

| 7.13 | Memory consumption evolution. The blue and red parts correspond to the                 |                   |

|      | Do_subtree and Activate contribution                                                   | 92                |

| 7.14 | Extrapolating results for $e18$ matrix on 100 and 400 CPU cores                        | 93                |

|      |                                                                                        |                   |

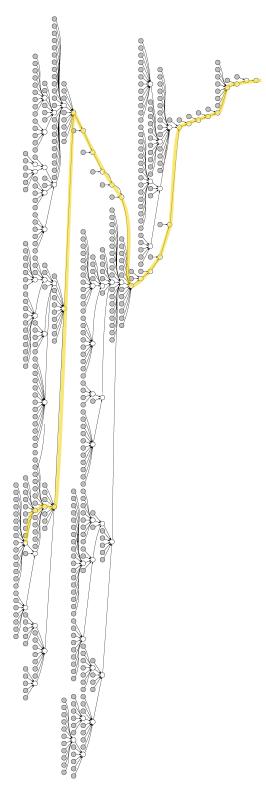

| 8.1  | Elimination tree for $cat\_ears\_4\_4$ matrix, rotated for 90 degrees to fit the page. |                   |

|      | The graph is extremely badly balanced and has a comb-like structure with a huge        |                   |

|      | number of Do_subtree kernels presented as grey nodes                                   | 100               |

| B.1  | Script for running experiments and automatically capturing meta-data                   | 120               |

| B.2  |                                                                                        | $\frac{120}{121}$ |

| B.3  | -                                                                                      | $\frac{121}{122}$ |

| B.4  | - · · · · · · · · · · · · · · · · · · ·                                                | $\frac{122}{123}$ |

| B.5  | · · ·                                                                                  | $123 \\ 124$      |

| B.6  | y i                                                                                    | $124 \\ 125$      |

| ט.ט  | Org-mode arricle contains both text and the analysis code                              | 140               |

LIST OF FIGURES

LIST OF FIGURES

# List of Tables

| 2.1 | Ranked first on the TOP500 list, illustrating the diversity of architectures used to construct modern HPC platforms. | 7  |

|-----|----------------------------------------------------------------------------------------------------------------------|----|

| 5.1 | Typical duration of runtime operations                                                                               | 49 |

| 6.1 | Machines used for the dense linear algebra experiments                                                               | 59 |

|     | Machines used for the sparse linear algebra experiments                                                              |    |

| 7.2 | Matrices used for the sparse linear algebra experiments                                                              | 80 |

| 7.3 | Linear Regression of Panel kernel                                                                                    | 83 |

| 7.4 | Linear Regression of Update kernel                                                                                   | 85 |

| 7.5 | Summary of the modeling of each kernel based on the e18 matrix on Fourmi (see                                        |    |

|     | Section 7.3 for more details)                                                                                        | 86 |

# Chapter 1

## Introduction

Computers have become an indispensable research tool in many scientific fields such as physics, medicine, engineering, etc. These machines can execute trillions of operations per second and therefore perform computations that are far beyond from what humans could manually do. Still, even such tremendous computational power is insufficient for solving certain computational problems. Programs performing simulations in particle physics, earthquakes or astronomy all study very large systems and have thus to perform vast amount of computation on huge data. High-Performance Computing (HPC) is a computer science discipline that focuses on these groups of applications as well as on the platforms required to execute them.

High power machines, often called *supercomputers*, went through an extremely rapid evolution in the past 50 years. Thanks to the miniaturization and frequency scaling of the microchips, the performance of the computers doubled approximately every 18 months. However, this trend stopped a decade ago due to the technological limitations, namely energy consumption and heat. In order to pursue performance growth, manufacturers started to produce computers with multiple cores per processor and started to add the accelerator units. This allowed for breaking the problems into smaller ones that can be executed in parallel. Therefore, modern HPC machines comprise thousands to millions of cores, interconnected by fast networks.

The HPC community maintains the list of the fastest 500 computers in the world: the TOP500 [Top]. This list ranks the computers by the achieved maximum number of FLOPS (FLoating-point Operations Per Second) measured with the LINPACK benchmark [Don88]. Today's fastest supercomputer is "Tianhe-2" in China with 3,120,000 processor cores and it reaches a peak performance of approximately 33 PetaFlops (10<sup>16</sup> floating-point operations per second). If the previous trends continue, it is expected that 1 ExaFlops (10<sup>18</sup> floating-point operations per second) will be reached in 2020.

The major challenge for achieving such a high performance is energy constraint. Supercomputers and data centers already consume as much electricity as a small city and the price for powering them for a few years is the same as the initial price of the hardware that it is composed of. Therefore, it is estimated that the power budget for the future fastest computers should not exceed 20 MegaWatts. This requires performance efficiency of 50 GFLOPS/Watt, which is far above the current maximum of 5,2 GFLOPS/Watt achieved by the L-CSC computer [Greb]. Hence, there is a huge energy-efficient computing movement in HPC that established a new supercomputer ranking. The Green500 list [Grea] is organized similarly to the TOP500, except that computers are ranked according to their energy efficiency.

The large diversity of hardware architectures and their respective complexity, on both TOP500 and Green500 lists, clearly indicate that no consensus has still been reached on the architecture of the future supercomputers. For example, the top three machines on the Green500 list all use differently designed accelerators produced by different vendors [Greb]. The technology is evolving extremely fast and it is hard to predict what kind of resources will be available to the applications developers.

Implementing codes whose performance is portable across such diverse and complex platforms

becomes extremely challenging. Having hundred times more processor cores rarely provides hundred times faster execution due to the overheads of parallelization, communication and critical path limits of the application. Such scaling issues are hard to overcome, as exploiting efficiently all resources provided by modern computer platforms is not trivial.

Until a few years ago, the dominant trend for designing HPC libraries mainly consisted of designing scientific software as a single whole that aims to cope with both the algorithmic and architectural needs. This approach may indeed lead to extremely high performance because the developer has the opportunity to optimize all parts of the code, from the high level design of the algorithm down to low level technical details such as data movements. However, such a development often requires a tremendous effort, and is very difficult to maintain. Achieving portable and scalable performance has thus become extremely challenging, especially for irregular codes.

There is a recent and general trend in using instead a modular approach where numerical algorithms are written at a high level independently of the hardware architecture as Directed Acyclic Graphs (DAG) of tasks. A task-based runtime system then dynamically schedules the resulting DAG on the different computing resources, automatically taking care of data movement and taking into account the possible speed heterogeneity and variability. In such a way, runtimes abstract the underlying architecture complexity through a common application program interface (API).

However, dynamic task-based runtimes are hard to develop and the evaluation of their performance raises two major challenges. First, these complex runtimes aim to support diverse platform and parameter configurations. Therefore, to ensure that they achieve good performance on a wide range of settings, numerous experiments need to be executed. Second, these runtimes use dynamic scheduling techniques, which leads to non-deterministic executions. From one execution to another, tasks are not executed in the same order or on the same resources, leading to different makespans, which makes performance evaluation and comparison even more difficult than in classical deterministic settings. Furthermore, this non-determinism often brings heisenbugs that are very hard to locate.

Hence, there is a huge need for a reliable experimental methodology allowing to produce reproducible results to evaluate the correctness of the execution and the good performance of the runtimes on a wide range of settings. A possible solution is to conduct such experimental studies using simulation, which can address the aforementioned issues.

In this thesis, we propose a sound methodology for experimentally evaluating the performance of HPC application implemented on top of dynamic task-based runtimes, using faithful simulation predictions. In our approach, the target high-end machines are calibrated only once to derive sound performance models. These models can then be used at will to quickly predict and study in a reproducible way the performance of resource-demanding parallel applications using solely a commodity laptop. This allows for obtaining performance predictions of classical linear algebra kernels accurate within a few percents and in a matter of seconds, which allows both runtime and application designers to quickly decide which optimization to enable or whether it is worth investing in additional hardware components or not. Moreover, this allows for conducting robust and extensive scheduling studies in a controlled environment whose characteristics are very close to real platforms while having a reproducible behavior.

#### 1.1 Contributions

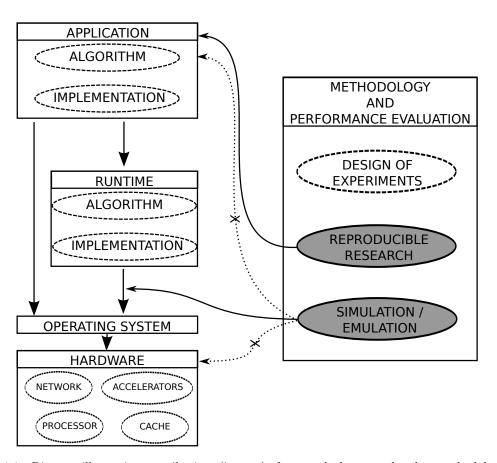

Figure 1.1 (left part) recaps the previously described system, where an application can be executed either directly on the operating system (OS) or on top of a runtime. The goal of our research was however not to directly contribute to the development of any of these blocks, but to propose a good methodology and performance evaluation techniques to study them (right part of Figure 1.1).

In such a complex, multi-layer systems, it is impossible to master every part. Therefore, during our research we closely collaborated with domain experts, most notably with:

Figure 1.1: Diagram illustrating contributions (in gray) of our work that are related to methodology and performance evaluation. In this thesis, for the simulation aspect of our work we consider solely the case where applications rely on a runtime. Our workflow for doing reproducible research is however completely general.

- 1. Application developers: Emmanuel AGULLO, Suraj KUMAR, Paul RENAUD-GOUD, Abdou GUERMOUCHE, Alfredo BUTTARI, and Florent LOPEZ.

- 2. Runtime developers: Samuel Thibault, and Marc Sergent.

- 3. Operating systems and computer architecture experts: Brice VIDEAU, Jean-François Méhaut, Augustin Degomme and numerous other researchers from teams MESCAL, MOAIS, NANOSIM, CORSE and TIMA in Grenoble as well as experts from ARM and the Barcelona Supercomputing Center.

Even though we studied several aspects in the area of methodology and performance evaluation, the main contributions of this thesis are twofold. First, we developed a unique workflow for doing **reproducible research** on a daily basis when conducting empirical studies on modern computer architectures. Second, we crafted a faithful **simulation of a dynamic runtime system** that aids at its evaluation.

#### 1.1.1 Methodology for conducting reproducible research

Computers, operating systems and software running on it have reached such a level of complexity that it has become very difficult (not to say impossible) to control them perfectly and to know every detail about their configuration and operation mode. Consequently, it becomes less and less reasonable to consider computer systems as deterministic. Experiments that focus on measuring the execution time or the performance of the application running on such setups have thus become non replicable by essence. Hence, there is an urgent need for sound experimental methodology.

We inspired on other tools and approaches developed in the last few years in the domain of reproducible research to develop a lightweight experimental workflow based on standard tools widely used in our community. We used such workflow extensively throughout three years of research, and we strongly believe that our scientific work greatly benefited from it. This workflow was published in:

- [1] L. Stanisic, A. Legrand, and V. Danjean. An effective git and org-mode based workflow for reproducible research. *ACM SIGOPS Operating Systems Review*, 49:61 70, 2015. Special Topic: Repeatability and Sharing of Experimental Artifacts.

- [4] L. Stanisic and A. Legrand. Effective reproducible research with org-mode and git. In 1st International Workshop on Reproducibility in Parallel Computing, Porto, Portugal, Aug. 2014.

- [7] L. Stanisic, and A. Legrand. Actes du 10ème Atelier en Évaluation de Performances, chapter Good practices for reproducible research, pages 29–30. Inria, 2014.

Moreover, we presented our solution on numerous occasions in order to encourage researchers from our community to redefine their practices and develop similar workflows that will aid them in their daily work. The most important events where our approach was presented are:

- LIG day on trace production in Grenoble, March 2015.

- Plafrim day on performance of parallel codes in Bordeaux, December 2014.

- REPPAR workshop on reproducibility in parallel computing in Porto, August 2014.

- AEP workshop on performance evaluation in Nice, June 2014.

- Join Laboratory for Petascale Computing (JLPC) summer school on performance metrics, modeling and simulation of large HPC systems in Nice, June 2014.

- SyncFree European project meeting in Paris, May 2014.

- COMPAS conference in Neuchâtel, April 2014.

- ANR SONGS plenary meetings in Lyon, June 2013, and in Nice, January 2014.

Additionally, our approach served as a base for a platform sharing HPC application traces, which is a joint project between researchers in Grenoble and Bordeaux [Traa].

Finally, we made a regular usage of a laboratory notebook comprising information about all the experiments we conducted during the last three years. We opened this laboratory notebook and made it publicly available so that anyone can inspect and possibly build upon our results [SSW].

#### 1.1.2 Simulating dynamic HPC applications

Runtime systems are a promising approach for efficiently exploiting the heterogeneous resources offered by modern computers. However, their development and optimal utilization is not easy to achieve, and it requires constant experimental validation on a wide range of different setups. Evaluating the performance of such systems is extremely challenging due to the diversity of the experimental machines as well as the complexity of the code of the both application and the runtime. Moreover, for the runtimes that use dynamic scheduling, the executions are non-deterministic which makes evaluation even more difficult.

To address these issues, we developed a coarse-grain simulation tool. Our solution can be executed quickly and on a commodity machine, in order to evaluate the performance of the long runtime execution on a large, hybrid clusters. Additionally, the simulation provides reproducible results, which makes debugging of both the code and the performance much easier. Our tool provides very accurate performance predictions for applications running on top of dynamic task-based runtime and it was presented in the following papers:

- [3] L. Stanisic, E. Agullo, A. Buttari, A. Guermouche, A. Legrand, F. Lopez, and B. Videau. Fast and Accurate Simulation of Multithreaded Sparse Linear Algebra Solvers. 2015. Submitted to the ICPADS conference.

- [2] L. Stanisic, S. Thibault, A. Legrand, B. Videau, and J.-F. Méhaut. Faithful Performance Prediction of a Dynamic Task-Based Runtime System for Heterogeneous Multi-Core Architectures. *Concurrency and Computation: Practice and Experience*, page 16, May 2015.

- [5] L. Stanisic, S. Thibault, A. Legrand, B. Videau, and J.-F. Méhaut. Modeling and simulation of a dynamic task-based runtime system for heterogeneous multi-core architectures. In *Euro-par 20th International Conference on Parallel Processing*, Euro-Par 2014, LNCS 8632, pages 50–62, Porto, Portugal, Aug. 2014. Springer International Publishing Switzerland.

This work was also presented on several occasions:

- ANR SOLHAR plenary meeting in Lyon, June 2015.

- Mont-Blanc meeting in Barcelona, October 2014.

- EuroPar conference Porto, August 2014.

- JointLab for Petascale Computing (JLPC) workshop in Nice, June 2014, and in Barcelona July 2015.

- ANR SONGS plenary meetings in Lyon, June 2012, in Nice, January 2014, and in Nancy, January 2015.

Finally, we emphasize that our solution is not merely a proof of concept. This tool has been fully integrated into a runtime, and can thus be used for performance evaluation studies of both applications (block Application in Figure 1.1) and runtime (block Runtime in Figure 1.1). Some researchers have already benefited from this tool, while investigating different scheduling algorithms for the studied application [ABED<sup>+</sup>15].

#### 1.2 Thesis organization

The rest of this thesis is organized as follows: Chapter 2 briefly describes the evolution of the HPC applications and machines. It states the challenges of efficiently programming in such context and introduces dynamic task-based runtimes as a possible solution. Developing such programs is a process that requires constant empirical validation, which may be prohibitive for large computer platforms. Therefore, simulation can be used to overcome such limits. In Chapter 3 we present state of the art related to the tools for doing reproducible research and to the techniques for doing different types of simulation. Chapter 4 addresses the question of developing a lightweight and effective workflow for conducting experimental research on modern parallel computer systems in a reproducible way. Our approach builds on two well-known tools, Git and Org-mode, and enables to address, at least partially, issues such as running experiments, provenance tracking, experimental setup reconstruction or replicable analysis. In Chapter 5, we present in detail how we ported a dynamic task-based runtime on top of a simulator. We also present the models that are essential to obtain good performance predictions. In Chapter 6, we show that our approach allows for obtaining predictions accurate within a few percents for two dense linear algebra applications on wide range of hybrid machines, within a few seconds on a commodity laptop. We validate our models by systematically comparing traces acquired in simulation with those from native executions. In Chapter 7, we show that it is also possible to conduct faithful simulation of the behavior of an irregular fully-featured library both in terms of performance and memory on multicore architectures. Finally, in Chapter 8, we conclude with the contributions of our study, as well as its current limitation and future directions.

# Chapter 2

# Background

#### 2.1 Programming challenges for HPC application developers

#### 2.1.1 HPC applications

HPC applications are computer programs that require high-level computational power. They include a wide range of scientific applications from various domains, such as molecular modeling, weather forecast, quantum mechanics, simulation for engineering/finance/biology, etc. For example, the SPECFEM3D [PKL $^+$ 11] application simulates seismic wave propagation on local to regional scales using continuous Galerkin spectral-element method. Another good representative is BigDFT [Big12] that proposes a novel approach for electronic structure simulation based on the Daubechies wavelets formalism [GNG $^+$ 08, Nus82].

Executing these applications on a commodity machine is possible, but it could take many months or even years to complete, which is too long for any practical purposes. One CPU being insufficient for such high software requirements, supercomputers were introduced. These machines typically comprise thousands of nodes interconnected through high-speed networks and possibly equipped with accelerators. For example, SPECFEM3D was executed in February 2013 on the IBM BlueWaters machine using 693,600 cores.

To continue with the progress in their domains, researchers need their applications to focus on more details which makes applications more complex, hence the need for even more computational power. Nevertheless, with the technology we currently have at our disposal, this requirement is not easy to fulfill. Table 2.1 shows the list of the officially most powerful machines in the world in the last years (ranked first on the TOP500 list), where the multiplicity of solutions can be clearly observed. Indeed, the choice of components and methods with which future supercomputers will be constructed is constantly debated between HPC experts, many new technologies emerging and showing promising performance results.

Table 2.1: Ranked first on the TOP500 list, illustrating the diversity of architectures used to construct modern HPC platforms.

| Date    | Name       | CPU             | Accelerator | Interconnect |

|---------|------------|-----------------|-------------|--------------|

| 06/2013 | Tianhe-2   | Intel Xeon      | Xeon Phi    | TH Exp.2     |

| 11/2012 | Titan      | AMD Opteron     | Kepler      | Cray Gemini  |

| 06/2012 | Sequoia    | IBM Power BQC   | /           | Custom       |

| 11/2011 | K computer | Fujitsu SPARC64 | /           | Tofu         |

| 11/2010 | Tianhe-1A  | Intel Xeon      | Fermi       | Proprietary  |

#### 2.1.2 Different architectures used in HPC

In the previous decades, computing power of individual CPUs mainly improved thanks to the frequency increase, miniaturization, and hardware optimizations (cache hierarchy and aggressive cache policies, out-of-order execution, branch prediction, speculative execution, etc.). However, frequency increase and hardware optimizations are now facing hard limits and incur unacceptable power consumption. Power consumption grows more than quadratically with the growth of frequency. Additionally, speculative execution performs many useless operations and although they seem free in terms of scheduling on the CPU resources, in terms of power utilization they waste a lot of energy. If supercomputers are to achieve a predicted performance in the following years, the power efficiency of individual CPUs will have to be reduced by a factor of 30.

Several different approaches are envisioned. The first one attempts to improve the power consumption and increase parallelism of standard Intel/AMD processors currently used in HPC. This is performed through various frequency scaling techniques, increased number of cores per CPU, additional support for vectorized instructions, and many other very sophisticated methods. Still, performance improvements introduced by each new generation of such processors are becoming less and less significant. To achive desired GFLOPS per Watt ratio, radical changes in the approach are needed.

Another approach is to build on existing low-power CPUs commonly used in embedded systems and to try to improve their performance, as proposed by the European Mont-Blanc project [Mon]. The Mont-Blanc project aims at developing scalable and power efficient HPC platform based on low-power ARM technology. ARM (Advanced RISC Machine and, before that, the Acorn RISC Machine) processors are particularly designed for portable devices as they have very low electric power consumption. Nowadays, these CPUs are embedded on almost all mobile phones and personal digital assistants. However, such CPUs have very different characteristics and using them in HPC is not straightforward.

Yet another solution is based on the use of large Non-Uniform Memory Access (NUMA) machines. These machines consist of multiple multi-core processors, each containing its own part of the memory hierarchy, interconnected with the other processors through PCI bus. The time processor needs to access the data in the memory is non-uniform as it depends whether the data is stored in local or distant memory bank. These architectures can achieve great performance for certain applications, however programming them efficiently is very hard as data locality has to be carefully controlled. Since obtaining a solution with optimally distributed data for a single NUMA machine is already a challenge, constructing a supercomputer with multiple nodes based on this architecture is even harder. With the current system this approach would be extremely complex to program, thus it is unlikely to scale well.