# Contributions of hybrid architectures to depth imaging: a CPU, APU and GPU comparative study

Issam Said

## ▶ To cite this version:

Issam Said. Contributions of hybrid architectures to depth imaging: a CPU, APU and GPU comparative study. Hardware Architecture [cs.AR]. Université Pierre et Marie Curie - Paris VI, 2015. English. NNT: 2015PA066531. tel-01248522v2

## HAL Id: tel-01248522 https://theses.hal.science/tel-01248522v2

Submitted on 20 May 2016  $\,$

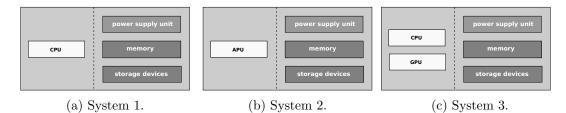

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE l'UNIVERSITÉ PIERRE ET MARIE CURIE

### spécialité Informatique

École doctorale Informatique, Télécommunications et Électronique (Paris)

présentée et soutenue publiquement par

## Issam SAID

pour obtenir le grade de

### DOCTEUR en SCIENCES de l'UNIVERSITÉ PIERRE ET MARIE CURIE

# Apports des architectures hybrides à l'imagerie profondeur : étude comparative entre CPU, APU et GPU

Thèse dirigée par Jean-Luc LAMOTTE et Pierre FORTIN

#### soutenue le Lundi 21 Décembre 2015

| après avis des <b>rapporteur</b><br>M. François BODIN | s<br>Professeur, Université de Rennes 1                          |

|-------------------------------------------------------|------------------------------------------------------------------|

| M. Christophe Calvin                                  | Chef de projet, CEA                                              |

| devant le <b>jury</b> composé de                      |                                                                  |

| M. François Bodin                                     | Professeur, Université de Rennes 1                               |

| M. Henri Calandra                                     | Expert en imagerie profondeur et calcul haute performance, Total |

| M. Christophe Calvin                                  | Chef de projet, CEA                                              |

| M. Pierre Fortin                                      | Maître de conférences, Université Pierre et Marie Curie          |

| M. Lionel LACASSAGNE                                  | Professeur, Université Pierre et Marie Curie                     |

| M. Jean-Luc LAMOTTE                                   | Professeur, Université Pierre et Marie Curie                     |

| M. Mike Mantor                                        | Senior Fellow Architect, AMD                                     |

| M. Stéphane VIALLE                                    | Professeur, SUPELEC campus de Metz                               |

"If I have seen further it is by standing on the shoulders of Giants."

— Isaac Newton

## Acknowledgements

Foremost, I would like to express my deepest thanks to my two directors, *Pr. Jean-Luc Lamotte* and *Dr. Pierre Fortin*. Their patience, encouragement, and immense knowledge were key motivations throughout my Ph.D. I thank them for having instructed me, for having guided me to compose this thesis, and for having steered me to the end. I thank them for having cheerfully assisted me in moments of frustration and of doubt. I would like to gratefully thank *Henri Calandra* for his trust, valuable recommendations, insights and useful discussions. He accompanied me throughout this adventure, I look forward to the next one.

I have been privileged and honored to have had my work been reviewed by Pr. François Bodin and Dr. Christophe Calvin. I am indebted to them for having taken the time out of their busy schedules, and for having spent efforts to go through, to give insightful comments, and to correct the ideas shared in this dissertation. I also thank the rest of the committee members: Pr. Lionel Lacassagne, M. Mike Mantor and Pr. Stéphane Vialle for having accepted to examine this dissertation and to give valuable feedbacks.

This work was a close partnership between Total, AMD, CAPS and Lip6. I would like to extend my gratitude to Total for funding this project. AMD is acknowledged for providing the hardware which was used at the heart of this work. CAPS is kindly acknowledged for the technical support and the sophisticated skills.

Immeasurable appreciation and deepest gratitude for the help and support are extended to the following persons, who in one way or another, have contributed in making this study possible. Bruno Conche for his endless support and logistic help, and more importantly for his energy that he did not spare in order to put this project together, without him it would not have been a success. Bruno Stefanizzi for having pointed me to the right way whenever I had questions or needed support from AMD. Laurent Morichetti, Joshua Mora and Robert Engel, each of whom had made each journey of mine to the AMD Sunnyvale campus, a pleasant experience. I thank them for sharing their experiences with me, and for finding answers to all of my questions. Greq Stoner and *Gregory Rodgers*, for the helpful discussions and the valuable information about the AMD hardware and software stack roadmaps. Terrence Liao and Rached Abdelkhalek, for their precious advices and for the brain storming sessions during my trips to Pau, France. Harry Zong, Jing Wen, Donny Cooper, Matthew Bettinger and Russell Jones for their precious help in setting up a remote work environment. Romain Dolbeau, for having put his rich technical expertise at my disposal. My fellow colleagues in the PE-QUAN team with whom I have shared memorable moments throughout this experience. The administrative staff of the PEQUAN team is also kindly acknowledged for having taken care of my professional trips.

On a more personal note, words cannot express my gratitude for my parents, *Khalifa* and *Moufida*, the reason of what I become today thank you for your great support and continuous care. I profusely thank my brothers *Bilel* and *Zied* for being there for me no matter what. *Asma*, thank you for being supportive and for the great moments we spent together discussing this project. *Rached*, thank you for your hospitality, for the time, for the trips and for the laughs and fears we lived together. *Saber*, thank you immensely for your wise thoughtful advices, and for the numerous funny moments we spent together. I thank my cousins and friends (*Khaled, Yasser, Rafik, Haithem, Fethi*,

Mohammed, Elkhal, John, Erick, Nefili, Layla, Justyna, Chris, Daniel, Jeaven, Binomi, Sahma, Saif, Sana, Sari, Hanen, and the list goes on) for the precious moments of joy that were much needed during this journey. Moktar and Souad, I owe you a deep sense of gratitude for you unconditional love and attention. Ludmila, Igor, Anna, Beji, and Lorita thank you for your never ending support, and more importantly for the initiation to the Russian "banya". To my wonderful wife Tatjana, whose sacrificial care for me, her quiet patience, her tolerance to my occasional vulgar moods, and her unwavering love made it possible for me to finish this work, I express my genuine appreciation. Finally, I thank my son Arsen, a treasure from the Lord that was offered to me and to my wife in the middle of this adventure, and who was the source of my inspiration and of my greatest happiness.

# Contents

| С | Contents |        |                                                               |    |

|---|----------|--------|---------------------------------------------------------------|----|

| 1 | Intr     | roduct | on                                                            | 1  |

| Ι | Sta      | te of  | the art                                                       | 5  |

| 2 | Geo      |        | s and seismic applications                                    | 7  |

|   | 2.1      | Introd | uction to seismic exploration                                 | 8  |

|   |          | 2.1.1  | Seismic acquisition                                           | 9  |

|   |          | 2.1.2  | Seismic processing                                            | 11 |

|   |          | 2.1.3  | Seismic interpretation                                        | 14 |

|   | 2.2      | Seismi | c migrations and Reverse Time Migration (RTM)                 | 14 |

|   |          | 2.2.1  | Description and overview of migration methods                 | 14 |

|   |          | 2.2.2  | Reverse Time Migration                                        | 16 |

|   | 2.3      |        | rical methods for the wave propagation phenomena              | 18 |

|   |          | 2.3.1  | The wave equation                                             | 19 |

|   |          |        | 2.3.1.1 Seismic waves and propagation media                   | 19 |

|   |          |        | 2.3.1.2 The elastic wave equation                             | 19 |

|   |          |        | 2.3.1.3 The acoustic wave equation                            | 21 |

|   |          | 2.3.2  | Numerical methods for wave propagation                        | 22 |

|   |          |        | 2.3.2.1 Integral methods                                      | 22 |

|   |          |        | 2.3.2.2 Asymptotic methods                                    | 23 |

|   |          |        | 2.3.2.3 Direct methods                                        | 23 |

|   |          |        | 2.3.2.3.1 Pseudo-Spectral Methods                             | 23 |

|   |          |        | 2.3.2.3.2 Finite Difference Methods                           | 23 |

|   |          | 0.0.0  | 2.3.2.3.3 Finite Element Methods                              | 24 |

|   |          | 2.3.3  | Application to the acoustic wave equation                     | 25 |

|   |          |        | 2.3.3.1 Numerical approximation                               | 25 |

|   |          |        | 2.3.3.2 Stability analysis and CFL                            |    |

|   |          |        | 2.3.3.3 Boundary conditions                                   | 28 |

| 3 | Hig      | h perf | ormance computing                                             | 29 |

|   | 3.1      | Overv  | iew of HPC hardware architectures                             | 30 |

|   |          | 3.1.1  | Central Processing Unit: more and more cores                  | 30 |

|   |          | 3.1.2  | Hardware accelerators: the other chips for computing          | 33 |

|   |          | 3.1.3  | Towards the fusion of CPUs and accelerators: the emergence of |    |

|   |          |        | the Accelerated Processing Unit                               | 36 |

|   | 3.2 | Progr   | amming r           | nodels in HPC                                                   | 41        |

|---|-----|---------|--------------------|-----------------------------------------------------------------|-----------|

|   |     | 3.2.1   | Dedicat            | ed programming languages for HPC                                | 41        |

|   |     |         | 3.2.1.1            | Overview                                                        | 41        |

|   |     |         | 3.2.1.2            | The OpenCL programming model                                    | 43        |

|   |     | 3.2.2   | Directiv           | e-based compilers and language extensions                       | 45        |

|   | 3.3 | Power   | consump            | tion in HPC and the power wall                                  | 45        |

| 4 | 0   |         | of a cool          | erated seismic applications                                     | 49        |

| 4 | 4.1 |         |                    | ations                                                          |           |

|   | 4.1 |         | · ·                | igration                                                        |           |

|   | 4.2 | 4.2.1   |                    | on of RTM algorithms                                            |           |

|   |     | 4.2.1   |                    | eld reconstruction methods                                      |           |

|   |     | 4.2.2   |                    |                                                                 |           |

|   |     |         | 4.2.2.1            | Re-computation of the forward wavefield                         |           |

|   |     |         | 4.2.2.2            | Storing all the forward wavefield                               |           |

|   |     |         | 4.2.2.3            | Selective wavefield storage (linear checkpointing)              |           |

|   |     |         | 4.2.2.4            | Checkpointing                                                   |           |

|   |     |         | 4.2.2.5            | Boundaries storage                                              |           |

|   |     |         | 4.2.2.6            | Random boundary condition                                       |           |

|   |     | 4.2.3   |                    | n multi-cores and hardware accelerators                         |           |

|   |     |         | 4.2.3.1            | RTM on multi-core CPUs                                          |           |

|   |     |         | 4.2.3.2            | RTM on GPUs                                                     | 58        |

|   |     |         | 4.2.3.3            | RTM on other accelerators                                       | 59        |

|   | 4.3 | Close   | to seismi          | cs workflows                                                    | 61        |

| 5 | The | esis po | sition an          | nd contributions                                                | 63        |

|   | 5.1 | Positi  | on of the          | study                                                           | 63        |

|   | 5.2 | Contr   | ibutions           |                                                                 | 65        |

|   | 5.3 | Hardy   | vare and s         | seismic material configurations                                 | 67        |

|   |     | 5.3.1   | The har            | dware configuration                                             | 68        |

|   |     | 5.3.2   | The nur            | nerical configurations of the seismic materials                 | 69        |

|   |     |         | 5.3.2.1            | The seismic source                                              | 69        |

|   |     |         | 5.3.2.2            | The velocity model and the compute grids $\ldots \ldots \ldots$ | 69        |

|   |     |         |                    |                                                                 |           |

| Π | Se  | ismic   | applica            | tions on novel hybrid architectures                             | <b>73</b> |

| 6 | Eva | luatio  | n of the           | Accelerated Processing Unit (APU)                               | 75        |

|   | 6.1 |         |                    | t strategies                                                    | 76        |

|   | 6.2 |         | -                  | nchmarks                                                        |           |

|   |     | 6.2.1   |                    | multiplication                                                  |           |

|   |     | 0.2.1   | 6.2.1.1            | Implementation details                                          |           |

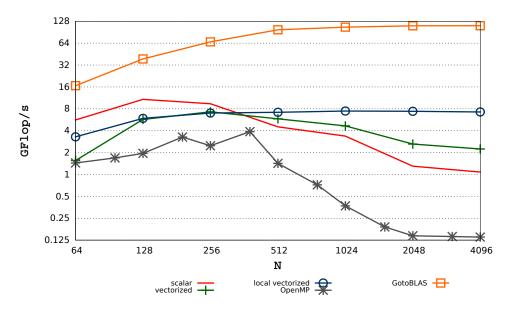

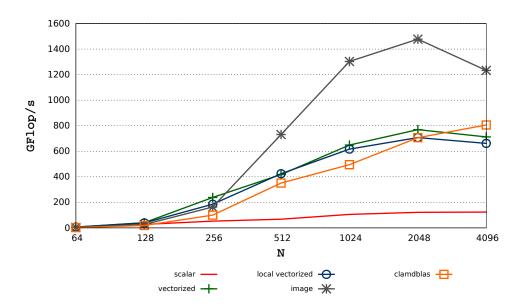

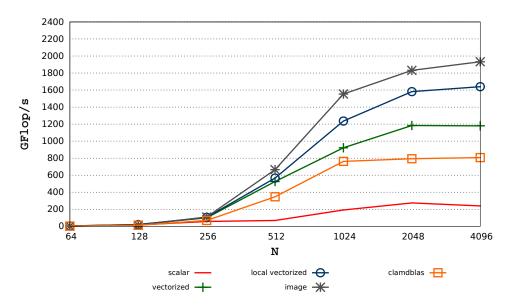

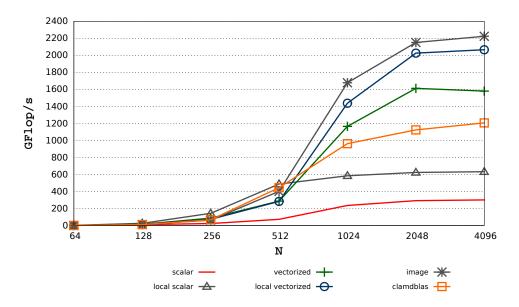

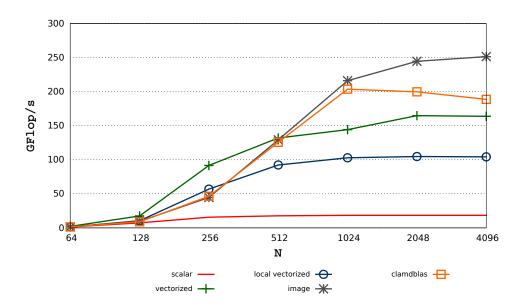

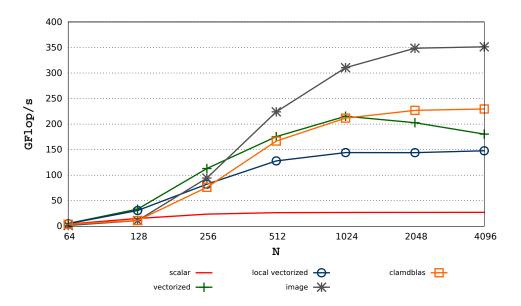

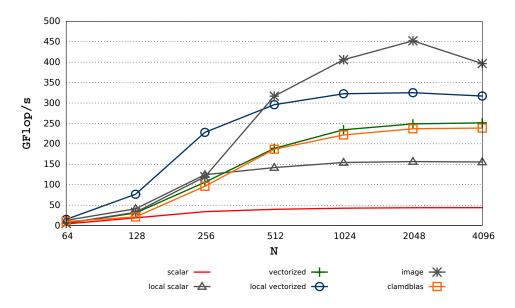

|   |     |         | 6.2.1.2            | Devices performance                                             |           |

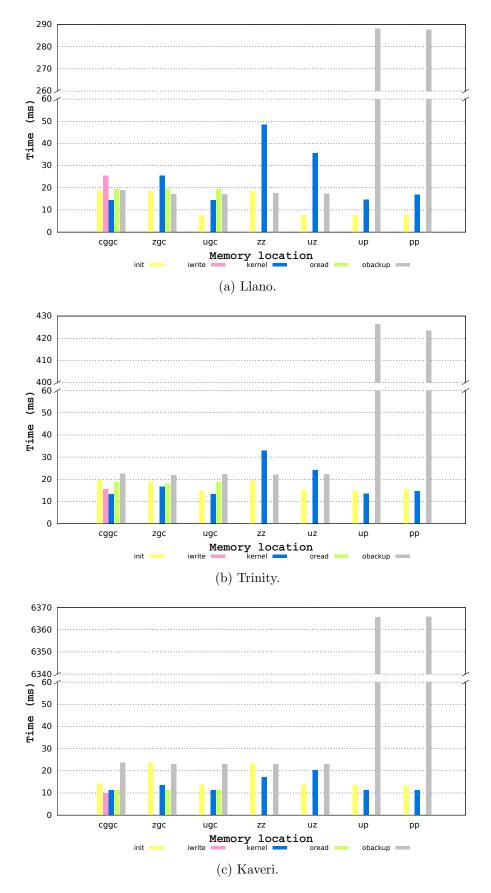

|   |     |         | 6.2.1.2<br>6.2.1.3 | Impact of data placement strategies on performance              |           |

|   |     |         | 6.2.1.3<br>6.2.1.4 | Performance comparison                                          |           |

|   |     | 6.2.2   |                    | ifference stencil                                               |           |

|   |     | 0.2.2   | 6.2.2.1            | Implementation details                                          |           |

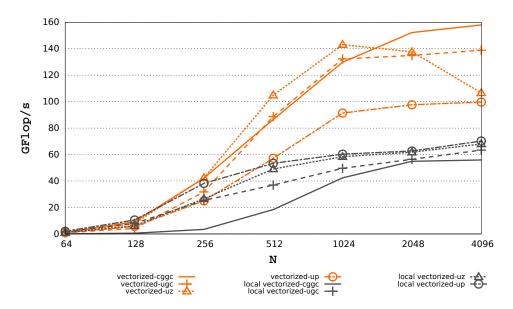

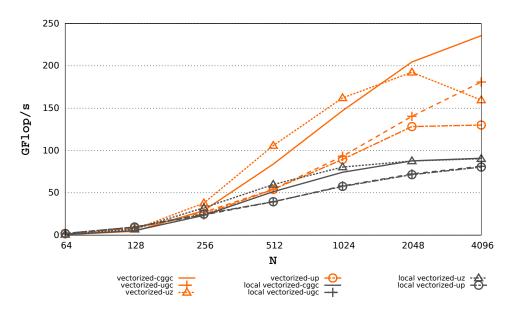

|   |     |         | 6.2.2.1<br>6.2.2.2 | Devices performance                                             |           |

|   |     |         | 6.2.2.2<br>6.2.2.3 |                                                                 |           |

|   |     |         | 0.2.2.3            | Impact of data placement strategies on performance              | 94        |

|   |      | 6.2.2.4 Performance comparison                                          | . 96  |

|---|------|-------------------------------------------------------------------------|-------|

|   | 6.3  | Power consumption aware benchmarks                                      | . 97  |

|   |      | 6.3.1 Power measurement tutorial                                        | . 97  |

|   |      | 6.3.1.1 Metrics for power efficiency                                    | . 98  |

|   |      | 6.3.1.2 Proposed methodology                                            | . 98  |

|   |      | 6.3.1.3 Hardware configuration                                          | . 101 |

|   |      | 6.3.1.4 Choice of applications and benchmarks                           | . 102 |

|   |      | 6.3.2 Power efficiency of the applicative benchmarks                    | . 102 |

|   | 6.4  | Hybrid utilization of the APU: finite difference stencil as an example  |       |

|   |      | 6.4.1 Hybrid strategy for the APU                                       | . 104 |

|   |      | 6.4.2 Deployment on CPU or on integrated GPU                            | . 106 |

|   |      | 6.4.3 Hybrid deployment                                                 | . 109 |

|   | 6.5  | Directive based programming on the APU: finite difference stencil as an |       |

|   |      | example                                                                 |       |

|   |      | 6.5.1 OpenACC implementation details                                    |       |

|   |      | 6.5.2 OpenACC performance numbers and comparison with OpenCL .          | . 115 |

| 7 | Seis | smic applications on one compute node                                   | 117   |

|   | 7.1  | Seismic modeling                                                        |       |

|   |      | 7.1.1 Description of the algorithm                                      |       |

|   |      | 7.1.2 Accelerating the seismic modeling using OpenCL                    |       |

|   |      | 7.1.3 Performance and power efficiency                                  |       |

|   |      | 7.1.4 OpenACC evaluation and comparison with OpenCL                     |       |

|   | 7.2  | Seismic migration                                                       |       |

|   |      | 7.2.1 Description of the algorithm                                      |       |

|   |      | 7.2.2 Accelerating the seismic migration using OpenCL                   |       |

|   |      | 7.2.3 Performance and power efficiency                                  |       |

|   |      | 7.2.4 OpenACC evaluation and comparison with OpenCL                     |       |

|   | 7.3  | Conclusion                                                              | . 130 |

| 8 | Lar  | ge scale seismic applications on CPU/APU/GPU clusters                   | 133   |

|   | 8.1  | Large scale considerations                                              | . 134 |

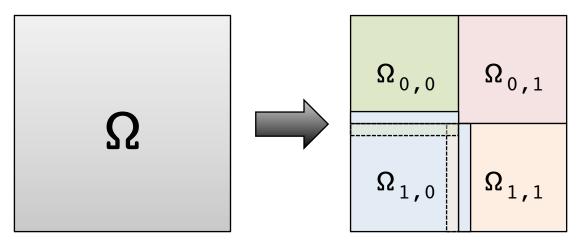

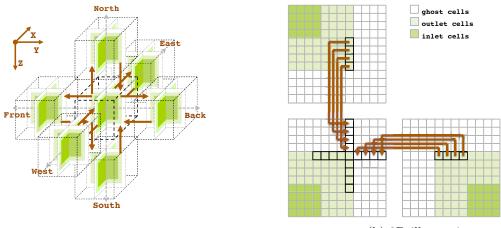

|   |      | 8.1.1 Domain decomposition                                              | . 134 |

|   |      | 8.1.2 Boundary conditions                                               | . 140 |

|   | 8.2  | Seismic modeling                                                        | . 141 |

|   |      | 8.2.1 Deployment on CPU clusters: performance issues and proposed       |       |

|   |      | $\operatorname{solutions}$                                              |       |

|   |      | 8.2.1.1 Implementation details                                          |       |

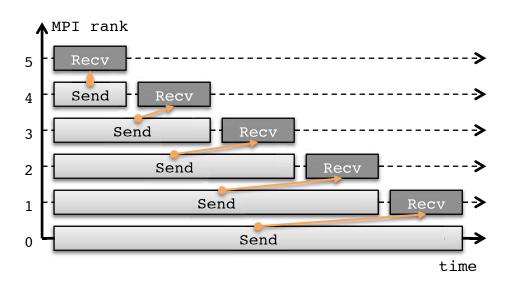

|   |      | 8.2.1.2 Communications and related issues                               |       |

|   |      | 8.2.1.3 Load balancing                                                  |       |

|   |      | 8.2.1.4 Communication-computation overlap                               |       |

|   |      | 8.2.1.4.1 Problems of non-blocking MPI communications                   |       |

|   |      | 8.2.1.4.2 Proposed solutions                                            |       |

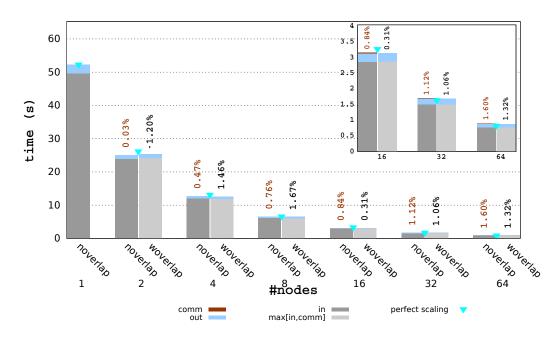

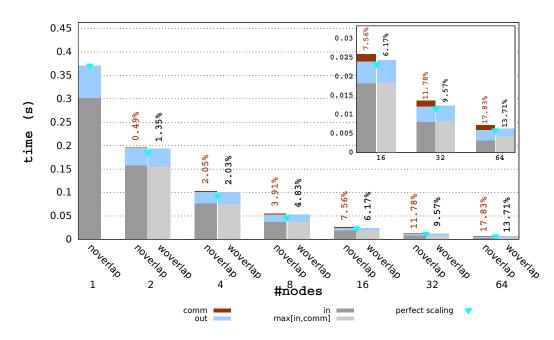

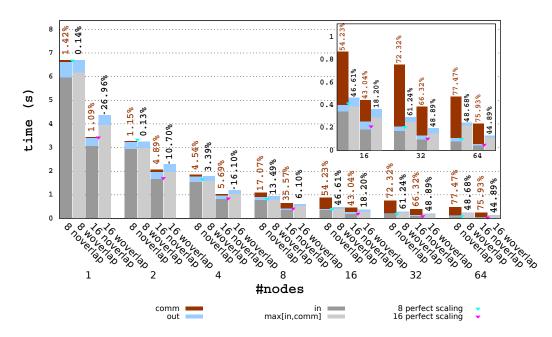

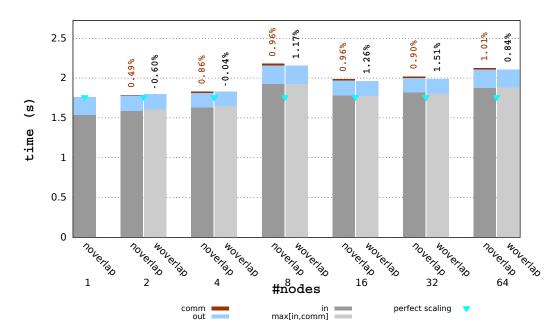

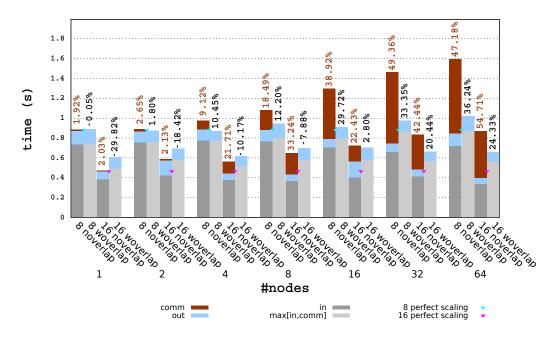

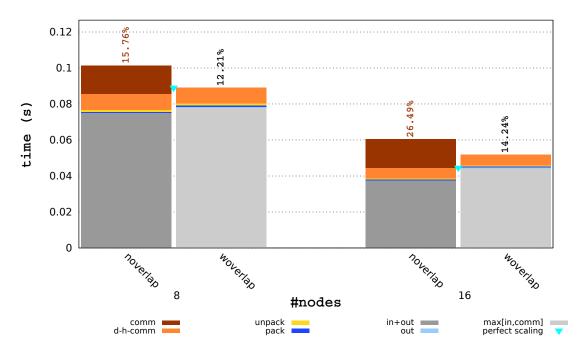

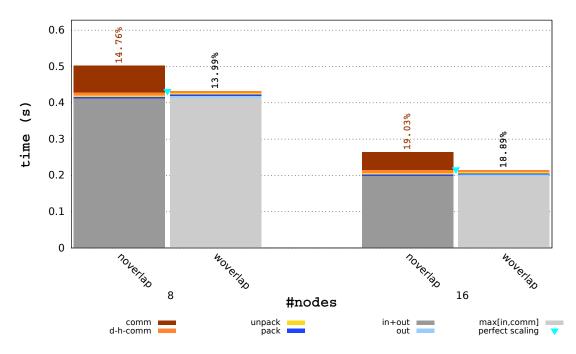

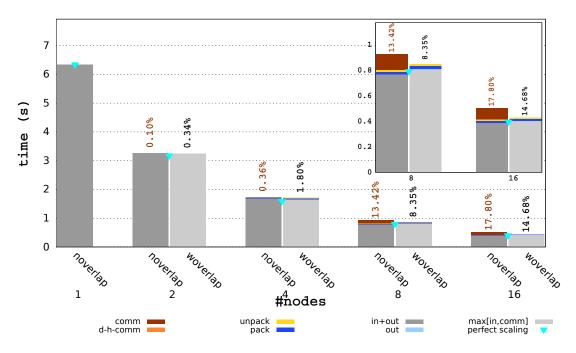

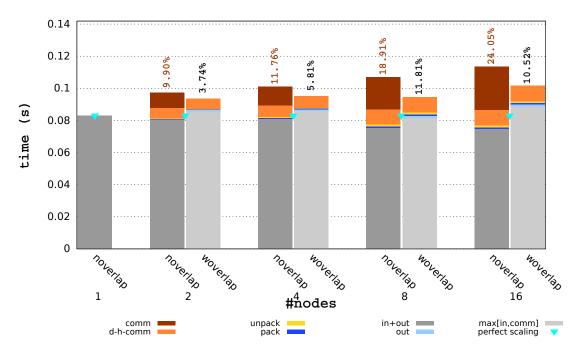

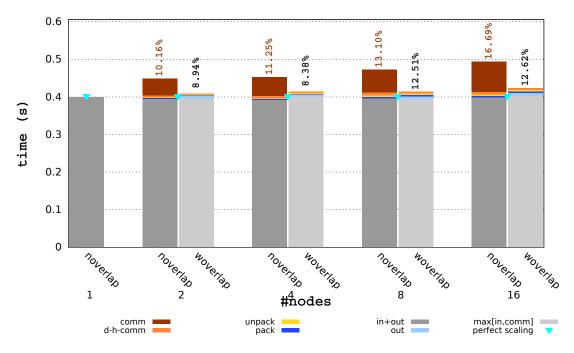

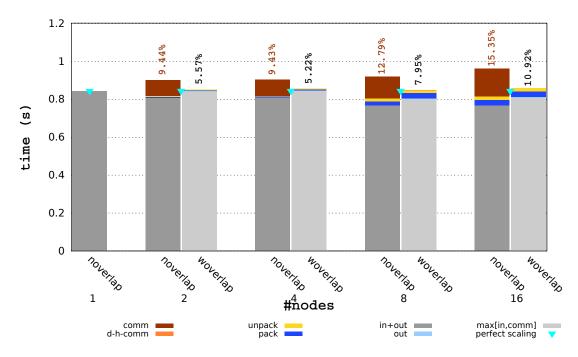

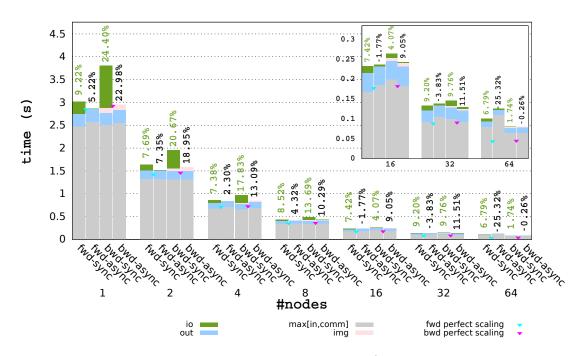

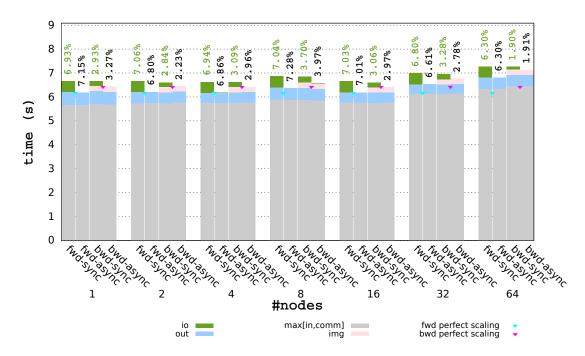

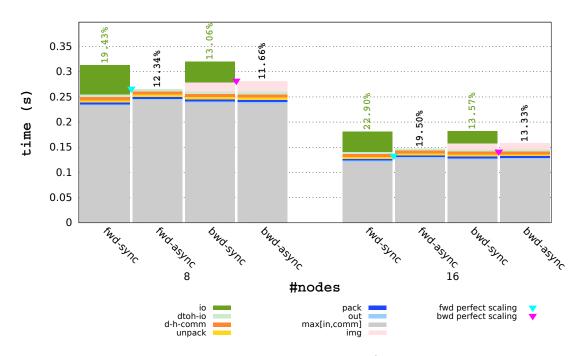

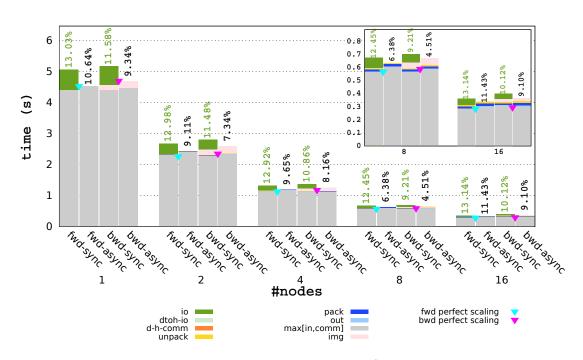

|   |      | 8.2.1.4.3 Performance results                                           |       |

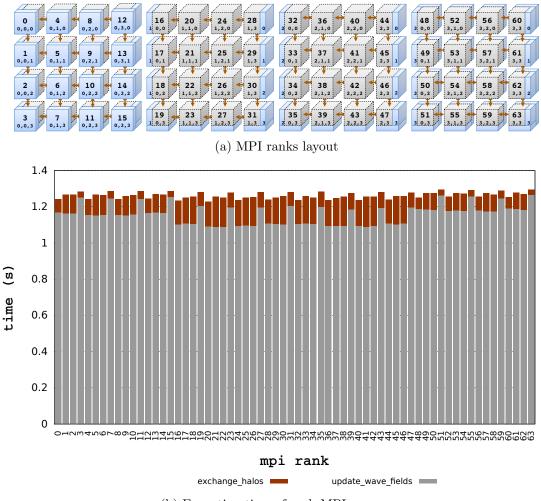

|   |      | 8.2.2 Deployment on hardware accelerators                               |       |

|   |      | 8.2.2.1 Implementation details                                          |       |

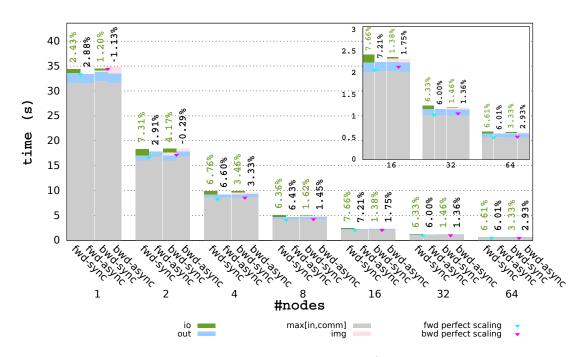

|   |      | 8.2.2.2 Performance results                                             | . 170 |

|    |                     |        | 8.2.2.2.1 Strong scaling tests $\ldots \ldots \ldots \ldots \ldots \ldots 172$                                                                                      |  |  |

|----|---------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    |                     |        | 8.2.2.2.2 Weak scaling tests $\ldots \ldots \ldots \ldots \ldots \ldots 174$                                                                                        |  |  |

|    | 8.3                 | Seismi | c migration                                                                                                                                                         |  |  |

|    |                     | 8.3.1  | Deployment on CPU clusters                                                                                                                                          |  |  |

|    |                     |        | 8.3.1.1 Implementation details                                                                                                                                      |  |  |

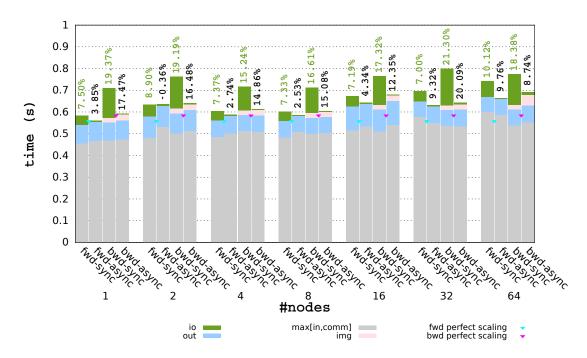

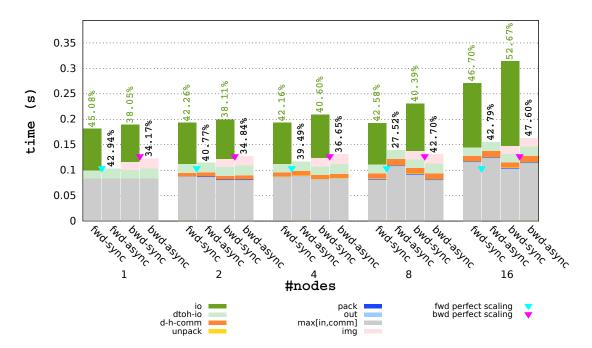

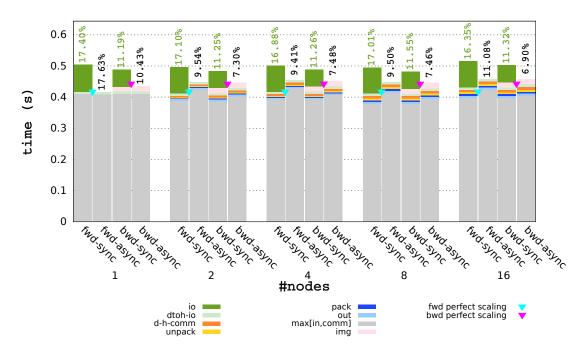

|    |                     |        | 8.3.1.2 Performance results                                                                                                                                         |  |  |

|    |                     |        | 8.3.1.2.1 Strong scaling tests $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 180$                                                                        |  |  |

|    |                     |        | 8.3.1.2.2 Weak scaling tests $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 182$                                                                   |  |  |

|    |                     | 8.3.2  | Deployment on hardware accelerators                                                                                                                                 |  |  |

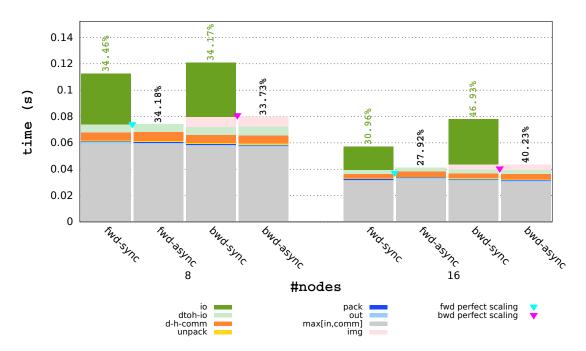

|    |                     |        | 8.3.2.1 Implementation details                                                                                                                                      |  |  |

|    |                     |        | 8.3.2.2 Performance results                                                                                                                                         |  |  |

|    |                     |        | 8.3.2.2.1 Strong scaling tests $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 186$                                                                        |  |  |

|    |                     |        | 8.3.2.2.2 Weak scaling tests $\ldots \ldots \ldots$ |  |  |

|    |                     | 8.3.3  | Performance comparison                                                                                                                                              |  |  |

|    |                     |        | 8.3.3.1 Comparison based on measured results                                                                                                                        |  |  |

|    |                     |        | 8.3.3.2 Comparison based on performance projection 194                                                                                                              |  |  |

|    | 8.4                 | Conclu | $1$ sion $\dots \dots \dots$                                        |  |  |

| 9  | Cor                 | clusio | as and perspectives 199                                                                                                                                             |  |  |

|    | 9.1                 | Conclu | sions                                                                                                                                                               |  |  |

|    | 9.2                 | Perspe | ctives                                                                                                                                                              |  |  |

| Bi | ibliog              | graphy | 219                                                                                                                                                                 |  |  |

| Li | List of Figures 221 |        |                                                                                                                                                                     |  |  |

| Li | st of               | Tables | 229                                                                                                                                                                 |  |  |

| Α  | List                | of pu  | plications 233                                                                                                                                                      |  |  |

This thesis is dedicated to all of my family for their love, endless support and encouragement. To my cousin Marwen (1993-2014). To my grandma Khadija (1930-2013).

## Chapter 1

# Introduction

For more than 150 years, after the world's first commercial extraction of rock-oil by *James Miller Williams* in *Oil Springs (Ontario, Canada)* in 1858, exploration and mining companies worldwide face the challenge of finding new oil reserves in order to satisfy an ever-growing energy demand. The oil discovery rate had continued to grow, and had peaked in the 1960s. Since then, it has declined with each passing decade. The giant oilfields — a giant oilfield is defined as containing more than 500 million barrels of ultimately recoverable oil — are less and less discovered and their production is dropping throughout the years, as skewed in table 1.1. In sharp contrast, the average age of the world's 19 largest giant fields is almost 70 years, and 70% of the daily oil supply comes from oilfields that were discovered prior to 1970 [199].

Today, most of the shallow and easily accessible basins have already been found. The alternative way to find new deposits is to explore much deeper below the surface in hostile locations and extreme or challenging environments (such as deepwaters, frigid zones and hot dusty deserts), where accessing the explored area is often difficult, and where the complex geologic structures make it harsh to prospect the subsurface and to extract the hydrocarbon energy stored in the rocks. Therefore, the cost of drilling in these complex topographies is rising as the number of major new discoveries is decreasing. As a matter of fact, the cost of drilling an onshore well is about \$3.5 to \$4.5 million, that of an offshore well ranges between \$23 and \$68 million, while the cost of deepwater drilling, in a complex geology for example, can grow up to \$115 million [36].

To face this challenge, Oil and Gas (O&G) firms are turning to modern exploration technologies that includes sophisticated survey techniques and cutting-edge science in

| date of discovery | number of discoveries | average production per field (MMbbls) |

|-------------------|-----------------------|---------------------------------------|

| pre-1950s         | 19                    | 557                                   |

| 1950s             | 17                    | 339                                   |

| 1960s             | 29                    | 242                                   |

| 1970s             | 24                    | 236                                   |

| 1980s             | 15                    | 176                                   |

| 1990s             | 11                    | 126                                   |

TABLE 1.1: Statistics about the discoveries of giant oilfields until the 1990s, in terms of number and current production in Million Barrels (MMbbls). From [199].

order to glean the location and character of crude oil deposits while reducing the uncertainty of exploration, and thus improving drilling success rates. Indeed, the industry is developing new seismic acquisition techniques and new imaging technologies that provide vital information needed before drilling. More importantly, seismic imaging technologies help to remotely identify oil accumulations trapped tens of kilometers underground and undersea. The seismic acquisition is the process of sending acoustic waves through the subsurface and collecting the echoes reflected by the rock layers, and *seismic imaging* (or *depth imaging*) delineates the subsurface geologic structures from the collected data. Amongst the seismic imaging techniques, *Reverse Time Migration* (RTM) is by far the most famous computer based technique used in the industry because of the quality and integrity of the images it provides. O&G companies trust RTM with crucial decisions on drilling investments. However, RTM consumes prodigious amounts of computing power across extremely large datasets (tens of terabytes of data), which requires large memory capacities and efficient storage solutions. Throughout the last decades, theses heavy requirements have somewhat hindered its practical success.

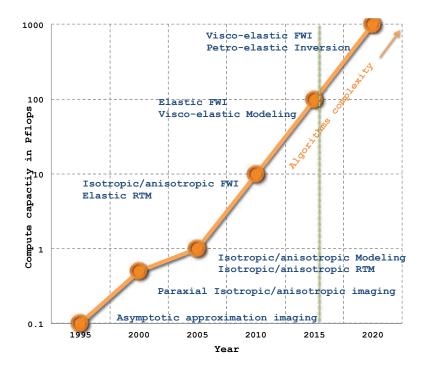

Given the enormous amounts of data that must be processed, analyzed, and visualized in the least amount of time, O&G organizations are today leveraging High Performance Computing (HPC) technologies for seismic imaging, to stay ahead. In particular, organizations are deploying ever more powerful and highly honed computational workflows on a variety of HPC facilities. With the advances in processor technology over the past few years, today's HPC clusters are capable of providing petaflops<sup>1</sup> of compute capabilities and are slowly heading to the exascale era<sup>2</sup>, making them an appropriate match for the challenges in the O&G industry. Today, it is not unusual for O&G companies to rely on clusters built around the latest multicore CPUs, with petabytes of storage and with the fastest-available network infrastructures, in order to spread workloads across an array of compute nodes [57, 145, 172]. Additionally, O&G exploration firms are trying to accelerate seismic processing workflows, such as RTM, by optimizing their increasingly sophisticated algorithms to take advantage of hardware accelerators, such as graphic processing units (GPUs) [23, 63, 147], field-programmable gate arrays (FPGAs) [63] and the Intel Xeon Phi processors [84]. GPUs are the most widely deployed, given the massively parallel nature of their architecture and hardware design which makes them a good fit for RTM (and similar algorithms such as Kirchhoff migration) workloads.

However, the deployment of seismic workloads on high-end CPU clusters and GPU based solutions have shown several restrictions in terms of performance, memory capacities and power consumption. The use of GPU technologies also introduces additional technical challenges to the table. Adapting seismic imaging applications to GPUs requires mastering novel programming models such as CUDA and OpenCL which may be considered as a difficult task for scientists (especially geophysicists) whose primary concern is introducing more physics and accuracy to the algorithms. Besides, unlike mainstream processors, a GPU acts like a co-processor in a system, and is interconnected to the main CPU via a PCI Express bus (gen 2 or gen 3). This implies particular manipulations, in terms of computations and memory management.

Recently, AMD has proposed the APU technology: a combination of a CPU and an integrated GPU on the same silicon die, and in a small power envelope. With the APUs,

<sup>&</sup>lt;sup>1</sup>A petaflops is 10<sup>15</sup> Flop/s, a Flop/s is a measure of computer performance that corresponds to the number of floating point operations a processor is capable to carry out per second.

<sup>&</sup>lt;sup>2</sup>When HPC facilities will be able to achieve a performance at the order of exaflops  $(10^{18} \text{ Flop/s})$ .

AMD has introduced a new on-chip interconnect that puts together the CPU and GPU featuring a unified memory between the CPU and the GPU. Throughout this work, we therefore assess the relevance of APUs in the seismic workloads arena. By means of memory, applicative and power efficiency benchmarks as well as a CPU/APU/GPU comparative study on both the node level and the large scale level, we try to find out whether the APU technology can deliver a compromise solution, in terms of application performance, power efficiency and programming complexity, that is profitable and valuable in an O&G exploration context.

The first part of the dissertation is dedicated to a state of the art review. We start in chapter 2, by introducing the different stages of the modern seismic exploration chain. We emphasize the workflow of the seismic migrations, that of the RTM in particular. Then we present the mathematical tools and numerical methods that are used in a seismic exploration context. In chapter 3, we summarize the current advances in HPC in terms of hardware architectures, programming models and power consumption. We follow up in chapter 4, by giving an overview of state-of-the-art accelerated implementations of the stencil computations (an important building block of the seismic applications), as well as state-of-the-art accelerated RTM implementations and similar workflows.

The chapter 5 is a detailed description of the position of this thesis as well as a presentation of our contributions.

We follow up with the second part of this thesis, which is dedicated to our contributions. In chapter 6, we start with a thorough evaluation of the APU technology. The evaluation includes the assessment of the new memory model, a performance study and comparison between CPU, GPU and APU by means of applicative benchmarks, a power efficiency evaluation (where we describe our power measurement methodology), the feasibility of the hybrid utilization (CPU+GPU) of APUs, and a performance study of directive based implementations of the stencil computations. Then in chapter 7, we study the performance, power efficiency and the programmability of two seismic applications at the node level: the seismic modeling, which is considered as the first step of the seismic migration workflow, and the RTM. We conduct a performance and power efficiency comparisons between the CPU, GPU and APU to assess the relevance of APUs in this context. In the chapter 8, we extend our study to the large scale implementations of the seismic modeling and of the seismic migration (RTM) on a CPU cluster, on a GPU cluster and on an APU cluster. We try throughout this chapter to find out whether the RTM implementation on the APU cluster might be a valuable solution that addresses the limiting factors on the CPU and GPU based solutions. Finally, we conclude in chapter 9 with a mention to possible perspectives.

# Part I

# State of the art

# Chapter 2

# Geophysics and seismic applications

#### Contents

| 2.1 | Intro | duction to seismic exploration                    | 8         |

|-----|-------|---------------------------------------------------|-----------|

| 2   | 2.1.1 | Seismic acquisition                               | 9         |

| 2   | 2.1.2 | Seismic processing                                | 11        |

| 2   | 2.1.3 | Seismic interpretation                            | 14        |

| 2.2 | Seisn | nic migrations and Reverse Time Migration (RTM)   | <b>14</b> |

| 2   | 2.2.1 | Description and overview of migration methods     | 14        |

| 2   | 2.2.2 | Reverse Time Migration                            | 16        |

| 2.3 | Num   | erical methods for the wave propagation phenomena | 18        |

| 2   | 2.3.1 | The wave equation                                 | 19        |

| 2   | 2.3.2 | Numerical methods for wave propagation            | 22        |

| 2   | 2.3.3 | Application to the acoustic wave equation         | 25        |

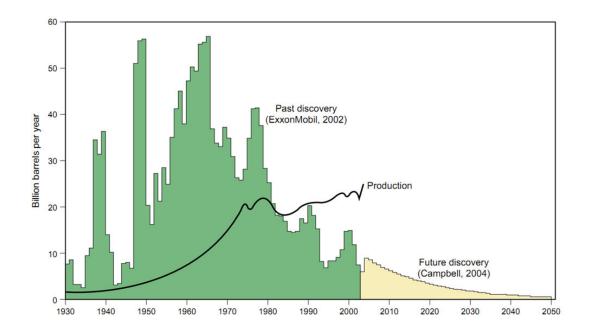

Hydrocarbon exploration remains very challenging for the mainstream O&G industry. Substantial efforts are put to maximize the production of discovered reservoirs and explore new ones, albeit very rare (see figure 2.1). The industry relies on geophysics and more specifically on *seismic exploration* to transform vibrations, induced in the earth from various sources, into interpretable subsurface pictures and models. The pressing need for sharper and more informative structural images pushes the industry to permanently innovate and tackle a host of grand challenges in terms of seismic technology: to identify lithology (rock types), to infer petrophysical properties, to estimate the fluid content etc.

In this chapter, we present a brief overview of the basic goals and procedures for seismic exploration. We define the seismic migration operation since it is considered as the main imaging tool for petroleum deposits mapping, and we emphasize on the *Reverse Time Migration* (RTM) which is being increasingly used by the industry at the heart of a wide range of seismic imaging applications. We also review some fundamental mathematics associated with the wave propagation phenomenon, being the essential and mandatory tool to help understand the physics behind the seismic exploration.

FIGURE 2.1: Oil discoveries and oil production, 1930 to 2050. Extracted from [25].

### 2.1 Introduction to seismic exploration

The principal goal of seismic exploration, more commonly referred to as exploration geophysics or also as reflection seismology and often abbreviated as seismic, is to obtain structural subsurface information from seismic data i.e. data collected by recording elastic or acoustic wave motion on Earth. Seismic is one of the geophysical methods, summarized in table 2.1, used in hydrocarbon exploration. The primary environments for seismic exploration are land (onshore), and marine (offshore). The land environment covers almost every type of terrain that exists on Earth, each bringing its own logistical problems. That includes jungle, desert, forest etc. The marine environment consists essentially of seas and oceans. However, there are also transition zones (TZ), i.e. the areas where the land meets the sea such as rivers, presenting unique challenges because the water is too shallow for large seismic vessels but too deep for the use of traditional methods of exploration on land.

| Method          | Measured parameter                                                            | Physical property                                        |

|-----------------|-------------------------------------------------------------------------------|----------------------------------------------------------|

| Gravity         | Spatial variations in the strength of<br>the gravitational field of the Earth | Density                                                  |

| Magnetic        | Spatial variations in the strength of the geomagnetic field                   | Magnetic susceptibility<br>and remanence                 |

| Electromagnetic | Response to electromagnetic radia-<br>tion                                    | Electric conductiv-<br>ity/resistivity and<br>inductance |

| Seismic         | Travel times of reflected/refracted seismic waves                             | Seismic velocity (and density)                           |

TABLE 2.1: A summary of the geophysical methods used in hydrocarbon exploration.From the University of Oslo, Department of Geosciences.

FIGURE 2.2: The seismic exploration workflow.

Seismic exploration allows the O&G industry to map out subsurface deposits of crude oil, natural gas, and minerals by seismically imaging the earth's reflectivity distribution. It is also used by petroleum geologists and geophysicists to interpret potential petroleum reservoirs, by extracting the seismic attributes out of the obtained images. The seismic exploration workflow, as described in figure 2.2, consists of three main stages: seismic acquisition, seismic processing and seismic interpretation<sup>1</sup>. For general informations about seismic exploration, the reader is kindly referred to Biondi [41], Coffeen [65], Sengbush [192] and Robein [181, 182].

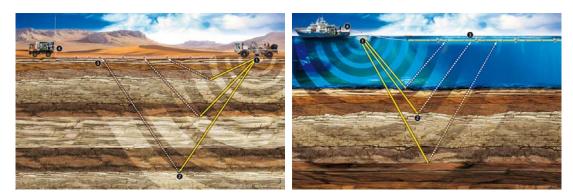

#### 2.1.1 Seismic acquisition

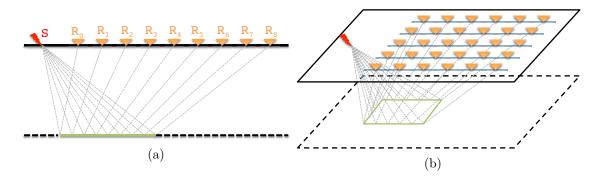

Seismic acquisition is the act of gathering data in the field, and making sure that it is of sufficient quality (this requires pre-processing such as noise attenuation and filtering). In seismic acquisition, an elastic or acoustic wavefield is emitted by a *seismic source* at a certain location at the surface. The reflected wavefield is measured by *receivers* located along lines (2D seismics) or on a grid (3D seismics). We refer to this process as a shot experiment. After each shot the source is moved to another location and the measurement is repeated. Figure 2.3 distinguishes between the land seismic acquisition (onshore) and the marine seismic acquisition (offshore). In land surveys, the seismic source can be a vibroseis or dynamite, the receivers are called geophones and are towed by trucks. In marine surveys, the source is often an air gun and the receivers are designated as hydrophones and are towed by vessels.

In order to collect data, many strategic choices have to be made. They are related to the physics and the location of the survey area, to the geometry of the acquisition

<sup>&</sup>lt;sup>1</sup>This categorization is becoming more and more obsolete as technologies, that repeatedly iterate through those three stages, are emerging [179].

(a) Onshore seismic acquisition.

(b) Offshore seismic acquisition.

FIGURE 2.3: Seismic acquisition steps at land (a) and at sea (b): 1) the seismic source emits controlled energy; 2) the seismic energy is transmitted and reflected from the subsurface layers; 3) the reflected energy is captured by receivers placed on the surface; 4) the acquisition systems record the data and pre-process it. From Sercel [193].

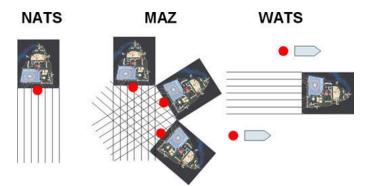

FIGURE 2.4: Seismic acquisition geometries: from left to right, Narrow Azimuth Towed Streamers, Multi-Azimuth, Wide Azimuth Towed Streamers. From PGS [174].

and to the accuracy of the targeted geophysical properties. These choices are often driven by economic considerations, since the cost of a survey may vary from \$18.000 to \$45.000 per square mile [21]. For example, specific acquisition parameters such as energy source effort and receiver station intervals, together with the data recording or *listening time*, have to be carefully defined. In addition, in the old days 2-D seismic reflection (see figure 2.5a) was the only tool for exploration because cost effective. Today, conventional 2-D seismic is only able to identify large structural traps while 3-D seismic (see figure 2.5b)<sup>2</sup> is able to pinpoint complex formations. Therefore, 3-D reflection has entirely replaced 2-D seismology in the O&G industry, albeit expensive. Furthermore, the acquisition geometry determines the coverage azimuth range and the consistency level of the illumination of reservoirs. Figure 2.4 represents schematic diagrams of the common acquisition geometries used in the O&G industry. The reader can find more detailed descriptions about the most common seismic acquisition geometries in [115]. Further, one can learn about cutting edge technologies in terms of seismic surveys, such as coil shooting in [101].

The basic principle of the seismic reflection is explained in figure 2.5. We differentiate between the 2-D seismic acquisition and the 3-D seismic acquisition, but the principle remains the same in the two cases. We activate a source (S) to send artificially-generated seismic waves into the subsurface. The waves get reflected off layer boundaries (called *reflectors* in the seismic literature). We record the arrival times and amplitudes of the reflected waves on the surface and detected by the receivers  $(R_{0..n})$ .

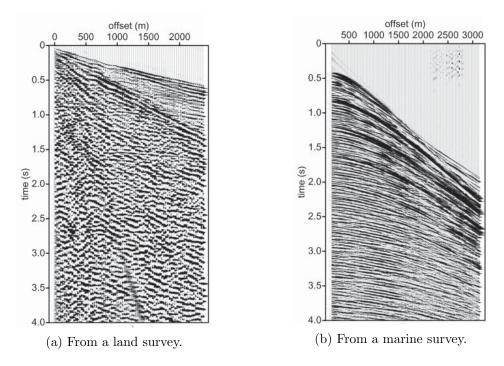

The size and scale of seismic surveys has increased alongside the significant concurrent increase in compute power during the last years. The collected data, i.e. *seismic traces* (see figure 2.6), is often humongous and was stored, in the past, in *tapes* and was very hard to process by computers. Each seismic trace corresponds to a seismic signal detected by one receiver throughout time. A wide variety of seismic data formats were proposed to digitize the seismic data and standardize its manipulation; the most famous ones in the industry are SEGY [191], SEP [200], SU [66] and RSF [148], to name a few. So far, the choices of seismic survey parameters such as the shot position (the position of the seismic source), the shot interval (the distance between two successive seismic perturbations), the receiver interval (the distance that separates two successive receivers situated in the same streamer), the shooting frequency (the frequency of activating the seismic source), etc. are of prime importance as they make immediate impact on the

$<sup>^{2}</sup>$ This is only a simplified illustration of the 3-D seismic reflection. In the industry, more than one seismic source is required to conduct a 3-D survey.

FIGURE 2.5: Seismic surveys in 2-D (a) and in 3-D (b). The seismic source is the red sign. Receivers are the orange triangles. Dotted black lines are basic representations of the subsurface reflectors. Green lines represent the covered area. Dashed gray lines illustrate the wave energy paths. The blue lines (in b) are called *streamers*.

generated seismic traces which are used in the following stages of the seismic exploration cycle.

#### 2.1.2 Seismic processing

In the seismic processing stage, we want to manipulate the gathered data, after acquisition, such that we generate an accurate image of the subsurface. A long run separates the raw data from being transformed into structural pictures. Processing consists of the application of a chain of computer treatments to the acquired data, guided by the hand

FIGURE 2.6: Example of seismic traces. Each wiggle is an illustration of the evolution of the wave amplitude, as well as the wave travel time, as a function of the "offset" (in meters) throughout time (in seconds) as measured by a given receiver. The offset is the distance between each receiver and the seismic source. Source *Drijkoningen*, *TU Delft* [78].

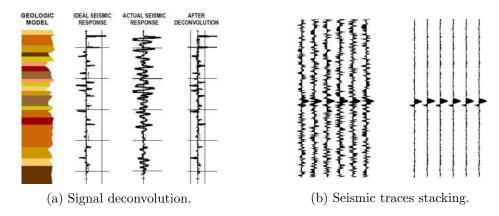

FIGURE 2.7: Signature deconvolution and stacking. Source CGG.

of processing geophysicists. There is neither a standard classification nor an order to define theses operations because they depend on the nature of the collected data, in the one hand, and because processing is a subjective manipulation, in the other hand. We try, throughout this section, to describe the most relevant processing routines and leave the opportunity to the reader to dive into the geophysics literature [59, 127, 143, 181], in order to learn more about seismic processing.

To begin with, the reflected seismic response can be a mixture of the seismic source pulse, the effect of the Earth upon that pulse, and background noise, all convolved together. The data is usually cleaned up from those spurious signals that might have been accumulated during seismic surveys. For instance, the seismic source may introduce signals, into the Earth, to which the underlying structures remain irresponsive because they do not depend on the signal put in. Those signals have to be removed. This is considered as *pre-processing* or *data conditioning*, and usually includes signal processing techniques, such as *signal deconvolution* and *anti-aliasing filtering*. Figure 2.7a shows an example of a seismic trace after applying a signal deconvolution.

Besides, seismic traces are usually sorted and those that share the same geometry properties are *stacked*, i.e. the signals are summed, to attenuate the background noise and thus increase the signal-to-noise ratio. The more seismic traces we can stack together into one seismic trace, the clearer is the seismic image. Stacking can be done by putting together traces from the same reflecting point (*Common Reflection Point (CRP) stacking* or *CRP gather*), from the same shot position (*Common Shot Gather (CSG)*), from the same midpoint (*Common Midpoint (CMP) stacking*) or from the same depth point (*Common Depthpoint (CDP) stacking*)<sup>3</sup> etc. [59]. Figure 2.7b emphasizes the noise attenuation after the CRP stacking of six seismic traces.

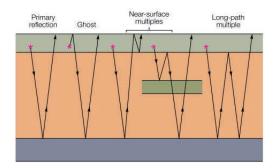

Furthermore, before arriving at the receivers the seismic energy may be reflected a number of times: this is known as the *multiple reflections* phenomenon (see figure 2.8) as opposed to *primary reflections*. For example, during offshore surveys, the energy bouncing back-and-forth within the water produces false reflections and obscures the real data. Multiple attenuation is needed to remove multiples embedded in the data without interfering with primary events. This is referred to as *Demultiple* in the literature, and many advanced numerical algorithms are proposed to do so, such as *Surface-Related Multiple Elimination* (SRME) [144]. Note that some research, such as Guitton [99], focus on imaging the multiples and integrating them to the primary reflections rather

<sup>&</sup>lt;sup>3</sup>In the case where the reflectors are horizontal, CDP is equivalent to CMP stacking.

FIGURE 2.8: Illustration of the multiple reflections. Source Ashton C. et al. [35].

than removing them. Another seismic processing is seismic traces interpolation. This manipulation is used to enhance the energy and highlight the areas close to the subsurface reflectors. Any missing seismic trace is filled in by signal interpolation.

At this point, the data is ready to more advanced processing operations such as *seismic imaging* or *inversions* [44]. The main goal of seismic imaging is to transform the pre-processed seismic traces to the most accurate possible graphical representation of the Earth's subsurface geologic structure. A key point in imaging is that the reflected wave is proportional to the amplitude of the incidence wave. The proportionality coefficient is called the *reflection coefficient*. Imaging has the objective of computing this reflection coefficient. Hence, the final image is a representation of the reflection coefficient at each point of the subsurface. This can be performed by means of *seismic migration*.

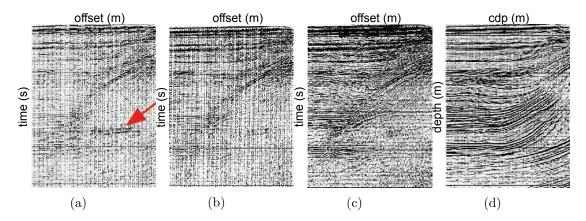

Migration is using the two-way travel time, amongst other attributes provided by seismic traces, to place (or migrate) the dipping temporal events in their true subsurface spatial locations. Processing these reflections produces a synthetic image of the subsurface geologic structure. We show in figure 2.9 an example of a seismic processing chain. The traces in 2.9a are subject to a water bottom multiple reflection (arrowed). In 2.9b, it is removed by demultiple and the image shows the result of suppressing the water bottom multiple. The seismic traces are, then, enhanced by interpolation in 2.9c. Finally, the image, in 2.9d most closely resembles the true sub-surface geology. It is obtained after seismic migration. More advanced processing techniques, such as *Prestack*

FIGURE 2.9: The result of a sequence of seismic processing algorithms. (a) represents the raw traces. From (a) to (b) demultiple is applied. From (b) to (c) interpolation is performed. From (c) to (d) seismic migration is used to produce the final subsurface image. Source CGG.

Depth Migration (PSDM), can significantly improve seismic imaging, especially in areas of complex geology. Finally, we recall the seismic processings are numerous and require advanced mathematical algorithms. Those are often applied to 3D seismic data which require enormous computing resources. Not to mention the massive volumes of data involved.

#### 2.1.3 Seismic interpretation

The final stage of the seismic exploration cycle is seismic interpretation. The purpose of interpretation is to interpret the processed seismic images and integrate other geoscientific information in order to make assessments of where the O&G reservoirs may be accumulated and to learn about their characterization. Interpreters or *interpretation* geophysicists, are involved at this stage to analyse the seismic data. Relevant information consist of structures and features which can be related to geological phenomena such as faults, fractures, anticlines etc. This can deliver valuable insights about the nature of rocks, about which time they were formed and about their environment.

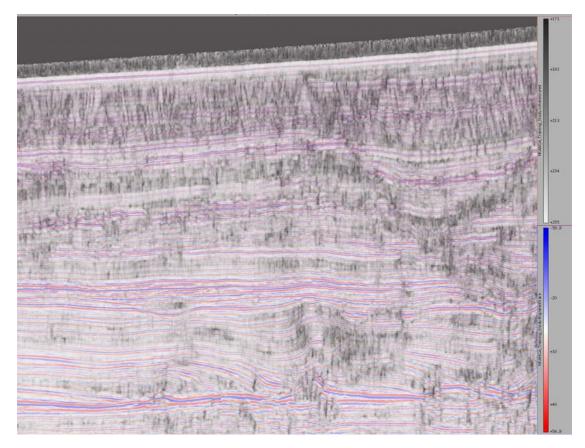

Computer algorithms are used to help interpret seismic data. For instance, numerical algorithms are used for the calculation of seismic attributes such as amplitude, phase and frequency based on the migrated seismic image. In practice, the seismic attributes (especially the amplitude) are related to the subsurface reflectivity which in turn provides information about the rock and the pressure-formation. Other seismic attributes are used in interpretation, namely *coherence*, *dip* and *azimuth*, and *gradient correlation cube*. For instance, the coherence is an attribute that measures the continuity between seismic traces in a specified window, applied on a seismic section. Figure 2.10 shows a composite of a section of a 3D seismic cube and a section of the corresponding coherence cube. For other examples of attributes calculation used in the interpretation stage we refer the reader to Abdelkhalek [22].

### 2.2 Seismic migrations and Reverse Time Migration (RTM)

In section 2.1 we have mentioned that seismic migration is classified as a final processing step in order to generate structural pictures of the subsurfaces. It is in fact the most important routine of the whole processing flow. In this section, we give a short overview of seismic migrations in general. We particularly insist on the Reverse Time Migration (RTM), where we describe the components of its workflow along with its advantages compared with the conventional migration techniques.

#### 2.2.1 Description and overview of migration methods

The purpose of migration is to reconstruct the reflectivity distribution of the buried structures on Earth, from the seismic data recorded at the surface. For that to do, reflections events (especially non *zero-offset* reflections) are collapsed and moved, i.e. migrated, to their proper spatial location. Schustler [188] explains how seismic traces are migrated, and enumerates the challenges that might be related to migration such as diffraction, out-of-plane reflections and conflicting dips.

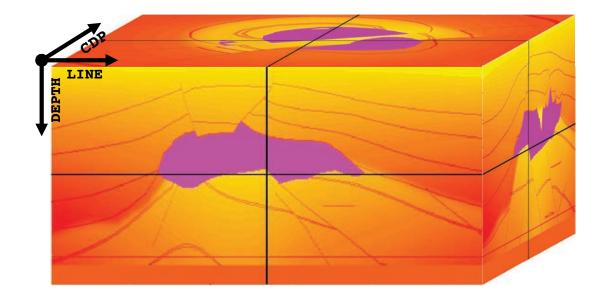

FIGURE 2.10: A seismic section (colored) superposed by its corresponding coherence attribute section (grayed). The color bar is the amplitude and the gray scale is to evalute the coherence. Courtesy of Abdelkhalek, Total S.A [22].

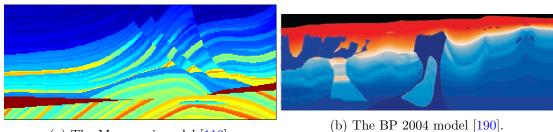

Migration relies upon pre-processed input data (seismic traces) and an accurate velocity model. Synthetic velocity models were proposed (see figure 2.11) by the O&G community in order to validate migration algorithms and display their potential power for imaging complex structures. However, in the case of real data, the velocity model of the subsurface is unknown. As a matter of fact, migration relies on various velocity estimation procedures, e.g. iterative prestack migration [42], to aid in imaging. In other words, migration is also a velocity analysis tool. Conceptually, migrations can be categorized with respect to different parameters. From a dimensionality perspective, migration is either 2D or 3D. 3D migration requires data to be acquired in 3D and presents rich azimuth content.

From data stacking standpoint, migration can be *prestack* or *poststack*. In poststack

(a) The Marmousi model [116].

FIGURE 2.11: Examples of synthetic velocity models provided by the O&G community.

migration, the seismic traces are stacked in bins, each of which is reduced to only one seismic trace. This is much less expensive to process but is also less accurate. In prestack migration, traces are not stacked and every single trace is processed which require huge computational effort.

Furthermore, we can categorize migrations upon wether they support or not lateral velocity variations. *Time* migration is insensitive to lateral variation of the velocities and is more appropriate to constant and depth dependent velocities. In the contrary, *depth* migration can handle strong variations of the velocities and is thus more appropriate for complex geological structures.

Mathematically, we can split migrations into two categories. The first one is *Ray-based* migrations, such as *Kirchhoff* migration and *Beam* migration [105]. The second is *Wave-field extrapolation* migrations, such as *One-way* migration and *Two-way* migration [159].

Historically, migration was achieved by graphical methods in the 1960's [194]. This was followed by diffraction summations. In the 1970's, several important developments took place. Based on the pioneering work of Jon Claerbout [59, 60], migration methods based on wave theory were developed. Claerbout derived migration as a finite-difference solution of an approximate wave equation. Kirchhoff wave-equation migration (Schneider [186], Gardner [89]), and frequency-wavenumber migrations (Gazdag [90] and Stolt [202]) appeared shortly thereafter. Those were initially time migration methods, but due to the pressing need for more accuracy they were changed into depth migrations. In the early 1980's, Baysal et al. [37] along with Whitmore [221] and McMechan [151], proposed the Reverse Time Migration, based on the exact wave equation. The last twenty years have seen extensions of these methods to three dimensions and to prestack migration, and enhancements of their efficiency and accuracy. For further reading about migrations, we refer to [42, 94].

#### 2.2.2 Reverse Time Migration

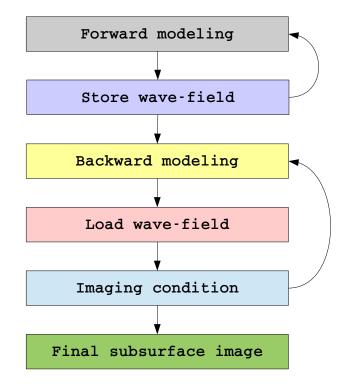

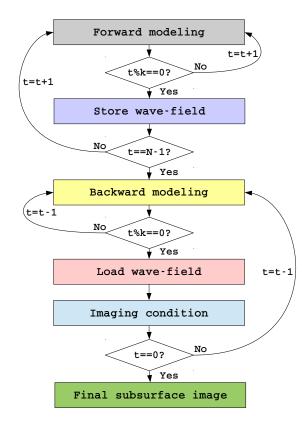

RTM is a two-way wave equation based pre-stack or post-stack depth migration. RTM is becoming more and more important as a tool of seismic imaging in the O&G industry. If the velocity model is complex or is subject to strong velocity gradients, such complexities will produce turning (or diving) rays and multiples when using conventional migration techniques (detailed in [188]). The RTM addresses these issues by directly using the two-way wave equation without any approximations or assumptions. The workflow of the RTM technique is depicted in the flowchart 2.12. Note that we do not mention in the figure that RTM also needs a velocity model as an input and that this workflow is repeated for each shot experiment. First, the source wavefield, i.e the wavefield whose origin is the seismic source, is propagated forward in time (we refer to this stage as *forward modeling* or also *seismic modeling*). Then, the receiver wavefield, i.e. a wavefield that is incident from the receivers, is then propagated back in time (this phase is called *backward modeling* or *retro-propagation*). Finally, the imaging condition is applied with respect to Claerbout's [58] imaging principle: "a reflector exists where the source and the receiver wavefields coincide in time and space".

As a matter of fact, the source wavefield and the receiver wavefield are cross-correlated throughout time. We denote I(x, y, z) the reflectivity coefficient of the subsurface, i.e. the resulting seismic image, at the coordinate (x, y, z). The source wavefield is presented by a  $(\mathbb{R}^3, \mathbb{N}) \to \mathbb{R}$  function S(x, y, z, t) and the receiver wavefield by a similar function R(x, y, z, t), each at the coordinate (x, y, z) and at time t. We can identify the RTM as

FIGURE 2.12: The Reverse Time Migration flowchart.

the linear operator described in the equation (2.1).

$$I(x, y, z) = \sum_{shot} \sum_{t} S_{shot}(x, y, z, t) * R_{shot}(x, y, z, t)$$

$$(2.1)$$

However, in some cases especially for large impedance contrasts and complex geological structures, the source and receiver wavefields can not be serrated efficiently. In these cases, the cross-correlation described in equation (2.1) leads to low frequency artefacts and illumination effects [123].

In order to eliminate the illumination effects, the image is often divided, after crosscorrelation, by the source illumination (see equation (2.2)), or by the receiver illumination (see equation (2.3)), or even better by a combination of both source illumination and receiver illumination (see equation (2.4)). This calculation corresponds to the imaging condition of the RTM algorithm.

$$I(x, y, z) = \frac{\sum_{shot} \sum_{t} S_{shot}(x, y, z, t) * R_{shot}(x, y, z, t)}{\sum_{shot} \sum_{t} S_{shot}^{2}(x, y, z, t)}$$

(2.2)

$$I(x, y, z) = \frac{\sum_{shot} \sum_{t} S_{shot}(x, y, z, t) * R_{shot}(x, y, z, t)}{\sum_{shot} \sum_{t} R_{shot}^2(x, y, z, t)}$$

(2.3)

$$I(x, y, z) = \frac{\sum_{shot} \sum_{t} S_{shot}(x, y, z, t) * R_{shot}(x, y, z, t)}{\sum_{shot} \sum_{t} S_{shot}^{2}(x, y, z, t)} + \frac{\sum_{shot} \sum_{t} S_{shot}(x, y, z, t) * R_{shot}(x, y, z, t)}{\sum_{shot} \sum_{t} R_{shot}^{2}(x, y, z, t)}$$

$$(2.4)$$

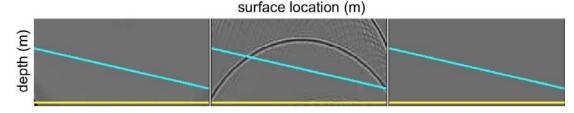

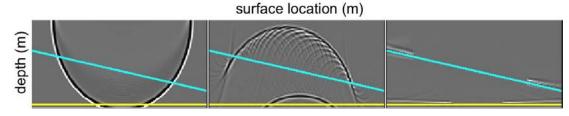

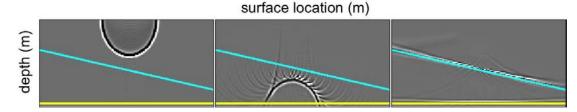

In the scope of this work we make use of the imaging condition defined in (2.2). We show an example of the RTM technique in figure 2.13, where we present the three different steps along with the resulting seismic image (see the dipping reflector).

(a) Snapshot at  $t = 1.20 \ s$  of the source wavefield (left), the receiver wavefield (middle) and the image progression (right). No reflector is imaged yet.

(b) Snapshot at  $t = 0.75 \ s$  of the source wavefield (left), the receiver wavefield (middle) and the image progression (right). The bottom reflector is almost fully imaged.

(c) Snapshot at  $t = 0.30 \ s$  of the source wavefield (left), the receiver wavefield (middle) and the image progression (right). All reflectors (the bottom and the shallow) are fully imaged.

FIGURE 2.13: A Reverse Time Migration example: the source and receiver wavefields are correlated, at three subsequent time-steps, in oder to image two reflectors. Source: Biondi [41].

## 2.3 Numerical methods for the wave propagation phenomena

Most differential equations are much too complicated to be solved analytically, thus the development of accurate numerical approximation schemes is essential to understand the behavior of their solutions. The wave equation, being a Partial Differential Equation (PDE), is no exception. This section presents an overview of the state-of-the-art numerical methods used for seismic modeling and seismic imaging. Given that RTM is based on the wave equation, we present the general equations that govern the propagation of waves in elastic and acoustic media. These methods were widely studied for seismic imaging and one can find more details in Virieux et al. [215] and in Carcione et al. [50].

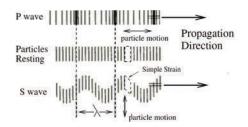

FIGURE 2.14: Particle motions for P (top) and S (bottom) waves.  $\lambda$  is the wavelength and the simple strain illustrates a unit deformation. From [189].

#### 2.3.1 The wave equation

#### 2.3.1.1 Seismic waves and propagation media

Before introducing the theory that governs the wave propagation phenomenon, we briefly recall the type of seismic waves and the nature of propagation media. A wave propagation is called *elastic* when the traversed medium can change in shape as a result of a deforming force otherwise the propagation is *acoustic*. If the medium has constant density, we call it *homogeneous*, *heterogeneous* if it has not. Besides, we call a medium *isotropic* if it has the same physical characteristics independently of directions. In the contrary, the medium is called *anisotropic*.

The seismic waves are either *body* waves, that is they travel through the interior of the Earth, or *surface* waves if they travel along the Earth's surface. We distinguish two types of body waves: *Compressional* waves, also referred to as *Primary* (*P*) waves<sup>4</sup>, and *Shear* waves, also called *Secondary* (*S*) waves. Figure 2.14 illustrates the propagation directions of P and S waves for small elemental volumes (*particles*). P waves propagate in parallel with the particle motion whereas S waves propagate perpendicularly to the particle motion. In homogeneous and isotropic media the velocities of P and S waves are, respectively,  $V_p = \sqrt{\frac{\lambda+2\mu}{\rho}}$  and  $V_s = \sqrt{\frac{\mu}{\rho}}$ , where  $\lambda$  and  $\mu$  are the *Lamé* parameters, and  $\rho$  is the density. Note that shear waves do not propagate in acoustic media (water for example) because the shear modulus  $\mu$  is null in fluids.

#### 2.3.1.2 The elastic wave equation

The general wave equation is established using the Newton's second law of motion and Hook's law, with some constraints considered: the media is elastic, isotropic and subject to infinitesimal displacements in order to satisfy the elasticity condition. For the sake of simplicity the motion of the wave is initially presumed to be one dimensional, the wave equation will be later derived to the three dimensional case. We denote the particle displacement  $\eta$ , the dimension of the wave motion Z, and the particle position is given by the z coordinate. Newton's law (2.5), for small elemental volumes, states that the acceleration ( $\gamma$ ) of a particle when multiplied by its mass (m) is equal to the sum of forces applied on it (f).

$$f = m\gamma \tag{2.5}$$

Considered that the pressure (p) is the force on an object that is spread over a surface area and given that the particles are infinitesimal (we consider the unit surface), the

<sup>&</sup>lt;sup>4</sup>Note that there are other types of wave, i.e. Love waves and Rayleigh waves, which are surface waves that we deliberately ignore here.

force is equivalent to the pressure differential. Similarly, here we consider studying the wave kinematics in a unit volume thus the mass can be replaced by the density ( $\rho$ ). Note that the variables in the equation are scalar fields since we consider 1D case and that in the 3D case vector fields should be considered instead. The equation (2.5) is then equivalent to the formula (2.6).

$$\frac{\partial \Delta p}{\partial z} = \rho \frac{\partial^2 \eta}{\partial t^2} \tag{2.6}$$

Hook's law (2.7) states that the *strain* (deformation) of an elastic object or material is proportional to the *stress* applied to it.

$$\Delta p = K \frac{\partial \eta}{\partial z},\tag{2.7}$$

where K is the *Bulk* modulus. The wave equation is thus derived as follows:

$$K\frac{\partial^2 \eta}{\partial^2 z} = \rho \frac{\partial^2 \eta}{\partial t^2} \tag{2.8}$$

Extending the equation to the 3D cartesian coordinate system (X, Y, Z), and using the indicial notation implies the system of equations (2.9) and (2.10) [24, 38]:

$$\frac{\partial \sigma_{xx}(x, y, z, t)}{\partial t} = (\lambda(x, y, z) + 2\mu(x, y, z)) \frac{\partial v_x(x, y, z, t)}{\partial x} + \lambda(x, y, z) \left( \frac{\partial v_y(x, y, z, t)}{\partial y} + \frac{\partial v_z(x, y, z, t)}{\partial z} \right) \\

\frac{\partial \sigma_{yy}(x, y, z, t)}{\partial t} = (\lambda(x, y, z) + 2\mu(x, y, z)) \frac{\partial v_y(x, y, z, t)}{\partial y} + \lambda(x, y, z) \left( \frac{\partial v_x(x, y, z, t)}{\partial x} + \frac{\partial v_z(x, y, z, t)}{\partial z} \right) \\

\frac{\partial \sigma_{zz}(x, y, z, t)}{\partial t} = (\lambda(x, y, z) + 2\mu(x, y, z)) \frac{\partial v_z(x, y, z, t)}{\partial z} + \lambda(x, y, z) \left( \frac{\partial v_x(x, y, z, t)}{\partial x} + \frac{\partial v_y(x, y, z, t)}{\partial y} \right) \\

\frac{\partial \sigma_{xy}(x, y, z, t)}{\partial t} = \mu(x, y, z) \left( \frac{\partial v_x(x, y, z, t)}{\partial z} + \frac{\partial v_z(x, y, z, t)}{\partial x} \right) \\

\frac{\partial \sigma_{yz}(x, y, z, t)}{\partial t} = \mu(x, y, z) \left( \frac{\partial v_y(x, y, z, t)}{\partial z} + \frac{\partial v_z(x, y, z, t)}{\partial x} \right) \\

\frac{\partial \sigma_{yz}(x, y, z, t)}{\partial t} = \mu(x, y, z) \left( \frac{\partial v_y(x, y, z, t)}{\partial z} + \frac{\partial v_z(x, y, z, t)}{\partial y} \right)$$

(2.9)

$$\frac{\partial v_x(x,y,z,t)}{\partial t} = \frac{1}{\rho(x,y,z)} \left( \frac{\partial \sigma_{xx}(x,y,z,t)}{\partial x} + \frac{\partial \sigma_{xy}(x,y,z,t)}{\partial y} + \frac{\partial \sigma_{xz}(x,y,z,t)}{\partial z} \right) \\

\frac{\partial v_y(x,y,z,t)}{\partial t} = \frac{1}{\rho(x,y,z)} \left( \frac{\partial \sigma_{xy}(x,y,z,t)}{\partial x} + \frac{\partial \sigma_{yy}(x,y,z,t)}{\partial y} + \frac{\partial \sigma_{yz}(x,y,z,t)}{\partial z} \right) \\

\frac{\partial v_z(x,y,z,t)}{\partial t} = \frac{1}{\rho(x,y,z)} \left( \frac{\partial \sigma_{xz}(x,y,z,t)}{\partial x} + \frac{\partial \sigma_{zy}(x,y,z,t)}{\partial y} + \frac{\partial \sigma_{zz}(x,y,z,t)}{\partial z} \right)$$

(2.10)

where  $v_x(x, y, z, t)$ ,  $v_y(x, y, z, t)$  and  $v_z(x, y, z, t)$ , are the components of the particles velocity vector at time t;  $\sigma_{ij}(x, y, z, t)$  with  $i, j \in (x, y, z)^2$  are the stress tensor components at time t (note that the tensor is symmetric, i.e.  $\sigma_{xz} = \sigma_{zx}$ );  $\rho(x, y, z)$  is the density of the medium;  $\lambda(x, y, z)$  and the *shear modulus*  $\mu(x, y, z)$  are the Lamé parameters that describe the linear-stress relation [196].

#### 2.3.1.3 The acoustic wave equation

The acoustic approximation states that shear effects in the data are negligible and that the dominant wave type is a compressional wave. Thus the shear modulus  $\mu(x, y, z)$  is null. The equations (2.9) and (2.10) are simplified as follows:

$$\frac{\partial \sigma_{xx}(x,y,z,t)}{\partial t} = \lambda(x,y,z) \left( \frac{\partial v_x(x,y,z,t)}{\partial x} + \frac{\partial v_y(x,y,z,t)}{\partial y} + \frac{\partial v_z(x,y,z,t)}{\partial z} \right) \\

\frac{\partial \sigma_{yy}(x,y,z,t)}{\partial t} = \lambda(x,y,z) \left( \frac{\partial v_y(x,y,z,t)}{\partial y} + \frac{\partial v_x(x,y,z,t)}{\partial x} + \frac{\partial v_z(x,y,z,t)}{\partial z} \right) \quad (2.11)$$

$$\frac{\partial \sigma_{zz}(x,y,z,t)}{\partial t} = \lambda(x,y,z) \left( \frac{\partial v_z(x,y,z,t)}{\partial z} + \frac{\partial v_x(x,y,z,t)}{\partial x} + \frac{\partial v_y(x,y,z,t)}{\partial y} \right) \\

\frac{\partial v_y(x,y,z,t)}{\partial t} = \frac{1}{\rho(x,y,z)} \frac{\partial \sigma_{xx}(x,y,z,t)}{\partial y} \quad (2.12)$$

$$\frac{\partial v_z(x,y,z,t)}{\partial t} = \frac{1}{\rho(x,y,z)} \frac{\partial \sigma_{zz}(x,y,z,t)}{\partial z}$$

The equation (2.11) implies that  $\frac{\partial \sigma_{xx}(x,y,z,t)}{\partial t} = \frac{\partial \sigma_{yy}(x,y,z,t)}{\partial t} = \frac{\partial \sigma_{zz}(x,y,z,t)}{\partial t}$ , which can lead to the hyperbolic 1<sup>st</sup> order system:

$$\frac{\partial p(x,y,z,t)}{\partial t} = K(x,y,z) \left( \frac{\partial v_x(x,y,z,t)}{\partial x} + \frac{\partial v_y(x,y,z,t)}{\partial y} + \frac{\partial v_z(x,y,z,t)}{\partial z} \right)$$

$$\frac{\partial v_x(x,y,z,t)}{\partial t} = \frac{1}{\rho(x,y,z)} \frac{\partial p(x,y,z,t)}{\partial x}$$

$$\frac{\partial v_y(x,y,z,t)}{\partial t} = \frac{1}{\rho(x,y,z)} \frac{\partial p(x,y,z,t)}{\partial y}$$

$$\frac{\partial v_z(x,y,z,t)}{\partial t} = \frac{1}{\rho(x,y,z)} \frac{\partial p(x,y,z,t)}{\partial z}$$

(2.13)

where  $p(x, y, z, t) = \frac{\sigma_{xx}(x, y, z, t) + \sigma_{yy}(x, y, z, t) + \sigma_{zz}(x, y, z, t)}{3}$  is the pressure field, and K(x, y, z) is the Bulk modulus. To complete the equation we have to add the seismic source term s(t), positioned at the coordinate  $(x_s, y_s, z_s)$ . The system of equations (2.13) becomes the following  $2^{nd}$  order equation:

$$\frac{1}{K(x,y,z)}\frac{\partial^2 p(x,y,z,t)}{\partial t^2} - \nabla \cdot \left(\frac{1}{\rho(x,y,z)}\nabla p(x,y,z,t)\right) = s(t)\delta(x-x_s)\delta(y-y_s)\delta(z-z_s)$$

(2.14)

where  $\nabla$ . is the *divergence* operator,  $\nabla$  the *gradient* operator and  $\delta$  the Dirac delta function. We define  $c = \sqrt{\frac{K}{\rho}}$  as the compressional particle velocity. The divergence and the gradient operators are correlated and are replaced by the *Laplace* operator  $\Delta$ . In

the case where the density  $\rho$  is constant, the equation (2.14) becomes:

$$\frac{1}{c^2(x,y,z)}\frac{\partial^2 p(x,y,z,t)}{\partial t^2} - \Delta p(x,y,z,t) = s(t)\delta(x-x_s)\delta(y-y_s)\delta(z-z_s)$$

$$with: \Delta p(x,y,z,t) = \frac{\partial^2 p(x,y,z,t)}{\partial x^2} + \frac{\partial^2 p(x,y,z,t)}{\partial y^2} + \frac{\partial^2 p(x,y,z,t)}{\partial z^2}.$$

(2.15)

Note that the displacement field u(x, y, z, t), which determines the displacement of the particles during the propagation, is governed by a similar equation as the equation (2.13). Solving the pressure field p(x, y, z, t) is thus equivalent to solving the displacement field u(x, y, z, t):

$$\frac{1}{c^2(x,y,z)}\frac{\partial^2 u(x,y,z,t)}{\partial t^2} - \Delta u(x,y,z,t) = s(t)\delta(x-x_s)\delta(y-y_s)\delta(z-z_s).$$

(2.16)

This is the acoustic wave equation that we tend to solve numerically in the rest of this section. It is also the equation used to simulate the wave propagation in the seismic modeling and in the seismic imaging, i.e. in the Reverse Time Migration.

#### 2.3.2 Numerical methods for wave propagation

Numerically, the solutions to the wave equation can be approximated using a wide variety of numerical methods. Depending on the targeted accuracy and on the available computational resources, one can consider a spectral formulation, a strong formulation or a weak formulation. One can also adopt a time-domain approach or a frequencydomain approach. The spectral formulation produces efficient results for simple geological structures whereas the strong formulation via finite-difference methods can give a good compromise between the quality of images and the computational costs. On the other hand, weak formulation via finite-elements, e.g. continuous or discontinuous Galerkin methods, are more suitable for areas with complex subsurfaces. For a thorough overview of the most common numerical methods used in resolving the wave equation we recommend the following two readings [50] and [215]. In this section, we briefly introduce the methods that we find most relevant to the acoustic wave equation solver.

#### 2.3.2.1 Integral methods

These methods are based on the Huygen's principle that states that every point in the wavefield can be considered as a secondary source. For the integral form of the scalar wave equation in homogeneous media we use the Green's function G

$$G(\mathbf{x}, \mathbf{x}_{\mathbf{s}}, t) = \frac{\delta(t - |\mathbf{x} - \mathbf{x}_{\mathbf{s}}|/c_0)}{4\pi |\mathbf{x} - \mathbf{x}_{\mathbf{s}}|}$$

(2.17)

$$p(\mathbf{x},t) = \int \int G(\mathbf{x},\mathbf{x}_{\mathbf{s}},t-t') \ q(\mathbf{x}_{\mathbf{s}},t') \ d\mathbf{x}_{\mathbf{s}} \ dt'$$

(2.18)

Green's function are used as a response to a source in the studied media. The source location is  $\mathbf{x}_{s}$ . p is the pressure generated by the particles displacement in media,  $c_{0}$  is the wave velocity and q is a mass flow rate per unit volume. These approaches are more efficient in homogeneous medium.

## 2.3.2.2 Asymptotic methods

They are also called ray-tracing methods and are used when the medium is heterogeneous. In such media, the Green's functions cannot be computed simply. An example of the asymptotic approach is the Kirchhoff approximation widely used in migration as described in [41]. Kirchhoff approximations are based on the assumption of high frequencies.

## 2.3.2.3 Direct methods

Direct methods are based on a discretization of the computational domain. The approximation of solutions to the PDE that defines the wave equation can be done using strong formulations such as finite-difference and pseudo-spectral approaches. We can also rely on weak formulations like finite-element and finite-volume methods. We also need a time integration in order to approximate the wave equation. Depending on the formulation chosen for the equation, the space and time derivatives can be either second or first order. The source term is added to the right hand side of the PDE in order to consider the inhomogeneous solutions.

**2.3.2.3.1** Pseudo-Spectral Methods Pseudo-spectral (PS) methods also known as the Fourier methods are strong formulations of partial differential equations. Using these approaches, pressure values  $p(\mathbf{x})$  are approximated using basis functions  $\psi_j$  like in equation (2.19)

$$p(\mathbf{x}) = \sum_{j=1}^{N} p(\mathbf{x}_j) \psi_j(\mathbf{x})$$

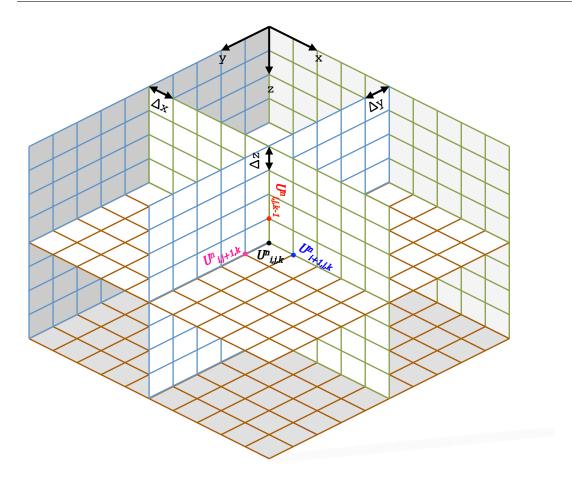

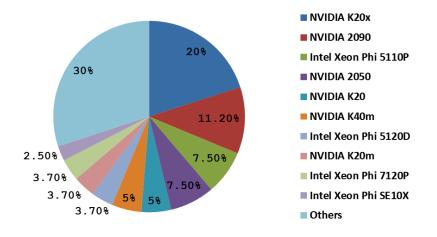

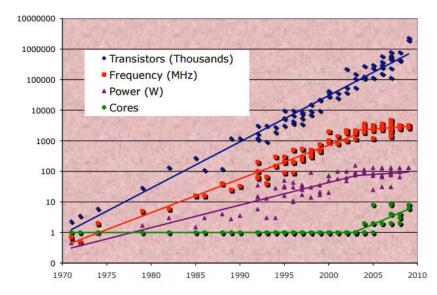

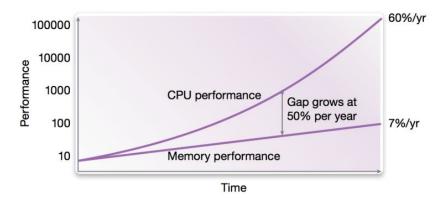

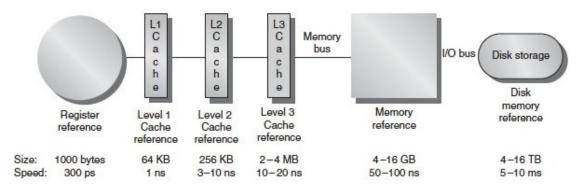

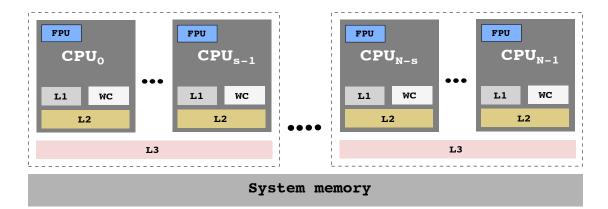

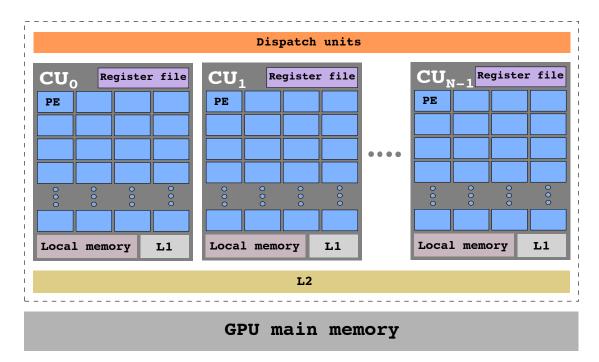

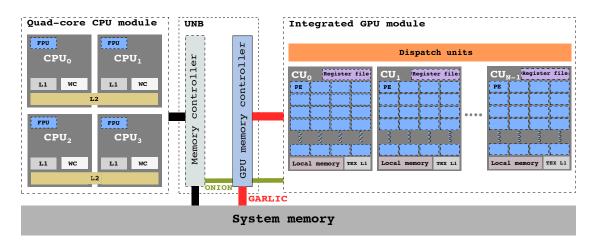

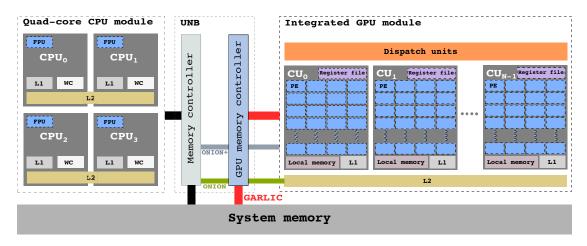

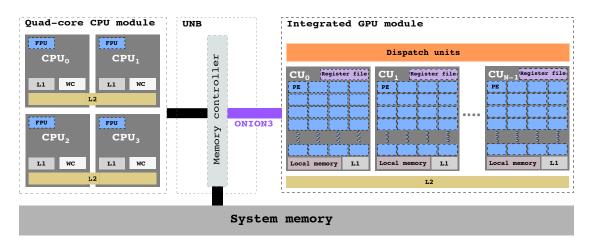

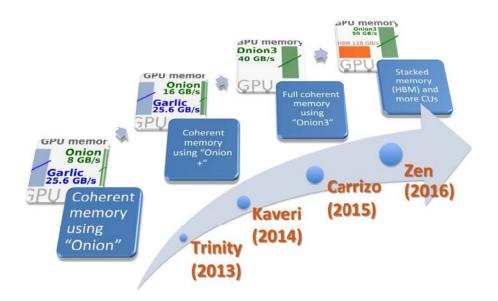

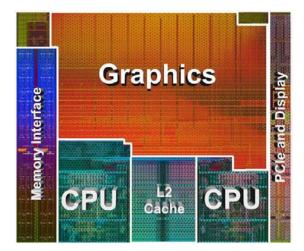

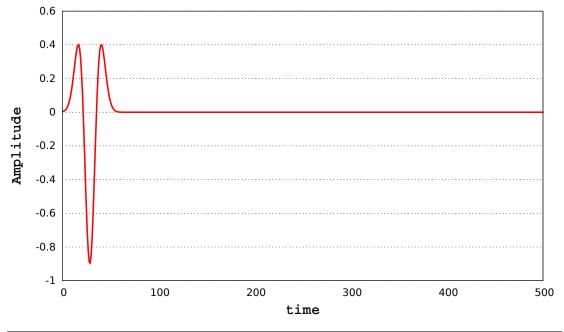

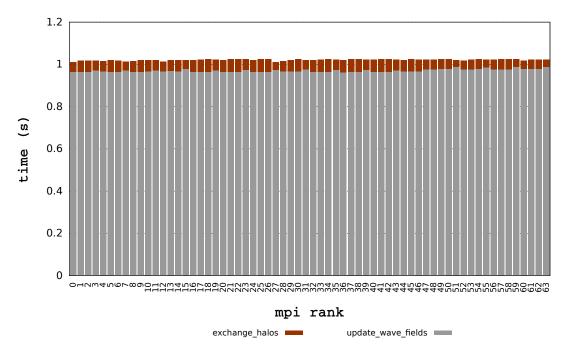

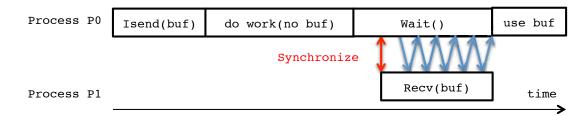

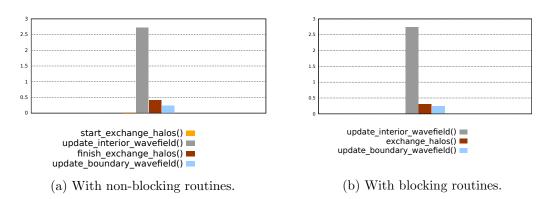

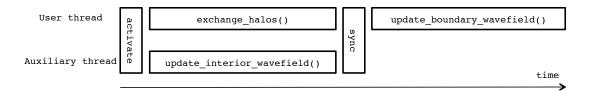

(2.19)