# Design, Optimization, and Formal Verification of Circuit Fault-Tolerance Techniques

Dmitry Burlyaev

#### ▶ To cite this version:

Dmitry Burlyaev. Design, Optimization, and Formal Verification of Circuit Fault-Tolerance Techniques. Modeling and Simulation. Inria Grenoble Rhône-Alpes, Université de Grenoble, 2015. English. NNT: . tel-01253368v1

## HAL Id: tel-01253368 https://theses.hal.science/tel-01253368v1

Submitted on 11 Jan 2016 (v1), last revised 10 May 2016 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique

Arrêté ministériel : 2 juillet 2012

Présentée par

## **Dmitry Burlyaev**

Thèse dirigée par **Pascal Fradet** et codirigée par **Alain Girault**

préparée au sein de l'INRIA et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# Design, Optimization, and Formal Verification of Circuit Fault-Tolerance Techniques

Conception, optimisation, et vérification formelle de techniques de tolérance aux fautes pour circuits

Thèse soutenue publiquement le **26 Novembre 2015**, devant le jury composé de :

#### Prof. Koen Claessen

Chalmers University, Rapporteur

**Dr. Arnaud Tisserand**

CNRS, Rapporteur

Prof. Florent de Dinechin

INSA Lyon, Examinateur

**Prof. Laurence Pierre**

Univ. Grenoble Alpes, Président

**Dr. Pascal Fradet**

INRIA, Directeur de thèse

Dr. Alain Girault

INRIA, Co-Directeur de thèse

### Acknowledgements

Je voudrais remercier mes directeurs, Pascal Fradet et Alain Girault, de leur aide, de leur patience, et du temps qu'ils ont consacré à me soutenir et m'encourager pendant ma thèse. Je vous suis reconnaissant pour tout, de la recherche de financement aux resultats scientifiques aboutis.

I also express gratitude to Vagelis, Sophie, Yoann, Gregor, Gideon, Peter, Helen, Christophe, Jean-Bernard, Adnan, Quentin, Willy and many many others. Our discussions helped me to be more fault-tolerant:)

Отдельную благодарность хочу выразить моим родителям за их каждодневную поддержку. Без Ваших советов эта работа никогда бы не была выполнена.

# Contents

| Li           | st of      | Figures                                                          | i               |

|--------------|------------|------------------------------------------------------------------|-----------------|

| Li           | st of      | Tables                                                           | iv              |

| $\mathbf{G}$ | lossa      | ry                                                               | vi              |

| 1            | Intr       | oduction                                                         | 1               |

|              | 1.1        | Problems and Contributions                                       | 2               |

|              | 1.2        | Outline                                                          | 4               |

| 2            | Circ       | cuits Fault-Tolerance and Formal Methods                         | 5               |

|              | 2.1        | Circuits Fault Tolerance                                         | Ę               |

|              |            | 2.1.1 Historical Roots of Fault-Tolerance                        | 6               |

|              |            | 2.1.2 Taxonomy of Faults                                         | 16              |

|              | 2.2        | 2.1.3 Conventional Fault-Tolerance Techniques                    | 10              |

|              | 2.2        | Formal Methods in Circuit Design                                 | 21              |

|              |            | 2.2.1 Model Checking                                             | 22              |

|              | 2.3        | 2.2.2 Theorem Proving                                            | $\frac{27}{34}$ |

|              | 2.3        | Conclusion                                                       | 34              |

| 3            | Ver        | ification-based Voter Minimization                               | 35              |

|              | 3.1        | Approach overview                                                | 35              |

|              | 3.2        | Syntactic Analysis                                               | 36              |

|              | 3.3        | Semantic Analysis                                                | 37              |

|              |            | 3.3.1 The precise logic domain $D_1$                             | 37              |

|              |            | 3.3.2 Semantic analysis with $D_1 \dots \dots \dots \dots \dots$ | 37              |

|              | 0.4        | 3.3.3 More Abstract Logic Domains                                | 39              |

|              | 3.4        | Inputs Specification                                             | 41<br>42        |

|              | 3.5<br>3.6 | Outputs Specification                                            | $\frac{42}{44}$ |

|              | 5.0        | 3.6.1 Precise modeling of SETs                                   | 45              |

|              |            | 3.6.2 Safe SET over-approximation                                | 46              |

|              | 3.7        | Experimental results                                             | 47              |

|              | 3.8        | Related work                                                     | 52              |

|              | 3.9        | Conclusion                                                       | 53              |

|              | <b></b>    |                                                                  |                 |

| 4            |            | ne-Redundancy Circuit Transformations                            | 55              |

|              | 4.1        | Basic notations and approach                                     | 56              |

|              | 4.2        | Triple-Time Redundancy                                           | 58              |

|              |            | 4.2.1 Principle of Triple-Time Redundancy                        | 58<br>59        |

|              |            | 4.2.3 TTR Control Block                                          | 61              |

|              |            | 4.2.4 Fault-Tolerance Guarantees                                 | 62              |

|              |            | 4.2.5 TTR Voting Mechanisms Minimization                         | 63              |

ii Contents

|          |        | 1                                                              | 3  |

|----------|--------|----------------------------------------------------------------|----|

|          | 4.3    | v v                                                            | 6  |

|          |        | 4.3.1 Principle of Dynamic Time Redundancy 6                   | 7  |

|          |        | 4.3.2 Dynamic Triple-Time Redundancy                           | 0  |

|          |        | 4.3.3 Dynamic Double-Time Redundancy                           | 8  |

|          |        | 4.3.4 Experimental results                                     | 1  |

|          | 4.4    | Double-Time Redundancy with Checkpointing                      | 3  |

|          |        | 4.4.1 Principle of Time Redundancy with Checkpointing 8        | 34 |

|          |        |                                                                | 6  |

|          |        |                                                                | 37 |

|          |        | •                                                              | 37 |

|          |        | *                                                              | 9  |

|          |        |                                                                | 0  |

|          |        |                                                                | )1 |

|          |        | v .                                                            | 3  |

|          |        |                                                                | 6  |

|          | 4.5    |                                                                | 8  |

|          | 1.0    |                                                                |    |

| <b>5</b> | For    | al proof of the DTR Transformation 10                          | 1  |

|          | 5.1    | Circuit Description Language                                   |    |

|          |        | 5.1.1 Syntax of LDDL                                           |    |

|          |        | 5.1.2 Semantics of LDDL                                        |    |

|          | 5.2    | Specification of Fault Models                                  | 5  |

|          | 5.3    | Overview of Correctness Proofs                                 | 7  |

|          |        | 5.3.1 Transformation                                           | 7  |

|          |        | 5.3.2 Relations between the source and transformed circuits 10 | 8  |

|          |        | 5.3.3 Key Properties and Proofs                                | 9  |

|          |        | 5.3.4 Practical issues                                         | 0  |

|          | 5.4    | Correctness Proof of the DTR Transformation                    | 1  |

|          |        | 5.4.1 Formalization of DTR                                     | 1  |

|          |        | 5.4.2 Relations between source and transformed circuits        | 5  |

|          |        | 5.4.3 Main theorem                                             | 8  |

|          |        | 5.4.4 Execution of a DTR circuit                               | 9  |

|          |        | 5.4.5 Lemmas on DTR components                                 |    |

|          | 5.5    | Conclusion                                                     |    |

| 6        | Con    | lusions 12                                                     | o  |

| J        | 6.1    | Summary                                                        |    |

|          | 6.2    | Future Work                                                    |    |

|          | 0.4    | tutute work                                                    | U  |

| Bi       | ibliog | aphy 13                                                        | 3  |

# List of Figures

| 2.1  | Predicted number of bit-flips vs the number of observed bit-flips [1]                                          | 9  |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Measured error rates dependency from supply voltage [2]                                                        | 10 |

| 2.3  | TMR scheme proposed by von Neumann                                                                             | 12 |

| 2.4  | TMR with only cells triplication for SEU masking                                                               | 13 |

| 2.5  | Full TMR with a triplicated voter                                                                              | 13 |

| 2.6  | Circuit realization of inter-clock time-redundant technique [3]                                                | 14 |

| 2.7  | Razor flip-flop for a pipeline stage [2]                                                                       | 15 |

| 2.8  | Voting element for a time-multiplexed circuit [4]                                                              | 16 |

| 2.9  | Memory storage with ECC protection [5]                                                                         | 18 |

| 2.10 | Three examples of state encoding for the FSM with 5 states                                                     | 20 |

|      | Circuit with a majority voter                                                                                  | 24 |

| 2.12 | Representations of the Boolean function $f_d(i, a, b, c) = (a \wedge b) \vee (b \wedge c) \vee (c \wedge a)$ . | 25 |

| 2.13 | A parametric OR-chain orN                                                                                      | 29 |

| 2.14 | Two abstraction levels of the processor AAMP5 operations [6]                                                   | 32 |

| 3.1  | Input interface as an NBA (a) and its deterministic version (b)                                                | 42 |

| 3.2  | Original circuit with the surrounding interface circuit                                                        | 43 |

| 3.3  | Combinational cones for SET modeling                                                                           | 46 |

| 3.4  | Logic Domain Comparison: Reachable State Space Size                                                            | 50 |

| 3.5  | Logic Domain Comparison: Size Ratio of RSS                                                                     | 51 |

| 4.1  | Digital Circuit before the transformation                                                                      | 56 |

| 4.2  | General scheme of a time-redundant circuit                                                                     | 57 |

| 4.3  | Transformed circuit for TTR                                                                                    | 59 |

| 4.4  | TTR memory block without voting                                                                                | 59 |

| 4.5  | TTR memory block with voting                                                                                   | 61 |

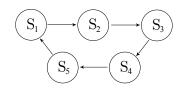

| 4.6  | TTR control block FSM                                                                                          | 61 |

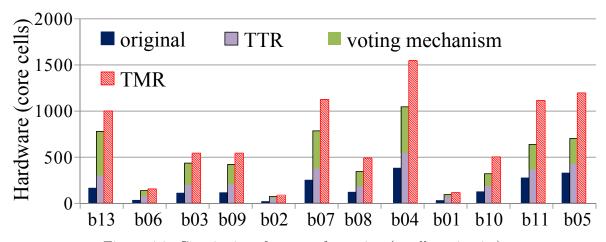

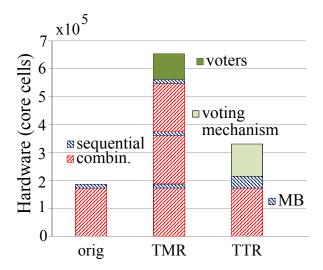

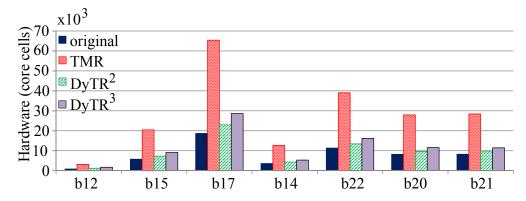

| 4.7  | Circuit size after transformation (largest circuits)                                                           | 64 |

| 4.8  | Circuit size after transformation (smallest circuits)                                                          | 64 |

| 4.9  | Transformed circuits profiling, circuit $b17$                                                                  | 65 |

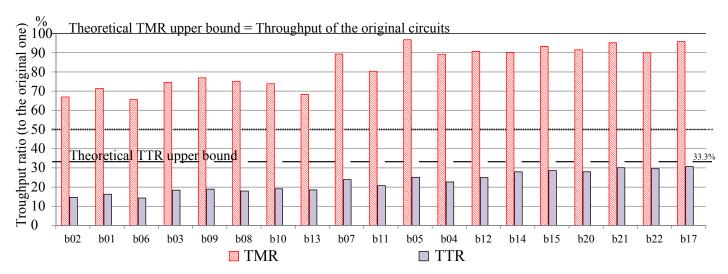

| 4.10 | Throughput ratio of TMR and TTR transformed circuits (sorted according to                                      |    |

|      | circuit size)                                                                                                  | 66 |

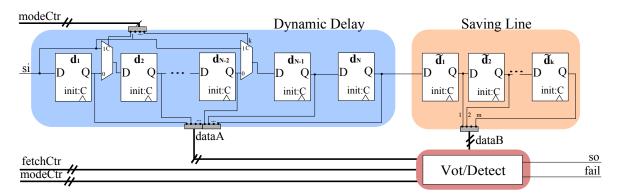

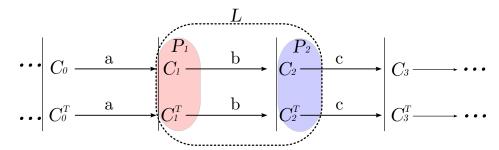

|      | Result of the circuit transformation $DyTR^N$                                                                  | 67 |

|      | General memory block structure for $DyTR^N$                                                                    | 68 |

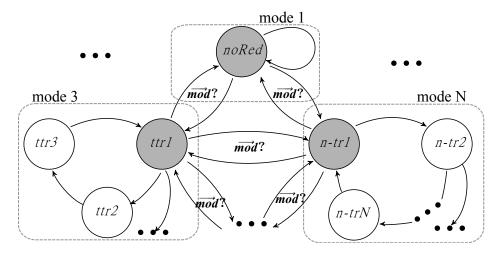

|      | Control block for the generic DyTR <sup><math>N</math></sup> transformed circuit                               | 70 |

| 4.14 | Memory block for DyTR <sup>3</sup>                                                                             | 71 |

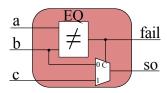

|      | VotA: voter with detection capability                                                                          | 72 |

| 4.16 | Control block for DyTR <sup>3</sup>                                                                            | 74 |

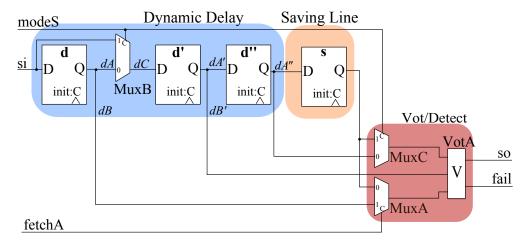

| 4.17 | Memory Block for DyTR <sup>2</sup>                                                                             | 79 |

| 4.18 | Control block for $DyTR^2$                                                                                     | 80 |

| 4.19 | Transformed circuits profiling (circuit $b21$ )                                                                | 82 |

| 4.20 | Circuit size after transformation, big circuits (for all $COM/SEQ > 8$ )                                       | 82 |

| 4.21 | Circuit size after transformation, small circuits (for all $COM/SEQ < 8$ )                                     | 83 |

iv List of Figures

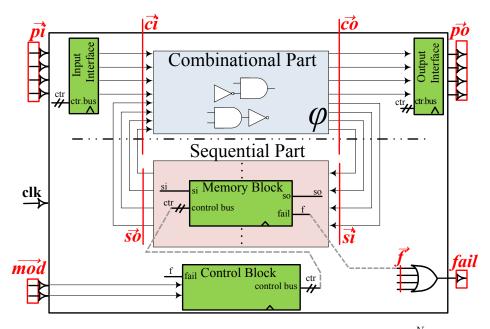

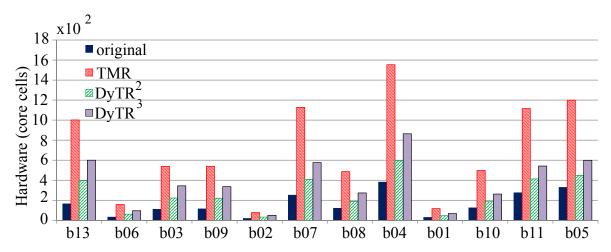

| 4.22 | Overview of the DTR transformation                                             | 84  |

|------|--------------------------------------------------------------------------------|-----|

| 4.23 | Transformed DTR circuit                                                        | 85  |

| 4.24 | DTR Memory Block                                                               | 86  |

|      | DTR input buffer ( $pi$ primary input)                                         | 87  |

|      | DTR Output Buffer ( $co$ is the output of the combinational part)              | 88  |

| 4.27 | FSM of the DTR control block: "=" denotes a guard, "=" an assignment and       |     |

|      | signals absent from an edge are set to 0. $f_i$ is a fail delayed on one cycle | 89  |

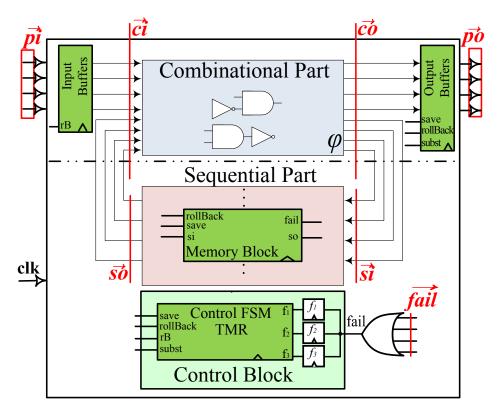

| 4.28 | Circuit size after transformation (large circuits)                             | 96  |

| 4.29 | Circuit size after transformation (small circuits)                             | 97  |

| 4.30 | Transformed circuits profiling (for $b17$ )                                    | 97  |

| 4.31 | Throughput ratio of TMR, and DTR transformed circuits (sorted according        |     |

|      | to circuit size)                                                               | 98  |

| 4.32 | Transformations overheads for throughput and hardware, the circuit $\it b21.$  | 99  |

| 5.1  | LDDL syntax                                                                    | 102 |

| 5.2  | $x \vdash C$ operator                                                          | 103 |

| 5.3  | Simple memory cell $(x \mid SWAP)$                                             | 103 |

| 5.4  |                                                                                | 103 |

| 5.5  | LDDL semantics for a clock cycle                                               | 105 |

| 5.6  | LDDL semantics with SET (main rules)                                           | 106 |

| 5.7  | Execution of source and transformed circuits described by predicates           | 108 |

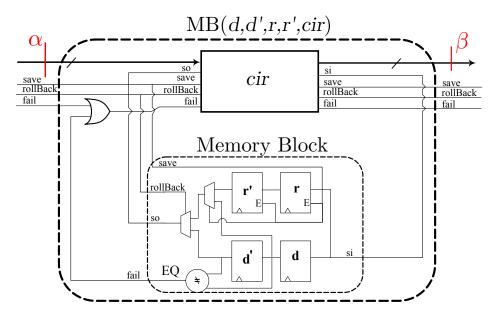

| 5.8  | The internal structure of $MB(d, d', r, r', cir)$                              | 112 |

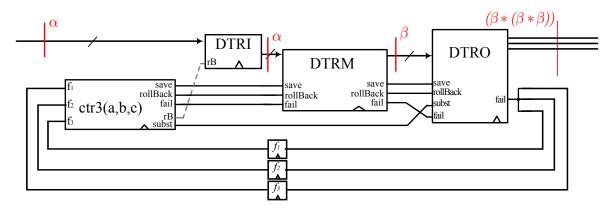

| 5.9  | DTR(C) transformation composition: the types of buses are marked with red.     | 115 |

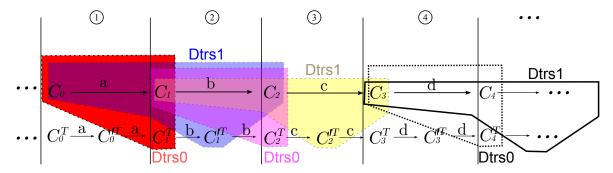

| 5.10 | DTR circuit step reduction described by predicates                             | 120 |

| 5.11 | DTR circuit stepg reduction from the state described by Dtrs0                  | 121 |

| 5.12 | Internal structure of a memory cell with an enable input                       | 123 |

| 6.1  | a) Sequential, b) parallel, and c) feedback circuit decomposition              | 131 |

# List of Tables

| 2.1.3 Hamming code $(7,4)$                                                                                                                                                   | 19 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2.0 Voter Minimization, Syntactic Analysis Step                                                                                                                            | 37 |

| 3.3.1 Operators for 4-value logic domain $D_1$                                                                                                                               | 38 |

| 3.3.3 Operators for 4-value logic domain $D_2$                                                                                                                               | 40 |

| 3.7.0 Voter Minimization, SEU model, Boolean domains $D_1 \mid D_2 \mid D_3$                                                                                                 | 47 |

| 3.7.0 Voter Minimization, SET model, Boolean domains $D_1 \mid D_2 \mid D_3$                                                                                                 | 50 |

| 3.7.0 Time and memory resources to calculate the RSS                                                                                                                         | 51 |

| 3.7.0 Frequency and area gain of optimized $vs$ full TMR                                                                                                                     | 52 |

| 4.3.2 Switching process $1 \mapsto 2. \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                 | 75 |

| $4.3.2$ Switching process $1 \mapsto 3. \dots $                        | 75 |

| 01                                                                                                                                                                           | 76 |

| $4.3.2$ Recovery procedure - DyTR <sup>3</sup> , mode $3. \dots \dots$ | 77 |

| 4.3.3 Switching process $1 \mapsto 2 \mapsto 1$ ; '?' is a don't care                                                                                                        | 80 |

| 4.4.6 Recovery process in DTR circuits                                                                                                                                       | 91 |

| 4.4.7 Recovery Process: Input/Output Buffers Reaction for an Error Detection at                                                                                              | ഹ  |

| cycle $i$                                                                                                                                                                    | 93 |

| 5.4.4 Cases of glitched signal (introduced by steps) and the resulting state corruptions. 1                                                                                  | 22 |

# Glossary

ALU Arithmetic Logic Unit.

ASIC Application-Specific Integrated Circuit.

**BDD** Binary-Decision Diagram.

**CIC** Calculus of Inductive Constructions.

CTL Computation Tree Logic.

**DMR** Double Modular Redundancy.

**DTR** Double-Time Redundant Transformation.

**ECC** Error-Correcting Code.

**EDA** Electronic Design Automation.

**ESA** European Space Agency.

**FF** flip-flop.

FPGA Field-Programmable Gate Array.

**FSM** Finite State Machine.

**HDL** Hardware Description Language.

IC Integrated Circuit.

ITP Interactive Theorem Prover.

LTL Linear Temporal Logic.

$\mathbf{MBU}$  Multiple-Bit Upset.

MVFS Minimum Vertex Feedback Set.

**RSS** Reachable State Space.

RTL Register-Transfer Level.

**SAA** South Atlantic Anomaly.

**SED** Single Event Disturb.

**SEFI** Single-Event Functional Interrupt.

viii Glossary

**SEGR** Single Event Gate Rupture.

**SEL** Single-Event Latchup.

**SER** Soft-Error Rate.

**SET** Single-Event Transient.

**SEU** Single-Event Upset.

**SHE** Single Hard Error.

**STMR** Selective Triple-Modular Redundancy.

${\bf TMR}$  Triple-Modular Redundancy.

${\bf TTR}$  Triple-Time Redundant Transformation.

${f VLSI}$  Very-Large-Scale Integration.

# Introduction

- "In 2008, a Quantas Airbus A330-303 pitched downward twice in rapid succession, diving first 650 feet and then 400 feet. ... The cause has been traced to errors in an on-board computer suspected to have been induced by cosmic rays." [7]

- "Canadian-based St. Jude Medical issued an advisory to doctors in 2005, warning that single bit-flips in the memory of its implantable cardiac defibrillators could cause excessive drain on the unit's battery." [8]

This list could be continued by other examples of drastic consequences of fault occurrences. Proper circuit functionality even under perturbations and faults has been always crucial in aerospace, defense, medical, and nuclear applications. Circuit tolerance towards transient faults (non-destructive, non-permanent) is an important research topic and an unavoidable characteristic of any circuit used in safety critical applications. Common sources of faults are natural radiation, such as neutrons of cosmic rays and alpha particles of packing or solder materials, capacitive coupling, electromagnetic interference, etc [7,9]. Nowadays, technology shrinking and voltage scaling increase electronics susceptibility and the risk of fault occurrences.

Circuit engineers use fault-tolerance techniques to mask or, at least, to detect faults. Regardless of the chosen technique, this step increases the level of complexity of the whole design. Commonly used simulation-based methodologies are not able to fully verify even the functional correctness due to the huge number of possible execution cases. The verification of fault-tolerance properties by checking all fault injection scenarios raises the order of complexity. Non-exhaustive manual checks or simulation-based techniques are error-prone and may miss a circuit corruption scenario that leads to the loss of the circuit functionality or to degraded quality of service.

Since engineers need their implementations to be simple and correct, they mostly use Triple-Modular Redundancy (TMR), a technique that triplicates the circuit and introduces majority voters. Modern EDA tools support TMR, as well as other basic techniques such as Finite State Machine (FSM) encoding [10–12], through automatic circuit transformations. While there are other more elegant and optimized fault-tolerance techniques [13, 14], their functional correctness and fault-tolerance properties are often not guaranteed.

Ensuring correctness of fault-tolerance techniques requires mathematically based techniques for the specification, development, and verification. Formalization of fault-models, circuit designs, and specifications gives a vast opportunity to create, to optimize, and to check the correctness of fault-tolerance techniques. Showing fault-tolerance properties w.r.t. the chosen fault-model eliminates all doubts about the circuit functionality under the faults whose occurrence and type are specified by the fault-model. Thanks to this formal verification, the overall probability of the system failure is purely the probability of faults occurring outside of the fault-model.

There are many different formal methods to verify properties of systems or circuits. In this dissertation, we mainly use static symbolic analysis and theorem proving.

#### 1.1 Problems and Contributions

Throughout the dissertation, we work with circuits described at the gate level (i.e., netlists of AND, OR, NOT gates plus flip-flops (FFs) – also called memory cells). This decision offers two main advantages:

- gate-level netlists can be captured in an elementary language, which simplifies formal circuit representations (e.g., as a transition system) and correctness proofs;

- it is easier to prevent synthesis tools from optimizing (undoing) our transformations at this late stage, as well as to integrate the circuit transformations in commercial logic synthesis tools that we use for benchmarking.

We address three problems of circuit fault-tolerance: an optimization of a standard fault-tolerance technique based on static analyses, the design of several new fault-tolerance techniques based on time redundancy, and the formal proof of their functional and fault-tolerance properties.

Verification-based optimization of fault-tolerance techniques. Making a circuit fault-tolerant always leads to overheads in terms of performance and hardware resources. The circuit transformations for fault-tolerance usually do not take into account any peculiarities and functionality of the original circuit. Moreover, they do not take into account neither how the circuit is used nor what fault-tolerance properties are indeed needed. There is significant room for optimizations if we take into account the circuit original design, its utilization, and the expected fault rate. For instance, if it is known that faults are less frequent than one fault per K clock cycles, it may be possible to suppress some fault-tolerance mechanisms which would be overkill for the required fault-tolerance property. A crucial point is that, while optimizing a fault-tolerant design, we have to be sure that the fault-tolerance and functional properties are not violated. The guarantees can be given if the design, its properties, the fault-model, and the optimization procedure are formally defined and taken into account.

Our first step is to consider error-masking mechanisms in fault-tolerance techniques as an object of optimization and to develop a verification-based approach to suppress them. For instance in TMR, error-masking mechanisms are majority voters introduced after triplicated memory cells. We propose an approach to minimize the number of voters in TMR with guarantees that, after this optimization, the circuit is still tolerant w.r.t. the given fault-model [15]. While the final goal is to suppress as many voters as possible, the developed methodology clarifies how to take into account the original circuit functionality and the circuit typical use. Many circuits have native error-masking capabilities due to the structure of its combinational part, embedded FSMs, or due to the way the circuit is commonly used and communicates with the surrounding device. The developed methods take these native error-masking properties into account and identify useless voters that can be suppressed without violation of the fault-tolerance properties. We demonstrate how to consider large class of fault-models of the form "at most one bit-flip or one wire-glitch every K clock cycle", where K is a chosen parameter.

The formalization of a circuit, its typical utilization, the fault-model as well as optimization steps using static analysis distinguish this work from [16-18] where probabilistic simulation-based approaches are followed. In our case, the circuit fault-tolerance is guaranteed w.r.t. its fault-model before and after optimizations.

Universal time-redundant techniques as circuit transformations. TMR has multiple advantages as a throughput comparable to the original one and unchanged input/ouput interfaces. However, the triple permanent hardware overhead is often prohibitive. Time-redundant techniques could produce circuits several times smaller than their TMR counterparts but would obviously reduce the circuit performance. However, many safety-critical applications may accept the reduced throughput to obtain strong fault-tolerance guarantees, small hardware overhead, and flexibility. Unfortunately, to the best of our knowledge, there is no simple and trusted alternative to TMR among time-redundant fault-tolerance techniques.

We propose a circuit transformation, called Triple-Time Redundant Transformation (TTR), that automatically makes any sequential circuit triple-time redundant and capable to mask any effect of a glitch occurrence. We explain that TTR circuits can also be optimized with the aforementioned voter minimization analysis because the error-masking analysis stays the same regardless of redundancy type (hardware redundancy in TMR and time redundancy in TTR).

Second, we introduce the notion of dynamic time redundancy, a circuit property that allows it to dynamically change the level of redundancy without interrupting the computation [19]. We also propose a family of circuit transformations that implements this property. The transformed circuit may dynamically adapt the throughput/fault-tolerance trade-off by changing its redundancy level. Therefore, time-redundancy can be used only in critical situations (e.g., above the South Atlantic Anomaly (SAA) or Earth poles where the radiation level increases), during the processing of crucial data (e.g., encryption of selected data), or critical processes (e.g., a satellite computer reboot). When hardware size is limited and fault-tolerance is only occasionally needed, the proposed scheme is a better choice than TMR, which incurs a constant hardware area overhead, or than TTR which has a constant throughput cost.

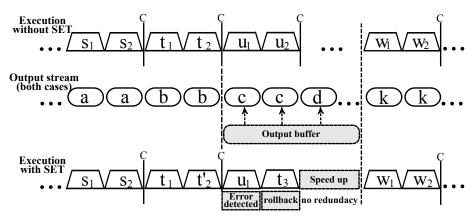

Third, we merge the proposed principle of dynamic time redundancy and a checkpointing-rollback mechanism to obtain the Double-Time Redundant Transformation (DTR). DTR is capable to recover from any transient fault consequences with only a double redundancy and without disturbing the input/output streams [20]. The recovery process remains transparent for the surrounding circuit. While TTR has similar error-masking properties, it introduces a higher throughput overhead than DTR. It allows us to state that DTR is an interesting logic-level time-redundant alternative to TMR in applications where a reduced throughput is tolerable.

All presented circuit transformations are technologically independent, do not require any specific hardware support, and are applicable to any circuit. Moreover, their fault-tolerance properties are formally provable which is crucial for safety-critical systems.

Formal proof of circuit transformation correctness. Universal fault-tolerance techniques have to be applicable to any circuit and, thus, are defined independently from a particular circuit implementation. The circuit transformations to implement these techniques are defined on the syntax of a Hardware Description Language (HDL). The functional correctness of the transformation as well as its fault-tolerance properties have to be assured independently from the circuit the transformation is applied to. The fault-tolerance properties rely on the notion of fault model that is formalized in the semantics of HDL. However, modern hardware description languages, like Verilog or VHDL, do not have formal semantics.

We propose a language-based approach to formally certify the functional and fault-

tolerance properties of circuit transformations using the Coq proof assistant [21]. We define the syntax and semantics of a simple gate-level functional HDL, called LDDL, to describe circuits. We focus on the DTR transformation whose complexity made it necessary to provide a formal proof for full assurance of its correctness. While we relied on many manual checks to design all presented transformations, only Coq allowed us to get complete correctness guarantees. The DTR transformation is defined as a recursive function on the LDDL syntax. The fault-model of the form "at most one transient fault every K cycle" is formalized in the language semantics. Proofs rely mainly on relating the execution of the source circuit without faults to the execution of the DTR circuit w.r.t. the fault-model.

To the best of our knowledge, our work is the first to certify automatic circuit transformations for fault-tolerance.

#### 1.2 Outline

The thesis is structured as follows: Chapter 2 starts by presenting background information on circuit fault tolerance (Section 2.1). It provides details about faults, their characteristics, and the techniques to make circuits fault-tolerant. Later (Section 2.2), we give an overview of the main approaches in formal hardware verification including model checking, symbolic simulation, and theorem proving. We focus on these formal techniques and their applications because they are used throughout the dissertation. The rest of the work is structured according to the problems-contributions list presented above.

Chapter 3 presents our formal solution to minimize the number of voters in TMR sequential circuits, keeping the required fault-tolerance properties. Chapter 4 starts with the presentation of the TTR circuit transformation explaining the main principle of any time-redundant transformation proposed in this dissertation. Then, it presents the idea of dynamic time redundancy and the corresponding circuit transformations with their properties. Chapter 4 ends by proposing the DTR transformation capable to mask any transient fault which makes it an interesting alternative to hardware redundant solutions. In Chapter 5, we present a language-based solution to certify circuit transformations for fault-tolerance in digital circuits. We focus on the details of the DTR correctness proof in the Coq proof assistant.

Finally, the thesis is summarized in Chapter 6, where contributions and future work perspectives are discussed.

# Circuits Fault-Tolerance and Formal Methods

Fault-tolerance has become a design characteristic of circuits as important as performance and power consumption [22]. Proper circuit functionality even under perturbations and faults has been always a crucial characteristic for safety-critical systems (e.g., aerospace, defense, and nuclear plants applications). Nowadays, circuit fault-tolerance is a research topic for many more devices due to the increased fault sensitivity caused by shrinking transistor sizes.

The integration of fault-tolerance techniques represents a new design step to already convoluted functional circuit design. These techniques can be implemented manually and the final system properties can be checked by simulations. However, as the design complexity increases, an even smaller percentage of circuit behavior scenarios can be covered by simulation methods. Consequently, it does not provide confidence in the design correctness, which is unacceptable for safety-critical applications. It is even a more challenging task to cover all possible system behaviors under faults due to the high number of fault injection cases. Formal hardware verification methods attempt to overcome the weakness of non-exhaustive simulation-based methods by proving the correspondence between the desired properties expressed in the specification and the implemented circuit design. Overall, formal methods are mathematically rigorous techniques for the specification, design, analysis, and verification of systems.

Section 2.1 provides a brief background on the topic of fault tolerance and its terminology. Section 2.1.1 explains the roots of the research domain and Section 2.1.2 provides details about faults, their classification, characteristics, and ways of modelling them. The fundamental principles and modern techniques to tolerate faults are presented in Section 2.1.3. We give an overview of the main approaches in formal hardware verification in Section 2.2: model checking and symbolic simulation in Section 2.2.1; theorem proving in Section 2.2.2. We outline the underlying theory behind these approaches and illustrate them on simple examples.

Section 2.3 concludes this chapter by explaining the research directions and motivations of the dissertation.

#### 2.1 Circuits Fault Tolerance

Fault tolerance is the ability of a system to operate according to its specification in the presence of faults [23].

The term fault is used to identify the initiating physical event whereas the term error identifies the undesired system state. The way how we model faults and their consequences is defined by a fault-model. A failure is an event that occurs when the delivered service deviates from correct one [23]. In these terms, fault tolerance is the ability to avoid failures in the presence of faults and, thus, to deliver the specified service and correct results. The

correctness of a computational process is defined by the absence of incorrect outputs. The correctness of the output result stays the most important characteristic of any computation performed by a system.

The only reason why a correctly designed system can return incorrect results and violate its specification is the existence of physical faults. They can be often avoided or their risk can be minimized by a range of measures, such as the use of highly reliable materials during the device manufacturing, the increase of voltage and frequency margins, *etc*. These measures form the fault-avoidance technique category [23]. Unfortunately, these techniques either cannot fully guarantee the absence of faults or they are not cost effective.

Nevertheless, the computational correctness under specific fault-models can be provided using fault-tolerance techniques [24]. The large range of fault-tolerance techniques has been developed at different abstraction levels of system design but all of them can be classified according to the redundancy type they rely on: hardware, time, or information redundancy. The most common techniques are discussed in Section 2.1.3.

The main principles and fault-tolerance techniques appeared with the first computers. We introduce fault tolerance from its historical retrospective in Section 2.1.1. Section 2.1.2 explains the difference between different fault types showing the main peculiarities of soft-errors. The vast research on fault-tolerance techniques is presented in Section 2.1.3 where the three fundamental redundancy types are introduced.

#### 2.1.1 Historical Roots of Fault-Tolerance

The lack of reliability in early computers of the 1940s-1950s [25, 26] gave rise to the fault-tolerance domain. Unreliable hardware components were the main issue. For instance, ENIAC [27] had only 54% of correct computations due to reliability-related issues. The EDAVAC computer of 1949 was the first one with an error-detection implemented with duplicated Arithmetic Logic Units (ALUs) [26]. Error-Correcting Codes (ECCs) for memory scrubbing and parity checking have been integrated later in 1951 in Univac I architecture [28] as well as in IBM 650 which used multiple redundant components.

New challenges for fault-tolerance research came when computers appeared in aerospace, military, and other safety critical applications in the 1960s [29]. The space programs and artificial satellites needed fault-tolerance techniques for electronics protection from harsh radiation environment. Hardware redundancy was extensively used to avoid potential costs of mission failures [30, 31].

Since the 1980s, the fourth computer generation gave birth to Very-Large-Scale Integration (VLSI) and the corresponding technological trend of feature size and power consumption minimization [32]. It leaded to an increased risk of soft errors in logic components [33,34]. If fault-tolerance techniques against soft errors could be found before only in special-purpose expensive computers (e.g., controlling aerospace missions), from now on, the increasing integration has raised the fault probability in any general-purpose system [35]. As a result, fault-tolerance techniques are nowadays used in a wide range of computer systems, from personal computers and corporate servers to embedded systems in automotive, health, railway, energy, and production industries.

#### 2.1.2 Taxonomy of Faults

Avizienis [23] classified all kind of existing faults in several subcategories (software or hardware, natural or human-made, etc). In the context of circuit fault tolerance, we consider the

subcategory of natural operational hardware faults. Natural faults, by definition, are caused by natural phenomena without human participation (versus human-made faults). Operational faults occur during the service delivery of a circuit. Thus, the development faults, caused by design mistakes, are commonly out of the scope of the fault-tolerance research domain.

Faults can be classified according to their source: *internal* and *external* ones. For instance, noise-related faults [32] or cross talks between wires can be considered as internal because their original cause is electrical disturbances inside the circuit. On the other hand, the sources of external faults exist outside of the system such as external electromagnetic fields, natural radiation in the form of neutrons of cosmic rays [36] and alpha particles emitted by packing or solder materials [37–40].

Moreover, faults can be further divided according to their persistence: they are either permanent or transient. A permanent fault is a hardware damage that is continuous in time (e.g., a wire break). Transient faults have non-destructive and non-permanent hardware effects. They manifest themselves as soft-errors and they can be represented as some information loss or a system incorrect state. Integrated Circuits (ICs) are now increasingly susceptible to transient faults [7,9].

A typical representative of natural operational hardware faults are faults caused by radiation. The increased risk of these faults results from the continuous shrinking of transistor size that makes components more sensitive to radiation [9]. Having been an object of attention in space and medical industries for many years [41], these faults represent a danger for all circuits manufactured at 90nm and smaller [22].

Space-based radiation comprises atomic particles that have been spread by stellar events within the solar system or beyond it [42]. The statistical correlation between radiation-induced faults in satellite electronics and solar activities was revealed by the Hiten satellite mission [43]. Earth's magnetosphere traps, slows, or deflects electrons, protons, and heavy ions (isotopes of atom from helium to uranium) emitted during solar events such as solar flares and mass coronal ejection, which reduces the rate and the impact of radiation particles on electronic devices used in the atmosphere. However, there is a region, called South Atlantic Anomaly (SAA), where the magnetic field extends downwards the Earth. High concentration of protons is observed in this region at lower altitudes, which constitutes a danger for satellites and planes.

But even on the ground radiation-related faults are common. Electronics materials contain high-density atoms due to their impurities. These atoms emit alpha particles that inject charges leading to soft errors [44]. Package materials are also a source of alpha particle emission and should be chosen carefully for safety-critical applications. Other sources of faults include energetic neutrons: if a neutron is captured by the nucleus of an atom in an electronic device, an alpha particle and oxygen nuclei are produced. There is a 0.95 probability that this will cause a soft error [45]. Since neutron flux is a function of altitude, neutron-based faults are more frequent for aerospace applications. For instance, computers at mountaintops experience over 10 times more soft error than at sea level [46], and electronics devices in airplanes 300 times more.

All radiation-related faults have the same physical nature, which consists in the material ionization caused by a high energetic particle hit. In particular, when a charged particle is passing through an electronic device, it ionizes the material along its path. Because of such ionization, free carriers are created around the particle track. In interaction with the internal electric field of the device, it may result in an electrical pulse or a glitch that disrupts normal

device operation. Such an effect, called a *soft error*, does not cause any permanent damage of the hardware but leads to a wrong system state. Since both supply voltage levels  $V_{DD}$  and the circuit nodes capacitance C are reducing with newer technologies, the charge stored on a circuit node  $(Q = V_{DD} \times C)$  is decreasing. It reduces the required charge from a radiation particle to reverse the node value. As a result, the increasing sensitivity is observed in both memory cells and logic network.

On the other hand, a large energy deposition by a passing particle can influence memory cells such that they loss their ability to change the state. Such *permanent* faults lead to hardware lasting rupture: Single-Event Latchup (SEL), Single Hard Error (SHE), Single Event Gate Rupture (SEGR), *etc.* SEL is a type of short circuit that may cause the loss of device functionality. High current may cause permanent device damage if the device is not power cycled as soon as high power consumption is detected. SHE leads to a stuck bit in a memory device. The output of such bit is stuck at logic 0 or 1, regardless of the input.

We focus in this dissertation on transient faults. The effects of all single transient faults can be grouped into two sub-categories, SEU and SET:

- **Single-Event Upset (SEU)** is the disturbance of a memory cell that leads to the change of its state, *i.e.*, a bit-flip. SEUs can be caused by a direct particle hit. A radiation particle creates a transient pulse that can be captured by the asynchronous loop forming the memory cell and can change its state. Historically, SEUs in memory cells were the main contributors to the fault rate due the sensitivity of memory elements [47].

- Single-Event Transient (SET) is a transient current in a combinational circuit induced by the passage of a particle. It may propagate through the combinational logic depending on its electrical characteristics and if not logically masked by circuit functionality. As a result, the outputs of the combinational circuit might be glitched and be incorrectly latched by memory cells. Since an SET may potentially lead to several bit-flips, SETs subsumes SEUs. SET-caused glitches are not attenuated because the logic transition time of gates is shorter than a typical glitch duration. Moreover, the increasing circuit clock frequencies increase the probability to latch a transient pulse. Nowadays, the combinatorial circuits are becoming as susceptible to faults as memory cells [48].

The classifications by NASA [49] and by ESA [50] also distinguish other transient faults. Some of them are given hereafter:

- **Single Event Disturb (SED)**: A momentary disturbance of the information stored in memory cells. It can manifest itself only when the information is incorrectly read out. The bits state remains correct.

- Single-Event Functional Interrupt (SEFI): A condition where the device stops operating in its normal mode, and usually requires a power reset or other special sequence to resume normal operations. It is a special case of an SEU changing an internal control signal.

- Multiple-Bit Upset (MBU): An event induced by a single energetic particle that causes multiple upsets or transients during its path through a device. The analysis of MBUs requires the knowledge about the circuit physical layout due to its spatial nature.

Even if they have different characteristics and behavior, any single radiation transient fault can be modeled as either an SEU or an SET. For instance, the effect of an SED can be modelled as an SET on the output of a memory cell. The memory cell will keep its correct state but its output will be read incorrectly. A SEFI is just a special case of an SEU: the term Single-Event Functional Interrupt (SEFI) is usually used when internal circuit design is unknown but it is necessary to describe its corruption. In such cases, one may say: "A SEFI interrupted CPU normal execution". The term SEU is more commonly used when a location of a bit-flip is known (e.g., a particular memory cell). An MBUs can be modelled as multiple SEUs [51].

#### 2.1.2.1 Fault Rate and Fault Model

Even in environments with high levels of ionizing radiations (e.g., space, particle accelerators), transient faults happen rare relatively to clock periods of modern devices. Below, we provide several observations of the fault rates in different environmental conditions.

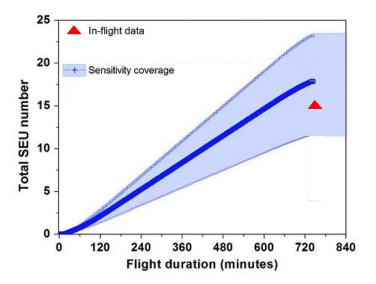

The experiments of TIMA laboratory with 1 Gbit of SRAM memory at 130 nm technology have shown that 15 soft-errors have been observed during the flight Los Angeles-Paris (23/4/2009) [1]. Among them, there were 5 SEUs and 4 MBUs. It verified the precision of the developed prediction tool MUCSA. The dependence between the flight length and the number of bit-flips is presented in Figure 2.1.

Figure 2.1: Predicted number of bit-flips vs the number of observed bit-flips [1].

In other experiments in Peru at 3800m, 1 Gbit of SRAM at 90 nm and 130 nm experienced 37 bit-flips during 5 months: 10 SEUs and 9 MBUs [1].

Soft-Error Rate (SER) can be as small as  $10^{-5}$  bit-upset/day for Vertex FPGAs [52] in terrestrial conditions.

At geosynchronous Earth orbit altitudes, Lockheed Martin Commercial Space Systems observed  $1.8 \times 10^{-10}$  errors/bit/day in SRAM  $0.25 \mu m$  devices [53]. During solar maximum condition, SER raised to  $1 \times 10^{-9}$  errors/bit/day. MBUs constituted 4-10% of all faults.

Microsemi Corporation [7] lists an extensive list which shows that the radiation-based soft-errors are widely observed and already leaded to incidents. Among others, let us cite:

• "In 2008, a Quantas Airbus A330-303 pitched downward twice in rapid succession, diving first 650 feet and then 400 feet. The cause has been traced to errors in an

on-board computer suspected to have been induced by cosmic rays."

• "Canadian-based St. Jude Medical issued an advisory to doctors in 2005, warning that SEUs to the memory of its implantable cardiac defibrillators could cause excessive drain on the unit's battery." The observed SER in defibrillators was  $9.3 \times 10^{-12}$  upsets/bit-hour [8].

Due to low fault rates on Earth or even in open space, the most common fault-model is a single fault, e.g., an SEU or an SET. If we relate SER with the number of system clock cycles between two consecutive faults, then we can introduce fault models of the form "at most n bit-flips within K cycles", denoted by SEU(n, K), and "at most n SETs within K cycles", denoted by SET(n, K).

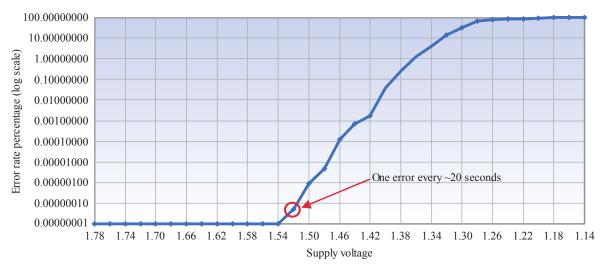

Besides radiation-related faults, it is worth to mention the faults caused by signal metastability during aggressive voltage scaling [2]. Voltage scaling is a technique to reduce circuit energy demands, it decreases the voltage in the circuit to minimize its power consumption. Figure 2.2 illustrates the dependency between voltage and error rates for an 18x18-bit multiplier at 90MHz in Xilinx XC2V250-F456-5 FPGA.

Figure 2.2: Measured error rates dependency from supply voltage [2]

As it is marked on the plot, when the voltage is 1.52 V, the error rate is one error per 20 seconds or per 1.8 billion operations. It corresponds to the fault model  $SET(1, 1.8 \times 10^9)$ .

#### 2.1.3 Conventional Fault-Tolerance Techniques

Any fault-tolerance technique is based on some sort of redundancy. There are three redundancy classes:

Hardware or spatial redundancy. It adds additional hardware resources to simultaneously produce several copies of the same computational result for their further comparison (resp. voting) to detect (resp. to mask) soft-errors. For instance, a duplicated system is capable to detect an error occurrence by comparing the states of its two redundant modules. The triplicated design can mask an error by majority voting. Additional hardware introduces the corresponding cost in terms of physical space, power, etc, but it allows avoiding significant performance degradation because redundant computations are performed in parallel.

Time or temporal redundancy. The redundant computations are performed sequentially multiple times re-using the same hardware resources. Thus, time redundancy trades-off performance for a low hardware cost. For instance, if a system re-computes its result twice for further comparison, it is capable to detect an error. If the computation is triplicated in time, the system can mask an error by voting on the redundant results.

**Information redundancy.** It adds extra information (bits) to be used for detection/correction purposes. To operate with and use this information, e.g., parity bits, a system also needs additional hardware and/or time resources that encode/decode this extra data.

Furthermore, there is an orthogonal classification of the redundancy types according to the system reaction upon error detection and the guarantees on the primary outputs correctness. In particular:

Active redundancy relies on an error-detection with a subsequent appropriate system reaction. For example, the system performs a global reset after an error-detection in any of its redundant copies.

Passive redundancy is based on fault-masking techniques to guarantee the correctness of the primary outputs. Any fault occurring in the system protected by passive redundancy does not change the system output behavior.

**Hybrid redundancy** incorporates both active and passive types of redundancy.

Since active redundancy does not guarantee the equivalence of output streams with and without fault occurrence, it is typically used in systems that can tolerate some temporal service quality degradation. As the European Space Agency (ESA) states: "In some applications it is sufficient to detect an error caused by an SEU and to flag the affected data as invalid or corrupted" [49].

The two observed classifications are orthogonal. There are systems where an error detection of active redundancy is realized through hardware duplication with comparison (hardware redundancy), error detection codes (information redundancy), or self-checking logic (time redundancy) [31].

The next three sections present hardware, time, and information redundancies in details.

#### 2.1.3.1 Hardware Redundancy

The lectures by von Neumann given in Princeton University in 1952 [54] can be considered as the first theoretical work about hardware redundancy. He proposed and analyzed Triple-Modular Redundancy (TMR) that stays to be the most popular approach for error masking in safety-critical applications.

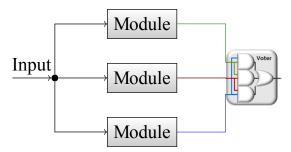

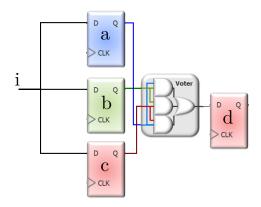

TMR relies on three redundant copies of an original system receiving the same inputs. Majority voters are introduced at the primary triplicated outputs. If at least two of three redundant outputs return correct values, the voters return the correct result, therefore masking one possible error. TMR is able to detect one or two errors and to correct one.

Double Modular Redundancy (DMR) represents the reduced version of TMR that has only two redundant modules and is only capable to detect one error. The generalized version of TMR, called N-modular redundancy, requires N redundant copies of a system to feed majority voters with N inputs. It can correct  $\lfloor \frac{N-1}{2} \rfloor$  errors and detect (N-1) errors. There are several versions of TMR that can be applied to circuits [12], in particular:

- 1. the whole circuit triplication with the insertion of a single majority voter at each primary output (as in the von Neumann's original TMR);

- 2. only memory cells are triplicated with a single voter after each triplicated cell and each primary output;

- 3. the whole circuit triplication with a single voter after each triplicated memory cell and each triplicated primary output;

- 4. the whole circuit triplication with three voters after each triplicated memory cell and each triplicated primary output.

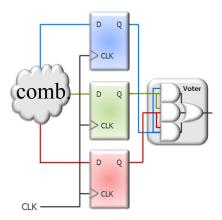

The first TMR version, depicted in Figure 2.3, is tolerant only to a single fault, temporal or permanent, occurring inside one of the redundant modules. When a fault occurs in a module, its state becomes corrupted and may stay erroneous forever if it does not have any additional error-masking mechanisms. This is why this scheme is tolerant only to a single internal fault of the modules. This TMR version may not be capable to tolerate a second fault occurring in a different module. If another fault occurs (even long after the first one) and corrupts the second module, the TMR structure would have two erroneous modules simultaneously and cannot guarantee anymore the correctness of primary outputs. Furthermore, if an SET corrupts an output voter, then the correctness of the output is not guaranteed. As a result, the first TMR modification is tolerant to the fault models (notations of Section 2.1.2.1):  $SEU(1,\infty)$  and  $SET(1,\infty)$ , provided that faults do not occur at the output voters.

Figure 2.3: TMR scheme proposed by von Neumann.

The second TMR version triplicates only memory cells introducing a single majority voter per each triplet, see Figure 2.4. This approach relies on the assumption that radiation effects cannot cause perturbations in a combinational circuit (which is not triplicated in this case). In other words, it protects only against SEUs. Indeed, an SET in the non-redundant combinational part could simultaneously corrupt three redundant memory cells and that error would not be masked after the voting on this triple. The second TMR version makes any circuit fault-tolerant to the fault model SEU(1,2). If an SEU happened every clock cycle, then one redundant cell could be corrupted at the end of the cycle i and the next fault could corrupt its redundant copy at the beginning of the cycle i + 1. In this case, the majority voting that happens after the triplicated cells would produce an incorrect result because two of three redundant cells have a wrong value.

The third version triplicates both the combinational and the sequential parts of the original circuit. Voters are inserted after each triplicated memory cell and each primary output but they are not triplicated. This scheme assumes that voters are fault-tolerant by

Figure 2.4: TMR with only cells triplication for SEU masking.

themselves. For instance, the voters could be radiation hardened and produced by a different technology than the rest of the circuit. This version can tolerate the fault models SEU(1,2) or SET(1,2) assuming no fault occurs at voters. Since the later fault-model subsumes the former one, we write just SET(1,2). Again, if faults happen every cycle, this TMR protection is not capable to mask them for the same reason as in the previous case.

The fourth TMR version works exactly as the third one but its voters are triplicated, see Figure 2.5. It tolerates the fault-model SET(1,2) without assumptions on voters. This TMR version is often referred as "full TMR" since all original circuit components and voters are triplicated. The first TMR version can be considered as the fourth one where voters after all triplicated memory cells have been suppressed.

Figure 2.5: Full TMR with a triplicated voter.

The second and the fourth TMR versions are well supported by the majority of existing Electronic Design Automation (EDA) synthesis tools like Xilinx XTMR tool [10,55], BYU Los Alamos National Laboratory B-TMR [56], Synopsys Synplify Premier [11], and Mentor Graphics Precision Hi-Rel [12]. The inclusion of TMR can be also done manually directly in VHDL, as it has been done in the LEON SPARC ESA microprocessor [49].

Since hardware redundancy introduces a high hardware overhead, it is usually used only in high reliability/availability applications (e.g., for aerospace and nuclear applications). In-

terestingly, hardware redundancy (as any other redundancy type) can be applied at different design abstraction levels, from transistors to the whole system. The NASA shuttle used five-time redundant on-board computers, the primary flight computer of Boeing 777 is triplicated [57], four-time component-level redundancy has been implemented in PPDS computer of NASA Orbiting Astronomical Observatory satellite [58], triplicated CPUs are used in automotive applications [59].

#### 2.1.3.2 Time Redundancy

The basic principle of all time redundant techniques is data re-computation for further comparison/voting. The hardware overhead of time redundancy is significantly lower than that of hardware-redundancy because the same hardware is used to re-compute. On the other hand, the performance degradation often prohibits the use of this technique in applications demanding high throughout (e.g., real-time).

We can distinguish time-redundant techniques based on the period  $\mathcal{P}$  (or granularity) of the re-computation of redundant results. For example, techniques that produce redundant information within one clock cycle have the re-computation period  $\mathcal{P} < 1$ . If a circuit recomputes its state after one cycle, then  $\mathcal{P} = 1$ ; and if it performs several times a multi-cycle computation, then  $\mathcal{P} > 1$ . The period of recomputation is connected with the abstraction level where a fault-tolerance technique is introduced: lower the level, shorter the period can be reached. We start the overview of time-redundant techniques with the low-level ones that have  $\mathcal{P} < 1$ .

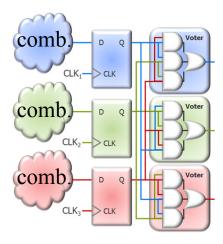

Nicolaidis et al. [3,60] presented a time-redundant IC transformation at the transistor level. Since an SET manifests itself for a limited duration of time in a combinational circuit, the circuit timing properties should be adjusted so that the correct values are present on the circuit outputs for a time duration greater than the duration of the transient fault. Consequently, if the signal is latched at three different instances of time with guarantees that a glitch can be latched only once, the majority voter after the memory cells is able to filter out the corrupted latched value. The implementation of such mechanism is presented in Figure 2.6.

Figure 2.6: Circuit realization of inter-clock time-redundant technique [3].

The three latching edges of the three clock lines are shifted relatively to each other on  $\delta$ , which is chosen based on the targeted transient pulse duration. This construction guarantees that a glitch in the combinational circuit cannot affect more than one latch, which assures the output correctness of the output latch. This time-redundant technique has an area

overhead of 15-23% and 10-15% depending on the SET pulse duration, 0.45ns and 0.15ns respectively. The performance degradation is 20-50% for 0.45ns and 10-22% for 0.15ns glitches. Fault-masking efficiency reaches 99-100%. In comparison, TMR required  $\sim 200\%$  of hardware overhead and 10-25% of performance penalty with the same circuits.

A similar technique with shifted clock edges has been presented for Field-Programmable Gate Arrays (FPGAs) [61,62]. The technique reaches 97-100% error-detection efficiency. Both in Application-Specific Integrated Circuits (ASICs) and FPGAs, the techniques require a strong control of the clock lines. In addition, these techniques usually do not guarantee 100% SET fault coverage.

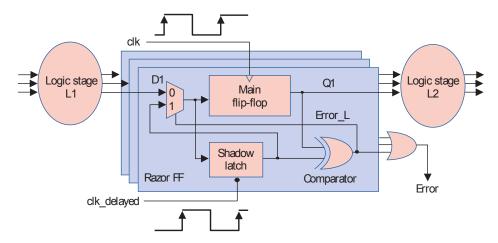

The same principle of shifted clock has been used for error-detection in the Razor CPU pipeline architecture and its variants [2, 63–65] where aggressive voltage scaling increases fault risks. A "shadow" latch with its own delayed clock line is annexed to each original memory cell of original pipeline stages, as shown in Figure 2.7. Both the main memory cell and its shadow latch take the same data and the comparison between their values implements an error detection mechanism. It may happen that the combinational stage logic L1 exceeds the intended delay due to subcritical voltage operation caused by aggressive voltage scaling. In this case, the main memory cell does not latch the correct data but the "shadow" latch successfully saves the correct combinational output because it operates using the delayed clock.

Figure 2.7: Razor flip-flop for a pipeline stage [2].

The recovery phase starts after an error-detection. Since the "shadow" latches contain the correct information, they can be used to re-calculate the values for the main memory cells in the pipeline. One of the proposed mechanisms [2] involves a pipeline control logic that stalls the entire pipeline for one cycle. This additional clock period allows every stage to re-compute its result using "shadow" latches values. This mechanism is a typical representative of an active fault-tolerance technique that imposes a performance penalty after an error-detection. Being developed to tolerate soft-errors to organize a safe voltage scaling, these techniques have a performance penalty as low as 0-2.5% while providing near 100% fault masking. However, all the mentioned restrictions (precise time properties tunings, additional clock lines, pipelined architecture) prevent the use of these approaches for FPGAs, where special circuitries to implement these techniques are not normally available in standard synthesis tools for commercial off-the-shelf FPGAs.

At Register-Transfer Level (RTL), time-redundancy can be realized in many forms with

different periods of re-computation. For instance, let us assume that an original circuit computes and returns the result during n clock cycles (a block of information). Its triple-time redundant version with  $\mathcal{P} = n$  works according to the next three-step scenario:

- 1. It fully computes and stores the result a first time. It takes n cycles.

- 2. It re-computes and stores the result a second time. It takes another n cycles.

- 3. Finally, it re-computes and stores the result a third time, again during n cycles.

With three independently calculated outputs, a corruption of any of them can be masked by voting. This approach is similar to software fault-tolerance techniques where a program is re-executed three times to produce three independent redundant computation results.

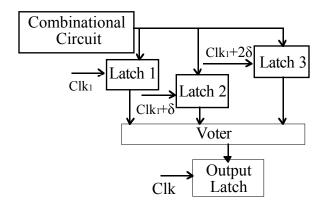

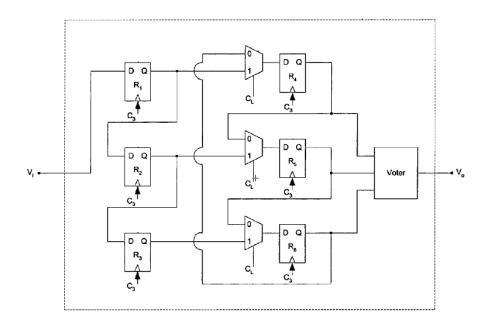

McElvain [4] presents an automatic circuit transformation technique to insert time-redundancy with the period  $\mathcal{P}=1$ . The combinational circuit is re-used three times consecutively to calculate three times the same bits. In other words, the combinational circuit is time-multiplexed. Every single bit is recomputed three times first before its successive bit is recomputed three times. The input and output streams of the circuit can be seen as upsampled (x3) versions of the corresponding input and output streams in the original circuit. A voting element depicted in Figure 2.8 is introduced to each output of the combinational circuit.

Figure 2.8: Voting element for a time-multiplexed circuit [4].

The memory cells  $R_1$ ,  $R_2$ , and  $R_3$  in each voting element are used to record the three successively recomputed bits. When the pipeline  $R_1 - R_2 - R_3$  is filled with redundant bits, the signal  $C_L$  is raised and the content of  $R_1 - R_3$  propagates to three cells  $R_4 - R_6$ . During the next three clock cycles these three redundant bits circulate in the loop  $R_4 - R_5 - R_6 - R_4$  ( $C_L = 0$ ) and the voter that takes the outputs of  $R_4 - R_6$  cells is capable to vote three times on the same redundant bits. Note that during the circulation of one bit-triple in  $R_4 - R_6$  cells, the cells  $R_1 - R_3$  are being filled with the next redundant bit-triple. This three-cycle period

repeats. As a result, the output of a voting element is error-free even if the combinational part experiences an SET.

We can notice that there is a single point of failure in this voting element (Figure 2.8): if the signal  $C_L$  is corrupted by an SET, it may corrupt two or even three cells  $R_4 - R_6$  that contain redundant information. In this case, the voter cannot mask an error.

Since each input and output is triplicated in time when the period  $\mathcal{P}=1$ , this fault-tolerant scheme can be considered as stream-oriented. This scheme is a typical representative of passive fault-tolerance techniques where error masking does not require a dedicated recovery process.

As an active fault-tolerance technique, we can consider schemes based on checkpointing and rollback. The circuit state (the content of its memory cells) is saved periodically and re-stored after an error detection. The circuit rolls-back to its previous correct state and re-computes the results previously computed. Since it relies on re-computation, this group of techniques can be also considered as time-redundant. Thus, the Razor architecture implements an active fault-tolerance technique with "shadow" latches keeping the circuit correct state.

Carven Chan et al. [66] show how checkpointing/rollback mechanisms can be automatically inserted at register-transfer level. The used Backwards Error Recovery (BER) takes snapshots of the system states and after an error detection rolls back within one clock cycle. Until this work, BER had been implemented only manually, e.g., for processors [67,68]. Using syntactic additions to standard Verilog HDL, the main circuit design is separated from the BER mechanism. The approach requires minimal modifications of an original Verilog design. A user must choose which signals to checkpoint, the conditions when their values are saved, the error-detection conditions when the states are restored, etc. All these circuit fault-tolerance actions are described as guarded operations [69] on the original circuit design. While flexibility and generality of this automatic approach makes it applicable to almost all cases where checkpointing/rollback are needed, the user-defined error-detection condition in the form of assertions does not guarantee to take into account all possible transient fault effects. It has not been investigated if a transient fault can corrupt simultaneously both a circuit and its checkpointed snapshot. If such possibility exists, the rollback may be performed to a wrong state. Therefore, its flexibility requires a deep understanding of the original circuit to make the proper decisions about checkpointing and rollback conditions. Similar approaches have been proposed in [70] with multi-cycles rollback from a register file and in [14] at a gate-level.

General hardware checkpointing/rollback techniques have also been proposed as microarchitectural transformations [14]. However, the resulting circuit is tolerant to SEUs but not to SETs. Indeed, an SET may corrupt both a cell (i.e., the current state) and its copy (i.e., its checkpoint) because they use the same input data signal that can be glitched by the same SET. As a result, when an error is detected, the rollback may return the circuit to an incorrect state.

The checkpointing/rollback mechanisms allow the system to reduce the performance penalty introduced by time-redundancy. Instead of triple-time redundancy a system can use a double-time redundant scheme with checkpointing/rollback to mask an error. As a result, the throughput loss can be reduced from triple to double one but the system obtains the same fault-tolerance properties. In general, the recovery (rollback and a third re-computation) disturbs the output stream and is not transparent to the surrounding circuit.

Besides performance penalty, another disadvantage of time-redundancy is that it does not mask a permanent fault because all redundant results computed on a permanently corrupted hardware will be wrong. In comparison, a single permanent fault in TMR does not lead to erroneous results since only one redundant module is out of order. TMR will however stop working upon the next fault (even transient) happening in another redundant module than the permanently corrupted one. Nevertheless, there are mixed forms of time redundancy with input data encoding (and an additional hardware cost) that are capable of detecting the effect of a permanent fault. One of them is alternating logic [71] that achieves error detection using time redundancy. The original combinational circuit is modified to implement a self-dual function. The first cycle, the signals propagate through the combinational circuit and its outputs are saved. The second cycle, an inverted version of the same signals is given to the combinational circuit. Comparing these two results, a circuit can detect a fault.

#### 2.1.3.3 Information Redundancy

Information redundancy adds extra bits to data, often using encoding, and uses this extra information for error-detection and error-correction. The most common circuit fault-tolerance techniques that use information redundancy are FSM encoding and memory encoding using Error-Correcting Codes (ECC).

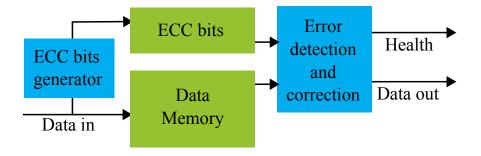

Error-Correcting Codes. Error-Correcting Codes (ECCs) are mainly used for memory storage protection [72]. ECC can protect large memory blocks imposing low hardware overhead but it is not so efficient when used for small memory storages or distributed elements [73]. They can be automatically introduced in a circuit design as shown in Figure 2.9. The integration of ECC requires extra memory and extra combinational logic in the form of an "ECC bit generator" and an "Error detection and correction" circuit. The ECC bit generator creates extra ECC bits from the stored data according to the chosen encoding scheme, e.g., Hamming(7,4) encoding [74]. When reading the memory, the ECC detection and correction logic checks the combination of ECC bits and regular data from the data memory. If no error is detected, the regular data is passed through unchanged. A single bit error can be corrected using ECC bits, e.g., in Hamming(7,4). Additionally, the "Health" flag indicates error detection. In Hamming(7,4) scheme, two errors also can be detected but not corrected and the ECC scheme can only signal about this event to the surrounding circuit.

Figure 2.9: Memory storage with ECC protection [5].

|      | 1     | 2     | 3     | 4     | 5     | 6     | 7     |

|------|-------|-------|-------|-------|-------|-------|-------|

| Data | $p_0$ | $p_1$ | $u_3$ | $p_2$ | $u_2$ | $u_1$ | $u_0$ |

| 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1    | 1     | 1     | 0     | 1     | 0     | 0     | 1     |

| 2    | 0     | 1     | 0     | 1     | 0     | 1     | 0     |

| 3    | 1     | 0     | 0     | 0     | 0     | 1     | 1     |

| 4    | 1     | 0     | 0     | 1     | 1     | 0     | 0     |

| 5    | 0     | 1     | 0     | 0     | 1     | 0     | 1     |

| 6    | 1     | 1     | 0     | 0     | 1     | 1     | 0     |

|      |       |       |       |       |       |       |       |

| 13   | 1     | 0     | 1     | 0     | 1     | 0     | 1     |

| 14   | 0     | 0     | 1     | 0     | 1     | 1     | 0     |

| 15   | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

Table 2.1.3: Hamming code (7,4).

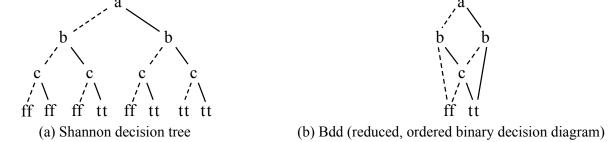

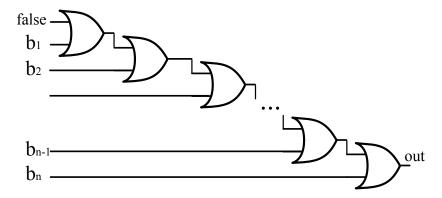

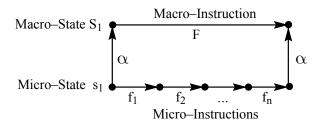

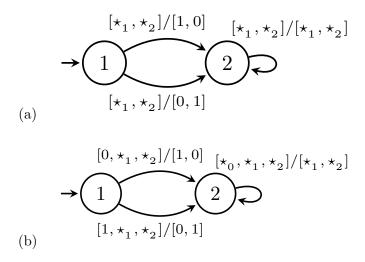

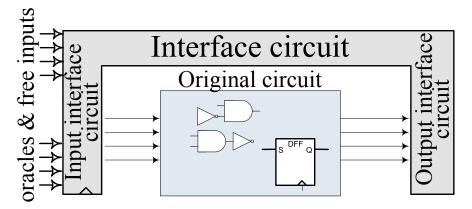

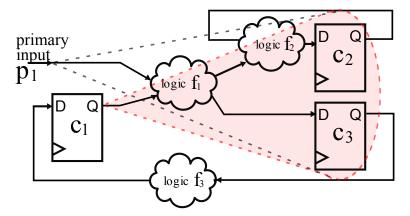

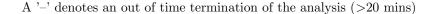

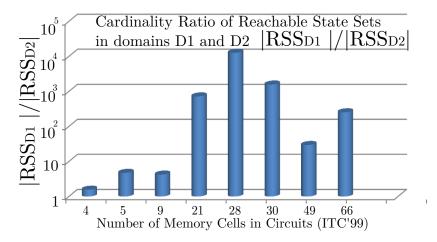

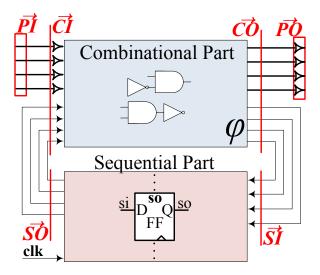

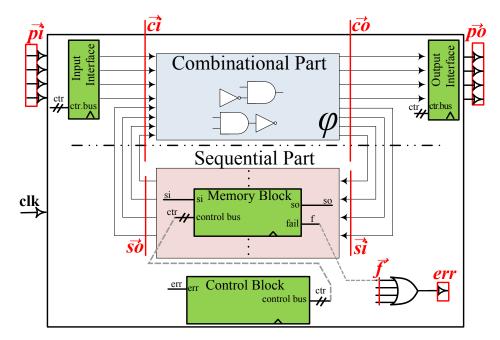

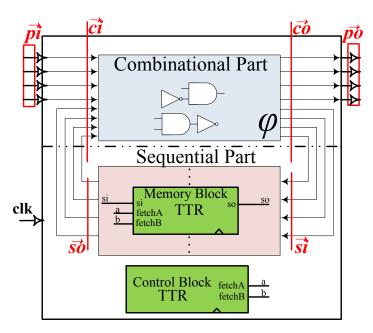

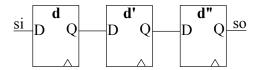

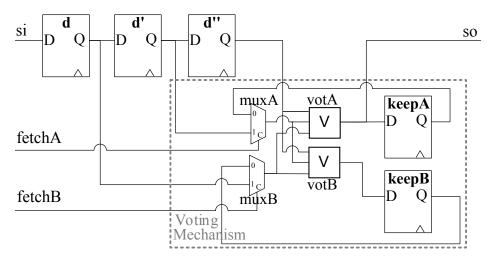

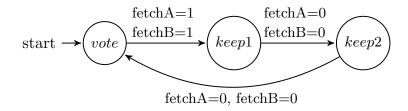

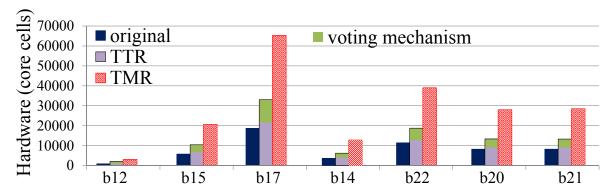

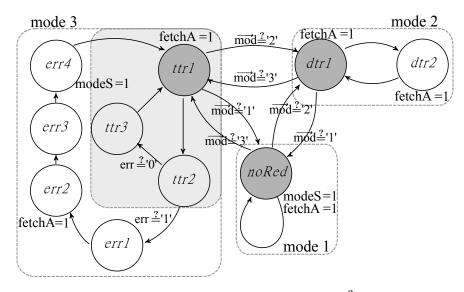

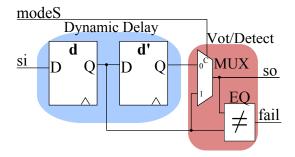

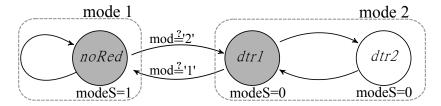

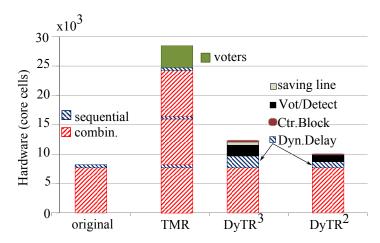

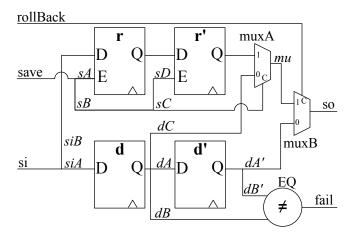

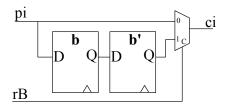

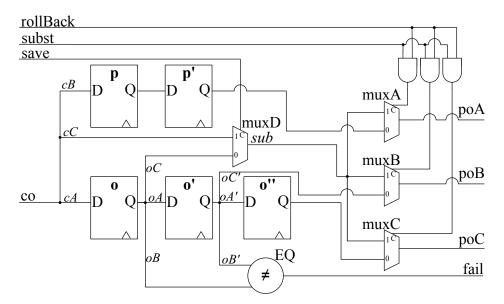

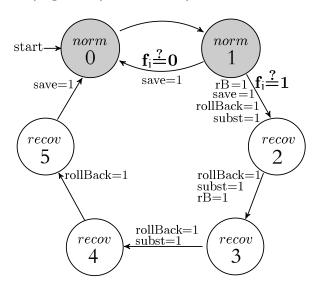

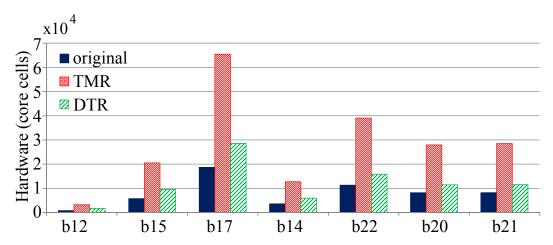

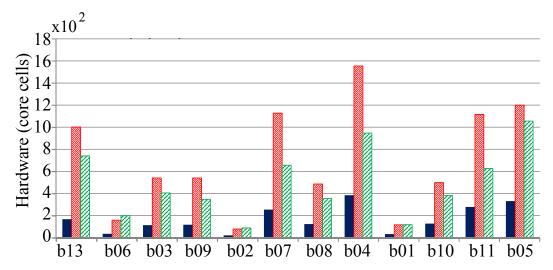

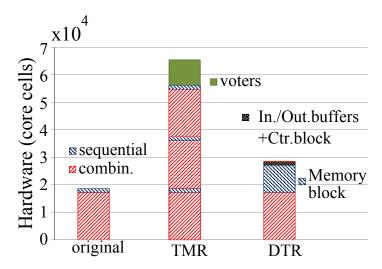

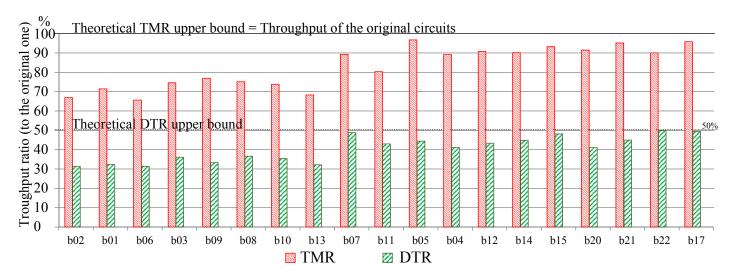

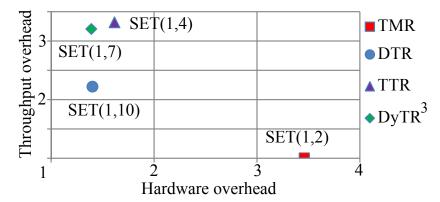

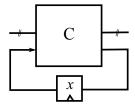

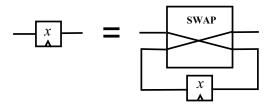

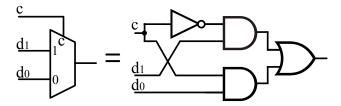

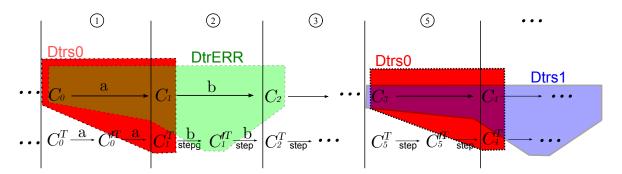

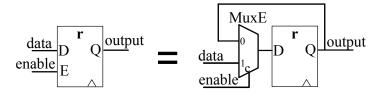

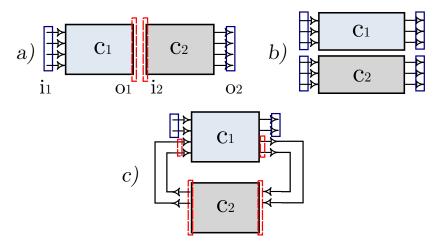

Historically, ECC has been introduced due to the high soft error rate in large memory banks. However, it introduces resilience against other fault types, e.g., a permanent fault in a single bit (a stuck bit).