# Electrical characterization and modeling of advanced SOI substrates

Luca Pirro

### ▶ To cite this version:

Luca Pirro. Electrical characterization and modeling of advanced SOI substrates. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2015. English. NNT: 2015GREAT096. tel-01254695

# HAL Id: tel-01254695 https://theses.hal.science/tel-01254695

Submitted on 12 Jan 2016  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ GRENOBLE ALPES

# THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES (NENT)

Arrêté ministériel : 7 août 2006

Présentée par

# Luca Pirro

Thèse dirigée par **Sorin CRISTOLOVEANU** et codirigée par **Irina IONICA**

préparée au sein du Laboratoire IMEP-LAHC dans l'École Doctorale EEATS

# Caractérisation et modélisation électrique de substrats SOI avancés

Thèse soutenue publiquement le **24 Novembre 2015**, devant le jury composé de :

Mme. Cristell MANEUX

Professeur des Universités, Université de Bordeaux, Rapporteur

M. Alexander ZASLAVSKY

Professeur des Universités, Brown University, Rapporteur

M. Jean-Pierre RASKIN

Professeur des Universités, Université catholique de Louvain, Membre

M. Frédéric ALLIBERT

Docteur, Ingénieur R&D, SOITEC, Membre

M. Gérard GHIBAUDO

Directeur de Recherche au CNRS, IMEP-LAHC, Invité

M. Sorin CRISTOLOVEANU

Directeur de Recherche au CNRS, IMEP-LAHC, Directeur de thèse

Mme. Irina IONICA

Maître de Conférences, IMEP-LAHC, Co-encadrante de thèse

To my family and to my girlfriend

# Acknowledgements

I would like to thank all the members of the jury for the time spent to evaluate this work and attend my Ph.D defense. Their comments/remarks allowed me to further improve this manuscript and gave me interesting ideas for future research. Thank you, Prof. Cristell Maneux, Prof. Alexander Zaslavsky, Prof. Jean-Pierre Raskin and Dr. Frédéric Allibert.

I would like to thank my supervisors, Prof. Sorin Cristoloveanu and Prof. Irina Ionica, for constant support and teaching. Thanks to them I have largely improved my professional knowledge. Moreover, I really appreciated the discussions and relations with them.

I am also very grateful to Prof. Gérard Ghibaudo for constant support and help. Despite the fact I was not officially one of his Ph.D. students, he gave me several suggestions and these results were obtained also thanks to him.

Particular acknowledges to Xavier Mescot and Martine Gri. Their help and support in the characterization laboratory were priceless. Without them this thesis would be of lesser quality.

I would also like to thank all my colleagues at IMEP-LAHC (and not only). Special thanks to my office-mates in A-287. They helped me during these three years and they supported me during the difficult periods. Professional and personal discussions have been the key to this successful Ph.D.

The SOI samples were provided by Soitec<sup>™</sup>.

I would like to also thank Dr. Lukas Czornomaz, Dr. Vladimir Dijara and Dr. Jean Fomperyne from IBM for the collaboration with them in Ruschilikon (CH). In one month I learned a lot, and I had the chance to see a different working approach. It was very interesting for me.

I would like to thank Dr. Julie Widiez, Mathilde Lemang and Sebastien Sollier from the CEA, for their collaboration on the characterization of III-V materials.

There are a lot of other people who helped/supported me during this work (directly or indirectly). Even if their names are not present in this list, I really appreciated their help and working with them. To all of them I give my deepest and most grateful thanks.

I was very lucky to meet and know all of you. Thanks!

# Abstract/Résumé

#### Title: Electrical characterization and modeling of advanced SOI substrates

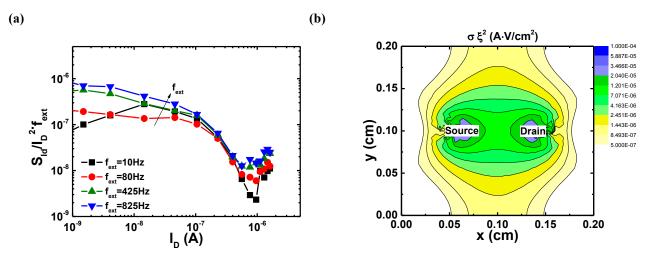

Silicon-on-insulator (SOI) substrates represent the best solution to achieve high performance devices. Electrical characterization methods are required to monitor the material quality before full transistor fabrication. The classical configuration used for SOI measurements is the pseudo-MOSFET. In this thesis, we focused on the enrichment of techniques in  $\Psi$ -MOSFET for the characterization of bare SOI and III-V wafers. The experimental setup for static  $I_D$ -V<sub>G</sub> was improved using a vacuum contact for the back gate, increasing the measurement stability. Furthermore, this contact proved to be critical for achieving correct capacitance values with split-CV and quasi-static techniques (QSCV). We addressed the possibility to extract Dit values from split-CV and we demonstrated by modeling that it is impossible in typical sized SOI samples because of the time constant associated to the channel formation. The limitation was solved performing QSCV measurements. Dit signature was experimentally evidenced and physically described. Several SOI structures (thick and ultra-thin silicon films and BOX) were characterized. In case of passivated samples, the QSCV is mostly sensitive to the silicon film-BOX interface. In non-passivated wafers, a large defect related peak appears at constant energy value, independently of the film thickness; it is associated to the native oxide present on the silicon surface. For low-frequency noise measurements, a physical model proved that the signal arises from localized regions surrounding the source and drain contacts.

Keyword: Silicon-on-insulator (SOI), pseudo-MOSFET (Ψ-MOSFET), static I<sub>D</sub>-V<sub>G</sub>, split-CV, quasi-

static capacitance (QSCV), low-frequency noise (LFN), III-V materials.

#### Titre: Caractérisation et modélisation électrique de substrats SOI avances

Les substrats Silicium-sur-Isolant (SOI) représentent la meilleure solution pour obtenir des dispositifs microélectroniques ayant de hautes performances. Des méthodes de caractérisation électrique sont nécessaires pour contrôler la qualité SOI avant la réalisation complète de transistors. La configuration classique utilisée pour les mesures du SOI est le pseudo-MOFSET. Dans cette thèse, nous nous concentrons sur l'amélioration des techniques autour du  $\Psi$ -MOFSET, pour la caractérisation des plaques SOI et III-V. Le protocole expérimental de mesures statiques I<sub>D</sub>-V<sub>G</sub> a été amélioré par l'utilisation d'un contact par le vide en face arrière, permettant ainsi d'augmenter la stabilité des mesures. De plus, il a été prouvé que ce contact est essentiel pour obtenir des valeurs correctes de capacité avec les méthodes split-CV et quasi-statique. L'extraction des valeurs de Dit avec split-CV a été explorée, et un model physique nous a permis de démontrer que ceci n'est pas possible pour des échantillons SOI typiquement utilisés, à cause de la constante de temps reliée à la formation du canal. Cette limitation a été résolue un effectuant des mesures de capacité quasi-statique (QSCV). La signature des  $D_{it}$  a été mise en évidence expérimentalement et expliquée physiquement. Dans le cas d'échantillons passivés, les mesures QSCV sont plus sensibles à l'interface silicium-BOX. Pour les échantillons non passivés, un grand pic dû à des défauts d'interface apparait pour des valeurs d'énergie bien identifiées et correspondant aux défauts à l'interface film de silicium-oxyde natif. Nous présentons des mesures de bruit à basses fréquences, ainsi qu'un model physique démontrant que le signal émerge de régions localisées autour des contacts source et drain.

**Mots cles:** Silicium-Sur-Isolant (SOI), pseudo-MOSFET ( $\Psi$ -MOSFET), statique I<sub>D</sub>-V<sub>G</sub>, split-CV, capacité quasi-statique (QSCV), bruit basse fréquence (LFN), semiconducteurs III-V.

# **Table of Contents**

| Acknowledgements |                                                                |    |

|------------------|----------------------------------------------------------------|----|

| Abstract/Rés     | sumé                                                           | v  |

| Chapter I: G     | eneral introduction                                            | 1  |

| I.1 MO           | S transistors: state of art and trends                         | 3  |

| I.2 SOI          | substrates                                                     | 9  |

| I.3 Obj          | ectives and organization of the thesis                         | 12 |

| Chapter II: I    | Pseudo-MOSFET for SOI characterization                         | 13 |

| II.1 The         | state-of-art in SOI electrical characterization                | 15 |

| II.2 Prin        | nciple of $\Psi$ -MOSFET and parameter extraction methods      | 17 |

| II.3 Imp         | pact of measurement                                            | 23 |

| II.3.1           | Measurement time setup                                         | 23 |

| II.3.2           | Quality of back contact                                        | 23 |

| II.3.3           | Role of the probes                                             | 24 |

| II.3.4           | Passivated top silicon film                                    | 30 |

| II.4 Exte        | ension of Ψ-MOSFET to new materials: III-V-on-insulator        | 32 |

| II.4.1           | Material characterization before bonding                       | 32 |

| II.4.2           | Ψ-MOSFET with pressure probes on III-V-on-insulator (III-V-OI) | 34 |

| II.4.3           | Ψ-MOSFET with metal contacts on III-V-OI                       | 35 |

| II.4.4           | Preliminary results of III-V transistors                       | 39 |

| II.5 Cor         | clusions and perspectives                                      | 41 |

| Chapter III:     | Split-CV in Ψ-MOSFET                                           | 43 |

| III.1 II         | ntroduction                                                    | 45 |

| III.1.1          | Split-CV in MOSFET devices                                     | 45 |

| III.1.2          | Split-CV in pseudo-MOSFET configuration: state of the art      | 48 |

| III.2 E          | Effective surface and improved measurement setup               | 51 |

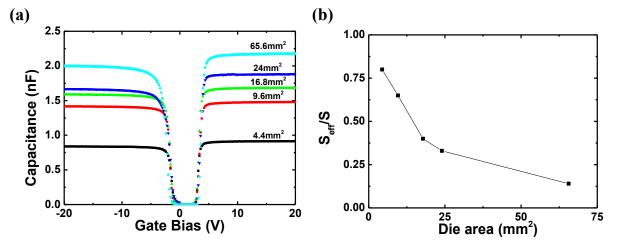

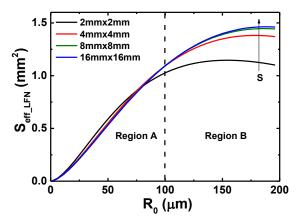

| III.2.1          | Dependency of S <sub>eff</sub>                                 | 51 |

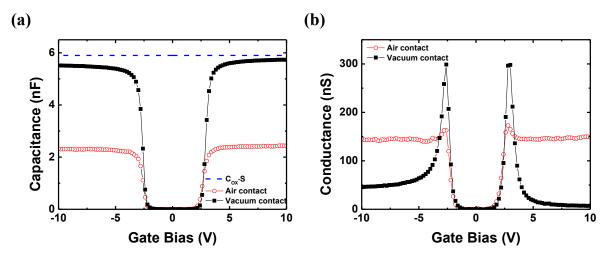

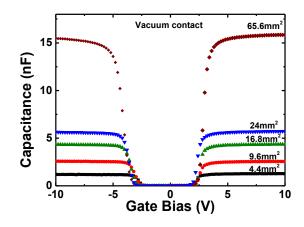

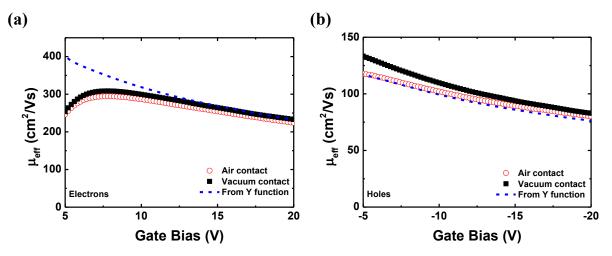

| III.2.2          | Improved measurement setup                                     | 52 |

| III.2.3          | Robustness of the technique (probe effects)                    | 56 |

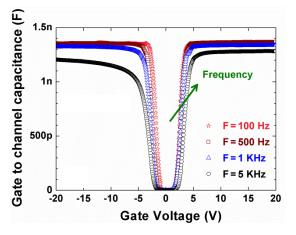

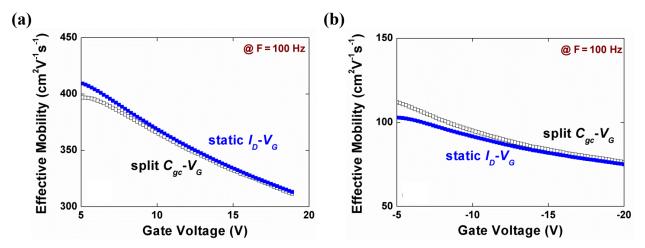

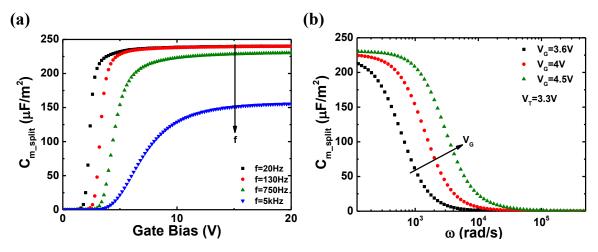

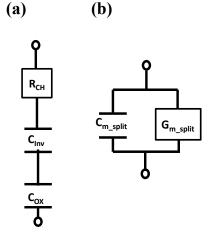

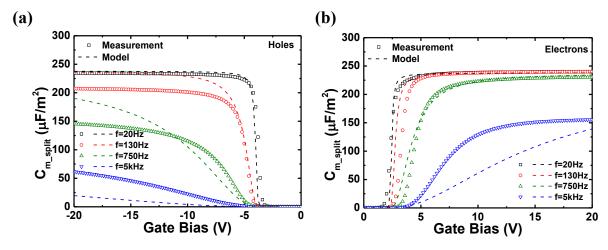

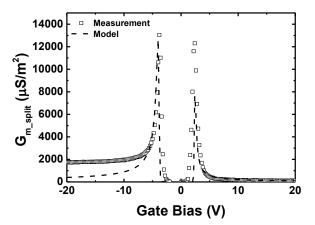

| III.3 F       | Frequency effects                                                      | . 59 |

|---------------|------------------------------------------------------------------------|------|

| III.3.1       | Model derivation                                                       | . 59 |

| III.3.2       | Model validation                                                       | . 61 |

| III.3.3       | <i>D<sub>it</sub></i> signature                                        | 65   |

| III.4 C       | Conclusions and perspectives                                           | 71   |

| Chapter IV:   | Quasi-static capacitance in Ψ-MOSFET                                   | 73   |

| IV.1 I        | ntroduction: quasi-static CV in MOS structures                         | 75   |

| IV.2 (        | Quasi-static capacitance in pseudo-MOSFET                              | 76   |

| IV.2.1        | Basics of QSCV for Ψ-MOSFET                                            | 76   |

| IV.2.2        | Comparison with LCR meter measurements                                 | 78   |

| IV.3 I        | mpact of measurement parameters                                        | 79   |

| IV.3.1        | Impact of back contact quality                                         | 79   |

| IV.3.2        | Impact of the probes                                                   | 80   |

| IV.3.3        | Impact of scan direction                                               | 81   |

| IV.4 <i>L</i> | D <sub>it</sub> model                                                  | 82   |

| IV.4.1        | Model derivation                                                       | 82   |

| IV.4.2        | Model validation                                                       | . 87 |

| IV.5 <i>I</i> | D <sub>it</sub> extraction procedure                                   | 91   |

| IV.6 C        | Characterization of non-passivated samples                             | 94   |

| IV.6.1        | Traps charging procedure                                               | . 95 |

| IV.6.2        | Example of <i>D<sub>it</sub></i> extraction for non-passivated samples | 99   |

| IV.7 S        | Surface potential computation                                          | 102  |

| IV.8 C        | Comparison of $D_{it}$ profiles for different samples                  | 105  |

| IV.9 C        | Conclusions and perspectives                                           | 109  |

| Chapter V:    | Low-frequency noise in Ψ-MOSFET                                        | 111  |

| V.1 I         | ntroduction to low-frequency noise                                     | 113  |

| V.1.1         | Noise parameters: the Power Spectral Density of a signal               | 114  |

| V.1.2         | LFN in MOSFETs                                                         | 115  |

| V.1.3         | State of art of LFN in pseudo-MOSFET                                   | 119  |

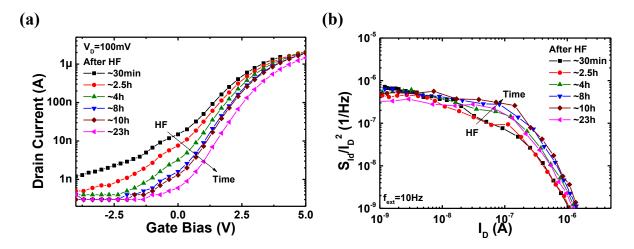

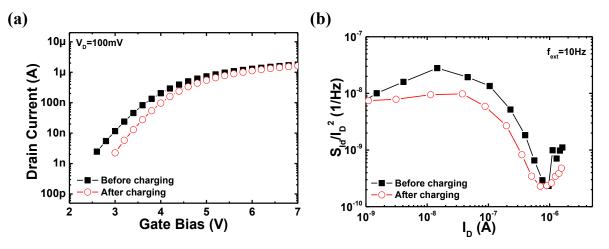

| V.2 I         | LFN characterization in Ψ-MOSFET                                       | 120  |

| V.2.1                                                                                     | Measurement setup                                   | 120                                                         |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|

| V.2.2                                                                                     | Reproducibility issues                              | 123                                                         |

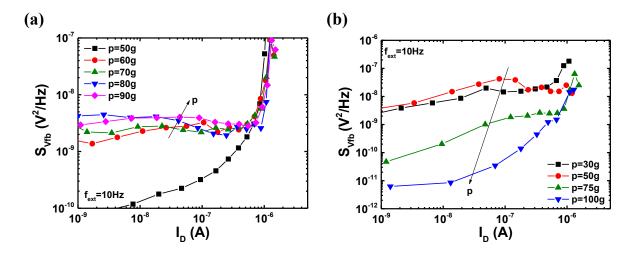

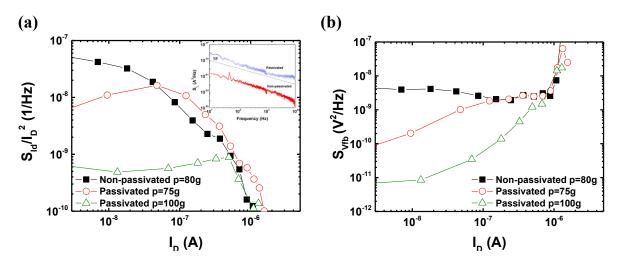

| V.2.3                                                                                     | Probe pressure impact                               | 125                                                         |

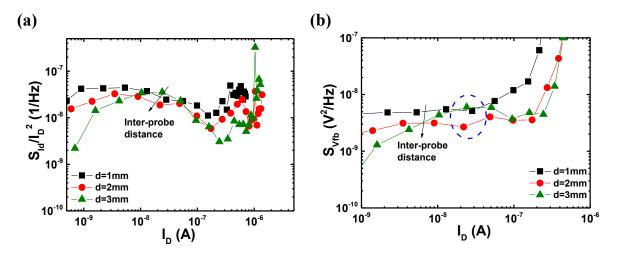

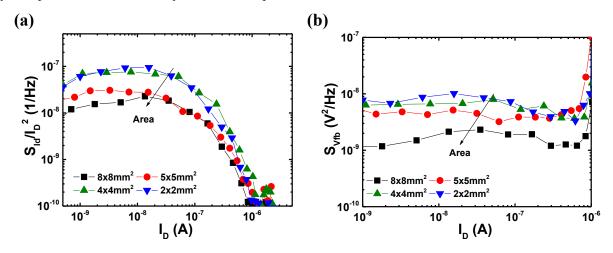

| V.2.4                                                                                     | Impact of inter-probe distance and die area         | 127                                                         |

| V.3 I                                                                                     | LFN in inhomogeneous material                       | 129                                                         |

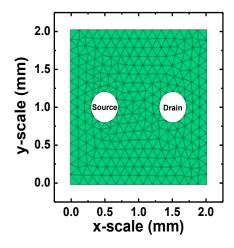

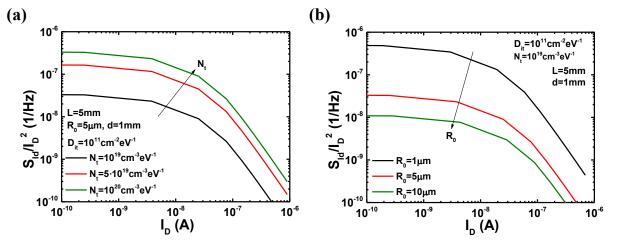

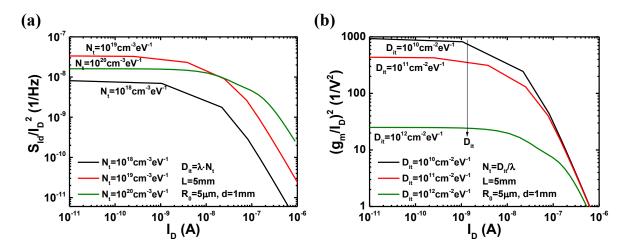

| V.3.1                                                                                     | Physical model                                      | 129                                                         |

| V.3.2                                                                                     | Computation of LF-noise                             | 131                                                         |

| V.4 I                                                                                     | Effective surface in LF-noise                       | 135                                                         |

| V.4.1                                                                                     | Why an effective surface?                           | 135                                                         |

| V.4.2                                                                                     | Quantification of effective surface                 | 136                                                         |

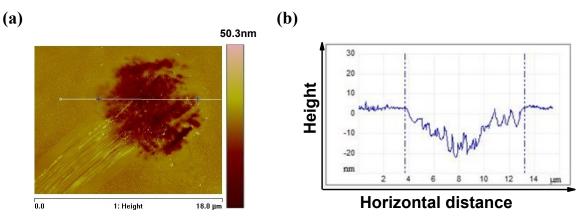

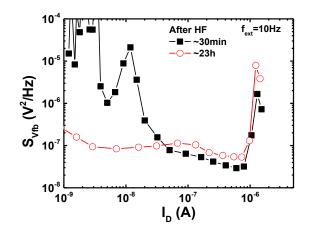

| V.5 I                                                                                     | Probe penetration effects                           | 138                                                         |

| V.5.1                                                                                     | Experimental evidences                              | 138                                                         |

|                                                                                           |                                                     |                                                             |

| V.5.2                                                                                     | Computation of induced defects by probe penetration | 141                                                         |

|                                                                                           | Computation of induced defects by probe penetration |                                                             |

| V.6 (                                                                                     |                                                     | 143                                                         |

| V.6 (<br>Chapter VI:                                                                      | Conclusions and perspectives                        | 143<br>145                                                  |

| V.6 (<br>Chapter VI:<br>VI.1 (                                                            | Conclusions and perspectives                        | 143<br>145<br>147                                           |

| V.6 Chapter VI:<br>VI.1 CVI.2 I                                                           | Conclusions and perspectives                        | 143<br>145<br>147<br>149                                    |

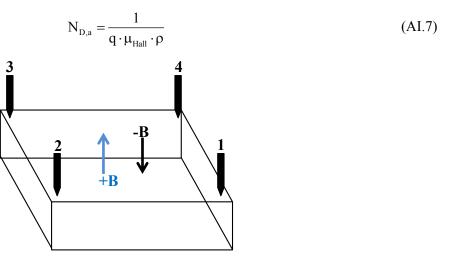

| V.6 Chapter VI:<br>VI.1 C<br>VI.2 I<br>Appendix I                                         | Conclusions and perspectives                        | 143<br>145<br>147<br>149<br>151                             |

| V.6 Chapter VI:<br>VI.1 C<br>VI.2 I<br>Appendix I<br>Van Der                              | Conclusions and perspectives                        | 143<br>145<br>147<br>149<br>151                             |

| V.6 Chapter VI:<br>VI.1 C<br>VI.2 I<br>Appendix I<br>Van Der<br>Hall effec                | Conclusions and perspectives                        | 143<br>145<br>147<br>149<br>151<br>151<br>152               |

| V.6 Chapter VI:<br>VI.1 C<br>VI.2 I<br>Appendix I<br>Van Der<br>Hall effec<br>Table of Ac | Conclusions and perspectives                        | 143<br>145<br>147<br>149<br>151<br>151<br>152<br>154        |

| V.6 Chapter VI:<br>VI.1 C<br>VI.2 I<br>Appendix I<br>Van Der<br>Hall effec<br>Table of Ac | Conclusions and perspectives                        | 143<br>145<br>147<br>149<br>151<br>151<br>152<br>154<br>156 |

# **Chapter I:** <u>General introduction</u>

In this chapter, the recent trends in microelectronics will be presented. The interest on using siliconon-insulator (SOI) substrates will be pointed out. SOI fabrication process, typical properties, related defects and characterization methods are discussed. The general objectives of the thesis are detailed.

# **Contents Chapter I**

| I.1 | MOS transistors: state of art and trends  | 3  |

|-----|-------------------------------------------|----|

| I.2 | SOI substrates                            | 9  |

| I.3 | Objectives and organization of the thesis | 12 |

### I.1 MOS transistors: state of art and trends

The concept for a Field Effect Transistor (FET) was invented by Lilienfeld [1] in 1930. It did not immediately catch the attention of the research community and the idea was not applied until 1948, when the first device was fabricated at Bell Labs [2]. After the fabrication of the first integrated circuit (IC) in the 1958 [3], the topic became hot and a lot of industrial companies and researches focused their attention on transistors.

Nowadays, MOS transistors are the base of all the integrated circuits which constitute the electronic devices largely present in our life: computers, cars, phones, etc., leading to huge market place that changed our social behavior [4].

#### Metal-oxide-semiconductor field effect transistor

The microelectronics world is based on simple devices that can operate together to compute complex functions. In general, these devices are classified according to their operation principle. We focus here on the metal-oxide-semiconductor field effect transistor (MOSFET), the primary device for circuits.

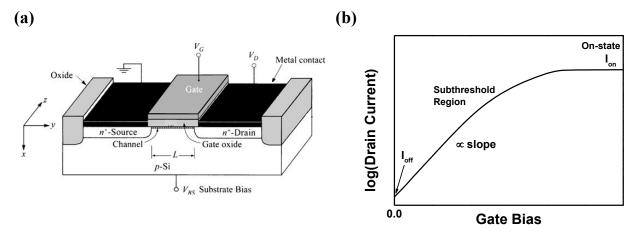

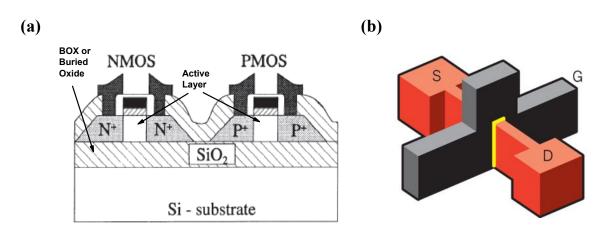

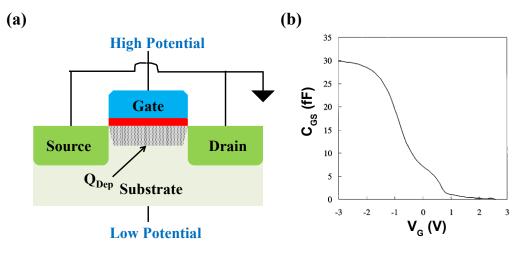

Figure I-1a shows the structure. It is easier to analyze it along the vertical (x) and horizontal (y) axis separately [5]:

- Along the *x*-axis we have a metal-oxide-semiconductor (MOS) structure. The semiconductor is typically nearly doped silicon (in the example, it is p-type, thus a n-MOSFET is obtained). On top of it, a silicon-dioxide layer is fabricated and serves as gate oxide. A conductive gate is placed on the top interface of the SiO<sub>2</sub>. The gate bias  $V_G$  controls the electronic bands bending in the silicon, at the interface with the gate oxide. A conduction channel made of electrons is induced if  $V_G > V_T$  (threshold voltage). For low values of gate bias, no free carriers are present in the channel;

- Along the *y*-axis two highly doped regions (source and drain) are made by implantation of the silicon next to the conduction channel. Considering the case of p-type silicon film, the source and drain contacts are  $n^{++}$  type. The source is grounded, while a bias is applied on the drain side (drain bias,  $V_D$ ). For  $V_G << V_T$ , no carrier flow is possible and the transistor is off. For gate bias values higher than the threshold voltage, a large current of electrons flows between source and drain contacts (drain current,  $I_D$ ), making the device "on".

Figure I-1b shows a schematic of drain current in logarithmic scale versus gate bias for standard ntype transistor. The characteristic has a clear switch behavior. Three regions related to the state of the device can be identified:

- Off-state:  $V_G \ll V_T$  and no current flow is possible. The current measured for  $V_G = 0$ , labeled  $I_{off}$ , governs the static power consumption. The off-state current has to be as small as possible to reduce power dissipation [5];

- On-state: for  $V_G > V_T$  the conduction channel is completely created. The measured drain current at given  $V_G$  and  $V_D$  is labeled  $I_{on}$ ;

• Subthreshold region: the channel starts to be created, but it is not yet complete. The slope of the  $I_D$  in logarithmic scale versus  $V_G$  (identified as subthreshold swing,  $S_s = 1/slope$ ) defines the speed at which the device can switch between on-state and off-state. High transistor performances are obtained for steep slope (fast on-off transition) [5].

# Figure I-1: (a) Schematic view of n-type MOSFET [5]. (b) Example of drain current in logarithmic scale versus gate bias for n-MOSFET.

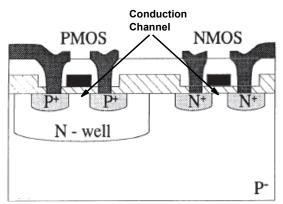

One of the main advantages of MOSFET is the possibility to co-integrate p-type and n-type devices on the same substrate, thanks to the use of implanted wells (CMOS technology) (Figure I-2). This allows the fabrication of integrated logic circuits which are small and fast.

Figure I-2: Example of co-integration of p-type and n-type bulk MOSFET [6].

#### **Microelectronics trends**

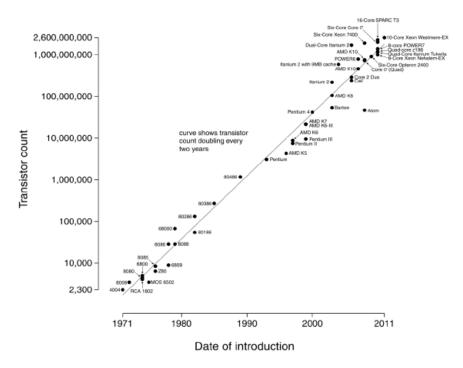

The transistor scaling down and performance improvements are the main topics of microelectronics industry and research. The mainstream is defined by the well-known "Moore's law" [7]: every decade of technology evolution corresponds to an extra order of magnitude in transistor density (Figure I-3). In order to drive the microelectronics research & development, the International Technology Roadmap for Semiconductors (ITRS) presents the state-of-art and provides guidelines and targets for the following years. Today the fabricated transistors have 22-30 nm gate length. The last updated report of IRTS in 2014 predicts that the logic industry will have transistors with sub-10 nm gate length in 2017 (7 nm node) [8].

#### Microprocessor Transistor Counts 1971-2011 & Moore's Law

However, physical limitations can compromise the device scaling down and limit the MOSFET performances:

- The decrease of the gate oxide thickness leads to an exponentially increase of the leakage current through the oxide (gate current,  $I_G$ ) with consequent loss of transistor-like behavior [9];

- Decreasing the MOSFET dimensions, mobility degradation is due to limitations of fabrication process

[10], [11]. The mobility degradation is smaller structures drastically limits the transistor speed;

- In high quality Si-SiO<sub>2</sub> interface, the subthreshold slope is not controlled by the transistor dimensions but is mainly a function of the temperature. Thus, at room temperature in the best case (SOI) it can be  $\approx 66 \text{ mV/dec}$  [5]. To obtain faster on-off transitions, new device architecture are demanded;

- Short-channel effects (SCE): around source and drain contacts, depletion regions are present [5].

When the device becomes smaller, the two depleted regions can overlap, leading to loss of electrostatic control of the gate bias. In order to fabricate faster and smaller transistors, new architectures are required such as multi-gate (MG) structures.

Several solutions were proposed to overcome the problems, such as the replacement of polyscristalline Si used as gate with metal [12], the use of high- $\kappa$  dielectric material instead of silicon-dioxide [13], the replacement of the silicon channel with new materials with high performances [14], [15], etc. Table I-1 reports the challenge for *near-term 2013-2020* according to ITRS predictions.

| Near-Term          | Summary of Issues                                                          |

|--------------------|----------------------------------------------------------------------------|

| 2013-2020          |                                                                            |

| Scaling Si CMOS    | • Scaling of fully depleted SOI and multi-gate (MG) structures             |

|                    | • Implementation of gate-all-around (nanowire) structures                  |

|                    | • Controlling source/drain series resistance within tolerable limits       |

|                    | • Further scaling of EOT with higher $\kappa$ materials ( $\kappa > 30$ )  |

|                    | • Threshold voltage tuning and control with metal gate and high-κ stack    |

|                    | <ul> <li>Inducing adequate strain in advanced structures</li> </ul>        |

| Implementation of  | Basic issues same as for Si devices listed above                           |

| high-mobility CMOS | • High- $\kappa$ gate dielectrics and interface state ( $D_{it}$ ) control |

| 0                  | • CMOS (n- and p-channel) solution with monolithic material integration    |

| channel materials  | • Epitaxy of lattice-mismatched materials on Si substrate                  |

|                    | • Process complexity and compatibility with significant thermal budget     |

|                    | limitations                                                                |

Table I-1: Near-term 2013-2020 challenges defined by ITRS 2013. Table adapted from the document [8].

The short-channel effects that strongly affect the performances of small devices can be limited by particular transistor architectures. Two main ways were explored:

- STMicroelectronics®, Samsung® and GlobalFroundries® moved to MOSFET fabricated on siliconon-insulator (SOI technology) (Figure I-4a). Fully-depleted (FDSOI) transistors lead to several practical advantages like the reduction of short-channel effect [16], [17], the possibility to use multiple threshold voltage [18], [19] and the capability to achieve high performances (*e.g.*, avoid mobility degradation) [20]–[22]. The transistor structure is still planar (*i.e.*, the conduction channel is on a twodimensional planes, as in Figure I-1a);

- Fin-shaped FET, called FinFET, is the architecture adopted by Intel®, Samsung®, TSMC and Global Foundries (Figure I-4b). In this case the gate surrounds 3 sides of the silicon film which acts as conduction channel (3D structure). This allows a better electrostatic control. However, the fabrication process is very different to the planar structure and huge economic effort was required to implement it. Note also that the FinFET fabrication is easier on SOI substrate [5]. The use of SOI improves the electrostatic isolation of the conduction channel and decreases the leakage current [6]. The feasibility and the interest of FinFET on SOI is documented in [23]–[27].

Hence, independently of the implemented MOSFET architecture (planar or 3D), it is clear that SOI substrates are superior for improving device performances. Thus, in this thesis we focus on SOI technology and, in the next sub-sections, after showing the schematic of SOI structure, a description of the main advantages and drawbacks arising from the use of SOI technology will be presented.

Figure I-4: (a) Example of p-type and n-type MOSFET co-integrated using silicon-on-oxide substrate [6]. (b) FinFET structure [28].

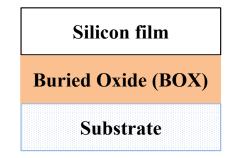

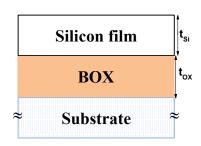

#### Silicon-on-insulator structure

The SOI substrate is a multi-layer stack with a top silicon film, that acts as active layer for the devices, a buried oxide (BOX) used to isolate the active layer from the substrate and a low-doped p-type substrate used as mechanical support of the structure [6] (see Figure I-5).

Figure I-5: Schematic of silicon-on-insulator (SOI) substrate.

#### Advantages of SOI technology

In MOSFET on bulk silicon (see Figure I-2) the conduction channel is confined close to the oxide interface. Most part of the thickness of the silicon substrate is not used but it is subject to parasitic effects such as current leakage, latch-up. Placing an oxide (called BOX or buried oxide) between the active layer and the substrate (see Figure I-4a), the conduction channel is isolated from the substrate, improving the transistor characteristics. This is the key point of SOI technology. Examples of benefits are:

- *Reduction of parasitic capacitances*; for example capacitances between source/drain contacts and the substrate are drastically reduced thanks to the presence of the BOX. Hence, devices fabricated on SOI work at higher frequencies than bulk technology [6];

- *Reduction of short-channel effects*: the surfaces of the source and drain junctions are now defined by the silicon film thickness. Thus, the depletion regions are spatially limited by the presence of the buried oxide and consequently they are reduced compared to a MOSFET on bulk silicon. In case of FDSOI, the gate has a better electrostatic control on the channel [16], [17];

- *Improved device isolation*: the buried oxide leads to better device isolation. Thus, phenomena like latch-up disappear leading to higher fabrication density [29];

- *Improvement of subthreshold swing*: in FDSOI devices, the depletion region is confined in the top silicon film leading to smaller associated capacitance. Hence, the slope of drain current in weak inversion is improved. Values close to the theoretical *66 mV/dec* can be achieved at room temperature [30], [31]. This allows the use of smaller threshold voltage and operating voltage, thus reducing the power consumption [32], [33];

- *Immunity against radiations*: devices fabricated on SOI substrate are less affected by external radiations. Since the active layer (top silicon film of the SOI structure) is isolated from the bulk substrate by the buried oxide, the impact of transient effects or ionization phenomena are drastically attenuated [30].

#### Issues with SOI technology

Despite the large numbers of advantages associated to SOI substrates, some drawbacks are still present:

- *SOI quality*: device performance improvements are obtained only in case of high quality SOI substrates. Thus, the carrier mobility in the silicon film has to be high and the density of defects low at silicon film-BOX interface;

- *Production costs*: SOI substrates are more expensive than bulk silicon. However, their use for mass production decreases the impact of the substrate price on the IC;

- *Interface coupling*: in FDSOI device, two silicon-SiO<sub>2</sub> interfaces are present: one between the conduction channel and gate oxide, and the second one between the Si layer and the buried oxide. In case of ultra-thin silicon films, electrical coupling can be present between the two interfaces. The models to describe the characteristics have to be adapted to the FDSOI case;

- *Floating-body effect*: the holes present in the channel are confined by the buried oxide and cannot be evacuated, affecting the device performances. An example is the enhancing of leakage current [34]–[36];

- *Self-heating effects*: the buried oxide has smaller thermal conductivity than bulk silicon material. Thus, for high current flow, the generated heat remains confined in the conduction channel decreasing the device performances. The problem is negligible for dynamic operation of the device [37].

### I.2 SOI substrates

#### SOI fabrication

The SOI technology started with Silicon-on-Sapphire wafers (SOS) [38]. SOS substrates improved the resistance of the integrated circuits against radiations. Consequently, this technology was very appealing for space and military applications. However, the high fabrication costs and insufficient crystal quality limited the market.

A step forward was the fabrication of devices on implanted oxygen layer which formed an insulating film under the transistor [39]. This opened the way to new fabrication processes like Separation by Implantation of Oxygen (SIMOX) [40], Bond-and-Etch-Back SOI (BESOI) [41] and Epitaxial Layer Transfer Wafer (ELTRAN) [42]. However, the interface quality was not high enough to introduce the SOI substrates in large-scale market.

The development of Smart-Cut<sup>™</sup> process [43] completely changed the SOI production. Today, the use of this technology allows the highest quality of silicon-on-insulator substrate [44].

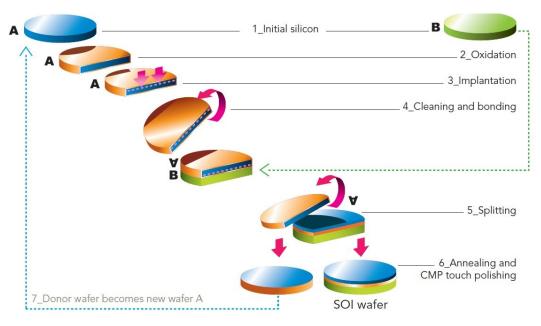

The main steps involved in the Smart-Cut<sup>TM</sup> fabrication process are (see Figure I-6):

- Two silicon wafers are required: a 'donor wafer' labeled A and a 'handle wafer' B;

- Thermal oxidation is performed on the wafer A, to growth SiO<sub>2</sub>, that will be the BOX of the final SOI substrate. The oxidation process allows a precise control of SiO<sub>2</sub> quality and thickness;

- Hydrogen implantation is performed through the fabricated oxide. This induces micro-cavities that define the future plan of fracture (dash line in Figure I-6 at step 3\_oxidation);

- The donor and handle wafers are cleaned. The surfaces are made hydrophilic;

- The two wafers are put in contact and annealed, in order to increase the pressure of hydrogen molecules in the micro-cavities. This leads to H<sub>2</sub> propagation which induces an horizontal fracture in the wafer A;

- The two wafers are thus separated. The wafer B is now an SOI substrate suitable for device fabrication, while the wafer A can be reused for another SOI fabrication process.

The Smart-Cut<sup>™</sup> technology has several advantages which justify its industrial interest:

- Low density of defects is present at the interface between the top silicon film and BOX;

- High quality silicon films are obtained;

- Conventional implantation and annealing tools are used;

- The top silicon film and BOX thickness can be easily adjusted to the wanted values.

Figure I-6: Schematic of Smart-Cut<sup>™</sup> process for SOI fabrication [45].

#### SOI characterization

SOI substrates are clearly an asset for high quality devices but they must be of high quality. The huge fabrication progress achieved thanks to Smart-Cut<sup>™</sup> leads todays to excellent quality substrates. However, as expressed by ITRS report, further developments on the SOI characterization (and monitoring) are required for two reasons [8]:

- Support the research and drive the next improvements on the fabrication processes;

- Monitor the fabricated substrates and their quality during mass production.

Structural characterization techniques for SOI substrates can be divided into two groups, according to their capability to investigate geometrical dimensions or defects of the material. The characterization of SOI substrates is more complex than standard bulk silicon. The presence of a supplementary oxide (the BOX) with an additional Si-SiO<sub>2</sub> interface requires adapted characterization methods and new approaches when the standard techniques fail.

Focusing on the geometrical dimensions, the key properties which require very accurate measurements are:

- *BOX* and *silicon film thickness*: a small variation of their values drastically affects the electrical performances of the fabricated devices. Thus, they are monitored with variable-angle single-wavelength reflectometry, single-wavelength ellipsometry and spectroscopic ellipsometry [30], [46];

- *Wafer flatness* is mandatory to make the SOI substrate compatible with all the tools required for MOSFET fabrication (especially for lithography steps).

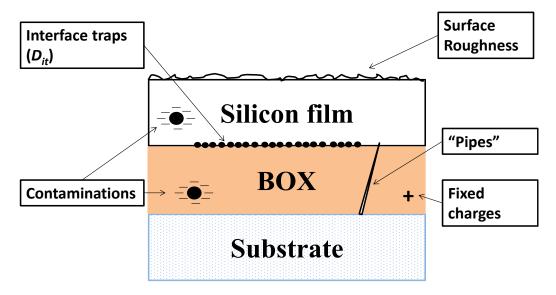

Structural defects are also present in the SOI substrate and they can degrade the performance of the future transistors [33]. The most important are (see the schematic in Figure I-7):

- Dislocations and stacking faults are found as in standard bulk silicon;

- *Surface roughness*: it is a critical parameter because it can decrease the breakdown voltage on the fabricated device;

- *Voids* can be present at the BOX interface especially due to dust. Today this type of defects is very rare;

- *"Pipes"*: are conductive vias which can be present in the oxide or in the silicon film. They act as a parallel resistor, increase the off-current and reduce the device immunity against radiations;

- *Metal or alkaline ions contaminations*: they can affect the fabrication process (metal contaminations) or the electrical properties of the structure (alkaline ions contaminations). They decrease the minority carrier lifetime and the mobility;

- *The level of residual oxygen or carbon in the silicon film*: *I*<sub>off</sub> is increased and the breakdown voltage is decreased if these impurities are present;

- Fixed charges in the BOX: they affect the transistor threshold voltage and the leakage current;

- *Interface traps density (D<sub>it</sub>)*: these defects are due to the silicon-silicon dioxide interface and they can limit the electric properties of the transistor: poor subthreshold swing and low carrier mobility.

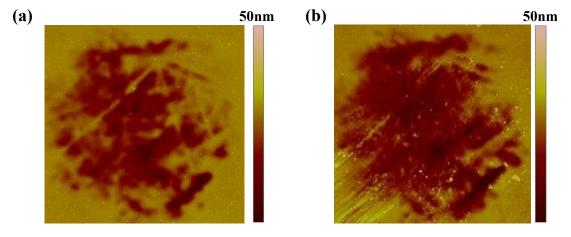

All these defects have to be minimized in a high quality SOI substrate. This is possible only improving the fabrication processes and monitoring the SOI production. Some examples of characterization methods for structural aspects of SOI are: AFM (Atomic Force Microscope), TRXF (Total Reflection at X Fluorescence) and SIMS (Secondary Ion Mass Spectroscopy).

Figure I-7: Example of defects on SOI structure.

#### Electrical characterization

The SOI substrate serves to fabricate a MOSFET and if the SOI substrate is low quality, the final transistor will have poor performance. Thus, the key point is to evaluate the electrical impact of the listed defects. The best configuration to electrically characterize a bare SOI wafer without fabrication of the entire device is the pseudo-MOSFET [6].

### I.3 Objectives and organization of the thesis

The previous section clearly showed the necessity to electrically characterize the SOI substrates after their fabrication and before the transistor production. The pseudo-MOSFET (see Sec. II.2) is the solution used ever since 1992. Its capability to measure carrier mobility and interface traps density was proved using  $I_D-V_G$  curves [6]. However, the reduction of the top silicon film and BOX thicknesses complicates the characterization and new techniques are required [46]–[52].

The objective of this thesis is to enrich the characterization techniques suitable for bare SOI substrates in pseudo-MOSFET configuration, mostly focusing on the investigation of the quality of the interface between the top silicon film and the BOX:

- Chapter II reviews the pseudo-MOSFET principle. The importance of measurement setup will be largely detailed. Some precautions on the setup will provide their benefits for stable and reproducible I<sub>D</sub>-V<sub>G</sub> analysis. The possibility to characterize new materials like InGaAs will be addressed.

- In Chapter III, the split-CV technique will be revisited. The capability to measure the effective carrier mobility with split-CV was already proved [53], [54]. Some aspects concerning the die surface which contributes to the whole signal are here clarified. The possibility to extract the interface traps density will be discussed from experimental and modeling point of view.

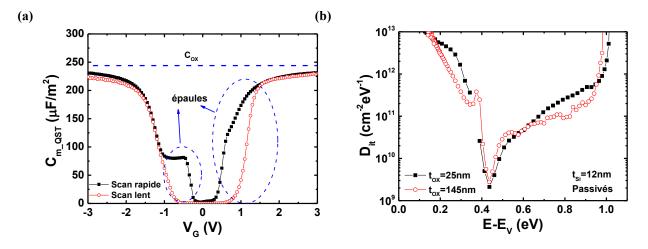

- Chapter IV presents the quasi-static capacitance measurements performed for the first time on bare SOI wafers to achieve interface characterization. After discussing the measurement setup, a physical model will be derived and validated in different configurations. A suitable procedure to compute interface traps density will be presented, tested and applied to characterize several SOI geometries, from thick to ultra-thin films and BOXs.

- The low-frequency noise measurements performed in pseudo-MOSFET configuration will be addressed in Chapter V. This technique was expected to allow the characterization of interface traps density. Diab *et al.* [55] already applied it in pseudo-MOSFET configuration but the extracted values of traps were not realistic and required explanations. Thanks to modeling, we explain the previous results. The capability to extract  $D_{it}$  in  $\Psi$ -MOSFET is discussed through model and experiments.

- o Chapter VI summarizes our results and addresses perspectives for future work.

# Chapter II: <u>Pseudo-MOSFET for SOI characterization</u>

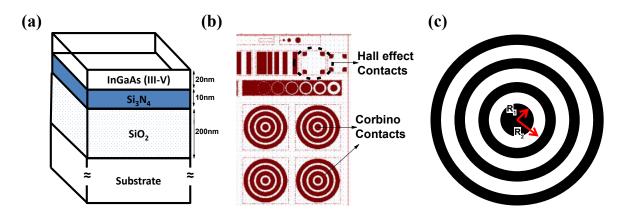

This chapter presents the characterization of bare SOI wafers performed using static drain current measurements in pseudo-MOSFET configuration. The principle of operation and measuring setup will be discussed. The impact of the quality of back contact and the role of the probes on the characteristics will be addressed. The characterization of III-V layers at different fabrication steps (from bulk material to fully fabricated device) is also shown.

# **Contents Chapter II**

| II.1 | The  | state-of-art in SOI electrical characterization                | . 15 |

|------|------|----------------------------------------------------------------|------|

| II.2 | Prin | ciple of $\Psi$ -MOSFET and parameter extraction methods       | . 17 |

| II.3 | Imp  | act of measurement                                             | . 23 |

| II   | .3.1 | Measurement time setup                                         | . 23 |

| II   | .3.2 | Quality of back contact                                        | . 23 |

| II   | .3.3 | Role of the probes                                             | . 24 |

| II   | .3.4 | Passivated top silicon film                                    | . 30 |

| II.4 | Exte | ension of $\Psi$ -MOSFET to new materials: III-V-on-insulator  | . 32 |

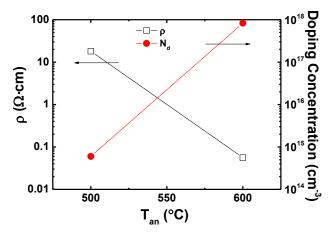

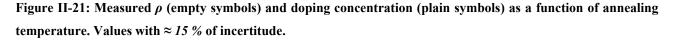

| II   | .4.1 | Material characterization before bonding                       | . 32 |

| II   | .4.2 | Ψ-MOSFET with pressure probes on III-V-on-insulator (III-V-OI) | . 34 |

| II   | .4.3 | Ψ-MOSFET with metal contacts on III-V-OI                       | . 35 |

| II   | .4.4 | Preliminary results of III-V transistors                       | . 39 |

| II.5 | Con  | clusions and perspectives                                      | . 41 |

### **II.1** The state-of-art in SOI electrical characterization

Accurate electrical characterization techniques are required to monitor the SOI material quality before pursuing device fabrication process. High transistor performances can be expected only if the carrier mobility in the top silicon film is high and the density of defects at Si film-buried oxide interface is low. In this context, we review here the electrical methods for SOI.

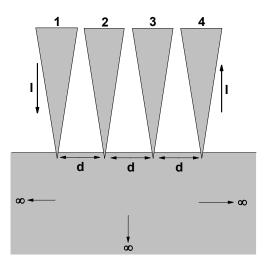

The simplest way to investigate the electrical properties of a material is the 4-probe resistivity measurement. In case of SOI, four needles are directly placed on the top surface of the Si film. A current *I* is imposed between the two external probes and the potential difference between the two inner probes is measured ( $\Delta V_{diff}$ ) (Figure II-1). Knowing the inter-probe distance (*d*), it is possible to directly compute the material resistivity [56]:

$$\rho = 2 \cdot \pi \cdot d \cdot F \cdot \frac{\Delta V_{\text{diff}}}{I}$$

(II.1)

where *F* is a correction factor taking into account the probe location with respect to the sample edges, the sample thickness and the probe diameter. Equation (II.1) is only valid if all the needles have the same interprobe distance *d* [56]. In case of large semiconductor samples, where the probes are placed far from the edges and *in-line* configuration is used (see Figure II-1), Eq. (II.1) can be re-written as a function of the sheet resistance  $R_{SH}$ :

$$\rho = 4.532 \cdot \mathbf{t}_{\mathrm{Si}} \cdot \frac{\Delta V_{\mathrm{diff}}}{\mathrm{I}} = \mathbf{t}_{\mathrm{Si}} \cdot \mathbf{R}_{\mathrm{SH}}$$

(II.2)

where  $t_{Si}$  is the silicon film thickness. The carrier mobility can be determined if the doping level is known. However, with this configuration the interface traps density, that qualifies the quality of the BOX-film interface, cannot be measured.

#### In-line probe configuration

Figure II-1: 4-probes measurement on infinite layer. 4 in-line needles are used.

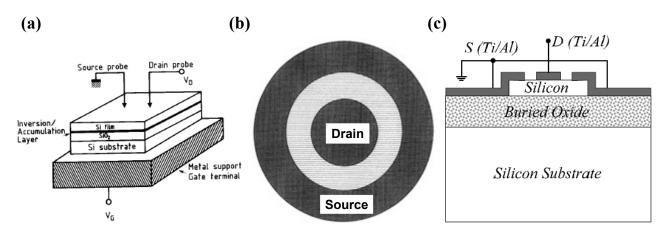

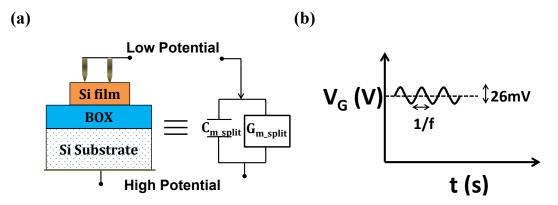

To overcome these limitations, a new method for SOI structure was proposed in 1992: the so-called pseudo-MOSFET ( $\Psi$ -MOSFET) (see Figure II-2a) [47], [57]. The silicon substrate is biased and used like a gate to create a conduction channel at the interface between the top Si and SiO<sub>2</sub> layers. Two probes with controlled pressure are directly placed on the top silicon surface to access the channel; they act as source and drain contacts. The structure is an upside-down MOSFET. Thus, the same characterization techniques classically used for standard MOSFET can be adopted to measure carrier mobility and  $D_{it}$  in SOI substrate.

There are two key issues with  $\Psi$ -MOSFET:

- 1 The dimensions of the conduction channel are generally not well defined;

- 2 The quality of the source and drain contacts and therefore the access resistance is dependent on the probe penetration into the silicon film. Thus, they are sensitive to the pressure applied on the probes.

A variant of the standard  $\Psi$ -MOSFET technique was proposed in 1997: the HgFET [58]. In this case, Hg circular contacts in Corbino configuration were used instead of adjustable pressure probe (see Figure II-2b). The channel geometry (length, width) is now clearly identified. However, in order to obtain good ohmic contacts, the silicon surface has to be cleaned to remove any existing oxide, such as the native oxide on the top silicon film. Furthermore the characterization will be time dependent because the contacts quality evolves in time.

Another possibility to characterize SOI substrates is to deposit metal contacts (source and drain) on the top of the silicon film (see Figure II-2c) [59], [60]. In this case the channel dimensions are also well defined. However, the configuration has several drawbacks: it requires fabrication steps, the contacts may not be ohmic, making the extraction procedure more complex.

In order to avoid contact related issues or uncertain channel definition, Ionescu *et al.* [61] and Van Den Daele *et al.* [62] merged the standard pseudo-MOSFET configuration with the 4-probes technique. This made the configuration pressure independent, leading to the characterization of ultra-thin SOI structures [62]. However, the interface traps density could be determined only through simulations.

Among all these variants, the standard pseudo-MOSFET with pressure probes remains the most suitable configuration for the characterization of bare SOI wafers, because it does not need fabrication steps for the contacts and it adapts easily to any type of measurement already existing in MOSFETs. We will see in the next sections and chapters how the use of optimized measurement setup and different techniques can lead to parameter extractions, suitable for SOI quality monitoring.

Figure II-2: (a) SOI structure characterized using standard pseudo-MOSFET configuration [47]. (b) Top view of HgFET contacts [63]. SOI wafer with fabricated source and drain contacts [64].

### **II.2** Principle of Ψ-MOSFET and parameter extraction methods

A detailed description of the  $\Psi$ -MOSFET and extraction methods for electrical parameters ( $\mu$ ,  $D_{it}$ ) from I<sub>D</sub>-V<sub>G</sub> characteristics will be provided in this section.

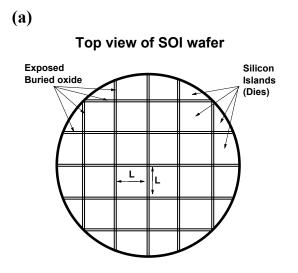

#### Sample preparation (between film and BOX via the sidewalls)

The pseudo-MOSFET configuration with pressure probes does not need contact process. Nevertheless, in order to avoid parasitic leakage currents, the SOI wafer needs a lithography step followed by etching to create square silicon islands (mesas) separated by 2 mm oxide (Figure II-3a). L is the side size of a mesa. These mesas define the dies or the tested regions on the SOI. Most of the analyses were performed on structures with 25 mm<sup>2</sup> effective area (*i.e.*, the mask size was 5 mm x 5 mm). However, other areas are available: 4.4 mm<sup>2</sup>, 9.6 mm<sup>2</sup>, 16.8 mm<sup>2</sup> and 65.6 mm<sup>2</sup>. Their use for some specific tests will be clearly indicated in the manuscript.

Figure II-3b shows the vertical cross-section of a silicon island. The Si thickness will be labeled  $t_{Si}$ . It is non-intentionally doped (NID) p-type:  $N_a \approx 5 \cdot 10^{14} \text{ cm}^{-3}$ . Two kinds of samples with different top interface quality were available:

- Passivated samples: the top silicon surface is covered with 4 nm dry silicon dioxide;

- Non-passivated samples: native oxide is present on the top of the Si layer.

The buried oxide will be labeled BOX and its thickness  $t_{OX}$ . The substrate of the SOI structures is made of p-type NID silicon.

**(b)**

Cross-section of silicon island

Figure II-3: (a) Top view of the SOI wafer after etching process. *L x L* isolated mesas separated by *2 mm* distance were obtained. (b) Vertical cross-section of a SOI island.

#### **Operation principle**

The electrical characterization was achieved using probe stations.  $\Psi$ -MOSFET is commonly performed using the adjustable pressure probe station from Jandel®. Four *in-line* needles with 1 mm interdistance are present. The pressure (p) can be precisely controlled between 0 g and 100 g, for each probe. Since we have no direct information concerning the effective surface where p is applied, the word "pressure" may sound incorrect. However, note that it is just a reference to better adjust (and repeat) the probe penetration into the silicon film and no direct physical meaning is given to p magnitude. The probe radius typically used was 40  $\mu$ m. The probe was made of WC.

Manual probe stations with micromanipulators can be also used, but the pressure cannot be precisely controlled.

In the following pages the principle to perform static drain current measurements  $(I_D-V_G \text{ and } I_D-V_D)$  will be explained. The particular setups required for capacitance or low-frequency noise measurements will be detailed in the corresponding chapters.

The SOI wafer is placed on a metallic chuck. Assuming that the top silicon film is grounded, the SOI substrate is polarized by  $V_G$  applied through the chuck and it *acts* as a gate.

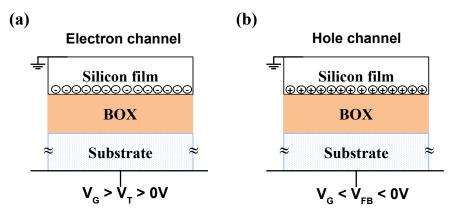

For  $V_G = 0 V$ , the electronic bands of the top silicon layer are already bent due to the different Fermi levels between the gate and the top Si film, to  $D_{it}$  and to fixed charges in the BOX. The flat band condition is achieved for  $V_G = V_{FB}$  (flat-band voltage). For  $V_{FB} < V_G < V_T$ , the electronic bands bend down with respect to the flat band condition, depleting the p-type Si film. Beyond  $V_T$  (threshold voltage), a conduction channel made of electrons is obtained (Figure II-4a). In case of  $V_G < V_{FB}$ , the conduction channel will be made of accumulated holes (electronic bands bent upwards) (Figure II-4b).

Figure II-4: SOI structure with positive (a) and negative (b) gate biases applied. Hole and electron channels are induced, respectively.

To perform current measurements, one of the two adjustable pressure probes placed on the silicon surface will act as drain, while the second one will be grounded. For symmetry reasons, the two probes have the same pressure. p is a major parameter to achieve good characteristics: if it is too small, Schottky barriers are obtained. In case of too large pressures, the probes can reach the BOX, damaging it and making the die not suitable for any further analysis [65].

The drain current  $(I_D)$  between the source and the drain contacts is obtained applying a bias  $(V_D > 0 V)$ .

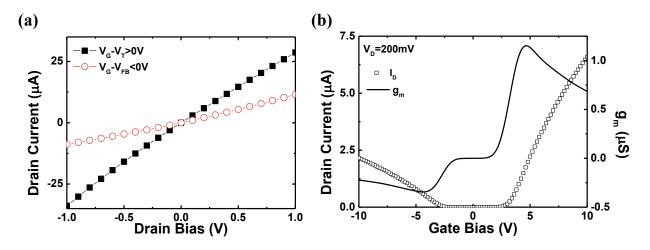

The first step is to verify if the contacts are Schottky or ohmic. In Figure II-5a, the drain current is measured as a function of  $V_D$  in case of positive ( $V_G - V_T > 0 V$ , plain symbols) and negative ( $V_G - V_{FB} < 0 V$ , empty symbols) overdrive gate voltage. Linear I<sub>D</sub>-V<sub>D</sub> dependency is found in both cases confirming the presence of ohmic contacts for both electrons and holes. Most of the extraction techniques (such as I<sub>D</sub>-V<sub>G</sub> or low-frequency noise) require measurements in the linear region, where  $V_D$  has no impact on the extracted parameters. However, to avoid parasitic effects due to too large electric field in the channel, we always used drain bias between 100 mV (low-frequency noise analysis) and 200 mV (static I<sub>D</sub>-V<sub>G</sub>) (see again Figure II-5a).

For material parameter extractions,  $I_D$ - $V_G$  measurements are required. Figure II-5b shows an example of  $I_D$  measured as a function of gate bias (empty symbols). Since the source and drain are metallic (instead of highly doped regions as in MOSFET) electrons (for  $V_G > 0$ ) and holes (for  $V_G < 0$ ) can be collected. The analysis of both types of carriers is therefore possible.

The transconductance  $(g_m = dI_D/dV_G)$  as function of gate bias (line) is also traced in Figure II-5b. The shape is similar to the one in MOSFETs.

Figure II-5: (a)  $I_D$  versus  $V_D$  performed on the same die in case of positive (plain symbols) and negative (empty symbols) overdrive bias. (b) Drain current (empty symbols) and transconductance (line) as a function of gate bias. The SOI structure had 88 nm top silicon film thickness and 145 nm BOX thickness and it was non-passivated.

#### Parameter extraction procedure

In case of fabricated transistors with width W and length L, the drain current measured in linear regime is directly proportional to the applied  $V_G$  and  $V_D$  [5]:

$$I_{\rm D} = \frac{W}{L} \cdot C_{\rm OX} \cdot \mu_{\rm eff} \cdot (V_{\rm G} - V_{\rm T}) \cdot V_{\rm D}$$

(II.3)

where  $C_{OX}$  indicates the gate oxide capacitance defined as  $\varepsilon_{OX}/t_{OX}$ , with  $\varepsilon_{OX}$  the oxide permittivity. The effective mobility  $\mu_{eff}$  takes into account the first order attenuation factor  $\theta_I$  due to access resistance  $R_{SD}$  impact [56]:

$$\mu_{\rm eff} = \frac{\mu_0}{1 + \theta_1 \cdot \left(V_{\rm G} - V_{\rm T}\right)} \tag{II.4}$$

where  $\mu_0$  is the low-field mobility. The transconductance  $g_m$  is defined as:

$$g_{m} = \frac{dI_{D}}{dV_{G}} = \frac{W}{L} \cdot C_{OX} \cdot \frac{\mu_{0}}{\left[1 + \theta_{1} \cdot \left(V_{G} - V_{T}\right)\right]^{2}} \cdot V_{D}$$

(II.5)

To extract the low-field carrier mobility from  $I_D$ - $V_G$  characteristics, erasing the effect of access resistance, the Y function method is largely used in MOSFET [66]. Using Eqs. (II.3) and (II.5), the Y function can be written as:

$$Y = \frac{I_{D}}{\sqrt{g_{m}}} = \sqrt{\frac{W}{L} \cdot \mu_{0} \cdot C_{OX} \cdot V_{D}} \cdot (V_{G} - V_{T})$$

(II.6)

The same equations are valid also in  $\Psi$ -MOSFET with two adjustments:

- The W/L ratio is defined by the so called geometrical factor  $f_G$  obtained by comparison of 4-probes and two needles configuration [47]:

$$f_G = \frac{W}{L} = 0.75$$

(II.7)

Recent works have shown that small die areas could lead to  $f_G$  variation [67]–[69]. In this work, large dies with respect to the inter-probe distance were used to avoid geometrical factor incertitude [70]. They will be detailed in the next section.

- In case of  $V_G < 0 V$ , a hole channel is induced (Figure II-5). The same equations remain valid but  $V_{FB}$  must replace  $V_T$ ;  $\mu_0$  and  $\mu_{eff}$  represent the hole mobility.

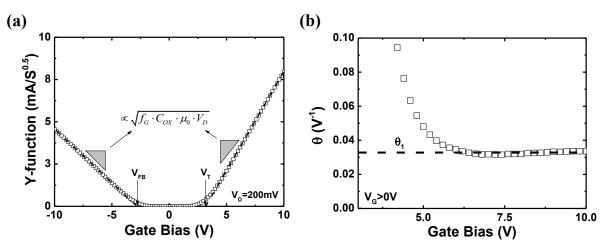

Figure II-6a presents the Y function computed from the data in Figure II-5b. In strong inversion (or accumulation) regime, the Y function is linearly dependent with respect to  $V_G$  (Eq. (II.6)).From the linear fit, the intercept with the *x*-axis yields  $V_T$  or  $V_{FB}$ , while the slope is directly proportional to the square root of the low-field mobility.

As for MOSFET, the attenuation factor  $\theta$  is defined as [66]:

$$\theta = \frac{\frac{I_{\rm D}}{g_{\rm m} \cdot (V_{\rm G} - V_{\rm T})} - 1}{V_{\rm G} - V_{\rm T}}$$

(II.8)

$\theta$  should be constant in strong inversion (or accumulation) regime (see Figure II-6b) and the limit to high gate bias values leads to the calculation of the first-order attenuation factor  $\theta_I$ . This allows the computation of the access resistance [66]:

$$R_{SD} \cong \frac{\theta_1}{f_G \cdot C_{OX} \cdot \mu_0} \tag{II.9}$$

Figure II-6: (a) Y function versus gate bias (data from Figure II-5a). The slope of the linear fit allows  $\mu_{\theta}$  calculation, while the intercepts with the x-axis lead to  $V_T$  and  $V_{FB}$ , respectively. (b)  $\theta$  as a function of  $V_G$ ; in strong inversion regime the constant value  $\theta$  is  $\theta_I$ .

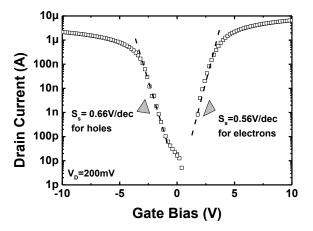

The slope of  $I_D$  in logarithmic scale versus gate bias under threshold voltage (or  $V_G > V_{FB}$  for holes channel) leads to the subthreshold swing  $(S_s)$  which gives access to  $D_{it}$  (interface traps density) [5]:

$$S_{s} = 2.3 \cdot \frac{k \cdot T}{q} \cdot \left(1 + \frac{C_{si} + q \cdot D_{it}}{C_{ox}}\right)$$

(II.10)

where the top silicon film capacitance is  $C_{Si} = \varepsilon_{Si}/t_{Si}$ .  $\varepsilon_{Si}$  is the silicon permittivity. Note that in SOI structures, two interfaces are present: one between the top silicon film and the BOX (called bottom interface) and a second one at the top surface of the silicon film (called top interface). Both of them can contribute to  $D_{it}$  via coupling effects. In case of thick  $t_{Si}$ , the coupling is low and  $D_{it}$  is dominated by the contribution of the bottom interface. In ultra-thin silicon layers (< 20 nm) stronger coupling is present and  $D_{it}$  gives an effective value of the contribution of both interfaces. Some models [49], [71], based on the double gate approach [72], were proposed to separate the defects contribution coming from the top silicon film-BOX interface and the traps placed on the surface of the Si layer.

Before applying these extraction procedures to evaluate material properties ( $\mu_0$ ,  $V_T$ ,  $V_{FB}$ ,  $D_{il}$ , etc.), we must define the best measurement setup and experimental parameters.

Figure II-7: Drain current in semi-logarithmic scale versus gate bias. The slopes of the linear regions lead to the estimation of subthreshold swing for holes and electrons. Same data as in Figure II-5a.

### **II.3** Impact of measurement

In this section we discuss the precautions on the measurement setup that may reduce parasitic effects. The importance of choosing good measurement times is presented in Sec. II.3.1. The role played by the back contact is addressed in Sec. II.3.2, while the impact of adjustable pressure probes on the characteristics is pointed out in Sec. II.3.3. Section II.3.4 shows the role of the quality of the top silicon film surface.

#### **II.3.1** Measurement time setup

In order to avoid transient effects and reduce noise, some measurement parameters have to be optimized [33]:

- $\circ$  *Hold time*: it is the time before starting the first measurement point and it must be long enough so that the structure is in equilibrium conditions at the beginning of the characterization. Used values range: *1-100 s*;

- *Delay time*: it is the time between two consecutive measurement points and it must be long enough to avoid any transient effects due to out-of-equilibrium state. A too long delay time can stress the device. All our measurements were obtained using a delay time between 0.4 s and 2 s.

- Integration time: the value obtained for each bias point is computed by integrating several measurements performed by the instrument at the same biasing condition. "Short" integration time means very short integration time range. The analysis is fast but usually the curves are noisy due to trapping/detrapping phenomena induced by surface defects. The use of "long" integration time reduces the noise on the characteristics becaue the structure is close to equilibrium condition; but the measurement is more time consuming. In this work, "medium" integration time was used for SOI structure with  $t_{Si} = 88 \text{ nm}$ , while "long" integration time was adopted in case of ultra-thin Si layers ( $t_{Si} < 20 \text{ nm}$ ).

#### **II.3.2** Quality of back contact

In  $\Psi$ -MOSFET configuration,  $V_G$  is directly applied on the structure through the chuck. Hence, the quality of the "*back contact*" (contact between the back of the SOI substrate and the metallic chuck) may affect the obtained characteristics. This problem never arises in case of fully fabricated transistors, because metallic contacts are used.

Two different cases will be investigated:

- *Air contact*: the wafer is just placed on the metallic chuck. No particular precautions are used to improve the contact;

- *Vacuum contact*: a vacuum system is used to "*stick*" the SOI to the metallic surface. This avoids any possible parasitic contributions due to poor contact.

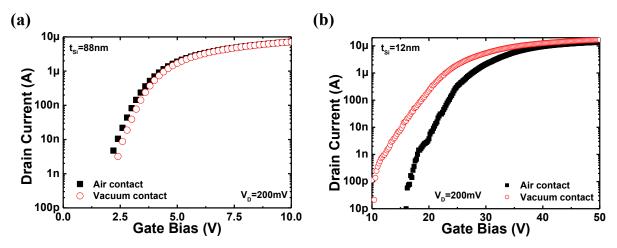

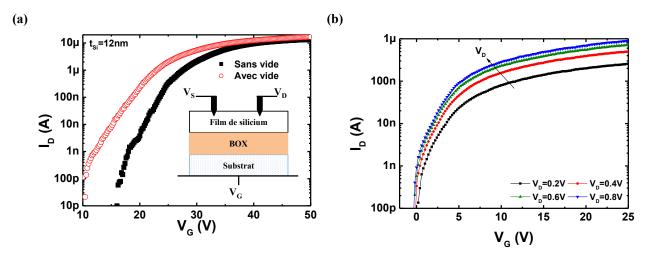

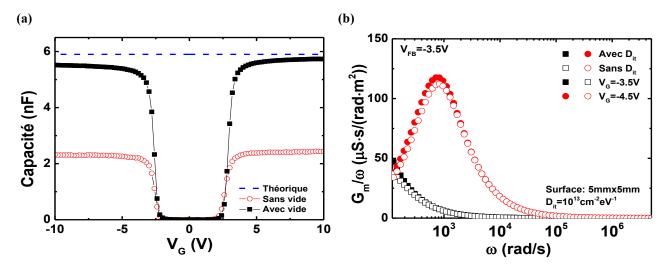

Figure II-8a shows the drain current versus gate bias on SOI structure with 88 nm top silicon film thickness and 145 nm BOX thickness. The top surface was non-passivated. The characterization was performed with (empty symbols) and without (plain symbols) vacuum system. The results obtained on SOI structure with the same  $t_{OX}$  but thinner silicon layer (12 nm) are presented in Figure II-8b. Variation of  $V_T$  and  $S_s$  are obtained in both cases, and there are stronger for the thinner silicon film. Vacuum system will be always used to avoid parasitic effects. In the chapter of split-CV measurements we will show that the vacuum contact is even more critical.

Figure II-8: Measured drain current versus gate bias in *88 nm* (a) and *12 nm* (b) thick SOI film. The buried oxide was in both cases of *145 nm* and the top surface non-passivated. Analysis performed without (plain symbols) and with (empty symbols) vacuum for the back contact.

## **II.3.3** Role of the probes

The probes have an important role on the obtained  $\Psi$ -MOSFET characteristics. It was proved that  $R_{SD}$  is directly related to the probe pressure [65]. Furthermore, the probe position on the silicon surface can affect  $f_G$  value [67], [68]. Several aspects will be addressed to clarify these effects and how they limit the extraction.

#### **Probe choice**

The Jandel® station has four *in-line* probes. In  $\Psi$ -MOSFET configuration only two probes are used, thus it is possible to choose among the four needles. We mainly considered the case with d = 1 mm.

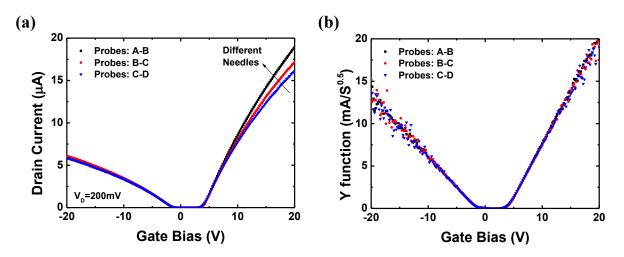

Figure II-9a shows the measured  $I_D$  as a function of  $V_G$  using different needles. Curves match for low  $V_G$  but for very large gate bias some differences are present. In this region,  $R_{SD}$  (which is probe related) becomes relevant, inducing  $I_D$  variations. The corresponding Y functions are shown in Figure II-9b. The impact of access resistance is removed in this case (see Eq. (II.6)) and the curves superpose. Thus, the choice of the probe is not critical in case of I<sub>D</sub>-V<sub>G</sub> characterization analyzed using the Y function.

Figure II-9: Measured drain current (a) and Y function (b) versus gate bias on the same SOI structure as in Figure II-8a. Different combinations of probes were used for the analysis. The inter-probe distance was kept constant to *1 mm*.

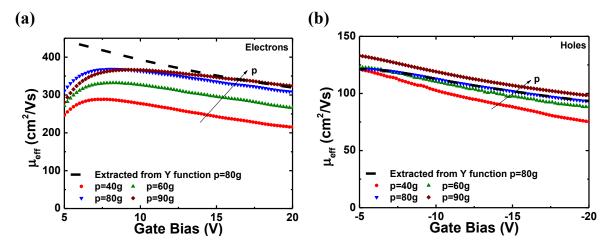

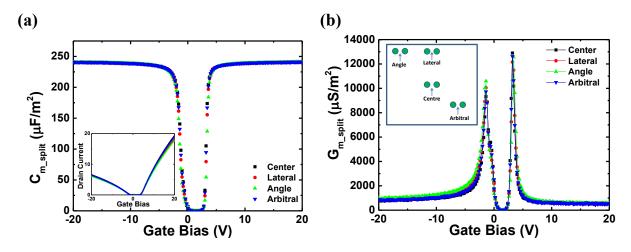

#### **Probes position**

Border effects influence the pseudo-MOSFET measurements because they can affect  $f_G$  [67]–[69]. To verify if the use of vacuum system attenuates their impact, several characterizations were performed on the same die changing the position of the probes. The same needles with the same pressure were used. The obtained  $I_D$  versus  $V_G$  are shown Figure II-10a. The corresponding positions on the silicon surface are represented schematically in the inset. Very close to the edges, the current flow is affected by border effects decreasing the measured  $I_D$  value [67]. The corresponding Y functions versus gate bias are shown in Figure II-10b and the computed low-field mobilities are reported in Table II-1. In case of  $V_G > 0$  V, the mobility measured close to the edges is underestimated. In the worst case, the impact is lower than 10 %. Even smaller impact is found in case of hole mobility.

$\mu_0$  cannot change in an homogenous material according to the contacts position. The different values of  $\mu_0$  are due to variation of the geometrical factor (lower than 10 %). In conclusion, placing the probes at the center of the structure, makes  $f_G$  variation negligible.

Figure II-10: Drain current (a) and Y function (b) versus gate bias for different probe positions. The SOI structure had 88 nm thick top silicon film and 145 nm BOX. The top surface was non-passivated. The die size L was 8 mm. The inset in Figure II-10a presents the corresponding probe position on the silicon surface.

| Position | $\mu_0$ electron (cm <sup>2</sup> /Vs) | $\mu_0$ hole (cm <sup>2</sup> /Vs) |

|----------|----------------------------------------|------------------------------------|

| Center   | 460                                    | 150                                |

| Lateral  | 442                                    | 149                                |

| Angle    | 431                                    | 143                                |

| Arbitral | 460                                    | 152                                |

Table II-1: Low-field mobility for electrons and holes computed from data in Figure II-10b for different needle positions.

#### **Probes pressure**

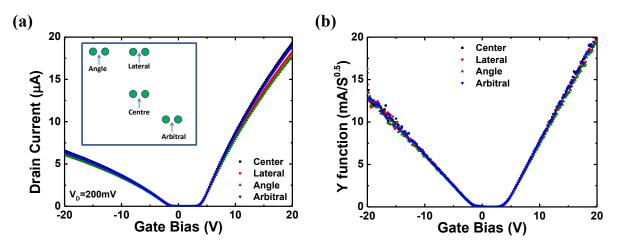

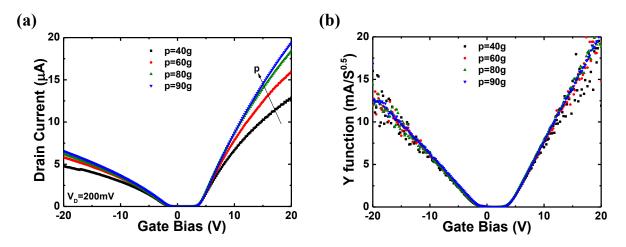

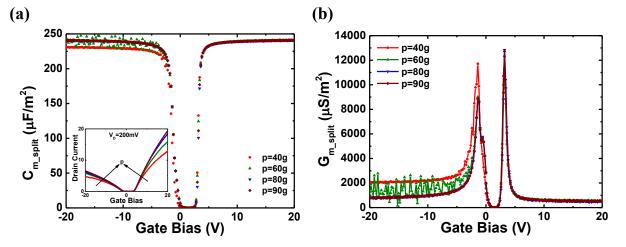

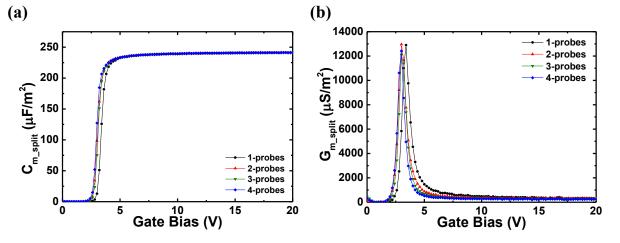

The impact of probes pressure was already studied in pseudo-MOSFET [65], [68], but without vacuum. Figure II-11 shows the measured  $I_D$  (a) and Y function (b) as a function of  $V_G$  for different p. The needles were placed on the top silicon film using the lowest pressure. Next, p was gradually increased step by step, without moving the probes. Larger pressure leads to stronger probe penetration into the silicon film [65]. The higher the pressure, the higher the measured drain current due to an improved contact (lower  $R_{SD}$ ). Y functions superpose and are stable as soon as the pressure is sufficient to have an acceptable contact (here p > 60 g).

Figure II-11: (a)  $I_D$  versus gate bias in case of different probe pressure. The SOI structure had 88 nm top silicon film and 145 nm BOX. Non-passivated top surface was used and L = 5 mm. The corresponding Y function is computed in Figure II-11b.

Mobility and  $R_{SD}$  variation with p are reported in Table II-2, for electrons and holes. Note that pressure effect is much stronger in case of  $V_G > 0$  V (electrons) than for the holes, where only one point (p = 60 g) is slightly different from the other values. However, despite a pressure variation higher than  $\approx 40$  %, the mobility change is less than  $\approx 10$  %. Once the needles have sufficiently penetrated into the silicon film to contact the channel (p = 60 g in this case), p has only a low impact on  $\mu_0$  thanks to the Y function method that removes  $R_{SD}$  effects.

| Pressure (g) | $\mu_0$ electron (cm <sup>2</sup> /Vs) | $R_{SD}$ electron ( $k\Omega$ ) | μ <sub>0</sub> hole<br>(cm²/Vs) | $R_{SD}$ hole $(k\Omega)$ |

|--------------|----------------------------------------|---------------------------------|---------------------------------|---------------------------|

| 40           | 420                                    | 7.5                             | 147                             | 22                        |

| 60           | 449                                    | 5.1                             | 128                             | 11                        |

| 80           | 460                                    | 3.3                             | 150                             | 13                        |

| 90           | 461                                    | 2.6                             | 153                             | 12                        |

Table II-2: Low-field mobility of electrons and holes computed from Figure II-11b and corresponding  $R_{SD}$  for different probe pressures.

#### Pressure of the probe and vacuum contact

In the previous section (Se. II.3.1) it was proved that the use of vacuum contact is mandatory in case of ultra-thin silicon film. Does the vacuum affect also the mobility-pressure trend?

To answer the question, SOI structure with ultra-thin silicon film (12 nm) and thick BOX (145 nm) was characterized using different probe pressure. Table II-3 shows the extracted low-field electron mobility obtained from characteristics measured with and without vacuum back contact for different probe pressure. p variation of  $\approx 40$  % induces almost 20 %  $\mu_0$  shift using vacuum back contact. In case of standard configuration, the variation is higher than 70 %, proving the importance of using the vacuum system, especially for ultra-thin films.

| Pressure (g) | $\mu_0 (cm^2/Vs)$<br>vacuum | $\mu_0 (cm^2/Vs)$<br>no vacuum |

|--------------|-----------------------------|--------------------------------|

| 40           | 443                         | 195                            |

| 50           | 462                         | 309                            |

| 60           | 426                         | 454                            |

| 70           | 509                         | 713                            |

Table II-3: Measured low-field mobility for different p and  $V_G > \theta V$ . Characterization performed on SOI wafer with 12 nm top silicon film and 145 nm BOX. The top surface was non-passivated. Comparison between measurements obtained with and without vacuum.

#### Radius and probe material

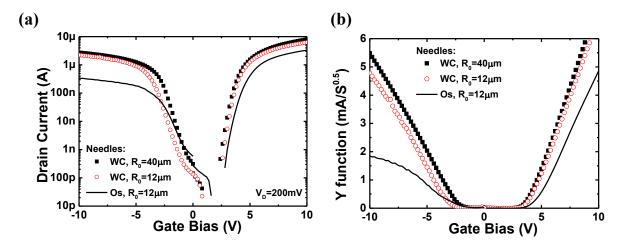

Our Jandel® station has tungsten carbide (WC) probes. Their radius is of 40  $\mu m$ . To investigate the impact of the probe radius  $R_0$ , we used a manual probe station. The needles were made of WC and they had  $R_0 = 12 \ \mu m$ . The inter-probe distance was kept constant:  $d \approx 1 mm$ .

Figure II-12 shows the measured drain current (a) and corresponding Y function (b) versus gate bias in case of Jandel® station (plain symbols) and manual probe station (empty symbols). The corresponding parameters extracted using Y function method are reported in Table II-4. The obtained electron and hole mobilities are lower in case of sharper tip, due to possible  $f_G$  and  $R_{SD}$  variation. Note that in manual probe station the probe pressure cannot be precisely adjusted. Agreement is found for threshold voltage, while a  $V_{FB}$  shift is measured. Thus, the probe radius has a sizeable effect on the characteristics and the extracted physical parameters [33], [68].

Additionally, we show the results obtained using tips made of different material, osmium (Os) in this example. The probe radius was 12  $\mu m$ . The corresponding measured current is shown in Figure II-12 (continuous line) and the extracted values are reported in Table II-4. The highest access resistance was found in this case. For  $V_G < 0 V$ , non-realistic low  $\mu_0$  mobility is measured, probably due to a non-ohmic contact. A clear shift of  $V_T$  and  $V_{FB}$  is also present. Thus, the extracted parameters are influenced by the probe material work function.

To perform wafer monitoring, it is important to use all the time tips with the same properties and adapted to the characterized material [73]. In this work, all the measurements performed on Si-SiO<sub>2</sub> wafers were obtained using WC tips with  $R_0 = 40 \ \mu m$ .

Figure II-12: Drain current (a) and Y function (b) versus gate bias on SOI structure with 88 nm top silicon film and 145 nm BOX. The top surface was non-passivated and L = 2 mm. Different tips were used: WC with  $R_0 = 40 \ \mu m$  from Jandel® station (plain symbols), WC (empty symbols) and Os (line) tips with radius  $R_0 = 12 \ \mu m$ from manual probe station. The inter-probe distance d was  $\approx 1 \ mm$ .

|                                        | WC                             | WC                 | Os                 |

|----------------------------------------|--------------------------------|--------------------|--------------------|

|                                        | $R_0 = 40 \ \mu m$             | $R_0 = 12 \ \mu m$ | $R_0 = 12 \ \mu m$ |

|                                        | $Jandel \mathbb{R} (p = 80 g)$ | Manual st.         | Manual st.         |

| $\mu_0$ electron (cm <sup>2</sup> /Vs) | 412                            | 349                | 220                |

| $V_T(\mathbf{V})$                      | 3.9                            | 3.9                | 4.5                |

| $\mu_0$ hole (cm <sup>2</sup> /Vs)     | 154                            | 137                | 29                 |

| $V_{FB}\left(\mathbf{V} ight)$         | -2.3                           | -2.9               | -2.3               |

| $\theta_l$ electron (1/V)              | 0.018                          | 0.033              | 0.054              |

| $\theta_l$ hole (1/V)                  | 0.089                          | 0.01               | -                  |

Table II-4: Extracted parameters from Figure II-12b for different needle properties.

#### Reproducibility of tests

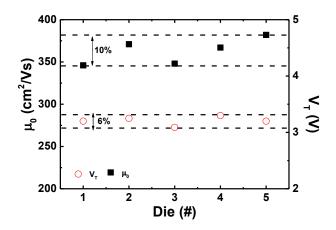

In pseudo-MOSFET configuration, the source and drain contacts are obtained using probes directly placed on top of the silicon surface. This can be a new source of variability added compared to standard transistors with fabricated metal contacts. In this section we investigated the reproducibility of material characterization (*i.e.*, parameter extraction) obtained using the Y function method on static  $I_D(V_G)$  curves. We also defined the order of magnitude of error bars of calculated  $\mu_0$  and  $V_T$ .

The fitting range of Y function can affect the obtained results: a maximum variation of  $\pm 4.5$  % is obtained for  $\mu_0$  and  $\pm 3$  % for  $V_T$ .

Figure II-13 shows the extracted low-field mobility (plain symbols) and threshold voltage (empty symbols) for different dies present on the same SOI wafer. The maximum incertitude of  $\mu_0$  is around  $\pm 5$  %. Lightly lower variation is found for  $V_T$  ( $\pm 3$  %). Thus, total error bars around 15 % represent a good estimation for the measurement technique.

Figure II-13: Extracted  $\mu_{\theta}$  (plain symbols) and  $V_T$  (empty symbols) from different dies present in the same SOI wafer with 88 nm thick Si film and 145 nm thick BOX. The top surface was non-passivated.

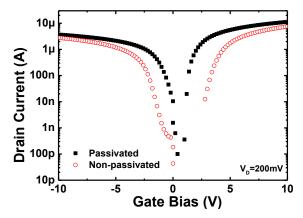

### **II.3.4** Passivated top silicon film

In the literature, one of the most frequent approaches to identify to which interface the characterization technique is sensitive, is the comparison between passivated and non-passivated SOI structures. *4 nm* dry oxide grown on the top silicon film improves the corresponding interface quality. Thus, the  $D_{it}$  associated to this interface decreases. Figure II-14 shows an example of the measured  $I_D$  versus  $V_G$  for passivated (plain symbols) and non-passivated (empty symbols) wafers. The different density of defects induces remarkable shifts of  $V_T$ ,  $V_{FB}$  and  $S_s$ .

Note that the penetration through the top oxide is easier in case of non-passivated sample (native SiO<sub>2</sub>) than passivated one (thermal SiO<sub>2</sub>). Thus, different probe pressures have to be used to achieve similar access resistance. In this example, p = 80 g for non-passivated sample leads to  $R_{SD} = 3.4 k\Omega$ , while p = 100 g on the passivated yields  $R_{SD} = 4.5 k\Omega$ .

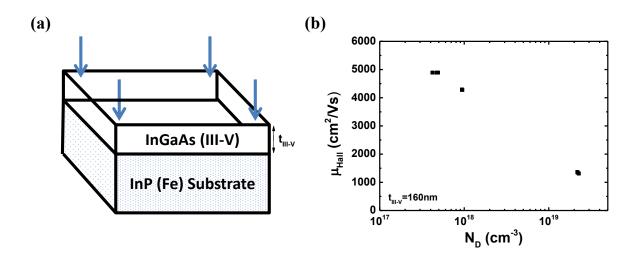

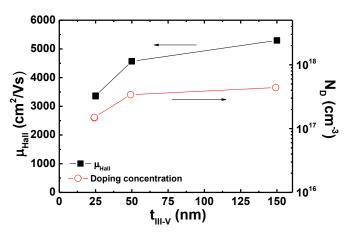

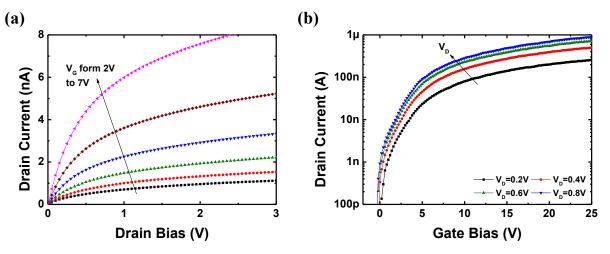

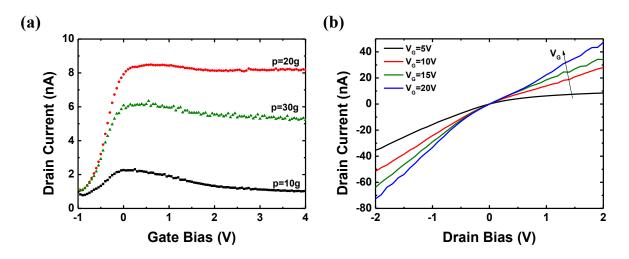

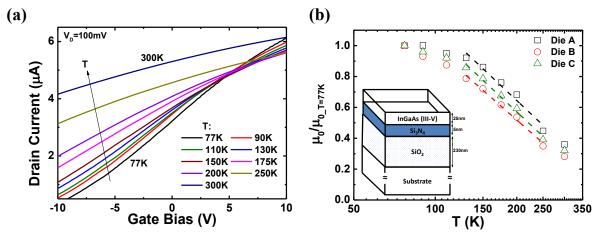

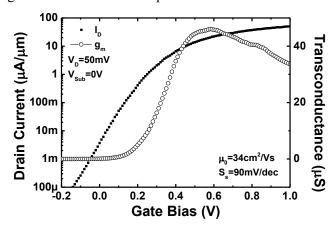

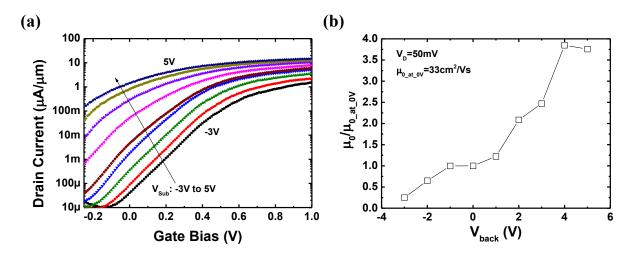

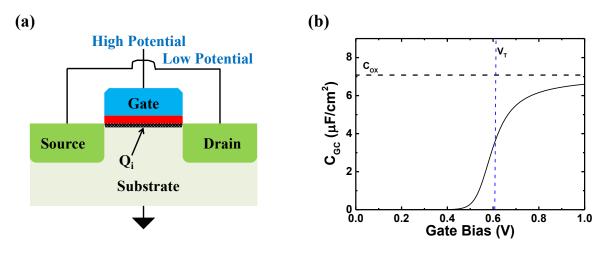

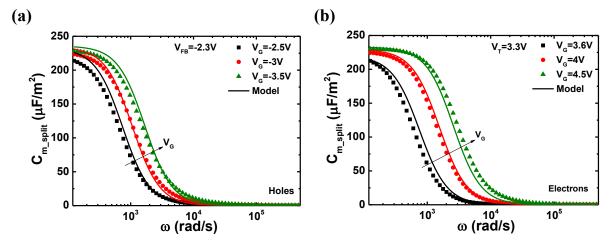

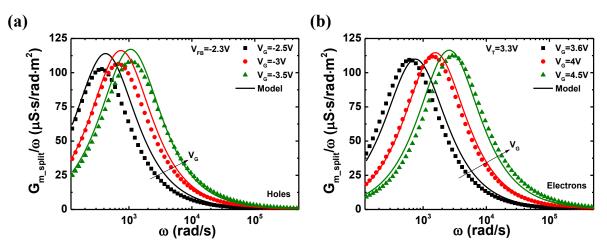

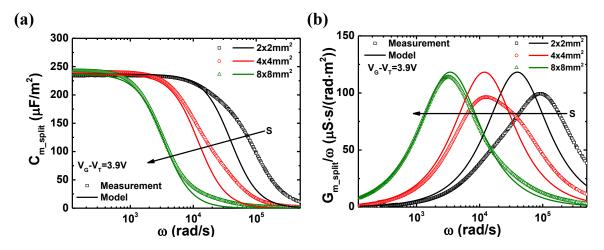

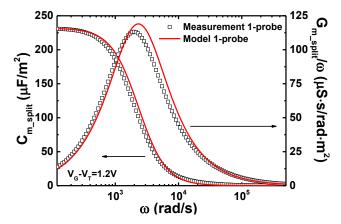

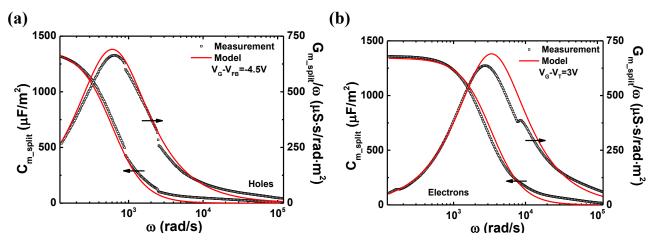

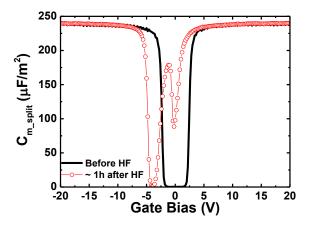

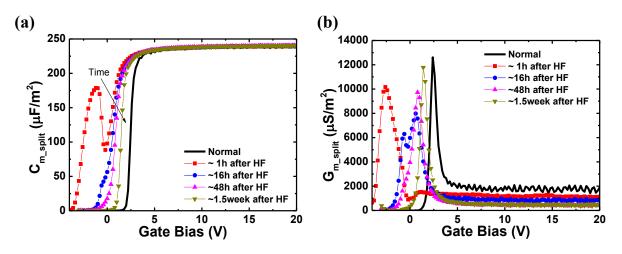

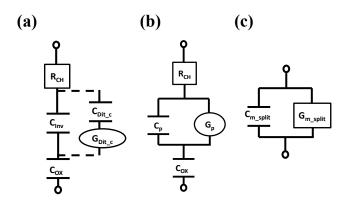

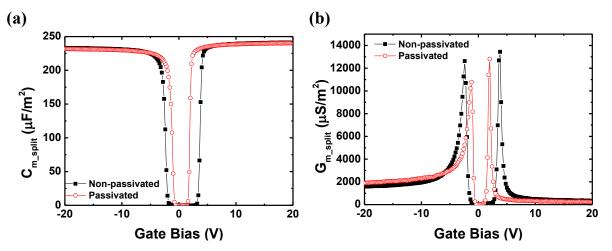

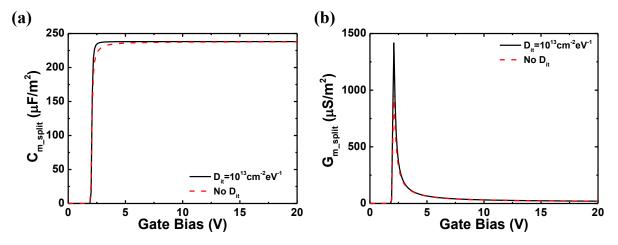

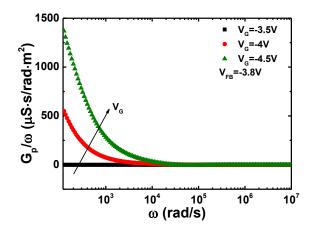

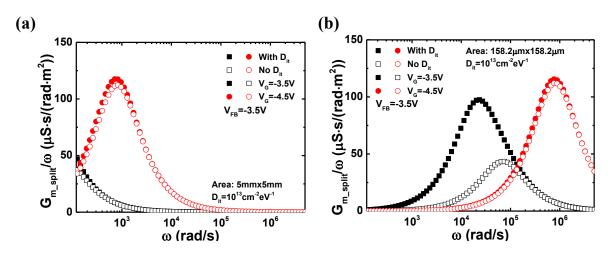

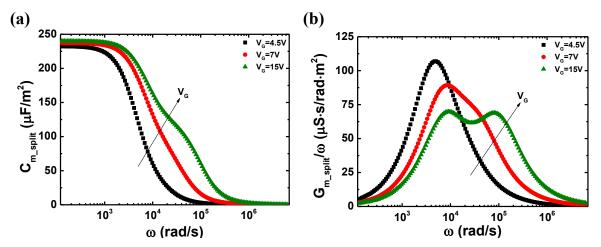

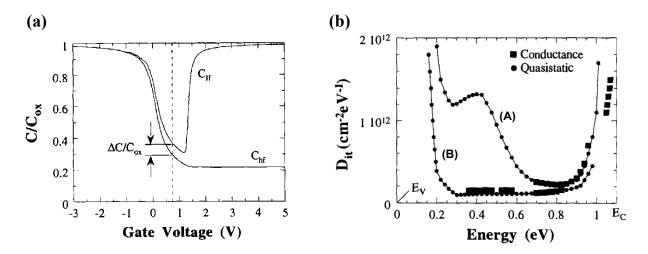

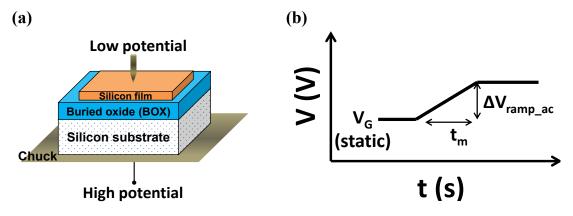

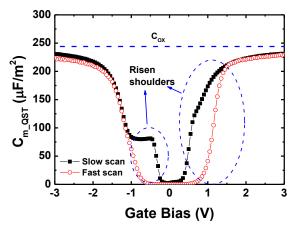

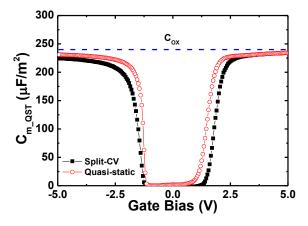

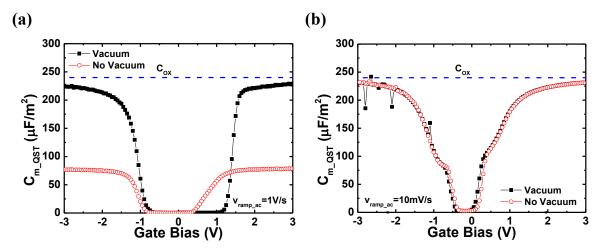

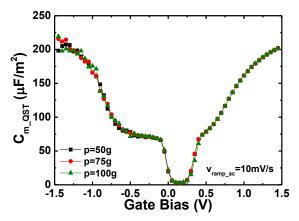

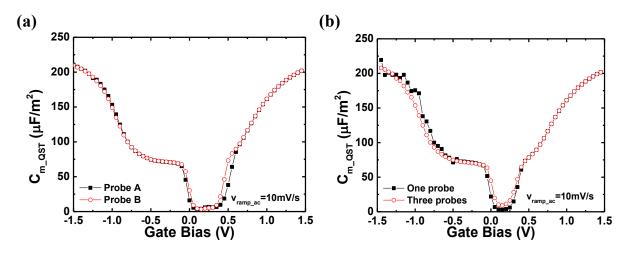

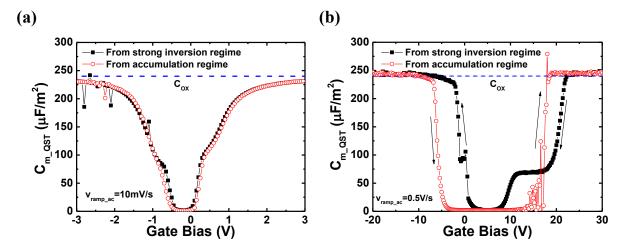

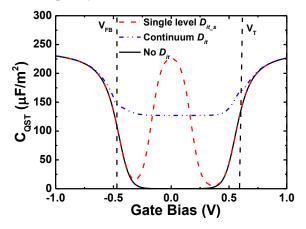

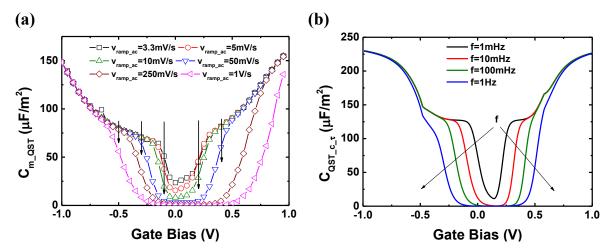

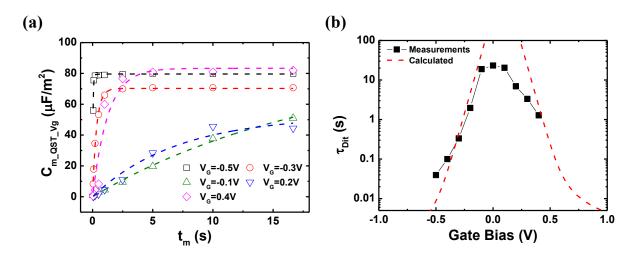

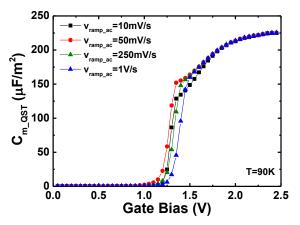

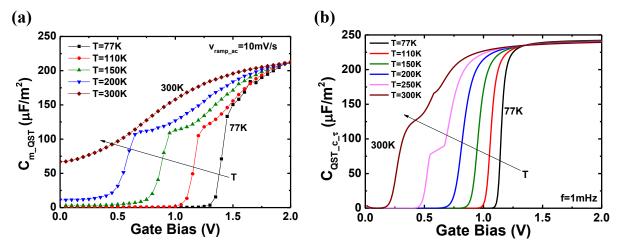

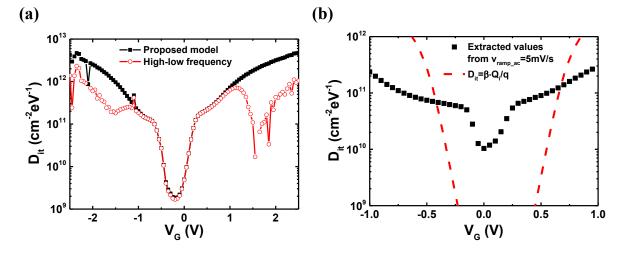

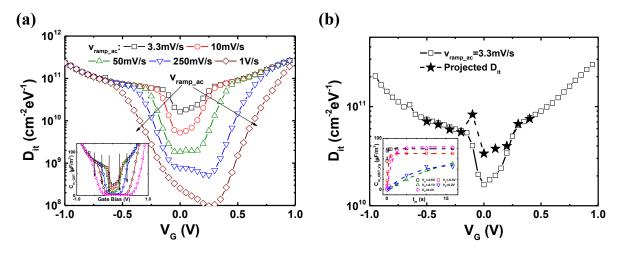

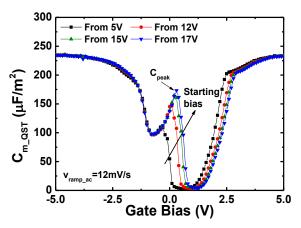

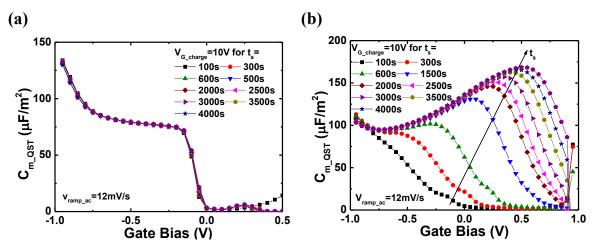

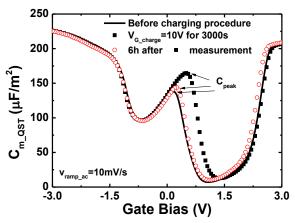

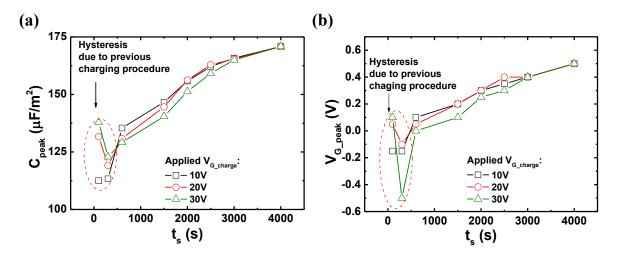

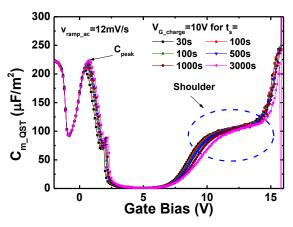

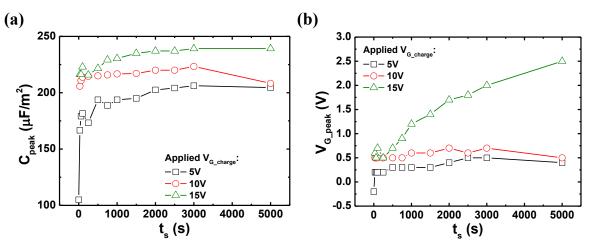

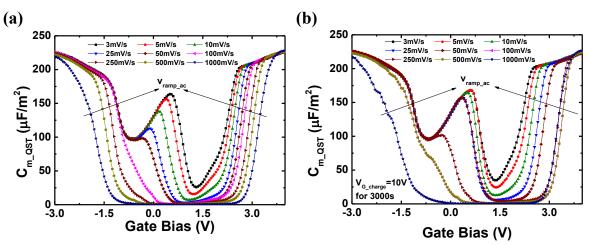

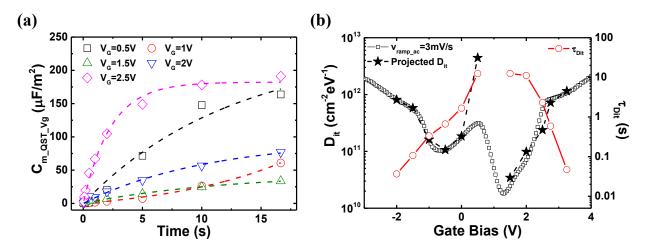

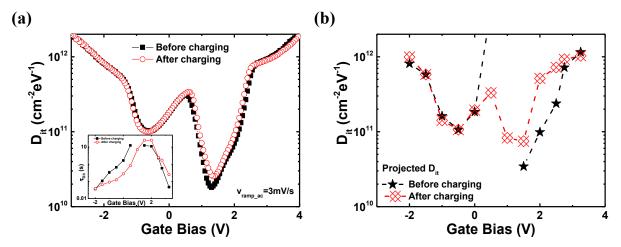

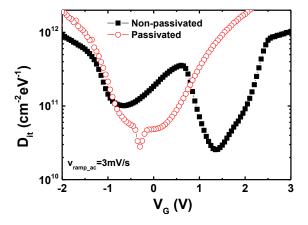

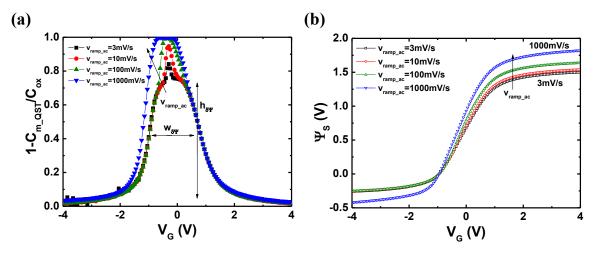

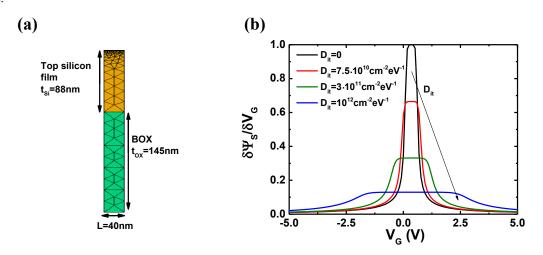

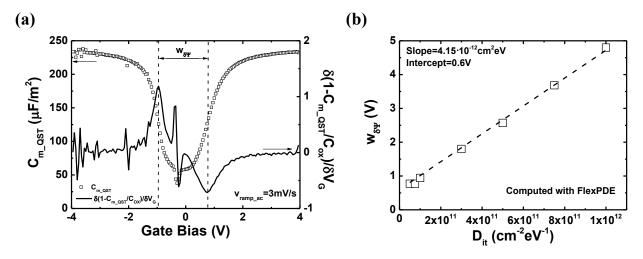

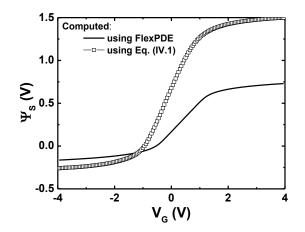

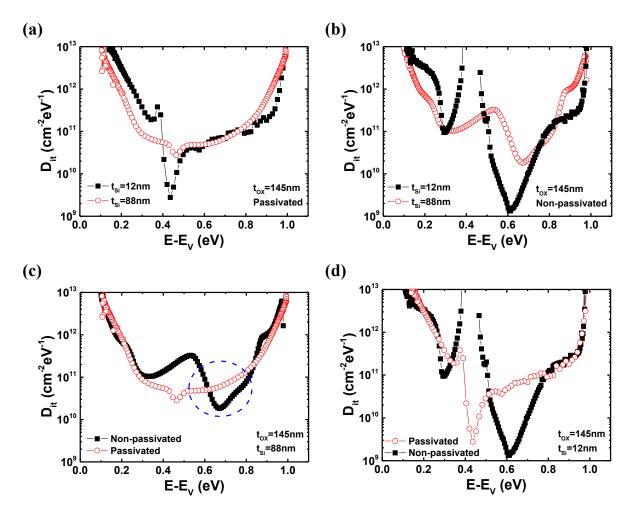

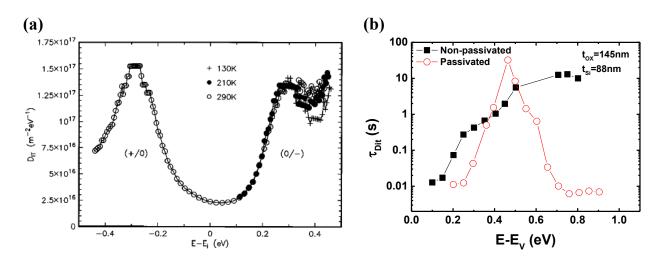

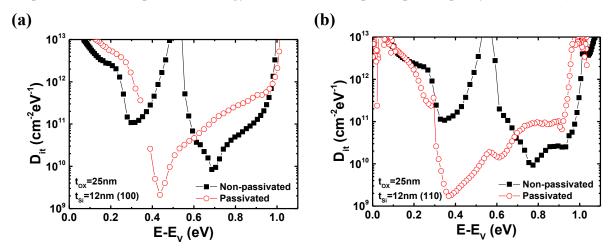

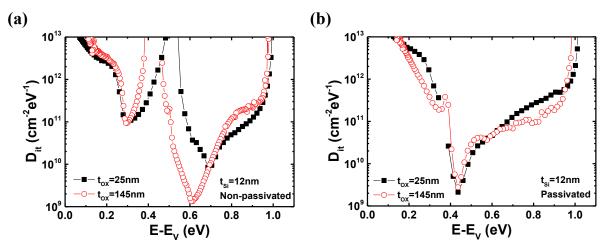

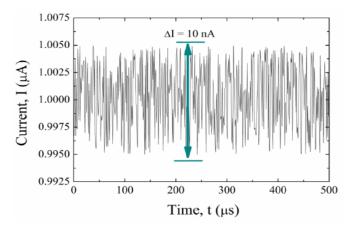

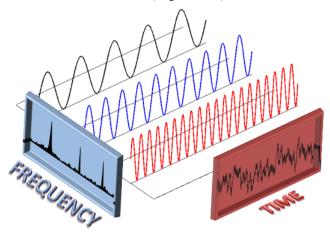

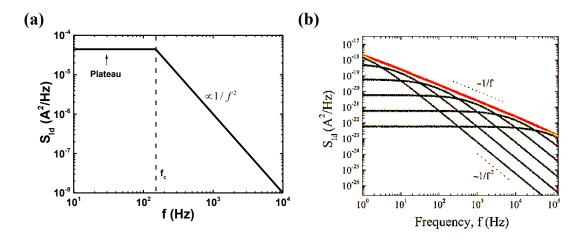

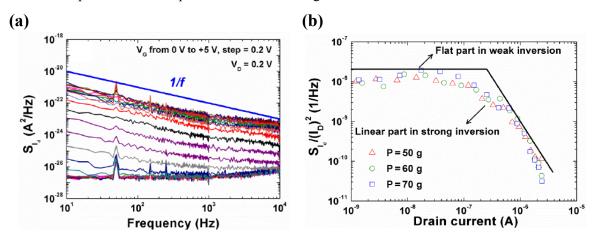

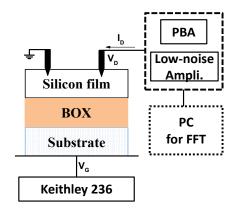

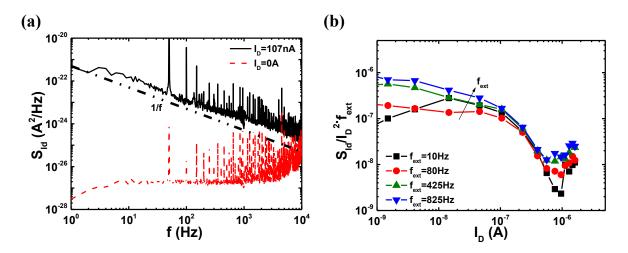

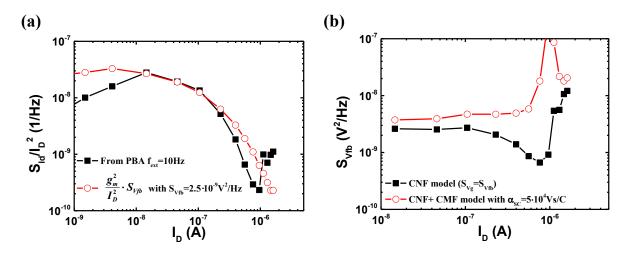

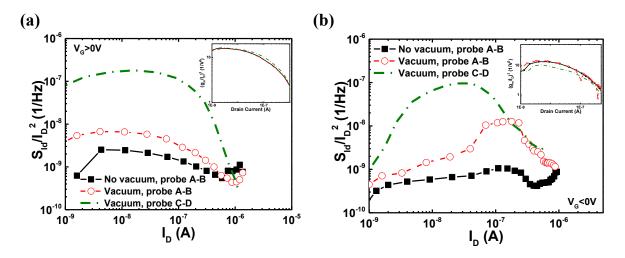

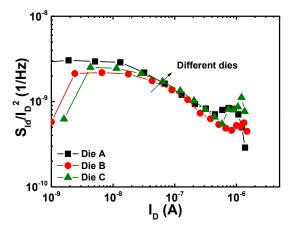

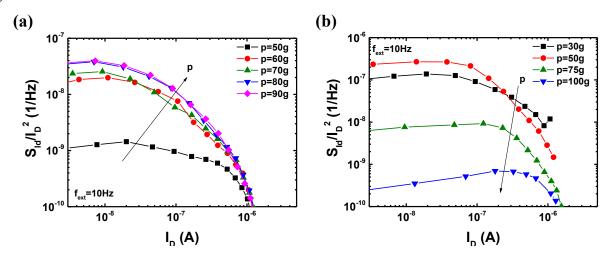

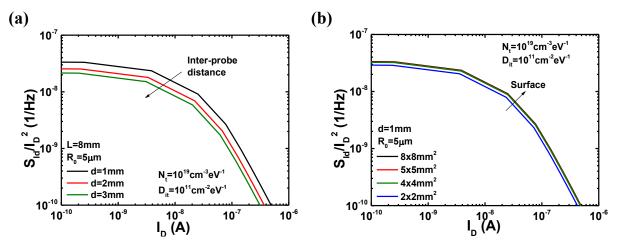

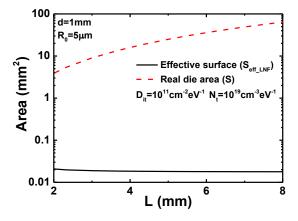

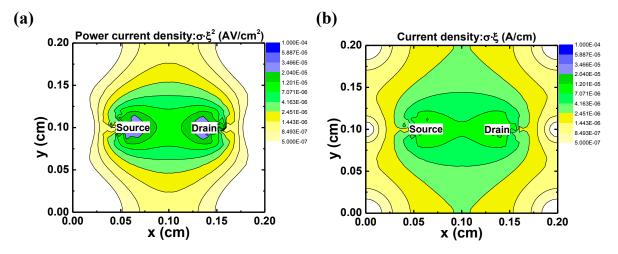

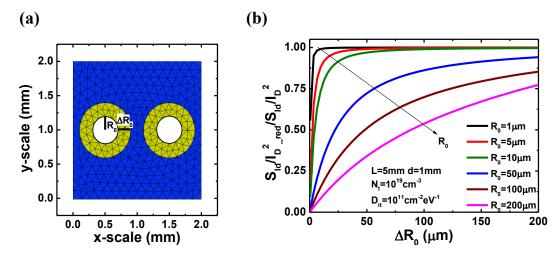

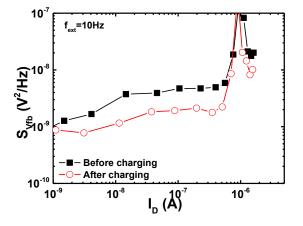

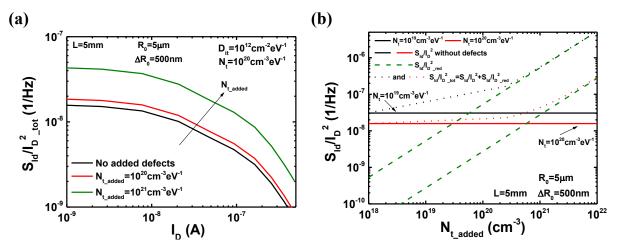

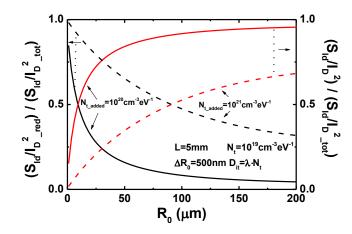

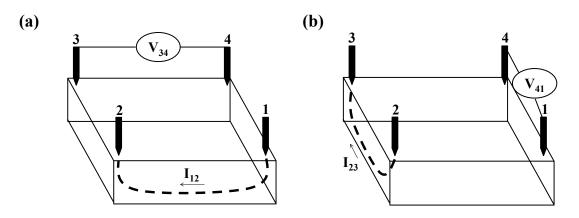

Figure II-14: Drain current as a function of gate bias for SOI structure with 88 nm top silicon film and 145 nm BOX. The passivated structure (plain symbols) was measured using p = 100 g, while in non-passivated sample (empty symbols) the tip pressure was 80 g.