# On Scalable Reconfigurable Component Models for High-Performance Computing

Vincent Lanore

# ▶ To cite this version:

Vincent Lanore. On Scalable Reconfigurable Component Models for High-Performance Computing. Software Engineering [cs.SE]. Ecole normale supérieure de lyon - ENS LYON, 2015. English. NNT: 2015 ENSL1051. tel-01257842

# HAL Id: tel-01257842 https://theses.hal.science/tel-01257842

Submitted on 18 Jan 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

en vue de l'obtention du grade de

Docteur de l'Université de Lyon, délivré par l'École Normale Supérieure de Lyon

discipline

# Informatique

laboratoire

Laboratoire de l'Informatique du Parallélisme

école doctorale

École doctorale en Informatique et Mathématiques de Lyon

présentée et soutenue publiquement le 10 décembre 2015 par Monsieur Vincent LANORE

# On Scalable Reconfigurable Component Models for High-Performance Computing

# directeur de thèse M. Christian Pérez

## devant la commission d'examen formée de

| Raymond      | Namyst    | Professeur, Univ. de Bordeaux     | Président    |

|--------------|-----------|-----------------------------------|--------------|

| Marco        | Danelutto | Professeur associé, Univ. de Pise | Rapporteur   |

| Laurence     | Duchien   | Professeure, Univ. de Lille 1     | Examinatrice |

| Laxmikant V. | Kale      | Professeur, Univ. de l'Illinois   | Examinateur  |

| Christian    | Pérez     | Directeur de recherche, Inria     | Directeur    |

| Jean-Bernard | Stefani   | Directeur de recherche, Inria     | Rapporteur   |

# Acknowledgements / remerciements

(English part) First, I want to thank all the members of the jury: Mr Raymond NAMYST and Ms Laurence Duchien for their presence at the defense; Mr Laxmikant V. Kale for his remote participation despite the time difference; Mr Marco Danelutto for reviewing the manuscript; and, especially, Mr Jean-Bernard Stefani for his presence at the defense, his review of the manuscript despite a very tight schedule, and his precious insight regarding the contents of the manuscript.

(French part) Je tiens à remercier tous ceux qui ont dû me supporter pendant la thèse : l'inénarrable professeur Simon ; François, pour son fascisme sans égal ; Mathias, mais pas pour ses pâtes carbo ; Fred, pour le beurre ; Julien, dont c'est clairement la faute ; Maxime, informaticien malgré lui ; Samantha, la reine des mouches ; sans oublier François (mais pas le même), Vincent, Clément et le reste des ambreux, pour m'avoir irrémédiablement condamné à ne pas avoir assez de temps libre. Je tiens également à remercier les autres lyonnais, ceux qui sont partis avant que je ne commence la thèse (coucou Hugo), et ceux que j'ai sans doute oublié. À cause de vous tous, je vais vraiment avoir du mal à quitter Lyon ; j'espère que vous êtes fiers de vous.

Un grand merci à toute ma famille qui m'a toujours soutenu dans mes études, et qui a toujours supposé que je savais ce que je faisais avec mes choix d'orientation.

Merci également à tout ceux qui m'ont poussé vers l'informatique et la recherche, sans qui je n'aurais jamais fait cette thèse. Je pense notamment aux enseignants qui ont participé à me donner le goût des maths, en particulier à M. Cozar qui m'a poussé vers l'ENS alors que je ne me donnais pas une chance.

Un grand merci bien sûr à toute l'équipe Avalon avec qui ça a été un plaisir de travailler pendant ces trois ans, et plus largement à tous ceux du LIP qui m'ont aidé au cours de la thèse. Merci en particulier à la team composants (Jérôme et Hélène), aux irremplaçables trolls du coin café (notamment Arnaud, Anthony, Laurent et Daniel), à Eddy avec qui j'ai eu beaucoup de plaisir à enseigner, et à tous ceux qui ont dû partager un bureau avec moi (Jonathan, Sylvain, Hélène et Jérôme). Merci à Cristian, avec qui j'ai eu beaucoup de plaisir à travailler lors de mon stage de master, et à Maverick, qui a été un stagiaire exemplaire. Je tiens à remercier tout particulièrement ceux qui m'ont aidé dans l'organisation de la soutenance, qui a été un moment particulièrement stressant pour moi : Violaine, Hélène, Jérôme, Jean-Christophe et Serge.

Enfin, et surtout, merci à Christian pour son encadrement tout au long de la thèse. Ça a été un grand plaisir de travailler avec lui pendant ces trois ans.

# Contents

| $\mathbf{C}_{0}$ | onter                     | nts                                   | i  |  |  |  |  |  |  |  |  |  |  |  |  |

|------------------|---------------------------|---------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|--|

| 1                | Intr                      | roduction                             | 1  |  |  |  |  |  |  |  |  |  |  |  |  |

| Ι                | Context and Related Works |                                       |    |  |  |  |  |  |  |  |  |  |  |  |  |

| 2                | Con                       | ntext                                 | 7  |  |  |  |  |  |  |  |  |  |  |  |  |

|                  | 2.1                       | High-Performance Computing            | 7  |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | 2.1.1 Hardware Architectures Today    | 7  |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | 2.1.2 HPC Applications                | 9  |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | 2.1.3 Focus: Adaptive Mesh Refinement | 12 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  | 2.2                       | Component Models                      | 15 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | 2.2.1 Common Concepts and Features    | 16 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | 2.2.2 Examples of Component Models    | 18 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  | 2.3                       | Conclusion                            | 20 |  |  |  |  |  |  |  |  |  |  |  |  |

| 3                | Rale                      | ated Works                            | 21 |  |  |  |  |  |  |  |  |  |  |  |  |

| J                | 3.1                       |                                       | 22 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  | 5.1                       |                                       | 22 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           |                                       | 23 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           |                                       | 23 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           |                                       | 24 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  | 3.2                       |                                       | 25 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  | 0.2                       | 1                                     | 25 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           |                                       | 25 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | 3.2.3 User-Driven                     | 26 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           |                                       | 27 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  | 3.3                       |                                       | 27 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  | 0.0                       |                                       | 27 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | 3.3.2 Appropriate Execution Model     | 27 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           |                                       | 28 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           |                                       | 29 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | 11 1                                  | 30 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  | 3.4                       |                                       | 30 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | •                                     | 30 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           |                                       | 31 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           |                                       | 31 |  |  |  |  |  |  |  |  |  |  |  |  |

|                  |                           | 3 4 4 Concluding remarks              | 31 |  |  |  |  |  |  |  |  |  |  |  |  |

| II | Con  | atributions                                                                                               | 33        |

|----|------|-----------------------------------------------------------------------------------------------------------|-----------|

| 4  | The  | DIRECTMOD Component Model                                                                                 | 35        |

|    | 4.1  | Preliminary Model                                                                                         | 36        |

|    |      | 4.1.1 Syntax                                                                                              | 36        |

|    |      | 4.1.2 Graphical Conventions and Example                                                                   | 38        |

|    |      | 4.1.3 Additional Definitions                                                                              | 41        |

|    |      | 4.1.4 Call-Stack Semantics                                                                                | 42        |

|    | 4.2  | The DIRECTMOD Component Model                                                                             | 44        |

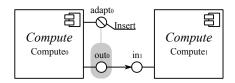

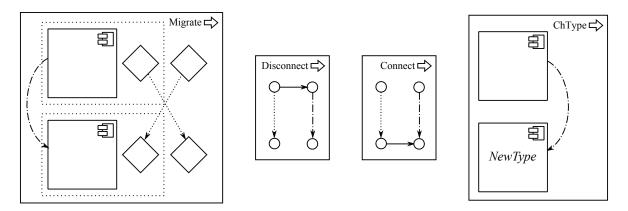

|    |      | 4.2.1 Transformations                                                                                     | 45        |

|    |      | 4.2.2 Transformation Adapters                                                                             | 47        |

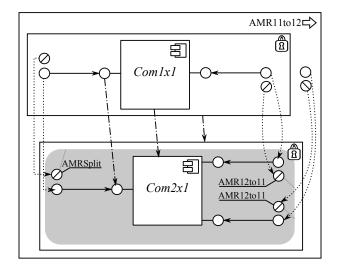

|    |      | 4.2.3 Domains                                                                                             | 48        |

|    |      | 4.2.4 Full Assembly                                                                                       | 50        |

|    |      | 4.2.5 Additional Notations and Definitions                                                                | 51        |

|    |      | 4.2.6 Full Semantics                                                                                      | 53        |

|    | 4.3  | Discussion and Evaluation                                                                                 | 57        |

|    | 1.0  | 4.3.1 Model-level Discussion                                                                              | 57        |

|    |      | 4.3.2 Implementation and Evaluation                                                                       | 60        |

|    | 4.4  | Conclusion                                                                                                | 62        |

|    |      |                                                                                                           |           |

| 5  |      | sex-based Locking of Component Assemblies                                                                 | 65        |

|    | 5.1  | Model and Algorithm                                                                                       | 66        |

|    |      | 5.1.1 Control Metadata                                                                                    | 66        |

|    |      | 5.1.2 Locking Paradigm                                                                                    | 68        |

|    |      | 5.1.3 Locking Algorithm                                                                                   | 71        |

|    |      | 5.1.4 Discussion                                                                                          | 74        |

|    | 5.2  | Evaluation                                                                                                | 74        |

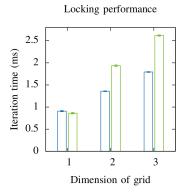

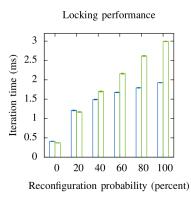

|    |      | 5.2.1 Locking Performance on Stencil Benchmark                                                            | 75        |

|    |      | 5.2.2 Software Engineering Properties on AMR Benchmark                                                    | 76        |

|    | 5.3  | Conclusion                                                                                                | 77        |

| c  | A C. |                                                                                                           | 70        |

| 6  | 6.1  | pecialization Model For Hierarchical Component Assemblies SpecMOD, A Calculus for Assembly Specialisation | <b>79</b> |

|    | 0.1  | 6.1.1 Assembly model                                                                                      | 80        |

|    |      | ·                                                                                                         |           |

|    |      | 6.1.2 Type System                                                                                         | 82        |

|    |      | 6.1.3 Well-Formedness                                                                                     | 83        |

|    |      | 6.1.4 Operational Semantics                                                                               | 85        |

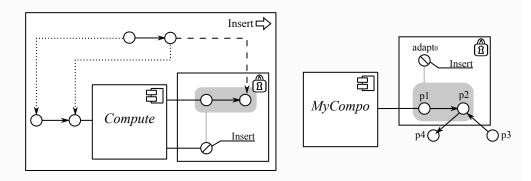

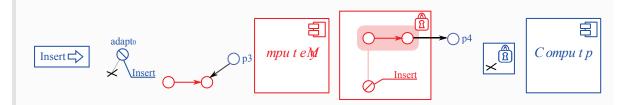

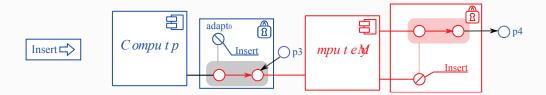

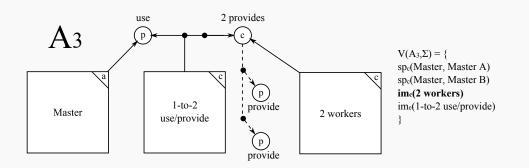

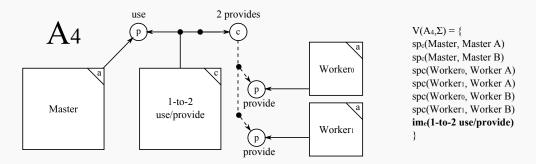

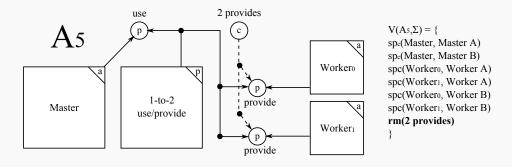

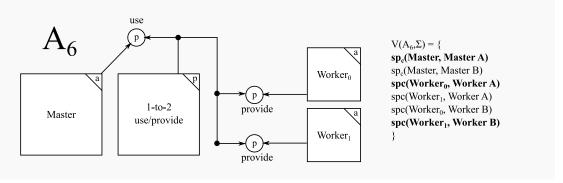

|    |      | 6.1.5 Full Example                                                                                        | 86        |

|    | 0.2  | 6.1.6 Calculus Variant: Reversible Operations                                                             | 89        |

|    | 6.2  | Encoding Additional Features                                                                              | 90        |

|    |      | 6.2.1 Hierarchy                                                                                           | 90        |

|    |      | 6.2.2 Genericity                                                                                          | 91        |

|    | 6.3  | Discussion and Use Case                                                                                   | 93        |

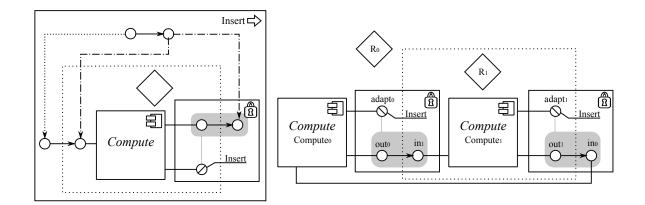

|    |      | 6.3.1 Specialisation Processes                                                                            | 93        |

|    |      | 6.3.2 Use Case: Compiling a High-level Language to DIRECTL2C                                              | 95        |

|    | 6.4  | Conclusion                                                                                                | 99        |

| 7  | Con   | clusion      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 1      | 01 |

|----|-------|--------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--------|----|

|    | 7.1   | Conclusion   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | <br>10 | 01 |

|    | 7.2   | Perspectives |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | <br>10 | 03 |

| Bi | bliog | graphy       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 1      | 05 |

# Chapter 1

# Introduction

Since the early days of computer programming, code reuse has been the focus of research. Software engineering research has developed over the years a variety of concepts to help code reuse, such as procedures or objects. Code reuse is important to avoid having to reinvent the wheel for each new project, when third-party code could be used instead. Moreover, even within a single application, code quickly becomes redundant. Proper reuse and/or factorization techniques can tremendously ease the development and maintenance of applications.

Component-based software engineering (CBSE) is a software engineering paradigm, introduced in the 1960s [74], which proposes to reuse code through composition. Code to be reused is encapsulated in entities called components which are meant to be composed. Let us say that some component A needs to reuse the code from some other component B, then A can be composed with B. This approach is different from object-oriented software engineering which uses inheritance as its main means of code reuse.

Component-based programming (CBP) is a direct application of this paradigm and consists in writing applications through component composition only. This approach assumes that there exist components, written by third-parties, which are available "on a shelf". These components can be composed using a dedicated language to form a full application. This process is called "component assembly". Component-based programming requires the use of a dedicated model, called a component model, which defines components and composition. Component models have been the focus of a lot of academic and industrial efforts in the last decades. Many component models, with various features and properties, have been proposed and implemented over the years.

Compared to other software engineering paradigms, component-based approaches have two main advantages: easy separation of concerns, and high-level view of application architecture. Separation of concerns (SoC) is the process of dividing an applications into parts (in our case: components) so that each part deals with a small number of specific "concerns". SoC is an important software engineering property which ensures applications parts are easy to write (less concerns means less complexity and skills involved), and easy to reuse (SoC means less dependencies). CBSE proposes both separation of concerns between components (each component deals with a specific task), and between the component level (low-level concerns) and the assembly level (high-level concerns, application structure). Moreover, a component assembly provides a convenient high-level view of an application structure. Indeed, low-level concerns are hidden within components and composition can be used to express meaningful interactions between parts of the application. Also, this high-level view provides convenient high-level mechanisms to tweak applications, e.g., to adapt them to specific use cases.

CBSE has been successfully applied to High-Performance Computing (HPC) applications. HPC applications are applications whose sequential execution time is ludicrously high (e.g.,

years or centuries) and which, consequently, target highly-parallel hardware architectures such as supercomputers or computer clusters. HPC applications include, for example, large-scale simulations in scientific domains such as climatology, chemistry or astrophysics. HPC applications tend to be large (e.g., hundreds of thousands of lines of codes), complex (e.g., cutting-edge physics/maths, fine-grained multithreaded synchronization) and to have drastic scalability requirements (e.g., hundreds of thousands of cores). Moreover, HPC applications require frequent adaptation and tweaking, to fit different use cases and target hardware architectures, over the course of their long lives (typically tens of years). CBSE has been used in this case to both ease the expression of parallelism (thanks to the assembly-level view offered by CBP) and ease adaptation to different use cases and hardware (by tweaking the assembly).

Unfortunately CBP has a hard time dealing with applications whose code, communication topology and/or data topology change during execution. One example of such an application, in HPC, is Adaptive Mesh Refinement (AMR), a computing technique which involves dynamic refinement of a mesh of data. From a CBP perspective, this kind of application is difficult to implement because the application structure (which highly influences the component assembly) changes dynamically during execution. Most existing component models do not provide the same benefits (e.g., assembly view, third-party reuse) during execution, as they do at assembly time. While it is possible to circumvent the problem by using large components which encapsulate the dynamic parts, this defeats the purpose of using components in the first place. Moreover, it would be interesting to express structure changes as assembly changes, in order to benefit from the high-level view provided by CBP. In order to do that, one must use a reconfigurable component model, i.e., a component model which supports assembly modification (reconfiguration) at runtime.

Reconfigurable component models exist in the literature but none of them is compatible with the scalability and performance requirements of HPC applications. Indeed, these models impose synchronization constraints (e.g., global synchronization before any reconfiguration) which limit scalability in the general case (e.g., global synchronization is known not to be a scalable operation). HPC applications are a particularly challenging case because they often require (in order to scale) fine-grain custom synchronization (e.g., point-to-point message-passing synchronization across millions of processes).

# **Problem**

The goal of the present thesis is to propose a reconfigurable component model compatible with HPC performance and scalability requirements. Such a model is important to help design, maintain and adapt HPC applications with dynamic structure, which are among the most complex HPC applications. This problem is not simple though, and presents several sub-problems.

The first sub-problem that must be addressed is the synchronization of concurrent reconfigurations. When several concurrent reconfigurations occur at once in an assembly, consistency and synchronization problems arise. This problem can be further decomposed into ensuring safety (i.e., consistency of application state during execution) and performance (i.e., minimizing reconfiguration time for HPC purposes).

The second sub-problem to be addressed is programmability of reconfigurable applications. Reconfigurable applications, and reconfigurable HPC applications in particular, typically are large and complex applications, which are difficult to develop. In addition, HPC applications must be easily adaptable to various hardware architectures. While high-level programmability-oriented features exist in the component literature (e.g., hierarchy, genericity), their use with reconfigurable assemblies is problematic (notably hierarchy).

In addition, solutions for these various problems can easily conflict and/or be difficult to reconcile. For example, performance and programmability are goals which typically hamper

one another. Also note that the proposed solutions must comply with the core principles of component-based programming, otherwise the software engineering benefits this approach provides may not longer hold.

## Contributions

For this thesis, we have decided not to focus on one particular sub-problem but, instead, to adopt a "vertical slice" approach. We have endeavoured to tackle both software-engineering-oriented and HPC-oriented problems in order to provide a full end-to-end solution and overview of the larger problem.

**DIRECTMOD** The main contribution of the thesis, and the cornerstone of our approach, is the DIRECTMOD formal component model. This model aims to:

- provide an assembly-level language for assembly transformations;

- ease the reuse of transformations;

- separate the synchronization and locking concerns from the rest of the application.

In order to achieve these goals, two novel concepts are introduced: domains and transformation adapters. Domains are special components which are responsible for safely executing transformations. Transformations adapters are special ports which explicitly connect a transformation to its target subassembly. We provide full syntax and semantics for DIRECTMOD in a formal fashion. This first contribution is evaluated both through a model-level analysis, and using DIRECTL2C, an implementation we developed. Evaluation deals with both the programmability capabilities of DIRECTMOD and its performance.

Efficient Locking Our second contribution is a set of models and tools to help with stopping running components in an efficient and reliable fashion. We present a formal model for a stopping paradigm called *mutex-based locking*, which is efficient but difficult to use. We then propose an algorithm which helps to implement mutex-based locking while relying on very little metadata. We evaluate this approach on a series of AMR-based benchmarks, which we compare in terms of code metrics and performance. While this approach does not work in the general case, it works well for a certain class of applications which include useful use cases such as stencil codes.

SPECMOD Our third contribution is SPECMOD, a formal calculus for specialization of hierarchical component assemblies. SPECMOD models the element-by-element specialization of component assemblies and provides a formal framework to express specialization algorithms. We show how SPECMOD can support hierarchy, genericity and—more importantly in the context of this thesis—assembly transformations. Full syntax and semantics of SPECMOD are provided. The generality of the model is extensively discussed through a series of examples and extensions of the model. Preliminary work to apply SPECMOD to DIRECTMOD, in order to improve the transformation and assembly description, is also presented and evaluated.

## Structure of this Document

The present thesis is divided into two parts. First, Part I presents the context of the thesis and relevant related works. This part is divided into Chapter 2, which gives the context on HPC and component models, and Chapter 3, which presents related works on reconfiguration in general. Second, Part II presents our contributions, one per chapter. This second part is divided into three chapters. Chapter 4 presents DIRECTMOD, which is a formal component model which

allows concurrent reconfiguration while preserving separation of concerns. Chapter 5 presents a series of models and tools aimed at stencil-style applications to help with efficient deadlock-free locking of component assemblies while requiring minimal metadata. Chapter 6 presents SpecMOD, a formal calculus for component assembly specialization which support genericity, hierarchy and Directmod-style transformations; usage with Directmod is also discussed. Finally, Chapter 7 concludes and present perspectives.

# Part I Context and Related Works

# Chapter 2

# Context

#### Contents

| 2.1 | High-Performance Computing            | 7  |

|-----|---------------------------------------|----|

|     | 2.1.1 Hardware Architectures Today    | 7  |

|     | 2.1.2 HPC Applications                |    |

|     | 2.1.3 Focus: Adaptive Mesh Refinement | 12 |

| 2.2 | Component Models                      | 15 |

|     | 2.2.1 Common Concepts and Features    | 16 |

|     | 2.2.2 Examples of Component Models    | 18 |

| 2.3 | Conclusion                            | 20 |

This chapter presents High-Performance Computing and Component Models, the two domains at the intersection of which lie the subject matter of the thesis. For each of those two domains, a presentation of the important concepts relevant to the understanding of the thesis is given. Section 2.1 presents High-Performance Computing (HPC), while Section 2.2 deals with component models.

# 2.1 High-Performance Computing

High-Performance Computing, abbreviated as HPC, is the domain of computer science that deals with applications with very large space and/or time requirements. Typically, a HPC application executing on a traditional desktop computer would take years or centuries to terminate. Alternatively, some HPC applications might require inordinate amounts of memory. HPC as a scientific domain deals with the development of new hardware and software techniques so as to be able to run more and more demanding applications.

HPC today deals with both unusual hardware architectures and unusual software, and a few notions about both are required to fully understand the context for the present thesis. Section 2.1.1 presents modern HPC hardware and afferent challenges, while Section 2.1.2 deals with HPC application characteristics, and finally Section 2.1.3 presents a specific HPC application (Adaptive Mesh Refinement) as a motivating example for this thesis.

## 2.1.1 Hardware Architectures Today

Over the years, a variety of different hardware architectures have been developed for HPC applications. Not all those architectures target the same kind of application, and their characteristics vary depending of their specific goals.

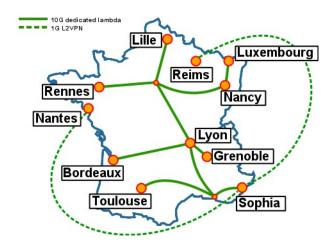

Figure 2.1: Grid'5000, an example of a computing grid.

High-performance hardware is a complex subject whose intricacies could easily fill a whole thesis, but this section gives only a brief overview. Indeed, the subject matter of the thesis requires no more than a coarse-grain understanding of the main characteristics of HPC hardware and underlying issues.

**Brief taxonomy** Most modern HPC architectures are collections of computing hardware, structured into large architectures. Different paradigms can be used to build such architectures. The most common of those paradigms are:

- Supercomputers are large, tightly-connected high-performance architectures built as a single machine. Supercomputers are different from the other approaches below in that they are designed from scratch as a single machine, instead of being a collection of smaller machines.

- Clusters are collections of desktop-style or server-style computers, assembled together using high-performance networks. The machines composing a cluster are typically called computing nodes (or just nodes). On many clusters (depending on the program used for resource reservations), users know the structure and can reserve specific subsets of the nodes for a given computing task.

- Computing grids are collections of clusters and supercomputers, often geographically distant from one another, connected to form a single infrastructure. While grids can be used to run applications on a single cluster or supercomputer, they also allow to run grid-wide applications. One example of a computing grid is Grid'5000 [10], an experimental platform regrouping clusters from sites all across France.

- Clouds are computing resources abstracted as on-demand services. Clouds typically try to hide away architectural information such as network topology or node location. While clouds are mostly known for non-HPC applications, there have been initiatives that try to use them for HPC (early examples include [92, 93]).

Size and parallelism HPC infrastructure are typically quite large and very parallel. For example, at the time of writing, the largest supercomputer is the Tianhe-2, developed at China's National University of Defense Technology [1], which sports 3,120,000 computing cores.

The point of those very large architectures is to push the boundaries of what a single application can compute in a reasonable time (up to months or years). Thus, such architecture are

not meant to be used by a lot of concurrent applications but, as much as possible, by large, very parallel applications.

There is a constant push towards larger architectures. At the time of writing, the largest supercomputers are capable of tens of quadrillions of floating point operations per second (i.e., tens of Pflop/s) [1]. This scale of architecture is called *petascale computing*, and a lot of initiatives are already working towards the next step, *exascale computing* (i.e., thousands of Pflop/s); see for example [18, 89, 46].

This race towards larger architectures means that architectures are more and more parallel. Indeed, as the frequency of circuits has pretty much stopped, increasing the power of chips was done by cramming more and more computing units in them, using the extra transistors predicted by Moore's law [76].

**Heterogeneity** In addition to being large and parallel, HPC architectures tend to be heterogeneous, in the sense that hardware inside a single architecture can be heterogeneous.

First, there might be heterogeneity inside computing nodes. Typically, a computing node can feature a hardware accelerator in addition to its CPU, such as a GPU, a FPGA, or an Intel MIC coprocessor. Also, HPC computing nodes may have non-uniform memory or processor architectures.

Second, there might be inter-node heterogeneity, either in the form of non-uniform access (due to network concerns), or simply different nodes hardware-wise. A typical example of internode heterogeneity is provided by computing grids.

Concluding remarks HPC architectures are very large, very parallel (up to millions of cores and growing), very complex, and can differ greatly from one another. This poses a challenge to programmers, particularly in a HPC context where making the most of every piece of hardware is crucial for performance.

## 2.1.2 HPC Applications

HPC applications are, by definition, applications with very large computing times and/or memory requirements, that target HPC hardware. HPC applications have other specific characteristics which are detailed in the present section.

**Application domains** HPC applications come from a variety of science and engineering domains. Typical examples of HPC applications include:

- climatology (e.g., [59]);

- engineering simulations (e.g., nuclear-waste disposal [80]);

- biology (e.g., DNA alignment [5], biomolecular dynamics [56]);

- physics (e.g., astrophysics [98, 94]);

- computational chemistry (e.g., quantum chemistry [3]).

A study conducted by PRACE (Partnership for Advanced Computing in Europe, a European organisation regrouping most Europe's world-class HPC infrastructures) [90] shows that, in practice, on large computers, physics and chemistry constitute the majority of applications.

**Scalability** Since HPC infrastructures are very parallel (up to millions of cores, see Section 2.1.1), HPC applications must be capable of such a level of parallelism.

Most HPC applications are moldable, i.e., the level of parallelism can be configured per-run at the start of the application or at compilation. Technically, any such application can run at arbitrarily high parallelism. However, the very point of parallelism is to improve computing

time as the number of cores/threads/processes increases, which is difficult. The relation between the amount of computing resources available to an application and its performance is called *scalability*. At the very best, the performance of an application (number of operations/time unit) can scale linearly with the number of computing resources <sup>1</sup>.

In practice linear scaling is difficult to attain for high resource counts as many phenomenons hamper scalability. At the very least, applications are held by Amdahl's law [6], which states that an application's performance has a sequential component which becomes dominant as the resource count go up, preventing linear scaling. Many other problems arise that hamper scalability, including:

- Algorithmic limitations: some problems cannot easily be parallelised (e.g.,, irregular meshes).

- Saturation of resources that arise with intensive use, e.g., network, memory bandwidth.

- Imperfect use of resources: it is difficult to ensure that every core/process/thread has work to do 100% of the time. This problem is called *load balancing*.

- Management/synchronisation overhead: managing thousands/millions of cores/processes/threads is no trivial task and may be imperfect or require resources in itself.

Scalability is a very central issue in HPC, a large part of the literature aiming at improving scalability through technologies, algorithms, and software optimisations.

In terms of figures, the largest HPC applications target million-cores architectures (see Section 2.1.1), and execution times of a few years at most. This means that the largest HPC applications require millions of *cpu.month*, i.e., millennia of *cpu* time.

**Languages and technologies** Most HPC applications are written in Fortran, C, or C++ [90]. All these languages have traditional call-stack-based executions, and a C-style memory model with pointers. From a software engineering perspectives, these languages feature functions, and module/objects for some of them.

Since HPC applications need to be very parallel, several technologies were developed to allow/ease parallel programming in C/C++/Fortran. The most prominent of these technologies are:

- MPI [50] (Message Passing Interface) is a widely-used standard in C++/Fortran HPC applications. It handles parallelism through message passing and has a distributed memory model, i.e., a MPI application is composed of several *processes* with their own memory which communicate by sending and receiving messages. A noteworthy feature of MPI is collective communications, i.e., procedures for communications involving many processes. Collective communications are usually very well-optimised and can bring a very noticeable increase in performance compared to using only point-to-point communications.

- Shared-memory technologies, such as OpenMP [38] and Intel TBB [84], rely on a shared memory approach, i.e., the application has several control threads that can access the same memory and must synchronise to avoid conflicts.

- Traditional thread libraries, e.g., PThreads [77], are low-level libraries that provide the basic primitives to create threads and synchronise them.

- Partitioned Global Address Space (PGAS) languages, e.g., UPC [47], Co-array Fortran [78], HPF [72], or XcalableMP [71]. These languages propose to abstract all the memories available in a (possibly distributed) system, as a single partitioned memory (the partition represents the various memory locations). This allows a shared-memory programming style, while still permitting to distinguish between memory locations.

<sup>&</sup>lt;sup>1</sup>Technically, superlinear performance increase with the number of computing cores exist, but is generally a side-effect of having other resources that come with the additional cores (e.g., memory).

In addition to those technologies, which are mostly aimed at CPU-based architectures, there exist technologies dedicated to accelerators such as CUDA [79], OpenCL [53] or FPGA suites.

A synthesis and detailed classification of these technologies can be found in [45].

**Complexity** HPC applications are very complex in several respects.

First, because of the need to increase performance as much as possible, HPC applications rely on noticeable amounts of highly-optimised low-level code. Such low-level code is not only verbose, but also difficult to write and error-prone. Examples of difficult code issues that HPC programmers must face include manual fine-grain memory management (possibly down to the bit), or thread-level synchronisation (very error-prone).

Second, HPC programmers need to have a variety of non-trivial skills. Indeed, HPC typically requires knowledge of parallelism, non-standard hardware, and understanding of the functional part of the application (which typically involves state-of-the-art science). For this reason, HPC applications are difficult to develop and maintain, as programmers with such skill combinations are difficult to find.

In addition, HPC applications need to be adapted to different hardware in the course of their life. Indeed, the lifetime of HPC applications (e.g., TURBOMOLE which was introduced in 1989 [3], was still used in 2008 [91]), is shorter than the lifetime of HPC hardware (years). As many HPC applications rely on hardware-dependent optimisations to make the most of state-of-the-art hardware, it is necessary to adapt these applications when moving to new hardware.

Moreover, as the power of HPC hardware grows, possibilities emerges of combining several existing codes. For example, it is now possible to combine a heat simulation code with a fluid physics code to perform a heat simulation on a dynamic fluid, which would have been too costly to compute twenty years ago Combining several existing code is often preferred to writing a new one from scratch, as it saves time and builds on already well-known and accepted tools. However, this process, referred to as *code coupling*, leads to applications made of several large and complex glued-together parts, increasing even further the skills and knowledge required to have a good understanding of the whole application.

Finally, HPC applications are large in terms of code size, typically in the hundreds of thousands/million range in terms of lines of code (LOC). While these sizes are not particularly noteworthy in themselves—a typical OS or car software ranging in the tens or hundreds of millions LOC—they can still be problematic, as they are very complex and often developed/maintained by very small academic teams.

**Dynamicity** Many HPC applications have some sort of dynamic structure that evolves during execution. As HPC applications are very parallel and very complex, it is often difficult to predict its behaviour and performance perfectly, and thus several optimisation techniques rely on decisions taken at runtime to optimise performance.

A first example of dynamicity is dynamic load balancing. To maximise performance, a HPC application must make sure every core/thread/process has work most of the time. Since it is often difficult to estimate the computation time of everything, some application rely on *dynamic load balancing*, i.e., they attribute work at runtime, based on the observed workload.

Another common example of dynamic behaviour in HPC application is resiliency, or fault tolerance. As HPC applications can take centuries of cpu time, hardware faults that would otherwise be negligible become a real problem. Such large application require software mechanisms to ensure it completes its computation without error. While some techniques to handle fault tolerance are not very dynamic (e.g., checkpointing), some HPC works advocate dynamic approaches, e.g., [48] proposes to proactively migrate tasks away from nodes that are about to fail.

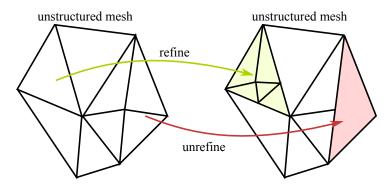

Figure 2.2: Illustration of mesh refinement and unrefinement on an unstructured mesh. Refinement adds nodes to the mesh, while unrefinement fuses several mesh elements together.

In addition, in order to use HPC platforms to their maximum, it can be interesting to have *malleable* HPC applications, i.e., applications whose resource allocation can change mid-execution. Some manner of adaptation of reconfiguration mechanism is required in such an application in order to make use of extra resources mid-execution, or to avoid crashing if resources are removed. Works advocating malleable approaches include [100, 44].

Finally, some HPC applications have a dynamic behaviour at functional level. Adaptive mesh refinement is an example of such application, and is presented in details in the next section.

Concluding remarks In this section on HPC applications, we have presented common characteristics of HPC applications, and the technologies that are commonly used. HPC applications are often very complex and, because of their long lives and the evolution of hardware, require important development, maintenance and adaptation efforts. Among HPC applications, those with dynamic structure are the most complex.

#### 2.1.3 Focus: Adaptive Mesh Refinement

Adaptive Mesh Refinement (AMR) is a computing technique which involves dynamic modification of a data mesh, in order to optimise both performance and precision.

**Principle** Many simulation applications rely on meshes as discrete representations of space. For example, the universe might be represented by a 3D grid, or a solid object might be represented by an object-shaped mesh. Simulation of a phenomenon on such a mesh typically involves attaching physical values to the vertices (e.g., temperature, electromagnetic field) and simulating the passage of time by computing step-by-step evolution of these values.

In such a context, the resolution of the mesh, i.e., the number of mesh elements per unit of simulated space, determines the precision of the simulation. Obviously, high-resolution meshes are more costly computing-wise, to the point where computing time (or memory) became a limit for high-precision simulations.

However, many physical simulations do not require high precision everywhere on their mesh. For example, density of matter in the universe might present high gradients inside galaxies (which requires high precision to properly simulate), but be very homogeneous in intergalactic space (which does not require high precision). Note however that high-gradient regions might move as time passes (e.g., a storm in a climate simulation).

In order to take advantage of this fact, a technique was introduced which consists in adapting the resolution of the mesh locally and dynamically, depending on gradient (i.e., on required

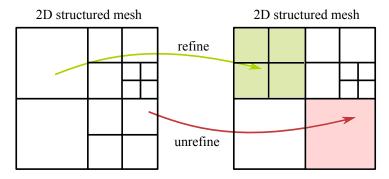

Figure 2.3: Illustration of mesh refinement and unrefinement on a structured 2D mesh.

precision). This approach allows to optimise the mesh resolution to have both high precision where it matters, and save on computing resources elsewhere. Figure 2.2 illustrates what mesh refinement means on an example unstructured mesh. This technique is called Adaptive Mesh Refinement, as it consists in changing the mesh refinement (i.e., its resolution) by adapting to simulated phenomenons.

**Unstructured meshes** For some applications, meshes are said to be *unstructured*, i.e., they can have pretty much any shape. For example, 3D models of objects are unstructured meshes. The mesh from Figure 2.2 is also unstructured.

Since unstructured meshes lack structural properties, they are difficult to work with. For example, it is difficult to have coordinates within a dynamic unstructured mesh. This makes it hard to provide application-agnostic support for such applications. However, there exist frameworks and libraries that targets unstructured mesh AMR applications, such as libmesh [66]. Such frameworks provide support for local reconfiguration and communication (e.g., communicating with neighbours in the mesh, local load balancing), along with global tools, e.g., for mesh partitioning.

Structured meshes In other cases, mesh are structured. The most common occurrence of structured mesh is 2D/3D grids in which cells can be further subdivided in 2D/3D grids respectively. Figure 2.3 presents an example of such a mesh: a 2D grid with local subdivisions. The number of times a cell has been recursively subdivided is called the *level of refinement*.

Since structured meshes have strong structural properties, it is easier to devise application-agnostic optimisations and tools for structured AMR. In particular, AMR framework that support structured meshes feature optimised data structures to represent the current state of the grid. Because of the recursive nature of structured AMR, these implementations, and related optimisations, are often based on quadtrees (for 2D AMR) or octrees (for 3D AMR) to represent the state of the mesh; those optimised tree structures are stored on every process and are used to locate neighbours. Examples of such frameworks include RAMSES [98], PARAMESH [73], and P4est [34].

One particular sub-category of structured AMR is meshes which follow the 2:1 rule [61]. The 2:1 rule is a constraint on refinement level which forces adjacent cells in a structured AMR mesh to have at most a difference one level of refinement. This means that a cell has at most 2 neighbours in a given direction (hence the 2:1 name).

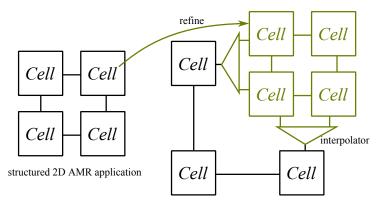

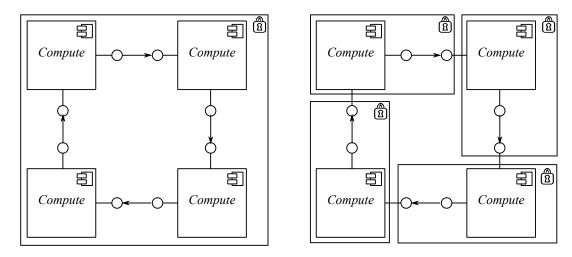

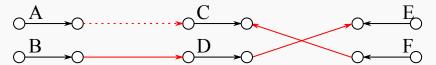

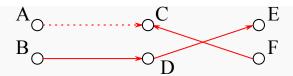

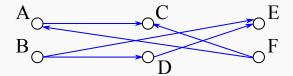

Figure 2.4 illustrates one possible way to implement 2D structured AMR that follows the 2:1 rule. Such an application can be built from computing cells, each responsible for the computation on a square of data of fixed resolution. When refining, as illustrated on the figure, one cell is

Figure 2.4: Application architecture before and after refinement of a 2D AMR structured mesh. Each cell is identical to every other, apart from the data it holds. All cells have the same resolution. Note the addition of interpolators to connect to adjacent cells with different levels of refinement.

replaced by four identical cells, and those cells are given interpolated data based on the data of the original cell before refinement. Interpolators are added between adjacent cells with different refinement levels, and are responsible for interpolating data so that each cells gets data with the correct resolution. Note that the 2:1 rule ensure that interpolators are at most two-to-one. While this way of implementing AMR is interesting because it builds upon reusable fixed-resolution cells, it also means refinement and unrefinement must modify the structure of the application.

Scalability issues Most traditional AMR approaches scale well up to a few thousands of cores, but struggle to scale further. This is due in most cases to an over-reliance on global representations and operations. For example, global partitioning steps in non-structured meshes are non-scalable because they require a global synchronisation. Another example is the use on quadtrees/octrees in traditional structured AMR implementations, which incurs a O(P) storage cost on each node, and a  $O(\log P)$  time to locate neighbours, where P is the number of processes.

While it is possible to have AMR applications that scale to large processor counts [68, 33], it is particularly difficult. Recent works [68] advocates the use of more distributed approaches, with less reliance on global representations. Not only does such an approach address some of the programmability concerns raised by highly-complex traditional implementations, but it scales more easily at an algorithmic level.

Complexity AMR applications are extremely complex to write, maintain, and adapt. Indeed, not only is runtime adaptation difficult in itself, but AMR specifically needs to have very high performance (otherwise, a simple non-adaptive mesh could be used instead). Currently, the programmer of an AMR application needs to be skilled in distributed computation, non-trivial data structures (octrees/quadtrees), and the functional part of the application (whatever is actually simulated), which often involves non-trivial maths (differential equations).

The dedicated frameworks mentioned above help separating concerns and removing some of the optimisation work from the user. However, by taking away control from the user, they also limit application-specific optimisations, constrain conjoint use of other HPC technologies, and make code coupling more complex.

There has been studies that applied component-based software engineering techniques to structured AMR [85, 82]. These techniques proved particularly natural to represent recursive

refinement as recursive transformation of component assemblies. However, current HPC component models are ill-suited to runtime reconfiguration, and several problems remain unsolved.

Concluding remarks We have presented AMR in detail as it is a motivating and difficult example of application reconfiguration at runtime. Indeed, not only does AMR constitute an example of actual application-driven reconfiguration, but it also has high performance and scalability requirements, and is complex from a software engineering standpoint. For these reasons, AMR ticks all the boxes to be a motivating use case for the thesis.

# 2.2 Component Models

As discussed in Section 2.1.2, HPC applications are often very complex and need to be maintained and adapted throughout their long lives. Such applications could benefit greatly from software engineering techniques, easing high-level adaptation and separation of concerns. This section presents one such technique.

This section deals with component models, which are one of the domains at the intersection of which the subject of the thesis is situated. This section is divided into Section 2.2.1 which presents common component concepts such as connectors or hierarchy, and Section 2.2.2 which lists noteworthy models.

**Definitions** Before getting to these two sections, we propose to define what exactly component models are. There are various ways to define components, a few of which are listed below:

A first way to define components, which is the way we used in Chapter 1, is to start with the definition of component-based software engineering (CBSE). It is a software engineering paradigm which proposes to use composition as the primary means of code reuse. The entities that are being composed to implement CBSE are called components. While it is technically possible to use CBSE as a design paradigm in many languages, such as object-oriented languages, the best way to practice CBSE is to use a dedicated language or model. Such languages or models provide abstractions and concepts which are designed to help with composition. A model defining what a component is is called a component model, while a language designed to compose components is called an assembly language. The process of writing an application as a composition of components is called component-based programming.

Another way to define component models is to start by defining the components themselves. A classical definition has been proposed by Clemens Szyperski [96]: A software component is a unit of composition with contractually specified interfaces and explicit context dependencies only. A software component can be deployed independently and is subject to third-party composition. This definition is similar to the previous one in that it defines components as a unit of composition, but is more precise regarding what a component is and how it is defined. There are two important characteristics of components given in this definition which are worth highlighting. First, components must have interfaces and explicit context dependencies only; this is an important constraint which ensures components are easy to compose by explicitly declaring all its dependencies in an interface. Second, components are subject to third-party composition, which means components (and their interface) must be written while keeping in mind they might be reused by persons other than the programmer. Third parties can reuse components easily because all their dependencies are contained in their interface (by definition).

Variations exist on the second definition approach. One important distinction is whether components are primarily runtime entities, or design-time entities. Some works define components as runtime entities (e.g., [86]) which means that the units of composition used to build an application must correspond to an actual runtime entity which is called a component. Other

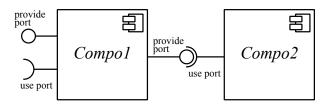

Figure 2.5: Example of components with use/provide ports. Components are represented by squares. The symbol at their top-right means they are software components.

works (e.g., HLCM [20]) present components as design-time entities which might not exist at runtime. For example, a component-based application might be compiled into a non-component-based language.

**Properties** The consequence of these definitions is that component-based approaches enforce, by construction, two important software engineering properties: reuse and separation of concerns.

Reuse is the process of using code written by third parties, which is a goal of components by definition. Reuse is an important property to minimize the cost of using third-party code, and minimize compatibility problems. Ideally, third-party components should be reusable as-is without modifying their code and with minimal extra "glue" code.

Separation of concerns (SoC) is the process of dividing an applications into parts (in this case: components) in such a fashion that each part deals with a small number of specific "concerns", i.e., aspects of the code related to a specific skill or characteristic of the application. In a context where an application is written by several persons, separation of concerns helps avoiding unnecessary conflict and helps minimizing the skill and knowledge required to write individual parts of the application.

## 2.2.1 Common Concepts and Features

The literature on component models is vast and many concepts have been proposed over the years. This sections reviews some of the most useful and common concepts used in existing component models. These concepts have been divided in three parts: first, essential concepts and definitions; second, common interface definitions; and then hierarchy and genericity which are two high-level ways to specify components.

Basic Concepts While, as illustrated by the definitions above, there are various ways to define components and component models, we provide a set of definitions of the basic concepts so that there is no ambiguity in the rest of the thesis.

**Definition 1** (Component). A component is a software unit, equipped with an interface, which is meant to be composed with other components using only the information contained in its interface.

**Definition 2** (Component assembly). A component assembly is the result of the composition of components.

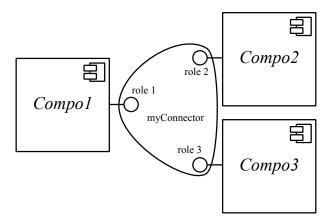

Figure 2.6: Example of components connected using a ternary connector with three roles.

**Definition 3** (Component model). A component model is a model which defines components, interfaces, and a way to compose components using their interfaces. In particular, composition semantics must be defined.

**Interfaces** The definitions given so far of components specify they must have interfaces but do not say what form these interfaces must have. There are various approaches to interfaces in the literature, two of which are presented below.

First, many component models use the notion of *ports* and *connection*, by analogy to physical plugs or electronic components. In such models, an interface is a list of ports, and components are composed by connecting their ports to ports of other components. A component model with ports provides a list of port types, details what connections are allowed between ports and what they mean.

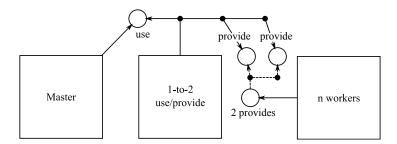

The most common way to define ports is to have *use ports* and *provide ports*. A provide port means that a component provides a specific service, and a use port means that a component requires an external service to work. A use port is meant to be connected to a provide port, and an assembly is typically required to have no unconnected use port. Depending on the model, provide may be used by several use ports or not, and use ports might use multiple provide ports or not. Component models with use/provide ports are easy to represent graphically; Figure 2.5 shows how such connections are usually depicted.

A more generalist approach to ports is to have *connectors*. Connectors are devices used to connect components, but as opposed to the use/provide approach, connectors may be typed and more than two ports may participate in a connector. The type of a connector can be used to encode different sorts of port connexions. For example, two given ports might be connected either by a local connection (e.g., a C++ pointer to an object interface), or by a distant one (e.g.,, a message-passing connection). Non-binary connectors can be used to encode non-binary port interactions such as collective communications. Examples of models with connectors include BIP [12, 13] and HLCM [20]. Figure 2.6 shows one possible convention to represent connectors.

**Hierarchy** Some component models from the literature allows to implement components using component assemblies. Such component models are called *hierarchical*, as components can be implemented by other components, which can in turn be implemented by other components, and so on, leading to a tree-like hierarchy of components.

In hierarchical component models, components which are implemented by component assemblies are called *composite components*, while components with direct implementations are called *primitive components*.

Hierarchy in component models is a high-level feature which allows to group components into higher-level components, possibly until the entire application is a single composite components. The structure given by the nesting of components is a tree whose leaves are primitive components, and whose non-tree vertices are composite components which model some logical part of the application. Such a structure is useful, as it allows modelling the structure of the application at various levels.

Examples of hierarchical component models include FRACTAL [30], BIP [12], HLCM [20], SOFA2 [32].

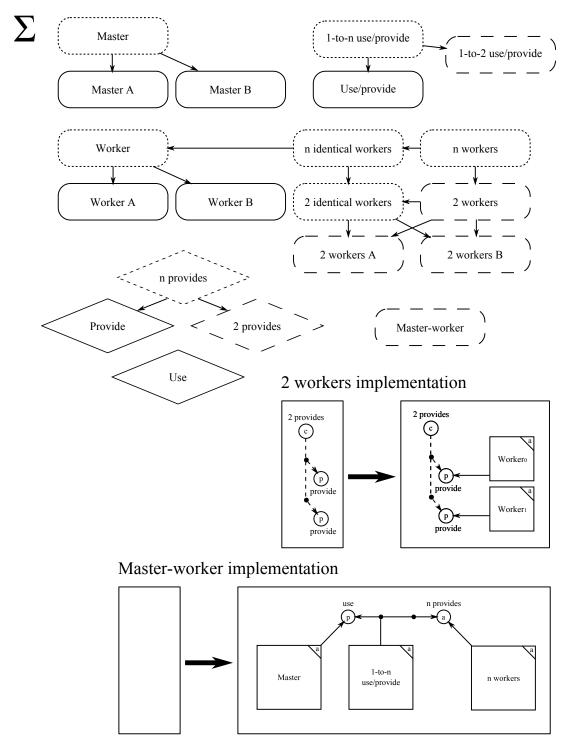

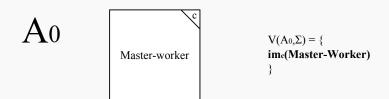

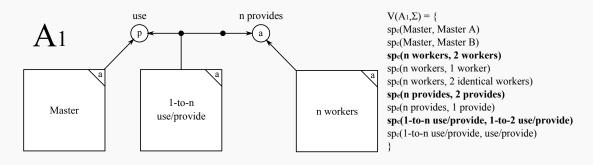

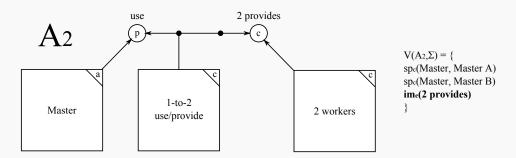

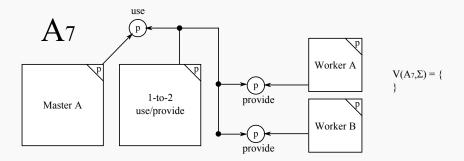

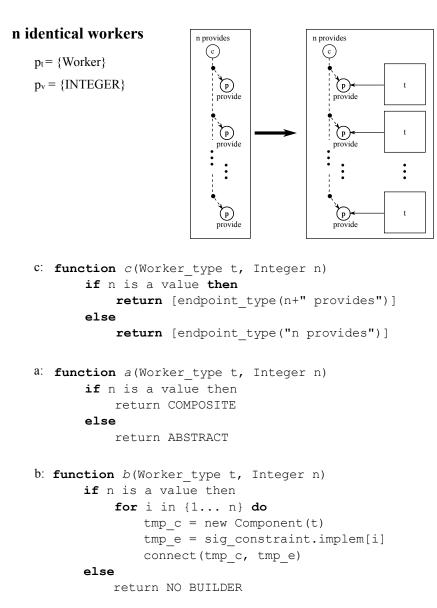

**Genericity** In some cases, it may be useful to parametrise components with types or value so as to make them more generic. For example, let us consider a composite component which is implemented by a set of workers; it would be natural to parametrise such a composite component with the number of workers, instead of having to specify a composite component for each value. Some component models provide the necessary concepts to parametrise components in such a fashion. Such models are called *generic*, and improve genericity as parametrised components are more versatile [22].

Examples of component models featuring genericity include HLCM [20].

# 2.2.2 Examples of Component Models

Since components were first proposed by [74], tens of component models have been proposed, ranging from tried and tested industrial models focused on reliable implementation, to formal academical component models. Classifications of component models exist in the literature, e.g., [70, 37], but we provide our own overview below, which focuses on some noteworthy models, include some models relevant specifically to the thesis.

**Fractal** Fractal [30] is a hierarchical component model with runtime components, that has been the focus of many research efforts. Fractal is noteworthy for its *membrane* concept and for its various implementations.

In Fractal, components (which are runtime entities) are divided into a membrane, an interface, and an implementation. The membrane is a set of components responsible for managing the lifecycle of the component and for providing other non-functional services. The membrane separates the component from the rest of the assembly, and is notably responsible for connecting the interface of the component to its implementation.

Fractal is a component model in the truest sense, i.e., it is not linked to a specific implementation. Many implementations of Fractal exist, based on various underlying technologies. Implementations of Fractal include, for example:

- Julia [30], based on Java;

- ProActive [15], a distributed implementation based on active objects;

- FracNet [88], a .NET implementation.

Fractal is discussed further in the next chapter, as it is a reconfigurable model.

BIP BIP [12, 13] is an academical hierarchical model built in the first place to allow formal proofs on component behaviour and composition. While BIP is not reconfigurable, and has no direct relation to the thesis, it is presented here because it features several noteworthy concepts/

BIP stands for Behaviour, Interaction, Priorities, which corresponds to a division of component assemblies into three layers. Each BIP components features a model of its behaviour as a finite state automaton; these component behaviours collectively form the Behaviour layer. In addition, components have ports which can be connected using connectors, forming the Interactions layer. Connectors in BIP are noteworthy in that they are built from a connector algebra, which allows the encoding of a variety of collective synchronisations. Finally, BIP assembly feature a Priorities layers composed of rules determining which inter-component interactions should be triggered first.

Another noteworthy feature of BIP is that it allows to fusion of connected components into larger components. The automaton-based behaviours connected through composite connectors can be compiled into larger automatons with an equivalent behaviour.

**HLCM** HLCM [20] is a hierarchical and generic academical component model, which is meant to be "compiled" into a lower-level model or language, through a semi-automated transformation phase.

HLCM was initially designed for HPC applications, as a way to reconcile high-level features (provided by HLCM) and performance (to be obtained after transformation to a low-level language). The high-level language in which HLCM assemblies are written is called HLA (High-Level Assembly). HLA is hierarchic, generic, based on connectors, and allows *abstract* components and connectors (i.e., components/connectors whose implementation has not been chosen yet).

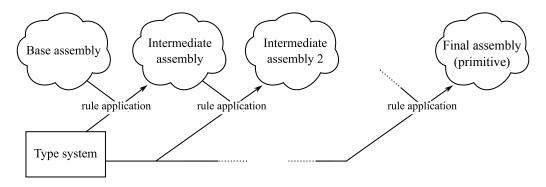

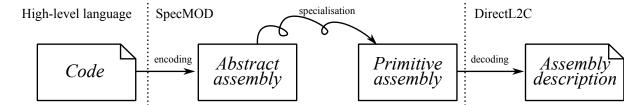

HLA assemblies are compiled into LLA (Low-Level Assemblies) which can then be transposed to various backend languages. Currently implemented backend languages are L2C, described below in more details, which is a zero-overhead low-level language designed for HPC, and Gluon++ which is a version of L2C based on Charm++ (a HPC language described in more details in the next chapter in Section 3.3.2). The transformation process (from HLA to LLA) consists in making individual specialisation decisions (e.g., choosing the implementation of an abstract connector or component, setting the value of a parameter, replacing a composite by its implementation), until the assembly is fully primitive.

HLCM is noteworthy because its transformation phase theoretically allows some optimisation or adaptation decisions to be taken automatically during the transformation phase. HLCM was developed in the Avalon team, as was L2C, and was a strong inspiration for the contribution presented in Chapter 6.

HPC component models Some component models have been specifically designed for use in HPC applications, or distributed applications in general. The CORBA Component Model [24] (CCM) and the Grid Component Model (GCM) [14] are notable examples of distributed models. However, they generate runtime overheads [102] that are acceptable for distributed application but not for HPC. The Common Component Architecture [41] (CCA) is the result of an US DoE effort to enhance composability in HPC. However, CCA is mainly a process-local standard that relies on external models such as MPI for inter-process communication. As a consequence, such interactions do not appear in component interfaces.

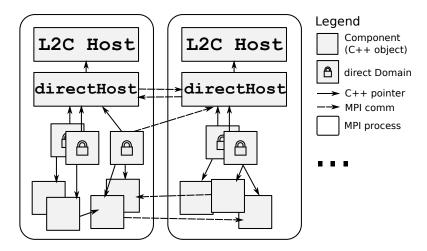

The Low Level Components [21] (L2C) is a minimalist HPC component model built, designed to have a negligible overhead at runtime. L2C is built on C++, MPI and Corba, which are common HPC technologies. Low overhead is achieved by removing all component-related infrastructure after instantiation of the components: two L2C components are, at runtime, C++ objects directly connected through C++/Corba connections or MPI communicators. As described in [21], L2C has been successfully used to describe a stencil-like application with performance similar to native implementations.

Non-HPC industrial models The more widely-used component models in the industry seldom provide a model in the formal sense, and instead focus on a specification and an implementation, often based on some existing widely-used language or technology. For example, JavaBeans [52] and OSGi [4] are based on Java, COM [26] was developed by Microsoft, and KobrA [8] is based on UML. Since those models are far from the subject of thesis, we do not present them in detail.

## 2.3 Conclusion

In this section, we have presented high-performance computing and component models, which make up the necessary context to understand the problem of the thesis and the contributions.

First, we have presented high-performance computing, notably HPC hardware architectures and HPC applications. We have introduced the main challenges of HPC which are scalability and managing the complexity of applications, and have presented Adaptive Mesh Refinement (AMR), a computing technique which serves as a motivating example for the contributions of the thesis.

Second, we have presented the general concepts and literature around component models. In particular, we have provided several definitions of "component"; we have presented common component concepts such as ports, connectors or hierarchy; and we have presented a handful of noteworthy component models including some models dedicated to HPC such as L2C or CCA.

# Chapter 3

# Related Works

## Contents

| 3.1 | Brief Taxonomy                              | 22 |

|-----|---------------------------------------------|----|

|     | 3.1.1 Application-Level                     | 22 |

|     | 3.1.2 Model-Level                           | 23 |

|     | 3.1.3 Autonomic                             | 23 |

|     | 3.1.4 Discussion                            | 24 |

| 3.2 | Specification and Related Issues            | 25 |

|     | 3.2.1 Code-based                            | 25 |

|     | 3.2.2 Formal transformations                | 25 |

|     | 3.2.3 User-Driven                           | 26 |

|     | 3.2.4 Discussion                            | 27 |

| 3.3 | Execution and Related Issues                | 27 |

|     | 3.3.1 Global Synchronization                | 27 |

|     | 3.3.2 Appropriate Execution Model           | 27 |

|     | 3.3.3 Locking                               | 28 |

|     | 3.3.4 Application Representation at Runtime | 29 |

|     | 3.3.5 Concluding remarks                    | 30 |

| 3.4 | Reconfigurable Component Models             | 30 |

|     | 3.4.1 Ad hoc reconfiguration                | 30 |

|     | 3.4.2 Controllers                           | 31 |

|     | 3.4.3 Global Reconfiguration                | 31 |

|     | 3.4.4 Concluding remarks                    | 31 |

| 3.5 | Conclusion                                  | 32 |

|     |                                             |    |

Application reconfiguration in the literature happens in a variety of contexts for a variety of reasons. Several very different approaches to reconfiguration exist that can vary widely in terms of goals and methods. Examples of reconfiguration are numerous and include, for example, updating the code of a web application without stopping it, reconfiguring a P2P network in the presence of churn, or adapting an embedded application to its environment.

As reconfiguration is the primary focus of the thesis, we consider the reconfiguration literature to be related works, as opposed to HPC and component concepts which are considered context. This chapter presents related work around reconfiguration, whether it is component-based or not, as ideas relevant to the thesis may come from non-component literature.

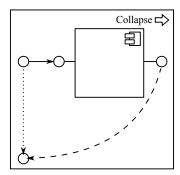

First, Section 3.1 gives a broad overview of reconfiguration approaches sorted by abstraction level, and discusses which are relevant to the thesis. Second, Section 3.2 discusses issues related

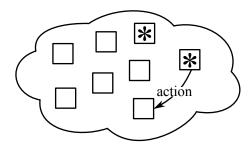

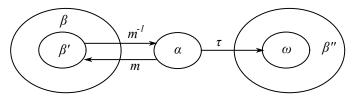

Figure 3.1: Application-level reconfiguration. The cloudy shape denotes the reconfigurable application, while the stars denote where reconfiguration logic is located, and the squares denote parts of the application.

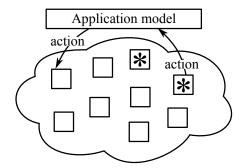

Figure 3.2: Model-level reconfiguration. The cloudy shape denotes the reconfigurable application, while the stars denote where reconfiguration logic is located, and the squares denote parts of the application.

to the specification of application transformations, and strategies from the literature to address these issues. Third, Section 3.3 discusses issues related to the execution of reconfigurations, such as consistency problems and application locking. Finally, Section 3.4 presents actual reconfigurable component models from the literature, and analyses their limitations regarding our specific HPC use case.

# 3.1 Brief Taxonomy

This section provides a simple coarse-grain taxonomy of reconfiguration approaches. There exist a variety of approaches in the literature that we have divided into broad categories, of increasing abstraction: application-level reconfiguration (Subsections 3.1.1), model-level reconfiguration (3.1.2), and autonomic reconfiguration (3.1.3). The relevancy for the thesis of each of these broad approaches is discussed in Section 3.1.4.

## 3.1.1 Application-Level

A first, seemingly easy, ad hoc approach to reconfiguration consists in writing the reconfiguration logic at the same level as the rest of the application. The programming model used for the application likely features the primitives which allow reconfiguration, things like object destruction and creation at runtime. Those primitives can be used by the application to reconfigure itself. We call this approach application-level, as reconfiguration is expressed and carried out at the same level of abstraction as was used to write the application itself. Figure 3.1 shows a simple diagram illustrating this kind of reconfiguration.

**Example:** ad hoc reconfiguration Some applications perform reconfiguration directly without relying on a third-party technology such as a framework or a language. We call this kind of reconfiguration ad hoc as it does not make use of reconfiguration-dedicated abstractions or technologies. Examples of such applications include AMR applications that do not use a dedicated framework such as the pkdgrav/gasoline computational astrophysics codes [95].

**Discussion** This approach is the most general as it does not make any assumption regarding how reconfiguration is decided or carried out. Applications with unusual reconfiguration patterns

might work, by default, only at that level of abstraction. In addition, this kind of approach does not restrict the kind of optimizations that can be performed, which can be useful in a HPC context to get maximum performance.

However, this approach is limited from a software engineering standpoint. Indeed, the absence of model-level enforced structure means that reconfiguration logic has to be *ad hoc*. One notable implication of relying on *ad hoc* reconfiguration is that reuse of third-party reconfiguration code is difficult, as no general framework for reconfiguration exists.

#### 3.1.2 Model-Level

Another possible approach to reconfiguration is to have an abstraction level above the application itself, which provides a model of the applications parts and ways to rearrange those parts. The reconfiguration logic itself might or might not be part of the reconfigurable parts, but all reconfiguration operations are expressed at model-level instead of application-level. We call this approach model-level control of reconfiguration as it relies on a dedicated model to express reconfiguration. Figure 3.2 shows a simple diagram illustrating this kind of reconfiguration, to be put in opposition with the diagram from Figure 3.1.

This approach brings several advantages. By relying on an intermediate model dedicated to reconfiguration, reconfiguration code is easier to write from the point of view of the developer. A reconfiguration-dedicated model is also much more likely to be easy to analyse for a program (e.g., for model-checking or automatic proof) than a general-purpose programming language (which is often not analysable at all). Finally, because such an approach sets conventions regarding how reconfiguration is performed, reusing third-party reconfiguration code is easier, as hypotheses can be made regarding how it operates.

**Example: reconfiguration DSLs** A *Domain-Specific Language* (DSL), is a programming language tailored for a specific task, as opposed to a general purpose language. DSLs trade their generality for specialized abstractions, and are typically easier to use and easier to analyse than general-purpose languages.

There exist reconfiguration DSLs, that is, DSLs made specifically to express reconfiguration in dynamic applications. By definition, reconfiguration DSLs rely on an application model dedicated to reconfiguration, and as such constitute model-level reconfiguration.

A good example of a such a reconfiguration DSL is FScript [39], which is used to reconfigure FRACTAL component assemblies. FScript provides abstractions and tools that help reconfiguration, such as the FPath tool, which helps with pattern-matching in FRACTAL assemblies. FPath is discussed in more details in the section dedicated to component models below (Section 3.4).

**Example:** specialised frameworks Other examples of model-level reconfiguration include frameworks specialised for a certain kind of dynamic applications. For example, AMR frameworks such as RAMSES [98] belong to this category. By providing abstractions tailored for a very specific type of applications, such frameworks are particularly efficient for writing such applications, but are also less generic which might be problematic when combining several forms of reconfiguration in a single application.

#### 3.1.3 Autonomic

A possible next step towards further abstraction is to use concepts from *autonomic computing* to get a general framework for reconfiguration. Application reconfiguration can be achieved using

Figure 3.3: The overall structure of a MAPE loop.

autonomic loops, that is, closed control loops which use principles from autonomic computing to decide reconfigurations.

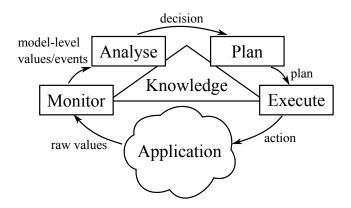

A widely-used autonomic loop is the *MAPE* loop, which divides reconfiguration into four distinct steps: Monitor, Analyse, Plan, and Execute. Figure 3.3 presents the overall MAPE loop and the four steps in question. These steps are: