# Design flow for the rigorous development of networked embedded systems

Alexios Lekidis

#### ▶ To cite this version:

Alexios Lekidis. Design flow for the rigorous development of networked embedded systems. Embedded Systems. Université Grenoble Alpes, 2015. English. NNT: 2015GREAM056. tel-01261936v2

# HAL Id: tel-01261936 https://theses.hal.science/tel-01261936v2

Submitted on 9 Jan 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ DE GRENOBLE

## **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : **Informatique** Arrêté ministérial : 7 août 2006

Présentée par

#### **Alexios Lekidis**

Thèse dirigée par Marius Bozga et codirigée par Saddek Bensalem

préparée au sein du laboratoire VERIMAG et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# Design flow for the rigorous development of networked embedded systems

Thèse soutenue publiquement le **10 Decembre 2015**, devant le jury composé de :

#### M. Ahmed Lbath

Professeur, Université Joseph Fourier Grenoble, Président

#### M. Roman Obermaisser

Professeur, Universität Siegen, Rapporteur

#### M. Roberto Passerone

Professeur, University of Trento, Rapporteur

#### M. Smail Niar

Professeur, Université de Valenciennes, Examinateur

#### M. Marius Bozga

Ingénieur de recherche, HDR, CNRS, Directeur de thèse

#### M. Saddek Bensalem

Professeur, Université Joseph Fourier Grenoble, Co-Directeur de thèse

# Abstract

Over the latest years the use of embedded devices has expanded rapidly due to the convenience they offer in daily life. Embedded devices are characterized by their tiny size, their portability as well as their ability to exchange data with other devices through a dedicated network unit. The analysis of the behavior and interactions between such devices lead to the emergence of a new system type, called networked embedded systems.

As the current popularity of networked embedded systems grows, there is a trend for addressing their existing design challenges in the development of functional applications. These challenges relate to the use of their limited hardware resources (e.g. processor memory, power unit) and the system heterogeneity in terms of software, hardware as well as communication mechanisms between the embedded devices. To this end, in this thesis we present a rigorous approach considering all the design challenges through a model-based design flow. The flow uses BIP as an underlying framework for the hierarchical construction of component-based systems and it is easily employed, as each step is fully supported by developed tools and methods. Its benefits include early-stage simulation and testing, verification of functional correctness, generation of deployable code and collection of performance data from real executions, in order to calibrate the developed models. Calibrated models represent faithfully the real system and can analyze system performance as well as evaluate accurately system requirements. Additionally, performance analysis results may provide design enhancements in the target system.

Our approach is demonstrated in several well-known application domains of networked embedded systems, namely the automotive, industrial automation, Wireless Sensor Network (WSN) and Internet of Things (IoT) systems. Each domain includes different characteristics and technologies, but also features different challenges. These challenges are considered by developed tools for each domain, which are validated against existing domain-specific, such as MATLAB/Simulink, RTaW-Sim, OPNET Modeler and Cooja. The validation is facilitated through case-studies in industrial or benchmark networked embedded systems. Our experiments illustrate the support of a better fine-grained analysis from the developed tools by initially providing similar simulation results and additionally offering capabilities for automated code generation as well as requirement verification.

# Résumé

Au cours des dernières années, l'utilisation d'appareils embarqués a augmenté rapidement en raison de la commodité qu'ils offrent dans la vie quotidienne. Les appareils embarqués se caractérisent par leur petite taille, leur portabilité ainsi que leur capacité d'échanger des données avec d'autres appareils grâce à leur service de communication réseau. L'analyse du comportement et les interactions entre ces appareils a abouti dans l'établissement d'un nouveau type de système, appelé systèmes embarqués en réseau.

En tant que la popularité actuelle des systèmes embarqués en réseau grandissent, il y a une tendance de relever leurs défis de conception existants afin de développer d'applications fonctionnelles. Ces défis concernent l'utilisation de leurs ressources matérielles limitées (p.ex. la mémoire du processeur, l'unité d'alimentation) et l'hétérogénéité du système en termes de logiciel, de matériel et aussi des mécanismes d'interaction entre les appareils. A cet effet, dans cette thèse nous présentons une approche rigoureuse considérant tous les défis grâce à un flot de conception basée sur techniques de modélisation. Le flot utilise le formalisme BIP pour la construction hiérarchique de systèmes autour de composants et il est facilement utilisé, car chaque étape est entièrement automatisée par des outils et méthodes développés. En plus, ce flot perme la simulation des systèmes à chaque étape de développement, la vérification par l'exploration de l'espace de conception, la génération de code et la calibration des modèles développés, afin de présenter fidèlement le système réel. Les modèles calibrés peuvent analyser la performance de system et aussi valider des exigences sur le system. Finalement, les résultats d'analyse de performance peuvent apporter des améliorations sur la conception de système cible.

Notre approche est présenté sur plusieurs bien connus domaines applicatifs des systèmes embarqués en réseau, comme les systèmes automobiles, les systèmes de l'automation industrielle, les systèmes de réseaux de capteurs sans fil (WSN systèmes) et les systèmes pour l'internet des objets (IoT systèmes). Chaque domaine inclut différentes caractéristiques et technologies, mais dispose également différent défis. Ces défis sont considérés par les outils développés pour chaque domaine, qui sont validées contre les outils existantes, comme MATLAB/Simulink, RTaW-Sim, OPNET Modeler et Cooja. La validation se fait grâce à les cas d'études sur les applications industrielles ou les benchmark réalistes des systèmes embarqués en réseau. Nos expérimentations illustrent le soutien d'une meilleure analyse par les outils développés en fournissant d'abord résultats similaires pendant la simulation et en plus les capacités de génération automatique de code et la vérification des exigences.

# Acknowledgments

The presented work is the outcome of my research efforts over these 4 years at Verimag. For this reason I would like to thank firstly my supervisors Marius Bozga and Prof. Saddek Bensalem. Marius was always there, even from my first day, to support and help me expecially in the difficult stages of this work and Prof. Saddek gave me motivation and research directions in the projects we have carried out.

I would also like to express my gratitude to Prof. Joseph Sifakis, for giving me the opportunity of joining Verimag as well as for his advice, help and his ideas on future research directions, such as the Internet of Things and the Real-Time Ethernet.

I am evenly grateful to all the jury members who were interested in my work and for all the time spent to review it.

A great thank goes to my collaborators all these years Paraskevas Bourgos, Prof. Panagiotis Katsaros, Emmanouela Stachtiari, Ayoub Nouri because without them this work would never be the same.

Additionally, I would like to thank my colleagues at Verimag. Firstly, I would include here Jacques Combaz, for his help and support during the time we were trying to have stable versions for new BIP tools. Then, I am really grateful to Ayoub Nouri for the time he devoted for corrections on chapters of this thesis. Afterwards, I would like to thank Petro Poplavko for his help and the understanding we had between each other all the years we shared the office. Moreover, I am grateful to Ananda Basu, Balaji Raman, Jean Quilbeuf, Pranav Tendulkar, Anakreontas Mentis, Dario Socci, Hosein Nazarpour, Souha Ben Rayana, Najah Ben Said and many more for the interesting discussions and the really enjoyful working environment.

I would like to thank my friends Christoforos, Vassilis, Katerina, Paraskevas, Dimitris who have been with me all these years and their support meant the world for me. Additional thanks goes to Tony, Thiago, Irini, Tasos, Stefano, Andy, Maciej, Audrey, Bogdan, Christoph, Alina, Rosi, Petra, Savina, Gözde and Dimitris with whom we shared great moments.

Finally, I would like to thank my family: my mother Haroula, my father Vassilis, my brother Panagiotis as well as my grandmothers Nitsa and Eleni who have provided unconditional support in all the stages of my life. As in life we are never alone, I left for the end my gratitude to a very important person in my life, Alexandra. Without her by my side I wouldn't have come this far..

# Contents

| Ι | Co   | ntext  |                                         | 9  |

|---|------|--------|-----------------------------------------|----|

| 1 | Intr | oducti | ion                                     | 11 |

|   | 1.1  | Netwo  | orked Embedded Systems                  | 12 |

|   |      | 1.1.1  | Heterogeneous Embedded Devices          | 12 |

|   |      | 1.1.2  | Heterogeneous networks and protocols    | 12 |

|   |      | 1.1.3  | Resource-constrained systems            | 13 |

|   | 1.2  | Functi | ional and Extra-Functional Requirements | 14 |

|   |      | 1.2.1  | Timing Constraints                      | 15 |

|   |      | 1.2.2  | Clock Synchronization                   | 15 |

|   |      | 1.2.3  | Energy and thermal constraints          | 16 |

|   | 1.3  | Develo | opment Methods                          | 16 |

|   |      | 1.3.1  | Classical methodologies                 | 17 |

|   |      | 1.3.2  | Model-based Design                      | 17 |

|   |      | 1.3.3  | Embedded system design methodologies    | 18 |

|   | 1.4  | Thesis | s Contribution                          | 19 |

|   | 1.5  |        | ization                                 | 20 |

| 2 | Net  | worke  | d Embedded Systems: A Background        | 23 |

| _ | 2.1  |        | fication of Networked Embedded Systems  | 23 |

|   |      | 2.1.1  | Automotive systems                      | 23 |

|   |      | 2.1.2  | Industrial Automation Systems           | 26 |

|   |      | 2.1.3  | Wireless Sensor Network systems         | 27 |

|   |      | 2.1.4  | IoT Systems                             | 29 |

|   | 2.2  |        | ologies and Communication Protocols     | 32 |

|   |      | 2.2.1  | Controller Area Network (CAN)           | 32 |

|   |      | 2.2.2  | CANopen                                 | 35 |

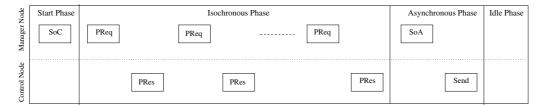

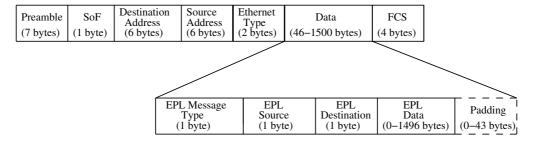

|   |      | 2.2.3  | Ethernet Powerlink (EPL)                | 43 |

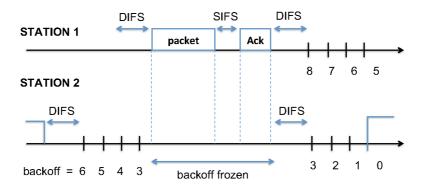

|   |      | 2.2.4  | IEEE 802.11                             | 47 |

|   |      | 2.2.5  | The 6LoWPAN protocol                    | 49 |

|   |      | 2.2.6  | Contiki OS                              | 51 |

|   | 2.3  |        | ary and Discussion                      | 55 |

|   |      |        |                                         |    |

| 3 |      |        | Framework                               | 57 |

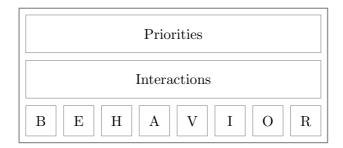

|   | 3.1  | Conce  | •                                       |    |

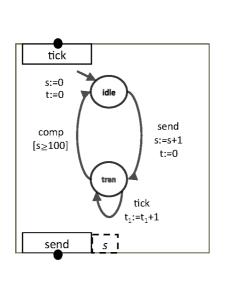

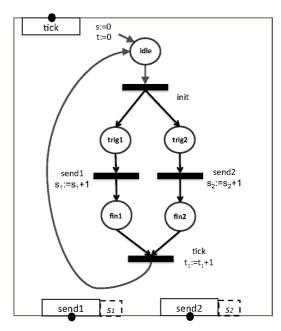

|   |      | 3.1.1  | Atomic components                       |    |

|   |      | 3.1.2  | Component composition                   | 60 |

6 Contents

|    | 3.2  | Modeling language                                                       | 64  |

|----|------|-------------------------------------------------------------------------|-----|

|    | 3.3  | Toolset                                                                 |     |

|    |      | 3.3.1 Language Factory                                                  | 69  |

|    |      | 3.3.2 Engine-based simulation                                           |     |

|    |      | 3.3.3 Verification                                                      |     |

|    |      | 3.3.4 Statistical Model Checking                                        |     |

|    | 3.4  | Design Flow                                                             |     |

|    | 3.5  | Summary                                                                 |     |

| II | Co   | ontribution                                                             | 75  |

| 4  | Rigo | orous Design Flow for Networked Embedded Systems                        | 77  |

| _  | 4.1  | Overview and design phases of the proposed flow                         |     |

|    | 4.2  | PPM: A programming model for networked embedded systems                 |     |

|    | 4.3  | Automated Code Generation from PPM specifications                       |     |

|    | 4.4  | System-level performance analysis methods                               |     |

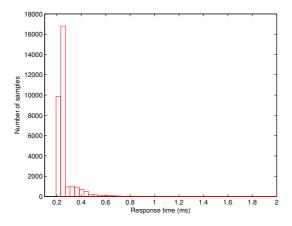

|    |      | 4.4.1 Distribution fitting                                              |     |

|    |      | 4.4.2 Model calibration                                                 |     |

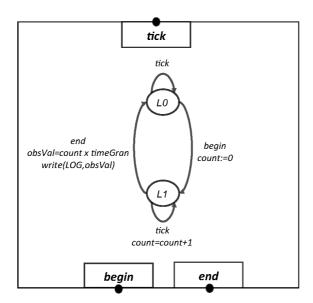

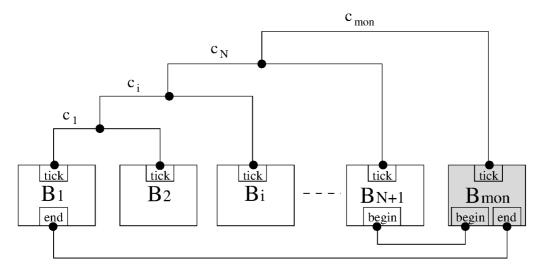

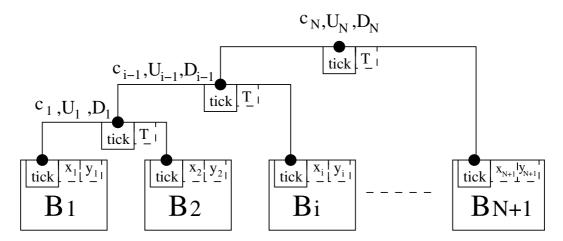

|    |      | 4.4.3 Monitoring performance information in the System Model            |     |

|    |      | 4.4.4 Improvement of simulation for the System Model                    | 91  |

|    | 4.5  | Conclusions                                                             |     |

| 5  | App  | plication of the Design Flow to Automotive Systems                      | 97  |

|    | 5.1  | Design phases of the automotive system flow                             |     |

|    | 5.2  | Modeling rules and principles                                           |     |

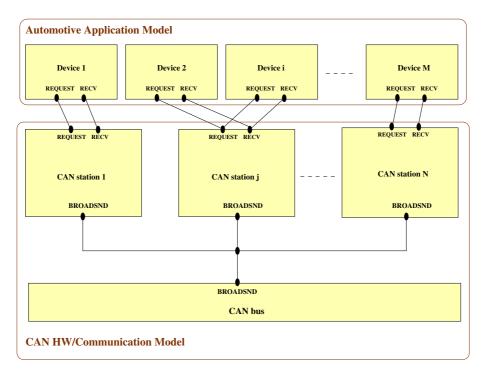

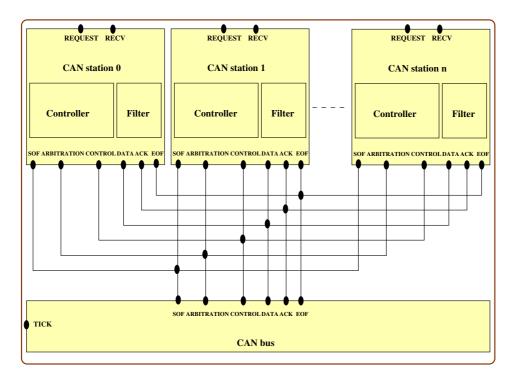

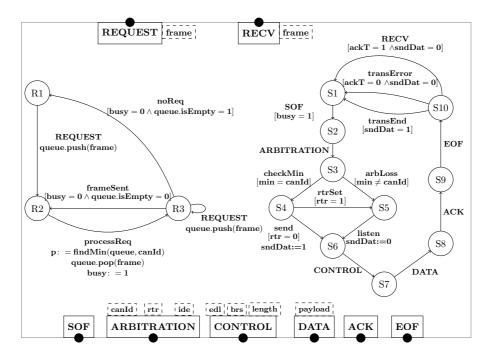

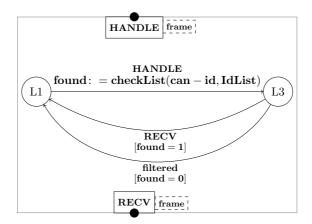

|    | 5.3  | CAN HW/Communication Model                                              |     |

|    | 5.4  | Tools for automotive system development: The NETCAR2BIP Translator $$ . |     |

|    | 5.5  | Case study: Powertrain Vehicle System                                   |     |

|    |      | 5.5.1 Modeling the Application Software                                 |     |

|    |      | 5.5.2 Requirement Description                                           |     |

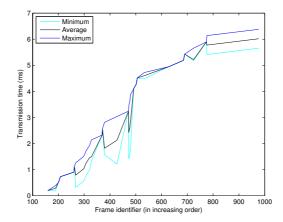

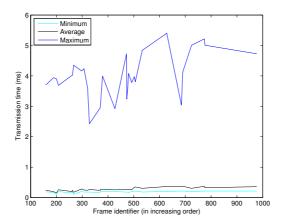

|    |      | 5.5.3 Experiment 1: Simulation                                          |     |

|    |      | 5.5.4 Experiment 2: Performance optimization                            |     |

|    | 5.6  | Summary and Discussion                                                  | 112 |

| 6  | App  | ·                                                                       | 115 |

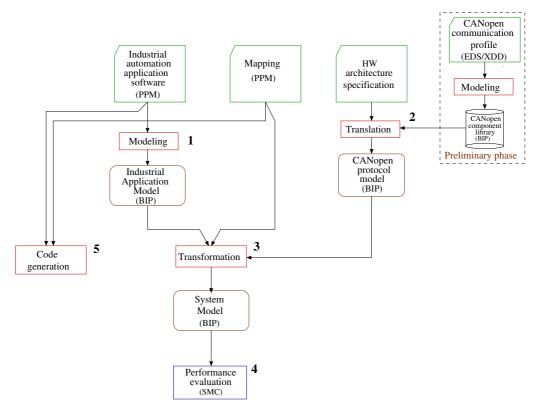

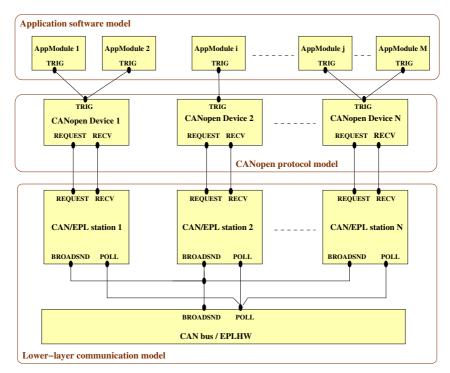

|    | 6.1  | Design phases of the industrial automation system flow                  |     |

|    | 6.2  | System modeling principles                                              |     |

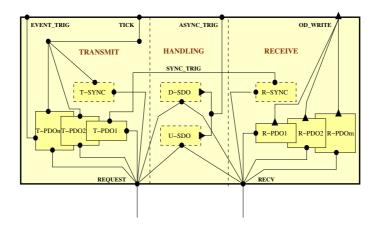

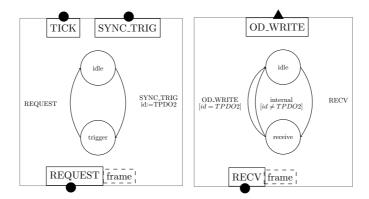

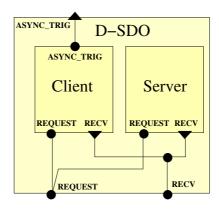

|    | 6.3  | CANopen protocol model                                                  | 119 |

|    | 6.4  | Tools for industrial automation system development: The CANopen2EPL     |     |

|    |      | Code Generator                                                          |     |

|    |      | 6.4.1 EPLNodeConf Device Configurator                                   |     |

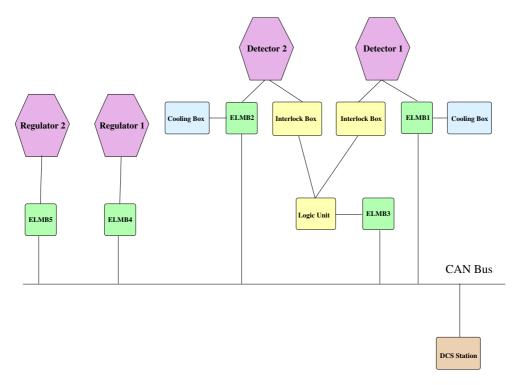

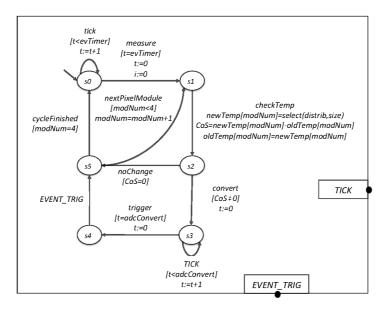

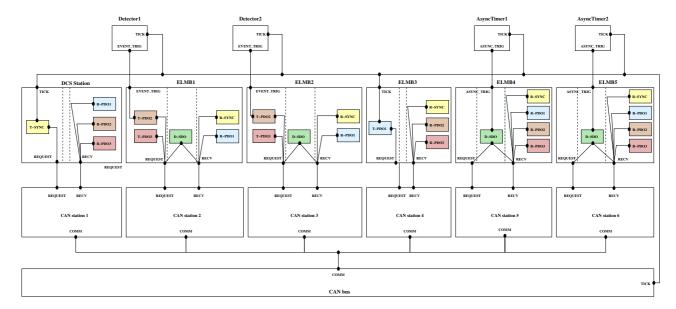

|    | 6.5  | Case study 1: Pixel Detector Control System                             |     |

|    |      | 6.5.1 Modeling the Application Software                                 |     |

|    |      | 6.5.2 Requirement Description                                           |     |

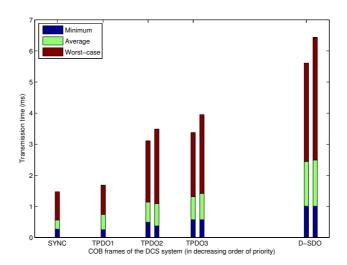

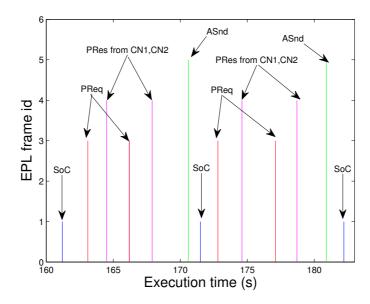

|    |      | 6.5.3 Experiments                                                       |     |

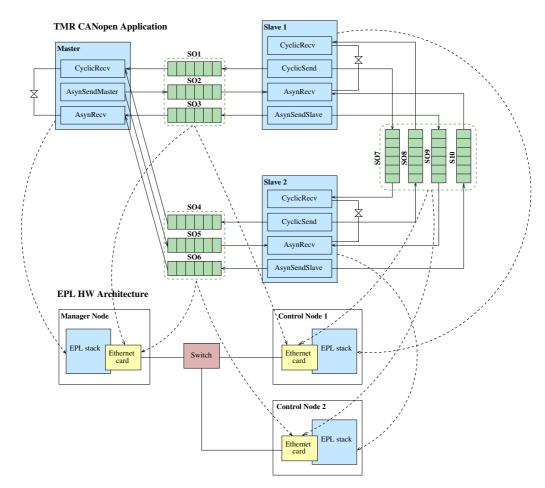

|    | 6.6  | Case study 2: Triple Modular Redundancy System                          |     |

|    |      | 6.6.1 Modeling the Application Software                                 |     |

|    |      | 6.6.2 Code generation                                                   |     |

|    |      | 6.6.3 Experiments                                                       | 135 |

Contents 7

|   | 6.7 | Summary and Discussion                                      | 1  | 37 |  |  |  |

|---|-----|-------------------------------------------------------------|----|----|--|--|--|

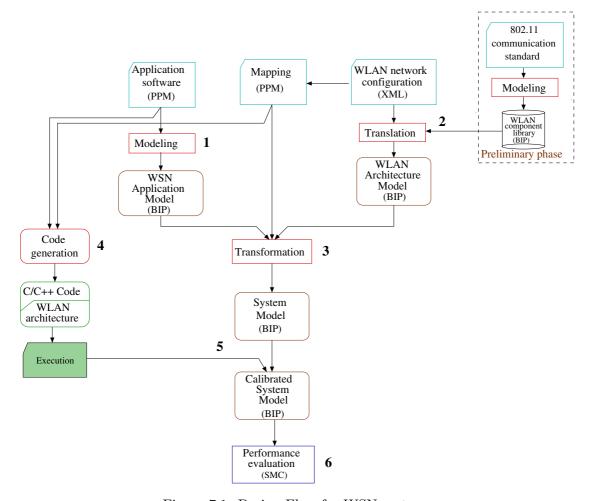

| 7 | Арр | plication of the Design Flow to WSN Systems                 | 1: | 39 |  |  |  |

|   | 7.1 | Design phases of the WSN system flow                        | 1  | 40 |  |  |  |

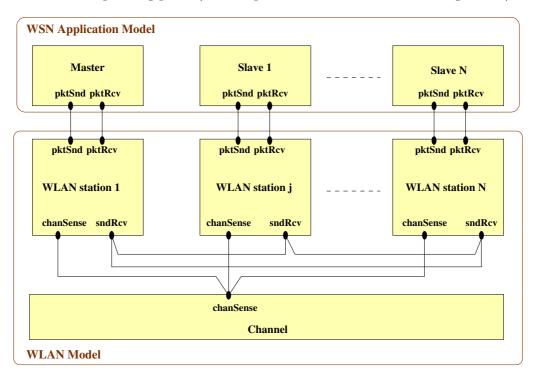

|   | 7.2 | System modeling principles                                  | 1  | 42 |  |  |  |

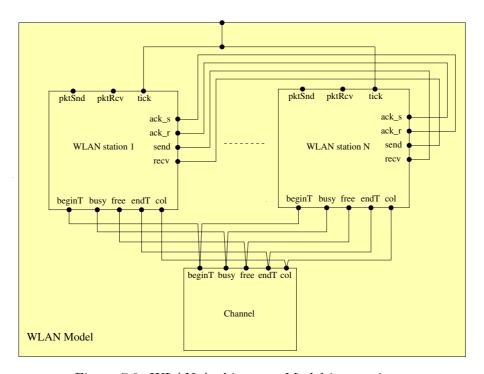

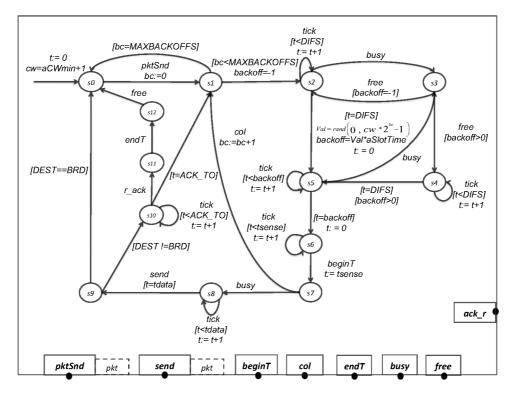

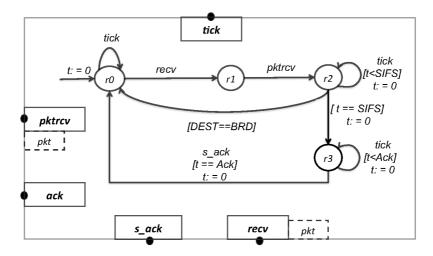

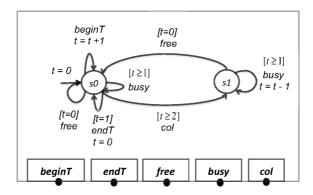

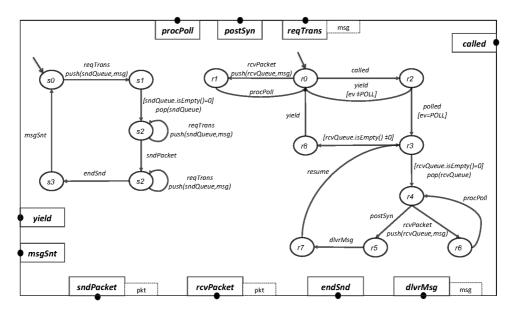

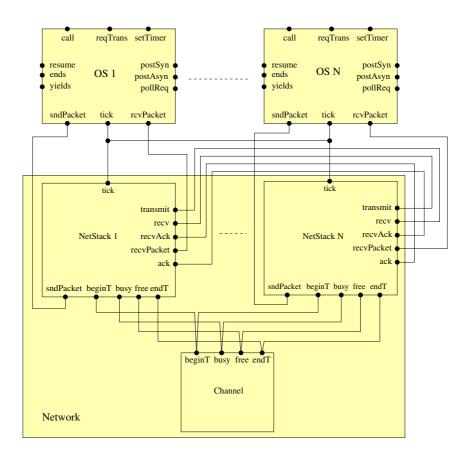

|   | 7.3 | WLAN architecture model                                     | 1  | 44 |  |  |  |

|   | 7.4 | Tools and methods for WSN system development                | 1  | 48 |  |  |  |

|   |     | 7.4.1 Translation of the WLAN network configuration $\dots$ | 1  | 48 |  |  |  |

|   |     | 7.4.2 Automated code generation for WSN                     | 1  | 49 |  |  |  |

|   |     | 7.4.3 Distribution Fitting                                  | 1  | 50 |  |  |  |

|   | 7.5 | Case study: Wireless Multimedia Sensor Network              | 1  | 52 |  |  |  |

|   |     | 7.5.1 Application overview                                  | 1  | 52 |  |  |  |

|   |     | 7.5.2 Modeling the Application Software                     | 1  | 55 |  |  |  |

|   |     | 7.5.3 Code generation                                       | 1  | 62 |  |  |  |

|   |     | 7.5.4 Requirement Description                               | 1  | 62 |  |  |  |

|   |     | 7.5.5 Experiments                                           | 1  | 63 |  |  |  |

|   |     | 7.5.6 Summary and Discussion                                | 1  | 66 |  |  |  |

| 8 | Apı | plication of the Design Flow to IoT Systems                 | 10 | 69 |  |  |  |

|   | 8.1 | - ·                                                         |    |    |  |  |  |

|   | 8.2 | · · · · · · · · · · · · · · · · · · ·                       |    |    |  |  |  |

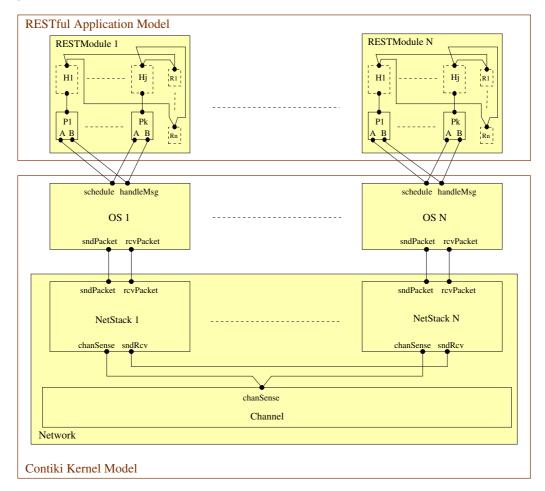

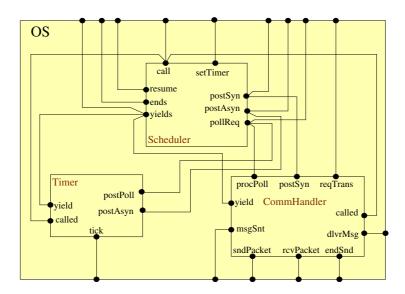

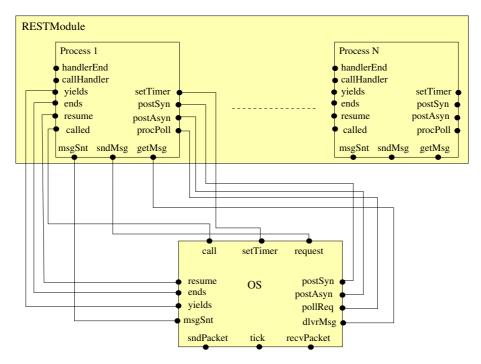

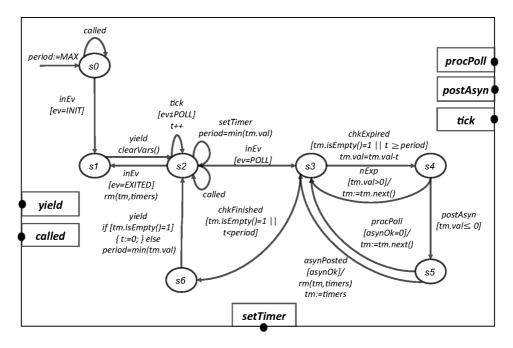

|   | 8.3 | Contiki OS Kernel Model                                     |    |    |  |  |  |

|   |     | 8.3.1 Modeling the Contiki Kernel                           | 1  | 74 |  |  |  |

|   |     | 8.3.2 Modeling the Contiki network stack                    |    |    |  |  |  |

|   |     | 8.3.3 Fault injection model                                 |    |    |  |  |  |

|   | 8.4 | Tools and methods for IoT system development                |    |    |  |  |  |

|   |     | 8.4.1 Translation of the WPAN network specification         |    |    |  |  |  |

|   |     | 8.4.2 Using the DSL application description                 |    |    |  |  |  |

|   |     | 8.4.3 BIP System Model Calibration                          |    |    |  |  |  |

|   | 8.5 | Case study 1: Smart Heating System                          |    |    |  |  |  |

|   |     | 8.5.1 Modeling the Application Software                     |    |    |  |  |  |

|   |     | 8.5.2 Requirement Description                               |    |    |  |  |  |

|   |     | 8.5.3 Experiments                                           |    |    |  |  |  |

|   | 8.6 | Case study 2: Building Automation System                    |    |    |  |  |  |

|   |     | 8.6.1 Modeling the Application Software                     |    |    |  |  |  |

|   |     | 8.6.2 Requirement Description                               |    |    |  |  |  |

|   |     | 8.6.3 Experiments                                           |    |    |  |  |  |

|   | 8.7 | Summary and Discussion                                      |    |    |  |  |  |

| 9 | Cor | nclusion                                                    | 10 | 97 |  |  |  |

| J | 9.1 | Summary                                                     |    |    |  |  |  |

|   | 9.1 | Perspectives                                                |    |    |  |  |  |

|   | 0.4 | 1 orspectives                                               | 1  | JO |  |  |  |

| 8               | Contents |

|-----------------|----------|

| List of figures | 201      |

| List of tables  | 205      |

| Bibliography    | 208      |

# Part

Context

### - Chapter 1 -

#### Introduction

The recent exponential increase in the use of embedded devices, has made a great impact on the modern society. The reason behind this increase is the commodity and utility they offer in every day life. Their main attributes include compact size, low-cost as well as the low-power that they consume while operating. The addition of networking capabilities lead to the emergence of *networked embedded systems*, a new type of distributed embedded systems with tremendous applications. Such systems are nowadays used in a variety of domains including health-care, transportation, agriculture, environmental monitoring, security systems, industrial process control, factory and building automation and control (BAC), high-energy physics, and many more.

In general, the development of functional networked embedded systems is challenging, even when complete knowledge of the application software and the interactions with the HW abstraction layers is assumed. This occurs due to their complexity and unpredictable behavior in terms of functionality as well as external factors (e.g. harsh environmental conditions). An example of unpredictable functional behavior is when developing software modules that depend on each other as well as on the underlying hardware architecture, in which case the communication and data processing latencies should be taken into consideration. Nevertheless, such details are not known during the development. Moreover, assuming that the functional errors are resolved, unpredictable behavior can be also identified in the deployment phase of an application, such as the conflicts that might occur in the network stack. From these examples we can reason that the time required for the design of networked embedded systems as well as additional effort for their a posteriori validation, which is a hardly predictable.

Nowadays, the academic and industrial focus lies towards techniques to improve the overall efficiency, performance and lifetime of networked embedded systems, whilst keeping the production cost low. This dissertation aims on providing solutions for the efficient design, validation and deployment of networked embedded systems. To this extent, in the following sections we introduce with some more details the main characteristics of such systems and discuss the most important design and development challenges. Then, we summarize our contribution and provide an insight on the overall organization of this document.

#### 1.1 Networked Embedded Systems

Networked embedded systems are complex heterogeneous systems. They usually consist of different devices, every one including specific sensors and actuators to gather data and to interact with their environment. Moreover, they are usually managed by different operating systems and support different network protocols and communication mechanisms for data exchange. All these make system design complex and each developer should be able to handle different coordination principles, as synchronous and asynchronous, objectand actor-based, and event- and data-based.

#### 1.1.1 Heterogeneous Embedded Devices

In general, embedded devices are deployed in the physical environment, in order to interact with it and collect measurements as well as to handle different types of events. The collected measurements may be exchanged with other embedded devices or base stations in the network and additionally the device may often indicate to them its own critical operating conditions, such as identified failures or insufficient energy. Therefore, an important characteristic of a networked embedded device is its high-degree of reactivity. In this sense, the device is not only able to gather measurements, but also to act rapidly in order to abstract these measurements and obtain useful data from them. Then, it can use this data to make inferences and perform dedicated operations.

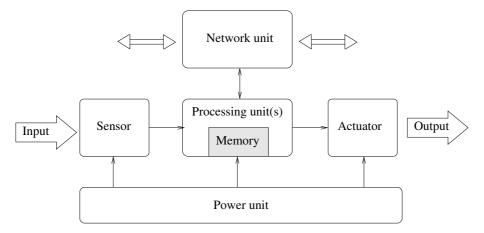

The typical architecture of a networked embedded device is illustrated in Figure 1.1. The device receives inputs from the external physical environment in the form of signals or probes that are measured by the sensor and performs control actions to them through the actuator unit. Accordingly, these actions produce data that are stored in the storage memory of the central processing unit in order to be displayed or exchanged with other devices and base stations through the network unit. Thus, the outputs of such a device are respectively in the form of displays or communication signals. Moreover, they are usually a function of its inputs and several other factors (e.g. elapsed time, current temperature, power consumption). Another source of reactive behavior in a device relates to its automatic configuration, during its initial deployment in the physical environment. Therefore, apart from the deployment itself, no further human intervention is required for the normal device operation.

Figure 1.1: Networked embedded device example

#### 1.1.2 Heterogeneous networks and protocols

An important characteristic of networked embedded systems is that they are distributed systems. This architecture usually involves a large number of independent devices that are spatially scattered in many different locations to process information in parallel. Additionally, these locations are often distant and therefore a distributed deployment allows networked embedded devices to use their network unit for delivering the gathered data to nearby devices in a collaborative and reliable manner.

Wired and wireless networks. Embedded devices are connected by either wired or wireless networks or often a combination of both. Wireless communication is becoming more and more widespread due to the avoidance of the cost and complexity from the installation of wires. Though the absence of wires is beneficial, it also introduces unpredictable latencies, which may worsen the overall performance especially in time-critical applications. Therefore, the selection of the communication network depends on the application characteristics or requirements and sometimes it is also quite challenging. For example in environmental monitoring applications, networked embedded devices can be deployed in mountains or forests, in order to gather data. The installation of wires in such areas is however not possible, therefore the only option for transmitting the data to central processing (base) stations is the use of wireless communication. Nevertheless, the harsh and unpredictable environmental conditions in these areas may lead to low performance and increased data losses.

Event- and time-triggered technologies. Most of the communication protocols that are currently found in networked embedded systems, employ two basic data exchange technologies, named event-triggered and time-triggered. On the one hand, in event-triggered technologies messages are transmitted to signal the occurrence of significant actions. Moreover, event-triggered technologies provide a high degree of flexibility, in order to exchange data whenever it is necessary as well as to support dynamic scheduling in the activation of the software tasks that service the events. This allows them to handle different functioning modes of the application. Besides their benefits, event-triggered technologies lack of predictability in the occurrence of events. Therefore, in a worst-case scenario multiple events may occur in approximately the same moment. As a result, the load in the communication medium would be sharply increased, leading to low system performance. On the other hand, in time-triggered technologies messages are transmitted in predetermined points in time (e.g. periodical transmission). Such technologies offer a restrictive design procedure, in that all software processes and their time specifications must be known in advance. They also support a static predetermined scheduling between the different processes, such as the periodic clock interrupts or time-slot allocation (e.g. in TDMA communication). This requires a lot of planning and deprives flexibility in the design phase, but in contrast to event-triggered technologies it also provides a predictable behavior to the system. The selection of the type of data exchange technology depends on the category and requirements of the application. For example time-critical applications are likely to employ time-triggered technologies, in order to ensure a high-level of predictability.

Dynamic reconfiguration. Communication in networked embedded systems is usually supported by several localization algorithms, which are mainly trying to identify the nearby devices (i.e. neighbors) as well as the closest route for delivering the data to the base station [LR04]. An advantage of such an architecture is data availability, meaning that in case of a device failure its data will be still accessible through a backup in another device, unlike a centralized architecture where the failure would be expanded in the entire

network and the data would be unrecoverable.

#### 1.1.3 Resource-constrained systems

Most of the embedded devices nowadays contain microprocessors as a part of their processing unit and are battery powered, which makes them respectively compact as well as portable and thus facilitates their deployment in the physical environment. Nevertheless, the use of batteries introduces significant resource constraints on the devices. Typical examples of such constraints relate to their processing power, memory size and energy they use while operating. The efficient use of these resources is of vital importance, since it determines the device lifetime. In detail, the design of networked embedded systems should ensure that the resources of the individual devices do not reach a critical state, or otherwise the devices will fail to process and exchange data and will require replacement. Nevertheless, since devices can be deployed in inaccessible areas (e.g. mountains, forests), they should not be replaced often upon failure. Moreover, neighbor devices may not notified of the failure and will continue data transmission to a non-operational device. Each such transmission would consequently lead to data loss, which will lead to a performance degradation in the system. Special attention should be also given to the restricted communication bandwidth and processing performance, which are offered by embedded devices and are a direct outcome of their scarce resources. For all these reasons they are usually described as resource-constrained devices. Recent efforts have been made in order to improve the resource exploitation in such devices by introducing proprietary technologies in their network stack [Zur05]. However, the development and maintenance cost of the produced embedded devices in this case cannot be justified from the novel capabilities that they offer.

Energy efficiency. This an important characteristic in networked embedded systems, since it determines the system lifetime. It is tightly connected to network communication, as transmission/reception consumes around 60% of the power resources in an embedded device [SHC+04]. This is due to certain event handling functionalities taking place in the sensor unit and keeping it constantly awake in order to process and respond to the received data. As an example, transmission/reception in wireless communication is supported by a radio transceiver, which is monitoring the shared communication channel even if nothing is happening. In this scope, many techniques have been defined to reduce the energy consumed for network communication. A commonly employed technique amongst them sets the sensor unit into a low-power (sleep-mode) state from which it is awakened at certain instants to process and handle incoming events (e.g. from the physical environment). Awakening could either be periodical, meaning that the device sets a timer and the sensor unit is notified to wake-up upon expiration [GS05], or based on wake-up signals from the device at asynchronous moments (e.g. in the occurrence of high-priority event) [CKH11] or sometimes even adaptive [BKL05].

#### 1.2 Functional and Extra-Functional Requirements

Up to this point we have described the main characteristics of networked embedded systems. These characteristics are considered during the system development, in order to ensure the benefits of using networked embedded systems (e.g. low-cost, compact size and low power consumption). More precisely, a set of system-level requirements are usually identified and addressed before the system development is initiated. Such requirements

are distinguished in two major categories, the functional requirements which are related to the functionality, correctness and robustness of the developed applications, as well as the extra-functional requirements which are related to the performance, efficiency and Quality of Service (QoS) of the entire system-under-study. Characteristic examples of functional requirements include the delivery of expected functionality, the absence of deadlocks as well as of other unexpected errors in the application software. However, special focus should also be given to extra-functional requirements, such as enforcing bounds on the communication and data processing latencies, energy consumption or maintaining the system temperature in specified levels. The significance of extra-functional requirements is depicted if we consider our earlier statement about the strong impact of non-efficient energy consumption on the probability of a device failure.

Further requirements are defined for networked embedded systems that may be classified in one of the aforementioned categories but are strongly influenced by the other. A typical example are the memory management requirements, which may be considered as functional, but are influenced by communication and data processing latencies. Although, functional requirements are concerning the application software as well as the code development and debugging, the extra-functional requirements are also affected directly by the choices of the hardware and network communication technologies that are made in the system as explained in the following section.

#### 1.2.1 Timing Constraints

In the category of extra-functional requirements the identified constraints concern the efficiency as well as the overall performance of the networked embedded system. The most important types of extra-functional requirements in this category relate to timing constraints and concerns dedicated time intervals for data handling (i.e. processing, storing). These constraints are related to certain time frames on which processing and exchange of data should be completed. The selection of these time frames depends on the system requirements and the type of employed communication technologies. The existing communication technologies used for networked embedded systems are organized into three main categories according to their overall impact on the system-under-study. The categories are hard real-time, soft real-time and best effort. Hard real-time are the technologies that set strict deadlines, which should be guaranteed to ensure a time-critical functionality. Typical examples in this category are the avionics or control systems. Soft real-time technologies also define deadlines, nevertheless they are not necessarily met in all cases. Likewise, an example in this category concerns building automation and healthcare systems. Finally, best effort technologies do not set any deadlines and may only define relative priorities between the messages. In this category we usually encounter systems that are used in agriculture or for environmental monitoring.

In particular, the extent on which the time constraints are satisfied in a networked embedded system is strongly influenced by the communication and data processing latencies that are produced during data exchange. These latencies usually depend on the employed hardware platforms as well as the network communication technologies and the mechanisms they use for data delivery.

#### 1.2.2 Clock Synchronization

A further issue that should be taken into account when enforcing timing constraints in distributed networked embedded systems lies in the different frequencies with which the hardware clocks of the individual devices advance over time. This causes a slight divergence

between every clock in the system, called *skew*. Therefore, if for example we consider a timing constraint between two events that occur in different nodes (e.g. transmission and reception of data), the achieved measurement won't be accurate due to the skew difference. In order to obtain the desired accuracy we would have to measure this duration according to a consistent notion of time in the system, named *common time reference*.

A possible question at this point would be on how to obtain this common time reference in a distributed system? A well-defined mechanism for answering to this question is by performing clock synchronization, in order to correct the skew of each clock. Clock synchronization involves message exchange in order to initially compute the difference between two or more nodes. Once this difference is computed the clocks can be corrected or adjusted in order to operate in a synchronized way. The interval where this difference is found over time determines the effectiveness of the protocol which is used to perform clock synchronization, also called synchronization accuracy. Several synchronization protocols have been proposed to compute this difference [SBK05], which are classified with respect to two basic criteria 1) their efficiency, in terms of synchronizing the clocks with the least number of messages (to ensure low resource consumption) and 2) their effectiveness denoting their ability of preventing message latencies from affecting the quality of synchronization. The commonly obtained synchronization accuracy of the synchronization protocols is usually in the microsecond scale.

#### 1.2.3 Energy and thermal constraints

The scarce resources pose significant constraints on the use of networked embedded systems and necessitate the introduction of management techniques to improve their efficiency. Efficiency improvements lead also to the reduction of the device failure rate in such systems when the device resources reach a critical point. The most prominent management techniques in this direction aim in introducing energy constraints to control the energy consumption in the system and thermal constraints to maintain the measured temperature of each device in the desired levels. The former define specific bounds for the consumed energy in the units of each device and provide efficient techniques for its dissipation in network communication [HCB00]. Additionally, the latter try to prevent peaks in the load of the processing unit in the individual devices of the networked embedded system, which will cause them to overheat and will accordingly degrade their performance as well as decrease their overall lifetime [FS13].

#### 1.3 Development Methods

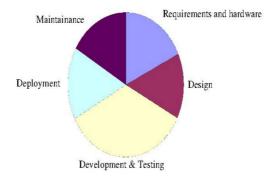

When considering the underlying effort for building a functional networked embedded system, the longest period is allocated in the application development and debugging (or testing) phase, as it was also described in the context of the makeSense project (Figure 1.2). Moreover, once the application is functional and properly tested, it is still uncertain that all the design or development errors were fixed before the deployment. Non-identified errors may concern conflicts in the network stack or even unexpected behaviors that were not taken into consideration during the development. In such a case it is extremely hard and time-consuming to fix these errors by the use of debugging techniques, even for developers with high-expertise i.e. complete knowledge of the application as well as the underlying hardware architecture (operating systems and network stack protocols).

<sup>&</sup>lt;sup>1</sup>https://www.sics.se/projects/makesense-easy-programming-of-integrated-wireless-sensor-networks

Figure 1.2: Time allocated in building networked embedded systems (source: makeSense project  $^{1}$ )

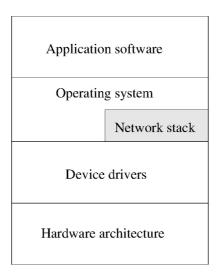

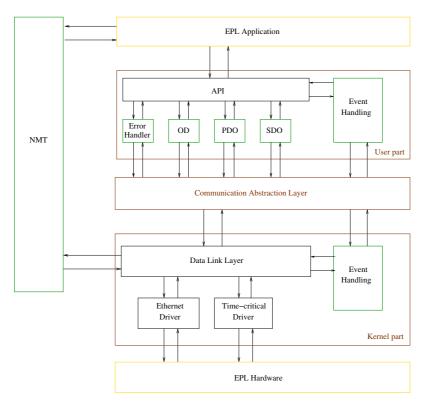

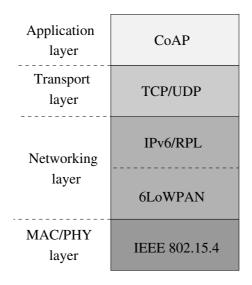

Traditional software development techniques implement software modules, in order to provide the ability of high-level interactions with the hardware. This does not require any knowledge of the actual hardware and the individual devices and is mainly done through the use of dedicated Application Programming Interfaces (API's). On the contrary, the development in networked embedded systems requires an adequate knowledge and understanding of different hardware architectures and network stack protocols, in order to initially select the most appropriate ones according to the needs and requirements of the system-under-study. This selection is connected to the extra-functional requirements as well as impacts the performance and efficiency of the overall system. Therefore, sufficient time should be allocated for it. Then, the development proceeds on defining the interactions amongst the different HW abstraction layers (Figure 1.3) in the mixed SW/HW architecture of each individual device. This procedure aids the application software in exchanging data with the hardware architecture.

Figure 1.3: Networked embedded devices SW/HW architecture

#### 1.3.1 Classical methodologies

Several classical methodologies are currently used in order to facilitate the development. In particular, a traditional and widely employed methodology follows the "V-Model" cycle

<sup>2</sup>. This methodology is based on an extension of the Waterfall SDLC model <sup>3</sup> and focuses on two main aspects, namely development and testing. A considerable drawback in the "V-model" is its underlying assumption that all the system requirements are initially well-known as well as that they can be used to build the system from scratch. However, system requirements are usually formulated and understood during the development and additionally system construction is rather incremental by reusing existing software modules and applying modifications to them. Moreover, since the development proceeds iteratively between different phases, identified errors in the application software or modifications of the hardware platforms may require an immediate return to a previous phase. As a result, the cycle as well as the overall development effort would be augmented.

A recently emerging methodology used by many developers to improve the derived limitations of the "V-Model" is "Agile/Scrum" [HC01]. Unlike the "V-Model" methodology "Agile/Scrum" focuses on the development of the simplest version of the system, which will adaptively evolve based on the requirements and needs of the system users. The evolution is supported by several iterations in which different functionalities of the system are initially developed and accordingly integrated, in order to perform a series of tests to them. Nevertheless, this methodology considers that coding and system design are performed in parallel. This is quite problematic as the changing requirements in each iteration lead to a unstructured development approach. Moreover, the constantly changing requirements in "Agile/Scrum" cannot provide a clear vision for the final system, which is of vital importance in system development. A direct consequence in this case would be the implementation of software modules for vague projects (in terms of time and overall cost), where the objective is not known.

#### 1.3.2 Model-based Design

An alternative to classical methodologies are model-based design techniques, which attempt to describe faithfully the behavior and functionality of the system through dedicated model artifacts. Model-based design allows the progressive system implementation, starting from the description of the application software to the development of software modules until the application deployment in the hardware architecture. Moreover, the developed model artifacts are reusable, thus they can be instantiated and parameterized according to the particular system-under-study. Furthermore, they can be used for early-stage simulation and testing, performance evaluation as well as verification of system requirements. Additionally, system design can be also enhanced by the presence of incremental component composition techniques, which will add a high-degree of productivity and correctness to the resulting system. More specifically, such techniques allow the system to be constructed incrementally through the composition of simple components in order to form more complex components. As an outcome, the debugging and identification of errors in simple components is easier and less time-consuming. The incremental system construction using model-based design is becoming extremely appealing for networked embedded systems, due the substantial reduction on the development time and effort that it offers. Many existing techniques in this scope rely on data-flow systems or finite state machines to facilitate the design of such systems as well as their validation through simulation or verification of system requirements.

The benefits of model-based design apart from incremental system construction include the support of separation of concerns during system design and development. Separation

<sup>&</sup>lt;sup>2</sup>http://ops.fhwa.dot.gov/publications/seitsguide/section3.htm

<sup>&</sup>lt;sup>3</sup>http://www.tutorialspoint.com/sdlc/sdlc\_waterfall\_model.htm

of concerns in networked embedded systems is two-fold and involves the separation of communication and computation as well as the separation of application from the architecture. The former denotes that the mechanisms and primitives of the protocols employed in the network stack should be handled independently from data handling (i.e. processing, storing). On the other hand, the latter is of vital importance as it allows the application to be developed independently from the hardware architecture. In this scope, developers have to specify and build separate artifacts for the software and the hardware architecture, which can be also reused in similar applications. Moreover, this is highly beneficial, since any modifications to any of them (i.e. application software or the hardware architecture) won't affect the other. Then, they should be able to define the optimal methodology for the deployment of the application on the target architecture by simultaneously ensuring its proper functionality.

#### 1.3.3 Embedded system design methodologies

Several methodologies exist currently in order to facilitate embedded system design by considering both the application software as well as the underlying hardware architecture. These methodologies are also enhanced by model-based design techniques to provide modeling, simulation and design space exploration capabilities during the early development stages. A notable modeling framework for such systems is Ptolemy II [BLL<sup>+</sup>08]. It is based on the Java programming language and focuses on embedded application software development rather than the deployment in hardware architectures. It supports several computational models, such as data-flow systems, finite state machines, Process Networks Kahn Process Network [TBHH07]), Synchronous/Reactive (SR) models. models are hierarchically mixed and controlled by a global scheduler. Another notable framework in this scope is metroII [DDG<sup>+</sup>13], which focuses both in the development of functional as well as hardware architecture models (e.g CPUs, memories, communication channels). metroII supports design space exploration as well as provides guarantees for the satisfaction of logical and time-based conditions that are linked to system requirements. Furthermore, openMETA [SBN<sup>+</sup>14] is a framework that supports a design flow for the systematic development of embedded systems. The supported flow allows the early design space exploration for hybrid dynamic models and the finite element analysis of thermal, mechanical and mobility requirements. Finally, the Generic Modeling Environment (GME) [LBM<sup>+</sup>01] uses metamodels based on UML to provide a flexible and extensible modular component architecture that allows the simulation, evaluation and optimization capabilities for for a target system domain. GME is also applied to the domain of embedded systems through the MILAN framework [BPL01].

Additional tools and techniques also exist to provide feedback in the system architecture by conducting a system-level performance analysis, such as the SymTA/S approach [HHJ<sup>+</sup>05]. SymTA/S is based on formal scheduling analysis techniques and symbolic simulation to determine performance data, such as end-to-end latencies, bus and processor utilization, and worst-case scheduling scenarios. A similar approach is supported by the MAST toolset [GHGGM01]. Additionally, in [WTVL06] the authors present the Modular Performance Analysis (MPA) method, used for the effective evaluation of Real-Time embedded systems through the Real-Time Calculus [TCN00].

Even though the aforementioned tool-supported frameworks facilitate embedded system design, they provide limited support for the operating systems and hardware architectures that are found in networked embedded systems as well as the protocols and interaction mechanisms that are used in the network stack of each embedded device. This motivated our research contribution of the following section.

#### 1.4 Thesis Contribution

In the scope of this dissertation we propose a novel method for providing systematic and generic solutions in the presented design challenges that are faced during the development of networked embedded systems. The method is based on a design flow with rigorous semantics, which uses model-based design techniques as well as incremental component construction to progressively build such systems by modular and reusable components. The flow covers all the levels in the design, namely the description of the application software, the modeling and implementation of software modules in a high-level for the application software as well as in a low-level for the hardware architecture through rapid prototyping techniques and finally the application deployment on the target architecture. Moreover, since it is model-based, it allows to capture all possible behaviors in a networked embedded system and furthermore provide simulation, performance evaluation and model-checking capabilities even in the early system development stages i.e. before it is implemented.

We advocate that the proposed design flow is rigorous as it involves the following capabilities:

- Open to standards: By this term we denote that it uses as input for the application software well-known specifications and standards. This allows to combine a high-degree of standardization with the necessary customizations to obtain a fully-fledged design of the networked embedded system architecture.

- Model-based: It uses a single semantic framework (BIP [BBS06]) to represent all the hardware/software layers of networked embedded systems, in order to maintain semantic coherency in the description of the application software and the underlying hardware architecture. Furthermore, the application software and hardware architecture models are developed independently according to the Y-chart design principle. This allows to consider the separation of concerns (Section 1.3.2), such that the development and modifications to any of them proceed independently, in order do not affect the other. Once built, these models are accordingly synthesized using the mapping procedure, which describes the application deployment in the hardware architecture.

- Component-based: It is using component composition to derive composite components from simpler components. To this extent, it supports component reusability, in order to reduce the development time and effort as well as to design and analyze the system incrementally.

- Correct-by-construction: This term denotes that the design flow leads to the construction of a final model for the system-under-study, which preserves in the entirety all the requirements of the initial input model for the application software model. This is accomplished by extensive use of formal design rules and transformations to proceed from one step to another in the flow.

- Tool-supported: This attribute denotes that the design flow includes tools, which are used to automate the transition between its different steps. These tools are either generic or specifically adapted to each category of each networked embedded system-under-study.

- Re-targetable: It can be deployed in a wide range of embedded systems featuring network communication between resource-constrained devices. Specifically, the

design flow provides support for several types of application software, operating systems as well as network stack protocols.

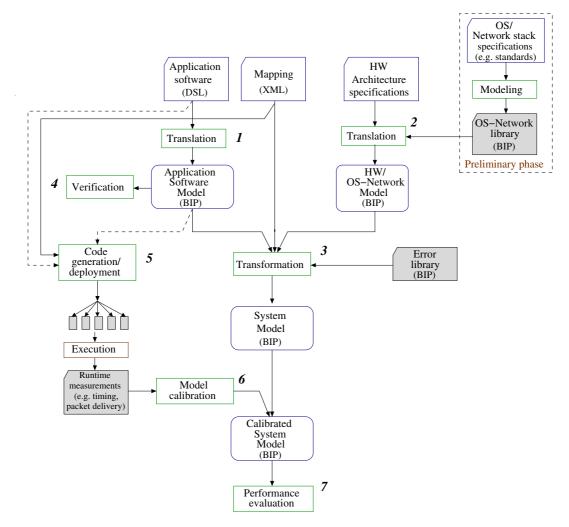

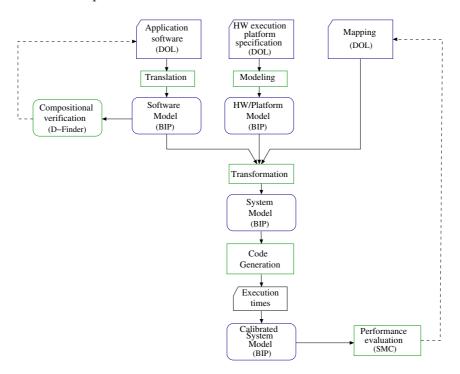

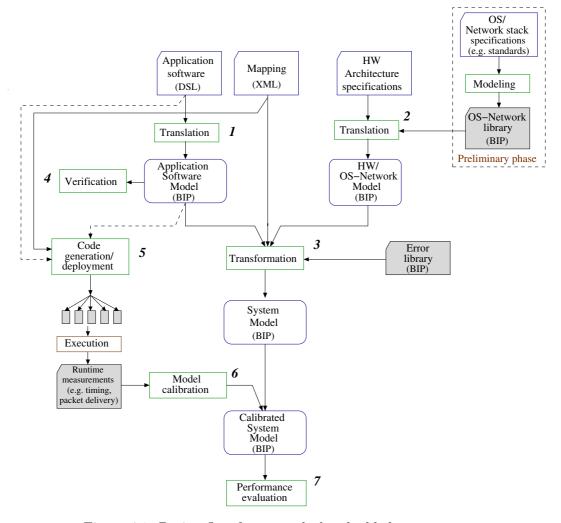

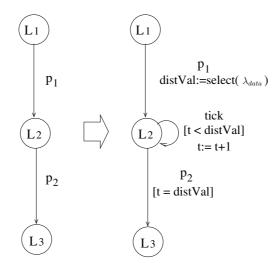

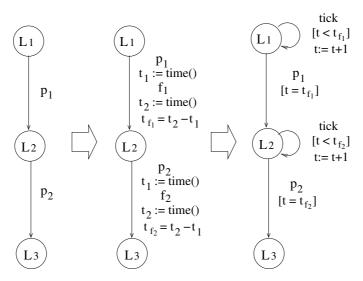

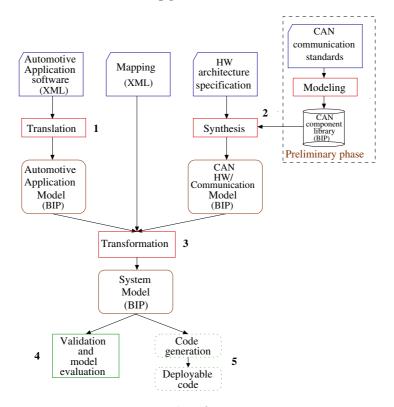

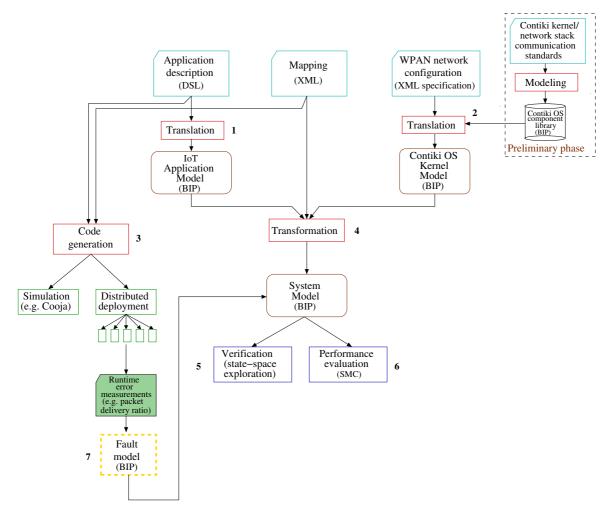

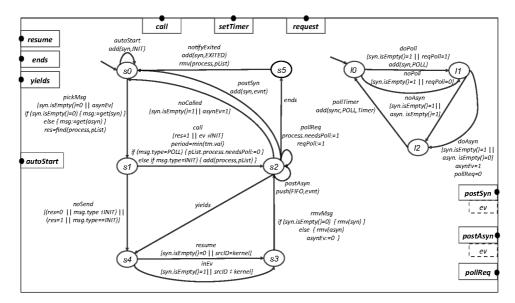

The proposed flow implements of an approach for rigorous design and development of functional networked embedded systems, illustrated in Figure 1.4. In this scope it involves several design phases, which aim in the independent development of the application software and the hardware architecture. Therefore, initially the application software is described in domain-specific languages or programming models and can be either translated to an Application Software Model (phase 1) or used to automatically generate deployable code for the target architecture (phase 5). The Application Software Model is then used to check correctness and the proper functionality in the application-level through verification techniques (phase 4). In the design flow we also synthesize a HW/OS-Network Model (phase 2) for the hardware architecture from model fragments for the operating systems as well as the network stack protocols that are used in the system (preliminary phase). The integration of the models from phase 1 and 2 allows the construction of a functional System Model, representing the entire system (phase 3). The System Model is further calibrated with performance data that are derived from the execution of the deployable code in a hardware architecture (phase 6). The resulting Calibrated System Model is used for the simulate and analyze the performance of the system, but also to evaluate functional and extra-functional requirements at the system-level. Furthermore, performance evaluation (phase 7) may also propose design enhancements for the system.

#### 1.5 Organization

The **first part** of this document provides a background to the area of networked embedded systems and an existing framework that is used in the context of this dissertation.

Chapter 2 describes the system categories of networked embedded systems, by extending the classification in [Zur05] to include the automotive, industrial automation, Wireless Sensor Network (WSN) as well as the recently emerged type of Internet of Things (IoT) systems. Furthermore, it describes characteristic technologies (e.g. operating systems, network stack protocols) that are used in this dissertation for each system category.

Chapter 3 presents BIP, a component-based framework which is used as a basis for the model-based design and incremental construction of networked embedded systems. It then proceeds on describing the concepts of the framework, the basic constructs that are used in its modeling language as well as its supported toolset. The chapter accordingly details on an existing system design flow that is defined through the BIP framework in the domain of manycore architectures.

The **second part** of this document refers to the thesis contribution, that is, a rigorous design flow for networked embedded systems and its application in such systems.

Chapter 4 provides a generic presentation of the proposed design flow and details on its benefits, namely early-stage simulation, validation and verification of functional and extra-functional system-level requirements. Accordingly, it presents the tools and methods that are used to fully automate its different phases. Specifically, the presented tools and methods allow (i) the description of the application software through a novel programming framework, (ii) the automated code generation for several hardware architectures of such systems, (iii) the construction of faithful system-level models and (iv) the system-level performance evaluation. The chapter additionally provides a discussion with respect to the existing BIP design flow for manycore architectures.

Figure 1.4: Rigorous design flow for networked embedded systems

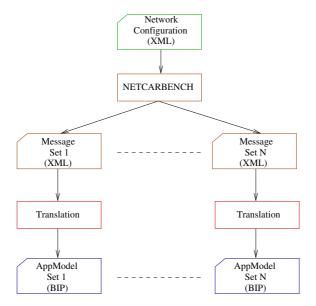

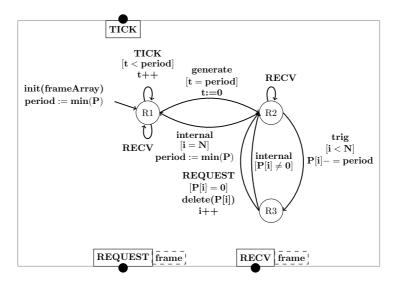

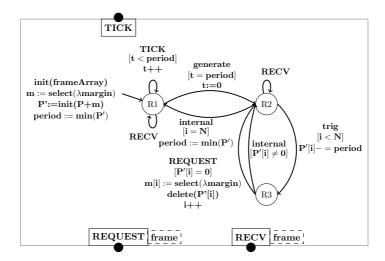

Chapter 5 demonstrates the flow in the domain of automotive systems through the CAN communication protocol [ISO03a] [ISO03b] as well as the newly introduced CAN FD protocol version [Bos12]. The chapter proceeds on describing the input application software in NETCARBENCH [BHN<sup>+</sup>07] and how it is progressively translated into a application-level model through a developed tool. The benefits of the resulting flow are illustrated through the simulation and performance evaluation of a powertrain automotive network, which is also configured optimally in order to avoid load peaks in the CAN network.

Chapter 6 demonstrates the flow in the domain of industrial automation systems using the CANopen communication protocol [CAN11]. The chapter details on the configuration flexibility and management capabilities that CANopen provides to the input application software as well as on rapid prototyping techniques that automate the generation of deployable code for Real-Time Ethernet hardware architectures [Dec05] using the Ethernet Powerlink protocol [Std14b] for network communication. The industrial automation flow is demonstrated through two case studies, each one focusing on a different type of industrial automation system. Specifically, the chapter initially presents the simulation and performance evaluation capabilities of the flow in the Pixel Detector Control System [KBI+02], which is constitutes a part of the ATLAS experiment at CERN's Large Hadron

1.5. Organization 23

Collider (LHC) particle accelerator and then it proceeds on describing the code generation capabilities through a Triple Modular Redundancy System [Kop11], providing support for fault-tolerance in safety-critical Real-Time Ethernet applications.

Chapter 7 demonstrates the flow in the widely popular application domain of WSN systems through the IEEE 802.11 standard [IEE12] for WLAN network communication. The WLAN network is described by input HW specifications, that are also used to configure the target architecture. Additionally, the chapter details on the automatic generation of deployable code based on the Linux sockets. Runtime measurements of the code are used by developed methods to derive performance data for calibration of system-level models. In this context, the flow is illustrated through a concrete case-study for multimedia transmission over a wireless network. Furthermore, the case-study proposes a software-based clock synchronization mechanism for improving the clock synchronization accuracy in such systems. The resulting accuracy is verified through dedicated extra-functional system-level requirements.

Chapter 8 demonstrates the flow in the emerging application domain of IoT systems through the Contiki operating system [DGV04] as well as the supported network stack protocols. The chapter details on the configuration of the underlying WPAN network through an input HW specification as well as presents a high-level Domain Specific Language (DSL) for the IoT application software. The IoT application software is either translated to an application-level model or used to generate deployable code for execution in dedicated hardware platforms. The execution of the code allows measuring software-dependent runtime constraints of the Contiki OS. The chapter proceeds on explaining dedicated techniques that were developed, in order to add these constraints to system-level models and accordingly obtain models that represent Contiki OS systems. The benefits of the resulting flow in IoT systems are illustrated through two case-studies, which focus on simulation and validation of functional and extra-functional system-level (e.g. thermal) requirements in a smart heating and a building automation system respectively.

Finally, **Chapter 9** draws a conclusion of this work by summarizing its key points and discusses future perspectives for the proposed design flow.

# - Chapter 2 -

#### Networked Embedded Systems: A Background

#### 2.1 Classification of Networked Embedded Systems

Network embedded systems are used in many different types of systems, which can be organized in the automotive, industrial automation, wireless sensor network systems categories as described in [Zur05]. This dissertation extends this classification to four categories in order to include the recently emerged type of IoT systems. In this chapter we provide a brief introduction to each category and accordingly describe representative technologies that are suitable for them in different HW abstraction layers (Chapter 1), namely from the operating system to the network communication through the supported protocol stack. As it is detailed each category has its own characteristics in terms of offered capabilities in the application or system level as well as requirements and constraints from their use and is additionally targeted to different lower-layer hardware architectures.

#### 2.1.1 Automotive systems

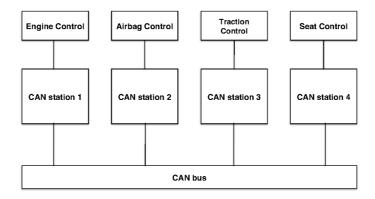

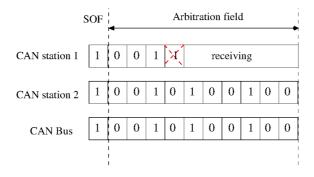

A modern automotive embedded system consists of several subsystems, which are comprised of one or several Electronic Control Units (ECUs). In turn, the ECU's are comprised of a micro-controller as well as a set of sensors and actuators and are able to communicate through the transmission of electronic signals. The subsystems that rely on network communication in automotive systems are divided into five main categories:

- The powertrain subsystem: Involves the generation of power in the engine (engine control) and transmission of it through the gear box to the driving axis and wheels (transmission and gear control) [CSB<sup>+</sup>06].

- The chassis subsystem: Provides functional units for in-vehicle active safety, driving dynamics and assistance and some of its main systems include the Antilock Braking System (ABS), EPS (electronic power steering), the suspension system and others.

- The body subsystem: Implements the in-vehicle body and comfort functions, such as the air condition and climate control

- Passive safety subsystem : Provides safety-related functions inside the vehicle and includes the airbags and seat belt pretensioners

• The telematics subsystem: Includes services related to multimedia technologies, such as the in-vehicle navigation system (GPS), monitor displays CD or DVD players. Most of these technologies use wireless communication.

Each subsystem involves a different set of communication requirements from its use, which are mainly described in terms of:

- fault tolerance, defining to which degree incorrect behavior is allowed in the subsystem

- predictability, in terms of real-time behavior that the subsystem offers

- minimum bandwidth, which is required for the subsystem to operate properly

- flexibility, allowing the transmission of both event- and time-triggered messages as well as defining the extent on which management of the overall load in the network is offered

There are several network technologies which were defined for the exchange of information in automotive systems. They are classified in two categories, namely wired and wireless. The wireless technologies were recently introduced to supply more bandwidth in automotive systems and are mainly based on Zigbee and Bluetooth. Nevertheless, the absence of real-time guarantees and proof of delivery for message exchange restrains their use in specific subsystems, such as the telematics subsystem. On the other hand, the wired technologies that are employed in automotive systems are distinguished according to their event or time triggered architecture. Characteristic examples belonging to the event-triggered category are the Controller Area Network (CAN) (see Section 2.2.1), the Local Interconnect Network [Wen00] and the MOST Bus [Coo10]. On the other hand time triggered communication protocols for automotive systems include the Time-Triggered CAN (TTCAN) [FMD+00], FlexRay [C+05]. There are also technologies that provide both event and time triggered communication, such as Volcano [Men].

Modern automotive systems can have up to 70 ECU's, which are responsible for the distribution of more than 2500 variables and signals. Therefore, the growing number of networked ECU's makes system design complex in terms of support and management of the network interconnecting all these ECUs. An efficient solution proposed by the automotive industry to this end was a common scalable electric/electronic architecture, which was standardized under the name AUTomotive Open System ARchitecture (AUTOSAR) [FMB<sup>+</sup>09].

#### The AUTOSAR architecture

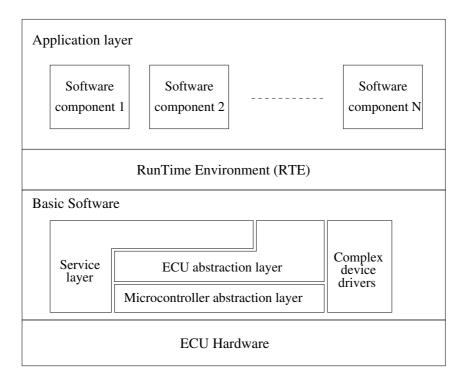

An initiative towards the direction of providing a common middleware for automotive systems was done through the AUTomotive Open System ARchitecture (AUTOSAR) standard [FMB<sup>+</sup>09]. AUTOSAR supports an architecture which improves the quality and reliability of automotive systems by distinguishing them in three layers, namely the Application, the RunTime Environment (RTE) and the basic software layers (Figure 2.1).

The Application layer defines several software components, which are generally provided by suppliers to exchange information through the RTE. Similarly, the basic software layer includes modules, which provide basic services to the architecture, such as network communication through the interaction with the ECU hardware. The modules of this layer have standardized interfaces which makes the whole architecture modular and hardware-independent. Finally, the RTE acts as a middleware between software components of

Figure 2.1: The AUTOSAR architecture

the application layer and the modules of the basic software layer. Moreover, it provides support for all types of communication in an ECU and to remove communication and hardware dependencies from the software components of the application layer.

#### Tools for automotive system development

A variety of tools exist in the market to provide support for the development of automotive applications as well as for testing and Hardware-In-the-Loop (HIL) simulation. They include the Renesas Development Environment <sup>1</sup>, the DSpace Automotive Simulation Models <sup>2</sup> as well as the Eclipse IDE libraries for automotive software development <sup>3</sup>. Furthermore, several tools are based on the AUTOSAR architecture to support a structured development for automotive systems. The most notable ones amongst them include the Simulink and Embedded Coder integrated environment provided by Mathworks' <sup>4</sup> as well as dedicated tools that are provided by Vector GmbH <sup>5</sup>. The latter include the DaVinci Developer <sup>6</sup> for the design of the BSW layer component and the DaVinci Configurator Pro <sup>7</sup> for the configuration and generation of the BSW layer components as well as the RTE layer. Even though powerful, the aforementioned tools are not capable of providing support for performance analysis of quantitative aspects in the system (e.g. timing and thermal information, energy consumption) or for addressing and verifying system requirements and are merely focused in a module-specific and comprehensive consistency

<sup>&</sup>lt;sup>1</sup>http://www.renesas.eu/applications/automotive/peer/manual\_softtools\_index.jsp

<sup>&</sup>lt;sup>2</sup>https://www.dspace.com/en/pub/home/products/sw/automotive\_simulation\_models.cfm

$<sup>^3</sup> http://www.eclipse.org/downloads/packages/eclipse-ide-automotive-software-developers-includes-incubating-components/keplersr2$

<sup>&</sup>lt;sup>4</sup>mathworks.com/solutions/automotive/standards/autosar.html

<sup>&</sup>lt;sup>5</sup>https://vector.com/

<sup>&</sup>lt;sup>6</sup>http://vector.com/vi\_davinci\_developer\_en.html

<sup>&</sup>lt;sup>7</sup>http://vector.com/vi\_davinci\_configurator\_pro\_en.html

check of parameters in the system. Moreover, the aforementioned tools are following the "V-Model" development cycle and therefore inherit its described limitations in Chapter 1.

#### 2.1.2 Industrial Automation Systems

Industrial automation systems are used in manufacturing, quality control and material handling processes. General purpose controllers for industrial processes include Programmable Logic Controller (PLC) devices as well as sensors and actuators. The exchanged data in industrial processes are stored in powerful computers, such as servers. The main concern in such systems is to assure real-time performance as well as efficiency in terms of resource usage, such as the energy or memory consumption. Typical examples of such systems are distributed control systems or safety critical systems.

The main technologies used nowadays in industrial automation systems are called fieldbus protocols. They provide a digital communication link between control devices (input or output), which serves as a Local Area Network (LAN). Fieldbus technologies offer several characteristics, such as installation flexibility, maintainability (monitoring and maintenance are handled through the network) and most of all configurability. The latter provides a high degree of parameterization in the control devices, thus making them reasonably intelligent. The most common solutions in the family of fieldbus protocols rely on the Real-Time or Industrial Ethernet [Dec05]. Real-Time Ethernet is using the standard Ethernet communication and apply modifications to extend it with real-time capabilities. Currently, a lot of Real-Time Ethernet solutions are in use, but only some of them are known due to their technical aspects and standardization status. Many of these solutions are defined in the IEC 61784-Part 1 [Std14a] and IEC 61784-Part 2 [Std14b] international standards for fieldbus communication and rely mainly on the master/slave architecture. In such an architecture a particular device manages the network and has uniformal control over the other devices.

The Real-Time Ethernet that employ a master/slave architecture are classified into three categories according to the implementation of the slave devices in the system. We hereby present these categories by evenly giving characteristic examples of technologies that are mainly described by the IEC 61784-Part 1 and IEC 61784-Part 2 international standards for each one of them. Moreover, for solutions that are not included in these standards, supporting material is provided.

The first category is using the TCP/IP protocol stack and hardware, such as the standard Ethernet controller as well as Ethernet switches. However, it does not provide guarantees for real-time performance as the communication latencies deriving from the use of switches as well as of the best-effort delivery service are unpredictable and result in an average data rate of 100 ms. Typical technology variants belonging in this category include Ethernet/IP, PROFINET Component Based Automation (CBA) and Modbus/TCP. The second category uses the same hardware, but employs an additional timing layer in the third layer (Internet) of the TCP/IP stack, in order to control access to the medium. Technology variants belonging in this category include PROFINET Real-Time (RT) and Ethernet POWERLINK (EPL) (see Section 2.2.3). An important feature of this category is that it provides better real-time performance (average data rate below 10 ms), which can be additionally ameliorated as some of the related technologies are also deployed using Ethernet hubs (e.g. Ethernet POWERLINK). Finally, the third category aims on achieving the best possible real-time performance for the most demanding class of applications. Nevertheless, this is not feasible without specific modifications on the underlying hardware. These modifications depend on the technology and can either concern the Ethernet controller or the Ethernet switches. Technologies related to this category

include PROFINET Isochronous Real Time (IRT), SERCOS III, EtherCAT and TTEthernet [Ste08]. The selection of the category as well as the specific master/slave solution for an application depends on its requirements and needs.

Even though Real-Time Ethernet technologies are widely used for industrial automation systems, application development is still challenging, due to their low level complexity as well as their high expertise needed for their configuration. Therefore, a higher layer of abstraction is required, which is typically found in application-layer protocols. An increasingly popular application-layer fieldbus protocol is CANopen (see Section 2.2.2), as it provides a vast variety of communication mechanisms, such as time or event-driven, synchronous or asynchronous as well as additional support for time synchronization and network management. Furthermore, it offers a high-degree of configuration flexibility, requires limited resources and has therefore been deployed on many existing embedded devices.

#### Tools for industrial automation system development

Currently, the development of industrial automation applications using the IEC 61784-Part 1 or IEC 61784-Part 2 standards is supported by dedicated development kits. The kits include the hardware platforms as well as for software tools and dedicated drivers to facilitate application development. Characteristic examples between them are the IXXAT Econ 100 platform and its native Soft-PLC programming environment provided by IXAAT <sup>8</sup> as well as the AM3359 Industrial Communications Engine (ICE) platform and the Code Composer Studio IDE provided by Texas Instruments 9. Although, the software tools are supporting the rapid and efficient implementation of complex applications, they cannot be used for early-stage simulation, or performance evaluation in the system. This increases the probability for the discovery of errors or unexpected behaviors during the deployment of the application in the hardware platform, even if it is found error-free during debugging. Yet another toolkit which provides support for the development and code generation in industrial automation applications is EtherLab <sup>10</sup>. Etherlab relies on the design of control modules in the Simulink/Real-Time workshop as well as provides various capabilities for test management and data logging server applications. Communication in the toolkit is realized through the EtherCAT protocol [Std14b]. However, all the presented tools require the presence of the specific hardware equipment and cannot be easily extended to support alternative Real-Time Ethernet solutions.

#### 2.1.3 Wireless Sensor Network systems

The recent availability of low-cost standard wireless network technologies offered new features in networked embedded systems. Such features include the high transmission rate (up to 54 Mb/s) and mostly the avoidance as well as cost of cabling. The former allows to maintain (or at least not significantly worsen) the real-time behavior of network embedded applications, whereas the latter minimizes the deployment complexity.

The introduction of wireless sensor networks has provided a huge technological advance in comparison with the previous approach which was followed. Specifically, sufficiently big and robust devices had to be built, containing the sensors in order to store data locally. Periodically, human intervention was required to collect this data and calibrate the sensors. Nevertheless, in case of a hardware failure all the gathered data would be lost. Instead,

<sup>&</sup>lt;sup>8</sup>http://www.ixxat.com/embedded-controller\_en.html

<sup>&</sup>lt;sup>9</sup>http://www.ti.com/tool/ccstudio

<sup>10</sup> http://www.etherlab.org/download/flyer.pdf

with the use of tiny, low-cost, low-power devices with wireless transmission capabilities the data are transferred to central stations and the configuration can be performed remotely.

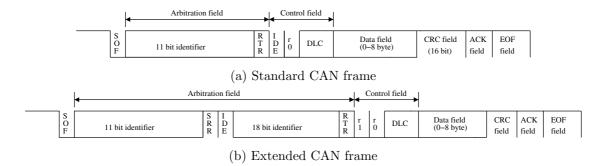

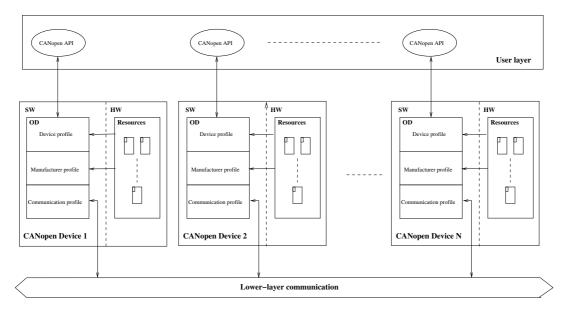

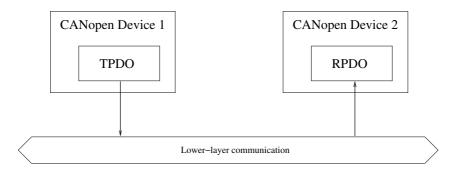

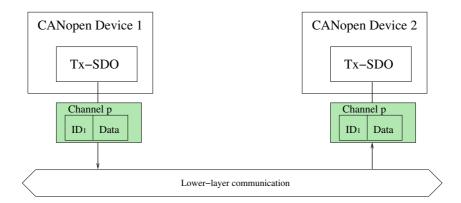

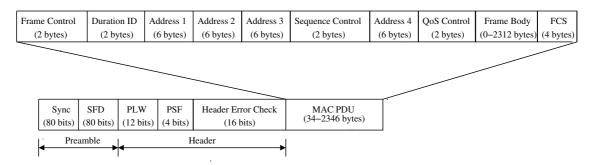

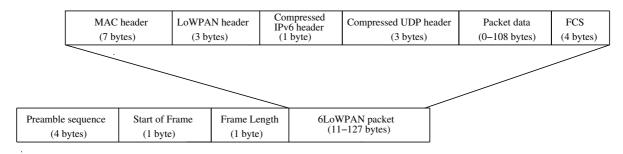

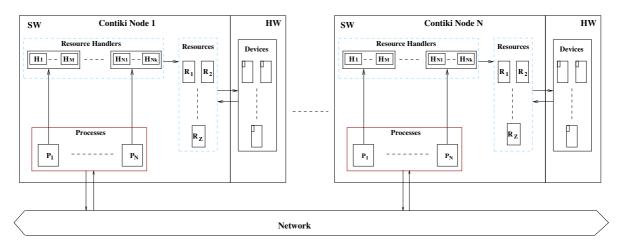

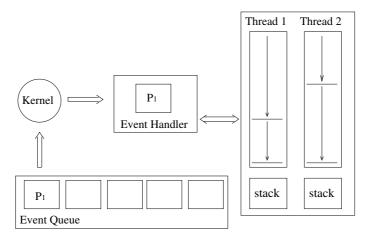

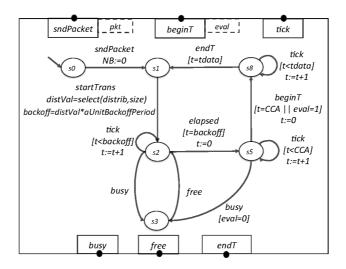

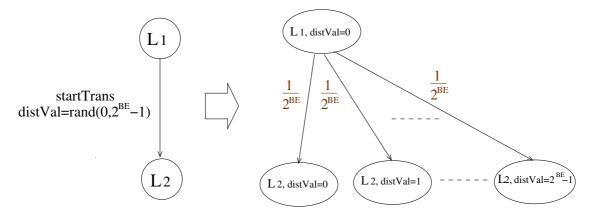

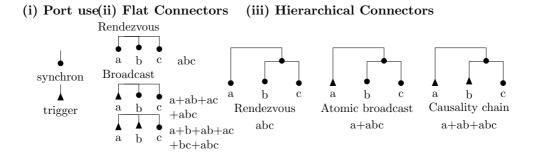

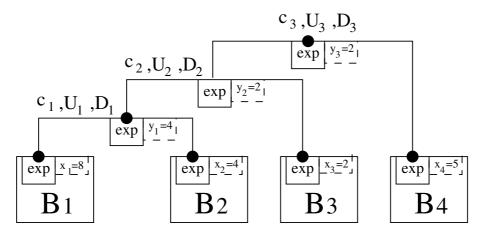

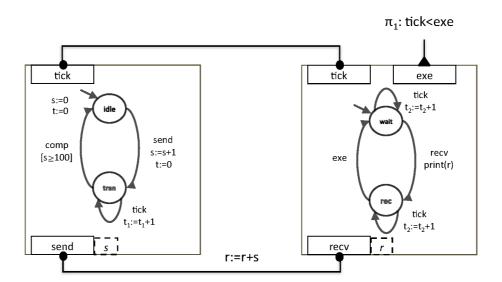

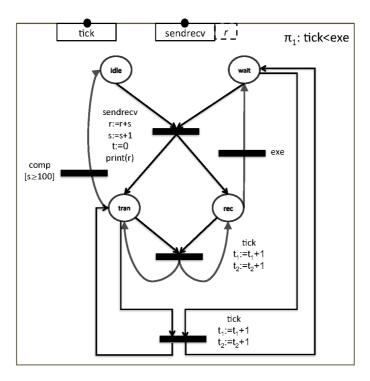

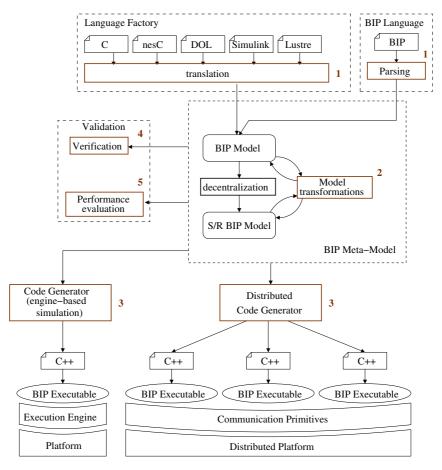

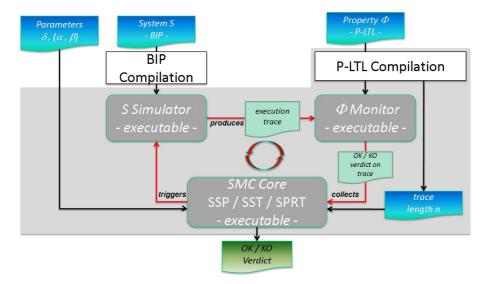

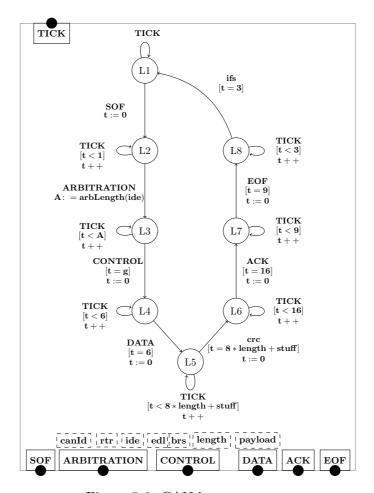

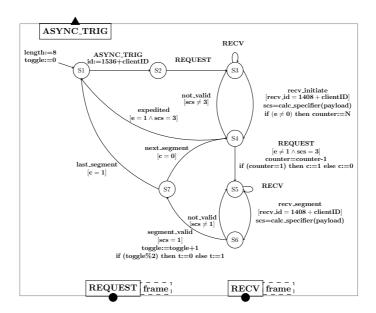

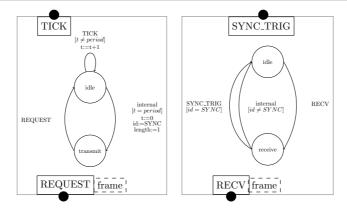

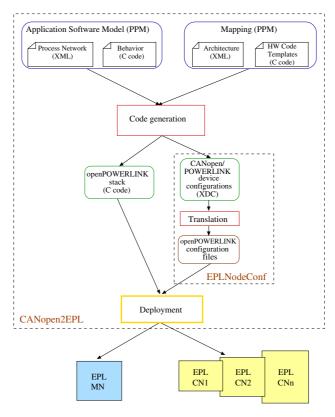

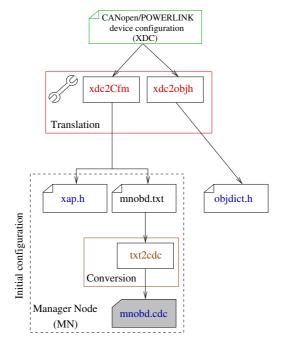

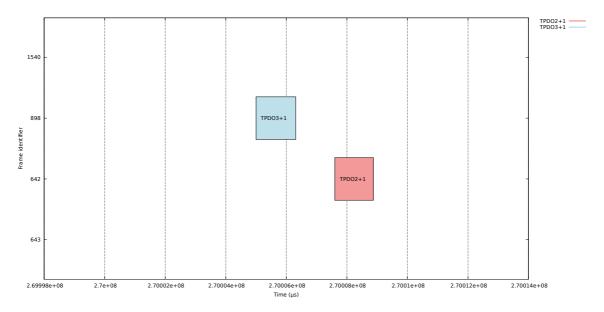

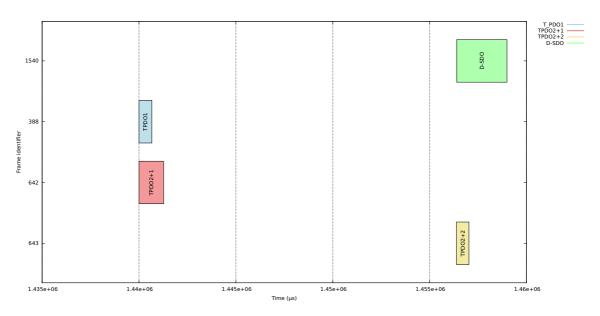

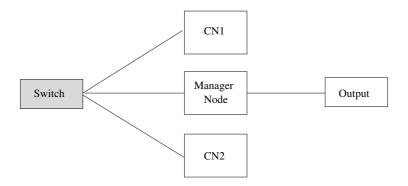

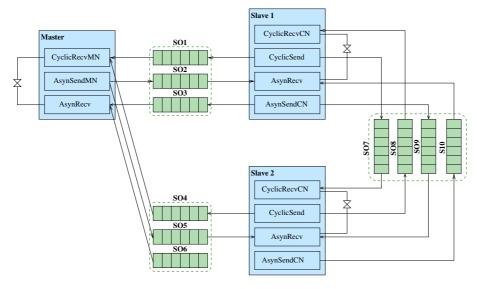

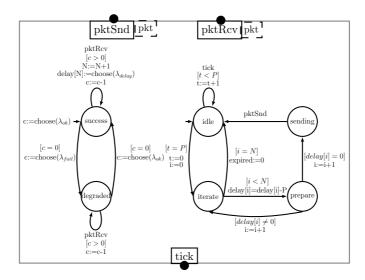

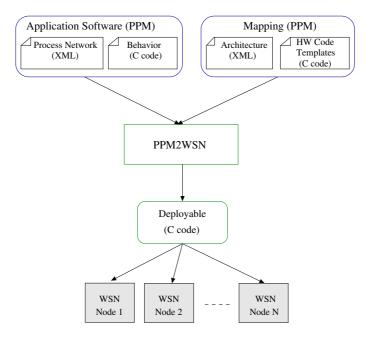

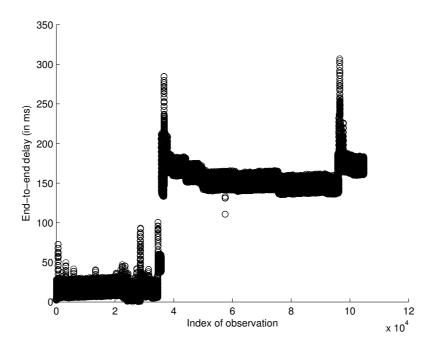

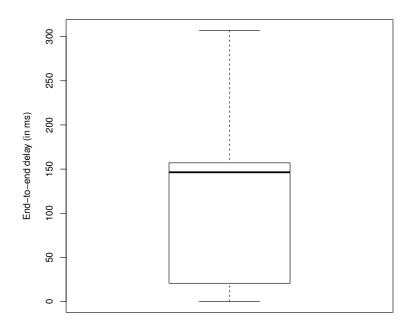

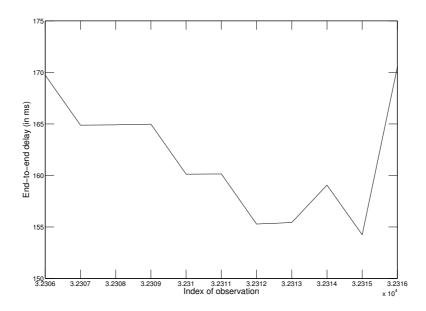

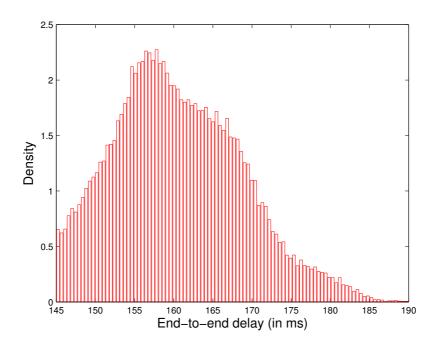

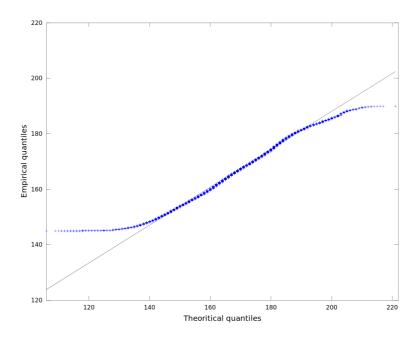

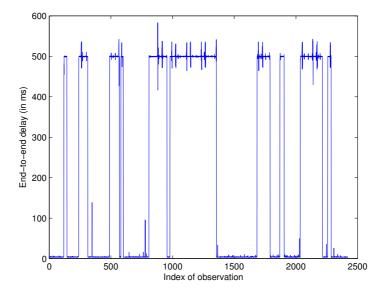

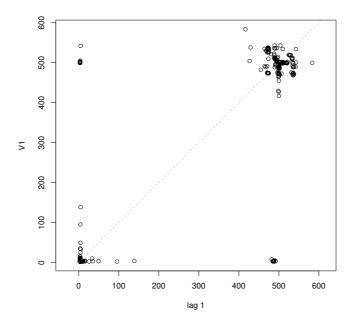

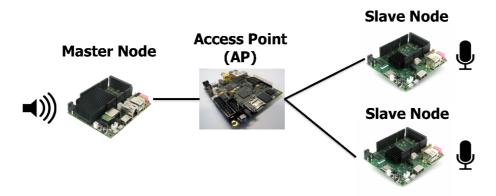

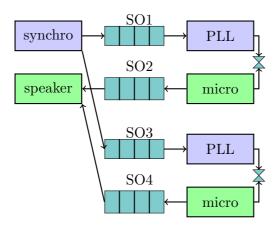

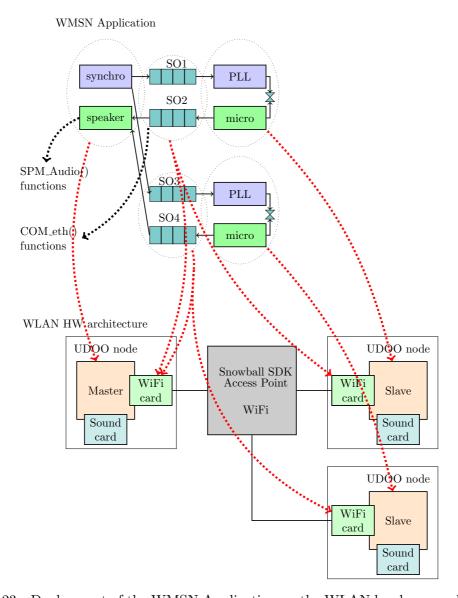

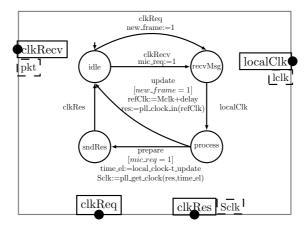

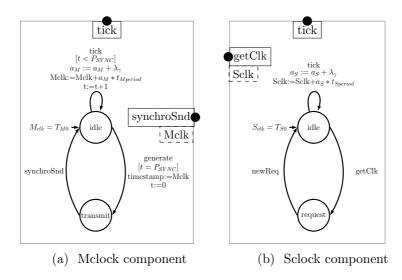

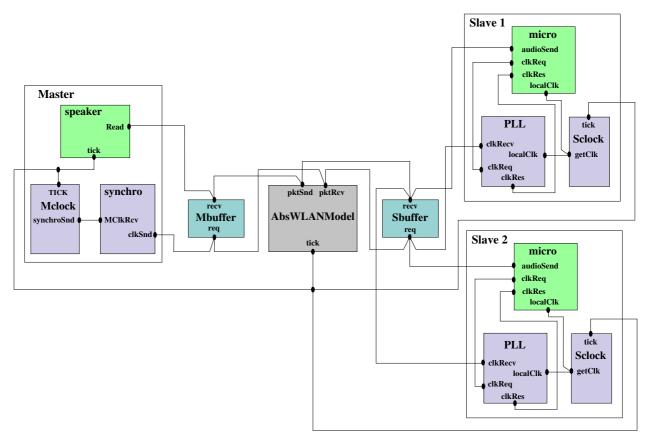

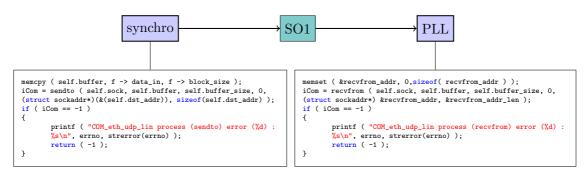

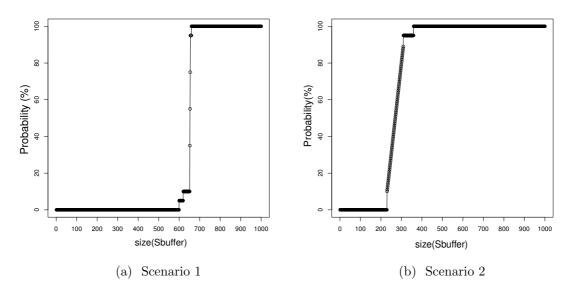

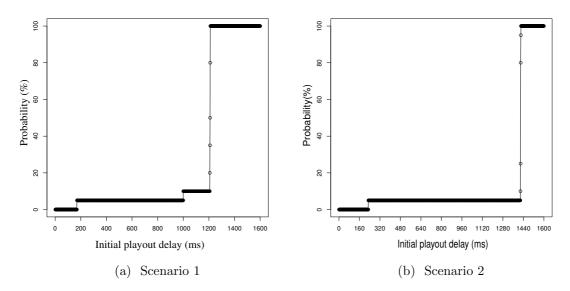

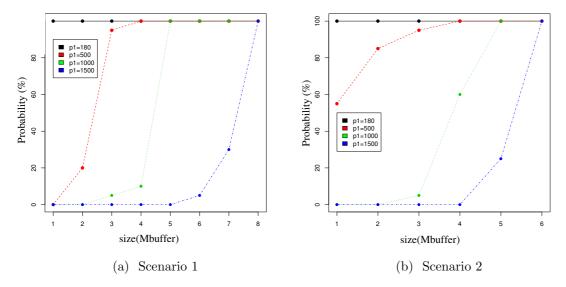

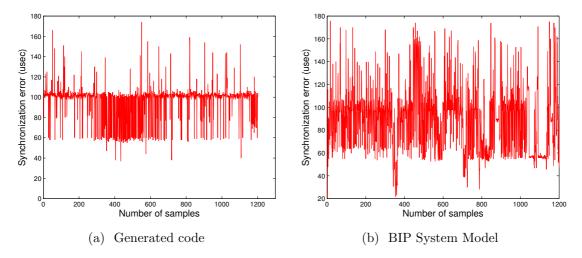

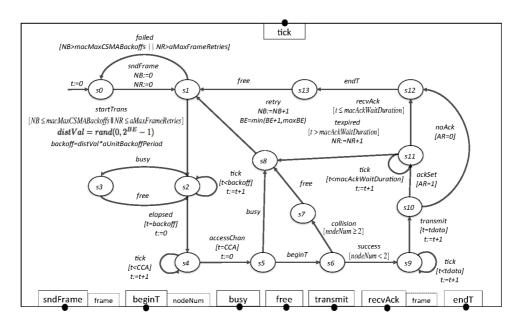

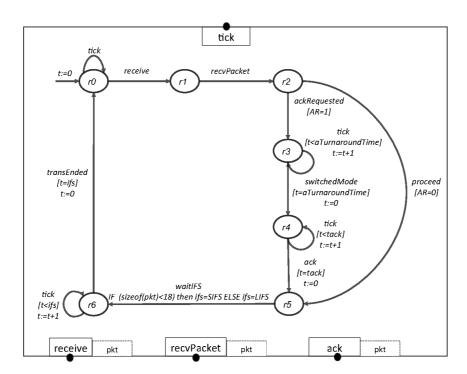

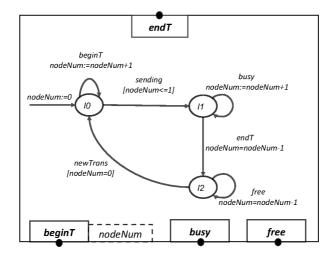

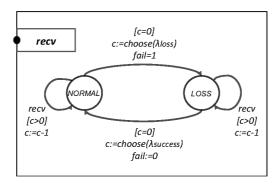

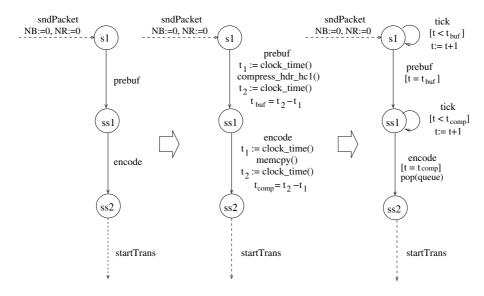

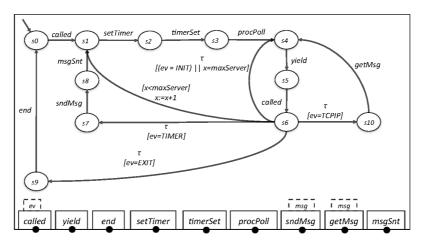

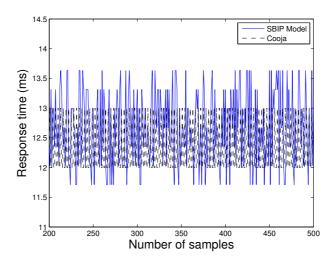

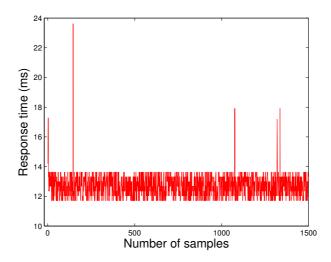

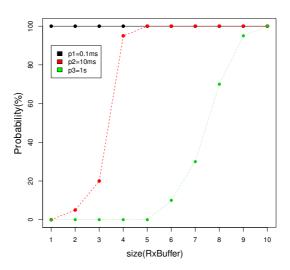

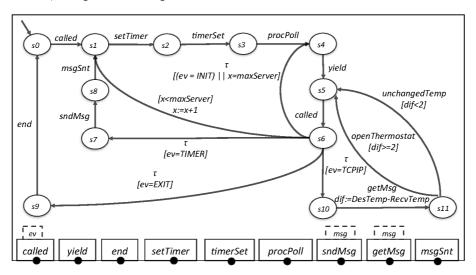

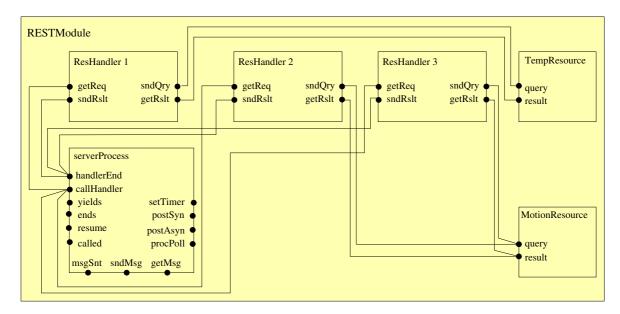

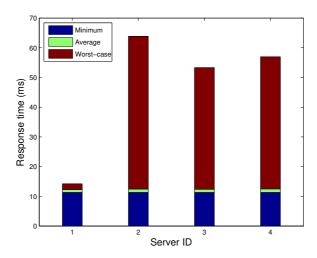

Although they provide several benefits, there are underlying challenges for the development of functional WSN applications with real-time abilities. This is due to the unpredictable network communication latencies that are imposed through the use of random access schemes, such as the Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA) technique (described in Section 2.2.4). Another source of non-deterministic behavior in wireless communication is the electromagnetic interference by electrical appliances or by nearby wireless networks, due to the use of radio channels. This interference may lead to error-prone data exchange or in increased packet losses. In both cases the performance of the network will be detiorated, thus leading to low reliability especially in applications with strict timing constraints for data handling.