# Study of task migration in a multi-tiled architecture. Automatic generation of an agent based solution Ashraf Elantably

# ▶ To cite this version:

Ashraf Elantably. Study of task migration in a multi-tiled architecture. Automatic generation of an agent based solution. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2015. English. NNT: 2015GREAT130. tel-01278646

# HAL Id: tel-01278646 https://theses.hal.science/tel-01278646

Submitted on 24 Feb 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# THÈSE

Pour obtenir le grade de

**DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE** Spécialité : Nano Electronique et Nano Technologies (NENT)

Arrêté ministériel : 7 août 2006

Présentée par Ashraf ELANTABLY

Thèse dirigée par Frédéric ROUSSEAU

préparée au sein Laboratoire TIMA et de l'École Doctorale Electronique Electrotechnique Automatique et Traitement du signal EEATS

# Étude de la migration de tâches dans une architecture multi-tuile Génération automatique d'une solution basée

sur des agents

Thèse soutenue publiquement le **16 Décembre 2015**, devant le jury composé de :

## Monsieur, Jean François MEHAUT

Professeur - Université Grenoble Alpes, Président **Monsieur, Fabiano HESSEL** Maître de conférences - Université de Porto Alegre, Rapporteur **Monsieur, Gilles SASSATELLI** CR CNRS (HdR) LIRMM, Rapporteur **Monsieur, Florent DE DINECHIN** Professeur - INSA Lyon, Examinateur **Monsieur, Olivier GRUBER** Professeur - Université Grenoble Alpes, Examinateur **Monsieur, Frédéric ROUSSEAU** Professeur - Université Grenoble Alpes, Directeur de thèse

# Acknowledgments

"Say: 'In the Bounty of Allâh, and in His Mercy; therein let them rejoice'. That is better than what they amass." **THE NOBLE QURAN**, Yunus 10:58.

I would like to sincerely thank my supervisor prof. Frédéric Rousseau for giving me the opportunity to work with him. I would like also to thank him for his guidance, friendliness, patience, kindness, and his continuous technical support during last four years and especially during writing this dissertation.

I would like to thank my thesis manuscript reviewers Dr. Fabiano Hessel and Dr. Gilles Sassatelli for their efforts, time taken to review this manuscript, and their constructive feedback and remarks. I would like also to thank prof. Jean-Francois Mehaut for presiding over my thesis defense committee, as well as the other members of the committee: prof. Olivier Gruber and prof. Florent de Dinechin for their questions and remarks.

I would like to thank my colleagues in SLS team members for their wonderful company especially Nicolas Fournel, Clément Deschamps and Etienne Ripert for their valuable contribution to the work of the project EURETILE. I would like to thank our partners in EURETILE project for their professionalism during the work in the project.

I would like to sincerely thank my family for their prayers, encouragement, and moral support during my studies. I would like as well to thank my wife for her support and my newly born baby for his delightful smiles and laughs that fill me with joy.

Ashraf Ahmed Mostafa El-Antably

January 2016

## Abstrait

Les systèmes multiprocesseurs sur puce (MPSoC) mis en œuvre dans les architectures multi-tuiles fournissent des solutions prometteuses pour exécuter des applications sophistiquées et modernes. Une tuile contient au moins un processeur, une mémoire principale privée et des périphériques nécessaires associés à un dispositif chargé de la communication inter-tuile. Cependant, la fiabilité de ces systèmes est toujours un problème. Une réponse possible à ce problème est la migration de tâches. Le transfert de l'exécution d'une tâche d'une tuile à l'autre permet de garder une fiabilité acceptable de ces systèmes. Nous proposons dans ce travail une technique de migration de tâches basée sur des agents. Cette technique vise les applications de flot de données en cours d'exécution sur des architectures multituiles. Une couche logicielle "middleware" est conçue pour supporter les agents de migration. Cette couche rend la solution transparente pour les programmeurs d'applications et facilite sa portabilité sur architectures multi-tuiles différentes. Afin que cette solution soit évolutive, une chaîne d'outils de génération automatique est conçue pour générer les agents de migration. Grâce à ces outils, ces informations sont extraites automatiquement des graphes de tâches et du placement optimisé sur les tuiles du système. L'algorithme de migration est aussi détaillé, en montrant les phases successives et les transferts d'information nécessaires. La chaîne d'outils est capable de générer du code pour les architectures ARM et x86. Cette technique de migration de tâche peut être déployée sur les systèmes d'exploitation qui ne supportent ni chargement dynamique ni unité de gestion mémoire MMU. Les résultats expérimentaux sur une plateforme x86 matérielle et une plateforme ARM de simulation montrent peu de surcoût en terme de mémoire et de performance, ce qui rend cette solution efficace.

## Abstract

Fully distributed memory multi-processors (MPSoC) implemented in multi-tiled architectures are promising solutions to support modern sophisticated applications; however, reliability of such systems is always an issue. As a result, a system-level solution like task migration keeps its importance. Transferring the execution of a task from one tile to another helps keep acceptable reliability of such systems. A tile contains at least one processor, private main memory and associated peripherals with a communication device responsible for inter-tile communications. We propose in this work an agent based task migration technique that targets data-flow applications running on multi-tiled architectures. This technique uses a middleware layer that makes it transparent to application programmers and eases its portability over different multi-tiled architectures. In order for this solution to be scalable to systems with more tiles, an automatic generation tool-chain is designed to generate migration agents and provide them with necessary information enabling them to execute migration processes properly. Such information is extracted automatically from application(s) task graphs and mapping on the system tiles. We show how agents are placed with applications and how such necessary information is generated and linked with them. The tool-chain is capable of generating code for ARM and x86 architectures. This task migration technique can be deployed on small operating systems that support neither MMU nor dynamic loading for task code. We show that this technique is operational on x86 based real hardware platform as well as on an ARM based simulation platform. Experimental results show low overhead both in memory and performance. Performance overhead due to migration of a task in a typical small application where it has one predecessor and one successor is 18.25%.

# Contents

| 1        | Rés  | umé     |                                                                                                    |

|----------|------|---------|----------------------------------------------------------------------------------------------------|

|          | 1.1  | Introd  | $\operatorname{uction}$                                                                            |

|          | 1.2  | Problé  | matique                                                                                            |

|          |      | 1.2.1   | L'environnement logiciel                                                                           |

|          |      | 1.2.2   | Hypothéses pour une solution de migration de tâches                                                |

|          | 1.3  | État d  | e l'art                                                                                            |

|          |      | 1.3.1   | Migration dans des architectures multi-tuiles                                                      |

|          | 1.4  | Métho   | dologie de la solution                                                                             |

|          |      | 1.4.1   | MProcFW                                                                                            |

|          |      | 1.4.2   | Transparence des points de migration                                                               |

|          |      | 1.4.3   | Gestion du problème d'incohérence de la communication                                              |

|          |      | 1.4.4   | Génération des agents de migration                                                                 |

|          |      | 1.4.5   | Principe de la migration                                                                           |

|          | 1.5  | Expéri  | imentations et résultats                                                                           |

|          |      | 1.5.1   | Description des plateformes                                                                        |

|          |      | 1.5.2   | Surcoût de performance                                                                             |

|          |      | 1.5.3   | Le surcoût de la migration par rapport à la taille de l'état de                                    |

|          |      |         | la tâche $\ldots$ |

|          |      | 1.5.4   | Variation du surcoût d'exécution de la migration                                                   |

|          |      | 1.5.5   | Le surcoût de migration par rapport au nombre de canaux $\ $ .                                     |

|          | 1.6  | Conclu  | usion                                                                                              |

| <b>2</b> | Inti | roducti | on                                                                                                 |

|          | 2.1  | Microp  | processor architectures                                                                            |

|          |      | 2.1.1   | What is architecture?                                                                              |

|          |      | 2.1.2   | Towards parallel architectures                                                                     |

|          |      | 2.1.3   | Multi-tiled architecture                                                                           |

|          | 2.2  | Task n  | nigration                                                                                          |

|          |      | 2.2.1   | Motivation                                                                                         |

|          | 2.3  | Outlin  | e                                                                                                  |

| 3        | Bac  | kgrour  | nd and problem statement                                                                           |

|          | 3.1  |         | vare/Software architecture                                                                         |

|          |      | 3.1.1   | Centralized shared memory architecture                                                             |

|          |      | 3.1.2   | Distributed memory architecture                                                                    |

|          | 3.2  | Genera  | al migration algorithm                                                                             |

|          | 3.3  |         | ss space transfer strategies                                                                       |

|          | 3.4  |         | tion approaches                                                                                    |

|          |      | 3.4.1   | Task replication                                                                                   |

|          |      | 3.4.2   | Task recreation                                                                                    |

|   |      | $3.4.3  \text{Cost}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                     |

|---|------|---------------------------------------------------------------------------------------------------------------------------|

|   | 3.5  | Parallel applications and dataflow programming model 39                                                                   |

|   | 3.6  | Problem statement                                                                                                         |

|   |      | 3.6.1 Software environment                                                                                                |

|   |      | B.6.2 Distributed Application Layer (DAL)                                                                                 |

|   |      | <b>3.6.3</b> Fault-avoidance solution description                                                                         |

| 4 | Sate | of the art 49                                                                                                             |

|   | 4.1  | Migration implementation                                                                                                  |

|   |      | 4.1.1 Migration using shared memory                                                                                       |

|   |      | 4.1.2 Migration using distributed memory                                                                                  |

|   |      | 1.1.3 Migration in NORMA architecture                                                                                     |

|   |      | 1.1.4 Migration points                                                                                                    |

|   |      | 1.1.5 Dynamic loading                                                                                                     |

|   | 4.2  | ssues of migration $\ldots$              |

|   |      | 4.2.1 Address collision                                                                                                   |

|   |      | 4.2.2 Address space dependence                                                                                            |

|   | 4.3  | Conclusion $\ldots \ldots 64$  |

| 5 | Tas  | migration methodology 65                                                                                                  |

|   | 5.1  | Solution overall description                                                                                              |

|   | 5.2  | ٩٢ ProcFW layer                                                                                                           |

|   |      | 5.2.1 Transparent migration points                                                                                        |

|   |      | 5.2.2 Overcoming communication inconsistency issue                                                                        |

|   |      | 5.2.3 Whole example of communication consistency preservation in                                                          |

|   |      | a migration $\ldots \ldots 76$ |

|   | 5.3  | Solution agents layer                                                                                                     |

|   | 5.4  | Migration principle                                                                                                       |

|   | 5.5  | Agents connection    81                                                                                                   |

|   | 5.6  | Blockage avoidance                                                                                                        |

|   | 5.7  | Migration algorithm    83                                                                                                 |

|   | 5.8  | MigSup routing algorithm 86                                                                                               |

| 6 | Aut  | matic generation and experimental results 89                                                                              |

|   | 6.1  | Platforms                                                                                                                 |

|   |      | 6.1.1 Simulation platform                                                                                                 |

|   |      | 6.1.2 Hardware platform                                                                                                   |

|   | 6.2  | Operating System    91                                                                                                    |

|   | 6.3  | Design flow                                                                                                               |

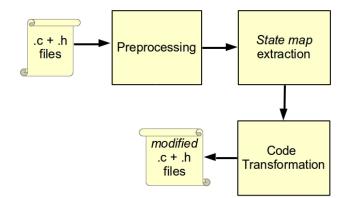

|   | 6.4  | SW synthesis tool                                                                                                         |

|   |      | $6.4.1  \text{Front-end}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                |

|   |      | 6.4.2 Back-end                                                                                                            |

|   | 6.5  | First experiments                                                                                                         |

|   |      | $6.5.1  \text{Simulation}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                               |

|    |                 | 6.5.2 HW platform                              | 102 |

|----|-----------------|------------------------------------------------|-----|

|    | 6.6             | Performance overhead                           | 103 |

|    | 6.7             | Migration overhead vs. task state size         | 104 |

|    | 6.8             | Variation of migration overhead                | 106 |

|    | 6.9             | Overhead versus number of channels             | 106 |

|    | 6.10            | Memory overhead                                | 110 |

|    | 6.11            | Rationale                                      | 112 |

| 7  | Con             | clusion and future work                        | 115 |

|    | 7.1             | Conclusion                                     | 115 |

|    | 7.2             | Fault tolerance increase: link integrity issue | 116 |

|    |                 | 7.2.1 Proposed solution                        | 117 |

|    |                 | 7.2.2 Example                                  | 120 |

|    |                 | 7.2.3 Conclusion                               | 122 |

|    | 7.3             | Address collision alleviation                  | 122 |

|    |                 | 7.3.1 Solution description                     | 124 |

|    |                 | 7.3.2 Example                                  | 126 |

|    |                 | 7.3.3 Conclusion                               | 127 |

| Α  | MPro            | cFW details                                    | 129 |

|    | A.1             | Tasks category                                 | 129 |

|    | A.2             | Channels category                              | 130 |

| в  | $\mathbf{List}$ | of publications                                | 131 |

| Bi | bliog           | raphy                                          | 133 |

# Chapter 1 Résumé

#### Contents

| 1.1 Iı | ntroduction                                                                 | <b>2</b>  |

|--------|-----------------------------------------------------------------------------|-----------|

| 1.2 P  | roblématique                                                                | <b>2</b>  |

| 1.2    | .1 L'environnement logiciel                                                 | 3         |

| 1.2    | .2 Hypothéses pour une solution de migration de tâches                      | 3         |

| 1.3 É  | tat de l'art                                                                | 4         |

| 1.3    | .1 Migration dans des architectures multi-tuiles                            | 4         |

| 1.4 N  | féthodologie de la solution                                                 | 7         |

| 1.4    | .1 MProcFW                                                                  | 8         |

| 1.4    | .2 Transparence des points de migration                                     | 8         |

| 1.4    | .3 Gestion du problème d'incohérence de la communication                    | 9         |

| 1.4    | .4 Génération des agents de migration                                       | 11        |

| 1.4    | .5 Principe de la migration                                                 | 12        |

| 1.5 E  | xpérimentations et résultats                                                | 13        |

| 1.5    | .1 Description des plateformes                                              | 14        |

| 1.5    | .2 Surcoût de performance                                                   | 14        |

| 1.5    | .3 Le surcoût de la migration par rapport à la taille de l'état de la tâche | 17        |

| 1.5    | .4 Variation du surcoût d'exécution de la migration                         | 18        |

| 1.5    | .5 Le surcoût de migration par rapport au nombre de canaux .                | 18        |

| 1.6 C  | onclusion                                                                   | <b>21</b> |

Le but de ce résumé long en français est de synthétiser le travail qui est décrit en anglais dans les chapitres de ce mémoire. Ce résumé commence par une introduction qui explique le contexte de ce travail et le problème ciblé, ainsi que la solution proposée. L'état de l'art décrit des travaux qui concernent le même sujet. Nous détaillons ensuite notre solution et la méthodologique, puis nous décrivons les expériences qui sont réalisées pour valider notre solution. Nous finissons par une conclusion et quelques perspectives.

## 1.1 Introduction

Les systèmes embarqués électroniques existent dans presque tous les aspects de notre vie quotidienne. De nouveaux marchés sont ouverts presque tous les jours en raison de leurs capacités croissantes, de leur puissance de calcul et de leur ubiquité. Grâce aux progrès en cours dans le domaine de l'électronique, plus de transistors peuvent être intégrés sur une seule puce, et par conséquent, des systèmes plus performants peuvent être construits.

L'unité qui est responsable de réaliser toute la logique et les calculs arithmétiques s'appelle un microprocesseur. Un microprocesseur est un circuit intégré numérique qui est capable de lire les instructions stockées dans une mémoire et les exécuter sur les données stockées et/ou d'entrée(s) et enfin à stocker le(s) résultat(s) dans une mémoire. C'est un dispositif programmable. Les circuits intégrés (ou puces) sont composés de dispositifs semi-conducteurs (transistors). Un circuit intégré a besoin de nombreux transistors pour avoir plus de fonctionnalités et de capacités de traitement, et la technologie permet l'intégration de toujours plus de transistors.

Le rythme avec lequel le nombre de transistors intégrés a augmenté sur une seule puce, jusqu'à présent, avait été observé par Gordon Moore en 1965 [1]. Il a remarqué que le nombre de transistors double tous les deux ans. Ceci, conduit à la possibilité d'avoir des architectures de microprocesseurs qui peuvent fournir des puissances de calcul de plus en plus élevées. Par conséquence, le domaine des systèmes embarqués s'est enrichi. Un système embarqué est un système qui est capable d'effectuer une (des) fonction(s) dédiée(s) nécessitant une puissance de calcul limitée.

Dans la section suivante, nous donnons un aperçu des architectures de microprocesseurs, examinons brièvement les questions liées à la technologie, mentionnons la migration des tâches et les définitions de base et pourquoi la migration de tâches semble une bonne solution à la problématique de cette thèse.

## 1.2 Problématique

Pour bien comprendre certaines hypothèses et le raisonnement derrière les choix de conception, il est nécessaire de mentionner que ce travail a été réalisé dans le cadre d'un projet européen FP7 EURETILE. Ce travail est donc très lié à celui de certains partenaires, et des décisions communes ont été prises pour développer un démonstrateur.

Les calculs effectués par les unités de traitement des tuiles peuvent entraîner une variation thermique importante et affecter l'intégrité des composants. La migration de tâches pourrait être une solution à cette contrainte thermique. Mais d'autres raisons pourraient bénéficier du support de la migration de tâches : équilibrage de charge entre tuiles, détection des problèmes de communication (congestion, rupture de liens) et adaptation en déplaçant des traitements sur une autre tuile, adaptation dynamique en fonction des applications pour une basse consommation (alimentation réduite de certaines tuiles).

#### 1.2.1 L'environnement logiciel

Dans le cadre du projet EURETILE, c'est l'aspect fiabilité, notamment par la détection des problèmes de communication (un composant matériel permettait de détecter ces problèmes), qui nous intéressait. La détection d'un problème entraînait la migration d'un nombre réduit de tâches pour assurer la continuité de traitement pour de grosses applications de calcul.

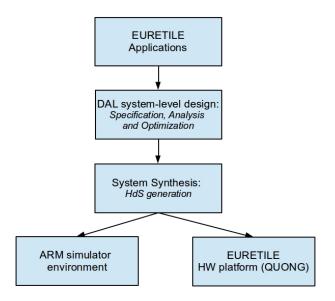

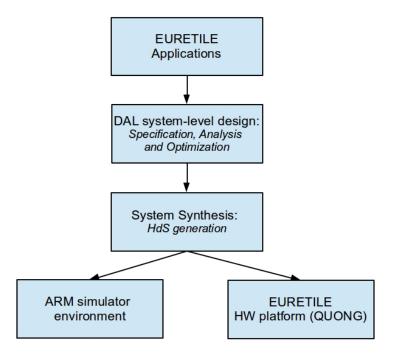

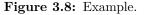

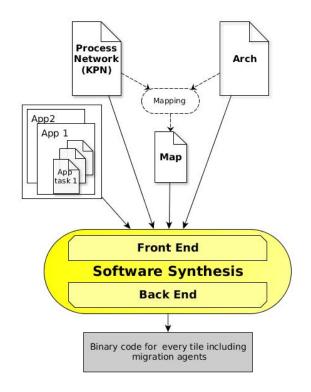

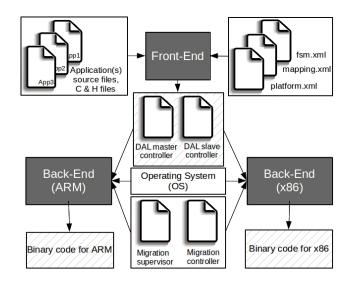

Les principales phases de l'environnement logiciel du projet sont illustrées sur la figure 1.1. La première étape est le développement d'applications. Les applications sont développées en langage C et peuvent s'exécuter en parallèle. Chaque application est divisée en un certain nombre de tâches. Ces applications entrent dans un processus de co-conception dans laquelle les spécifications de niveau système sont analysées. Les applications sont simulées en couvrant plusieurs scénarios pour trouver la meilleure réalisation en fonction des objectifs de conception spécifiés. Dans cette phase, un modèle de programmation avancé est introduit. Il est appelé couche d'application distribuée (DAL). DAL permet la programmation des applications dynamiques à grande échelle, l'introduction d'un modèle à deux niveaux de réseau de processus, des mécanismes de contrôle, et une API complète. Tous ces modèles sont raffinés pour produire du logiciel, et notre participation au projet EURETILE s'est focalisée dans la couche logicielle de bas niveau (logiciel dépendant du matériel ou HdS). Ainsi, DAL présente les premiers niveaux des mécanismes de tolérance aux pannes qui nécessitent une prise en charge complète de la plateforme et du logiciel de bas niveau.

#### 1.2.2 Hypothéses pour une solution de migration de tâches

Plusieurs hypothèses sont envisagées pour la mise en œuvre de la migration de tâches :

- 1. Les tâches qui migrent ne sont pas redémarrées à destination, mais reprises, ce qui implique le transfert d'état de la tâche. Il faut donc garantir la mise en pause d'une tâche sur la tuile source et sa reprise sur la tuile destination.

- 2. L'architecture du système doit être prise en considération. Les systèmes multi-tuiles n'ont généralement pas d'espace d'adressage accessible dans une mémoire partagée. Cela rend le transfert de l'état de la tâche effectué par communication explicite entre la tuile.

- 3. La migration de tâche doit être capable de fonctionner sur des systèmes d'exploitation légers, c'est à dire ne nécessitant pas des fonctionnalités spéci-

**Figure 1.1:** Vue globale de l'environnement logiciel du projet EU-RETILE.

fiques qui existent dans des systèmes d'exploitation plus sophistiques (MMU ou chargement dynamique).

4. La solution de migration devrait être compatible avec le flot de conception de DAL.

# 1.3 État de l'art

La migration de tâches a été mise en œuvre de manières différentes et dans des couches logicielles différentes. Les techniques d'implémentation varient selon des paramètres tels que l'architecture du système et les capacités du système d'exploitation. En plus, il y a plusieurs difficultés qui rendent l'implémentation difficile. Le chapitre 4 est dédié à la description des implémentations pour des architectures différentes et nous mentionnons les travaux de recherche correspondants. Cependant, dans cette section, nous nous focalisons sur les solutions qui concernent la migration de tâche dans des architectures multi-tuiles. Nous étudions ces solutions dans la section suivante en montrant comment elles se différencient de celle proposée dans ce travail.

#### 1.3.1 Migration dans des architectures multi-tuiles

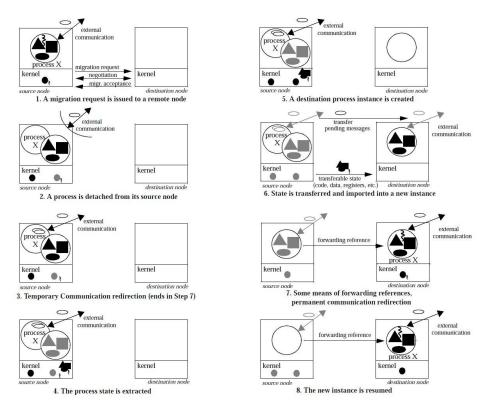

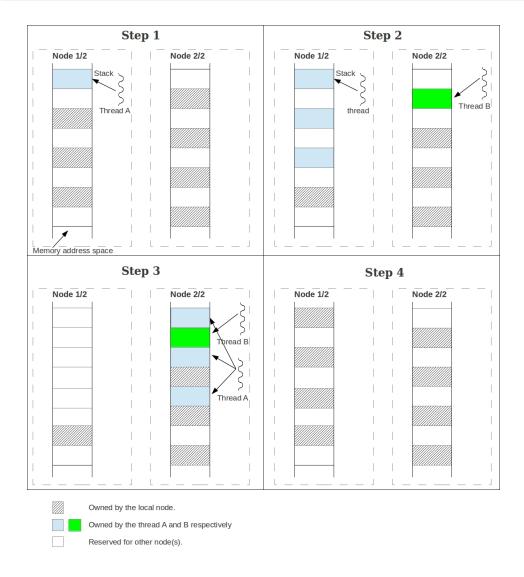

Les architectures des systèmes multi-tuiles sont des architectures NORMA, c'est à dire qu'un processeur (élément de traitement) d'une tuile ne peut pas accéder à la mémoire d'une autre tuile. Il existe des solutions récentes de migration de tâches qui sont proposées dans [24, 25, 26, 27, 29]. Elles visent des architectures multi-tuiles à base de NoC.

Dans [24], un système d'exploitation est utilisé sur lequel un chargeur dynamique est conçu pour soutenir le transfert du code de la tâche qui doit migrer. Toutefois, la migration du contexte de tâche (l'état de la tâche) n'est pas pris en charge. Par conséquence, cette technique est efficace seulement pour les tâches qui n'ont pas d'état ou si l'application ou la tâche redémarre sur la tuile destination. La migration de tâches est appliquée dans le contexte de la reconfiguration dynamique et pour une meilleure performance. Il est affirmé que le coût de la migration est amorti par le gain de performances à cause du redéploiement de la tâche. Il n'est pas mentionné, cependant, comment la solution est transparente vis à vis de l'application. Contrairement à cette solution, notre solution supporte les applications avec des tâches qui ont un état, c'est à dire un ensemble d'information qui permet la poursuite du traitement sur la tâche destination. De plus, notre solution fonctionne sur du matériel réel. [28] propose une solution assez similaire, mais sans transfert de code.

Dans [25], les auteurs déploient une technique de migration de tâches ciblant des MPSoCs basés sur une NoC qui ne comprend pas de transfert de code. En ce qui concerne la communication, un message MPSoC Passing Interface MMPI est utilisé. C'est un modèle de programmation parallèle qui rend le programme indépendant du placement optimisé de la tâche. La solution est basée sur les agents (tâches) maître (master) et esclaves (slaves) qui gèrent le processus de migration. Le maître réside dans un élément de traitement (Processing element PE) séparé et fonctionne sur le système d'exploitation Linux. Les esclaves sont exécutés sur MicroC/OS-II. Il est indiqué que cette technique fonctionne sur une plateforme de simulation.

Dans [26], ce travail se préoccupe principalement de fournir des plates-formes pour simuler la migration de tâches dans des architectures différentes. Par conséquent, le processus de migration n'est pas représenté du point de vue algorithmique ou méthodologique. Les plates-formes de simulation supportées sont des architectures à accès mémoire uniforme et des clusters (UMA et NORMA). Pour obtenir les résultats, des expériences de migration sont exécutés sur ces platesformes. Ils utilisent une couche logicielle «middleware» qui fournit des APIs pour supporter la migration. Ils appliquent la réplication de tâches de sorte que toutes les tâches pouvant migrer, un réplicat est déployé sur toutes les tâches. L'impact pour répliquer toutes les tâches sur tous les éléments de traitement PE n'est pas représenté et limite l'évolutivité de la solution. La migration de communication est gérée par un composant qu'ils ont ajouté à la plateforme de simulation. Il s'agit d'un ordonnanceur runtime de ressource RTR «RunTime Resource Scheduler». Ce composant est responsable de la gestion de toutes les ressources matérielles et toutes les communications. Les résultats expérimentaux sont présentés d'une manière relative entre les différentes techniques de décision de déploiement. Des applications multimédias différentes sont exécutées. Les résultats montrent seulement l'impact du redéploiement en ce qui concerne, par exemple, l'amélioration de la communication sur le NoC. Ce qui peut expliquer pourquoi il n'y a pas beaucoup de différence entre certains cas où les décisions de déploiement peuvent conduire aux mêmes résultats.

Dans [27], les auteurs abordent le problème d'incohérence de la communication de la migration de tâches. Ils utilisent une solution basée sur des agents pour gérer la communication avant, pendant et après le processus de migration. Ils utilisent la méthode de commutation de protection «protection switching method» pour résoudre le problème d'incohérence, via la retransmission sans arrêter la communication. Contrairement à la solution proposée dans ce travail, aucun système d'exploitation n'est utilisé dans ce travail. Cela signifie que l'ensemble des logiciels de bas niveau est évidemment fait sur mesure comme notamment les pilotes de communication qui supportent des fonctions spécifiques. La cohérence de la communication est abordée ici, mais ce modèle ne semble pas pouvoir être générique pour s'adapter à différentes plateformes. Aucun détail n'est donné sur la transparence d'une telle solution vis à vis du programmeur.

Les travaux proposés dans [29] utilisent la migration de tâches pour améliorer l'adaptabilité du système MPSoC. La solution cible des applications décrites dans le modèle de calcul polyhédrique (Polyhedral Process Network PPN). Le modèle PPN est un cas particulier des réseaux de Khan KPN). Chaque tâche est basée sur une boucle avec deux compteurs. Les tâches ne peuvent pas avoir d'état, et par conséquent, la migration de tâches peut être vue comme une migration de communication, c'est à dire un processus de transfert qui concerne le contenus des files d'entrée et de sortie, et les deux compteurs de la boucle. La solution est basée sur une couche logicielle intermédiaire «middleware» qui fournit les APIs. La communication est initiée coté récepteur. Quand les données d'entrée sont reçues, elles sont stockées dans les files d'entrée correspondantes, et restent présentes même après leur consommation par la tâche. Elles ne sont supprimées que quand les données de sortie sont produites. Cette technique est utilisée car elle est simple à mettre en œuvre. L'interface réseau (NI) est étendue pour produire une interruption à la réception d'un message particulier, ce qui déclenche l'envoi d'un message par le gestionnaire d'exécution vers la tuile source de la migration et interrompt la tâche. La tuile source envoie ensuite aux tuiles voisines un message pour la migration. L'interface réseau nécessite donc d'être modifiée, contrairement à notre solution. Il n'est pas clairement indiqué dans l'article si une tâche peut avoir plusieurs canaux en entrée ou en sortie, et ce qui se passe quand les tâches voisines (prédécesseur ou successeur) sont sur la même tuile, ce qui suppose la mise en œuvre de communication inter-tuile. De plus, les opérations de lecture et écriture n'étant pas atomiques, il n'est pas précisé comment on garantit de ne pas perdre de données quand une interruption se produit pendant une lecture.

À notre connaissance, il n'y a pas de travail équivalent au notre dans la littérature avec la mise en œuvre d'une solution complète, évolutive et qui génère automatiquement les ajouts (couche logicielle) pour une exécution sur une plateforme multi-tuiles existantes. En effet, presque toutes les implémentations et leurs validations sont effectuées soit sur des plateformes de simulation ou des plateformes ad-hoc basées sur des FPGA. Les mesures sont aussi données de manière relative et sont rarement représentées de manière absolue. Cela rend les surcoûts pas très clairs et une analyse comparative très difficile. Des questions telles que la transparence pour les programmeurs d'applications et la portabilité sur différentes architectures de base sont rarement expliquées, ce qui pose la question sur la façon dont la solution est applicable à des applications existantes ou comment adapter la solution de migration à différentes architectures. Enfin, il n'y a aucune technique qui étudie l'influence de performance de migration en fonction du nombre de voisins dans une architecture distribuée. Notre solution est expliquée avec des détails à la fois méthodologiques et algorithmiques. Notre méthode est déployée dans un outil de génération automatique, ce qui rend possible son utilisation pour différentes architectures et pour différentes applications.

## 1.4 Méthodologie de la solution

L'objectif de cette section est d'expliquer comment les problèmes de migration de tâches sont gérés. Les détails qui sont données dans cette section répondent à la question : *Comment le processus de la migration de tâches a lieu ?* Les solutions sont expliquées selon les deux perspectives méthodologiques et algorithmiques.

Ce travail décrit le processus de migration de la décision de migration de la tâche jusqu'à sa reprise sur la tuile destination en se focalisant aussi sur l'aspect communication pour ne pas perdre de données. Les algorithmes utilisés pour prendre la décision de migrer une tâche ne font pas partie de ce travail. Dans la spécification initiale, on laisse le concepteur système indiquer les tâches critiques, qui pourront subir une migration, ainsi que les tuiles qui seront en charge d'exécuter la solution de déploiement de tâche initiale et la tuile destination qui accueillera la tâche après migration.

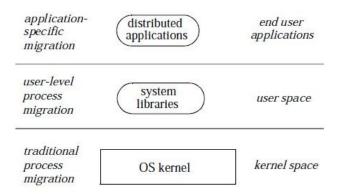

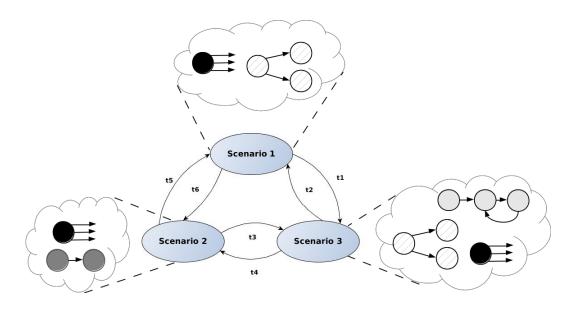

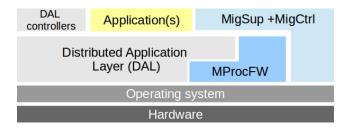

Les architectures distribuées sont intrinsèquement décentralisées. La décentralisation est attribuée au fait que chaque tuile exécute sa propre copie du système d'exploitation. C'est pourquoi, la solution de migration de tâches est basée sur des agents répartis sur les tuiles de manière à décider et exécuter la migration. Afin de permettre à ces agents d'exercer leurs rôles dans la migration, une couche logicielle intermédiaire «middleware» (appelée Multi-Processing FrameWork MProcFW) est développée pour fournir des APIs nécessaires qui facilitent l'exécution de la migration. Ces API sont invoquées par les agents, et font le lien entre le système d'exploitation et la couche logicielle applicative. Par conséquent, cette caractéristique offre une bonne portabilité sur différentes architectures et une transparence vis à vis des applications. La solution réside dans deux couches logicielles : la couche application où les agents résident et la couche «middleware» où MProcFW fournit les API nécessaires.

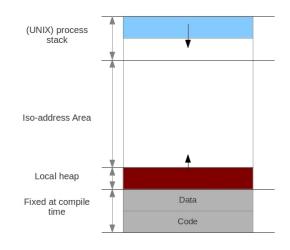

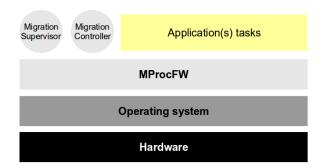

#### 1.4.1 MProcFW

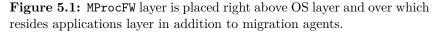

La couche MProcFW est conçue pour fournir des API nécessaires pas seulement pour faciliter la migration, mais aussi pour permettre le contrôle des tâches des applications. MProcFW se situe au-dessus de la couche de système d'exploitation dans l'architecture logicielle (figure 1.2). Les APIs de MProcFW peuvent être classés en deux catégories comme suit :

- Un catégorie qui contient toutes les APIs qui contrôlent les tâches, c'est à dire création, démarrage, pause, arrêt ou migration. Ces APIs sont applelées dans la couche d'application par des tâches spécifiques (ou agents).

- Un catégorie qui contient toutes les APIs qui contrôlent les canaux de communication en créant, l'ouverture, l'envoi, la réception et la fermeture des canaux. Ces APIs sont appelées par la couche d'application.

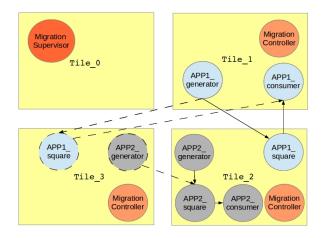

| Migration<br>Supervisor | Migration<br>Controller | Application(s) tasks |  |  |  |  |  |

|-------------------------|-------------------------|----------------------|--|--|--|--|--|

|                         | MProcFW                 |                      |  |  |  |  |  |

|                         | Operating system        |                      |  |  |  |  |  |

|                         |                         | Hardware             |  |  |  |  |  |

**Figure 1.2:** L'architecture logicielle du système. La couche MprocFW réside directement au-dessus le système d'exploitation.

#### 1.4.2 Transparence des points de migration

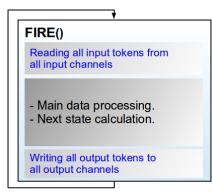

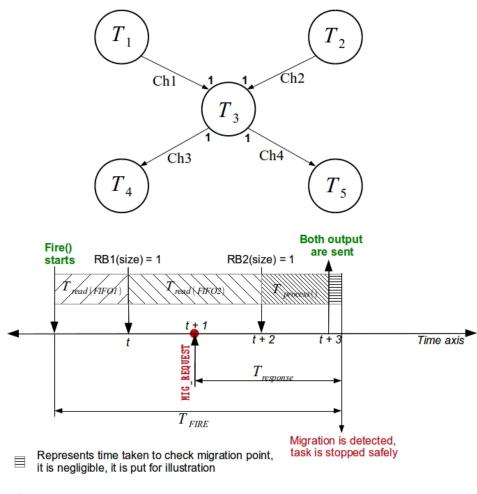

Notre technique de migration de tâches est basée sur des points de migration [9, 10, 32, 33]. Un point de migration est un point prédéfini dans le code applicatif où une requête de migration est traitée. La tâche concernée doit être arrêtée en toute sécurité et son exécution reprise à partir de ce point de migration. MProcFW spécifie un modèle de tâches en boucle, et toutes les tâches doivent être conformes à ce modèle.

Le modèle de tâche est présenté dans le code 1.1. La procédure INIT est principalement responsable de l'allocation de mémoire pour l'état de la tâche et de l'initialisation des variables nécessaires. L'initialisation est exécutée une seule fois au démarrage de chaque tâche de l'application. L'exécution principale est composée d'itérations de la procédure FIRE. La procédure FIRE est composée de trois parties pour la lecture des données (jetons) d'entrée, le traitement et l'écriture des données en sortie. A la fin de l'application, la procédure FINISH est appelée pour nettoyer la mémoire allouée par la procédure INIT. La communication via les canaux utilise les procédures **read** et **write**.

```

procedure INIT(TaskStructure *t) // initialization

initialize();

end procedure

procedure FIRE(TaskStructure *t) // execution

Ch_FIFO->read(buf, size); // read i/p from fifo

process(); // processing data

Ch_FIFO->write(buf, size); // write o/p to fifo

end procedure

procedure FINISH(TaskStructure *t) // cleanup

cleanup();

end procedure

```

Listing 1.1: Le modèle d'une tâche de flux de données (Data-flow task model). TaskStructure est une structure de données qui contient tous les paramètres d'une tâche.

#### 1.4.3 Gestion du problème d'incohérence de la communication

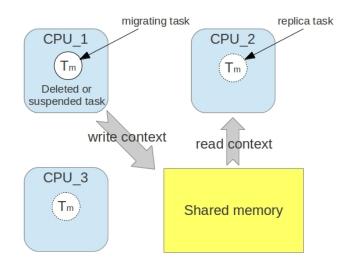

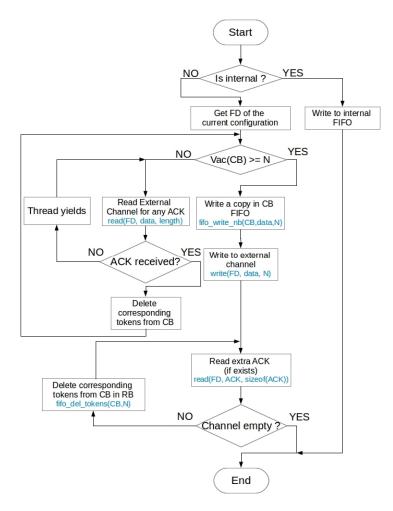

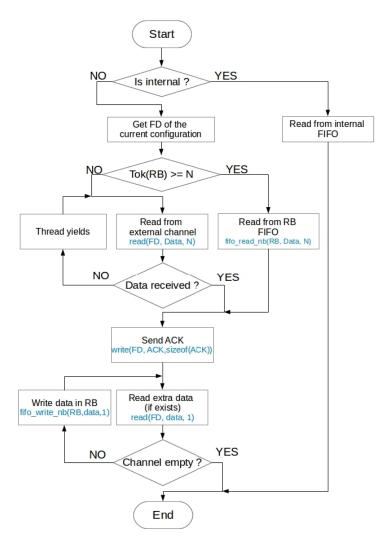

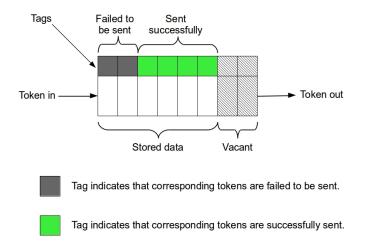

L'incohérence de communication provient du fait que les tâches qui migrent changent de tuile d'exécution. Cela rend la reprise de la communication entre la tâche qui vient de migrer et ses voisins impossible sans modification des canaux qui les relient. En conséquence, ces canaux doivent être changés pour que la reprise de l'exécution se fasse de façon correcte. Les tâches voisines doivent évidement être informées de la migration. De plus, l'incohérence de communication peut aussi être attribuée à la possibilité d'avoir des données non-traitées qui résident dans les files d'entrée de la tâche qui migre et qui ne sont pas encore consommées. La reprise d'exécution doit se faire en conservant ces données. Afin d'effectuer une migration avec succès, il faut transférer toutes les données qui restent dans les files d'entrées à la tuile source à la tuile de destination, mais, ce transfert doit être fait de manière transparente vis à vis des développeurs d'applications et si possible sans utiliser des services ou des dispositifs spécifiques de communication.

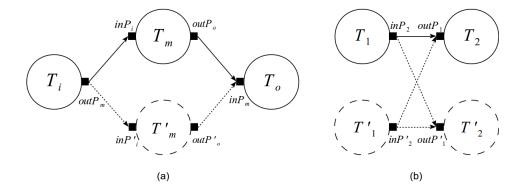

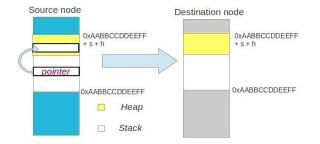

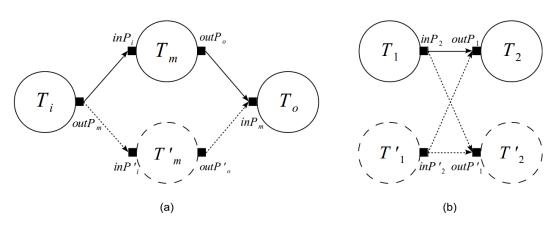

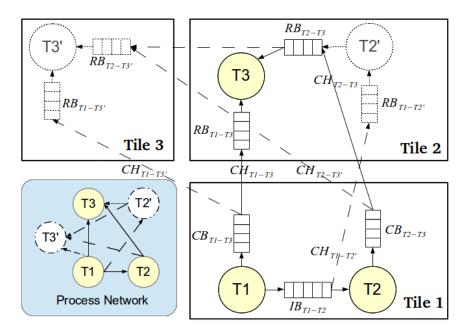

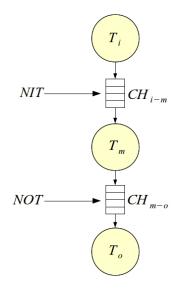

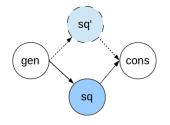

Nous proposons deux solutions pour résoudre les deux problèmes mentionnés précédemment. La première concerne la modification des canaux d'une manière transparente. Pour cela, nous proposons un nouveau type de canal appelé «canal reconfigurable». Un canal configurable relie une tâche qui peut migrer et une tâche voisine. Un tel canal possède trois extrémités dépendant du sens du canal : un canal d'entrée de la tâche à migrer possède une seule extrémité pour recevoir des données et deux extrémités pour lire les données. Un canal de sortie de la tâche à migrer possède deux extrémités d'entrée et une extrémité de sortie. Un canal configurable est composé de deux branches, chaque branche étant un canal ordinaire mais un seul canal est activé à la fois. Ceci facilite la connexion entre une tâche qui peut migrer et son réplicat d'un côté, et un voisin d'un autre. Lorsque il y a une migration, tous les canaux configurables sont mis à jour par la commutation entre leurs branches. Ce processus de mise à jour est fait de manière transparente pour les tâches qui ne détectent rien. En effet, le numéro de port (d'extrémité) reste fixe mais l'identifiant du canal change. Ce changement est effectué par l'invocation de l'API spécifique (Mproc\_channel\_update) pour faire la commutation entre les deux branches. La figure 1.3 illustre ce principe avec un canal d'entrée de la tache qui peut migrer et un canal de sortie (figure 1.3.a). On peut observer les deux branches de chaque canal reconfigurable. La figure 1.3.b généralise ce concept par montrer les branches de deux canaux configurables dans le cas où les deux tâches reliées peuvent migrer.

**Figure 1.3:** Canaux configurables.  $T_m$  est une tâche qui peut migrer,  $T_i$  et  $T_o$  sont respectivement les prédécesseur et successeur.  $T'_m$  est le réplicat. (a) Seul  $T_m$  peut migrer. (b)  $T_1$  et  $T_2$  peuvent migrer.

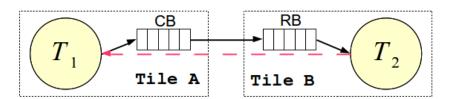

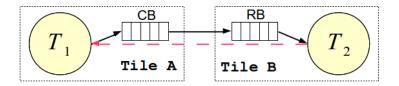

La deuxième solution cible le problème des données non traitées dans une FIFO liée à la tâche qui peut migrer. Le but est de proposer une méthode qui permet le transfert des données après migration des données non consommées au début de la migration. Cette solution doit être transparente pour le programmeur c'est à dire sans devoir modifier le code de l'application. Nous ajoutons alors un protocole pour la communication entre les tâches de l'application : chaque tâche qui transmet les données à une autre, sauvegarde un copie des données transmises dans une file qui s'appelle une file de copie (copy buffer CB). Côté réception, toutes les données reçues par une tâche sont stockées dans une file qui s'appelle une file de réception (receive buffer RB) (figure 1.4). Dès qu'une tâche consomme une donnée de la file de réception, elle transmet au coté émetteur l'information de consommation, ce qui permet supprimer la donnée correspondante dans CB. Ce protocole permet d'avoir toujours une copie de toutes les données non-traitées, par conséquence, lorsque la migration est effectuée, les copies sauvegardées coté émetteur peuvent être retransmises à la tuile destination pour synchroniser les nouvelles files de réception. Cette synchronisation est effectuées par l'invocation de l'API de MprocFW (MProc\_channel\_synchronize décrite dans l'annexe A).

Figure 1.4: Protocole "Write-with-copy"

#### 1.4.4 Génération des agents de migration

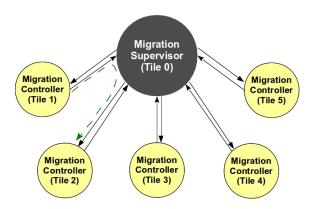

Le nombre et le rôle des agents de migration sont déterminés en fonction de l'approche choisie : entièrement distribuée, entièrement centralisée, semi-distribuée.

Entièrement distribuée : tous les agents ont le même rôle qui inclut à la fois la décision de migration et son exécution. Cette approche correspond bien à la nature de l'architecture dans le projet EURETILE. Cependant, cette approche nécessite une conception complexe des agents de migration. Un autre inconvénient de cette approche est que la décision de migration peut être prise par un certain nombre de différents agents dans le même temps, qui peut conduire à de l'instabilité ou un blocage si deux tâches adjacentes dans le même réseau de processus migrent en même temps. En effet, l'incohérence des données et des canaux peut entraîner un blocage avant la reprise.

**Entièrement centralisée** : Il existe un agent pour l'ensemble du système qui est responsable à la fois de prendre la décision de migration et son exécution. Cela évite la complexité de l'approche entièrement distribuée, car le développement d'un agent centralisé est relativement facile. Mais cela peut aussi entraîner un nombre important de communications et des difficultés de synchronisation.

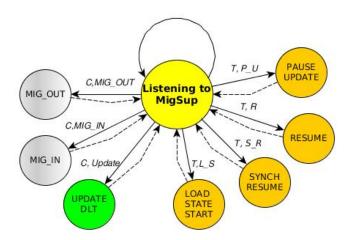

**Semi-distribué** : deux types d'agents sont conçus avec des responsabilités différentes. Un agent de migration est centralisé et est chargé de prendre la décision de migration et un autre agent est responsable de l'exécution des commandes de migration. La complexité du développement de cette approche est intermédiaire entre les deux approches précédentes. Cette solution correspond bien à la nature décentralisée de l'architecture du projet EURETILE par groupe de tuiles, constituant un cluster. La complexité de la conception des agents est relativement atténuée, mais au détriment de la communication nécessaire afin de coordonner tous les agents nécessaire à la migration. La troisième approche est adoptée en raison de ses avantages par rapport aux deux autres. Elle fournit une solution générique qui correspond à une architecture multi-tuile distribuée. Avec une telle hiérarchie distribuée, les agents ont différentes responsabilités. Un des agents (le maître) gère un groupe d'agents esclaves, ce qui rend la migration a deux niveaux : la prise de décision est différent du niveau d'exécution de la décision. Par conséquence, il existe deux types d'agents selon le rôle de chacun d'eux :

- i **MigSup**, C'est l'agent superviseur de la migration qui est chargé de prendre les décisions de migration. Il initie la migration via l'envoi de commandes de la tuile source à une tuile destination.

- ii **MigCtrl**, C'est l'agent contrôleur de la migration qui est responsable de l'exécution des commandes de migration envoyées par MigSup, en transférant état de la tâche de sa tuile source vers la tuile destination, en prenant en charge les communications avec les voisins, et en assurant la reprise d'exécution sur la tuile destination. MigCtrl est capable d'exécuter des commandes de migration sur la tuile en raison de sa capacité à accéder à la mémoire principale privée.

Le système est divisé en groupes de tuiles (clusters). La migration ne peut se dérouler qu'à l'intérieur d'un même cluster. Il existe un seul agent MigSup par cluster tandis qu'un MigCtrl existe sur chaque tuile. Les API fournies par MProcFW ne sont suffisantes pour la gestion de la migration, il faut aussi que les agents disposent des informations sur le placement des tâches sur les tuiles. Cette information est maintenant disponible sous la forme de tables, ce qui permet aux agents de connaître les tâches voisines et leur placement (déploiement) ainsi que les destinations de migrations pour les taches concernées. Deux tables sont nécessaires :

- 1. "Global View Table" **GVT** contient des informations sur toutes les tâches qui peuvent migrer dans un cluster. GVT est composée d'un certain nombre d'enregistrements correspondants au nombre de tuiles du cluster. Dans un enregistrement, on retrouve la liste des tâches qui peuvent migrer, leur tuile source et leur tuile destination. GVT est utilisée par MigSup, par conséquence, une seule GVT existe par cluster.

- 2. "Destination look-up table" **DLT** contient plus de détails sur les tâches qui peuvent migrer tels que les emplacements de tous les voisins, et tous les identifiants de canaux reliés à cette même tâche. Ce tableau permet à MigCtrl d'avoir toutes les informations pour gérer la suspension et la reprise correcte de l'exécution après migration.

#### 1.4.5 Principe de la migration

L'algorithme de migration est conçu en deux parties distinctes :

i La partie qui concerne la prise de la décision de migration.

ii La partie qui concerne l'exécution de la migration.

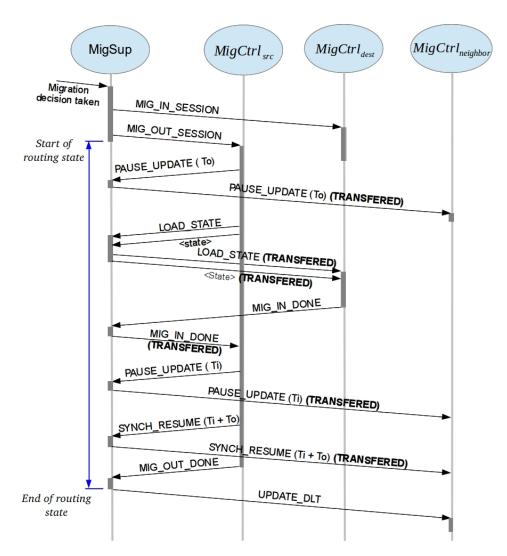

La première partie, la prise de décision est faite par l'agent MigSup. Les critères de décision, la méthode de décision, les valeurs ou paramètres des informations permettant cette prise de décision ne font pas partie du travail de thèse. Néanmoins à titre d'exemple, dans le contexte du projet EURETILE, un composant spécifique permettait de récupérer des informations sur l'état du matériel de l'architecture multi-tuile (température des unités de traitement, état des liens - opérationnel , défaillant - entre les routeurs du réseau sur puce connectant les tuiles au sein d'un cluster), ce qui permettait de décider ou non d'initier une migration. La responsabilité de l'exécution de la migration est donnée à l'agent MigCtrl. MigSup initie la migration en informant les agents MigCtrl des tuiles concernées, ce qui permet de démarrer le processus de migration.

## 1.5 Expérimentations et résultats

La solution proposée dans ce travail a été implémentée, c'est à dire que le flot de production de code initial a été modifié pour ajouter les agents, et la couche d'API MprocFW. Le code ainsi obtenu peut alors être compilé pour obtenir un ensemble de fichiers binaires à exécuter sur les différentes tuiles de l'architecture. Deux types d'architectures distinctes sont visées : le domaine de l'embarqué avec des cœurs de calcul ARM v7 dans une plateforme de simulation, et le domaine du calcul haute performance avec une plateforme existante composée de 16 tuiles, chaque tuile intégrant un cœur x86 (Xéon). L'exécution d'une application mettant en œuvre la migration sur ces deux plateformes permet alors d'une part de valider la solution, mais aussi de mesurer les coûts et les performances de la solution pour une analyse de la méthode. Par exemple, nous étudierons l'impact sur la mémoire, sur le temps d'exécution en cas de migration, mais aussi l'influence du nombre de canaux sur les performances.

L'application de démonstration est une petite application, avec trois tâches. En fait, cette application est dupliquée pour obtenir un ensemble d'applications à exécuter. L'intérêt d'une petite application est d'une part sa facilité de mise en œuvre, d'autre part, les résultats obtenus permettront de valider la méthode sur une application défavorable. Le temps d'exécution ou la taille mémoire de l'application sont petits, et le surcoût mémoire ou la perte de performance est plus significatif.

Les résultats les plus difficiles à obtenir sont ceux provenant des expérimentations faites sur l'architecture multi-tuile matérielle. En effet, l'accès (distant) à la machine a été limité à quelques semaines dans le cadre du projet EURETILE, mais aussi aucune solution de deboggage n'était disponible, car c'est le chargement des binaires autour de DNA-OS n'offre pas cette possibilité. Les mises au point ont toujours été faite dans un premier temps à l'aide de la plateforme de simulation ARM pour la vérification de la fonctionnalité (application et algorithme de migration). La mise au point pour la plateforme matérielle a été plus délicate.

#### 1.5.1 Description des plateformes

Si les deux plateformes matérielles diffèrent, le système d'exploitation utilisé pour toutes les expérimentations est le même. Il s'agit de DNA-OS [14], un système d'exploitation développé au TIMA et porté sur les deux architectures (en 32 bits). DNA-OS est léger, et son mécanisme de génération n'inclut que les fonctionnalités nécessaires à l'application. Il supporte les architectures SMP, possède un ordonnanceur coopératif, et la communication est basée sur un système de fichiers virtuel. La libc est largement supportée. Néanmoins, il ne possède ni support MMU, ni chargement dynamique.

#### 1.5.1.1 Domaine de l'embarqué : plateforme de simulation ARM

La plateforme de simulation a été développée au TIMA en SystemC TLM [45]. Elle est composée de tous les composants ou périphériques nécessaires tels que TTY, afficheurs... Chaque cœur ARM cortex A9 utilise un émulateur QEMU. Chaque tuile contient une mémoire privée, et un composant spécifique (composant de communication) permettant l'interface avec le NoC. Ce composant spécifique est proche du composant physique utilisé dans la seconde plateforme. Néanmoins, il a nécessité une adaptation du pilote. L'instanciation de plusieurs tuiles permet de créer un cluster à l'aide de scripts. Pour un temps de simulation raisonnable, on est aujourd'hui limité à 128 tuiles. Chaque tuile exécute sa propre copie du système d'exploitation.

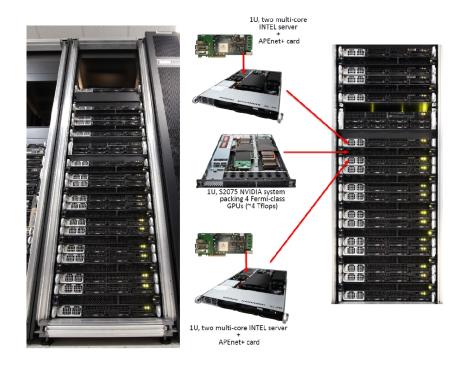

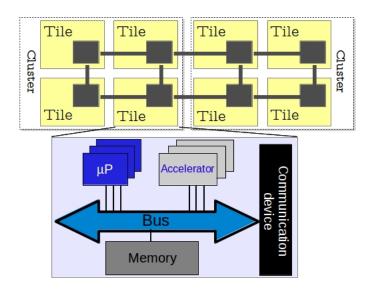

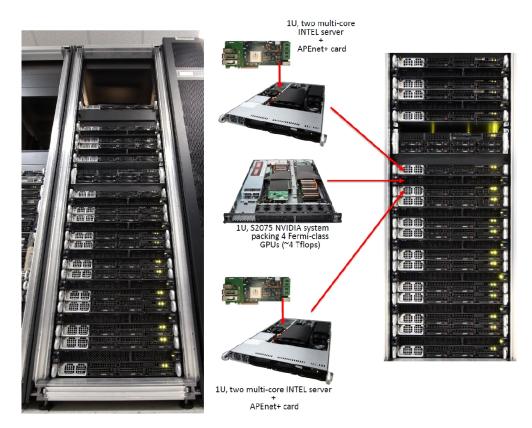

# 1.5.1.2 Domaine du calcul haute performance : plateforme matérielle x86

La plateforme matérielle, développée par l'INFN Rome (Italie) - coordinateur du projet EURETILE, est basée sur les processeurs Intel (Xéon SMP) et fournit un environnement pour du calcul scientifique haute performance [46]. Plusieurs mécanismes spécifiques et performants permettent les communications entre tuiles (infiniband, APEnet+). La plateforme est composée de 16 tuiles (figure 1.5). Tous les composants à l'intérieur d'une tuile sont connectés via un bus PCIe. Une machine serveur est installée pour faciliter les connexions à distance et le chargement des binaires sur les tuiles.

#### 1.5.2 Surcoût de performance

Le surcoût de performance à cause de la migration est le temps additionnel sur le temps d'exécution d'une demande en raison de la migration. Le temps d'exécution mesuré est le temps total écoulé depuis de départ de l'application jusqu'à la fin, y

Figure 1.5: Plateforme matérielle 16 tuiles pour le calcul haute performance.

compris la communication inter-tuile. De part notre solution basée sur des agents, il y a deux composantes à ce surcoût :

- a Le temps d'exécution normal des agents de migration.

- b Le temps écoulé à cause de la migration.

Pour évaluer le surcoût de migration, nous avons effectuer la mesure dans trois cas différents pour une même application :

- 1. Cas 1 (C1) : Aucun agent de migration existe. Le temps d'exécution de l'application est mesurée.

- 2. Cas 2 (C2) : Les agents de migration existent et s'exécutent mais aucune migration n'a lieu. Ce cas est évaluer pour les mesurer le surcoût introduit par les agents de migration par rapport à cas 1.

- 3. Cas 3 (C3) : Les agents de migration s'exécutent et une migration est effectuée à un moment arbitraire. Ce cas est conçu pour les mesurer le surcoût introduit par les deux agents de migration et le processus de migration par rapport à des cas 1 et 2.

Quatre tuiles sont utilisés sur lesquelles deux applications identiques s'exécutent, chaque application contient trois tâches. Les tâches sont : la tâche du générateur,

| Cas           | temps de départ  | temps de fin     | temp d'exécution | Surcoût |  |  |  |  |

|---------------|------------------|------------------|------------------|---------|--|--|--|--|

|               | $(\mu s)$        | $(\mu s)$        | $(\mu s)$        | (%)     |  |  |  |  |

|               | Application 1    |                  |                  |         |  |  |  |  |

| 1             | $65 \ 027 \ 461$ | $67 \ 247 \ 538$ | $2 \ 220 \ 077$  | N/A     |  |  |  |  |

| 2             | $28 \ 401 \ 948$ | $30\ 623\ 281$   | $2 \ 221 \ 332$  | 0.06    |  |  |  |  |

| 3             | $21 \ 754 \ 757$ | $24 \ 379 \ 930$ | $2\ 625\ 173$    | 18.25   |  |  |  |  |

| Application 2 |                  |                  |                  |         |  |  |  |  |

| 1             | 33 163 108       | $35 \ 387 \ 392$ | 2 224 284        | N/A     |  |  |  |  |

| 2             | $28 \ 687 \ 143$ | $30 \ 911 \ 856$ | $2 \ 224 \ 713$  | 0.02    |  |  |  |  |

| 3             | 40 811 884       | $43 \ 358 \ 217$ | $2\ 546\ 333$    | 14.49   |  |  |  |  |

Table 1.1: Les temps d'exécutions et le surcoût à cause de migration.

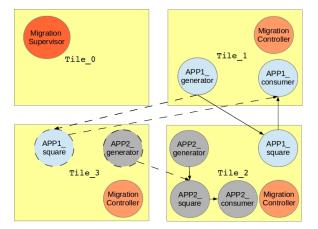

la tâche de traitement et la tâche du consommateur. Toutes les tâches ont des états. Le placement des agents et de l'application est représenté dans la figure 1.6. Les résultats sont donnés dans tableau 1.1.

Figure 1.6: Le placement des agents et les applications sur les quatre tuiles.

On remarque que les agents de migration ajoutent un surcoût négligeable car l'augmentation du temps d'exécution pour les deux applications est de l'ordre de 0,02% - 0,06%. Sachant que dans les situations typiques, une migration n'est pas un événement ordinaire qui a lieu régulièrement, il n'y a presque aucun coût de déploiement des agents dans les applications.

Le surcoût du à la migration est d'environ 18% du temps d'exécution par rapport aux cas 1 de l'application 1, mais seulement de 14% pour l'application 2. La différence vient de plusieurs facteurs : la tâche qui peut migrer n'est pas la même, et le nombres de canaux connectés est différent. Pour l'application 1, APP1\_square a deux voisins s'exécutant sur des tuiles différentes, ce qui augmente le temps notamment pour la gestion des canaux, alors que l'application 2 où APP1\_generator est la tâche qui migre a un seul voisin et un seul canal (de sortie).

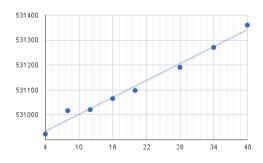

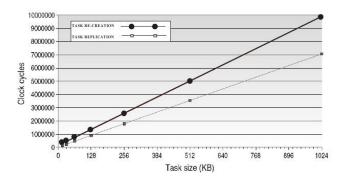

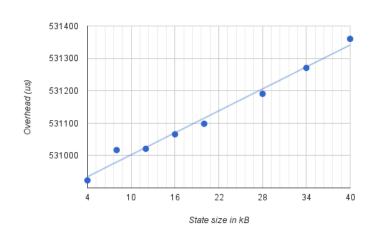

# 1.5.3 Le surcoût de la migration par rapport à la taille de l'état de la tâche

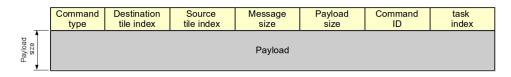

L'objectif de cette série d'expériences est d'étudier le surcoût causé par la taille de l'état de la tâche. L'impact est mesuré en faisant varier la taille de l'état (taille d'un tableau). Les expériences sont effectuées sur la même plateforme 4-tuiles avec la même application et le même placement donné dans la figure 1.6. La taille de l'état de **APP1\_square** est augmentée et le temps d'exécution incluant une migration est mesuré. La charge utile "payload" de données dans chaque paquet du réseau est limitée à 4 ko, c'est à dire que les tailles de l'état d'une tâche qui sont inférieures ou égalent à 4 ko sont envoyés dans un seul paquet. Les paquets de taille supérieure à 4 ko sont divisés en plusieurs paquets de 4 ko. Le tableau 1.2 donne les différentes tailles et les surcoûts de migration correspondants. La relation entre le surcoût et la taille est montrée dans la figure 1.7. On observe un loi d'évolution linéaire.

**Figure 1.7:** Le surcoût de la migration  $(\mu s)$  vs. la taille de l'état de la tâche (ko).

Table 1.2: Taille de l'état de la tâche vs. le surcoût de migration.

| Taille $(ko)$ | Surcoût $(\mu s)$ | Pourcentage d'augmentation (%) |

|---------------|-------------------|--------------------------------|

| 4             | $530 \ 923$       | -                              |

| 8             | $531\ 017$        | 0.0176                         |

| 12            | $531 \ 021$       | 0.0184                         |

| 16            | $531\ 066$        | 0.0268                         |

| 20            | $531 \ 099$       | 0.033                          |

| 28            | 531  191          | 0.0504                         |

| 34            | $531\ 271$        | 0.0654                         |

| 40            | $531 \ 360$       | 0.0823                         |

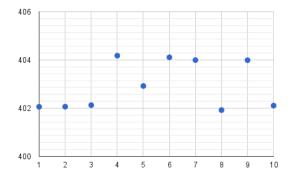

#### 1.5.4 Variation du surcoût d'exécution de la migration

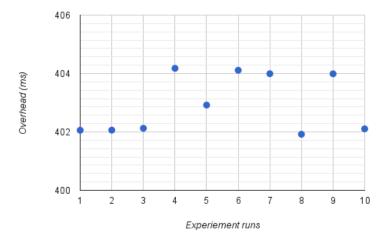

L'objectif de cette série d'expériences est d'étudier si le temps écoulé par la migration varie quand elle est répétée dans les mêmes conditions. Ceci permet d'évaluer le déterminisme de l'algorithme de la migration. Avec cette information, nous pourrons prédire le temps de migration et offrir une certaine qualité de service.

| Expérience | Temps de départ   | Temps de fin      | Temps d'exécution | Surcoût         |

|------------|-------------------|-------------------|-------------------|-----------------|

|            | $(\mu s)$         | $(\mu s)$         | $(\mu s)$         | Cas 1 $(\mu s)$ |

| 1          | 27 801 647        | $30 \ 425 \ 029$  | $2\ 623\ 382$     | 402 057         |

| 2          | $45 \ 614 \ 455$  | $48\ 237\ 843$    | $2\ 623\ 387$     | $402 \ 062$     |

| 3          | $78\ 243\ 189$    | $80 \ 866 \ 640$  | $2\ 623\ 450$     | 402  125        |

| 4          | $36 \ 361 \ 808$  | $38 \ 987 \ 310$  | $2\ 625\ 503$     | 404 177         |

| 5          | $121 \ 649 \ 077$ | $124 \ 273 \ 322$ | $2\ 624\ 246$     | 402 920         |

| 6          | $24 \ 258 \ 600$  | $26\ 884\ 037$    | $2\ 625\ 437$     | 404 111         |

| 7          | $56\ 529\ 629$    | $59\ 154\ 948$    | $2\ 625\ 319$     | 403 994         |

| 8          | $69 \ 221 \ 222$  | $71 \ 844 \ 467$  | $2\ 623\ 245$     | 401 920         |

| 9          | $31 \ 294 \ 232$  | $33 \ 919 \ 547$  | $2\ 625\ 315$     | 403 990         |

| 10         | $88\ 779\ 483$    | $91 \ 402 \ 913$  | $2\ 623\ 430$     | 402  105        |

| Temps mo   | yen $(\mu s)$     |                   |                   | 402 946         |

| Temps max  | $404 \ 177$       |                   |                   |                 |

| Temps mir  | 401 920           |                   |                   |                 |

| Écart-type | 1 004             |                   |                   |                 |

| Différence | $2\ 258$          |                   |                   |                 |

| Pourcentag | ge de (Max-Min)   | à temps moy       | en                | 0.56%           |

Table 1.3: Variation du surcoût de migration en modifiant la date de migration.

Plusieurs expériences de migration sont répétées, avec chaque fois la même tâche qui migre, mais à une date arbitraire. A chaque expérience, tout le système est réinitialisé, la machine doit redémarrer pour éviter l'influence de la mémoire cache. La taille de l'état de la tâche est fixée dans toutes les expériences et ne dépasse pas 4 ko. Les résultats sont donnés dans le tableau 1.3. La gamme de variation des surcoûts mesurés (différence entre maximum et minimum) est de 2.25 ms, comme illustré dans la figure 1.8. Les chiffres montrent que la variation du surcoût due à la migration est limitée (de l'ordre de 0,6%) avec un écart type très faible (environ 1 ms). Cela contribue à une bonne estimation du surcoût de la migration et surtout rend les coûts de migration déterministes.

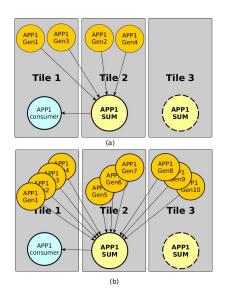

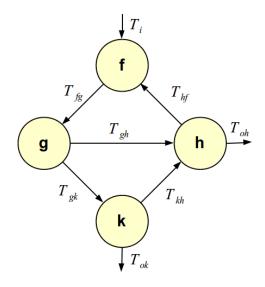

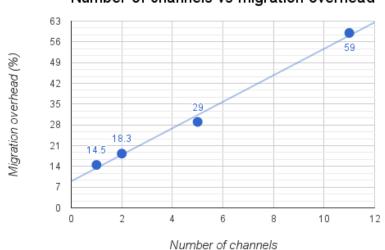

#### 1.5.5 Le surcoût de migration par rapport au nombre de canaux

La méthode de migration proposée dans notre travail, est basée sur des agents déployés sur une architecture distribuée, ce qui implique un échange de commandes

Figure 1.8: Variation du surcot de migration.

entre les différents agents et les tuiles impliquées dans la migration. Pour cette raison, le temps de migration dépend du nombre de tuiles voisines impliquées, notamment dans les communications avec la tâche qui doit migrer. L'objectif des expériences décrites dans cette sous-section est d'étudier l'influence du nombre de canaux sur le surcoût de migration. Le principe de l'application de calcul du carré est reprise mais en modifiant le nombre de générateurs pour faire varier le nombre de canaux.

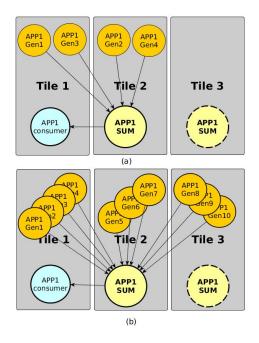

Le graphe de tâches de l'application 1 a été modifié pour produire les deux exemples suivants :

- i Quatre générateurs comme indiqué (Figure 1.9.(a)). Ils sont répartis sur tile\_1 et tile\_2.

- ii Dix générateurs (Figure 1.9.(b)). Ils sont répartis sur les tuiles tile\_1, tile\_2 et tile\_3.

Les temps d'exécution sont mesurés dans le cas 2 (avec agents sans migration) et 3 (avec agents et migration). Les résultats sont présentés dans le tableau 1.4.

| Cas             | Temps de départ    | Temps de fin     | Temps d'exécution | Surcoût     |  |  |  |  |

|-----------------|--------------------|------------------|-------------------|-------------|--|--|--|--|

|                 | $(\mu s)$          | $(\mu s)$        | $(\mu s)$         | Cas 2 (%)   |  |  |  |  |

|                 | Quatre générateurs |                  |                   |             |  |  |  |  |

| 2               | 17 482 080         | 19  565  805     | 2 083 724         | N/A         |  |  |  |  |

| 3               | $24 \ 940 \ 435$   | $27 \ 628 \ 979$ | $2\ 688\ 544$     | 29          |  |  |  |  |

| Dix générateurs |                    |                  |                   |             |  |  |  |  |

| 2               | $30 \ 300 \ 077$   | $32\ 434\ 774$   | $2 \ 134 \ 697$   | N/A         |  |  |  |  |

| 3               | 33 822 369         | $37 \ 231 \ 950$ | $3 \ 409 \ 580$   | <b>59.7</b> |  |  |  |  |

**Table 1.4:** Surcoûts de la migration dans les cas de quatre générateurset dix générateurs.

Nous pouvons aussi étudier la relation entre le nombre de canaux et les surcoûts

**Figure 1.9:** Placement optimisé de l'application modifiée sur un plateforme de trois tuiles. (a) Quatre générateurs. (b) Dix générateurs.

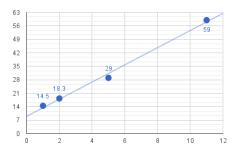

de performance due à la migration par la consolidation de toutes les mesures de toutes les expériences présentées dans les sections précédentes. Nous avons listé dans le tableau 1.5 toutes les expériences avec le nombre de canaux et de leurs surcoûts de migration correspondants. La relation est linéaire entre le nombre de canaux et le surcoût de performance comme présenté dans la figure 1.10.

Table 1.5: Nombre de canaux par rapport les surcoût de performance.

| Expérience          | Nombre de canaux | Surcot cause de migration (%) |

|---------------------|------------------|-------------------------------|

| (App2) in table 1.1 | 1                | 14.5                          |

| (App1) in table 1.1 | 2                | 18.3                          |

| In table 1.4        | 4                | 29                            |

| In table 1.4        | 10               | 59.7                          |

Figure 1.10: Le surcoût de la migration (%) vs. nombre de canaux.

## 1.6 Conclusion

Nous avons proposé une solution de migration de tâche basée sur des agents. Cette solution cible les architectures multi-tuiles, et présente un faible impact en terme de surcout de performance. La solution est expliquée à la fois de point de vue méthodologique et algorithmique avec les détails de mise en œuvre. Un flot de génération a été développé dans le cadre du projet européen FP7 EURETILE, ce qui a permis de nombreuses expérimentation à la fois sur une architecture ARM en simulation, mais aussi sur une architecture x86 existante en exécution.

La solution proposée présente plusieurs avantages. Elle est transparente pour le programmeur d'applications. La solution est basée sur une couche logicielle intermédiaire conforme à POSIX. Elle est donc portable sur d'autres architectures et d'autres systèmes d'exploitation. Aucun service spécifique d'un système d'exploitation n'est nécessaire (pas d'utilisation de la mémoire virtuelle ou de chargement dynamique), et même un système d'exploitation léger supporte la méthode. Dans ce contexte de système d'exploitation léger, on a montré que le cot était déterministe.

# Chapter 2 Introduction

| Contents |       |                                                                 |           |  |  |  |

|----------|-------|-----------------------------------------------------------------|-----------|--|--|--|

| 2.1      | Mic   | roprocessor architectures                                       | <b>24</b> |  |  |  |

|          | 2.1.1 | What is architecture?                                           | 24        |  |  |  |

|          | 2.1.2 | Towards parallel architectures                                  | 25        |  |  |  |

|          | 2.1.3 | Multi-tiled architecture                                        | 27        |  |  |  |

| 2.2      | Task  | $\alpha$ migration $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 28        |  |  |  |

|          | 2.2.1 | Motivation                                                      | 29        |  |  |  |

| 2.3      | Out   | line                                                            | 30        |  |  |  |

As computers are getting more and more pervasive, there is hardly an aspect in our lives nowadays in which they do not exist. New markets are being opened to computers almost everyday due to their increasing capabilities, computation power and ubiquitousness. Their versatile functionalities are ranging from simple management of automatic garden watering to sophisticated robots that discover distant planets' surfaces. Thanks to ongoing and outstanding advancements in electronics, more transistors can be integrated on a single chip, hence, better computers can be built.

The unit that is responsible for undergoing all the logic and arithmetic computations and incorporates all functions of Central Processing Unit CPU inside a computer is called a microprocessor. A microprocessor is a digital integrated circuit that is capable of reading instructions stored in a memory and executing them on stored and/or input data and finally storing the outcome on a memory, i.e. it is a re-programmable device. Integrated circuits (or chips) are made of semiconductor devices (called transistors). The more features and capabilities an integrated circuit has, the more transistor it needs. As a result, technology has been being more and more developed and advanced to house bigger numbers of transistors.

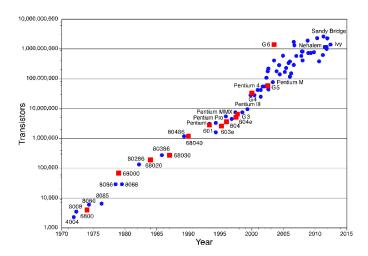

The pace with which the number of transistors is being increased on a single chip until now had been observed by Gordon Moore in 1965 [1]. He observed that the number of transistors doubles every almost two years, as depicted in Fig 2.1. This, consequently, leads to the possibility of better and more fledged microprocessor architectures that can deliver higher and higher computation powers. This, also

**Figure 2.1:** Moore's law, number of transistors doubles every two years. The source of the photo is in [2]

leads to computers invading wider and wider aspects.

Computers, in time, not only do not need much space to exist but also they are becoming more and more portable enriching the embedded systems field. An embedded system is a system that is capable of performing dedicated function(s) for specific purpose(s) with limited supply of power. These systems are classified according to the manner with which they deliver their outputs; some must deliver the output of their processing in predefined hard timed-deadlines as in *hard realtime* systems, others are not constrained stringently by time, i.e. their outputs can be accepted within a relatively acceptable delay from their deadlines like in *soft real-time* systems.

In the following section, we give an overview of microprocessors architectures, look briefly at technology-related issues, mention task migration basic definition and how it proposes a good system-level solution for some of these issues and finally mention how this work is planned.

## 2.1 Microprocessor architectures

A microprocessor is the unit that is responsible for performing computations and processing digital data. This unit incorporates the functions of a Central Processing Unit CPU. It is built on a single chip that sometimes houses other peripherals beside the CPU rendering it to be micro-controller.

#### 2.1.1 What is architecture?

Architecture is an assembly of disciplines that describe the design and implementation of a microprocessor. It covers three aspects of microprocessor design:

- i *Instruction-set*, it is the set of instructions visible to the programmer (compiler). They are the basic instructions that only can be executed by the real hardware. They stand in the middle between software and hardware, i.e. whatever the type of the software; it must be entirely converted to these instructions.

- ii Organization, it includes high-level aspects of the design like the memory system, the memory interconnect, and the design of the internal processor (like arithmetic, logic, branching, and data transfer are implemented).

- iii *Hardware design*, it refers to the specifics of the microprocessors including logic design, clock rates, transistor and packaging technology.

#### 2.1.2 Towards parallel architectures

Microprocessor architectures have different impacts on the computer systems. They affect performance, power consumption and how it can be programmed. Although architectures keep getting more sophisticated, this cannot continue indefinitely. This is due to the fact that higher attained speeds of microprocessors can no longer increase the throughput of the whole computer systems that require not only CPUs but also memories, networks and power. Because of the fact that developing all the components (processor, memory, interconnect ... etc.) in a computer system cannot result in the same speedup, latency of some components can dominate the speedup of another. As a result, ongoing speed enhancements in processors are blocked by the latencies of other components like memory. This makes further architecture development in uniprocessor systems infeasible due to the diminishing returns. This can be briefly explained as follows:

- *Hitting memory wall*: speed of memory access is not increasing with the same rate as that of microprocessor. Consequently, ongoing increase in microprocessor speed requires larger caches. Larger caches solution is not considered to be free, i.e. its cost diminishes the benefit of the bigger size.

- Wire delay: wire delay does not scale well with transistor performance, i.e. while transistors are getting smaller and more efficient, wire delays are becoming dominant. This makes wire delay a limitation in designing computers.

- *Hitting power wall*: since transistors are becoming more and more numerous because they are smaller, power needs to be brought to and distributed among the chip gates. Heat results from power distribution anomalies in a filled area with transistors. That is why distributing the power, removing the heat, and preventing hot spots have become increasingly difficult challenges. Unlike in the past when area made the most important limitation in designing integrated circuits in general, power now makes the major limitation to using transistors.

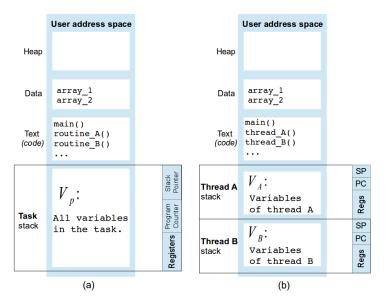

That is why the trend now is to have multiple microprocessors (or cores) in single chip (or multiple processor system-on-chip MPSoC) and they are all there for executing different parallelized applications where an application (it is, sometimes, called *job*) is split into a number of processes and a process has a number of threads. As a result parallel architectures emerged where every processor executes a thread so that a number of threads are executed in a simultaneous manner. All microprocessor architectures are categorized according to the taxonomy that was put by Michael J. Flynn [3] in 1966. They are categorized such that an architecture must be one of the following four ones:

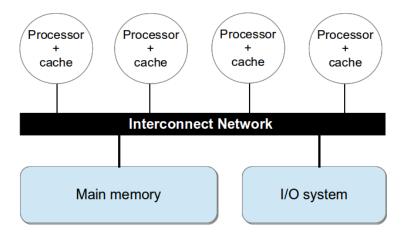

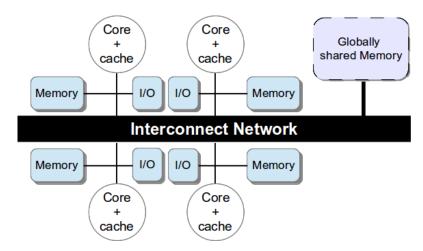

- 1. *Single Instruction Single Data* SISD: This is the category in which a uniprocessor is used to execute instructions one by one.