# A variability study of PCM and OxRAM technologies for use as synapses in neuromorphic systems

Daniele Garbin

### ▶ To cite this version:

Daniele Garbin. A variability study of PCM and OxRAM technologies for use as synapses in neuromorphic systems. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2015. English. NNT: 2015GREAT133. tel-01278998

# HAL Id: tel-01278998 https://theses.hal.science/tel-01278998v1

Submitted on 25 Feb 2016

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ GRENOBLE ALPES

# **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nanoélectronique et nanotechnologies

Arrêté ministériel : 7 août 2006

Présentée par

### Daniele GARBIN

Thèse dirigée par Prof. Gérard GHIBAUDO et codirigée par Dr. Barbara DE SALVO

préparée au sein du CEA-LETI dans l'École Doctorale d'Électronique, Électrotechnique, Automatique et Traitement du Signal

# Étude de la variabilité des technologies PCM et OxRAM pour leur utilisation en tant que synapses dans les systèmes neuromorphiques

Thèse soutenue publiquement le 15 décembre 2015, devant le jury composé de :

### M Daniele IELMINI

Prof., Politecnico di Milano, Italie, Rapporteur

### M Giacomo INDIVERI

Prof., Swiss Federal Institute of Technology in Zurich, Suisse, Rapporteur M Ian O'CONNOR

Prof., Ecole centrale de Lyon, Président

### **Mme Elisa VIANELLO**

Dr. Ing., CEA-Leti Grenoble, Co-encadrant de thèse

### M Quentin RAFHAY

MCF, Université Grenoble Alpes (IMEP-LAHC), Co-encadrant de thèse

### M Gérard GHIBAUDO

DR, CNRS Université Grenoble Alpes (IMEP-LAHC), Directeur de thèse

### **Mme Barbara DE SALVO**

HDR, Dr. Ing. CEA-Leti Grenoble, Co-directeur de thèse, Invité

### M Olivier BICHLER

Dr. Ing. CEA-List Gif-sur-Yvette, France, Invité

# Abstract

Title: A variability study of PCM and OxRAM technologies for use as synapses in neuromorphic systems.

The human brain is made of a large number of interconnected networks which are composed of neurons and synapses. With a low power consumption of only few Watts, the human brain is able to perform computational tasks that are out of reach for today's computers, which are based on the Von Neumann architecture. Neuromorphic hardware design, taking inspiration from the human brain, aims to implement the next generation of non-Von Neumann computing systems. In this thesis, emerging non-volatile memory devices, specifically Phase-Change Memory (PCM) and Oxidebased resistive memory (OxRAM) devices, are studied as artificial synapses for use in neuromorphic systems. The use of PCM devices as binary probabilistic synapses is proposed for complex visual pattern extraction applications. The impact of the PCM programming conditions on the system-level power consumption is evaluated. A programming strategy is proposed to avoid the PCM resistance drift. It is shown that, using scaled devices, it is possible to reduce the synaptic power consumption. The OxRAM resistance variability is evaluated experimentally through electrical characterization, gathering statistics on both single memory cells and at array level. A model that allows to reproduce OxRAM variability from low to high resistance state is developed. An OxRAM-based convolutional neural network architecture is then proposed on the basis of this experimental work. By implementing the computation of convolution directly in memory, the Von Neumann performance bottleneck is avoided. The robustness of the neuromorphic system to OxRAM variability is demonstrated for complex visual pattern recognition tasks such as handwritten characters and traffic signs recognition.

# Résumé

Titre : Étude de la variabilité des technologies PCM et OxRAM pour leur utilisation en tant que synapses dans les systèmes neuromorphiques.

Le cerveau humain est composé d'un grand nombre de réseaux interconnectés, dont les neurones et les synapses en sont les briques constitutives. Caractérisé par une faible consommation de puissance, de quelques Watts seulement, le cerveau humain est capable d'accomplir des tâches qui sont inaccessibles aux systèmes de calcul actuels, basés sur une architecture de type Von Neumann. La conception de systèmes neuromorphiques vise à réaliser une nouvelle génération de systèmes de calcul qui ne soit pas de type Von Neumann. L'utilisation de mémoires non-volatile innovantes en tant que synapses artificielles, pour application aux systèmes neuromorphiques, est donc étudiée dans cette thèse. Deux types de technologies de mémoires sont examinés: les mémoires à changement de phase (Phase-Change Memory, PCM) et les mémoires résistives à base d'oxyde (Oxide-based resistive Random Access Memory, OxRAM). L'utilisation des dispositifs PCM en tant que synapses de type binaire et probabiliste est étudiée pour l'extraction de motifs visuels complexes, en évaluant l'impact des conditions de programmation sur la consommation de puissance au niveau système. Une nouvelle stratégie de programmation, qui permet de réduire l'impact de la dérive de la résistance des dispositifs PCM (dit « drift ») est ensuite proposée. Il est démontré qu'en utilisant des dispositifs de tailles réduites, il est possible de diminuer la consommation énergétique du système. La variabilité des dispositifs OxRAM est ensuite évaluée expérimentalement par caractérisation électrique, en utilisant des méthodes statistiques, à la fois sur des dispositifs isolés et dans une matrice mémoire complète. Un modèle qui permets de reproduire la variabilité depuis le niveau faiblement résistif jusqu'au niveau hautement résistif est ainsi développé. Une architecture de réseau de neurones de type convolutionnel est ensuite proposée sur la base de ces travaux éxperimentaux. La tolérance du système neuromorphique à la variabilité des OxRAM est enfin démontrée pour des tâches de reconnaissance de motifs visuels complexes, comme des caractères manuscrits ou des panneaux de signalisations routières.

# Contents

| $\mathbf{A}$ | ckno | wledgments                                               | 1  |

|--------------|------|----------------------------------------------------------|----|

| In           | trod | uction                                                   | 2  |

| 1            | Em   | erging Non Volatile Memories and Neuromorphic Systems    | 4  |

|              | 1.1  | The semiconductor memory market                          | 4  |

|              | 1.2  | Emerging non-volatile memory technologies                | 7  |

|              |      | 1.2.1 PCRAM                                              | 8  |

|              |      | 1.2.2 STT-RAM                                            | 10 |

|              |      | 1.2.3 CBRAM                                              | 11 |

|              |      | 1.2.4 OxRAM                                              | 12 |

|              |      | 1.2.5 Comparison of NVM technologies                     | 15 |

|              | 1.3  | Neuromorphic systems                                     | 15 |

|              |      | 1.3.1 Neurons and Synapses                               | 19 |

|              |      | 1.3.2 Non-volatile memory devices as artificial synapses | 21 |

|              |      | 1.3.3 Fully connected neural networks                    | 23 |

|              |      | 1.3.4 Convolutional neural networks                      | 24 |

|              |      | 1.3.5 Learning                                           | 27 |

|              |      | 1.3.6 Applications                                       | 31 |

|              | 1.4  | Conclusion                                               | 31 |

| <b>2</b>     | Neı  | uromorphic Systems based on PCRAM synapses               | 33 |

|              | 2.1  | Introduction                                             | 33 |

|              |      | 2.1.1 The 2-PCM Synapse refresh scheme                   | 35 |

|              | 2.2  | PCM binary synapse                                       | 37 |

|              | 2.3  | Neuromorphic Architecture                                | 38 |

|              |      | 2.3.1 Operation of the system                            | 41 |

|              |      | 2.3.2 System performance                                 | 44 |

|              | 2.4  | Power consumption analysis                               | 45 |

|              |      | 2.4.1 Learning mode power consumption                    | 46 |

|              |      | 2.4.2 Read mode power consumption                        | 47 |

|              | 2.5  | Resistance drift                                         | 48 |

|              |                                                      | 2.5.1 Drift mitigation strategy                                   |    |  |  |  |

|--------------|------------------------------------------------------|-------------------------------------------------------------------|----|--|--|--|

|              | 2.6                                                  | Simulations using scaled devices                                  | 52 |  |  |  |

|              | 2.7                                                  | Conclusion                                                        | 53 |  |  |  |

| 3            | OxRAM technology: failure mechanisms and variability |                                                                   |    |  |  |  |

|              | 3.1                                                  | · ·                                                               | 55 |  |  |  |

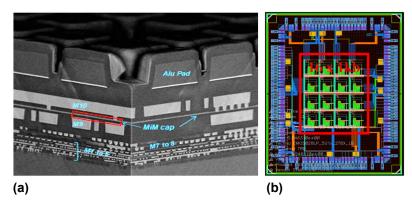

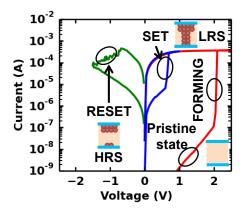

|              | 3.2                                                  | Device operation                                                  | 56 |  |  |  |

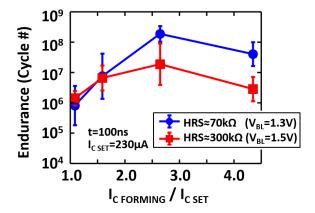

|              | 3.3                                                  | Endurance: failure mechanisms                                     |    |  |  |  |

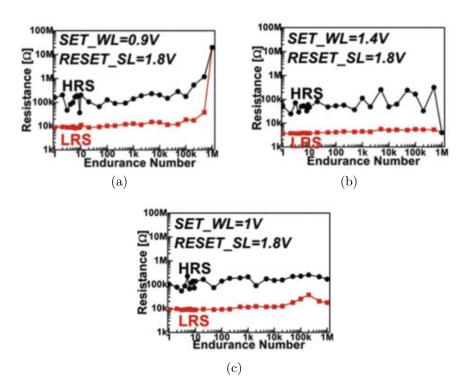

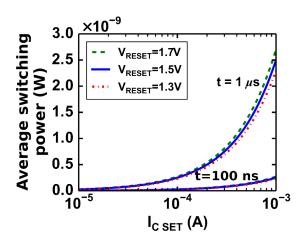

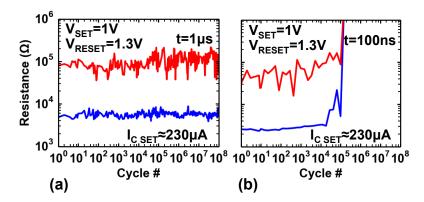

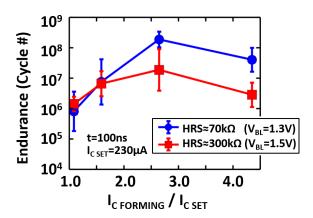

|              |                                                      | 3.3.1 Endurance improvement for low programming current           | 62 |  |  |  |

|              | 3.4                                                  |                                                                   | 63 |  |  |  |

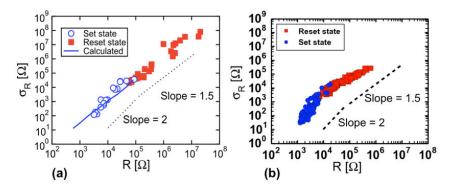

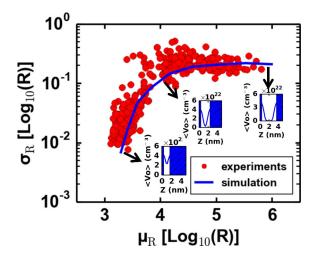

|              | 3.5                                                  | Variability Modelling: 3D resistor network approach               | 66 |  |  |  |

|              | 3.6                                                  | Continuity of variability from LRS to HRS: model calibration      | 70 |  |  |  |

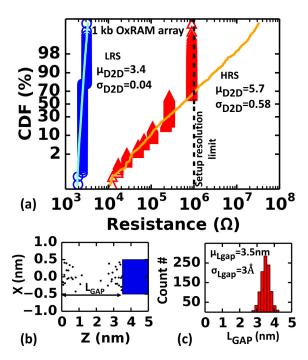

|              | 3.7                                                  | Variability from 28 nm memory array demonstrator                  | 72 |  |  |  |

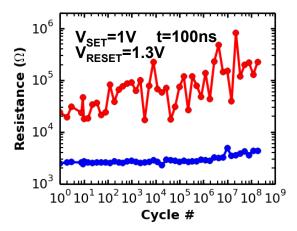

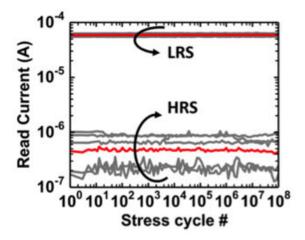

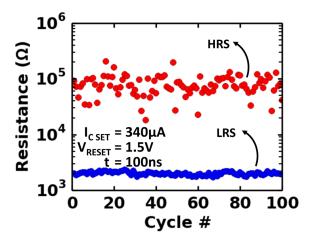

|              |                                                      | 3.7.1 Cycle-to-cycle variability                                  |    |  |  |  |

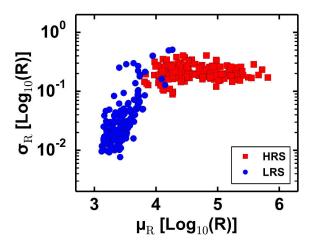

|              |                                                      | 3.7.2 Device-to-device variability                                | 74 |  |  |  |

|              | 3.8                                                  | Conclusion                                                        | 76 |  |  |  |

| 4            | OxI                                                  | RAM devices as artificial synapses for convolutional neural net-  |    |  |  |  |

|              | wor                                                  | v -                                                               | 77 |  |  |  |

|              | 4.1                                                  | Introduction                                                      |    |  |  |  |

|              | 4.2                                                  | Multilevel synapse with binary OxRAMs in parallel                 | 8  |  |  |  |

|              |                                                      | 4.2.1 LTP and LTD curves on OxRAM synapses                        | 82 |  |  |  |

|              | 4.3                                                  | Convolutional Neural Network architecture                         | 85 |  |  |  |

|              |                                                      | 4.3.1 Impact of OxRAM programming conditions                      | 91 |  |  |  |

|              | 4.4                                                  | Unsupervised learning                                             | 92 |  |  |  |

|              | 4.5                                                  | Synaptic weight resolution                                        | 94 |  |  |  |

|              |                                                      | 4.5.1 Analog vs. digital integration neuron                       | 96 |  |  |  |

|              | 4.6                                                  | Tolerance to variability                                          | 98 |  |  |  |

|              | 4.7                                                  | Conclusion                                                        | .0 |  |  |  |

| 5            | Con                                                  | iclusions 1                                                       | 02 |  |  |  |

|              | 5.1                                                  | Future perspectives                                               | 04 |  |  |  |

| $\mathbf{A}$ | The                                                  | Xnet simulator 1                                                  | 06 |  |  |  |

| В            | Aut                                                  | hor's publications                                                | 08 |  |  |  |

|              |                                                      | •                                                                 |    |  |  |  |

| $\mathbf{C}$ | Rés                                                  | umé en français 1                                                 | 1. |  |  |  |

|              | C.1                                                  | Mémoires non-volatiles émergentes et systèmes neuromorphiques 1   |    |  |  |  |

|              |                                                      | C.1.1 Technologies de mémoire non volatile émergentes             |    |  |  |  |

|              |                                                      | C.1.2 Systèmes neuromorphiques                                    |    |  |  |  |

|              | C.2                                                  | Systèmes neuromorphiques basés sur des synapses de type PCRAM . 1 | 16 |  |  |  |

|         | Technologie OxRAM : mécanismes de défauts et variabilité Dispositifs OxRAM en tant que synapses pour des réseaux de neurones | 117 |

|---------|------------------------------------------------------------------------------------------------------------------------------|-----|

|         | convolutifs                                                                                                                  |     |

| Bibliog | graphy                                                                                                                       | 125 |

# Acknowledgments

This PhD thesis was prepared at the Université Grenoble Alpes, CEA LETI and IMEP-LAHC. First of all, I would like to thank my PhD thesis directors Prof. Gérard Ghibaudo and Dr. Barbara De Salvo, for their precious guidance and wisdom. Then, I would like to thank my advisors Dr. Elisa Vianello and Dr. Quentin Rafhay for supporting me and helping me improve during these three years. I thank all the LCM team: Luca Perniola, Eric Jalaguier, Gabriele Navarro, Véronique Sousa, Gabriel Molas, Alain Persico, Christelle Charpin, Sophie Bernasconi, Carine Jahan, Rémi Coquand, Etienne Nowak, Laurent Grenouillet, Cathérine Carabasse, Jean-François Nodin, Guillaume Bourgeois, Jérôme Lozat and Khalil El Hajjam. I would like to thank Dr. Olivier Joubert and the LabEx Minos for supporting my PhD thesis under Grant ANR-10-LABX-55-01.

I am deeply grateful to Dr. Olivier Bichler for our nice and fruitful collaboration. I would also like to thank Dr. Christian Gamrat for welcoming me during the time that I spent in CEA LIST. I thank Alain Lopez, Jacques Cluzel, Denis Blachier, Carlo Cagli, Giovanni Romano, Olga Cueto, and all the people from LCTE and LICL laboratories for their support. I thank our collaborators from STMicroelectronics for providing most of the samples that I tested during this research.

I thank all the PhD students, interns and postdocs who shared with me coffee breaks, lunches, trips and happy moments during the last three years: Marinela, Thanasis, Manan, Boubacar, Quentin, Thomas, Gabriele, Giorgio, Thérèse, Jérémy, Florian, Yann, Sebastien, Amine, Julien, Issam, Sarra, Heimanu, Rémi, Luca, Niccolò, Thilo, Julia, Mourad, Mouhamad, Giuseppe, Cécile, Adam, Daeseok, Luc, Martin, Davide, Marco, Aurore, Fabien, Loïc, Romain, Vincent, Jose, Mathilde, Corentin, Anouar, Mathias, Patricia, Alexandre, Anthony, Louise, Jessy and all those people that i may have forgotten in this list. I would also like to thank Sabine, Brigitte, Sylvaine and Malou for their help during these three years.

I am grateful to Prof. Ian O'Connor, Prof. Daniele Ielmini and Prof. Giacomo Indiveri for accepting to review this thesis and attending my PhD defense.

Last but not least, I thank my family for their support and for always being there for me.

# Introduction

The human brain is made of a large number of interconnected networks which are composed of neurons and synapses. With a low power consumption of only few Watts, the human brain is able to perform computational tasks that are out of reach for today's computers, currently are based on the Von Neumann architecture. Neuromorphic hardware design, taking inspiration from the human brain, aims to implement the next generation of non-Von Neumann computing systems. Neuromorphic systems are designed to perform, in a power efficient way, those tasks at which the human brain is excellent, as for example the recognition of complex visual and auditory patterns.

Emerging Non-Volatile Memory (NVM) devices have been studied in the recent years as possible solutions to implement artificial synapses in neuromorphic hardware systems. In this work, emerging NVM devices, in particular Phase-Change Memory (PCM) and Oxide-based resistive memory (OxRAM) devices, are studied having in mind the central role that they will play in future memory and computing architectures. We investigate the use of these devices for the implementation of artificial synapses, with a special focus on device variability and its impact on the performance of neuromorphic computing systems.

# Manuscript outline

In Chapter 1, we introduce the context and motivation behind the research conducted during the preparation of this PhD. Given the interdisciplinarity involved in this project, this chapter describes in depth the basics concepts that are needed to contextualize this research, in the framework of both conventional memory and neuromorphic computing architectures.

In Chapter 2, we focus on PCM technology, one of the most mature among the emerging non-volatile memory technologies. PCM devices offer the possibility of multilevel programming by gradually changing the size of the crystalline portion of the active phase-change material. We analyze the drawbacks related to the use of the multilevel PCM synapse approach. Therefore, driven by the motivation to overcome the limitations associated to the multilevel programming, we explore by simulations the use of PCM synapses operated in binary mode, where only two

resistance states are exploited. The use of the proposed binary PCM synapse is studied in a neuromorphic system designed for complex visual pattern extraction.

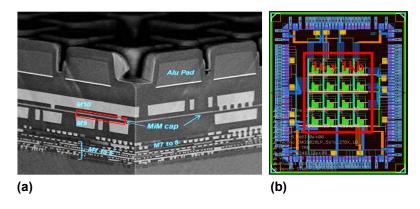

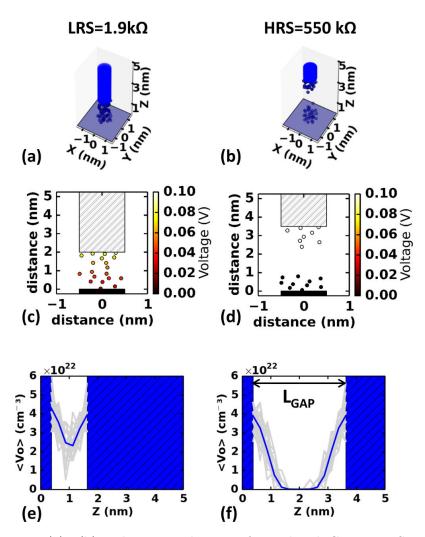

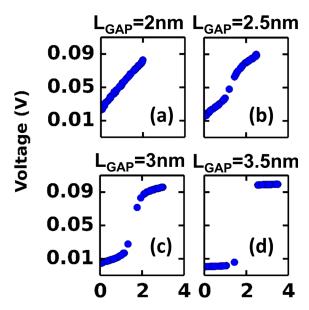

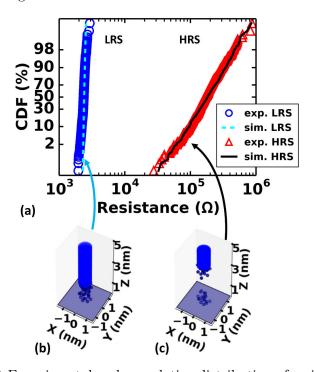

In Chapter 3, we investigate the binary operation of OxRAM devices. Since variability is the main drawback of OxRAM technology, we carry out an extensive work of electrical characterization on single bitcells and on 16 kb memory array, in order to understand the source of variability. Starting from the electrical characterization results, we develop a simplified trap-assisted tunneling model to reproduce the OxRAM variability from low (LRS) to high resistance state (HRS), highlighting the continuity of the mechanisms involved in the variability. We carry out this analysis with a dual goal. On one hand, the developed model provides an insight on the source of variability in OxRAM, suggesting technology guidelines for the improvement of reliability. On the other hand, the computational efficiency of the developed model allows to simulate large memory arrays and take into account the synaptic variability corresponding to a wide range of programming conditions in neuromorphic system simulations.

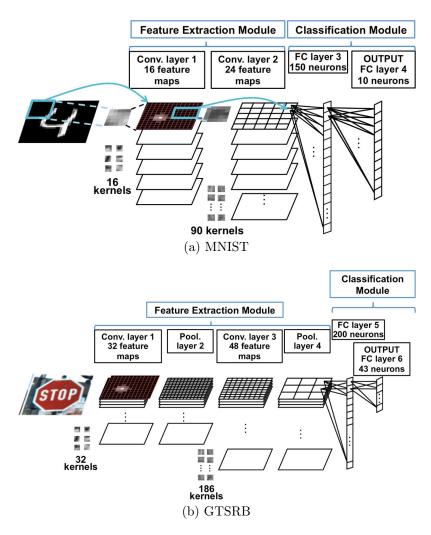

In Chapter 4 we propose an OxRAM-based synapse design that combines together the advantages of multilevel and binary approaches. Using such synapses, we propose a hardware implementation of a convolutional neural network (CNN) for complex visual applications such as handwritten digits and traffic signs recognition. We investigate the tolerance of the proposed network to both temporal and spatial synaptic variability.

In Chapter 5 we provide a general conclusion of the research carried out for this thesis. Finally, we provide a perspective on the future work that needs to be done for the further progress of the research on neuromorphic hardware.

# Chapter 1

# Emerging Non Volatile Memories and Neuromorphic Systems

In this chapter, we introduce the context and motivation behind the research conducted during the preparation of this PhD. On one side, emerging Non-Volatile Memory (NVM) devices are studied having in mind the central role that they will play in the memory architectures of the future. On the other side, a novel application of NVM devices, which has gained a large interest over the last few years, is investigated: the implementation of artificial synapses in brain-inspired computing architectures. Given the interdisciplinarity involved in this project, this chapter describes in depth the basics concepts that are needed to contextualize this research, in the framework of both conventional memory and neuromorphic computing architectures.

# 1.1 The semiconductor memory market

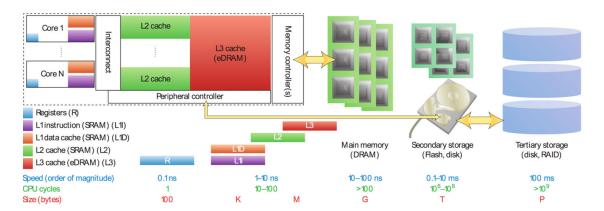

The design of today's computing systems is based on the Von Neumann architecture [1]. In this architecture, a marked distinction exists between the role of the Central Processing Unit (CPU) and the Memory Unit (MU). The CPU is in charge of performing the arithmetic operations, logic functions, control tasks and input/output operations that are specified by a set of instructions, i.e. a computer program, which is stored in the MU. The MU contains both the code of the computer programs and the data. Data comprise the information that has to be processed by the CPU and the results of the computation [1].

The simplest architecture for organizing memory is the *flat* memory architecture. In this architecture, data are stored in a single, large memory unit block in the form of array. However, the memory access time and the power consumption associated to the access to information increase with the size of the memory array. Hence, memory power and access time dominate the total power and performance when a large storage is required for computation [2]. In fact, a gap exists between processor and

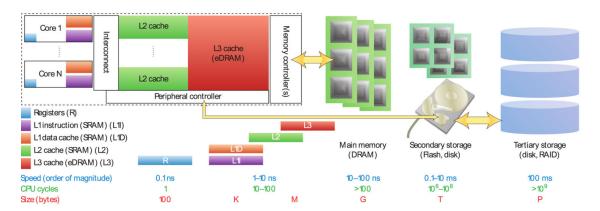

Figure 1.1. The memory hierarchy in computers. Small amounts of high-performance volatile and expensive memory are close to the CPU. Large amounts of slower, non volatile and low-cost storage units are far from the CPU at the bottom of the hierarchy. Source: [4].

memory in terms of performance: computation performance is typically limited by how fast the data in memory can be accessed, with latency and bandwidth being the main limiting factors. This gap is commonly referred to as the memory bottleneck [2].

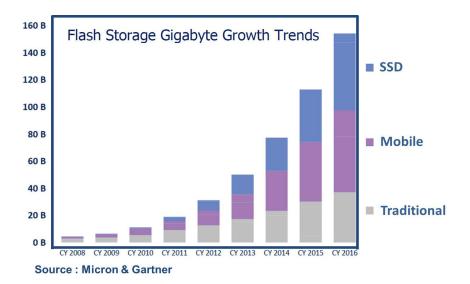

In more advanced memory architectures, memory is not *flat*. It is structured as a hierarchy of volatile and non-volatile memory devices, in order to achieve an optimal trade-off between cost and performance. The goal of this memory hierarchy, shown in Figure 1.1, is to mitigate the problem of the memory bottleneck, bridging the performance gap between the fast CPU and the slower memory and storage technologies, keeping the system costs down [3]. As illustrated in Fig. 1.1, at the top of the hierarchy, close to the CPU unit, is the memory that is accessed most frequently. Static Random Access Memory (SRAM) is the technology of choice because it allows the fastest operation speed. However, due to the large silicon area required, it is also the most expensive technology [4]. The technology adopted for the main memory is typically the Dynamic Random Access Memory (DRAM), which often resides in a different chip than the CPU because the technology process is different. For over 30 years, SRAM [5] and DRAM [5] technology have dominated the memory market [6]. Both SRAM and DRAM, however, are volatile memories, i.e. the information stored in memory is lost when the device is turned off. At the bottom of the memory hierarchy, magnetic Hard Disk Drives (HDDs) have been used for over 50 years [7] as a first choice for non-volatile storage solutions. Since the advent and explosive growth of portable devices such as music players and cellular phones, however, Flash memory [8], [9] has forced its way into the information storage hierarchy, between DRAM and HDD, as non-volatile storage solution. As shown in Fig. 1.2, the growth of Flash technology has exploded over the last few years,

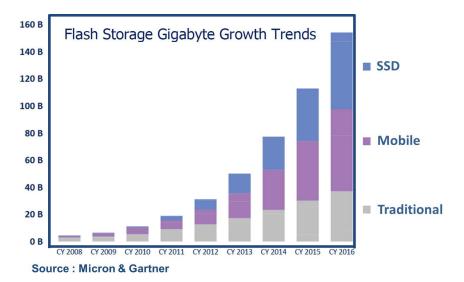

Figure 1.2. Flash storage gigabyte growth trends, source: [12].

and it has become the dominant data storage technology for mobile applications. Enterprise-scale computing systems and cloud data storage systems are also starting to adopt Flash technology to complement the HDD storage units with Solid-State Drives (SSDs) [10]. The Flash memory market in this segment is forecast to grow over the next few years, also thanks to the adoption of vertically 3D stacked cells solutions [11].

However, Flash technology is facing challenges in scaling due to intrinsic physical limitations related to the technology, such as floating gate interference [13], reduced coupling between control and floating gate [14], short channel effects [13] and small electron charge in the floating gate [15], [16]. The emergence of a non-volatile memory technology able to combine at the same time high performance, high density and low cost can potentially lead to deep changes in the memory/storage hierarchy [3]. A non-volatile memory with latency compared to DRAM would be a game changer in storage tiering [17]. For these reasons, research efforts are being done in order to find new non-volatile memory solutions, with better scalability compared to Flash and possibility of vertical 3D stacking. Such a technology would allow to reach the highest possible densities achievable with future technology nodes [3] and offer the possibility to mitigate the problem of the memory bottleneck.

Considering the semiconductor memory market, two main types of memory business can be considered:

• The standalone memory market, with focus on density and performance. It is a very concentrated market with 5 Integrated Device Manufacturers (IDMs) holding 95% of the total business: Samsung, Micron/Intel, SK Hynix, Toshiba and SanDisk.

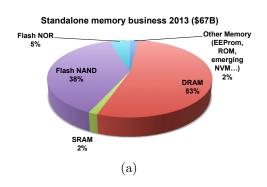

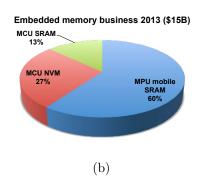

Figure 1.3. (a) Standalone and (b) embedded memory market in 2013. Source: [18].

• The embedded memory market, with low power consumption and high thermal stability being some of the most restricting specifications. There are two types of embedded memory, depending on the level of system integration. I System on Chip (SoC) such microcontrollers (MCUs) for smart cards, automotive or mobile microprocessors (MPUs) for portable systems. II System in Package (SiP) where a number of integrated circuits are enclosed in a single module (package). The embedded memory market is more fragmented, with foundries manufacturing the bulk part of the total production [18].

As shown in Fig. 1.3a, Flash NAND technology and DRAM currently dominate the standalone memory market, representing about 90% of overall memory sales. A low-cost emerging memory technology with densities larger than Flash and speed comparable to DRAM can possibly conquer a large portion of the market. After 2020, emerging NVM could also replace SRAM in the MCU and MPU embedded memory business [18] (Fig. 1.3b).

## 1.2 Emerging non-volatile memory technologies

In the quest for innovative non-volatile memory solutions, different technologies have emerged in research over the last 15 years [19], [20]. These technologies are free from the limitations of Flash, which are low endurance (i.e. a limited number of write operations is possible), need for high voltage supply for programming, long write time and complex erase procedure [4]. Another limitation of Flash is the fact that it is a Front-End-Of-Line (FEOL) technology, difficult to co-integrate with sub-32 nm CMOS [16].

The main emerging non-volatile memory technologies are the following:

- Phase-Change Random Access Memory (PCRAM or PCM);

- Spin-Transfer-Torque Magnetic Random Access Memory (STT-MRAM);

- Conductive-Bridging Random Access Memory (CBRAM);

- metal Oxide resistive Random Access Memory (OxRAM).

These emerging memory technologies store information using physical mechanisms which do not rely on storing charge in a capacitor or the floating gate of a transistor as in the case of SRAM, DRAM and Flash. They are integrated in the Back-End-Of-Line. It is worth noticing that in literature the generic term resistive RAM (RRAM or ReRAM) is often used to generically refer to both OxRAM and CBRAM. In the next sections, an overview of the main emerging non-volatile memory technologies will be given, with details on some important properties and performance aspects.

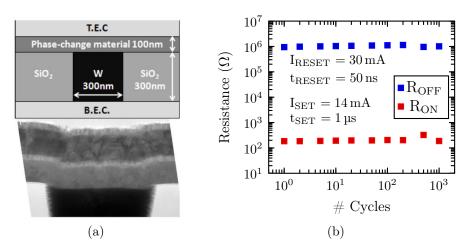

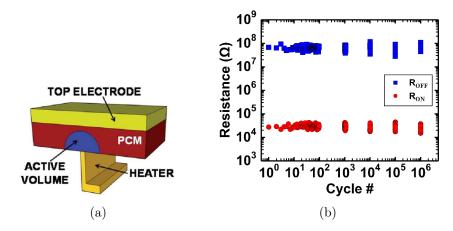

### 1.2.1 PCRAM

Phase-Change Random Access Memory (PCRAM, or PCM) working principle is based on the electrical properties of phase-change materials. Phase-change materials, in fact, feature a high contrast in resistivity between amorphous and crystalline phases. The amorphous phase is characterized by a high electrical resistivity, while the crystalline phase features low resistivity [21]. In PCRAM it is possible to switch the material between amorphous and crystalline phase multiple times. Most of phase-change materials are chalcogenides, which are alloys featuring at least one element from the VI group of the periodic table. Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) is one of the most studied chalcogenide phase-change materials. Other examples are GeTe, GeSeTe<sub>2</sub>, AgSbSe<sub>2</sub> [21] and different variants obtained by doping [22], [23] or enrichment of alloying elements [24], [25]. GaSb is an example of phase-change material that is not a chalcogenide [26].

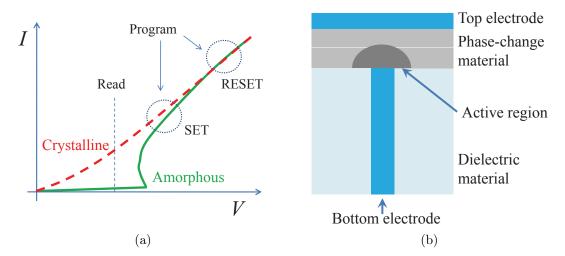

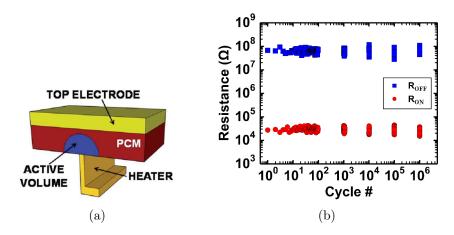

In PCRAM, the phase-change material is switched between amorphous and crystalline phase by Joule heating. Figure 1.4a shows the shape of typical current-voltage characteristics for crystalline and amorphous phases of phase-change materials. Crystallization is achieved by heating the material above its crystallization temperature (SET operation). Amorphization is achieved by melting the material in the liquid state and rapidly quenching it into the disordered amorphous phase (RESET operation). These operations are performed by electrical current pulses: high-power pulses are required for the RESET operation, moderate power but longer duration pulses are used for the SET operation. In order to retrieve the information, low power pulses are used to sense the resistance of the device [21]. Figure 1.4b shows schematically a mushroom-shaped PCRAM cell. The device is composed of a phase-change material sandwiched between a top electrode and a bottom electrode in the form of small cross-section heater plug. The active region is defined as the portion of the phase-change material that actually undergoes phase switching. It is located right above the heater plug, where the temperature reaches the highest value due to high current density.

Figure 1.4. (a) Typical current-voltage characteristics of crystalline and amorphous phases of phase-change materials. (b) Schematic cross-section of a phase-change memory cell. Source: [27].

One of the limiting factors for the adoption of PCRAM technology is the relatively high RESET current [28]. However, the programming current scales down with device area. In ultra-scaled devices with 10 nm feature size, the RESET current is shown to decrease down to the microampere range [29]. Furthermore, material and interface engineering can significantly contribute to the reduction of the RESET current [23], [30].

One of the attractive features of PCRAM is the possibility of achieving multilevel-cell (MLC) storage. This means that the device can be programmed into multi-level resistance states, in addition to the full SET and RESET resistance levels. This is obtained by modulating the ratio between the crystalline and amorphous region size within the active region. MLC functionality is an efficient way of decreasing the cost of memory, because it alows to store more information for a given silicon area [31]. However, in phase change materials the amorphous intermediate resistance states drift with time t towards higher resistance values, following a  $R(t) = R_0(t/t_0)^{\nu}$  relationship, where  $R_0$  is the resistance at initial time  $t_0$ , and  $\nu$  is the drift coefficient, which depends on the material and on the device morphology [32]. As a consequence, after a certain amount of time has passed after programming, it is a not trivial task to distinguish the programmed states. Only using advanced cell readout methodologies which are intrinsically resilient to resistance drift, a reliable 2 bits/cell storage and data retention at high temperature can be achieved [31].

### 1.2.2 STT-RAM

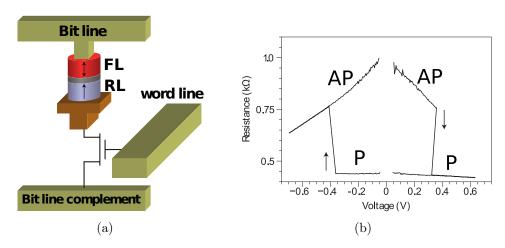

In Spin-Transfer-Torque Magnetic Random Access Memory (STT-MRAM) devices, information is stored in the orientation of the magnetization of a nano-scale ferromagnetic layer. Figure 1.5a shows the schematic view of a typical STT-MRAM bit-cell. The main component of STT-MRAM is the Magnetic Tunnel Junction (MTJ), which consists of two magnetic layers separated by a tunneling barrier, composed of a thin layer of insulating MgO. The orientation of the magnetization of the Free Layer (FL) can be switched between two states and is used to store information. The magnetization of the Reference Layer (RL) is permanent and it serves the function of a stable reference for the magnetic orientation [33]. If the orientation of RL and FL are the same, the device is said to be in Parallel (P) state. If the orientation of the two layers is opposite, the device is in the Anti-Parallel (AP) state. The STT-MRAM working principle is based on two phenomena that have been discovered during the last two decades: the Tunnelling Magneto-Resistance (TMR) effect and the Spin-Transfer Torque (STT) effect. The TMR effect [34] is the cause of the resistivity contrast between the resistance  $R_{\rm P}$  in the P state and the resistance  $R_{AP}$  in the AP state. The resistance of the device can be sensed in order to determine which is the magnetic state of the FL, so the stored information can be retrieved. The STT effect [35]–[37] is the effect which allows to switch the magnetic orientation of the FL. When electrons flow through the MTJ, a torque is exerted on the magnetization of the FL. If the torque is large enough, the magnetic state of the FL can be switched and information is written. The write operation is achieved according to the direction of the current flow. If a positive voltage is applied to the device, a non-polarized current, i.e. featuring electrons with random spin orientation, is injected in the direction that goes from the RL to the FL. Electrons with a spin opposite to the RL magnetization orientation are mostly reflected. Only the electrons with a spin having the same orientation as the RL magnetization will be transmitted by tunneling through the MTJ and will transfer their spin to the FL by STT. The result is that the MTJ will be in the parallel state. If a negative voltage is applied to the device, the electrons are injected from the FL to the RL. At the interface between the tunneling barrier and the RL, electrons with the same orientation as the RL will be transmitted through the MTJ. Electrons with an opposite spin will be reflected back in the FL and switch its magnetization to the AP state. In summary, as shown in Fig. 1.5b, a positive voltage leads to AP-to-P transition. A negative voltage leads to P-to-AP transition [38].

STT-MRAM is expected to have a very high endurance [38]. This is due to the fact that no magnetic degradation mechanism is associated to the switching of the magnetization orientation. In fact, no atoms are moved during write operations, contrary to PCRAM, CBRAM or OxRAM. However, the dielectric breakdown of the MgO tunnel barrier can occur if the voltage across the tunnel barrier exceeds roughly 400 mV [38], [39].

Figure 1.5. (a) Schematic view of an STT-MRAM bit cell. The MTJ is composed of a permanent reference layer (RL), a tunnel barrier and a free layer (FL) element, with both layers magnetized perpendicular to the plane of the junction. (b) Typical resistance-voltage characteristics, showing switching between antiparallel (AP) to parallel (P) states (positive bias) and vice versa. Source: [38].

### 1.2.3 CBRAM

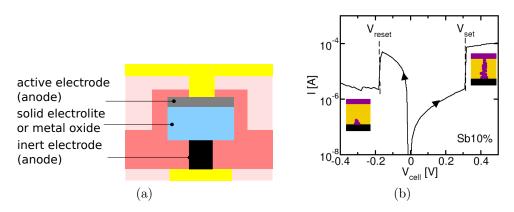

As shown in Fig. 1.6a, the structure of Conductive-Bridging Random Access Memory (CBRAM) devices consists of a Metal-Insultator-Metal structure where the top electrode (anode) is electrochemically active or oxidized under positive bias, and the bottom electrode (cathode) is electrochemically inert. The insulating materials between top and bottom electrode can be solid electrolytes [40] or metal oxides [41], [42]. Upon application of a positive voltage on the anode, mobile metal ions from the anode migrate, driven by the electric field, into the solid electrolyte or oxide and reduce on the inert cathode, forming a conductive filaments (CF) composed of element of the top electrode (typically Cu or Ag), bridging top and bottom electrode and bringing the device to the Low Resistance State (LRS, SET operation). When the voltage is reversed, metal ions migrate back to the anode dissolving the CF and bringing the device into the High Resistance State (RESET operation) [43], [44]. Figure 1.6b shows typical current voltage characteristics of CBRAM. A resistance ratio between HRS and LRS higher than 10<sup>6</sup> has been demonstrated by interface engineering of chalcogenide CBRAM with dual-layer electrolyte stack [45], [46]. Due to the fact that the migration of ions is a stochastic process, the configuration of the CF is different after each SET and RESET operation. This results in large resistance variability, especially in the HRS [4].

Figure 1.6. (a) Schematic view of CBRAM device [47]. (b) Typical CBRAM current-voltage characteristics [40].

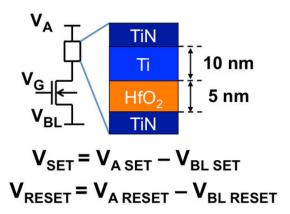

### 1.2.4 OxRAM

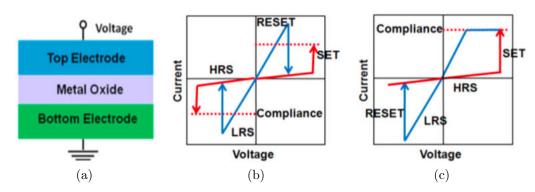

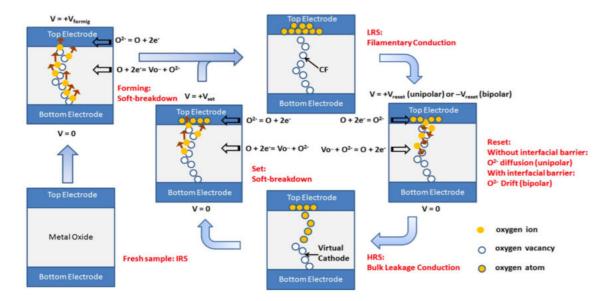

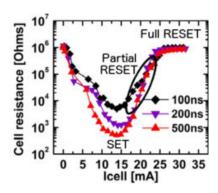

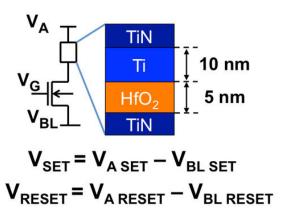

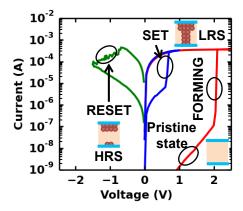

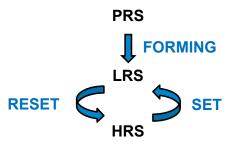

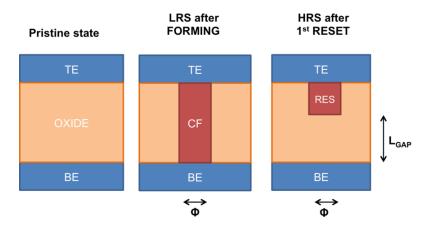

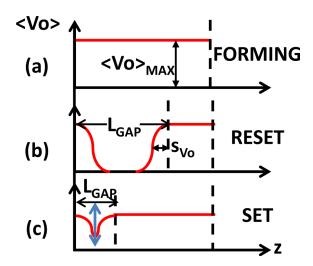

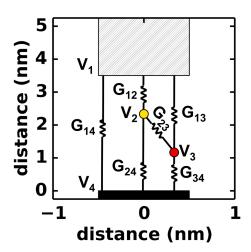

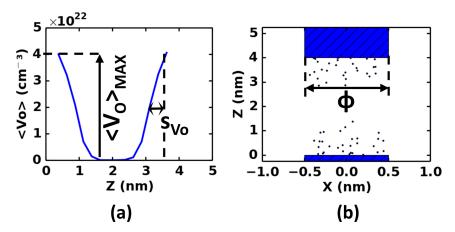

Similarly to CBRAM, Oxide-based resistive RAM (OxRAM) devices are also composed of a simple MIM structure, where a metal oxide is sandwiched between a top and a bottom electrode as shown in Fig. 1.7a. The application of an electric field on the device induces the creation and motion of oxygen vacancies V<sub>O</sub>, resulting in the possibility of repeatedly form and destruct V<sub>O</sub>-rich conductive filaments (CFs) in the oxide. This corresponds to a change in the resistance of the device, which can be switched between Low Resistance State (LRS) and High Resistance State (HRS) with SET and RESET operation, respectively. Figure 1.8 is a schematic illustration of the switching processes. Usually for the fresh samples in the pristine resistance state, a forming or electroforming process is needed to form a Conductive Filament (CF) in the oxide layer for the first time [48]. During the forming process, oxygen ions drift towards the top electrode interface driven by the orientation of the electric field. The formation of an interface oxide layer occurs if the top electrode material is oxidizable. Otherwise, oxygen accumulates in the form of nonlattice atoms if the top electrode material is inert. Thus, the top electrode/oxide interface behaves like an oxygen reservoir [49] for the subsequent SET/RESET operations. According to the polarity of the voltage needed to SET and the RESET the device, OxRAM operation is classified into two switching modes: unipolar and bipolar. Figures 1.7b and 1.7c show a schematic of the current-voltage characteristics for the two switching modes.

• In the unipolar switching mode (Fig. 1.7b), the SET and RESET operations depend only on the amplitude of the applied voltage. Thus, they can be achieved using the same programming polarity. For the RESET operation, current flowing through the CF causes Joule heating. The rising temperature activates the thermal diffusion of oxygen ions, which will diffuse away from the CF due to the concentration gradient [50], bringing the device to HRS. If

Figure 1.7. (a) Schematic of MIM structure of OxRAM devices and (b) Schematic unipolar and (c) bipolar current-voltage characteristics [48].

Figure 1.8. Schematic illustration of the working principle of OxRAM. Source: [48].

SET and RESET operations can equally occur at both positive and negative voltage polarities, the unipolar switching mode mode is also called *nonpolar*.

• In bipolar switching (Fig. 1.7c), the SET and RESET operations are performed at reverse voltage polarities. The interfacial oxide layer at the top electrode may present a significant diffusion barrier. In this case, thermal diffusion caused by Joule heating and concentration gradient alone is not sufficient, so a reverse electric field is needed to improve oxygen ions migration in the RESET process.

In order to achieve the required high temperature at the CF for the RESET

process, usually the unipolar devices requires a higher programming current compared to bipolar devices. In both switching modes, the SET operation occurs by dielectric soft breakdown, similarly to the forming operation. SET operation, however, typically requires a lower voltage compared to the forming one [48]. In order to avoid a permanent dielectric breakdown in the forming and set process, a current limitation, or compliance, is needed. The compliance current is usually provided by the semiconductor parameter analyzer in the case of devices composed of the MIM structure only (1R devices). In the case of 1T1R device, the compliance current is obtained via the selection transistor. Self-compliance 1D1R devices, with a diode as selector device, are an attractive solution for high-density crossbar structures [51].

One of the biggest advantages of this technology is the fact that it relies on simple structure and on materials that are widely used in semiconductor processes and current CMOS technologies. Some OxRAM material examples are  $HfO_x$ ,  $TiO_x$ ,  $AlO_x$  and  $TaO_x$ .

Although the device working principle is simple, the physics that govern the functioning of OxRAM devices are not fully understood yet. There are controversies about the shape of the conductive filament and the role that top and the bottom electrodes play in the switching mechanisms. The characteristics of the oxygen vacancies in terms of thermal stability and mobility are topics of intense research [44], because they are related to memory performance and reliability, such as high temperature data retention and speed. Physical observation of real-time formation and dissolution of CF with in-situ TEM is an active research field [52]–[54], because it can give guidelines for the improvement of the variability issue.

### OxRAM variability

One of the main issues for the manufacturing and industrialization of OxRAM devices is the reproducibility of their electrical characteristics. Large resistance variations occur in fact not only between devices (device-to-device variability – d2d), but also between consecutive programming cycles of the same device (cycle-to-cycle variability -c2c). The problem of variability has been holding OxRAM technology back from commercialization despite its many attractive features, because it limits the size of the memory array that can be implemented. In fact, as the number of devices increases, the distributions of the devices in LRS and HRS tend to overlap, thus making it impossible to sense the difference between LRS and HRS state and thus retrieve information. The resistance variability in High-Resistance State (HRS) is typically larger than the variability of the Low-Resistance State (LRS) [48]. The HRS variability has been modeled introducing a variation on a tunneling barrier thickness [55], [56]. For LRS, it has been attributed to geometric variability of the conductive filament (CF) shape (i.e. CF radius, constriction point...) [48], [57], [58]. However, a unified model able to reproduce the variability from HRS to LRS [59] is still lacking.

### 1.2.5 Comparison of NVM technologies

Table 1.1 presents a benchmark of the different emerging nonvolatile memory technologies. Practically unlimited endurance and good speed are advantages of STT-MRAM technology. However the relatively low resistance ratio achievable in MTJ requires a memory cell architecture that limits its device density. OxRAM features better endurance and speed than PCM and CBRAM, but the problem of variability is much worse than that of PCM and STT-MRAM. In addition, all these memories promise to scale further than Flash and DRAM. When these emerging NVM memories were proposed, there was hope that one of them could become the universal memory, able to make a revolution in the memory hierarchy by meeting all specifications in terms of power consumption, high temperature data retention, speed, endurance, density, scalability and low cost [60]-[62]. However, as it can be evinced from Table 1.1, researchers now generally agree that the possibility of universal memory technology is not very realistic. Application-driven design imposes different specifications about memory performance at each level of the memory hierarchy. These specifications require trade-offs in device characteristics that are hard to obtain with an individual memory technology [4].

## 1.3 Neuromorphic systems

In addition to a drastic change in the organization of the memory hierarchy in traditional Von Neumann computing architectures, emerging non-volatile memories have been indicated as key players in a computation paradigm shift, beyond the traditional Von Neumann architecture, thanks to their use as nanoscale artificial synapses in neuromorphic hardware [64].

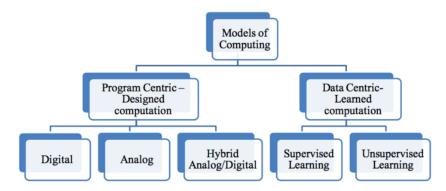

Neuromorphic hardware refers to an emerging field of computing systems design. It takes inspiration from biological neural networks that exist in mammalian nervous system and cerebral cortex. Research in neuromorphic hardware is interdisciplinary, requiring knowledge from computational neuroscience, neurobiology, machine learning, computer science, VLSI design and nanotechnology [65]. Unlike conventional Von Neumann computing architectures, in neuromorphic architectures memory and processing are not isolated tasks. They are interleaved entities, and memory participates in the task of processing the information [66]. Figure 1.9 shows the spectrum of models of computing, from the traditional program-centric Von Neumann-like architectures to emerging data-centric, learned computation models. In the era of the internet of things, with 10 billion devices networked together today (50 billion by 2020) [67], a huge amount of data has to be processed. New models of computation that learn from data, rather than executing instruction provided by programmers, are thus fundamental. The human brain is an example provided by nature of a computing system that learns from data in an efficient way. As

|                |              | PCRAM              | STT-<br>MRAM         | CBRAM              | OxRAM              |

|----------------|--------------|--------------------|----------------------|--------------------|--------------------|

| Feature        | Demonstrated | 45                 | 65                   | 20                 | 5                  |

| Size F (nm)    | Projected    | 8                  | 16                   | 5                  | <5                 |

| Cell Area      | Demonstrated | $4F^2$             | $20F^2$              | $4F^2$             | $4F^2$             |

| Cen Area       | Projected    | $4F^2$             | $8F^2$               | $4F^2$             | $4F^2$             |

| Programming    | Demonstrated | 3                  | 1.8                  | 0.6                | 1                  |

| Voltage (V)    | Projected    | <3                 | <1                   | < 0.5              | <1                 |

| Programming    | Demonstrated | 100                | 35                   | <1                 | <1                 |

| Time (ns)      | Projected    | < 50               | <1                   | <1                 | <1                 |

| Programming    | Demonstrated | $6 \cdot 10^{-12}$ | $2.5 \cdot 10^{-12}$ | $8 \cdot 10^{-12}$ | $<1\cdot 10^{-12}$ |

| Energy (J/bit) | Projected    | $1 \cdot 10^{-15}$ | $1.5 \cdot 10^{-13}$ | N.A.               | $1 \cdot 10^{-16}$ |

| Read           | Demonstrated | 1.2                | 1.8                  | 0.2                | 0.1                |

| Voltage (V)    | Projected    | <1                 | <1                   | < 0.2              | 0.1                |

| Retention      | Demonstrated | >10yr              | >10yr                | >10yr              | >10yr              |

| Time           | Projected    | >10yr              | >10yr                | >10yr              | >10yr              |

| Endurance      | Demonstrated | $10^{9}$           | $> 10^{12}$          | $10^{10}$          | $10^{12}$          |

| (nb. cycles)   | Projected    | $10^{9}$           | $> 10^{15}$          | $> 10^{11}$        | $> 10^{12}$        |

Table 1.1. Comparison of the performance of the different emerging nonvolatile memory technologies according to the 2013 International Technology Roadmap for Semiconductor (ITRS) [63], with projections for year 2026.

Figure 1.9. Taxonomy for traditional and emerging models of computation. Source: [63].

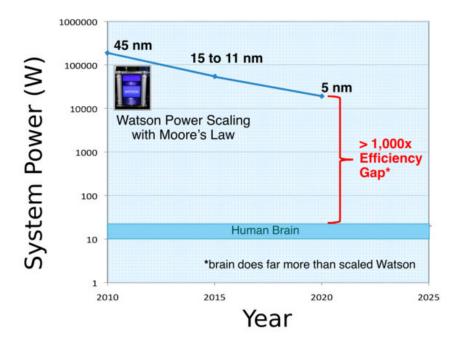

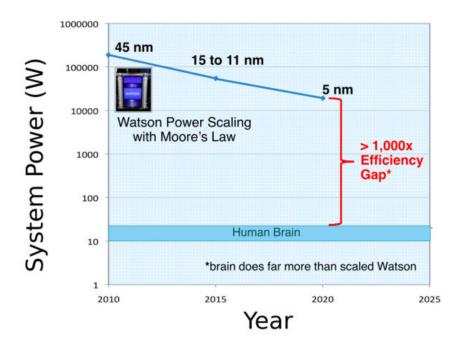

Figure 1.10. Comparison between power consumption of extremely scaled IBM Watson supercomputer and the human brain [68].

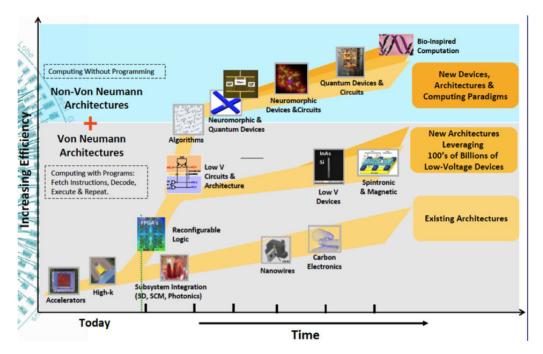

shown in Fig. 1.10, even with extreme scaling, power consumption associated to the Von Neumann computing architecture is orders of magnitude larger than the power required by the human brain. The invention of new architectures is thus required in order to face this challenge, bridging the gap of efficiency that exists between conventional computing architectures and the human brain. In the quest for more efficient computation, neuromorphic hardware has been proposed as a new generation of computing systems, with a complementary role with respect to Von Neumann machines (Fig. 1.11).

Figure 1.11. Proposed future computing roadmap with emerging non-Von Neumann architectures [68].

Historically, the interest on neuromorphic computing systems originated in the 1940s, with the presentation of the computational model for neural networks developed by McCulloch and Pitts [69]. In the late 1940s Hebb made the hypothesis that brain plasticity is at the basis of the human learning mechanism [70]. Researchers started applying these concepts to computational models in 1948 with Turing's B-type machines [71]. In 1957, Rosenblatt developed the perceptron algorithm for image recognition [72], implemented in hardware as the "Mark I Perceptron" or the first neuromorphic machine. Over the next years, the field was relatively stagnant because of the limitations of computational machines that processed neural networks [73]. The emergence of greater computational efficiency, together with advances with the backpropagation algorithm [74], revived the research activity in neuromorphic computing. During the 1980s, parallel distributed processing systems started to be adopted to simulate large-scale neural networks [75]. Mead introduced VLSI design concepts for the design of bio-inspired systems [76], with the design of the first silicon artificial retina and neuro-inspired learning chips on silicon. Neurocomputers, i.e. dedicated hardware implementations of processors specialized for neural computations, emerged in the period from 1980s to early 1990s. The ZISC (Zero Instruction Set Computing) processor [77] was proposed by IBM. The ETANN (Electrically Trainable Artificial Neural Network) chip, featuring 10240 floating-gate synapses was presented by Intel [78]. Other examples of neurocomputers from that period are L-Neuro by Philips, ANNA by AT& T, SYNAPSE 1 by Siemens [79], and

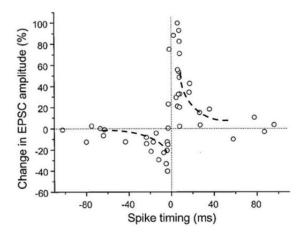

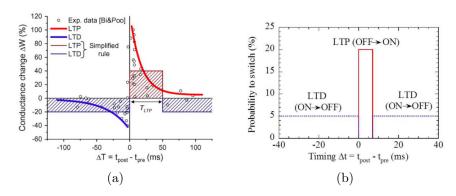

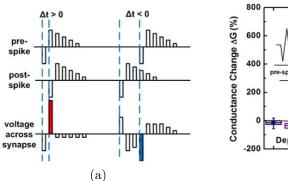

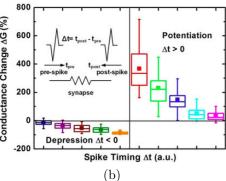

MIND-1024 by CEA [80]. Research advancements in neuroscience during the 1990s, particularly the interest in synaptic plasticity [81] and unsupervised learning rules like spike timing dependent plasticity (STDP) [82] represented a turning point in the field [83]. The progress in the field of emerging non-volatile resistive memory technologies brought new life to research in neuromorphic hardware in the 2000s.

In the next section, we will briefly discuss the characteristics of biological neural networks, composed of neurons and synapse. This is useful to understand which characteristics have to be emulated in order to efficiently implement in hardware a bio-inspired architecture.

### 1.3.1 Neurons and Synapses

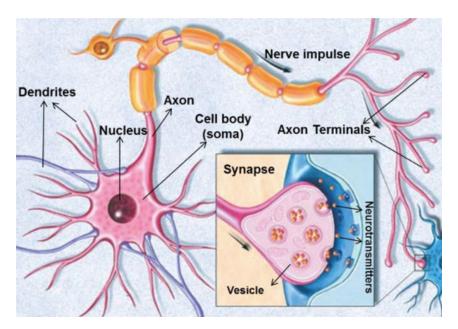

The human brain is composed by a large number of interconnected networks, where the fundamental building blocks are neurons and synapses. It is estimated that in the human brain there are about 10<sup>11</sup> neurons, and 10<sup>15</sup> synapses [84]. Neural networks perform different intelligent functions inside the brain such as perception of stimuli, recognition, movement, speech.

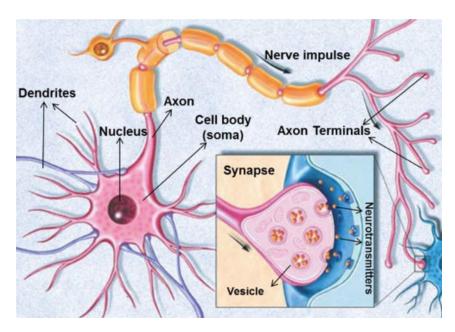

The neuron is an electrically excitable cell that processes and transmits information through electrical signals. Neurons are connected to each other via the synapses, to form neural networks. The signals that are exchanged between neurons are called action potentials or spikes. As shown in Fig. 1.12, a neuron consists of three main parts: the dendrites, the soma and the axon.

- The dendrites are the input vectors through which signals are received. The dendrites allow the cell to receive signals from a large (>1000) number of neighboring neurons.

- The main body of the neuron is the soma. It performs an integrate-and-fire function: as positive and negative signals (exciting and inhibiting, respectively) reach the soma from the dendrites, the membrane voltage of the cell is affected.

- Once the membrane voltage of the soma reaches a certain threshold value, the neuron produces a spike wich is transmitted along the axon to all other connected neurons dendrites.

The synapse is the connecting unit between the axon of a presynaptic neuron (pre-neuron, i.e. the neuron that is sending a spike), and a post-synaptic neuron (post-neuron, i.e. the neuron which is receiving the signal). In a synapse, the voltage spike of the presynaptic neuron activates the voltage-controlled calcium channels present in the presynaptic membrane. The rapid influx of Ca<sup>2+</sup> into the presynapse triggers the release of chemical substances (the neurotransmitters) in the synaptic cleft. Neurotransmitters bind to receptors located on the membrane of the postsynaptic cell. The binding of the transmitters to the postsynaptic receptors causes ionic

Figure 1.12. Schematic view of the basic structure of a neuron cell. Inset shows a zoom of the biological synapse. Source: [85].

channels to open or close, thus changing the ability of ions to flow into or out of the postsynaptic neuron. The selective permeability of these channels allow ions to move along their electrochemical gradient, inducing a ionic current that changes the membrane potential of the neuron (Post-Synaptic Potential, PSP). The change can be positive (Excitatory Post-Synaptic Potential, EPSP) or negative (Inhibitory Post-Synaptic Potential, IPSP).

In the post-neuron, all ionic currents incoming from multiple synapses are summed over time and when a threshold potential is reached, an action potential (spike) is generated and sent along the axon. After that, the membrane potential of the neuron goes back to the resting threshold potential. An important characteristics of synapses is the fact that they are *plastic*: their weight, i.e. the efficiency in the transmission of signals through the synapse, changes over time according to the relative timing at which pre-synaptic and post-synaptic spikes occur. This plasticity, which is described in more detail in Section 1.3.5, is a key factor in learning and remembering.

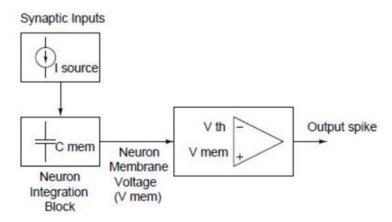

One of the simplest artificial neuron model is, the Integrate and Fire (IF) neuron model. Figure 1.13 shows the concept of a simple IF neuron. It sums over time (integrates) the incoming excitatory and inhibitory signals inside the neuron integration block using a capacitor. More advanced designs also work with this principle [86]. This integration leads to an increase in the membrane potential of the neuron  $V_{\text{mem}}$ . When  $V_{\text{mem}}$  reaches the threshold value  $V_{\text{th}}$ , the neuron generates an output spike. After the neuron has fired the membrane potential is restored to a resting value, by

Figure 1.13. Schematic image shown the basic concept of an Integrate and Fire neuron [86].

discharging the the capacitor  $C_{\text{mem}}$ .

Many designs for the hardware implementation of artificial neurons on silicon, based on standard VLSI CMOS technology, have been proposed in the literature [86]. Research activity is being carried out to optimize power and area efficiency of neurons. Some example feature the use of non-volatile memories [87].

However, given the fact that the number of synapses is about 4 orders of magnitude larger than the number of neurons, the real challenge is to find an efficient design for the synapse, in order to be able to integrate large-scale neural networks on chip. The hardware implementation of artificial synapses is discussed in the next section.

### 1.3.2 Non-volatile memory devices as artificial synapses

Multiple solutions to implement artificial synapses using available VLSI devices such as Flash, DRAM and SRAM have been proposed in the literature [66]. These approaches have the advantage of relying on already available standardized design tools and a mature fabrication process. However, some limitations exist with this approach [65]. Flash devices are not an ideal candidate for the implementation of bio-inspired learning rules because they are 3-terminal devices, while real synapses are 2-terminal. During synaptic learning individual synapses may undergo weight modification asynchronously, which is not straightforward to achieve with the addressing schemes required for Flash arrays. Flash devices also require high operating voltages in order to program the cell. In many cases, complex pre-synaptic circuitry is required to implement timing dependent learning rules. This is necessary in the case of NOR Flash, because of the differences in the physics involved in the writing and erasing of the floating gate devices, but not in the case of NAND Flash. Furthermore, Flash endurance is limited, which implies a limited amount of learning operations can occur. Synapses based on DRAM technology are volatile and require refresh cycles

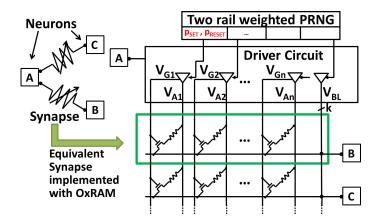

to retain the synaptic weight, since the information is stored as charge accumulated on a capacitor. Typically the implementation of learning rules based on DRAM synapse requires more than 10 additional transistors [88], [89]. The capacitor element itself is also area-consuming. The SRAM based synapses are affected even worse by the problem of large area consumption and are also volatile. When the network is turned off, the synaptic weights stored in SRAM are lost, so they need to be stored to a nonvolatile memory unit during or after the learning, which leads to additional power and area consumption. The limitations of available VLSI technologies for the implementation of artificial synapses provided the motivation for research in synaptic emulation using emerging non-volatile memory technologies. Recent research in nanoscale devices and materials has demonstrated the possibility of emulating the behavior of real synapses in artificial neural networks, and in particular to reproduce their plasticity and non-volatility characteristics [66], [90]–[104]. The basic idea behind this approach is to emulate the behavior of the synapse, which is a communication channel featuring variable efficiency, as a tunable resistor, implemented with a non-volatile memory (NVM) device. Some advantages of using emerging NVMs as artificial synapses are low-cost, full CMOS compatibility, high density, low-power consumption, high endurance, high temperature retention [28], [48]. NVM devices are 2-terminal, as in the case of real synapses, and offer the possibility of 3D integration.

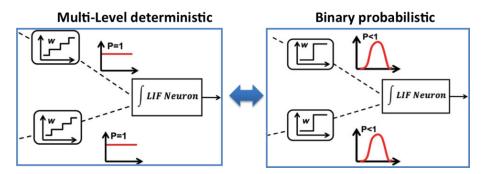

Two main device categories can be identified for the implementation of artificial synapses: multilevel and binary devices.

#### Multilevel

In the multilevel (or analog) approach, the possibility of programming individual NVMs at multiple resistance levels is exploited. Some examples feature the use of OxRAM and CBRAM devices, where multilevel resistance levels are obtained by tuning compliance current during SET operation, or modulating the applied voltage [96]. However, this implementation is not ideal from a practical perspective. It requires the adoption of complicated neuron spike shapes [90], or the generation of spikes with increasing amplitude while keeping a history of the previous state of the synaptic device, leading to additional overhead in the neuron circuitry.

A better candidate for the multilevel approach is PCRAM technology, which offers the possibility of gradually increasing the conductance of the device by applying identical SET pulses, gradually increasing the size of the crystalline region in the active phase-change material. However, the reset process is not gradual but abrupt.

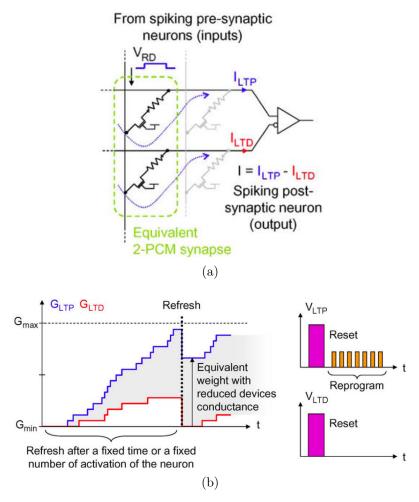

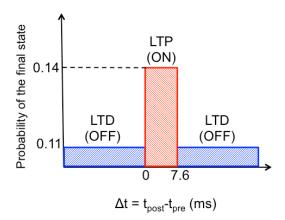

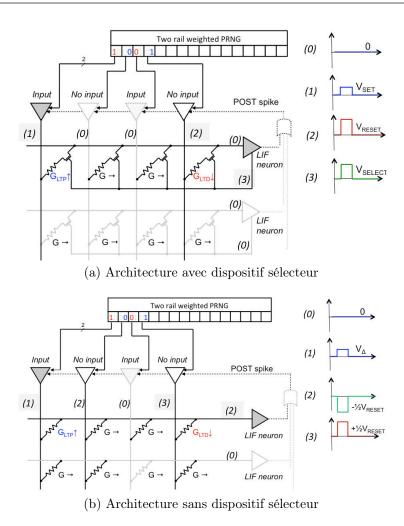

This led to the proposition of the use of two PCRAM devices per synapse, in the 2-PCM approach proposed in [101] and recently adopted in [104]. These two devices are connected in a complementary configuration, where each device has an opposite contribution to the neuron's integration. When the equivalent synapse needs to be potentiated, the Long Term Potentiation (LTP) PCRAM device is partially crystallized with a weak SET operation. This increases the equivalent

weight of the synapse. On the contrary, when the synapse must be depressed, it is the Long Term Depression (LTD) PCM device that undergoes partial crystallization. Since the contribution of the to the neuron's integration is negative, the equivalent weight of the synapse is decreased. With this solution, since gradual crystallization is achieved with successive identical voltage pulses, the pulse generation scheme is greatly simplified. However, a systematic refresh scheme is needed to reset the devices by retaining the weight of the synapse.

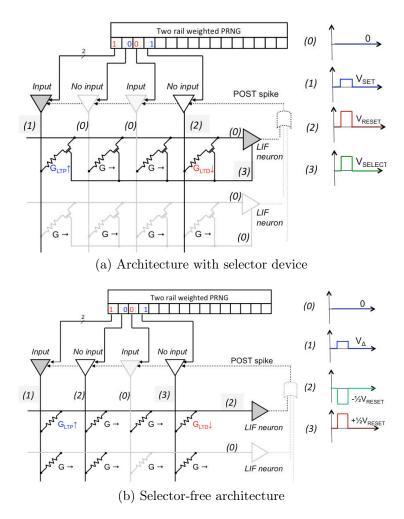

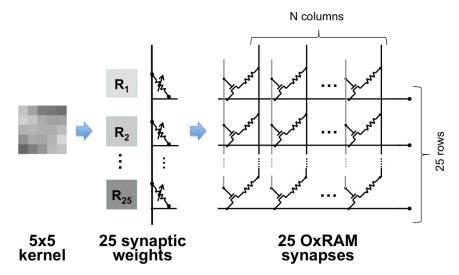

### **Binary**

With the binary approach, only two resistance levels per NVM device are used: the low and high resistance states (LRS and HRS). The advantage of this approach resides in the fact that it relies on programming schemes that are by all means similar to the ones used for conventional memory applications. Since only two sates of the device are exploited, simple SET and RESET pulses are required, optimized for speed and power consumption. It has been demonstrated that for some applications, such as the detection of cars driving in different lanes of a motorway [105], a single device associated to a stochastic learning rule (Section 1.3.5), is enough to achieve detection rates comparable to the ones obtained with multilevel synapses. In Chapter 4 we will illustrate how, by connecting n devices in parallel, it is possible to obtain a multilevel conductance behavior using binary devices. Since parallel conductance sum up, the conductance of the equivalent synapses ranges from the sum of the n conductance in the HRS to the sum of all the n conductance in the LRS. The use of multiple devices is necessary for applications that are more complex than detection, such as visual pattern recognition. This strategy comes at the cost of an increased number of devices needed to build a synapse. The binary approach offers the advantage of a simple programming methodology for the NVM devices, in which standard SET and RESET pulses, optimized for high endurance and low-power consumption, are used to switch the device resistance from LRS to HRS and vice versa.

### 1.3.3 Fully connected neural networks

The artificial synapses described in Section 1.3.2 have been proposed in the literature for the implementation of artificial neural networks composed of CMOS neurons and NVM-based synapses [66], [90]–[104]. The network topology that has been mostly investigated in the literature is the fully connected neural network. In this neural network topology, neurons are organized in layers. The first neuron layer is connected to the input of the network, while the last neuron layer represents the output of the system. The neuron layers between input and output are generally referred to as *hidden* layers. For a system designed for visual applications such as pattern detection or recognition, the raw data to be processed can be a static picture [96] or a video [101]. For auditory application the raw data is sound [105]. The raw

# Fully Connected Neural Network topology

m neurons m × n synapses n neurons

Figure 1.14. Fully connected neural network topology. Each neuron is connected to every neuron of the upper layer by a large number of synapses.

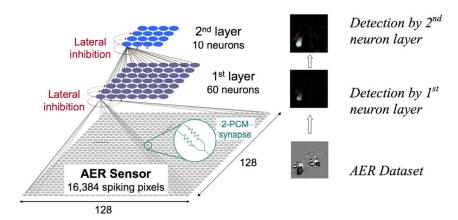

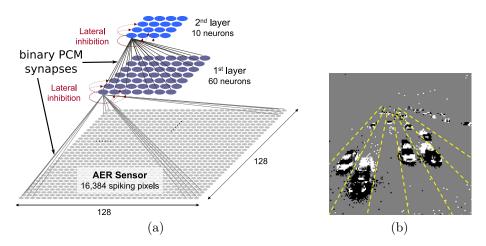

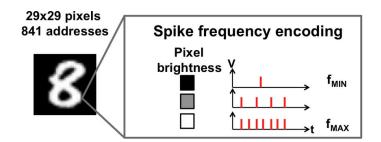

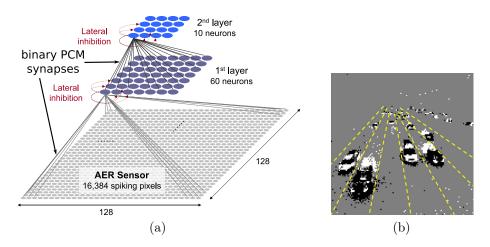

data is converted into voltage spikes with a given encoding rule, and fed as an input to the network. The conversion of the data to "spike language" understandable by the network can be implemented with a simple algorithm, such as linear conversion from pixel brightness to spike frequency. It can also be obtained with bio-inspired sensors such as artificial retina [106] or cochlea [107], or even electroencephalography (EEG) recording [95]. In the fully connected neural network topology, each neuron is connected to every neuron of the next layer as shown in Fig. 1.14. The spike signals propagate through from input to output through the hidden layers of the network, undergoing a transformation that is defined by the weight of the synapses. The output neuron layer can be composed of a single or multiple neurons. A single neuron is used if the network is used to detect a pattern in time. An example is detecting a specific sound pattern hidden by white noise [105]. Multiple output neurons can be used to perform a classification task, such as the classification of the sound of different vowels [95], the orientations of a segment [96] or the shape of simple visual patterns [100]. Figure 1.15 shows an example of a neuromorphic system with fully connected topology and multiple output neurons. The input of the network is connected to a bio-inspired artificial retina sensor, using Address-Event Representation (AER) data. The artificial retina records a video of cars passing on different lanes of a motorway. The neuromorphic system is used to detect cars passing on different lanes: when a car is driving on a given lane, a corresponding output neuron is activated. This allows to extract information about when and which lane a car is driving on.

### 1.3.4 Convolutional neural networks

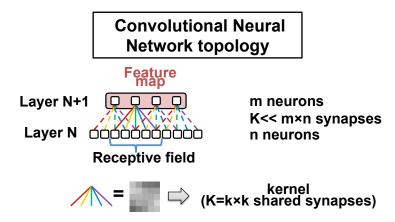

Fully connected neural network topologies are often limited to a maximum number of hidden layers equal to one or two. Further increasing the number of layers explosively increases the complexity of the network and the number of required synapses, without necessarily improving the performance of the network for pattern

Figure 1.15. Fully connected neuromorphic system for visual pattern extraction from video of cars driving on different lanes [101].

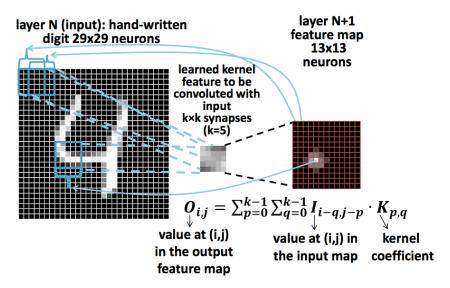

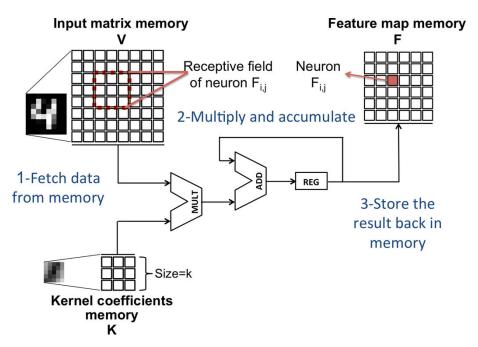

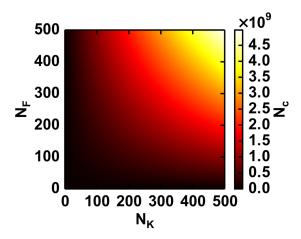

recognition applications. Convolutional Neural Networks (CNNs), often referred to as deep neural networks, are composed of a cascade of many layers. The first layers of a CNN are convolutional layers, with a topology schematized in Fig. 1.16. Neurons of a convolutional layer are organized in feature maps. Each neuron of a feature map is connected to a small subset of neurons (receptive field) of the previous layer. A small set of synapses (kernel, or filter bank) is shared among different neurons to connect layer N and N+1 through a convolution operation. Figure 1.17 illustrates the operation of convolution where layer N is a handwritten digit 4, and the kernel feature is a diagonal edge. The kernel corresponds to a feature that has to be localized in the input image. A peak in the convolution signal means that the feature is present in the input pattern, and the feature map indicates where the feature is present in the input field. At each convolutional layer, the input pattern undergoes a transformation to a higher, more abstract representation. In the case of image recognition applications, for examples, the learned kernel features in the first convolutional layer typically represent simple edges or segments with a given orientation. The features of the second layer typically represent particular arrangements of edges in more complex shapes. The kernel features of the next layer layer may represent more complex combinations that correspond to parts of objects. After the convolutional layers, a classifier with fully connected topology is used to classify objects as combinations of the different parts extracted by the previous convolutional layers.

CNNs are based on the property that many natural signals feature a hierarchic structure, where higher-level complex features are a composition of lower-level simple ones. In the examples of visual images, local combinations of edges are arranged into motifs, motifs are arranged into parts composing different objects. Similar hierararchic structures exist in natural speech signal, where different sounds compose phones, which in turn form phonemes, then syllables, then words and finally full

Figure 1.16. Convolutional neural network topology. A small set of synapses (kernel) is shared among different neurons to connect layer N and N+1 through a convolution operation.

Figure 1.17. Schematic illustration of the convolution operation between an input image representing the handwritten digit "4" and a kernel feature representing a diagonal edge. The resulting feature map holds information about where the kernel feature is present in the input image.

complex sentences [108]. The organization of convolutional layers in CNNs are inspired by the complex cells in visual neuroscience [109], and the CNN hierarchic structure is inspired by the neuronal hierarchy in the visual cortex [110].

Software implementations of CNNs were originally developed in the early 1990s and used for applications such as speech recognition [111] and document reading [112]. Since the early 2000s CNNs have been applied with great success in applications such as traffic sign recognition [113], the analysis of biological images [114], and the detection of faces, complex text, pedestrians on the streets and human bodies in

natural images [115]–[120]. A major recent practical success of software implementations of CNNs is the face recognition software proposed by Facebook, which is based able to match human performance in people's faces recognition tasks [121].

Hardware implementations of CNNs, exploiting the energy efficiency of NVMs as discussed in Chapter 4, would open the way to advanced complex pattern recognition in smart and portable devices, where low power consumption is a crucial factor to take into account.

### 1.3.5 Learning

In the previous sections, the concept of synapses as connections with tunable weight in artificial neural networks has been introduced. In this section, we will introduce the concept of learning, i.e. how the weight of each synapse of a neural network is defined in the network, starting from the input stimuli.

### Supervised learning

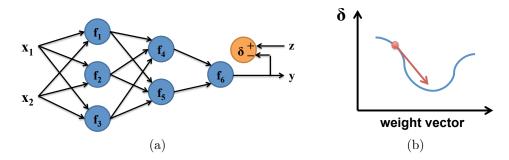

In the framework of artificial neural networks, the most common form of machine learning is supervised [108]. In supervised training, the network learns from data but an external supervision is needed, in the form of a labeled training data set, to guide the learning process towards correct results. The backpropagation algorithm is one of the most used supervised learning algorithm. In order to explain this algorithm, let's consider a hypothetical system designed for image classification, where images of objects have to be classified into n different categories. At the initial state, the network is untrained, i.e. the synaptic weights are random. In order to determine the good synaptic weights, first a training data set has to be collected. It consists of a large set of examples, where each object image is labeled with its corresponding category. Then the network undergoes training, which is done in software simulation. A flowchart illustrating the algorithm that is executed is presented in Fig. 1.18. At every step of the training (training epoch), the machine is shown one of the images of the training data set and produces an output. The output of the network is in the form of neuron activity of the n output neurons, one for each object category. It is desired that only the output neuron associated to the category of the image that we show is activated. However, this is unlikely to happen before training, because we still need to "teach" to the network which object belongs to which category. In order to quantify the goodness of the network output, the objective function  $\delta$  is determined as schematically represented in Fig. 1.19a. It measures the error, i.e. the distance between the actual network output y and the desired output pattern z. The internal adjustable parameters of the machine are then adjusted to reduce this error. These adjustable parameters are the synaptic weights, which define the transformation performed by the machine from input to output. In a typical deep-learning system such as a convolutional neural network, there may be tens or hundreds of millions

Figure 1.18. Flowchart of the supervised learning algorithm.

of these synaptic weights. The set of synaptic weights of the system is called the weight vector. To properly adjust the weight vector, the backpropagation algorithm computes a gradient vector. The gradient vector describes, for each weight, by how much the error would decrease (or increase) if the synaptic weights were changed by a tiny amount. The key insight of the backpropagation algorithm is that gradient vector of the objective function can be computed backwards from the output to the input of the network. The weight vector is then adjusted in the opposite direction to the gradient vector. The objective function is a complex function in the multidimensional weight space, featuring multiple local minima and maxima. Figure 1.19b gives a schematic example of an objective function  $\delta$  as a function of a one-dimensional weight vector. Thanks to the gradient vector we can follow the direction of steepest descent in this multidimensional function, towards a global minimum where the error is the lowest on average [108].

The optimal weight vector determined with backpropagation, which makes sure that the network performs the best on the training data set, is also the one that most likely will perform well on new images that do not belonging to the training data set, with images that the network didn't "see" before, in a process which is

Figure 1.19. (a) Schematic representation of the computation of the objective function  $\delta$  as the distance between the desired output of the network z and the actual network output z. Adapted from [122]. (b) Illustration of the gradient descent process, performed to minimize the error of the network thanks to the backpropagation algorithm.

called generalization. Once the weight vector is defined with training in computer simulation, it is possible to import the weight in the artificial neural network. In the case of an artificial neural network where the synapses are implemented with NVM devices, each device is programmed to the resistance level determined by the backpropagation learning algorithm.

### Unsupervised learning

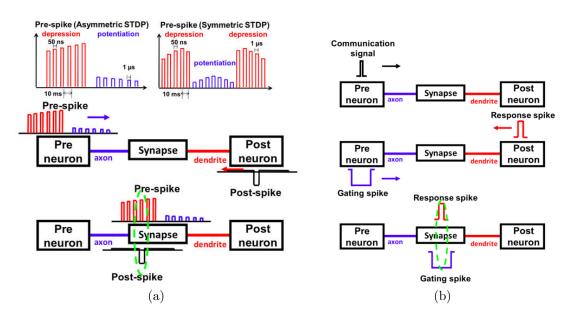

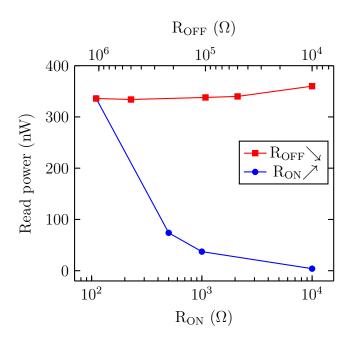

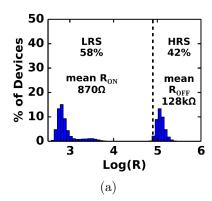

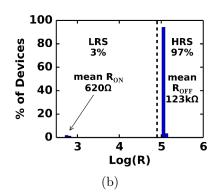

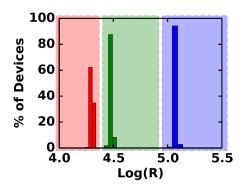

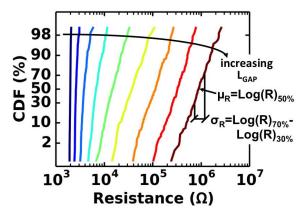

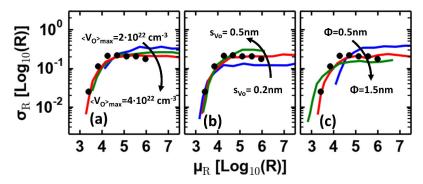

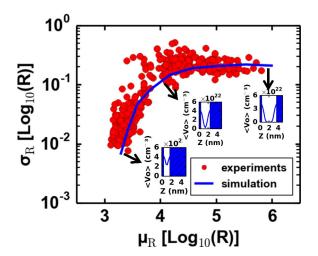

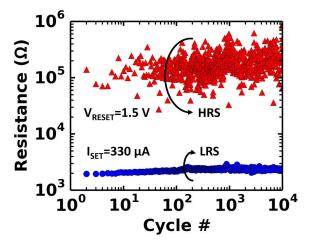

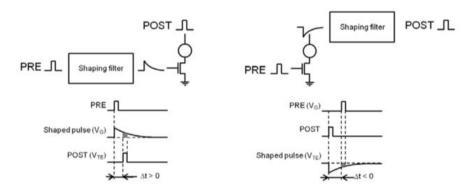

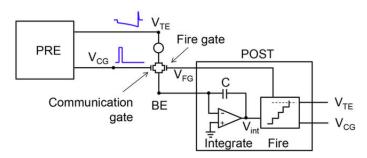

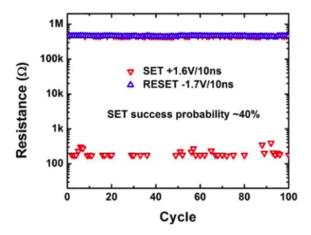

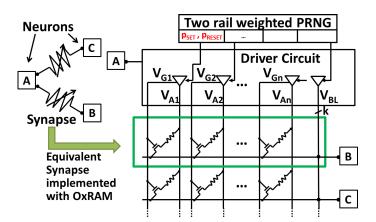

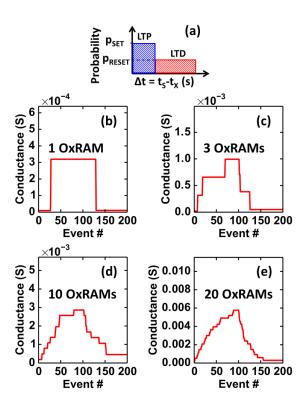

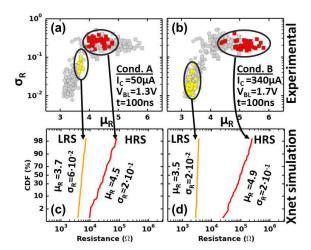

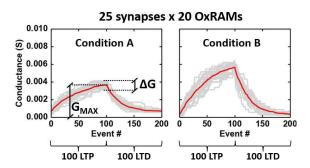

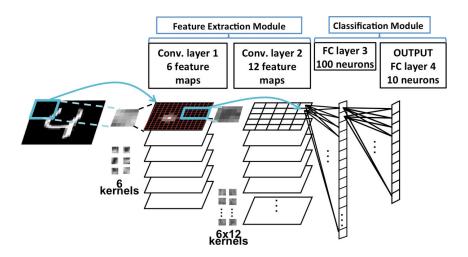

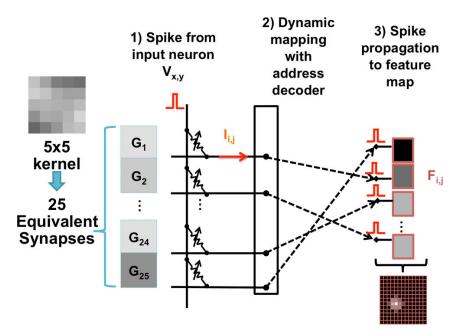

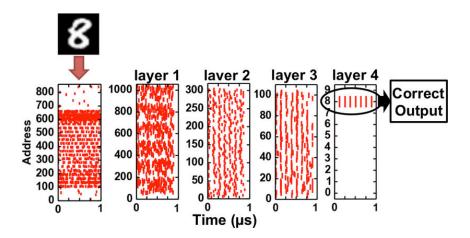

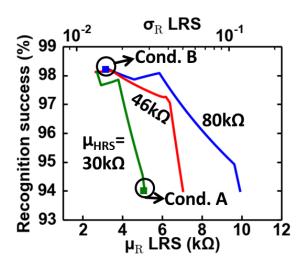

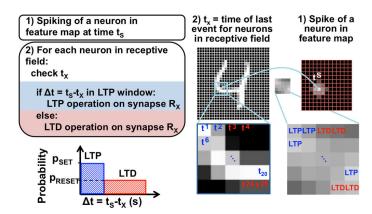

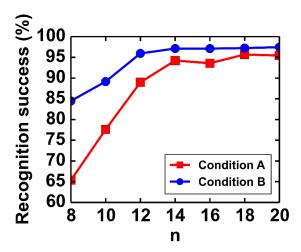

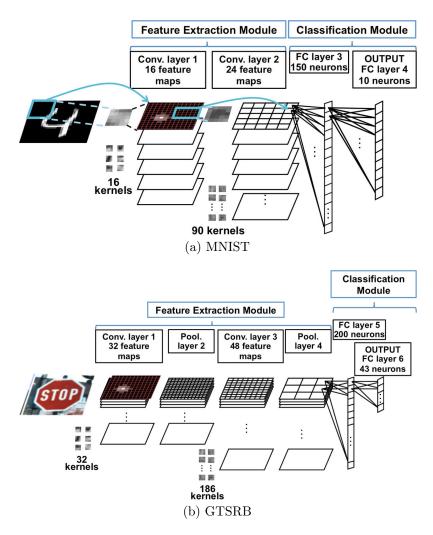

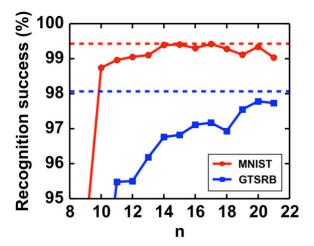

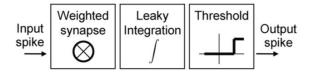

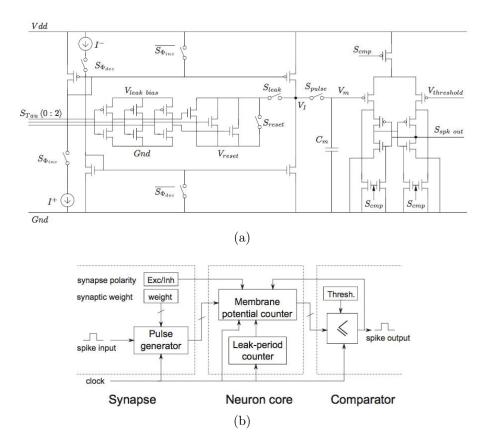

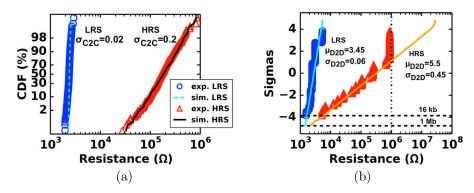

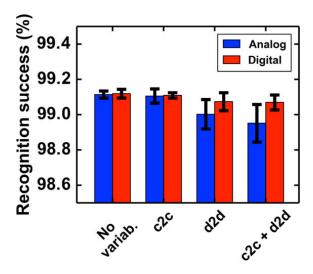

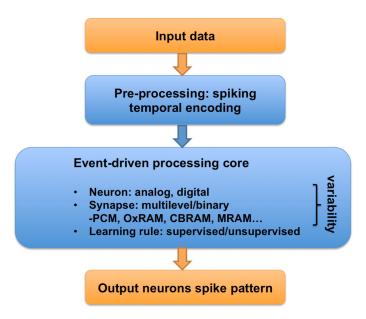

While supervised learning offers the possibility to achieve excellent performance, similar to the human one, even on very complex recognition tasks such as face recognition [121], its main limitation is the need of a labeled training data set, which can require hundreds of millions of elements in order to achieve excellent performance [108]. If we take inspiration from human learning, we realize that it is largely unsupervised: the structure of the world is learned by observing it, not by using a huge database of labeled examples, as it happens in supervised learning. Even though human learning is still relatively obscure and still object of research, the biological process known as Spike Timing Dependent Plasticity (STDP) is widely believed to play a key role in learning and storing information in the brain [82].