# Techniques de multiplexage pour un système d'émulation et de prototypage rapide à base de FPGA

Mariem Turki

#### ▶ To cite this version:

Mariem Turki. Techniques de multiplexage pour un système d'émulation et de prototypage rapide à base de FPGA. Modélisation et simulation. Université Pierre et Marie Curie - Paris VI; Université de Sfax (Tunisie), 2014. Français. NNT: 2014PA066698 . tel-01281361

## HAL Id: tel-01281361 https://theses.hal.science/tel-01281361

Submitted on 2 Mar 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Thèse de doctorat de l'université Pierre et Marie Curie -Paris VI L'école Nationale d'ingénieurs de sfax - Université de Sfax

Présentée par : Mariem TURKI

Pour obtenir le grade de

### Docteur de l'Université Pierre et Marie Curie

Spécialité Informatique et Micro-Electronique

ET

## Docteur de l'Ecole Nationale d'Ingénieurs de Sfax Spécialité Ingénierie des Systèmes Informatiques

## TECHNIQUES DE MULTIPLEXAGE POUR UN SYSTÈME D'ÉMULATION ET DE PROTOTYPAGE RAPIDE À BASE DE FPGA

Soutenue le 17 Septembre 2014, devant le jury composé de :

| Pr. | Rached Tourki    | FSM     | Rapporteur         |

|-----|------------------|---------|--------------------|

| Pr. | Smail Niar       | LAMIH   | Rapporteur         |

| Pr. | Bertrand Granado | LIP6    | Examinateur        |

| Pr. | Mohamed Masmoudi | ENIS    | Examinateur        |

| Pr. | Habib Mehrez     | LIP6    | Directeur de thèse |

| Pr. | Mohamed Abid     | ENIS    | Directeur de thèse |

| M.  | Zied Marrakchi   | Flexras | Invité             |

#### Résumé

De nos jours, la complexité de la conception des circuits intégrés et du logiciel croit régulièrement, faisant croître le besoin de la vérification dans chaque étape du cycle de conception. Le prototypage matériel sur une plateforme multi-FPGA présente le meilleur compromis entre le temps de conception d'un circuit et le temps d'exécution d'une application par ce circuit. Pour l'implémenter sur cette plateforme, une opération de partitionnement est effectuée afin de créer des partitions capables de s'intégrer dans chaque FPGA. Par conséquent, des signaux coupés à l'interface des partitions doivent passer d'un FPGA à un autre. Cependant, le nombre de traces physiques inter-FPGA est limité ce qui crée des problèmes de routabilité du circuit prototypé.

Cette thèse touche surtout la partie post-partitionnement et s'intéresse au problème de routage inter-FPGA. Ainsi, les principaux travaux de cette thèse sont les suivants :

- •Dans un premier temps, nous nous intéressons au développement d'un générateur de benchmarks qui permet, à l'aide d'une description architecturale simple du benchmark, de générer un circuit modélisé avec le langage de description matérielle VHDL. Le générateur utilise un ensemble de composants ce qui donne aux benchmarks un aspect réel semblable à celui des circuits industriels. Ces circuits de tests nous serviront pour évaluer les performances des techniques développées dans cette thèse.

- •Dans un deuxième temps, nous proposons de développer un outil spécifique qui intervient après le partitionnement pour prendre en compte la contrainte liée à la limitation du nombre de fils d'interconnexion entre les FPGAs. Cet outil est basé sur une approche itérative visant à réduire le taux de multiplexage (nombre de signaux qui partagent un seul fil physique). Le routage en lui même est assuré par l'algorithme de routage Pathfinder adapté. Cet algorithme servira comme point de départ pour les techniques de routage développées durant cette thèse. Des adaptations adéquates seront faites pour cibler un réseau de routage inter-FPGA. Dans une deuxième partie, nous essayons de déterminer la meilleure forme du signal à router (bi-points ou multi-points) ainsi que le graphe de routage utilisé. Pour cela, nous proposons des scénarios de test afin de sélectionner les critères qui donnent la fréquence de fonctionnement la plus performante.

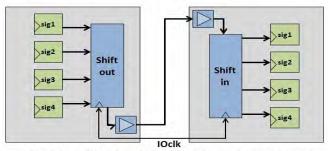

- •Par la suite, nous présentons une description détaillée des IPs de multiplexage utilisés. Ces IPs sont insérés dans les parties émettrices et réceptrices d'un canal de communication. Ces IPs incluent des composants spécifiques appelés SERDES pour assurer la sérialisation/déserialisation des données à transmettre. L'insertion de ces composants peut créer des problèmes de routabilité intra-FPGA. Ainsi, dans une deuxième partie, nous proposons un algorithme de placement basé sur l'estimation de la congestion afin d'améliorer la routabilité du circuit.

Mots-clés: FPGA (Field Programmable Gate Array), Prototypage, Routage, Pathfinder, Itératif, Multiplexage, Graphe de routage, Benchmarks.

#### Abstract

With the ever increasing complexity of system on chip circuits, the software and hard-ware developers can no longer wait for the fabrication phase to test their designs. Multi-FPGA-based prototyping is an important verification method since it presents a best compromise between the time of circuit design and the execution time of an application by the circuit. To implement a design into a multi-FPGA platform, a partitioning operation is performed to create partitions which can fit into each FPGA. Consequently, cut signals which appear at the interfaces are transmitted between pairs of FPGA. However, the number of physical traces inter-FPGA is limited, which creates problems of routability of the prototyped design.

This thesis mainly deals with the post-partitioning task and addresses the problem of inter-FPGA routing. Thus, the main contributions of this thesis are:

- •Firstly, we focus on the development of a benchmark generator which, using a simple architectural description of the benchmark, generates a circuit modelled with the hardware description language VHDL. The generator uses a set of industrial components providing benchmarks with real behaviour similar to that of industrial circuits. These benchmarks are used to evaluate the performance of the techniques developed in this thesis.

- •In a second step, we propose a specific tool which acts after the partitioning to handle the constraints related to the limited number of interconnection between FPGAs. This tool is based on an iterative approach and aims to reduce the multiplexing ratio (the number of signals that share the same physical wire). The routing task itself is operated by the Pathfinder routing algorithm which is widely used by academic and industrial researchers. This algorithm is used as a starting point for routing techniques developed in this thesis. In a second part, we try to identify the best shape of the routed signals and the appropriate routing graph. For this reason, we propose scenarios to select criteria that give the best system frequency.

- •Finally, we present a detailed description of the architecture of the multiplexing IPs. These IPs are inserted in the transmitting and receiving FPGAs of a communication channel. These IPs include specific components called SERDES for serialization/descrialization of the data. The insertion of these IPs can create problems of intra-FPGA routability. Thus, in a second part, we propose a placement algorithm based on congestion estimation to improve the routability of the circuit.

**Keywords:** FPGA (Field Programmable Gate Array), Prototyping, Routing, Pathfinder, Iterative, Multiplexing, Routing graph, Benchmarks.

A mes parents pour leur amour et leur soutien A mon mari pour sa patience et son encouragement A toute ma famille et tous mes amis

#### Remerciements

Je voudrais exprimer ma plus grande gratitude à mes directeurs de thèse, Habib Mehrez, Professeur à Paris 6, et Mohamed ABID, Professeur à l'ENIS pour la confiance qu'ils m'ont accordée tout au long de ma thèse, ainsi que pour leur grande disponibilité, motivation et encouragement.

Je suis extrêmement reconnaissante à mon encadrant Zied Marrakchi pour ses conseils précieux et son support technique qui ont permis de me guider durant cette thèse. Zied Marrakchi a réussi, avec son dynamisme, son talent et surtout sa patience, à orienter les travaux de cette thèse vers le bon chemin.

J'adresse mes remerciements à monsieur Rached Tourki, professeur à la faculté des sciences à Monastir, et monsieur Smail Niar, professeur à l'université de valenciennes, qui m'ont fait l'honneur d'être rapporteurs de cette thèse.

Je tiens également à remercier messieurs Bertrand Granado, professeur au laboratoire Lip6 de Paris 6 et Mohamed Masmoudi, professeur à l'Ecole Nationale d'Ingénieurs de Sfax, qui ont bien voulu accepter d'évaluer ce travail en participant à mon jury de thèse.

Je voudrais aussi adresser mes sincères remerciements à monsieur Abdelmalek si-Mrabet pour sa gentillesse et ses réponses techniques.

Je souhaite ensuite saluer mes collègues au LIP6, Emna Amouri, Andi Drebes et Vinod Pangratious sans oublier mes amis à l'ENIS, Saoussen, Bouthaina, Nihel et Rania pour la bonne ambiance qu'ils ont créée durant la thèse.

Je témoigne ma plus profonde affection à mes parents et mes deux sœurs pour leur amour et leur perpétuel soutien. J'envoie également mes sentiments les plus tendres à mon mari, pour son soutien quotidien et son encouragement.

Pour terminer, je m'excuse auprès de ceux que j'aurais pu oublier, et à qui j'adresse évidemment mes sincères remerciements.

## Table des Matières

| $\mathbf{R}$              | ésum   | ıé                           |                                                                   |     | i  |

|---------------------------|--------|------------------------------|-------------------------------------------------------------------|-----|----|

| A                         | bstra  | ct                           |                                                                   | ii  | ίi |

| $\mathbf{R}$              | emer   | cieme                        | ${f nts}$                                                         | vi  | ίi |

| $\mathbf{T}_{\mathbf{i}}$ | able ( | $\mathbf{des} \; \mathbf{M}$ | atières                                                           | i   | X  |

| Ta                        | able ( | des fig                      | gures                                                             | X   | v  |

| Li                        | ste d  | les tab                      | oleaux                                                            | xi  | X  |

| 1                         | Intr   | $\operatorname{roduct}$      | ion                                                               |     | 1  |

|                           | 1.1    | Les b                        | uts de recherche et contributions                                 | •   | 1  |

|                           |        | 1.1.1                        | Problème de routage inter-FPGA                                    | •   | 2  |

|                           |        | 1.1.2                        | Problème de routage intra-FPGA                                    | •   | 5  |

|                           |        | 1.1.3                        | Limitation des benchmarks de test                                 | •   | 6  |

|                           | 1.2    | Plan                         |                                                                   | •   | 7  |

| 2                         | Éta    | t de l'                      | art : Plateformes matérielles                                     | 9   | 9  |

|                           | 2.1    | Introd                       | luction                                                           |     | 9  |

|                           | 2.2    | Vérifi                       | cation des SoCs                                                   | . 1 | 0  |

|                           |        | 2.2.1                        | Simulation logique                                                | . 1 | 1  |

|                           |        | 2.2.2                        | Émulation matérielle                                              | . 1 | 2  |

|                           |        | 2.2.3                        | Prototypage matériel                                              | . 1 | 4  |

|                           |        | 2.2.4                        | Synthèse : Comparaison entre les différents types de vérification | . 1 | 5  |

|                           | 2.3    | Archi                        | tecture FPGA                                                      | . 1 | 6  |

|                           |        | 2 3 1                        | Bloc logique de base du FPGA                                      | 1   | 6  |

|   |     | 2.3.2    | Ressources de routage                               | 17 |

|---|-----|----------|-----------------------------------------------------|----|

|   |     | 2.3.3    | Éléments spécifiques                                | 19 |

|   | 2.4 | Exemp    | oles de FPGA industriels                            | 20 |

|   |     | 2.4.1    | Architecture du Virtex VI                           | 20 |

|   |     | 2.4.2    | Architecture du Virtex 7                            | 23 |

|   |     | 2.4.3    | Architecture du Stratix V                           | 24 |

|   | 2.5 | Platefo  | ormes industrielles de prototypage                  | 26 |

|   |     | 2.5.1    | Plateformes matérielles                             | 26 |

|   |     | 2.5.2    | Plateformes de prototypage complètes                | 27 |

|   | 2.6 | Conclu   | asion                                               | 29 |

| 3 | Éta | t de l'a | art : Flot logiciel pour plateforme Multi-FPGA      | 31 |

|   | 3.1 | Introd   | $\operatorname{uction}$                             | 31 |

|   | 3.2 | Modél    | isation RTL du système sur puce                     | 33 |

|   | 3.3 | Synthè   | ese logique et mapping                              | 33 |

|   | 3.4 | Partiti  | onnement                                            | 35 |

|   | 3.5 | Routa    | ge des signaux inter-FPGA                           | 36 |

|   |     | 3.5.1    | Technique des fils virtuels : Avec ordonnancement   | 37 |

|   |     | 3.5.2    | Technique de routage sans ordonnancement            | 42 |

|   | 3.6 | Placen   | nent intra-FPGA                                     | 45 |

|   |     | 3.6.1    | Placement par le recuit simulé                      | 45 |

|   |     | 3.6.2    | Fonction coût                                       | 46 |

|   |     | 3.6.3    | Réduction de la congestion                          | 47 |

|   | 3.7 | Routa    | ge Intra-FPGA                                       | 48 |

|   |     | 3.7.1    | Algorithme de routage PathFinder                    | 48 |

|   | 3.8 | Conclu   | asion                                               | 51 |

| 4 | Gér | nérateu  | r de benchmarks                                     | 53 |

|   | 4.1 | Introd   | $\operatorname{uction}$                             | 53 |

|   | 4.2 | Les ar   | chitectures multiprocesseurs                        | 54 |

|   |     | 4.2.1    | Caractéristiques des architectures multiprocesseurs | 54 |

|   |     | 4.2.2    | Caractéristiques du générateur de benchmarks        | 55 |

|   | 4.3 | L'envi   | ronnement DSX SystemC                               | 56 |

|   |     | 4.3.1  | Chaine de compilation de DSX_SystemC                                     | 56           |

|---|-----|--------|--------------------------------------------------------------------------|--------------|

|   |     | 4.3.2  | Bibliothèque SoCLib de composants                                        | 57           |

|   | 4.4 | Enviro | onnement DSX_VHDL                                                        | 58           |

|   |     | 4.4.1  | Génération de la netlist synthétisable                                   | 58           |

|   |     | 4.4.2  | Chaine de compilation de DSX_VHDL                                        | 60           |

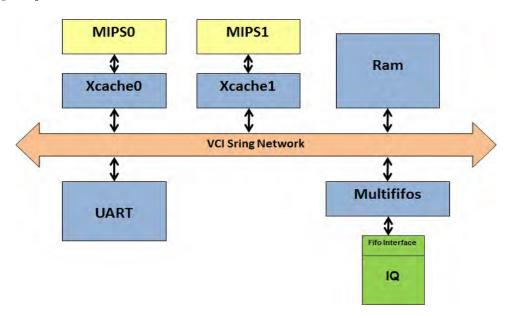

|   |     | 4.4.3  | Exemple de benchmark généré                                              | 66           |

|   | 4.5 | Métho  | dologie de synthèse logique rapide                                       | 66           |

|   | 4.6 | Résult | ats expérimentaux                                                        | 69           |

|   | 4.7 | Conclu | ısion                                                                    | 70           |

| 5 |     | _      | s de multiplexage proposées pour une plateforme de prototy-              | <b>-7</b> -1 |

|   | •   |        |                                                                          | 71           |

|   | 5.1 |        |                                                                          | 71           |

|   | 5.2 | _      |                                                                          | 72           |

|   |     | 5.2.1  |                                                                          | 72           |

|   | ۲.0 | 5.2.2  |                                                                          | 75           |

|   | 5.3 |        |                                                                          | 77           |

|   | 5.4 |        |                                                                          | 79           |

|   | 5.5 | -      |                                                                          | 81           |

|   |     | 5.5.1  |                                                                          | 82           |

|   |     | 5.5.2  |                                                                          | 82           |

|   |     | 5.5.3  |                                                                          | 87           |

|   | 5.6 | Conclu | ısion                                                                    | 88           |

| 6 | Rés | ultats | expérimentaux                                                            | 91           |

|   | 6.1 | Introd | $\operatorname{uction}$                                                  | 91           |

|   | 6.2 | Modèl  | e de calcul de la période d'émulation                                    | 92           |

|   |     | 6.2.1  | Architecture des IPs de multiplexage                                     | 93           |

|   |     | 6.2.2  | Période d'émulation                                                      | 95           |

|   | 6.3 | Enviro | onnement d'expérimentation                                               | 98           |

|   |     | 6.3.1  | Outil de partitionnement WASGA                                           | 98           |

|   |     | 6.3.2  | Plateforme matérielle de prototypage                                     | 99           |

|   |     | 6.3.3  | Comparaison des performances des IPs de multiplexage avec et sans SERDES | 99           |

|    | 6.4   | Comp    | araison des résultats de routage : Branche ou Signal?                             | . 100 |

|----|-------|---------|-----------------------------------------------------------------------------------|-------|

|    |       | 6.4.1   | Scénario 1 : Routage de signaux multi-points sur graph unidirectionne             | el100 |

|    |       | 6.4.2   | Scénario 2 : Routage de branches sur un graphe unidirectionnel                    | . 101 |

|    |       | 6.4.3   | Scénario 3 : Routage de signaux multi-terminaux sur un graphe bi-<br>directionnel | . 101 |

|    |       | 6.4.4   | Scénario 4 : Routage de branches sur un graphe bidirectionnel                     |       |

|    |       | 6.4.5   | Comparaison des résultats de routage de chaque scénario                           |       |

|    | 6.5   |         | araison des techniques de routage : itératif ou constructif?                      |       |

|    | 6.6   | -       | araison des résultats de prototypage des flots Wasga et Certify                   |       |

|    | 0.0   | 6.6.1   | Objectifs de partitionnement                                                      |       |

|    |       | 6.6.2   | Résultats de prototypage des flots Wasga et Certify                               |       |

|    | 6.7   |         | usion                                                                             |       |

|    | 0.1   | Concr   | ubloii                                                                            | . 100 |

| 7  | Inse  | ertion  | des IPs de multiplexage et gestion de la congestion                               | 111   |

|    | 7.1   | Introd  | $\operatorname{luction}$                                                          | . 111 |

|    | 7.2   | Spécif  | ication des IPs de multiplexage                                                   | . 112 |

|    |       | 7.2.1   | Architecture de l'IP émettrice                                                    | . 112 |

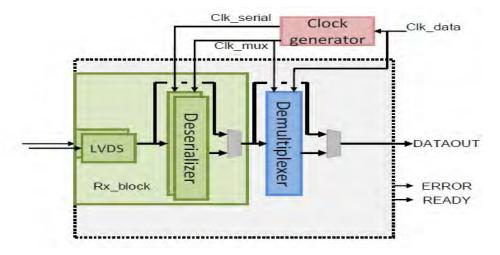

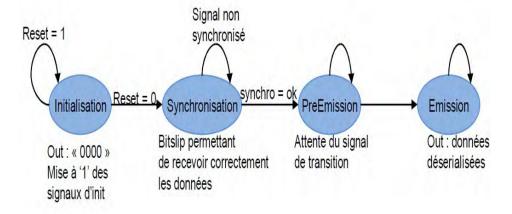

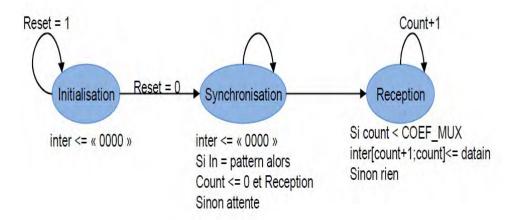

|    |       | 7.2.2   | Architecture de l'IP réceptrice                                                   | . 114 |

|    |       | 7.2.3   | Générateur d'horloge                                                              | . 116 |

|    |       | 7.2.4   | Environnement de vérification                                                     | . 117 |

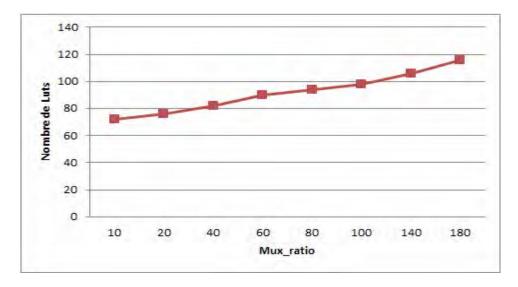

|    |       | 7.2.5   | Variation de taille de l'IP de multiplexage                                       | . 117 |

|    | 7.3   | Techn   | ique de placement basée sur l'estimation de congestion                            | . 118 |

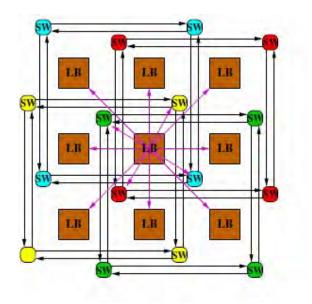

|    |       | 7.3.1   | Architecture du FPGA cible                                                        | . 118 |

|    | 7.4   | Placer  | ment avec estimation de congestion                                                | . 119 |

|    |       | 7.4.1   | Placement recuit simulé                                                           | . 119 |

|    |       | 7.4.2   | Estimation de congestion                                                          | . 120 |

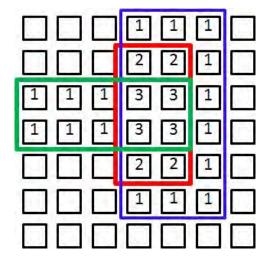

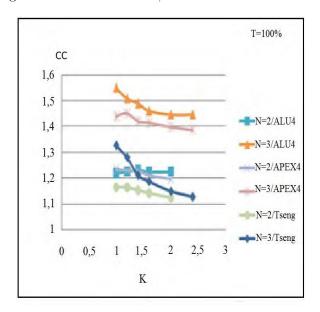

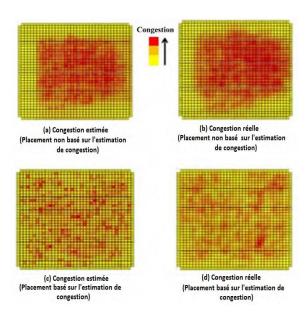

|    |       | 7.4.3   | Qualité de l'estimation de congestion                                             | . 126 |

|    |       | 7.4.4   | Résultats                                                                         | . 127 |

|    | 7.5   | Concl   | usion                                                                             | . 128 |

| C  | onclu | ısion e | t Perspectives                                                                    | 129   |

| Li | ste d | les pub | olications                                                                        | 132   |

| TABLI  | E DES   | MATIÈRES                                       | xiii  |

|--------|---------|------------------------------------------------|-------|

| Référe | ences I | Bibliographiques                               | 135   |

| Annex  | ces     |                                                | 140   |

| .1     | Fichie  | ers d'entrée pour la génération d'un benchmark | . 141 |

|        | .1.1    | Description de l'architecture                  | . 141 |

|        | .1.2    | Description des metadonnées                    | . 144 |

.2

## Table des figures

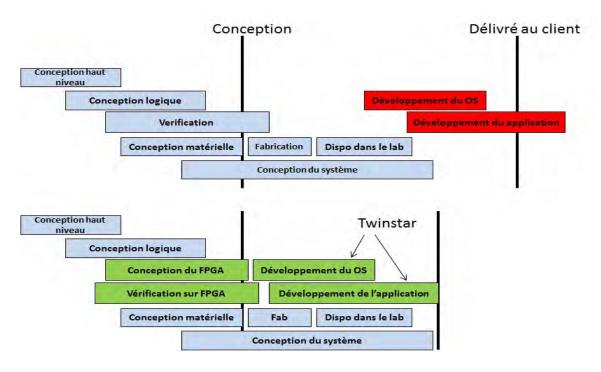

| 2.1  | Réduction du temps de conception d'un SoC en permettant la vérification matérielle et la validation logicielle[1] | 10 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Emulateur Palladium supportant 256M de portes                                                                     | 13 |

| 2.3  | Caractéristiques des différentes techniques de vérification matérielle                                            | 15 |

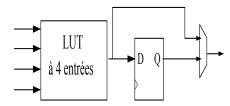

| 2.4  | Bloc logique de base (BLE)                                                                                        | 17 |

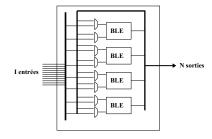

| 2.5  | Cluster de N blocs logiques                                                                                       | 17 |

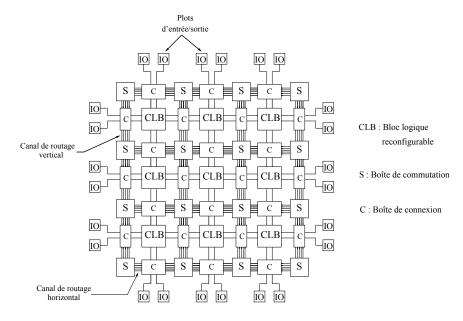

| 2.6  | Architecture FPGA matricielle                                                                                     | 18 |

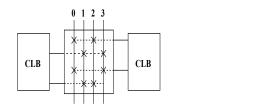

| 2.7  | Boîte de connexion avec une flexibilité $\mathrm{Fc}=2$                                                           | 18 |

| 2.8  | boîte de commutation avec une flexibilité Fs $=3$                                                                 | 18 |

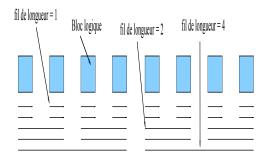

| 2.9  | Canal de routage composé de fils de différentes longueurs [2]                                                     | 19 |

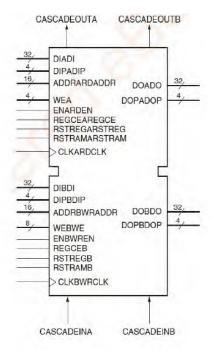

| 2.10 | Architecture d'une SLICEM                                                                                         | 21 |

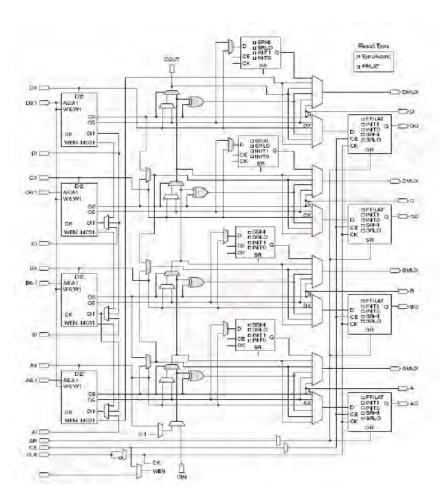

| 2.11 | Architecture d'un BlockRAM du Virtex VI                                                                           | 21 |

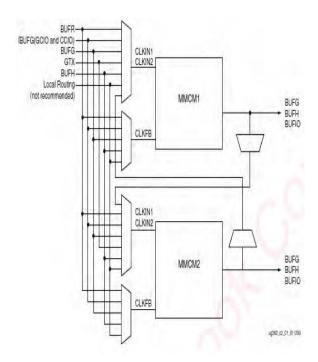

| 2.12 | Architecture d'un Block CMT du Virtex VI                                                                          | 23 |

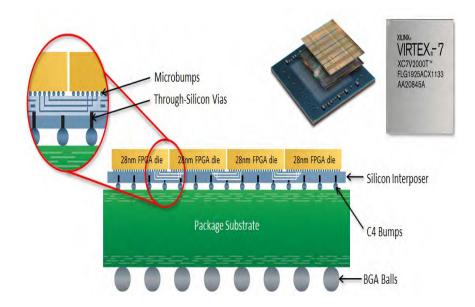

| 2.13 | Architecture d'un Virtex 7                                                                                        | 24 |

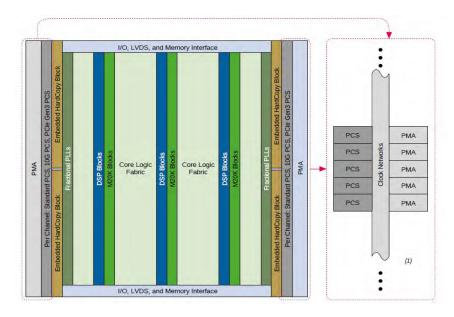

| 2.14 | Architecture d'un Stratix V                                                                                       | 25 |

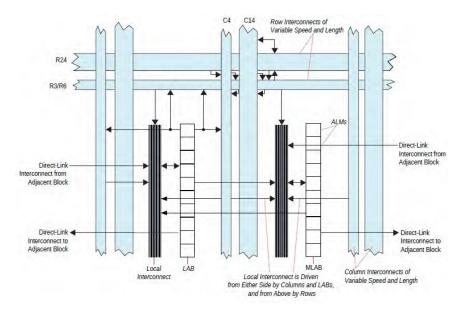

| 2.15 | Architecture d'un LAB de Stratix V                                                                                | 25 |

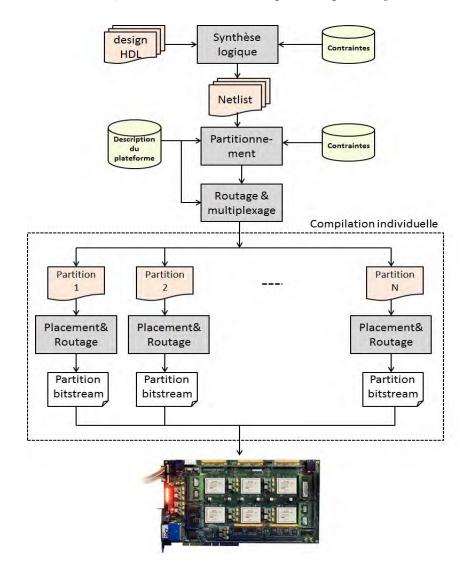

| 3.1  | Flot de prototypage matériel                                                                                      | 32 |

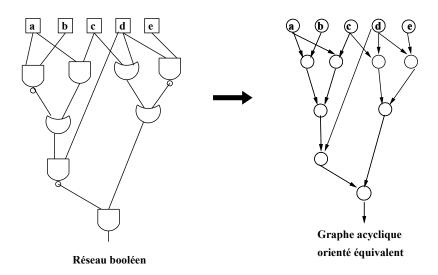

| 3.2  | Représentation du circuit avec un graphe acyclique orienté                                                        | 33 |

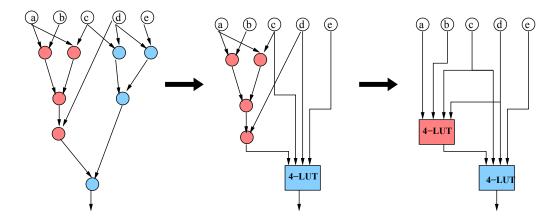

| 3.3  | Exemple de projection structurelle                                                                                | 34 |

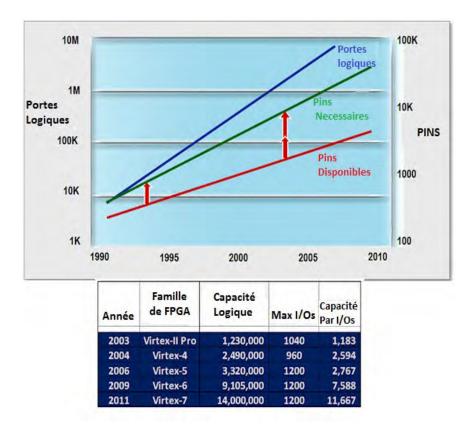

| 3.4  | Nombre de Pin par rapport à la taille logique d'un FPGA                                                           | 37 |

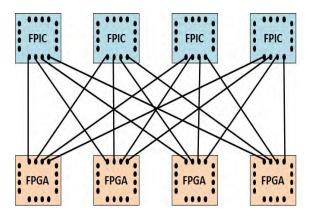

| 3.5  | Interconnexions à travers des circuits FPICs                                                                      | 38 |

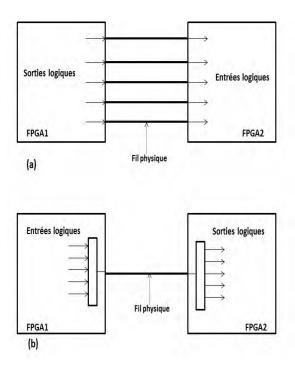

| 3.6  | (a) Transfert de signaux non multiplexés, (b) Transfert de signaux multiplexés                                    | 38 |

| 3.7  | Domaine d'horloge                                                                                                 | 39 |

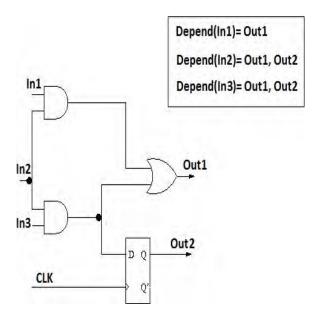

| 3.8  | Calcul de la dépendance                                                                                           | 40 |

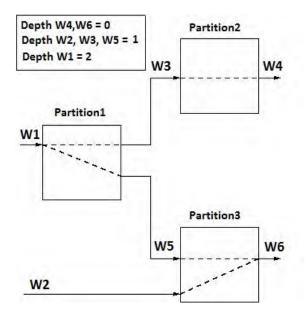

| 3.9  | Calcul du Depth                                                                                         | 41 |

|------|---------------------------------------------------------------------------------------------------------|----|

| 3.10 | Les différentes parties de la netlist finale                                                            | 42 |

| 3.11 | Multiplexage des signaux                                                                                | 43 |

| 3.12 | Rectangle englobant un signal connectant 5 blocs logiques [2]                                           | 46 |

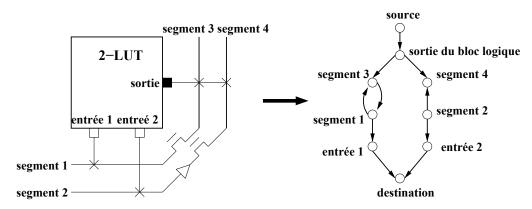

| 3.13 | Modélisation d'une architecture FPGA par un graphe de routage                                           | 48 |

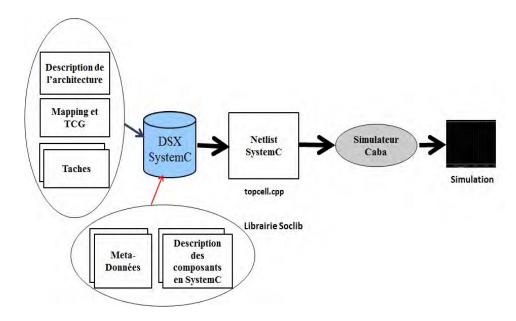

| 4.1  | Schéma descriptif des flux d'entrée et de sortie de DSX_SystemC                                         | 57 |

| 4.2  | Les différentes parties de la netlist .vhd                                                              | 58 |

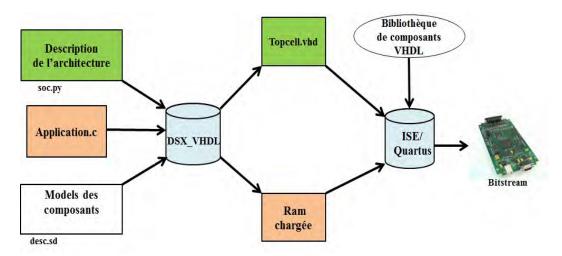

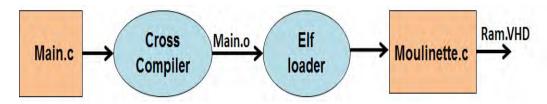

| 4.3  | Chaîne de compilation de DSX_VHDL                                                                       | 60 |

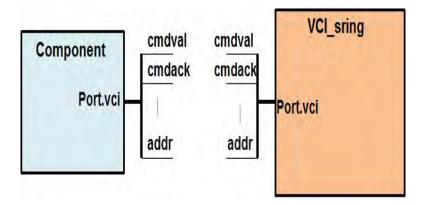

| 4.4  | Exemple de port composé                                                                                 | 61 |

| 4.5  | Chaîne de compilation de l'application                                                                  | 62 |

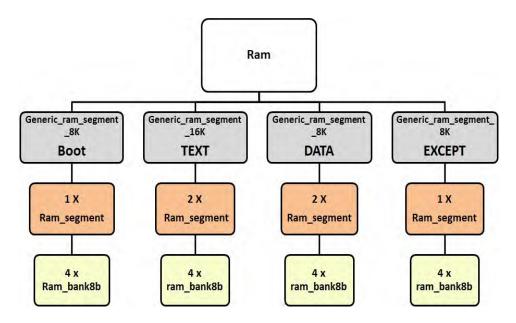

| 4.6  | La structure d'un exemple de Ram générée                                                                | 63 |

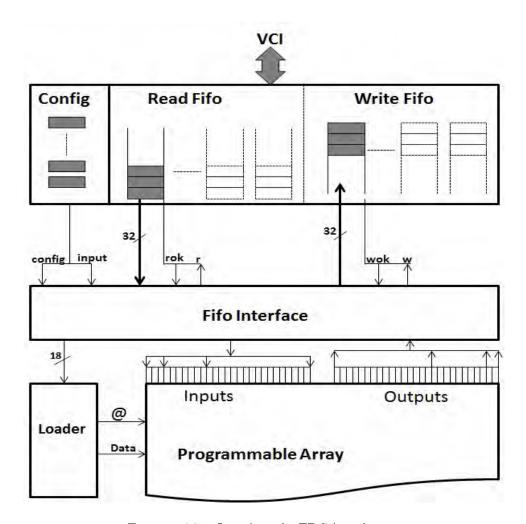

| 4.7  | Interface du FPGA embarqué                                                                              | 65 |

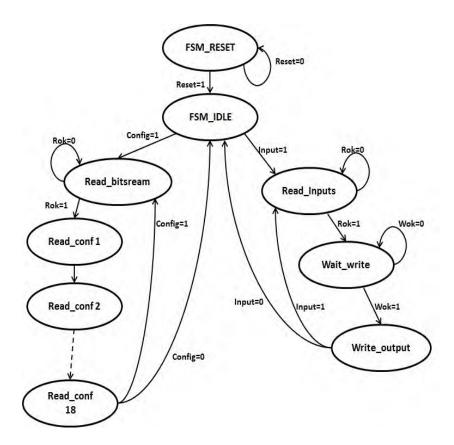

| 4.8  | Automate de configuration et de fonctionnement de l'e-FPGA                                              | 66 |

| 4.9  | Intégration d'une fifo asynchrone                                                                       | 67 |

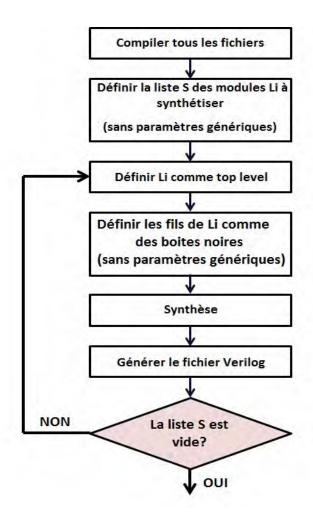

| 4.10 | Graphe de la méthode de synthèse logique proposée                                                       | 68 |

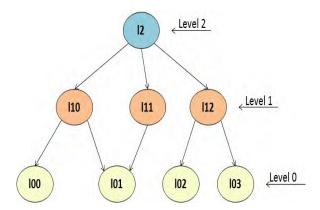

| 4.11 | Les différents niveaux d'un design hiérarchique                                                         | 69 |

| 5.1  | Exemple de hops combinatoires                                                                           | 73 |

| 5.2  | Sélection des signaux non qualifiés pour le multiplexage                                                | 74 |

| 5.3  | Signal appartenant à un chemin demi-cycle                                                               | 74 |

| 5.4  | Signal d'horloge traversant une partie logique                                                          | 75 |

| 5.5  | Domaine d'horloge du système prototypé                                                                  | 75 |

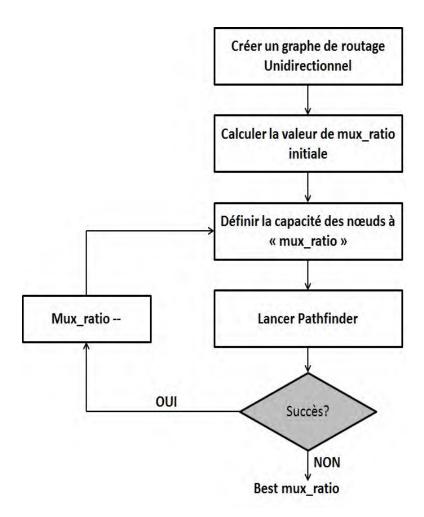

| 5.6  | Approche itérative pour la réduction du taux de multiplexage                                            | 76 |

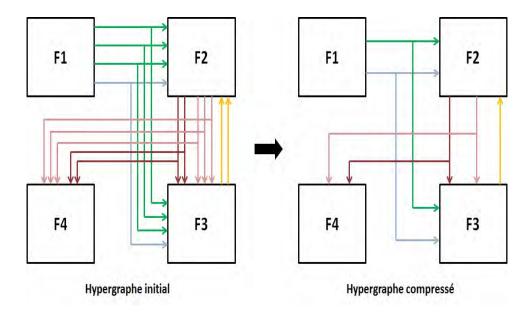

| 5.7  | Réduction du taux de multiplexage par une approche itérative                                            | 77 |

| 5.8  | Exemple montrant l'inconvénient d'un algorithme de routage constructif basé sur l'évitement d'obstacles | 78 |

| 5.9  | Résolution d'un conflit de routage durant deux itérations                                               | 79 |

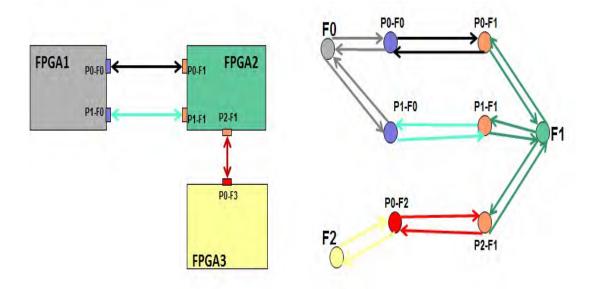

| 5.10 | Modélisation des ressources inter-FPGAs par un graphe de routage                                        | 82 |

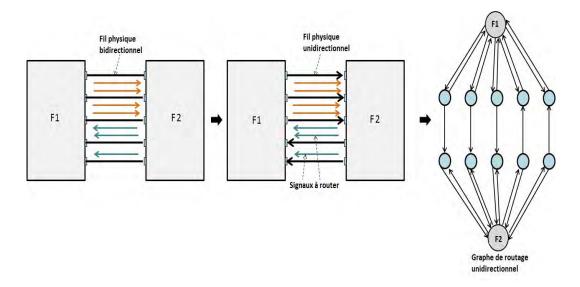

| 5.11 | Les étapes de routage sur un graphe unidirectionnel                                                     | 84 |

| 5.12 | Sélection des fils unidirectionnels proportionnellement aux signaux                                     | 85 |

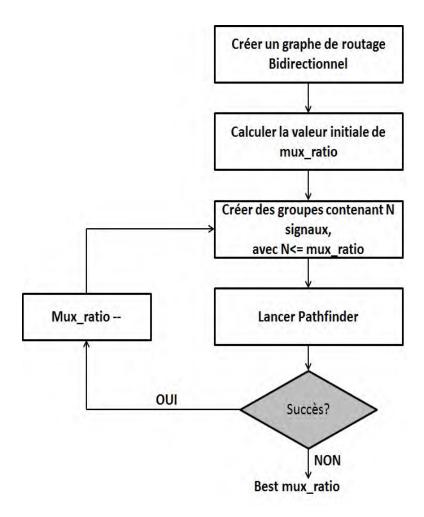

| 5.13 | Les étapes de routage sur un graphe bidirectionnel                                                      | 86 |

| 5.14 | Exemple de regroupement de signaux/branches                                                             | 87 |

| 5.15 | Possibilités de routage d'un signal multi-destinations                                         |

|------|------------------------------------------------------------------------------------------------|

| 6.1  | Exemples d'architectures d'IPs de multiplexage                                                 |

| 6.2  | Exemple de signal routé à travers deux hops de routage                                         |

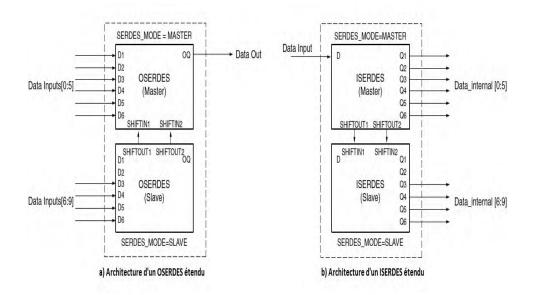

| 6.3  | Architecture matérielle des composants SERDES                                                  |

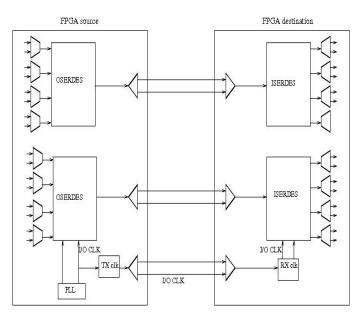

| 6.4  | Insertion des IPs de multiplexage dans les FPGAs source et destination 95                      |

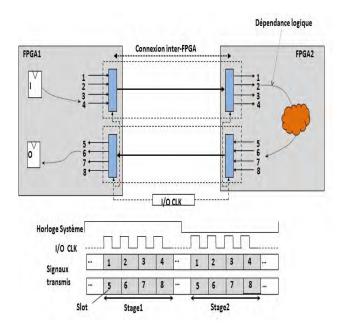

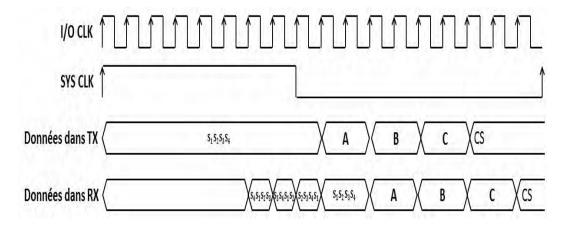

| 6.5  | Chronogramme du fonctionnement d'un IP de multiplexage 96                                      |

| 6.6  | Domaine d'horloge du système prototypé                                                         |

| 6.7  | Carte Dini à base de 6 Virtex 6                                                                |

| 6.8  | Comparaison des performances de deux architectures d'IPs de multiplexage 100                   |

| 6.9  | solution de routage non optimisée sur un graphe unidirectionnel $102$                          |

| 6.10 | Taux de multiplexage non équilibré entre les paires de FPGA 106                                |

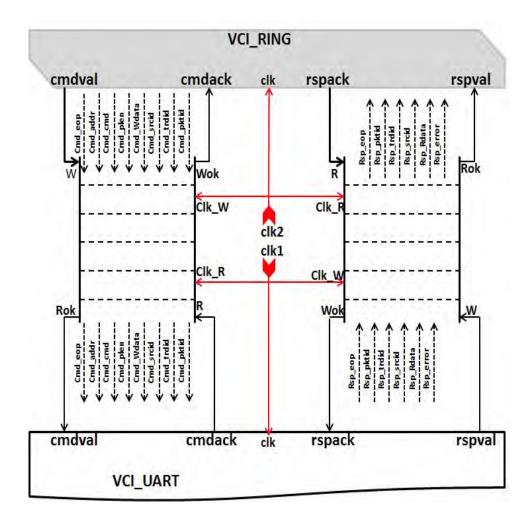

| 7.1  | Environnement des IPs de multiplexage                                                          |

| 7.2  | Architecture de l'IP émettrice                                                                 |

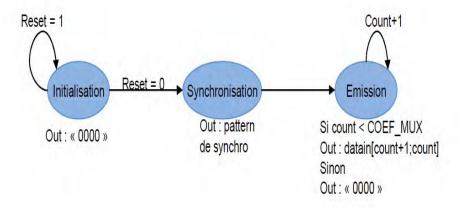

| 7.3  | Machine d'état du mécanisme d'envoi de données                                                 |

| 7.4  | Machine d'état du bloc multiplexeur                                                            |

| 7.5  | Architecture de l'IP réceptrice                                                                |

| 7.6  | Machine d'états du désérialisateur                                                             |

| 7.7  | Machine d'états du bloc démultiplexeur                                                         |

| 7.8  | Variation de la taille d'un IP par rapport au taux de multiplexage 117                         |

| 7.9  | Architecture FPGA matricielle                                                                  |

| 7.10 | Exemple de répartition de congestion suivant le nombre de rectangles englobant 121             |

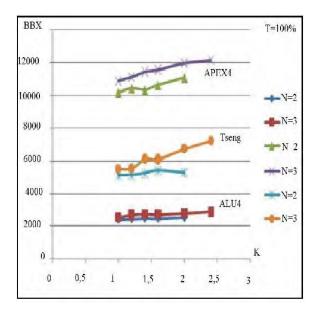

| 7.11 | L'effet de variation du paramètre K sur le coefficient de congestion 123                       |

| 7.12 | L'effet de variation du paramètre K sur la somme des demi périmètres des rectangles englobants |

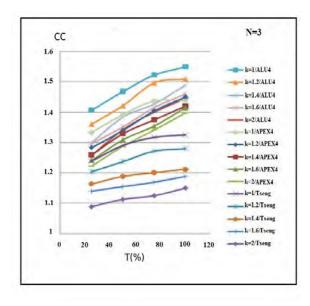

| 7 13 | L'effet de variation de T sur le coefficient de congestion                                     |

|      | La carte de congestion du circuit ALU4                                                         |

| 15   | Exemple d'architecture à base de deux processeurs MIPS                                         |

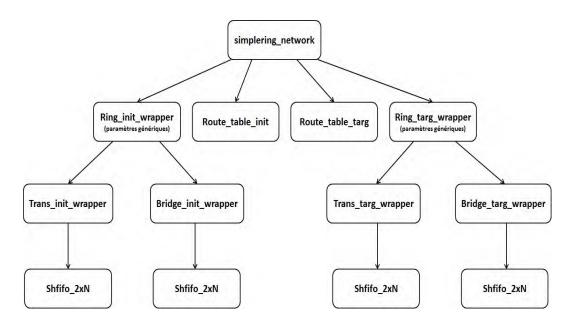

| 16   | Niveaux hiérarchique du bus local "sring"                                                      |

|      |                                                                                                |

## Liste des tableaux

| 4.1 | Durée de synthèse et résultats de prototypage de quelques benchmarks générée                                        | s 70 |

|-----|---------------------------------------------------------------------------------------------------------------------|------|

| 6.1 | Comparison des résultats de routage des différents scénarios                                                        | 102  |

| 6.2 | Caractéristiques des benchmarks                                                                                     | 103  |

| 6.3 | Comparaison de la fréquence du système après routage par les algorithmes itératif et constructif                    | 104  |

| 6.4 | Caractéristiques des benchmarks                                                                                     | 107  |

| 6.5 | Comparaison entre la fréquence de fonctionnement résultante du prototypage par les flots de WASGA et CERTIFY        | 107  |

| 7.1 | L'impact du placement basé sur l'estimation de congestion sur la surface du FPGA et sur le délai du chemin critique | 127  |

## Chapitre 1

## Introduction

Avec la tendance mondiale vers le numérique, la complexité de la conception des circuits intégrés et du logiciel croit régulièrement tandis que la durée de vie des circuits et des produits se réduit. Par conséquent, les développeurs du matériel et du logiciel ne peuvent plus attendre jusqu'à la phase de fabrication pour tester leur circuit [3]. La vérification est une étape importante pour la création du produit final et c'est une composante clé pour la réussite de la commercialisation dans les délais prévus. Actuellement, la vérification occupe environ 60% à 80% du temps de conception d'un SoC [4]. Avant de produire le silicium réel, il n'y a que trois possibilités de vérification : une simulation, une émulation et un prototype sur FPGA.

#### 1.1 Les buts de recherche et contributions

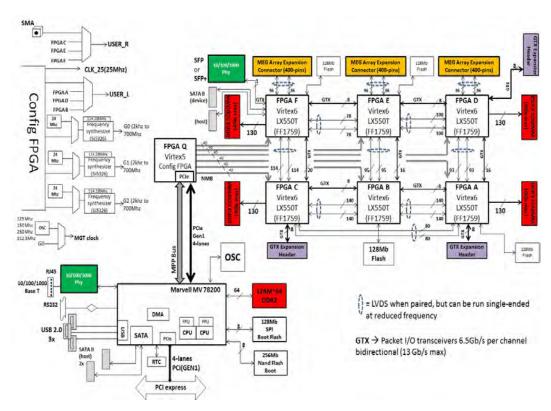

Le prototypage matériel sur plateforme FPGA présente le meilleur compromis entre le temps de conception d'un circuit et le temps d'exécution d'une application par ce circuit. L'avantage principal de l'utilisation d'une carte à base de circuit FPGA est sa capacité d'exécution à grande vitesse, proche des conditions réelles, un modèle à un cycle/bit précis [5]. D'autre part, la disponibilité des outils CAO pour les circuits FPGA ont simplifié le processus d'implémentation, ce qui rend le chemin entre la modélisation du SoC et son implémentation sur FPGA plus simple. Cependant, lorsque la taille d'un circuit dépasse la capacité logique d'un FPGA, une plateforme de prototypage multi-FPGA est utilisée pour supporter la totalité du circuit. La surface en silicium d'un circuit fabriqué avec la technologie FPGA est estimée à 40 fois plus grande qu'avec celle des ASIC [6]. Du coup, le circuit prototypé doit être partitionné sur une plateforme multi-FPGA. Le nombre de FPGA, dépendant de l'application à tester, varie entre quelques [7] et 60 FPGAs [1]. Une plateforme complète de prototypage propose une carte à base de circuits FPGA et un flot logiciel assurant l'implémentation du circuit à vérifier sur la carte. Cependant, rare sont les environnements de prototypage complets qui ont été proposés dans l'état de l'art. Les industriels tel que Dinigroup [8], Aldec [9] et Gidel [10] produisent une multitude de

cartes multi-FPGA à base de circuit Xilinx et/ou Altera sans proposer les outils CAO qui automatisent le flot de l'implémentation. Récemment, Synopsys a lancé son environnement de prototypage Certify [11], qui, à part les cartes Haps multi-FPGA [12], offre un flot logiciel permettant de gérer des systèmes contenant des millions de LUTs. Pareil pour S2C [13] et Cadence [14] qui offrent un environnement complet pour un prototypage rapide sur FPGA.

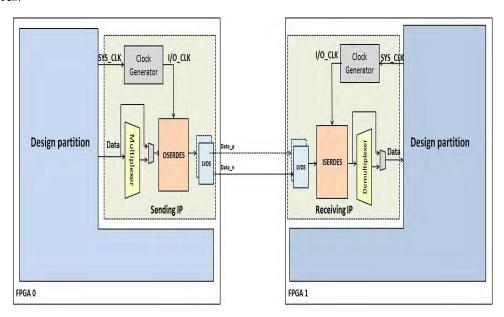

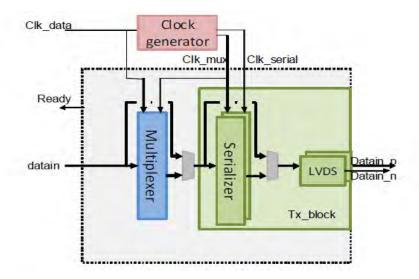

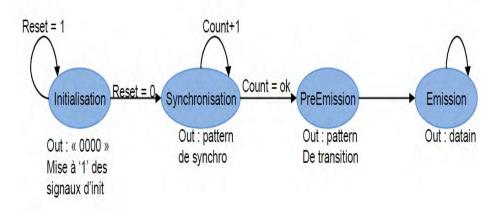

Vu l'importance de la vérification dans le cycle de vie d'un système sur puce et le nombre réduit des plateformes de prototypage matériel, un projet financé par System@tic [15] a été lancé, visant la conception d'un environnement complet de prototypage. Le projet couvre un aspect matériel (conception de carte multi-FPGA assuré par REFLEX CES [16]) et un aspect logiciel assuré par Flexras [17], Adacsys [18] et le Laboratoire d'Informatique de Paris 6 (LIP6)(Laboratoire d'accueil des travaux de cette thèse). Les études faites durant cette thèse touchent surtout la partie post-partitionnement. En effet, lorsqu'un système est partitionné sur une carte multi-FPGA, des signaux coupés à l'interface des partitions doivent passer d'un FPGA à un autre. Cependant, le nombre de fils physiques inter-FPGA est limité ce qui crée des problèmes de routage du circuit prototypé. La solution proposée est de grouper un certain nombre de signaux ensemble et les faire passer à travers le même fil physique. Une fois le routeur détermine l'ensemble des groupes, des IPs de multiplexage(sérialisation/désérialisation) seront insérés dans les parties émettrices et réceptrices de chaque groupe de signaux. Cette étape, étant effectuée après le partitionnement et le routage, pourrait créer un problème de routage intra-FPGA à cause de la partie logique récemment insérée (les IPs de multiplexage).

Les solutions développées pour remédier à ces deux problèmes doivent être validées en utilisant des gros benchmarks de test ayant des caractéristiques spécifiques permettant de mettre en valeur les performances de ces techniques.

Les travaux de cette thèse s'intéressent à la résolution des problèmes suivants :

- Lorsque la taille d'un circuit à tester dépasse la capacité logique d'un seul FPGA, ce circuit est partitionné sur une carte multi-FPGA ayant un nombre limité de connexions physiques inter-FPGA. Dans ce cas, il s'agit d'un problème de routage inter-FPGA.

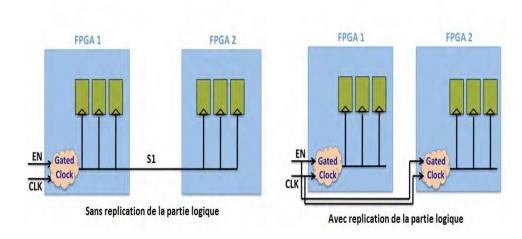

- Après l'insertion d'IPs de multiplexage dans les FPGAs sources et destinations, la congestion augmente dans les FPGAs et le circuit risque de ne pas pouvoir être routé. Dans ce cas, nous parlons d'un problème de routage intra-FPGA.

- Problème de limitation de benchmarks de test qui répondent à un certain nombre d'exigences requises par la nature des techniques à valider.

#### 1.1.1 Problème de routage inter-FPGA

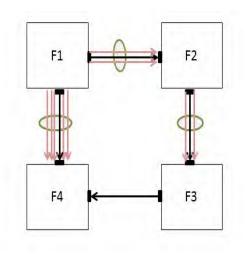

Comme nous l'avons expliqué, dans le cas où le nombre de cellules logiques d'un circuit dépassent largement le nombre de blocs logiques d'un seul FPGA, ce circuit devrait être partitionné sur une carte multi-FPGA.

La manière dont le circuit est découpé a un effet très important sur les performances du système de prototypage. L'outil de partitionnement permet d'obtenir une répartition du circuit objet du prototypage sur les FPGA de la carte. Cette répartition tente de tirer le meilleur profit de l'architecture du FPGA en tenant compte des contraintes imposées par celle-ci en termes de ressources logiques disponibles mais aussi du nombre de liens physiques inter-FPGA. En effet, l'étude dans [19] a montré que les FPGA disposent d'un nombre limité de ressources d'entrée-sortie. Or, a priori, cette ressource matérielle détermine le nombre de signaux qui peuvent apparaître à l'interface de deux parties et qui doivent passer d'un FPGA à un autre.

Face à cette limitation physique de ressources de routage inter-FPGA, des études dans la littérature ont proposé des approches basées sur le partage des ressources là où plusieurs signaux peuvent être transmis à travers le même fil physique. Le routage des signaux peut se faire à travers des algorithmes statiques qui ne dépendent pas de la variation de la valeur de chaque signal au cours du temps [20] [21] [22] [23]. Chaque signal est transmis durant un cycle donné indépendamment de son activité. Alternativement, une approche dynamique a été proposée dans [24] selon laquelle seuls les signaux qui ont changé de valeur sont transmis. Les approches dynamiques dépendent de l'activité du système à prototyper. Par contre, la disponibilité des ressources de routage est déterminée au cours de l'exécution de l'application, ce qui nécessite plus de ressources logiques dans chaque FPGA pour le contrôle des opérations de communication. En plus, pour des applications complexes avec une activité importante, les algorithmes dynamiques sont moins robustes face aux variations de la fréquence, et les risques de transmission de données erronées sont plus importants. Par conséquent, nous nous intéressons dans cette thèse aux méthodes statiques.

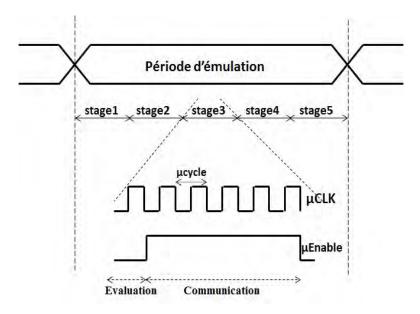

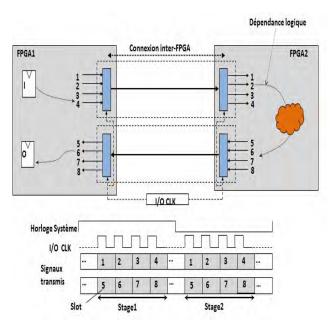

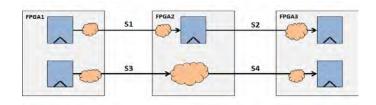

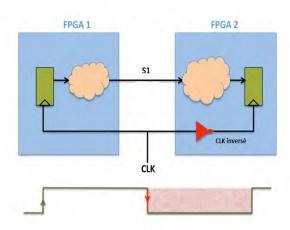

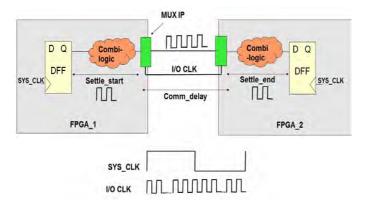

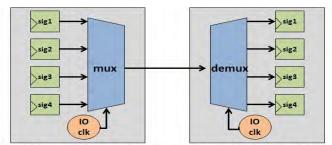

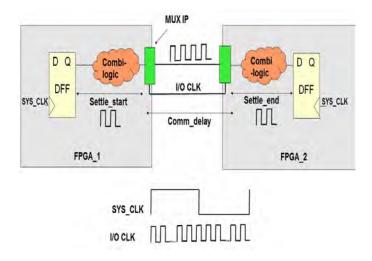

La technique des «fils virtuels» ou «virtual wires» [20] consiste à faire passer la valeur de plusieurs signaux logiques par le même canal physique (multiplexage). Les connexions sont établies via un réseau de communication pipeliné et routé statiquement. Le multiplexage permet d'augmenter l'efficacité de la bande passante tout en affectant plusieurs signaux à un pin. En effet, l'idée consiste à construire des canaux de communication logiques au-dessus des canaux de communication physiques qui sont les fils d'interconnexion dont on dispose entre deux FPGAs. Un canal de communication logique permet de virtualiser le transfert des signaux d'un FPGA à l'autre. Pour assurer cette virtualisation, il a fallu diviser la période de l'horloge d'émulation en un certain nombre de microcycles. Donc chaque signal multiplexé est transmis pendant un microcycle.

L'inconvénient de cette technique c'est qu'elle multiplexe tous les signaux sans tenir compte des signaux qui passent par le chemin critique. D'autre part, cette technique étant basée sur l'ordonnancement des signaux, est peu robuste du fait que la probabilité d'erreur est importante (erreurs dues au non-respect des contraintes temporelles). En cas d'erreur, il est nécessaire de retransmettre tous les signaux pendant une autre période d'émulation, et par conséquent dégrader la performance du système d'émulation.

Une autre technique a été proposée [21] dont le but est de déterminer, en utilisant la

programmation linéaire, quels sont les signaux qui doivent être multiplexés, et ceux qui ne le doivent pas. Une autre particularité de cette méthode, c'est que tous les signaux sont envoyés plusieurs fois dans la même période d'émulation, mais la valeur de chaque signal n'est évaluée qu'une seule fois. L'apport de cette méthode est qu'elle est facile à implémenter. En effet, toute erreur dans la transmission d'un signal est rectifiable pendant seulement quelques microcycles, contrairement à la méthode des virtual wires ou il faut toute une période d'émulation pour le faire.

Cependant, cette technique n'est pas basée sur l'ordonnancement, du coup, tous les signaux sont transmis plusieurs fois pendant la même période ce qui dégrade la performance du système de prototypage.

Dans cette étude, nous proposons de développer un outil spécifique qui intervient après le partitionnement pour prendre en compte la contrainte liée à la limitation du nombre de fils d'interconnexion entre deux FPGA.

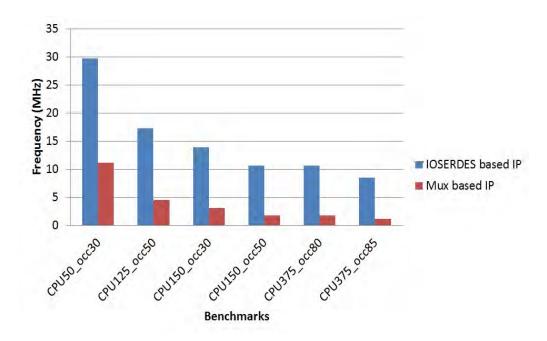

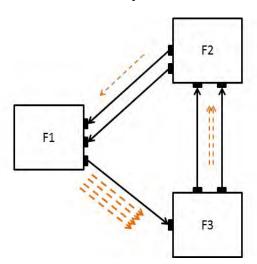

L'objectif est donc de développer un outil de routage, basé sur le multiplexage des signaux entre les FPGA pour résoudre la contrainte limitant le nombre de connexions physiques disponibles. Un ensemble de signaux ayant la même source et les mêmes destinations sont routés à travers le même chemin. Pour tracer les propriétés de notre outil de routage, il a fallu examiner les inconvénients des techniques proposées dans l'état de l'art. En effet, la technique des fils virtuels et celle de la programmation linéaire utilisent le multiplexage pour transmettre les signaux d'un FPGA à un autre. Cette technique (le multiplexage) nous semble inévitable à cause de la grande limitation des ressources inter-FPGA. Bien évidemment, le multiplexage a un coût en termes de fréquence de fonctionnement, mais aussi en termes de surface logique (nombre de portes logiques). En effet, transférer la valeur de plusieurs signaux logiques à travers le même canal physique a un impact sur la performance du circuit. Il se traduit par une réduction de la fréquence de fonctionnement du circuit. Cette fréquence dépend essentiellement de deux paramètres : le taux de multiplexage et le nombre de stages par période. Le taux de multiplexage est le nombre de signaux transmis à travers le même lien physique. Le nombre de stage est le nombre de fois un signal est coupé entre deux registres.

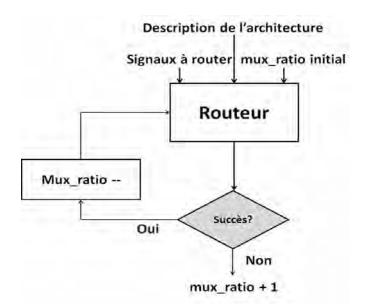

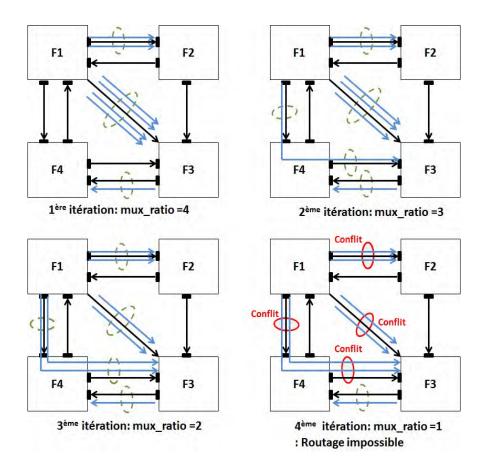

Avec la technique des fils virtuels qui est basé sur l'ordonnancement, le nombre de stages par période est important contrairement à la technique de la programmation linéaire qui vise à diminuer le nombre de stages en sélectionnant les signaux qui ne doivent pas être multiplexés, mais en contrepartie, le taux de multiplexage est très grand du fait que tous les signaux sont transmis dans chaque stage. Pour remédier à ce problème, nous décidons de sélectionner, suivant des critères précis, les signaux qui ne doivent pas être multiplexés afin d'obtenir un nombre de stages réduit. Pour diminuer le taux de multiplexage, notre outil de routage effectuera plusieurs itérations. A travers ces itérations, le taux de multiplexage se décrémente jusqu'à ce qu'aucune solution de routage n'est trouvée.

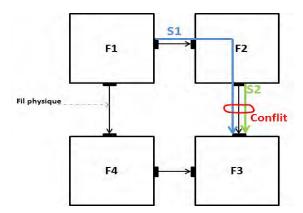

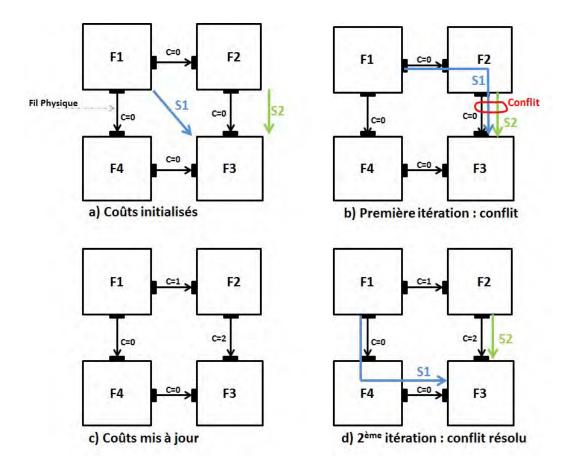

D'autre part, pour trouver un chemin de routage entre la source et la destination d'un signal, les techniques proposées dans l'état de l'art utilisent un algorithme constructif basé sur l'évitement de congestion. Avec des taux de multiplexage réduits, cette méthode

conduit à un blocage rapide au niveau du routage qui ne se résout qu'en utilisant des taux de multiplexage plus grands, ce qui dégrade remarquablement la fréquence de fonctionnement du système à tester. Pour cette raison, nous proposons bâtir notre outil de routage en utilisant un algorithme basé sur la négociation de la congestion. Par conséquent, tous les signaux négocient leurs besoins d'utiliser une ressource afin de construire un chemin de routage entre la source et la destination de chaque signal.

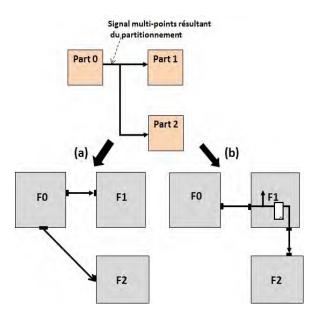

Finalement, la performance du routeur dépend de la forme du signal à router. En effet, un signal peut être bi-points (ayant une source et une seule destination), mais aussi il peut avoir plusieurs destinations. Des plateformes matérielles proposent des traces physiques multi-points pour router les signaux multi-destinations. Les auteurs de [25] proposent une approche pour router ce type signaux. Mais comme la plupart des plateformes matérielles comportent uniquement des traces physiques bi-points, les techniques développées dans cette thèse ciblent uniquement ce type de plateformes. Les techniques de multiplexage dans [21] et [20] agissent sur des signaux bi-points. Même les signaux ayant plusieurs destinations sont décomposés sous forme de branches. Dans notre étude, nous allons définir plusieurs scénarios pour déterminer celui qui donne les meilleurs résultats de point de vue fréquence de fonctionnement. Dans chaque scénario, nous varions la forme du signal ainsi que le graphe de routage correspondant. Par conséquent, l'outil de routage essaie de définir le taux de multiplexage et les groupes de signaux qui sont transmis ensemble via les mêmes fils physiques.

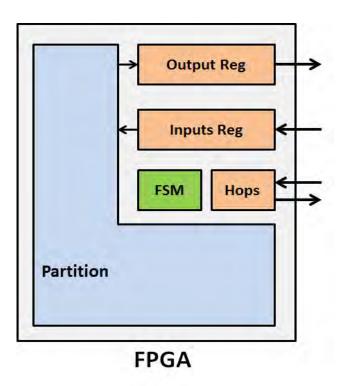

Le choix des signaux à regrouper influe considérablement sur la performance de l'outil de routage. De l'autre côté, une fois les groupes de signaux sont déterminés, la gestion des canaux de communication logique doit être assurée par un matériel spécifique, appelé IPs de multiplexage. Ce matériel supplémentaire comporte des éléments mémoires et des portes combinatoires qui doivent être ajoutés de part et d'autre du canal de communication physique (sur le FPGA émetteur et sur le FPGA récepteur) ce qui peut causer des problèmes de routage à l'intérieur du FPGA lui-même.

#### 1.1.2 Problème de routage intra-FPGA

La surface d'un FPGA inclut les ressources de routage et les ressources logiques. Contrairement à un circuit intégré à application spécifique (ASIC), 80% de la surface totale d'un FPGA est dédiée aux ressources de routage [26]. Cependant, il est parfois impossible de router tous les signaux d'un circuit malgré que le nombre de blocs logiques ne dépasse pas la surface logique disponible sur ce FPGA. En effet, Ce problème de routage est essentiellement dû à la congestion : une répartition non étudiée des blocs logiques, peut créer, d'une part, des zones dans lesquelles les ressources de routage sont fortement demandées et qui dépassent largement les ressources disponibles, et d'autre part des zones légèrement congestionnées la ou les ressources ne sont pas toutes exploitées.

Pour remédier à ce problème, des travaux ont été faits pour une meilleure gestion des

ressources de routage. Des solutions architecturales ont été proposées visant à agir sur la taille de la largeur du canal de routage tout en la rendant variable selon le besoin de l'application. Dans [27], les auteurs ont estimé que la congestion est généralement localisée au centre du FPGA. Pour cette raison, ils ont proposé d'augmenter la largeur du canal seulement au milieu du FPGA et d'utiliser des canaux qui sont moins larges dans reste du circuit. Cette technique n'avait pas donné des résultats suffisants pour justifier l'effort supplémentaire nécessaire pour la conception physique d'un tel FPGA. Une technique itérative qui a été proposée et qui vise à ajuster, durant un certain nombre d'itérations, le placement des blocs logiques selon l'information sur la congestion crée par le routage [28]. Cette technique est très gourmande de point de vue temps de compilation puisque le placement et le routage se refont à chaque itération.

Notre objectif est donc de développer une technique de placement intra-FPGA, qui permet de placer les blocs logiques en se basant sur l'estimation de la congestion mise à jour à fur et à mesure de l'évolution du placement. Cette technique permettra de répartir les blocs logiques dans toute la surface de l'FPGA tout en évitant de créer des zones congestionnées dans un temps relativement acceptable et ainsi, améliorer la routage du circuit.

#### 1.1.3 Limitation des benchmarks de test

Les techniques de multiplexage développées dans le cadre de cette thèse seront évaluées à travers une série de tests en utilisant un ensemble de benchmarks. Par contre, le plus grand défi était de trouver des benchmarks spécifiques qui nous permettent de valider et évaluer ces techniques. En effet, nous cherchons des benchmarks suffisamment grands et dont la taille dépasse largement la capacité des FPGAs actuels, afin de pouvoir les tester sur une carte multi-FPGAs. D'autre part, nous nous intéressons aux benchmarks hétérogènes qui contiennent un mixe de différents composants. Ces circuits hétérogènes permettent de bien évaluer le degré d'adaptabilité et de flexibilité de nos algorithmes. La dernière caractéristique des benchmarks requis c'est la testabilité. En d'autres termes, nous devons toujours avoir la controlabilité et l'observabilité du circuit sous test (application software exécutée par le matériel).

En menant une recherche sur ce qui existe, nous n'avons pas trouvé de benchmarks qui répondent à nos besoins. En effet, la première initiative de génération de benchmarks de test a été faite par CBL <sup>1</sup> [29, 30] et MCNC <sup>2</sup>[31]. Ces circuits sont des simples fonctions (pas d'application software) qui ne sont pas suffisamment grands pour cibler des opérations de partitionnement et de multiplexage. En fait, le plus grand circuit généré est le s38584 et il contient seulement 2904 blocs logiques(LUT) [32].

Plus récemment, des chercheurs ont développé un programme de génération de benchmark

<sup>1.</sup> Collaborative Benchmarking Laboratory, North Carolina State University, Raleigh, NC.

<sup>2.</sup> Microelectronics Center of North Carolina

1.2 Plan 7

GNL <sup>3</sup> [33] qui permet de créer des netlists ayant des comportements assez réalistes. Ce programme est basé sur la règle de Rent [34] pour contrôler la complexité des interconnexions entre les taches. En effet, l'utilisateur définit le nombre de blocs logiques, le nombre de flip flop, la profondeur combinatoire, le nombre d'entrées/sortie et aussi l'exposant rent. Par la suite, le programme GNL suit une approche bottom-up. Donc il commence par établir les connexions entre un certain nombre de blocs logiques ce qui en résulte la formation de clusters. Ces clusters eux-mêmes vont être connectés ensemble jusqu'à ce que tous les clusters seront combinés en un seul circuit. A chaque niveau, le programme vérifie si l'exposant rent fixé par l'utilisateur est respecté. L'inconvénient de ce générateur réside dans le fait que les circuits générés sont composés de ressources logique homogènes (pas de DSP, Ram..), en plus aucune application n'est générée pour tester ces circuits.

En 2005, la suite de benchmarks IWLS a été publiée dans le workshop IWLS (International Workshop on Logic and Synthesis)[35]. Elle contient des circuits déjà publiés dans des conférences précédentes, des circuits publiés par des communautés de développeurs de code libre et encore par des circuits industriels. Malgré la diversité et la taille relativement grande de ces circuits, mais ils n'offrent aucune solution de testabilité durant l'implémentation sur la carte multi-FPGA.

Notre objectif c'était donc de développer un générateur de benchmarks, qui permet, à l'aide d'une description architecturale simple du benchmarks, de générer le circuit demandé modélisé avec le langage de description matérielle VHDL. Le générateur utilise un ensemble de composant de la bibliothèque Soclib [36], ce qui donne aux benchmarks un aspect réel semblable à celui des circuits industriels.

#### 1.2 Plan

Le présent manuscrit est réparti en chapitres. Le premier chapitre commence par une introduction sur le prototypage matériel ainsi que la problématique posée.

Dans le deuxième chapitre nous comparons les différentes méthodes de vérification : la simulation, l'émulation et le prototypage matériel. Comme ce dernier présente le meilleur compromis entre le temps de mise en œuvre et le temps d'exécution, nous présenterons quelques plateformes de prototypage commerciales qui existent sur le marché.

Le troisième chapitre décrit le flot de prototypage complet tout en mettant en œuvre les parties qui sont concernées par les travaux de cette thèse. Pour ces parties, nous donnerons une présentation détaillée sur les différentes techniques proposées dans la littérature.

Par la suite, nous détaillons l'environnement proposé pour la génération de netlists de circuits complexes qui serviront de benchmarks pour valider les outils et les techniques qui seront développés au cours de cette thèse. Cette étude couvrira les volets matériels et logiciels. Deux types d'architectures matérielles seront proposés : des architectures multiprocesseurs et des architectures multi-coprocesseurs.

<sup>3.</sup> gnl is the acronym for Generate Net List

Le cinquième chapitre dresse un état de l'art des solutions envisageables pour assurer le multiplexage des signaux. Dans un premier temps, nous proposons un outil de routage itératif qui tente de réduire le taux de multiplexage durant un certain nombre d'itérations. Le routage en lui-même est assuré par l'algorithme de routage Pathfinder [37] qui est largement utilisé par les chercheurs académiques et industriels. Cet algorithme servira comme point de départ pour les techniques de routage développées durant cette thèse. Des adaptations adéquates seront faites pour cibler un réseau de routage inter-FPGA. Dans une deuxième partie, nous essayons de déterminer la meilleure forme de signal avec laquelle il doit être routé. Pour cela, nous proposons des scénarios de test afin de sélectionner celui qui donne la fréquence de fonctionnement la plus performante.

Le sixième chapitre présentera les résultats expérimentaux des techniques proposées. Nous mettrons en valeur la performance de ces techniques à travers des comparaisons avec avec les méthodes proposées dans l'état de l'art ainsi qu'avec celles de l'outil industriel Certify. Dans le dernier chapitre, une description détaillée des IPs de multiplexage sera présentée. Ces IPs sont insérés dans les parties émettrices et réceptrices d'un canal de communication. Ces IPs inclus des composants spécifiques appelés SERDES pour assurer la sérialisation/déserialisation des données à transmettre. Dans une deuxième partie, nous proposons notre algorithme de placement basé sur l'estimation de congestion. Cet algorithme sera implémenté dans un outil de placement développé dans le LIP6 et destiné aux FPGAs de la CEA puisque nous n'avons pas la possibilité d'agir sur les outils de placement et routage de Xilinx ou Altera.

Enfin, une conclusion résumera les différents points traités dans ce manuscrit, et abordera les perspectives relatives à ces travaux.

## Chapitre 2

# État de l'art : Plateformes matérielles

| Sommaire |       |                                                                     |    |

|----------|-------|---------------------------------------------------------------------|----|

| 2.1      | Intr  | oduction                                                            | 9  |

| 2.2      | Véri  | fication des SoCs                                                   | 10 |

|          | 2.2.1 | Simulation logique                                                  | 11 |

|          | 2.2.2 | Émulation matérielle                                                | 12 |

|          | 2.2.3 | Prototypage matériel                                                | 14 |

|          | 2.2.4 | Synthèse : Comparaison entre les différents types de vérification . | 15 |

| 2.3      | Arcl  | nitecture FPGA                                                      | 16 |

|          | 2.3.1 | Bloc logique de base du FPGA                                        | 16 |

|          | 2.3.2 | Ressources de routage                                               | 17 |

|          | 2.3.3 | Éléments spécifiques                                                | 19 |

| 2.4      | Exe   | mples de FPGA industriels                                           | 20 |

|          | 2.4.1 | Architecture du Virtex VI                                           | 20 |

|          | 2.4.2 | Architecture du Virtex 7                                            | 23 |

|          | 2.4.3 | Architecture du Stratix V                                           | 24 |

| 2.5      | Plat  | eformes industrielles de prototypage                                | 26 |

|          | 2.5.1 | Plateformes matérielles                                             | 26 |

|          | 2.5.2 | Plateformes de prototypage complètes                                | 27 |

| 2.6      | Con   | clusion                                                             | 29 |

#### 2.1 Introduction

Le prototypage matériel a été proposé pour une vérification rapide des systèmes sur puce avant d'atteindre la phase de fabrication. Il permet de réduire remarquablement le temps de conception d'un circuit en guidant le concepteur à faire des choix stratégiques de son système. Dans ce chapitre, nous allons commencer par une comparaison du prototypage matériel par rapport à d'autres méthodes de vérification. Par la suite, il est nécessaire d'examiner avec plus de détails l'architecture de l'élément de base des plateformes de prototypage qui est le "FPGA". La dernière partie de ce chapitre est dédiée à la présentation de quelques exemples de plateformes matérielles industrielles. Ces plateformes sont classées sous forme de deux types : plateformes complètes fournissant la carte multi-FPGA ainsi que le flot logiciel d'implémentation sur la carte. Mais aussi un second type qui regroupe tous les industriels qui commercialisent des plateformes matérielles, sur étagère ou sur mesure, sans aucun logiciel qui automatise le flot d'implémentation.

Figure 2.1 – Réduction du temps de conception d'un SoC en permettant la vérification matérielle et la validation logicielle[1]

#### 2.2 Vérification des SoCs

Les concepteurs doivent s'assurer de la conformité de leur produit à ses spécifications à chaque étape de conception avant d'atteindre la phase de fabrication. Par conséquent, la vérification peut occuper jusqu'à 80% du cycle de réalisation du système sur puce [4] tout en diminuant le temps de mise sur le marché du produit final comme le montre la figure 2.1. En effet, traditionnellement, l'étape de validation ne peut commencer réellement qu'après la fabrication, le test et la mise en place du circuit dans le laboratoire. L'impacte de la vérification consiste à permettre la validation du matériel mais aussi du logiciel très tôt dans le cycle de développement du SoC ce qui permet d'accélérer le temps de la mise

sur le marché.

Le recours à la vérification a augmenté à partir des années 90 la où plusieurs erreurs de conception ont été découvertes et médiatisées, entre autres, celle du Pentium d'Intel en 1994 (bug FDIV du Pentium) [38], erreur du démarrage de la machine équipée d'un Pentium III [39], TLB bug du Phenom de AMD [40]. Ces erreurs ont coûtées des centaines de millions de dollars à l'époque. De ce fait, plus vite l'erreur est détectée, plus son coût de correction est faible. Généralement, il existe plusieurs méthodes de vérification matérielle que l'on peut citer essentiellement la simulation, l'émulation et le prototypage matériel.

#### 2.2.1 Simulation logique

La simulation emploie des méthodes d'exécution et de calcul sur ordinateur. Cette technique offre une grande observabilité, une grande souplesse et une grande flexibilité. Elle peut intervenir dans plusieurs niveaux puisque pour un même système, plusieurs modèles à différents niveaux d'abstraction peuvent être utilisés. Plus le modèle est précis, plus les calculs pour la simulation sont nombreux et par conséquent, plus l'exécution est lente. Dans le domaine de conception des circuits monopuces, le système peut être modélisé selon 6 niveaux d'abstraction :

- Le niveau spécification fonctionnelle modélise le comportement global du système sans aucune précision vis à vis de sa réalisation finale. Ici, on travaille à un très haut niveau d'abstraction, une simulation à ce niveau permet de très rapidement simuler une spécification fonctionnelle et permettra, par son analyse, de mettre en évidence les besoins du système.

- Le niveau architectural modélise le système comme un ensemble de modules travaillant en parallèle et communiquant entre eux. A ce niveau, les différentes tâches du système sont allouées à des sous-systèmes. Chaque sous-système est modélisé au niveau fonctionnel. La granularité concernant les interactions est au niveau transactionnel (TLM). Ce type de simulation est particulièrement utile pour l'exploration d'architecture et le développement des parties logicielles du système.

- Le niveau micro-architecture correspond à la même simulation qu'au niveau architectural sauf qu'ici, les interactions entre sous-systèmes ne sont plus des transactions mais des signaux. La précision du modèle est donc au cycle d'horloge prêt au niveau de la communication entre sous-systèmes. Ce niveau de modélisation permet la réalisation de premières mesures de performances ainsi que le développement des pilotes de bas niveau («drivers») des logiciels embarqués.

- Le niveau RTL modélise un circuit comme un ensemble de registres et de relations logiques entre registres. Ce modèle est à bas niveau d'abstraction, le système entier est simulé au cycle d'horloge prêt. Ce niveau est particulièrement utilisé pour la mise au point des sous-ensembles matériels qui composent le système. De nos jours, plusieurs outils permettant de faire la simulation à ce niveau d'abstraction, à noter le Modelsim [41] et le Isim de Xilinx [42].

- Le niveau porte logique décrit le système complet comme un assemblage de portes logiques. Ce niveau est obtenu après synthèse. De nos jours, les outils permettant le passage du niveau RTL au niveau porte logique sont automatisés et suffisamment fiables pour ne pas avoir à travailler à ce niveau pour la conception d'un ASIC. Cependant, dans les flots d'émulation qui nécessitent eux aussi une phase de synthèse, le niveau de fiabilité est moins élevé et il s'avère parfois nécessaire d'effectuer des simulations à ce niveau pour trouver une erreur de synthèse.

- Le niveau analogique est le plus bas niveau d'abstraction utilisé en simulation. A ce niveau existent des outils d'extraction de paramètres électriques à partir du plan de masse. On travaille ici avec des modèles précis des transistors, dépendant de la technologie utilisée.

Pour conclure, la simulation est donc utile à toutes les phases de conception. Cette technique est très efficace de part sa grande souplesse, sa grande flexibilité, observabilité, contrô-labilité et un temps de mise en œuvre souvent court. Cependant, plus on avance dans le processus de conception et plus la précision du modèle nécessaire augmente, ce qui implique plus de calculs et donc une vitesse d'exécution moindre. La simulation trouve donc ses limites lorsqu'il faut jouer de longues séquences de tests à un bas niveau d'abstraction.

#### 2.2.2 Émulation matérielle

L'émulation utilise des modèles physiques qui imitent le comportement matériel. Les modèles utilisés offrent une grande observabilité du système, proches de celles des simulateurs, mais leur vitesse d'exécution est beaucoup plus rapide. Un émulateur pourra fonctionner à 1MHz là ou une simulation tourne à 10Hz. Les émulateurs puissants sont souvent à base de processeurs, mais il existe encore des machines qui sont à base de circuits FPGAs.

#### 2.2.2.1 Emulateurs à base de processeurs

Le marché de ce type d'émulateurs est dominé par Cadence avec son émulateur Palladium [43]. Présent sur le marché depuis Janvier 2002, l'émulateur Palladium est basé sur l'utilisation parallèle de plusieurs dizaines de milliers de microprocesseurs spécialement conçus pour les besoins de l'émulation. La plus petite machine a une capacité d'émulation relativement grande. En combinant plusieurs machines, on peut étendre la capacité d'émulation jusqu'à deux billions de portes logiques. Cette machine offre des fréquences de fonctionnant allant jusqu'à 1GHz. Toutes les techniques d'émulation et de co-émulations sont supportées. La capacité de déboguage est excellente, comparable à celle des solutions concurrentes. Un des gros avantages de Palladium est d'être une machine multi-domaines et multi-utilisateurs, c'est à dire que plusieurs circuits peuvent être émulés en même temps sur la même machine. Cela permet d'optimiser l'utilisation de la machine. La figure 2.2 représente la machine Palladium capable de supporter jusqu'à 256M de portes logiques. A

part sa grande taille, cette machine est très onéreuse avec un prix de l'ordre de 12 millions de dollars.

FIGURE 2.2 – Emulateur Palladium supportant 256M de portes

#### 2.2.2.2 Emulateurs à base de circuits FPGA

Deux grandes industries qui domine le marché des émulateurs à base de circuits FPGA : Synopsys avec son émulateur Zebu [44] et Mentor graphics avec son émulateur Veloce [45].

La solution Zebu de Synopsys : La société Eve a proposé une famille d'émulateurs nommée ZeBu (Zero Bug) avant d'être achetée par Synopsys. Cette famille d'émulateurs est un ensemble de circuits FPGA standards. La première machine fut le modèle ZeBu-ZV utilisant deux FPGAs Xilinx Virtex2, la carte s'installant sur le bus PCI d'un PC. Les dernières machines apparues sont utilisées pour la vérification des SoCs ayant une taille logique qui varie entre 20 et 200 millions de portes. Quelle que soit la machine Zebu considérée, ces machines ont toutes, les mêmes capacités de déboguage, à savoir, une visibilité sur l'ensemble des registres et mémoires du circuit. L'utilisateur a le choix entre effectuer un déboguage dynamique (sélection à la volée des signaux observés) et lent (fréquence à quelques kilohertz) ou un déboguage statique (sélection à la compilation des signaux observés). En mode statique, le déboguage n'altère pas la vitesse d'exécution de la plateforme mais, seule une courte fenêtre temporelle est observable. Les machines ZeBu supportent l'ensemble des techniques d'émulation et de co-émulation et offrent une fréquence d'émulation très élevée, allant jusqu'à 100MHz.

La solution Veloce 2 de Mentor qui propose des machines d'émulation à base de circuit FPGAs spécifiques. La capacité logique de ces émulateurs varie entre 16 millions et 2 billions de portes logiques. Cet émulateur cible les SoCs multi-puces ainsi que les grands

processeurs et GPU. Pour mettre un œuvre un tel SoC, des outils de partitionnement automatiques sont disponible ainsi que des outils de déboggage offrant une bonne visibilité pour les signaux au cours de l'exécution. La fréquence de fonctionnement peut aller jusqu'à 100MHz.

#### 2.2.3 Prototypage matériel

Le prototypage est une technique proche de l'émulation, consistant à réaliser un prototype du système avec des modèles physiques très rapides (FPGA) mais qui n'offrent quasiment pas d'observabilité. Le prototypage vise à vérifier la fonctionnalité du système final, à aider au développement des logiciels embarqués. Cette technique est celle qui offre la meilleure vitesse d'exécution (jusqu'à plusieurs dizaines de méga hertz). Elle intervient, en général, lorsque le matériel a atteint un certain niveau de maturité. De plus, il arrive que l'environnement du circuit soit impossible à modéliser. Dans ce cas, il faut vérifier le système dans son environnement, en temps réel. Le prototypage est la seule technique offrant une vitesse d'exécution suffisante pour couvrir ce besoin. La nuance entre émulation et prototypage se situe au niveau de la mise en œuvre et de la capacité de déboguage des machines. Les émulateurs sont avant tout des machines conçues pour réaliser un déboguage matériel rapide et efficace. Elles ont des flots de mise en œuvre assez rapides, de l'ordre de quelques heures. Par contre, pour un flot de prototypage n'est pas automatisé, le partitionnement d'un circuit entre les différents FPGAs de la plateforme de prototypage n'est pas aisé et engendre des temps de mise en œuvre assez longs, pouvant atteindre plusieurs mois.

Au cours de la conception d'un système sur puce, la question qui peut se poser est : pourquoi faire le prototypage? Une partie de la réponse peut être présentée dans les points suivants :

- Seul le prototypage à base de circuits FPGA fournit à la fois la vitesse et la précision nécessaire pour tester correctement de nombreux aspects du design. Le logiciel peut être validé sur un système virtuel avec une performance encore plus élevée, mais ça serai au dépend de la précision qui vient du fait d'employer le RTL réel.

- La vérification d'un SoC est souvent très compliquée parceque l'état actuelle du système dépend de plusieurs variables, entre autres, son état précédent, ses entrées. Le prototypage permet d'exécuter le système en temps réel ce qui permet d'apercevoir les effets immédiats des conditions temps réel, les entrées et le changement des sorties.

- Au début d'un projet, les concepteurs doivent prendre des décisions fondamentales à propos du choix de la technologie de conception de la puce, la performance, la consommation d'énergie... Certains de ces choix sont mieux réalisés en utilisant des outils de modélisation algorithmique, mais quelques expériences supplémentaires pourraient également être effectuée en utilisant les FPGA. Par conséquent, un circuit FPGA est utilisé pour prototyper une idée à partir de sa modélisation en RTL. Une fois dans le FPGA, les informations préliminaires peuvent être recueillies pour aider à conduire

l'optimisation de l'algorithme et l'architecture éventuelle du SoC.

• Un système de prototypage est considéré comme autonome. En effet, un FPGA peut être configuré, par exemple à partir d'une carte mémoire flash EEPROM ou autre support autonome, sans supervision par un PC hôte. Le prototype peut donc tourner de façon autonome et être utilisé pour tester la conception de SoC dans des situations tout à fait différentes de celles fournies par d'autres techniques de vérification, comme l'émulation, qui reposent sur l'intervention d'une machine hôte. Dans les cas extrêmes, le prototypage pourrait être pris complètement hors du laboratoire et dans les environnements de la vie réelle sur le terrain pour servir comme étant une démonstration.

# 2.2.4 Synthèse : Comparaison entre les différents types de vérification

La figure 2.3 présente les caractéristiques des 3 méthodes de vérification matérielle précédemment citées. La simulation offre une grande souplesse, simplicité d'utilisation, grande

FIGURE 2.3 – Caractéristiques des différentes techniques de vérification matérielle

observabilité, un temps de mise en place assez court. De part ses qualités, la simulation est l'outil fondamental dans la conception des systèmes sur puce. Cependant, cette technique a une faible vitesse d'exécution au niveau RTL ce qui limite son utilisation.

L'émulation, quant à elle, offre une souplesse, observabilité et une vitesse d'exécution supérieure par rapport à la simulation moyennant un flot de mise en œuvre plus ou moins complexe et un important budget de fonctionnement.

Enfin, le prototypage matériel, avec un temps modéré de mise en œuvre et d'exécution, offre la meilleure solution aux développeurs pour réussir la conception de leurs produits dans les plus courts délais. En plus, une plateforme de prototypage est beaucoup moins chère qu'un émulateur matériel. Par conséquent, et dans un stade avancé dans la conception d'un système sur puce, le prototypage matériel permet d'anticiper le développement du logiciel et le circuit est prêt rapidement. En plus la capacité logique de la plateforme de prototypage est assez grande et peut atteindre 500 millions de portes logiques. Dans le reste de ce manuscrit, nous nous intéressons au prototypage matériel ainsi qu'aux plateformes de prototypage qui existent sur le marché. Mais en premier lieu, nous allons nous attarder sur la description de l'élément de base des plateformes matérielles qui est le FPGA

# 2.3 Architecture FPGA

Les plateformes de prototypage matériel sont conçues à base de circuits FPGA. Deux grands fabricants s'imposent sur le marché des FPGA qui sont Altera et Xilinx. L'architecture d'un FPGA, qui a beaucoup progressé ces dernières années, varie de l'un à l'autre tout en gardant l'aspect reconfigurable de ces circuits. En effet, un FPGA (Field Programmable Gate Array) est un circuit logique intégré qui peut être reprogrammé après sa fabrication, permettant ainsi d'implémenter plusieurs applications.

Un FPGA est formé d'un réseau de blocs logiques configurables connectés par un réseau d'interconnexion configurable. Récemment, un FPGA peut intégrer d'autres composants permettant d'améliorer sa performance.

# 2.3.1 Bloc logique de base du FPGA

Le bloc logique de base d'un FPGA, nommé BLE (Basic Logic Element) est composé d'une table de transcodage (LUT : Look Up Table) à K entrées et d'une bascule suivies d'un multiplexeur. Le BLE peut fonctionner soit en mode combinatoire si sa sortie est fournie par la LUT, soit en mode séquentiel si sa sortie vient de la bascule.

Une table de transcodage à K entrées (K-LUT) contient  $2^K$  bits de configurations. Elle est capable d'implémenter n'importe quelle fonction booléenne ayant au plus K entrées. Des études ont été menées sur le nombre d'entrées des LUTs. Les auteurs de [46] [47] ont montré que le choix de 4 entrées est un bon compromis entre les performances du circuit et les contraintes des algorithmes de placement-routage, leur complexité et leur efficacité. La figure 2.4 montre la structure d'un bloc logique de base ayant 4 entrées. La 4-LUT utilise 16 bits SRAM (static random access memory) pour implémenter n'importe quelle fonction booléenne à 4 entrées.

Les éléments logiques de base peuvent être rassemblés en clusters hiérarchiques afin

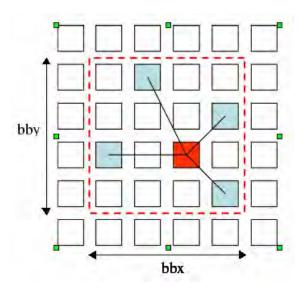

de réduire la connectivité globale et favoriser une connectivité locale et rapide. Un cluster est caractérisé par le nombre de BLEs (N) qu'il contient et le nombre de ses entrées (I). Le nombre de BLEs N est typiquement entre 4 et 10 dans les FPGAs modernes. Chaque entrée d'un BLE peut être connectée à n'importe quelle entrée parmi les I entrées du cluster ou à n'importe quelle sortie des BLEs contenus dans le cluster. Le schéma d'un cluster est illustré par la figure 2.5.