## Modeling and characterization of electrical effects of Ge integration in Metal/High-k/SiGe MOS structures

Assawer Soussou

### ► To cite this version:

Assawer Soussou. Modeling and characterization of electrical effects of Ge integration in Metal/Highk/SiGe MOS structures. Micro and nanotechnologies/Microelectronics. Université de Grenoble, 2014. English. NNT: 2014GRENT018. tel-01282054

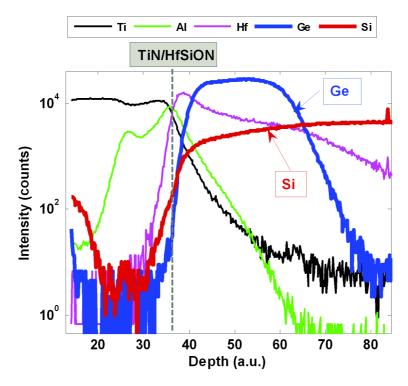

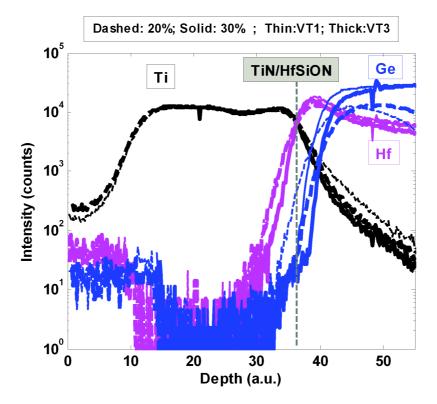

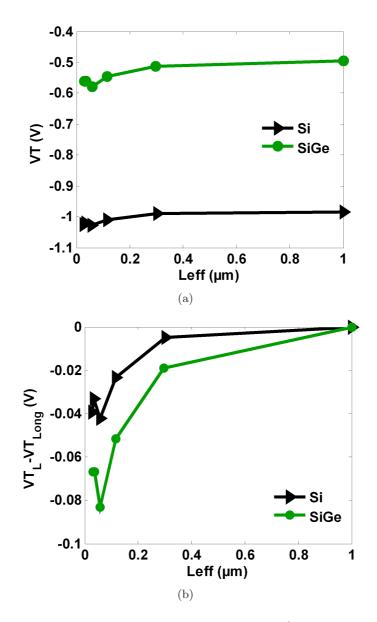

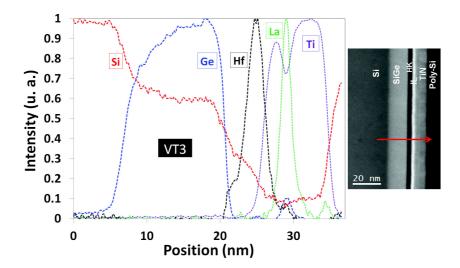

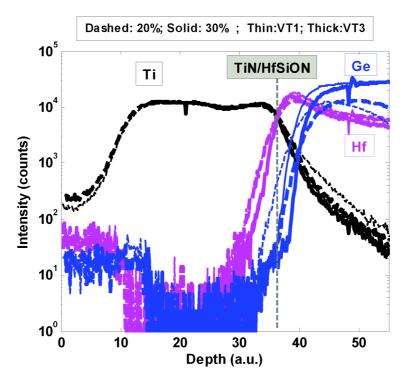

## HAL Id: tel-01282054 https://theses.hal.science/tel-01282054

Submitted on 3 Mar 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano électronique et Nano Technologies

Arrêté ministériel : 7 août 2006

Présentée par

## Assawer SOUSSOU

Thèse dirigée par **Gérard GHIBAUDO** et codirigée par **Charles LEROUX** et **Denis RIDEAU**

préparée au sein du laboratoire IMEP-LAHC, le CEA-Leti et de l'entreprise STMicroelectronics dans l'École Doctorale « Electronique, Electrotechnique, Automatique et Traitement du Signal »

# Modeling and characterization of electrical effects of Ge integration in Metal/High-k/SiGe MOS structures

Thèse soutenue publiquement le « **03 Avril 2014** », devant le jury composé de :

Mr. Brice GAUTIER PR, INSA de Lyon, Président Mr. Pascal MASSON PR, Université de Nice Sophia Antipolis, Rapporteur Mme. Daniella MUNTEANU DR, CNRS Marseille, Rapporteur Mr. Denis RIDEAU ING, STMicroelectronics, Co-encadrant Mr. Charles LEROUX ING, CEA-Grenoble, Co-encadrant Mr. Gérard GHIBAUDO Directeur de thèse DR, CNRS Alpes,

This thesis is dedicated to my parents, my grandmother and persons who believe in me.

#### Acknowledgements

Writing this dissertation has been one of the most significant academic challenge I have ever had to face. Unless the support, encouragement and guidance of the following people, this thesis would not have been completed. It is a pleasure to thank them for their contribution and valuable assistance in the preparation and completion of this study.

Foremost, I owe my deepest gratitude to my supervisor Dr. Gérard Ghibaudo. Without your continuous optimism concerning this work, enthusiasm, encouragement and support this study would hardly have been completed. Your wisdom and immense knowledge inspired and motivated me. Despite your many other academic and professional commitments, you often have been present for discussion and have painstakingly e-mailed the information I needed. I consider it an honor to work with you and to present our methods to extract electrical parameters in MOSFETs in the ULIS conference. My sincere thanks also for offering me the three months opportunity in the IMEP lab and leading me finishing this manuscript in excellent atmosphere. I could not have imagined having a better advisor and mentor for my PhD study.

I would like to express my special appreciation and sincere gratitude to my co-advisor Dr. Charles Leroux. Over the past three years, you have been a tremendous mentor for me. I would like to thank you for encouraging my research and for allowing me to grow as a research scientist. Your good advice, excellent guidance, caring, kindness and continual support have been invaluable on both an academic and a personal level. During this thesis, you spent countless hours proofreading, listening to me talk about my research and patiently corrected my writing. You deserve very special thanks for believing in me.

I am deeply grateful to my second co-advisor Dr. Denis Rideau for his help and motivation. Your critiques helped to mold my analysis and always forced me to think beyond and improve things. Working with you is a priceless experience that has turned me from a young student into a professional in numerical simulation.

I would like to thank Professor Brice Gautier for serving as my committee member. I would also like to express my gratitude to Professor Pascal Masson and Dr. Daniella Muntenau for reviewing this thesis. Thank you for letting my defense be an enjoyable moment and for your brilliant comments and suggestions.

I am grateful to Dr. Gilles Reimbold and Ing. Clément Tavernier for making it possible to carry out this work in their teams.

My appreciation and thanks go also to Gregory Bidal, Olivier Saxod, Mustapha Rafik, Giovanni Romano, Alain Toffoli, Vincent Delaye, Philippe Blaise, Francois Bertin, Guillaume Audoit and Qentin Rafhay. Collaborations and discussions with you were always a great pleasure, and led to significant improvements in the content and exposition of this work. I have benefited from your priceless skills.

Special thanks goes to the members of my research group who have made working at CEA enjoyable and eventful: Sylvain, Jean, Alexandre, Xavier, Mikael, Masahiro, Carlos, Denis, Guillaume, Jonathan, Joanna, Rabah and Fabienne. I also thank Marie-anne, Pierrette, Sébastien and François for thier encouragements. I am indebted to my many colleagues at ST-Crolles who supported me: Amina, Ben, Seb, Zahi, Joris, Floria, Frédéric, Gabriel, Olivier Nier, Sylvain, Yvan, Komiatchou, François, Fabio, Salim, Michel, Benoit Legoix, Vincent, Patrick, Xavier, Guillaume, Nayera, Emmanuel, Cheikh and Jérôme. I am also gratful to my colleagues at IMEP-LAHC Tapas and Ramin.

I would also like to thank all of my friends who supported me in writing, and incented me to strive towards my goal.

Finally, a special thanks to my family. Words cannot express how grateful I am to my parents for all of the sacrifices that you have made on my behalf.

# Contents

| Α        | Acknowledgements   |                                                                                          |            |  |  |

|----------|--------------------|------------------------------------------------------------------------------------------|------------|--|--|

| G        | enera              | l introduction                                                                           | 9          |  |  |

| 1        | MO                 | MOS capacitor C-V characteristic : basic principles and simulation                       |            |  |  |

|          | 1.1                | Introduction                                                                             | 18         |  |  |

|          | 1.2                | Basic principles of MOS capacitor                                                        | 18         |  |  |

|          |                    | 1.2.1 Ideal MOS capacitor                                                                | 18         |  |  |

|          |                    | 1.2.2 Real (Non-ideal) MOS capacitor                                                     | 23         |  |  |

|          |                    | 1.2.3 Capacitance-voltage measurements                                                   | 30         |  |  |

|          | 1.3                | MOS capacitance simulation                                                               | 32         |  |  |

|          |                    | 1.3.1 Modeling of quantum confinement                                                    | 32         |  |  |

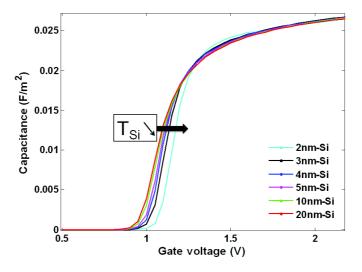

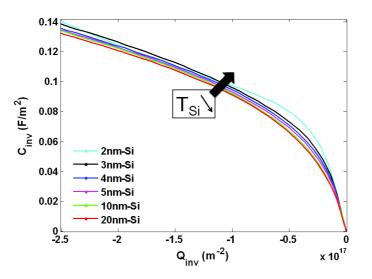

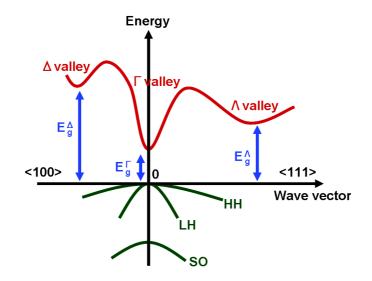

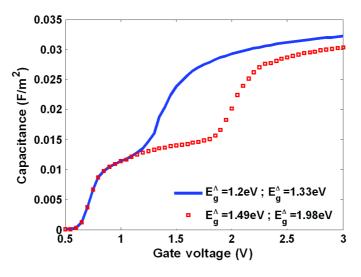

|          |                    | 1.3.2 C-V simulations of Si nMOSFETs                                                     | 41         |  |  |

|          | 1.4                | Conclusion                                                                               | 43         |  |  |

| <b>2</b> | C-V                | simulations of SiGe devices                                                              | 45         |  |  |

|          | 2.1                |                                                                                          | <b>4</b> 6 |  |  |

|          | 2.1<br>2.2         | Strained SiGe/Si electrostatics modeling                                                 | 46         |  |  |

|          | 2.2                | 2.2.1 Strained $SiGe$ on $Si$                                                            | 46         |  |  |

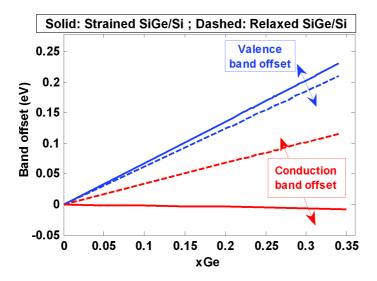

|          |                    | 2.2.2 Strain effects on the $SiGe$ band structure $\ldots$                               | 48         |  |  |

|          |                    | 2.2.2       Strain cheets on the Stee Sand Strateduce         2.2.3       Charge density | 55         |  |  |

|          |                    | 2.2.4 Strained $SiGe/Si$ band structure                                                  | 57         |  |  |

|          | 2.3                | SiGe/Si heterostructure modeling                                                         | 61         |  |  |

|          | 2.3<br>2.4         | SiGe-based pFETs and C-V characteristics                                                 | 68         |  |  |

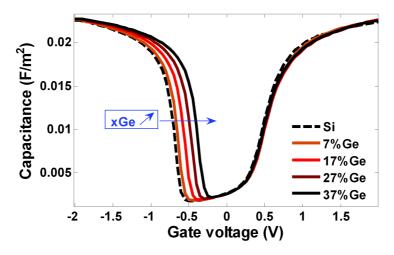

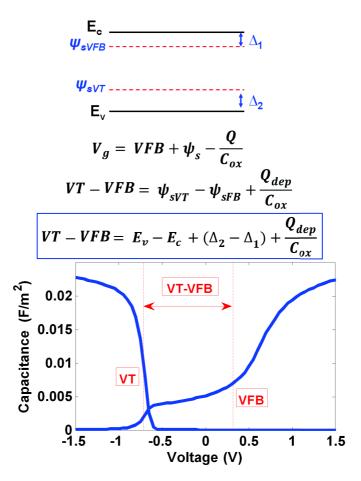

|          | 2.1                | 2.4.1 Bands offset effects                                                               | 68         |  |  |

|          |                    | 2.4.2 SiGe strain effects                                                                | 69         |  |  |

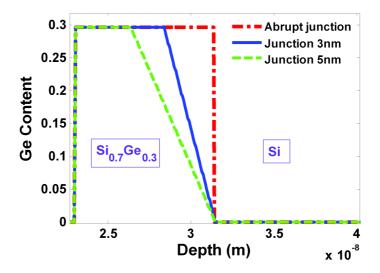

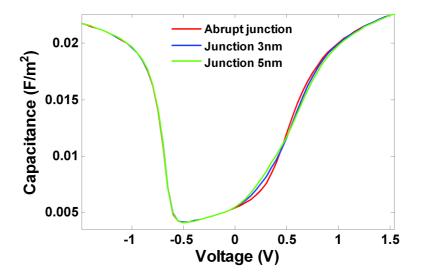

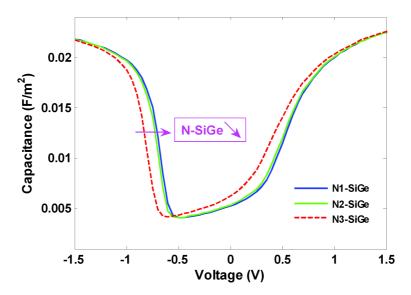

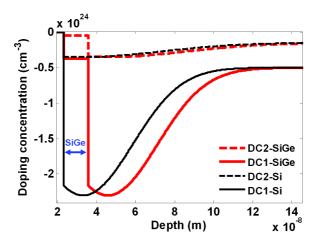

|          |                    | 2.4.3 <i>Ge</i> profile effects                                                          | 71         |  |  |

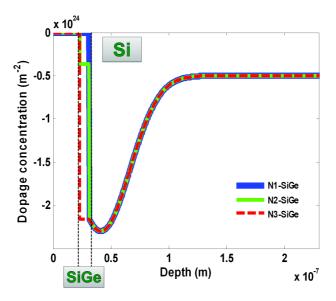

|          |                    | 2.4.4 SiGe dopant concentration effects                                                  | 72         |  |  |

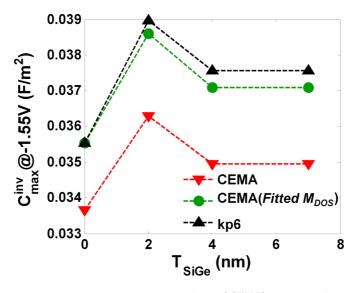

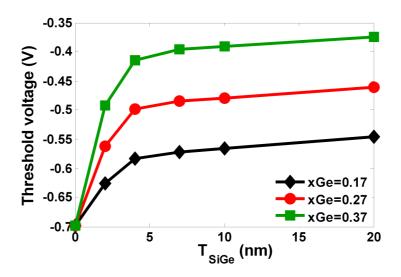

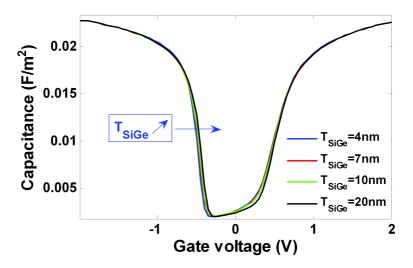

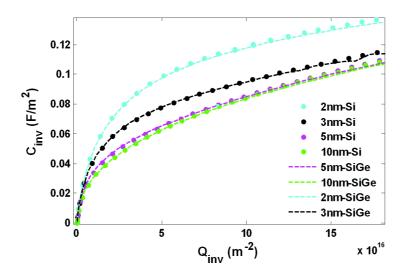

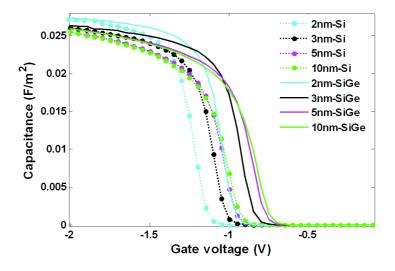

|          |                    | 2.4.5 Ge concentration and SiGe thickness effects                                        | 73         |  |  |

|          | 2.5                | Conclusion                                                                               | 74         |  |  |

| 3        | VТ                 | VFB and EOT parameters extraction                                                        | 75         |  |  |

| U        | <b>ч</b> г,<br>3.1 | Introduction                                                                             | 76         |  |  |

|          | $3.1 \\ 3.2$       | Validation of parameters extraction methods                                              | 76         |  |  |

|          | 0.4                | 3.2.1 Validation of VT and VFB extraction method                                         | 76         |  |  |

|          |                    | 3.2.2 Application of v r and v r b extraction methods on measurements                    | 83         |  |  |

|     | 3.3        | EOT extraction method in the FDSOI devices                                                                         | 86          |

|-----|------------|--------------------------------------------------------------------------------------------------------------------|-------------|

|     |            | 3.3.1 EOT extraction in FDSOI nFETs                                                                                | 86          |

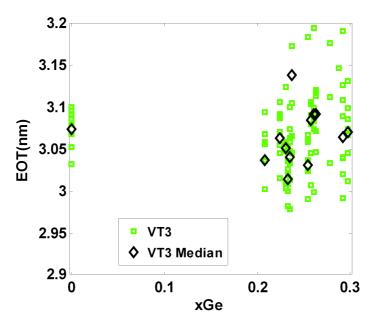

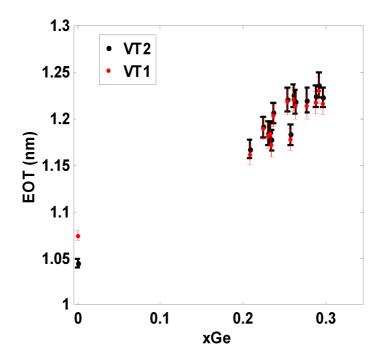

|     |            | 3.3.2 EOT extraction in FDSOI pFETs                                                                                | 101         |

|     | 3.4        | Conclusion                                                                                                         | 106         |

| 4   | Con        | manium impact in Si Ca pEETa acta stack                                                                            | 07          |

| 4   | <b>Ger</b> | manium impact in $Si_{1-x}Ge_x$ pFETs gate stack       1         Introduction       1                              | . <b>07</b> |

|     | 4.1        | Measurements                                                                                                       |             |

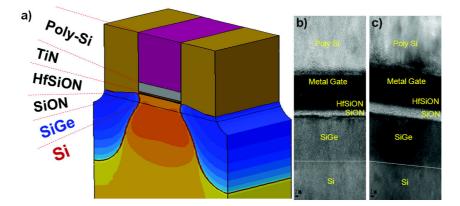

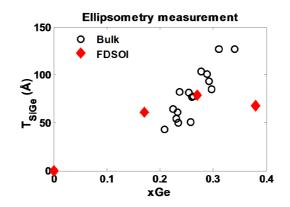

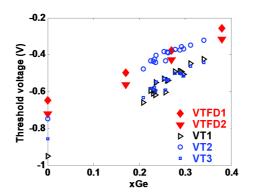

|     | 4.2        | 4.2.1 SiGe bulk pMOSFETs                                                                                           |             |

|     |            | 4.2.2 <i>SiGe</i> FDSOI pFETs                                                                                      |             |

|     | 4.3        | Simulations                                                                                                        |             |

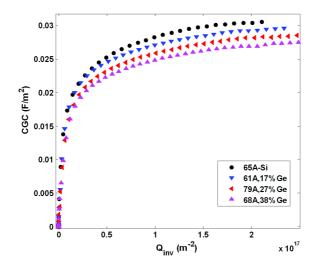

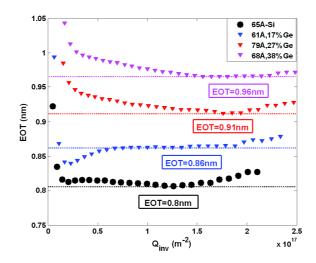

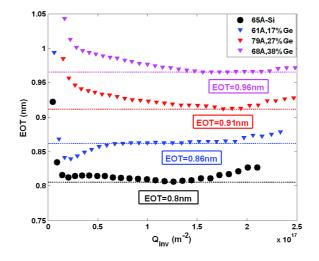

|     | 4.4        | Ge impact on EOT parameter                                                                                         |             |

|     | 4.5        | Si <sub>1-x</sub> Ge <sub>x</sub> material $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |             |

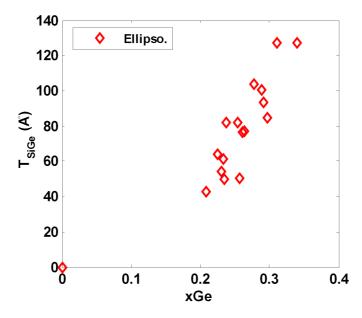

|     | 4.0        | 4.5.1 Ge concentration and $SiGe$ thickness                                                                        |             |

|     |            | 4.5.2 Doping concentration profile                                                                                 |             |

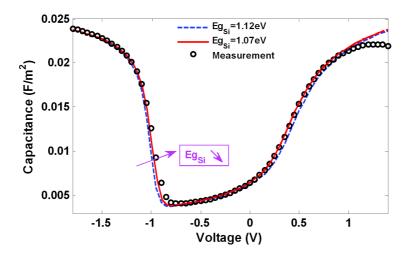

|     |            | 4.5.3 SiGe energy band gap                                                                                         |             |

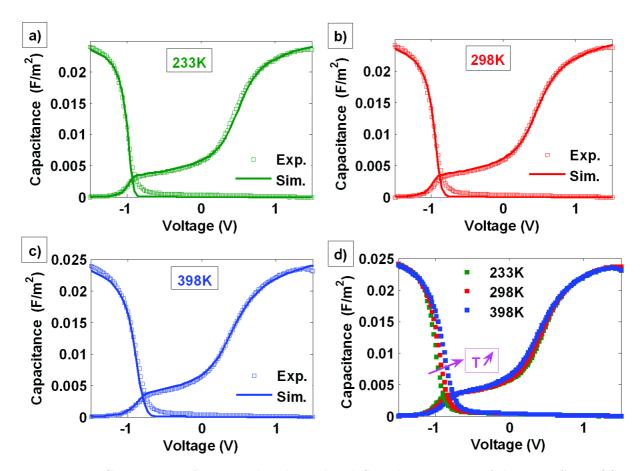

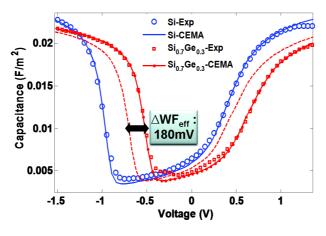

|     | 4.6        | Ge impact on C-V characteristic                                                                                    |             |

|     | 1.0        | 4.6.1 (VT-VFB) parameters                                                                                          |             |

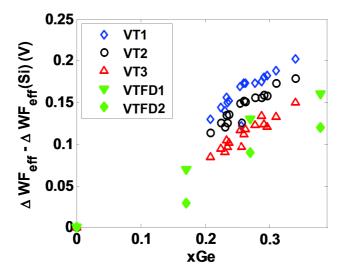

|     |            | 4.6.2 Effective metal gate work function                                                                           |             |

|     | 4.7        | Effective metal gate work function shift                                                                           |             |

|     | 4.8        | Ge impact on VT and VFB understanding                                                                              |             |

|     | 1.0        | 4.8.1 Oxide charges and interface states effects                                                                   |             |

|     |            | 4.8.2 Physicochemical analysis of dipoles and charges at oxide/gate stack                                          |             |

|     |            | 4.8.3 $\Delta WF_{eff}$ shift in the literature                                                                    |             |

|     | 4.9        | Impact of gate length reduction                                                                                    |             |

|     | -          | Conclusion                                                                                                         |             |

|     | 1.10       |                                                                                                                    |             |

| G   | enera      | l conclusion 1                                                                                                     | .45         |

| Bi  | hliog      | graphy 1                                                                                                           | 49          |

|     | onog       | rapny                                                                                                              | 10          |

| Su  | ımma       | ary 1                                                                                                              | .64         |

| Ъı  | ublice     | ations                                                                                                             | .65         |

| 1 ( |            | 10005                                                                                                              | .00         |

| R   | ésum       | é 1                                                                                                                | .67         |

|     | .1         | Introduction et contexte                                                                                           | 167         |

|     | .2         | Simulation des capacités MOS                                                                                       | 168         |

|     |            | .2.1 Validation des résultats de simulation Poisson-Schrödinger                                                    | 169         |

|     |            | .2.2 Analyse du modèle analytique et validation pour les structures $SiO_2/Si$                                     |             |

|     |            | Bulk dans un n-MOSFET                                                                                              |             |

|     |            | .2.3 Validation des simulations C-V du $SiO_2/Si$ n-MOSFET                                                         | 172         |

|     | .3         | Simulation des C-V des transistors intégrant du SiGe                                                               | 175         |

|     |            | .3.1 L'alliage Silicium Germanium                                                                                  |             |

|     |            | .3.2 L'héterojonction SiGe-contraint/Si                                                                            |             |

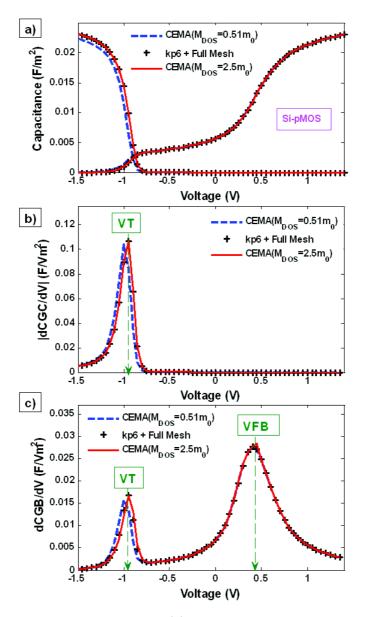

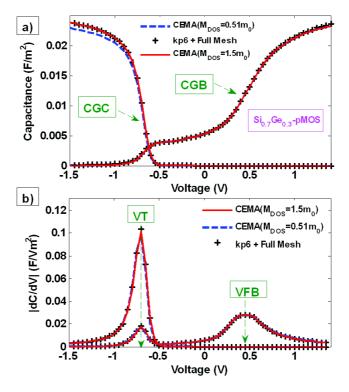

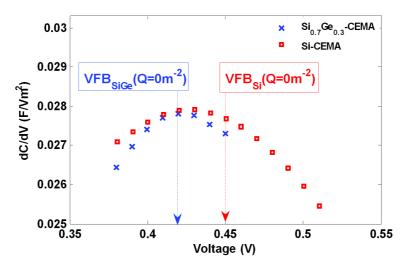

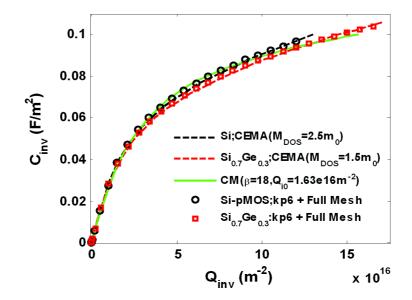

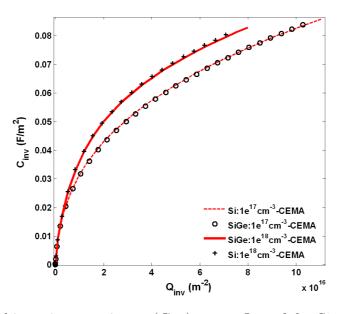

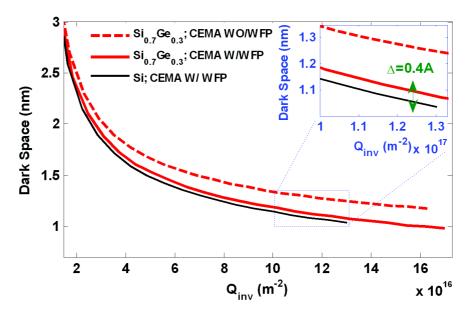

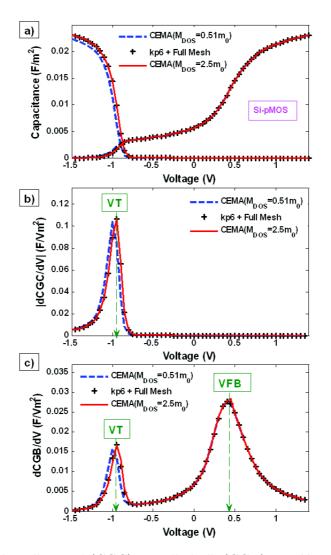

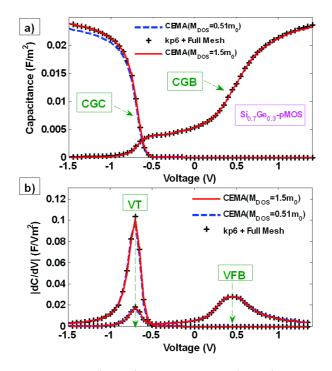

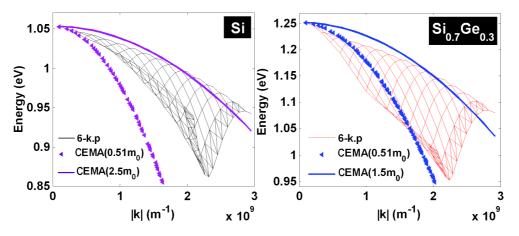

|     |            | .3.3 Simulation des C-V des pMOS à base de Si et SiGe                                                              |             |

|     | .4         | Méthodes d'extraction de VT, VFB et EOT                                                                            | 178         |

#### CONTENTS

|    | .4.1    | Extraction de VT et VFB dans les pMOSFET $Si_{1-x}Ge_x/Si$ |

|----|---------|------------------------------------------------------------|

|    | .4.2    | Extraction de l'EOT dans les pFET FDSOI $Si_{1-x}Ge_x$     |

| .5 | Effet ( | de l'intégration du Ge dans les structures MOS             |

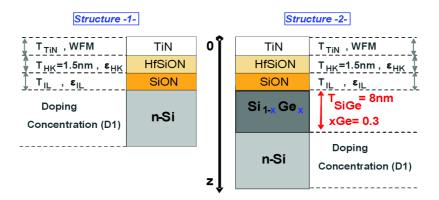

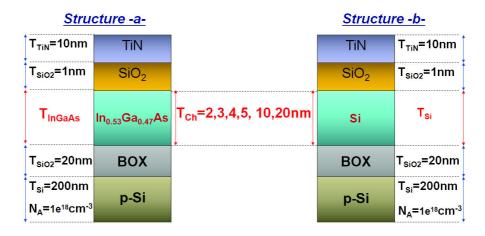

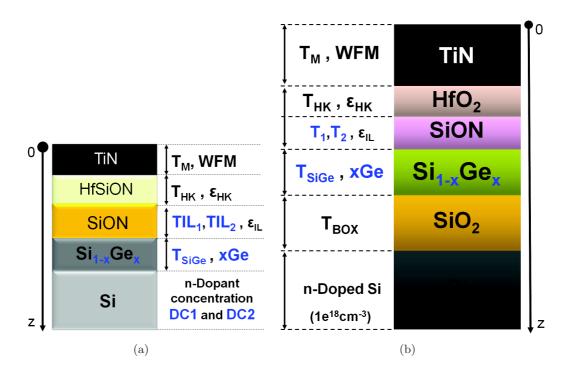

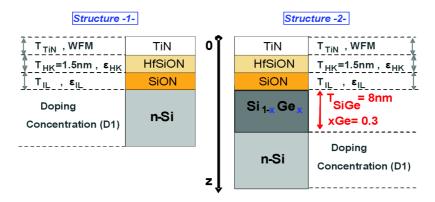

|    | .5.1    | Dispositifs étudiés                                        |

|    | .5.2    | Décalage de travail de sortie effectif de la grille        |

|    | .5.3    | Étude des états d'interface                                |

|    | .5.4    | Étude des charge dans l'oxyde                              |

|    | .5.5    | Étude des charge dans l'oxyde high-k et des dipôles        |

|    | .5.6    | Conclusion                                                 |

CONTENTS

# General introduction

#### Contents

| High-k dielectrics integration 10 | ) |

|-----------------------------------|---|

| Threshold voltage adjust          | 2 |

| FDSOI structures                  | } |

| Purpose of this thesis            | ł |

| Organization of the thesis 16     | ; |

|                                   |   |

The downscaling of metal-oxide-semiconductor field-effect transistor (MOSFET) geometry has been a very successful process to improve the performances of CMOS devices. The guideline of the technology improvements in MOSFET fabrication is the International Technology Roadmap for Semiconductors (ITRS). According to the ITRS [1], devices which enter the mass production in 2014 should integrate further ultrathin EOT with higher-k materials as dielectrics. Table 1 reports the 2014 ITRS target of the physical gate length, equivalent oxide thickness and threshold voltage for bulk and fully depleted SOI (FDSOI) devices.

| ITRS target                        | Bulk | FDSOI |

|------------------------------------|------|-------|

| Physical gate length (nm)          | 18   | 18    |

| Equivalent oxide<br>thickness (nm) | 1.04 | 1.2   |

| Threshold voltage (V)              | 0.3  | 0.22  |

Table 1: ITRS target of the physical gate length, equivalent oxide thickness and threshold voltage for bulk and fully depleted SOI (FDSOI) devices which enter the mass production in 2014 [1].

Nevertheless, conventional scaling down of MOSFET dimensions, according to aggressive ITRS requirements, faces physical and economical limits. Further CMOS scaling for sub-45nm node [2] relies on new materials integration such as metal gate electrode together with high-k dielectric and new channel materials, or alternative device structures, such as fully depleted SOI devices.

To be able to achieve the ITRS roadmap objectives, low threshold voltage metal gate MOS-FETs, especially with small EOT, has been a challenging problem for implementation in the manufacturing CMOS flow at every new technological node. In practice, the threshold voltage of a MOSFET is controlled by the adjustment of two parameters: the work functions of the gate and substrate. In this introduction, we firstly introduce high-k dielectrics integration, the MOS threshold voltage adjust and FDSOI structures. Then, we describe problems and explore the purpose of this thesis. Finally, the organization of the thesis is presented.

#### High-k dielectrics integration

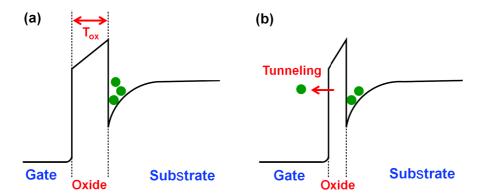

As device scaling progresses, gate dielectric physical thickness becomes extremely thin. The oxide thickness shrinking leads to a leakage current increase because of the quantum mechanical tunnel effect (figure 1). In order to reduce the probability that an electron passes through the dielectric (tunneling between gate and channel), the potential barrier between channel and gate should be thicker in space or higher in energy. Silicon dioxide  $(SiO_2)$  has been widely used as

Figure 1: Band diagram of structures with a thick (a) and thin (b) gate dielectric. In the thin oxide structure, a leakage current increases because of the quantum mechanical tunnel effect.

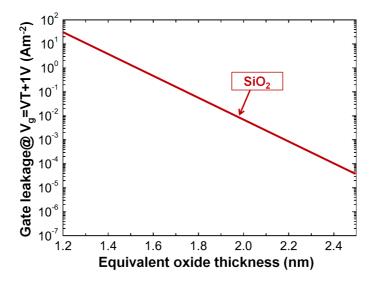

gate dielectric because of its high insulation, passivation, and process compatibility with Si [1]. However, as device miniaturisation continues, physical thickness of  $SiO_2$  gate insulator becomes ultrathin. This results in significant carriers tunneling from the MOSFET channel to the gate electrode leading to an undesired gate leakage current increase (figure 2). Therefore, scaling of MOSFETs with  $SiO_2$  gate dielectrics reaches its limit. High-k materials have been promising candidates to substitute the  $SiO_2$  dielectrics and break its limitation.

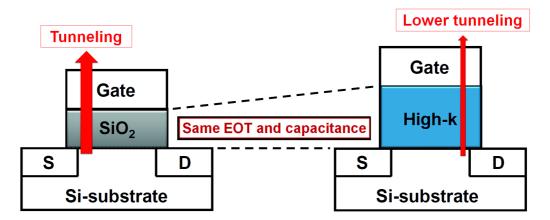

Indeed, high-k oxides have high dielectric constants. Thus, their introduction allows a dielectric thickness increase (which should decrease the gate leakage) for the same gate oxide capacitance  $(C_{ox})$  (figure 3):

$$C_{ox} = \frac{\varepsilon_{ox}}{T_{ox}} \tag{1}$$

where  $\varepsilon_{ox}$  and  $T_{ox}$  are the dielectric constant and thickness.

Figure 2: Inversion gate leakage as a function of equivalent oxide thickness for  $SiO_2$  dielectric [3][4].

It is worth noting that the figure of merit which expresses scaling of high-k gate dielectrics is the equivalent oxide thickness (EOT), given by:

$$EOT = \frac{\varepsilon_{SiO_2}}{\varepsilon_{high-k}} . T_{high-k}$$

<sup>(2)</sup>

where  $\varepsilon_{SiO_2}$  and  $\varepsilon_{high-k}$  are the  $SiO_2$  and high-k dielectric constants.  $T_{high-k}$  is the high-k physical thickness.

Figure 3: High-k gate dielectrics introduction allows the dielectric thickness increase and gate leakage decrease for a same gate oxide capacitance.

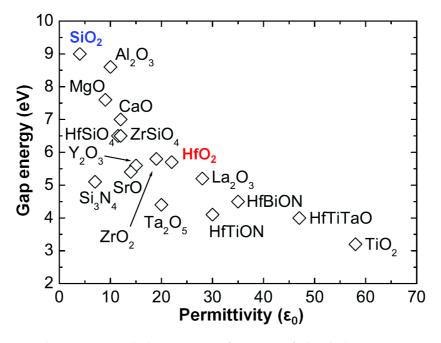

Equation 2 and figure 3 show that using a material with a dielectric constant n times larger than the  $SiO_2$  one, gives the possibility to obtain the same  $C_{ox}$  with n times larger thickness. However, high-k dielectrics have a smaller potential barrier height than  $SiO_2$  oxide (figure 4). Thus, carriers in the inversion layer of a MOSFET featuring high-k dielectrics feel a thicker but lower potential barrier than in  $SiO_2$  devices [5]. Anyway, despite of the lower potential barrier, high-k insulator MOSFETs outperform  $SiO_2$  devices in terms of leakage [6][7].

Figure 4: Band gap energy dielectrics as a function of the dielectric permittivity [8].

#### Threshold voltage adjust

Actually, the threshold voltage (VT) of MOSFETs is controlled by the adjustment of two parameters: the work functions of the gate (WFG) and of the substrate (WFS)( $VT \sim WFG - WFS$ ).

In Poly-Si gate bulk MOSFETs, the work function of a polycrystalline-Silicon gate is adjusted by doping the gate p+ or n+ for p-channel and n-channel MOSFETs respectively. The channel work function is adjusted by appropriately doping the substrate to provide an acceptable work-function difference and charge depletion [9].

Beyond the 45nm node, the integration of high-k dielectrics and metal gates would be mandatory for high-performance and low-power advanced CMOS applications.

Indeed, introducing metal gates can:

(i) solve the problem of poly depletion in inversion. Poly-depletion effect adds an equivalent oxide thickness up to 0.5 nm to the gate stack, which is significant in front of the overall targetted EOT, around 1nm [2].

(ii) eliminate boron penetration from the p-doped polysilicon gate into the channel region in conventional CMOS.

(iii) avoid the high poly electrode resistance.

Selecting the metal gate material, the workfunction of the metal gate should be given a high consideration since it influences the MOSFET threshold voltage  $(VT \sim WFG - WFS)$ .

A bandedge metal gate was reported to be the optimal choice for sub-45 nm high performance applications (about 4.2 eV for nMOS and 5.1 eV for pMOS) [10][11].

For conventional metal gate CMOS applications on Silicon, a p+ metal work function is required for the pMOS transistor. Whereas, an n+ metal work function is needed for the nMOS transistor. In order to satisfy the optimal n and pMOS threshold voltages, a dual metal gate solution would be ideal. But, it is difficult to identify, complicate and expensive to implement into devices [12]. Instead, a single midgap metal could be used. The VT could be therefore adjusted by suitable implants for n and p types MOSFETs.

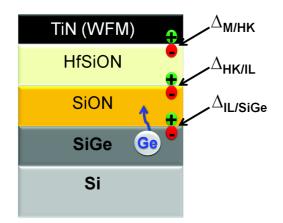

Metal nitrides e.g. TiN are being considered as potential candidates for the mid-gap electrode due to their high thermal stability and compatibility with conventional CMOS processing [13]. Indeed, the Fermi level of the TiN gate (WFG~ 4.55-4.7 eV [14]) lies midway between the valence and conduction band edges of the Silicon, i.e., at midgap, assuming that the same gate material can be used for both p- and n-channel MOSFETs. In metal gate/high-k based MOS-FETs, low threshold voltage is achieved by the incorporation of an interface dipole layer in the gate dielectric stack [15][16]. The interface dipole layer either increases, or decreases the effective gate work function by creating a localized electric field in the metal gate/high-k stack. The interface dipole layers are separately formed in n-channel and p-channel MOSFETs. LaOx and AlOx capping on high-k dielectrics have been shown to be effective in modulating the effective metal gate work function toward the n and p type band edge respectively [17][18][19][20].

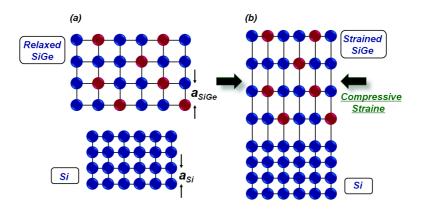

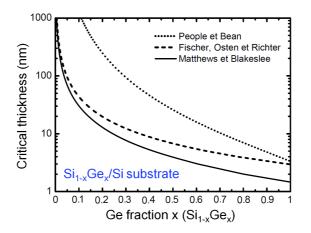

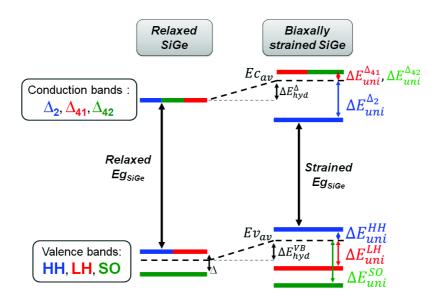

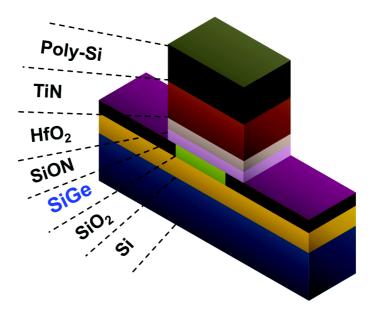

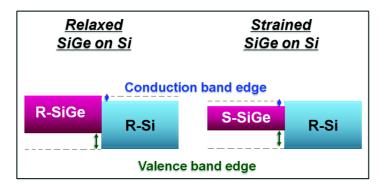

The pMOS metal gate work function optimisation using AlOx capping is not sufficient to maintain low VT. The VT adjust can be tailored by accommodating the substrate work function. To this end, new materials e.g. SiGe have been introduced in the channel of the pMOS. The large SiGe valence-band offset with respect to Si allows the achievement of low pFET threshold voltage [21]. Moreover, the SiGe is also an attractive channel material due to its high carrier mobility and compatibility with conventional CMOS processes [21]. The combination of high-k dielectric and SiGe channel may present a practical device architecture to achieve high-performance and low-power application with low VT [8].

#### **FDSOI** structures

CMOS on thin-film Silicon-On-Insulator (SOI) is considered as a very attractive technology for further CMOS dimension downscaling and performance enhancement.

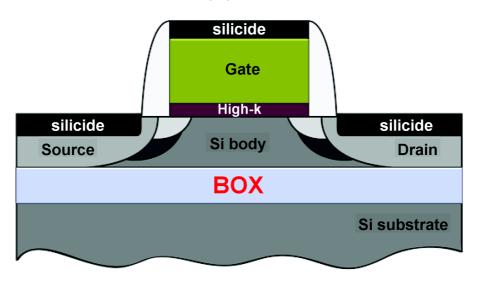

Figure 5 shows a cross-section of a SOI device. The advantages of SOI technology over conventional bulk Si CMOS come from its buried oxide layer (commonly called BOX). They consist of:

(i) lateral and vertical dielectric isolation providing reduced parasitic capacitances and leakage currents when compared to junction isolation [22],

(ii) thinned films and dielectric isolation offering tighter transistor packing density and simplified processing [23],

(iii) SOI devices yield improved switching speed and reduced power consumption. The operating speed is also improved since the isolated channel from substrate bias prevents the increase in a threshold voltage of stacked SOI transistors [23].

We distinguish between two types of SOI transistors. If the Silicon film (typically 100 nm or more) on the BOX layer is thicker than the body depletion region depth, the film is partially depleted (PD) SOI. This technology is called partially depleted (PD) SOI. However, if the

Silicon film thickness is thin enough (typically 50 nm or less) or the body doping concentration is low enough, the ultra thin film is fully depleted (FD). The obtained device is called fully depleted (FD) SOI. FD SOI transistors have more advantages than PD SOI transistors in terms of extremely low sub-threshold swing ( <65 mV/decade), no floating-body effects, and low threshold voltage variation with temperature (2-3 times less). Moreover, undoped or very slightly doped UTB devices minimize impurity scattering and reduce threshold voltage variation resulting from random dopant fluctuation [23].

Figure 5: Cross-section of a SOI MOSFET.

#### Purpose of this thesis

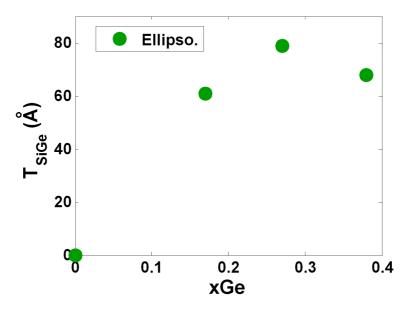

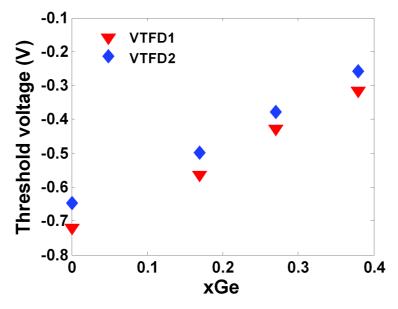

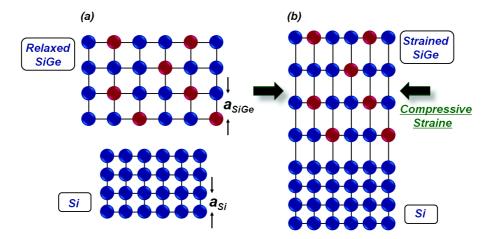

To reduce the high bulk pMOS threshold voltage, strained Silicon Germanium on Silicon buffer layer has been successfully introduced in the 32-28nm industrial bulk process [21][24]. The threshold voltage reduction is achieved by narrowing the channel band gap on the valence band side. For this reason, recently SiGe has been integrated also in the body of FDSOI pFETs [25].

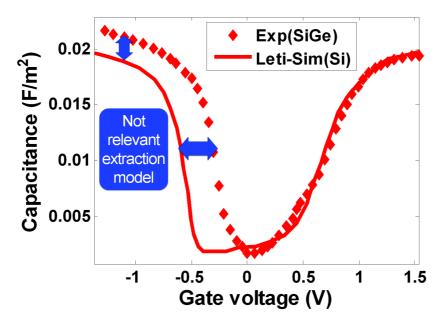

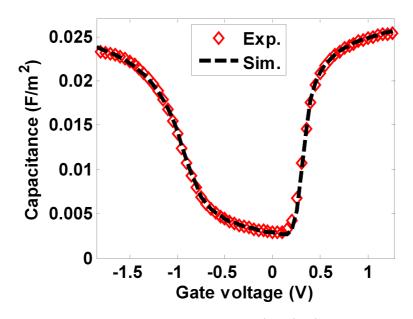

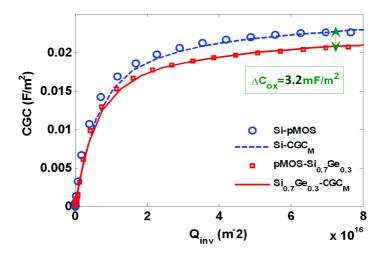

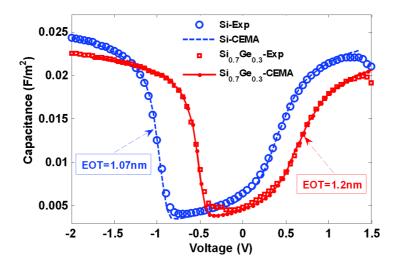

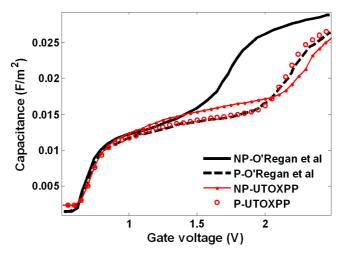

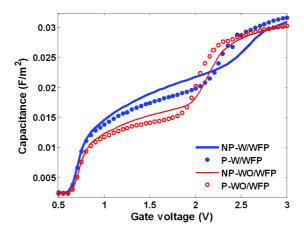

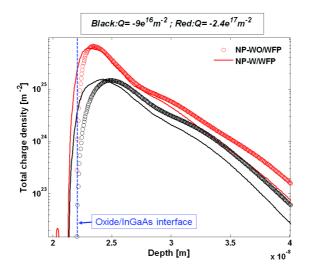

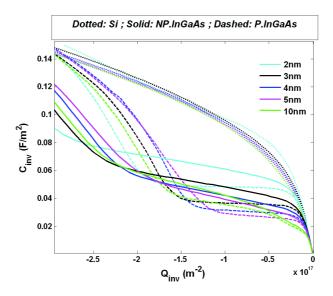

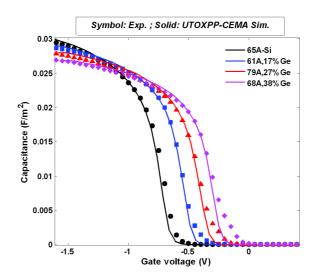

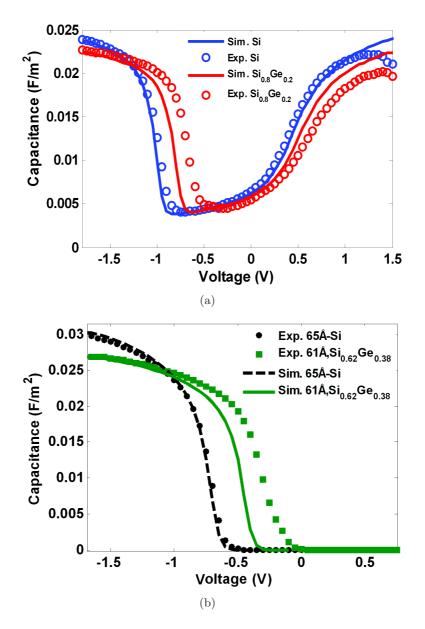

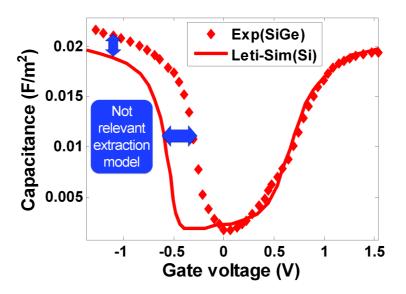

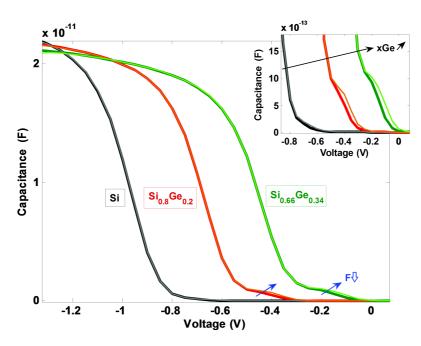

Nevertheless, SiGe incorporation in pMOS transistors generates problems. One of the problematics is that the simulation model for pure Si is not valid for SiGe devices modeling. Moreover, before this thesis, electrical parameters (threshold voltage, flat band voltage (VFB) and EOT) were extracted using the extraction model on pure Si [26]. Figure 6 compares the measured capacitance versus gate voltage of the SiGe bulk pMOSFET to the obtained curve using the extraction model on pure Si. It is clear from this figure that the extraction model is not relevant for SiGe devices.

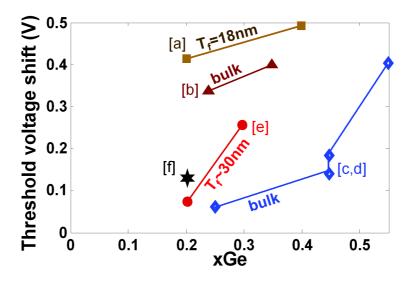

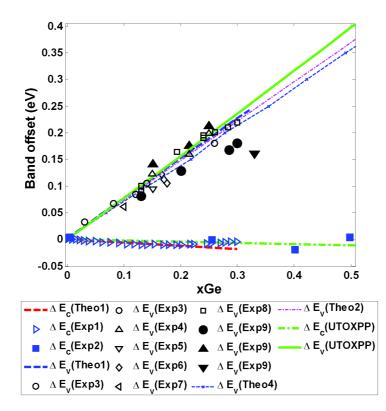

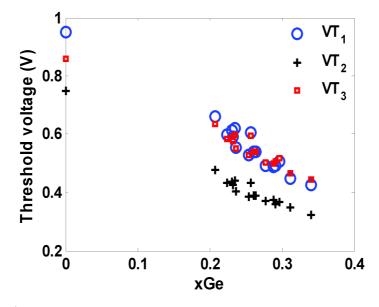

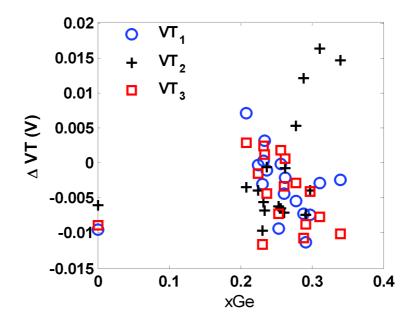

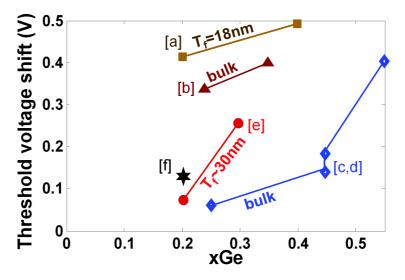

Another issue is to maintain good threshold voltage centering when introducing SiGe in the pMOS. Figure 7 illustrates published reports on threshold voltage (VT) shift as a function of the *Ge* concentration. In this figure, data for both bulk and FDSOI pFETs are reported. Unexplained large discrepancy of VT shift is noticed making accurate VT centering very problematic. This justifies the investigation and results presented all along the manuscript.

The purpose of this thesis is to provide better insight on these issues. The first challenge is to find which simulation model should be used to predict the gate capacitance accurately. Furthermore, the problem is to find out how electrical parameters (threshold voltage, flat band voltage (VFB) and EOT) will be extracted when introducing SiGe in the pMOS. The second problem is to understand the Ge impact on VT, VFB and EOT in  $Si_{1-x}Ge_x$  pMOS for better VT contol.

Figure 6: Measured (symbol) SiGe bulk pMOSFET capacitance versus gate voltage compared to the obtained curve using the extraction model on pure Si (line) [26].

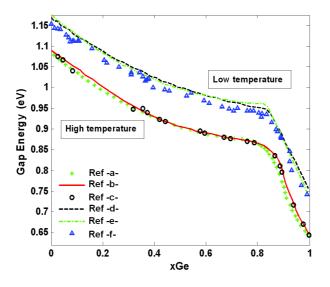

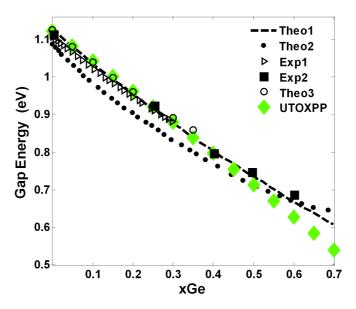

Figure 7: Published data of VT shift for SiGe pMOS as a function of the Ge content.(References: [a]: [27]; [b]: [28]; [c]: [29]; [d]: [30]; [e]: [31]; [f]: [32].)

#### Organization of the thesis

The core of this document includes 4 chapters. The basic background of ideal and real MOS capacitors are presented in chapter 1. In this chapter, UTOXPP Poisson-Schrödinger simulation results are also validated. Chapter 2 focuses on strained SiGe/Si heterostructure band structure modeling. This chapter discusses the theoretical impact of the SiGe incorporation on the C-V characteristic. In chapter 3, we propose simple methods to extract VT, VFB and EOT parameters in  $Si_{1-x}Ge_x$  pMOS. The extraction methods are first validated by simulations and then applied to C-V measurements. An investigation of the *Ge* integration electric impact in both pMOS bulk and FDSOI technologies is explored in chapter 4. In this chapter, evaluation of the role of Germanium on pMOS gate stack parameters (Effective work function and Equivalent oxide thickness) is presented. Finally, this document is finalized by conclusions and suggestions for future work.

# Chapter 1

# MOS capacitor C-V characteristic : basic principles and simulation

#### Contents

| 1.1 | $\mathbf{Intr}$ | oductior  | 1                                                                                                      | <b>18</b> |

|-----|-----------------|-----------|--------------------------------------------------------------------------------------------------------|-----------|

| 1.2 | Basi            | ic princi | ples of MOS capacitor                                                                                  | 18        |

|     | 1.2.1           | Ideal M   | OS capacitor                                                                                           | 18        |

|     |                 | 1.2.1.1   | Accumulation region                                                                                    | 19        |

|     |                 | 1.2.1.2   | Flat bands                                                                                             | 20        |

|     |                 | 1.2.1.3   | Depletion region                                                                                       | 21        |

|     |                 | 1.2.1.4   | Threshold voltage                                                                                      | 21        |

|     |                 | 1.2.1.5   | Inversion region                                                                                       | 22        |

|     | 1.2.2           | Real (N   | on-ideal) MOS capacitor                                                                                | 23        |

|     |                 | 1.2.2.1   | Effect of the bulk oxide charges                                                                       | 23        |

|     |                 | 1.2.2.2   | Effect of interface fixed oxide charges                                                                | 24        |

|     |                 | 1.2.2.3   | Effect of interface trapped charges                                                                    | 25        |

|     |                 | 1.2.2.4   | Flat band voltage expression                                                                           | 26        |

|     |                 | 1.2.2.5   | Electric effect of oxide charges                                                                       | 28        |

|     | 1.2.3           | Capacit   | ance-voltage measurements                                                                              | 30        |

| 1.3 | MO              | S capaci  | $tance simulation \ldots \ldots$ | <b>32</b> |

|     | 1.3.1           | Modelin   | g of quantum confinement                                                                               | 32        |

|     |                 | 1.3.1.1   | 1D Poisson equation                                                                                    | 32        |

|     |                 | 1.3.1.2   | 1D Schrödinger equation                                                                                | 33        |

|     |                 | 1.3.1.3   | Poisson-Schrödinger results validation                                                                 | 34        |

|     |                 | 1.3.1.4   | Analytical model analysis for $SiO_2/Si$ bulk n-MOSFETs $\ .$ .                                        | 37        |

|     | 1.3.2           | C-V sim   | nulations of Si nMOSFETs                                                                               | 41        |

| 1.4 | Con             | clusion   |                                                                                                        | <b>43</b> |

#### 1.1 Introduction

Capacitance-voltage (C-V) characteristic offers a wealth of device and process information, including bulk and interface charges. It is commonly used for extracting common MOS device parameters such as oxide capacitance, oxide thickness, doping density, flat band voltage, threshold voltage, metal-semiconductor work function difference, etc..

This chapter will review basic principles of ideal and real MOS capacitors allowing threshold voltage and flat band voltage definition. Effects of oxide charges and interface traps on the C-V response will be investigated and testing C-V configuration will be explored.

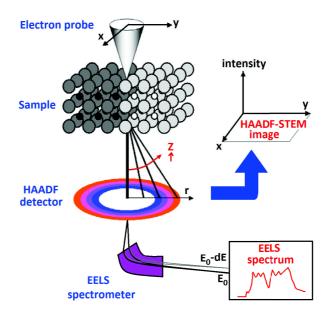

In this thesis, C-V simulations have been performed using UTOXPP Poisson-Schrödinger solver. The second section of this chapter introduces the Poisson-Schrödinger solver and its enhancements implemented in UTOXPP simulator. The MOS-capacitor simulation results will be compared to the measured C-V characteristic in order to validate the C-V simulation model.

#### **1.2** Basic principles of MOS capacitor

Before characterizing electrically the real MOS device by considering the defects contained in the oxide, at first, the ideal MOS structure will be studied. This section adresses the basic principles of MOS capacitor. The first part exposes the different MOS operation gate bias modes. The second part assesses the oxide defects and interface traps impact on the C-V characteristic and the flat band voltage in real MOS capacitor.

#### 1.2.1 Ideal MOS capacitor

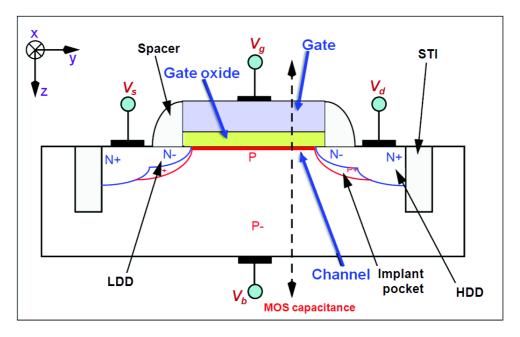

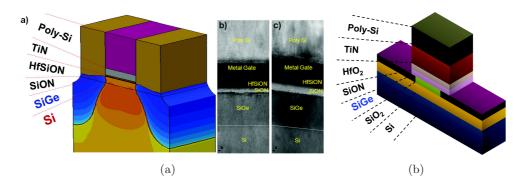

The metal-oxide-semiconductor (MOS) capacitor is the core of the MOS technology. Figure 1.1 presents a schematic MOS transistor of the actual C28nm node. In the z direction (perpendicular to the oxide/substrate interface), the charge concentration in the channel is modulated by a MOS capacitance between the semiconductor substrate and gate electrode located above an oxide layer. A voltage drop across the oxide induces a conducting channel between the source and drain contacts via the field effect.

The MOS structure is called ideal if the following two conditions are met:

(a) The work function of metal (WFM) and work function of semiconductor (WFS) are equal (WFM=WFS) when no voltage applied to the structure.

(b) Both the oxide and oxide/semiconductor interface are assumed to be free of charges and defect states. So, the electric field is zero everywhere in the absence of any applied voltage.

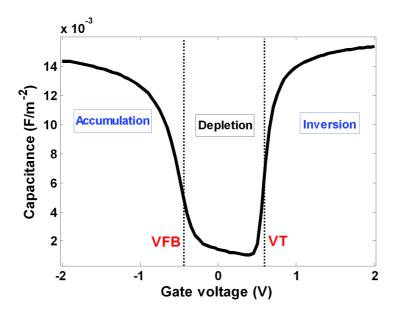

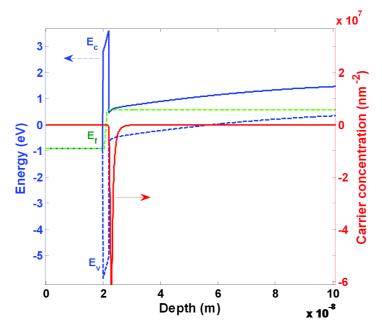

Depending on the applied gate voltage, the carrier concentration is changed due to the relative position of Fermi level versus conduction and valence bande edge. So, MOS capacitance will also vary with the applied gate to substrate voltage. In general, MOS capacitor operates at three different bias conditions. The three modes of operation, accumulation, depletion and inversion are represented by the behaviour of the capacitance with the gate voltage variation (C-V) (figure 1.2). The accumulation, flat bands, depletion, threshold voltage and inversion MOS regimes will now briefly be discussed for the case of the Si n-MOSFET ( $T_{SiO2} = 2nm, N_A = 10^{17} cm^{-3}$ ).

Figure 1.1: Schematic MOS transistor of the actual C28nm node.

Figure 1.2: Simulated C-V characteristic of the Si n-MOSFET ( $T_{SiO2} = 2nm, N_A = 10^{17} cm^{-3}$ ) showing the accumulation, depletion and inversion regimes.

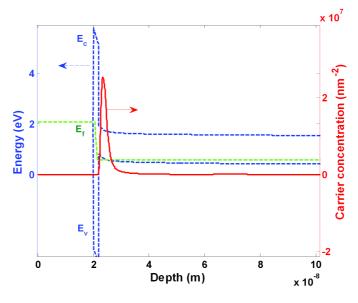

#### 1.2.1.1 Accumulation region

Figure 1.3 shows the conduction and valence bands bending, the Fermi level and the carrier concentration as a function of the distance along the z direction. When a negative voltage  $V_g$  is applied to the gate terminal of the MOS structure, the metal part becomes negatively charged and the semiconductor part becomes positively charged. Then, there occurs an internal electric field in the upwards direction from semiconductor to metal. This electric field piles up holes of

p-type semiconductor to the semiconductor/oxide interface, where an accumulation region of holes is obtained. The change in the free carrier concentration at the interface also affects the bands curve of the Si at the interface as shown in Figure 1.3.

Figure 1.3: Energy bands structure and carrier concentration profile in the accumulation region.

#### 1.2.1.2 Flat bands

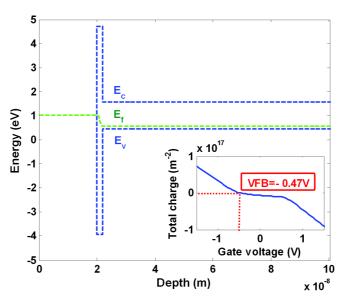

The energy bands and the carrier concentration are plotted in the figure 1.4 as a function of the distance along the z direction. At Vg = -0.47V, the total charge in the MOS structure is zero. This corresponding applied gate voltage is called 'flat band voltage' (VFB).

Figure 1.4: Energy bands structure in the Flat band voltage condition.

#### 1.2.1.3 Depletion region

Figure 1.5 presents the energy bands structure and carrier concentration in the depletion regime. When a gate voltage  $V_g > VFB$  (slightly positive) is applied to metal terminal of MOS structure, the metal part becomes positively charged and the semiconductor part becomes negatively charged. Under the influence of the electric field holes at the interface of semiconductor are pushed towards the bulk Silicon. So, majority carrier hole density decreases at the oxide/semiconductor interface. This surface region is the depletion region where only ionized acceptor atoms remain. Thus, the charge depletion is limited by the Si dopant concentration.

Figure 1.5: Energy bands structure and carrier concentration profile in the depletion region.

#### 1.2.1.4 Threshold voltage

The turn-on region for a MOSFET corresponds to the inversion region on its C-V plot (figure 1.2). When a MOSFET is turned on, the channel formed corresponds to strong generation of inversion charges. It is these inversion charges that conduct current between source and drain electrodes. The threshold voltage (VT) can be commonly defined as the point on the C-V curve for which the electron concentration at the semiconductor interface equals the hole concentration in the bulk. This curve point corresponds to the onset of strong inversion where the device begins to conduct. This parameter, which is fundamental for MOSFET modeling and characterization, has been given several definitions [33][34]. There exist numerous methods to extract the value of threshold voltage [35][36]. Various extractor circuits have also been proposed [37][38] to automatically measure this parameter. But, it may be essentially understood as the gate voltage value at which the transition between weak and strong inversion takes place in the MOSFET channel. Different available methods have been reviewed and scrutinized in the litterature [39][40][41][42][43].

In this thesis, we have used three methods to extract the threshold voltage of the bulk MOSFET and FDSOI transistors:

(i) The first method consists of extracting the threshold voltage in MOS transistors biased in the

linear region. This extraction method is based on the measurement of the static drain current versus gate voltage characteristics. The VT extraction is done using low drain voltages (Vd) so that the device operates in the linear region [43][35][44]. VT is defined as the gate voltage corresponding to a certain predefined practical constant drain current (Icc). This method is widely used in industry because of its simplicity. The threshold voltage can be determined quickly with only one voltage measurement [43].

(ii) The threshold voltage is also extracted from the maximum of the gate capacitance derivative with respect to gate voltage (see chapter 3). In this method VT is defined from the commonly known "maximum of the transconductance derivative" method [45]. It is a conceptually correct method based on the transconductance  $(g_m)$  change [46] and consists of measuring the variation in  $g_m$  with respect to gate voltage and determining the maximum of this variation.

(iii) The threshold voltage is defined at 40% of  $C^{max,inv}$ , the gate capacitance maximum value at strong inversion (see chapter 4).

#### 1.2.1.5 Inversion region

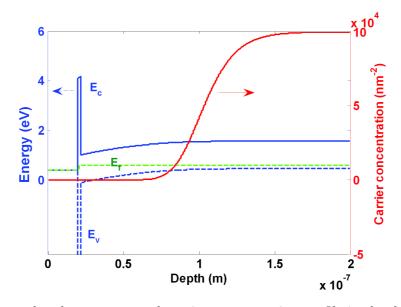

Figure 1.6 illustrates the energy bands structure and carrier concentration in the inversion regime. When a positive voltage  $V_g$  higher than the threshold voltage (VT) is applied, minority carrier electrons in the bulk of p-type Silicon are accumulated at the semiconductor surface under strong electric field. In this case electron concentration at the surface becomes higher than the hole concentration in the bulk Si. As a result, conduction and valence bands bend down at the semiconductor/oxide interface.

Figure 1.6: Energy bands structure and carrier concentration profile in the inversion region.

#### 1.2.2 Real (Non-ideal) MOS capacitor

In the theoretical treatment of an ideal MOS capacitor, the metal work function (WFM) and semiconductor work function (WFS) are equal in the absence of an applied voltage  $(V_g=0)$ . Moreover, oxide layers are treated as ideal insulators, where there are no traps or states at oxide/semiconductor interface. However, an ideal MOS device does not agree with experimental results. Actually, in real MOS devices, the metal and semiconductor work functions are different at  $(V_g=0)$ . Besides, the oxide/semiconductor interface and bulk oxide are far from beeing electrically neutral. Some impurities or defects can be incorporated into the oxide during oxide growth or subsequent fabrication process steps. This results in the dielectric contamination with various types of charges and traps. The presence of oxide defects can strongly affect the threshold voltage and flat band voltage. As a result, the C-V characteristic in real MOS capacitor may be modified.

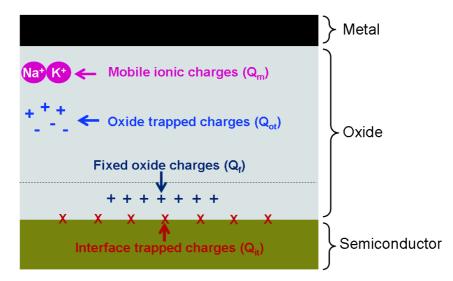

Four different types of oxide charges can be identified in real MOS devices [47]. These are shown schematically in figure 1.7. These are: oxide trapped charges  $(Q_{ot})$ , mobile ionic charges in the oxide  $(Q_m)$ , interface fixed oxide charges  $(Q_f)$  and interface-trapped charges  $(Q_{it})$ . Each type of oxide charge can cause a shift  $(Q_{ot}, Q_m \text{ and } Q_f)$  or deformation  $(Q_{it})$  of the C-V curve.

Figure 1.7: Distribution of charges inside the gate-oxide.

In this section, the main defects commonly observed in insulators will be briefly described. Their impact on the C-V characteristic will also be assessed.

#### 1.2.2.1 Effect of the bulk oxide charges

The bulk oxide charges regroups:

(a) Mobile ionic charges which are due to alkali metal ions in the oxide such as  $Li^+$ ,  $Na^+$  and  $K^+$  [47]. These impurities cause reliability problems under high temperature and high voltage operations. So, they can migrate from an interface to another under high bias-temperature conditions.

(1.1)

(b) The oxide fixed charges which may be positive or negative due to defects in the bulk of the oxide. Trapping may result from ionizing radiation, avalanche injection, or other similar processes [47].

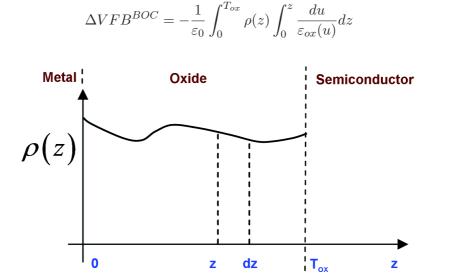

These defects may be distributed unevenly in the bulk oxide. In that case, their charge density  $\rho(z)$  varies with distance. The origin of the z-axis is taken at the metal/oxide interface as shown in figure 1.8. At the flat band condition, using Gauss's law and the superposition theorem, the effects of all oxide layers comprised between zero and  $T_{ox}$  are added. So, the gate voltage shift  $\Delta VFB^{BOC}$ , which is necessary to ensure a flat band condition at the oxide/semiconductor interface, is found to be:

Figure 1.8: Oxide charges distribution as a function of distance.

The effect of each charge layer depends on its distance from the metal/oxide interface as given in equation 1.1. A layer has no effect if it is located at the metal/oxide interface (z=0) and has a maximum effect if it is located at the oxide/semiconductor interface.

#### 1.2.2.2 Effect of interface fixed oxide charges

Fixed oxide charges are positive or negative charges located near the oxide/semiconductor interface. They are due primarily to structural defects (ionized Silicon) in the oxide layer [48]. The density of this charge depends on oxidation process and temperature. Fixed oxide charge does not move and exchange charge with the underlying semiconductor. It is also insensitive to the applied electric field variation.

Fixed charges dispersed randomly across the oxide/semiconductor interface may cause a gate voltage shift of the real C–V curve with respect to the ideal one. The gate voltage shift  $\Delta VFB^{FOC}$  is given by:

$$\Delta VFB^{FOC} = -\frac{Q_f}{\varepsilon_{SiO_2}\varepsilon_0}EOT \tag{1.2}$$

#### 1.2. BASIC PRINCIPLES OF MOS CAPACITOR

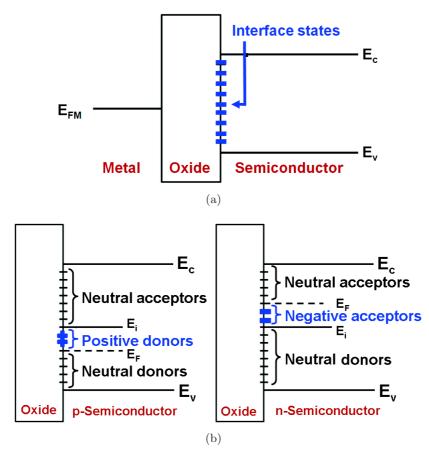

#### **1.2.2.3** Effect of interface trapped charges

Interface trapped charges, also called as the interface states or traps are positive or negative charges located at or very close to the semiconductor/oxide interface. They are attributed to dangling bonds and other native defects at this interface. Unlike fixed charge or trapped charge, interface trapped charge is in electrical communication with the semiconductor. Indeed, they are distributed along the bandgap of the semiconductor (figure 1.9.a). Electrons or holes get trapped in these states and act like charges at the interface. The probability that an electron or hole occupies a given interface state depends on its energetic location relative to the Fermi energy.

Figure 1.9: (a) MOS structure Energy band diagram, depicting the distribution of interface states along the bandgap of the semiconductor at the semiconductor/oxide interface. (b) Schematic presentation of donors and acceptors distribution in the gap of p and n-type semiconductors in flat band condition.

Presumably, every interface has both kind of states, donor states and acceptor states. An acceptor state is neutral when it is not occupied. It becomes negatively charged when it captures an electron. However, a donor state is neutral when it traps an electron (or emits a hole). It becomes positively charged when it is not occupied. The sum of these states is the equivalent interface states density  $(D_{it})$  distribution with a characteristic energy level called the charge-neutrality level  $E_i$ . The interface states which exist in the upper half of the semiconductor

band-gap (E>  $E_i$ ) are acceptor states. Whereas, the interface states which exist in the lower half of the band-gap are donor states (E<  $E_i$ ). Indeed, interface states are occupied only when these are below the Fermi level. The charge of the interface states is then a function of the substrate doping type and gate voltage applied across the MOS capacitor. Figure 1.9.b schematizes the interface traps distribution in the gap of p and n-type semiconductors in flat band condition. This figure shows that the trapped charges in the interface states are negative for the n-type substrate and positive in the case of p-type substrate.

The MOS structure bias variation induces the Fermi level change. Therefore, the interface states may be charged and neutralized during the C-V measurement (figure 1.9.b). These charges cause a flat band voltage shift  $\Delta VFB^{IT}$  expressed as:

$$\Delta VFB^{IT} = -\frac{Q_{it}(\Psi_s)}{\varepsilon_{SiO_2}\varepsilon_0}EOT$$

(1.3)

#### 1.2.2.4 Flat band voltage expression

Here, we describe first the flat band voltage expression in real MOS devices introducing monolayer oxide. Then, the VFB expression will be explored for bilayer insulator. Given VFB expressions will be simplified under the assumption of a contant oxide charge distribution.

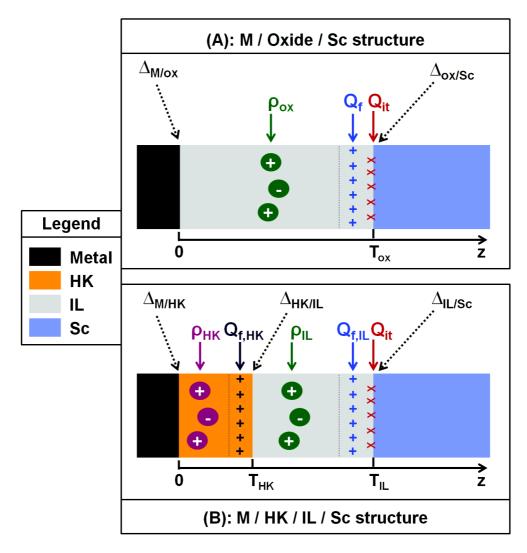

For a practical MOS structure integrating one oxide layer only, there exist oxide charges, interface traps and dipoles present at each gate stack interface. As shown in the subsection 1.2.2.1, defects are distributed unevenly in the bulk oxide. Whereas, interface fixed charges and interface traps are located close to the oxide/semiconductor interface. In order to express the flat band voltage in actual MOS devices, we have taken into account (see figure 1.10.(A)):

(i) the metal and semiconductor work functions difference (WMS = WFM - WFS). WFS is the Fermi level in the semiconductor at flat band condition. In FDSOI devices, the thin body is beeing undoped so there is neither depletion nor accumulation regimes. Therefore, it seems difficult to define VFB. Nevertheless, the VFB definition at zero charges (see subsection 1.2.1.2) can be conserved for FDSOI transistors.

- (ii) the oxide charges density  $\rho_{ox}$  in the bulk of the oxide.

- (iii) the interface oxide charges  $Q_{f,ox}$ .

- (iv) the interface traps  $Q_{it}$ .

- (v) the dipoles  $\Delta_i$  at each oxide metal gate stack interface "i".

The flat band voltage can be expressed as a function of these quantities and oxide thickness  $(T_{ox})$  as follows [49]:

$$VFB = WMS - \frac{1}{\varepsilon_{ox}\varepsilon_{0}} \left( \int_{0}^{T_{ox}} Q_{f,ox} \delta(T_{ox}) z dz + \int_{0}^{T_{ox}} Q_{it}(\Psi_{s}) \delta(T_{ox}) z dz \right) - \frac{1}{\varepsilon_{0}} \int_{0}^{T_{ox}} \rho(z) \int_{0}^{z} \frac{du}{\varepsilon_{ox}(u)} dz + \sum_{i} \Delta_{i}$$

(1.4)

#### 1.2. BASIC PRINCIPLES OF MOS CAPACITOR

where  $\delta$  is the delta function ( $\delta(z = T_{ox}) = 1$  and  $\delta(z \neq T_{ox}) = 0$ ). The formula 1.4 is valid for any charge distribution in the oxide. For a constant oxide charge density, it becomes:

$$VFB = WMS - \frac{Q_{f,ox} + Q_{it}(\Psi_s)}{\varepsilon_{SiO_2}\varepsilon_0}EOT - \frac{\rho_{ox}T_{ox}^2}{2\varepsilon_{ox}\varepsilon_0} + \sum_i \Delta_i$$

(1.5)

The oxide fixed charge is constant when appling an electric field whereas  $Q_{it}$  is a function of the surface potential  $(\Psi_s)$ .

Figure 1.10: MOS capacitor cross sections. (A) metal gate (M) on oxide only and (B) metal gate on high-k (HK) and interfacial layer (IL). The various charges and dipoles at gate stack interfaces are indicated.

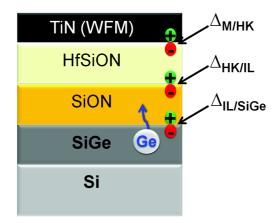

For two layers insulators (figure 1.10.(B)), consisting of a gate, a high-k dielectric (HK), an interfacial oxide (IL) and a substrate (Sc), the flat band voltage is written as:

$$VFB = WMS + \Delta VFB(HK) + \Delta VFB(IL) + \sum_{i} \Delta_{i}$$

(1.6)

where

$$\sum_{i} \Delta_{i} = \Delta_{M/HK} + \Delta_{HK/IL} + \Delta_{IL/Sc}$$

(1.7)

In equation 1.6,  $\Delta VFB(HK)$  is the VFB shift due to the fixed charge density  $Q_{f,HK}$  at the HK/IL interface  $(\Delta_{HK/IL}^{Ch})$  and charge density  $\rho_{IL}(z)$  in the high-k insulator  $(\Delta_{HK}^{Ch})$ . The  $\Delta VFB(HK)$  is given by:

$$\Delta VFB(HK) = \Delta_{HK/IL}^{Ch} + \Delta_{HK}^{Ch} = -\frac{T_{HK}}{\varepsilon_{HK}\varepsilon_0} Q_{f,HK} - \frac{1}{\varepsilon_{HK}\varepsilon_0} \int_0^{T_{HK}} \rho_{HK}(z) z dz$$

(1.8)

The  $\Delta VFB(IL)$  is the VFB shift caused by: the interface traps  $Q_{it}$  ( $\Delta VFB^{IT}$ ), the fixed charge density  $Q_{f,IL}$  at the IL/semiconductor interface ( $\Delta_{SiGe/IL}^{Ch}$ ) and charge density  $\rho_{IL}(z)$  in the IL ( $\Delta_{IL}^{Ch}$ ) (figure 1.10.(B)). The  $\Delta VFB(IL)$  expression is:

$$\Delta VFB(IL) = \Delta VFB^{IT} + \Delta_{SiGe/IL}^{Ch} + \Delta_{IL}^{Ch} = -\frac{Q_{it(\Psi_s)} + Q_{f,IL}}{\varepsilon_{SiO_2}\varepsilon_0}EOT - \int_{T_{HK}}^{T_{HK}+T_{IL}} \rho_{IL}(z) \left(\frac{T_{HK}}{\varepsilon_{HK}\varepsilon_0} + \frac{z - T_{HK}}{\varepsilon_{IL}\varepsilon_0}\right) dz$$

(1.9)

Under the assumption of a constant oxide charge distribusion,  $\Delta VFB(HK)$  and  $\Delta VFB(IL)$  VFB shifts become:

$$\begin{cases} \Delta VFB(HK) = -\frac{Q_{f,HK}}{\varepsilon_{HK}\varepsilon_{0}}T_{HK} - \frac{\rho_{HK}}{\varepsilon_{HK}\varepsilon_{0}}\frac{T_{HK}^{2}}{2} \\ \Delta VFB(IL) = -\frac{Q_{it}(\Psi_{s}) + Q_{f,IL}}{\varepsilon_{SiO_{2}}\varepsilon_{0}}EOT - \frac{\rho_{IL}}{\varepsilon_{IL}\varepsilon_{0}}\frac{T_{IL}^{2}}{2} + \frac{\rho_{IL}}{\varepsilon_{HK}\varepsilon_{0}}T_{IL}T_{HK} \end{cases}$$

(1.10)

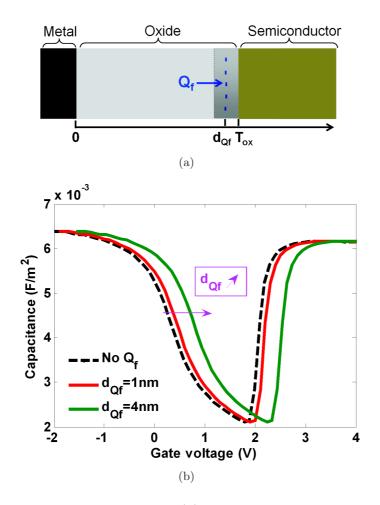

#### **1.2.2.5** Electric effect of oxide charges

As shown in subsection 1.2.2.2, fixed charge in the oxide induces a gate voltage shift of the measured C–V curve. A negative (or positive) fixed charge at the oxide/semiconductor interface shifts the flat band voltage by an amount which equals the charge divided by the oxide capacitance (equation 1.2). The shift decreases linearly as the position of the fixed charge relative to the gate electrode is reduced. It becomes zero if the charge is located at the metal/oxide

28

interface. Figure 1.11 illustrates the impact of oxide fixed charge on C-V characteristic using UTOXPP simulations. Clearly, the C-V plot including  $-5 \times 10^{19}$  cm<sup>-3</sup> oxide fixed charge peak is shifted toward more positive bias voltage in comparison to the ideal C-V curve (with no oxide fixed charge). Moreover, it is important to notice that the C-V shift is higher when the negative fixed charge peak position being far from the gate (400mV C-V shift versus 100mV) (figure 1.11.b).

Figure 1.11: (a) Simulated MOS structure. (b) Simulated C-V curves of the Si nMOSFET (EOT=5nm) considering an ideal  $SiO_2$  oxide (dashed curve) and  $-5 \times 10^{19}$  cm<sup>-3</sup> oxide fixed charge peak at  $d_{Qf}$  position (solid curves).

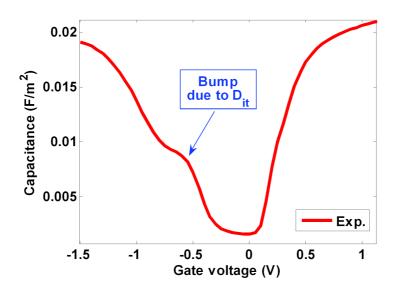

Charge due to interface states also yields a shift in flat band voltage (see subsection 1.2.2.3). However, as the applied voltage is varied, the Fermi energy at the oxide/semiconductor interface changes. This Fermi energy level evolution affects the occupancy of the interface states. The presence of the surface trapped charges are observable in the measured C-V characteristic. So, a distortion and bump is appeared in the C-V plot (figure 1.12).

Figure 1.12: Distortion and bump of the measured Si nMOSFET C-V characteristic due to interface trapped charges.

#### 1.2.3 Capacitance-voltage measurements

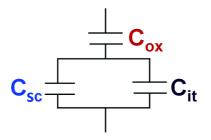

C-V testing is widely used to determine semiconductor parameters, particularly in MOS capacitor and MOSFET structures. C-V measurements can reveal for example oxide thickness, oxide charges, interface trap density [50][51], threshold voltage and flat band voltage.

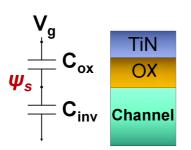

The equivalent circuit of a MOSFET is shown in figure 1.13. In a real MOSFET there will also be parasitic capacitances between the gate and source/drain and between the substrate and source/drain. But, for a large area MOSFET, these are usually negligible. The total capacitance C is given by:

$$\frac{1}{C} = \frac{1}{C_{ox}} + \frac{1}{C_{sc} + C_{it}}$$

(1.11)

where  $C_{sc}$  is the semiconductor capacitance.  $C_{ox}$  and  $C_{it}$  being oxide and interface traps capacitances.

Figure 1.13: Equivalent circuit of a MOSFET.  $C_{ox}$ ,  $C_{sc}$  and  $C_{it}$  are the dielectric, semiconductor and interface trap capacitances respectively.

#### 1.2. BASIC PRINCIPLES OF MOS CAPACITOR

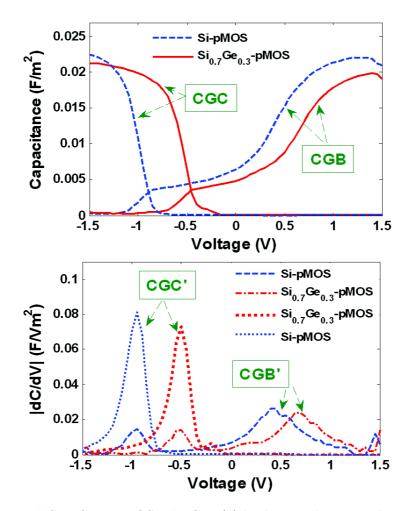

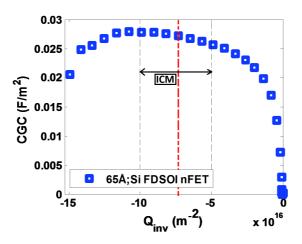

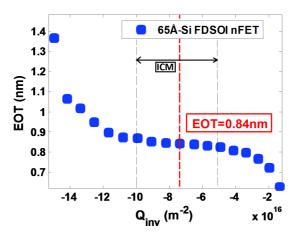

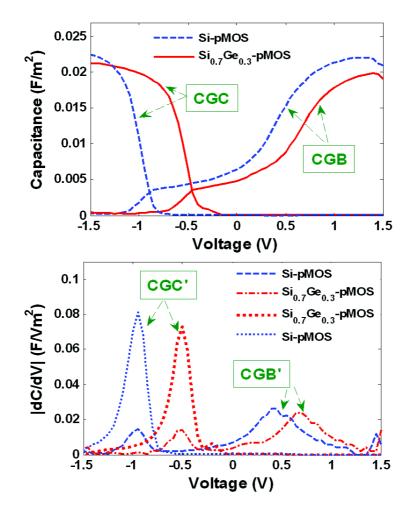

Since the inversion charge is supplied by the source and drain and the depletion charge by the substrate, measurements of the inversion and depletion capacitances can be obtained separately. This is known as the split C-V technique [52][53]. Figure 1.14 reports the measurement configurations and examples of C-V measurement results of the *Si* pMOSFET.

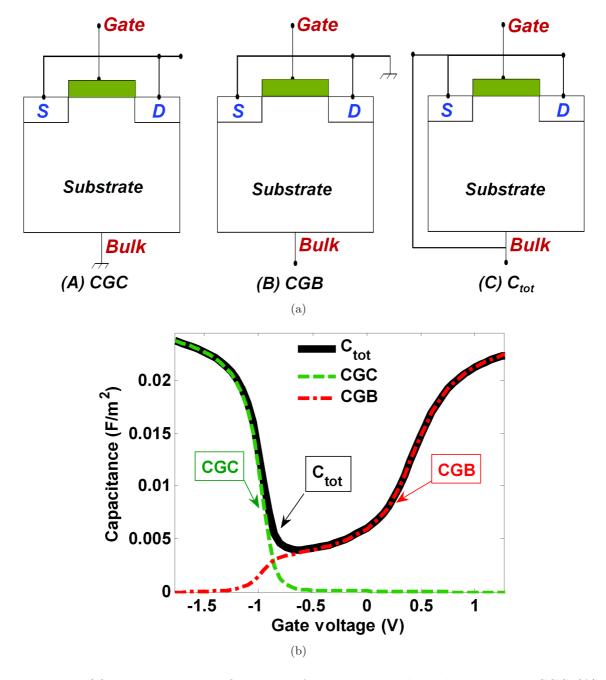

Figure 1.14: (a) Measurement configurations for the gate-to-channel capacitance CGC (A), gate-to-bulk capacitance CGB (B) and total capacitance  $C_{tot}$  (C). (b) Measured CGC, CGB and  $C_{tot}$  characteristics for the *Si* pMOSFET.

In the gate-to-channel (CGC) configuration (figure 1.14.a(A)) the gate, drain and source are connected to the LCR meter while the bulk is tied to ground. This configuration measures the change in inversion charge with the applied voltage (figure 1.14.b):

$$CGC = \frac{\partial Q_{inv}}{\partial V_q} \tag{1.12}$$

The gate-to-bulk capacitance (CGB) is measured with the source and the drain terminals grounded (figure 1.14.a(B)). It approaches  $C_{ox}$  in accumulation and the series combination of  $C_{ox}$  and  $C_{dep}$  in depletion (figure 1.14.b).

The total capacitance  $C_{tot}$  (equation 1.11) is measured with the interconnected source, drain and bulk and gate connected to the LCR meter figure 1.14.b(C). The measured  $C_{tot}$  shows the inversion, depletion and accumulation regimes (figure 1.14.b).

#### **1.3 MOS capacitance simulation**

This section presents a validation of UTOXPP Poisson-Schrödinger simulation results by comparison to other solvers and literature results. In the second part, UTOXPP C-V simulations will be validated for *Si* nMOSFETs with Polysilicon and metal gate.

#### 1.3.1 Modeling of quantum confinement

The trend toward smaller MOSFET devices with thinner gate oxide is resulting in the increasing importance of quantum mechanical effects. For actual device simulations, predicting these quantum effects requires solving the Schrödinger equation self-consistently with the Poisson equation. The coupled resolution of Poisson and Schrödinger equations computes the electrostatic potential and charge density distribution in the simulated structure for different gate voltages  $(V_q)$ .

In this report, the electrostatic potential variation in the MOS structure is considered along the z direction (perpendicular to the oxide/substrate interface).

#### 1.3.1.1 1D Poisson equation

The electrostatics within a MOS device are described by the Poisson equation [54]:

$$\frac{\partial}{\partial z} [\varepsilon_r(z) \frac{\partial}{\partial z}] \phi(z) = -\frac{q}{\varepsilon_0} \rho(z) \tag{1.13}$$

where q is the elementary electron charge,  $\varepsilon_r$  is the dielectric constant,  $\phi$  is the electric potential and  $\rho$  is the charge density distribution. The dielectric constant  $\varepsilon_r(z)$  depends to the relative material and z position.

#### 1.3. MOS CAPACITANCE SIMULATION

The charge density  $\rho(z)$  is decomposed into charge carrier densities of electrons n(z) and holes p(z) and the ionized dopant concentration of acceptor  $N_A$  and donator  $N_D$  atoms:

$$\rho(z) = p(z) + N_D(z) - n(z) - N_A(z) \tag{1.14}$$

#### 1.3.1.2 1D Schrödinger equation

Within the effective mass approximation, for a particle of mass m under a potential V(z), the one-dimensional, time independent Schrödinger equation is given by [54]:

$$-\frac{\hbar^2}{2}\frac{\partial}{\partial z}\left[\frac{1}{m_i(z)}\frac{\partial}{\partial z}\right]\psi_{i,v}(z) + V(z)\psi_{i,v}(z) = E^z_{i,v}\psi_{i,v}(z)$$

(1.15)

where  $m_i$  is the effective mass,  $\hbar$  is the Planck constant h divided by  $2\pi$ ,  $\psi_{i,v}$  is the wave function of the v-th subband of the i band, V is the potential energy determined by the Poisson equation resolution (1.13) and  $E_{i,v}^z$  corresponds to the energy level.

The numerical resolution of the equation (1.15) computes the wave functions  $\psi_{i,v}$  and eigenenergies  $E_{i,v}^z$ . The inversion layer electron density appearing in the 1D Poisson equation (1.14) is obtained by summing over all subbands to get [54]:

$$n(z) = \sum_{i,v} \frac{m_{xy}^{v}}{\pi \hbar^{2}} g_{v} k_{B} T \ln \left[ 1 + \exp \frac{E_{F} - E_{i,v}^{z}}{k_{B} T} \right] |\psi_{i,v}(z)|^{2}$$

(1.16)

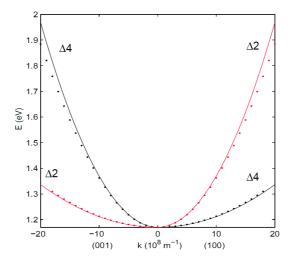

In (1.16),  $E_F$  is the Fermi level,  $k_B$  is the Boltzmann constant, T is the temperature,  $m_{xy}^v$  is the inplane effective mass of the v-th subband and  $g_i$  ( $g_1 = 2$  for the  $\Delta_2$ -band, and  $g_2 = 4$  for the  $\Delta_4$ -band) is the corresponding band degeneracy.

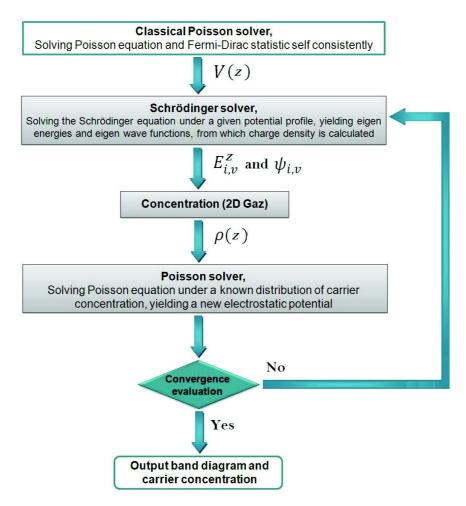

Thus, to calculate the charge density  $\rho$  given by (1.14) along the z direction in the MOS structure, the Shrödinger equation (1.15) should be numerically solved. To do so, the electrical potential is needed. It's determined by the Poisson equation solution (1.13). To this end, the charge density calculation is necessary. As a result, both Poisson and Shrödinger equations have common variables. That's why, these equations should be self consistently solved. The self-consistent calculation is carried out as described in the flow chart shown in Figure 1.15.

An initial classical solution of the Poisson equation in conjunction with the Fermi-Dirac distribution is given to the Schrödinger solver as an initial guess of the potential profile. Then, the carrier (electons and holes) concentration is derived from the obtained eigen energies and eigen wave functions. The second Poisson solver calculates the potential distribution with the knowledge of carrier concentration as a function of position.

Figure 1.15: Flow chart of the Poisson-Schrödinger self-consistent solution.

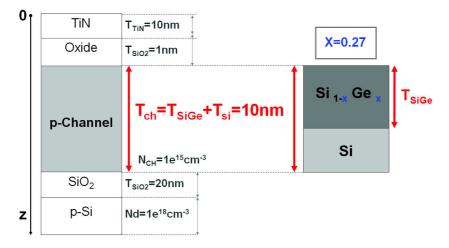

#### 1.3.1.3 Poisson-Schrödinger results validation

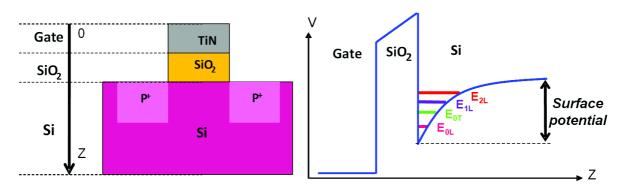

The simulated structure described in figure 1.16 consists of a TiN metal gate and a  $SiO_2$  oxide on a p-doped Si substrate ( $N_{Dop} = 10^{18} \text{cm}^{-3}$ ). Figure 1.17 compares the 1D self-consistent

Figure 1.16: Simulated structure of the  $SiO_2/Si$  n-MOSFET.

#### 1.3. MOS CAPACITANCE SIMULATION

Poisson-Schrödinger (PS) simulation results obtained using UTOXPP (PS.UTOXPP), the PS developed at Leti (PSL) and Synopsys Poisson-Schrödinger (PS.Synopsys). All simulations consider: the effective mass approximation (EMA), the wave functions penetration into the oxide and 20nm of quantum box. For the WFP, we used 3eV of oxide barrier height and  $0.5m_0$  of effective mass.

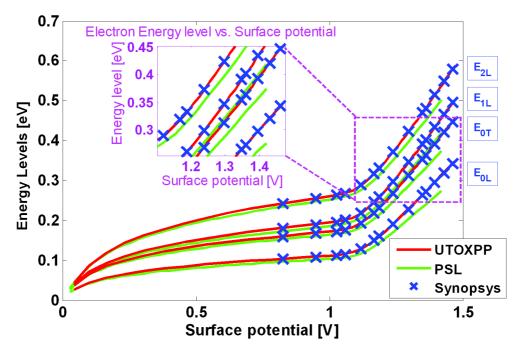

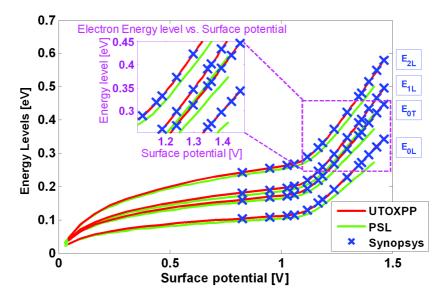

Figure 1.17: The first four energy levels obtained using PS.UTOXPP, PSL and PS.Synopsys for a different surface potentials in the inversion regime.

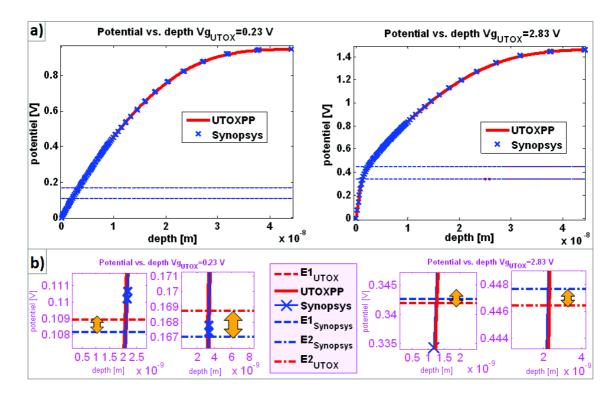

Very good agreement is noticed between the PS.UTOXPP and Synopsys results. Discrepancy is observed for PSL energy levels. Figure 1.18 reports the energy levels and electrostatic potential profile as a function of the z position at weak and strong inversion. The first two eigenenergies computed using UTOXPP are close to Synopsys results.

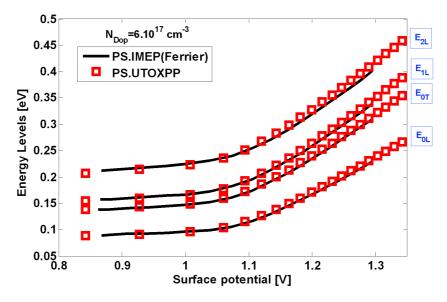

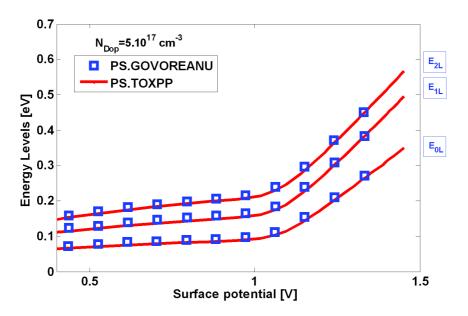

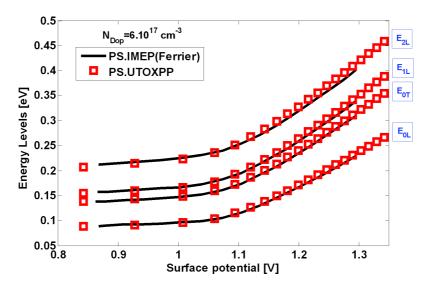

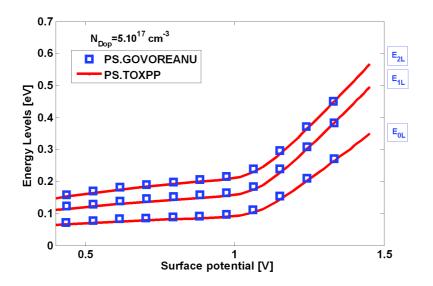

The PS.UTOXPP results were compared to data from literature for Si substrate doped at  $5.10^{17}$  cm<sup>-3</sup> in the inversion regime (see figure 1.19 and figure 1.20). Inspite of the global agreement observed for the different Si doping, it is recommended that the PS results comparison should be careful. Indeed, Poisson-Schrödinger results depend on different parameters such as the size of the quantum box (where the Poisson and Schrödinger equations are self-consistently solved), the number of energy levels taken into account to compute the charge concentration and wave functions penetration into the oxide.

Figure 1.18: (a) The first two energy levels and electric potential profile as a function of the z position computed using the PS.UTOXPP and Synopsys at weak and strong inversion. (b) Zoom on the first two energy levels obtained using the PS.UTOXPP and Synopsys at weak and strong inversion.

Figure 1.19: Comparison of the first four energy levels calculated using the PS.UTOXPP and PS.IMEP [55] for a different surface potentials in the inversion regime.

Figure 1.20: The first three  $\Delta_2$  subbands obtained using the PS.UTOXPP and PS.Govoreanu [56] for a different surface potentials in the inversion regime.

#### **1.3.1.4** Analytical model analysis for $SiO_2/Si$ bulk n-MOSFETs

Quantum confinement modeling at Silicon/oxide interface typically requires numerical selfconsistent Poisson-Schrödinger simulations [57][58]. Analytical alternatives [59] such as the triangular well approximation and the variational approach are proposed to model the eigenenergies and wave functions. However, these analytical models are accurate enough to model only the charge located in the first subband [60]. This is satisfactory for charge and C-V modeling. Whereas, the tunneling current computation needs an accurate determination of the second subband which also have a significant contribution [60]. In order to calculate different energy levels with more precision, an improved triangular well approximation has been proposed by Ferrier et al. [55]. In this approach, the effective electric field for each subband is expressed by:

$$F_{i,v} = \frac{Q_{dep} + f_{i,v}.Q_{inv}}{\epsilon_s} \tag{1.17}$$

where  $\epsilon_s$  is the substrate permittivity.  $Q_{dep}$  and  $Q_{inv}$  stand respectively for depletion and inversion charge expressed as:

$$Q_{dep} = \sqrt{2.q.N_a.\epsilon_s.V_s} \tag{1.18}$$

$$Q_{inv} = q \cdot \sum_{i} n_{i,v} \tag{1.19}$$

where  $V_s$  is the band bending in the Si substrate (the surface potential),  $N_a$  the Si p-doping concentration and  $n_{i,v}$  the electron concentration on the  $i^{th}$  subband of the v band.

In this model, the energy levels obtained using the conventional triangular well approximation  $(E_{i,v}^{TWA})$  [61] has been corrected by the non-linearity potential well  $(\Delta E_{i,v}^{NL})$  and the wave function penetration  $(\Delta E_{i,v}^{WFP})$  corrections as:

$$E_{i,v} = E_{i,v}^{TWA} - \Delta E_{i,v}^{NL} - \Delta E_{i,v}^{WFP}$$

$$(1.20)$$

where

$$E_{i,v}^{TWA} = \left(\frac{\hbar^2}{2m_v}\right)^{1/3} \cdot \left[\frac{3\pi \cdot q \cdot F_{i,v}}{2} \cdot \left(i + \frac{3}{4}\right)\right]^{2/3}$$

(1.21)

$$\Delta E_{i,v}^{NL} = \frac{4q.N_a}{15.\epsilon_s} \cdot \left(\frac{\hbar^2}{2.q.m_v.F_{i,v}}\right)^{2/3} \cdot \left[\frac{3\pi}{2} \cdot \left(i + \frac{3}{4}\right)\right]^{4/3}$$

(1.22)

$$\Delta E_{i,v}^{WFP} = \frac{\hbar . m_{ox} . F_{i,v}}{m_{v} . \sqrt{2 . m_{ox} . \left(\phi_{ox} - E_{i,v}^{TWA}\right)}}$$

(1.23)

In the above equations,  $\phi_{ox}$  is the oxide barrier height.  $m_{ox}$  and  $m_v$  are the oxide and Si effective masses.

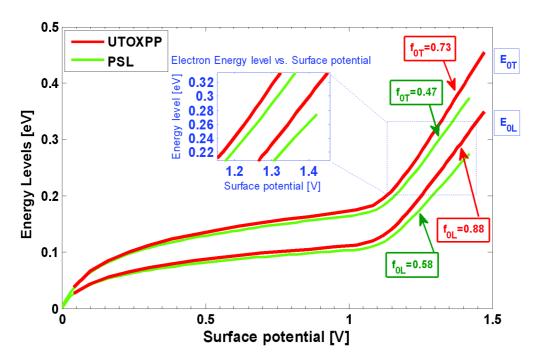

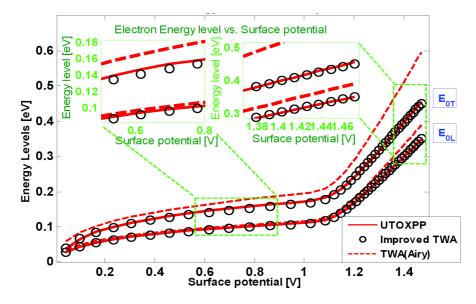

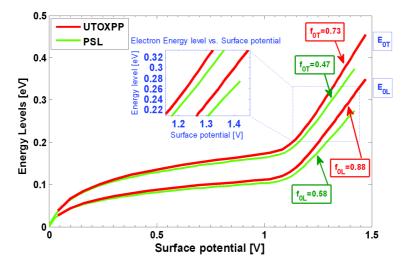

Using the improved triangular well approximation model (Improved TWA), J. Coignus et al [60] have compared the obtained energy levels from (1.20) to those calculated using the Poisson-Schrödinger PSL simulator. The  $f_{i,v}$  parameters introduced in the equation (1.17) to reproduce the numerical results have been found to be equal to  $f_{0L} = 0.58$  and  $f_{0T} = 0.47$  respectively for the  $\Delta_2$  and  $\Delta_4 Si$  conduction bands.

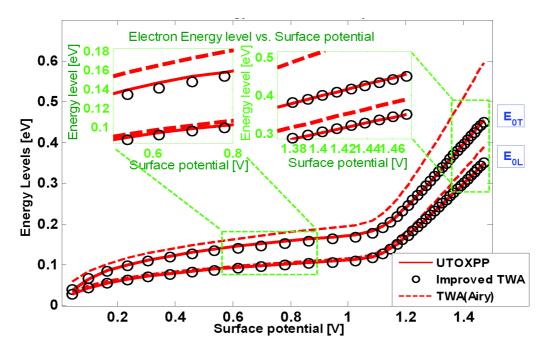

A similar study has been achieved using Poisson-Schrödinger UTOXPP results. The figure 1.21 shows that the analytical model takes well into account the wave functions penetration into the oxide. We reproduce the PS.UTOXPP eigenenergies using  $f_{0L} = 0.88$  and  $f_{0T} = 0.73$  respectively for the  $\Delta_2$  and  $\Delta_4$  Si conduction bands in strong inversion. These  $f_{i,v}$  values are similar to those found by B.Govoreanu et al [56] ( $f_{0L} = 0.86$  and  $f_{0T} = 0.61$ ).

Indeed, the  $f_{i,v}$  parameters are extracted by comparing the eigenenergies calculated using the Poisson-Schrödinger simulator to the analytical one (equation (1.20)).

The Improved TWA estimates precisely the effective electric field for each subband. Nevertheless, the comparison of the different  $f_{i,v}$  values corresponding to each PS simulator shows a discrepancy (see figure 1.22).

Furthermore, even if we obtain similar energy levels at the same surface potential (figure 1.19), the  $f_{i,v}$  values extracted from the PS.IMEP ( $f_{0L} = 0.65$  and  $f_{0T} = 0.43$  respectively for the  $\Delta_2$  and  $\Delta_4$  Si conduction bands [55]) are different than those extracted from the PS.UTOXPP (table 1.1).

| $f_{i,v}$ comparison | PSL [60] | UTOXPP | <b>PS.IMEP</b> [55] |

|----------------------|----------|--------|---------------------|

| $f_{0L}$             | 0.58     | 0.88   | 0.65                |

| $f_{0T}$             | 0.47     | 0.73   | 0.43                |

Table 1.1: Comparison of first two  $f_{i,v}$  values extracted from PSL, PS.UTOXPP and PS.IMEP.

Figure 1.21: The first two subbands obtained using the PS.UTOXPP and Improved TWA model for a different surface potentials in the inversion regime.

Figure 1.22: The first two subbands obtained using the PS.UTOXPP and PSL for a different surface potentials in the inversion regime.

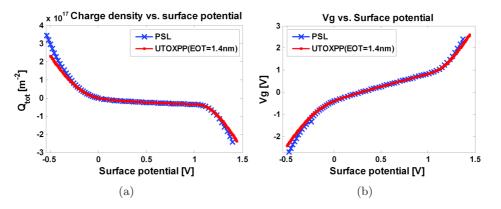

As a conclusion, in order to compare the Poisson-Schrödinger simulator results, it is not relevant to compare the  $f_{i,v}$  parameters of the effective electric field (equation 1.17). Besides,

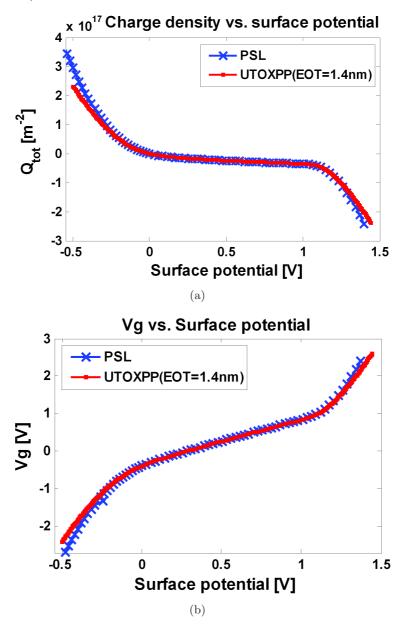

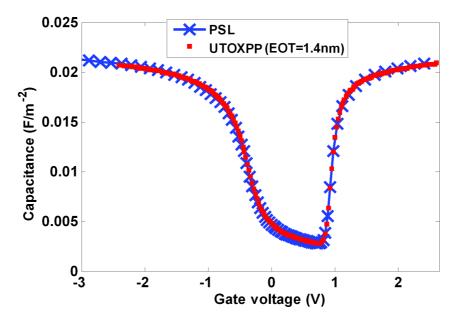

it is important to investigate the impact of the simulation results discrepancy between the PS.UTOXPP and PSL simulator (shown in figure 1.22) on the C-V characteristic. Indeed, the observed eigenenergies discrepancy  $(E_{0L}(UTOXPP) - E_{0L}(PSL) \approx 35meV$  at  $V_s = 1.4V)$  is also noticed in the evolution of the semiconductor total charge as a function of the surface potential  $(Q_{tot}(UTOX) - Q_{tot}(PSL)) = 4.08 \times 10^{16}m^{-2}$  at  $V_s = 1.4V)$  (figure 1.23.a). The gate voltages  $(V_g)$  computed using the PSL and UTOXPP are also slightly different (figure 1.23.b). However, the comparison of the obtained C-V characteristic shows no influence on the C-V response (figure 1.24).

Figure 1.23: The evaluation of the total charge (a) and gate voltage (b) as a function of the surface potential.

Figure 1.24: Comparison of the C-V calculated using UTOXPP and PSL simulators. (Si n-MOSFET with  $T_{SiO2} = 0.8nm$ ,  $T_{HfO2} = 3nm$ ).

#### 1.3.2 C-V simulations of Si nMOSFETs

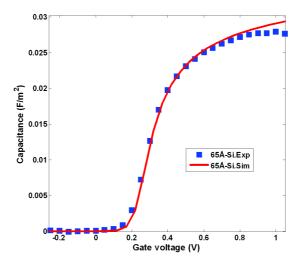

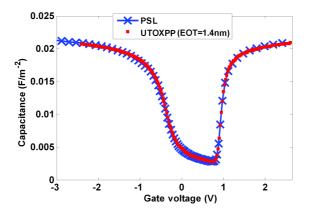

In this section, we validate the UTOXPP C-V simulations by comparison to measurements.

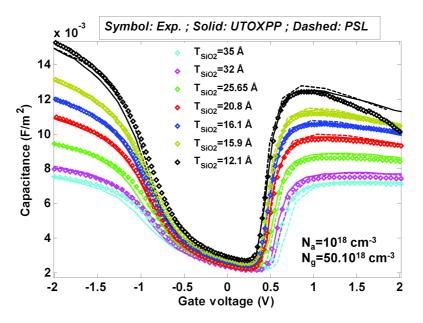

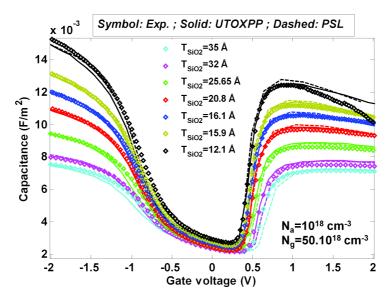

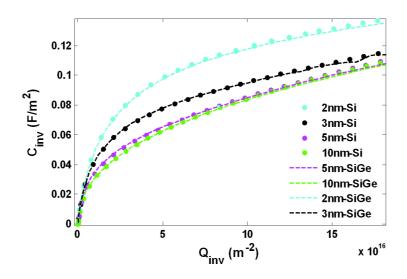

To this end, we have considered the N<sup>+</sup> polysilicon gate/ $SiO_2/Si$  nMOSFET. The  $SiO_2$  insulator thickness was varied from 12Å to 35Å. The C-V measurements for the different oxide thicknesses are plotted in figure 1.25. The gate capacitance increases for a thinner dielectric (see equation 1.11). A very good agreement is noticed between the simulated (lines) and measured C-V curves (symbols). Besides, a comparison between the simulation results using UTOXPP and PSL is also performed. A good matching is observed (figure 1.25).

The corresponding equivalent oxide thickness of each Si nMOSFET can be extracted thanks to C-V simulations. Indeed, it consists of determining the  $SiO_2$  thickness, needed as C-V simulation input, to fit the measured C-V. Table 1.2 shows a very good adequacy between the EOT Ellipsometry measurements and values extracted using UTOXPP and PSL, evidencing the usefulness of the C-V simulation model.

| Ellipsometry<br>EOT (Å) | 35 | 32 | 25.65 | 20.8 | 16.1 | 15.9 | 12.1 |

|-------------------------|----|----|-------|------|------|------|------|

| PSL (Å)                 | 35 | 32 | 26.5  | 22   | 19   | 17.5 | 14.5 |

| UTOXPP (Å)              | 35 | 32 | 26.5  | 22   | 19.5 | 17.5 | 14.5 |

Table 1.2: Comparison of the measured EOT (by Ellipsometry) to values extracted from the PSL and UTOXPP.

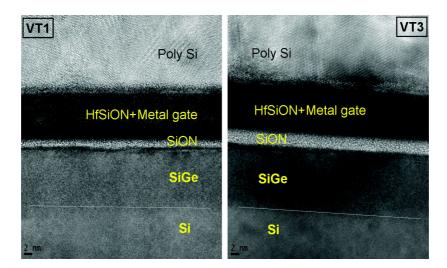

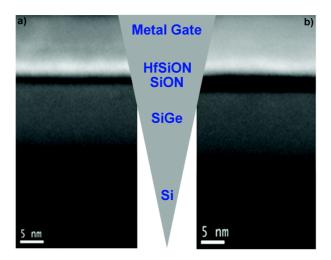

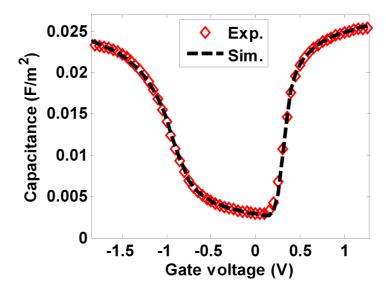

In addition, UTOXPP C-V simulations of MOSFETs integrating a metal gate and bilayer insulators were also validated during this thesis. The C-V characteristic of the metal/HfSiON/SiON/Si

Figure 1.25: C-V simulations of N<sup>+</sup> polysilicon gate/ $SiO_2/Si$  nMOSFET using UTOXPP and PSL simulator. The  $SiO_2$  thickness was varied from 1.2nm to 3.5nm.

nMOSFET has been simulated using UTOXPP. Figure 1.26 illustrates a very good fit of the measured C-V proving the validity of the C-V UTOXPP model.

Figure 1.26: Measured and simulated C-V of Metal/HK/IL/Si nMOSFET. The HK and IL physical thicknesses are 1.4nm and 1.3nm respectively. The Si concentration doping is  $4.10^{17}$  cm<sup>-3</sup>.

## 1.4 Conclusion

In this chapter, basic principles of ideal and real MOS capacitors have been explored. The MOS capacitor evidences three different gate bias operation modes which are the accumulation, depletion and inversion regimes. In advanced CMOS technologies, oxide defects and dipoles at gate stack interfaces have a prominent influence on the C-V characteristic. Here, the oxide defects and interface traps impact on the C-V characteristic have been addressed evaluating the flat band voltage expression in the real MOS capacitor.

In actual ultra-thin devices, predicting the quantum effects requires Poisson-Schrödinger simulation. In the second section, UTOXPP Poisson-Schrödinger simulation results was validated by comparison to PSL solver and literature results. Afterwards, UTOXPP C-V simulation model is validated for *Si* nMOSFETs with polysilicon and metal gate.

MOS CAPACITOR C-V CHARACTERISTIC

## Chapter 2

# C-V simulations of SiGe devices

## Contents

| <b>2.1</b> | Intro                                      | $oduction  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                |  |

|------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>2.2</b> | $\mathbf{S}\mathbf{t}\mathbf{r}\mathbf{a}$ | ined SiGe/Si electrostatics modeling 46                                                                                                    |  |

|            | 2.2.1                                      | Strained $SiGe$ on $Si$                                                                                                                    |  |

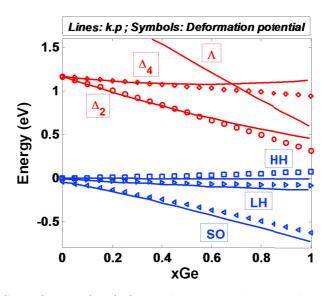

|            | 2.2.2                                      | Strain effects on the $SiGe$ band structure $\ldots \ldots \ldots \ldots \ldots \ldots 48$                                                 |  |

|            |                                            | 2.2.2.1 EMA model and deformation potential                                                                                                |  |

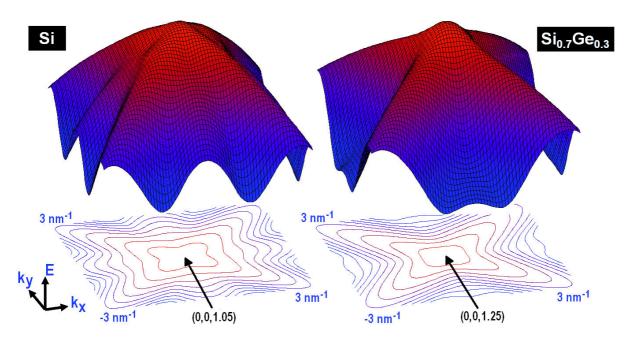

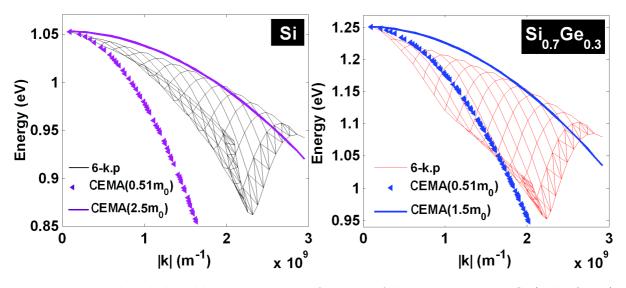

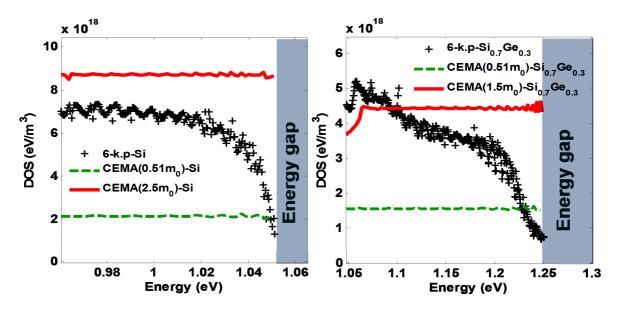

|            |                                            | 2.2.2.2 6-Band k.p model                                                                                                                   |  |

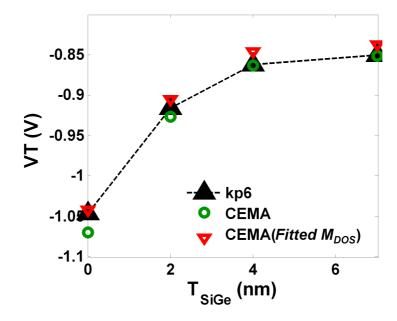

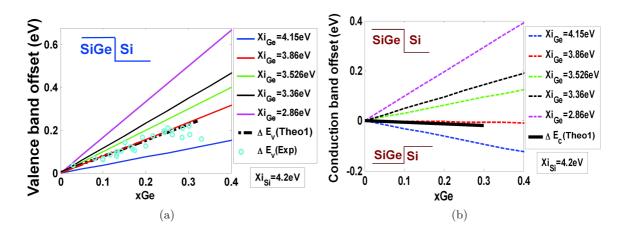

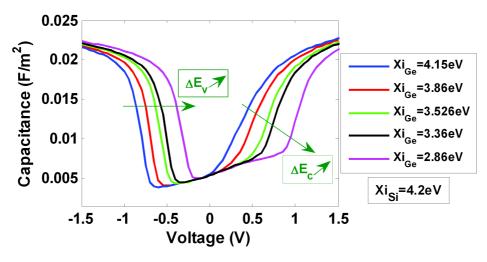

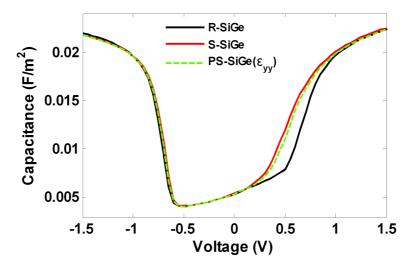

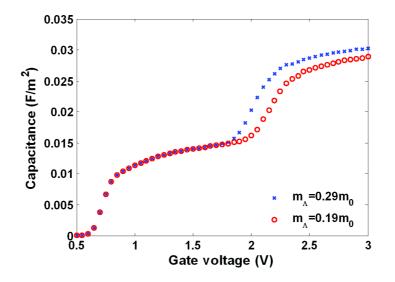

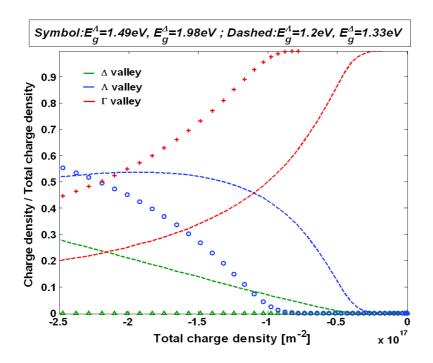

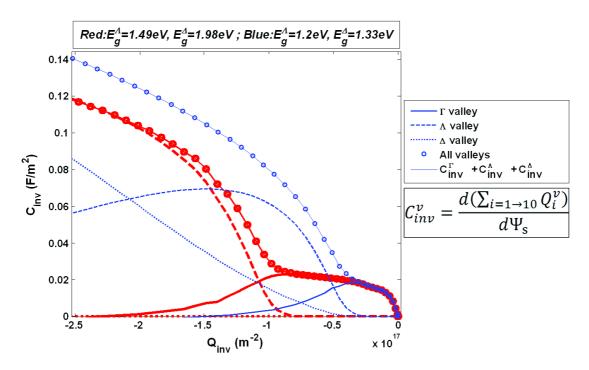

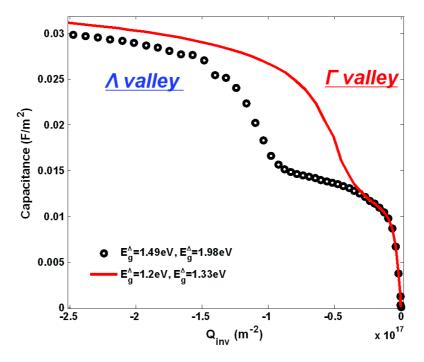

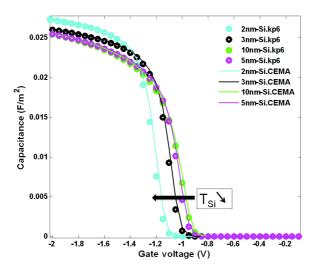

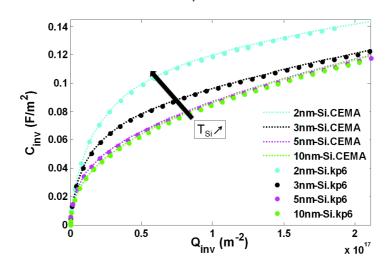

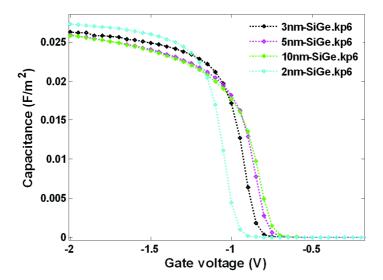

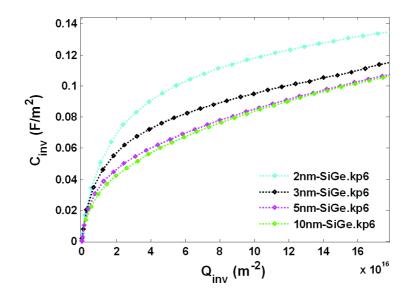

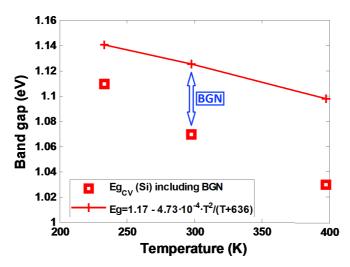

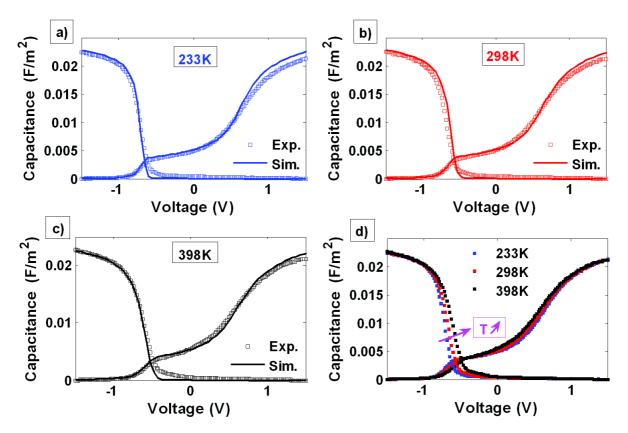

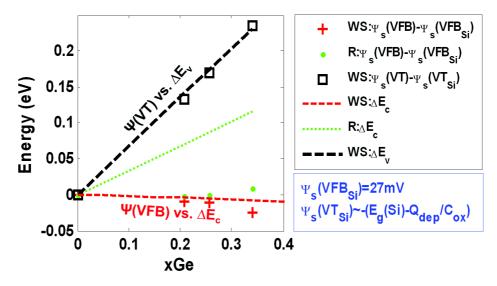

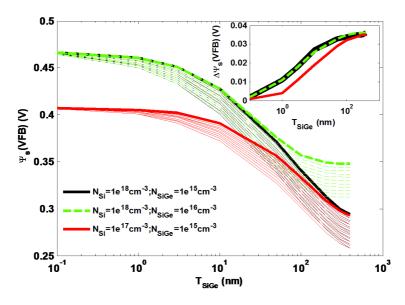

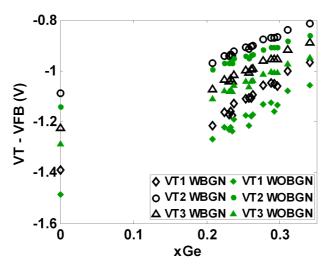

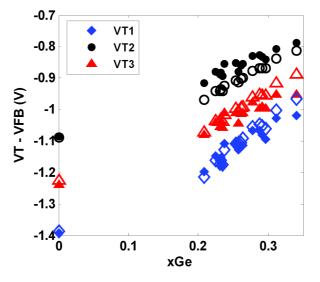

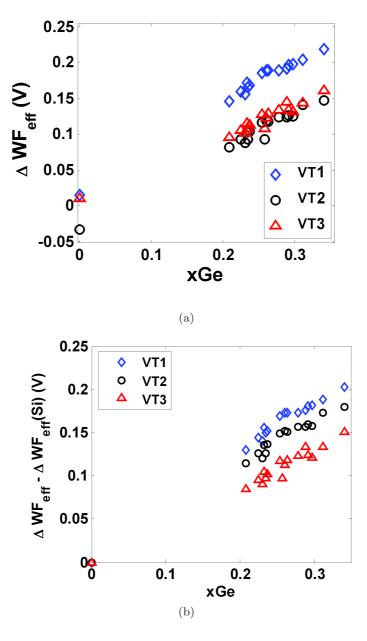

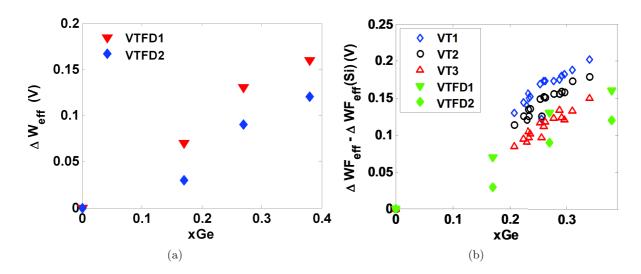

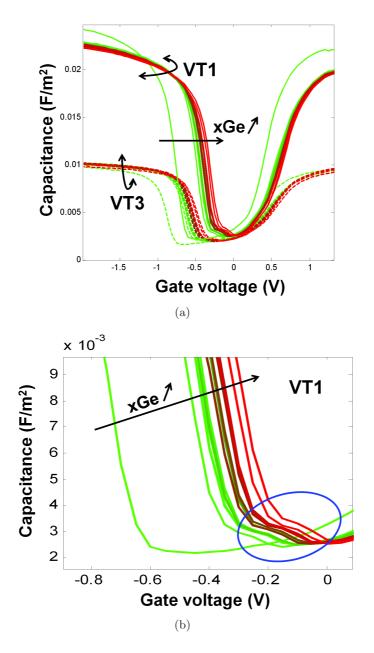

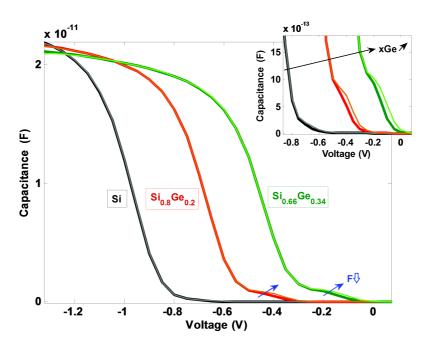

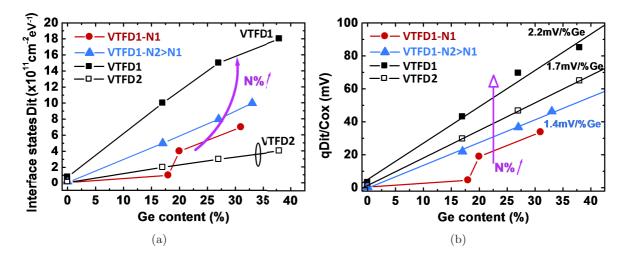

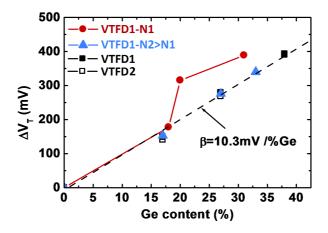

|            |                                            | 2.2.2.3 Application to confined $SiGe/Si$                                                                                                  |  |