# Conception et réalisation de circuits de génération de fréquence en technologie FDSOI 28nm

Alexandre Fonseca

#### ▶ To cite this version:

Alexandre Fonseca. Conception et réalisation de circuits de génération de fréquence en technologie FDSOI 28nm. Autre. Université Nice Sophia Antipolis, 2015. Français. NNT: 2015NICE4100 . tel-01284746

### HAL Id: tel-01284746 https://theses.hal.science/tel-01284746

Submitted on 8 Mar 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITE NICE SOPHIA ANTIPOLIS POLYTECH'NICE-SOPHIA

## **École Doctorale des Sciences et Technologies de** l'Information et de la Communication

Électronique pour Objets Connectés

#### **THESE**

Pour obtenir le titre de **Docteur en Sciences spécialité Électronique** de l'Université Nice Sophia Antipolis

présentée et soutenue par

### **Alexandre FONSECA**

## Conception et réalisation de circuits de génération de fréquences en technologie FDSOI 28nm

Thèse dirigée par Philippe LORENZINI et Gilles JACQUEMOD Soutenue le 2 Décembre 2015

#### Jury:

| H. BARTHELEMY  | Rapporteur   | Professeur, Université du Sud Toulon Var |

|----------------|--------------|------------------------------------------|

| Y. DEVAL       | Rapporteur   | Professeur, ENSEIRB Bordeaux             |

| P. LORENZINI   | Directeur    | Professeur, UNS Sophia Antipolis         |

| G. JACQUEMOD   | Co-directeur | Professeur, UNS Sophia Antipolis         |

| E. de FOUCAULD | Encadrant    | Ingénieur, CEA-LETI Grenoble             |

| P. NOUET       | Examinateur  | Professeur, Polytech'Montpellier         |

| R.M. SAUVAGE   | Invitée      | Ingénieur, DGA Bagneux                   |

## **Avant-propos**

Le travail présenté dans ce mémoire a été effectué au sein du Laboratoire d'Architectures et Infrastructures Radiofréquences (LAIR) du Département Architecture Conception et Logiciels Embarqués (DACLE) du Laboratoire d'Electronique et de Technologie de l'Information (LETI) du Département de Recherche technologique (DRT) du Commissariat à l'Energie Atomique (CEA), situé sur le site de Grenoble.

Je remercie en premier lieu Monsieur Marc Belleville et Monsieur Pierre Vincent pour m'avoir accueilli dans le département/laboratoire.

Je remercie également Monsieur Philippe Lorenzini et Monsieur Gilles Jacquemod, mes codirecteurs de thèse pour m'avoir proposé ce sujet passionnant, m'avoir conseillé techniquement tout au long de ma thèse et m'avoir aidé à rédiger ce mémoire.

Je remercie vivement Monsieur Emeric de Foucauld, mon tuteur désigné, et Monsieur Gérard Billiot, un expert de la microélectronique radiofréquence, pour m'avoir guidé et conseillé avec une disponibilité exemplaire tout au long de mes trois années de thèse.

J'adresse également mes remerciements à Messieurs H. Barthélémy, Y. Deval, pour m'avoir fait l'honneur de présider, de rapporter et d'examiner ce travail.

Je tiens à exprimer toute ma sympathie aux toute l'équipe du LAIR qui m'a accompagnée au cours de ces trois années de thèse et plus particulièrement à J. Prouvée, O. Rozeau, D. Morche, M. Pelissier, G. Waltener, C.Jany ainsi qu'à mes collègues thésards M. Verdy, A. Ratiu, O.Martin, P. Moron Guerra et G. Tant.

Enfin, il me tient à cœur de remercier ma femme, Mme Tânia Emanuelle Mende De Almeida, mon meilleur ami Pierre Pétolat, et ma mère pour m'avoir soutenu et aidé dans les moments difficiles.

## **Sommaire**

| Avan  | t-prop   | os        |                                                                | 1  |

|-------|----------|-----------|----------------------------------------------------------------|----|

| Somr  | maire .  |           |                                                                | ii |

| Gloss | saire    |           |                                                                | 1  |

| Intro | ductio   | n généra  | ale                                                            | 3  |

| 1.    | Des c    | bjets co  | ommunicants vers les objets connectés                          | 3  |

| 2.    | Trava    | aux de Tl | hèse                                                           | 5  |

| Chap  | itre I - | Standar   | d, technologie et architecture pour l'autonomie                | 7  |

| 1.    | Intro    | duction   |                                                                | 7  |

| 2.    | Le sta   | andard E  | Bluetooth Low Energy                                           | 7  |

|       | 2.1.     | Blueto    | oth Low Energy et Internet des Objets                          | 7  |

|       |          | 2.1.1.    | L'émergence de l'IOT                                           | 7  |

|       |          | 2.1.2.    | Avantages du BLE pour l'IOT                                    | 8  |

|       |          | 2.1.3.    | Transaction BLE type                                           | 10 |

|       |          | 2.1.4.    | Spécifications du BLE                                          | 11 |

|       | 2.2.     | Comm      | unications sans fil                                            | 12 |

|       |          | 2.2.1.    | Bases de fonctionnement d'un lien radio                        | 12 |

|       |          | 2.2.2.    | Composants d'un module radio                                   | 17 |

|       |          | 2.2.3.    | Influence des blocs sur les performances                       | 18 |

|       | 2.3.     | Synthè    | se de fréquences pour le BLE                                   | 19 |

|       |          | 2.3.1.    | Caractéristiques d'une synthèse                                | 19 |

|       |          | 2.3.2.    | Transposition en fréquence non idéale                          | 22 |

|       |          | 2.3.3.    | Résumé des spécifications pour la synthèse                     | 22 |

|       | 2.4.     | Conclu    | sion : L'apport du BLE                                         | 22 |

| 3.    | La te    | chnologi  | ie CMOS FDSOI                                                  | 23 |

|       | 3.1.     | Les enj   | jeux de l'évolution microélectronique                          | 23 |

|       | 3.2.     | Evoluti   | ion de la technologie microélectronique                        | 25 |

|       |          | 3.2.1.    | La fin de la loi de Moore ?                                    | 25 |

|       |          | 3.2.2.    | Limitations des transistors MOS Bulk dus aux nœuds agressifs   | 27 |

|       |          | 3.2.3.    | La technologie FDSOI                                           | 30 |

|       |          | 3.2.4.    | La variabilité de la tension de seuil dans les nœuds agressifs | 32 |

|       |          | 3.2.5.    | Méthodes de simulation de la variabilité                       | 33 |

|       |          | 3.2.6.    | Méthodes de correction de la variabilité                       | 35 |

|       | 3.3.     | Conclu    | sion                                                           | 36 |

| 4.    | Archi    | tectures  | s de synthèse de fréquences                                    | 36 |

|      | 4.1.      | Introdu   | uction                                                             | 36 |

|------|-----------|-----------|--------------------------------------------------------------------|----|

|      | 4.2.      | Archite   | ectures de synthèse                                                | 37 |

|      |           | 4.2.1.    | Types d'asservissement                                             | 37 |

|      |           | 4.2.2.    | Types de PLL                                                       | 39 |

|      |           | 4.2.3.    | Types d'oscillateurs                                               | 41 |

|      |           | 4.2.4.    | PLL Entière Vs Fractionnaire                                       | 43 |

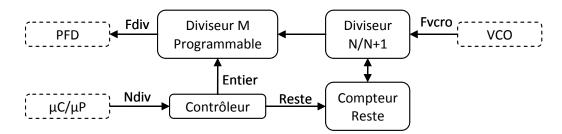

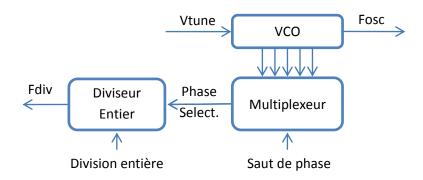

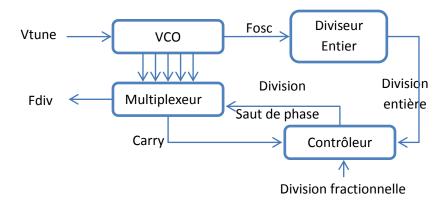

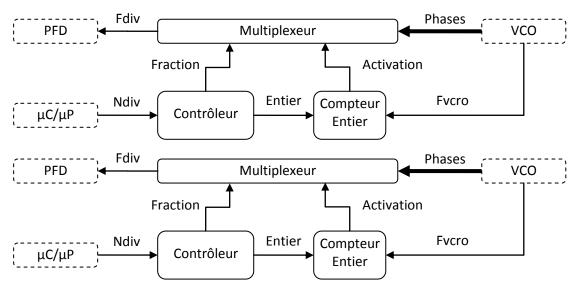

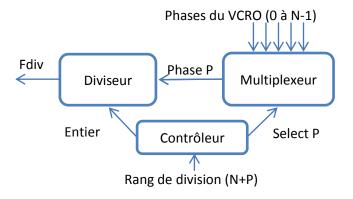

|      |           | 4.2.5.    | Diviseurs fractionnaire : modulo variable Vs commutation de phases | 45 |

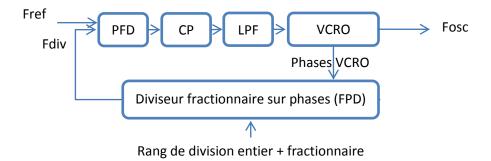

|      | 4.3.      | La PLL    | à diviseur fractionnaire sur phase (FPD)                           | 48 |

|      |           | 4.3.1.    | Différents chemins menant à la même architecture                   | 48 |

|      |           | 4.3.2.    | Historique et état de l'art de la PLL FPD                          | 48 |

|      |           | 4.3.3.    | Création Vs réutilisation des phases du VCRO                       | 51 |

|      |           | 4.3.4.    | DPLL à TDC implicite Vs TDC explicite                              | 52 |

|      |           | 4.3.5.    | Diviseur à commutation Vs resynchronisation                        | 52 |

|      |           | 4.3.6.    | Exemple d'implémentation FPD                                       | 53 |

|      |           | 4.3.7.    | Amélioration de la base de temps                                   | 54 |

|      | 4.4.      | Conclu    | sion                                                               | 55 |

| 5.   | Concl     | lusion    |                                                                    | 55 |

| Chap | itre II - | - Modéli  | isation système                                                    | 58 |

| 1.   | Intro     | duction . |                                                                    | 58 |

|      | 1.1.      | Métho     | dologie de modélisation                                            | 58 |

| 2.   | Etude     | e du bloc | C VCRO - Diviseur                                                  | 59 |

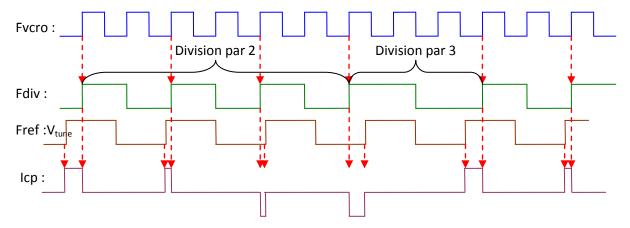

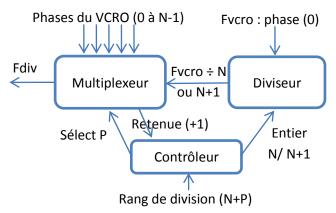

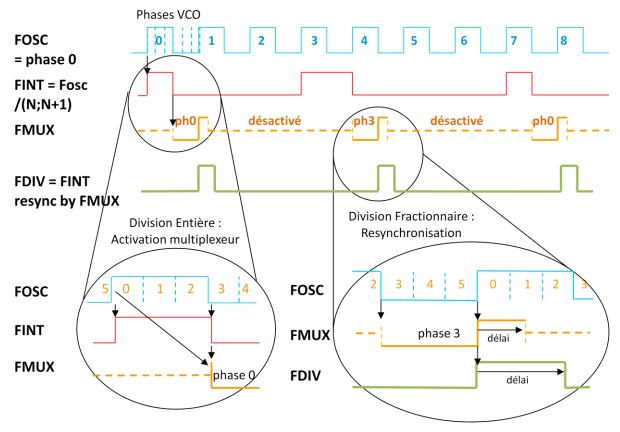

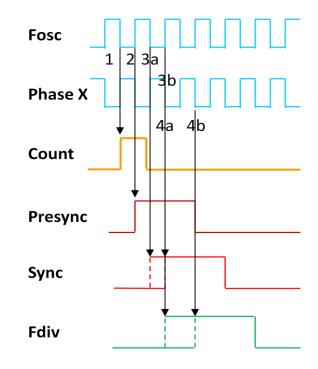

|      |           | 2.1.1.    | Diviseur par commutation et diviseur par resynchronisation         | 59 |

|      | 2.2.      | Modèle    | es                                                                 | 61 |

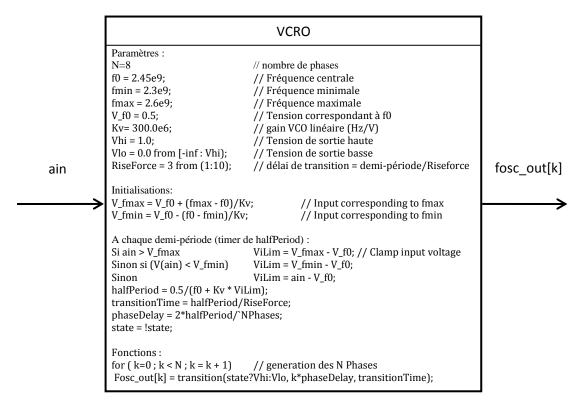

|      |           | 2.2.1.    | VCRO à phases multiples                                            | 61 |

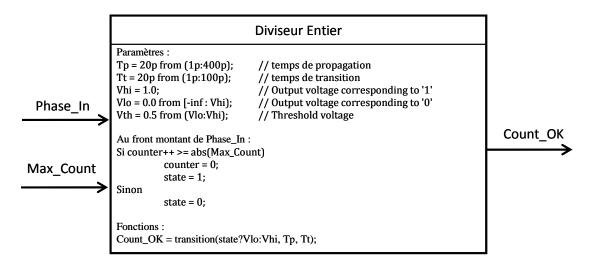

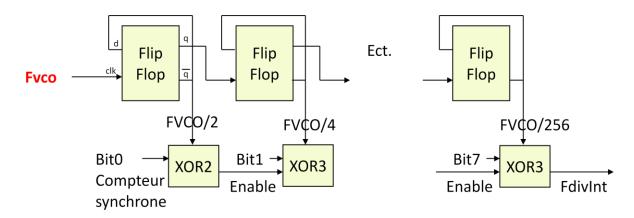

|      |           | 2.2.2.    | Diviseur entier                                                    | 62 |

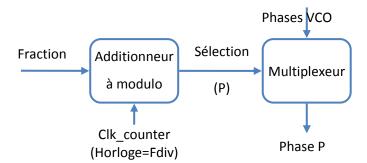

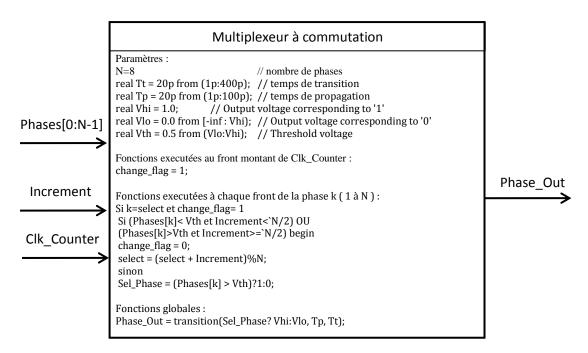

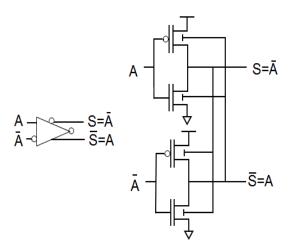

|      |           | 2.2.3.    | Multiplexeur à commutation                                         | 63 |

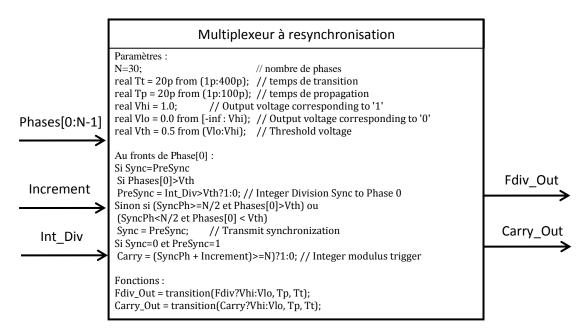

|      |           | 2.2.4.    | Multiplexeur à resynchronisation                                   | 64 |

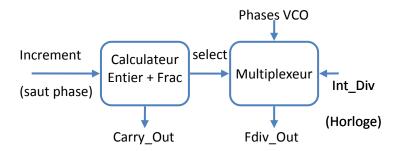

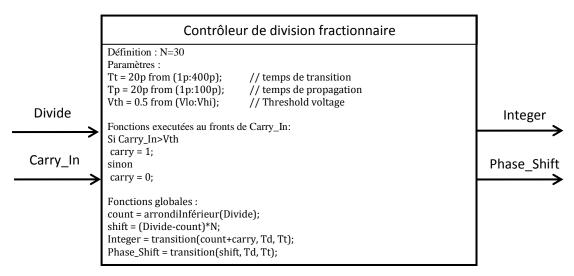

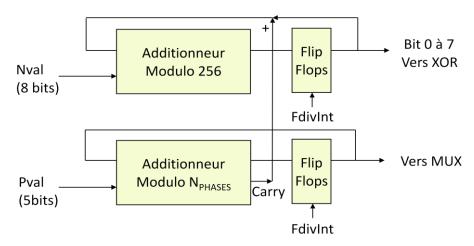

|      |           | 2.2.5.    | Contrôleur de division fractionnaire                               | 66 |

|      | 2.3.      | Résulta   | ats                                                                | 67 |

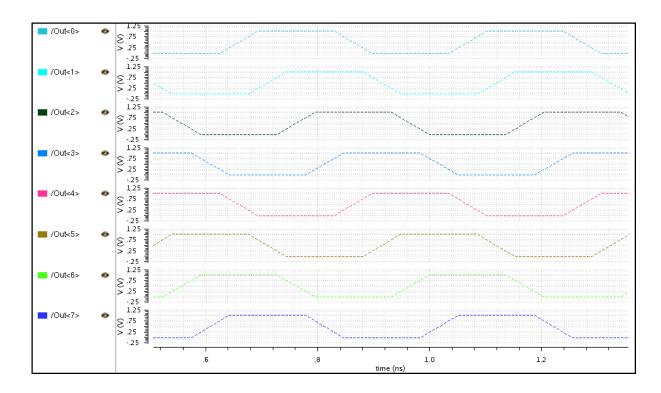

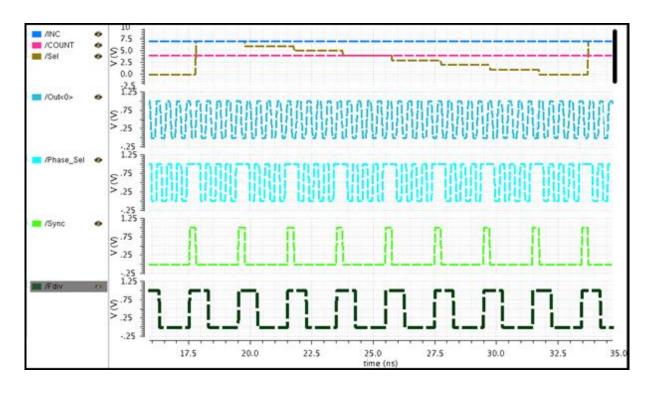

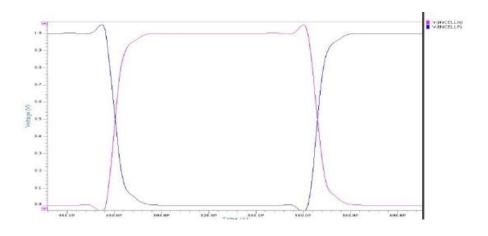

|      |           | 2.3.1.    | Simulation temporelle des phases du VCO                            | 67 |

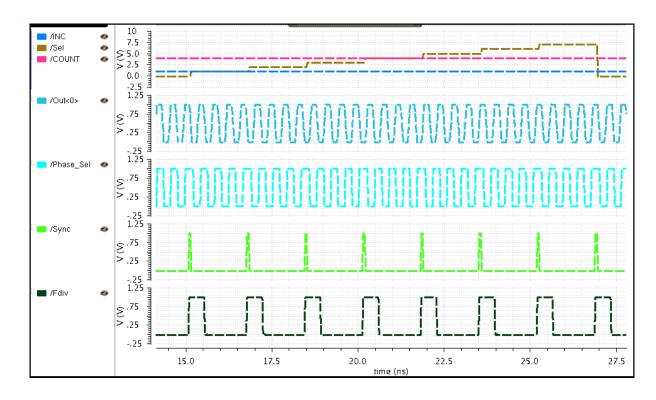

|      |           | 2.3.2.    | Simulation du FPD à commutation de phases                          | 68 |

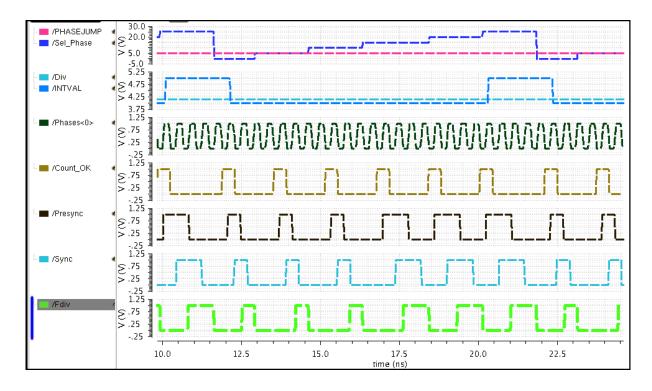

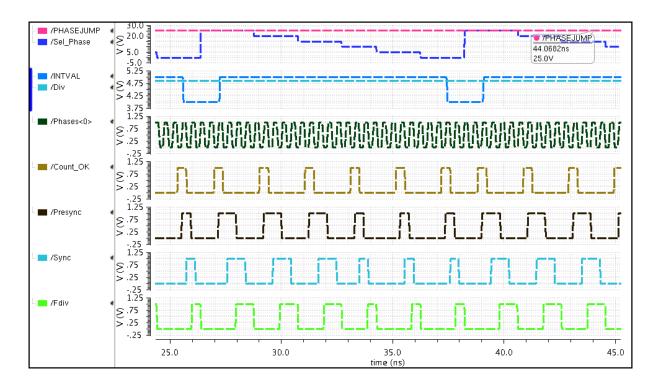

|      |           | 2.3.3.    | Simulation du FPD à resynchronisation par phase                    | 69 |

|      | 2.4.      | Conclu    | sion                                                               | 71 |

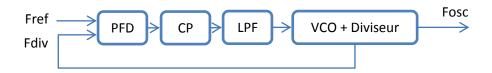

| 3.   | Etude     | e d'une f | PLL à base de diviseur FPD                                         | 71 |

|      | 3.1.      | Introdu   | uction                                                             | 71 |

|      | 3.2.      | Modèle    | es                                                                 | 72 |

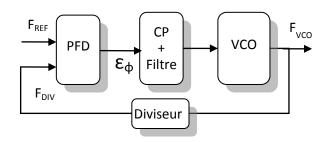

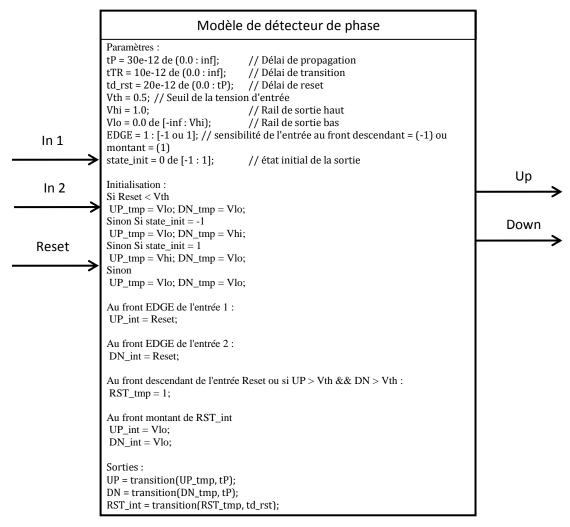

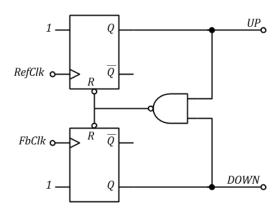

|      |           | 3.2.1.    | Détecteur de Fréquence et Phase (PFD)                              | 72 |

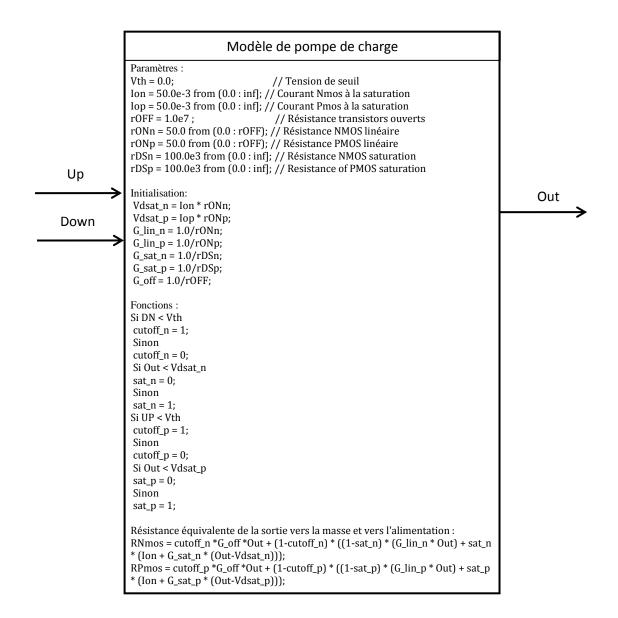

|      |           | 3.2.2.    | Pompe de Charge (CP)                                               | 73 |

|      |          | 3.2.3. Filtre Passe-Bas (LPF)                                         | 74  |

|------|----------|-----------------------------------------------------------------------|-----|

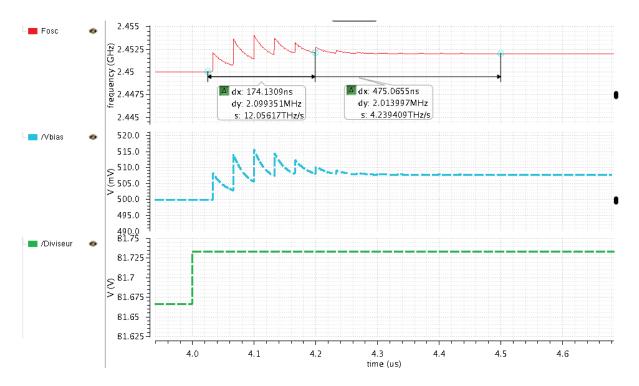

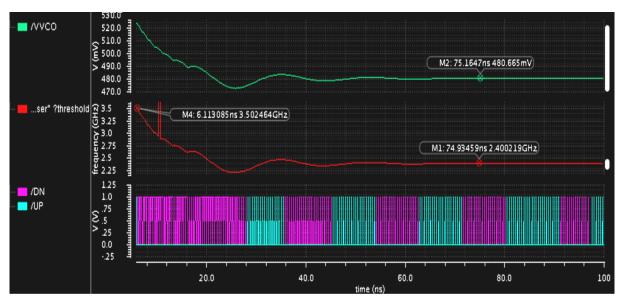

|      | 3.3.     | Simulation temporelle de la PLL fractionnaire                         | 74  |

|      | 3.4.     | Conclusion                                                            | 75  |

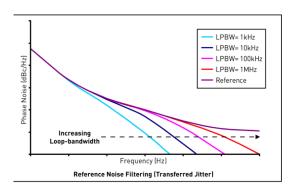

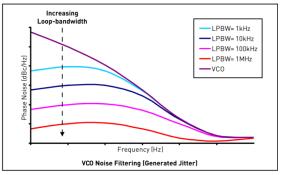

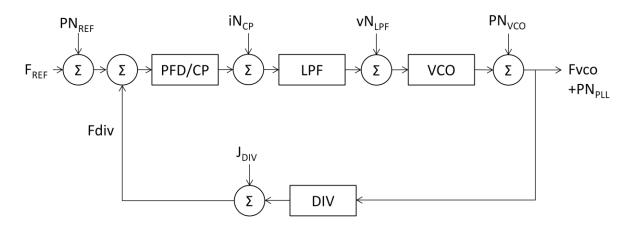

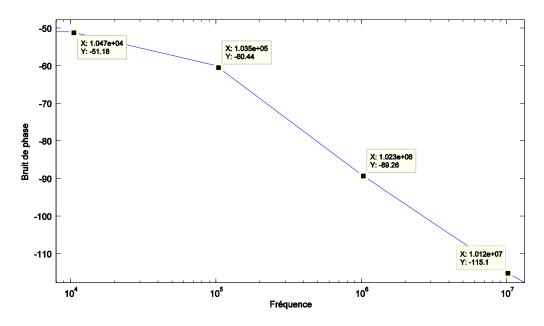

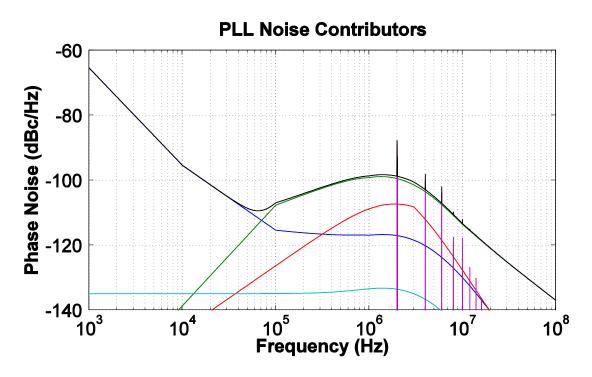

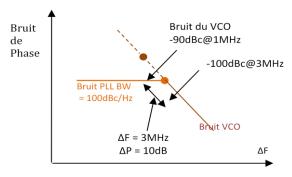

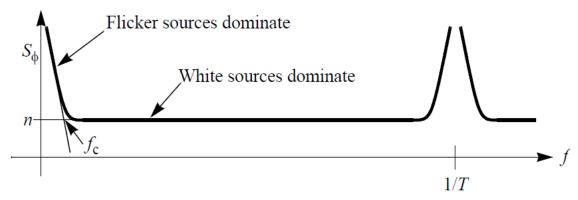

| 4.   | Etud     | e du bruit de phase                                                   | 76  |

|      | 4.1.     | Introduction                                                          | 76  |

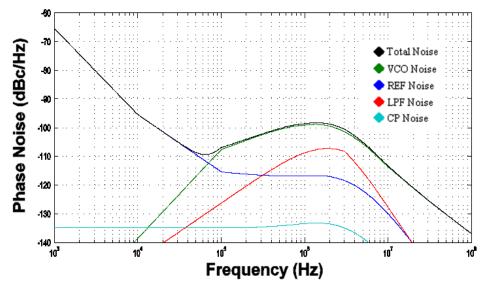

|      | 4.2.     | Extraction du bruit de chaque contributeur                            | 77  |

|      | 4.3.     | Résultats                                                             | 79  |

|      |          | 4.3.1. Simulation dans le domaine temporel                            | 79  |

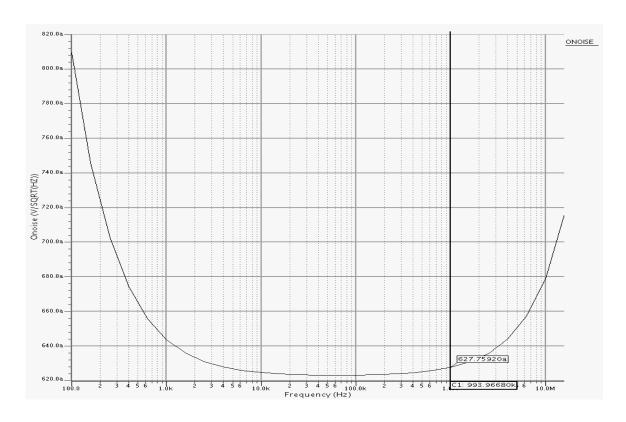

|      |          | 4.3.2. Simulation dans le domaine fréquentiel                         | 80  |

|      | 4.4.     | Conclusion                                                            | 81  |

| 5.   | Etud     | e de génération des spurious                                          | 82  |

|      | 5.1.     | Introduction                                                          | 82  |

|      | 5.2.     | Modèles                                                               | 83  |

|      |          | 5.2.1. Méthode temporelle                                             | 83  |

|      |          | 5.2.2. Méthode fréquentielle                                          | 85  |

|      | 5.3.     | Résultats                                                             | 85  |

|      |          | 5.3.1. Simulation temporelle                                          | 85  |

|      |          | 5.3.2. Simulation fréquentielle                                       | 86  |

|      | 5.4.     | Conclusion                                                            | 87  |

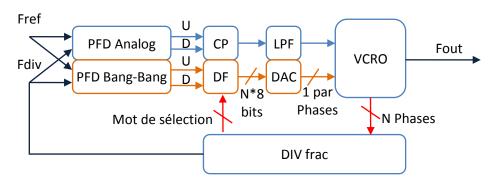

| 6.   | Etud     | e de calibration des phases                                           | 88  |

|      | 6.1.     | Introduction                                                          | 88  |

|      | 6.2.     | Architectures de calibration                                          | 88  |

|      |          | 6.2.1. Calibration par comparateur Bang-Bang, Filtre numérique et DAC | 89  |

|      |          | 6.2.2. Calibration par Vtune distribué par multiplexeur analogique    | 89  |

|      |          | 6.2.3. Conclusion sur l'architecture de calibration                   | 90  |

|      | 6.3.     | Modélisation                                                          | 90  |

|      | 6.4.     | Résultats de calibration progressive                                  | 91  |

|      | 6.5.     | Conclusion                                                            | 93  |

| 7.   | Conc     | lusion                                                                | 93  |

| Chap | itre III | – Conception, réalisation et test de VCRO                             | 96  |

| 1.   | Intro    | ductionduction                                                        | 96  |

| 2.   | Spéci    | ifications                                                            | 97  |

| 3.   | Imple    | émentation transistor, Layout & Simulation                            | 98  |

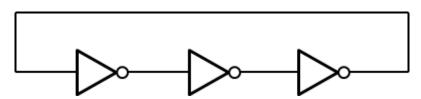

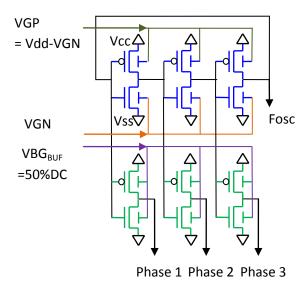

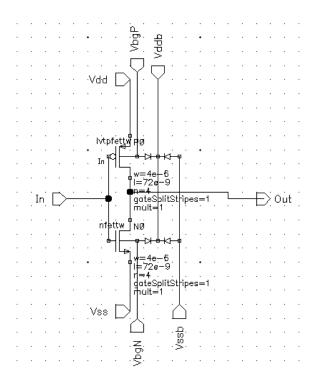

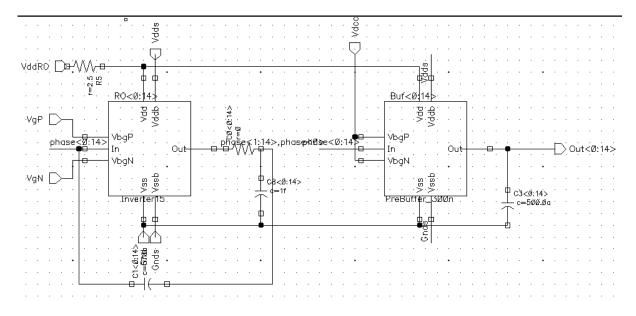

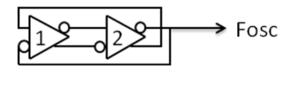

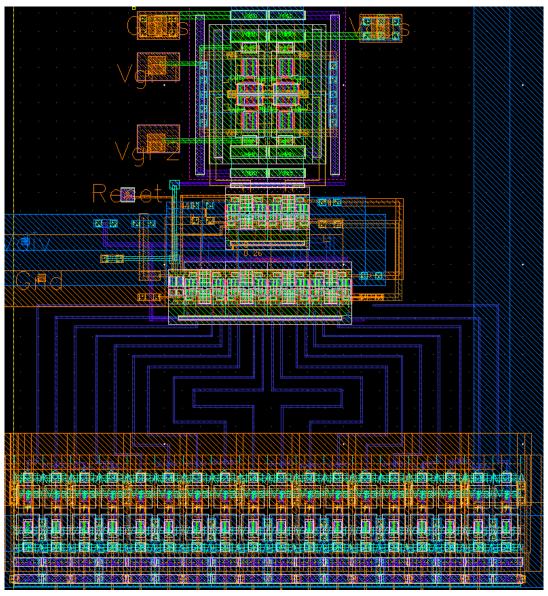

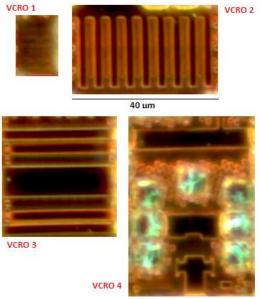

|      | 3.1.     | VCRO single ended à 6 phases (3 inverseurs)                           | 98  |

|      |          | 3.1.1. Introduction                                                   | 98  |

|      |          | 3.1.2. Implémentation                                                 | 98  |

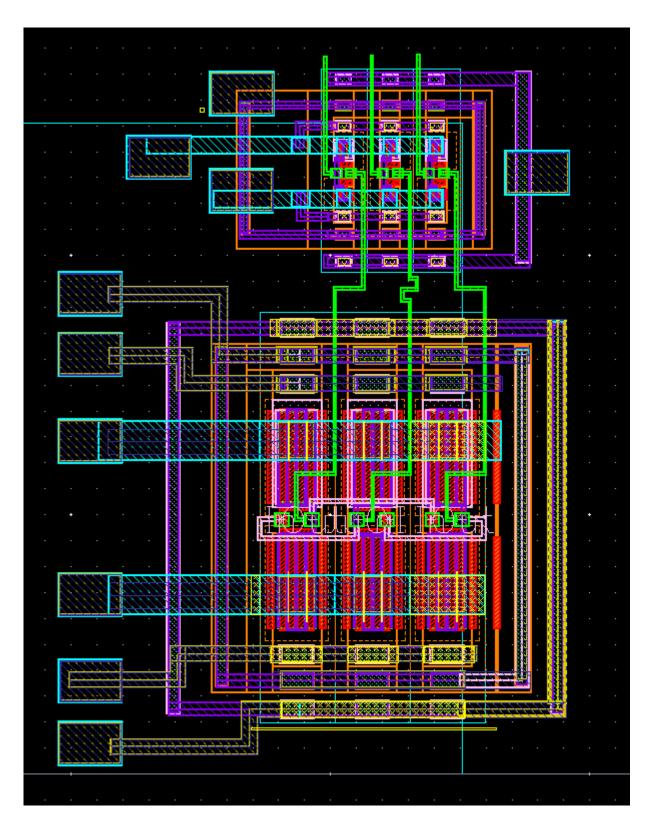

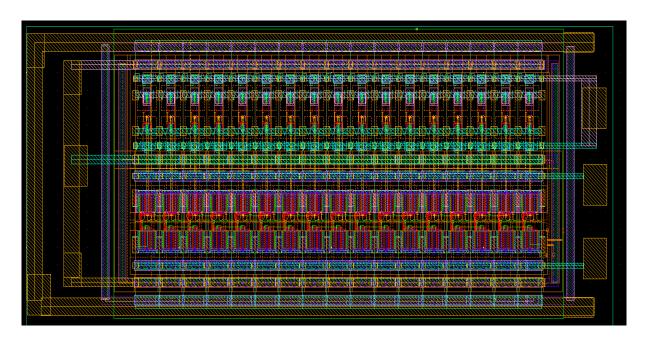

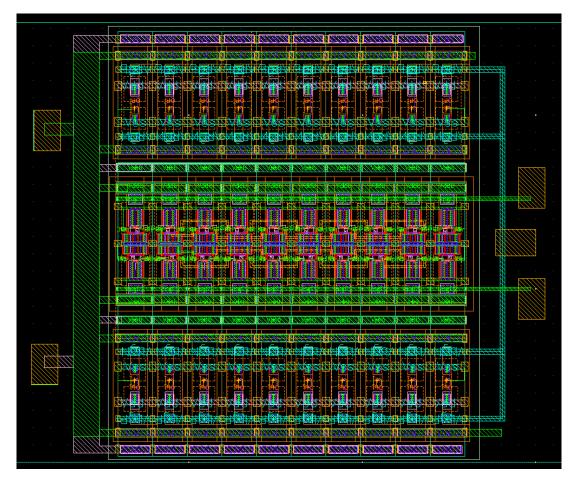

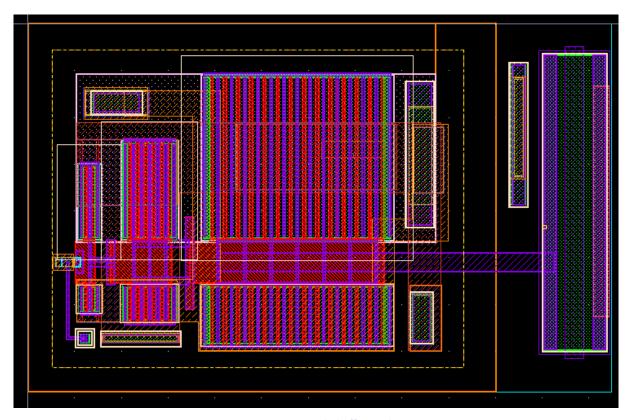

|      |          | 3.1.3. Layout                                                         | 101 |

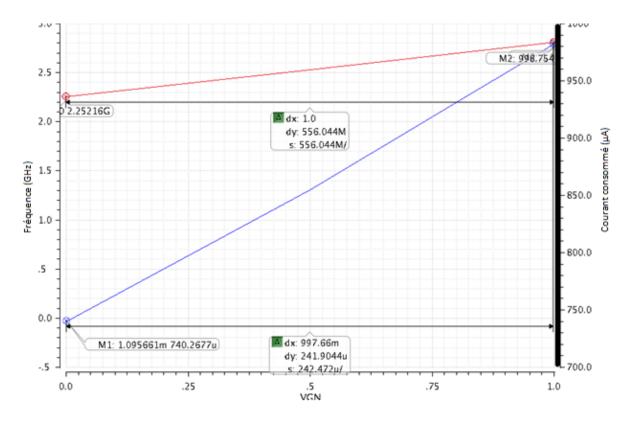

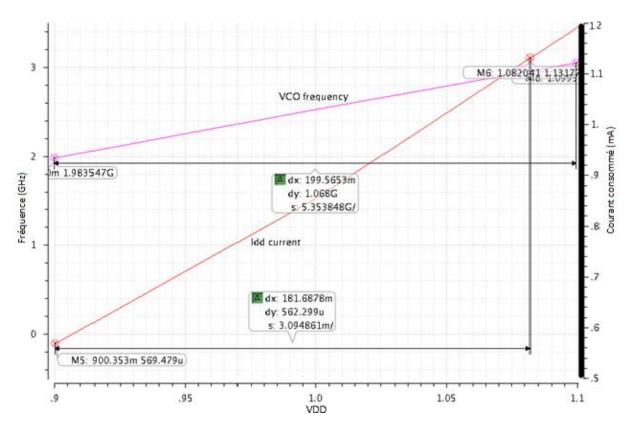

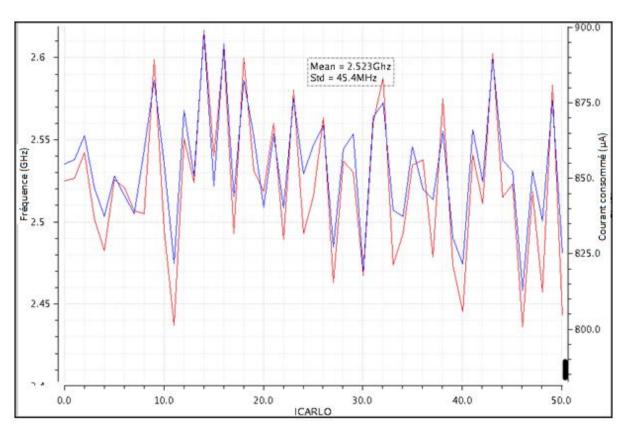

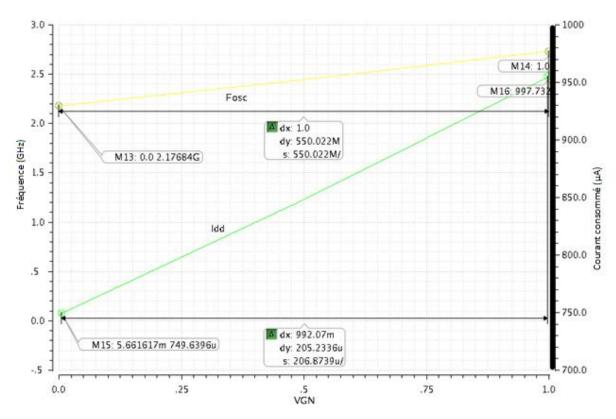

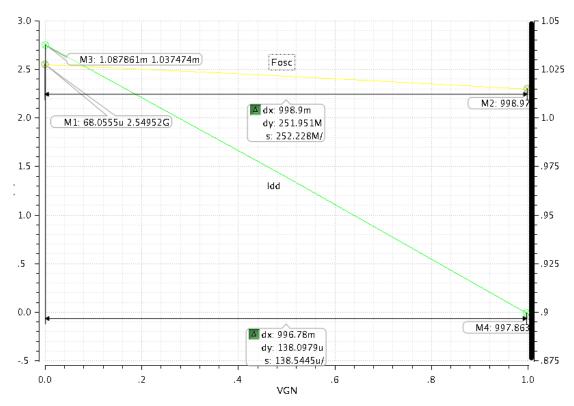

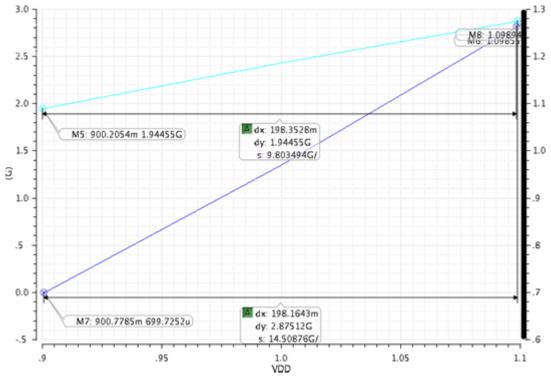

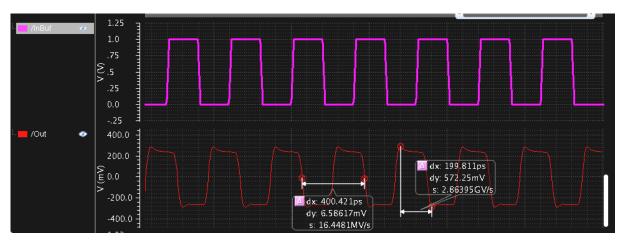

|      |          | 3.1.4. Simulation                                                     | 104 |

|      | 3.2.    | VCRO single ended à 30 phases (15 inverseurs)     | 106 |

|------|---------|---------------------------------------------------|-----|

|      |         | 3.2.1. Implémentation                             | 106 |

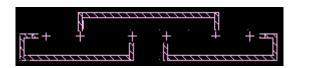

|      |         | 3.2.2. Layout                                     | 107 |

|      |         | 3.2.3. Simulation                                 | 108 |

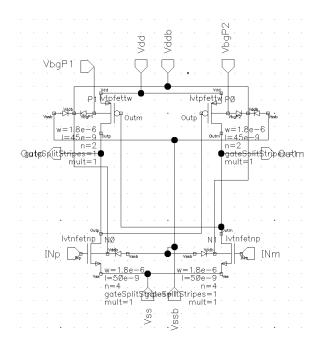

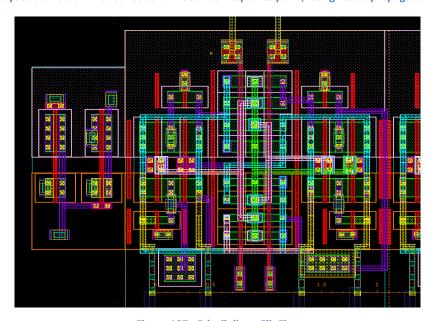

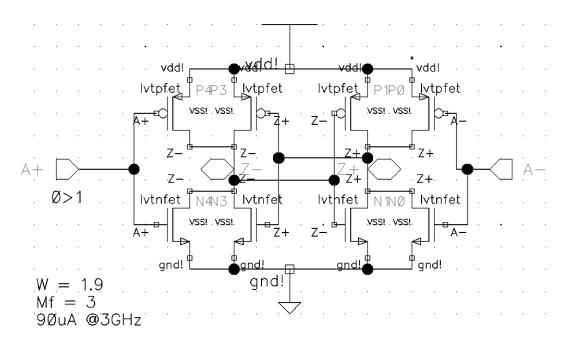

|      | 3.3.    | VCRO différentiel à 16 phases (8 cellules)        | 110 |

|      |         | 3.3.1. Implémentation                             | 110 |

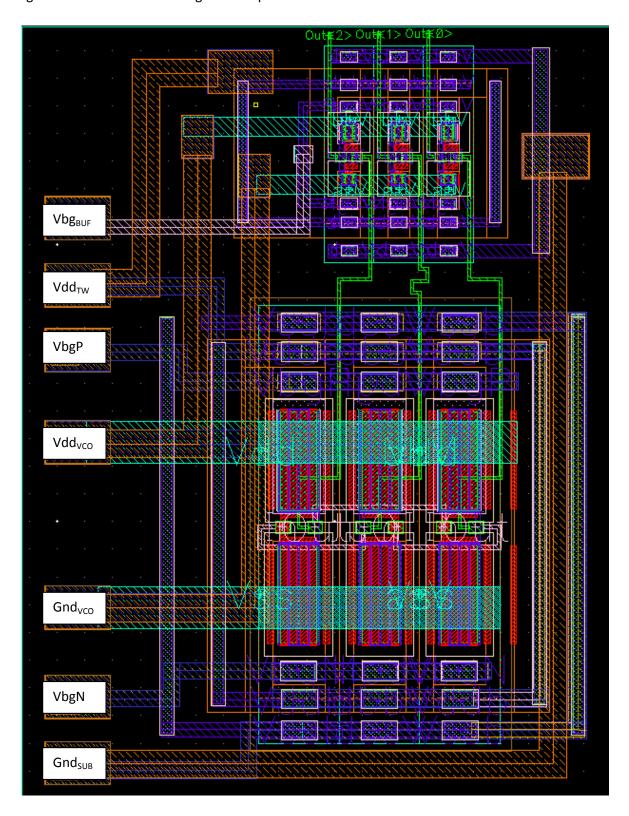

|      |         | 3.3.2. Layout                                     | 111 |

|      |         | 3.3.3. Simulation                                 | 112 |

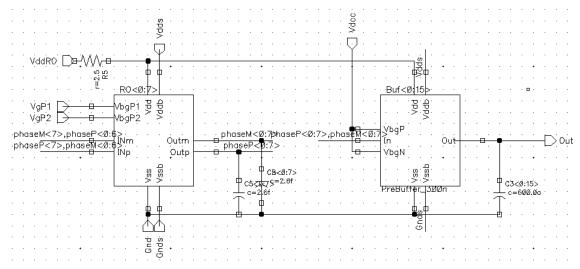

|      | 3.4.    | VCRO différentiel à 16 phases à 4x Fout           | 114 |

|      |         | 3.4.1. Implémentation                             | 114 |

|      |         | 3.4.2. Layout                                     | 117 |

|      |         | 3.4.3. Simulation                                 | 119 |

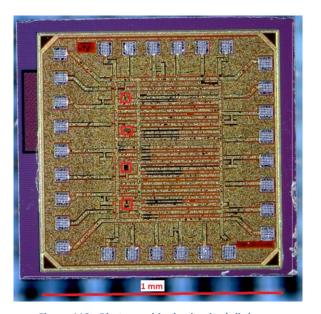

| 4.   | Réali   | isation                                           | 121 |

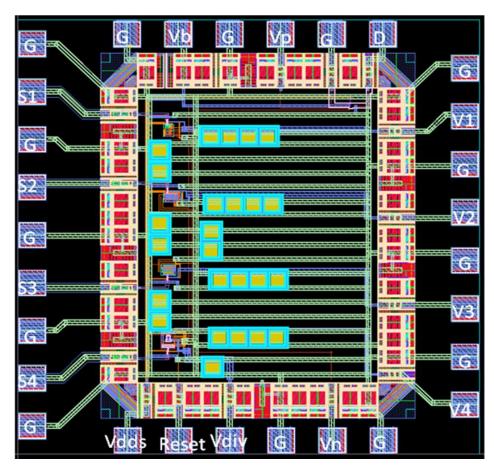

|      | 4.1.    | Dessin des masques                                | 121 |

|      | 4.2.    | Simulations post layout                           | 121 |

|      | 4.3.    | Fabrication                                       | 123 |

|      | 4.4.    | Récapitulatif et Conclusion                       | 123 |

| 5.   | Mesu    | ures et tests des VCRO                            | 124 |

|      | 5.1.    | Introduction                                      | 124 |

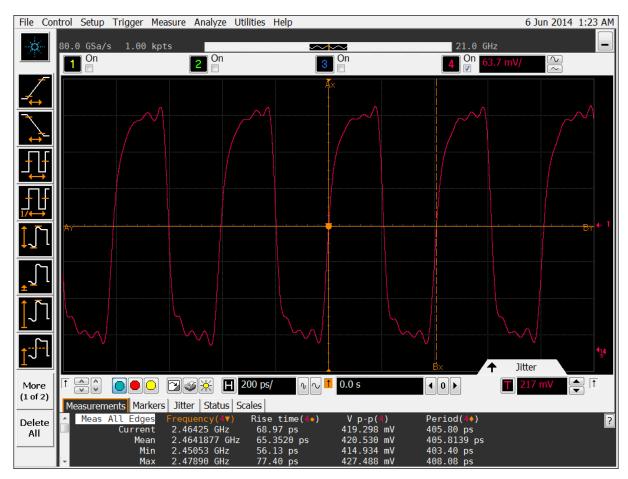

|      | 5.2.    | Mesure à fréquence nominale                       | 124 |

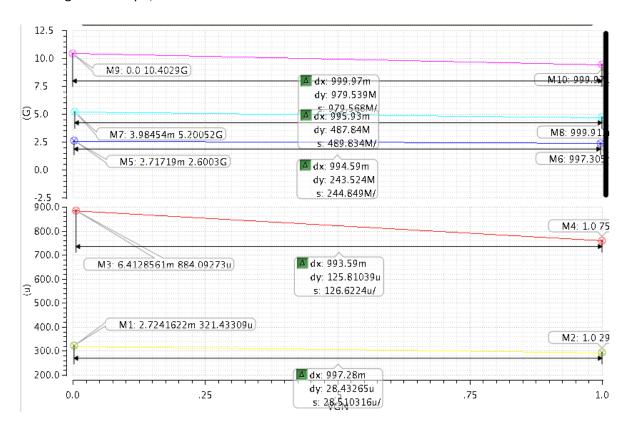

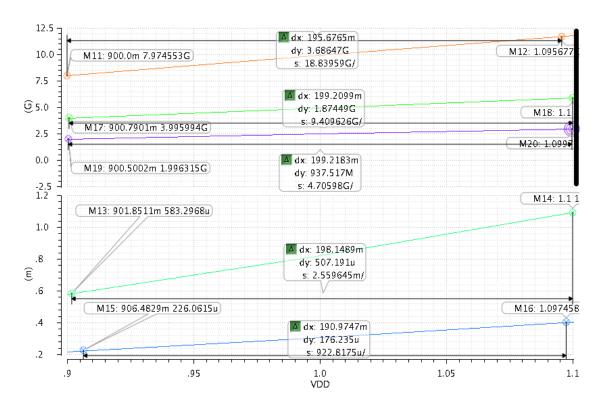

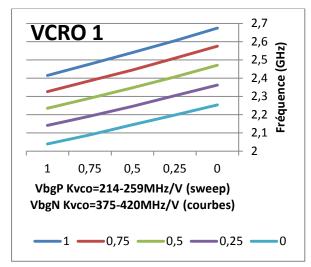

|      | 5.3.    | Mesures de la fréquence d'oscillation des VCRO    | 125 |

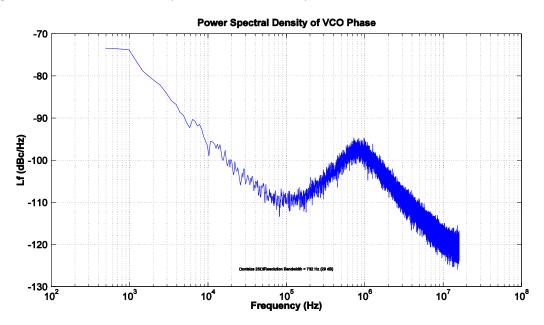

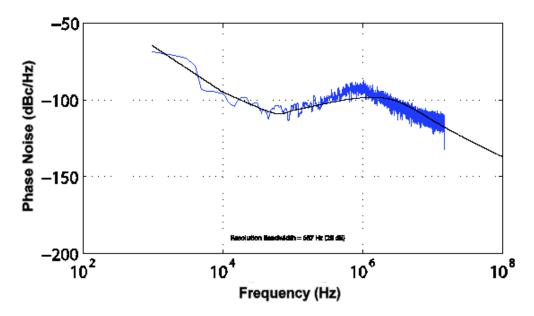

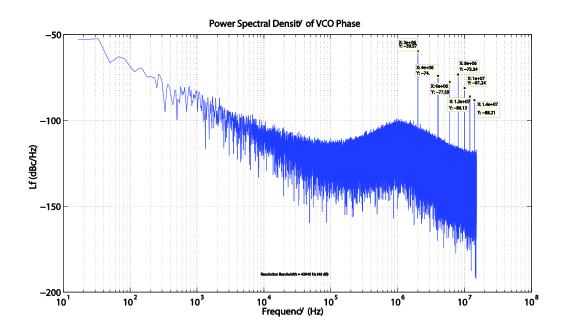

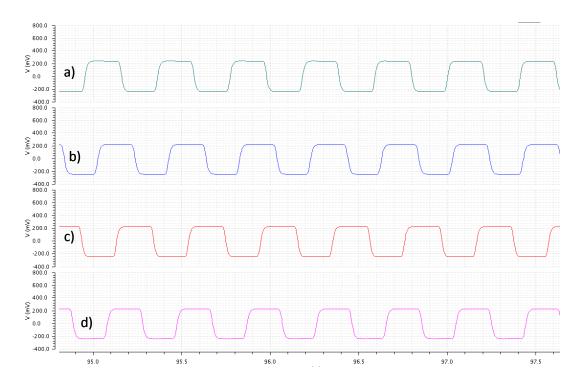

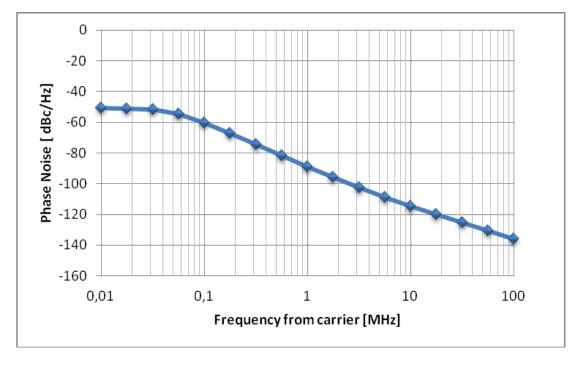

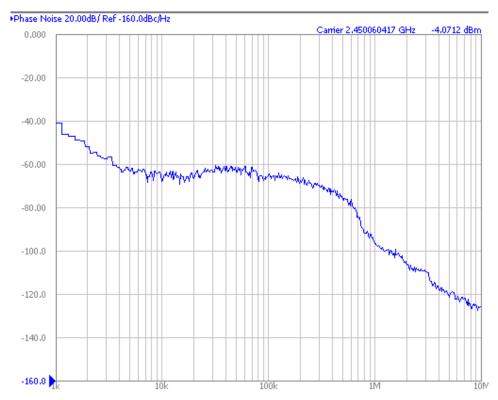

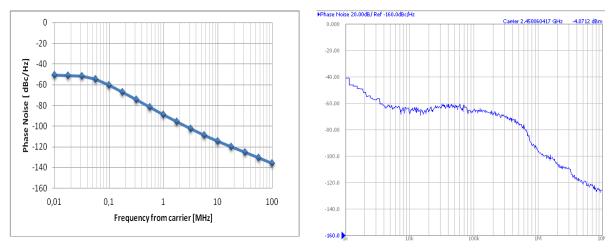

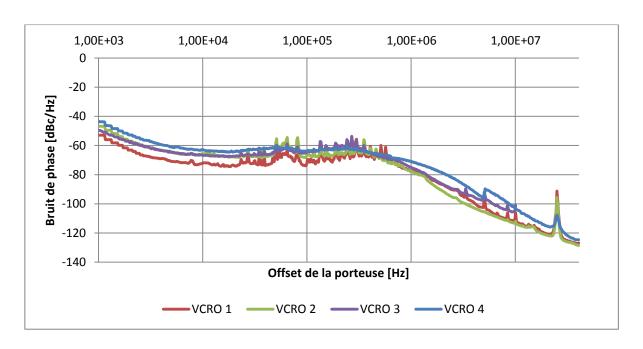

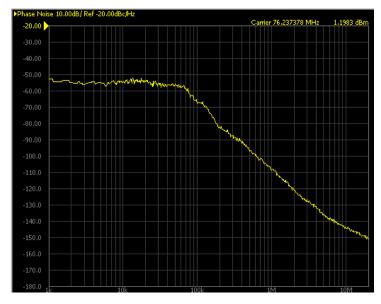

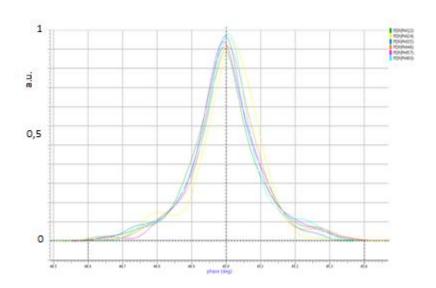

|      | 5.4.    | Mesure du bruit de phase des VCRO                 | 127 |

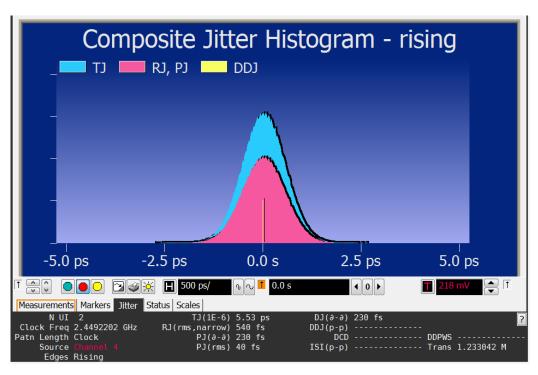

|      | 5.5.    | Mesure du bruit de phase en boucle fermée         | 129 |

|      | 5.6.    | Conclusion                                        | 130 |

| 6.   | Conc    | clusion                                           | 132 |

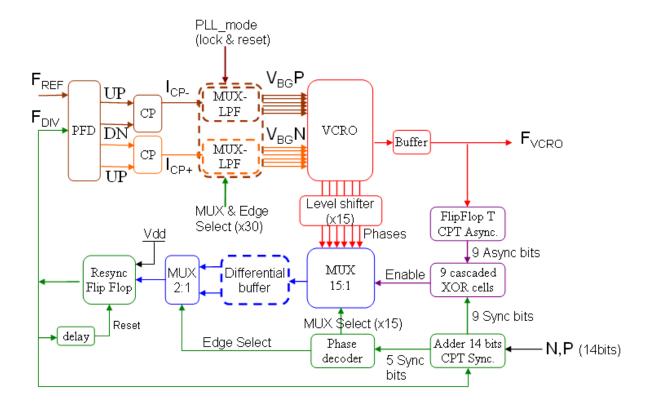

| Chap | itre IV | / – Etude de la PLL à resynchronisation de phases | 134 |

| 1.   | Intro   | oduction                                          | 134 |

| 2.   | Divis   | eur fractionnaire                                 | 134 |

|      | 2.1.    | Introduction                                      | 134 |

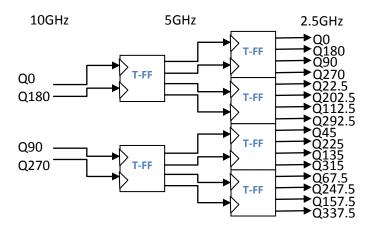

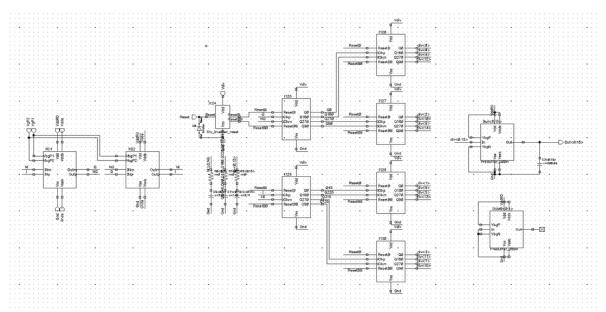

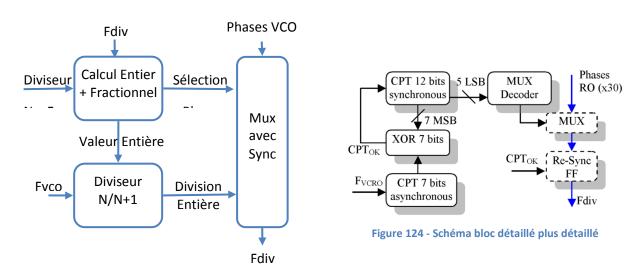

|      | 2.2.    | Architecture                                      | 135 |

|      | 2.3.    | Spécifications                                    | 135 |

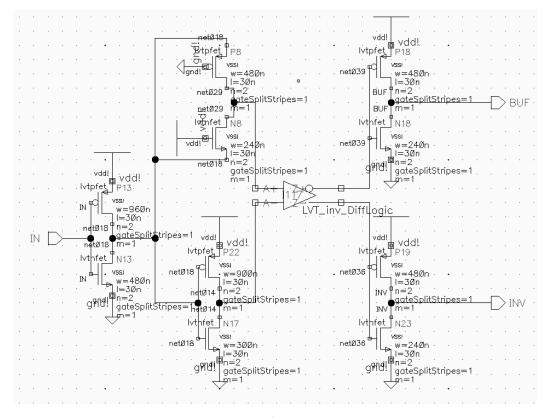

|      | 2.4.    | Implémentation au niveau transistor               | 135 |

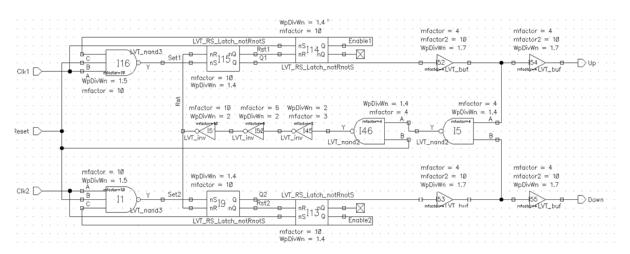

|      |         | 2.4.1. Calculateur                                | 135 |

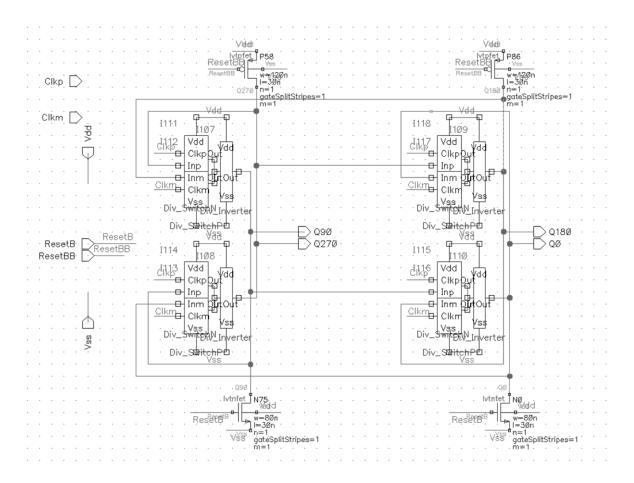

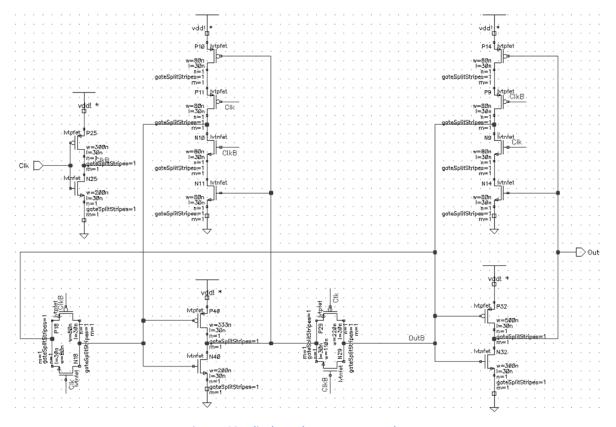

|      |         | 2.4.2. Diviseur Entier                            | 137 |

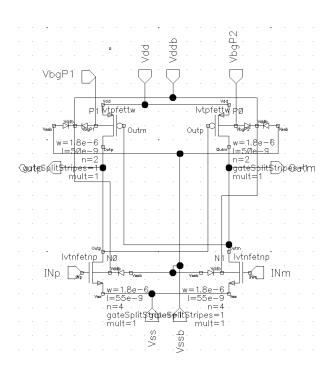

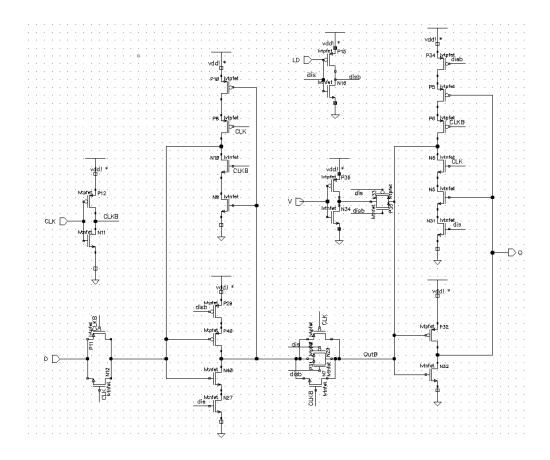

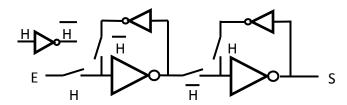

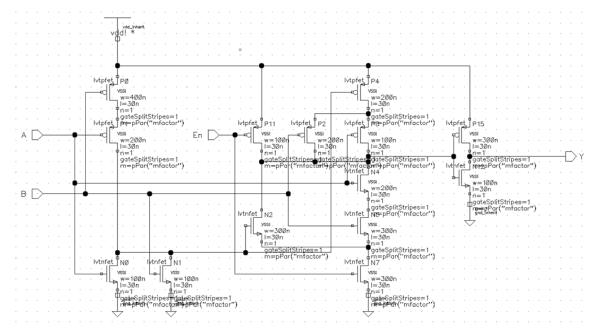

|      |         | 2.4.3. Multiplexeur à resynchronisation           | 139 |

|      |         | 2.4.4. Conclusion                                 |     |

|      | 2.5.    | Simulation                                        | 143 |

|      | 2.6.    | Conclusion                                        | 145 |

|      |         |                                                   |     |

| 3.     | Détec   | teur de <sub>l</sub>         | ohase et filtre                         | 145 |  |  |

|--------|---------|------------------------------|-----------------------------------------|-----|--|--|

|        | 3.1.    | Introdu                      | ction                                   | 145 |  |  |

|        | 3.2.    | Spécific                     | ations                                  | 146 |  |  |

|        | 3.3.    | Implém                       | entation                                | 146 |  |  |

|        |         | 3.3.1.                       | Comparateur de phases                   | 146 |  |  |

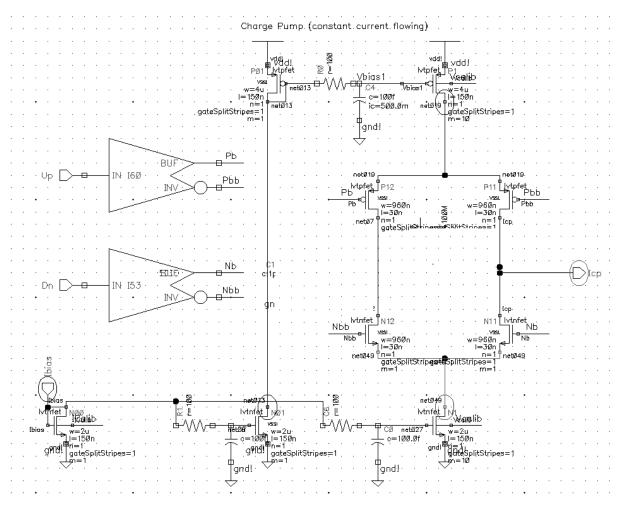

|        |         | 3.3.2.                       | Pompe de charge                         | 147 |  |  |

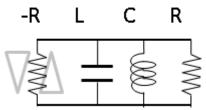

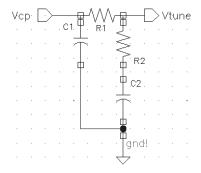

|        |         | 3.3.3.                       | Filtre de boucle                        | 149 |  |  |

|        | 3.4.    | Simulat                      | ion                                     | 149 |  |  |

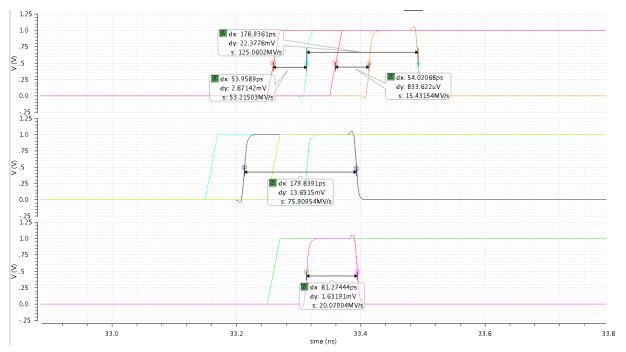

|        |         | 3.4.1.                       | Comparateur de phases                   | 150 |  |  |

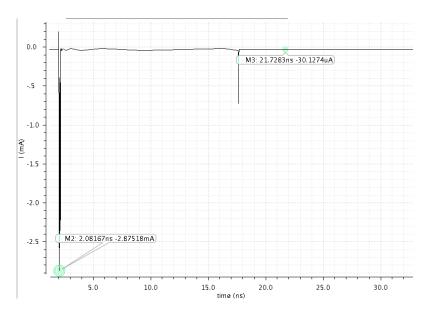

|        |         | 3.4.2.                       | Pompe de charge                         | 151 |  |  |

|        |         | 3.4.3.                       | Filtre de boucle                        | 152 |  |  |

|        | 3.5.    | Conclus                      | ion                                     | 152 |  |  |

| 4.     | Buffer  | 50Ω                          |                                         | 152 |  |  |

|        | 4.1.    | Introdu                      | ction                                   | 152 |  |  |

|        | 4.2.    | Spécific                     | ations                                  | 153 |  |  |

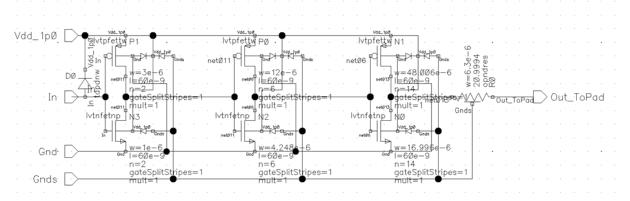

|        | 4.3.    | Implém                       | entation                                | 153 |  |  |

|        | 4.4.    | Layout.                      |                                         | 153 |  |  |

|        | 4.5.    | Simulat                      | ion                                     | 154 |  |  |

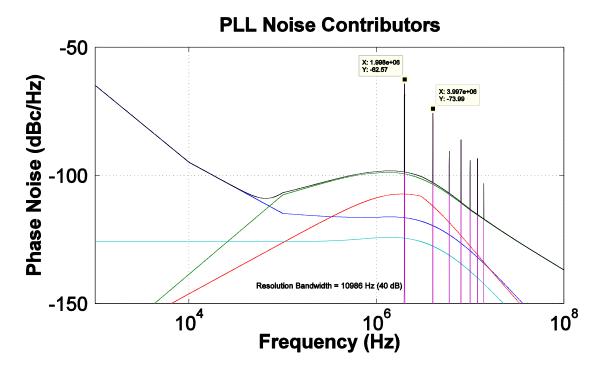

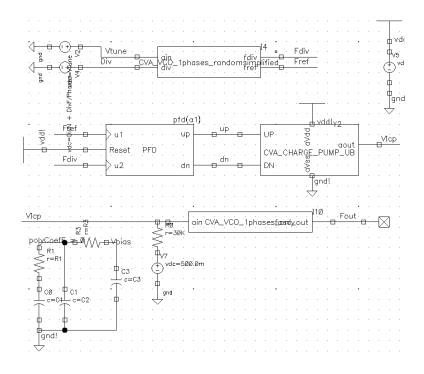

| 5.     | PLL     |                              |                                         | 155 |  |  |

|        | 5.1.    | Introdu                      | ction                                   | 155 |  |  |

|        | 5.2.    | Simulat                      | ion                                     | 155 |  |  |

|        | 5.3.    | Conclus                      | ion                                     | 156 |  |  |

| 6.     | Persp   | ectives                      |                                         | 156 |  |  |

|        | 6.1.    | Introdu                      | ction                                   | 156 |  |  |

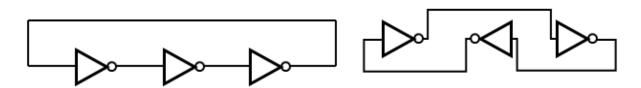

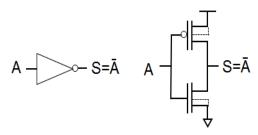

|        | 6.2.    | Logique                      | complémentaire                          | 157 |  |  |

|        | 6.3.    | Oscillate                    | eur en anneau en logique complémentaire | 159 |  |  |

| 7.     | Concl   | usion                        |                                         | 159 |  |  |

| Concl  | usion ( | Générale                     |                                         | 161 |  |  |

| Public | ations  |                              |                                         | 163 |  |  |

| Référ  | ences   |                              |                                         | 164 |  |  |

| Anne   | xes     |                              |                                         | 167 |  |  |

| 1.     | Modè    | le de VC                     | RO à phases                             | 167 |  |  |

| 2.     | Modè    | le de div                    | riseur entier                           | 168 |  |  |

| 3.     | Modè    | le du mu                     | ultiplexeur à commutation               | 169 |  |  |

| 4.     |         |                              | ultiplexeur à resynchronisation         |     |  |  |

| 5.     |         |                              | ntrôleur                                |     |  |  |

| 6.     | Modè    | le de dé                     | tecteur de phase                        | 172 |  |  |

| 7.     |         | Nodèle de pompe de charge173 |                                         |     |  |  |

| 8.  | Fonction d'estimation de la DSP du bruit de phase à partir des mesures des périodes | 174 |

|-----|-------------------------------------------------------------------------------------|-----|

| 9.  | Modélisation du bruit de phase et des spurious à partir du mismatch                 | 175 |

| 10. | Fonction de génération de mismatch des phases en fonction du jitter RMS             | 179 |

## **Glossaire**

| ACK    | Acknowledgement                                                                     |

|--------|-------------------------------------------------------------------------------------|

| BER    | Bit Error Rate                                                                      |

| BG     | Back Gate (Grille arrière des transistors FDSOI)                                    |

| BLE    | Bluetooth Low Energy                                                                |

| Вох    | Buried Oxide - oxyde enterré                                                        |

| BW     | Bandwidth                                                                           |

| CML    | Current Mode Logic                                                                  |

| CMOS   | Complementary Metal Oxide Semiconductor                                             |

| СР     | Charge Pump                                                                         |

| CSR    | Cambridge Silicon Radio                                                             |

| DAC    | Digital to Analog Converter                                                         |

| DCVSL  | Differential Cascode Voltage-Switch Logic                                           |

| DCVSLR | Differential Cascode Voltage-Switch Logic with series Resistor                      |

| DF     | Digital Filter - Filtre numérique                                                   |

| DLL    | Delay Locked Loop                                                                   |

| DSP    | Densité spectrale de puissance                                                      |

| DTC    | Digital to Time Converter - Générateur de délai ajustable numériquement             |

| FDSOI  | Fully Depleted Silicon on Insulator - complètement appauvri de silicium sur isolant |

| FOM    | Figure of Merit - figure de mérite                                                  |

| FPD    | Fractional Phase Divider - Diviseur fractionnaire à phases                          |

| GFSK   | Gaussian Frequency Shift Keying                                                     |

| ILO    | Injection Locked Oscillator                                                         |

| IOT    | Internet des Objets                                                                 |

| IP     | Intellectual Property                                                               |

| ISM    | Industrial, Scientific and Medical                                                  |

| LPF    | Low Pass Filter                                                                     |

| MCS    | MonteCarlo Simulation                                                               |

| PFD    | Phase Frequency Detector                                                            |

| PLL    | Phase Locked Loop                                                                   |

| PLS    | Post Layout Simulation                                                              |

| PN     | Phase Noise                                                                         |

| SNR    | Signal to noise Ratio                                                               |

| TDC    | Time to Digital Converter                                                           |

| TF     | Transformée de Fourier                                                              |

| UTBB   | Ultra Thin Body and BOx - canal et oxyde ultra fin                                  |

| VCO    | Voltage Controlled Oscillator - oscillateur contrôlable en tension                  |

| VCRO   | Voltage Controlled Ring Oscillator - oscillateur en anneau contrôlable en tension   |

## Introduction générale

# 1.Des objets communicants vers les objets connectés

Depuis plusieurs décennies, les objets communicants ont envahi notre quotidien et le nombre de données transmises, associées à de nombreux standards de communication sans fil, a également explosé. De nos jours, les objets sont connectés entre eux, sans parfois d'intervention humaine, et connectés à Internet; on parle alors d'Internet des objets (IOT : Internet of Things). Toutefois, parmi toutes les données disponibles sur internet, qui sont au nombre inimaginable de 50 pétaoctets (50 000 téraoctets), quasiment toutes ont été créées ou insérées par un humain. Le problème est que l'homme est limité en temps, en attention et en précision, et devrait se consacrer à d'autres activités, plus basiques ou plus créatives, que seul un humain peut effectuer.

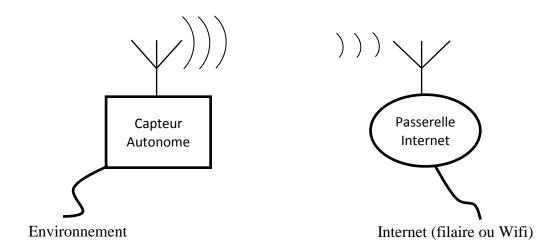

C'est de cette constatation que l'IOT fut imaginé, pour que les objets du quotidien puissent fournir des données à Internet pour les usagers (cf. Figure 1). Ces objets connectés, permettent l'utilisation intelligente des données collectées automatiquement, qu'elles soient sécuritaires, médicales, alimentaires, vestimentaires, météorologiques, de trafic, sociales, professionnelles ou commerciales. Ainsi la capture, le traitement des données et la prise de certaines décisions sont automatisés.

Figure 1 - Principe de l'internet des objets

Une grande partie des applications de l'IOT demande des objets communicants sans fil fonctionnant sur batterie (mobilité et facilité d'installation) à faible coût et longue autonomie (petite

batterie ou récupération d'énergie et faible consommation). La transmission d'une faible quantité de données à intervalle régulier d'un grand nombre d'objets vers Internet impose l'utilisation d'une passerelle, fixe (domicile, lieux publics, etc.) ou mobile (Smartphone). Les standards de radiocommunications adaptés à ces applications sont par exemple Bluetooth Low Energy (BLE) [1], ANT+ [2], ou ZigBee [3].

Récapitulatif des points que l'objet communicant de demain doit respecter :

- Communication radio sans fil sur batterie (mobilité, facilité d'installation) ou autonome en énergie (Récupération d'énergie)

- Bon marché (faible coût, batterie peu chère, pas d'entretien)

- Autonome et sans maintenance (faible consommation et/ou récupération)

La communication sans fil est le but premier, le deuxième point viendra avec son utilisation massive. Toutefois, l'autonomie longue et durable, qui nous fera oublier que ces objets intelligents sont parmi nous, n'est pas acquise et doit être recherchée.

Même (ou surtout) si ces objets utilisent la récupération d'énergie, ils doivent consommer très peu pour pouvoir s'autoalimenter et être bas coût. Pour avoir une faible consommation, il faut que la radio et le capteur consomment peu. Si le capteur peut facilement être optimisé pour consommer peu, la diminution de la consommation de la radio passera par :

- Utilisation parcimonieuse,

- Economie de trames,

- Economie de bit par trame,

- Distance d'émission faible,

- Rendement radio élevé.

En conclusion, le déploiement à grande échelle de l'internet des objets en général et des réseaux de capteurs en particulier, nécessite le développement de circuits et systèmes électroniques de plus en plus économes en énergie. Les circuits de génération de fréquences sont connus pour être un des blocs particulièrement énergivores. L'objectif de ce travail de thèse est double, d'une part développer une synthèse de fréquences très faible consommation et d'autre part démontrer les performances de la technologie FDSOI pour des applications analogiques et radiofréquences.

Pour illustrer nos travaux de thèse, nous avons choisi comme exemple d'application le standard Bluetooth Low Energy (BLE). L'objectif qui a été fixé est l'optimisation de l'architecture d'une PLL pour parvenir à une consommation inférieure au milliwatt.

#### 2. Travaux de Thèse

Dans le premier chapitre seront exposés les trois ingrédients nécessaires pour obtenir un objet communicant autonome à longue durée de vie, tel que l'IOT l'envisage. Le premier ingrédient est le standard, BLE dans notre cas, spécialement développé pour les objets autonomes, leur permettant de transmettre peu de données à intervalles réguliers avec un bon rendement. Le deuxième ingrédient est la technologie CMOS avancée : le FDSOI, qui permet de créer des blocs analogiques et radiofréquences avec une consommation plus faible par rapport aux technologies précédentes et des dispersions technologiques plus faibles que les technologies actuelles. Cette diminution permet de réaliser des circuits plus performants sur une même surface. Le troisième ingrédient est l'architecture de la synthèse de fréquences du module radiofréquence qui joue énormément sur la consommation et donc l'autonomie. Ce bloc est très important car il génère la fréquence permettant de communiquer sur le canal radio.

Le deuxième chapitre analyse les résultats de trois types de modélisation système de l'architecture particulière de cette synthèse de fréquence, et propose, en conclusion, les modifications à apporter pour satisfaire le cahier des charges. La première étude concerne le fonctionnement de l'architecture et doit permettre de définir les points clés à respecter pour son implémentation. La deuxième étude concerne le comportement des bruits afin de définir les meilleurs paramètres architecturaux permettant de respecter les spécifications. Enfin, la dernière étudie l'impact de l'architecture sur la génération de raies spectrales parasites pour estimer leur amplitude en fonction de la variabilité du signal de contre-réaction, afin d'en limiter les effets.

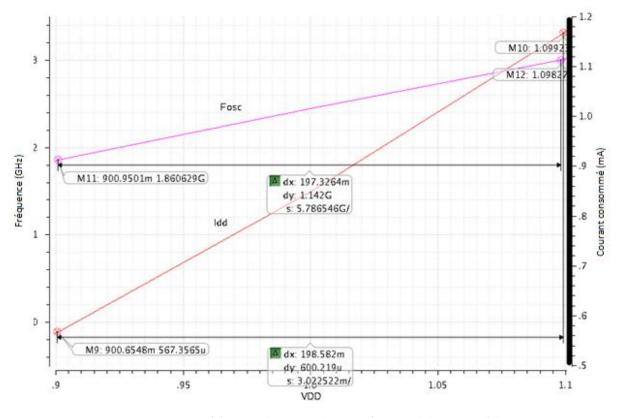

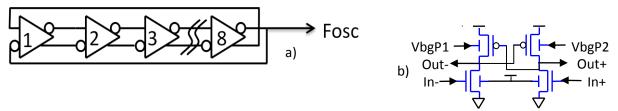

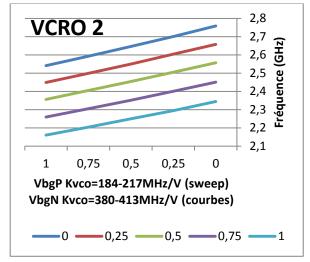

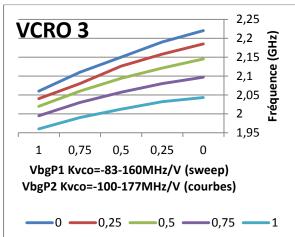

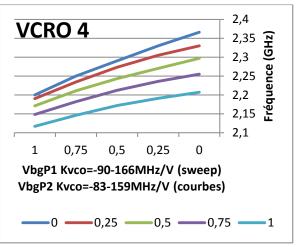

Le troisième chapitre est ainsi consacré à la conception, la réalisation et le test de VCRO en technologie FDSOI 28nm. Plusieurs topologies sont présentées et intégrées sur un circuit de test. Les premiers résultats de mesure sont encourageants, mais nécessitent sans doute d'être complétés. En effet, la sensibilité des circuits à la tension d'alimentation (pushing de l'ordre de 5 GHz/V) a rendu les mesures du bruit de phase très délicates. La consommation mesurée reste inférieure à 0,8 mA et la surface de chaque VCRO est de l'ordre de 600  $\mu$ m².

Dans le quatrième et dernier chapitre, nous proposons une topologie de la PLL à resynchronisation de phases, chaque bloc ayant été conçu et optimisé au niveau circuit. Nous terminons ce chapitre par quelques pistes d'amélioration, notamment la technique d'autocalibration par auto-polarisation de la grille arrière en utilisant une logique complémentaire qui a fait l'objet d'un dépôt de brevet. Une conclusion générale terminera ce mémoire.

# Chapitre I - Standard, technologie et architecture pour l'autonomie

#### 1.Introduction

Dans ce chapitre sont exposés les trois points les plus importants pour obtenir un système cohérent en termes d'économies d'énergie, permettant de concevoir des objets communicants par ondes radiofréquences autonomes et à longue durée de vie.

Le premier point est le standard de communication radiofréquence BLE qui a été optimisé pour consommer moins que sa version initiale (Bluetooth standard). Cette partie explique pourquoi le standard a été créé et rappelle son fonctionnement et ses caractéristiques. On détaillera ce standard après avoir expliqué les bases du fonctionnement des communications radiofréquences (RF) et les spécifications qu'une synthèse de fréquences doit respecter, ainsi que les caractéristiques du standard BLE qui permettent d'offrir une faible consommation.

Le deuxième point est la technologie CMOS FDSOI qui permet de fabriquer des circuits très économe en énergie. Cette partie discute les qualités du FDSOI qui nous aiderons à atteindre les spécifications, ainsi qu'à effectuer une analyse comparative des technologies CMOS précédentes.

Enfin, le troisième point concerne l'architecture du système radiofréquence, qui doit être conçue en suivant une approche bas coût et faible consommation. Dans cette partie sont présentés les différents types de synthèse de fréquences, de PLL, d'oscillateurs et de diviseurs et en particulier l'architecture à diviseur à commutation de phases. Pour conclure il sera expliqué quels sont les avantages espérés d'utiliser ces trois points ensemble.

## 2.Le standard Bluetooth Low Energy

#### 2.1. Bluetooth Low Energy et Internet des Objets

#### 2.1.1. L'émergence de l'IOT

Les télécommunications radiofréquences sont utilisées depuis longtemps pour la radiodiffusion sur de grandes distances vers un grand nombre de récepteurs, de par la facilité et leur faible coût de déploiement (peu de travaux de câblage, peu d'émetteurs nécessaires). Depuis que la

technologie nécessaire pour établir des télécommunications radiofréquences (émission et réception) a été rendu portable, celles-ci se sont développées exponentiellement et aujourd'hui le monde compte plus de terminaux mobiles que d'habitants [4]. La prochaine étape du développement des télécommunications est l'IOT, dont l'idée de base est de rendre les objets du quotidien communicants et autonomes pour qu'ils nous libèrent de tâches ingrates et répétitives de récupérations de données. Les premiers objets à être connectés sont ceux qui sont connectés au réseau électrique, car ils n'ont pas d'exigence sévère d'économie d'énergie. Mais les nombreuses applications mobiles ont un déploiement limité, de par leur manque d'autonomie vis-à-vis de l'utilisateur, et surtout électrique, car le résultat est mitigé si nous devons les recharger régulièrement. Leur autonomie doit augmenter pour que le marché croisse. En 2016 plus de la moitié des mobiles seront des Smartphones avec accès à Internet. Ces Smartphones peuvent servir de passerelle vers l'Internet pour les objets connectés à proximité de l'utilisateur, via un standard adapté à la faible consommation, tel que le BLE.

#### 2.1.2. Avantages du BLE pour l'IOT

Le BLE, renommé Bluetooth Smart pour les consommateurs, est un standard de communication de type réseau personnel sans fil (WPAN). Il a été défini par le Bluetooth Special Interest Group (SIG)

en ayant en tête la réutilisation du hardware Bluetooth existant avec un protocole totalement différent, avec comme destinée l'IOT. Ces objets communicants du quotidien, existants ou à inventer, ont généralement besoin d'envoyer l'état d'un capteur ou de recevoir une commande (quelques octets) à intervalle régulier, comme par exemple dans le domaine médical, le sport, la sécurité ou la domotique.

L'objectif du BLE est simple : apporter à l'objet distant (capteur autonome) de quoi pouvoir transmettre et recevoir quelques octets à bonne distance (cent mètres en champ libre) avec une autonomie élevée (par rapport aux standards existants) de plusieurs mois à quelques années (en fonction de la périodicité de réveil) à partir d'une pile bouton, pour obtenir un prix très faible (quelques euros).

La solution retenue par le BLE pour réussir cela est de favoriser l'autonomie de l'objet recueillant les données par rapport au routeur qui le connecte à Internet ou à l'utilisateur. La solution technique est de désactiver complètement la radio quand on ne communique pas de données (pas d'écoute côté objet). Le routeur doit écouter le canal radio jusqu'à ce que l'objet se

réveille et lui envoie les données, après quoi le routeur peut en envoyer à son tour avant que la cible se rendorme.

Toute cette communication est optimisée :

- Pas de dialogue d'établissement de la communication, (dé-) connexion, etc.

- Pas d'envoi de données si le routeur ne répond pas

- Pas d'accusé de réception à un accusé de réception (lazy acknowledgement)

- Transaction complète limitée à 3ms (dont 1ms de calcul de trame)

Une autonomie de plusieurs années est possible de la manière suivante :

- Faible consommation hors communication (capteur, calcul trame, veille)

- Faible rapport cyclique d'utilisation de la radio (optimisation protocole)

- Faible consommation de la radio

La consommation des modules radio BLE existants est de 18mA [5] à 10mA [6] sous 3V en communication et de  $0.5\mu A$  à  $2\mu A$  en veille profonde (quelle que soit la tension). Concernant le rapport cyclique d'utilisation de la radio, la périodicité des transactions varie de quelques minutes pour un capteur de température jusqu'à 250ms pour un capteur de présence, pour un temps de transaction minimum de 3ms.

En optimisant la consommation de la radio, on peut gagner en autonomie, surtout sur les objets les plus réactifs. Le Tableau 1 démontre cela pour 3 périodicités différentes, avec une radio à l'état de l'art existant (15mW) et une autre 5 fois plus économe, une pile bouton d'énergie (EBATTERIE) égale à 200mWh et un temps de transaction (DACTIF) constant de 3ms. Les formules utilisées permettent de calculer le rapport cyclique d'utilisation de la radio (1) et l'autonomie (2). On constate qu'en diminuant la consommation de la radio par 5, on augmente l'autonomie de 1,5 à 4,8 fois selon le temps de veille programmé. En concevant une PLL très faible consommation (<1mW) grâce au FDSOI, cela permettrait de concevoir une radio pour le Bluetooth LE consommant moins de 3mW.

$$\alpha = \frac{D_{ACTIF}}{Periode} \tag{1}$$

$$Autonomie = \frac{E_{BATTERIE}}{P_{VEILLE} + \alpha \cdot P_{RADIO}}$$

(2)

Tableau 1 - Comparaison du gain de l'autonomie en fonction de l'intervalle de communication

| Périodicité | P <sub>MAX</sub> Radio | P <sub>MOY</sub> Radio | P <sub>MOY</sub> Veille | Autonomie | Gain  |

|-------------|------------------------|------------------------|-------------------------|-----------|-------|

| 60s         | 15mW                   | 750nW                  | 1μW                     | 13,0 ans  | -     |

| 60s         | 3mW                    | 150nW                  | 1μW                     | 19,9 ans  | x1,53 |

| 10s         | 15mW                   | 4,5μW                  | 1μW                     | 4,15 ans  | -     |

| 10s         | 3mW                    | 0,9μW                  | 1μW                     | 12 ans    | X2,9  |

| 1s    | 15mW | 45μW  | 1μW | 6 mois    | -     |

|-------|------|-------|-----|-----------|-------|

| 1s    | 3mW  | 9μW   | 1μW | 27,7 mois | x4,6  |

| 250ms | 15mW | 180μW | 1μW | 46 jours  | X0,01 |

| 250ms | 3mW  | 36μW  | 1μW | 225 jours | x4,8  |

#### 2.1.3. Transaction BLE type

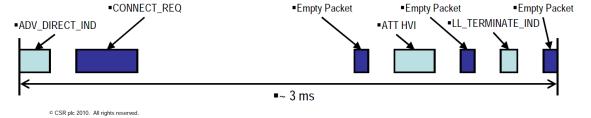

La Figure 2 illustre une transaction BLE type, donné par le manuel de fonctionnement de BLE et réalisé par la société CSR [7]. Cet exemple montre la simplicité de l'établissement de la communication et la rapidité de la transaction.

| Time<br>(us) | Master Tx                      | Radio Active<br>(us) | Slave Tx                                   |

|--------------|--------------------------------|----------------------|--------------------------------------------|

| 0            |                                | 176                  | ADV_DIRECT_IND                             |

| 326          | CONNECT_REQ                    | 352                  |                                            |

| 1928         | Empty Packet                   | 80                   |                                            |

| 2158         |                                | 144                  | Attribute Protocol Handle Value Indication |

| 2452         | Empty Packet (Acknowledgement) | 80                   |                                            |

| 2682         |                                | 96                   | LL_TERMINATE_IND                           |

| 2928         | Empty Packet (Acknowledgement) | 80                   |                                            |

Figure 2 - Détails temporels d'une transaction BLE

#### 2.1.3.1. Signalement

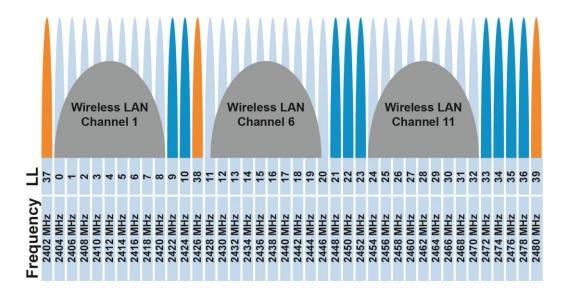

Le protocole BLE est simple: la passerelle (maître) écoute le réseau sur 3 fréquences de signalement (advertising) où l'objet distant (esclave) doit émettre pour signaler qu'il s'est réveillé. Ce sont les canaux 37 à 39 (2402, 2426 et 2480MHz) qui occupent ces fonctions, ils ont été choisis pour être en dehors des canaux WiFi les plus utilisés et ainsi diminuer les possibilités de collisions (cf. Figure 3). L'esclave peut transmettre 8 à 39 octets dans la trame de signalement, le maître peut ensuite répondre qu'il a reçu les données ou engager une connexion qui permettra d'envoyer des données à l'esclave.

Figure 3 - Répartition des canaux BLE de signalement (orange) et les canaux les plus utilisés du WiFi (1, 6, 11)

#### **2.1.3.2. Connexion**

Le maître capte le signalement de l'esclave et y répond avec une requête de connexion dans la foulée. Puis au bout d'un temps borné entre 1,25ms à 11,25ms, le maître envoie un paquet vide pour signaler qu'il est prêt à recevoir.

#### 2.1.3.3. Transmission des données

L'esclave ayant reçu la demande de connexion prépare les données à envoyer (mesures des capteurs, mise en forme et calcul de la trame) et envoie la trame dès qu'il reçoit le paquet vide signalant la disponibilité du maître.

#### 2.1.3.4. Fin de transmission

A la fin de chaque paquet, le maître acquitte l'avoir reçu avec un paquet vide. Si l'esclave ne le reçoit pas, il retransmettra le paquet en question, sinon il enverra le paquet suivant ou alors un paquet de fin de transmission.

#### 2.1.3.5. Récapitulatif

La transmission complète s'opère en trois millisecondes s'il n'y a pas de problème de transmission (BER élevé) impliquant une retransmission d'une trame. Cette rapidité de transmission permet d'économiser de l'énergie au niveau de l'esclave mais aussi de laisser du temps libre au maître pour communiquer avec d'autres esclaves.

#### 2.1.4. Spécifications du BLE

Les spécifications des standards Bluetooth Low Energy [7] et Bluetooth « standard » [8] ont été regroupées dans le Tableau 2 pour comparaison. Elles seront expliquées dans la section suivante.

Tableau 2 - Comparaison des spécifications du Bluetooth 'normal' et du Bluetooth Low Energy

| Modules Radio                | Bluetooth Low Energy                                     | Bluetooth « standard »                   |

|------------------------------|----------------------------------------------------------|------------------------------------------|

| Portée (en champ libre)      | 150m                                                     | 100m                                     |

| PIRE (Puissance d'émission)  | 10mW (10dBm)                                             | 100mW (20 dBm)                           |

| Consommation en standby      | 1μΑ                                                      | 1mA                                      |

| Consommation RF active       | <15mA                                                    | <30mA                                    |

| Consommation                 | 0,5 à 0,01 (a.u.)                                        | 1 (référence)                            |

| Autonomie sur pile           | 20-70M connexions (>1an)                                 | 7j (standby) ou 4h (voix)                |

| Mode de communication        | Advertising (écoute du maître)                           | Connexion (par l'esclave)                |

| Topologie                    | Etoile                                                   | Etoile                                   |

| N° d'esclaves pour un maître | Limité par le TDMA ~1000@4s                              | 7 + 255 en standby (parked)              |

| Latence (non connecté)       | 6ms                                                      | 100ms                                    |

| Durée de trame               | 3ms                                                      | 100ms                                    |

| Connexion                    | Périodique de 7,5ms à 32s                                | Continue                                 |

| Données utile trame          | 1 à 31 octets                                            | 0 à 343 octets                           |

| Voix possible                | Non                                                      | Oui                                      |

| Fréquence                    | 2402 à 2480 MHz                                          | 2400 à 2483,5 MHz                        |

| Canaux radio                 | 40 x 2MHz                                                | 79 x 1MHz                                |

| Modulation                   | 1Mbit/s GFSK                                             | 1-3Mbit/s GFSK                           |

| Indice de modulation         | 0,5                                                      | 0,35                                     |

| Débit utile de données       | 0,27Mbit/s                                               | 0,7-2,1Mbit/s                            |

| Robustesse                   | AFH <sup>1</sup> , 24-bit CRC, 32-bit MIC <sup>2</sup> , | Fast AFH, 24-bit CRC, FEC <sup>5</sup> , |

|                              | lazy and low power ACK                                   | fast ACK                                 |

| Sécurité                     | 128-bit AES <sup>4</sup> CCM <sup>5</sup>                | 56/128 AES CCM                           |

| Profils de communication     | Unique : GATT <sup>6</sup>                               | 35+ profils spécialisés                  |

<sup>&</sup>lt;sup>1</sup> AFH: Adaptative Frequency Hopping = Saut de fréquence adaptatif

#### 2.2. Communications sans fil

#### 2.2.1. Bases de fonctionnement d'un lien radio

#### 2.2.1.1. Bilan de liaison

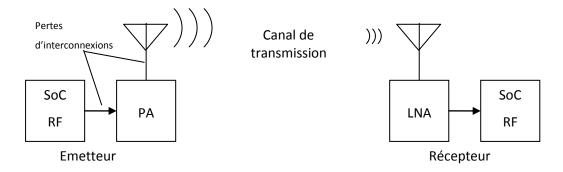

Les communications sans fil numériques permettent de transmettre des données entre un émetteur et un récepteur par le biais des ondes radioélectriques (ondes électromagnétiques à fréquence inférieure à 300GHz) par le biais d'antennes (monopole/dipôle, boucle, patch ou parabole). Pour permettre la communication, le bilan de liaison [9] (cf. Figure 4) doit être positif (de 3

<sup>&</sup>lt;sup>2</sup> MIC : Message Integrity Check = Vérification d'intégrité du message

<sup>&</sup>lt;sup>3</sup> AES: Advanced Encryption Standard

<sup>&</sup>lt;sup>4</sup> CCM: Counter with Cipher Block Chaining-Message Authentication Code

<sup>&</sup>lt;sup>5</sup> FEC : Forward Error Correction <sup>6</sup> GATT : Generic ATTribute Profile

à 10dB), c'est-à-dire que la somme de la puissance d'émission et des gains d'amplification (dB, dBm ou dBi) doit être supérieure à la somme des pertes et de la sensibilité du récepteur :

- + Puissance d'émission (dBm)

- + Gain d'amplificateur de puissance (dB)

- + Gain d'antenne d'émission (dBi)

- + Gain d'antenne de réception (dBi)

- Pertes du canal de transmission (dB)

- Pertes d'adaptation d'impédance des interconnexions (dB)

- Sensibilité du récepteur (dBm)

- = Bilan de liaison (dB)

Figure 4 - Lien radio et bilan de liaison

La puissance d'émission s'entend à la sortie du circuit (System on Chip - SoC) radiofréquence (RF). Le gain d'amplification est celui de l'amplificateur de puissance (Power Amplifier - PA). Le gain d'antenne dépend de sa directivité, une antenne parabolique est directionnelle et possède un gain d'antenne élevé par rapport à une antenne isotrope (uniforme dans toutes les directions) qui est le référentiel OdBi. Une antenne directionnelle permet d'économiser de l'énergie en n'émettant que dans la direction du récepteur mais n'est pas envisageable pour des objets mobiles à bas coût (pas d'antenne active), l'antenne doit donc être isotrope (ou s'en rapprocher) pour émettre et recevoir dans toutes les directions. Les pertes en espace libre (sans obstacle) dépendent de la fréquence du signal émis. Pour la bande utilisée par le BLE, ISM 2,4GHz, les pertes sont d'environ 80dB à 100 mètres et proportionnelles au carré de la distance. Chaque obstacle supplémentaire (arbre, vitre ou mur) ajoute des pertes et diminue la portée (respectivement 10, 2 et 20dB). Comme l'atténuation dans l'air des ondes électromagnétiques est proportionnelle au carré de la distance, la distance de communication maximum théorique est proportionnelle à la racine carrée du rapport entre la puissance de l'émetteur et la sensibilité du récepteur.

Les pertes d'adaptation apparaissent à chaque interconnexion de composants (puce, guide d'onde, antenne, etc.) côté émission ou réception et doivent être minimisées pour gagner en consommation pour la même portée. La sensibilité du récepteur dépend de nombreux critères comme la bande passante du signal reçu ou la puissance allouée à l'amplification. Communément, moins le signal contient d'informations, plus il est facile de les extraire, et souvent un module radio dépense plus d'énergie à la réception qu'à l'émission à cause de l'amplification du signal.

#### 2.2.1.2. Réglementation

La puissance émise par l'antenne est règlementée en termes de Puissance Isotrope Rayonnée Equivalente (PIRE – en Watts), c'est la puissance maximale d'émission définie dans la direction où la puissance émise est maximale. Chaque pays réglemente l'attribution des licences d'émission (voir Tableau 3) et la PIRE par bande de fréquence. Certaines bandes sont libres d'exploitation (pas de licence), comme par exemple la bande ISM à 2,45GHz (de 2400 à 2500 MHz) utilisée par le BLE. Sur cette bande la PIRE en France est limitée à 100 mW (20 dBm) pour la bande 2 400 à 2 483,5 MHz sauf en France métropolitaine et en extérieur de 2 454 à 2483,5 MHz où elle est limitée à 10 mW (10 dBm); cette dernière limitation n'est pas présente dans les DOM-TOM et le reste de l'Europe.

Bandes ISM PIRE Utilisateurs licenciés Bande Extérieur 6,765 - 6,795 MHz 30,0 kHz Services fixes et mobiles 13,553 - 13,567 MHz 14,0 kHz Services fixes et mobiles 26,957 - 27,283 MHz 10mW 326,0 kHz Bande radio civile 40,660 - 40,700 MHz 40,0 kHz 16,4mW Services fixes et mobiles 433,05 - 434,79 MHz 10mW (α Radio Amateur & radar 1,74 MHz ≤10%) 2,4 - 2,5 GHz 100 MHz 100mW 10mW (F > Radio Amateur, lien microondes & radar 2454 MHz) 5,725 - 5,875 GHz 150 MHz 25mW Radio Amateur, stations terrestres, lien microondes & radar 24 - 24,25 GHz 250 MHz 100mW Radio Amateur & radar 61 - 61,5 GHz 500 MHz 100mW lien microondes et radar 122 - 123 GHz 1 GHz 100mW Radio Amateur et lien microondes 244 - 246 GHz 2 GHz 100mW Radio Amateur, Radar & Radio Astronomique

Tableau 3 - Allocation des fréquences ISM en France

2.2.1.3. Fréquence porteuse et types de modulation

Pour envoyer un signal radio, une porteuse P(t) (fréquence centrale de la bande de fréquence allouée) est modulée pour y insérer les données à envoyer. Pour récupérer les données cette porteuse doit être démodulée par la méthode appropriée au type de modulation.

$$P(t) = A * \cos(B\omega t + \theta + C)$$

(3)

A, B et C représentent les trois types de modulation possible, à savoir, la modulation d'amplitude, de fréquence et de phase. Les données sont codées selon le standard : soit sur une

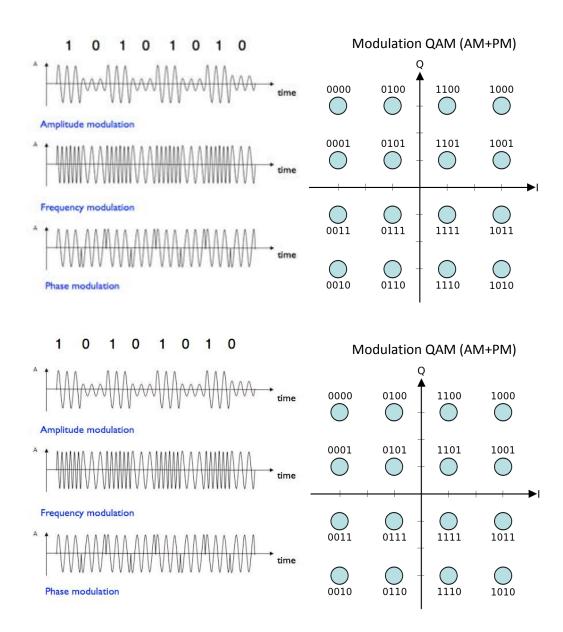

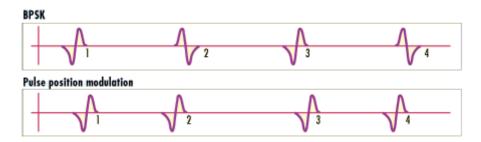

faible occupation spectrale (Figure 5), par modulation d'amplitude (AM), de fréquence (FM), de phase (PM) ou une combinaison amplitude/phase (QAM), soit ou sur une large occupation spectrale (Figure 6) en de courtes impulsions (IR-UWB), par modulation de phase ou de position.

Figure 5 - Types de modulation à bande étroite (AM, FM, PM et QAM)

Figure 6 - Modulation bande large par impulsion (IR-UWB)

Le débit de données maximum théorique est fixé par le nombre de bits codés par symbole (nombre de valeurs de fréquence, de phase et/ou d'amplitude discrétisées) et la fréquence de modulation de ces symboles. La bande passante occupée est proportionnelle à la fréquence de modulation mais aussi au facteur de modulation.

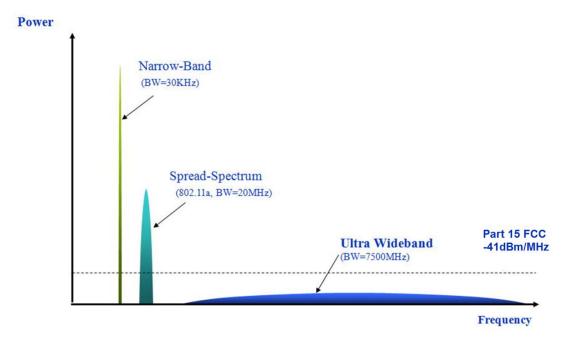

#### 2.2.1.4. Etalement spectral et sensibilité

En augmentant le facteur de modulation, on occupe un spectre plus important, illustré par la Figure 7, et on améliore donc la portée de détection par le récepteur. C'est le choix qui a été fait pour le BLE pour améliorer la portée sans changer ni la fréquence de modulation ni la puissance d'émission par rapport au Bluetooth. De plus pour simplifier les objets communicants et le protocole de communication, un seul débit est possible en BLE (1Mbps).

Figure 7 - Occupation spectrale de différents standards

#### 2.2.1.5. Bruit, SNR et BER

Chaque composant depuis la modulation des données dans l'émetteur jusqu'à la démodulation des données dans le récepteur ajoute son bruit propre (thermique, flicker, intermodulations, distorsions) au signal et fait baisser le rapport signal à bruit (SNR). D'autres bruits peuvent s'ajouter au signal dans le canal de propagation, ceux-ci proviennent de réflexions du signal ou d'interférences avec des signaux perturbateurs (blockers) à proximité fréquentielle. Ainsi, même si le signal reçu a une puissance suffisante, si le SNR est trop faible le décodage des données est impossible. Les diverses corrections d'erreurs (CRC, redondance de données, multi-antennes)

permettent d'en corriger une partie. Au final c'est le taux d'erreur binaire (BER) qui exprime la qualité d'une transmission numérique.

La sensibilité du récepteur est proportionnelle au débit binaire, associé à un certain type et vitesse de modulation. Les spécifications de sensibilité sont donc données pour un certain BER (0.1% en Bluetooth) à un certain débit binaire. Quand la réception est mauvaise (SNR faible), les erreurs de décodage entrainent une chute du débit binaire, car les paquets doivent être réémis jusqu'à bonne réception (acknowledge). Avec certains standards comme le WiFi, il est possible de diminuer le débit pour garder un bon BER. Le BLE n'étant pas prévu pour une application haut débit mais vise une économie d'énergie, il n'y a pas de changement de modulation possible, ni de réémission en cas de non réception (en mode non connecté).

#### 2.2.2. Composants d'un module radio

Les composants constitutifs d'un module de communication radiofréquence dépendent de l'architecture et de la modulation utilisée. Il sera présenté ici les composants typiques d'un module Bluetooth avec un émetteur à modulation directe et à démodulation hétérodyne.

#### 2.2.2.1. Emetteur à modulation directe

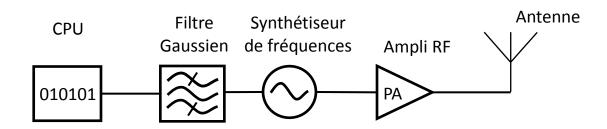

Figure 8 - Schéma synthétique d'un émetteur à modulation directe

La modulation directe (cf. Figure 8) signifie que le signal en bande de base module directement la fréquence d'un oscillateur commandé dont la fréquence est centrée sur celle du canal. Selon les spécifications du Bluetooth, le signal en bande de base (données numériques à émettre) doit passer par un filtre gaussien avant de moduler les sauts de fréquence pour la vitesse de transition et donc l'occupation spectrale du signal RF généré. La synthèse de fréquence transpose le signal de modulation autour de la fréquence du canal, puis l'amplificateur de puissance amplifie le signal RF modulé pour qu'il soit émis par l'antenne.

#### 2.2.2.2. Récepteur à démodulation hétérodyne

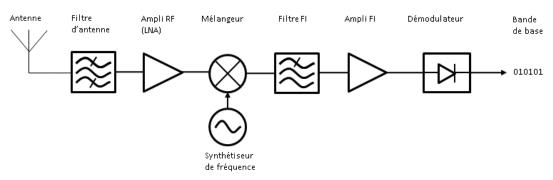

Figure 9 - Schéma synthétique d'un récepteur hétérodyne

Un récepteur hétérodyne (cf. Figure 9) utilise un mélangeur pour transposer le signal RF vers une fréquence plus basse, celle-ci pouvant être nulle (Zéro-IF). Il convient alors d'éliminer la fréquence image d'un récepteur hétérodyne. En multipliant le signal de l'antenne avec un signal à fréquence fixe, des intermodulations sont produites. Le filtre FI ne garde que le signal à la fréquence intermédiaire (F<sub>ANTENNE</sub> — F<sub>SYNTHESE</sub>) et après amplification le démodulateur extrait les données numériques. Il existe de nombreux types de démodulateur (démodulation I/Q, discriminateur à délai, détecteur de quadrature, etc.), mais ce n'est pas l'objet de ces travaux. Finalement, les données sont traitées par un processeur numérique.

#### 2.2.2.3. Réutilisation de blocs

La synthèse de fréquences et l'antenne sont communes à l'émission et à la réception, et ne peuvent donc être utilisées simultanément. L'antenne est seulement commutée d'une voie vers l'autre. La synthèse doit pouvoir être modulée directement (méthode économe en énergie).

#### 2.2.3. Influence des blocs sur les performances

Le LNA (low noise amplifier) effectue la première étape d'amplification du signal reçu par l'antenne. Son bruit doit être extrêmement bas car il est ensuite amplifié par toute la chaine de réception.

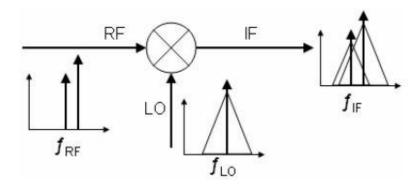

Le mélangeur transpose le signal reçu à la fréquence radio vers une fréquence plus basse en le mélangeant (multiplication) au signal fourni par le synthétiseur de fréquences, il doit être le plus linéaire possible sous peine de diminuer le rapport signal à bruit en générant des intermodulations non désirées.

Le synthétiseur de fréquences fabrique la fréquence nécessaire à la transposition, à partir d'un oscillateur de référence (généralement à quartz). Il doit avoir un faible bruit de phase sinon une

partie des signaux adjacents au signal RF recherché se retrouvera dans la bande de fréquence du signal utile après transposition. L'importance de la synthèse de fréquence est détaillée dans la section suivante car c'est le composant que nous avons choisi de concevoir et optimiser en technologie FDSOI.

Le filtre de fréquence intermédiaire (FI) et l'amplificateur associé élève la valeur du signal pour que le démodulateur puisse différencier les bits de données. L'amplificateur ou le démodulateur s'adapte à la puissance de réception (dynamique du signal) pour éviter la saturation et réussir à décoder le signal.

Les filtres RF et FI ajoutent un peu de bruit mais ont surtout une précision assez faible s'ils sont intégrés, et peuvent donc avoir une bande passante autre que celle conçue.

#### 2.3. Synthèse de fréquences pour le BLE

Comme vu précédemment, la synthèse de fréquences est un bloc constitutif du module radio nécessaire pour transposer le signal vers (et depuis) le canal de communication radiofréquence. A partir d'un signal de référence à fréquence fixe, la synthèse doit générer une fréquence réglable pour adresser tous les canaux de communications du standard visé, en respectant les spécifications de ce dernier. De plus, en émission, la synthèse peut avoir à générer un signal modulé si l'architecture de modulation choisie est la modulation directe.

#### 2.3.1. Caractéristiques d'une synthèse

Les performances que doit respecter une synthèse de fréquences utilisée dans un module de communication radiofréquence sont décrites ci-dessous, et sous chaque section sont expliqués les objectifs qui ont été fixés.

#### 2.3.1.1. Consommation

La consommation du générateur de fréquences est un des paramètres les plus importants pour l'autonomie du système. Pour augmenter cette autonomie, on peut, quand le lien radiofréquence le permet, diminuer la puissance d'émission. Mais on peut aussi, au prix d'une complexité non négligeable, diminuer la consommation des autres composants. La consommation de la synthèse de fréquences de l'émetteur/récepteur n'est pas une donnée spécifiée par le standard, mais la consommation totale en émission/réception est conseillée à moins de 15mW. Néanmoins, pour parvenir à une bonne autonomie de l'objet communicant, il faudrait que la consommation soit autour de 3 milliwatts. Le synthétiseur de fréquences consomme habituellement jusqu'à 30% du

total du module radio [10, p., 5], et donc l'objectif de consommation fixé pour ce travail de thèse est de l'ordre du milliwatt.

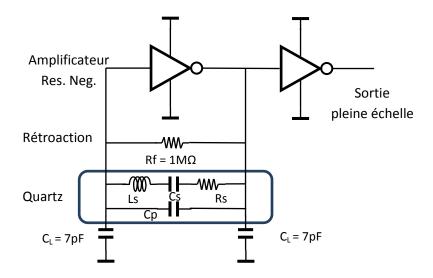

#### 2.3.1.2. Surface occupée

La surface occupée par la synthèse, mais surtout celle de la radio est décisive, car elle impacte directement le coût de la solution. C'est pour cela qu'il a été choisi de se concentrer sur une architecture très faible surface, tel qu'un oscillateur en anneau. Ce type d'oscillateur est connu pour avoir un très mauvais comportement en termes de bruit de phase (jitter) mais être très agressif vis-àvis de la surface de silicium et de la consommation. L'objectif est alors d'intégrer un VCO, basé sur un oscillateur en anneau, dans une PLL afin de diminuer ce bruit de phase par un asservissement (calibration) du système en utilisant les grilles arrières des transistors MOS FDSOI de chaque inverseur.

#### 2.3.1.3. Gamme de fréquences

La synthèse doit respecter la gamme de fréquences fixée par le standard, en tenant compte des variations technologiques de plus en plus importantes avec l'évolution de la microélectronique (loi de Moore). Pour respecter, ce point les oscillateurs en anneau utilisent couramment une calibration au démarrage. Pour le BLE, la gamme de fréquence est de 2400 à 2480 MHz.

#### 2.3.1.4. Dynamique de Fréquence

La dynamique de fréquence est l'écart maximum entre deux fréquences à synthétiser, pour le BLE c'est 78MHz. Après une calibration initiale de la fréquence centrale de l'oscillateur, l'oscillateur doit avoir une dynamique de fréquence suffisante, ce qui est rarement un problème pour les oscillateurs en anneau.

#### 2.3.1.5. Pas de synthèse

Le pas de synthèse est l'écart minimal adressable par la synthèse entre deux canaux de fréquences du standard choisi, 2MHz dans le cas du BLE. Il est fixe et déterminé par l'architecture, à cause du type de diviseur (entier ou fractionnaire), du pas du diviseur et de la fréquence de référence.

#### 2.3.1.6. Temps de démarrage et de commutation de canal

Le temps de démarrage est celui que la synthèse met pour atteindre la fréquence cible à partir de l'alimentation du circuit. Ce paramètre va impacter la consommation moyenne, car plus le

démarrage est lent, plus la consommation moyenne sera élevée. La vitesse de démarrage dépend du facteur de qualité de l'oscillateur, qui influence le temps de stabilisation de la fréquence et le temps d'accrochage de la PLL. Ce dernier dépend de la bande passante et de la marge de phase du système bouclé. Dans le cas d'un oscillateur en anneau, le démarrage est très rapide (moins de 100 périodes) car le facteur de qualité est faible.

Le temps de commutation de canal est celui que met la synthèse à passer d'une fréquence cible à une autre. Ce paramètre dépend principalement de la bande passante et de la marge de phase du système de synthèse. Une bande passante trop faible limite la vitesse de synchronisation, et une marge de phase non optimale (z=1/V2; MP=67°) ralentit la stabilisation. Le standard Bluetooth définit un délai maximum de 150 microsecondes pour changer de canal. L'oscillateur en anneau et la PLL à bande passante élevée permettent d'effectuer la commutation de canal très rapidement.

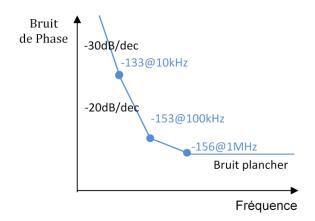

#### 2.3.1.7. Bruit de phase et Spurious

Le bruit de phase est la performance en termes de modulation de la phase d'un dispositif électronique dont la sortie est périodique. Il exprime la densité spectrale de puissance qui n'est pas à la fréquence de la porteuse. Le bruit de phase est défini par convention par la puissance par bande de un Hertz, par rapport à la puissance de la porteuse, à un certain éloignement de celle-ci. Son unité est le dBc/Hz (ou dBrad²/Hz) à (x) Hertz de la porteuse. Ex : -90dBc/Hz@1MHz.

#### 2.3.1.8. **Pushing**

Le pushing est une spécification de l'oscillateur faisant partie de la synthèse en boucle ouverte. Il représente la variation de la fréquence de sortie de l'oscillateur en fonction de la variation de la tension d'alimentation. Il donne une idée de la réjection ou sensibilité de l'oscillateur à une alimentation qui n'est pas stable ou propre. Cela permet d'estimer le bruit créé en sortie en fonction du bruit sur la tension d'alimentation et donc de définir les spécifications de bruit de l'alimentation.

#### 2.3.1.9. Pulling

Le pulling est aussi une spécification de l'oscillateur en boucle ouverte et représente la variation de la fréquence de sortie en fonction de la charge vue à sa sortie. Si la charge varie dans le temps, cela produira du bruit de phase supplémentaire que l'asservissement essaiera de supprimer. Ce phénomène peut se produire si la charge en sortie est un multiplexeur (état ouvert / passant) à une fréquence différente ou un modulateur donc la tension analogique moyenne fait évoluer les capacités parasites des transistors.

#### 2.3.2. Transposition en fréquence non idéale

Figure 10 - Transposition en Fréquence avec du Bruit

La fréquence générée par la synthèse va permettre de transposer un des canaux de communication en bande de base pour décodage. Si la fréquence générée est bruitée, les signaux adjacents au canal, potentiellement plus puissants, seront aussi transposés en basse fréquence (cf. Figure 10), diminuant le SNR du signal reçu.

#### 2.3.3. Résumé des spécifications pour la synthèse

Le Tableau 4 rappelle les spécifications que doit attendre la PLL que nous désirons concevoir dans ce travail de thèse.

| Spécification      | Valeur      | Unité           |

|--------------------|-------------|-----------------|

| Consommation       | ~1          | mW              |

| Surface            | <0,01       | mm <sup>2</sup> |

| Gamme de fréquence | 2402 à 2480 | MHz             |

| Dynamique          | 78          | MHz             |

| Pas de synthèse    | 2           | MHz             |

| Démarrage          | <1          | ms              |

| Délai de saut      | <150        | μs              |

| Bruit de phase     | <-90        | dBc@1MHz        |

| Spurious           | <-70        | dBc@1MHz        |

Tableau 4 - Résumé des spécifications de la synthèse de fréquence à concevoir

#### 2.4. Conclusion : L'apport du BLE

Le Bluetooth Low Energy est un standard de communication réellement adapté aux communications à faible consommation. Il permet la mise en œuvre de plusieurs solutions simplificatrices pour la conception et le fonctionnement du module radio, permettant d'augmenter grandement la longévité des objets connectés sur batterie. La synthèse de fréquences étant un bloc important et consommateur d'énergie au sein d'un module radio, nous nous fixons comme objectif

des spécifications drastiques de consommation et de bruit de phase pour améliorer l'autonomie des objets de demain en utilisant le BLE.

## 3.La technologie CMOS FDSOI

#### 3.1. Les enjeux de l'évolution microélectronique

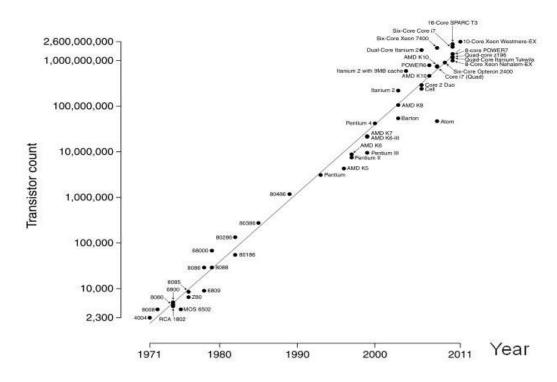

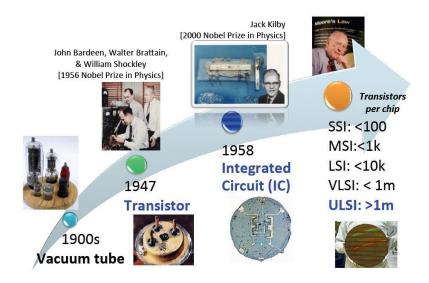

Chaque année, de nouvelles technologies microélectroniques sont disponibles, apportant des innovations et des améliorations à notre vie. Tout cela est possible grâce à des circuits aux performances de plus en plus élevées et des fonctions de plus en plus complexes. Cette augmentation de performances, continue depuis plus de 40 ans, a été rendu possible par la miniaturisation des composants élémentaires, les transistors. La prédiction de Gordon Moore [11], connu comme la loi de Moore (la densité des transistors sur une puce double tous les 18 mois, voir Figure 11), a été prouvée comme étant étrangement précise, en partie parce-que cette loi a été la clé de voûte de la planification à long terme de la recherche et développement des industries de semiconducteurs.

Figure 11 - La loi de Moore et le nombre de transistors dans les microprocesseurs

Les technologies actuelles permettent de concevoir des puces ayant des transistors aux dimensions atomiques. Dans le futur, les transistors seront tellement petits que la physique quantique sera prépondérante pour déterminer leurs propriétés. Pour AMD la fin de la loi de Moore est à

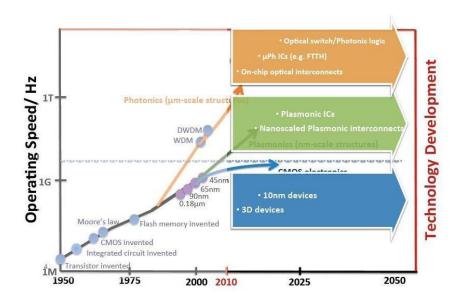

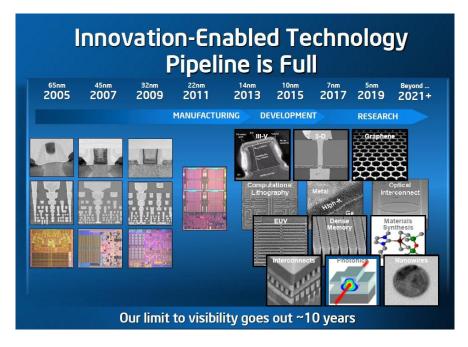

l'horizon [12]. Les physiciens tel que M. Kaku ont aussi prédit la fin de la loi de Moore [13]. Qu'est-ce qu'il y aura après le silicium et la technologie CMOS ? Il y a beaucoup de propositions : nanotubes de carbone, graphène, optique, dispositifs moléculaires, etc. (voir Figure 12 [4] et Figure 13 [14]).

Figure 12 - Tendances des technologies électroniques [4]

Figure 13 - Point de vue d'Intel sur les innovations technologique en électronique [14]

Un des points important est la manufacturabilité, qui peut être résumé par la capacité à fabriquer des circuits intégrés rentables. Jusqu'à maintenant, les solutions industrielles mettent en avant la technologie CMOS à base de silicium. Pour passer outre le problème de technologies agressives comme le nœud 28 nm et en deçà, deux nouvelles solutions sont apparues : les transistors FinFet et les transistors UTBB-FDSOI.

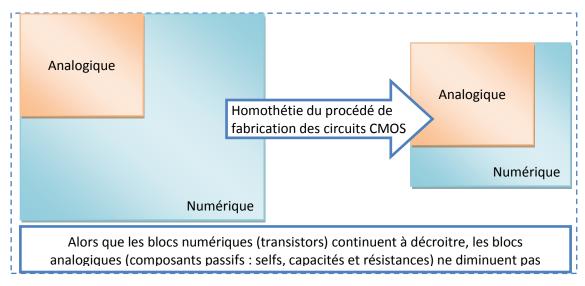

De plus, alors que les blocs numériques subissent directement la loi de Moore par une diminution de leur surface, les blocs analogiques, en raison notamment des composants passifs, ne suivent pas cette loi (voir Figure 14 [15]). Les blocs numériques, n'ayant comme spécification que le temps de propagation et la consommation maximum, peuvent être conçus de taille minimale contrairement aux blocs analogiques qui eux doivent respecter une panoplie de spécifications. Ces spécifications dépendent de l'erreur relative entre composants dont les dimensions, à cause des variations des procédés de fabrication, doivent rester grandes par rapport au minimum technologique. Cela se traduit, au fil des nœuds technologiques, par une diminution proportionnelle des blocs numériques et une diminution beaucoup moins rapide des blocs analogiques et RF.

Le seul moyen permettant de diminuer la taille totale d'un circuit mixte (analogique, RF et mixte) est soit de passer des fonctions analogiques dans le domaine numérique soit d'améliorer la technologie (variabilité, capacités parasites, courant de fuite, variations en fonction de la température, etc.) pour que les blocs analogiques réduits gardent leurs performances.

Figure 14 - Le problème de diminution de taille de l'analogique

# 3.2. Evolution de la technologie microélectronique

#### 3.2.1. La fin de la loi de Moore?

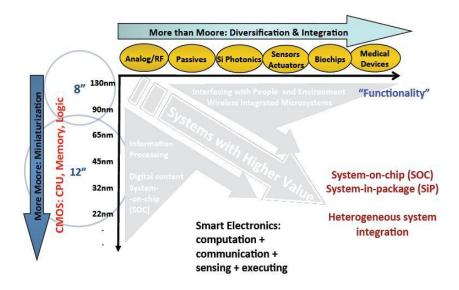

L'histoire de la microélectronique peut être résumée par la Figure 15. En effet, la microélectronique est présente dans tous les aspects de notre vie de tous les jours et les circuits intégrés permettent de réaliser de plus en plus de fonctions complexes. Depuis quelques années, deux domaines existent : « More Moore » et « More than Moore », comme expliqués en Figure 16.

Figure 15 - L'histoire de la microélectronique

Figure 16 - More Moore Vs More than Moore

Le domaine du « More Moore » est défini internationalement comme la tentative de développer des technologies CMOS avancées afin de réduire les coûts associés par fonction, tout en augmentant les performances des circuits. Presque 70% du total du marché total des composants semiconducteurs est impacté par la miniaturisation du CMOS avancé dans le domaine « More Moore ». Ces 70% comprennent trois groupes de composants de taille similaire : les microprocesseurs, les mémoires de masse et la logique numérique.

"More than Moore" est basé sur, ou dérivé de, la technologie silicium, mais pas nécessairement dans le sens de la loi de Moore. Cela se réfère à un ensemble de technologies qui permettent des fonctions micro-nano-électroniques non-numériques, comme :

- Radiofréquences

- Haute tension et puissance

- Eclairage et imagerie à base de composants à l'état solide

- Ultrason médical, circuits bioconnectés, laboratoire sur puce et microfluidique

- Récupération d'énergie

- Capteur et actionneurs sur plateforme CMOS

Les composants "More than Moore" fournissent la conversion des informations nonnumériques ou non-électroniques, comme mécanique, thermique, acoustique, chimique, optique et biomédical, en données numériques et vice-versa.

Dans le futur, les transistors seront si petits que la physique quantique prendra le pas sur la physique classique et les électrons commenceront à fuir en dehors des fils par exemple. La fin de la loi de Moore est à l'horizon, due aux inconvénients des transistors MOS Bulk sur les nœuds agressifs (14nm et en dessous).

#### 3.2.2. Limitations des transistors MOS Bulk dus aux nœuds agressifs

Qu'est que qu'un bon transistor pour les applications numériques ? C'est un interrupteur idéal, à savoir :

- Pas de fuite quand il est ouvert

- Pas de pertes ohmiques quand il est fermé

- Capable de commuter à faible V<sub>TH</sub> et donc faible Vdd (faible consommation)

Pour pouvoir suivre la loi de Moore, les tailles des transistors silicium sur substrat doivent diminuer, ce qui induit certains inconvénients. Le premier concerne l'oxyde de grille. Pour pouvoir garder constant le champ électrique entre drain et source, la tension d'alimentation doit diminuer proportionnellement à la taille du transistor. Une des conséquences de cette diminution est le besoin de diminuer l'épaisseur d'oxyde pour diminuer la tension de seuil du transistor, de 300nm sur les générations MOS précédentes, jusqu'à 1,2nm aujourd'hui. Et comme ce n'est pas un isolant parfait, il fuit et peut éventuellement claquer si le champ électrique est trop grand. Avec l'arrivée du nœud 90nm, les technologues ont introduit l'isolant « High-K » (Oxyde d'Hafnium, HfO<sub>2</sub>) où k est la constante diélectrique, qui correspond à la capacité à isoler.

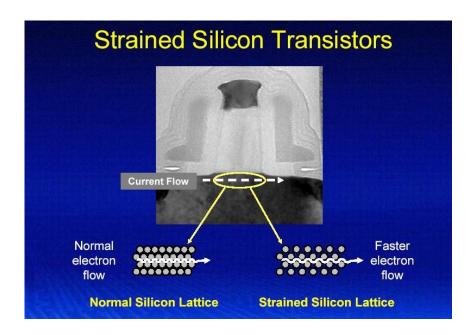

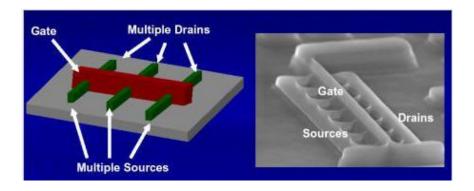

Les technologies diminuant, le courant y est limité. Le courant I<sub>DS</sub> dépend de la taille du canal d'inversion. Plus le canal est court, moins les porteurs ont le temps d'accélérer sous l'effet du champ électrique (saturation de la vitesse). Le silicium contraint, imagé sur la Figure 17 [16], est une des solutions que les ingénieurs ont inventée pour augmenter la mobilité des porteurs.

Figure 17 - Silicium contraint introduit par Intel [16]

La mise en conduction apparait sous l'effet qu'un champ électrique suffisamment élevé, créé par la tension de grille, et qui va générer une couche d'inversion : le canal de conduction. La diminution et le contrôle du seuil est important pour les circuits à basse consommation (faible tension d'alimentation). L'introduction d'une grille métallique associée à un diélectrique High-K, appelée « High-K MG », favorise cette mise en conduction.

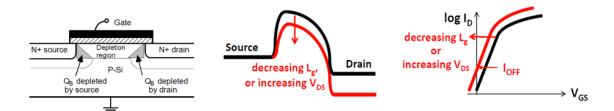

La réduction de la taille des transistors induit des effets de canal court (SCE – Short Channel Effect) et de diminution du seuil induite par le drain (DIBL - Drain Induced Barrier Lowering), le transistor fuira d'autant plus (voir Figure 18).

Figure 18 - SCE et DIBL

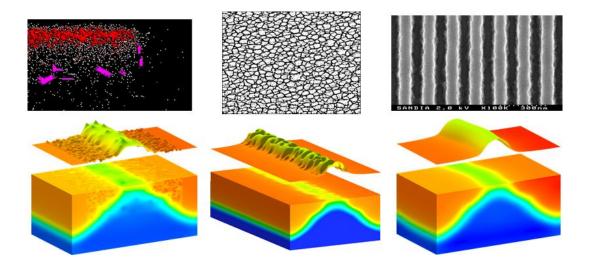

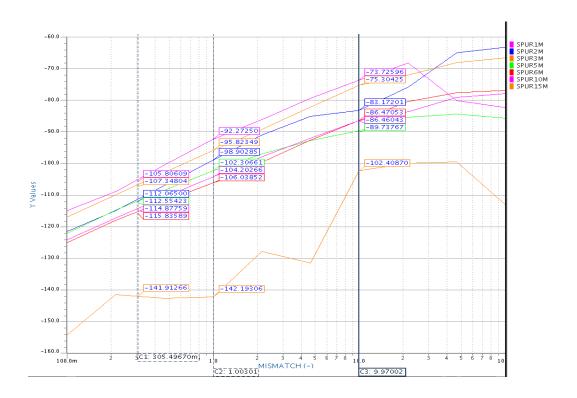

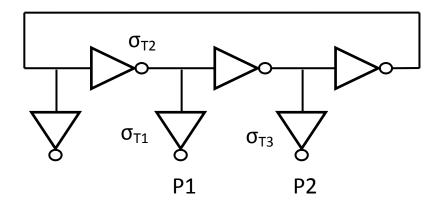

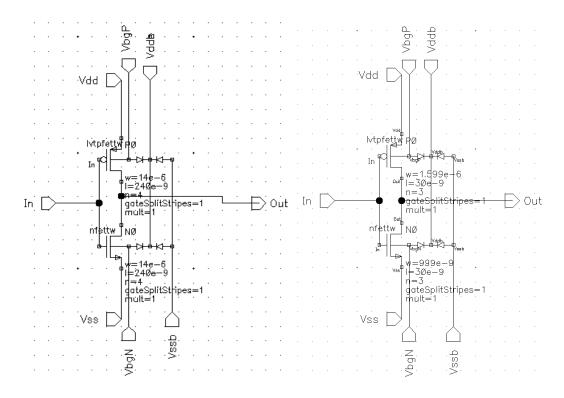

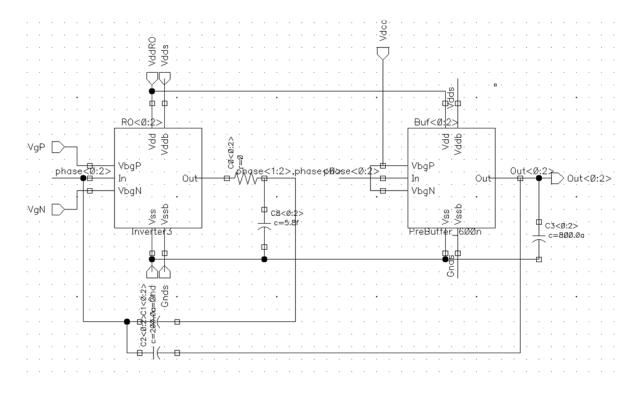

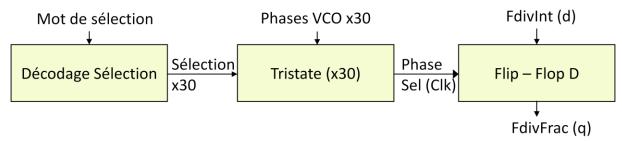

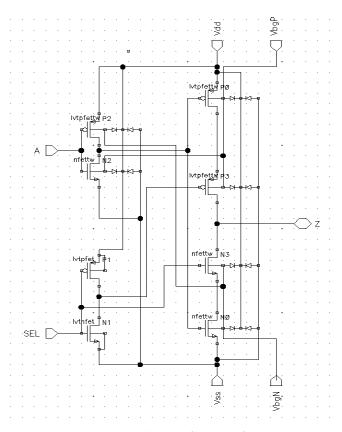

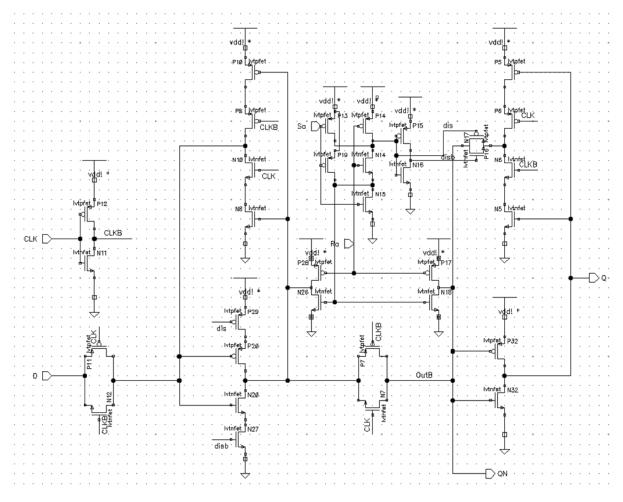

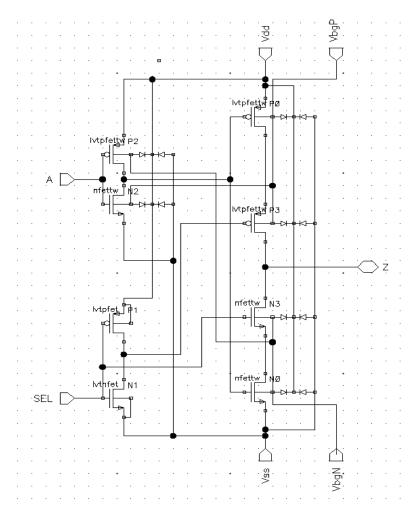

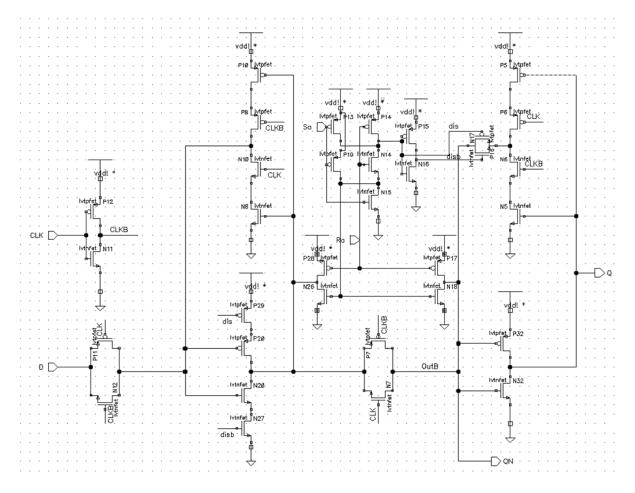

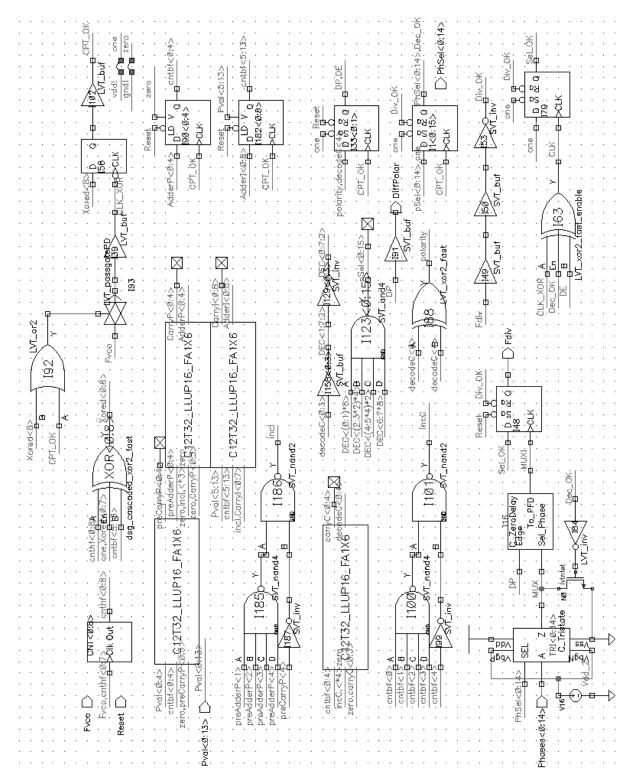

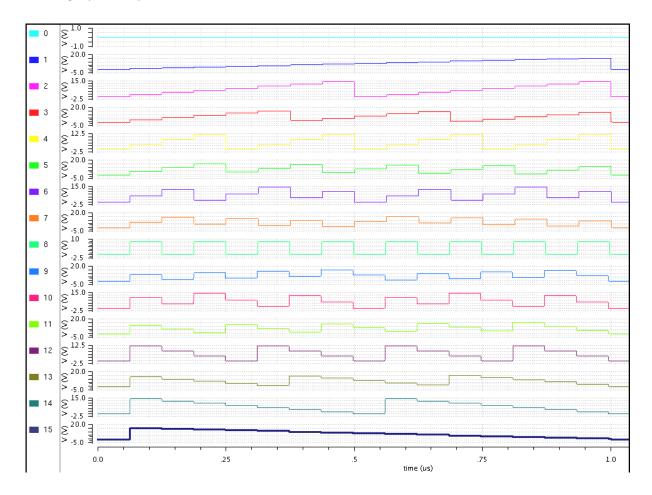

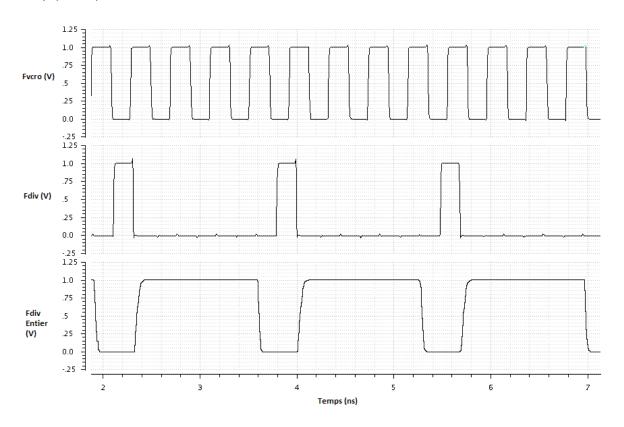

Le dernier problème, et non le moindre, concerne la variabilité. Au fur et à mesure que les transistors sont réduits vers la dizaine de nanomètres, la variation de la tension de seuil devient un problème préoccupant. Comme montré sur la Figure 19 [17], cela est du aux fluctuations aléatoires des dopants (RDF - Random Dopant Fluctuations) dans la région du canal ainsi qu'à la rugosité des interfaces (LER - Line Edge Roughness), et dans une moindre mesure, par la variation de l'épaisseur d'oxyde.