# Development and characterization of plasma etching processes for the dimensional control and LWR issues during High-k Metal gate stack patterning for 14FDSOI technologies

Onintza Ros Bengoetxea

### ▶ To cite this version:

Onintza Ros Bengoetxea. Development and characterization of plasma etching processes for the dimensional control and LWR issues during High-k Metal gate stack patterning for 14FDSOI technologies. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2016. English. NNT: 2016GREAT009 . tel-01285187

# HAL Id: tel-01285187 https://theses.hal.science/tel-01285187

Submitted on 8 Mar 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano-Électronique et Nano-Technologies

Arrêté ministériel : 7 août 2006

Présentée par

### Onintza ROS BENGOETXEA

Thèse dirigée par **Erwine PARGON** et codirigée par **Pascal GOURAUD**

préparée au sein du Laboratoire LTM (CNRS/UJF-Grenoble1/CEA) et la société STMicroelectronics dans l'École Doctorale EEATS

# Development and characterization of plasma etching processes for the dimensional control and LWR issues during High-k Metal gate stack patterning for 14FDSOI technologies

Développement et caractérisation des procédés de gravure plasma impliqués dans la réalisation de grille métallique de transistor pour les technologies FDSOI 14nm : contrôle dimensionnel et rugosité de bord

Thèse soutenue publiquement le « 29 Janvier 2016 », devant le jury composé de :

### M. Christophe VALLÉE

Professeur, LTM Grenoble (CNRS), Président

### M. Rémi DUSSART

Professeur, GREMI Orléans (CNRS), Rapporteur

### M. Christophe CARDINAUD

Directeur de Recherche, IMN Nantes (CNRS), Rapporteur

### **Mme. Sophie BOUCHOULE**

Chargée de Recherche, LPN Marcoussis (CNRS), Examinateur

### Mme Erwine PARGON

Chargée de Recherche, LTM Grenoble (CNRS), Directeur de Thèse

### M. Pascal GOURAUD

Ingénieur Gravure, STMicroelectronics, Co-encadrant

### M. Sébastien BARNOLA

Responsable de Laboratoire, LETI Grenoble (CEA), Invité

### Remerciements

Ce travail de thèse a été réalisé dans le cadre d'une convention CIFRE tri-partite entre la société STMicroelectronics, le Laboratoire des Technologies de la Microélectronique (CNRS-LTM) et le Laboratoire d'Electronique et de Technologies de l'Information (CEA-LETI).

Je tiens donc à remercier Isabelle Thomas pour m'avoir accueilli dans l'équipe R&D Gravure à ST Crolles, ainsi qu'Olivier Joubert pour m'avoir convaincu de faire une thèse et m'avoir ouvert les portes de son laboratoire. Egalement je dois remercier Sébastian Barnola, responsable de l'équipe de gravure au sein du LETI pour sa collaboration et pour m'avoir donné accès aux outils de son laboratoire.

Je souhaite également remercier l'ensemble des membres du jury qui m'ont fait l'honneur de juger mon travail : Christophe Vallée qui a présidé le jury, Rémi Dussart et Christophe Cardinaud qui ont accepté d'être rapporteurs et qui ont porté un grand intérêt au manuscrit, et enfin Sophie Bouchoule qui a accepté d'assister à ma présentation et d'examiner mon travail.

J'aimerais également remercier ma directrice de thèse, Erwine Pargon, pour avoir suivi mon travail et pour sa disponibilité surtout dans la période de rédaction qui est sans doute le moment le plus difficile de la thèse. T'inquiètes, je vais écrire mes publies... ©

Puis, bien sûr, je veux remercier mon co-encadrant chez ST, Pascal Gouraud, qui m'a beaucoup aidé au cours de ces trois ans. Merci pour m'avoir appris les enjeux de la microélectronique et la gravure, un domaine complètement inconnu pour moi il y a trois ans... ainsi que les subtilités de la culture et de la langue Française! Même après trois ans j'arrive encore à faire des petites fautes! On dira que c'est « le charme » de l'accent Espagnol! J'espère que ces échanges continueront encore longtemps et que les mots écrits sur mes cartes postales ne disparaîtront pas complétement!

Je continue par l'équipe de gravure R&D qui m'a si bien accueilli durant ces trois ans ! François (Le coach !), JP (Celui qui ne fume « jamais »), Phillipe (maintenant, le mot « Plancha » aura une tout autre signification pour toi...), Fanny, Enrique, Laurent (blagueur d'élite), Marc (Je suis curieuse de savoir ce que ça aurait donné un DRI avec toi....), Sébastien, Claire, Cecile, Delia (Team-Building Leader!), Pierre, Emeline, Linda (C'est l'heure du thé!), Latifa (Le soleil marocain!), Olivier (Eh Toto y a t'il ta tata ? Y est pas y est pas !), mais également les ASRD, Fred, Frank, Nolwenn, Jean-Seb et Sabrina parce que ce sont nos chevaliers de l'ombre, et sans eux cela serait impossible de faire avancer toutes nos manipes ! Puis également, je dois dire un mot pour Steddy, les TPP et l'équipe de maintenance gravure car ils ont toujours été patient quand je faisais planter leur machines...  $\odot$

Mais bien sûr une thèse ne se fait pas toute seule, alors je veux remercier toutes les personnes qui ont travaillé avec moi et qui m'ont aidé à bien mener cette thèse. Je commence par l'équipe de métro/litho (Bertrand, Julien, Laurène, Jean-Damien, Maxime, Jonathan, Bastien, Alain....) qui sont toujours été motivés et m'ont aidé à réussir mes procédés de litho de plus en plus compliqués! Une thésarde a toujours beaucoup d'imagination! L'équipe de PI (Benjamin, Claire, Jean Christophe...) qui m'ont aidé à faire avancer mes projets, à Vincent, qui a toujours été disponible pour m'aider avec le wet, à l'équipe de dépôt (Pierre, Florien, Maxime, Carlos...) qui m'ont tout appris sur la RF-PVD, l'équipe carac (Laurent, Véronique, Christophe, Germain, David, Florent, Alexandre....) qui m'ont accompagné dans mes longues après-midis devant le SEM et ils m'ont appris à utiliser Siltrac (à 5 on y arrive!)

Je n'oublie pas bien sûr le LTM, qui m'ont également très bien accueilli! Je commence par Marc Fouchier, qui a beaucoup contribué à ma thèse et m'a tout appris sur l'AFM et la métro rugo, Laurent, Camille, Maxime, Eddy (Merci pour ta patience au TEM et pour ta compagnie à ev3!) Seb, Mika, Gilles (Les longues conversations aux sujets atypiques au carré vont me manquer...) Emilie (Toujours Fun, Toujours Cool!), Bernard, Michel, Malou et Sylvaine (On ne trouvera jamais plus efficaces!), Dave, Martin, Jumana, Karim et son gang, Cecile...

Et finalement, est arrivé le tour aux CDD, j'y inclus les post-docs, thésards, alternants, DRIs, stagiaires, passagères, amis... tous ces gens avec qui j'ai partagé autant de moments et qui ont rendu ces trois années uniques! Merci à la « Pinky Promise » pour tous ces paries absurdes, à Bastien, organisateur official de toute activité/voyage... Next stop, Mexique! Carrément oui! à Carlos, (Bilan : No se yo si has gravado muchas placas...), à Mokrane (pour tout ce qu'on a partagé!), à Romu (Pulse!), à Paulin et Manon pour ce road-trip aux US!, Manu (Je sais que c'était toi qui faisait du pie...), à Phil (Azkenean hainbeste espero zenuen esaldia! Hau guztiz ulertzen duzunerako, zihurrenik oso urrun egongo naiz jada! Faltan botako ditut zure tuntuntxantxak!) Odile (La maman de l'équipe!), Jérôme (No Limit! L'homme qui pensait que 500wb n'était pas assez...) Paul, Dana, Romain, Melisa, Florentin, Vahagn, Maxime, Alexandru, Laurent (My Gossip Girl!), Sophie, Reynald, Jeremy, Alexandra, Imane (djobi, djoba!), Nouredine, Remi (Désolé pour le bruit de fond pendant ton stage!), Marion, Antoine, Aurélien S, Maxime GB, Aurélien T. (RDV aux US) Mathieu F, Juh (choisi ton concert!) Jonani, Boris, Darayus, Giulio 2, Giulio & Zini (Laurea Sbagliata!), Rob, Lucia (Encore?), Los quimicos locos! (Alex, Marina, Fuad, Toc, Charlie, Laz, Flo, Noemie, etc...), Geek-ohm, François, Adrien, Emilie, Antoine et André (Parce que j'ai quitté la chimie pour faire une thèse en Electronique!) Johanna, Tanju, Domi, Mattheus, Solenn et Thomas (pour toutes ces folies en montagne!) Etienne et Pablo (pour ces journées de dure escalade!) et tant d'autres personnes qui m'ont toujours accompagnée!

Je finis, sans doute, par remercier ma famille et sur tout mon compagnon pour m'avoir soutenu, supporté et motivé pendant tout ce temps, et pour m'avoir accompagné dans cette aventure et les prochaines à venir!

# Development and characterization of plasma etching processes for the dimensional control and LWR issues during High-k Metal gate stack patterning for 14FDSOI technologies

(Abstract)

In a transistor manufacturing process, patterning is one of the hardest stages to control. Along with downscaling, the specifications for a transistor manufacturing have tightened up to the nanometer scale. Extreme metrology and process control are required and Critical Dimension Uniformity (CDU) and Line Width Roughness (LWR) have become two of the most important parameters to control.

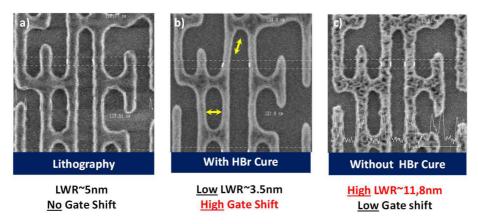

So far, to meet the requirements of the latest CMOS technologies, post-lithography treatments such as plasma cure treatments have been introduced to increase photo-resist stability and to improve LWR prior to pattern transfer. However, conventional post-lithography treatments are no more efficient to address the specifications of 14nm gate patterning where more complicated designs are involved.

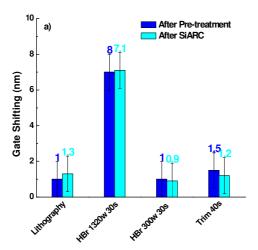

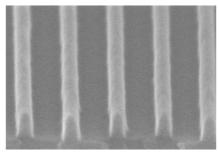

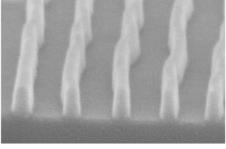

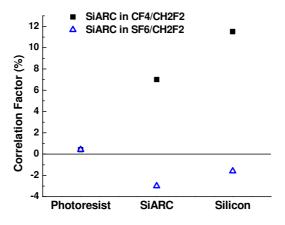

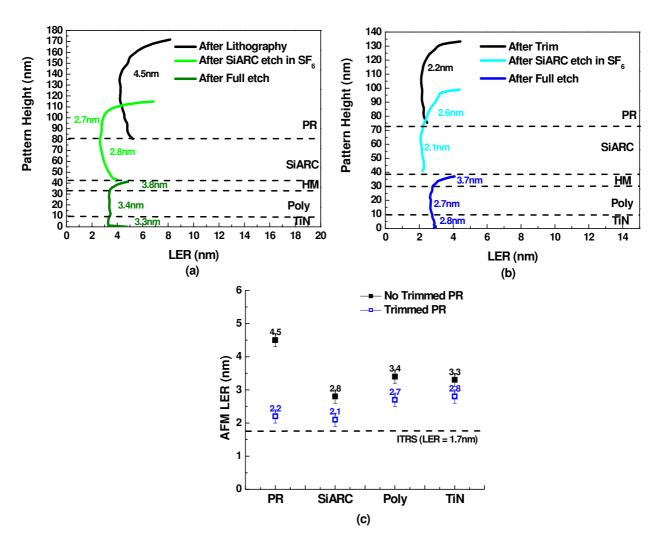

In this work, we have studied limitations of cure pretreatments in 2D gate integrations. In fact, the HBr plasma post-lithography treatment was identified as being responsible of a local pattern shifting that result in a loss of the device's electrical performance. Preliminary results show that, cure step removal helps to control pattern shifting but to the detriment of the LWR. Indeed, if no cure treatment is introduced in the gate patterning process flow, photoresist patterns undergo severe stress during the subsequent Si-ARC plasma etching in fluorocarbon based plasmas. In this work, the mechanisms that drive such resist degradation in fluorocarbon plasmas have been studied and improved SiARC etch process condition shave been proposed. Besides, we evaluate how the state-of-art gate etch process can be improved, by investigating the impact of each plasma etching step involved in the high-K metal gate patterning on both LWR and gate shifting. The goal of this study is to determine if the TiN metal gate roughness can be modified by changing the gate etch process conditions. Our research reveals that addition of N<sub>2</sub> flash steps prevents from gate profile degradation and sidewall roughening. In revenge, the TiN microstructure as well as the HKMG etch process has no impact on the gate final roughness. However, the TiN LER is strongly modified during the wet cleaning process. This modification results from the dissolution of TiN sidewall passivation layers that are formed during plasma processing. Although the TiN LER is also modified during wet process, the hard mask patterning process still remains the main contributor for gate roughening.

Keywords: Plasma etching, Gate shifting, Photoresist degradation, Roughness, HKMG, 14FDSOI.

# Développement et caractérisation des procédés de gravure plasma impliqués dans la réalisation de grille métallique de transistor pour les technologies FDSOI 14nm : contrôle dimensionnel et rugosité de bord

(Abstract)

Dans le procédé d'élaboration d'un transistor, la définition des motifs de grilles est une des étapes les plus dures à contrôler. Avec la miniaturisation des dispositifs, les spécifications définies pour la structuration des transistors se sont resserrées jusqu'à l'échelle du nanomètre. Ainsi, le Contrôle Dimensionnel (CD) et la rugosité de bord des lignes (LWR) sont devenus les paramètres les plus importantes à contrôler. Précédemment, pour atteindre les objectifs définis pour les précédentes technologies CMOS, des traitements post-lithographiques tels que les traitements plasma à base d'HBr ont été introduits pour améliorer la résistance des résines aux plasmas de gravure et minimiser la rugosité des motifs de résine avant leur transfert dans l'empilement de grille. Cependant, ces méthodes conventionnelles ne sont plus satisfaisantes pour atteindre les spécifications des nœuds avancés 14FDSOI, qui font intervenir des schémas complexes d'intégration de motifs. Dans ces travaux, les limitations des traitements plasma HBr pour réaliser des motifs de grille bidimensionnels comme définis par les règles de dessin ont été mises en évidence. En effet, il s'avère que les traitements par plasma HBr sont responsables d'un déplacement local du motif de grille, qui entraine sur le produit final une perte de rendement. Des résultats préliminaires montrent que le retrait de cette étape de traitement réduit le phénomène de décalage des grilles, au détriment de la rugosité des motifs de résines. En effet, les résines non traités par plasma subissent d'importantes contraintes lors de l'étape de gravure SiARC en plasma fluorocarbonnés, ce qui génère une nette augmentation de la rugosité de la résine qui se transfère par la suite dans les couches actives du dispositif. Dans cette thèse, j'ai étudié les mécanismes de dégradation des résines dans des plasmas fluorocarbonés. Cette compréhension a abouti au développement d'une nouvelle chimie de gravure plasma de la couche de SiARC qui limite la dégradation des résines. De plus, j'ai évalué comment le procédé complet de gravure de grille métallique peut être amélioré pour réduire la rugosité et la déformation des motifs en travaillant sur chacune des étapes impliquées. Le but de cette étude est d'identifier les étapes de gravure ayant un rôle dans la rugosité finale de la grille. Mes travaux montrent que l'ajout des étapes de nitruration limite la dégradation du profil de grille et de la rugosité des flancs. Au contraire, la microstructure du film de TiN ainsi que les procédés de gravure de grille métal n'ont pas d'impact sur la rugosité finale du dispositif. Cependant, nos travaux ont montré que les étapes de nettoyage ont un fort impact sur la rugosité finale du TiN dû à la dissolution des couches de passivation générées pendant les procédés de gravure par plasma. Mis appart cette modification de la rugosité du TiN lors des procédés de nettoyage, le transfert du motif de grille lors des étapes de gravure du masque dur reste toujours le principal contributeur de la rugosité finale de grille.

**Mots Clés:** Gravure par Plasma, déplacement de grille, Dégradation des résines, Rugosité, grille métallique, 14FDSOI.

### **Nomenclature**

**OES** Optical Emission Spectroscopy

**PR** Photoresist

RF-PVD Radio Frequency Physical Vapor **AFM** Atomic Force Microscopy Deposition **ALD** Atomic Layer Deposition **RMS** Root Mean Square **AR-XPS** Angle Resolved X-ray Photoelectron **SiARC** Silicon Anti Reflective Coating Spectroscopy **CD** Critical Dimension **SoC** Spin on Carbon **CD-SEM** Critical Dimension Scanning Electron **STG** Side Tuning Gas Microscopy **Td** Degradation Temperature **CF** Correlation Factor **Te** Electron Temperature **CVD** Chemical Vapor Deposition **Tg** Glass Transition Temperature **DC** Direct Current **TGA** Thermo Gravimetrical Analysis **ER** Etch Rate **VUV** Vacuum Ultra Violet **ESC** Electro Static Chuck **XRD** X-ray Diffraction FC Fluorocarbon **ACF** Auto Correlation Function FDSOI Fully Depleted Silicon On Insulator **ITRS** International Technology Roadmap for FTIR Fourier Transform Infra Red Semiconductors Spectroscopy ME Main Etch **GS** Gate Shifting **OE** Over Etch **HK** High K **PSD** Power Spectral Density **HKMG** High-K Metal Gate **OPC** Optical Proximity Correction **HM** Hard Mask **PAB** Post Applied Bake **ICs** Integrated Circuits **PEB** Post Exposure Bake **LER** Line Edge Roughness PAG Photo Acid Generator **LSR** Light Signal Reflectometry **STI** Shallow Trench Isolation LWR Line Width Roughness **XPS** X-Ray Photoelectron Spectroscopy Ne Electron Density **LELE** Litho-Etch Litho-Etch

**RIE** Reactive Ion Etching

MOS Metal Oxide Semiconductor

# Index

| Nomeno   | clature                                                            | 4  |

|----------|--------------------------------------------------------------------|----|

| General  | Introduction                                                       | 8  |

| I Cha    | apter I. Introduction                                              | 10 |

| I.1      | Microelectronic context                                            | 10 |

| I.2      | Electronic circuit manufacturing                                   | 14 |

| I.3      | Gate Patterning                                                    | 15 |

| I.3.     | 1 Lithography                                                      | 16 |

| I.3.     | 2 Etch                                                             | 18 |

| I.4      | Challenges in Gate Patterning                                      | 24 |

| I.4.     | 1 Challenges related to the lithography step                       | 24 |

| I.4.     | 2 Challenges related to the dry etch processes                     | 29 |

| I.4.     | 3 Lithography & Etch: A Combined Interaction                       | 30 |

| I.5      | Objectives of this work                                            | 34 |

| Bibliogr | aphy of Chapter I                                                  | 36 |

| II Cha   | apter II. Experimental Set up                                      | 42 |

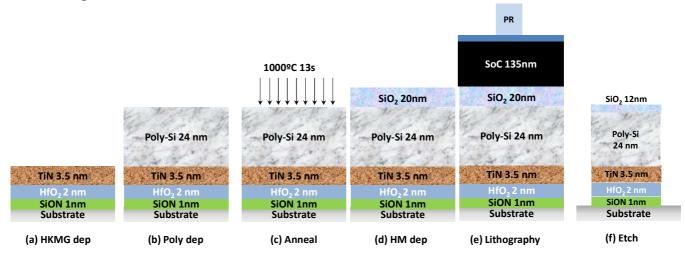

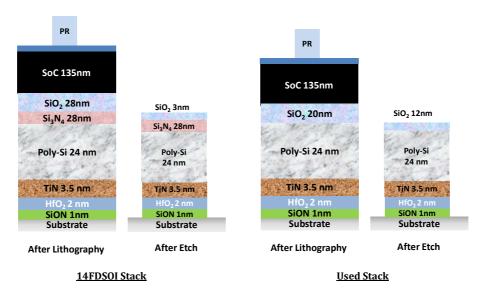

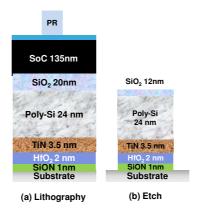

| II.1     | The gate patterning process                                        | 42 |

| II.2     | Equipments for gate patterning: Deposition and Etch reactors       | 43 |

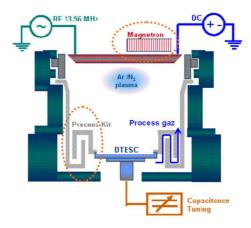

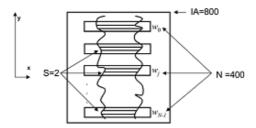

| II.2     | .1 The Endura RF-PVD TiN deposition reactor                        | 44 |

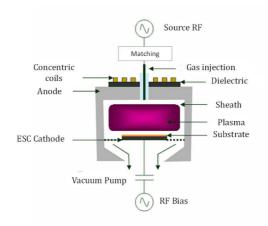

| II.2     | .2 The LAM KiyoEx etch reactor                                     | 47 |

| II.3     | Characterization techniques                                        | 52 |

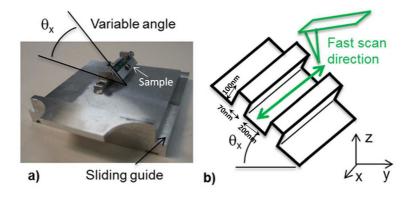

| II.3     | .1 Material physic-chemical characterization techniques            | 52 |

| II.3     | .2 Process Qualification techniques                                | 65 |

| Bibliogr | aphy of Chapter II                                                 | 76 |

| III Cha  | apter III. Gate shifting phenomenon on 14FDSOI Gate etch processes | 80 |

| III.1    | Gate Shifting Issue                                                | 81 |

| III.     | 1.1 The Gate shifting phenomenon                                   | 81 |

| III.     | 1.2 Origin of gate shifting                                        | 82 |

| III.2    | Mechanisms responsible for gate shifting during cure step          | 83 |

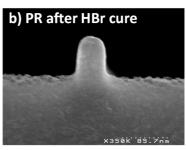

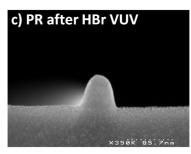

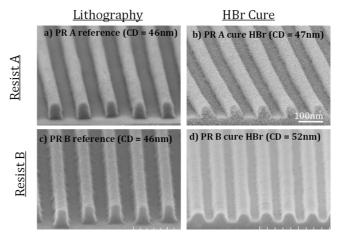

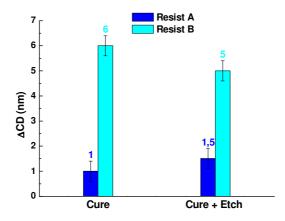

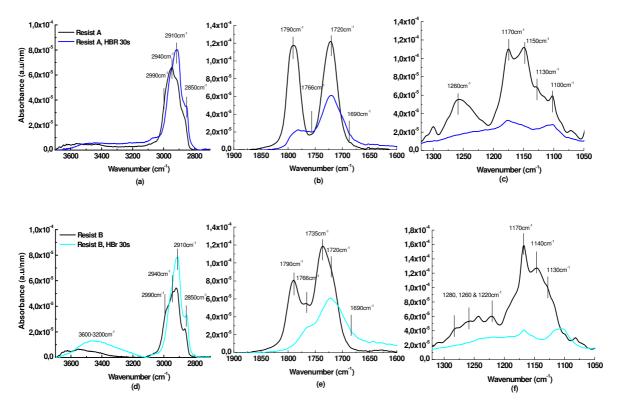

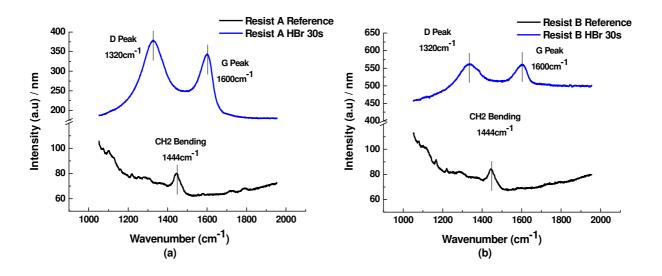

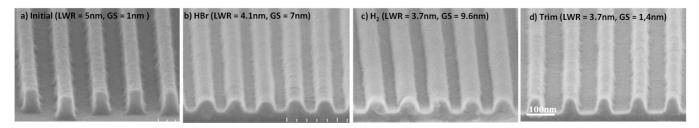

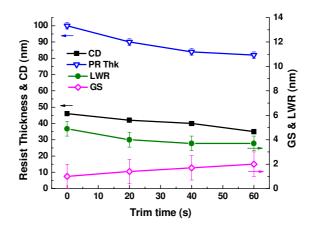

| III.     | 2.1 Impact of HBr cure step on photoresist patterns                | 83 |

| III.     | 2.2 Resist flowing mechanism                                       | 87 |

| III.     | 2.3 Pattern deformation mechanism                                  | 94 |

| III.3    | Towards gate shifting improvement                                  | 96 |

| III.     | 3.1 Metrology                                                      | 96 |

|      | III.3.2   | Impact of HBr cure plasma parameters on gate shifting and LWR                        | 97            |

|------|-----------|--------------------------------------------------------------------------------------|---------------|

|      | III.3.3   | Impact of cure plasma chemistries on gate shifting and LWR                           | 102           |

|      | III.3.4   | Gate shifting and LWR transfer after etch                                            | 108           |

| II   | I.4 Co    | nclusion                                                                             | 109           |

| Bibl | iograph   | y of Chapter III                                                                     | 110           |

| IV   | Chapte    | r IV. Photoresist LWR degradation during SiARC process and transfer into the g       | ate stack 114 |

| IV   | /.1 Im    | pact of SiARC plasma etching process on gate patterning and roughness                | 115           |

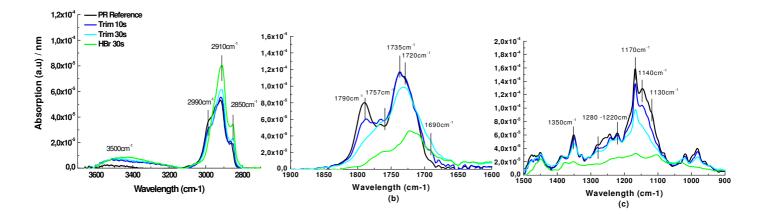

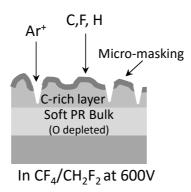

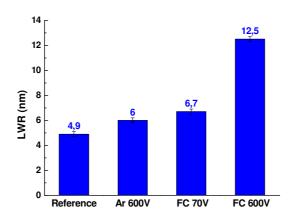

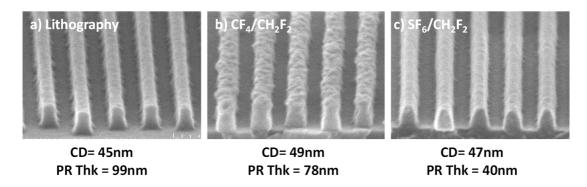

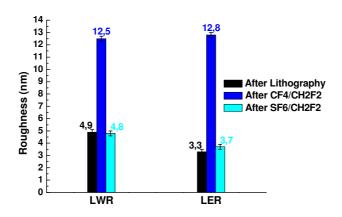

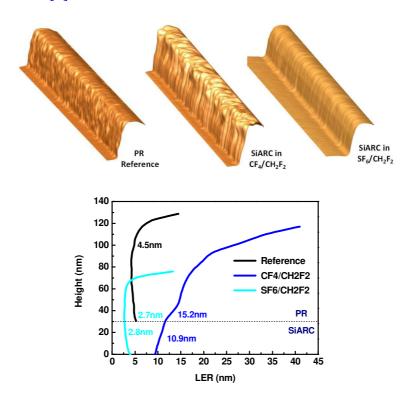

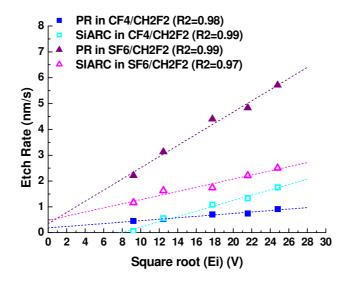

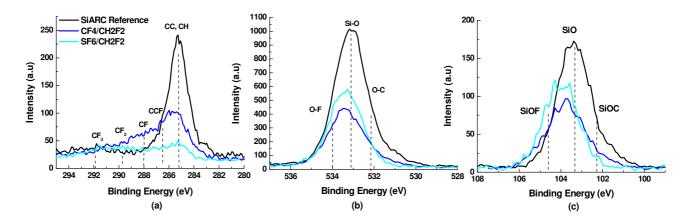

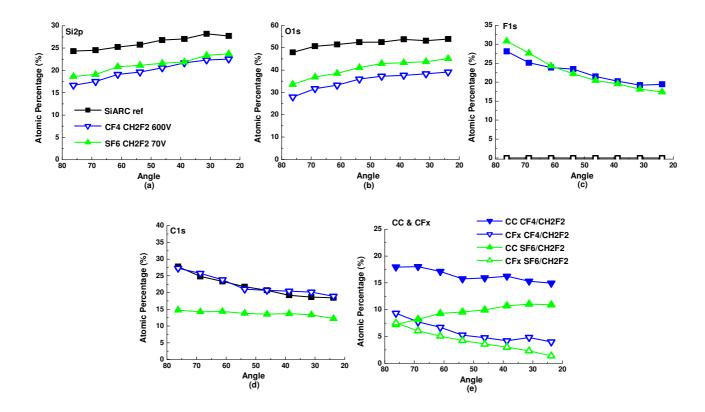

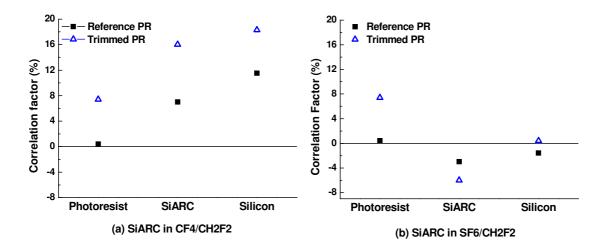

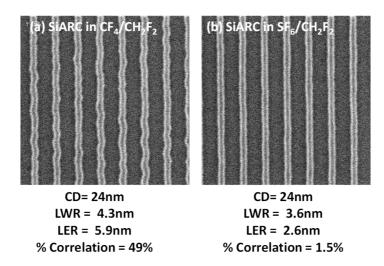

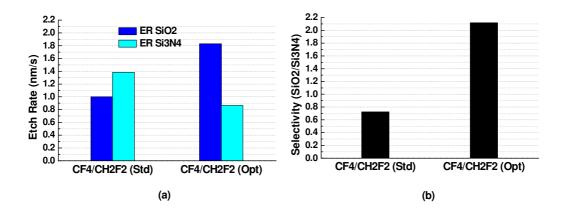

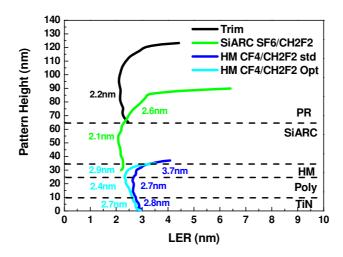

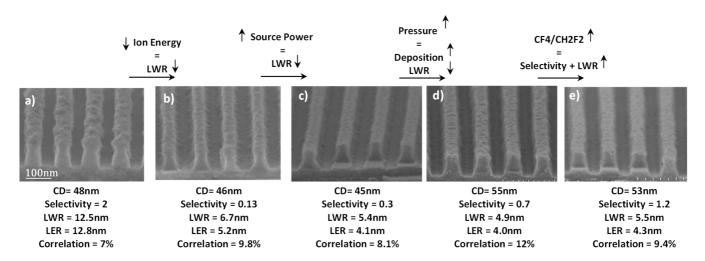

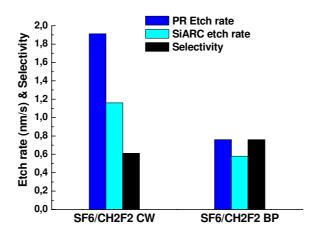

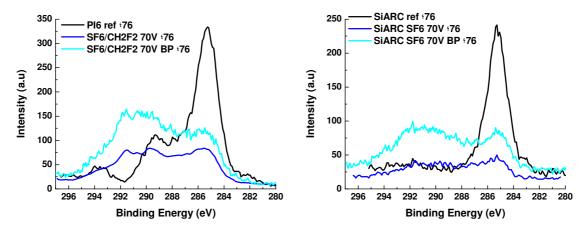

|      | IV.1.1    | Photoresist degradation in CF <sub>4</sub> /CH <sub>2</sub> F <sub>2</sub> plasmas   | 115           |

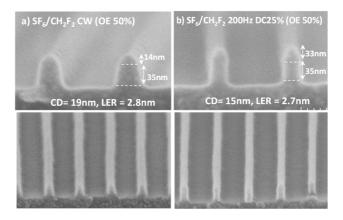

|      | IV.1.2    | SF <sub>6</sub> /CH <sub>2</sub> F <sub>2</sub> plasma chemistries for SiARC etching | 130           |

| IV   | 7.2 Pa    | ttern transfer into gate stack (HM/Silicon/TiN)                                      | 141           |

|      | IV.2.1    | Impact of SiARC etch process in the LER transfer for HKMG patterning                 | 141           |

|      | IV.2.2    | Impact of Trim step addition in the LER transfer for HKMG patterning                 | 145           |

|      | IV.2.3    | Impact of HM etch process in the LER transfer for HKMG patterning                    | 149           |

| IV   | 7.3 Ge    | neral conclusion                                                                     | 151           |

| Bibl | iograph   | y of Chapter IV                                                                      | 153           |

| V    | Chapte    | r V. LWR issue during TiN metal gate etching processes                               | 156           |

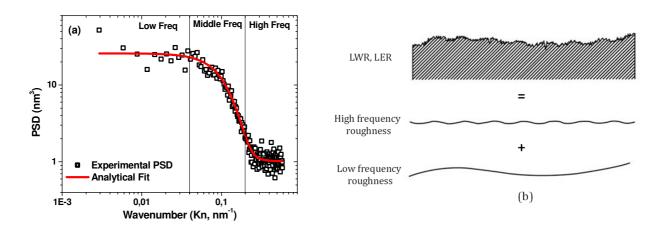

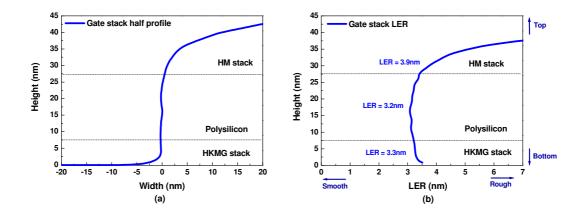

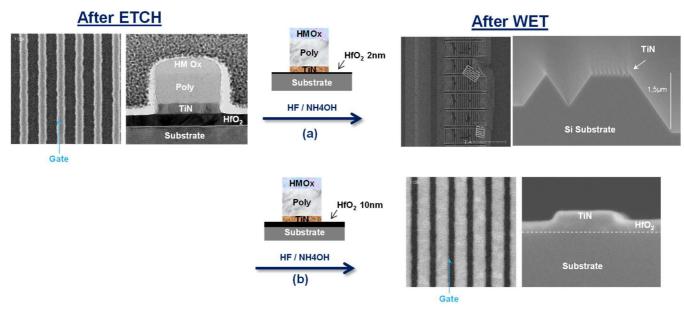

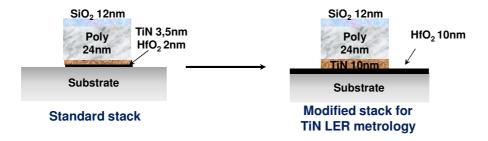

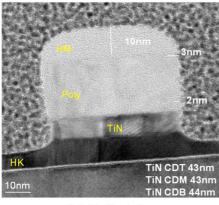

| V    | .1 M      | etrology of HKMG Line Edge Roughness                                                 | 156           |

|      | V.1.1     | Metrology issue for accurate TiN LER determination                                   | 156           |

|      | V.1.2     | TiN LER metrology by CD-SEM                                                          | 157           |

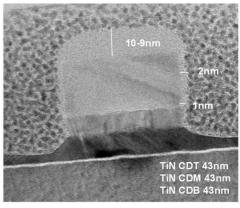

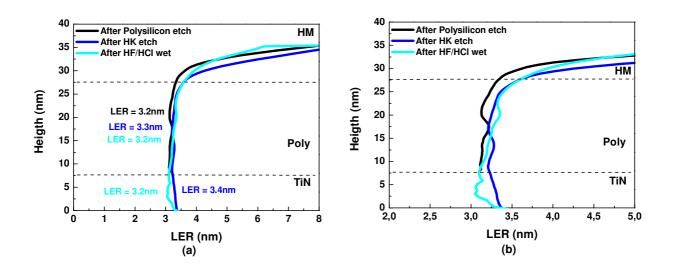

| V    | .2 In     | pact of TiN etch process to gate stack in final roughness                            | 161           |

|      | V.2.1     | Process description                                                                  | 161           |

|      | V.2.2     | Impact of TiN etch process steps onto the gate LER                                   | 162           |

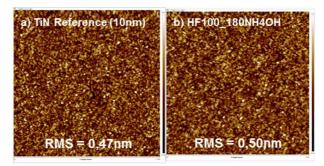

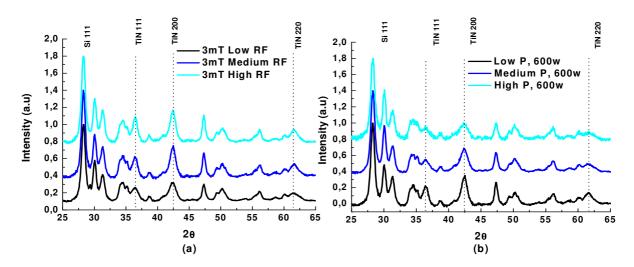

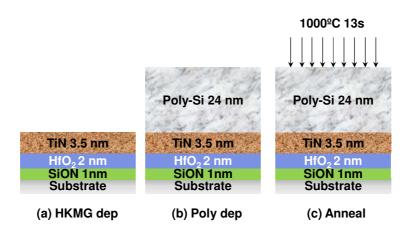

| V    | .3 Im     | pact of TiN deposition parameters                                                    | 170           |

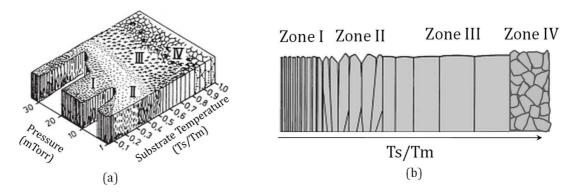

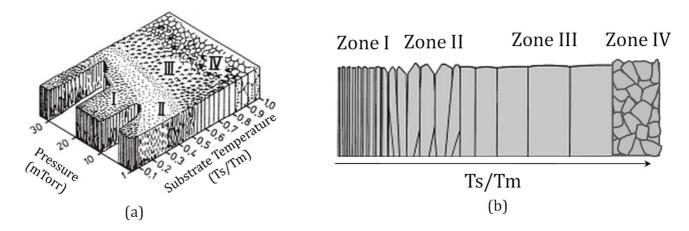

|      | V.3.1     | TiN deposition                                                                       | 170           |

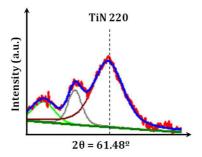

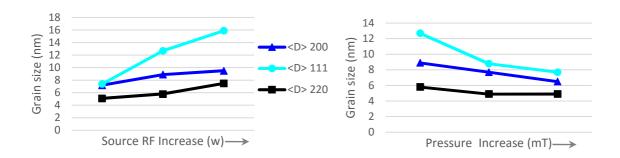

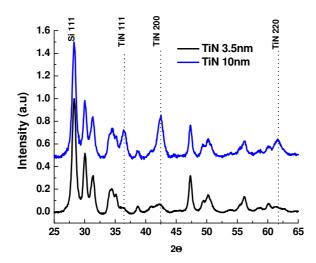

|      | V.3.2     | Film characterization                                                                | 166           |

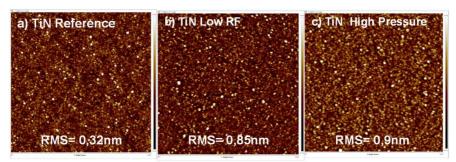

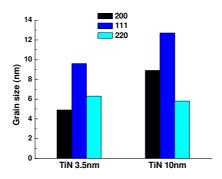

|      | V.3.3     | Impact of TiN granulometry on TiN surface roughness                                  | 168           |

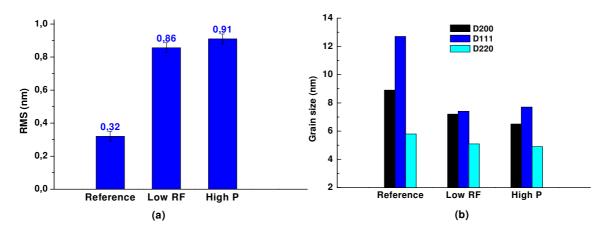

|      | V.3.4     | Impact of TiN granulometry on TiN sidewall roughness (LER)                           | 169           |

|      | V.3.5     | Conclusion                                                                           | 173           |

| V    | .4 Ge     | neral Conclusion                                                                     | 179           |

| Bibl | iograph   | y of Chapter V                                                                       | 180           |

| Gen  | eral Cor  | nclusion                                                                             | 182           |

| Ann  | ex I Til  | N deposition by RF-PVD                                                               | 189           |

| Ann  | ex II Op  | timization of SiARC etch chemistries                                                 | 190           |

| Ann  | ex III In | npact of TiN film thickness on the material properties                               | 196           |

### **General Introduction**

The microelectronic industry has been one of the most important industry sectors for the last 60 years. The first transistor was made by Bell laboratories in the late 40s. It was made up of a pure germanium crystal and its size was about the palm of a hand. From that day, the microelectronic industry has well developed. Today, transistors are nanometer scale devices made of a number of different materials stacked in complicated integrations. Now, transistors are the core of most of our electronic devices; from cars and mobile phones to pacemakers, and their applications are countless: Automotive, Biology, Security, Medicine...

Such a huge evolution is the result of a lot of hard work carried out by engineers and scientists whose goal was to improve the transistor manufacturing process in order to achieve the best performances. This led to a continuous decrease of the transistor dimension and an increase of the transistor density per chip. However, the pursuit for the transistor miniaturization results in an increased complexity of the integrated circuits and therefore, transistor manufacturing becomes more and more challenging.

To assist this increasing complexity, the "International Technology Roadmap for Semiconductor" (ITRS), defines every year the goals to be obtained by the semiconductor industry. Thus, in a transistor manufacturing process, gate patterning has become one of the hardest stages to control. Along with downscaling, the ITRS specifications for a transistor manufacturing have tightened up to the nanometer scale. Extreme metrology and process control are required and the gate Critical Dimension Uniformity (CDU) and Line Width Roughness (LWR) have become two of the most important parameters to control. In 2011, the ITRS affirmed that the gate CD non-uniformity should not exceed 10% (for 14nm technologies) while the LWR should not be higher than 12% of the gate dimension. In other words, for a gate pattern of 20nm, the ITRS predicts a gate size variation of 20±2nm with a sidewall roughness (LWR) of 2.4nm.

Nowadays, the best lithography conditions allow the definition of photo-resist patterns with a minimum roughness of 4-5nm and a CD non-uniformity of around 2%, which will be then transferred to the underlying layers by plasma etch processes. This means that in order to achieve the specifications defined for the latest CMOS technologies, new strategies need to be implemented to control this variability.

So far, post-lithography treatments such as plasma cure treatments have been introduced to increase photo-resist stability and to improve LWR prior to pattern transfer. However, conventional post-lithography treatments are no longer efficient to address the specifications for 14nm gate patterning where more complicated designs are seen.

The goal of this work is to evaluate the impact of subsequent etch steps in the dimensional control and LWR of a 14FDSOI gate pattern. Thus, the work is particularly dedicated to the understanding of the gate pattern deformations during the etch process and the LWR evolution at each process step.

The first chapter is dedicated to recall of the context in which this work has been carried out. A brief summary of the state-of-art is proposed followed by a discussion about the main challenges concerning gate patterning processes.

The second chapter is dedicated to the description of the experimental setup. In this chapter, a detailed description of the substrates and etch conditions is given. Besides, the operating principle of certain characterization techniques is described to better understand the results obtained in the following sections.

The third chapter describes the challenges encountered due to the addition of cure steps on 14FDSOI gate integrations where complicated 2D patterns are defined. A particular attention was paid to the understanding of the observed phenomena in order to propose solutions to prevent gate pattern degradation.

The fourth chapter, focuses more particularly on the photoresist degradation during the etch process. Besides, the evolution of the gate LWR during the hard-mask patterning process is studied.

Finally, the last chapter is dedicated to the study of the LWR evolution along a gate stack consisting in a polysilicon/metal/high-k stack. More particularly, the study is focused on the impact of High-K Metal Gate etch steps on the final gate roughness.

This was a CIFRE PhD carried out in collaboration with STMicroeletronics (ST) and the LTM Laboratory (CNRS). All the experiments were carried out in an industrial environment (i.e. Industrial reactor) and on real ST substrates to better answer to ST challenges in terms of CD control and LWR for advanced 14FDSOI technologies. At the beginning of this PhD, this product was in progress of development and was scheduled to be released by 2015.

# **Chapter I. Introduction**

### I.1 Microelectronic context

Microelectronics is the science that studies and manufactures integrated circuits at a microscopic scale. This includes the manufacturing of transistors, capacitors, inductors, diodes and a number of different electronic components.

The origin of the semiconductor industry stands in 1947, where the first bipolar transistor was developed over a germanium mono-crystal by J. Bardeen, W. Brattain and W.B. Shockley from Bell Laboratories [1]. However, it was only in 1960 that this industry exploded thanks to the development of the first transistor made of a metal deposed over an oxide and a semiconductor material, or "Metal Oxide Semiconductor" (MOS) transistor, by D. Khan and M. Attala [2].

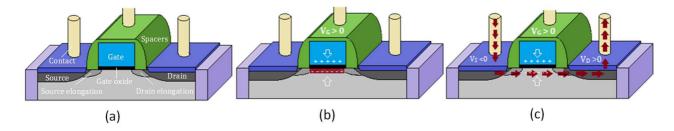

Each MOS transistor allows the transfer of the electric charge, though the charge carriers could be either holes or electrons. Thus, two different transistors are defined: n-MOS transistors (when the transferred charges are electrons) and p-MOS (when the transferred charges are holes). To choose the charge carrier's nature, the substrates are doped either choosing N-type (i.e. Phosphor) or P-type dopants (i.e. Boron). A schematic representation of an n-MOS transistor operating principle is shown in Figure I.1.

**Figure I-1** Schematic representation of n-MOS transistor operating principle. (a) Illustration of the MOS components at  $V_G=0$ , (b) Formation of the conduction channel with a  $V_G>0$  and (c) conduction of electrons at  $V_D>0$  [3].

The n-MOS transistor is composed of four electrodes, the substrate (i.e. Silicon, P doped), the gate, the source (N doped) and the drain (N doped) (Figure I.1a). To each one of these electrodes, a different voltage will be applied, identified as  $V_G$ ,  $V_S$  and  $V_D$ . When no potential is applied ( $V_G = 0$ ), no charge is formed in the MOS junction. However, since the substrate potential is always kept to zero, if a potential is applied into the gate electrode ( $V_G > 0$ ) an electric field is formed in the MOS junction. This electric

field will repulse the holes present in the semiconductor surface to create an N-type inversion channel where electrons will conduct (Illustrated by the red zone in Figure I.1b). Typically, the source potential is equal to zero ( $V_S=0$ ) while the drain is elevated to a higher potential ( $V_D>0$ ). Therefore, the electron conduction occurs from source to drain (Figure I.1c).

The combination of n-type and p-type MOS transistors leads to a latter exploration of the CMOS technology (Complementary MOS), which allows the definition of the first logic functions and enabled the fabrication of integrated circuits. Thus, the first integrated circuit was then born in 1960, and the first microprocessor was built by Intel in 1971 [4]. Since then, the dimensions of the integrated circuit main elements (i.e. the MOS transistors) have been progressively reduced to improve their performance and reduce the manufacturing costs. This led to an explosion of the semiconductor market in order to offer smaller products to the consumers that integrate more functionalities. Thus, in 1974, the Moore's law was established, an economic trend that forecasted that the number of transistors composing a microprocessor should double every two years [5]. This trend was followed by the formation of the ITRS (International Technology Roadmap for Semiconductor) in 1997, an industrial organization that predicts the evolution of the microelectronic industry and defines the goals to be achieved for the years to come. As an example, the gate dimensions defined by the ITRS in 2011 for the following years are listed in Table I.1 [6].

Table I-1Gate length evolution between 2012 and 2017 as defined by the ITRS 2011

| Year of Production | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 |

|--------------------|------|------|------|------|------|------|------|------|------|

| Gate length (nm)   | 22   | 20   | 18   | 17   | 15   | 14   | 13   | 12   | 11   |

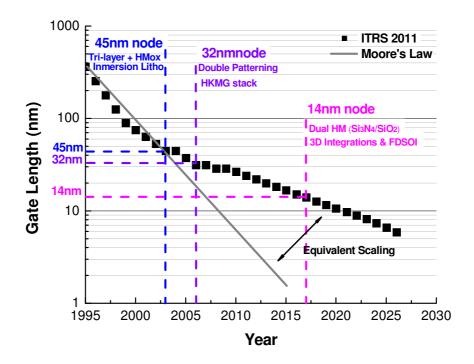

Therefore, the semiconductor industry has increased the complexity of the developed transistors in order to achieve the ambitious goals defined by the Moore's law and the ITRS. This increased complexity includes reduction of gate dimensions, addition of new materials into gate stacks, improvement of the masking strategies and the development of new manufacturing processes. Figure I.2 illustrates the gate length evolution as predicted by the 2011 ITRS compared with the gate length as defined by the Moore's law.

**Figure I-2** 2011 ITRS predictions for the gate physical length evolution between 1995 and 2030. The ITRS trend is compared to the gate length evolution as defined by the Moore's law. After the 45nm node, the difficulties to obtain performing MOS transistors lead to a change in the gate integrations. Reprinted from ITRS 2011 [6].

As it can be observed in Figure I.2, the first gate integrations (i.e. before 45nm technologies), agree with the trends defined by the Moore's law. At that time, the transistors were carried out with the classical MOS stack, which consisted in a polysilicon gate over a silicon gate oxide layer. However, along with transistor downscaling, more aggressive targets were defined in terms of gate dimensions and uniformity control. This resulted in an increased complexity of the transistor manufacturing process, and more particularly reviewing the masking strategies, and materials stacks used for feature definition.

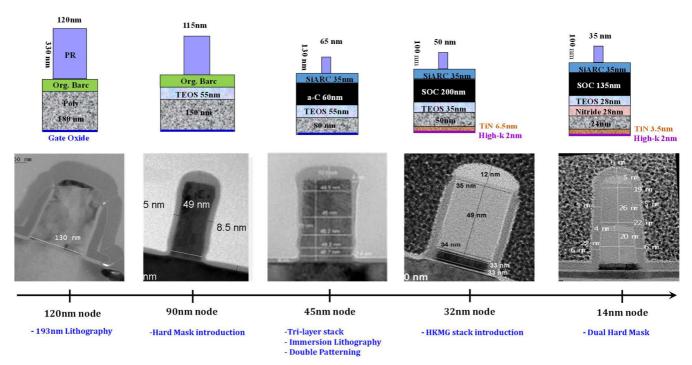

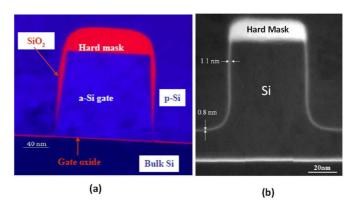

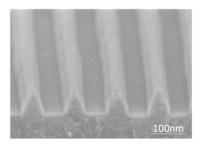

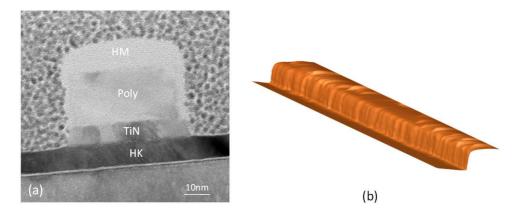

As an example, Figure I.3 shows the gate stack evolution from the 120nm node until the 14nm node. In the first raw, the full gate stack is schematically illustrated where the increasing stack complexity, and the reduced dimensions are also described. In the second raw, TEM images of the gate stacks after full etch are also shown.

Figure I-3 Gate stack evolution from 90nm to 14nm technological nodes

Initially for the 120nm node, the gate patterns were defined using a simple photoresist mask (Fig I.3); and the gate dimensions were reduced by only reducing the photoresist pattern dimensions. However, due to the limited photoresist budget, this strategy was not adapted to define smaller gate patterns. Thus, already for the 90nm node, oxide hard masks were introduced (Fig I.3). With this strategy, the pattern dimensions were still reduced by reducing the resist pattern dimensions, while the hard-mask was used to improve the pattern transfer into silicon. However, below the 45nm node, the classic lithography could not resolve the novel design targets and other strategies, such as, tri-layer lithography stack depositions, immersion lithography and double patterning techniques had to be implemented to achieve the gate patterning (Fig I.3) (i.e. these new strategies will be further described in section I.3).

However, the smaller the gate dimensions, the more challenging becomes the MOS manufacturing and as it can be observed in Figure I.2, for the 32nm node and beyond, the gate length predicted by the Moore's law cannot be reached, and we slightly move away from the specified trend. This deviation occurred because the small MOS devices undergo a loss in their electrical performances due to physical failure effects such as, polysilicon depletion [7] or gate leakage because of the extreme reduction of the oxide thickness [8]. As a result, the engineers realized that it was not possible to continue with the classical CMOS downscaling and other strategies need to be found. Thus, with the arrival of the 32nm node, TiN metal and HfSiON high-k materials were added into the gate stack leading to the first HKMG integrations (Fig I.3). This marked a breakdown for the semiconductor industry, which moved into a new trend, based in an "Equivalent Scaling", which consists in carrying out bigger transistors but with optimized gate integrations that allow reaching performances that are equivalent to those of "ideally" small transistors (Fig I.2).

Taking advantage of this new scaling trend, the transistor downscaling continued its course until the 14nm node. For this new integration the gate stack was again in order to meet the specifications. In fact, due to the continuous reduction of the oxide layer thickness, the HfSiON high-k material was no longer efficient to avoid gate leakage and was replaced by  $HfO_2$  materials [8]. Besides, due to manufacturing modifications, the traditional oxide hard mask was not sufficient to assure suitable gate patterning and

the masking strategy was also improved by addition of a dual hard masks formed by SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> stacks (Fig I.3).

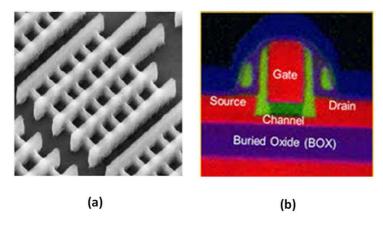

However, to keep on with the ITRS downscaling, modifying the gate stacks seemed not sufficient. The gate leakage effects due to the extremely thin oxide layer depositions and the limited control of source and drain electrodes become important failure sources, and new transistor integrations are required. Some industries such as IBM and Intel bet for 3D integrations like FinFET integrations. Such transistors are based on fins on which field effect transistors are built and are wrapped around by the gate structures (Figure I.4a). These 3D structures are assumed to achieve higher performances at lower voltages; however, they suppose an increase challenge in terms of manufacturing [9] [10].

**Figure I-4** SEM image of a FinFET and (a) TEM-EDX image of a FD-SOI gate integration. In (b) different materials are identified by different colors.

Other companies, like STMicroelectronics, preferred remaining on planar structures, and bet for new strategies such as the « Fully Depleted Silicon On Insulator" (FDSOI) integrations (Figure I.4b). The idea is to add a buried oxide (BOX) within the silicon substrate to physically limit vertically the source and drain zones and reduce the leak currents between the junctions and the substrate. This enables a better control of the gate electrode ( $V_G$ ) on the carrier density conduction along the conduction channel [11]. This strategy should help to achieve the performances established by the ITRS without moving into more complicated 3D integrations.

This PhD work was carried out at STMicroelectronics, and is therefore focused on the development of the 14FDSOI technologies with 14nm gate integrations, or in other words, HKMG integrations on SOI wafers.

### I.2 Electronic circuit manufacturing

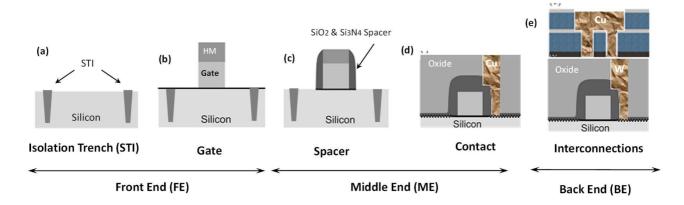

The 14FDSOIintegrated circuit manufacturing process counts with more than 300 technological steps and is divided into five main sections (Figure I.5).

- 1. **Active zone and Isolation trench (STI) formation:** To separate N-MOS and P-MOS active zones present within the SOI substrate.

- 2. **The Gate fabrication:** The formation of the transistor MOS junctions.

- 3. **Formation of the gate spacer and Source & Drain areas**: Dopant implantation to form the Source and drain regions. Spacers are deposited to avoid short-cuts between source, drain and gate electrodes.

- 4. **Contact Formation**: Deposition of the first metal layer (in W) over each electrode (Gate, Source & Drain) to enable interconnection.

5. **Interconnection**: elaboration of the 9 different metal levels (in Cu) that allow the connection between different transistors.

**Figure I-5** Five main sections involved in the 14FDSOI integrated circuit manufacturing: (a) STI formation, (b) Gate formation (c) Spacer deposition and implantation of source and drain electrodes, (d) Contact of all Source, drain and gate electrodes by a first W metal layer (To simplify, only the drain contact is shown) and (e) Interconnection of all the transistors by the formation of 9 different metal levels using Copper (Cu) as connection metal.

These five sections are grouped into three main stages: The "Front End of line" (FE) which involves the fabrication of the active part of the integrated circuit (the transistors) (cf fig I.5 a, b); the "Middle End of line" (ME) for the fabrication of the first contact levels (cf. fig I.5c, d), and the "Back End of line" (BE) (cf.fig I.5e) which includes the fabrication of the different metal interconnections that allow the communication between different transistors.

To develop each one of these structures (Active, Gate, Spacer...), typically a four step process flow is followed:

- 1. Material deposition and polishing (to flatten the material surface).

- 2. Lithography, to imprint a pattern into a photoresist

- 3. Etch, which transfers the photoresist pattern into the whole material stack by plasma or wet processes

- 4. Wet cleaning, to remove the residual polymers after etch processes.

Some of the described sections can also include other process steps such as: Epitaxial crystalline material growth (i.e. for Contact fabrication), implantation (i.e. the introduction of particular chemical elements into materials for example for the formation of Source & Drain zones) and thermal treatments.

In my PhD, I have worked on the FE process, and more particularly on the development of plasma etch processes for 14nm gate patterning.

### **I.3 Gate Patterning**

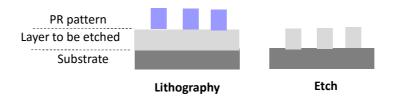

**Gate patterning is carried out following a top-down approach.** This consists in using two different steps for material structuration: The lithography, where the gate pattern is imprinted over a photoresist film, and the etching process, where the photoresist pattern is transferred into the remaining gate stack.

Figure I-6 Schematic representation of the top-down approach

### I.3.1 Lithography

The lithography consists in the definition of gate designs into a photoresist film and is therefore the stage where the dimensions of the imprinted features are defined. Thanks to the improvements done at this manufacturing level, the pattern's Critical Dimension (CD) is reduced and the transistor density within a wafer can be increased.

A schematic design of the complete lithography process is shown in Figure I.7.

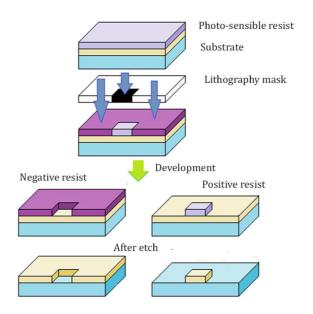

Figure I-7 Principle of lithography [3]

In the lithography process, the photoresist film is exposed to UV irradiation through a quartz mask where the desired gate features have been designed. This mask covers certain parts of the photoresist while the remaining film is exposed to the UV irradiation. Under exposure, the resist undergoes several chemical reactions that make it soluble in a specific solvent (i.e. Developer, typically TMAH for "Tetra-Methyl Ammonium hydroxide"). The difference in the solubility between the exposed and un-exposed resist allows imprinting the mask features into the photoresist film (i.e. for positive zone PR). This process is carried out in five steps:

1. **Layer deposition:** First, the lithography tri-layer stack is deposited over the polysilicon wafer using the Spin Coating technique. This consists in: an amorphous carbon planarizing layer (Spin on Carbon SoC), that improves the surface uniformity of the polysilicon wafer; an anti-reflective coating (SiARC), which absorbs the reflected wavelengths and avoids photoresist pattern degradation by UV back scattering; and the photoresist (PR) which consist in a chemically amplified resist.

Chemically amplified photoresist are extremely sensitive resist materials that by action of one only photon undergo several chemical reactions. These photoresist include: a *polymer* (composed of different monomers that improve the PR thermal stability, adhesion or etch resistance...), a *Photo-Acid Generator* (PAG, containing photo-catalytic groups which under UV exposure are transformed into acids), and a *quencher* (i.e. a basic component that limits the photo-catalytic reaction and controls the acid diffusion within the photoresist film).

- 2. **Post applied bake (PAB):** Is a soft bake condition (T~100°C) used for solvent desorption and resist densification after deposition. The PAB temperature is chosen so that no thermal degradation of the un-exposed photoresist occurs during the baking process and is therefore dependent on the polymer material.

- 3. **Exposure:** consist in the exposition of the photo resist to a specific wavelength through a lithography mask. Due to this exposure, the PAG undergoes photo-catalytic reactions that lead to acid formation. An example of the photo-catalytic reactions using a "tri-phenyl-sulfonium antimony hexafluoride" PAG is shown in figure I.8 [12].

**Figure I-8** Tri-phenyl-sulfonium antimony hexafluoride Photo Acid Generator (PAG) photo-catalytic reaction to form H\*SbF<sub>6</sub>- acids. [12]

**4. Post Exposure Bake (PEB):** In this step, the photoresist is heated until the activation temperature for the photoresist deprotection reaction is reached. At this temperature, the acids (H<sup>+</sup>) generated by the PAG photo-catalytic reaction react with the polymer material which undergoes an ester photolysis. This results in the cleavage of each monomer's active groups and the formation of soluble resist material. The PEB temperature is dependent on the activation energy for the deprotection reaction, and therefore changes from one polymer to another. A schematic representation of the polymer deprotection reaction is shown in Figure I.9 [13].

**Figure I-9**Example of the deprotection reaction of a AZ/Clariant193nm Photoresist in presence of an acid (H+). Ester hydrolysis leads to a detachment of monomers active groups and the formation of a soluble polymer backbone in basic solution [13].

5. **Development:** In this final step, the exposed polymer material is dissolved selectively towards the non-exposed material using an adapted solution. In the given example, since the resulting polymer matrix presents an acid nature, it will be soluble in basic solutions such as TMAH. This results in the transfer of the mask features into the photoresist film.

### *I.3.2* Etch

Once the photoresist patterns have been defined by the lithography step, the etching processes will be used to remove the material from the zones that were not covered by the photoresist (c.f Figure I.7).

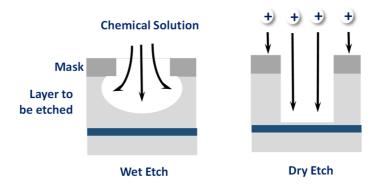

Depending on the applications, the photoresist pattern transfer can be carried out using either the wet etching or the plasma etching.

Historically, wet etching was used for pattern transfer. This technique is very **selective** and allows the removal of a material's layer without damaging the underlying materials. In the latest technologies, for example for the 28nm node, it is still used for the elaboration of N-MOS and P-MOS HKMG integrations [14]. However, wet solutions lead to an **isotropic** etching of active materials where the directionality of the etching process cannot be controlled. Along with downscaling, wet etching became less suitable for the definition of small patterns and an increasing interest grew towards plasma etching processes.

Plasma etch processes are **less selective** than wet processes but **anisotropic**, and allow transferring the lithography patterns vertically into the whole gate stack. Thanks to the definition of vertical gate patterns, a strong fidelity and an improved dimensional control can be obtained.

**Figure I-10**Differences between a wet etch process and a plasma etching process [15]

For the gate patterning process, since complicated gate stacks with a number of different materials need to be etched with an extreme pattern fidelity and anisotropy, plasma etch processes are preferred.

### I.3.2.1 Plasmas used for dry etch processes

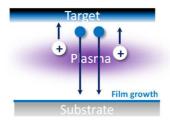

A plasma is an ionized gas that is composed of ions(positive and negative), electrons, and neutral species (molecules, atoms and radicals). These species interact between each other and result in a globally neutral environment.

Each plasma is characterized by its **electron density**,  $n_e$  (i.e. the amount of generated plasma electrons) and the **electron temperature**,  $T_e$  (or the average kinetic energy of plasma electrons). Thus, depending on these two magnitudes different types of plasmas can be described such as "hot plasmas" (i.e. T>10<sup>6</sup>K,

which are typically used in fusion physics) and "cold plasmas" (T<10<sup>6</sup>K, typically used for microelectronic applications).

For Microelectronic applications, we will therefore use "Cold plasmas" at low pressures (i.e. 1mT-1T). These are plasmas in a non-thermodynamic equilibrium (i.e. the electron temperature ( $T_e \sim 2$ -3eV) is very superior to the ion temperature ( $T_i < 0.1 \text{eV}$ )) where the ion (and electron) proportion ( $\sim 10^8 - 10^{12} \text{ cm}^{-3}$ ) is low as compared to the proportion of neutral species ( $\sim 10^{13} - 10^{17} \text{cm}^{-3}$ ).

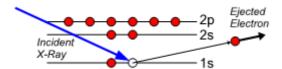

For our applications, plasmas are generated in an "inductively coupled plasma" (ICP) reactor where the gas is confined between two electrodes. When a certain voltage is applied, an electric field builds up and the electrons absorb enough electrical power to be heated. These energetic electrons collide with the surrounding neutrals and sustain the plasma discharge by the formation of plasma species. As a result of these collisions, several chemical reactions may occur:

Dissociation:  $e^- + A_2 \rightarrow 2A + e^-$

Ionization:  $e^- + A \rightarrow A^+ + 2e^-$

Excitation:  $e^- + A \rightarrow A^* + e^-$

Generally, the excitation reactions are always followed by a relaxation reaction ( $A^* + e^- \rightarrow A + hv$ ) that leads to the formation of energetic photons (VUV) that contribute to the etch process (i.e. photoresist modification, default generation, photo-etching...) [16] [17]

An important notion on the plasma discharge is the frequency at which electron/neutral collisions occurs. Thus, the electron **mean free path** ( $\lambda$ ), represents the average distance that an electron can cross without colliding with another molecule within the gas phase. This distance depends on the electron temperature and the gas pressure and is described by the following formula:

$$\lambda = \frac{kT}{\sqrt{2\pi}d^2P}$$

(Eq. I.1)

Where, k is the Boltzmann constant (1.38x10<sup>-23</sup> J/K), T is the gas temperature in K, d is the particle diameter in meters and P is the gas pressure in Pascal.

Depending on the mean free path, electrons will undergo more or less collisions within the gas phase where they will lose a certain part of their energy. Thus, the **ionization degree** ( $\alpha$ ) of a plasma, or the ratio between ion density and the neutral density, depends on the amount of collisions happening within the gas phase that is dependent on the electron density and temperature (ne and Te). For microelectronics, the plasma ionization degree is typically less than  $10^{-2}$ . At the same time, the electron density ( $n_e$ ), typically of  $1x10^{11}$  cm- $^3$ , is directly related to the applied electrode power, while the electron temperature ( $T_e$ ), typically of 2-3eV, is dependent on the working pressure.

### I.3.2.2 Plasma etch mechanisms

The main interest on plasma etching or Reactive Ion Etching (RIE) is the possibility to combine chemical etching (to improve the selectivity) and physical etching (to increase anisotropy).

### a) Chemical etching

Chemical etching involves the reactions taking place between reactive radicals and material surfaces. For example, if we consider silicon etching in  $SF_6$  plasmas, the chemical etching mechanism consists in four mains steps described as follows [18] [19] [20]:

- 1. Creation of reactive radicals in gas phase i.e.  $SF_6+e^-\rightarrow SF_5+F+e^-$

- 2. Adsorption of reactive species on the silicon surface i.e. Si+ F → SiF

- 3. Formation of volatile reaction products i.e.  $4F + Si \rightarrow SiF_4(g)$

- 4. Desorption of reaction products

This reaction is also possible with other halogens such as Chlorine and Bromine leading to the formation of  $SiCl_4$  and  $SiBr_4$  volatile species. Since the etching mechanism is based on a thermodynamic reaction, the chemistry choice is done depending on the material to be etched, so that the reaction products are stable volatile compounds. For example, silicon oxide is typically etched in fluorocarbon based chemistries by the formation of  $SiF_2$ ,  $SiF_4$ , CO and  $CO_2$  volatile compounds [21]. Carbon based photoresist are etched in oxygen based plasmas and several metals such as Aluminum are only etched in chlorine based chemistries [22].

Thus, the chemical etching is an isotropic process that is responsible for the improved selectivity during a plasma etching process. In fact, a specific chemistry can be chosen whose radicals are reactive to one of the materials, and form volatile compounds, while they are not reactive towards a second material. Thus, really good selectivities can be obtained for thin film etching in a presence of a patterned mask.

### b) Physical etching

Physical etching corresponds to a material sputtering when it is exposed to an energetic ion bombardment. When an ion collides with a material, the material's surface atoms receive enough energy to be removed from the material surface.

This process is defined by the **etch yield (Y)**, or, the number of surface atoms removed per incident ion; and is theoretically represented as follows [23] [24]:

$$Y = A \times \sqrt{E_i - E_{th}}$$

(Eq.I.2)

Where, A is a proportionality factor that is dependent on the incident ion sputtering angle,  $E_i$  is the ion energy and  $E_{th}$  is the threshold ion energy, or the minimum energy required for surface sputtering, which is dependent on the target material nature, and the incident ion nature. Therefore, the sputtering of a surface atom only occurs if  $E_i > E_{th}$ .

For lower ion energies ( $E_i \sim 0-10 eV$ ), other reactions may also occur at the substrate surface, such as, the migration of adsorbed species (i.e. Fluorine), the reorganization and mixing of the reactive surface layer and desorption of surface species.

Thanks to the directionality of incident ions during a physical sputtering process, a good anisotropy can be obtained, but, the etch selectivity is reduced.

### c) Radical/ion Synergy

In a plasma etching process the advantages of chemical etching and physical etching are combined. Therefore, a good selectivity can be obtained, thanks to the selective reactions of radical species and also a good anisotropy is obtained, due to the directional ion bombardment.

Besides, the etch rates are strongly increased compared to the etch rates obtained for chemical or physical etching processes separately. This is due to the combined effect of radicals and ions. Ion bombardment enhances atom bindings breaking in the substrate surface. This leads to an increased adsorption of radicals and helps the formation of volatile species. Desorption of such species is also improved by the ion bombardment which generally speeds up the etching process [25]. Thanks to this radical/ion synergy the plasma etch processes are great interest for pattern transfer.

The plasma etch mechanisms are based in the fact that radical species and ions do not have the same angular distribution. The neutral species are isotropic, and lead to a lateral etching; while the ions, are anisotropic and are accelerated towards the substrate (i.e. by the electrostatic sheath). This results in a directional etching that speeds up the vertical etch rate as compared to the lateral etch rate and therefore a good anisotropy can be obtained.

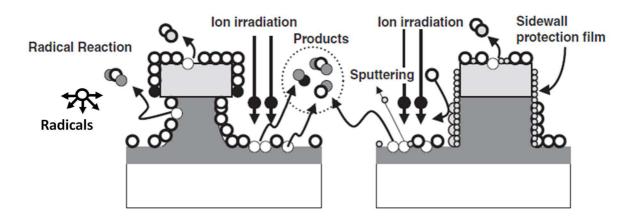

To further decrease the lateral etching component and improve the anisotropy, passivating agents can be introduced in the gas phase. These are molecules that present a high sticking coefficient that are deposited on all the surfaces exposed to the plasma. These molecules can be adsorbed in the pattern sidewalls during the etching process to form a thin passivation layer that block the lateral etching. Therefore, the lateral etching on pattern sidewalls results from a deposition/etch competition that is driven by two components: the lateral etching induced by reactive radicals and the sidewall deposition promoted by sticky molecules.

To better explain the principle of the reactive ion etching (RIE) processes, Image I.11 illustrates the mechanisms taking place during a simple patterning process.

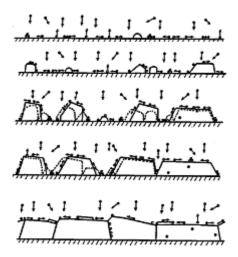

Figure I-11 Schematic representation of the mechanisms happening during plasma etching [79]

The passivating molecules can be either added intentionally to the gas phase (i.e.  $CH_2F_2$  addition) or are produced during the process due to the formation of non-volatile etch by-products (i.e.  $SiBr_x$  species) Depending on the plasma process conditions, the main two passivation mechanisms are:

- **Sidewall passivation formed from gas phase:** As an example, we can consider the silicon etching process in HBr/O<sub>2</sub> chemistries [26]. In this process, the Silicon is etched in HBr chemistries by formation of SiBr<sub>4</sub> volatile species. In addition less volatile SiBr<sub>x</sub> bi-products can be released into the gas phase and redeposit on all the surfaces exposed to the plasma and more specifically on the pattern sidewalls. There, they can be oxidized by oxygen radicals present in the plasma phase and form a thick SiO<sub>x</sub>Br<sub>y</sub> passivation layer that protects the profile from lateral etching. The passivation layers obtained by this mechanism present a non-uniformity of the passivation thickness along the sidewall and are typically thicker at the top of the etched patterns. (cf. Figure I.12a)

- Sidewall passivation formed by by-product sputtering from the bottom of the structures: Also known as "Direct line of sight deposition mechanism" [27] [28]. It has been shown that the silicon etch of horizontal surfaces proceeds through the formation of a fluorocarboned layer [29]. This fluorocarbon deposition is then sputtered from the bottom of the pattern due to ion bombardment and is re-deposited over silicon sidewalls forming a uniform passivation layer over the whole gate profile (cf. Figure I.12b).

**Figure I-12** TEM images of silicon gate patterns etched in (a) HBr/O<sub>2</sub> and (b) SF<sub>6</sub>/CH<sub>2</sub>F<sub>2</sub> plasmas.

The development of plasma etch processes is based on a fine comprehension of the passivation layer formation mechanisms which are key parameters to obtain anisotropic etch profiles.

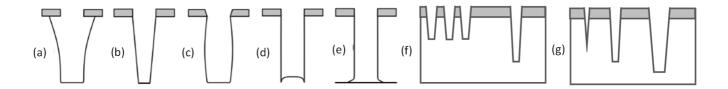

### d) Profile deformation mechanisms during plasma etching

As explained in the previous section, the plasma etch processes are ruled by the flux of neutral species (etching or passivating species) and the ion flux bombarding the surface. Depending on these two components, the patterning processes can undergo different modifications that degrade the patterned profiles. Depending on the origin of these deformations, we can differentiate three different mechanisms for pattern degradation:

Due to the difference in the ratios of neutral species and ions, there is a competition on the passivation/etch mechanisms that induce pattern deformations such as, undercutting and formation of tapered profiles.

• **Undercut**: consists in a lateral etching of the pattern sidewalls often due to a lack of passivation. For example, silicon etching in SF<sub>6</sub> plasmas without addition of any passivating agent may lead to silicon undercut (Fig I.13a).

• **Tapered profiles**: If the Passivation/etch mechanisms are not well controlled, the mask's dimensions may be modified which leads to the formation of tapered profiles. For example, if the sidewall deposition over the mask is too strong, the mask width can be progressively increased during the etching process leading to tapered profiles [30](Figure I.13b). The same may occur when the mask is consumed due to ion bombardment [31]. If we consider for example a PR mask, the sputtering yield is more efficient at 60° and therefore, the mask's sharp corner are eroded [32]. If the mask is eroded significantly, then, the bottom edge will also move leading to a tapered profile [33].

Other profile deformations, such as bowing, notching and micro-trenching, are caused when ions are directed towards the substrate with an off-normal incident angle. This is most likely due to charging effect [34], but can also be influenced by ion's transversal temperature [35] or ion scattering on hard mask facets [36]. These three phenomena are illustrated in Figure I.13.

- **Bowing**: is a CD loss under the mask level because the ion trajectory is distorted and they are directed towards the sidewalls (Fig I.13c). This effect is typically observed in the etching of low-k materials because they are fragile and they are etched following an ion enhanced etching mechanism [37].

- **Micro-trenching:** Though most incident ions are perpendicular to the substrate surface, they also present a lateral component that affects their trajectory. In some cases, they can also be reflected and displaced along the pattern vertical sidewall leading to higher ion fluxes near the base of the feature. This effect is called micro-trenching [38] (Fig I.13d).

- **Notching**: The notching effect is the lateral etching of underlying layers during the etch process (Figure I.13e). This can occur either due to positive charging of the underlying layer, which can deflect the ions towards the sidewalls (i.e. at low bias voltages) [39], or due to isotropic etching of sidewall passivation layers [40].

And finally we find the deformations related to the etch rate uniformity and the CD control such as loading and Aspect Ratio Dependent Etching (ARDE) effects.

- Loading: Consists in a consumption of the reactive species by the wafer or the reactor walls that results in a reduced etch rate. In practice, it results in a decrease of the etching rate with an increase in the amount of exposed material to be etched. The loading effect can be observed at a wafer scale (macro-loading) or locally at a feature-scale (micro-loading). The loading effect depends on the density of the features to be etched, the chamber volume (i.e. larger volumes reduce the loading effect) [32], the gas flow rate (i.e. ER increases with increasing flow rate) [41] and the lifetime of the reactive species (Fig I.13 f).

- **Aspect Ratio Dependent Etch rate (ARDE)**: is the etch rate dependence on the aspect ratio of the structure to be etched. This effect is attributed to the difference in flux of neutral species, ions, and ion energy as a function of the pattern aspect ratio and results in a lower ER for structures having higher aspect ratios. This issue is mostly important for hole or trench etch processes (Fig I.13 g).

A schematic representation of all the etch degradation mechanisms is shown in Fig I.13.

**Figure I-13**Schematic representation of the gate profiles obtained during plasma etching: (a) Undercut (b) tapered profile (c) bowing (d) micro-trenching (e) notching, (f) Micro-loading and (g) ARDE.

All these profile degradation mechanisms become even more critical for gate integrations where small gate patterns need to be etched with strong uniformity and pattern fidelity.

### I.4 Challenges in Gate Patterning

As already explained, for the gate patterning process, lithography and etch steps follow each other to carry out the definition of gate patterns. However, with the increased complexity of the gate stacks and the dimension reduction, the gate patterning process becomes more and more challenging. Therefore, in this section, we will discuss about the main challenges encountered for both, lithography and plasma etching processes that limit the definition of ultimate gate patterns.

### I.4.1 Challenges related to the lithography step

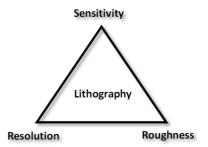

To ensure a good photoresist pattern definition, lithography has to meet three requirements: Resolution, Sensibility and Roughness.

### I.4.1.1 Resolution

The Resolution (R) is the smallest interval feasible between two photoresist patterns. Along with downscaling, the lithography needs to achieve the definition of smaller photoresist patterns and for this, the image resolution at very small scales needs to be improved.

The lithography Resolution (R) is expressed by the following Rayleigh criteria:

$$R = k \frac{\lambda}{NA}$$

(Eq. I.3)

Where k is an empirical constant (varies between 0.5-1 and depends on process conditions),  $\lambda$  is the light wavelength used for the PR exposition and NA is the numerical aperture of the lithography system (proportional to the environment refraction index, n, and the size of the optical lenses).

To improve the pattern resolution, it seems clear that the exposition wavelength ( $\lambda$ ) needs to be decreased. This is the reason for which at the late 90s we moved from KrF lasers emitting 248nm light towards ArF lasers with a 193nm light emission. Clearly changing the exposition wavelength also implies adapting the photoresist materials. Thus, the photo-resist platforms evolved from 248nm based photoresist towards 193nm photoresists. An illustration of both resist platforms is shown in Fig I.14.

(a) 248nm Photoresist

(b) 193nm Photoresist

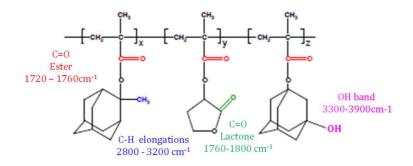

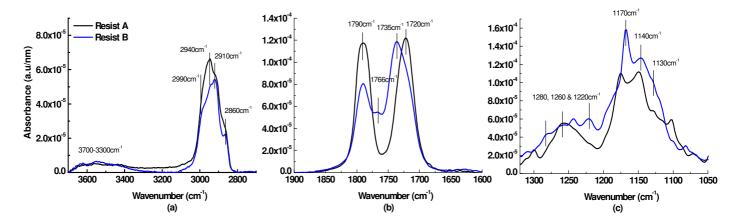

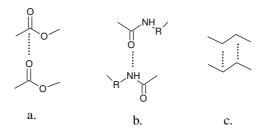

**Figure I-14** Structure of a (a) 248nm photo-resist based in a poly(hydroxystyrene) polymer matrix and a (b) 193nm photo-resist composed of three monomers: Methyl adamantane (MAMA) for thermal stability, a lactone group ( $\alpha$ GBLMA) to improve PR solubility in the developer solution, and a polar group (HAMA) to improve the adhesion of the film to the substrate.

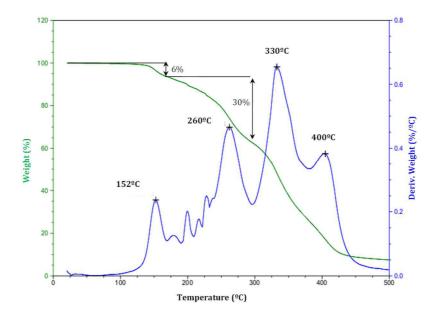

The 248nm photoresist (fig 13a) typically contained benzene rings that improve the PR resistance to etch processes. However, these structures strongly absorb the 193nm irradiation and therefore, the photo-catalytic reactions at such low exposition wavelengths were not efficient. Thus, lithographers moved towards acrylate based polymers which do not absorb the 193nm wavelength (Fig 13b). These photoresist contain different monomers, each of them with a specific function, such as, C-rich *protective groups* to improve the PR thermal stability, *lactone groups* to improve the PR solubility in the developer, or *polar groups* for adhesion enhancement. However, they are more sensitive to plasma etch processes due to the absence of benzene groups in the polymer chain. Besides, to avoid pattern collapse or ARDE issues in small PR patterns, the lithography tends to reduce the deposited photoresist thickness.

However, this strategy is not sufficient to ensure proper pattern definition for the latest CMOS technologies. Another option to further improve the resolution is increasing the numerical aperture (NA) or in other words, working in an environment whose refractive index is higher than 1 (n>1). Thus, from the 45nm technological node, *immersion lithography* where lithography scanners are submerged in a water environment (n= 1.44) have been introduced to improve the resolution.

Since then, the immersion lithography has reached its limitations and the dimension reductions with this technique have been at a standstill. Therefore, other lithography strategies such as Extreme UV lithography [42] or e-beam [43] lithography are under development. However, these strategies being expensive and not mature at this moment, to improve the gate pattern resolution, most companies use double patterning strategies at least until the 14nm technological node.

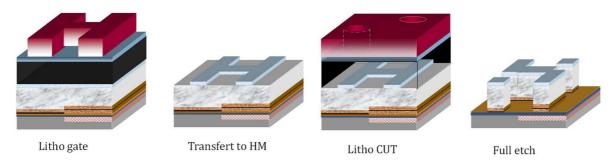

The double patterning process enables to double the pattern density from a conventional 193nm immersion lithography step. The main advantage of this technique is that it enables the definition of structures beyond resolution capability of existing lithographic tools without drastic changes in manufacturing infrastructures. There are two main types of double patterning technology: pattern-splitting type such as Litho-Etch-Litho-Etch process (LELE) [44] and self-aligned double patterning (SADP) [45].

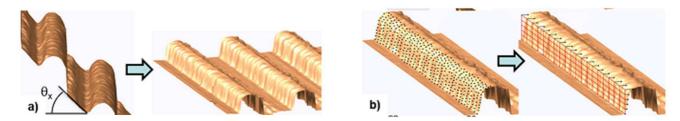

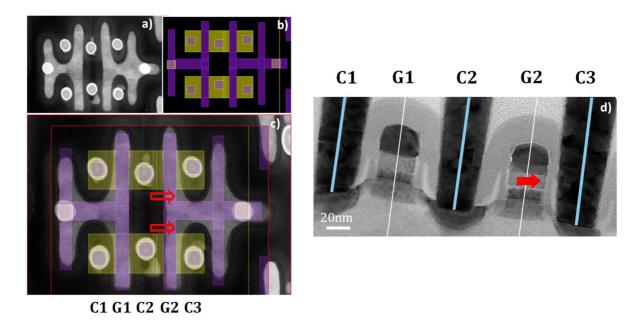

At ST Microelectronics, the LELE approach is used. It consists in the definition of the gate pattern in two steps using a litho-etch-litho-etch (LELE) approach. In a first step, referred as GATE etch, a first resist pattern (typically composed by gate lines) is transferred into the HM stack (Fig I.15).

Then a new lithography stack is deposited over the already patterned HM layer and a second lithography is done with a different mask design (Referred as CUT). This second lithography is used to cut the gate lines in different positions. Combination of both lithography patterns will define the final gate 2D patterns which are then transferred into the full stack.

**Figure I-15** Double patterning process: a first lithography step is used for gate pattern definition which is transferred to the HM layer. Then, in a second lithography step, the CUT definition is carried out. This new mask is used to cut the gate lines at certain points and define the final gate pattern at the HM layer. Finally, the gate pattern is transferred into the full stack.

### I.4.1.2 <u>Sensitivity</u>

The photoresist sensitivity is its efficiency to undergo photo-catalytic and deprotection reactions under UV exposure. For example, a very sensitive photoresist will undergo many photocatalytic reactions under low UV expositions. In other words, a lower UV dose, or the amount of UV irradiation per cm², is required for resist exposition. Working at lower doses is advantageous because it results in a reduction of the exposition time and therefore allows increasing the *throughput*, or the amount of processed wafers. Besides, at lower doses, a better control of the deprotection reactions can be obtained which can improve the pattern resolution.

To further improve the photoresist sensibility, chemists play with the polymer and PAG compositions to obtain more sensitive photoresists. For example, they will choose polymers with lower activation energies for the deprotection reactions (lower PEB) so that they react more easily with the PAG acids. Thus, we will be able to reduce the PAG concentration within the resist film and therefore, reduce the acid formation. This allows a better control of the deprotection reaction and limits the diffusion of the acid groups towards the non-exposed photoresist patterns. Due to these modifications, the photoresist chemistry has strongly changed. The first 193nm photoresist generation consisted in simple methyl methacrylate based polymers with only three different monomers [46]. Today, the 193nm photoresist present really complicated chemistries with 6 or more different monomers. This means that moving towards more sensitive photoresist may become a challenge for plasma etch processes.

### I.4.1.3 Roughness

The Roughness is an irregularity on the pattern line edge that results in variations of the average gate dimension or Critical Dimension (CD). To characterize the pattern roughness two parameters are used, the Line Width Roughness (LWR) that represents the CD standard deviation along an "infinite" line; and the Line Edge Roughness (LER) that represents the line edge variations.

$$LWR = 3 \sqrt{\sum_{i=l}^{n} \frac{(CD_i - \overline{CD})^2}{n}} LER = 3 \sqrt{\sum_{i=l}^{n} \frac{(x_i - \overline{x})^2}{n}}$$

(Line length)

Figure I-16 Schematic representation of roughness parameters: LWR and LER.

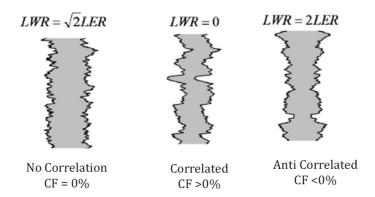

The line's right edge and left edge roughness variations can be correlated, not correlated or anticorrelated. An illustration is shown in Figure I.17.

**Figure I-17** Schematic representation gate patterns with no correlation, correlated sidewalls and anti-correlated sidewalls. CF refers to Correlation Factor.

The correlation degree between both line edges is defined by the correlation factor (or correlation coefficient,  $\rho$ ), which is given by:

$$\rho = \frac{\sigma_L^2 + \sigma_R^2 - \sigma_{CD}^2}{2\sigma_L \sigma_R}$$

Where,  $\sigma_{CD}$  is the standard deviation of the line width and  $\sigma_L$ ,  $\sigma_R$ , are the standard deviations of the left and right edges, i.e. the LWR, LER left and LER right respectively. The correlation coefficient can vary between -1 to +1. When the left and right edges of the patterns are uncorrelated (i.e. if the edge positions are independent from each other), the LWR and the LER are related by  $\sigma_{LWR} = \sqrt{2}\sigma_{LER}$ , resulting in a null correlation factor. The correlation coefficient is positive when the edges are correlated (i.e. when they tend to follow each other in phase which corresponds to wiggled patterns). If they are perfectly correlated,  $\rho = 1$  and then,  $\sigma_{LWR} = 0$ , even if  $\sigma_{LER} \neq 0$ . The correlation coefficient is

negative when the edges are anti-correlated, i.e. when they tend to follow each other in opposition of phase. In this situations, the LWR and LER are related by LWR = 2LER.

The origin of the photoresist LER is attributed to many contributors, such as, the lithography mask roughness [47], the resolution (i.e. the contrast between the exposed and un-exposed PR patterns) [48], the "shot noise" (i.e. the statistic variation of the applied dose) [49] or the acid diffusion within the unexposed photoresist pattern [50] [51].

Unfortunately, all these contributors are correlated and it becomes complicated to find a good compromise to reduce the PR LER but keeping a good pattern resolution and PR sensibility. For example, by increasing the acid diffusion length, the LER can be improved. However, if the acid diffuses too much within the PR film, then, the resolution will be degraded ref. The same occurs if too sensitive resists are chosen. In this case, the dose needs to be reduced to keep a good resolution, but at low doses, due to the shot noise effect, the LER is degraded. To improve the LER either we work at high doses, or we increase the acid diffusion, but both degrade the resolution. In conclusion, there is no way to improve the Sensitivity (i.e. dose reduction) and the resolution (i.e. pattern definition) keeping low LER values. This is described as the "lithography incertitude principle" (i.e. LSR principle) and resumes the challenges to find a good compromise between Sensibility/Resolution/LER.

Figure I-18 Lithography incertitude principle

Along with downscaling, finding a good compromise becomes more and more challenging because, to pattern small gate designs, extremely sensitive photoresist are required, which supposes a problem in terms of pattern LER degradation.

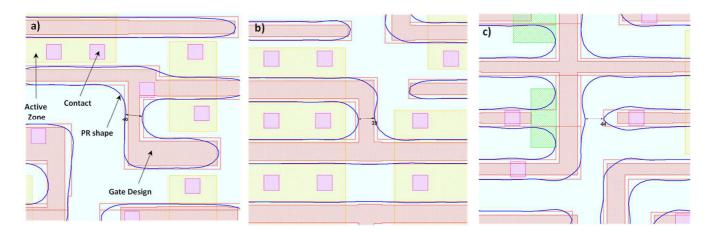

Besides, the increasing pattern density and the mask design complexity make of pattern resolution a very critical point. For example, in the logic integrations of the latest CMOS devices, we can find 2D gate structures that are not easy do define at the lithography level. Some examples are shown in Figure I.19.

**Figure I-19**(a, b & c) Three examples of 2D structures designed for the latest logic CMOS technologies. The gate designs are represented in red. Pink squares represent contact position while orange and green squares represent the active zones. The photoresist pattern shape is illustrated by the contour defined by the blue lines. To better identify the PR pattern shape deformations, the resist profile and the designed structures are overlapped.

Due to resolution problems U-Shape structures are not patterned with a good fidelity (i.e. rounded corners, short line ends....). To improve the pattern definition, the lithography benefits of the "Optical Proximity Correction" (OPC) models which correct and modify the mask design considering the lithography pattern deformations in order to improve the PR pattern definition [52] [53]. However, even with the addition of all the lithography corrections, the definition of small gate features still remains a challenge in some gate integrations.

### I.4.2 Challenges related to the dry etch processes

Gate etching itself is also a very challenging process because, perfectly anisotropic gate profiles need to be patterned over gate stacks comprising a wide number of different materials. Thus, an etch process needs to respect five criteria: a good anisotropy, strong selectivity, CD control, etch rate uniformity and low damage. Considering the ITRS specifications for the latest CMOS technologies, these criteria become more and more difficult to respect.

- Anisotropy: In the gate etch processes, perfectly anisotropic (vertical) gate profiles need to be

obtained without impacting the selectivity or damaging the underlying layers. For this, the ion

bombardment as well as the deposition and etch mechanisms need to be controlled at a

nanometer scale.

- **Selectivity**: The etch selectivity is the etch rate ratio between the etch rate of the etched material relative to that of the masking material or the underlying layer.

$$S = \frac{ER_{etched material}}{ER_{underlying material}}$$

(Eq. I.4)

Ideally, the selectivity should be infinite or at least >>1. A good selectivity is extremely important because usually the etch processes need to be stopped on ultra-thin layers. For example, in the case of the  $HfO_2$  HK etching, the process has to be stopped on the underlying silicon where the source and drains will be elaborated, without consuming or damaging it. These processes are often carried out in  $BCl_3/Cl_2$  chemistries. As it will be explained in Chapter II (section II.2.2.3),  $BCl_3$  addition improves the selectivity because in presence of silicon it

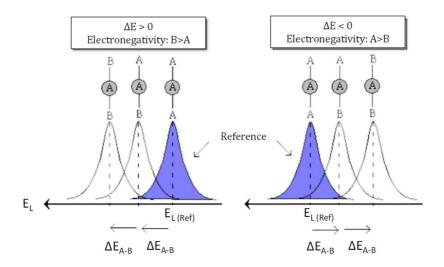

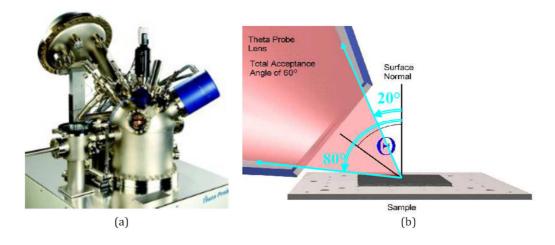

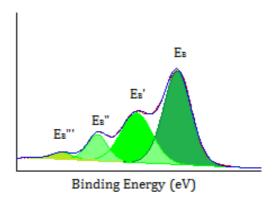

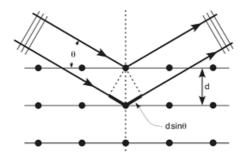

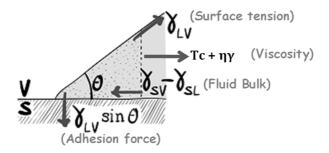

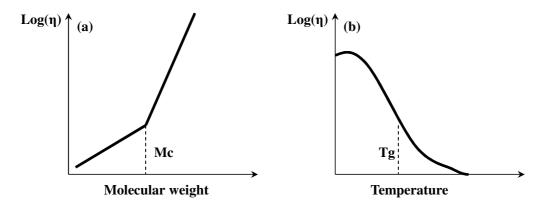

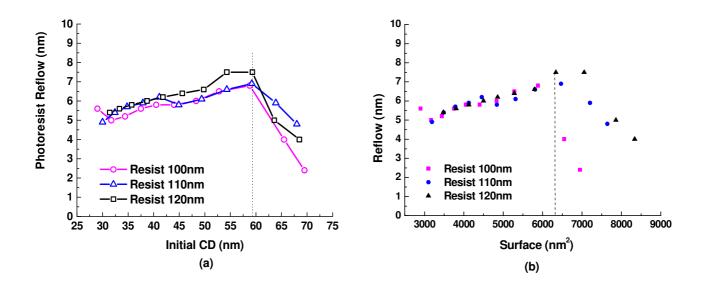

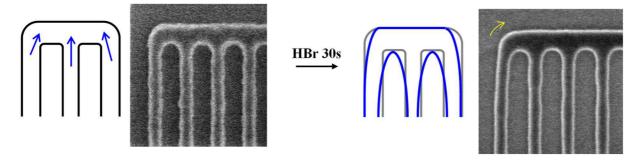

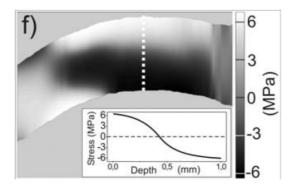

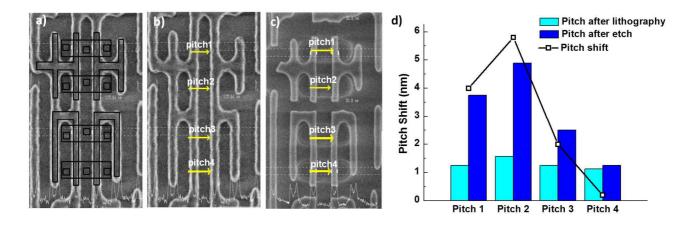

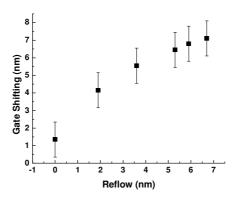

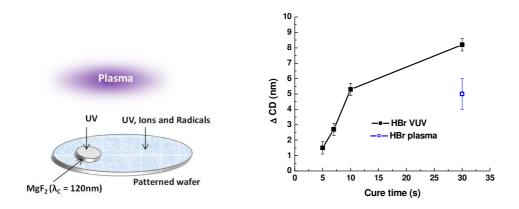

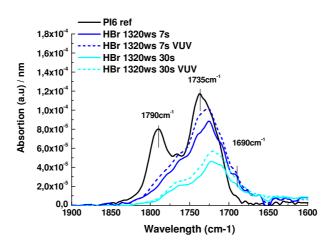

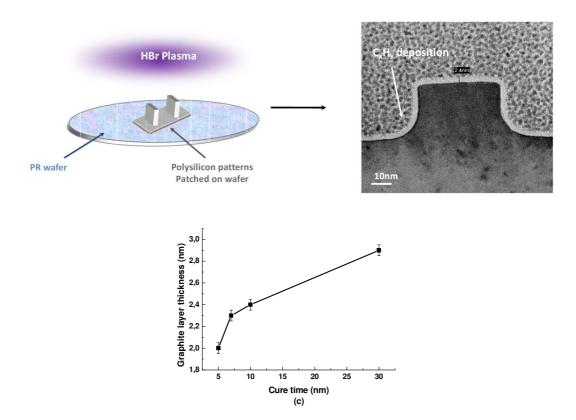

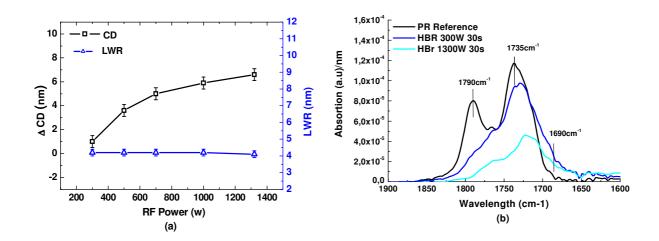

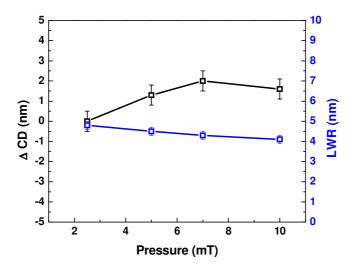

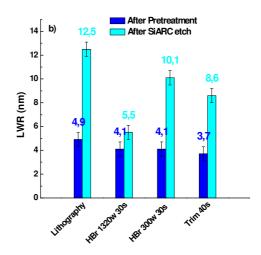

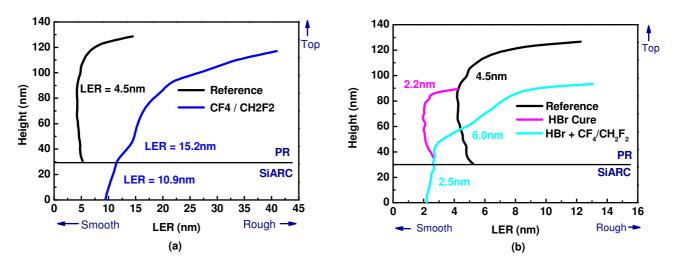

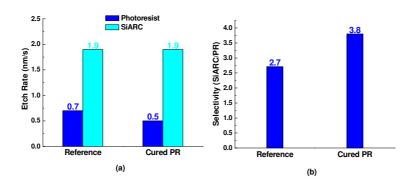

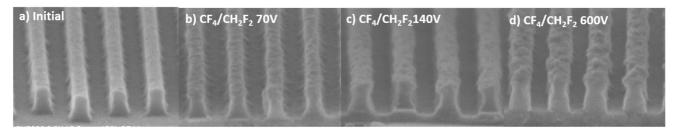

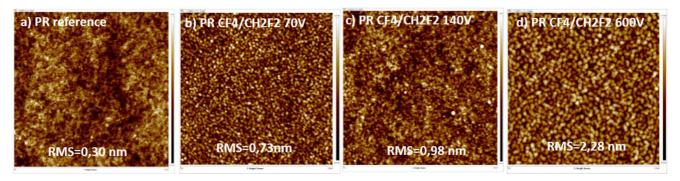

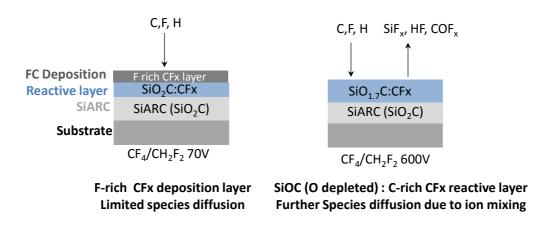

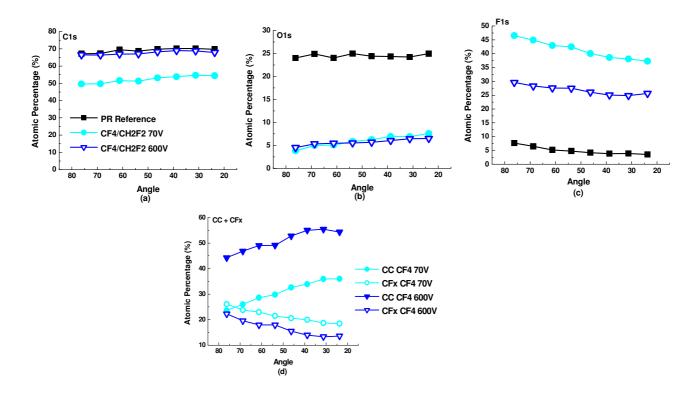

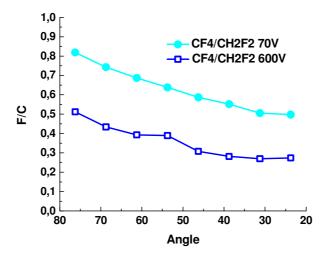

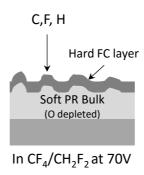

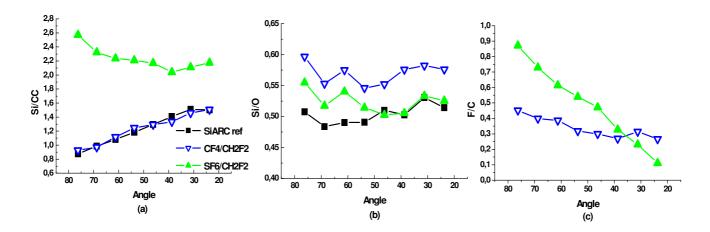

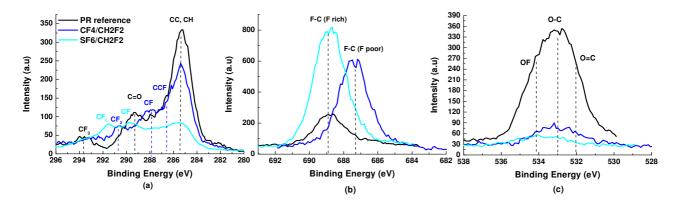

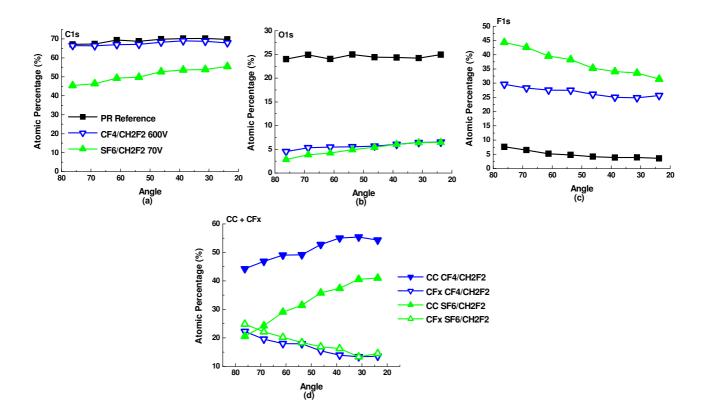

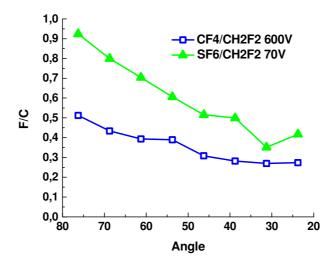

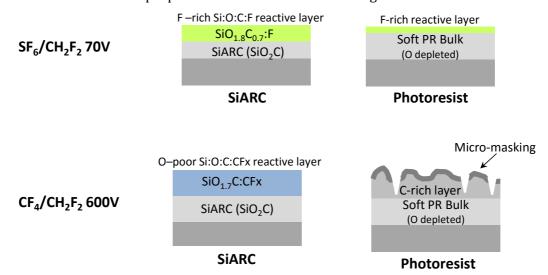

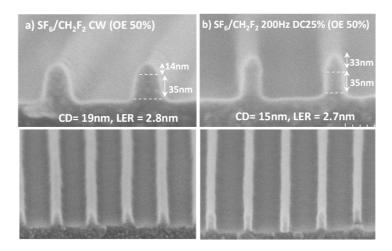

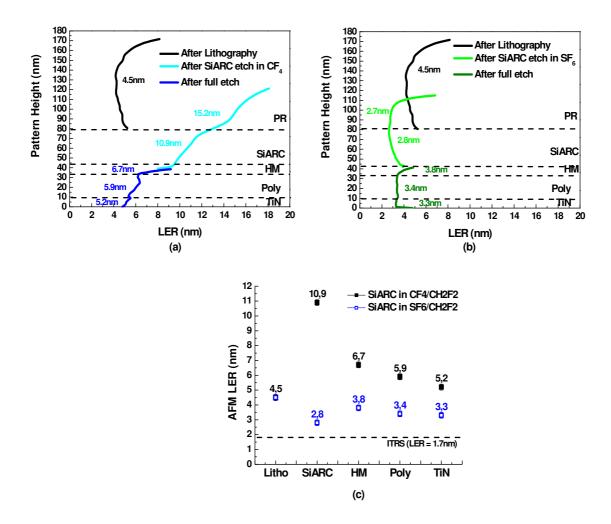

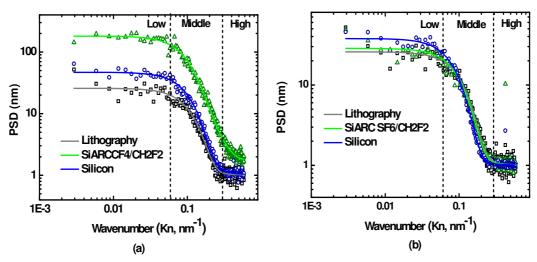

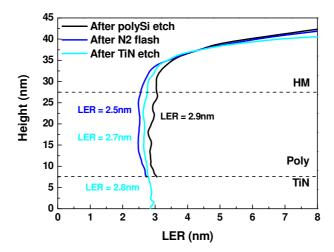

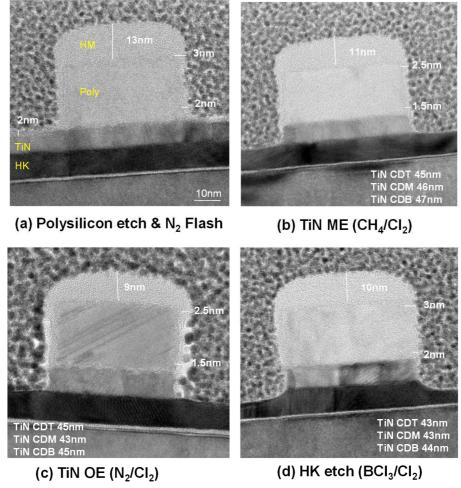

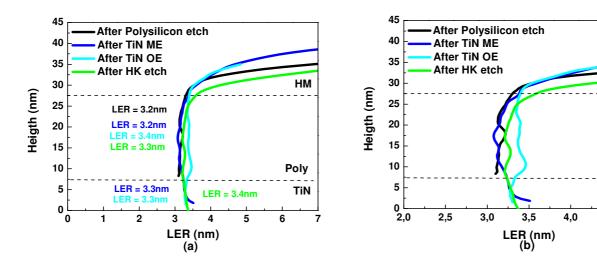

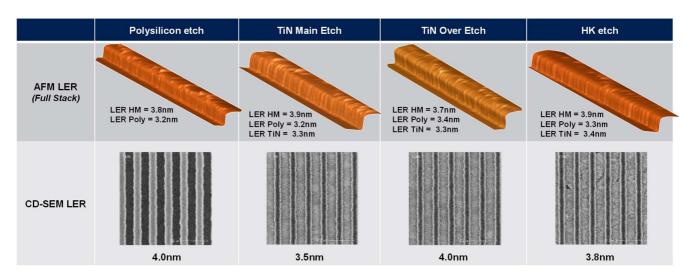

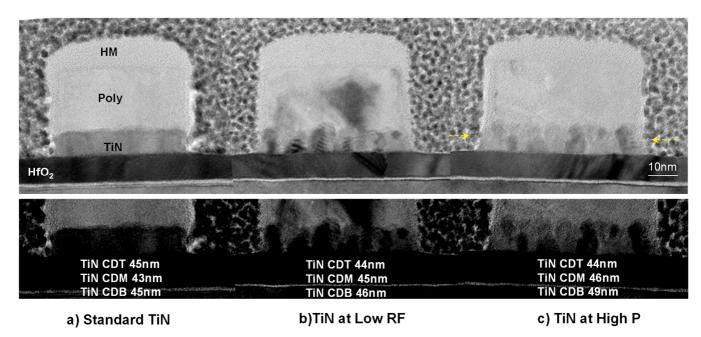

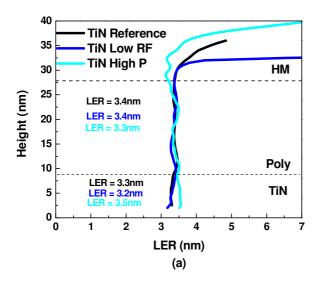

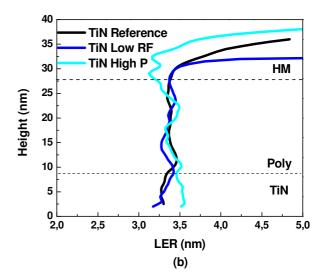

initiates a  $BCl_x$  deposition process that stop the silicon etch reaction. By this way, an infinite selectivity is obtained [54].