## Low power architecture for fall detection system

Thi Khanh Hong Nguyen

## ▶ To cite this version:

Thi Khanh Hong Nguyen. Low power architecture for fall detection system. Other. Université Nice Sophia Antipolis, 2015. English. NNT: 2015NICE4093. tel-01288526

# HAL Id: tel-01288526 https://theses.hal.science/tel-01288526

Submitted on 15 Mar 2016

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### UNIVERSITE NICE-SOPHIA ANTIPOLIS

## **ECOLE DOCTORALE STIC**

#### SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION

# THESE

pour obtenir le titre de

## Docteur en science

De l'Université Nice-Sophia Antipolis

Mention:

Présentée et soutenue par

Thi Khanh Hong NGUYEN

## Low power architecture for Fall Detection System

Thèse dirigée par Cecile BELLEUDY et Van Tuan PHAM

Soutenue le 18 Novembre 2015

#### Jury:

Mme. Nathalie Julien Professeur à l'Université Rapporteur de Bretagne Sud

M. Bertrand Granado Professeur à l'Université de

Pierre and Marie Curie

Rapporteur

Mme. Cecile BELLEUDY Maitre de Conférences, HDR,

Université Nice Sophia Antipolis

M. Van Tuan PHAM Co-directeur Associate Professeur,

Université de Science et Technologie,

Université de Da Nang.

Directeur de recherche de INRIA M. François Brémond Examinateur

Directrice

# **Contents**

| Abstract                                                                | ix   |

|-------------------------------------------------------------------------|------|

| Résumé                                                                  | xi   |

| Acknowledgement                                                         | xiii |

| Chapter 1. Introduction                                                 | 1    |

| 1.1 The healthcare systems                                              | 2    |

| 1.1.1 The healthcare system based on sensors                            | 2    |

| 1.1.2 The healthcare system based on audio                              | 4    |

| 1.1.3 The healthcare system based on communication network              | 4    |

| 1.1.4 The healthcare system based on intelligent video surveillance     | 5    |

| 1.2 Fall Detection Approaches.                                          | 6    |

| 1.2.1 Classification Fall Detection Approach                            | 6    |

| 1.2.2 Efficient Architecture for Fall Detection on heterogeneous platfo | orm8 |

| 1.3 Research questions                                                  | 11   |

| 1.4 Thesis contributions                                                | 12   |

| 1.5 Publications                                                        | 14   |

| 1.5.1 International journal publication                                 | 14   |

| 1.5.2 International conference's publication                            | 14   |

| 1.5.3 Other publications                                                | 15   |

| 1.6 Thesis Organization                                                 | 15   |

| Chapter 2. Fall Detection Algorithm                                     | 17   |

| 2.1 Overview of Fall Detection algorithm                                | 17   |

| 2.1.1 Definition of falling event                                       | 17   |

| 2.1.2 Fall Detection algorithms                                         | 18   |

| 2.2 Proposed Fall Detection Algorithm                                   | 22   |

| 2.2.1 Object Segmentation                                               | 23   |

| 2.2.2 Object Enhancement                                                | 25   |

| 2.2.3 Object Feature Extraction                                         | 28   |

| 2.3 Recognition event                                                   | 36   |

| 2.3.1 Threshold-based algorithm                                         | 36   |

| 2.3.2 Neural Network algorithm                                                  | 37 |

|---------------------------------------------------------------------------------|----|

| 2.3.3 Hidden Markov Model algorithm.                                            | 39 |

| 2.4 Evaluation                                                                  | 40 |

| 2.4.1 DUT-HBU database                                                          | 40 |

| 2.4.2 Performance measurement.                                                  | 44 |

| 2.4.3 Performance of the system based on Hidden Markov Model                    | 51 |

| 2.4.5 Analysis of error recognition                                             | 54 |

| 2.5 General discussion                                                          | 57 |

| 2.5.1 Performance under real-life conditions                                    | 58 |

| 2.5.2 Usability                                                                 | 58 |

| 2.6 Conclusion                                                                  | 58 |

| Chapter 3. Power and Time Model Methodology for Fall Detection System           | 61 |

| 3.1 Power and energy consumption characterization and estimation in MPSoC       | 62 |

| 3.2 Power consumption modeling approaches                                       | 63 |

| 3.2.1 Low-level power consumption estimation techniques                         | 63 |

| 3.2.2 High-level power consumption estimation techniques                        | 67 |

| 3.3 Execution time estimation approaches                                        | 73 |

| 3.3.1 Static timing estimation                                                  | 73 |

| 3.3.2 Dynamic timing estimation.                                                | 74 |

| 3.3.3 Timing estimation tools                                                   | 75 |

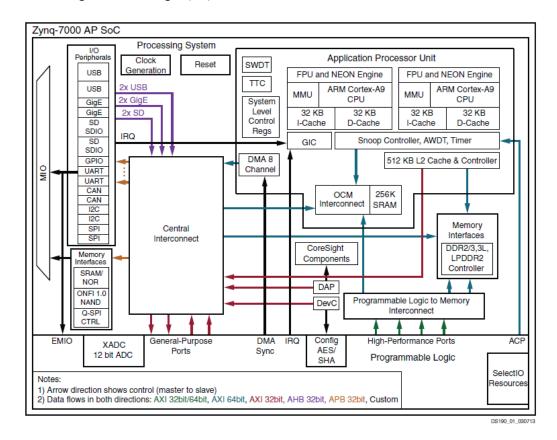

| 3.4 Heterogeneous platform: Zynq7000 AP SoC platform                            | 77 |

| 3.4.1 Motivation.                                                               | 77 |

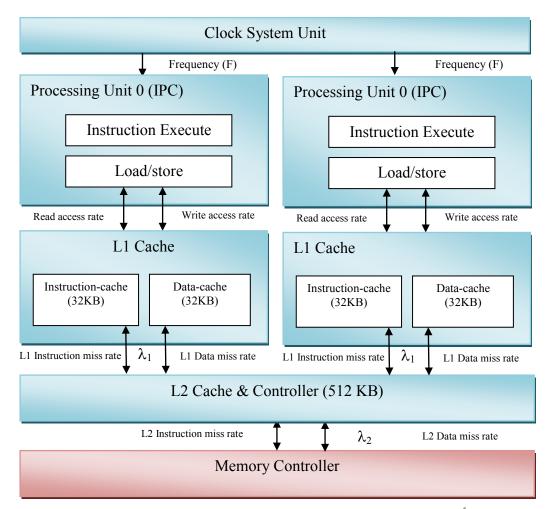

| 3.4.2 Description of Zynq-7000 AP SoC                                           | 78 |

| 3.4.3 The Performance Monitor Unit (PMU)                                        | 79 |

| 3.5 Power/execution time models for video applications                          | 81 |

| 3.5.1 Power estimation methodology for Fall Detection System                    | 81 |

| 3.5.2 Power measurement                                                         | 83 |

| 3.5.3 Execution time measurement                                                | 85 |

| 3.6 Proposed power model of the Fall Detection System on heterogeneous platform | 86 |

| 3.6.1 Power models for processor                                                | 86 |

| 3.6.2 Power models for hardware                                                 | 95 |

| 3.6.3 Power consumption models for heterogeneous architecture                   | 97 |

| 3.7 Execution time models for heterogeneous platform                              | 97  |

|-----------------------------------------------------------------------------------|-----|

| 3.7.1 Execution time models for processor                                         | 98  |

| 3.7.2 Times models for hardware acceleration (FPGA)                               | 100 |

| 3.8 Conclusion                                                                    | 101 |

| Chapter 4. Low Cost Architecture for Fall Detection System                        | 103 |

| 4.1 High level synthesis tools based on C/C++ specification                       | 104 |

| 4.1.1 CATAPULT                                                                    | 104 |

| 4.1.2 Program In Chip Out (PICO) tool's                                           | 105 |

| 4.1.3 GAUT, SPARK tools                                                           | 105 |

| 4.1.4 Vivado HLS tool                                                             | 106 |

| 4.2 Low power techniques                                                          | 108 |

| 4.3 Video applications and Fall Detection System implemented on various platforms | 111 |

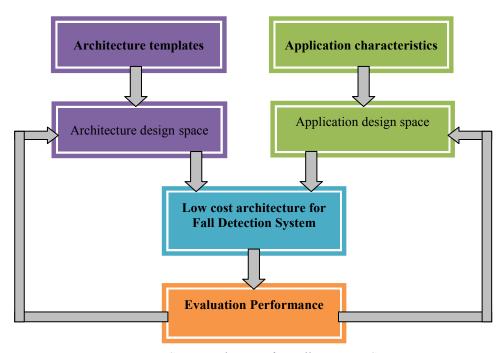

| 4.4 Overview of low cost architecture methodology                                 | 114 |

| 4.5 Software development and testing                                              | 116 |

| 4.5.1 Case study                                                                  | 116 |

| 4.5.2 Primary implementation and experiment results for the Fall Detection Sys    | tem |

| on software                                                                       | 117 |

| 4.5.3 Performance evaluation for the Fall Detection System                        | 120 |

| 4.6 Hardware development and testing                                              | 124 |

| 4.7 Application of parallelism techniques                                         | 124 |

| 4.7.1 Intra-task parallelism technique.                                           | 125 |

| 4.7.2. Inter-task parallelism technique                                           | 130 |

| 4.8 Design Space Exploration Architecture for Fall Detection System               | 131 |

| 4.8.1 Methodology                                                                 | 132 |

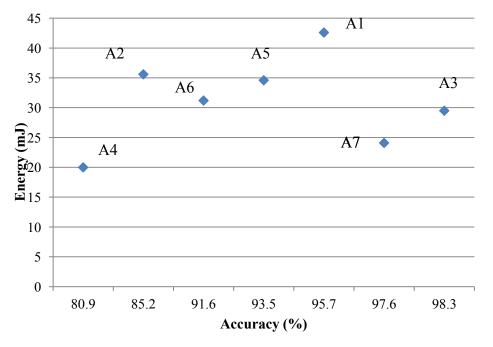

| 4.8.2 Model results                                                               | 134 |

| 4.9. Conclusion                                                                   | 136 |

| Chapter 5. Conclusions and perspectives                                           | 139 |

| 5.1 Conclusion                                                                    | 140 |

| 5.2 Perspectives                                                                  | 141 |

| 5.2.1 Improve the Fall Detection Algorithm                                        | 142 |

| 5.2.2 Power/execution time optimization                                           | 142 |

| 5.2.3 Camera network                                                              | 143 |

|         | 5.2.4 Solutions for combination of many equipments for the Fall Detection System | 143 |

|---------|----------------------------------------------------------------------------------|-----|

| Append  | lix                                                                              | 145 |

| Bibliog | raphy                                                                            | 147 |

# **Figures**

| Figure 1.1-A model of the healthcare system based on sensors stuck on human body [8]          | 3        |

|-----------------------------------------------------------------------------------------------|----------|

| Figure 1.2-Welfare Techno House system [9]                                                    | 3<br>1   |

| Figure 1.3-A circular microphone array used to automatically detects falling actions[6]       |          |

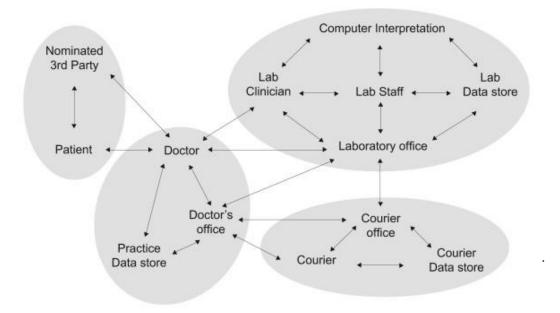

| Figure 1.4-A possible communication pathways for a laboratory test [10]                       |          |

| Figure 1.5-A person is monitoring the healthcare camera in a hospital [12]                    |          |

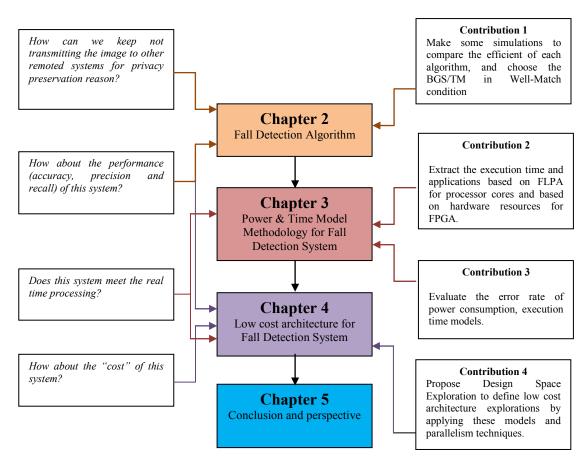

| Figure 1.6-An outline of the different chapters, research questions and contributions in this |          |

| thesis                                                                                        | 10       |

| Figure 2.1-A typical fall while walking                                                       | 19       |

| Figure 2.2-Some typical types of non-fall action                                              |          |

| Figure 2.3-Block diagram of Fall Detection System.                                            |          |

| Figure 2.4-Detecting the fall by video analysis                                               | 20       |

| Figure 2.5 (a) Estimated background; (b) Frame input; (c) Background Subtraction metho        |          |

| (d) Adaptive GMM method                                                                       | 25       |

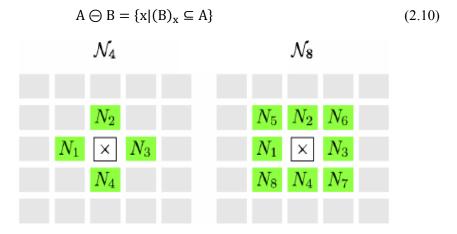

| Figure 2.6-Structuring elements in Mathematical morphology                                    |          |

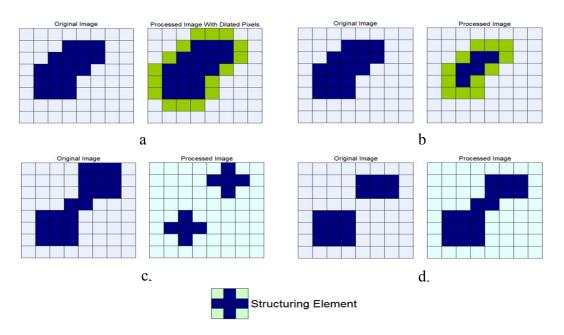

| Figure 2.7-Example of Mathematical morphology operations [62]                                 |          |

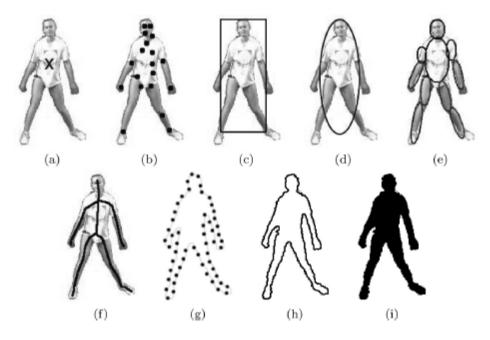

| Figure 2.8-Object representations. (a) Centroid, (b) multiple points, (c) rectangular patch,  |          |

| [64] (d) Elliptical patch, (e) part-based multiple patches, (f) object skeleton, (g) Complete |          |

| object contour, (h) control points on object contour, (i) object silhouette                   |          |

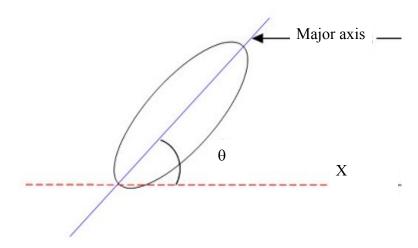

| Figure 2.9-Vertical angle $\theta$                                                            |          |

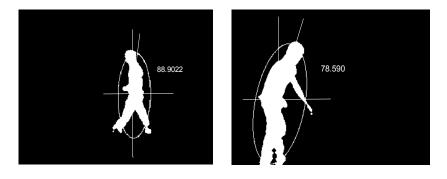

| Figure 2.10-Ellipse model for fall action                                                     |          |

| Figure 2.11-Current angle of object                                                           |          |

| Figure 2.12-Motion History Image. (a) MHI of slow action (b) MHI of fast action               |          |

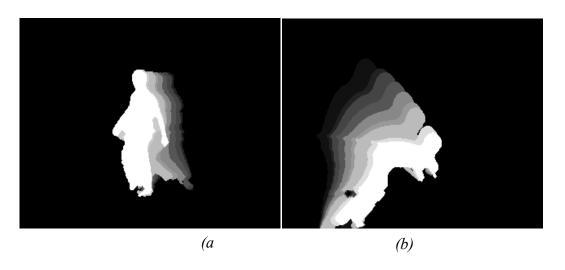

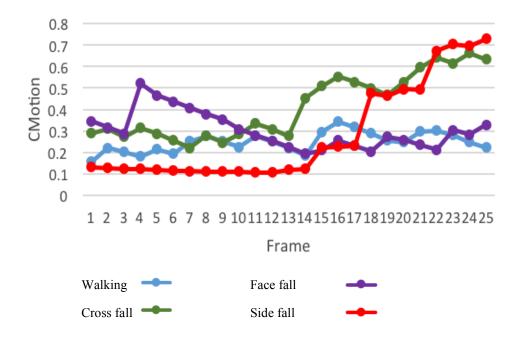

| Figure 2.13-The variable of coefficient of motion                                             | 34       |

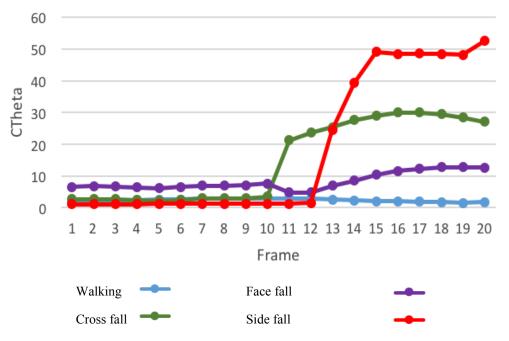

| Figure 2.14-Deviation of the angle ( $C_{Theta}$ )                                            |          |

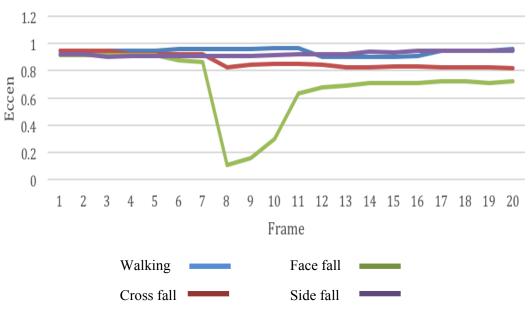

| Figure 2.15-Eccentricity.                                                                     |          |

| Figure 2.16-The position of falling compared with angles of camera                            |          |

| Figure 2.17-Daily activities look like falling                                                |          |

| Figure 2.18-Confusion matrix                                                                  |          |

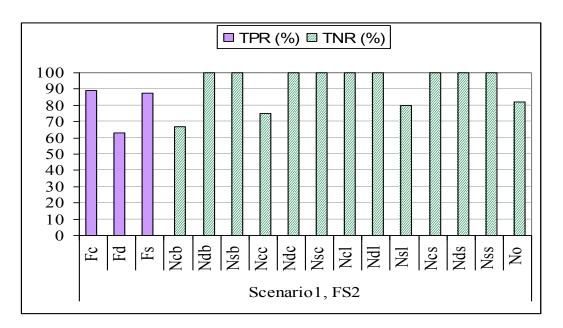

| Figure 2.19-Evaluating TPR and TNR of ALL three tests (FS1, SN1)                              |          |

| Figure 2.20-Evaluating TPR and TNR of ALL three tests (FS1, SN2)                              |          |

| Figure 2.21-Evaluating TPR and TNR of ALL three tests (FS2, SN1)                              |          |

| Figure 2.22-Evaluating TPR and TNR of ALL three tests (FS2, SN2)                              |          |

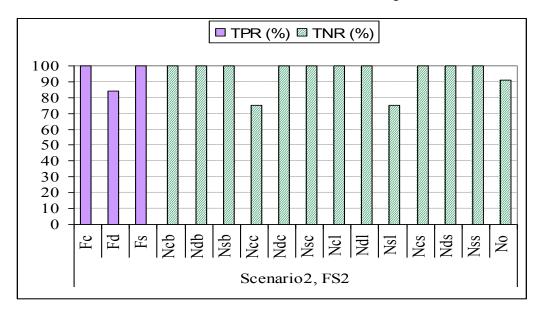

| Figure 2.23-Evaluating three tests for four different models                                  |          |

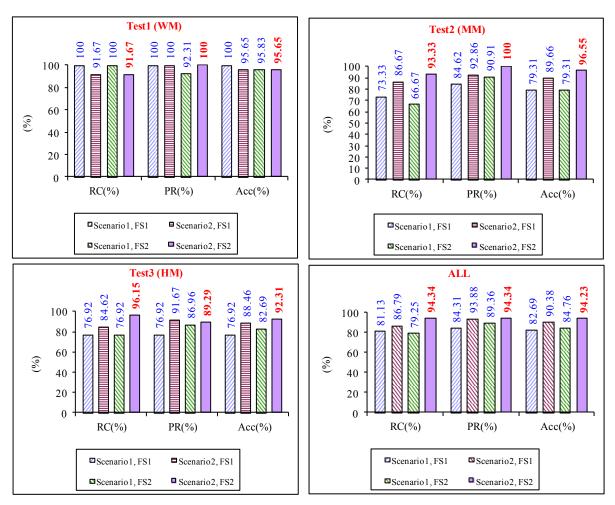

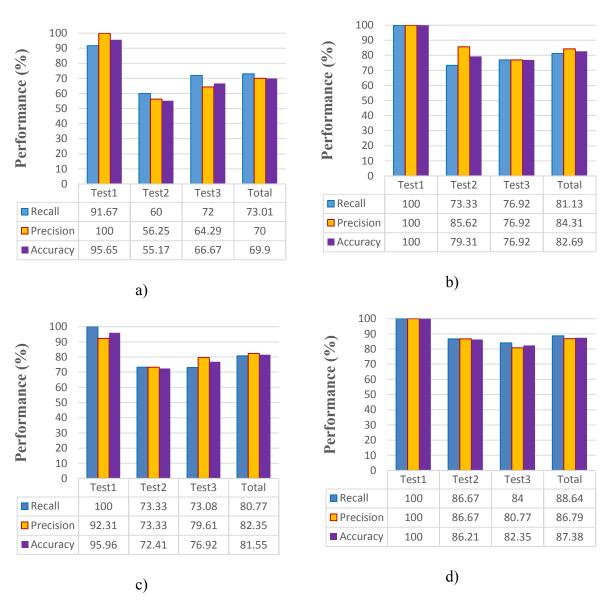

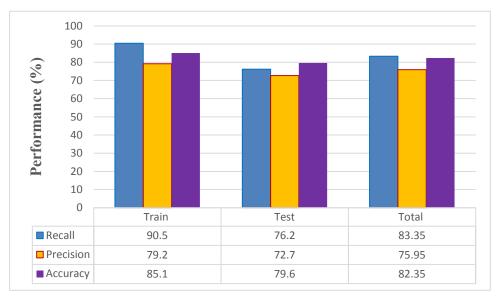

| Figure 2.24-Statistical results following to Recall (RC) [%], Precision (PR) [%] and          |          |

| Accuracy (Acc)                                                                                | 52       |

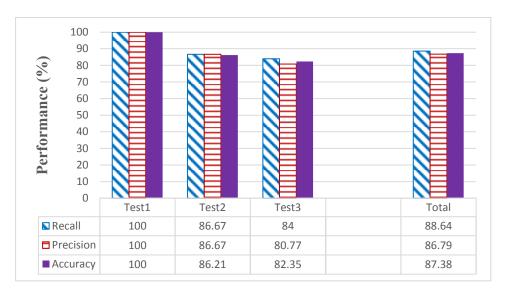

| Figure 2.25-Recognition performance derived from                                              |          |

| Figure 2.26-Extracted object under not good environment's brightness                          |          |

| Figure 2.27-Object is obscured some parts of body                                             |          |

| Figure 2.28-Many objects are moving at the same time                                          |          |

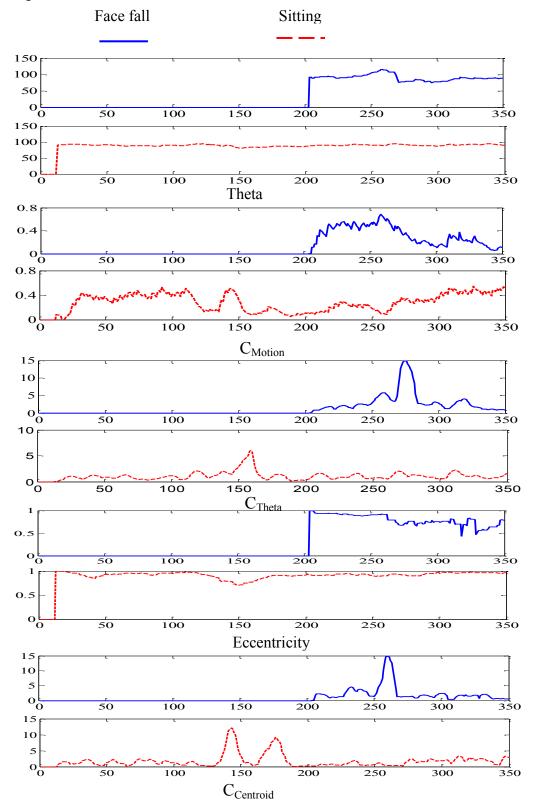

| Figure 2.29-Comparison the five features of face fall and sitting action                      |          |

| 5 T                                                                                           | /        |

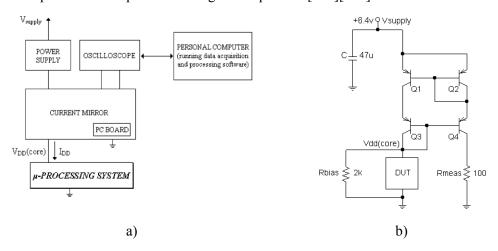

| Figure 3.1-(a) Experimental Setup for current measurement, (b) The simple current mirror      | <b>.</b> |

| DUT is the Device Under Test [116]                                                            |          |

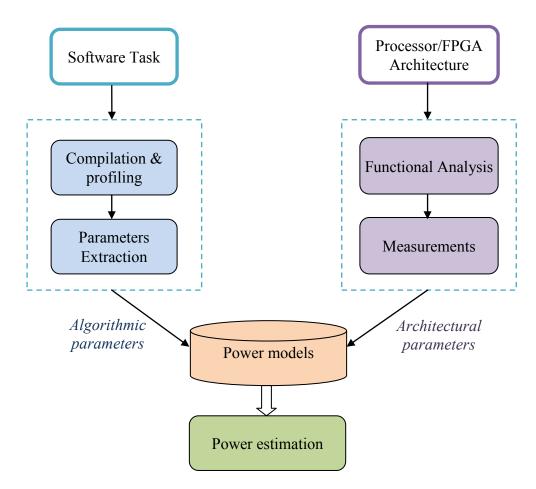

| Figure 3.2-The Functional Methodology[121]                                                    |          |

| <del>-</del>                                                                                  |          |

| Figure 3.3-Zynq-7000 All Programmable SoC Overview[144]                                | 79    |

|----------------------------------------------------------------------------------------|-------|

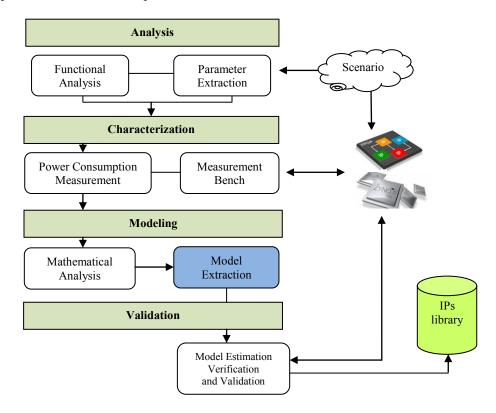

| Figure 3.4-Functional Level Power Analysis Methodology [147]                           | 82    |

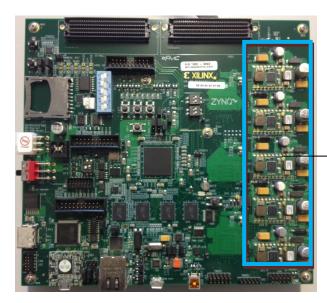

| . Figure 3.5-Integrated Texas Instruments digital power controller on Zynq-7000 Ap SoC | 83    |

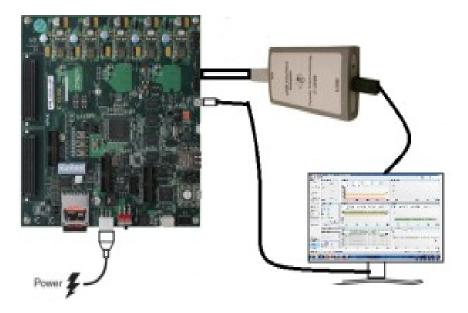

| Figure 3.6-Measurement environment for Zynq-7000 AP SoC platform                       | 84    |

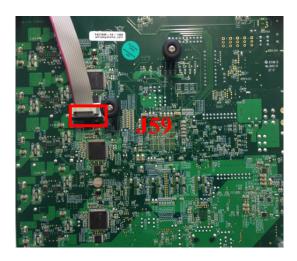

| Figure 3.7-Power Measurement probes across jumper for Zynq-7000 AP SoC                 | 85    |

| Figure 3.8-Framework for extracting power models                                       | 87    |

| Figure 3.9-Functional Blocks of Dual Core ARM Cortex A9 processor                      | 89    |

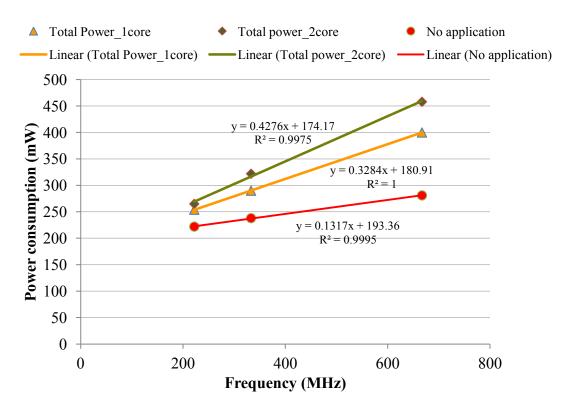

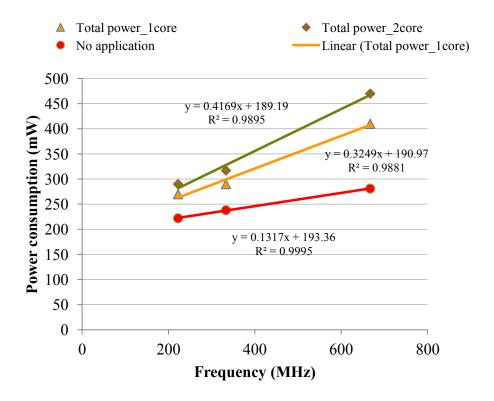

| Figure 3.10-Power models of Object Segmentation with $320x240$ input images on SW      | 90    |

| Figure 3.11-Power models of Mathematical Morphology with 640x480 input image on S      | W.90  |

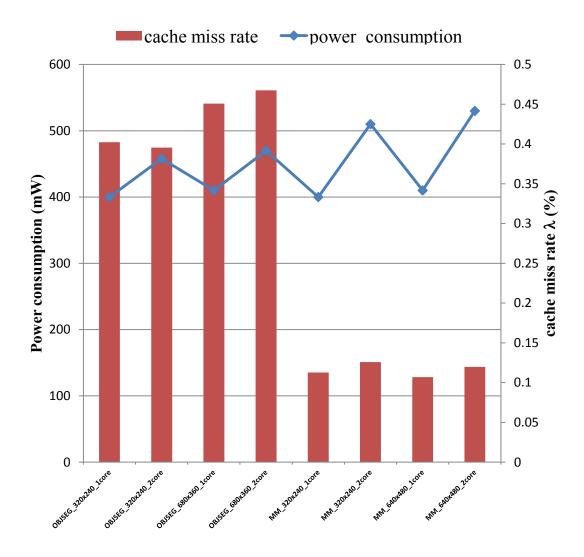

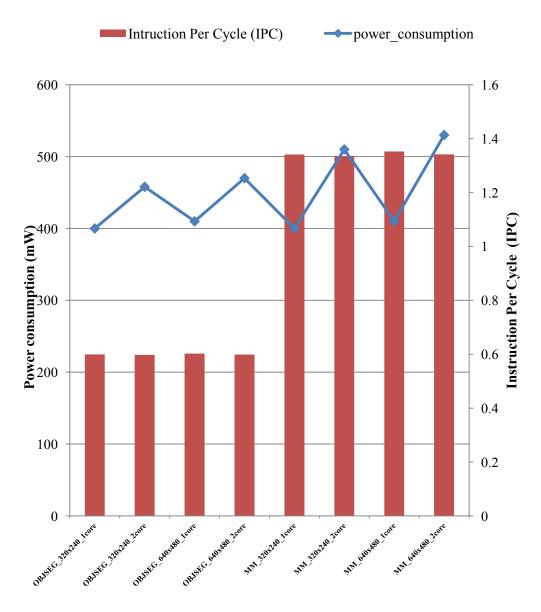

| Figure 3.12-The power consumption and cache miss rate of Object Segmentation and       |       |

| Mathematic Morphology with various resolutions                                         | 91    |

| Figure 3.13-The power consumption and Instruction per Cycle (IPC) of Object Segmenta   | ıtion |

| and Mathematic Morphology with various resolutions                                     | 92    |

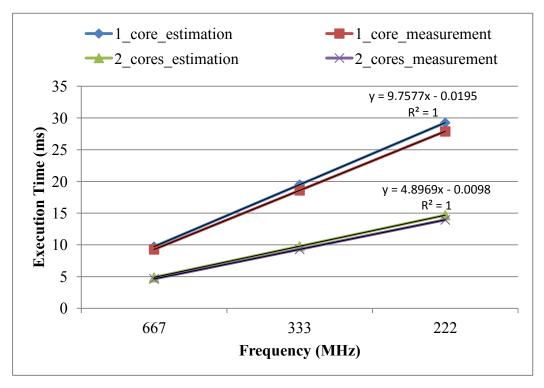

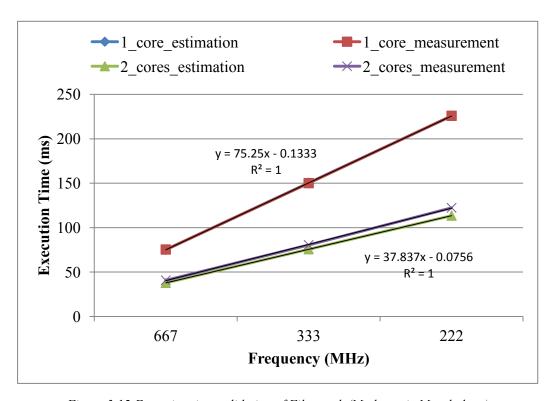

| Figure 3.14-Execution time validation of Object Segmentation task                      | 99    |

| Figure 3.15-Execution time validation of Filter task (Mathematic Morphology)           | 99    |

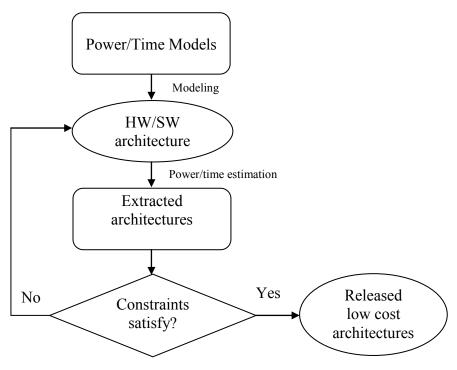

| Figure 4.1-Our low cost architecture design methodology for Fall Detection System      | 115   |

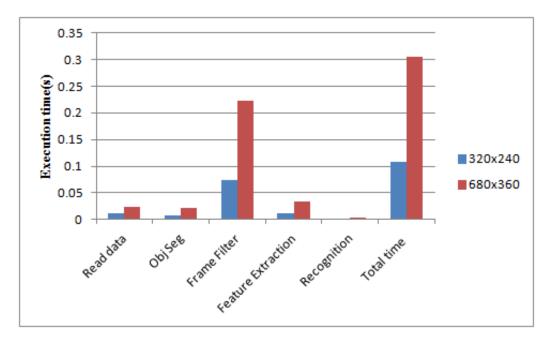

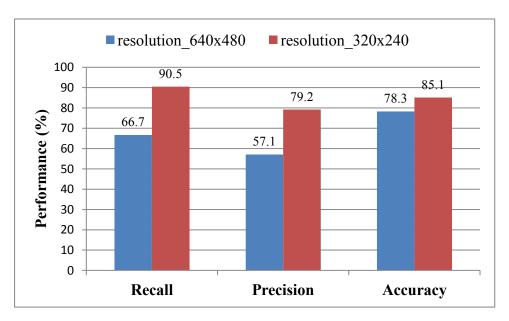

| Figure 4.2-Comparison execution times at two image resolutions on one core             | 120   |

| Figure 4.3-The results of Template Matching Algorithm with resolution 320x240          | 122   |

| Figure 4.4-The performance comparison of two resolutions                               | 123   |

| Figure 4.5-Design Space Exploration for Fall Detection System                          | 132   |

| Figure 4.6-Architecture exploration for Fall Detection System                          | 135   |

# **Tables**

| Table 2.1-Classifier of videos according to activities                              | 41      |

|-------------------------------------------------------------------------------------|---------|

| Table 2.2-Glossary of action classification                                         |         |

| Table 2.3-Performance of the Model 1                                                |         |

| Table 2.4-Performance of the Model 2                                                |         |

| Table 2.5-Performance of the Model 3                                                |         |

| Table 2.6-Performance of the Model 4                                                |         |

| Table 2.7-Classifier of videos according to activities                              |         |

| Table 3.1-Model parameters                                                          |         |

| Table 3.2-Power model of Object Segmentation and Filter task                        | 89      |

| Table 3.3-Maximum and average errors for power consumption model on processors      |         |

| Table 3.4-The power consumption on FPGA                                             |         |

| Table 3.5-Hardware resources and power consumption on different input image resolu  |         |

|                                                                                     | 96      |

| Table 3.6-The validation of power consumption model on FPGA                         | 97      |

| Table 3.7-Estimation of Execution time on hardware for video applications           | 100     |

| Table 4.1-Fall Detection System implements on different frequencies                 | 118     |

| Table 4.2-The Power/Energy of Fall Detection System on SW                           | 119     |

| Table 4.3-Classification of videos                                                  | 121     |

| Table 4.4-Confusion matrix                                                          | 122     |

| Table 4.5-The relationship between Accuracy performance with resolution and frame   | rate of |

| input video                                                                         | 123     |

| Table 4.6-Summary the results on hardware                                           | 124     |

| Table 4.7-Task regroups Architecture 2 with 320x240 resolutions                     | 126     |

| Table 4.8-The relationship of power and energy per frame at different frequencies   | 126     |

| Table 4.9-Example of frequency for different frame rate                             | 126     |

| Table 4.10-Task regroups case 4                                                     | 127     |

| Table 4.11-The estimation power/energy per frame at different frequencies (A4)      | 127     |

| Table 4.12-Intra-task parallelism technique                                         | 128     |

| Table 4.13-The inter-task technique with scheduling of five consecutive frames      | 130     |

| Table 4.14-The relationship between energy and accuracy in different architectures  | 135     |

| Table 4.15-The power/energy consumption and architectures based on inter-task techn | ıique   |

|                                                                                     | 136     |

## **Abstract**

Nowadays, fall detection is a major challenge in the public health care domain, especially for the elderly living alone. Falls are the leading cause of injury deaths among older adults, those aged 65 or older. Moreover, the lack of medical staff, who take care of rehabilitants in hospital, is an urgent problem in the 21<sup>st</sup> century. Therefore, the demand for surveillance systems, especially for fall detection, has considerably increased within the healthcare industry.

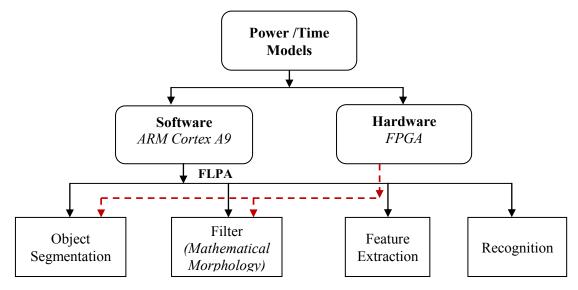

This thesis presents an exploration for a Fall Detection System based on camera under an algorithmic and architectural point of view. The studied Fall Detection System is suitable not only for the elderly living alone, but also for rehabilitants in hospitals. Our system is composed of four modules: Object Segmentation, Filter, Feature Extraction and Recognition and can give an urgent alarm for detecting different kinds of fall.

Firstly, different algorithms are proposed and studied for the modules which compose the Fall Detection System like the Background Subtraction-Neural Network (BGS-NN), the Background Subtraction-Template Matching (BGS-TM), the Background Subtraction-Hidden Markov Model (BGS-HMM), and the Gaussian Mixture Model (GMM-HMM). In order to evaluate the efficiency of these algorithms, a comparison is made on the accuracy (Acc), precision (PR) and recall (RC) performance. This comparison leads to select the BGS/TM which will be used for the remainder of this research work. This algorithm is simulated on Matlab with 91.67% (RC), 100% (PR) and 95.65% (Acc) and implemented on ZYNQ platform by using C++ and OpenCV. Furthermore, in order to evaluate the efficiency of our Fall Detection System, a DUT-HBU database which is classified with different actions: fall, non-fall (sitting, lying, creeping, etc.) in three camera directions (face, sides and cross) is created and used for simulation, evaluation and implementation purposes.

Secondly, the aim is to define a methodology to explore low cost architectures for this fall detection system. As we consider heterogeneous architecture, new power consumption and execution time models for processor core and FPGA are defined according to the different configurations of the target architecture (ZYNQ platform) and the features of the applications like: core frequency, number of processor cores, image resolution. To validate the accuracy of the proposed models, we also analyze the error rate of these models that show that they don't exceed 3.5%. The power consumption and execution time models are then extended to hardware/software architectures according to the assignment of the Fall Detection System tasks and have been coupled with an accuracy model to evaluate the performance of this system. With these extended models, our approach targets to explore low cost architecture

by defining a suitable Design Space Exploration methodology. We also apply two techniques for parallelization which are based on intra-task and inter-task static scheduling with the aim to enhance the accuracy and the power consumption of this system. As example, first execution on ARM Cortex A9 processor of ZYNQ platform achieves an accuracy of 62% with energy per frame of 43mJ/f. When the parallel techniques based on hardware/software architecture are applied, the frame rate of our system is considerably increased and the accuracy rate reaches 98.3% with energy per frame of 29.5mJ/f.

## Résumé

De nos jours, la détection de chute est un défi majeur dans le domaine de la santé publique, en particulier pour les personnes âgées vivant seules. Les chutes sont la principale cause de décès, suite à des blessures, chez les personnes âgées de plus de 65 ans. Par ailleurs, le manque de personnel médical, par exemple pour les patients en rééducation, dans les hôpitaux ou les maisons de retraite, est un problème important mondial pour le 21ème siècle. Par conséquent, le développement de systèmes de surveillance, en particulier pour la détection de chute, devient une nécessité pour le secteur de la santé.

Le but de cette thèse est de concevoir un système de détection de chute basée sur une surveillance par caméra et d'étudier à la fois les aspects algorithmiques et architecturaux. Notre système de détection de chute est conçu non seulement pour les personnes âgées vivant seules, mais aussi pour les personnes en réadaptation à l'hôpital ou placée en maison de retraite. Notre système se compose de quatre modules: la segmentation d'objet, le filtrage, l'extraction de caractéristiques et la reconnaissance qui permettent en plus de la détection de chute d'identifier le type de ces chutes (avant, arrière, coté) dans le but de définir un niveau d'alarme.

Dans un premier temps, différents algorithmes ont été étudiés pour réaliser les traitements des modules qui composent notre système de détection de chute comme le Background Subtraction-Neural Network (BGS-NN); le Background Subtraction-Template Matching (BGS-TM); le Background Subtraction-Hidden Markov Model (BGS-HMM); et le Gaussian Mixture Model (MGM-HMM). Afin d'évaluer l'efficacité de ces algorithmes, une comparaison est effectuée sur les paramètres qui permettent d'évaluer la performance du système soit: Accuracy (Acc), Precision (PR), Recall (RC). Le résultat de cette comparaison nous a amené à sélectionner le BGS/TM qui sera utilisé dans la suite de ces travaux de recherche. La simulation de cet algorithme sous Matlab a permis d'évaluer le RC à 91,67%, le PR à 100% et l'ACC à 95,65%. Cet algorithme a aussi été testé après implémentation sur une plateforme ZynQ en utilisant le langague C++ et OPENCV. De plus, afin de mieux évaluer l'efficacité du système de détection de chute proposé, une base de donnée DTU-HBU a été construite et classifiées selon les différentes actions: chute, non-chute (assis, couché, rampant, etc.) selon trois angles de caméra (de face, de côtés et de biais).

Dans un second temps, l'objectif a été de définir une méthodologie permettant de sélectionner les architectures à faible coût qui présenteraient les meilleures performances. Comme nous considérons des architectures hétérogènes, un premier travail fut de définir des modèles de consommation et du temps d'exécution pour différentes cibles technologiques,

processeur et FPGA. A titre d'exemple, la plateforme ZYNQ a été considérée. Les différentes configurations de cette plateforme ont été caractérisées pour les algorithmes de détection de chute. En particulier, des paramètres comme la fréquence, le nombre de cœurs actifs, la résolution de l'image ont été pris en compte. Pour valider la précision des modèles proposés, des expérimentations ont été menées et l'erreur pour ces tests n'a pas excédé 3,5%. Ces modèles ont ensuite été étendus à des architectures hétérogènes et complétés par un modèle de l'Accuracy (ACC) qui permet d'évaluer la performance du système complet. Sur la base de ces modèles, notre approche vise à explorer les architectures à faible coût par la définition d'une méthodologie adaptée de DSE. Afin d'exploiter le parallélisme offert par la plateforme ZYNQ, deux techniques d'ordonnancement statique (Intra tâche et inter tâche) ont été utilisées dans le but de réduire la consommation d'énergie tout en possédant une performance adaptée. Les résultats obtenus montrent qu'une première implémentation fournit un ACC=62% avec une énergie par image de 43 mJ alors qu'après optimisation, l'ACC atteint 98,3% pour une énergie de 29,5 mJ.

# Acknowledgement

I would like to express my deep and sincere gratitude to all those who have helped and supported me the possibility to complete this thesis.

I am deeply indebted to my supervisor and principal academic advisor, Mme Cecile BELLEUDY, who has always been amazingly thoughtful, enthusiasm and sharp. Her constructive advice, belief and support, from research strategy and general approach to detailed writing styles, have been invaluable. Mme Cecile BELLEUDY has given me trust, especially in difficult moments, and certain freedom to develop a research topic.

My deepest gratitude also goes to Associate Professor Van Tuan PHAM that I am truly passionate about, for his continual guidance on the first ideals for this research topic. I sincere thank him to give me an opportunity to participate the co-research project between University of Nice Sophia Antipolis and University of Danang under supporting of EMMA's program in ten months.

I would also like to thank my official referees, Professor N. Julien and Professor Bertrand Granado, for their thoughtful and detailed review, constructive criticism and excellent advice during the preparation of this thesis.

I wish to express my sincere thanks to Human Behaviour Understanding group in Da nang University of Technology (HBU-DUT) for working together in developing the algorithm of Fall Detection, the database called HBU-DUT and some achievements in simulation during the first PhD's year.

I warmly thank the members of the MCSOC group for their valuable advices on my research methodology and contributions. Special thanks also go to Professor VERDIER François, Mr PEGATOQUET Alain and Mr BILAVARN Sébastien.

During this time I have collaborated with many colleagues for whom I have great regard, and I wish to extend my warmest thanks to all those who have helped me with my work for all their help, support, interest and valuable hints. Special thanks also go to Professor DAUVIGNAC Jean Yves, Professor AUGUIN Michel, Mme PROSILLICO Marie Hélène and Mme GUYON Marie-France for all their administrative supports.

My deepest gratitude also goes to the board of principals at the College of Technology, University of Danang. Futhermore, I want to thank all my colleagues of the Electronic Department to share the teaching work for me during last 4 years. Thanks for all

Vietnamese friends support and share the difficult and unforgettable moments in research and in my life.

I owe my loving thanks to my family for all their love and encouragement. Without their encouragement and understanding it would have been impossible for me to begin, continue and finish this work. Thanks for my little daughter giving me the most motivation to finish this PhD. I love you all dearly.

This work was support by the Vietnam Ministry of Education and Training and the ten months of Erasmus Mundus Mobility with Asia - EMMA in Exchange Doctoral Research project.

# **Chapter 1. Introduction**

Currently, accompanying with the development of society, e-health systems are playing increasingly important roles in our lives. Among them, medical care and falling accidents for the elderly seem to draw attention as important topics in healthcare and human behaviour recognition domains. In addition, to efficiently monitor the situation of patients, there is at least a medical staff (i.e. a doctor or a nurse) who presents next to patients for hours. The extremely increasing demands on healthcare services have been, thus, urging the development of new generation of surveillance systems. These novel systems can be benefit from new advances in sensors, digital video processing, and broadband access network infrastructures. Therefore, the health services today have been dominated by high-tech devices as well as automatic systems which have greatly facilitated the higher ability in convenience, fast response, and high reliability.

According to the statistics given in the international advisory conference on innovation, training of health forces in the 21st century took place on 28/04/2011 in Hanoi, Vietnam showed that there were only 0.5 doctors and/or 0.8 nurses per 1000 population. It means that according to the World Health Organization (WHO) Vietnam should add about 80 thousand health forces to meet the general requirements [1]. That was the general reality of the countries on over the world, including developing countries. In addition, another study of the elderly from Vietnam Association of Rheumatology, every year, every three people over 65 years old have at least one person fell. The accident was the sixth most common causes of death for the elderly, in which the incidence of falls was the majority [2]. In Vietnam, the proportion of people of 60 years and older increased from 6.7% in 1979 to 9.2% in 2006 [3]. Vietnamese life expectancy at birth increased from 66 years in 1990 to 72 years in 2006 and the average life expectancy of elderly Vietnamese is 73 years old [4].

The application of the intelligent video surveillance for taking care the elderly at home or the rehabilitants in Vietnam's hospital is proposed to find out the solutions for this reality in Vietnam. Before more details of this approach are discussed, many approaches applied in healthcare systems based intelligent surveillance (sensors, audio, video, communication networks) as following sections will be reviewed. For this intelligent video surveillance system, usually the performance is the main objective but today the power consumption is also a critical parameter and more especially for autonomous object. The challenge is to build some tools or some ways to evaluate the performance, the recognition rate, and the power consumption at early step of the design.

These ways help in reducing the time-to-market for a quality product. In this thesis, a new Fall Detection algorithm is proposed and a methodology is defined to design low cost architectures.

#### 1.1 The healthcare systems

With the rapid development of science and technology, surveillance systems are developing quickly. Nowadays, these systems not only generally monitor but also enable to analyse and process the captured data to activate an alarm when there are abnormal actions. This feature is quite suitable for a healthcare system.

#### 1.1.1 The healthcare system based on sensors

#### 1.1.1.1 Sensors worn on human body

A sensor is an electronic device that easily detects events or changes from the external environment, and then the received signals are transformed into an electrical or optical signal to control other devices. There are many sensors such as micro switches, spirit levels, accelerometers, and gyroscopes that are embedded in garments, or walking sticks [5]. The sensor systems can be stuck at the area where needs to collect the surroundings and then transmit to the central processor and finally process it for a specific purpose. Sensor and its essential features have been implemented in industrial and in medical equipment in particular. By capturing signals from sensors, doctors or healthcare scientists have a chance to easily monitor or even remotely diagnosis while patients are in hospital, clinic or even at home. The model of a healthcare system based on sensors is depicted in Figure 1.1.

A sensor mounted on body generally divides into three main factors: wireless, wire, and integrated in patients' body [6]. There are specific sensors for each part of the body and for each surveillance. Wearable embedded systems use sensors that can detect changes in postures, activities or motions of the person wearing devices. A wearable motion detection device using tri-axial accelerometer, which can detect and predict events based on tri-axial acceleration of human upper trunk, was designed and realized, [7]. With this method, the elderly who suffer from chronic diseases can be not only monitored effectively, but the early symptoms of the disease are also found. Wearable devices are simple and cheap; however, they might disturb the user's normal life. In addition, the issue of surveillance is that the elderly often forget to wear this equipment, and it depends on the ability and willingness of the elderly.

Figure 1.1-A model of the healthcare system based on sensors stuck on human body [8].

#### 1.1.1.2 Ambient sensors

Due to the adverse effects of the wearable devices, some ambience systems which are not stuck directly on the human body are researched and applied recently. Welfare Techno House in Japan is an excellent example for the ambience systems [9].

Figure 1.2-Welfare Techno House system [9]

In this system, automated electrocardiogram (ECG) measurements can be taken while the subjects are in bed, in the bathtub, and on the toilet, without their awareness and without using body surface electrodes. The sensors are installed in furniture and/or sanitary goods and the subject needs to attach the sensor. The heart rate and body weight can be obtained without any special measurement and the subject can receive daily physiological parameters without any awareness and discomfort. It is useful for understanding personal health status and daily activity information without the use of

invasive measurements. Some monitoring devices in the Welfare Techno House are shown in Figure 1.2.

#### 1.1.2 The healthcare system based on audio

The healthcare system based on sound includes circular microphone array located in a room or relatively narrow and quiet space. When a sound is detected, the sound system will automatically amplify the signal, then identify and classify whether it is sound caused by the monitoring action or not [6]. However, this is the main limitation of this kind of the sound system, because it is usually placed in daily life environment, it is easily disturbed by surroundings noise, like falling objects or crying, etc. Furthermore, the sound also depends on each patient, type of actions or the position. Therefore, this system is not reliable enough to apply in the real life. A sound falling detection system consisting of the circular microphone array is depicted in Figure 1.3 [6].

Figure 1.3-A circular microphone array used to automatically detects falling actions [6]

#### 1.1.3 The healthcare system based on communication network

The care of patients now is involved in many different individuals, namely doctors, nurses, patients and their families. All of them need to share patient information and discuss their management. As a result, communication technologies are becoming a significant role in supporting health services. However, it is generally accepted that there is still a gap in applying communication technologies in healthcare systems, especially in rural areas where voice-mail or electronic mail is still not available.

A communication system involves people, the messages they wish to convey, the technologies that mediate conversations, and the organisational structures that define and constrain the conversations that are allowed to occur [10]. A possible communication pathway for a laboratory test, ordered by a general practitioner is shown in Figure 1.4.

There are significant organisational and communication challenges facing those delivering healthcare in the community. The model of shared care often adopted means that many different healthcare professionals may be involved in the management of an

individual patient. Even apparently simple activities such as ordering a laboratory test in general practice, and receiving the report, can involve many individuals, and many opportunities for inefficiency and errors.

Figure 1.4-A possible communication pathways for a laboratory test [10]

### 1.1.4 The healthcare system based on intelligent video surveillance

Ambience systems use sensors installed in the living environments that certainly does not disturb the users. However, these kinds of sensor-based ambient systems normally result in high false alarm rate. Several studies have been proposed recently to use vision-based systems. Visual surveillance systems have been installed at many places in our lives, for instance offices, factories, schools or buildings. They recorded visual as well as any actions in the camera's area. At present, a variety of cameras are adopted to obtain the real-time situation for the elderly at home, and elderly abnormality is judged according to the above situations.

According to abnormality types and credibility, the systems analyse, process, and evaluate patients' situation to make some correction measurements in advanced in order to notify the guardian or those who concern. In today's modern life, intelligent video surveillance for elderly people living alone is an important application in the field of intelligent video surveillance. To reduce the workload of the remote monitoring staffs, the scene images are pre-processed by using techniques like image processing, or data mining, etc. After that, the captured scene images are transmitted by the internet or other communication methods to the distant guardian, and then these signals are carefully examined. By using intelligent video surveillance, people can effectively monitor their family as well as their business and issue warnings via computers or gadgets as soon as possible with many benefits. If there is any unusual events, user can take the warning to

others who are nearer to that area to prevent a bad outcome. An example of using intelligent video surveillance in hospital is illustrated in Figure 1.5. In addition, Ming-Liang Wang et al. [11] has proposed a video surveillance system using an omnidirectional charge-coupled device (CCD) camera which is adopted to provide a 360° view angle of the indoor scene in a single image. The authors combined different algorithms for robust human motion tracking such as motion history image (MHI), Continuously Adaptive Mean Shift (CamShift) and optical flow in order to increase the robustness of the surveillance and tracking system. And for the human activity recognition, they use a calibrated one-to-one correspondence between the ground locations and the omni-directional vision sensor (ODVS) images.

Figure 1.5-A person is monitoring the healthcare camera in a hospital [12]

#### 1.2 Fall Detection Approaches.

### 1.2.1 Classification Fall Detection Approach

The biggest advantage of video surveillance is the ability of real time execution by using standard computing platforms and low cost cameras. The methods have the capability to deal with robustness, however, still leave a widen horizon for further research and development. There are some different types of fall detection as follows[13]:

#### 1.2.1.1 Spatiotemporal

Shape modelling using spatiotemporal features provides crucial information of human activities, which is used to detect different events. Image analysis requires efficient and accurate shape modelling methods [14]. Homa Foroughi et al. [15] proposed a novel approach for human fall detection based on combination of integrated time motion images and eigenspace technique. Integrated Time Motion Image (ITMI) is a type of spatio-temporal

database that includes motion and time of motion occurrence. Based on these observations, they extracted some motion information from the video sequences. Although, this motion information can be used directly in motion classification, they used eigenspace techniques for feature. Finally a multilayer perceptron (MLP) Neural Network is used for precise classification of motions and determination of a fall event.

#### 1.2.1.2 Inactivity/change of shape

This algorithm bases on shape change analysis as well as inactivity detection. Vinay Vishwakarma et al. presented an approach for human fall detection consists of two parts: object detection and the use of a fall model. The authors used an adaptive background subtraction method to detect a moving object and mark it with its minimum-bounding box. The fall model uses a set of extracted features to analyze, detect and confirm a fall. Then they implemented a two-state finite state machine (FSM) to continuously monitor people and their activities [16].

#### 1.2.1.3 Posture

The use of posture information contributes towards accurate fall detection. Different body positions are used to calculate postures. Specific types of postures are identified and localised in image sequences. Generally, model dependent methods obtain postures relatively easy and are robust to occlusion to an extent after labelling the body parts. Rita Cucchiaraour et al. proposed a human behaviour classification by the posture of the monitored person and, consequently, detected corresponding events and alarmed situations, like a fall. There are two phases in this project: firstly, posture classification performed frame-by-frame. This classification exploits simple visual features. Secondly, the obtained posture is further validated exploiting the information extracted by a tracking module in order to take into account the reliability of the classification of the first phase. This is motivated by the concept of "posture state" defined in a state-transition graph that takes into account for the classification the reliability of the track and acquired knowledge of the people's average behaviour in changing their posture [17].

#### 1.2.1.4 3D head position analysis

Head position analysis is based on head tracking that determines the occurrence of large movement within the video sequences. Different state models are used to track the head based on the magnitude of the movement. In 3D head motion analysis methods, the principle of faster vertical motion than horizontal motion during a fall is applied. The head is initially located and then the 3D head position is estimated using fiHead. The idea of using appropriate thresholds to distinguish a fall from other actions is applied by computing vertical and horizontal velocities of the head [18][19].

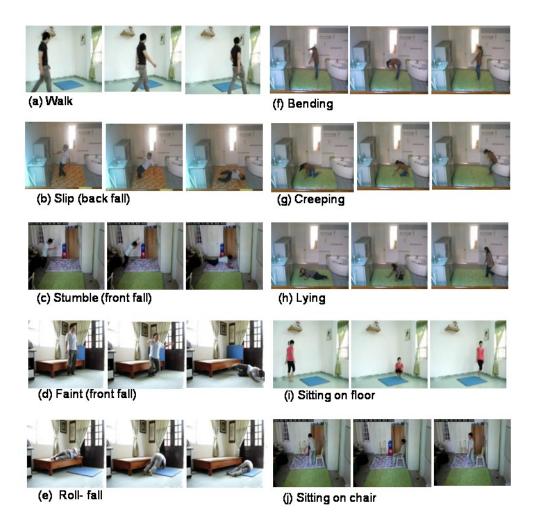

In this thesis, we propose algorithms for the Fall Detection System including Object Segmentation, Object Enhancement, Feature Extraction and Recognition modules. To understand the behaviour of human object inside the video, the five features are calculated by the different positions of object performed frame by frame. The postures of object which are classified in our DUT-HBU dataset: fall and non-fall (bending, sitting, lying, creeping, etc.) are used for evaluation of this system. Our system is evaluated in terms of the accuracy, recall and precision performance. We also compare the performances among various algorithms such as BackGround Subtraction/Hidden Markov Model (BGS-HMM), Gaussian Mixture Model/Hidden Markov Model (GMM-HMM), BackGround Subtraction/Neural Network (BGS-NN), and BackGround Subtraction/Template Matching (BGS-TM).

#### 1.2.2 Efficient Architecture for Fall Detection on heterogeneous platform

Currently, the advanced co-design step can lead to many solutions, especially in video processing: there are many ways of partitioning a system, and of writing the software with the chosen hardware. It is now well-known that the software has a very considerable impact on the final power consumption of a system. To find the best solution is a complex task.

New System on Chips (SOCs) that combine processor cores and field-programmable gate array (FPGA) architecture will help to build complex and performing systems. Some examples of video processing on heterogeneous architecture are shown as follows:

Eduardo Gudis, Pullan Lu et al. [20] have described an architecture framework using heterogeneous hardware accelerators for embedded vision applications. They presented a framework using an extensive library of pipelined real time vision hardware accelerators and service-based software architecture. Their framework allows the service-based software to take advantages of the hardware acceleration blocks available and perform the remainder of the processing in software. Three applications - Video stabilization (pre-processing), Moving Target Indication, and Contrast Normalization - were implemented on two Xilinx Zynq platforms: (1) the Xilinx ZC702 evaluation board with 7020-1part, and (2) a custom board with 7045-1 board.

Another video application applied OpenCV which is implemented on Zynq platform is illustrated in [21]. Road sign recognition is an autonomous application in driver assistance systems and road sign maintenance. This algorithm is presented using the Xilinx Zynq-7020 chip on a Zedboard to scan 1920×1080 images taken by an ON Semiconductor VITA-2000 sensor attached via the FPGA Mezzanine Card (FMC) slot. The Programmable Logic section of the Zynq is used to perform essential image preprocessing functions and colour based on filtering of the image. Software classifies the shapes in the filtered image, and they used OpenCV's template matching function to

identify the signs from a database of United Kingdom road signs. The system was designed in six weeks, and can process one frame in approximately 5 seconds. This is a promising start for a real-time System on Chip based approach to the problem of road sign recognition and also for using the Zynq platform for rapid deployment of these types of applications.

In addition, the jpeg decoder, image rectification, Semi Global Matching algorithm, and Stixel clustering are the applications which are accelerated on FPGA by using Xilinx Zynq 7045. In [22] Gilliland. S et al. evaluated the performance of an FPGA based embedded ARM processor system to implement signal processing for ultrasonic imaging and non-destructive testing applications. FPGA based on embedded processors possesses many advantages including a reduced overall development time, increased performance, and the ability to perform hardware-software (HW/SW) codesign. This study examined the execution performance of split spectrum processing, chirplet signal decomposition, Wigner-Ville distributions and short time Fourier transform implementations on two embedded processing platforms - a Xilinx Virtex-5 FPGA with embedded MicroBlaze processor and a Xilinx Zynq FPGA with embedded ARM processor. Overall, the Xilinx Zynq FPGA significantly outperforms the Virtex-5 based system in software applications.

Dobai and Sekanina [23] demonstrated evolutionary design of switching image filters on the platform. The investigated implementations included virtual reconfigurable circuits and the use of dynamic partial reconfiguration. The achieved results demonstrated the advantages and disadvantages of the Zynq platform. The observations intended to be useful for designers who would develop evolvable hardware on this new platform. They presented the time required to evaluate one filter candidate (individual), the time for a generation of filter candidates (4 individuals), the number of generation per second and the relative acceleration in comparison ARM processor (without the PL). First, the pure software-based approach was evaluated on the ARM processor of the available Zynq device. Second, they compared the processor of Zyng with a desktop processor (Intel i5). The code in language C was pre-ported to that processor. According to this experiment, the Intel i5 processor was 5 and 6 times faster than the ARM processor of the Zynq device. The third experiment was to determine the magnitude of the FPGA-based acceleration of the filter evolution. The implementation revealed that the operational frequency of the pure virtual reconfigurable circuits (VRC) and hybrid VRC-DPR (dynamic partial reconfiguration) approach was 203.6 MHz and 265.3 MHz, respectively. The hybrid approach was able to evaluate the candidate filters approximately by 30% faster. On the other hand, the VRC approach mutated the circuit in negligible time and the hybrid approach required more time. The hybrid approach changed the interconnections similarly to the pure VRC approach but the replacement of the processor elements by dynamic partial reconfiguration (PEs by DPR) takes longer.

Monson et al. developed their application in High-Level Synthesis (HLS) for FPGAs making it possible to "run" C code on FPGAs and thereby making modern programming environments available to FPGA developers. In their research, C code for a complex optical-flow algorithm was optimized for both a desktop PC and a FPGA-based system, the Xilinx Zynq-7000, which is a device containing both a programmable fabric and two ARM cores. They discussed how the code was optimized and restructured to execute effectively on the programmable fabric and the ARM cores. The resulting Zynq version of the C code was competitive with the desktop PC but only consumed 1/7 as much energy.

In the other co-design Digital Signal Processor (DSP)/FPGA, Giuseppe Baruffa et al [24] presented the architecture of a DSP/FPGA based hardware platform, which is conceived leverage programmable logic processing power definition video processing. Their system was reconfigurable and scalable, since multiple boards may be parallelized to speed-up the most demanding tasks. The application frameworks, JPEG 2000 and H.264, both at high dimension (HD) and Super HD (SHD) resolutions have been simulated and performed on the embedded processing cores. The issues such as real-time, or near real-time encoding was viable, the modularity of the architecture allowed parallelization and performance scalability were proposed in this study. Cooperation of FPGA and DSP processing modules was required to fulfil the proposed objectives. Performance results showed that real-time encoding and decoding of HD and SHD video were possible by using a parallelized configuration.

In addition of co-design, Felix Büsching et al. [25] proposed an outdoor fall detection system. The system consisted of an Android smartphone and an INGA wireless sensor node. This node was equipped with an accelerometer, a gyroscope and a barometric pressure sensor. However, only the accelerometer for the fall detection was utilized. In the system, the smartphone was used as a counterpart. It was implemented for the three different applications to:

- a) send a text message with a predefined text to a predefined phone number;

- b) all raw data which is transmitted to the smart phone and processed a fall detection;

- c) work as a standalone fall detection and alert system applying the same algorithms as the second application. Nevertheless, this application only utilized the acceleration sensor of the smartphone.

The research works described below show that this kind of video application needs heterogeneous architecture (Processor cores + FPGA) to meet a sufficient frame rate. So in this thesis, we consider this type of architecture (Zynq platform) and we firstly define the power and execution time models for different target circuit: processor core, FPGA with the aim to evaluate the performance (recognition rate and energy) of the fall detection system. Our models are determined based on the Functional Level Power

Analysis for the processor cores and related with hardware resources for FPGA. In order to find architectures and suitable configuration which allow an acceptable fall recognition rate, we propose a new methodology for exploring low cost architectures and by applying parallelism techniques such as intra-task and inter-task static scheduling based on hardware/software architecture for Fall Detection System.

#### 1.3 Research questions

The problem landscape of implementing the video processing has many facets. Within the limited framework of this thesis, all aspects of this research domain cannot be addressed. We focus on the following questions:

1. How can we avoid transmitting the image to other remote systems for privacy reason?

When the Fall Detection System works, all activities of a person are recorded and processed. The video content will automatically be analysed and carried out by computer or hardware device. If a falling is occurred, the system will immediately send a warning of FALL or NON FALL to the remote monitoring center. It also provides the exact cause of human falling and all input video are processed inside closed system.

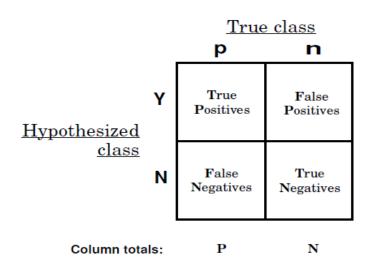

#### 2. How are the performances (accuracy, precision and recall) of this system?

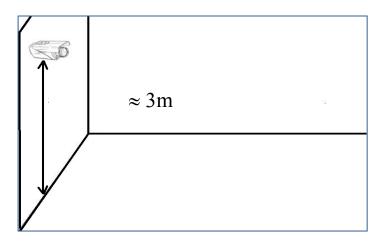

Fall detection is a challenge in the public healthcare system, especially for the elderly, and reliable surveillance is a necessity to mitigate the effects of falls. The technology and products related to fall detection have always been in high demand within the security and the health-care industries. An effective Fall Detection System is required to provide urgent support and to significantly reduce the medical care costs associated with falls. Therefore, we first should have a database with various kinds of human activities. In this system, the DUT-HBU dataset [26] is used and all video data are compressed in .avi format and captured by a single camera in a small room with the changeable conditions such as brightness, objects, direction of camera, etc. In this database, the fall direction is subdivided into three basic directions which are Direct fall, Cross fall, and Side fall. In terms of non-fall videos, usual activities which can be misrecognized with fall action such as lying, sitting, creeping, and bending are also classified into three mentioned directions. Moreover, to evaluate the efficient and accuracy of a system, we analyse the Precision (PR), Recall (RC) and Accuracy (Acc).

#### 3. How does a video system meet the real-time processing?

Designing a real-time system requires a holistic approach that is considered many aspects such as algorithms, architectures, and implementation methods of applications in order to meet a specified deadline. The constraints on the considered video processing are that the system must be able to maintain an average processing rate higher than the required frame rate in order to get a sufficient accuracy for fall detection recognition rate. This requires a deterministic and bounded execution time. In our system, we apply parallelism techniques based on hardware/software architecture to improve the execution time and by this way the performance of our system.

12

#### 4. How is the "cost" of this system?

Fall detection systems based on cameras have proven to offer a promising solution which is complementary to the wearable sensors. One advantage of visual-based fall detections is they can be installed in-door and not required to be worn by any users. The cameras can be wall- or ceiling-mounted, depending on the interests on orientation and field of view of the frames to be captured. Besides, the recorded video allows more efficient use of multiple events analysis and post verification. Moreover, cameras are increasingly becoming a strong candidate for the choice of fall detection sensor due to the rapid drop of camera costs. So far, different visual-based fall detection techniques have been identified. Nevertheless, the development of such systems has been implemented as software-based solutions on computers.

In addition, we want to design a standalone Fall Detection System corresponding with the less energy consumption and the higher performance. Therefore, in our system, we try to extract the power consumption and execution time models for processor cores and FPGA to explore the low cost architectures which offer sufficient frame rate, low power/energy consumption and an adequate accuracy rate based on Design Space Exploration methodology. Some parallelism techniques are also applied to improve the execution time and by the way the performance of Fall Detection System.

#### 1.4 Thesis contributions

Most of video surveillance for fall detection researches includes two or three modules to detect the behaviour of human object. They recognise the movement of object by analysis of shape of object modeling in several frames or the different centroid of object or by comparing with the available template, etc. Therefore, it is also necessary to explore the algorithms which provide a high performance of recognition ability for a Fall Detection System. In addition, the algorithms have usually been compared together by simulating on Matlab and evaluated the reliable performance by a database. Besides, several video applications such as object segmentation, video compression format

(H.264 or MPEG4), filter (sobel, canny, etc.), and recognition (using Neural Network, Template Matching, etc.) have been studied on power/energy consumption characterization and modeling at different levels for embedded video system. Many methodologies have handled the low and high level models related to the processor, memory or FPGAs. In this thesis, the first main contribution is to propose efficient algorithms for the Fall Detection System which consists not only to signalize a fall but also the type of this fall in order to determine the urgency of the situation. Comparing to others fall detection, our system consists of 4 modules: Object Segmentation, Filter, Feature Extraction and Recognition with an automatic alarm whenever FALL is occurred. Then, in order to find out fall detection architectures which meet users and application constraints, power consumption and execution time models are defined taking into account architecture and application parameters. Thus, low cost architectures for our system are explored by using the parallelism techniques to find out the heterogeneous architectures which couple the energy consumption and fall detection accuracy rate. To achieve this goal, we intend to pursue the methodology scheduled as follows:

13

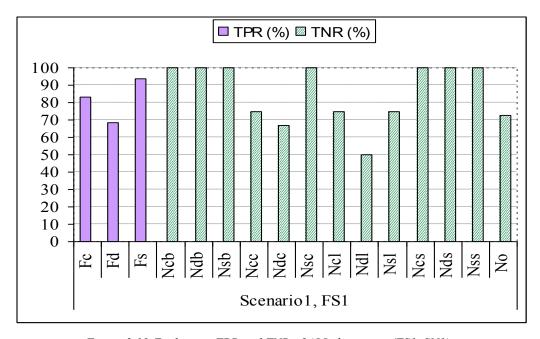

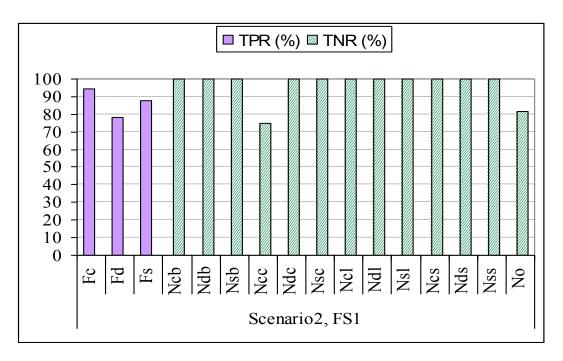

- (1) We determine recent algorithms which are applied on each module of Fall Detection System and our system also give an urgent alarm for detecting different kinds of fall. We make then various simulations to compare the recognition rate performances among algorithms such as BackGround Subtraction/Hidden Markov Model (BGS-HMM), Gaussian Model/Hidden Markov Model (GMM-HMM), BackGround Subtraction/Neural Network (BGS-NN) and BackGround Subtraction/Template Matching (BGS-TM). In this thesis, in order to evaluate the efficiency of the Fall Detection System, a DUT-HBU database which is classified with different actions: fall, non-fall (sitting, lying, creeping, etc.) in three camera directions (face, sides and cross) is created and used for simulation, evaluation and implementation purposes. The testing databases are then regrouped into three different scenarios types: well-matched (WM), medium-mismatched (MM) and highly-mismatched (HM). We select the BGS/TM algorithm, which is sufficient for recognition performance by using the well-matched test in this database, and is in order to implementation purpose. Some factors which affect to the quality of recognition in this system such as environment brightness, occlusion of object, many movement objects appearing in a frame at the same time are also analysed.

- (2) In order to find out a suitable architecture for the proposed algorithm, power consumption and execution time models are proposed for processor cores based on Functional Level Power Analysis (FLPA) and FPGA related with the hardware resources and then for heterogeneous architecture. Our video application was implemented on processor cores (ARM Cortex A9 processor) of ZYNQ Platform different configurations. TI USB Interface Adapter PMBus

associated with TI Fusion Digital Power Designer GUI are used to measure the power consumption on processor cores. Some tasks of the application are also synthesized, and characterized on FPGA by using Vivado 2012.4 tool. The curve fitting of regression law is used to get the mathematic models for power consumption and execution time which depend on algorithm and architecture parameters, such as operating frequencies, number of cores, image resolution. The error rate of these models is then evaluated and used for exploring the architecture for the Fall Detection System.

(3) By extending the power consumption and execution time models, we propose a Design Space Exploration methodology to define low cost architecture for Fall Detection System. In this methodology, in order to explore heterogeneous architectures for our system, two parallelism techniques *intra-task* and *inter-task* static scheduling are applied. The low cost architectures are selected with the compromising of energy consumption and accuracy rate performance of the Fall Detection System.

#### 1.5 Publications

#### 1.5.1 International journal publication

- [1] Hong. Nguyen.T.K, Cecile. Belleudy and Tuan.V.Pham, "Performance and Evaluation Sobel Edge Detection on Various Methodologies", 2014 International Conference on Advances in Electronics Engineering, 19-20 February, 2014.

- This paper has been extended and published in International Journal of Electronics and Electrical Engineering Vol. 2, No. 1, March, 2014.

- [2] Hong Thi Khanh Nguyen, Cecile Belleudy and Pham Van Tuan "Fall Detection Application on an ARM and FPGA Heterogeneous Computing Platform" International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol.3, Issue 8, August, 2014.

### 1.5.2 International conference's publication

- [3] Hong. Nguyen.T.K, Cecile. Belleudy and Tuan.V.Pham, "Power Evaluation of Sobel Filter on Xilinx Platform", IEEE FTFC, 4-6 May, 2014, Monaco.

- [4] Hong Thi Khanh Nguyen, Hassoon Fahama, Cecile. Belleudy and Tuan.V.Pham "Low Power Architecture Exploration for Standalone Fall Detection System Based on Computer Vision", IEEE-EMS2014 European Modelling Symposium 2014, 21st 23rd October, 2014, Pisa, Italy.

#### 1.5.3 Other publications

- [5] Hong. Nguyen. T. K, Cecile Belleudy and Tuan.V.Pham, "FPGA-based Object Segmentation of Fall detection", RUNSUD 2013, 23-24 April, 2013.

- [6] Thi Khanh Hong Nguyen, Cecile. Belleudy and Tuan.V.Pham, "Low Power Exploration Design Flow for Fall Detection System", COLLOQUE NATIONAL of GDR SoC-SiP, 11-13 juin 2014 in Paris.

- [7] Hong Thi Khanh Nguyen, Cecile. Belleudy and Tuan.V.Pham, "Low cost architecture for Fall Detection System", e-PSP 2014, 27th November, 2014, Biot, France.

#### 1.6 Thesis Organization

This thesis is divided into 5 chapters. After the introduction in Chapter 1, we present the Fall Detection approaches and analyse the comparison of the performance of these approaches by their simulation on Matlab in Chapter 2. In Chapter 3 the extraction of the execution time and power models based on Function Level Power Analysis for processor cores and based on hardware resources for FPGA is discussed. And then the Design Space Exploration methodology including two parallelism techniques (intra-task and inter-task static scheduling) which is applied to explore low cost architectures for this system based on heterogeneous architectures with different configurations is described in Chapter 4. Finally, Chapter 5 contains the conclusions and proposals for the future works of this work.

Figure 1.6-An outline of the different chapters, research questions and contributions in this thesis

# Chapter 2. Fall Detection Algorithm

Nowadays, fall detection is a serious challenge in the public health care domain, especially for the elderly living alone. There are some health care systems based on sensors, audio, communication network and video processing. In our work, we develop a Fall Detection System based on video processing. The Fall Detection System is developed in two sides: algorithms and architectures. In this Chapter, we study and make the simulations of algorithms used in the Fall Detection System.

In Section 2.1 of this chapter, the overview of Fall Detection System describes the definition of a falling event and the Fall Detection approaches which are currently used in recognition the postures or action of human object. The most important part is in Section 2.2 where we propose studied algorithms for the Fall Detection System including four modules: Object Segmentation, Object Enhancement, Feature Extraction and Recognition. In order to understand the behaviour of human object in our system, some recognition models are studied and illustrated more detail in Section 2.3. Moreover, the DUT-HBU database which is classified with different actions: fall, non-fall (sitting, lying, creeping, etc.) in different directions of camera (face, sides and cross) is used for evaluation our system. The system is evaluated in terms of the accuracy, recall and precision performance. Finally, the results on Matlab's simulation in comparing the performances among these algorithms such as BackGround Subtraction/Hidden Markov Model (BGS-HMM), Gaussian Mixture Model/Hidden Markov Model (GMM-HMM), BackGround Subtraction/Neural Network (BGS-NN), BackGround and Subtraction/Template Matching (BGS-TM) are shown in Section 2.4. At the end of this Chapter, we make the general discussion about parameters which impact on the quality of recognition ability in the Fall Detection System.

## 2.1 Overview of Fall Detection algorithm

#### 2.1.1 Definition of falling event

According to the World Health Organization (WHO), there is no any specific definition of falls. In our work, falling accident is defined as "the loss of balance with involuntary causes the body suddenly fell to the ground". Accidental falls are always dangerous for children, adults, especially the elderly and cause serious consequences.

Sudden fall (or falls by accident) is often affected by the impact and the external factors and by many different reasons, such as: slip and fall, walk and fall, fall from

heights, etc. Unexpected fall mainly for the elderly (or falls not by accident) may occur by many reasons. When considering the characteristics of the falls, the following factors are generally considered:

- Direction falls: front, sides, behind.

- Position of the body before and after the fall: lying, sitting, standing, kneeling, and leaning.

- Speed of fall: rapidly or slowly falling down with wobbled knees.

- Active or react before falling: legs or arms raise high, head thrown back, head peers ahead.

Daily actions are mistaken as falling like running, sit down, laying and etc.

These above mentioned factors are used to classify and build scenarios, various situations of fall and then used to train and build the fall detection, evaluation and development in our system.

There are four stages in the process of falls include [10]: pre-fall, fall phase (main phase), after falling phase and recovery phase.

- In the pre-fall phase, people are doing the normal activities in daily (probably occur with sudden movements like sitting or lying down quickly). Fall detection system distinguishes this stage with the following phase.

- Fall phase includes sudden movement of the body to the ground, and ends with a crash to the ground. The period of this phase is usually very short, 300-500 ms [11], it is determined from 400-800 ms.

- In the after falling phase, the body is not a normal movement, still lying on the ground.

- Recovery phase: the falling elderly can stand up by themselves or by the other helps.

#### 2.1.2 Fall Detection algorithms

Nowadays, fall detection is a major challenge in the public health care domain, especially for the elderly living alone. In 2013, the Center for Disease Control and Prevention<sup>1</sup> (CDC) reported that rate of fall injuries for adults from 85 years old and older was almost ten times than that for adults between 65 and 74 in the United State<sup>2</sup>. This statistic also shows that falls are the primary reason of injury related to death for seniors aged 65 and older. Along with the population explosion of the elderly in the world, the demand for surveillance systems, especially for fall detection, has considerably increased within the healthcare industry. Developing intelligent surveillance systems take an important role, especially vision-based systems, which can

\_

<sup>1</sup> http://www.cdc.gov/

<sup>&</sup>lt;sup>2</sup> http://www.cdc.gov/injury/wisqars/pdf/leading cause of nonfatal injury 2012-a.pdf

automatically monitor and detect falls. It has been proved that the medical consequences of a fall are highly contingent upon the response and rescue time. Thus, a highly-accurate automatic Fall Detection System is an important part of the living environment for the elderly to expedite and improve the medical care. In order to provide immediate medical attention, and contribute to solve the lack of manpower in the health sector, many Fall Detection Systems have been studied recently. Several studies have been proposed to use vision-based systems. By using a single camera, Rougier et al. [27] propose an algorithm based on a combination of motion history and human shape variation which provides promising results on video sequence of daily activities and simulated falls. In order to reduce the occlusion areas by cause of the irrelevant position of camera or movement of object, several research works have developed to use multiple cameras [28]. Rougier and his research group [29] present a new method to detect falls by analysing human shape deformation during video sequences captured from four cameras. The shape matching technique is used to track the person's silhouette along the video sequence. Auvinet et al. [30] reconstruct 3-D volume of a person from eight cameras using calibration information. If a big portion of the body volume is near the ground for a period of time they recognise it as a fall.

Figure 2.1-A typical fall while walking

Figure 2.2-Some typical types of non-fall action

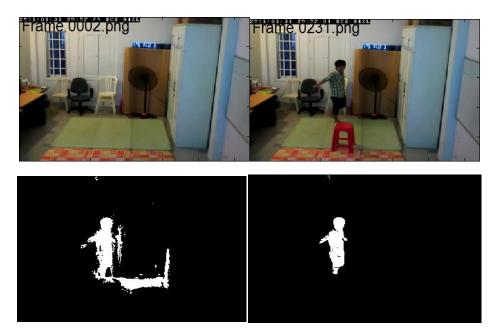

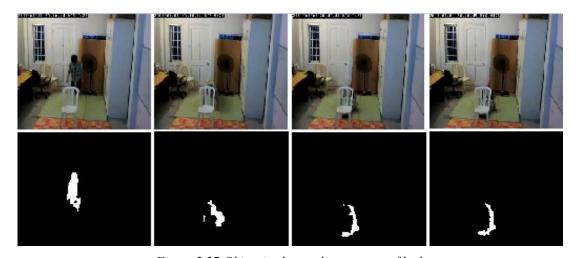

In most of the developed camera-based systems, the algorithms mainly carried out in four phases as illustrated in Figure 2.3. Among them, Object Segmentation plays an important role in ensuring system robustness. From the practical aspects, the system should be able of dealing with lighting changes, movement through clutter areas, unexpected objects overlapping in the visual field and objects being introduced or

removed from the scene. First, moving object is segmented from each frame of the input video in the first module of the following diagram. An Object Enhancement is also used to improve the impact of noise in order to get the better object for the next modules. Afterwards, an ellipse model is built from the segmented object and used for extracting five features. These features are applied for training by recognition models. From the trained features, probability of each observed input data is calculated. By looking at the output results from sequential frames stored in a buffer, a final decision is made. Figure 2.4 shows the process of fall detection by video.

20

Figure 2.3-Block diagram of Fall Detection System.

Figure 2.4-Detecting the fall by video analysis

## 2.1.2.1 Object Segmentation

Video signal including sequence of frames captured from the camera is put into Object Segmentation module to extract objects from the background. The output of this module is a stain, shape of the moving object. This is the first module in the Fall Detection System, therefore, its accuracy makes a considerable impact to next processing modules.

Human objects are extracted from the background of an image by using the Object Segmentation algorithms. The object is segmented based on the difference between two consecutive frames in the time domain [31] or the type of removing background from an image [32][33]. In recent years, Background Subtraction method has become more popular and many thanks go to the development of optimization techniques in estimating dynamic background [34]. Stauffer and Grimson [35] have done

the Gaussian mixture model which is very flexible and suitable for objects moving slower than the background.

21

Because monitored objects continuously move up, so objects are tracked to set the connection of objects via consecutive frames in the sequence images. To achieve accurate detection, tracking objects have the ability to handle the causes which are happened by segmented objects are not perfect and handle the occlusion by camera angles. Cheng and Hwang present not only the partial adaptive sample called Kalman algorithm [36] but also the combination of statistical data in order to detect multi-objects [34] with high accuracy and reliability. Comaniciu et al. propose tracking method in which the moving average values changed based on the centre of the image [37]. In this method, human object is performed as the convolution of the object's properties with the central image are calculated the cost vie spatial. One of the biggest advantages of this method is less computation complexity compared to other methods.

# 2.1.2.2 Object Enhancement