# Electrical and physicochemical characterization of metal gate processes for work function modulation and reduction of local VTH variability in 14FDSOI technologies

Carlos Augusto Suarez Segovia

## ► To cite this version:

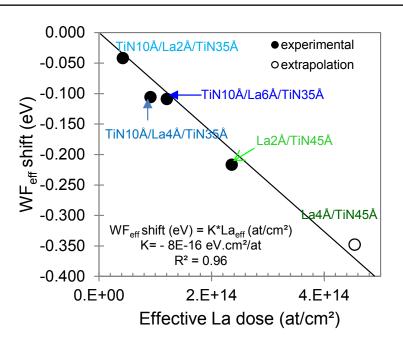

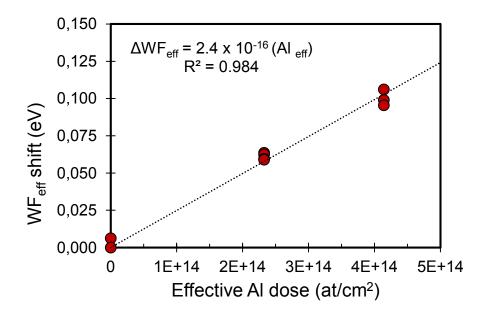

Carlos Augusto Suarez Segovia. Electrical and physicochemical characterization of metal gate processes for work function modulation and reduction of local VTH variability in 14FDSOI technologies. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2016. English. NNT: 2016GREAT011. tel-01288566

## HAL Id: tel-01288566 https://theses.hal.science/tel-01288566

Submitted on 15 Mar 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Communauté Suniversité Grenoble Alpes

# THÈSE

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano Electronique et Nano Technologies

Arrêté ministériel : 7 août 2006

Présentée par

# **Carlos Augusto SUAREZ SEGOVIA**

Thèse dirigée par **Gerard GHIBAUDO** et codirigée par **Charles LEROUX et Florian DOMENGIE**

préparée au sein de la société STMicroelectronics, du laboratoire CEA-Leti (Grenoble) et de l'IMEP-LAHC et de l'Ecole Doctorale EEATS

Electrical and physicochemical characterization of metal gate processes for work function modulation and reduction of local V<sub>TH</sub> variability in 14FDSOI technologies

Thèse soutenue publiquement le **4 février 2016**, devant le jury composé de :

Mme. Catherine DUBOURDIEU DR, CNRS Ecole Centrale de Lyon, Président Mme. Nathalie MALBERT PR, Université de Bordeaux, Rapporteur M. Brice GAUTIER PR. INSA Lyon, Rapporteur M. Florian DOMENGIE ING, STMicroelectronics, Examinateur M. Charles LEROUX ING, CEA-LETI, Examinateur M. Gerard GHIBAUDO DR. CNRS Alpes, Directeur de thèse

## Acknowledgments

While this thesis is written in English, I feel nice to write most of these acknowledgements in French and Spanish, as it will enforce my thanks.

J'aimerais tout d'abord remercier sincèrement mon encadrant de thèse, Charles Leroux, de m'avoir toujours guidé et poussé pendant ces 3 années de thèse. J'ai particulièrement apprécié ta rigueur scientifique et toutes les discussions que nous avons pu avoir. Charles, grâce à toi j'ai beaucoup appris sur les techniques d'analyse capacitive et de photoémission interne et sur les techniques d'extraction des paramètres électriques. Merci pour la confiance que tu m'as accordé et pour le regard critique et objectif que tu as porté sur mes résultats. Cela m'a aidé à m'améliorer, à me remettre en question quand cela était nécessaire et à mieux choisir mes expériences.

Je tiens à remercier Pierre Caubet et Florian Domengie, qui a pris le relais de l'encadrement industriel chez STMicroelectronics Crolles, suite au changement de poste de Pierre. Merci à vous deux de m'avoir formé sur les équipements de dépôt et caractérisation de la grille métallique en salle blanche et de m'avoir appris plein d'astuces pour l'organisation de mes expériences et pour la gestion de mes lots. Merci pour vos conseils, bonnes idées et coups de main essentiels pour la réussite de cette thèse.

Merci également à Gérard Ghibaudo de l'IMEP-LAHC d'avoir bien voulu diriger cette thèse. Merci pour ta disponibilité dans la gestion administrative de mon travail, ton accueil et ton soutien notamment dans la rédaction de mon manuscrit et dans les différentes conférences internationales.

Je tiens à saluer la qualité de votre encadrement, votre patience et votre disponibilité, ce fut très agréable de travailler avec vous au quotidien pendant ces 3 années de thèse.

Je tiens à remercier également les membres du jury, Mme. Catherine Dubourdieu, Mme. Nathalie Malbert, ainsi que M. Brice Gautier d'avoir bien voulu évaluer mes travaux. Merci de m'avoir fait l'honneur de votre présence à ma soutenance de thèse et d'avoir bien voulu faire le déplacement jusqu'à Grenoble.

Je remercie les responsables hiérarchiques des différentes structures dans lesquelles j'ai travaillé. D'une part, j'ai été accueilli au sein de l'unité Process Development chez STMicroelectronics Crolles menée par Jean Galvier, et plus particulièrement l'équipe métal R&D, dirigée par Maxime Mellier, à qui je remercie d'avoir participé à la valorisation de mon travail au sein de l'entreprise et ses conseils précieux pour la présentation de mes résultats. Merci aussi à Olivier Hinsinger de m'avoir donné les ressources nécessaires à mon travail. Je n'ai jamais été en manque de silicium !

D'autre part, je tiens à remercier Gilles Reimbold de m'avoir accueilli dans son équipe de caractérisation et tests électriques du CEA-LETI-Minatec. Merci à Jacques Cluzel et Denis Blachier, mâitres des SIAM et du banc IPE, respectivement, de m'avoir formé sur ces bancs de test électrique et de mesures de photoémission interne. Merci à Giovanni Romano, Alain Toffoli, Rabah Kies et Fabienne Allain, qui méritent d'être cités pour l'aide technique qu'ils mon apporté pour la mise en place de mes mesures.

Mes expériences n'auraient pu être menées à bien sans la participation de plusieurs experts process R&D de ST Crolles. Je remercie tout particulièrement à l'ensemble des membres du module "Gate Stack" mené par Stéphane Zoll. Merci donc à Vincent Joseph, en charge de graver par solution chimique chaque empilement de grille sacrificielle de cette thèse. Merci également à Olivier Gourhant, en charge de la réalisation des différents oxydes et recuits thermiques pour mes études de diffusion à différentes températures. Merci aussi à Virginie Beugin pour les dépôts d'oxyde high-k et les échanges instructifs. J'ai aussi bénéficié de l'expertise device de l'éminent Olivier Weber et de l'aide précieuse de Nicolas Degors et Stéphane Martin pour l'embarquement de mes structures de test. Merci aussi à Jean Philippe Manceau et Mustapha Rafik de l'équipe de caractérisation électrique de ST d'avoir partagé avec moi leurs premiers échantillons. Merci aussi à Nelly Guillot pour son aide vitale pour débloquer mes lots et faire avancer mes manips exotiques.

Une pensée particulière pour Karen Dabertrand de l'équipe de métrologie et pour Marc Juhel de l'équipe de caractérisation physique de ST pour les échanges instructifs sur les avantages et limitations des équipements XRF et SIMS, respectivement. Je n'oublie pas la collaboration avec la plateforme de nanocaractérisation du CEA-Leti Minatec pour la caractérisation physicochimique de mes échantillons, en particulier avec Patrick Gergaud et Frédéric Fillot en XRD et avec Eugénie Martinez en XPS.

Je voudrais également remercier tous les membres de l'équipe de caractérisation électrique du LETI pour les échanges intéressants que nous avons eus et pour votre bonne humeur : Xavier Garros, Mikaël Cassé, William van den Daele, Carlo Cogli et Jean Coignus. Je remercie également Stéphane Becu, Alain Lopez et Matthieu Nongaillard. Enfin, je remercie également tous les doctorants et stagiaires du labo d'avoir mis une ambiance très positive, en particulier mes collègues de bureau Blend Mohammad, à qui je remercie pour les discussions très productives et tous les bons moments passés ensemble, et Alexandre Vernet, pour ses interminables explications sur l'évolution de la grammaire française. Merci aussi à Assawer, Jonathan, Guillaume, Johan, Antoine, Remy, Alexandre S., Giulio2, Cheikh, Illias, Clément, Niccolò, Philippe, Genaro, Gauthier, Julien pour les repas et sorties de labo, les matchs de foot, votre sympathie et votre disponibilité.

Merci également à tous les gens de l'équipe métal à ST pour leur convivialité au quotidien, leur bonne humeur contagieuse, leur dynamisme et leurs coups de mains. Je remercie profondément à Magali Grégoire, Sebastien Petitdidier, Katia Haxaire, Yannick Le Friec, Julie Poulet, Nicolas C, Jerôme, Etienne, Thierry, Eric, GG et bien d'autres.

Une pensée particulière aux doctorants de l'IMEP-LAHC qui m'ont chaleureusement accueilli et m'ont permis de rédiger ma thèse dans le calme et la bonne humeur. Et aux doctorants de ST pour la bonne ambiance pendant les repas à midi: Giulio1, Boris, Darayus, Nayera, Hassan, Antoine, etc. Merci aussi à mon pote Omar qui est venu voir ma soutenance à Grenoble.

Merci aussi à mes potes thésards ou pas, qui m'ont accompagné au quotidien au cours de ces dernières années sur Grenoble : Onintza, Bastien, Romu, Mokrane, Lucia, Giulio1, Mathilde et Bruna. Merci pour les sorties ski, les soirées raclettes, les balades en montagne, les soirées salsa et les beaux voyages que nous avons partagés !

Por último, quisiera agradecer a mi familia. A mis padres Carlos Suarez Carrillo y Silvia Segovia, por haberme dado la vida, por todo su apoyo y por haber sido una constante fuente de fortaleza y amor a lo largo de mi vida. Y a mis hermanos Rodrigo y Diego. Sin su apoyo, no estoy seguro de haber llegado hasta aquí.

# Contents

| Acknowledgments i |       |          |                                                                                                 |          |  |

|-------------------|-------|----------|-------------------------------------------------------------------------------------------------|----------|--|

| G                 | enera | al intro | oduction                                                                                        | 1        |  |

| 1                 | Gat   | e stac   | k technology for 14 nm FDSOI MOSFET devices                                                     | <b>5</b> |  |

|                   | 1.1   |          |                                                                                                 |          |  |

|                   |       | MOSI     | FET device performance                                                                          | 6        |  |

|                   |       | 1.1.1    | MOSFET operation                                                                                | 6        |  |

|                   |       | 1.1.2    | Metal-Oxide-Semiconductor gate stack properties                                                 | 9        |  |

|                   |       | 1.1.3    | MOSFET performance parameters influenced by the gate                                            |          |  |

|                   |       |          | stack                                                                                           | 18       |  |

|                   |       |          | stack fabrication process                                                                       | 23       |  |

|                   |       | 1.2.1    | Oxidation methods and Gate dielectrics                                                          | 23       |  |

|                   |       | 1.2.2    | Metal gate electrode and deposition techniques                                                  | 27       |  |

|                   |       |          | 1.2.2.1 Thin metal gate films deposition techniques                                             | 28       |  |

|                   |       |          | 1.2.2.2 Deposition of ultra-thin Titanium nitride films                                         |          |  |

|                   |       |          | and Aluminum and Lanthanum monolayers by                                                        |          |  |

|                   |       |          | RF-PVD magnetron sputtering                                                                     | 34       |  |

|                   | 1.3   | Metal    | gate integration in 14 nm Fully-Depleted SOI devices $\ldots$                                   | 36       |  |

|                   |       | 1.3.1    | FDSOI architecture                                                                              | 36       |  |

|                   |       |          | 1.3.1.1 Multi- $V_{TH}$ offer                                                                   | 37       |  |

|                   |       |          | 1.3.1.2 Effective work function requirements for                                                |          |  |

|                   |       |          | Fully-Depleted SOI devices                                                                      | 38       |  |

|                   |       | 1.3.2    | Sacrificial metal gate-first process integration                                                | 39       |  |

|                   |       | 1.3.3    | Random local $V_{TH}$ fluctuations $\ldots \ldots \ldots \ldots \ldots \ldots$                  | 41       |  |

|                   | 1.4   | Concl    | usion $\ldots$ | 44       |  |

| <b>2</b>          | Pro   | cess     | flow and test methodology for electrical and                                                    |          |  |

|                   | phy   | sicoch   | emical characterization of gate stack                                                           | 45       |  |

|                   | 2.1   | Techn    | iques of electrical characterization                                                            | 46       |  |

|                   |       | 2.1.1    | Test structures                                                                                 | 46       |  |

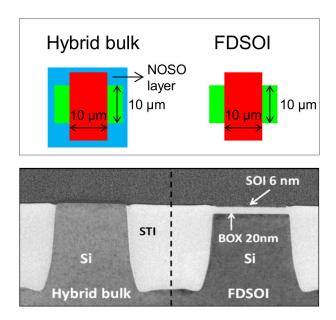

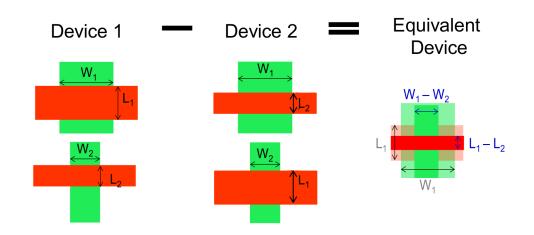

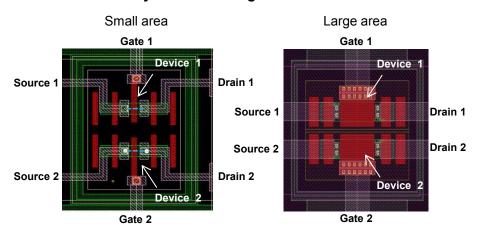

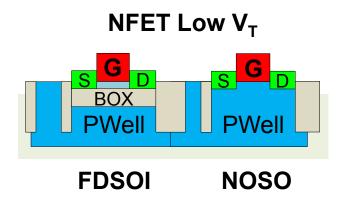

|                   |       |          | 2.1.1.1 Hybrid devices                                                                          | 48       |  |

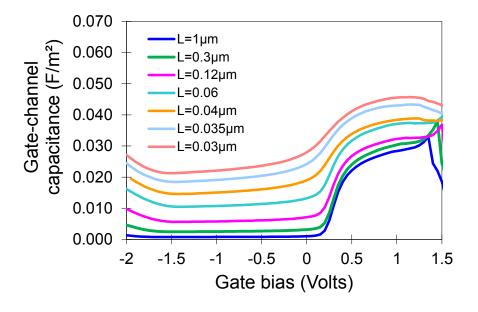

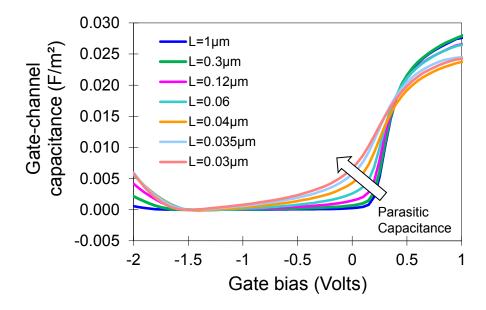

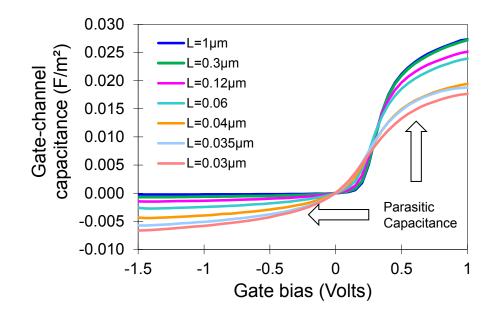

|                   |       |          | 2.1.1.2 Short channel test structures                                                           | 49       |  |

|                   |       |          | 2.1.1.3 Matching test structures                                                                | 54       |  |

|                   |       | 2.1.2    | Process flow simplification for nominal devices and specific                                    |          |  |

|                   |       |          | research wafers                                                                                 | 56       |  |

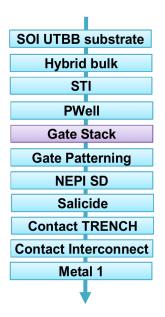

|                   |       |          | 2.1.2.1 Nominal devices $\ldots$                                                                | 56       |  |

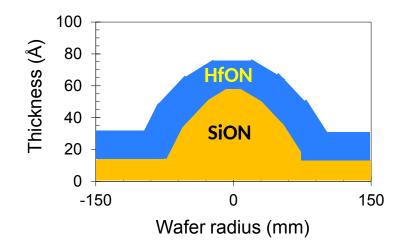

|                   |       |          | 2.1.2.2 Devices with beveled oxide $\ldots \ldots \ldots \ldots$                                | 58       |  |

|                   |       | 2.1.3    | Measurements and electrical parameters extraction $\ . \ . \ .$                                 | 62       |  |

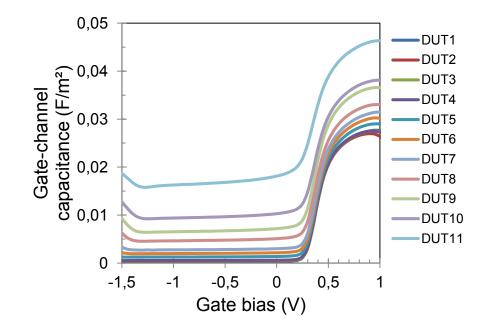

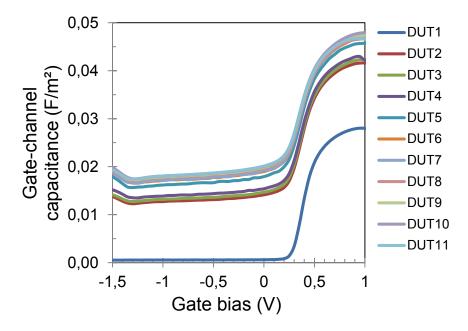

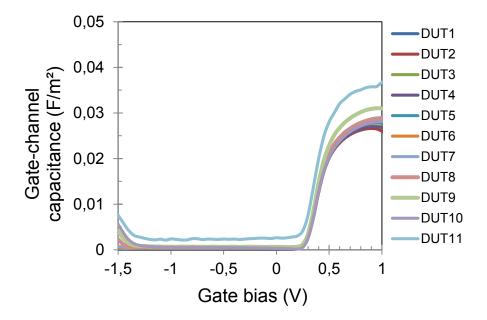

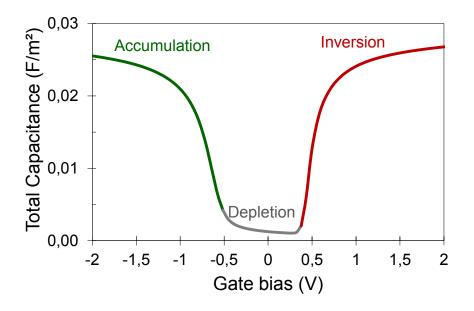

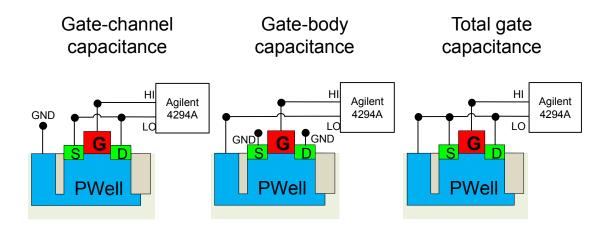

|                   |       |          | 2.1.3.1 Experimental set up for C-V measurements                                                | 62       |  |

|   |            | 2.1.3                  | 3.2 Extraction of electrical parameters from C-V characteristics                                 | 64  |

|---|------------|------------------------|--------------------------------------------------------------------------------------------------|-----|

|   | 2.2        | Physicocher            | mical characterization                                                                           | 67  |

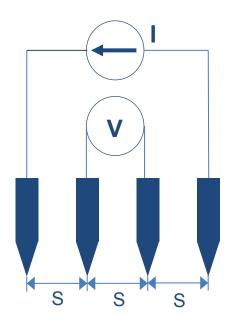

|   | 2.2        | •                      | r-point probe resistance measurement                                                             | 67  |

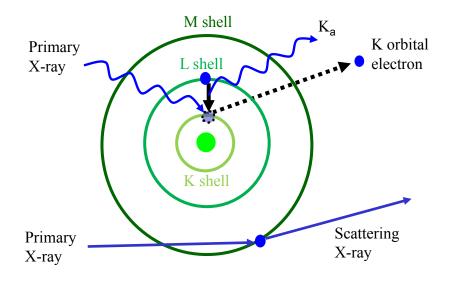

|   |            |                        | ay Fluorescence                                                                                  | 68  |

|   |            | 2.2.2 A-IG<br>2.2.2    | •                                                                                                | 69  |

|   |            | 2.2.2                  | -                                                                                                | 09  |

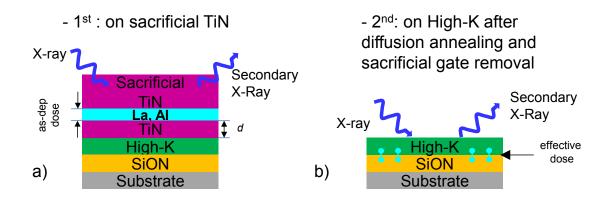

|   |            | 2.2.2                  | diffusion of gate additives                                                                      | 70  |

|   |            | 2.2.3 Seco             | ondary Ion Mass Spectrometry                                                                     | 70  |

|   |            |                        |                                                                                                  | 71  |

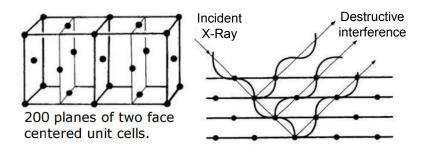

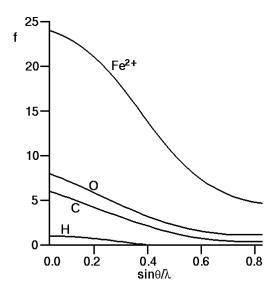

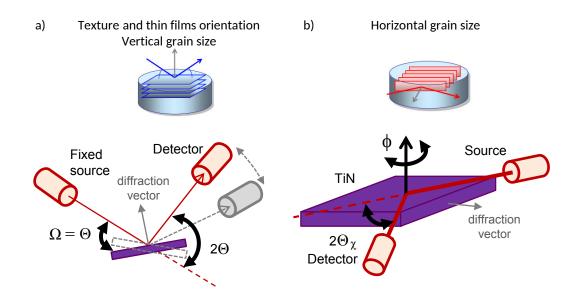

|   | <b>9</b> 9 |                        | ay Diffraction                                                                                   | 80  |

|   | 2.3        |                        |                                                                                                  |     |

| 3 |            |                        | x function modulation by accurate control of<br>crificial lanthanum and aluminum into gate stack |     |

|   |            |                        | d NFET devices                                                                                   | 81  |

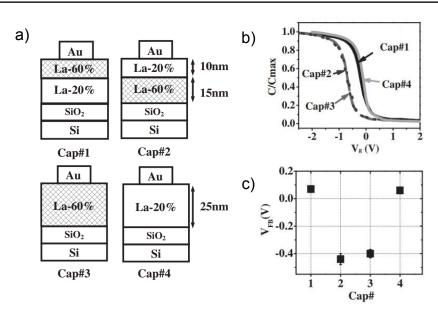

|   | 3.1        | 0                      | e art of lanthanum in gate stack                                                                 | 82  |

|   | -          |                        | thanum oxide as alternate gate dielectrics                                                       | 82  |

|   |            |                        | thanum incorporation into Hf-based dielectrics                                                   | 83  |

|   |            |                        | thanum incorporation into TiN                                                                    | 84  |

|   | 3.2        |                        | vork function modulation by accurate control of                                                  |     |

|   | 0          |                        | anthanum diffusion                                                                               | 86  |

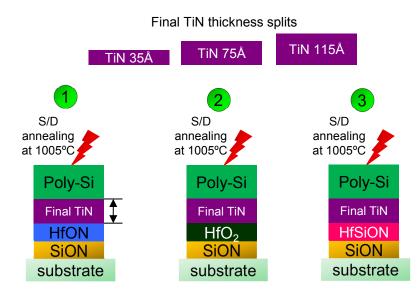

|   |            | •                      | ice fabrication and electrical characterization                                                  | 86  |

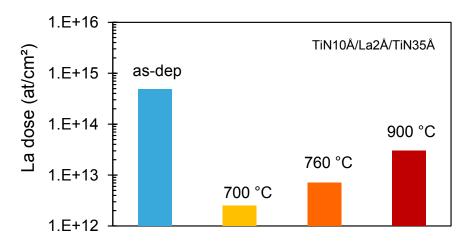

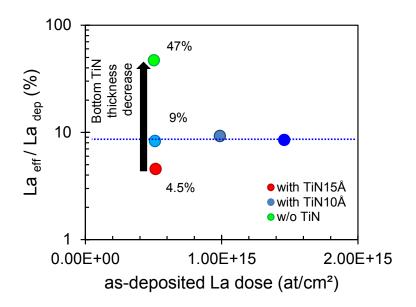

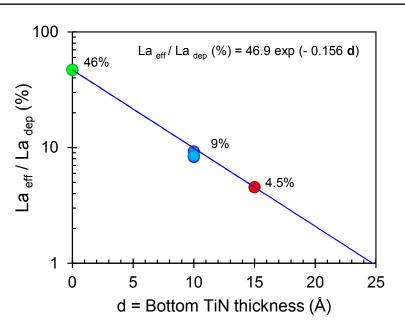

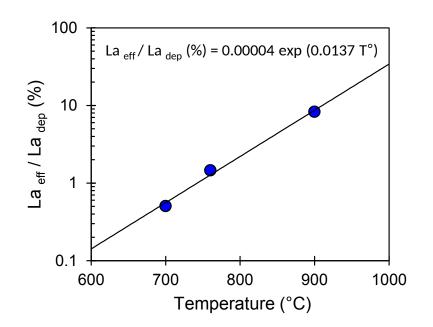

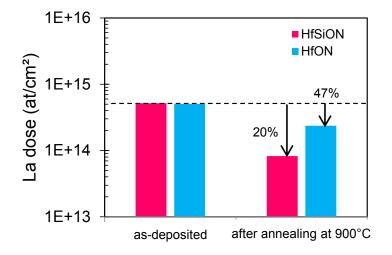

|   |            |                        | usion characterization by X-Ray Fluorescence                                                     | 91  |

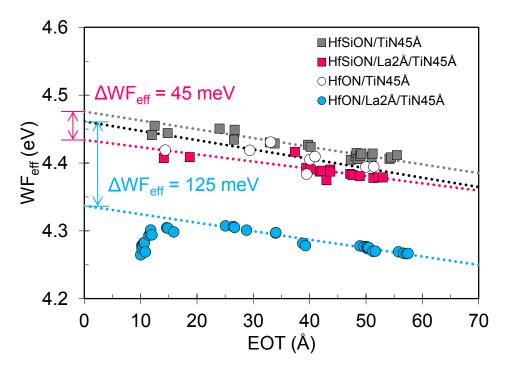

|   |            |                        | nence of high- $\kappa$ dielectrics on the effective work function                               | 01  |

|   |            |                        | induced by lanthanum incorporation                                                               | 97  |

|   | 3.3        |                        | e art of aluminum in gate stack                                                                  | 102 |

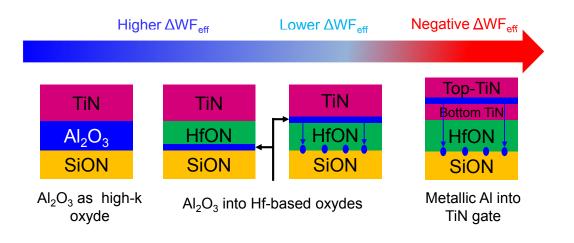

|   | 0.0        |                        | minum oxide as alternative gate dielectrics                                                      | 103 |

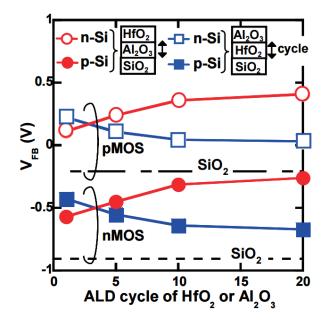

|   |            |                        | minum incorporation into Hf-based gate dielectrics                                               | 103 |

|   |            |                        |                                                                                                  | 105 |

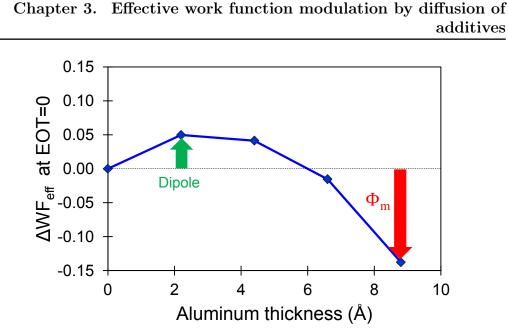

|   | 3.4        |                        | vork function modulation by accurate control of                                                  | 100 |

|   |            |                        | luminum diffusion                                                                                | 107 |

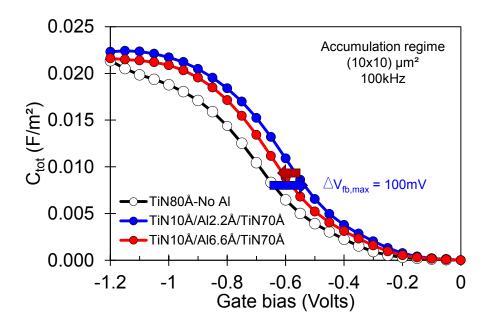

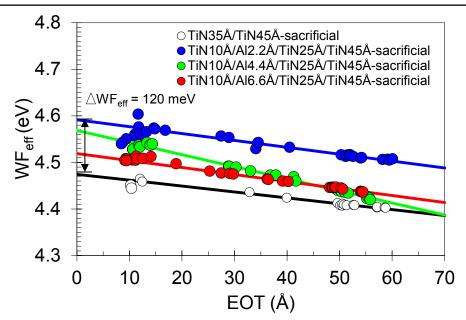

|   |            | 3.4.1 Devi             | ice fabrication and electrical characterization                                                  | 107 |

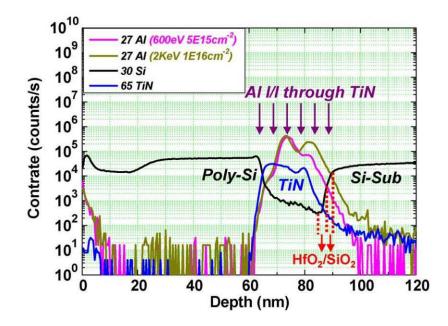

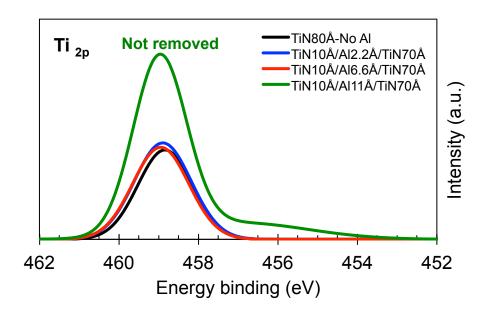

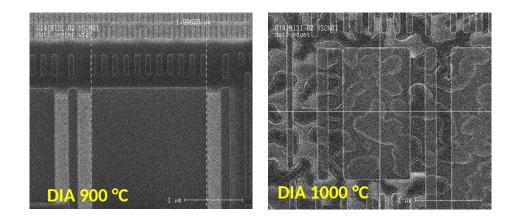

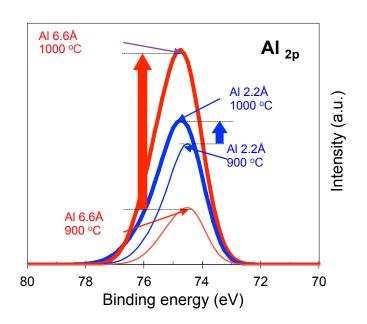

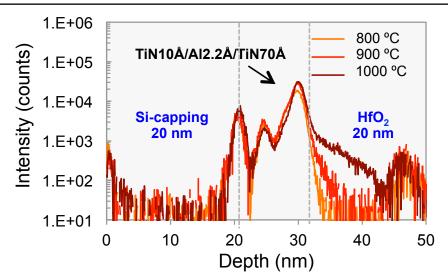

|   |            | 3.4.2 Diffu            | usion characterization by X-Ray Spectroscopy                                                     | 113 |

|   |            |                        | nence of high- $\kappa$ dielectrics on the effective work function                               |     |

|   |            | $\operatorname{shift}$ | induced by aluminum incorporation                                                                | 121 |

|   | 3.5        |                        | s standard final approach                                                                        | 124 |

|   | 3.6        |                        |                                                                                                  | 127 |

| 4 | Rol        | e of TiN or            | n effective work function and matching of 14 nm                                                  | L   |

|   | FDS        | SOI devices            | 3                                                                                                | 129 |

|   | 4.1        | State of the           | e art of the modification of the effective work function                                         |     |

|   |            | induced by             | the TiN                                                                                          | 130 |

| Bibliography                 |                                                                          |                                                                                                |     |  |  |

|------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|--|--|

| Conclusions and Perspectives |                                                                          |                                                                                                |     |  |  |

| 4.4                          | Conclu                                                                   | ision                                                                                          | 166 |  |  |

|                              | 4.3.4                                                                    | TiN microstructure versus thickness                                                            | 164 |  |  |

|                              | 4.0.0                                                                    | with TiN microstructure engineering $\ldots$                                                   | 160 |  |  |

|                              | 4.3.3                                                                    | deposited by RF-PVD $\ldots$ Electrical impact and local $V_{TH}$ variability improvement      | 156 |  |  |

|                              | 4.3.2                                                                    | deposited by RF-PVD                                                                            | 152 |  |  |

|                              | 4.3.1                                                                    | Impact of pressure conditions on microstructure of TiN                                         |     |  |  |

| 4.3                          | Impact of deposition process on TiN microstructure and local variability |                                                                                                | 149 |  |  |

|                              |                                                                          | effective work function                                                                        | 147 |  |  |

|                              | 4.2.4                                                                    | HfON/SiON stacks                                                                               | 145 |  |  |

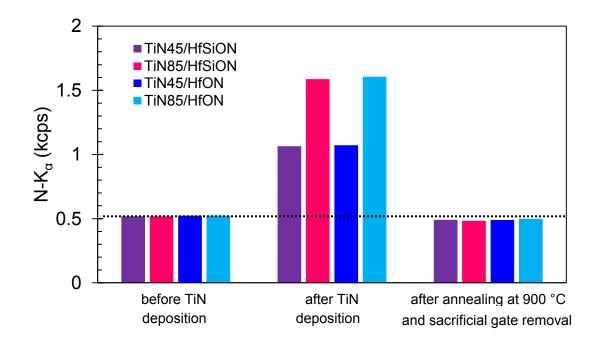

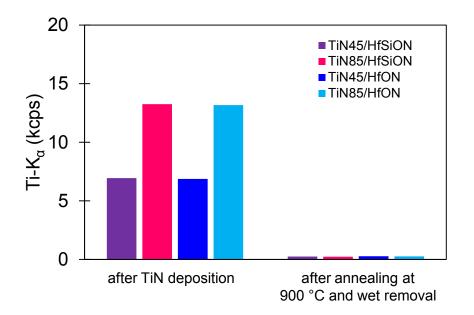

|                              | 4.2.3                                                                    | Titanium and nitrogen diffusion into HfSiON/SiON and                                           | 110 |  |  |

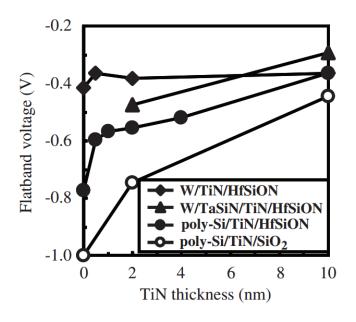

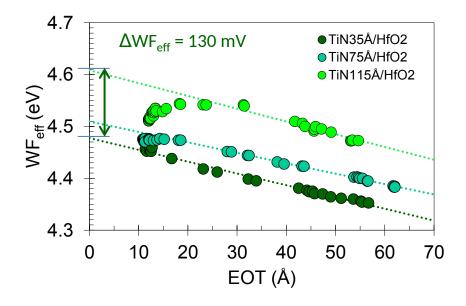

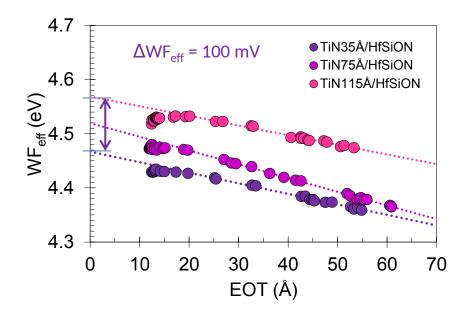

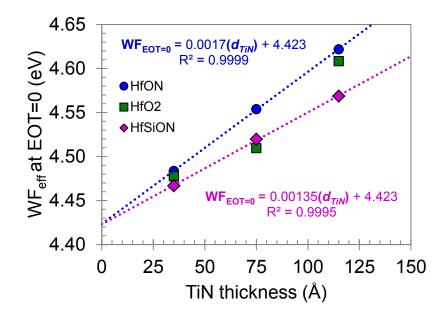

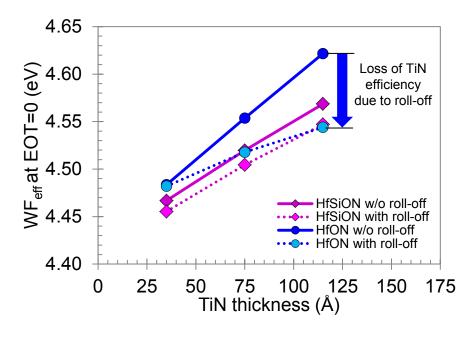

|                              | 4.2.2                                                                    | Influence of high- $\kappa$ dielectrics on the work function shift<br>induced by TiN thickness | 140 |  |  |

|                              |                                                                          | function                                                                                       | 134 |  |  |

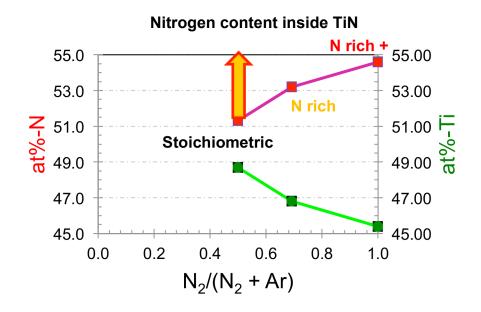

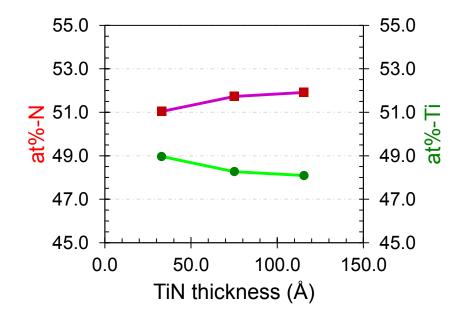

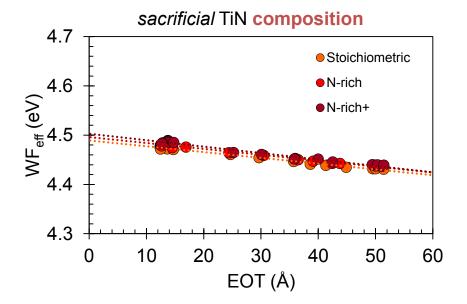

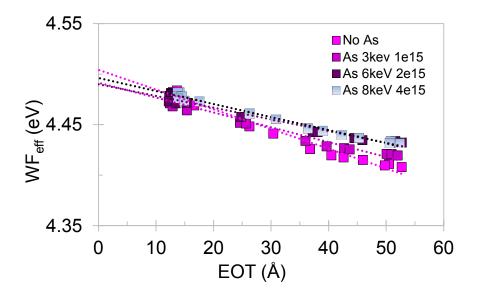

|                              | 4.2.1                                                                    | Impact of nitrogen content into TiN on the effective work                                      | 104 |  |  |

| 4.2                          | function of 14 nm FDSOI devices                                          |                                                                                                | 134 |  |  |

| 4.2                          | Chara                                                                    | effective work function                                                                        | 133 |  |  |

|                              | 4.1.4                                                                    | Effect of the reduction of oxygen vacancy defects on                                           |     |  |  |

|                              | 4.1.3                                                                    | Effect of the oxygen incorporation in TiN gate on the effective work function                  | 132 |  |  |

|                              | 1.1.2                                                                    | composition in TiN gate                                                                        | 132 |  |  |

|                              | 4.1.2                                                                    | thickness                                                                                      | 130 |  |  |

|                              | 4.1.1                                                                    | Modulation of the effective work function by tuning TiN                                        | 100 |  |  |

## Context

Digital electronics are omnipresent across the globe today, enriching people's lives and making communication and sharing easier than ever. This revolution is the consequence of the miniaturization of electronic systems over the past few decades. At the heart of each of these digital devices are semiconductor chips that provide the intelligence and power to drive the device. Each chip is made up with billions of transistors. The simultaneous manufacturing of these billions of transistors on a single wafer made possible the creation of integrated circuits To build better digital devices and performing complex logic operations. enhance the user experience, the size of the transistors must be reduced while increasing performance and reducing power consumption. This trend was first predicted by Intel co-founder Gordon Moore, who observed that the number of components in integrated circuits had doubled every two years from the invention of the integrated circuit in 1958, by Jack Kilby and Robert Noyce, From the beginning of mass production, the number of until 1965 [1]. transistors that the industry was able to place on a chip did double every two vears. In every new generation, the down-scaling of the horizontal along with the vertical dimensions of devices allows the increase of productivity and performances [2]. This prediction, now known as the Moore's law, is responsible for the evolution of today's complementary metal-oxide-semiconductor (CMOS) This law is now used in the semiconductor industry to guide technology. long-term planning and to set targets for research and development. In the 1960's the integrated circuits market was broadly based on Bipolar Junction Transistors (BJT) due to their high switching speed and low power consumption atsmaller sizes. But since 1975,integration of Field-Effect-Transistor (FET), invented by Dawon Kahng and Martin Atalla in 1959, dominated even though they were found to be slower switching devices than the bipolar transistors [3]. This was caused by the failure of BJTs to demonstrate rapid decrease in the power per circuit compared to FETs. As linear dimensions reached the half-micron level in the early 1990s, the performance advantage of bipolar transistors was overcome by FETs, then used in the CMOS circuit production until today.

For the fabrication of logic gates, most advanced integrated circuits use CMOS technology. CMOS uses both n-channel and p-channel MOSFET devices to achieve a high speed with low power dissipation. The aggressive scaling of CMOS has marked milestones in the evolution of the gate stack at STMicroelectronics. First, with the introduction of the couple high- $\kappa$  metal gate (HKMG) stack that has been integrated in the conventional SiO<sub>2</sub>/Poly-Si gate stack to continue the down-scaling of CMOS transistors while keeping overall performances. The introduction of a high- $\kappa$  dielectric is indeed key in order to keep low gate leakage current and enhance the gate stack capacitance density, thereby increasing the transistor ON-current ( $I_{ON}$ ), which leads to an increase of the circuit speed. In addition, the introduction of metal gate electrodes are required to be included in gate stack in order to lower gate resistance and eliminate poly silicon depletion and boron penetration effects, for improved performance and reliability [4], but also because of thermal instability of high- $\kappa$ dielectrics in contact with Poly-Si above temperatures which can exceed 1000 °C [5]. Second, with the integration of an ultra-thin buried oxide (BOX) for V<sub>TH</sub> variability improvement, back-bias efficiency and better short channel immunity compared to bulk technologies. Besides, this buried oxide layer eliminates the need to add dopants to the channel, thus making it fully depleted. This technology is called Fully-Depleted Silicon-On-Insulator (FDSOI) technology.

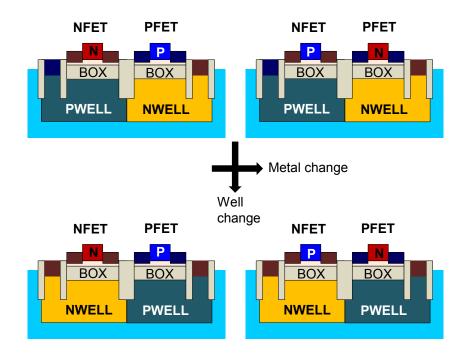

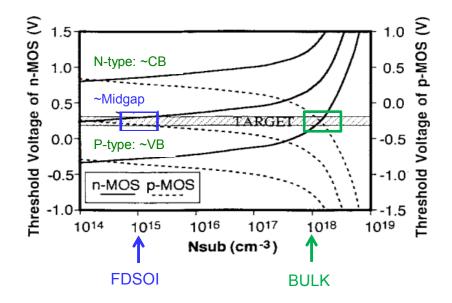

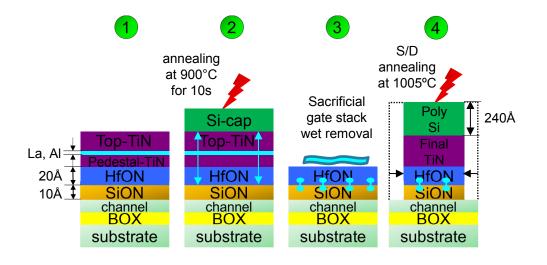

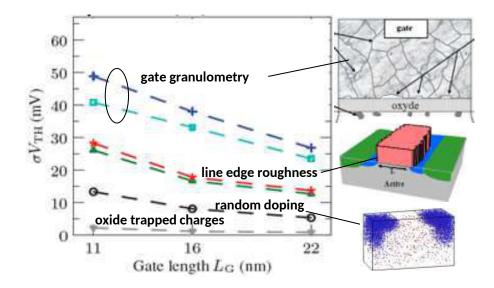

In this context, the  $V_{TH}$  for CMOS logic applications is mainly tuned through the work function of the metal gate, and not anymore by Poly-Si or channel doping. Metal gate electrodes with the correct work functions are therefore required for high performance CMOS logic applications. These requirements are not similar in FDSOI and bulk devices, as will be detailed in Furthermore, one technical challenge in metal electrode this thesis work. research is that the metal work function is process-dependent and depends on the electrical properties of the underlying high- $\kappa$  film [6], leading to an effective work function. The gate-first integration has been chosen for the integration of the metal gate stack in FDSOI devices manufactured at STMicroelectronics. In a gate-first approach, the metal electrode is deposited before the source drain dopant activation annealing at more than 1000 °C. In a gate-last approach, the metal electrode is thus deposited after the source drain dopant activation annealing. The choice of a gate-first integration limits the choice of metal electrode materials and the tuning of  $V_{TH}$  becomes more complex. On the other hand, a gate-last approach significantly increases the process complexity, the manufacturing cost, and the design rules are more restricted. On the other hand, although the main source of local  $V_{TH}$  variability related to the Random Dopant Fluctuations (RDF) in the channel has been suppressed in undoped channel FDSOI devices, some simulations predict that the Metal Gate Granularity (MGG) becomes more important in scaled devices and must be investigated.

### Objectives of this Ph. D. thesis

At the beginning of this Ph.D., the 14 nm FDSOI product was in progress of development and was scheduled to be released by end 2015. The couple TiN/HfON had been retained in 14 nm FDSOI manufacturing process for their thermal stability and reduced gate leakage currents. Based on the state of the

art, it was known that the presence of lanthanides in the dielectric shifts the effective work function towards the N+ values and the presence of alumina towards the P+ values. Nevertheless, a clear understanding of the diffusion of such additives and a methodology to provide a relationship between this diffusion and their impact on the effective work function was lacking. On the other hand, the optimal metal gate deposition conditions to face the local  $V_{\rm TH}$  variability induced by the metal granularity were unknown.

The main objectives of this thesis are, on one hand, the understanding of the modulation of the effective work function through the incorporation of additives such as aluminum, lanthanum and nitrogen following a *sacrificial* metal gate-first approach, and on the other hand, the study of the impact of the TiN microstructure on the  $V_{TH}$  variability of adjacent MOSFET pairs placed the one from the other at minimal spacing authorized by the design rules. The goal is to validate the sacrificial gate-first integration to successfully achieve the threshold voltage requirements of the 14FDSOI technology and to propose metal deposition conditions to further reduce the local  $V_{TH}$  variability in advanced FDSOI nodes.

### Outline

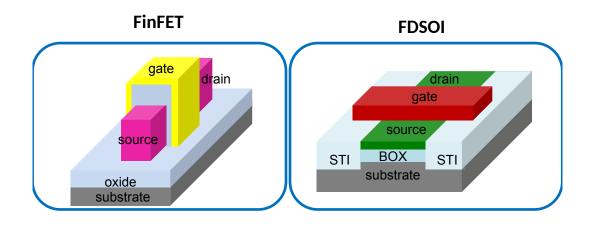

The first chapter introduces the gate stack technology as well as the current process challenges in gate stack integration with the aggressive scaling of Fully-Depleted Silicon on Insulator (FDSOI) MOSFET devices. The gate stack properties and their correlation with the main MOSFET performance parameters are reviewed in this chapter. The methods for dielectric growth as well as the metal deposition techniques are also described in this chapter. In particular, the deposition by Radio Frequency Physical Vapor Deposition of titanium nitride, lanthanum and aluminum layers is detailed. These metals are currently used in the development of the 14 nm FDSOI devices. We also describe in this chapter the Fully-Depleted Silicon on Insulator (FDSOI) architecture and its capability to offer multi threshold voltage  $(V_{TH})$  solutions. We define the requirements of the effective work function of the metal for such devices and the interest of the sacrificial metal gate-first approach as a process scheme able to achieve this target by precisely controlling the amount of additives incorporated into the gate stack. Finally, the need to investigate the microstructure of metal gates is introduced.

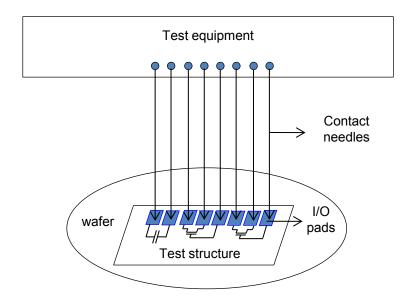

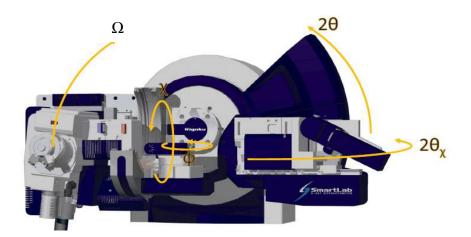

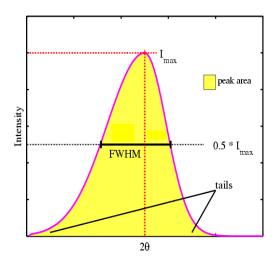

The second chapter introduces the techniques of electrical and physicochemical characterization used in this thesis. The implementation of specially designed test structures and a simplified process flow for metal gates investigation. The Capacitance-Voltage (C-V) analysis techniques employed to characterize the modulation of the effective work function with the additives incorporation into gate stack and to identify its physical origin are described in this chapter. Furthermore, a new methodology based on X-Ray Fluorescence is presented and validated in order to precisely characterize the percentage of effective diffusion of aluminum and lanthanum into high- $\kappa$ /bottom oxide stack. Finally, the two X-Ray diffraction configurations used to fully study the microstructure of TiN layers are detailed.

The third chapter focuses on the impact of the incorporation of lanthanum (La) and aluminum (Al) in a *sacrificial* gate-first approach on the effective work function of 14 nm FDSOI devices. This chapter covers the study of the process variations used to incorporate La in a sacrificial gate approach in NFET devices, the electrical measurements and the diffusion characterization of lanthanum into the HfON/SiON stack by the methodology based on X-Ray Fluorescence introduced in the second chapter. The influence of high- $\kappa$ dielectrics on the effective work function shift induced by lanthanum incorporation is also studied. Similarly, the study of the process variations used to incorporate aluminum following a *sacrificial* gate-first approach in NFET devices as well as the electrical characterization are described in this chapter. Likewise, the diffusion characterization of aluminum into the HfON/SiON stack and the influence of high- $\kappa$  dielectrics on the effective work function shift induced by aluminum incorporation are also presented and discussed in this chapter. Finally, the benefit of the sacrificial gate-first approach compared to a standard gate-first approach is discussed, as well as the perspectives for future research.

The final chapter focuses on the impact of nitrogen, adjusted by the thickness and composition of TiN layers, on the effective work function of FDSOI devices. Afterwards, the incorporation of nitrogen into gate stack is characterized by the physicochemical measurements. Finally, an innovative process for metal deposition by RF-PVD at room temperature, allowing the modification of the microstructure of TiN, is proposed in order to further reduce the local  $V_{\rm TH}$  variability in FDSOI devices.

This CIFRE Ph.D. thesis work has been carried out in collaboration with STMicroelectronics in Crolles, the CEA-LETI and the IMEP-LAHC laboratories in Grenoble. All the devices and blanket wafers were manufactured at STMicroelectronics in an industrial environment to better propose solutions to STMicroelectronics challenges in terms of  $V_{TH}$  modulation as well as of the reduction of  $V_{TH}$  variabilities for advanced FDSOI technologies. Electrical characterizations were performed in the Laboratoire de Caractérisations et Test Electrique (LCTE) of the CEA-LETI.

# Gate stack technology for 14 nm FDSOI MOSFET devices

#### Contents

| 1.1 | Impact of Metal-Oxide-Semiconductor gate stack<br>properties on MOSFET device performance | 6  |

|-----|-------------------------------------------------------------------------------------------|----|

| 1.2 | Gate stack fabrication process                                                            | 23 |

| 1.3 | Metal gate integration in 14 nm Fully-Depleted SOI devices                                | 36 |

| 1.4 | Conclusion                                                                                | 44 |

This chapter introduces the gate stack technology as well as the current process challenges in gate stack integration with the aggressive scaling of Fully-Depleted Silicon on Insulator (FDSOI) MOSFET devices.

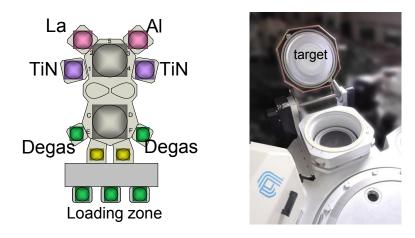

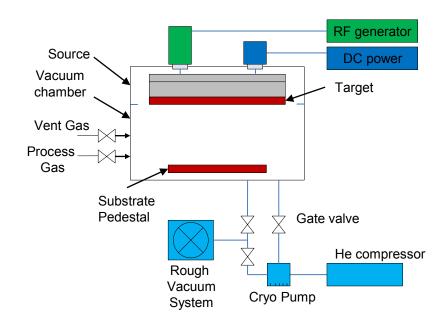

The gate stack properties and their correlation with the main MOSFET performance parameters are reviewed in the section 1.1 of this chapter. The section 1.2 extensively describes the methods for dielectric growth as well as the metal deposition techniques. In particular, the deposition by Radio Frequency Physical Vapor Deposition of titanium nitride, lanthanum and aluminum layers is detailed. These metals are currently used in the development of the 14 nm FDSOI devices.

The section 1.3 of this chapter presents the Fully-Depleted Silicon on Insulator (FDSOI) architecture and its capability to offer multi threshold voltage ( $V_{TH}$ ) solutions. In this context, the requirements for the effective work function of the metal are defined. The sacrificial metal gate-first approach is described as a process scheme able to achieve this target by precisely controlling the amount of additives incorporated into the gate stack.

# 1.1 Impact of Metal-Oxide-Semiconductor gate stack properties on MOSFET device performance

### 1.1.1 MOSFET operation

The Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) device is based on the field effect mechanism [7]. In physics, the field effect refers to the modulation of the electrical conductivity of a material by the application of an external electric field. In MOSFETs, this field effect is then related to the control of the semiconductor conductivity near its surface.

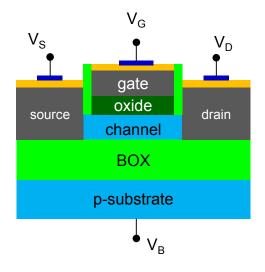

A MOSFET is a four-terminal device, but it can be seen as a combination of two orthogonal two-terminal devices, as shown in Fig. 1.1. The objective is to control the current flow between two ohmic contacts, the *source* and the *drain*, by the modulation of the charges in the semiconductor channel. Charge carriers in the semiconductor channel are controlled by two other terminals, the *gate* and the *body* or *substrate*, by capacitive coupling<sup>1</sup>. The threshold voltage ( $V_{TH}$ ) is the minimum gate-to-body voltage difference that is needed to create a conductive channel between the source and drain terminals. It is the conductive channel that allows the carriers to flow from the source to the drain.

Figure 1.1: Schematic diagram of a four terminal n-channel MOSFET device.

The simplest MOS structure is the MOS capacitor and it is composed of a p-type or n-type doped silicon, a gate oxide and a layer of metal or polycrystalline

<sup>&</sup>lt;sup>1</sup>In electronics, coupling is the transfer of energy from a medium to another medium.

silicon. By applying Kirchhoff's voltage law, the potential difference between the gate and the body terminals  $(V_G)$  can therefore be decomposed as follows :

$$V_G = \Phi_m - \Phi_{\rm sc} + V_{\rm ox} + V_{\rm sc} \tag{1.1}$$

where  $q\Phi_m$  corresponds to the difference between the metal Fermi level and its vacuum level,  $q\Phi_{sc}$  corresponds to the difference between the semiconductor Fermi level and its vacuum level,  $V_{ox}$  is the drop voltage across the oxide and  $V_{sc}$ is the potential drop in the semiconductor.

The relationship between the charges in the semiconductor  $Q_{sc}$  and the potential at the semiconductor surface ( $V_{sc}$ ) can be described by the Poisson equation for electrostatics, according to classical electrodynamics [7]. However, for ultra-thin oxide thicknesses and low field strengths, such interactions are better described by quantum Poisson-Schrödinger simulations (section 2.1.3). The charges induced in the semiconductor may be of three types : majority carriers, minority carriers and depletion charge. The type of charges can be controlled by the voltage applied to the gate, specifically by the  $V_{sc}$ . Indeed, the ability to induce and modulate a conducting sheet of minority carriers at the semiconductor/oxide interface is the basis of the operation of the MOSFET.

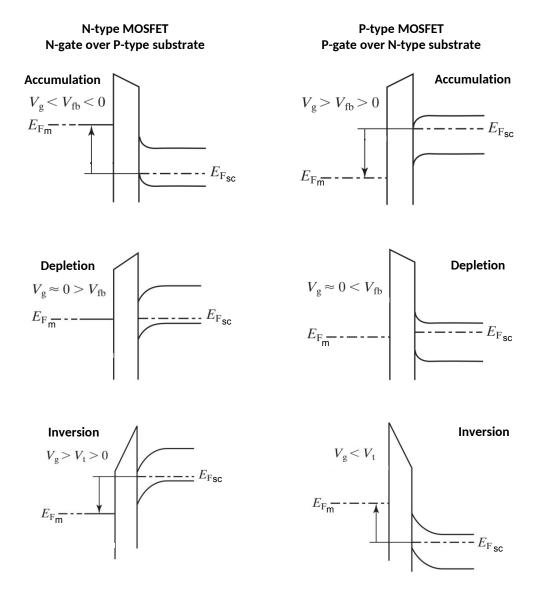

Let's take the example of p-type semiconductor substrate. For an n-type semiconductor, the sign of  $V_{sc}$  has to be switched, as shown in Fig. 1.2.

- $V_{sc} < 0$ : Accumulation regime. Majority carriers are attracted to the surface of the semiconductor.

- $0 < V_{sc} < \Phi_{fi}$ : *Depletion* regime. Majority carriers are pushed towards the bulk silicon, and so, their density decreases at the semiconductor/oxide interface. The only remaining charges are the thermally ionized dopant atoms at room temperature.

- $\Phi_{\rm fi} < V_{\rm sc} < 2\Phi_{\rm fi}$ : Weak inversion or subthreshold regime. Minority carriers density starts to increase, but charges are essentially the thermally ionized dopant atoms at room temperature. Transistor is in the "off" state or weak inversion under threshold voltage.

- $2\Phi_{\rm fi} < V_{\rm sc}$ : Strong inversion regime. The transistor is in the "on" state. Minority carriers density becomes much more important than the doping concentration. The channel is formed between the source and the drain.

Figure 1.2: Energy band diagrams of the two dominant types of MOS capacitors.

The heavily doped (n+ for NFETs and p+ for PFETs) source/drain regions, are used to make an ohmic contact with the conductive channel for  $|V_G| > |V_{TH}|$  so that a voltage difference between the source and the drain ( $V_{DS}$ ) will result in a current flow ( $I_{DS}$ ) of minority carriers (electrons for NFETs and holes for PFETs) from the positive voltage at the drain terminal to the negative voltage at the source. This current flow of minority carriers is also known as drive current and is one of the main MOSFET device performance parameters. In the "off" state, the drive current is very small (ideally zero) and in the "on" state, it is a function of both  $V_G$  and  $V_{DS}$ .

#### 1.1.2 Metal-Oxide-Semiconductor gate stack properties

#### Gate dielectric capacitance and equivalent oxide thickness

The capacitance is the ability of a body to store an electrical charge. The most common form of energy storage device is the parallel plate capacitor, which consists of two electrical conductors (plates) separated by a dielectric (i.e. an electrical insulator that can be polarized by the application of an electric field). When a potential difference V is applied to the conductors, an electric field develops across the dielectric, causing positive charge (+Q) on one plate and negative charge (-Q) on the other plate. The capacitance C is defined as the ratio of charge on each conductor to the voltage V between them (C = Q/V).

In a Metal-Oxide-Semiconductor capacitor, one of the plates is the metal gate and the other, is the silicon substrate. However, in the MOS capacitor the applied voltage may be used to control the type of interface charge induced in the channel (majority carriers, minority carriers, and depletion charge). The dielectric consists of the gate oxide with a relative permittivity  $\varepsilon_{ox}$  (commonly known as the dielectric constant) and thickness  $T_{ox}$ . Consequently, the gate dielectric capacitance per unit area ( $C_{ox}$ ) can be expressed as follows :

$$C_{\rm ox} = \frac{\varepsilon_0 \varepsilon_{\rm ox}}{T_{\rm ox}} \tag{1.2}$$

where  $\varepsilon_0 = 8.854... \ge 10^{-12} \text{ F/m}$  is the vacuum permittivity.

In order to quickly compare different dielectric materials to the industry standard silicon oxide  $(SiO_2)$  dielectric, a new definition has been proposed :

$$C_{\rm ox} = \frac{\varepsilon_0 \varepsilon_{\rm SiO2}}{EOT} \tag{1.3}$$

where EOT (Equivalent Oxide Thickness) is defined as :

$$EOT = T_{\rm ox} \frac{\varepsilon_{\rm SiO2}}{\varepsilon_{\rm ox}} \tag{1.4}$$

Both EOT and  $C_{ox}$  are important gate stack properties that influence the performance parameters of MOSFET devices such as the drive current ( $I_{DS}$ ) and the threshold voltage ( $V_{TH}$ ), as will be detailed in section 1.1.3.

#### Flat band voltage

The gate bias  $(V_G)$  always corresponds to the potential difference between the metal and semiconductor Fermi levels,  $E_{F,m}$  and  $E_{F,sc}$ , respectively. The energy band diagram of the MOS structure for  $V_G = 0$  is quite complex and shows band bending due to the semiconductor and metal work function difference. The flat band voltage  $(V_{fb})$  is a special bias condition which corresponds to the gate bias with no charge in the substrate. In other words,  $V_{fb}$  is the bias condition leading

to no band bending at the substrate interface. It corresponds to  $Q_{sc} = 0$ , and for constant doping level in semiconductor, it usually leads to  $V_{sc} = 0$ . However, at flat band condition, the term  $V_{ox}$  is not necessarily zero [7] [8]. Indeed, it is influenced by oxide stack charges density and interfacial voltage drops [9]. The flat band expression can thus be deduced from Eq. 1.1

$$V_{\rm fb} = \Phi_m - \Phi_{\rm sc} + V_{\rm ox} \tag{1.5}$$

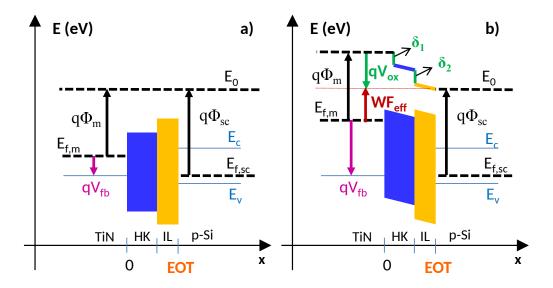

Considering a p-type substrate and an bilayer high- $\kappa/SiO_2$  oxide stack with no oxide charges at all, the energy band diagram of the MOS structure at flat band condition is described in Fig. 1.3a.  $E_0$ ,  $E_C$ , and  $E_V$  are the energy of vacuum level, the energy of the bottom of the conduction band, and the energy of the top of the valence band of silicon, respectively.

Figure 1.3: Energy band diagram of the MOS structure at the flat band condition a) without any oxide charge and b) with charges in the oxide and dipoles at high- $\kappa$  interfaces.

However,  $V_{\rm fb}$  for real devices is a process-dependent parameter and its control is currently one of the most serious problems, especially in bilayer high- $\kappa/{\rm SiO}_x$  oxide structures, currently used in 14 nm FDSOI technology and other modern MOSFET technologies. Gate stack charges density and interfacial voltage drops due to the formation of an electrostatic dipole ( $\delta$ ) at both high- $\kappa$ interfaces have been reported as the origins of the V<sub>fb</sub> shift. An energy band diagram for such non-ideal MOS structure at flat band condition is shown in Fig. 1.3b [9]. Note that the vacuum level is influenced by the presence of charges and interfacial drops. As a result, processes variations lead to an effective work function (WF<sub>eff</sub>) different from  $\Phi_m$ . The effective work function is of first interest, since it drives  $V_{TH}$ . In the next sections, we first describe the gate stack charges and the interface electrostatic dipole and their impact on  $V_{fb}$ . Next, the expression of  $WF_{eff}$  in the case of a bilayer high- $\kappa/SiO_x$  oxide structure will be defined, as well as the considerations assumed and validated to simplify the  $WF_{eff}$  expression in this thesis work.

#### Gate stack charges density and its impact on flat band voltage

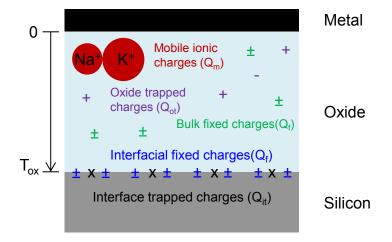

In real MOSFET devices, four general types of charges can be identified and associated to the Si/SiO<sub>2</sub> system [10] [11] [12]: bulk or interfacial fixed charges  $(Q_f)$ , mobile ionic charges  $(Q_m)$ , interface trapped charges  $(Q_{it})$ , and oxide trapped charges  $(Q_{ot})$ . The origin of these charges has been related to some impurities or defects incorporated into the oxide during oxide growth or subsequent fabrication process steps.

The mobile ionic charges  $(Q_m)$  are primarily due to positive alkali ions in the oxide such as Na<sup>+</sup>, K<sup>+</sup> and Li<sup>+</sup> [10], incorporated during device processing steps. These impurities cause reliability problems under high temperature and high voltage operations as they can migrate from an interface to another.

The oxide trapped charges  $(Q_{ot})$  may be positive or negative due to holes or electrons trapped in the bulk of the oxide. Trapping may result from ionizing radiation, avalanche injection, or other similar processes. Unlike fixed charge, oxide trapped charge is generally annealed out by low temperature (< 500 °C) treatment, although neutral traps may remain [11].

The fixed oxide charges  $(Q_f)$  are positive or negative charges located in the dielectric or at Si/SiO<sub>x</sub> interface. In a bilayer high- $\kappa$ /SiO<sub>x</sub> oxide structure, fixed charges can be located at: a) bulk high- $\kappa$  layer, b) high- $\kappa$ /SiO<sub>x</sub> interface, c) bulk SiO<sub>x</sub> layer, d) SiO<sub>x</sub>/Si interface, and e) metal/high- $\kappa$  layer [13]. We name  $Q_{Si/SiO_x}$  the sheet of charges at SiO<sub>x</sub>/Si interface and  $Q_{SiO_x/HK}$  the sheet of charges at high- $\kappa$ /SiO<sub>2</sub> interface. Fixed oxide charges do not move and exchange charge with the underlying silicon. They also do not change with the applied voltage [11].

The interface trapped charges ( $Q_{it}$ ) are positive or negative charges located at the Si/SiO<sub>x</sub> interface. They are due to structural, oxidation-induced defects, radiation-induced defects or other dangling bonds at this interface. Unlike fixed charge or trapped charge, interface trapped charge is in electrical communication with the underlying silicon and can thus be charged or discharged, depending on the surface potential V<sub>sc</sub>. Most of the interface trapped charges can be neutralized by low temperature (450 °C) hydrogen annealing or forming gas annealing [11].

The location of these charges is illustrated in Fig. 1.4.

Figure 1.4: Location of charges in thermally oxidized silicon according to [10].

The effect of each charge on the V<sub>fb</sub> condition depends on its distance from the oxide/semiconductor interface and can be calculated from Gauss Law. This is why it is convenient to separate the charges between bulk charges and interface charges. From Gauss Law application, we can deduce the V<sub>fb</sub> shift induced by each type of oxide charge:  $\Delta V_{\rm fb}^{bulk}$ ,  $\Delta V_{\rm fb}^{f}$ , and  $\Delta V_{\rm fb}^{it}$  for bulk charges, interface fixed charges, and interface trapped charges, respectively. Bulk charges include the mobile ionic charges, the oxide trapped charges and the bulk fixed charges and their impact on flat band voltage is given by:

$$\Delta V_{\rm fb}^{bulk} = -\frac{1}{\varepsilon_0} \int_0^{T_{ox}} \rho(z) \int_0^z \frac{du}{\varepsilon_{ox}(u)} dz \tag{1.6}$$

where  $\rho(\mathbf{z})$  is the gate dielectric charge distribution per unit volume. For a constant bulk charge density in a dielectric layer, the voltage drop will then vary with the square of its thickness. Interface fixed charges for a bilayer high- $\kappa/\text{SiO}_x$  oxide structure can be expressed as follows:

$$\Delta V_{\rm fb}^f = -\frac{Q_{\rm Si/SiO_x}}{\varepsilon_0 \varepsilon_{\rm SiO_2}} \text{EOT} - \frac{Q_{\rm SiO_x/HK}}{\varepsilon_0 \varepsilon_{\rm SiO_2}} \text{EOT}_{HK}$$

(1.7)

A sheet of charges at the high- $\kappa/\text{SiO}_x$  interface or at  $\text{SiO}_x/\text{Si}$  interface induces a voltage drop which increases linearly with the distance from the gate. Finally, interface trapped charges located at the  $\text{Si}/\text{SiO}_x$  interface influences the V<sub>fb</sub> as follows:

$$\Delta V_{\rm fb}^{it} = -\frac{Q_{it}(V_{\rm sc})}{\varepsilon_0 \varepsilon_{\rm SiO_2}} \text{EOT}$$

(1.8)

It is therefore evident that the presence of charges in the oxide changes  $V_{\rm fb}$ . As the threshold voltage is related to the  $V_{\rm fb}$ , charges also directly influence the threshold voltage and most of the performance parameters of MOSFET devices, which will be described in section 1.1.3. Even worst, charges affect not only threshold voltages but also effective mobilities, and device stability in MOS devices, and also junction leakage, noise, and breakdown voltage in discrete transistors and digital integrated circuits. In addition, defects are undesirable for four reasons. Firstly, charges trapped in defects shift the gate threshold voltage of the transistor. Secondly, the trapped charge changes with time so  $V_{\rm TH}$  shifts with time, leading to instability of operating characteristics. Thirdly, trapped charge scatters carriers in the channel and lowers the carrier mobility. Fourthly, defects are the starting point for electrical failure and oxide breakdown [14], and then they cause unreliability.

#### Interface electrostatic dipole

Discrepancies between  $WF_{eff}$  obtained through electrical measurements and  $\Phi_m$  in high- $\kappa$  metal gate stacks have also been related to other electrostatic effects. Indeed, although differences in fixed charges could explain some of the differences in the relative shifts, only fixed charges was not sufficiently appropriate to explain a part of the potential drop, which was independent of the thickness of the oxides. Several models have therefore been proposed to explain such discrepancies at various locations in the gate stack, in particular at metal/high- $\kappa$  interface and at high- $\kappa/SiO_x$  interface. We present here a synthesis of the most important hypothesis, the interpretations of experimental results, and the latest progress on the understanding of this electrical behaviour.

At first, the presence of metal-induced gap states (MIGS) was proposed at the metal/high- $\kappa$  interface [15]. Oxygen vacancies in high- $\kappa$  oxides, leading to charge transfer from oxygen vacancies to the gate electrode [16], was also mentioned as a possible cause of the V<sub>fb</sub> shift. Indeed, reduction/oxidation ambient annealing experiments were performed to introduce/annihilate the oxygen vacancies of  $HfO_2$  and to investigate the origin of  $V_{fb}$  shifts [17]. Positive and negative  $V_{\rm fb}$  shifts were observed by switching from annealing in a oxidizing to a reducing atmosphere, respectively. It was stated that the  $V_{\rm fb}$ modulation was caused by a change of the oxygen vacancy concentration in the  $HfO_2$  near the metal/ $HfO_2$  contact. The origins of this  $V_{fb}$  shift was also related to the electrical effect of a dipole layer at metal/high- $\kappa$  interface due to the group electronegativity difference between metal gate and Hf in dielectrics [18]. According to this model, the modulation of the capping dielectric material which it is in contact with metal can also modulate the  $V_{fb}$  shift. The polarity of these shifts was also consistent with the difference in mean electronegativity for each dielectric relative to that of  $HfO_2$  [19]. The hypothesis of the formation

of an electric dipole at metal/high- $\kappa$  interface was compatible with the V<sub>fb</sub> shifts successfully achieved by capping the top surface of the high- $\kappa$  layer with additives such as aluminum [20] or lanthanum [21], in a conventional gate-first flow with the highest temperature in the range between 985 °C and 1050 °C. At the time, this was considered as the experimental demonstration that the metal/high- $\kappa$  interface is the key reason for the observed WF<sub>eff</sub> variations.

Nevertheless, other experiments demonstrated that  $V_{fb}$  shift is modulated predominantly by the high- $\kappa/SiO_2$  interface, at least in the case of low annealing temperature (500 °C) for which no interdiffusion of Hf and metallic atoms occurs during device fabrication [22], [23].

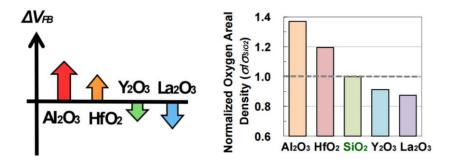

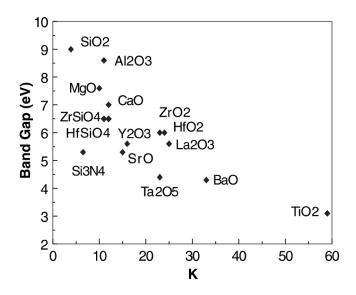

the oxygen vacancy formation [24] and a material Once again, electronegativity differences 25 at the bottom interface were considered to be the origin of the dipole creation. Some authors also concluded that generated oxygen vacancy forms an additional dipole different from the initially existing dipole at high- $\kappa/SiO_2$  interface and therefore the V<sub>fb</sub> shift is determined by the contribution of two types of dipoles at high- $\kappa/SiO_2$  interface [26]. An interesting point is that the interface dipole direction of  $La_2O_3/SiO_2$  or  $Y_2O_3/SiO_2$  is opposite to that of  $Al_2O_3/SiO_2$  or  $HfO_2/SiO_2$ , as shown in Fig. 1.5 on the left. In order to explain the direction and magnitude of the  $V_{fb}$  shift induced by the dipole formed at high- $\kappa/SiO_2$  interface, K. Kita and A. Toriumi proposed a model which takes into account the oxygen behaviour at the interface, since oxygen is the common atom for both materials high- $\kappa$  and SiO<sub>2</sub> and not the metal cations in high- $\kappa$  oxides [27]. In this model, the number of oxygen atoms per unit area ( $\sigma$ ) for various high- $\kappa$  oxides and SiO<sub>2</sub> was calculated from the weight and the density of each oxide, extracted from their crystallographic data. The results were normalized and ordered in relation to the ratio of  $\sigma/\sigma_{SiO_2}$ , as shown in Fig. 1.5 on the right.

Figure 1.5: On the left, experimentally observed  $V_{\rm fb}$  shift due to dipole formed at high- $\kappa/{\rm SiO}_2$  interface. On the right, relative areal oxygen density of various oxides at interfaces normalized by that of SiO<sub>2</sub> calculated using their molar volume [27].

According to this model, the bonds at the interface are strained because of the deformation due to  $\sigma$  difference, leading to an increase of free energy of the interface. The free energy of the interface should be therefore minimized by a movement of oxygen from larger  $\sigma$  side to the smaller  $\sigma$  side. For example, the oxygen is transferred from SiO<sub>2</sub> to high- $\kappa$  in the cases of Y<sub>2</sub>O<sub>3</sub> and La<sub>2</sub>O<sub>3</sub>, while it is transferred from high- $\kappa$  to SiO<sub>2</sub> in the cases of Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> [27]. As a result, a charge imbalance at interface is induced by the movement of oxygen since oxygen is negatively charged. This model explains the formation of an equal amount of charges of opposite sign at high- $\kappa$ /SiO<sub>2</sub> interface.

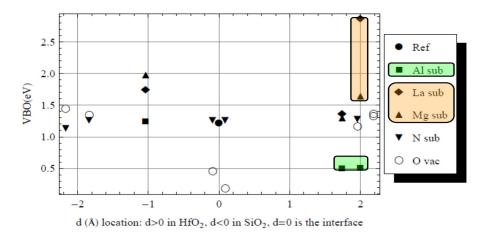

On the other hand, ab initio simulations performed recently on interface between HfO<sub>2</sub> and SiO<sub>2</sub> revealed that a substitution of Hf by La and Mg increases the valence band offset (VBO) at this interface and a substitution of Hf by Al decreases the valence band offset (VBO) [28], compared to reference interface, as shown in Fig. 1.6. These results are in agreement with WF<sub>eff</sub> shifts direction, since VBO shift is equal to the opposite effect of an electrostatic dipole  $(-\delta)$  [25]. In other words, ab initio simulations demonstrated that interfacial Hf substitution by La and Mg shifts WF<sub>eff</sub> towards N+ level, whereas Al shifts WF<sub>eff</sub> towards P+.

Figure 1.6: Valence band offsets for different additives at the  $HfO_2(001)/SiO_2(101)$  interface [25].

Finally, it should be noted that the V<sub>fb</sub> shifts successfully achieved by capping the top surface of the high- $\kappa$  layer were performed in a conventional gate-first flow with temperatures in the range between 985 °C and 1050 °C. At these temperatures, diffusion of species must be taken into account. These experiments were misunderstood at the time, but the latest models described above clearly show that an energetically favorable dipole layer is formed at high- $\kappa$ /SiO<sub>x</sub> interface. For this reason, a new methodology based on X-Ray Fluorescence will be proposed and validated in section 2.2.2.2 for accurate in-line characterization of the effective diffusion of species into the oxide gate stack after annealing.

#### Semiconductor doping density

For an intrinsic semiconductor, the Fermi level is at the midgap. However, for an n-doped semiconductor the Fermi level is above the intrinsic level, and for a p-doped semiconductor it is below the intrinsic level.  $q\Phi_{\rm fi}$  is the difference between the intrinsic Fermi level of silicon (E<sub>i</sub> = 4.61 eV) and the resulting Fermi level energy after doping (E<sub>F,sc</sub>) and is given by the Eq. 1.9.

$$E_i - E_{\rm F,sc} = q\Phi_{\rm fi} = k_b T \ln\left(\frac{N_{\rm sc}}{n_i}\right) \tag{1.9}$$

where  $k_b$  is the Boltzmann constant, T is temperature in Kelvin,  $N_{sc}$  is the substrate doping concentration in cm<sup>-3</sup>, q is the elementary charge in C and  $n_i$  is the intrinsic carrier concentration of silicon in cm<sup>-3</sup>. Thus, the silicon work function can be expressed as follows:

$$q\Phi_{\rm sc} = 4.61eV + q\Phi_{\rm fi} \tag{1.10}$$

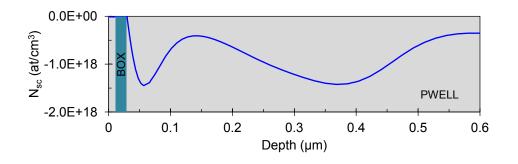

In practice, silicon substrate is doped with boron (for P-type Si) or phosphorus (for N-type Si) impurities by a series of ion implantation processes, followed by an annealing. As a result, the donors (or acceptors) impurities are not evenly distributed into the semiconductor and therefore the doping is not constant through the semiconductor. In Fig. 1.7, the dopant concentration profile below the buried oxide (BOX) of the 14 nm FDSOI technology after PWELL implantations and annealing at 1050 °C for 5 s has been simulated with Synopsis TCAD tool. As  $\Phi_{sc}$  is a parameter related to the doping substrate level, it will be determined through C-V analysis.

Figure 1.7: Dopant concentration profile below the buried oxide (BOX) of the 14 nm FDSOI technology after PWELL implantations and annealing at 1050 °C for 5 s simulated with Synopsis TCAD tool. *Courtesy of B. Mohamad.*

#### Metal effective work function

The work function of the metal is defined as the minimum energy needed to remove an electron from the metal to a point in the vacuum immediately outside the metal surface. In a MOS system, however, the metal work function seems to be dependent on the processes, leading to an effective work function. WF<sub>eff</sub> takes into account not only  $q\Phi_m$  but also the potential drop in the dielectric ( $V_{\text{ox}}$ ) at flat band voltage in real MOS devices, as shown in Fig. 1.3b. Indeed, including the vacuum level in the equation of the flat band voltage, WF<sub>eff</sub> expression is given by the work function of the metal ( $q\Phi_m$ ) plus the impact of charges density and interfacial dipoles ( $\delta$ ) on the potential drop across the oxide ( $qV_{\text{ox}}$ ) (see first part of Eq. 1.11), and it can be obtained by adding  $q\Phi_{\text{sc}}$  to V<sub>fb</sub> (see second part of Eq. 1.11). Indeed, in chapter 2, we will see that V<sub>fb</sub> and  $q\Phi_{sc}$  can be automatically and accurately determined by the measurement of the capacitive response (CV) of a MOS device, and then WF<sub>eff</sub> directly obtained by adding  $q\Phi_{\text{sc}}$  to V<sub>fb</sub>.

$$WF_{eff} = q\Phi_m + qV_{ox} = qV_{fb} + q\Phi_{sc}$$

(1.11)

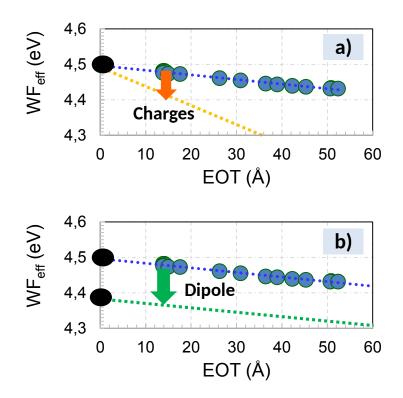

Considering constant values of permittivity along the thickness of the oxide and assuming a uniformly distributed charge per unit volume, it can be proved that  $V_{\rm fb}$  shift induced by bulk charges (Eq. 1.6) results in a quadratic modification of the  $V_{\rm fb}$  vs EOT plot for a given oxide [13]. On the contrary,  $V_{\rm fb}$ shift induced by interfacial fixed charges (Eq. 1.7) results in a linear modification of the  $V_{\rm fb}$  vs EOT plot for a given oxide. Now then, it has been experimentally demonstrated that  $V_{\rm fb}$  vs EOT plot is described by a straight line for SiO<sub>x</sub> and HfO<sub>x</sub> oxides [13] [9]. Therefore, by neglecting the impact of bulk charges in the dielectric layers and only considering the presence of interfacial fixed charges and potential drops induced by dipoles at the interfaces ( $\delta$ ), the WF<sub>eff</sub> should be rewritten as follows [9]:

$$\frac{\mathrm{WF}_{\mathrm{eff}}}{q} = \Phi_m - Q_{\mathrm{Si/SiO}_x} \left(\frac{\mathrm{EOT}}{\varepsilon_{\mathrm{SiO}_2}}\right) - Q_{\mathrm{SiO}_x/HK} \left(\frac{EOT_{\mathrm{HK}}}{\varepsilon_{SiO2}}\right) + \delta \tag{1.12}$$

Finally, recent studies demonstrated that by subtracting the potential drop due to  $\text{SiO}_x/\text{Si}$  interfacial fixed charges from the WF<sub>eff</sub>, gate stacks with various HfO<sub>2</sub> thickness all lead to the same value. This independence of WF<sub>eff</sub> shift with HfO<sub>2</sub> thickness implies the absence of any isolated fixed charge at HfO<sub>2</sub>/SiO<sub>2</sub> interface or in HfO<sub>2</sub> bulk. Indeed, any charge at HfO<sub>2</sub>/SiO<sub>2</sub> interface or in HfO<sub>2</sub> bulk would lead to increasing WF<sub>eff</sub> shift when HfO<sub>2</sub> thickness increases [25]. Based on these results, the WF<sub>eff</sub> expression may be rewritten in an even simpler way:

$$\frac{WF_{\text{eff}}}{q} = \Phi_m - Q_{\text{Si/SiO}_x} \left(\frac{\text{EOT}}{\varepsilon_{\text{SiO}_2}}\right) + \delta$$

(1.13)

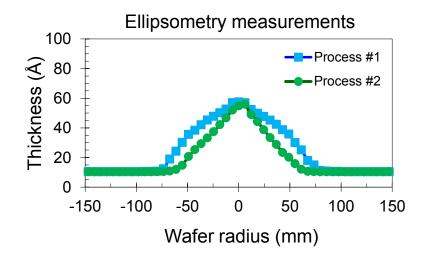

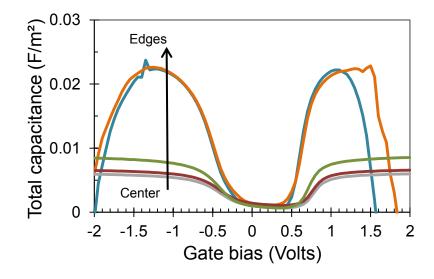

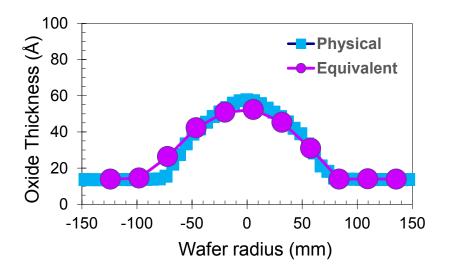

Eq. 1.13 is the WF<sub>eff</sub> expression used in this work.  $Q_{Si/SiO_x}$  will be extracted from a WF<sub>eff</sub> vs EOT for each manufactured device in this work. In summary, to design and accurately tune the threshold voltage (V<sub>TH</sub>) in CMOS devices, comprehensive and quantitative understanding of WF<sub>eff</sub> shift is strongly required. In section 2.1.2.2, a practical technique implemented on MOSFET devices completely manufactured at STMicroelectronics's 300 mm wafer fab is described in order to distinguish between an effect of charges density into gate stack or a potential offset induced by dipoles ( $\delta$ ). The methodology consists of varying the SiO<sub>x</sub> layer along the wafer to decouple the impact of charges from the interface electrostatic dipole. The influence of fixed charges on V<sub>fb</sub> should depend on the thickness of SiO<sub>x</sub> layers, whereas the influence of dipoles at high- $\kappa$ /SiO<sub>x</sub> interface does not depend on the insulator thicknesses.

# 1.1.3 MOSFET performance parameters influenced by the gate stack

The MOSFET is the predominant semiconductor device in very large scale integrated circuits. Besides the ability to pack more and more transistors within the same given silicon area, another motivation to further reduce the size of transistors is to improve the performance of the resulting integrated circuits in terms of operating speed and power dissipation. Drive current, transconductance, channel conductance, threshold voltage, reliability and direct tunneling current density or gate leakage density are the main device performance parameters that are somewhat influenced by the MOSFET gate stack properties.

#### Threshold voltage

The threshold voltage equals the sum of the flat band voltage, plus the semiconductor surface potential ( $V_{sc}=2\Phi_{fi}$  at threshold condition [8]), plus the voltage across the oxide due to the depletion charges (sign + for NFET devices and sign - for PFET devices).

$$V_{\rm TH} = V_{\rm fb} + 2\Phi_{\rm fi} \pm \frac{\sqrt{4\varepsilon_{\rm sc}qN_{\rm sc}\Phi_{\rm fi}}}{C_{\rm ox}}$$

(1.14)

where  $V_{\rm fb}$  is given by the sum of the effective work function defined in Eq. 1.12 and the silicon workfunction determined from Eq. 1.10,  $\Phi_{\rm fi}$  is the potential difference between the intrinsic Fermi level of silicon and the resulting Fermi level after doping (defined in Eq. 1.9),  $\varepsilon_{\rm sc}$  is the semiconductor permittivity and  $N_{\rm sc}$  is the substrate doping concentration (cm<sup>-3</sup>). It is convenient to reformulate the V<sub>TH</sub> in order to explicitly show its dependence with WF<sub>eff</sub> and EOT. The expression is obtained by substitution of  $V_{\rm fb}$  by Eq. 1.11 and  $C_{\rm ox}$  by Eq. 1.3:

$$V_{\rm TH} = \frac{\rm WF_{eff}}{q} - \Phi_{\rm sc} + 2\Phi_{\rm fi} \pm \frac{\rm EOT\sqrt{4\varepsilon_{\rm sc}qN_{\rm sc}\Phi_{\rm fi}}}{\varepsilon_0\varepsilon_{\rm SiO_2}}$$

(1.15)

#### Drive current

For small drain-to-source voltages, MOSFET transistor acts as a linear resistor whose resistance is modulated by the gate-to-source voltage. In this regime, the MOSFET can be used as a switch for analog and digital signals or as an analog multiplier. The drive current ( $I_{DS}$ ), defined as the current flow of minority carriers from the positive voltage at the drain terminal to the negative voltage at the source can be written as follows [7]:

- For

$$|V_{\rm DS}| \ll (V_G - V_{\rm TH})$$

$$I_{\rm DS} = (W/L)C_{\rm ox}\mu(V_G - V_{\rm TH})V_{\rm DS}$$

(1.16)

- For

$$V_{DS} > (V_G - V_{TH})$$

$$I_{\rm DS} = (W/L)C_{\rm ox}\mu \frac{(V_G - V_{\rm TH})^2}{2}$$

(1.17)

where W is the width of the transistor channel, L is the channel length,  $\mu$  is the channel carrier mobility,  $V_G$  is the voltage applied to the gate terminal,  $V_{DS}$  is the drain to source voltage and  $V_{TH}$  is the threshold voltage. An increased  $I_{DS}$  thus requires a reduction in the channel length or an increase in the gate dielectric capacitance.

#### Gate leakage current

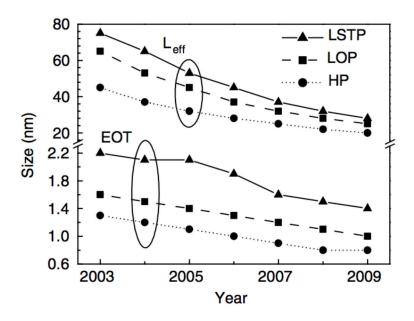

Fig. 1.8 shows the 2004 International Technology Roadmap for Semiconductor (ITRS) trends for effective channel length ( $L_{eff}$ ) and equivalent oxide thickness (EOT) scaling for Low Standby Power (LSTP), Low Operating Power (LOP) and High-Performance logic (HP) technologies. However, this reduction in the oxide thickness causes an important current flow through the gate, which depends exponentially on the thickness of the oxide [29]. This gate current, also known as gate leakage current, represents a limiting factor in device down-scaling and affects the performance of MOSFET devices.

Figure 1.8: Short-term ITRS 2004 projections of effective channel length ( $L_{eff}$ ) and equivalent oxide thickness (EOT) for Low Standby Power (LSTP), low operating power (LOP), and high performance logic (HP) technologies.

Moreover, for oxides with thicknesses in the order of a few nanometers, direct tunneling even at lower applied voltages is no longer negligible. In general, the direct tunneling current  $J_G$  through the energy gap of an insulator or semiconductor is given by [30]:

$$J_G = \frac{2q}{(2\pi)^3\hbar} \int_0^\infty (f_1 - f_2) \left[ \int \int P dk_y dk_z \right] dE$$

(1.18)

where P is the tunneling probability, E is the total electron energy,  $k_y$  and  $k_z$  are the wave vectors in the plane of the barrier (perpendicular to the tunneling direction), and  $f_1$  and  $f_2$  are the probabilities of occupation of the states on each side of the barrier, given by the Fermi-Dirac distribution functions.

Solving such integral is not a trivial problem. It implies the knowledge of the probability of tunneling through the barrier and requires solving Schrödinger equation for the electron wave function. Some hypothesis or other considerations are therefore needed in order to find approximate solutions. The physical mechanisms of tunneling in modern MOS transistors include effects such as carrier quantization and valence band tunneling. Various compact models taking into account such effects have already been proposed [31]. Here, it will be only cited the quasi-empirical model derived by Lee and Hu [32], which takes into account the availability of carriers in the material from where

the carriers are tunneling, and the availability of states in the receiving material. Neglecting high order terms of this complex model, the direct tunneling current  $J_G$  can be rewritten as follows [33]:

$$J_G = b \exp\left\{-afEOT\right\} \tag{1.19}$$

where a is a constant, b is a pre-exponential factor, and f is entirely dependent on the essential material properties of the gate dielectric. Simplifying to the first order f can be expressed by [33]:

$$f = \kappa (m_{\text{eff}}\phi_b)^{1/2} \tag{1.20}$$

where  $\kappa$  is the permittivity of the gate dielectric,  $m_{eff}$  is the tunneling effective mass of carrier in the dielectric, and  $\phi_b$  is the tunneling barrier height. It should be noted from Eqs. 1.19 and 1.20 that direct tunneling increases exponentially with the reduction of the equivalent oxide thickness (EOT) and the attenuation of the leakage current is determined by f. The insertion of a high- $\kappa$  gate dielectric has therefore successfully allowed the reduction of the high levels of gate leakage current. However, it is worth noting that the direct tunneling for a given EOT is not exclusively determined by the value of  $\kappa$ , but also by  $m_{eff}$  and  $\phi_b$ , which strongly affect the tunneling characteristics. For Poly-Si/SiO<sub>2</sub> devices,  $J_G = 1A/cm^2$  at  $V_{ox} = 1V$  and a difference in EOT of just 2.1 Å can lead to a decade of magnitude change in the gate leakage current density [33].

Nevertheless, although the successful introduction of the high-k oxide has permitted the aggresive scaling of MOSFET devices, the ultimate down-scaling limit will be set by other factors such as noise, reliability, drain current reduction, direct tunneling between the source and drain, on-chip interconnections, power dissipation, or even the atomic dimensions [31] [14].

#### Transconductance

The transconductance, in MOSFET transistors, is the change in the drain current divided by the small change in the gate/source voltage with a constant drain/source voltage. It is given by the following equations [7]:

- For

$$|V_{DS}| \ll (V_G - V_{TH})$$

$$g_{\rm m, \ lin} = (W/L)C_{\rm ox}\mu V_{\rm DS} \tag{1.21}$$

- For  $V_{DS} > (V_G - V_{TH})$

$$g_{\rm m, \, sat} = (W/L)C_{\rm ox}\mu(V_G - V_{\rm TH})$$

(1.22)

#### Channel conductance

The channel conductance quantifies the drain current variation with a drain-source voltage variation while keeping the gate-source voltage constant, and it can be calculated from the equations below[7]:

- For

$$|V_{\rm DS}| \ll (V_G - V_{\rm TH})$$

$$g_{\rm d, \, lin} = (W/L)C_{\rm ox}\mu(V_G - V_{\rm TH})$$

(1.23)

- For

$$|V_{DS}| > (V_G - V_{TH})$$

$$g_{\rm d,\,sat} = 0 \tag{1.24}$$

As can be seen from these expressions, high values of drive current, channel conductance and transconductance are obtained for large carrier mobilities, large gate insulator capacitances (i.e., thin gate insulator layers), and large gate width to gate length ratios.

In summary, most of the performance parameters of MOSFET devices cited above are strongly influenced by the effective work function and by the gate dielectric capacitance. In this thesis, we will study the impact of the metal process conditions and materials on both the effective work function (WF<sub>eff</sub>) and the equivalent oxide thickness (EOT). In particular, the impact of the incorporation of lanthanum and aluminum in a *sacrificial* metal gate-first approach on both electrical parameters will be investigated.

### **1.2** Gate stack fabrication process

#### **1.2.1** Oxidation methods and Gate dielectrics

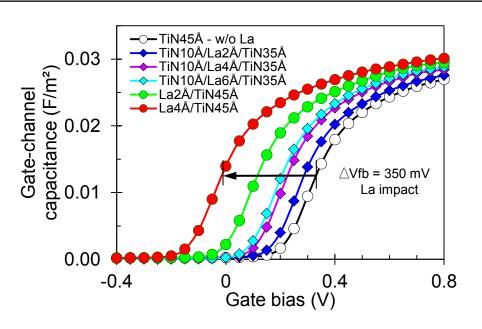

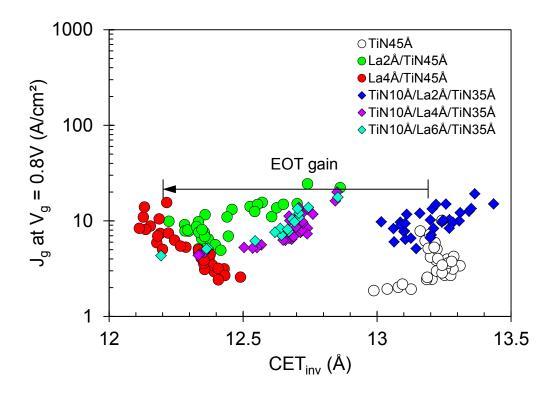

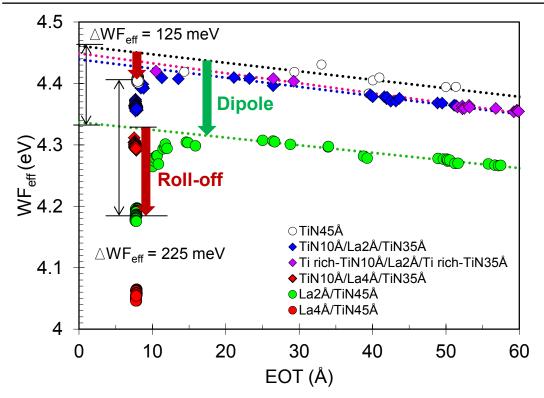

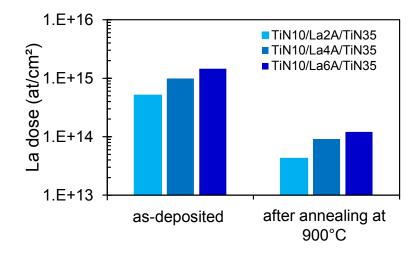

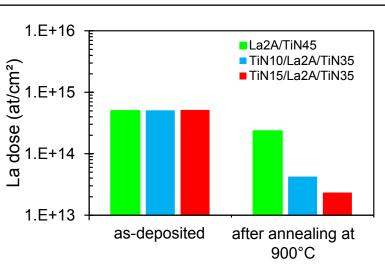

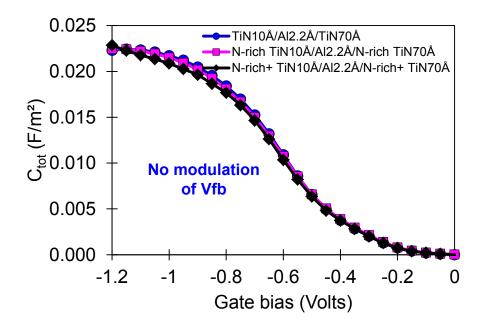

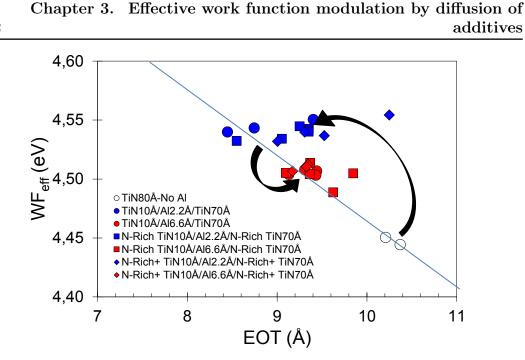

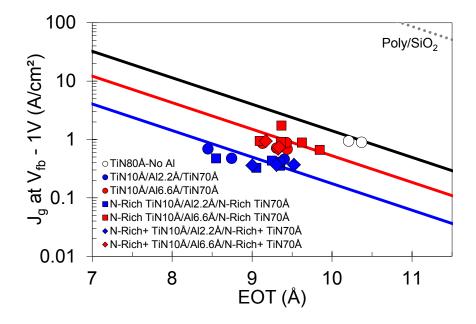

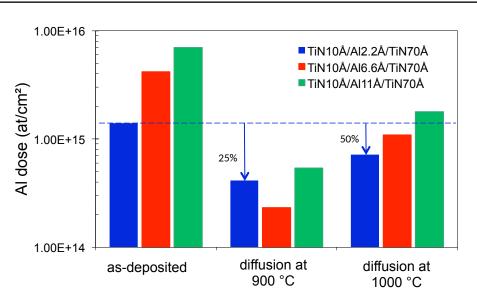

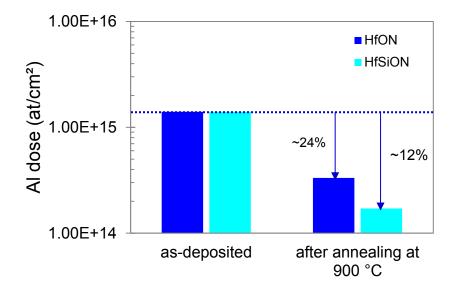

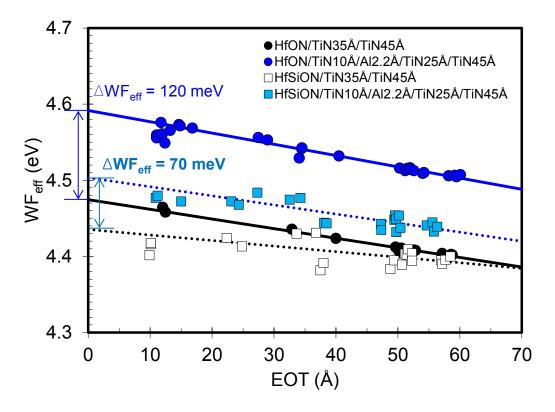

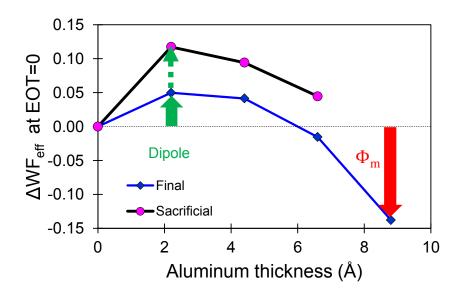

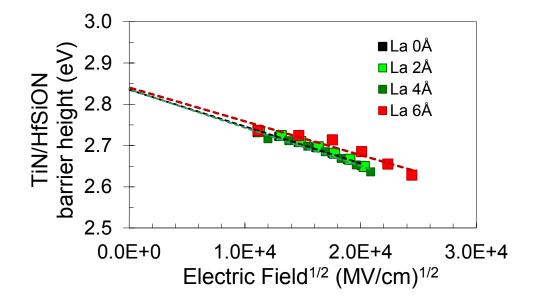

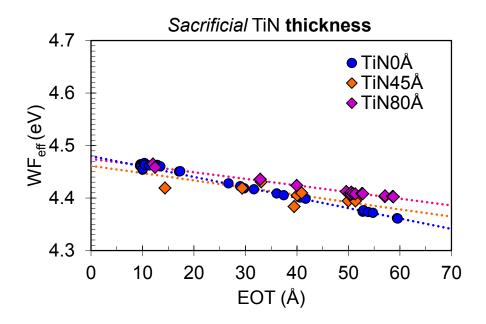

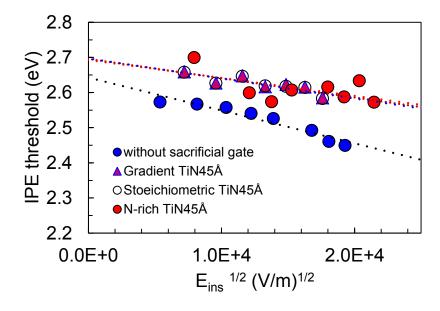

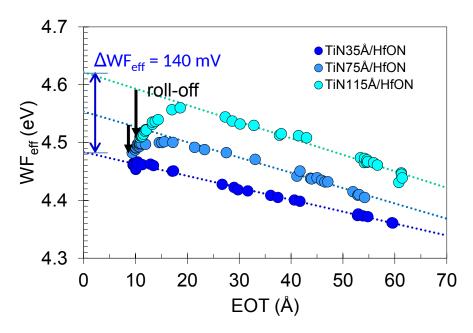

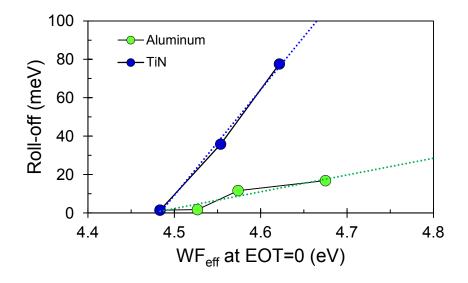

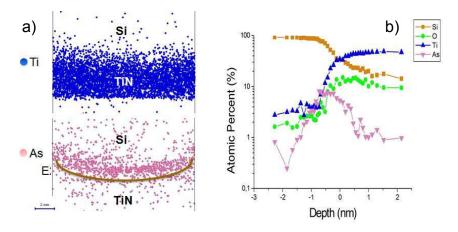

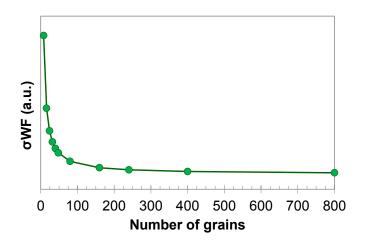

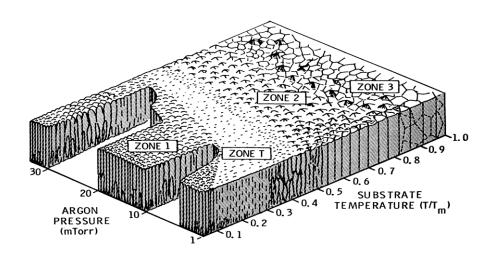

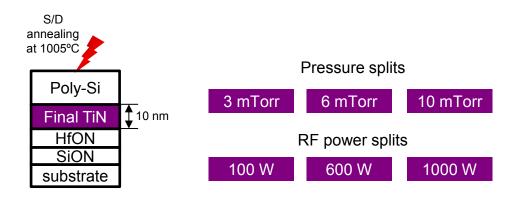

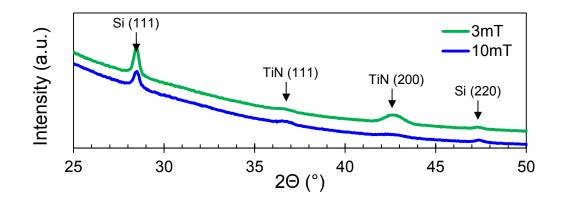

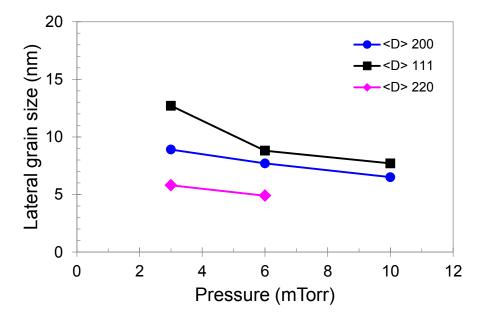

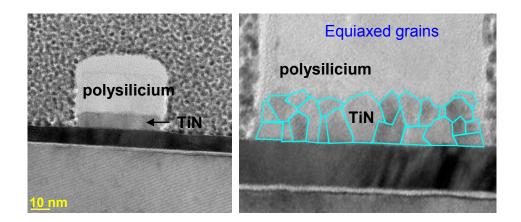

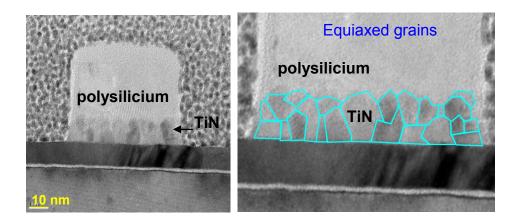

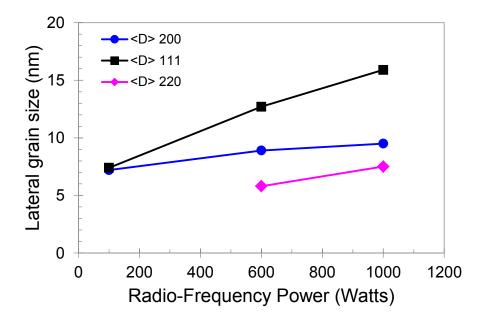

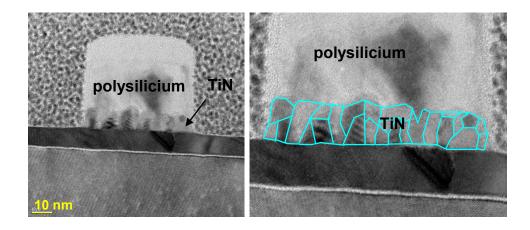

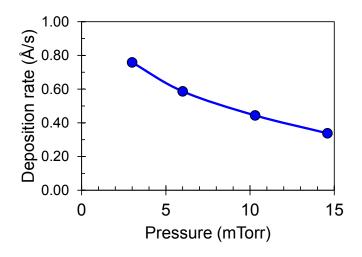

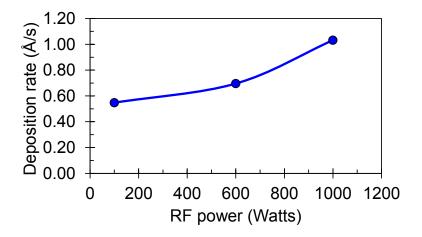

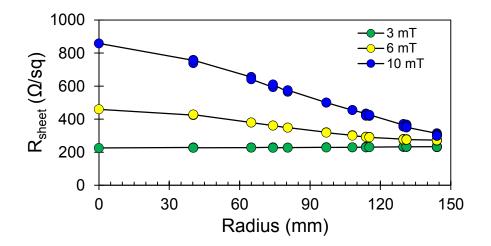

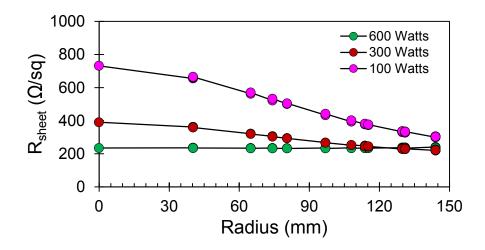

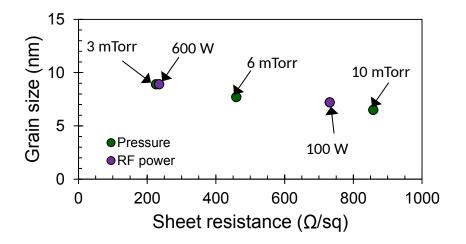

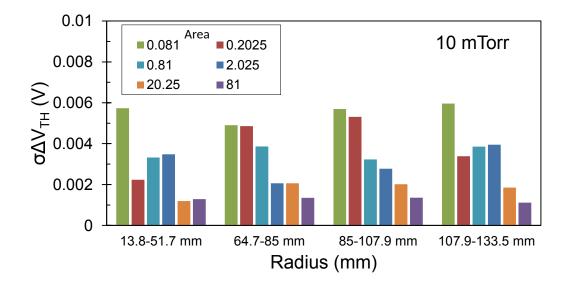

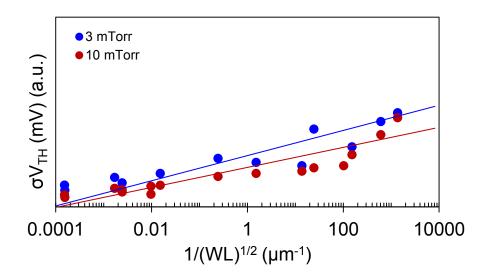

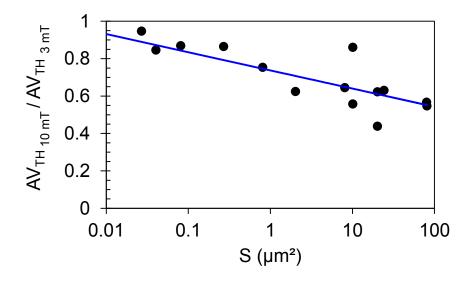

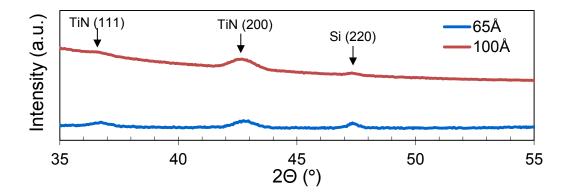

The gate dielectrics allows to insulate the gate electrode from the silicon in MOSFET devices. Although various methods, such as vapor phase reaction [34], plasma anodization<sup>2</sup> [35, 36], wet and dry thermal oxidations [37] and wet anodization [38] have been developed for the growth of oxide silicon films, the dominant technology is the thermal oxidation due to its ability to produce a minimum, stable density of oxide fixed charges and interface traps at the oxide/semiconductor interface.