## Introduction of Fault-Tolerance Mechanisms for Permanent Failures in Coherent Shared-Memory Many-Core Architectures

César Fuguet Tortolero

### ▶ To cite this version:

César Fuguet Tortolero. Introduction of Fault-Tolerance Mechanisms for Permanent Failures in Coherent Shared-Memory Many-Core Architectures. Distributed, Parallel, and Cluster Computing [cs.DC]. Université Pierre et Marie Curie - Paris VI, 2015. English. NNT: 2015PA066462. tel-01292995

### HAL Id: tel-01292995 https://theses.hal.science/tel-01292995

Submitted on 24 Mar 2016  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE DE DOCTORAT DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

Specialité

### Informatique

École Doctorale Informatique, Télécommunication et Électronique (Paris)

Presentée par

### César Armando FUGUET TORTOLERO

Pour obtenir le grade de

### DOCTEUR de l'UNIVERSITÉ PIERRE ET MARIE CURIE

Sujet de la thèse :

### Introduction de mécanismes de tolérance aux pannes franches dans les architectures de processeur « many-core » à mémoire partagée cohérente

soutenue le 25 November, 2015 devant le jury composé de :

| M. Fabien CLERMIDY   | Examinateur        | CEA (Grenoble)                           |

|----------------------|--------------------|------------------------------------------|

| M. Philippe Coussy   | Rapporteur         | Lab-STICC (Lorient)                      |

| Mme. Agnès Fritsch   | Examinatrice       | Thales Communications & Security (Paris) |

| M. Alain GREINER     | Directeur de thèse | LIP6 (Paris)                             |

| M. Lionel Lacassagne | Examinateur        | LIP6 (Paris)                             |

| M. Gilles Sassatelli | Rapporteur         | LIRMM (Montpellier)                      |

#### Dissertation submitted to THE UNIVERSITY PIERRE ET MARIE CURIE

#### Department of

#### **Computer Sciences**

École Doctorale Informatique, Télécommunication et Électronique (Paris)

Presented by

### César Armando FUGUET TORTOLERO

For the degree of

### DOCTOR OF PHYLOSOPHY

Subject:

### Introduction of Fault Tolerance Mechanisms for Permanent Failures in Coherent Shared-Memory Many-Core Architectures

Defense on 25 November 2015 Committee:

| M. Fabien CLERMIDY<br>M. Philippe Coussy | Examiner<br>Reviewer | CEA (Grenoble)<br>Lab-STICC (Lorient) |

|------------------------------------------|----------------------|---------------------------------------|

| Mme. Agnès Fritsch                       | Examiner             | Thales Communications &               |

|                                          |                      | Security (Paris)                      |

| M. Alain Greiner                         | Advisor              | LIP6 (Paris)                          |

| M. Lionel LACASSAGNE                     | Examiner             | LIP6 (Paris)                          |

| M. Gilles Sassatelli                     | Reviewer             | LIRMM (Montpellier)                   |

## Résumé

L'augmentation continue de la puissance de calcul requise par les applications telles que la cryptographie, la simulation, l'analyse et distribution de paquets réseau ou le traitement du signal a fait évoluer la structure interne des processeurs vers des architectures massivement parallèles (dites « many-core »). Ces architectures peuvent contenir des centaines, voire des milliers de cœurs afin de fournir une puissance de calcul importante avec une consommation énergétique raisonnable.

Néanmoins, l'importante densité de transistors fait que ces architectures sont très susceptibles aux pannes matérielles. L'augmentation dans la variabilité du processus de fabrication, et dans les facteurs de stress des transistors, dégrade à la fois le rendement de fabrication, et leur durée de vie.

Nous proposons donc un mécanisme complet de tolérance aux pannes franches, permettant les architectures « many-core » à mémoire partagée cohérente de fonctionner dans un mode dégradé. Ce mécanisme permet à ces architectures de s'autoreconfigurer afin de supporter aussi bien des défauts de fabrication, que des pannes de vieillissement après que la puce est en service dans l'équipement.

Le mécanisme s'appuie sur un logiciel embarqué et distribué dans des mémoires sur puce (« firmware »), qui est exécuté par les cœurs à chaque démarrage du processeur, sans aucune intervention externe. Ce logiciel implémente plusieurs algorithmes distribués permettant de localiser les composants défaillants (cœurs, bancs mémoires, et routeurs des réseaux sur puce), de reconfigurer l'architecture matérielle, et de fournir une description complète de l'infrastructure matérielle fonctionnelle au système d'exploitation.

Notre proposition est évaluée en utilisant un prototype virtuel précis au cycle d'une architecture « many-core » existante. Nous évaluons à la fois sa latence, et son coût en surface de silicium.

## Remerciements

Je remercie M. Alain Greiner, professeur à l'Université Pierre et Marie Curie (UPMC) et membre du Laboratoire d'Informatique de Paris 6 (LIP6), pour avoir dirigé mes travaux de recherche. Je vous remercie d'abord pour m'avoir accueilli au laboratoire en 2011 pour faire un stage, et puis pour m'avoir proposé ce sujet de thèse, intéressant et passionnant. Merci pour votre encadrement tout au long de ces derniers quatre ans, ce fût un grand plaisir de travailler, et surtout d'apprendre à vos côtés.

J'exprime mes remerciements aux membres du jury. Je remercie M. Philippe Coussy, professeur au laboratoire Lab-STICC (Université de Bretagne-Sud), et M. Gilles Sassatelli, directeur de recherche au LIRMM (CNRS, Université de Montpellier 2), pour avoir accepté d'être rapporteurs de mon travail, et pour ses remarques très constructives. Je remercie M. Lionel Lacassagne, professeur au laboratoire LIP6, d'avoir participé et d'être président de mon jury de thèse. Je remercie également M. Fabien Clermidy, chef du laboratoire LISAN (CEA-LETI), et Mme. Agnès Fritsch, chef du laboratoire des architectures avancées à Thales, d'avoir participé à mon jury.

Je tiens à remercier M. Pirouz Bazargan, maître de conférence au LIP6, et M. Jean-Luc Danger, directeur d'études à Telecom ParisTech, pour avoir participé à mon jury de mi-parcours, et pour les remarques très constructives à mon travail.

Je remercie aux membres du laboratoire LIP6 pour créer un environnement de travail agréable et amical. Je remercie tout particulièrement à Abdelmalek Si-Merabet, Franck Wajsbürt, Pirouz Bazargan, Quentin Meunier et Manuel Bouyer. Je remercie Mme. Marie-Minerve Louërat, responsable du département SoC au LIP6, pour son aide sur le plan administratif, et je tiens aussi à remercier Mme. Shahin Mahmoodian pour sa disponibilité au secrétariat.

Je remercie pour leur amitié à tous mes collègues doctorants et ingénieurs : Clément D., Hao L., Mohammed K., Joël P., Cédric B., Benoît V., Alexandre B., Laurent L., Jean-Baptiste B. et Vanessa T.. Je remercie Kamel Hacene, que j'ai eu le plaisir d'encadrer pendant son stage sur la tolérance aux pannes dans les NoCs 3D.

Je remercie M. Gérard Paez-Monzon, professeur à l'Université des Andes (Venezuela) et ancien doctorant au LIP6, pour m'avoir introduit dans le monde de la conception des circuits numériques.

Finalement, j'étends mes remerciements à ma famille. Je remercie à ma mère et mon père pour faire de moi la personne que je suis, pour leur amour, et pour m'avoir appris à atteindre mes objectifs avec travail et patience. Merci à ma sœur Maria Alejandra, et mes neveux Antonio, Maria, et Andrés qui me donnent toujours le sourire. Je remercie ma compagne Liliana pour son amour, ses encouragements et son soutien tous les jours.

## Contents

| R  | ésum     | é        |                                                  | V    |

|----|----------|----------|--------------------------------------------------|------|

| R  | emer     | ciemen   | ıts                                              | VII  |

| Li | ist of   | Figures  | 3                                                | XIV  |

| Li | ist of . | Algorit  | hms                                              | XV   |

| Li | ist of ' | Tables   |                                                  | XVII |

| 0  | utlin    | e        |                                                  | 1    |

| 1  | Prol     | blem D   | efinition                                        | 3    |

|    | 1.1      | Motiv    | ation                                            | . 4  |

|    | 1.2      | Many     | -core Architectures                              | . 5  |

|    | 1.3      | Netwo    | ork-on-Chip (NoC)                                | . 6  |

|    |          | 1.3.1    | Globally-Asynchronous Locally-Synchronous (GALS) | . 6  |

|    |          | 1.3.2    | Routing Algorithm                                | . 7  |

|    | 1.4      | Tera-S   | Scale Architecture (TSAR)                        | . 8  |

|    |          | 1.4.1    | Memory Hierarchy                                 | . 9  |

|    |          | 1.4.2    | Network-on-Chips                                 | . 10 |

|    |          | 1.4.3    | IO Subsystem.                                    | . 11 |

|    | 1.5      | Fault-   | Tolerance                                        | . 12 |

|    |          | 1.5.1    | NoCs Routing Algorithm Reconfiguration           | . 14 |

|    |          | 1.5.2    | Distributed Algorithms                           | . 14 |

|    | 1.6      | Proble   | em Definition                                    | . 15 |

| 2  | Stat     | e of the | Art                                              | 17   |

|    | 2.1      | Fault-   | Tolerance in Many-Core Processors                | . 18 |

|    |          | 2.1.1    | Many-Core Yield Enhancement                      | . 18 |

|    |          | 2.1.2    | Many-Core Self-Organization                      | . 18 |

|    |          | 2.1.3    | Many-Core Distributed Cores Diagnosis            | . 19 |

|    | 2.2      | Fault-   | Tolerant Routing Algorithms for NoCs             | . 20 |

|    |          | 2.2.1    | Fault-Tolerant Routing Based on Virtual Channels |      |

|    |          | 2.2.2    | Segment-Based Routing Algorithm                  | . 20 |

|   |      | 2.2.3  | Logic-Based Distributed Routing (LBDR)              | 21 |

|---|------|--------|-----------------------------------------------------|----|

|   |      | 2.2.4  | Cycle-Free Contour Fault-Tolerant Routing Algorithm | 22 |

|   | 2.3  | Concl  | usion                                               | 24 |

| 3 | Dist | ribute | d Recovery Firmware                                 | 25 |

|   | 3.1  | Globa  | l Procedure                                         | 26 |

|   | 3.2  | Hardv  | ware-Based NoC Fault Detection                      | 28 |

|   | 3.3  | Distri | buted Software-Based Fault Location                 | 28 |

|   | 3.4  | Hardv  | ware-Assisted NoC Reconfiguration                   | 30 |

|   |      | 3.4.1  | Broadcast Support With Holes                        | 31 |

|   |      | 3.4.2  | 3D NoCs Reconfiguration                             | 31 |

|   |      | 3.4.3  | Memory Segment Reallocation                         | 31 |

|   | 3.5  | OS Lo  | ading                                               | 31 |

|   | 3.6  | Concl  | usion                                               | 32 |

| 4 | Dist | ribute | d Fault-Location                                    | 33 |

|   | 4.1  | Intrac | cluster Phase                                       | 34 |

|   |      | 4.1.1  | Software-Based Self-Test (SBST)                     | 35 |

|   |      | 4.1.2  | Intracluster Local Neighbors' Discovery             | 37 |

|   |      | 4.1.3  | Local Leader Election                               | 40 |

|   |      | 4.1.4  | Gateway Hardware Barrier                            | 41 |

|   | 4.2  | Interc | cluster Phase                                       | 42 |

|   |      | 4.2.1  | Intercluster Neighbors' Discovery                   | 42 |

|   | 4.3  | Coher  | rence Networks                                      | 49 |

|   |      | 4.3.1  | Intracluster Coherence Networks Test                | 51 |

|   |      | 4.3.2  | Intercluster Coherence Networks Test                | 51 |

|   | 4.4  | Fault- | Free Spanning Tree Construction                     | 52 |

|   |      | 4.4.1  | FFST's Data Structure                               | 53 |

|   |      | 4.4.2  | FFST's Construction Algorithm                       | 55 |

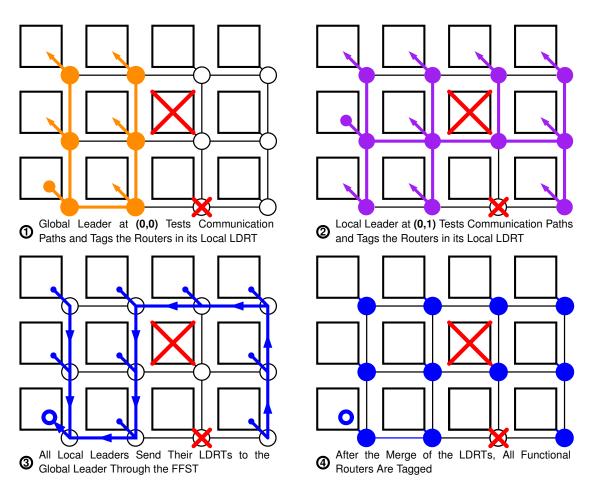

|   | 4.5  | Map o  | of Operational Resources                            | 61 |

|   |      | 4.5.1  | Distributed Information Gathering                   | 61 |

|   |      | 4.5.2  | Black-Holes Location Procedure                      | 62 |

|   | 4.6  | Concl  | usion                                               | 64 |

| 5 | NoC  | Recon  | figuration                                          | 67 |

|   | 5.1  | Intro  | duction                                             | 68 |

|   | 5.2  | Recon  | nfiguration Procedure                               | 69 |

|   |      | 5.2.1  | Supported NoC Faulty Topologies                     | 70 |

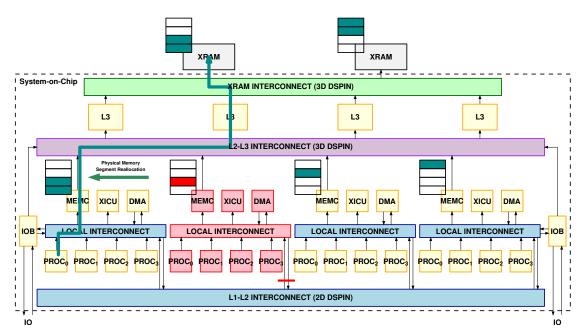

|   | 5.3                                                                                      | Memory Segment Reallocation                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                          | 5.3.1 Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                                                                          | 5.3.2 Limitations of the Segment Reallocation Mechanism 75                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 5.4                                                                                      | Broadcast Support With Holes in the NoC                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                                                          | 5.4.1 Recovery Broadcast Replication Policy                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                                                          | 5.4.2 Verification of the Recovery Broadcast Replication Policy 80                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 5.5                                                                                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6 | Exp                                                                                      | erimental Results and Evaluation 83                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 6.1                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 6.2                                                                                      | Virtual Simulation Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 6.3                                                                                      | Fault Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 6.4                                                                                      | Performance Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                                          | 6.4.1 Distributed Software-Based Fault Location Latency 88                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                                                                                          | 6.4.2 NoC Reconfiguration Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                                          | 6.4.3 Available Computational Power                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                                                                          | 6.4.4 Linux Kernel Boot in a Defective Architecture                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 6.5                                                                                      | Hardware Cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 6.6                                                                                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7 | Faul<br>Laye                                                                             | lt-Tolerance Extension for Interconnects above the Computational<br>er                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 7.1                                                                                      | 3D NoCs Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 7.2                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 1.2                                                                                      | Physical Address Space Distribution for L3 Cache Controllers 99                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 7.2<br>7.3                                                                               | Physical Address Space Distribution for L3 Cache Controllers       99         Fault-Tolerance Mechanism Overview.       100                                                                                                                                                                                                                                                                                                                                                       |

|   | 7.3                                                                                      | Fault-Tolerance Mechanism Overview.   100                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                                                                                          | Fault-Tolerance Mechanism Overview.       100         Software-Based Fault Location on the 3D NoCs       100                                                                                                                                                                                                                                                                                                                                                                      |

|   | 7.3                                                                                      | Fault-Tolerance Mechanism Overview.       100         Software-Based Fault Location on the 3D NoCs       100         7.4.1       Specific Test Hardware Mechanism.       101                                                                                                                                                                                                                                                                                                      |

|   | 7.3<br>7.4                                                                               | Fault-Tolerance Mechanism Overview.       100         Software-Based Fault Location on the 3D NoCs       100         7.4.1       Specific Test Hardware Mechanism.       101         7.4.2       Black-hole Location Procedure       101                                                                                                                                                                                                                                          |

|   | 7.3                                                                                      | Fault-Tolerance Mechanism Overview.       100         Software-Based Fault Location on the 3D NoCs       100         7.4.1       Specific Test Hardware Mechanism.       100         7.4.2       Black-hole Location Procedure       100         Reconfigurable Routing Algorithm for 3D NoCs       100                                                                                                                                                                           |

|   | 7.3<br>7.4                                                                               | Fault-Tolerance Mechanism Overview.100Software-Based Fault Location on the 3D NoCs1007.4.1 Specific Test Hardware Mechanism1017.4.2 Black-hole Location Procedure101Reconfigurable Routing Algorithm for 3D NoCs1037.5.1 L2-L3 CMD NoC Recovery Routing Algorithm103                                                                                                                                                                                                              |

|   | <ul><li>7.3</li><li>7.4</li><li>7.5</li></ul>                                            | Fault-Tolerance Mechanism Overview.100Software-Based Fault Location on the 3D NoCs1007.4.1Specific Test Hardware Mechanism1017.4.2Black-hole Location Procedure1017.4.2Black-hole Location Procedure1017.4.3Black-hole Location Procedure1017.4.4Black-hole Location Procedure1017.5.1L2-L3 CMD NoC Recovery Routing Algorithm1037.5.2L2-L3 RSP NoC Recovery Routing Algorithm103                                                                                                 |

|   | <ul><li>7.3</li><li>7.4</li><li>7.5</li><li>7.6</li></ul>                                | Fault-Tolerance Mechanism Overview.100Software-Based Fault Location on the 3D NoCs1007.4.1Specific Test Hardware Mechanism1007.4.2Black-hole Location Procedure1007.4.2Black-hole Location Procedure1007.4.2Black-hole Location Procedure1007.5.1L2-L3 CMD NoC Recovery Routing Algorithm1037.5.1L2-L3 CMD NoC Recovery Routing Algorithm1037.5.2L2-L3 RSP NoC Recovery Routing Algorithm103Faulty Routers in the Bottom Layer103                                                 |

|   | <ul> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ul>              | Fault-Tolerance Mechanism Overview.100Software-Based Fault Location on the 3D NoCs1007.4.1 Specific Test Hardware Mechanism1017.4.2 Black-hole Location Procedure101Reconfigurable Routing Algorithm for 3D NoCs1037.5.1 L2-L3 CMD NoC Recovery Routing Algorithm1037.5.2 L2-L3 RSP NoC Recovery Routing Algorithm103Faulty Routers in the Bottom Layer103Hardware-Assisted Reconfiguration of the 3D NoCs103                                                                     |

|   | <ul><li>7.3</li><li>7.4</li><li>7.5</li><li>7.6</li></ul>                                | Fault-Tolerance Mechanism Overview.100Software-Based Fault Location on the 3D NoCs1007.4.1 Specific Test Hardware Mechanism1017.4.2 Black-hole Location Procedure101Reconfigurable Routing Algorithm for 3D NoCs1037.5.1 L2-L3 CMD NoC Recovery Routing Algorithm1037.5.2 L2-L3 RSP NoC Recovery Routing Algorithm103Faulty Routers in the Bottom Layer103Hardware-Assisted Reconfiguration of the 3D NoCs103Evaluation103                                                        |

|   | <ul> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ul>              | Fault-Tolerance Mechanism Overview.100Software-Based Fault Location on the 3D NoCs1007.4.1 Specific Test Hardware Mechanism.1017.4.2 Black-hole Location Procedure101Reconfigurable Routing Algorithm for 3D NoCs1037.5.1 L2-L3 CMD NoC Recovery Routing Algorithm.1037.5.2 L2-L3 RSP NoC Recovery Routing Algorithm103Faulty Routers in the Bottom Layer103Hardware-Assisted Reconfiguration of the 3D NoCs.1037.8.1 Performance Evaluation103                                   |

|   | <ul> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> <li>7.8</li> </ul> | Fault-Tolerance Mechanism Overview.100Software-Based Fault Location on the 3D NoCs1007.4.1Specific Test Hardware Mechanism.1017.4.2Black-hole Location Procedure101Reconfigurable Routing Algorithm for 3D NoCs1037.5.1L2-L3 CMD NoC Recovery Routing Algorithm.1037.5.2L2-L3 RSP NoC Recovery Routing Algorithm103Faulty Routers in the Bottom Layer103Hardware-Assisted Reconfiguration of the 3D NoCs.1037.8.1Performance Evaluation1037.8.2Hardware Cost103                   |

|   | <ul> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ul>              | Fault-Tolerance Mechanism Overview.100Software-Based Fault Location on the 3D NoCs1007.4.1Specific Test Hardware Mechanism1017.4.2Black-hole Location Procedure101Reconfigurable Routing Algorithm for 3D NoCs1037.5.1L2-L3 CMD NoC Recovery Routing Algorithm1037.5.2L2-L3 RSP NoC Recovery Routing Algorithm103Faulty Routers in the Bottom Layer103Hardware-Assisted Reconfiguration of the 3D NoCs1007.8.1Performance Evaluation1077.8.2Hardware Cost1077.8.2Hardware Cost107 |

| A Reconfigurable Cycle-Free Routing Algorithm | 113 |

|-----------------------------------------------|-----|

| Bibliography                                  | 113 |

# **List of Figures**

| 1.1  | Variability-Induced Failure Rates for Two Canonical Circuit Types | 4  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Examples of NoC Topologies                                        | 6  |

| 1.3  | X-First Routing Example                                           | 8  |

| 1.4  | TSAR 2D-Mesh                                                      | 9  |

| 1.5  | TSAR Flattened Global View                                        | 10 |

| 1.6  | TSAR 3D Stacking Technology                                       | 11 |

| 2.1  | LBDR: Examples of Topologies                                      | 21 |

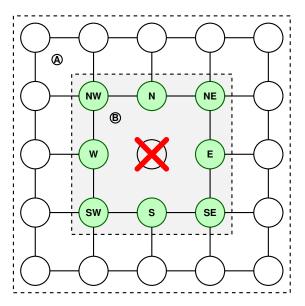

| 2.2  | Contour of a Faulty Router                                        | 22 |

| 2.3  | The Nine Contour Types for Single-Faulty-Router Topologies        | 23 |

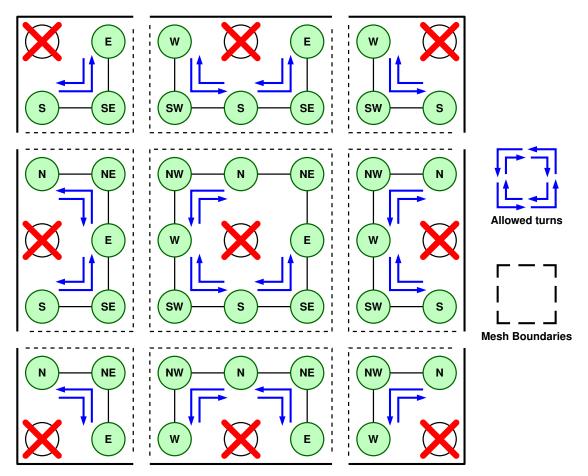

| 3.1  | Global Procedure Flow Diagram                                     | 27 |

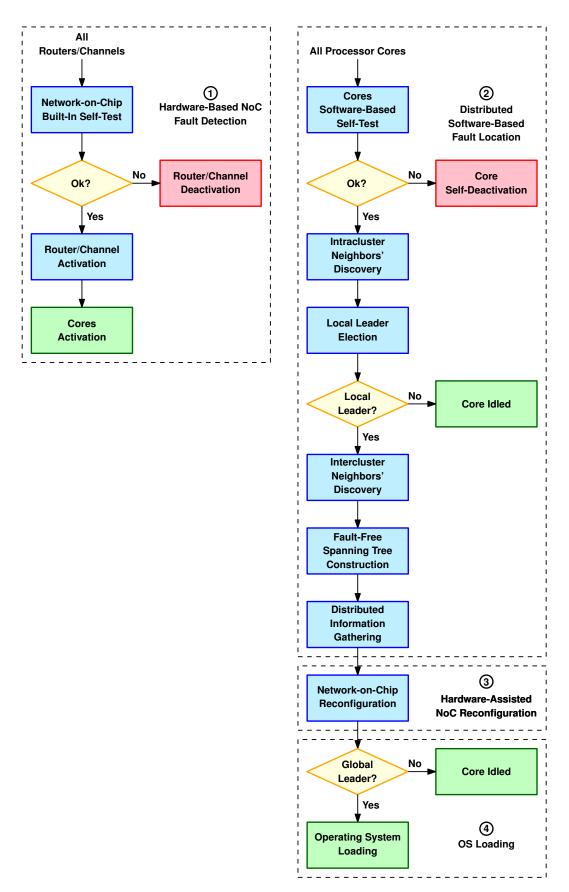

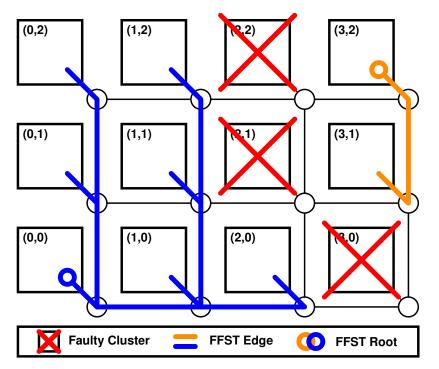

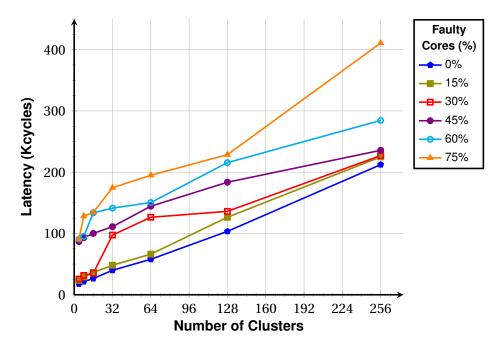

| 3.2  | FFST Example in a Mesh with a Faulty Router                       | 29 |

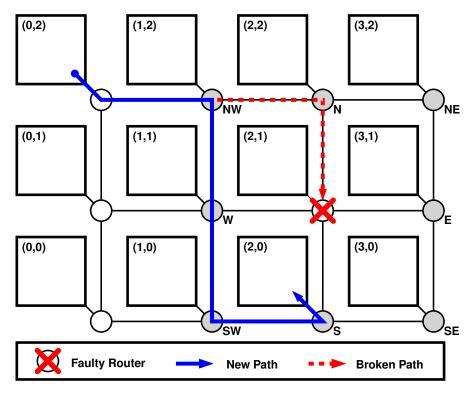

| 3.3  | NoC Reconfiguration Example                                       | 30 |

| 4.1  | Software-Based Memory Test.                                       | 36 |

| 4.2  | TSAR CMD Local Interconnect: Multiplexing at Targets              | 40 |

| 4.3  | Gateway Hardware Barrier                                          | 43 |

| 4.4  | Intercluster Neighbors                                            | 44 |

| 4.5  | Interconnection Path Between Neighbor Clusters                    | 45 |

| 4.6  | Interconnection Path Between Neighbor Clusters (Faulty)           | 49 |

| 4.7  | Processor Core Triggering the Coherence Network Test              | 50 |

| 4.8  | FFST's Data Structure                                             | 54 |

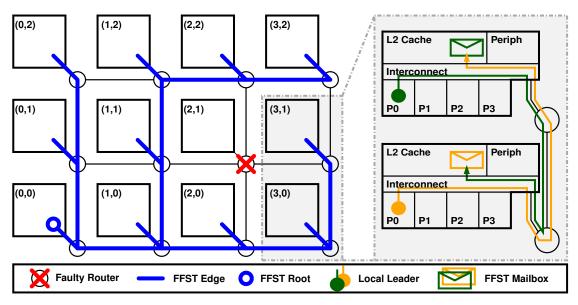

| 4.9  | Example of a FFST and its Logical Representation                  | 55 |

| 4.10 | Example $TREE_r$ Array of the Global Leader                       | 55 |

| 4.11 | Software Mailboxes Between Two Neighbor Clusters                  | 56 |

| 4.12 | FFST Construction Algorithm Example                               | 58 |

| 4.13 | FFST Example With Two Partitions                                  | 59 |

| 4.14 | Black-Hole Location Procedure                                     | 64 |

| 5.1  | Distribution of the Physical Address Space in TSAR                | 71 |

| 5.2 | Reallocation of a Physical Memory Segment                                     | 72  |

|-----|-------------------------------------------------------------------------------|-----|

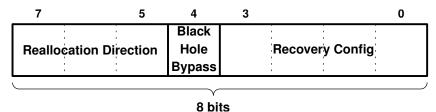

| 5.3 | NoC Routers' Reconfiguration Register                                         | 72  |

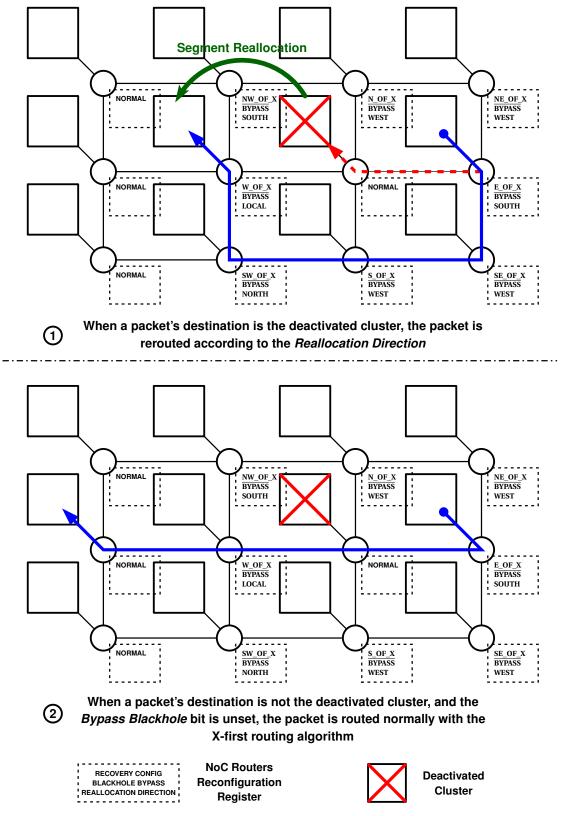

| 5.4 | Example of a Physical Memory Segment Reallocation                             | 74  |

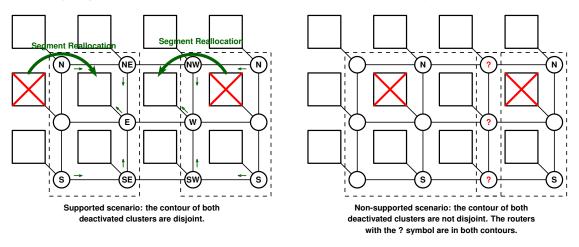

| 5.5 | Supported Scenario for the Physical Memory Segment Reallocation               | 75  |

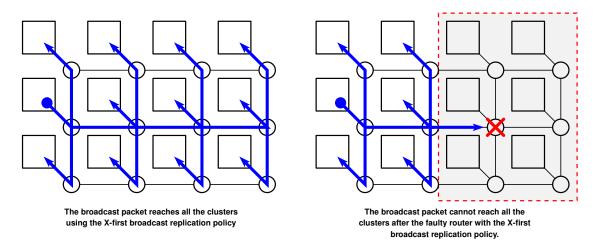

| 5.6 | Example of Packet Broadcasting With the X-First Replication Policy            | 76  |

| 5.7 | Recovery Broadcast Replication Policy                                         | 77  |

| 5.8 | Examples of the Recovery Broadcast Replication                                | 78  |

| 5.9 | X-First Router: Channel Dependency Graph                                      | 80  |

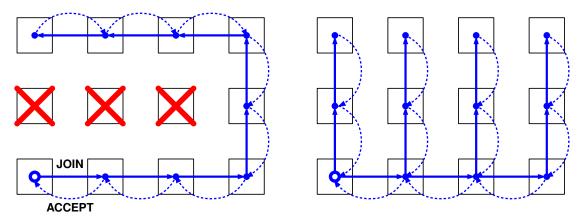

| 6.1 | TSAR Cluster with the Fault-Tolerance Additional Hardware                     | 85  |

| 6.2 | TSAR Virtual Prototype (Logical View)                                         | 86  |

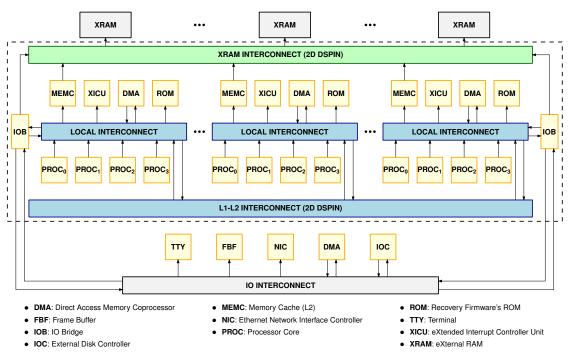

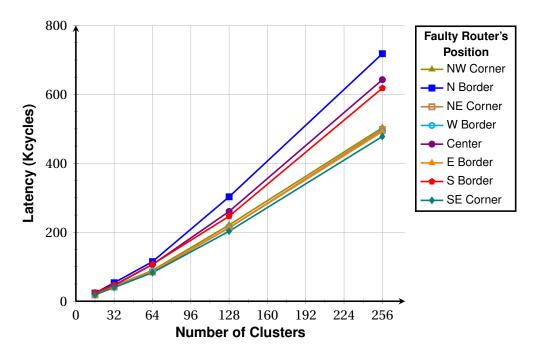

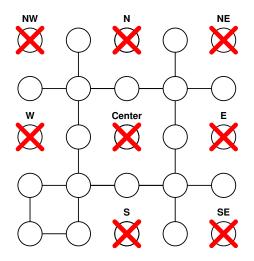

| 6.3 | Fault-Free Spanning Tree's Construction Latency                               | 88  |

| 6.4 | Example of a Strongly Modified Topology                                       | 89  |

| 6.5 | Black-Hole Location Procedure Latency                                         | 90  |

| 6.6 | Faulty Router's Positions for the Black-Hole Location Latency Plots $\ . \ .$ | 90  |

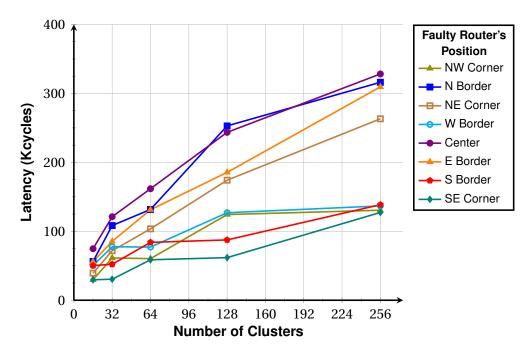

| 6.7 | Network-on-Chip Reconfiguration's Latency.                                    | 92  |

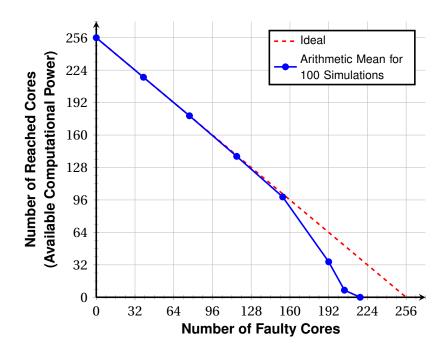

| 6.8 | Mean Available Computational Power                                            | 93  |

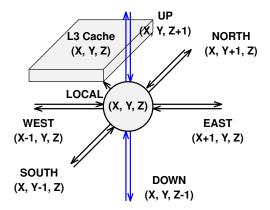

| 7.1 | 3D Router in the L2-L3 Interconnect                                           | 98  |

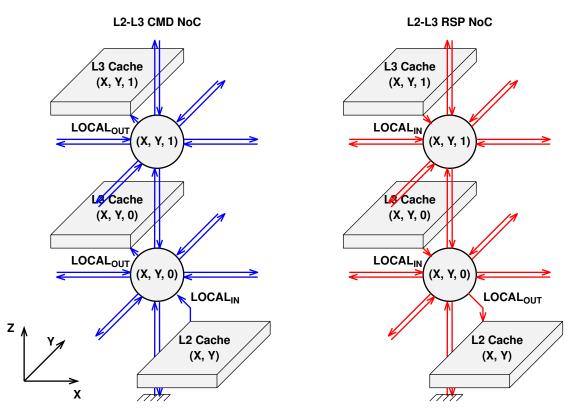

| 7.2 | Interconnection Computational Layer $\rightarrow$ L2-L3 NoC                   | 99  |

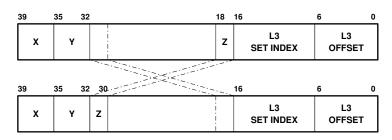

| 7.3 | Physical Address Format in the L2-L3 CMD NoC                                  | 00  |

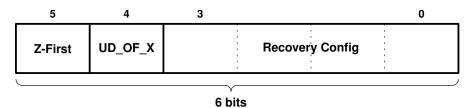

| 7.4 | Reconfiguration Register for L2-L3 NoC Routers                                | 03  |

| 7.5 | Examples of the 3D Recovery Routing Algorithm (CMD)                           | 04  |

| 7.6 | Example of the 3D Recovery Routing Algorithm (RSP)                            | .06 |

# List of Algorithms

| 4.1 | Local Neighbors' Discovery                  | 38  |

|-----|---------------------------------------------|-----|

| 4.2 | Local Leader Election                       | 40  |

| 4.3 | Neighbor Clusters' Discovery                | 47  |

| 4.4 | Tag X-First Path Algorithm                  | 63  |

| 5.1 | Recovery Broadcast Replication Policy       | 79  |

| 7.1 | Tag ZXY Path Algorithm                      | 102 |

| A.1 | Reconfigurable Cycle-Free Routing Algorithm | 114 |

## List of Tables

| 1.1 | Routing Algorithms Used on TSAR 3D NoCs               | 11 |

|-----|-------------------------------------------------------|----|

| 5.1 | Routers Routing Decision                              | 73 |

| 6.1 | Available Computational Power: Number of Faulty Cores | 93 |

## Outline

The always increasing performance demands of applications such as cryptography, scientific simulation, network packets dispatching, signal processing or even general-purpose computing has made of many-core architectures a necessary trend in the processor design. These architectures can have hundreds or thousands of processor cores, so as to provide important computational throughputs with a reasonable power consumption.

However, their important transistor density makes many-core architectures more prone to hardware failures. There is an augmentation in the fabrication process variability, and in the stress factors of transistors, which impacts both the manufacturing yield and lifetime. A potential solution to this problem is the introduction of fault-tolerance mechanisms allowing the processor to function in a degraded mode despite the presence of defective internal components.

We propose a complete in-the-field reconfiguration-based permanent failure recovery mechanism for shared-memory many-core processors. This mechanism is based on a firmware (stored in distributed on-chip read-only memories) executed at each hardware reset by the internal processor cores without any external intervention. It consists in distributed software procedures, which locate the faulty components (cores, memory banks, and network-on-chip routers), reconfigure the hardware architecture, and provide a description of the functional hardware infrastructure to the operating system.

Our proposal is evaluated using a cycle-accurate SystemC virtual prototype of an existing many-core architecture. We evaluate both its latency, and its silicon cost.

### **Detailed Content**

- *Chapter 1-Problem Definition*, presents the motivation of this work, the context of the treated problem (many-cores, networks-on-chip, fault-tolerance, etc.), and the questions to which this work intends to answer. Additionally, this chapter describes the TSAR architecture, which is used to demonstrate our fault-tolerance mechanism.

- *Chapter 2-State of the Art*, analyzes the state-of-the-art research in the field of permanent failures recovery in many-core architectures. It presents some solutions dealing with faulty cores, or faulty NoC routers. This chapter is concluded with the problems that in our knowledge are not yet solved.

- *Chapter 3-Distributed Recovery Firmware*, presents the general principles of the proposed in-the-field software-based fault-tolerance mechanism. It gives a brief description of the software-based procedures for the location of faults, and the reconfiguration of the hardware; and introduces other contributions of this work, like the reallocation of a physical memory segment when there is a deactivated cluster, the support of broadcast communications even when the NoC is partially defective, or a reconfigurable fault-tolerant algorithm for 3D NoCs.

- *Chapter 4-Distributed Fault-Location*, presents a detailed description of the proposed software-based fault-location procedure. This chapter describes the different distributed procedures of the recovery firmware, defines the properties that these procedures must satisfy, and proves these properties. Additionally, it presents a software, but hardware-assisted mechanism to test the coherence NoCs in the TSAR architecture.

- *Chapter 5-NoC Reconfiguration*, presents the software-based distributed procedure to reconfigure the NoCs. Additionally, it presents the mechanism allowing to reallocate the physical memory segment of a deactivated cluster to one of its neighbors, and a fault-tolerant routing algorithm supporting broadcast communications.

- *Chapter 6-Experimental Results and Evaluation*, presents the evaluation in terms of latency, and silicon cost of the proposed fault-tolerance mechanism, that has been implemented in a cycle-accurate virtual prototype of the TSAR architecture.

- *Chapter 7-Fault-Tolerance Extension for Interconnects above the Computational Layer*, presents an extension to the fault-tolerance mechanism to support permanent failures in 3D NoCs. This chapter describes a software-based fault-location, and fault-reconfiguration procedure for these NoCs; and a 3D fault-tolerant routing algorithm.

# Chapter 1

## **Problem Definition**

## Contents

| 1.1 | Motiv  | ation                                              |

|-----|--------|----------------------------------------------------|

| 1.2 | Many   | core Architectures                                 |

| 1.3 | Netwo  | ork-on-Chip (NoC)                                  |

|     | 1.3.1  | Globally-Asynchronous Locally-Synchronous (GALS) 6 |

|     | 1.3.2  | Routing Algorithm                                  |

| 1.4 | Tera-S | Scale Architecture (TSAR)                          |

|     | 1.4.1  | Memory Hierarchy                                   |

|     | 1.4.2  | Networks-on-Chip                                   |

|     | 1.4.3  | IO Subsystem                                       |

| 1.5 | Fault- | Tolerance                                          |

|     | 1.5.1  | NoCs Routing Algorithm Reconfiguration             |

|     | 1.5.2  | Distributed Algorithms                             |

| 1.6 | Probl  | em Definition                                      |

### 1.1 Motivation

Many-core architectures are a current trend in processor design to face the augmentation on the performance demands of modern systems [1]. These architectures take benefit of the increasing transistor density of circuits by the integration of hundreds or thousands of small cores in a single chip. However, as a consequence of the very high transistor density, the reliability in this kind of architecture is a major concern. The technology scaling improves the transistor density but arises the two following consequences: (1) augmentation in the process variability that impacts the manufacturing yield and (2) augmentation of the stress factors of transistors that impacts the lifetime of Integrated Circuits (ICs) [2].

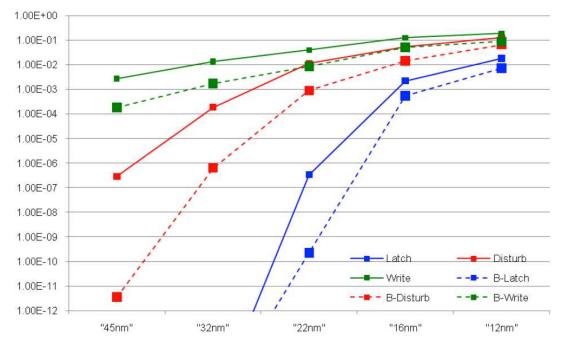

The International Technology Roadmap for Semiconductors (ITRS) [3] estimates that in the near-future, "the cost of ensuring that each transistor in a large integrated circuit to function within specification may become to high to be practical" and therefore, there will be a high percentage of non-functional devices right after fabrication. In the ITRS design report at 2011, the Figure 1.1 shows failure probabilities predictions (y-axis) against the technology nodes (x-axis) for two major components in the digital CMOS design: SRAM bitcell and latch. The figure shows that failure probabilities can reach 10% for SRAM cells in the 16nm technology if traditional circuit design approaches continue unchanged; therefore shows the necessity of introducing new circuit and architecture techniques.

Figure 1.1 - Variability-Induced Failure Rates for Two Canonical Circuit Types (source: ITRS [3])

A potential solution to this massively defective circuit problem can be the introduction of fault-tolerance mechanisms. These mechanisms improve both yield and lifetime factors by allowing hardware to function, in a possibly degraded mode, despite the presence of defective internal components. Such a solution is achieved by designing systems that can dynamically self-reconfigure to deactivate the internal failing devices. In order to enable self-reconfiguration during the entire life-time of the circuit, fault-tolerance should be achieved by means of on-chip components without any external intervention. Such kind of solutions are denominated "in-the-field". These solutions improve the manufacturing yield by allowing to produce circuits with a tolerated percentage of faulty internal devices and also to improve the circuit's lifetime by allowing it to reconfigure when it is already in service after manufacturing (in the field).

### 1.2 Many-core Architectures

Many-core architectures exploit thread level parallelism through hundreds or thousands of cores and therefore, applications should exhibit highly parallel behaviors. Some examples of applications are cryptography, finance, weather forecasting, scientific simulation, network packets acquisition and dispatching, or signal processing (e.g. video compression). They can also be used in embedded environments for automotive or aerospace applications.

In order to reduce architecture bottlenecks, and therefore improve the parallel execution, many-cores are usually organized in clusters, interconnected through a Network-on-Chip (NoC), where each cluster contains various components such as one or more cores, local memory banks and internal peripherals. This organization allows a scalable performance by providing important memory and communication bandwidths.

The communication between cores can be implemented using whether a shared memory or a message-passing paradigm. On the former, all cores share the same address space, thus any processor core can write or read any memory location (local or remote). On the latter, all processor cores in a cluster have a private address space, and hence software needs to explicitly move data from the local memory bank to the remote memory bank by means of message passing in order to perform communication between clusters. This work is interested in many-core architectures implementing a shared memory address space.

Additionally, to reduce access time and to decrease demands on external memories, processors implement a memory hierarchy containing one or more levels of cache memory (lower levels) followed by external main memory and disk (higher levels). When one or more cache levels are private to a processor core in a shared memory architecture, a cache coherence problem exists. As a data replica can be at several private caches, modifications on a replica should be propagated to all other replicas in order to have a consistent view of the memory by all processor cores. The propagation of changes on replicas could be done by software or hardware. This work is interested in architectures guarantying cache coherence by hardware.

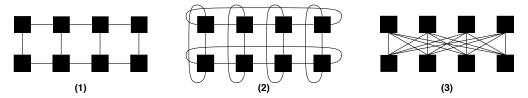

Figure 1.2 - Examples of NoC Topologies: (1) 2D Mesh, (2) 2D Torus, (3) 4 × 4 Crossbar

### 1.3 Network-on-Chip (NoC)

NoCs are in charge of the interconnection of internal devices in many-core architectures. Basic components of NoCs are routers and communication channels: routers are in charge of the routing of incoming packets from one input channel to one output channel; and channels are buffering devices connecting one output port of a router to an input port of another router.

In general, to avoid communication bottlenecks, the NoCs use regular topologies providing a scalable communication bandwidth. When the number of devices is small, they can be interconnected using a fully connected topology like a crossbar (see Figure 1.2 (3)). Otherwise, if the number of devices is important, the NoCs use partially connected topologies like multidimensional meshes. Figure 1.2 (1) and Figure 1.2 (2) show a Two-Dimensional (2D) mesh and torus respectively. In this work, we consider many-core architectures implementing multidimensional meshes for the inter-cluster connections as they are the most commonly used. Such topologies allow, on the one hand to reduce the silicon cost by the implementation of simple routing algorithms, and on the other hand to reduce the use of long wires that incur important delays and power dissipation [4].

### 1.3.1 Globally-Asynchronous Locally-Synchronous (GALS)

One important feature proposed by modern NoCs is the implementation of the Globally-Asynchronous Locally-Synchronous (GALS) approach. As the size of the systems grows, is becoming harder to provide a single clock through the whole chip because of the skew. The skew is produced among other reasons, by the delay incurred by wires while sending the clock signal to the different sequential devices of the chip. When the clock signal has significantly different arrival times to the different devices, timing violations may occur. Moreover, with the increment in the clock frequency such violations are becoming more important.

The term GALS was firstly used by Chapiro [5] and it is a technique consisting in dividing the chip in several clock-independent regions (clock domains). Each region is locally synchronous but may be asynchronous with respect to other regions. In order to allow communication between clock domains, the regions can use bi-synchronous FIFOs at their interfaces. The advantages of this technique are: modularity, scalability, smaller clock wires length because there is no need of circuit's global clock, power consumption improvements and fault-tolerance.

The power consumption can be improved in two ways: 1) smaller clock wire lengths results in smaller wire resistance and decreases power consumption, and 2) as each region can work with different clock frequencies, one can for example dynamically slow down the clock of currently unused regions or regions executing some low priority task. Regarding fault-tolerance, because there are several clocks, the failure of one of them only affects the concerned region.

### 1.3.2 Routing Algorithm

The routing algorithm defines which network path is used by packets in order to go from a source cluster to a destination cluster.

When the path is always the same for all packets transferred between a given pair of clusters, the routing algorithm is deterministic, and the path depends only on the packet's destination. Otherwise, when the path depends on the destination and on the link status (e.g. network congestion), the routing algorithm is adaptive. The adaptive routing algorithms use network resources better but they are more expensive than deterministic counterparts. In particular, adaptive solutions do not guarantee the in-order delivery property and therefore, need specific hardware in the Network Interface Controllers (NICs) to reorder packets. This kind of mechanism is then not always scalable with respect to area, energy consumption and latency. Therefore, deterministic routing algorithms are commonly preferred in NoCs.

The routing algorithm can be implemented using whether routing tables (a.k.a. forwarding tables) or a logic-based circuit. When using the former, there is one table per router that contains at least one entry per destination (per node in the network). Each entry contains the output port associated to a destination. When using a deterministic algorithm, there is exactly one entry per destination. In the case of logicbased routing algorithms, the output port is computed by a hardwired combinational circuit that takes as an input the destination of the packet. Routing tables are more flexible concerning topologies but they are not scalable because the number of entries depends on the number of nodes in the network. As a consequence, the logic-based implementations are preferred for NoCs because of their scalability as the area does not depend on the network size.

An important property that routing algorithm must guarantee is that a packet always reaches its destination. Therefore, it must guard against livelock and deadlock situations. The former arises when a packet can be routed an unbounded time in the network. The latter arises when a packet cannot advance towards its destination because it waits for a network resource to be freed by another packet. Both problems can be solved by implementing some restrictions on the routing algorithm. In the case of livelocks, the number of forwarding options of routers should be restricted to avoid the packet to be redirected indefinitely without reaching its destination. When using deterministic routing algorithms there is a unique possible path between any pair of clusters and therefore there is no risk of livelock. In the case of deadlock situations, they can be avoided by eliminating cycles in the dependency graph of the network resources [6].

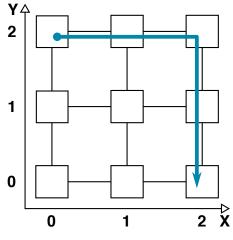

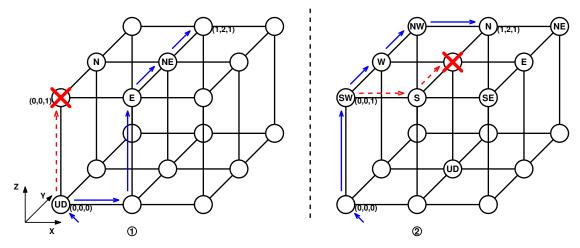

Figure 1.3 – X-First Routing Example

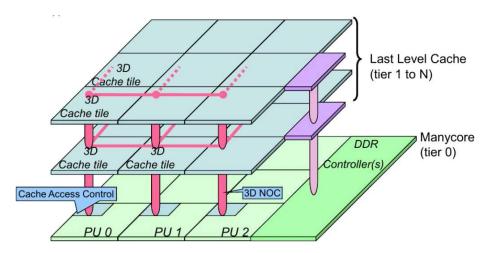

Usually used livelock-free, deadlock-free, deterministic and logic-based routing algorithms are the Dimension-Order Routing (DOR) algorithms. These algorithms work on multidimensional meshes or torus. The packets are routed in a specified order of dimensions until it reaches its destination. Figure 1.3 shows an example for a 2D mesh: a packet is first routed on the X dimension and then on the Y dimension. This specific case of DOR algorithms is called X-first routing (a.k.a. XY routing).

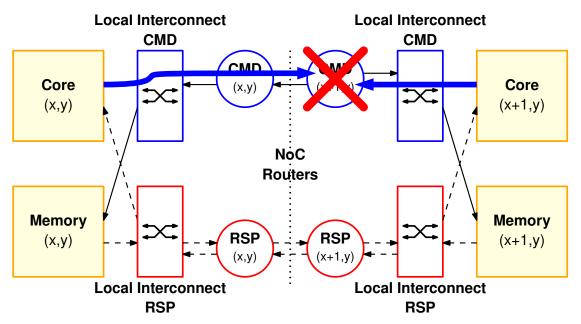

DOR algorithms have the advantage to be simple, and therefore cost-effective solutions for NoCs. However, they do not support irregular topologies. When some NoC routers or channels are faulty in a regular topology, it may become irregular, and then DOR algorithms cannot support it. In such cases, the communication between clusters is broken, and the entire chip is useless. This is why some modifications need to be introduced in such algorithms in order to support some irregular topologies while preserving their low-cost, deadlock free and livelock free properties. Such modifications will be presented in Section 1.5.

### **1.4 Tera-Scale Architecture (TSAR)**

The architecture used by this work to validate and evaluate the proposed fault tolerance technique is TSAR.

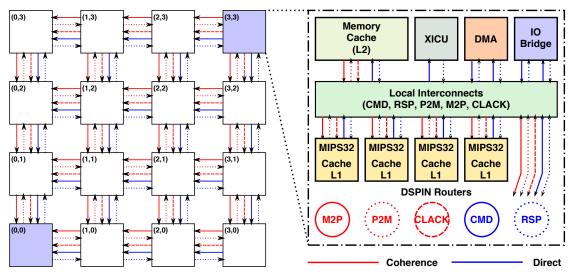

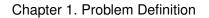

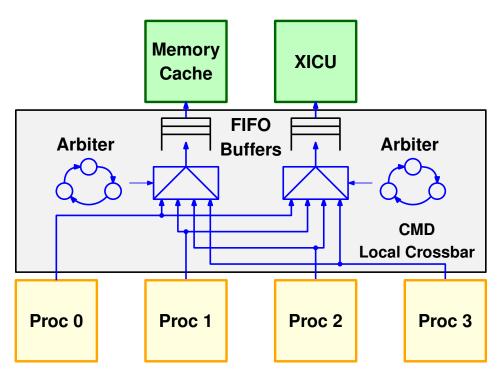

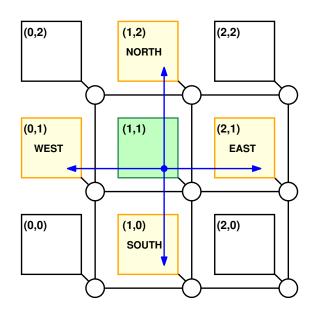

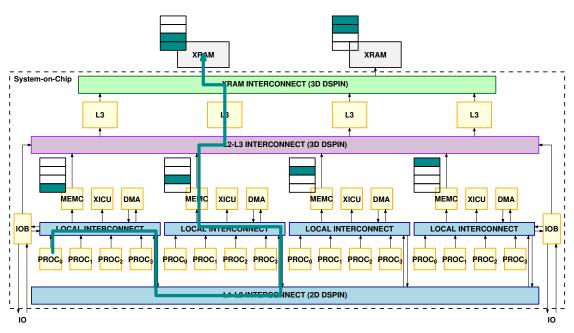

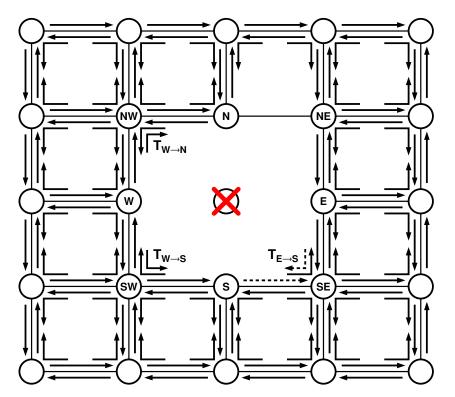

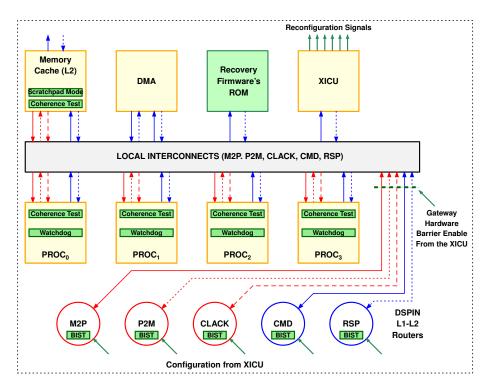

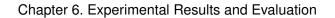

TSAR [7] is a scalable, cache-coherent, shared-memory many-core jointly designed by BULL, LIP6 and CEA-LETI in the framework of the European CATRENE SHARP project. It supports up to 1024 processor cores organized as a mesh of clusters, where each cluster contains up to 4 processor cores as shown in Figure 1.4. Each processor core has a private L1 data cache and L1 instruction cache. Additionally, each cluster contains a shared L2 cache controller, which can be accessed by any processor core in the system, an interrupt controller (XICU) and a Direct Access Memory (DMA) controller.

Figure 1.4 – TSAR 2D-Mesh

### 1.4.1 Memory Hierarchy

In Tera-Scale Architecture (TSAR) the memory is logically shared but physically distributed. This means that every memory location is shared and can be accessed by any processor core, but the address space is physically distributed in every cluster. Each cluster manages an exclusive segment of the physical address space defined by the most significant bits of the physical address. As a result of this address space distribution, the TSAR is a Non-Uniform Memory Access (NUMA) architecture, i.e., the memory access latency is not uniform for the entire address space but depends on the distance between the processor core and the target memory location.

The physical address space length is 1 Terabyte (40 bits addresses) but to be energy efficient, this architecture uses 32-bits, single instruction issue, RISC cores with a 4 Gigabytes address space (32-bits addresses). These cores implement the MIPS32 Instruction Set Architecture (ISA) with a Memory Management Unit (MMU) containing two separates Translation Lookaside Buffers (TLBs): one for data and one for instructions. This custom MMU implementation allows, in particular, to maintain the TLBs coherence by hardware.

In addition to the L1 and L2 cache controllers, TSAR implements a third level of cache (L3). Nominal capacities of L2 and L3 caches are 256 Kbytes and 1 Mbyte, respectively. The L1 data and instruction caches have each 16 Kbytes. The Figure 1.5 contains a flattened global view of the TSAR architecture with its memory hierarchy.

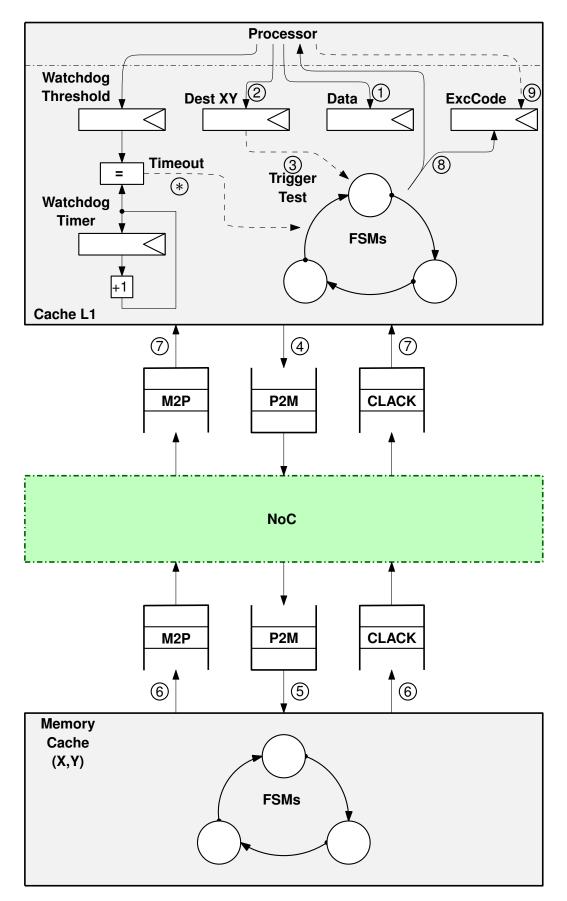

Regarding cache coherence, because L1 caches are private but L2 caches are shared, TSAR implements a hardware cache-coherence protocol called Distributed Hybrid Cache Coherence Protocol (DHCCP). The L1 caches implements a *write-through* policy while the L2 caches implements a *write-back* policy.

Figure 1.5 – TSAR Flattened Global View

### 1.4.2 Networks-on-Chip

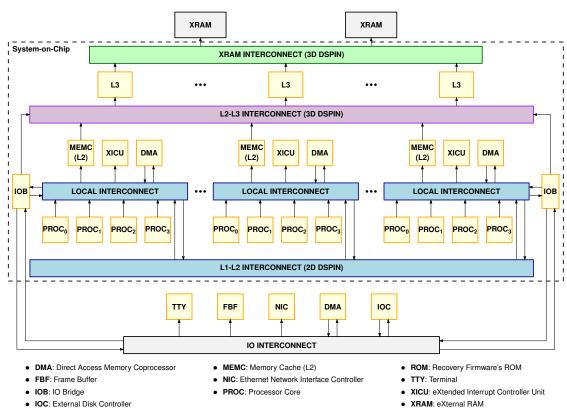

Several independent internal NoCs are implemented in TSAR. The Figure 1.6 shows the physical implementation. It relies on a Three-Dimensional (3D) stacking technology: in the first layer (called computational layer) are the cores, L1 cache and L2 caches. The other layers contain the distributed L3 cache.

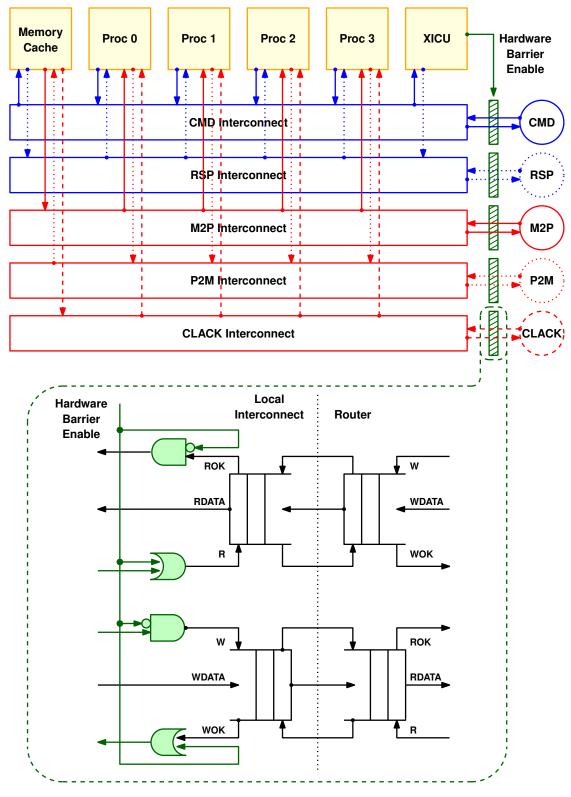

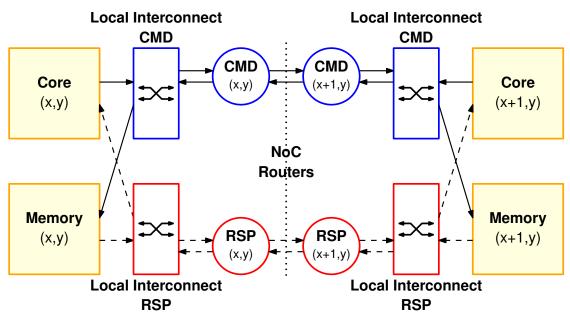

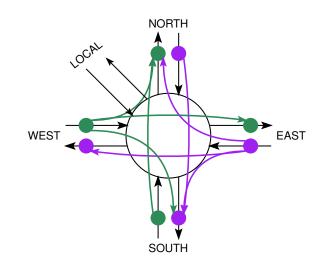

The computational layer of TSAR (shown in Figure 1.4) implements five physically independent NoCs (CMD, RSP, M2P, P2M & CLACK): two for the direct traffic (normal read and write transactions triggered by L1 cache controllers or DMA-capable internal peripherals) and three for the coherence traffic (triggered by L1 and L2 cache controllers to maintain the memory coherency). The CMD and RSP NoCs transport the commands and responses of the direct transactions, respectively. The M2P and CLACK NoCs transport commands from the L2 cache to L1 cache controllers and the P2M NoC transport commands from the L1 cache to L2 cache controllers. These three independent NoCs are required by the coherence protocol because some transactions need three phases. Thus, for deadlock avoiding, the messages on each phase must use independent networks.

The five NoCs in the computational layer implement a two-level hierarchical structure: local and global. The local interconnect uses a crossbar for intracluster communication, and the global interconnect uses the 2D-mesh Distributed, Scalable, Programmable, Integrated Network (DSPIN) for intercluster communication.

Figure 1.6 - TSAR 3D Stacking Technology (source: Guthmuller, Miro-Panades, and Greiner [8])

Miro Panades, Greiner, and Sheibanyrad [9] define the DSPIN NoC infrastructure which is intended for clustered shared memory multiprocessor architectures. It implements a 2D mesh topology and uses the deterministic, deadlock and livelock free, in-order delivery, X-first routing algorithm. Additionally, it implements the GALS approach, i.e., each cluster in the architecture can have its own clock source with a possibly different frequency with respect to other clusters. The communication between clock domains is achieved through bi-synchronous FIFO buffers in the router-to-router interconnection channels.

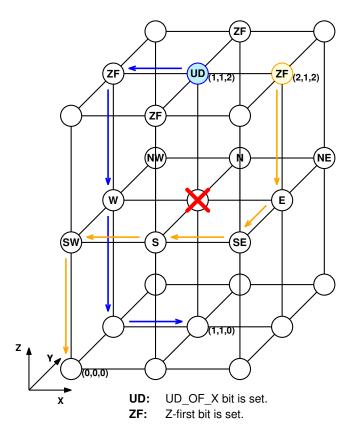

Guthmuller, Miro-Panades, and Greiner [8] define the L3 cache architecture implemented in TSAR. The L3 cache layers use a 3D version of the DSPIN infrastructure for NoCs. There are two independent 3D NoCs for L2 and L3 cache controllers command and response traffics. Additionally, there are two 3D NoCs for command and response traffics between L3 cache controllers and the external memory banks (XRAM). Table 1.1 shows the routing algorithms used by these NoCs. In summary, TSAR implements nine internal NoCs.

| NoC                                                                                 | Routing Algorithm                      |

|-------------------------------------------------------------------------------------|----------------------------------------|

| $L2 \rightarrow L3$ $L3 \rightarrow L2$ $L3 \rightarrow XRAM$ $XRAM \rightarrow L3$ | ZXY<br>XYThenDown<br>XYThenDown<br>ZXY |

Table 1.1 - Routing Algorithms Used on TSAR 3D NoCs

#### 1.4.3 IO Subsystem

Input/Output (IO) peripherals are connected to an external IO interconnect. TSAR implements bridges placed in specific clusters of the computational layer to access this interconnect.

As shown in Figure 1.4, TSAR implements two IO bridges: one on cluster (0, 0) and another on cluster (*XSIZE* – 1, *YSIZE* – 1) where *XSIZE* and *YSIZE* are the size of the 2D mesh on *X* and *Y* dimensions, respectively. These two clusters are called in the remainder of this document as IO clusters. The two IO bridges are connected to the same IO interconnect and therefore, provide two different paths to access external peripherals. This redundancy is important for fault-tolerance purposes: if one IO cluster is faulty, the other one can be used.

### 1.5 Fault-Tolerance

Fault tolerant systems are capable of operating despite the presence of faults. For this purpose, systems must implement fault tolerance techniques whose complexity depends on the reliability requirements. One of the requirements that must be defined is the kind of tolerated faults.

When classifying faults by duration, two coarse categories can be distinguished: permanent faults and transient faults. Permanent faults remain in existence indefinitely and transient faults appear and disappear within short periods of time. The formers can appear as the consequence of manufacturing defects or aging; the latter can appear because of external disturbances effects like radiation. In modern ICs the problem of permanent failures is becoming important because of the process variability, and the accelerated aging issues of current technology nodes. Such issues are a consequence of the technology scaling and the related very high transistor density. This work focusses in fault tolerance techniques for permanent failures.

There are several types of fault tolerance techniques. The dynamic reconfiguration approach tries to recover a desirable state of the system when faults have been detected. The reconfiguration can consist in replacing faulty components by backup spares, or isolating faulty components from the rest of the system. Techniques that isolate and deactivate faulty components, are called graceful degradation techniques. Such techniques use the redundant hardware resources of the system to allow a degraded operational mode. This work focusses on this kind of techniques.

Regarding many-core architectures, graceful degradation techniques are an interesting fault tolerance approach because these architectures are inherently redundant (several identical cores, memory banks and NoC routers). Therefore, one can imagine various operational modes where faulty cores, memory banks or NoC resources are deactivated and the remainder of the system continues to perform its functions with only a limited performance degradation.

The system reconfiguration can be performed by means of external or internal devices (or both). When the reconfiguration is performed autonomously by internal devices, the system is called in-the-field self-reconfigurable (a.k.a. self-healing systems or self-adaptable systems). Such systems are able to *heal* themselves after the occurrences of failures on internal devices during its entire lifetime. Therefore, they

can self-reconfigure to recover from manufacturing defects or from components wear-out. This work searches an in-the-field self-reconfiguration solution that improves both manufacturing yield and lifetime of many-core processor chips.

The reconfiguration-based fault tolerances approaches involve four issues [10]: fault detection, fault location, fault containment, and fault recovery. Fault detection is the ability of a system to recognize that a fault occurred; fault location is the process of determining where a fault has occurred; fault containment is the process of isolating a fault and preventing its effects from propagating throughout the system; and fault recovery is the ability of the system to regain an operational mode via reconfiguration.

### **Fault Detection**

The first process performed in any reconfiguration-based fault tolerance technique is the fault detection. In this process the erroneous behavior of internal components is detected, in order to allow a subsequent location and deactivation of failed components.

This work tries to reuse existent fault detection techniques and therefore, it focusses on how to solve the fault location, fault containment and fault recovery issues. Hereafter a brief introduction of some existent fault detection techniques is presented.

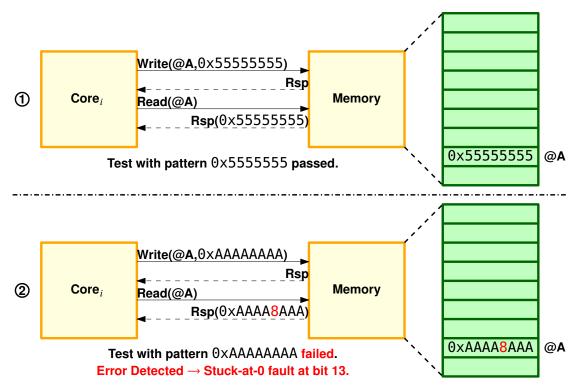

In general, the fault detection process consists on applying test patterns to the inputs of the Device Under Test (DUT), and the outputs are compared to expected values. Errors are detected when there are differences between the obtained values and the expected ones. For the purpose of applying test patterns, there are several techniques and among these techniques there are: Automated Test Equipment (ATE), Built-In Self-Test (BIST) and Software-Based Self-Test (SBST).

The ATE is an external test equipment that is connected to inputs and outputs of the entire chip. It performs comparisons against expected values in order to detect errors. This approach is not suited for in-the-field fault detection.

The BIST techniques were introduced to perform test at the system nominal clock frequency and allow the DUT to self-diagnose. In this technique, dedicated test pattern generators and analyzers are introduced in the chip. However, when the complexity of the DUT is important, the BIST overhead may also be important.

Finally, the SBST solution uses the internal processor cores to run test procedures that are generally stored either in internal or external Read-Only Memory (ROM). These test procedures allow the core to diagnose itself and the memory subsystem. As the core uses its native instruction set to generate and analyze test patterns, there is no need of additional test-specific hardware. Test procedures write and read different memory locations, and perform comparisons to detect erroneous behaviors. Like BISTs, the SBSTs can be run in the field at the nominal clock frequency of the system.

In this work we plan to use pre-existent BIST solutions for the NoCs, and pre-existent SBSTs solutions for the processor cores and memories. NoC routers have a rather low hardware complexity, and the associated overhead of the BIST mechanism is not important.

In order to implement the fault detection on NoCs, this work intends to use a distributed BIST like the one defined by Zhang, Greiner, and Benabdenbi [11]. This BIST is distributed in every router, and it performs the router deactivation when a fault is detected at every processor power-on.

Regarding the processor cores, several SBST solutions exist [12]–[14]. These solutions allow the test of a core and the memory subsystem, by means of self-testing programs. As reference, in Kranitis, Paschalis, Gizopoulos, *et al.* [12], the authors propose a SBST for a MIPS32 processor with a 5-stage pipeline. This SBST achieves a 92% fault coverage, with a latency of 10 Kcycles, and 7 Kbytes of code.

### 1.5.1 NoCs Routing Algorithm Reconfiguration

The use of regular topologies in the NoCs, provides an intrinsic redundancy which can be used for fault-tolerance. In fact, in this kind of topology there are several paths between any pair of communicating nodes. However, in order to reduce the silicon cost and guaranty in-order delivery, the NoCs use deterministic routing algorithms where any pair of nodes communicate to each other through a deterministic path. In this scenario, when there is a faulty router in a path, the communication is broken. Therefore, it is necessary to introduce a reconfiguration mechanism in the routers in order to modify their routing algorithm and then, reestablish communication by bypassing the faulty components. However, this reconfiguration must guaranty that the new routing algorithm is deadlock and livelock free.

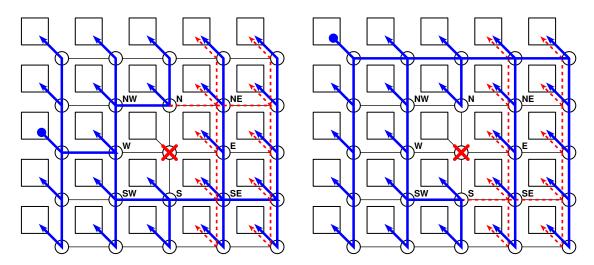

The solution proposed by Zhang, Greiner, and Taktak [15] deals with the reconfiguration of the 2D DSPIN interconnect in order to bypass a faulty router. This solution consists in the introduction of a configuration register in the DSPIN routers that allows modifying the default X-first routing. However, this solution needs that the faulty routers (creating *holes* in the network) are precisely located, and it requires a reconfiguration communication infrastructure to reliably reconfigure the routers. This work searches solutions to these two problems.

### 1.5.2 Distributed Algorithms

The location of faulty routers is required to reconfigure the remaining routers and adapt to the new irregular topology. The main problem is to centralize all this distributed information (location of faulty routers) to compute a new global routing algorithm.

This work will search a solution to locate faulty routers by executing a distributed firmware. The goal is to reuse the processor cores to reduce the overall hardware

cost of the solution. However, this implies that the fault tolerance mechanism is running on an unreliable hardware as some processor cores, memory banks or communication links can be faulty.

For this reason, the solution to this problem requires distributed algorithms. Such algorithms are executed in parallel by processor cores, but they need to work coordinately in order to centralize the distributed gathered information and take consensual decisions. Moreover, these algorithms must consider the problem of being executed on unreliable hardware and this is one of the main challenges that this work has to face.

### 1.6 Problem Definition

The technology scaling allows circuits to improve their computational power by increasing the transistor density. However, there is also an increase of the probability of failures, and the cost of ensuring that every transistor in the chip works within the specifications is becoming not practical. A possible approach to deal with these defective chips is to introduce reconfiguration-based fault-tolerant mechanisms. Such mechanisms can improve both the manufacturing yield and lifetime by allowing the circuits to work degradedly despite the presence of faults.

Many-core architectures are inherently redundant. They contain multiple cores and memory banks. The regular NoC topologies provide redundant communication paths between internal components. Therefore, the general question to which this work will intend to answer is: **how to take benefit of the many-core architectures' intrinsic redundancy in order to tolerate permanent failures in cores, memory banks and NoC components?**. This work considers in-the-field reconfiguration (i.e. after the chip manufacturing) without any external intervention. Besides, in order to reduce the overhead of the fault-tolerance mechanism, this work focusses in solutions reusing at maximum the existent hardware for the reconfiguration (e.g. reuse of internal cores, memories and communication infrastructure). Such a solution can be based on distributed software procedures executed in parallel by all processor cores, on the one hand, to provide scalable reconfiguration times and, on the other hand, to provide robustness because the reconfiguration does not depend on a unique non-faulty device.

Regarding the fault-tolerance on the NoCs, our work relies upon two existent technologies: the first, proposed by Zhang, Greiner, and Benabdenbi [11] provides a BIST for the detection and deactivation at every hardware reset of the faulty routers in a 2D mesh NoC; the second, proposed by Zhang, Greiner, and Taktak [15] provides a reconfigurable dead-lock free routing function for this kind of NoC which allows bypassing the deactivated faulty routers. However, in order to perform the reconfiguration of the NoC, we need to locate the deactivated routers, compute the new global routing algorithm, and provide a reliable communication infrastructure to reconfigure the routers. Thus, this work intends to answer the two following questions: (1) how to locate the faulty routers, faulty cores, and faulty memory banks in order to build a map of the operational hardware devices ? and (2) how to reconfigure the routers reliably when the existent hardware communication infrastructure is partially defective?. As explained in Section 1.1, many-core architectures have several internal NoCs allowing the transmission of different types of messages (e.g. normal memory accesses, hardware cache coherence) between different internal devices. This work considers the reconfiguration of all internal NoCs to effectively increase the fault tolerance in many-cores.

Additionally, we focus in many-core processors capable of executing commodity Operating Systems (OSs) like Linux or NetBSD. Such OSs need to determine the complete description of the hardware in order to initialize their internal data structures. In the presence of hard faults, the available devices may change and thus, the OS needs to know about these changes. Our work answers the following question: how to transmit the map of the functional hardware devices to the OS so as to support its execution on a degraded architecture?.

# Chapter 2

## State of the Art

## Contents

| 2.1            | Fault- | Tolerance in Many-Core Processors                   | 18 |

|----------------|--------|-----------------------------------------------------|----|

|                | 2.1.1  | Many-Core Yield Enhancement                         | 18 |

|                | 2.1.2  | Many-Core Self-Organization                         | 18 |

|                | 2.1.3  | Many-Core Distributed Cores Diagnosis               | 19 |

| 2.2 Fault-Tole |        | Tolerant Routing Algorithms for NoCs                | 20 |

|                | 2.2.1  | Fault-Tolerant Routing Based on Virtual Channels    | 20 |

|                | 2.2.2  | Segment-Based Routing Algorithm                     | 20 |

|                | 2.2.3  | Logic-Based Distributed Routing (LBDR)              | 21 |

|                | 2.2.4  | Cycle-Free Contour Fault-Tolerant Routing Algorithm | 22 |

| 2.3            | Concl  | usion                                               | 24 |

This chapter analyses the state-of-the-art research in the field of permanent failures recovery in many-core architectures. It is divided in three sections.

The first section presents fault-tolerance techniques dealing with permanent failures in many-core processors. The second section focuses in the NoC, and presents some fault-tolerant routing algorithms to support faulty routers or links. Finally, there is a conclusion section, where we present the problems that in our consideration are not yet solved, and for which we will propose a solution.

## 2.1 Fault-Tolerance in Many-Core Processors

This section presents three solutions related to the problem of supporting permanent failures in many-core processors.

#### 2.1.1 Many-Core Yield Enhancement

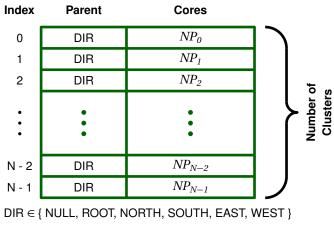

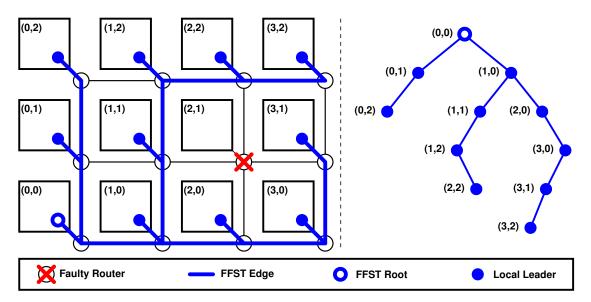

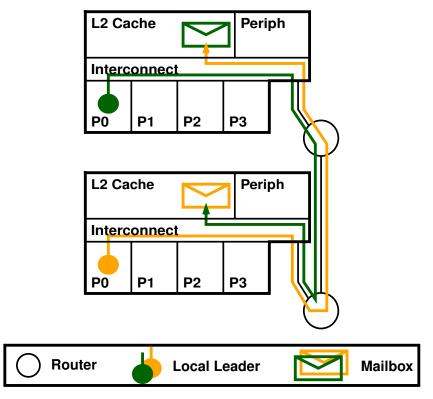

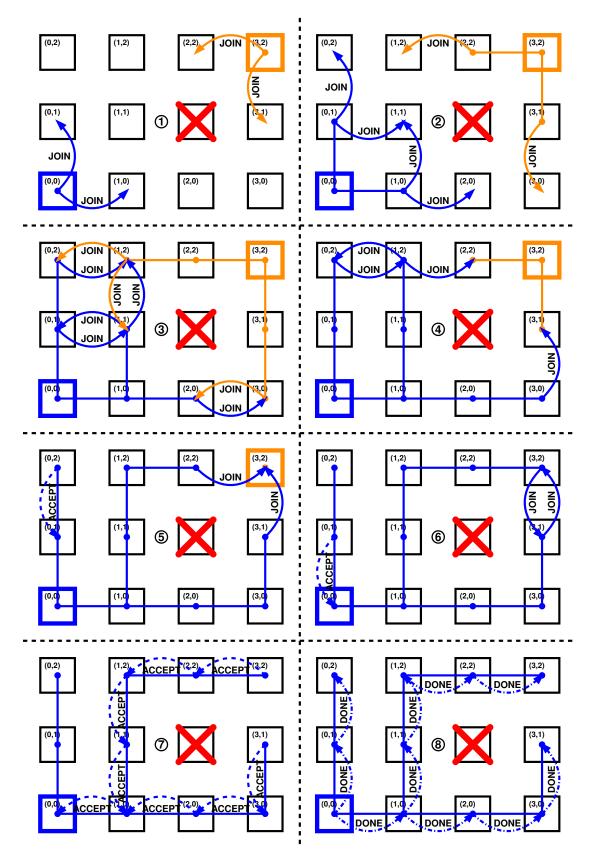

In Zhang, Han, Xu, *et al.* [16], the authors propose the **N+M** fault-tolerance technique for yield enhancement. This technique uses a core-level redundancy scheme where a N-core processor is fabricated with M spare cores.