# Abstraction techniques for scalable soft error analysis and mitigation

Adrian Evans

## ► To cite this version:

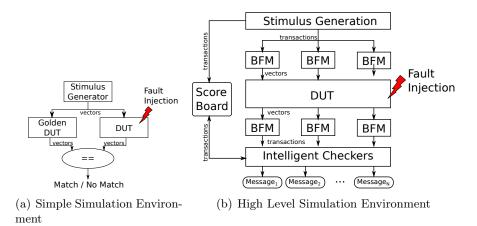

Adrian Evans. Abstraction techniques for scalable soft error analysis and mitigation. Micro and nanotechnologies/Microelectronics. Université de Grenoble, 2014. English. NNT: 2014GRENT035. tel-01294383

# HAL Id: tel-01294383 https://theses.hal.science/tel-01294383v1

Submitted on 29 Mar 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Micro et Nano Électronique

Arrêté ministériel : 7 août 2006

## Présentée par Adrian EVANS

Thèse dirigée par Michael NICOLAIDIS

préparée au sein du laboratoire TIMA dans l'École Doctorale Électronique, Électrotechnique, Automatique et Traitement du signal

# Techniques d'abstraction pour l'analyse et la mitigation des effets dus à la radiation

Thèse soutenue publiquement le **19 juin 2014**, devant le jury composé de :

#### **Professeur Dominique HOUZET**

INPG (Laboratoire GIPSA, Grenoble), Président **Dr. Jean ARLAT** CNRS (LAAS, Toulouse), Rapporteur **Professeur Luis ENTRENA ARRONTES** Universidad Carlos III de Madrid, Rapporteur **Dr. Michael NICOLAIDIS** CNRS (Laboratoire TIMA, Grenoble), Directeur de thèse

## Acknowledgments

Undertaking a PhD has been an exciting and challenging experience and I have learned a great deal about the topic matter as well as about scientific research in general. I am indebted to numerous people; more than I can fully acknowledge here.

First and foremost, I wish to thank my thesis supervisor, Michael Nicoloaidis, who welcomed me warmly when I arrived at the TIMA laboratory. Over the last three years, his guidance and insight have been invaluable. He has also taught me a great deal about the importance of protecting intellectual property.

I wish to express my thanks to Jean Arlat for his contributions to the RIIF workshop and to him, Luis Entrena and Dominique Houzet for serving on my thesis committee and providing their feedback.

To Dan Alexandrescu, CEO of iROC Technologies, I am beholden for his encouragement, for granting me time to write my thesis and for helping me to obtain numerous reference materials. To the entire staff at iROC Technologies, I wish to express my thanks for providing a warm environment where I have learned immensely from experts in the field of soft errors. I especially thank Enrico Costenaro with whom I collaborated on the work on the analysis of transient errors and Jocelyne Baudoin who helped manage the time I spent working on my thesis.

The first year of my thesis was spent at the TIMA Laboratory and I wish to express my thanks to Dominique Borrione, director of the laboratory. Mounir Benabdenbi helped me with my course work and Lorena Anghel was of great assistance with the organization of the RIIF Workshop. Laurence Ben Tito and Anne-Laure Fourneret-Itie helped me navigate the administrative procedures.

Furthermore, I wish to express my thanks to Shi-Jie Wen of Cisco Systems who encouraged many parts of the work in this thesis. His help in gaining access to actual designs for the portion of the work on selective flip-flop mitigation and his support for extending the work on combinatorial SET analysis were extremely valuable.

The work related to RIIF was highly collaborative. I would like to thank Oliver Bringmann who was the co-chair of the RIIF workshop as well as Pedro Reviriego Vasallo and Alfonso Sánchez Macián of the University of Nebrija who helped develop the parser and test cases for RIIF.

The work on Bloom Filters was a collaboration with Salvatore Potarelli and Marco Ottavi at the University of Rome "Tor Vergata". The technical interaction was very enjoyable and I wish to acknowledge the Median Cost Action which covered my travel expenses for several trips.

In addition, I would like to thank Li Chen and Hao Xie of the University of Saskatchewan who lead the implementation of the work on redundant logic.

Last, but certainly not least, I express my sincere thanks to my wife Anne and my children Zoë and Ben who have been extremely patient while I have spent many hours in front of the computer. Anne's precious help in proofreading my manuscript is sincerely appreciated.

# Contents

| 1 | Intr | ntroduction                                        |                 |  |  |  |  |  |

|---|------|----------------------------------------------------|-----------------|--|--|--|--|--|

|   | 1.1  | Introduction to Soft Errors and System Reliability | 2               |  |  |  |  |  |

|   | 1.2  | Soft Error Effects                                 | 3               |  |  |  |  |  |

|   |      | 1.2.1 Sources of Natural Radiation                 | 3               |  |  |  |  |  |

|   |      | 1.2.2 Brief History of Soft Error Effects          | 6               |  |  |  |  |  |

|   |      | 1.2.3 Taxonomy of Radiation Effects                | 7               |  |  |  |  |  |

|   |      | 1.2.4 Summary of Radiation Effects                 | 10              |  |  |  |  |  |

|   | 1.3  | Masking Effects                                    | 10              |  |  |  |  |  |

|   |      | 1.3.1 Logical Masking                              | 10              |  |  |  |  |  |

|   |      | 1.3.2 Temporal De-Rating                           | 11              |  |  |  |  |  |

|   |      | 1.3.3 Electrical Masking                           | 13              |  |  |  |  |  |

|   |      | 1.3.4 Functional Masking                           | 13              |  |  |  |  |  |

|   |      | 1.3.5 Computing the Overall SER                    | 14              |  |  |  |  |  |

|   | 1.4  | Current SER Trends                                 | 15              |  |  |  |  |  |

|   |      | 1.4.1 Combinatorial SER                            | 16              |  |  |  |  |  |

| 2 | Roł  | ust Sequentials                                    | 19              |  |  |  |  |  |

| 4 | 2.1  | 1                                                  | 20              |  |  |  |  |  |

|   | 2.2  |                                                    | $\frac{20}{22}$ |  |  |  |  |  |

|   | 2.2  | · ·                                                | $\frac{22}{22}$ |  |  |  |  |  |

|   |      |                                                    | 23              |  |  |  |  |  |

|   |      |                                                    | 20<br>24        |  |  |  |  |  |

|   |      |                                                    | 26              |  |  |  |  |  |

|   |      |                                                    | 27              |  |  |  |  |  |

|   |      |                                                    | $\frac{-}{29}$  |  |  |  |  |  |

|   |      |                                                    | 31              |  |  |  |  |  |

|   |      |                                                    | 32              |  |  |  |  |  |

|   |      |                                                    | 35              |  |  |  |  |  |

|   |      |                                                    | 36              |  |  |  |  |  |

|   |      |                                                    | 38              |  |  |  |  |  |

|   |      |                                                    | 39              |  |  |  |  |  |

|   | 2.3  | ·                                                  | 41              |  |  |  |  |  |

|   | 2.4  |                                                    | 42              |  |  |  |  |  |

| 3 | Sin  | le Event Effect Analysis                           | 45              |  |  |  |  |  |

| J | 3.1  | •                                                  | <b>4</b> 5      |  |  |  |  |  |

|   | 0.1  |                                                    | $43 \\ 47$      |  |  |  |  |  |

|   |      |                                                    | 49              |  |  |  |  |  |

|   |      |                                                    | 49<br>56        |  |  |  |  |  |

|   |      | · -                                                | 50<br>57        |  |  |  |  |  |

|   |      | U.I.T Maryunai Ontun Dever rechniques              | 51              |  |  |  |  |  |

|     | 3.1.5 Formal Techniques                                                                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 3.1.6 Probabilistic Techniques                                                                                                  | D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 3.1.7 Comparison of Analysis Techniques                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.2 | Networking Case Study                                                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

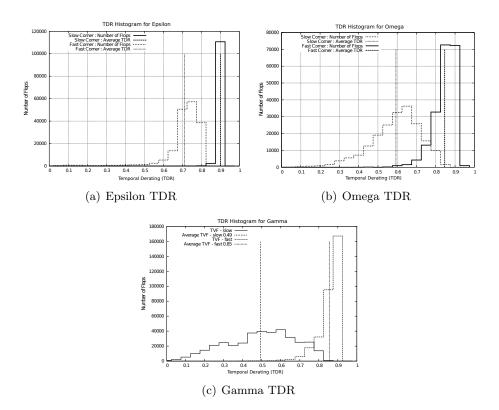

|     | 3.2.1 Temporal De-Rating                                                                                                        | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 3.2.2 Classifying Failure Effects                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

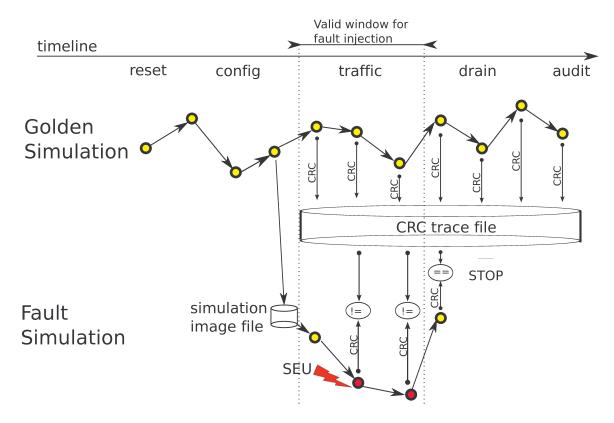

|     | 3.2.3 Testbench Environment                                                                                                     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 3.2.4 Simulation Speedup and CPU Efficiency                                                                                     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

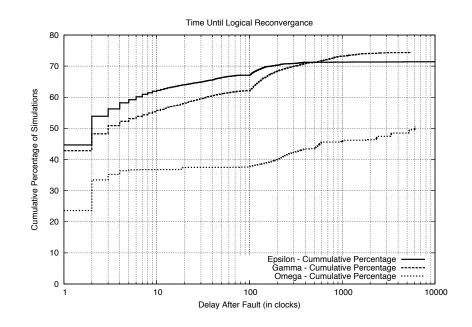

|     | 3.2.5 Logical De-Rating Results                                                                                                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 3.2.6 Summary of Simulation Results                                                                                             | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 3.2.7 Combining the Results                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

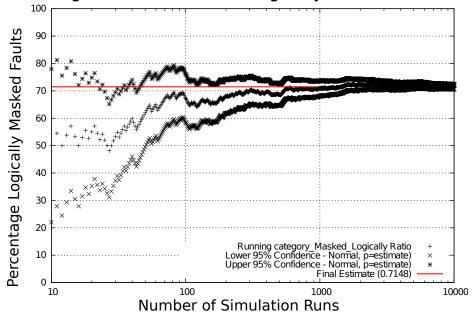

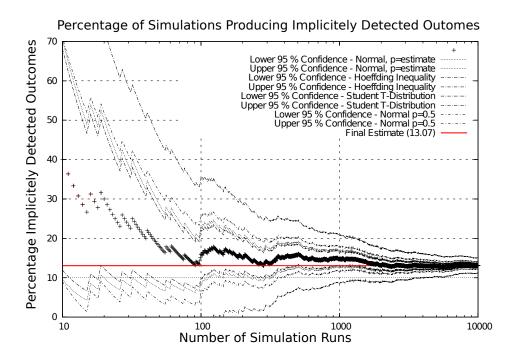

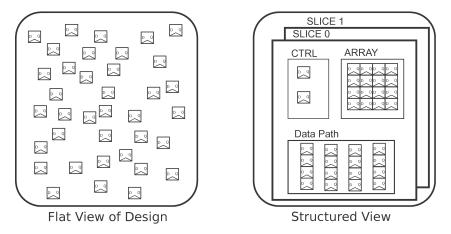

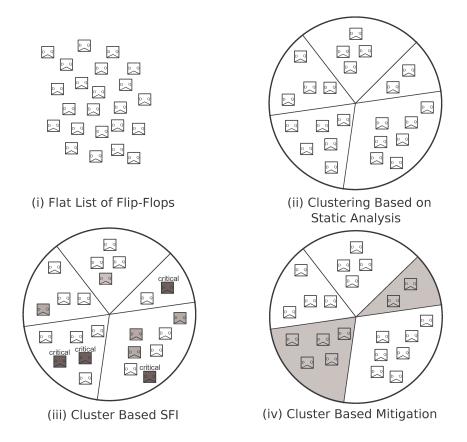

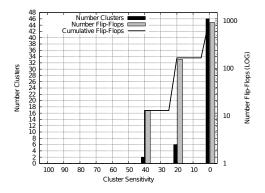

| 3.3 | Statistical Analysis of Fault Injection Results                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4 | Conclusions                                                                                                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| _   |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.1 |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.2 | 5 I                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 0                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 0                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.3 |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 0                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.4 |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 3                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.6 | $Conclusions \dots \dots$ | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Hie | erarchical Single Event Transient Analysis                                                                                      | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.1 |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -   |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.2 |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.3 |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | _                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.5 | •                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.6 | Conclusions                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 3.3<br>3.4<br><b>Teo</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br><b>Hie</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5             | 3.1.6       Probabilistic Techniques       66         3.1.7       Comparison of Analysis Techniques       66         3.2.1       Temporal De-Rating       66         3.2.2       Classifying Failure Effects       66         3.2.3       Testbench Environment       66         3.2.4       Simulation Speedup and CPU Efficiency       66         3.2.5       Logical De-Rating Results       66         3.2.6       Summary of Simulation Results       66         3.2.7       Combining the Results       77         3.3       Statistical Analysis of Fault Injection Results       77         3.4       Conclusions       77         4.1       Introduction       77         4.1       Proposed Clustering Techniques       77         4.1.1       Proposed Clustering Techniques       77         4.2       Flat SFI Results       77         4.2       Static Clustering Techniques       77         4.2.1       Bus Based Clustering       78         4.2.1       Bus Based Clustering       88         4.3.1       Bus Based Clustering       88         4.3.3       Simulation Results       88         4.3.4       Hierarchical Clustering |

| 6 | Reli       | ability Modeling with RIIF                                    | 105   |  |  |  |  |  |  |

|---|------------|---------------------------------------------------------------|-------|--|--|--|--|--|--|

|   | 6.1        | 1 Introduction                                                |       |  |  |  |  |  |  |

|   | 6.2        | Elements of the RIIF Language                                 | 108   |  |  |  |  |  |  |

|   |            | 6.2.1 Components and Parameters                               | 108   |  |  |  |  |  |  |

|   |            | 6.2.2 Failure Modes                                           | 109   |  |  |  |  |  |  |

|   |            | 6.2.3 Complex Components                                      | 109   |  |  |  |  |  |  |

|   |            | 6.2.4 Environments                                            | 110   |  |  |  |  |  |  |

|   | 6.3        | Worked Examples                                               | 111   |  |  |  |  |  |  |

|   |            | 6.3.1 Board Level Example                                     | 111   |  |  |  |  |  |  |

|   |            | 6.3.2 Soft IP Example                                         | 114   |  |  |  |  |  |  |

|   |            | 6.3.3 Scrubbed Memory Example                                 |       |  |  |  |  |  |  |

|   | 6.4        | Extensions to RIIF                                            |       |  |  |  |  |  |  |

|   |            | 6.4.1 Faults versus Errors                                    |       |  |  |  |  |  |  |

|   |            | 6.4.2 Mission Profiles and Timelines                          |       |  |  |  |  |  |  |

|   | 6.5        | Conclusion                                                    | 122   |  |  |  |  |  |  |

| 7 | Con        | clusions                                                      | 123   |  |  |  |  |  |  |

| • | 7.1        | Simulation Analysis and Selective Mitigation                  |       |  |  |  |  |  |  |

|   | 7.2        | Hierarchical SET Analysis                                     |       |  |  |  |  |  |  |

|   | 7.3        | RIIF                                                          |       |  |  |  |  |  |  |

|   | 7.4        | Summary                                                       |       |  |  |  |  |  |  |

|   |            |                                                               |       |  |  |  |  |  |  |

| Α |            | of Bloom Filters to Protect TCAMs                             | 127   |  |  |  |  |  |  |

|   | A.1        | Introduction                                                  |       |  |  |  |  |  |  |

|   | A.2        | Existing TCAM Protection Techniques                           |       |  |  |  |  |  |  |

|   | A.3        | Background on Bloom Filters                                   |       |  |  |  |  |  |  |

|   | A.4        | Application Aware Hashing                                     |       |  |  |  |  |  |  |

|   | A.5        | Error Detection Architecture                                  |       |  |  |  |  |  |  |

|   | A.6<br>A.7 | Experimental Results                                          |       |  |  |  |  |  |  |

|   | Π.1        |                                                               | 107   |  |  |  |  |  |  |

| В | App        | proximate Logic Functions for Protection of Combinatorial Log | ic139 |  |  |  |  |  |  |

|   | B.1        | Introduction to Logic Repair                                  | 139   |  |  |  |  |  |  |

|   | B.2        | Overview of Approximate Logic Functions                       | 140   |  |  |  |  |  |  |

|   | B.3        | Proposed Algorithm                                            |       |  |  |  |  |  |  |

|   | B.4        | Experimental Results                                          |       |  |  |  |  |  |  |

|   | B.5        | Conclusions                                                   | 147   |  |  |  |  |  |  |

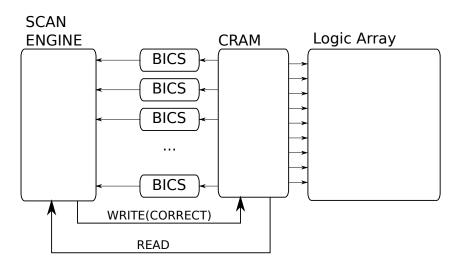

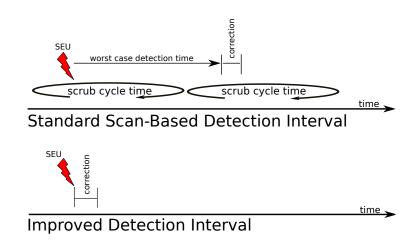

| С | Pro        | tection of FPGA CRAM or TCAMs using BICS                      | 149   |  |  |  |  |  |  |

|   | C.1        | Overview of SRAM Based FPGAs and TCAMs                        |       |  |  |  |  |  |  |

|   | C.2        | Overview of BICS                                              | 150   |  |  |  |  |  |  |

|   | C.3        | Use of BICs to Protect CRAMs                                  |       |  |  |  |  |  |  |

|   | C.4        | Extension to TCAMs                                            | 152   |  |  |  |  |  |  |

|   | C.5        | Summary                                                       | 152   |  |  |  |  |  |  |

|   |            |                                                               |       |  |  |  |  |  |  |

v

## Bibliography

153

# Glossary

- ACE Architecturally Correct Execution. 56, 57

- ACL Access Control List. 130, 131, 152

- ADD Algebraic Decision Diagram. 47, 57–59, 92

- ALU Arithmetic Logic Unit. 56, 90, 96, 100–103

- ASIC Application Specific Integrated Circuit. 48, 52, 63, 65, 124, 125

- AVF Architectural Vulnerability Factor. 46, 56, 62, 110, 114, 122

- **BDD** Binary Decision Diagram. 47, 57, 58, 92, 140

- **BFM** Bus Functional Model. 50

- **BICS** Built-In Current Sensor. 2, 150–152

- **BPSG** Boron Doped Phosphosilicate Glass. 6

- CAM Content Addressable Memory. 127, 128, 130, 132, 133

- **CED** Concurrent Error Detection. 140

- CEU Code Emulated Upset. 53–55

- CLA Carry Lookahead Adder. 91

- **CRAM** Configuration RAM. 149–152

- CRC Cyclical Redundancy Check. 68, 123, 124

- DAG Directed Acyclical Graph. 120

- DICE Dual-Interlocked storage Cell. 20, 22, 23, 40, 42

- ${\bf DPM}\,$  Defects per Million. 48

- **DSTB** Douple Sampling with Time Borrowing. 31, 32, 42, 43

- **DUE** Detected Uncorrected Error. 47, 63, 107, 114, 116

- **DUT** Device Under Test. 49, 50

- **DVS** Dynamic Voltage Scaling. 21, 27

- ECC Error Correcting Code. 16, 18, 54, 63, 65, 94, 95, 112, 114, 118, 127, 150, 152

- EDA Electronic Design Automation. 90, 122, 126

- **EDC** Error Detection Correction. 35, 36, 41, 42

- EDM Error Detection Mechanism. 54, 55

- EDR Electrical De-Rating. 13, 46, 58, 91–93, 97, 100, 102, 103, 125

- **EM** Electro-Migration. 126

- EPP Error Propagation Probability. 91, 101, 142, 143

- FDD First-level Dynamically Dead. 56

- **FDR** Functional De-Rating. 13, 14, 46, 48, 50, 61, 62

- **FDSOI** Fully Depleted Silicon on Insulator. 15, 123

- **FI** Fault Injection. 54

- FIFO First-In First Out. 65, 66

- **FIT** Failure in Time. 11, 14, 15, 90, 93, 96, 99–102, 105–108, 114, 115, 117, 141, 145–147

- FPGA Field Programmable Gate Array. 38, 46, 51–53, 149–152

- **FR** Fault Reduction. 142–144

- HCI Hot Carrier Injection. 20, 126

- HDL Hardware Description Language. 79

- HPC High Performance Computing. 78

- **HSEET** Hierarchical Soft Error Estimation Tool. 92

- **IC** Integrated Circuit. 107, 108, 122

- IoT Internet of Things. 16

- IP Intellectual Property. 107, 114, 115

- LDR Logical De-Rating. 46, 51, 56–58, 60, 91–93, 95, 97, 100–102, 107

- LUT Look Up Table. 52

- **MBE** Multiple Bit Error. 112

- **MBU** Multiple Bit Upset. 40, 63, 106, 110, 112, 114, 117

- MDR Memory De-Rating. 46, 115

- MoRV Modelling Reliability under Variability. 126

- MOS Metal Oxide Semiconductor. 8

- MTBF Mean Time Between Failure. 108

- **NBTI** Negative Bias Temperature Inversion. 20, 126

- NDA Non-Disclosure Agreement. 47

- NMI Non-Maskable Interrupt. 53

- **NP** Network Processor. 47, 63, 73, 77

- OO Object Oriented. 117, 122

- **PIPB** Propagation Induced Pulse Broadening. 13

- PLA Programmable Logic Array. 140

- **PLL** Phase Locked Loop. 8

- **PVF** Program Vulnerability Factor. 46, 56

- **PVT** Process, Voltage, Temperature. 30

- **QoS** Quality of Service. 48, 127, 130, 131

- **RAID** Redundant Array of Independent Disks. 110

- RIIF Reliability Information Interchange Format. 2, 3, 47, 90, 103, 106, 108–112, 114, 116–118, 120–122, 125, 126

- **RTL** Register Transfer Language. 3, 46, 51, 53, 57, 63, 66, 67, 78, 79, 89, 90, 92–94, 96, 100, 101, 103

- **SBU** Single Bit Upset. 106, 109, 110, 112, 114, 117, 118

- **SDC** Silent Data Corruption. 47, 63, 78, 109, 110, 114, 116, 118, 125

- **SDF** Standard Delay Format. 52, 58, 62, 100, 102

- **SEB** Single Event Burnout. 8

- **SEC** Single Error Correct. 118

- SECDED Single Error Correct, Double Error Detect. 109, 110, 112, 114

- **SEE** Single Event Effect. 150

- **SEFI** Single Event Functional Interrupt. 8, 106

- **SEGR** Single Event Gate Rupture. 8

- **SEL** Single Event Latchup. 8

- SER Soft Error Rate. 7–10, 15, 16, 18, 21–23, 28, 63, 73, 76, 89–95, 100, 102, 103, 106, 107, 125, 128

- SET Single Event Transient. 2, 3, 7, 8, 10–14, 18, 20–27, 29–32, 34–36, 38, 40, 42, 43, 47, 49, 52, 53, 57, 58, 61, 62, 89–93, 95, 96, 100–102, 125, 141, 147

- SEU Single Event Upset. 7, 8, 10–14, 20–22, 24–26, 28–30, 32, 34–40, 42, 43, 49, 52, 53, 56, 57, 59, 61, 63–66, 68–70, 78, 80, 83, 87, 102, 110, 114, 123, 125, 127, 134, 150

- **SEUT** Single Event Upset Tolerant. 23

- SFI Statistical Fault Injection. 71, 77, 79

- **SHE** Single Bit Hard Error. 118

- SoC System on Chip. 47, 107, 108, 114, 122, 123

- SOI Silicon on Insulator. 4

- **SOP** Sum of Products. 140, 146, 147

- STA Static Timing Analysis. 63

- SWIFI Software Implemented Fault Injection. 53–56

- TCAD Technology CAD. 93, 106

- TCAM Ternary Content Addressable Memory. 2, 106, 127, 128, 130–138, 152

- **TD** Transition Detector. 36, 37

- **TDR** Temporal De-Rating. 11, 12, 23, 24, 42, 46, 57, 58, 61–63, 70, 91–93, 97, 100, 102

- TDTB Transition Detector with Time Borrowing. 31, 32, 42

- TFIT Transistor FIT. A tool developed by IROC Technologies to estimate the SER sensitivity of individual cells. These can be memory cells, sequential cells or combinatorial cells. 93

- **TID** Total Ionizing Dose. 9

- **TMR** Triple Modular Redundancy. 38, 83

- **TVF** Temporal Vulnerability Factor. 11

- UCLI Unified Command Line Interface. 67

${\bf ULA}\,$ Ultra Low Alpha. 3

${\bf VPI}$ Verilog Procedural Interface. 67, 78

# Chapter 1 Introduction

### Contents

| 1.1 | Intro           | oduction to Soft Errors and System Reliability | <b>2</b> |  |  |  |  |

|-----|-----------------|------------------------------------------------|----------|--|--|--|--|

| 1.2 | $\mathbf{Soft}$ | Error Effects                                  | 3        |  |  |  |  |

|     | 1.2.1           | Sources of Natural Radiation                   | 3        |  |  |  |  |

|     |                 | 1.2.1.1 Alpha Particles                        | 3        |  |  |  |  |

|     |                 | 1.2.1.2 Cosmic Radiation                       | 4        |  |  |  |  |

|     |                 | 1.2.1.3 Thermal Neutrons                       | 4        |  |  |  |  |

|     | 1.2.2           | Brief History of Soft Error Effects            | 6        |  |  |  |  |

|     | 1.2.3           | Taxonomy of Radiation Effects                  | 7        |  |  |  |  |

|     |                 | 1.2.3.1 SEUs                                   | 7        |  |  |  |  |

|     |                 | 1.2.3.2 SETs                                   | 8        |  |  |  |  |

|     |                 | 1.2.3.3 SEFI                                   | 8        |  |  |  |  |

|     |                 | 1.2.3.4 SEL                                    | 8        |  |  |  |  |

|     |                 | 1.2.3.5 SEGR                                   | 8        |  |  |  |  |

|     |                 | 1.2.3.6 Clock Network Faults                   | 8        |  |  |  |  |

|     |                 | 1.2.3.7 Power Supplies                         | 9        |  |  |  |  |

|     |                 | 1.2.3.8 Dose Effects                           | 9        |  |  |  |  |

|     | 1.2.4           | Summary of Radiation Effects                   | 10       |  |  |  |  |

| 1.3 | Mas             | king Effects                                   | 10       |  |  |  |  |

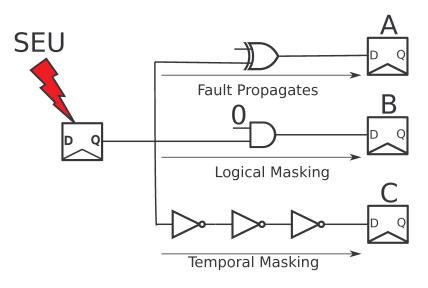

|     | 1.3.1           | Logical Masking                                | 10       |  |  |  |  |

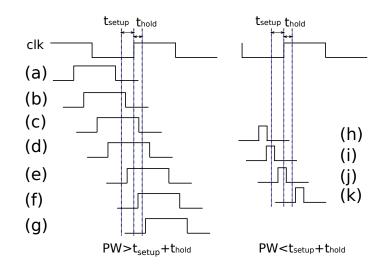

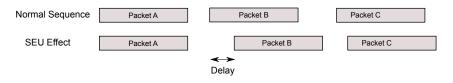

|     | 1.3.2           | Temporal De-Rating                             |          |  |  |  |  |

|     | 1.3.3           | Electrical Masking                             |          |  |  |  |  |

|     | 1.3.4           | Functional Masking 1                           |          |  |  |  |  |

|     | 1.3.5           | 5.5 Computing the Overall SER                  |          |  |  |  |  |

| 1.4 | Curi            | rent SER Trends                                | 15       |  |  |  |  |

|     | 1.4.1           | Combinatorial SER                              | 16       |  |  |  |  |

## 1.1 Introduction to Soft Errors and System Reliability

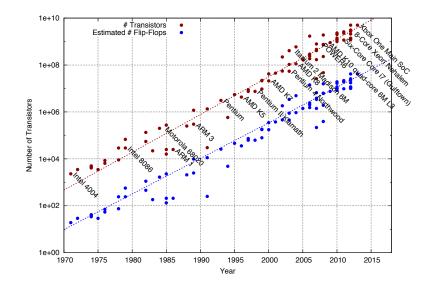

Electronic systems based on complex silicon devices play an increasingly critical role in our lives and it is extremely important that they function reliably. Faults induced by the effects of natural radiation are a significant source of failure and there exists a vast body of research devoted to analyzing and mitigating these effects. Much of the academic work has focussed on achieving accurate results when analyzing relatively small circuits. In industry, the size of circuits continues to grow and integrated circuits with over ten million flip-flops are very common.