# Framework pour une exécution efficace sur systèmes GPU et CPU+GPU

Jean-François Dollinger

#### ▶ To cite this version:

Jean-François Dollinger. Framework pour une exécution efficace sur systèmes GPU et CPU+GPU. Hardware Architecture [cs.AR]. Université de Strasbourg, 2015. English. NNT: 2015STRAD019. tel-01298088

# HAL Id: tel-01298088 https://theses.hal.science/tel-01298088

Submitted on 5 Apr 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Université de Strasbourg Université de Strasbourg

# École Doctorale Mathématiques, Sciences de l'Information et de l'Ingénieur

Laboratoire des sciences de l'ingénieur, de l'informatique et de l'imagerie (ICube)

# THÈSE présentée par :

## Jean-François DOLLINGER

Soutenue le : 01 juillet 2015

pour obtenir le grade de : Docteur de l'Université de Strasbourg

discipline/spécialité: Informatique

# A framework for efficient execution on GPU and CPU+GPU systems

Thèse dirigée par :

M. CLAUSS Philippe Professeur, Unistra, Strasbourg

Rapporteurs:

M. COHEN Albert Directeur de Recherche INRIA, ENS, Paris

M. BODIN François Professeur, IRISA, Rennes

Examinateurs:

Professeur, Universität des Saarlandes, Saar-

M. HACK Sebastian brücken, Allemagne

M. LOECHNER Vincent Maître de conférences, Unistra, Strasbourg

# Contents

| 1        | Rés  | umé e   | n Français                                       | 1       |

|----------|------|---------|--------------------------------------------------|---------|

|          | 1.1  | Introd  | luction                                          | 1       |

|          | 1.2  | Prédic  | etion et sélection adaptative de version de code | 1       |

|          |      | 1.2.1   | Introduction                                     | 1:      |

|          |      | 1.2.2   | Vue d'ensemble du framework                      | 1:      |

|          |      | 1.2.3   | Equité                                           | 14      |

|          |      | 1.2.4   | Prédiction                                       | 14      |

|          |      | 1.2.5   | Expérimentations                                 | 16      |

|          | 1.3  | Calcul  | l hétérogène : CPU vs GPU                        | 1'      |

|          |      | 1.3.1   | Introduction                                     | 1'      |

|          |      | 1.3.2   | Code CPU                                         | 18      |

|          |      | 1.3.3   | Code GPU                                         | 18      |

|          |      | 1.3.4   | Expérimentations                                 | 19      |

|          | 1.4  | Calcul  | l hétérogène : CPU + GPU                         | 19      |

|          |      | 1.4.1   | Introduction                                     | 19      |

|          |      | 1.4.2   | Génération de code                               | 20      |

|          |      | 1.4.3   | Répartition de charge                            | 2       |

|          |      | 1.4.4   | Multiversioning                                  | 23      |

|          |      | 1.4.5   | Consommation d'énergie                           | 23      |

|          |      | 1.4.6   | Experimentations                                 | 2       |

|          | 1.5  | Paralle | élisation spéculative                            | $2^{2}$ |

|          |      | 1.5.1   | Introduction                                     | $2^{2}$ |

|          |      | 1.5.2   | Problématique                                    | 2!      |

|          |      | 1.5.3   | Machine virtuelle                                | 2!      |

|          |      | 1.5.4   | Contributions                                    | 2!      |

| <b>2</b> | Inti | roducti | ion                                              | 27      |

|          | 2.1  | Conte   | xt                                               | 2       |

|          | 2.2  | Proble  | ematic                                           | 28      |

|          | 2.3  | Outlin  | ne                                               | 30      |

| 3        | Cor  | ıtext a | and related work                                 | 3       |

|          | 3.1  | Genes   | is of GPU computing                              | 32      |

|          | 3.2  | GPU a   | architecture                                     | 3       |

|          |      | 3.2.1   | CUDA                                             | 36      |

4 CONTENTS

|   |      | 3.2.2  | Processor space                   |        | <br> | <br> |   | <br>• | 36       |

|---|------|--------|-----------------------------------|--------|------|------|---|-------|----------|

|   |      | 3.2.3  | Software model                    |        | <br> | <br> |   |       | 38       |

|   |      | 3.2.4  | Memory space                      |        | <br> | <br> |   |       | 39       |

|   |      | 3.2.5  | OpenCL                            |        | <br> | <br> |   |       | 41       |

|   |      | 3.2.6  | CUDA vs OpenCL                    |        | <br> | <br> |   |       | 42       |

|   | 3.3  | Direct | ive languages                     |        | <br> | <br> |   |       | 42       |

|   | 3.4  | Appro  | aches to performance modelling    |        | <br> | <br> |   |       | 43       |

|   | 3.5  | Optim  | nization techniques               |        | <br> | <br> |   |       | 44       |

|   |      | 3.5.1  | Hand-tuning vs. Automatic optimis | zation | <br> | <br> |   |       | 44       |

|   |      | 3.5.2  | Static methods                    |        | <br> | <br> |   |       | 45       |

|   |      | 3.5.3  | Hybrid methods                    |        | <br> | <br> |   |       | 46       |

|   |      | 3.5.4  | Dynamic methods                   |        | <br> | <br> |   |       | 48       |

|   |      | 3.5.5  | Conclusion                        |        | <br> | <br> |   |       | 48       |

|   | 3.6  | Hetero | ogeneous computing                |        | <br> | <br> |   |       | 49       |

|   |      | 3.6.1  | Static partitioning               |        | <br> | <br> |   |       | 50       |

|   |      | 3.6.2  | Hybrid partitioning               |        | <br> | <br> |   |       | 51       |

|   |      | 3.6.3  | Dynamic partitioning              |        | <br> | <br> |   |       | 51       |

|   |      | 3.6.4  | Conclusion                        |        | <br> | <br> |   |       | 52       |

|   | 3.7  | Polyto | ppe Model                         |        |      |      |   |       | 53       |

|   |      | 3.7.1  | SCoP                              |        | <br> | <br> |   |       | 54       |

|   |      | 3.7.2  | Polyhedral model illustration     |        |      |      |   |       | 56       |

|   |      | 3.7.3  | Access functions                  |        | <br> | <br> |   |       | 56       |

|   |      | 3.7.4  | Scattering matrix                 |        |      |      |   |       | 58       |

|   |      | 3.7.5  | Dependence                        |        |      |      |   |       | 61       |

|   |      | 3.7.6  | Transformations                   |        |      |      |   |       | 62       |

|   |      | 3.7.7  | Integer points counting           |        |      |      |   |       | 63       |

|   | 3.8  |        | G                                 |        |      |      |   |       | 64       |

|   | 3.9  |        | O                                 |        |      |      |   |       | 64       |

|   |      | Par4A  |                                   |        |      |      |   |       | 65       |

|   |      |        | eam                               |        |      |      |   |       | 65       |

|   |      |        |                                   |        |      |      |   |       |          |

|   |      |        | on compilers                      |        |      |      |   |       | 66       |

|   |      |        | ies                               |        |      |      |   |       | 66       |

|   | 3.15 | Specul | lative parallelization            |        | <br> | <br> |   | <br>• | 67       |

| 4 | Cod  | o wore | ioning and profiling for GPU      |        |      |      |   |       | 69       |

| 4 | 4.1  |        | uction                            |        |      |      |   |       | 69       |

|   | 4.2  |        | ed Work                           |        |      |      |   |       | 71       |

|   | 4.3  |        | work overview                     |        |      |      |   |       | 73       |

|   | 4.4  |        | ng                                |        |      |      |   |       | 75<br>75 |

|   | 7.7  | 4.4.1  | Equity                            |        |      |      |   |       | 75       |

|   |      | 4.4.2  | Static performance factors        |        |      |      |   |       | 76       |

|   |      | 4.4.3  | Dynamic performance factors       |        |      |      |   |       | 76       |

|   |      | 4.4.4  | CUDA grid size evaluation         |        |      |      |   |       | 86       |

|   | 4.5  |        | me prediction                     |        |      |      |   |       | 88       |

|   |      |        | r · · · · · · · · · · · ·         |        | <br> | <br> | • | <br>• | 00       |

CONTENTS 5

|    |                      | 4.5.1 Prediction                                        | 88  |

|----|----------------------|---------------------------------------------------------|-----|

|    | 4.6                  | Experiments                                             | 90  |

|    |                      | 4.6.1 Testbed                                           | 90  |

|    |                      | 4.6.2 Prediction accuracy                               | 93  |

|    | 4.7                  | Perspectives and conclusion                             | 94  |

| 5  | Het                  | erogeneous computing                                    | 95  |

|    | 5.1                  | CPU vs GPU execution: a dynamic approach                | 96  |

|    |                      | 5.1.1 Introduction                                      | 96  |

|    |                      | 5.1.2 CPU vs GPU attempt                                | 97  |

|    |                      | 5.1.3 Early termination of CPU and GPU codes            | 99  |

|    |                      | 5.1.4 Experimentations                                  | 102 |

|    |                      | 5.1.5 Perspective and limitations                       | 105 |

|    | 5.2                  | CPU vs GPU execution: a hybrid approach                 | 106 |

|    | 5.3                  | CPU + GPU joint execution                               | 108 |

|    |                      | 5.3.1 Introduction                                      | 108 |

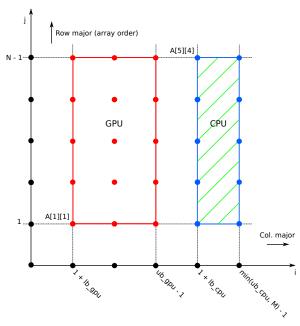

|    |                      | 5.3.2 Code generation                                   | 111 |

|    |                      | 5.3.3 CPU+GPU Runtime                                   | 113 |

|    |                      | 5.3.4 Evaluation                                        | 117 |

|    |                      | 5.3.5 Multiversioning                                   | 120 |

|    |                      | 5.3.6 Power-guided scheduling                           | 131 |

|    |                      | 5.3.7 Perspectives and conclusion                       | 134 |

| 6  | $\operatorname{Thr}$ | read Level Speculation                                  | 139 |

|    | 6.1                  | CPU speculative execution                               | 139 |

|    |                      | 6.1.1 Introduction                                      | 139 |

|    | 6.2                  | Overview of our system                                  | 141 |

|    | 6.3                  | Binary skeletons                                        | 144 |

|    |                      | 6.3.1 Guarding code                                     | 146 |

|    |                      | 6.3.2 Initialization code                               | 146 |

|    |                      | 6.3.3 Verification code for speculative parallelization | 147 |

|    | 6.4                  | Memory backup                                           | 148 |

|    | 6.5                  | Experimental results                                    | 150 |

|    | 6.6                  | Memory backup extensions                                | 155 |

|    | 6.7                  | GPU extension proposal                                  | 155 |

|    |                      | 6.7.1 Verification code                                 | 155 |

|    |                      | 6.7.2 Memory address space                              | 156 |

|    |                      | 6.7.3 Finding adequate block size                       | 157 |

|    | <i>a</i> o           | 6.7.4 CPU + GPU execution                               | 157 |

|    | 6.8                  | Conclusions and perspectives                            | 158 |

| 7  | Con                  |                                                         | 161 |

|    | 7.1                  | Contributions                                           | 161 |

|    | 7.2                  | Perspectives                                            | 163 |

| Bi | ibliog               | graphy                                                  | 165 |

6 CONTENTS

# List of Figures

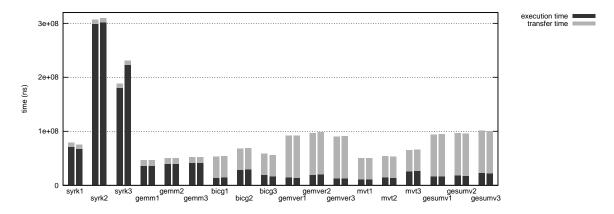

| 1.2 | Comparaison entre temps d'exécution prédit (barre gauche) et effectif (barre droite) sur PolyBench avec le jeu de données standard sur GTX 590                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

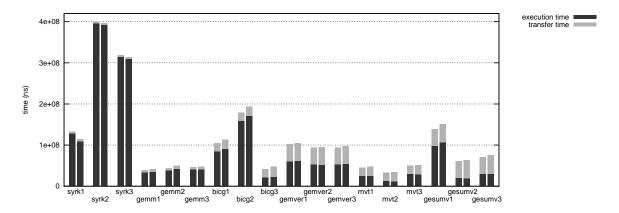

| 1.3 | Comparaison entre temps d'exécution prédit (barre gauche) et effectif (barre droite) sur PolyBench avec le jeu de données standard sur GTX 680                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17 |

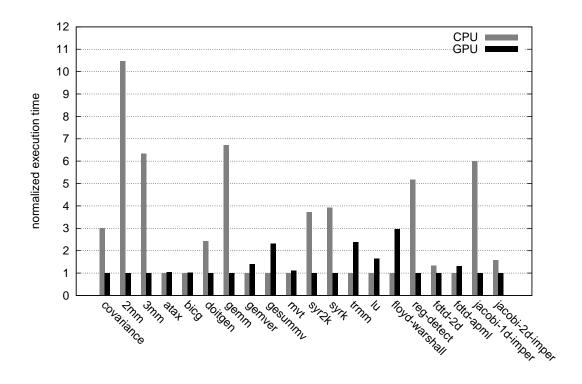

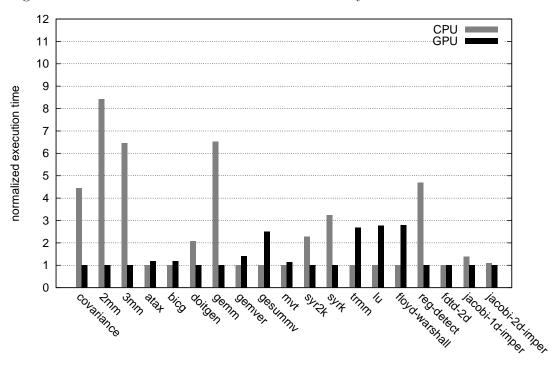

| 1.4 | Temps d'exécution normalisé pour le jeu de données standard sur Poly-Bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20 |

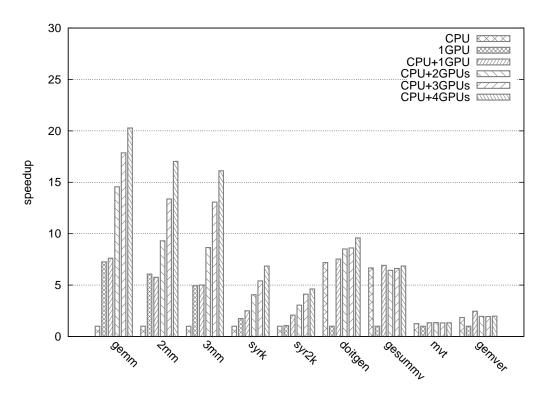

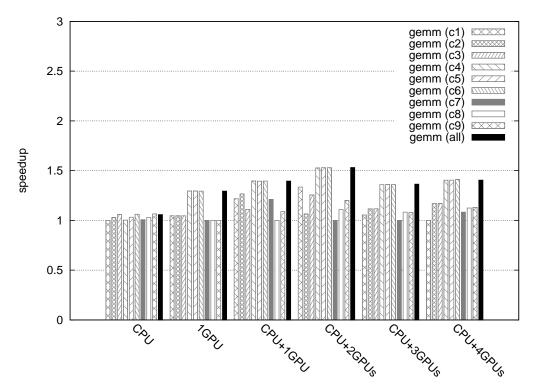

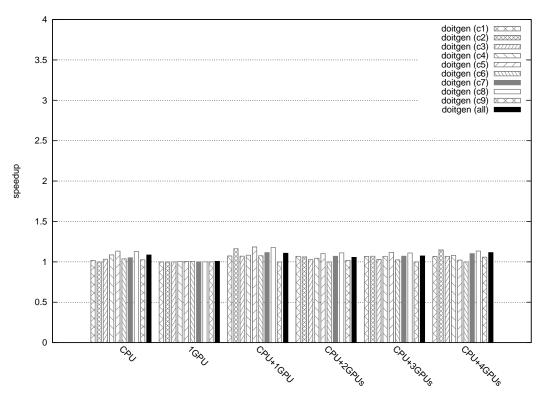

| 1.5 | Speedup to execution time on CPU or GPU alone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 |

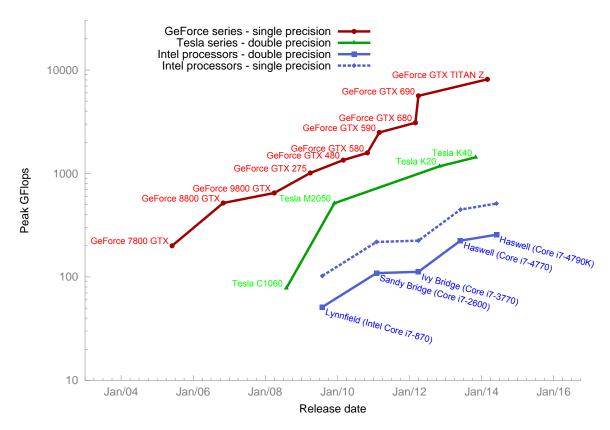

| 3.1 | Recomputed theoretical peak performance trends between Intel CPUs and Nvidia GPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32 |

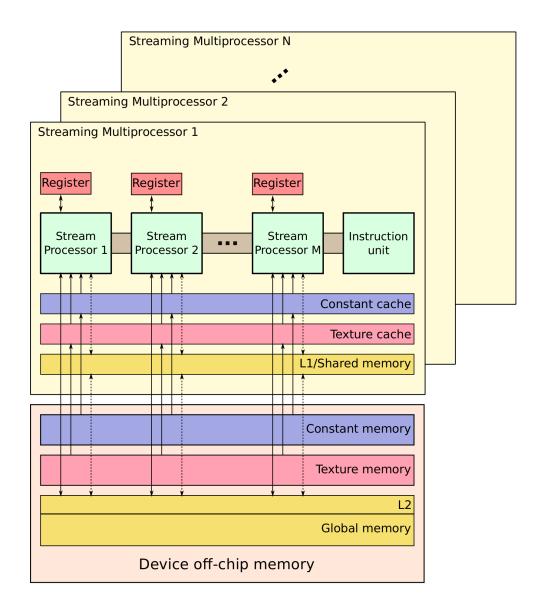

| 3.2 | Nvidia discrete graphics card architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35 |

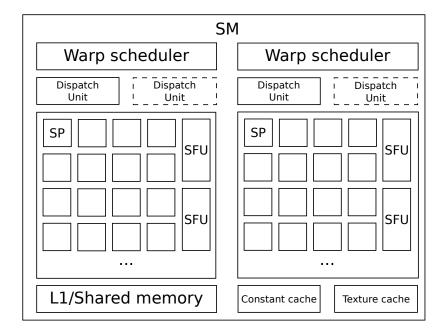

| 3.3 | Insight of a Streaming Multiprocessor (SM) organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37 |

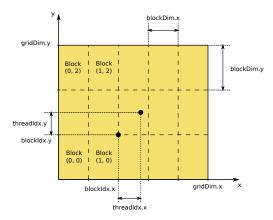

| 3.4 | CUDA execution model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38 |

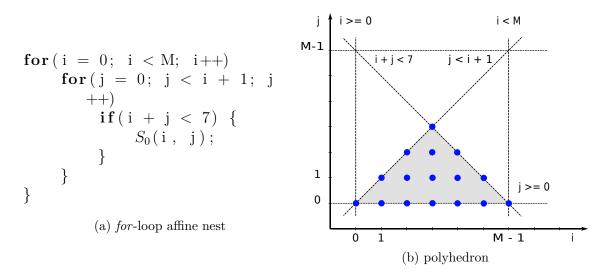

| 3.5 | Illustration of a loop nest and its associated polyhedron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56 |

| 3.6 | Constraint inequalities and associated constraint matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56 |

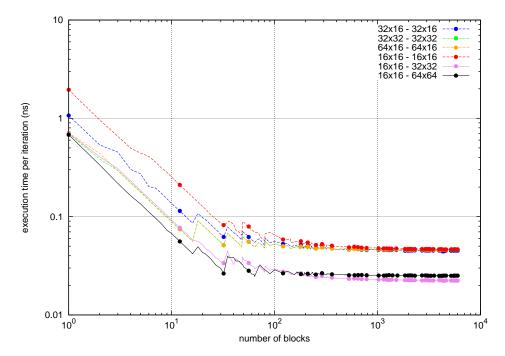

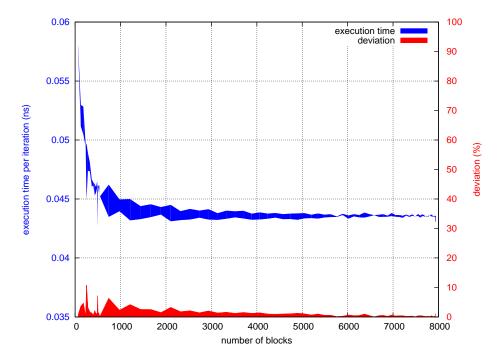

| 4.1 | Comparison of actual execution time per iteration for several block - tile sizes for $gemm \ (matrix \ size = 1024 * 1024). \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70 |

| 4.2 | Example of a CPU ranking table and prediction for gemm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72 |

| 4.3 | Global framework workflow overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73 |

| 4.4 | Comparison (top) and deviation (bottom) of actual execution time per iteration to empirically demonstrate commutativity of the block dimensions for same. Plank/Tile sires 22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 × 16/22 | 75 |

| 1 E | sions for gemm, $Block/Tile$ size: $32 \times 16/32 \times 16$ , $NK = 2000$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75 |

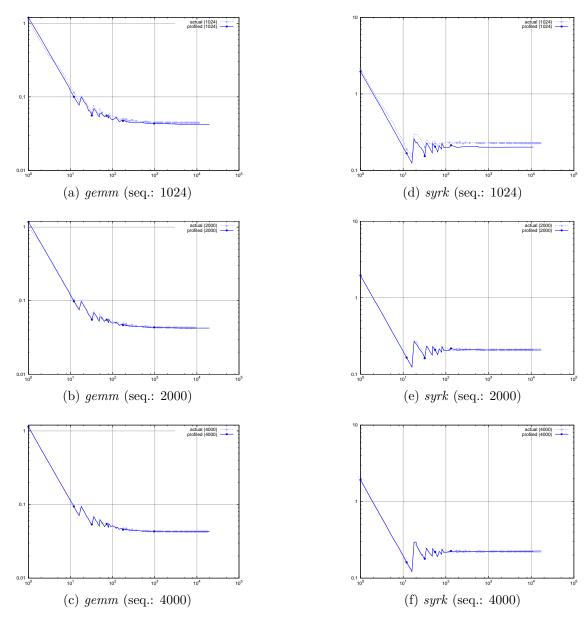

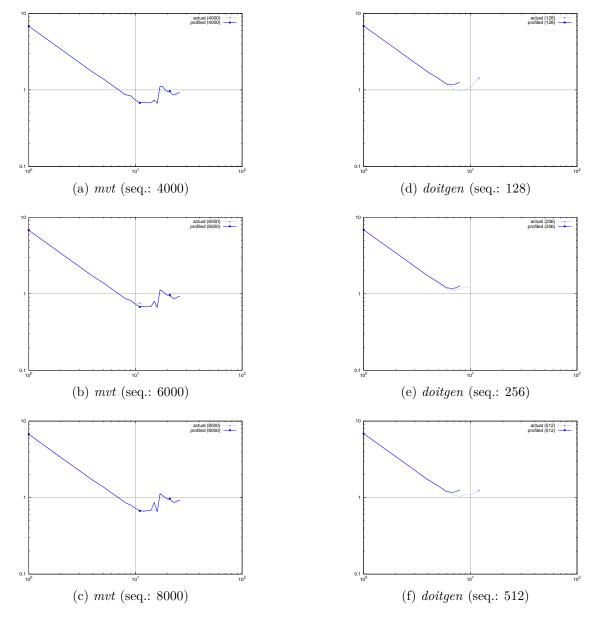

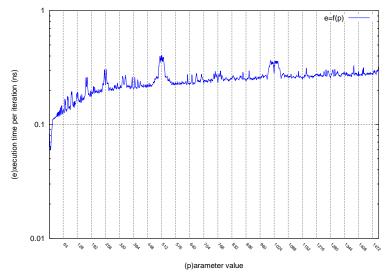

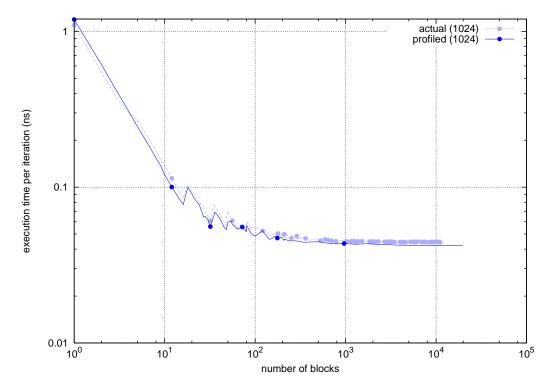

| 4.5 | Comparison between profiled and measured execution times per iteration (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79 |

| 4.6 | Comparison between profiled and effective execution times per iteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10 |

| 1.0 | (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80 |

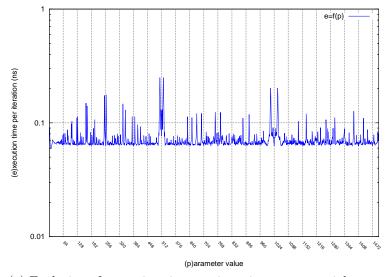

| 4.7 | Sequential parameters influence for different tile configurations for <i>syrk</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81 |

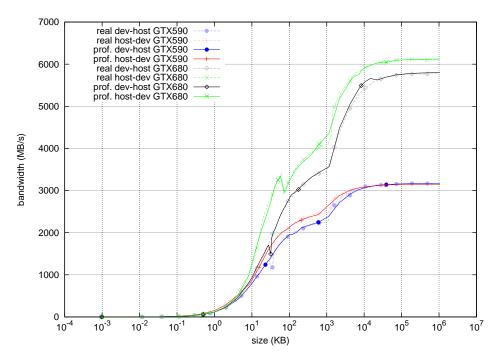

| 4.8 | Bandwidth evaluation on Asus P8P67-Pro motherboard with Asus GTX 590 GPU and Asus P8P67-Deluxe with Nvidia GTX 680 GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82 |

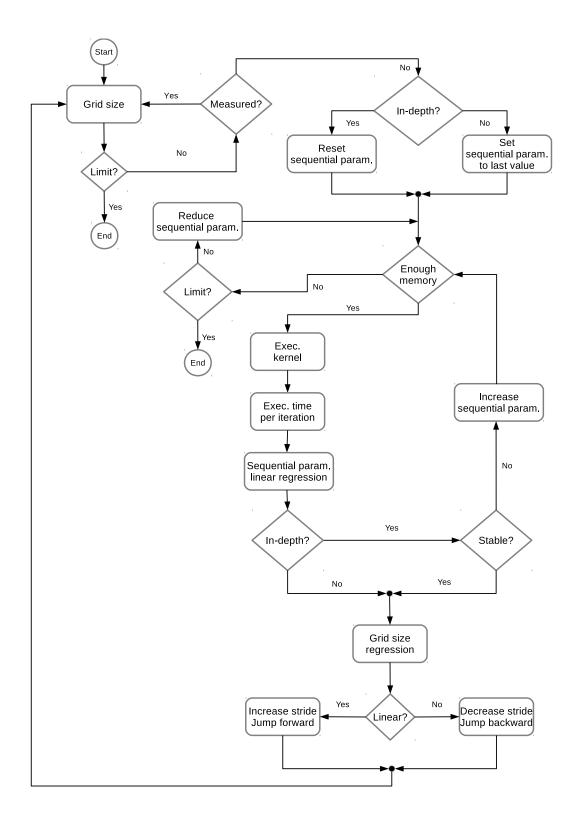

| 4 Q | Profiling flow chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83 |

8 LIST OF FIGURES

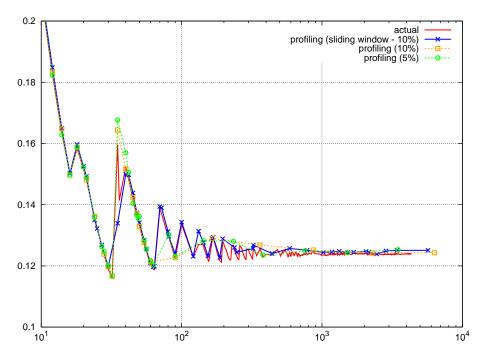

| 4.10 | Demonstration of the capability of our profiler to map the actual execution time per iteration measurements (solid) for gemm, Block/Tile size: |       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | $16 \times 16/128 \times 128$ , $NK = 2000$ . The profiler makes use of a paramet-                                                             |       |

|      | ric sliding window to perform measurements in a wider spectrum (solid,                                                                         |       |

|      | cross). This configuration is compared to a single point based decision,                                                                       |       |

|      | with a maximum allowed deviation of $10\%$ (dashed, square) and $5\%$                                                                          |       |

|      | $(dashed, circle). \dots \dots$          | 85    |

|      | A code version (a) and its associated prediction code (b)                                                                                      | 89    |

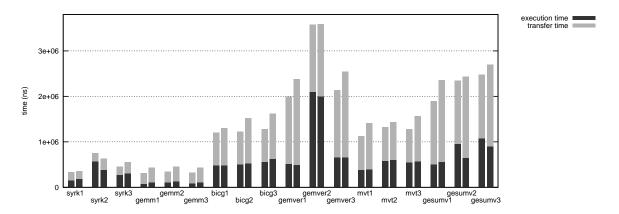

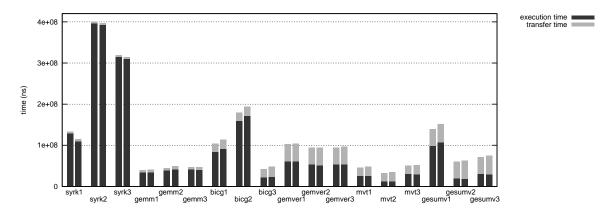

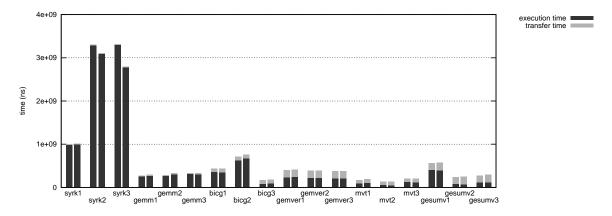

| 4.12 | Comparison between prediction (left bar) and real (right bar) execution times on PolyBench with small dataset on GTX590                        | 90    |

| 4.13 | Comparison between prediction (left bar) and real (right bar) execution                                                                        |       |

|      | times on PolyBench with standard dataset on GTX590                                                                                             | 91    |

| 4.14 | Comparison between prediction (left bar) and real (right bar) execution times on PolyBench with large dataset on GTX590                        | 91    |

| 4.15 | Comparison between prediction (left bar) and real (right bar) execution times on PolyBench with small dataset on GTX680                        | 92    |

| 4 16 | Comparison between prediction (left bar) and real (right bar) execution                                                                        | 92    |

| 1.10 | times on PolyBench with standard dataset on GTX680                                                                                             | 92    |

| 4.17 | Comparison between prediction (left bar) and real (right bar) execution                                                                        | 02    |

| 1.11 | times on PolyBench with large dataset on GTX680                                                                                                | 92    |

| 5.1  | GPU kernel termination algorithm with thread election                                                                                          | 97    |

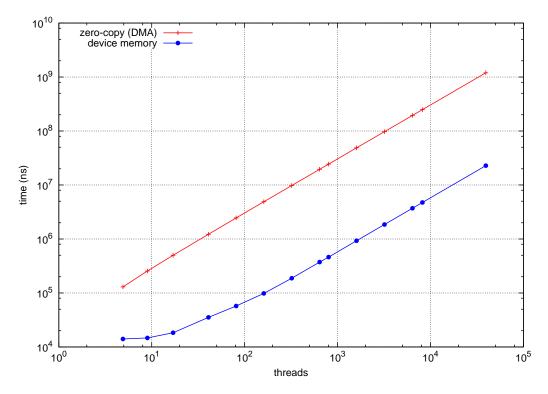

| 5.2  | Comparison of execution time between zero-copy (accessing central me-                                                                          |       |

|      | mory) and memcpy (accessing device off-chip memory) techniques when                                                                            |       |

|      | varying the number of threads                                                                                                                  | 101   |

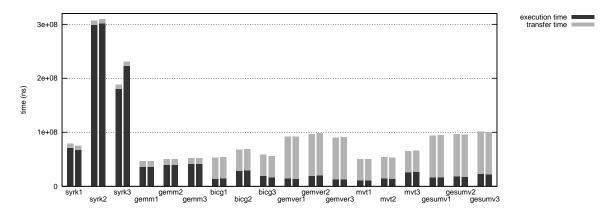

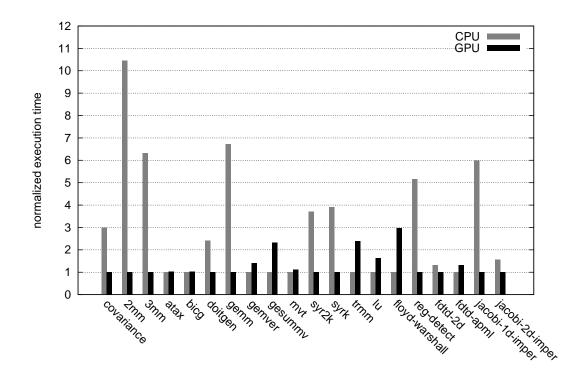

| 5.3  | Normalized execution time for the PolyBench standard dataset                                                                                   | 103   |

| 5.4  | Normalized execution time for the PolyBench large dataset                                                                                      | 103   |

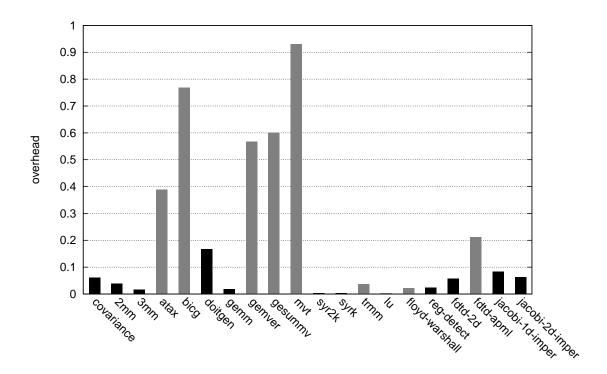

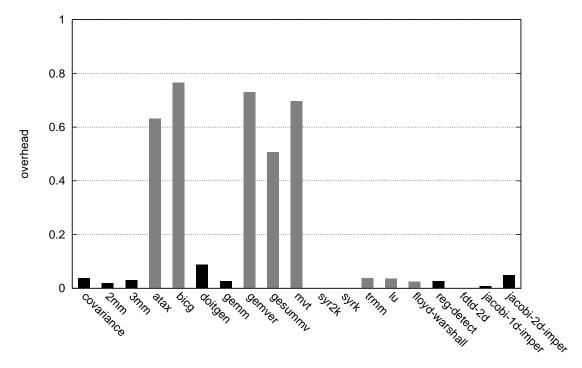

| 5.5  | Overhead to the single-PU execution time for the PolyBench standard                                                                            |       |

|      | dataset                                                                                                                                        | 104   |

| 5.6  | Overhead to the single-PU execution time for the PolyBench large dataset                                                                       | t.104 |

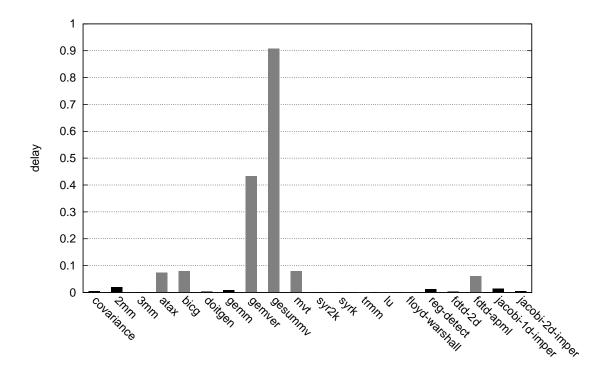

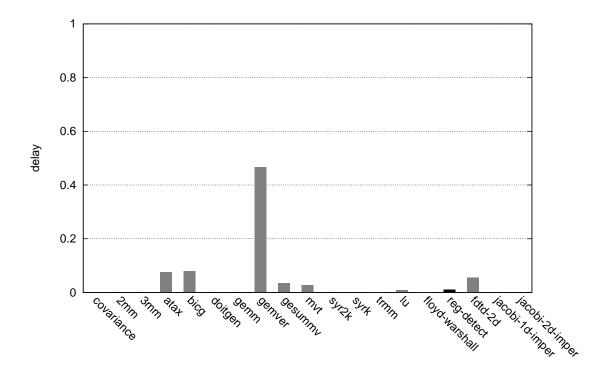

| 5.7  | Delay to shut the computation down on the PU that lost the race, for                                                                           |       |

|      | standard dataset                                                                                                                               | 105   |

| 5.8  | Delay to shut the computation down on the PU that lost the race, for                                                                           |       |

|      | large dataset.                                                                                                                                 | 106   |

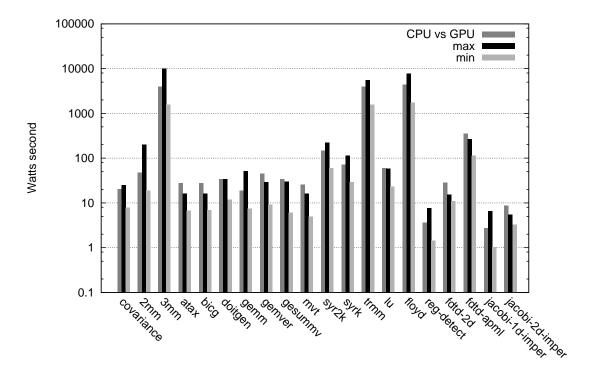

| 5.9  | Energy consumption resulting from simultaneously running CPU and                                                                               |       |

|      | GPU codes, for standard dataset. Energy consumption is expressed                                                                               |       |

|      | in Watts second and originates from the product of maximal device                                                                              |       |

|      | consumption (measured for a reference code at wall socket) by execution                                                                        |       |

|      | time                                                                                                                                           | 107   |

| 5.10 | Evaluation of the execution time per iteration for gemm for various block                                                                      |       |

|      | sizes and sequential parameter fixed to 1024                                                                                                   | 110   |

| 5.11 | Illustration of the mechanisms required for communication                                                                                      | 112   |

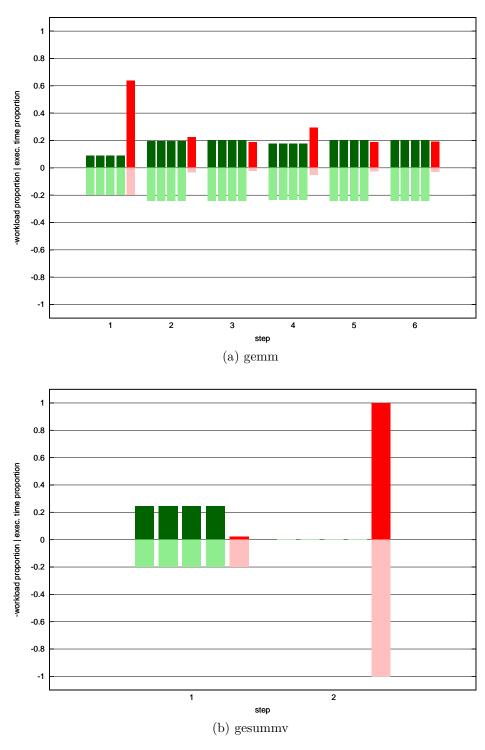

|      | Scheduler algorithm steps for <i>gemm</i> and <i>gesummv</i> . GPU is eliminated                                                               |       |

|      | after first step in gesummv                                                                                                                    | 116   |

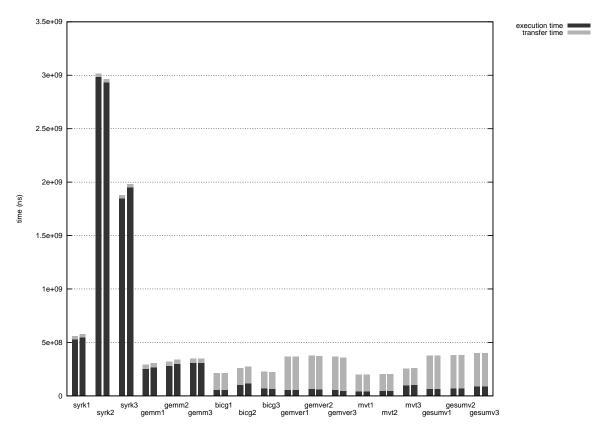

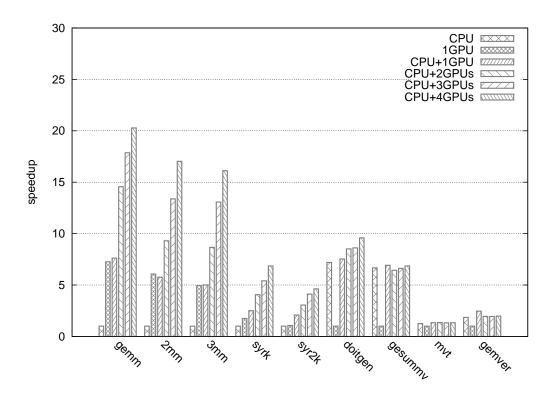

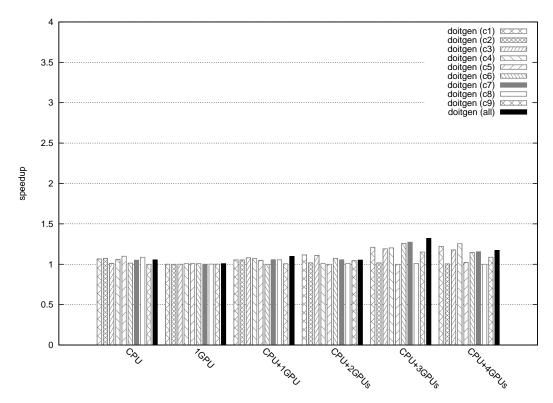

| 5.13 | Speedup to execution time on CPU or GPU alone                                                                                                  | 119   |

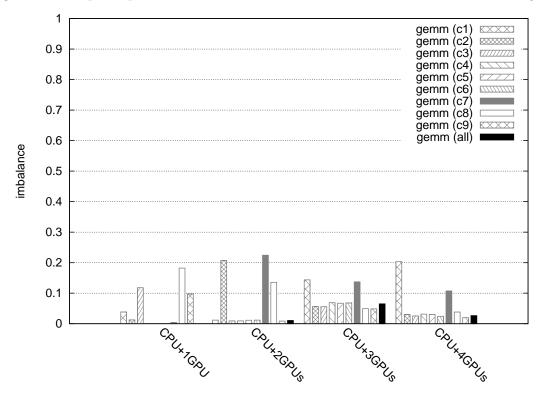

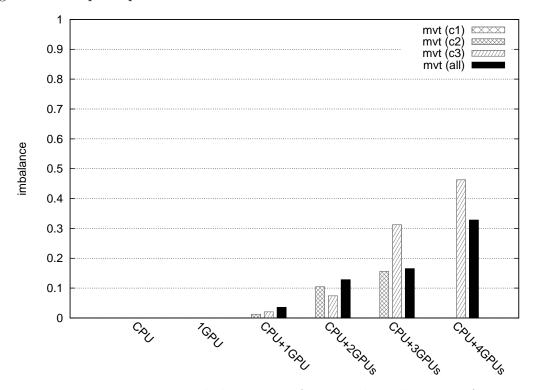

|      | Execution time imbalance ratio for several combinations of PUs                                                                                 | 119   |

LIST OF FIGURES 9

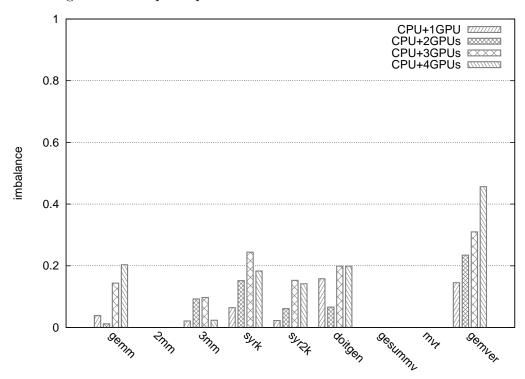

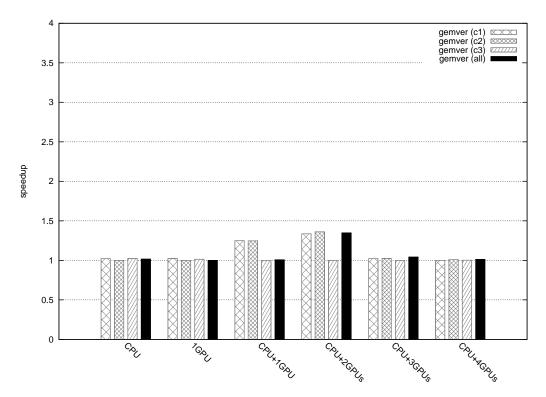

|      | Speedup to execution time of slowest code version combination for gemm            | .121    |

|------|-----------------------------------------------------------------------------------|---------|

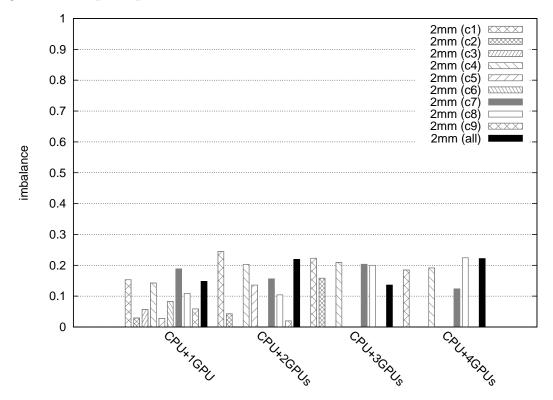

| 5.16 | Execution time imbalance ratio for several combination of code versions           |         |

|      | for <i>gemm.</i>                                                                  | 121     |

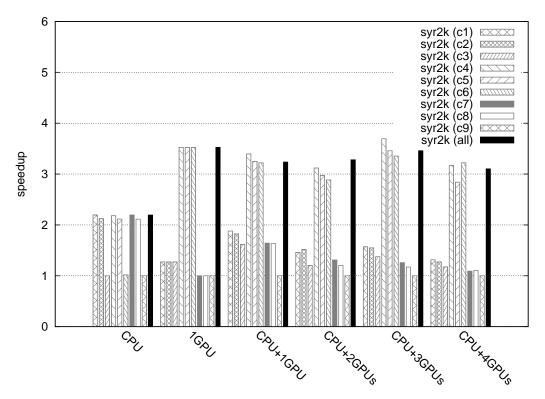

|      | Speedup to execution time of slowest code version combination for $syr2k$ .       | 122     |

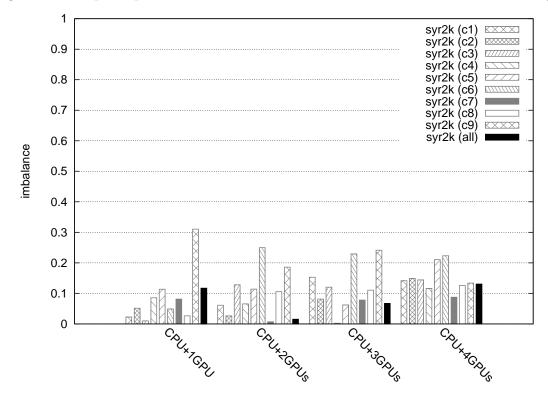

| 5.18 | Execution time imbalance ratio for several combination of code versions           |         |

|      | for $syr2k$                                                                       | 122     |

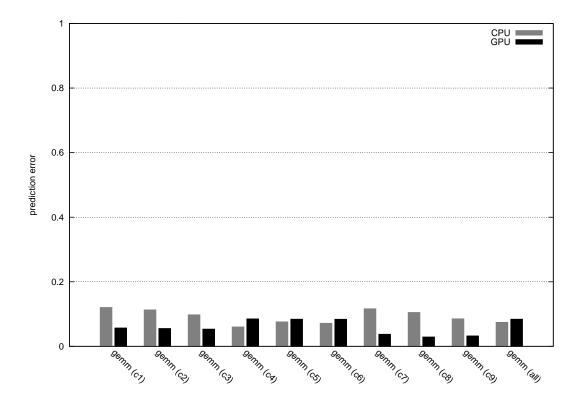

| 5.19 | Average prediction error ratio of CPU and GPU for gemm                            | 123     |

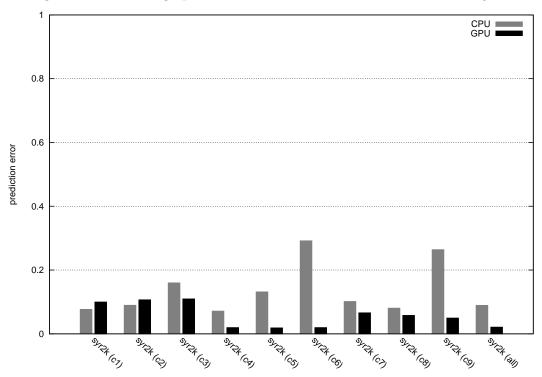

| 5.20 | Average prediction error ratio of CPU and GPU for syr2k                           | 123     |

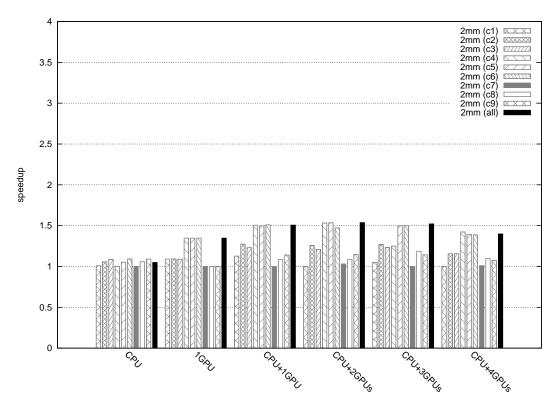

| 5.21 | Speedup to execution time of slowest code version combination for 2mm.            | 124     |

|      | Average prediction error ratio of CPU and GPU for 2mm                             | 124     |

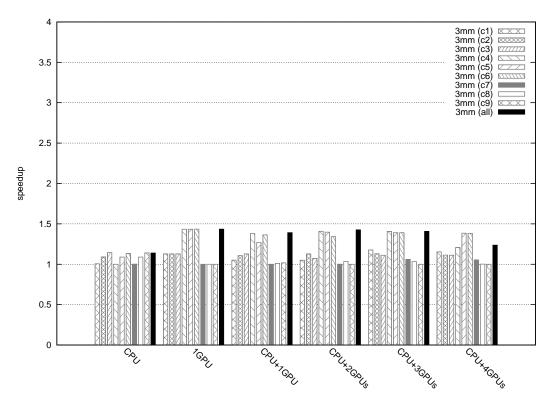

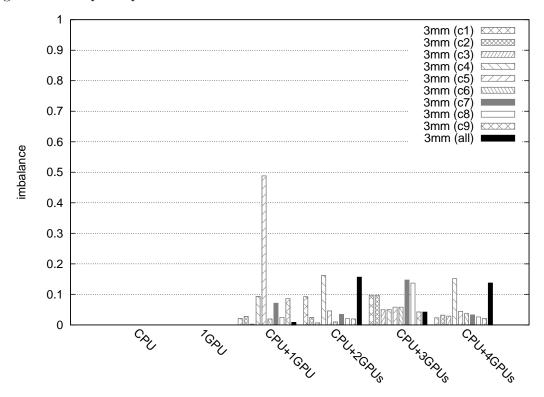

| 5.23 | Speedup to execution time of slowest code version combination for 3mm.            | 125     |

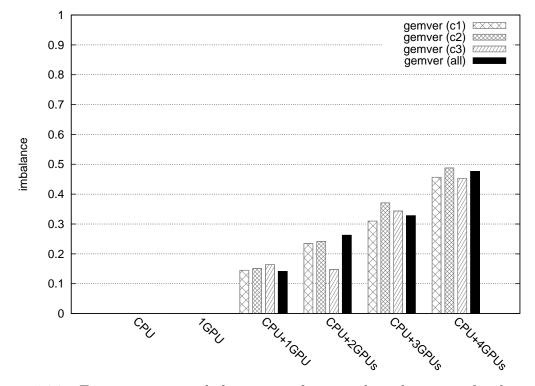

|      | Execution time imbalance ratio for several combination of code versions           |         |

|      | for <i>3mm</i>                                                                    | 125     |

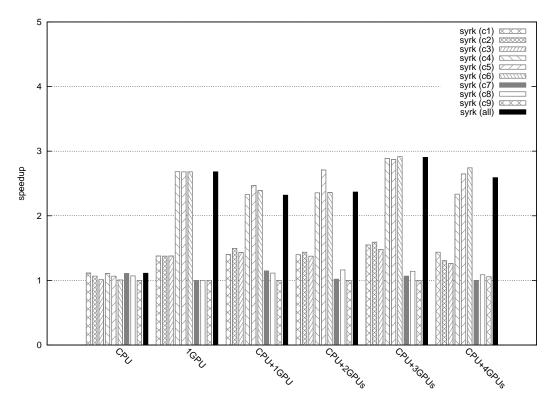

| 5.25 | Speedup to execution time of slowest code version combination for <i>syrk</i> .   | 126     |

|      | Execution time imbalance ratio for several combination of code versions           |         |

| 0.20 | for $syrk$                                                                        | 126     |

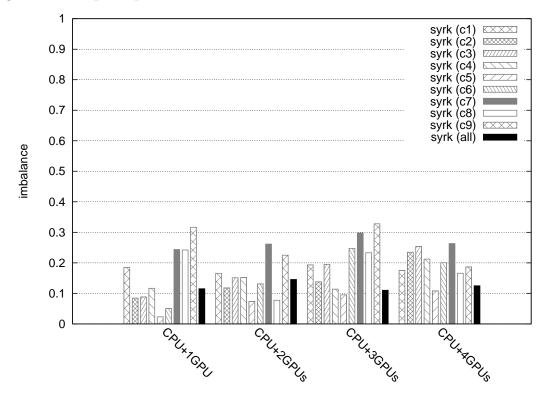

| 5 27 | Speedup to execution time of slowest code version combination for <i>doitgen</i>  |         |

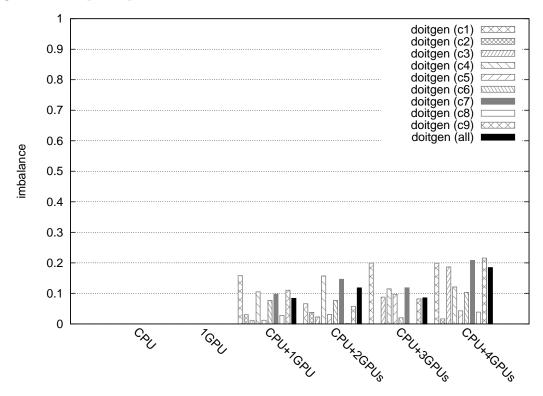

|      | Execution time imbalance ratio for several combination of code versions           | . 1 2 1 |

| 0.20 | for doitgen.                                                                      | 127     |

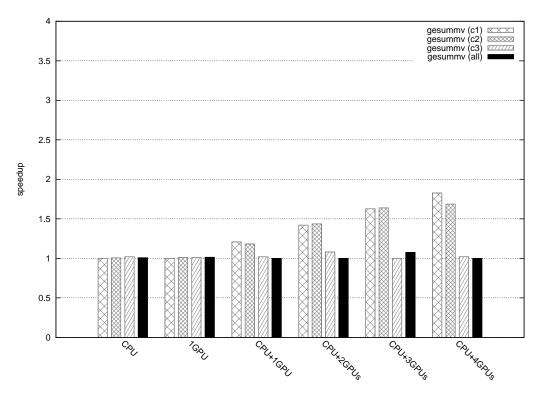

| 5 20 | Speedup to execution time of slowest code version combination for ge-             | 141     |

| 0.23 | summv.                                                                            | 128     |

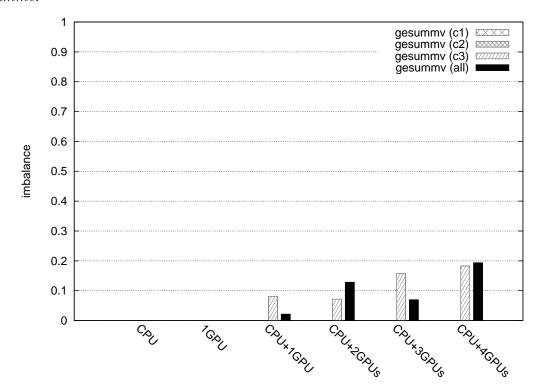

| 5.30 |                                                                                   | 120     |

| 5.50 |                                                                                   | 128     |

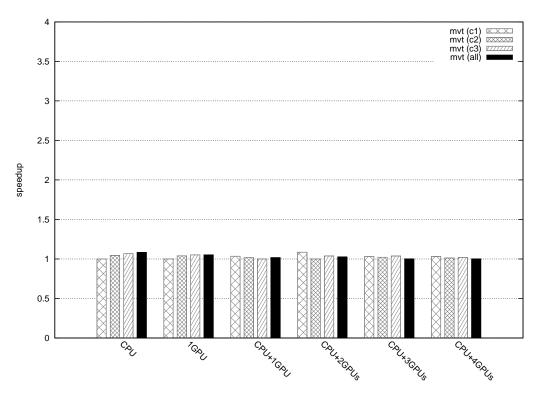

| 5 21 | for gesummv                                                                       | 129     |

|      | Execution time imbalance ratio for several combination of code versions           | 125     |

| ე.ე∠ |                                                                                   | 129     |

| E 22 |                                                                                   |         |

|      | Speedup to execution time of slowest code version combination for <i>gemver</i> . | . 10(   |

| 0.54 | Execution time imbalance ratio for several combination of code versions           | 190     |

| F 9F | for gemver.                                                                       | 130     |

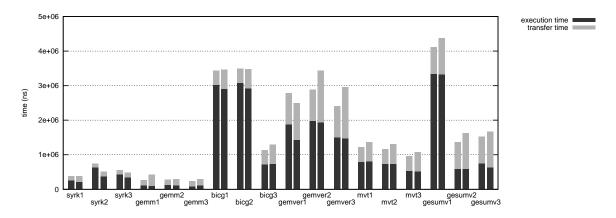

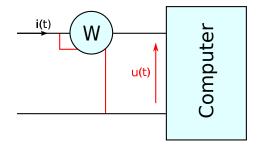

|      | Scheme of the measurement platform circuit with Wattmeter                         | 131     |

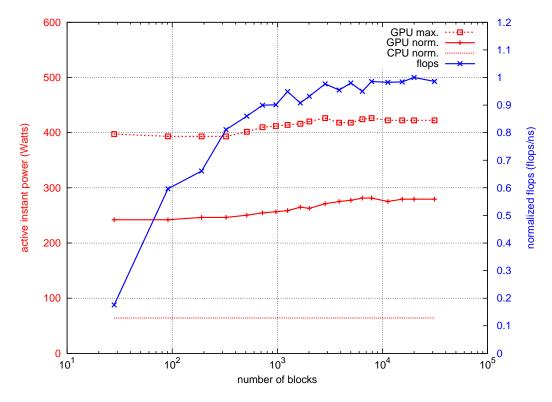

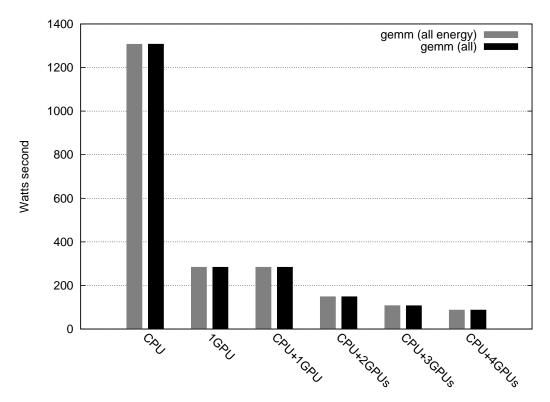

|      | Instant power consumption (y) and normalized flops (y2) for gemm                  | 133     |

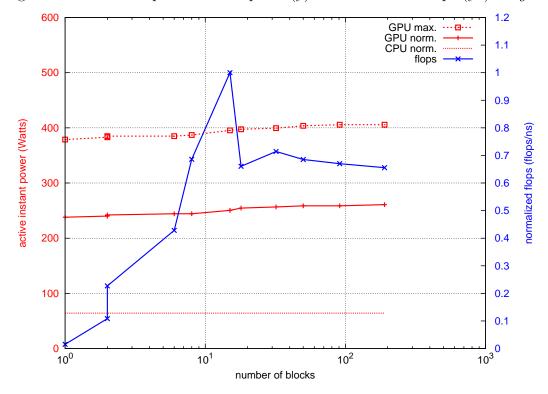

|      | Instant power consumption (y) and normalized flops (y2) for doitgen.              | 133     |

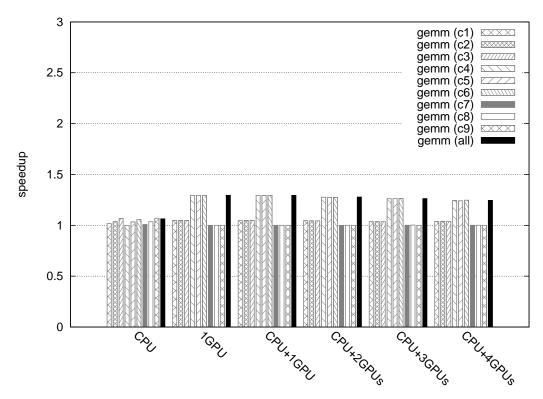

| 5.38 | Speedup to execution time of slowest code version combination for gemm            | 105     |

| - 00 | with energy-enabled scheduler                                                     | 135     |

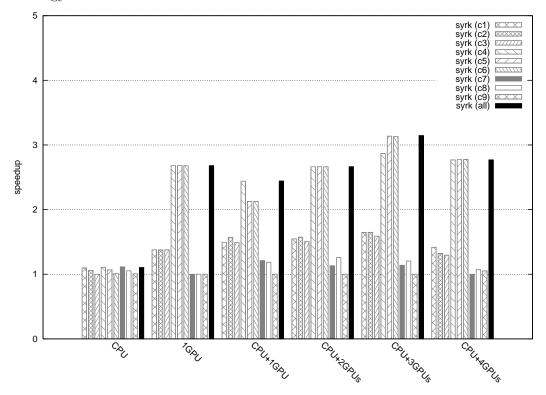

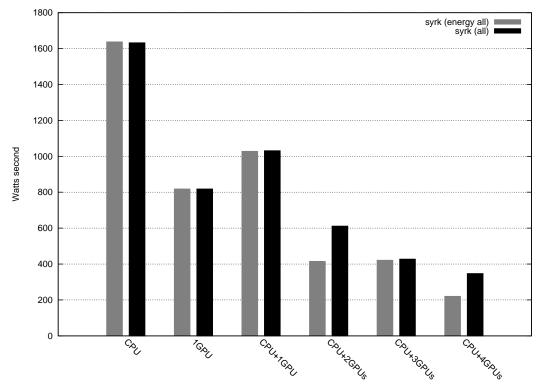

| 5.39 | Speedup to execution time of slowest code version combination for syrk            |         |

|      | with energy-enabled scheduler                                                     | 135     |

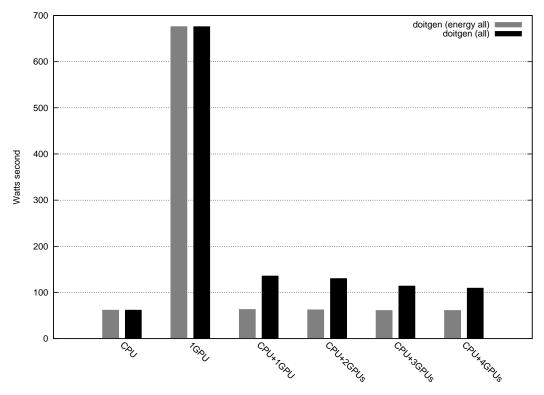

| 5.40 | Speedup to execution time of slowest code version combination for doit-           |         |

|      | gen with energy-enabled scheduler                                                 | 136     |

| 5.41 | Comparison of energy consumption for <i>gemm</i> between energy enabled           |         |

|      | scheduler (left bar) and iteration count based elimination (right bar)            | 137     |

| 5.42 | Comparison of energy consumption for syrk between energy enabled                  |         |

|      | scheduler (left bar) and iteration count based elimination (right bar)            | 137     |

| 5.43 | Comparison of energy consumption for <i>doitgen</i> between energy enabled        |         |

|      | scheduler (left bar) and iteration count based elimination (right bar)            | 138     |

| 6 1  | Static-dynamic collaborative framework                                            | 1 16    |

| 6.1  | Static-dynamic conaborative framework                                             | 142     |

10 LIST OF FIGURES

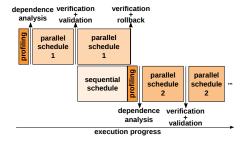

| 6.2 | The chunking mechanism                                                 | 143 |

|-----|------------------------------------------------------------------------|-----|

| 6.3 | Alternate execution of different versions during one loop nest's run   | 143 |

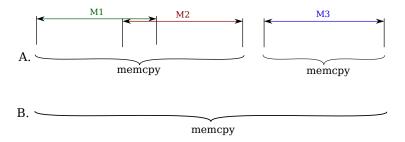

| 6.4 | memcpy merging strategy                                                | 149 |

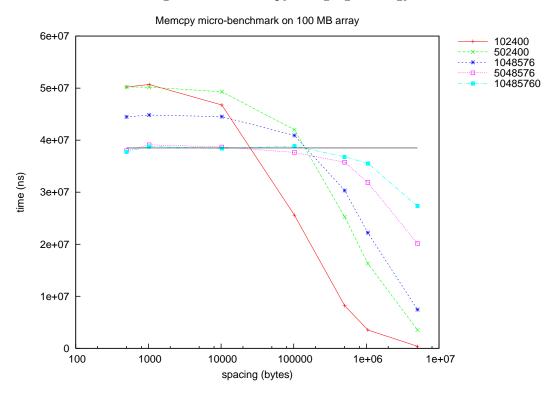

| 6.5 | memcpy behaviour on multiple spacing configurations, for different ch- |     |

|     | unk sizes                                                              | 149 |

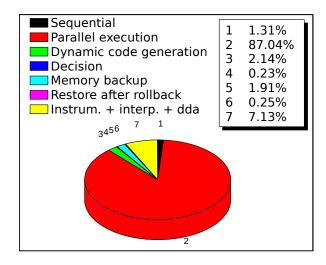

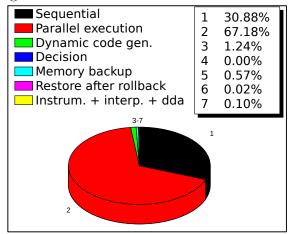

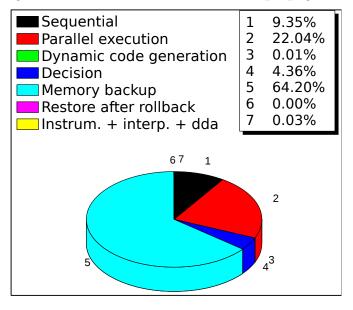

| 6.6 | Runtime overhead of covariance                                         | 152 |

| 6.7 | Runtime overhead of backpropagation                                    | 152 |

| 6.8 | Runtime overhead of adi                                                | 152 |

# Chapitre 1

# Résumé en Français

### 1.1 Introduction

Le rapide déploiement d'applications graphiques fin des années 80 et le surcoût occasionné en terme de consommation de ressources a poussé à l'utilisation de coprocesseurs spécialisés appelés Graphics Processing Unit (GPU). A leur origine les GPUs présentent une architecture peu flexible n'autorisant qu'un certain spectre d'applications; seul un nombre restreint d'opérations précâblées étaient exposées aux programmeurs. Avec l'arrivée des langages CUDA en 2007 et OpenCL en 2009, le modèle de programmation s'est affranchi des contraintes de programmabilité archaïques inhérentes aux GPUs d'ancienne génération. Aujourd'hui, les GPUs se révèlent être une alternative viable pour des traitements autres que graphiques, en particulier pour combler l'insatiable demande en performance de la communauté scientifique.

Malgré les efforts de simplification engagés par les fournisseurs de puces graphiques, le portage d'un code pour une exécution efficace sur GPU n'est pas chose aisée. Un programmeur doit non seulement se familiariser avec le modèle de programmation, mais également avoir une connaissance fine de l'architecture et transformer le code pour utiliser le GPU à son plein potentiel.

Les nids de boucles concentrent la majorité du temps d'exécution d'un programme. Le modèle polyédrique est une représentation mathématique d'un nid de boucles affine paramétré, soit un nid de boucles dont les accès mémoire et les bornes de boucles sont exprimés via des combinaisons affines des paramètres et des itérateurs des boucles englobantes. Ce cadre théorique autorise l'application de transformations de code automatiques (e.g. inversion de boucles, tuilage, skewing, etc.) tout en préservant la sémantique initiale. Mes travaux de thèse ainsi que les outils utilisés s'appuient principalement sur le modèle polyédrique.

Des outils de parallélisation automatiques polyédriques tels que PLUTO [25], C-to-CUDA [15], PPCG [145], R-Stream [131], Par4All [7, 9], sont capables de générer du code optimisé pour une architecture cible. Ces outils manipulent des SCoP (Static Control Parts) renfermant une succession de nids de boucles affines. Le processus typique de compilation, du fait de sa nature statique, réduit le champ des opportunités des compilateurs. A défaut de générer du code performant dans toutes les situations, les performances restent généralement moyennes car issues d'heuristiques : il est néces-

saire de considérer les paramètres dynamiques et l'ensemble des ressources de calcul d'un système.

Les performances d'une version de code peuvent varier en fonction du contexte d'exécution; elles sont fonction des paramètres de nid de boucles. Pour répondre à cette problématique, le "multiversioning" consiste à produire plusieurs versions de code sémantiquement équivalentes au programme original. La meilleure des versions doit être sélectionnée à l'aide d'une prédiction du temps d'exécution sur GPU.

Pour tirer les meilleures performances des systèmes hétérogènes, c'est à dire de systèmes hébergeant des processeurs aux architectures différentes, il est nécessaire de déterminer les affinités entre les codes et les Unités de Calcul (processeur central, GPU, accélérateurs, etc.), appelées UC dans la suite du texte. Nous présentons une méthode dynamique capable de sélectionner l'architecture cible la plus adaptée, tout en tenant compte de l'impact de l'environnement d'exécution. Celle-ci consiste à exécuter simultanément un même code sur plusieurs processeurs et sélectionner le plus rapide. Pour cela nous proposons une technique d'interruption anticipée de codes exécutés sur GPU et CPU.

Une autre méthode que nous avons implémentée consiste à exploiter toutes les ressources de calcul; elle requiert l'ajustement de la charge de travail attribuée à chaque UC. En effet, pour être performante, la distribution d'un calcul requiert de partager équitablement les temps d'exécution. Nous présentons un ordonnanceur guidé par des prédictions de temps d'exécution et capable, si c'est avantageux, de sélectionner l'architecture adéquate ou d'utiliser conjointement plusieurs UCs pour effectuer un calcul. La taille de la charge de travail est raffinée successivement jusqu'à obtenir des temps d'exécution équivalents sur toutes les UCs engagées.

# 1.2 Prédiction et sélection adaptative de version de code

#### 1.2.1 Introduction

Rendre les performances d'un programme adaptative au contexte d'exécution est un travail difficile et fastidieux, surtout pour des architectures complexes tels que les CPU généralistes ou les cartes accélératrices. La prédiction des performances d'un code est souvent difficile statiquement. En effet, l'efficacité d'un code varie selon l'architecture, la charge et les jeux de données à traiter. Pour ces raisons, les compilateurs peuvent difficilement prendre des décisions statiquement. Les techniques de compilation iteratives facilitent la recherche de la meilleure des versions pour un contexte donné, mais négligent généralement la variation des paramètres d'entrée et/ou du matériel. Les compilateurs devraient fournir un moyen au programme de s'adapter par le biais de la compilation dynamique (JIT) ou du multiversioning. La compilation dynamique a l'inconvénient d'introduire un surcoût, potentiellement non négligeable. Si l'objectif de l'utilisateur est uniquement la performance, le multiversioning est mieux adapté. Les versions de code, toutes sémantiquement équivalentes, mais de caractéristiques de performance différentes, sont choisies en fonction du contexte d'exécution. Ainsi, nous

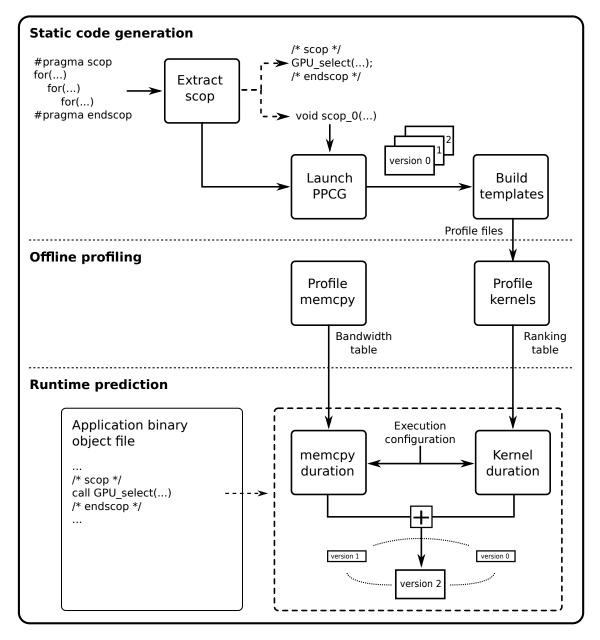

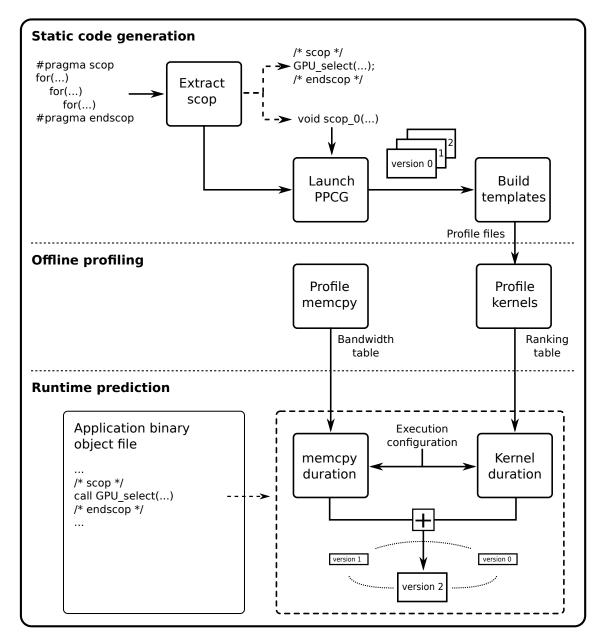

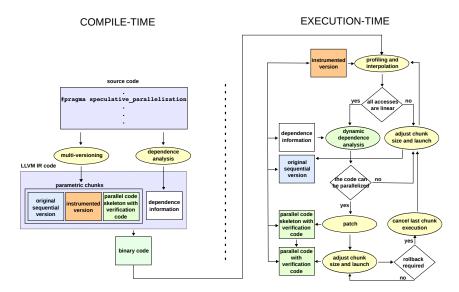

FIGURE 1.1 – Vue d'ensemble de l'infrastructure du framework.

avons développé un framework capable de prédire des temps d'exécution et de sélectionner la meilleure version d'un code sur une architecture hétérogène CPU+GPU.

#### 1.2.2 Vue d'ensemble du framework

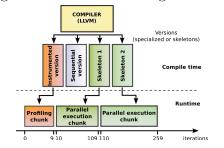

Le framework, représenté en Fig. 1.1, repose sur trois étapes : génération de code, profilage et prédiction. Les nids de boucles annotés dans le code source original sont extraits dans des fonctions. Plusieurs versions de ces nids de boucles sont générées à l'aide de PPCG, un compilateur polyédrique source-à-source capable de produire du code CUDA optimisé à partir de code C. Elles diffèrent par leur ordonnancement, taille de tuile et de bloc CUDA, utilisation de mémoire partagée, etc. PPCG a été

modifié afin de produire certaines informations issues de la compilation, notamment les polynômes d'Ehrhart représentant la taille du domaine d'itération et de la grille CUDA. Les fichiers générés sont transmis à un ensemble de programmes afin de construire le code de profilage et de prédiction.