# Electrical characterization & TEM study of the physical mechanism simplied in reliability issues of Ge-rich GST phase-change memories

Martin Coué

### ▶ To cite this version:

Martin Coué. Electrical characterization & TEM study of the physical mechanism simplied in reliability issues of Ge-rich GST phase-change memories. Electronics. Université Grenoble Alpes, 2016. English. NNT: 2016GREAT018. tel-01304128

## HAL Id: tel-01304128 https://theses.hal.science/tel-01304128v1

Submitted on 19 Apr 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano-électronique & Nano-technologies

Arrêté ministériel: 7 août 2006

Présentée par

### Martin COUÉ

Thèse dirigée par Barbara DE SALVO

préparée au sein du CEA Leti dans l'École Doctorale Electronique, Electrotechnique, Automatique et Traitement du Signal

# Caractérisation électrique et étude TEM des problèmes de fiabilité dans les mémoires à changement de phase enrichis en germanium

Thèse soutenue publiquement le **03/03/2016**, devant le jury composé de :

### Monsieur Christophe VALLÉE

Professeur des universités, UGA Polytech', Grenoble, France (Président)

### Madame Caroline BONAFOS

Directrice de recherche, CEMES-CNRS, Toulouse, France (Rapporteur)

### **Monsieur Salvatore LOMBARDO**

Directeur de recherche, CNR-IMM, Catania, Italie (Rapporteur)

### Monsieur Abdelkader SOUIFI

Prof., Institut de Nanotechnologies, Lyon, France (Membre)

### Madame Véronique SOUSA

Ing., CEA-LETI, Grenoble, France (Membre)

### **Monsieur Vincent DELAYE**

Ing., CEA-LETI, Grenoble, France (Membre)

### Madame Barbara DE SALVO

Directrice de recherche, CEA-Leti, Grenoble, France (Directrice de thèse)

# Contents

| In | trod | uction |                                                            | 1  |

|----|------|--------|------------------------------------------------------------|----|

| 1  | Pha  | ase-Ch | ange Memories                                              | 3  |

|    | 1.1  | Conte  | ${ m ext}$                                                 | 3  |

|    |      | 1.1.1  | The semiconductor memory market                            | 3  |

|    |      | 1.1.2  | Introduction to non-volatile memories                      | 4  |

|    |      | 1.1.3  | Focus on Flash non-volatile memory technologies and market | 5  |

|    |      | 1.1.4  | Limits of Flash technology and solutions                   | 9  |

|    | 1.2  | Emerg  | ging non-volatile memories                                 | 11 |

|    | 1.3  | Histor | ry of Phase-Change Memories                                | 14 |

|    |      | 1.3.1  | The beginning of Random Access Memories                    | 14 |

|    |      | 1.3.2  | Birth of Phase-Change Memories                             | 15 |

|    |      | 1.3.3  | Hibernation                                                | 15 |

|    |      | 1.3.4  | Rebirth                                                    | 16 |

|    | 1.4  | Worki  | ing Principle of a PCM device                              | 16 |

|    |      | 1.4.1  | Structure and operation of a PCM device                    | 16 |

|    |      | 1.4.2  | Phase-change transitions                                   | 18 |

|    |      | 1.4.3  | I-V and R-I characteristics                                | 20 |

|    | 1.5  | Streng | gths and weaknesses of Phase-Change Memories               | 22 |

|    |      | 1.5.1  | Strengths                                                  | 22 |

|    |      | 1.5.2  | Weaknesses                                                 | 23 |

|    | 1.6  | Struct | tures of PCM cells                                         | 24 |

|    |      | 1.6.1  | Lance-type structure                                       | 24 |

|    |      | 1.6.2  | Edge structure                                             | 25 |

|    |      | 1.6.3  | Bridge structure                                           | 25 |

|    |      | 1.6.4  | Confined structure                                         | 26 |

|    |      | 1.6.5  | $\mu$ trench structure                                     | 27 |

|    |      | 1.6.6  | Wall structure                                             | 27 |

|    | 1.7  | Physic | cs of crystallization in Phase-Change materials            | 28 |

|    |      | 1.7.1  | Nucleation                                                 | 28 |

|    |      | 1.7.2  | Growth                                                     | 31 |

|    | 1.8  | Relial | bility issues of Phase-Change Memories                     | 32 |

|    |      | 1.8.1  | Target specifications                                      | 33 |

|    |      | 1.8.2  | Retention of the RESET state                               | 34 |

|    |      | 1.8.3  | Retention of the SET state                                 | 36 |

|    | 1.9  | PhD :  | goals & outline                                            | 37 |

ii Contents

|        |         | characterization of Ge-rich PCM devices                                                                          |

|--------|---------|------------------------------------------------------------------------------------------------------------------|

| 2.1    | Mater   | rial characterization                                                                                            |

|        | 2.1.1   | Crystallization temperatures                                                                                     |

|        | 2.1.2   | Activation energies of conduction                                                                                |

|        | 2.1.3   | Kissinger analysis                                                                                               |

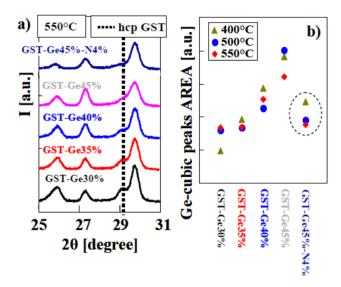

|        | 2.1.4   | X-Rays Diffraction measurements                                                                                  |

| 2.2    | Electr  | rical characterization of a PCM cell                                                                             |

|        | 2.2.1   | Description of the PCM cells under study                                                                         |

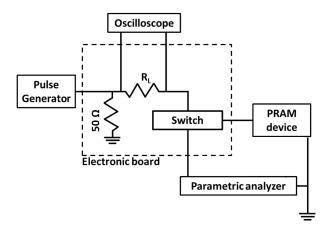

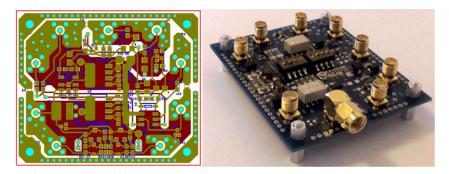

|        | 2.2.2   | The equipment                                                                                                    |

| 2.3    | Devic   | es performances                                                                                                  |

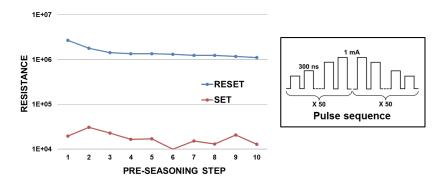

|        | 2.3.1   | Seasoning                                                                                                        |

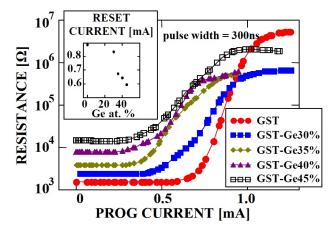

|        | 2.3.2   | RESET characteristics                                                                                            |

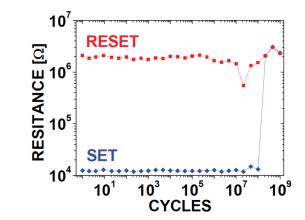

|        | 2.3.3   | Endurance                                                                                                        |

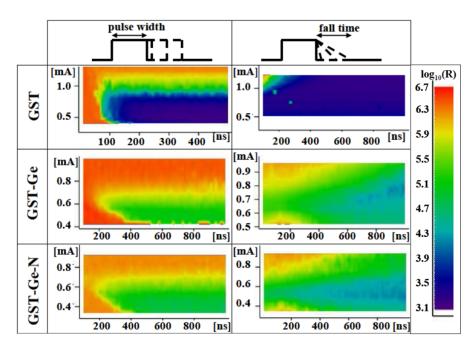

|        | 2.3.4   | Crystallization speed                                                                                            |

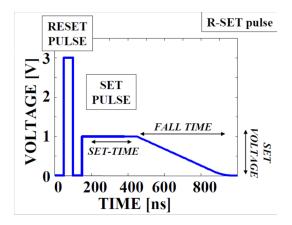

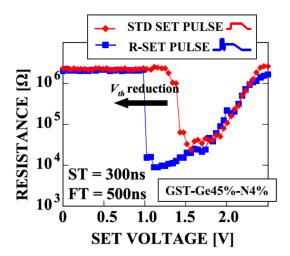

|        | 2.3.5   | The R-SET pulse                                                                                                  |

| 2.4    | Relial  | bility study                                                                                                     |

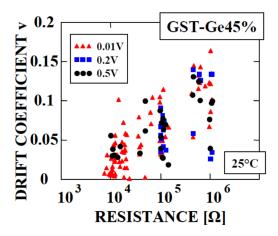

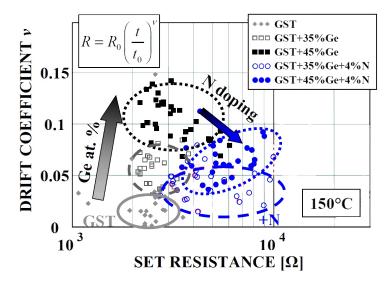

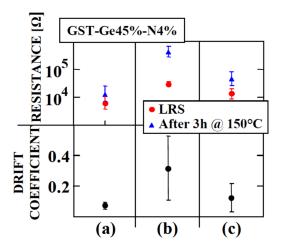

|        | 2.4.1   | Resistance drift of the SET state                                                                                |

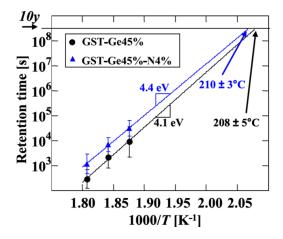

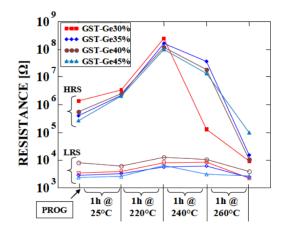

|        | 2.4.2   | Retention of the RESET state                                                                                     |

| 2.5    | Chapt   | ter conclusion                                                                                                   |

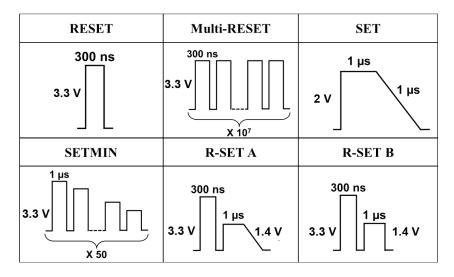

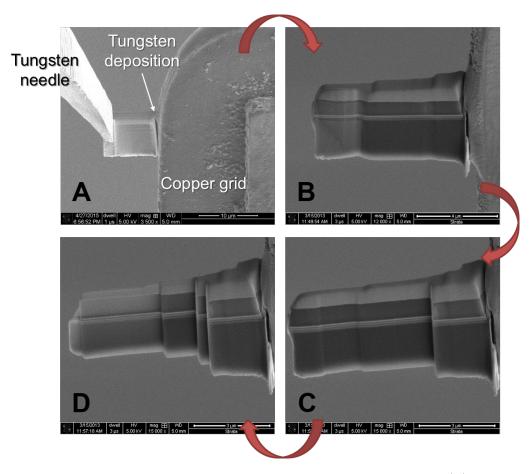

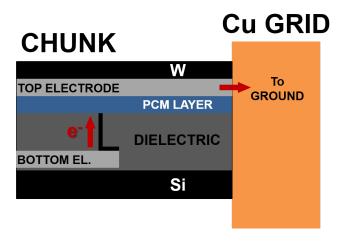

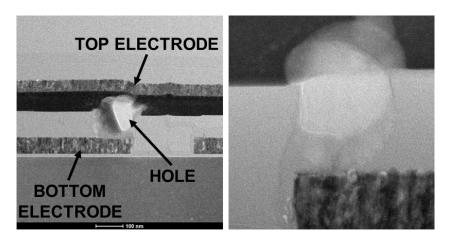

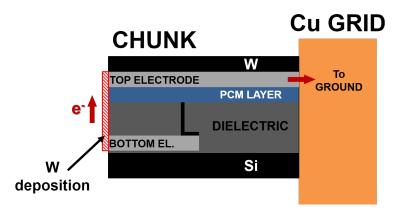

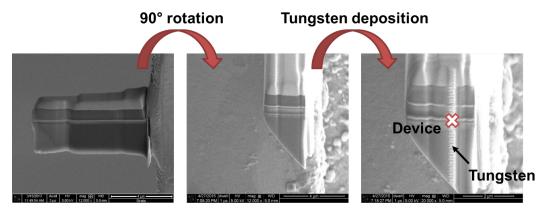

|        | 3.1.1   | le Preparation  Electrical characteristics and programming of the devices under analysis  Extracting the devices |

|        | 3.1.3   | Avoiding Electrostatic Discharges                                                                                |

| 3.2    | Resul   | ts                                                                                                               |

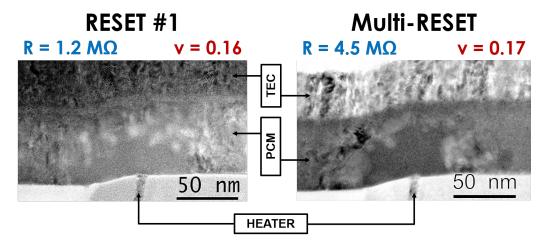

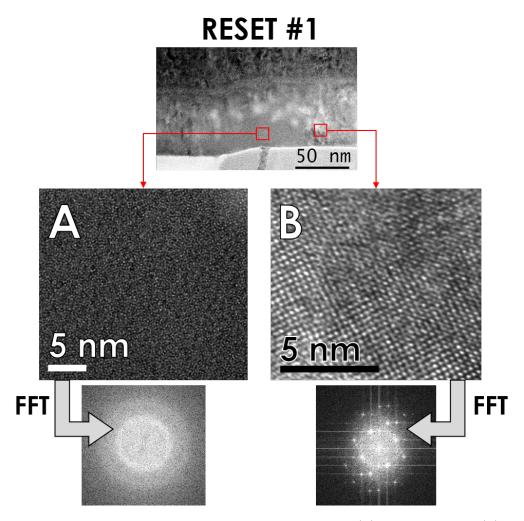

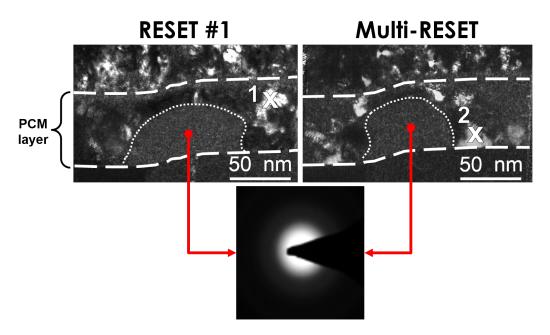

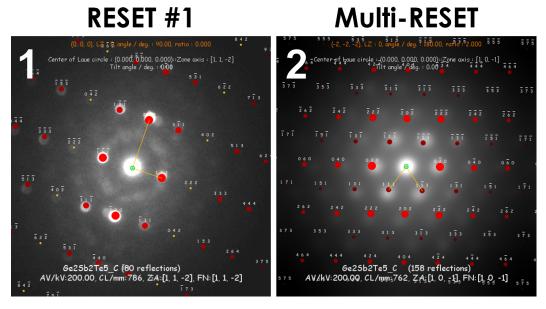

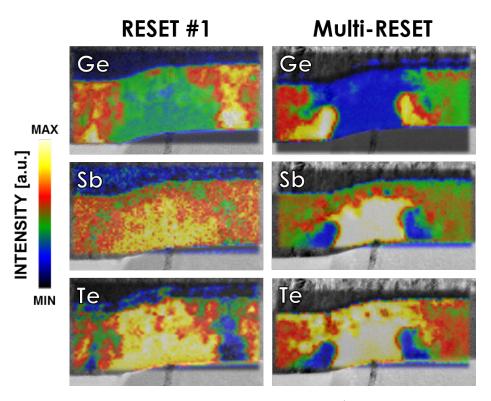

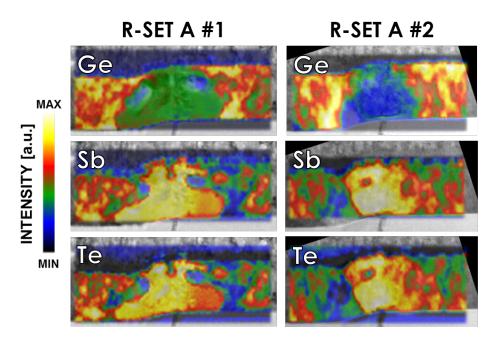

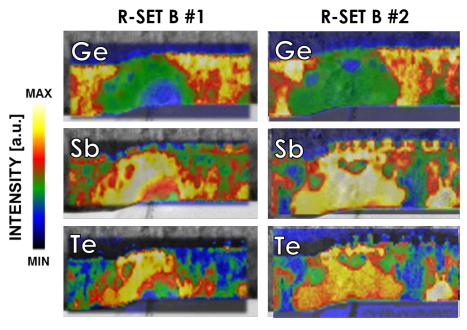

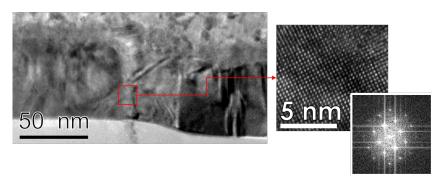

|        | 3.2.1   | RESET & Multi-RESET                                                                                              |

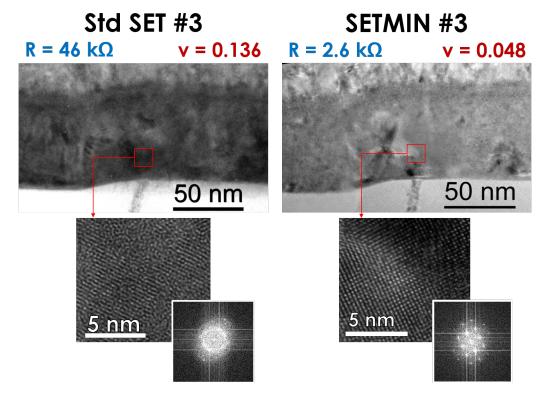

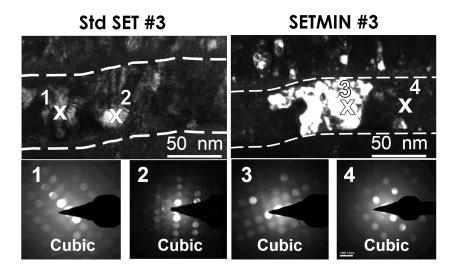

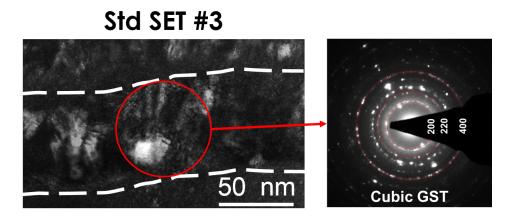

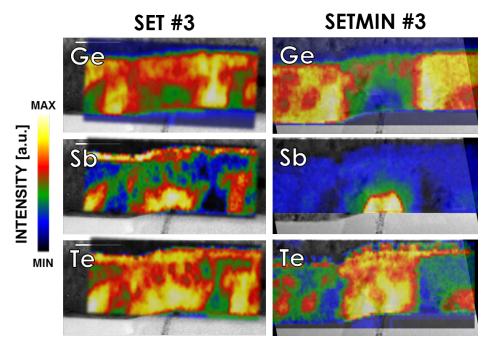

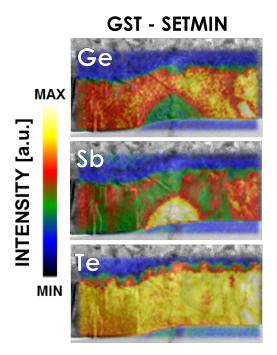

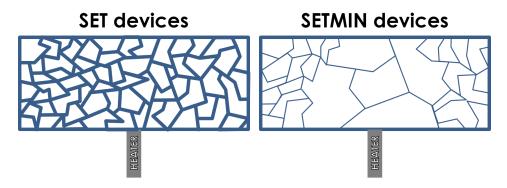

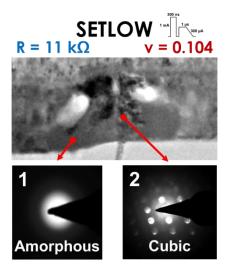

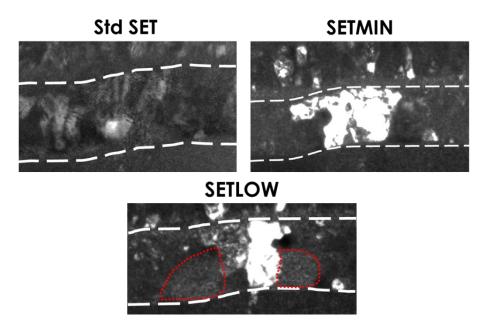

|        | 3.2.2   | Standard SET & SETMIN                                                                                            |

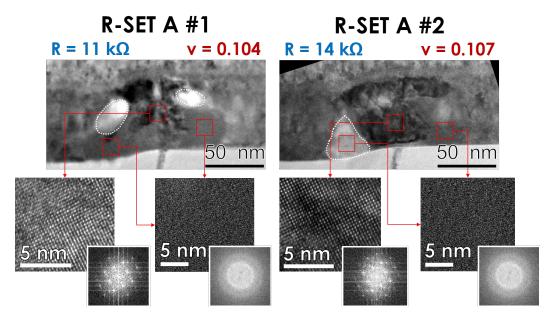

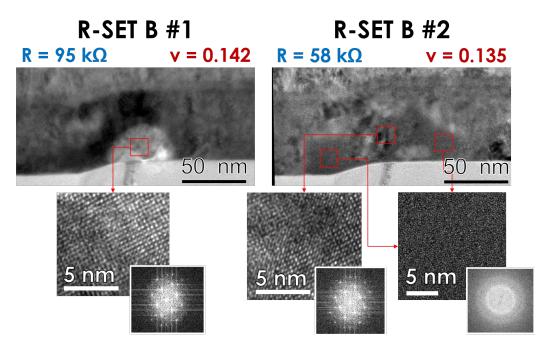

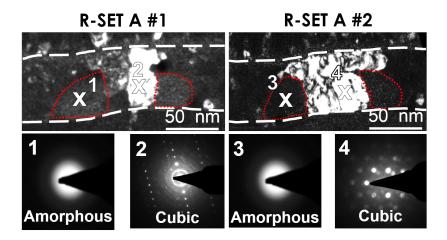

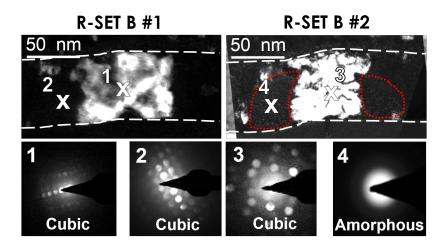

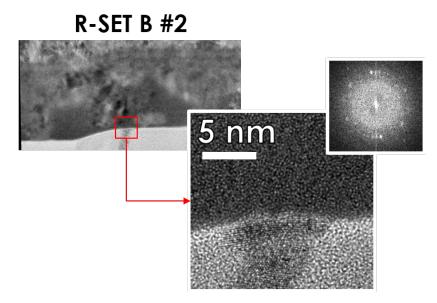

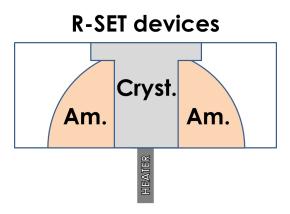

|        | 3.2.3   | R-SET                                                                                                            |

|        | 3.2.4   | GST 225                                                                                                          |

|        | 3.2.5   | Quantitative analyses                                                                                            |

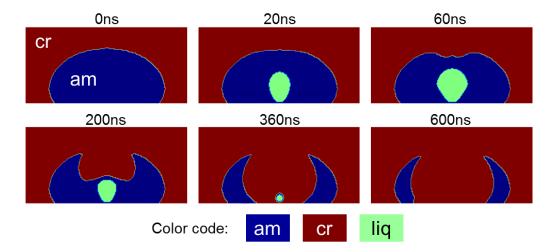

| 3.3    | Simul   | ations                                                                                                           |

| 3.4    |         | ssion                                                                                                            |

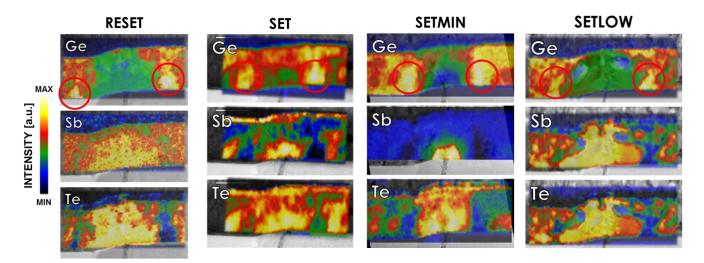

|        | 3.4.1   | Morphological interpretation of the drift phenomenon                                                             |

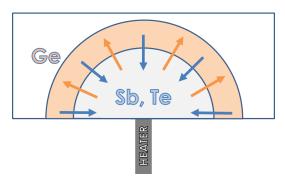

|        | 3.4.2   | Concentration of elements and retention of the RESET state                                                       |

| 3.5    | Chapt   | ter conclusion                                                                                                   |

|        | 1       |                                                                                                                  |

| Gener  | al cond | clusion                                                                                                          |

| Public | ations  | & Conferences                                                                                                    |

| . abne | anons   | & Comercines                                                                                                     |

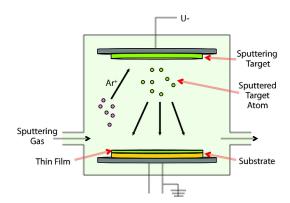

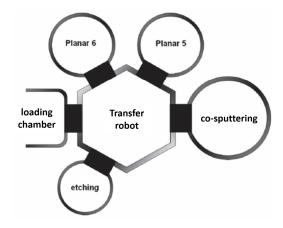

| A Do   | positio | n of the Phase-Change Material                                                                                   |

| iii |

|-----|

|     |

|     |

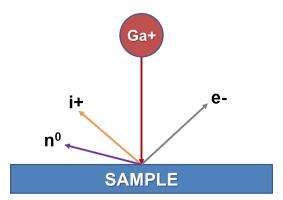

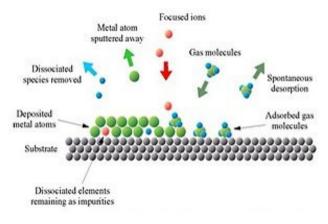

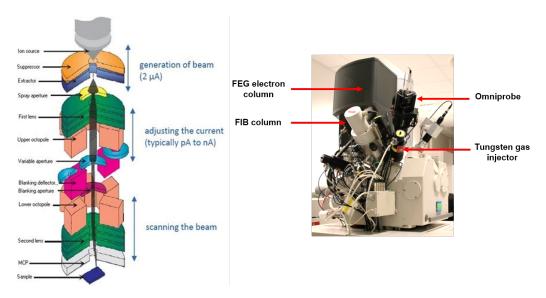

| В            | The   | FIB instrument                                               | 97  |

|--------------|-------|--------------------------------------------------------------|-----|

|              | B.1   | Principle                                                    | 97  |

|              | B.2   | The instrument                                               | 98  |

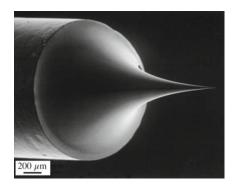

|              | B.3   | Ion Beam Source                                              | 99  |

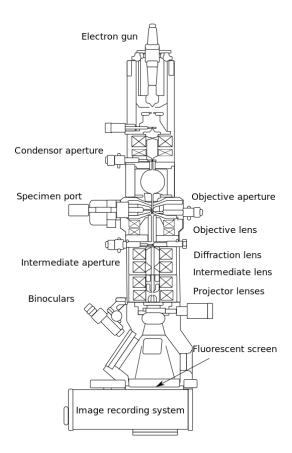

| $\mathbf{C}$ | Trai  | nsmission Electron Microscopy                                | 101 |

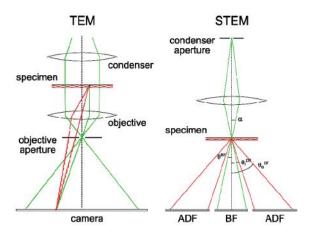

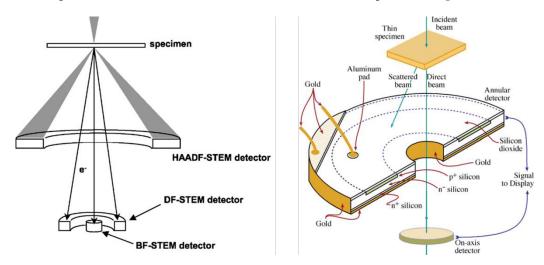

|              | C.1   | Principle                                                    | 101 |

|              | C.2   | The TEM instrument                                           | 103 |

|              |       | C.2.1 The electron gun                                       | 103 |

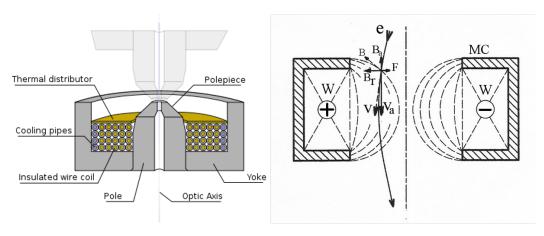

|              |       | C.2.2 Electromagnetic lenses                                 | 105 |

|              |       | C.2.3 Apertures                                              | 105 |

|              |       | C.2.4 Detectors and display                                  | 106 |

|              | C.3   | Bright Field imaging in conventional TEM mode                | 106 |

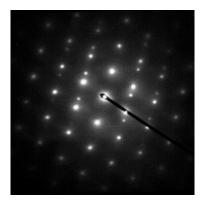

|              | C.4   | Diffraction Patterns and Dark Field imaging                  | 107 |

|              |       | C.4.1 Diffraction Patterns                                   | 107 |

|              |       | C.4.2 Dark Field imaging                                     | 108 |

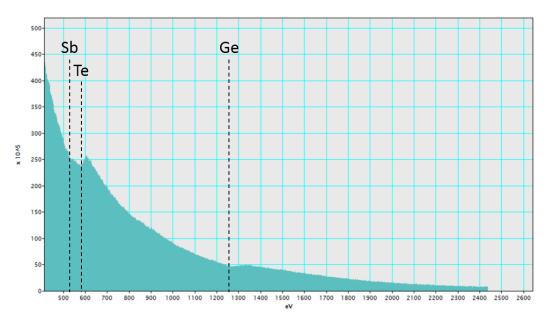

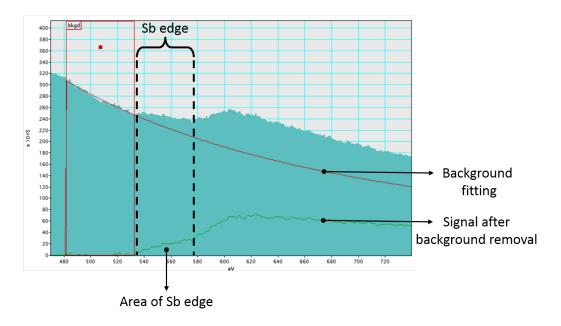

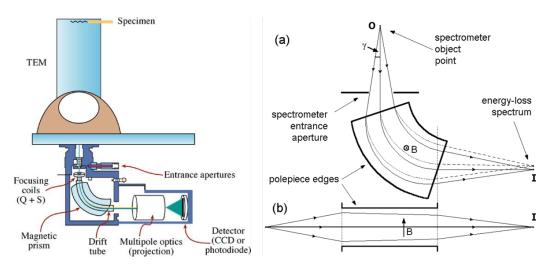

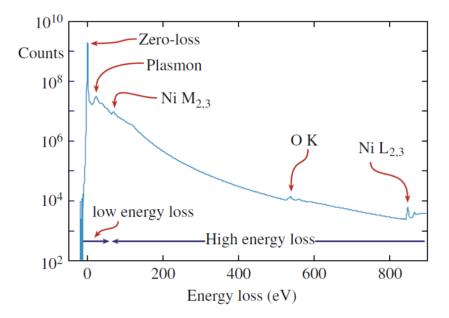

|              | C.5   | Electron Energy Loss Spectroscopy                            | 108 |

| $\mathbf{D}$ | The   | simulation tool                                              | 111 |

|              | D.1   | The Level Set Method                                         | 111 |

|              | D.2   | Simulation of nucleation and growth                          | 111 |

|              |       | D.2.1 Nucleation                                             | 112 |

|              |       | D.2.2 Growth                                                 | 112 |

|              | D.3   | Coupling the Level Set Method with an electro-thermal solver | 112 |

|              | D.4   | Numerical methods and implementation                         |     |

| Bi           | bliog | graphy                                                       | 115 |

# Introduction

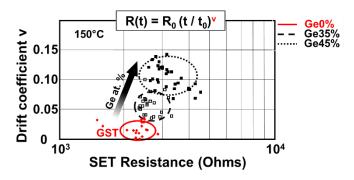

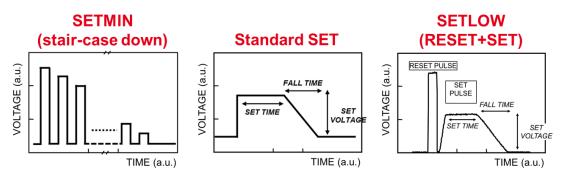

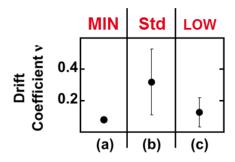

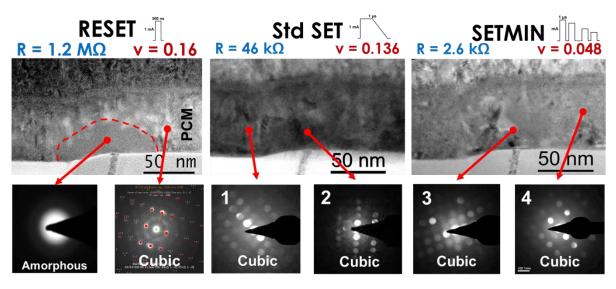

Since the invention of the first electronic computers by Alan Turing in 1937 [Turing 1937], the importance of memories in our daily life hasn't stopped to rise. Nowadays they can be found in a vast range of electronic systems such as personal computers, laptops, cellphones, televisions, appliances, and many others. As the applications of these memories have grown more and more various, different kind of technologies have been developed to answer specific needs. In particular, the development of embedded nonvolatile memories (eNVMs) has become a major need for the industry as the market of autonomous, decentralized and mobile units has risen up during the last decade. If flash technology has been dominating the market until now, its limitations have been reached, opening the way to a new era for non-volatile memories. Thanks to their scalability, endurance, write performances and low cost per bit when compared to other eNVMs, Phase Change Memories (PCMs or PRAMs) are often seen as one of the most promising technology to completely re-think the design of the memory subsystem, allowing to gain orders of magnitude improvements in speed and/or power consumption and to improve the memory hierarchy gap (as storage-class memory between the CPU and hard-disk). Moreover, PCMs offer great potential for low density embedded memories (to be integrated in microcontrollers and Systems on Chip (SoC)). Finally, exciting new applications and markets can be addressed, as new functionalities coupled with logic circuits to enable block power-down (in the Internet-of-Thing "Normally-Off" applications), or use as artificial synapses in neuromorphic systems for Big-Data analytics. However, some requirements still need to be fulfilled, in particular concerning the reliability of the memories when exposed to high temperatures. During the last few years, many efforts have been made to improve the thermal stability of PCMs, and notable progress has been achieved in this way by experimenting innovative materials such as germanium-enriched Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (Ge-rich GST). Unfortunately this solution raises another issue, which is the drift of the resistance over time. This phenomenon, already observed and studied in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) and other phase change materials was especially known to increase the resistance of the RESET state, but has been proven recently to have also an impact on the SET state of Ge-rich GST devices. In this thesis, we have investigated physical mechanisms governing Reliability of Ge-rich Phase-Change Memories by means of intensive electrical characterization & TEM analyses.

# Phase-Change Memories

In the following chapter we will present the context of this work with a rapid overview of the semiconductor memory market and a comparison of emerging non-volatile memories. We will then focus on the PCM technology, introducing its working principle, its advantages, and its drawbacks. The main structures of PCM cells will be detailed before going into the physics of crystallization in phase-change materials. The goals and outline of this thesis will be given after presenting the main topic of our studies, namely the reliability issues of Phase-Change Memories (PCM), with the description of the mechanisms responsible for the loss of data.

### 1.1 Context

### 1.1.1 The semiconductor memory market

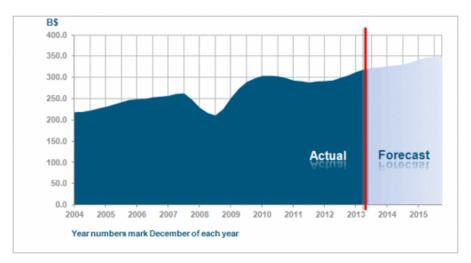

Since the invention of the first transistor by Bell Labs (USA) in 1947, the market of Integrated Circuits (IC) has impressively soared, and the total revenue now exceeds 300 billion dollars (fig.1.1).

Figure 1.1: Worldwide semiconductor industry revenue, data from WSTS [Statistics 2013]

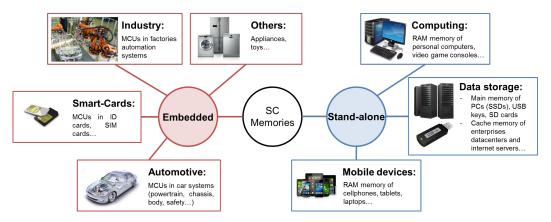

The semiconductor (SC) memory market represents a consistent share of the IC market, with approximately \$82B of revenues in 2013 (1/4 of IC revenues) [De Charentenay 2015]. It is divided into two main categories depending on the type of system in which the memories are integrated. Fig.1.2 shows some application fields for both categories: *stand-alone* memories are mainly dedicated to data

storage and main RAM memories of computers, servers, cellphones, video game consoles or tablets; *embedded* memories regroup all applications where the memory device is co-integrated with the CMOS elements on the same chip (System on Chip or SoC), like microcontrollers (MCUs) for the automotive and industrial fields, smart-cards (SIM cards, ID cards...), mobile Micro Processor Units (MPUs) for cellphones, and other general electronic purposes like appliances or toys.

Figure 1.2: Stand-alone and embedded applications of semiconductor memories.

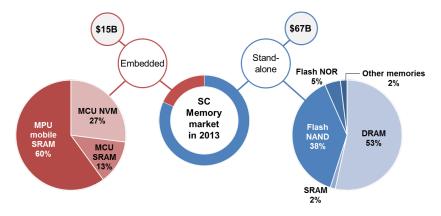

The distribution of the SC market revenues is detailed in fig. 1.3, with \$67B for stand-alone applications and \$15B for embedded systems. Flash and DRAM share most of the stand-alone sales with respectively 43% and 53% of the revenues in 2013 while SRAM is the most represented technology in embedded systems with 73% of the embedded market revenues.

Figure 1.3: The semiconductor memory market in 2013.

### 1.1.2 Introduction to non-volatile memories

Random-Access Memory The role of Random-Access Memory (RAM) in modern computers is of primary importance. It is used to store temporarily all the data (text, images...) and software (word processors, web browsers, video games...)

1.1. Context 5

which are in use, as well as a part of the Operating System (DOS, Windows, Mac OS, Linux...). For example, when the user opens a software (originally installed and stored on the hard drive), the computer stores it temporarily in the RAM memory, faster to access than the hard drive. In this case, Random-Access Memory thus enables a much faster communication between the Central Processing Unit (CPU) - the heart of the computer which processes the data - and the software being used. Such a memory must therefore provide very low accessing times and a high reliability to ensure a proper user experience.

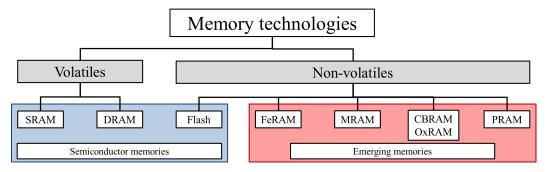

Two types of Random Access Memories Random-Access Memories are divided into 2 categories: volatile and non-volatile. Volatile memories like Static RAM (SRAM) and Dynamic RAM (DRAM) Data stored in volatile memories will be lost once power is switched off while non-volatile memories (NVMs) can keep the information even without any power source.

Figure 1.4: Organization chart of the main memory technologies. [Natarajan 2009]

Figure 1.4 shows an organization chart of the main memory technologies (including technologies already on the market and others that are currently under development). While the volatile Dynamic and Static RAMs (respectively DRAM and SRAM) have been dominating the field of RAM memories for decades since the 60's, new types of non-volatile RAMs have risen up during the last twenty years, especially flash memory which has become the new dominant technology on the market. Besides DRAM, SRAM and flash, new alternatives are being explored, representing the so-called emerging memories technologies.

### 1.1.3 Focus on Flash non-volatile memory technologies and market

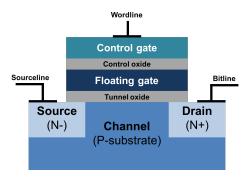

Flash technology: the floating gate transistor To store data, a flash memory cell uses a MOSFET transistor in which a floating gate (typically made of polycrystalline silicon) is inserted in-between the control gate and the MOSFET channel. This floating gate is electrically isolated from the rest of the device by two insulating layers, namely the control oxide and the tunnel oxide (fig.1.5).

In this type of memory the information is stored by transferring electrons in or out of the floating gate, which modifies the threshold voltage of the MOSFET and enables the creation of two distinct states (binary 1 or 0).

Figure 1.5: Schematic of a floating gate transistor used in flash technology.

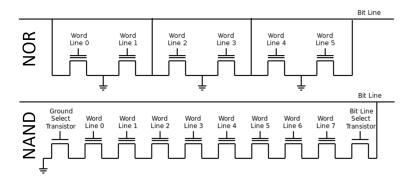

Flash memories are divided in two different groups depending on the cells arrangement in the memory arrays:

- the NOR architecture in which cells are connected in parallel (fig.1.6), enabling to access each individual cell separately. NOR devices are mainly used for instruction codes storage in operating systems of cellphones, motherboard or microcontrollers.

- the NAND architecture in which cells are connected in series (fig.1.6), which forbids the access to individual cells but enables to store a high volume of data. NAND flash is the main technology used in USB storage devices as well as most memory card formats and solid-state drives available today.

Figure 1.6: The NOR and NAND architectures of Flash memories.

The simplicity of Flash structure makes it a highly scalable technology, but the two architectures do not require the same space for each cell: while one cell occupies an area of  $4F^2$  in the NAND architecture, this value rises to  $10F^2$  in the NOR one, even when using exactly the same semiconductor device fabrication because NOR Flash cells require a separate metal contact for the drain of each cell.

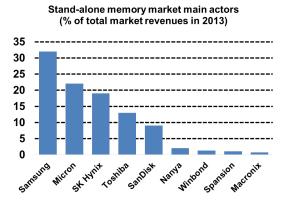

**Stand-alone memory applications** The stand-alone memory market is currently dominated by 5 integrated device manufacturers (Samsung, Micron, SK

1.1. Context 7

Hynix, Toshiba and SanDisk) which share 95% of the overall revenues in 2013 (fig.1.7). If we focus on non-volatile memories, Flash represents approximately 95% of global NVMs sales for stand-alone applications, driven by the expansion of NAND memory over the past few years.

Figure 1.7: Main actors of the stand-alone memory market (reproduced from [Tortorelli 2015]).

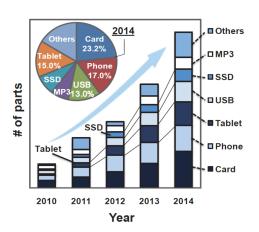

As NAND memory is mainly dedicated to store a large amount of data, user data storage is thus the main market aimed by this technology typically found in USB keys, memory cards, cellphones, tablets and most recently in Solid-State Disks (SSD). Fig.1.8 shows a analysis of the NAND market evolution between 2010 and 2014 [Choi 2014]. The explosion of the mobile devices market, coupled to the progressive replacement of Hard Drive Disks (HDDs) by Solid-State Disks (SSDs) are two of the main reasons why NAND rules over the NVM market for stand-alone applications.

Figure 1.8: Analysis of the NAND market evolution between 2010 and 2014 (reproduced from [Choi 2014]).

This rise has been made possible essentially by the cost diminution of NAND memories with the reduction of cells size thanks to the improvements of lithography techniques. From 1998 to 2012 the size of a NAND cell has been indeed divided by 1000 [Burr 2013], leading to a radical decrease of NAND cost from approximately \$10k/GBit in 1995 to \$0.05/GBit in 2015 [De Charentenay 2015].

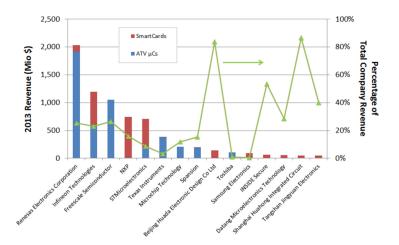

Embedded applications Concerning embedded memories, we will focus on the MCU market since it is the main field of applications for embedded non-volatile memories (eNVMs). This market is less concentrated than the stand-alone memory market with the top ten producers being large semiconductor IC manufacturers (fig.1.9).

Figure 1.9: Main actors of the MCU market (automotive & Smartcards) [Strenz 2014].

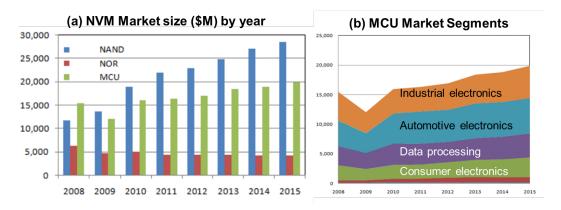

Fig.1.10 compares the evolution of market size for stand-alone Flash (NAND and NOR) and MCUs [Baker 2012]. Although NAND Flash still represents the most rapidly growing market, MCU sales are also growing steadily and are expected to reach \$20B by the end of the year 2015.

Figure 1.10: The evolution of the MCU market from 2008 to 2015 (reproduced from [Baker 2012]).

Embedded NVMs are currently estimated to represent 50% of the MCU market, with expectations to see this number rising up in the next years [Niebel 2011], making this field a strong driver for eNVM innovations.

MCUs are used in a wide variety of applications, with very special specifications for each of them. Fig.1.11 displays the main criteria that eNVMs must fulfill to address each application [Baker 2012].

1.1. Context

| Market                    | Fast Code<br>Execution                  | Robust/ZD<br>Quality                        | Pgm/Erase<br>Endurance                       | Read/Pgm/<br>Erase Pwr                   | Sector Size<br>P/E Time                      |

|---------------------------|-----------------------------------------|---------------------------------------------|----------------------------------------------|------------------------------------------|----------------------------------------------|

| Auto P-Train<br>& Chassis | 3-5<br>High<br>compute<br>power req     | 5<br>Mission- and<br>safety-critical        | 4<br>Increasing<br>EE Emul<br>Requirement    | 3<br>Self-heating,<br>Perf. tradeoff     | 2<br>Cost of boot<br>blocks, Factory<br>Pgm. |

| Auto Body                 | 2<br>Moderate<br>compute<br>power       | 5<br>Mission- and<br>safety-critical        | 3<br>Increasing<br>EE Emul<br>Requirement    | 4<br>Many<br>always-on<br>devices        | 3<br>Cost of boot<br>blocks, etc.            |

| Industrial<br>Control     | 3-5<br>High<br>compute<br>power req     | 3<br>Also control<br>critical<br>functions  | 2<br>Moderate EE<br>Emulation<br>Req.        | 4<br>Many apps<br>are low<br>power       | 3<br>Cost of boot<br>blocks                  |

| Portable &<br>Consumer    | 2<br>Moderate for<br>many apps          | 2<br>Shorter<br>lifetimes,<br>less critical | 2<br>Moderate EE<br>Emulation<br>Req.        | 4<br>Many apps<br>are low<br>power       | 3<br>Cost of boot<br>blocks                  |

| Smart Cards               | 2<br>Less<br>important<br>than pwr, etc | 2<br>Shorter<br>lifetimes in<br>many cases  | 5<br>EE function<br>with frequent<br>updates | 5<br>Critical for<br>contactless,<br>etc | 5<br>Also important for<br>contactless, etc  |

Figure 1.11: Requirements for each eNVM application with relative importance (max = 5, min = 1) [Baker 2012].

Since a single technology cannot answer all these needs, different types of Flash architectures have been developed:

- the 1T-NOR architecture where a single floating-gate transistor is used to store data

- the 2T-NOR (or EEPROM) where 2 transistors are used in series

- the 1.5T Flash (or split-gate) in which the control gate only covers part of the tunnel oxide and floating gate

The main applications, advantages and drawbacks of these technologies are summarized in fig.1.12.

### 1.1.4 Limits of Flash technology and solutions

As said above, Flash technology is based on floating gate transistors: to reduce the size of a Flash cell it is thus necessary to shrink the dimensions of the oxides layer surrounding the floating gate. But this shrinking will soon reach its limits as physical issues start to appear when the tunnel oxide is too thin: there is indeed a threshold value for the oxide thickness below which the electrons can escape the floating gate because of quantum tunnelling effects. Scaling down the tunnel oxide also affects the endurance of the cell: as the electric field applied to the device gets stronger and stronger with smaller dimensions, more defects appear in the oxide layer, fostering

|              | 1T                                    | 2T                                       | Split-gate                    |

|--------------|---------------------------------------|------------------------------------------|-------------------------------|

|              | CG<br>FG<br>p-well                    | BL PMD So FG AG So i-pWell Burried nWell | CG Erasing MG D S Programming |

| Applications | Automotive                            | User data storage                        | Various                       |

| Advantages   | High reliability, small dimensions    | Low power consumption                    | Speed, reliability, low power |

| Drawbacks    | High tension, high current, low speed | High tension, big dimensions             | Complexity of fabrication     |

Figure 1.12: Main Flash architectures used in embedded applications [Strenz 2011].

the electrons leakage from the floating gate. Another important issue when scaling down Flash memories lays in the increase of interference between neighboring cells. A capacitive coupling can indeed appear because of the modification of the transistor's threshold voltage implied by the charge stored in a neighboring cell. It is thus necessary to keep a certain distance between the cells to ensure the reliability of the devices. At last, shrinking the dimensions of the floating gate transistor implies that fewer electrons can be stored in the floating gate. This leads to another issue, as reliability problems start to appear when dimensions do not enable more than 10 electrons to be stored, so that quantum effects must be taken into account.

As these intrinsic physical limits cannot be avoided with the current materials and architectures used in Flash fabrication, other solutions are considered to increase its density. Some studies are currently focusing on new materials with better performances for the floating gate, like silicon nitride (SiN) or nanocrystals which lower the leakage of charges towards the tunnel oxide. The control oxide could also be replaced by high permittivity materials (or "high k materials") like HfO<sub>2</sub>, ZrO<sub>2</sub> or AlO<sub>3</sub>, which ensure a good coupling between the control gate and the floating gate while limiting the leakage current. At last, electrostatic interference between neighboring cells can be lowered by using low permittivity materials (SiO<sub>2</sub>, SiOCH...) to separate each transistor.

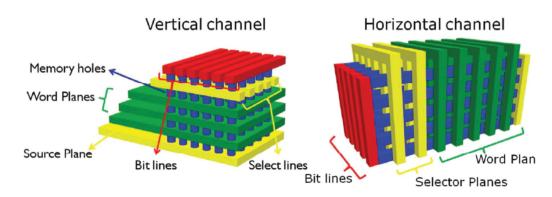

Besides these researches for alternative materials, new types of architectures have also been considered to further decrease the cost of Flash memories. As opposed to the currently adopted planar structures, three-dimensional architectures have been introduced: one approach, called the stacked architecture, consists in several layers of classical planar memories which are interconnected by metallic junctions [Jung 2006]. In other architectures like BiCS [Tanaka 2007], TCAT [Jang 2009], VSAT [Kim 2009] or VG-NAND [Lue 2010], the transistor channel and the gate form crossed 3D structures as depicted in fig.1.13.

Figure 1.13: Schematic of 3D Flash architectures with vertical transistor channels (left) or horizontal (right) [Arreghini 2013].

### 1.2 Emerging non-volatile memories

In order to overcome the limits of current technologies (in terms of scaling, performance or cost), several new technologies have been intensively studied in the last decades. Their working principles, main characteristics and application fields are briefly reviewed in the next paragraphs.

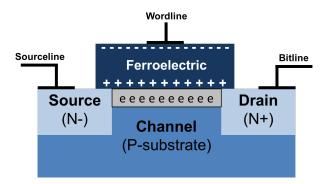

Ferroelectric RAM (FeRAM) This type of RAM exploits the two stable polarization states of a ferroelectric material (typically lead zirconate titanate Pb(Zr, Ti)O<sub>3</sub> or PZT) which naturally contains electric dipoles, because of the distribution of anions and cations inside its structure. The application of an electrical field to the material enables to change its polarization state durably, and thus to program the device in two distinct states (fig.1.14). The 1T-1C (one transistor and one capacitor) storage cell design in an FeRAM is similar in construction to the storage cell in widely used DRAM since both cell types include one capacitor and one access transistor. In a DRAM cell capacitor, a linear dielectric is used, whereas in an FeRAM cell capacitor the dielectric structure includes ferroelectric material.

Figure 1.14: Schematic of a FeRAM cell.

To read the information, the cell is set to its "0" polarization state. If this implies a change of polarization, a charge variation is measured, meaning that the cell was in

its state "1". If no variation is measured, then the cell was in a state "0". This means that the reading step in a FeRAM cell is a destructive process. The advantages of this technology over Flash are its lower power consumption, faster write performance and greater number of write-erase cycles. But the working principle of FeRAM implies that the information stored in one cell is lost after reading, because the cell has to be put back in its "0" state, because of its lower density (thus higher cost), its small scaling potential and the difficulties usually encountered during the integration of the devices, FeRAM is generally not considered as a future alternative to Flash memories at this date.

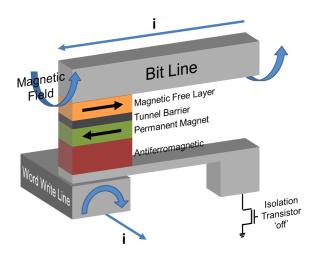

Magnetic RAM (MRAM) MRAMs can be seen as the magnetic version of FeRAMs as they use the two stable magnetic states of a ferromagnetic material. An MRAM cell is made of two ferromagnetic plates which can both hold a magnetization, separated by a thin insulating layer (fig.1.15). One of the two plates is a permanent magnet set to a particular polarity while the other plate's polarity can be changed by the means of an external magnetic field applied to the cell. This change of polarity induces a change of the cell's resistance, and thus enables the distinction between two resistive states, making it suitable for memory applications.

Figure 1.15: Schematic of a classic MRAM cell.

The main drawback of this technology comes from the many different layers needed for its fabrication, using multiple materials which are not usual in the microelectronic field, making it difficult to integrate in the production lines of current microelectronic manufacturers. Moreover the first generation of MRAMs had a limited scaling potential, with high currents needed for the programmation and a small resistance window between the two resistive states. More recently, the Spin-Transfer Torque MRAMs (STT-MRAM) technology has been introduced, in which the orientation of the free magnetic layer is modified using a spin-polarized current rather than an external magnetic field. Thanks to this new technique, STT-MRAMs could theoretically reach similar performances than SRAM with densities close to DRAM

but much lower power consumption than the latter, and an unlimited lifetime since no electronic nor material movement is engaged.

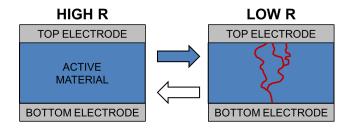

Resistive RAMs (RRAMs): Oxide Resisitive RAM (OxRRAM) & Conductive-Bridging RAM (CBRAM) OxRRAM and CBRAM technologies are both based on the reversible change of resistance inside an active material by the creation and destruction of a conductive filament between the two electrodes (fig.1.16).

Figure 1.16: Schematic of the working principle of CBRAM/OxRRAM device. The application of an electrical pulse to the cell enables the reversible creation of a conductive filament inside the active material (typically  $GeS_2$  or  $GdO_x$  in CBRAMs, and  $HfO_2$  or  $TiO_2$  in OxRRAMs).

In the case of CBRAM, the active material is a solid electrolyte (e.g.  $GeS_2$  or  $GdO_x$  for example) surrounded by two solid metal electrodes. One of these electrode is inert (e.g. platinum or tungsten) while the other one is electrochemically active (e.g. copper or silver), leading to redox reactions with the active material when a voltage or current pulse is applied to the cell, and thus to the creation (or destruction) of a conductive filament.

In an OxRRAM cell, the active material is usually a very thin layer (a few nanometers) made of a transition metal oxide (e.g. HfO<sub>2</sub> or TiO<sub>2</sub>). In its initial state, the oxide layer is insulating, and a first electrical stress is needed to make it conductive (the so-called "forming" step). The reversible switching between the high and low resistance states is then induced by the application of an electrical pulse to the cell, creating (or erasing) a conductive filament which is thought to be made of oxygen vacancies [Waser 2009].

It should be said that for both technologies, the physics implied in the formation and destruction of the conductive filament is not totally understood at this date and still being discussed.

When compared to Flash memory, CBRAM and OxRRAM exhibit faster write times, higher endurance and lower power consumption. Moreover these technologies theoretically need only a few ion widths to work, making them scalable to sizes much smaller than Flash. Their integration in the Back-End-Of-Line is also much simpler, leading to simpler construction and lower costs. But because of the great variability of the cells performances, and because we still don't have a full understanding of the physics involved in their working process, these technologies are still not enough mature to be brought to the market.

**Phase-Change RAM (PRAM)** Phase-Change RAMs (also known as PCM, PCRAM, Ovonic Unified Memory, Chalcogenide RAM or C-RAM) use the two resistive states of a chalcogenide material to store data. As this technology is the main interest of this work, its working principle and other characteristics will be detailed throughout the next sections and chapters.

Finally, the main characteristics, advantages and drawbacks of the emerging technologies introduced above are summed up in table 1.1 [Tortorelli 2015].

| Table 1.1: Main characteristics | , advantages and drawback | s of emerging NVMs | [Tortorelli 2015]. |

|---------------------------------|---------------------------|--------------------|--------------------|

|---------------------------------|---------------------------|--------------------|--------------------|

|                | FeRAM            | MRAM                             | CBRAM        | OxRRAM                |

|----------------|------------------|----------------------------------|--------------|-----------------------|

| Maturity       | High             | Medium                           | Low          | Low                   |

| Scaling        | Low              | Medium                           | Unknown      | High                  |

| potential      |                  |                                  |              |                       |

| Cell surface   | $20 \text{ F}^2$ | $6 \text{ F}^2 - 40 \text{ F}^2$ | $4 F^2$      | $4 	ext{ } 	ext{F}^2$ |

| Speed          | High             | High                             | Medium       | Medium                |

| Data retention | Good             | Medium                           | Unknown      | Unknown               |

| Endurance      | High             | High                             | Medium       | Medium                |

| Power          | Low              | Variable                         | Low          | Low                   |

| consumption    |                  |                                  |              |                       |

| Integration    | Medium           | Low                              | High         | High                  |

| ease           | Medium           | LOW                              | 111811       | 111811                |

| Cost           | High             | High                             | Unknown      | Unknown               |

|                | Destructive      | Integration,                     | Variability, | Variability,          |

| Drawbacks      | reading,         | scaling                          | under-       | under-                |

|                | scaling          | scanng                           | standing     | standing              |

### 1.3 History of Phase-Change Memories

### 1.3.1 The beginning of Random Access Memories

The basic principles of electronic computers as we know them today were first stated by Alan Turing in 1937 [Turing 1937]. The functionality of this new kind of technology relied on a form of memory to store all the information and data needed, and so were created paper punched cards used in the very first computer devices. The limits of this technique were however quickly reached, and Turing pointed out the need of new types of memories to allow the full development of computers [Turing 1947]. Magnetic core memories were invented a few years later and used as the main memory of the first commercialized electronic computers, but the real revolution started in the late 60's with the rise of solid state memories. This new era gave birth to Random Access Memories (RAM) such as Static RAM (SRAM) and Dynamic RAM (DRAM), more practical and much denser than magnetic core memories. But

unlike the latter, SRAM and DRAM are both volatile, meaning they lose all the information they have been storing once power is turned off. Further research was therefore needed to develop a new kind of solid state memory with a density similar to SRAM and DRAM, but non-volatile, and here was the opportunity for Phase Change RAMs to make their first appearance on the memory stage.

### 1.3.2 Birth of Phase-Change Memories

The idea of using the peculiar behaviors of phase-change materials to make solid state memories was already explored since the early 60's: the first patent on the subject was filled in 1961 by Dewald, Northover and Pearson, who developed the idea of "multiple resistance semiconductor elements" [Dewald 1966]. In their patent they describe the main operations of a two-terminal device "capable of operating in two resistance states", i.e. a low resistance state (LRS or SET) and a high one (HRS or RESET). They also mention a threshold value of the voltage applied to the cell "for changing the resistance state of [the device] from a first discrete high resistance state to a second discrete low resistance state". These concepts are still applicable to modern phase-change memories (PCM), but the real breakthrough in PCM history came from the work of Standford Ovshinsky, considered as the father of PCM. Since 1960 Ovshinsky had been working on chalcogenides which are compounds or alloys containing at least one element from column VI of the periodic table, and first published his findings in 1968 [Ovshinsky 1968]. In this paper he reports the functionality of memory devices integrating an alloy of tellurium, arsenic, silicon and germanium, demonstrating the possibility to switch multiple devices continuously over a period of many months, which was a first at the time. This ground-breaking demonstration and the interest it drew from industrials constitute the real starting point of PCMs development.

### 1.3.3 Hibernation

In the 70's, other research teams started to work on their own PCM devices: in 1970, R. G. Neale, D. L. Nelson (both from Energy Conversion Devices) and G. E. Moore (Intel) developed the first 256-bit PCM array. But unfortunately the expansion of PCM technology quickly had to face some technical limitations. Back in 1970, the minimum feature size which could be printed on integrated circuit was about 10  $\mu$ m. With this geometry, the volume of phase-change material needed to be switched was too large, resulting in huge power consumption: the cells of Neale et al. required 5  $\mu$ s, 200 mA at 25 V bias to RESET the device and 10 ms, 5 mA at 25 V bias for the SET operation, consuming much more energy than other competitive memories at the time. Because of this inferiority in power efficiency the 256-bit array was never commercialized, and interest in PCMs took a step back.

Figure 1.17: Schematic of a 1T1R PCM device.

### 1.3.4 Rebirth

Two decades later, in 1990, the first rewritable CD based on chalcogenides was commercialized by PANASONIC, following the discovery of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) which still remains the most studied phase-change material to date. The interest in phase-change materials quickly rose up again, and 9 years later, when the lithographic technics reached the 180 nm node and that the power needed to switch the devices seemed reasonable, the Ovonyx joint venture was created Tyler Lowrey and Ward Parkinson along with Energy Conversion Devices, the company created by Ovshinsky in 1960, to commercialize phase-change memories. Things started to accelerate: in February 2000, just one year after the creation of Ovonyx, a license agreement was found with Intel which started to invest in the PCM technology. Ten months later, another agreement was found with STMicroelectronics, announcing the imminent commercialization of the first PCM devices, and the beginning of the modern era for PCM technology.

The main events in the history of phase change memories are listed in the table 1.2:

### 1.4 Working Principle of a PCM device

### 1.4.1 Structure and operation of a PCM device

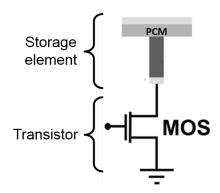

A PCM device is divided into two main parts (fig.1.17): the storage element in which data is stored and the access transistor which enables to program or read the device. Those devices are often referred to as 1T1R devices (one transistor, one resistive element), as opposed to 1R devices which don't integrate any transistor and which are usually dedicated to research purposes where it is not needed to work on a full array of memories.

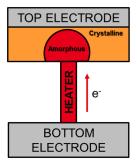

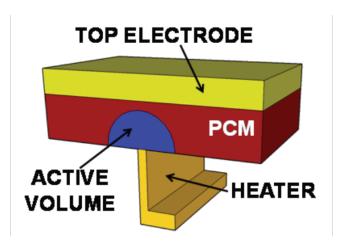

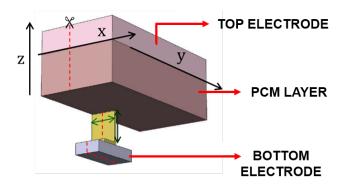

The structure of the storage element in a typical PCM cell is very simple: it is a two-terminal device consisting in two electrodes (bottom & top) enclosing a heater and a layer of chalcogenide glass (fig.1.18).

Chalcogenide glasses are materials containing one or more chalcogenide elements

Table 1.2: main events of Phase-Change Memories history.

| Year    | Event                                                                         |

|---------|-------------------------------------------------------------------------------|

| 1966    | First patent on PCM technology granted to Dewald et al.                       |

|         |                                                                               |

| 1968    | Ovshinsky publishes his findings on phase change threshold switching          |

| 1970    | First 256-bit PCM array by Neale et al.                                       |

| 1990    | First R/W phase change CD                                                     |

| 1999    | Ovonyx joint venture is formed to commercialize PCM technology                |

| 2000    | Intel invests in Ovonyx and licenses its technology                           |

|         | STMicroelectronics also licenses the technology from Ovonyx                   |

| 2002    | Macronix files a patent application for transistor-less PCM                   |

| 2003    | Samsung begins work on PCM technology                                         |

| 2003-05 | PCM-related patent applications filed by Toshiba, Hitachi, Macronix, Renesas, |

|         | Elpida, Sony, Matsushita, Mitsubishi, Infineon and more                       |

| 2004    | Samsung announces successful 64 Mbit PCM array                                |

| 2005    | Samsung announces successful 256 Mbit PCM array, touts 400 $\mu$ A program-   |

|         | ming current [Samsung 2005]                                                   |

| 2005    | Intel increases investment in Ovonyx                                          |

| 2005    | Hitachi and Renesas announce 1.5 V PCM with 100 $\mu A$ programming current   |

|         | [Hitachi 2005]                                                                |

| 2005    | Samsung licenses PCM technology from Ovonyx                                   |

| 2006    | BAE Systems begins selling the first commercial PCM chip [Purvis 2006]        |

| 2006    | Samsung announces 512 Mbit PCM device [EETimes 2006]                          |

| 2006    | Intel and STMicroelectronics show a 128 Mbit PCM chip                         |

| 2007    | Hynix begins pursuing PCM by licensing Ovonyx' technology                     |

| 2008    | Intel and STMicroelectronics announce four-state MLC PCM [Greene 2008]        |

| 2000    | and begin shipping samples to customers.                                      |

| 2008    | Numonyx announces mass production 128 Mbit PCM device to selected cus-        |

| 2008    | tomer                                                                         |

| 2009    | Samsung announces mass production start of 512 Mbit PCM device                |

| 2009    | Numonyx announces 1 Gb 45 nm product [Numonyx 2009]                           |

| 2010    | Samsung releases 512Mbit PCM with 65 nm process, in Multi-Chip-Package        |

| 2010    | [Krishnamurthy 2011]                                                          |

| 2011    | Samsung presented 58 nm 1.8V 1Gb PCM [Chung 2011]                             |

| 2012    | Samsung presented 20 nm 1.8V 8Gb PCM                                          |

| 2012    | Micron announces availability of Phase-Change Memory for mobile devices -     |

| 2012    | the first PCM solution in volume production [Krishnamurthy 2012]              |

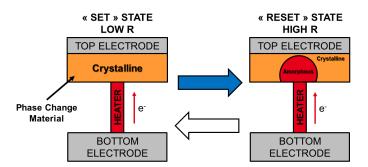

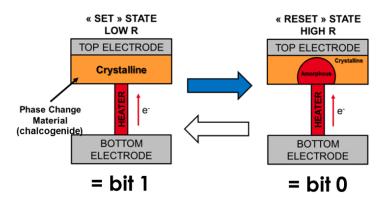

Figure 1.18: Schematic of the working principle of a PCM device. The reversible transition from the low resistance crystalline state (SET state, bit 0, left of the picture) to the high resistance amorphous state (RESET state, bit 1, right of the picture) is thermally induced by the application of a current pulse to the phase-change material through a resistive heater.

(elements from column VI of the periodic table excluding oxygen) and their unique properties are at the heart of the PCM technology. The operation of a PCM device relies indeed on the large resistivity contrast (typically 3 orders of magnitude) between the amorphous and crystalline phases of these materials to store data, i.e. bits 0 or 1. The cell can thus operate in two states depending on the chalcogenide state:

- the amorphous, high resistance state represents a binary 0;

- the crystalline, low resistance state represents a binary 1.

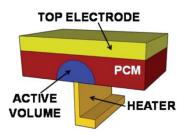

The device structure described in fig.1.18 is called the lance-type structure. Other PCM structures exist and will be discussed later in this chapter, but most of them derive from the lance-type one, which is the most straightforward to fabricate. In such a device the role of the heater is to enable a good heat confinement and provide an efficient joule heating of the phase-change material to fulfill the low power/energy requirements. It must then dissipate a large power and be able to sustain a large temperature gradient, so materials with high electrical resistivity and low thermal conductivity are required (titanium, tungsten, silicon and nitrogen are typically used). Clearly the choice of the phase-change material has a crucial impact on the memory performances since it will define the intrinsic limits of the device, but the structure and the scaling of the cells also have an important role to play. Indeed, shrinking the dimensions of the cell, and especially the contact area between the heater and the chalcogenide layer, can drastically change the performances of the device, in particular its power consumption. These parameters will be detailed in the next chapter when we will focus on the different ways to optimize a phase-change memory.

### 1.4.2 Phase-change transitions

What makes the PCM technology interesting is that the transition between the crystalline and amorphous phases (fig.1.19) is reversible, thermally-induced and there-

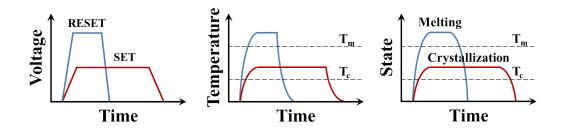

Figure 1.19: Principle of the phase change transitions. During the RESET operation, the material is melted then quenched to the amorphous phase. During the SET operation, the material is heated above  $T_c$  for a sufficient time to enable the reorganization of atoms into the crystalline phase. [Terao 2009]

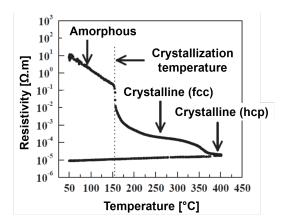

fore simply achievable by the application of electrical pulses to the cell (fig.1.20): if the device is initially in a low resistive crystalline state, the amorphization of the chalcogenide (RESET or write operation) is achieved by raising the temperature of the material above the melting point  $T_m$  (650°C in GST) thanks to Joule effect, and then by quenching it in a disordered amorphous phase. The recovering of the crystalline state (SET or erase operation) is achieved by heating the phase-change material above the crystallization temperature  $T_c$  (150°C in GST) without exceeding the melting point. Both operations do not require the same amount of time nor energy: because of the high temperatures which need to be reached during the RESET operation, this step is the most power consuming. But it is also the shortest to achieve (typically a few tens of nanoseconds) when compared to the times needed during the SET operation to ensure the good recrystallization of the chalcogenide (usually in the 100 ns - 1  $\mu$ s range).

Figure 1.20: Schematic of the electrical pulses applied to program the cell into the RESET or SET state (left), along with the temperature profile inside the device during the pulses (middle) and the corresponding states of the phase-change material (right). [Hubert 2013]

### 1.4.3 I-V and R-I characteristics

A PCM device can be characterized by monitoring the evolution of the current passing through the cell as a function of the voltage (I-V characteristic), and the

evolution of its resistance as a function of the current (R-I characteristic).

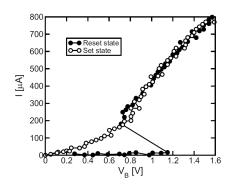

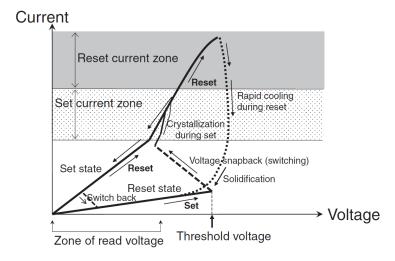

Figure 1.21: Typical I-V curve of a PCM device showing the SET & RESET characteristics, and the typical snap back observed for  $V \geq V_{th}$  [Ielmini 2007a].

Fig.1.21 illustrates a typical I-V curve obtained on a 1R device. The SET state characteristic is splitted in two linear parts (ohmic conduction) while the RESET state characteristic is a bit more peculiar: when low voltage pulses are applied to the cell, the current stays very low because the phase-change material is in a very resistive amorphous phase. But when the voltage reaches a particular value  $V_{th}$ , the so-called threshold voltage, a switch is observed with a characteristic snap back in the I-V curve. This switching phenomenon is the heart of the PCM technology: once the threshold voltage is reached, the material switches to a high conductive state (ON-state) which allows the recrystallization of the chalcogenide thanks to the Joule heating induced by the increased current. The switching phenomenon thus enables the recrystallization of the material with only a few volts applied to the cell. Without this peculiar behavior, PCM devices would need much higher voltages to operate (tens or even hundreds of volts) and would be destroy even before the beginning of recrystallization. While this phenomenon is essential for the functionnality of PCM devices, its physical interpretation is still discussed [Wong 2010] and will be more detailed in section 1.7. The process described in this paragraph are summed up in fig. 1.22.

Figure 1.22: Schematic voltage-current characteristics of a PCM device [Terao 2009].

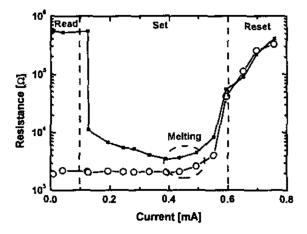

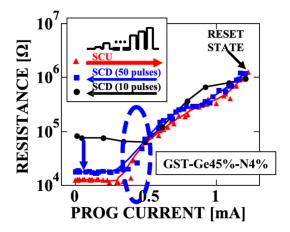

The resistance versus programming current characteristics of PCM devices allow to determine the amount of current needed to program the cells in the desired state. Fig.1.23 displays a classic R-I curve of a PCM device initially in a SET state or a RESET state. Each point corresponds to the final resistance of the cell achieved after the application of a current pulse of specific intensity. The graph is divided in three current ranges: the READ region at low currents corresponding to the values used for the reading of the devices; the SET region corresponding to the values needed to recrystallize the phase-change material, and the RESET region corresponding to the current values enabling the amorphization of the chalcogenide.

Figure 1.23: Classic R-I curves of a PCM device starting from a RESET state(filled circles) and from a SET state (white circles) [Pirovano 2003].

The physics of phase-change transformations will be discussed later in this chapter.

# 1.5 Strengths and weaknesses of Phase-Change Memories

### 1.5.1 Strengths

Write/erase speed The speed of the write (RESET) and erase (SET) operations is determined by the time needed to respectively melt and crystallize the phase-change material. As the melting of the material is a very fast process, the amorphization step, governed by the thermal constant of the cell, is a fast procedure which can be achieved in a few nanoseconds: studies have shown the feasibility of achieving a RESET state with 10 ns pulses [Ottogalli 2004]. On the other hand, the crystallization step is a longer process since more time is needed for atoms to be reorganized inside the material. The SET operation is typically achieved in times varying between a few tens of nanoseconds to a few microseconds, and is thus the limiting step of PCM operation speed. However, studies performed on Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>2</sub> have demonstrated crystallization times shorter than 100 ns [ITRS 2012]. When

compared to Flash memories which typically need several tens of microseconds for the erasing operation, PCM cells are then much faster than NAND and NOR technologies.

Resistance window and endurance The resistance window of a PCM cell is defined as the gap between the resistances of the RESET and SET states. A good resistance window is thus necessary to distinguish both states. A typical Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>2</sub> PCM cell exhibits resistance windows of at least 2 orders of magnitude, which is enough to ensure a good distinction between the two resistive states, and therefore a reliable reading of the information. The endurance of a memory device is defined as the number of write/erase cycles that one cell can sustain before failure. Concerning PCM cells, failures correspond to devices stuck in the low or high resistive state (because of interdiffusion of atoms inside the phase-change layer or voids creation for example), forbidding further programming. It has been demonstrated that the programming currents used to program the cells have a direct impact on their endurance: high programming currents will lead to faster failures [Lai 2003]. Endurance greater than 10<sup>12</sup> cycles for a single device has been demonstrated, while typical values for Flash memories do not exceed 10<sup>6</sup> cycles.

Multi-Level capability The PCM technology also allows to store more than one bit per cell. These type of memories are called "Multi-Level Cells" (MLC) and represent an efficient way to increase the memory density, i.e. the number of bits per unit area. This technology can be achieved in PCM devices by different means:

- the first method consists in programming the PCM in an intermediate state between the SET and RESET states, either by partially amorphizing a cell originally programmed in a SET state, or by partially recrystallizing a cell originally programmed in a RESET state. This method has been proven to be functional with 2 bits per cell in a 256 Mbits demonstrator [Bedeschi 2009], and up to 4 bits per cell in smaller arrays [Nirschl 2007].

- the over way to store more than one bit per cell is to increase the number of active zones inside one cell, i.e. to use several layers of phase-change materials which can be amorphized or recrystallized instead of just one. For example it is possible to fabricate PCM cells with 3 phase-change layers in parallel [Oh 2009] or in series [Gyanathan 2012] to create 4 distinct resistive states and thus to store 2 bits per cell.

### 1.5.2 Weaknesses

**Programming currents** As it has been described previously, the writing operation is accomplished by melting and quenching the phase-change material inside the cell. It is thus necessary to heat the material above its melting temperature  $T_m$ , which is a very energy consuming step. High values of write current (called RESET current or  $I_{RESET}$ ), typically 200  $\mu$ A for 45 nm devices [Servalli 2009], are needed

to provide an efficient Joule heating, and this is one of the main PCM drawbacks since it directly affects the performances and the dimensions of the cells. Indeed, a full PCM device is made of the actual PCM cell in series with an access device (transistor or diode) which provides current to the cell: the more current is needed, the bigger the access device has to be. This is thus a limiting factor for scaling down the devices, and therefore a limiting factor to increase the density of the PCM technology. Moreover, since the memory arrays are powered by a limited source, a lower  $I_{RESET}$  would allow to program more cells in parallel, and increase the capacity of the arrays [Ahn 2005]. These are the reasons why the reduction of the RESET current has been one of the main topic of research since the beginning of PCM development. Several solutions can be considered:

- as the amount of current needed is directly proportional to the volume of phase-change material which has to be amorphized (the so-called active zone), decreasing this volume leads to smaller values of  $I_{RESET}$ . Since the active zone is defined by the contact area between the heater and the phase-change material as well as the thickness of the phase-change layer, efforts have been made to reduce those two parameters by exploiting new types of cell structures, which are described in section 1.6.

- the optimization of the cell structure can also enable a better confinement of current, leading to lower power consumption (see "confined structures" detailed in next section)

- another solution is to improve the interface between the heater and the phase-change material by adding a thin layer of a dielectric material. Indeed, studies have shown a large decrease of the reset current in PCM cells integrating a thin layer of TiO<sub>2</sub> or HfO<sub>2</sub> with up to 78% of current reduction compared to standard GST cells [Hubert 2011]. This reduction appears to be mainly due to a decrease of the equivalent contact area with the creation of small conductive filaments through the thin films, and a better thermal efficiency. In fact, the thermal conductivity of such materials being lower than materials used for the heater (typically tungsten or TiN), the thermal energy loss through the heater are lowered [Matsui 2006, Choi 2010], increasing therefore the temperature reached inside the phase-change material for the same amount of current. Less current is thus needed to program the cells integrating an interface layer.

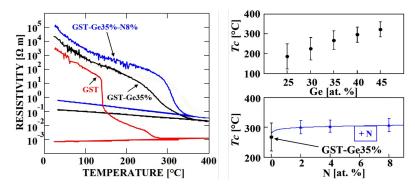

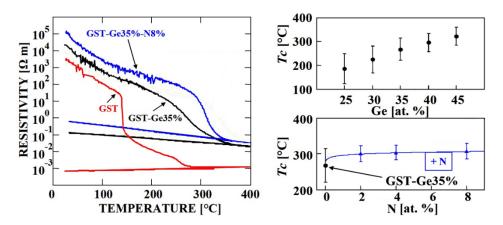

- at last, it is also possible to modify the phase-change material itself by changing its stoechiometry or by doping it with elements like nitrogen, carbon or SiO<sub>2</sub>, which will modify the melting and crystallization temperatures of the material.

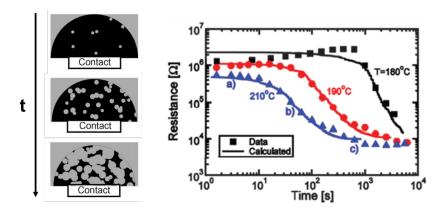

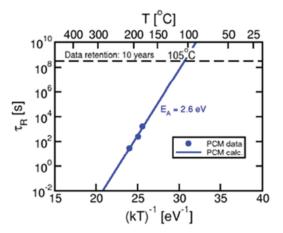

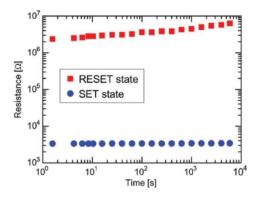

**Programmed states stability** Another challenge for the development of Phase-Change Memories is to limit the loss of data in the RESET and SET states, which results respectively from the recrystallization of the amorphous phase and the drift of the resistance. Indeed, the amorphous phase of chalcogenides is unstable: it tends

naturally towards recrystallization, which leads to the loss of data in the RESET state. This process is thermally activated, and while typical GST cells can remain in the RESET state for tens of years at room temperature, only a few papers show data retention longer than 10 years at 85°C (which is the typical criterion for non-volatile memories applications) for this material [Kim 2005, Pirovano 2004]. Data in the SET state can also be lost because of the drift of the resistance over time, which is a phenomenon well known for the RESET state but which can also be detrimental for the SET state. As these reliability issues are the main topic of this thesis, they will be described in more details in section 1.8 of this chapter.

### 1.6 Structures of PCM cells

As it has been introduced in section 1.5, the size of the cell, the volume of phase-change material to melt, the thermal and electrical confinements as well as the contact area between the heater and the phase-change material are key parameters when it comes to lowering the write current. Since the beginning of PCM hystory, many efforts have been made to find solutions enabling to minimize it by changing the structure of the cells. In the next sections, we present the evolution of PCM cells architectures as it can be found in literature.

### 1.6.1 Lance-type structure

Fig.1.24 describes the first PCM cell concept, known as the lance-type structure. This type of cell can be realized by the etching of a via in the dielectric material deposited over the bottom electrode. The via is then filled with a metal, typically tungsten or TiN, to create the plug. After this step, a chemical-mechanical polishing (CMP) is performed to ensure a good planarity of the surface, before the deposition of the phase-change material.

Figure 1.24: The lance-type structure.

The reduction of the contact area in the lance-type structure thus depends on the etching and lithography technology resolution available.

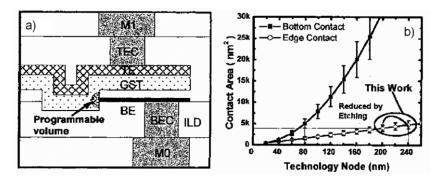

### 1.6.2 Edge structure

In an edge-type PCM cell, the heater is no longer vertical like in the lance-type structure, but horizontal. An example of this type of cell is proposed in fig.1.25. The phase-change material is deposited so that a lateral contact with the exposed surface of the heater is obtained.

Figure 1.25: a) The edge-type structure. b) Comparison between the lance-type structure and the edge structure [Raoux 2008].

The contact area is thus defined by the thickness of the horizontal layer (BE) and its width. Results from [Raoux 2008] shows the advantages of such a geometry over the lance-type structure. However, difficulties are often encountered to ensure a perfect lateral contact with the material during the deposition.

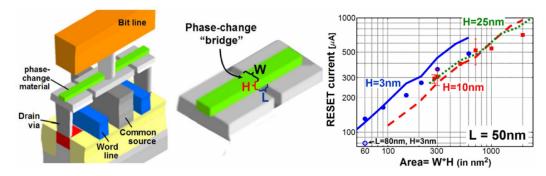

### 1.6.3 Bridge structure

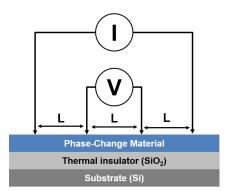

The bridge structure consists in two vertical electrodes separated by a thin insulating gap, and connected together only by a narrow line of phase-change material, hence the name "bridge structure". Fig.1.26 shows a schematic of this type of structure [Raoux 2008]. The gap between the two electrodes defines the bridge length (L). The phase-change material is deposited by magnetron sputtering to create the bridge, with thickness down to 3 nm (H), with a width (W) defined by electron-beam lithography, down to 20 nm [Chen 2008].

In this type of cell no heater is needed since the rise of the temperature is located inside the phase-change material (self-heating cell). Therefore, the cross-sectional area of the bridge (WxH) defines the current needed for the RESET operation. The advantage of this structure is the possibility to achieve very small contact area dimensions, enabling to reach RESET current as low as 150  $\mu$ A, but with an endurance not exceeding 30000 cycles [Chen 2006].

### 1.6.4 Confined structure

In a confined-type cell, the phase-change material is confined in the same hole than the heater, replacing it partially or totally (fig.1.27).

Figure 1.26: Scheme of the bridge struture (left) with the selector device, and experimental results for the RESET currents as a function of the cross-sectional area of the phase-change material, for different thickness H.[Raoux 2008, Chen 2008].

Figure 1.27: TEM images of a confined PCM cell [Lee 2007].

The confinement obtained by the surrounding dielectric material allows a better electrical confinement of the active volume, leading to lower  $I_{RESET}$  values. In addition to being very scalable, this structure shows indeed a big improvement on RESET currents, reducing more than twice the current needed for the write operation, and endurance up to  $10^8$  cycles [Lee 2007]. Just like standard lance-type cells, the contact area in confined cells is determined by the lithography resolution. The drawback of this architecture is that the whole volume of phase-change material is amorphized or recrystallized in the write/erase process. This is an issue when dealing with multi-bit capability since it is thus very difficult to achieve an intermediate state between the RESET state and the SET state.

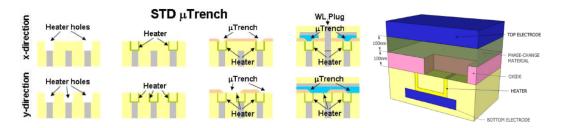

### 1.6.5 $\mu$ trench structure

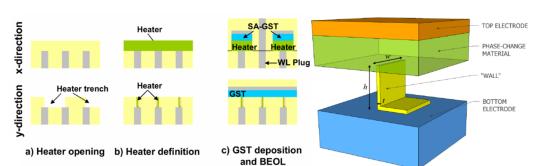

This type of structure was introduced in 2004 by STMicroelectronics [Pellizzer 2004] and is the structure used in the first real industrial PCM product. Fig.1.28 displays a schematic of a  $\mu$ trench cell.

Figure 1.28: Schematic of a  $\mu$ trench cell (right) and process flow (left, [Pirovano 2007]).

To fabricate a this type of structure, the bottom electrode and the dielectric material (SiO<sub>2</sub>) are first deposited. Then a squared via is opened in the dielectric material by Deep UV (DUV) light lithography before the deposition of the metal layer (WSi in the case of the devices fabricated here at the LETI) to create the "ring". The via is then filled with the dielectric and a final CMP leaves the ring surface exposed. Another dielectric (SiN) is deposited and etch to open the trench, on which the phase-change material is deposited. The final step consists in the deposition of the top electrode. The contact area is defined by the control of the metal layer thickness, which therefore also defines the contact area and thus the RESET current.

### 1.6.6 Wall structure

Fig.1.29 shows a schematic of the wall-type cell. The wall structure is a direct evolution of the  $\mu$ trench structure. It relies on the fabrication of a via in which a thin layer of a conductive material is deposited, etched, and then planarized, but unlike in the  $\mu$ trench process, the PCM layer and the heater are etched at the same time (self aligned process). This structure is thus highly scalable, reaching sublithographic sizes. The result is a very small contact area between the heater and

the phase-chage material, leading to lower RESET currents [Servalli 2009].

Figure 1.29: Schematic of a wall-type cell (right) and corresponding process flow (left, [Servalli 2009]).

### 1.7 Physics of crystallization in Phase-Change materials

The studies presented in this work have been performed in an effort to understand the physical process responsible for the loss of data in the RESET and SET states of Phase-Change Memories. As we have seen in section 1.5 when we introduced the drawbacks of Phase-Change Memories, the loss of data in the SET state comes from the resistance drift of the crystalline material, while the loss of data in the RESET state is due to the recrystallization of the amorphous phase. It is therefore important to understand the physics governing the crystallization of phase-change materials as it will enable us to identify the critical parameters involved, and give us the tools to develop a numerical model to simulate phase-change transitions. This numerical model, used for the simulations presented in chapter 4, is detailed in appendix B.

Two mechanisms are involved in the crystallization process of an amorphous material: nucleation, which initiates the crystallization by creating small crystalline nuclei, and then the growth of these nuclei enabling them to reach a macroscopic size.

### 1.7.1 Nucleation

The process implied during the nucleation step can be described by referring to the Classical Nucleation Theory (CNT). This theory developed by Gibbs in the 70's relies on the main assumption that the composition of the material stays unchanged during the crystallization and that the process is limited by diffusion.

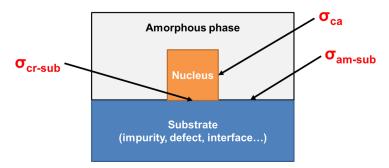

Two types of nucleation can happen: homogeneous nucleation or heterogeneous nucleation. The homogeneous nucleation occurs at any site of the bulk material, while heterogeneous nucleation is ignited by the presence of preferential nucleation sites inside the amorphous material like impurities or interfaces.

Our numerical model used for the simulations takes into account both homogeneous nucleation, occurring in the bulk of the phase-change material, and heterogeneous nucleation, present around impurities and at the external boundaries of the

material. Only the heterogeneous nucleation is described in details hereafter, but homogeneous nucleation is treated in a similar manner.

As we have said, the heterogeneous nucleation model includes the presence of defects, impurities and other potential substrates like foreign particles which act as nucleation sites (fig.1.30) and add extra interfaces energies. The total free energy resulting from the creation of a square shaped nucleus in such a system is then given by equation 1.1:

Figure 1.30: Schematic of the heterogeneous nucleation principle. Impurities, defects and other substrates contribute to the formation of nuclei by adding extra interfaces energies.

$$\Delta G = G_{am} - G_{cr} = r^3(-\Delta G_v) + 5r^2\sigma_{ac} + r^2\chi > 0$$

(1.1)

Where r is the side length of the nucleus,  $\sigma_{ac}$  is the interfacial energy per unit area between the crystalline nucleus and the amorphous phase matrix,  $\chi = \sigma_{cr-sub} - \sigma_{am-sub} < 0$  (in  $J.m^2$ ) is the surface energy, describing the chemical affinity between the phase-change material and the surrounding materials (with  $\sigma_{cr-sub}$  and  $\sigma_{am-sub}$  being respectively the energies of the crystal-substrate and amorphous-substrate interfaces), and  $\Delta G_v$  is the difference between the Gibbs free energy per unit volume of the amorphous and crystalline phase.  $\Delta G_v$  represent the driving force of crystallization and is given by the relation Thompson-Spaepen (eq.1.2):

$$\Delta G_v(T) = G_{am} - G_{cr} = \frac{L_m}{T_m} \times T \times \ln(\frac{T_m}{T})$$

(1.2)

Where  $L_m$  is the latent heat of melting and  $T_m$  the melting temperature of the material.

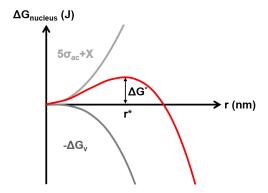

Knowing the values of the parameters  $L_m$ ,  $T_m$ ,  $\Delta G_v$ ,  $\sigma_{ac}$  and  $\chi$  for the material of interest, we can plot the variation of  $\Delta G$  as a function of the nucleus size r (fig.1.31).

The curve obtained shows a maximum at  $r = r^*$  Given that  $\frac{d\Delta G}{dr}(r^*) = 0$ , we can calculate  $r^*$ :

$$r^{\star} = 4 \frac{\sigma_{ca}}{\Delta G_v} \tag{1.3}$$

This parameter, of the order of a few nanometers, tends to infinity when T gets closer to  $T_m$ .

Figure 1.31: Variation of  $\Delta G$  as a function of the nucleus size r for a given temperature. The curve shows a maximum at  $r = r^*$  corresponding to the energy barrier  $\Delta G^*$  which has to be overcome to create a stable nucleus.

The minimum energy needed to form a stable nucleus is thus given by:

$$\Delta G^{\star} = \frac{4(\chi + 5\sigma_{ca})^3}{27\Delta G_v^2} \tag{1.4}$$

From here we can determine the rate of nucleation in stationary state, given by eq.1.5:

$$I_s = N \times \gamma \times O_n \times Z_e \times \exp(-\frac{\Delta G^*}{k_B T})$$

(1.5)

Where N is the density of nucleation sites,  $\gamma$  is the atomic jump frequency,  $Z_e$  is the Zeldovich factor, and  $O_n^*$  is the number of atoms at the surface of the critical size nucleus which is given by, in the case of heterogeneous nucleation:

$$(O_n^{\star}) = 5\left(\frac{r^{\star}}{d}\right)^2 \tag{1.6}$$

Which leads to:

$$(O_n^{\star}) \times (Z_e) = 0.456 \left(\frac{M}{\rho}\right)^{1/3} \sqrt{\frac{\chi + 5\sigma_{ca}}{RT}} N_a^{1/6}$$

(1.7)

With R the gas constant and  $N_a$  the Avogadro number.

The Zeldovich factor is given by equation 1.8:

$$Z_e = \left(\frac{\Delta G_{mol}(T)}{6\pi RT n^*(T)}\right)^{1/2} \tag{1.8}$$

Where  $n^*(T)$  is the number of atoms inside the critical size nucleus and  $\Delta G_{mol}(T)$  the molar free energy of the amorphous/crystalline transition (in  $J.mol^{-1}$ ).

In the case of Phase-Change Memories, the electrical pulses applied to the cells imply a very fast increase and decrease of temperature (respectively in the order of  $10^{12}$  K/s and  $10^{10}$ ). Because of this, a transient nucleation nucleation rate is used [Hyot 2002]:

$$I = I_s \exp(\frac{-\tau}{\delta t}) \tag{1.9}$$

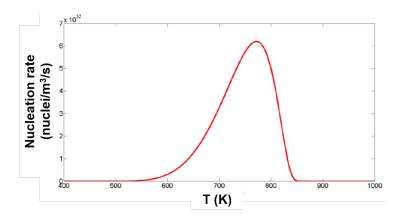

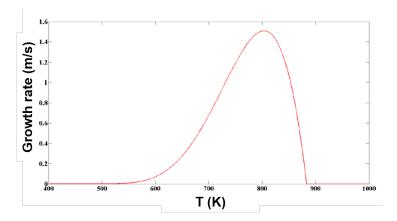

in which  $\tau$  is the time needed to establish the stationary state of nucleation and  $\delta t$  is the isothermal holding time based on the local temperature variation rate  $\delta T/\delta t$ . Knowing the values, for a specific material, of the thermodynamical parameters involved in this model, it is then possible to calculate the nucleation rate for any temperature. Fig.1.32 displays the nucleation rate in GST as a function of temperature (values for the thermodynamic parameters taken from [Gliere 2011]).

Figure 1.32: Evolution of the nucleation rate of GST as a function of temperature, showing a maximum around  $800~\mathrm{K}$ .

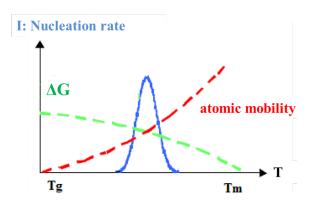

The gaussian-like shape of this curve, with a maximum around T = 800 K, is due to the fact that the nucleation mechanism is governed by two main forces: the driving energy of the crystallization ( $\Delta G_v$ ) and the atoms mobility, as shown in fig.1.33. At low temperatures (close to the glass transition temperature), the atomic mobility is low and so is the nucleation rate, even if the driving force of nucleation is strong. At high temperatures (close to the melting temperature), the atomic mobility increases strongly. However, the nucleation rate is still low because the driving force for crystallization is vanishing.

The nucleation rate rises and reaches its maximum at an intermediate temperature. This results from a trade-off between the two opposite effects which govern the mechanism.

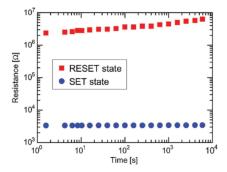

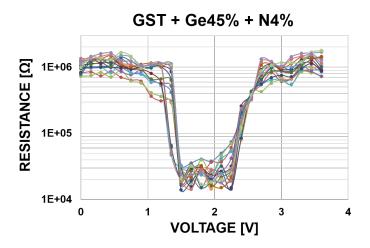

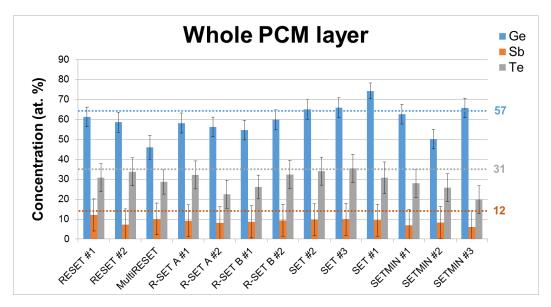

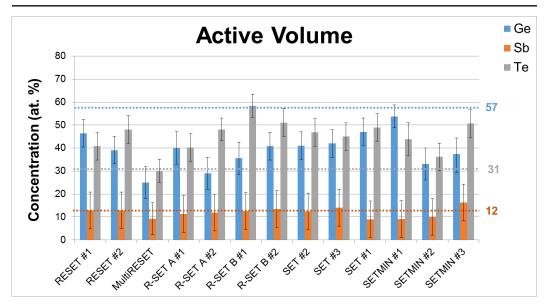

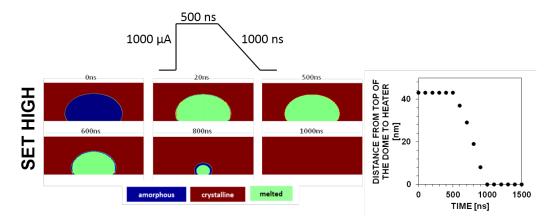

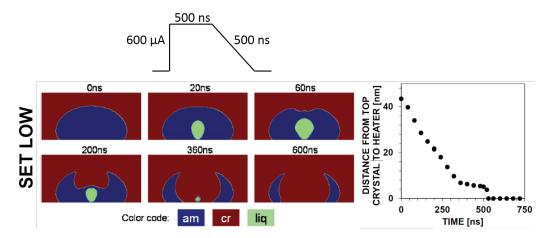

### 1.7.2 Growth