# Analysis and modeling of mismatch phenomena for advanced MOSFET s

Lama Rahhal

#### ▶ To cite this version:

Lama Rahhal. Analysis and modeling of mismatch phenomena for advanced MOSFET s. Micro and nanotechnologies/Microelectronics. Université de Grenoble, 2014. English. NNT: 2014GRENT061 . tel-01305050

#### HAL Id: tel-01305050 https://theses.hal.science/tel-01305050v1

Submitted on 20 Apr 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ DE GRENOBLE

#### **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano électronique et Nano Technologies

Arrêté ministériel: 7 août 2006

Présentée par

#### Lama RAHHAL

Thèse dirigée par **Gérard GHIBAUDO** and Co-Encadrée par **Aurélie BAJOLET**

Préparée au sein de l'Institut de Microélectronique Electromagnétisme et Photonique et le Laboratoire d'Hyperfréquences et de Caractérisation (IMEP/LAHC) et de l'entreprise STMicroelectronics dans l'École Doctorale d'Electronique, Electrotechnique, Automatique et Traitement du Signal (EEATS)

# Analyse et modélisation des phénomènes de mismatch des transistors MOSFET avancées

Thèse soutenue publiquement le « 06 Novembre 2014 », devant le jury composé de :

Mr. Abdelkader SOUIFI

Pr, INSA-Lyon Président

Mr. Jean-Michel PORTAL

Pr, Aix-Marseille Université Rapporteur

M. Nathalie MALBERT

Pr, Université de Bordeaux Rapporteur

M. Aurélie BAJOLET

ING, STMicroelectronics Crolles Co-Encadrante

Mr. Gérard GHIBAUDO

Pr, CNRS Alpes - IMEP/INPG Directeur de thèse

#### UNIVERSITÉ DE GRENOBLE

#### **THESIS**

To obtain the degree of

#### DOCTOR FROM UNIVERSITE DE GRENOBLE

Specialty: Nano technology and Nano electronics

Ministerial Order: 6 August 2006

Presented by

#### Lama RAHHAL

Directed by Gérard GHIBAUDO and co supervised by Aurélie BAJOLET

Prepared at Institut de Microélectronique Electromagnétisme et Photonique et le Laboratoire d'Hyperfréquences et de Caractérisation (IMEP/LAHC) and STMicroelectronics at École Doctorale d'Electronique, Electrotechnique, Automatique & Traitement du Signal (EEATS)

### **Analysis and modeling of mismatch phenomena for advanced MOSFET**

| To My Mum and the Memo                                    | ry of my dad       |

|-----------------------------------------------------------|--------------------|

| You are always present in my heart, in my mind and in eve | ry step of my life |

|                                                           |                    |

|                                                           |                    |

|                                                           |                    |

|                                                           |                    |

|                                                           |                    |

|                                                           |                    |

### Acknowledgments

I start by thanking all the persons I met and collaborated with during the course of my Ph.D. at ST, IMEP, in Grenoble and Crolles, and in all the conferences and meetings I attended.

My thanks go to Pr. Abdelkader SOUIFI and Pr. Nathalie MALBERT and Pr. Jean Michel Portal for accepting to be part of my thesis Jury.

My thanks also go to my thesis director, Gerard GHIBAUDO. Thank you, Gerard, for your constant availability and all the scientific goals you helped me achieve. I appreciated working with you on a scientific and human level. Thank you for your good humor, your modesty and your constant encouragement.

I also thank my co-supervisor Aurelie BAJOLET for believing in me. Thank you, Aurelie, for your scientific and human advice, constant help and all the hours and energy you dedicated to my thesis.

My thanks also go to Emanuel VINCENT for giving me the opportunity to work in the ECR team. I would also like to thank my line DDCC manager Julien ROSA for his management qualities, for his deep knowledge on electrical characterization, and for his advice. I also thank you, Julien, for your constant good humor and for listening to all my knee and kiné stories and daily adventures hehehe (with the participation of Xavier, Wafa and Stephane too :P) !!!! I appreciated being part of your team. I also thank the DDCC Team, Antoine CROS, Sebastien HANDLER, Stephane RICQ, Jean-Philippe MANCEAU, Cheikh DIOUF and Flore KERGOMARD for the great team environment. You all participated to this thesis and were part of this work and the articles produced. My thanks also go to Helene PITOLET who accepted me in her team for an internship that resulted into this Ph.D. thesis. Thank you, Helene, for giving me this opportunity and for being a nice and agreeable colleague. My thanks also go to Xavier FEDERSPIEL. Thank you, Xavier, for all the scientific discussions, especially in the last part of this thesis, and also for being a nice, friendly and smiley desk neighbor.

My thanks also go to Guillaume BERTRAND for all the work, measurements and discussions he helped me achieve for chapter III.

My thanks to Damien ANGOT who has contributed in chapter VI of this thesis. Thank you for all the manip we did together:) Working with you was very agreeable!

My thanks also go to my ST friends Wafa ARFAOUI, Anna SZUCS, Kaya-Can AKYEL, Flore KERGOMARD and Antoine CROS, once again. I appreciated all our pausescafé and funny discussions.

Thanks to all ST colleagues for making this Ph.D nice and humanly agreeable.

I would also like to thank my friends and second family in Grenoble, especially Christine HAJJAR, Christine BAKHOUS, George BAKHOUS, Micheline BAKHOUS, Chady NASRALLAH, Joseph KORTBAOUI, Roberto MRAD, Chirine et Charbel El KAED, who made my thesis years full of laughter and funny moments. I also thank you for being there in good and hard moments.

To my family who always loved and supported me. All my thanks and love to: Mama (Elham ATALLAH), Nayla RAHHAL, Dima RAHHAL, Nadim RAHHAL, Rawad RAHHAL, Uncle Riad RAHHAL, tante Berte HOJEIBAN, Uncle George HOJEIBAN, Ali HAMIE, Daniel HAMIE, Ziad RAHHAL, Marwan RAHHAL and his familly, Tante Victoria EL HAJJ, Tante May RAHHAL, Beit MALEK (in total :P). Thank you for loving me, for being always there for me, for all your encouragements, prayers, constant help, support and endless love.

To my dad Rabih RAHHAL who helped me be the person I am now. Thank you for your love, for all your advices and all your lectures :D. Now that I write this acknowledgement, it is the ninth anniversary of your death. I wish that you are content and at peace. I dedicate this manuscript and every step of my life to your memory. I wish that you are not worried any more about your teenage girl. This girl has grown up and became a doctor, she will be strong and move on as she promised you. Ok she still gets herself in trouble sometimes :P hmmmm... most of the times :D but more importantly she loves and misses you so much.

Finally to Giuseppe SCHIAVONE, my dearest one, thank you for your love, your constant help, support and encouragements. Thank you for all your Grenoble allez/retour plane trips: D, for standing my moody states.... With you, life is full of laugher, love, joy and hope. With you, life is simply better.

It is always hard to put an end to these three years. They were full of good and hard moments. Many PLANE TRIPS!!! (PS: for the future ST mismatch Ph.D., you will probably read this thesis, and so you won't think I'm crazy :P, I have plane phobia :\$) and conferences.

Many experiments that worked and others that did not.... Many joyful moments and disappointing ones... But most importantly, if I went back in time I would definitely do it again.

# **Table of contents**

| ACKNOWLEDGMENTS                                                                | 6       |

|--------------------------------------------------------------------------------|---------|

| TABLE OF CONTENTS                                                              | 9       |

| LIST OF ACRONYMS                                                               | 14      |

| GENERAL INTRODUCTION                                                           | 15      |

| CHAPTER I                                                                      | 19      |

| TRANSISTOR MOSFET: THEORY, CHARACTERIZATION AND MI                             | ISMATCH |

| CONCEPT                                                                        |         |

| I.1 MOSFET transistor                                                          | 20      |

| I.1.1 Operation principle                                                      | 20      |

| I.1.2 Electrical figures of merits for static performance                      |         |

| I.1.3 Operating Regimes                                                        | 22      |

| I.1.4 Parasitic effects due to the Miniaturization of MOS transistors          | 28      |

| I.2 Methodology of extraction of MOS transistors parameters                    | 31      |

| I.2.1 Maximum slope method                                                     | 32      |

| I.2.2 Constant current method                                                  | 33      |

| I.2.3 Y function method                                                        | 34      |

| I.3 Types of electrical variability                                            | 36      |

| I.4 Local variability                                                          | 37      |

| I.4.1 Measurement phase                                                        | 37      |

| I.4.2 Gaussian distribution verification                                       | 38      |

| I.4.2.a Data plot                                                              | 38      |

| I.4.2.b Gaussian law verification                                              | 39      |

| I.4.3 Data filtering and separation between systematic and stochastic mismatch | 40      |

| I.4.4 Concept and computation of systematic mismatch                           | 41      |

| I.4.4.a Concept of systematic mismatch                                         | 41      |

|                                                                                                                                                                         | 42                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| I.4.4.c Confidence interval                                                                                                                                             | 42                             |

| I.4.5 Stochastic mismatch                                                                                                                                               | 43                             |

| I.4.5.a Concept and computation of stochastic mismatch                                                                                                                  | 43                             |

| I.4.5.b Confidence interval                                                                                                                                             | 44                             |

| I.4.5.c Deviations from Pelgrom's Law                                                                                                                                   | 45                             |

| I.5 Mismatch measurement system and test structures                                                                                                                     | 46                             |

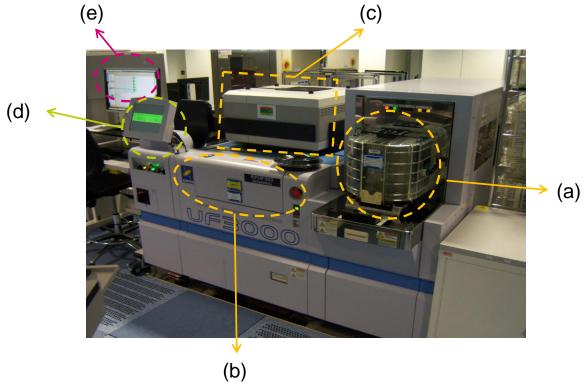

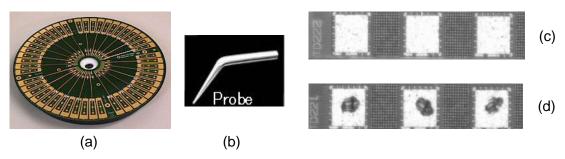

| I.5.1 Mismatch measurement system                                                                                                                                       | 46                             |

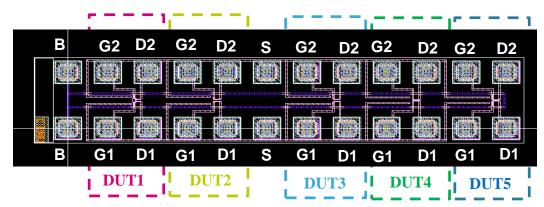

| I.5.2 Mismatch test structures                                                                                                                                          | 47                             |

| I.6 Stochastic mismatch contributions and effects in Bulk technology: state of the art                                                                                  | 48                             |

| I.7 Improvements due to FD SOI technology                                                                                                                               | 51                             |

| I.7.1 Main advantages of SOI over BULK technology                                                                                                                       | 52                             |

| I.7.2 Stochastic mismatch contributions and effects in FD SOI technology: State of the art                                                                              | 53                             |

| I.8 Conclusions                                                                                                                                                         | 55                             |

| CHAPTER II                                                                                                                                                              | 56                             |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT                                                               |                                |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTAGE                                                                                                                  |                                |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT                                                               | GE AND                         |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT MISMATCH MODEL                                                | GE AND57                       |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT MISMATCH MODEL  II.1 Introduction and motivation of this work | GE AND57                       |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT MISMATCH MODEL  II.1 Introduction and motivation of this work | <b></b> 57 59 63               |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT MISMATCH MODEL  II.1 Introduction and motivation of this work | 57 59 63                       |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTAGE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT MISMATCH MODEL  II.1 Introduction and motivation of this work | 57 57 59 63 64                 |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT MISMATCH MODEL  II.1 Introduction and motivation of this work | 57                             |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT MISMATCH MODEL  II.1 Introduction and motivation of this work | <b> 57  59  63  64  65  65</b> |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT MISMATCH MODEL  II.1 Introduction and motivation of this work | <b>5E AND</b>                  |

| NEW METHOD FOR THE EXTRACTION OF THE THRESHOLD VOLTACE CURRENT GAIN FACTOR MISMATCH AND NEW DRAIN CURRENT MISMATCH MODEL  II.1 Introduction and motivation of this work | <b>GE AND</b>                  |

# CASCODE CONFIGURATION AS A SUBSTITUTE TO LDE MOSFET FOR IMPROVED ELECTRICAL MISMATCH PERFORMANCE

| III.1 Introduction and motivation of this work                                                          | 75      |

|---------------------------------------------------------------------------------------------------------|---------|

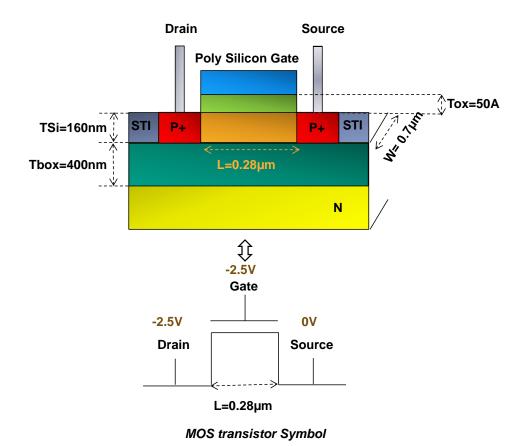

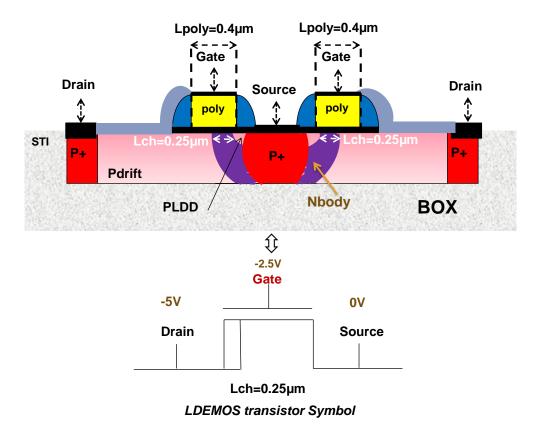

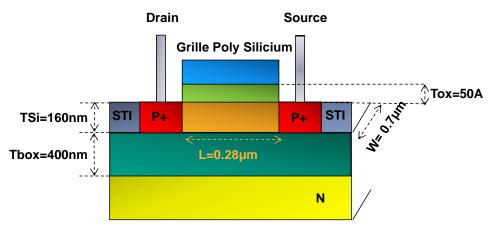

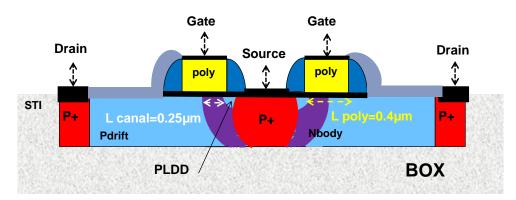

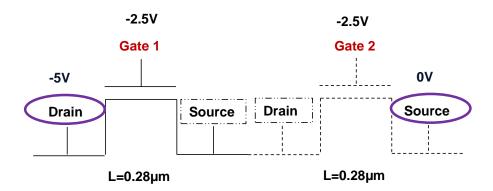

| III.2 Experimental details                                                                              | 77      |

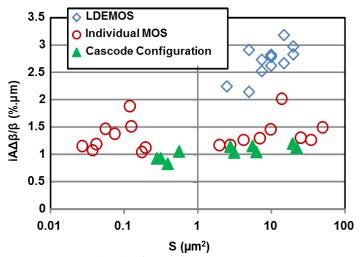

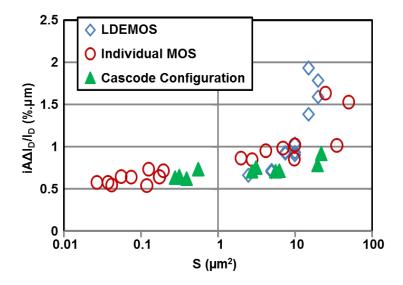

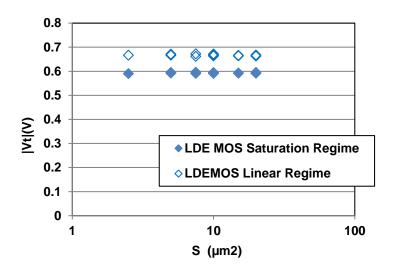

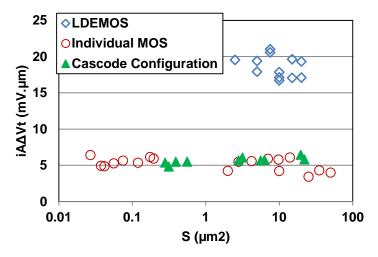

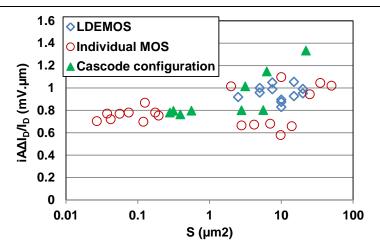

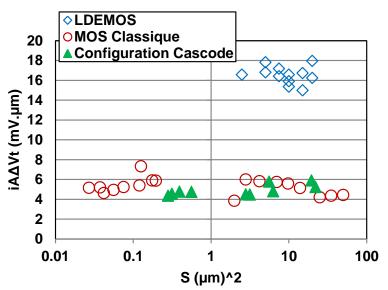

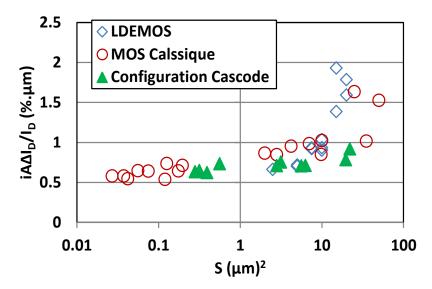

| III.3 Vt, $\beta$ and $I_D$ mismatches comparison for LDEMOS, Individual and cascode configuration devi | ices 78 |

| III.3.1 Linear Regime                                                                                   | 78      |

| III.3.1.a Vt and β mismatch                                                                             | 78      |

| III.3.1.b I <sub>D</sub> mismatch                                                                       | 82      |

| III.3.2 Saturation Regime                                                                               | 85      |

| III.3.2.a Vt mismatch                                                                                   | 85      |

| III.3.2.b I <sub>D</sub> mismatch                                                                       | 88      |

| III.4 Conclusions and perspectives                                                                      | 92      |

| CHAPTER IV                                                                                              | 94      |

| PERFORMANCES IN 28NM GATE FIRST BULK TECHNOLOGY  IV.1 Introduction (State of the art)                   | 95      |

| IV.2 Experimental setup                                                                                 | 95      |

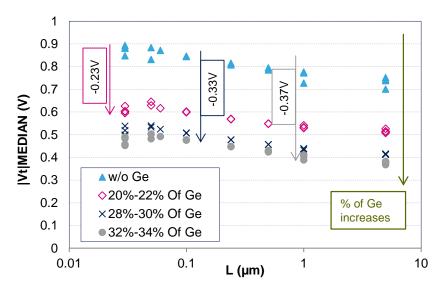

| IV.3 Electrical parameters mismatch characterization on transistors without pocket implants             | 97      |

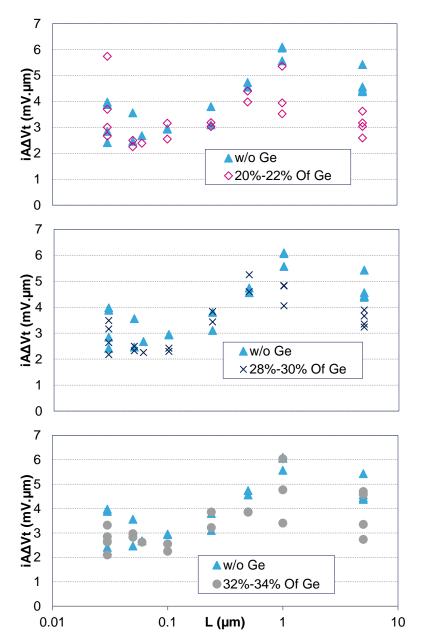

| IV.3.1 Threshold Voltage mismatch                                                                       | 97      |

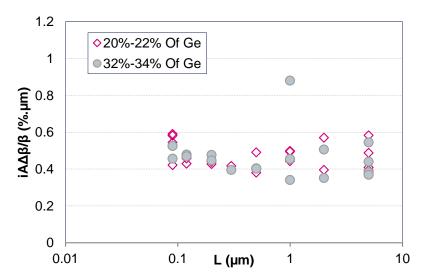

| IV.3.2 Current gain factor mismatch                                                                     | 100     |

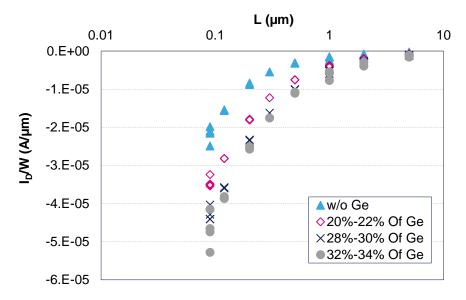

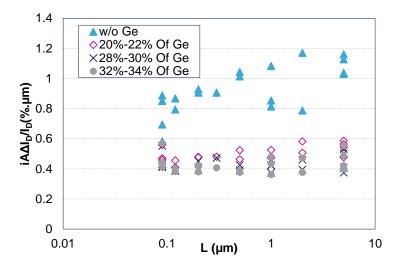

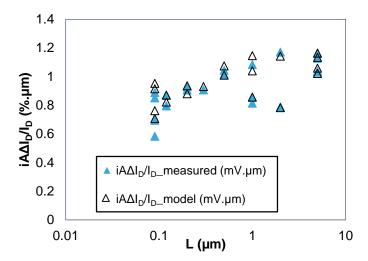

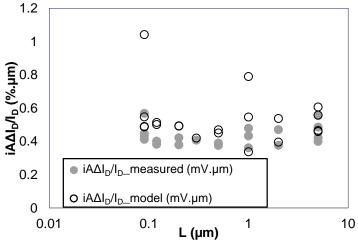

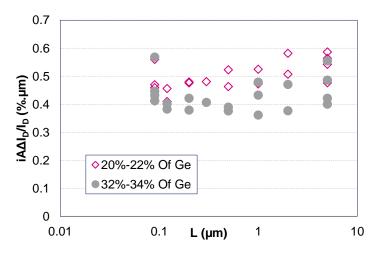

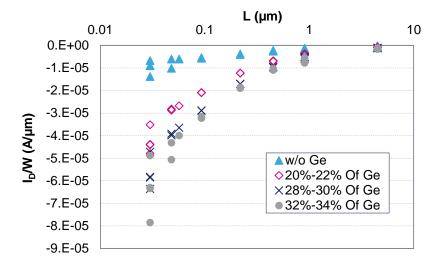

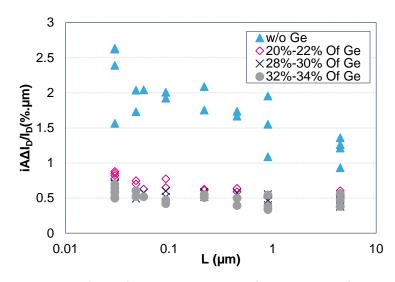

| IV.3.3 Drain current mismatch                                                                           | 102     |

| IV.4 Electrical parameters mismatch characterization on transistors with heavily pocket implants        | 105     |

| IV.4.1 Threshold Voltage mismatch                                                                       | 105     |

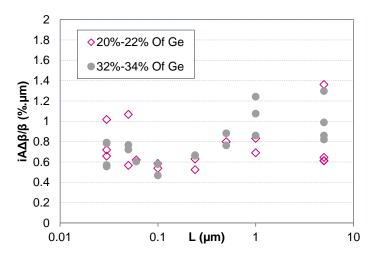

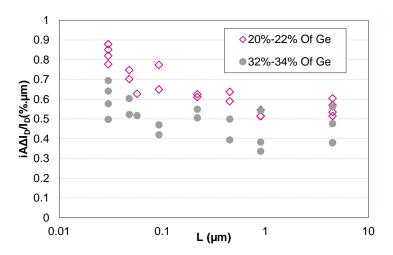

| IV.4.2 Current gain factor mismatch                                                                     | 108     |

| IV.4.3 Drain current mismatch                                                                           | 109     |

| IV.5 Conclusions                                                                                        | 112     |

| CHAPTER V                                                                                               | 114     |

# MISMATCH CHARACTERIZATION OF 20NM GATE-LAST BULK CMOS TECHNOLOGY

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 115                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| V.2 Experimental details                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 115                |

| V.3 Comparison of devices with channel pocket implants and different oxide thicknesses EO                                                                                                                                                                                                                                                                                                                                                                                   | T (Tox) in         |

| 20nm Gate-Last technology                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 117                |

| V.3.1 Threshold Voltage mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                            | 117                |

| V.3.2 Current gain factor mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                          | 122                |

| V.3.3 Drain Current mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                | 122                |

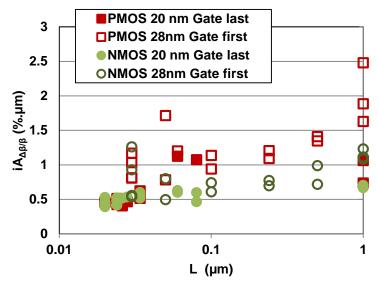

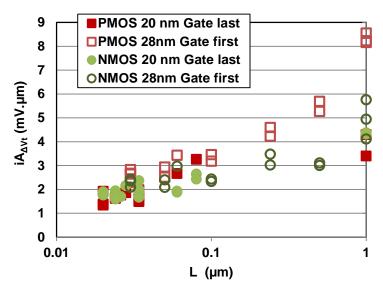

| V.4 Comparison between 28nm Gate-first and 20 nm Gate-last Bulk technologies                                                                                                                                                                                                                                                                                                                                                                                                | 125                |

| V.4.1 Threshold Voltage mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                            | 125                |

| V.4.2 Current gain factor mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                          | 128                |

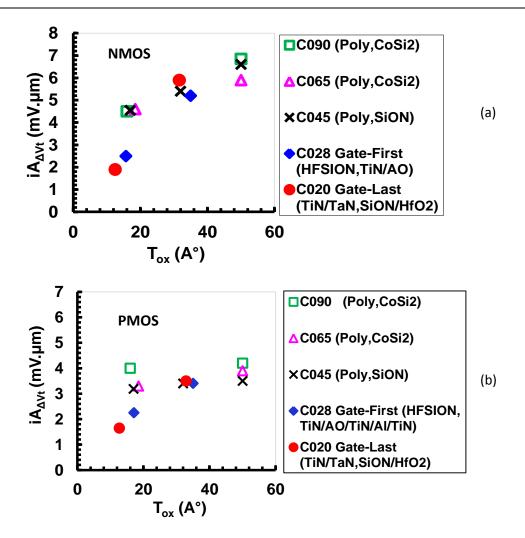

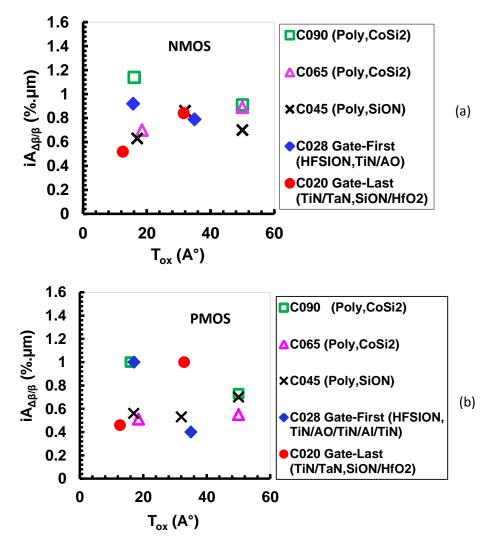

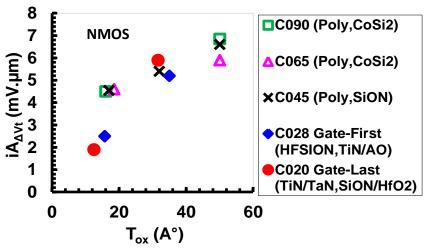

| V.5 Vt and β mismatch trends as a function of Tox                                                                                                                                                                                                                                                                                                                                                                                                                           | 129                |

| V.6 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 131                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |

| MISMATCH BEHAVIOR IN ADVANCED FD SOI CMOS TECHNOLOGI                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |

| VI.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 134                |

| VI.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 134                |

| VI.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 134<br>135         |

| VI.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |

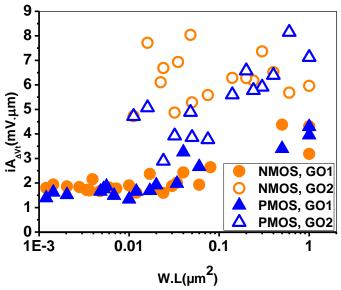

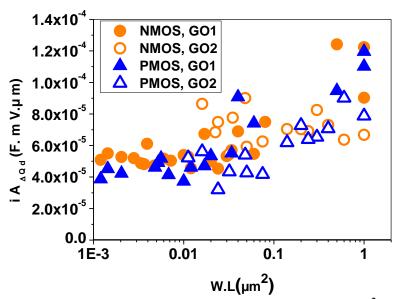

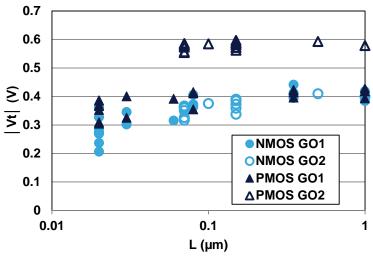

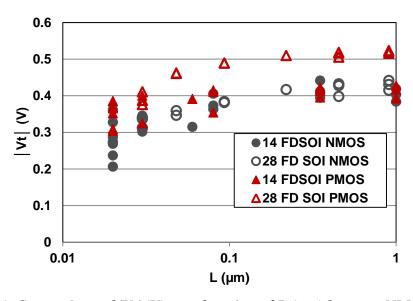

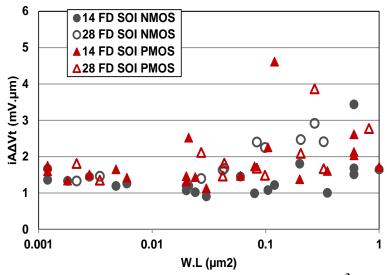

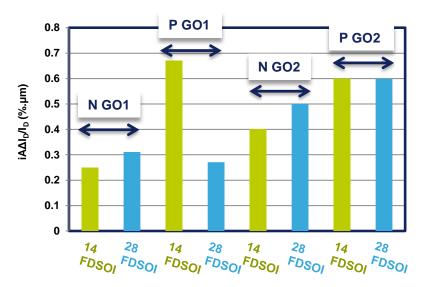

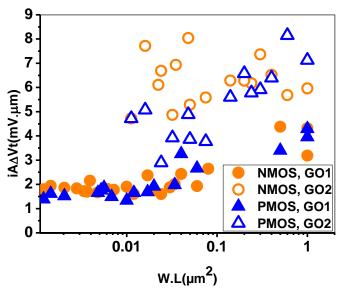

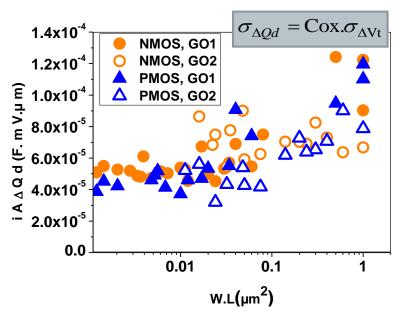

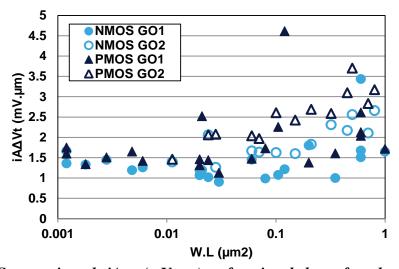

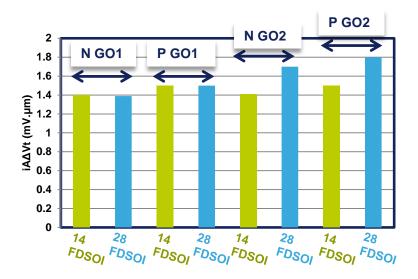

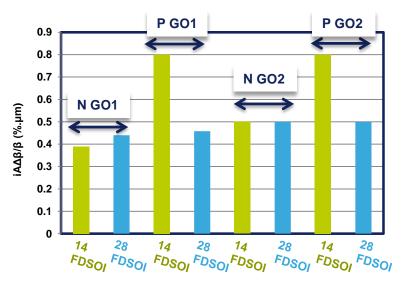

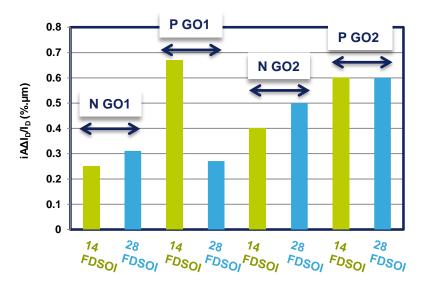

| VI.1 Introduction  VI.2 Mismatch behavior in 14nm and 28 nm FD SOI CMOS technology  VI.2.1 Experimental details  VI.2.2 Effect of EOT: Comparison between GO1 and GO2 for 14nm FD SOI technology  VI.2.2.a Threshold Voltage mismatch                                                                                                                                                                                                                                       | 134135136137       |

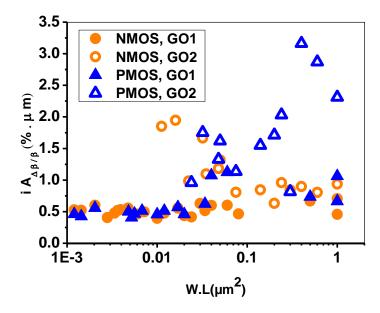

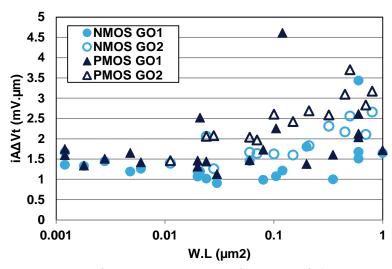

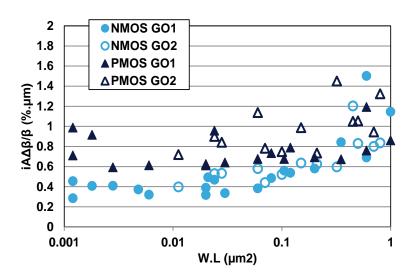

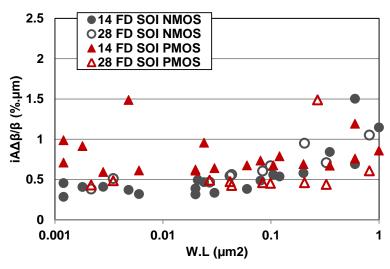

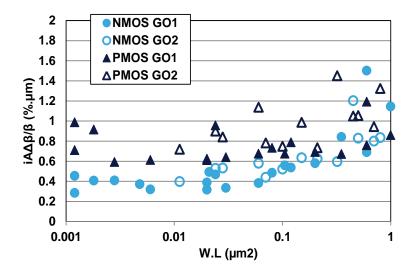

| VI.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 134135135136137138 |

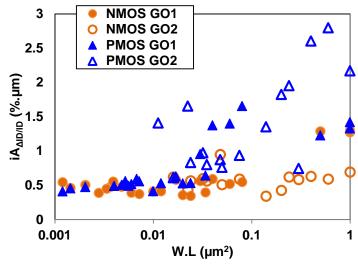

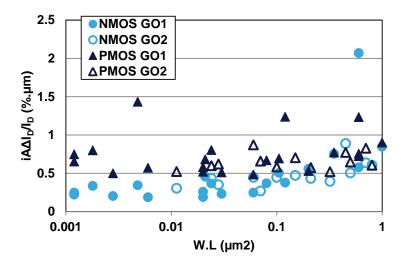

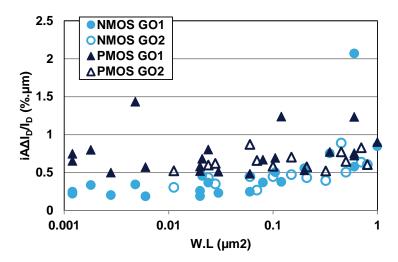

| VI.1 Introduction  VI.2 Mismatch behavior in 14nm and 28 nm FD SOI CMOS technology  VI.2.1 Experimental details.  VI.2.2 Effect of EOT: Comparison between GO1 and GO2 for 14nm FD SOI technology  VI.2.2.a Threshold Voltage mismatch  VI.2.2.b Current gain factor mismatch  VI.2.3.c Drain current mismatch                                                                                                                                                              |                    |

| VI.2 Mismatch behavior in 14nm and 28 nm FD SOI CMOS technology  VI.2.1 Experimental details  VI.2.2 Effect of EOT: Comparison between GO1 and GO2 for 14nm FD SOI technology  VI.2.2.a Threshold Voltage mismatch  VI.2.2.b Current gain factor mismatch  VI.2.3.c Drain current mismatch  VI.2.3 Comparison between 28nm and 14 nm FD SOI technologies                                                                                                                    |                    |

| VI.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |

| VI.2 Mismatch behavior in 14nm and 28 nm FD SOI CMOS technology  VI.2.1 Experimental details  VI.2.2 Effect of EOT: Comparison between GO1 and GO2 for 14nm FD SOI technology  VI.2.2.a Threshold Voltage mismatch  VI.2.2.b Current gain factor mismatch  VI.2.3.c Drain current mismatch  VI.2.3 Comparison between 28nm and 14 nm FD SOI technologies  VI.2.3.a Threshold Voltage mismatch  VI.2.3.b Current gain factor mismatch  VI.2.3.b Current gain factor mismatch |                    |

| VI.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |

| VI.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |

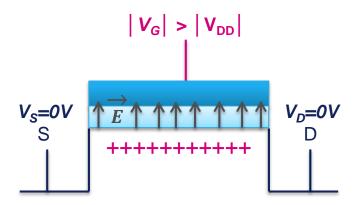

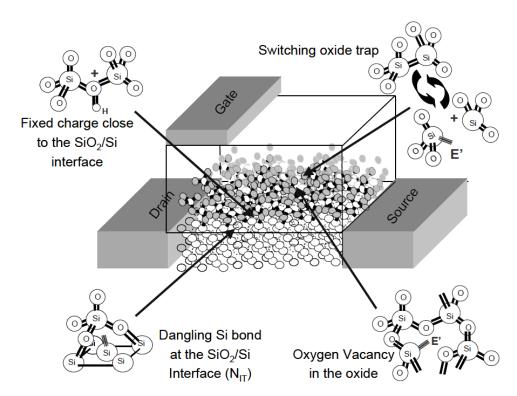

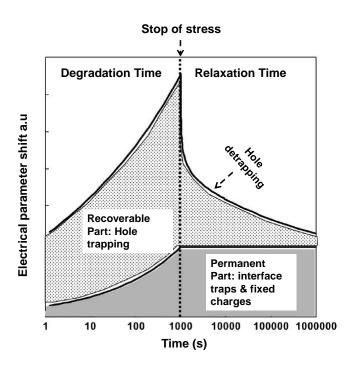

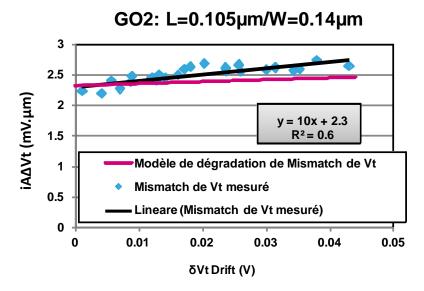

| VI.3.2 Experimental details                                                             | 148 |

|-----------------------------------------------------------------------------------------|-----|

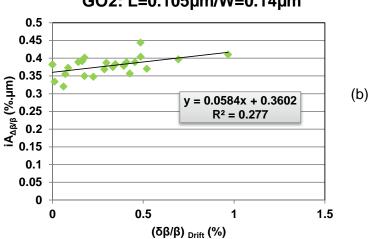

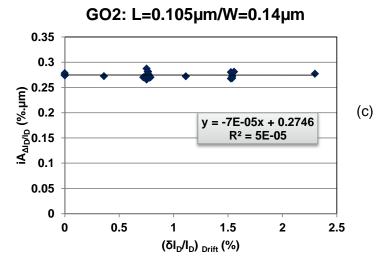

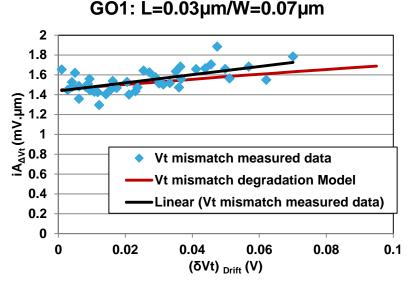

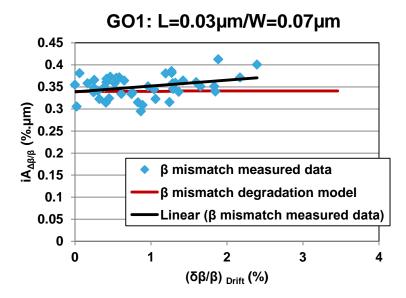

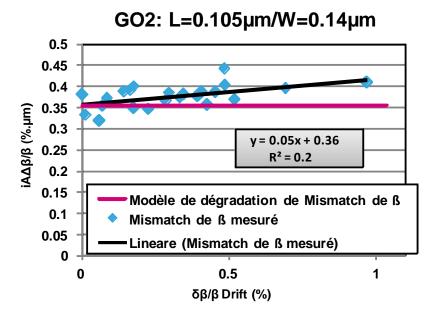

| VI.3.3 Mismatch behavior in response to NBTI stress for GO1 and GO2 28nm FD SOI devices | 150 |

| VI.3.3.a Experimental results                                                           | 150 |

| VI.3.3.b Theoretical models and discussions                                             | 155 |

| VI.4 Conclusions                                                                        | 159 |

| GENERAL CONCLUSIONS AND PERSPECTIVES                                                    | 161 |

| AUTHOR PUBLICATIONS                                                                     | 167 |

| International Conferences:                                                              | 167 |

| Journals:                                                                               | 167 |

| BIBLIOGRAPHY                                                                            | 169 |

| APPENDIX A                                                                              | 187 |

| APPENDIX B                                                                              | 188 |

| Thesis Abstract in French / Résumé de thèse en Français                                 | 188 |

| B.I Introduction Générale                                                               | 188 |

| B.II Motivations et objectifs de cette thèse                                            | 189 |

| B.III Principaux résultats et conclusions générales                                     | 190 |

| B.IV Articles                                                                           | 215 |

| B.V Bibliographies                                                                      | 216 |

| RÉSUMÉ:                                                                                 | 217 |

| ABSTRACT:                                                                               | 217 |

## List of acronyms

MOSFET: Metal-Oxide-Semiconductor Field Effect Transistors

SRAM: Static Random Access Memory

**EOT: Electrical Oxide Thickness**

SCZ: Space Charged Zones

FD SOI: Fully Depleted Silicon On Insulator

PD SOI: Partially Depleted Silicon On Insulator

**BOX**: Buried Oxide

SCE: Short Channel Effect

DIBL: Drain Induced Barrier Lowering

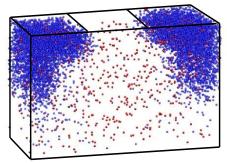

**RDF: Random Dopant Fluctuations**

LER: Line Edge Roughness

PGG: Poly-Gate Granularity

MGG: Metal Gate Granularity

LDE: Lateral drain extended

NBTI: Negative-Bias Temperature Instability

### **General Introduction**

#### **General challenges in Microelectronics**

As its name suggests, the field of microelectronics focuses on the study and fabrication of electronic components at the micro and nano scale, connected together on the same substrate to form Integrated Circuits (IC). The role of IC is to implement one or many electronic functions of different complexity levels on the same chip. IC find extensive use in electronic systems such as smart phones, numerical televisions, credit cards, computers, videogame consoles, devices for automotive, military and even aerospace applications. Any perspective progress towards enhancing such systems starts from improvements in the field of microelectronics. The driving parameters in research aimed at achieving enhanced IC performance are speed, integration density, and reduced power consumption and production costs.

The basic components of integrated circuits are transistors, diodes, resistors, capacitors, and inductors. In 1965 Gordon Moore in [Moore 65] predicted that the number of transistors that can be hosted in circuits of a given size will roughly double with every year of development, enabling exponential improvement in system-level performance. Moore revised his prediction at a later date [Moore 75] and modified it by stating that the number of transistors in microprocessors would double every two years. This prediction is known as "scaling trend", and reflects the research efforts that pursue the continuous miniaturization of the dimensions of MOS transistors. MOS with reduced size achieve high saturation current, which translates into an increase in the operating speed of the products. The challenge with such devices is however to maintain the leakage current low enough in order to limit the power consumption of products, especially if powered by batteries.

Another challenge faced by researchers chasing the "scaling trend" is the transistor local variability. This phenomenon is a consequence of process variations (random microscopic fluctuations of the device architecture) and causes identically designed transistors to exhibit different electrical behavior. It became mandatory, therefore, for the microelectronics industry to understand the physical causes of such variability, to quantify them, and to propose

solutions that enable reduced variability, with the aim of guaranteeing reliable performance in integrated circuits.

#### **Motivation of this work**

For correct operation, certain analog (current mirrors, amplifiers, etc.) and digital (Static Random Access Memory, SRAM) circuits require pairs of transistors, which are identically designed and laid out in an identical environment, in order to ensure identical electrical performances. Real devices, however, suffer from random local variations in the electrical parameters, a problem referred to as mismatch. Pelgrom *et al.* demonstrated a mismatch law that establishes a direct dependency between the local fluctuations of an electrical parameter P and the channel area (denoted as S) through a coefficient A [Pelgrom89]. This, in combination with the miniaturisation of MOSFET devices, has set the ground for an increasing interest in achieving a deeper understanding of the causes of the mismatch phenomena and characterising their effects, with the objective of guaranteeing reliable integrated circuits performance.

In light of the presented scenario, the purpose of the work reported in this thesis is to:

- o Optimize the measurement methodology of mismatch phenomena;

- Characterize different configurations of MOS transistors in order to propose optimized design architectures for specific applications;

- Analyze and model the mismatch phenomena observed in advanced Bulk and Silicon

On Insulator (SOI) MOSFET transistors;

- Analyze and model the mismatch phenomena with the transistor aging in advanced MOSFET transistors.

#### Thesis layout

The first chapter presents the concept of MOS transistor, reviews extraction techniques and the principles of variability. The following chapters are centered on four major subjects, as outlined below.

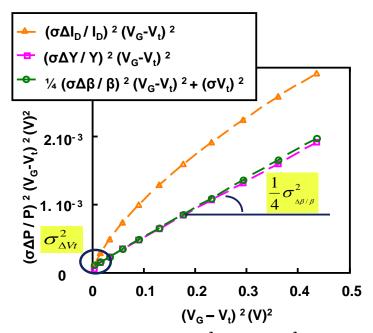

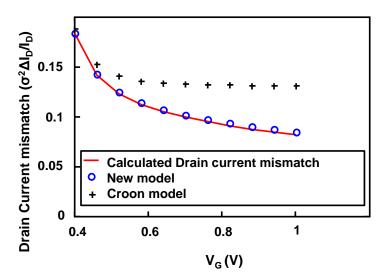

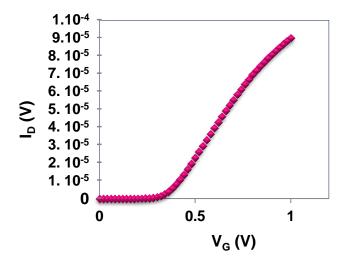

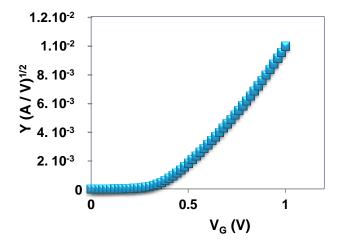

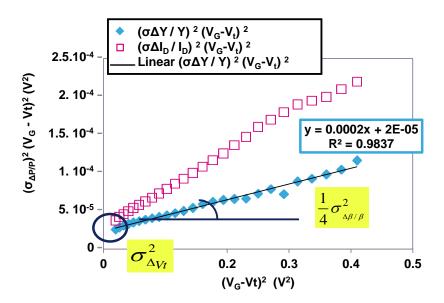

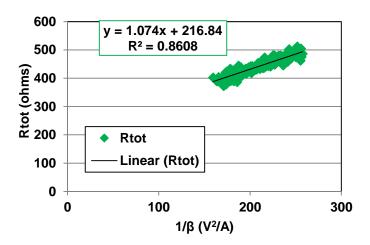

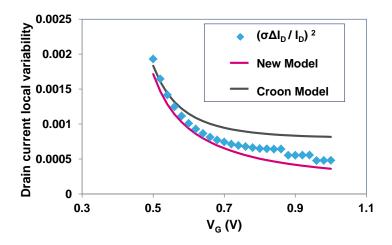

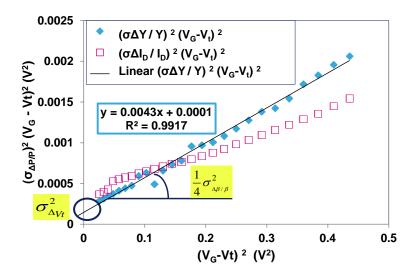

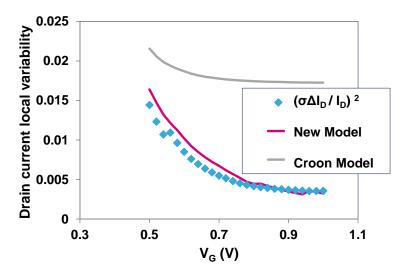

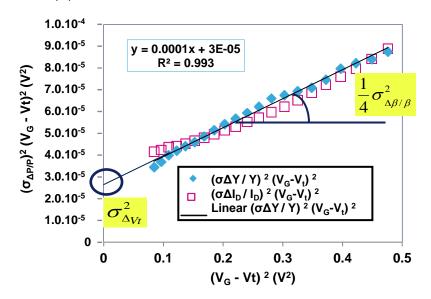

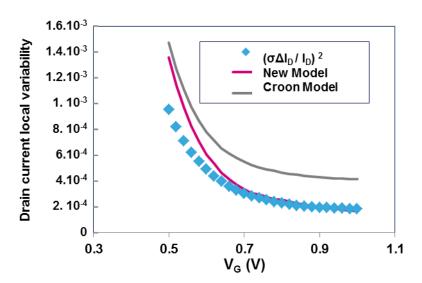

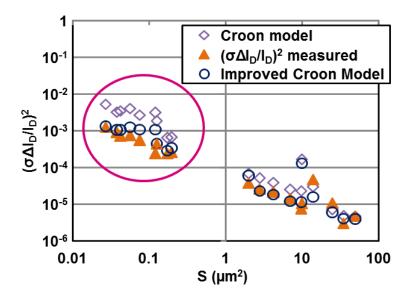

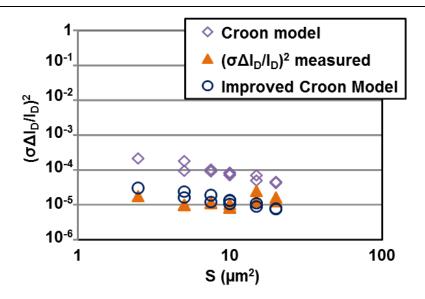

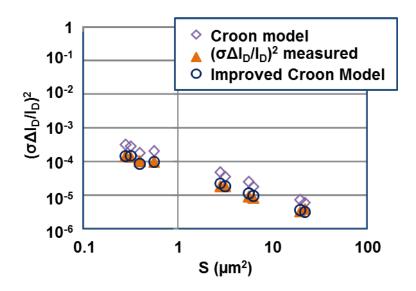

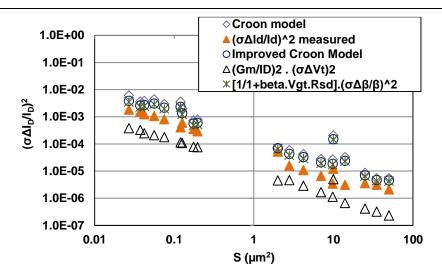

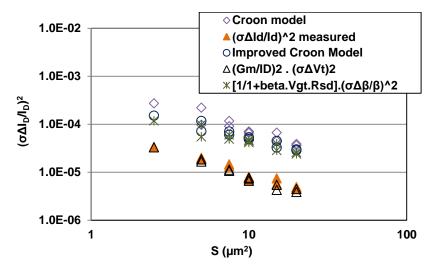

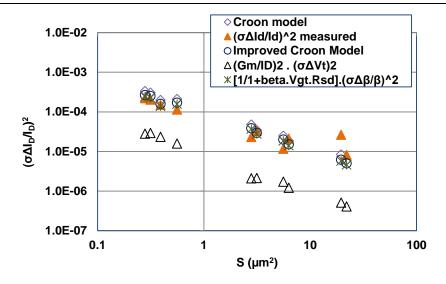

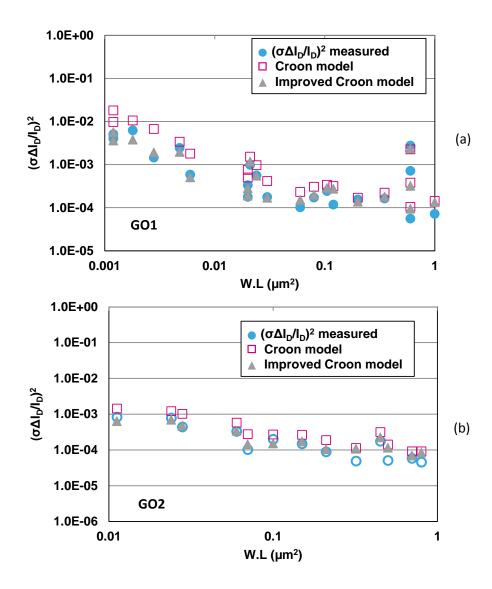

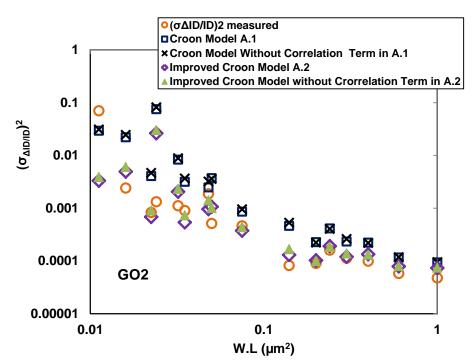

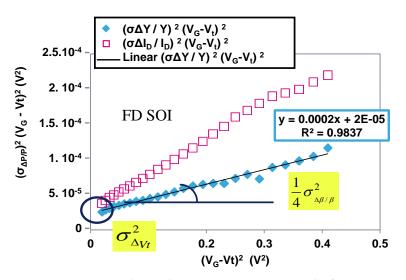

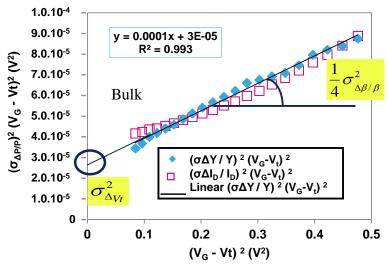

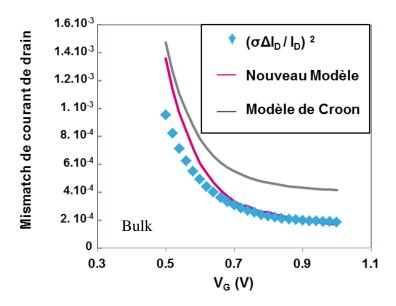

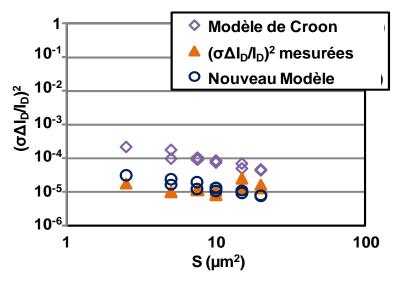

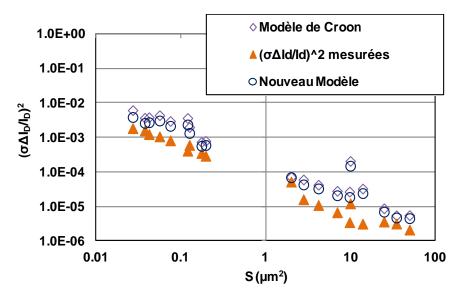

- Chapter II focuses on the methodologies for the extraction and modeling of the electrical parameters of MOS transistors. A new methodology of mismatch extraction parameters is proposed, with a thorough discussion of its advantages and applications. A new drain current mismatch model is also proposed which expands from the strategy published by Croon [Croon07] by adding an Rsd contribution and neglecting the mutual correlation between parameters.

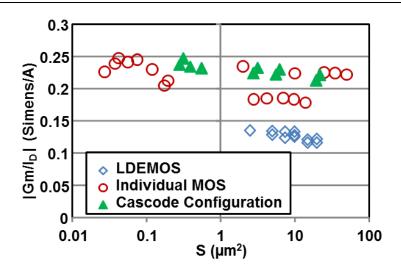

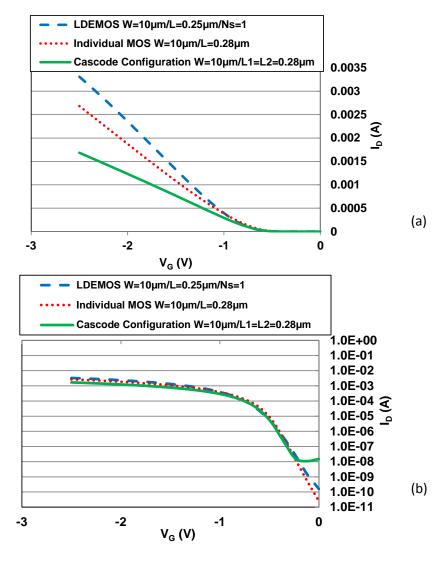

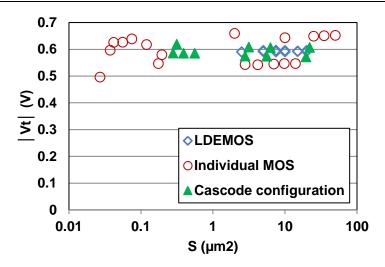

- Chapter III focuses on the characterization of MOS transistors of different design architectures in various configurations for high drain current design applications. A comparison of three different MOS transistor types and configurations for high drain current applications is reported. Conclusions and perspectives are discussed in detail, with the aim of proposing the most convenient MOS configuration or type for specific applications.

- After these methodology and design considerations, the studies are oriented on mismatch phenomena in advanced technologies:

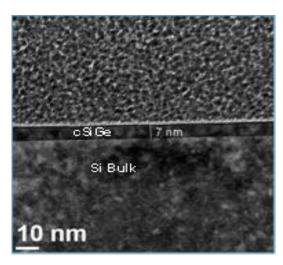

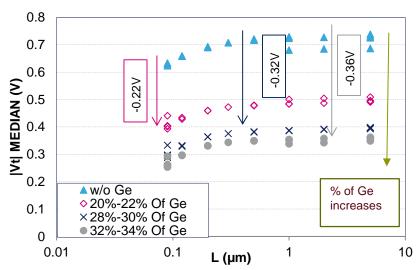

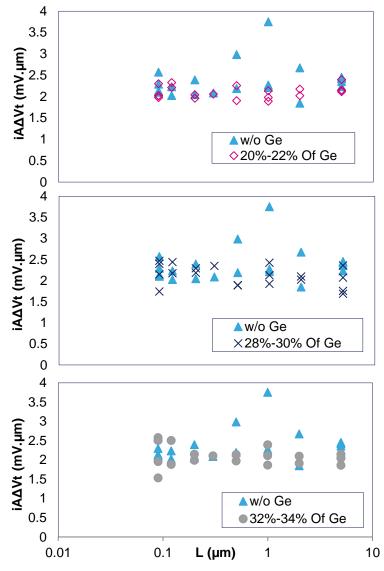

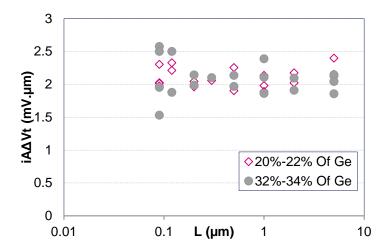

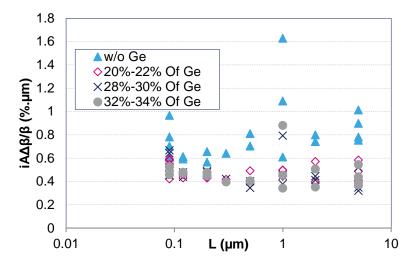

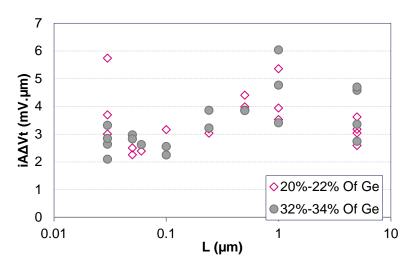

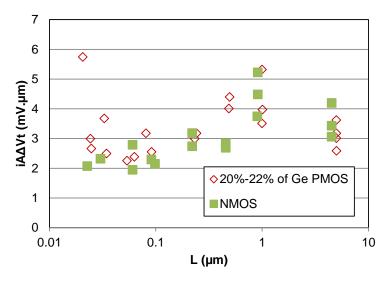

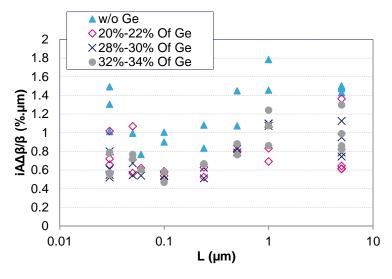

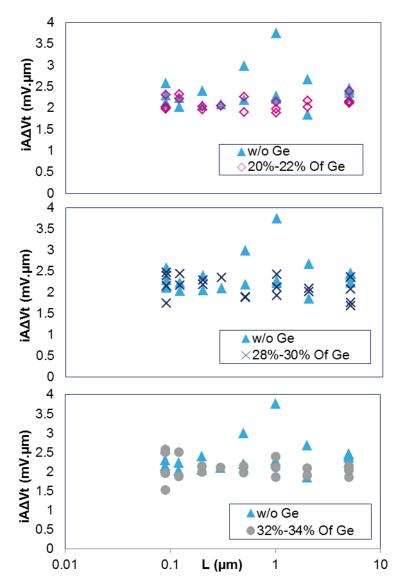

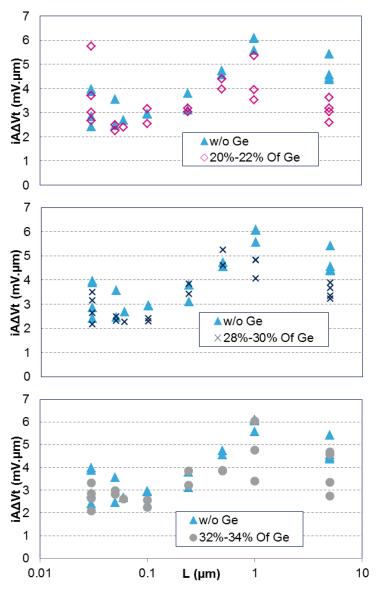

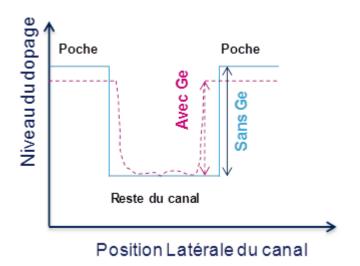

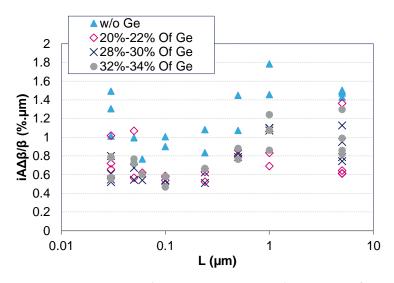

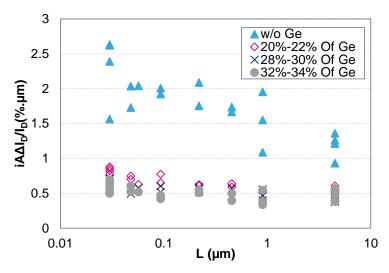

- O Chapter IV treats the effect of Germanium (Ge) on mismatch phenomena in the case of the PMOS 28 nm Bulk technology node. The conducted work comprises a detailed study on threshold voltage, current gain factor and drain current for transistors with and without pocket implants.

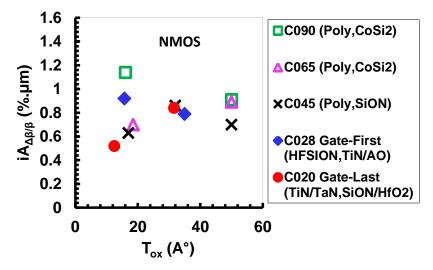

- o In chapter V, the contribution of the metal gate granularity to electrical parameters mismatch is studied and potential solutions to eliminate the associated effects are discussed. This study is conducted on 20nm Gate—last BULK technology, and a performance comparison is presented with respect to the 28nm Bulk technology. A general review of the mismatch contributions in Bulk technology is further discussed by analyzing the observed trends over the technology nodes from 90nm BULK ST down to 20 nm.

- Chapter VI discusses two aspects of advanced FDSOI technologies. The mismatch trends of 14nm Fully Depleted Silicon On Insulator (FD SOI) technology are first presented, followed by a comparison with the 28nm FD

SOI technology. The second aspect is instead centered on the mismatch trends observed with MOS transistor aging. To this end, NBTI stress tests have been conducted on PMOS 28nm FDSOI transistors, and a general study of the mismatch of electrical parameters as a function of the quantity of produced traps or defects is presented.

A final section concludes this manuscript by summing up the reported findings and offering perspectives for future work.

## **Chapter I**

# Transistor MOSFET: Theory, characterization and mismatch concept

After a brief description of MOS transistor concept, types, operation regimes and electrical parameters, this chapter mainly discusses the different types of electrical variability, focusing particularly on the concept of stochastic mismatch.

#### This chapter is divided in eight sections:

- Section I presents the concepts of Bulk MOS transistor and operation regimes.

- Section II is focused on the electrical parameters extraction methods used in this thesis.

- Section III introduces the different types of electrical variability.

- Section IV explains the local variability phenomenon called mismatch and further presents the differentiation between stochastic and systematic mismatch. This section also explains in detail the mismatch causes, extraction techniques, and effects.

- Section V describes the measurement system and the test structures used in this thesis to characterize the stochastic mismatch.

- Section VI presents the present state of the art for BULK technology in terms of mismatch.

- Section VII explains the improvement in MOS transistors performance achieved by adopting the SOI technology. This section also provides a detailed description of the state of the art for this technology in terms of mismatch.

- Finally, section VIII draws global conclusions from all the concepts illustrated in the chapter.

#### I.1 MOSFET transistor

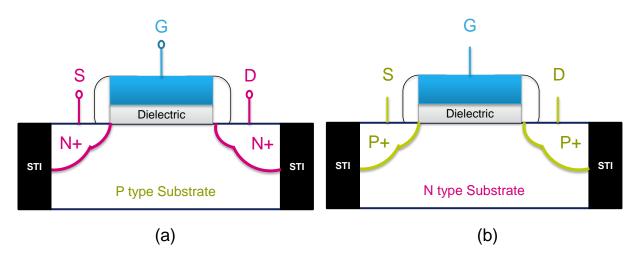

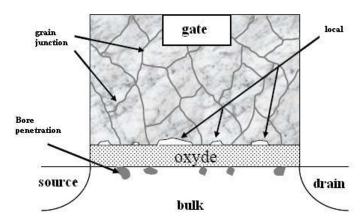

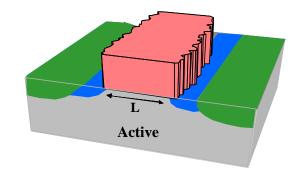

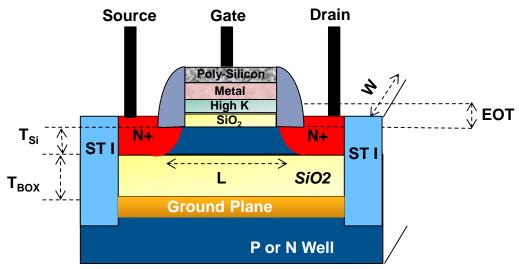

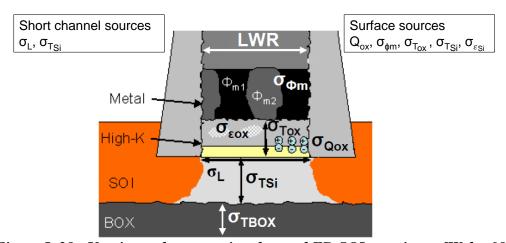

One of the basic elements of integrated circuits is the Metal Oxide Semiconductor Field-Effect (MOSFET) transistor. This device is comparable to an electrical switch, as its principal function is to alternatively pass or block an electrical current. The MOS transistor in Figure I. 1 is fabricated on bulk silicon, over active zones isolated by two trenches of oxide called STI (shallow trench isolation). It is mainly composed of:

- o A silicon substrate doped P (NMOS transistor) or N (PMOS transistor).

- An insulating dielectric layer. It is usually SiO<sub>2</sub>, or a high-K dielectric placed above an SiO<sub>2</sub> interfaced layer in advanced technologies.

- A commanding gate, which can be patterned in Poly-silicon or composed of a stack of metals in advanced technologies.

- Two highly doped charge tanks with a doping concentration of opposite type to the substrate called source and drain.

Figure I. 1: a) NMOSFET BULK transistor b) PMOSFET BULK transistor

#### I.1.1 Operation principle

The operation of MOSFET transistors is based on the 'field' effect, where the local density of mobile charges in the semiconductor is electrostatically modulated by:

O Applying a potential difference between the Gate and the source  $(V_{GS})$ . This potential difference creates inversion charges (minority carriers) at the surface of the semi-conductor by a transversal field effect through the dielectric.

O Applying a potential difference between the source and the drain  $(V_{DS})$ . This potential difference allows the circulation of the minority carriers between the source and the drain and thus creates a drain current  $(I_D)$ .

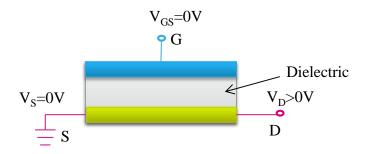

If the applied  $V_{GS}$  is lower than a potential called threshold voltage (Vt), the transistor is blocked and no current circulates between the source and the drain as shown in Figure I. 2.a. However, if  $V_{GS}$  is equal or higher than Vt, the minority carriers are modulated vertically to the surface of the semiconductor, and a region called channel is formed on the oxide/semiconductor interface. The minority carriers can also be modulated horizontally by applying a  $V_{DS}$ , and thus forming a drain current that circulates between drain and source, as shown in Figure I. 2.b.

a- Empty channel => I<sub>DS</sub>=0A=> Blocked channel

b- Channel filled of minority carriers =>  $I_{DS} \dagger 0A$  => Passing channel

Figure I. 2 Example of Field effect in the case of NMOS transistor [Skotnicki03]

#### I.1.2 Electrical figures of merits for static performance

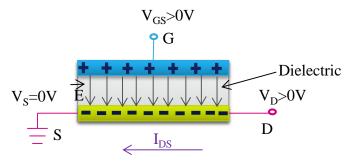

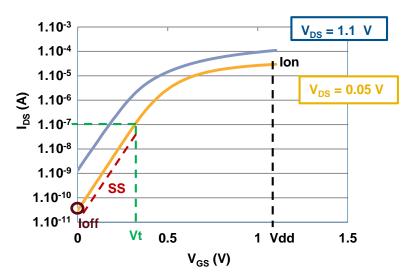

The performance of MOS transistors in static regime can be evaluated by measuring: the drain current when the transistor is in the open state (Ioff) (Blocked channel), the drain current when the transistor is in the closed state (Ion) (Passing channel), the sub-threshold swing (SS), the Ion/Ioff ratio and the threshold voltage (Vt), as shown in Figure I. 3.

- o *Ioff* is measured between source and drain when  $V_{GS}$ =0V, and  $V_{DS}$ = $V_{DD}$  (NMOS) /  $V_{DS}$ =- $V_{DD}$  (PMOS). Note that  $V_{DD}$  is the power supply voltage. This current is mainly composed of the contributions of leakage currents between for instance the gate and the substrate, the gate and the drain, the gate and the source, the drain and the substrate, the source and the substrate. *Ioff* also depends on the amplitude of the potential barrier between the channel and the source/drain.

- o *Ion* is measured between source and drain when  $V_{GS}=V_{DS}=V_{DD}$  (NMOS) or  $V_{GS}=V_{DS}=V_{DS}=V_{DD}$  (PMOS). This current is mainly modulated by  $V_{DS}$ . When  $V_{DS}$  is increased the drain current is also increased as shown in Figure I. 3.

The objective of an ideal transistor is to have an *Ioff* as low as possible, an *Ion* as high as possible and a transition between *Ioff* and *Ion* as abrupt as possible. This transition is characterized by the sub threshold swing (SS). Note that the theoretical limit of the sub threshold swing is of 60mV/decade at 300K of temperature. The *Ion/Ioff* ratio is mainly used as a single global performance parameter of the transistor. The higher the value of *Ion/Ioff*, the better the device. Finally, the threshold voltage (*Vt*) represents the barrier separating the blocked mode from the passing mode.

Figure I. 3:  $I_{DS}(V_{GS})$  characteristic for two different  $V_{DS}$  values (NMOS transistor).

#### I.1.3 Operating Regimes

Considering the Metal/Oxide/Semiconductor structure (MOS capacitor), if a voltage  $(V_{GS})$  is applied to the gate, the energy bands at the interface between the oxide and the

semiconductor bend. The MOS capacitor goes through different regimes as a function of the applied gate voltage.

#### We introduce:

- $\circ$   $\Phi_S$ : The potential at oxide/semi-conductor interface

- $\Phi_F$ : The Fermi potential, it represents the difference between the extrinsic Fermi level (for a doped semiconductor with acceptor doping  $N_A$  in the case of NMOS and donor doping  $N_D$  in the case of PMOS) and the intrinsic Fermi level (for the undoped semiconductor).

- o  $\Phi_m$ : The metal work function

- o  $\Phi_{SC}$ : The semiconductor work function

- $\circ$   $V_{FB}$ : The flat band voltage, the required gate voltage to push  $\Phi_S$  to 0, thus producing flat bands in the semiconductor. In the case of an ideal MOS transistor (no traps or charges in the oxide/semiconductor interface),  $V_{FB}$  is thus equal to the difference between  $(\Phi_m)$  and  $(\Phi_{SC})$ .

Adding the source and drain to the MOS capacitor, the difference of the types of doping between the substrate and the source/drain junctions creates a potential barrier  $\Phi_D$ , where its height can also be modulated by the applied gate voltage.

The different operation regimes of the MOS transistor thus arise from the different applied gate voltages and consequently from the different values of  $\Phi_S$ . Considering the case of NMOS transistors:

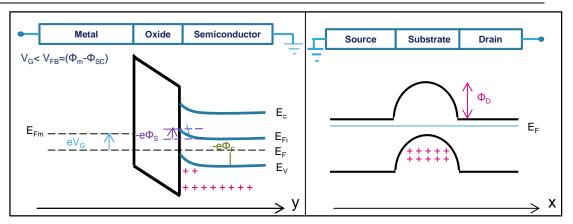

#### a- Accumulation regime: $V_{GS} < V_{FB} => \Phi_S < \theta$

The energy bands of the semiconductor bend down as shown in Figure I. 4. The gate attracts holes from the substrate to the Oxide/Semiconductor interface. This phenomenon is called accumulation.

As a consequence, the potential barrier  $(\Phi_D)$  is very high for the electrons present in the source to cross it. Even if a drain voltage  $(V_{DS})$  is applied no drain current is observed.

Figure I. 4: Energy bands and potential barrier in Accumulation Regime (NMOS transistor) [Mathieu 01]

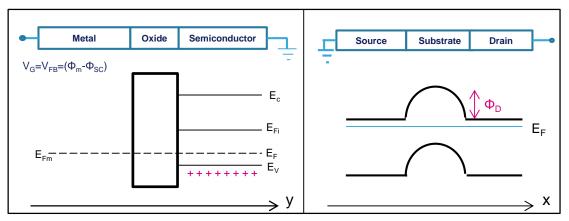

#### b- Flat band regime: $V_{GS} = V_{FB} = \Phi_{m} - \Phi_{SC} \implies \Phi_{S} = 0$

The energy band of the semi-conductor doesn't bend. The potential barrier  $(\Phi_D)$  is still very high for the electrons present in the source to cross it as shown in Figure I. 5.

Figure I. 5: Energy bands and potential barrier in Flat band Regime (NMOS transistor).

[Mathieu 01]

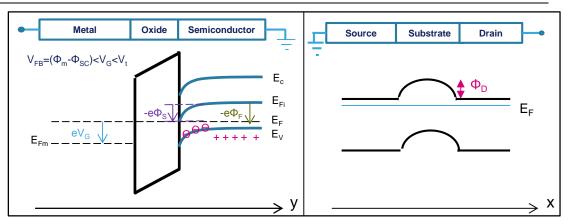

#### c- Depletion regime: $V_{FB} = \Phi_{m}$ - $\Phi_{SC} < V_{GS} < Vt => 0 < \Phi_{S} < \Phi_{F}$

The semiconductor energy bands bend upward as shown in Figure I. 6. The holes are rejected from the Oxide/Semiconductor interface to the substrate. An empty zone of mobile carriers is formed with a depletion charge Qd.

The potential barrier  $(\Phi_D)$  starts to decrease, but is still too high for the electron to cross it. Also, in this case, even if a drain voltage  $(V_{DS})$  is applied, no drain current is observed.

Figure I. 6: Energy bands and potential barrier in Depletion Regime (NMOS transistor).

[Mathieu 01]

#### d- Inversion Regime:

#### Weak inversion regime: $V_{FB} = \Phi_{m} - \Phi_{SC} < V_{GS} < Vt$ and $\Phi_{F} < \Phi_{S} < 2\Phi_{F}$

The semiconductor energy bands bend more compared with the depletion regime and the potential barrier  $(\Phi_D)$  height is thus decreased. Some electrons present in the source manage to cross  $\Phi_D$  by thermal activation, and an inversion zone at the Oxide/Semiconductor interface starts to form. However the density of the electrons at the interface is lower than the density of the holes in the substrate. The electrons thus circulate due to a charge gradient (from the high concentration region, the Source, to the low concentration region, the drain). A diffusion drain current is thus formed that evolves exponentially with  $V_G$ .

The threshold voltage (Vt) is defined as the voltage that causes the concentration of the electrons at the interface to be equal to the concentration of the holes in the substrate, in other term when  $\Phi_S = 2\Phi_F$ . This potential marks the state change of the transistor, which switches from weak to strong inversion regime. Vt can be expressed as shown in Equation I.1.

$$Vt = V_{FB} + 2\Phi_F - \frac{Qd}{Cox} \tag{I. 1}$$

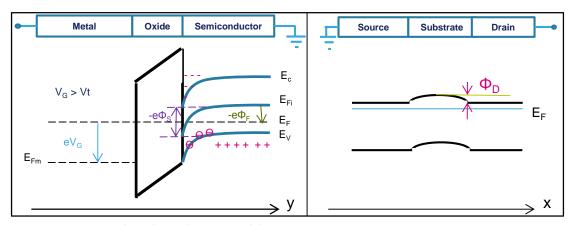

#### $\circ$ Strong inversion regime: $V_{GS} > Vt$ and $\Phi_S > 2\Phi_F$

The semiconductor energy bands bend in such a way that  $\Phi_S > 2\Phi_F$ . The potential barrier  $(\Phi_D)$  drastically decreases and the electrons can easily cross the barrier as shown in Figure I. 7. The concentration of the electrons at the interface becomes much higher than the concentration of the holes in the substrate. The electrons can thus

circulate in the channel from the source to the drain due to the applied  $V_{DS}$ , following the drift-diffusion law.

Figure I. 7: Energy bands and potential barrier in Strong Inversion Regime (NMOS transistor) [Mathieu 01]

$V_{DS}$  determines the regime of operation of the transistor. Three regimes can be observed: Linear, non-linear and saturation regimes.

We introduce the channel effective potential Veff(x), where x is the coordinate that spans the length of the channel. At the source (x=0),  $Veff=V_{GS}$ , while at the drain (x=d),  $Veff=V_{GS}-V_{DS}$ .

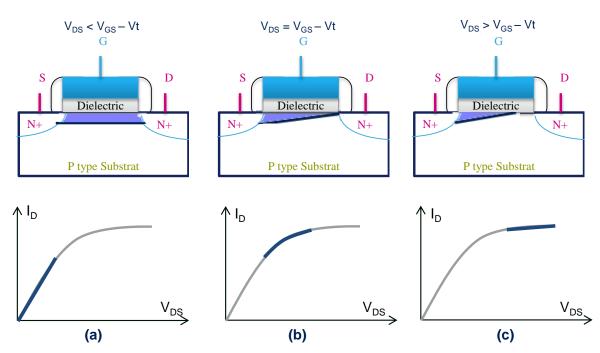

#### d.1 - Linear Regime: $V_{DS} < V_{GS} - Vt$

The channel is almost equipotential Veff(x=0)  $\approx$  Veff(x=d) as shown in Figure I. 8.a.

- The electrons concentration is almost uniform along the channel

- The inversion channel extends over the entire area between the source and the drain

The MOS transistor operates like a resistor controlled by both the gate and the drain voltage.  $I_D$  increases linearly with  $V_{DS}$ , and is given by Equation I.2.

$$I_D = \beta . (V_{GS} - Vt - \frac{V_{DS}}{2}).V_{DS}$$

(I. 2)

$$\beta = \frac{W}{L} \mu_0 Cox,$$

where:

$\beta$  is the current gain factor given by Equation I.3.

W is the transistor width

L is the transistor length

$\mu_0$  is the low field mobility

Cox is gate oxide capacitance.

#### <u>d.2 – Non-Linear or pinch off Regime: $V_{DS} = V_{GS} - Vt$ </u>

By increasing  $V_{DS}$ , the potential changes along the channel and is reduced considerably at the drain side, Veff(x=0) > Veff(x=d). The electrons concentration at the drain side is decreased, implying an augmentation of the channel electrical resistance. The drain current continues to increase with  $V_{DS}$ , but less rapidly than in the linear regime, until reaching the pinch off point P shown in Figure I. 8.b.

At the pinch-off point, saturation is achieved with  $V_{DS} = V_{GS} - Vt$ . The channel effective potential becomes equal to  $V_{GS}$  at the source and  $V_{GS} - V_{GS} + Vt$  at the drain. This means that in the proximity of the drain the gate voltage is just enough to form the inversion layer and the electron concentration is almost negligible. The channel becomes more resistive and the drain current reaches saturation. Moreover, any higher potential applied to the drain will cause the channel effective potential at the drain side to be reduced below the threshold voltage and the region near the drain will be depleted.

#### <u>d.3 - Saturation Regime: $V_{DS} \ge V_{GS} - Vt$ </u>

The region near the drain is not in strong inversion regime any more (Veff (x=d) < V<sub>GS</sub> - V<sub>GS</sub> + Vt), but rather in weak inversion regime. The electrons spread out and part of the channel is disconnected. While the depletion region lacks mobile carriers, there is no restriction on current flow through it: if an electron with initial velocity enters the depletion region from one side, and if there is a field across the region, this electron will be dragged by the field. The drain current is therefore quasi-independent of V<sub>DS</sub> and is controlled only by V<sub>GS</sub> and the I<sub>D</sub>(V<sub>DS</sub>) characteristic becomes flat, as shown in Figure I. 8.c. Note that when V<sub>DS</sub> is increased, the pinch-off point moves towards the source and the channel length is decreased.

Considering  $V_{DS,sat} = V_{GS} - Vt$ , the saturation drain current can be written as Equation I.4:

$$I_D = \frac{\beta}{2} . (V_{GS} - Vt)^2$$

(I. 4)

Figure I. 8: Energy bands and potential barrier in Strong Inversion Regime (NMOS transistor) [Skotnicki03]

#### I.1.4 Parasitic effects due to the Miniaturization of MOS transistors

In 1975 Gordon Moore predicted that the numbers of transistors in circuits of a given size will double every two years, allowing an exponential performance enhancement. The miniaturization of MOS transistors that enables the increase in device number per area unit allows the saturation current to be high enough to increase the operating speed of the products. The challenge in this case is to prevent disruptive increase of leakage currents, in order to limit the power consumption of these products, especially if battery powered.

The miniaturization of MOS transistors also induces parasitic phenomena, disrupting the electrical operation of ideal devices and it is necessary to understand and control such effects. In this paragraph, we introduce the main parasitic effects encountered and mentioned in this work and some of their control techniques.

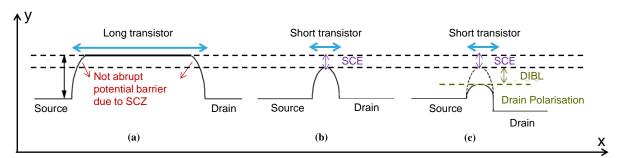

- 1- Short channel effect (SCE) and Drain induced barrier Lowering (DIBL). In real devices, the n/p junctions between the source/drain extensions and the channel are not abrupt. These junctions create depleted zones (depletion charge) of a few nanometers uncontrolled by the gate polarization. In these regions called Space Charge Zones (SCZ), the potential is decreased in a quadratic fashion.

- o Linear regime.

- For long transistors, the surface potential is constant along the channel except near the source and the drain junctions due to the SCZs, as shown in Figure I.

9.a.

- For short transistors, the SCZs approach each other with the reduction of the gate length, until they are partly overlapped. In this case, the flat behavior of the surface potential noticed for long transistors is no more observed, as shown in Figure I. 9.b. The depletion charge in the channel is not completely controlled by the gate polarization but majorly by the junction zones. The potential barrier ( $\Phi_D$ ) is thus decreased. As a consequence the inversion regime is quickly reached and Vt is lowered. This phenomenon is called short channel effect (SCE).

#### Saturation regime.

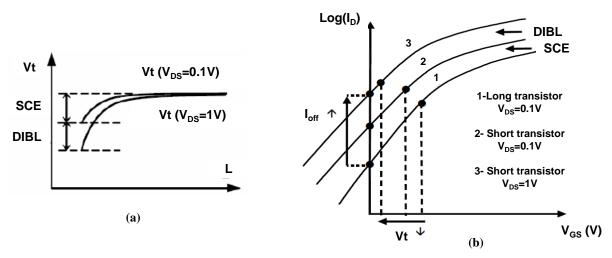

In addition to the SCE, when polarizing the drain with a strong drain field the potential barrier will also decrease as shown in Figure I. 9.c. This phenomenon, called Drain Induced Barrier Lowering (DIBL), induces a further lowering of Vt compared to the case of linear regime shown in Figure I. 10.a and b.

Figure I. 9: Surface potential in Strong Inversion Regime as a function of transistor length (NMOS transistor) [Skotnicki03][Gallon 07]

SCE and DIBL denote a loss of the electrostatic control of the channel by the gate, due to the miniaturization of the channel length. The gate modulation of the channel potential barrier in less efficient, implying a degradation of SS. The uncontrolled decrease of the potential barrier will induce an uncontrolled lowering of the threshold voltage Vt, and a significant degradation of Ioff as shown in Figure I. 10.b.

Figure I. 10: Short channel effect and Drain induced barrier lowering effect on (a) threshold voltage as a function of L and (b)  $I_D(V_{GS})$  characteristic for long and short devices [Skotnicki03][Gallon 07]

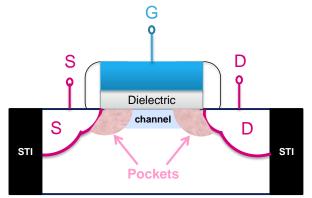

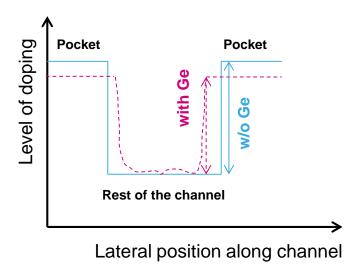

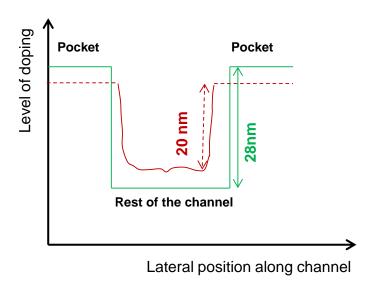

The SCZ mainly extends a few nanometers in the channel, due to its low doping as compared to the source/drain. To eliminate the SCE and DIBL effects, two highly doped regions called pockets or halo, having the same doping type as the substrate, are implanted near the source and the drain as shown in Figure I. 11. This pocket implantation limits the extension of the SCZ and thus of the SCE.

Figure I. 11: Transistor NMOS with pocket implant

For small gate lengths, the pocket regions are close to each other's forming a homogenous channel controlled by the gate polarization. As the pockets are highly doped, the channel doping is increased, increasing the potential barrier and thus *Vt*. This phenomenon is called reverse short channel effect.

2- Gate leakage due to the reduction of the oxide thickness (*Tox*).

In the purpose of granting sufficient drain current, it is important to maintain high Cox value as shown in Equations I.2, I.3 and I.4. The traditional technique to improve the

capacitive coupling between the gate and the channel is to reduce the oxide thickness (*Tox*). However, by decreasing the oxide thickness to a few Angstroms, it becomes more probable for the minority carriers to cross the potential barrier of the dielectric. A leakage gate current can be observed between the gate and the substrate and the gate and the source drain extensions. To face this issue, the silicon dioxide is replaced by a high-k material in advanced technologies such as HfO<sub>2</sub> and HfSiON. This enables larger oxide thickness for a given target Cox value, limiting therefore the gate leakage.

The high-k layer is usually deposited on a  $SiO_2$  interfacial layer. As a consequence, instead of considering the oxide thickness Tox as in the case of simple silicon dioxide dielectric, an equivalent oxide thickness (EOT) is considered, equal to the sum of the contributions of the  $SiO_2$  interfacial layer and the high-k dielectric layer.

#### 3- Increasing EOT due to Poly-Silicon Gate

The Poly-Silicon gate is known to induce a depletion layer between the gate itself and the oxide, thus increasing the EOT. One of the main solutions to this problem is the use of a metal gate. The metal gate technology, even with its difficulty of integration (compatibility with the gate oxide, chemical contamination, etc. [Tavel 01]) has another advantage over the poly-silicon technology, which is given by its low resistivity. This enables a decrease of the delay in signal propagation in high frequency applications.

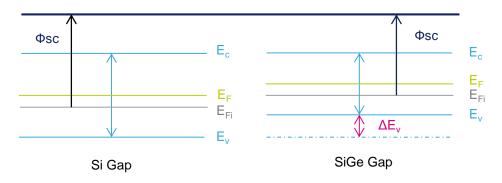

By using a metal gate, the threshold voltage will be dependent of the gate material through  $V_{FB}$  ( $V_{FB} = \Phi_{m^-} \Phi_{SC}$ ).

#### I.2 Methodology of extraction of MOS transistors parameters

The development of MOS transistors technology leads to additional complexities that make the calculation of its electrical parameters increasingly difficult. Several methods for measuring these electrical parameters under static conditions exist, meeting various constraints such as repeatability, ease and speed of measurement and reliability.

While the drain current  $(I_D)$  can be directly extracted for a known gate and drain voltage, the extraction of the threshold voltage (Vt) and current gain factor  $(\beta)$  is more complex. Some of the most known and used methods to extract these two parameters are the constant current

method [Deen 90], the maximum slope method [Hao 85], the three-point method [Hamer 86], the Y function method [Ghibaudo 88] and the shift & ratio method [Taur 92].

In this thesis the constant current, maximum slope and Y function methods are used and thus detailed below.

#### I.2.1 Maximum slope method

The drain current  $I_D$  is measured as a function of gate bias  $(V_{GS})$  in linear regime. The Trans-conductance (Gm) is then calculated using Equation I.5.

$$Gm = \frac{\partial I_D}{\partial V_{GS}} \tag{I. 5}$$

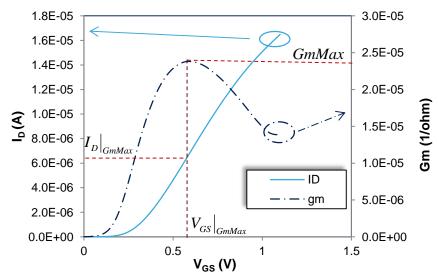

$I_D$  and Gm are plotted as a function of  $V_{GS}$ , as shown in Figure I. 12 with drain bias  $V_{DS} = 50mV$ .

As shown in Figure I. 12, the maximum value of Gm ( $y = G_{mMax}$ ) and the inflection point ( $y = I_D|_{GmMax}$ ) of the  $I_D(V_{GS})$  characteristic are obtained for the same gate bias  $V_{GS}|_{GmMax}$ . Note that the inflection point marks the transition of MOS transistor from weak to strong inversion regime. The current gain factor  $\beta_{extrapolated}$  can thus be extracted at the maximum Gm point using Equation I.6, while the threshold voltage  $Vt_{extrapolated}$  can be extracted using Equation I.7.

$$\beta_{extrapolated} = \frac{G_{m.Max}}{V_{DS}} \tag{I. 6}$$

$$Vt_{extrapolated} = V_{GS}\big|_{GmMax} - \frac{I_D\big|_{GmMax}}{G_{mMax}}$$

(I. 7)

Figure I. 12: Maximum slope method for linear regime ( $V_{GS}$ =1.1V,  $V_{DS}$ =50mV), for Bulk transistors with W=0.135 $\mu$ m and L=0.04 $\mu$ m

This is a reproducible method that gives a physical value of threshold voltage [Ghibaudo 89]. However, [Ghibaudo 89] shows that this value depends on the mobility attenuation factor  $\theta_1$ . If  $\theta_1$  is large, the extrapolated Vt can deviate from the real Vt value as shown in Equation I.8.

$$Vt_{extrapolated} = Vt - \theta_1 \cdot (V_{GS}|_{GmMax} - Vt)^2$$

(I. 8)

Although a method has been demonstrated at a later stage [Shimizu 02] to extract Vt and  $\beta$  in saturation regime, the values of Vt and  $\beta$  used in this thesis were extracted in linear regime.

#### I.2.2 Constant current method

The threshold voltage is defined as the necessary gate voltage to obtain a defined current level *Icc* as shown in Equation I.9.

$$Icc = I_{Normalized} \cdot \frac{W}{I}$$

(I. 9)

Usually, the normalized current is defined in weak inversion mode, where the drain current equation follows an exponential law as a function of  $V_G$ .

The constant current method is faster than the maximum slope method. Indeed, while the maximum slope method is based on scanning the  $gm(V_{GS})$  curve to find the maximum

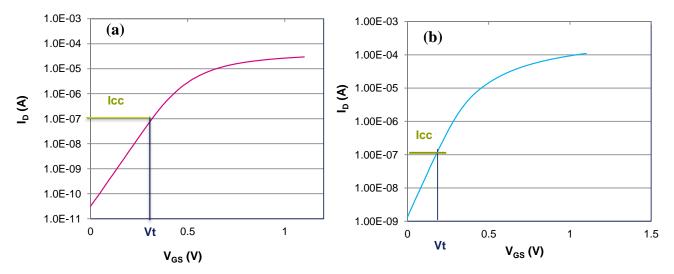

slope, the constant current method is based on classical interpolation extractions such as dichotomy, and thus requires less measurement points. This method is also reproducible and can be used in linear and saturation regimes as shown in Figure I. 13.

Figure I. 13: Constant current method for (a) linear regime ( $V_{GS}$ =1.1V,  $V_{DS}$ =50mV) and (b) saturation regime ( $V_{GS}$ =1.1V,  $V_{DS}$ =1.1V), for Bulk transistors with W=0.135 $\mu$ m and L=0.04 $\mu$ m

The disadvantage of this method is that it only enable the extraction of Vt values.

#### I.2.3 Y function method

The drain current equation as a function of  $V_G$ , in linear regime, can be written as shown in Equation I.10.

$$I_{D} = \frac{W}{L} \cdot \mu_{0} \cdot C_{OX} \frac{V_{G} - Vt}{1 + \theta_{1} \cdot (V_{G} - Vt) + \theta_{2} \cdot (V_{G} - V_{T})^{2}} \cdot V_{D}$$

(I. 10)

Where  $\theta_1$  (defined in Equation I.11 where  $\theta_{1,0}$  is the intrinsic mobility reduction factor) and  $\theta_2$  are the mobility attenuation factors, and  $\beta$  is the current gain factor (defined in Equation I.12).

$$\theta_1 = \theta_{10} + \beta . Rsd \tag{I. 11}$$

$$\beta = \frac{W}{L} \cdot \mu_0 \cdot C_{OX} \tag{I. 12}$$

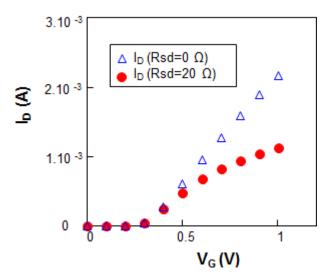

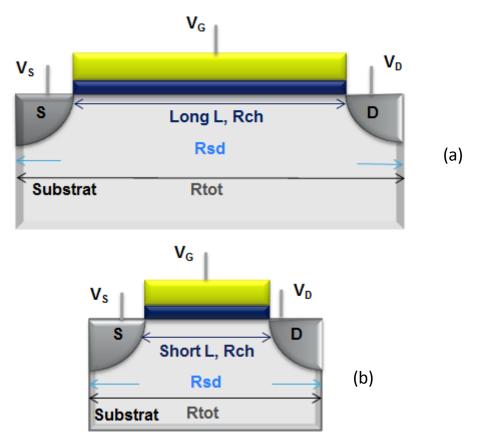

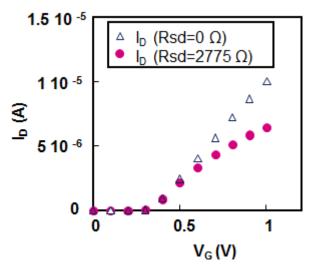

As shown in Equation I.11,  $\theta_1$  depends on Rsd values. For short gate lengths Rsd has an large impact on the values of  $I_D$  in strong inversion regime, as shown in Figure I. 14. It is thus mandatory to extract Vt and  $\beta$  values in a method that overcomes the influence of Rsd.

Figure I. 14: Calculated drain current values as a function of gate voltage, for Rsd=20 $\Omega$  and Rsd=0 $\Omega$ . (FD SOI transistors with W=0.08 $\mu$ m/L=0.05 $\mu$ m and V<sub>D</sub> =50mV).

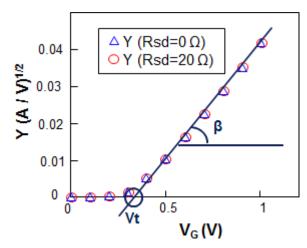

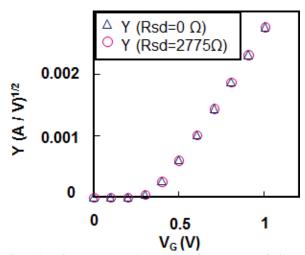

The Y function given by Equation I.13, which has been introduced as a simple method to extract the MOS transistor's parameters [Ghibaudo88] & [Fleury08], is immune to Rsd values as shown in Figure I. 15.

$$Y = \frac{I_D}{\sqrt{Gm}} \tag{I. 13}$$

The trans-conductance *Gm* is defined as

$$Gm = \frac{\partial I_D}{\partial V_G} = \frac{W}{L} . \mu_0 . C_{OX} \frac{V_D}{(1 + \theta_1 . (V_G - Vt))^2},$$

(I. 14)

so that the Y function can be written as shown in Equation I.15

$$Y = \frac{I_D}{\sqrt{Gm}} = \sqrt{\frac{W}{L}Cox\mu_0 V_D}.(V_G - V_t) if \theta_2 = 0$$

(I. 15)

Note that in practice  $\theta_2 \approx 0$  except for very high  $V_G$  values [Fleury08].

Figure I. 15: Calculated Y function values as a function of gate voltage, for Rsd=20 $\Omega$  and Rsd=0 $\Omega$ . (FD SOI transistors with W=0.08 $\mu$ m/L=0.05 $\mu$ m and V<sub>D</sub> =50mV).

In strong inversion regime, the  $Y(V_G)$  characteristic varies linearly with  $V_G$  as shown in Figure I. 15. It is thus easy to extract the threshold voltage value by extrapolating the value at Y=0 of the linear portion of the  $Y(V_G)$  curve, as shown in Figure I. 15. Moreover, the current gain factor  $(\beta)$  can also be extracted by calculating the slope of the linear region of  $Y(V_G)$ .

### I.3 Types of electrical variability

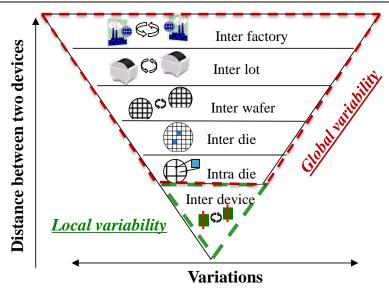

When measuring the electrical variability of MOS transistors between two factories, two lots, two wafers or two separate dies, the global devices variability is characterized as shown in Figure I. 16. Often, this global variability is due to different fabrication processes, such as the use of different fabrication tools between two factories or the temperature gradient effect during the oxidation or annealing steps of the back end fabrication. In contrast, the local devices variability, also called mismatch, is characterized by measuring two identical MOS devices:

- Placed in pairs

- Spaced by the minimum allowed distance

- o Laid out in identical environment

- Electrically independent with symmetric connections

Figure I. 16: Different types of electrical variability [Mezzomo10b][Croon 04]

### I.4 Local variability

We will first introduce the concept of statistical local variability computation, allowing the decomposition of the local variability into systematic and stochastic mismatch. Then we will define each type of variability and we will mostly concentrate on the stochastic mismatch.

### I.4.1 Measurement phase

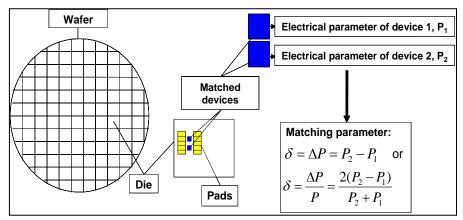

With the aim of measuring the local variability, a 300mm wafer is considered as an example. The measurements are conducted on two identical devices (MOS transistors in this case) within the same die. The electrical parameter  $P_1$  of device1 (MOS1) and the electrical parameter  $P_2$  of device2 (MOS2) are measured, then  $\Delta P$  or  $\frac{\Delta P}{P}$  are calculated as shown in Figure I. 17.

Figure I. 17: Measurement of the electrical parameters P1 and P2 for a pair of devices

This measurement is repeated for N pairs of MOS transistors. A large number of transistors in pairs (70 pairs and above) are considered to assure a significant statistical population.

#### I.4.2 Gaussian distribution verification

### I.4.2.a Data plot

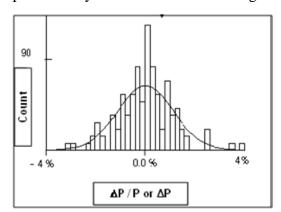

When the N samples of  $\Delta P$  or  $\frac{\Delta P}{P}$  are plotted as a function of their number of occurrence, a Gaussian shape is usually obtained as shown in Figure I. 18.

Figure I. 18: An example of statistical plot of the number of occurrences of each measured value of  $\Delta P$  or  $\frac{\Delta P}{P}$

This Gaussian plot is characterized by its mean value  $(\overline{\Delta P} \text{ or } \overline{\frac{\Delta P}{P}})$  (Equation I.16) and its standard deviation  $(\sigma_{\Delta P} \text{ or } \sigma_{\frac{\Delta P}{P}})$  (Equation I.17).

$$\overline{\Delta P} = \frac{1}{N} \sum_{i=1}^{N} \Delta P \tag{I. 16}$$

$$\sigma_{\Delta P} = \sqrt{\frac{1}{N-1} \cdot \sum_{i=1}^{N} (\Delta P - \overline{\Delta P})^2}$$

(I. 17)

#### I.4.2.b Gaussian law verification

Theoretically, considering a finite number of samples, the random measured variable  $\Delta P$  or  $\frac{\Delta P}{P}$  is Gaussian if its probability density function is of the form:

$$f(\Delta P) = \frac{1}{\sigma_{\Lambda P} \cdot \sqrt{2.\pi}} \exp\left(-\frac{(\Delta P - \overline{\Delta P})^2}{2.\sigma_{\Lambda P}^2}\right)$$

(I. 18)

In practice, however, even if considering an important number of samples, the experimental data doesn't perfectly follow this law. Thus, a test to verify that the experimental distribution matches the normal law is mandatory. The chi-squared test enables to validate or to reject the Gaussian distribution.

To explain how this test works, the hypothesis H is first considered: the distribution of the experimental data is Gaussian.

The  $\chi^2$  function expresses the difference between:

- the observed (O<sub>i</sub>) frequency of occurrence of the measured data

- the expected (E) frequency of occurrence of the data calculated using Equation I.18

$\chi^2$  is defined as:

$$\chi^{2} = \sum_{i=1}^{k} \frac{(Oi - Ei)^{2}}{Ei}$$

(I. 19)

where k represents the number of classes (the number of intervals over which the distribution is divided to determine the frequency of occurrence:  $[\Delta P_i - \Delta P_{i-1}]$ ).

To verify the H hypothesis, an assessment parameter  $\chi^2_{\alpha}$  must be defined, which depends on the confidence level  $(1-\alpha)$  and on the degrees of freedom  $\nu$  [Montgomery01], with

$$v = k - m - 1 \tag{I. 20}$$

where m represents the number of parameters to be determined and k is chosen from the Cochran criterion [Cochran54], which states that all classes should have a theoretical non-zero value and 80% of the classes should have a theoretical value greater than or equal to 5. In our

case k = 56 and m = 2 (2 parameters,  $\overline{\Delta P}$  and  $\sigma_{\Delta P}$ ), thus  $\nu > 30$ .  $\chi^2_{\alpha}$  can in this case be written as shown in Equation I.21:

$$\chi_{\alpha}^{2} = \frac{1}{2} \cdot (Z_{\alpha} + \sqrt{2\nu - 1})^{2}$$

(I. 21)

where  $Z_{\alpha}$  represents the standard deviation number from the normal central limit theorem and can be extracted from Table I.1 below.

**Table I.1:**  $Z_{\alpha}$  values of the central limit theorem

| $(1-\alpha)$ | 99.73% | 99%  | 98%  | 96%  | 95.45% | 95%  | 90%   | 80%  | 68.27% | 50%    |

|--------------|--------|------|------|------|--------|------|-------|------|--------|--------|

| $Z_{lpha}$   | 3      | 2.58 | 2.33 | 2.05 | 2      | 1.96 | 1.645 | 1.28 | 1      | 0.6745 |

In our case we consider a restricted interval  $\left[\overline{\Delta P} - 3\sigma_{\Delta P}; \overline{\Delta P} + 3\sigma_{\Delta P}\right]$ , thus our confidence level is 99%, and consequently  $Z_{\alpha} = 2.58$ .

Once all parameters have been evaluated, the test requires to verify whether  $\chi^2 < \chi_\alpha^2$ , in which case H will be accepted, else H will be rejected.

The chi-squared test methodology can therefore be conducted on our data to identify whether it follows a Gaussian distribution or not.

### I.4.3 Data filtering and separation between systematic and stochastic mismatch

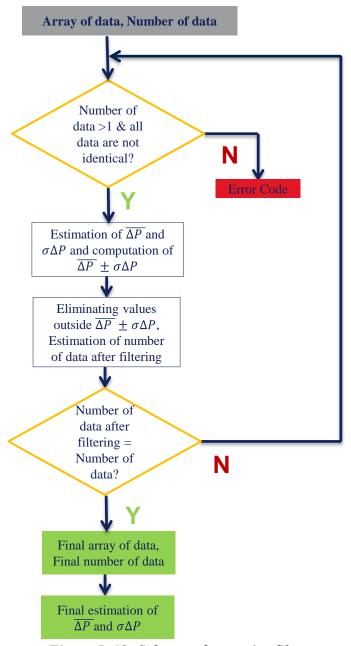

The experimental data must be filtered to exclude erroneous values arising from measurement errors such as high probe resistance [Cathignol07], or technology defects during MOS transistor fabrication. After verifying that the data follows a Gaussian law, and computing the mean and the standard deviation, a recursive filter is applied to obtained  $\Delta P$  or  $\frac{\Delta P}{P}$  values. The used filter is of iterative type: it selects only the values between  $\overline{\Delta P} \pm 3.\sigma_{\Delta P}$  with a 99% probability of occurrence, and repeats this action until no values of  $\Delta P$  or  $\frac{\Delta P}{P}$  outside  $\overline{\Delta P} \pm 3.\sigma_{\Delta P}$  are present, as shown in Figure I. 19.

After eliminating all the erroneous data, a final estimation of  $\overline{\Delta P}$  and  $\sigma_{\Delta P}$  is calculated. At this point a separation between stochastic and systematic mismatches can be introduced by associating  $\overline{\Delta P}$  to systematic mismatch and  $\sigma_{\Delta P}$  to stochastic mismatch.

Figure I. 19: Scheme of recursive filter

### I.4.4 Concept and computation of systematic mismatch

### I.4.4.a Concept of systematic mismatch

Systematic mismatch is mainly caused by the difference in the environment where the pair of examined devices is laid out. Tuinhout in [Tuinhout96] [Tuinhout97b] explained that systematic mismatch arises mainly due to inadequate design practices For example, the use of a metallic cover over only one device of the pair can induce local differences in terms of mechanical constraints, which in turn induce systematic mismatch. The same author also identified in [Tuinhout03] the phenomena that can induce differences in the measurement

conditions for the pair of devices, thus inducing systematic mismatches. As systematic mismatch is mostly due to design factors, it can also be reduced by following more mismatch-aware practices. One of the techniques to reduce this kind of local variability is the use of dummies in MOS transistors conception. Dummy devices are not connected to the pair of transistors, but are placed on both sides of the gate to assure the same surrounding environment for both transistors of the pair.

### I.4.4.b Systematic mismatch computation

Systematic mismatch is usually considered to be negligible compared to stochastic mismatch. To validate this hypothesis, a zero-mean test is considered.

This test is used to validate or reject the following hypothesis:

- H: the experimental values follow a Gaussian distribution with  $\Delta P = 0$ .

For this test, the reduced centered variable of [Pergoot95] for a confidence level of 1-K=99% is considered, defined as:

$$Z = \frac{\overline{\Delta P}}{\sqrt{\frac{2.\sigma_{\Delta P}^2}{N}}}$$

(I. 22)

where N is the number of samples.

The comparison parameter for this test is  $Z_{k/2}$ , which for K = 1% is equal to 2.58.

Based on these parameters, if  $Z \le Z_{K/2}$ , H will be accepted and the systematic mismatch can be deemed negligible, else H is rejected.

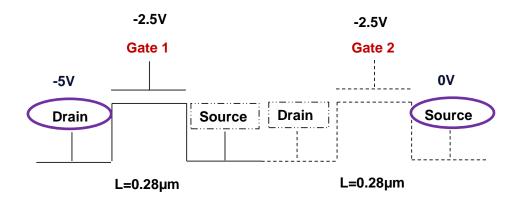

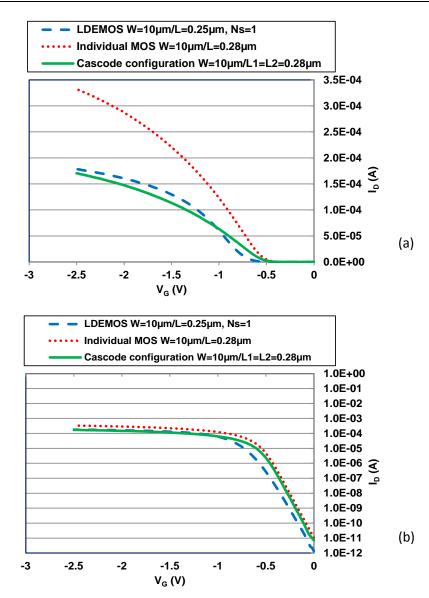

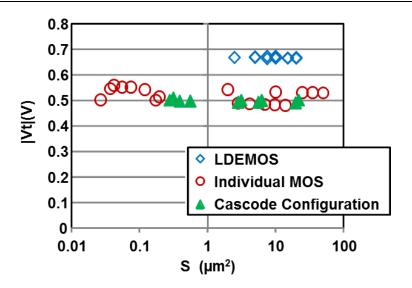

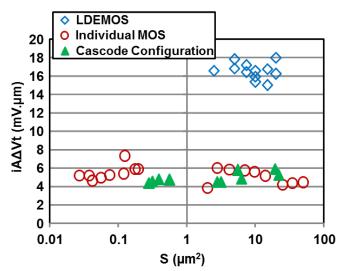

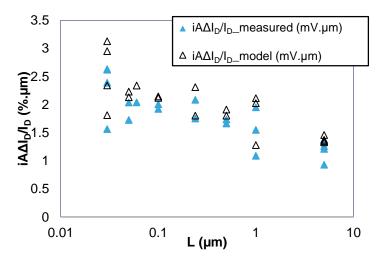

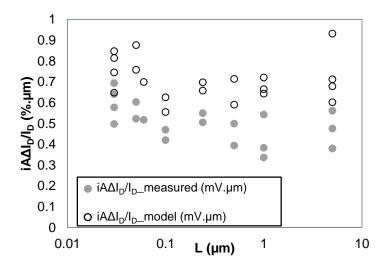

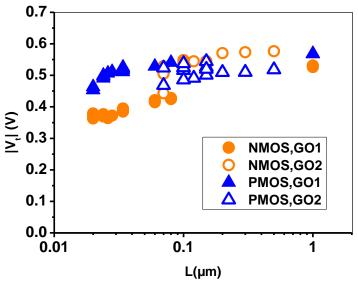

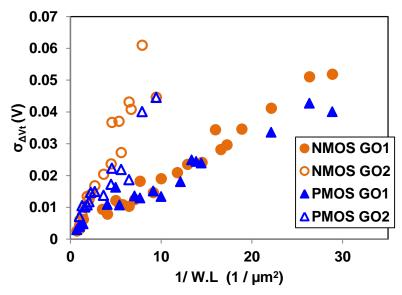

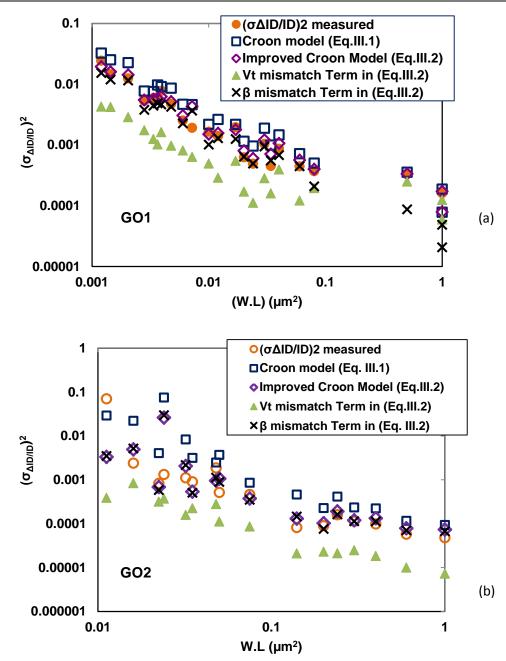

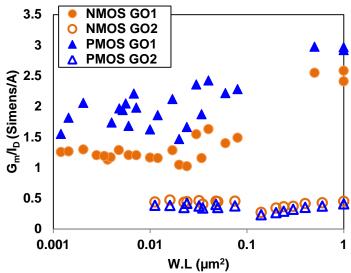

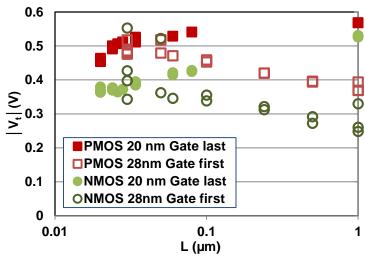

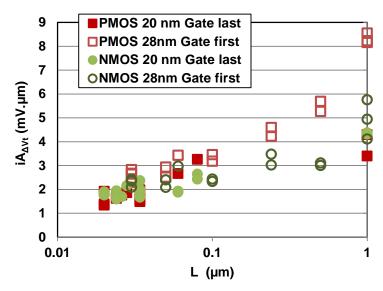

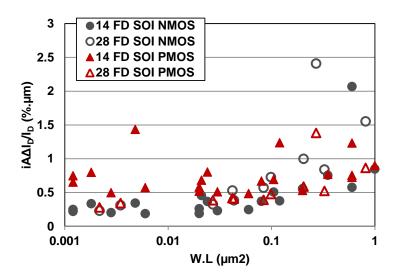

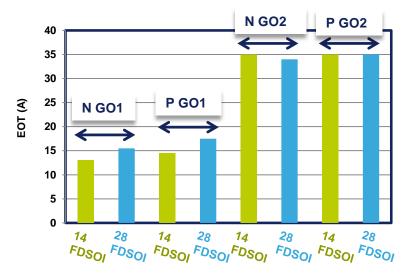

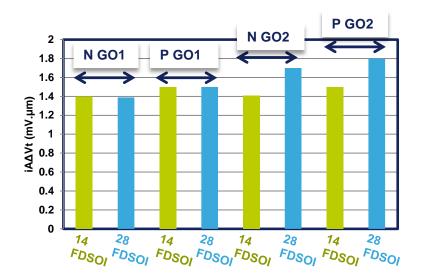

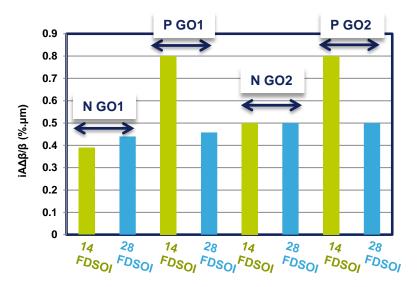

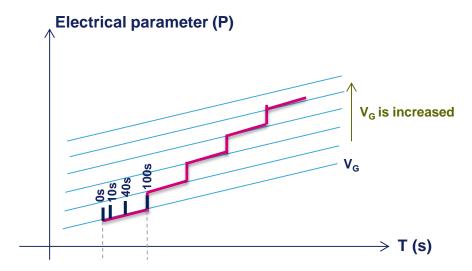

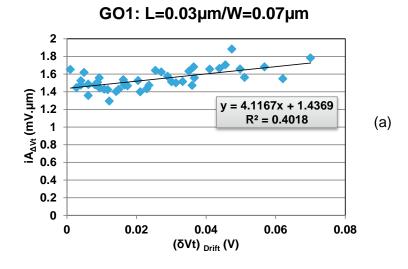

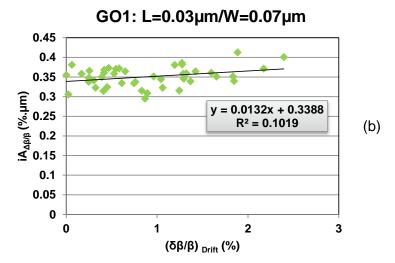

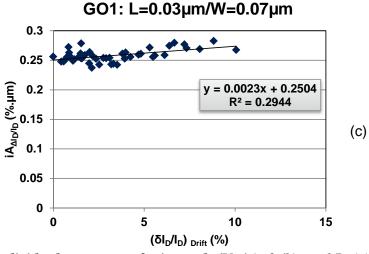

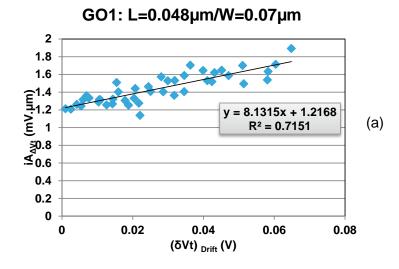

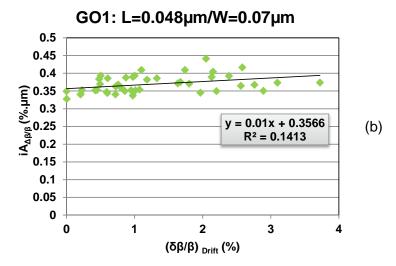

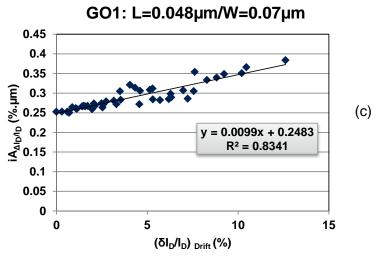

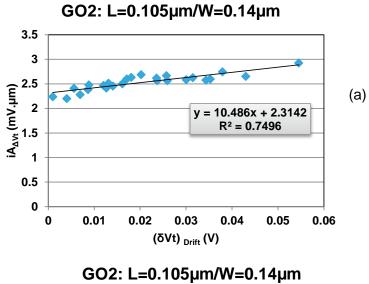

### I.4.4.c Confidence interval