### Rétro-ingénierie des plateformes pour le déploiement des applications temps réel

Rania Mzid

#### ▶ To cite this version:

Rania Mzid. Rétro-ingénierie des plateformes pour le déploiement des applications temps réel. Système d'exploitation [cs.OS]. Ecole Nationale des Ingénieurs de Sfax; Université de Bretagne Occidentale, 2014. Français. NNT: . tel-01316089

### HAL Id: tel-01316089 https://theses.hal.science/tel-01316089

Submitted on 14 May 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Ecole Nationale des Ingénieurs de Sfax et Université de Bretagne Occidentale

### Thèse

présentée pour obtenir le grade de docteur

spécialité : Informatique

par

Rania MZID

# Rétro-ingénierie des plateformes pour le déploiement des applications temps réel

Thèse soutenue 12 Mai 2014, devant le jury composé de :

Mohamed JMAIEL **Président** ENIS Mohamed KHALGUI **Rapporteur** INSAT

Pierre BOULET Rapporteur Université Lille 1

Jérôme DELATOURExaminateurESEOJean-Philippe BABAUDirecteurUBOMohamed ABIDDirecteurENIS

Chokri MRAIDHA Encadrant CEA-LIST

TECHNO-THÈSE CEA-TUNISIE EN CO-TUTELLE ENTRE L'ÉCOLE DOCTORALE SCIENCES ET TECHNOLOGIES DE L'ENIS DE L'Université de Sfax et l'École Doctorale Santé, Information, Communication, Mathématique, Matière de L'Université de Bretagne Occidentale

### Table des matières

| Ta | ble d  | es mat   | ières                                                                | ii |

|----|--------|----------|----------------------------------------------------------------------|----|

| Ta | ıble d | es figu  | res                                                                  | vi |

| Li | ste de | es table | aux                                                                  | ix |

| 1  | Intr   | oductio  | on                                                                   | 1  |

|    | 1.1    | Conte    | xte                                                                  | 2  |

|    | 1.2    | Proble   | ématique                                                             | 3  |

|    | 1.3    | Contr    | ibutions                                                             | 3  |

|    | 1.4    | Orgar    | nisation du document                                                 | 4  |

| 2  | État   | de l'ar  | t                                                                    | 6  |

|    | 2.1    | Introd   | luction                                                              | 7  |

|    | 2.2    | Doma     | ine de l'étude                                                       | 7  |

|    |        | 2.2.1    | Les systèmes temps réel embarqués                                    | 7  |

|    |        |          | 2.2.1.1 Mise en œuvre des systèmes temps réel embarqués              | 8  |

|    |        |          | 2.2.1.2 Vérification des applications temps réel embarquées          | 10 |

|    |        | 2.2.2    | Ingénierie Dirigée par les modèles (IDM)                             | 13 |

|    |        |          | 2.2.2.1 Modèles, méta-modèles et transformations de modèles          | 14 |

|    |        |          | 2.2.2.2 Approche MDA                                                 | 15 |

|    |        |          | 2.2.2.3 Caractérisation d'une plateforme dans un cadre IDM           | 17 |

|    |        | 2.2.3    | Synthèse                                                             | 17 |

|    | 2.3    | Les pl   | ateformes d'exécution                                                | 18 |

|    |        | 2.3.1    | Représentations des plateformes d'exécution dans l'IDM               | 18 |

|    |        | 2.3.2    | Modélisation des plateformes d'exécution                             | 19 |

|    |        |          | 2.3.2.1 Modèle de plateforme pour l'analyse d'ordonnançabilité       | 19 |

|    |        |          | 2.3.2.2 Langages de modélisation des plateformes                     | 20 |

|    |        | 2.3.3    | Synthèse                                                             | 24 |

|    | 2.4    | Platef   | ormes cibles et processus de développement des STRE                  | 25 |

|    |        | 2.4.1    | Prise en compte des plateformes pour la vérification des contraintes |    |

|    |        |          | temporelles des applications                                         | 26 |

|     |      | 2.4.2   | Prise en compte des plateformes lors du déploiement des applications    | 29 |

|-----|------|---------|-------------------------------------------------------------------------|----|

|     |      | 2.4.3   | Synthèse et discussion                                                  | 30 |

|     | 2.5  | Concl   | usion                                                                   | 32 |

| 3   | DRI  | M : un  | processus pour le déploiement multiplateforme des applications temps    |    |

| rée |      |         |                                                                         | 34 |

|     | 3.1  | Introd  | luction                                                                 | 35 |

|     | 3.2  |         | ibution à la prise en compte explicite des plateformes logicielles pour |    |

|     |      |         | yse                                                                     | 35 |

|     |      | 3.2.1   | Modèles de plateformes de point de vue analyse dans l'IDM               | 35 |

|     |      | 3.2.2   | Identification des besoins pour une plateforme abstraite d'analyse      | 37 |

|     | 3.3  | Proces  | ssus DRIM                                                               | 38 |

|     |      | 3.3.1   | Vue d'ensemble du processus DRIM                                        | 38 |

|     |      | 3.3.2   | La phase de refactoring                                                 | 40 |

|     | 3.4  | Concl   | usion                                                                   | 42 |

|     |      |         |                                                                         |    |

| 4   | Mét  | hodolo  | gie de modélisation dans DRIM                                           | 43 |

|     | 4.1  | Introd  | luction                                                                 | 44 |

|     | 4.2  | Descri  | iption du langage de modélisation                                       | 44 |

|     |      | 4.2.1   | Le méta-modèle DRIM : un méta-modèle pour la description des pla-       |    |

|     |      |         | teformes logicielles                                                    | 44 |

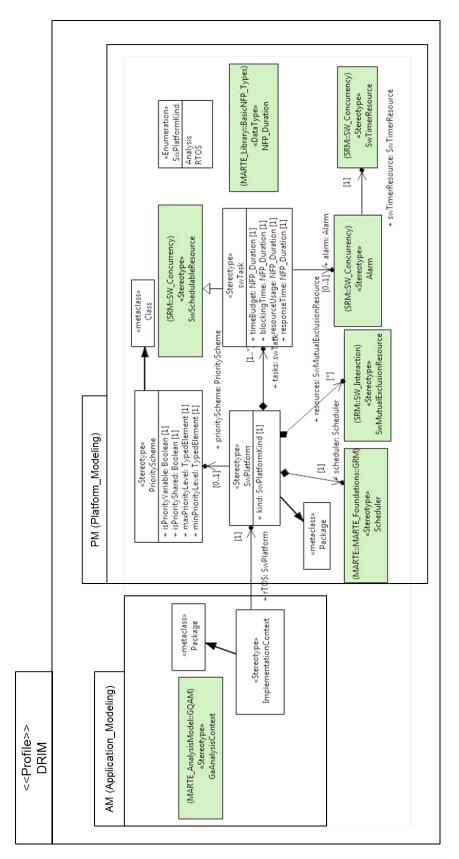

|     |      | 4.2.2   | Le profil DRIM : une extension du profil MARTE                          | 48 |

|     |      |         | 4.2.2.1 Implantation du méta-modèle DRIM dans un profil UML             | 48 |

|     |      |         | 4.2.2.2 Identification des concepts pour la modélisation des applica-   |    |

|     |      |         | tions dans DRIM                                                         | 50 |

|     | 4.3  | Règles  | s méthodologiques de modélisation                                       | 52 |

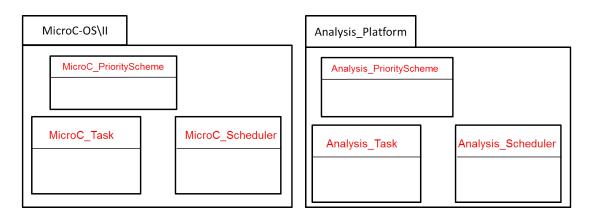

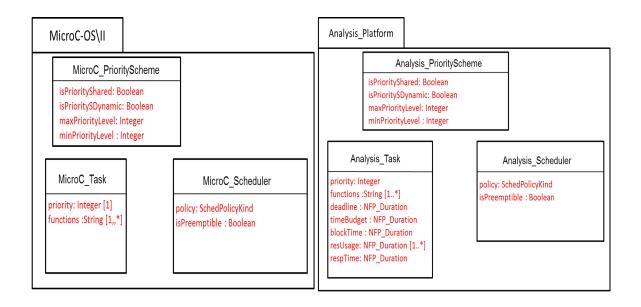

|     |      | 4.3.1   | Les règles de modélisation de plateformes                               | 52 |

|     |      |         | 4.3.1.1 Les règles liées aux éléments UML                               | 53 |

|     |      |         | 4.3.1.2 Les règles de stéréotypage                                      | 57 |

|     |      | 4.3.2   | Les règles de modélisation des applications temps réel                  | 60 |

|     | 4.4  | Concl   | usion                                                                   | 63 |

| 5   | Mise | e en œı | uvre du processus DRIM                                                  | 64 |

|     | 5.1  | Introd  | luction                                                                 | 65 |

|     | 5.2  | Évalua  | ation de faisabilité du déploiement                                     | 65 |

|     |      | 5.2.1   | Test de l'ordonnanceur                                                  | 65 |

|     |      | 5.2.2   | Test des ressources partagées                                           | 67 |

|     |      | 5.2.3   | Identification des tests pour la notion de priorité                     | 69 |

|     |      |         | 5.2.3.1 Test des niveaux de priorité distincts                          | 69 |

|     |      |         | 5.2.3.2 Test des niveaux de priorité égaux                              | 70 |

|     |      |         | 5.2.3.3 Test de priorité dynamique                                      | 72 |

|    | 5.3   | Génér   | ration et validation des modèles d'implémentation                    | 74    |

|----|-------|---------|----------------------------------------------------------------------|-------|

|    |       | 5.3.1   | Phase de Portage                                                     | 74    |

|    |       |         | 5.3.1.1 Définition des règles de correspondance                      | 74    |

|    |       |         | 5.3.1.2 Principe de portage                                          | 76    |

|    |       | 5.3.2   | Phase de validation du Portage                                       | 85    |

|    | 5.4   | Phase   | de refactoring                                                       | 90    |

|    |       | 5.4.1   | NPAP: Un patron pour une nouvelle assignation des valeurs des prio-  |       |

|    |       |         | rités                                                                | 91    |

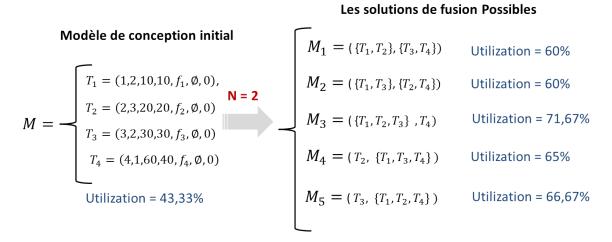

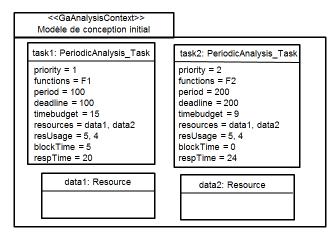

|    |       | 5.4.2   | DPMP : Un patron pour la fusion des tâches de priorités distinctes   | 94    |

|    |       | 5.4.3   | EPMP : Un patron pour la fusion des tâches de priorités égales       | 97    |

|    |       | 5.4.4   | SRMP: Un patron pour la fusion des ressources partagées              | 100   |

|    | 5.5   | Concl   | usion                                                                | 107   |

| 6  | Éva   | luation | s et expérimentations                                                | 108   |

|    | 6.1   | Introd  | luction                                                              | 109   |

|    | 6.2   | Conte   | xte                                                                  | 109   |

|    |       | 6.2.1   | Qompass-Architect                                                    | 109   |

|    |       | 6.2.2   | Définition des critères d'évaluation                                 | 110   |

|    | 6.3   | Étude   | de cas : Application de Contrôle de Robot                            | 111   |

|    |       | 6.3.1   | Aperçu global sur le système étudié                                  | 112   |

|    |       | 6.3.2   | Spécification de l'application de contrôle de robot                  | 113   |

|    |       |         | 6.3.2.1 Fonctionnement                                               | 113   |

|    |       |         | 6.3.2.2 Contraintes temps réel                                       | 114   |

|    |       | 6.3.3   | Modélisation de l'application de contrôle de robot                   | 114   |

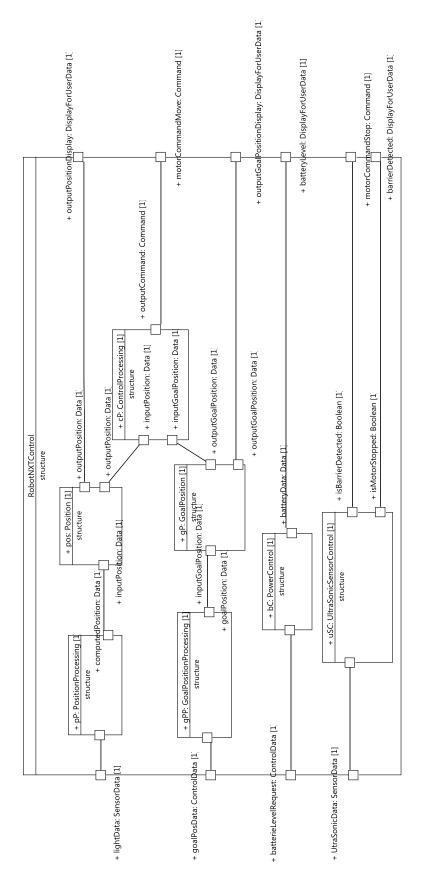

|    |       |         | 6.3.3.1 Description fonctionnelle : Diagramme de structure composite | e 115 |

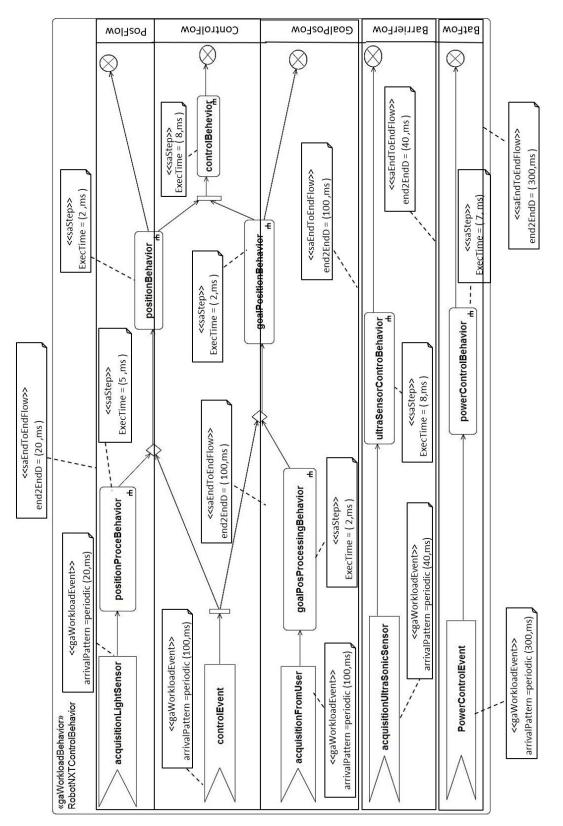

|    |       |         | 6.3.3.2 Description comportementale : Diagramme d'activité           | 115   |

|    |       | 6.3.4   | Génération d'un modèle de conception initial pour l'application de   |       |

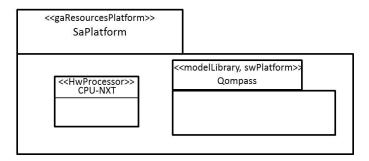

|    |       |         | contrôle de robot                                                    | 118   |

|    | 6.4   | Résult  | tats et discussion                                                   | 122   |

|    |       | 6.4.1   | Déploiement de l'application sur un RTOS qui peut varier             | 122   |

|    |       | 6.4.2   | Déploiement de l'application sur un RTOS fixe                        | 125   |

|    | 6.5   | Concl   | usion                                                                | 131   |

| 7  | Con   | clusior | n et perspectives                                                    | 133   |

|    | 7.1   | Bilan   |                                                                      | 134   |

|    | 7.2   | Perspe  | ectives                                                              | 135   |

| Li | ste d | es Publ | ications                                                             | 137   |

| Bi | bliog | raphie  |                                                                      | 138   |

| A  | For   | nulatio | on MILP du patron DPMP                                               | 144   |

B Modèles des plateformes logicielles

149

# Table des figures

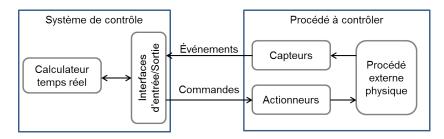

| 2.1 | Architecture d'un système temps réel                                                                                                                                                   | 7  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

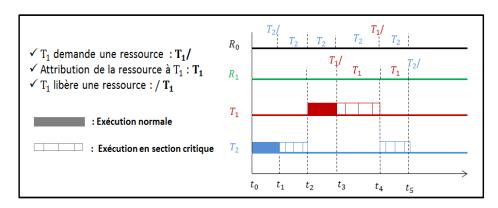

| 2.2 | Situation d'inversion de priorité entre $T_1$ et $T_2$                                                                                                                                 | 12 |

| 2.3 | Situation d'inter-blocage                                                                                                                                                              | 13 |

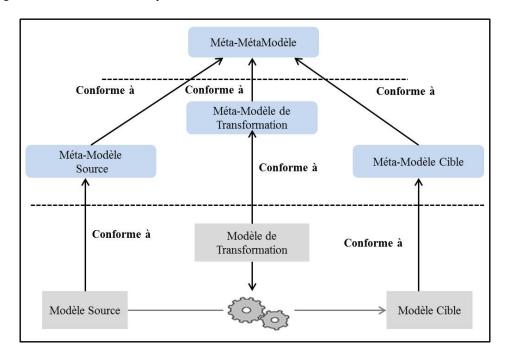

| 2.4 | Transformation de modèles                                                                                                                                                              | 15 |

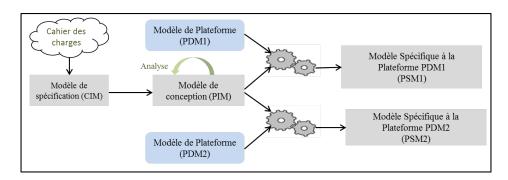

| 2.5 | Processus de développement des systèmes temps réel embarqués dans un cadre MDA                                                                                                         | 16 |

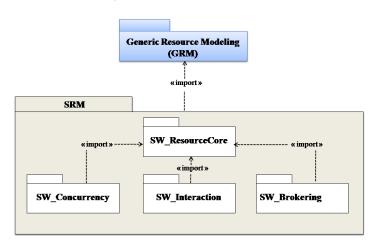

| 2.6 | Structure du profil SRM                                                                                                                                                                | 23 |

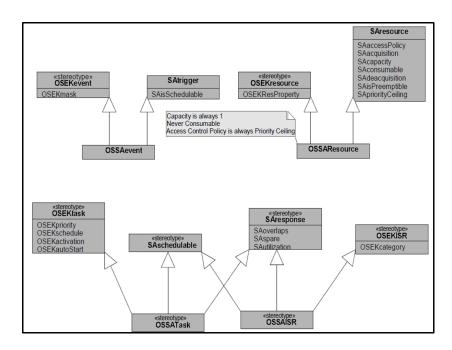

| 2.7 | Extrait du sous-profil définit dans [60] pour l'analyse les systèmes OSEK                                                                                                              | 27 |

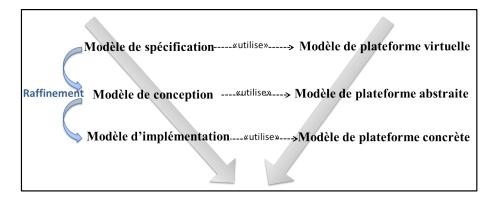

| 3.1 | Les niveaux de plateformes de point de vue analyse dans un flot IDM                                                                                                                    | 36 |

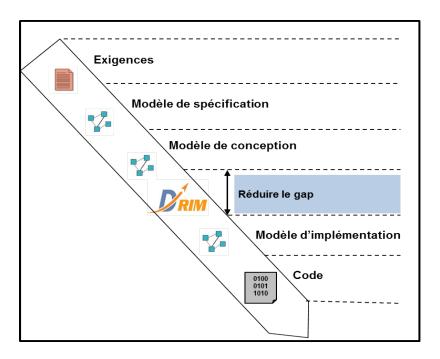

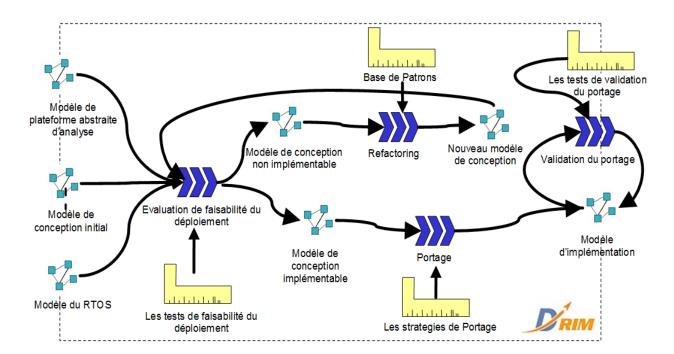

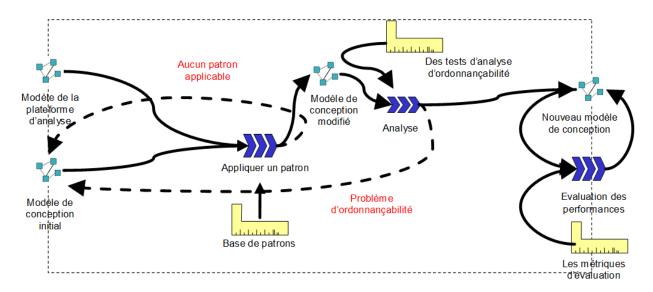

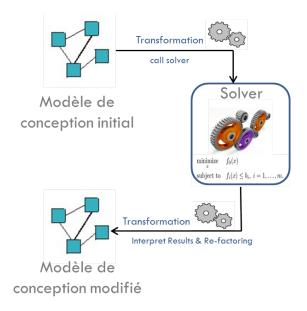

| 3.2 | Le processus DRIM dans un flot orienté modèle                                                                                                                                          | 39 |

| 3.3 | Le processus DRIM                                                                                                                                                                      | 40 |

| 3.4 | La phase de refactoring                                                                                                                                                                | 41 |

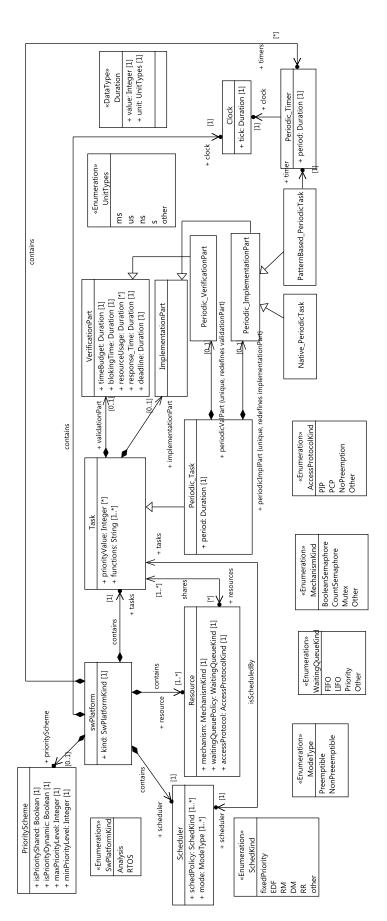

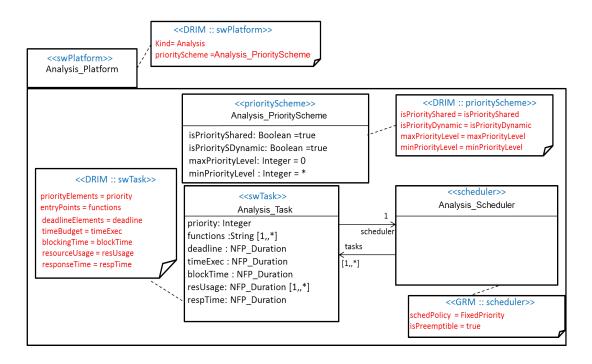

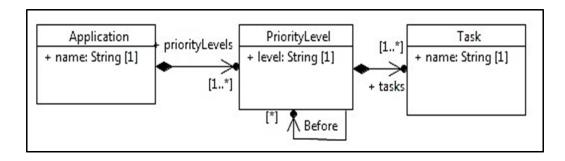

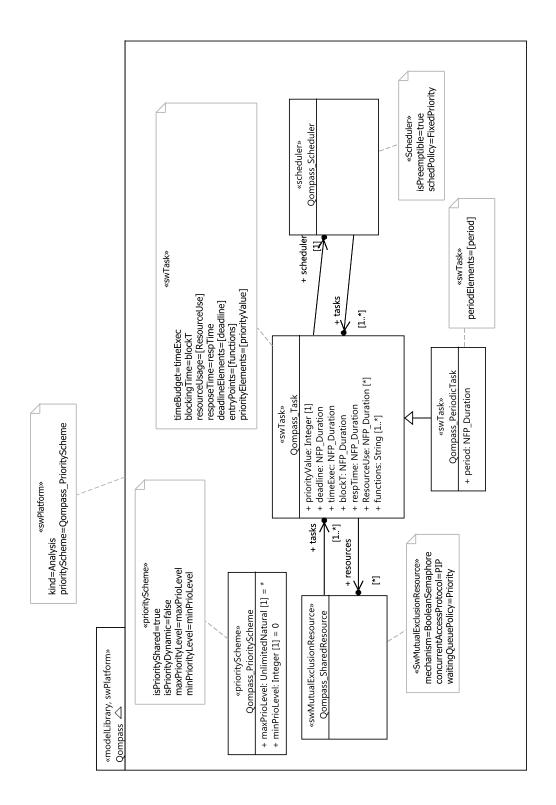

| 4.1 | Le méta-modèle DRIM pour la description des plateformes logicielles                                                                                                                    | 45 |

| 4.2 | Une contrainte OCL sur le méta-modèle DRIM pour limiter le choix de la politique d'ordonnancement et du mode d'un ordonnanceur pour une configuration d'une pla-                       |    |

|     | teforme abstraite d'analyse                                                                                                                                                            | 46 |

| 4.3 | Une contrainte OCL sur le méta-modèle DRIM pour définir une seule implémenta-<br>tion des ressources partagées pour une configuration donnée d'une plateforme abs-<br>traite d'analyse | 47 |

| 4.4 | <i>Une contrainte OCL sur le méta-modèle DRIM pour éliminer une situation non si- gnificative pour l'implémentation des ressources partagées</i>                                       | 48 |

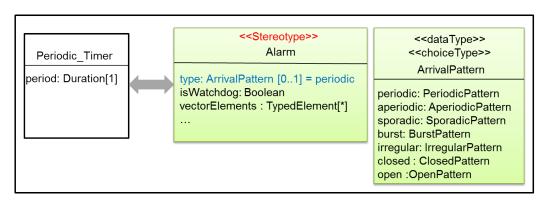

| 4.5 | Correspondance entre le concept Periodic_Timer du méta-modèle et le stéréotype «Alarm» de SRM                                                                                          | 49 |

| 4.6 | Le profil DRIM : une extension du profile MARTE                                                                                                                                        | 51 |

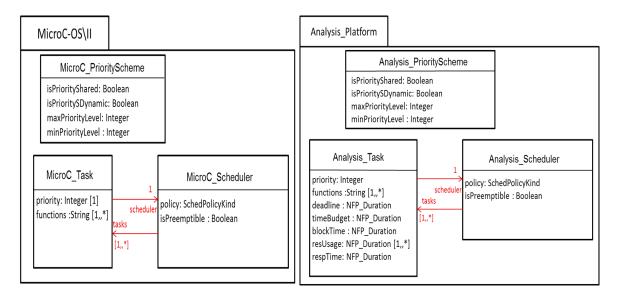

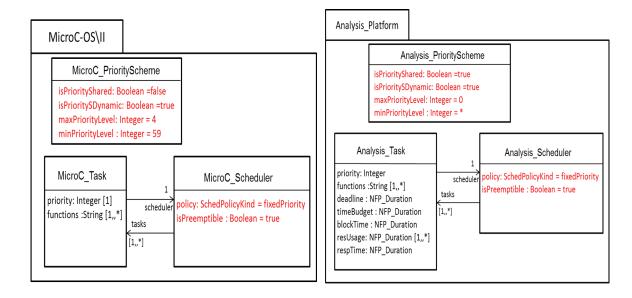

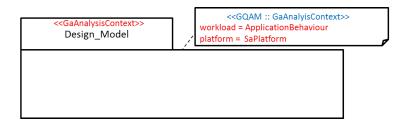

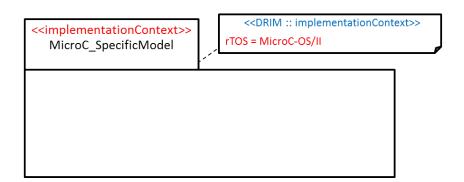

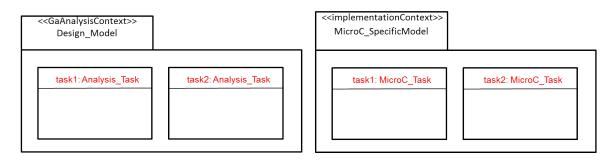

| 4.7 | Exemple d'application de la première règle pour MicroC-OS/II et une plateforme d'analyse                                                                                               | 53 |

| 4.8 | Exemple d'application de la deuxième règle pour MicroC-OS/II et une plateforme d'analyse                                                                                               | 54 |

| 4.9 | Exemple d'application de la troisième règle pour MicroC-OS/II et une plateforme d'analyse                                                                                              | 54 |

| 4.10 | Exemple d'application de la quatrième règle pour MicroC-OS/II et une plateforme d'analyse   | Į  |

|------|---------------------------------------------------------------------------------------------|----|

| 111  | Exemple d'application de la cinquième règle pour MicroC-OS/II et une plateforme             |    |

| 4.11 | d'analyse                                                                                   | Į  |

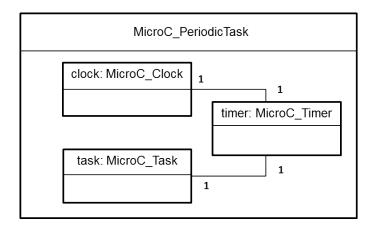

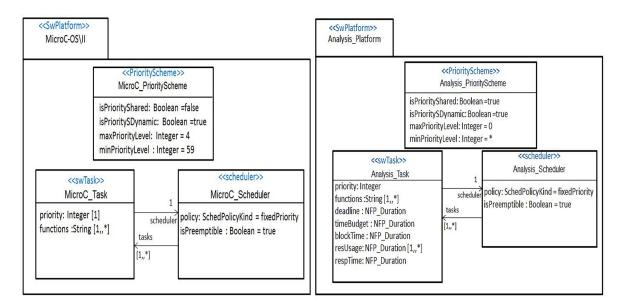

| 4.12 | Exemple de motif de conception pour la description d'une tâche périodique dans              |    |

|      | MicroC-OS/II                                                                                | Į  |

| 4.13 | Exemple d'application de la septième règle pour MicroC-OS/II et une plateforme              |    |

|      | d'analyse                                                                                   | Į  |

| 4.14 | Exemple d'application de la huitième et neuvième règle pour MicroC-OS/II                    | Į  |

|      | Exemple d'application de la huitième et neuvième règle pour une plateforme d'analyse        | (  |

|      | Exemple d'application de la première règle pour créer un modèle de conception de            |    |

| 1.10 | l'application                                                                               | (  |

| 4 17 | Exemple d'application de la deuxième règle pour créer un modèle de l'application spé-       | •  |

| 1.17 | cifique au noyau MicroC-OS/II                                                               | (  |

| 4 18 | Exemple d'application de la troisième règle pour créer un modèle de conception et un        | `  |

| 4.10 | modèle d'implémentation d'une application                                                   | (  |

| A 10 | Exemple d'application de la quatrième règle pour créer un modèle de conception et un        | `  |

| 4.17 | modèle d'implémentation d'une application                                                   | (  |

|      | mouele a implementation a une application                                                   | ,  |

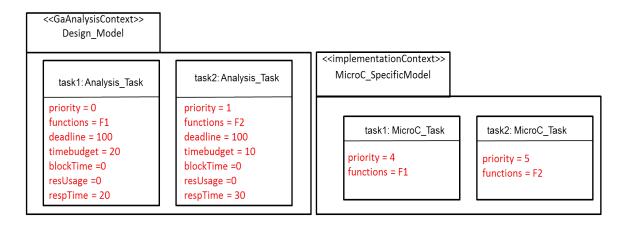

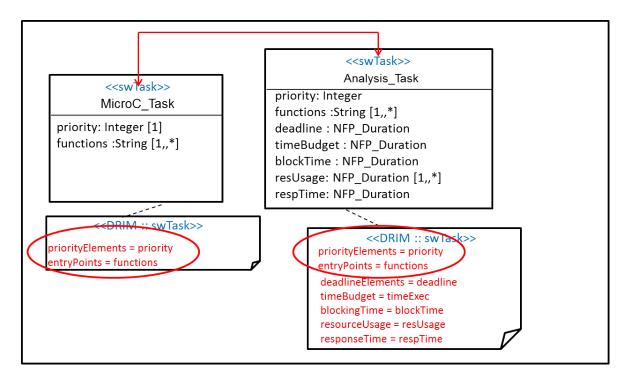

| 5.1  | Un exemple qui illustre une correspondance entre une tâche MicroC-OS/II et une              |    |

|      | tâche d'une plateforme abstraite d'analyse                                                  | 7  |

| 5.2  | <i>Un exemple de modèle de conception, plateforme abstraite d'analyse et RTOS : entrées</i> |    |

|      | pour l'algorithme de portage                                                                | 8  |

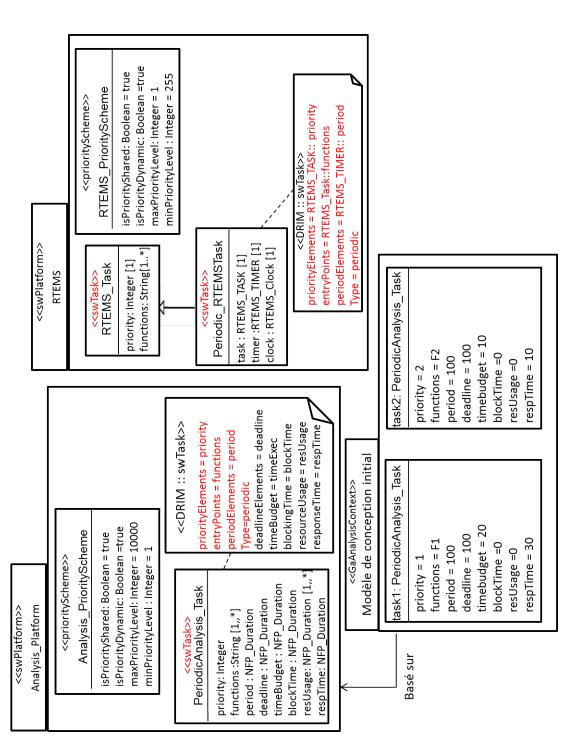

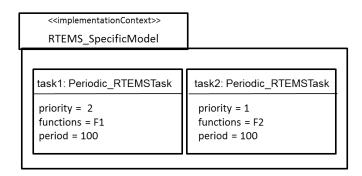

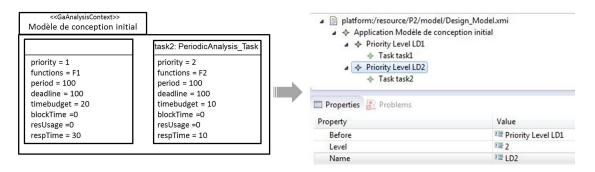

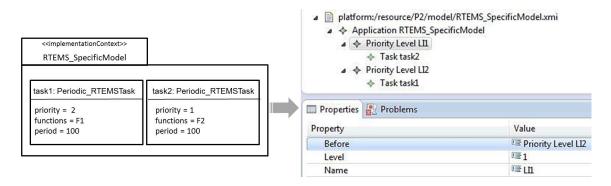

| 5.3  | Le modèle spécifique à RTEMS généré par l'algorithme de portage                             | 8  |

| 5.4  | Le méta-modèle utilisé pour la vérification de la propriété P2                              | 8  |

| 5.5  | Modèle de conception de la Figure 5.2 comme instance du méta-modèle utilisé pour la         |    |

|      | vérification de la propriété P2                                                             | 8  |

| 5.6  | Modèle d'implémentation de la Figure 5.3 comme instance du méta-modèle utilisé              |    |

|      | pour la vérification de la propriété P2                                                     | (  |

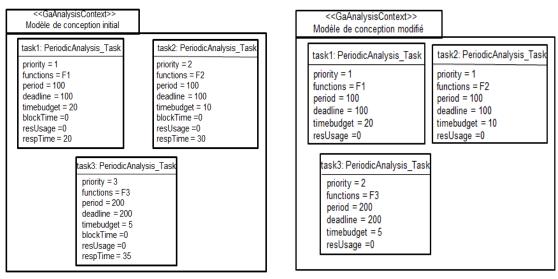

| 5.7  | Exemple d'application du patron NPAP                                                        | (  |

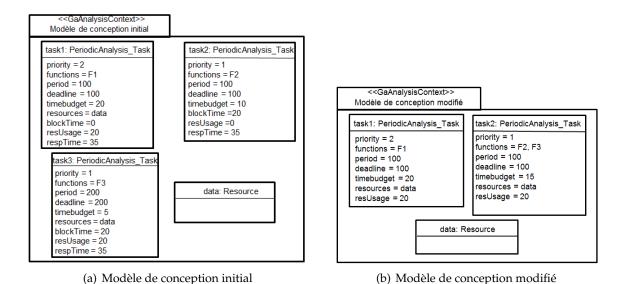

| 5.8  | Fusion de deux tâches en suivant le patron DPMP                                             | (  |

| 5.9  | DPMP :Un problème combinatoire                                                              | (  |

|      | Application du patron DPMP                                                                  | •  |

|      | Fusion de deux tâches en suivant le patron EMPM                                             | (  |

|      | Exemple d'application du patron EPMP                                                        | (  |

|      | Les différentes situations possibles à l'implémentation pour une tâche $T_i$ afin d'accéder |    |

| 0.10 | aux deux ressources $R_n$ et $R_m$                                                          | 1  |

| 5 14 | Application du patron SRMP pour la fusion des deux resources $R_n$ et $R_m$                 | 1  |

|      | Exemple d'application du patron SRMP                                                        | 1  |

| 0.10 | Exemple a application au pation ordin                                                       | 1, |

| 6.1  | La méthodologie Optimum dans un flot IDM                                                    | 1  |

viii Table des figures

| 6.2  | Brique Lego NXT                                                                          | 112 |

|------|------------------------------------------------------------------------------------------|-----|

| 6.3  | Architecture matérielle cible                                                            | 113 |

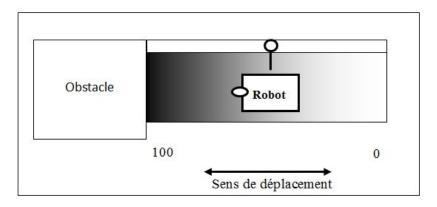

| 6.4  | Description du comportement du robot                                                     | 113 |

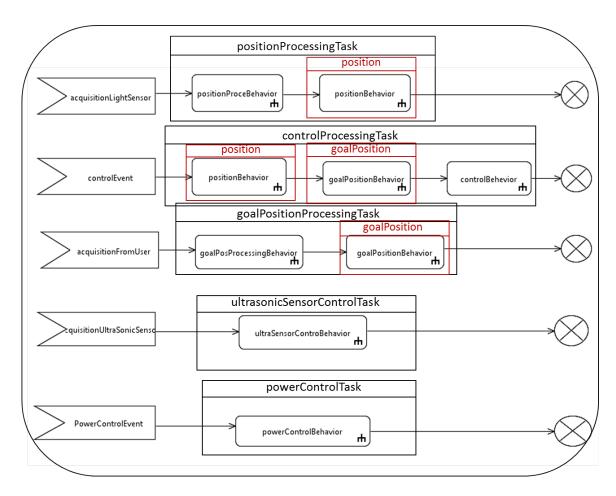

| 6.5  | Description fonctionnelle de l'application de contrôle de robot                          | 116 |

| 6.6  | Description comportementale niveau système de l'application de contrôle de robot .       | 117 |

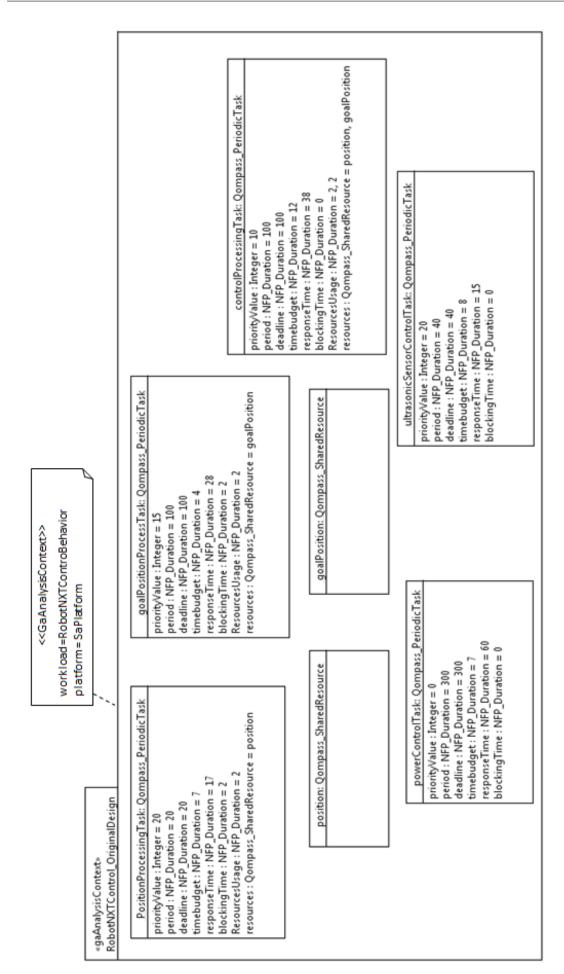

| 6.7  | Description de la plateforme utilisée au niveau conception                               | 118 |

| 6.8  | Modèle d'allocation des tâches et des ressources pour l'application de contrôle du robot | 119 |

| 6.9  | Exemple de modèle de conception initial de l'application de contrôle du robot généré     |     |

|      | par Qompass-Architect                                                                    | 120 |

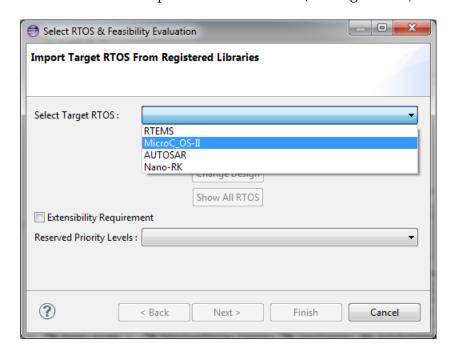

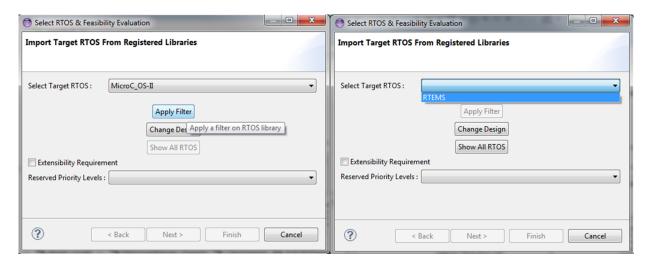

| 6.10 | Sélection d'un RTOS cible à partir d'une librairie de modèle                             | 122 |

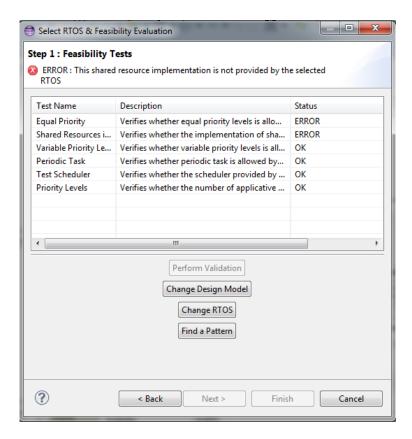

| 6.11 | Évaluation de faisabilité du modèle de conception initial pour MicroC-OS/II              | 123 |

| 6.12 | Application du filtre pour guider l'utilisateur à choisir le RTOS approprié              | 124 |

| 6.13 | Sélection du RTOS cible et limitation du nombre des niveaux de priorité distincts        |     |

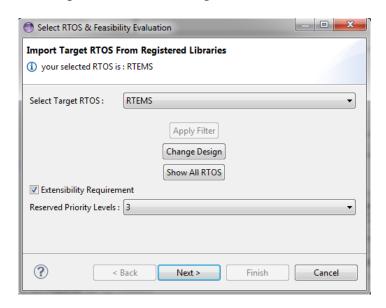

|      | pour des besoins d'extensibilité                                                         | 125 |

| 6.14 | Évaluation de faisabilité du déploiement du modèle de conception initial pour RTEMS      |     |

|      | en limitant le nombre des niveaux de priorité distinct à 3                               | 126 |

| 6.15 | Liste des patrons proposée par l'outil Qompass lié au problème de déploiement du         |     |

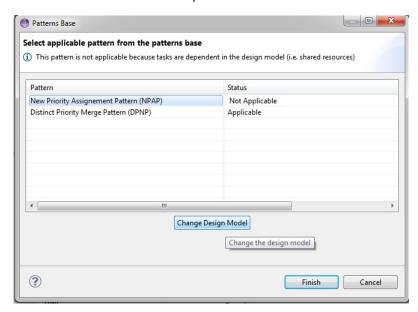

|      | nombre des niveaux de priorité distincts                                                 | 126 |

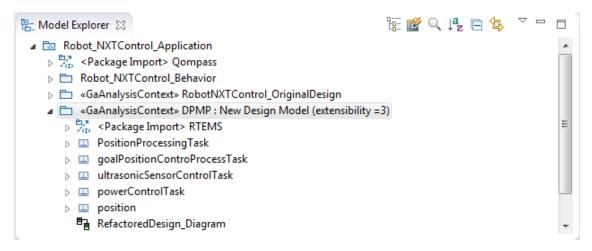

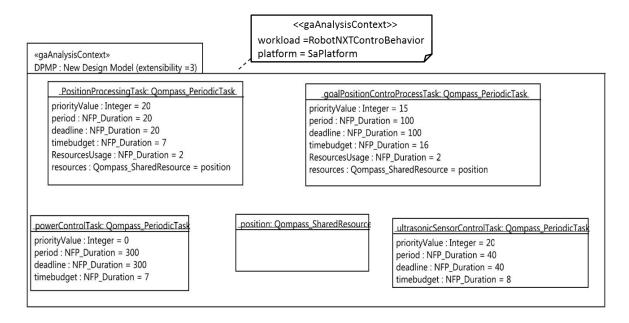

|      | Génération d'un nouveau modèle de conception en appliquant le patron DPMP                | 127 |

| 6.17 | Modèle de conception de l'application de contrôle de robot généré suite à l'application  |     |

|      | du patron DPMP                                                                           | 128 |

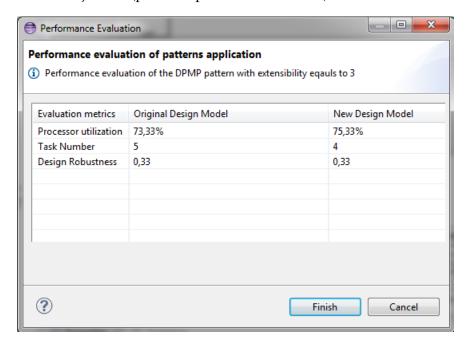

| 6.18 | Évaluation des performances du modèle de conception généré suite à l'application du      |     |

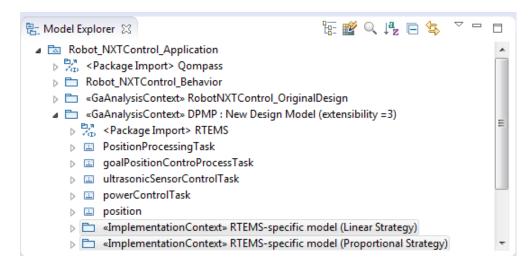

|      | DPMP                                                                                     | 129 |

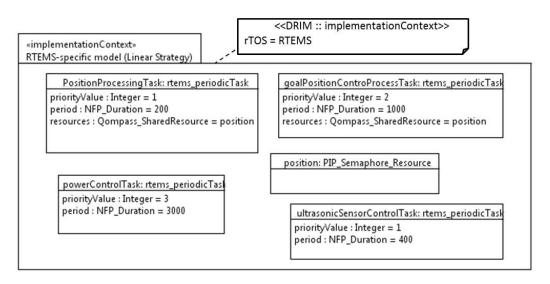

|      | Génération des modèles de l'application de contrôle de robot spécifiques à RTEMS .       | 129 |

|      | Un modèle de l'application de contrôle de robot spécifique à RTEMS                       | 130 |

| 6.21 | Vérification du modèle spécifique à RTEMS (Validation du portage)                        | 131 |

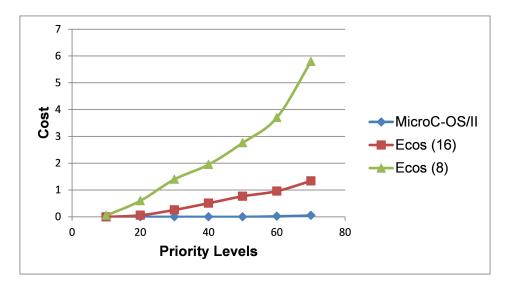

| A.1  | Évaluation du patron DPMP                                                                | 147 |

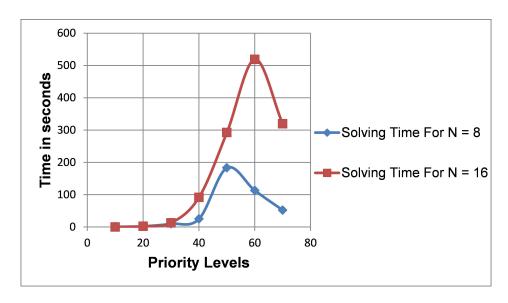

|      | Évaluation du temps de résolution du programme linéaire du patron DPMP                   | 148 |

|      | Extrait de la transformation d'appel du solveurpour l'exéution du programme linéaire     |     |

|      | du patron DPMP                                                                           | 148 |

|      | ,                                                                                        |     |

| B.1  | Modèle d'une configuration possible de la plateforme abstraite d'analyse associée à      |     |

|      | Qompass                                                                                  | 150 |

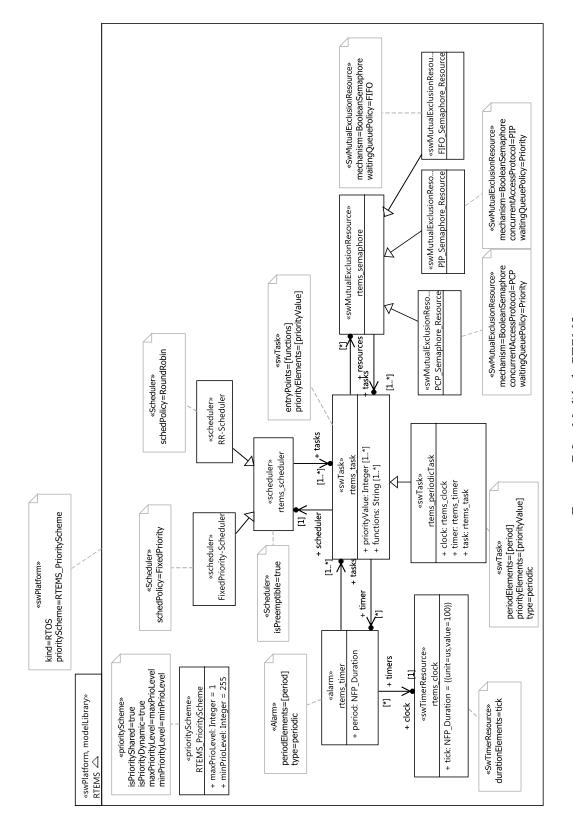

| B.2  | Modèle de RTEMS                                                                          | 151 |

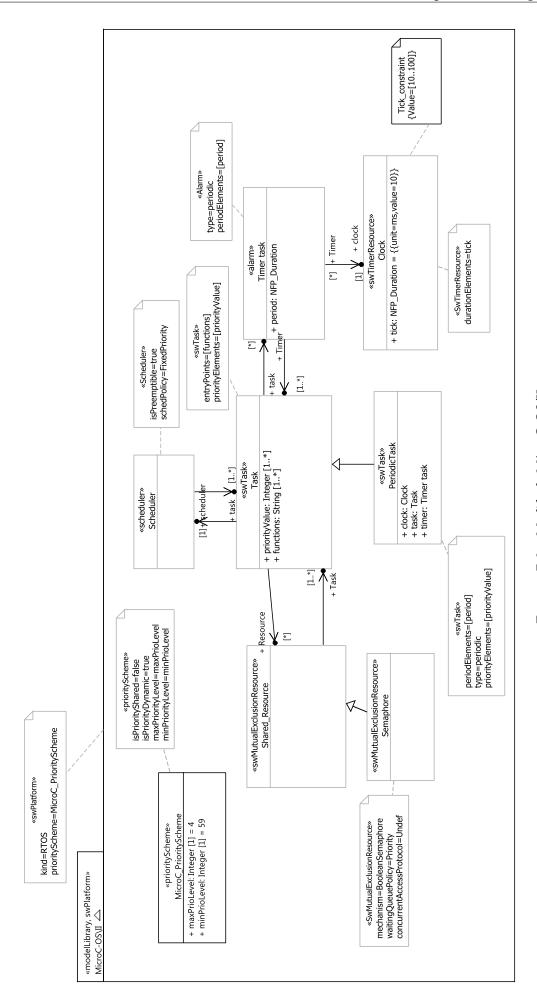

| B.3  | Modèle de MicroC-OS/II                                                                   | 152 |

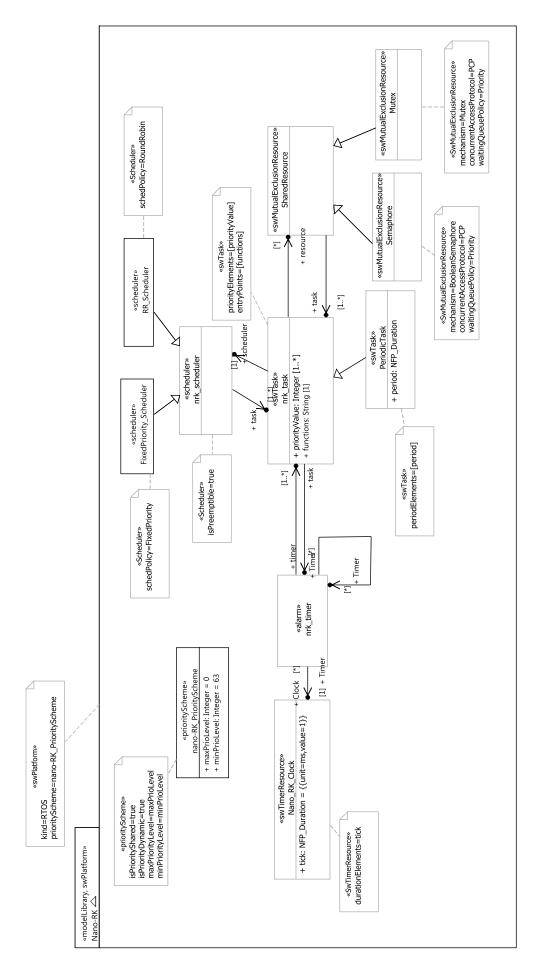

| B.4  | Modèle de nano-RK                                                                        | 153 |

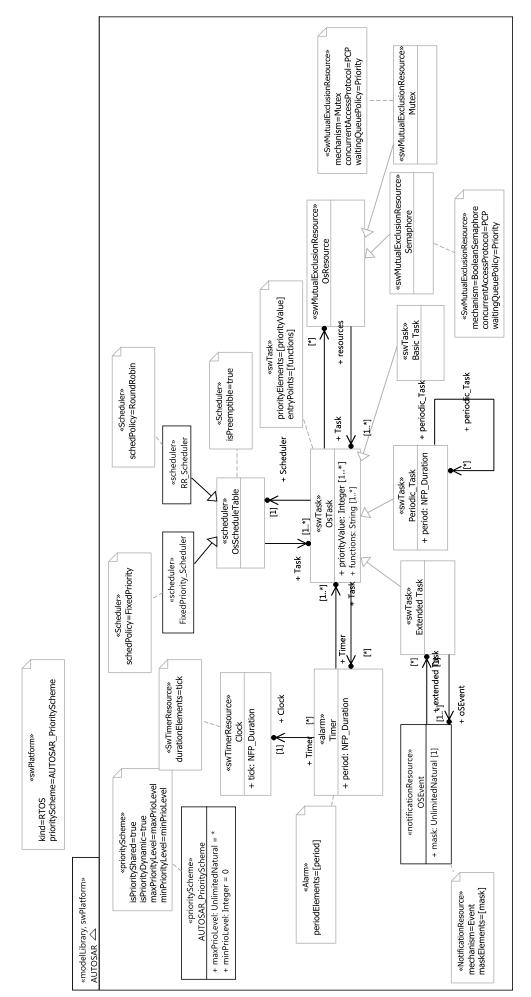

| B.5  | Modèle de AUTOSAR-OS                                                                     | 154 |

### Liste des tableaux

| cution                                                                       | 25                                                                               |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Comparaison des langages de modélisation des plateformes logicielles d'exé-  |                                                                                  |

| cution                                                                       | 32                                                                               |

| Correspondance entre les concepts du méta-modèle DRIM et les concepts de     |                                                                                  |

| MARTE                                                                        | 49                                                                               |

| Liste des tests de faisabilité du déploiement identifiés dans cette étude    | 73                                                                               |

| Les caractéristiques de l'algorithme NPAP en termes de complexité et de ter- |                                                                                  |

| minaison                                                                     | 93                                                                               |

| Les caractéristiques de l'algorithme EPMP en termes de complexité et de ter- |                                                                                  |

| minaison                                                                     | 99                                                                               |

| Les caractéristiques de l'algorithme SRMP en termes de complexité et de ter- |                                                                                  |

| minaison                                                                     | 104                                                                              |

| Description des patrons proposés                                             | 106                                                                              |

| Résultats de vérification temporelle du modèle de conception initial donnés  |                                                                                  |

| par Qompass                                                                  | 121                                                                              |

| Classification des RTOS selon les familles identifiées                       | 124                                                                              |

| Résultats de vérification temporelle du nouveau modèle de conception pro-    |                                                                                  |

| duit suite à l'application du patron DPMP                                    | 128                                                                              |

|                                                                              | Comparaison des langages de modélisation des plateformes logicielles d'exécution |

## **Chapitre 1**

## Introduction

| 1.1 | Contexte                 |

|-----|--------------------------|

| 1.2 | Problématique 3          |

| 1.3 | Contributions            |

| 1.4 | Organisation du document |

2 Introduction

#### 1.1 Contexte

Les systèmes temps réel embarqués (STRE) sont désormais présents dans plusieurs domaines d'application tels que la télécommunication, l'automobile, l'aéronautique, etc. Devant assurer de plus en plus de fonctionnalités, ces systèmes ont tendance à être de plus en plus complexes [27][46]. En plus de cette complexité, des contraintes concurrentielles liées au marché des systèmes temps-réel embarqués viennent s'ajouter. Ces contraintes obligent les industries à fournir un produit innovant tout en optimisant son coût et son temps de mise sur le marché (*time to market*).

Afin de répondre à cette complexité croissante, l'innovation technologique s'oriente vers une montée en niveaux d'abstraction. Depuis plusieurs années, les couches d'abstraction logicielles ont vu le jour. Notamment, les systèmes d'exploitation ont permis d'abstraire les préoccupations liées à la plateforme matérielle. L'apparition de ces systèmes a permis, d'une part, aux développeurs de se décharger de la complexité du développement qui résulte de l'utilisation des langages machines. D'autre part, leur utilisation facilite le portage des applications sur différents supports matériels. Les systèmes d'exploitation constituent ainsi des supports d'exécution logiciels pour les applications.

Aujourd'hui, les systèmes d'exploitation tendent à leur tour à évoluer et se diversifier. Ceci a paradoxalement complexifié les cycles de développement [50] et a poussé les recherches vers une nouvelle montée en niveau d'abstraction. En effet, les besoins de réutilisation et de portage des applications sur différents systèmes (ou sur plusieurs versions d'un même système), orientent le développement logiciel vers une conception de l'application indépendante de tout système d'exploitation. L'ingénierie dirigée par les modèles (IDM)[76] propose un cadre aux développeurs pour séparer la conception de l'application de son implémentation. Elle prône pour cela l'utilisation des modèles et des transformations des modèles. Les modèles décrivent les systèmes, tandis que les transformations automatisent leur manipulation et leur intégration dans un processus de développement génératif.

Par ailleurs, l'aspect critique des systèmes temps réel embarqués qui résulte principalement des contraintes temps réel exigées par l'application, nécessite de faire appel à des techniques de vérification. L'application de ces techniques permet de prouver qu'un système respecte ses contraintes de temps. Dans ce contexte, l'IDM préconise la vérification des modèles de haut niveau pour une détection plus rapide et efficace des erreurs de développement.

C'est dans ce contexte que cette thèse se situe. Nous nous intéressons au développement des systèmes temps réel embarqués en suivant la ligne de l'IDM. Plus précisément, l'objectif est d'assurer le déploiement d'une application temps réel sur différents systèmes d'exploitation temps réel (RTOS). Ce déploiement doit permettre le portage de l'application d'un RTOS à un autre tout en assurant le respect des contraintes de temps de celle-ci à l'implémentation.

Problématique 3

#### 1.2 Problématique

Standardisée par l'OMG, l'approche MDA (Model-Driven Architecture) [65] définit un cadre pour un processus de type IDM, et plus particulièrement pour la mise en œuvre d'une application sur différentes plateformes logicielles d'exécution. En suivant cette discipline, les concepteurs ont la possibilité de décrire leur application dans un modèle de conception indépendant de toute plateforme logicielle (PIM, Platform Independant Model). A partir de ce modèle, plusieurs modèles de l'application spécifiques à différents RTOS doivent pouvoir être automatiquement générés (PSM, Platform Specific Model) à l'aide des transformations de modèles.

En outre, dans une approche MDA, une vérification des contraintes de temps de l'application peut être réalisée au niveau conception (c'est-à-dire au niveau du PIM). A ce niveau, l'utilisation des techniques d'analyse à savoir les techniques d'analyse d'ordonnançabilité [80], a pour objectif d'éliminer (tôt dans le cycle de développement) les défauts de conception. Cela permet de détecter les architectures non faisables menant à des systèmes défaillants c'est-à-dire des systèmes qui ne respectent pas les contraintes de temps de l'application. Toutefois, afin d'être vérifié un modèle doit être exécutable, c'est à dire il doit avoir une sémantique permettant son interprétation. Par conséquent, l'application des techniques d'analyse d'ordonnançabilité nécessite de faire une abstraction de certaines informations de la plateforme logicielle (afin d'obtenir un PIM interprétable). Cette abstraction se traduit en général par des hypothèses sur l'implémentation dans le but de garder la portabilité (l'indépendance par rapport au RTOS) du PIM.

Du fait de la grande variété des RTOS qui existent aujourd'hui, le déploiement de ce PIM sur un de ces RTOS est une tâche qui n'est pas triviale. En effet, même si tous ces RTOS partagent à peu près les mêmes concepts, la caractérisation de ces concepts peut varier d'un RTOS à un autre, d'une famille à une autre ou d'un standard à un autre [5][6]. De ce fait, les hypothèses sur l'implémentation considérées au niveau conception pour vérifier les contraintes de temps, peuvent être non vérifiées pour le RTOS cible. Dans ce cas, le PIM est considéré non-implémentable sur ce RTOS. Par ailleurs, au niveau implémentation, ces hypothèses peuvent avoir une sémantique différente de celle spécifiée au niveau conception. Dans un tel scénario, le PSM résultant n'est pas équivalent au PIM et ainsi les contraintes de temps peuvent être affectées. Pour remédier à ces problèmes, le concepteur effectue une itération sur le modèle de conception (PIM) en le modifiant dans le but de trouver une solution réalisable. Ces modifications sont, d'une part, basées sur l'expérience du concepteur ce qui augmente considérablement le cycle de développement et, d'autre part, réduisent la portabilité du PIM.

#### 1.3 Contributions

L'objectif de cette thèse est de guider le déploiement d'une application temps réel sur différents systèmes d'exploitation temps réel (RTOS) en respectant les principes du MDA,

4 Introduction

d'une part, et en assurant la préservation des propriétés temporelles à l'implémentation d'autre part. Pour cela, cette thèse contribue en deux points :

- L'introduction de la notion de plateforme abstraite pour l'analyse, plus précisément une plateforme logicielle abstraite pour l'analyse d'ordonnançabilité. Cette plateforme est utilisée au niveau conception pour vérifier les contraintes de temps de l'application et pour préparer la phase de déploiement tout en restant indépendant du RTOS cible.

- Proposition du processus DRIM qui permet de guider le raffinement du modèle de l'application indépendant de tout RTOS (PIM) à un modèle de celle-ci spécifique à un RTOS particulier (PSM). Ce processus repose sur une description explicite de la plateforme abstraite d'analyse et du RTOS cible. Il intègre un ensemble de phases intermédiaires entre la conception et l'implémentation permettant ainsi de (1) détecter les modèles de conception (i.e. PIM) non-implémentables pour un RTOS donné, (2) guider l'utilisateur pour le choix d'un RTOS approprié pour une application particulière, (3) effectuer le refactoring du PIM au travers l'application des patrons pour trouver une solution implémentable pour un RTOS donné et (4) générer plusieurs modèles de l'application spécifiques à différents RTOS (i.e. PSM) en assurant le respect des contraintes de temps à l'implémentation. Une méthodologie pour la description des modèles dans DRIM a été présentée et une mise en œuvre de ce dernier pour les systèmes temps réel s'exécutant sur une architecture monoprocesseur a été également exposée.

#### 1.4 Organisation du document

Le manuscrit est organisé selon le plan suivant :

Le deuxième chapitre présente le contexte de cette étude qui aborde le domaine du développement logiciel pour les systèmes temps-réel embarqués. Tout d'abord, nous introduisons les systèmes temps réel embarqués et l'ingénierie dirigée par les modèles (IDM) utilisée pour leur mise en œuvre dans cette étude. Ensuite, nous nous focalisons sur la notion de la plateforme logicielle au sens de l'IDM et nous faisons un tour d'horizon des différents langages proposés dans la littérature pour modéliser cette dernière. Enfin, nous exposons les différentes approches connexes à nos travaux. À partir de cette étude, nous positionnons nos travaux et nous donnons les grandes lignes de nos contributions.

Le troisième chapitre donne un aperçu global des contributions de cette thèse. Nous commençons par expliquer notre contribution pour une prise en compte explicite de la plate-forme logicielle, dite abstraite, utilisée pour l'analyse d'ordonnançabilité au niveau conception. Ensuite, nous présentons un processus que nous appelons DRIM (Design Refinement toward Implementation Methodology). Ce processus définit un ensemble d'étapes intermédiaires entre la phase de conception et la phase d'implémentation du flot IDM permettant ainsi le déploiement d'une application temps réel sur différents RTOS.

Dans le quatrième chapitre, nous introduisons un langage pour la description des différents modèles intervenant dans le processus DRIM et nous présentons une méthodologie pour la description de ces différents modèles en nous basant sur le langage proposé. Les résultats de ce chapitre constituent la base du cinquième chapitre de ce rapport, qui présente une mise en œuvre du processus DRIM. L'objectif de cette mise en œuvre est de détailler les techniques permettant de guider le déploiement des applications visées dans cette étude (i.e. des applications temps-réel s'exécutant sur une architecture mono-processeur et présentant des tâches qui ne peuvent être dépendantes qu'en partageant des données en exclusion mutuelle.)

Le sixième chapitre décrit les expérimentations menées dans cette étude pour évaluer le processus DRIM. Ces expérimentations sont basées sur l'automatisation de ce dernier et une présentation d'un cas d'étude permettant ainsi de vérifier son applicabilité. L'évaluation réalisée a permis non seulement d'explorer les différentes facettes du processus mais elle a montré sa capacité à détecter les problèmes potentiels de déploiement plus tôt dans le cycle d'une part et à suivre la ligne du MDA en garantissant la portabilité de l'application d'autre part.

Enfin, dans le dernier chapitre, nous concluons cette thèse par le bilan des travaux effectués avant d'aborder quelques perspectives à nos travaux.

### **Chapitre 2**

# État de l'art

| 2.1 | Introd | luction                                                              | 7  |

|-----|--------|----------------------------------------------------------------------|----|

| 2.2 | Doma   | iine de l'étude                                                      | 7  |

|     | 2.2.1  | Les systèmes temps réel embarqués                                    | 7  |

|     | 2.2.2  | Ingénierie Dirigée par les modèles (IDM)                             | 13 |

|     | 2.2.3  | Synthèse                                                             | 17 |

| 2.3 | Les pl | ateformes d'exécution                                                | 18 |

|     | 2.3.1  | Représentations des plateformes d'exécution dans l'IDM               | 18 |

|     | 2.3.2  | Modélisation des plateformes d'exécution                             | 19 |

|     | 2.3.3  | Synthèse                                                             | 24 |

| 2.4 | Platef | ormes cibles et processus de développement des STRE                  | 25 |

|     | 2.4.1  | Prise en compte des plateformes pour la vérification des contraintes |    |

|     |        | temporelles des applications                                         | 26 |

|     | 2.4.2  | Prise en compte des plateformes lors du déploiement des applications | 29 |

|     | 2.4.3  | Synthèse et discussion                                               | 30 |

| 2.5 | Concl  | usion                                                                | 32 |

Ce chapitre vise deux objectifs. Il s'intéresse tout d'abord à introduire le contexte de cette étude et les concepts mis à contribution. Il vise ensuite à positionner les contributions de cette thèse par rapport aux travaux existants.

Introduction 7

#### 2.1 Introduction

L'objectif de ce chapitre est de positionner les contributions de cette thèse face aux travaux existants. Pour cela, ce chapitre est divisé en trois parties. Dans la première partie, nous débuterons par une introduction aux systèmes temps réel embarqués et l'ingénierie dirigée par les modèles en mettant l'accent sur les concepts mis à contribution dans la suite de cette étude. Cette partie a pour but de familiariser le lecteur avec le contexte d'étude de nos travaux. La deuxième partie de ce chapitre s'intéresse à la notion de plateforme d'exécution et traite en particulier la problématique de modélisation des plateformes. Dans la troisième partie, nous proposons une synthèse permettant de classifier les travaux de recherche qui concernent les processus de développement des systèmes temps réel embarqués. Ainsi, nous distinguons les processus qui se focalisent sur l'aspect temps réel et ceux qui s'intéressent au problème de déploiement. Nous nous intéressons, en particulier, à la considération des plateformes logicielles pour des activités d'analyse ou de déploiement. Au terme de ce chapitre, nous serons alors en mesure de définir les grandes lignes de nos contributions.

#### 2.2 Domaine de l'étude

Cette partie a pour but de familiariser le lecteur avec le contexte d'étude de nos travaux. Pour cela, elle introduit tout d'abord les systèmes temps réel embarqués. Ensuite, elle présente l'ingénierie dirigée par les modèles utilisée pour leur développement. Nous signalons que nous précisons au fur et à mesure les hypothèses que nous avons considérées lors de nos travaux.

#### 2.2.1 Les systèmes temps réel embarqués

Les systèmes temps réels sont des systèmes réactifs. Un système réactif est un système assujetti à l'évolution dynamique d'un procédé qui lui est connecté et qu'il doit piloter en réagissant à tous ses changements d'état dans un temps fini et déterminé [36]. L'architecture classique des systèmes temps réel est illustrée par la figure 2.1. Ces systèmes sont constitués essentiellement de deux sous-systèmes : le procédé à contrôler et le système de contrôle.

FIGURE 2.1 – Architecture d'un système temps réel

Le procédé communique via des capteurs et des actionneurs. Les capteurs récupèrent

des informations du procédé et les transmettent au système de contrôle sous forme d'événements et de données. Les actionneurs commandent le procédé afin de réaliser une tâche bien définie. Le système de contrôle est composé d'un calculateur auquel sont liées des interfaces d'entrées/sorties qui servent à communiquer avec les capteurs et les actionneurs. Le calculateur exécute un algorithme de contrôle en respectant des propriétés temporelles et envoie des ordres de commande aux actionneurs via l'interface de communication. Le procédé contrôlé est souvent appelé l'environnement du système de calcul temps réel. Un système temps réel est dit embarqué lorsque le système de contrôle est enfoui à l'intérieur de l'environnement avec lequel il interagit, comme un calculateur dans un avion ou une voiture. Pour les systèmes temps réel, la validité d'une action dépend du temps qui s'écoule entre la fin de la réalisation de l'action de contrôle et l'événement qui l'a déclenchée. Autrement dit, il est nécessaire que les réactions du système aux événements soient effectuées en un temps inférieur à une borne maximale. Cette borne caractérise une contrainte temps réel. Selon qu'il faille absolument respecter les contraintes ou qu'il soit possible de les violer occasionnellement, ces systèmes sont qualifiés de critiques, fermes ou non critiques. Ainsi, les systèmes critiques nécessitent le respect strict des contraintes. Les systèmes fermes admettent le non-respect de certaines contraintes selon des critères définis par le contexte de l'application. Enfin les systèmes non critiques tolèrent une probabilité de contraintes non satisfaites.

**Hypothèse**. Dans le cadre de ce travail, nous nous intéresserons aux *systèmes temps réel critiques*. Par conséquent, toutes les contraintes temporelles spécifiées par l'application doivent être systématiquement respectées.

#### 2.2.1.1 Mise en œuvre des systèmes temps réel embarqués

Un système contrôle embarqué se compose : (a) d'une application chargée de piloter le procédé, (b) d'un support d'exécution matériel et/ou logiciel pour permettre l'exécution de l'application.

#### Architecture matérielle

Les supports d'exécution matériels s'articulent aujourd'hui autour de quatre types d'architectures : (a) monoprocesseur, (b) multiprocesseurs, (c) multi-cœurs et (d) distribuée [85]. Ainsi, lorsqu'une puissance de calcul importante est nécessaire, des architectures multiprocesseurs ou multi-cœurs enrichissent l'approche monoprocesseur d'un parallélisme matériel pour le traitement des données. Par contre, les architectures distribuées sont utilisées pour des installations qui sont écalées géographiquement.

**Hypothèse.** Dans cette étude, nous supposons que l'architecture matérielle est *monoprocesseur*.

Domaine de l'étude

#### Développement des applications temps réel embarquées

Une application temps réel décrit la réalisation des différentes fonctions de contrôle du procédé physique. Comme nous l'avons déjà mentionné, cette application est soumise, en plus, à des contraintes temporelles. Une technique très répandue pour la prise en compte des contraintes temporelles est la concurrence ou la programmation multi-tâches [22]. En effet, cette technique permet d'exprimer le parallélisme dans une application logicielle. Elle englobe également des techniques pour assurer la communication et la synchronisation entre des entités concurrentes (appelées tâches).

**Hypothèse.** Dans cette étude, nous admettons que les tâches du système ne peuvent être dépendantes qu'en partageant des données en exclusion mutuelle.

La mise œuvre d'une application multi-tâches sur une architecture monoprocesseur peut suivre une approche logicielle ou mixte. Dans une approche logicielle, tout le traitement est effectué par un programme logiciel s'exécutant sur le processeur. Une approche mixte consiste à mettre en œuvre conjointement (co-design) la configuration matérielle et la programmation logicielle [83]. Cette approche consiste à implanter une partie du traitement sur des circuits spécialisés tels que l'ASIC (Application Specific Integrated Circuit)[82], DSP (Digital Signal Processing)[14] et l'autre partie du traitement sur le processeur lui-même.

**Hypothèse.** Cette étude s'inscrit dans le cadre de développement des systèmes temps réel embarqués pour une composante matérielle donnée. Toutes les fonctionnalités de l'application sont supposées être *mises en œuvre de manière logicielle*.

Afin de faciliter la mise en œuvre d'une application multi-tâches sur une architecture monoprocesseur, un support d'exécution logiciel (système d'exploitation temps réel)[87] offre des services d'exécution tout en masquant les spécificités du matériel sous-jacent.

**Hypothèse.** Dans cette étude, nous nous intéressons à mettre en œuvre des applications logicielles dont l'exécution repose sur un *système d'exploitation temps réel*. Les systèmes d'exploitation envisagés sont supposés disponibles. Cependant aucun système particulier n'est imposé.

#### Système d'exploitation temps réel

Un exécutif temps réel ou système d'exploitation temps réel (appelé en anglais Real-Time Operating System ou RTOS) est composé d'un noyau temps réel et de modules ou bibliothèques complétant le noyau et facilitant le développement de l'application. Un système d'exploitation est dit temps réel lorsqu'il implémente les mécanismes et les services qui, si utilisées correctement peuvent garantir les délais souhaités. Pour la prise en compte des aspects temps-réel, un exécutif temps réel doit en particulier :

- gérer la concurrence par l'adoption d'une stratégie pour partager le temps processeur, à travers des techniques d'ordonnancement temps-réel, entre les différentes tâches en attente d'exécution;

- gérer l'accès aux données et aux ressources partagées à travers des techniques de synchronisation adaptées aux contraintes au temps-réel;

offrir des mécanismes de communication adaptés au temps-réel entre les entités concurrentes du système de contrôle;

- gérer les horloges pour la manipulation du temps;

- assurer une gestion prédictible de la mémoire

**Hypothèse.** Nous nous intéressons aux différents artéfacts du noyau temps réel liés à *la concurrence, au partage de ressources logicielles* et *à la gestion du temps,* que nous supposons suffisants pour la réalisation des applications visées par cette étude.

Il existe aujourd'hui dans la littérature trois principaux standards pour les RTOS: POSIX [5], OSEK/VDK [6] et ITRON[3]. En général, un noyau temps réel peut être conforme à un de ces standards, il peut être commercial tel que VxWorks [2] ou open source comme RTEMS [8]. Dans tous les cas, un noyau temps réel doit accomplir les fonctionnalités décrites ci-dessus. Cependant, les mécanismes mis en œuvre pour la réalisation de ces fonctionnalités peuvent varier d'un noyau à un autre. L'ordonnanceur est l'élément de base d'un noyau temps réel, qui permet de planifier l'exécution des différentes tâches (déterminer l'ordre d'allocation des tâches au processeur). Un ordonnanceur est caractérisé par sa politique d'ordonnancement citefixed [93] [54] et son mode (préemptif ou non préemptif). Selon le noyau, une ou plusieurs politiques sont supportées et un des deux modes (ou les deux) est possible. Ces différents paramètres qui caractérisent l'ordonnanceur ont un impact direct sur l'exécution de l'application et par la suite sur les propriétés temporelles.

#### 2.2.1.2 Vérification des applications temps réel embarquées

Les applications temps réel embarquées possèdent deux aspects : un aspect fonctionnel et un aspect non-fonctionnel. Par conséquent, la vérification de ces applications passe par la vérification de ces deux aspects. Pour l'aspect fonctionnel, la vérification consiste à vérifier que le système produit un résultat correct pour chaque ensemble de données en entrées [35][12] [39]. En ce qui concerne l'aspect non-fonctionnel, la vérification consiste à assurer que le système respecte les contraintes non-fonctionnelles telles que les contraintes temporelles, les contraintes de consommation mémoire ou d'énergie. Parmi les techniques de vérification de l'aspect non-fonctionnel, on distingue les techniques statiques basées sur l'analyse et les techniques dynamiques basées sur la simulation ou le test.

**Hypothèse.** Dans cette étude, nous nous intéressons à la vérification de *l'aspect non-fonctionnel* en particulier les *contraintes temporelles* en utilisant les *techniques d'analyse statiques*. Nous nous visons plus précisément *l'analyse d'ordonnançabilité*.

#### Techniques d'analyse d'ordonnançabilité

Les techniques d'analyse d'ordonnançabilité permettent de vérifier si une configuration donnée de tâches est ordonnançable, c'est-à-dire que leur charge de calcul (*load*) est réalisable sur la plateforme cible en respectant les contraintes temporelles qui leur sont affectées. En effet, l'exécution de chaque tâche doit respecter un délai maximum définissant ainsi une

Domaine de l'étude 11

échéance à ne pas dépasser. L'échéance d'une tâche est l'instant auquel l'exécution de la tâche doit se terminer. Le dépassement d'une échéance constitue une faute temporelle. La vérification des échéances est fortement liée à l'algorithme d'ordonnancement temps réel utilisé pour créer cette configuration de tâches. En fait, les algorithmes d'ordonnancement permettent d'établir « au mieux » les niveaux de priorité des tâches pour un contexte applicatif donné.

L'analyse d'ordonnançabilité offre deux techniques pour vérifier la faisabilité d'un système : une technique basée sur les tests de faisabilité et une technique basée sur le calcul de bornes maximales sur les temps de réponse des tâches [23]. La première technique consiste à définir des conditions nécessaires et /ou suffisantes applicables sous certaines hypothèses du système. Ces conditions font en général appel à une description simple de l'application. Par exemple, selon [54], un système ordonnancé en utilisant Rate Monotonic (RM) ou Deadline Monotonic (DM) est faisable si et seulement si :

$$\sum_{i=1}^{n} \frac{c_i}{P_i} \le n(2^{\frac{1}{n}} - 1) \tag{2.1}$$

Dans cette expression  $C_i$  définit le temps d'exécution d'une tâche  $T_i$ ;  $P_i$  est sa période d'activation et n étant le nombre de tâches. On note par  $D_i$  l'échéance de la tâche  $T_i$ . Cette condition est applicable si toutes les tâches applicatives sont périodiques et indépendantes et que l'échéance de chaque tâche est égales à sa période  $(P_i = D_i)$ . Pour des descriptions plus élaborées de l'application, la deuxième technique consiste à calculer une borne maximale du temps de réponse de chaque tâche et à vérifier si cette borne est inférieure à son échéance. Si les temps de réponse de toutes les tâches applicatives sont inférieurs à leurs échéances, on peut confirmer que l'application respecte ses contraintes de temps. Dans ce cas, la formule de calcul du temps de réponse dépend de l'application et de la politique d'ordonnancement considérée. Par exemple si toutes les tâches sont indépendantes et pour un ordonnanceur préemptif à priorité fixe [52], le temps de réponse est la plus petite solution de l'équation :

$$Rep_i = c_i + \sum_{T_i \in HP} \left\lceil \frac{Rep_i}{P_j} \right\rceil * c_j$$

(2.2)

$R_i$  représente le temps de réponse de la tâche  $T_i$  et  $HP_i$  correspond à l'ensemble des tâches ayant des priorités supérieures ou égales à  $T_i$ . Dans le cas où les tâches sont dépendantes par partage des ressources logicielles (gestion d'accès aux sections critiques), un nouveau terme  $B_i$  s'ajoute à la formule précédente.

$$Rep_i = c_i + B_i + \sum_{T_i \in HP} \left\lceil \frac{Rep_i}{P_j} \right\rceil * c_j$$

(2.3)

$B_i$  représente le temps de blocage maximal, il correspond au temps pendant lequel une tâche reste bloquée en attendant la libération d'une ressource exclusive par une ou plusieurs tâches

de priorité inférieure.

#### Analyse d'ordonnançabilité et protocoles de synchronisation

Le partage de ressources dans un système temps réel peut être à l'origine de deux problèmes : inversion de priorité et inter-blocage. Une inversion de priorité survient lorsqu'une tâche est bloquée par une tâche de priorité moindre ne partageant pas de ressource avec la tâche plus prioritaire. On ne peut alors plus prévoir le temps de blocage de la tâche de plus haute priorité. Figure 2.2 ci-dessous illustre une situation d'inversion de priorité pour un système de trois tâches tel que  $p_1 > p_2 > p_3$  et une ressource  $R_0$  partagée entre  $T_1$  et  $T_3$ . Dans ce cas l'exécution de la tâche  $T_1$  qui est la plus prioritaire est bloquée par la tâche  $T_2$  qui est moins prioritaire. Le temps de blocage supplémentaire du à l'inversion de priorité est  $t_5 - t_4$ .

FIGURE 2.2 – Situation d'inversion de priorité entre  $T_1$  et  $T_2$

Un inter-blocage survient si les tâches du système partagent plus d'une ressource à la fois. La Figure 2.3 illustre une situation d'inter-blocage pour un système de deux tâches tel que  $p_1 > p_2$  qui partagent deux ressources  $R_0$  et  $R_1$ . Dans ce cas, les deux tâches sont en interblocage car la tâche  $T_1$  qui est la plus prioritaire demande la ressource  $R_0$  pour terminer son exécution par contre cette ressource est utilisée par  $T_2$ . De même  $T_2$  ne peut pas prendre  $R_1$ pour terminer son exécution. Pour résoudre ces problèmes (inversion de priorité et interblocage), une solution classique est d'utiliser les protocoles où les conflits sont résolus en réalisant des ajustements sur les priorités des tâches lors de l'accès à la section critique. Les protocoles les plus connus sont Priority Ceiling Protocol (PCP) [43] et Priority Inheritance Protocol (PIP) [81]: Dans le protocole PIP, la tâche qui utilise la ressource hérite de la priorité de la tâche qui demande la ressource et qui se trouve en tête de liste dans la file d'attente. Ceci permet de diminuer le temps de blocage de la tâche la plus prioritaire en inhibant la préemption de la tâche qui possède la ressource par des tâches de priorité moyenne. Ce protocole est capable de gérer juste l'inversion de priorité sans résoudre le problème d'inter-blocage. Le protocole PCP suppose que chaque tâche possède une priorité fixe et que les ressources utilisées sont connues avant le début de l'exécution. Chaque ressource est caractérisée par Domaine de l'étude 13

FIGURE 2.3 – Situation d'inter-blocage

un plafond de priorité (priority ceiling) qu'on note  $\pi_i$ . On définit aussi le plafond de priorité courant du système que l'on note  $\gamma = Max_i(\pi_i)$ . Si aucune ressource n'est utilisée  $\gamma = \delta$  qui est une priorité plus basse que n'importe quelle priorité dans le modèle. Une  $T_i$  tâche ne peut prendre une ressource libre  $R_j$  que si la priorité de la tâche  $T_i$  est strictement supérieure à  $\gamma$ . Dans le cas échéant, la tâche  $T_i$  est bloquée et la tâche  $T_j$  qui bloque cette dernière hérite la priorité de  $T_i$ . La tâche  $T_j$  est exécutée avec cette priorité jusqu'à ce qu'elle libère toutes les ressources ayant un plafond de priorité supérieur à la priorité de tâche  $T_i$ . L'utilisation de ce protocole permet d'éviter les deux problèmes mentionnés (inversion de priorité et inter-blocage). Le calcul du temps de blocage dépend fortement du protocole utilisé pour accéder à une ressource partagée. La formule de calcul du temps de blocage dans le cas où le protocole PCP est utilisé est donnée ci-dessous :

$$B_i = \max_{T_j \in HP, R_k \in R} \{ U_{R_k, T_j} : p_j < p_i \text{ and } \pi_k \ge p_i \}$$

(2.4)

Dans cette expression, R est l'ensemble des ressources qui constituent le système et  $C_{(R_k,T_j)}$  correspond à l'utilisation de la ressource  $R_k$  par la tâche  $T_j$ . Le temps de blocage  $B_i$  représente la durée de la plus grande section critique parmi celles des tâches de priorités inférieures ou égales à  $p_i$  et dont la ressource relative  $R_k$  est telle que  $\pi_k$  est supérieure ou égale à  $p_i$ .

De part de leur nature, les systèmes temps réel embarqués requièrent un processus de développement rigoureux afin d'atteindre la correction fonctionnelle et temporelle. La partie qui suit introduit alors une ingénierie émergente qui offre des solutions pour le développement de tels systèmes, c'est l'ingénierie dirigée par les modèles.

#### 2.2.2 Ingénierie Dirigée par les modèles (IDM)

L'ingénierie dirigée par les modèles (IDM) propose l'amélioration du développement de systèmes complexes en permettant de se concentrer sur des préoccupations plus abstraites que la programmation classique au travers de modèles. Cette ingénierie offre un cadre méthodologique outillé aux développeurs des systèmes temps réel embarqués, qui se concentre

désormais sur l'élaboration des modèles abstraits, plutôt que sur des concepts liés à l'algorithmique et la programmation. Cette partie introduit cette nouvelle technologie en se focalisant sur les aspects importants pour cette étude.

#### 2.2.2.1 Modèles, méta-modèles et transformations de modèles

De nombreux travaux [24] [16] [77] [37] se sont intéressés à l'IDM, ce qui a permis de clarifier les concepts liés à celle-ci. En nous basant sur ces travaux, nous définissons succinctement dans ce qui suit les notions de base de l'IDM.

#### Modèles

Un modèle est une représentation abstraite d'un système réalisée dans une intention particulière. Un modèle peut représenter un système dans sa totalité (la structure, le comportement et les propriétés non-fonctionnelles) ou bien il peut représenter juste un aspect du système en occultant ces autres aspects. Les différentes étapes d'un flot de développement d'une application nécessitent différents types de modèles définis avec une précision adaptée et contenant des informations pertinentes pour l'utilisation qui en est faite. Dans un cadre IDM, un modèle doit être interprétable (non-ambigu) afin qu'il puisse être manipulé de manière automatique (outillage). Ceci n'est possible que si ce dernier est exprimé dans un langage clairement structuré et interprétable, appelé méta-modèle.

#### Méta-modèles

Un *méta-modèle* est un modèle qui définit un langage de modélisation [69]. Un méta-modèle définit précisément les concepts d'un langage de modélisation ainsi que les relations entre ces concepts. Un méta-modèle est écrit dans un langage appelé méta-langage. Un modèle bien formé est *conforme* à son méta-modèle. A partir d'un *modèle bien formé*, il est possible de le transformer en un autre modèle ou bien de générer du code ou de la documentation. Cependant, la vérification de cette relation de conformité est importante avant toute transformation ou génération. En effet, il est nécessaire de s'assurer qu'un modèle est syntaxiquement et sémantiquement conforme à son méta-modèle avant de produire une application à partir de celui-ci.

#### Transformations de modèles

La transformation de modèles est un processus de conversion d'un ensemble de modèles d'une application donnée à d'autres modèles de la même application [65]. Une transformation de modèles définit un ensemble de règles pour passer d'un modèle source conforme à un méta-modèle source à un modèle cible conforme à un méta-modèle cible. Ces règles sont définies au niveau du méta-modèle et seront exécutées sur les modèles pour passer d'un modèle à un autre. La transformation de modèles peut être du type transformation de modèle

Domaine de l'étude 15

en modèle dans le but de raffiner ou changer (refactoring [59]) le modèle source. Ce type de transformation peut être modélisé par les langages de transformations de graphes tels que QVT (Query/View/Transformation) [67] ou (Atlas Transformation Language) ATL [47]. La transformation de modèles peut aussi être de type transformation de modèle en texte dans le but de générer du code ou de la documentation par exemple.

Hypothèse. Seules les transformations de modèle à modèle sont utilisées dans cette étude.

FIGURE 2.4 – Transformation de modèles

#### 2.2.2.2 Approche MDA

A partir de ces principes très généraux, plusieurs approches ont été proposées [65] [26] [84] pour intégrer les notions de l'IDM dans un cadre méthodologique et mettre en œuvre ses principes.Parmi ces approches, nous nous intéressons dans cette étude à l'approche MDA (Model Driven Architecture) [65] sur laquelle repose ce travail. Lancé en 2000 par l'OMG, le MDA vise à améliorer la portabilité, la maintenance et la réutilisation des modèles en préconisant l'utilisation de plusieurs types de modèles. En faisant une séparation claire entre les modèles de l'application indépendants des plateformes et les plateformes elles-mêmes, le MDA permet le déploiement d'une même application sur différentes plateformes. Dans un cadre MDA, ce déploiement se concrétise par une transformation de modèles ayant comme entrées le modèle de l'application indépendant de toute plateforme technologique (PIM) et le modèle de plateforme cible (PDM) et comme sortie le modèle de l'application spécifique à la plateforme correspondante (PSM). Le principe clé de l'approche MDA pour la mise en œuvre des principes de l'IDM consiste à s'appuyer sur l'utilisation des standards. Pour cela,

le MDA préconise l'utilisation du standard UML pour la description des différents modèles et méta-modèles et sur le standard MOF (Meta Object Facility) [69] pour la description des méta-métamodèles.

FIGURE 2.5 – Processus de développement des systèmes temps réel embarqués dans un cadre MDA

Pour les systèmes temps réel embarqués, le processus de transformation des exigences en un système final en suivant une approche MDA est constitué des activités de conception, d'analyse et de déploiement. Afin de répondre au mieux aux objectifs du MDA, les activités d'analyse sont réalisées plut tôt dans le cycle en particulier au niveau conception ou PIM. Cette pratique permet de détecter rapidement les erreurs de développement, ce qui diminue considérablement le coût de traitement de ces erreurs et réduit le délai de mise sur le marché (time-to-market). Figure 2.5 illustre le principe de développement des systèmes temps réel embarqués dans un cadre MDA. En effet, le modèle de spécification, le CIM (Computation Independent Model) dans une approche MDA, traduit les exigences fonctionnelles et les contraintes temporelles du cahier des charges. A partir de ce modèle, l'activité de conception décrit une réalisation possible de l'application en introduisant des choix architecturaux (introduction de la concurrence, dépendance de données, etc.) mais tout en restant indépendant de la technologie logicielle(PIM). Une activité d'analyse permet de valider ces choix afin de vérifier si les contraintes temporelles sont respectées. Ensuite, la phase de déploiement permet de générer à partir de ce PIM, plusieurs modèles spécifiques à différentes plateformes logicielles(PSM).

Avec cette initiative sur le MDA, l'OMG a introduit le concept de plateforme, cependant aucune précision n'est donnée sur sa forme et sur sa prise en compte dans le processus de développement. Cela ouvre la possibilité de plusieurs interprétations de la notion de plateforme et de modèle de plateforme. De plus la façon de transformer un PIM en PSM en tenant compte de cette dernière n'est pas détaillée. En effet, lors du passage du PIM vers PSM à l'aide d'une transformation, le PDM peut être décrit soit implicitement dans la transformation ou dans l'application faisant ainsi une partie intégrante de la transformation ou de l'application, soit il est décrit explicitement dans des modèles à part, et il sera alors passé en entrée de la transformation, avec le PIM.

Domaine de l'étude 17

#### 2.2.2.3 Caractérisation d'une plateforme dans un cadre IDM

Dans le cadre d'une ingénierie dirigée par les modèles, Atkinson et Kühne [17] définissent une plateforme, comme étant un système permettant la réalisation des objectifs d'une application. Par cette définition, les auteurs cherchent à montrer que l'exécution n'est pas le seul objectif d'une plateforme. En effet, au sens de l'IDM, une plateforme peut être utilisée pour des activités d'analyse, stockage de donnée ou même pour la représentation des modèles.

Dans ce même contexte, Almeida [13] introduit deux types de plateformes : plateforme abstraite et plateforme concrète. Une plateforme abstraite au sens d'Almeida est une plateforme fictive définissant un ensemble de concepts qui peuvent ne pas avoir une implantation réelle. Dans son approche, Almeida introduit aussi une plateforme abstraite comme étant une plateforme idéale de point de vue du développeur de l'application. Cette plateforme est définie pour une utilisation précise à une phase donnée du cycle de développement (généralement pour garantir l'indépendance par rapport à une plateforme d'exécution). CORTA [33] est un exemple de plateforme abstraite définit dans un cadre IDM pour la spécification des applications multi-tâches d'une façon indépendante des exécutifs temps réel. Contrairement à une plateforme abstraite, une plateforme concrète pour Almeida ne peut être qu'une plateforme d'exécution.

Selic [79] [78] définit une plateforme comme un ensemble de ressources qui fournit des services qui peuvent être accessibles par un ou plusieurs clients (des applications). Selic souligne ,à ce titre, qu'une plateforme au travers ses ressources et services doit être en mesure de satisfaire le besoin de l'application.

Face à cette diversité, l'OMG propose sa propre définition pour le concept de plateforme. Cette définition, dont la traduction est donnée ci-dessous, spécifie qu'une plateforme fournit un ensemble de fonctionnalités, au travers d'interfaces et des patrons d'utilisation de ces fonctionnalités.

« Une plateforme est un ensemble de sous-systèmes et de technologies qui fournissent un ensemble cohérent de fonctionnalités au travers d'interfaces et la spécification de patrons d'utilisation que chaque sous-système qui dépend de la plateforme peut utiliser sans être concerné par les détails et sur la façon dont les fonctionnalités sont implantées » [65]

En gros, une plateforme dans l'IDM est plus qu'une plateforme d'exécution. Elle est dite abstraite, si elle est définie pour une utilisation prévue, autre que l'exécution telle que l'analyse ou la simulation, à un instant donné du cycle de développement. Sinon, elle est dite concrète.

#### 2.2.3 Synthèse

Nous avons évoqué dans cette première partie les points clés de cette étude dans le but cadrer le contexte de nos travaux. Nous avons ainsi introduit les systèmes temps réel embarqués. Plus précisément, nous avons fixé les hypothèses considérées dans cette étude pour

la conception de ces systèmes. Nous considérons, dans cette thèse, des applications temps réel s'exécutant sur une architecture monoprocesseur et ayant comme support d'exécution logiciel un système d'exploitation temps réel (RTOS). Nous avons montré que, de part leur nature, ces systèmes requièrent une étape de vérification supplémentaire par rapport aux systèmes classiques en particulier une vérification des contraintes temporelles se basant sur des techniques d'analyse d'ordonnançabilité. Nous avons également présenté l'ingénierie dirigée par les modèles, en particulier, nous avons détaillé l'approche MDA et nous avons survolé des travaux qui ont abordés la notion de plateforme dans le cadre de l'IDM. Ces deux points constituent la base des contributions de cette thèse.

#### 2.3 Les plateformes d'exécution

Il n'existe pas à nos jours une définition unique et précise du concept plateforme. Classiquement, une plateforme référence la structure matérielle permettant l'exécution du logiciel. Cette vision a rapidement évolué avec la montée en niveau d'abstraction et l'apparition de la structuration en couches des plateformes [57]. Cette représentation en couches successives d'infrastructure matérielle, de système d'exploitation, de machine virtuelle et d'intergiciel rend la distinction entre l'application et la plateforme fortement liée au point de vue où l'on se place. En effet, un système d'exploitation peut être vu comme une application du point de vue d'un fournisseur de support matériel, et comme une plateforme d'exécution du point de vue d'un développeur d'applications logicielles. Par conséquent, la caractérisation d'un système comme étant une plateforme ne dépend pas de la nature du système lui-même mais plutôt de l'utilisation prévue pour ce système dans un contexte donné.

**Hypothèse.** Dans cette étude, nous faisons une abstraction de l'architecture matérielle et nous nous intéressons uniquement *aux plateformes logicielles*. En outre, nous considérons les systèmes d'exploitation temps réel (*RTOS*) comme plateformes d'exécution pour les applications visées dans cette étude.

#### 2.3.1 Représentations des plateformes d'exécution dans l'IDM

Dans un cycle de développement basé sur les modèles, une plateforme logicielle d'exécution peut être représentée dune façon enfouie, implicite ou explicite.

La représentation enfouie est généralement utilisée dans les approches qui visent la génération du code d'une application à travers les transformations de type modèles en texte. Dans ce cas, les caractéristiques de la plateforme sont capturées dans la transformation. On peut citer dans ce contexte l'outil OCARINA [45] qui permet la génération de code Ada ou C pour l'intergiciel PolyORB II [91] à partir d'une description AADL [68] de l'application.

La représentation implicite est basée sur la définition d'un méta-modèle de la plateforme considérée [74] [28] [51]. Ce méta-modèle est implémenté sous forme d'un profil UML ou d'un DSL (Description Specification Language) et est utilisé pour la description du modèle applicatif. Dans ce cas, la plateforme est représentée de façon implicite dans l'application.

Dans une représentation explicite, la plateforme est décrite dans un modèle indépendant de la transformation et de l'application. Dans ce cas, la génération des modèles applicatifs spécifiques à une plateforme se traduit par une transformation du type modèle en modèle ayant comme entrées : le modèle de l'application indépendant de toute plateforme et le modèle de plateforme.

**Hypothèse.** Afin de répondre aux principes de le MDA, dans ce travail, nous adoptons *une représentation explicite* des plateformes d'exécution (RTOS).

Cette dernière hypothèse exige alors la définition des modèles de plateformes d'exécution (en d'autres termes des modèles des RTOS), ce qui nécessite l'utilisation d'un langage approprié adapté à nos besoins de modélisation. Cette problématique est l'objet de la partie suivante.

#### 2.3.2 Modélisation des plateformes d'exécution

Selon [61], un modèle de plateforme est une représentation abstraite mais suffisamment précise d'une plateforme d'exécution. Un modèle de plateforme doit être focalisé sur les aspects de celle-ci nécessaires pour son utilisation. En effet, une plateforme d'exécution logicielle peut être modélisée par exemple dans le but de conception d'une application (description d'une application multi-tâches), d'analyse ou de génération de code. La précision du modèle de cette plateforme dépend fortement de l'objectif pour lequel ce modèle a été crée.

Hypothèse. Dans cette thèse, nous nous intéressons à la modélisation des plateformes d'exécution logicielles (RTOS) dans le but de permettre le déploiement d'une application sur un RTOS en assurant le respect des contraintes temporelles. Plus précisément, les modèles des plateformes considérés dans cette étude se limitent aux concepts des RTOS nécessaires pour la vérification temporelles en utilisant les techniques d'analyse d'ordonnançabilité.

#### 2.3.2.1 Modèle de plateforme pour l'analyse d'ordonnançabilité

Dans le contexte de modélisation des plateformes logicielles, Marvie et al. [73] proposent de modéliser une plateforme selon trois vues distinctes : (a) une vue statique des ressources fournies par la plateforme (telles que les tâches logicielles pour un système d'exploitation multi-tâches), (b) une vue dynamique des traitements réalisés par la plateforme (telles que la création et l'activation d'une tâche) et (c) une vue qui traite le cycle de vie des ressources sous l'influence des traitements qui leurs sont appliqués (le cycle de vie d'une tâche est, par exemple, borné par sa création et sa destruction). Dans la même vision, Thomas [86] identifie quatre axes pour modéliser une plateforme logicielle d'exécution : (1) la caractérisation des concepts d'une plateforme (les ressources d'une plateforme)(2) la caractérisation des traitements (les services associées aux ressources).(3) la caractérisation des règles d'utilisation d'une plateforme (des contraintes et des patrons d'utilisation des ressources et des services offertes par une plateforme).(4) La caractérisation de comportement observable d'une plate-

forme (le cycle de vie d'une ressource sous l'influence des services).

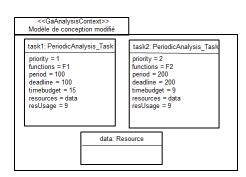

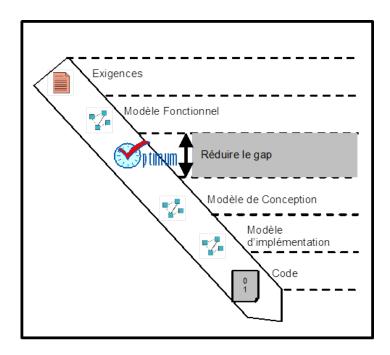

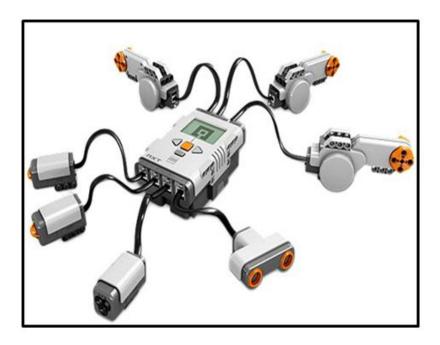

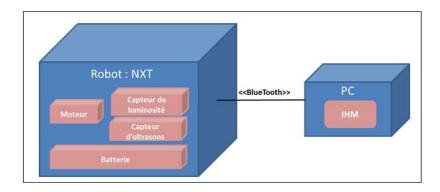

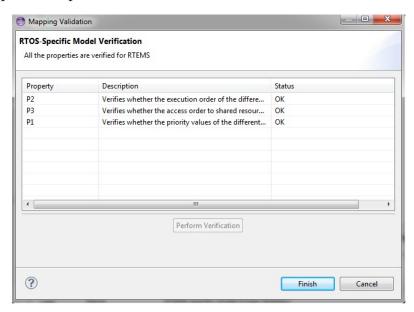

Un modèle de plateforme logicielle pour l'analyse d'ordonnançabilité doit être focalisé sur les aspects de celle-ci nécessaires pour vérifier les contraintes de temps d'une application. En d'autres termes, ce modèle décrit uniquement les éléments de la plateforme qui interviennent pour la vérification temporelle. Citons quelques concepts d'une plateforme logicielle d'exécution nécessaires pour la vérification temporelles des applications visées dans cette étude :