### Improving the Hybrid model MPI+Threads through Applications, Runtimes and Performance tools Aurèle Maheo

#### ▶ To cite this version:

Aurèle Maheo. Improving the Hybrid model MPI+Threads through Applications, Runtimes and Performance tools. Distributed, Parallel, and Cluster Computing [cs.DC]. Université de Versailles-Saint Quentin en Yvelines, 2015. English. NNT: 2015VERS039V. tel-01318684

### HAL Id: tel-01318684 https://theses.hal.science/tel-01318684

Submitted on 19 May 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Thesis submitted to obtain the grade of Doctor in Philosophy of Université de Versailles-Saint-Quentin-en-Yvelines

École doctorale de Sciences et Technologie de Versailles Specialized in **Computer Sciences**

By Aurèle MAHEO

#### Improving the Hybrid model MPI+Threads through Applications, Runtimes and Performance tools

## Hosted by Exascale Computing Research, Versailles, France

Defended on 25 of September 2015 in front of the following doctoral committee :

| Pr. Raymond NAMYST<br>Pr. Allen Malony<br>Pr. Gaël Thomas<br>Pr. Michael KRAJECKI<br>Dr. Patrick CARRIBAULT | Professor at the University of Versailles<br>Professor at the University of Bordeaux<br>Professor at the University of Oregon<br>Professor at Télécom SudParis<br>Professor at the University of Reims<br>Research Engineer, CEA, DAM<br>Research Engineer, CEA, DAM | PhD Advisor<br>Referee<br>Examiner<br>Examiner<br>Examiner<br>Examiner<br>Examiner |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Dr. Marc PERACHE                                                                                            | Research Engineer, CEA, DAM                                                                                                                                                                                                                                          | Examiner                                                                           |

UNIVERSITE PARIS-SACLAY

#### Thèse présentée pour obtenir le grade de **Docteur de** I'Université de Versailles-Saint-Quentin-en-Yvelines

École doctorale de Sciences et Technologie de Versailles Spécialité : **Informatique**

Présentée par Aurèle MAHEO

# Amélioration du modèle hybride MPI+Threads à travers les applications, les supports d'exécution et outils d'analyse de performance

Organisme d'accueil: Exascale Computing Research, Versailles, France

Soutenue le 25 Septembre 2015 devant la commission d'examen composée de :

| Professeur à l'université de Versailles | Directeur de thèse                                                                                                                                                                       |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Professeur à l'université de Bordeaux   | Rapporteur                                                                                                                                                                               |

| Professeur à l'université de l'Oregon   | Rapporteur                                                                                                                                                                               |

| Professeur à Télécom SudParis           | Examinateur                                                                                                                                                                              |

| Professeur à l'Université de Reims      | Examinateur                                                                                                                                                                              |

| Ingénieur de recherche, CEA,DAM         | Examinateur                                                                                                                                                                              |

| Ingénieur de recherche, CEA,DAM         | Examinateur                                                                                                                                                                              |

|                                         | Professeur à l'université de Bordeaux<br>Professeur à l'université de l'Oregon<br>Professeur à Télécom SudParis<br>Professeur à l'Université de Reims<br>Ingénieur de recherche, CEA,DAM |

#### Acknowledgements / Remerciements

Au moment de terminer ce manuscrit, il me semblait opportun de jeter un coup d'oeil dans le rétroviseur. Je n'ai pas accompli cette thèse seul et beaucoup de personnes de valeur ont apporté leur concours à sa réalisation.

Je voudrais tout d'abord remercier M. Allen Malony et M. Raymond Namyst, en tant que rapporteurs de ma thèse et d'avoir accepté de juger mes travaux. Merci également à M. Gaël Thomas et M. Michael Krajecki d'avoir bien voulu être mes examinateurs.

Je voudrais ensuite exprimer ma gratitude au Professeur William Jalby pour avoir accepté d'être mon directeur de thèse.

Mes pensées vont ensuite à mes tuteurs Marc Pérache et Patrick Carribault qui m'ont accompagné pendant ces trois (ou quatre !) années. Je voudrais tout spécialement saluer Patrick qui m'a réellement impressionné, tout d'abord en tant qu'enseignant pour ses qualités pédagogiques, puis comme encadrant pour sa rigueur intellectuelle, qui a su m'inculquer ce fameux "esprit recherche". Je remercie chaleureusement Marc pour son encadrement également et ses qualités humaines. Merci à eux deux d'avoir su être à l'écoute quand je me suis senti dans l'impasse. Je m'estime chanceux d'avoir bénéficié de leur encadrement.

I would like to thank Dr Sameer Shende for welcoming me in University or Oregon. I'm very excited to continue this collaboration !

Je tiens ensuite à saluer l'équipe MPC, à commencer tout d'abord par les "anciens". Merci à Jean-Yves pour sa bonne humeur, merci de m'avoir légué l'appartement, perpétuant ainsi une tradition consistant à garder le bien au sein de l'équipe MPC. Je crains malheureusement - et ce n'est pas faute d'avoir essayé ! - qu'il ne restera pas dans l'équipe. Merci à Jean-Baptiste pour ses encouragements, à Sébastien, et à Emmanuelle qui devrait également tenter l'aventure transatlantique, Camille et Antoine, et sans oublier Jérôme, le Bordelais spécialiste des tâches.

Salut à mes camarades du mihps et tout spécialement aux motivés (Nicolas, Zakaria, Caner) qui ont décidé que 5 ans d'étude, c'était pas encore assez. Rappelons tout de même que nous fûmes les patients zéro de ce beau Master, soyons fiers !

Je n'oublie pas les autres exascaliens, Franck, Augustin mon voisin du 2.2, Vincent, Michel et l'équipe MAQAO.

J'adresse un salut particulier à Andres qui n'est certainement pas pour rien dans le choix de cette aventure !

Je salue également les autres collègues ou compagnons d'infortune de thèse (hum) que j'ai pu rencontrer lors de conférences, doctoriales ou autres. Il y eut de belles rencontres, des échanges intéressants et des occasions de sortir un peu de mon quotidien.

Et pour sortir un peu du cadre de la thèse, je n'oublie mes amis et proches qui ont réussi m'arracher les yeux de l'écran (pas facile). Salut aux collègues plongeurs, c'est toujours agréable de pouvoir faire quelques bulles entre deux chapitres de manuscrit ! Je pense tout d'abord à Mathieu et Pierre, merci pour ces cavales à droite et gauche, les balades á vélo (le bonheur est simple). Merci à celles et ceux qui, sans être présents physiquement, n'en sont pas moins précieux pour moi. Clin d'oeil à mon vieux camarade Samir, occupé á parcourir l'Outback australien puis la terre du milieu, mais jamais loin par la pensée (et par Messenger :)) ! Je lui souhaite de tout coeur de trouver son petit coin de paradis. Peut-être aura-t-on l'occasion d'explorer des territoires vierges et de palmer un peu parmi les coraux ? Enfin, *no worries !*

Merci à Anaïs, une londonienne qui compte beaucoup pour moi, et avec qui j'ai toujours grand plaisir á échanger. Merci pour son esprit positif et sa gentillesse.

Je tiens à dire à Timothée qu'il a été un ami très précieux tout au long de ce parcours, pour son soutien sans failles. Je crois que nous avons tous deux parfaitement intégré le concept de "reprise d'études". Je n'oublierai ni sa présence ni son amitié. J'espère le convaincre un jour d'aller chausser des skis dans les Rocheuses !

Mes dernières pensées vont mes proches, spécialement mes neveux et nièces, que j'ai toujours plaisir à retrouver ! Je voudrais terminer par rendre hommage à mes parents pour leur soutien inconditionnel et pour avoir su me donner de par leur exemple l'envie nécessaire de me dépasser et d'aller aussi loin que possible.

## Contents

| Сс | Contents<br>List of Figures |                                                                                                                       |    |

|----|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|----|

| Li |                             |                                                                                                                       |    |

| 1  |                             | mé en français                                                                                                        | 13 |

|    | 1.1                         | Contexte                                                                                                              | 13 |

|    | 1.2                         | 1.1.2       Modèle hybride MPI+OpenMP                                                                                 |    |

|    |                             | <ul><li>1.2.1 Supports exécutifs OpenMP pour les codes MPI+OpenMP</li></ul>                                           |    |

|    |                             | 1.2.3       Hybridisation de l'opération collective MPI_Allreduce         1.2.4       Opérations collectives unifiées | 19 |

|    |                             | <ul> <li>1.2.4 Operations conectives unnees</li></ul>                                                                 | u  |

|    | 1.3                         | Conclusion et perspectives                                                                                            | 25 |

|    |                             | 1.3.2 Perspectives à long terme                                                                                       |    |

#### I Context

2

| Intro | roduction on High Performance Computing                                 | 31   |

|-------|-------------------------------------------------------------------------|------|

| 2.1   | High Performance Computing for numerical simulation                     | . 31 |

|       | 2.1.1 Numerical simulation for physic models                            | . 31 |

|       | 2.1.2 Parallel machines to support numerical simulation                 | . 32 |

| 2.2   |                                                                         |      |

|       | 2.2.1 From sequential to multicore machines                             |      |

|       | 2.2.2 Heterogeneous architectures                                       |      |

|       | 2.2.3 Memory hierarchy                                                  | . 35 |

|       | 2.2.4 Distributed memory systems and shared memory systems              |      |

|       | 2.2.5 From UMA to NUMA architectures                                    | . 37 |

| 2.3   |                                                                         |      |

| 2.4   | -                                                                       |      |

|       | 2.4.1 Message Passing models                                            |      |

|       | 2.4.2 Partitioned Global Address Space                                  |      |

|       | 2.4.3 Thread-based models                                               |      |

|       | 2.4.4 Task parallelism                                                  | 41   |

| 2.5   | •                                                                       |      |

|       | 2.5.1 Adequation with underlying topology                               | 41   |

|       | 2.5.2 Memory scalability of domain decomposition method using MPI model |      |

|       | 2.5.3 Problems with load balancing                                      |      |

|       | 2.5.4 Optimization of MPI for shared memory                             |      |

| 2.6   |                                                                         |      |

| 2.7   |                                                                         |      |

| 3  | Foc | us on h  | nybrid model MPI+OpenMP                                                        | 45 |

|----|-----|----------|--------------------------------------------------------------------------------|----|

|    | 3.1 | Definir  | ng MPI+OpenMP programming model                                                | 45 |

|    | 3.2 | Advan    | tages and issues of hybrid MPI+OpenMP model                                    | 45 |

|    |     | 3.2.1    | Adequation between programming model and hardware                              | 45 |

|    |     | 3.2.2    | Reduce memory footprint                                                        | 46 |

|    |     | 3.2.3    | Better load balancing                                                          | 47 |

|    |     | 3.2.4    | Drawbacks                                                                      | 47 |

|    | 3.3 | Taxon    | omy of hybrid MPI+OpenMP model                                                 | 47 |

|    |     | 3.3.1    | Granularity of OpenMP                                                          | 47 |

|    |     | 3.3.2    | Thread Placement                                                               | 51 |

|    |     | 3.3.3    | Overlapping between communications and computations                            | 51 |

|    | 3.4 | Requir   | rements of MPI runtimes                                                        | 52 |

|    |     | 3.4.1    | Thread support                                                                 | 52 |

|    |     | 3.4.2    | Interoperability between MPI and OpenMP                                        | 53 |

|    | 3.5 | Identify | y bottlenecks in hybrid programming                                            | 53 |

|    |     | 3.5.1    | Overhead of OpenMP runtimes                                                    | 53 |

|    |     | 3.5.2    | Lack of parallelism and resource usage                                         | 55 |

|    |     | 3.5.3    | Complexity of Hybrid MPI+OpenMP codes                                          | 55 |

|    |     | 3.5.4    | Performance analysis of MPI+OpenMP codes                                       | 55 |

|    | 3.6 | Thesis   | contributions                                                                  | 56 |

|    |     | 3.6.1    | Reduce overhead of OpenMP runtimes in the context of fine grain parallelism in |    |

|    |     |          | MPI+OpenMP model                                                               | 56 |

|    |     | 3.6.2    | Study Collective operations in a hybrid context                                | 57 |

|    |     | 3.6.3    | Standard performance analysis of OpenMP codes                                  | 58 |

|    | 0-  | ntrik    | tiono                                                                          | 50 |

| II | U0  | ntribu   | luons                                                                          | 59 |

| 4  | Оре | nMP ru   | Intimes for MPI+OpenMP applications                                            | 61 |

| 4 | Ope | enmP runtimes for MPI+OpenMP applications                                             | 61 |

|---|-----|---------------------------------------------------------------------------------------|----|

|   | 4.1 | Constraints on OpenMP runtime in hybrid MPI+OpenMP codes                              | 61 |

|   |     | 4.1.1 Need of efficient mechanisms for OpenMP constructs                              | 61 |

|   |     | 4.1.2 Need of a flexible runtime                                                      | 62 |

|   | 4.2 | Impacts of NUMA effects on OpenMP runtimes                                            | 62 |

|   | 4.3 | Related Work                                                                          | 63 |

|   | 4.4 | NUMA aware runtime                                                                    | 64 |

|   |     | 4.4.1 Hierarchical tree                                                               | 64 |

|   |     | 4.4.2 Application to thread activation and thread synchronization                     | 64 |

|   |     | 4.4.3 Explore different tree shapes                                                   | 67 |

|   |     | 4.4.4 Handle tree shapes in a dynamic way                                             | 69 |

|   | 4.5 |                                                                                       |    |

|   |     | 4.5.1 Bypassing the tree                                                              | 69 |

|   |     | 4.5.2 Apply bypassing to thread activation and thread synchronization                 | 71 |

|   |     | 4.5.3 Implementation                                                                  | 73 |

|   |     | 4.5.4 Experimental results                                                            | 73 |

|   | 4.6 | Discussion about hierarchical work stealing                                           | 75 |

|   |     | 4.6.1 Strategies for work stealing                                                    | 77 |

|   |     | 4.6.2 Implementations of hierarchical work stealing                                   | 78 |

|   | 4.7 | Conclusion                                                                            | 80 |

| 5 | Stu | dy Collective operations in hybrid MPI+OpenMP context                                 | 81 |

|   | 5.1 | Tackle the problem of sequential time in Fine Grain pattern: Focus on MPI collectives | 81 |

|   |     | 5.1.1 Related Work on optimizing MPI collectives and reduction collectives            | 82 |

|   | 5.2 | Discussion about hybridization of MPI collectives                                     | 83 |

|   |     | 5.2.1 Split communicators with threads                                                | 84 |

|   |     | 5.2.2 Message tiling and parallelizing computations using threads                     | 85 |

|   | 5.3 | Contribution: Use OpenMP threads to optimize MPI_Allreduce                            | 85 |

| Bi | Bibliography 135         |                                                                                                                                                                                                                                                   |                                                    |

|----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| в  | Imp                      | plementation of OpenMP Tools API inside MPC                                                                                                                                                                                                       | 131                                                |

| A  | Hie                      | rarchical barrier inside MPC                                                                                                                                                                                                                      | 129                                                |

| 7  | 7.1                      | Anclusion and Perspectives         Contributions                                                                                                                                                                                                  | . 122<br>. 122<br>. 123                            |

|    | 6.7                      | OMPT       6.6.1       Implementation inside MPC framework       6.6.2         6.6.2       Guiding OpenMP loops tuning using OMPT       6.6.3         6.6.3       Estimate overhead of OpenMP runtimes       6.6.3         Conclusion       6.6.3 | . 113<br>. 114<br>. 116                            |

|    | 6.6                      | <ul> <li>6.5.1 Targeted OpenMP constructs and provided events</li></ul>                                                                                                                                                                           | . 109<br>. 112                                     |

|    | 6.3<br>6.4<br>6.5        | 6.2.1       Instrumentation                                                                                                                                                                                                                       | . 105<br>. 106<br>. 106<br>. 106<br>. 107<br>. 107 |

| 6  | <b>Ana</b><br>6.1<br>6.2 |                                                                                                                                                                                                                                                   | . 103<br>. 104                                     |

|    | 5.4<br>5.5<br>5.6        | Contribution: Unified collectives in runtime5.5.1Case study of unified barrier in hybrid MPI+OpenMP context5.5.2Implementation5.5.3Experiments5.5.4Conclusion and Future work about Unified Collectives                                           | . 96<br>. 97<br>. 98<br>. 100<br>. 101             |

|    |                          | 5.3.1Hybrid Allreduce approach5.3.2Rank Shifting5.3.3Implementation5.3.4Experimental environment5.3.5Microbenchmarks5.3.6Real World application5.3.7Conclusion and future work about optimizing MPI collectives                                   | . 86<br>. 89<br>. 89<br>. 90<br>. 90               |

## **List of Figures**

| 1.1  | Architectures ccNUMA                                                                      |    |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | Taxonomie hybride MPI+OpenMP                                                              | 15 |

| 1.3  | Activation hiérarchique des threads                                                       | 17 |

| 1.4  | Vue matérielle de l'approche Masteronly                                                   | 19 |

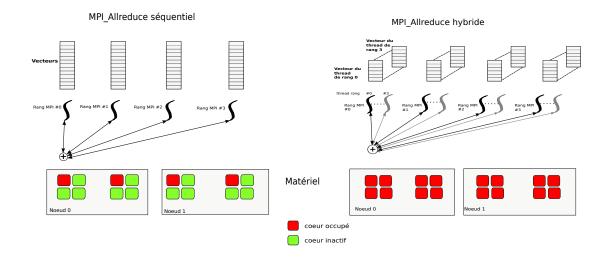

| 1.5  | MPI_Allreduce hybride                                                                     | 20 |

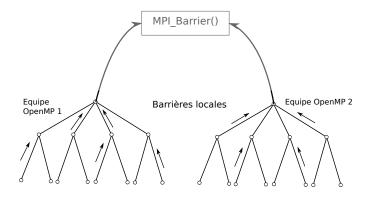

| 1.6  | Barrière unifiée MPI+OpenMP sans optimisation                                             | 21 |

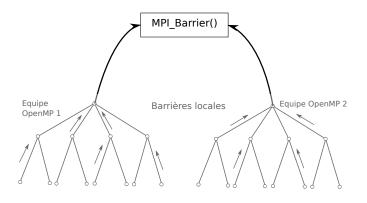

| 1.7  | Première étape de la barrière unifiée: synchronisation des équipes OpenMP                 | 22 |

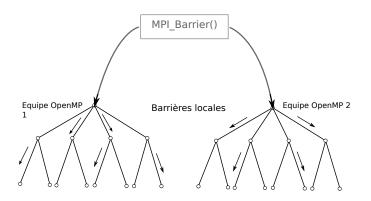

| 1.8  | Seconde étape de la barrière unifiée: appel de la barrière MPI                            | 22 |

| 1.9  | Troisième étape de la barrière unifiée: libération des équipes OpenMP                     | 22 |

|      | Insertion des événements relatifs aux régions parallèles OpenMP à l'intérieur du support  |    |

|      | d'OpenMP                                                                                  | 24 |

| 1.11 | Insertion des évévements relatifs aux tâches implicites à l'intérieur du support d'OpenMP | 24 |

|      |                                                                                           |    |

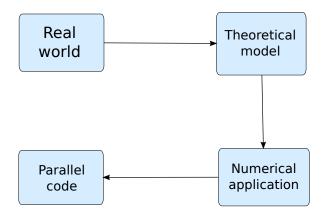

| 2.1  | Process for numerical simulation                                                          | 32 |

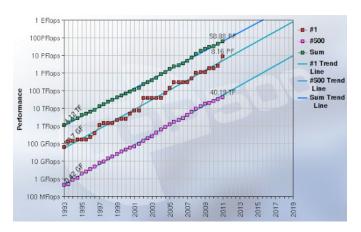

| 2.2  | Evolution of performances from the first to the last machine in Top500 ranking            | 32 |

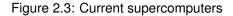

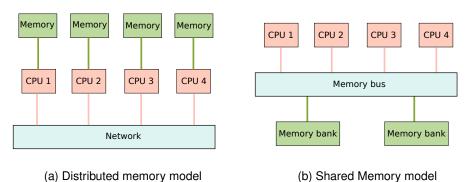

| 2.3  | Current supercomputers                                                                    | 33 |

| 2.4  | Evolution of processors following Moore's law                                             | 34 |

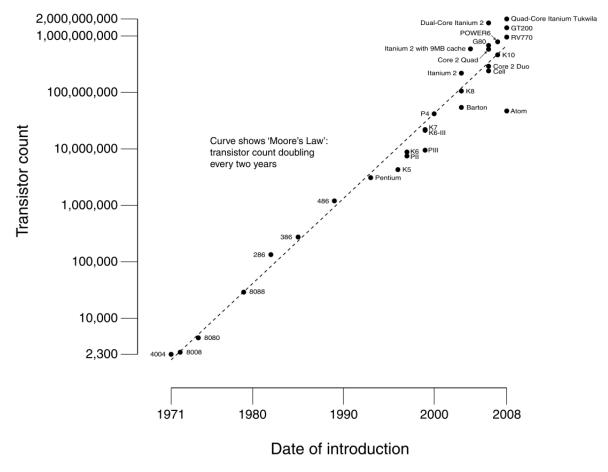

| 2.5  | Memory hierarchy                                                                          | 35 |

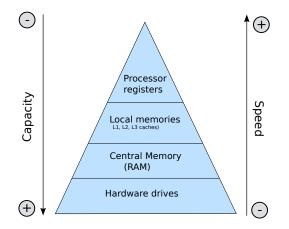

| 2.6  | Distributed memory model Vs Shared memory model                                           | 36 |

| 2.7  | Uniform Access to Memory                                                                  | 37 |

| 2.8  | ccNUMA architecture                                                                       | 38 |

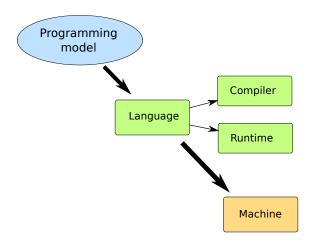

| 2.9  | From the programming model to the language, from the language to the program              | 39 |

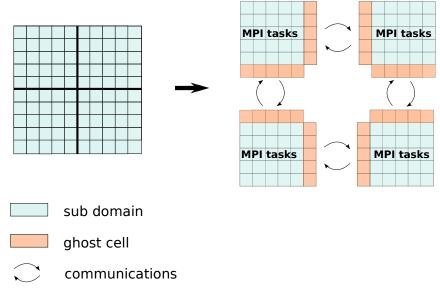

|      | Domain decomposition of a 2D mesh with MPI                                                | 42 |

|      |                                                                                           |    |

| 3.1  | Memory representation of a pure MPI code and hybrid MPI+OpenMP code, using domain         |    |

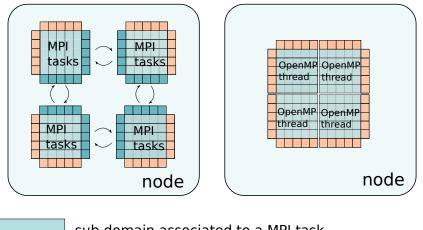

|      | decomposition                                                                             | 46 |

| 3.2  | Hybrid MPI+OpenMP taxonomy                                                                | 48 |

| 3.3  | Execution timeline with Fine-Grain parallelism                                            | 49 |

| 3.4  | Comparison between classic OpenMP and SPMD                                                | 50 |

| 3.5  | Thread placement of hybrid programming model                                              | 52 |

| 3.6  | Overhead of OpenMP model                                                                  | 54 |

| 3.7  | OpenMP overhead with Fine-Grain code                                                      | 54 |

| 3.8  |                                                                                           | 56 |

| 3.9  |                                                                                           | 57 |

|      | Targeted modes for unified collectives                                                    |    |

|      | •                                                                                         |    |

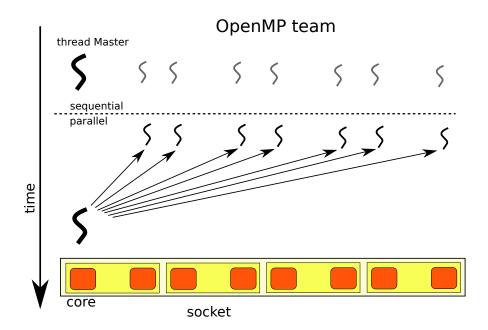

|      | Centralized approach for thread activation                                                | 62 |

| 4.2  | Hierarchical thread activation                                                            | 65 |

| 4.3  | Hierarchical thread activation - 1st stage                                                | 66 |

| 4.4  | Hierarchical thread activation - 2nd stage                                                | 66 |

| 4.5  | Hierarchical thread activation - 3rd stage                                                | 67 |

| 4.6  | Hierarchical thread activation - 4th stage                                                | 67 |

| 4.7  | Different tree shapes                                                                     | 68 |

| 4.8  | Logic view of a 128-core node                                                             | 70 |

| -    | U                                                                                         | 2  |

| 5.1       Hardware view of Master approach       82         5.2       Hybrid MPL Allreduce       86         5.3       Algorithm for Hybrid MPL Allreduce       87         5.4       Different behavior of the reduction following ordering of the communicator       88         5.5       Rank Shifting of Hybrid MPL Allreduce       86         5.6       Algorithm for Rank Shifting       86         5.7       IMB - Hybrid MPL Allreduce with MPC (4 128-core nodes, 1 MPI task per node)       91         5.8       IMB - Hybrid MPL Allreduce with MPC (4 128-core nodes, 1 MPI task per node)       91         5.9       IMB - Hybrid MPL Allreduce with IntelMPI (4 128-core nodes, 1 MPI task per node)       91         5.10       IMB - Comparison between MPC, BullxMPI, IntelMPI, and the best hybrid combination for<br>MPC and IntelMPI (4 128-core nodes, 1 task per node)       92         5.11       MC - Comparison between MPC, IntelMPI, BullxMPI, and best hybrid combination for<br>MPC and IntelMPI (8 18-core nodes, 1 task per node)       92         5.12       MC - Comparison between MPC, IntelMPI, BullxMPI, and best hybrid combination for<br>MPC and IntelMPI (8 16-core nodes, 1 task per node)       94         5.13       Combination of MPI and OpenMP used as SPMD       95         5.14       Example of unified barrier: Barrier of OpenMP teams       96         5.15       Global MPI+OpenMP bar    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.9       IMB - Hybrid MPI_Allreduce with IntelMPI (4 128-core nodes, 1 MPI task per node)       91         5.10       IMB - Comparison between MPC, BullxMPI, IntelMPI, and the best hybrid combination (4       92         5.11       MC - Comparison between MPC, IntelMPI, BullxMPI, and best hybrid combination for       92         5.12       MC - Comparison between MPC, IntelMPI, BullxMPI, and best hybrid combination for       93         5.12       MC - Comparison between MPC, IntelMPI, BullxMPI, and best hybrid combination for       94         5.12       MC - Comparison between MPC, IntelMPI, BullxMPI, and best hybrid combination for       94         5.12       MC - Comparison between MPC, IntelMPI, BullxMPI, and best hybrid combination for       94         5.13       Combination of MPI and OpenMP used as SPMD       94         5.14       Example of unified Allreduce operation       96         5.15       Global MPI+OpenMP barrier without optimization       97         5.16       First stage of unified barrier: Call MPI barrier       96         5.19       Comparison between hybrid barrier and optimized hybrid barrier implemented in MPC (1       128-core node)         5.20       Timeline comparing execution of regular and optimized unified barrier, with the different stages       100         6.1       Infrastructure of performance analysis       106         6.2       Corres |

| 5.11 MC - Comparison between MPC, IntelMPI, BullxMPI, and best hybrid combination for<br>MPC and IntelMPI (4 128-core nodes, 1 task per node)       93         5.12 MC - Comparison between MPC, IntelMPI, BullxMPI, and best hybrid combination for<br>MPC and IntelMPI (8 16-core nodes, 1 task per node)       94         5.13 Combination of MPI and OpenMP used as SPMD       96         5.14 Example of unified Allreduce operation       96         5.15 Global MPI+OpenMP barrier without optimization       97         5.16 First stage of unified barrier: Barrier of OpenMP teams       96         5.17 Second stage of unified barrier: Call MPI barrier       96         5.19 Comparison between hybrid barrier and optimized hybrid barrier implemented in MPC (1<br>128-core node)       100         5.20 Timeline comparing execution of regular and optimized unified barrier, with the different<br>stages       100         6.1 Infrastructure of performance analysis       100         6.2 Corresponding OMPT events to OpenMP constructs       100         6.3 Insert event callbacks related to parallel regions       100         6.4 Insert event callbacks related to implicit tasks inside OpenMP runtime       100         6.5 Interaction between OMPT, runtime and tool       110         6.6 Initialization of OMPT       110         6.7 Frame management with OMPT       112                                  |

| MPC and IntelMPI (8 16-core nodes, 1 task per node)       94         5.13 Combination of MPI and OpenMP used as SPMD       95         5.14 Example of unified Allreduce operation       96         5.15 Global MPI+OpenMP barrier without optimization       97         5.16 First stage of unified barrier: Barrier of OpenMP teams       98         5.17 Second stage of unified barrier: Call MPI barrier       98         5.18 Third stage of unified barrier: Release OpenMP teams       98         5.19 Comparison between hybrid barrier and optimized hybrid barrier implemented in MPC (1       106         128-core node)       100         5.20 Timeline comparing execution of regular and optimized unified barrier, with the different stages       100         6.1 Infrastructure of performance analysis       106         6.2 Corresponding OMPT events to OpenMP constructs       108         6.3 Insert event callbacks related to parallel regions       108         6.4 Insert event callbacks related to implicit tasks inside OpenMP runtime       108         6.5 Interaction between OMPT, runtime and tool       110         6.6 Initialization of OMPT       110         6.7 Frame management with OMPT       112                                                                                                                                                                                                   |

| 6.2       Corresponding OMPT events to OpenMP constructs       108         6.3       Insert event callbacks related to parallel regions       108         6.4       Insert event callbacks related to implicit tasks inside OpenMP runtime       108         6.5       Interaction between OMPT, runtime and tool       110         6.6       Initialization of OMPT       110         6.7       Frame management with OMPT       112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>6.9 Implemented and not implemented OMPT events inside MPC</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

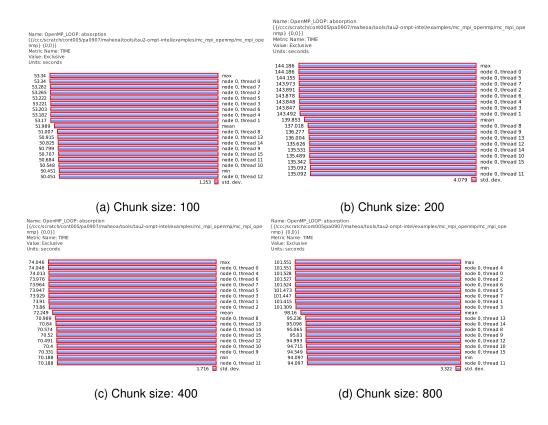

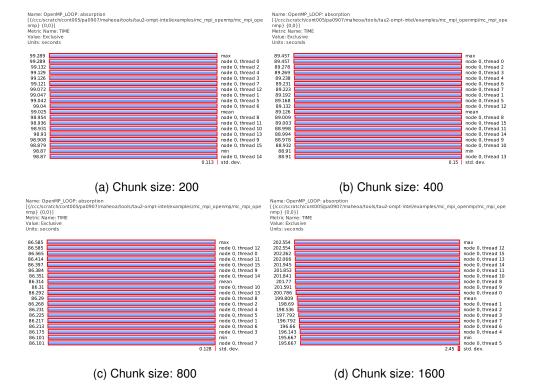

| <ul> <li>6.12 Tune loops of the absorption function depending on the chunk size, with static scheduling, running with MPC - with the help to OMPT and TAU</li> <li>6.13 Tune loops of the absorption function depending on the chunk size, with static scheduling,</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

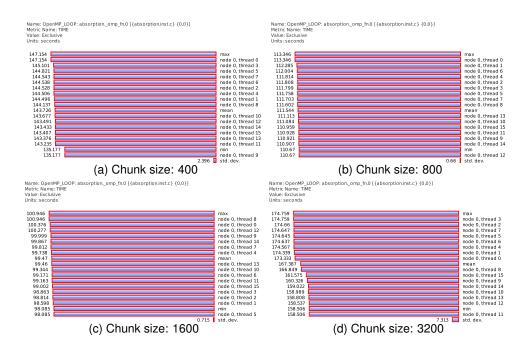

| running with Intel OpenMP - with the help to OMPT and TAU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | Tune loops of the absorption function depending on chunk size, with dynamic scheduling, running with Intel OpenMP - with the help to OMPT and TAU                                                                                                                                                                            |          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

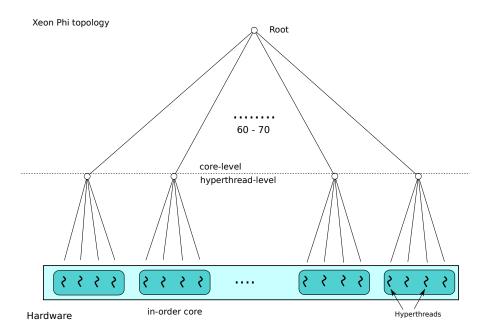

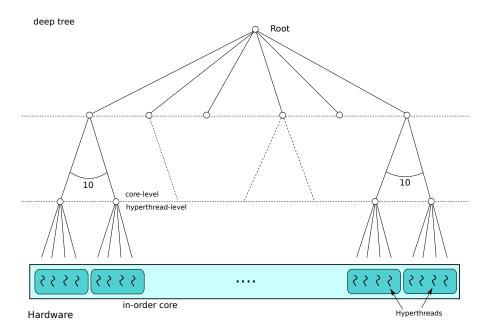

| 7.2<br>7.3 | Non Uniform Input Output Access architecture gathering a NUMA node and a hardware accelerator, communicating through a PCI Express bus       1         Topology of Xeon Phi architecture       1         Increase depth of the tree for Xeon Phi       1         Generalization of the unified barrier with n models       1 | 24<br>25 |

| A.1        | Implementation of the hierarchical barrier inside MPC framework                                                                                                                                                                                                                                                              | 29       |

|            | Implementation of OMPT events inside OpenMP parallel region function                                                                                                                                                                                                                                                         | 33       |

### **Chapter 1**

### Résumé en français

Cette partie présente un résumé en français de la thèse, et en reprend les éléments clés. Le lecteur voulant approfondir un sujet particulier est invité à consulter les chapitres correspondants.

#### 1.1 Contexte

#### 1.1.1 Introduction

Le domaine du calcul haute performance s'adresse aux machines massivement parallèles utilisées pour les applications ayant trait à la simulation numérique. Cette discipline et les moyens de calcul associés sont apparus lors de la Seconde Guerre Mondiale, avec notamment le fameux projet Manhattan, dans le but de concevoir la première bombe atomique. De nos jours, de nombreux projets d'envergure sont menés à l'aide de la simulation numérique, dont voici quelques exemples:

- Dans le domaine de l'astrophysique, DEUS (Dark Energy Universe Simulation) vise à estimer l'impact de l'énergie noire dans l'univers.

- Le projet The Human Brain Project est une initiative européenne visant à simuler le cerveau humain, en modélisant ses processus biologiques.

Cependant, ces applications requièrent des capacités de calcul conséquentes. C'est ainsi que les supercalculateurs ont émergé dans le but d'aider les scientifiques à mener à bien leurs simulations. Les premiers supercalculateurs sont apparus dans les années 1960, avec le CDC-6600. Dans les années 1970, Seymour Cray fonde Cray Research et une nouvelle famille d'ordinateurs parallèles, en premier lieu le Cray-1. La puissance d'un superordinateur est estimé par le nombre de calculs en virgule flottante qu'il est capable d'effectuer par seconde (FLOP). Si les premières machines parallèles développaient seulement quelques mégaflops, en 2001, la machine Earth Simulator affichait 40 téraflops. Aujourd'hui, les supercalculateurs sont composés d'armoires reliées en réseau rapide, et sont capables de développer une puissance de calcul de l'ordre du pétaflop (10<sup>15</sup> opérations par seconde). Cependant, la communauté scientifique a aujourd'hui les yeux rivés sur l'Exascale (10<sup>18</sup> opérations par seconde).

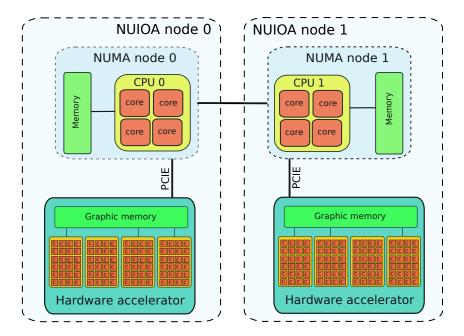

Les processeurs actuels sont équipés de plusieurs coeurs de calcul, obligeant les programmeurs à rendre leurs codes parallèles. De plus, les processeurs graphiques (GPUs), à l'origine destinés à l'interfaçage entre le système et l'utilisateur, puis dédiés au rendu graphique dans le contexte des jeux vidéos, sont désormais utilisés pour effectuer du calcul. Ces tendances ont influencé l'évolution des supercalculateurs. Ainsi, originellement composés de systèmes à mémoire distribuée, les machines actuelles intègrent de plus en plus d'unités de calcul à l'intérieur d'un noeud physique.

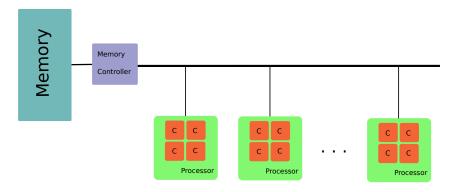

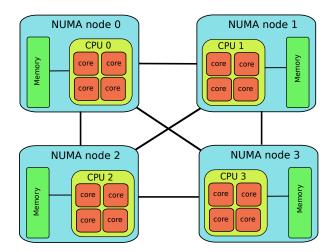

Les architectures parallèles se sont également complexifiées: dans les systèmes dits UMA (Uniform Memory Access), les unités de calcul partagent un même bus pour accéder à la mémoire centrale. Mais

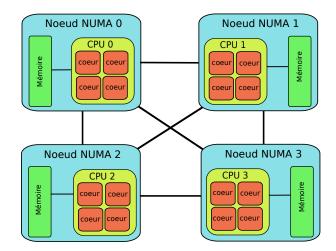

Figure 1.1: Architectures ccNUMA

la multiplication des coeurs a conduit à saturer la bande passante disponible. Ceci a obligé les constructeurs à concevoir des systèmes plus complexes, tels les architectures NUMA (figure 1.1). Dans ce type d'architectures, on définit comme bloc de base l'ensemble constitué d'un processeur relié à un banc mémoire local: on appelle cet ensemble un noeud NUMA. La localité des données constitue une caractéristique importante pour ce type d'architecture, et peut fortement influencer les performances des applications. En effet, la latence d'accès à une donnée peut être très variable selon que cette donnée se situe dans un banc mémoire local ou alors dans un banc mémoire appartenant à un noeud NUMA distant. Ce phénomène est appelé l'effet NUMA.

Pour programmer ces machines et les exploiter au mieux, plusieurs modèles de programmation ont été conçus, et peuvent être répartis entre plusieurs familles:

- Modèles à passage de messages, tel que MPI (Message Passing Interface)

- PGAS (Partitioned Global Address Space)

- Modèles à base de threads: Posix Threads, OpenMP

- Modèles à base de tâches: Cilk

MPI est le modèle principalement utilisé pour paralléliser les applications à travers les clusters de calcul. Cependant, avec l'évolution des supercalculateurs et la diminution de la quantité de mémoire disponible par coeur, la librairie MPI montre de plus en plus de limites concernant le passage à l'échelle des codes de calcul.

C'est pourquoi les scientifiques cherchent désormais à coupler MPI avec un modèle adapté aux machines à mémoire partagée. OpenMP, modèle à base de threads, est un choix privilégié car considéré comme un standard. De plus, il supporte les langages C, C++ et Fortran. Cependant, combiner MPI et OpenMP, modèles munis de paradigmes et de sémantiques différents, est loin d'être une tâche aisée.

#### 1.1.2 Modèle hybride MPI+OpenMP

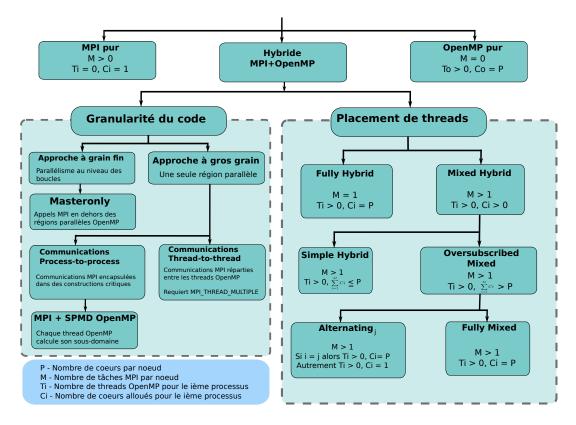

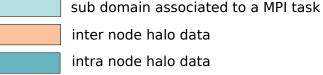

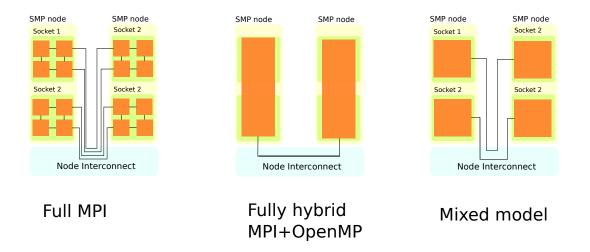

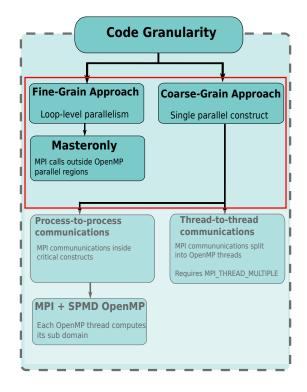

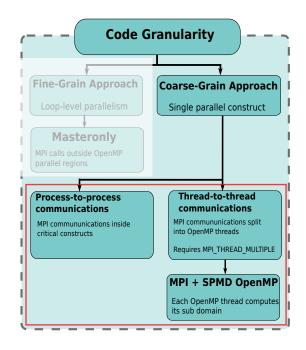

Nous présentons ainsi une taxonomie décrivant les différentes manières de combiner ces deux modèles, à travers deux principaux aspects: la granularité du code et le placement (figure 1.2).

Au niveau du code, différentes granularités sont possibles s'agissant du mélange de MPI et de OpenMP:

Figure 1.2: Taxonomie hybride MPI+OpenMP

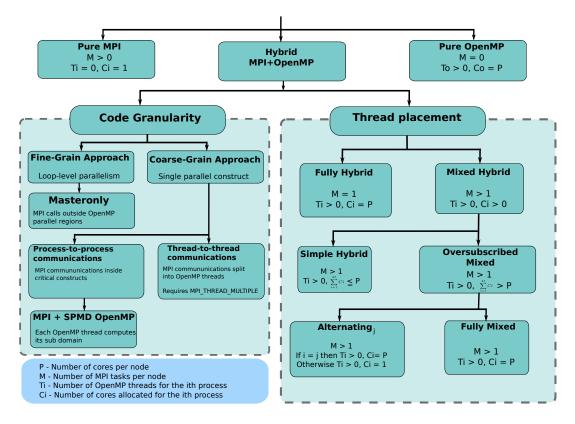

**Parallélisme à grain fin.** Ce mode consiste, à partir d'un code MPI, à paralléliser des boucles de calcul à l'aide de la construction #pragma omp parallel for. On peut décomposer le temps d'exécution d'un code hybride à grain fin à l'aide de l'équation suivante:

$$Ttot = Tseq + Tcomm + \frac{Tcompute}{P}$$

(1.1)

où *Ttot*, *Tseq*, *Tcomm*, *Tcompute* et *P* sont respectivement le temps total d'exécution, la partie séquentielle, le temps passé dans les communications, le temps passé dans le calcul et le nombre de threads OpenMP.

Plusieurs inconvénients sont à noter concernant cette approche. Tout d'abord, quand des boucles parallèles sont exécutées, deux niveaux de parallélisme sont imbriqués: l'un avec MPI et le second avec OpenMP. Mais en dehors des boucles parallèles, nous perdons un niveau de parallélisme. De plus, les coeurs utilisés par les threads OpenMP deviennent alors inactifs.

Troisièmement, le support OpenMP est susceptible d'être accédé de manière très fréquente dans ce mode, car OpenMP est utilisé uniquement pour paralléliser les boucles, structures potentiellement nombreuses dans le code.

**Parallélisme à gros grain.** Dans ce mode, on ouvre une ou plusieurs régions parallèles OpenMP. Cette approche est susceptible d'offrir plus de parallélisme avec OpenMP. Cependant, il est possible que ces régions parallèles contiennent des appels à des primitives MPI, ce qui reviendrait alors pour une fonction MPI donnée, à faire un appel par thread OpenMP de chaque tâche MPI. Pour résoudre ce problème, deux variantes du parallélisme à gros grain sont possibles: Process-to-process communications et Thread-to-thread communications. Avec la variante Process-to-process, on s'assure qu'un appel à une fonction MPI donnée est effectuée par tâche MPI à l'aide de constructions critiques telles

que #pragma omp single ou #pragma omp critical. Dans la variante Thread-to-thread, on parallélise les communications en utilisant plusieurs threads. Et ce faisant, il est alors possible de recouvrir les communications MPI avec du calcul.

Le placement décrit différentes manières de répartir les tâches MPI et les threads OpenMP au sein d'un noeud de calcul. Le premier mode, *Fully hybrid*, utilise MPI pour les communications inter-noeuds et remplit les coeurs du noeud de calcul avec des threads OpenMP. Avec l'approche *Mixed Hybrid*, plusieurs tâches MPI sont lancées par noeud de calcul. Il est possible de surcharger les coeurs avec des tâches MPI ou des threads OpenMP (c'est le mode *Oversubsribed Mixed*).

Suite à l'étude de la taxonomie du modèle hybride MPI+OpenMP, nous présentons différents problèmes freinant le passage à l'échelle des codes MPI+OpenMP:

- Fréquence d'accès à la couche OpenMP dans le mode à grain fin

- Sous-utilisation des coeurs de calcul en dehors des constructions OpenMP, toujours concernant le parallélisme à grain fin

- · Complexité des codes MPI+OpenMP dans une approche à gros grain

- Nécessité de pouvoir analyser les performances des codes hybrides pour permettre le passage à l'échelle

#### 1.2 Contributions

#### 1.2.1 Supports exécutifs OpenMP pour les codes MPI+OpenMP

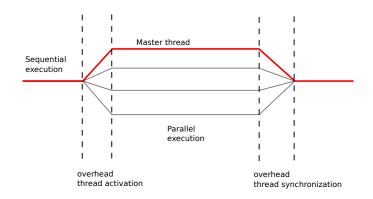

Tout d'abord, considérant le modèle OpenMP comme étant situé en haut de la pile logicielle, il est nécessaire d'avoir de bonnes performances au niveau du support exécutif d'OpenMP. Ainsi, nous nous concentrons sur le surcoût induit par les entrées et sorties dans le moteur d'exécution depuis l'application, à savoir lorsqu'on entre et sort d'une région parallèle, respectivement.

Ceci nous amène à nous intéresser à l'optimisation des support exécutifs OpenMP pour les codes hybrides MPI+OpenMP et en environnement NUMA. Il s'agit d'obtenir un surcoût minimal d'une part dans un contexte où les coeurs de calcul sont partagés entre les tâches MPI et les threads OpenMP, donc l'espace pour chaque équipe OpenMP peut varier. D'autre part, le parallélisme hiérarchique induit par les systèmes NUMA doit être pris en compte, notamment les effets NUMA associés.

Nous pouvons illustrer l'impact des effets NUMA sur le surcoût d'un support exécutif OpenMP en prenant l'exemple de l'activation des threads lors de l'ouverture d'une région parallèle. Dans une implémentation dite centralisée, le thread Master doit réveiller lui-même tous les autres threads. Si le coût pour activer un thread est minime si celui-ci se trouve sur le même socket que le thread Master, il devient important si le thread à réveiller se situe sur un socket distant. Il est donc important d'utiliser des mécanismes adaptés en environnement NUMA.

Cependant, plusieurs contributions ont proposé des optimisations concernant les supports exécutifs OpenMP, suivant plusieurs directions:

- Implémentation des threads OpenMP: Pour démarrer leur exécution rapidement ou effectuer un ordonnancement efficace, une implémentation légère des threads peut constituer une piste intéressante. Par exemple, une contribution introduit le concept de microVP, implémenté dans le support MPC. Ces microVPs ordonnancent des threads légers appelés microthreads, utilisant la pile du microVP.

- Placement hiérarchique des threads: ForestGOMP propose une représentation hiérarchique des threads, via son outils BubbleSched. Les threads appartenant à une équipe OpenMP sont regroupés au sein d'une même bulle, et la bulle est éclatée suivant la topologie NUMA.

Affinité mémoire: Le placement des threads peut évoluer durant l'exécution d'une application parallèle. Cependant, il est important de s'intéresser aux interactions entre un thread et les données accédées par ce thread (lecture ou écriture). Il peut alors s'avérer pertinent de migrer les données afin de les garder le plus proche possible du thread en question.

Parmi ces différentes pistes, nous nous sommes concentrés sur comment intégrer la topologie NUMA dans la représentation des threads.

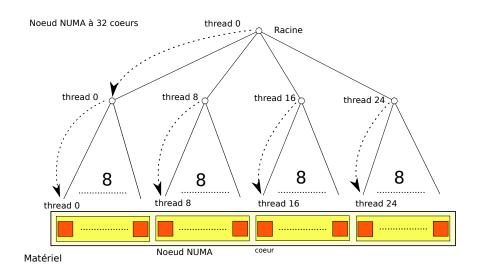

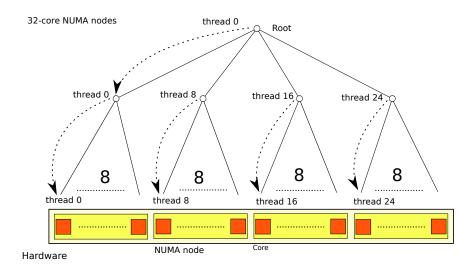

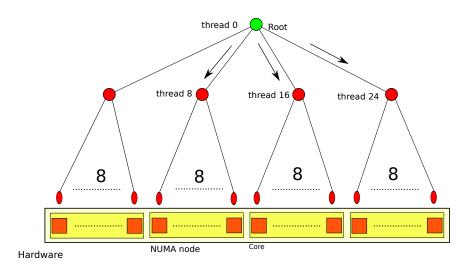

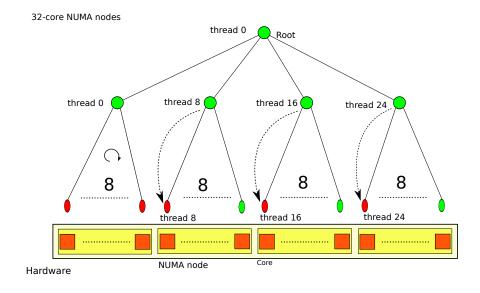

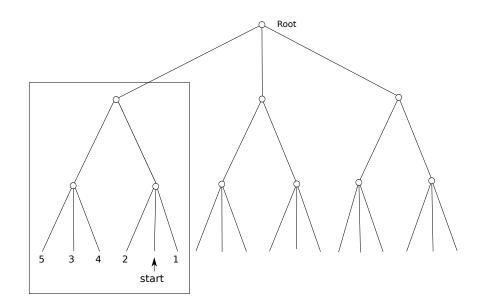

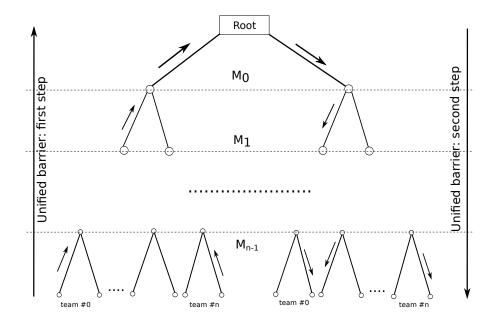

Figure 1.3: Activation hiérarchique des threads

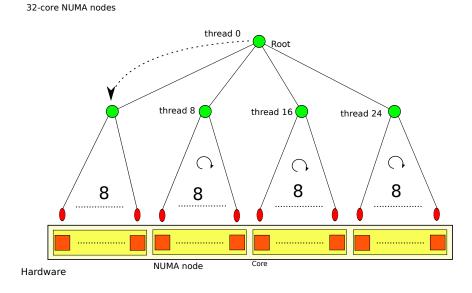

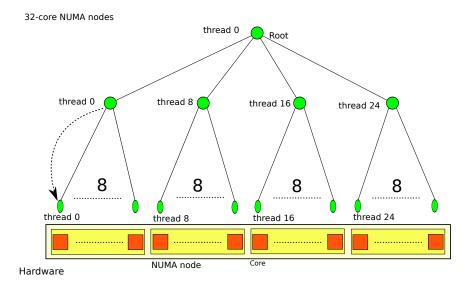

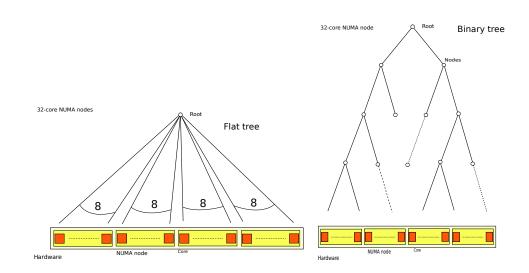

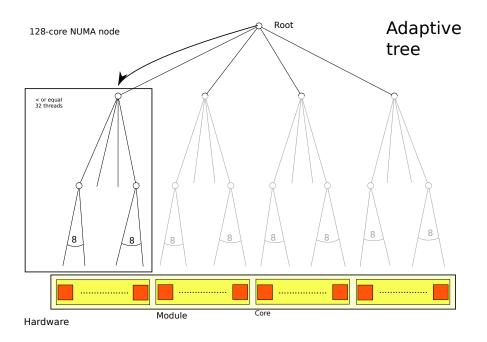

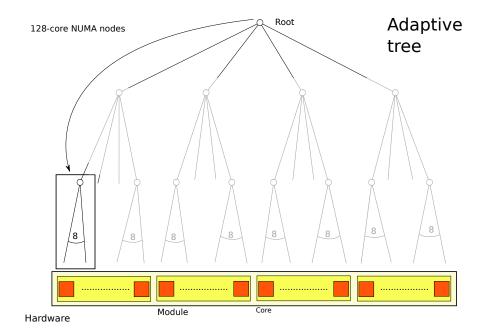

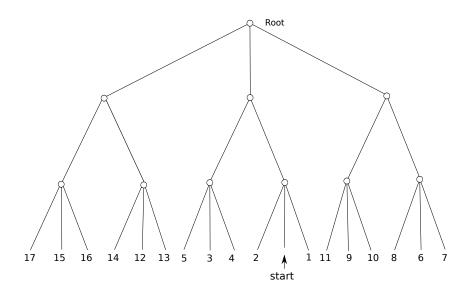

Un travail préliminaire a donc consisté à implémenter une représentation hiérarchique des threads à l'aide d'un arbre équilibré, avec une racine, des noeuds et des feuilles (figure 1.3). Les threads sont répartis sur l'arbre. Cette structure permet au thread Master de déléguer le travail d'activation des threads.

Cependant, pour un nombre réduit de threads OpenMP, l'arbre topologique ne convient peut-être pas, et un arbre plat (avec une racine et une feuille par thread) est sans doute la forme d'arbre la plus adaptée. A contrario, pour un grand nombre de threads, un arbre profond tel un arbre binaire permet de minimiser la contention dûe à l'activation des threads à chaque étage.

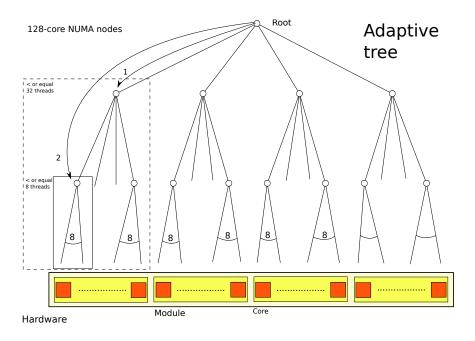

#### Arbre adaptatif

Notre première contribution consiste en un arbre adaptatif, dont la forme change au cours de l'exécution de l'application. Nous construisons un arbre topologique, et l'utilisons en fonction du nombre de threads demandé. Le principe est le suivant: nous utilisons un sous-arbre de l'arbre topologique si le nombre de threads demandés peut être contenu dans ce sous-arbre. Dans ce cas, nous déplaçons la racine initialement placée en haut de l'arbre topologique à la racine du sous-arbre.

Le mécanisme d'arbre adaptatif est transparent pour les implémentations des constructions OpenMP telles que l'activation et la synchronisation des threads. Celles-ci prennent simplement en compte la racine retournée par l'algorithme de court-circuit.

#### **Expérimentations**

L'arbre adaptatif a été implémenté au sein de la version 2.5.0 du framework MPC. La forme initiale de l'arbre suit la topologie matérielle, à l'aide de l'outil HWLOC (HardWare LOCality).

#### Algorithm 1 Bypassing

**Require:** *tree*, *numthreads*

- $\texttt{1:} node \leftarrow tree.root$

- 2: while  $node.typechildren \neq LEAF$  and  $numthreads \leq node.children[0].maxindex$  do

- 3:  $node \leftarrow node.children[0]$

- 4: end while

- 5:  $tree.newroot \leftarrow node$

- 6: return tree.newroot

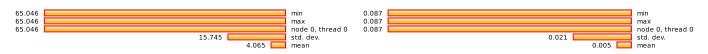

Cette approche a été évaluée sur deux configurations matérielles: 1 noeud composé de 4 processeurs Nehalem EX X7550 à 2 GHz (Tera-100), totalisant 32 coeurs de calcul 1 second noeud Bull Coherency Switch contenant 16 processeurs Intel Xeon E7-4800, avec un total de 128 coeurs de calcul.

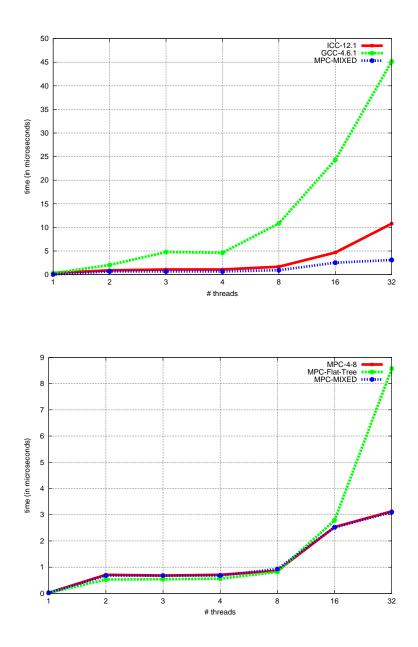

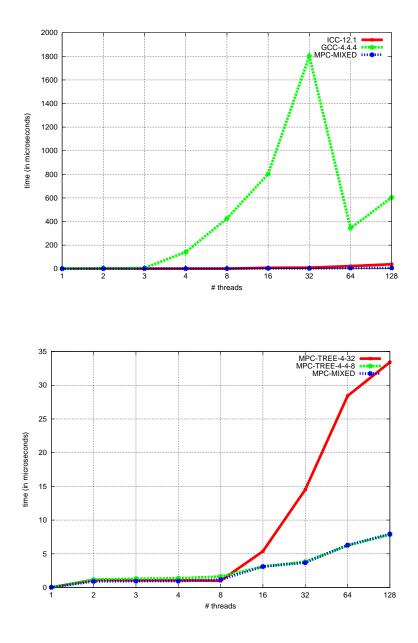

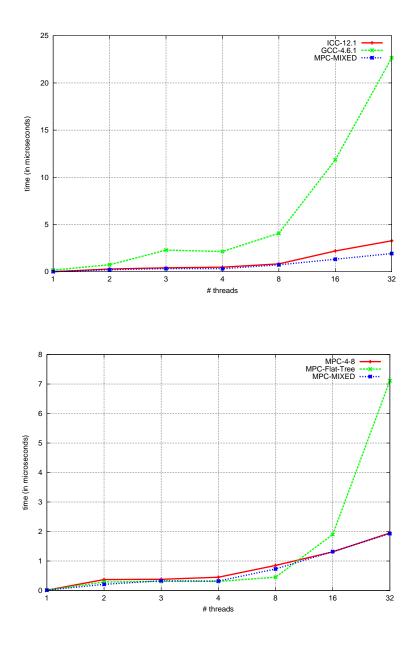

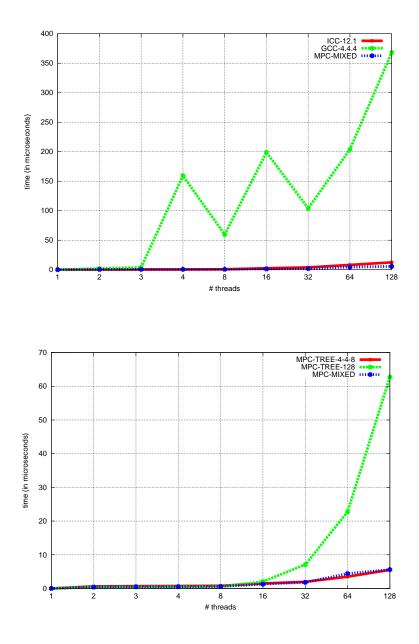

Nous avons comparé le surcoût du support OpenMP de MPC utilisant l'approche adaptative, tout d'abord par rapport à d'autres formes d'arbres dans le même support, puis par rapport aux supports OpenMP des compilateurs GCC 4.4.4 et ICC 12.1. Ces comparaisons ont été effectuées sur les deux configurations matérielles présentées, et en se focalisant sur l'activation des threads dans une région parallèle et leur synchronisation dans le cas d'une barrière OpenMP.

Nous nous sommes servis de la suite de microbenchmarks EPCC pour estimer le surcoût du support MPC.

Les expérimentations décrites suivantes ont été menées sur le noeud large contenant 128 coeurs.

Nous montrons tout d'abord que l'arbre adaptatif permet un surcoût inférieur aux autres formes d'arbres (4-32, 4-4-8), concernant l'activation des threads, sur une plage de 1 à 128 threads lancés. La forme d'arbre 4-32, même si elle offre de bonnes performances jusqu'à 8 threads, devient inefficace au-delà car les threads ne peuvent plus être contenus dans un seul socket, et cette forme d'arbre ne respecte pas la topologie. La forme d'arbre 4-4-8 fournit de bonnes performances sur toute la plage de threads car elle suit la topologie matérielle, mais demeure moins compétitive que l'arbre adaptatif jusqu'à 8 threads.

Toujours avec la même configuration matérielle, nous obtenons de bons résultats par rapport à d'autres supports OpenMP. Les performances obtenues avec la librairie libGOMP de GCC 4.4.4 sont largement en deçà de celles de MPC et de ICC 12.1. Sur 128 threads, nous obtenons un surcoût de 8 microsecondes environ avec MPC et l'arbre adaptatif activé, contre 39 microsecondes environ avec ICC 12.1.

#### 1.2.2 Etude des opérations collectives dans un contexte hybride MPI+OpenMP

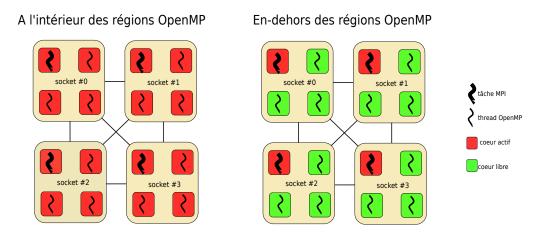

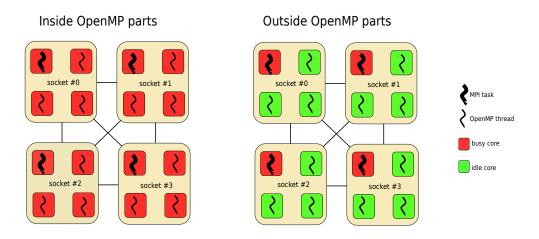

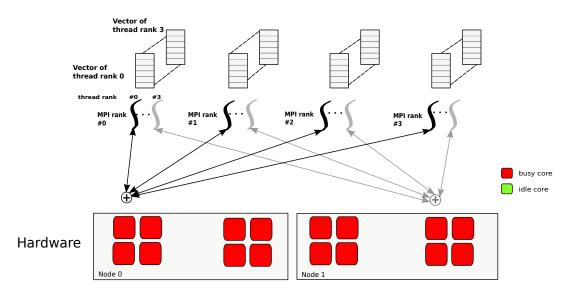

D'autres goulets d'étranglements que le surcoût des supports exécutifs OpenMP ont été identifiés, freinant le passage à l'échelle des codes MPI+OpenMP, telles que le ratio des parties séquentielle et communication dans le temps total d'exécution, ou la sous-utilisation des coeurs de libre en mode *Masterlonly* (figure 1.4).

Ces aspects nous ont conduit à nous intéresser aux opérations collectives MPI, et notamment les opérations relatives aux réductions. L'optimisation des opérations collectives MPI fait l'objet d'intenses recherches, desquelles nous avons dégagé deux axes: l'utilisation de la mémoire partagée et l'exploitation de la topologie matérielle et réseau sous-jacents.

De nombreuses contributions s'appuient sur la mémoire partagée pour optimiser les opérations collectives. L'une d'entre elles se concentre les opérations de réduction et présente deux algorithmes: *Recursive Halving and Doubling*, et *Binary Blocks*, décomposant une réduction en deux opérations: Reduce\_Scatter et Allgather. Le principe pour ces deux algorithmes est de découper les vecteurs de départ récursivement, et à chaque étape, une moitié est envoyée à la tâche MPI voisine. Une autre

Figure 1.4: Vue matérielle de l'approche Masteronly

contribution propose deux variantes pour paralléliser l'opération MPI\_Allreduce. Dans la première variante, chaque processus MPI divise son espace mémoire en autant de sous-blocs que de processus, et calcule une réduction locale, stockée dans le premier bloc mémoire. La seconde variante permet d'optimiser le trafic mémoire: les réductions locales sont stockées suivant une approche cyclique.

Exploiter la topologie réseau et matérielle est une autre manière d'optimiser les opérations collectives. Il peut par exemple s'agir de concevoir des algorithmes ayant connaissance de la topologie réseau, en utilisant des sous-communicateurs. Par ailleurs, le framework *HierKNEM* inclut des algorithmes permettant de séparer les communications inter-noeud des communications intra-noeud.

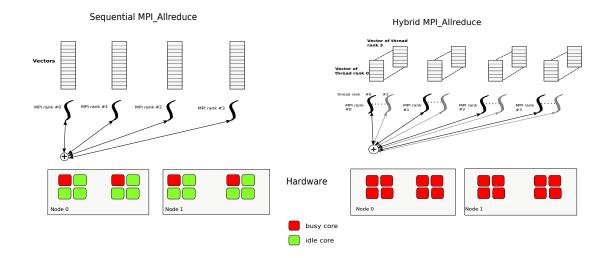

#### 1.2.3 Hybridisation de l'opération collective MPI\_Allreduce

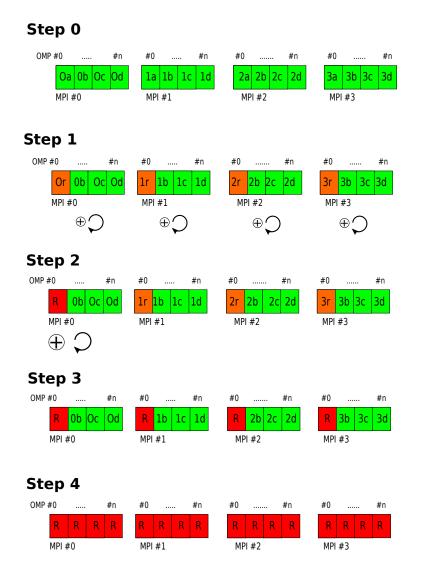

Notre seconde contribution se concentre sur l'opération collective Allreduce et consiste à découper les vecteurs de l'opération Allreduce en plusieurs blocs, à l'aide des coeurs de libres. Ainsi, chaque thread OpenMP a en charge d'effectuer l'opération sur un sous-ensemble du vecteur de départ (figure 1.5).

La conséquence principale de l'algorithme consiste à dupliquer les appels au support exécutif de MPI, mais le motif de communication demeure le même pour tous les appels: tous les rangs MPI effectuent une réduction vers un même rang MPI destination, la tâche MPI destination effectue la rédution, puis diffuse le résultat vers toutes les autres tâches. La raison est que les threads OpenMP possèdent une copie du même communicateur d'entrée, avec un ordre des tâches MPI identiques. Ceci peut générer de la contention et du déséquilibre.

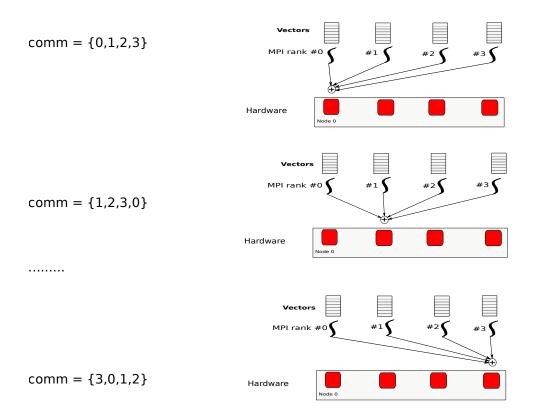

Pour pallier à ce défaut, nous proposons une technique complémentaire, appelée Rank Shifting. Celle-ci consiste à donner un rôle différent à chaque thread OpenMP, en effectuant un décalage au niveau du sous-communicateur. Par exemple, le thread de rank 0 aura une copie identique du communicateur de départ. En revanche, le thread de rang 1 fera un décalage de telle sorte que le premier rang MPI dans son sous-communicateur sera celui de rang 1, et ainsi de suite pour les autres threads OpenMP. Dans le cas où il y a plus de threads que de tâches MPI et que nous arrivons au dernier rang MPI, nous effectuons une rotation de sorte à revenir à la première tâche MPI. Cette technique permet donc de rééquilibrer les communications entre tâches MPI.

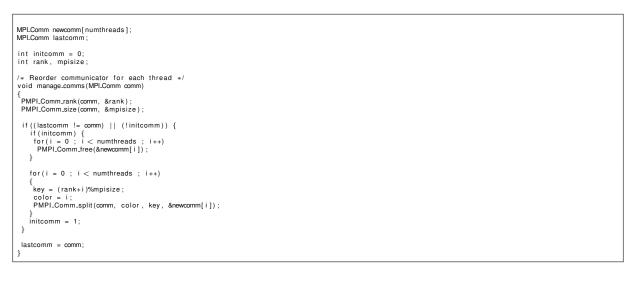

Les algorithmes présentés ont été implémentés dans un wrapper, qui capture les appels à MPI\_Allreduce via l'interface PMPI. Ce wrapper est compilé en tant que librairie partagée et préchargé à l'aide de la variable d'environnement LD\_PRELOAD, lorsque l'on exécute une application. Grâce à cette approche,

Figure 1.5: MPI\_Allreduce hybride

notre implémentation fonctionne avec n'importe quel support exécutif MPI et OpenMP. Cependant, l'implémentation doit fournir le support MPI\_THREAD\_MULTIPLE, du fait que l'on effectue des appels concurrents à la couche MPI.

#### **Expérimentations**

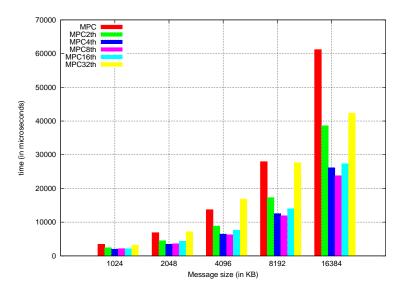

Nous avons dans un premier temps évalué l'hybridisation de la collective MPI\_Allreduce sur la suite Intel MPI Benchmarks 3.2, sur quatre noeud large contenant 128 coeurs de calculs, avec une tâche MPI par noeud.

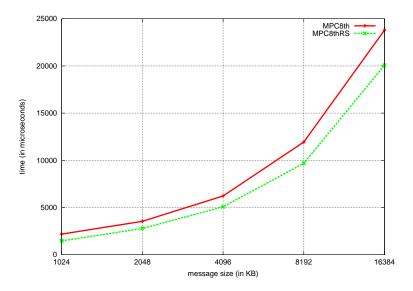

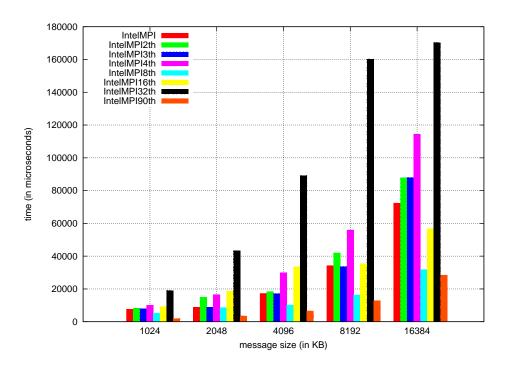

Une première expérimentation a consisté à observer le gain de l'hybridisation sur le framework MPC. Nous obtenons la plus grosse accélération en utilisant 8 threads pour l'hybridisation (gain de 2,57), sur une taille de message de 16Mo. La méthode du Rank Shifting sur cette hybridisation apporte une accélération additionnelle de 18,6%. En testant l'hybridisation de la collective avec le support IntelMPI, nous obtenons une accélération maximale de 2,55 avec 90 threads, par rapport aux résultats sans hybridisation avec IntelMPI.

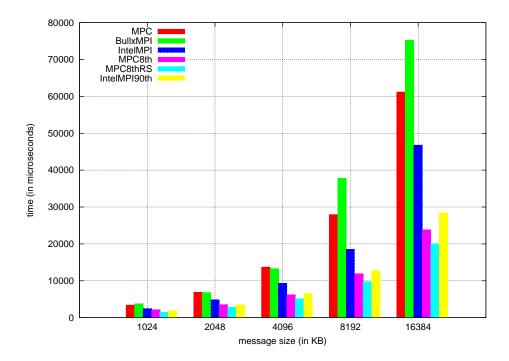

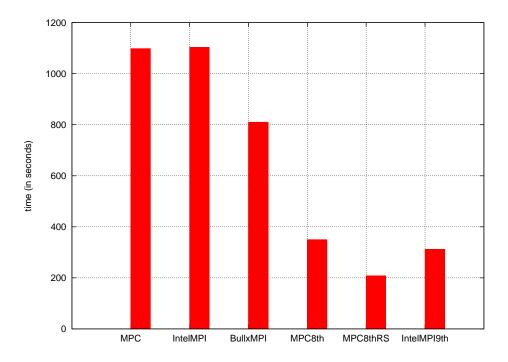

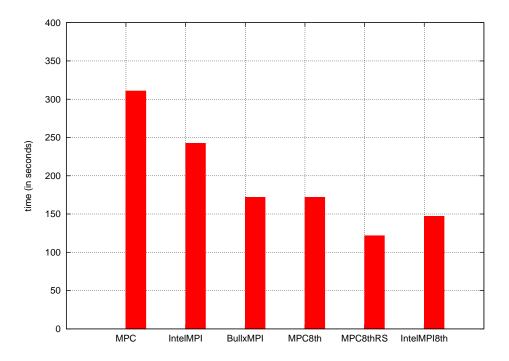

Nous avons dans un second temps évalué notre approche avec une application hybride MPI+OpenMP: MC. Il s'agit d'un code simulatant des déplacements aléatoires de particules, basé sur des méthodes de Monte Carlo. OpenMP est utilisé pour paralléliser les boucles de calcul. Les particules se déplacent sur un domaine unidimensionnel, répliqué sur chaque tâche MPI. L'application contient une opération collective MPI\_Allreduce, servant à mettre à jour l'état du maillage à chaque itération de la simulation.

Nous avons tout d'abord mesuré le temps d'exécution de MC avec différents supports exécutifs: MPC, IntelMPI et BullxMPI. Les noeuds de calcul sont intégralement remplis quand les boucles OpenMP sont exécutés. Nous obtenons les meilleures performances avec BullxMPI.

Nous avons ensuite mesuré les temps d'exécution de MC avec les mêmes supports exécutifs, mais en appliquant l'hybridisation de MPI\_Allreduce. L'hybridisation n'est pas applicable avec BullxMPI, car celui-ci ne supporte pas le niveau de multithreading MPI\_THREAD\_MULTIPLE. Pour MPC, nous obtenons la meilleure performance avec 8 threads, performance encore améliorée en appliquant la méthode du Rank Shifting (accélération totale de 5.29 par rapport à MPC sans hybridisation). Avec IntelMPI, la

```

int main(int argc, char **argv)

{

MPI_Init(&argc, &argv);

#pragma omp parallel

{

/* Code to be executed */

#pragma omp barrier

#pragma omp single

{

MPI_Barrier();

}

/* Code to be executed */

}

MPI_Finalize();

}

```

meilleure hybridisation est obtenue avec 9 threads.

#### 1.2.4 Opérations collectives unifiées

Nous revenons au parallélisme à gros grain dans le contexte du modèle hybride, et soulignons la complexité de mise en oeuvre de cette approche. OpenMP peut être utilisé dans une optique SPMD (Single Program Multiple Data), ou à mémoire distribuée. A chaque thread OpenMP est assigné un sousdomaine à calculer. Il est possible d'effectuer des opérations collectives telles que diffusion ou réduction en utilisant OpenMP avec ce mode-ci. Si l'on se replace dans un contexte hybride, et couplons MPI avec OpenMP dans un mode SPMD, nous pouvons réfléchir aux moyens de concevoir des opérations collectives impliquant aussi bien des tâches MPI que des threads OpenMP.

Le fait de concevoir des collective mettant en jeu aussi bien des tâches MPI que des threads OpenMP implique une forte coopération entre le support MPI et celui de OpenMP.

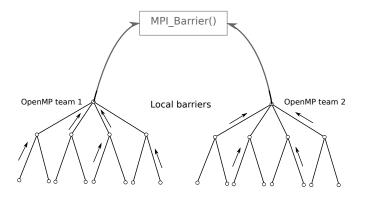

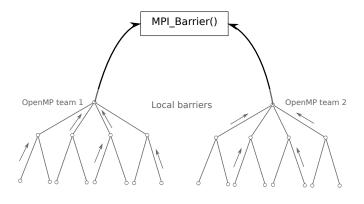

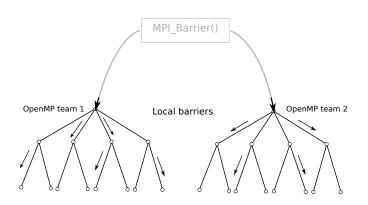

Nous motivons notre approche à l'aide d'une preuve de concept, qui est une barrière unifiée, synchronisant toutes les tâches MPI et tous les threads de toutes les équipes OpenMP.

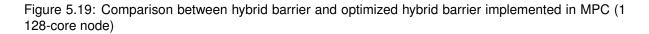

Nous commençons par décrire une implémentation de la barrière unifiée à l'aide de constructions existantes MPI et OpenMP (figure 1.6). Pour synchroniser l'ensemble des tâches MPI et des threads OpenMP, une première barrière OpenMP est nécessaire, puis un appel à MPI\_Barrier() et une seconde barrière OpenMP. Cependant, en examinant l'exécution de cette barrière, nous constatons que des optimisations sont possibles. Pour une meilleure compréhension, nous allons décomposer chaque barrière OpenMP en deux semi-barrières: la première semi-barrière se charge de synchroniser les threads, et la seconde semi-barrière libère les threads afin qu'ils continuent leur exécution.

A la fin de la première barrière OpenMP, un seul thread exécute la barrière MPI alors que les autres threads continuent leur exécution et commencent à exécuter la seconde barrière OpenMP. Ils se retrouvent donc à la fin de la semi-barrière à attendre le dernier thread.

Notre contribution concernant cette partie consiste donc à proposer une version optimisée de la barrière unifiée, proposant un appel à une seule fonction, et implémentée au niveau du support exécutif. Dans cette version optimisée, nous effectuons une première semi-barrière OpenMP (figure 1.7). Puis le dernier thread arrivé appelle une barrière MPI (figure 1.8), puis nous effectuons la seconde semi-barrière OpenMP (figure 1.9). Cette conception fonctionne avec toute implémentation de la barrière MPI.

Nous avons implémenté une version optimisée de cette barrière unifiée dans le framework MPC, cette librairie offrant une vision commune entre les tâches MPI et les threads OpenMP. L'idée est

Figure 1.7: Première étape de la barrière unifiée: synchronisation des équipes OpenMP

Figure 1.8: Seconde étape de la barrière unifiée: appel de la barrière MPI

Figure 1.9: Troisième étape de la barrière unifiée: libération des équipes OpenMP

d'effectuer cette opération en un seul appel.

#### Expérimentations

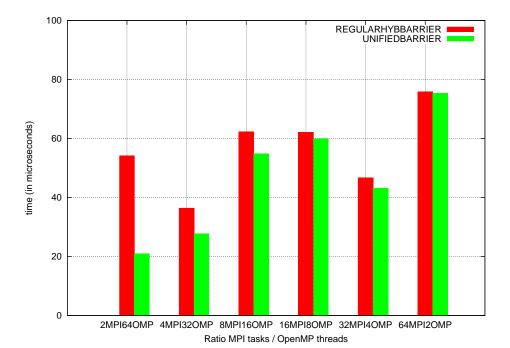

Pour valider notre approche, nous avons comparé les performances de notre barrière unifiée optimisée avec une implémentation classique d'une barrière unifiée. Pour ce faire, nous avons modifié la suite de microbenchmarks EPCC, et avons effectué des expérimentations sur un noeud large BCS contenant 128 coeurs de calcul, en testant différents ratios de tâches MPI et de threads OpenMP, de telle sorte de remplir le noeud de calcul.

Avec la barrière unifiée optimisée, nous obtenons la meilleure accélération avec une configuration avec 2 tâches MPI et 64 threads OpenMP par tâche. Nous expliquons ce résultat du fait que notre version optimisée économise un appel à une barrière OpenMP entière, ce qui a pour conséquence de gagner un temps significatif avec un grand nombre de threads. En revanche, nous avons une accélération négligeable avec 64 tâches MPI et 2 threads OpenMP par équipe. Nous estimons qu'avec cette configuration, nous passons la majorité du temps dans la barrière MPI, et l'optimisation sur les barrières OpenMP a donc peu d'incidence sur le temps total d'exécution.

#### 1.2.5 Analyse des performances des codes MPI+OpenMP au niveau applicatif et du support d'exécution

Dans la dernière partie, nous nous intéressons aux divers problèmes susceptibles de freiner les performances des codes MPI+OpenMP et empêcher leur passage à l'échelle. Identifier ces goulets d'étranglement est une tâche complexe pour des codes s'exécutant sur des milliers, voire des millions de coeurs de calcul. Cette tâche est complexifiée par le fait que ces problèmes peuvent provenir d'une mauvaise conception de l'application ou bien du support d'exécution, a fortiori lorsque deux supports d'exécution cohabitent, dans le cadre des codes hybrides. Des outils deviennent alors nécessaires afin d'identifier ces problèmes. Nous introduisons dans cette dernière partie ce qui a trait à l'analyse de performances des applications parallèles.

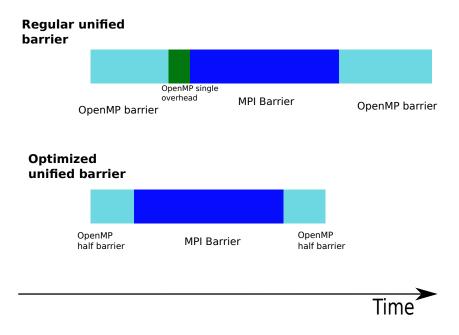

L'analyse de performance des applications parallèles peut être décomposée en trois étapes:

- Instrumentation: Une première étape consiste à instrumenter l'application à analyser, à savoir insérer des sondes soit dans le code source, soit dans l'exécutable ou bien encore dans le support d'exécution.

- Mesure: La seconde étape permet de mesurer différentes parties de l'application cible à l'aide de l'instrumentation effectuée. Plusieurs techniques sont répandues lors de cette étape, telles que le profilage, permettant par exemple de mesurer le temps passé dans des fonctions, ou bien le traçage, consistant à suivre l'exécution de différentes parties de l'application au fil du temps.

- Analyse: La dernière étape permet d'effectuer une analyse des faiblesses de l'application à partir des mesures effectuées, et comprend des fonctionnalités permettant de visualiser les mesures effectuées.

Nous nous focalisons maintenant sur l'étape d'instrumentation et examinons de quoi nous avons besoin pour instrumenter des codes MPI+OpenMP. Des outils d'instrumentation existent pour les codes MPI tels que PMPI.

On trouve diverses contributions proposant des langages pour instrumenter les codes OpenMP: OpenMP Pragma And Region Instrumentor (OPARI), un compilateur source à source permettant de localiser les directives OpenMP dans le code source et d'insérer des fonction à l'aide de l'interface POMP. OpenMP Runtime API (ou Collector API), conçu au sein du compilateur OpenUH, permet d'insérer des événements dans un support d'exécution OpenMP. ORA est notamment supporté par l'outil TAU.

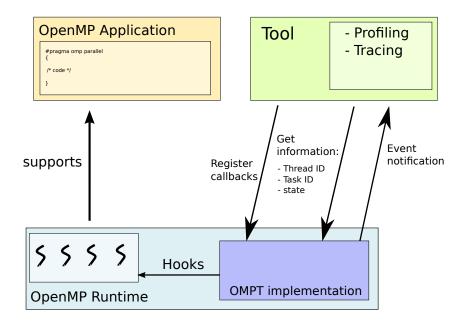

Enfin, nous introduisons OMPT, basé sur les mêmes techniques que Collector API, à savoir l'insertion d'événements dans un support d'exécution. OMPT fournit un plus large panel d'événements que Collector API et est intégré au standard OpenMP.

OMPT, qui doit être implémenté dans un support exécutif OpenMP, fait l'interface entre le support d'exécution et un outil d'analyse de performance.

Les événements fournis par OMPT sont associés aux constructions OpenMP, et sont généralement utilisés par paire: une paire d'événements pour les région parallèles ou encore les boucles OpenMP. Voici quelques exemples d'événements associés à des constructions OpenMP:

- ompt\_event\_parallel\_begin / ompt\_event\_parallel\_end

- ompt\_event\_loop\_begin / ompt\_event\_parallel\_end

Ces événements, insérés dans un support d'OpenMP, permettent à l'outil de prendre connaissance de l'activité des threads OpenMP, à quel moment ils exécutent des constructions, etc.

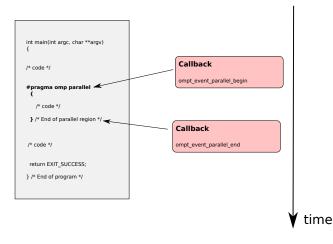

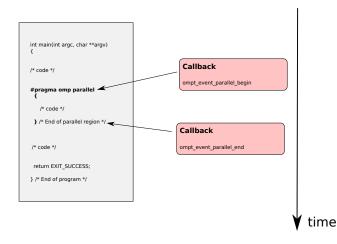

Figure 1.10: Insertion des événements relatifs aux régions parallèles OpenMP à l'intérieur du support d'OpenMP

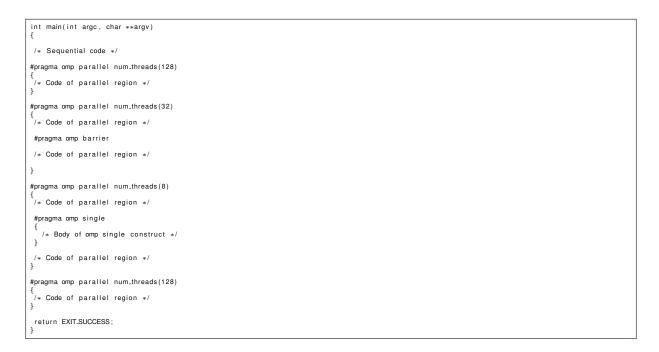

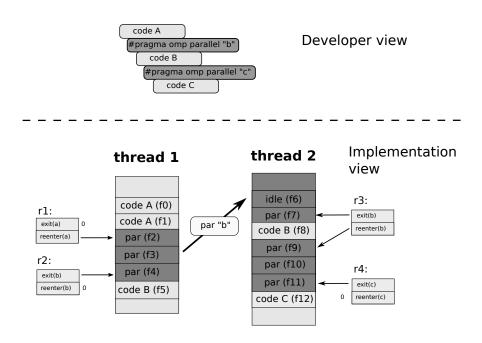

La figure 1.10 présente un exemple de code contenant une région parallèle OpenMP et montre où doivent être insérés les événements afin d'instrumenter ladite région parallèle.

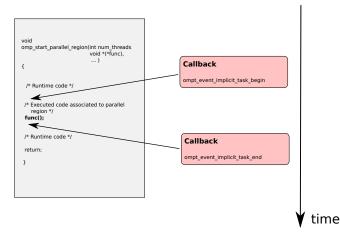

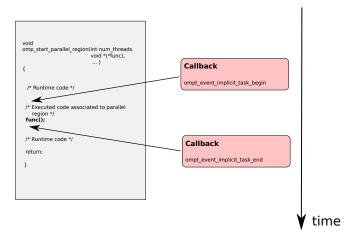

D'autres événements permettent d'étudier l'efficacité du support exécutif OpenMP, tels que la paire ompt\_event\_implicit\_task\_begin et ompt\_event\_implicit\_task\_end, permettant de mesurer le temps d'exécution du code parallèle. On peut alors déduire le surcoût du support exécutif.

Figure 1.11: Insertion des évévements relatifs aux tâches implicites à l'intérieur du support d'OpenMP

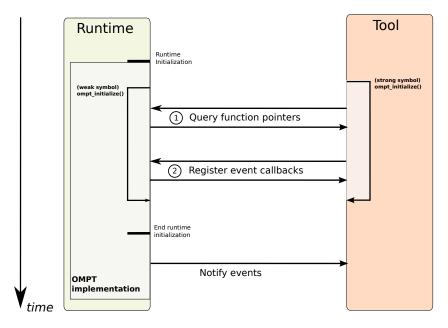

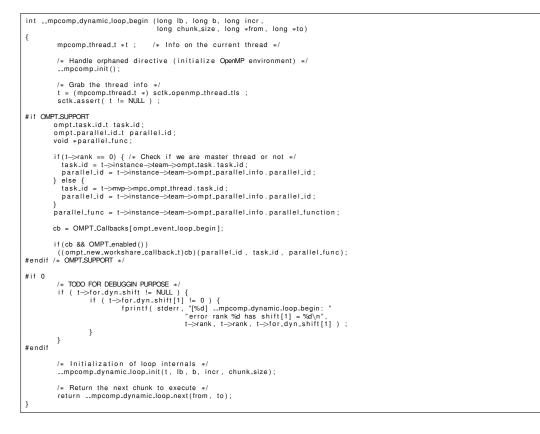

Le code de la figure 1.11 présente le squelette d'une implémentation d'une région parallèle OpenMP. La figure montre où doivent être placés les événements relatifs aux tâches implicites dans le support. La façon dont OMPT s'interface avec l'outil est la suivante: OMPT est démarré à l'initialisation du support OpenMP et arrêté à la terminaison de ce dernier. Pour initialiser l'outil, la norme propose une fonction ompt\_initialize, qui doit être implémenté aussi bien du côté du support que celui de l'outil. Une fois OMPT initialisé, l'outil enregistre des callbacks relatifs aux événements susceptibles de l'intéresser, et OMPT doit notifier l'outil lorsque des événements enregistrés par ce dernier sont rencontrés.

Nous présentons ici notre dernière contribution, à savoir l'implémentation de l'outil d'instrumentation OMPT dans le support exécutif MPC, puis son évaluation sur des application MPI+OpenMP.

Les événements OMPT liés aux principales constructions OpenMP ont été implémentés dans la version 2.5.0 du support MPC.

Il est à noter que, puisque la majorité des événements est fournie par paires (une pour l'entrée dans une construction OpenMP et une pour la sortie), des fonctions d'entrée et de sortie sont requises pour insérer ces événements. Cependant, Il n'y a pas de fonction générée pour la construction #pragma omp loop schedule(static), et une seule fonction est générée pour #pragma omp single: la fonction retourne 0 ou 1 selon que le thread courant exécute la construction ou non.

Ces problèmes nous ont poussé à modifier l'interface de GCC avec le support d'exécution afin de générer les fonctions requises, permettant l'insertion des événements OMPT liés à ces deux constructions.

Une fois l'outil OMPT implémenté dans le support MPC, nous nous sommes dans un premier temps concentrés sur une étude sur les boucles OpenMP et comment il est possible de les optimiser à l'aide de OMPT. Nous avons donc repris l'application MPI+OpenMP MC, en nous focalisant sur les boucles OpenMP, en étudiant comment il était possible d'optimiser les boucles en réglant la politique d'ordonnancement et la taille des blocs.

Nous avons tout d'abord comparé les politiques d'ordonnancement statique et dynamique pour une boucle d'une fonction donnée, et avons observé un ralentissement très important lorsque l'on passe de la politique statique à la politique dynamique. Plusieurs raisons peuvent expliquer ce ralentissement:

- Dans la norme OpenMP, lorsqu'aucune taille de bloc est spécifiée avec la politique d'ordonnancement statique, la boucle est divisée en autant de blocs que de threads. Ce cas implique un minimum d'intervention du support exécutif, alors que pour la politique d'ordonnancement dynamique, chaque thread choisit un bloc de taille 1 à exécuter, et ceci jusqu'à l'exécution complète de la boucle. Dans ce dernier cas, le support d'exécution est plus sollicité que pour la politique statique.

- La politique d'ordonnancement dynamique autorise un équilibrage de travail entre les threads. Aussi, nombre de supports exécutifs OpenMP implémentent des algorithmes de vol de travail. Il est possible qu'un mauvaise implémentation du vol de travail gêne le travail des threads, ou génère de la contention au niveau des communication.

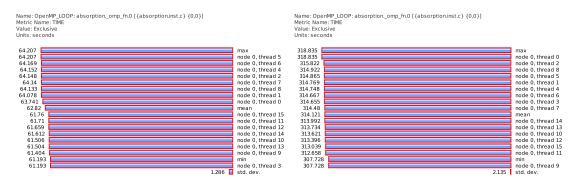

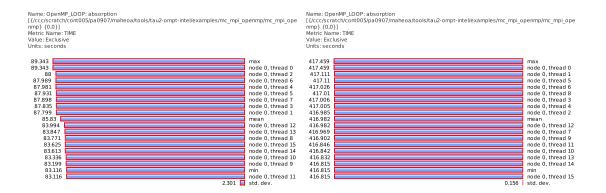

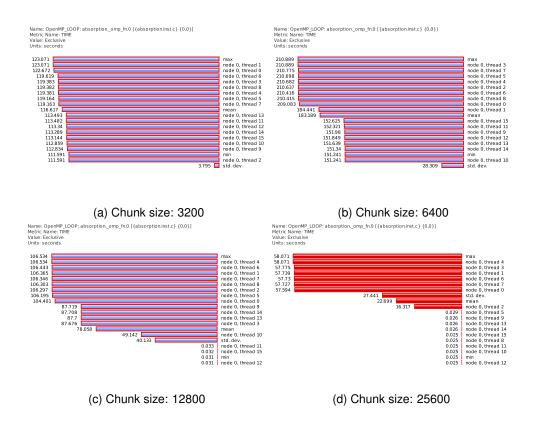

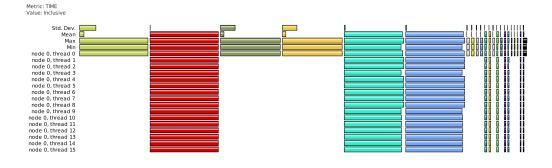

Par ailleurs, nous nous servons de OMPT afin de déterminer de manière empirique la meilleure combinaison entre la politique d'ordonnancement et la taille de blocs en terme de performances. Nous comparons les performances des boucles avec les supports MPC OpenMP et Intel OpenMP.

Enfin, nous pouvons utiliser OMPT afin d'estimer le surcoût du support OpenMP de MPC, à l'aide de la paire d'événements ompt\_event\_implicit\_task\_begin / ompt\_event\_implicit\_task\_end. Le surcoût est déduit en comparant le temps passé dans une région parallèle et celui passé dans une tâche implicite, puisqu'il s'agit du temps mis pour réveiller les threads.

#### **1.3 Conclusion et perspectives**

Cette thèse s'est intéressée à différents aspects du modèle hybride MPI+OpenMP, et s'est focalisée sur les limitations venant avec ce modèle, empêchant le passage à l'échelle des codes parallèles. Nous avons présenté des contributions proposant des solutions à ces freins:

- Arbre adaptatif: Afin de répondre au besoin d'efficacité des supports exécutifs OpenMP dans un contexte hybride, notre première contribution a consisté proposer un arbre adaptatif permettant d'optimiser l'activation et la synchronisation des threads en environnement NUMA, et sur un large spectre de threads.

- Hybridisation de l'opération collective MPI\_Allreduce: Nous avons proposé une méthode permettant d'accélérer l'opération collective MPI\_Allreduce, en utilisant les threads OpenMP et ainsi réutilisant les coeurs de calcul inactifs. Cette contribution répond une limitation rencontrée avec le parallélisme à grain fin.

- Opérations collectives unifiées: Nous avons introduit le concept d'opérations collectives unifiées, ceci afin d'assurer une meilleure coopération entre MPI et OpenMP utilisé dans le mode SPMD. Nous motivons notre approche avec une preuve de concept, la barrière unifiée.

- Implémentation et évaluation de l'outil d'instrumentation OMPT: Enfin, nous nous concentrons sur l'analyse de performance des codes MPI+OpenMP et proposons une implémentation de l'outil d'instrumentation OMPT, ainsi que son évaluation sur une application MPI+OpenMP, en ciblant les boucles OpenMP.

Nous terminons en abordant quelques axes de réflexion concernant le modèle hybride.