# Mapping of large task network on manycore architecture Karl-Eduard Berger

#### ▶ To cite this version:

Karl-Eduard Berger. Mapping of large task network on manycore architecture. Distributed, Parallel, and Cluster Computing [cs.DC]. Université Paris Saclay (COmUE), 2015. English. NNT: 2015SACLV026. tel-01318824

#### HAL Id: tel-01318824 https://theses.hal.science/tel-01318824

Submitted on 20 May 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

NNT: 2015SACLV026

# THESE DE DOCTORAT DE L'UNIVERSITE PARIS-SACLAY

PREPAREE A

"L'UNIVERSITE VERSAILLES SAINT-QUENTIN EN YVELINES"

ECOLE DOCTORALE N° 580 Sciences et technologies de l'information et de la communication

Mathématiques et Informatique

Par

#### M. Karl-Eduard Berger

Placement de graphes de tâches de grande taille sur architectures massivement multicoeur

Thèse présentée et soutenue à CEA Saclay Nano-INNOV, le 8 décembre 2015 :

#### Composition du Jury:

M., El Baz, Didier Chargé de recherche CNRS, LAAS Rapporteur M, Galea, François Chercheur, CEA **Encadrant CEA** M, Le Cun, Bertrand Maitre de conférence PRISM Co-directeur de thèse Mme, Munier, Alix Professeur des universités, UPMC Examinatrice M, Nace, Dritan Professeur des universités HEUDIASYC Président M., Pellegrini, François Professeur des universités, LABRI Rapporteur M, Sirdey, Renaud Directeur de recherche, CEA Directeur de thèse

Titre : Placement de graphes de tâches de grande taille sur architectures massivement multicoeurs

Mots clés : Placement de tâches, recherche opérationnelle, architectures manycoeurs

**Résumé :** Ce travail de thèse de doctorat est dédié à l'étude d'un problème de placement de tâches dans le domaine de la compilation d'applications pour des architectures massivement parallèles. Ce problème placement doit être résolu dans le respect de trois critères: les algorithmes doivent être capables de traiter des applications de tailles variables, ils doivent répondre aux contraintes de capacités des processeurs et prendre en compte la topologie des architectures cibles. Dans cette thèse, les tâches sont organisées en réseaux de communication, modélisés sous forme de graphes. Pour évaluer la qualité des solutions produites par les algorithmes, les placements obtenus sont comparés avec un placement aléatoire.

Cette comparaison sert de métrique d'évaluation des placements des différentes méthodes proposées. Afin de résoudre à ce problème, trois algorithmes de placement ont été développés. Task-wise Placement et Subgraph-wise Placement s'appliquent dans des cas où les poids des tâches et des arêtes sont unitaires.

Regret-based Approach est une heuristique de construction progressive basée sur la théorie des jeux qui s'applique sur des graphes dans lesquels les poids des tâches et des arêtes sont variables similairement aux valeurs qu'on peut retrouver dans des cas industriels.

Afin de vérifier la robustesse de l'algorithme, différents types de graphes de tâches de tailles variables ont été générés.

**Title:** Mapping of large task networks on manycore architecture

**Keywords:** Tasks mapping, Operational Research, manycore architecture

**Abstract:** This Ph.D thesis is devoted to the study of the mapping problem related to massively parallel embedded architectures. This problem has to be solved considering three criteria: heuristics should be able to deal with applications with various sizes, they must meet the constraints of capacities of processors and they have to take into account the target architecture topologies. In this thesis, tasks are organized in communication networks, modeled as graphs. In order to determine a way of evaluating the efficiency of the developed heuristics, mappings, obtained by the heuristics, are compared to a random mapping. This comparison is used as an evaluation metric throughout this thesis. The existence of this metric is motivated by the fact that no comparative heuristics can be found in the literature at the time of writing of this thesis.

In order to address this problem, three heuristics are proposed. They are able to solve a dataflow process network mapping problem, where a network of communicating tasks is placed into a set of processors with limited resource capacities, while minimizing the overall communication bandwidth between processors. Task-wise Placement and Subgraph-wise Placement are applied on task graphs where weights of tasks and edges are unitary set. Then, in a will to address problems that can be found in industrial cases, application cases are widen to tasks graphs with tasks and edges weights values similar to those that can be found in the industry. A progressive construction heuristic named Regret Based Approach, based on game theory, is proposed In order to check the strength of the algorithm; many types of task graphs with various sizes are generated.

To Hélène, Stefan and Maximilien Berger, Ingeborg und Günter Berger, Mireille and Martial Labouise, Jeanne Clermon et Huguette Chaumereux, And my friend Kristina Guseva.

He who loves practice without theory is like the sailor who boards ship without a rudder and compass and never knows where he may cast.

Leonardo de Vinci

## Contents

| A            | cknov  | vledge                 | ment                                                     | 1  |

|--------------|--------|------------------------|----------------------------------------------------------|----|

| P            | ublica | ations                 |                                                          | 5  |

| R            | ésum   | é                      |                                                          | 7  |

| $\mathbf{A}$ | bstra  | $\operatorname{ct}$    |                                                          | 9  |

| R            | ésum   | é Fran                 | çais                                                     | 11 |

| In           | trodu  | ıction                 |                                                          | 17 |

| 1            | Con    | text                   |                                                          | 25 |

|              | 1.1    | Introdu                | uction                                                   | 25 |

|              | 1.2    | Moore                  | 's law                                                   | 26 |

|              | 1.3    | Embed                  | lded systems                                             | 28 |

|              |        | 1.3.1                  | What is an embedded system?                              | 28 |

|              |        | 1.3.2                  | Massively parallel embedded systems                      | 29 |

|              | 1.4    | Manyc                  | ore architectures                                        | 30 |

|              |        | 1.4.1                  | Parallel architectures                                   | 30 |

|              |        | 1.4.2                  | Massively Parallel Processor Architectures (MPPA)        | 32 |

|              | 1.5    | SDF a                  | nd CSDF dataflow programming models                      | 34 |

|              | 1.6    | $\Sigma C$ pro         | ogramming language and compilation                       | 36 |

|              |        | 1.6.1                  | $\Sigma$ C programming language                          | 36 |

|              |        | 1.6.2                  | An Example $\Sigma C$ Application: Laplacian of an Image | 37 |

|              |        | 1.6.3                  | The compilation process                                  | 39 |

|              | 1.7    | Formal                 | lization of the DPN mapping problem                      | 41 |

|              | 1.8    | A meti                 | ric to evaluate the quality of solutions                 | 43 |

|              |        | 1.8.1                  | Approximation measure of Demange and Paschos             | 43 |

|              |        | 1.8.2                  | Random-based approximation metric                        | 44 |

|              | 1.9    | $\operatorname{Graph}$ | Theory Background                                        | 45 |

|              |        | 1.9.1                  | Some Definitions                                         | 45 |

|              |        | 1.9.2                  | Breadth-First Traversal (BFT) algorithm                  | 47 |

|              |        | 1.9.3                  | Notion of affinity                                       | 47 |

|              | 1 10   | Conclu                 | sion                                                     | 48 |

ii CONTENTS

| <b>2</b> | Stat | te of the Art of the Mapping Problem                           |

|----------|------|----------------------------------------------------------------|

|          | 2.1  | Introduction                                                   |

|          | 2.2  | The importance of mapping applications                         |

|          | 2.3  | Partitioning problems                                          |

|          |      | 2.3.1 Bipartitioning algorithms                                |

|          |      | 2.3.2 Multilevel approaches                                    |

|          | 2.4  | Quadratic Assignment Problems (QAP)                            |

|          | 2.5  | Mapping problems                                               |

|          |      | 2.5.1 Two-phases mapping heuristics                            |

|          |      | 2.5.2 One-phase mapping heuristics                             |

|          | 2.6  | Solvers                                                        |

|          |      | 2.6.1 Metis, Parmetis, hMetis, kMetis                          |

|          |      | 2.6.2 Scotch and PT-Scotch                                     |

|          |      | 2.6.3 Jostle: Parallel Multi-Level Graph Partitioning Software |

|          |      | 2.6.4 Other solvers                                            |

|          | 2.7  | Discussion                                                     |

|          |      | 2.7.1 Overview                                                 |

|          |      | 2.7.2 Our work                                                 |

|          | 2.8  | Conclusion                                                     |

| 3        | Two  | o Scalable Mapping Methods                                     |

|          | 3.1  | Introduction                                                   |

|          | 3.2  | Subgraph-Wise Placement                                        |

|          |      | 3.2.1 Creation of a Subgraph of Tasks                          |

|          |      | 3.2.2 Subgraph to node affinity                                |

|          |      | 3.2.3 Complexity of the algorithm                              |

|          |      | 3.2.4 Conclusion                                               |

|          | 3.3  | Task-Wise Placement                                            |

|          | 0.0  | 3.3.1 Distance affinity                                        |

|          |      | 3.3.2 The mapping procedure                                    |

|          |      | 3.3.3 Complexity of the Algorithm                              |

|          |      | 3.3.4 Conclusion                                               |

|          | 3.4  | Results                                                        |

|          | J. 1 | 3.4.1 Execution Platform                                       |

|          |      | 3.4.2 Instances                                                |

|          |      | 3.4.3 Computational results                                    |

|          | 3.5  | Conclusion                                                     |

| 4        | Reo  | ret-Based Mapping Method                                       |

| I        | 4.1  | Introduction                                                   |

|          | 4.1  | Game theory background                                         |

|          | 4.4  | 4.2.1 Overview of game theory                                  |

|          |      | 4.2.1 Overview of game theory                                  |

|          |      |                                                                |

|          |      | 4.2.3 Decision theory                                          |

| CONTENTS | iii |

|----------|-----|

|----------|-----|

| 4.3    | Regret | theory                                                  | 91  |

|--------|--------|---------------------------------------------------------|-----|

|        | 4.3.1  | External regret, internal regret and swap regret        | 92  |

|        | 4.3.2  | Formal definition                                       | 93  |

|        | 4.3.3  | Use of regret theory in the literature                  | 94  |

| 4.4    | Regret | Based Heuristic                                         | 96  |

|        | 4.4.1  | Task-Wise Placement behavior on non-unitary task graphs | 96  |

|        | 4.4.2  | Introduction of the task cost notion                    | 97  |

|        | 4.4.3  | A new task selection model based on regret theory       | 97  |

|        | 4.4.4  | Description of the algorithm                            | 98  |

|        | 4.4.5  | Complexity of the algorithm                             | 98  |

| 4.5    | GRAS   | P Principles for RBA                                    | 101 |

|        | 4.5.1  | Definition of the GRASP procedure                       | 101 |

|        | 4.5.2  | GRASP and RBA                                           | 102 |

| 4.6    | Applic | ation of the heuristic                                  | 102 |

|        | 4.6.1  | Execution platform                                      | 102 |

|        | 4.6.2  | Instances                                               | 102 |

|        | 4.6.3  | The node layout                                         | 104 |

|        | 4.6.4  | Random weight generation                                | 104 |

|        | 4.6.5  | Experimental protocol                                   | 105 |

|        | 4.6.6  | Experimental results and analysis                       | 106 |

|        | 4.6.7  | Experimental results and analysis using GRASP procedure | 111 |

| 4.7    | Conclu | sion                                                    | 117 |

| Conclu | sion   |                                                         | 119 |

iv CONTENTS

# List of Figures

| 1    | Domino circle with double 4 form                                                                                                                                                                                                                                                                                                 | 18 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

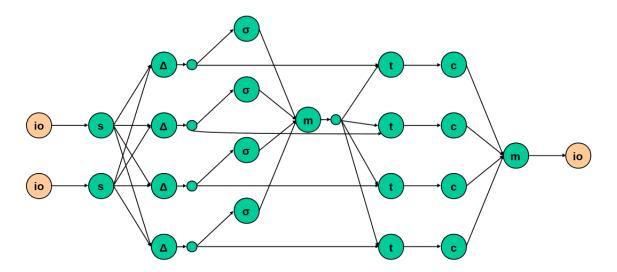

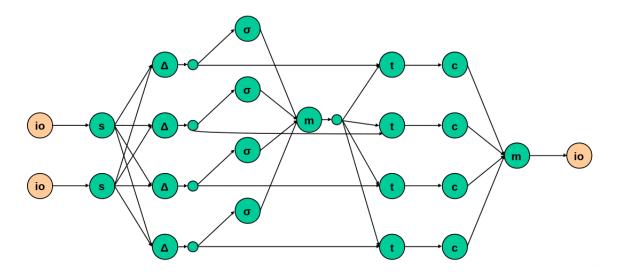

| 2    | A dataflow process network graph example of a motion detection application.                                                                                                                                                                                                                                                      | 19 |

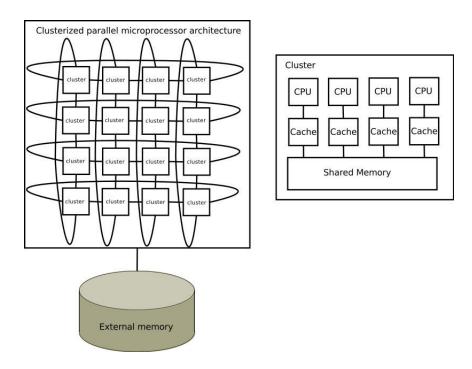

| 3    | Clusterized parallel microprocessor architecture                                                                                                                                                                                                                                                                                 | 20 |

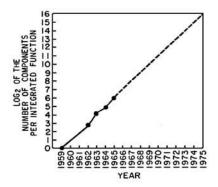

| 1.1  | Moore's 1965 prediction of the doubling of the number of minimum cost                                                                                                                                                                                                                                                            |    |

|      | component on chip each year, extrapolated to 1975                                                                                                                                                                                                                                                                                | 27 |

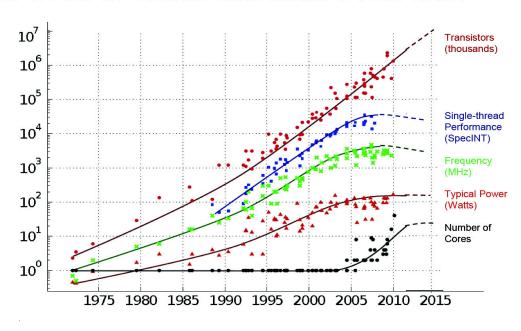

| 1.2  | Evolution during the last 35 years of the number of transistors, single thread performance, frequency, typical power and number of cores. Image from C. Moore (original data by M. Horowitz, F. Labonte, O. Shacham,                                                                                                             |    |

|      | K. Olukotun, L. Hammond and C. Batten).                                                                                                                                                                                                                                                                                          | 28 |

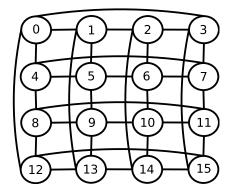

| 1.3  | Undirected 2-dimensional cyclic mesh. Each vertices correspond to a clus-                                                                                                                                                                                                                                                        |    |

|      | ter and each edge to a communication channel                                                                                                                                                                                                                                                                                     | 33 |

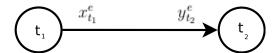

| 1.4  | Synchronous Dataflow illustration                                                                                                                                                                                                                                                                                                | 36 |

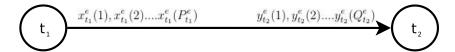

| 1.5  | Cyclo-Static Dataflow illustration                                                                                                                                                                                                                                                                                               | 36 |

| 1.6  | A dataflow process network of a motion detection application to map on                                                                                                                                                                                                                                                           |    |

|      | a torus node architecture target                                                                                                                                                                                                                                                                                                 | 37 |

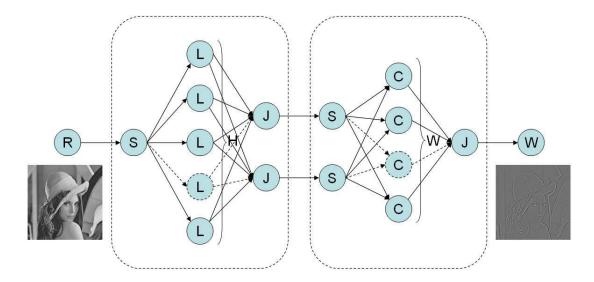

| 1.7  | Dataflow process network for the Laplacian computation of an image                                                                                                                                                                                                                                                               | 38 |

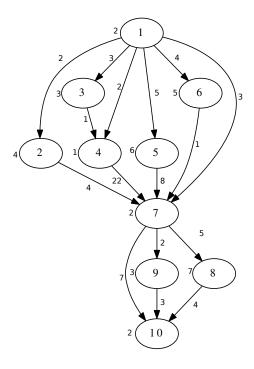

| 1.8  | A task graph for a fictitious program. Vertices are numbered, vertex and                                                                                                                                                                                                                                                         |    |

|      | edges weights are noted besides them                                                                                                                                                                                                                                                                                             | 40 |

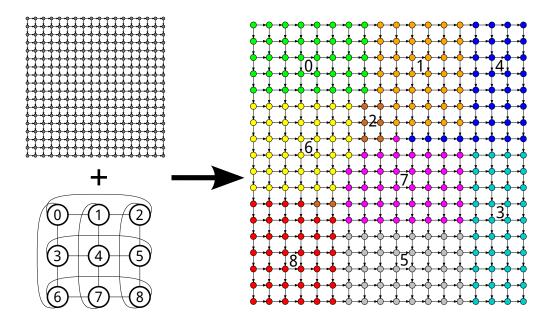

| 1.9  | Mapping of a DPN on a parallel architecture. The grid on the upper left corner represents a task graph, the torus on the lowest left corner represents the target architecture. The graph on the right size represent the tasks graphs and colors indicates on which node the task is mapped. Each color corresponds to one node | 41 |

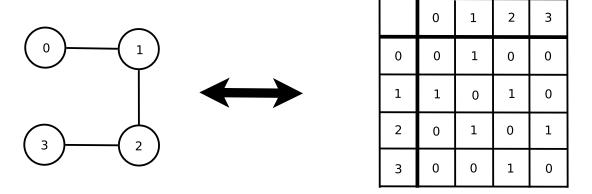

| 1.10 | A non-oriented simple fictitious graph with its associated adjacency matrix.                                                                                                                                                                                                                                                     | 47 |

| 1.10 | 11 non offened simple neutrous graph with its associated adjacency matrix.                                                                                                                                                                                                                                                       | 11 |

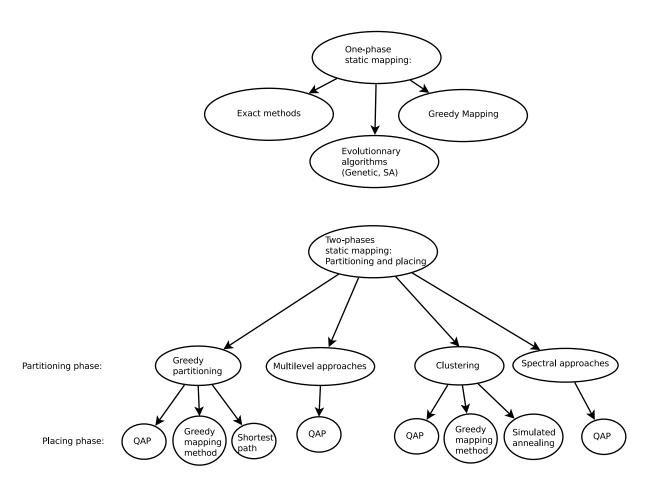

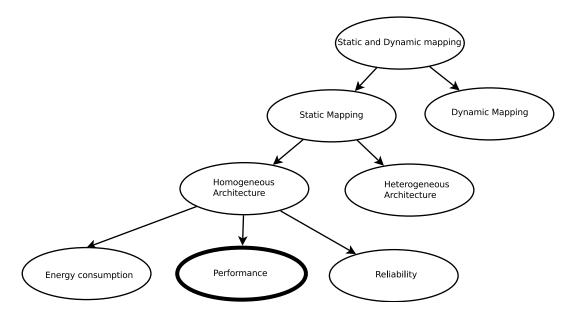

| 2.1  | The state of the art has been filtered using the above personal criteria. Placing heuristics are not exhaustive, only those which appeared frequently are cited                                                                                                                                                                  | 55 |

| 2.2  | Decision tree which shows how the state of the art of one-phase mapping is organized. The focus is set on the performance of static mapping heuristics which are developed for homogeneous target architectures. This                                                                                                            | 00 |

|      | classification is inspired by a survey of Singh <i>et al.</i> [171]                                                                                                                                                                                                                                                              | 60 |

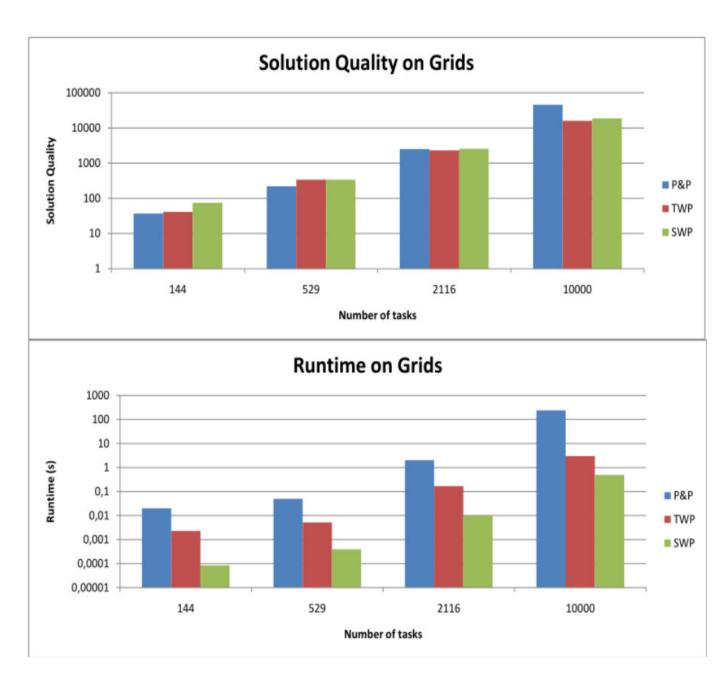

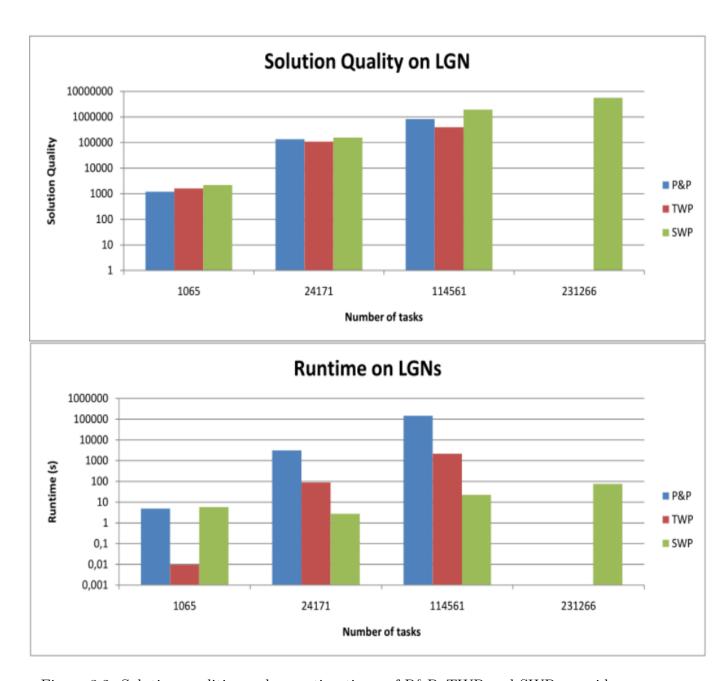

| 3.1  | Solution qualities and execution times of P&P, TWP and SWP on grids.                                                                                                                                                                                                                                                             | 81 |

vi LIST OF FIGURES

| 3.2 | Solution qualities and execution times of P&P, TWP and SWP on grids.                         | 82  |

|-----|----------------------------------------------------------------------------------------------|-----|

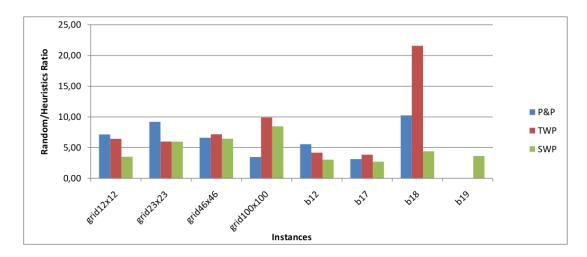

| 3.3 | $\frac{Random}{P\&P}$ , $\frac{Random}{TWP}$ , $\frac{Random}{SWP}$ ratios on Grids and LGNs | 83  |

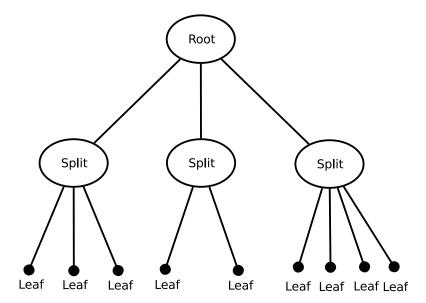

| 4.1 | A decision tree. Each circle is a node. Data are split into smaller groups                   |     |

|     | depending on a rule defined by the decision maker. At the end of the tree,                   |     |

|     | each leaf contains a various amount of data                                                  | 90  |

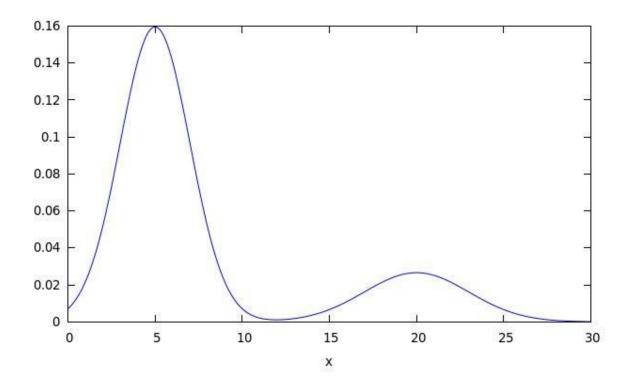

| 4.2 | weight density function $(m_0 = 5, s_0 = 2, m_1 = 15, s_1 = 3)$                              | 105 |

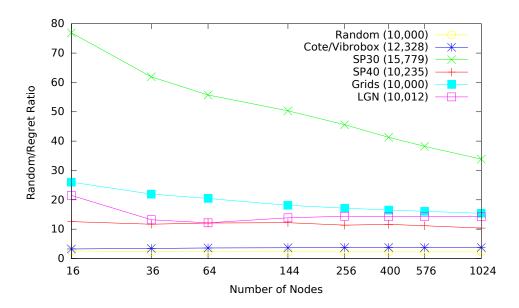

| 4.3 | $\frac{Random}{Regret}$ for task graphs with an order of magnitude of 10,000 tasks           | 106 |

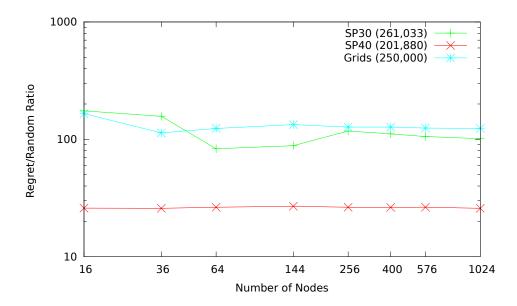

| 4.4 | $\frac{Random}{Regret}$ for task graphs with an order of magnitude of 200,000 tasks          | 107 |

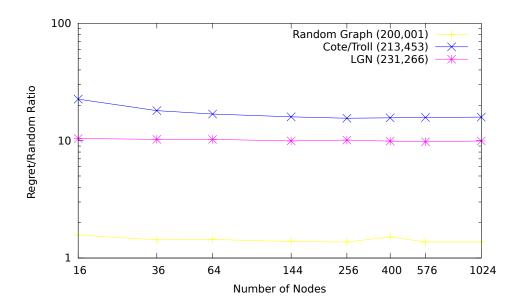

| 4.5 | $\frac{Random}{Regret}$ for task graphs with an order of magnitude of 200,000 tasks          | 108 |

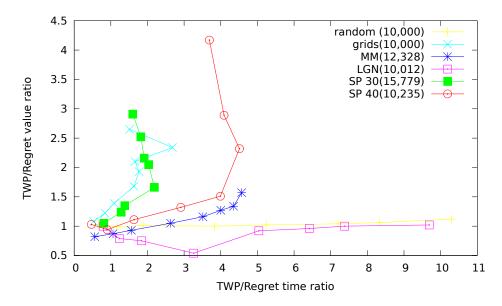

| 4.6 | Ratio $\frac{TWP}{Regret}$ for task graphs with an order of magnitude of 10,000 tasks.       | 109 |

|     |                                                                                              |     |

# List of Tables

| 1                        | Etat de l'art résumé. Les données en vert correspondent aux caractérisques nécessaires pour la résolution du problème                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                   |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.1                      | Summary of Flynn's taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                   |

| 2.1<br>2.2               | Related works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67<br>68             |

| 3.1<br>3.2<br>3.3<br>3.4 | Grid shaped task topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79<br>79<br>80<br>80 |

| 4.1                      | Prisoners' dilemna [151]. If $A$ stays silent and $B$ betrays, $B$ goes free and $A$ stays 10 years in prison. If $B$ stays silent and $A$ betrays, $A$ goes free and $B$ stay 10 years in prison. If both remain silent, both of them stay 3 years in prison. Otherwise, if both betrays each other, they stay in prison for 5 years. If $A$ and $B$ cooperate, they stay 3 years in prison. If not, either the betrayer is free or stays 5 years in prison. What is the best strategy? Dixit and Nalebuff offer alternatives like mixing moves, strategic moves, bargaining, concealing and revealing about this problem [43] | 87                   |

| 4.2                      | Task graphs with several topologies. Shown values are the number of tasks, the number of edges and the diameter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 103                  |

| 4.3                      | Ratio $\frac{Random}{Regret}$ for task graphs with an order of magnitude of 10,000 tasks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 106                  |

| 4.4                      | Ratio $\frac{Random}{Regret}$ for task graphs with an order of magnitude of 10,000 tasks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 107                  |

| 4.5                      | Ratio $\frac{Random}{Regret}$ for task graphs with an order of magnitude of 200,000 tasks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107                  |

| 4.6                      | Ratio $\frac{Random}{Regret}$ for task graphs with an order of magnitude of 200,000 tasks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 108                  |

| 4.7                      | Ratio $\frac{Random}{Regret}$ for task graphs with an order of magnitude of 1 and 2 million tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 108                  |

| 4.8                      | Cumulated percentage of solution values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 111                  |

| 4.9                      | Solution Quality and Time Ratios $\frac{Regret}{GRASP}$ for task graphs with an order of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

|                          | magnitude of 10,000 tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 112                  |

| 4.10                     | Solution Quality and Time Ratios $\frac{Regret}{GRASP}$ for task graphs with an order of magnitude of 10,000 tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 113                  |

viii LIST OF TABLES

| 4.11 | Solution Quality and Time Ratios $\frac{Regret}{GRASP}$ for task graphs with an order of |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | magnitude of 200,000 tasks                                                               | 113 |

| 4.12 | Solution Quality and Time Ratios $\frac{Regret}{GRASP}$ for task graphs with an order of |     |

|      | magnitude of 200,000 tasks                                                               | 113 |

| 4.13 | Solution Quality and Time Ratios $\frac{Regret}{GRASP}$ for partial GRASPs for task      |     |

|      | graphs with an order of magnitude of 10,000 tasks                                        | 115 |

| 4.14 | Solution Quality and Time Ratios $\frac{Regret}{GRASP}$ for partial GRASPs for task      |     |

|      | graphs with an order of magnitude of 10,000 tasks                                        | 115 |

| 4.15 | Solution Quality and Time Ratios $\frac{Regret}{GRASP}$ for partial GRASPs for task      |     |

|      | graphs with an order of magnitude of 200,000 tasks                                       | 115 |

| 4.16 | Solution Quality and Time Ratios $\frac{Regret}{GRASP}$ for partial GRASPs for task      |     |

|      | graphs with an order of magnitude of 200,000 tasks                                       | 116 |

# List of Algorithms

| 1 | Breadth-first traversal for SWP (BFT1)                                      | 71  |

|---|-----------------------------------------------------------------------------|-----|

| 2 | Computation of subgraph to nodes affinity                                   | 72  |

| 3 | Subgraph Wise Placement(SWP)                                                | 74  |

| 4 | updateAffinities algorithm computing the distance affinities for the input  |     |

|   | task toward all nodes. The complexity of the algorithm is $\mathcal{O}(tn)$ | 76  |

| 5 | Task-Wise Placement (TWP)                                                   | 77  |

| 6 | compute Regret                                                              | 99  |

| 7 | Regret-based Task Placement                                                 | 100 |

| 8 | GRASP procedure                                                             | 101 |

## Acknowledgement

First of all, I want to thank all my Ph.D. advisors. First Renaud Sirdey, my thesis director. He provided me with numerous advices, both professional or personal. His enthusiasm and ideas were always encouraging and he always knew how to reassure, motivate and help me persevere on my thesis when times were hard. Secondly, I would like to thank Bertrand Le Cun, my thesis co-director for his perpetual ideas and suggestions which led to several final results in my thesis. Thanks to his advices, I have learned to adapt to the numerous problems that raised during these three years and remain focused on them.

My foremost appreciation goes to my CEA Ph.D. supervisor François Galea. I was surprised to see how easy it was to work together in spite of our differences. Indeed, during those three years of Ph.D, I have learned more things about computer science than during my master and bachelor years and this, simply by working and chatting with him, observing him and listening to him. All too many times, have I walked out of his office without having understood in depth the meanings of his ideas but, after working on some of my shortcomings, I realized that his ideas were brilliant and would allow me to go forward in my research work. Moreover, and that is unusual: I have deeply appreciated his high degree of commitment and personal investment in my thesis. He always managed to find the time to check on my work and get me some feedback, whether positive or negative. I feel truly blessed to have had him as a Ph.D advisor.

I wish to thank François Pellegrini and Didier El Baz for accepting to review my thesis. A special thanks to François Pellegrini for all remarks and correction he made during his reviews, they have been highly appreciated. I also want to express my sincere appreciation to Alix Munier and Alain Bui for accepting to examine my thesis work. Finally, I wish to thank Dritan Nice for chairing the Ph.D comity.

Now let's talk about the serious stuff. On my first day at the CEA, I was afraid to meet an old bunch of researchers. I was pleasantly surprised to meet people who were actually and dynamic and who had one thing in common: a strong motivation to do research and transmit what they have learned. I immediately got locked in the Ph.D cage that I have managed to escape 2 years later for 6 months before being thrown back inside it again. Therefore I wish to thank all my cage mates: Oana Stan, Safae Dahmani, Simon Fau, Vincent Legout, Dang Phuong N'Guyen, Khanh Do Xuan, Jad Khatib, Paul-Antoine Arras and Rania Mamesh. I also worked for six months in a real office with Laure Abdallah. Having Laure as a co-worker was incredible. The last 10 months in the Ph.D cage were simply awesome thanks to Jad Khatib, Khanh Do Xuan, Rania Mamesh and of course Paul-Antoine Arras.

2

Another surprise consisted in all the extra trips that have been organized with my colleagues at the time: the amusement parks (i.e. Europa Park, Porto Aventura or Parc Asterix by night) the Christmas Markets of Strasbourg, the long week-end in a huge villa in Ramatuelle and the week-end in Barcelona. Many thanks to all members of these trips: Loic Cudennec, Pascal Aubry, Sergiu Carpov, Cyril Faure, Oana Stan, Julien Hervé, Kods Trabelsi, Selma Azaiez, Safae Dahmani, Vincent Legout, Alexandre Aminot and Aziz Dziri.

I also have to thanks Marie-Bénédicte Jacques and especially Patrick Ruf for all the advices they provided me in improving my writing skills and the quality of my work. And for the long chat we had in their office.

I have to mention my Wood Work Out (WWO) and running mates: Daniela Cancila, Luca Incarbone, Vincent Leboeuf, Alain Giraud, Alexandre Aminot, Aziz Dziri, Andrea Castagnatti and Pascal Aubry.

One special thanks goes to Oana Stan. Indeed, her Ph.D work inspired me during these 3 years and without her advices and her work, my work would have been long and far much more difficult. She fortunately provided me her precious help.

Additionally, I am grateful to Cyril Faure whose advice enabled me to both chair the Ph.D association and to teach during my research work. It really took a lot of effort but with some organization skills, I managed not to burn out.

Another special thanks goes to Fabrice de Mayran de Chamisso. We shared the same ideas and feelings about how things are going and it was always fun to chat and to deepen ideas and concepts. Moreover, he often gave me some tips which have been useful in many of my computations.

Many thanks to Sylvie Esterlin-Thiollier. Working with her for preparing the Ph.D's arrivals and some formations for Ph.D was appreciated and her help very valuable. Our lunches were always interesting, I learned many valuable things and I met several interesting people thanks to her!

The last special thanks goes to Thierry Goubier, who virtually demolished many times my car and often proudly made many pertinent and rightful demonstrations about why I should stop buying German cars and how they suck. Actually, he often had a point.

I wish to cite everyone I met at CEA but there are too many of them. So I apologize for not mentioning everyone's name, but I wish to thanks all the members of the DACLE department and INSTN I met. The coffee breaks, the discussions, the after-works, the picnics, lunches, more coffee breaks, more discussions, more jokes... Thanks for that.

During one and half year, I chaired the CEA Ph.D. association of Ile-de-France. I created a project which gathered many Ph.D associations in order to perform social events (like afterworks or actions for cancer cure). By chatting with many other Ph.D. candidates that I met through the association, I realized what a thesis is and how difficult it is to pursue and to finish it. Moreover, this networking boost allowed me to meet a lot of interesting profiles. I wish to thank all Ph.Ds members of any Ph.D. association.

What would I have done without my Rock'n Roll friends and my favorite trip and dance partner: Cédric Salmon? Without forgetting to mention Emmanuel Gaudry, Adrien Nahlovksy, Gilbert Bienaimé, Rittchy de Triolet, Olivier Bernard and Juliette Bour. A special thanks goes to my roommate Juliette Ledouce for enduring me the last

Acknowledgement 3

two years of my Ph.D. I also wish to cite very valuable friends that I met during the time I worked my thesis like Emmanuelle Cazayus, Marie André-Ratsimbazafy, Melisande de Lassence, Emmanuelle Brun, Marc Rivault, Cécile Bouton and Julie Loffi.

I also wish to thank Sophie Grousset, Bénédicte Leclec'h, Ejona Kishta, Anne Vajou, Margot Didier and Hayfa Alaya who provided me with the help I needed in dire times.

A great thank you to Mathilde Adorno for the domino illustration she made foor my paper.

A thank you goes to Julie Loffi who helped me in my thesis defense preparation by inviting me in Japan and for having, with Aziz Dziri, prepared the last details of it. And for enduring me while I was getting nervous a couple of hours before the defense.

Another thank you goes to Hélène and Stefan Berger, Soukaina Bel-Hadj and Julie Loffi which were my syntax error trackers for the last version of this manuscript.

I wish also to thank more long-term friends for having supported and encouraged me throughout all these years: Rafael Perez, Soukaina Bel-Hadj Soulami, Amine Amokrane, Fodhil Babaali, Amaury Vannier-Moreau, Laurent Bourasseau (who kicked my ass many times during my Master time), Nadjet Beghoul and of course the Valdès-Forain Family and the Dargouge Family.

Before ending my acknowledgment, I would like to make a special dedication to one of my dearest friend: Kristina Guseva. We met under very strange circumstances and we quickly became very good friends. She provided me with very pertinent advice and has always been there when I needed someone. She always made fun of me in a way that always made me smile. Unfortunately, Kristina passed away too early at the age of 27 after a difficult battle against cancer. Kristina, I miss you.

Last but not least, I have to thank my family for everything. First to my parents Hélène and Stefan Berger that I truly love. My first student years were chaotic but they helped me to stay focused on studies and thanks to their help, I was able to write this thesis. One never says enough to his parents how much one loves them and is grateful for what they did. To mein little Bruder Maximilien Berger. To my French grand-parents: Mireille and Martial Labouise, my grand-aunts Jeanne Clermon and Huguette Chaumereux. Also to my German grand-parents: Ingeborg and Gunter Berger. I deeply regret that I could'nt finish my Ph.D before the death of meine Oma. Last, I also wish to thank Ina, Maria, Adrien and Axel Berger and other Berger relatives for everything.

The last thanks I wish to provide concern a living creature who just doesn't give a damn about the fact I did a Ph.D or anything else in my life and has a very special way of loving me by ignoring me: my cat Isis.

## **Publications**

- K.E. Berger et F.Galea. "An efficient parallelization strategy of Dynamic programming on GPU"

- PCO'13,IPDPSW'13,Boston,2013

- K-E. Berger , B. Le Cun, F. Galea and R. Sirdey. "Placement de graphes de flots de données de grande taille"

- Roadef'14, Bordeaux,2014

- K-E. Berger , B. Le Cun, F. Galea and R. Sirdey. "Fast Generation Of Large Task Network Mappings"

- PCO'14,IPDPSW'14, Phoenix,2014

- Electronique et RO, GT OSI, UPMC, Paris, 2014

- K-E. Berger , B. Le Cun, F. Galea and R. Sirdey. "Un modèle de regret pour le placement de graphe de tâches de grande taille"

- Roadef'15, Marseille, 2015

- K-E. Berger , B. Le Cun, F. Galea and R. Sirdey. "Mapping of large task graphs with a regret model"

- Soumis à Computer & OR, Elsevier

## Résumé

Ce travail de thèse de doctorat est dédié à l'étude de problèmes de placement de tâches dans le domaine de la compilation d'applications pour des architectures massivement parallèles. Ce problème vient en réponse à certains besoins industriels tels que l'économie d'énergie et la demande de performances pour les applications de type flots de données synchrones. Ce problème de placement doit être résolu dans le respect de trois critères : les algorithmes doivent être capables de traiter des applications de tailles variables, ils doivent répondre aux contraintes de capacités des processeurs et prendre en compte la topologie des architectures cibles. Dans cette thèse, les tâches sont organisées en réseaux de communication, modélisés sous forme de graphes.

Pour évaluer la qualité des solutions produites par les algorithmes, les placements obtenus sont comparés avec un placement aléatoire. Cette comparaison sert de métrique d'évaluation des placements des différentes méthodes proposées. La création de cette métrique est due au fait de l'absence d'heuristiques dans la littérature avec lesquelles nous pouvons nous comparer au moment de la rédaction de ce manuscrit.

Afin de résoudre ce problème, deux algorithmes de placement de réseaux de tâches de grande taille sur des architectures clusterisées de processeurs de type many-coeurs ont été développés. Ils s'appliquent dans des cas où les poids des tâches et des arêtes sont unitaires. Le premier algorithme, nommé Task-wise Placement, place les tâches une par une en se servant d'une notion d'affinité entre les tâches. Le second, intitulé Subgraph-wise Placement, rassemble les tâches en groupes puis place les groupes de tâches sur les processeurs en se servant d'une relation d'affinité entre les groupes et les tâches déjà affectées. Ces algorithmes ont été testés sur des graphes, représentant des applications possédant des topologies de types grilles ou de réseaux de portes logiques. Les résultats des placements sont comparés avec un algorithme de placement, présent dans la littérature, qui place des graphes de tailles modérées et ce à l'aide de la métrique définie précédemment.

Les cas d'application des algorithmes de placement sont ensuite orientés vers des graphes dans lesquels les poids des tâches et des arêtes sont variables, similairement aux valeurs qu'on peut retrouver dans des cas industriels. Une heuristique de construction progressive basée sur la théorie des jeux a été développée. Cet algorithme, nommé Regret Based Approach, place les tâches une par une. Le coût de placement de chaque tâche en fonction des autres tâches déjà placées est calculé. La phase de sélection de la tâche se base sur une notion de regret présente dans la théorie des jeux. La tâche qu'on regrettera le plus de ne pas avoir placée est déterminée et placée en priorité. Afin de

8 Résumé

vérifier la robustesse de l'algorithme, différents types de graphes de tâches (grilles, logic gate networks, series-parallèles, aléatoires, matrices creuses) de tailles variables ont été générés. Les poids des tâches et des arêtes ont été générés aléatoirement en utilisant une loi bimodale paramétrée de manière à obtenir des valeurs similaires à celles des applications industrielles. Les résultats de l'algorithme ont également été comparés avec l'algorithme Task-Wise Placement, qui a été spécialement adapté pour les valeurs non unitaires. Les résultats sont également évalués en utilisant la métrique de placement aléatoire.

#### Abstract

This Ph.D thesis is devoted to the study of the mapping problem related to massively parallel embedded architectures. This problem arises from industrial needs like energy savings, performance demands for synchronous dataflow applications. This problem has to be solved considering three criteria: heuristics should be able to deal with applications with various sizes, they must meet the constraints of capacities of processors and they have to take into account the target architecture topologies. In this thesis, tasks are organized in communication networks, modeled as graphs.

In order to determine a way of evaluating the efficiency of the developed heuristics, mappings, obtained by the heuristics, are compared to a random mapping. This comparison is used as an evaluation metric throughout this thesis. The existence of this metric is motivated by the fact that no comparative heuristics can be found in the literature at the time of writing of this thesis.

In order to address this problem, two heuristics are proposed. They are able to solve a dataflow process network mapping problem, where a network of communicating tasks is placed into a set of processors with limited resource capacities, while minimizing the overall communication bandwidth between processors. They are applied to task graphs where weights of tasks and edges are unitary set. The first heuristic, denoted as Taskwise Placement, places tasks one after another using a notion of task affinities. The second algorithm, named Subgraph-wise Placement, gathers tasks in small groups then place the different groups on processors using a notion of affinities between groups and processors. These algorithms are tested on tasks graphs with grid or logic gates network topologies. Obtained results are then compared to an algorithm present in the literature. This algorithm maps task graphs with moderated size on massively parallel architectures. In addition, the random based mapping metric is used in order to evaluate results of both heuristics.

Then, in a will to address problems that can be found in industrial cases, application cases are widen to tasks graphs with tasks and edges weights values similar to those that can be found in the industry. A progressive construction heuristic named Regret Based Approach, based on game theory, is proposed. This heuristic maps tasks one after another. The costs of mapping tasks according to already mapped tasks are computed. The process of task selection is based on a notion of regret, present in game theory. The task with the highest value of regret for not placing it, is pointed out and is placed in priority. In order to check the strength of the algorithm, many types of task graphs (grids, logic gates networks, series-parallel, random, sparse matrices) with various size are generated.

Tasks and edges weights are randomly chosen using a bimodal law parameterized in order to have similar values than industrial applications. Obtained results are compared to the Task Wise placement, especially adapted for non-unitary values. Moreover, results are evaluated using the metric defined above.

#### Contexte et modélisation

Il existe actuellement un grand nombre d'applications parallèles développées pour répondre aux problèmatiques des domaines à la fois du traitement de signal et du multimédia. Ces applications ont différentes propriétés et nous n'en citerons que deux: d'une part, les niveaux de parallélisme mis en place pour exploiter au mieux les architectures sur lesquelles elles doivent s'executer et d'autre part l'espace mémoire nécéssaire à leur exécution.

Les travaux qui ont mené à cette thèse portent sur l'exécution de ces applications sur un type d'architecture bien spécifique: les architectures embarquées massivement multicœurs. Ce type d'architectures peuvent se définir comme un ensemble de processeurs pour chacun desquels est associé un cache. Les processeurs sont connectés à une mémoire partagée. Cet ensemble formant un nœud de calcul. L'architecture est donc composée de plusieurs nœuds de calcul reliés soit sous forme de réseau tore, soit sous forme de grille. Plusieurs autres topologies existent, mais cette thèse ne traitera que de l'architecture en tore. On peut citer, comme exemple de cette dernière, la puce MPPA de Kalray qui contient 16 cœurs. Chacun de ces cœurs regroupent 16 processeurs et sont regroupés entre eux par un réseau tore.

Ce type d'architecture massivement manycœurs est spécifique à la programmation parallèle. Leur exploitation est difficile, malgré toutes les potentialités qu'elles offrent. En effet, il est nécessaire d'optimiser la communication inter-nœuds, de garantir l'absence d'inter-blocages et de gérer efficacement les accès concurrents pour en garantir une meilleure utilisation. En outre, l'aspect embarqué de ces architectures rajoute de la complexité à leur pratique : les ressources sont limitées par la mémoire et la bande passante de l'architecture cible.

Une solution proposée par le CEA-LIST est l'élaboration d'un langage de programmation  $\Sigma C$  avec une chaîne de compilation associée. Son modèle est celui de la programmation dataflow cyclo-statique. Dans la programmation data-flow, une application est composée de plusieurs ensembles de tâches parallèles communiquant entre elles par des canaux de communication de données de type FIFO. La synchronisation est effectuée par les données. Dans la programmation dataflow cyclo-statique, le graphe de tâches est défini au moment de la compilation de l'application et demeure inchangé pendant son exécution. La quantité de données produites et consommées est connue et chaque tâche peut, de manière cyclique, s'exécuter avec suffisamment de données sur ses ports

d'entrées et produire des données sur ses ports de sorties.

Dans la chaîne de compilation associée se retrouvent quatre grandes parties : la génération du code, l'instanciation du parallélisme, l'allocation des ressources et la génération de l'exécutable. L'attention de ces travaux se porte sur l'allocation des ressources et plus précisément sur le partitionnement et le placement du graphe de tâches sur l'architecture cible. Les applications actuelles présentent des niveaux de parallélisme de plus en plus importants. Elles sont modélisées par des graphes de tâches statiques de grande taille, sont exécutées sur des architectures massivement parallèles et elles doivent tenir compte des contraintes de capacité des processeurs. Quant au problème du placement, au moment de l'écriture de cette thèse, l'heuristique de placement utilisée dans  $\Sigma C$  ne parvient pas à trouver une solution dans un temps acceptable lorsque le nombre de tâches dépasse 2000. L'objectif de cette thèse est de développer une heuristique capable de surmonter cette limite, de placer les graphes sur des architectures de taille supérieure à 256 nœuds, tout en respectant les contraintes de capacités.

Le problème du placement associé se modélise de la manière suivante :

$$\begin{cases}

\operatorname{Min} \sum_{t \in T} \sum_{t' \neq t} \sum_{n \in N} \sum_{n \neq n'} x_{tn} x_{t'n'} q_{tt'} d_{nn'}, \\

\text{t. q.} \\

\sum_{n \in N} x_{tn} = 1 \ \forall t \in T, \\

\sum_{t \in T} w_{tr} x_{tn} \leq C_r \ \forall n \in N, r \in R, \\

x_{tn} \in \{0, 1\} \ \forall t \in T, n \in N.

\end{cases} \tag{1}$$

avec comme paramètres  $C_{nr}$  la capacité d'un nœud  $n \in N$  pour une ressource  $r \in R$ ,  $w_{tr}$  la quantité de ressource r requis par une tâche  $t \in T$ . Comme variable de décision,  $x_{tn} = 1$  si la tâche t est placée sur le nœud n.

#### Etat de l'art

L'état de l'art peut se résumer part le tableau 1. Les solveurs parallèles SCOTCH et Métis sont capables de placer des graphes de tâches allant jusqu'à un milliard de sommets. Cependant, seul SCOTCH tient compte de la topologie cible, et aucun des deux n'est capable de résoudre le problème du placement en respectant les contraintes de capacité.

D'autres approches développées par le CEA-List pour la chaîne de compilation  $\Sigma$ C prennent en compte les contraintes de capacité et la topologie de l'architecture cible mais ne sont pas capables de passer à l'échelle au delà de 2 000 tâches.

Cette étude montre qu'il existe un besoin de méthodes de placement qui prennent en compte la topologie et les contraintes de capacité de l'architecture cible et qui sont capables de placer des graphes de tâches dont le nombre varie entre quelques centaines et quelques milliers de sommets.

| Nom                                       | Contraintes    | # de tâches | Topologie |

|-------------------------------------------|----------------|-------------|-----------|

| (PT-)SCOTCH - Pellegrini et al.           | Load Balancing | $> 10^9$    | Yes       |

| (Par)Metis - Karypis, Kumar <i>et al.</i> | Load Balancing | $> 10^9$    | No        |

| ΣC toolchain                              | Capacité       | < 2000      | Yes       |

| Partitioning & Placing (GRASP + SA)       |                |             |           |

| Sirdey et al.                             |                |             |           |

| ΣC toolchain                              | Capacité       | < 2000      | Yes       |

| Parallel Simulated Annealing              |                |             |           |

| Galea et al.                              |                |             |           |

Table 1: Etat de l'art résumé. Les données en vert correspondent aux caractérisques nécessaires pour la résolution du problème

#### Les contributions de la thèse

Les contributions de la thèse se résument en trois aspects: la mise en place d'une métrique d'évaluation du placement des graphes de tâches de grande taille, des méthodes de placement de graphes de tâches unitaires (les poids des tâches et des arêtes sont fixés à 1) de grande taille et des méthodes de placement de graphes de tâches non-unitaires de grande taille.

#### Une métrique d'évaluation de placement

En recherche opérationnelle, afin d'évaluer la qualité d'une solution obtenue à l'aide d'une heuristique, on compare généralement cette solution à l'optimal ou à une borne inférieure (s'il s'agit d'un problème de minimisation). Dans le cadre de cette thèse, la borne de comparaison est la valeur minimale de placement. Toutefois, au vu de la taille importante des instances, cette valeur ne peut être connue et le problème de trouver des bornes de qualité suffisante et supportant l'échelle du nombre de tâches reste ouvert.

Afin de définir une métrique permettant d'évaluer la qualité du placement, on s'est inspiré de l'approche différentielle de Demange et Paschos [41]. Ces auteurs tiennent compte à la fois de l'optimal et de la pire solution pour définir un rapport d'approximation, et tentent de s'éloigner le plus possible de la pire solution. La considération de ces deux extrema permet de normaliser l'évaluation de la qualité du problème de RO associé. Néanmoins, pour les problèmes de grande taille, la définition de ces deux extrema est impossible pour le moment.

Des alternatives ont été considérées, alternatives pouvant être appliquées sur des instances de grande taille et qui permettent de garantir l'objectivité de la mesure de qualité. L'idée a ensuite émergé d'utiliser une statistique sur les placements aléatoires. Les tâches sont placées au hasard sans biais algorithmique et le calcul d'une moyenne sur plusieurs tirages permet d'obtenir une référence stable qui ne représente ni l'optimum ni le pire des cas mais représente en quelque sorte un investissement nul en matière d'intelligence algorithmique.

Cette référence a permis de définir une métrique d'évaluation de la qualité des placements effectués par les heuristiques développées dans ces travaux. Cette évaluation dépend donc de l'importance de la distance de la solution par rapport à la valeur donnée par la statistique obtenue.

# Placement de graphe de tâches unitaires de grande taille

Une première approche gloutonne nommée Task-Wise Placement (TWP) a été développée. Cette méthode utilise une notion d'affinité de distance afin de déterminer à la fois la tâche à placer en priorité et le nœud sur lequel cette tâche doit être affectée. Les tâches non encore affectées sont stockées dans un espace d'attente. Ce processus est répété de manière itérative jusqu'à épuisement du stock de tâches. L'affinité de distance mesure l'intérêt de placer la tache t sur un nœud n vis à vis des tâches déjà placées. Lorsqu'un nœud est saturé, une autre méthode de placement est utilisée : les nœuds non saturés dans le voisinage direct du nœud sont sélectionnés. Un parcours en largeur commençant avec la première tâche sélectionnée par l'algorithme permet de déterminer un ordre de sélection des tâches. Ainsi, seules les tâches non affectées sont considérées et un nombre équivalent au nombre de nœuds non saturés est sélectionné. Les tâches sont ensuite placées sur les nœuds leur correspondant.

Une deuxième approche gloutonne intitulée Subgraph-Wise Placement (SWP) est une méthode de placement à deux phases. Un sous-graphe est déterminé à partir du sommet qui a le moins de voisins puis est construit grâce à un algorithme de parcours en largeur. Sa taille dépend de la capacité maximale restante sur les nœuds multipliée par un facteur  $\frac{1}{2}$ . Un calcul d'affinités entre le sous-graphe et les nœuds contenant des tâches est alors effectué et permet de placer le sous-ensemble de tâches sur le nœud avec lequel il a le plus d'affinités.

Les instances utilisées sont des modélisations de grilles ou de réseaux de portes logiques. Les architectures cibles sur lesquelles les instances doivent être utilisées sont des tores carrés de longueur de lien égale à 1. La taille des instances varie de quelques centaines à plusieurs centaines de milliers de sommets.

Les deux approches sont ensuite comparées à l'approche utilisée dans la chaîne de compilation  $\Sigma C$ . Les approches développées dans la thèse sont capables de placer des grilles sur des architectures assez facilement et avec des temps d'exécution globalement plus rapides que ceux de  $\Sigma C$ . Sur des réseaux de porte logique, TWP est jusqu'à soixante fois plus rapide que  $\Sigma C$  avec une solution de meilleure qualité. En revanche, malgré le fait que SWP ne soit pas capable de fournir un placement de meilleure qualité que  $\Sigma C$ , cette approche est plus rapide que l'algorithme de comparaison à une échelle de  $10^i$ , i variant en fonction de la taille de l'instance.

#### Placement de graphe de tâches non-unitaires de grande taille

Les heuristiques développées précédemment ne sont pas aussi performantes sur des cas non-unitaires, c'est à dire des instances dont les poids des tâches et des arêtes diffèrent de 1. Une nouvelle approche gloutonne a donc été mise au point. Il s'agit d'un placement à une phase qui adapte une notion de regret inspirée de la théorie des jeux et l'applique lors de l'étape de la sélection de la tâche à placer. Au lieu de calculer les affinités des tâches entre elles, le calcul sera effectué en déterminant le coût du placement de la tâche t par rapport à tous les nœuds disponibles. Ensuite, pour chaque tâche présente dans l'espace d'attente, les coûts sont triés par ordre croissant. On calcule ensuite la différence de coût de placement sur les nœuds pour chaque tâche et de manière itérative en utilisant l'approche de Kilby[104]. Ce calcul de différence correspond au regret. La tâche ayant le regret le plus fort sera ensuite placée prioritairement sur le nœud de coût le plus faible.

Pour vérifier la robustesse de ces travaux, un panel plus complet d'instances a été constitué. Les grilles et les réseaux de portes logiques, ainsi que des instances issues du Matric Market de Walshaw, des graphes aléatoires et des graphes de séries parallèles seront utilisés. Ces derniers sont très proches des graphes de type dataflow mais s'en différencient par la présence de liens entre des nœuds non consécutifs. Pour chaque type d'instance, 30 graphes de poids de tâches distincts sont générés. La moyenne de la valeur du placement sur ces 30 graphes distincts est ensuite calculée afin d'éviter les cas particuliers. Le nombre de nœuds varie de 16 à 1024, et leur capacité totale dans le système est fixée à 105% de la somme totale du poids des tâches. Trois ordres de grandeur sont utilisés pour les instances : 10 000, 200 000 et 1 000 000 de sommets. L'heuristique fournit les meilleurs résultats pour des instances de type séries-parallèles, indépendamment du nombre de sommets. Les capacités de l'heuristique ont ensuite été comparées à une version non-unitaire de TWP avec un ordre de grandeur de 10 000 sommets et un nombre de nœuds variables. Il en résulte que l'approche par le regret produit une qualité de placement jusqu'à 5 fois meilleure que celle de TWP et jusqu'à 10 fois plus rapide.

Pour exploiter la variabilité dans l'espace des solutions possibles, une heuristique semi-gloutonne proposée par Hart et Shogan [78] a été utilisée. Cette méthode a généré plusieurs solutions issues d'une procédure aléatoire. La construction de ces solutions peut s'effectuer en parallèle en modifiant les caractéristiques de l'aléatoire. Ce principe a été appliqué à l'heuristique développée dans ces travaux, et un choix aléatoire est effectué pour sélectionner les tâches à placer lorsqu'il existe plusieurs valeurs de regret égales. 30 solutions sont construites en parallèle, desquels on tire la meilleure valeur de placement ainsi que le pire temps d'exécution. Les résultats de cette approche indiquent que, dans la quasi-totalité des cas, il est possible d'améliorer la qualité de la solution au détriment des temps d'exécution qui demeurent acceptables. Il est aussi apparu qu'il existe une corrélation entre la qualité de la solution et son temps d'exécution, dans le sens où moins l'heuristique met de temps à générer la solution, meilleure celle-ci est. Une table de probabilité cumulée d'obtention de la meilleure solution parmi les 10 premiers

lancements a été construite, table qui montre qu'en fonction du taux de dégradation de qualité accepté diminue aussi le nombre de solution requis.

#### Conclusion et perspectives

Cette thèse présente plusieurs méthodes de placement adaptées pour les architectures massivement multicœurs, ainsi qu'une métrique d'évaluation de la qualité de placement pour les instances de grande taille.

Il est possible de généraliser les méthodes de placement proposées ici sur des architectures hétérogènes ou, dans un autre contexte, de les paralléliser pour placer des graphes de plus grande taille dans des temps humainement acceptables.

De plus, l'élaboration d'une méthode de raffinement pourrait améliorer la qualité de la production et également permettre d'utiliser l'heuristique semi-gloutonne dans un cadre d'optimisation plus poussée des solutions.

Enfin, la métrique d'évaluation pourrait être généralisée sur d'autres variantes du problème de placement, ou sur des problématiques dont les instances ont le même ordre de grandeur que ceux traités dans les travaux ici présentés.

## Introduction

Computers have become more and more powerful through the last decades and this trend is not likely to stop in the near future. Despite of all these advances, researchers are still looking for solutions to combinatorial problems. The word "combinatorial" is often synonym with computational difficulty. Combinatorics corresponds to the study of several approaches able to determine and manipulate many configurations of discrete-state events that constitute a combinatorial object. The configuration depends on the combinatorial problem to solve. Combinatorial algorithms can be defined as techniques for the manipulation of combinatorial objects such as permutations, arrangements or combinations. The goal of such algorithms is to find patterns which provide acceptable solutions depending on multiple constraints.

As an example of combinatorial complexity, we will use Terquem's dominoes problem: dominoes is a Chinese game played with 28 rectangular tiles with a line dividing its face into two square ends. Each end is marked with a number of spots or pips which varies from 0 to 6. Each tile corresponds to one unique double combination of tile numbers. The traditional basic game variant is the blocking game. In this variant, all 28 tiles are shuffled face down. Each player picks up 7 tiles amongst the 28. One player starts the game by placing one tile down. The placed tile will serves as starting domino. If the second player possesses a tile with the same end value, he places this tile at this end. The game ends when one of the players has no more tiles. The most common dominous game variant consists in the double-n form where n=6 whereas several domino games exist with a maximum tile end value  $n \in \{6, 9, 12, 15, 18\}$ . The higher the number, the more the game becomes complicated. In 1847, Orly Terquem stated the following problem: for any general value of n, is it possible to take the complete set of dominoes and finish the game without any dominoes left on the table? In order to solve this problem, dominoes are modeled by a graph. Vertices are labeled from 0 to n. Each domino corresponds to an edge. A tile with i pipes on one end and j pipes on the other end will be represented by edge (i, j). Moreover, some of the tiles have the same number of pipes. So all vertices i have a loop (i,i). The number of edges including loops is  $\frac{(n+1)(n+2)}{2}$ , making the graph complete. In order to solve the problem, a Eulerian cycle must be found. Terquem then stated a new problem which appeared to be combinatorial: how many different cycles exist when n = 6? A solution has been proposed by a work of M. Reiss in Nouvelles Annales Mathématiques (1971) confirmed by another approach, much simpler, proposed by G. Tarry in 1886: the number of possible configurations is 129, 976, 320. However, these approaches do not take into account tiles with the same end values. Adding these

Figure 1: Domino circle with double 4 form.

tiles adds some complexity because it exists 3<sup>7</sup> ways to insert the seven missing doubles into a cycle of 2-combination. This means, it exists 284, 258, 211, 840 possible ways to use the complete set of 28 dominoes and finish the game with no tile left! Starting from a problem dealing with a small number of elements, it occurs that the possible solution space contains several billions of elements. This example illustrates the fact that combinatorial problems are often associated with large numbers. Now that we described the nature of combinatorics, we will go back to the 2010's.

Nowadays, many applications in the industrial world imply combinatorial subproblems. The resource allocation, the traveling salesman or the knapsack problems are classical combinatorial problems that can be found in many applications. In "the Art of Computer Programming" [108], Knuth proposed a methodology which allows to identify possible solutions to these new combinatorial problems. It consists in five basic types of questions which arise when combinatorial problems are studied:

- 1. Existence: Is there any arrangement X that conforms to the pattern?

- 2. Construction: If so, can such an X be found quickly?

- 3. Enumeration: How many different arrangements X exist?

- 4. Generation: Can all arrangements  $X_1, X_2, ....$  be visited systematically?

Introduction 19

Figure 2: A dataflow process network graph example of a motion detection application.

5. Optimization: Which arrangements maximize or minimize f(X), given an objective function f.

The limits for combinatorial problems are either the required computational time which is not humanly acceptable or overflowing memory size that cannot been dealt by hardware. This is why, despite of the fact that heuristics do not lead to the optimal solution, the obtained values might be the best we can get within those limits. The main question is: how can we obtain an optimal solution within acceptable time or/and without overflowing the memory size for this kind of problems? By the time of writing this dissertation, no one is able to provide an answer.

Limits are often set by hardware. Until the 2000 decade, Moore's Law was a good indicator in the prediction of the performance of new microprocessors. For each new generation of hardware, new optimization challenges also appear for performance enhancement. With the end of the frequency version of Moore's law, new clusterized embedded parallel microprocessor architectures, known as manycores, are currently emerging. New challenges consist in applying combinatorial optimization techniques to problems in software compilation of applications, like in signal processing, image processing or multimedia, on these massively parallel architectures. Such applications can be represented under the static dataflow parallel programming model, in which one expresses computationintensive applications as networks of concurrent processes (also called agents or actors) interacting through (and only through) unidirectional FIFO channels. They provide strong guarantee of determinism, absence of deadlocks and execution in bounded memory. The main difficulty in the development of this kind of applications for those architectures consists in handling resource limitations, a high exploitation difficulty of massive parallelism and global efficiency. On top of more traditional compilation aspects, compiling a dataflow program in order to achieve a high level of dependability and performance on such complex processor architectures involves solving a number of difficult, large-size discrete optimization problems among which graph partitioning, quadratic assignment

Figure 3: Clusterized parallel microprocessor architecture.

and (constrained) multi-flow problems are worth mentioning.

Our applicative work focuses on the problem of mapping a dataflow process network (DPN), illustrated by Figure 2, on a clusterized parallel microprocessor architecture composed of a number of nodes, each of these node being a small symmetric multiprocessor system (SMP), interconnected by an asynchronous packet network, as shown in Figure 3. A DPN is modeled by a graph where the vertices are the tasks to be placed, and the edges represent communication channels between tasks. Vertices are weighted with one or more quantities which correspond to processor resources consumption and the edges are weighted with an inter-task communication outflow value. The aim of our problem is to maximize inter-task communication inside SMPs while minimizing inter-node communication under capacity constraints to be respected in terms of task resource occupation on the SMPs.