# Communication support in multi-core architectures through hardware mechanisms and standardized programming interfaces

Thiago Raupp Da Rosa

## ▶ To cite this version:

Thiago Raupp Da Rosa. Communication support in multi-core architectures through hardware mechanisms and standardized programming interfaces. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2016. English. NNT: 2016GREAT029. tel-01327969

## HAL Id: tel-01327969 https://theses.hal.science/tel-01327969

Submitted on 7 Jun 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : Nanoélectronique et nanotechnologies

Arrêté ministériel: 7 août 2006

Présentée par

## Thiago RAUPP DA ROSA

Thèse dirigée par **Fabien CLERMIDY** et codirigée par **Romain LEMAIRE**

préparée au sein du Laboratoire Intégration Silicium des Architectures Numériques dans l'École Doctorale Électronique, Électrotechnique, Automatique & Traitement du Signal (EEATS)

Support des communications dans des architectures multicœurs par l'intermédiaire de mécanismes matériels et d'interfaces de programmation standardisées

## M. Frédéric ROUSSEAU

Professeur, Université Grenoble Alpes, TIMA, Président

## M. Gilles SASSATELLI

Directeur de Recherche, HDR, LIRMM, Rapporteur

## M. Sébastien PILLEMENT

Professeur, École Polytechnique de l'Université de Nantes, Rapporteur

#### M. Fabien CLERMIDY

Docteur, HDR, CEA-LETI, Directeur de thèse

## M. Romain LEMAIRE

Docteur, CEA-LETI, Co-encadrant de thèse, Invité

## UNIVERSITE GRENOBLE ALPES

## Abstract

## Communication Support in Multi-core Architectures through Hardware Mechanisms and Standardized Programming Interfaces

The application constraints driving the design of embedded systems are constantly demanding higher performance and power efficiency. To meet these constraints, current SoC platforms rely on replicating several processing cores while adding dedicated hardware accelerators to handle specific tasks. However, developing embedded applications is becoming a key challenge, since applications workload will continue to grow and the software technologies are not evolving as fast as hardware architectures, leaving a gap in the full system design. Indeed, the increased programming complexity can be associated to the lack of software standards that supports heterogeneity, frequently leading to custom solutions. On the other hand, implementing a standard software solution for embedded systems might induce significant performance and memory usage overheads. Therefore, this Thesis focus on decreasing this gap by implementing hardware mechanisms in co-design with a standard programming interface for embedded systems. The main objectives are to increase programmability through the implementation of a standardized communication application programming interface (MCAPI), and decrease the overheads imposed by the software implementation through the use of the developed hardware mechanisms.

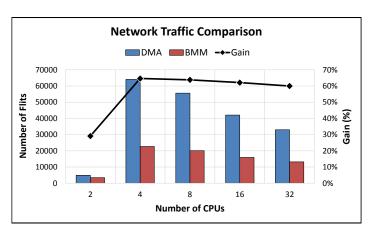

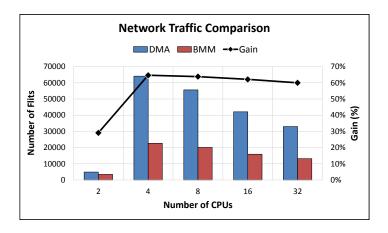

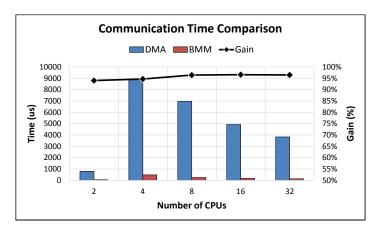

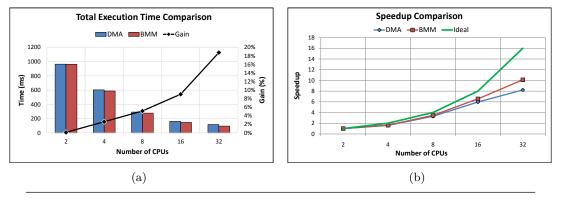

The contributions of the Thesis comprise the implementation of MCAPI for a generic multi-core platform and dedicated hardware mechanisms to improve communication connection phase and overall performance of data transfer phase. It is demonstrated that the proposed mechanisms can be exploited by the software implementation without increasing software complexity. Furthermore, performance estimations obtained using a SystemC/TLM simulation model for the reference multi-core architecture show that the proposed mechanisms provide significant gains in terms of latency (up to 97%), throughput (40x increase) and network traffic (up to 68%) while reducing processor workload for both characterization test-cases and real application benchmarks.

#### UNIVERSITE GRENOBLE ALPES

## Résumé

Support des communications dans des architectures multicœurs par l'intermédiaire de mécanismes matériels et d'interfaces de programmation standardisées

L'évolution des contraintes applicatives imposent des améliorations continues sur les performances et l'efficacité énergétique des systèmes embarqués. Pour répondre à ces contraintes, les plateformes « SoC » actuelles s'appuient sur la multiplication des cœurs de calcul, tout en ajoutant des accélérateurs matériels dédiés pour gérer des tâches spécifiques. Dans ce contexte, développer des applications embarquées devient un défi complexe, en effet la charge de travail des applications continue à croître alors que les technologies logicielles n'évoluent pas aussi vite que les architectures matérielles, laissant un écart dans la conception complète du système. De fait, la complexité accrue de programmation peut être associée à l'absence de standards logiciels qui prennent en charge l'hétérogénéité des architectures, menant souvent à des solutions ad hoc. A l'opposé, l'utilisation d'une solution logicielle standardisée pour les systèmes embarqués peut induire des surcoûts importants concernant les performances et l'occupation de la mémoire si elle n'est pas adaptée à l'architecture. Par conséquent, le travail de cette Thèse se concentre sur la réduction de cet écart en mettant en œuvre des mécanismes matériels dont la conception prend en compte une interface de programmation standard pour systèmes embarqués. Les principaux objectifs sont ainsi d'accroître la programmabilité par la mise en œuvre d'une interface de programmation : MCAPI, et de diminuer la charge logiciel des cœurs grâce à l'utilisation des mécanismes matériels développés.

Les contributions de la thèse comprennent la mise en œuvre de MCAPI pour une plate-forme multicœur générique et des mécanismes matériels pour améliorer la performance globale de la configuration de la communication et des transferts de données. Il est démontré que les mécanismes peuvent être pris en charge par les interfaces logicielles sans augmenter leur complexité. En outre, les résultats de performance obtenus en utilisant un modèle SystemC/TLM de l'architecture multicœurs de référence montrent que les mécanismes proposés apportent des gains significatifs en termes de latence, débit, trafic réseau, temps de charge processeur et temps de communication sur des cas d'étude et des applications complètes.

# Contents

| A  | bstra | ct          |                                                         | iii |

|----|-------|-------------|---------------------------------------------------------|-----|

| R  | ésum  | ıé          |                                                         | v   |

| C  | onter | $_{ m nts}$ |                                                         | vi  |

| Li | st of | Figure      | es es                                                   | xi  |

| Li | st of | Table       | 5                                                       | xii |

| A  | bbre  | viation     | us                                                      | xv  |

| In | trod  | uction      |                                                         | 1   |

| 1  | Mu    | lti-core    | e Systems Overview: Hardware and Software Related Works | 7   |

|    | 1.1   | Multi-      | core Architectures                                      | 7   |

|    | 1.2   | Applic      | cation Programming Interfaces                           | 15  |

|    |       | 1.2.1       | Custom APIs                                             | 15  |

|    |       | 1.2.2       | Standard APIs                                           | 16  |

|    |       | 1.2.3       | MCAPI                                                   | 18  |

|    | 1.3   | Comm        | nunication Hardware Mechanisms                          | 20  |

|    |       | 1.3.1       | Synchronization/Communication Set-Up                    | 20  |

|    |       | 1.3.2       | Data Transfer                                           | 23  |

|    |       | 1.3.3       | Thesis Positioning                                      | 25  |

|    | 1.4   | Refere      | ence Architecture                                       | 27  |

| 2  | MC    |             | Mapping and Overhead Characterization                   | 33  |

|    | 2.1   |             | PI Standard and Specification                           |     |

|    | 2.2   |             | PI Implementation                                       |     |

|    |       | 2.2.1       | Data Structures                                         |     |

|    |       |             | 2.2.1.1 MCAPI Attributes Structure                      |     |

|    |       |             | 2.2.1.2 FIFO Structure                                  | 40  |

|    |       |             | 2.2.1.3 Request Structure                               |     |

|    |       | 2.2.2       | Connection Set-up non-blocking Functions                |     |

|    |       | 2.2.3       | MCAPI non-blocking Operations                           |     |

|    |       | 2.2.4       | Data Transfer                                           |     |

|    | 23    | Perfor      | mance Limitations of Software Implementation            | 45  |

viii Contents

|              |       | 2.3.1            | Communication Set-up Overheads           | . 45                                           |

|--------------|-------|------------------|------------------------------------------|------------------------------------------------|

|              |       | 2.3.2            | Data Transfer and FIFO Control Overheads |                                                |

| 3            | Con   | amuni            | cation Set-up Support                    | 49                                             |

|              | 3.1   |                  | nunication Set-up Polling Phases         | . 49                                           |

|              | 3.2   |                  | Synchronizer Mechanism                   |                                                |

|              | 3.3   |                  | PI Modifications                         |                                                |

| 4            | Dat   | a Tran           | asfer Support                            | 59                                             |

| -            | 4.1   |                  | Transfer Phase                           |                                                |

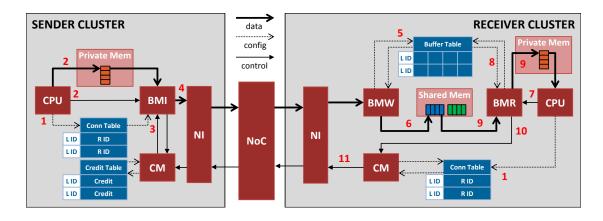

|              | 4.2   |                  | Manager Mechanism                        |                                                |

|              | 1.2   | 4.2.1            | Table Structures                         |                                                |

|              |       | 4.2.1            | Connection Set-up                        |                                                |

|              |       | 4.2.3            | Data Transfer Requests                   |                                                |

|              |       | 4.2.3            |                                          |                                                |

|              |       |                  | 1                                        |                                                |

|              |       | 4.0.4            | 4.2.3.2 Read Request                     |                                                |

|              |       | 4.2.4            | Data Transfer Operations                 |                                                |

|              |       | 4.2.5            | Buffer Manager Interface (BMI)           |                                                |

|              |       | 4.2.6            | Buffer Manager Write (BMW)               |                                                |

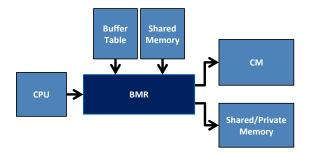

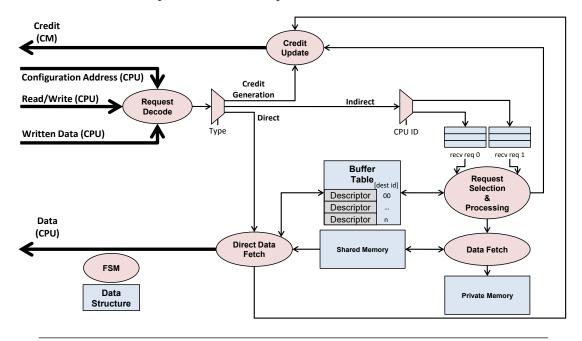

|              |       | 4.2.7            | Buffer Manager Read (BMR)                |                                                |

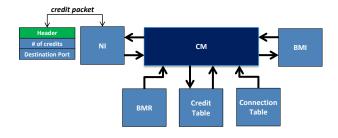

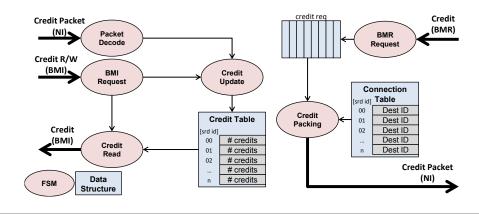

|              |       | 4.2.8            | Credit Manager (CM)                      |                                                |

|              | 4.3   | MCAI             | PI Modifications                         | . 76                                           |

| 5            | Exp   | erimei           | ntal Results and Validation              | 81                                             |

|              | 5.1   | Simula           | ation Environment                        | . 81                                           |

|              |       | 5.1.1            | Simulation Scenarios                     | . 82                                           |

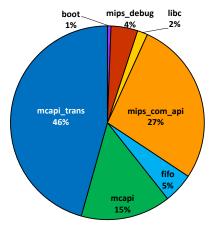

|              | 5.2   | MCAF             | PI Memory Footprint                      | . 84                                           |

|              |       | 5.2.1            | Transport Layer Code                     | . 84                                           |

|              |       | 5.2.2            | MCAPI Structures                         | . 87                                           |

|              | 5.3   | Comm             | nunication Set-up Characterization       | . 88                                           |

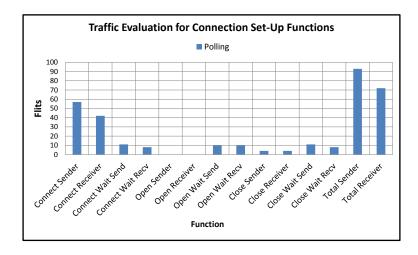

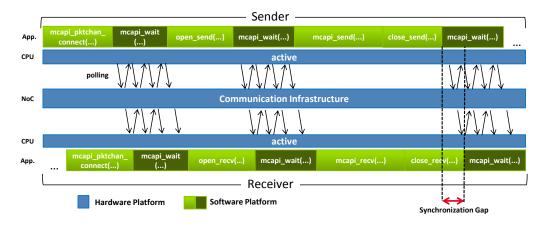

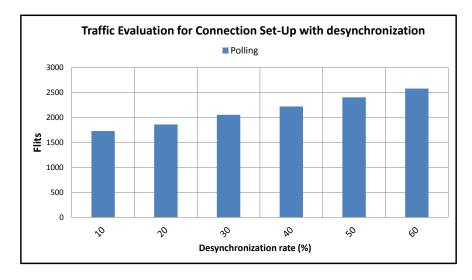

|              |       | 5.3.1            | Network Load                             | . 90                                           |

|              |       | 5.3.2            | CPU Load                                 | 0.1                                            |

|              | 5.4   | Data 7           | Transfer Characterization                | . 94                                           |

|              |       | 5.4.1            | Throughput Evaluation                    |                                                |

|              |       | 5.4.2            | Latency Evaluation                       |                                                |

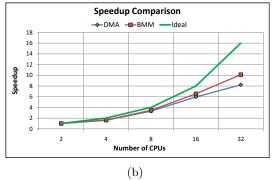

|              |       | 5.4.3            | Network Load                             |                                                |

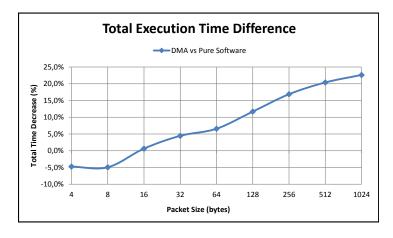

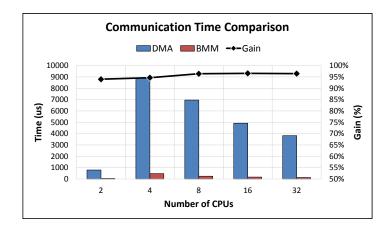

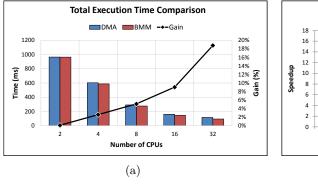

|              |       | 5.4.4            | Communication and Total Execution Times  |                                                |

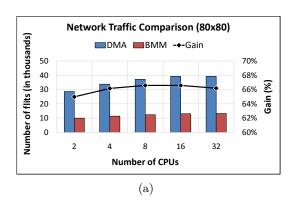

|              | 5.5   |                  | marks Validation                         |                                                |

|              | 0.0   | 5.5.1            | SUSAN                                    |                                                |

|              |       | 5.5.2            | Dijkstra                                 |                                                |

|              |       | 0.0.2            | Dijkstra                                 | . 103                                          |

| Co           | onclu | sion a           | nd Perspectives                          | 107                                            |

| $\mathbf{A}$ | List  | of Pu            | blications                               | 111                                            |

|              |       |                  |                                          |                                                |

| В            |       | umė ei<br>Introd | n Français                               | $\begin{array}{c} 113 \\ {}^{113} \end{array}$ |

|              |       | 11111100         | THE HALL                                 | ≺                                              |

Contents

|         | B.1.1 Organisation de la Thèse                         |

|---------|--------------------------------------------------------|

| B.2     | Vue d'ensemble des Systèmes Multi-cœurs                |

|         | B.2.1 Architecture de Référence                        |

|         | B.2.2 Positionnement de la Thèse                       |

| B.3     | Mise en Œuvre de MCAPI et Caractérisation des Surcoûts |

|         | B.3.1 Limitations de Performance                       |

| B.4     | Support pour la Configuration de la Communication      |

| B.5     | Support pour les Transferts de Données                 |

| B.6     | Résultats Expérimentaux et Validation                  |

|         | B.6.1 SUSAN                                            |

| B.7     | Conclusion                                             |

|         |                                                        |

|         |                                                        |

| Bibliog | craphy 127                                             |

# List of Figures

| 1 2  | Application deployment in a multi-core architecture                      |    |

|------|--------------------------------------------------------------------------|----|

| 1.1  | Design complexity forecast for SoCs                                      | 8  |

| 1.2  | SoC architecture template.                                               | Ĉ  |

| 1.3  | Block diagrams for biggle.LITTLE and CELL processors                     | 10 |

| 1.4  | Tomahawk block diagram overview                                          | 11 |

| 1.5  | General overview of Magali processing cores                              | 11 |

| 1.6  | Communication set-up steps used by packet and scalar channels            | 21 |

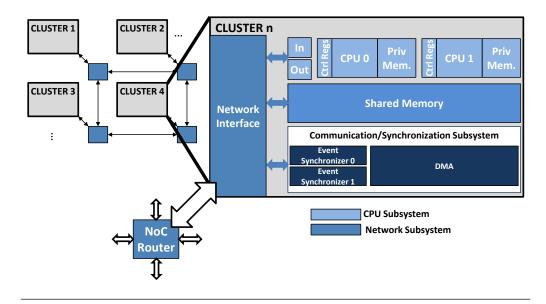

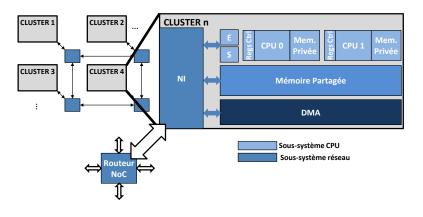

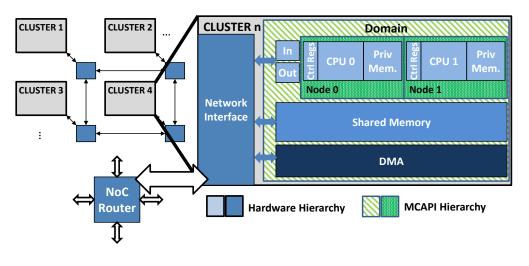

| 1.7  | Reference architecture block diagram and hierarchy                       | 28 |

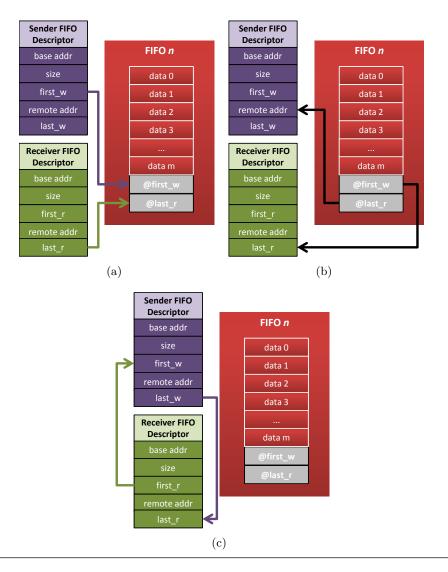

| 1.8  | FIFO descriptor initialization and update                                | 30 |

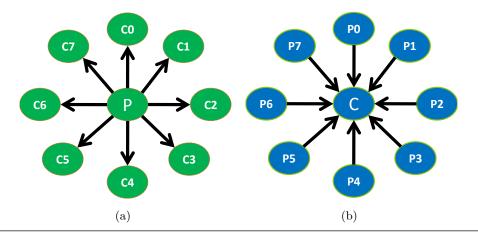

| 2.1  | MCAPI Communication Modes                                                | 34 |

| 2.2  | MCAPI architecture mapping                                               | 36 |

| 2.3  | MCAPI attributes organization in the Shared Memory                       |    |

| 2.4  | FIFO structure                                                           |    |

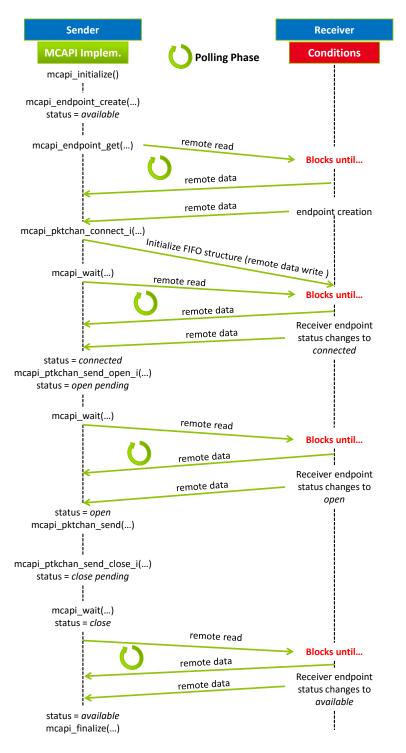

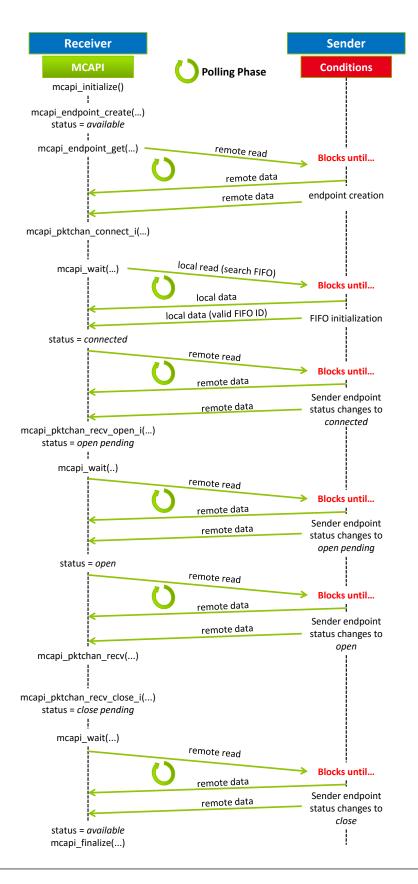

| 2.5  | Channel Set-Up Functions                                                 |    |

| 2.6  | Generated traffic during channel set-up                                  |    |

| 2.7  | Synchronization gap between the connection set-up steps                  |    |

| 2.8  | Generated traffic during channel set-up with desynchronization           |    |

| 2.9  | Initialization and pointer exchanging of FIFO structure                  | 48 |

| 3.1  | Connection set-up polling phases in the sender side                      |    |

| 3.2  | Connection set-up polling phases in the receiver side                    |    |

| 3.3  | Cluster block diagram with Event Synchronizer                            |    |

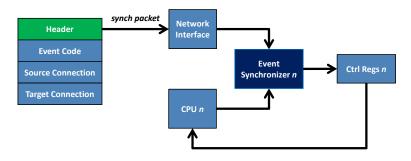

| 3.4  | Synchronization packet and Event Synchronizer block interactions         |    |

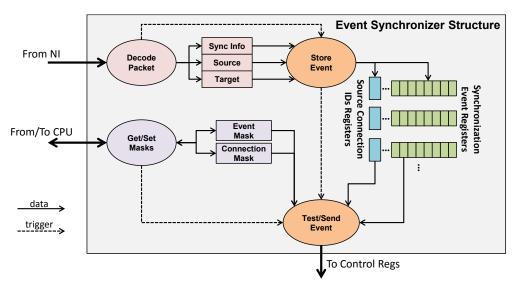

| 3.5  | Event Synchronizer structural view.                                      |    |

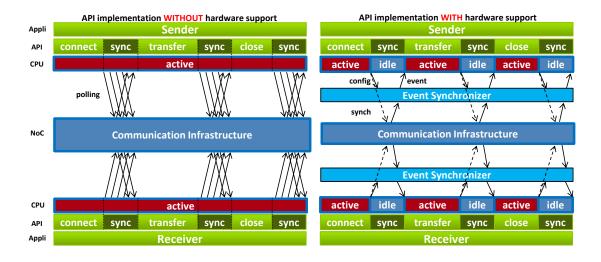

| 3.6  | Comparison of the hardware platform utilization with and without the ES. |    |

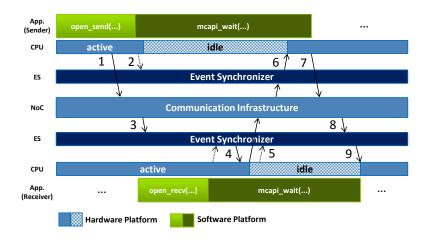

| 3.7  | Communication opening diagram using the Event Synchronizer               | 56 |

| 3.8  | Source code of the wait_synch function                                   | 57 |

| 3.9  | Source code of the send_synch function                                   | 58 |

| 3.10 | ing step in the sender side                                              | 58 |

| 4.1  | Steps performed during data transfer using pure software implementation. | 60 |

| 4.2  | Partitioning schemes options to implement a buffer management solution   | ,  |

|      | in hardware                                                              | 62 |

| 4.3  | Cluster block diagram with BMM modules                                   | 63 |

| 4.4  | Partitioning of BMM blocks regarding communication sides                 | 64 |

xii List of Figures

| 4.5        | Buffer Manager Mechanism operation                                                                                                        | . 70  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|

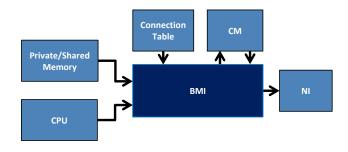

| 4.6        | Buffer Manager Interface connected modules                                                                                                | . 71  |

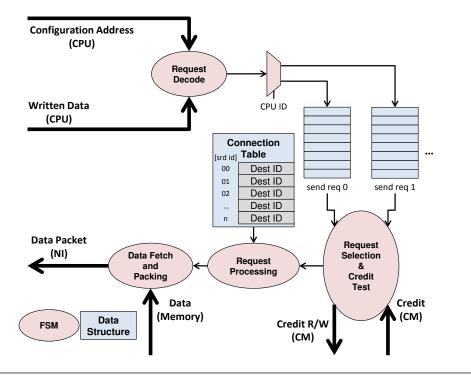

| 4.7        | Buffer Manager Interface functional description                                                                                           | . 72  |

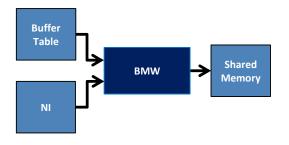

| 4.8        | Buffer Manager Write connected modules                                                                                                    | . 73  |

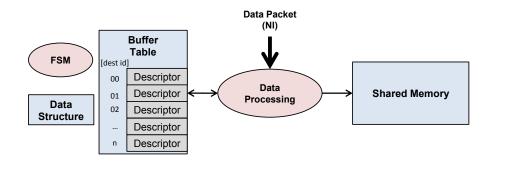

| 4.9        | Buffer Manager Write functional description                                                                                               | . 73  |

| 4.10       | Buffer Manager Read connected modules                                                                                                     | . 74  |

|            | Buffer Manager Read functional description                                                                                                |       |

|            | Credit Manager connected modules                                                                                                          |       |

|            | Credit Manager functional description                                                                                                     |       |

| 5.1        | Ping-Pong application with multiple connections                                                                                           |       |

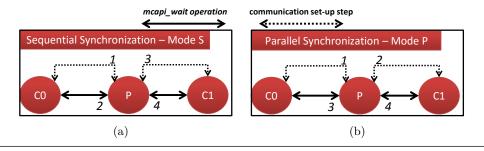

| 5.2        | Sequential and parallel synchronization schemes                                                                                           |       |

| 5.3        | Software layers proportional contribution in the entire software stack                                                                    |       |

| 5.4        | Difference in the total execution time for the ping-pong application                                                                      | . 87  |

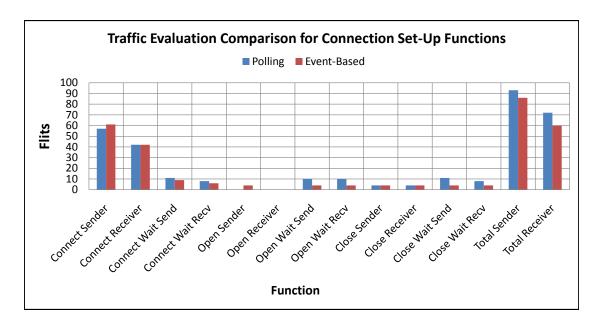

| 5.5        | Number of flits sent by each connection set-up function using polling and event-based approaches.                                         | . 89  |

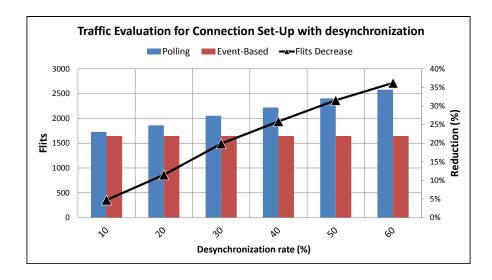

| 5.6        | Number of flits sent in the communication set-up phase using polling and                                                                  |       |

|            | event-based approaches for several desynchronization rates                                                                                | . 90  |

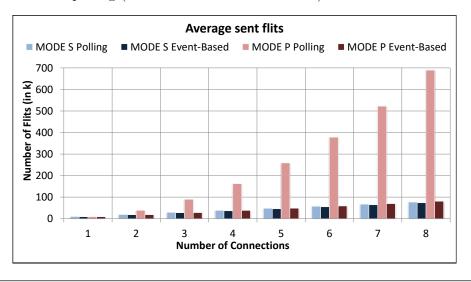

| 5.7        | Number of flits sent by the ping process for different number of connec-                                                                  |       |

|            | tions in both synchronization schemes                                                                                                     | . 91  |

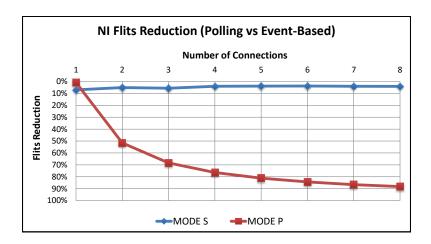

| 5.8        | Decrease in the number of sent flits when using ES in both synchronization                                                                | 0.0   |

| <b>-</b> 0 | modes                                                                                                                                     | . 92  |

| 5.9        | Total execution time of ping-pong application for a different number of                                                                   | 0.9   |

| F 10       | connections in both synchronization modes                                                                                                 | . 93  |

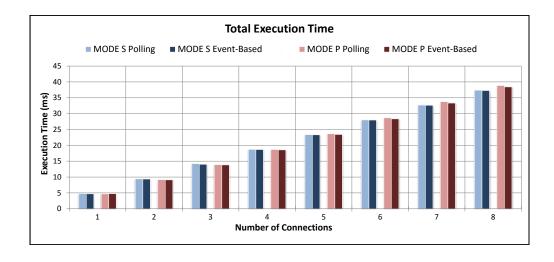

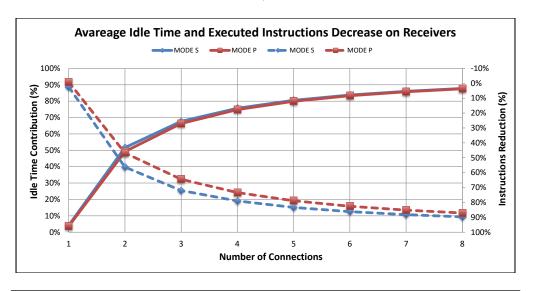

| 5.10       | Relation between idle time (solid line) and reduction in the number of executed instructions (dotted line) for both synchronization modes | . 93  |

| E 11       | Total execution time divided between idle and active times                                                                                |       |

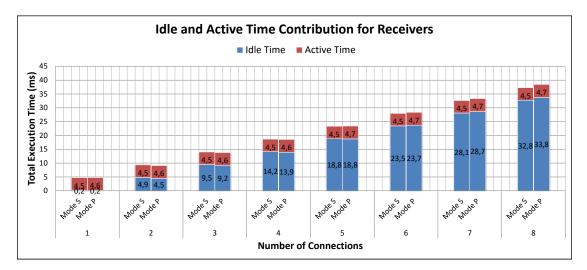

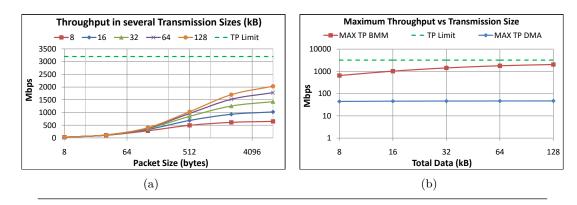

|            | Throughput comparison between BMM and DMA                                                                                                 |       |

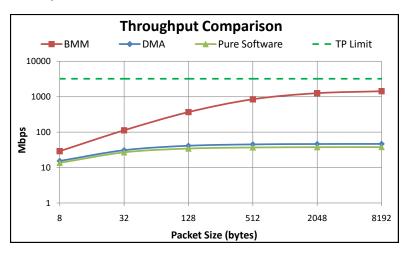

|            | Maximum achievable throughput for different amounts of transmitted data                                                                   |       |

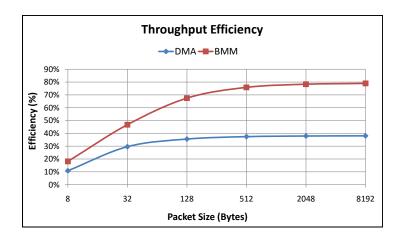

|            | Throughput efficiency comparison between BMM and DMA                                                                                      |       |

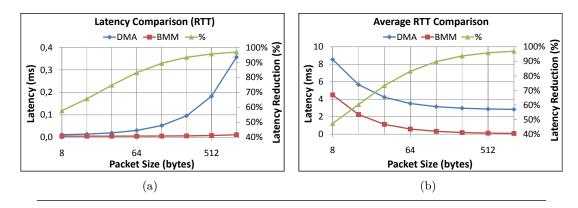

|            | Round-trip time evaluation                                                                                                                |       |

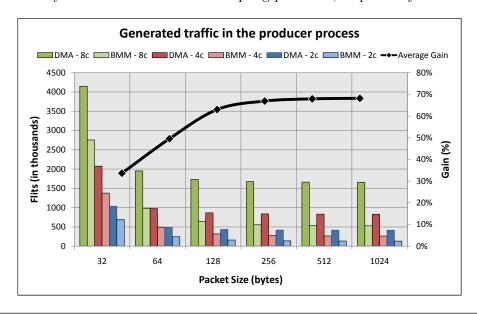

|            | Total number of flits sent by for the ping process to transfer 128 kB of                                                                  | . 91  |

| 5.10       | data                                                                                                                                      | 98    |

| 5 17       | Communication time using DMA and BMM for different packet and FIFO                                                                        | . 50  |

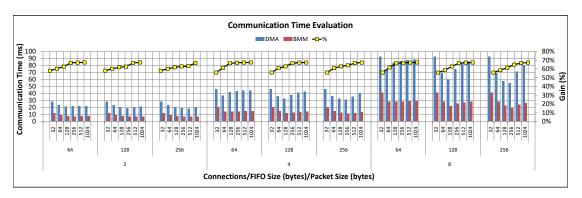

| 0.11       | sizes with different number of connections                                                                                                | 90    |

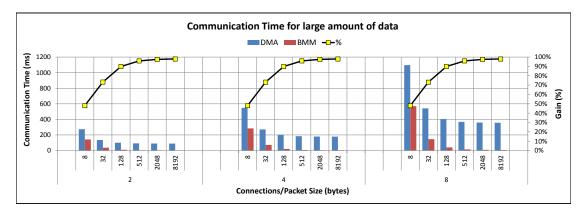

| 5 18       | Communication time comparison for a data transfer of 128 kB                                                                               |       |

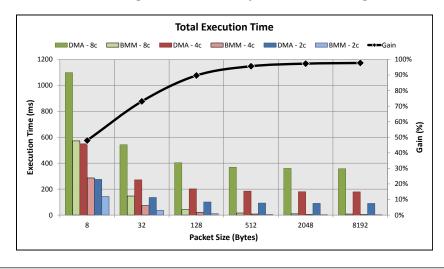

|            | Ping-pong application execution time to transfer 128 kB of data                                                                           |       |

|            | Average number of flits sent by each task for SUSAN benchmark                                                                             |       |

|            | Average communication time comparison between BMM and DMA for                                                                             | . 102 |

| J          | SUSAN benchmark.                                                                                                                          | . 103 |

| 5.22       | Average total execution time and speedup comparison between BMM and                                                                       |       |

|            | DMA for SUSAN benchmark                                                                                                                   | . 103 |

| 5.23       | Average number of flits sent by each task for Dijkstra benchmark                                                                          |       |

|            | Average communication time comparison between BMM and DMA for                                                                             |       |

|            | Dijkstra benchmark                                                                                                                        | . 105 |

| 5.25       | Average total execution time and speedup comparison between BMM and                                                                       |       |

|            | DMA for Dijkstra benchmark                                                                                                                | . 106 |

# List of Tables

| 1.1 | Multi-core architectures summary and comparison                                               | 14 |

|-----|-----------------------------------------------------------------------------------------------|----|

| 1.2 | Comparison of different software standards for multi-core programming                         | 18 |

| 1.3 | Thesis positioning regarding communication and programmability aspects                        |    |

|     | in relation to the state-of-the-art                                                           | 26 |

| 1.4 | Cluster address map                                                                           | 28 |

| 1.5 | Packets used to exchange data and control through the NoC                                     | 29 |

| 2.1 | Non-exhaustive list of MCAPI functions                                                        | 37 |

| 2.2 | Request structure fields                                                                      | 41 |

| 3.1 | MCAPI communication set-up events                                                             | 56 |

| 4.1 | Buffer Manager mapping into the Global Address Map                                            | 66 |

| 4.2 | Buffer Manager request parameters encoding                                                    | 67 |

| 4.3 | Write requests encoding                                                                       | 68 |

| 4.4 | Read requests encoding                                                                        | 69 |

| 5.1 | Architecture parameters used in the simulations                                               | 82 |

| 5.2 | Code sizes for different implementations of software API layers in the reference architecture | 84 |

| 5.3 | Number of cycles spent by each function in the transport layer to complete                    |    |

|     | a mcapi_pktchan_send_open_i function                                                          | 85 |

| 5.4 | Memory footprint for the different versions of functions affected by the                      |    |

|     | use of BMM, DMA and ES                                                                        | 86 |

| 5.5 | Size of MCAPI structures placed in the Shared Memory                                          | 87 |

| 5.6 | Evaluation of data structures memory footprint                                                | 88 |

# Abbreviations

API Application Programming Interface

APU Accelerated Processing Unit

BMM Buffer Manager Mechanism

COBRA Cognitive Baseband Radio

CPU Central Processing Unit

CSDF Cyclo-Static Data Flow

DMA Direct Memory Access

DSP Digital Signal Processing

DVFS Dynamic Voltage and Frequency Scaling

EDGE Enhanced Data Rate for GSM Evolution

ES Event Synchronizer

FIFO First-In First-Out

FFT Fast Fourier Transform

FPGA Field-Programmable Gate Array

FSM Finite State Machine

GALS Globaly Asynchronous Locally Synchronous

GPP General Purpose Processor

GPU Graphics Processing Unit

GSM Global System for Mobile Communications

**HPC** High-Performance Computing

HSPA High Speed Packet Access

IFFT Inverse Fast Fourier Transform

IoT Internet of Things

IPC Inter-Process Communication

ISS Instruction Set Simulator

xvi Abbreviations

ITRS International Technology Roadmap for Semiconductors

LTE Long Term Evolution

LSB Least Significant bit

MAC Media Access Control

MCAPI Multi-core Communications API

MIMD Multiple Instruction, Multiple Data

MPI Message Passing Interface

MPSoC Multiprocessor System-on-Chip

MSB Most Significant Bits

NI Network Interface

NoC Network on Chip

PE Processing Engine

PGAS Partitioned Global Address Space

POSIX Portable Operating System Interface for UNIX

QoS Quality of Service

RDMA Remote Direct Memory Access

RTT Round-Trip Time

SCC Single-chip Cloud Computer

SDF Synchronous Data Flow

SDR Software Defined Radio

${f SIMD}$  Single Instruction, Multiple  ${f D}$ ata

SMP Symmetric Multi-Processors

SoC System-on-Chip

TLM Transaction Level Modeling

VLIW Very Long Instruction Word

The technology scaling predicted by Moore's law [1] continuously allows the integration of a higher number of components in a single chip, named SoCs (System-on-Chip). In the past few decades, along with increasing transistor count, the SoC performance could be improved by simply increasing its operating frequency. However, due to technology scaling limitations such as the power wall [2], this approach has reached its limit. Thus, in order to further increase embedded systems performance, architectures with multiple processing cores have been widely used in the past few years.

Nowadays, in addition to the higher performance requirement, multiple application fields (e.g., communication standards, high-quality video processing and computer vision) also impose low-power consumption as a primary constraint. Therefore, hardware accelerators might be employed to achieve higher power efficiency, i.e., higher performance with lower power consumption, since they are designed to execute specific tasks with a limited amount of resources, e.g., an FFT (Fast Fourier Transform) block, or a DSP (Digital Signal Processing) processor.

On the other hand, the addition of multiple processing cores coupled with dedicated hardware accelerators increases the system complexity and renders the application development a key challenge for two main reasons [3]. Firstly, embedded application workloads continue to grow in diverse fields (e.g. spatial, automotive, etc.) [4]. Secondly, the software technologies are not evolving as fast as hardware architectures, leaving a gap in the full system design [5]. In other words, custom software solutions that take benefit of given hardware platform aspects are required to decrease software overhead and fully explore each hardware architecture. Moreover, it force the users to build custom infrastructures to support their programming requirements, decreasing code compatibility, portability and reuse.

A solution to decrease this gap is the implementation of standard software APIs (Application Programming Interface), which is the approach adopted by several works presented in Section 1.2. However, these standards were developed in the context of SMP (Symmetric Multi-Processors) systems, and impose limitations regarding hardware

heterogeneity and memory footprint when addressing embedded systems. Indeed, the induced overhead might compromise the application performance and, consequently, violate the initial constraints. Hence, multi-core programming in embedded systems is hindered by the lack of flexible and general-purpose support.

Therefore, a flexible and lightweight standard specifically designed for embedded systems that addresses both homogeneous and heterogeneous architectures is desired. By using such solution, the software overhead could be decreased and applications could be efficiently ported between different architectures. A promising solution of software standards for embedded system is proposed by the Multi-Core Association (MCA), called Multi-core Communication API (MCAPI) [6]. This standard has been subject of many works, such as [5, 7–12]. Yet, as shown by some of these works, the application performance is also directly affected by the software stack/support efficiency, since MCAPI does not target a specific hardware architecture and a simple implementation will not take benefit of hardware aspects.

To counterpart this issue, the addition of hardware mechanisms able to handle and speed-up the inter-process communication can increase the overall system performance. On the other hand, most of the time, these mechanisms are not flexible to couple with different types of architectures and/or do not take into account the increased complexity in software development to manage them. Thus, it is mandatory to co-design hardware and software to increase the programmability of multi-core architectures and achieve the expected performance requirements. Moreover, the use of a standard software API is essential for code reuse and compatibility.

## Motivation

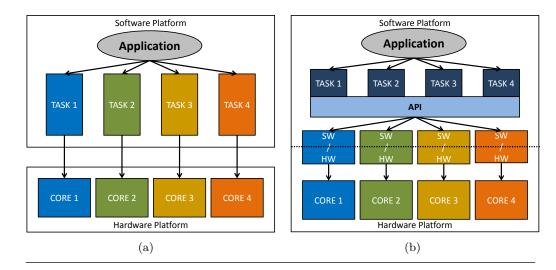

This work is motivated by the need of co-designing hardware and software in order to increase applications programmability and efficiency while keeping good performance. The main idea of this approach is represented in Figure 1. The scenario illustrating a given application deployment in a heterogeneous hardware platform is depicted in Figure 1(a). In this scenario, the programmer needs to consider each processing core characteristics in order to code a given task accordingly. Although this approach allows the application to take advantage of hardware features, it compromises programmability, code reuse and portability.

On the other hand, Figure 1(b) illustrates that an API might increase the aforementioned aspects, allowing programmers, developers and users to abstract hardware

Figure 1: Application deployment in a multi-core architecture. (a) Without software support. (b) With software support.

details. Nonetheless, the application performance must be preserved, since the application requirements, e.g., output frame rate or data transfer rate, still have to be respected. Therefore, as both hardware and software support play an important role in the overall application performance, hardware or software mechanisms might be used by the API to extract the required performance leveraging on hardware features.

Therefore, this thesis focuses on developing the elements introduced in Figure 1(b). From the software side, a standard API targeting embedded systems is chosen, which allows to increase programmability and code portability/reuse at the same time. As the selected standard focuses on inter-process communication, the hardware mechanisms focus on increasing the communication performance. Furthermore, the different communication modes supported by the API are taken into account in order to co-design the mechanisms accordingly. In summary, the main objective is to propose hardware mechanisms that can alleviate the overheads imposed by the software implementation and increase communication performance.

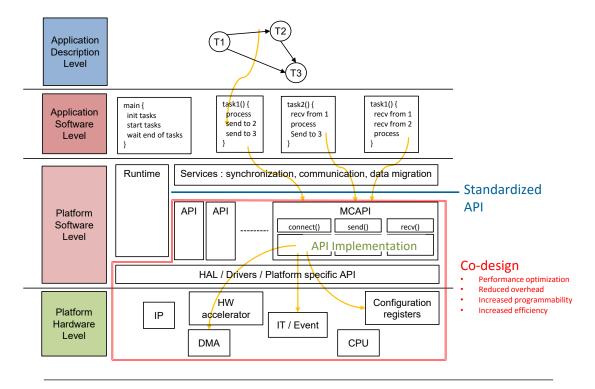

## Contributions

In order to achieve the main objective, the developments performed during this thesis concern platform software and hardware levels, as highlighted by the red line in Figure 2. At the platform software level, the APIs and HAL (Hardware Abstraction Layer) must be developed to couple with the reference architecture and increase software programmability. Next, in order to increase application performance without increasing software

complexity, the addition of modules or mechanisms in the platform hardware level must take into account the software level. Thus, three main contributions are presented:

FIGURE 2: Co-design approach regarding different abstraction levels.

# • Implementation and evaluation of a standard API for inter-process communication.

MCAPI allows the applications to express inter-process communication in a standardized manner, increasing code portability and reuse. Therefore, the communication can be implemented independently from the hardware architecture. Additionally, we characterized the overhead imposed by the software implementation, showing which points must be improved in order to avoid performance losses.

# • Design and evaluation of a hardware mechanism to improve communication set-up performance.

We developed a hardware mechanism in co-design with MCAPI in order to decrease network traffic and processor workload during the communication set-up phase. Due to the co-design approach, this mechanism can be easily accessed and programmed at the API level, making the hardware modifications transparent to the application.

Design and evaluation of a hardware mechanism to improve data transfer performance.

We co-designed a hardware mechanism with MCAPI, which implements a FIFO-like communication channel and handles the data transfer phase. This mechanism is programmed through memory-mapped registers, making it flexible to be used by processors or hardware accelerators. Similarly to the communication set-up mechanism, the software modifications are performed only at API level, without increasing programming complexity.

## Thesis Organization

The thesis is divided into Introduction, five main chapters, and Conclusion. The Introduction describes the context of this work and presents its motivation and contributions. Chapter 1 places the thesis in relation with the state-of-the-art and provides background in multi-core architectures and software programming interfaces. Since this work is inserted in the context of multi-core architectures programmability, the hardware-software co-design aspect is also discussed, as well as hardware mechanisms looking for performance improvements. Additionally, it presents the reference architecture used to develop the contributions of this thesis.

Chapter 2 presents the MCAPI standard and the design choices performed to implement the specification for the reference architecture. Furthermore, an analysis is carried out to evaluate the main drawbacks and bottlenecks in the referred implementation.

Then, Chapter 3 presents the Event Synchronizer mechanism, which is the second contribution of this thesis. It also presents the polling processes present in the MCAPI implementation and the modifications performed in the MCAPI implementation to take advantage of the Event Synchronizer. Chapter 4 presents the third contribution of this thesis, which is the Buffer Manager Mechanism. Initially, the data transfer phase and the software implementation are reviewed. Then, the proposed mechanism is described. Furthermore, the modifications performed in the MCAPI implementation to take advantage of the Buffer Manager are presented in the end of the chapter.

The environment set-up, experimental results and benchmark validation are described in Chapter 5. The objective is to characterize the mechanisms proposed in Chapters 3 and 4, as well as evaluate the MCAPI implementation described in Chapter 2 in terms of memory footprint. Furthermore, the performance gains obtained with the proposed mechanisms are validated through the execution of image processing and path calculation benchmarks. Finally, conclusion and perspectives are drawn.

# Chapter 1

# Multi-core Systems Overview: Hardware and Software Related Works

This chapter places the thesis in relation with the state-of-the-art and provides background for multi-core architectures and software programming interfaces. Since this work is inserted in the context of multi-core architectures programmability, the hardware-software co-design aspect is also discussed. Therefore, Section 1.1 presents examples of recent multi-core platforms, providing insights to architecture trends. Then, Section 1.2 gives multiple options of software support that can be applied on these architectures. Section 1.3 introduces works related to hardware mechanisms looking for improving the performance of such architectures and discuss their support or interaction regarding the software level. Finally, the reference architecture used to develop the contributions of this thesis is presented in Section 1.4.

## 1.1 Multi-core Architectures

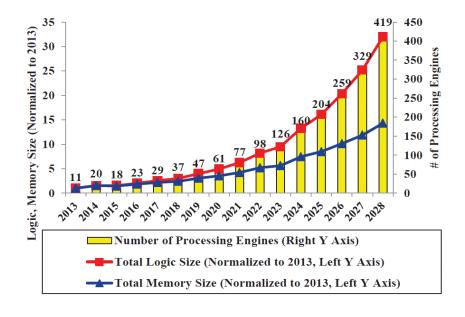

Multi-core architectures have been used in the past years as solution to meet application constraints in several areas, such as high-bandwidth digital communication, gaming, augmented reality and high-quality image and video encoding. In addition, according to ITRS [13], the number of processing engines in a single device is expected to grow exponentially in the next years, as depicted in Figure 1.1, which confirms the importance of further developing such architectures.

Besides the processing engine count, the core types must also be considered. When more than one core type is employed, the multi-core platform can be classified as heterogeneous. On the other hand, homogeneous architectures are composed of a single replicated processing engine, which can be either general purpose processors (GPPs) (e.g., Intel's multi-core CPUs, SCC [14]) or DSP processors [15]. Both homogeneous and heterogeneous architectures have their advantages and drawbacks. While applications are easier to code and parallelize in homogeneous architectures, the power efficiency of heterogeneous solutions is higher due to the specialized hardware units employed to execute specific tasks.

Figure 1.1: Design complexity forecast for SoCs in terms of processing engines, logic and memory sizes [13].

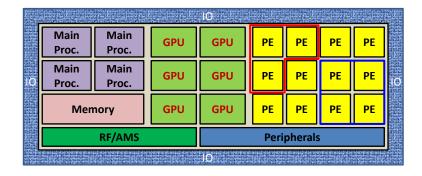

In fact, heterogeneous solutions are being widely employed in both industry and academy. Additionally, according to ITRS, the SoC template consists of few processing cores (4 cores, currently), GPUs (Graphics Processing Unit) and several processing engines (PEs) to execute specific tasks (Figure 1.2), which characterizes a heterogeneous architecture. Furthermore, "due to the continuously increasing demand for high-definition audio and video playback, the number of GPUs is expected to rapidly increase" [13]. Therefore, it is safe to affirm that heterogeneous architectures will be preferred over homogeneous architectures due to the increased performance and higher power efficiency.

The industry has already demonstrated many examples of architectures composed of GPPs and GPUs, such as Tegra from NVIDIA, Exynos from Samsung, Ax series from Apple, Fusion APU from AMD and Ivy, Sandy and Haswell architectures from Intel.

FIGURE 1.2: SoC architecture template for consumer portable devices [13].

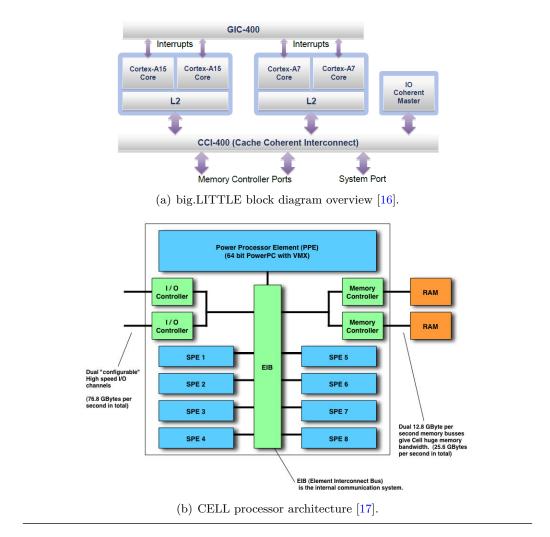

Figure 1.3 details the block diagram of two industry architectures: big.LITTLE [16] and Cell Processor [17], from ARM and STI, respectively.

Figure 1.3(a) shows the big.LITTLE block diagram, which consists of an ARM Cortex-A15 pair (big) and an ARM Cortex-A7 pair (LITTLE) connected by the cache coherent ARM CoreLink CGI-400 interconnect. The idea is to take advantage of different workload patterns in mobile applications to switch the operation between the different cores. The "big" cores are used when high processing power is needed, while the "LITTLE" cores are employed to execute simpler tasks. This architecture is used in the Exynos 5 [18] and 7 Octa from Samsung and in Qualcomm Snapdragon 808 and 810 processors.

The Cell processor block diagram is presented in Figure 1.3(b). It is composed of one Power Processor Element (PPE) and eight Synergistic Processing Elements (SPEs). The interconnection is performed by the Element Interconnect Bus (EIB), which is a set of 4 ring buses. The SPEs are responsible to execute computing intensive tasks assigned by the PPE, which can also run an operating system and applications. This architecture is used in PlayStation 3 gaming console and was developed in co-operation between Sony, Toshiba and IBM [17].

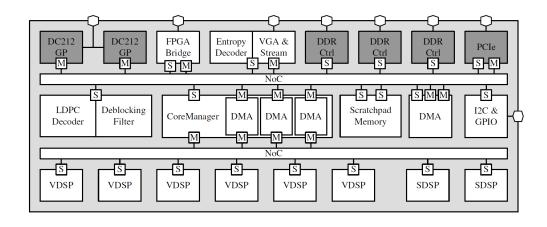

Heterogeneous multi-core architectures are also research subject in the academy, and several examples can be highlighted. The Tomahawk MPSoC [19] targets baseband communications and multimedia applications. The platform is composed by two Tensilica processors (DC212), six fixed-point DSP units (VDSP), two scalar floating-point DSP units (SDSP), among other specialized hardware blocks, as depicted in Figure 1.4. All components are connected by two crossbar-like master/slave NoCs. The application control and scheduling is centralized in the CoreManager unit. The platform is programmed using a C-based programming model. The programmer explicitly assigns the C-functions that will be executed as tasks in a given PE using special #pragma directives. Before task execution, program and input memories are copied from the global

FIGURE 1.3: Block diagrams for biggle.LITTLE and CELL processors.

to the local PE memory. After task completion, the local PE memory is copied back to the global memory.

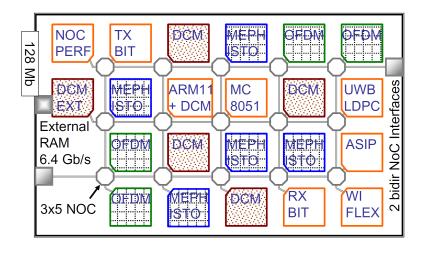

There are also architectures targeting only a single application field, such as Magali [20], X-GOLD SDR 20 [21] and COBRA [22]. These architectures are focused mainly on Software Defined Radio (SDR) applications. Magali [20] is an evolution of the Faust [23] platform, which is composed of 23 processing units, including VLIW DSP processors, blocks dedicated for FFT/IFFT processing, a hardware block for managing configuration and data (DCM) and an ARM processor working as a centralized general manager. These units are connected by a 3x5 mesh asynchronous NoC (ANoC), as presented in Figure 1.5. Also, this architecture supports dynamic data-flow reconfiguration. Using a data-flow programming model, the ARM processor configures the Communication and Configuration Controllers (CCCs), which are in charge to manage the communication in a distributed way. The data flow is statically defined at compile time, but the number of data to be exchanged between the different units can be modified dynamically. When

Figure 1.4: Tomahawk block diagram overview [19].

a new configuration of a given task is missing, the CCC requests a configuration to one of the DCMs, which stores all the configurations defined at compile time.

The X-GOLD SDR20 [21] platform supports the implementation of the physical layer signal processing for GSM, EDGE, HSPA, LTE and others. The processor contains an SDR subsystem, an ARM subsystem and a power management unit. The ARM subsystem is composed by the ARM 1176 core, local memories, a DMA, external memory interface, an audio DSP processor, among other peripherals. The SDR subsystem is composed by SIMD clusters and an accelerator cluster. The SIMD cluster is composed by four SIMD cores, two RC1632 scalar cores, a shared memory, a multi-layer local bus, and a bridge to connect the cluster to the Global Bus. The scalar cores are intended to be used for tasks without parallelism. Similarly, the Accelerator cluster contains five accelerators in total. Each accelerator is composed of a RC1632 control processor and the actual accelerator core, plus a shared memory. In the same way of the SIMD

FIGURE 1.5: General overview of Magali processing cores [20].

cluster, the interconnection is done via a multi-layer local bus. Additionally to the clusters and ARM subsystem, a dedicated mechanism allows synchronization between tasks. However, there is no mention about the programming model or tool chain to assist the programmer developing applications for this platform.

Lastly, the COBRA (Cognitive Baseband Radio) platform [22] is a multi-core SDR platform based on the ADRES baseband processor [24]. This processor consists of one or more VLIW processors and a set of Coarse Grain Array (CGA) resources. Each VLIW processor is able to run the application sequential code, while the CGA runs the parallel code. The COBRA platform contains 2 ADRES baseband processors, 2 DIFFS (Digital Front For Sensing), 2 flexible forward error correction (FlexFEC), a Viterbi accelerator and an ARM core for task controlling. All parts are programmable in C or high level assembly. The interconnection is done via buses and crossbars. From the memory hierarchy point of view, there are local memories, which are connected to each thread and store local variables, and a shared memory, which stores shared variables that are used by different threads or implement FIFO communication between threads. The application are implemented using the MPA tool [25], which uses the application C code and a file specifying the parallelization as input. Then, the tool analyzes the dependencies in the C code, performs the parallelization and inserts FIFO buffers at the points where communication between threads is needed.

However, more recent architectures are focused on flexibility and distributed control, such as Flextiles [26] and P2012 [27]. The FlexTiles platform targets high performance and dynamic algorithms in embedded products with low power consumption. The architecture is scalable, and there is not a fixed number of cores that the platform supports. Indeed, it is composed by general purpose processing (GPP) nodes, DSP processors, Accelerators Interfaces (AIs), an embedded FPGA, I/Os and a DDR controller. The GPPs are used as masters while the DSP processors, eFPGA and I/Os are used as slaves.

The interconnection infrastructure employs a NoC for communication. The interface between NoC and GPP nodes, DDR controller, I/Os and eFPGA Configuration Controller is done via a Network Interface (NI). In addition, for the DSP nodes, an AI is used between the DSP core and the NI. The platform is not yet implemented in silicon. However, for future implementations, it is proposed the use of 3D stacking technology. In this case, eFPGA module is placed in a different layer from the GPP nodes.

The programmer's view is a set of concurrent threads with different priorities that can address domain-specific accelerators to meet application constraints. The application is programmed in C or C++ language, while the accelerated parts are described in

the respective accelerator language. The application parallelism is expressed by describing the threads as series of data-flow graphs and combining them with priority orders and synchronization mechanisms. In fact, the application is defined as a set of static clusters. Then, a cluster is described using Synchronous Data Flow (SDF) or Cyclo-Static Data Flow (CSDF) models of computation, where each producer/consumer is defined as an actor.

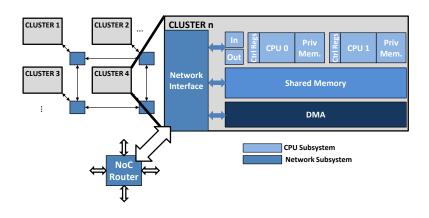

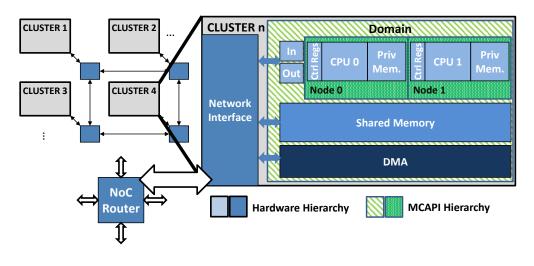

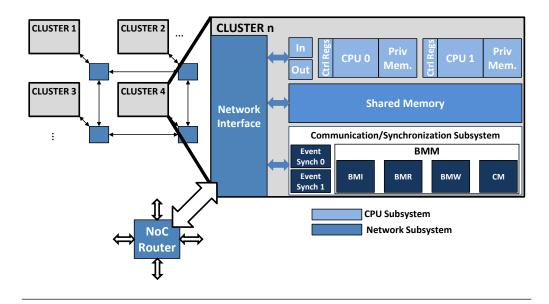

Finally, Platform 2012 [27] is a multi-core architecture composed of processor clusters in a GALS approach targeting applications such as digital communication standards, gaming, augmented reality, high-quality audio and video, etc. Each cluster is composed of a computer engine called ENCore, which can be composed from 1 to 16 PEs (STxP70-V4), a cluster controller and several Hardware Accelerators (HWPEs). The cluster controller is responsible for booting and initializing the ENCore PE, application deployment, error handling and also energy management. In fact, each cluster has his own cluster controller, characterizing a distributed controlling approach. The ANoC performs communication intra (between HWPEs and ENCore engine) and inter-cluster.

The platform supports three classes of programming models: (i) Native Programming Layer (NPL); (ii) Standards-based Programming Models; (iii) Advanced Programming Models. Using (i) the platform resources are accessed through a low-level C-based API. In (ii) some standard programming models can be used to program the platform, such as OpenCL and OpenMP. Finally, (iii) offer a midway productivity/performance trade-off between the other two. From the software viewpoint, the 2012 architecture is PGAS – Partitioned Global Address Space, where all processors have full visibility on all the memories with no aliasing, i.e., a processor located in a given cluster can load and store directly in remote L1 memory of other clusters.

Table 1.1 compares the mentioned architectures regarding their target applications (specific, semi-specific or generic), inter-process communication (IPC), communication control, hardware characteristics (interconnection and processing engines) and support for application programming.

The architectures' target applications differ and a trend can not be identified. However, with mobile devices supporting multiple features (4G and 5G standards, highquality video playback, etc) and Internet of Things (IoT) becoming increasingly in evidence, architectures targeting specific application niches are not suitable. The predominant inter-process communication implementation is through shared memories with centralized communication control. On the other hand, architectures supporting a high number of processing nodes must implement distributed control to avoid a bottleneck in the system. Moreover, only P2012 supports standard programming models. Therefore,

Table 1.1: Multi-core architectures summary and comparison.

|                         | Target        | Ę                 | Communication            | Communication Interconnection | Main Processing | Hardware                        | Application        |

|-------------------------|---------------|-------------------|--------------------------|-------------------------------|-----------------|---------------------------------|--------------------|

| Architecture            | Application   | IPC               | Control                  | Infrastructure                | Engine          | Accelerators                    | Programming        |

| hia I ITPTI E [16]      | Conomic       | Charod Momorit    | Controlized              | Proprietary                   | ARM-based       |                                 |                    |

|                         | Central       | Shared intelliory | Centrangea               | Interconnect                  | processors      | ı                               |                    |

| Cell [17]               | Generic       | Shared Memory     | Centralized              | Ring buses                    | Power PC        | Synergistic<br>Processing Units | ı                  |

| Tomohomb [10]           | Somi Specific | Shared Momert     | Contralized              | No. besed                     | Toncilies DC919 | VDSPs, SDSPs,                   | C-based;           |

| TOIIIAIIAWA [13]        | nemi-pherime  | Shared intemoty   | Centrangen               | INOC-Dased                    | rensinca DO212  | LDPC Decoder, etc               | #pragmas           |

| Danat [99] /Magal: [90] | Chooifo       | Mosesso Dossins   | Partially                | None bear                     | ARM-based       | FFT, IFFT,                      | Data-flow          |

| raust [20]/ Magan [20]  | Specific      | Message r assing  | Distributed              | INOC-Dased                    | processor       | VLIW DSPs, etc                  | configuration      |

| V COI D 90090 [91]      | Chooif        | Chound Massoure   | Continuition             | Due beend                     | ARM-based       | SIMD processors,                |                    |

| A-GOLD 3DR20 [41]       | Specific      | Shared Memory     | Centranzea               | Dased<br>Dased                | processor       | Audio DSP, etc                  | 1                  |

| CORP A [99]             | Crosific      | Cherod Momorite   | Controling               | Crossbars and                 | ADRES           | DIFFS, FlexFEC,                 | MDA tool           |

| CODIG [42]              | omeda         | Shared Memory     | Centrangen               | sesnq                         | CINION          | Viterbi accelerator             | INTLA COOL         |

| Floortiles [98]         | Comognio      | Shared Memory and | Dietributed              | None bosed                    | CDD             | DGD, OFDCA                      | Thread-based;      |

| r icanica [20]          | Ceneric       | Message Passing   | Distributed              | INOC-Dased                    | 3115            | Doi s, er i da                  | specific languages |

| P2012 [27]              | Generic       | Shared Memory     | Partially<br>Distributed | NoC-based                     | STxP70-V4       | HWPEs                           | Multiple options   |

the multi-core architecture presented in Section 1.4 is used as reference, taking flexibility and scalability as the main target constraints.

## 1.2 Application Programming Interfaces

Besides the hardware architecture, efficient implementation of the software stack is also important for two main aspects: application performance and portability/code reuse. Usually, the application take advantage of Application Programming Interfaces (APIs) or another software component that interfaces with the hardware. Parallel and distributed computing have well established software standards for both shared memory and message passing paradigms. On the other hand, the lack of standards for embedded systems often leads to custom solutions.

#### 1.2.1 Custom APIs

Several works present implementations of lightweight solutions for well-known standard APIs when targeting embedded systems. In [28], only a set of MPI ([29]) functions are implemented for four different network topologies. The code size is reported to be between 11 kB and 16 kB. Similarly, [30] and [31] present optimizations for a set of MPI functions. However, since only a set of MPI functions is implemented, application portability might be compromised. Other works present solutions with specific architecture constraints, such as [32], where a processor with enough processing power to run a full MPI implementation is needed, or such as [33], where the solution targets CPU-GPU architectures. Even though these implementations take advantage of MPI, they can not be considered a standard. Furthermore, [34] and [35] report performance overheads induced by software implementation that might compromise the application constraints.

Moreover, other custom software solutions can be highlighted. C-Heap [36] (CPU-controlled Heterogeneous Architectures for Signal Processing) is a combination of an architecture template with a protocol for cooperation and communication between autonomous tasks. The architecture template is a MIMD (Multiple Instruction Multiple Data) architecture, and has a main processor controlling the other processing devices.

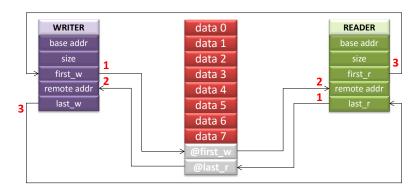

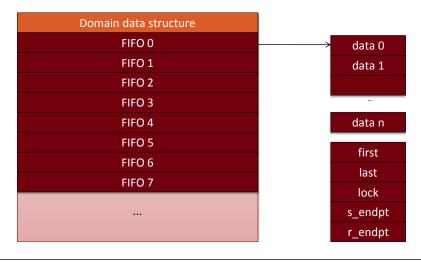

The communication protocol is implemented using FIFO-based communication between the tasks. In this model, the communication is divided between synchronization and data transportation. As the FIFOs are implemented using shared memories, no data copy is necessary and only synchronization primitives are needed. In this architecture, the data transfers are based on tokens. Therefore, the tasks need to claim and release tokens to manage the buffer memory space using primitives. These primitives, used by the tasks, control the allocated space in a FIFO manner to implement a channel FIFO buffer. Therefore, it provides flexibility to tune the FIFO and token sizes for an application even after a silicon tape-out. Also, the number of FIFOs and their interconnection structure can be changed in order to map different applications on the same hardware.

In [37], a message passing library with limited number of functions is presented. The focus is to decrease the overhead imposed when setting up and controlling the communication and in the data transfer. The library uses semaphores for data synchronization, which are explicitly informed in the functions calls. The synchronization can be done by polling or by waiting for an interruption for a given semaphore. Although performance gains are shown, the library provides limited functionality and is not based on a widely used standard.

A different approach is proposed in [38], where a programming interface to express communication constraints at language level is presented. The constraints are evaluated by the operating system, which configures the communication hardware accordingly. The base programming language is the X10, which offers type safety, system modularity, portioned global address space, dependent types, transactional memory, among other features. The optimizations in the communication are done by resource allocation and data pre-fetching through DMA.

Nevertheless, the main issue related to these solutions are code portability and reuse, since the API, software framework or programming language are not widely employed. Therefore, as the multi-core hardware is evolving faster than software technologies, other software standards are necessary to address embedded systems capabilities [5].

## 1.2.2 Standard APIs

Implementing a standard software solution provides benefits such as code portability and code reuse. An example of a well-know standard is the OpenMP API [39]. It supports multi-platform shared memory multiprocessing programming in C, C++, and Fortran. In a multi-thread implementation, the master thread forks a specified number of slave threads to work over a given set of data. Then, each slave thread executes its parallelized code section. After the slaves processing completion, the slave threads join back into the master thread, which continues to execute until the end of the program or until the next fork. Thus, the work-sharing constructs can be used to divide a task among threads so that each one executes its allocated part of the code.

The code section that will be executed in parallel is defined by a preprocessor directive, e.g. #pragmas in C language. The number of threads that will be generated can be defined by the user, or left to be managed by the runtime environment. In the later case, the runtime environment allocates threads to processors depending on usage, machine load and other factors.

Another standard is the MPI (message passing interface) [29], which is a message passing library standard for parallel programming. Therefore, MPI is not a library itself, but the specification for developers and users of what this library should be. The goal of the MPI is to provide a widely used standard for writing message passing programs. The interface specifications are defined for C/C++ and Fortran.

The main advantages of using MPI includes the portability, since there is no need to modify the source code when porting an application to a different platform that supports the MPI standard, and functionality, with more than 115 routines implemented already in MPI-1. Also, implementations are available at both vendor and public domain [40].

Initially, MPI was designed to be used in distributed memory architectures. However, as the architecture trends changed, shared memory SMPs (Symmetric Multi-Processors) were combined over networks, creating hybrid distributed/shared memory systems. Then, the MPI implementors adapted the libraries to handle both types of underlying memory architectures. Nowadays, MPI can run virtually on any kind of memory architecture (distributed, shared or hybrid), but the programming model remains as a distributed memory model. As a drawback, all parallelism is explicit, i.e. the programmer is responsible for correctly identifying parallelism and implementing parallel algorithms using the MPI constructs.

More recently, languages such as OpenCL [41] and OpenCV [42] were developed to program heterogeneous multi-core platforms. OpenCL is an open standard maintained by the technology consortium Khronos Group. It has been adopted by Intel, AMD, NVIDIA, Altera, Samsung, ARM, among others. The OpenCL framework is used for writing programs that execute across heterogeneous platforms consisting of CPUs, GPUs, DSP units and other processors. Also, it includes a language (based on C99) for writing kernels, and APIs that are used to define and then control the platforms.

The programming language used to write computation kernels is based on C99 with some limitations and additions. It omits the use of function pointers, recursion, bit fields, variable-length arrays, and standard C99 header files, but provides some extensions. The platform model considers one host device and one or more compute devices. In turn, each compute device is composed of one or more compute units that can be divided processing elements. The applications written in OpenCL are managed by the host, which submits

the work to compute devices. The memory management is explicit, which means that the programmer must move the data manually from/to any memory level, e.g. from host memory to local memory, or vice-versa.

OpenCV s an open-source library including several hundreds of computer vision algorithms that can take advantage of multi-core processing. It was firstly developed by Intel, and now is supported by Itseez. The main focus is on real-time image processing, but the functions also cover several areas such as machine learning, camera calibration, stereo, 3D, among others. The library is written in C++, but there are interfaces in Phyton, Java and Matlab.

Table 1.2 compares the aforementioned standards and also MCAPI, which is introduced in the next section. Although multiple standards are available to implement parallel applications, embedded systems with limited memory and power budgets are not addressed. Indeed, the OpenCL standard does target embedded systems, but it imposes a model between host and computing devices that might not fit in some platforms. In the same way, OpenMP API focus only on shared memory architectures and benefits mainly SMP (Symmetric Multiprocessing) machines, lacking support for heterogeneity. On the other hand, MPI and OpenCV could be explored by embedded systems. However, OpenCV needs to be executed on top of an operating system or other run-time environment, which prohibits its use for platforms with limited resources. Similarly, the implementation of the entire MPI standard is too heavyweight for such architectures [5].

| API/Library | $egin{array}{c} \mathbf{Target} \ \mathbf{Architecture} \end{array}$ | Target Application   | Language               |

|-------------|----------------------------------------------------------------------|----------------------|------------------------|

| OpenMP      | Shared Memory based                                                  | Fork-join algorithms | C, C++, Fortran        |

| MPI         | Any                                                                  | Generic              | Any                    |

| OpenCL      | Heterogenous                                                         | Generic              | OpenCL, C99            |

| OpenCV      | Any                                                                  | Computer Vision and  | C++ and interfaces for |

|             |                                                                      | Machine Learning     | other languages        |

| MCAPI       | Any                                                                  | Generic              | Any                    |

Table 1.2: Comparison of different software standards for multi-core programming.

#### 1.2.3 MCAPI

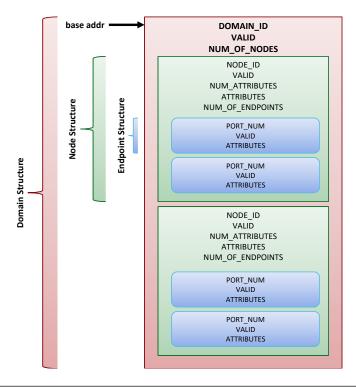

The MCAPI (Multicore Communications API) specification [6] was created by the Multicore Association, an association with several industry companies, and defines an API and semantics for communication and synchronization between processing cores in embedded systems. This API uses the message passing communication model. The purpose is to capture the basic elements of communication and synchronization that are required for closely distributed embedded systems. The primary goals of MCAPI implementations are extremely high performance and low memory footprint. Additionally, MCAPI

intends to be scalable and to virtually support any number of cores, each with a different processing architecture and running the same, different, or no operating system at all. Thus, MCAPI aims to provide source-code compatibility that allows applications to be ported from one operating environment to another.

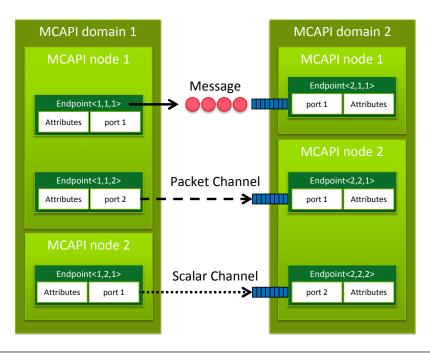

Three communication modes are provided: messages, packets, and scalars. Also, MCAPI provides a limited number of calls with sufficient communication functionality while keeping it simple enough to allow efficient implementations. In comparison with other communication APIs such as MPI, the MCAPI targets inter-core communication in a multi-core chip, while MPI was developed targeting inter-computer communication. Furthermore, other characteristics differ MCAPI from MPI, such as the support of quality of service and priorities, the absence of collective communications, no concept of groups, no synchronization methods (barriers, fences, locks), among others. Similarly, in comparison with OpenCL and OpenCV, which more closely resembles a programming model, MCAPI does not focus on architecture or application type, but in the interprocess communication. Nevertheless, both standards can take benefit of MCAPI to implement their low layers communication protocols.

Although the standard does not entirely cover multi-core programming, it provides a solution for the communication aspect and capability to implement a significant amount of applications. Additionally, multiple implementation examples are already available. For example, the MCAPI implementation presented in [5] is publicly available and can run on Linux computers. It separates the implementation in 2 layers: common code with MCAPI function calls as presented in the specification, and a transport layer, implementing the MCAPI functionalities through Posix shared memory and semaphores. Another example of implementation using shared memory was performed by Mentor Graphics [7]. In [8], the standard was extended to allow inter-chip communication. Finally, works presenting MCAPI implementations for FPGA [9–11] and Intel's SCC [12] are also available.

Thus, the MCAPI standard is a relevant development choice in the context of this thesis. As mentioned, the MCAPI is an increasingly popular standard, which allows the implementation described in Chapter 2 to be compared with other solutions, which is performed in Section 5.2. In addition, the MCAPI main characteristics, i.e., focus on embedded systems, low memory footprint, high communication performance, scalability and heterogeneity, are fully compatible with the objectives of this thesis.

## 1.3 Communication Hardware Mechanisms

Improving communication performance has been research subject for many years. Initially, the main concern was to decouple communication and computation in clusters of processors through hardware support for inter-process communication [43]. However, as showed in [44], both hardware support and software programming model must be addressed in order to successfully implement efficient communication. Yet, the Authors in [44] propose a custom programming model as solution. Similarly, [45] presents software optimizations to increase communication performance in SMP clusters by decreasing synchronization overhead.

Nonetheless, the research on hardware/software co-design for embedded systems must present different solutions, since its characteristics greatly differ from SMPs. In addition, multi-core architectures present high programmability complexity due to limited software capabilities, e.g., smaller operating systems to couple with limited memory resources. Usually, increasing programmability induces performance overheads [10–12, 46]. Thus, it is mandatory to co-design hardware and software to increase programmability while meeting application constraints in multi-core architectures. Although aiming a specific SoC and proposing a software custom solution, an example of hardware/software co-design is presented in [47] and shows significant performance gains.

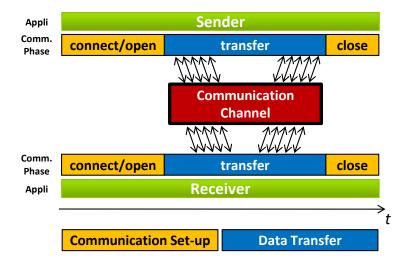

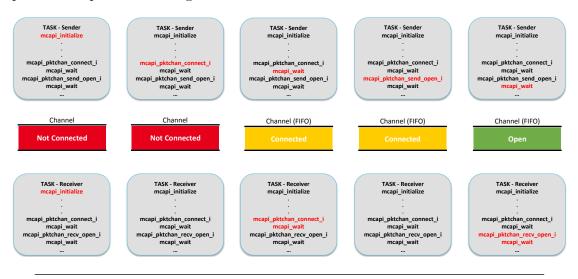

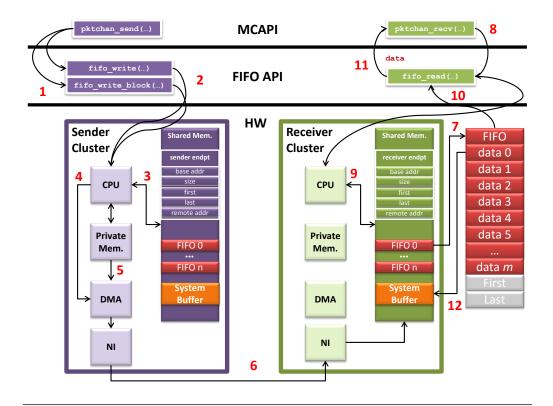

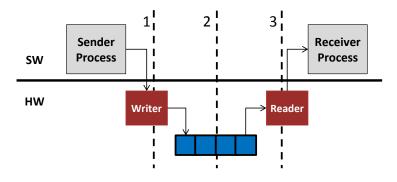

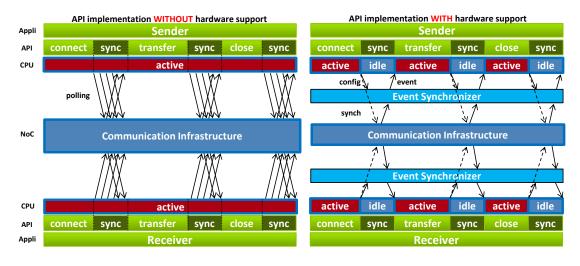

Since MCAPI targets inter-process communication, the research must focus on solutions that improve this aspect. Considering the three communication modes, messages is the most simple, since the data can be transferred by informing only the endpoint identifiers. However, for packet and scalar channels, specific actions must be executed by both communication endpoints before and after exchanging data. Indeed, for these modes, the communication process can be split in two phases: communication set-up and data transfer, as depicted in Figure 1.6. The first phase is used to establish a connection, allocate and deallocate resources, while the second one is where the data is actually exchanged. Therefore, both phases must be taken into account when developing the hardware mechanisms. The following sections describe related works for synchronization mechanisms (that could be used during communication set-up) and data transfer support. In the end, the work presented in this thesis is compared to the works described in both sections.

#### 1.3.1 Synchronization/Communication Set-Up

The communication set-up can be considered a set of synchronization steps, since the MCAPI standard defines conditions that can be interpreted as a barrier, or a lock

FIGURE 1.6: Communication set-up steps used by packet and scalar channels.

in shared resource. According to [48], an ideal synchronization mechanism has to be flexible, scalable, contention free and present low latency and low overhead. Based on these characteristics, a mechanism focused on thread synchronization is proposed in [49]. The idea is to take advantage of the "weak synchronization principle" and tightly-coupled accelerators to achieve high core utilizations. Although the mechanism is easily usable by the applications, its flexibility is limited. This limitation is related to the fact the mechanism only solves the issue of scheduling synchronization for multi-core architectures employing tightly-coupled cores.

A more flexible solution is presented in [50], where the scratch-pad memory is used to virtualize synchronization and communication operations. This way, the software layer can issue operations by writing in the virtual addresses. The synchronization primitives are provided by counters and queues. The counters provide software notifications upon completion of a given number of synchronization operations, e.g. a barrier, in the pre-configured address. Queues are used to send and received data, but can also be used to implement a lock or a semaphore. The main drawback of this solution is related to the architecture constraints, since communication operations are expected to be handled by a remote DMA (RDMA) due to address translation when accessing remote memories. Moreover, the software support for the proposed mechanisms is not mentioned.

Optimizations aiming the MPI standard in heterogeneous SMPs clusters are proposed in [51]. In this work, barrier operations are optimized automatically according to architecture profile. This is achieved by selecting different barrier algorithms according to profiles extracted for different system topologies. This solution provides higher

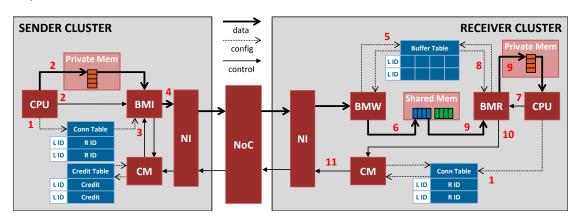

flexibility in relation to the target architecture and performance. However, implementing this solution in embedded systems might induce significant processing and memory footprint overheads.