## Towards thermoelectric metamaterials based on vertical superlattices: fabrication and challenges

Jayalakshmi Parasuraman

#### ▶ To cite this version:

Jayalakshmi Parasuraman. Towards thermoelectric metamaterials based on vertical superlattices: fabrication and challenges. Electronics. Université Paris-Est, 2013. English. NNT: 2013PEST1092. tel-01329533

#### HAL Id: tel-01329533 https://theses.hal.science/tel-01329533v1

Submitted on 9 Jun 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **Ecole Doctorale**

Mathématiques, Sciences de l'Information et de la Communication (MSTIC)

#### **THÈSE**

pour obtenir le grade de Docteur de l'Université Paris-Est

Spécialité : Electronique, Optronique et Systèmes

présentée et soutenue publiquement par

Jayalakshmi PARASURAMAN

Le 28 juin 2013

Vers des Métamateriaux Thermoélectriques à Base de Super-Réseaux Verticaux : Principes et Défis Technologiques.

Towards Thermoelectric Metamaterials Based on Vertical Superlattices: Principles and Technological Challenges.

Thèse dirigée par Tarik BOUROUINA Yamin LEPRINCE-WANG et suivie par Philippe BASSET

#### Jury

Yong CHEN, Directeur de Recherche, PASTEUR, ENS, Paris Bernard LEGRAND, Chargé de Recherche, IEMN, CNRS Patrice CHANTRENNE, Professeur, CETHIL, CNRS-INSA Lyon Tarik BOUROUINA, Professeur, ESYCOM, ESIEE Paris Yamin LEPRINCE-WANG, Professeur, UPEMLV Philippe BASSET, Professeur associé, ESYCOM, ESIEE Paris Rapporteur Rapporteur Examinateur Directeur Co-directrice Examinateur

WWW. PHDCOMICS. COM

"I almost wish I hadn't gone down that rabbit-hole—and yet—and yet—it's rather curious, you know, this sort of life!"

- Alice

"Success is not a result of spontaneous combustion. You must set yourself on fire." - Fred Shero

#### Acknowledgements

WWW. PHDCOMICS. CON

I would like to take this opportunity to thank a whole bunch of important people who have really helped me to get to this very significant step in my professional life. First and foremost, I am deeply indebted to Prof. Tarik Bourouina, my thesis director, for his undertaking, direction, interest, enthusiasm and efforts in realizing the many facets of this work. My big thanks are definitely also due to Prof. Yamin Leprince-Wang of LPMDI, my codirector of thesis, for undertaking me as a student under her very busy wing. Her good cheer, incisiveness and optimism and encouragement has been very constructive through this work. My deepest gratitude is also to Dr. Philippe Basset, my thesis supervisor, for his tolerance, understanding, and perseverance over me coupled with his cool attitude over these years. Through my work, I had the very fortunate opportunity of collaborating with Prof. Dan Angelescu, to whom I am deeply grateful for including me in some of his projects, some of which are among my favorite portions of this thesis. It was fun, instructive and challenging and his direction kept me motivated to achieve the best I could. I am also deeply thankful to Anand Summanwar, whose PhD work has directed my own and provided new goals to reach.

I must've created an ESIEE first of sorts to have worked in the cleanroom for 5 years! I hardly think any words can describe my gratitude to the SMM staff for helping me through many sticky situations in and out the cleanroom. Specifically I'd like to thank Frédéric Marty, Lionel Rousseau, Nicolas Pavy and Bruno Mercier for all their time, help, and guidance to my million and one questions on processes, operational procedures, recipes and what not! I would also like to thank Farbod Ghasseimi for all his ever-ready help with the PCB designs. Additionally I would like to thank all our collaborators in my project – the professors and

students at INSA, CETHIL/MATHEIS – Lyon for all their work and involvement in my thesis.

I am also deeply grateful to Prof. Yong Chen of Ecole Nationale Superior, Paris, and Dr. Catherine Schwob of INSP, who welcomed me to their labs to perform experiments. I also thank Sisi Li of ENS-Paris for her assistance with the electrospinning setup.

What's a PhD without funding! And for this I owe my thanks to the ANR grant that funded me for most part of my work. All the comics appearing on this thesis have been used with the permission Jorge Cham of PhD Comics<sup>TM</sup>.

Life at ESIEE would've been a drag if it hadn't been for Kim Nguyen, my BFF and office mate at ESIEE-Paris. Her positive outlook and sheer goodness made many things fun. I would also like to thank my other friends at ESIEE – Ayyaz, Maurine, and Noha for all the coffees/teas, lunches and conversations, both professional and personal.

Happiness is where the home is! And if the home front hadn't supported me, nothing would've mattered. And for this I owe my heartfelt gratitude to my husband Shravan, who only has pride when he talks about his 'nanotechnology wife' and motivated me through some difficult patches. My parents and grandparents have been my strength, my constant source of encouragement and have forever believed in me and supported every crazy decision of mine, including doing this PhD! For this I am eternally lucky. My in-laws have been amazingly supportive too and this makes me twice as lucky. My best friends across the globe in India and the US have kept me company in spirit, calls and online throughout never letting me feel the onus of the work upon me and most importantly, keeping me in good cheer even without being physically present. Sandhya, Vidhya and Kavitha – I don't know what I'd have done without you! You've seen it all with me and have kept me company from the different parts of the world that you're in. I love you guys! Ashwin, you're my reality meter. You keep me grounded as you do push me to the stars and for this, I'm thankful. Sachin, you're my gossip buddy and those everyday chats of ours kept me going more than you probably know.

What probably really impacted this thesis is my own biggest blessing – my little boy Aarav, who was single handedly responsible for about a year's work in lapse when he was born. Even with everything that achieving this PhD means, he is still by far, my hugest accomplishment and my biggest pride. Look Aanu – Amma's a PhD! I dedicate this thesis to him. Thanks y'all!

## Resumé

Les métamatériaux offrent la possibilité d'obtenir des propriétés physiques nettement améliorées en comparaison avec celles des matériaux naturels. Dans ce travail, nous explorons une nouvelle variété de métamatériaux thermoélectriques à base de micro- et nanostructuration du silicium, sous la forme de super-réseaux verticaux, avec comme visée applicative la récupération d'énergie thermique ainsi que le refroidissement. En outre, nous focalisons nos efforts sur une méthodologie expérimentale permettant la réalisation de ces métamatériaux par des moyens simples et peu coûteux. La première partie de cette thèse sert d'introduction aux phénomènes thermiques qui constituent la base de la conduction électrique et de la dissipation de chaleur dans les nanostructures, respectivement par émission thermoionique et par la diffusion de phonons. Cette partie détaille également les principes et résultats de caractérisation thermique à l'aide des méthodes 3 et 2. La deuxième partie de cette thèse décrit les approches de micro- et nano-structuration descendante "top-down" et ascendante "bottom-up", en vue de la fabrication de super-réseaux nanométriques sur du silicium monocristallin. La nouvelle architecture verticale proposée soulève des défis technologiques qui sont traités à travers l'exploration de techniques expérimentales originales pour produire, d'une manière efficace et sur de grandes surfaces, des structures submicroniques à fort facteur de forme. Ces techniques comprennent l'utilisation de motifs résultant de lithographie traditionnelle combinée à l'extrusion pour en produire des structures volumiques. En outre, l'utilisation de nanofibres et de diblocs copolymères comme nano-motifs géométriques sont également présentés pour nous rapprocher davantage de l'objectif ultime du projet.

Mots clés: Métamatériaux, Superréseaux, micro et nano-structures en silicium, DRIE.

### **Abstract**

Metamaterials offer the benefit of obtaining improved physical properties over natural materials. In this work, we explore a new variety of thermoelectric metamaterials based on silicon micro- and nanostructuration, in the form of vertical superlattices for use in energyrelated applications. Additionally, we focus on a route towards fabricating these materials using simple and low-cost means compared to prior attempts. The first part of this thesis serves as an introduction to the thermal phenomena which form the basis for electrical conduction and heat dissipation by thermionic emission and phonon scattering at the nanoscale. These principles forms the crux of the device. This section also details the and 2 characterization principles and results using the 3 methods for thermal measurement. The second part of this thesis describes both top-down and bottom-up approaches towards fabricating nanoscale superlattices from single-crystalline silicon. The novel proposed vertical architecture raised technological challenges that were tackled through the exploration of original experimental techniques for producing high aspect ratio (HAR) structures in an effective manner and over large surface areas. These techniques include the use of traditional lithography patterning and subsequent extrusion of volumetric structures. Additionally, the use of nanofibers and diblock copolymers as templates for further etching of HAR silicon nanostructures are also presented to bring us closer to the ultimate goal of the project.

Keywords: Metamaterials, Superlattices, HAR structures, DRIE.

## Table of contents

| Table of contents                                                        |  |

|--------------------------------------------------------------------------|--|

| List of symbols and acronyms                                             |  |

| List of tables                                                           |  |

| List of figures                                                          |  |

| Chapter 1. Introduction                                                  |  |

| 1.1. Background and motivation                                           |  |

| 1.2. Thermoelectric metamaterials                                        |  |

| 1.2.1 Peltier effect in metal-semiconductor junctions                    |  |

| 1.2.2 Thermionic emission                                                |  |

| 1.2.3 Barrier thickness requirements                                     |  |

| 1.3. Conclusions from previous work                                      |  |

| 1.4. Objectives and scope of this thesis                                 |  |

| 1.5. Thesis outline and organization                                     |  |

| References                                                               |  |

| Part I – Metamaterials and vertical superlattices                        |  |

| Chapter 2. State of the art of structured metamaterials                  |  |

| 2.1. Introduction                                                        |  |

| 2.2. Metamaterials based on multi-layered thin film stacks               |  |

| 2.2.1 Giant magnetoresistance (GMR)                                      |  |

| 2.2.2 III-V semiconductor superlattices                                  |  |

| 2.3. Metamaterials based on silicon and nano-structuration               |  |

| 2.3.1 Photonic crystals                                                  |  |

| 2.3.2 Phononic crystals                                                  |  |

| 2.3.3 Vertical structures as opposed to planar                           |  |

| 2.4. Conclusions.                                                        |  |

| Chapter 3. Towards TE materials based on vertical superlattices          |  |

| 3.1. Vertical superlattices.                                             |  |

| 3.2. Materials and process selections.                                   |  |

| 3.2.1 The first material.                                                |  |

| 3.2.2 The second material.                                               |  |

| 3.2.3 Material choices and limitations.                                  |  |

| 3.3. Characterization of microsuperlattices                              |  |

| 3.3.1 Thermal conductivity of nanomaterials                              |  |

| 3.3.2 Measuring principle of thermoelectric power for metallic materials |  |

| 3.3.3 Development of characterization tools for thermal measurements     |  |

| on superlattices                                                         |  |

| 3.3.4 Calculation for sample design and <i>in situ</i> characterization  |  |

| $3.3.4.1~3\omega$ method                                                 |  |

| $3.3.4.1~3\omega$ method.                                                |  |

| 3.3.5 Devices for measurement atop the superlattices                     |  |

| 3.4. On chip facilitation                                                |  |

| 3.4.1 Primary PCB                                                        |  |

| 3.4.2 Secondary PCB.                                                     |  |

| J.T.4 DCCOHUALY I CD                                                     |  |

|             | 3.4.3 Challenges in wire bonding                                       | 46  |

|-------------|------------------------------------------------------------------------|-----|

| 3.5         | 5. Test device and results                                             | 46  |

|             | 3.5.1 Fabrication of test devices                                      | 46  |

|             | 3.5.2 Experimental setup.                                              | 47  |

|             | 3.5.3 Results and discussion                                           | 48  |

|             | 3.5.4 Conclusions and perspectives                                     | 49  |

| 3.6         | 5. Fabrication of microsuperlattices                                   | 50  |

|             | 7. Challenges in fabrication                                           | 50  |

|             | 3.7.1 Electrodeposition                                                | 51  |

|             | 3.7.2 Copper polishing challenges                                      | 54  |

|             | 3.7.3 Silicon polishing challenges                                     | 56  |

|             |                                                                        |     |

| Conclusion  | ns of Part I                                                           | 57  |

|             | S                                                                      | 59  |

|             |                                                                        |     |

| Part II – H | ligh aspect ratio (HAR) silicon-based micro and nanostructures         | 65  |

|             |                                                                        |     |

|             |                                                                        |     |

| Chapter 4.  | Top down approach to achieving HAR Si-based micro- and nanostructures  | 67  |

|             | Obtaining HAR silicon structures by pattern transfer using             |     |

|             | Deep reactive ion etching (DRIE)                                       | 67  |

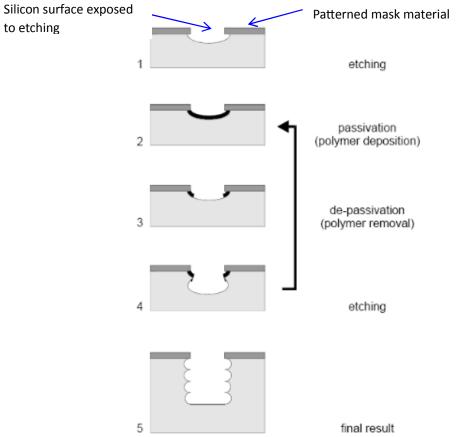

|             | 4.1.1 Bosch DRIE.                                                      | 68  |

|             | 4.1.2 Cryogenic DRIE                                                   | 70  |

| 4.2.        | Lithographically-defined patterns as etching mask for HAR structures   | 70  |

|             | Non-conventional techniques for achieving micro-nanopatterns           | 72  |

|             | 4.3.1 Soft lithography techniques                                      | 73  |

|             | 4.3.2 Non-lithography based patterning techniques                      | 74  |

| 4.4.        | Conclusions.                                                           | 75  |

|             |                                                                        |     |

|             |                                                                        |     |

| Chapter 5.  | Deep reactive ion etching (DRIE) on lithography-defined                |     |

| •           | Sub-micron features.                                                   | 77  |

| 5.1.        | Introduction                                                           | 77  |

|             | Results from Bosch DRIE process                                        | 78  |

| 5.3.        | Results from cryogenic DRIE process.                                   | 83  |

|             | Aspect ratio vs. feature size                                          | 85  |

|             | Conclusions                                                            | 86  |

|             |                                                                        |     |

| Chapter 6.  | Electrospinning for advanced transfer of HAR micro- and nanostructures | 89  |

|             | Introduction                                                           | 89  |

|             | Electrospinning to achieve nanofibers                                  | 89  |

|             | Electrospinning using PS 12.5% and Gelatin 10%                         | 92  |

|             | DRIE on nanofiber templates                                            | 97  |

|             | 6.4.1 Nano-trenches.                                                   | 97  |

|             | 6.4.2 Nano-walls.                                                      | 98  |

|             | 6.4.3 Nanofibers trial#2.                                              | 101 |

|             | 6.4.4 Aligned nanofibers.                                              | 103 |

| 6.5         | Conclusions                                                            | 104 |

| Chapter 7. Focuse                       | ed ion beam (FIB) patterning and subsequent DRIE etching        |

|-----------------------------------------|-----------------------------------------------------------------|

| 7.1. Basic 1                            | principles                                                      |

|                                         | ching                                                           |

|                                         | results                                                         |

|                                         | usions                                                          |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                                                 |

| Chapter 8 Advan                         | nced transfer of mico- and nanostructures by Bottom-up approach |

| -                                       | Diblock copolymers                                              |

| •                                       | 1 2                                                             |

|                                         |                                                                 |

|                                         | 1 •                                                             |

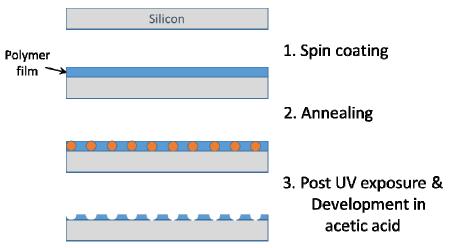

|                                         | Fabrication process.                                            |

|                                         | 8.2.1.1 Spin coating.                                           |

|                                         | 8.2.1.2 Annealing.                                              |

| 8                                       | 8.2.1.3 UV exposure                                             |

|                                         | 8.2.1.4 Acetic acid development.                                |

|                                         | g experiments                                                   |

|                                         | RIE etching of polymer                                          |

| 8.3.2 I                                 | FIB etching                                                     |

| 8.3.3 I                                 | FIB patterning followed by DRIE etching                         |

| 8.3.4 I                                 | DRIE etching of copolymer – Bosch process                       |

| 8.4. Copoly                             | ymer alignment experiments and perspectives                     |

|                                         | Electric field alignment                                        |

|                                         | Shearing alignment                                              |

| 8.5. Conclu                             | usions and perspectives                                         |

| 0.01 0011011                            | perspecta (estimated)                                           |

| Conclusions of Pa                       | art II                                                          |

| References                              |                                                                 |

|                                         |                                                                 |

| Part III. Perspecti                     | ives, future work and conclusions                               |

|                                         |                                                                 |

|                                         | possible bottom up approaches                                   |

| 9.1. Introdu                            |                                                                 |

|                                         | s alumina formed by self-organized anodizing                    |

|                                         | Fabrication                                                     |

|                                         | Porous alumina sample results                                   |

|                                         | Conclusions                                                     |

| 9.3. Black                              | silicon templates as mask                                       |

|                                         | etic opals fabricated by Langmuir-Blodgett method as masks      |

|                                         | Langmuir-Blodgett films                                         |

|                                         | Fabrication of synthetic opals                                  |

|                                         | Sample results.                                                 |

|                                         | uperlattices.                                                   |

|                                         | ary of results.                                                 |

| 7.0. Dumin                              | ur vi 100uito                                                   |

| Defense                                 | ,                                                               |

| Appendix A. Basic thermoelectric principles                            | 167  |

|------------------------------------------------------------------------|------|

| A.1. Seebeck effect                                                    | 167  |

| A.2. Thermoelectric figure of merit                                    | 171  |

| A.3. Peltier effect                                                    | 171  |

| References                                                             | 175  |

| Appendix B. Black Silicon                                              | 177  |

| B.1. Introduction                                                      | 177  |

| B.2. Fabrication parameters                                            | 177  |

| B.3. Applications of black silicon                                     | 179  |

| B.4. Conclusions                                                       | 180  |

| References                                                             | 181  |

| Résumé long en français                                                | I    |

| 1.1. Introduction                                                      | III  |

| 2.0. Fabrication de super-réseaux verticaux                            | VII  |

| 2.1 Choix des matériaux                                                | VII  |

| 2.2 Etude de caractérisation                                           | VII  |

| 3.0. Fabrication de nanostructures à haut facteur de forme en silicium | XI   |

| 3.1 Nanostructures obtenues par lithographie conventionnelle           | XI   |

| 3.2 Fabrication de nanostructures par approche <i>bottom up</i>        | XI   |

| 3.2.1 Résultats obtenues par la technique d'Electrospinning            | XII  |

| 3.2.2 Par diblock copolymères                                          | XIV  |

| 4.0. Conclusions et perspectives                                       | XV   |

| Références                                                             | XVII |

#### List of symbols and acronyms

TE Thermoelectics

TEM Thermoelectric Module

RTG Radioactive Thermoelectric Generator

Z Thermoelectric figure of merit

SL Superlattice

TEP Thermoelectric Power

TCR Temperature Coefficient of Resistance

MEMS Micro Electro Mechanical Systems

PVD Physical Vapour Deposition

RIE Reactive Ion Etching

DRIE Deep Reactive Ion Etching

AR Aspect Ratio

HAR High Aspect Ratio

FOM Figure Of Merit

SEM Scanning Electron Microscope

FIB Focused Ion Beam

ALD Atomic Layer Deposition

SThM Scanning Thermal Microscope

AFM Atomic Force Microscope

PCB Printed Circuit Board

BNC Baynoet Neil-Concelman

CMP Chemical Mechanical Polishing

DMF Dimethyl Formalamide

PS Polystyrene

PMMA Poly Methyl Methacrylate

PDMS | Poly Dimethyl Siloxane

UV Ultraviolet

AA Acetic Acid

LB Langmuir-Blodgett

BS Black Silicon

## List of Tables

| Table 3.1. | The numerical data pertinent to different materials as compared with highly doped <i>p</i> and <i>n</i> type Silicon. The highlighted boxes in blue represent the values of the material most desired with respect to our selection of the second material | 26  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2. | Metal diffusion into silicon at elevated temperatures                                                                                                                                                                                                      | 27  |

| Table 3.3. | Experimentally extracted diffusivity values for silicon                                                                                                                                                                                                    | 48  |

| Table 5.1. | Parameters for deep etching of sub-micron features using Bosch process                                                                                                                                                                                     | 80  |

| Table 5.2. | Process parameters for the cryogenic etch process (Set 3)                                                                                                                                                                                                  | 85  |

| Table 6.1. | Process parameters for various experiments of electrospinning to obtain nanofibers                                                                                                                                                                         | 93  |

| Table 6.2. | Standard Bosch process conditions.                                                                                                                                                                                                                         | 97  |

| Table 6.3. | Electrospinning parameters for Set II experiments                                                                                                                                                                                                          | 101 |

| Table 7.1. | Process parameters for standard cryogenic etch process                                                                                                                                                                                                     | 110 |

| Table 8.1. | Different test conditions for UV exposure and acetic acid development                                                                                                                                                                                      | 122 |

| Table 8.2. | RIE etch test parameters for etching away the polymer film                                                                                                                                                                                                 | 126 |

| Table 8.3. | Parameters for cryogenic etch of copolymer                                                                                                                                                                                                                 | 129 |

| Table 8.4. | Bosch DRIE etching parameters for copolymer etching                                                                                                                                                                                                        | 132 |

| Table 9.1. | Comparison of porous alumina characteristics with different electrolytes                                                                                                                                                                                   | 154 |

| Table 9.2. | Summary of HAR results achieved in silicon with possible future prospects of work to achieve nanosuperlattices                                                                                                                                             | 160 |

| Table B.1. | Range of cryogenic DRIE parameters for BS formation                                                                                                                                                                                                        | 178 |

| Table B.2. | Sample parameters to achieve BS and their physical characteristics under SEM                                                                                                                                                                               | 178 |

## List of Figures

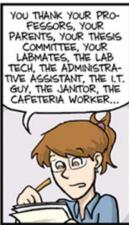

| Figure 1.1. | Illustration of FOM optimization and representation of the trade-offs. In the case of a semiconductor material, doping concentration is used as a tuning parameter                         | 3  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

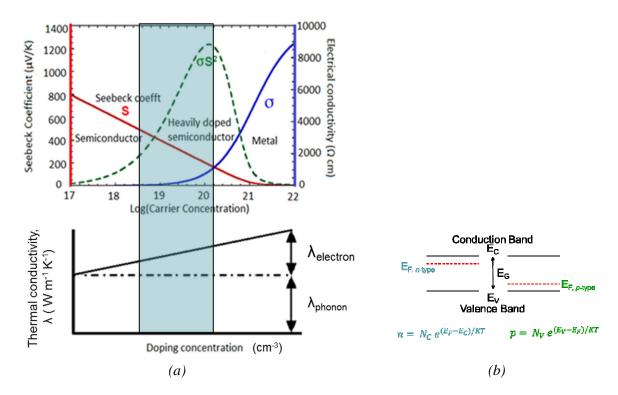

| Figure 1.2. | Illustration of a typical metal-semiconductor-metal junction in (a) <i>n</i> -type configuration and (b) <i>p</i> -type configuration                                                      | 5  |

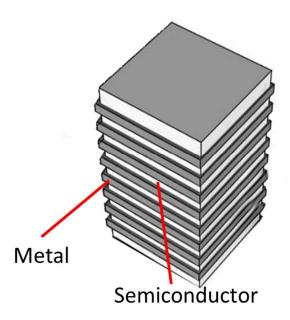

| Figure 1.3. | Schematic diagram of a typical two material superlattice structure                                                                                                                         | 6  |

| Figure 1.4. | Representation of barrier thresholds for increased thermionic emission                                                                                                                     | 6  |

| Figure 1.5. | Schematic representation of planar superlattices used in the traditional approach                                                                                                          | 8  |

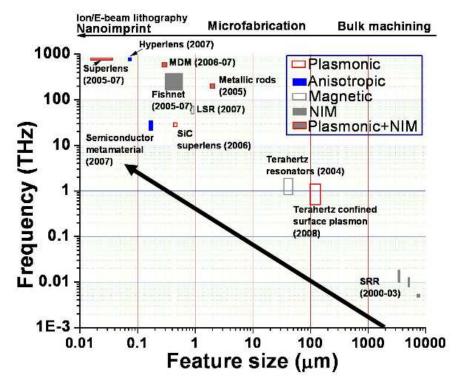

| Figure 2.1. | Progress made in scaling metamaterials from microwave to optical frequencies with change in feature size and the fabrication technology listed on top.                                     | 18 |

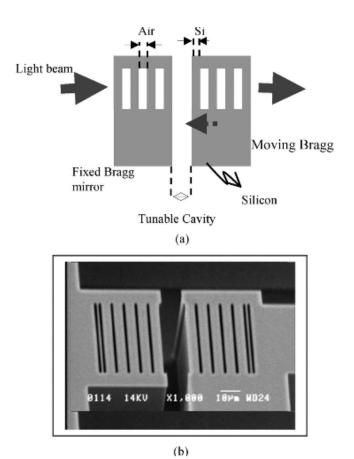

| Figure 2.2. | (a) Schematic of the vertical Bragg mirror and (b) its realization imaged under SEM                                                                                                        | 21 |

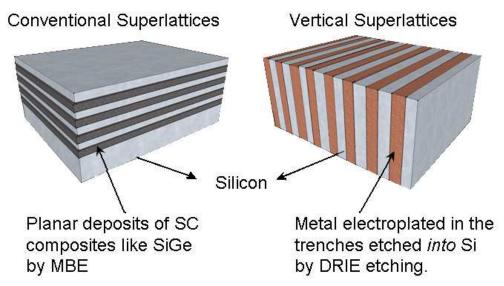

| Figure 3.1. | Comparison of conventional superlattices with vertical superlattices                                                                                                                       | 23 |

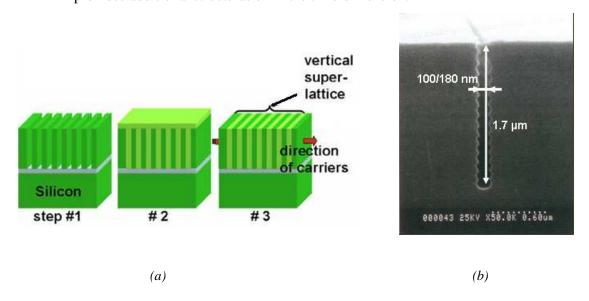

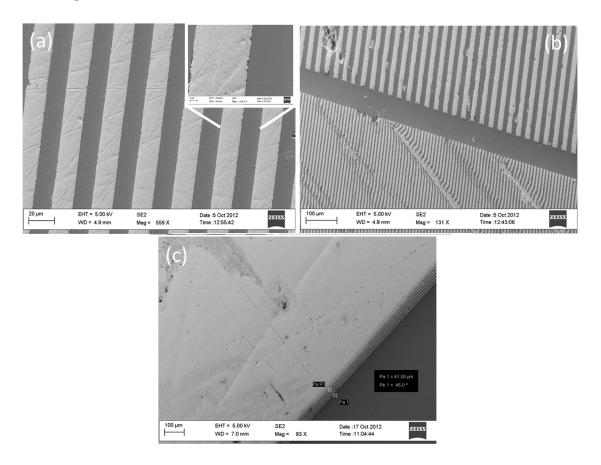

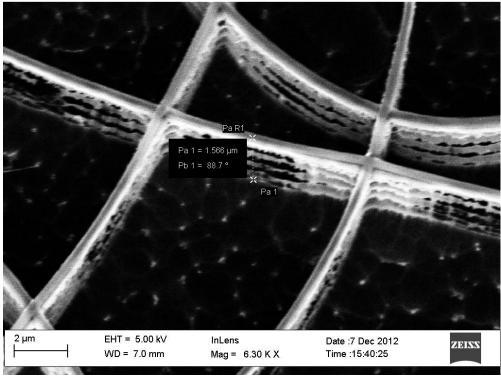

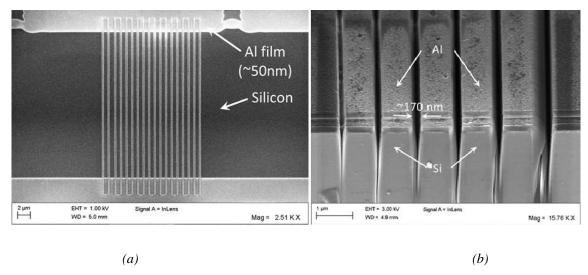

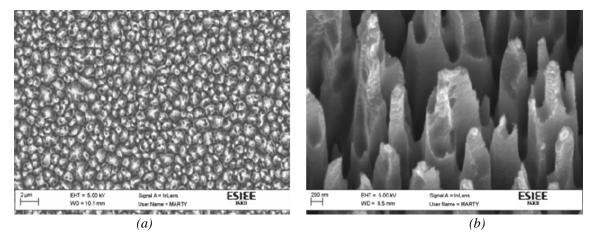

| Figure 3.2. | (a) Schematic of vertical superlattices (b) SEM image of scalloping effect from DRIE.                                                                                                      | 24 |

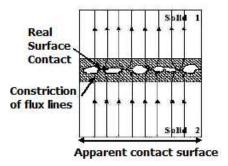

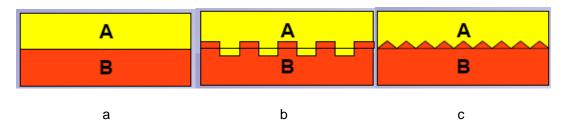

| Figure 3.3. | Representation of the phenomenon of constriction of flux lines during real contact <i>vs.</i> apparent contact of two surfaces                                                             | 30 |

| Figure 3.4. | Perfect contact interface for materials A / B. (a) surface with only the Kapitza resistance (b, c) non-planar interfaces - the Kapitza resistance and the constriction resistance involved | 30 |

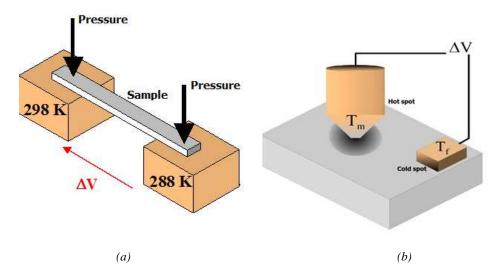

| Figure 3.5. | (a) Principle of the measurement of the thermoelectric power on sample plates and (b) principle of the measurement of the thermoelectric power of bulk sample (device tip)                 | 32 |

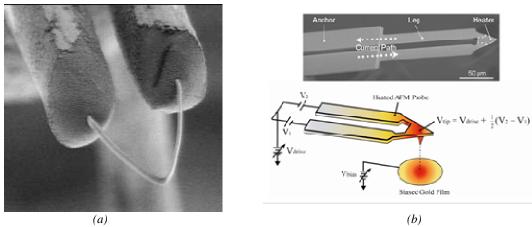

| Figure 3.6. | (a) Scanning thermal microscope tip and (b) heated Si AFM tip heated                                                                                                                       | 33 |

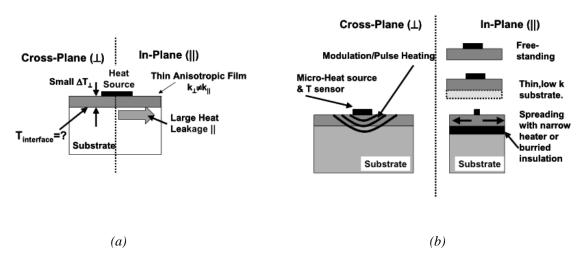

| Figure 3.7. | Illustration of (a) thin film sample configuration and characterization challenges and (b) strategies to overcome these challenges (reproduced from [87])                                  | 34 |

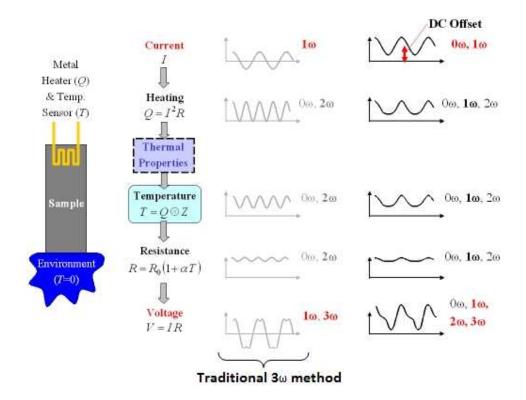

| Figure 3.8. | Illustration of the $1\omega$ , $2\omega$ and $3\omega$ methods for thermal measurements                                                                                                   | 36 |

| Figure 3.9. | Schematic illustration of 1D heater                                                                                                                                                        | 36 |

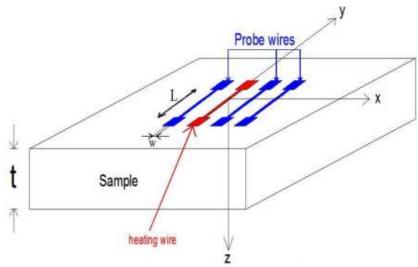

| Figure 3.10. | Schematic illustration of our sample (reproduced from [96])                                                                                                                                                    | 40 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

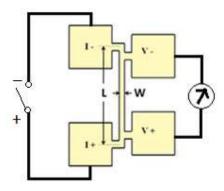

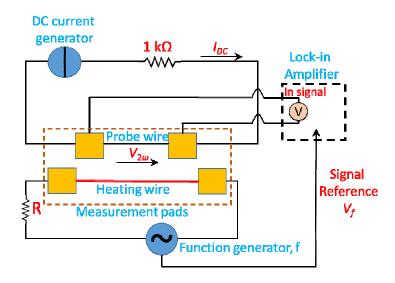

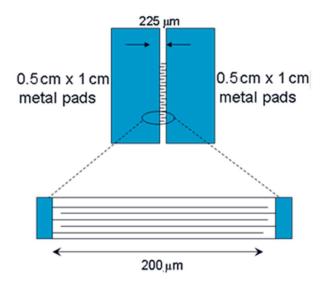

| Figure 3.11. | Configuration for the proposed $2\omega$ measurement device                                                                                                                                                    | 42 |

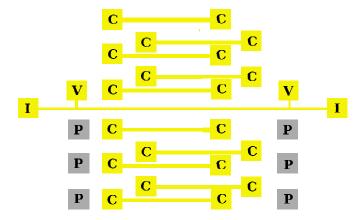

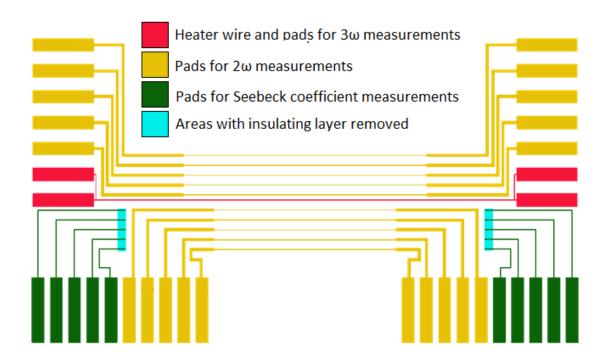

| Figure 3.12. | Final version of the measurement structures to be fabricated on top of the superlattices                                                                                                                       | 43 |

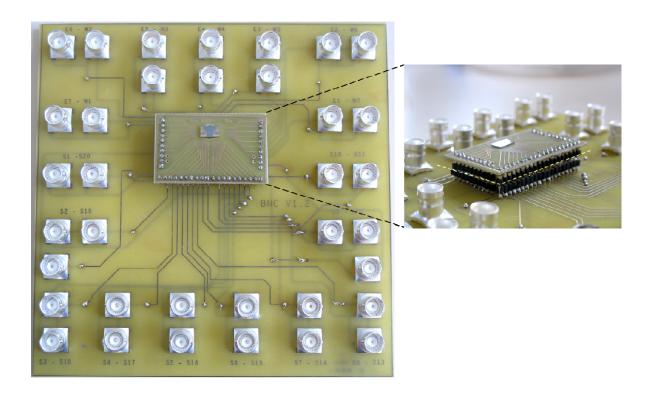

| Figure 3.13. | Completed PCB 2-board assembly. The secondary PCB (bottom) remains common across changing primary PCBs (top) with different samples.                                                                           | 45 |

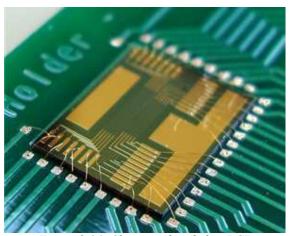

| Figure 3.14. | Chip wire-bonded to PCB                                                                                                                                                                                        | 45 |

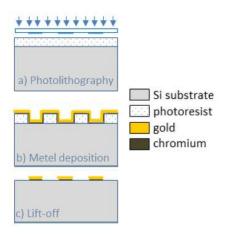

| Figure 3.15. | Fabrication process for creating test measurement devices on pure silicon substrate by lift-off                                                                                                                | 47 |

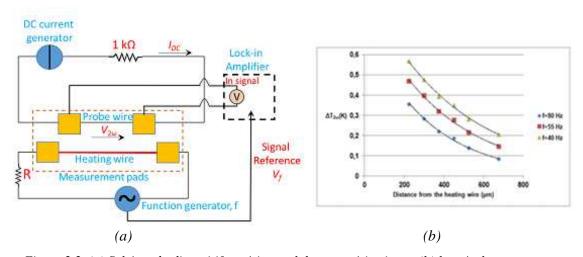

| Figure 3.16. | Schematic of the experimental setup for measurements on fabricated samples (modified from [96])                                                                                                                | 48 |

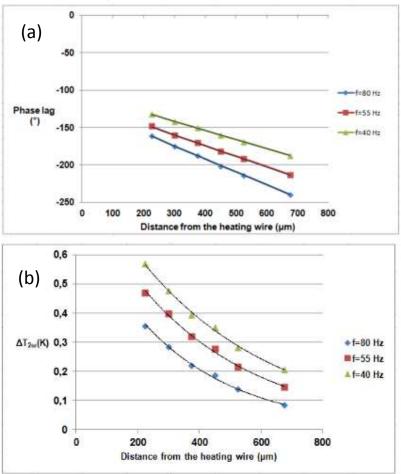

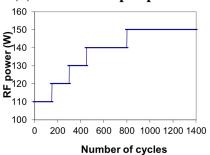

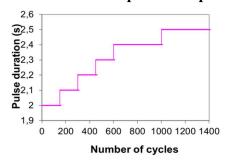

| Figure 3.17. | Results of experimentally determined (a) phase lag and (b) $\Delta T_{2\omega}$ as a function of the distance from the heating wire for $I_{ac} = 60$ mA for different frequencies (reproduced from [96])      | 49 |

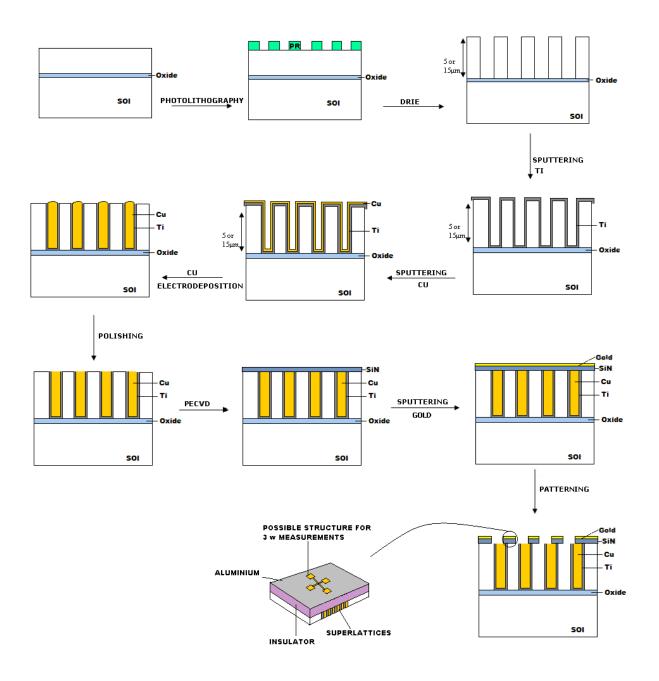

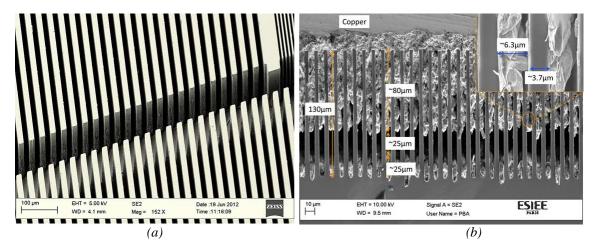

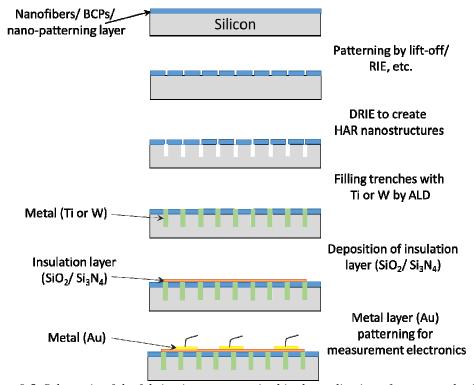

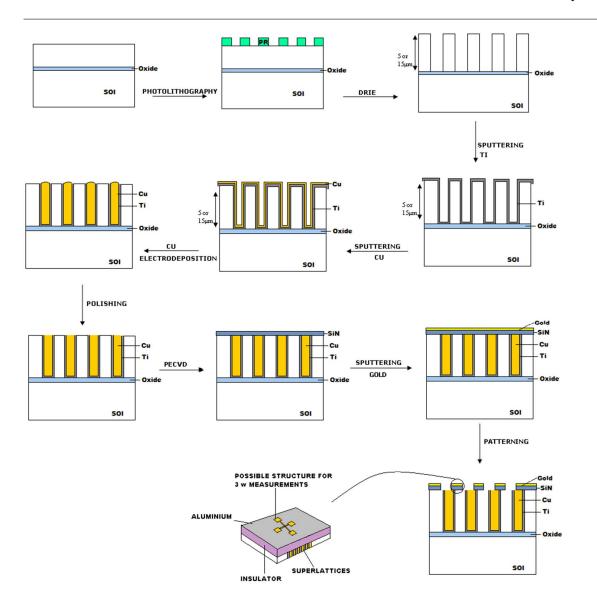

| Figure 3.18  | Process flow for the fabrication of microscale superlattices in silicon                                                                                                                                        | 52 |

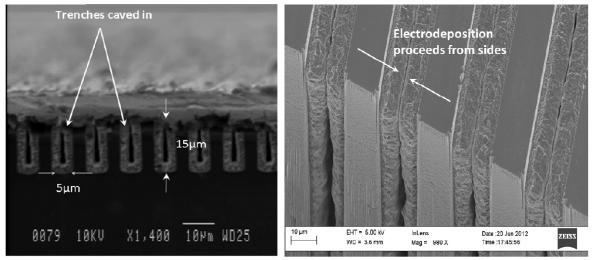

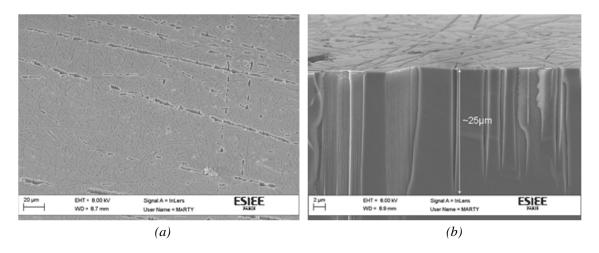

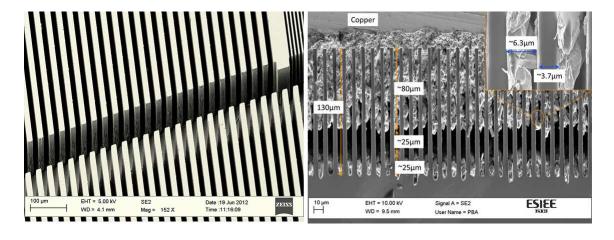

| Figure 3.19. | SEM images of (a) microsuperlattices post 100 µm-DRIE etch and (b) cross section of microsuperlattices post Cu electrodeposition on sputtered Ti adhesion layer.                                               | 53 |

| Figure 3.20. | (a) 'Dog-ear syndrome' when plating with higher current resulting in caved trenches and (b) properly electroplated trenches showing evidence of plating proceeding sideways and resulting in a central 'crack' | 54 |

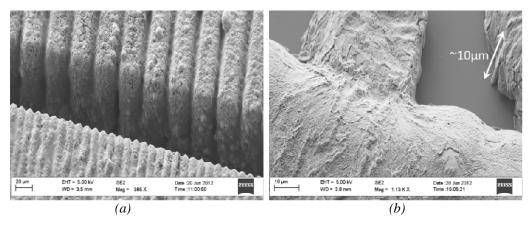

| Figure 3.21. | (a) Trenches after 6 hours of electrodeposition and (b) Measure of excess copper on top of the trenches                                                                                                        | 54 |

| Figure 3.22. | Sequence of nitric acid brushes to remove excess copper on top of superlattices.                                                                                                                               | 55 |

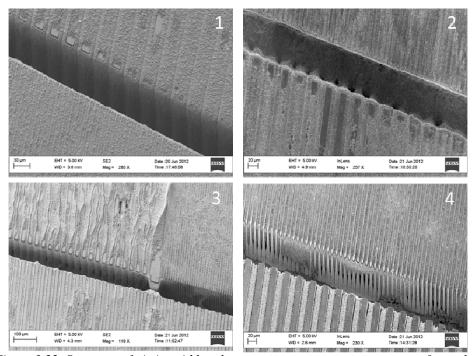

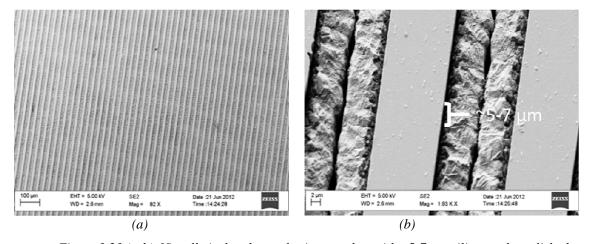

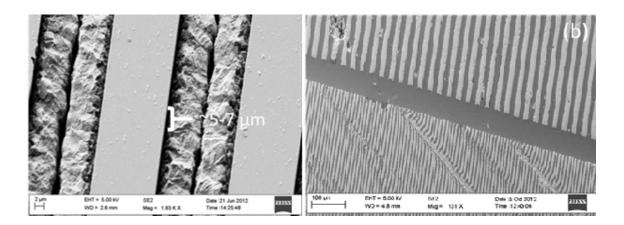

| Figure 3.23. | Visually isolated superlattice trenches with ~5-7 µm silicon to be polished.                                                                                                                                   | 55 |

| Figure 3.24  | <ul> <li>(a) Good results – electrically isolated trenches post-Si polishing,</li> <li>(b) Broken trenches from polishing action and (c) Ridge formed at the edge of pattern by discarded Si.</li> </ul>       | 56 |

|              |                                                                                                                                                                                                                |    |

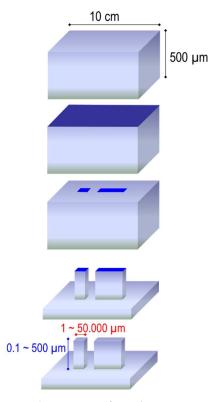

| Figure 4.1. | Sketch of the typical main steps for achieving vertical HAR silicon structures. Once the mask patterns are achieved on the top substrate surface (in this case using lithography on a thin-film deposited layer) one proceeds to DRIE for extruding those surface patterns into high-aspect ratio (HAR) structures having vertical sidewalls | 67 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.2. | Steps in a typical 'Bosch' DRIE                                                                                                                                                                                                                                                                                                              | 69 |

| Figure 4.3. | Typical Bosch process etching showing scalloping on the side walls on a circular trench of 75 $\mu$ m etched to a depth of ~300 $\mu$ m                                                                                                                                                                                                      | 69 |

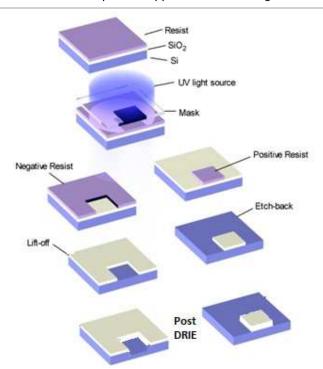

| Figure 4.4. | Illustration of the use of positive and negative photoresists to obtain contrasting thin film patterns on the wafer using the same mask. When needed, the thin film pattern can be used to produce etching of the underlying bulk of the substrate material                                                                                  | 71 |

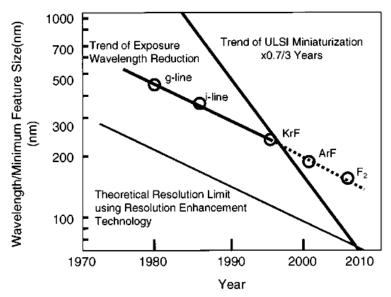

| Figure 4.5. | Comparison of photolithography wavelength trends with reduction in IC size                                                                                                                                                                                                                                                                   | 72 |

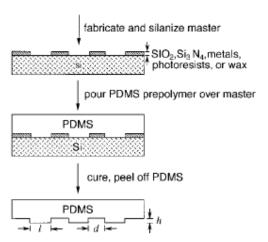

| Figure 4.6. | Replica molding process to create PDMS 'molds' from a 'master' substrate                                                                                                                                                                                                                                                                     | 73 |

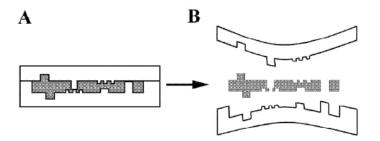

| Figure 4.7. | Schematic illustration of making replicas from a PDMS master. The white surfaces show PDMS masters which mold the grey substrate in between. Once cured, the two PDMS molds can then be peeled away leaving a patterned substrate behind                                                                                                     | 74 |

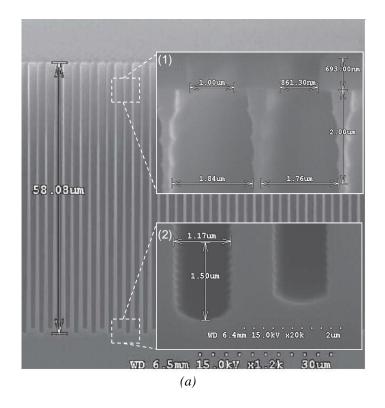

| Figure 5.1. | (a) Etch results with standard, non-optimized process, showing excessive bowing on top – inset (1) and available space at the bottom – inset (2) and (b) Etch results with increased passivation reduced bowing on top – inset (1) and narrowed trenches at the bottom – inset (2)                                                           | 79 |

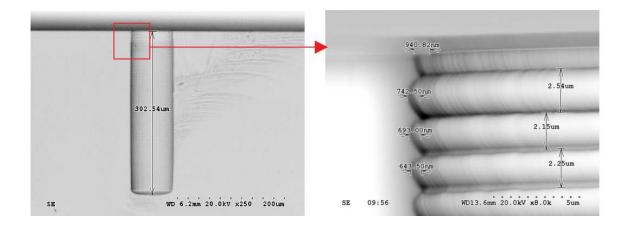

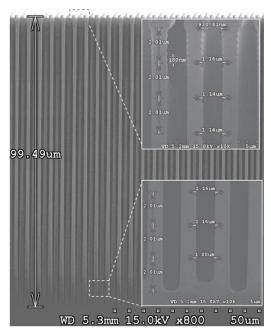

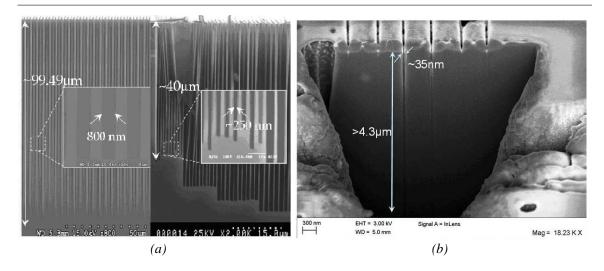

| Figure 5.2. | Extremely high aspect ratio (124:1) trenches having a width of 800 nm and a depth of 99.4 μm obtained using Set 1 parameters                                                                                                                                                                                                                 | 80 |

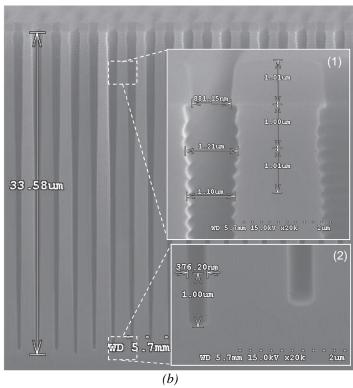

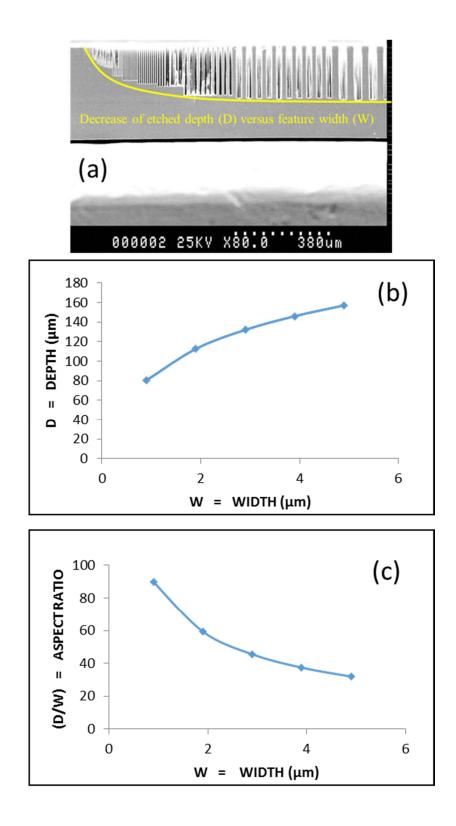

| Figure 5.3. | (a) SEM image illustrating the typical trend of etched depth (D) versus feature size (W); (b) and (c) are the corresponding graphical trends for both the etched depth (D) and the aspect ratio (D/W), respectively, which have opposite variations                                                                                          | 82 |

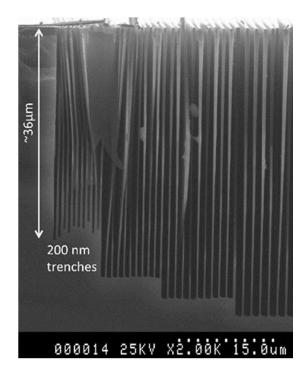

| Figure 5.4. | 250 nm-wide trenches with a depth of 40 µm (aspect ratio 160:1) obtained through the process in Set 2. Some of the walls collapsed during the dicing procedure                                                                                                                                                                               | 83 |

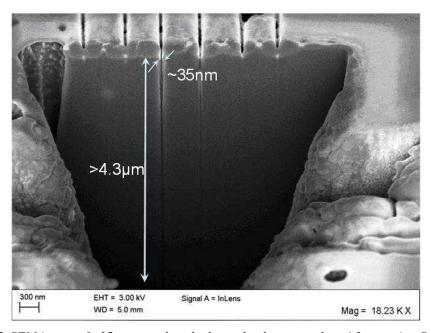

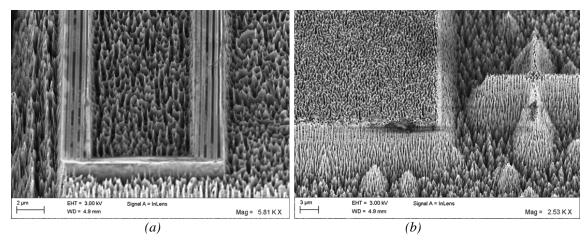

| Figure 5.5. | SEM image of ~35 nm trench etched to a depth greater than 4.3 µm using Set 3 parameters, hence with aspect ratio >125:1. A rectangular hole was etched using the FIB to allow cross-sectional visualization                                                                                                                                  | 85 |

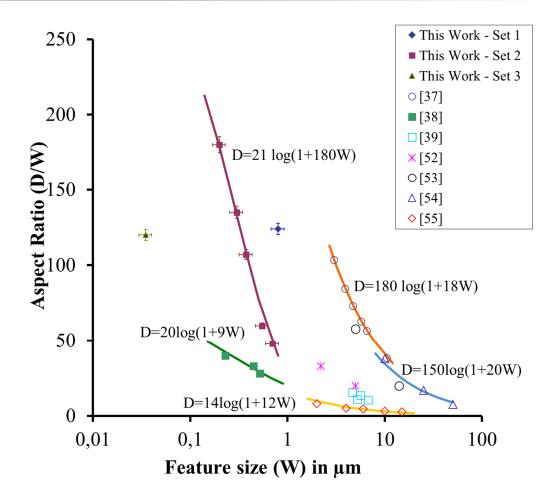

| Figure 5.6.  | Aspect ratio vs. feature size as studied by various groups in the micrometer range plotted on a logarithmic scale                                                                | 8  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

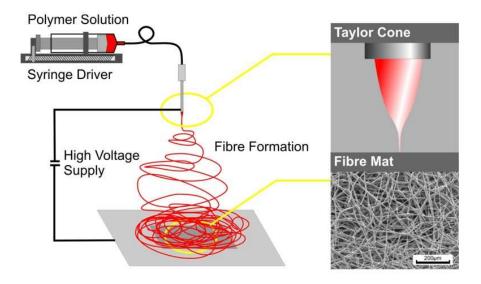

| Figure 6.1.  | Schematic of the electrospinning process                                                                                                                                         | 9  |

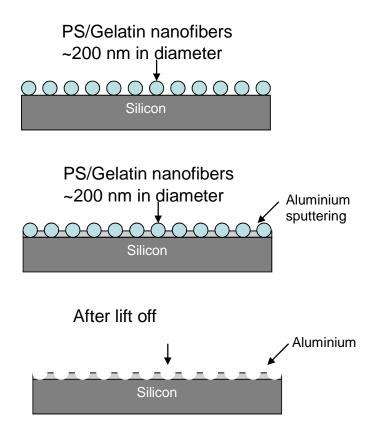

| Figure 6.2.  | Post processing steps of nanofibers to obtain HAR micro- and nanostructures in silicon.                                                                                          | 9  |

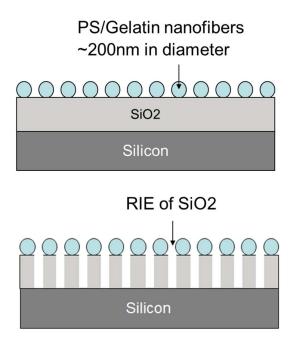

| Figure 6.3.  | Illustration of post processing step to obtain nanofibers on SiO <sub>2</sub> or using PS as mask to produce nanowalls                                                           | 9  |

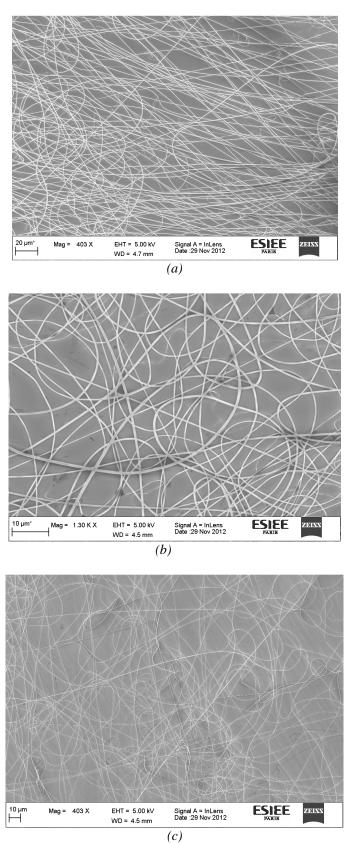

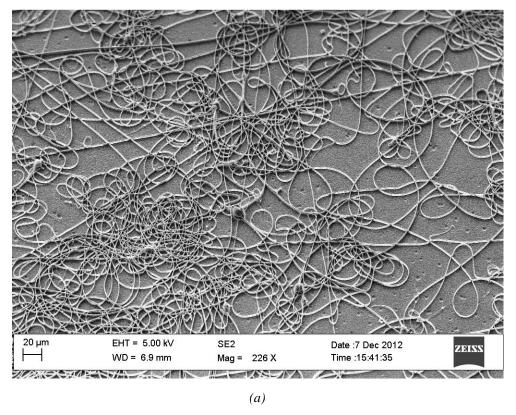

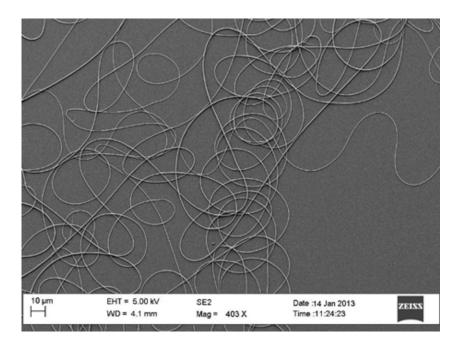

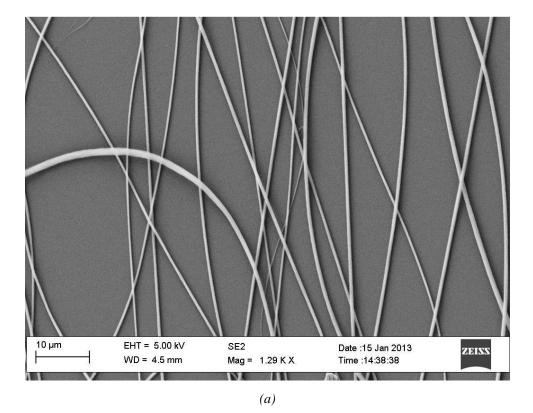

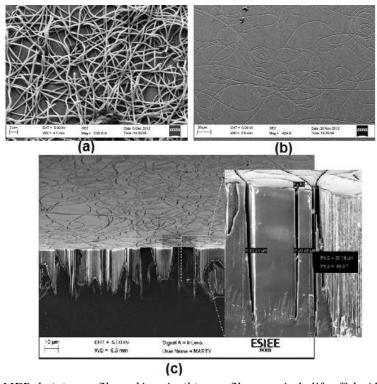

| Figure 6.4.  | SEM images of the nanofibers obtained through electrospinning –  (a) Sample 1, (b) Sample 6 and (c) Sample 22                                                                    | 9  |

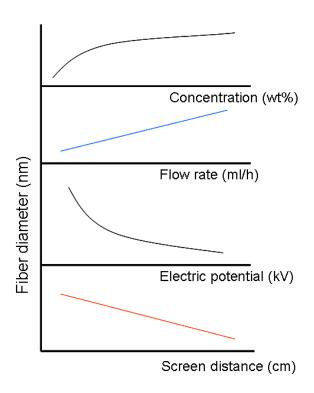

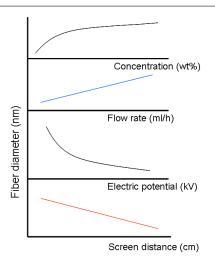

| Figure 6.5.  | Trend of effect of variation of electrospinning parameters on nanofiber diameter.                                                                                                | 9  |

| Figure 6.6.  | SEM image of (a) Sample 22 after Al deposition and before lift-off and (b) after lift-off                                                                                        | 9  |

| Figure 6.7.  | Partially successful Gelatin lift-off of Sample 23                                                                                                                               | 9  |

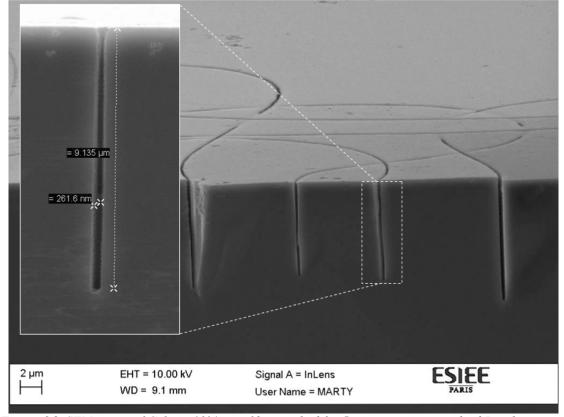

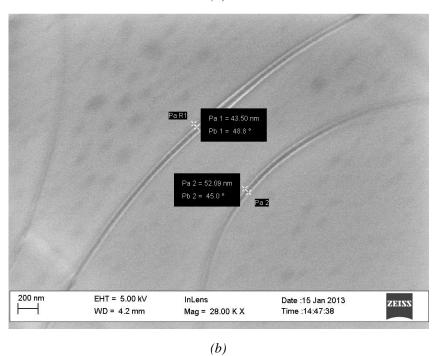

| Figure 6.8.  | SEM image of Gelatin 10% nanofibers etched for 5 minutes using standard Bosch process. The result is a 261 nm-wide, 9.1 µm-deep trench, corresponding to an aspect ratio of 35:1 | 9  |

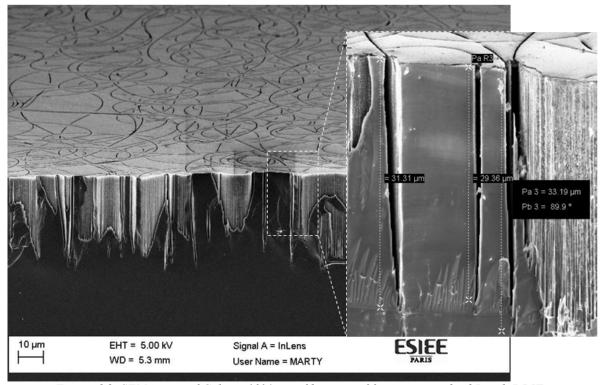

| Figure 6.9.  | SEM image of Gelatin 10% nanofibers post 30 minutes standard Bosch DRIE.                                                                                                         | 9  |

| Figure 6.10. | SEM image of the same sample shown in Figure 6.9, highlighting the undercut                                                                                                      | 9  |

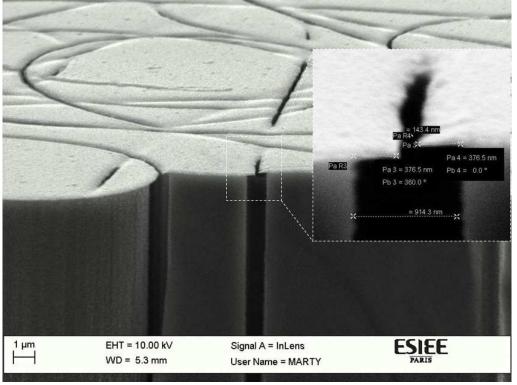

| Figure 6.11. | (a) Nano-wall formation with PS 12.5% template on SiO <sub>2</sub> and (b) closer-up view                                                                                        | 10 |

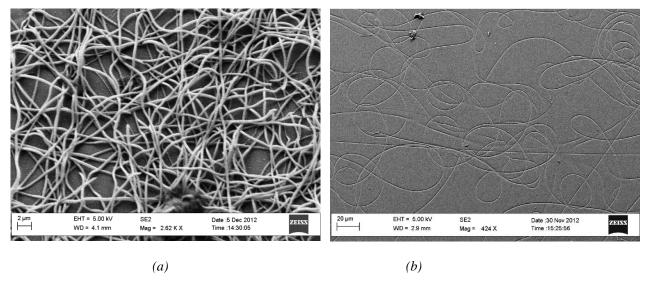

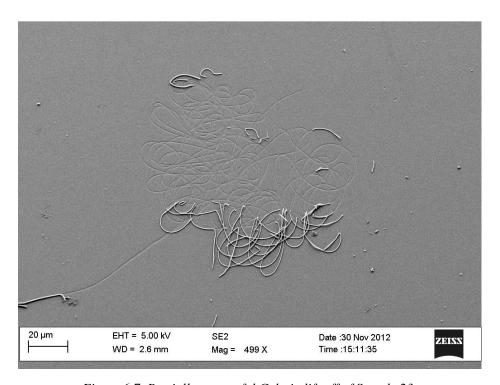

| Figure 6.12. | Set II nanofibers (a) before Al lift-off and (b) post lift-off                                                                                                                   | 10 |

| Figure 6.13. | SEMs of nanofiber-based trenches post 30 minutes standard Bosch DRIE in (a) top view and (b) cross-sectional view                                                                | 10 |

| Figure 6.14. | Photograph of sample prepared with strips of parallel conducting aluminum tape meant to act as alignment aides during electrospinning of nanofibers.                             | 10 |

| Figure 6.15. | (a, b) SEM images of 'quasi-aligned' nanofibers using parallel strips of conducting Al tape as electrodes                                                                        | 10 |

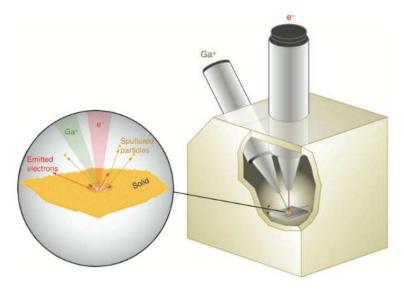

| Figure 7.1.  | Dual beam microscope having one column each for SEM and FIB                                                                                                                      | 10 |

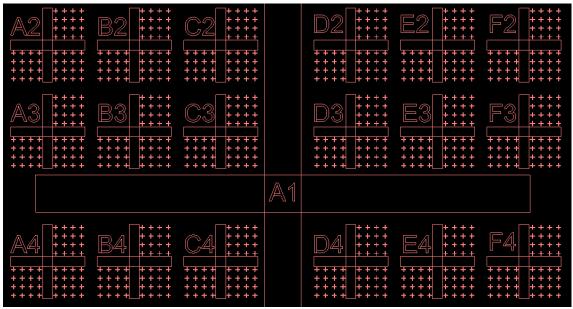

| Figure 7.2.  | Magnified view of one of the higher level crosses on the mask showing the other 2 levels of crosses for easy identification under the microscope                                                                           |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7.3.  | (a, b) Sets of lines/slices created by ion milling using FIB on Al over Si                                                                                                                                                 |

| Figure 7.4.  | SEM image after cryogenic etching of (a) FIB lines from Figure 7.2 (a) and (b) different parts of the same sample exhibiting a variety of BS surfaces.                                                                     |

| Figure 7.5.  | Cryogenic DRIE etch results for slices shown in Figure 7.3 (b)                                                                                                                                                             |

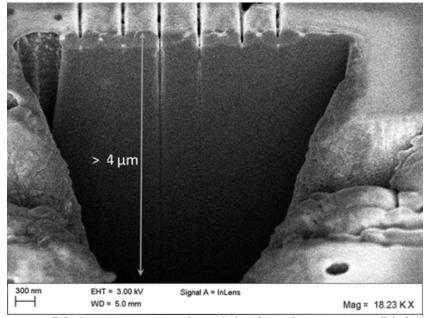

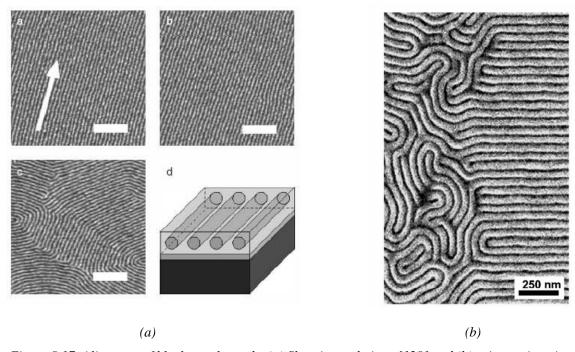

| Figure 8.1.  | Bulk configurations of diblock copolymer phases for increasing volume, <i>f</i> , of Polymer A to Polymer B                                                                                                                |

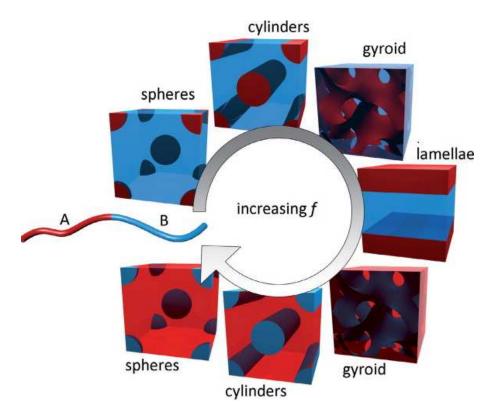

| Figure 8.2.  | Illustration of possible nanotechnological applications of block copolymers                                                                                                                                                |

| Figure 8.3.  | Chemical structure of PS-b-PMMA                                                                                                                                                                                            |

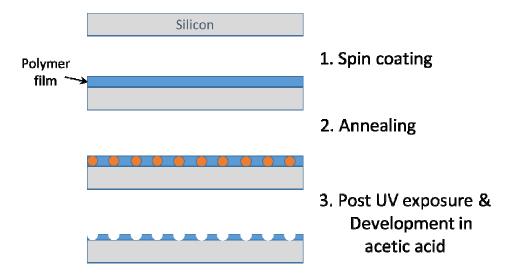

| Figure 8.4.  | Schematic illustration of the process to obtain self-assembling block copolymer patterns on a substrate                                                                                                                    |

| Figure 8.5.  | Illustration of the spin coating process                                                                                                                                                                                   |

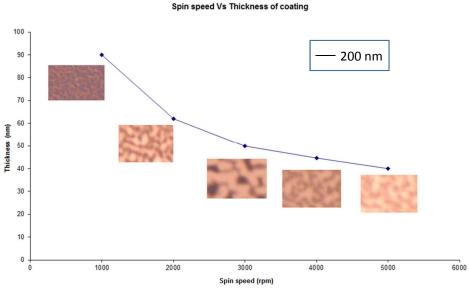

| Figure 8.6.  | Spin speed <i>vs.</i> thickness obtained of polymer films with optical microscope images of films annealed after deposition at different spin speeds                                                                       |

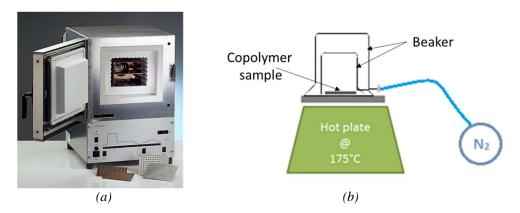

| Figure 8.7.  | Annealing setup for copolymer samples in (a) oven (not actual) and (b) hot plate                                                                                                                                           |

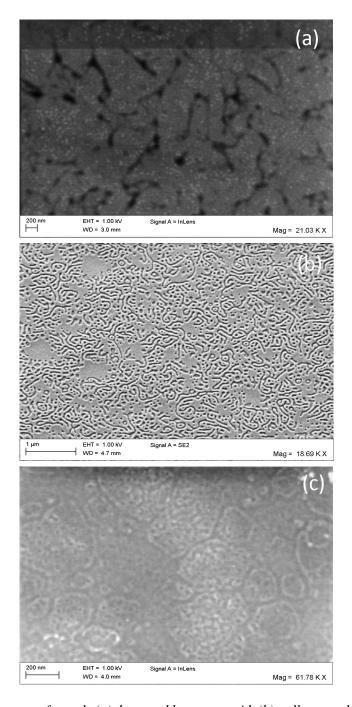

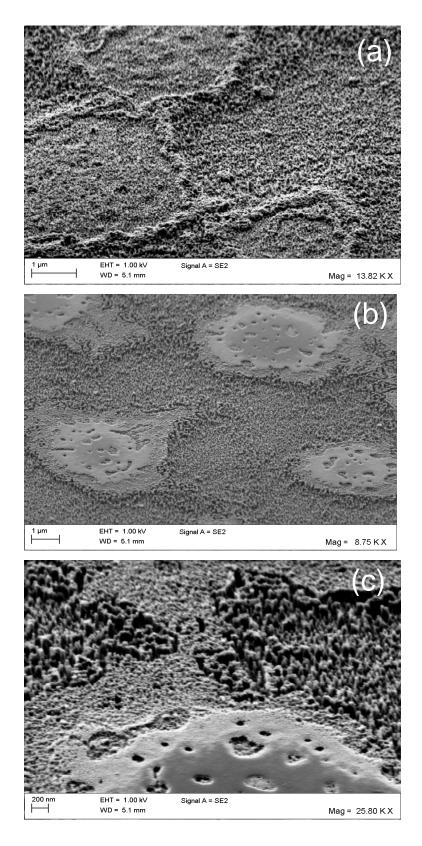

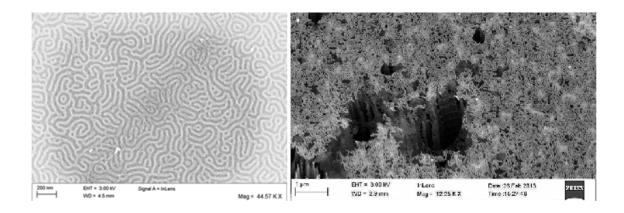

| Figure 8.8.  | SEM images of sample (a) destroyed by strong acid, (b) well-exposed and developed and (c) destroyed by over-exposure to UV                                                                                                 |

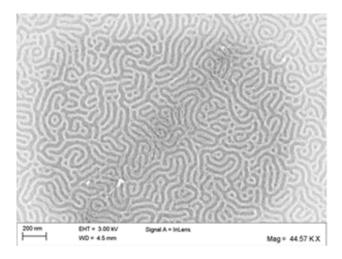

| Figure 8.9.  | SEM image of P6402 samples annealed for 5 hours on a hotplate and then exposed to UV for 30 minutes and developed in 60% acetic acid for 30 minutes                                                                        |

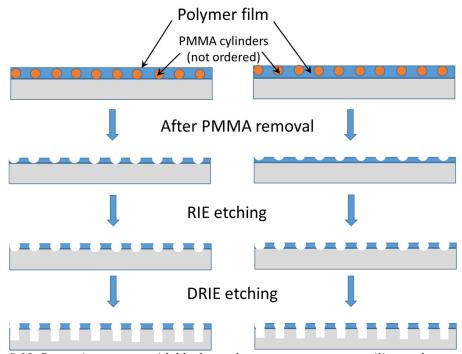

| Figure 8.10. | Patterning process with block copolymer nanostructure on silicon substrate: (a) PS domains after PMMA removal, (b) after RIE etching of polymer film, and (c) DRIE etching of exposed silicon using copolymer as template. |

| Figure 8.11. | Successful RIE etching: 30 W/15 mT/40 V/90 s                                                                                                                                                                               |

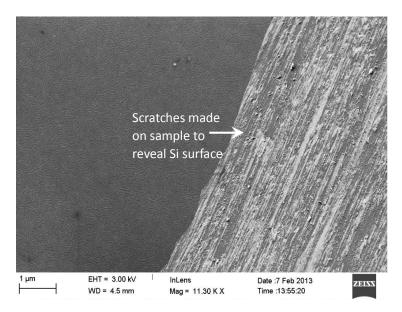

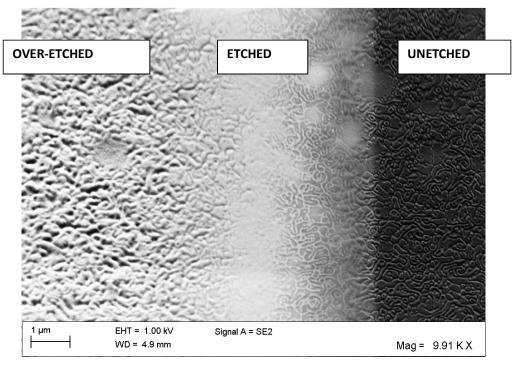

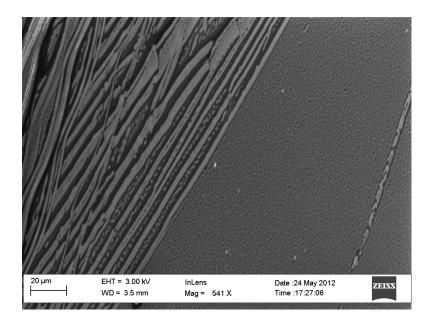

| Figure 8.12. | End of FIB etching using ion milling of 5 nA over an area of $\sim 10 \mu\text{m}^2$ . Clearly the left part of the image shows the patterns etched into the substrate while the middle part has begun etching and the right part remains unetched. | 128 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

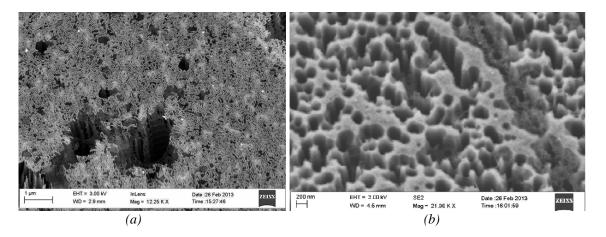

| Figure 8.13. | (a) 'Nano-black silicon', (b) polymer islands free of black Si and (c) copolymer pattern-template for nano-black silicon peaks                                                                                                                      | 131 |

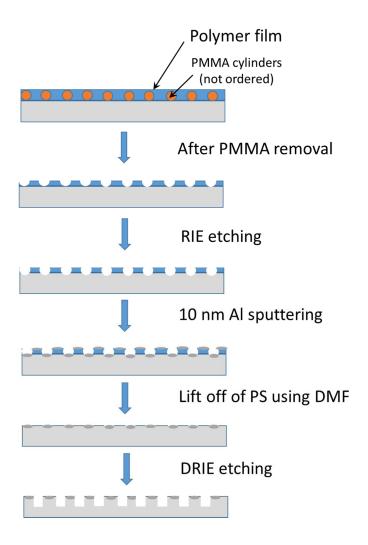

| Figure 8.14. | Schematic illustration of transfer of copolymer patterns to Al by lift-off                                                                                                                                                                          | 132 |

| Figure 8.15. | SEM image of block copolymer DRIE (a) post Al-lift off and (b) after Al-etch.                                                                                                                                                                       | 133 |

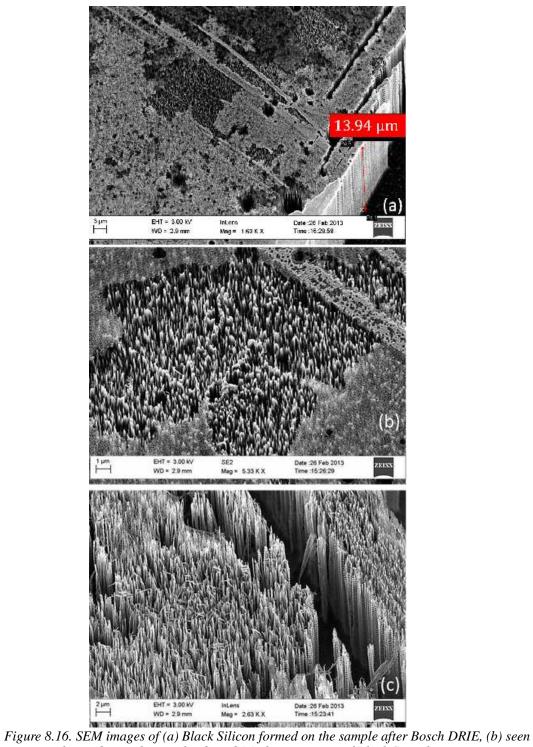

| Figure 8.16. | SEM images of (a) Black Silicon formed on the sample after Bosch DRIE, (b) seen alongside copolymer islands and (c) closer-up view of Black Si peaks                                                                                                | 134 |

| Figure 8.17. | Alignment of block copolymer by (a) shearing technique and (b) using an imaging layer                                                                                                                                                               | 135 |

| Figure 8.18. | . Schematic of a single 'cell' of the electric field layout. The electrodes in between the pads vary in dimension from 2 $\mu m$ -32 $\mu m$                                                                                                        | 136 |

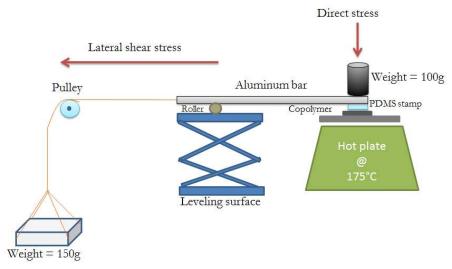

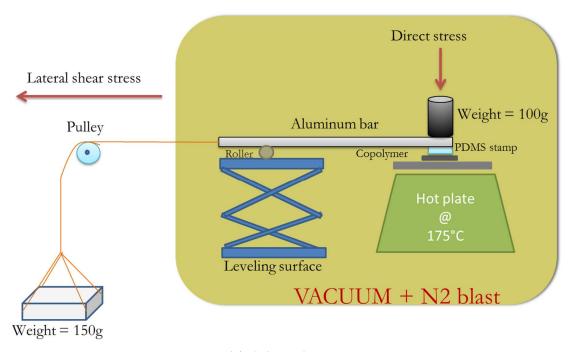

| Figure 8.19. | Illustration of the shear setup for aligning block copolymer                                                                                                                                                                                        | 137 |

| Figure 8.20. | Peeled off layers from excessive weight during shearing of PS-PMMA                                                                                                                                                                                  | 138 |

| Figure 8.21. | Modified shear alignment setup                                                                                                                                                                                                                      | 138 |

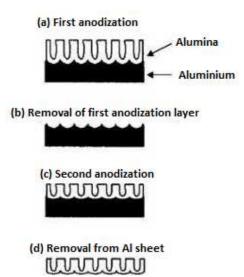

| Figure 9.1.  | Two-step anodization process for fabrication of porous alumina                                                                                                                                                                                      | 155 |

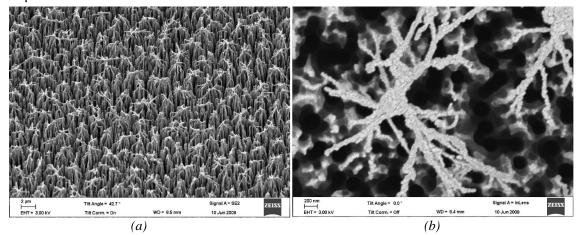

| Figure 9.2.  | SEM images of porous alumina in (a) top view and (b) cross-sectional view                                                                                                                                                                           | 156 |

| Figure 9.3.  | SEM images of (a) black silicon with aluminium on top and (b) closer up view                                                                                                                                                                        | 156 |

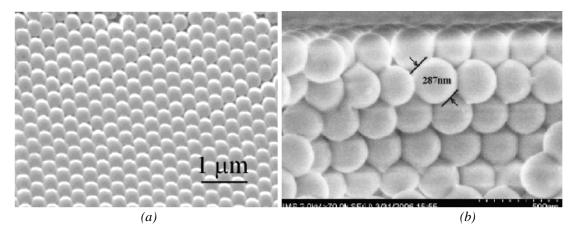

| Figure 9.4.  | SEM images of opals obtained by L-B method by (a) M.Bardosova, et al and (b) J. F. Dechézelles, et al                                                                                                                                               | 158 |

| Figure 9.5.  | Schematic of the fabrication steps required in the realization of nanosuperlattices                                                                                                                                                                 | 159 |

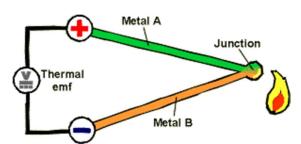

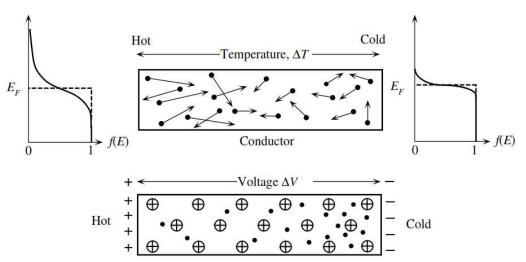

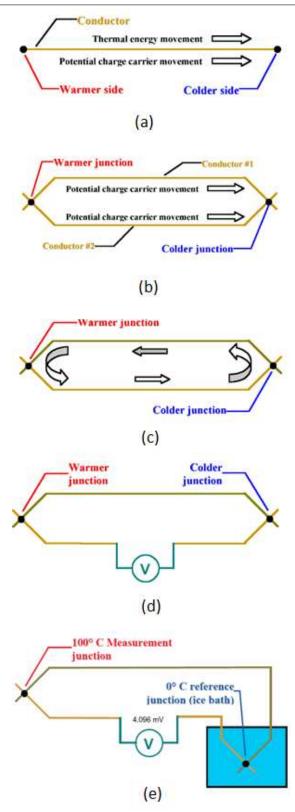

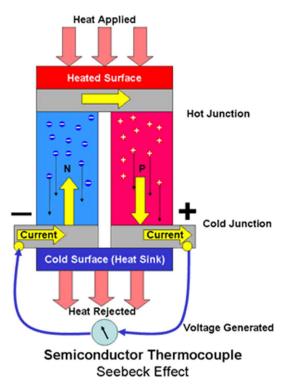

| Figure A.1. | Illustration of (a) the Seebeck effect between two metals and (b) sketch of electron velocities with longer arrows in the hot region, the corresponding energy distributions and the resultant equilibrium state, which leads to more electrons in the cold region, thus creating a voltage difference between the two regions                                                                                                                                                                    | 167 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure A.2. | Illustration of (a) capacity for charge carrier movement when excited by a thermal gradient, (b) similar conductors used to complete the circuit resulting in canceling out of net potential created, (c) dissimilar conductors employed to result in continuous flow of current in the closed circuit when the temperature gradient is maintained, (d) breaking the circuit allows for measurement of this voltage and (e) example of a thermocouple using a 0°C reference (reproduced from [5]) | 169 |

| Figure A.3. | Seebeck effect at the junction of two dissimilar semiconductors                                                                                                                                                                                                                                                                                                                                                                                                                                   | 170 |

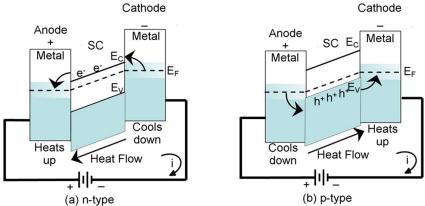

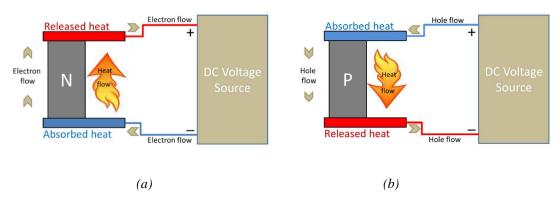

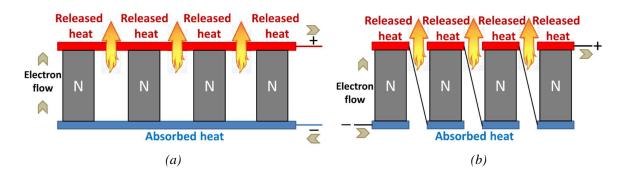

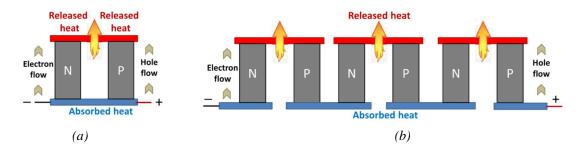

| Figure A.4. | Illustration of Peltier Effect in (a) <i>n</i> -type and (b) <i>p</i> -type material                                                                                                                                                                                                                                                                                                                                                                                                              | 172 |

| Figure A.5. | Similar semiconductor material electrically connected in (a) parallel and (b) series. In both cases, they are connected thermally in parallel                                                                                                                                                                                                                                                                                                                                                     | 174 |

| Figure B.1. | SEM images of (a) top view and (b) side view of BS samples                                                                                                                                                                                                                                                                                                                                                                                                                                        | 179 |

# Chapter 1 Introduction

#### 1.1. Background and motivation

With increasing demand for sustainable energy technologies, research in the area has escalated over the past couple of decades. Conventional renewable energy sources (solar, wind, and geothermal) supply only a small fraction of the electricity consumed, owing primarily to their relatively high cost with the key limitation of the wastage of heat as a by-product [1-5]. With the possibility of heat being an untapped source with huge potential, there is also significant interest in finding high efficiency and cost-effective technologies for generating electricity from residual heat.

A typical thermoelectric device consists of two different materials connected at both ends which either generates electrical power when subjected to a temperature difference (Seebeck effect) or generates a temperature difference when supplied with electrical power (Peltier effect). Depending on what effect takes place, the device may act as an electrical power generator or a refrigerator. In current world applications, thermoelectrics thus far have only found use in niche applications such as Peltier coolers for small-scale or localized cooling, mainly due to their moderate energy conversion efficiency and relatively high cost. In these applications, conventional mechanical refrigerators do not scale well from the weight, cost and efficiency point of view. Thermoelectric devices have also been used in radioisotope thermal generators for deepspace satellites [6-9] and remote electrical power generation for unmanned systems. Additional applications such as vehicle exhaust waste heat recovery [10-12] and autonomous sensors on the body [13-15] are actively being studied. Thermoelectric coolers are currently widely used for cooling of infrared detector cameras and temperature stabilization of semiconductor lasers. The use of Peltier coolers in relation to refrigeration of biological specimens/samples is an upcoming application of thermoelectrics as well. They offer an environmentally "green" solution as opposed to conventional methods using chlorofluorocarbons which are harmful to the atmosphere in terms of waste gas released. However, most efforts to this end are restricted to small-scale applications requiring localized cooling of small components in portable systems. Recently, a thermoelectric climate control system has been commercialized, and applications for small-scale beverage Chapter 1 Introduction

coolers are expanding as well [16]. In general, when considering the performance of small electronic systems, cooling is considered as a fundamental limit of performance improvement because temperature directly relates to noise. For example, cooling of laser diodes and infrared detectors to temperatures (T), between 100 and 200 K, would greatly improve performance and sensitivity of the device, hence leading to further applications that it can be put to use to. Thus, the payoff for the development of low-temperature thermoelectric refrigeration devices is escalating, and the requirement for compounds with properties optimized over wide temperature ranges has led to a much-expanded interest in new thermoelectric materials.

On the other hand, electrical power generation applications are also being investigated by the automotive industry, among others, as a means to produce electrical power from wasted heat of the engines for development of the 'next generation vehicle'. The research in applications range from power generation utilizing waste engine heat from the exhaust and radiator cooling system to seat coolers/warmers for comfort or electronic component cooling including beverage heaters or coolers [16-18]. In a similar manner, the deep space applications of NASA's *Voyager* and *Cassini* missions use radioactive thermoelectric generators (RTGs) to produce electrical energy [19-21]. In this case, the primary heat is produced by a radioactive material as it decays into non-radioactive state.

Study of thermoelectric materials is an extremely well-studied area of research spanning over 5 decades. Of particular interest when studying these materials are their characteristics that govern their performance in related applications. Traditionally, a good thermoelectric material is described based on its Figure of Merit (FOM), Z, which is defined as the dimensionless quantity

$$ZT = \frac{\sigma S^2 T}{\lambda} \tag{1.1}$$

where,  $\sigma$  is electrical conductivity of the material;  $\lambda$ , its thermal conductivity; S, the Seebeck coefficient of the material and T, the absolute temperature of the device. This dimensionless quantity, ZT, quantifies the material's ability to produce thermoelectric power.

An ideal thermoelectric material would thus have a high electrical conductivity to minimize Joule heating, low thermal conductivity to prevent thermal shorting and a high Seebeck coefficient to maximize the conversion efficiency between heat and electricity. But when attempting to achieve the qualities desired as discussed above, one is faced with some trade-offs in trying to maximize each of these quantities. Figure 1.1 (a) [23] is an illustration of the trade-

offs encountered through the maximization of the figure of merit of a 'natural' thermoelectric material. For instance, consider the example of metals as a thermoelectric material. A high electrical conductivity is almost always accompanied by a high thermal conductivity *and* a low Seebeck coefficient. On the other hand, for an engineered semiconductor material, the parameter that helps in achieving maximum ZT is the doping concentration. When the doping is high and the Fermi level of the semiconductor is around its band edge (the conduction band for an n-type semiconductor and the valence band for a p-type semiconductor – see Figure 1.1 (b)), the charge carriers occupy the highest energy state for excitation. Hence when provided with the momentum, they are released into the conduction band and thereby enhance the electrical conductivity of the material. The effects of the different thermoelectric properties with respect to the level of doping in the semiconductor are illustrated in the Figure 1.1 (a). As can be inferred, the semiconductor doping level can be used as a tuning parameter to maximize  $\sigma S^2$  which is shown in green as the bell curve, which is the quantity directly proportional to increasing ZT. The desired properties are highlighted by the blue region in the image.

Figure 1.1. (a) Illustration of FOM optimization and representation of the trade-offs. In the case of a semiconductor material, doping concentration is used as a tuning parameter (reproduced from [23]) and (b) Representation of the band energies and Fermi levels for highly doped n-type and p-type semiconductors.

Also it can be noted from Figure 1.1 (a) that the lattice contributions of the thermal conductivity,  $\lambda_{phonon}$  increase with doping over the electronic contributions,  $\lambda_{electron}$ . Typically

$\lambda_{electron}$  is  $1/3^{rd}$   $\lambda_{phonon}$  [19]. Thus, since the phonons are the vibrational lattice components that primarily carry heat, they can be dissipated by interface scattering and thus it is beneficial to maximize their contributions with higher doping [19].

Over the years, semiconductor composites such as Bismuth Telluride (Bi<sub>2</sub>Te<sub>3</sub>), Silicon Germanium (SiGe), *etc*. have found applications in thermoelectricity with *ZTs* in the range of 1-3 [24-28].

Continued interest in improving the thermoelectric figure of merit, ZT has led to research for new engineered materials and metamaterials, including material nanocomposites with improved thermal characteristics for applications in micro and nanoscale devices. The most actively studied materials of this kind include, but are not restricted to, improved Silicon Germanium stacked superlattice structures [29, 30] and thermoelectric oxide materials [31]. One can also cite other advanced materials such as half-Heusler alloys [32], Skutterudites [33] and complex chalcogenides [34], which are beyond the scope of this thesis.

#### 1.2. Thermoelectric metamaterials

Appendix I recalls the basic theoretical background on thermoelectric effects. Detailed explanations of the basic thermoelectric effects like the Seebeck, Peltier effects and the physics of these phenomena are explained in detail. In the next few sections, we concentrate on the thermoelectric behavior of metal-semiconductor multi-layered stacks, with special interest to those with nanometric thicknesses, namely, thermoelectric superlattices.

#### 1.2.1 Peltier effect and thermionic emission in metal-semiconductor junctions

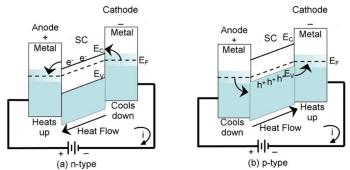

While the Peltier effect in semiconductor pairs gave rise to the concept of thermoelectric generators and thermoelectric coolers (see Appendix I for more details), it is interesting to revisit the Peltier effect in metal-semiconductor-metal junctions as it is very relevant to the work done in this thesis. Figure 1.2 [35] is an illustration of a typical metal-semiconductor-metal junction (a) in *n*-type configuration and then (b) in *p*-type configuration.

Consider the current flow in the clockwise direction. For electrons to enter the semiconductor conduction band from the metal, they must overcome the difference between  $E_C$  and  $E_{F.}$

Figure 1.2. Illustration of a typical metal-semiconductor-metal junction in (a) n-type configuration and (b) p-type configuration (redrawn from [35]).

Only the 'hottest electrons' (those with the highest kinetic energy) are likely to surmount the barrier (by thermionic emission). These electrons travel from right to left encountering no barrier while entering the metal again, hence creating depletion on the cathode and a gain on the anode. Therefore, one side heats up while the other cools down. The same concepts hold good for the *p*-type material with the primary charge carriers being the holes instead of the electrons.

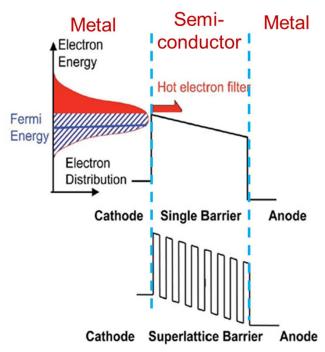

#### 1.2.2. Thermionic emission

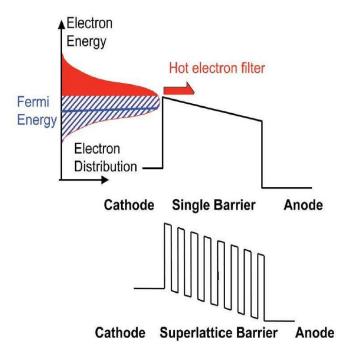

Considering a multilayered metal-semiconductor stack (Figure 1.3), the band offset between each pair of junctions (Figure 1.4) acts as a 'hot electron filter', allowing through, only the highest energy electrons [35] surmount the barrier by *Thermionic Emission*. These hottest electrons will be the main contributors to the electrical conduction. Furthermore, in case each succeeding layer interface is spaced very close (nanometric range) from one another, we can also have *Phonon Scattering*, which is a mechanism which by scattering the heat carrying lattice vibrational component, the phonons, can reduce thermal conductivity at the interfaces between successive layers when they are in the nanometer scale. At the end, the net result can be a reduction of thermal conductivity while maintaining a high electrical conductivity, leading to a potential increase of the figure of merit, ZT, which scales as  $\sigma/\lambda$ .

#### 1.2.3. Barrier thickness requirements

It has been theoretically ascertained in literature that thermoelectric parameters are enhanced when the layer thickness is lesser than the mean-free-path of the electrons. (~100 nm for most semiconductor [36]).

Figure 1.3. Schematic diagram of a typical two material superlattice structure.

Figure 1.4. Representation of barrier thresholds for increased thermionic emission.

To ensure thermionic emission, i.e., by overcoming the energy barriers, the barrier thickness should be greater than 10 nm at ambient temperatures. If the barrier is inferior to 10 nm, there is a *tunneling effect*, i.e., the electrons simply pass through the barrier rather than overcoming them. The thermionic emission threshold and succession of barriers is shown in Figure 1.4 [36]. It then follows that a succession of barriers might be better than a single barrier for increased thermionic emission. Concluding from the above-stated points, we can conservatively conclude that barrier thickness should be between 10 and 100 nm.

Having a succession of barriers allows for heat dissipation by band offset as well as electrical conduction by thermionic emission. Through research of previous work done in this area, it has been theoretically concluded that a resultant structure made with this concept will have better thermoelectric properties when compared to bulk material. We therefore arrive upon the structure of a *superlattice* (see Figure 1.3). A superlattice is a metamaterial which is composed of a heterogeneous material resulting from a multilayer structure of two or more materials with a succession of potential barriers, thus allowing better thermoelectric conversion than classical bulk materials by cross-plane carrier transport.

#### 1.3 Conclusions from previous work

Whilst trying to introduce some novelty into solving this conundrum, it is important to take the inferences from the work done by other groups in this area. The following is a synopsis of the conclusions drawn from the bibliography of the relevant papers:

- ❖ Tall metal barriers associated with a degenerated semiconductor will increase the density of 'hot electrons' that are filtered [37].

- ♦ Multiple barriers using Metal-Semiconductor Interfaces can increase thermoelectric power factor due to non-conservation of lateral momentum [37].

- ❖ Controlled roughness at heterostructure interfaces can break the in-plane translation variance and lateral momentum conservation. This allows the high-energy electrons in any direction to participate in current transport [41].

- Reducing barrier thickness increases thermionic emission. However reducing them too much may result in *Tunneling* [40].

It thus follows that we are likely to have an effective device in fabricating a superlattice using a metal-semiconductor junction ensuring that they are spaced closely to each other (in the nanometer scale) to allow 'hot-electron' filtering and effective thermoelectric cooling.

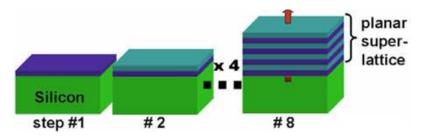

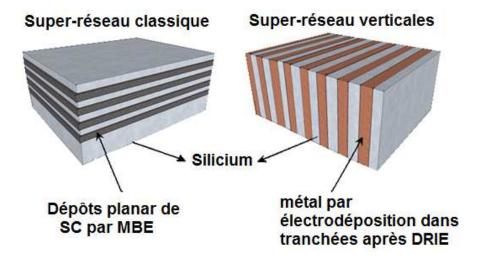

Traditionally, superlattices have been fabricated in the planar form [43-47]. Typically, to accomplish this requires multiple planar deposits using molecular beam epitaxy (MBE) which is a very expensive form of depositing successive ultrathin layers. Figure 1.5 is a schematic representation of conventional planar superlattices.

Figure 1.5. Schematic representation of planar superlattices used in the traditional approach.

#### 1.4. Objectives and scope of this thesis

The focus of this thesis is on the study and realization of new silicon-based structured metamaterials with improved thermoelectric performances and which might be suitable for use in various applications such as hot-spot cooling on overheating chips, to construct more efficient thermoelectric modules for use in refrigeration and in energy harvesting, as described the applications of thermoelectric devices in the previous section. The motivation behind using silicon as the base material stems from its familiarity in the semiconductor and MEMS industries whilst being able to accurately control dimensions of the structures to be fabricated down to the nanoscale and with extremely high aspect ratio, which appears as a great advantage towards achieving a new class of novel thermoelectric metamaterials based on vertical superlattices, as detailed hereafter. The technologies for working with silicon are fairly well developed and this presents us with the opportunity to improve further open studied techniques to achieve high aspect ratio feature sizes in the nanoscale as is required towards reaching our objective. Besides, working with silicon reduces the cost of the end product and it allows co-integration with electronic circuits as well. These are other driving forces behind exploring technologies in making metamaterials using silicon in order to enhance thermoelectric performances for usage in on-chip thermal management.

With the Moore's law predicting the number of transistors on an IC doubles approximately every two years [42], the dissipation of heat is also a significant issue preventing the realization of more advanced devices due to high device failure rate as the heat overcomes the device

capabilities. The inclusion of microscale integrated coolers on the microprocessor chips could be a highly significant advancement, allowing higher clock speeds to be realized.

The ultimate objective of our research team is to design, produce and use thermoelectric devices fashioned from improved thermal property materials for heat dissipation of a hot spot on a chip. The basic thermoelectric device built in this thesis involves metamaterials in the form of 'vertical superlattice' structures in silicon. Conventional superlattices have been already fabricated but they are limited to the planar form [23] involving multiple-layer deposition of ultra-thin films. Indeed, the traditional way of fabrication superlattices involves multiple planar deposits using molecular beam epitaxy (MBE) leading to nanoscale multi-layered material stacks, which turns out to be an extremely lengthy and expensive fabrication step. The key disadvantages of such structures can be summarized as below:

- Energy conversion efficiency is proportional to the number of layers in the superlattices In other words, efficient devices need a large number of deposits.

- ❖ Such devices only transmit electrons whose kinetic energy (KE) in the direction perpendicular to the potential barrier is large enough. Therefore, many "hot electrons" with large in-plane momentum are blocked by the barrier and do not contribute to heat transfer. The electrons have to be seen as carriers of an electrical charge as well as heat quanta, namely phonons.

Hence, the refrigeration function is not cost effective compared to the traditional techniques, even by using chemical vapour deposition (CVD) instead of MBE.

In this thesis we propose exploring a solution to the disadvantages of the conventional superlattices: *Vertical superlattices in silicon*. The main advantages of these are as below:

- ❖ Vertical Superlattices could be fabricated directly into Silicon with just 3 main steps: (i) a single patterning step, (ii) a single etch step with high aspect ratio and finally (iii) a conformal deposit of a complementary material to silicon.

- Proceeding this way greatly facilitates in principle, the manufacturing process and it also significantly reduces the manufacturing costs.

- ❖ The proposed approach offers alternative shapes to the one-dimensional periodic superlattices. Several two-dimensional shapes, either periodic or not, can be considered.

- \* High-energy electrons in any direction can potentially contribute to heat transfer, therefore increasing electrical conductivity by further introduction of *controlled*