###

#### ▶ To cite this version:

Oumar Maïga. An integrated language for the specification, simulation, formal analysis and enactment of discrete event systems. Other [cs.OH]. Université Blaise Pascal - Clermont-Ferrand II, 2015. English. NNT: 2015CLF22662. tel-01330780

### HAL Id: tel-01330780 https://theses.hal.science/tel-01330780

Submitted on 13 Jun 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre : D. U : 2662

E D S P I C: 738

#### UNIVERSITE BLAISE PASCAL - CLERMONT II

ECOLE DOCTORALE SCIENCES POUR L'INGENIEUR DE CLERMONT-FERRAND &

UNIVERSITE DES SCIENCES, TECHNIQUES ET TECHNOLOGIES DE BAMAKO

### Thèse

Présentée par

Oumar Y. MAIGA

pour obtenir le grade de

## DOCTEURD'UNIVERSITÉ

**SPECIALITE**: Informatique

#### Titre de la thèse :

# An Integrated Language for the Specification, Simulation, Formal Analysis and Enactment of Discrete Event Systems

Soutenue publiquement le 22/12/2015 devant le jury :

Prof. Jean-François Santucci

Prof. Claudia Frydman

Prof. Mamadou Kaba Traoré

Prof. Ouaténi Diallo

Prof. Moussa Lô

Dr. Jacqueline Konaté

Rapporteur et examinateur Rapporteur et examinateur Directeur de thèse

Co-directeur de thèse

Examinateur

Examinateur

### **Abstract**

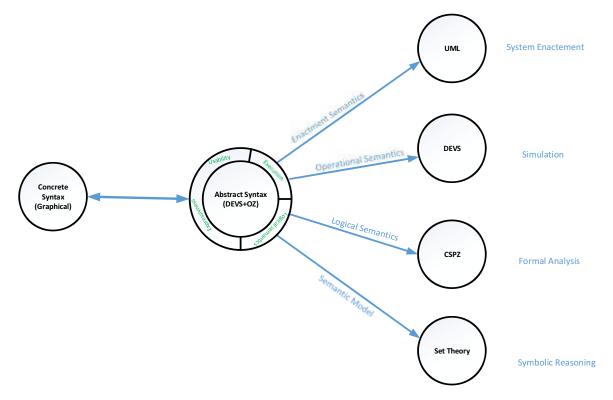

This thesis proposes a methodology which integrates formal methods in the specification, design, verification and validation processes of complex, concurrent and distributed systems with discrete events perspectives. The methodology is based on the graphical language HILLS (High Level Language for System Specification) that we defined. HiLLS integrates software engineering and system theoretic views for the specification of systems. Precisely, HiLLS integrates concepts and notations from DEVS (Discrete Event System Specification), UML (Unified Modeling Language) and Object-Z. The objectives of HILLS include the definition of a highly communicable graphical concrete syntax and multiple semantic domains for simulation, prototyping, enactment and accessibility to formal analysis. Enactment refers to the process of creating an instance of system executing in real-clock time. HILLS allows hierarchical and modular construction of discrete event systems models while facilitating the modeling process due to the simple and rigorous description of the static, dynamic, structural and functional aspects of the models.

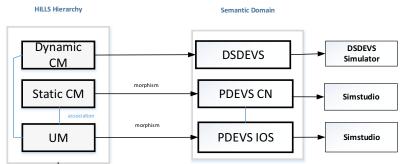

Simulation semantics is defined for HiLLS by establishing a semantic mapping between HiLLS and DEVS; in this way each HiLLS model can be simulated by a DEVS simulator. This approach allow DEVS users to use HiLLS as a modeling language in the modeling phase and use their own stand alone or distributed DEVS implementation package to simulate the models.

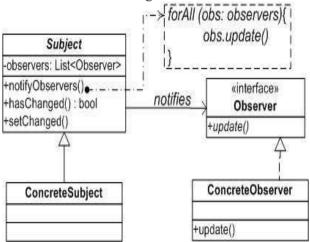

An enactment of HiLLS models is defined by adapting the observer design-pattern to their implementation.

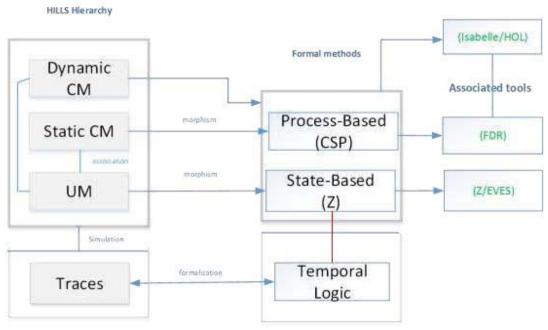

The formal verification of HiLLS models is made by establishing morphisms between each level of abstraction of HILLS and a formal method adapted for the formal verification of the properties at this level. The formal models on which are made the formal verification are obtained from HILLS specifications by using the mapping functions. The three levels of abstraction of HILLS are: the Composite level, the Unitary level and the Traces level. These levels correspond respectively to the following levels of the system specification hierarchy proposed by Zeigler: CN (Coupled Network), IOS (Input Output System) and IORO (Input Output Relation Observation). We have established morphisms between the Composite level and CSP (Communicating Sequential Processes), between Unitary level and Z and we expect to use temporal logics like LTL, CTL and TCTL to express traces level properties. HiLLS allows the specification of both static and dynamic structure systems. In case of dynamic structure systems, the composite level integrates both sate-based and process-based properties. To handle at the same time state-based and process-based properties, morphism is established between the dynamic composite level and CSPZ (a combination of CSP and Z);

The verification and validation process combine simulation, model checking and theorem proving techniques in a common framework. The model checking and theorem proving of HILLS models are based on an integrated tooling framework composed of tools supporting the notations of the selected formal methods in the established morphisms.

We apply our methodology to modeling of the Alternating Bit Protocol (ABP) and the Automated Teller Machine (ATM).

The thesis has contributed to the following publications:

- 1. Ighoroje, U.B., Maïga, O., Traoré, M.K. The Formal Framework for the DEVS Driven Modeling Language. In Proceedings of European Modeling and Simulation Symposium (EMSS) 2011, Rome (Italy), September 2011.

- 2. Ighoroje, U.B., Maïga, O., Traoré, M.K.: The DEVS-driven modeling language: syntax and semantics definition by meta-modeling and graph transformation. In: Proceedings of the 2012 Symposium on Theory of Modeling and Simulation DEVS Integrative M&S Symposium Article No. 49. Society for Computer Simulation International San Diego, CA, USA (2012).

- 3. Maïga O., Ighoroje U.B. and Traoré M.K. Intégration des Méthodes formelles dans la spécification et la vérification et validation des modèles de simulation. In Proceedings of MOSIM 2012, Bordeaux (France), June 2012.

- 4. Maïga O., Ighoroje U.B. and Traoré M.K.. DDML: A support for communication in Modeling and Simulation. 3rd IEEE Track on Collaborative Modeling and Simulation-CoMetS'12. Toulouse (France), June 2012.

- 5. Maïga O and Traoré M.K. Approche Formelle de vérification et validation des modèles de simulation. In : Journées Scientifiques de l'Ecole Doctorale des Sciences pour l'Ingénieur (EDSPI), Clermont-Ferrand (France), June 2013.

- 6. Maïga O. and Traoré M.K. An Integrated approach to the specification, simulation, formal analysis and enactment of discrete event systems. AUSTECH 2015, Abuja, Nigeria, October 2015.

- 7. Aliyu H. O., Maïga O., Abdoul-Wahab H. I. and Traoré M.K. Introducing HiLLS: High Level Language for System Specification. AUSTECH 2015, Abuja, Nigeria, October 2015. *Best Presentation Award*.

- 8. Maïga O., Aliyu H. O. and Traoré M.K. A New Approach to Modeling Dynamic Structure Systems. Accepted for publication at European Simulation and Modeling Conference (ESM'2015), Leicester, United Kingdom, October 2015.

- 9. Aliyu H. O., Maïga O. and Traoré M.K. A Framework for Discrete Event Systems enactment. Accepted for publication at European Simulation and Modeling Conference (ESM'2015), Leicester, United Kingdom, October 2015.

#### Papers under review:

- 1. Aliyu H. O., Maïga O. and Traoré M.K. AnnoGram4MD: A Language for Annotating Grammars for High Quality Metamodel Derivation. Submitted to the 28<sup>th</sup> International Conference on Software Engineering, Austin,TX, May 14-22, 2016

- 2. Aliyu H. O., Maïga O., and Traoré M.K. Yet another Visual Language for DEVS. International Journal of Modeling and Simulation and Scientific Computing.

**Keywords:** HiLLS, System Theory, Software Engineering, Modeling and Simulation, formal methods, Verification and Validation, Enactment

### Résumé

Titre: Un Langage Intégré pour la Spécification, Simulation, Analyse Formelle et En-action des Systèmes à évènements discrets.

Cette thèse propose une méthodologie qui intègre les méthodes formelles dans la spécification, la conception, la vérification et la validation des systèmes complexes concurrents et distribués avec une perspective à événements discrets. La méthodologie est basée sur le langage graphique HILLS (High Level Language for System Specification) que nous avons défini. HiLLS intègre des concepts de génie logiciel et de théorie des systèmes pour une spécification des systèmes. Précisément, HiLLS intègre des concepts et notations de DEVS (Discrete Event System Specification), UML (Unified Modeling Language) et Object-Z. Les objectifs de HILLS incluent la définition d'une syntaxe concrète graphique qui facilite la communicabilité des modèles et plusieurs domaines sémantiques pour la simulation, le prototypage, l'enaction et l'accessibilité à l'analyse formelle. L'Enaction se définit par le processus de création d'une instance du système qui s'exécute en temps réel (par opposition au temps virtuel utilisé en simulation). HiLLS permet la construction hiérarchique et modulaire des systèmes à événements discrets grâce à une description simple et rigoureuse des aspects statiques, dynamiques et fonctionnels des modèles.

La sémantique pour simulation de HiLLS est définie en établissant un morphisme sémantique entre HiLLS et DEVS; de cette façon chaque modèle HiLLS peut être simulé en utilisant un simulateur DEVS. Cette approche permet aux utilisateurs DEVS d'utiliser HiLLS comme un langage de spécification dans la phase de modélisation et d'utiliser leurs propres implémentations locales ou distribuées de DEVS en phase de simulation.

L'enactment des modèles HiLLS est basé sur une adaptation du patron de conception Observateur pour leur implémentation.

La vérification formelle est faite en établissant un morphisme entre chaque niveau d'abstraction de HiLLS et une méthode formelle adaptée pour la vérification formelle des propriétés à ce niveau. Les modèles formels sur lesquels sont faites les vérifications formelles sont obtenus à partir des spécifications HiLLS en utilisant des morphismes. Les trois niveaux d'abstraction de HiLLS sont : le niveau composite, le niveau unitaire et le niveau des traces. Ces niveaux correspondent respectivement aux trois niveaux suivants de la hiérarchie de spécification des systèmes proposée par Zeigler : CN (Coupled Network), IOS (Input Output System) et IORO (Input Output Relation Observation). Nous avons établi des morphismes entre le niveau Composite et CSP (Communicating Sequential Processes), entre le niveau unitaire et Z, et nous utilisons les logiques temporelles telles que LTL, CTL et TCTL pour exprimer les propriétés sur les traces. HiLLS permet à la fois la spécification des modèles à structures statiques et les modèles à structures variables. Dans le cas des systèmes à structures variables, le niveau composite intègre à la fois des propriétés basées sur les états et les processus. Pour prendre en compte ces deux aspects, un morphisme est défini entre le niveau Composite de HiLLS et CSPZ (une combinaison de CSP et Z).

Le processus de vérification et de validation combine la simulation, la vérification exhaustive de modèle (model checking) et la preuve de théorèmes (theorem proving) dans un Framework

commun. La vérification exhaustive et la preuve de théorèmes sur les modèles HiLLS sont basées sur les outils associés aux méthodes formelles sélectionnées dans les morphismes.

Nous appliquons la méthodologie de modélisation de HiLLS à la modélisation du Alternating Bit Protocol (ABP) et à celle d'un guichet automatique de dépôt de billet (Automated Teller Machine) (ATM).

Cette thèse a contribué aux publications suivantes:

- 1. Ighoroje, U.B., Maïga, O., Traoré, M.K. The Formal Framework for the DEVS Driven Modeling Language. In Proceedings of European Modeling and Simulation Symposium (EMSS) 2011, Rome (Italy), September 2011.

- 2. Ighoroje, U.B., Maïga, O., Traoré, M.K.: The DEVS-driven modeling language: syntax and semantics definition by meta-modeling and graph transformation. In: Proceedings of the 2012 Symposium on Theory of Modeling and Simulation DEVS Integrative M&S Symposium Article No. 49. Society for Computer Simulation International San Diego, CA, USA (2012).

- 3. Maïga O., Ighoroje U.B. and Traoré M.K. Intégration des Méthodes formelles dans la spécification et la vérification et validation des modèles de simulation. In Proceedings of MOSIM 2012, Bordeaux (France), June 2012.

- 4. Maïga O., Ighoroje U.B. and Traoré M.K.. DDML: A support for communication in Modeling and Simulation. 3rd IEEE Track on Collaborative Modeling and Simulation-CoMetS'12. Toulouse (France), June 2012.

- 5. Maïga O and Traoré M.K. Approche Formelle de vérification et validation des modèles de simulation. In : Journées Scientifiques de l'Ecole Doctorale des Sciences pour l'Ingénieur (EDSPI), Clermont-Ferrand (France), June 2013.

- 6. Maïga O. and Traoré M.K. An Integrated approach to the specification, simulation, formal analysis and enactment of discrete event systems. AUSTECH 2015, Abuja, Nigeria, October 2015.

- 7. Aliyu H. O., Maïga O., Abdoul-Wahab H. I. and Traoré M.K. Introducing HiLLS: High Level Language for System Specification. AUSTECH 2015, Abuja, Nigeria, October 2015. *Prix de la Meilleure Présentation*.

- 8. Maïga O., Aliyu H. O. and Traoré M.K. A New Approach to Modeling Dynamic Structure Systems. Accepted for publication at European Simulation and Modeling Conference (ESM'2015), Leicester, United Kingdom, October 2015.

- 9. Aliyu H. O., Maïga O. and Traoré M.K. A Framework for Discrete Event Systems enactment. Accepted for publication at European Simulation and Modeling Conference (ESM'2015), Leicester, United Kingdom, October 2015.

#### Articles en cours d'évaluation:

- 1. Aliyu H. O., Maïga O. and Traoré M.K. AnnoGram4MD: A Language for Annotating Grammars for High Quality Metamodel Derivation. Submitted to the 28<sup>th</sup> International Conference on Software Engineering, Austin,TX, May 14-22, 2016

- **2.** Aliyu H. O., Maïga O. and Traoré M.K. Yet another Visual Language for DEVS. International Journal of Modeling and Simulation and Scientific Computing.

**Mots clés:** HiLLS, Théorie des Systèmes, Génie logiciel, Modélisation et Simulation, Méthodes Formelles, Vérification et Validation, Enaction

### **Acknowledgment/Remerciements**

Je tiens tout particulièrement à exprimer ma plus profonde gratitude à Pr Mamadou Kaba Traoré de l'Université Blaise Pascal de Clermont, pour avoir dirigé ces travaux et m'avoir soutenu dans toutes les phases. Je remercie également mon Co-directeur de thèse Pr Ouaténi Diallo pour son accompagnement et ses conseils précieux.

Mes remerciements vont aux mes membres du GReP (Groupe de Recherche du Pôle) avec mention spéciale à Hamzat Aliyu pour sa collaboration et les nuits blanches à travailler sur HiLLS. Mes remerciements vont également à l'endroit de Bright Ighoroje et Hamidou Togo pour leurs apports et observations au développement de la thèse.

Je remercie le Chef de D.E.R de mathématiques et d'informatique Dr Yaya Koné pour son suivi dans les démarches administratives ainsi que toute l'administration de la Faculté des Sciences et Techniques (FST) de l'Université de Sciences, des Techniques et Technologie de Bamako (USTTB). Mes remerciements vont également à Pr Françoise Paladian, directrice de l'Ecole Doctorale des Sciences pour l'Ingénieur (EDSPI) de Clermont-Ferrand ainsi qu'à toute son équipe pour leur soutien administratif.

Je remercie Mme Jacqueline Girard, directrice du Pôle Universitaire et Technologique de Vichy (PUTV) et toute son équipe avec une mention spéciale pour Isabelle Vairet. Je remercie toute l'équipe du LIMOS (Laboratoire d'Informatique de Modélisation et d'Optimisation des Systèmes) de Clermont-Ferrand pour leur accueil pendant toute la durée de la thèse.

Mes remerciements vont à tout le staff de l'AUF (Agence Universitaire de la Francophonie), plus particulièrement Michel Namar et Birama Seyba Traoré pour leur soutien et accompagnement.

Mes remerciements vont également au coordinateur du PFF (Programme de Formation des Formateurs) pour sa disponibilités et son accompagnement pendant la formation doctorale et pour les supports accordés pour les conférences scientifiques.

Je tiens enfin, à remercier ma famille et mes amis pour leurs encouragements, et particulièrement Bintou pour avoir supporté mes multiples longues absences et m'avoir soutenu pendant tout le projet.

# **Table of Content**

| List of figures                                          | 10 |

|----------------------------------------------------------|----|

| List of abbreviations                                    | 13 |

| I. General introduction                                  | 14 |

| I.1 Context                                              | 15 |

| I.2 Objectives                                           | 17 |

| I.3 Outline                                              | 18 |

| II. State of the art                                     | 19 |

| II.1 Introduction                                        | 20 |

| II.2 Modeling and Simulation                             | 20 |

| II.2.1 Simulation life Cycle                             | 20 |

| II.2.2 Verification and Validation                       | 21 |

| II.2.3 DEVS-Based Modeling and Simulation Framework      | 23 |

| II.3 Formal Methods                                      | 46 |

| II.3.1 Z language                                        | 48 |

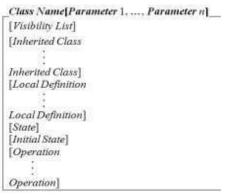

| II.3.2 Object-Z                                          | 49 |

| II.3.3 CSP                                               | 52 |

| II.3.4 Formal Verification and Validation of DEVS models | 53 |

| II.4 System Design                                       | 57 |

| II.4.1 Unified Modeling Language                         | 57 |

| II.4.2 Object-Oriented design patterns                   | 59 |

| II.4.3 Enactment of discrete event systems               | 60 |

| II.5 Language engineering                                | 62 |

| II.5.1. Definition of a Language                         | 62 |

| II.5.2 Visual Languages                                  | 63 |

| II.5.3 Integrating Heterogeneous languages               | 65 |

| II.5.4 Language integration techniques                   | 69 |

| II.5.5 Integrated languages for system specification     | 71 |

| II.6 Conclusion                                          | 73 |

| III. The High Level Language for Systems Specification   | 75 |

|                                                          |    |

| III.2 Informal Presentation of HiLLS          | 77  |

|-----------------------------------------------|-----|

| III.3 HiLLS Abstract Syntax                   | 80  |

| III.3.1 Object-Z concepts Metamodel           | 81  |

| III.3.2 System Theory concepts from DEVS      | 83  |

| III.3.3 Object Orientation Concepts from EMOF | 86  |

| III.3.4 HiLLS Complete Metamodel              | 87  |

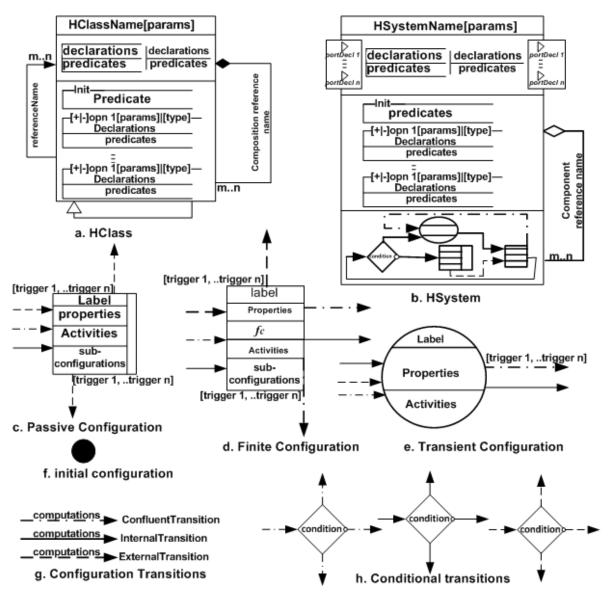

| III.4 HiLLS Concrete Syntax                   | 92  |

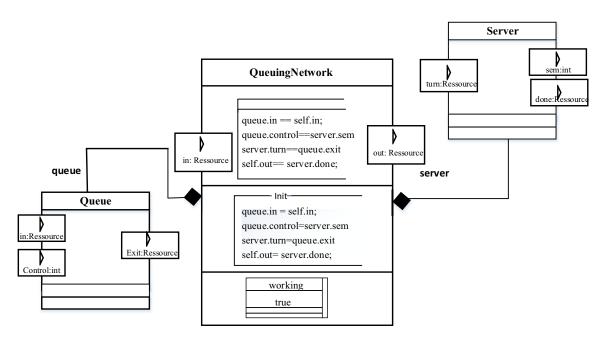

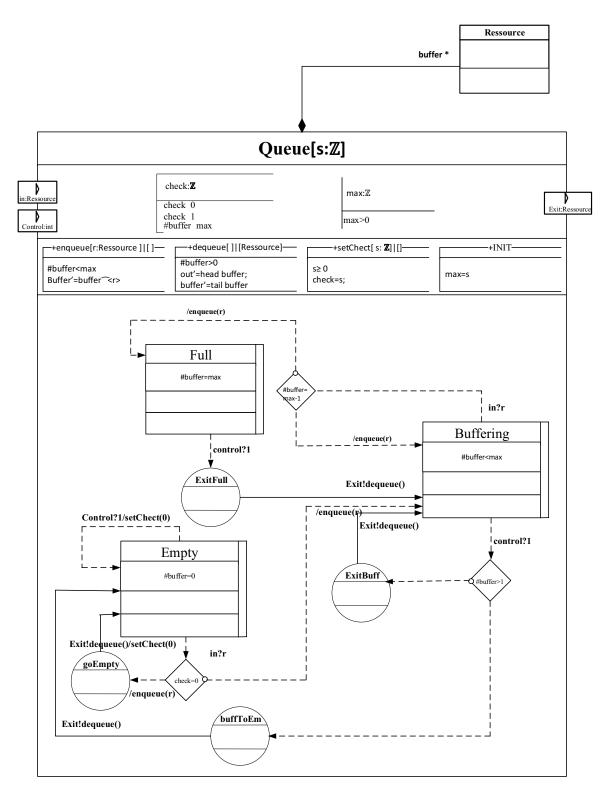

| III.5 Queuing Network example                 | 94  |

| III.6 Set-theoretic semantics of HiLLS        | 98  |

| III.6.1 Formalization                         | 99  |

| III.6.2 Closure under coupling of HILLS       | 109 |

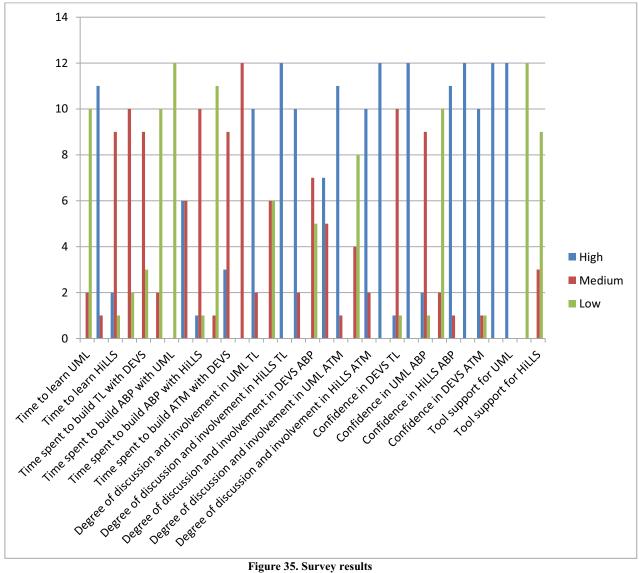

| III.7 HiLLS Usability Assessment              | 112 |

| III.8 Conclusion                              | 113 |

| IV. Translational Semantics of HiLLS          | 115 |

| IV.1 Introduction                             | 116 |

| IV.2 Operational Semantics for Simulation     | 117 |

| IV.2.1 Semantic mapping to DEVS               | 118 |

| IV.2.2 Semantic mapping to DSDEVS             | 122 |

| IV.3 Operational Semantics for Enactment      | 124 |

| IV.3.1 Enactment                              | 124 |

| IV.3.2 Enactment Methodology                  | 124 |

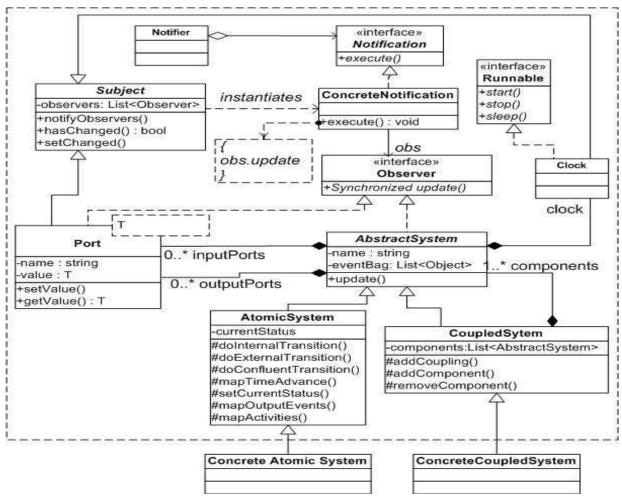

| IV.3.3 Metamodel of the framework             | 125 |

| IV.3.4 Enactment protocol                     | 126 |

| IV.3.5 Implementation                         | 127 |

| IV.3.5 Traffic Light Example                  | 127 |

| IV.4 Semantic mapping to Z                    | 132 |

| IV.5 Semantic mapping to CSP                  | 139 |

| IV.6 Tooling Framework                        | 144 |

| VI.7 Conclusion                               | 145 |

| V. Application                                | 146 |

| V.1 Introduction                              | 147 |

| V.2 Alternating Bit Protocol                  | 148 |

| V.2.1 HiLLS specification of ABP              | 149 |

|-----------------------------------------------|-----|

| V.2.2 Equivalent models of the ABP in DEVS    | 156 |

| V.2.3 Z specification and Analysis of the ABP | 159 |

| V.3 Automated Teller Machine (ATM)            | 166 |

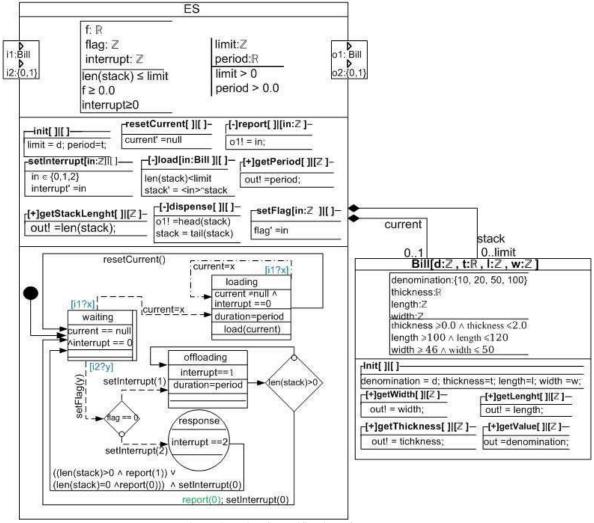

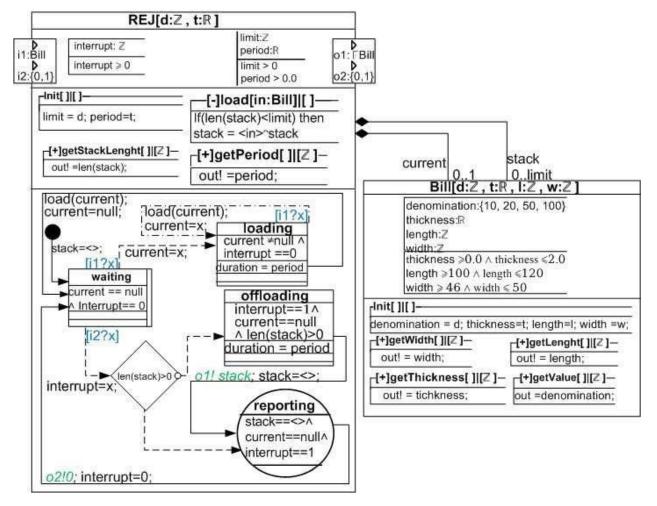

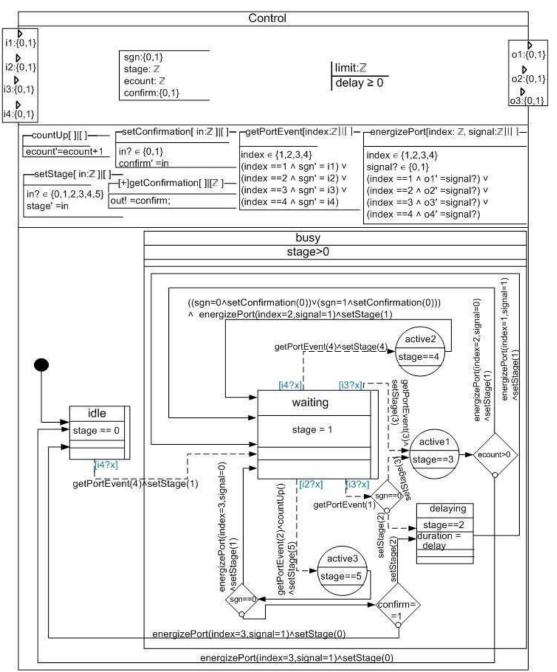

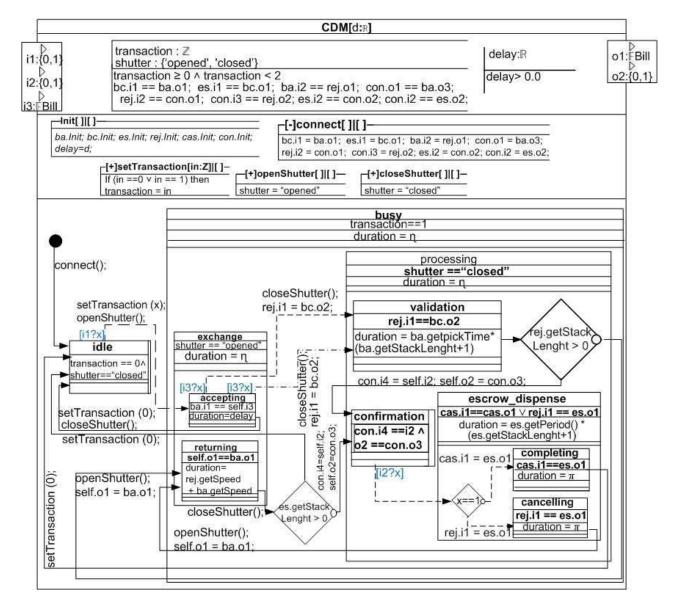

| V.3.1 HiLLS specification of ATM              | 167 |

| V.3.2 DSDEVS specification of ATM             | 179 |

| V.4 Conclusion                                | 184 |

| VI. General conclusion                        | 185 |

| References                                    | 188 |

# List of figures

| Figure 1: Simulation Life Cycle                                                    | 21  |

|------------------------------------------------------------------------------------|-----|

| Figure 2. Taxanomy of Verification, Validation and Testing Techniques [Balci 1997] | 23  |

| Figure 3. M&S Entities and Relationships between them [Zeigler et al. 2000]        | 24  |

| Figure 4. Experimental Frame and its Components [Zeigler 1983]                     | 25  |

| Figure 5. System at OF level                                                       | 27  |

| Figure 6. Example of transitions occurrences                                       | 30  |

| Figure 7. Example of Coupled Model                                                 | 31  |

| Figure 8. Correspondence between Model Hierarchy and Simulation Tree               | 31  |

| Figure 9. Sending of initialization message                                        | 32  |

| Figure 10. Sending of done messages to parents                                     | 32  |

| Figure 11. Sending star message                                                    | 33  |

| Figure 12. Simstudio components                                                    | 39  |

| Figure 13. the Stack specification in Z                                            | 49  |

| Figure 14. Template of Object-Z class                                              | 50  |

| Figure 15. A sample model in Object-Z                                              | 51  |

| Figure 16. Observer design pattern                                                 | 59  |

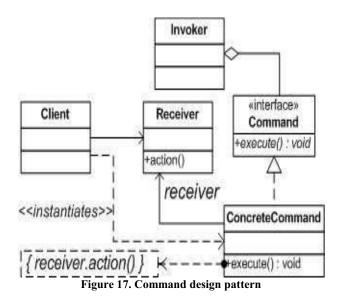

| Figure 17. Command design pattern                                                  | 60  |

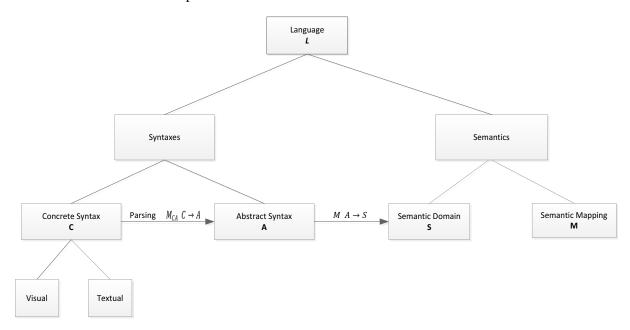

| Figure 18. Defining a language                                                     | 62  |

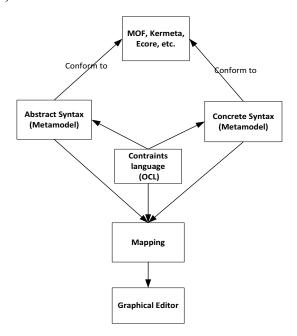

| Figure 19. Mapping between abstract and concrete syntaxes                          | 64  |

| Figure 20. HiLLS definition elements                                               | 76  |

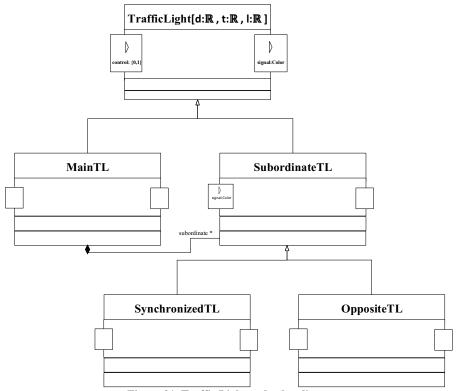

| Figure 21. Traffic Light and subordinate                                           | 77  |

| Figure 22. Traffic Light                                                           | 78  |

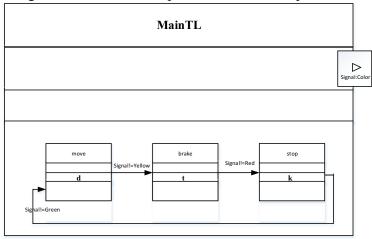

| Figure 23. Behavior of SynchronizedTL                                              | 79  |

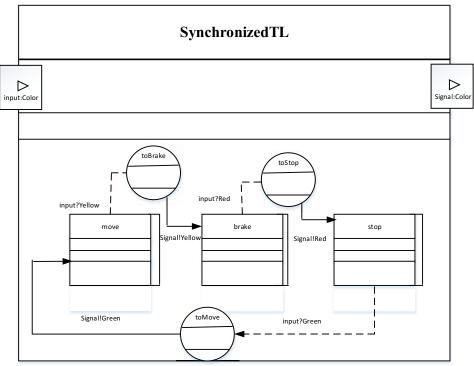

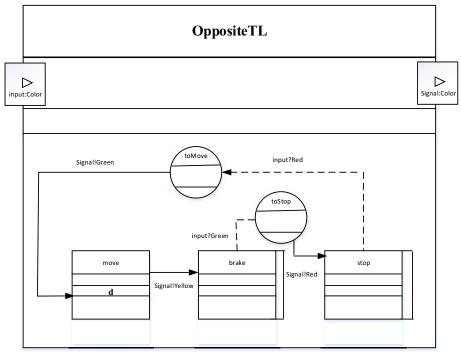

| Figure 24. Behavior of OppositeTL                                                  | 79  |

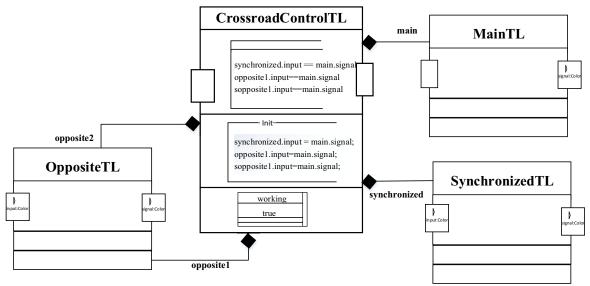

| Figure 25. Crossroad control traffic lights                                        | 80  |

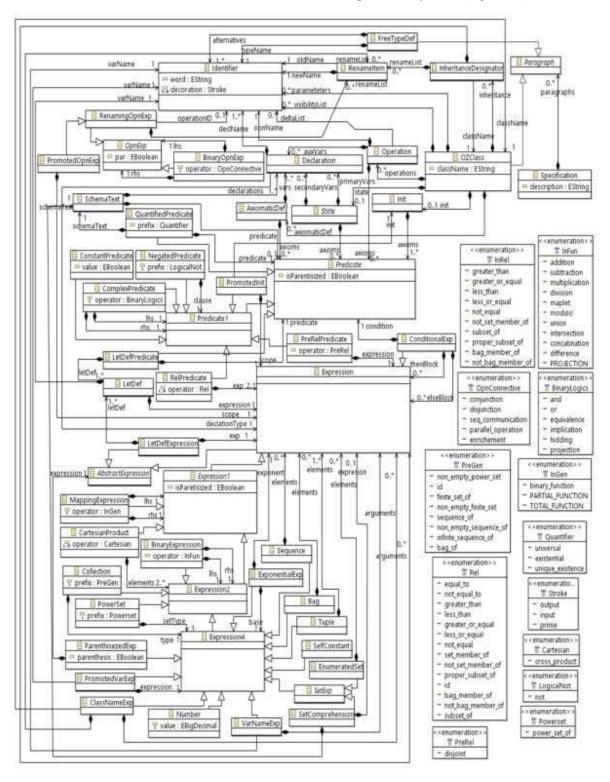

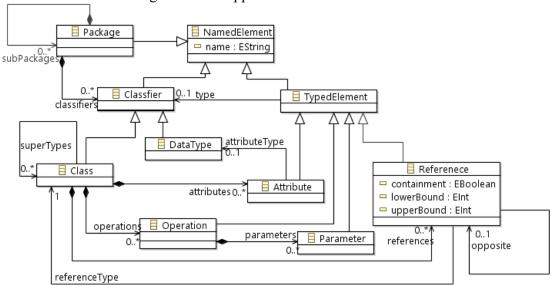

| Figure 26. Object-Z Metamodel                                                      | 82  |

| Figure 27. Discrete Event (part) Metamodel                                         | 84  |

| Figure 28. OCL Constraints of Discrete Event Metamodel                             | 85  |

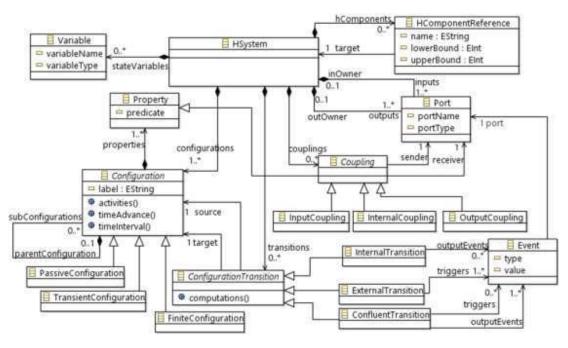

| Figure 29. HiLLS Object Oriented part metamodel                                    | 87  |

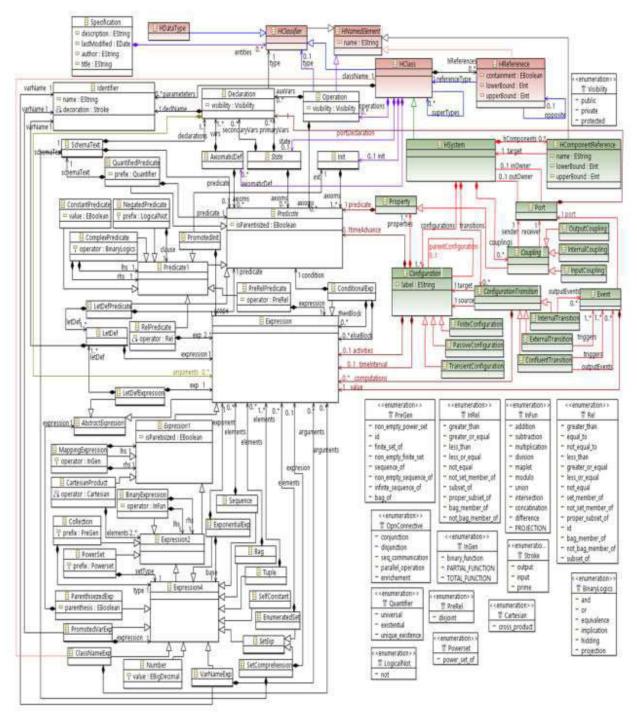

| Figure 30. Complete Metamodel integrating the different parts                      | 89  |

| Figure 31. OCL constraints                                                         | 90  |

| Figure 32. HiLLS Concrete Syntax                                                   | 94  |

| Figure 33. Queueing Network                                                        | 95  |

| Figure 34. HSystem of the Queue                                                    | 97  |

| Figure 35. Survey results                                                          | 113 |

| Figure 36. From HILLS to Formal Methods                                            |     |

| Figure 37. HiLLS operational Semantics mappings                                    | 118 |

| Figure 38. controlled Trafficlight                                                 | 121 |

| Figure 39. Observer pattern with asynchronous notification                         | 125 |

| Figure 40. Metamodel of enactment framework                    | 126 |

|----------------------------------------------------------------|-----|

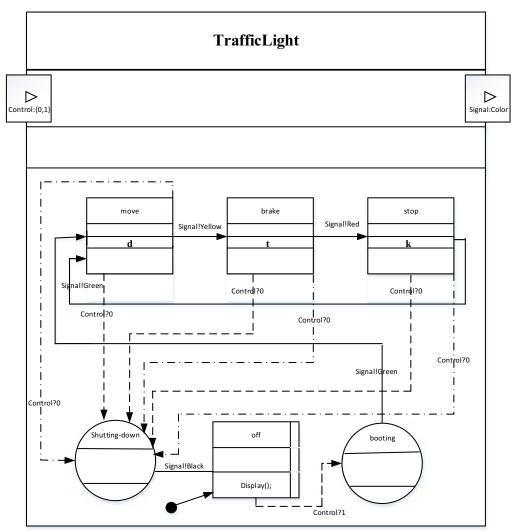

| Figure 41. Specification of traffic light system               | 127 |

| Figure 42 Control unit of the traffic light system             | 129 |

| Figure 43 Display unit of the traffic light system             | 130 |

| Figure 44 Coupled traffic light system                         | 131 |

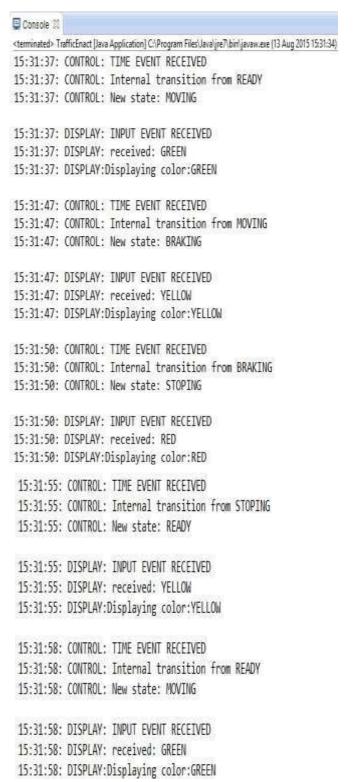

| Figure 45 Results of the enactment of the traffic light system | 132 |

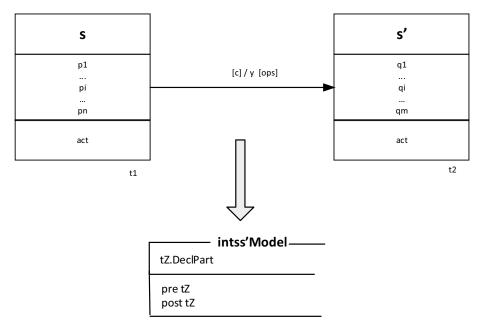

| Figure 46. Translation of an internal transition to Z          | 135 |

| Figure 47. Conditional internal transition to Z                | 136 |

| Figure 48. External Transition translation to Z                | 137 |

| Figure 49. Conditional external transition to Z                | 137 |

| Figure 50. Confluent transition to Z                           | 138 |

| Figure 51. Confluent conditional transition to Z               | 139 |

| Figure 52. Illustration of HILLS to CSP translation            | 142 |

| Figure 53. Translation of HILLS composite model to CSP         | 143 |

| Figure 54. Overview of HiLLS tooling Framework                 | 145 |

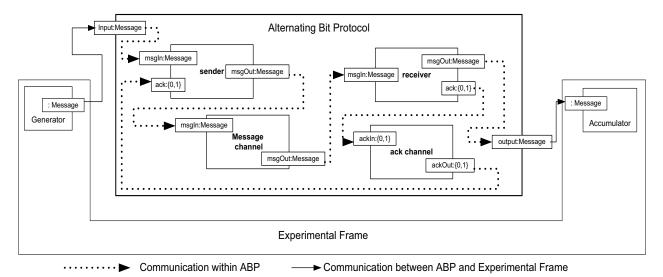

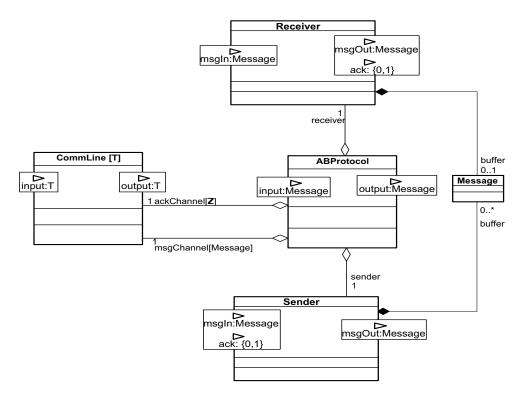

| Figure 56. HiLLS metamodel of the alternating bit protocol     | 150 |

| Figure 57. Message HClass                                      | 150 |

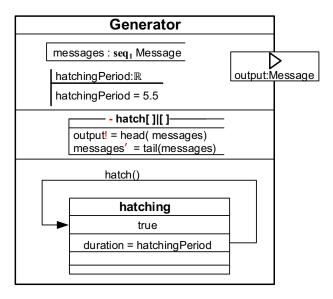

| Figure 58. HiLLS model of the Generator                        | 151 |

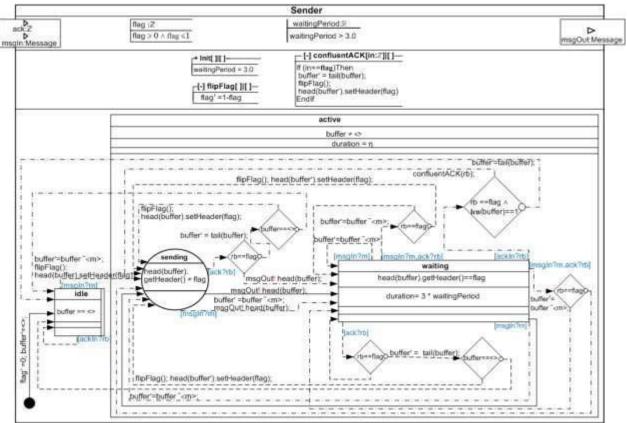

| Figure 59. HiLLS model of the Sender                           | 152 |

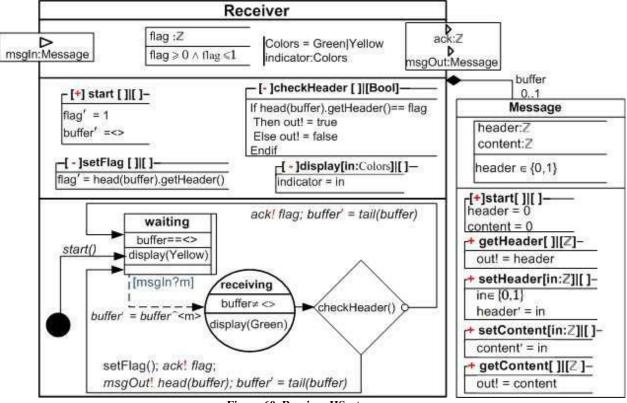

| Figure 60. Receiver HSystem                                    | 153 |

| Figure 61. The HiLLS model of the Medium                       | 154 |

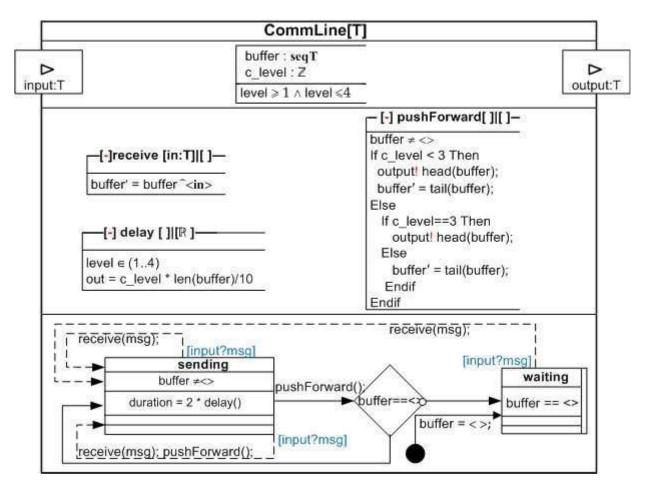

| Figure 62. The Model of accumulator                            | 155 |

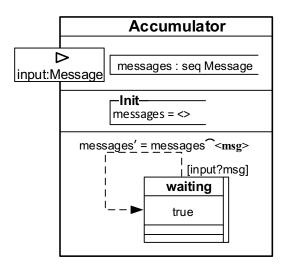

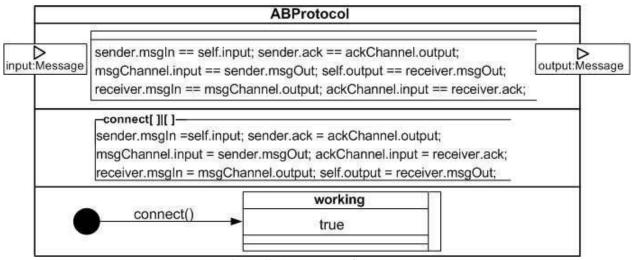

| Figure 63. ABProtocol HSystem                                  | 155 |

| Figure 64. couplings mapping                                   | 158 |

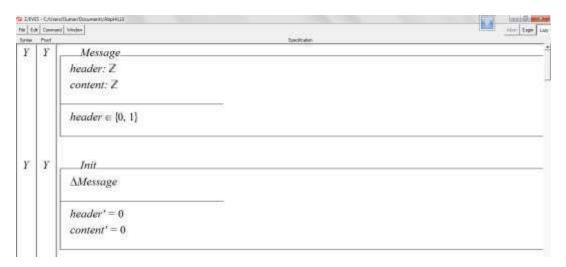

| Figure 65. Message and Init                                    | 159 |

| Figure 66.getHeader and setHeader                              | 160 |

| Figure 67. getContent and setContent                           | 160 |

| Figure 68. Receiver in Z                                       | 160 |

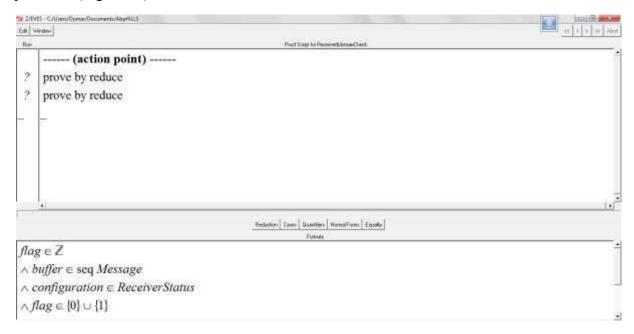

| Figure 69. Show proof of Receiver State schema                 | 161 |

| Figure 70. Proof of Reciver state schema                       | 161 |

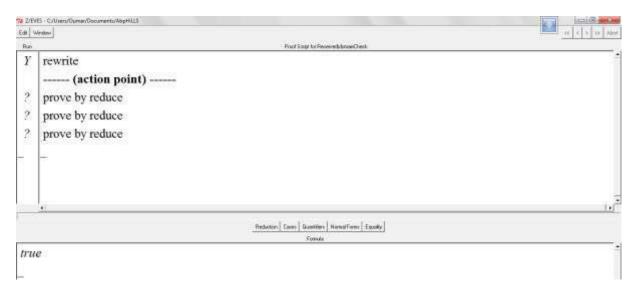

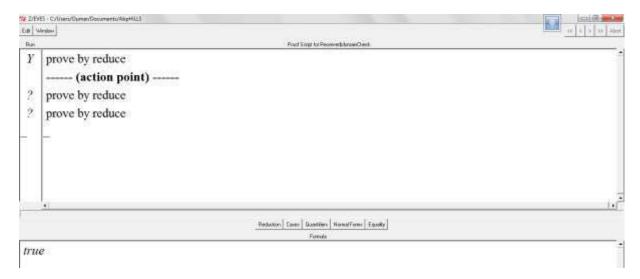

| Figure 71. proof by reduce of Receiver state schema            | 162 |

| Figure 72. Init and waiting2sendingTransition                  | 162 |

| Figure 73. show Proof on waiting2sendingTransitionExt          | 163 |

| Figure 74. sendint2waintingTransitionINT1                      | 163 |

| Figure 75. sending2waitingTransitionINT2                       | 163 |

| Figure 76. syntax error in sending2waitingTransitionINT2       | 164 |

| Figure 77. Existence of initial state                          |     |

| Figure 78. unsuccessful proof of the theorem                   | 165 |

| Figure 79. proof of the theorem                                | 165 |

| Figure 80. Trajectories in Z                                   | 166 |

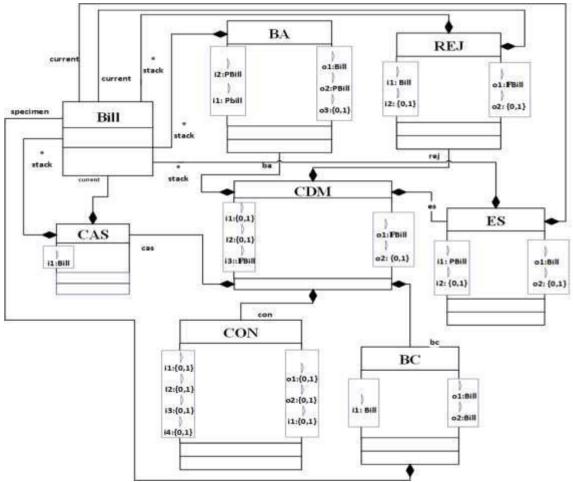

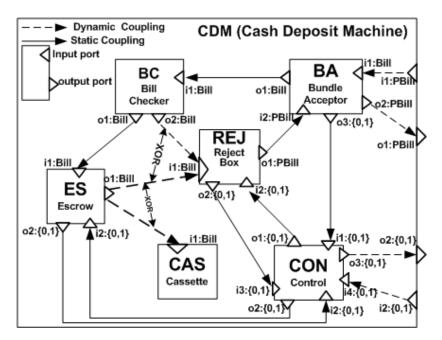

| Figure 81. Domain Model of the CDM                             | 167 |

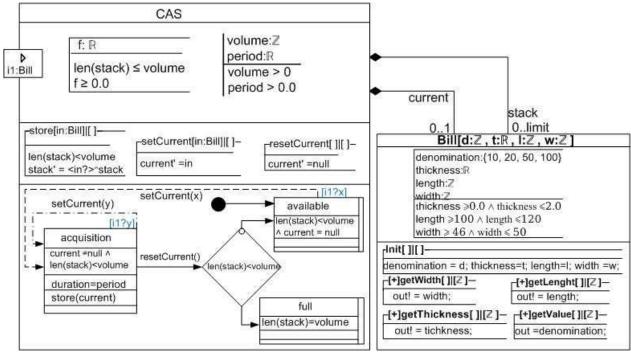

| Figure 82. HiLLS specification of the Cassette                 | 169 |

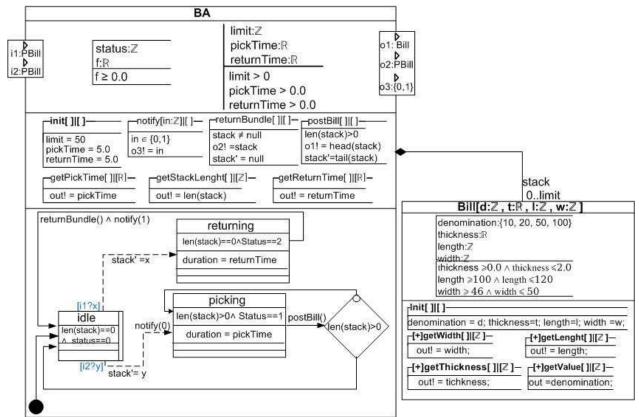

| Figure 83. HiLLS specification of the Bundle Acceptor            | . 170 |

|------------------------------------------------------------------|-------|

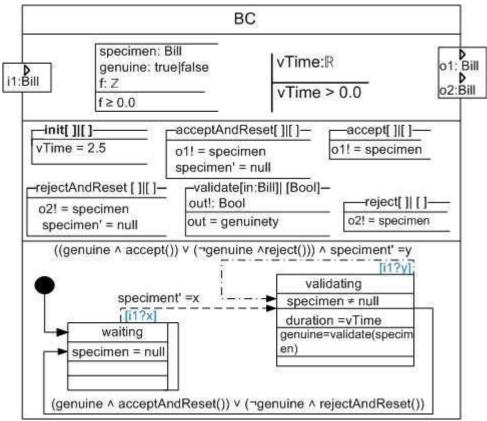

| Figure 84. HiLLS specification of the Bill Checker               |       |

| Figure 85. HiLLS specification of the Escrow                     | . 172 |

| Figure 86. HiLLS' specification of Bill and Reject box           | . 174 |

| Figure 87. HiLLS specification of the Control board              | . 176 |

| Figure 88. HiLLS specification of the Cash Deposit Machine (CDM) | . 178 |

| Figure 89. Block diagram illustrating the structure of the CDM   | . 179 |

### List of abbreviations

ABP Alternating Bit Protocol

ATM Automated Teller Machine

BPMN Business Process Modeling Notation

CCS Calculus of Communicating Systems

CDEVS Classic DEVS

CDM Cash Deposit Machine

CSP Communicating Sequential Processes

CSPZ CSP combined with Z

CTL Computaion Tree Logic

DDML DEVS Driven Modeling Language

DEVS Discrete Event System Specification

DSDEVS Dynamic Structure DEVS

DSL Domain Specific Language

DSML Domain Specific Modeling Language

ERD Entity Relationship Diagrams

FDR Failure Divergence Refinement

GPPL General Purpose Programming Language

HiLLS High Level Language for System Specification

LTS Labelled Transition System

PDEVS Parallel DEVS

SLC Simulation Life Cycle

UML Unified Modeling Language

USTTB Université des Sciences, des Techniques et des Technologies de Bamako

SysML System Modeling Language

ZCCS Z combined with CCS

# I. General introduction

#### I.1 Context

It is a known fact that software development projects have low level of success compared to projects in other domains like construction. Success in these domains is due to well-defined engineering methodologies and standards. To increase success in software and hardware systems development there is a need to define principles, languages, methodologies and tools that help projects managers, designers and developers in the different steps. Over the years multiple development methods and software life cycle models classified as classic approaches and agile methodologies have been proposed. Classical approaches (Waterfall model, incremental methods etc.) articulate around four main phases: specification, design, implementation, verification and validation. The differences between them reside in how steps follow each other, details of each step and how verification and validation is conducted through the different phases. A common critic of most of these approaches is that error is detected very late or interaction with the product is very late. While classical approaches follow rigorously a requirement document and a defined project plan, agile methodologies (eXtreme Programming, Scrum, Feature Driven Development, Adaptive Software Development) focus on the interaction with the customer, changes in requirements and proposition of an early version of the software. A list of recommendations to complement the deficiencies of software development can be to:

- Capture Requirement in a precise and unambiguous way

- Integrate Many languages in one or different phases

- Detect and correct errors in the early phases

- Conduct Verification and validation through all the phases

- Make an early version of the software available

- Use Formal methods in complement to simulation and testing

- Use Object-Orientation Principles in design and implementation

- Generate code from models

In modeling and analysis of complex systems, it is important that the abstract model should accurately capture the structural and behavioral aspects of the system to make verification and validation using techniques such as simulation and formal analysis effective and the implementation of the system possible. System development generally requires knowledge of the system domain, modeling methodology, and model analysis and execution techniques. Domain experts are concerned with system characteristics, problems and behavior. Modeling experts use mathematical formalisms, algorithms, and/or computer programs to develop abstractions of systems. These abstractions must be translated into some semantic domain to investigate system properties. Due to the difference in concerns and expertise between experts involved in the system development, it is required to utilize a framework that supports communication and cooperation between domain experts and experts in other domains like modeling and simulation and formal methods. What is needed to achieve this is an intermediate notation which is highly communicable, expressive, and low enough to reduce the complexity of code synthesis for simulation, prototyping, enactment and formal analysis. This representation should be able to express the structural and behavioral characteristics of complex systems without ambiguities. In the area of software, systems, business processes and data engineering some notables languages such as Unified Modeling Language <sup>TM</sup> (UML) [OMG 2010a], System Modeling Language <sup>TM</sup> (SysML) [OMG 2010b], Business Process Modeling Notation (BPMN) [OMG 2012] and Entity Relationship Diagrams (ERD) [Chen 1976] respectively have been used as specifications that provide easy visual constructs that facilitate cooperation between domain engineers and technical experts. Employing similar constructs for real-time, concurrent and distributed systems modeling with discrete event perspective would facilitate the system development process; this is a part of the objectives of this thesis.

Over the years, several modeling techniques for dynamic systems have been developed. The Discrete Event System Specification (DEVS) [Zeigler 1976] formalism has emerged as a preferred formalism because other formalisms have been proven to have an equivalent DEVS representation [Vangheluwe 2000]. Although DEVS is specifically tailored to suit discrete event systems, it supports full range of dynamic system representation. In particular, a Differential Equation System Specification (DESS) can have an approximate Discrete Time System Specification (DTSS) by selection of a sufficiently small constant time interval (discretization). A DTSS model, in turn has an equivalent DEVS representation. Also, quantization of a DESS system can result in an approximate DEVS model. As such, approximate models of continuous and hybrid systems can be developed with DEVS. DEVS also promotes separation of concerns by separating the model, simulator, and experimental frame thereby facilitating system development. The DEVS simulation protocol is well defined. However, DEVS is semi-formal and it does not provide concrete guidelines to express system structure, behavior, and traces. The modeler is free to develop system models in ways that are most appealing. The absence of a common agreed concrete syntax for DEVS has led to different implementations such as DEVSJAVA [Sarjoughian and Zeigler 1998], SimBeans [Präehofer et al. 1999], James II [Himmelspach and Uhrmacher 2004], etc. that makes collaboration between modelers and communicability of models difficult. An Objective of this thesis is to define a new language that reuse DEVS and provide a concrete syntax for modeling systems and make models communicable and improve collaboration.

Simulation and testing have been used as traditional methods of verification and validation to assess the qualities of the models by exploring some of the possible situations and scenarios and comparing with system specification. The limitation of simulation is that it does not guarantee that a verified system is error free because only some part of the system behavior is explored. On the other hand, formal analysis involves using deductive verification, axioms, and proof rules to determine the correctness of systems or models. They derive static properties when simulation derives dynamic properties. Formal methods have been used in the specification, development and verification of software and hardware systems but its use with computer simulation has not been explored exhaustively. Formal methods can be a good compliment of simulation thereby contributing to the reliability and robustness of systems [Micheal 1997]. Mathematical proof of correctness is the most effective means of model verification and validation if its applicability is possible [Balci 1997]. Formal analysis techniques allow for exhaustive check for the conformity of the specification to requirements and rigorous proof of assertions about the system. Advances in Formal methods have increased the range of systems that this can be applied to. Hence, integrating formal methods with a well-established simulation technique like DEVS would enable to derive premises or logical consequences of the model and confirm that the abstract specification conforms to the operational specification [Traoré 2006]. A goal of this thesis is to complement simulation-based verification by formal analysis techniques to check the multiple aspects of systems properties.

The increasing complexity of hardware systems, software systems and embedded systems often requires the use of different languages for modeling their different aspects. In general a system

development requires many models that provide several complementary views on the system structure and behavior. Communication between experts is constrained by the disparateness of the descriptions of the various aspects of the system in their respective domains. Usually, an exhaustive study of a complex system is done by adopting one of the two following prevalent methods:

- a. Creating different models of the same system with different formalisms to express the aspects of the system required by experts of different domains.

- b. Transforming a model defined in a specific formalism into models of other languages to carry out the investigations.

These methods are not without serious drawbacks. In addition to the difficulty of mutual communication between experts, the use of (a) is haunted by an arduous task of updating the different versions of the specification to maintain consistency. The time and efforts required to specify different models in different languages, yet for the same system could dissuade one from embarking on that track. By taking benefits of the Model-Driven Engineering (MDE), method, (b) solves the problem of manually specifying multiple models of same system. However, it is still characterized by inconsistencies resulting from two sources:

- Difference in the capabilities of different formalisms to effectively create abstractions of certain aspects of a system.

- Misinterpretations of the source model by the target languages due to lack of precisely defined semantics for the source language.

To handle the presented challenges, a system development methodology should provide a language with a concrete syntax that promotes communicability of models and collaboration between experts. Since DEVS is proven to be a common denominator for discrete event systems modeling and simulation, it can be used as a base formalism in a system development methodology with a provided concrete syntax to solve the communication and collaboration issues. The development methodology should include other analysis techniques to complement simulation to cover different aspects of system behavior. It is also important to maintain consistency between the different views of the system during the development process; this is an aspect of system development addressed by the language proposed in this thesis.

#### I.2 Objectives

Our objective is the definition of a modeling language called HiLLS with support for a precise and consistent unification of the various aspects of a system in one model. This approach is expected to make the model adaptable to multiple analysis techniques. The objectives of HiLLS include:

- *High communicability*: define a graphical concrete syntax for HiLLS that is easy to learn and communicate and make sharing and discussing models between experts simple thereby facilitating their cooperation.

- *High expressive power:* define the abstract syntax of HiLLS by integrating DEVS and Object-Z to support the precise modeling of complex systems with discrete event perspective. HiLLS inherits the expressiveness and properties of DEVS and Object-Z.

- Simulation applicability: adopt DEVS as a semantic domain for HiLLS by defining a semantic mapping from HiLLS to DEVS so that HiLLS models can be simulated by using DEVS existing simulators.

- Amenability to formal analysis: make HiLLS models amenable to formal analysis so that the user can analyze static and dynamic properties of the model by generating the formal models and verification conditions from it to ease the verification process

- *Hierarchy and Modularity*: adopt modular and hierarchical structuring concepts from the DEVS formalism and object oriented structuring concepts from Object-Z and MOF (Meta Object Facility).

- Availability of supporting tools: provide supporting tools that facilitates the design of graphical models as well as automated code synthesis for simulation and integrated support for visualization and formal analysis.

- Automated code synthesis: Generate code from HiLLS models to reduce error in translation process.

- Executability of models: provide enactment semantics for the automatic generation of a real-time executable code of the system from the HiLLS models.

- Maintainability of consistency between all the views: use HiLLS specifications as front-ends from witch other views are generated to maintain consistency between the different views and reduce the task of updating them.

#### I.3 Outline

Chapter II explores the state of the art in the modeling and simulation domain in general and DEVS-based modeling and simulation framework in particular. We discuss formal methods with focus on Z, Object-Z and CSP formal notations. We present also Formal analysis of DEVS models. Chapter III introduces the HiLLS language and presents its objectives. It presents the abstract syntax, concrete syntax and the set-theoretic semantics of HiLLS. Chapters IV presents the operational and logical semantics of HiLLS. Application of HiLLS to the modeling and analysis of the ABP (Alternating Bit Protocol) and ATM (Automated Teller Machine) is discussed in chapter V. The general conclusion of the thesis is drawn in chapter VI.

# II. State of the art

#### **II.1 Introduction**

Nowadays, the daily life of a man occurs in an environment made up of complex systems going from simple tools of entertainment to critical systems such as embedded systems on medical systems, individuals cars, trains, planes and materials whose failures can be fatal for him. The study of these systems is done through experiments of various kinds. The construction of physical models to test certain characteristics of the system are often very dangerous, expensive, and even impossible in much of cases. One of the methods making it possible to study systems consists in characterizing the system studied by a system of equations and the use of mathematical techniques to determine the analytical solution or approximate solution by using approximation techniques. These methods known as analytical methods present some limits, they are difficult to use in the study of some category of systems like manufacturing systems, military systems, etc.

Simulation exceeds the limits of the analytical and numerical methods in the study of complex dynamic systems. It is largely used in industry and academia. It covers all the scientific, economic and social fields. Simulation has been applied to aeronautics, urban and interurban transportation systems, demography; propagation of epidemics, etc. Simulation has several advantages such as the facilitation of the experimentation process by using less financial and data-processing resources. Simulation is used to check that our models give us coherent results compared to the data of the real system and in conformity with the formal and verifiable requirements of this last.

Different simulation approaches exist in the literature: discrete-time, continuous and discrete-event simulations. For a comprehensive view on simulation, reader can consult the following papers: [Kreutzer 1986], [MacDougall 1987] and [Fishwick 1995]. In the simulation area, the discrete-event simulation approach has emerged as well accepted system analysis technique. Some known formalisms like UML integrate discrete-event modeling techniques in the specification and analysis of systems. Our thesis concentrates on the discrete-event approach to systems modeling and analysis.

This chapter presents modeling and simulation in general and DEVS-based modeling and simulation in particular as a background for the operational semantics of HiLLS. The chapter also discusses formal methods with focus on Z, Object-Z and CSP formal notations, existing formal verification approaches of DEVS models and basic concepts of the formal languages used as logical semantic domain for HiLLS. Basic concepts of system design and language engineering are presented as background respectively for enactment methodology of HiLLS and the integration approach used to define HiLLS. Related work of integrated languages is also discussed.

#### **II.2 Modeling and Simulation**

#### **II.2.1 Simulation life Cycle**

Simulation process turns around three main activities: modeling, simulation and the verification and validation activities (Figure 1). The modeling phase consists of using a particular simulation modeling approach to create an abstraction of the real or proposed system of interest named the problem entity in [Sargent 2000]. The conceptual model is the simplified representation of the problem entity developed in the analysis and modeling phase for a particular study. The computer

programming and implementation phase consists to build the computerized model. Inferences about the problem entity are obtained by conducting computer experiments on the computerized model in the experimentation phase.

Figure 1: Simulation Life Cycle

The modeling and simulation process needs to ensure different kind of validity relation between the problem entity, the conceptual model and the computerized model. Conceptual model validity is defined as determining that the theories and assumptions underlying the conceptual model are correct and that the model representation of the problem entity is reasonable for the intended purpose of the model. Computerized model verification is defined as ensuring that the computer programming and implementation of the conceptual model is correct. Operational validity is defined as determining that the model's output behavior has sufficient accuracy for the model's intended purpose over the domain of the model's intended applicability. Data validity is defined as ensuring that the data necessary for model building, model evaluation and testing, and conducting the model experiments to solve the problem are adequate and correct".

#### II.2.2 Verification and Validation

Different definitions of model verification and validation exist in the literature with different formulations. The definition adopted in [Sargent 2000] is "ensuring that the computer program of the computerized model and its implementation are correct". In [Sargent 2000] Model validation is adopted to mean "substantiation that a computerized model within its domain of applicability possesses a satisfactory range of accuracy consistent with the intended application of the model". Validation is the process of comparing real system data and collected as simulation results with respect to experimentation conditions [Zeigler et al. 2000]. Different V&V techniques exist in the literature.

[Sargent 2000] gives a non-exhaustive list of techniques that can be applied in the V&V process:

- Animation (Displaying the operational behavior graphically and values of various performance measures through time),

- Comparison to Other Models (Various results of the simulation model being validated are compared to results of other models that have been validated),

- Face Validity (asking people knowledgeable about the system whether the model and/or its behavior are reasonable),

- Degenerate Tests (testing the degeneracy of the model behavior by appropriate selection of values of the input and internal parameters),

- Event Validity (comparing event occurrences in the model to that of the system),

- Extreme Condition Tests (testing how model react to unlikely combination of factors),

- Historical Data Validation (compare model to system by using the system's collected data),

- Internal Validity (analyzing the degree of variability in model behavior),

- Parameter Variability–Sensitivity Analysis (testing the effect of input and parameters variability upon the model's behavior and output),

- Multistage Validation (developing the model's assumptions, testing the assumptions and testing input-output relationship between the system and the model) etc.

A recommended procedure for some of these techniques in V&V is given by the author in another paper [Sargent 2001]. In model testing, the model is subjected to test data or test cases to determine if it functions properly. These techniques are independent from the modeling language used.

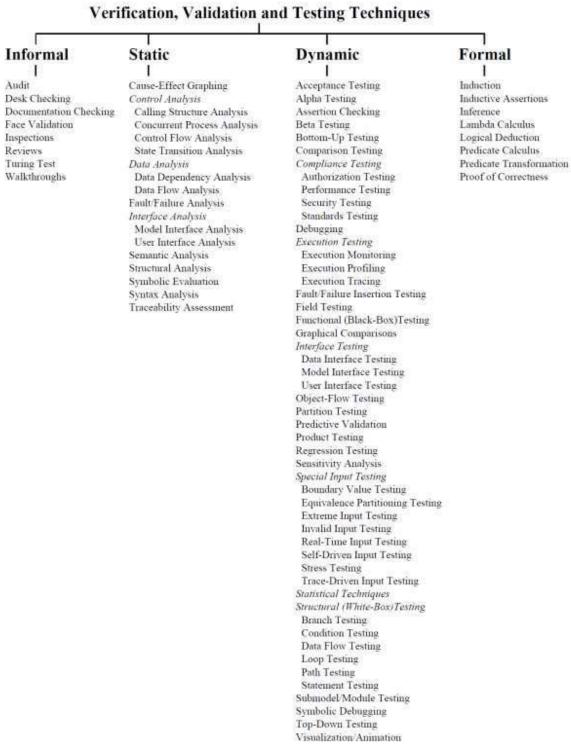

[Balci 1997] gives a list of principles and techniques in verification, validation and accreditation of simulation models that can help in assessing model credibility. Taxonomy of more than 77 V&V techniques is provided to assist simulation practitioners in selecting proper approaches for simulation model V&V (Figure 2). Taxonomy of 38 V&V techniques is presented for object-oriented simulation models. The cited principles turn around the application of V&V in the entire M&S lifecycle:

- The specification of simulation objectives and conditions

- Clear specification of the requirements,

- The nature of V&V results,

- Detection of error in M&S phases etc.

The techniques include those presented in [Sargent 2000]. Some techniques come from software engineering and others are specific to simulation field. The selection of V&V method may depend on model type, simulation type, problem domain, and M&S objectives.

Figure 2. Taxanomy of Verification, Validation and Testing Techniques [Balci 1997]

#### **II.2.3 DEVS-Based Modeling and Simulation Framework**

#### II.2.3.1 Entities of the Framework

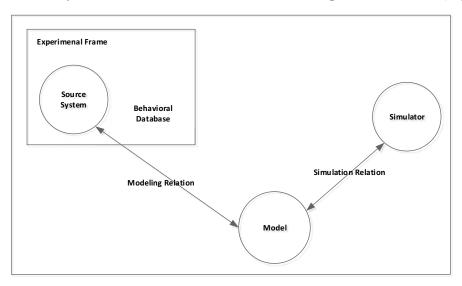

The DEVS formalism defines a modeling and simulation framework composed of the following entities: the source system, the model, the simulator and the experimental frame (Figure 3).

Figure 3. M&S Entities and Relationships between them [Zeigler et al. 2000]

#### II.2.3.1.1 Source System

The source system is real or virtual system concerned by the modeling and simulation process. It is the source of observables data that constitutes behavioral database. The term system in this thesis is used for any entity of the real world, phenomenon or process that can be represented in form computable by a machine.

#### II. 2.3.1.2 Model

The model is a simplified and abstract representation of the system. This representation can be physical, mathematic or logical. A model is used to study the structure and behavior of a system in a particular context. The results of the study are only meaningful in the specified context. The specification of models in the DEVS framework obeys to a hierarchy proposed by Zeigler [Zeigler et al. 2000].

#### **II. 2.3.1.3 Simulator**

A Simulator is an engine capable of reproducing the behavior of a model. The type of simulator used depends of the formalism used to create the associated model.

#### II. 2.3.1.4 Modeling and simulation relations

The existing relations between these entities are: the modeling relation between the system and the model and simulation relation between the model and the simulator. The modeling relation refers to the degree at which the Model faithfully represents the System and the simulation relation refers to correspondence between model design and its implementation.

#### II.2.3.1.5 Experimental Frame

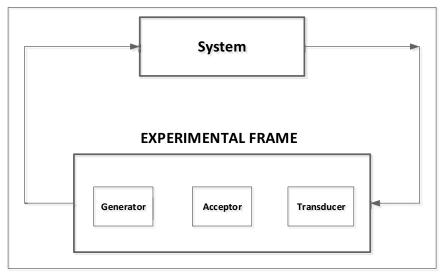

The experimental frame (Figure 4) defines the limited set of circumstances under which the system is observed, modeled and studied. The operational formulation of the objectives of the experimentation is a part of the experimental frame specification in a context. There is no agreed framework for the factors that can characterize a context. There are similarities between the acts of specifying a model for a real system and that of specifying a context. However, there is a common agreement to recognize that a model of context must make explicit at least the underlying objectives, assumptions and constraints of the study.

Figure 4. Experimental Frame and its Components [Zeigler 1983]

The set of experimentation circumstances defined by a frame consists of input, output, run control and summary variable sets. Constraints are imposed on the time segments of input and run control variables. Formally, the experimental frame is the following structure:

$EF = \langle T, I, O, C, \Omega_I, \Omega_C, SU \rangle$ , where:

- T is the time base

- I is the set of input variables, inputs are received from the model

- 0 is the set of output variables, outputs are sent to the model

- C is the set of run control variables which will be monitored to avoid situation that violate the frame constraints

- $\Omega_I$  is the set of input segments,

- $\Omega_C$  is the set of run control segments, i.e., constraints on the combinations of run control variables (including temporal constraints) which capture the domain operation required by the frame. Input/output behavior of a model in this frame is accepted as long as the run control constraints are not violated.

- *SU* is the set of summary mappings which are statistical and other aggregations of the input/output behavior into reduced and manageable spaces.

Different definitions of experimental frame and propositions for its structure and components have been proposed in the literature [Zeigler 1976] [Rozenblit 1985]. In most of the propositions, an experimental frame is composed of three type of components interconnected as shown in Figure 4. This structuration of the experimental frame allows the separation between a model and

the different contexts in which it can be experimented. So a model can be experimented using different experimental frames.

- **Generator:** Produces the input segments sent to a model. A generator is generally modeled in DEVS as a component without input port that generates outputs within constant or variable period of time.

- **Acceptor:** Continually tests the run control segments for satisfaction of the given constraints.

- **Transducer:** Collects the input/output data and computes the summary mappings. This is generally modeled by a DEVS model without output.

In [Rozenblit 1991] the basic experimental frame/model coupling results in the architecture where control of frame components is concentrated within the master experimental frame module whereas the simulators are responsible for execution of model component's dynamics. The centralized architecture involves a single experimental frame module directly linked to the global coordinator.

In [Traoré and Muzy 2005], authors advocated the separation between a model and its context, as a systematic part of the M&S process like the separation between a model and its simulator. This separation of concerns gives the following pairs: system/context pair, model/frame pair, and simulator/experimenter pair. In this approach experimenters adhere to the same message passing protocol as simulators during simulation.

#### II.2.3.2 System Specification Hierarchy

The systems specification hierarchy is the basis for a framework for modeling and simulation. We base our understanding of a system on Zeigler's hierarchy of system specification [Zeigler et al. 2000]. This framework employs a general concept of dynamical systems and identifies useful ways in which such systems can be specified. The proposed hierarchy is composed of five levels: OF, IORO, IOFO, IOS, and CN. This hierarchy is organized such that knowledge about the system is increased in higher levels; and knowledge of lower levels can be derived from higher levels. Modeling the structure of a system is done at the IOS and CN level. Knowledge of the behavior is given at the IORO level and this can be derived from IOFO knowledge. Usually, simulation algorithms are applied to the model to generate the behavior (IORO).

#### III. 2.3.2.1 Observation Frame (OF)

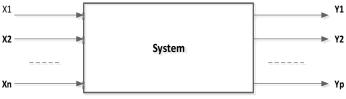

This level is concerned by how to stimulate the system with input, what variables to measure and how to observe them over a time base. It is the input output observation frame.

An observation frame is a structure of the form =< X, Y, T >, where X is the input interface, Y is the output interface and T is the time base.

At this level the system is seen a black box with input and output ports (Figure 5).

Figure 5. System at OF level

$$X = X_1 \times X_2 \times ... \times X_n$$

$$Y = Y_1 \times Y_2 \times ... \times Y_n$$

#### III.2.2.2.2 Input Output Relation Observation (IORO)

This level establishes a relation between input segments and output segments i.e. for each input segment  $\omega \in (X,T)$  applied to the system it associates a corresponding output segment  $\rho \in (Y,T)$  observed in the same time interval.

An IORO is a structure of the form  $IORO = \langle X, Y, T, \Omega, R \rangle$ , where  $\langle X, Y, T \rangle$  is an Observation Frame,  $\Omega = (X, T)$  is the set of input segments and R is the input/output relation that define the behavior of the system.

$R = \{(\omega, \rho) / dom(\omega) = dom(\rho)\} \subset \Omega \times (Y, T)$ , with  $\omega$  an input segment and  $\rho$  an output segment.

dom(f) is the observation time interval of f.

#### III.2.3.2.3 Input Output Function Observation (IOFO)

This level adds the knowledge of the initial state and every input stimulus produces a unique output.

Given an  $IORO = \langle X, Y, T, \Omega, R \rangle$  with  $R = \{(\omega, \rho)/dom(\omega) = dom(\rho)\} \subset \Omega \times (Y, T)$ . For each  $(\omega, \rho)$  we can find a function  $f_i \in F = \{f_1, f_2, ..., f_i, ...\}$  such that  $\rho = f_i(\omega)$ . The input/output relation R is partitioned to a set of functions  $F = \{f_1, f_2, ..., f_i, ...\}$ .

An IOFO structure is defined as follows:

$$IOFO = \langle X, Y, T, \Omega, F \rangle$$

$X, Y, T, et \Omega$  are the same as in IORO;

$f \in F \Rightarrow f \subseteq \Omega \times (Y,T)$  is a function, and if  $\rho = f(\omega)$  then  $dom(\rho) = dom(\omega)$ .

Given an  $IOFO = \langle X, Y, T, \Omega, F \rangle$  one can derive an  $IORO = \langle X, Y, T, \Omega, R \rangle$ , with  $R = \bigcup_{f \in F} f$ .

#### III.2.3.2.4 Input Output System (IOS)

The objective of this level is to determine how states are affected by inputs; given a state and an input what is the state after the input stimulus is over? What output event is generated by a state?

At IOFO level we know the initial state but not the other states (intermediary states and final states). IOFO is extended to IOS by defining the set of states and transitions.

An IOS is a structure of the form  $IOS = \langle X, Y, T, \Omega, Q, \Delta, \Lambda \rangle$ , where  $X, Y, T, et \Omega$  are the same as in IOFO; Q is the set of states;  $\Delta: Q \times \Omega \to Q$  is the global state transition function and  $\Lambda: Q \times X \to Y$  (or  $\Lambda: Q \to Y$ ) is the output function.

#### III.2.3.2.5 Coupled Network (CN)

This level defines the components and how they are coupled together. The components can be specified at lower levels or can even be structure systems themselves-leading to hierarchical structure.

A CN level structure is of the following form:

$$CN = \langle T, X_N, Y_N, D, \{M_d/d \in D\}, \{I_d/d \in D \cup \{N\}, \{Z_d/d \in D \cup \{N\}\}\}\} > 0$$

where,  $X_N$  is the set of input;

Y<sub>N</sub> is the set of output;

D is the set of components names;

$\forall d \in D, M_d$  is an IOS or a CN;

$\forall d \in D \cup \{N\}, I_d \subseteq D \text{ is the set of influencer of d,}$

$Z_d:\times_{i\in I_d} YX_i \to XY_d$  is coupling function

$$YX_i = X_i \text{ if } i = N$$

$= Y_i \text{ if } i \neq N$

$$XY_d = Y_d \text{ if } d = N$$

$$= X_d \text{ if } d \neq N$$

#### II.2.3.3 DEVS Modeling formalism

Models in DEVS are distinguished into atomic and coupled models [Zeigler et al. 2000]. Atomic models are component models that cannot be decomposed. The behavior of atomic models are specified in terms of input and output events, state space, transition functions from state to state, output functions and time advance function. Coupled models are hierarchical composition of atomic or coupled models. Two versions of DEVS exist: the original sequential version called Classic DEVS (CDEVS) [Zeigler 1976] and the parallel version called Parallel DEVS (PDEVS) [Chow 1996]. For the rest of the document the term DEVS refer to PDEVS.

#### II.2.3.3.1 Atomic DEVS

A DEVS atomic model is a structure of the form:  $M = \langle X, Y, S, \delta_{int}, \delta_{ext}, \delta_{conf}, \lambda, ta \rangle$ , where

$X = \{(p, v), p \in IPort \land v \in dom(p)\}$  is the set of inputs, IPort is the set of input ports,

$Y = \{(q, v), q \in OPort \land v \in dom(q)\}$  is the set of outputs, OPort is the set of output ports,

S is the state space,

$\delta_{int}: S \to S$  is the internal transition function

$\delta_{ext}: Q \times X^b \to S$  is the external transition function

$\delta_{conf}: S \times X^b \to S$  is the confluent transition function which resolves collision between internal and external events

$\lambda: S \to Y^b$  is the output function,

$ta: S \to \mathbb{R}^+ \cup \{+\infty\}$  is the time advance function.

Atomic DEVS provides a more appropriate way of modeling a system at IOS level

The semantics of an atomic model is as follows: at each time, the model is in some state s. If the lifetime of the state elapse i.e. e = ta(s) then the model send and output  $y = \lambda(s)$ ; if he receives no input within this simulation cycle he goes to the next state  $s' = \delta_{int}(s)$  (internal transition) with a new lifetime ta(s') else the next state is  $s' = \delta_{con}(s,x)$  (confluent transition, where x is the set of all events received by the model in this simulation cycle). If events are received before the time elapse e < ta(s) then the next state is  $s' = \delta_{ext}(s,e,x)$  (external transition, x is the set of events received) with a new lifetime ta(s'). See [Zeigler et al 2000] for more details of simulation algorithms for DEVS.

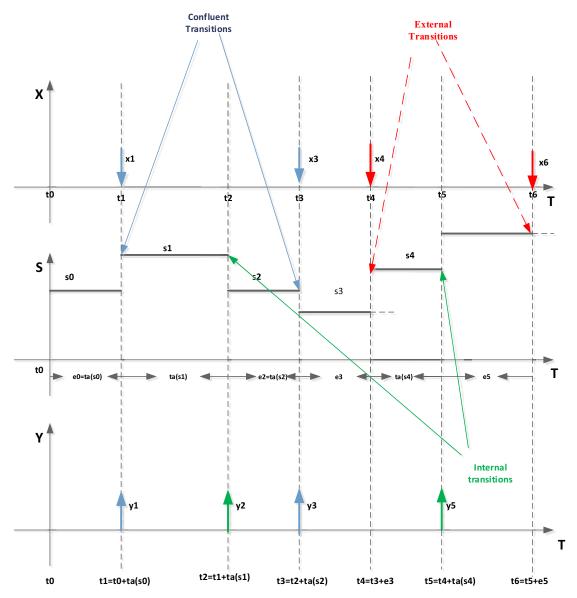

In the example of the following figure (Figure 6), the model is initially in state  $s_0$ , after the expiration of the duration  $t(s_0)$  and the reception of the input bag  $x_1$ , an output bag  $y_1 = \lambda(s_0)$  is sent at the time instant  $t_1$  and the model execute confluent transition with the new state defined by  $s_1 = \delta_{con}(s_0, x_1)$  for a new duration equal to  $ta(s_1)$ . In this state no event is received before the total expiration of the duration  $(s_1)$ , this results in an output bag  $y_2 = \lambda(s_1)$  and an internal transition with new state defined by  $s_2 = \delta_{int}(s)$  for a new duration  $ta(s_2)$ . In state  $s_3$ , the model is stimulated by the input bag  $x_4$  at the time instant  $t_4$  before the expiration of its duration  $(e_3 < ta(s_3))$ ; this results in an external transition with new state  $s_4 = \delta_{ext}(s_3, e_3, x_4)$

Figure 6. Example of transitions occurrences

#### II.2.3.3.2 Coupled DEVS

A coupled model is a structure of the form:  $M = \langle X, Y, D, \{M_d\}_{d \in D}, EIC, EOC, IC \rangle$ , where

X and Y are the same as in the case of atomic model,

D is the set of names of models which compose M;

$M_d$  is the model wich name is d;

$EIC \subseteq \{((M, ip_M), (d, ip_d))/ip_M \in IPorts_M, ip_d \in IPorts_d\}$  is the external input coupling relation

$EOC \subseteq \{((d, op_d), (M, op_M))/op_M \in OPorts_{M,} op_d \in OPorts_d\}$  is the external output coupling relation

$IC \subseteq \{((a, op_a), (b, ip_b))/op_a \in OPorts_a, ip_b \in IPorts_b\}$  is the internal coupling relation;

Coupled DEVS provides basic concepts that appropriately capture the different aspects of a system at CN level.

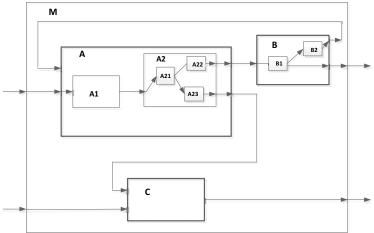

A DEVS model is simulated by following a well-defined simulation protocol. We explain this protocol by considering the example of Figure 7.

Figure 7. Example of Coupled Model

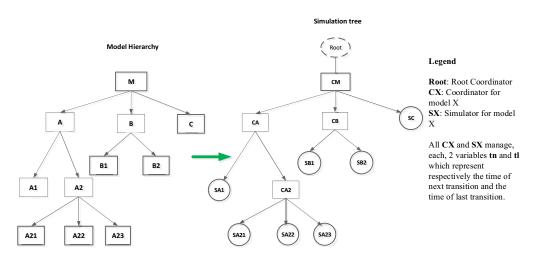

From each coupled model hierarchy corresponds a simulation tree; the corresponding simulation tree of the coupled model of Figure 7 is shown on Figure 8.

Figure 8. Correspondence between Model Hierarchy and Simulation Tree

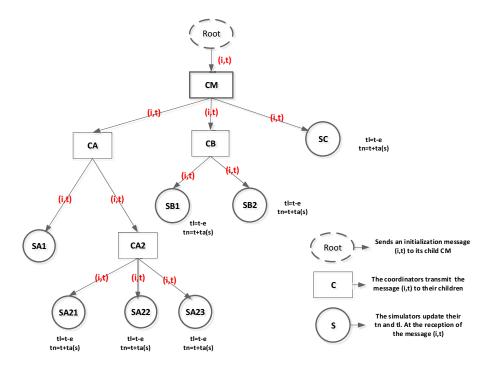

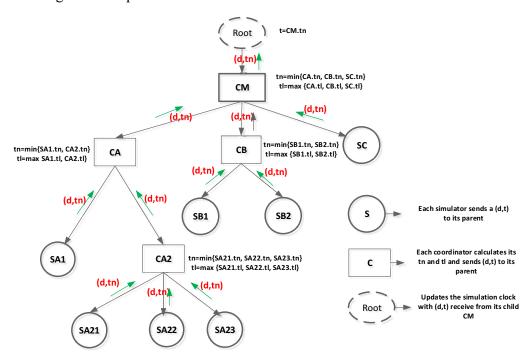

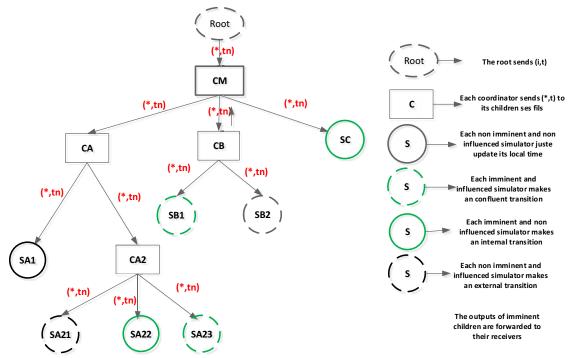

The Root coordinator is responsible of starting the simulation at a time t by sending an initialization message (i,t) to its child CM. When CM receives the message (i,t), it forwards it to its children so that they can forward it also to their children in case of coordinators or update their tl and tn in case of simulators. The initialization process is shown on Figure 9 and Figure 10.

Figure 9. Sending of initialization message

After the updates of their tn and tl, each simulator sends a done message to its parent coordinator which also calculates its tn and tl and sends it to its parent. This process ends with the sending of the done message of the top-level coordinator to the root coordinator.

Figure 10. Sending of done messages to parents

The root coordinator sends a first message (\*,t) message to its child CM (Figure 11) so that it can forward it to its children.

Figure 11. Sending star message

At the reception of the (\*,t) message, imminent simulators send their outputs to their respective parents coordinators and all the simulators (including the imminent ones) wait for eventual inputs to decide which transition to perform. Each coordinator will send the received outputs as input to its children by analyzing coupling relations of the coupled model associated to it. Imminent components that are not influenced will make internal transition. Imminent and influenced components will make confluent transition. Non-imminent and influenced components will external transition. The cycle ends by sending of (d,tn) done message by all the components (including non-imminent and influenced components that have not performed any transition) to their parent coordinators like in the end of the initialization process.

An important property of the DEVS formalism is the closure under coupling property which ensures that any coupled model has an equivalent atomic model.

#### II.2.3.3.3 Modeling with DEVS

#### II.2.3.3.3.1 University Bus System

A bus shuttles between a downtown station and a university station, providing students and non-students with a transportation service. The growing number of users leads the university administration to set up a study to evaluate the performances of the bus system. We then consider a model for the UBS, with user identification possibilities. A user enters the model when he lines up in a station. He exits from the model when he gets off the bus at a station.

The university Bus System is a DEVS atomic model.

$$UBS = \langle X, Y, S, \delta_{int}, \delta_{ext}, \delta_{conf}, \lambda, ta \rangle$$

$$X = \{Hello1, Hello2\} \text{ et } Y = \{Bye1, Bye2\}$$

$Hello1, Hello2, Bye1, Bye2 \in \{(identity, statut) / statut \in \{"Student", "non - Student"\} \}$  and identity is a string.

$$S = \{W_d, W_u, B, P, D, S'\}$$

$W_d$  is the ordered list of users waiting at the downtown station,

$W_u$  is the ordered list of users waiting at the university station,

B is the ordered list of passengers in the bus,

$P \in \{1,2,3,4\}$  is the current position of the bus (1: downtown station, 2: university station, 3: from downtown to the university, 4: from the university to downtown),

D is the duration of the current action,

$S' \in \{"loading", "unload", "travel"\}$  is the current status of the bus,

$\tau$  is the current simulated time..

#### Internal transition function $\delta_{int}$ : $S \rightarrow S$

$$\delta_{int}(W_d, W_u, B, P = 4, D, S = \text{travel}, \tau) =$$

$$= (W_d, W_u, B, P = 1, D = 0, S = \text{unload}, \tau = \tau + D) \text{ if } B \neq \emptyset$$

$$= (W_d, W_u, B, P = 1, D = v, S = \text{load}, \tau = \tau + D) \text{ if } W_d \neq \emptyset \text{ and } B = \emptyset$$

$$= (W_d, W_u, B, P = 3, D = \beta_1, S, \tau = \tau + D) \text{ si } W_d = \emptyset \text{ et } B = \emptyset$$

If the bus arrives at the university station (the travel time is elapsed, then an internal transition must occur), it must stop to let the passengers get off. If the bus is empty, the users waiting at the station can immediately start getting in it. If the bus was empty, and no one was waiting at the station, a stop is not required.

$$\begin{split} \delta_{int}(W_d,W_u,B,P&=1,D,S=\text{unload},\tau) = \\ &= (W_d,W_u,B=rest(B),P,D=\mu,S,\tau=\tau+D) \ if \ B \neq \emptyset \\ &= (W_d,W_u,B,P,D=0,S=\text{load},\tau=\tau+D) \ if \ B = \emptyset \end{split}$$

All the passengers in the bus must get off when the bus stops at the station. They do it, one by one. When all the passengers get off the bus, the users waiting at the station can start getting in it.

$$\delta_{int}(W_d, W_u, B, P = 1, D, S = \text{load}, \tau) =$$

$$= (W_d, W_u, B, P = 3, D = \beta_1, S = \text{"travel"}, \tau = \tau + D) \text{ if } W_d = \emptyset \text{ or } ||B|| = \alpha$$

$$= (W_d = rest(W_d), W_u, B = B + first(W_d), P, D = \mu, S, \tau = \tau + D)if W_d \neq \emptyset \land ||B|| < \alpha$$

If there is no one waiting, the bus can start its travel to the other station. Also if the bus is full, the bus can start its travel to the other station. If not, users can get in it, one by one.

Similar specifications are done at the following lines for the case the downtown station is considered.

$$\begin{split} \delta_{int}(W_d,W_u,B,P=3,D,S=\text{travel},\tau) = \\ &= (W_d,W_u,B\neq\emptyset,P=2,D=0,S=\text{unload},\tau=\tau+D) \text{ if } B\neq\emptyset \\ &= (W_d,W_u,B,P=1,D=\upsilon,S=\text{load},\tau=\tau+D) \text{ if } W_u\neq\emptyset \text{ and } B=\emptyset \\ &= (W_d,W_u,B,P=3,D=\beta_2,S,\tau=\tau+D) \text{ if } W_u=\emptyset \text{ and } B=\emptyset \\ \delta_{int}(W_d,W_u,B,P=2,D,S=\text{unload},\tau) = \\ &= (W_d,W_u,B=rest(B),P,D=\mu,S,\tau=\tau+D) \text{ if } B\neq\emptyset \\ &= (W_d,W_u,B,P,D=0,S=\text{load},\tau=\tau+D) \text{ if } B=\emptyset \\ \delta_{int}(W_d,W_u,B,P=2,D,S=\text{load},\tau) = \\ &= (W_d,W_u,B,P=3,D=\beta_1,S=\text{"travel"},\tau=\tau+D) \text{ if } W_u=\emptyset \text{ or } \|B\|=\alpha \\ &= (W_d,W_u=rest(W_u),B=B+first(W_u),P,D=\mu,S,\tau=\tau+D) \text{ if } W_u\neq\emptyset \text{ } \land \|B\|<\alpha \\ \alpha\in\mathbb{N} \text{ is the capacity of the bus} \end{split}$$

$\beta_1 \in \mathbb{R}^+$  est le temps de Voyage de la gare du centre-ville jusqu'à la gare de l'université,

$\beta_2 \in \mathbb{R}^+$  is the travel time from downtown station to university station

$\mu \in \mathbb{R}^+$  is the time for a user to get in the bus

$v \in \mathbb{R}^+$  is the time for a user to get from the bus

first(list) returns the first element of list

rest(list) returns list, which has been reordered after its first element has been removed,

||B|| gives the number of element of list B,

"list + element" performs an adding of "element" to "list", and reorders "list",

#### External transition function $\delta_{ext}$ : $Q \times X \rightarrow S$

$$\delta_{ext} \big( (W_d, W_u, B, P, D, S, \tau), e, (x_1, x_2) \big) =$$

$$= (W_d + x_1, W_u, B, P, D = D - e, S, \tau = \tau + D) \text{if } x_1 \neq \emptyset \text{ and } x_2 = \emptyset$$

$$= (W_d, W_u + x_2, B, P, D = D - e, S, \tau = \tau + D) \text{if } x_1 = \emptyset \text{ and } x_2 \neq \emptyset$$

$$= (W_d + x_1, W_u + x_2, B, P, D = D - e, S, \tau = \tau + D) if x_1 \neq \emptyset \text{ and } x_2 \neq \emptyset$$

A user can line up at the downtown station, at any time. Then, the time he enters the UBS is updated to the current time, and the time he enters the bus is set to  $+\infty$ . Similar situation at the university station. Situation where two users line up simultaneously at the downtown and the university station.

Confluent transition function:

$$\delta_{conf}$$

:  $S \times X^b \to S$

$\delta_{conf}(s,x) = \delta_{ext}(s,ta(s),x) \ \forall s \in S$

# Output function $\lambda: S \to Y$

$$\lambda(W_d, W_u, B \neq \emptyset, P = 1, D, S = "unload", \tau) = (Bye1 = first(B), Bye2 = \emptyset)$$

$$\lambda(W_d, W_u, B \neq \emptyset, P = 2, D, S = "unload", \tau) = (Bye1 = \emptyset, Bye2 = first(B))$$

A passenger who gets off the bus at any station exits the system too.

$$\lambda(W_d, W_u, B \neq \emptyset, P, D, S, \tau) = (Bye1 = \emptyset, Bye2 = \emptyset)$$

in all other cases.

Time advance function  $ta: S \to \mathbb{R}^+ \cup \{+\infty\}$

$$ta(W_d, W_u, B, P, D, S, \tau) = D$$

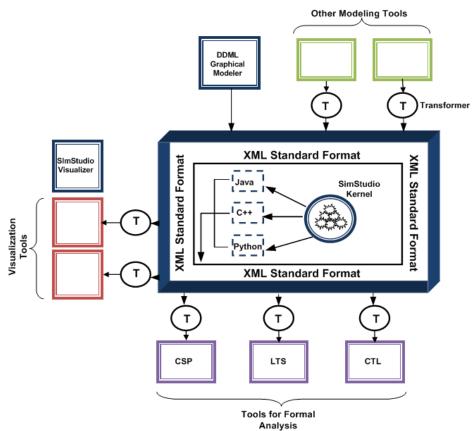

## II.2.3.4 DEVS modeling Tools

Over the years, several modeling platforms and tools have been developed based on DEVS theory and its extensions. DEVS models have been constructed using programming languages or some XML-based storage structures. Most of these platform dependent methods take advantage of reusability in object oriented programming by extending and reusing classes of DEVS models. Some notable platform-dependent tools include:

- DEVS-Scheme [Zeigler 1990]: is a knowledge-based environment for modeling and simulation based on the Scheme functional language (a variation of Lisp)

- DEVS-C++ [Zeigler et al. 1996] is a DEVS-based modeling and simulation environment written in C++, which implements parallel execution and supports large-scale systems

- DEVSim++ [Kim 1994] is an object-oriented DEVS simulator implemented in C++ that defines basic classes that can be extended by users to define their own atomic and coupled DEVS components

- ADEVS [Nutaro 1999] provides a C++ library based on DEVS, which developers can use to build their own models, and supports integration with other simulation environments

- DEVSJAVA [Sarjoughian and Zeigler 1998] is a DEVS-based modeling and simulation environment that provides Java classes for users to implement their own models. It also supports PDEVS, DSDEVS, RT-DEVS and 2D/3D cellular automata models. Distributed simulation is also possible due to the integration of several distributed implementations of DEVS abstract simulators. DEVSJava is now a part of DEVS-Suite, which provides some graphical facilities for modeling and simulation activities [Kim et al. 2009].

- VLE [Quesnel et al. 2009] is a modeling library that in addition to the DEVS formalism, implements in C++ several modeling formalisms like Petri nets, 2D/3D cellular automata, Quantized State Systems, etc. and allow heterogeneous integration of models of these

formalisms in PDEVS coupled model and their simulation by PDEVS simulators. Coupled models can be created in VLE graphically but atomic models are defined textually in C++. VLE integrates particular ports called initialization and observation ports respectively used for initialization and observation of models. The observation ports are connected to EOV (Eyes of VLE) which present simulation results in different forms.

- CD++[Wainer 2009] provides a C++ library to specify models in CDEVS, PDEVS and Cell-DEVS, an extension integrating cellular automata and DEVS. DEVS models and Cell-DEVS models can be mixed in the same simulation in CD++. CD++ integrates multiple simulation algorithms implementations including parallel and distributed simulation strategies. CD++ also provides an Eclipse plugin allowing the edition of DEVS and Cell-DEVS models both textually and graphically, as well as the graphical visualization of Cell-DEVS simulation results.

- SimBeans [Präehofer et al. 1999] is a component-based software architecture based on Java and JavaBeans. The idea is to provide a set of layered components that can be used in model creation, output results analysis, and visualization using DEVS.

- PythonDEVS [Bolduc and Vangheluwe 2002] is a basic implementation of CDEVS in Python programming language.

- JDEVS [Filippi and Bisgambiglia 2004] is a DEVS modeling and simulation environment written in Java. It allows general-purpose, component-based, object-oriented, visual simulation of models

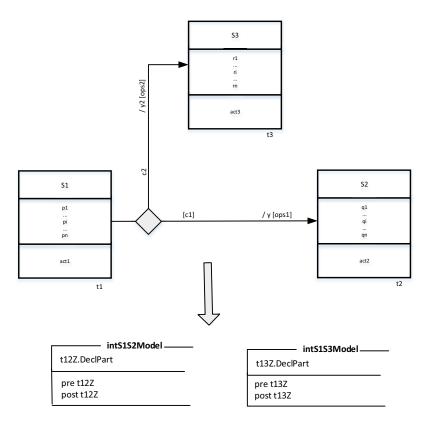

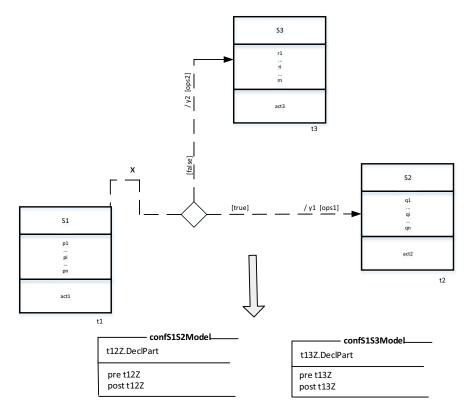

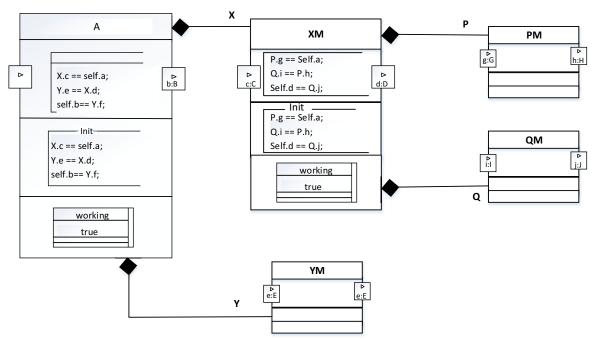

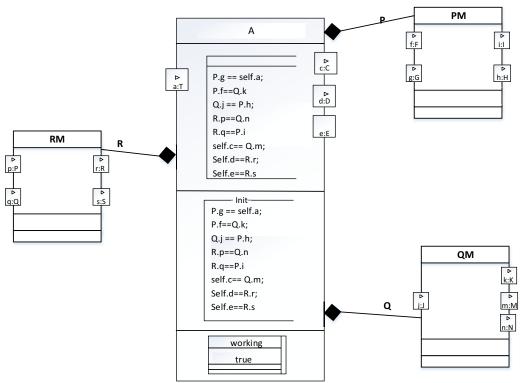

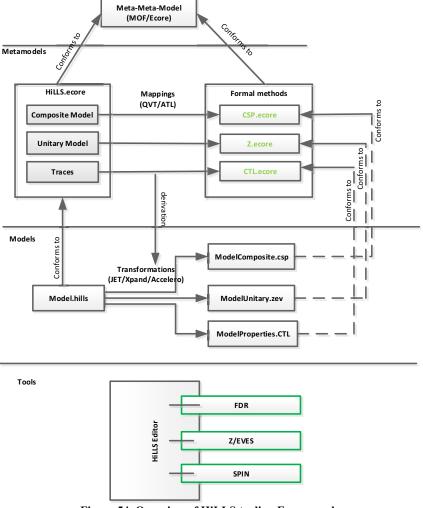

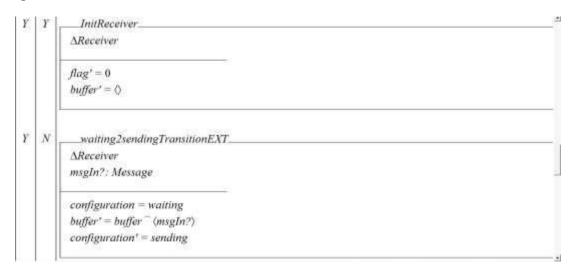

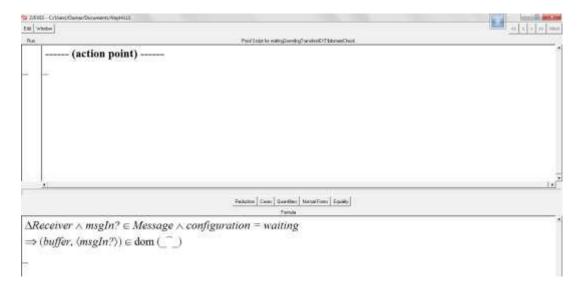

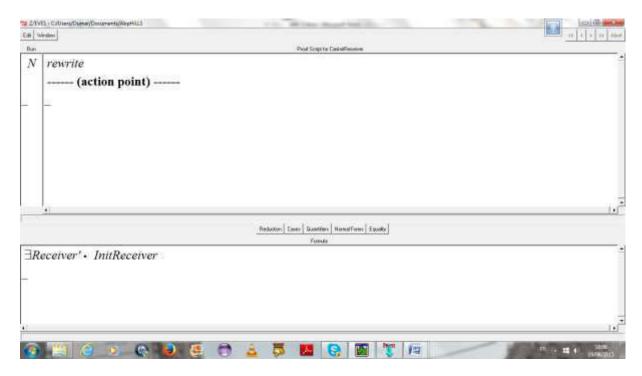

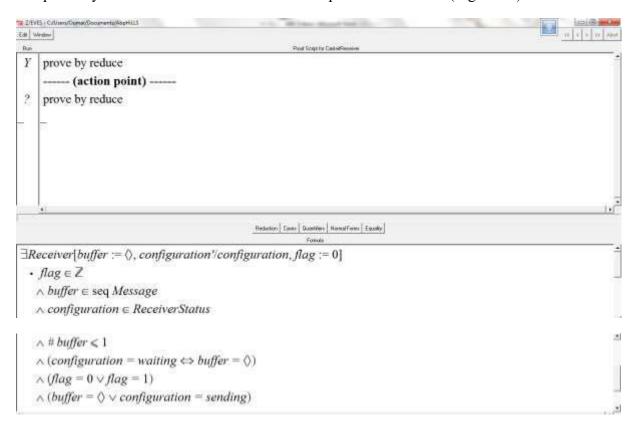

- James II [Himmelspach and Uhrmacher 2004] implements DEVS theory including PDEVS, PdynDEVS and cellular automata to model and simulate agent systems. The toolkit supports software-in-the-loop simulation to test agents in virtual environments. James II integrates sequential and multi-threaded implementations of various simulation algorithms.