# Compensation numérique pour convertisseur large bande hautement parallélisé.

Nicolas Le Dortz

#### ▶ To cite this version:

Nicolas Le Dortz. Compensation numérique pour convertisseur large bande hautement parallélisé.. Autre. CentraleSupélec, 2015. Français. NNT: 2015CSUP0002 . tel-01331558

#### HAL Id: tel-01331558 https://theses.hal.science/tel-01331558

Submitted on 14 Jun 2016

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^{\circ}$  d'ordre : 2015-02-TH

#### **SUPELEC**

#### ÉCOLE DOCTORALE STITS

"Sciences et Technologies de l'Information des Télécommunications et des Systèmes"

#### THÈSE DE DOCTORAT

**DOMAINE: STIC** Spécialité : Électronique

Soutenue le 14 janvier 2015 par:

#### Nicolas LE DORTZ

Compensation numérique pour convertisseur large bande hautement parallélisé

Directeur de thèse: Philippe BÉNABÈS HDR - SUPELEC

#### Composition du jury:

Examinateur: Philippe BÉNABÈS HDR - SUPELEC

Dominique DALLET Professeur - IMS Bordeaux Rapporteur:  ${\bf Examinateur}:$ David DECLERCQ Professeur - ENSEA

Examinateur: Pierre DUHAMEL Professeur - CNRS-LSS Rapporteur: Andreas KAISER Professeur - IEMN

${\bf Examinateur}:$ Caroline LELANDAIS-PERRAULT Enseignant chercheur - SUPELEC

Membre invité : Thierry SIMON Ingénieur - STMicroelectronics Membre invité: Pascal URARD Ingénieur - STMicroelectronics Membre invité : Filipe VINCI DOS SANTOS Enseignant chercheur - SUPELEC

Président du jury : Pierre DUHAMEL Professeur - CNRS-LSS

#### Abstract

Because of their parallel scalable structure, time-interleaved analog-to-digital converters (TIADC) seem to be the holy grail of analog-to-digital conversion. Theoretically, their sampling speed can be increased, very simply, by duplicating the sub-converters. The real world is different because mismatches between the converters strongly reduce the TIADC performance, especially when trying to push forward the sampling speed, or the resolution of the converter. In this thesis, I show that this limitation can be alleviated by using background digital mismatch calibration.

The first part of the thesis is dedicated to studying the mismatches themselves. The various technological sources of offset, gain, skew and bandwidth mismatches are explained. Following this explanation is the derivation of a frequency model that gives an insight of the way the mismatch errors affect the TIADC output signal. Performance metrics such as the SNDR and the SFDR are expressed as the function of the mismatch levels.

In the second part of the thesis, I introduce new background digital mismatch calibration techniques that are able to reduce the offset, gain, skew and bandwidth mismatch errors. In the proposed calibration methods, the mismatches are estimated by using the statistical properties of the input signal. The calibration algorithms are shown to converge for non-stationary signals, provided that the input signal autocovariance is well-conditioned. Digital FIR filters are used to recover the correct output samples.

In the third part, a 1.6 GS/s TIADC test chip, implementing offset, gain and skew mismatch calibration, demonstrates a reduction of the mismatch spurs down to a level of -70 dBFS, up to an input frequency of 750 MHz. Temperature measurements of the chip emphasize the need for background calibration by showing the mismatch variations with respect to the temperature. The circuit achieves the lowest level of mismatches among TIADCs in the same frequency range, with a reasonable power and area, despite the overhead caused by the calibration.

# Contents

| 1 | Intr | Introduction                                              |    |  |  |

|---|------|-----------------------------------------------------------|----|--|--|

|   | 1.1  | The challenges of high speed analog-to-digital conversion | 1  |  |  |

|   | 1.2  | Analog-to-Digital converter architectures                 | 3  |  |  |

|   | 1.3  | Mismatches in TIADCs                                      | 5  |  |  |

|   | 1.4  | Mismatch calibration prior art                            | 6  |  |  |

|   |      | 1.4.1 Foreground mismatch calibration                     | 7  |  |  |

|   |      | 1.4.2 Background mismatch calibration                     | 7  |  |  |

|   |      | 1.4.2.1 Mixed mismatch calibration                        | 8  |  |  |

|   |      | 1.4.2.2 Digital mismatch calibration                      | 9  |  |  |

|   | 1.5  | Aim of this work and outline                              | 0  |  |  |

| _ | 3.50 |                                                           | _  |  |  |

| 2 |      |                                                           | 2  |  |  |

|   | 2.1  |                                                           | 12 |  |  |

|   | 2.2  |                                                           | 13 |  |  |

|   | 2.3  |                                                           | 16 |  |  |

|   | 2.4  |                                                           | 19 |  |  |

|   |      | 2.4.1 Circuit sources                                     | 19 |  |  |

|   |      | 2.4.2 Effects on the output signal                        | 21 |  |  |

|   |      | 2.4.3 Consequences on the TIADC performance               | 23 |  |  |

|   |      | 2.4.3.1 SNDR degradation                                  | 23 |  |  |

|   |      | 2.4.3.2 SFDR degradation                                  | 25 |  |  |

|   | 2.5  | Transfer function mismatches                              | 27 |  |  |

|   | 2.6  | Gain mismatches                                           | 29 |  |  |

|   |      | 2.6.1 Circuit sources                                     | 30 |  |  |

|   |      | 2.6.2 Effects on the output signal                        | 30 |  |  |

|   |      | 2.6.3 Consequences on the TIADC performance               | 32 |  |  |

|   | 2.7  | Skew mismatches                                           | 34 |  |  |

|   |      | 2.7.1 Circuit sources                                     | 35 |  |  |

|   |      | 2.7.2 Effects on the output signal                        | 35 |  |  |

|   |     | 2.7.3  | Consequences on the TIADC performance                    |

|---|-----|--------|----------------------------------------------------------|

|   | 2.8 | Bandy  | width mismatches                                         |

|   |     | 2.8.1  | Circuit sources                                          |

|   |     | 2.8.2  | Effects on the output signal                             |

|   |     | 2.8.3  | Consequences on the TIADC performance                    |

|   | 2.9 | Conclu | usion                                                    |

| 3 | Bac | kgrour | nd digital mismatch calibration                          |

|   | 3.1 | Introd | luction                                                  |

|   | 3.2 | Requir | rements on the input signal                              |

|   |     | 3.2.1  | Foreword                                                 |

|   |     | 3.2.2  | Wide Sense Stationary processes                          |

|   |     | 3.2.3  | Non-stationary processes                                 |

|   |     | 3.2.4  | Application to digital communications signals            |

|   | 3.3 | Overa  | ll mismatch calibration architecture                     |

|   | 3.4 | Offset | mismatch calibration                                     |

|   |     | 3.4.1  | Introduction                                             |

|   |     | 3.4.2  | Offset mismatch correction                               |

|   |     |        | 3.4.2.1 Principle                                        |

|   |     |        | 3.4.2.2 Circuit implementation                           |

|   |     | 3.4.3  | Offset mismatch estimation                               |

|   |     |        | 3.4.3.1 General idea                                     |

|   |     |        | 3.4.3.2 Theoretical explanation                          |

|   |     |        | 3.4.3.3 Circuit implementation                           |

|   |     |        | 3.4.3.4 Accuracy analysis                                |

|   |     | 3.4.4  | Conclusion                                               |

|   | 3.5 | Gain r | mismatch calibration                                     |

|   |     | 3.5.1  | Introduction                                             |

|   |     | 3.5.2  | Gain mismatch correction                                 |

|   |     |        | 3.5.2.1 Principle                                        |

|   |     |        | 3.5.2.2 Circuit implementation                           |

|   |     | 3.5.3  | Gain mismatch estimation                                 |

|   |     |        | 3.5.3.1 General idea                                     |

|   |     |        | 3.5.3.2 Theoretical explanation – WSS process            |

|   |     |        | 3.5.3.3 Theoretical explanation – non-stationary process |

|   |     |        | 3.5.3.4 Circuit implementation                           |

|   |     |        | 3 5 3 5 Accuracy analysis                                |

|   |     | 3.5.4   | Conclusion                                                  | $^{\prime}3$ |

|---|-----|---------|-------------------------------------------------------------|--------------|

|   | 3.6 | Skew    | mismatch calibration                                        | 73           |

|   |     | 3.6.1   | Introduction                                                | 73           |

|   |     | 3.6.2   | Skew mismatch correction                                    | 74           |

|   |     |         | 3.6.2.1 General idea                                        | 74           |

|   |     |         | 3.6.2.2 Theoretical explanation                             | 75           |

|   |     |         | 3.6.2.3 Circuit implementation                              | 76           |

|   |     |         | 3.6.2.4 Accuracy analysis                                   | 79           |

|   |     | 3.6.3   | Skew mismatch estimation                                    | 32           |

|   |     |         | 3.6.3.1 General idea                                        | 32           |

|   |     |         | 3.6.3.2 Theoretical explanation – WSS process               | 33           |

|   |     |         | 3.6.3.3 Theoretical explanation – non-stationary process 8  | 37           |

|   |     | 3.6.4   | Generalization                                              | 39           |

|   |     |         | 3.6.4.1 Circuit implementation                              | 39           |

|   |     |         | 3.6.4.2 Accuracy analysis                                   | 90           |

|   |     | 3.6.5   | Conclusion                                                  | )2           |

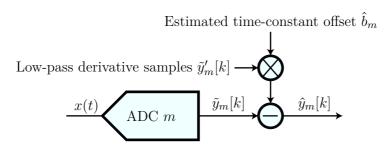

|   | 3.7 | Bandy   | width mismatch calibration                                  | 93           |

|   |     | 3.7.1   | Introduction                                                | 93           |

|   |     | 3.7.2   | Bandwidth mismatch correction                               | 93           |

|   |     |         | 3.7.2.1 General idea                                        | 93           |

|   |     |         | 3.7.2.2 Theoretical explanation                             | )4           |

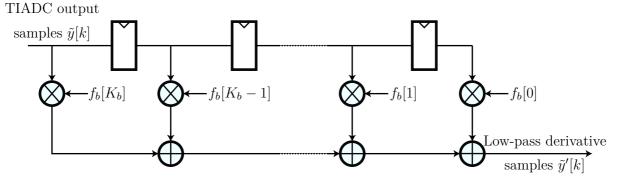

|   |     |         | 3.7.2.3 Circuit implementation                              | 96           |

|   |     | 3.7.3   | Bandwidth mismatch estimation                               | 9            |

|   |     |         | 3.7.3.1 General idea                                        | 9            |

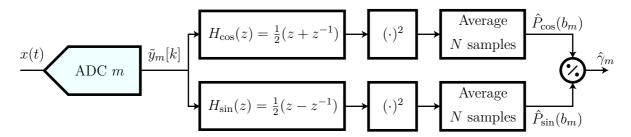

|   |     |         | 3.7.3.2 Cosine and sine filtering                           | )1           |

|   |     |         | 3.7.3.3 Theoretical explanation – WSS process               | )3           |

|   |     |         | 3.7.3.4 Theoretical explanation – non-stationary process 10 | )5           |

|   |     |         | 3.7.3.5 Circuit implementation                              | )6           |

|   |     | 3.7.4   | Accuracy analysis                                           | )7           |

|   |     | 3.7.5   | Conclusion                                                  | )8           |

|   | 3.8 | Concl   | usion                                                       | .0           |

| 4 | Dig | ital mi | ismatch calibration circuit implementation 11               | 1            |

|   | 4.1 |         | luction                                                     |              |

|   | 4.2 |         | ll architecture                                             |              |

|   |     | 4.2.1   | Analog front-end                                            |              |

|   |     | 4.2.2   | Mismatch calibration                                        |              |

|   |     |         |                                                             |              |

|   | 4.3 | Measu  | rements                                         | 7 |

|---|-----|--------|-------------------------------------------------|---|

|   |     | 4.3.1  | Measurement test bench                          | 7 |

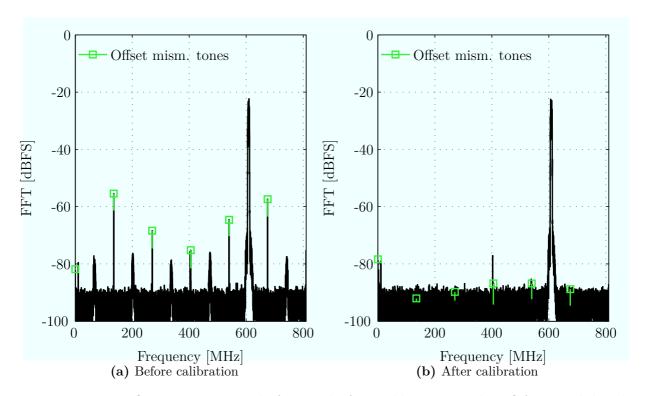

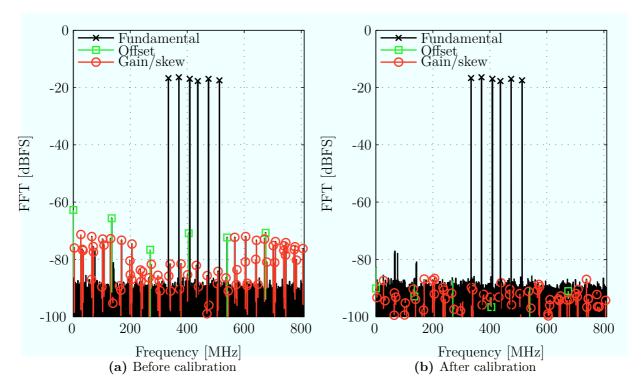

|   |     | 4.3.2  | Mismatch calibration performance                | 8 |

|   |     | 4.3.3  | Mismatch characterization                       | 9 |

|   |     |        | 4.3.3.1 Mismatch variations vs. input frequency | 0 |

|   |     |        | 4.3.3.2 Mismatch variations vs. temperature     | 2 |

|   |     | 4.3.4  | Performance with non sinusoid inputs            | 5 |

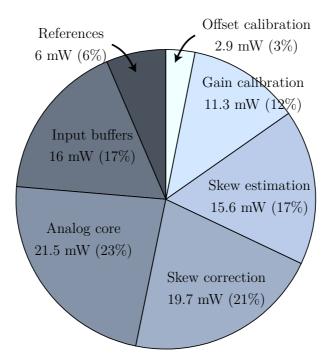

|   |     | 4.3.5  | Power consumption breakdown                     | 6 |

|   | 4.4 | Comp   | arison with state of the art                    | 7 |

|   | 4.5 | Conclu | usion                                           | 8 |

| 5 | Con | clusio | n 130                                           | 0 |

|   | 5.1 | Summ   | nary                                            | 0 |

|   | 5.2 | Perspe | ectives and future work                         | 2 |

# List of Figures

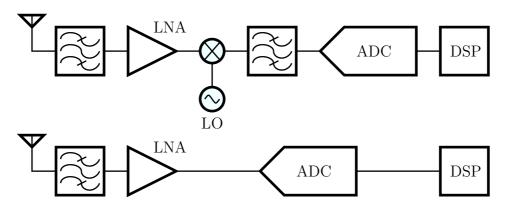

| 1.1  | Traditional IF sampling vs. direct RF sampling                           |

|------|--------------------------------------------------------------------------|

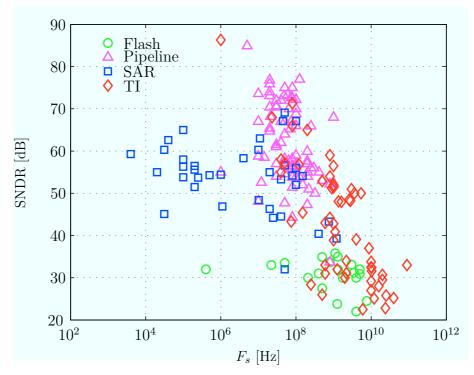

| 1.2  | ADC architectures classified vs. sampling frequency and SNDR             |

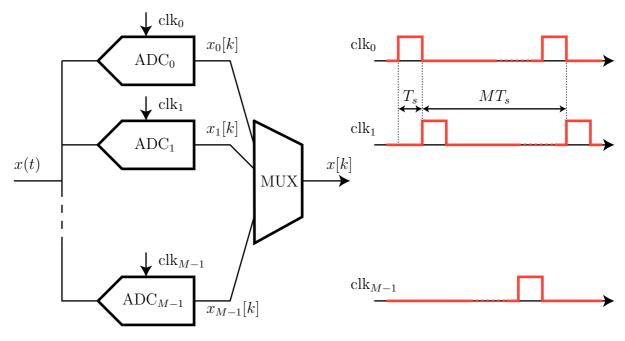

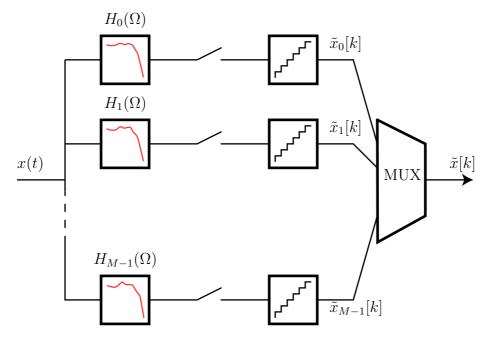

| 1.3  | Principle of a time-interleaved ADC                                      |

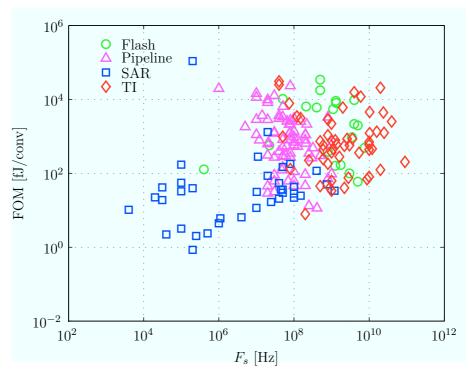

| 1.4  | ADC architectures classified vs. sampling frequency and FOM              |

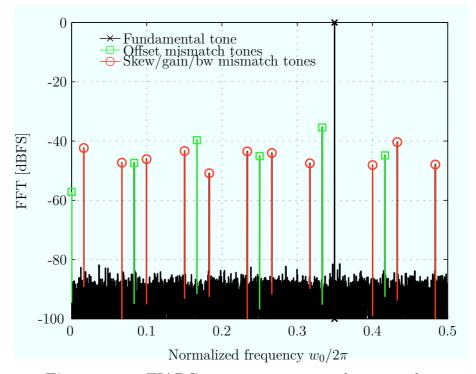

| 1.5  | TIADC output spectrum with mismatches                                    |

| 2.1  | Full rate and sub-sampled Dirac combs                                    |

| 2.2  | Threshold voltage standard deviation vs. transistor dimensions 18        |

| 2.3  | Schematic of a NMOS differential pair                                    |

| 2.4  | Model of a TIADC with offset mismatches                                  |

| 2.5  | Illustration of offset mismatch tones in TIADC output spectrum 23        |

| 2.6  | Output spectrum of a TIADC with offset mismatches                        |

| 2.7  | SNDR vs. RMS offset mismatch level                                       |

| 2.8  | Model of a TIADC with transfer function mismatches                       |

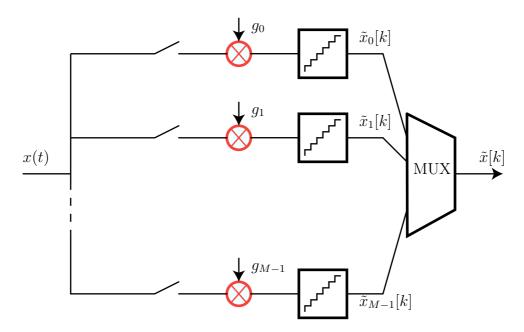

| 2.9  | Model of a TIADC with gain mismatches                                    |

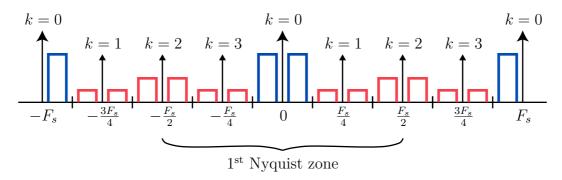

| 2.10 | Illustration of TIADC output spectrum with gain mismatch aliases 31      |

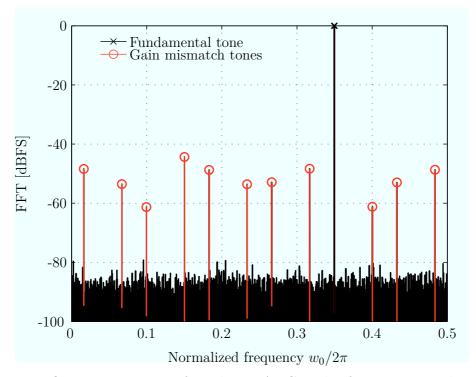

| 2.11 | Output spectrum of a TIADC with gain mismatches                          |

| 2.12 | SNDR vs. RMS gain mismatch level                                         |

| 2.13 | Model of a TIADC with skew mismatches                                    |

| 2.14 | Illustration of TIADC output spectrum with skew mismatch aliases 36      |

| 2.15 | Output spectrum of a TIADC with skew mismatches                          |

| 2.16 | SNDR vs. input frequency for different RMS skew mismatch levels 38       |

| 2.17 | Model of a TIADC with bandwidth mismatches                               |

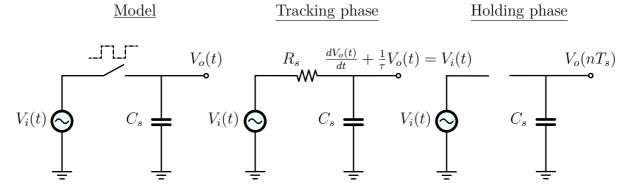

| 2.18 | Operation principle of a T&H circuit                                     |

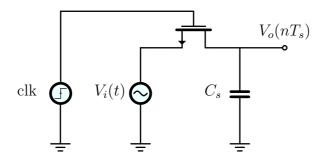

| 2.19 | Realization of a basic T&H circuit with a NMOS transistor                |

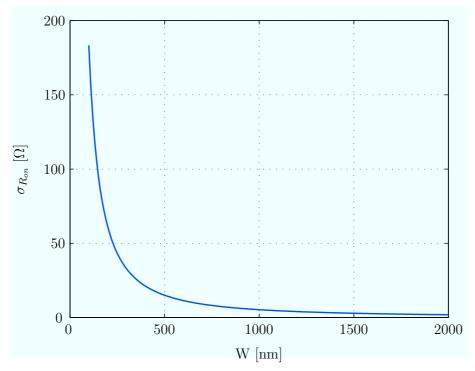

| 2.20 | Standard deviation of NMOS on-resistance vs. transistor width 42         |

| 2.21 | Illustration of TIADC output spectrum with bandwidth mismatch aliases 43 |

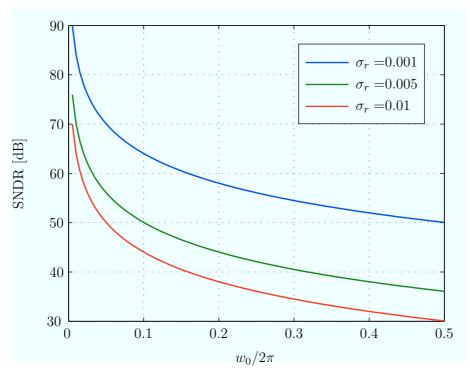

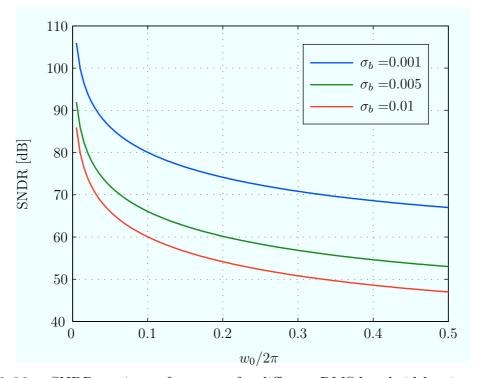

| 2.22 | SNDR vs. input frequency for different RMS bandwidth mismatch levels 45  |

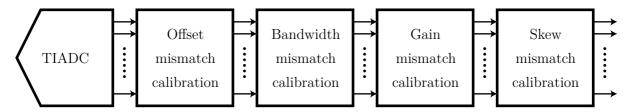

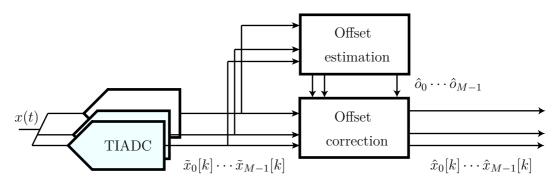

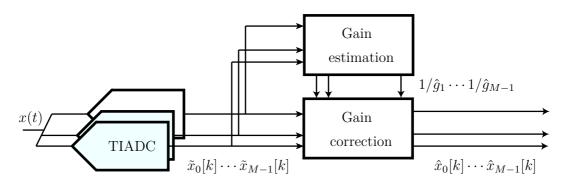

| 3.1  | Overall mismatch calibration structure                                   |

| 5.2  | Offset mismatch campration block diagram                                      |

|------|-------------------------------------------------------------------------------|

| 3.3  | Offset mismatch correction block diagram                                      |

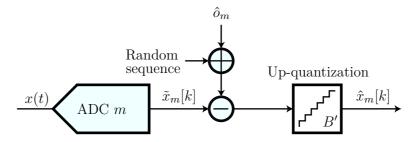

| 3.4  | Spectrums after offset mismatch correction                                    |

| 3.5  | Offset mismatch estimation block diagram                                      |

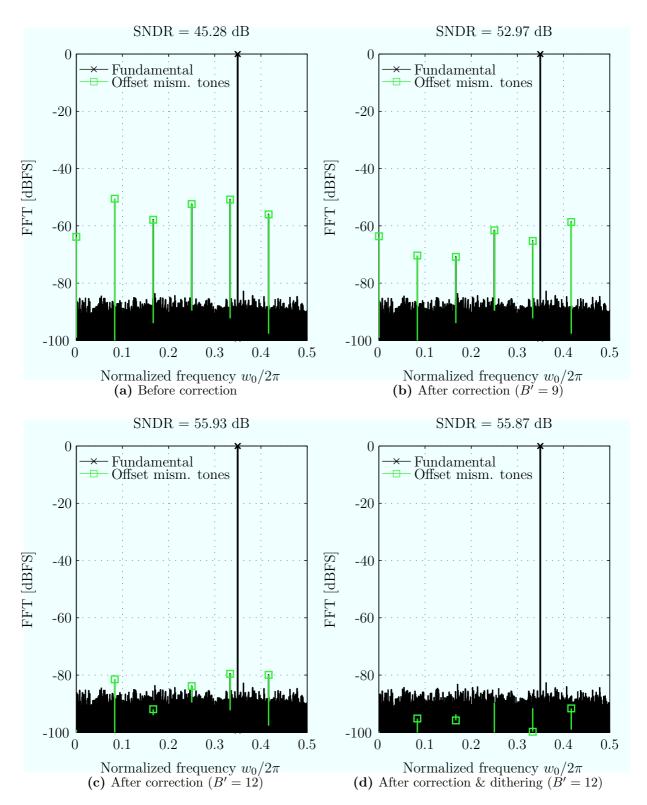

| 3.6  | Frequency response of the offset mismatch estimation filter                   |

| 3.7  | Gain mismatch calibration block diagram                                       |

| 3.8  | Gain mismatch correction block diagram                                        |

| 3.9  | Output spectrum before and after gain mismatch correction 68                  |

| 3.10 | Gain mismatch estimation block diagram                                        |

| 3.11 | Alternative implementation of the gain mismatch estimation                    |

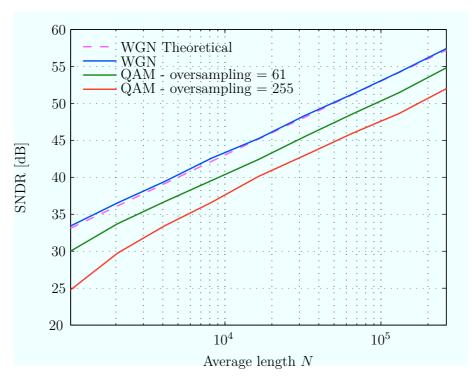

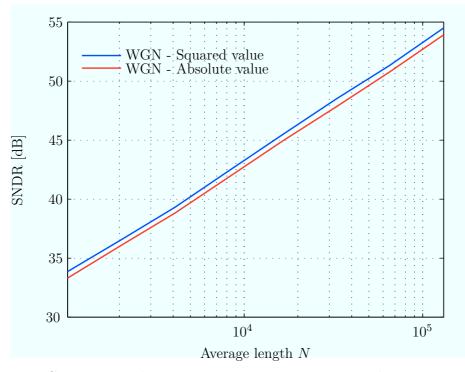

| 3.12 | Gain mismatch estimation accuracy vs. average length                          |

| 3.13 | Gain mismatch estimation accuracy vs. type of estimation                      |

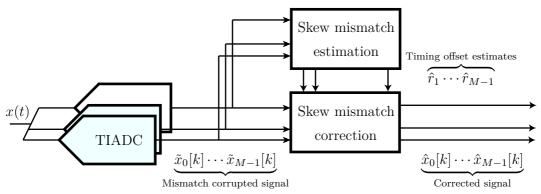

| 3.14 | Skew mismatch calibration block diagram                                       |

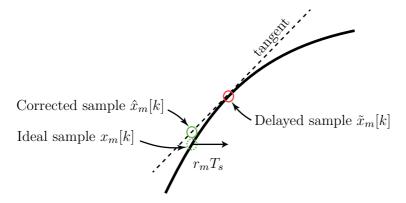

| 3.15 | Skew mismatch correction illustration                                         |

| 3.16 | Skew mismatch correction block diagram                                        |

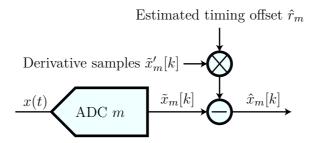

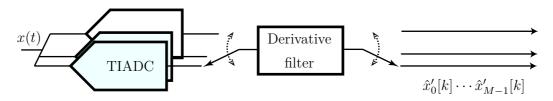

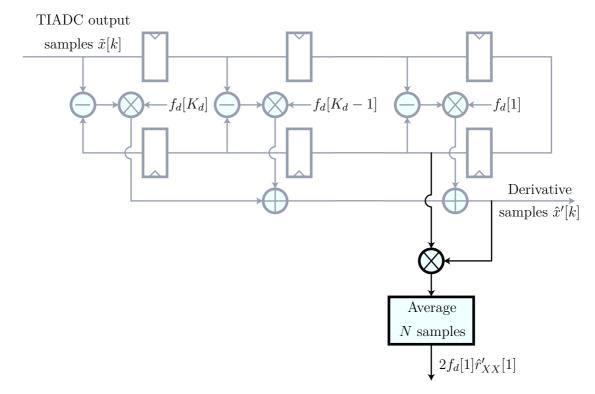

| 3.17 | Calculation of TIADC output signal derivative                                 |

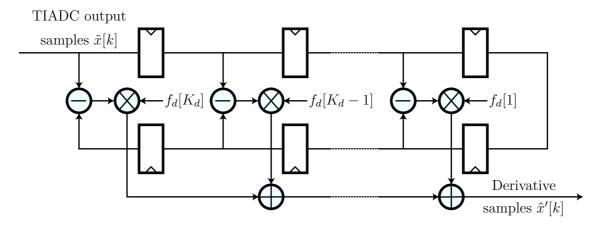

| 3.18 | Efficient derivative filter implementation                                    |

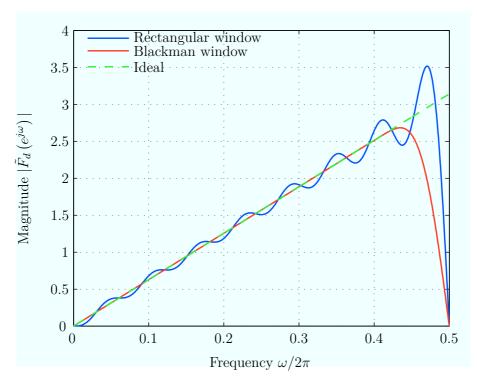

| 3.19 | Frequency response of the derivative filter for different windows             |

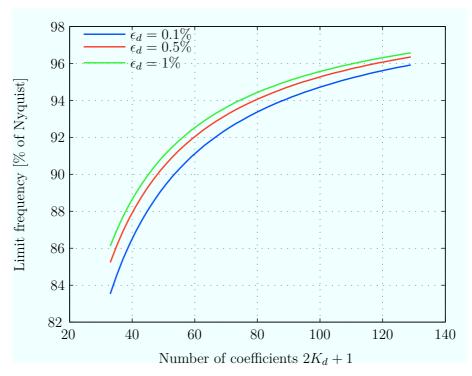

| 3.20 | Cut-off of the derivative filter vs. number of coefficients                   |

| 3.21 | SNDR before and after skew mismatch correction vs. input frequency 80         |

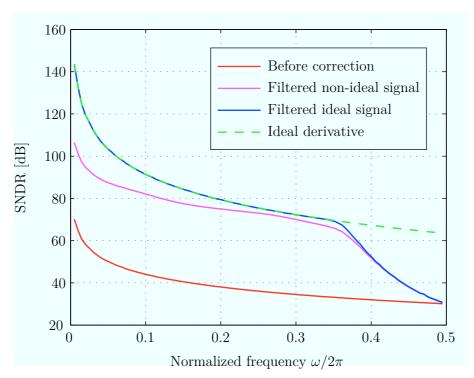

| 3.22 | Output spectrum before and after skew mismatch correction                     |

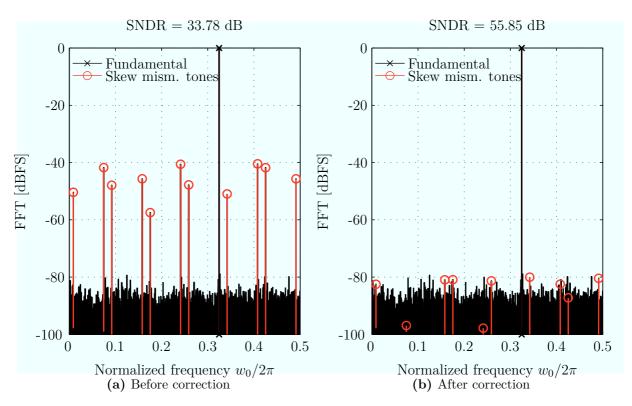

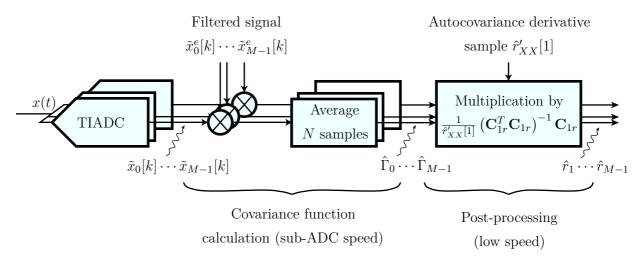

| 3.23 | Skew mismatch estimation block diagram                                        |

| 3.24 | Autocovariance derivative calculation                                         |

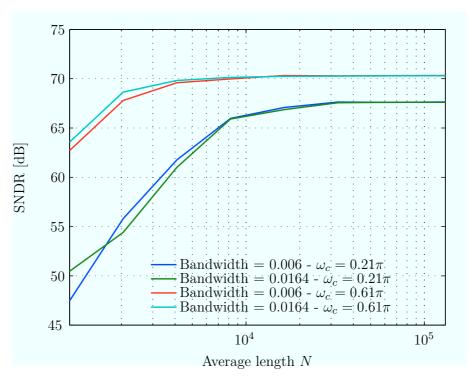

| 3.25 | Skew mismatch estimation accuracy vs. average length 99                       |

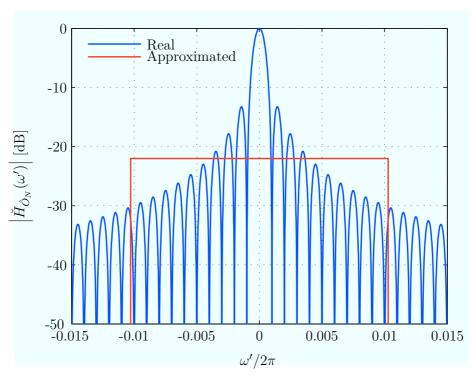

| 3.26 | Bandwidth mismatch correction block diagram                                   |

| 3.27 | Efficient low-pass derivative filter implementation                           |

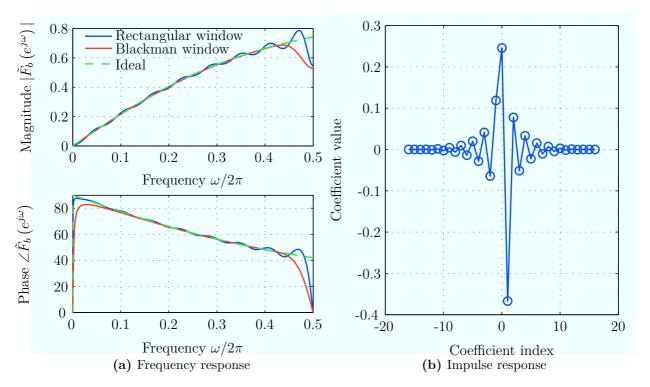

| 3.28 | Frequency response of the low-pass derivative filter for different windows 97 |

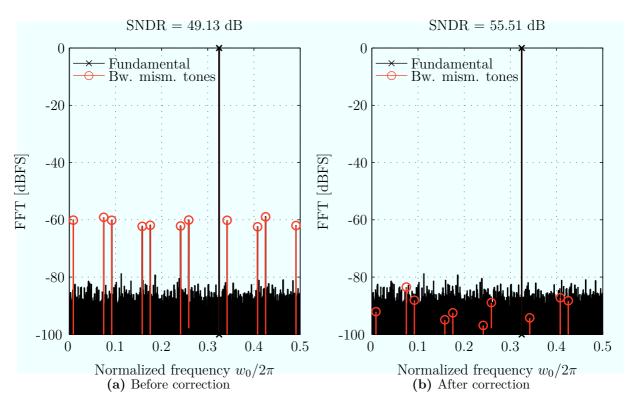

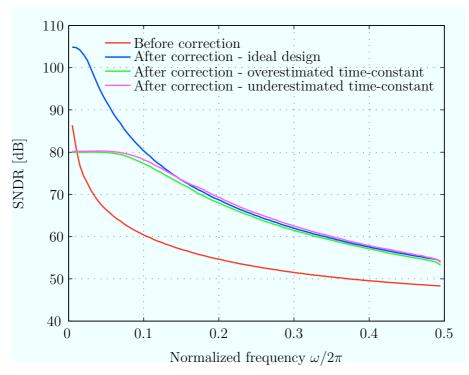

| 3.29 | Output spectrum before and after bandwidth mismatch correction 98             |

| 3.30 | Bandwidth mismatch estimation accuracy vs. input frequency 99                 |

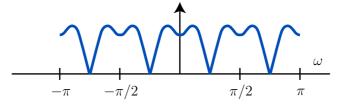

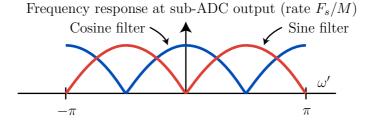

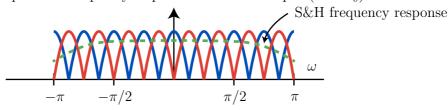

| 3.31 | Effects of upsampling on filter frequency response                            |

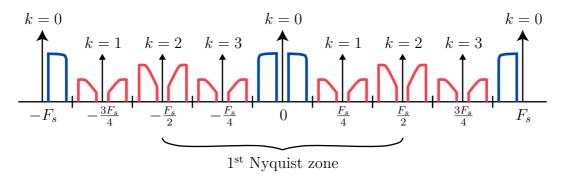

| 3.32 | Spectral interpretation of sine and cosine filtering                          |

| 3.33 | Bandwidth mismatch estimation block diagram                                   |

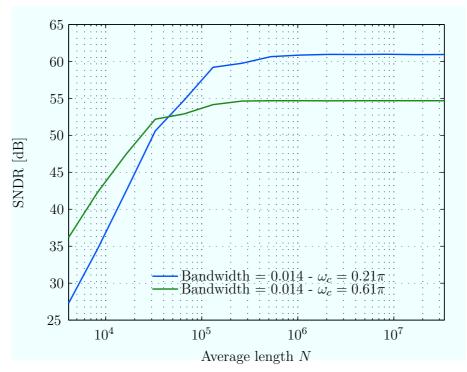

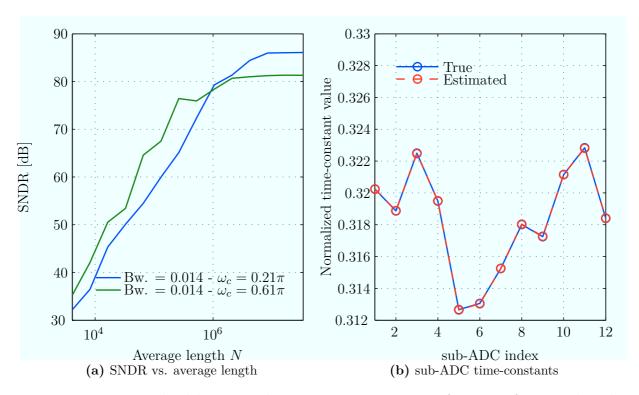

| 3.34 | Bandwidth mismatch estimation accuracy vs. average length 108                 |

| 3.35 | Bandwidth mismatch estimation accuracy vs. average length 109                 |

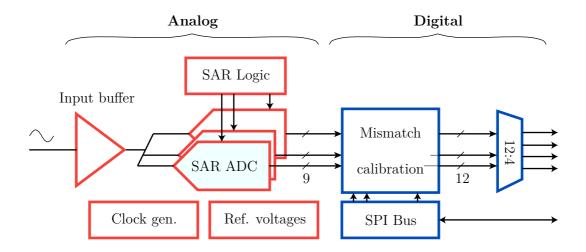

| 4.1  | Overall architecture of the circuit                                           |

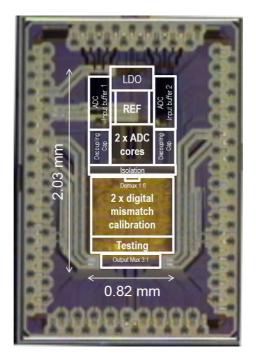

| 4.2  | Die photo of the chip                                                         |

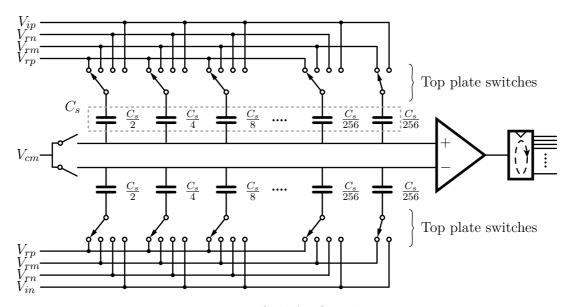

| 4.3  | Sub-ADC architecture                                                          |

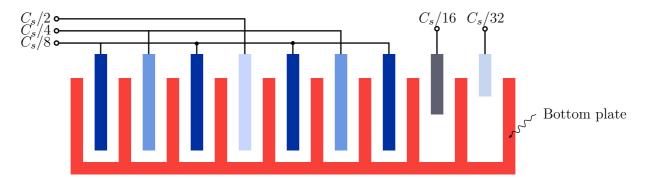

| 4.4  | Custom layout of the binary weighted capacitor array           | 114 |

|------|----------------------------------------------------------------|-----|

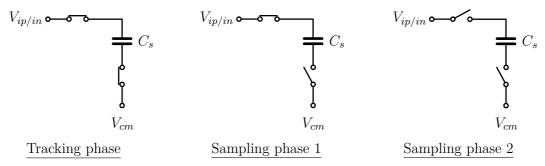

| 4.5  | Bottom plate sampling principle                                | 114 |

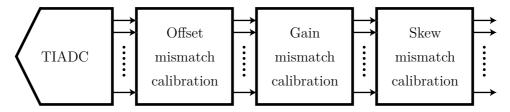

| 4.6  | Mismatch calibration structure                                 | 115 |

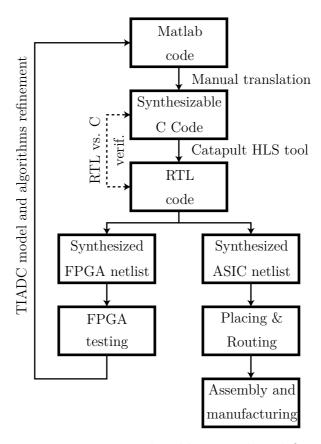

| 4.7  | Mismatch calibration digital flow                              | 116 |

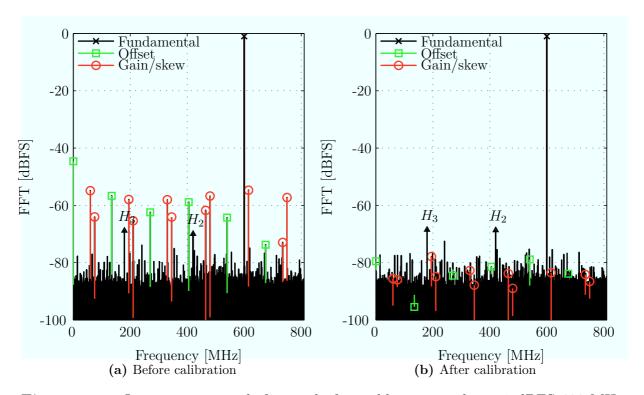

| 4.8  | Output spectrum before and after calibration with a sine input | 118 |

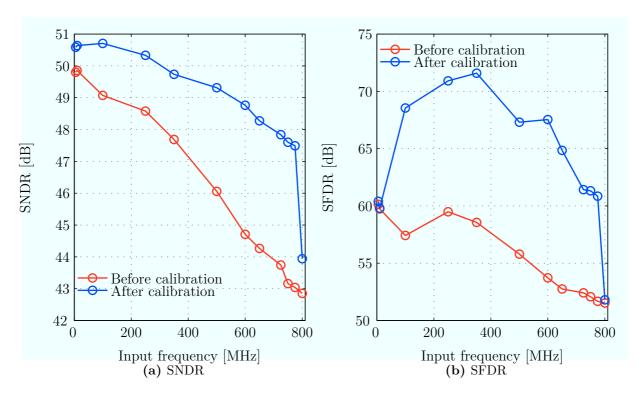

| 4.9  | Measurement of SNDR and SFDR vs. input frequency               | 119 |

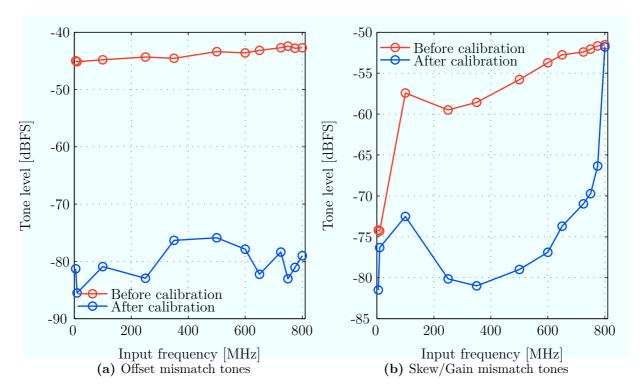

| 4.10 | Measurement of highest mismatch tones vs. input frequency      | 120 |

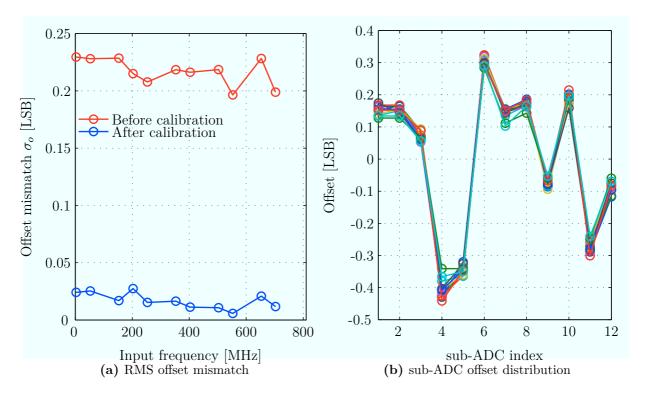

| 4.11 | Offset mismatch measurements vs. input frequency               | 121 |

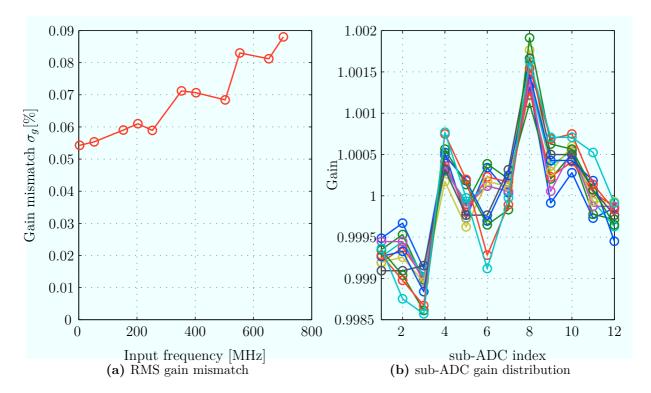

| 4.12 | Gain mismatch measurements vs. input frequency                 | 122 |

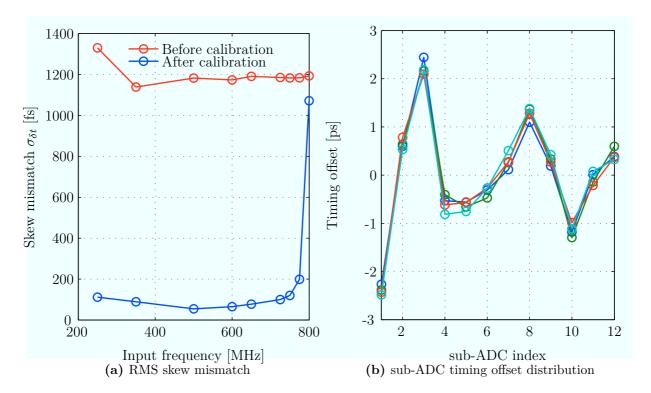

| 4.13 | Skew mismatch measurements vs. input frequency                 | 123 |

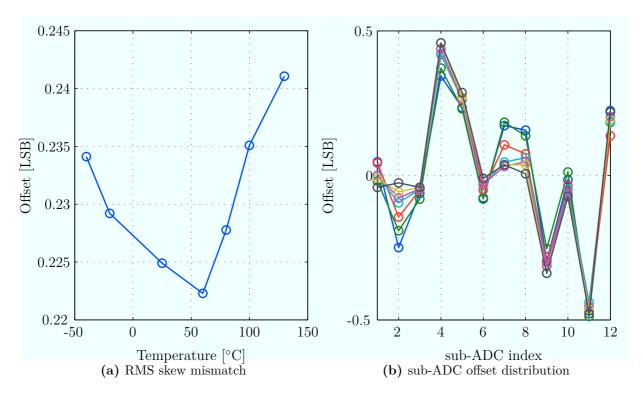

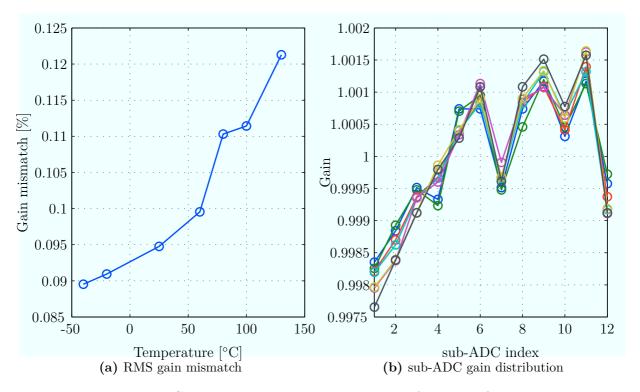

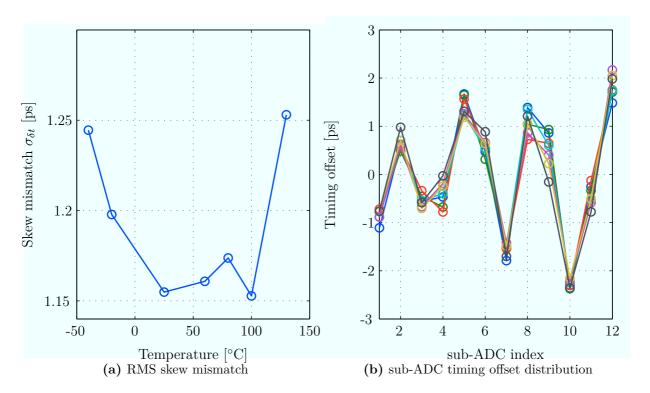

| 4.14 | Offset mismatch measurements vs. temperature                   | 124 |

| 4.15 | Gain mismatch measurements vs. temperature                     | 124 |

| 4.16 | Skew mismatch measurements vs. temperature                     | 125 |

| 4.17 | Output spectrum before and after calibration (QAM)             | 126 |

| 4.18 | Output spectrum before and after calibration (multitone)       | 127 |

| 4.19 | Circuit power breakdown                                        | 128 |

# Aknowledgements

As I am writing the last words of this dissertation, it is time for me to look back at these 3 years of work during which I crossed the path of many talented people. My PhD work was an incredible experience on a purely technical basis, but I would certainly not have achieved as much without the precious advice of colleagues, professors or simply friends.

First I want to thank Pascal Urard, my manager at ST, who gave me the opportunity to join his team in 2010, for what was then a 4-month internship. He was the first in ST to envision that blind digital mismatch calibration for TIADCs could be successful. From 2010, he was critical in convincing the most skeptical people about the potential of digital mismatch calibration. His hard work left me with free hands to focus on the research, and without his relentless obstination, the results of my PhD would certainly not have reached the same extent. More than a colleague, Pascal has been a confident and a friend with whom I shared more than professional experiences. The wonderful hiking and backcountry skiing trips that we went on together were a necessary escape from my day-to-day work.

Then, I want do deeply acknowledge Thierry Simon, my closest colleague at ST, who shares a significant part of the credit for this work. His skills in digital design made it possible to put together a functional testchip that demonstrated the benefits of digital mismatch calibration. Our numerous challenging discussions forced me to always go deeper in understanding the principles underlying mismatch calibration. I think our collaboration was ideal in many ways, particularly because we understood each other really well, and because we had complementary skills. I am also very grateful to the ADC analog design team, particularly Jean-Pierre Blanc, Sarah Verhaeren and Emmanuel Rouat for providing the analog front-end of the TIADC presented in this dissertation. A special thank you goes to Stéphane Le Tual who made me discover ADC design, and was always available to answer my endless questions about analog design. I have been particularly happy to count him as a friend an a colleague. I also want to express my gratitude to Frederic Paillardet for his circuit-debugging skills, to Andreia Cathelin for the valuable guidance, Dimitri Goguet for the lab support, and Pascale Maillet Contoz,

for the administrative support. Finally, among my colleagues, I cannot forget to express my gratitude to Fabien Todeschnini and Florian Barrau, with whom I have shared the CIFRE PhD experience at ST (and numerous coffee breaks).

My work at Supélec was quite different from the one I was doing at ST, and it was an opportunity for me to think more about the theoretical basis for my work. I want to thank Caroline Lelandais-Perrault, my PhD advisor, for her continued support. She made sure that I took the time to think about the theoretical proofs of my work, which to my opinion, is as important as having a circuit realization. Our discussions about the tiniest theoretical details helped make sure that I was not leaving any aspect behind. Then, I thank Philippe Benabes, for accepting me as one of his PhD students, and for his valuable opinions on my work. I am also grateful to him for communicating about our work to the Supélec community. I also acknowledge Stéphane Font, Filipe Vinci, and my other colleagues at Supélec for having made me discover the academic word, and for their permanent positive mood. A last thank you goes to Luc Batalie and Alexandra Siebert for their administrative support.

I have also been lucky to spend one year as a visiting researcher at UC Berkeley. I thank Borivoje Nikolic for integrating me in his research group, for supporting me throughout my stay in California, and for having me meet key people in my field. He also provided me with very valuable feedback on my presentations and papers, which greatly improved my technical communication skills. I have also deeply enjoyed the company of my friends Camilo, Miki, Dajana and Luis, with whom I often enthusiastically worked late at night in the lab.

My last words go the people who often had to stand me after a day of work. I particularly think about Pierre and Quentin, my roommates in Grenoble, and Antoine and Kilian who have accepted to host me numerous times when I was staying in Paris. I also thank my friend Alan (and his wife Fanny). Having gone through the PhD experience himself, he gave me critical advice and shared his insights about the academic world. I would also like to deeply thank my parents and my brother for their lifetime support. My final thoughts are for my dear Amanda (and Pepper) who has been wonderful in cheering me up in the past throughout this adventure.

## List of abbreviations

ADC Analog-to-Digital Converter

**ASIC** Application-specific integrated circuit

CAD Computer Aided Design

CMOS Complementary Metal Oxyde Semiconductor

CTFT Continuous-Time Fourier Transform

**DC** Direct Current

**DFT** Discrete Fourier Transform

**DNL** Differential Non-Linearity

**DOCSIS** Data Over Cable Service Interface Specification

**DTFT** Discrete-Time Fourier Transform

**DTPSD** Discrete-Time Power Spectral Density

DVB-S Digital Video Broadcasting - Satellite

**ENOB** Effective number of bits

FDSOI Fully Depleted Silicon On Insulator

FFT Fast Fourier Transform

FIR Finite Impulse Response

**FOM** Figure Of Merit

FPGA Field Programmable Gate Array

**HFB** Hybrid Filter Bank

INL Integral Non-Linearity

LMS Least Mean Square

LSB Least Significant Bit

LVT Low Voltage Threshold

MOM Metal Oxide Metal (capacitor)

MSB Most Significant Bit

MUX Multiplexer

**NL-HFB** Non-Linear Hybrid Filter Bank

NMOS N-type Metal Oxyde Semiconductor (transistor)

**OFDM** Orthogonal Frequency Division Multiplexing

PAPR Peak to Average Power ratio

PMOS P-type Metal Oxyde Semiconductor (transistor)

**PSD** Power Spectral Density

**QAM** Quadrature-Amplitude Modulation

**RC** Resitance Capacitor

RMS Root Mean Square

S&H Sample and Hold

SAR Successive Approximation Register

SFDR Spurious-Free Dynamic Range

SHA Sample and Hold Amplifier

SNDR Signal-to-Noise and Distorsion Ratio

**SNR** Signal-to-Noise Ratio

**T&H** Track and Hold

**THD** Total Harmonic Distorsion

TIADC Time-Interleaved Analog-to-Digital Converter

WSCS Wide-Sense Cyclostationary

WSS Wide-Sense Stationary

# Chapter 1

### Introduction

# 1.1 The challenges of high speed analog-to-digital conversion

In modern communication systems, the information between a transmitter and a receiver is carried on continuous-time *analog* signals. This can be done either through physical media, like copper wires (e.g. TV cable, phone line) or optic fiber (e.g local networks, Internet), but the signal can also be transmitted in the vacuum via electromagnetic waves (e.g. WiFi, satellite). However, the information carried by the analog signal is usually processed by *digital* circuits. Digital circuits have certain advantages as compared to their analog counterparts:

- Complex signal processing is easier performed in the digital domain

- Digital compression algorithms and error correcting codes enable to encode signals that carry more data on a given bandwidth

- Digital designs are easier to adapt to different CMOS technologies

- Digital designs benefit from the semi-automated CAD tools for synthesis, placing and routing.

- Digital circuits are more robust to noise

- The simulation of digital circuits is faster than the simulation of analog circuits

The conversion from the analog domain to the digital domain is performed by Analog-to-Digital Converters (ADC), which are often a bottleneck in modern communication systems. The purpose of an ADC is to sample and quantize a continuous-time analog signal in order to obtain discrete-time quantized values.

For these reasons, the trend is to reduce the analog circuitry by sampling the received signal at an earlier stage at the receiver end.

The extreme case – where the market is going nowadays – is RF (Radio-Frequency)

direct sampling, which consists in sampling the continuous-time signal without converting it upstream to IF (Intermediate Frequency) with analog mixers. The block diagrams shown in Figure 1.1 illustrate the difference between IF sampling and direct RF sampling.

Figure 1.1 – Traditional IF sampling vs. direct RF sampling

However, moving the ADC ahead in the reception chain increases the performance requirements on the ADC. One can cite cable TV (CATV) as an example to illustrate the requirements of RF-direct sampling.

In cable TV transmissions, the signal is carried on a coaxial cable, and occupies a frequency band that goes from 54 MHz to 1002 MHz (EIA Specifications in North America). In the most common standard in use today (DOCSIS 3.0 [1]), the channels are transmitted on 6 MHz frequency wide channels distributed across the full frequency band. Those channels use QAM 256 constellations as a modulation scheme. Future improvements of this standard (DOCSIS 3.1 [2]) include increasing the size of the constellations (up to QAM 2048) as well as using OFDMA signals instead of the 6 MHz channels currently in use. Plus, certain service providers want to use the cable as a mean of transmitting other types of multimedia data (gaming, video streaming, HDTV) under the MoCA standard (Multimedia over Coax Alliance). This standard uses a band that can go from 500 MHz to 1650 MHz. To summarize, the signal that is transmitted on the cable can span a frequency band going from 54 MHz to 1650 MHz, and is encoded using complex modulation techniques such as QAM2048 and OFDMA.

Performing direct RF sampling of this kind of signal requires the ADC to be capable of sampling at a frequency  $F_s$  at least equal to twice the signal bandwidth – i.e. at least 3.2 GS/s for the cable TV application. In terms of resolution, the ADC is required to quantize the signal with enough precision to make the demodulation possible. An effective resolution of 10 bits is a minimum requirement for the cable TV application.

#### 1.2 Analog-to-Digital converter architectures

Over the years, numerous ADC architectures have been proposed, such as flash ADCs, pipeline ADCs, Successive Approximation Register (SAR) ADCs and Time Interleaved ADCs (TIADC). They differ by the sampling frequency and the effective resolution that they achieve. Figure 1.2 shows a classification of the ADCs published between 1997 and 2014 at the International Solid State Circuit Conference (ISSCC) and the VLSI Symposium. Flash ADCs are known to be fast ADCs with a low resolution whereas SAR

Figure 1.2 – Different ADC architectures classified with respect to their sampling frequency and their SNDR (from data published at the ISSCC and the VLSI symposium between 1997 and 2014 [3])

ADCs enable to achieve a higher SNDR at a lower sampling frequency. Pipeline ADCs have long been the dominating architecture for achieving a high sampling speed (> 100 MHz) with a good SNDR but they are now surpassed by TIADCs.

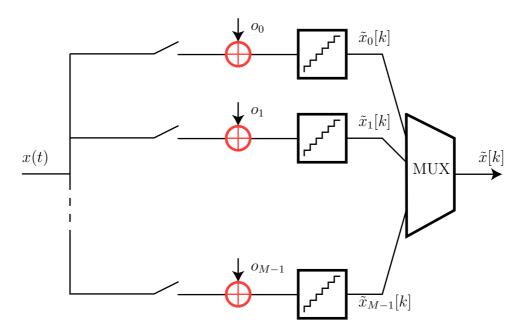

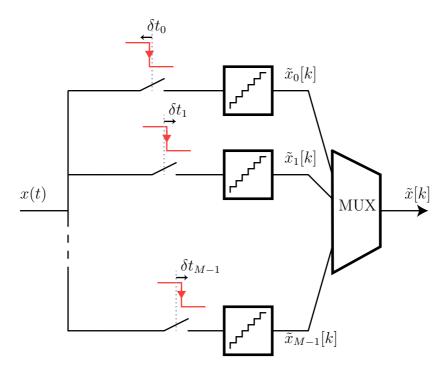

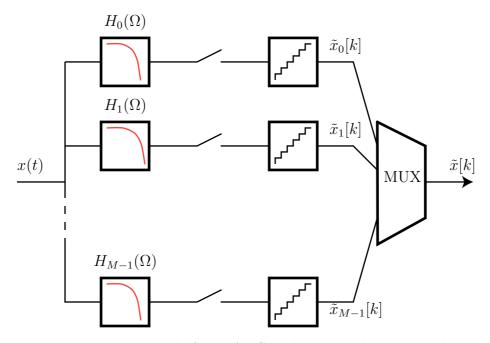

Invented in 1980 [4], the TIADC is the only architecture that reaches a sampling frequency of the order of 1 GS/s with a SNDR over 50 dB (around 8 effective bits). Distinguishing TIADCs from the other ADC families is not completely accurate because TIADCs are comprised of several sub-ADCs belonging to one of the other ADC families (for example SAR ADCs). Time interleaving consists in having several "low frequency" sub-ADCs sample the signal one after an other (as illustrated in Figure 1.3), in order to increase the overall sampling frequency.

Figure 1.3 – Principle of a time-interleaved ADC

Time-interleaving also improves the energy efficiency of the analog-to-digital conversion because each of the sub-ADCs can be designed to operate in its most energy efficient frequency zone. The scatter plot in Figure 1.4 classifies the different ADC architectures based on their Figure of Merit (FOM) and their sampling frequency. The FOM is an indicator that measures the energy that an ADC uses per conversion step. It takes into account the power consumption, the effective resolution, and the sampling frequency of the ADC. It is defined as follows:

$$FOM = \frac{P}{2^{ENOB}F_s} \tag{1.1}$$

where P is the power consumption of the ADC, ENOB = (SNDR - 1.76)/6.02 is the effective number of bits of the ADC and  $F_s$  is the sampling frequency. The idea behind this metric is that doubling the sampling frequency of an ADC is as hard as improving its effective resolution or reducing its power consumption by a factor of 2.

Whereas time-interleaved pipeline ADCs [5, 6, 7, 8, 9] were very popular a few years ago to achieve a sampling frequency of the order of 1 GS/s, they seem to be slowly replaced by time-interleaved SAR ADCs [10, 11, 12, 13]. Time-interleaved SAR ADCs enable to achieve sampling frequencies above 10 GS/s [14, 15], and they hold the record of the highest published sampling speed with 90 GS/s (for 5.5 bits of effective resolution) [16]. The performance of pipeline ADCs tends to worsen with technology scaling because the gain of the MOSFET transistors decreases at each technology node. On the other hand, SAR ADCs do not require dynamic circuits (see Chapter 4), and gain from technology

Figure 1.4 – Different ADC architectures classified with respect to their sampling frequency and their Walden FOM (from data published at the ISSCC and the VLSI symposium between 1997 and 2014 [3])

scaling thanks to their seemingly digital nature. Very recently, hybrid flash/SAR time-interleaved ADCs have been published [17]. The idea is to convert the Most Significant Bits (MSB) of the signal at a high speed using a single low resolution flash ADC ( $\approx 4$  bits) and resolve the remaining Least Significant Bits (LSB) using time-interleaved SAR ADCs.

#### 1.3 Mismatches in TIADCs

Theoretically, increasing the sampling frequency of a TIADC is simply done by increasing the number of sub-ADCs. However, at some point, the performance becomes limited by the mismatches between the sub-converters. Indeed, the sub-ADCs have slightly different characteristics due to random physical variations happening during the manufacturing process (see Chapter 2). These mismatches degrade the TIADC digital output signal, and the noise power at the output of the TIADC becomes higher than the one of a single sub-ADC.

The mismatches can be classified in different categories depending on their source. In real circuits, the mismatches that most commonly limit the TIADC performance are:

— the offset mismatches that occur when the sub-ADCs have different offsets

- the gain mismatches that occur when the sub-ADCs have different gains

- the timing skew mismatches that occur when the sub-ADCs sample the signal with different timing offsets

- the bandwidth mismatches that occur when the sub-ADCs have different input bandwidths

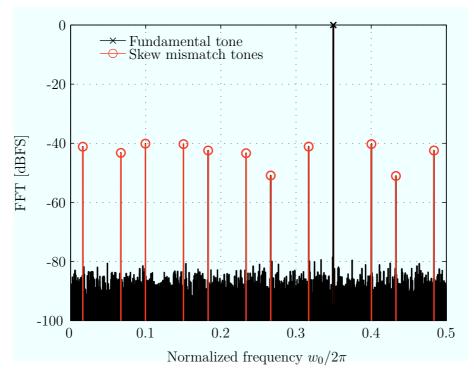

The sources and the effects of the mismatches are more detailed in Chapter 2. Figure 1.5 shows the output spectrum of a TIADC having offset, gain, skew and bandwidth mismatches. The offset mismatch noise takes the form of spurious tones at fixed frequencies,

Figure 1.5 – TIADC output spectrum with mismatches

whereas the skew, gain and bandwidth mismatch noises consist of attenuated aliases of the input signal.

Since the invention of the first TIADC [4], reducing the mismatches has been a challenge. This challenge is still existing today and a lot of research is being done to develop calibration techniques to reduce the effects of the mismatches.

#### 1.4 Mismatch calibration prior art

There are numerous types of mismatch calibration techniques, and the aim of this section is to give an overview of the different paths that have been explored in the state of the art.

#### 1.4.1 Foreground mismatch calibration

Foreground calibration techniques [18, 19] require an offline phase where the converter is in "calibration mode". During the offline phase, a known signal, for example a sine wave with a known amplitude and a known frequency, is connected at the input of the TIADC. In the circuit presented in [16], the timing offsets are adjusted in the analog domain with a fixed-frequency sine input. In [20], the offset mismatches are calibrated in the foreground by trimming the comparators of the sub-ADCs. Foreground mismatch calibration is however not suitable for applications where the converter is always 'on', for example in communications receivers. Indeed, temperature variations and circuit aging may require the calibration to be done frequently, or even continuously. These techniques can however find their application in high-end measurement systems where the equipment can either self-calibrate or be sent to calibration. This dissertation focuses on TIADCs in the context of communication systems For that reason, foreground calibration techniques will not be further discussed.

#### 1.4.2 Background mismatch calibration

The alternative to foreground calibration is background calibration, where the mismatch calibration is performed during the normal operation of the converter, in the background.

Some background calibration techniques require the input signal to be slightly modified in the analog domain. Those techniques are referred as *non blind* calibration techniques. For example, offset and gain mismatch calibrations can be performed with the help of a random signal that is added to the analog input signal [21] or, multiplied with it [22]. The techniques presented in [23] and [24] perform bandwidth mismatch calibration by adding a known sine wave to the TIADC input signal.

On the other hand, blind calibration techniques do not require any modification of the input signal, which reduces the risk of adding other sources of noise. Naturally, blind background calibration techniques are the most challenging to develop because only a limited prior knowledge about the signal is available. In reality, none of these methods is fully blind. They require some information about the input signal, usually expressed in term of spectral content or statistical properties. Among blind calibration techniques, fully digital calibration techniques are performed entirely in the digital domain while mixed mismatch calibration techniques partly operate in the digital domain and partly in the analog domain.

#### 1.4.2.1 Mixed mismatch calibration

Most mixed mismatch calibration techniques have a structure where a digital unit controls a feedback to the analog front-end to trim some parts of the circuit. The goal of the digital unit is to detect the mismatches and to adaptively control a feebback to adjust the analog front-end.

The chip reported in [25] is an exception to this rule as it embeds an all-analog background skew mismatch calibration. The clock phases in the analog front-end can be shifted using delay lines based on a comparison with a reference clock signal.

The offset mismatches are often calibrated by equalizing the sub-ADC output averages [26, 27]. The offset mismatches can then be corrected in the analog domain, for example through digitally controlled current sources embedded in the track-and-hold amplifiers of the sub-ADC [28]. Other techniques involve auto-zeroing comparators that reduce the offset of each comparator individually, thereby reducing the offset mismatches [29, 30].

In a quite similar way, the gain mismatches can be calibrated by equalizing the output powers of the sub-ADCs [26]. Alternatively, it is possible to estimate the gain mismatches in the frequency domain by measuring the mismatch noise that appears in a frequency band free of signal [31]. In [32], the circuit uses a random chopper Sample and Hold Amplifier (SHA) in which the signal is multiplied in the analog domain by a random sequence. The offset mismatches are then estimated by equalizing the averages of the chopped sub-ADC outputs. The gain mismatches are estimated by equalizing the cross-products between the chopped output and the non-chopped output of each sub-ADC.

Skew mismatch calibration usually involves more complex techniques. The estimation of the timing mismatches can either be performed in the time domain or in the frequency domain. The techniques described in [33, 34, 35] are time based ones. The timing offsets are estimated through the minimization of a cost function calculated from cross-correlations between adjacent channels, and the sub-ADCs sampling instants are adjusted with variable delay lines. In [32], one of the two sub-ADC outputs of the 2-channel TIADC is digitally delayed to match the samples of the second channel. The technique however requires the input signal to be bandlimited to the Nyquist frequency of a single sub-ADC.

Some mixed calibration methods require the use of one or more redundant sub-ADCs. It the case of the circuit described in [20] that detects the timing mismatches in the digital domain, by minimizing the cross-covariance between each sub-ADC output and the ouput of a redunda. The timing offsets are adjusted in the analog domain by controlling adjustable delay lines. In [11, 27], the circuit has two redundant sub-ADCs, one that serves as a reference and the other one that is slightly delayed. The difference between the delayed reference ADC and the reference ADC gives a coarse approximate of the signal derivative, which is used in a correlation-based adaptive algorithm to adjust the

timing offsets through a bank of capacitors. In the TIADC circuit presented in [14], the skew mismatch calibration is performed in two phases. First, a time-to-digital signature is stored by inputting a known binary signal, generated by a DAC, into a reference ADC. Then the sub-ADC to be calibrated are disconnected from the array one after the other and replaced by the reference ADC. Their sampling times are adjusted in the analog domain by comparing their output to the reference ADC signature with the same binary signal at the input. In [17], the timing delays are adjusted through programmable delay lines by comparing the output of the sub-ADCs to the output of a flash ADC running at the TIADC overall sampling frequency.

Other approaches [36, 37, 18] propose to randomly reorganize the sampling order of the channels in order to spread out the mismatch noise across the entire spectrum. In the circuit described in [14], the offset mismatch noise is spread out by randomly connecting together unit differential pairs in the comparator pre-amplifier.

Not many mixed bandwidth mismatch calibration techniques have been proposed. One can cite the patent [38]. It describes a TIADC where the bandwidth of each sub-ADC can be adjusted through a variable boost capacitor contained in the bootstrapped switch.

#### 1.4.2.2 Digital mismatch calibration

Digital mismatch calibration techniques have some advantages as compared to mixed calibration methods. First, they do not require any modification of the analog front-end, and they can therefore potentially be adapted to any TIADC architecture. Second, they benefit from technology scaling and from semi-automated CAD tools. However, certain functions that can be performed in the analog domain at a low cost – adjusting the delay of a sub-ADCs for example – require complex operations in the digital domain.

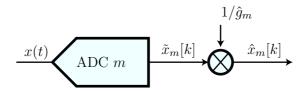

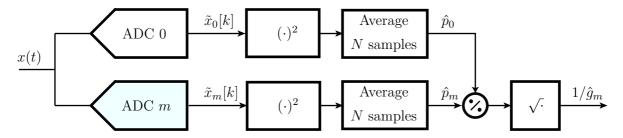

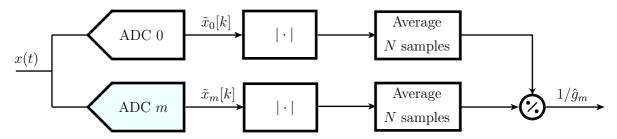

Correcting the offset mismatches and the gain mismatches in the digital domain is generally easy. Offset mismatch correction just requires to subtract each relative offset from each sub-ADC output [11, 39, 27]. Gain mismatch correction can be done by multiplying the output signal of each sub-ADC by the inverse of the corresponding estimated gain [35, 39]. The estimation of the offset and gain mismatches can be done similarly as in the mixed calibration case, by equalizing respectively the sub-ADC output averages, or the sub-ADC output squared average.

Solutions for fully digital calibration of the skew and bandwidth mismatches have been investigated a lot from a theoretical point of view but no integrated circuit demonstrating their efficiency has yet been published. In [40, 41], the authors propose to compensate the gain and the timing mismatches adaptively by retrieving the Wide Sense Stationarity of the signal at the TIADC output. The mismatches are digitally corrected by using a

FIR filter with variables coefficients. The work is then extended in [42, 43] to the case of arbitrary transfer function mismatches. Those methods are computationally costly as they require FIR filter with variable coefficients [44]. The skew mismatch calibration technique proposed in [45, 46] extends the work done in [47] to more than 2 interleaved ADCs. The idea is to pass the sub-ADC output signals through an Hadamard transform in order to separate the desired signal from the aliasing terms. This work is extended to the case of signals in arbitrary Nyquist zones in [48].

The skew mismatch calibration technique presented in [49, 50, 51, 52] assumes that the input signal is spectrally full, except for a small frequency band. The calibration is iteratively done by minimizing the power of the mismatch noise in this "out-of-band". The skew mismatch calibration method described in [31] uses the same principle, and the sampling errors are corrected using a first order Taylor approximation, which requires the computation of the signal derivative.

The principle of minimizing the out-of band noise was also extended to the case of generalized frequency mismatch calibration [53, 54]. In [42, 43], the frequency response of each sub-ADC is approximated by a polynom. Some papers solely deal with the problem of reconstructing a signal that is corrupted by the mismatch errors. The work done in [55, 56] uses linear interpolation to correct timing errors. An other solution, often more computationally complex, is to use fractional delay filters as explained in [57, 58]

#### 1.5 Aim of this work and outline

This dissertation focuses on the fully digital mismatch calibration of the offset, gain, timing and bandwidth mismatches.

As reviewed above, the state-of-the-art solutions in this domain are, on many aspects, theoretical. Even, if numerical simulations prove their efficiency, most calibration techniques presented before would add an important power/area overhead to the TIADC if they were to be integrated on a circuit. This is especially true with the skew and bandwidth mismatch calibration techniques because of the complex correction filters that are required. Plus, the proposed calibration methods are always iterative and they would need an extremely long time to converge if applied on real telecommunication signals (instead of sine or multitone inputs). Finally, in most of the published work, it is assumed that the TIADC input signal is Wide Sense Stationary (WSS), which is generally not the case in practice. Real communication signals are at best Wide Sense Cyclostationary (WSCS) or non stationary. The work presented in this dissertation aims at filling these gaps.

The content of Chapter 2 is mostly a reformulation of previous work, explaining the

sources of the mismatches, and their effects on the output signal. It provides the reader with performance indicators (such as SNDR of SFDR) as a function of the mismatch levels.

Chapter 3 is the heart of this dissertation as it describes direct, i.e. non iterative, fully digital blind mismatch calibration techniques for reducing the effects of the offset mismatches, the gain mismatches, the skew mismatches and the bandwidth mismatches. The theoretical assumptions behind these techniques are carefully investigated, and it is shown that convergence is insured for non-stationary signals provided that certain conditions are met.

Chapter 4 describes the circuit realization of a TIADC embedding the offset, gain and skew mismatch calibration techniques detailed in Chapter 3. The measurements from the 1.62 GS/s TIADC test-chip are analyzed and prove the viability of fully digital mismatch calibration techniques.

Chapter 5 summarizes the findings given in this dissertation and presents some perspective to further improve calibration techniques for TIADCs.

# Chapter 2

# Mismatches in Time-Interleaved ADCs

#### 2.1 Introduction

This chapter gives an overview of the sources of mismatch in TIADCs. The effects of the mismatches on the output signal are analyzed in order to provide performance metrics (SNDR and SFDR) based on the level of the mismatches. These performance indicators are useful both during the TIADC design process itself and for determining the accuracy of the mismatch calibration algorithms.

Although the mismatch problem was initially mentioned in the paper of Black and Hodges [4], the first efforts to analytically derive the effects of offset and gain mismatches on a TIADC performance were published in [59].

The analysis was later extended in [60] with a general frequency model that describes the effects of the mismatches. The model was also used to derive SNDR expressions as function of the level of the mismatches (offset, gain, skew).

The specific skew mismatch problem is also mentioned in papers dealing with non-uniform sampling (which includes timing jitter) such as [61, 19, 62, 63]. Those papers show the effects of non-uniform sampling for a sine input signal.

Later, an approach based on Hybrid Filter Banks (HFB) was proposed in order to model the mismatch effects for arbitrary input signals. This approach is extensively described in several articles [64, 65, 66] that include the effects of offset mismatches, gain mismatches, skew mismatches as well as bandwidth mismatches (first order or more). The specific case of a sine input is used to derive SNDR expressions as function of the mismatch level. HFB modeling is extended in [67, 68] to encompass non-linearity mismatches through the use of Non-Linear HFB (NL-HFB).

A probabilistic approach is proposed in [69]. The authors derive the probability

distribution of the SNDR assuming Gaussian random distributions for the offsets, gains and timing offsets.

Finally, whereas most of the literature analyzes the mismatch effects with sine input signals, the work presented in [70] analyzes skew mismatch effects for wide-band input signals. The authors show that for wide-band applications, evaluating the performances of a TIADC with sine inputs often leads to over-pessimistic requirements on the timing matching requirements.

This chapter re-demonstrates some of the results given in the literature by deriving a TIADC output spectrum when different types of mismatches are present. The reasoning that leads to these results is important because it gives a good sense of how the mismatches affect a TIADC performance. The chapter also introduces most of the notations that are used throughout this dissertation

#### 2.2 Ideal Time-Interleaved ADC

First, the proposed modeling technique is applied to an ideal TIADC in order to introduce notations and explain the modeling principle in a simple case. With no imperfections nor mismatches, the derivation of the TIADC output spectrum unsurprisingly leads to the well-known output spectrum of an ideal ADC.

The continuous analog input signal of the TIADC is denoted x(t). Depending on the applications x(t) can either be a deterministic signal – for example a sine wave – or a realization of Wide Sense Stationary (WSS) random process (see in Chapter 3) – for example a complex wideband communication signal. This dissertation focuses on Nyquist converters, which means that the input signal is assumed to be bandlimited to the first Nyquist zone. If the signal is deterministic, its Continuous Time Fourier Transform (CTFT)  $^1$ ,  $X(\Omega)$ , verifies

$$X(\Omega) = 0 \text{ for} |\Omega| > \frac{\Omega_s}{2}$$

(2.1)

where  $\Omega_s = 2\pi F_s$  is the sampling pulsation<sup>2</sup>.

In a TIADC, the analog input signal x(t) is sampled by M sub-ADCs. Each sub-ADC is indexed by m with  $m \in \mathcal{M} = \{0, \dots, M-1\}$ . The discrete sequence of samples at the output of each sub-ADC is denoted  $\{x_m[k], m \in \mathcal{M}\}$ . In the case of an ideal TIADC,

$$R_{xx}(\Omega) = 0 \text{ for } |\Omega| > \frac{\Omega_s}{2}$$

<sup>1.</sup> The CTFT is here defined as  $X(\Omega) = \int_{-\infty}^{+\infty} x(t)e^{-j\Omega t}dt$

<sup>2.</sup> If the signal is a WSS random process then its power spectrum density is zero outside the first Nyquist zone

each sub-ADC's output signal can be expressed

$$x_m[k] = x((kM+m)T_s) \text{ with } k \in \mathbb{N}$$

(2.2)

For a frequency analysis, it is easier to express the sampled signal in a continuous time form. Sampling a continuous signal at a frequency  $F_s = 1/T_s$  can be done by multiplying the signal with a Dirac comb defined as follows:

$$c(t) = \sum_{k=-\infty}^{+\infty} \delta(t - kT_s)$$

(2.3)

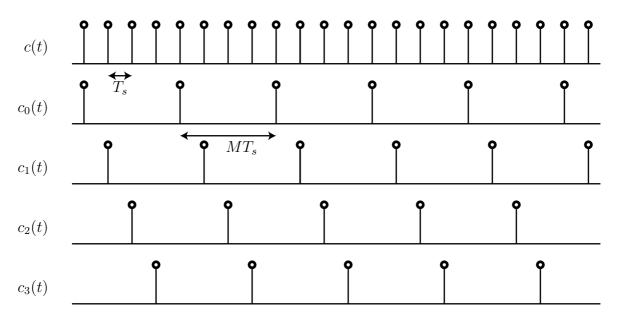

Figure 2.1 – Full rate and sub-sampled Dirac combs for M=4 sub-ADCs

The sampled signal denoted  $x_s(t)$  is therefore obtained by multiplying the continuoustime input signal x(t) by the Dirac comb c(t)

$$x_s(t) = x(t)c(t) (2.4)$$

In a TIADC, each sub-ADC samples the input signal at a rate  $F_s/M$  and each sub-ADC m has a delay  $mT_s$ . The sampled sub-ADC output signals, denoted  $\{x_m(t), m \in \mathcal{M}\}$ , are now equal the product between the input signal x(t) and the respective sub-sampling Dirac combs  $\{c_m(t), m \in \mathcal{M}\}$  (see illustration in Figure 2.1)

$$x_m(t) = x(t)c_m(t) (2.5)$$

where

$$c_m(t) = \sum_{k=-\infty}^{+\infty} \delta(t - (kM + m)T_s)$$

(2.6)

The sampled TIADC output signal is obtained by adding together the sampled signals  $\{x_m(t), m \in \mathcal{M}\}$  from all the sub-ADCs. When there are no mismatches, the sampled signal at the output of the TIADC is equal to the ideal sampled signal  $x_s(t)$  defined in equation 2.4

$$x_s(t) = \sum_{m=0}^{M-1} x_m(t) \tag{2.7}$$

The output spectrum of an ideal TIADC is therefore the same as the output spectrum of a regular ADC. The output spectrum, denoted  $X_s(\Omega)$ , is obtained by taking the CTFT of the sampled signal  $x_s(t)$  defined in equation 2.4. The product in the time domain becomes a convolution product in the frequency domain  $^3$ , which yields

$$X_s(\Omega) = \frac{1}{2\pi} X(\Omega) * C(\Omega)$$

(2.8)

In the above equation 2.8,  $C(\Omega)$  is the CTFT of the Dirac comb c(t), which is also a Dirac comb in the frequency domain:

$$C(\Omega) = \frac{2\pi}{T_s} \sum_{k=-\infty}^{+\infty} \delta(\Omega - k\Omega_s)$$

(2.9)

Replacing  $C(\Omega)$  in the equation of the TIADC output spectrum 2.8 yields a spectrum that contains replica of the input spectrum centered at frequencies multiple of  $\Omega_s$ , a well known phenomenon in sampling theory:

$$X_s(\Omega) = \frac{1}{T_s} \sum_{k=-\infty}^{+\infty} X(\Omega - k\Omega_s)$$

(2.10)

The above expression can directly be linked to the Discrete Time Fourier Transform (DTFT) of x[n]. Indeed, an other way of writing the sampled signal  $x_s(t)$  is

$$x_s(t) = \sum_{n = -\infty}^{+\infty} x(t)\delta(t - nT_s)$$

(2.11)

$$= \sum_{n=-\infty}^{+\infty} x(nT_s)\delta(t - nT_s)$$

(2.12)

Taking the CTFT of the above expression and replacing  $x(nT_s)$  by x[n] leads to the

<sup>3.</sup> The normalization by  $\frac{1}{2\pi}$  appears because of the use of angular frequencies in the CTFT.

DTFT of x[n]:

$$X_s(\Omega) = \sum_{n=-\infty}^{+\infty} x[n]e^{-j\Omega nT_s}$$

(2.13)

which is periodic of period  $\Omega_s = \frac{2\pi}{T_s}$ . The DTFT will be denoted  $X_{2\pi}(\omega)$  where  $\omega = \Omega T_s$  is the normalized angular frequency <sup>4</sup>

$$X_{2\pi}(\omega) = X_s(\Omega)|_{\Omega = \frac{\omega}{T_s}} = \sum_{k=-\infty}^{+\infty} x[n]e^{-j\omega n}$$

(2.14)

In the following sections, the mismatches are added to the model in order to characterize their effects on the TIADC output spectrum.

#### 2.3 Mismatches in CMOS technology

Before diving into the problem of modeling TIADC mismatches, it is useful to do a quick summary of the origin of mismatches in circuits. According to Pelgrom [71]

Mismatch that can be observed between the parameters of a group of equally designed devices [...] is the result of several random processes which occur during every fabrication phase of the devices.

The word "devices" can here be replaced by "transistor", "resistor", "capacitor" or "inductor" depending of the type of circuit under analysis. Mismatches can be classified according to the scale at which they happen. Thus, it is possible to distinguish

- Lot to lot mismatches, which consequence is to make devices of different lots have different physical properties.

- Wafer to wafer mismatches are mismatches that occur between devices from different wafers belonging to the same lot

- Die to die mismatches happen among devices from different dies of the same wafer

- Within die mismatches occur between devices in the same circuit

The first three types of mismatches can be excluded from our analysis because we are only interested in the mismatches between the sub-circuits (sub-ADCs) of a larger circuit (TIADC). More specifically, our interest goes toward transistors and capacitors, which are the main constituents of ADCs. In the remainder of this chapter, we will see that most of the TIADC mismatches originate from parameter variability in transistors and capacitors.

Among those parameters, the transistor threshold voltage has a particular role. The threshold voltage is indeed a parameter of the transistor that affects the properties of

<sup>4.</sup> From now on, each spectrum denoted with the subscript  $2\pi$  correspond to a DTFT, and is consequently periodic in  $\omega$  with period  $2\pi$ .

numerous basic circuits, and from which other important parameters can be derived, such as the on-resistance of a switch. As we will see later in this chapter, understanding transistor threshold variability is useful to analyze the sources of offset mismatches, skew mismatches and bandwidth mismatches.

Threshold variability can be induced by

- Random dopant fluctuations in the channel<sup>5</sup> or in the source and drain [73]

- Effective channel length variability due to line edge roughness happening during the lithography process [74]

- Electron mobility variability caused by random strain variation [75]

- Surface roughness causing gate oxide thickness variations [76]

It is not the purpose of this document to analyze all the sources of variability. The simple (and old) model presented in [71] is used. It states that the variance of the threshold voltage fluctuations from one device to an other is:

- inversely proportional to the area of the devices

- proportional to the square distance between the two devices. This type of mismatch is called fixed mismatch and can be due for example to gradient effects on the wafer.

This model can be summarized by the following expression <sup>6</sup>:

$$\sigma_{V_{th}}^2 = \frac{A_{V_{th}}^2}{WL} + S_{V_{th}}^2 D^2 \tag{2.15}$$

where W is the gate width of the device, L the channel length, D the distance between two devices and  $A_{V_{th}}$  and  $S_{V_{th}}$  are proportionality constants that depend on the technology. We here assume that the distances between devices in the design are sufficiently small so that the fixed part of the mismatches can be neglected. With that approximation, the standard deviation of the threshold voltage variation becomes inversely proportional to the square root of the device area:

$$\sigma_{V_{th}} = \frac{A_{V_{th}}}{\sqrt{WL}} \tag{2.16}$$

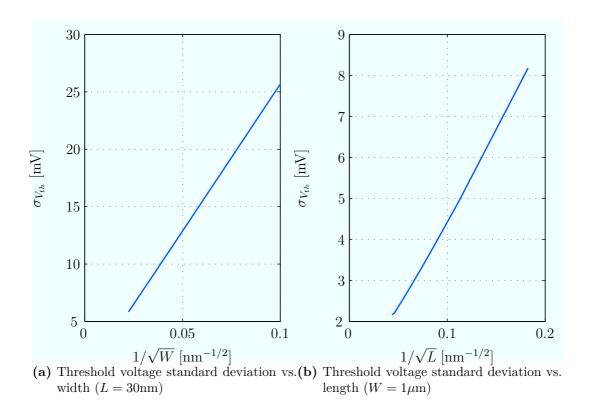

One can naturally wonder if this model, which dates from 1989, is still valid in today advanced CMOS technologies. The plots in Figure 2.2 show the standard deviation of the threshold voltage obtained from Monte-Carlo simulations of NMOS transistors in 28nm FDSOI CMOS technology, as a function of the width and the length of the transistor. It

<sup>5.</sup> In FDSOI technology, the channel is not doped, which decreases random dopant fluctuation [72]

<sup>6.</sup> The mismatches coming from the body-effect are here neglected, so that the standard deviation for  $V_{th}$  is the same as the standard deviation of  $V_{th0}$ . The formula in Pelgrom's model is actually  $\sigma_{V_{th0}} = \frac{A_{V_{th0}}}{\sqrt{WL}} + S_{V_{th0}}D^2$  and  $V_{th} = V_{th0} + K\left(\sqrt{|V_{sb}| + 2\phi_F} - \sqrt{2\phi_F}\right)$

turns out that, for sufficiently small devices (L < 500 nm and  $W < 2\mu$ m), the Pelgrom model seems to be valid with  $A_{V_{th}} \approx 1.4$  mV ·  $\mu$ m.

The typical threshold voltage of a LVT NMOS transistor in 28nm FDSOI is around 360 mV for a minimum length device (L=30 nm). It means that a minimum length transistor of 1  $\mu m$  wide can expect to have RMS threshold variability  $\sigma_{V_{th}}=1.4/\sqrt{0.03\times 1}=8$  mV. This represents a mismatch of 8/360=2.2%.

Figure 2.2 – Threshold voltage standard deviation as a function of transistor dimensions. Calculated from 50 Monte-Carlo simulations of a LVT-NMOS transistor in 28nm FDSOI ( $V_{gs}=1~{\rm V}$ )

Of course, this is a simplified analysis that does not pretend to summarize the complex concept of transistor mismatches in advanced CMOS technology.

Capacitors are another fundamental element in ADC designs. For example, they act as the storage element during the sampling of an analog signal. Capacitors manufactured on silicon can be of different types. In the past, parallel plate capacitors made of two metal plates with oxide in between were commonly used. Nowadays, thanks to the increasing metal interconnect density and the increasing number of available metal layers, Metal-Oxide-Metal (MOM) capacitors become the norm. They are comprised of several interdigitated metal fingers that store electrical charges laterally.

Mismatches in capacitors have to main causes [77]:

- dielectric thickness variations

- edge effects

However, the capacitor mismatch behavior also obeys Pelgrom's law, thereby yielding a standard deviation of the variations inversely proportional to the area (and therefore to the capacitance) of the device [78, 79]:

$$\sigma_C = \frac{A_{C1}}{C} = \frac{A_{C2}}{\sqrt{WL}} \tag{2.17}$$

where  $A_{C1}$  and  $A_{C2}$  are constants that depend on the type of capacitor and the technology.

In the next sections, we will see how these technology variations cause mismatches in a TIADC.

#### 2.4 Offset mismatches

The model of the TIADC presented in Section 2.2 does no take into account the mismatches between the converters. The aim of this section is to model the effects of offset mismatches.

Intuitively, the offset mismatches can be seen as a periodic sequence that is added to the signal. This sequence has a period M because the same offset is added to the output signal every M samples. Because of its periodicity, the sequence can be expressed in the frequency domain by its Fourier series, i.e. a sum of weighted tones at fixed frequencies. Since the mismatch sequence adds up to the signal, the output spectrum is therefore degraded by spurious tones. The mathematical framework developed for the ideal TIADC proves this intuition.

#### 2.4.1 Circuit sources

Depending of the architecture of the sub-ADC, one or several comparators are used during the quantization phase. For example, a B-bit flash ADC requires  $2^B$  comparators whereas a Successive Approximation Register (SAR) ADC only uses one. The offset mismatches happen when the comparators inside the sub-ADCs have different offsets. The offset sources in a comparator can be classified into two categories [30]:

- the static input offset, which is a static offset caused by the mismatches between the internal devices of the comparator (essentially transistors). Although the static input offset may slowly vary with temperature, it can be considered as a fixed offset.

- the input referred supply noise, which is an offset due to the comparator supply voltage variations. Input referred supply noise is by definition varying.

Comparators are usually made of several gain stages that amplify a voltage difference. Each of the stages has its own offset, which yield a global input referred offset. For instance, in high-speed ADCs, the comparator is usually made of one or two stages of pre-amplifiers followed by a latch comparator [15].

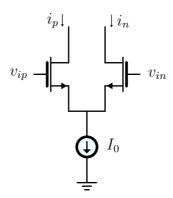

A simplest example of such an amplifier is a differential pair, which converts a voltage difference into a current difference. A NMOS differential pair is made of saturated NMOS transistors with sources connected to a current source  $I_0$ , as illustrated in Figure 2.3. If

Figure 2.3 – Schematic of a NMOS differential pair

the two transistors of the pair have the same voltage on their gate, the current in each branch is  $I_0/2$ . On the other hand, different gate potentials yield different currents in each branch because changing the gate-source voltage changes the biasing points of the transistors. The offset of a differential pair is characterized by the fact that a current difference is observed at the output while no voltage difference is applied at the input. Or conversely, the offset is the opposite of the voltage difference that has to be applied at the input such that no current difference appears at the output. The offset can be caused by

- mismatches between the sizes of the two transistors of the pairs

- mismatches between the loads of each branch

- mismatches of threshold voltage between the two transistors

- mismatches of current factor between the two transistors

In advanced CMOS technology such as 28nm FDSOI, the  $V_{th}$  mismatches dominate. If there is a threshold voltage difference  $\Delta V_{th}$  between the two transistors of the pair, the input referred offset is:

$$V_{os} = \Delta V_{th} \tag{2.18}$$

For example, a differential pair made of two minimum-length  $1\mu m$  NMOS transistors would have an offset standard deviation

$$\sigma_{V_{os}} = \sigma_{V_{th}} \approx 8 \text{ mV}$$

(2.19)

This value corresponds to 4 LSB in a 9-bit ADC with a peak-to-peak input range of 1V.

In a single ADC, the comparator offsets yield different effects depending on the architecture that is used. In a flash ADC, they create DNL errors since different comparators with different offsets are used to compare the signal to the different reference voltages. In a SAR ADC, the same comparator is used to determine all the bits. A comparator offset therefore only creates a global offset.

When only a single ADC is used, a global offset is not a big issue because telecommunication signal do not contain any information at DC<sup>7</sup>. The offset mismatch problem arises when several converters, with different global offsets, are interleaved.

#### 2.4.2 Effects on the output signal

When a TIADC has offset mismatches, a different offset is added to the output of each sub-converter, as illustrated in Figure 2.4. Assuming no quantization, the sampled

Figure 2.4 – Model of a TIADC with offset mismatches

signal at the output of each sub-ADC becomes

$$\tilde{x}_m[k] = x_m[k] + o_m \tag{2.20}$$

where  $o_m$  is the offset of the sub-ADC m.

Similar to the ideal TIADC case, the above expression can also be written in a continuous time form by adding an offset to the continuous-time signal, and by multiplying

<sup>7.</sup> However, an important offset can reduce the dynamic range of the ADC

it by the corresponding sub-sampling Dirac comb:

$$\tilde{x}_m(t) = (x(t) + o_m)c_m(t) = x_m(t) + o_m c_m(t)$$

(2.21)

The continuous TIADC output signal is obtained by adding the output signals of the sub-converters together:

$$\tilde{x}_s(t) = x_s(t) + \sum_{m=0}^{M-1} o_m c_m(t)$$

(2.22)

The above equation 2.22 shows that the TIADC output signal is a sum of the ideal output signal and weighted Dirac combs. Translating this expression into the frequency domain, through the CTFT, yields

$$\tilde{X}_s(\Omega) = X_s(\Omega) + \sum_{m=0}^{M-1} o_m C_m(\Omega)$$

(2.23)

The CTFT  $C_m(\Omega)$  of the sub-sampling Dirac combs  $c_m(t)$  are also Dirac combs:

$$C_m(\Omega) = \frac{2\pi}{MT_s} e^{-j\Omega mT_s} \sum_{k=-\infty}^{+\infty} \delta\left(\Omega - k\frac{\Omega_s}{M}\right)$$

(2.24)

Replacing  $C_m(\Omega)$  by its expression in equation 2.23 leads to

$$\tilde{X}_s(\Omega) = X_s(\Omega) + \frac{2\pi}{MT_s} \sum_{m=0}^{M-1} o_m e^{-j\Omega m T_s} \sum_{k=-\infty}^{+\infty} \delta\left(\Omega - k \frac{\Omega_s}{M}\right)$$

(2.25)

The above expression can be rearranged by inverting the two sums and by noticing, because of the Dirac impulses, that the exponential terms  $e^{j\Omega mT_s}$  only need to be evaluated at the frequencies  $\Omega = k\frac{\Omega_s}{M}$  and can be rewritten  $e^{-j2\pi\frac{km}{M}}$ . The spectrum of the sampled output of the TIADC can thus be expressed

$$\tilde{X}_s(\Omega) = X_s(\Omega) + \frac{2\pi}{MT_s} \sum_{k=-\infty}^{+\infty} O_k \delta\left(\Omega - k \frac{\Omega_s}{M}\right)$$

(2.26)

where  $O_k$  are the Fourier coefficients associated to the sequence of offsets  $\{o_0, o_1, \cdots, o_{M-1}\}$

$$O_k = \sum_{m=0}^{M-1} o_m e^{j2\pi \frac{km}{M}} \tag{2.27}$$

The DTFT of the TIADC output signal  $\tilde{x}[n]$  is therefore

$$\tilde{X}_{2\pi}(\omega) = X_{2\pi}(\omega) + \frac{2\pi}{M} \sum_{k=0}^{M-1} O_k \delta_{2\pi} \left(\omega - k \frac{2\pi}{M}\right)$$

(2.28)

Figure 2.5 – Illustration of offset mismatch tones in TIADC output spectrum

where  $\delta_{2\pi}(\omega)$  is the periodized Dirac comb DTFT, defined as follows:

$$\delta_{2\pi}(\omega) = \frac{1}{T_s} \sum_{k=-\infty}^{+\infty} \delta\left(\frac{1}{T_s} \left(\omega - 2k\pi\right)\right)$$

(2.29)

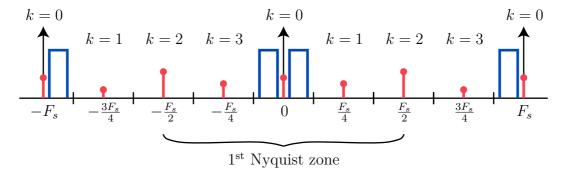

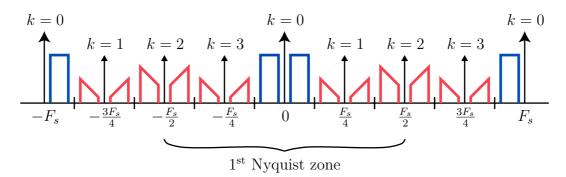

As expected, the TIADC output spectrum is comprised of the ideal signal spectrum, and spurious tones at frequencies multiple of  $2\pi/M$  (equivalent of  $F_s/M$ ). This is illustrated in Figure 2.5.

### 2.4.3 Consequences on the TIADC performance

The output spectrum in Equation 2.28 can be used to derive important ADC performance metrics such as the SNDR and the SFDR. As those metrics are calculated with a sine input, let the input signal be  $x(t) = A\cos(\Omega_0 t + \phi)$ . The DTFT of  $x[n] = x(nT_s)$

$$X_{2\pi}(\omega) = A\pi e^{j\omega\phi} \left(\delta_{2\pi}(\omega - \omega_0) + \delta_{2\pi}(\omega + \omega_0)\right)$$

(2.30)

where  $\omega_0 = \Omega_0 T_s$ .

### 2.4.3.1 SNDR degradation

Replacing the ideal signal DTFT by the expression given above in Equation 2.28 gives the TIADC output spectrum with offset mismatches:

$$\tilde{X}_{2\pi}(\omega) = \underbrace{A\pi e^{j\omega\phi} \left(\delta_{2\pi}(\omega - \omega_0) + \delta_{2\pi}(\omega + \omega_0)\right)}_{\text{Original sine tones}} + \underbrace{\frac{2\pi}{M} \sum_{k=0}^{M-1} O_k \delta_{2\pi} \left(\omega - k \frac{2\pi}{M}\right)}_{\text{Offset mismatch spurious tones}}$$

(2.31)

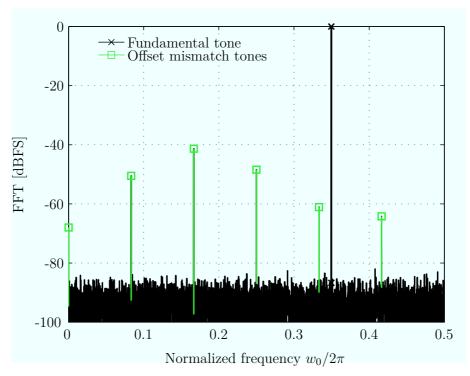

As illustrated in Figure 2.6, the output spectrum is comprised of the original sine tone, as well as offset mismatch spurious tones.

The SNDR is usually calculated for a full range sine input. It means that the sine wave

Figure 2.6 – Output spectrum of a 9-bit TIADC with offset mismatches (M=12,  $\omega_0=0.7\pi$ ,  $\sigma_o=2\times \text{LSB}$ ,  $N_{\text{FFT}}=12\times 4096$ )

takes values between  $-2^{B-1} \times \text{LSB}$  and  $2^{B-1} \times \text{LSB}$ , and consequently that  $A = 2^{B-1} \text{LSB}$ . The SNDR, in this case, is the ratio (in dB) between the signal power and the offset mismatch noise power <sup>8</sup>:

$$SNDR = 10 \log_{10} \left( \frac{2 \times 2^{2B-2} \times LSB^2}{\frac{4}{M^2} \sum_{k=0}^{M-1} O_k^2} \right)$$

(2.32)

The above expression 2.32 can be simplified using the Plancherel theorem that states that

$$\sum_{k=0}^{M-1} O_k^2 = M \sum_{m=0}^{M-1} o_m^2 = M^2 \sigma_o^2$$

(2.33)

where  $\sigma_o = \sqrt{\frac{1}{M} \sum_{m=0}^{M-1} o_m^2}$  is the Root Mean Square (RMS) offset mismatch level. Since the offsets are usually specified in number of LSBs, it is more convenient to express their RMS value in LSBs as well. For that, we define  $\sigma_o^{\rm LSB} = \sigma_o/{\rm LSB}$  and the final SNDR expression is:

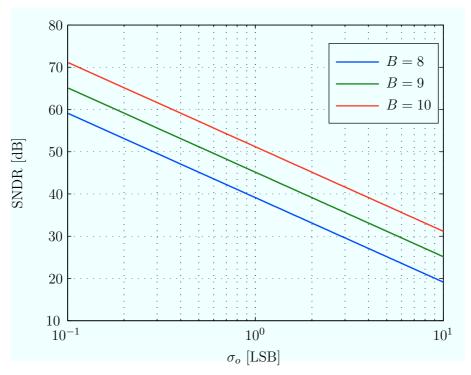

$$SNDR = 20 \log_{10} \left( \frac{2^{B-1}}{\sqrt{2}\sigma_o^{LSB}} \right)$$

(2.34)

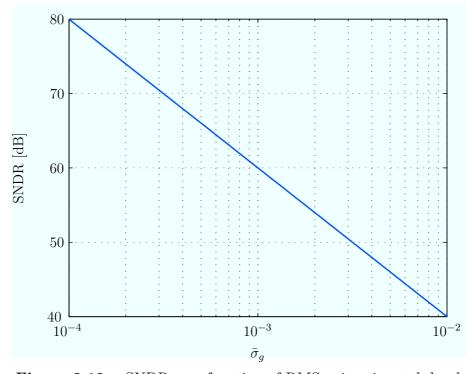

Figure 2.7 illustrates the above expression for different RMS offset mismatch levels. Ba-

<sup>8.</sup> The quantization noise is not taken into account in the calculation of the noise because we are interesting in measuring the effects of the offset mismatches only

sically, multiplying the amount of offset mismatch by 2 decreases the SNDR by 6 dB, which is equivalent to loosing 1 bit of effective resolution.

Figure 2.7 – SNDR as a function of RMS offset mismatch level

### 2.4.3.2 SFDR degradation

While the SNDR is an important metric to characterize an ADC performance, the SFDR is also often used to characterize offset mismatch noise. Indeed, since the offset mismatch noise takes the form of spurious tones, it is interesting to know the power of the highest tone relative to the power of the signal.

The worst case SFDR is obtained when the offset mismatch noise is concentrated in one spurious tone of index  $k_0$ . For a fixed  $\sigma_o$ , this translates into:

$$O_k = M\sigma_o \delta[k - k_0] \tag{2.35}$$

where  $\delta[\cdot]$  is the Kronecker delta function. The values of the offsets  $\{o_m, m \in \mathcal{M}\}$  are given by the inverse DFT of the  $\{O_k, k \in \mathcal{M}\}$

$$o_m = \frac{1}{M} \sum_{k=0}^{M-1} O_k e^{j2\pi \frac{km}{M}}$$

(2.36)

When only  $O_{k_0}$  is non-zero, as expressed in equation 2.35, the above expression becomes:

$$o_m = \sigma_o e^{j2\pi \frac{k_0 m}{M}} \tag{2.37}$$

Since the offsets are real valued,  $k_0$  can either be equal to 0 or to  $\frac{M}{2}$ . The case  $k_0 = 0$  can be discarded because it corresponds to the spurious tone that falls at DC. The case  $k_0 = \frac{M}{2}$ , corresponding to a tone at the Nyquist frequency, is only possible if M is even, which yields the following offset values:

$$o_m = \sigma_o e^{j\pi m} = \sigma_o (-1)^m \tag{2.38}$$

In this case, the expression of the worst case SFDR is the ratio between the power of the positive side (or the negative side) of the fundamental, and the power of the unique offset mismatch tone

$$SFDR_{worst} = 20 \log_{10} \left( \frac{2^{B-1}LSB}{2 |O_{k_0}|/M} \right) = 20 \log_{10} \left( \frac{2^{B-1}}{2\sigma_o^{LSB}} \right) = SNDR - 3 dB \qquad (2.39)$$

When M is even, the expression of the worst case SFDR is 3 dB lower than the SNDR (Equation 2.32) because even if all the offset mismatch noise is concentrated in one spurious tone, the calculation of the SFDR takes into account either the positive side, or the negative side of the spectrum.

When M is odd, it is not possible for the offset mismatch noise to be concentrated in only one spurious tone. In general, the spurious tones go in pairs, and the case where M is even is a particular case, where the two tones of the pairs are at half the Nyquist frequency. The fact that the offsets are real-valued implies that  $O_k = O_{M-k}^* \ \forall k \in \mathcal{M}$ . Consequently, the tone with index k and the tone with index M-k have the same power. When M is odd, the worst case SFDR is obtained when the offset mismatch noise is only concentrated in one pair of tones, respectively indexed by  $k_0$  and  $M-k_0^9$ . The two tones of the pair both have the same power since  $|O_{k_0}| = |O_{M-k_0}^*|$ , and according to the Plancherel theorem