## Design of an integrated streak camera based on a time correlated single photon counting system

Imane Malass

#### ▶ To cite this version:

Imane Malass. Design of an integrated streak camera based on a time correlated single photon counting system. Signal and Image processing. Université de Strasbourg, 2016. English. NNT: 2016STRAD001. tel-01332682

## HAL Id: tel-01332682 https://theses.hal.science/tel-01332682

Submitted on 16 Jun 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE STRASBOURG

## ÉCOLE DOCTORALE MATHEMATIQUES, SCIENCES DE L'INFORMATION ET DE L'INGENIEUR

## THÈSE Présentée par

## Imane MALASS soutenue le : 13 MAI 2016

pour obtenir le grade de Docteur de l'université de Strasbourg

Discipline : Électronique, Électrotechnique et Automatique

Spécialité : Micro et Nanoélectronique

## Design of an Integrated Streak Camera based on a Time Correlated Single Photon Counting System

**DIRECTEUR DE THESE:**

**UHRING Wilfried** Professeur, Université de Strasbourg, France

**CO-DIRECTEUR DE THESE:**

**LE NORMAND Jean-Pierre** MCF HDR, Université de Strasbourg, France

**RAPPORTEURS:**

**CALMON Francis** Professeur INSA de Lyon, France **CHARBON Edoardo** Professeur EPFL, Lausanne, Suisse

**AUTRES MEMBRES DU JURY:**

NORMAND Stéphane Chercheur Ingénieur HDR, CEA, Saclay, France

**DUMAS Norbert** MCF, Université de Strasbourg, France

**MEMBRE INVITE:**

**LEONARD Jérémie** Chargé de recherche HDR, IPCMS, Strasbourg, France

## **Imane Malass**

# Design of an Integrated Streak Camera based on a Time Correlated Single Photon Counting System

### Résumé

Nous présentons une caméra à balayage de fente intégrée basée sur un système de comptage de photon unique résolu en temps (TCSPC-SC) employant l'architecture linéaire « streak » pour surmonter la limitation de l'espace inhérent aux systèmes TCSPC bidimensionnels. Cette solution permet l'intégration de fonctionnalités électroniques complexes dans les pixels sans l'inconvénient d'un faible facteur de remplissage conduisant à une faible efficacité de détection. Le TCSPC-SC se compose de deux blocs principaux: une photodiode à avalanche (SPAD) et un bloc de mesure de temps, les deux blocs sont intégrés en technologie 180 nm CMOS standard. La structure de la SPAD utilisée a été sélectionnée parmi 6 structures différentes après un processus de caractérisation précise et approfondie. Le bloc de mesure du temps se compose d'un TDC hybride capable d'atteindre des résolutions de temps élevées et ajustables avec une large dynamique de mesure grâce à un système de conversion de temps (TDC) hybride qui combine l'approche analogique basée sur un convertisseur de temps vers amplitude(TAC), et les approches numériques utilisant une boucle à verrouillage de retard (DLL) et un compteur numérique 12 bit-. Le TDC hybride a été spécialement conçu pour être utilisé dans un système TCSPC qui intègre une ligne de TDC nécessitant ainsi une conception appropriée pour limiter la consommation d'énergie et la surface d'occupation et parvenir à une architecture flexible et facilement extensible. Suite à la conception et la réalisation de ces deux blocs dans une technologie180 nm CMOS standard, une structure de test de la caméra à balayage de fente (TCSPC-SC) qui englobe 8 unités a été réalisée dans le but final de mettre en œuvre un modèle TCSPC-SC complet et plus large.

## Résumé en anglais

In this work we present a TCSPC Streak Camera (TCSPC-SC) that takes advantage of the streak mode imaging to overcome the space limitation inherent to 2D TCSPC sensor arrays. This cost-effective solution allows the integration of complex functionalities in the pixel without the inconvenience of low fill factor that leads to low detection efficiency. The TCSPC-SC consists of two main building blocks: a SPAD and a time measurement block both integrated in 180 nm Standard CMOS technology. The SPAD was selected among 6 different SPAD structures following a thorough characterization process to fully determine its performance figures. The time measurement block consists of a hybrid TDC capable of achieving high adjustable time resolutions with large dynamic range owing to a time conversion scheme that combines traditional Analog Time to Amplitude Converter (TAC), Digital DLL-based and counter-based TDC. Furthermore, the hybrid TDC was especially designed to be used in a TCSPC system that incorporates an array of TDCs which required a careful design to limit power consumption and occupation area in order to achieve a flexible and easily scalable architecture. These two building blocks were both fabricated in a 180 nm standard CMOS technology and employed to demonstrate a TCSPC Streak Camera (TCSPC-SC) test structure that englobes 8 units in order to demonstrate the system's operation principle with the final aim of implementing complete and bigger TCSPC-SC model in the near future

## **Acknowledgement**

The work presented in this document would not have been possible without the help and the guidance of several individuals who in one way or another contributed to this project.

First and foremost, my deepest and utmost gratitude goes to my advisor Wilfried Uhring without whom I wouldn't have had the chance to do this thesis. His guidance, vast knowledge and support were essential for the completion of this work and his great personal qualities added considerably to my PhD experience. It was a true pleasure to witness up-close the remarkable joy and enthusiasm he has for his research and I cannot find words to express my gratitude for his kindness and the friendship he extended toward me since I started working with him.

My sincere gratitude also goes to my co-advisor Jean-Pierre Le Normand for his guidance, his patience and his vital assistance especially during the long nights preceding a deadline. I enjoyed sharing the same office with him and I am profoundly grateful for his kindness and the friendliness we shared.

I would like to take this opportunity to express my earnest gratitude to Professor Luc Hebrard. Pr. Hebrard was not directly involved in my PhD project but this achievement is in part a result of his guidance and excellent pedagogical skills. I have nothing but great admiration for Pr. Hebrard and I consider it a true privilege to be one of his students.

I would like to sincerely thank Foudil Dadouche, Norbert Dumas and Jean-Baptiste Schell for offering their help whenever it was needed. My thanks also goes to Pr. Daniel Mathiot, Freddy Anstotz, Frédéric Antoni, Jean-Baptiste Kamerer and Nicolas Collin.

I would like to thank the Microelectronic group in the Institut Pluridisciplinaire Hubert CURIEN (IPHC), I especially thank Claude Colledani, Frédéric Morel and Gregory Bertolone for kindly providing me with their much appreciated help and technical support.

To my fellow PhD students Fitsum Aweke, Julien Zelgowski, Laurent Osberger, Marwa Garci, Octavian Maciu, Rémi Bonnard, Simon Paulus, Thomas Regrettier, and Vincent Wlotzko, thank you for all the pleasant discussions and the fun times.

Last but not least I wish to express my deepest and utmost gratitude to my parents, Moustafa and Ghada, without whom none of this would have been possible. I am forever indebted to them for all their hard work, dedication and support over the years and to them I dedicate this thesis.

## **Abstract**

Streak cameras have been traditionally based on the vacuum tube technology, a mature and ultrafast technology that, despite great performance figures, suffer from bulkiness, fragility and expensive cost. In recent, Many efforts have been made to find a solid state alternative to the vacuum technology and several integrated streak cameras have been realized in (Bi)CMOS technology allowing a temporal resolution close to 1 ns and most of these devices are specifically designed to operate in single shot mode, their sensitivity represents a real issue for measurements of weak optical signals.

This problem can be resolved in the case of recurrent optical phenomena by employing the time correlated single photon counting (TCSPC), a technique that takes advantage of high gain photon detectors such as Photo-Multiplier Tubes (PMTs) and (MCPs) to measure weak optical signals. These mature technologies are capable of achieving very good performances but they are also expensive, cumbersome, fragile, and require high operating voltages (~kV) which makes them unsuitable for the fabrication of miniaturized portable TCSPC imaging systems. Following the emergence of Silicon Photo Multiplier (SiPM) based on single photon avalanche diodes (SPADs) integrated in standard CMOS technology in the 2000's; several integrated 2D-TCSPC systems have been demonstrated. These 2D systems consist of SPAD arrays integrated in 2D with their associated electronics resulting in a tradeoff between high photon detection efficiency and advanced electronic functionalities. The use of 3 dimensional (3D) heterogeneous integration with deep-submicron CMOS readout electronics represents a good solution to the previously mentioned limitations but the 3D technology is still new, immature and highly costly.

In this work we present a TCSPC Streak Camera (TCSPC-SC) that takes advantage of the streak mode imaging to overcome the space limitation inherent to 2D TCSPC sensor arrays. This costeffective solution allows the integration of complex functionalities in the pixel without the inconvenience of low fill factor that leads to low detection efficiency. The TCSPC-SC consists of two main building blocks: a SPAD and a time measurement block both integrated in 180 nm Standard CMOS technology. The SPAD was selected among 6 different SPAD structures following a thorough characterization process to fully determine its performance figures. The time measurement block consists of a hybrid TDC capable of achieving high adjustable time resolutions with large dynamic range owing to a time conversion scheme that combines traditional Analog Time to Amplitude Converter (TAC), Digital DLL-based and counter-based TDC. Furthermore, the hybrid TDC was especially designed to be used in a TCSPC system that incorporates an array of TDCs which required a careful design to limit power consumption and occupation area in order to achieve a flexible and easily scalable architecture. These two building blocks were both fabricated in a 180 nm standard CMOS technology and employed to demonstrate a TCSPC Streak Camera (TCSPC-SC) test structure that englobes 8 units in order to demonstrate the system's operation principle with the final aim of implementing a complete and bigger TCSPC-SC model in the near future.

## **Contents**

| 1 | Int  | roduction                                 | 1        |

|---|------|-------------------------------------------|----------|

|   | 1.1  | The Origin of Photography                 | 1        |

|   | 1.2  | From Photography to Cinematography        | 2        |

|   | 1.3  | The Emergence of CMOS Imagers             | 6        |

|   | 1.3. | CCD Cameras                               | <i>6</i> |

|   | 1.3. | 3.2 CMOS Cameras                          | 8        |

|   | 1.4  | Streak Mode Cameras                       | 9        |

|   | 1.4. | 1 Streak-Mode Imaging Concept             | 9        |

|   | 1.4. | 2 The Conventional Streak Camera          | 10       |

|   | 1.4. | .3 Integrated Streak Camera               | 13       |

|   | 1.5  | Time Correlated Single Photon Counting    | 15       |

|   | 1.5. | Fundamentals and History of TCSPC         | 15       |

|   | 1.5. | 5.2 TCSPC Building Blocks                 | 17       |

|   | 1    | 1.5.2.1 Discriminators                    | 18       |

|   | 1    | 1.5.2.2 Time Measurement in TCSPC Systems |          |

|   | 1    | 1.5.2.3 Detectors                         |          |

|   | 1.6  | This Thesis                               | 27       |

|   | 1.6. | 5.1 Aim                                   | 27       |

|   | 1.6. | - 0-                                      |          |

| 2 | Sin  | ngle Photon Avalanche Diodes              | 29       |

|   | 2.1  | Avalanche Photodiodes in Geiger Mode      | 29       |

|   | 2.1. | 1 The SPAD Biasing Cycle                  | 30       |

|   | 2.1. | 2 Figures of Merit for Individual SPADs   | 31       |

|   | 2    | 2.1.2.1 Dark Count Rate                   | 31       |

|   | 2    | 2.1.2.2 Afterpulsing                      | 31       |

|   | 2    | 2.1.2.3 Photon Detection Probability      | 32       |

|   | 2    | 2.1.2.4 Timing Resolution (litter)        | 32       |

| 2   | 2.1.3   | Figure of Merit for SPAD Arrays                                        | .32 |

|-----|---------|------------------------------------------------------------------------|-----|

|     | 2.1.3.2 | 1 Fill Factor                                                          | .32 |

|     | 2.1.3.2 | Pixel Pitch                                                            | .33 |

|     | 2.1.3.3 | 3 CrossTalk                                                            | .33 |

| 2   | 2.1.4   | Quenching Electronics                                                  | .33 |

|     | 2.1.4.2 | 1 Passive Quenching                                                    | .34 |

|     | 2.1.4.2 | 2 Active Quenching                                                     | .36 |

|     | 2.1.4.3 | Mixed Active-Passive Quenching                                         | .37 |

| 2   | 2.1.5   | SPAD progress and physical implementation                              | .38 |

|     | 2.1.5.2 | 1 Early SPADs                                                          | .38 |

|     | 2.1.5.2 | 2 Technological requirements                                           | .39 |

|     | 2.1.5.3 | Fabrication technology: CMOS vs Custom technologies                    | .40 |

| 2.2 | SPA     | D Structures and Characterization Set Up                               | .41 |

| 2   | 2.2.1   | SPAD Structures                                                        | .41 |

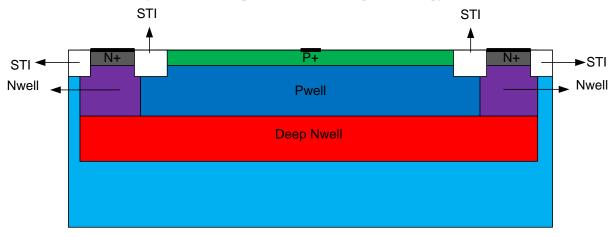

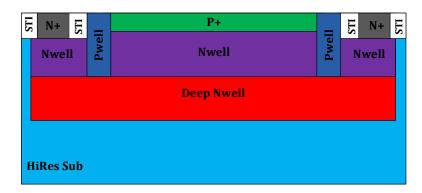

|     | 2.2.1.2 | Structure A (P+ Nwell with STI guardring)                              | .41 |

|     | 2.2.1.2 | 2 Structure B (P+ Nwell Deep Nwell with STI guard ring)                | .42 |

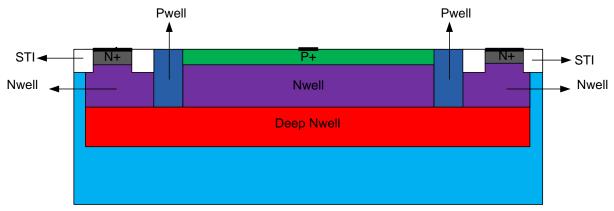

|     | 2.2.1.3 | Structure C (P+ Nwell Deep Nwell with Pwell guard ring)                | .42 |

|     | 2.2.1.4 | Structure D (P+ Pwell Deep Nwell with no guard ring)                   | .43 |

|     | 2.2.1.2 | Structure E (P+ Pwell Deep Nwell with STI guard ring)                  | .43 |

|     | 2.2.1.2 | 2 Structure F (P+ Nwell Deep Nwell with a double Pwell-STI guard ring) | .44 |

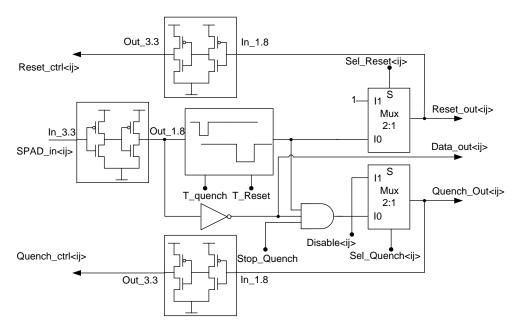

| 2   | 2.2.2   | SPAD Versatile Characterization Circuit                                | .44 |

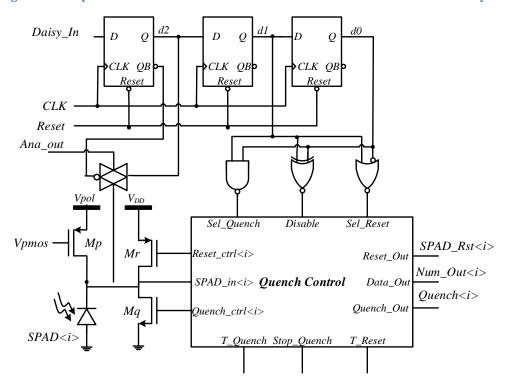

|     | 2.2.2.2 | 1 Circuit Structure                                                    | .44 |

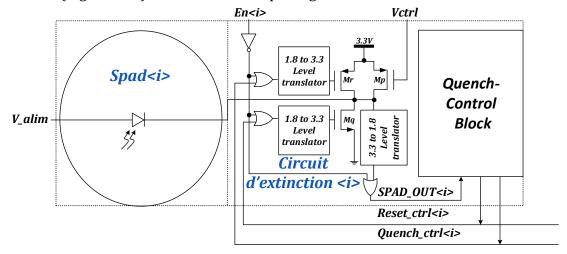

|     | 2.2.2.2 | Pixel Structure                                                        | .46 |

|     | 2.2.2.3 | 3 Versatile Quenching Control System                                   | .47 |

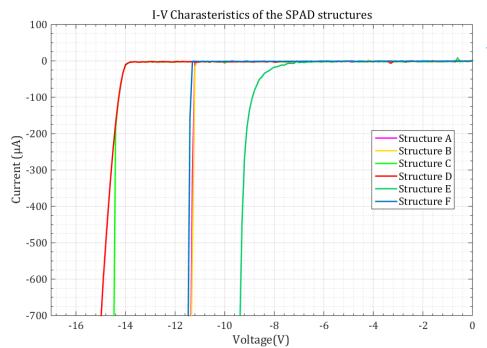

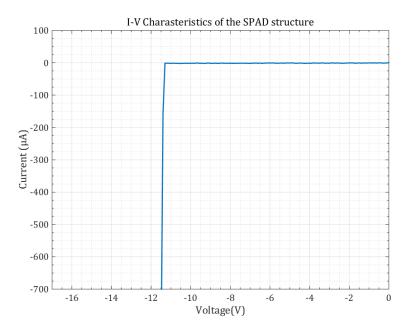

| 2.3 | Cha     | racterization Results                                                  | .49 |

| 2   | 2.3.1   | Breakdown voltage                                                      | .49 |

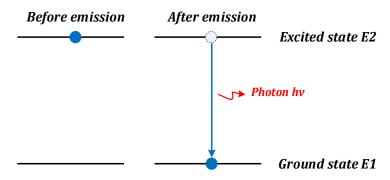

| 2   | 2.3.2   | Electroluminescence light emission test                                | .50 |

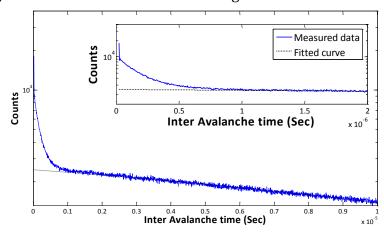

| 2   | 2.3.3   | Dark count rate                                                        | .51 |

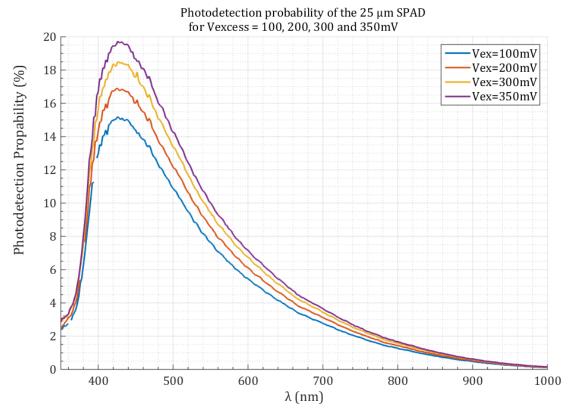

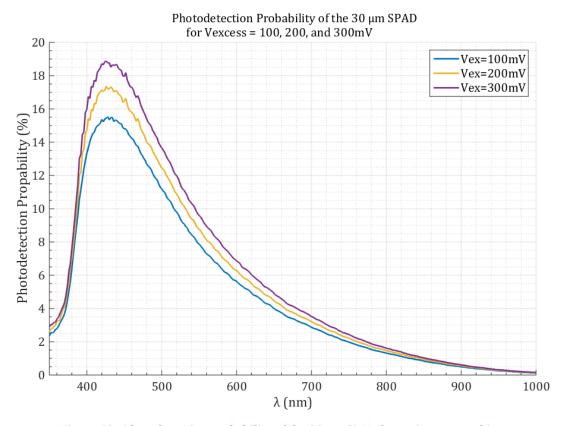

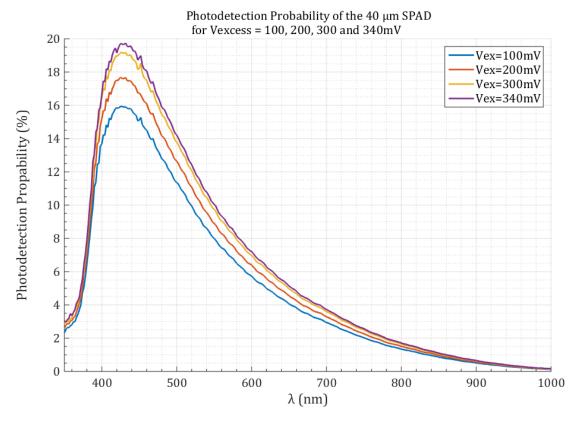

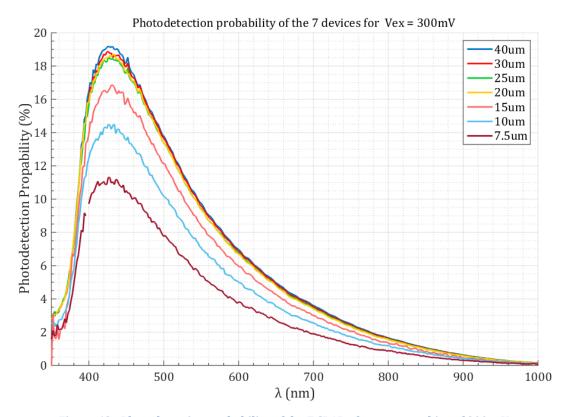

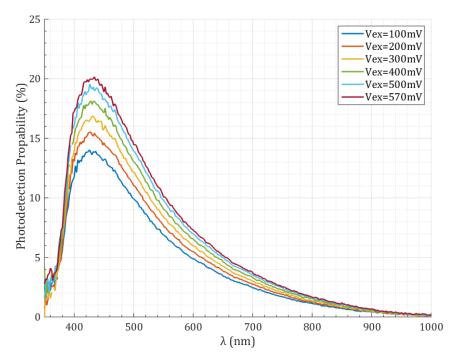

| 2   | 2.3.4   | Photodetection probability                                             | .54 |

| 2   | 2.3.5   | Timing resolution (Jitter)                                             | .59 |

| 2   | 2.3.6   | Conclusion                                                             | .62 |

| 3 Time | to Digital Converter                               | 63 |

|--------|----------------------------------------------------|----|

| 3.1 T  | DC Operation Metrics                               | 64 |

| 3.1.1  | Time Resolution                                    | 64 |

| 3.1.2  | Dynamic Range                                      | 65 |

| 3.1.3  | Quantization Error                                 | 65 |

| 3.1.4  | Offset                                             | 65 |

| 3.1.5  | Gain Error                                         | 66 |

| 3.1.6  | Non-linearity errors                               | 66 |

| 3.1.7  | Single Shot Precision                              | 67 |

| 3.1.8  | Conversion Time                                    | 68 |

| 3.1.9  | Dead Time                                          | 68 |

| 3.1.10 | Power Dissipation                                  | 68 |

| 3.2 A  | nalog TDC Architectures                            | 69 |

| 3.2.1  | Time to Analog Converter                           | 69 |

| 3.2.2  | Dual Slope TDC                                     | 70 |

| 3.3 Ba | asic TDC architectures                             | 71 |

| 3.3.1  | Counter Based TDC                                  | 71 |

| 3.3.2  | Delay Line Based TDC                               | 71 |

| 3.3.3  | Delay Locked Loop Based TDC                        | 73 |

| 3.4 A  | dvanced TDC Architectures for Sub-Gate Resolutions | 74 |

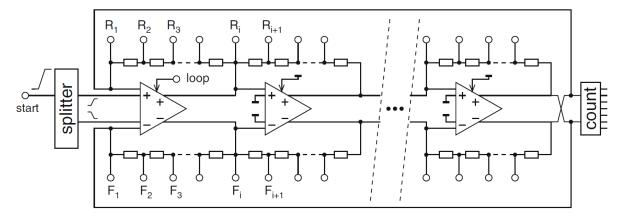

| 3.4.1  | Parallel Delay Elements Based TDC                  | 74 |

| 3.4.2  | Pulse Shrinking TDC                                | 75 |

| 3.4.3  | Vernier Delay Line                                 | 76 |

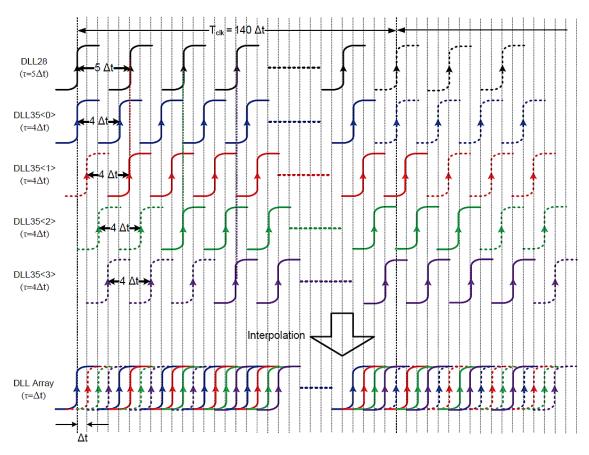

| 3.4.4  | DLL Arrays                                         | 78 |

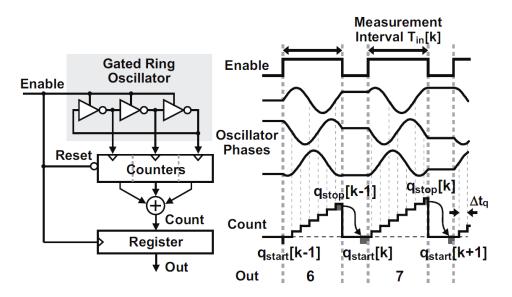

| 3.4.5  | Gated Ring Oscillator TDC                          | 79 |

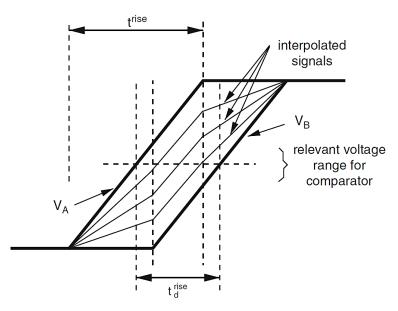

| 3.4.6  | Local Passive Interpolation TDC                    | 81 |

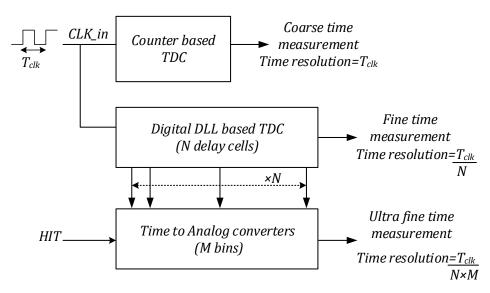

| 3.5 T  | he Hybrid Time to Digital Converter                | 83 |

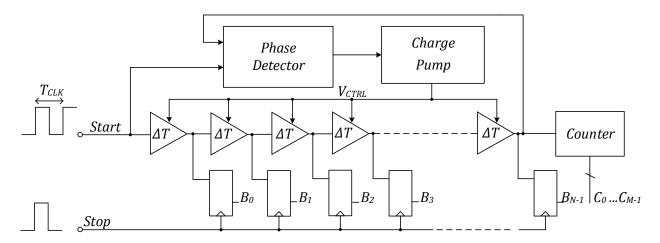

| 3.5.1  | Delay Locked Loop                                  | 85 |

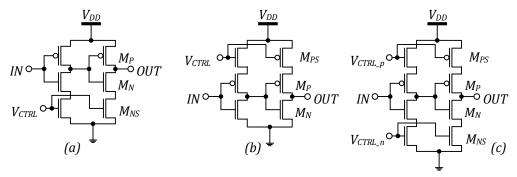

| 3.5.   | 1.1 Voltage-controlled Delay Line                  | 86 |

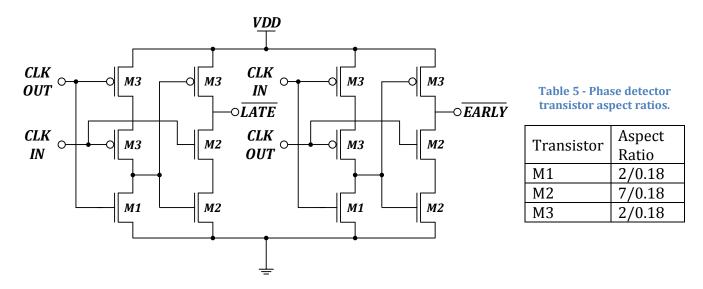

| 3.5.   | 1.2 Phase Detector                                 | 91 |

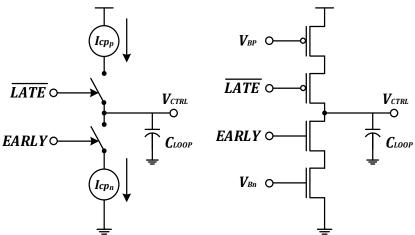

| 3.5.   | 1.3 Charge Pump and Loop Capacitor                 | 96 |

|   |     | 3.5.1   | .4    | DLL Simulation Results                           | 101 |

|---|-----|---------|-------|--------------------------------------------------|-----|

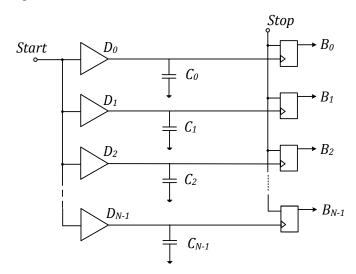

|   | 3   | 3.5.2   | Th    | e Time Sampling Unit                             | 103 |

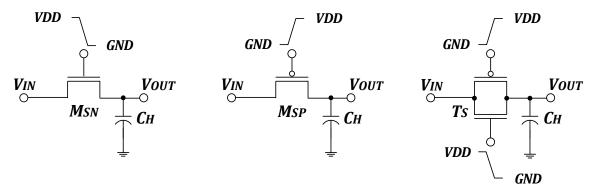

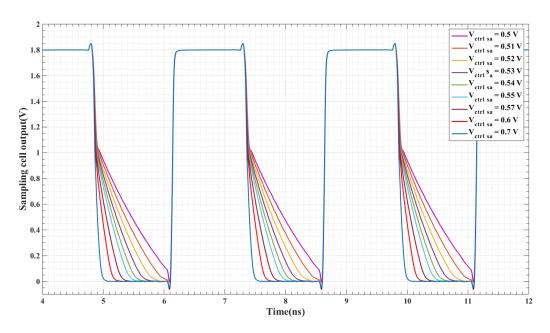

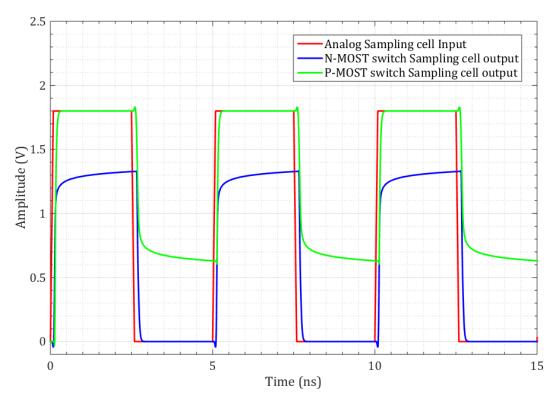

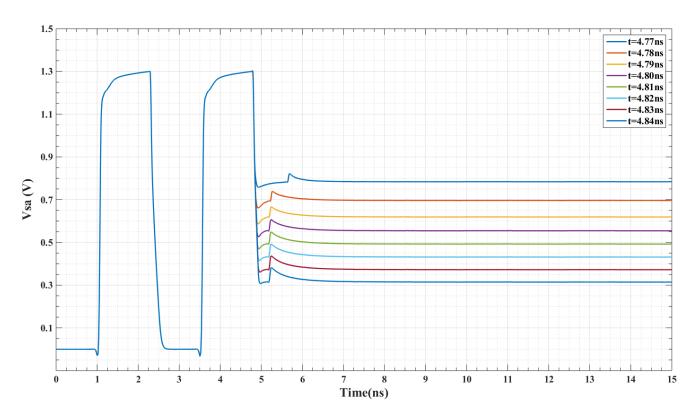

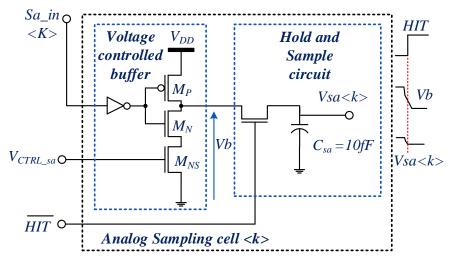

|   |     | 3.5.2   | .1    | The Analog Sampling Line                         | 104 |

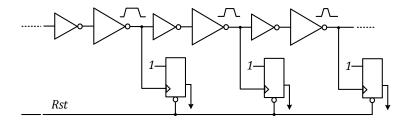

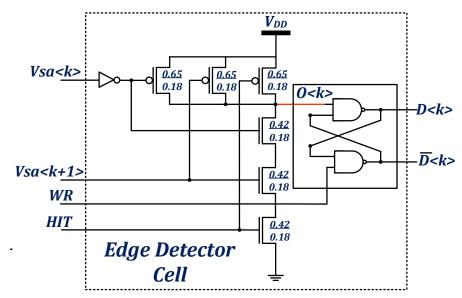

|   |     | 3.5.2   | .2    | The Edge Detector Line                           | 110 |

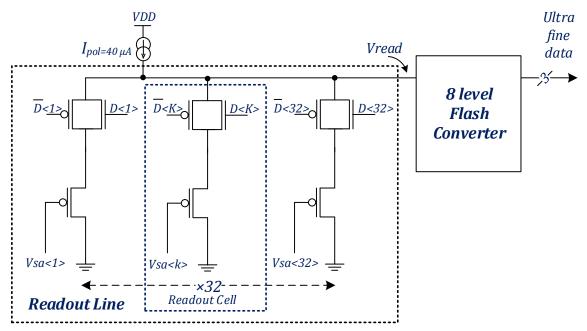

|   |     | 3.5.2   | .3    | The Readout Line                                 | 112 |

|   |     | 3.5.2   | .4    | The 3 Level Flash Converter                      | 115 |

|   |     | 3.5.2   | .5    | TSU State Machine                                | 120 |

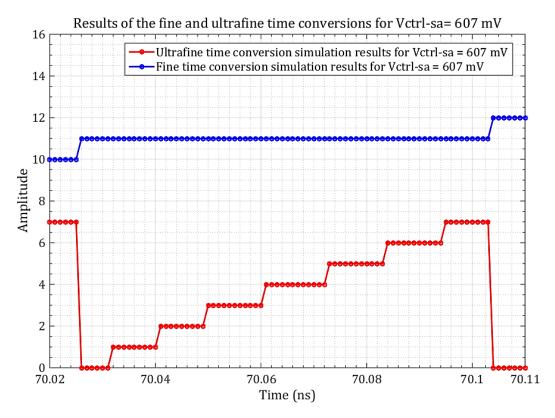

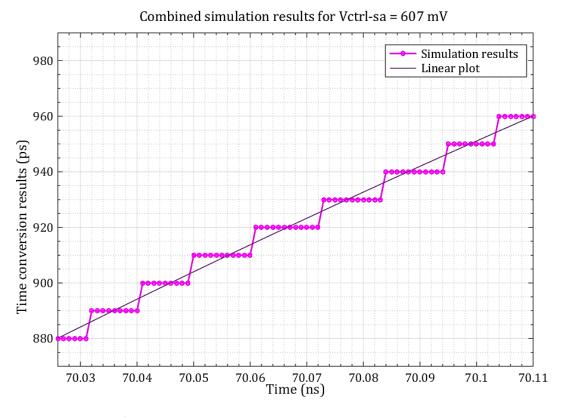

|   | 3   | 3.5.3   | Sin   | nulation Results                                 | 122 |

|   | 3   | 3.5.4   | Cha   | aracterization Results                           | 124 |

|   | 3.6 | Co      | nclus | sion                                             | 127 |

| 4 | T   | The TO  | CSPC  | Streak Camera                                    | 133 |

|   | 4.1 | TC      | SPC   | Unit                                             | 134 |

|   | 4   | ł.1.1   | Arc   | chitecture                                       | 134 |

|   | 4   | ł.1.2   | Op    | eration Principle                                | 136 |

|   | 4.2 | Str     | eak.  | Architecture                                     | 136 |

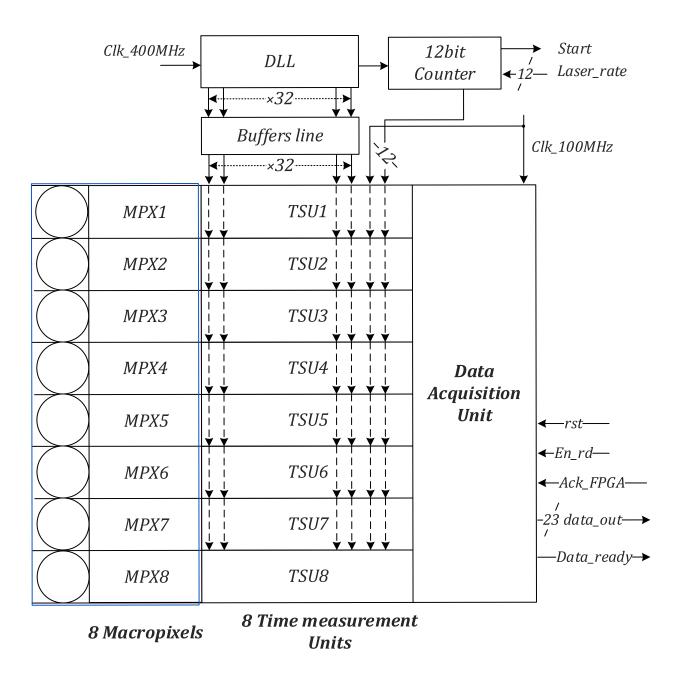

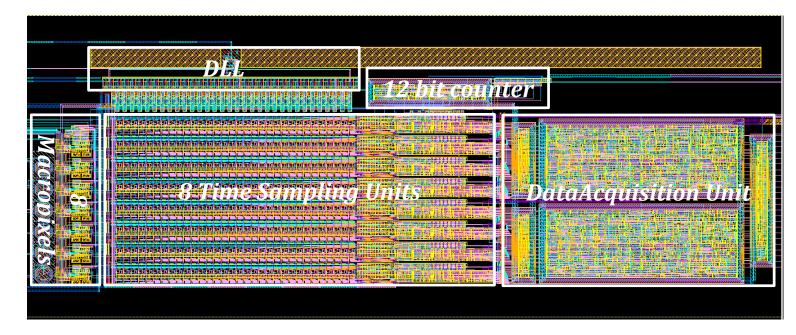

|   | 4.3 | Da      | ta Ao | equisition Unit                                  | 139 |

|   | 4.4 | Hi      | gh Tł | nroughput Time Correlated Single Photon Counting | 141 |

|   | 4   | ł.4.1   | SN    | R Optimization                                   | 141 |

|   | 4   | 1.4.2   | Eff   | iciency Improvement                              | 146 |

|   |     | 4.4.2   | .1    | Counting loss in a TCSPC system                  | 146 |

|   |     | 4.4.2   | .2    | TCSPC system as a queuing model                  | 147 |

| 5 | C   | Conclu  | sion  | and Future Work                                  | 155 |

| 6 | E   | Bibliog | grap  | hy                                               | 159 |

| 7 | L   | ist of  | Pub   | lications                                        | 173 |

| Ω | Г   | FCIIN   | (F D  | F I A THESE DE DOCTORAT                          | 175 |

## **List of Figures**

| Figure 1 - "Point de vue du Gras", 1826. The oldest surviving camera photograph t         | aken by  |

|-------------------------------------------------------------------------------------------|----------|

| Niépce                                                                                    | 2        |

| Figure 2 - "Boulevard du Temple". First ever photograph of a human taken by Dag           | uerre in |

| Paris, 1838                                                                               | 2        |

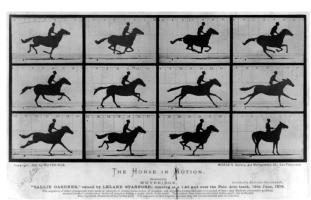

| Figure 3 - 'The horse in motion', first high speed sequence" taken by Muybridge in 18     | 386 3    |

| Figure 4 - Le prince 16 lens receiver                                                     | 3        |

| Figure 5 - Operation principle of a Kinematograph                                         | 4        |

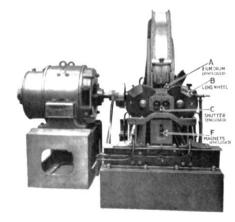

| Figure 6 - Photograph of the Heape and Grylls's Machine for High-speed Photograph         | y [1] 4  |

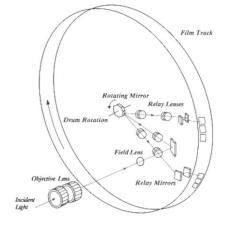

| Figure 7 - Operation principle of a drum camera                                           | 4        |

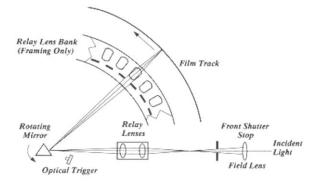

| Figure 8 - Operation principle of a rotating mirror camera                                | 4        |

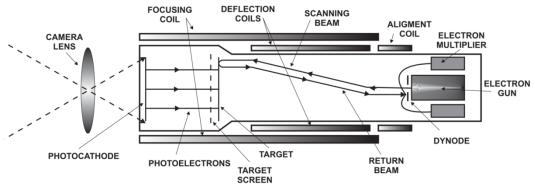

| Figure 9 - Operation principle of an Orthicon tube                                        | 5        |

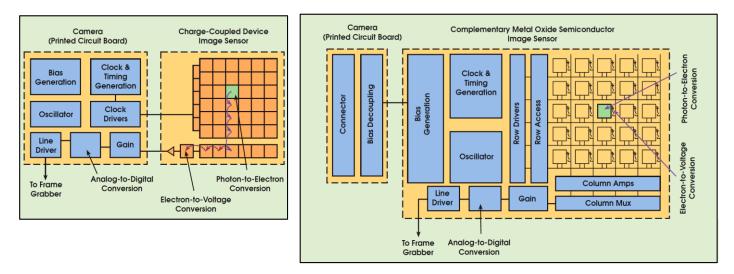

| Figure 10 - Typical architecture of a CMOS camera (left) and a CCD camera (right) [7      | ] 6      |

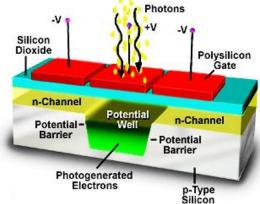

| Figure 11 - Schematic cross section of a buried channel MOS capacitor, the basic CCD      | sensing  |

| element in CCDs [13]                                                                      |          |

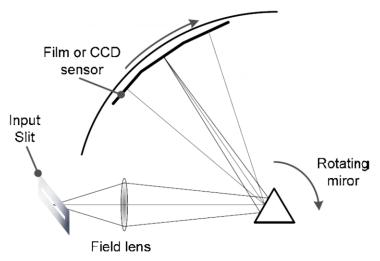

| Figure 12 - Principle of the rotating mirror high speed video camera [15]                 | 9        |

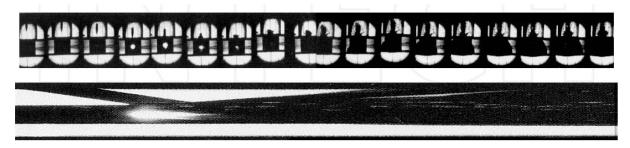

| Figure 13 - Illustration of the streak imaging concept: frame record at $100\ 000$ fps (t | op) and  |

| streak record at $0.53\ mm/\mu s$ (bottom) of a ballistic event acquired by a Cordin Mo   | del 330  |

| camera [5]                                                                                | 10       |

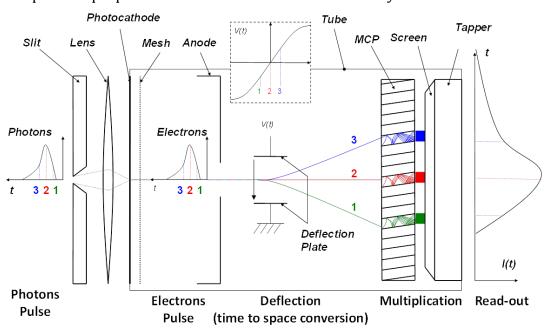

| Figure 14 - Operation principle of a conventional streak camera [15]                      |          |

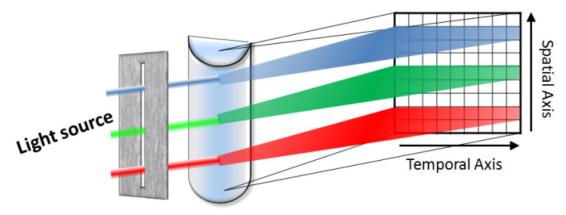

| Figure 15 - Optical setup of a MISC [35]                                                  | 13       |

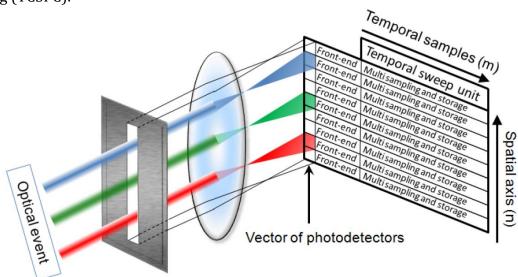

| Figure 16 - Optical setup and architecture of a VISC [40]                                 | 14       |

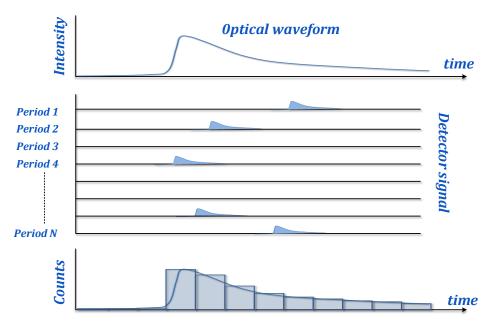

| Figure 17 - TCSPC Measurement Principle                                                   | 15       |

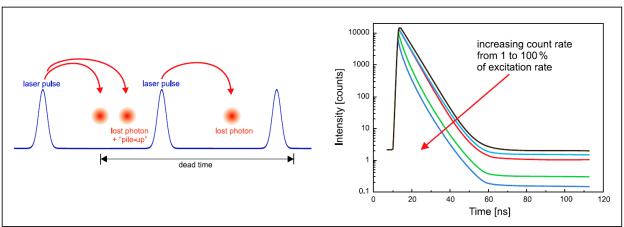

| Figure 18 - Distortion of the TCSPC measurement by pile-up effect [48]                    | 16       |

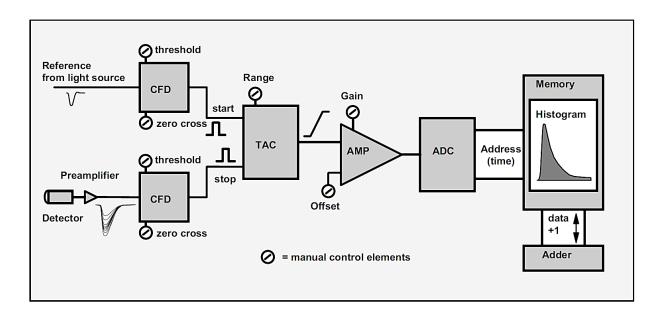

| Figure 19 - Classic TCSPC setup [49]                                                      | 17       |

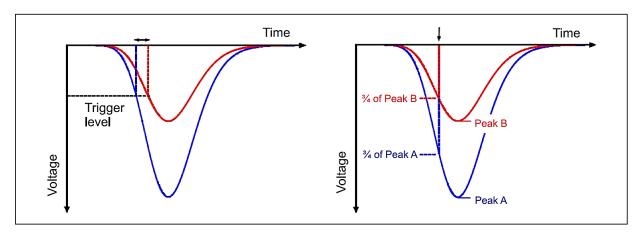

| Figure 20 - Comparison between level trigger (left) and CFD operation (right). [48]       | 18       |

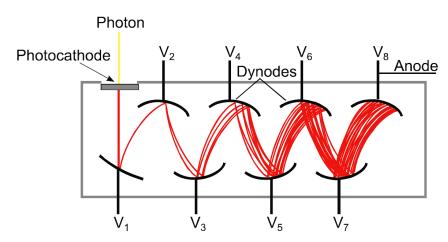

| Figure 21 - Operation principle of a photomultiplier tube [51]                            | 21       |

| Figure 22 - Timing jitter in time resolved measurements due to output pulse an            | nplitude |

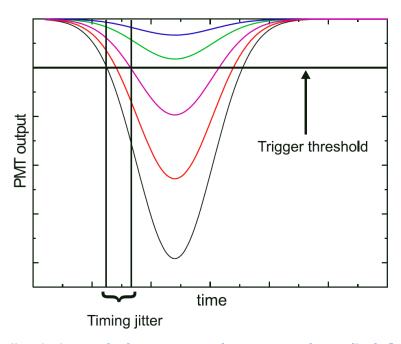

| fluctuation when using a simple level trigger [51]                                        | 22       |

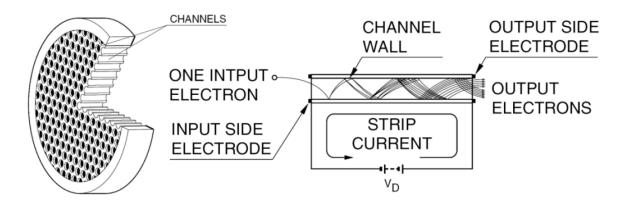

| Figure 23 - MCP schematic and operating mechanism [54]                                    | 23       |

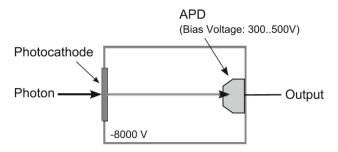

| Figure 24 - Schematic of a hybrid PMT [51]                                                | 24       |

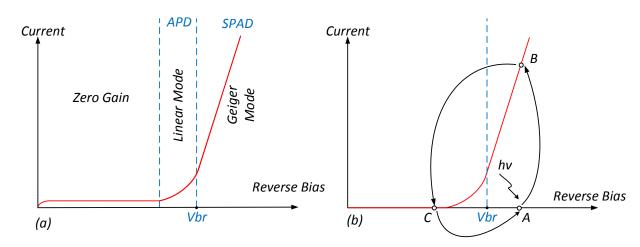

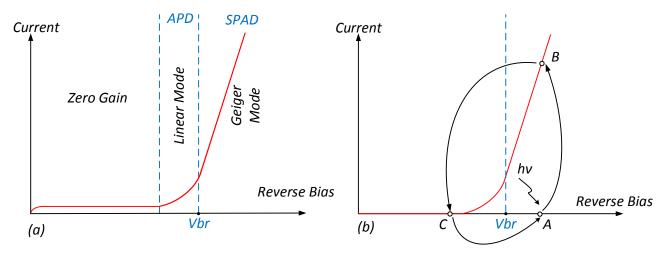

| Figure 25 - The photodiode gaining modes (a) and the SPAD biasing cycle (b)               | 24       |

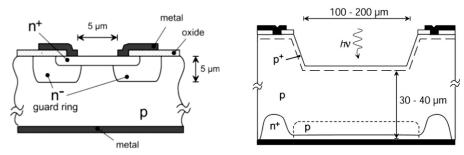

| Figure 26 - Cross section of a thin-junction (left) and a thick-junction (right) SPAD     | devices  |

| [56]                                                                                      | 25       |

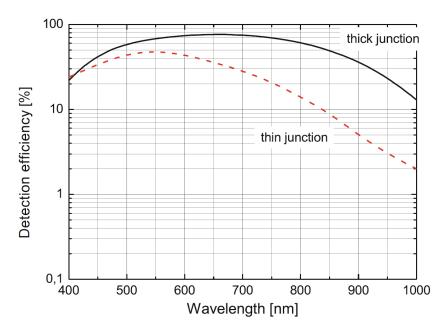

| Figure 27 - Typical detection efficiency of a thick-junction SPAD and a thin-junction     | on SPAD  |

| [51]                                                                                      |          |

| Figure 28 - The photodiode gaining modes (a) and the SPAD biasing cycle (b)               | 31       |

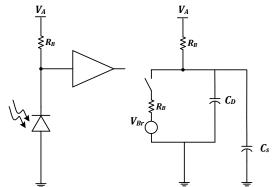

| Figure 29- A basic Passive Quenching Circuit and its equivalent circuit [76]              | 34       |

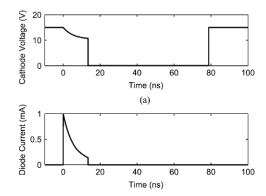

| Figure 30 - (a) Cathode voltage and (b) Diode current waveforms for a SPAD connected                         | to a  |

|--------------------------------------------------------------------------------------------------------------|-------|

| Passive Quenching Circuit [76]                                                                               |       |

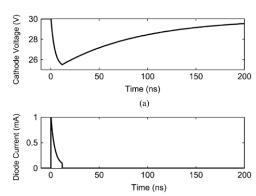

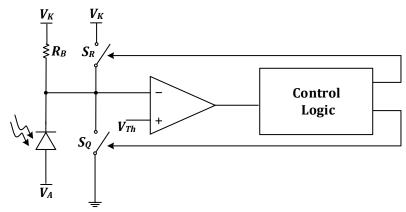

| Figure 31 - Basic Active Quenching Circuit [76]                                                              | 36    |

| Figure 32 - Cathode voltage (a) and diode current waveforms (b) for a SPAD connected to                      | o an  |

| Active Quenching Circuit [76]                                                                                | 36    |

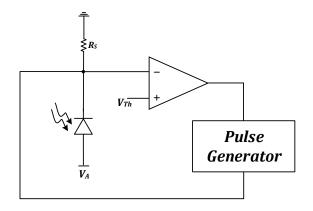

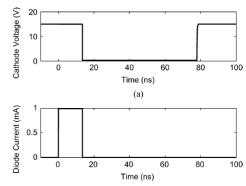

| Figure 33 - Basic diagram of a mixed active-passive quenching circuit [76]                                   | 37    |

| Figure 34 - (a) Cathode voltage and (b) Diode current wave forms for a SPAD connected                        | to a  |

| Mixed Active-Passive Quenching Circuit [76]                                                                  | 37    |

| Figure 35 - Cross section of the first planar SPAD structure devised by Haitz [56]                           | 38    |

| Figure 36 - Schematic cross section of the double epitaxial SPAD device structure [56]                       | 38    |

| Figure 37 - Schematic cross section of the first CMOS SPAD devised by Rochas [82]                            | 39    |

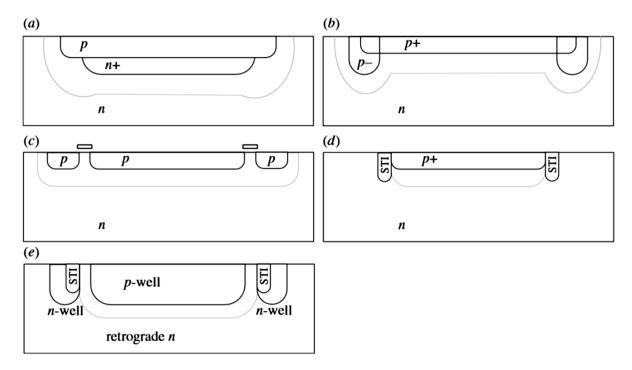

| Figure 38 - Prominent SPAD structures for premature edge breakdown prevention [86] .                         | 40    |

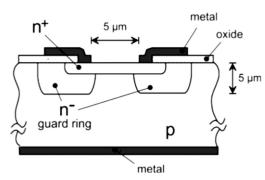

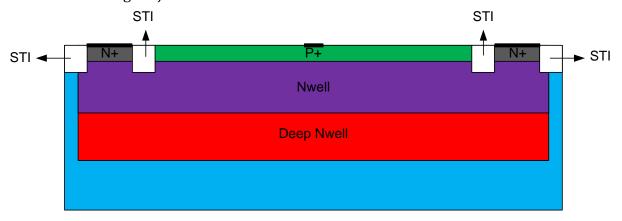

| Figure 39 - Cross-section of the P+/NWELL structure with STI guard ring                                      | 41    |

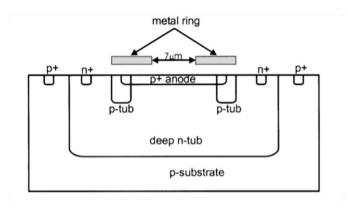

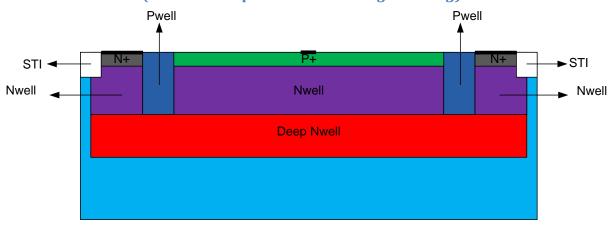

| $Figure\ 40\ -\ Cross-section\ of\ the\ P+/NWELL\ Deep\ Nwell\ structure\ with\ Pwell\ guard\ ring$          | 42    |

| $Figure\ 41\ -\ Cross-section\ of\ the\ P+/NWELL\ Deep\ Nwell\ structure\ with\ Pwellguard\ ring$            | 42    |

| Figure 43 - Cross-section of the P+/PWELL Deep Nwell structure with no guard ring $\dots$                    | 43    |

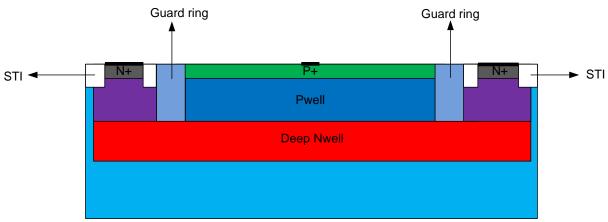

| Figure 42 - Cross-section of the P+/PWELL Deep Nwell structure with STI guard ring                           | 43    |

| Figure 44 - Cross-section of the P+/NWELL Deep Nwell structure with a double Pwell-                          | -STI  |

| guard ring                                                                                                   | 44    |

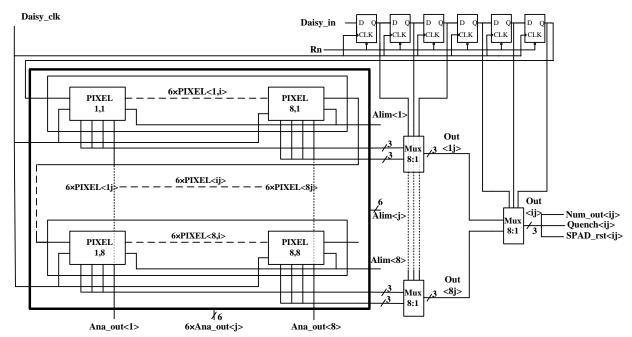

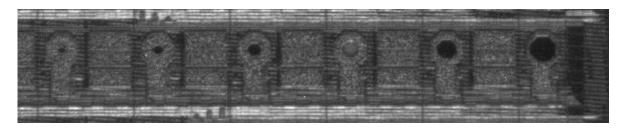

| Figure 45 - Illustration of the proposed $8x8$ pixels array along with the daisy_chain regi                  | ster  |

| and the multiplexing system.                                                                                 | 45    |

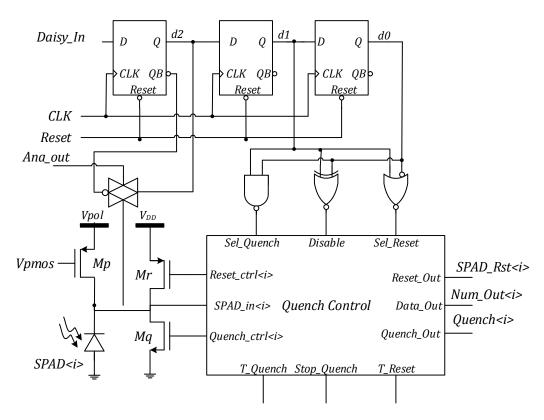

| Figure 46 - Description of one pixel of the SPAD array: the SPAD is controlled by a versa                    | atile |

| quenching circuit configurable via the daisy chain                                                           | 46    |

| Figure 47 - Detail of the versatile quenching control.                                                       | 48    |

| Figure 48 - I-V measurement results of the demonstrated SPAD structures                                      | 49    |

| Figure 49 - Spontaneous emission phenomenon                                                                  | 50    |

| Figure $50$ - Electroluminescence light emission test results for SPAD structures A (a), B (b)               | o), C |

| (c), D (d), E (e) and F (f)                                                                                  | 51    |

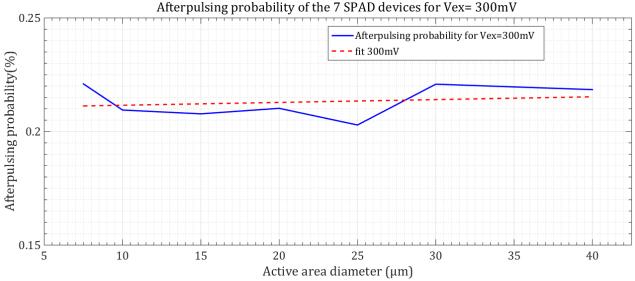

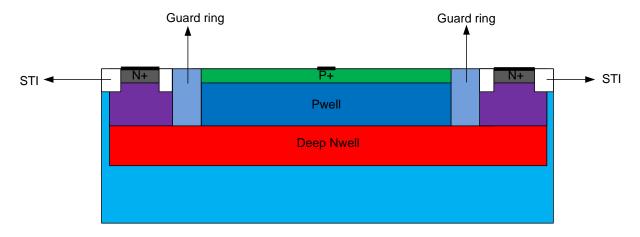

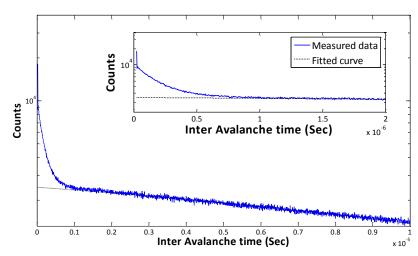

| Figure $51$ - Afterpulsing measurement results for a dead time of $30\ ns$ and an excess bia                 |       |

| 300 mV                                                                                                       |       |

| Figure $52$ - Afterpulsing probability measurement results for the 7 devices with an exception $\frac{1}{2}$ | cess  |

| bias of 300 mV                                                                                               | 52    |

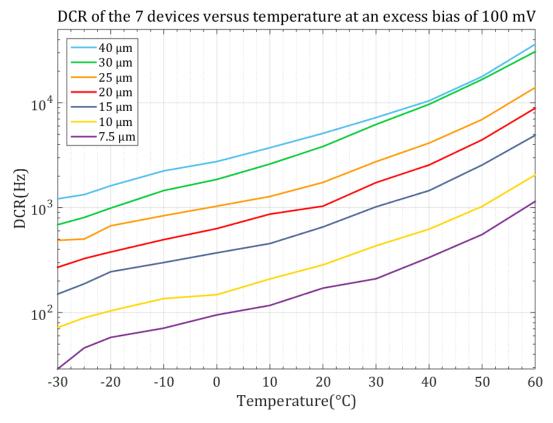

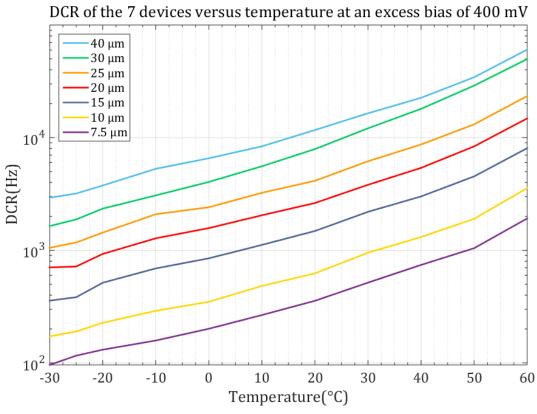

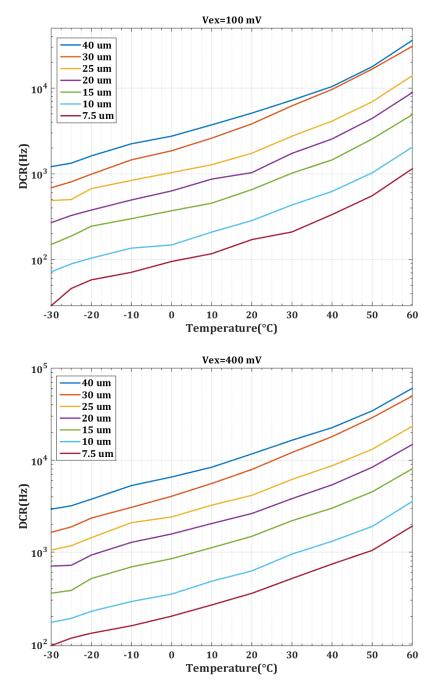

| Figure 53 - DCR of the 7 devices versus temperature at an excess bias of 100 mV and 400                      |       |

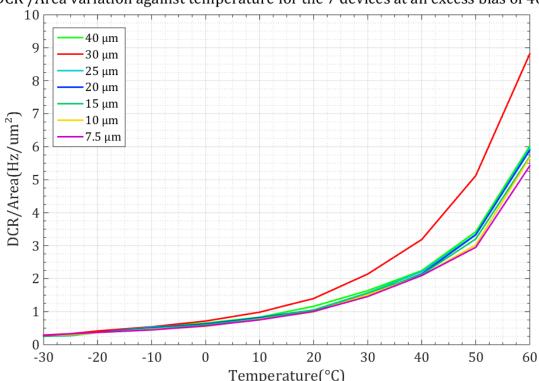

| Figure 54 - DCR /Area variation against temperature for the 7 devices at an excess bia                       |       |

| 400 mV                                                                                                       |       |

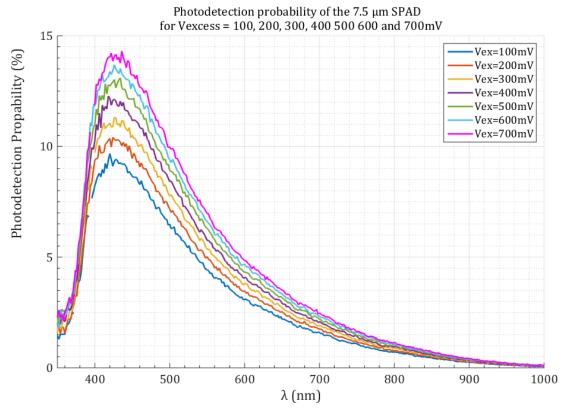

| Figure 55 - Photodetection probability of the 7.5 µm SPAD for various excess bias                            |       |

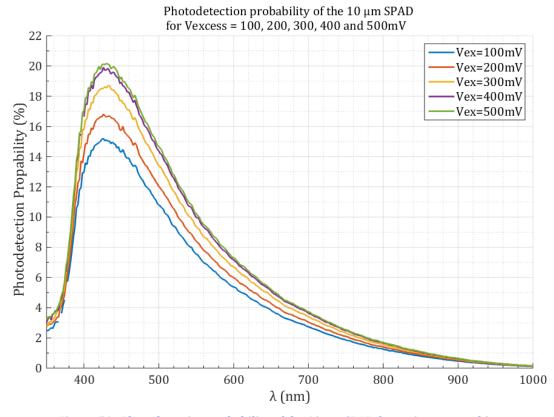

| Figure 56 - Photodetection probability of the 10 μm SPAD for various excess bias                             |       |

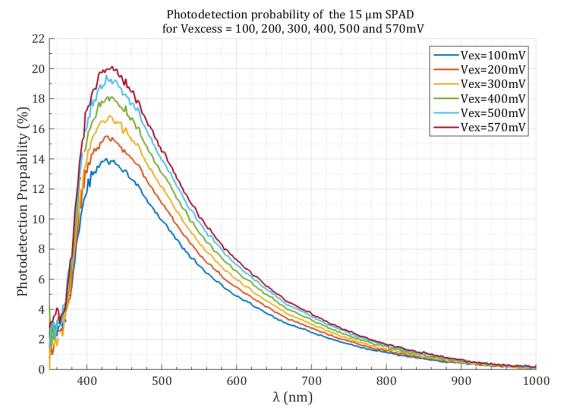

| Figure 57 - Photodetection probability of the 15 μm SPAD for various excess bias                             |       |

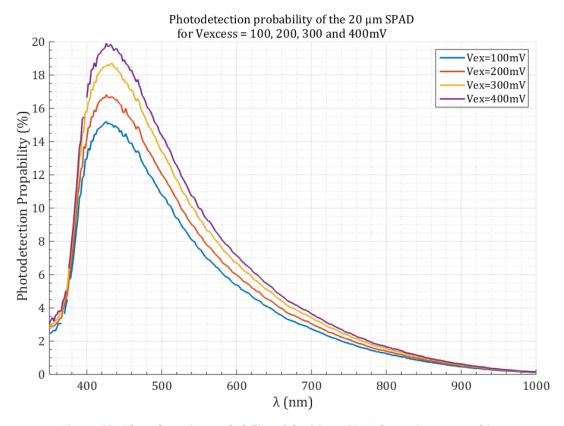

| Figure 58 - Photodetection probability of the 20 um SPAD for various excess bias                             |       |

|                                                                                                              |       |

| Figure 59 - Photodetection probability of the 25 $\mu m$ SPAD for various excess bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 60 - Photodetection probability of the 30 $\mu m$ SPAD for various excess bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57      |

| Figure 61 - Photodetection probability of the 40 $\mu m$ SPAD for various excess bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58      |

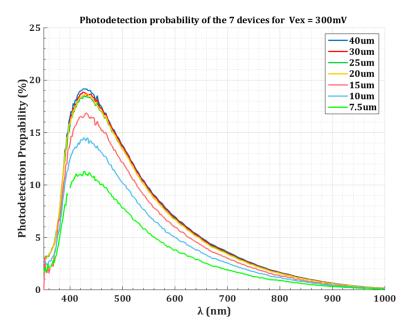

| Figure 62 - Photodetection probability of the 7 SPADs for an excess bias of 300 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58      |

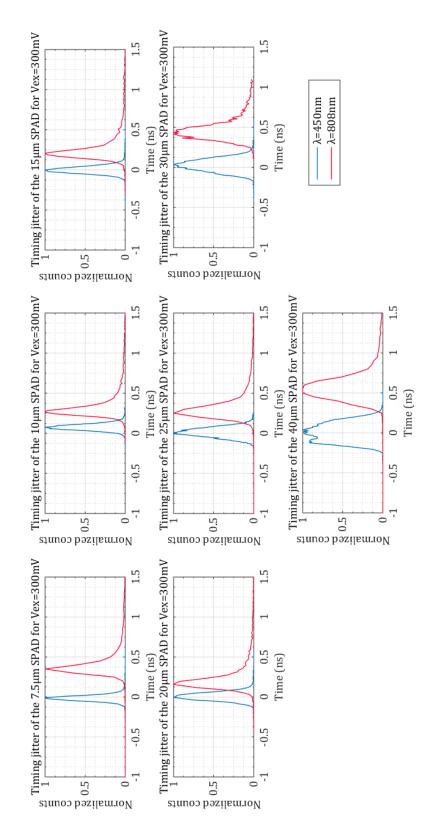

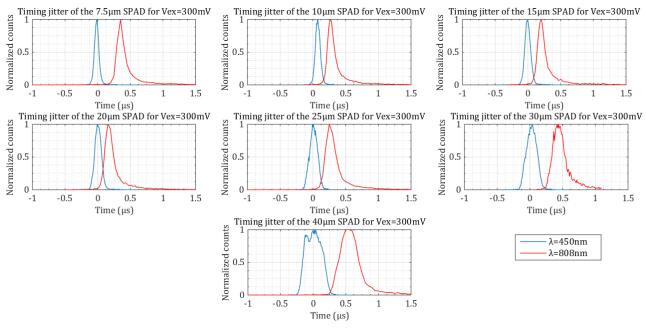

| Figure 63 - Normalized timing response measurement results using a 450 nm and an 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 08 nm   |

| laser with an excess bias of 300mV for the 7 SPAD diameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60      |

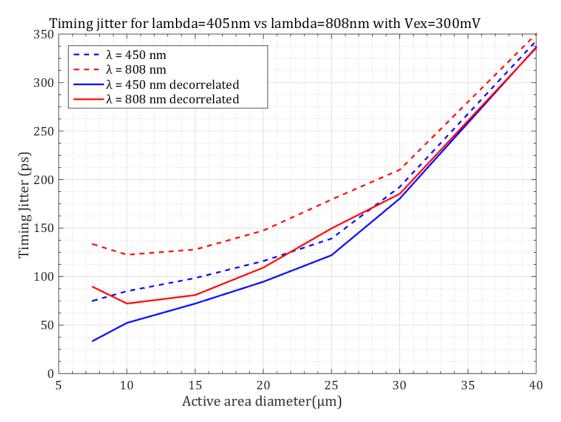

| Figure 64 - Timing jitter results for $\lambda$ = 450 nm and $\lambda$ = 808 nm at an excess bias of 300 nm at an excess bias | 00 mV   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61      |

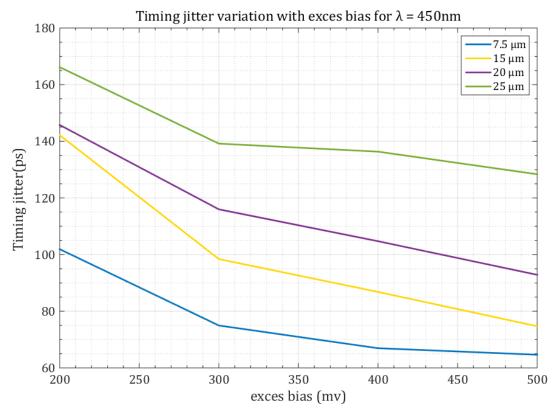

| Figure 65 - Timing jitter variation of the 7.5 $\mu m$ SPADs as a function of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| bias for $\lambda$ = 405 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61      |

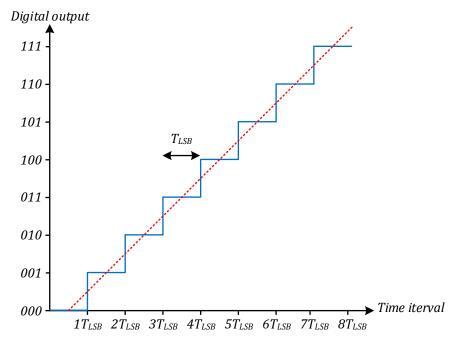

| Figure 66 - ideal input-output characteristic of a TDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64      |

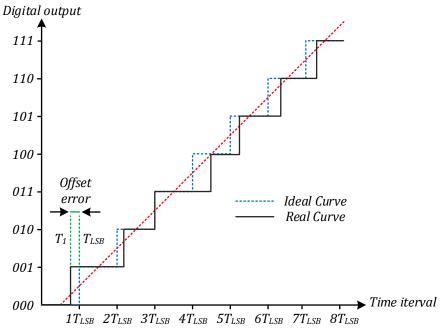

| Figure 67 - Input-output characteristic with offset error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65      |

| Figure 68 - Input-output characteristic of a TDC with gain error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

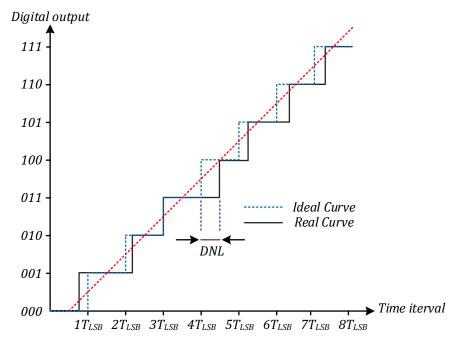

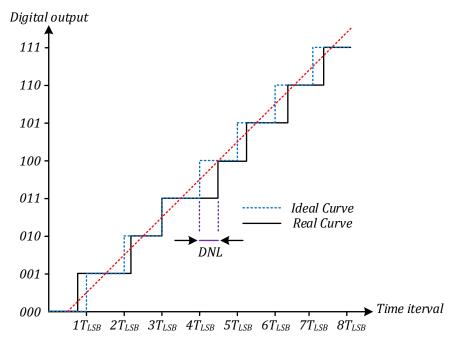

| Figure 69 - Input-output characteristic of a TDC with DNL error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 67      |

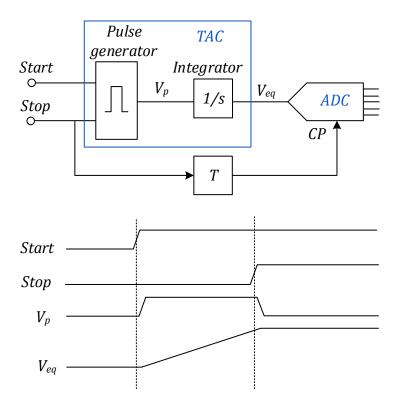

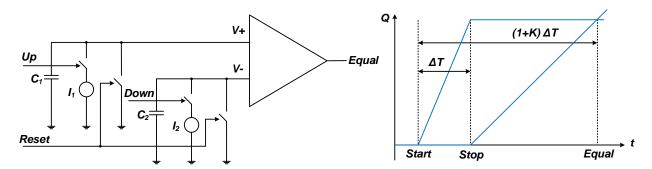

| Figure 70 - Block and signal diagram of a time to analog converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69      |

| Figure 71 - basic time stretcher realization and the corresponding timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70      |

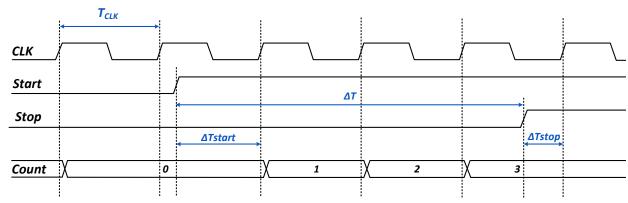

| Figure 72 - operation principle of a counter based TDC [104]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71      |

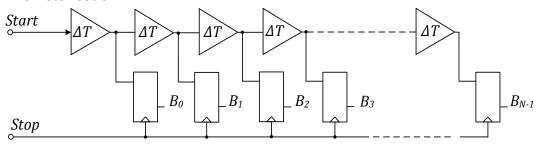

| $Figure \ 73 - Implementation \ of \ a \ Delay \ line \ based \ TDC \ using \ a \ buffer \ as \ a \ delay \ elementation \ of \ a \ Delay \ elementation \ elementation \ of \ a \ Delay \ elementation \ elementation \ of \ a \ Delay \ elementation \ of \ $                                                                                                                                                                                                                                                                                                             | t72     |

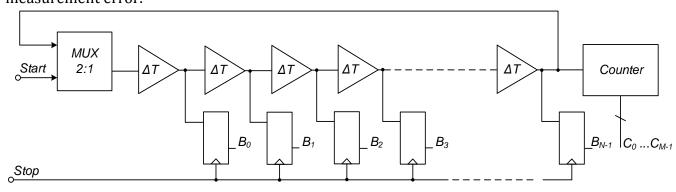

| Figure 74 - schematic representation of looped TDC architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72      |

| Figure 75 - Implementation of a DLL based TDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73      |

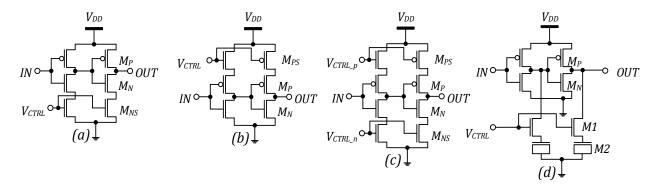

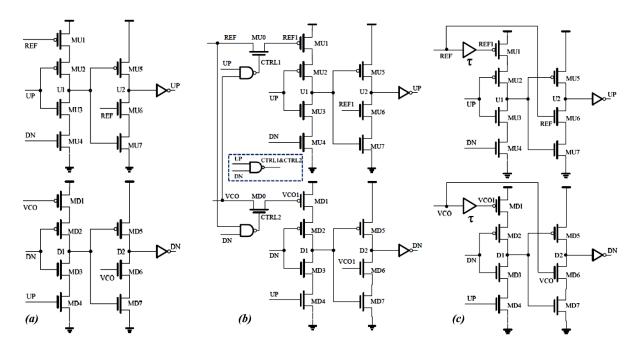

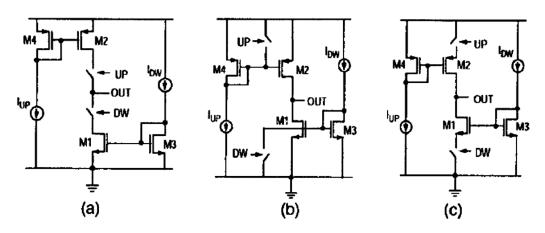

| Figure $76$ - The $3$ types of current starved inverters used as tunable delay elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | in the  |

| DLL based TDC: N-side (a), P-side (b), and both (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

| Figure 77 - Implementation of a parallel delay elements based TDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74      |

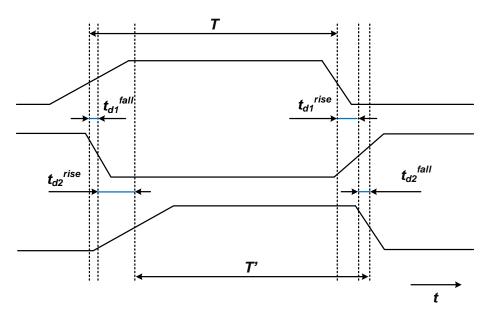

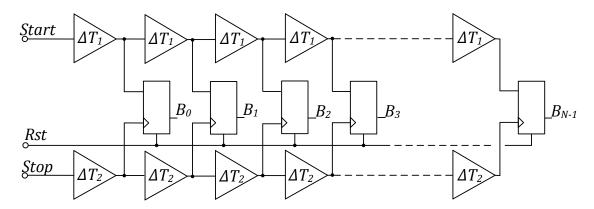

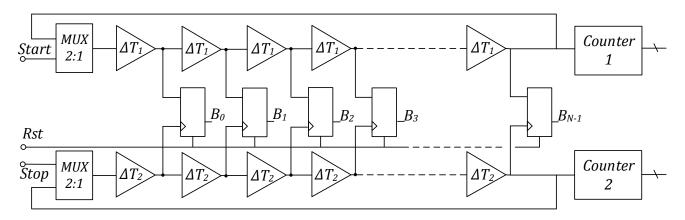

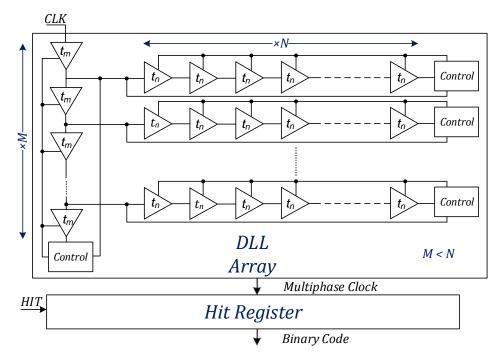

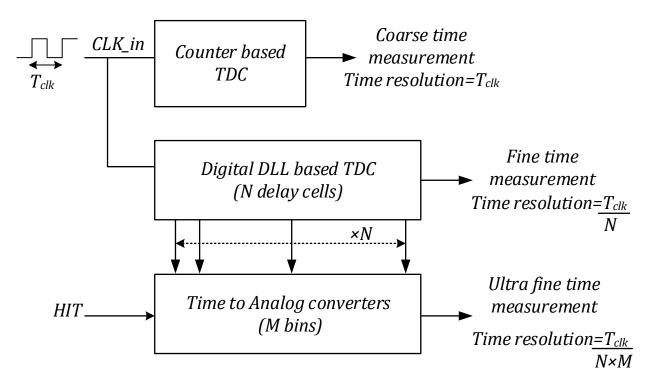

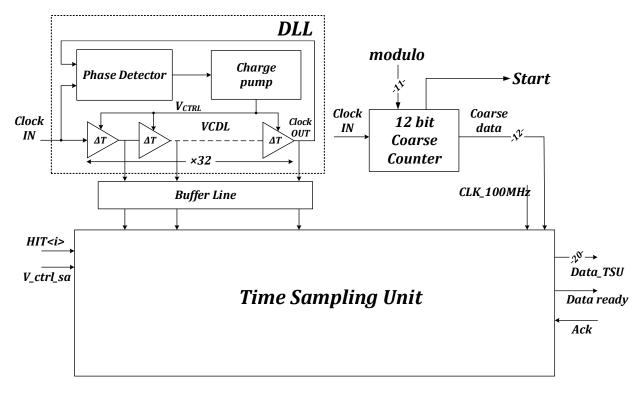

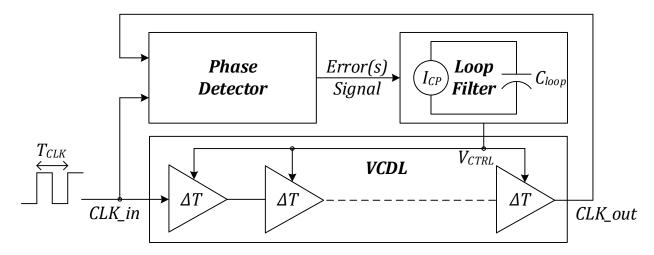

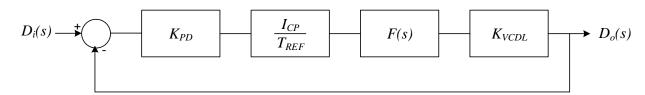

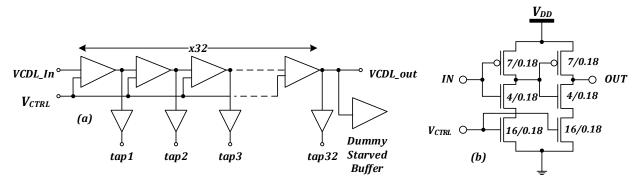

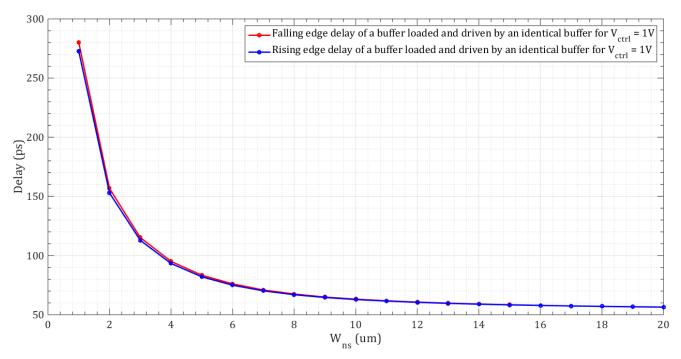

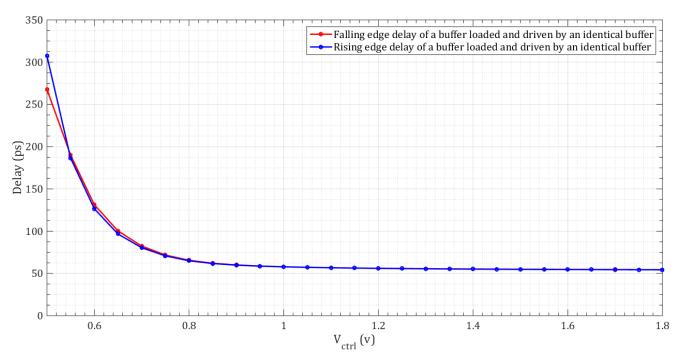

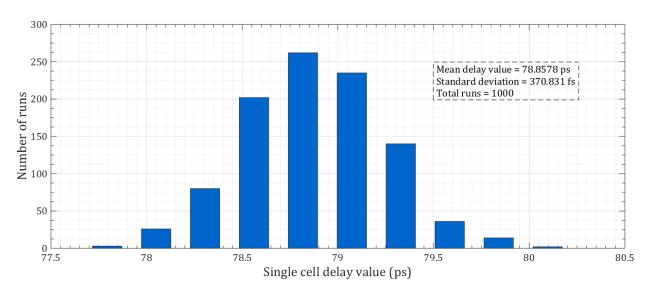

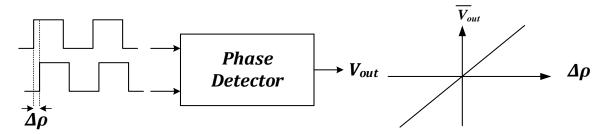

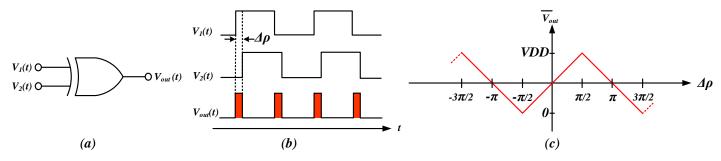

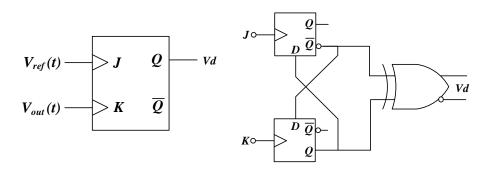

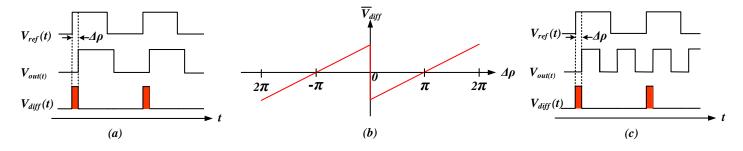

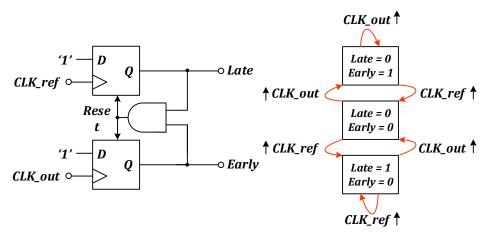

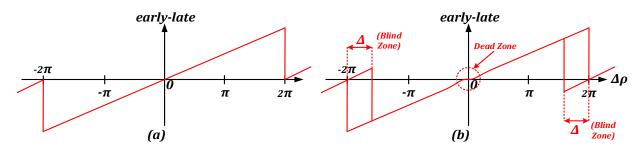

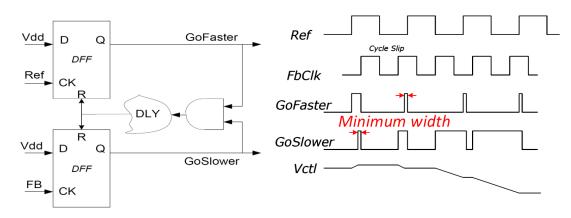

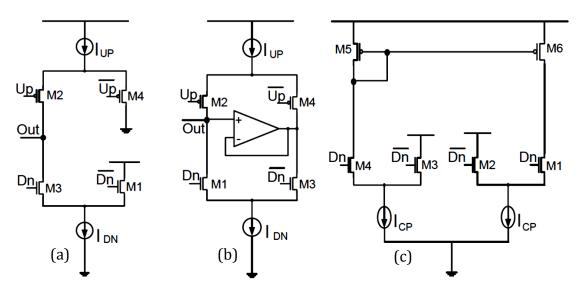

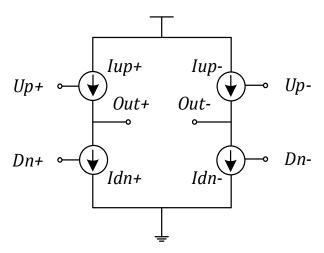

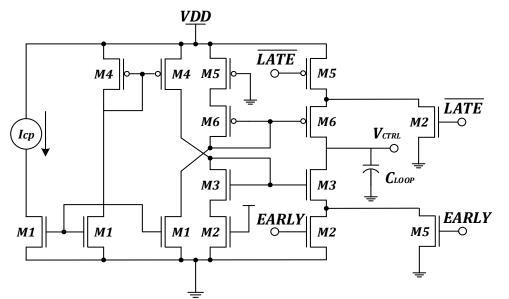

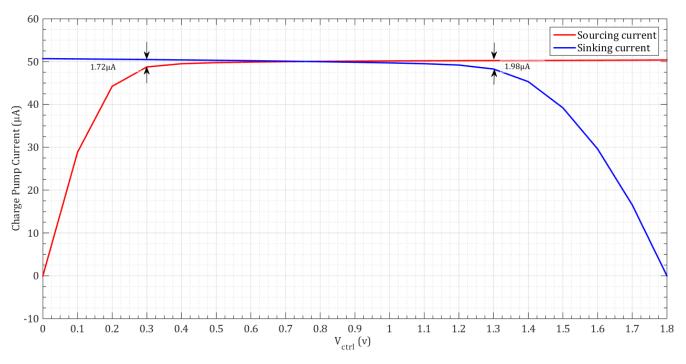

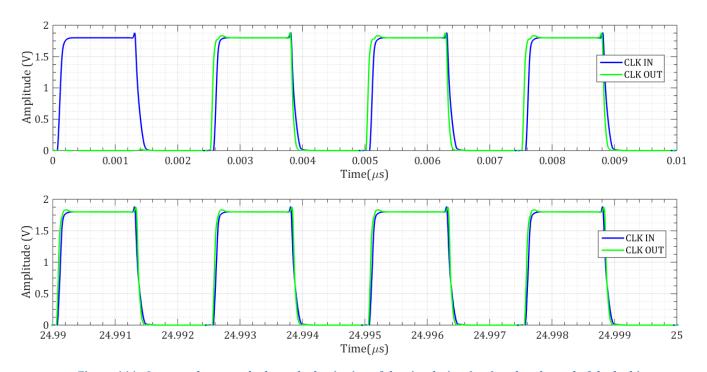

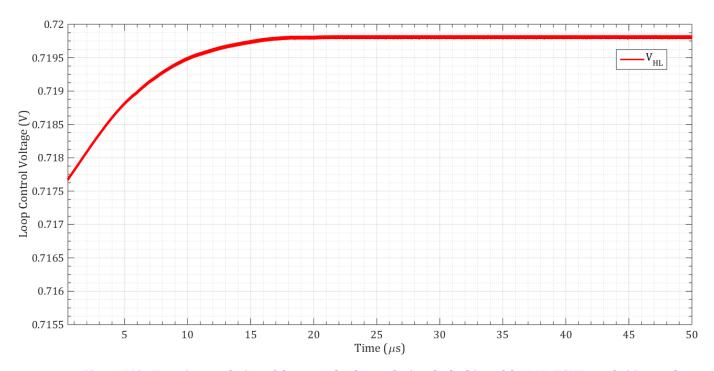

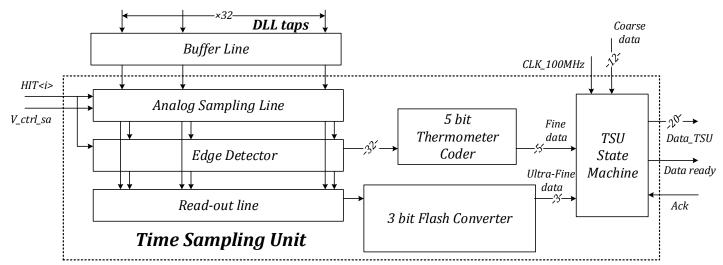

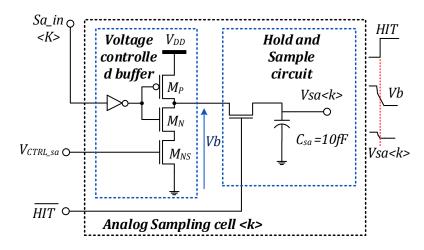

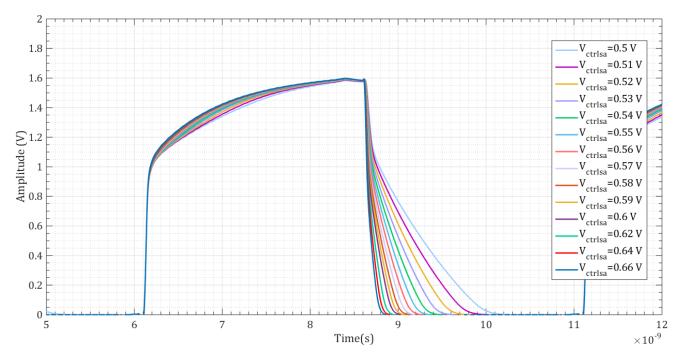

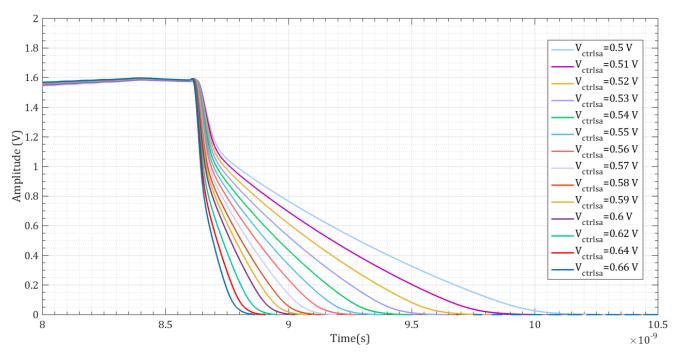

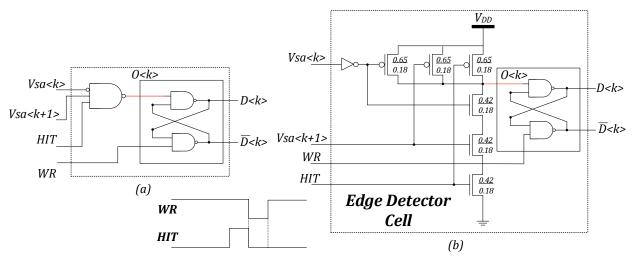

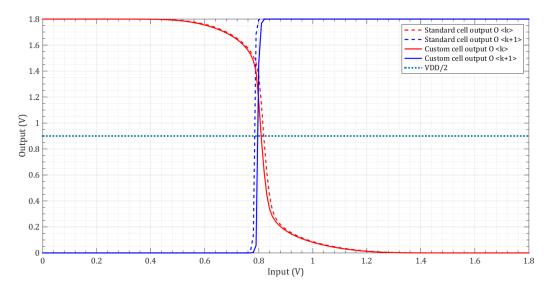

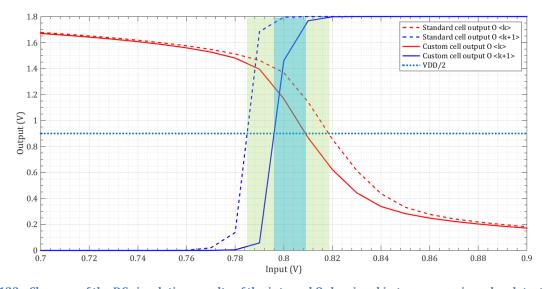

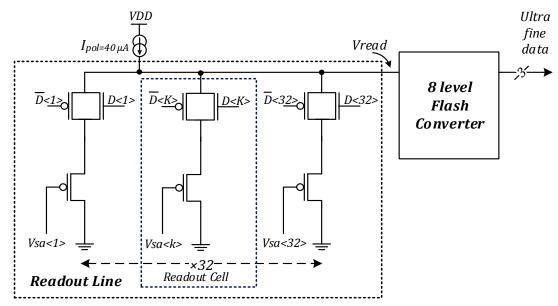

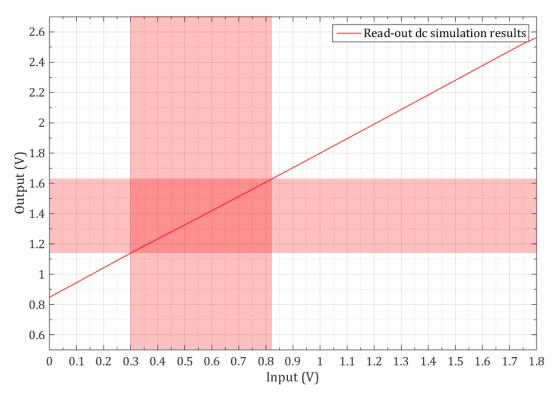

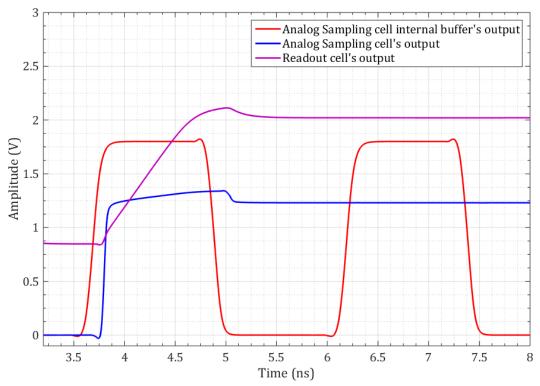

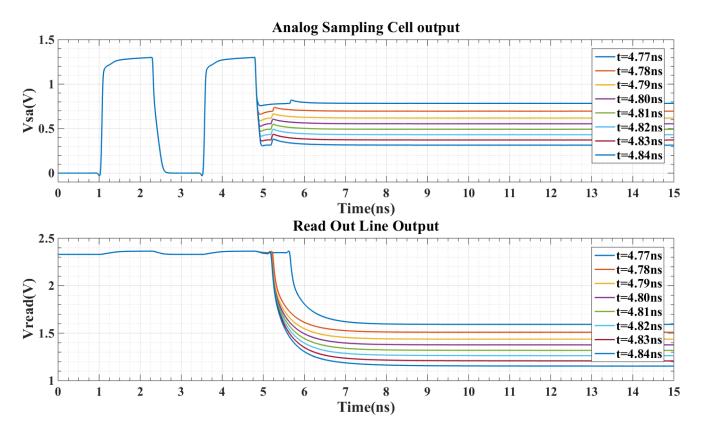

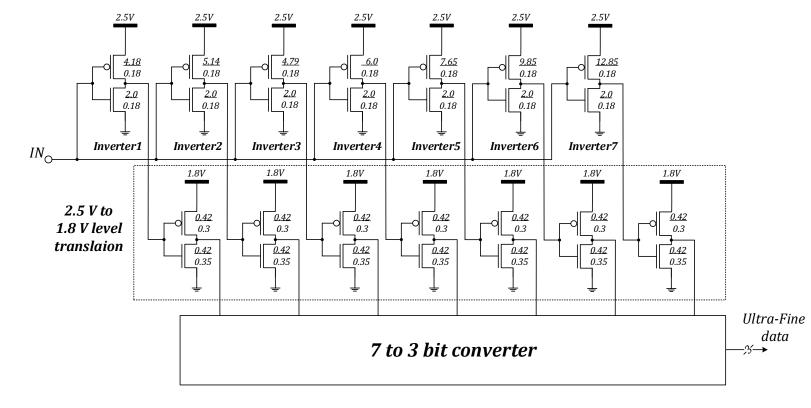

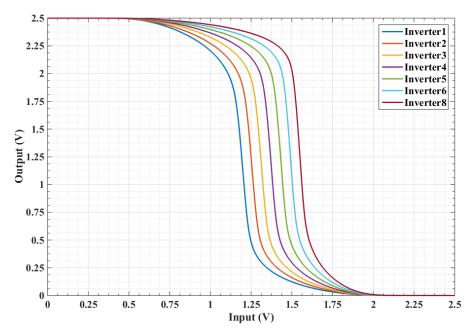

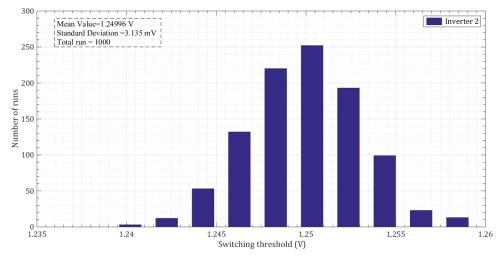

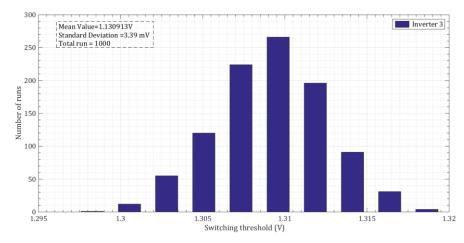

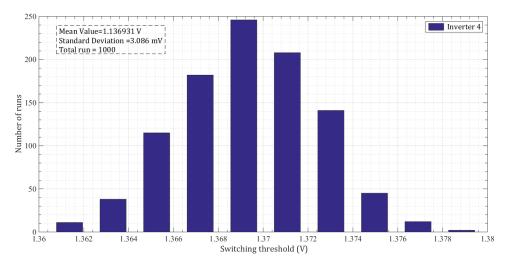

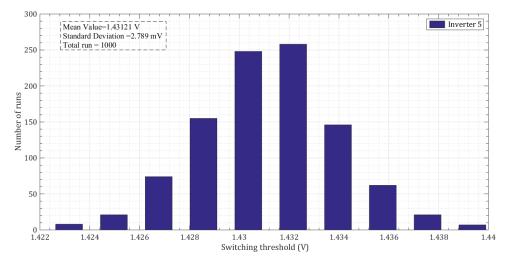

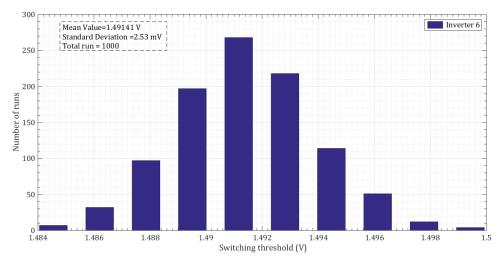

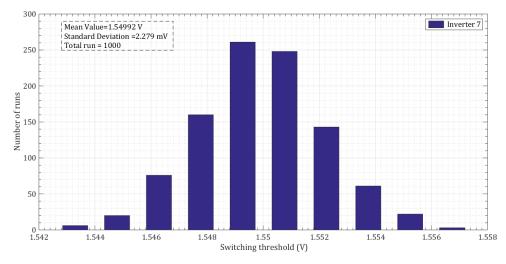

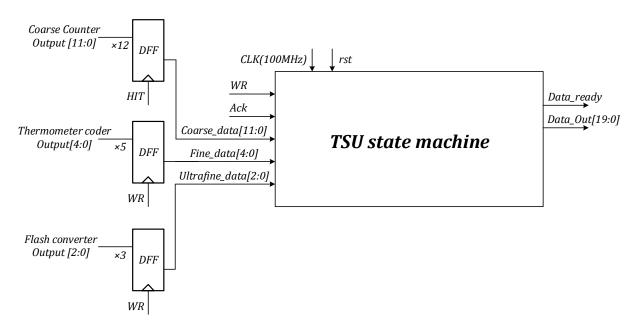

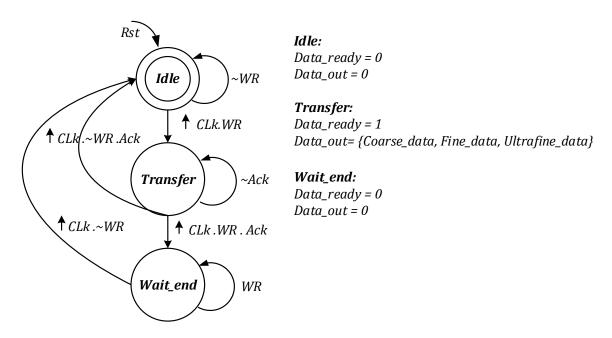

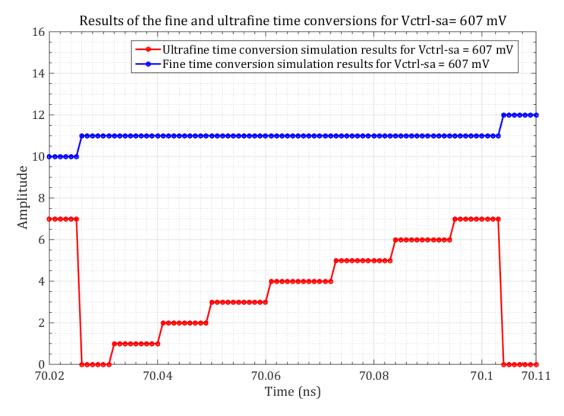

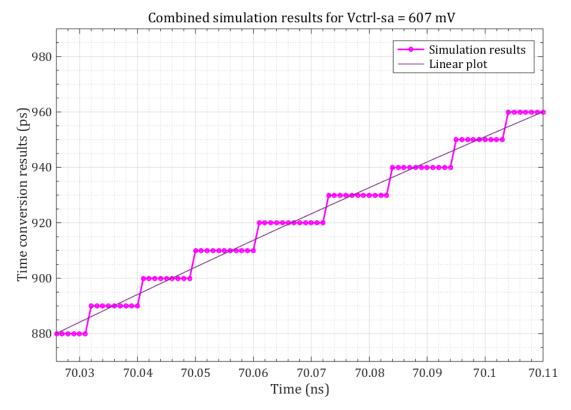

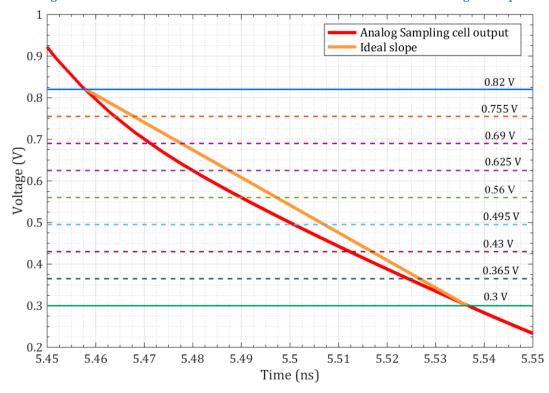

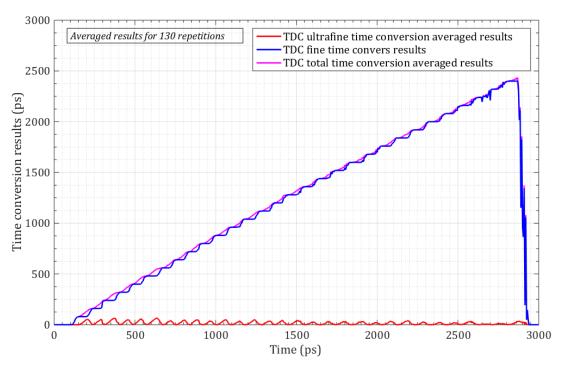

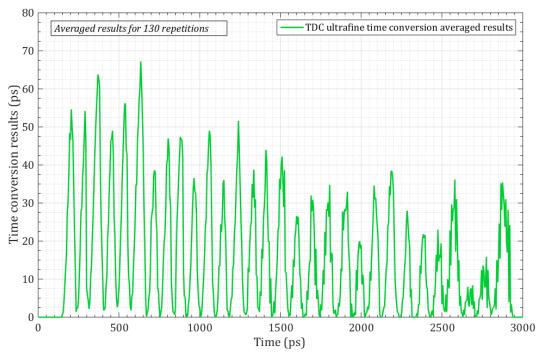

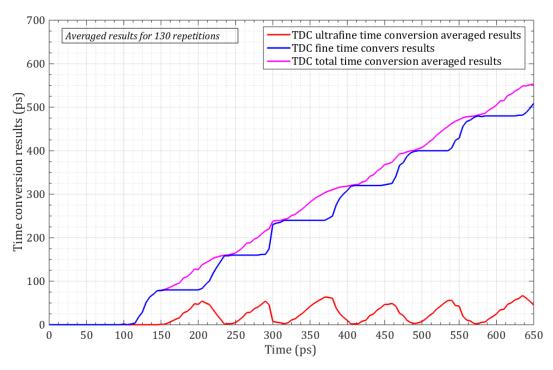

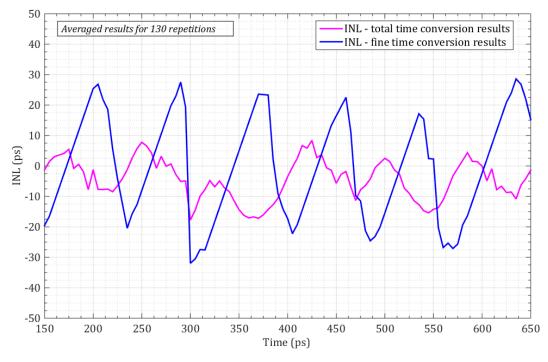

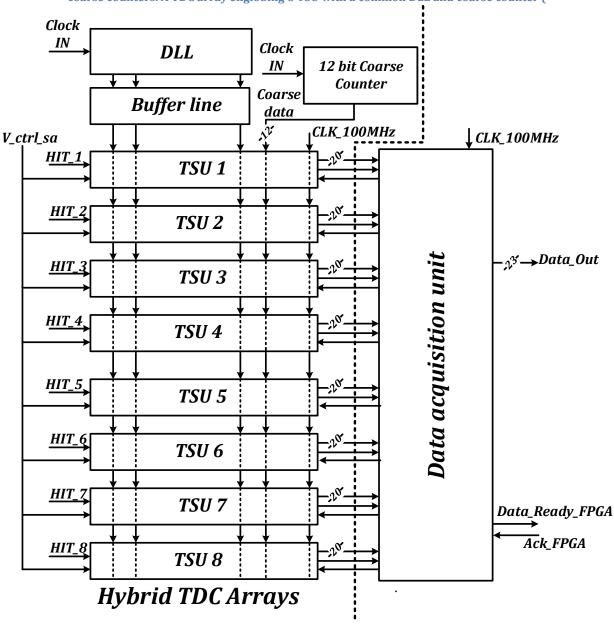

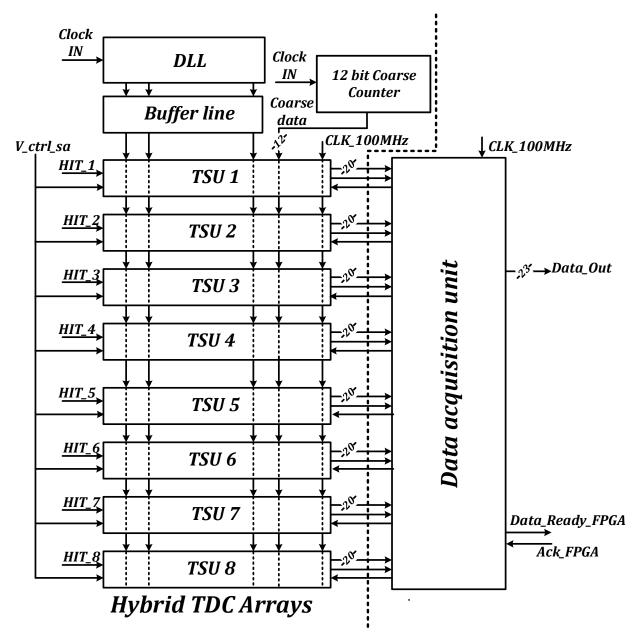

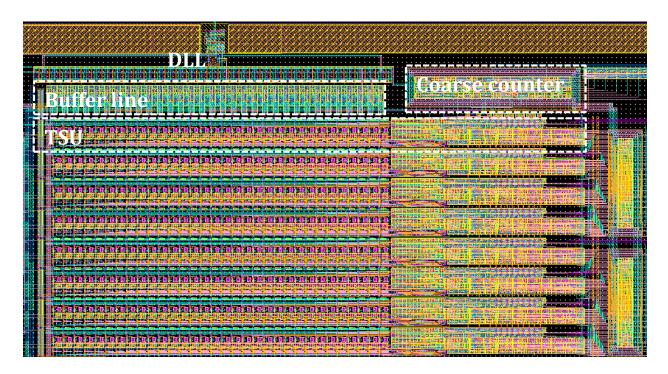

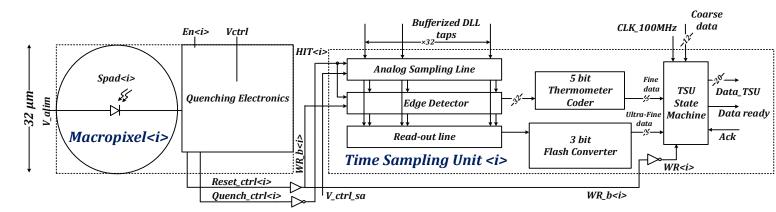

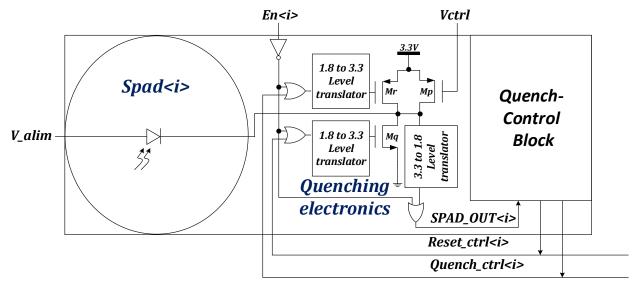

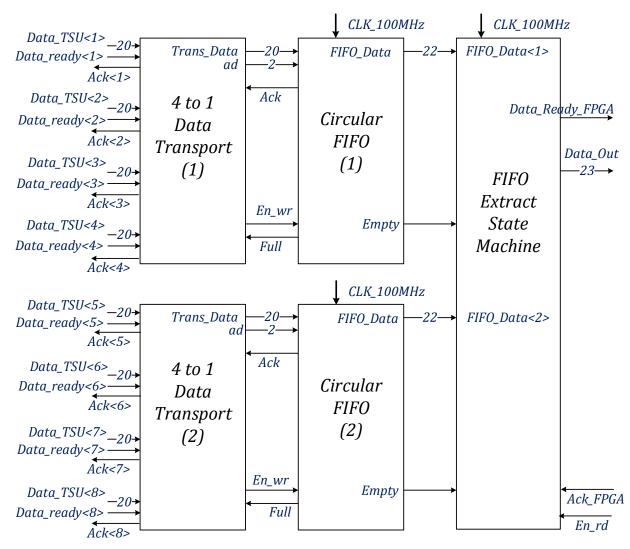

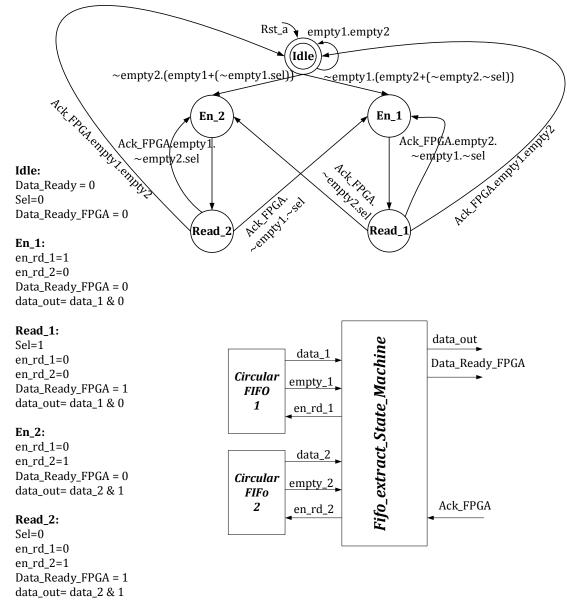

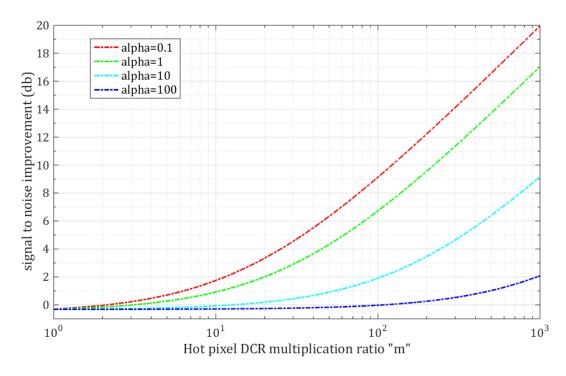

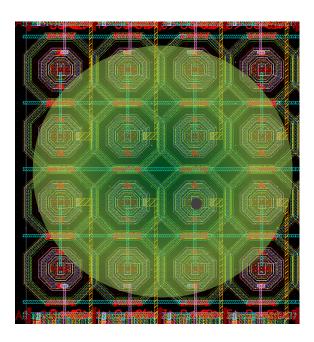

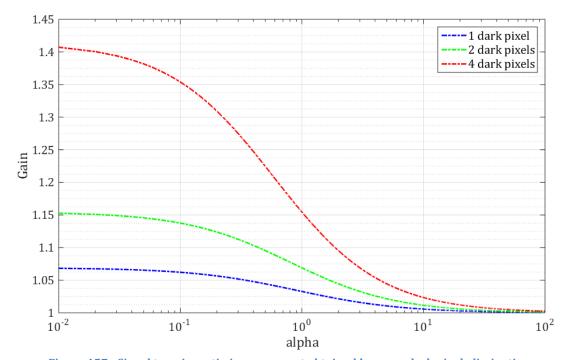

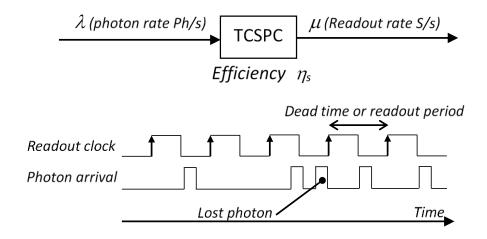

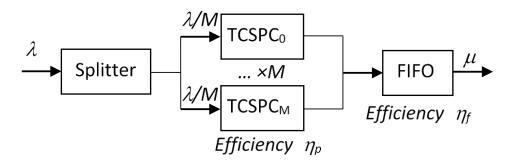

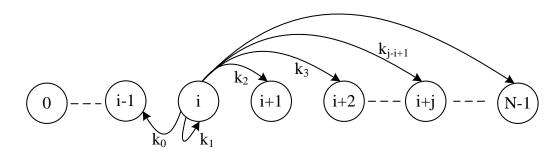

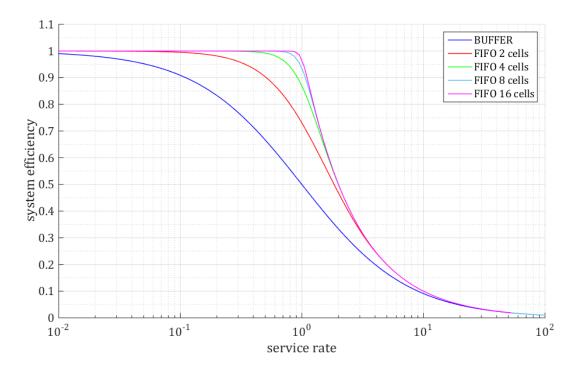

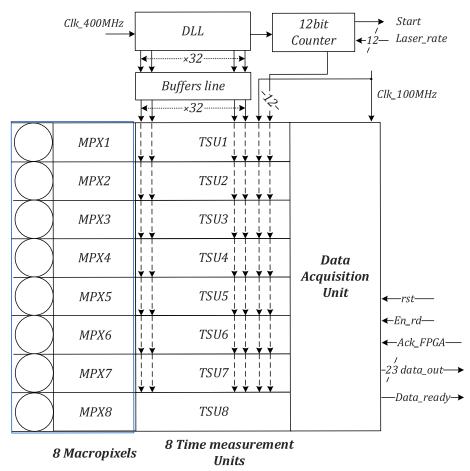

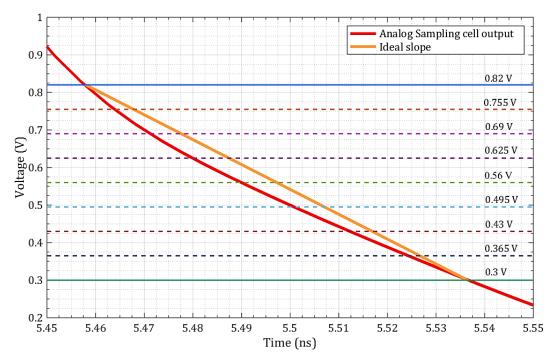

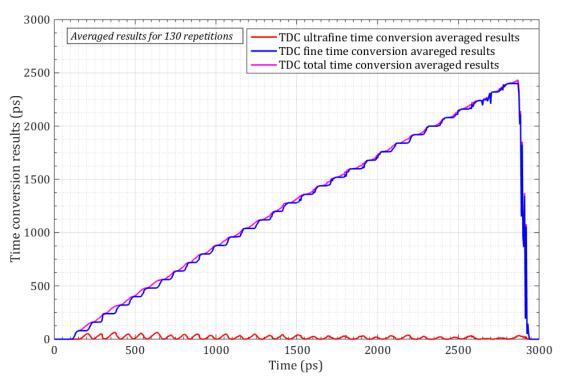

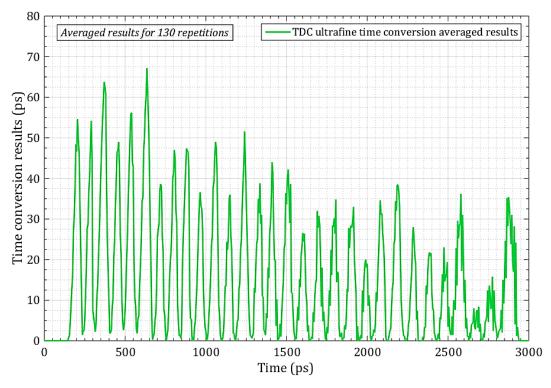

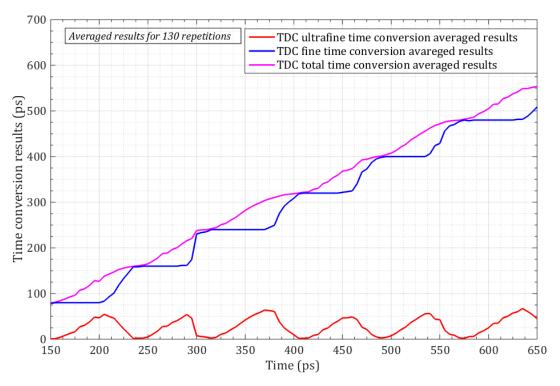

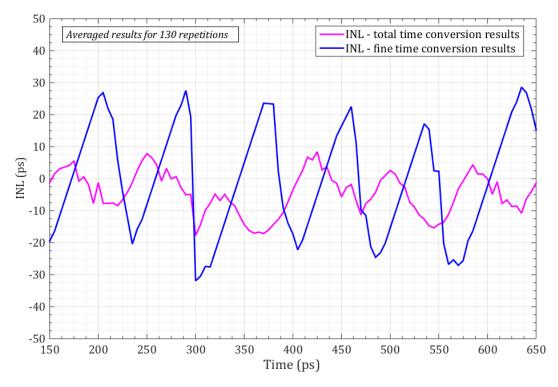

| Figure 78 - Cut-out of a pulse shrinking TDC line showing the pulse width reduction $\frac{1}{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | as the  |