## Modélisation l'immunité électromagnétique des composants en vue de la gestion de l'obsolescence des systèmes et modules électroniques.

Mohamed Amellal

#### ▶ To cite this version:

Mohamed Amellal. Modélisation l'immunité électromagnétique des composants en vue de la gestion de l'obsolescence des systèmes et modules électroniques.. Electronique. INSA de Rennes; Université Sidi Mohamed ben Abdellah (Fès, Maroc), 2015. Français. NNT: 2015ISAR0037. tel-01333563

## HAL Id: tel-01333563 https://theses.hal.science/tel-01333563

Submitted on 17 Jun 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Modélisation l'immunité électromagnétique des composants en vue de la gestion de l'obsolescence des systèmes et modules électroniques.

#### M. Mohamed Ramdani

Enseignant Chercheur HDR - ESEO Angers / Invité

M. Jean-Luc Levant

Expert CEM - Atmel Nantes / Invité

Thèse soutenue le 14.12.2015 devant le jury composé de :

#### M. Moulhime El Bakkali

Professeur - USMBA de Fès / Président du jury

M. Bélahcène Mazari

Docteur HDR, Groupe CESI / Rapporteur

Mme. Fatima ERRAHIMI

Professeur – USMBA de Fès / Rapporteur

M. Abdelhak Ziyyat

Professeur – Faculté des Sciences de Oujda / Rapporteur

M. Saad Bennani Doss

Professeur - USMBA de Fès / Examinateur

M. Richard Perdriau

Enseignant Chercheur HDR - ESEO Angers / Co-encadrant de thèse

M. M'hamed Drissi

Professeur des universités-directeur de l'INSA de Rennes / Co-directeur de thèse

M. Ali Ahaitouf

Professeur des universités - LERSI et FST de Fès / Co-directeur de thèse

# Modélisation de l'immunité électromagnétique des composants en vue de la gestion de l'obsolescence des systèmes et modules électroniques.

#### Mohamed AMELLAL

## En partenariat avec

## Remerciements

"La reconnaissance silencieuse ne sert à personne." - Gladys Bronwyn Stern

Les remerciements dans une thèse semblent souvent être une formalité. Pourtant, comment passer devant une telle occasion pour exprimer son remerciement, sa gratitude et son respect à ces gens sans lesquels cette thèse ne serait qu'une simple aventure scientifique.

Ma première pensée est pour toutes ces personnes qui m'ont posé cette question : "Alors cette thèse, elle avance ?... La soutenance c'est quand ?...", cette question aussi simple qu'elle soit n'a pas cessé de me motiver et me faire avancer. Je vous dis aujourd'hui merci.

Toute thèse a une histoire, ou plutôt un déclencheur (une personne, une rencontre, un sujet). A ce titre, je tiens à remercier plusieurs personnes. Parmi ces personnes, mon encadrant Mohamed Ramdani, qui au fil des années est devenu un ami. Qu'il trouve ici toute l'expression de ma reconnaissance pour son soutien et ses conseils. Merci pour son amitié, son soutien et surtout pour sa présence pendant les moments difficiles mais aussi pendant les moments de joie.

Je remercie aussi une autre personne, mon directeur de thèse Ali Ahaitouf, qui sans lui je n'aurais jamais pu faire cette thèse. Je le remercie de m'avoir poussé dans cette direction et d'avoir cru en mes capacités depuis mes années d'université à la FST.

Merci à Richard Perdriau mon co-encadrant de thèse et mon allié face aux contraintes CEM spécifiques aux mémoires et aux micro-contrôleurs. Je me dois de reconnaître la chance que j'ai eue d'avoir près de moi une personne comme lui. Merci pour ses conseils, ses discussions et sa disponibilité.

Merci à M'hamed Drissi pour avoir accepté de diriger cette thèse et pour m'avoir offert un cadre de travail souple et adapté à la co-tutelle.

Il va être difficile de remercier toutes ces personnes qui ont croisé le chemin de ma thèse. Mais j'ai une pensée particulière à quelques partenaires du laboratoire ESEO-EMC (Jean-Luc Levant) et quelques membres du groupe de travail du projet SEISME (Etienne Sicard, Frédéric Lafon) pour leurs idées, intérêts et leurs temps.

Merci à mes collègues d'équipe de recherche, Ala Ayed et Sjoerd Op't Land pour leur présence et aide au quotidien sur tant de petits sujets.

Je voudrais remercier également les personnes qui ont accepté de faire partie de mon Jury de thèse malgré toutes les contraintes et qui ont eu la lourde tâche d'évaluer et critiquer mon travail. Merci à Mme. Fatima Errahimi, Mr. Abdelhak Ziyyat et Mr. Bélahcène Mazari d'avoir accepté d'être rapporteurs, ainsi qu'à Mr. Jean-Luc levant et Mr. Saad Bennani Doss, d'être examinateurs. Je remercie également Mr. Moulhime El Bakkali d'avoir accepter d'être président du jury malgré ses contraintes et son planning chargé.

Je remercie tous mes proches et tous ceux qui m'ont soutenu, aidé dans la vie quotidienne et réussi à me remotiver pour relever la tête. Merci à mes parents, mes sœurs et ma belle famille pour leur soutien inépuisable. Aujourd'hui, c'est une consécration pour nous tous. J'espère avoir été à la hauteur de leurs espérances et qu'ils seront fiers que leurs fils, petit frère et beau frère est bientôt docteur.

Merci à Sarrah mon épouse, mon binôme et partenaire de toujours, présente dans tous mes moments de doute, de malheur et de bonheur malgré sa préparation de thèse. J'espère ne pas l'avoir traumatisée avec la CEM et mes projets d'articles au plein milieu de la nuit. Qu'elle me pardonne pour le temps que je n'avais pas passé avec elle.

Enfin, je voudrais remercier particulièrement deux personnes, Ladji et Ghassan qui ont toujours fait en sorte de me faire sentir en famille même loin des miens.

Je dédie cette thèse à mes nièces et neveux. J'espère qu'elle leur sera une source de fierté et d'inspiration pour leurs avenirs.

Je dédie également cette thèse à vous Papa et Maman, en souhaitant qu'elle effacera tous les torts que j'ai pus faire par le passé.

## Résumé

De nos jours, l'évolution croissante des domaines d'application des circuits intégrés impose aux industriels de nouvelles contraintes de conception. Afin de réaliser des circuits électroniques plus denses et plus performants, ils cherchent à faire cohabiter plusieurs types de composants sur des surfaces plus petites et, de surcroît, fonctionnant à des fréquences de plus en plus élevées. Cependant, cette cohabitation pourrait générer des problèmes de CEM (compatibilité électromagnétique).

Les travaux présentés dans ce mémoire rentrent dans le cadre du projet de recherche SEISME (Simulation de l'Emission et de l'Immunité des Systèmes et Modules Electroniques). Ils décrivent des méthodologies de mesure et de modélisation de l'immunité conduite des circuits intégrés complexes comme les mémoires non volatiles ou bien les micro-contrôleurs. L'objectif est d'étudier l'influence des changements de composants et de cartes sur le comportement électromagnétique d'un système électronique.

Dans cette perspective, afin de valider son utilisation dans le cas des circuits intégrés complexes, une étude détaillée de la norme de mesure DPI (Direct Power injection) est d'abord proposée. Basé sur cette dernière, un nouveau prototype de dispositif d'injection est réalisé. Ce multiplexeur permet de superposer un signal agresseur à un signal fonctionnel, avec un chevauchement de leurs bandes de fréquences. Ainsi, il est possible d'agresser une broche fonctionnelle (horloge par exemple) d'un circuit intégré pendant son fonctionnement. Ensuite, une procédure de mesure globale d'immunité conduite est présentée. Elle permet de caractériser la susceptibilité conduite des circuits complexes en tenant compte des différents modes de fonctionnement et avec la possibilité d'utiliser un critère d'immunité fonctionnel ou électrique. Grâce à l'application de cette procédure à deux mémoires non volatiles compatibles broche à broche (mêmes caractéristiques mais de deux fournisseurs différents), il est possible de constater l'influence des technologies de fabrication sur l'immunité conduite de ce type de circuits. Par conséquent, l'effet du changement de composant sur le comportement électromagnétique d'un système électronique devient prédictible.

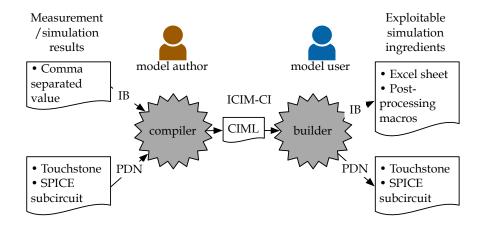

Enfin, deux méthodologies de modélisation sont proposées, l'une au niveau composant et l'autre au niveau carte. La démarche de modélisation au niveau composant repose sur le standard ICIM-CI (Integrated Circuit Immunity Model-Conducted Immunity) et vise à générer un modèle d'immunité simulable et prédictif. Grâce à l'application de cette démarche dans le contexte des mémoires non volatiles, il est possible de prédire leur immunité dans le cas de modification

d'une l'impédance d'entrée par rajout d'éléments de filtrage par exemple. En ce qui concerne la modélisation au niveau carte, une procédure basée sur la proposition de modèle EBIM-CI (Electronic Board Immunity Model-Conducted Immunity) est développée. Elle consiste à générer un modèle d'immunité d'une carte électronique en utilisant les modèles des différents composants qui la constituent. Un cas d'étude a été défini. Le modèle issu de cette approche permet de simuler l'immunité conduite globale du démonstrateur ainsi que de prédire le comportement électromagnétique de ce dernier lors du changement d'un ou plusieurs composants.

## **Abstract**

Nowadays, the growing evolution of application fields for integrated circuits sets new constraints for designers and manufacturers. Due to continuous technological advances in integrated circuits, those have become smaller, denser and operational at higher frequencies. The miniaturization of integrated circuits has led to the reduction of power consumption and, thus, noise margins. Mixing digital and analog functions inside the same chip also makes electromagnetic interferences (EMIs) more likely to spread and cause disturbances. As a result, complex ICs with coexisting different functions represent a challenge from an EMC point of view, as interferences can cause critical functional failures.

The work presented in this manuscript falls within the SEISME project which aims, among others, to perform the simulation of both the emission and the immunity of electronic systems and modules at different levels (IC, PCB, equipment, system). More precisely, this work deals with the development of measurement and modeling methodologies for the characterization of the conducted immunity of complex ICs, such as microcontrollers and non-volatile memories. The main goal is to study the effect of component and/or board replacement on the electromagnetic behavior of a complete electronic system.

In this context, a thorough study of the Direct Power Injection (DPI) technique is presented, thus validating its use for complex integrated circuits. Based on this study, a new prototype for the disturbance coupling path is proposed. It consists of a multiplexer that enables the superposition of a disturbance signal and a functional one with overlapping frequency bands. Therefore, it is possible to disturb an IC functional pin (a clock for instance) during its operation. Moreover, measurement procedure for conducted immunity is introduced. Its advantage is to make it possible to characterize the immunity of complex ICs by taking into account different operation modes as well as flexible immunity criteria (electrical / functional). Thanks to the application of this methodology for two different, non-volatile, pin-to-pin-compatible memories (having the same characteristics but different manufacturers), the influence of fabrication technology on the conducted immunity of such ICs is better identified and understood. As a consequence, the effect of changing components on the electromagnetic behavior of an electronic system has become predictable.

As far as modeling aspects are concerned, two methodologies are presented in this manuscript. The first one deals with the immunity at the component level whereas the other involves board

level immunity. At the IC level, the modeling approach is rather based on the ICIM-CI (Integrated Circuit Immunity Model-Conducted Immunity) draft standard which makes it possible to extract simulation models that can be incorporated within IC design flows. Once applied to the context of non-volatile memories, this approach allows predicting their immunity in the case of modified input impedance, for example. As far as immunity modeling at the board level is concerned, the idea is to make use of ICIM-CI models corresponding to different ICs on the PCB in order to construct an Electronic Board Immunity Model for Conducted Immunity (EBIM-CI). A case study has been defined and the extracted model makes it possible to simulate the demonstrator's global conducted immunity as well as to predict its electromagnetic behavior following the replacement of one or more components.

# Table des matières

| K  | Kesume (Français/English) |           |              |                                                         |    |

|----|---------------------------|-----------|--------------|---------------------------------------------------------|----|

| Li | ste de                    | es figure | es           |                                                         | X  |

| Li | Liste des tableaux        |           |              | xiv                                                     |    |

| 1  | Intr                      | oductio   | n général    | e                                                       | 2  |

| 2  | Gén                       | éralités  | sur la co    | ompatibilité électromagnétique et la CEM des circuits   | S  |

|    | inté                      | grés      |              |                                                         | 8  |

|    | 2.1                       | Généra    | alités sur l | a compatibilité électromagnétique                       | 8  |

|    |                           | 2.1.1     | Introduc     | ction                                                   | 8  |

|    |                           | 2.1.2     | Sources      | des perturbations électromagnétiques                    | 10 |

|    |                           |           | 2.1.2.1      | Sources intentionnelles                                 | 11 |

|    |                           |           | 2.1.2.2      | Sources non intentionnelles                             | 12 |

|    |                           | 2.1.3     | Couplag      | ge des perturbations électromagnétiques                 | 13 |

|    |                           |           | 2.1.3.1      | Couplage rayonné                                        | 14 |

|    |                           |           | 2.1.3.2      | Couplage conduit                                        | 15 |

|    | 2.2                       | CEM o     | des circuit  | s intégrés                                              | 16 |

|    |                           | 2.2.1     | Evolutio     | on des circuits intégrés                                | 16 |

|    |                           | 2.2.2     | Emissiv      | ité des circuits intégrés                               | 17 |

|    |                           |           | 2.2.2.1      | Origine des émissions parasites des circuits intégrés . | 17 |

|    |                           |           | 2.2.2.2      | Méthodes normalisées de mesure de l'émission des        |    |

|    |                           |           |              | circuits intégrés                                       | 18 |

|    |                           |           | 2.2.2.3      | Modélisation de l'émission conduite des circuits inté-  |    |

|    |                           |           |              | grés et des cartes électroniques                        | 20 |

|    |                           | 2.2.3     | Immuni       | té des circuits                                         | 21 |

|    |                           |           | 2.2.3.1      | Influence des perturbations sur le comportement des     |    |

|    |                           |           |              | circuits intégrés                                       | 21 |

|   |     |         | 2.2.3.2    | Méthodes normalisées de mesure de l'immunité des       |    |

|---|-----|---------|------------|--------------------------------------------------------|----|

|   |     |         |            | circuits intégrés                                      | 23 |

|   |     |         | 2.2.3.3    | Techniques d'amélioration de l'immunité des sys-       |    |

|   |     |         |            | tèmes électroniques                                    | 25 |

|   |     |         | 2.2.3.4    | Modélisation de l'immunité conduite des circuits inté- |    |

|   |     |         |            | grés et des cartes électroniques                       | 27 |

|   | 2.3 | Conclu  | ision      |                                                        | 29 |

| 3 | Mét | hodolog | gie de mes | ure de l'immunité conduite pour les circuits intégrés  |    |

|   | com | plexes  |            |                                                        | 30 |

|   | 3.1 | Introdu | action     |                                                        | 30 |

|   | 3.2 | Modèl   | e existant |                                                        | 31 |

|   |     | 3.2.1   | La norme   | e BCI                                                  | 31 |

|   |     | 3.2.2   | La norme   | e DPI                                                  | 32 |

|   |     | 3.2.3   | Composa    | ants étudiés                                           | 34 |

|   |     |         | 3.2.3.1    | Présentation générale                                  | 34 |

|   |     |         | 3.2.3.2    | Protocole SPI                                          | 36 |

|   | 3.3 | Caract  | éristiques | d'injection                                            | 37 |

|   |     | 3.3.1   | Critère d  | 'immunité                                              | 37 |

|   |     |         | 3.3.1.1    | Critère fonctionnel                                    | 37 |

|   |     |         | 3.3.1.2    | Critère électrique                                     | 38 |

|   |     | 3.3.2   | Chemin     | de couplage                                            | 38 |

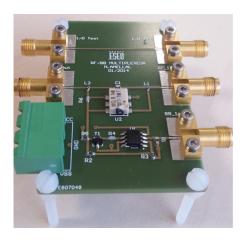

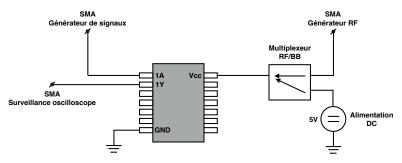

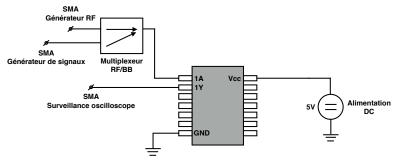

|   |     |         | 3.3.2.1    | Conception et contraintes du multiplexeur RF/BB        | 41 |

|   |     |         | 3.3.2.2    | Conception des pistes et des transitions               | 42 |

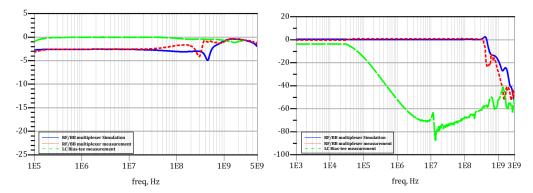

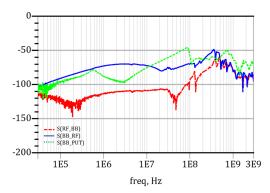

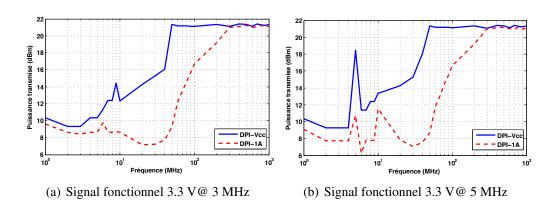

|   |     |         | 3.3.2.3    | Simulations et mesures des caractéristiques du multi-  |    |

|   |     |         |            | plexeur                                                | 43 |

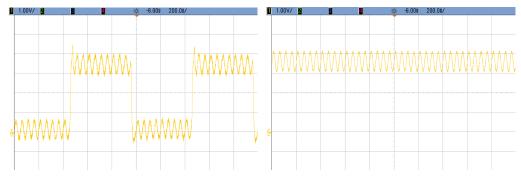

|   |     |         | 3.3.2.4    | Validation du multiplexeur : Étude détaillée sur l'in- |    |

|   |     |         |            | verseur SN74LS04D                                      | 46 |

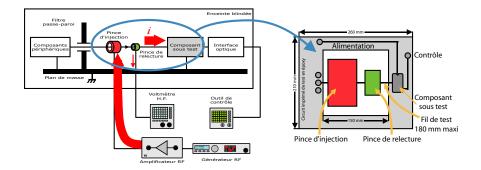

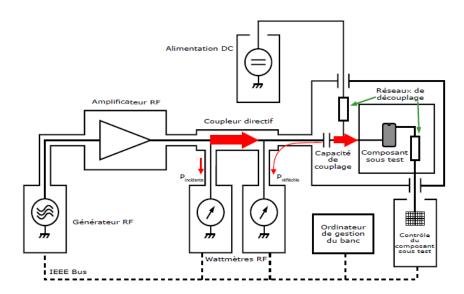

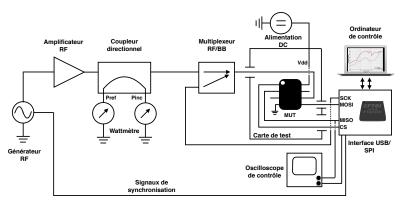

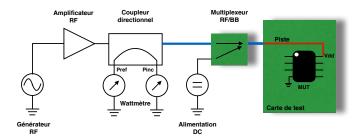

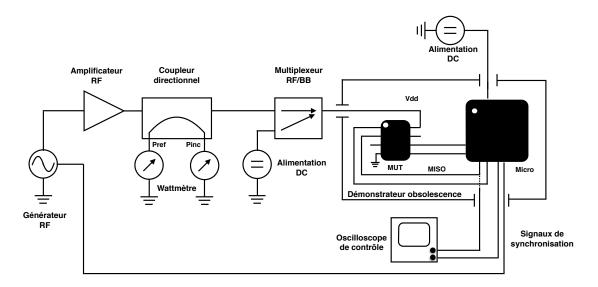

|   |     | 3.3.3   | Système    | de mesure                                              | 49 |

|   |     |         | 3.3.3.1    | Interface de communication et de contrôle              | 49 |

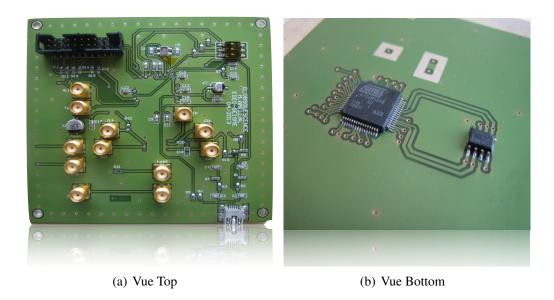

|   |     |         | 3.3.3.2    | Carte de test                                          | 50 |

|   |     |         | 3.3.3.3    | Mise en œuvre du système de mesure                     | 50 |

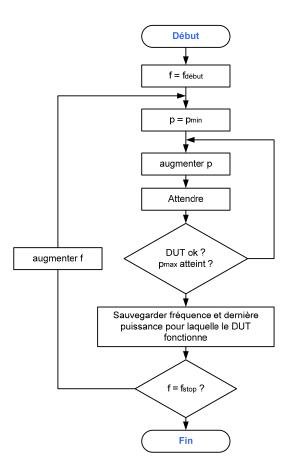

|   |     | 3.3.4   | Logiciel   | de gestion et algorithme de mesure                     | 53 |

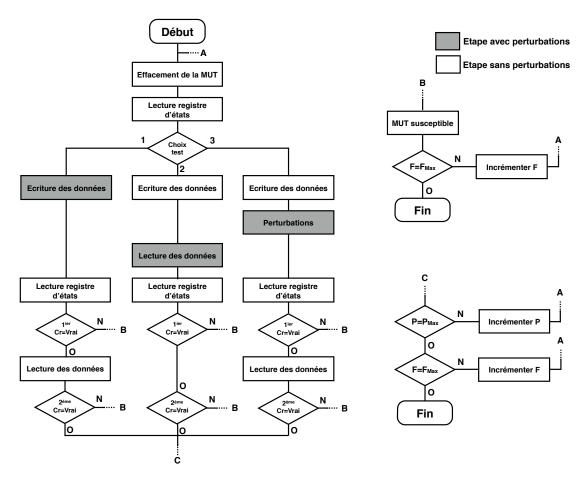

|   |     |         | 3.3.4.1    | Algorithme de mesure                                   | 53 |

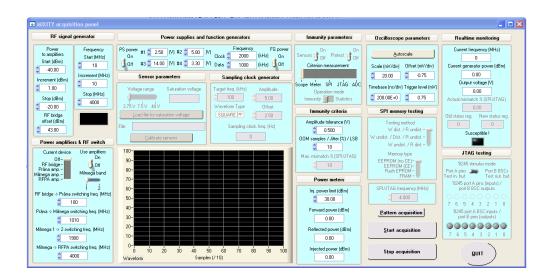

|   |     |         | 3.3.4.2    | Logiciel de gestion                                    | 54 |

|   |     |         | 3.3.4.3    | Banc d'agression conduite                              | 55 |

|   | 3.4 | Résulta | ats de mes | ure et discussions                                     | 58 |

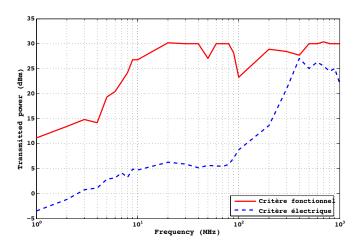

|   |     | 3.4.1   | Immunit    | é et critère de test                                   | 58 |

|    |        | 3.4.2    |              | té et fréquence de communication SPI                    |      |

|----|--------|----------|--------------|---------------------------------------------------------|------|

|    |        | 3.4.3    |              | té et phase d'accès mémoire                             |      |

|    |        | 3.4.4    |              | té et technique de conception                           |      |

|    |        | 3.4.5    |              | té et broche d'injection                                |      |

|    | 3.5    | Concl    | usion        |                                                         | . 69 |

| 4  | Mét    | hodolog  | gie de con   | struction d'un modèle d'immunité pour la gestion d      | le   |

|    | l'ob   | solescer | ice          |                                                         | 71   |

|    | 4.1    | Introd   | uction       |                                                         | . 71 |

|    | 4.2    | Modél    | isation niv  | veau composant                                          | . 72 |

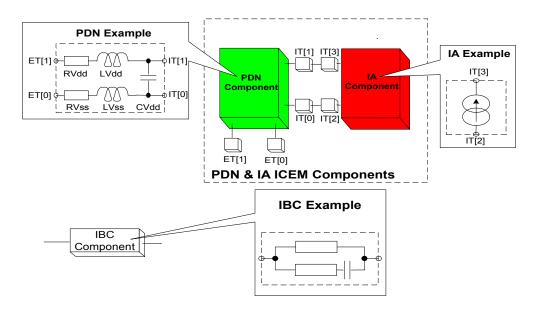

|    |        | 4.2.1    | Modèle       | d'émission ICEM-CE                                      | . 72 |

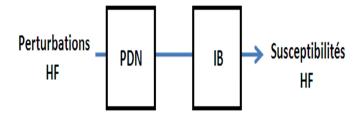

|    |        | 4.2.2    | Modèle       | de susceptibilité ICIM-CI                               | . 74 |

|    |        |          | 4.2.2.1      | Présentation de la norme                                | . 74 |

|    |        |          | 4.2.2.2      | Composant PDN                                           | . 76 |

|    |        |          | 4.2.2.3      | Composant IB                                            | . 76 |

|    |        | 4.2.3    | Dévelop      | pement du modèle ICIM-CI pour les mémoires              | . 77 |

|    |        |          | 4.2.3.1      | Structure du modèle                                     | . 77 |

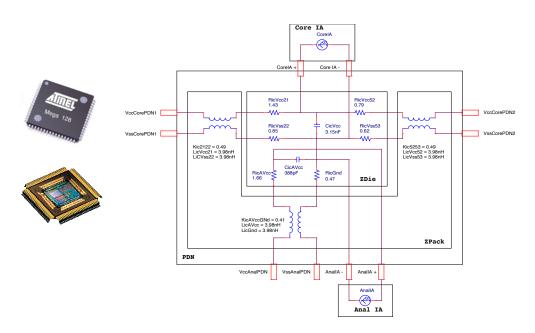

|    |        |          | 4.2.3.2      | Extraction et modélisation du PDN                       | . 78 |

|    |        |          | 4.2.3.3      | Extraction du IB                                        | . 79 |

|    |        |          | 4.2.3.4      | Validation du modèle                                    | . 82 |

|    | 4.3    | Prédic   | tion de l'ii | mmunité d'une carte électronique dans le cas d'un chan- |      |

|    |        | gemen    | it de comp   | osant                                                   | . 84 |

|    |        | 4.3.1    | Modélis      | ation niveau carte                                      | . 84 |

|    |        |          | 4.3.1.1      | Modèle EBIM-CI                                          | . 85 |

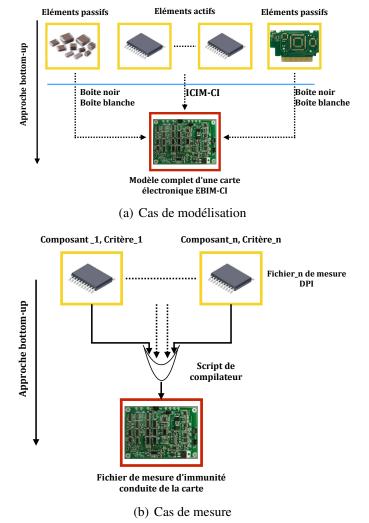

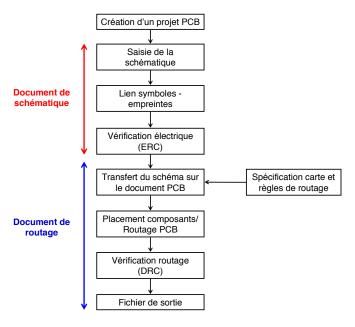

|    |        | 4.3.2    | Procédu      | re de modélisation                                      | . 86 |

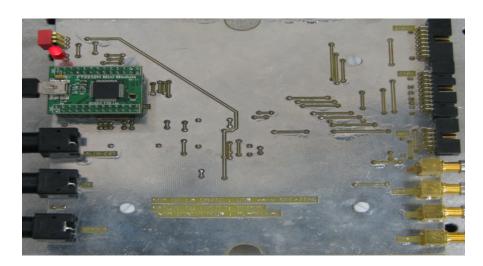

|    |        |          | 4.3.2.1      | Présentation de l'application étudiée                   | . 86 |

|    |        |          | 4.3.2.2      | Présentation générale de la procédure                   | . 87 |

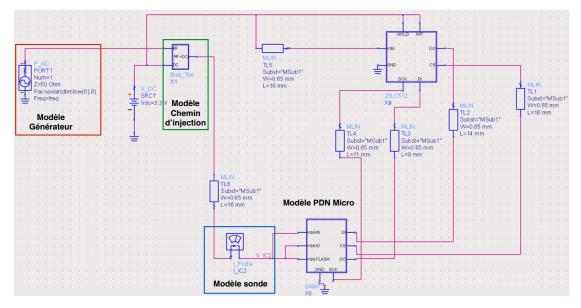

|    |        |          | 4.3.2.3      | Extraction du modèle                                    | . 88 |

|    |        |          | 4.3.2.4      | Simulation et validation du modèle                      | . 90 |

|    | 4.4    | Conclu   | usion        |                                                         | . 97 |

| 5  | Con    | clusion  | générale     |                                                         | 99   |

| Li | stes d | es publ  | ications     |                                                         | 103  |

| Bi | bliogi | raphie   |              |                                                         | 111  |

| Annexes | 113                                                        |

|---------|------------------------------------------------------------|

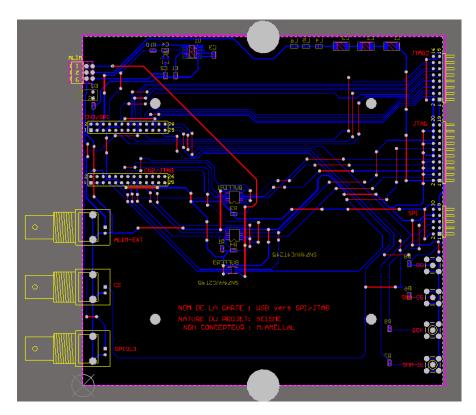

| A       | Annexes 1 - REALISATION DU LAYOUT DU MULTIPLEXEUR RF/BB113 |

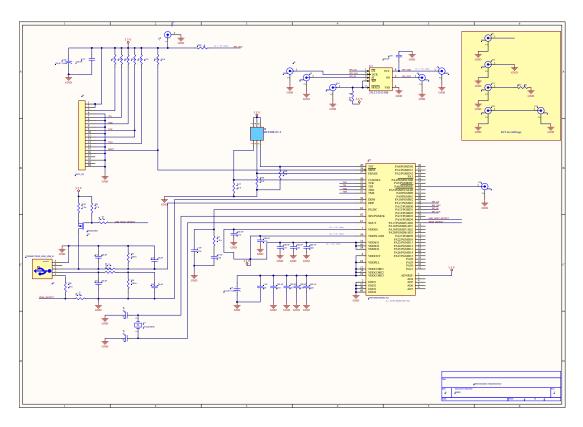

| В       | Annexes 2 - SCHEMAS ELECTRIQUE ET LAYOUT DE LA CARTE       |

|         | DE CONTROLE USB/SPI                                        |

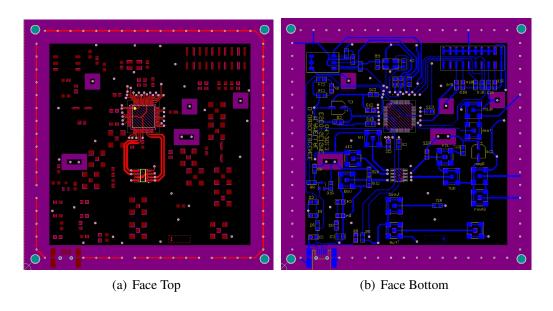

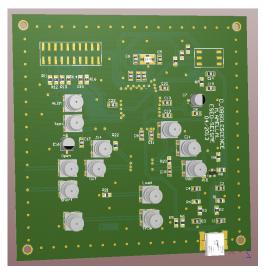

| C       | Annexes 3 - SCHEMAS ELECTRIQUE ET LAYOUT DU DEMONS-        |

|         | TRATEUR D'OBSOLESCENCE                                     |

# Table des figures

| 1.1  | Exemple d'un assemblage de circuits intégrés provenant de fournisseurs |    |

|------|------------------------------------------------------------------------|----|

|      | différents monté sur la carte électronique d'un smartphone             | 3  |

| 2.1  | Représentation des différents aspects de la CEM                        | 9  |

| 2.2  | Exemple de propagation des perturbations électromagnétiques dans un    |    |

|      | avion                                                                  | 10 |

| 2.3  | Sources d'émissions radio                                              | 12 |

| 2.4  | Exemple d'application de la technique CPL                              | 12 |

| 2.5  | Exemple de pics de courant consommés par un circuit intégré            | 13 |

| 2.6  | Les différents modes de couplage d'une perturbation électromagnétique. | 14 |

| 2.7  | Exemple de couplage entre deux interconnexions                         | 15 |

| 2.8  | Évolution de la longueur de canal d'un transistor                      | 16 |

| 2.9  | Exemple de tension parasite causée par la commutation simultanée et    |    |

|      | son spectre[14]                                                        | 18 |

| 2.10 | Méthodes standardisées de caractérisation de l'émission des circuits   |    |

|      | intégrés                                                               | 19 |

| 2.11 | Structure de base du modèle d'émission conduite xxEM-CE                | 20 |

| 2.12 | Phénomène de latchup dans les circuits intégrés                        | 22 |

| 2.13 | Marges de bruit en entrée d'un circuit élémentaire numérique           | 22 |

| 2.14 | Méthodes standardisées de caractérisation de l'immunité des circuits   |    |

|      | intégrés                                                               | 23 |

| 2.15 | Exemple de résultat de mesure d'immunité rayonnée avec la méthode NFS. | 24 |

| 2.16 | Simulation des performances CEM durant les différentes phases de       |    |

|      | conception d'un système électronique                                   | 26 |

| 2.17 | Structure de base du modèle d'immunité conduite xxIM-CI                | 28 |

| 3.1  | Vue d'ensemble du système de mesure BCI appliqué à un circuit intégré. | 31 |

| 3.2  | Vue d'ensemble du système de mesure DPI dans la norme actuelle         | 32 |

| 3.3  | Procédure de test DPI                                                  | 33 |

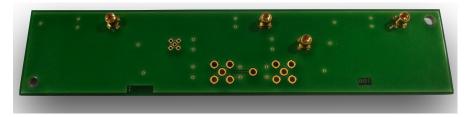

| 3.4  | Vue générale des mémoires étudiées                                     | 35 |

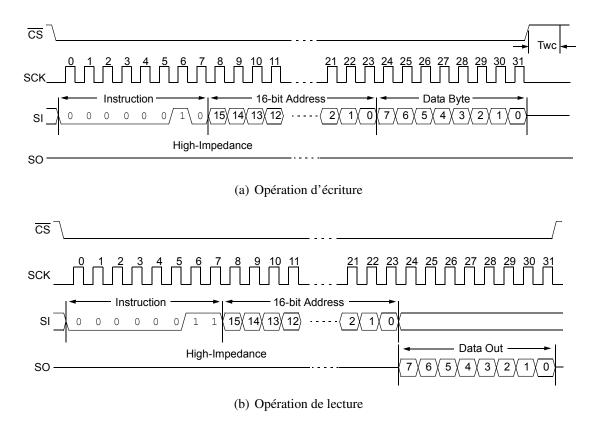

| 3.5  | Chrono-gramme d'accès mémoire en lecture et en écriture                     | 36 |

|------|-----------------------------------------------------------------------------|----|

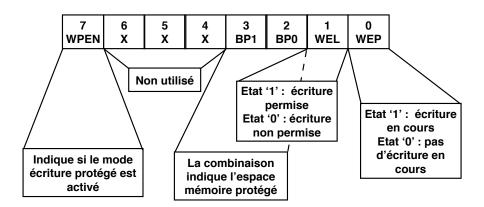

| 3.6  | Composition du registre d'états interne d'une mémoire non volatile de       |    |

|      | type SPI                                                                    | 38 |

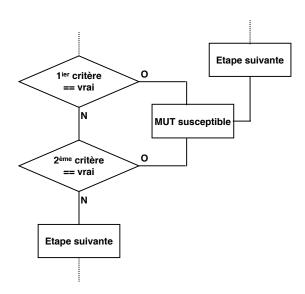

| 3.7  | Algorithme de test du critère d'immunité                                    | 39 |

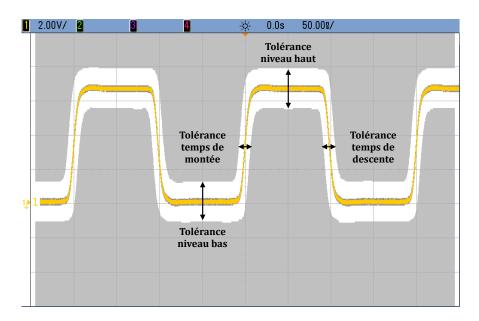

| 3.8  | Exemple de mise en place du critère de test électrique                      | 39 |

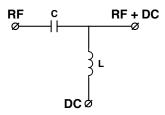

| 3.9  | Schéma fonctionnel d'un chemin de couplage DPI                              | 40 |

| 3.10 | Exigences du chemin de couplage LC, lorsqu'il est connecté à une entrée     |    |

|      | logique                                                                     | 40 |

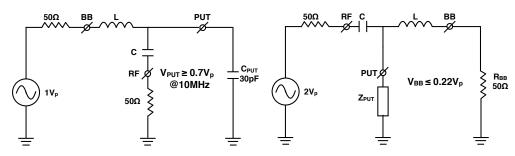

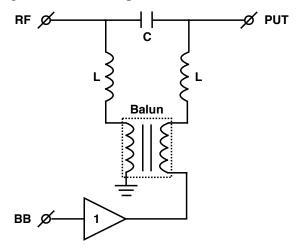

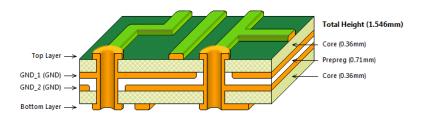

| 3.11 | Schéma fonctionnel du multiplexeur RF/BB                                    | 42 |

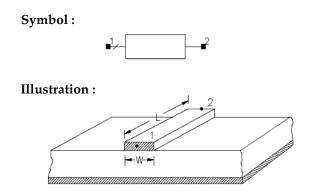

| 3.12 | Empilement et géométrie des couches du PCB utilisé                          | 43 |

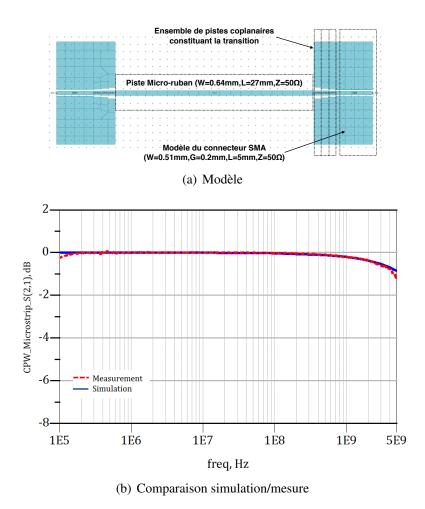

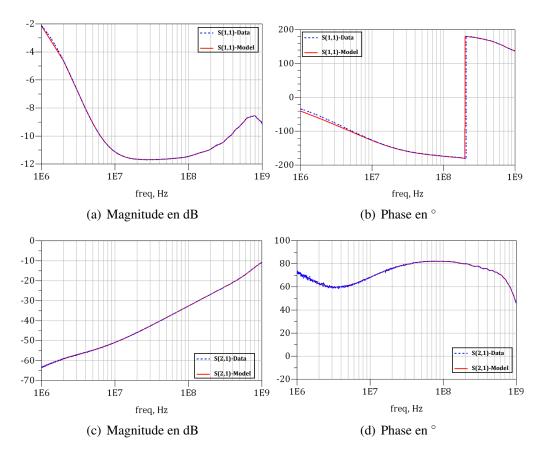

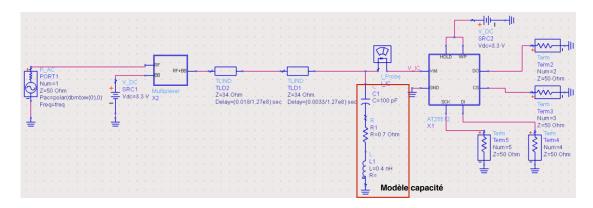

|      | Modélisation et comparaison simulation/mesure de la transition connecteur-  |    |

|      | piste-connecteur                                                            | 44 |

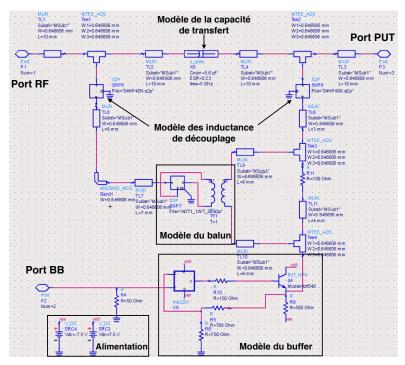

| 3.14 | Schéma général de la simulation et de l'implémentation du multiplexeur      |    |

|      | RF/BB                                                                       | 45 |

| 3.15 | Comparaisons mesures simulations des différentes caractéristiques du        |    |

|      | multiplexeur RF/BB                                                          | 46 |

| 3.16 | Signal de sortie du multiplexeur RF/BB dans le domaine temporel dans        |    |

|      | le cas d'une émulation d'injection de puissance                             | 47 |

| 3.17 | Configuration de mise en œuvre du SN74LS04D                                 | 47 |

| 3.18 | Résultats de caratérisation DPI du SN74LS04D                                | 48 |

| 3.19 | Schéma de l'interface SPI/USB                                               | 49 |

| 3.20 | Carte Valeo de mesure DPI et son kit de calibrage                           | 51 |

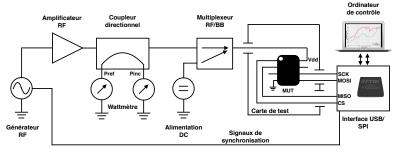

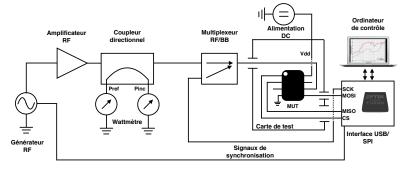

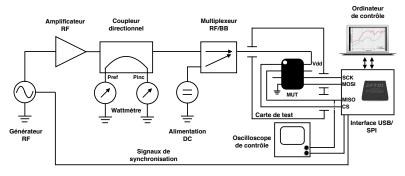

| 3.21 | Schéma général des quatre mises en œuvre des mesures DPI pour les           |    |

|      | mémoires SPI                                                                | 52 |

| 3.22 | Algorithme général de la procédure de test DPI pour les mémoires SPI.       | 54 |

|      | Interface graphique de commande                                             | 55 |

| 3.24 | Banc de mesure d'immunité conduite du laboratoire ESEO-EMC                  | 58 |

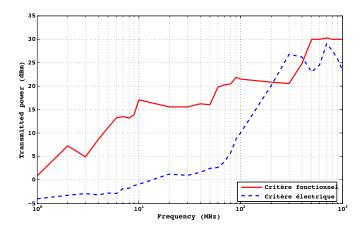

| 3.25 | Immunité conduite de la mémoire Microchip en fonction du critère de test.   | 59 |

| 3.26 | Immunité conduite de la mémoire Atmel en fonction du critère de test        | 60 |

| 3.27 | Variation de l'immunité conduite de la mémoire ATMEL en fonction de         |    |

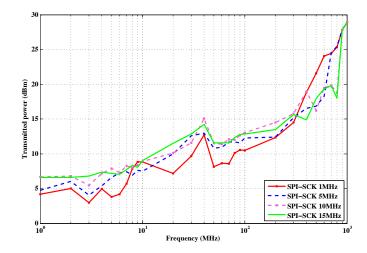

|      | la fréquence de communication SPI                                           | 60 |

| 3.28 | Immunité conduite de la mémoire Microchip en fonction de la phase           |    |

|      | d'accès                                                                     | 61 |

| 3.29 | Immunité conduite de la mémoire Atmel en fonction de la phase d'accès       | 61 |

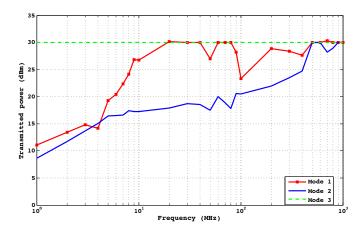

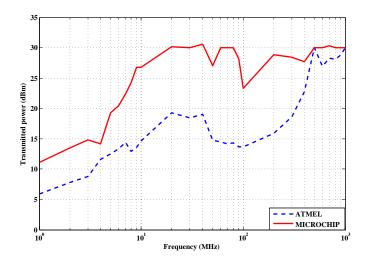

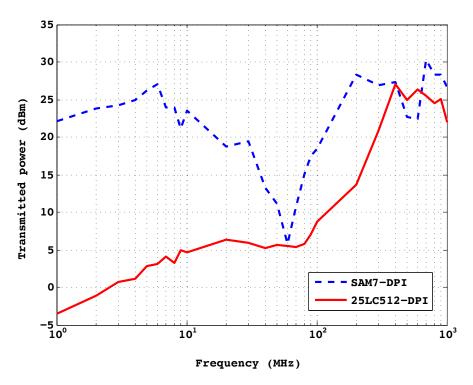

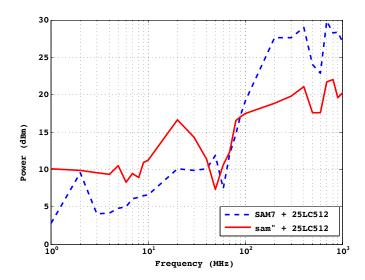

|      | Immunité conduite en écriture en fonction de la technologie de fabrication. | 62 |

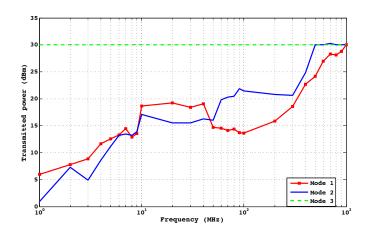

|      | Immunité conduite en lecture en fonction de la technologie de fabrication.  |    |

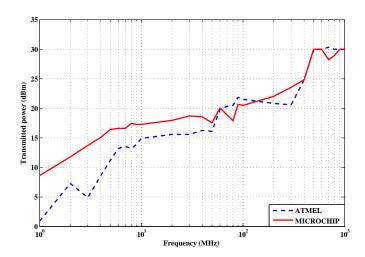

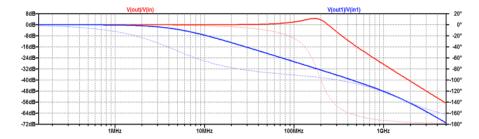

|      | Simulation des fonctions de transferts des modèles des mémoires étudiées.   |    |

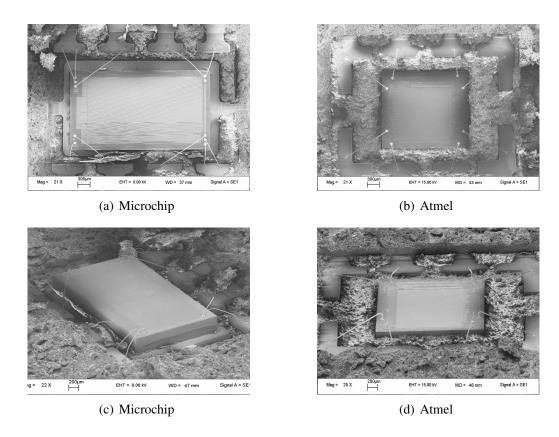

| 3.33 | Résultats de l'analyse technologique - ouverture chimique                   | 65 |

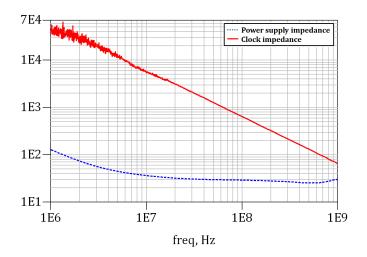

|      | Modélisation et simulation de l'impédance de la broche d'alimentation .                | 66 |

|------|----------------------------------------------------------------------------------------|----|

| 3.35 | L'immunité conduite en écriture de la mémoire Microchip en fonction la broche agressée | 67 |

| 3.36 | L'immunité conduite en lecture de la mémoire Microchip en fonction la                  |    |

|      | broche agressée                                                                        | 68 |

| 3.37 | Mesure de l'impédance d'entrée de la 25LC512 ( $\Omega$ )                              | 68 |

| 4.1  | Architecture générale du modèle ICEM-CE                                                | 73 |

| 4.2  | Exemple de modèle ICEM-CE - Source ATMEL                                               | 73 |

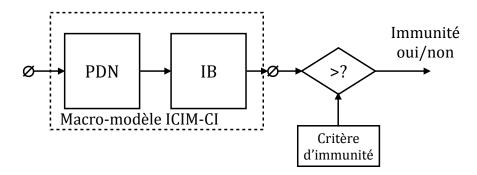

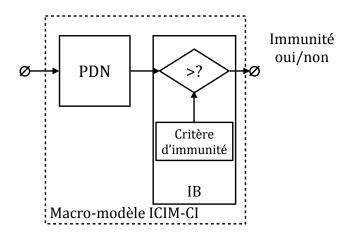

| 4.3  | Architecture générale d'un macro-modèle ICIM-CI[60]                                    | 75 |

| 4.4  | Schéma d'utilisation et d'échange d'un macro-modèle ICIM-CI                            | 75 |

| 4.5  | Macro-modèle ICIM-CI avec un critère extérieur                                         | 77 |

| 4.6  | Macro-modèle ICIM-CI avec un critère intégré                                           | 77 |

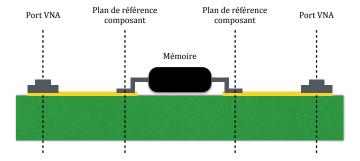

| 4.7  | Localisation du plan de référence pour l'extraction des paramètres S                   | 78 |

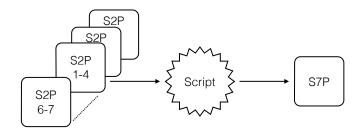

| 4.8  | Génération de la matrice S7P à partir de matrice S2P                                   | 79 |

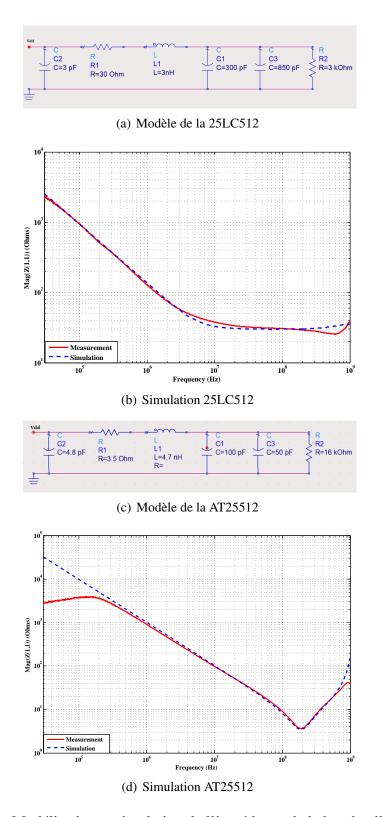

| 4.9  | Exemples de confrontation modèle PDN et paramètres S mesurées par le                   |    |

|      | VNA                                                                                    | 80 |

| 4.10 | Principe de mesure de la puissance transmise pendant test DPI                          | 80 |

| 4.11 | Principe d'extraction de la puissance transmise à la MUT en simulation                 | 81 |

| 4.12 | Simulation du composant IB pour la mémoire 25LC512 de Microchip .                      | 82 |

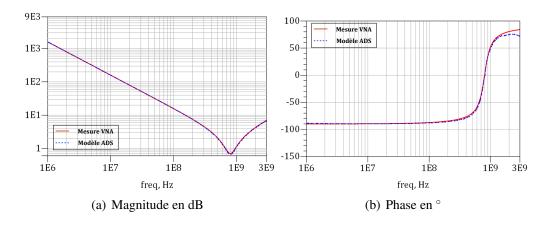

| 4.13 | Schéma général de la simulation du nouveau environnement de test                       | 83 |

| 4.14 | Confrontation entre le modèle de la capacité 100 pF et les paramètres S                |    |

|      | mesurés par le VNA                                                                     | 83 |

| 4.15 | Confrontation mesure DPI et simulation du modèle ICIM-CI dans le                       |    |

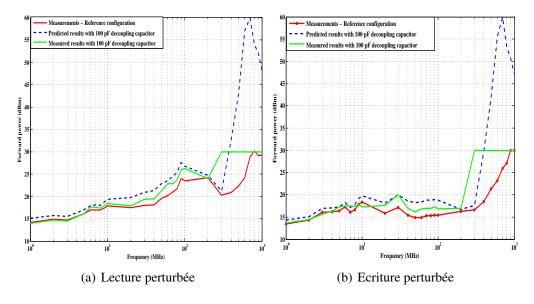

|      | nouveau environnement de test                                                          | 84 |

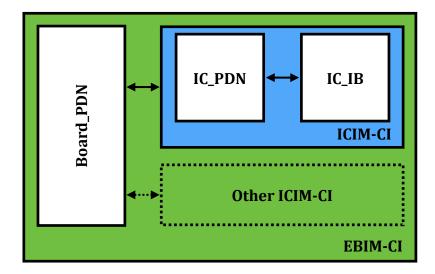

| 4.16 | Architecture générale d'un macro-modèle EBIM-CI                                        | 85 |

| 4.17 | Détails du démonstrateur obsolescence ( $\mu C$ + mémoire SPI)                         | 87 |

| 4.18 | Approche hiérarchique bottom-up pour une carte électronique                            | 88 |

| 4.19 | Mise en œuvre de la mesure DPI grâce démonstrateur obsolescence ( $\mu C$              |    |

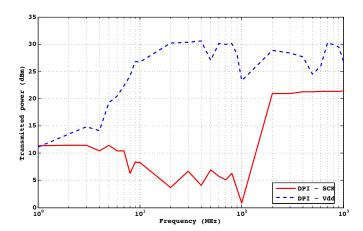

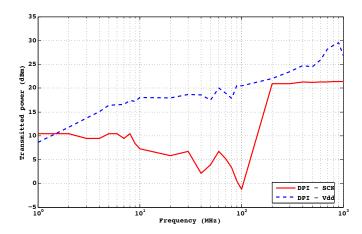

|      | + mémoire SPI) dans le cas des mémoires                                                | 90 |

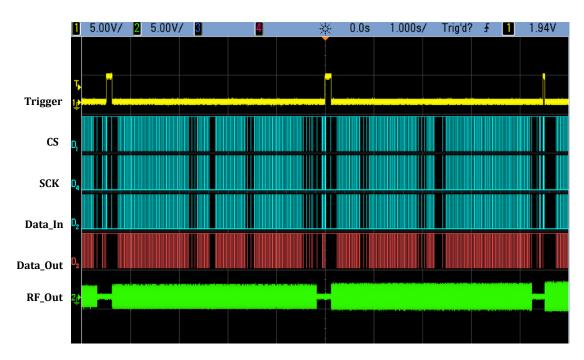

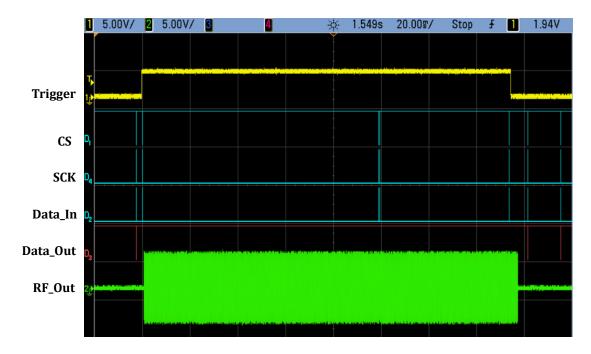

| 4.20 | Synchronisation des perturbations électromagnétiques avec la phase de                  |    |

|      | lecture du démonstrateur obsolescence ( $\mu$ C + mémoire SPI)                         | 91 |

| 4.21 | Synchronisation des perturbations électromagnétiques avec la phase                     |    |

|      | d'écriture du démonstrateur obsolescence ( $\mu C$ + mémoire SPI)                      | 91 |

| 4.22 | Courbes d'immunité de la mémoire et du µC réalisées sur le démonstra-                  |    |

|      | teur obsolescence                                                                      | 92 |

| 4.23 | Principe d'extraction de la partie IB du modèle ICIM-CI dans le cas des                |    |

|      | uС                                                                                     | 92 |

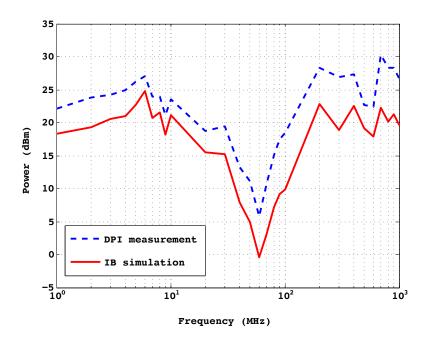

| 4.24 | Comparaison entre la mesure DPI et simulation du modèle ICIM-CI           |

|------|---------------------------------------------------------------------------|

|      | dans le cas du $\mu C$ Sam7                                               |

| 4.25 | Représentation du modèle microstrip line sous ADS de Agilent[70] 93       |

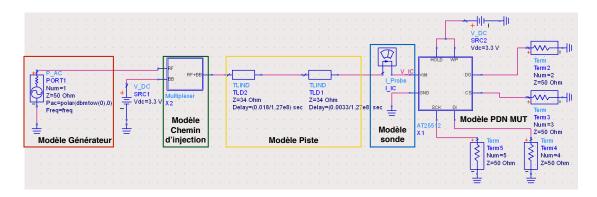

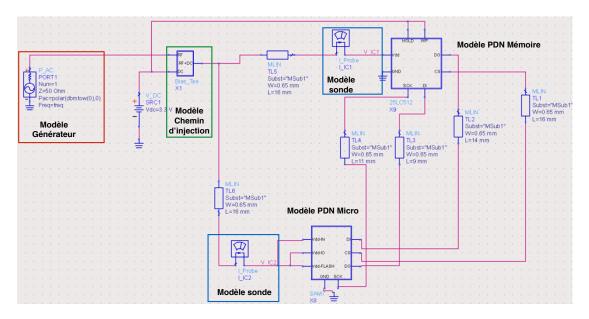

| 4.26 | Schéma général de la mise ne œuvre de la simulation du modèle EBIM-CI 94  |

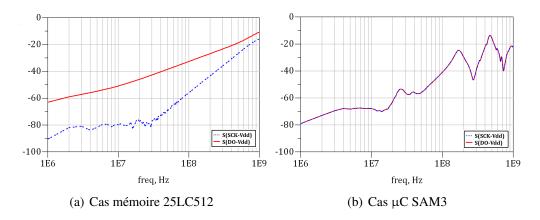

| 4.27 | Magnitude en dB du coefficient de transmission entre la broche d'ali-     |

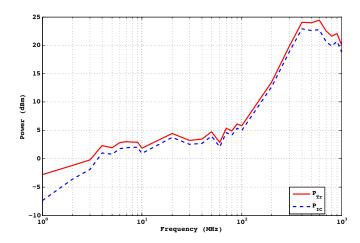

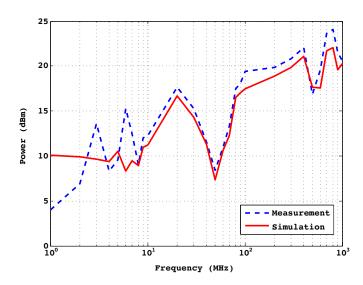

|      | mentation et les broches de sorties mesuré par le VNA 95                  |

| 4.28 | Confrontation mesure DPI et simulation du modèle EBIM-CI dans le          |

|      | cas de la mémoire 25LC512 et du µC SAM3                                   |

| 4.29 | Courbes d'immunité conduite prédites dans le cas du changement du $\mu C$ |

|      | SAM7 par le $\mu$ C SAM3                                                  |

| 5.1  | Flot de conception d'un circuit imprimé                                   |

| 5.2  | Layout du multiplexeur RF/BB                                              |

| 5.3  | Vue générale du module FTDI2232H                                          |

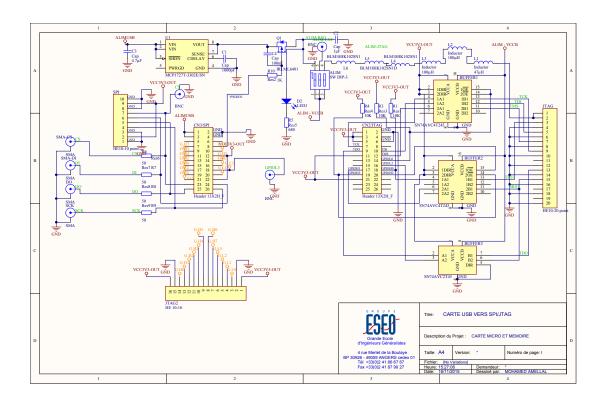

| 5.4  | Schéma électrique général de la carte de contrôle USB/SPI                 |

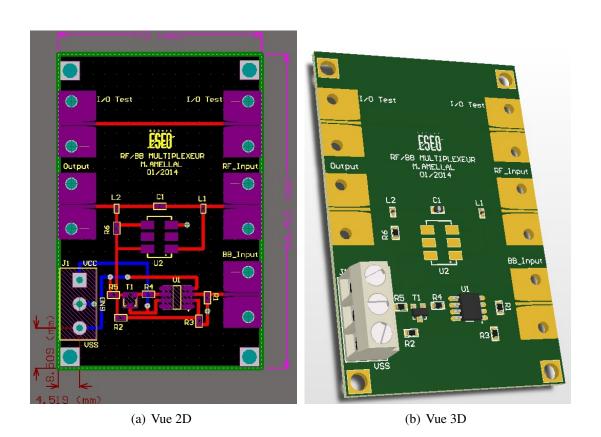

| 5.5  | Layout de la carte de contrôle USB/SPI - Vue 2D                           |

| 5.6  | Schéma électrique général du démonstrateur d'obsolescence                 |

| 5.7  | Layout du démonstrateur d'obsolescence - Vue 2D                           |

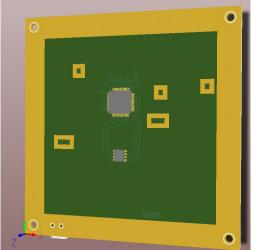

| 5.8  | Layout du démonstrateur d'obsolescence - Vue 3D                           |

|      |                                                                           |

# Liste des tableaux

|     | Principales sources de perturbation électromagnétique                    |    |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | Principales caractéristiques des méthodes de mesures de susceptibilité   | 25 |

| 3.1 | Caractéristiques générales des mémoires étudiées                         | 35 |

| 3.2 | Valeurs du couple $(W_{CPW},G)$ calculées pour une impédance caractéris- |    |

|     | tique de $50 \Omega$                                                     | 43 |

| 3.3 | Configurations des mises en œuvre des mesures DPI pour les mémoires      |    |

|     | SPIs                                                                     | 50 |

| 3.4 | 1                                                                        |    |

|     | deux mémoires                                                            |    |

| 3.5 | Synthèse des différentes mesures de cotation des mémoires étudiées       | 65 |

| 4.1 | Caractéristiques du modèle ICIM-CI relatif aux mémoires et micro-        |    |

|     | contrôleurs                                                              | 90 |

## 1 Introduction générale

## **Problématique**

L'essor important que connaissent les applications industrielles utilisant des systèmes électroniques embarqués, que ce soit dans le domaine aéronautique, spatial, ou encore automobile, permet aux industriels d'offrir des solutions techniques et économiques concurrentielles. Ce développement se manifeste par des performances croissantes, une intégration poussée et des coûts attractifs. Néanmoins, cette évolution technologique rapide et l'élargissement continu des domaines d'utilisation ne pourraient aboutir que par une meilleure compréhension des divers mécanismes de conception, de réalisation, et surtout, de fiabilité de ces systèmes électroniques. Garantir les performances souhaitées, indépendamment de l'environnement d'utilisation, devient aujourd'hui l'enjeu majeur pour les industriels concernés.

Un des éléments clés de la réussite des challenges d'intégration et d'évolution technologique est la maîtrise de la compatibilité électromagnétique et de ses risques.

En effet, depuis de nombreuses années, les problèmes liés à la compatibilité électromagnétique des systèmes et circuits électroniques sont au cœur des préoccupations des industriels. Assurer le bon fonctionnement de ces derniers, sans qu'ils soit perturbés par un tiers, ou qu'ils perturbent eux-mêmes leurs voisinage, devient vital à tous les niveaux de conception. L'exemple des circuits intégrés illustre parfaitement ce défi. D'une part, l'augmentation de l'intégration des fonctions logiques au sein d'un même composant conduit à l'accroissement des émissions parasites. D'autre part, la réduction des tensions d'alimentation et l'augmentation des fréquences de fonctionnement impactent négativement les niveaux de susceptibilité face aux perturbations électromagnétiques.

La susceptibilité et l'émissivité sont donc les deux aspects indissociables dont il faut tenir

FIGURE 1.1 – Exemple d'un assemblage de circuits intégrés provenant de fournisseurs différents monté sur la carte électronique d'un smartphone

compte dans la conception des circuits électroniques afin d'assurer un bon voisinage entre les différents circuits d'un équipement ou d'un système donné.

Si l'émission électromagnétique (causes et conséquences), est désormais maîtrisée et bénéficie d'un nombre de normes de modélisation, l'immunité quant à elle manque à ce jour de ressources et de normes qui permettront de tenir compte de cet aspect dès la phase de conception.

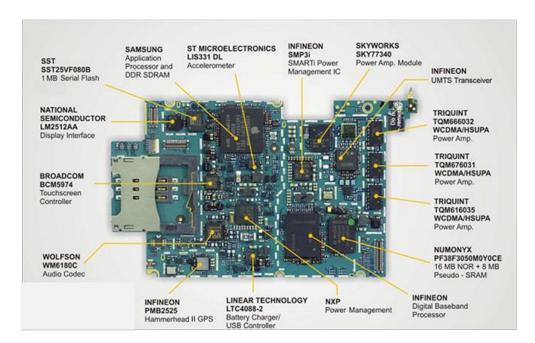

Cette problématique prend plus d'ampleur avec la diversification des architectures et des technologies des circuits intégrés qui partagent le même support, et qui à un niveau supérieur devront évoluer dans le même environnement (Figure 1.1).

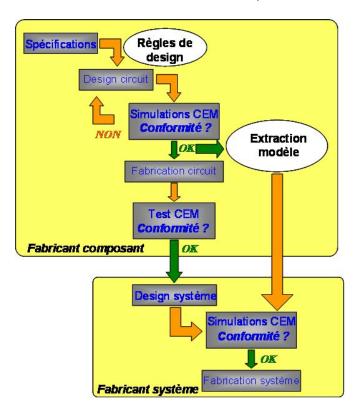

Dans cette perspective, un nouveau concept d'obsolescence électromagnétique est apparu et vise à se prémunir contre les risques d'obsolescence des composants ou systèmes électronique dans l'étude CEM. Qu'il s'agisse d'une obsolescence liée soit à l'évolution du processus de fabrication chez un même fondeur, soit à une décision de changement de fabricant (optimisation des coûts), la prédiction de l'effet du changement d'un composant par un autre sur les performances électromagnétiques représente actuellement un nouveau défi dans la conception des systèmes électroniques. De plus, en adoptant une approche hiérarchique bottom-up, ce concept peut intervenir à plusieurs niveaux d'un système et en particulier au niveau des circuits intégrés.

### **Contexte**

Les travaux de cette thèse rentrent de la cadre du projet SEISME (Simulation de l'Emission et de l'Immunité des Systémes et des Modules Electroniques). Ce projet vient suite à des besoins exprimés par les industriels de l'électronique embarquée. Ces derniers souffrent d'un manque au niveau des processus pour traiter par simulation numérique la non régression des performances CEM, ceci dans l'optique de réduire le nombre d'essais CEM.

Le projet SEISME est articulé autour de trois objectifs principaux. Le premier objectif concerne le développement de prototypage virtuel. Il est question de définir les outils, les modèles et les méthodes de test et de calcul pour l'analyse CEM lors d'une modification de composants ou d'équipements électroniques durant leur cycle de vie. Le second objectif vise à renforcer le test virtuel. Ce dernier permettra de réduire le nombre de tests de requalification CEM d'un équipement et d'un système électronique. Pour les industriels cela est synonyme de réduction des délais et des coûts de ces essais CEM. Enfin le dernier objectif se focalise sur les propositions de standardisation des modèles. Il s'agit de créer un projet unifié au sein des comités normatifs internationaux de la IEC (International Electrotechnical Commission) regroupant des propositions de modèles composants/carte/équipement électronique et de leurs méthodes d'extraction.

Ce projet est organisé selon cinq Work Packages (WP):

- Le WP 1 et le WP3 couvrent la problématique du changement de composants élémentaires. Dans ce cas il s'agit de mesures et de modèles au niveau composants et circuits intégrés. Cette problématique intéresse principalement les équipementiers automobiles qui sont plutôt mono cartes.

- Le WP 2 couvre la problématique du changement de cartes électroniques. Dans ce cas il est question de mesures et de modèles au niveau cartes électroniques. C'est une problématique qui intéresse principalement les équipementiers avioniques qui disposent de calculateurs multi-cartes.

- Le WP 4 concerne la problématique du changement d'équipements électroniques . Il s'agit dans ce cas de mesures et de modèles au niveau équipements électroniques. C'est une problématique qui concerne principalement les systémiers, avioniques et automobiles.

- Le WP5 a un rôle plus transversal en proposant pour chaque WP des structures de modèles et les méthodes de mesures pour extraire ces modèles. Cette approche transverse permet plus facilement d'envisager la création de standards de modèles.

## Objectifs et originalité de la démarche

L'objectif des travaux de cette thèse est de développer une méthodologie pour la caractérisation de l'immunité conduite des circuits intégrés complexes, ainsi que l'extraction et la construction de macro-modèles d'immunité pour les circuits intégrés et les cartes électroniques.

Les mémoires non volatiles et les micro-contrôleurs représentent un cas d'étude intéressant. D'une part, ils assurent des fonctions cruciales dans les systèmes électroniques actuels et présentent des modes de fonctionnement variés. D'autre part, la diversité des fabricants et des technologies ainsi que leur interchangeabilité font deux des sujets parfaits pour l'étude de l'obsolescence.

La première étape consiste à développer des procédures de mesure pour l'étude de l'immunité conduite des mémoires non volatiles et ainsi détenir une base solide pour identifier l'influence de la technologie de fabrication sur leur susceptibilité. Ensuite, il s'agira de développer une méthodologie pour l'extraction et la construction de macro-modèles d'immunité, au niveau composant, en se basant sur les normes existantes. Ces modèles serviront enfin de base de modélisation au niveau carte, afin d'étudier l'influence de changement d'un composant sur le comportement électromagnétique global d'une application.

## **Structure**

Dans le premier chapitre de ce manuscrit, des notions générales relatives à la compatibilité électromagnétique sont exposées. Ainsi, à travers une étude bibliographique de l'évolution des paramètres technologiques des circuits intégrés, ce chapitre introduit les différents aspects de la CEM des circuits intégrés, plus particulièrement sur l'immunité des composants.

Le deuxième chapitre expose la méthodologie de mesure d'immunité conduite développée dans le cadre de cette thèse. Le principe de mesure est d'abord introduit afin de déterminer les points critiques à traiter. Ensuite, les modifications et adaptations apportées à la norme à travers l'approche proposée sont détaillées, suivies par les algorithmes de test et les configurations de mesures développées. Enfin, les résultats obtenus par l'intermédiaire de notre procédure sont exposés.

Le dernier chapitre, quant à lui, traite de la modélisation des circuits intégrés dans le but de prédire leur immunité. Il est question dans un premier temps de proposer une démarche d'extraction du modèle d'immunité pour les circuits étudiés au niveau composant, en se

basant sur les normes en vigueur. Cette démarche sera validée grâce à la corrélation des résultats des mesures et simulations. Ensuite, une méthode de prédiction de l'immunité d'une carte est présentée. Elle repose sur l'étude de l'interaction des différents modèles proposés auparavant et vise à prédire le comportement électromagnétique d'une carte électronique lors d'un changement de composant.

# 2 Généralités sur la compatibilité électromagnétique et la CEM des circuits intégrés

"Si on commence avec des certitudes, on finit avec des doutes. Si on commence avec des doutes, on finit avec des certitudes." - Francis Bacon

#### 2.1 Généralités sur la compatibilité électromagnétique

#### 2.1.1 Introduction

Le 29 juillet 1967, un avion s'apprêtait à décoller d'un porte-avions américain lorsque l'une de ses roquettes prenait accidentellement feu et causait un désastre faisant une centaine de victimes, des dizaines de blessés mais aussi plusieurs millions de dollars de dégâts. L'enquête a démontré qu'un radar du porte- avions avait induit une surtension suffisante sur les câblages des roquettes placées sous l'avion pour activer la mise à feu[1]. Ce dysfonctionnement fait partie d'un ensemble d'exemples qui illustrent les conséquences des interférences entre les ondes électromagnétiques et les équipements et systèmes électroniques. L'étude de ces phénomènes est appelée la compatibilité électromagnétique (CEM).

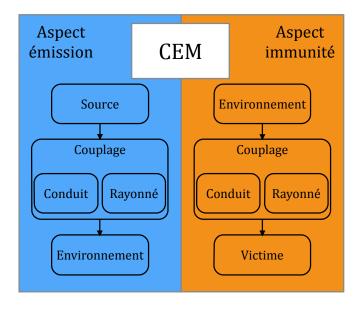

La compatibilité électromagnétique est définie comme "l'aptitude d'un dispositif, d'un appareil ou d'un système à fonctionner dans son environnement électromagnétique de façon satisfaisante et sans produire lui-même des perturbations électromagnétiques intolérables pour d'autres équipements qui se trouvent dans cet environnement".

De cette définition découlent deux notions fondamentales de la CEM. La figure 2.1

représente ces différents notions.

- La première partie de la définition met en évidence le concept de l'immunité d'un système ou d'un composant. Cette première notion se traduit par le fait que ces derniers doivent conserver leur fonctionnalité, ainsi que leurs spécifications, lorsqu'ils sont exposés à un certain niveau de perturbations électromagnétiques, notamment issues de leur environnement de fonctionnement. Dans cette approche ils sont considérés comme des victimes.

- La deuxième partie quant à elle introduit la notion d'émissivité. En effet, un système ou un composant doit pouvoir fonctionner correctement sans générer des perturbations électromagnétiques au-delà d'un niveau préalablement défini, ceci afin de ne pas influencer de manière trop importante l'environnement électromagnétique dans lequel il est situé. Dans ce cas de figure il est considéré comme agresseur ou source d'agression.

Cependant, il existe une autre notion, qui n'apparaît pas directement dans la définition de la CEM : C'est la notion de canal. Ce dernier véhicule les perturbations de l'agresseur vers la victime. Il peut se manifester sous deux aspects suivant sa nature. Il peut être un milieu comme le vide ou l'air ou bien un matériau non conducteur, on parle alors de couplage rayonné. Le canal peut aussi être un conducteur électrique, auquel cas on parlera de couplage conduit.

L'étude de la compatibilité électromagnétique est devenue une étape importante dans la réalisation des systèmes électroniques à cause de l'essor qu'a connu l'électronique durant les dernières décennies. En effet, les évolutions technologiques permettent une

FIGURE 2.1 – Représentation des différents aspects de la CEM

intégration de plus en plus poussée des fonctions électroniques. Elles autorisent ainsi une miniaturisation accrue des dispositifs, rendant possible le partage du même environnement. Par conséquent il est important et nécessaire d'assurer le bon fonctionnement des différentes parties qui évoluent dans cet environnement.

Par ailleurs, l'étude de la CEM est inévitablement liée à l'ordre de grandeur de l'objet sur lequel elle est menée. La figure 2.2 illustre la propagation d'une perturbation électromagnétique dans un système. Les circuits intégrés représentent le noyau des systèmes électroniques et sont le dernier maillon de la chaîne de traitement du signal du système. Cependant, une agression électromagnétique qui attaque le système peut se propager jusqu'aux composants via les chemins de couplage en passant par les équipements et les cartes électroniques jusqu'à ces derniers.

Dans cette optique, l'étude de la CEM des circuits intégrés devrait représenter le point de départ de toute caractérisation électromagnétique d'un système électronique complexe.

FIGURE 2.2 – Exemple de propagation des perturbations électromagnétiques dans un avion

#### 2.1.2 Sources des perturbations électromagnétiques

Afin de comprendre l'émissivité des circuits, il est important de s'intéresser dans un premier temps aux sources de perturbations. En effet, l'environnement électromagnétique comprend en plus des sources de perturbations. Elles sont soit naturelles, soit artificielles et créées par l'homme afin d'assurer des fonctions du quotidien. Elles peuvent être intentionnelles ou non intentionnelles.

Le tableau 2.1 résume les principales sources de perturbations d'origine naturelle et humaine.

#### Sources de perturbations d'origine Sources de perturbations d'origine naturelle humaine — Bruits statique et ther-— Réseaux électriques et ses dérivés (lignes haute tension, interrupteurs mique. des circuits de puissance, moteurs — Foudre (proche ou électriques, redresseurs,...). lointaine). — Équipements industriels et com-— Brouillage d'origine solaire (ondes merciaux grand public et médical siffleuses, rayons cos-(four micro-ondes, néons, équipemigues et solaires,...). ments médicaux,...). — Systèmes de communications (stations d'émissions de télévision, radio, radars, téléphonies mobiles, émetteurs/récepteurs Wifi, ...).

Tableau 2.1 – Principales sources de perturbation électromagnétique.

#### 2.1.2.1 Sources intentionnelles

L'essor que connait aujourd'hui la radio communication implique un élargissement et une densification importante de son spectre essentiellement sur la bande de 100 MHz — 10 GHz. Si les niveaux d'émissions sont réglementés par l'ITU (International Telecommunication Union), cet environnement électromagnétique très dense représente autant de sources de perturbations potentielles (Figure 2.3).

En effet, l'évolution rapide et permanente de cet environnement a permis l'apparition de plus en plus de nouvelles applications avec des niveaux d'émissions plus ou moins élevés. Ces dernières constituent un grand danger pour les systèmes et équipements qui ne les exploitent pas. Ceci est fonction de la distance séparant les émetteurs de ces dispositifs électroniques. D'ailleurs, cela pourrait représenter à terme, une réelle limite à la maîtrise de notre environnement.

Les sources de perturbations rayonnées (émissions radio) ne sont pas les seules à évoluer et à se densifier. L'apparition de réseaux électriques intelligents utilisant le principe de courants porteurs en ligne (CPL) est un exemple concret de source de perturbations conduites. Les courants à basse, moyenne et haute tension sont aujourd'hui couramment utilisés pour porter des informations pour contrôler et superviser une installation électrique. Ces derniers peuvent être des sources de perturbations non négligeables pour les dispositifs électroniques.

FIGURE 2.3 – Sources d'émissions radio

La figure 2.4 représente une application typique de la technique CPL, qui permet de faire passer des données informatiques sur le réseau électrique, et ainsi étendre un réseau local existant ou partager un accès Internet existant via les prises électriques.

FIGURE 2.4 – Exemple d'application de la technique CPL

#### 2.1.2.2 Sources non intentionnelles

La nature regorge de sources de perturbations électromagnétiques non intentionnelles. La foudre peut créer une décharge électrique de forte puissance susceptible d'influencer le fonctionnement de tout système électronique.

Un autre phénomène naturel auquel les spécialistes s'intéressent de plus en plus est le rayonnement cosmique. En effet, de par ses conséquences dévastatrices sur notre planète, ce type de rayonnement peut mettre hors service toute une installation spatiale à cause de l'énorme onde électromagnétique qu'il génère.

Par ailleurs, il existe une source de perturbations ayant les mêmes conséquences sur le fonctionnement du circuit intégré, c'est le circuit intégré lui même. Du fait de son activité interne toujours plus grande, il est à l'origine d'une émission électromagnétique

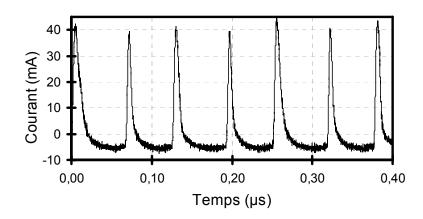

non négligeable. L'activité interne se traduit par la commutation de centaines de milliers de portes logiques à chaque front d'horloge. Des courants importants sont appelés sur les alimentations durant un temps très court, comme le montre la figure 2.5. Ce cas de figure est la principale cause d'émissivité conduite de bon nombre de circuits intégrés[2].

Hormis cet aspect conduit, le fonctionnement des circuits intégrés peut aussi entraîner des émissions électromagnétiques rayonnées. En effet, l'augmentation continue des fréquences de fonctionnement de ces derniers, associée à une densification et une réduction des distances entre circuits, favorise l'apparition d'antennes émettrices parasites. Elles sont non intentionnelles et adaptées à la longueur d'onde des signaux transitant sur ces pistes. Le circuit devient alors une source d'émission rayonnée au regard des circuits voisins.

FIGURE 2.5 – Exemple de pics de courant consommés par un circuit intégré

#### 2.1.3 Couplage des perturbations électromagnétiques

Comme expliqué auparavant, les perturbations électromagnétiques se propagent de la source à la victime via le canal de propagation. A ce stade il est important de distinguer entre mode de couplage et type de couplage.

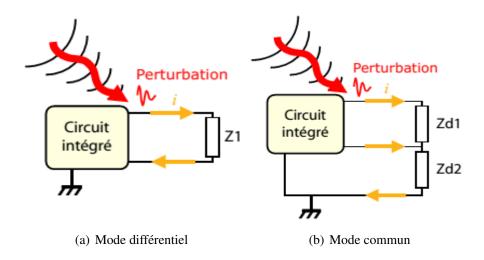

Il existe deux modes de couplage, le mode commun et le mode différentiel[3]. La figure 2.6 résume les deux modes.

Dans le cas d'un couplage en mode différentiel (Figure 2.6(a)), le courant se propage dans un sens dans l'un des conducteurs et dans le sens inverse dans l'autre. En d'autre termes, le chemin de retour ne passe pas directement par la référence du système. En mode commun (Figure 2.6(b)), le courant se propage dans les deux conducteurs dans le même sens et revient par la masse.

Pour chaque mode, deux types de couplage se présentent, à savoir, le couplage conduit et le couplage rayonné.

#### 2.1.3.1 Couplage rayonné

Le couplage rayonné d'une perturbation électromagnétique est évoqué lorsque le support de propagation n'est pas un conducteur. Deux cas de figure sont possibles en fonction de la distance (d) entre la source d'agression et la victime et la longueur d'onde considérée  $\lambda$ .

**Champ proche :** On parle de champ proche si  $d \ll \frac{\lambda}{2\pi}$ . Dans ce cas, une des composantes de l'onde (électrique ou magnétique) est prédominante par rapport à l'autre. La composante électrique domine si l'impédance de l'onde est supérieure à l'impédance du vide. Dans le cas contraire, c'est la composante magnétique.

**Champ lointain :** Dans le cas où  $d \gg \frac{\lambda}{2\pi}$ , le champ lointain est évoqué. Dans ce cas de figure, les deux composantes de l'onde sont orthogonales et forment ainsi le champ électromagnétique.

Avec l'augmentation de la densité des circuits complexes et l'utilisation des nouvelles technologies d'assemblage, ce type de couplage est fréquemment rencontré dans le cas des circuits intégrés comme les MCM (Multi-Chip Module), les SIP (System In Package) et les POP (Package on Package).

FIGURE 2.6 – Les différents modes de couplage d'une perturbation électromagnétique.

## 2.1.3.2 Couplage conduit

Mise à part les différentes manières dont il peut se manifester, le couplage conduit est le type de couplage le plus fréquent dans le cas des circuits intégrés. Ceci est dû à la multitude des mécanismes qui peuvent favoriser la propagation de l'agression électromagnétique entre plusieurs circuits intégrés d'un PCB ou à l'intérieur du circuit lui même. Par exemple le couplage sur les pistes du PCB, les rails d'alimentation ou bien les plans de masse.

Le couplage conduit peut prendre plusieurs formes. Lorsque plusieurs circuits se partagent une même portion de circuit, l'impédance de celle-ci n'est pas nulle. La tension parasite créée à ses bornes chaque fois qu'un courant circule est automatiquement ramenée au dispositif agressé. Ceci donne lieu à un couplage par impédance commune.

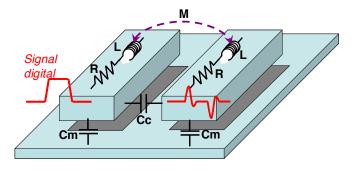

Dans le cas où deux circuits sont très proches, un couplage par diaphonie peut être observé. Il est soit de nature inductive, soit de nature capacitive. La figure 2.7 décrit ce phénomène.

Dans le premier cas, le courant circulant dans le circuit agresseur induit une tension perturbatrice proportionnelle à la valeur de l'inductance mutuelle entre les deux circuits. Dans le deuxième cas, une différence de potentiel au niveau du circuit agresseur fait apparaître un courant perturbateur au niveau de la victime proportionnel à la valeur de la capacité.

Par ailleurs, le couplage conduit des perturbations à l'intérieur d'un circuit intégré est spécialement impacté par les rails d'alimentation et le substrat. Ainsi suivant la topologie de ses rails d'alimentation et de masse, les performances électromagnétiques du circuit peuvent varier. Il est donc souhaitable, dans la limite du possible, de définir une paire d'alimentation différente pour chaque partie du circuit intégré, afin de réduire le couplage entre les différents blocs.

D'un autre côté, du fait que l'ensemble des blocs d'un même circuit partage le même substrat, les blocs bruyants peuvent injecter du bruit dans le substrat. C'est le cas des

FIGURE 2.7 – Exemple de couplage entre deux interconnexions.

blocs numériques. Ce bruit va se propager vers des blocs sensibles tels que les blocs analogiques et éventuellement les perturber[4]. De plus, la propagation du bruit dépend fortement du type de dopage employé, de la présence d'anneaux de garde, de caissons d'isolation....

## 2.2 CEM des circuits intégrés

## 2.2.1 Evolution des circuits intégrés

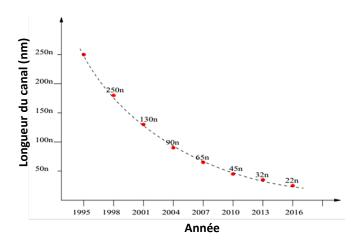

La microélectronique a connu une fantastique évolution depuis l'invention du premier circuit intégré en 1958 par l'Américain *Jack Kilby*. Cette évolution suit la loi de Moore[5], qui prévoit que tous les 18 mois, le nombre de transistors sur une même surface de silicium double. Ainsi la technologie d'intégration a évolué de l'échelle SSI (Small Scale Integration) avec moins de 12 portes par boîtier, à l'échelle ULSI (Ultra Large Scale Integration) avec plus de 10<sup>5</sup> portes. Ce résultats est devenu possible grâce à la réduction des tailles de lithographie qui caractérisent les longueurs minimales des canaux des transistors, mais aussi grâce à l'amélioration des procédés de fabrication des circuits intégrés. La figure 2.8 illustre cette tendance à la miniaturisation.

Alors que cette évolution a permis un énorme essor technologique en rendant possible la construction de circuits performants en termes de vitesse d'exécution et de consommation d'énergie, elle s'accompagne de plusieurs contraintes. C'est le cas d'inter-compatibilité entre d'un côté les différents blocs d'un même circuit et d'un autre côté entre les circuits intégrés sur une même carte.

Pour faire face à ces contraintes, une des solutions envisagées vise à réduire les lon-

FIGURE 2.8 – Évolution de la longueur de canal d'un transistor

gueurs des interconnexions entre circuits en les rapprochant. Des nouvelles méthodes d'intégration sont désormais utilisées, comme l'intégration sur puce ou System on Chip (SoC), et l'intégration sur boîtier ou System in Package (SiP). Cependant, l'augmentation du niveau d'intégration s'est accompagnée de plusieurs changements au niveau des caractéristiques des circuits intégrés, qui impactent directement le comportement électromagnétique de ces derniers.

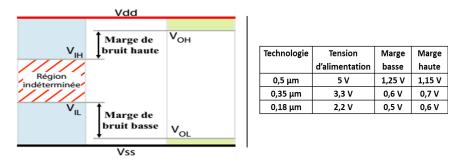

D'abord, l'augmentation des fréquences de fonctionnement et l'accroissement de la complexité de conception implique une augmentation à la fois des niveaux des émissions parasites[6], mais aussi la diminution de l'immunité des composants électroniques[7]. Ensuite, l'amélioration de la consommation des circuits a une influence sur l'immunité. En effet, la diminution des tensions d'alimentations augmente la vulnérabilité des circuits face aux agressions électromagnétique, à cause de la réduction des seuils de commutation et des marges de bruit, ce qui se traduit par des niveaux d'immunité plus bas[8].

Tous ces paramètres doivent être pris en considération lors de la conception des systèmes électroniques mais aussi des circuits intégrés, afin de bien estimer les performances des équipements.

## 2.2.2 Emissivité des circuits intégrés

## 2.2.2.1 Origine des émissions parasites des circuits intégrés

Comme déjà évoqué, les émissions électromagnétiques des systèmes électroniques trouvent leur origine au cœur des circuits intégrés. L'activité interne des circuits intégrés dû notamment à la commutation simultanée des portes logiques, génère des pics de courant importants. De plus, l'ensemble des interconnexions constituées par les broches des boîtiers et le réseau d'alimentation interne, représente autant de chemins de couplage qui, dès lors qu'ils sont traversés par un courant variable, induisent une variation de potentiel[9][10].

De ce fait, le courant de commutation se transforme en un bruit lié au passage de ce courant au travers des inductances parasites des différentes interconnexions[11]. L'amplitude de ce bruit est donnée par l'équation (2.1), où L représente l'inductance parasite du chemin d'alimentation.

$$V_{Noise} \approx L. \frac{di}{dt}$$

(2.1)

Par ailleurs, étant donné que le chemin d'alimentation est aussi constitué de petites résistances parasites, dont la valeur varie entre  $100 \text{ m}\Omega$  et  $10 \Omega[12]$ , le bruit engendré

FIGURE 2.9 – Exemple de tension parasite causée par la commutation simultanée et son spectre[14].

par le courant appelé lors de la commutation des circuits au travers des ces résistances devient contraignant. Les conséquences de ce bruit se manifestent par une chute de potentiel et une dégradation des vitesses de commutation des portes logiques[13].

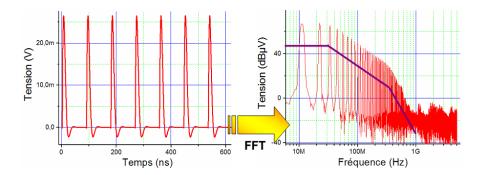

La figure 2.9 présente un exemple de bruit de commutation simultanée ainsi que sa transformée de Fourier. La forme des pics de courant observés présente des temps de montée et de descente rapides et leurs spectre couvre quasiment deux décades du spectre radio-fréquence.

A ce jour, plusieurs solutions ont été proposées pour réduire l'effet des ces émissions[15]. L'idée principale est de contrôler l'impédance des chemins d'alimentation, en agissant par exemple sur les structures d'alimentation, le type de boîtier ou simplement par l'ajout de capacités de découplage[16][17] sur les PCB.

D'autre techniques préconisent d'isoler les blocs les plus émissifs directement sur le silicium, en prévoyant des caissons d'isolation et des anneaux de garde.

Enfin, d'autres stratégies consistent à venir réduire localement les variations de tension sur la source d'émission, en implantant des régulateurs de tension intégrés au plus près des blocs bruyants[18].

## 2.2.2.2 Méthodes normalisées de mesure de l'émission des circuits intégrés

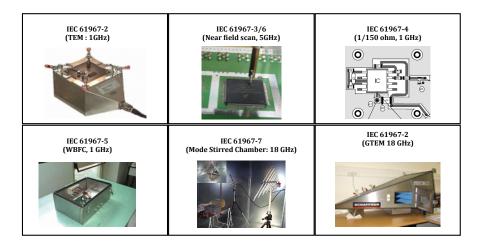

Afin de caractériser l'émissivité des systèmes électroniques (circuits intégrés ou équipements) et de gérer les problèmes liés aux interférences électromagnétiques, des méthodes et des approches de mesures ont été développées. Les procédures de mesure sont décrites dans le document *IEC-61967*[19]. Les différentes méthodes normalisées les plus utilisées sont représentées dans la figure 2.10.

La méthode de mesure la plus utilisée dans le cas des émissions conduites est la mesure l $\Omega/150~\Omega[20]$ . Cette méthode permet la mesure de l'émission conduite sur une ou plusieurs broches de masse d'un circuit intégré en caractérisant l'amplitude de l'ensemble

FIGURE 2.10 – Méthodes standardisées de caractérisation de l'émission des circuits intégrés.

des courants de retour à la masse d'un circuit sur une résistance 1  $\Omega$ . Pour caractériser l'émission conduite des broches d'alimentation et des E/S, une résistance de 150  $\Omega$  est alors utilisée. Dans les deux cas de figure la bande de fréquence peut aller jusqu'à quelques GHz.

Les cellules "TEM" (Transverse Electromagnetic) et "GTEM" (Gigahertz Transverse Electromagnetic) permettent la mesure rayonnée des composants dans un espace restreint[21]. Leur utilisation pour la caractérisation de l'émission rayonnée des circuits va jusqu'à 1 GHz ou 18 GHz, dans le cas respectif de la cellule "TEM" ou la cellule "GTEM". Une cellule "TEM" est un guide d'onde rectangulaire avec un conducteur central interne connecté à un ou deux terminaux. Elle forme ainsi une ligne coaxiale d'impédance caractéristique  $50~\Omega$ . Sa géométrie impose la propagation d'ondes en mode transverse électromagnétique jusqu'à la fréquence de coupure de la cellule.

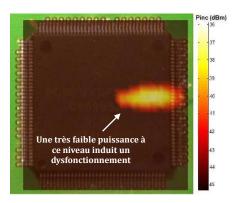

La méthode mesure "NFS" (scan champ proche) est une autre technique de mesure non invasive de l'émission rayonnée[22]. Elle peut être utilisée pour la caractérisation des cartes électroniques et des circuits intégrés. Elle permet de détecter et de cartographier les sources de rayonnement à la surface des composants électroniques. Elle fournit alors une image permettant de distinguer les chemins par lesquels s'écoulent les courants parasites. Le scan champ proche est donc principalement dédié au diagnostic des problèmes liés à l'émission rayonnée.

Pour la mesure d'émission, des techniques de mesures normalisées sont utilisées dans l'industrie jusqu'à 3 GHz que ce soit en mode conduit ou rayonné. Dans la bande 3-10 GHz des solutions existent mais seule la technique rayonnée est utilisée. Dans la bande 10-40 GHz, il est nécessaire de développer de nouvelles méthodes pour couvrir les besoins de l'industrie dans les années à venir.

# 2.2.2.3 Modélisation de l'émission conduite des circuits intégrés et des cartes électroniques

Comme expliqué auparavant, le phénomène d'émissions conduites se traduit par la circulation de perturbations électromagnétiques (courant / tension parasites) dans des conducteurs métalliques. L'origine de ces perturbations est due aux variations de courant et tension, qui génèrent des harmoniques dans un spectre de fréquence très large.

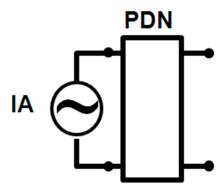

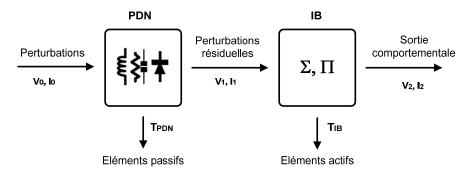

Le modèle proposé pour la simulation des émissions conduites est représenté dans la figure 2.11 (où xx est remplacé par IC dans le cas d'un circuit intégré ou bien par EB dans le cas d'une carte électronique). Il repose sur les mêmes éléments dans les deux cas de figures : circuits intégrés ou cartes électroniques. Ce modèle est décrit par un générateur de bruit IA (Internal Activity) et une impédance associée PDN (Passive Distribution Network). Ces deux blocs sont caractérisés en fonction de la fréquence et peuvent être extraits par mesure ou bien par simulation.

Le modèle CEM des émissions conduites au niveau circuit intégré existe déjà. Il est désormais une norme (IEC62014-3) pour le calcul des émissions conduites. Il a été mis en œuvre pour la modélisation de plusieurs types de composants de niveaux de complexité différents. Une étude détaillée de ce modèle et de ses différents éléments est proposée dans le chapitre 4.

Au niveau carte électronique, les travaux de proposition de modèle et de normalisation sont toujours au stade de projet. L'idée est d'étendre les structures de modèles proposés au niveau circuit intégré aux cartes électroniques. Une approche de modélisation dite «Bottom-Up» est proposée pour modéliser les émissions conduites. Cette méthodologie s'appuie sur l'encapsulation de modèles. Il est ainsi possible de structurer le modèle autour de macro-modèles hiérarchiques résumant les sous-éléments fonctionnels d'une carte électronique.

FIGURE 2.11 – Structure de base du modèle d'émission conduite xxEM-CE.

## 2.2.3 Immunité des circuits

L'immunité d'un circuit qualifie la robustesse de celui-ci face aux perturbations électromagnétiques. On distingue l'immunité interne de l'immunité externe en fonction de la localisation de la source par rapport au circuit victime.

Selon le point d'observation, la frontière entre l'immunité interne et externe peut varier. En effet, pour un équipement électronique, il est question d'immunité interne dans le cas de couplage de perturbations entre les différentes cartes le constituant. Toute autre perturbation est considérée comme externe.

Dans le cas d'une carte électronique, on parle d'immunité interne lorsque les composants présents sur la carte se perturbent entre eux.

Enfin, pour un circuit intégré, l'immunité interne représente le couplage des perturbations entre les fonctions électroniques sur le même substrat.

Dans le cadre de cette thèse, nous nous intéressons à décrire l'immunité des circuits intégrés. Dans ces conditions, nous considérons comme limite entre interne-externe le circuit intégré et son environnement extérieur, en d'autres termes le boîtier du circuit.

## 2.2.3.1 Influence des perturbations sur le comportement des circuits intégrés

Les perturbations électromagnétiques impactent fortement les performances d'un système électronique. Cela dit, les effets observés varient suivant la nature du circuit. Ainsi, le comportement des circuits numériques à ces perturbations est sensiblement différent de celui des circuits analogiques[23].

Pour un circuit analogique, l'apparition des effets de la perturbation, comme un décalage du signal utile ou une fluctuation de tension d'alimentation, varie en fonction du mode de fonctionnement dans la bande de fréquence du composant et hors bande[24][25]. Cependant, ces conséquences présentent un caractère temporaire. Une fois la perturbation disparue, le comportement du composant redevient souvent nominal. Pour les composants numériques ce n'est pas forcément le cas.

En effet, plusieurs phénomènes dûs notamment aux perturbations électromagnétiques peuvent être observés pour ce type de circuit intégré.

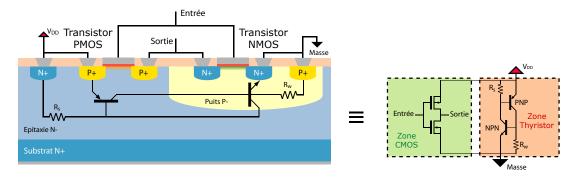

Le phénomène de latchup: Ce phénomène correspond à la mise en conduction d'un thyristor (structure PNPN) parasite présent dans tous les circuits intégrés de technologie CMOS entre l'alimentation et la masse [26][27]. La figure 2.12 illustre ce phénomène dans le cas d'une structure d'inverseurs en technologie CMOS.

Il crée un chemin de conduction parasite direct entre la masse et l'alimentation. Il

cause par conséquent un échauffement supplémentaire important dans le circuit et entraîne une forte augmentation de la consommation. Le court circuit engendré peut conduire à la destruction du circuit si le courant de l'alimentation n'est pas contrôlé.

FIGURE 2.12 – Phénomène de latchup dans les circuits intégrés

Seuil de commutation: La miniaturisation des circuits intégrés associée à la réduction des tensions d'alimentation engendre une diminution des marges de tension. Par conséquent, les seuils de basculement des inverseurs sont réduits. Ce qui rend ainsi les circuits intégrés vulnérables face aux interférences électromagnétiques. La figure 2.13 montre l'évolution des marges de bruit en fonction de l'évolution des technologies.

Si une perturbation est suffisante pour que la somme du signal logique et de la perturbation dépasse le seuil haut de commutation ( $V_{IH}$ ), une inversion de l'état de sortie peut alors être observée[28].

FIGURE 2.13 – Marges de bruit en entrée d'un circuit élémentaire numérique

**Délais de propagation :** Toujours à cause de la diminution des marges de tension, une perturbation peut créer une importante variation sur les fronts d'horloge des circuits intégrés, ce qui peut engendrer l'apparition de gigue et de situation de méta-stabilité. De plus si la fréquence du circuit augmente, alors sa

période et par la même occasion ses marges de délai diminuent. Cela pose de nombreuses contraintes de plus en plus strictes au niveau de la conception des circuits synchrones puisque les signaux doivent être en phase avec l'horloge. Une perturbation qui n'est guère suffisante pour modifier l'état logique peut toujours engendrer une erreur dynamique. Une désynchronisation totale du séquencement des opérations d'un circuit intégré en retardant ou en avançant les fronts d'horloge peut alors se produire.

## 2.2.3.2 Méthodes normalisées de mesure de l'immunité des circuits intégrés

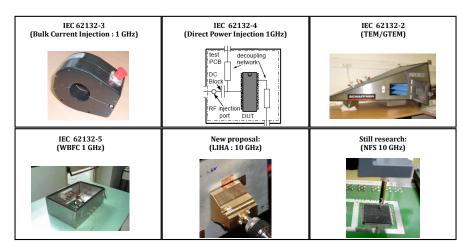

Au niveau de la caractérisation de l'immunité des circuits intégrés, il existe plusieurs méthodes standardisées. Les méthodes de mesure les plus utilisées pour les circuits intégrés sont limitées aujourd'hui en fréquence autour de 1 GHz, mais des travaux d'extension en fréquence sont en cours et les résultats obtenus sont prometteurs. La figure 2.14 montre les différentes méthodes de mesure de susceptibilité de la norme *IEC-62132*[29].

Pour étudier l'immunité conduite, l'injection directe de puissance (DPI) et l'injection de

FIGURE 2.14 – Méthodes standardisées de caractérisation de l'immunité des circuits intégrés.

courant (BCI) sont les méthodes les plus utilisées. La DPI est une méthode d'injection conduite de perturbations radio-fréquences directement sur une broche du circuit intégré. La BCI est utilisée pour caractériser l'immunité des systèmes électroniques. Contrairement à l'injection directe de puissance, elle ne demande pas de modification matérielle du système sous test. Une étude plus détaillée de ces deux méthodes est présentée dans le chapitre 3.

La méthode "Work Bench Faraday Cage" (WBFC) est une proposition néerlandaise[30]. Elle se base sur l'hypothèse selon laquelle les circuits intégrés sont fortement atteints par

FIGURE 2.15 – Exemple de résultat de mesure d'immunité rayonnée avec la méthode NFS.

les perturbations issues de câbles directement connectés au circuit imprimé. De ce fait la perturbation RF est injectée vers le composant sous test au travers d'une impédance de  $150~\Omega$  représentative de la longueur de câble des équipements. La carte sur laquelle est monté le circuit intégré est quant à elle placée à l'intérieur d'une cage de Faraday.

En ce qui concerne l'immunité rayonnée, le NFS (Near-field Scan)[31] et la GTEM[32] sont les méthodes utilisées pour caractériser ce type de comportement au niveau circuit intégré mais aussi au niveau système. En effet, le NFS permet la détection des zones sensibles sur tous types de cartes comme le montre la figure 2.15, cependant cette méthode reste plus un outil d'analyse qu'une méthode de mesure de qualification.

Dans le cas d'une mesure GTEM, le DUT est soudé sur une carte de  $10 \times 10$ cm de dimension de la même manière que dans le cas d'une mesure TEM. Elle offre la possibilité d'injecter des signaux RF dont la fréquence peut atteindre 24 GHz. La face supérieure de la carte (côté composant) est un plan conducteur venant au plus proche des broches du circuit. Cette couche de métal permet de fermer la cellule GTEM qui devient alors analogue à un conducteur coaxial d'impédance caractéristique  $50~\Omega$ , où le septum joue le rôle de l'âme centrale. La gamme de fonctionnement de la cellule va de 150kHz à 6GHz et offre un champ électrique E uniforme suivant l'équation (2.2), avec P la puissance injectée, h la distance entre le septum et le composant et  $Z_C$  l'impédance caractéristique de la cellule[33].

$$E = \frac{\sqrt{Z_C \cdot P}}{h} \tag{2.2}$$

Les principales caractéristiques des méthodes précédemment citées sont résumées dans le tableau 2.2.

| Méthode                 | Nature   | Fréquence<br>d'utilisation | Avantages                                                                               | Inconvénients                                                                           |

|-------------------------|----------|----------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|