# Optimisation énergétique de processus de traitement du signal et ses applications au décodage vidéo

Erwan Nogues

#### ▶ To cite this version:

Erwan Nogues. Optimisation énergétique de processus de traitement du signal et ses applications au décodage vidéo. Traitement du signal et de l'image [eess.SP]. INSA de Rennes, 2016. Français. NNT: 2016ISAR0004. tel-01359031v2

## HAL Id: tel-01359031 https://theses.hal.science/tel-01359031v2

Submitted on 12 Sep 2016

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Spécialité : Traitement du Signal et de l'Image

LABORATOIRE: IETR

Energy Optimization of Signal Processing on MPSoCs and its Application to Video Decoding

#### Thèse soutenue le 02.06.2016

devant le jury composé de :

#### **Emmanuel Casseau**

Professeur à l'Université de Rennes 1 / Président

#### **Bertrand Granado**

Professeur à l'Université Pierre et Marie Curie / Rapporteur

#### Cécile Belleudy

Maître de Conférences HDR à l'Université de Nice Sophia Antipolis / Rapporteur **Dominique Ginhac**

Professeur à l'Université de Bourgogne Franche-Comté / Examinateur

Eduardo Juárez

Associate professor à l'Université Polytechnique de Madrid / Examinateur

Maître de Conférences HDR à l'Université de Bretagne Sud / Examinateur Maxime Pelcat

Maître de Conférence à l'INSA Rennes / Co-Encadrant

#### Daniel Ménard

**Eric Senn**

Professeur à l'INSA Rennes / Directeur de thèse

# Energy Optimization of Signal Processing on MPSoCs and its Application to Video Decoding

**Erwan Nogues**

# Contents

| A | ckno | wledgements                                                                                                                         | 1      |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------|--------|

| 1 | Intr | coduction                                                                                                                           | 3      |

|   | 1.1  | General Context: Video in Mobile Networks                                                                                           | 3      |

|   |      | 1.1.1 The Video Eco-system                                                                                                          | 4      |

|   |      | 1.1.2 An Increasing Use of Mobile Devices for Video Applications                                                                    | 4      |

|   |      | 1.1.3 MPSoC Architectures: Making High Performance Mobile Systems                                                                   | 5      |

|   |      | Possible 1.1.4 Enhanced Software-based Energy Management in MPSoCs                                                                  | о<br>5 |

|   |      | 1.1.4 Emilanced Software-based Energy Management in Mr Socs 1.1.5 A Wider Range of Supported Applications in Mobile Devices - HEVC: | J      |

|   |      | a Promising New Standard                                                                                                            | 5      |

|   | 1.2  | Objectives of the Thesis                                                                                                            | 6      |

|   | 1.3  | Contributions of the Thesis                                                                                                         | 7      |

|   | 1.4  | Outline                                                                                                                             | 8      |

|   |      |                                                                                                                                     | Ü      |

| Ι | Sco  | ope and Motivations                                                                                                                 | 9      |

| 2 | Em   | bedded Video Context                                                                                                                | 11     |

|   | 2.1  | Motivation for Energy Optimization                                                                                                  | 11     |

|   | 2.2  | Video Applications                                                                                                                  | 11     |

|   |      | 2.2.1 The Video Chain and its Energy Consumption                                                                                    | 11     |

|   |      | 2.2.2 The MPEG Video Compression Standards                                                                                          | 15     |

|   | 2.3  | Energy in Electronic Components                                                                                                     | 20     |

|   |      | 2.3.1 Sources of Energy Consumption                                                                                                 | 20     |

|   |      | 2.3.2 Static Part                                                                                                                   | 20     |

|   |      | 2.3.3 Dynamic Part                                                                                                                  | 22     |

|   |      | 2.3.4 Comparison between Dynamic and Static Parts                                                                                   | 22     |

|   |      | 2.3.5 Techniques for Energy Reduction                                                                                               | 22     |

|   | 2.4  | Performance and Quality Assessment                                                                                                  | 31     |

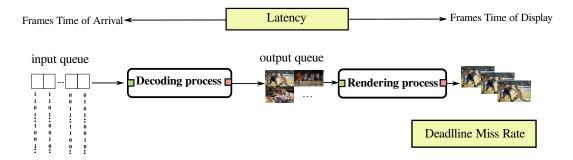

|   |      | 2.4.1 Video Decoding Set-up                                                                                                         | 32     |

|   |      | 2.4.2 Deadline Miss Rate (DMR)                                                                                                      | 32     |

|   |      | 2.4.3 Latency                                                                                                                       | 32     |

|   |      | 2.4.4 Power and Energy                                                                                                              | 33     |

CONTENTS

|    | 2.5 | Conclu  | sion                                                               | 33          |

|----|-----|---------|--------------------------------------------------------------------|-------------|

| 3  | Low | Power   | r decoders                                                         | 35          |

|    | 3.1 | Introd  | $\operatorname{uction}$                                            | 35          |

|    | 3.2 |         | Level Approaches to Low Power Decoding                             | 35          |

|    |     | 3.2.1   | Changing Resolution                                                | 36          |

|    |     | 3.2.2   | Changing Sampling Time                                             | 36          |

|    |     | 3.2.3   | Changing Quality                                                   | 37          |

|    |     | 3.2.4   | Scalable Extensions of Video Compression Standards                 | 38          |

|    | 3.3 |         | ase of Specialized Circuits for Low Power Decoding                 | 38          |

|    | 0.0 | 3.3.1   | Application Specific Integrated Circuit                            | 38          |

|    |     | 3.3.2   | Digital Signal Processors - DSP                                    | 30          |

|    | 3.4 |         |                                                                    | 36          |

|    | 3.4 |         | ase of Software-based Video Decoding Based on a General Purpose    | 20          |

|    |     | Proces  |                                                                    | 39          |

|    |     | 3.4.1   | Intel-based implementations                                        | 39          |

|    |     | 3.4.2   | ARM-based implementations                                          | 40          |

|    |     | 3.4.3   | Software-based Implementations                                     | 41          |

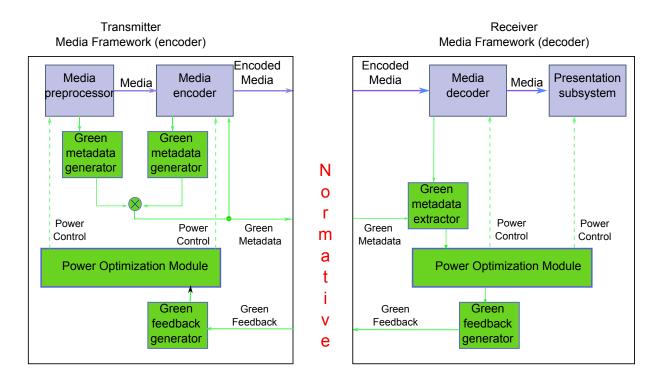

|    | 3.5 |         | ormative Approach: MPEG Green Metadata                             | 41          |

|    |     | 3.5.1   | Scope and Requirements                                             | 41          |

|    |     | 3.5.2   | Current Green Metadata Proposals                                   | $4^{\circ}$ |

|    |     | 3.5.3   | Conclusion on Low Power Decoders                                   | 45          |

|    |     |         |                                                                    |             |

| II | Co  | ntribu  | ıtions                                                             | 47          |

| 4  | Ene | rgy Efl | ficient Rapid Prototyping of Signal Processing                     | 49          |

|    | 4.1 | Introd  | $\operatorname{uction}$                                            | 49          |

|    |     | 4.1.1   | Motivation                                                         | 49          |

|    |     | 4.1.2   | Related Work                                                       | 50          |

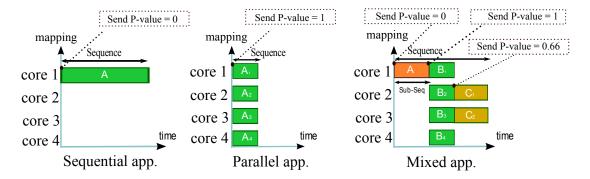

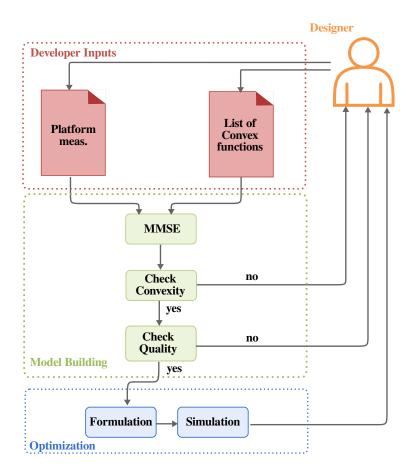

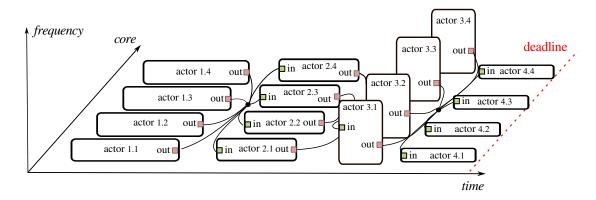

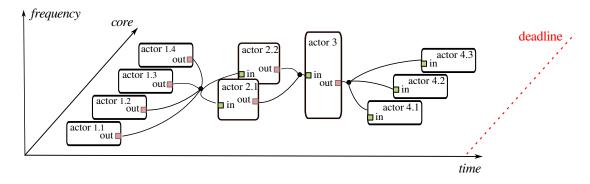

|    | 4.2 | Assiste | ed Design of Signal Processing Applications                        | 52          |

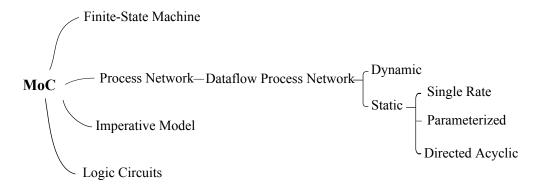

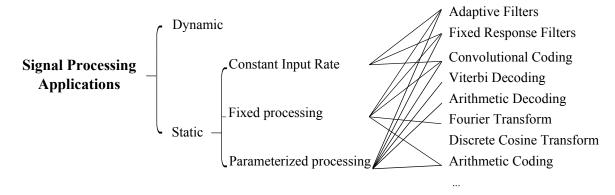

|    |     | 4.2.1   | Models Of Computation                                              | 52          |

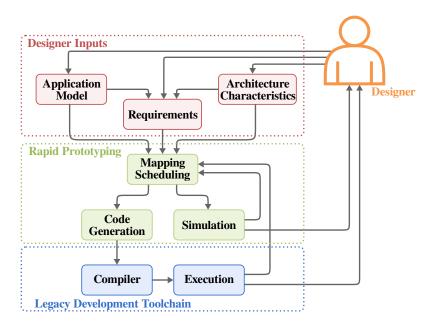

|    |     | 4.2.2   | Rapid Prototyping                                                  | 53          |

|    |     | 4.2.3   | Assisted Design using Algorithm Dataflow Modeling and Online Power |             |

|    |     | 1.2.15  | Optimization                                                       | 54          |

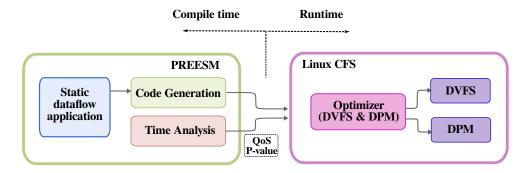

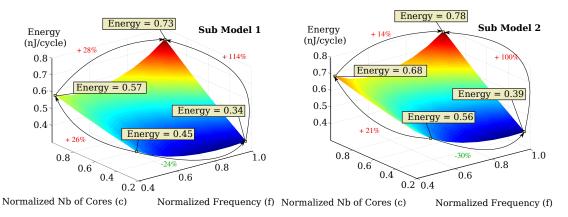

|    | 4.3 | Energy  | Optimization of an Application Described with a Dataflow Model of  | Ο.          |

|    | 1.0 |         | itation                                                            | 58          |

|    |     | 4.3.1   | Description of the Energy Model of an Application Considered as a  | 90          |

|    |     | 4.5.1   |                                                                    | 58          |

|    |     | 420     | "Black Box"                                                        |             |

|    | 4.4 | 4.3.2   | Framework Description for Minimizing Energy on a Real Platform     | 64          |

|    | 4.4 |         | sion of the Energy Optimisation Problem to MPSoCs with DVFS and    |             |

|    |     |         |                                                                    | 71          |

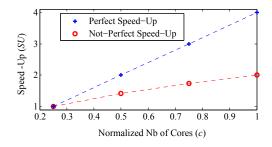

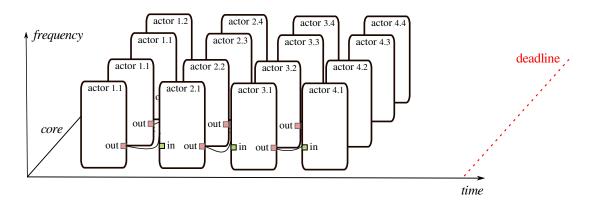

|    |     | 4.4.1   | An Extension to Multicore Plaforms                                 | 71          |

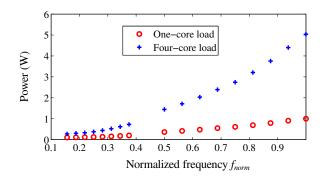

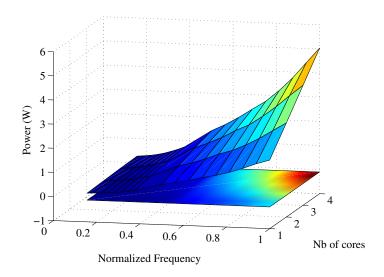

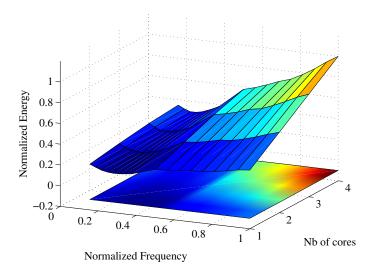

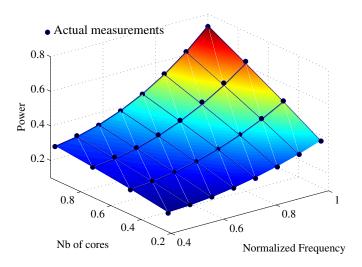

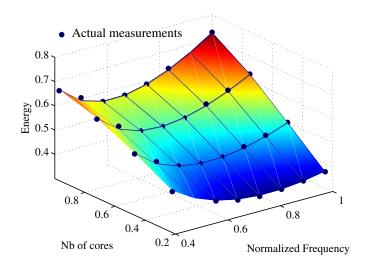

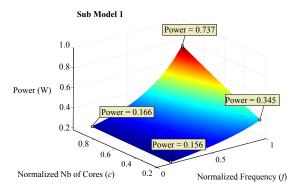

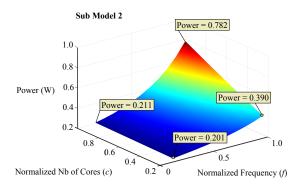

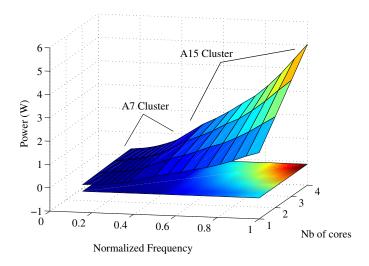

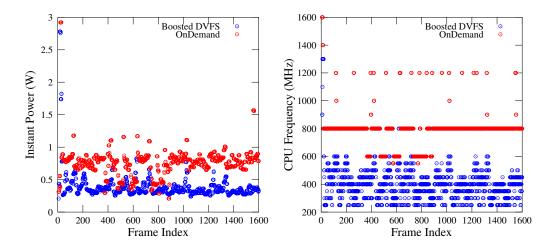

|    |     | 4.4.2   | Multicore Energy Modeling with DVFS and DPM                        | 72          |

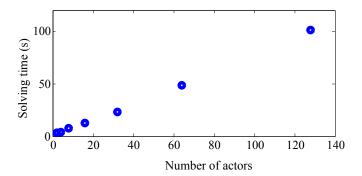

|    |     | 4.4.3   | Extension of the Convex Solver Framework to Solve the MPSoC En-    |             |

|    |     |         | ergy Optimization Problem                                          | 74          |

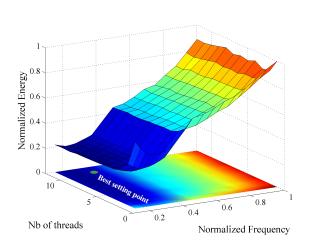

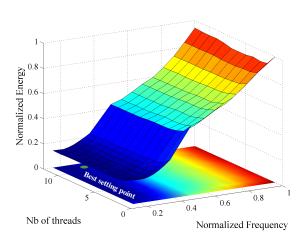

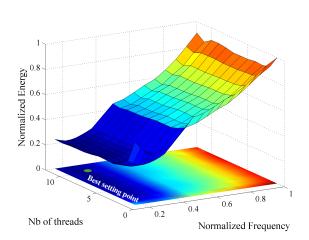

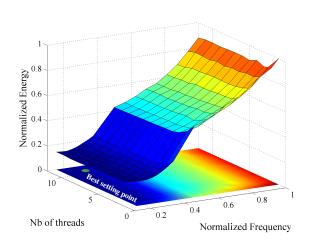

|    |     | 4.4.4   | Exploiting the MPSoC Energy Model to Explore the Design Space      |             |

|    |     |         | for Signal Processing Applications                                 | 76          |

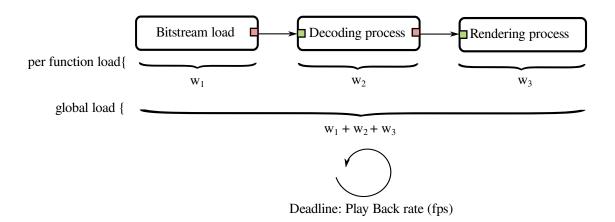

|    | 4.5 | Energy  | Efficient Offline Video Decoding: Use Case and Application to HEVC | 84          |

|    |     | 4.5.1   | Context of an HEVC Decoder                                         | 84          |

|    |     | 4.5.2   | Experimental Set-up                                                | 85          |

*CONTENTS* iii

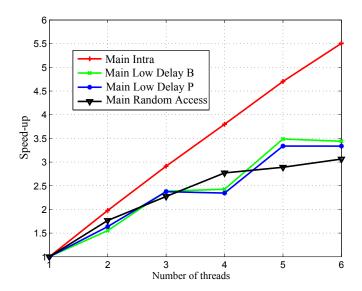

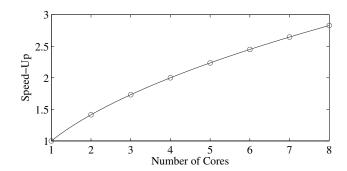

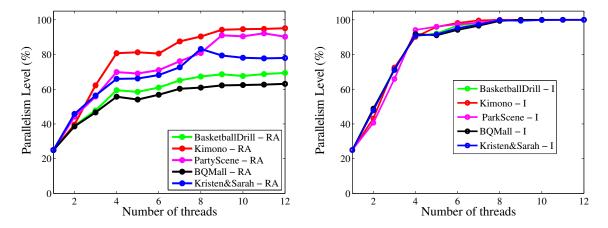

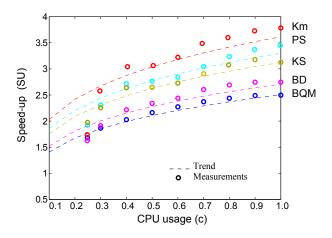

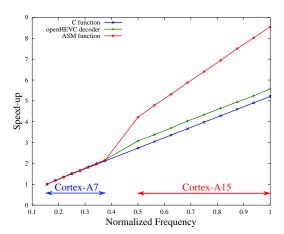

|   |     | 4.5.3 HEVC Decoder Parallelism and Speed-up                            | 86   |

|---|-----|------------------------------------------------------------------------|------|

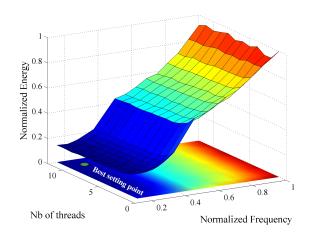

|   |     | 4.5.4 Determining the Most Energy Efficient Point at the Design Phase  | 86   |

|   |     | 4.5.5 Experimental Verification of the Offline Decoding Energy Optimal |      |

|   |     | Setting Point                                                          |      |

|   | 4.6 | Conclusion and Perspectives                                            | 93   |

| 5 | Vid | leo Aware DVFS for Energy Efficient Video Decoding                     | 95   |

|   | 5.1 | Introduction                                                           | 95   |

|   | 5.2 | Existing HEVC Decoder Implementations                                  |      |

|   |     | 5.2.1 Low Power HEVC Decoders                                          |      |

|   |     | 5.2.2 DVFS-Based Video Decoders for GPP                                | 96   |

|   |     | 5.2.3 Dynamic Frequency Scaling Policies                               |      |

|   |     | 5.2.4 HEVC Decoders with Integrated DVFS                               | 97   |

|   |     | 5.2.5 Contributions of the Chapter                                     |      |

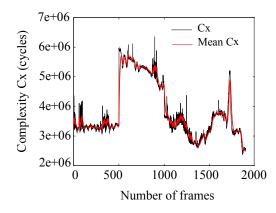

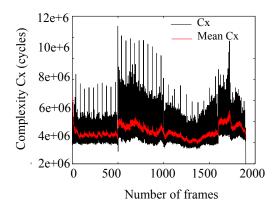

|   | 5.3 | HEVC Decoding System Analysis                                          | 99   |

|   |     | 5.3.1 Decoder Architecture and Performance                             |      |

|   |     | 5.3.2 Performance Metrics                                              |      |

|   | 5.4 | Characteristics of the ARM big.LITTLE Targeted Platform                | 103  |

|   |     | 5.4.1 General set-up                                                   |      |

|   |     | 5.4.2 Quasi-Heterogeneous Architecture                                 |      |

|   |     | 5.4.3 Power Management                                                 |      |

|   | 5.5 | DVFS Assisted HEVC Decoder                                             |      |

|   |     | 5.5.1 State-of-the-Art Method 1: Optimal DVFS HEVC Decoder             |      |

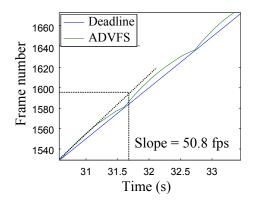

|   |     | 5.5.2 Proposed Method 2: Boosted DVFS HEVC Decoder                     |      |

|   |     | 5.5.3 Proposed Method 3: Adaptive DVFS HEVC Decoder                    |      |

|   | 5.6 | Performance Results                                                    |      |

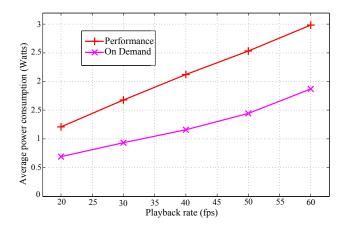

|   |     | 5.6.1 Power Performance                                                |      |

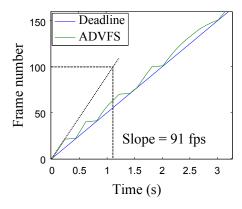

|   |     | 5.6.2 Optimal DVFS accuracy                                            |      |

|   |     | 5.6.3 Selected Frequencies                                             |      |

|   |     | 5.6.4 On-core - Off-core Power Consumption                             |      |

|   |     | 5.6.5 Real Time and Latency performance                                |      |

|   | 5.7 | Conclusion                                                             | 118  |

| 6 | Mo  | dified Decoder for Energy Efficient HEVC Decoding                      | 119  |

|   | 6.1 | Introduction                                                           |      |

|   | 6.2 | Approximate Computing                                                  |      |

|   | 6.3 | Proposed Method: Algorithmic-level Approximate Computing               |      |

|   |     | 6.3.1 Techniques of Approximate Computing                              |      |

|   |     | 6.3.2 Classifying Application Signal Processing Blocks                 |      |

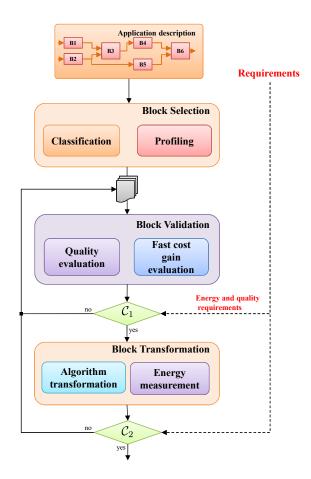

|   |     | 6.3.3 A New Design Method for Algorithmic-level Approximate Computing  |      |

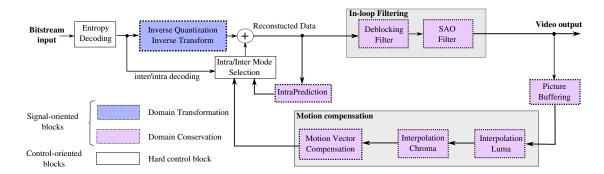

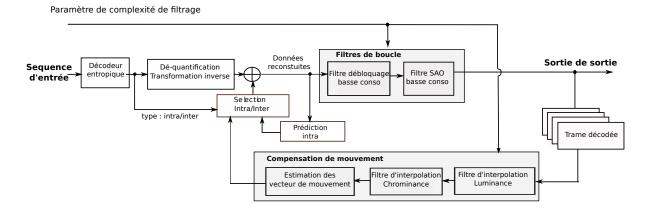

|   | 6.4 | Algorithmic-level Approximate Computing of an HEVC Decoder             |      |

|   |     | 6.4.1 Decomposition of HEVC Decoding into Signal Processing Blocks     |      |

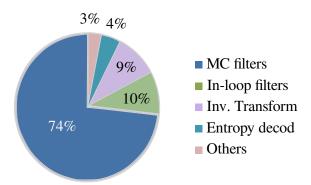

|   |     | 6.4.2 Classification of the Signal Processing Blocks                   |      |

|   |     | 6.4.3 Profiling Results                                                |      |

|   |     | 6.4.4 HEVC Decoder Block Selection                                     |      |

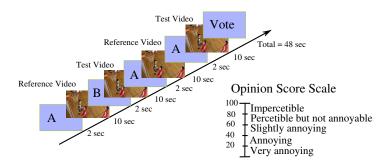

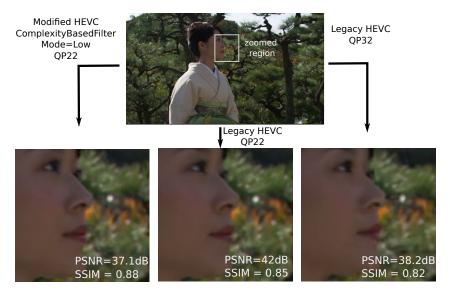

|   |     | 6.4.5 Quality Evaluation for HEVC Decoder Block Validation             |      |

|   | 6.5 | HEVC Decoder Block Transformations                                     |      |

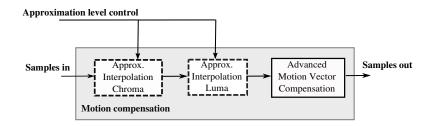

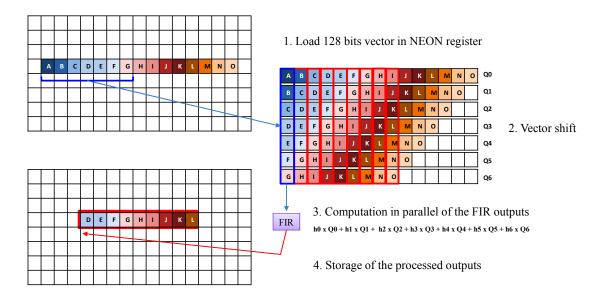

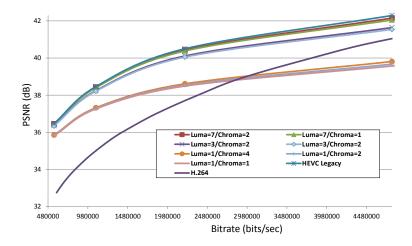

|   |     | 6.5.1 Block Class Modification of the Motion Compensation Filters      |      |

|   |     | 6.5.2 Complexity Reduction of MC Filters                               | -132 |

iv CONTENTS

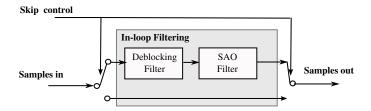

|   |       | 6.5.3        | Computation Skipping of the Motion Compensation Filters and In-                                                             |              |

|---|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------|--------------|

|   |       | _            | loop Filters                                                                                                                |              |

|   | 6.6   | <del>-</del> | ${ m iments}$                                                                                                               |              |

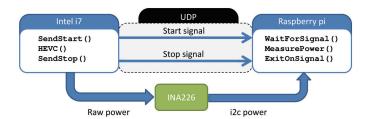

|   |       | 6.6.1        | Experimental Set-up                                                                                                         |              |

|   |       | 6.6.2        | Energy and Power measurements                                                                                               |              |

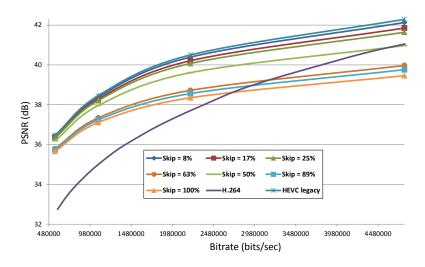

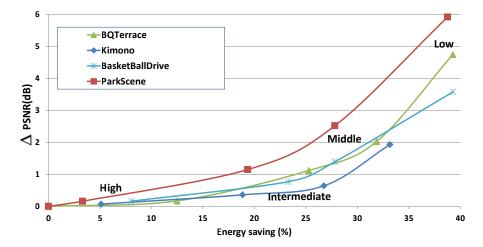

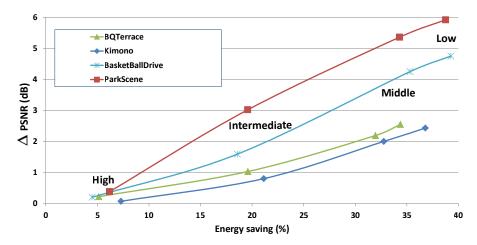

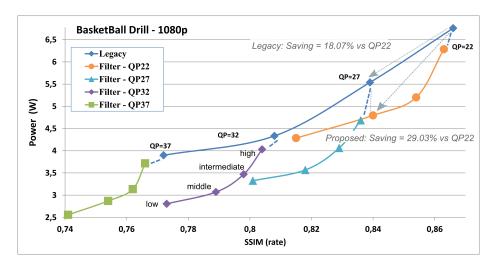

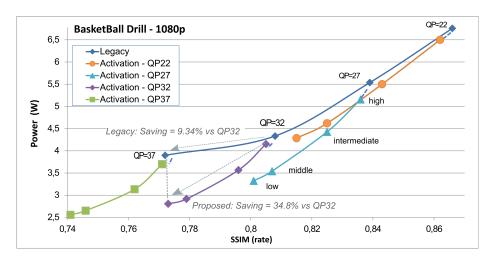

|   |       | 6.6.3        | Energy Reduction and QoS Tradeoff exploration                                                                               |              |

|   | 6.7   | -            | sal for Green Metadata Extension                                                                                            |              |

|   | 6.8   | Concl        | usion                                                                                                                       | ւ46          |

| 7 | Con   | clusio       | n 1                                                                                                                         | 49           |

|   | 7.1   |              | ary                                                                                                                         | 49           |

|   | 7.2   |              | e Work                                                                                                                      |              |

|   | •     | 7.2.1        | Energy modeling and Design Enhancement                                                                                      |              |

|   |       |              | 7.2.1.1 Enhanced Energy Modeling                                                                                            |              |

|   |       |              | 7.2.1.2 Support of Complex Applications                                                                                     |              |

|   |       | 7.2.2        | Video Power Efficiency                                                                                                      |              |

|   |       |              | 7.2.2.1 Video Encoding on Different Hardware Platforms 1                                                                    |              |

|   |       |              | 7.2.2.2 Embedded DVFS Video Players                                                                                         |              |

|   |       |              | 7.2.2.3 New Interpolation Filters for Future Video Coding - An                                                              |              |

|   |       |              | Alternative for Low Power Decoders                                                                                          | 152          |

|   |       |              | 7.2.2.4 New Interpolation Filters combined with Approximate Com-                                                            |              |

|   |       |              | puting Operators for ASICs                                                                                                  | 152          |

| A | Frei  | nch Su       | mmary 1                                                                                                                     | <b>53</b>    |

|   | A.1   | Introd       | $egin{array}{c} \operatorname{luction} & \ldots & $ | 153          |

|   |       | A.1.1        | Sources de consommation sur les systèmes embarqués                                                                          | 153          |

|   |       | A.1.2        | Contexte de la vidéo en électronique embarquée                                                                              | 154          |

|   |       | A.1.3        | Problématique de la thèse                                                                                                   | 155          |

|   |       | A.1.4        | Plan                                                                                                                        | 155          |

|   | A.2   | Protot       | sypage rapide sur systèmes multicoeurs                                                                                      | 155          |

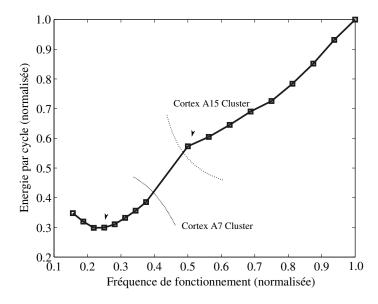

|   |       | A.2.1        | Modélisation de l'énergie pour un processeur à fréquence variable 1                                                         |              |

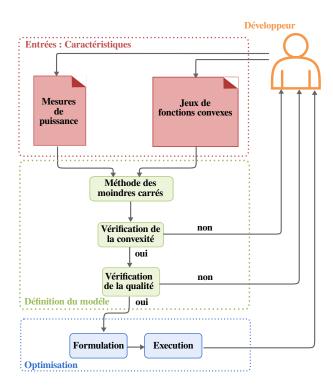

|   |       | A.2.2        | Flux de travail                                                                                                             | 157          |

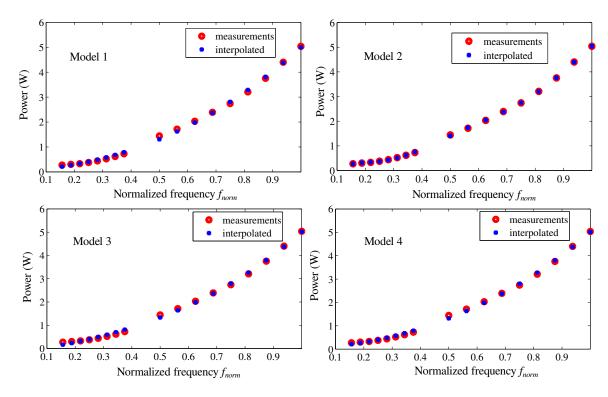

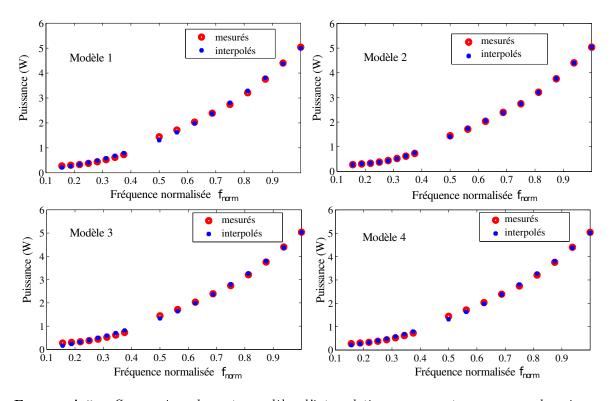

|   |       | A.2.3        | Évaluation du modèle                                                                                                        | 158          |

|   |       | A.2.4        | Discussions                                                                                                                 | 160          |

|   | A.3   | Décod        | eur embarqué $\operatorname{HEVC}$ avec ajustement dynamique de la fréquence $1$                                            | 160          |

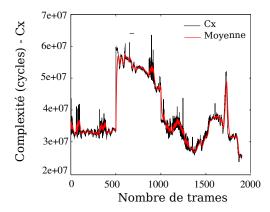

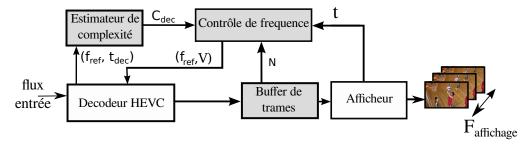

|   |       | A.3.1        | 1                                                                                                                           | 160          |

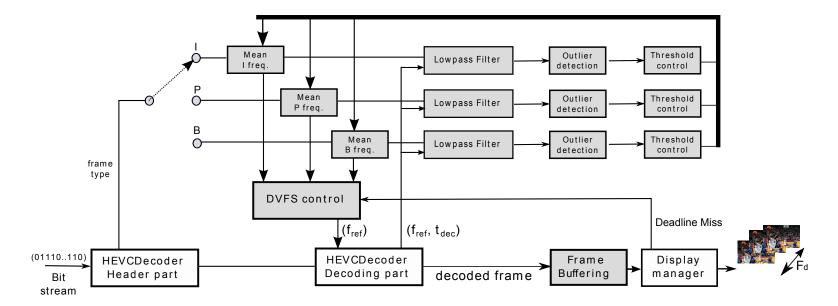

|   |       | A.3.2        | Architecture de la proposition                                                                                              | 160          |

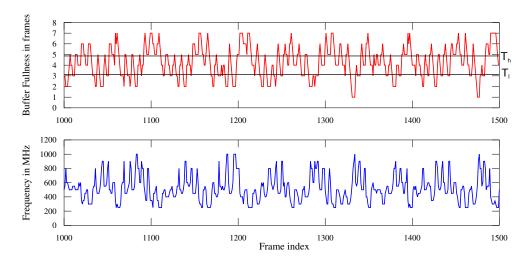

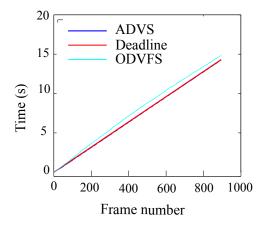

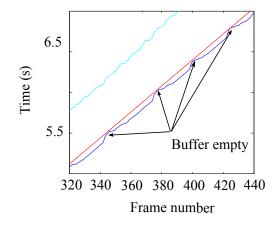

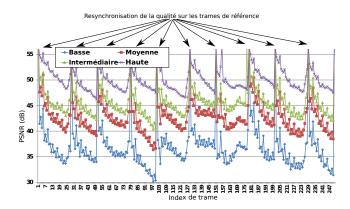

|   |       | A.3.3        |                                                                                                                             | 161          |

|   | A.4   |              | eur modifié HEVC                                                                                                            | L <b>6</b> 3 |

|   |       | A.4.1        | Génération de filtres simplifiés                                                                                            | 164          |

|   |       | A.4.2        | ±                                                                                                                           | 165          |

|   |       | A.4.3        |                                                                                                                             | 165          |

|   |       |              | A.4.3.1 Séquences de test                                                                                                   | 166          |

|   |       |              |                                                                                                                             | 166          |

|   | A.5   | Concl        |                                                                                                                             | 167          |

|   |       |              | A.5.0.3 Perspectives                                                                                                        | 167          |

| A | crony | /ms          | 1                                                                                                                           | 77           |

#### Acknowledgements

First, I would like to thank my thesis director Pr. Daniel Ménard and my advisor Dr. Maxime Pelcat for their guidance, their support, and their trust for the last years. Thank you for giving me the opportunity to pursue a PhD on such an interesting topic and in such a motivating and friendly working environment. Daniel, thank you for your advice during all this work, your great expertise and your strategic orientations to move forward. Maxime, thank you for your open-mindedness at any time during this PhD, your capability to be source of proposals and being always ready to help. All and all, we made a great team.

I want to thank also Pr. Jean-François Nezan to encourage me to start this PhD and put everything together so I could meet Daniel and Maxime. It's been a long trip since Sofia, Studentskigrad, July 1998.

I want to express my gratitude to Pr. Bertrand Granado and Dr. Cécile Belleudy for being part of the PhD committee and for taking time to review this thesis. I also want to thank Pr. Emmanuel Casseau for presiding the PhD committee and Pr. Dominique Ginhac, Dr. Eduardo Juárez and Dr. Eric Senn for being members of the PhD committee.

I also would like to thank Pr. Olivier Desforges and Pr. Luce Morin for welcoming me within the IETR Image group. More generally, I want to thank all the members of the image group for making me feel part of the team from the beginning.

Special thanks to all my very talented office-mates during this work, I learned a lot: Karol Desnos, Julien Heulot, Antoine Lorence, Judicaël Menant and Alexandre Mercat. Thanks also to Wassim Hamidouche, Erwan Raffin and Mickael Raulet for their support on HEVC. Thanks to Alexandre Sanchez for our interesting talks about Malotru. Also, thanks to Frédéric Garesché for his IT support and many thanks to Corinne Calo, Aurore Gouin and Jocelyne Trémier for their administrative support.

I am also very grateful to all the students that helped me with their hard work: Romain Berrada, Louis-Paul Cordier, Glenn Herrou, Morgan Lacour, Kévin Reuzé, Ladislas Robin and Simon Urosevic.

I would like to thank all the people from the Green Video project, especially Xavier Ducloux. I really appreciated our technical discussions.

My PhD also started very well with a good kick-off with Simon Holmbacka, my Linux friend for Finland.

I would like to thank Pr. Arnaud Martin and Dr. Mouloud Kharoune for giving me the opportunity of my first teaching experience at IUT Lannion. Teaching was a primary goal of doing a PhD.

Finally, thanks also to my former and new colleagues for their support: Anis, Christophe, Daniel, Fred, Jean-François, Jean-Yves, Landry, Laurent, Pascal (x2), Pierre (x2), Pierrick, Michel, Nicolas, Sébastien, Thierry, Yannick.

Je tiens aussi à remercier ma famille : Yvon, Marie-Annick, Sébastien, Carole, Maurice et Marie-Madeleine pour leurs encouragements et leur soutien durant ces années de thèse.

Enfin, je ne remercierai jamais assez ma chère compagne, Aude, qui m'aura encouragé à démarrer ce projet pas comme les autres dès que l'idée a germé dans mon esprit. Et merci de m'avoir toujours soutenu. Merci aussi à mes deux petits fans, Louise et Martin. On aura passé du bon temps à discuter tous les matins sur le chemin de l'école. Au final, cette expérience restera unique.

Introduction

#### 1.1 General Context: Video in Mobile Networks

More than ever, we live in a society where images are everywhere. In particular, our daily lives have been invaded by images and videos. The time when the only way to watch a content was to sit in front of a television is over. Modes of video utilization have been much disrupted over the last fifteen years. This progress was made possible thanks to the availability of efficient coding techniques, communication systems capable of supporting large bandwidth, and highly performing electronic systems. All these elements combined supply a virtuous circle where improved coding techniques enable better contents to be transmitted, increased communication bandwidth makes it possible to address more people or more advanced features, and new generations of electronic components provide better conditions to watch video. All in all, people can now access video content just about anywhere and on a wide range of devices.

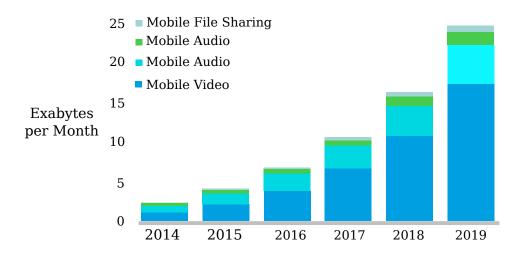

Figure 1.1: Cisco analysis of data exchange of mobile networks [Cis15]

4 Introduction

As a consequence, networks are now primarily used to supply video content to users. Cisco regularly publishes the data usage within the worldwide network [Cis15]. As depicted in Figure 1.1, data exchange is exploding together with the increasing number of supported video applications.

#### 1.1.1 The Video Eco-system

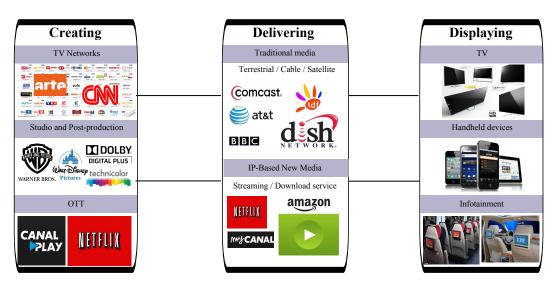

For a long time, the video eco-system has been limited to broadcasting video contents. These contents were traditionally centralized on servers owned by broadcasters. This situation drastically changed with the arrival of new uses cases. The production of video content is much easier today than it used to be. Video transmission is made possible by advanced network capabilities and video processing can be performed on a wide range of devices. As depicted in Figure 1.2, the content is not only focused on TV networks and studio production. Over-The-Top (OTT) service providers are likely to have a major role in the new eco-system thanks to IP-based media services. Furthermore, video decoders are embedded onto a wide range of devices: from TV to mobiles or tablets. The requirements are then different if the video content targets high definition televisions or midrange smartphones.

Figure 1.2: The Video Ecosystem

The final cut is done by the user experience. The user requirement is to access video content with a minimum of Quality of Service (QoS) or Quality of Experience (QoE). The metrics for the evaluation of quality are numerous: image resolution, sampling frequency of the video, latency or up-time of the device...

#### 1.1.2 An Increasing Use of Mobile Devices for Video Applications

The video eco-system is now driven by the utilization of video in mobility. This fact is mainly due to the increasing use of video sharing applications (e.g. Youtube, Netflix), social networks (e.g. Facebook, Instagram), IPTV on mobile and video-conferencing. These new practices, combined with the recent advances on network capabilities, induce an exponentially growing traffic. However, what characterizes mobile devices is their capacity of being autonomous and guaranteeing an utilization in mobility. The challenges for these devices are to support ever more complex features (e.g. new video codecs), to remain extensible to

new features and to function under the very strict power envelope offered by batteries. For example, Carollet al. report that the processing resources can consume more than 60% of the total power consumption to play back an H.264/AVC video [RJS+10]. Software-based solutions are some of the possible alternatives for video processing. Indeed, they offer flexibility to adapt devices to new features and video codecs. However, it is a difficult task to design software-based video decoders that are also energy efficient.

# 1.1.3 MPSoC Architectures: Making High Performance Mobile Systems Possible

Video processing is achieved with sophisticated algorithms that demand a lot of computational power. The common way to improve system performance accordingly is to increase the processing frequency and process more in the same period of time. However, increasing processor clock frequency is only possible to a certain extent because of power dissipation. The phenomenon is known as the power wall and pressures the semiconductor industry to switch to multicore architectures. Such a solution can provide more computational capabilities for a given power budget. Thanks to this technological advance, applications such as video decoding, that were traditionally hardwired, can now be processed in software [BAMG+13, CAMJ14, CAML+13a, RNH+15, CPG+13].

Embedded systems benefit from the multicore architecture enhancements to improve their computational capabilities. As of today, modern designs of portable devices use multicore architecture to support high-end features [exy13].

#### 1.1.4 Enhanced Software-based Energy Management in MPSoCs

Energy efficiency is critical to handheld devices. On top of providing high performing processors, the modern SoCs also provide means to control the power consumption of the device. At a synthetic level, the power consumption of an electronic device is composed of two elements, the static power and the dynamic power.

Firstly, the static power does not depend of the processing load. It depends on the circuit fabrication technology and area (number of transistors). To reduce it, the processor shall enter into sleep modes when idling. Secondly, the dynamic power is determined by the processing activity together with the voltage supply and the processing frequency. Scaling down the frequency of operation and the voltage supply reduces the dynamic power. On the one hand, mechanisms like Dynamic Power Management (DPM) are now available in SoCs to reduce the static power by shutting down blocks or clocks during idle periods. On the other hand, Dynamic Voltage Frequency Scaling (DVFS) adapts dynamically both the frequency and the supply voltage. These mechanisms are made available at the user space level to design low power embedded software implementations.

# 1.1.5 A Wider Range of Supported Applications in Mobile Devices - HEVC: a Promising New Standard

From the application point of view, the challenge lies in providing high compression rates for the transfer of videos. Motion Picture Expert Group (MPEG) introduced in 2013 the High Efficiency Video Coding (HEVC) standard that improves the bitrate by 50% compared to its predecessor H.264 at the same video quality. As an example, this surplus of bandwidth can be used by service providers to offer the video services to more devices. The video streaming case is the typical example of how the video offer can make the most

6 Introduction

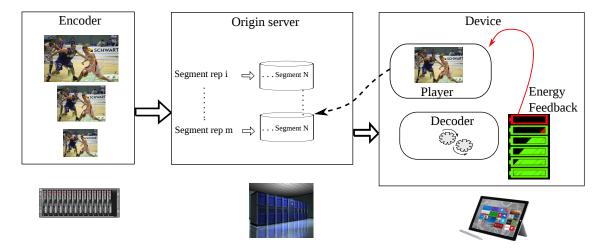

of the latest technological advances. It is implemented via the MPEG Dynamic Adaptive Streaming over HTTP (DASH) standard [Sod11].

Wide range of available versions

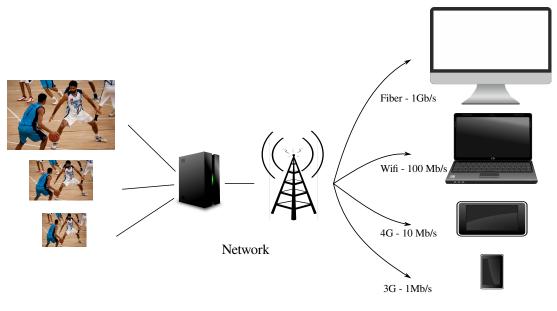

Wide range of devices

Figure 1.3: Example of streaming applications using the diversity of the network and addressing a wide range of devices

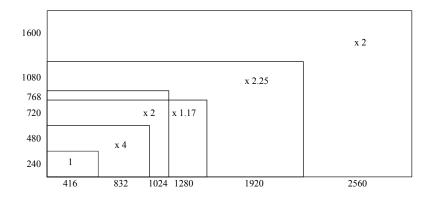

As depicted in Figure 1.3, several versions of the same content are available at the MPEG DASH server level. Depending on the network capabilities of the physical layer and on the features supported by the device, the initial content can be scaled down to adapt its payload. For example, the resolution can be resized, the display frame rate can be reduced or the quality can be lowered. All these features are intrinsically supported by HEVC. The feasibility of HEVC decoding on a wide range of devices is thus essential to the adoption of the standard. MPEG paid a special attention at the design phase of HEVC to take into account its complexity. Therefore, software based implementations like OpenHEVC [Ope] are available. They enable quick market penetration of this new standard with no hardware upgrade.

To be widely adopted, a new standard such as HEVC needs to prove itself in terms of energy efficiency. HEVC shall use efficiently all the latest technical advances of the underlying platform, i.e. parallelism, multicore architecture and low power design techniques. On top of that, MPEG acknowledged that low power video decoding is a real challenge. Therefore, the standardization body launched an ad-hoc working group also called Green Metadata [Gre13] to offer means to reduce the power consumption of the video decoding.

## 1.2 Objectives of the Thesis

The main objective of this thesis is to analyze how the low power management techniques embedded in modern System-on-Chip (SoC) can be utilized together with the application requirements to meet user expectations. Even though numerous techniques exist on Multiprocessor SoC (MPSoC) to design applications in a low power fashion, using them on a complex use case is far from easy.

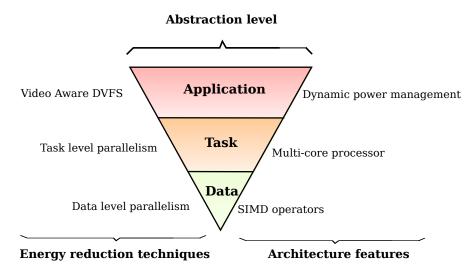

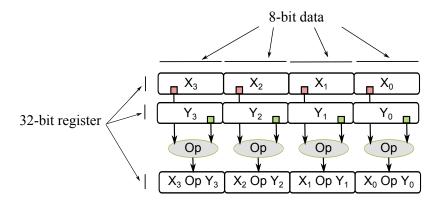

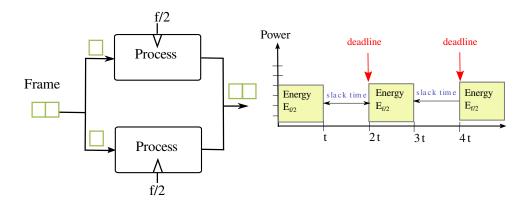

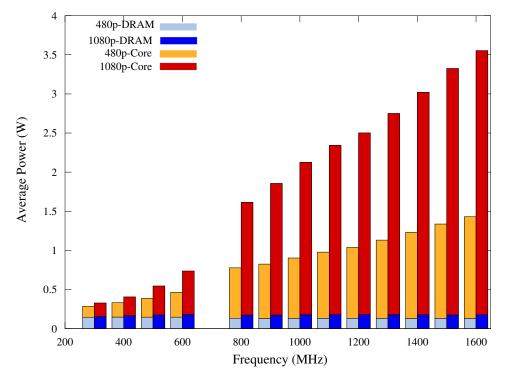

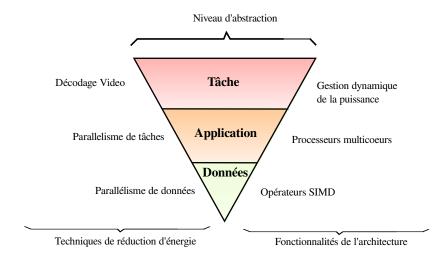

By using a top-down approach as shown in Figure 1.4, this thesis aims at providing a comprehensive analysis of the energy efficiency at the different steps of the design phases. At a low level of abstraction, we present how data parallelism can be exploited with Single Instruction Multiple Data (SIMD) operators. Then we present how task level parallelism and multi-threading can be efficiently mapped onto MPSoC to reduce the energy. Finally dynamic frequency scaling can be used at a top level set-up to use efficiently the dynamic power reduction.

Another objective is also to analyze how the low power management techniques can be used efficiently for a given application and how application characteristics shall be taken into account. The analysis shall result in solutions to implement the energy efficiency paradigm that gathers real-time QoS and overall QoE requirements.

The targeted application is the cutting edge video coding standard, HEVC. This class of applications faces a real implementation challenge on embedded systems. Indeed, it requires much computing resources, and consequently energy, to achieve real-time performance.

Figure 1.4: Energy efficient design methodology

#### 1.3 Contributions of the Thesis

Based on the scheme depicted in Figure 1.4, the main contributions of this thesis are:

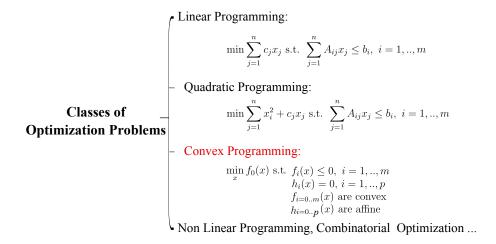

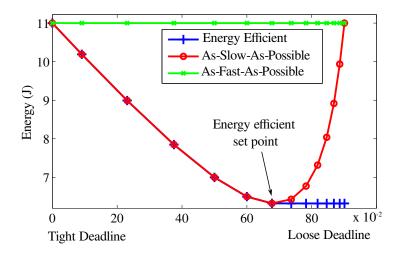

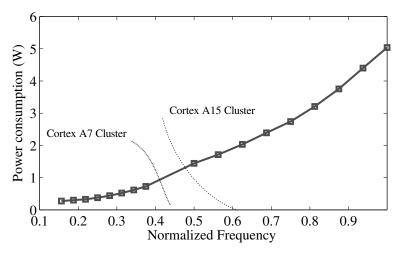

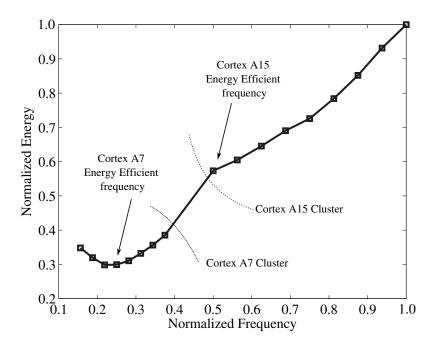

- 1. A framework offering Rapid Prototyping of Signal Processing Applications. We propose here to characterize a MPSoC in terms of power and energy [HNP+14]. We introduce an energy model that takes into account globally the SoC dynamic frequency scaling capabilities, deep sleep modes and parallelism levels [NPM+16]. Moreover, by injecting the application characteristics in the platform energy model, we propose to solve the energy minimization problem under real-time constraints. The proposed formulation of the problem exploits the convex properties of the power measurements guaranteeing to find an optimal solution in a polynomial time [NPM+16]. Using a model of a State-of-the-Art architecture, we find the most energy efficient operating point of the MPSoC. The modeling proposition is also validated on a real SoC with the HEVC application.

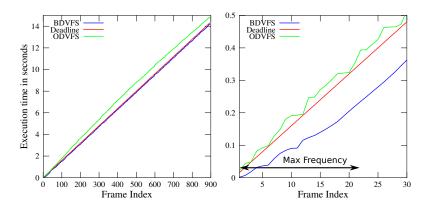

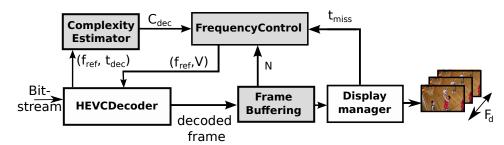

- 2. A real-time low power HEVC decoder using efficiently the DVFS capabilities of a General Purpose Processor (GPP)-based MPSoC. Typical technical techniques of the control of the control

8 Introduction

niques fail to assess the high variations of the per-frame processing. We propose here to use the DVFS capabilities of the MPSoC to reduce the power consumption. We show how our proposed implementations can achieve close-to-optimal performance with tight real-time requirements [NBP+15, RNH+15]. We propose two solutions: either intrusive with the inclusion of DVFS inside the HEVC decoder or non-intrusive where only the real-time requirements of the system are required. As a conclusion to this contribution, the results prove that HEVC can be implemented in real-time on an on-the-shelf GPP and therefore be deployed on a wide range of consumer electronic devices with no dedicated circuit.

3. A modified **HEVC** decoder with tunable image quality. This last contribution proposes to use the error tolerance property of video applications. Indeed, multimedia applications are inherently error tolerant since the final applications quality is left to the Human Visual System (HVS). Therefore, strict exactness may not be required and an imprecise result can be sufficient. We propose a framework based on approximate computing to save energy while decoding HEVC. We dive into the decoder itself from an algorithm signal processing point of view. The induced quality loss can be controlled at the device level according to the desired energy/quality tradeoff. It also provides a very fine grain tuning capability [NHP+14, NRPM15c, NRPM15a].

All these contributions were developed as part of the FUI project called Greenvideo [FUI] and were also promoted to the MPEG GreenMetadata Ad-Hoc group [FDM<sup>+</sup>15] through several contributions [NDR<sup>+</sup>14, NRQ<sup>+</sup>15, RNQ<sup>+</sup>15, RLP<sup>+</sup>15].

#### 1.4 Outline

The thesis is organized in two parts: Part I introduces the background, concepts and research issues, and Part II presents and evaluates the contributions of the thesis.

In Part I, Chapter 3 recalls the context and the motivations of the thesis. It particularly focuses on the video use case and presents the different parts of a complete video processing chain. Then, the different techniques of low power design are described as well as their influence on the different sources of power consumption. Chapter 3 presents the related work on low power decoders and especially for HEVC standard. It emphasizes the importance of coupling the platform low power techniques with the application requirements.

In Part II, a new energy model for MPSoC is introduced in Chapter 4. The model is used in the context of a rapid prototyping framework. Performance evaluations for offline HEVC decoding are given. Following the design flow of Figure 1.4, Chapter 5 takes into account the real-time characteristics of the HEVC decoders to propose efficient low power implementations. The performances are thoroughly evaluated on a wide range of video sequences. Chapter 6 introduces an approach based on approximate computing and proposes an evolution of the standard HEVC decoder that offers large power savings with a controlled decoding distortion. This approach is presented within the MPEG GreenMetadata initiative and motivates the use of a metadata to control the tradeoff between the decoder power consumption and the decoding quality.

Finally, Chapter 7 concludes this work and opens potential research directions for future works.

# Part I Scope and Motivations

Embedded Video Context

### 2.1 Motivation for Energy Optimization

When using a portable device for video applications, any user wishes the battery life to last longer. Hence, there is already a large demand for increased battery life on devices and this phenomenon keeps accelerating with the success of media applications. At the heart of embedded processing systems, video applications such as streaming (e.g. Video On Demand (VOD) service), conferencing and sharing use a major part of the energy budget.

In this section, the main features of video applications are described first. Then the scope of analysis is focused on the decoding part, especially on electronic portable devices. Finally the performance of these devices is analyzed through the power and energy perspective.

## 2.2 Video Applications

#### 2.2.1 The Video Chain and its Energy Consumption

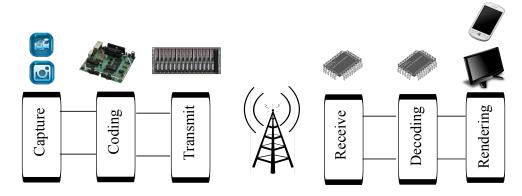

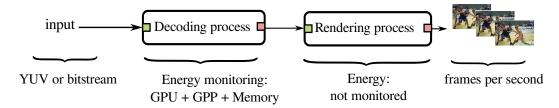

The video chain is split into several components from the capture to the rendering, as presented in Figure 2.1. In this section, we detail the different elements of this chain.

Figure 2.1: Components of the video chain

#### Video Capture

Initially, video cameras were developed for the television industry and were capable of capturing scenes in motion pictures. Over the last decades, these sensors have evolved along with the type of applications. Associated with them, a wide a range of services are now possible. Because the camera is located at the very beginning of the video chain, the type of camera is determined by the targeted type of application:

- professional video cameras are high-end devices that create electronic images in movement. Developed originally for a use in television studios, they are now also used for other applications like music or personal videos.

- camera recorders combine a camera with a video recorder. These cameras are mobile and are used in many fields like live journalism, movies, etc. With the arrival of digital video cameras, camera recorders have an in-built digital recording device.

- Closed-circuit television (CCTV) generally uses zoom cameras for security purposes, and monitoring purposes. CCTV cameras are generally small, discreet and robust to hostile environment.

- webcams provide images in real-time to a computer or a computer network. The video stream may be saved, viewed or sent on to other networks via systems such as the internet, and email as an attachment.

- camera phones are generally designed to be small and simpler than separate digital cameras. Their usual fixed-focus lenses and smaller sensors limit their performance in poor lighting.

- stereo cameras embed two lenses with a dedicated image sensor for each lens. They are generally used to capture 3D videos. The distance between the two cameras are generally similar to the distance between human eyes.

- scientific cameras are devices dedicated to a targeted application. The most common applications include astronomy with on-board devices, robotics, or medical devices. They are designed to work in a large, and non-visible, spectrum. For example, infrared is used for night vision and hyperspectral cameras are used to detect tumors in medical applications.

From an energy point of view, the list above can be sorted by type of power supply. For example, camera phones or on-board cameras are supplied by a battery and strongly necessitate an energy efficient design. It is also a fast growing market as they can be embedded barely anywhere (carried by people or drones).

The case of a mobile phone camera can be considered as one the most sensitive cases. Thanks to the recent advances in electronic devices, Complementary Metal Oxide Semiconductor (CMOS) image sensors require only a few mWatts [Fos94]. This power consumption can be considered as negligible compared to the other entities of the system.

#### Video Transmission

#### Current Status of the Video Transmission Energy Consumption

Within the production - distribution - consumption chain of multimedia content, the distribution segment represents something significant in terms of energy consumption. Digital terrestrial TV (DTTV) is specifically considered in this section.

The reduction of the consumption of this segment is becoming a real challenge for broadcast operators since they switched from the analog to the digital domain in the last decade. For example, 15000 transmitters are deployed in France with transmitted power ranging from a few Watts to several kWatts. DTTV uses Coded Orthogonal Frequency Division Multiplex (COFDM) multicarrier waveforms as modulation, characterized with a high Peak to Average Power Ratio (PAPR). Therefore, the power amplifiers cannot be used at their saturation level and the average power of the transmitted signal is about 12 dB below the peak power. The resulting energy efficiency ratio for a transmitter is between 10% and 20%, for first generation digital transmitters delivering from 500 Watts to 10 kWatts [NT].

#### Reducing the power consumption of the broadcast network

From about 2010, the transmitter manufacturers have been working a lot on reducing the energy consumption of their products, under the pressure of the network operators. Several directions are followed in that purpose. After the successful deployment of digital TV, network operators shifted their priority from coverage to energy efficient of the transmitter. Several solutions were developed for that purpose.

- the reduction of the energy consumption of the digital part of the transmitter. A transmitter is composed of a digital modulator plus some monitoring facilities that control the whole transmitter and its cooling system. The energy consumption of the digital modulator is independent from the antenna output power of the transmitter. The digital modulator is implemented with hardwired logic and programmable technologies like FPGAs and CPUs. These technologies continuously evolve towards more energy efficient solutions. The digital modulator part of the transmitter energy is then reduced but it represents a limited share of the global energy consumption. The benefits on the whole transmitter energy consumption is thus limited, except for low power transmitters (below 1 kWatts).

- Reduction of the energy consumption of the power amplifiers. This is the main part of the consumption of a high power transmitter. It requires 1 kWatts or more of power. As presented before, the low efficiency of this part results from the high PAPR of the modulated signal and the inherent low efficiency of the analog RF power amplifiers. Manufacturers seek low power designs with the following items. At first, different approaches exist for reducing the PAPR [VEWT96, JW08] of the multicarrier waveforms, including standardized ones like in the latest second generation DTTV standards, such as DVB-T2. Tradeoffs have to be made as reducing the PAPR introduces noise and degrades the signal quality. This PAPR reduction is performed in the digital modulator, as it is closely coupled to the waveform generation function. It brings a gain of a few percents in power amplifier efficiency.

Another option is to linearize power amplifiers. Adequate digital pre-processing compensates the inherent non-linearities of power amplifiers [SS83, SM98]. Using linearized amplifiers, the average operating power can be raised, thus increasing the energy efficiency, while maintaining the same signal quality at the output. This pre-processing is digitally performed at the output of the modulator. It is using a return channel so that the processing can dynamically adapt itself to the characteristics of the power amplifier, including variations linked to the power supply, the temperature, and even the memory effect of the power transistors. This approach brings a gain of a few more percents in power efficiency.

Finally, new amplifier technologies have better energy efficiency. Traditional Class AB amplifiers have a limited efficiency ratio (typically 25%). Alternative amplifier architectures, such as Doherty ones, bring higher efficiency (up to 40%) and are widely adopted in the latest generations of transmitters [IWC+01]. One drawback is the limited bandwidth of such architectures. Most implementations are not wide band (460 - 860 MHz). Other amplifier technologies are used in lower power systems such as the cellular phone base stations: Envelop Tracking power supplies [WYK+05] and Switched Mode amplifiers [MBM+98]. They are not really usable in the broadcast environment, where many low power amplifier modules must be parallelized to get the required power level. Implementation complexity would then be far too high.

By following all these technical directions at the same time, transmitter manufacturers are improving significantly the efficiency of their products. The latest high power transmitter now reach 40 to 45 % efficiency, which is typically twice the efficiency met 10 years ago.

#### Video Rendering

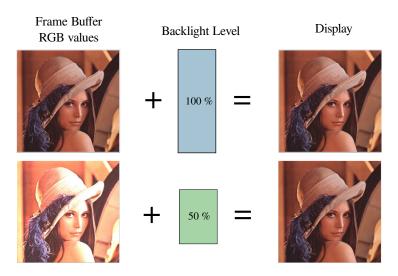

Video rendering is a mirror image of video capture. It also addresses a wide range of components that are tightly coupled with the user-defined applications. From cinema large screens to smart watches, power consumption constraints are drastically different. Within the scope of handheld devices, the rendering and display elements utilize a large share of the overall power budget. Ma et al. [Sam12a] showed indeed that in a phone reading streaming video, 400 mWatts are needed for the display, 300 mWatts for the video decoding, 250 mWatts for the idle part, and 300 mWatts for downloading the video. The measurements were done on a mid-range smartphone when a video sequence is being played.

Depending on the underlying technologies, several proposals were formulated to reduce the power consumption of the display device. Chang et al. [CCS04] proposed back light scaling for LCD systems. The induced distortion is compensated by an appropriate image mechanism to keep the perceived image contrast as close as possible as the original one. Shin et al. [SKCP11] propose a new principle applicable to the OLED technology adopted in newer equipments. Power consumption is then improved but it highly relies on the hardware technology used by the end device.

#### Discussion

In the above approaches, the reduction of energy consumption in the video chain is obtained by two different techniques. A first technique consists in improving the overall efficiency of the process. It is typically the case in the transmission part. The purpose of transmission energy optimization techniques can be rephrased as to do the same for less energy. The obtained improvements rely on technological advances and are generally independent from the video use case.

The second technique uses a singular property of the video context. Indeed, from a unique original scene or content to be captured, the final content that is delivered can take various forms. This so-called *scalability* is possible in different components of the chain from the capture to the delivery. Obtaining the correct energy balance in the chain from end to end is then a key challenge and it shall be emphasized that with the explosion of video capable devices, one source of video is likely to address a wide range of terminals with different features and capabilities.

In this thesis, we focus on the video decoding component of the chain and provide guidelines to reduce decoder energy consumption. Reducing of a few Watts the power consumption of billions of devices can have have a major impact at a large scale. The objective of our study is to propose new techniques for two objectives: improve the video processing efficiency and adapt the content to the device. The cornerstone of the decoding system is the compression technology. The rest of this section describes the main features of it.

#### 2.2.2 The MPEG Video Compression Standards

The most critical part of a video chain is the compression part since it provides means to transmit complex video contents to various supports.

#### Techniques of Modern Video Coding

Video coding belongs to the source coding theory and aims at reducing the data size of the video. The final goal of video coding is to make content broadcasting easier [SS95]. For example, a typical bandwidth needed for transmitting a high definition video content is 600 Mbits/sec. After compression, the bandwidth can be reduced to 7 Mbits/sec.

The principle of video coding is based on the high statistical redundancy of video sequences both in time and in space domains. The basic statistical property that compression techniques leverage on is the correlation between pixels. This correlation appears in both space (adjacent pixels in an image are similar), and time (colocated pixels in past and future frames are similar to the current pixel).

Thus, it is assumed that the color of a particular pixel of an image can be predicted from the neighboring pixels of the same image (using intra-frame coding techniques) or pixels of a neighboring image (using inter-frame techniques). Intuitively, it is obvious that in certain circumstances, for example, when changing plan within a sequence, the temporal correlation between neighboring pixels between images is small or zero. In this case, techniques that use the spatial correlation are the most appropriate. However, if the correlation between pixels in adjacent frames is large, for example, in the case when two consecutive frames have a similar or identical contents, it is preferable to use a so-called inter coding technique which uses the temporal prediction. In a typical compression scheme, an adaptive combination between the two predictions (temporal and spatial) is used to achieve significant data compression.

Because implementing the complete video chain is a complex task, and to ensure a tight relation between the encoding and the decoding processes, a working group gathering video experts was created to standardize efficient compression systems within a single set of specifications. This group is called Motion Picture Expert Group (MPEG) and brings together many experts from the electronic component industry, information technology and telecommunications.

#### General structure of MPEG

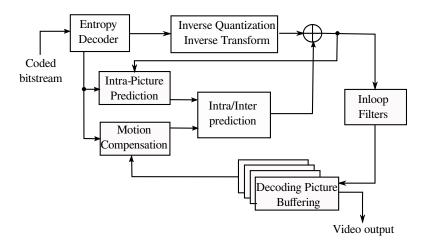

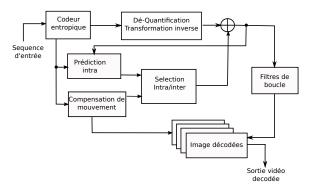

MPEG meetings began in the late 80's to develop a first standard. MPEG then quickly produced new series of international standards, including the still popular MPEG-2, primarily targeting applications related to digital TV. The basic framework of the transform-based motion-compensated decoders, followed by all MPEG decoders, is depicted in Figure 2.2.

In the first step, the entropy decoder extracts the different syntax elements from the video stream using arithmetic coding, after which the residual data (non-predicted data) are

Figure 2.2: Basic modules of the video decoder

dequantized and transformed using an inverse Discrete Cosine Transform (DCT) process. The prediction of the frames is then applied, and can be either of intra- or inter-frame type depending on the input bitstream parameters. In the case of the inter-frame prediction, a prediction is computed based on the previously decoded pictures and estimates of the motion vectors between pictures at a fractional pixel level. Finally, the in-loop filters are applied on the reconstructed data to reduce potential artifacts due to compression and increase picture quality.

H.264 is introduced here as an canonical example of an MPEG codec. H.264/AVC is based on this framework and is widely adopted thanks to its bitrate / distorsion performance [OBL+04]. Amongst its main features, H.264/AVC uses a Context-adaptive binary arithmetic coding (CABAC) or Context-adaptive Huffman variable-length coding (CAVLC) as entropy coding scheme. CABAC is an arithmetic coding producing excellent results in terms of compression, but at the cost of a complexity higher than CAVLC. CAVLC is an adaptive Huffman coding of variable length, which is a less complex alternative to CABAC coding.

The motion estimation and compensation can be performed over several already coded reference images. The choice of the reference image occurs at the macroblock and submacroblock levels. This allows the decoder to use in some cases up to 16 reference images and up to 4 different references for the same macroblock. For certain types of scenes, such as rapid changes, repetitive flashes or recurring scenes, this scheme provides a significant reduction of the actual bitrate. A motion compensation can use seven different block sizes  $(16 \times 16, 16 \times 8, 8 \times 16, 8 \times 8, 8 \times 4, 4 \times 8, 4 \times 4)$  to define moving zones with accuracy. The precision for motion compensation is based on quarter-pixel for luma data. Motion compensation of chroma values uses the same principle with an eighth-pixel precision.

Finally, an anti-block filter or deblocking filter is carried out in the coding loop and operated on the  $4 \times 4$  blocks so as to reduce artifacts due to block processing.

The output frames are traditionally coded with 8-bit data format on 3 components called YUV (one luma, Y and two chrominance, UV components). To increase the perceived quality, higher bit-depths (e.g. precision of 10 bits) have been proposed more recently. These methods are called High Dynamic Range (HDR) [RHD+10].

#### Legacy HEVC

Video coding standards such as High Efficiency Video Coding (HEVC) manipulate images represented as fields of color pixels. Next section introduces the different types of possible image organizations.

#### Image Organization

An image or a video frame is a rectangular region containing pixels (pels, samples) to be compressed. One of the characteristics of natural images is the strong similarity between neighboring pixels. Indeed, unless they belong to different objects, pixels are likely to be strongly correlated.

There are three components per image: luma (Y), chroma blue (Cb, U), and chroma red (Cr, V). The Y component is associated to gray levels, which enables the Human Visual System (HVS) to distinguish shapes. The later two components (Cb and Cr) represent a transition from gray towards respectively blue and red.

The selection of (Y,Cb,Cr) triplets over the primary (Red,Green,Blue) triplets captured by the HVS has to do with the fact that the HVS is more sensitive to gray levels, and less sensitive to colors. As a consequence, chrominance values can be subsampled without loosing perceptual information.

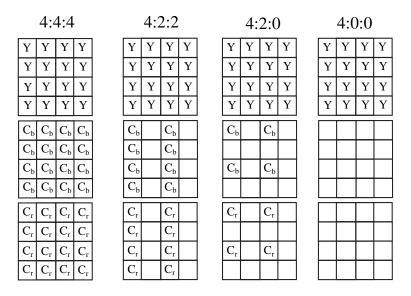

Image compression standards, including MPEG HEVC, use 4:4:4, 4:2:2, 4:2:0, or 4:0:0 subsampling patterns. The former specifies full resolution where all chrominance samples are kept. The later indicates a monochrome image (no chrominance samples are kept). 4:2:2 and 4:2:0 indicate that a subset of chrominance values is kept. The 4:2:2 pattern is for full horizontal resolution and half vertical resolution. 4:2:0 specifies half resolution in both directions. The subsampling patterns are illustrated below Figure 2.3.

Figure 2.3: Image subsampling patterns

When 4:4:4 sampling is used, each component may be coded independently as if three different images were coded independently. This means that the samples of a component will be processed before the next component is coded. The alternative is to interleave the components; block-by-block, the Y, Cb, then Cr values are coded. Using the MPEG HEVC codec, the components are processed using either 4:2:2 or 4:2:0 subsampling.

Finally, the bit-depth is defined for all the different components. The current range varies from 8 to 14 bits. The bit depth for luma pixels can differ from the bit depth of chroma pixels.

#### Main improvements

HEVC is the latest video compression standard from MPEG [SOHW12a]. The first version of HEVC was finalized in January 2013 by ITU-T Video Coding Experts Group (VCEG) and the ISO/IEC Moving Picture Experts Group (MPEG) under a partnership known as the joint collaborative team on video coding (JCT-VC). The HEVC standard brings a gain of up to 50% in terms of subjective video quality [OSS+12b] with respect to the H.264/AVC high profile [WSBL03].

Moreover, the second version of the HEVC standard embeds new coding functionalities, including an efficient coding of video at high bit depth (up to 14 bits) and with high color format fidelity: 4:2:2 and 4:4:4. The HEVC rate-distortion gain together with these new functionalities foster the proliferation of new video services such as video transmission at ultra high quality over broadband and wireless networks for both fixed and mobile devices.

Compared to H.264/AVC, HEVC advances lie in:

- in-built parallelism: compared to H.264/AVC where parallelism was thought afterwards, HEVC standard includes different levels of parallelism: independent slices, tiles and a *wavefront* mechanism. These levels are defined in the HEVC standard to simultaneously process multiple regions of a single image [SSM14].

- intra-prediction is improved for video and still images. There are two categories of intra-predictions: angular prediction and planar prediction [LBH<sup>+</sup>12].

- inter-prediction is improved and generalized compared to H.264/AVC. It uses advanced motion vector prediction based on motion vector competition [HOB+12].

- in-loop filtering: HEVC contains a deblocking filter as in H.264/AVC. It also adds a new filtering stage called sampling adaptive offset (SAO) which provides both subjective and objective improvements [NBF+12].

- improvements of the CABAC performance to approach ever closer to the inherent entropy coding bound [SB12].

#### **Profiles**

HEVC addresses a wide range of applications. To support the application variations without altering the core specifications, HEVC supports several profiles similarly to prior standards. Three profiles are defined in the first version of the standard.

- Main profile is used in the typical applications using 8-bit data per sample with a luma component for the brightness and two chroma components that have half the luma resolution both horizontally and vertically (4:2:0),

- Main Still Picture profile is used for still photography or snapshot extraction from video sequences. It is a subset of the capabilities of the Main profile.

- Main 10 profile is used for to support 10 bits per sample of the decoded frame. This profile aims at integrating the main HDR improvements.

As stated before, the main profile is widely used in various systems like TV broadcasting, video streaming or video on mobiles.

To test and validate a decoder implementation, reference bitstreams are provided by the BBC [bbc]. They are also used in the research area to compare and benchmark decoder implementations. For performance evaluation, this thesis uses test sequences from the Main profile.

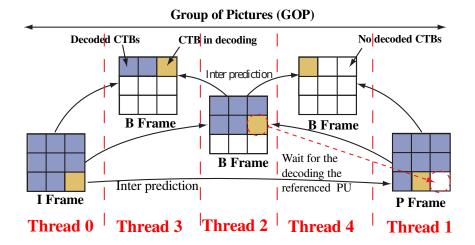

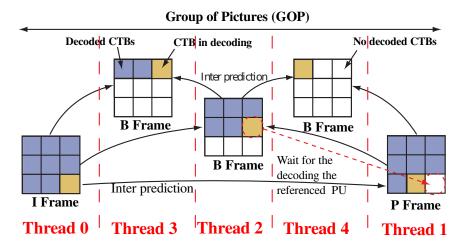

#### Frame organization

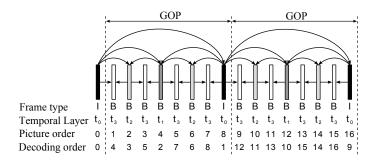

To achieve high levels of compression, motion prediction is essential and frames can be predicted from each other using motion vectors from a reference picture or frame. The notion of Group of Pictures (GOP) defines the order in which intra coded pictures and inter coded pictures are arranged. A GOP consists of a sequence of images encoded together in an encoded video stream. The types of these images follow a pattern that is repeated periodically until the end of the encoding. The visible images are generated from the coded images in a GOP. A GOP can contain the following types of images:

- I-frame (intra coded image) or Reference frame. It can be decoded independently from any preceding or following frame. Each GOP begins with a frame of this type.

- **P-frame** (predictive-coded picture). This frame includes difference information (motion compensated prediction) from an I-frame or a P-frame temporally prior to it. It is also a reference frame (i.e. it can be used for predicting other frames).

- **B-frame** (bidirectional predictive coded frame). A B-frame includes difference information from I-, P- or B- frames temporally located in the past or in the future within a GOP. To avoid excessive prediction error propagation, B-frames are generally not used as a reference frame.

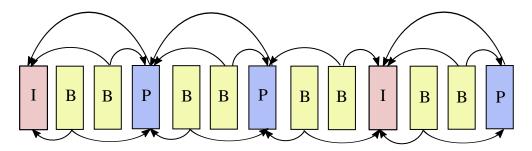

Figure 2.4 presents a typical organization of a GOP where arrows signify "is predicted from".

Figure 2.4: Typical GOP organization

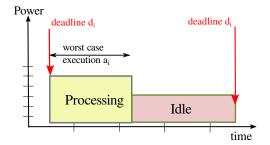

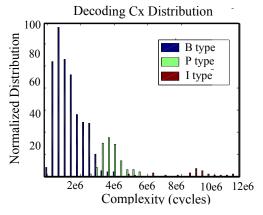

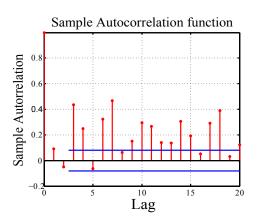

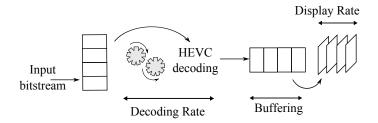

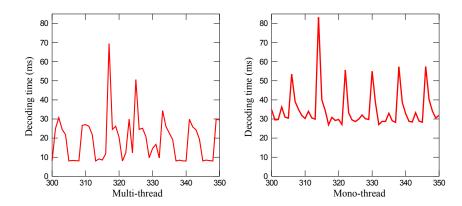

The purpose of using different types of frames is to improve the compression ratio while containing the image distortion and providing random access to a stream. However, each type of frame requires a very different processing load and a very different amount of memory. This property is a real issue to design efficient implementations of decoders [CAMJ14, NBP+15]. Indeed, some frames can require a high processing load when others much less but they are usually all under the same real-time constraint.

#### 2.3 Energy in Electronic Components

With the recent advances in the semiconductor industry, a wide range of techniques are now available to design in a low power fashion electronic systems. This section recalls the different parts of energy consumption and the techniques to reduce them.

#### 2.3.1 Sources of Energy Consumption

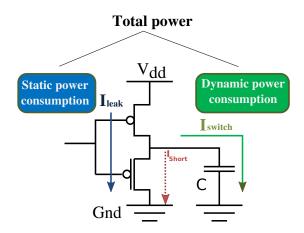

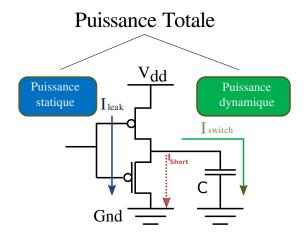

The power consumption in System-on-Chip (SoC) is often modeled by the CMOS industry with three components as described in Figure 2.5 [Mud01].

Figure 2.5: Power consumption: split between the static part and the dynamic part

They gather the essential properties for logic designers, architects and system builders. The power consumption is given by Equation (2.1).

$$P_{tot} = P_{dyn} + P_{short} + P_{stat} (2.1)$$

The dynamic power  $P_{dyn}$  is consumed by the charging and discharging of the capacitive load on the output of each gate. The second component  $P_{short}$  captures the power resulting from a short-circuit current which momentarily flows between the supply voltage and the ground due to a short-circuit current appearing when a CMOS logic gate output switches. However this component is relatively small compared to the others [Mud01]. Hence it is neglected in the rest of the document. While the two first components are related to the circuit activity. The third component is due to the leakage current and is not related to the gate state.

#### 2.3.2 Static Part

The static part of the power dissipation occurs even when a device is in standby mode. It has been neglected for a long time as it was not representing an important part of the total power dissipation. However, it becomes significant as the technology scales down. Typically, CMOS technology has been promoted for its low static power. Unfortunately, technology shrinking leads to smaller geometries which exacerbate leakage.

Static power is due to different leakage currents. Up to six sources of leakage can be considered [RMMM03] but the two main components [KAB+03] are, firstly, sub-threshold leakage and, secondly, gate leakage. Gate leakage current is due to the tunneling current

through the gate oxide insulation. As devices were scaled down, gate oxide thicknesses have decreased and an increasing probability of tunneling effect has emerged. The sub-threshold leakage current is due to a weak inversion current between the source and drain even if the transistor is OFF (subthreshold region). The sub-threshold leakage current is governed by thermodynamics, more specifically in the Boltzmann distribution [Fra06]. Equation (2.2) recalls in a compact form the static power [SNPF04].

$$P_{stat} = V_{dd}.N.I_s.e^{-V_{th}/U_t}$$

(2.2)

with  $V_{dd}$  the supply voltage,  $V_{th}$  the threshold voltage,  $I_s$  the average transistor current per cell,  $U_t$  the thermal voltage

Predictions of the SIA Roadmap [SIA] forecast supply voltage  $(V_{dd})$  as low as 0.8 to 0.5 V in year 2018. Since a reduction of  $V_{dd}$  requires an additional reduction of the transistor threshold voltage  $(V_{th})$  to maintain speed, this will result in an exponential increase of the static power consumption. As a consequence, the static power on its own may already exceed the required maximum total power consumption in stand-by mode for certain applications. When the activity is very low, i.e. when very few gates are switching during a clock cycle, the static power becomes a significant contributor to the total power consumption.

Table 2.1 [SNPF04] summarizes predictions of the main parameters required for the next generations of Bulk MOSFET devices in 2018, related to High Performance (HP), Low Operating Power (LOP) and Low Standby Power (LSTP) devices. LSTP transistors have high  $V_{th}$  with reduced leakage compared to other devices. Oppositely, HP transistors have the largest drive current for maximum speed at the cost of larger leakage.

| MOS  | Physical                | Supply  | Threshold | Ion             | Ioff                           | Ion/Ioff  |

|------|-------------------------|---------|-----------|-----------------|--------------------------------|-----------|

| Type | $\operatorname{length}$ | Voltage | Voltage   | $[\mu A/\mu m]$ | $[\mathrm{nA}/\mathrm{\mu m}]$ |           |

|      | [nm]                    | [V]     | [V]       |                 |                                |           |

| HP   | 7                       | 0.7     | 0.11      | 2190            | 500                            | 4380      |

| LOP  | 9                       | 0.5     | 0.17      | 950             | 30                             | 31 667    |

| LSTP | 10                      | 0.8     | 0.4       | 990             | 0.1                            | 9 900 000 |

Table 2.1: Parameters' impact on power consumption [SNPF04]

New design methodologies taking into account the contribution of leakage will be required for the conception of innovative SoC. State-of-art technologies (e.g. 28 nm widely available from 2015) are already largely impacted by leakage.

Similarly to previous design methodologies, solutions can be proposed at different levels, namely at circuit, architecture, and system levels. At the circuit level, many techniques have been proposed:

- Threshold voltage  $V_{th}$  optimization

- Multi  $V_{th}$  technology, with fast low  $V_{th}$  transistors

- Electrical regulation of  $V_{th}$  with body biasing (VTCMOS, Variable Threshold)

- Transistor optimization

- Transistor size optimization

- High- $\kappa$  Metal Gate

- Gated-Vdd, with  $V_{dd}$  switched off in sleeping mode

This last technique is used for power-gating mechanisms. Some sophisticated mechanisms can be adopted to define a complete set of power-supply domains.

#### 2.3.3 Dynamic Part

Dynamic power represents the amount of power consumed when the device is operating. It creates activity at the output of the gates when bits are changing from "0" to "1" or vice versa.

$$P_{dun} = \alpha.C.f.V_{dd}^2 \tag{2.3}$$

where C is the total capacitance seen by the outputs of the gates,  $V_{dd}$  is the supply voltage, f is the frequency of operation, and  $\alpha$  is the processor activity (number of modified gates per clock change)

It clearly shows that, as the performance increases with the speed and the frequency, the dynamic power also increases. The dynamic power is also linked to the data activity and is in fact closely tied to the number of transistors that change state.

At the circuit level, the parameters to reduce dynamic power are the following: reduce activity when it is not necessary, reduce the capacitance due to wires between cells, and reduce the operating frequency (and the associated voltage) when possible. This latter is possible if the considered application has some intrinsic slack times.

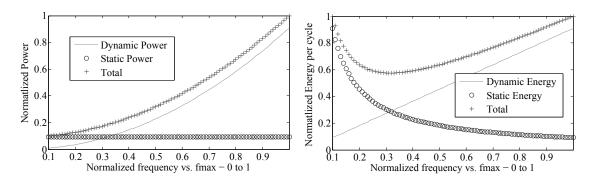

#### 2.3.4 Comparison between Dynamic and Static Parts

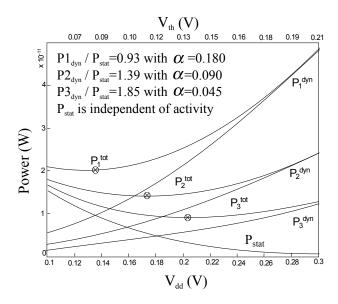

Some digital architectures are better than others in terms of leakage. Schuster *et al.* [SNPF04] propose a comparison of the dynamic power consumption versus the static power. Tradeoffs between dynamic and static power can be described from a theoretical point of view with the aim of understanding the influence of architectural parameters on this tradeoff and on total power consumption.

Equation (2.1) is formulated again in Equation (2.4) as the dynamic and static contributions from technological features.

$$P_{tot} = P_{dyn} + P_{stat} = \alpha.C.V_{dd}^{2}.f + V_{dd}.N.I_{s}.e^{-V_{th}/U_{t}}$$

(2.4)

with N the number of cells,  $\alpha$  the average cell activity, C the equivalent cell capacitance, f the operating frequency,  $I_s$  average transistor current per cell,  $U_t$  the thermal voltage.

As it can be observed in Figure 2.6, the ratio of dynamic power,  $P_{dyn}$ , over static power,  $P_{stat}$ , at the minimum of total power consumption is not constant and depends on some parameters like the activity but also on the processing frequency. In this thesis, these two parameters are adapted to the video applications to reduce system power consumption.

Subthreshold leakage is considered in static power in Figure 2.6, while gate and junction leakage are neglected. Whereas  $P_{dyn}$  decreases in a quadratic manner with the reduction of  $V_{dd}$ ,  $P_{stat}$  increases instead (due to a reduced  $V_{th}$ ). The total power presents thus a minimum i.e. an optimal power consumption (marked with a  $\oplus$  symbol in Figure 2.6).

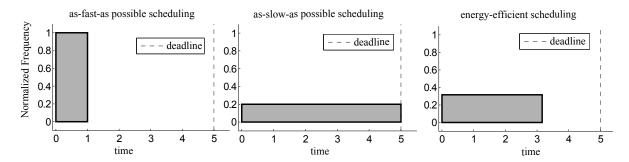

#### 2.3.5 Techniques for Energy Reduction

In this thesis, the Multiprocessor SoC (MPSoC) family is targeted. This section reviews power reduction techniques in modern microprocessors. Low power modes exploit application slack times to reduce power consumption.

**Figure 2.6:** Total Power  $(P_{tot})$ , dynamic Power  $(P_{dyn})$ , and static Power  $(P_{stat})$  of a single square transistor, as a function of  $V_{dd}$  and  $V_{th}$  for three different circuit activities  $\alpha$  [SNPF04]

#### Different Classes of Techniques

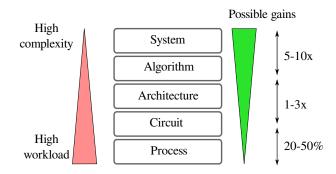

Figure 2.7 recalls the different architecture abstraction levels where energy saving and low power design can be taken into account. At low levels, low power techniques can be performed regardless of the application itself. These techniques were intensively discussed over the past decades [PMvKS95, RCN02].

Figure 2.7: Design phases versus possible energy gains

At the lowest level, low power techniques rely on advances in the technologies and processes of the silicon industry. They require high investments.

At the next level, and among the most popular techniques, clock gating and power gating are generally implemented onto modern SoCs to provide techniques to design in a low power fashion [RTM+10]. They are independent from the application itself but are used by upper levels design techniques where an application knowledge is needed. Clock gating is used to turn clock tree branches off whenever they are not used [WPW00]. This technique principally reduces the dynamic power part and can be implemented at different levels of the processors from functional units to complete cores. Power gating targets the reduction of static power consumption by shutting-down cores during the idle phases [JMSN05]. The implementation relies on a multi-threshold CMOS process. Low  $V_{th}$  transistors are used for logic blocks. They provide low latency but at the expense of a high leakage current.

High  $V_{th}$  transistors are used for switching transistors. These transistors control the supply of the logic blocks and provide low leakage current.

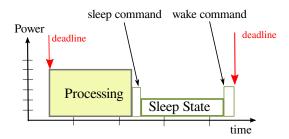

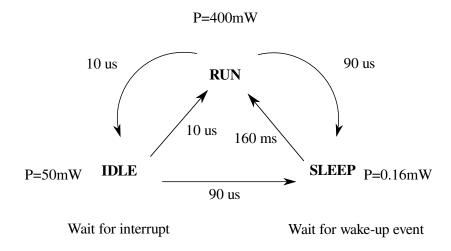

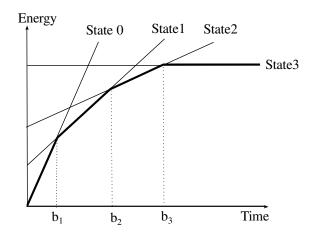

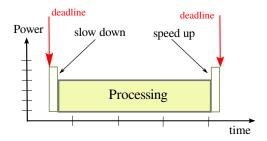

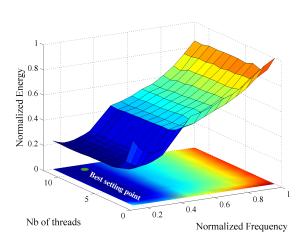

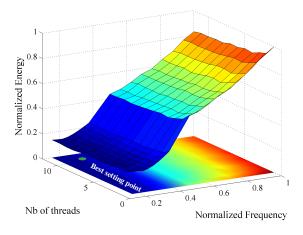

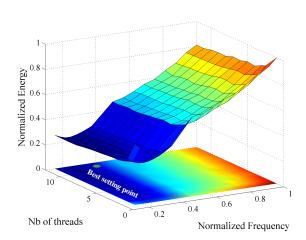

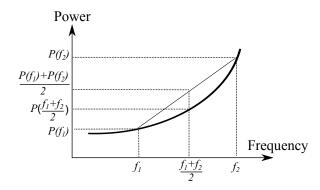

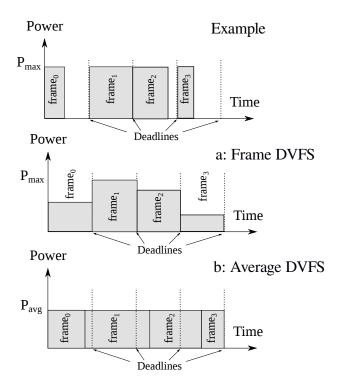

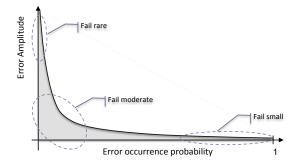

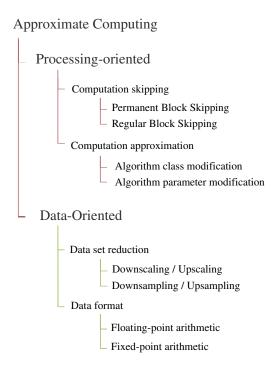

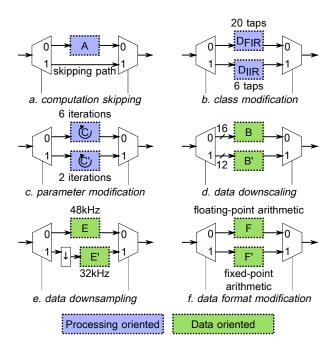

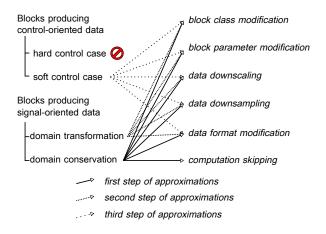

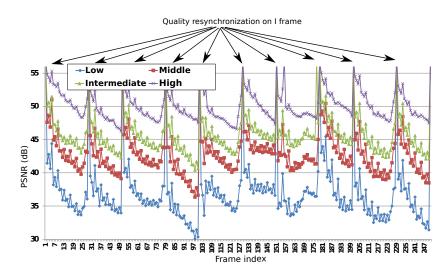

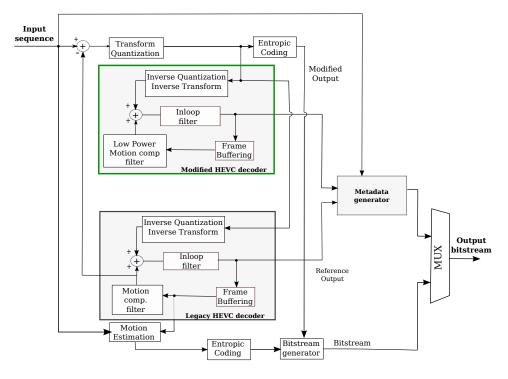

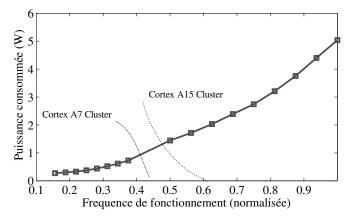

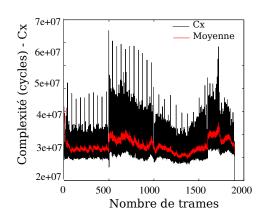

The next class of techniques works at the architecture level. This class seeks two important goals: exploiting the parallelism and speculate on the application behavior regarding the data usage and related processing operations.