# Extending Polyhedral Techniques towards Parallel Specifications and Approximations

Alexandre Isoard

#### ▶ To cite this version:

Alexandre Isoard. Extending Polyhedral Techniques towards Parallel Specifications and Approximations. Other [cs.OH]. Université de Lyon, 2016. English. NNT: 2016LYSEN011. tel-01369014

### HAL Id: tel-01369014 https://theses.hal.science/tel-01369014

Submitted on 20 Sep 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Numéro National de Thèse : 2016LYSEN011

### THÈSE de DOCTORAT DE L'UNIVERSITÉ DE LYON

opérée par

### l'École Normale Supérieure de Lyon

### École Doctorale N° 512 École Doctorale en Informatique et Mathématiques de Lyon

**Discipline**: Informatique

Soutenue publiquement le 05/07/2016, par :

### Alexandre ISOARD

# Extending Polyhedral Techniques towards Parallel Specifications and Approximations

Extension des techniques polyédriques vers les spécifications parallèles et les approximations

#### Devant le jury composé de :

Albert Cohen RapporteurJ. (Ram) RAMANUJAM RapporteurSamuel BAYLISS Examinateur François Irigoin Examinateur REDDY BONDHUGULA Uday Examinateur Alain Darte Directeur de thèse

### Remerciements

Je tiens à remercier chaleureusement avant tout Alain Darte qui m'a encadré pendant toute cette thèse avec le sérieux d'un directeur, l'enthousiasme d'un collègue, la complicité d'un ami et l'affectif d'un grand frère, et sans qui cette thèse n'aurait jamais pu avoir lieu. Je retiendrai particulièrement son intégrité et sa rigueur scientifique qui font de ses critiques des arguments précis et décisifs qui ont su susciter d'innombrables fois une ingéniosité bienvenue. Je n'aurais jamais pu progresser aussi vite sans nos discussions enflammées au coin d'un tableau, triant entre mes balourdises et mes avancées subtiles. Je crois d'ailleurs que beaucoup des idées novatrices de cette thèse sont issues de nos nombreux quiproquos fortuits mais dont la résolution a souvent été source de découvertes.

Je tiens ensuite à remercier mes rapporteurs et plus généralement tous les membres de mon jury : merci Albert, Ram, Samuel, François et Uday d'avoir accepté de voyager jusque là et de relire et juger de mon travail. Je tiens aussi à remercier Paul Feautrier dont l'expertise sans égale du monde polyédrique nous a été d'un recours irremplaçable. De même, mes discussions avec Tomofumi Yuki ont été d'une aide incomparable et nombre de mes présentations ont gagné en clarté grâce à lui.

Je n'oublie pas les personnes qui ont été d'une aide indirecte mais tout autant nécessaire pour ce travail, à savoir : mes deux colocataires, François Gindraud et Clément Lagisquet, dont l'aide logistique et la qualité des repas et des discussions partagés ont fait de ces quelques années passées ensemble un régal; Maroua Maalej, ma collègue de bureau préférée, mais aussi une amie qui a toujours été là pour me motiver, me donner conseil, et me faire goûter les spécialités tunisiennes, autant culinaires que linguistiques et spirituelles; Laure Gonnord qui a été d'un support sans faille pour un peu tout mais surtout aussi, avec Nicolas Louvet, pleine d'idées pour l'enseignement. Et je tiens aussi à remercier nos super assistantes, infailliblement de bonne humeur et toujours d'un grand secours : Laetitia Lecot, Evelyne Blesle et Chiraz Benamor.

J'ai beaucoup apprécié mes interactions scientifiques avec nombre de mes collègues au LIP mais aussi plus loin. Je pense particulièrement aux nombreux doctorants et stagiaires, Lucie Martinet, Guillaume Iooss, Aurélien Cavelan, Oguz Kaya, Guillaume Aupy, Aurélie Lagoutte, Julien Herrmann, Bertrand Simon, Loïc Pottier, Yannick Leo, Romain

Labolle...mais aussi aux nombreux chercheurs, Thierry Dumont, Violaine Louvet, Sanjay Rajopadhye, P. Sadayappan, Sven Verdoolaege, Tobias Grosser, Louis-Noël Pouchet, Béatrice Creusillet, Ronan Keryell, Fabrice Rastello, Christophe Alias...Malheureusement, ces listes seraient bien trop longues pour citer tout le monde!

Et bien sûr, je remercie ma famille, qui a toujours été à mes côtés et ce, depuis bien longtemps; elle, tient la place la plus au chaud.

Et pour finir, merci à Stephen Neuendorffer de m'avoir offert l'opportunité, décisive pour mon futur, de travailler au sein de Xilinx.

### Résumé

Guidé par le double objectif de performance et d'énergie, les infrastructures de calcul d'aujourd'hui évoluent vers des architectures d'une complexité croissante, incluant des organisations sophistiquées de la mémoire et l'utilisation d'accélérateurs matériels. Elles exigent que l'utilisateur ou le compilateur soient capables d'extraire le parallélisme, d'optimiser la localité et d'expliciter les mouvements de données. Cette thèse, motivée par le problème pratique du transfert automatique de noyaux de calcul vers des accélérateurs tels que GPUs ou FPGAs, a également eu comme objectif principal d'étendre les techniques polyédriques (adaptées à la manipulation de noyaux de calcul à base de boucles et de tableaux) dans les multiples directions nécessaires pour répondre à un tel problème : paramètres, approximations, parallélisme.

Notre premier résultat est une analyse (exacte ou avec approximation) des ensembles de données à copier vers et depuis un accélérateur pour le tuilage paramétrique quand un noyau est transféré tuile par tuile, éventuellement de manière pipelinée, et en exploitant la réutilisation des données entre tuiles. Notre deuxième résultat, nécessaire pour être en mesure d'allouer les tableaux locaux induits par ces mouvements de données, est de généraliser le concept et la construction des conflits entre éléments d'un tableau aux spécifications parallèles, en particulier aux ordres partiels (par opposition à un ordre total pour un programme séquentiel) qui peuvent prendre en compte certains constructeurs parallèles de langages tels qu'OpenMP ou X10. Notre troisième résultat est, sur la base de cette analyse, de généraliser la contraction de tableaux à base de treillis (réseaux euclidiens), précédemment limitée à un ensemble d'éléments en conflits convexe, au cas où cet ensemble est décrit comme une union d'ensembles convexes, une situation courante lors de l'utilisation de tuilage. Nous combinons tous ces résultats dans une proposition pour la génération automatique de code pour GPUs exploitant leurs différents niveaux de mémoire et de parallélisme. Nous pensons que nos différents résultats contribuent également à l'extension des techniques polyédriques, à l'analyse des programmes parallèles et à la compilation vers d'autres accélérateurs tels que les FPGAs.

# Table des matières

| Introduction (en anglais)   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | In | Introduction (en français) 1 |          |                                                |    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------|----------|------------------------------------------------|----|--|

| 1.1       Architecture de processeurs et modèle de calcul       12         1.1.1       CPU       13         1.1.2       GPU       16         1.2       Techniques polyédriques       19         1.2.1       Partie à contrôle affine et statique (SCoP)       20         1.2.2       Représentation par contraintes       21         1.2.3       Représentation d'un SCoP       23         1.2.4       Relations       25         1.2.5       Dépendances       25         1.2.6       Transformations de boucles       27         1.2.7       Tuilage (tiling)       29         2       Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points </th <th>In</th> <th>trod</th> <th>uction</th> <th>(en anglais)</th> <th>7</th> | In | trod                         | uction   | (en anglais)                                   | 7  |  |

| 1.1.1 CPU       13         1.1.2 GPU       16         1.2 Techniques polyédriques       19         1.2.1 Partie à contrôle affine et statique (SCoP)       20         1.2.2 Représentation par contraintes       21         1.2.3 Représentation d'un SCoP       23         1.2.4 Relations       25         1.2.5 Dépendances       25         1.2.6 Transformations de boucles       27         1.2.7 Tuilage (tiling)       29         2 Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1 Motivation       33         2.2 Prérequis       36         2.2.1 Notations et définitions       36         2.2.2 Réutilisation inter-tuiles des données       37         2.3 Gestion des tuiles non alignées       40         2.3.1 Approche exacte par équations ensemblistes       41         2.3.2 Fonctions par points       45         2.3.3 Le cas des approximations       47         2.4 Conclusion       52         3 Analyse de durée de vie pour spécifications parallèles       54         3.1.1 Vivacité, conflits et réutilisation       55         3.1.2 Indices simultanément en vie       58         3.2 Extensions à quelques cas particuliers       59         3.2.1 Ordonn                              | 1  | Co                           | ntexte   | et travaux connexes                            | 12 |  |

| 1.1.2       GPU       16         1.2       Techniques polyédriques       19         1.2.1       Partie à contrôle affine et statique (SCoP)       20         1.2.2       Représentation par contraintes       21         1.2.3       Représentation d'un SCoP       23         1.2.4       Relations       25         1.2.5       Dépendances       25         1.2.6       Transformations de boucles       27         1.2.7       Tuilage (tiling)       29         2 Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       55                                                                                                 |    | 1.1                          | Archit   | tecture de processeurs et modèle de calcul     | 12 |  |

| 1.2       Techniques polyédriques       19         1.2.1       Partie à contrôle affine et statique (SCoP)       20         1.2.2       Représentation par contraintes       21         1.2.3       Représentation d'un SCoP       23         1.2.4       Relations       25         1.2.5       Dépendances       25         1.2.6       Transformations de boucles       27         1.2.7       Tuilage (tiling)       29         2       Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation                                                                               |    |                              | 1.1.1    | CPU                                            | 13 |  |

| 1.2.1       Partie à contrôle affine et statique (SCoP)       20         1.2.2       Représentation par contraintes       21         1.2.3       Représentation d'un SCoP       23         1.2.4       Relations       25         1.2.5       Dépendances       25         1.2.6       Transformations de boucles       27         1.2.7       Tuilage (tiling)       29         2       Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices si                                                                               |    |                              | 1.1.2    | GPU                                            | 16 |  |

| 1.2.2       Représentation par contraintes       21         1.2.3       Représentation d'un SCoP       23         1.2.4       Relations       25         1.2.5       Dépendances       25         1.2.6       Transformations de boucles       27         1.2.7       Tuilage (tiling)       29         2       Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers                                                                               |    | 1.2                          | Techn    | niques polyédriques                            | 19 |  |

| 1.2.2       Représentation par contraintes       21         1.2.3       Représentation d'un SCoP       23         1.2.4       Relations       25         1.2.5       Dépendances       25         1.2.6       Transformations de boucles       27         1.2.7       Tuilage (tiling)       29         2       Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers                                                                               |    |                              | 1.2.1    | Partie à contrôle affine et statique (SCoP)    | 20 |  |

| 1.2.3       Représentation d'un SCoP       23         1.2.4       Relations       25         1.2.5       Dépendances       25         1.2.6       Transformations de boucles       27         1.2.7       Tuilage (tiling)       29         2       Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particu                                                                               |    |                              | 1.2.2    | _ ,                                            | 21 |  |

| 1.2.4       Relations       25         1.2.5       Dépendances       25         1.2.6       Transformations de boucles       27         1.2.7       Tuilage (tiling)       29         2       Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                       |    |                              | 1.2.3    |                                                | 23 |  |

| 1.2.6       Transformations de boucles       27         1.2.7       Tuilage (tiling)       29         2       Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                 |    |                              | 1.2.4    | <del>-</del>                                   | 25 |  |

| 1.2.7 Tuilage (tiling)       29         2 Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1 Motivation       33         2.2 Prérequis       36         2.2.1 Notations et définitions       36         2.2.2 Réutilisation inter-tuiles des données       37         2.3 Gestion des tuiles non alignées       40         2.3.1 Approche exacte par équations ensemblistes       41         2.3.2 Fonctions par points       45         2.3.3 Le cas des approximations       47         2.4 Conclusion       52         3 Analyse de durée de vie pour spécifications parallèles       54         3.1 Motivation       54         3.1.1 Vivacité, conflits et réutilisation       55         3.1.2 Indices simultanément en vie       58         3.2 Extensions à quelques cas particuliers       59         3.2.1 Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                     |    |                              | 1.2.5    | Dépendances                                    | 25 |  |

| 2       Réutilisation inter-tuiles pour le tuilage paramétrique       32         2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                             |    |                              | 1.2.6    | Transformations de boucles                     | 27 |  |

| 2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                              |    |                              | 1.2.7    | Tuilage (tiling)                               | 29 |  |

| 2.1       Motivation       33         2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                              | 2  | Ré                           | utilisat | tion inter-tuiles pour le tuilage paramétrique | 32 |  |

| 2.2       Prérequis       36         2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                    | _  |                              |          | - 9 <b>-</b> -                                 |    |  |

| 2.2.1       Notations et définitions       36         2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                              |          |                                                |    |  |

| 2.2.2       Réutilisation inter-tuiles des données       37         2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 2.2                          |          | •                                              |    |  |

| 2.3       Gestion des tuiles non alignées       40         2.3.1       Approche exacte par équations ensemblistes       41         2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |                              |          |                                                |    |  |

| 2.3.1 Approche exacte par équations ensemblistes       41         2.3.2 Fonctions par points       45         2.3.3 Le cas des approximations       47         2.4 Conclusion       52         3 Analyse de durée de vie pour spécifications parallèles       54         3.1 Motivation       54         3.1.1 Vivacité, conflits et réutilisation       55         3.1.2 Indices simultanément en vie       58         3.2 Extensions à quelques cas particuliers       59         3.2.1 Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 2.3                          |          |                                                |    |  |

| 2.3.2       Fonctions par points       45         2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3 Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 2.0                          |          |                                                |    |  |

| 2.3.3       Le cas des approximations       47         2.4       Conclusion       52         3       Analyse de durée de vie pour spécifications parallèles       54         3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                              | _        |                                                |    |  |

| 2.4 Conclusion       52         3 Analyse de durée de vie pour spécifications parallèles       54         3.1 Motivation       54         3.1.1 Vivacité, conflits et réutilisation       55         3.1.2 Indices simultanément en vie       58         3.2 Extensions à quelques cas particuliers       59         3.2.1 Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                              |          | · ·                                            |    |  |

| 3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 2.4                          |          | * *                                            |    |  |

| 3.1       Motivation       54         3.1.1       Vivacité, conflits et réutilisation       55         3.1.2       Indices simultanément en vie       58         3.2       Extensions à quelques cas particuliers       59         3.2.1       Ordonnancements complètement séquentiels       60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3  | Δη                           | alvse d  | de durée de vie pour spécifications parallèles | 54 |  |

| 3.1.1 Vivacité, conflits et réutilisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | J  |                              | •        |                                                |    |  |

| 3.1.2 Indices simultanément en vie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 0.1                          |          |                                                |    |  |

| 3.2 Extensions à quelques cas particuliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                              | -        |                                                |    |  |

| 3.2.1 Ordonnancements complètement séquentiels 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 3 9                          | -        |                                                |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | J.∠                          |          | 1 1 1                                          |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                              |          |                                                |    |  |

Table des matières vi

|    | 3.3           | Ordres partiels et au delà                                              | 68<br>69<br>72 |  |

|----|---------------|-------------------------------------------------------------------------|----------------|--|

|    | 3.4<br>3.5    | Liens avec les travaux précédents                                       |                |  |

| 4  | All           | location mémoire                                                        | 77             |  |

|    | 4.1           | Motivation                                                              | 77             |  |

|    | 4.2           | Présentation intuitive de l'approche                                    | 79             |  |

|    | 4.3           | Contexte                                                                | 81             |  |

|    |               | 4.3.1 Ensemble de conflits                                              | 81             |  |

|    |               | 4.3.2 Allocation modulo                                                 | 82             |  |

|    | 4.4           | Allocation gloutonne et construction de réseaux                         | 83             |  |

|    |               | 4.4.1 Sélection de bases dans l'espace des allocations                  | 83             |  |

|    |               | 4.4.2 Sélection de bases dans l'espace des réseaux                      |                |  |

|    |               | 4.4.3 Combinaison des deux approches                                    |                |  |

|    | 4.5           | Évaluation                                                              | 96             |  |

|    |               | 4.5.1 Région en $L$ inversé et scripts optimisés                        | 96             |  |

|    |               | 4.5.2 Filtre floutant ("Blur")                                          |                |  |

|    |               | 4.5.3 Tuilage en diamant                                                | 99             |  |

|    |               | 4.5.4 Comparaison de nos allocations avec d'autres approches            |                |  |

|    | 4.6           | Travaux connexes                                                        |                |  |

|    |               | 4.6.1 Lien avec l'ordonnancement multi-dimensionnel et le tuilage       | 101            |  |

|    |               | 4.6.2 Lien avec la réutilisation entre tableaux de Bhaskaracharya et al | 102            |  |

|    |               | 4.6.3 Lien avec les vecteurs d'occupation universels (UOV)              | 104            |  |

|    | 4.7           | Conclusion et travaux futurs                                            | 105            |  |

| 5  | Tra           | ansfert de noyaux de calcul                                             | 107            |  |

|    | 5.1           | Motivation                                                              |                |  |

|    | 5.2           | Pipeline et double tampon                                               |                |  |

|    | 5.3           | Dérivation des conflits mémoire                                         |                |  |

|    | 5.4           | Dimensionnement et allocation de la mémoire locale                      |                |  |

|    | 5.5           | Vers une génération de code pour GPGPU                                  |                |  |

|    |               | 5.5.1 Choix de la bande de boucles permutables                          |                |  |

|    |               | 5.5.2 Prise en compte de la séquentialité                               |                |  |

|    |               | 5.5.3 Kernels et transferts entre mémoire CPU et mémoire GPU            |                |  |

|    |               | 5.5.4 Hiérarchie de tuilage                                             |                |  |

|    |               | 5.5.5 Blocks et transferts entre mémoire globale et mémoire partagée    |                |  |

|    |               | 5.5.6 Threads et transferts entre mémoire partagée et registres         |                |  |

|    | 5.6           | Conclusion                                                              | 135            |  |

| Co | Conclusion    |                                                                         |                |  |

| Bi | Bibliographie |                                                                         |                |  |

### **Abstract**

Guided by both performance and power objectives, today's computing infrastructures evolve toward architectures with an increasing complexity, including sophisticated memory organizations and the use of hardware accelerators. They require the user or the compiler to be able to perform parallelism extraction, locality optimization, and explicit data movements. This thesis, motivated by the practical problem of the automatic offloading of computational kernels on accelerators such as GPU or FPGA, had also as primary objective to extend polyhedral techniques (good for handling loop and array-based kernels) in the multiple directions required to address such a problem: parameters, approximations, parallelism.

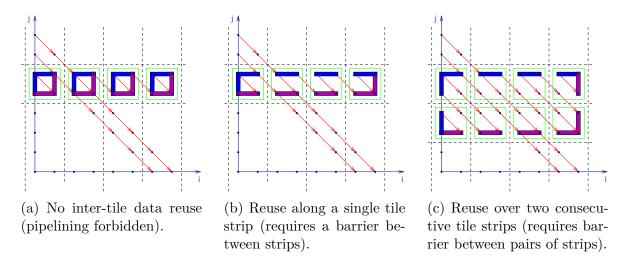

Our first result is an analysis (exact or with approximations) of the necessary copy-in and copy-out data for parametric tiling when a kernel is offloaded tile by tile, possibly in a pipelined fashion, and data reuse between tiles is exploited. Our second result, required to be able to allocate local arrays induced by data movements, is to generalize the concept and construction of conflicting array elements to parallel specifications, in particular partial orders (and not a total order as for a sequential program) that can capture parallel constructs of languages such as OpenMP or X10. Our third result is, based on this analysis, to generalize lattice-based array contraction, previously restricted to a convex set of conflicting elements, to the case where this set is described as a union of convex sets, a common situation when using tiling. We combine all these results into a proposal for the automatic code generation for GPUs exploiting their different levels of memory and parallelism. We believe our different results also contribute to the extension of polyhedral techniques, the analysis of parallel programs, and the compilation towards other accelerators such as FPGAs.

# **Contents**

| Introduction (in french) 1 |                 |                                                |                                        |      |  |  |  |  |

|----------------------------|-----------------|------------------------------------------------|----------------------------------------|------|--|--|--|--|

| In                         | $\mathbf{trod}$ | uction                                         | (in english)                           | 7    |  |  |  |  |

| 1                          | Bac             | kgrour                                         | nd and Related Work                    | 12   |  |  |  |  |

|                            | 1.1             | Proces                                         | ssor Architecture and Processing Model | . 12 |  |  |  |  |

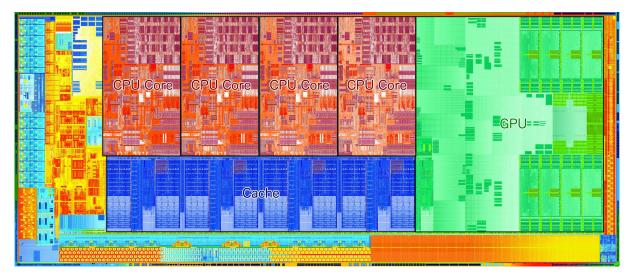

|                            |                 | 1.1.1                                          | CPU                                    |      |  |  |  |  |

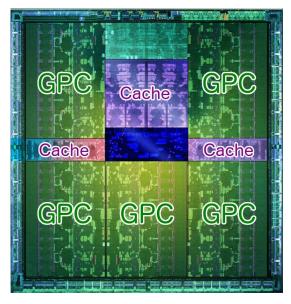

|                            |                 | 1.1.2                                          | GPU                                    | . 16 |  |  |  |  |

|                            | 1.2             | Polyhe                                         | edral Techniques                       |      |  |  |  |  |

|                            |                 | 1.2.1                                          | Affine Static Control Part             |      |  |  |  |  |

|                            |                 | 1.2.2                                          | Constraint Representation              |      |  |  |  |  |

|                            |                 | 1.2.3                                          | SCoP Representation                    |      |  |  |  |  |

|                            |                 | 1.2.4                                          | Relations                              |      |  |  |  |  |

|                            |                 | 1.2.5                                          | Dependences                            |      |  |  |  |  |

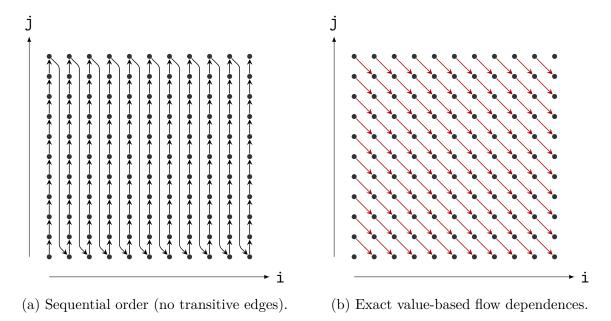

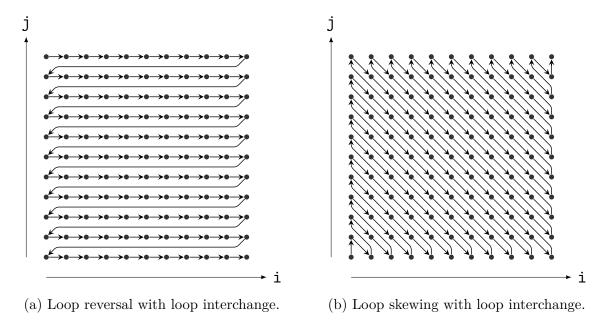

|                            |                 | 1.2.6                                          | Loop Transformations                   |      |  |  |  |  |

|                            |                 | 1.2.7                                          | Tiling                                 |      |  |  |  |  |

| 2                          | Inte            | r-Tile                                         | Reuse for Parametric Tiling            | 32   |  |  |  |  |

| 4                          | 2.1             |                                                | ation                                  |      |  |  |  |  |

|                            | 2.2             |                                                | quisites                               |      |  |  |  |  |

|                            | 2.2             | 2.2.1                                          | Notations and Definitions              |      |  |  |  |  |

|                            |                 | 2.2.1                                          | Inter-Tile Data Reuse                  |      |  |  |  |  |

|                            | 2.3             |                                                | g with Unaligned Tiles                 |      |  |  |  |  |

|                            | ۷.0             | 2.3.1                                          | Exact Approach with Set Equations      |      |  |  |  |  |

|                            |                 | 2.3.1 $2.3.2$                                  | Pointwise Functions                    |      |  |  |  |  |

|                            |                 | 2.3.2 $2.3.3$                                  | The Case of Approximations             |      |  |  |  |  |

|                            | 2.4             |                                                | usion                                  |      |  |  |  |  |

|                            | 2.4             | Concre                                         |                                        | . 02 |  |  |  |  |

| 3                          | Live            | Liveness Analysis over Parallel Specifications |                                        |      |  |  |  |  |

|                            | 3.1             | Motiva                                         | $\operatorname{ation}$                 |      |  |  |  |  |

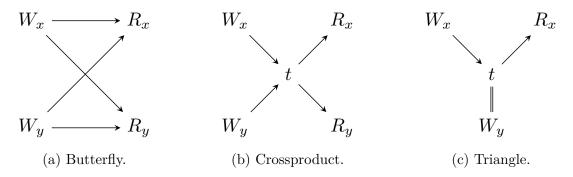

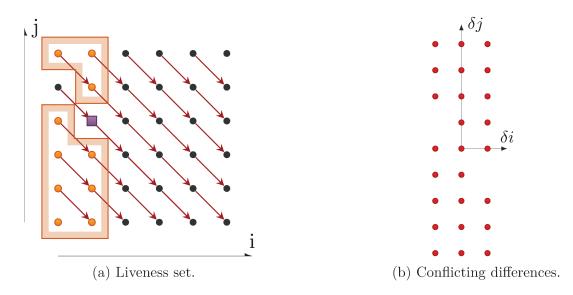

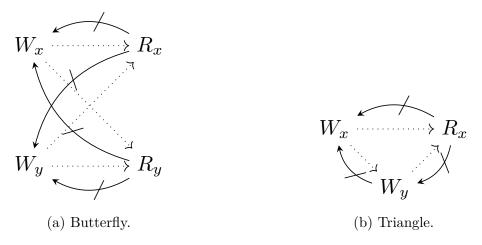

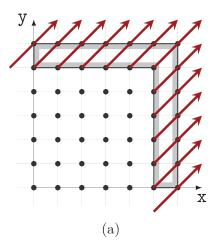

|                            |                 | 3.1.1                                          | Liveness, Conflicts, and Reuse         | . 55 |  |  |  |  |

|                            |                 | 3.1.2                                          | Simultaneously Live Indices            |      |  |  |  |  |

|                            | 3.2             | Specia                                         | d Case Extensions                      | . 59 |  |  |  |  |

|                            |                 | 3.2.1                                          | Fully Sequential Schedules             | . 60 |  |  |  |  |

|                            |                 | 3.2.2                                          | Affine Schedules and Parallel Loops    | . 64 |  |  |  |  |

CONTENTS ix

|    | 3.3           | Partial Orders and Beyond                               | 67<br>68<br>69<br>72<br>74 |  |  |  |

|----|---------------|---------------------------------------------------------|----------------------------|--|--|--|

|    | 3.5           | Conclusion                                              | 75                         |  |  |  |

| 4  |               | Iemory Allocation                                       |                            |  |  |  |

|    | 4.1           | Motivation                                              | 77                         |  |  |  |

|    | 4.2           | Intuition of the Approach                               | 79                         |  |  |  |

|    | 4.3           | Background                                              | 81                         |  |  |  |

|    |               | 4.3.1 Conflict Set                                      | 81                         |  |  |  |

|    |               | 4.3.2 Modular Mappings                                  | 82                         |  |  |  |

|    | 4.4           | Greedy Mapping and Lattice Constructions                | 83                         |  |  |  |

|    |               | 4.4.1 Basis Selection in Mapping Space                  | 83                         |  |  |  |

|    |               | 4.4.2 Basis Selection in Lattice Space                  | 88                         |  |  |  |

|    |               | 4.4.3 Combining the Two Approaches                      | 94                         |  |  |  |

|    | 4.5           | Evaluation                                              | 96                         |  |  |  |

|    |               | 4.5.1 Reverse- $L$ Shaped Region and Optimizing Scripts | 96                         |  |  |  |

|    |               | 4.5.2 Blur Filter                                       | 98                         |  |  |  |

|    |               | 4.5.3 Diamond Tiling                                    | 99                         |  |  |  |

|    |               | 1 11 0                                                  | 99                         |  |  |  |

|    | 4.6           | Related Work                                            |                            |  |  |  |

|    |               | 4.6.1 Link with Multi-Dimensional Scheduling and Tiling |                            |  |  |  |

|    |               | 4.6.2 Link with Bhaskaracharya et al. Intra-Array Reuse |                            |  |  |  |

|    |               | 4.6.3 Link with Universal Occupancy Vectors             |                            |  |  |  |

|    | 4.7           | Conclusion and Future Work                              | 105                        |  |  |  |

| 5  | Ker           | nel Offloading                                          | 107                        |  |  |  |

|    | 5.1           | Motivation                                              | 108                        |  |  |  |

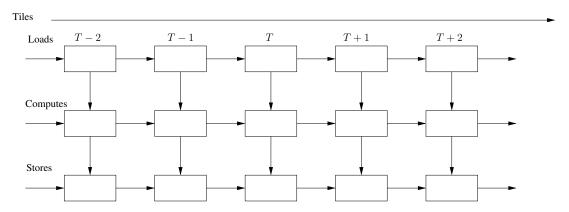

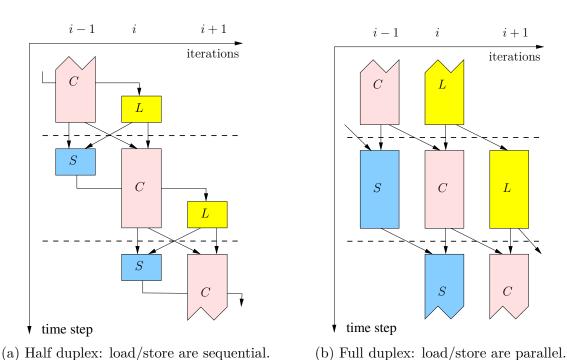

|    | 5.2           | Pipelining and Double Buffering                         | 110                        |  |  |  |

|    | 5.3           | Deriving Memory Conflicts                               | 112                        |  |  |  |

|    | 5.4           | Size and Mapping of Local Memory                        | 117                        |  |  |  |

|    | 5.5           | Targeting GPGPU                                         |                            |  |  |  |

|    |               | 5.5.1 Choice of Permutable Loop Band                    | 124                        |  |  |  |

|    |               | 5.5.2 Handling Sequentiality                            |                            |  |  |  |

|    |               | 5.5.3 Kernels and Host/Device Memory Transfers          | 127                        |  |  |  |

|    |               | 5.5.4 Tiling Hierarchy                                  |                            |  |  |  |

|    |               | 5.5.5 Blocks and Global/Shared Memory Transfer          |                            |  |  |  |

|    |               | 5.5.6 Threads and Shared/Register Memory Transfer       | 135                        |  |  |  |

|    | 5.6           | Conclusion                                              | 135                        |  |  |  |

| Co | Conclusion 13 |                                                         |                            |  |  |  |

| Bi | Bibliography  |                                                         |                            |  |  |  |

### Introduction

À notre époque moderne, les ordinateurs sont omniprésents. Ils ont des applications dans des domaines aussi divers que la médecine, la physique, les mathématiques, l'économie, ainsi que la photographie, le cinéma, la musique, et même la littérature. Ils promettent toujours plus de performances pour une consommation moindre. Cependant, il devient de plus en plus difficile d'utiliser efficacement cette puissance de calcul. Pour comprendre pourquoi, nous avons besoin d'un peu de contexte.

À l'heure actuelle, le parallélisme et l'efficacité énergétique font partie des défis majeurs. Alors que la fabrication des microprocesseurs suit grossièrement la loi de Moore, accumulant toujours plus de transistors sur une même puce, les avantages jadis offerts par ce rétrécissement sont devenus de plus en plus ténus. Jusqu'aux environs de la dernière décennie, des transistors plus petits demandaient une énergie de commutation plus faible, tout en offrant une vitesse plus élevée, et pour une tension plus faible. Dans l'ensemble, ceci conduisait à une fréquence plus élevée et une meilleure performance globale sans augmentation significative de la densité d'énergie et des exigences en refroidissement, suivant ainsi le principe de réduction de Dennard [34, 69]. Mais, comme on a pu le voir sur le marché grand public, la fréquence d'horloge n'a pas augmenté depuis 2006, où elle semble plafonner aux alentours de 3,5 à 4 GHz.

En pratique, parce que la tension de fonctionnement approche la tension de seuil intrinsèque au silicium et que les courants de fuite augmentent avec des transistors si petits, les effets quantiques ont mis un terme au principe de réduction de Dennard, limitant sévèrement toute possibilité d'amélioration significative de la fréquence d'horloge. Pour compenser cette perte, les fabricants de microprocesseurs se sont dirigés vers plus de parallélisme. En effet, puisqu'on a la possibilité de disposer de plus en plus de transistors, en augmentant le nombre d'opérations pouvant être faites en parallèle par cycle, on peut espérer augmenter d'autant les performances et ce, même à fréquence d'horloge constante. Le parallélisme a cependant un coût qui est que les programmes doivent être, de fait, conçus de l'application jusqu'à la machine avec, à l'esprit, parallélisme et concurrence.

Sur un aspect différent mais non moins important, la mémoire est devenue de plus

en plus problématique. Alors que les processeurs et la mémoire ont co-évolués vers un débit plus élevé, ils n'ont pas progressé au même rythme. Il est bien connu qu'un écart de performance s'est creusé entre le processeur et la mémoire, le débit du premier s'étant amélioré plus rapidement que le débit et la latence de la seconde. Notamment, plus grande est la mémoire et plus loin elle est du processeur, plus il faut de temps pour accéder à son contenu. Ceci a motivé l'utilisation d'une hiérarchie mémoire, où une petite mémoire embarquée sur la puce met « en cache » une plus grande mémoire externe, et ainsi de suite. De cette façon, des données qui devaient normalement être lues depuis la mémoire globale peuvent être récupérées plus rapidement depuis la mémoire locale, à la condition qu'elles y soient déjà. La mise en cache vient donc, elle aussi, avec un coût, qui est que les programmes doivent être conçus cette fois-ci avec, à l'esprit, la localité des données et le « pipelining ».

Ceci nous amène à notre problème actuel : comment programmer efficacement ces machines? En effet, le parallélisme se trouve généralement dans des algorithmes qui travaillent de façon aussi individuelle que possible en termes d'accès mémoire, où deux opérations différentes manipulent des données aussi espacées que possible. D'un autre côté, la localité est, elle, fournie par des algorithmes qui travaillent sur leurs données de façon aussi compacte que possible, où deux opérations différentes manipulent des données aussi proche que possible. Pour concilier ces deux objectifs apparemment antinomiques, il nous faut regarder au plus près de l'architecture, où les concepts tels que ligne de cache et mémoire partagée aident à produire des programmes à la fois parallèles et soucieux de la localité. Mais cela signifie aussi que les algorithmes deviennent de plus en plus dépendants des architectures sous-jacentes à un moment où les langages s'en éloignent pour offrir plus de flexibilité, portabilité et simplicité d'utilisation.

Cela signifie que le compilateur pour la partie la plus « statique » (et l'environnement d'exécution et système d'exploitation pour la partie la plus « dynamique ») est aujour-d'hui la pièce centrale du puzzle. En effet, un compilateur idéal transformerait un morceau de code portable, écrit dans un langage de programmation de haut niveau avec principalement la correction de l'algorithme à l'esprit, en un fichier binaire adapté à l'architecture, en se chargeant donc, entre autres, des considérations de localité et de parallélisme de manière entièrement automatique. A cet égard, bien qu'imparfaits dans la pratique, les compilateurs sont, lentement mais sûrement, de plus en plus à même de gérer la grande diversité des problèmes posés par la parallélisation et la vectorisation automatiques.

Le développement de tels compilateurs est difficile car ils ont une forte contrainte à respecter : peu importe la complexité du programme source, le code produit devra calculer le même résultat que l'original. Pour se simplifier la tâche, les compilateurs se concentrent

sur des optimisations à petite échelle où des propriétés locales garantissent la correction de la transformation. Cependant, optimiser pour le parallélisme et la localité nécessite des analyses et des transformations de code de plus grande envergure, mélangeant potentiellement plusieurs boucles ou fonctions, transformations auxquelles les compilateurs ne se risquent que très rarement. Pour aller dans ce sens, un important cadre d'étude, offrant à la fois rigueur mathématique et expressivité, est fourni par les analyses et optimisations polyédriques. Construit sur la base de l'arithmétique des inégalités affines, ce « modèle » de programmes et de transformations permet de décrire des morceaux de code avec une précision suffisante pour garantir la correction des transformations et une flexibilité assez grande pour représenter entièrement la plupart des transformations de programmes les plus courantes au sein d'un cadre commun.

Néanmoins, le « modèle polyédrique » central a de fortes limitations. Dans sa forme la plus simple, il nécessite une description exacte des calculs et des accès aux données, un ordonnancement séquentiel (total) des calculs, et, par nature, uniquement des analyses et optimisations qui peuvent être décrites par des inégalités affines portant sur les variables du programme, les paramètres, les accès mémoire, ou les spécifications des ordonnancements. Le but et la portée de cette thèse étaient d'étendre (c'est-à-dire de développer de nouvelles techniques) et d'élargir (c'est-à-dire de répondre à de nouvelles applications et problèmes) les techniques polyédriques vers de nouvelles directions, en particulier le tuilage paramétrique (qui a souvent été considéré comme un problème quadratique), les spécifications parallèles (par exemple, le pipelining et le traitement des ordres partiels), et les approximations (pas juste une description exacte des informations pertinentes).

Avant de présenter l'agencement de cette thèse, évoquons un peu l'histoire cachée qui a conduit aux travaux décrits dans ce manuscrit. Notre point de départ était d'étendre la thèse d'Alexandru Plesco [60], dans laquelle avait été conçue une méthode pour le transfert sur FPGA d'un noyau (petit morceau de code) par blocs de calcul, grâce au tuilage de boucles. Notre objectif était de mieux comprendre la réutilisation de données inter-tuiles et les mouvements de données associés au transfert de noyau, dans un cadre plus conceptuel et plus général, car ceux-ci apparaissent de plus en plus importants à optimiser, non seulement pour les FPGAs mais aussi pour les multicœurs et les GPUs. C'est, par exemple, la motivation première d'OpenAcc [58], même si, en l'occurrence, l'utilisateur est toujours responsable de l'orchestration de ces mouvements de données. De même, les transferts de données dans PPCG [75], un compilateur polyédrique pour GPU, étaient assez similaires, en particulier pour les mouvements de la mémoire globale à la mémoire partagée. Néanmoins, dans PPCG, ainsi que dans les travaux d'A. Plesco, les tailles de tuiles doivent être fixées avant la compilation, ce qui rend difficile la modélisation

statique des performances et de l'influence du choix des tailles de tuile. Pour le cas des FPGAs, ce travail était même d'autant plus pénible que la technique, mise en œuvre en amont d'un outil de synthèse de haut niveau (HLS), n'était que semi-automatique et nécessitait des modifications manuelles du code ainsi généré. Pour évaluer les performances des différentes tailles de tuiles, il était donc nécessaire d'effectuer, manuellement, toutes ces modifications, pour chaque taille de tuiles!

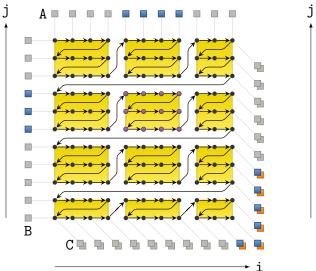

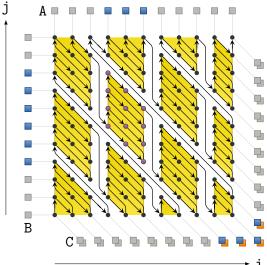

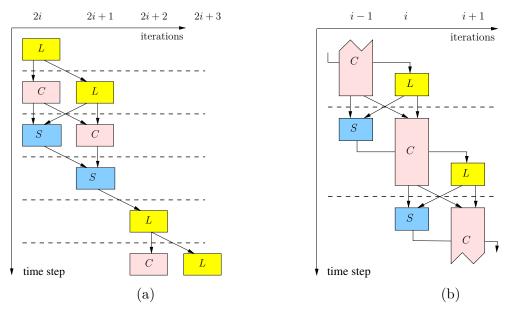

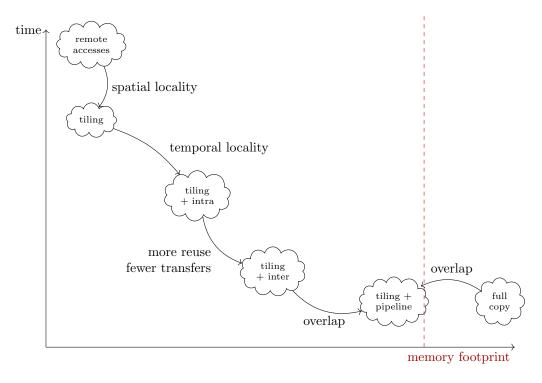

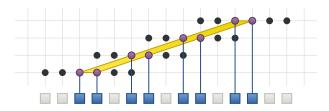

Nous avons donc d'abord travaillé sur la façon de rendre la technique précédente paramétrique en la taille des tuiles, avec l'objectif double de rendre la génération de code plus générique et de permettre, potentiellement, de concevoir des modèles de sélection de taille de tuiles. Nous avons également considéré l'impact des approximations sur l'analyse et les optimisations associées. Il s'est avéré que, lorsque les tuiles (contenant éventuellement du parallélisme) sont exécutées en séquence (le long des axes qui les définissent), c'est-à-dire d'une façon localement parallèle mais globalement séquentielle (LPGS), le problème peut être résolu de manière entièrement paramétrique en dépit de son caractère intrinsèquement quadratique.

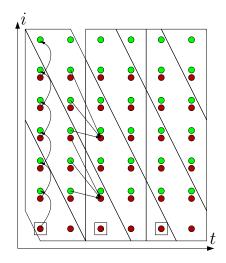

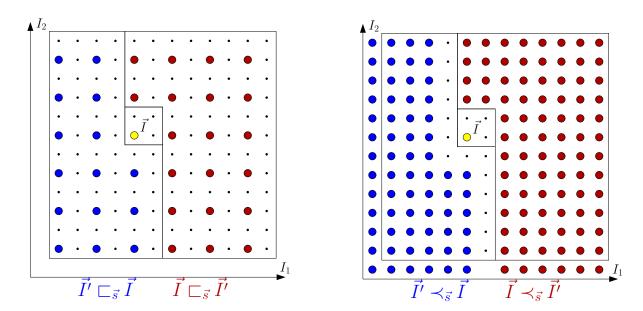

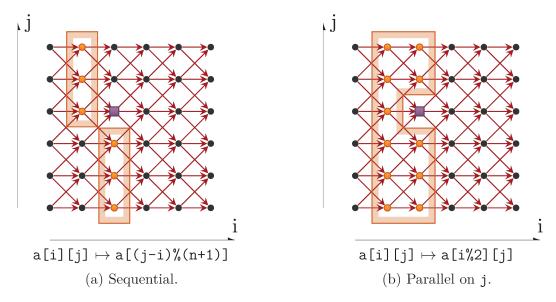

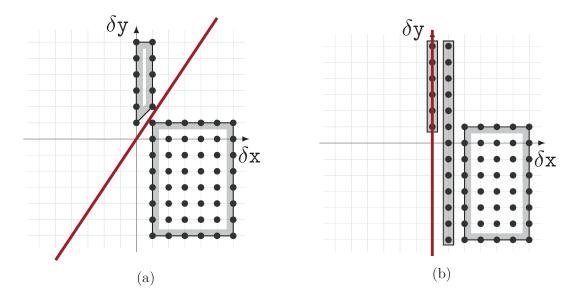

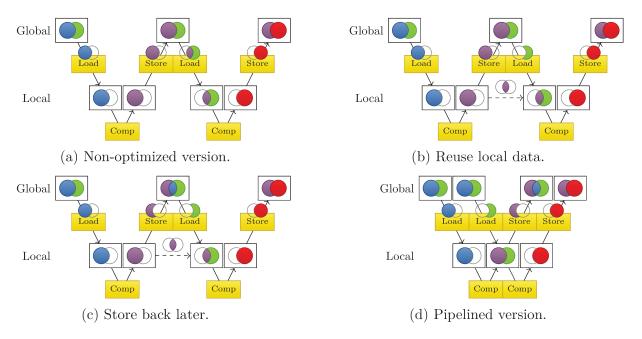

Nous souhaitions ensuite appliquer les techniques standard de contraction mémoire pour définir l'allocation des données transférées en mémoire locale. Ces techniques requièrent une analyse de la durée de vie des éléments de tableaux (c'est-à-dire, savoir quand un élément est « mort » et son emplacement réutilisable) et, plus précisément, une analyse d'interférences qui décrit les éléments d'un tableau qui peuvent partager le même emplacement mémoire. Cependant, pour superposer communications et calculs, nous utilisions une spécification pipelinée pour exprimer l'ordre des chargements, déchargements, et tâches de calcul, donc une spécification exprimant un certain parallélisme. Il nous est alors apparu que, même sous cette forme restreinte de parallélisme, certaines propriétés intuitives, vraies pour des calculs totalement ordonnés, ne pouvaient plus s'appliquer. Ceci nous a amenés à revoir et à étendre les techniques polyédriques standard pour l'analyse des durées de vie et la construction des interférences dans le cas d'ordonnancements parallèles.

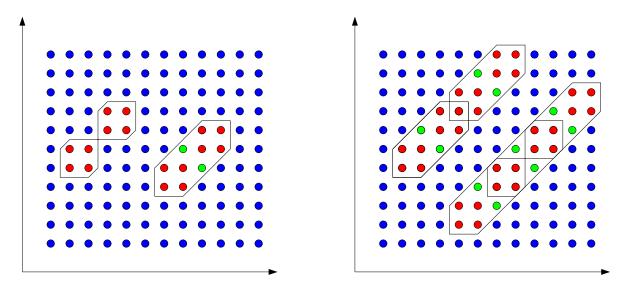

Enfin, en utilisant cette analyse, il restait à appliquer les techniques standard de contraction de tableaux pour allouer les données transférées dans la mémoire locale. Pour beaucoup d'exemples, une technique à base de modulos successifs [54] était suffisante pour obtenir une bonne allocation. Cependant, lors de discussions en marge du colloque IM-PACT'14, Uday Bondhugula et son élève S. G. Bhaskaracharya nous ont montré quelques exemples tuilés où la théorie d'allocation de mémoire basée sur les treillis (réseaux euclidiens) [32] nécessitait une sélection adéquate de base pour produire une bonne allocation. Nous avons alors travaillé indépendamment d'eux, et même en concurrence avec eux, sur

le problème de l'extension de l'allocation mémoire basée sur les treillis au cas où les interférences sont décrites par une union non-convexe de polyèdres, un cas qui arrive en effet fréquemment dans les situations parallèles et/ou tuilées. Ceci nous a conduits à une solution différente, avec quelques découvertes communes, comme le fait que la recherche de directions d'allocation est similaire à la recherche de directions d'ordonnancement, mais avec des contraintes (d'interférence au lieu de dépendance) qui sont non orientées.

Cette thèse raconte les détails de cette histoire. Elle est organisée de la façon suivante :

Contexte et travaux connexes où nous dressons une esquisse des architectures matérielles actuelles et donnons une vue générale de leurs capacités, de leurs limites, et des considérations associées. Nous passons aussi brièvement en revue ce qu'est la représentation polyédrique et quelques applications courantes auxquelles nous nous référerons dans la suite de la thèse.

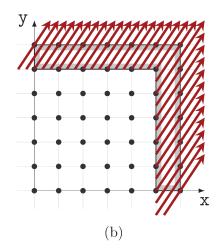

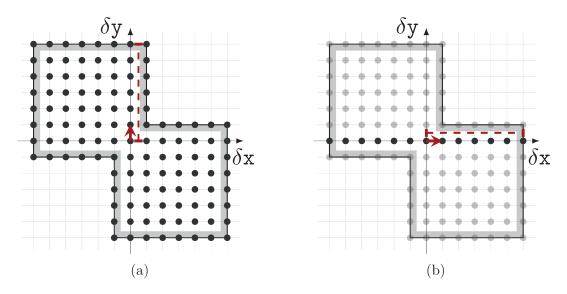

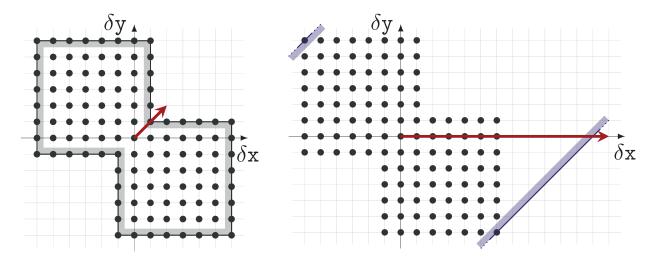

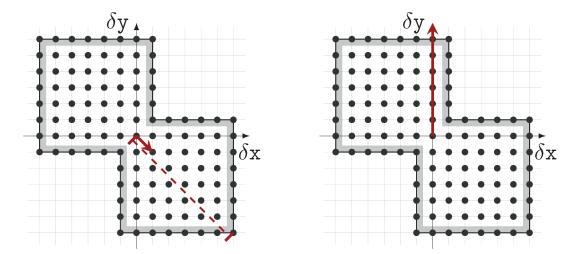

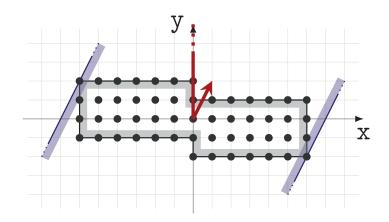

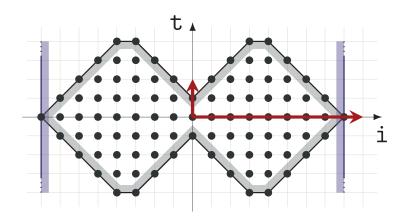

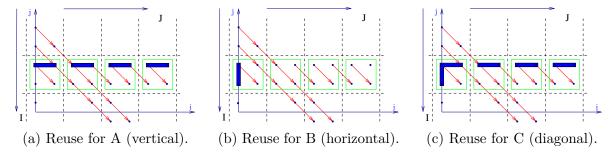

Réutilisation inter-tuiles pour le tuilage paramétrique où nous motivons, décrivons et traitons le tuilage avec des tailles de tuiles paramétriques et réutilisation des données inter-tuiles, c'est-à-dire comment exploiter la réutilisation des données non seulement dans une tuile, mais aussi entre des tuiles successives et ce, d'une manière paramétrique. L'ordonnancement parallèle spécifique que nous avons choisi pour orchestrer les communications et les calculs, une forme de pipeline logiciel des tuiles, est ce qui a motivé notre analyse des ordonnancements parallèles décrits par une relation « happens-before » (ordre de précédence dans toute exécution).