# Continuous time signal processing for wake-up radios Alin Ratiu

### ▶ To cite this version:

Alin Ratiu. Continuous time signal processing for wake-up radios. Networking and Internet Architecture [cs.NI]. INSA de Lyon, 2015. English. NNT: 2015ISAL0078. tel-01375171

### HAL Id: tel-01375171 https://theses.hal.science/tel-01375171v1

Submitted on 13 Apr 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Université de Lyon

### DOCTORAL THESIS

# Continuous Time Signal Processing for Wake-Up Radios

Author:

Alin Ratiu

Supervisor:

Dominique Morche

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

at the

Commissariat à l'Energie Atomique LETI / DACLE / SCCI / LAIR

October 8, 2015

### Abstract

### Continuous Time Signal Processing for Wake-Up Radios

by Alin Ratiu

Wake-Up Receivers (WU-RX) have been recently proposed as candidates to reduce the communication power budget of wireless networks. Their role is to sense the environment and wake up the main receivers which then handle the bulk data transfer. Existing WU-RXs achieve very high sensitivities for power consumptions below  $50\mu$ W but severely degrade their performance in the presence of out-of-band blockers. We attempt to tackle this problem by implementing an ultra low power, tunable, intermediate frequency filtering stage. Its specifications are derived from standard WU-RX architectures; it is shown that classic filtering techniques are either not tunable enough or demand a power consumption beyond the total WU-RX budget of  $100\mu$ W. We thus turn to the use of Continuous Time Digital Signal Processing (CT-DSP) which offers the same level of programmability as standard DSP solutions while providing an excellent scalability of the power consumption with respect to the characteristics of the input signal. A CT-DSP chain can be divided into two parts: the CT-ADC and the CT-DSP itself; the specifications of these two blocks, given the context of this work, are also discussed.

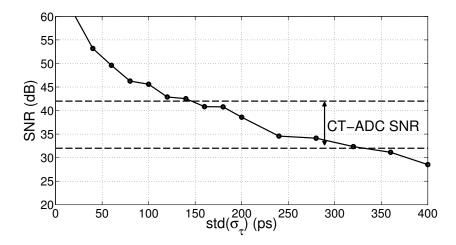

The CT-ADC is based on a novel, delta modulator-based architecture which achieves a very low power consumption; its maximum operation frequency was extended by the implementation of a very fast feedback loop. Moreover, the CT nature of the ADC means that it does not do any sampling in time, hence no anti-aliasing filter is required. The proposed ADC requires only  $24\mu W$  to quantize signals in the [10MHz 50MHz] bandwidth for an SNR between 32dB and 42dB, resulting in a figure of merit of  $3-10 {\rm fJ/conv}-{\rm step}$ , among the best reported for the selected frequency range.

Finally, we present the architecture of the CT-DSP which is divided into two parts: a CT-IIR and a CT-FIR. The CT-IIR is implemented by placing a standard CT-FIR in a feedback loop around the CT-ADC. If designed correctly, the feedback loop can now cancel out certain frequencies from the CT-ADC input (corresponding to those of out-of-band interferers) while boosting the power of the useful signal. The effective amplitude of the CT-ADC input is thus reduced, making it generate a smaller number of tokens, thereby reducing the power consumption of the subsequent CT-FIR by a proportional amount. The CT-DSP consumes around  $100\mu$ W while achieving more than 40dB of out-of-band rejection; for a bandpass implementation, a 2MHz passband can be shifted over the entire ADC bandwidth.

## Acknowledgements

First of all, I would like to thank my advisor, Dominique Morche for providing me with a very interesting research topic. He gave me the liberty to work as I desired but, at the same time, knew when to step in and bring his vast experience in systems analysis. From him, I have learned about the importance of strategy and positioning even in a scientific field such as microelectronics.

I would also like to thank our collaborators from Columbia University, Sharvil Patil for inspiring me with his ambition as well as Prof. Yannis Tsividis for teaching me about the importance of rigor in scientific writing.

I also thank Bruno Allard, Xuefang Lin-Shi and Jacques Verdier for giving me the opportunity of pursuing a PhD under the guidance of INSA de Lyon, as well as for the assistance and feedback they provided over the years.

Thanks also to the members of my defense committee, Prof. Pieter Harpe, Dominique Dallet, Hassan Aboushady, Stéphane Le Tual, Prof. Yannis Tsividis, and Bruno Allard for their interest, time and feedback given to me. A special thanks to Prof. Pieter Harpe and Stýhane Le Tual for their detailed and constructive comments they gave me regarding this manuscript.

I would also like to thank my fellow PhD students, especially Matthieu Verdy, for teaching me about Linux development, Robert Polster, for the interesting discussions regarding circuit design and finally, David Buffeteau for the time he took helping me improve this manuscript. I take this opportunity to send a big thank you to the rest of the LAIR team at CEA for their support and hospitality.

I thank the testing team, especially Sylvain Dumas and Christian Chancel for the support they offered in PCB design and in preparing the testing equipment as well as the testing software.

Finally, I thank my family for the support they have offered my throughout the years as well as for inspiring me to pursue a career which eventually lead to this PhD.

### INSA Direction de la Recherche - Ecoles Doctorales - Quinquennal 2011-2015

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                                  | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СНІМІЕ    | CHIMIE DE LYON http://www.edchimie-lyon.fr Sec: Renée EL MELHEM Bat Blaise Pascal 3º etage 04 72 43 80 46 Insa: R. GOURDON secretariat@edchimie-lyon.fr                                          | M. Jean Marc LANCELIN Université de Lyon – Collège Doctoral Bât ESCPE 43 bd du 11 novembre 1918 69622 VILLEURBANNE Cedex Tél: 04.72.43 13 95 directeur@edchimie-lyon.fr                                                                              |

| E.E.A.    | ELECTRONIQUE, ELECTROTECHNIQUE, AUTOMATIQUE http://edeea.ec-lyon.fr  Sec: M.C. HAVGOUDOUKIAN Ecole-doctorale.eea@ec-lyon.fr                                                                      | M. Gérard SCORLETTI Ecole Centrale de Lyon 36 avenue Guy de Collongue 69134 ECULLY Tél: 04.72.18 60.97 Fax: 04 78 43 37 17 Gerard.scorletti@ec-lyon.fr                                                                                               |

| E2M2      | EVOLUTION, ECOSYSTEME, MICROBIOLOGIE, MODELISATION http://e2m2.universite-lyon.fr  Sec: Safia AIT CHALAL Bat Atrium- UCB Lyon 1 04.72.44.83.62 Insa: S. REVERCHON Safia.ait-chalal@univ-lyon1.fr | M. Fabrice CORDEY Laboratoire de Géologie de Lyon Université Claude Bernard Lyon 1 Bât Géode – Bureau 225 43 bd du 11 novembre 1918 69622 VILLEURBANNE Cédex Tél: 04.72.44.83.74 Sylvie.reverchon-pescheux@insa-lyon.fr fabrice.cordey@univ-lyon1.fr |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-<br>SANTE<br>http://www.ediss-lyon.fr<br>Sec : Safia AlT CHALAL<br>Bat Atrium – UCB Lyon 1<br>04 72 44 83 62<br>Insa :<br>Safia.ait-chala@univ-lyon1.fr              | Mme Emmanuelle CANET-SOULAS INSERM U1060, CarMeN lab, Univ. Lyon 1 Bâtiment IMBL 11 avenue Jean Capelle INSA de Lyon 696621 Villeurbanne Tél: 04.72.11.90.13 Emmanuelle.canet@univ-lyon1.fr                                                          |

| INFOMATHS | INFORMATIQUE ET MATHEMATIQUES http://infomaths.univ-lyon1.fr  Sec : Renée EL MELHEM Bat Blaise Pascal 3° etage infomaths@univ-lyon1.fr                                                           | Mme Sylvie CALABRETTO LIRIS – INSA de Lyon Bat Blaise Pascal 7 avenue Jean Capelle 69622 VILLEURBANNE Cedex Tél: 04.72. 43. 80. 46 Fax 04 72 43 16 87 Sylvie.calabretto@insa-lyon.fr                                                                 |

| Matériaux | MATERIAUX DE LYON http://ed34.universite-lyon.fr  Sec: M. LABOUNE PM: 71.70 —Fax: 87.12 Bat. Direction 1er et. Ed.materiaux@insa-lyon.fr                                                         | M. Jean-Yves BUFFIERE INSA de Lyon MATEIS Bâtiment Saint Exupéry 7 avenue Jean Capelle 69621 VILLEURBANNE Cedex Té1: 04.72.43 71.70 Fax 04 72 43 85 28 Ed.materiaux@insa-lyon.fr                                                                     |

| MEGA      | MECANIOUE, ENERGETIOUE, GENIE CIVIL, ACOUSTIQUE http://mega.universite-lyon.fr  Sec: M. LABOUNE PM: 71.70 -Fax: 87.12 Bat. Direction 1 <sup>st</sup> et. mega@insa-lyon.fr                       | M. Philippe BOISSE INSA de Lyon Laboratoire LAMCOS Bătiment Jacquard 25 bis avenue Jean Capelle 69621 VILLEURBANNE Cedex Tél: 04.72.43.71.70 Fax: 04 72 43 72 37 Philippe.boisse@insa-lyon.fr                                                        |

| ScSo      | ScSo*<br>http://recherche.univ-lyon2.fr/scso/<br>Sec: Viviane POLSINELLI<br>Brigitte DUBOIS<br>Insa: J.Y. TOUSSAINT<br>viviane.polsinelli@univ-lyon2.fr                                          | Mme Isabelle VON BUELTZINGLOEWEN Université Lyon 2 86 rue Pasteur 69365 LYON Cedex 07 Tél: 04.78.77.23.86 Fax: 04.37.28.04.48 isavonb@dbmail.com                                                                                                     |

<sup>\*</sup>ScSo : Histoire, Géographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie

# Contents

| A | Abstract         |         |                                                     | i    |

|---|------------------|---------|-----------------------------------------------------|------|

| A | Acknowledgements |         |                                                     |      |

| A | bbre             | viation | 18                                                  | xvi  |

| 1 | Inti             | oduct   | ion: Wake-Up Radios                                 | 1    |

|   | 1.1              | Power   | Considerations in Wireless Sensor Networks          | . 2  |

|   | 1.2              | Wake-   | -Up Receivers State of the Art                      | . 4  |

|   |                  | 1.2.1   | Architecture Considerations                         | . 4  |

|   |                  | 1.2.2   | Performance Analysis of Existing WU-RXs             | . 7  |

|   | 1.3              | Propo   | osed WU-RX architecture                             | . 0  |

|   |                  | 1.3.1   | Proposed System                                     | . 9  |

|   |                  | 1.3.2   | Low Power – Low Sensitivity WU-RX                   | . 10 |

|   |                  | 1.3.3   | High Sensitivity WU-RX                              | . 10 |

|   |                  | 1.3.4   | Interferer Resilient WU-RX                          | . 15 |

|   | 1.4              | Tunab   | ole Filter Design                                   | . 17 |

|   |                  | 1.4.1   | Continuous Time Analog Domain Filters               | . 17 |

|   |                  | 1.4.2   | Discrete Time Charge Domain Filters                 |      |

|   |                  | 1.4.3   | Digital Signal Processing                           | . 18 |

|   |                  | 1.4.4   | Continuous Time Digital Signal Processing           | . 19 |

|   |                  | 1.4.5   | Tunable Filter Choice                               | 19   |

|   | 1.5              | Study   | of the Proposed CT Filtering Architecture           | . 20 |

|   |                  | 1.5.1   | Single Tone Reception                               | . 20 |

|   |                  | 1.5.2   | Single Tone Reception with an Interferer            | . 23 |

|   |                  | 1.5.3   | Single Tone Reception with Two Interferers          | . 26 |

|   | 1.6              | Wake-   | -Up Receiver Design Conclusions                     | . 28 |

| 2 | Cor              | ntinuou | us Time Processing Chain                            | 29   |

|   | 2.1              | Classi  | fication of the Different Signal Processing Domains | . 29 |

|   | 2.2              | Descri  | iption of the CT-DSP Chain                          | . 30 |

Contents vi

|   |     | 2.2.1   | CT-ADC                                        | 31  |

|---|-----|---------|-----------------------------------------------|-----|

|   |     | 2.2.2   | CT-DSP                                        |     |

|   | 2.3 | Co-De   | esigning the CT-ADC with the CT-DSP           | 41  |

|   | 2.4 | Propo   | osed CT-ADC Architecture                      | 45  |

|   |     | 2.4.1   | Filtering CT-ADC Principle                    | 46  |

|   |     | 2.4.2   | Reducing the Input Event Rate                 | 47  |

|   |     | 2.4.3   | Effects on the Linearity of the Conversion    | 49  |

|   | 2.5 | CT-A    | DC/DSP Conclusion                             | 52  |

| 3 | Ene | ergy Ei | fficient CT-ADC                               | 53  |

|   | 3.1 | Previo  | ous Work                                      | 53  |

|   |     | 3.1.1   | Basic Architectures                           | 53  |

|   |     | 3.1.2   | Improved Delta-Modulator Based CT-ADCs        | 55  |

|   | 3.2 | Propo   | osed CT-ADC                                   | 56  |

|   |     | 3.2.1   | Improved Commutation Scheme                   | 57  |

|   |     | 3.2.2   | Proposed Architecture                         | 58  |

|   |     | 3.2.3   | Features                                      | 61  |

|   |     | 3.2.4   | Possible Errors                               | 62  |

|   | 3.3 | Transi  | istor-Level Implementation                    | 66  |

|   |     | 3.3.1   | Comparators                                   | 66  |

|   |     | 3.3.2   | Transconductance                              | 72  |

|   |     | 3.3.3   | Threshold Management                          | 76  |

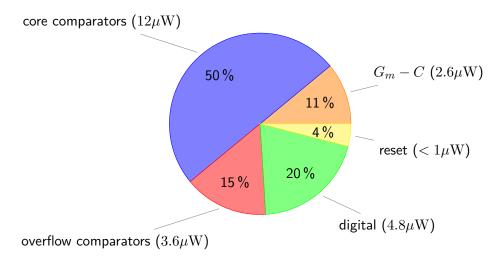

|   |     | 3.3.4   | Breakdown of the CT-ADC Power Consumption     | 79  |

|   | 3.4 | Measu   | rement Results                                | 80  |

|   |     | 3.4.1   | Single Tone Input: Noise                      | 80  |

|   |     | 3.4.2   | Two Tone Input: Linearity                     | 84  |

|   | 3.5 | CT-A    | DC Conclusion                                 | 86  |

| 4 | Pov | ver Sca | alable CT-DSP                                 | 87  |

|   | 4.1 | CT-D    | SP Architecture                               | 87  |

|   |     | 4.1.1   | Dual FIR – IIR Implementation                 | 88  |

|   |     | 4.1.2   | CT Digital Filter Design                      | 89  |

|   |     | 4.1.3   | Architecture Simulation                       | 91  |

|   |     | 4.1.4   | CT-DSP Specifications                         | 96  |

|   | 4.2 | CT D    | elay Cell                                     | 98  |

|   |     | 4.2.1   | State of the Art for Asynchronous Delay Cells | 98  |

|   |     | 4.2.2   | Delay Cell Design                             | 99  |

|   |     | 4.2.3   | Delay Cell Architecture                       | 102 |

|   |     | 4.2.4   | Calibration and Matching                      | 106 |

|          |       | 4.2.5   | Delay Architecture Summary                                                                           | 109  |

|----------|-------|---------|------------------------------------------------------------------------------------------------------|------|

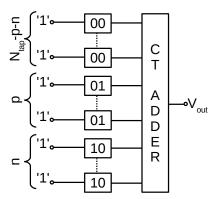

|          | 4.3   | CT A    | dder                                                                                                 | 110  |

|          |       | 4.3.1   | Previous Work                                                                                        | 110  |

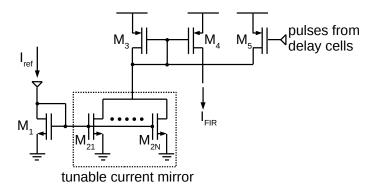

|          |       | 4.3.2   | Proposed Weighted-CT-Adder                                                                           | 112  |

|          |       | 4.3.3   | Adder Performance                                                                                    | 117  |

|          | 4.4   | DF-C    | Г-АDC                                                                                                | 118  |

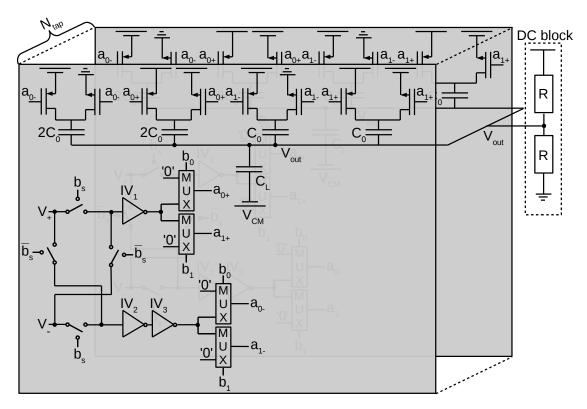

|          |       | 4.4.1   | $\label{eq:ct-adc} \mbox{CT-ADC} - \mbox{CT-FIR Integration} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 119  |

|          |       | 4.4.2   | Dispatcher                                                                                           | 120  |

|          |       | 4.4.3   | Voltage Gain and Filtering                                                                           | 121  |

|          |       | 4.4.4   | Feedback $G_m$                                                                                       | 122  |

|          | 4.5   | Simula  | ation/Measurements Results                                                                           | 123  |

|          |       | 4.5.1   | DF-CT-ADC Performance                                                                                | 123  |

|          |       | 4.5.2   | CT-FIR Performance                                                                                   | 126  |

|          |       | 4.5.3   | Interferer Rejection                                                                                 | 128  |

|          |       | 4.5.4   | Power Consumption Scaling                                                                            | 131  |

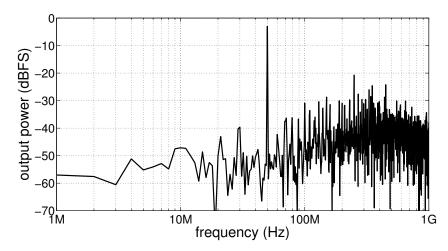

|          |       | 4.5.5   | Noise                                                                                                | 132  |

|          |       | 4.5.6   | Comparison with State of the Art                                                                     | 133  |

|          | 4.6   | CT-D    | SP Conclusion                                                                                        | 136  |

| 5        | Con   | clusio  | ${f n}$                                                                                              | 137  |

|          | 5.1   | Motiva  | ations and Contributions of this Work                                                                | 137  |

|          | 5.2   | Impro   | vements of the Proposed Design                                                                       | 139  |

|          |       | 5.2.1   | CT-ADC                                                                                               | 139  |

|          |       | 5.2.2   | DF-CT-ADC Feedback Path                                                                              | 141  |

|          |       | 5.2.3   | CT-DSP Delay Cells                                                                                   | 143  |

|          | 5.3   | Future  | e Work                                                                                               | 143  |

| <b>A</b> | Con   | anon N  |                                                                                                      | 1 45 |

| A        | əqu   | arer IV | Voise Analysis                                                                                       | 145  |

| В        | The   | 28nm    | UTBB FDSOI CMOS Technology                                                                           | 151  |

| Bi       | bliog | graphy  |                                                                                                      | 155  |

List of Figures viii

# List of Figures

| 1.1  | lot node available power versus its lifetime when powered by different           | 0  |

|------|----------------------------------------------------------------------------------|----|

| 1.0  | types of batteries: [2]                                                          | 2  |

| 1.2  | Representation of a duty cycled wireless network with synchronization            |    |

|      | packets as well as a zoomed in view of an arbitrary moment in time where         | _  |

|      | node A initiates communication with node B                                       | 3  |

| 1.3  | View of a network with wake-up radios; in this representation no duty-           |    |

|      | cycling is applied                                                               | 4  |

| 1.4  | Standard receiver architectures: heterodyne (a) and homodyne (b)                 | 5  |

| 1.5  | Architecture of the Uncertain IF receiver [4]                                    | 5  |

| 1.6  | State of the art in frequency references: power consumption versus preci-        |    |

|      | sion [5], [6], [7], [8], [4], [9], [10], [11], [12]                              | 6  |

| 1.7  | Spectrum of the signal at different points inside the Uncertain IF architecture. | 6  |

| 1.8  | State of the art low power data receivers and WU-RXs. The radio sensi-           |    |

|      | tivities have been normalized to a data-rate of 100kbps                          | 8  |

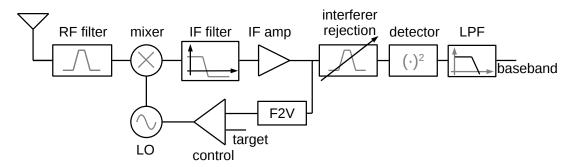

| 1.9  | Top level view of the proposed WU-RX architecture                                | 10 |

| 1.10 | Proposed WU-RX architecture in low power – low sensitivity mode                  | 10 |

| 1.11 | Proposed WU-RX architecture in high sensitivity mode                             | 11 |

| 1.12 | Model of the simulation bench used to characterize prospective sensitivity       |    |

|      | improvements by reducing the IF bandwidth                                        | 12 |

| 1.13 | IF signal-to-noise ratio required for a robust demodulation of the IF signal.    | 12 |

| 1.14 | Frequency estimated by a zero crossing detector versus the $SNR_{in}$            | 13 |

| 1.15 | Frequency control loop.                                                          | 14 |

| 1.16 | Evolution of the local oscillator instantaneous frequency for different values   |    |

|      | of the input $SNR_{in}$                                                          | 14 |

| 1.17 | Proposed WU-RX architecture                                                      | 15 |

| 1.18 | View of the WU-RX IF with an input signal configuration described by             |    |

|      | $SNR_{in}$ and $SIR_{in}$                                                        | 20 |

| 1.19 | Single tone reception scenario                                                   | 21 |

| 1.20 | Baseband SNR $(SNR_{BB})$ versus the input SNR $(SNR_{in})$ for different values |    |

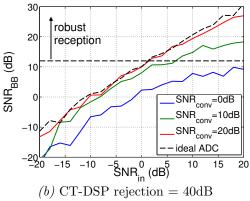

|      | of $SNR_{conv}$                                                                  | 22 |

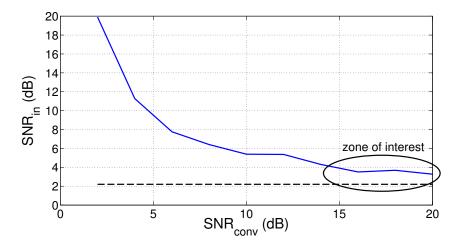

| 1.21 | Required $SNR_{in}$ versus the $SNR_{conv}$ for achieving a BER of 1e-3          | 23 |

|      |                                                                                  |    |

List of Figures ix

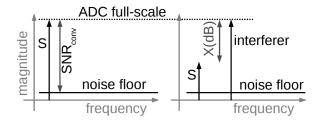

| 1.22 | The SNR constraint for the analog to digital conversion                              | 24 |

|------|--------------------------------------------------------------------------------------|----|

| 1.23 | Useful signal & interferer reception scenario                                        | 24 |

| 1.24 | Required $SNR_{in}$ and $SIR_{in}$ for different values of the conversion precision, |    |

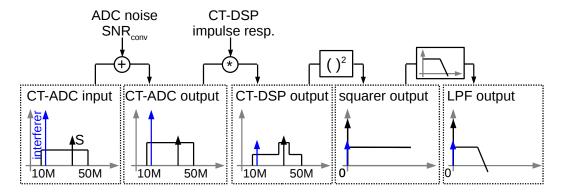

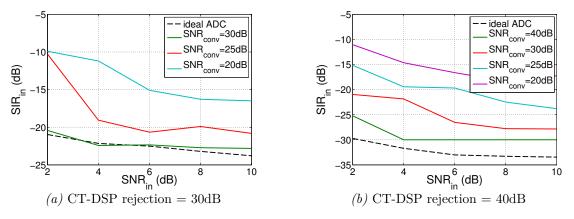

|      | $SNR_{conv}$ , and CT-DSP rejection level                                            | 25 |

| 1.25 | The SFDR constraint for the analog to digital conversion                             | 26 |

| 1.26 | Useful signal with two interferers reception scenario                                | 27 |

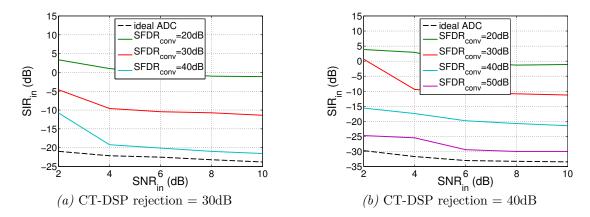

| 1.27 | Required $SNR_{in}$ and $SIR_{in}$ for different values of the conversion linearity, |    |

|      | $SFDR_{conv}$ , and CT-DSP rejection level                                           | 27 |

| 2.1  | Classification of systems according to the continuous / discrete nature of           |    |

|      | the time and amplitude [36]                                                          | 30 |

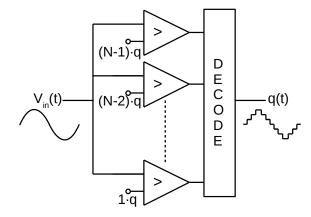

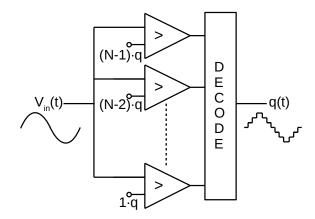

| 2.2  | Implementation of an N-level flash CT-ADC                                            | 31 |

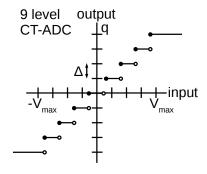

| 2.3  | Input-output characteristic of a 9 level flash CT-ADC                                | 32 |

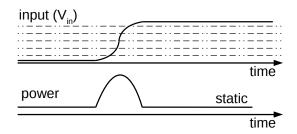

| 2.4  | Representation of the activity dependent power dissipation of a CT-ADC               |    |

|      | [36]                                                                                 | 32 |

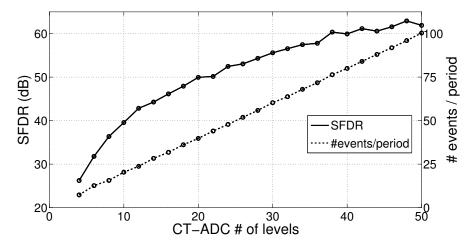

| 2.5  | Comparison between the spectral representation of a signal at the output             |    |

|      | of a CT-ADC and that of a sampled ADC for a single tone, sinusoid input.             | 34 |

| 2.6  | SFDR and number of events generated per period for a CT-ADC with an                  |    |

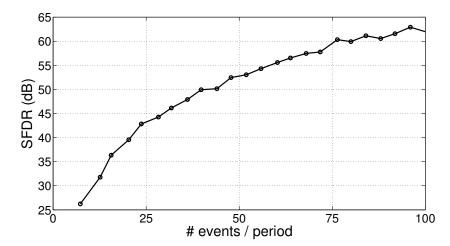

|      | input sinusoid versus the ADC number of levels, $N$                                  | 34 |

| 2.7  | SFDR versus the number of events generated per period for a CT-ADC                   |    |

|      | with an input sinusoid for different ADC number of levels, $N.$                      | 35 |

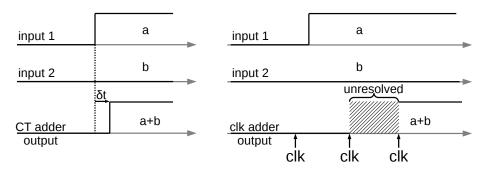

| 2.8  | Operation principle of a CT adder (left) and of a sampled adder (right)              | 37 |

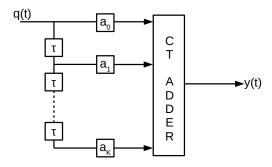

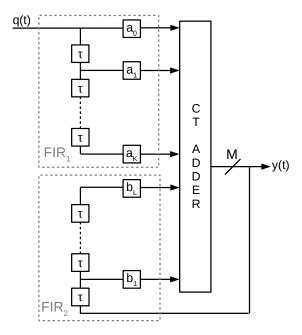

| 2.9  | Architecture of a CT finite impulse response (FIR) filter                            | 38 |

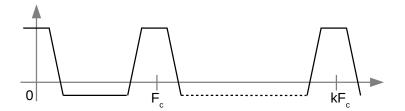

| 2.10 | Spectral representation of the transfer function of a low-pass FIR filter            |    |

|      | which has the values of all of its delay cells equal to $\tau = 1/F_c$               | 38 |

| 2.11 | Architecture of a CT infinite impulse response (IIR) filter                          | 39 |

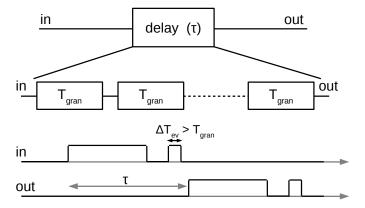

| 2.12 | Operation principle of a continuous time delay cell                                  | 40 |

| 2.13 | Details regarding the equiripple filter design specifications for a lowpass          |    |

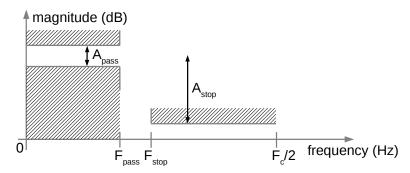

|      | filter implementation.                                                               | 42 |

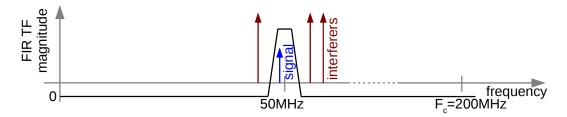

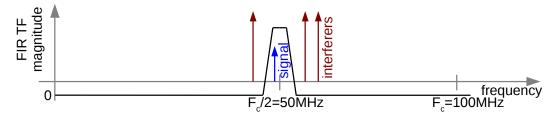

| 2.14 | FIR transfer function example using a bandpass implementation                        | 43 |

| 2.15 | FIR transfer function example using a highpass implementation                        | 43 |

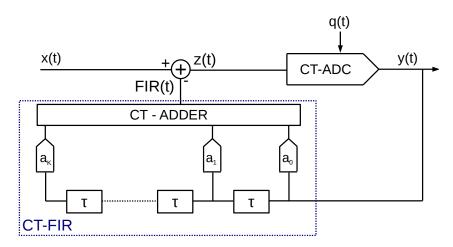

| 2.16 | FIR transfer function example using spectrum repetitions to filter out               |    |

|      | unwanted interferers                                                                 | 43 |

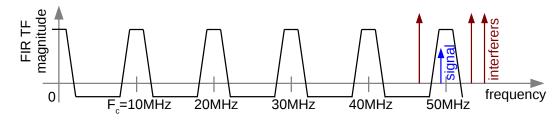

| 2.17 | Achievable CT FIR filter rejection levels versus the FIR order for the               |    |

|      | previously presented filter design methods                                           | 44 |

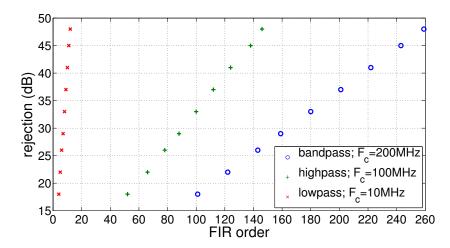

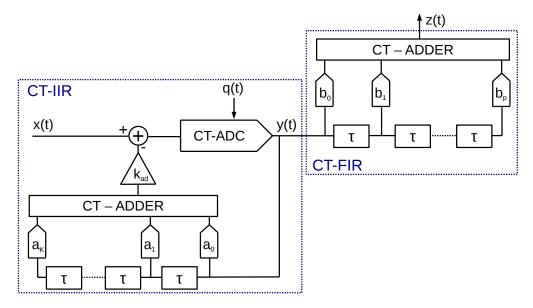

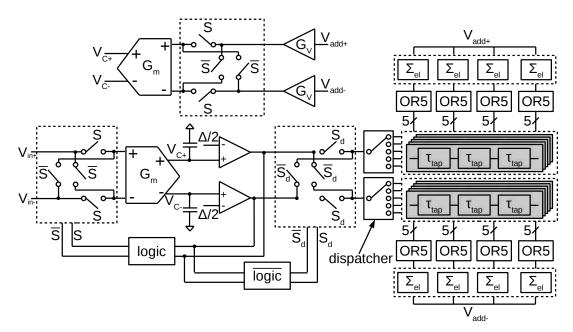

| 2.18 | Proposed DF-CT-ADC architecture                                                      | 46 |

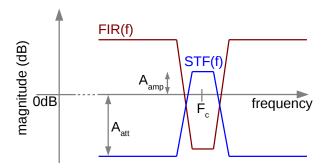

| 2.19 | Representation of the required feedback FIR transfer function and of the             |    |

|      | resulting signal transfer function.                                                  | 47 |

List of Figures

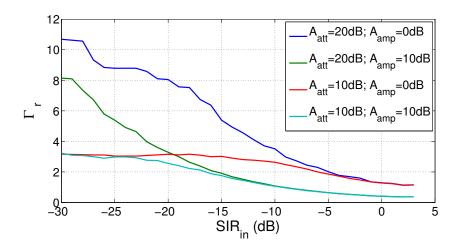

| 2.20 | Event rate reduction offered by the proposed solution versus the $SIR_{in}$      |    |

|------|----------------------------------------------------------------------------------|----|

|      | for different values of $A_{amp}$ and $A_{att}$                                  | 48 |

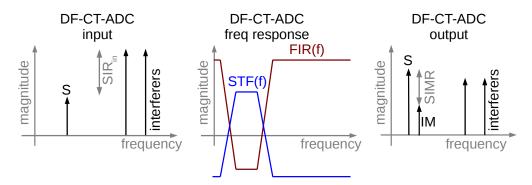

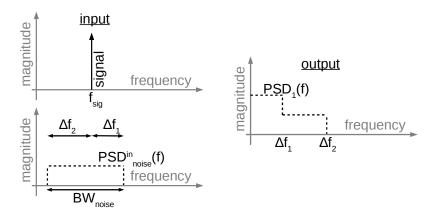

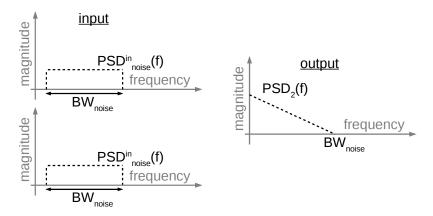

| 2.21 | Frequency domain representation of the signals at the input and at the           |    |

|      | output of the DF-CT-ADC                                                          | 49 |

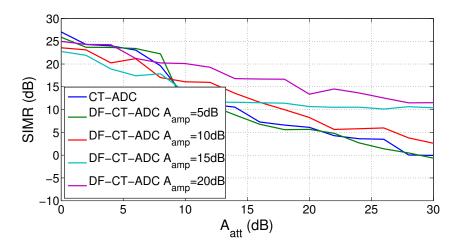

| 2.22 | Output SIMR for a 22 level ADC with an input signal at $-30 \mathrm{dB}$ of SIR  |    |

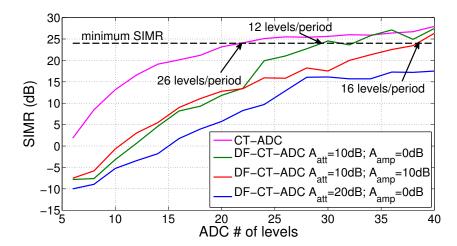

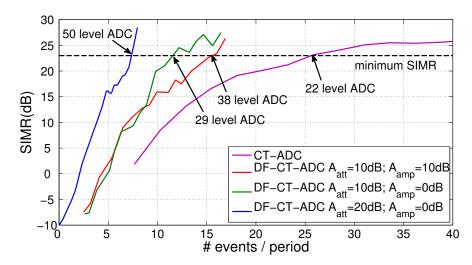

|      | and different configurations of the proposed DF-CT-ADC                           | 50 |

| 2.23 | Output SIMR for different values of $A_{att}$ and $A_{amp}$ versus the number of |    |

|      | CT-ADC levels for different configurations of the proposed DF-CT-ADC.            | 51 |

| 2.24 | Output SIMR versus the average number of events triggered per signal             |    |

|      | period for different values of the CT-ADC quantization level                     | 52 |

| 3.1  | Architecture of an $N$ -level flash CT-ADC                                       | 54 |

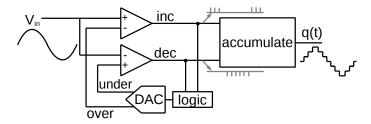

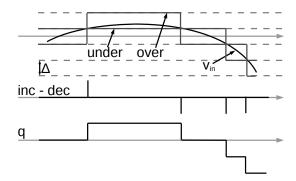

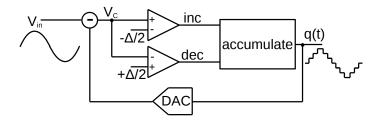

| 3.2  | Architecture of a delta modulator based CT-ADC                                   | 54 |

| 3.3  | Evolution of the input, output and some key internal signals of a delta          |    |

|      | modulator based CT-ADC                                                           | 55 |

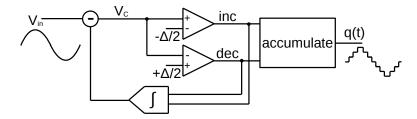

| 3.4  | Architecture of a delta modulator based CT-ADC which uses fixed com-             |    |

|      | parator thresholds                                                               | 56 |

| 3.5  | Architecture of a delta modulator based CT-ADC which uses fixed com-             |    |

|      | parator thresholds and has a fast feedback loop                                  | 57 |

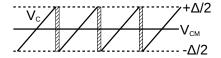

| 3.6  | Evolution of $V_C$ , the signal at the input of the comparators, in a standard   |    |

|      | delta modulator based CT-ADC                                                     | 57 |

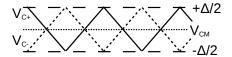

| 3.7  | Evolution of a differential version of $V_C$ , the signal at the input of the    |    |

|      | comparators, in the proposed delta modulator based CT-ADC                        | 58 |

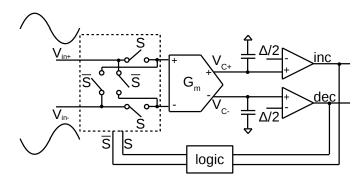

| 3.8  | Front end of the proposed CT-ADC architecture                                    | 58 |

| 3.9  | Logic required to control the input switches (DAC) of the proposed CT-           |    |

|      | ADC architecture.                                                                | 59 |

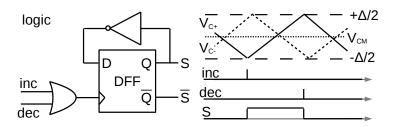

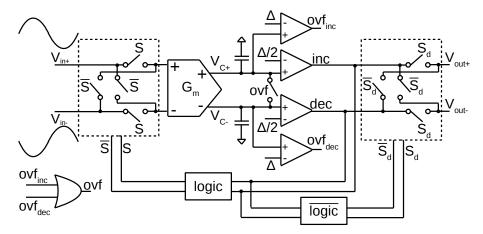

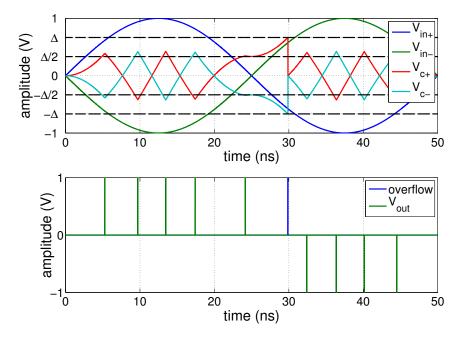

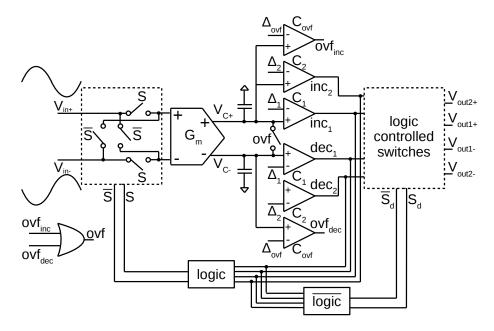

| 3.10 | Full view of the proposed CT-ADC architecture                                    | 60 |

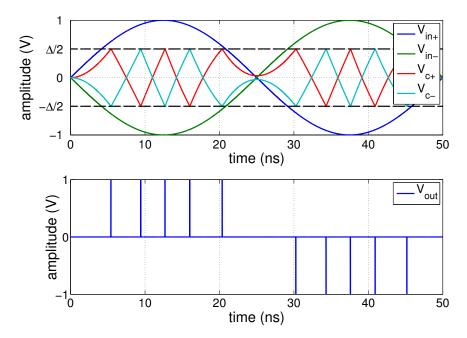

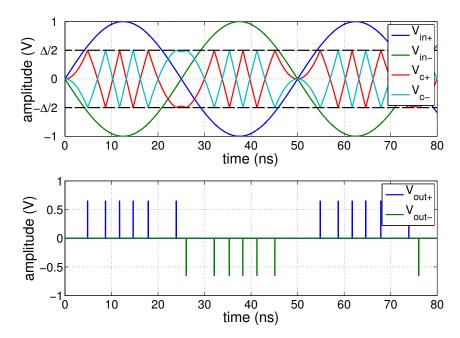

| 3.11 | View of the input, output and some key internal signals of the proposed          |    |

|      | CT-ADC                                                                           | 60 |

| 3.12 | Input and output signals as well as the voltage across the capacitors            | 62 |

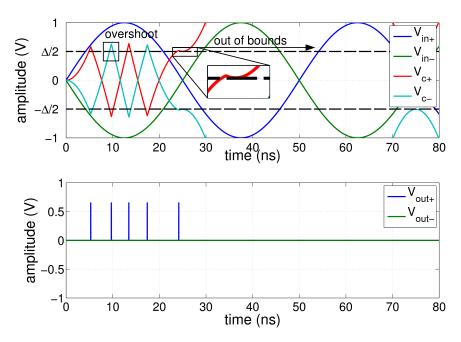

| 3.13 | Input and output signals as well as the voltage across the capacitors for a      |    |

|      | CT-ADC with a non-zero delay in the feedback path                                | 63 |

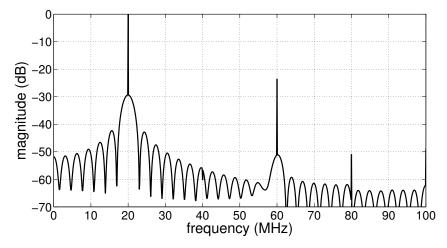

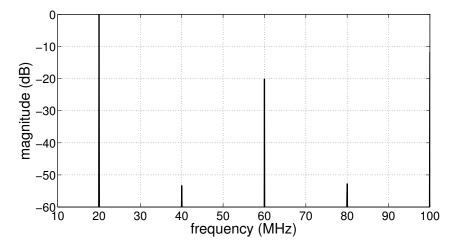

| 3.14 | Spectrum of the output signal containing periods when the CT-ADC goes            |    |

|      | out of bounds.                                                                   | 64 |

| 3.15 | Proposed CT-ADC with overflow comparators                                        | 65 |

| 3.16 | Input, output and some key internal signals around an overflow event             | 65 |

| 3.17 | Spectrum of the CT-ADC output signal with overflow comparator correction.        | 66 |

| 3.18 | Transistor level implementation of the continuous time comparators               | 67 |

| 3.19 | First order model of the comparator behavior.                                    | 69 |

List of Figures xi

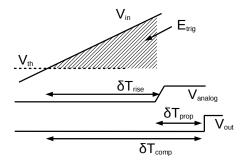

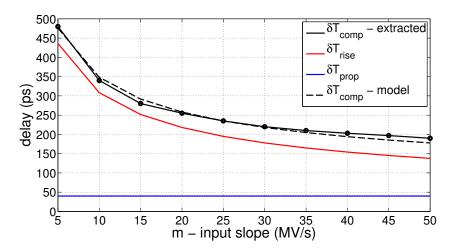

| 3.20 | Extracted comparator delay as well as a model for the rise and propagation   |    |

|------|------------------------------------------------------------------------------|----|

|      | delays                                                                       | 69 |

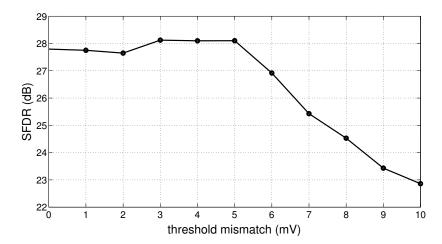

| 3.21 | SFDR degradation of the proposed CT-ADC architecture with a single           |    |

|      | input tone at 10MHz versus and an artificially injected threshold mismatch;  |    |

|      | the absolute value of $\Delta$ is 40mV                                       | 70 |

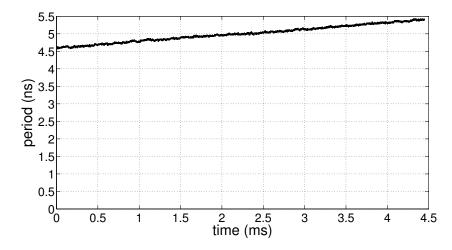

| 3.22 | Measured drift of the time between two consecutive output pulses for a       |    |

|      | constant DC input; this time is proportional to the instantaneous value of   |    |

|      | Δ                                                                            | 71 |

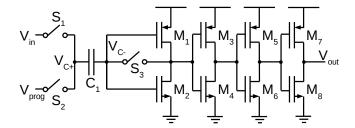

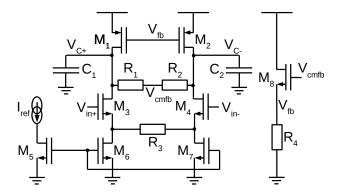

| 3.23 | Transistor level implementation of the transconductance                      | 72 |

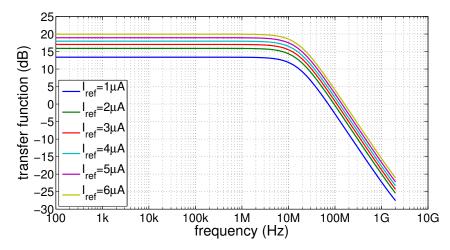

| 3.24 | Voltage transfer function of the proposed $G_m - C$ implementation for       |    |

|      | different values of $I_{ref}$                                                | 73 |

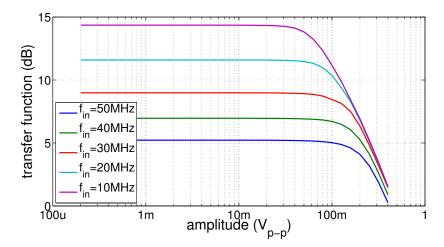

| 3.25 | Degradation of the voltage gain versus the input peak-to-peak swing at       |    |

|      | different input frequencies                                                  | 74 |

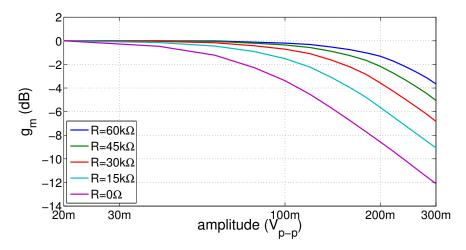

| 3.26 | $g_m$ normalized to its maximum value versus the input voltage difference    |    |

|      | for different values of the degeneration resistance                          | 75 |

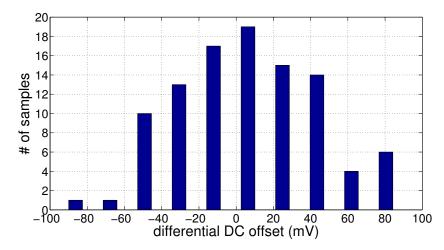

| 3.27 | Sampled PDF of the $G_m-C$ output differential DC offset over 100 MC         |    |

|      | simulations                                                                  | 76 |

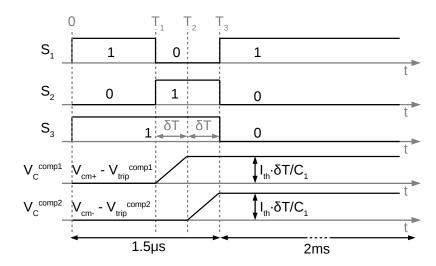

| 3.28 | Proposed threshold setting mechanism                                         | 77 |

| 3.29 | Design of the charge pump used to set comparator thresholds                  | 78 |

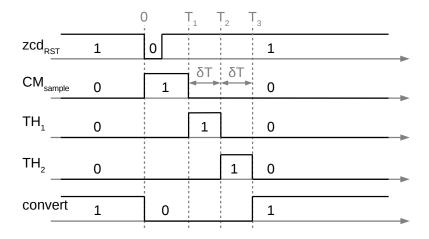

| 3.30 | Reset and control signals used for the proposed threshold setting mechanism. | 79 |

| 3.31 | Breakdown of the CT-ADC power consumption                                    | 80 |

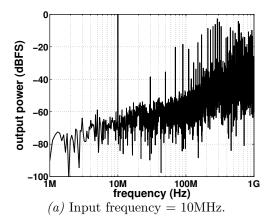

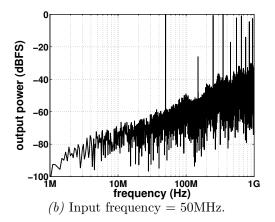

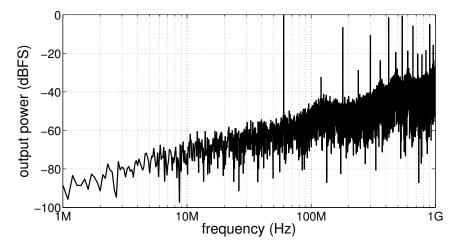

| 3.32 | Spectrum of the signal observed at the output of the proposed CT-ADC         |    |

|      | for different input frequencies                                              | 81 |

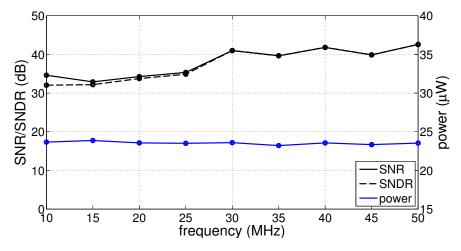

| 3.33 | The output SNR and SNDR versus the input tone frequency                      | 81 |

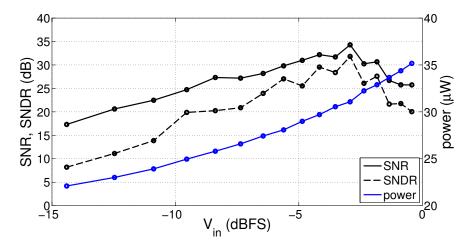

| 3.34 | The output SNR, SNDR as well as the ADC power consumption versus             |    |

|      | the input signal amplitude (normalized to full scale)                        | 82 |

| 3.35 | The output spectrum for an input consisting of an out-of-band tone located   |    |

|      | at 60MHz; no aliasing is observed.                                           | 82 |

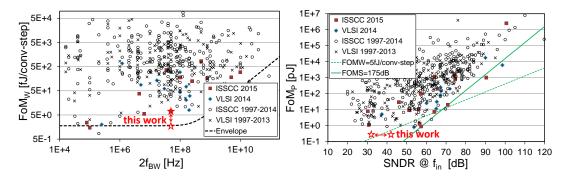

| 3.36 | Walden and Energy figures of merit of recent state of the art ADC imple-     |    |

|      | mentations                                                                   | 84 |

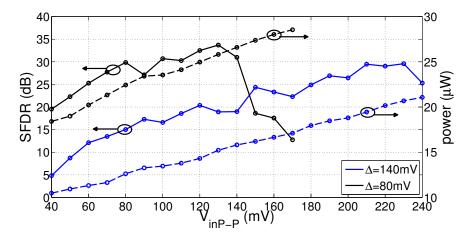

| 3.37 | SFDR of the proposed CT-ADC versus the input peak-to-peak swing for          |    |

|      | two values of $\Delta$ .                                                     | 85 |

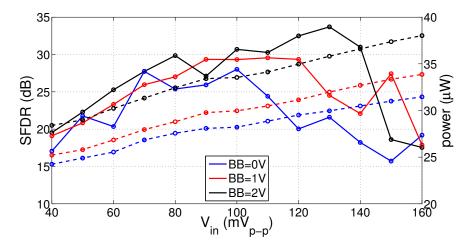

| 3.38 | SFDR of the proposed CT-ADC versus the input peak-to-peak swing for          |    |

|      | different values of the back-bias voltage                                    | 86 |

|      |                                                                              |    |

| 4.1  | Architecture of the proposed CT-DSP                                          | 88 |

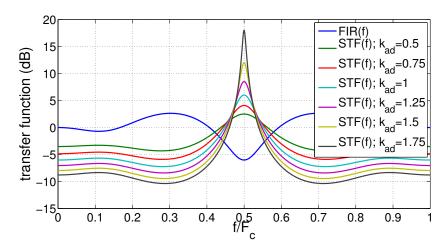

| 4.2  | Example of the IIR transfer function for different values of the adder       |    |

|      | conversion gain, $k_{ad}$ .                                                  | 89 |

List of Figures xii

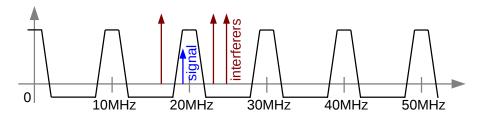

| 4.3  | Example of a CT-DSP frequency response along with a possible configura-           |

|------|-----------------------------------------------------------------------------------|

|      | tion of the IF signal                                                             |

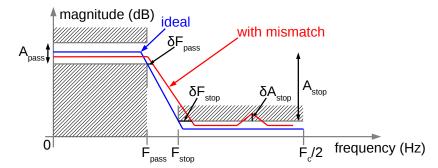

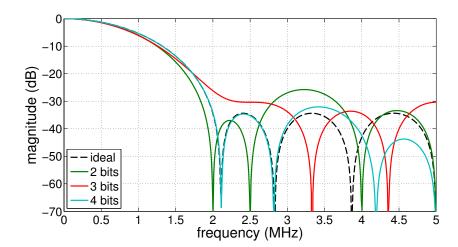

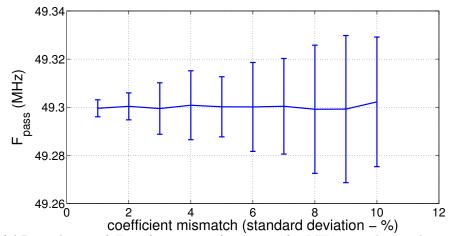

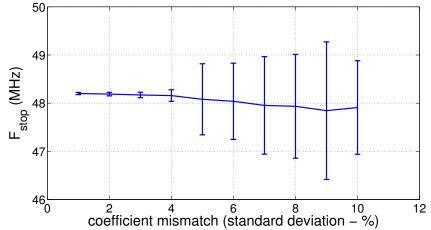

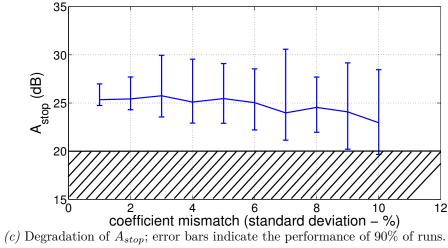

| 4.4  | Changes observed by adding mismatch to an ideal CT-FIR transfer function. 92      |

| 4.5  | Effects of delay cell mismatch on the transfer function of a $9^{th}$ order FIR   |

|      | filter                                                                            |

| 4.6  | Effects of delay cell jitter on the noise floor of the CT-DSP output 94           |

| 4.7  | CT-FIR transfer functions obtained using different representations of its         |

|      | coefficients                                                                      |

| 4.8  | Effects of coefficient mismatch on the transfer function of a $9^{th}$ order FIR  |

|      | filter                                                                            |

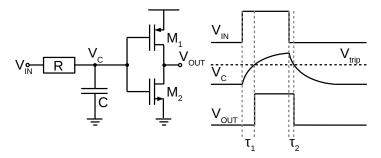

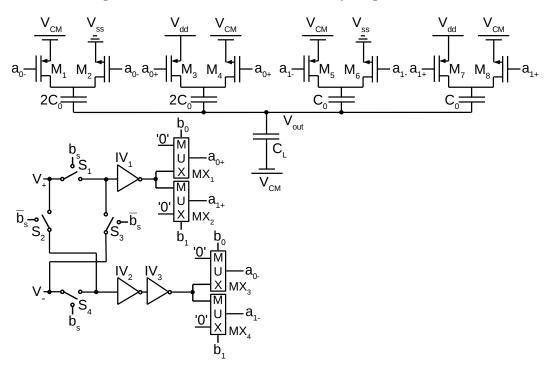

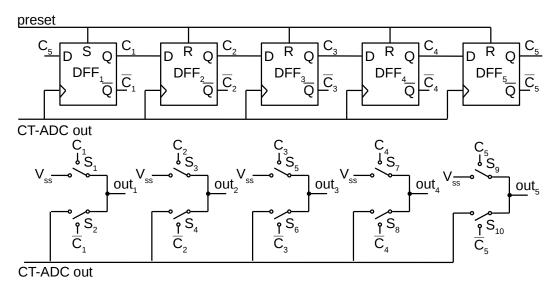

| 4.9  | RC based, mixed-signal delay cell                                                 |

| 4.10 | CMOS thyristor based, mixed signal delay cell                                     |

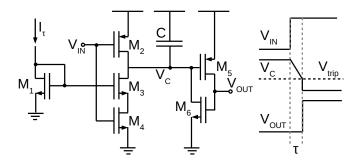

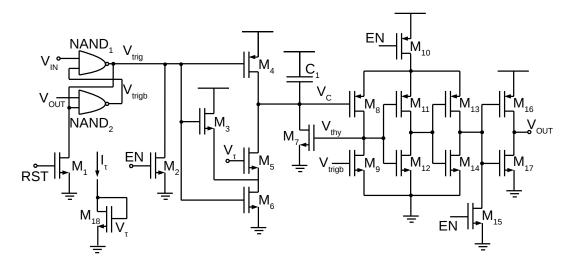

| 4.11 | Transistor level implementation of the proposed delay cell                        |

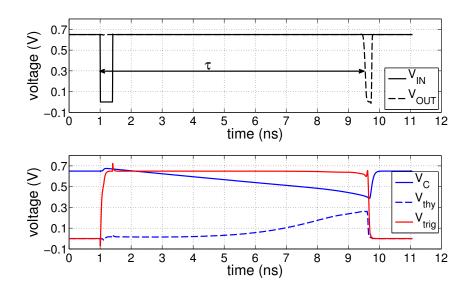

| 4.12 | Time domain evolution of different delay cell signals during a delay event. $100$ |

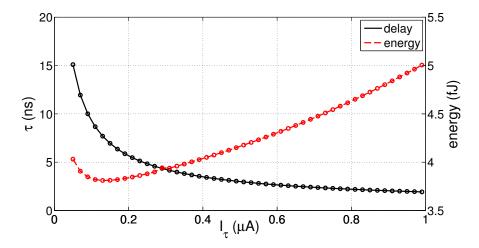

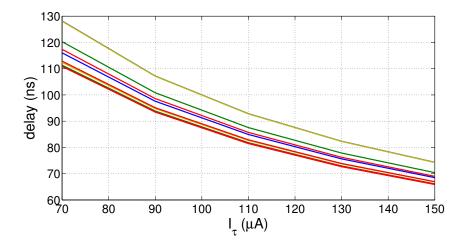

| 4.13 | Value of the delay cell versus the tail current                                   |

| 4.14 | Classic delay cell architecture in the context of our FIR filter 103              |

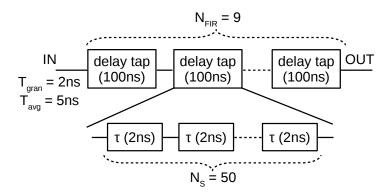

| 4.15 | Delay tap architecture based on a parallel elementary delay arrangement. 103      |

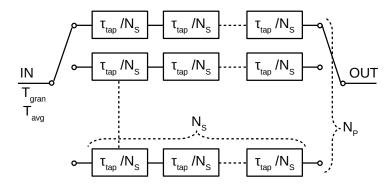

| 4.16 | Programmable parallel delay tap architecture                                      |

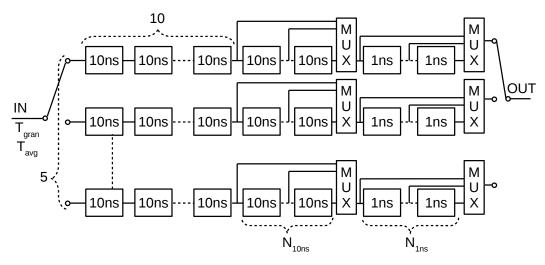

| 4.17 | Value of a delay tap versus the control current for different MC runs $108$       |

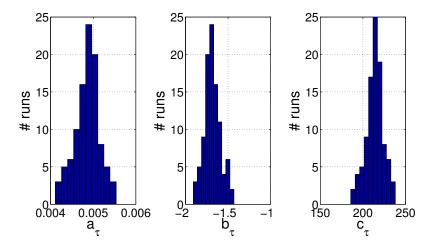

| 4.18 | PDFs of the three parameters describing the statistical link between the          |

|      | value of each elementary delay and the control current                            |

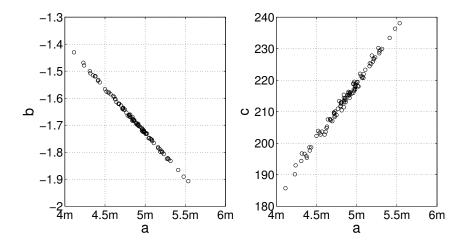

| 4.19 | Correlation between $b$ and $a$ (left); $c$ and $a$ (right)                       |

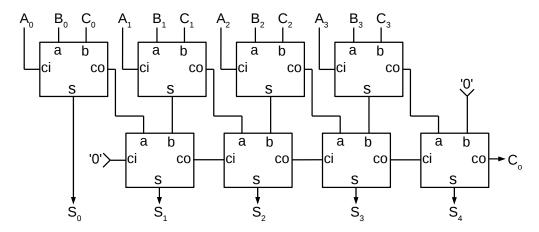

| 4.20 | Architecture of a 3 input (4 bits) Carry Save Adder                               |

| 4.21 | Charge pump based analog adder                                                    |

| 4.22 | Proposed elementary adder cell                                                    |

| 4.23 | Proposed full adder cell                                                          |

| 4.24 | Scenario used to illustrate the operation principle of the proposed weighted      |

|      | adder                                                                             |

| 4.25 | Elementary adder with its coefficient equal to 10 and with input $V_+$ active     |

|      | $(at V_{dd})$                                                                     |

| 4.26 | Elementary adder with its coefficient equal to 01 and with input $V_+$ active     |

|      | $(at V_{dd})$                                                                     |

| 4.27 | Elementary adder with its coefficient equal to 00 and with input $V_+$ active     |

|      | $(at V_{dd})$                                                                     |

| 4.28 | Lumped representation of the proposed CT adder                                    |

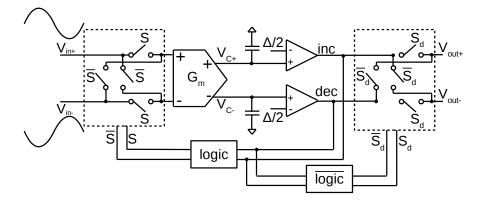

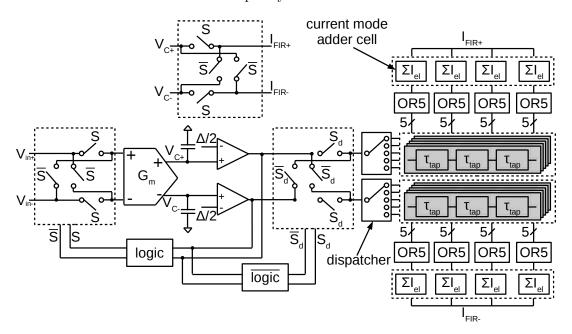

|      | View of the complete DF-CT-ADC implementation                                     |

| 4.30 | Schematic of the dispatching circuit used to split the CT-ADC output in           |

|      | 5 parallel streams                                                                |

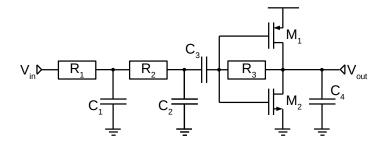

| 4.31 | Schematics of the active voltage gain stage used in the feedback loop of  |      |

|------|---------------------------------------------------------------------------|------|

|      | the DF-CT-ADC                                                             |      |

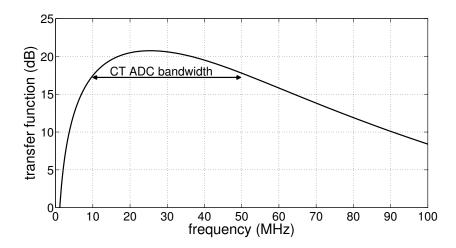

|      | Voltage transfer function of the $G_V$ block                              |      |

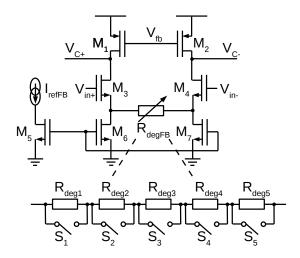

|      | Schematics of the feedback $G_m$ cell                                     | 122  |

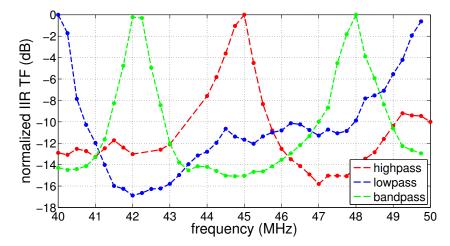

| 4.34 | Highpass, lowpass and bandpass configurations for the DF-CT-ADC trans-    |      |

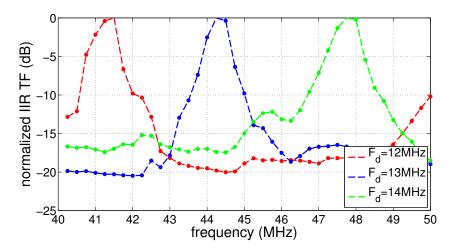

|      | fer function                                                              | 124  |

| 4.35 | Tuning the center frequency of the DF-CT-ADC signal transfer function.    | 125  |

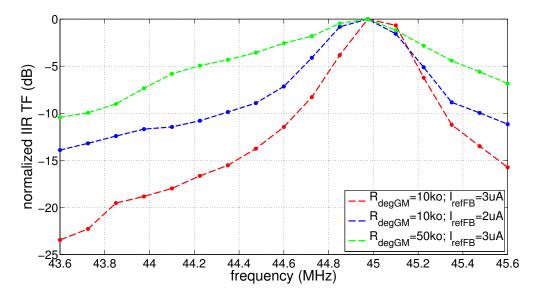

| 4.36 | DF-CT-ADC transfer functions for different configurations of the feedback |      |

|      | loop voltage gain                                                         | 126  |

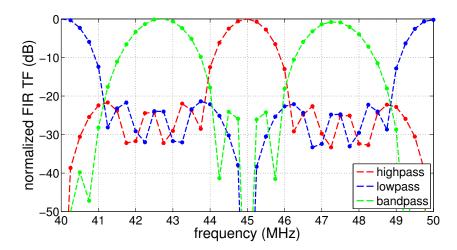

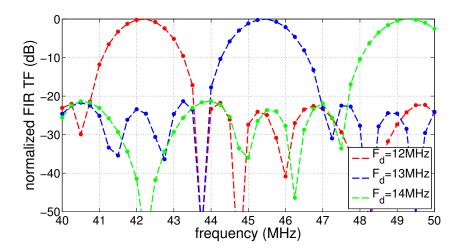

| 4.37 | Highpass, lowpass and bandpass configurations for the CT-FIR transfer     |      |

|      | function                                                                  | 127  |

| 4.38 | Tuning the central frequency of the CT-FIR filter transfer function       | 128  |

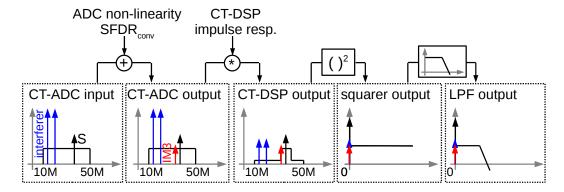

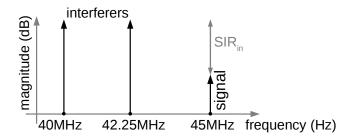

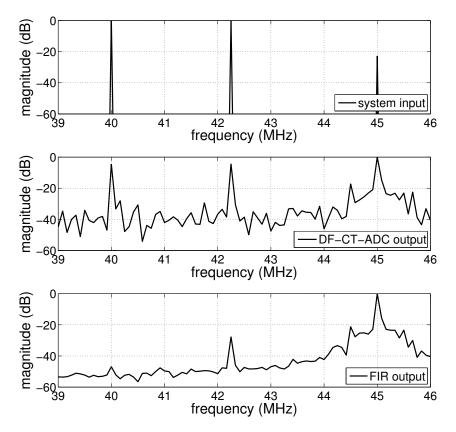

| 4.39 | Input scenario used to test the performance of the proposed CT-DSP. $$    | 128  |

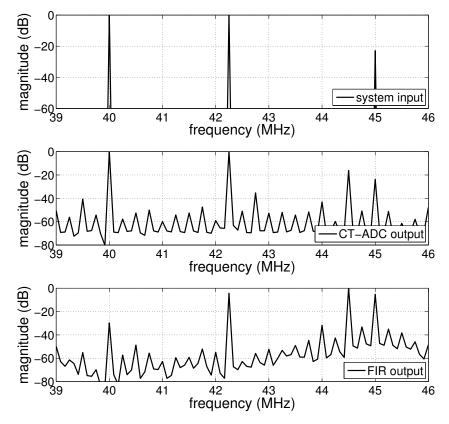

| 4.40 | Spectrum of the signal at various points in the proposed system (DF-CT-   |      |

|      | ADC & CT-FIR)                                                             | 129  |

| 4.41 | Spectrum of the signal at various points in the proposed system with no   |      |

|      | feedback loop around the ADC (CT-ADC & CT-FIR)                            | 130  |

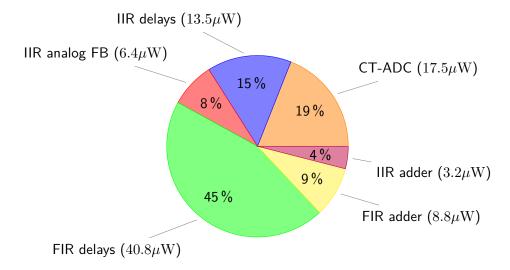

| 4.42 | Breakdown of the complete DF-CT-ADC-DSP power consumption                 | 131  |

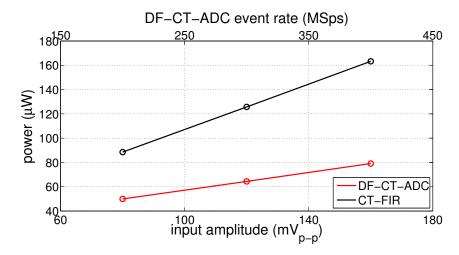

| 4.43 | CT-DF-ADC and CT-FIR power consumption versus the input amplitude         |      |

|      | (system event rate). Note that the power consumption of the CT-ADC is     |      |

|      | included in both previously defined systems                               | 132  |

| 4.44 | Output spectrum of a full-scale, 50MHz single tone input, for a transient |      |

|      | noise simulation of the entire system                                     | 133  |

|      |                                                                           | 1.40 |

| 5.1  | Concept of the improved CT-ADC design                                     |      |

| 5.2  | Switchable, current mode FIR adder cell                                   |      |

| 5.3  | DF-CT-ADC architecture using the proposed current mode adder              | 142  |

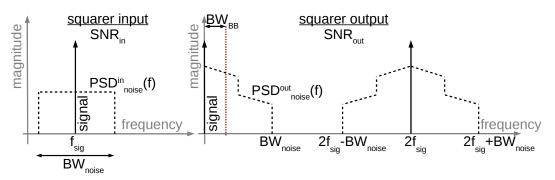

| A.1  | Scenario used to study the noise performance of a squarer                 | 145  |

| A.2  | Baseband noise generated by the cross-mixing of the IF noise with the     |      |

|      | signal component.                                                         | 147  |

| A.3  | Baseband noise generated by the self-mixing of the bandlimited IF noise.  |      |

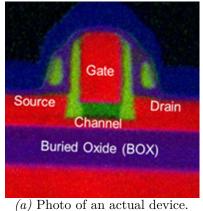

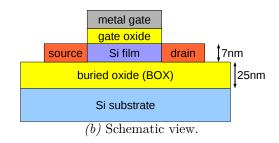

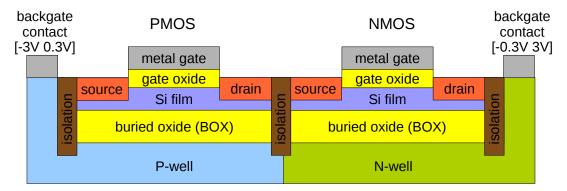

| B.1  | Cross sectional view of an UTBB FDSOI transistor [89]                     | 151  |

| B.2  | Sectional view of an FDSOI PMOS transistor next to an FDSOI NMOS          |      |

|      | transistor, along with the allowed backgate bias voltages                 | 152  |

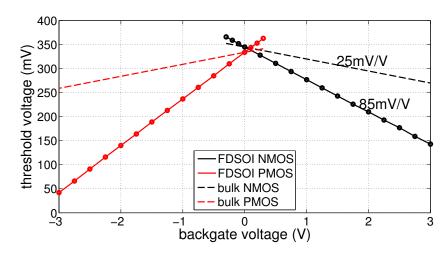

| В 3  | Threshold voltage variation of FDSOI and standard bulk transistors        | 159  |

List of Tables xiv

# List of Tables

| 1.1 | WU-RX state of the art. Note that the sensitivities and data-rates are               |

|-----|--------------------------------------------------------------------------------------|

|     | given as reported in the original publications and have not been normalized          |

|     | to 100kbps                                                                           |

| 1.2 | LO precision for different values of the $SNR_{in}$                                  |

| 1.3 | Comparison of different tunable filter solutions and the components they             |

|     | require                                                                              |

| 1.4 | Performance limits of the IF interferer rejection stage according to the             |

|     | specifications of the CT-ADC and the CT-DSP                                          |

| 2.1 | FIR and IIR filter comparison                                                        |

| 2.2 | Comparison of existing CT-ADC/DSP implementations with the require-                  |

|     | ments of our application                                                             |

| 2.3 | Estimation of the power requirements of our CT-ADC/DSP implementa-                   |

|     | tion based on results from literature                                                |

| 2.4 | CT-ADC operating point for different configurations of the DF-CT-ADC. 52             |

| 3.1 | Sizing of the comparator components                                                  |

| 3.2 | Sizing of the $G_m - C$ components                                                   |

| 3.3 | Sizes of various components used in the design of the charge pump 79                 |

| 3.4 | Comparison with state of the art discrete time ADCs with bandwidths                  |

|     | smaller than 100MHz                                                                  |

| 3.5 | Comparison with existing continuous time ADCs                                        |

| 3.6 | Speed of the logic block for different values of the back-bias voltage 85            |

| 4.1 | CT-DSP specifications                                                                |

| 4.2 | Sizing of the elementary delay cell components                                       |

| 4.3 | Comparison of the proposed elementary delay cell with previous works 102             |

| 4.4 | RMS jitter of a delay tap with different configurations $(N_S \text{ and } N_P)$ 106 |

| 4.5 | Performance of the proposed delay tap calibration method 109                         |

| 4.6 | Summary of the delay cell architecture and its performance                           |

| 4.7 | Component sizes of an elementary adder cell                                          |

| 4.8 | Energy required by an elementary adder cell to process a single CT-ADC               |

| _   | token                                                                                |

List of Tables xv

| 4.9  | Sizing of the components used for the dispatcher                                         |

|------|------------------------------------------------------------------------------------------|

| 4.10 | Sizing of the components used in the active voltage gain stage $121$                     |

| 4.11 | Sizing of various components used in the design of the feedback $\mathcal{G}_m$ cell 123 |

| 4.12 | Coefficients which demonstrate the transfer function reconfigurability of                |

|      | the DF-CT-ADC                                                                            |

| 4.13 | Simulated IIR feedback configurations                                                    |

| 4.14 | Rejection performance achieved by the proposed DF-CT-ADC 126 $$                          |

| 4.15 | Highpass, lowpass and bandpass CT-FIR configurations                                     |

| 4.16 | Power breakdown of the proposed CT-ADC-DSP system with and without                       |

|      | DF-CT-ADC feedback                                                                       |

| 4.17 | Comparison between the proposed DF-CT-ADC-DSP and other, state of                        |

|      | the art, CT-DSP implementations                                                          |

| 4.18 | Comparison between the proposed DF-CT-ADC and existing analog or                         |

|      | digital IIR filter implementations                                                       |

| 4.19 | Comparison between the proposed CT-FIR and existing analog or digital                    |

|      | FIR filter implementations                                                               |

## Abbreviations

ACK ACKnowledge

ADC Analog to Digital Converter

AGC Automatic Gain Control

BB Base Band

CT-ADC Continuous - Time Analog to Digital Converter

CT-DSP Continuous - Time Digital Signal Processor

DF-CT-ADC Digitally Filtering - Continuous Time - Analog to Digital Converter

DFF Data Flip Flop

DSP Digital Signal Processing

F2V Frequency TO Voltage

FDSOI Fully Depleted Silicon On Insulator

FIR Finite Impluse Response

FoM Figure of Merit

IF Intermediate Frequency

IM InterModulation

ISM Industrial Scientific and Medical

IoT Internet of Things

LNA Low Noise Amplifier

LO Local Oscillator

LPF Low Pass Filter

MAC Medium Access Control

MC Monte Carlo

NF Noise Figure

OA Operational Amplifier

OOK ON OFF Keying

Abbreviations xviii

OTA Operational Transconductance Amplifier

RF Radio Frequency

RTC Real Time Clock

RX Receiver

SFDR Spurious Free Dynamic Range

SIMR Signal to InterModulation Ratio

SIR Signal to Interferer Ratio

SNR Signal to Noise Ratio

TX Transmitter

UTBB Ultra Thin Body and Buried oxide

WU-RX Wake Up Radio

## Chapter 1

# Introduction: Wake-Up Radios

HE Internet of Things (IoT) represents the network which results by extending the Internet Protocol beyond its initial goal of enabling worldwide machine-tomachine communications. A "thing" in the IoT can be any object which has the possibility of sending data over a network. The applications include, but are not limited to, environment monitoring, infrastructure management, manufacturing, energy management, healthcare systems and transportation. According to some technology specialists the IoT is predicted to be the third big industrial revolution which occurred in the past 50 years, after the invention of computers and the Internet. However, due to the projected size of the IoT - between 50 and 100 trillion objects [1] - a key factor in its success is minimizing the implementation and operation costs. The cost of an IoT node can be lowered by increasing the level of integration of its electronic circuits: solutions with a minimum of off-chip components are thus preferred. Second, operation costs can be reduced by minimizing the maintenance required by an IoT network. The things should be capable of operating autonomously for extended periods of time without human intervention. Consequently, a key challenge in the development of the IoT is designing low power communication systems thus enabling a long thing lifetime on nomad power sources such as batteries or energy harvesters.

The next part of this chapter introduces the energy constraints related to IoT nodes based on different forms of energy harvesting. It is showed that, in order to achieve the targeted IoT node lifetimes, the power requirements of IoT circuits need to be drastically reduced. Therefore, a new concept in receiver design is presented, the Wake-Up Receiver (WU-RX), which thanks to its low power consumption, greatly reduces the total power requirements of IoT transceivers. After an analysis of existing state of the art designs, a new WU-RX architecture is proposed and analyzed. Finally, in the last part of this chapter, the focus shifts to the most critical block of the proposed WU-RX architecture,

the tunable filter. A set of specifications is derived, which further serves as a foundation for its design which is discussed in the rest of this manuscript.

### 1.1 Power Considerations in Wireless Sensor Networks

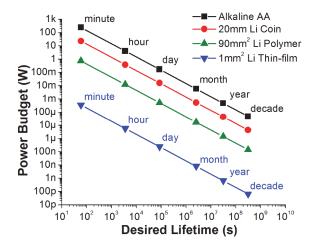

The power budget of an IoT node is determined by the energy sources it has access to. Figure 1.1 plots the amount of power available for a node versus its required lifetime for different types of batteries powering it: [2]. By targeting lifetimes of several years, it can be seen that the maximum power budget is around several tens of  $\mu$ W, around two orders of magnitude below the power consumption of the state of the art in low power receivers - 4mW [3]. Currently, the preferred solution for overcoming this power budget gap is by employing receiver duty cycling which consists in only turning ON the receiver for very short periods of time thus saving power.

FIGURE 1.1: Iot node available power versus its lifetime when powered by different types of batteries: [2].

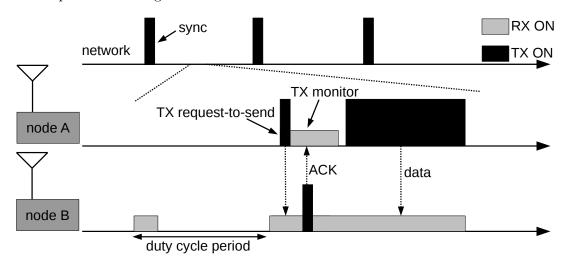

Before discussing alternative solutions which lower the power consumption of duty cycled receivers, it is important to understand the main trade-offs related to the design of a classic duty-cycled network (Figure 1.2). One of the basic hypothesis for efficient duty cycling is the fact that the network is perfectly synchronized: if the node A wants to emit a packet to node B, it is supposed that node A has perfect knowledge of the moments when node B is online. This synchronization problem is usually solved at the network level by sending sync packets which reset the internal timer of each node. The maximum time between the synchronization instants is set by the drift of each node's internal time reference which, in turn, is inversely proportional to the amount of power the time reference consumes. The network synchronization mechanism as well as a zoomed in

view of an arbitrary moment in time when node A initiates a communication with node B are represented in Figure 1.2.

Figure 1.2: Representation of a duty cycled wireless network with synchronization packets as well as a zoomed in view of an arbitrary moment in time where node A initiates communication with node B.

This solution works well for networks where the average time between two consecutive exchanges for any node is much smaller than the sync period, as the synchronization adds very little overhead. However, this is not the case for IoT networks: nomad nodes are expected to exchange a very small amount of data, with an average time between consecutive communications in the order of tens of seconds, or even minutes. Consequently, due to synchronization issues, there will be scenarios where duty-cycled IoT networks will exchange more sync packets rather than actual data packets, drastically increasing the synchronization overhead with respect to the actual communication.

Another drawback of duty-cycled networks is linked to the propagation delay of a packet through the network. In order to meet the restrictive power budgets of IoT nodes, imposed by the availability of nomad power sources, existing low power receivers need to be heavily duty-cycled, such that their *average* power consumption becomes sufficiently low. This has the negative effect of increasing the propagation time of the information through the network. This situation becomes even worse for mesh networks, where the worst case node-to-node propagation delay is multiplied by the number of hops between the source of the information and its destination.

Alternatively, a new paradigm for IoT receiver and network design can potentially solve the previously presented problems. The technique consists of adding a supplementary receiver to each IoT node, called henceforth wake-up receiver (WU-RX). The WU-RX monitors the communication channel and only switches ON the main receiver (also referred to as the data receiver) when it receives an actual communication request. The

advantage of such a scheme lies in the fact that the two receivers can now be optimized separately. The WU-RX is switched ON for relatively long periods of time and spends very little of its time actually receiving data, it can thus be optimized for low power consumption while it is in monitoring mode. On the other hand, the data receiver will spend almost the entirety of its ON time actually receiving information and thus can be optimized for a small energy consumption per received bit.

The previously described WU-RX scheme can be implemented either in a completely asynchronous network or in a duty cycled network. Figure 1.3 showcases the asynchronous WU-RX principle: the receiving node B keeps the WU-RX turned ON all the time and is ready to react whenever a TX-request-to-send packet is received. This solution completely obliviates the need for real time clocks (RTCs) thus allowing for a very flexible implementation of the network. The disadvantage of this approach is the fact that the budget for the WU-RX is very low making its design potentially troublesome. Alternatively, the WU-RX itself can be duty cycled opening up new possibilities concerning the trade-off between the power consumed by the RTCs (impacting its drift) and the power spent monitoring to the channel. In conclusion, the WU-RX principle represents a substantial expansion of the design space of low power radios, potentially enabling the implementation of more energy efficient trade-offs.

FIGURE 1.3: View of a network with wake-up radios; in this representation no duty-cycling is applied.

### 1.2 Wake-Up Receivers State of the Art

### 1.2.1 Architecture Considerations

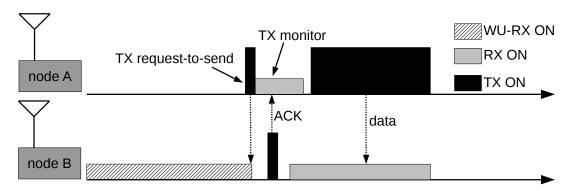

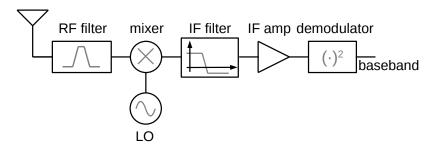

Choices concerning the design of modern WU-RX can be explained by analyzing the two classic and ubiquitous receiver topologies: the heterodyne and homodyne receiver, which are portrayed in the Figure 1.4(a) and Figure 1.4(b). The key in achieving a low power consumption is the removal of the most power consuming blocks: the RF gain stage and

the frequency synthesis in the heterodyne receiver and the large RF gain stage in the homodyne receiver.

FIGURE 1.4: Standard receiver architectures: heterodyne (a) and homodyne (b).

A true, low power receiver can be implemented by removing the most power consuming blocks from the previously presented architectures and by combining them. What results is an architecture known as the "Uncertain IF" receiver [4], shown in Figure 1.5. The frequency synthesis is completely removed from the heterodyne architecture and replaced by a simple free running LO. This enables a downconversion to an uncertain intermediate frequency which has a frequency precision defined by that of the local oscillator. At this point, it is possible to amplify the signal with a rather low power consumption as the operating frequency is expected to be lower than 100MHz. Finally, since the exact frequency of the signal is unknown, the demodulation is done through energy detection rather than by using a mixer, as in the case of the original homodyne receiver.

FIGURE 1.5: Architecture of the Uncertain IF receiver [4].

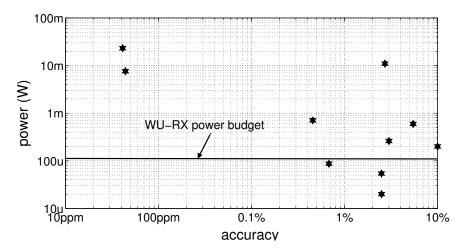

Relaxing the frequency precision requirement of the local frequency reference enables a substantial reduction in its power budget. This trade-off is showcased by comparing different state of the art frequency references: Figure 1.6. High precision systems with a frequency uncertainty of smaller than 100ppm require a power of at least several mW - this is equivalent to a frequency precision of 240kHz for an operation in the ISM band at 2.4GHz. On the other hand, ultra low power frequency references, usually implemented

as free running oscillators, achieve power consumptions which fit in the WU-RX budget but are limited in precision: around 1% which corresponds to 24MHz for an oscillating frequency of 2.4GHz.

FIGURE 1.6: State of the art in frequency references: power consumption versus precision [5], [6], [7], [8], [4], [9], [10], [11], [12].

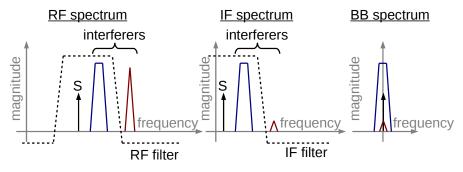

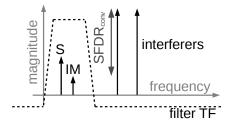

The IF filter must be designed with a transfer function wide enough to accommodate the imprecision linked to the free running oscillator. Low power frequency references for the 2.4GHz band thus require the use of a very wide IF filter passband (up to 24MHz), much wider than that required by the WU-RX communication speed (which is usually limited to 100kbps). Consequently, the IF filter can only be used to minimize the noise bandwidth before the demodulation stage and cannot be used for efficient interferer rejection. This situation is illustrated in Figure 1.7: interferers located inside the RF filter passband cannot usually be filtered by the subsequent IF filter stage, as the latter's passband is expected to be widest. These interferers are then downconverted to DC by the energy detector thereby irremediably corrupting the baseband signal. Consequently, it will be seen that most WU-RX implementations have a very limited interferer resilience.

FIGURE 1.7: Spectrum of the signal at different points inside the Uncertain IF architecture.

Another drawback of the Uncertain IF architecture stems from the removal of the frontend high frequency gain stage. The result is a low power radio with a degraded noise figure (NF). Moreover, the demodulator is most of the time implemented using the non-linearity of a diode, in which case, it can be shown [4] that its conversion gain  $(k_{conv})$ is proportional to the voltage swing presented at its input:  $k_{conv} = V_{pp}/(4nV_t)$ , where  $V_{pp}$  is the demodulator input peak-to-peak swing, n – subthreshold factor and  $V_t$  – the thermal voltage. Reducing the RF gain results in a lower amplitude signal at the input of the demodulator which decreases its gain thus also degrading its noise figure. To combat this, several strategies have been adopted in literature. As a possible solution, active noise cancellation [13] can be combined with RF envelope detection in order to reduce the noise contribution of the squarer. This solution is however limited by the fact that the envelope detector needs to be used at RF thus requiring it to function at a very low input swing due to the lack of an energy efficient way of providing gain. Another solution, proposed in [14], uses baseband correlators along with information redundancy to improve the effective sensitivity of the receiver at the cost of a reduced data-rate. However, such a scheme can be used at the output of any WU-RX implementation. To provide a fair comparison we are going to focus on the raw bit error rate measured at the output of the demodulator, which is entirely defined by the signal-to-noise ratio of the signal at that point.

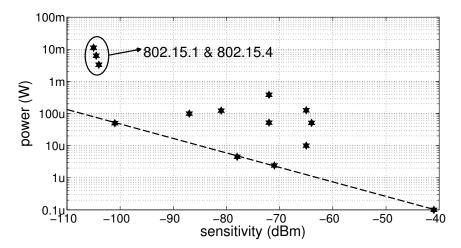

### 1.2.2 Performance Analysis of Existing WU-RXs

The mode of operation described in the introduction of this chapter demands the WU-RX to have a sensitivity as high as that of the data receiver. Any difference in the sensitivities of the two receivers is essentially wasted by either waking up on incoming communication requests which are then too faint for establishing a data transfer (WU-RX is more sensitive) or by missing TX-request-to-send packets which could otherwise be treated by the data receiver (data receiver is more sensitive). Similarly, the performance of the two radios must be identical in the presence of interferers.

The performance of the existing state of the art WU-RXs as well as state of the art data receivers is presented in Figure 1.8 (for WU-RXs, we have normalized the reported sensitivities to a data-rate of 100kbps), a comparison table is also given in Table 1.1. A careful analysis of the data provided in Figure 1.8 shows that next generation WU-RXs should have an improved sensitivity in order to match that of data receivers. Furthermore, as it is shown in Table 1.1, a key feature missing from existing WU-RXs is the robustness to interferers; the interferer rejection achieved currently by WU-RXs is far from that required by modern data receivers.

FIGURE 1.8: State of the art low power data receivers and WU-RXs. The radio sensitivities have been normalized to a data-rate of 100kbps.

TABLE 1.1: WU-RX state of the art. Note that the sensitivities and data-rates are given as reported in the original publications and have not been normalized to 100kbps.

| reference    | frequency          | sensitivity        | interferer<br>rejection | power              | data-rate          | process | modulation |

|--------------|--------------------|--------------------|-------------------------|--------------------|--------------------|---------|------------|

| [4]          | $2 \mathrm{GHz}$   | $-72 \mathrm{dBm}$ | n/a                     | $52\mu\mathrm{W}$  | 100kbps            | 90nm    | OOK        |

| [15]         | $915 \mathrm{MHz}$ | -83dBm             | 10 dB                   | $121\mu\mathrm{W}$ | 10kbps             | 90nm    | OOK        |

| [14]         | 868 MHz            | $-72 \mathrm{dBm}$ | n/a                     | $2.4 \mu W$        | 20kbps             | 130nm   | OOK        |

| [16]         | $2.45\mathrm{GHz}$ | -88dBm             | n/a                     | $50\mu\mathrm{W}$  | 250kbps            | 65nm    | OOK        |

| [17]         | $816 \mathrm{MHz}$ | -71dBm             | < 10dB                  | $382\mu\mathrm{W}$ | 125kbps            | 40nm    | FSK        |

| [18]         | $2.4\mathrm{GHz}$  | -97 dBm            | 22 dB                   | $99\mu W$          | $10 \mathrm{kbps}$ | 65nm    | OOK        |

| 802.15.1[19] | $2.4 \mathrm{GHz}$ | -70dBm             | 27dB<br>@3MHz           | n/a                | 1Mbps              | n/a     | GFSK       |

| 802.15.4[20] | 2.4GHz             | -85dBm             | 31dB<br>@10MHz          | n/a                | 250kbps            | n/a     | QPSK       |

Moreover, depending on the radiated output power, the ISM band may require transmitters to use spread spectrum techniques such as frequency hopping. Consequently, the WU-RX should also be designed to match these multi-channel requirements in order to avoid limiting choices related to the design of the transmitters.

We can thus define 3 development directions for the improvement of existing WU-RXs:

- power: reducing the power consumption will always improve the quality of the resulting networks.

- sensitivity: despite existing of WU-RX implementations with sensitivities close to those required by low power communication standards, improvements of this performance parameter can increase the communication range of IoT nodes.

- interferer robustness & multichannel capabilities: current WU-RXs have a limited multichannel operation and usually suffer from a very poor interferer rejection.

In conclusion, the current state of the art shows that existing WU-RX implementations severely lack in interferer rejection. As a consequence, this work is focused on the description and implementation of a block designed to improve this performance metric as well as to enable multichannel operation. The proposed system is compatible with most of the existing WU-RX implementations; however, it is important to define a precise setting for our application. Thus, in the next part of this chapter, we propose a new WU-RX architecture which attempts to solve some of the problems presented earlier and is compatible with the system described in the following chapters of this manuscript. Results from a set of architecture simulations of the proposed WU-RX will serve as specifications and as starting point for the design of the proposed IF interferer rejection block.

### 1.3 Proposed WU-RX architecture

From the previous discussion we have seen that there is a clear trade-off between the sensitivity of a WU-RX and its power consumption: a design achieving around  $-100 \mathrm{dBm}$  requires a power of  $50 \mu\mathrm{W}$  while a design achieving  $-40 \mathrm{dBm}$  requires only  $0.1 \mu\mathrm{W}$ , corresponding to a relative power reduction of more than two decades. Systems are usually designed to always operate in "worst-case" scenarios and do not scale their power consumption according to the strength of the input signal. This means that the  $50 \mu\mathrm{W}$  design will always consume the same amount of power regardless of the strength of the input signal (even if it is at  $-40 \mathrm{dBm}$ ). We can thus conclude, that a true, low-power WU-RX implementation needs to be capable of scaling its power consumption according to environment conditions such as received signal strength and presence (or lack) of strong interferers.

We propose a multi-stage WU-RX architecture conceived to achieve a scalable power consumption – sensitivity trade-off. Its design, presented in the next part of this chapter, is based on three different operation modes: an ultra-low power, low sensitivity mode; a high sensitivity mode; and finally, an interferer resistant mode. The following architecture analysis is only used to determine the specifications of the tunable filtering system required to enable efficient interferer rejection. The implementation of the latter will then be discussed for the rest of this manuscript.

### 1.3.1 Proposed System

To achieve a scalable performance level along with a scalable power consumption we propose a WU-RX architecture in which the most power consuming blocks can be

switched ON and OFF according to the current environment conditions. A top level view of the proposed system is presented in Figure 1.9.

FIGURE 1.9: Top level view of the proposed WU-RX architecture.

In the following paragraphs we discuss different WU-RX configurations where we estimate their power consumption as well as their sensitivity and interferer resilience. The control of the architecture configuration can be handled at a higher abstraction level and is beyond the scope of this manuscript.

### 1.3.2 Low Power – Low Sensitivity WU-RX

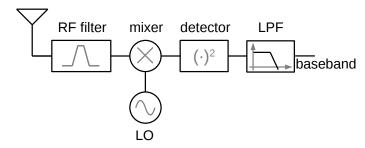

The low power – low sensitivity mode is activated only when environment conditions are extremely favourable (strong received signal with no interferers). All intermediate frequency blocks are deactivated, as it consists of a simple energy detector placed at the output of an uncertain receiver front end, as shown in Figure 1.10. The IF bandwidth depends on the precision of the free running oscillator frequency, which is determined by its implementation. No IF amplification is used to boost the signal, as we assume it is sufficiently strong for a correct demodulation.

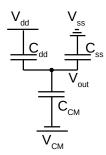

${\tt Figure~1.10:~Proposed~WU-RX~architecture~in~low~power-low~sensitivity~mode.}$

#### 1.3.3 High Sensitivity WU-RX

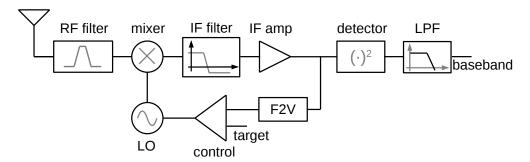

In the high sensitivity WU-RX mode, all IF blocks of the original architecture, except the tunable IF filter, are switched ON, as seen in Figure 1.11.

FIGURE 1.11: Proposed WU-RX architecture in high sensitivity mode.

With respect to the previous mode, the sensitivity is increased by the following mechanisms which are described below: increased direct path IF gain and a more narrow IF bandwidth.

### Increasing the IF Gain

As shown in [21], boosting the power of the IF signal increases the sensitivity of the demodulator thereby improving the sensitivity of the WU-RX. In fact, the demodulator, which is usually a squarer block, has a conversion gain which depends on the input signal amplitude: increasing the signal amplitude increases the conversion gain which improves the receiver noise figure. Based on results from literature, we estimate the sensitivity of such a system can be improved from -40 dBm to beyond -70 dBm for a total power consumption under  $50 \mu \text{W}$  ([22] and [4]).

#### Decreasing the IF Bandwidth

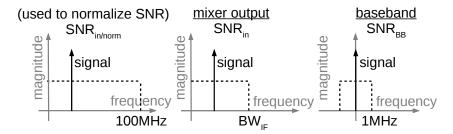

The sensitivity of the previously presented WU-RX architecture is limited by the wide IF bandwidth which can be as high as 100MHz [4] while the useful IF signal has a bandwidth of only several hundreds of kHz (imposed by the communication data-rate). The demodulator, implemented as an energy detector, then integrates its input noise over the entire bandwidth and downconverts it to baseband. The sensitivity can thus be improved by limiting the width of the IF stage passband, but this requires an improved precision of the local oscillator frequency. To illustrate prospective sensitivity improvements achieved by reducing the IF bandwidth, a set of simulations is done, in which we determine the minimum IF input signal-to-noise ratio  $(SNR_{in})$  for a given bandwidth  $BW_{IF}$  which results in 12dB of baseband SNR  $(SNR_{BB})$ , corresponding to a bit error rate (BER) of 1e-3. A representation of the simulation test bench is given in Figure 1.12; note that the first spectral representation of the signal is used only to normalize the SNR to a constant bandwidth and is obtained by extending the IF noise power from  $BW_{IF}$  to 100MHz – it never actually occurs in the proposed system.

FIGURE 1.12: Model of the simulation bench used to characterize prospective sensitivity improvements by reducing the IF bandwidth.

FIGURE 1.13: IF signal-to-noise ratio required for a robust demodulation of the IF signal.

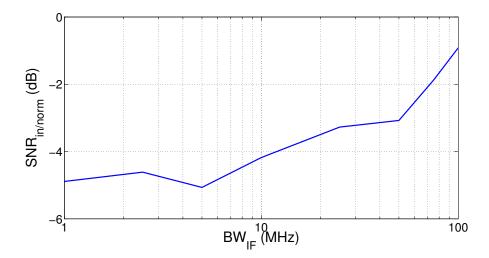

Results are plotted in Figure 1.13; the  $SNR_{in}$  has been computed by normalizing the integrated noise to a bandwidth of 100MHz, according to equation 1.1. It can be seen that by reducing the bandwidth from 100MHz to about 10MHz improves the sensitivity of the receiver by about 3dB.

$$SNR_{in/norm} = SNR_{in} - 10log_{10} \frac{BW_{IF}}{100MHz}$$

(1.1)

We now propose a new scheme aimed at improving the local oscillator precision by constructing a feedback loop which senses the frequency of the IF signal (through the use of the F2V – frequency to voltage – block) and controls the local oscillator, as showed initially in Figure 1.11 on the preceding page. At this point, we operate under the assumption that the IF signal does not contain any interferers. Compared to a standard PLL, the proposed LO control scheme does not employ any blocks running at RF other than the local oscillator itself. Consequently, its power requirements are not expected to increase dramatically [23].

A brief overview of the prospective performance of the proposed system is presented next.

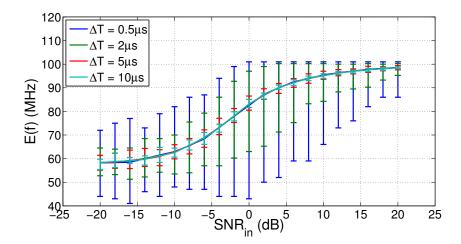

The proposed frequency locking mechanism achieves a precision which is limited by the estimation of the central frequency at IF level. At lower input signal levels, corresponding to a lower  $SNR_{in}$ , a bias in the estimation of the signal frequency is induced by the IF noise. To illustrate this we consider a scenario where the useful signal is situated at 100MHz, the IF bandwidth is [0Hz-100MHz] and the input SNR is defined as  $SNR_{in}$ . As an estimator, we use the average 0 crossing frequency computed over an interval ranging from  $0.5\mu$ s to  $10\mu$ s; the estimated frequency is thus given by equation 1.2 with N – the number of 0 crossings occurring in the time interval  $\Delta T$ . Results are plotted in Figure 1.14: the solid lines represent the "average" result while the error bars represent the most extreme cases occurring over the course of 100 MC (Monte Carlo) simulations.

$$E(f) = \frac{N-1}{2 \cdot \Delta T} \tag{1.2}$$

FIGURE 1.14: Frequency estimated by a zero crossing detector versus the  $SNR_{in}$ .

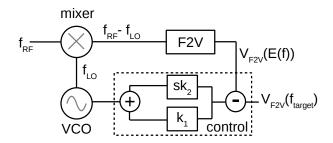

It can be seen that, for low signal strengths, the estimated frequency of the IF signal is very close to the middle of the IF noise bandwidth, 50MHz rather than to the frequency of the useful signal (100MHz). Moreover, the random nature of the IF noise increases the standard deviation observed between two consecutive estimations of the central frequency for a given estimation window. Having constructed the central frequency estimator, we now inject its output into a proportional – derivative (PD) controller which is used to tune the local VCO frequency. A more detailed view of the frequency control loop is given in Figure 1.15. Note that  $V_{F2V}(f)$  represents the voltage output of the F2V block when presented a signal of frequency f.

The frequency precision achieved by the proposed LO calibration loop is assessed through a series of simulations in which, initially, the useful signal is located at 100MHz and a 50MHz target is given to the control loop ( $f_{target}$ ). The frequency estimation is done over

FIGURE 1.15: Frequency control loop.

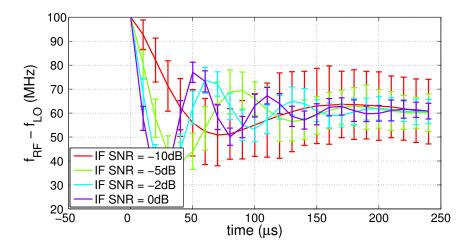

a duration  $\Delta T = 10\mu s$ . The evolution of the instantaneous frequency of the oscillator over a duration of  $250\mu s$  is plotted in Figure 1.16; as previously, the solid lines represent the evolution of the "average" result, while the error bars represent the most extreme cases occurring over the course of 100 MC simulations.

FIGURE 1.16: Evolution of the local oscillator instantaneous frequency for different values of the input  $SNR_{in}$ .

The coefficients chosen for the control loop have been optimized for an  $SNR_{in}$  of -10dB; the under-damped behavior of the control loop for other values of the  $SNR_{in}$  can be easily corrected by adjusting the corrector coefficients. In steady state, depending on the value of  $SNR_{in}$ , the frequency precision of the local oscillator is reduced from an initial value of 100MHz to values given in Table 1.2.

Table 1.2: LO precision for different values of the  $SNR_{in}$

| $SNR_{in}$       | $\Delta F_{LO}$ |

|------------------|-----------------|

| 0dB              | 7MHz            |

| -2dB             | 10MHz           |

| -5dB             | 15MHz           |

| $-10\mathrm{dB}$ | 28MHz           |

Comparing results from Table 1.2 with those from Figure 1.13 on page 12, we conclude that the proposed frequency calibration mechanism operates correctly at around -5dB of  $SNR_{in}$  which reduces the IF uncertainty to about 15MHz thereby improving the sensitivity of the WU-RX by 3dB with respect to the initial configuration (BW of100MHz). Despite the modest improvement in the sensitivity, this result is very useful as it drastically limits the IF bandwidth which relaxes the requirements of the interferer rejection stage.

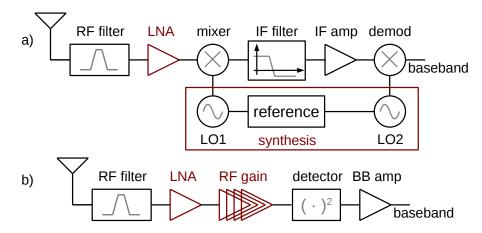

#### 1.3.4 Interferer Resilient WU-RX

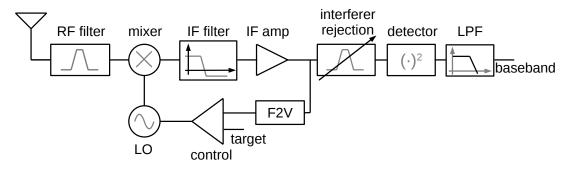

In this operation mode, all blocks of the initially proposed architecture are switched ON. For completeness, a view of the resulting architecture is given in Figure 1.17. Interferer rejection can only be achieved using filters which have bandwidths similar to that of the useful signal – up to 1MHz. This cannot be done at RF, since it would demand a filter with a quality factor which is too large. On the other hand, descending the signal to IF would solve the filter quality issue but would introduce another problem related to the frequency uncertainty of the useful signal. To solve this, we propose the use of a tunable IF filtering stage which is used to scan the entire IF band and attempt a demodulation at each frequency point in the search for the wake-up signal.

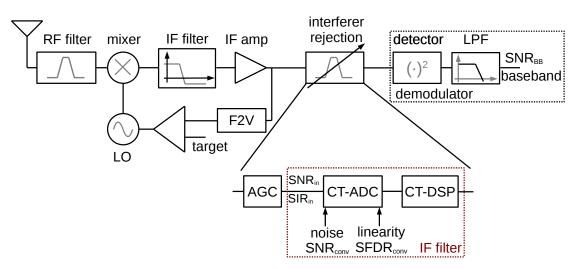

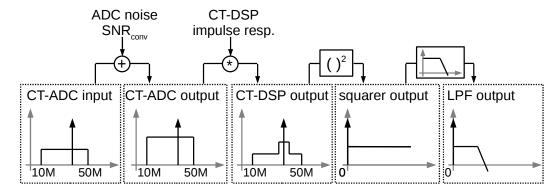

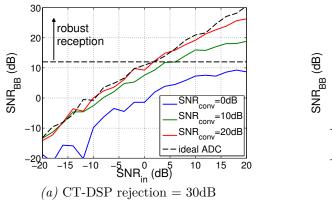

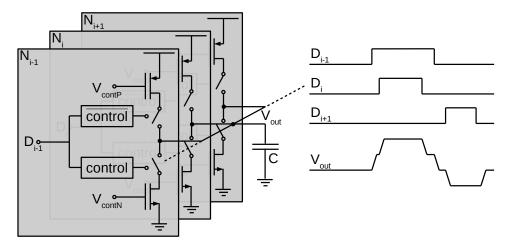

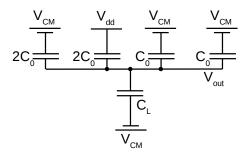

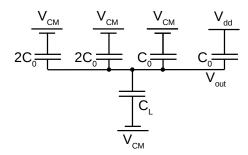

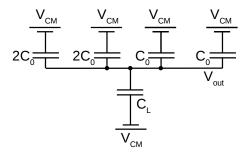

FIGURE 1.17: Proposed WU-RX architecture.