# Conception de circuits analogiques et numériques avec des transistors organiques flexibles

Miguel Angel Torres Miranda

#### ▶ To cite this version:

Miguel Angel Torres Miranda. Conception de circuits analogiques et numériques avec des transistors organiques flexibles. Electronics. Université Pierre et Marie Curie - Paris VI, 2015. English. NNT: 2015PA066693. tel-01380685

# HAL Id: tel-01380685 https://theses.hal.science/tel-01380685

Submitted on 13 Oct 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse de Doctorat de L'Université Pierre et Marie Curie

École Doctorale Informatique, Télécommunications et Électronique (EDITE)

Présentée par :

### Miguel Angel TORRES-MIRANDA

Pour obtenir le grade de :

### Docteur de l'Université Pierre et Marie Curie

Sujet de la thèse :

# Conception de Circuits Analogiques et Numériques avec des Transistors Organiques Flexibles

Date de soutenance : 1er Septembre 2015

#### Le jury est composé de :

| M. Hamid Kokabi        | Président du Jury     |

|------------------------|-----------------------|

| M. Boris Murmann       | Rapporteur            |

| M. Hagen Klauk         | Rapporteur            |

| M. Lionel Hirsch       | Examinateur           |

| Mme. Barbara Stadlober | Examinatrice          |

| M. Franck Wajsburt     | Examinateur           |

| M. Yvan Bonnassieux    | Co-directeur de Thèse |

| M. Hassan Aboushady    | Directeur de Thèse    |

# Design of Analog & Digital Circuits using Flexible Organic Electronics

A dissertation by:

## Miguel Angel TORRES-MIRANDA

Submitted to obtain the PhD degree from:

## Université Pierre & Marie Curie (UPMC)

Defense date: September 1st, 2015

### Committee in charge:

| Mr. Hamid Kokabi       | UPMC, France                   |

|------------------------|--------------------------------|

| Mr. Boris Murmann      | Stanford University, U.S.A     |

| Mr. Hagen Klauk        | Max Planck Institute, Germany  |

| Mr. Lionel Hirsch      | University of Bordeaux, France |

| Mme. Barbara Stadlober | Joanneum Research, Austria     |

| Mr. Franck Wajsburt    | UPMC, France                   |

| Mr. Yvan Bonnassieux   | Ecole Polytechnique, France    |

| Mr. Hassan Aboushady   | UPMC, France                   |

# Acknowledgements

I would like to thank my advisor Hassan Aboushady and co-advisor Yvan Bonnassieux for their time and their technical advices during my thesis.

I would like to thank the doctoral school EDITE: École Doctorale Informatique, Télécommunications et Électronique of Université Pierre et Marie Curie for funding this thesis work during 3 years. I was also partly funded by the European Institute of Technology (EIT), ICT Labs as a part of a program of Innovation and Entrepreneurship for PhD Candidates across Europe. I received several fundings, notably the one who allowed a research internship resulting in a collaboration (chapter 4 and 6) with the group of Dr. Barbara Stadlober, Joanneum Research, Weiz, Austria.

I would like to thank A. Al-Mutairi for his collaboration in the fabrication steps with the Orgatech Technology, Dennis Tondelier for his technical advices with the OTFT fabrication by shadow masks, Chang-Hyun Kim for his advices with modeling the experimental curves and the ORGATECH team at LPICM for the realization of a part of the experimental part in their facilities.

I would like as well to thank Andreas Petritz, Alexander Fian, Christine Prietl for helping me in the fabrication of the samples by photolithography, Herbert Gold for the mask layout design and the colleagues of the group of Micro and Nanostructuring of the Materials Department in the Joanneum Research center in Weiz, Austria, especially to Dr. Barbara Stadlober for being invited and funded for the realization of the experimental part in their facilities and the sample fabrication.

A big thank to Franck Wajsburt of LIP6/UPMC for his time and collaboration with the development of the Alliance CAD tools for the OTFT Technology.

I would like to thank as well Denis Crété of the Unité Mixte de Physique CNRS/Thales, Palaiseau, France and Jean-Charles Vanel of LPICM, Ecole Polytechnique, Palaiseau, France for helping him in the measurement process of the plastic circuits.

I would like to thank also to the master student Joao Cabral for his technical collaboration on the system level design of a sigma delta modulator and to all of the master students and colleagues at LIP6 which I work with during the thesis.

Finally I would like to thank my family and friends in Panama and in France for their patient and time during my long three years of thesis.

Miguel Angel TORRES-MIRANDA

# Contents

| Li | et of Figures                                                                     | iz |  |  |  |  |

|----|-----------------------------------------------------------------------------------|----|--|--|--|--|

| Li | ot of Tables                                                                      | XV |  |  |  |  |

| Aj | Appendixxv                                                                        |    |  |  |  |  |

| Pa | rt I Introduction to Electronics with Organics and Flexible Materials             |    |  |  |  |  |

| 1  | Introduction                                                                      | 1  |  |  |  |  |

|    | 1.1 Introduction                                                                  |    |  |  |  |  |

|    | 1.2 Outline                                                                       | 2  |  |  |  |  |

| 2  | Problem Definition and Motivation                                                 |    |  |  |  |  |

|    | 2.1 Introduction                                                                  |    |  |  |  |  |

|    | 2.1.1 Technology Process                                                          |    |  |  |  |  |

|    | 2.2 State of the Art of Compact Models for Circuit Design with Spice Simulators . | 8  |  |  |  |  |

|    | 2.3 State of the Art of Organic Thin Film Transistors                             | 14 |  |  |  |  |

|    | 2.4 State of the Art of Circuits                                                  | 15 |  |  |  |  |

|    | 2.4.1 Amplifiers on Flexible Foils                                                | 15 |  |  |  |  |

|    | 2.4.2 Comparators                                                                 | 10 |  |  |  |  |

|    | 2.4.3 Analog to Digital Converters                                                | 17 |  |  |  |  |

|    | 2.4.4 CAD Tools for Emerging Technologies                                         | 18 |  |  |  |  |

|    | 2.5 State of the Art of Applications                                              | 19 |  |  |  |  |

|                                                               | 2.5.1 Signal Treatment Systems                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                    |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

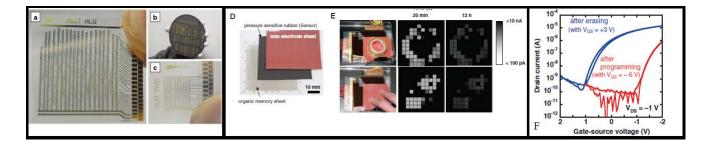

|                                                               | 2.5.2 Pressure Sensors                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                                                    |

|                                                               | 2.5.3 Flexible Displays                                                                                                                                                                                                                                                                                                                                                                                                                 | 20                                                    |

|                                                               | 2.5.4 RFID Tags                                                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                    |

|                                                               | 2.5.5 Energy management for flexible devices                                                                                                                                                                                                                                                                                                                                                                                            | 21                                                    |

|                                                               | 2.5.6 Smart Textiles                                                                                                                                                                                                                                                                                                                                                                                                                    | 22                                                    |

|                                                               | 2.5.7 e-Health applications with flexible and biocompatible materials                                                                                                                                                                                                                                                                                                                                                                   | 22                                                    |

| 2.6                                                           | Major Contributions                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                    |

|                                                               | 2.6.1 Technology Process                                                                                                                                                                                                                                                                                                                                                                                                                | 23                                                    |

|                                                               | 2.6.2 Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                    |

|                                                               | 2.6.3 Layout Design Automation Tools                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                    |

| 2.7                                                           | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                    |

| . **                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |

| rt II                                                         | Technology Process                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |

| CO                                                            | NFIDENTIAL: Systematic Parameter Characterization & Mismatch Model                                                                                                                                                                                                                                                                                                                                                                      |                                                       |

|                                                               | NFIDENTIAL: Systematic Parameter Characterization & Mismatch Model Analog Design                                                                                                                                                                                                                                                                                                                                                        | 29                                                    |

|                                                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |

| for                                                           | Analog Design                                                                                                                                                                                                                                                                                                                                                                                                                           | 29                                                    |

| <b>for</b> 3.1                                                | Analog Design                                                                                                                                                                                                                                                                                                                                                                                                                           | 29<br>31                                              |

| <b>for</b> 3.1 3.2                                            | Analog Design  Introduction  Mismatch Model Development                                                                                                                                                                                                                                                                                                                                                                                 | 29<br>31<br>34                                        |

| <b>for</b> 3.1 3.2                                            | Analog Design  Introduction  Mismatch Model Development  Manufacturing Technology Process                                                                                                                                                                                                                                                                                                                                               | <ul><li>29</li><li>31</li><li>34</li><li>34</li></ul> |

| <b>for</b> 3.1 3.2                                            | Analog Design  Introduction  Mismatch Model Development  Manufacturing Technology Process  3.3.1 Engineering the Polymeric Gate Dielectric                                                                                                                                                                                                                                                                                              | 29<br>31<br>34<br>34<br>35                            |

| for<br>3.1<br>3.2<br>3.3                                      | Analog Design  Introduction  Mismatch Model Development  Manufacturing Technology Process  3.3.1 Engineering the Polymeric Gate Dielectric  3.3.2 Engineering the Semiconductor Pentacene Layer                                                                                                                                                                                                                                         | 29<br>31<br>34<br>34<br>35<br>39                      |

| for<br>3.1<br>3.2<br>3.3                                      | Analog Design  Introduction  Mismatch Model Development  Manufacturing Technology Process  3.3.1 Engineering the Polymeric Gate Dielectric  3.3.2 Engineering the Semiconductor Pentacene Layer  3.3.3 Source and Drain Metal Deposition and Contact Resistance Calculation                                                                                                                                                             | 29<br>31<br>34<br>34<br>35<br>39                      |

| for<br>3.1<br>3.2<br>3.3                                      | Analog Design  Introduction  Mismatch Model Development  Manufacturing Technology Process  3.3.1 Engineering the Polymeric Gate Dielectric  3.3.2 Engineering the Semiconductor Pentacene Layer  3.3.3 Source and Drain Metal Deposition and Contact Resistance Calculation  Electrical & Mismatch Characterization                                                                                                                     | 29<br>31<br>34<br>35<br>39<br>39                      |

| for<br>3.1<br>3.2<br>3.3                                      | Introduction  Mismatch Model Development  Manufacturing Technology Process  3.3.1 Engineering the Polymeric Gate Dielectric  3.3.2 Engineering the Semiconductor Pentacene Layer  3.3.3 Source and Drain Metal Deposition and Contact Resistance Calculation  Electrical & Mismatch Characterization  3.4.1 Characteristics I-V Curves, Mobility and Ageing Effects                                                                     | 29<br>31<br>34<br>35<br>39<br>39<br>39<br>42          |

| <ul><li>for</li><li>3.1</li><li>3.2</li><li>3.3</li></ul> 3.4 | Analog Design Introduction Mismatch Model Development Manufacturing Technology Process 3.3.1 Engineering the Polymeric Gate Dielectric 3.3.2 Engineering the Semiconductor Pentacene Layer 3.3.3 Source and Drain Metal Deposition and Contact Resistance Calculation Electrical & Mismatch Characterization 3.4.1 Characteristics I-V Curves, Mobility and Ageing Effects 3.4.2 Modeling and Mismatch of Extracted Parameters in OTFTs | 29<br>31<br>34<br>35<br>39<br>39<br>39<br>42          |

|                                                               | 2.7                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.5.4 RFID Tags                                       |

|         | 4.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50                         |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|         |        | 4.1.1 Frequency Behavior of Transistors                                                                                                                                                                                                                                                                                                                                                                                                                            | 51                         |

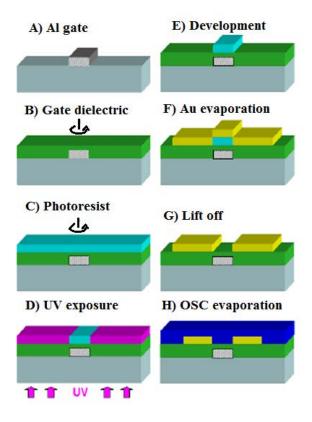

|         | 4.2    | Manufacturing Technology Process                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52                         |

|         |        | 4.2.1 Photolithography and Self Alignment Process Technology                                                                                                                                                                                                                                                                                                                                                                                                       | 53                         |

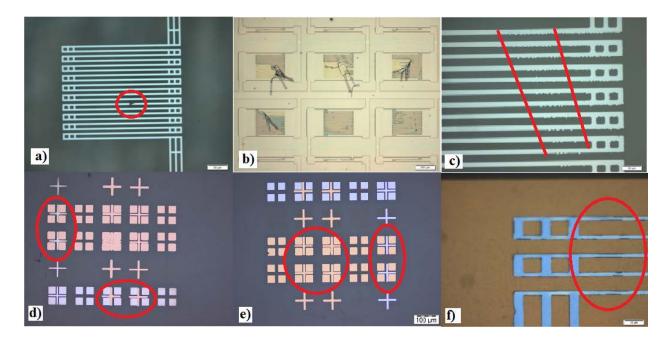

|         |        | 4.2.2 Issues and Difficulties of Manufacturing Structures by Photolithography                                                                                                                                                                                                                                                                                                                                                                                      | 55                         |

|         |        | 4.2.3 Engineering the Polymeric Gate Dielectric                                                                                                                                                                                                                                                                                                                                                                                                                    | 57                         |

|         |        | 4.2.4 Engineering the Semiconductor Pentacene Layer                                                                                                                                                                                                                                                                                                                                                                                                                | 57                         |

|         | 4.3    | Electrical Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59                         |

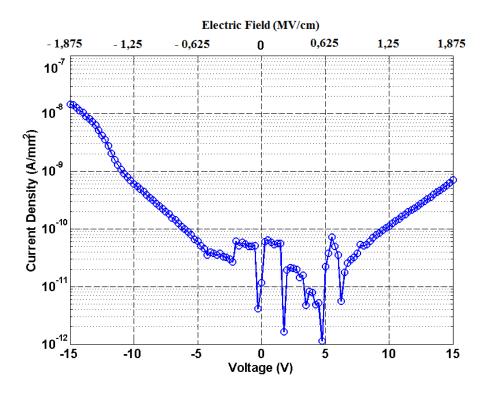

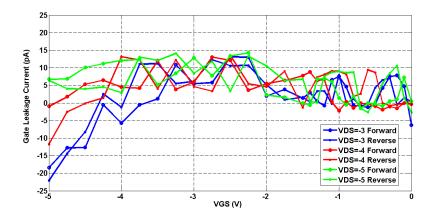

|         |        | 4.3.1 Gate Leakage Current Voltage Curves                                                                                                                                                                                                                                                                                                                                                                                                                          | 59                         |

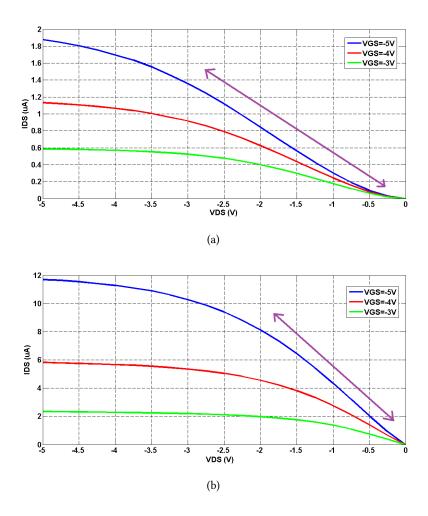

|         |        | 4.3.2 Engineering the Source and Drain Contact Resistance                                                                                                                                                                                                                                                                                                                                                                                                          | 61                         |

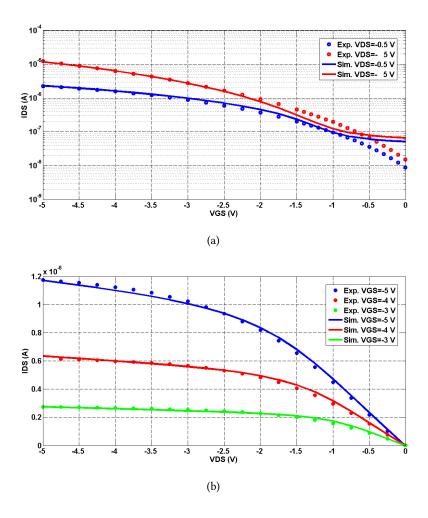

|         |        | 4.3.3 Extraction of Parameters and Modeling of OTFTs                                                                                                                                                                                                                                                                                                                                                                                                               | 63                         |

|         | 4.4    | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66                         |

| _       |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

| Pa<br>— | rt III | I Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| 5       | CO     | NFIDENTIAL: Design of Functional Analog Circuits with Few Organic                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

|         | Tra    | ansistors                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71                         |

|         | 5.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71                         |

|         | 5.2    | Gain Equations of a Diode Load Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                           | 72                         |

|         |        | 5.2.1 Sizing OTFTs                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74                         |

|         | 5.3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

|         |        | 6 OTFT Fully Differential Voltage Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                        | 74                         |

|         |        | 6 OTFT Fully Differential Voltage Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                        | 74<br>75                   |

|         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

|         |        | 5.3.1 Simulation Results for the Orgatech Technology                                                                                                                                                                                                                                                                                                                                                                                                               | 75                         |

|         | 5.4    | <ul> <li>5.3.1 Simulation Results for the Orgatech Technology</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            | 75<br>77                   |

|         | 5.4    | <ul> <li>5.3.1 Simulation Results for the Orgatech Technology</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            | 75<br>77<br>78             |

|         | 5.4    | <ul> <li>5.3.1 Simulation Results for the Orgatech Technology</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            | 75<br>77<br>78<br>80       |

|         | 5.4    | <ul> <li>5.3.1 Simulation Results for the Orgatech Technology</li> <li>5.3.2 Simulation Results for the Joanneum Research Technology</li> <li>5.3.3 Comparison of Performances of Both Technologies</li> <li>9 OTFT Source Coupled Latch Comparator</li> <li>5.4.1 Simulation Results for the Orgatech Technology</li> </ul>                                                                                                                                       | 75<br>77<br>78<br>80<br>81 |

|         | 5.4    | <ul> <li>5.3.1 Simulation Results for the Orgatech Technology</li> <li>5.3.2 Simulation Results for the Joanneum Research Technology</li> <li>5.3.3 Comparison of Performances of Both Technologies</li> <li>9 OTFT Source Coupled Latch Comparator</li> <li>5.4.1 Simulation Results for the Orgatech Technology</li> <li>5.4.2 Simulation Results for the Joanneum Research Technology</li> <li>5.4.3 Comparison of Performances of Both Technologies</li> </ul> | 75<br>77<br>78<br>80<br>81 |

|   |     | 5.5.2 Transistor Level Simulation Results for the Orgatech Technology          | 89  |

|---|-----|--------------------------------------------------------------------------------|-----|

|   |     | 5.5.3 Transistor Level Simulation Results for the Joanneum Research Technology | 89  |

|   |     | 5.5.4 Comparison of Performances of Both Technologies                          | 90  |

|   | 5.6 | A Discussion on Yield with Monte Carlo Simulations                             | 91  |

|   |     | 5.6.1 Monte Carlo Simulations for the Differential Amplifier                   | 92  |

|   | 5.7 | Conclusion                                                                     | 93  |

| 6 | co  | NFIDENTIAL: Implementation of Analog & Digital Circuits on Plastic             | 96  |

|   | 6.1 | Introduction                                                                   | 96  |

|   | 6.2 | Testing Plastic Circuits                                                       | 97  |

|   | 6.3 | Characterization of Moderate Gain-Fast Inverters and Logic Gates               | 100 |

|   | 6.4 | Characterization of Analog Circuits                                            | 105 |

|   |     | 6.4.1 Moderate Gain-Fast Differential Voltage Amplifier                        | 106 |

|   |     | 6.4.2 Fast Source Coupled Latch Comparator                                     | 108 |

|   | 6.5 | Discussion of the Results                                                      | 113 |

|   | 6.6 | Conclusion                                                                     | 114 |

| 7 | Ope | en Source CAD Layout Tools for Thin Film Emerging Technologies                 | 115 |

|   | 7.1 | Introduction to Alliance CAD Tools                                             | 115 |

|   | 7.2 | Alliance Concept for Emerging Printed and Flexible Technologies                | 116 |

|   | 7.3 | Proof of Concept for a Layout of Integrated Circuits with Organic TFTs         | 118 |

|   |     | 7.3.1 Graal environment for symbolic layout design                             | 118 |

|   |     | 7.3.2 Design Rules for Organic Thin Film Transistor Technology                 | 119 |

|   |     | 7.3.3 Differential Amplifier Layout                                            | 121 |

|   |     | 7.3.4 Comparator Layout                                                        | 123 |

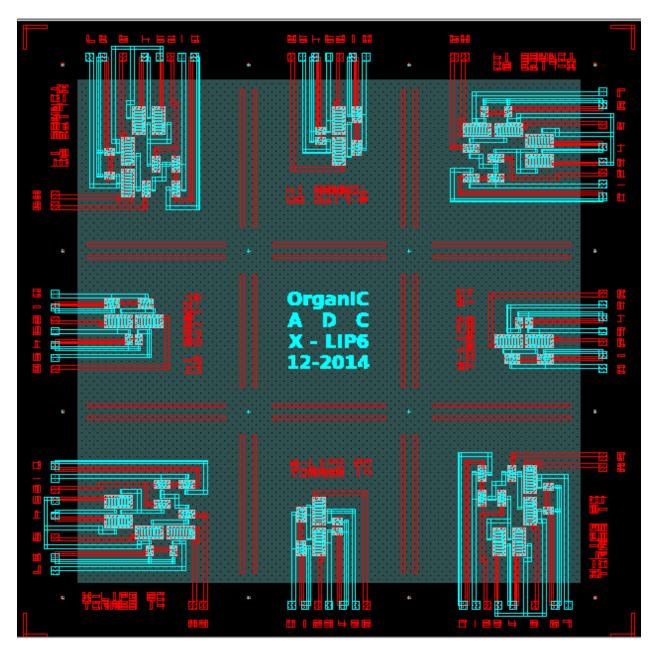

|   |     | 7.3.5 Sigma Delta Modulator Layout                                             | 124 |

|   | 7.4 | Conclusion                                                                     | 124 |

### **Part IV Conclusions**

vii

| 8  | Coı  | clusion and Future Work                                                         | 129 |

|----|------|---------------------------------------------------------------------------------|-----|

|    | 8.1  | Research Overview                                                               | 129 |

|    |      | 8.1.1 Design Kit with Organic Transistors                                       | 129 |

|    |      | 8.1.2 Circuit Design of Functional Analog and Digital Circuits on Plastic Foils | 130 |

|    |      | 8.1.3 Customization of the Alliance CAD Systems for Emerging TFT Technologies   | 131 |

|    | 8.2  | Future Work                                                                     | 131 |

| 9  | List | of Publications                                                                 | 133 |

| Ap | pen  | ices                                                                            | 134 |

| Αŗ | pen  | ix A                                                                            | 135 |

|    | A.1  | Analog to Digital Converters Principal Relations                                | 135 |

|    |      | A.1.1 Conventional Oversampled Analog to Digital Converters Signal to Noise     |     |

|    |      | Ratio Relation                                                                  | 136 |

|    |      | A.1.2 Analog to Digital Converters based on Sigma Delta Modulators Signal to    |     |

|    |      | Noise Ratio Relation                                                            | 136 |

| Aŗ | pen  | ix B                                                                            | 139 |

|    | B.1  | Alliance CAD Tools in CMOS Design                                               | 139 |

| Re | fere | ces                                                                             | 142 |

viii Contents

# **List of Figures**

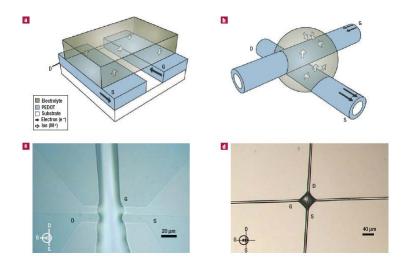

| 2.1  | Image of the four possible OTFT FET Structures                                  | 6  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Image of the thermal evaporation method with the different parts involved       |    |

|      | during the fabrication of thin film devices                                     | 7  |

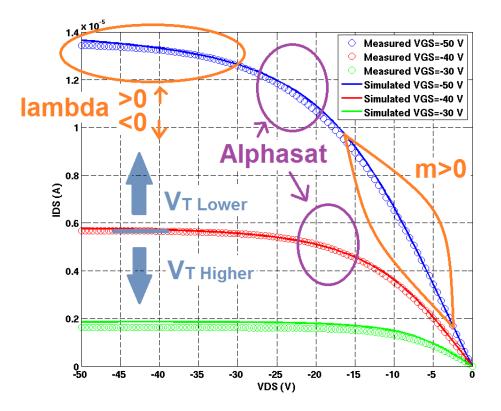

| 2.3  | Numerical parameters used to fit the models, in the output curve                | 11 |

| 2.4  | a-Si TFT Small Signal Model used as our OTFT Model in ELDO Spice. Note the      |    |

|      | different thin films composed on an organic transistor                          | 13 |

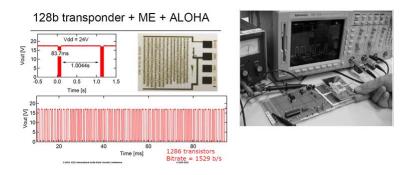

| 2.5  | Digital Systems with Flexible and Organic Transistors                           | 19 |

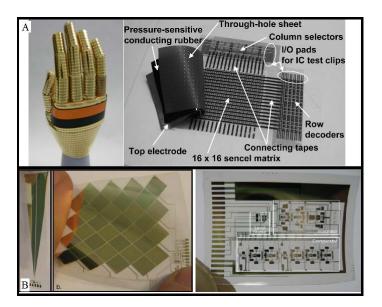

| 2.6  | Pressure sensor applications with flexible materials                            | 20 |

| 2.7  | Displays with flexible materials                                                | 20 |

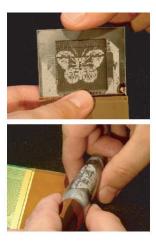

| 2.8  | RFID Tag with flexible materials                                                | 21 |

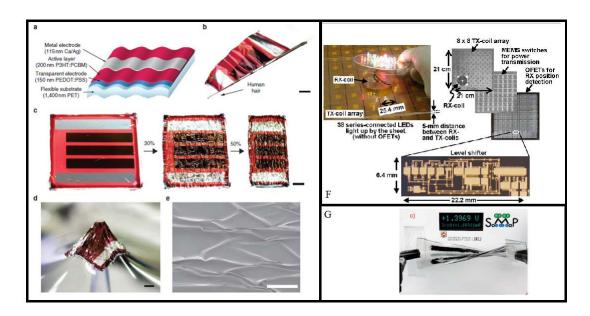

| 2.9  | Energiy Management Applications with Flexible and Organic Materials             | 22 |

| 2.10 | Textile Applications with flexible materials                                    | 23 |

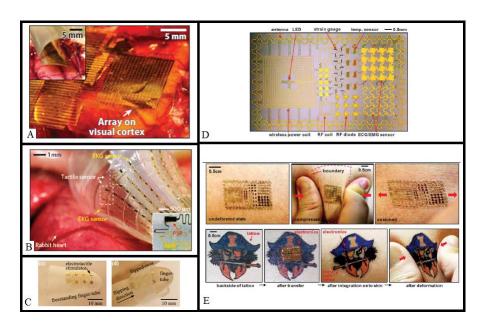

| 2.11 | e-Health Applications with flexible and biocompatible materials                 | 24 |

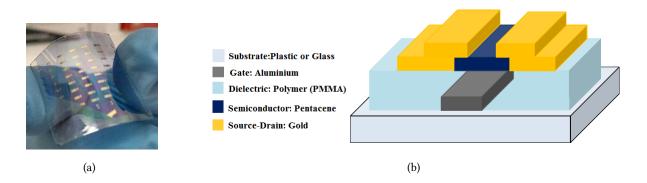

| 3.1  | a) Organic thin film transistor (OTFT) photography on a plastic substrate. b) A |    |

|      | 3D structure showing the different materials and layers with a bottom gate-top  |    |

|      | contact structure                                                               | 30 |

| 3.2  | a) Microscopic image of an OTFT. The changing colors are due to the light       |    |

|      | refraction in the inhomogeneous thickness of the dielectric. b) Experimental    |    |

|      | curve of the capacitance of the polymeric dielectric layer as a function of the |    |

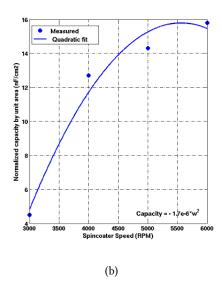

|      | spin-coater rotation speed                                                      | 34 |

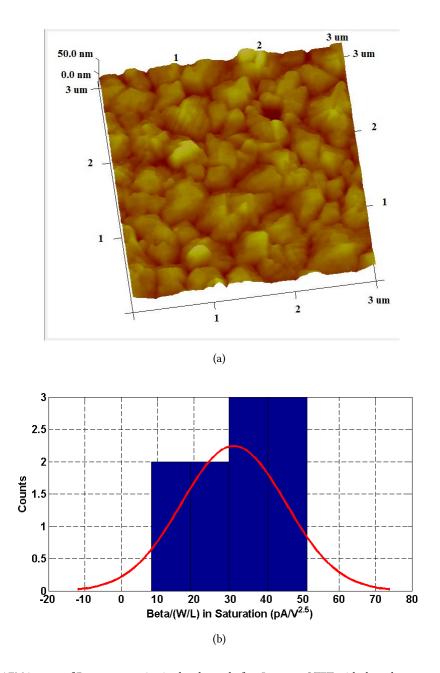

| 3.3  | a) Typical AFM images of Pentacene grains in the channel of an L=30 $\mu$ m OTFT                           |    |

|------|------------------------------------------------------------------------------------------------------------|----|

|      | with the substrates at T=25 C, during its deposition. The grains diameters are in                          |    |

|      | average 0,5 $\mu$ m. b) Histogram of the beta factor in saturation                                         | 37 |

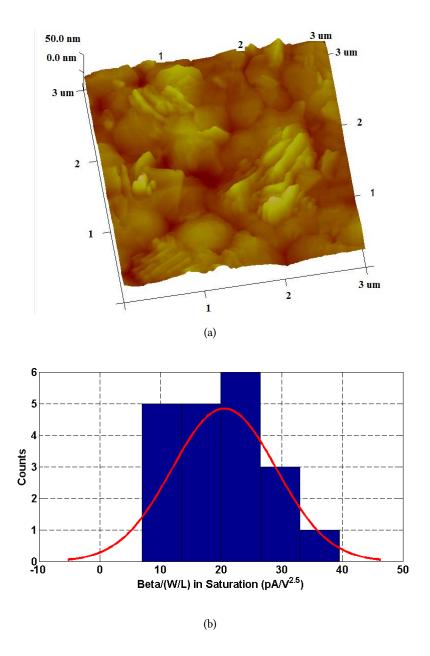

| 3.4  | a) Typical AFM images of Pentacene grains in the channel of a L=30 $\mu \rm m$ OTFTs                       |    |

|      | with the substrates heated to T=50 C, during its deposition. b) Histogram of the                           |    |

|      | beta factor in saturation. The diameter of the grain domains is doubled till $1\mu\mathrm{m}$ ,            |    |

|      | doubling the substrate heating temperature. Note that the parameter beta has                               |    |

|      | less variation compared to Fig.3.3                                                                         | 38 |

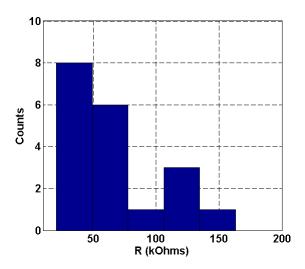

| 3.5  | Histogram of the computed source and drain contact resistance for several                                  |    |

|      | measured OTFTs                                                                                             | 39 |

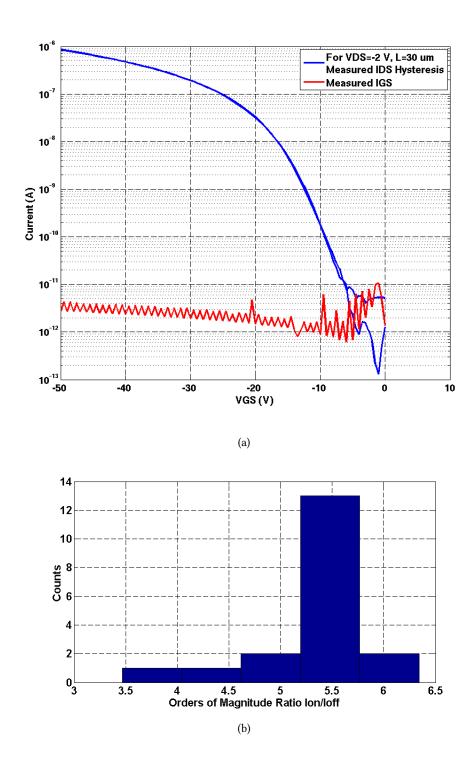

| 3.6  | a) Transfer curve of hysteresis in blue and gate leakage current in red. b)                                |    |

|      | Histogram of the ratio between the ON and the OFF drain source current                                     | 40 |

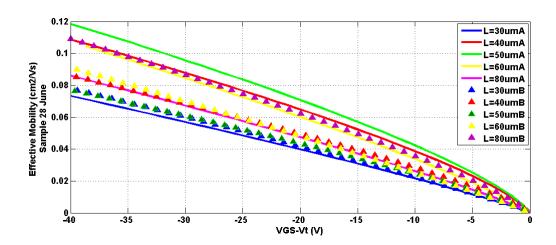

| 3.7  | Effective mobility vs. Overdrive voltage for 10 measured OTFT                                              | 42 |

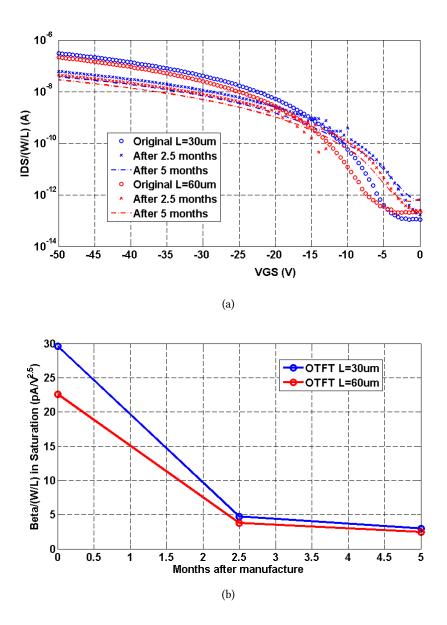

| 3.8  | a) Transfer curves in the linear regime for typical $30\mu\mathrm{m}$ and $60\mu\mathrm{m}$ channel length |    |

|      | OTFT measured in the saturation regime, several months later. b) Degradation                               |    |

|      | of beta factor in saturation with time.                                                                    | 43 |

| 3.9  | Experimental and fitted curves of a typical OTFT with 30 $\mu$ m channel length and                        |    |

|      | $1000\mu\mathrm{m}$ channel width. a) Transfer curves in the linear and in the saturation                  |    |

|      | regime.b) Fitted output curves                                                                             | 44 |

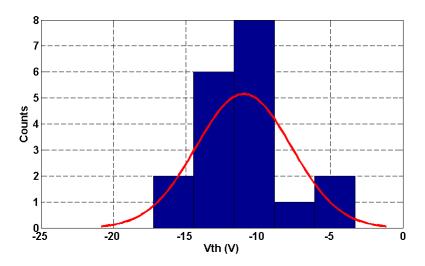

| 3.10 | Histogram of the threshold voltage for several measured OTFTs                                              | 45 |

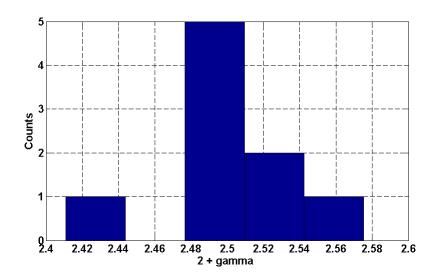

| 3.11 | Histogram of the 2+gamma power parameter                                                                   | 45 |

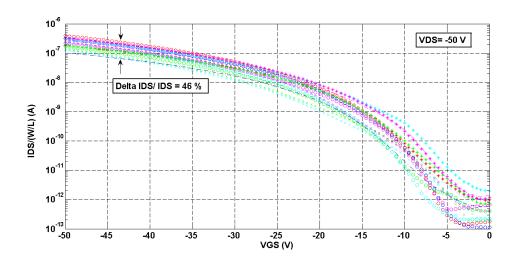

| 3.12 | Transfer curves for 15 OTFTs measured                                                                      | 46 |

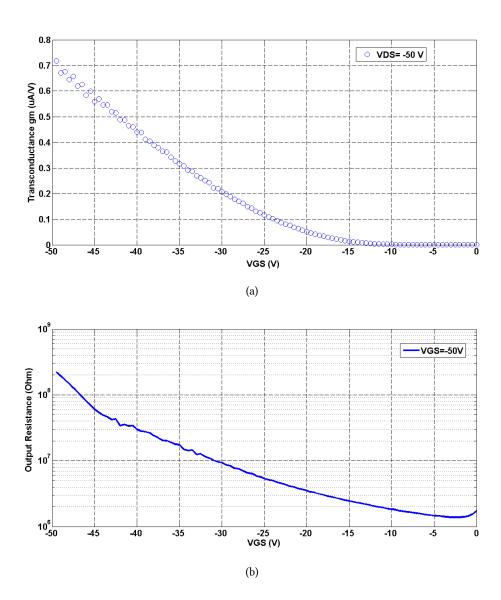

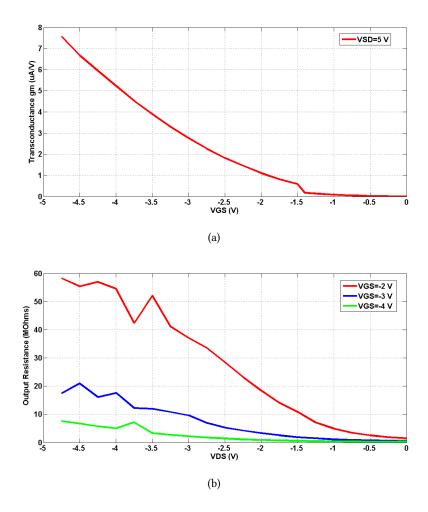

| 3.13 | a) Transconductance vs. Gate-source voltage. b) Output resistance vs.                                      |    |

|      | Drain-source voltage for an L=30 $\mu$ m OTFT                                                              | 48 |

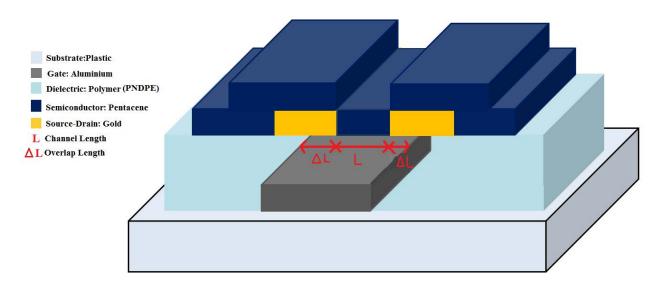

| 4.1  | 3D image of Joanneum Research?s Organic Thin Film Transistor layout with a                                 |    |

|      | bottom gate-bottom contact transistor geometry. Note the remark in red with                                |    |

|      | the overlap and channel length                                                                             | 53 |

| 4.2  | Fabrication process of organic thin film transistors by photolithography,           |    |

|------|-------------------------------------------------------------------------------------|----|

|      | self-aligning the source and drain contacts with the gate                           | 55 |

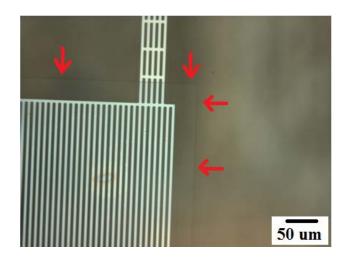

| 4.3  | Several typical defects occurring during the fabrication of organic thin film       |    |

|      | transistors by photolithography.                                                    | 56 |

| 4.4  | Edge of the dielectric layer after precise patterning                               | 58 |

| 4.5  | Current density of a capacitor with 80 nm of thickness                              | 58 |

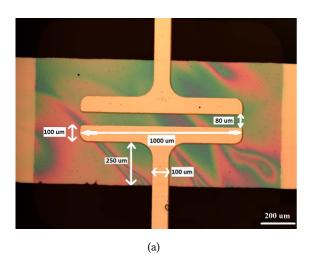

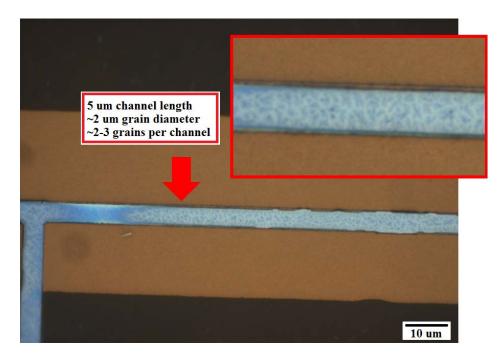

| 4.6  | Microscope image of the channel region of an OTFT with a channel length of          |    |

|      | 5 $\mu$ m. Note, that in the zoomed image only 2-3 grains are present between the   |    |

|      | contact edges.                                                                      | 60 |

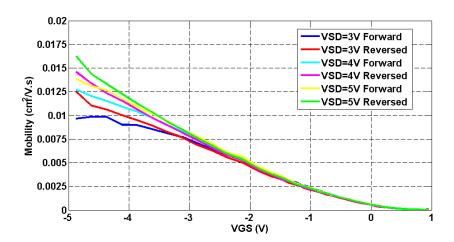

| 4.7  | Saturation mobility vs. gate-source voltage of a 10 mm wide and a 2 $\mu$ m channel |    |

|      | long OTFT in forward and reverse bias measurement                                   | 60 |

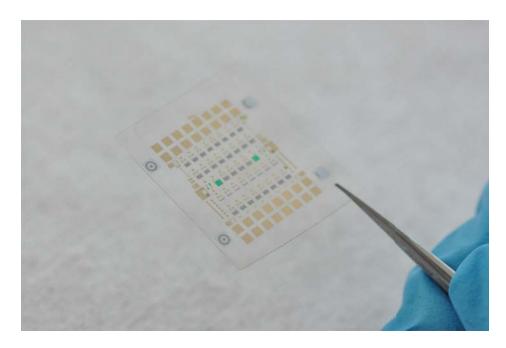

| 4.8  | Photo of the sample fabricated for testing OTFTs with very large widths and         |    |

|      | short channel length and large-area capacitors. Active area 1 inch square           | 61 |

| 4.9  | Gate leakage current in an OTFT of width = 10 mm and length = 2 $\mu$ m             | 61 |

| 4.10 | a)Measured output curves of the same OTFT. The violet arrow indicates the           |    |

|      | S-Shape characteristic of a non-linear contact resistance or injection in the       |    |

|      | channel. b) Measured output curves of the same OTFT. The violet arrow indicates     |    |

|      | the S-Shape characteristic of a non-linear contact resistance or injection in the   |    |

|      | channel                                                                             | 63 |

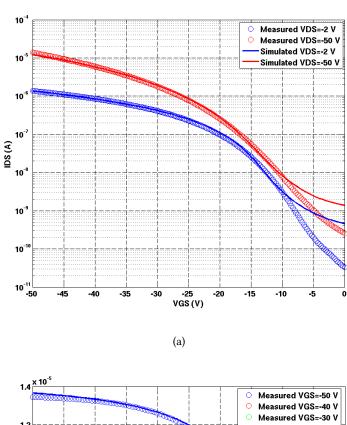

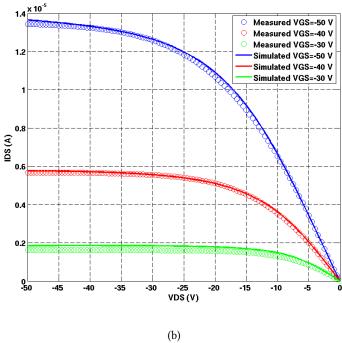

| 4.11 | a) Comparison of measured and modelled transfer curve of an OTFT with W =           |    |

|      | 14 mm and L = 2 $\mu$ m. b) Comparison of measured and modelled output curves of    |    |

|      | the same OTFT.                                                                      | 65 |

| 4.12 | a) Calculated transconductance from the OTFT of Fig. 4.11(a) b) Calculated          |    |

|      | output conductance of the same OTFT                                                 | 66 |

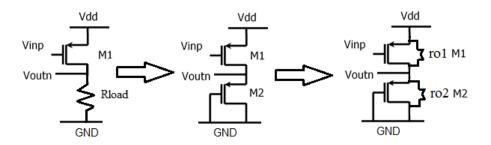

| 5.1  | Schematics of a single Input-Output amplifier with a resistance load, a diode       |    |

|      | connected transistor load and the output small signal resistances                   | 73 |

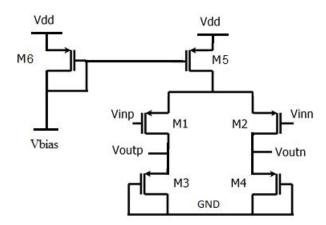

| 5.2  | Schematic of a fully differential voltage amplifier with diode load transistor and  |    |

|      | a current source                                                                    | 75 |

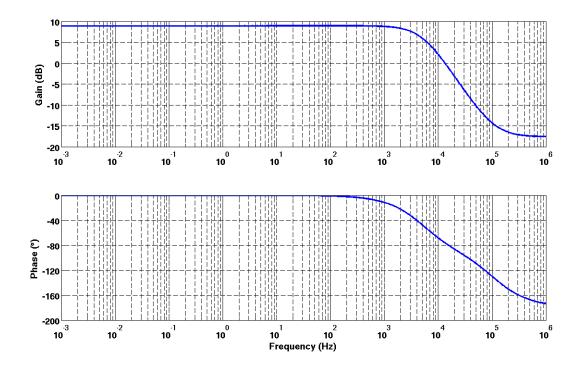

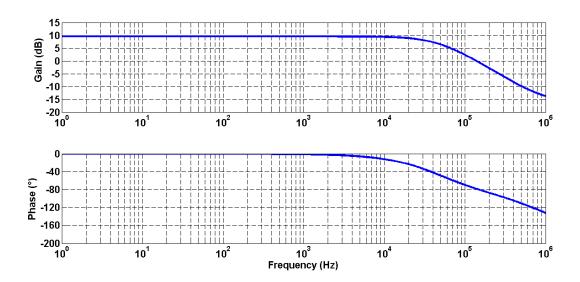

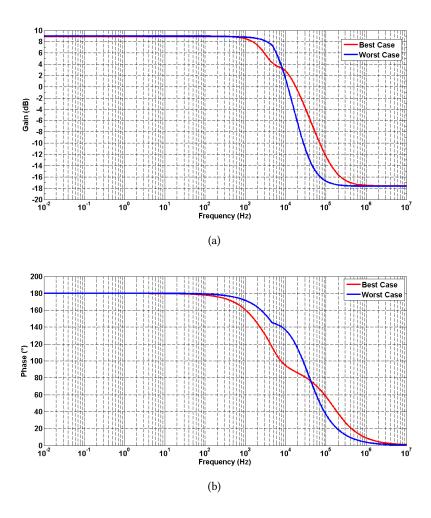

| 5.3                                                                             | Gain and phase bandwidth curves of the amplifier with the Orgatech Technology                  | 76 |  |  |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----|--|--|

| 5.4 Gain and phase bandwidth curves of the amplifier with the Joanneum Research |                                                                                                |    |  |  |

|                                                                                 | Technology                                                                                     | 78 |  |  |

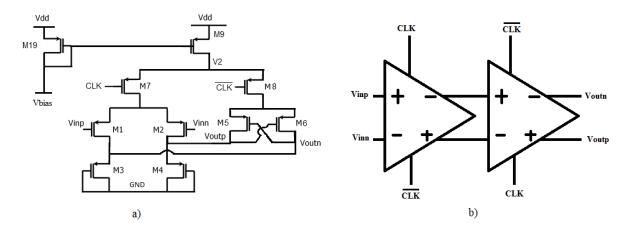

| 5.5                                                                             | a) Schematics of a source coupled latch(SCL) comparator. b) 2-stage SCL                        |    |  |  |

|                                                                                 | comparator with inverted clocks.                                                               | 81 |  |  |

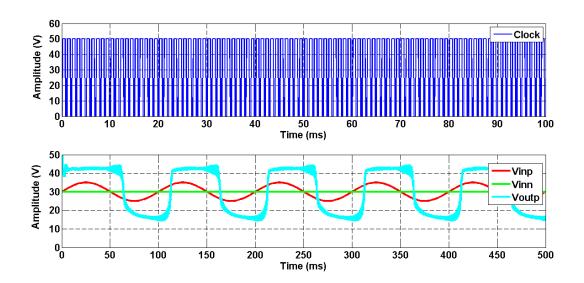

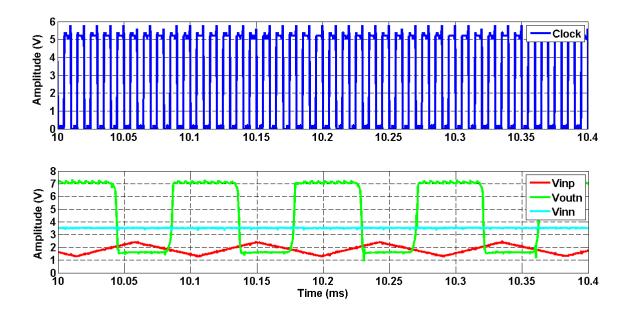

| 5.6                                                                             | Simulations results for the comparator with the conditions on Table 5.4                        | 82 |  |  |

| 5.7                                                                             | Simulations results for the comparator with the conditions on Table 5.5                        | 82 |  |  |

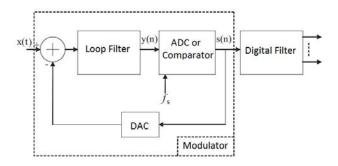

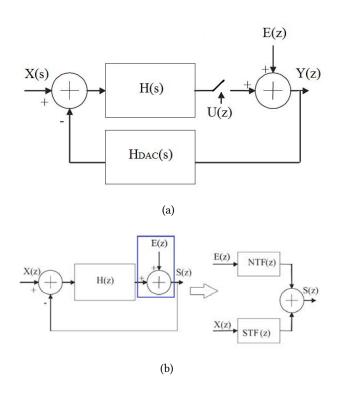

| 5.8                                                                             | Block model of a Sigma Delta Analog to Digital Converter                                       | 86 |  |  |

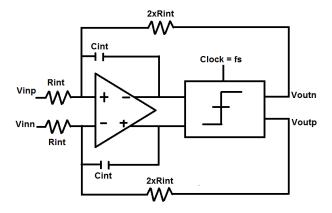

| 5.9                                                                             | Schematic of the Sigma Delta Modulator                                                         | 86 |  |  |

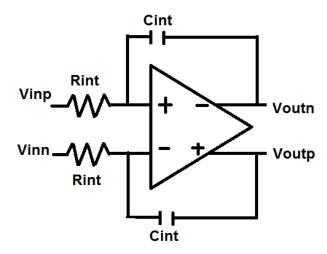

| 5.10                                                                            | Schematic of the RC active integrator                                                          | 87 |  |  |

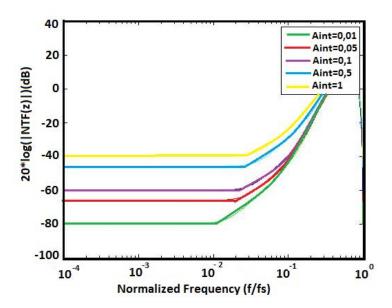

| 5.11                                                                            | Graphic of the Noise Transfer Function (NTF) vs. the normalized frequency for                  |    |  |  |

|                                                                                 | different Aint=1/ $f_s$ RC values, a DC gain of 9 dB and a $f_s$ of 1024 Hz                    | 89 |  |  |

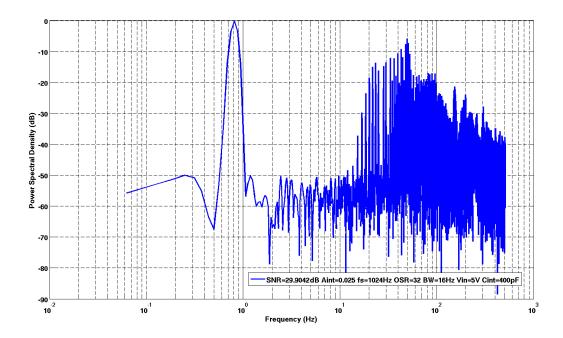

| 5.12                                                                            | Power Spectral Density versus Frequency with organic transistor-level                          |    |  |  |

|                                                                                 | simulations of the proposed Sigma Delta Modulator with the Orgatech Technology.                | 90 |  |  |

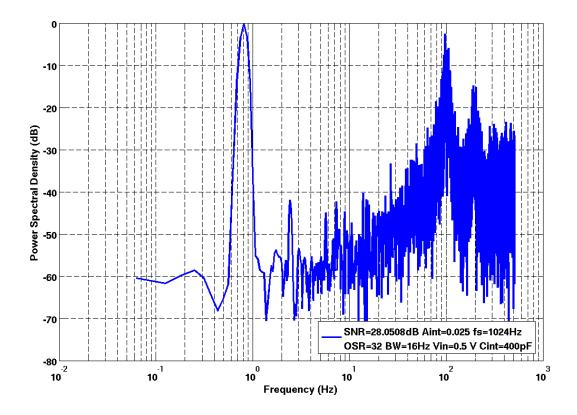

| 5.13                                                                            | Power Spectral Density versus Frequency with organic transistor-level                          |    |  |  |

|                                                                                 | simulations of the proposed Sigma Delta Modulator with the Joanneum Research                   |    |  |  |

|                                                                                 | Technology                                                                                     | 91 |  |  |

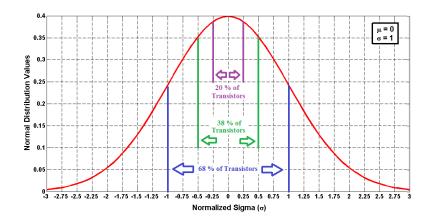

| 5.14                                                                            | Graphic of the normal distribution with mean $\mu$ = 0 and standard deviation $\sigma$ =1 $$ . | 93 |  |  |

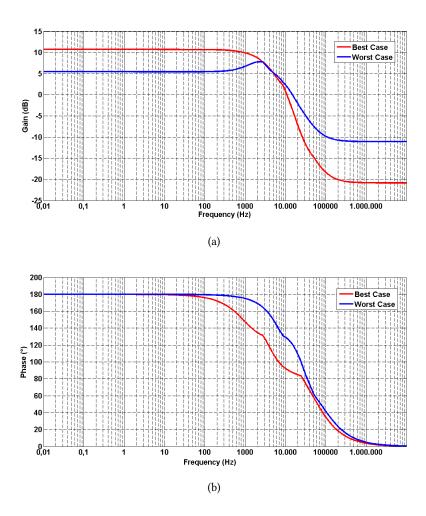

| 5.15                                                                            | Monte Carlo Simulations with a variation of 2V on the $V_{Th}$ with an uncorrelated            |    |  |  |

|                                                                                 | variation in each OTFT in the circuit. a) Best and worst case of the gain                      |    |  |  |

|                                                                                 | bandwidth curve. b) Best and worst case of the phase bandwidth curve                           | 94 |  |  |

| 5.16                                                                            | Monte Carlo Simulations with a variation of 41% on the mobility with a                         |    |  |  |

|                                                                                 | correlated variation in all of the OTFT in the circuit. a) Best and worst case of              |    |  |  |

|                                                                                 | the gain bandwith curve. b) Best and worst case of the phase bandwidth curve                   | 95 |  |  |

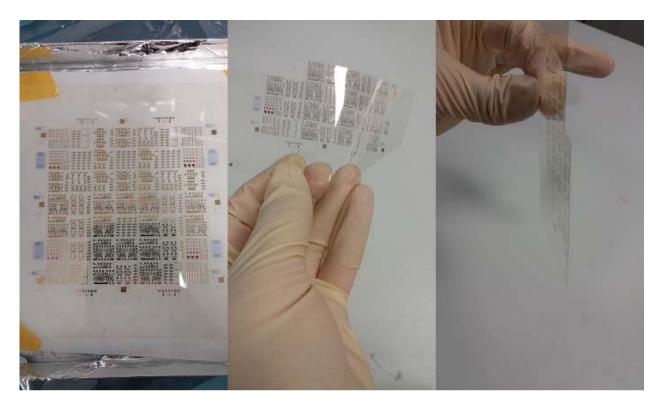

| 6.1                                                                             | Photos of the test sample fabricated to evaluate the performance of the different              |    |  |  |

|                                                                                 | analog and digital basic circuits. Note how thin and flexible the sample is                    | 98 |  |  |

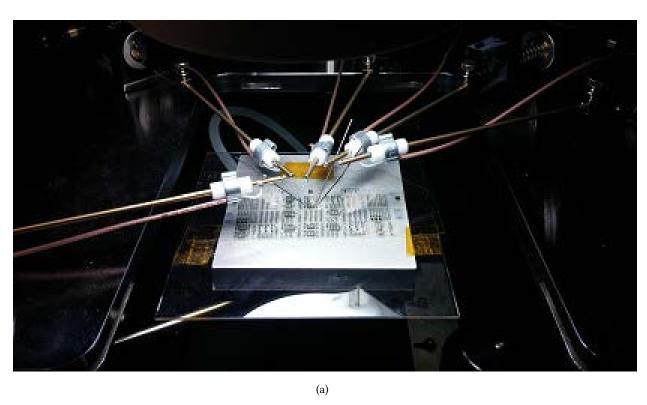

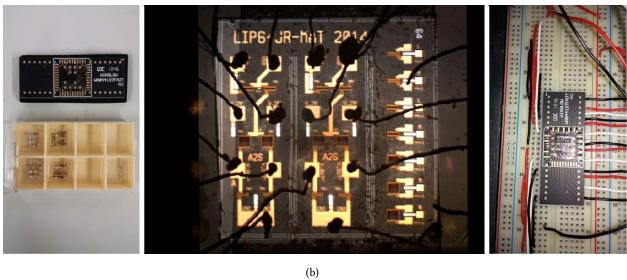

| 6.2                                                                             | a) Photo of the measurement setup with needle probes for circuits with few pads.               |    |  |  |

|                                                                                 | b) Photos of the low temperature bonding process to test circuits with many pads.              | 99 |  |  |

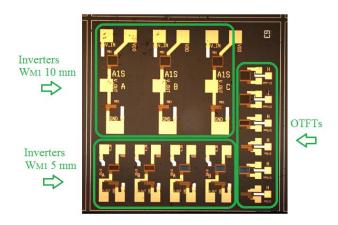

| 6.3  | Fabricated die of a total area of 9 x 9 mm <sup>2</sup> incorporating different inverters and  |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | single transistors                                                                             | 101 |

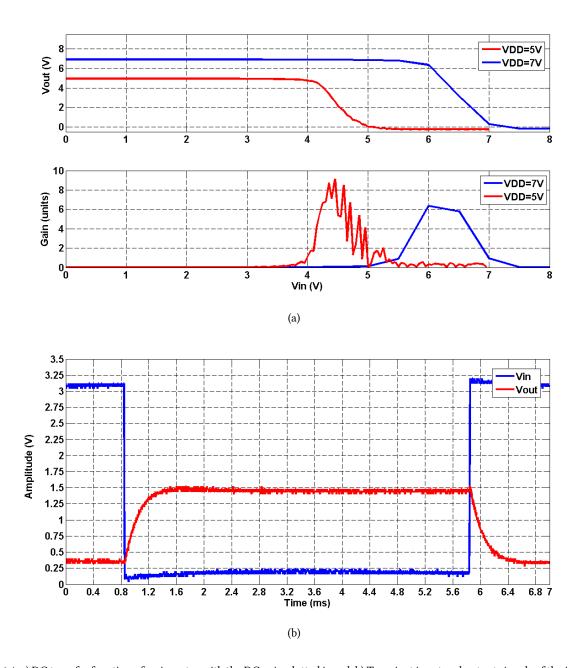

| 6.4  | a) DC transfer function of an inverter with the DC gain plotted in red. b)                     |     |

|      | Transient input and output signals of the inverter                                             | 102 |

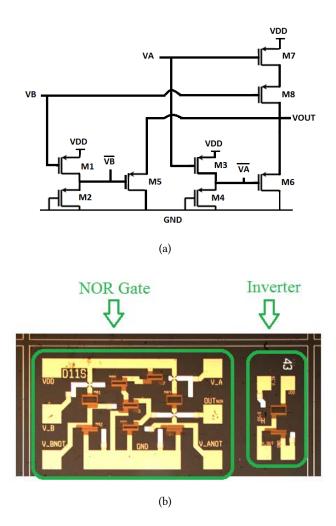

| 6.5  | a) Schematics of a NOR Gate. b) Implementation of the die with a total area of                 |     |

|      | 4,5 x 9 mm <sup>2</sup> with a NOR logic gate in plastic electronics                           | 104 |

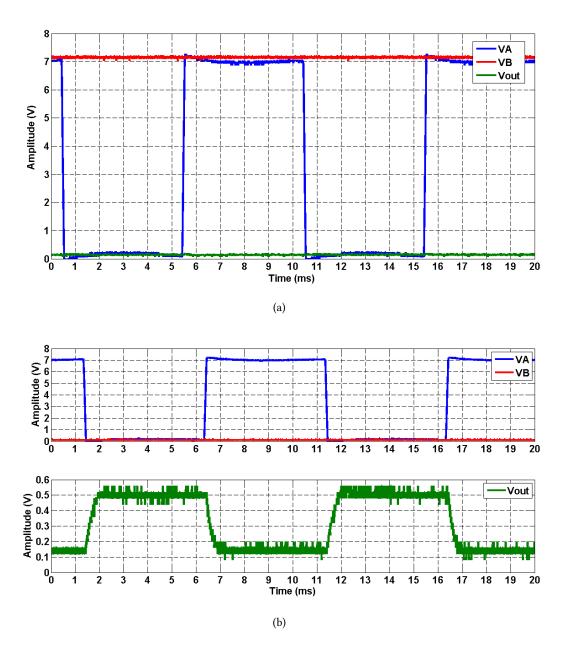

| 6.6  | a) Transient signals of a NOR Gate with VB ON. b) Transient signals of a NOR                   |     |

|      | Gate with VB OFF                                                                               | 105 |

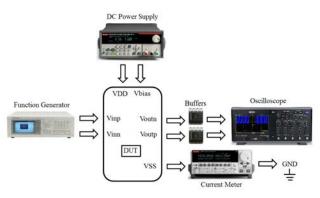

| 6.7  | Test Set-Up for the measurement of Analog Circuits                                             | 106 |

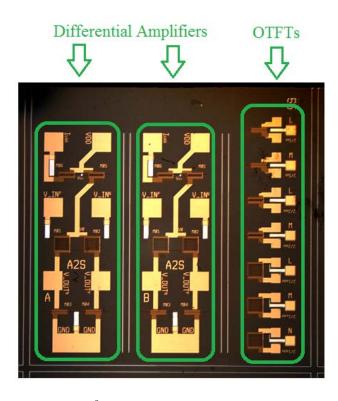

| 6.8  | Fabricated die of a total area of 9 x 9 mm <sup>2</sup> incorporating 2 differential amplifier |     |

|      | (A2S) and single transistors with variable dimension                                           | 107 |

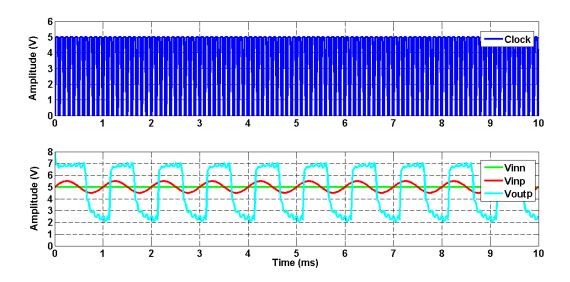

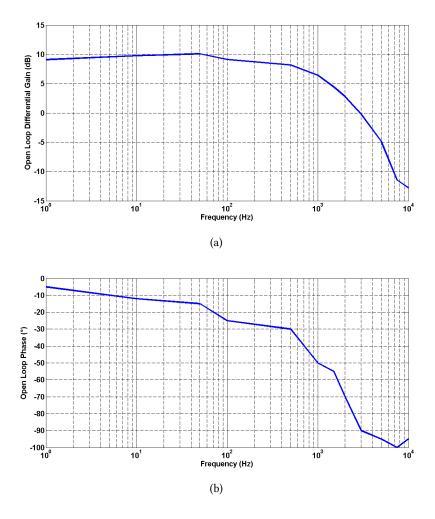

| 6.9  | a) Open loop differential gain versus frequency. b) Open loop phase versus                     |     |

|      | frequency                                                                                      | 109 |

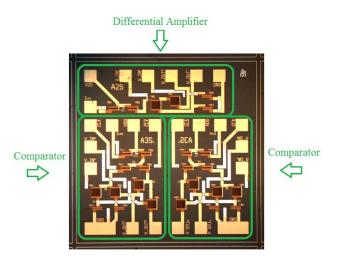

| 6.10 | Fabricated die of a total area of 9 x 9 mm <sup>2</sup> incorporating 2 source coupled latch   |     |

|      | comparators (A3S) and a differential amplifier (A2S). The comparator circuit                   |     |

|      | occupies a relatively small area of 5 x 8 mm <sup>2</sup>                                      | 111 |

| 6.11 | The comparator transient signals                                                               | 112 |

| 7.1  | Alliance Logo                                                                                  | 116 |

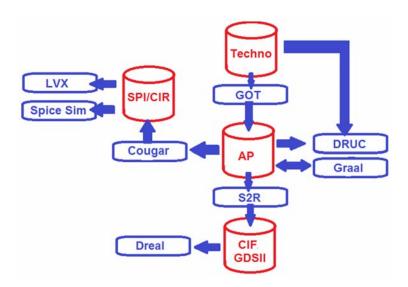

| 7.2  | Design Flow for the Organic Circuits with the Alliance CAD Tools                               | 117 |

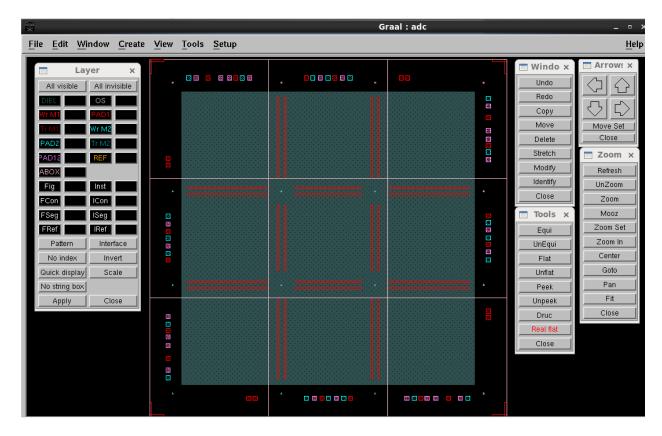

| 7.3  | Graal Design Environment                                                                       | 119 |

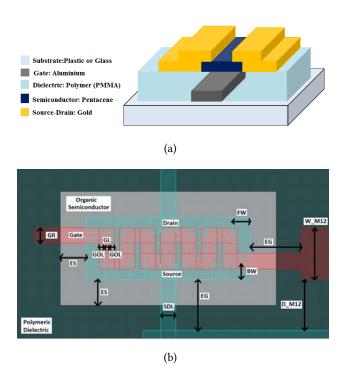

| 7.4  | a) 3D image of the Organic Thin Film Transistor in the Orgatech/LPICM-Ecole                    |     |

|      | Polytechnique technology. b) Top view of the OTFT with the design rules                        | 121 |

| 7.5  | Layout of the differential amplifier using Alliance CAD Tools                                  | 122 |

| 7.6  | Layout of the source coupled latch comparator presented in Chapter 5                           | 123 |

| 7.7  | Layout of the 2 diffrent cells that compose a Sigma Delta Modulator                            | 125 |

| A.1  | a) Block model of a continuous time sigma delta modulator. b) Block model of a                 |     |

|      | discrete time sigma delta modulator                                                            | 137 |

# **List of Tables**

| 2.1 | Organic thin film transistors already presented in our groups                       | 14 |

|-----|-------------------------------------------------------------------------------------|----|

| 2.2 | State of the Art of amplifiers fabricated with flexible organic materials           | 16 |

| 2.3 | State of the Art of comparators fabricated with flexible organic materials          | 17 |

| 2.4 | Different Organic ADC specifications in the litterature. The ** means that the      |    |

|     | ADCs are not fully manufactured with OTFTs                                          | 18 |

| 3.1 | Mean, standard deviations and percentage of variations of samples presented in      |    |

|     | Fig.3.3 and Fig.3.4                                                                 | 36 |

| 3.2 | Summary of parameters in the model for this OTFT technology                         | 49 |

| 4.1 | Dielectric characterization of several capacitors                                   | 59 |

| 4.2 | Summary of parameters in the model for our OTFT technology                          | 64 |

| 5.1 | Fully differential voltage amplifier specifications presented in Fig.5.2            | 77 |

| 5.2 | Fully differential voltage amplifier specifications presented in Fig.5.2            | 79 |

| 5.3 | State of the Art of amplifiers fabricated with flexible organic transistor          |    |

|     | technologies. PL stands for photolithography and SM for shadow mask. 1S for         |    |

|     | 1-stage, 2S for 2-stage, 3S for 3 -Stage. And L. for load. The (*) means that these |    |

|     | are simulation results.                                                             | 80 |

| 5.4 | Fully differential comparator specifications presented in Fig.5.5                   | 83 |

| 5.5 | Fully differential comparator specifications presented in Fig.5.5                   | 84 |

| 5.6 | Comparison of the tested comparator with the State of the Art. SM stands for  |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | shadow masks fabracation and PL for photolithography. L stands for transistor |     |

|     | load. Sw.Cap stands for switched capacitors. The (*) means that these are     |     |

|     | simulation results.                                                           | 85  |

| 5.7 | Different Organic ADC specifications in the literature. The * means that this |     |

|     | work is based for the moment on simulations results. The ** means that the    |     |

|     | ADCs are not fully manufactured with OTFTs. JR stands for Joanneum Research   |     |

|     | and MPI for the Max Planck Institute.                                         | 92  |

| 6.1 | Inverter specifications                                                       | 103 |

| 6.2 | NOR Logic Gate Table                                                          | 104 |

| 6.3 | NOR Gate specifications                                                       | 106 |

| 6.4 | Fully differential voltage amplifier specifications                           | 110 |

| 6.5 | State of the Art of amplifiers fabricated with flexible organic transistor    |     |

|     | technologies                                                                  | 111 |

| 6.6 | Fully differential comparator specifications                                  | 112 |

| 6.7 | Comparison of the tested comparator with the State of the Art                 | 113 |

| 7.1 | Alliance CAD Tools implemented for the Organic Transistor Technology          | 116 |

| 7.2 | Organic Thin Film Transistor Technology Layout Layers                         | 118 |

| 7.3 | Design Rules for the Orgatech/LPICM-Ecole Polytechnique Technology            | 120 |

| B.1 | Alliance CAD Tools implemented for conventional Si CMOS Technology. With      |     |

|     | an (*) the ones implemented for the Organic Transistor Technology             | 141 |

Introduction to Electronics with Organics and Flexible Materials

# Introduction

#### 1.1 Introduction

Electronics circuits and sensors using flexible materials is the next big revolution in the large fields of materials, devices and information technology due to its low cost fabrication process and its compatibility with stretchable, conformal and biological materials.

In the era of "Internet of Things", conventional expensive, bulky and rigid silicon is not the only answer for sensor interfaces. Electronic devices based on flexible materials are an interesting approach to interface with sensors connected to our everyday life, e.g.: clothes, packages, skin and into the human body.

In this thesis, we propose a formalization of the:

- Transistor fabrication process using organic and flexible materials.

- Analog and digital circuit design using these transistors.

The main contribution of this work can be summarized in the following:

- A design kit for two technologies: the first by shadow masks with an easy-to-fabricate procedure, the second by self-alignment and photolithography.

- Modeling and parameter extraction for process variation aware analog design.

- Customization of an open source VLSI CAD tools (Alliance©) for circuit design and layout of OTFT.

- Design, fabrication and measurement of OTFT analog front-ends (Voltage amplifiers, Comparators, Analog-to-Digital Converters) and basic digital circuits (Inverters, Logic Gates).

#### 1.2 Outline

The thesis report is divided in 8 chapters of content and a final chapter of conclusion and perspectives. In this first chapter we present a brief summary of what is the subject about and the outline of each chapter.

Chapter 2 presents the motivation of this work, a summary of basic concepts not treated in the subsequent chapters and an extensive description of the State of the Art in the different fields of research involving devices with flexible and organic materials.

Chapter 3 presents a detailed description of one of the two technologies optimized in this work: Organic Thin Film Transistors (OTFTs) fabricated by means of thermal evaporation and shadow masks at Orgatech in LPICM/Ecole Polytechnique, France. An extraction of the parameters of several fabricated OTFTs is shown. The adapted a-Si TFT Spice Model present in commercial simulators is used to model the transistors. A mismatch model will be presented with an statistical analysis.

Chapter 4 presents the description of the second technology presented in this work and developed at Joanneum Research, Austria: OTFTs with channels patterned by contact photolithography and self-alignment of source and drain with the gate. An optimization of several process parameters is presented such as the dielectric thickness, the semiconductor layer and a reduction in the contact resistance. Finally, those parameters were extracted and the transistors modeled with the a-Si TFT Spice model as well.

Chapter 5 presents the design of different analog basic blocks with the OTFTs based on the adapted model presented in chapter 2 and 3. The simulation results of different analog basic blocks with the technology developed in chapter 3 and 4. An amplifier, a comparator and a sigma delta modulator are designed using few OTFTs. A comparison among them and with the state of the art is done.

Chapter 6 presents the measurement of several analog and digital circuits in order to evaluate the performances of the Joanneum Research technology presented already in chapter 4. Good circuit performances such as gain, bandwidth, power consumptation and functional signals will be shown.

Chapter 7 presents the design of the layout of the sigma delta modulator developped in chapter 5, with the tools of a free and open source CAD system, Alliance ©. Simple standard circuit cells from the designed analog blocks will be shown.

Chapter 8 shows finally the conclusion of this work with the different results and a perspective of the future works in both groups.

# **Problem Definition and Motivation**

#### 2.1 Introduction

The Age of Internet of Things is here and is demanding us computational capability everywhere at anytime. Conventional silicon electronics has improved our lives in the last 40 years, however it has also arrived to a challenging period where people do not need only ultra low power and ultra fast devices, but also a close interaction with the technology. Bulky and rigid devices cannot accomplish these tasks because almost all of the objects around us, and moreover the human body are not hard but soft, conformal and mechanically dynamic. Electronics devices fabricated with flexible and stretchable materials looks forward to fill this gap. However the research field is also very challenging due to the lower electrical performances of the plastic materials compared to the crystalline semiconductors. It is necessary, as well, to differentiate both technologies not as competitors but as complementaries for the benefit of our everyday life.

Devices on plastic materials could be fabricated with organic and inorganic thin films deposited on top of a flexible substrate. Inorganic materials have better electrical properties because of the high temperature (and hence polycristalline structure) deposition process, however the most important disadvantages are the complex and expensive fabrication procedures which after all, make them a worse choice for commercialization. Organic materials on the contrary have at the moment of this thesis, lower performance properties than inorganic ones, however they could be deposited with low temperatures procedures, such as printing methods which makes a more interesting approach from an economic point of view. In fact, the possiblity of manufacture devices at a large scale and in large surfaces by conventional industrial process such as Roll to

Roll (R2R) and Sheet to Sheet (S2S) printing make organic thin film devices a better solution than inorganic ones. However some drawbacks need to be overcome to attain an industrial level of production compared to silicon electronics, for example the reliability of the devices, the increase in the amount of data driven and the decrease in the energy consumption.

In the last two decades, recent developments have shown the potential of these flexible devices which will be summarized in section 2.5. These connected devices with sensors on flexible materials need as well, signal treatment with at least a minimum of circuits serving as primary interfaces between them and a conventional electronic system. The state of the art in these basic signal treatment circuits will be shown in section 2.4. The OTFTs which are the base for those circuits and their models will be introduced in sections 2.3 and 2.2. A simple introduction to the manufacture process of those OTFTs is presented in the next section 2.1.1. Finally the principal contributions of this thesis work are presented in section 2.6.

#### 2.1.1 Technology Process

In order to manufacture circuits and systems, sensors and transistors are needed for the signal treatment. A thin film transistor (TFT) is an stack of layers each one with an electrical property. In this work, a conventional Field Effect Transistor (FET) structure is fabricated with a gate electrode, a dielectric as a buffer layer, a semiconductor as the active layer, and 2 contacts to manage the charge carrier injection to the semiconductor layer. Each of these layers could be deposited by different methods: thermal evaporation, spin-coating, ink-jet printing, among others.

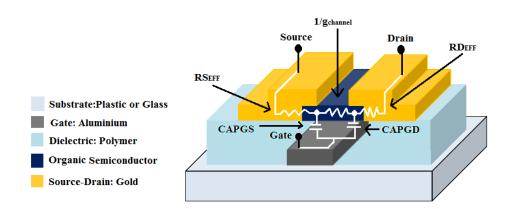

There are four basic OTFT structures presented in Fig. 2.1, explained in detail in [1] depending on the position of the gate and the contacts. In general when fabricating the transistor by shadow masks or photolithographic procedures it is important to reduce the overlap capacitances of the source and drain contacts with the gate. Therefore the gate is deposited as the first layer and then the rest of them, taking care to align the source and drain contacts with it.

The contact separation defines the channel length and its interface with the semiconductor determines the injection of charge carriers in the channel. As explained in [2], the contacts over the semiconductor layer allows a higher injection of those charge carriers in the channel compared to the coplanar structure with the contacts under the semiconductor layer. Therefore in

Fig. 2.1: Image of the four possible OTFT FET Structures.

order to reduce this contact resistance, in this work, the technology developed at LPICM-Ecole Polytechnique by shadow masks, is a bottom gate-top contact transistor structure. In the case where the contacts are defined by contact photolithography process as in Joanneum Research, the semiconductor has to be deposited at the end to avoid affecting this layer with other chemical or physical treatments. For this case, in this work, a bottom gate-bottom contact transistor structure is adopted.

The two basic deposition methods developped in this thesis are:

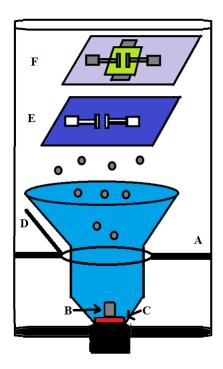

a)Physical Vapor Deposition (PVD) Process: is used to deposit solid materials such as the metals for the contacts (aluminium and gold) and the organic semiconductors in a high vacuum, typically with a pressure lower than  $10^{-5}$ mbar without another agent in the vacuum chamber. There are different possibilities: The simplest one is a thermal evaporation where the material to be deposited is in a solid state and placed in a furnace to be sublimated and then directed towards a substrate where it desublimates. In Fig. 2.2, there is shown a figure representing this process where A) represents the vacuum chamber, B) the material to be sublimated, C) the furnace where it is placed, D) the shutter or valve that opens when the material arrive to the necessary sublimation temperature and is ready to be deposited. E) is the shadow masks that filters the materials to a particular shape needed to create a device. And F) is the substrate where the material is going to be deposited. A variation of this PVD procedure is when the material grains are thus ejected to the substrate to be deposited.

The Chemical Vapor Deposition (CVD) Process: is another process where the material to be deposited is in a chamber with the present of a precursor volatile agent which will react with the surface of the substrate in order to have an uniform layer. The most used CVD procedures are at

Fig. 2.2: Image of the thermal evaporation method with the different parts involved during the fabrication of thin film devices.

Low Pressure (LPCVD), Plasma Enhanced (PECVD), Atomic Layer (ALCVD), among others. This process is not used in this work.

b) Solution based deposition procedures: these deposition methods are used to deposite liquid or sol-gel state materials with the need of a baking step in order to harden and to dry the layer over the substrate. It is used conventionally for the dielectric and the photo resistive layers in the photolithography process. There are different possibilites: the spin-coating process is where the liquid solution of the material is deposited by a needle and then it is spreaded with a uniform layer over all of the sample by an spinning of the substrate at several hundreds or thousands of revolution per minutes (RPM). In reality the layer has some non-uniformities in the thickess under 100 nm that makes quite difficult to control with precision.

Another possibility not used in this thesis would be to ink-jet print the solution with a commercial printer. In this case, the solution is deposited over the substrate drop by drop with a precision pico litter ink-jet head. The advantage of this process is the high precision in the feature printed and the low cost of the overall process that is achieved, however a disadvantage is the viscosity of

the solution that is needed in order to avoid clogging of the print heads. The slow speed making those features which could extend till hours for a simple device is also a disadvantage.

The photolithographic procedures are also used in the fabrication of OTFTs and are further explained in chapter 4.

# 2.2 State of the Art of Compact Models for Circuit Design with Spice Simulators

Compact models are a set of one dimensional physical equations which describe the behaviour of a transistor in the different regions of operation following the classical procedure described for conventional MOSFET transistors, [3]. The idea is to describe the dependence of the drain source current equation in terms of the gate source and the drain source voltage with the least possible quantity of parameters. This is done in order to reduce the time of the simulations. The equations are thus implemented in an Spice-like simulator to obtain an electrical model with a discret device structure (resistors, capacitors, voltage and current dependent sources)

Two characteristics curves are needed to describe the DC behavior of a transistor, the transfer and the output curve. The transfer curve describe the transition of the drain source current from an Off state (or leakage regime) with almost no current in the channel to a subthreshold regime with a small drain source current in the channel and then to a linear above treshold regime with a considerable high current in the channel. The output curves however, describe the transition of a transistor from a linear resistor (voltage dependent) behavior to a current source (voltage independent) behavior.