## Electro-thermal characterization, TCAD simulations and compact modeling of advanced SiGe HBTs at device and circuit level

Rosario d'Esposito

#### ► To cite this version:

Rosario d'Esposito. Electro-thermal characterization, TCAD simulations and compact modeling of advanced SiGe HBTs at device and circuit level. Electronics. Université de Bordeaux, 2016. English. NNT: 2016BORD0147 . tel-01386487

## HAL Id: tel-01386487 https://theses.hal.science/tel-01386487

Submitted on 24 Oct 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. N° d'ordre: 2016BORD0147

# THÈSE

#### PRÉSENTÉE À

## L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÉNIEUR

## Par Rosario D'ESPOSITO

POUR OBTENIR LE GRADE DE

#### DOCTEUR

SPÉCIALITÉ: ÉLECTRONIQUE

\*\*\*\*\*

## Electro-thermal characterization, TCAD simulations and compact modeling of advanced SiGe HBTs at device and circuit level

\*\*\*\*\*

Soutenue le: 29 Septembre 2016

Après avis de :

M. Raymond QUÉRÉ M. Gilles DAMBRINE Professeur, XLIM, Université de Limoges Professeur, IEMN, Université de Lille Rapporteur Rapporteur

Devant la Commission d'Examen formée de:

| M. Niccolò RINALDI<br>M. Raymond QUÉRÉ<br>M. Gilles DAMBRINE<br>Mma Gristell MANEUX | Professeur<br>Professeur<br>Professeur | Università di Napoli<br>XLIM<br>IEMN | Président du jury<br>Rapporteur<br>Rapporteur |

|-------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------|-----------------------------------------------|

| Mme Cristell MANEUX                                                                 | Professeur                             | Université de Bordeaux               | Examinateur                                   |

| M. Didier CÉLI                                                                      | Senior Member du Staff Technique       | STMicroelectronics                   | Examinateur                                   |

| M. Bertrand ARDOUIN                                                                 | Directeur Général                      | XMOD Technologies                    | Examinateur                                   |

| M. Thomas ZIMMER                                                                    | Professeur                             | Université de Bordeaux               | Directeur de thèse                            |

| M. Sébastien FRÉGONÈSE                                                              | Chargé de Recherche                    | CNRS                                 | Co-encadrant de thèse                         |

To Marco Di Rosa, a genius guy, a great friend

To all the people that supported me in this work

## Table of contents

| Abstrac | ct                                                          | iv |

|---------|-------------------------------------------------------------|----|

| Résum   | é                                                           | v  |

| Acknow  | wledgments                                                  | vi |

| Chapte  | r 1 General introduction                                    | 1  |

| 1.1     | THz waves and applications                                  | 1  |

| 1.2     | SiGe BiCMOS technology                                      | 2  |

| 1.3     | Thermal issues in SiGe technologies                         | 4  |

| 1.4     | This work                                                   | 7  |

| 1.4     | 4.1 Motivation                                              | 7  |

| 1.4     | 4.2 Organization                                            |    |

| Chapte  | r 2 Device characterization in SiGe HBT technologies        | 10 |

| 2.1     | Introduction                                                |    |

| 2.2     | Compact modeling: the HiCuM model                           |    |

| 2.3     | Modeling of device self-heating in compact simulators       | 12 |

| 2.4     | Self-heating effect on the device DC and AC characteristics | 13 |

| 2.5     | Extraction of the R <sub>th</sub>                           | 16 |

| 2.6     | Extraction of the Z <sub>th</sub>                           |    |

| 2.0     | 6.1 Theoretical formulation                                 | 21 |

| 2.7     | Recursive thermal network model                             | 24 |

| 2.8     | Behavior of the transistor under two tones excitation       |    |

| 2.9     | Conclusion                                                  |    |

| Chapte  | r 3 Impact of BEOL in single finger devices                 |    |

| 3.1     | Introduction                                                |    |

| 3.2     | State of the art in the study of the BEOL impact            |    |

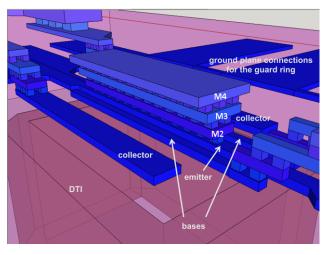

| 3.3     | Test structures in 0.34x5µm <sup>2</sup> geometry           |    |

| 3.4     | Test structures characterization                            |    |

| 3.4     | 4.1 DC characterization                                     |    |

| 3.4     | 4.2 Thermal characterization                                |    |

| 3.4     | I.3 Small signal RF characterization                                  | 43 |

|---------|-----------------------------------------------------------------------|----|

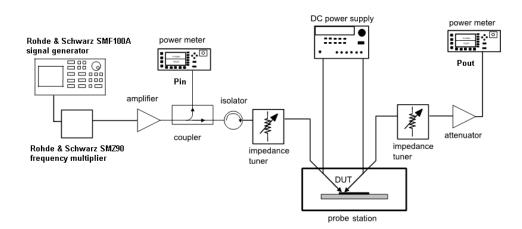

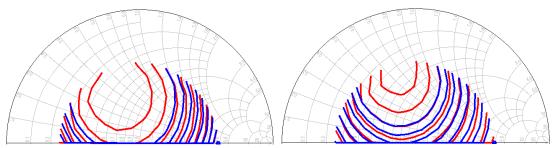

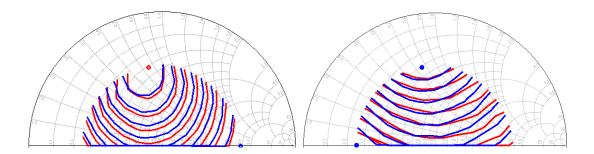

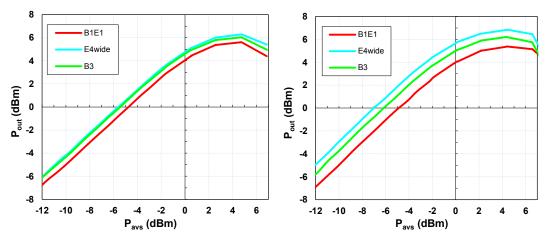

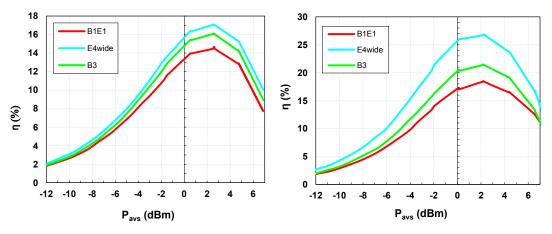

| 3.4     | 4.4 Large signal measurements                                         | 44 |

| 3.5     | Test structures in 0.22x5µm <sup>2</sup> geometry                     | 47 |

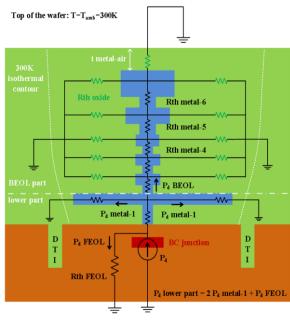

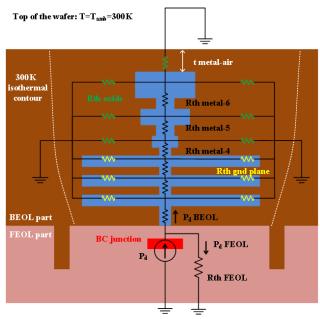

| 3.6     | Thermal modeling of the BEOL metallization                            | 49 |

| 3.6     | 5.1 DC measurements                                                   | 50 |

| 3.6     | 5.2 Low frequency measurements                                        | 50 |

| 3.6     | 5.3 Pulsed measurements                                               | 52 |

| 3.6     | 5.4 Large signal two tones simulations                                | 52 |

| 3.7     | Static and dynamic thermal characterization                           | 54 |

| 3.8     | 3D TCAD thermal simulations                                           | 55 |

| 3.8     | 3.1 Thermal parameters and doping dependence                          | 57 |

| 3.9     | Conclusion                                                            | 60 |

| Chapter | 4 Impact of BEOL and transistor layout change in multi-finger devices | 62 |

| 4.1     | Introduction                                                          | 62 |

| 4.2     | Improving thermal stability in multifinger transistors                | 62 |

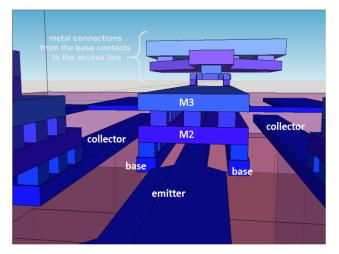

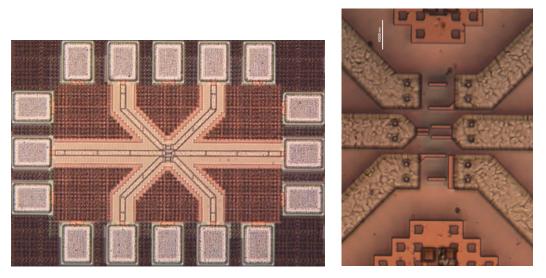

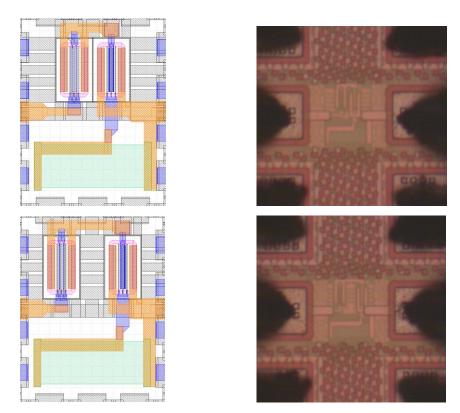

| 4.3     | Description of the test structures                                    | 63 |

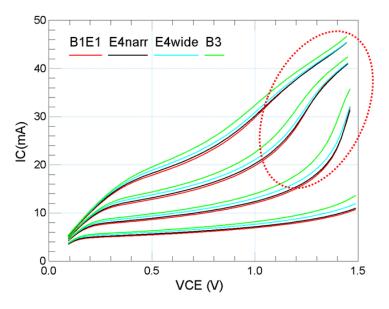

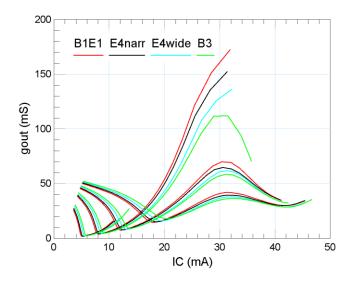

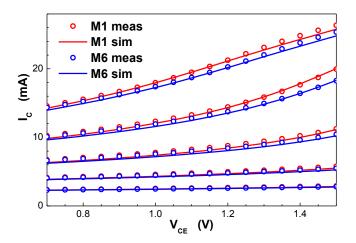

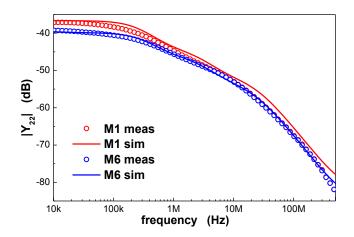

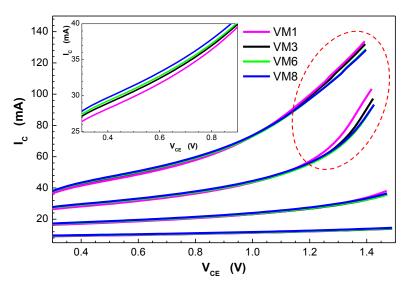

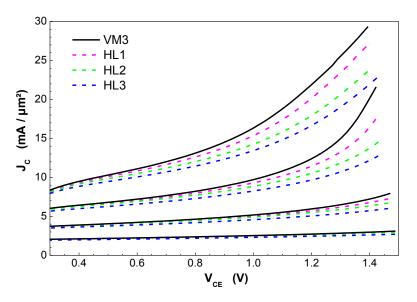

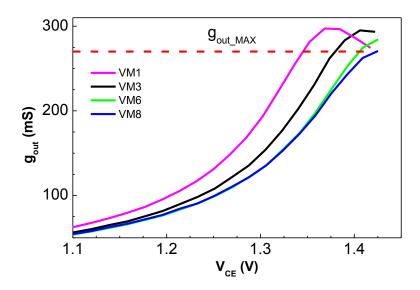

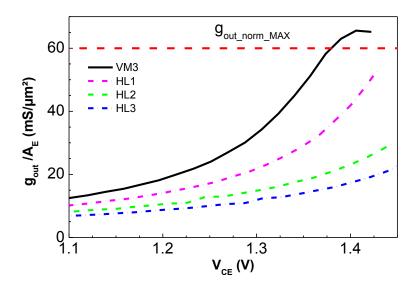

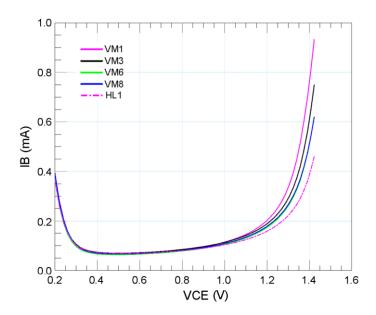

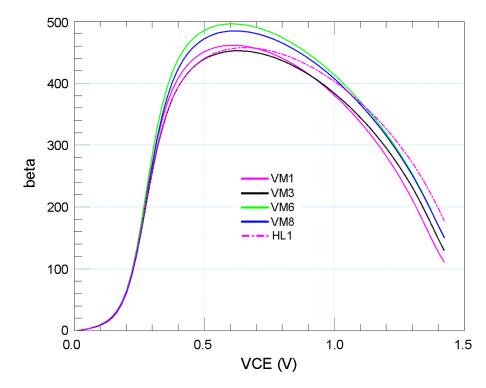

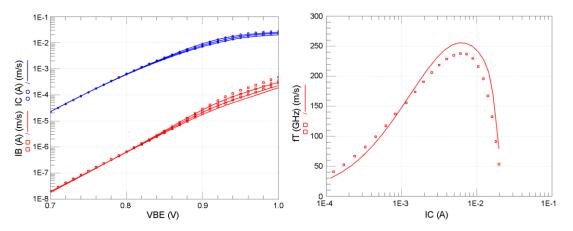

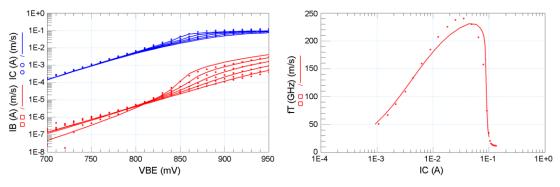

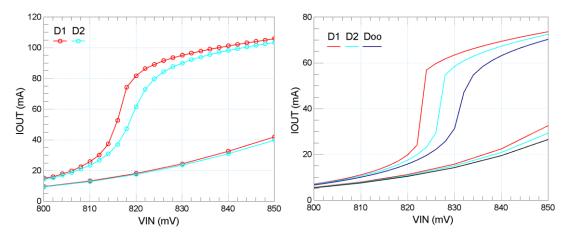

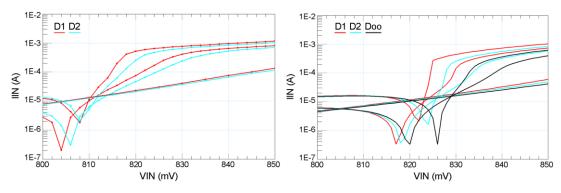

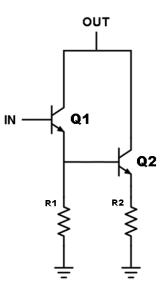

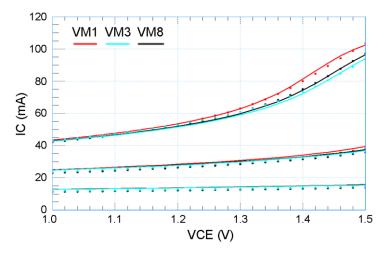

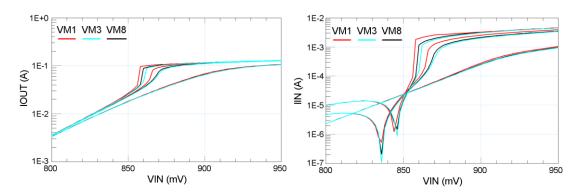

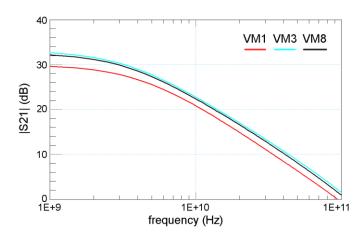

| 4.4     | DC electrical characterization                                        | 66 |

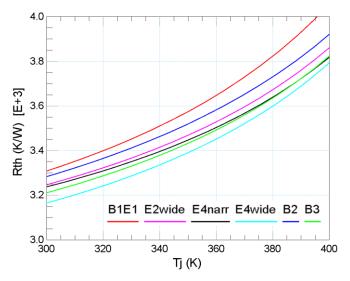

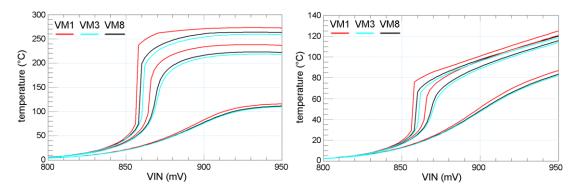

| 4.5     | Thermal characterization                                              | 71 |

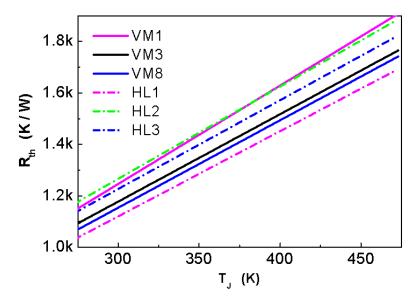

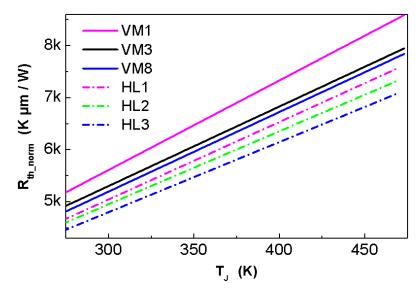

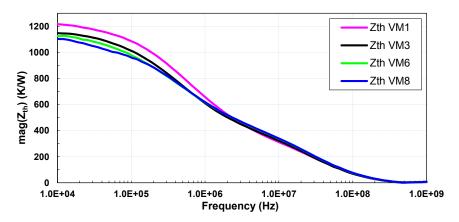

| 4.5     | 5.1 Thermal resistance extraction                                     | 71 |

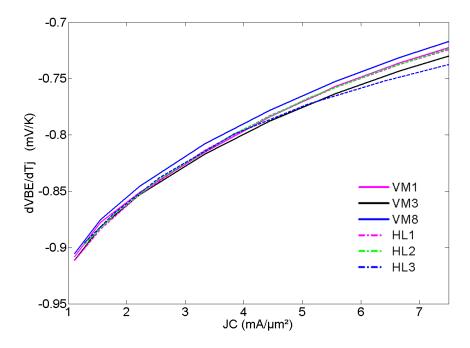

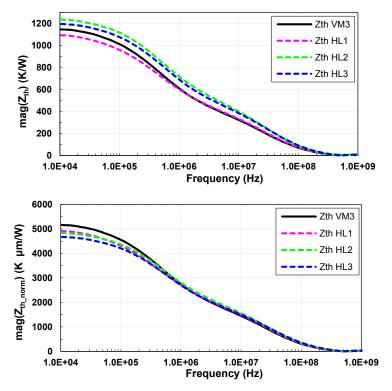

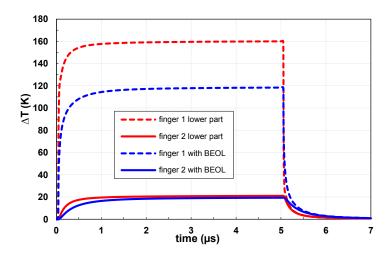

| 4.5     | 5.2 Thermal impedance extraction                                      | 74 |

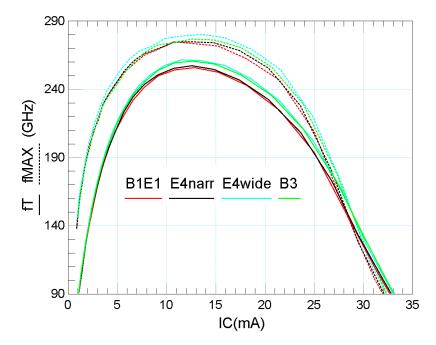

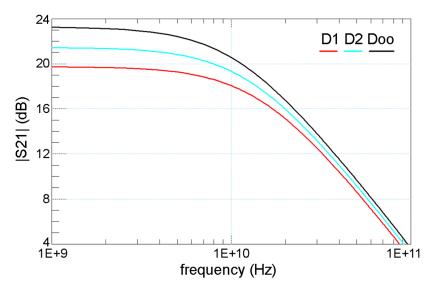

| 4.6     | Small signal AC characterization                                      | 76 |

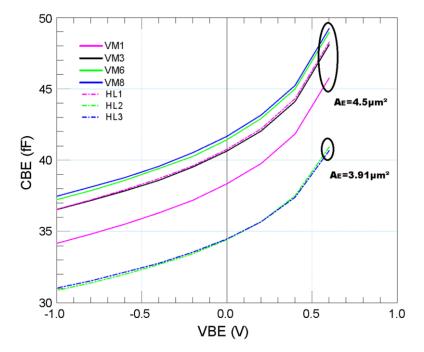

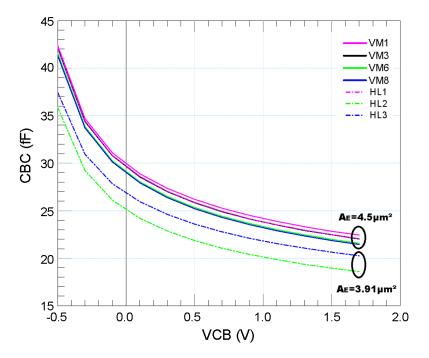

| 4.6     | 5.1 C <sub>BE</sub> and C <sub>BC</sub> capacitances                  | 76 |

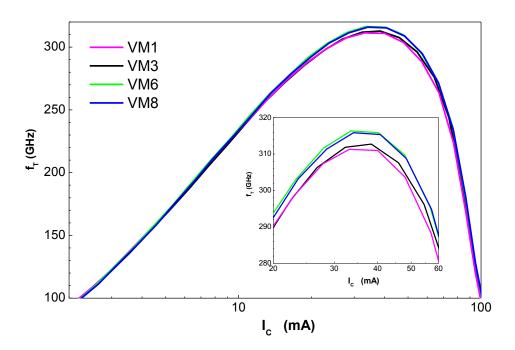

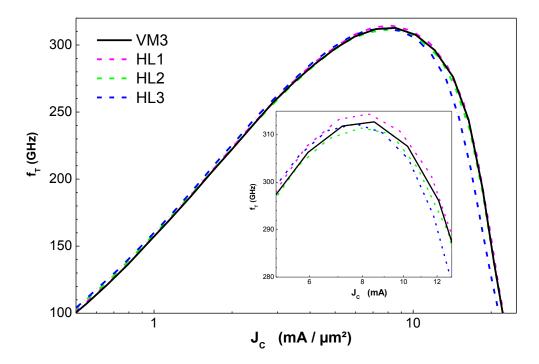

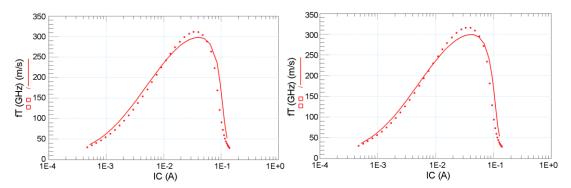

| 4.6     | 5.2 Transit frequency                                                 | 77 |

| 4.7     | Conclusion                                                            | 79 |

| Chapter | 5 Thermal modeling of state of the art multi-finger SiGe HBTs         | 80 |

| 5.1     | Introduction                                                          | 80 |

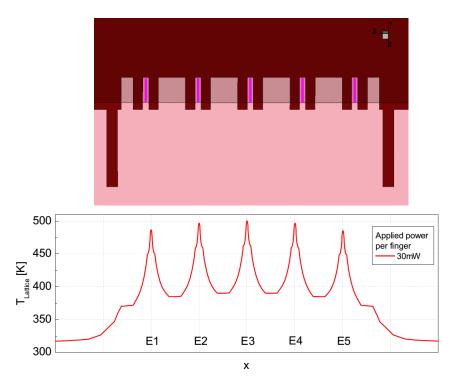

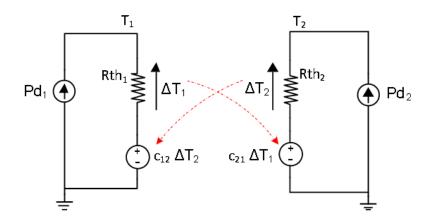

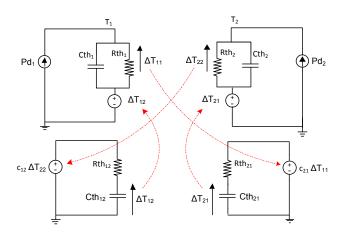

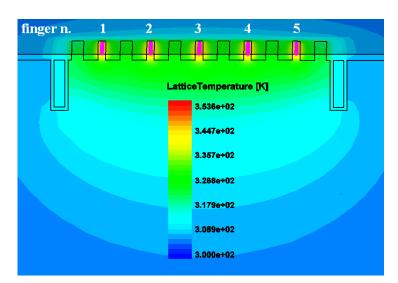

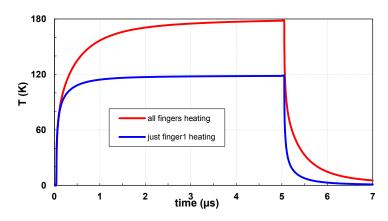

| 5.2     | Intra-device thermal interactions in multi-finger HBTs                | 80 |

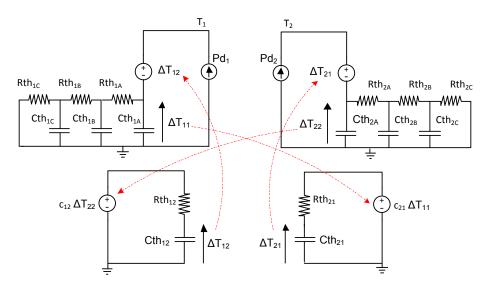

| 5.3     | The model proposed for transient intra-device thermal coupling        | 82 |

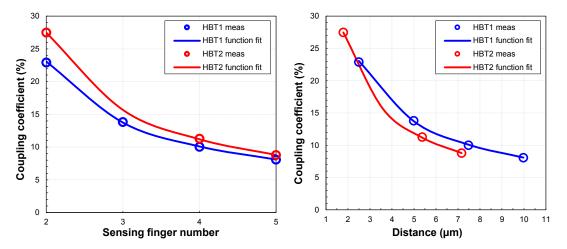

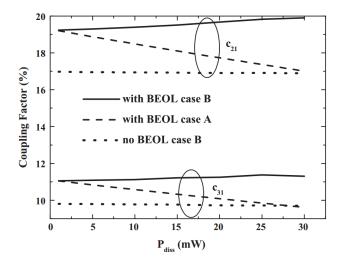

| 5.4     | The thermal coupling coefficients                                     | 84 |

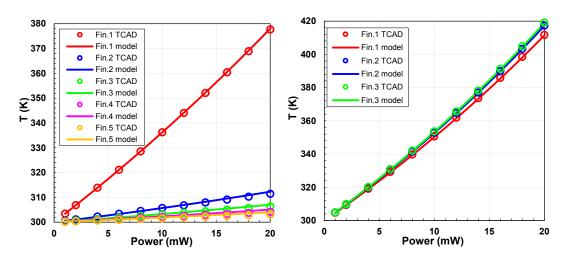

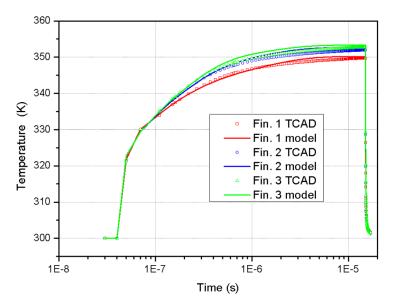

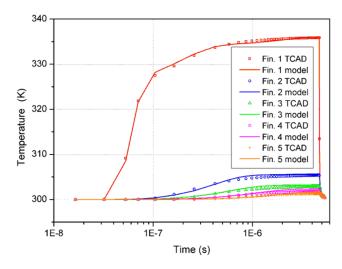

| 5.5     | Validation of the model with TCAD simulations                         | 86 |

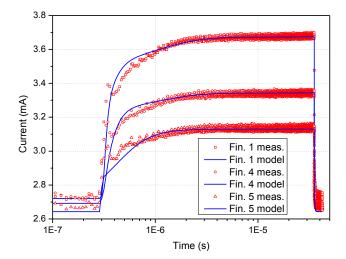

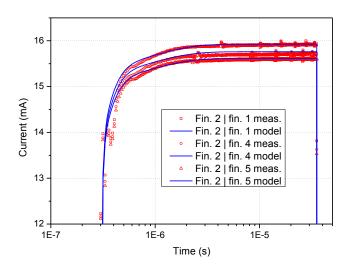

| 5.6     | Model validation with on-wafer measurements                           | 89 |

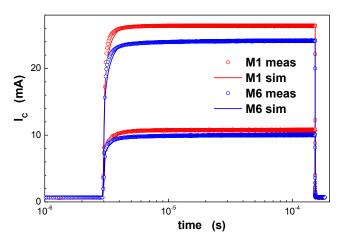

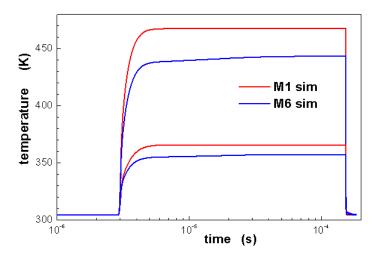

| 5.6     | 5.1 Pulsed measurements                                   |     |

|---------|-----------------------------------------------------------|-----|

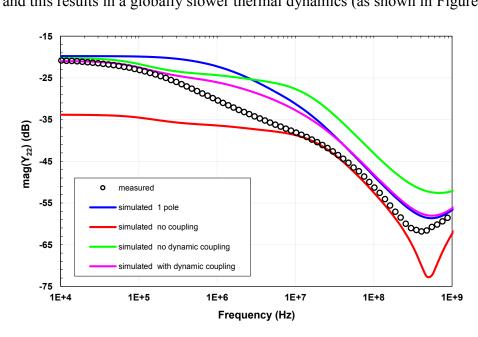

| 5.6     | 5.2 Low frequency measurements                            |     |

| 5.7     | Thermal impact of the BEOL                                |     |

| 5.8     | Conclusion                                                |     |

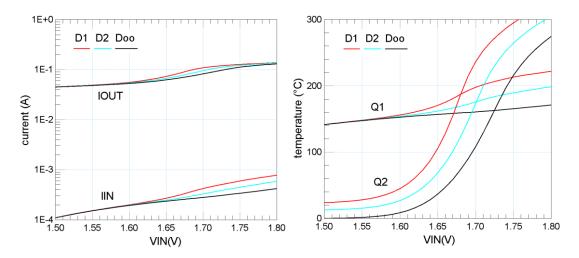

| Chapter | r 6 Modeling of thermal interactions at circuit level     |     |

| 6.1     | Introduction                                              | 97  |

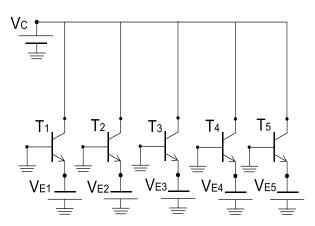

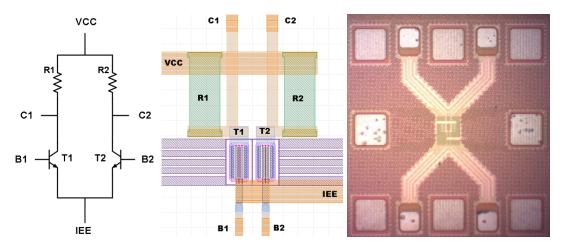

| 6.2     | Differential pair for model verification                  |     |

| 6.3     | Dedicated circuits to study inter-device thermal coupling |     |

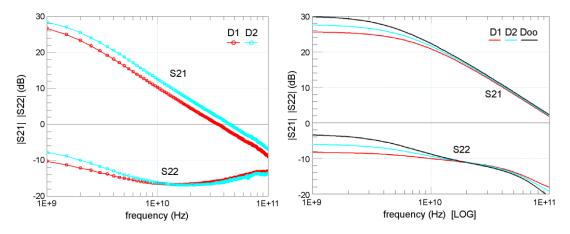

| 6.3     | 3.1 Cascode amplifier                                     |     |

| 6.3     | 3.2 Two stages Darlington amplifier                       |     |

| 6.4     | BEOL thermal impact at circuit level                      |     |

| 6.5     | Conclusion                                                | 110 |

| Summa   | ry of the work                                            |     |

| Gene    | eral conclusions                                          |     |

| Persp   | pectives                                                  |     |

| Bibliog | raphy                                                     | 116 |

| List of | publications                                              |     |

| Résumé  | é substantiel                                             |     |

## Abstract

This work is focused on the characterization of electro-thermal effects in advanced SiGe hetero-junction bipolar transistors (HBTs); two state of the art BiCMOS processes have been analyzed: the B11HFC from Infineon Technologies (130nm) and the B55 from STMicroelectronics (55nm).

Special test structures have been designed, in order to evaluate the overall electro-thermal impact of the back end of line (BEOL) in single finger and multi-finger components. A complete DC and RF electrical characterization at small and large signal, as well as the extraction of the device static and dynamic thermal parameters are performed on the proposed test structures, showing a sensible improvement of the DC and RF figures of merit when metal dummies are added upon the transistor. The thermal impact of the BEOL has been modeled and experimentally verified in the time and frequency domain and by means of 3D TCAD simulations, in which the effect of the doping profile on the thermal conductivity is analyzed and taken into account.

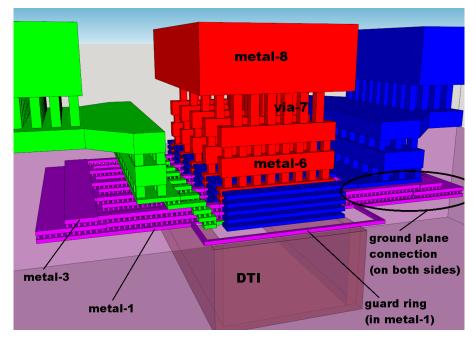

Innovative multi-finger transistor topologies are designed, which allow an improvement of the SOA specifications, thanks to a careful design of the drawn emitter area and of the deep trench isolation (DTI) enclosed area.

A compact thermal model is proposed for taking into account the mutual thermal coupling between the emitter stripes of multi-finger HBTs in dynamic operation and is validated upon dedicated pulsed measurements and TCAD simulations.

Specially designed circuit blocks have been realized and measured, in order to verify the accuracy of device compact models in electrical circuit simulators; moreover the impact on the circuit performances of mutual thermal coupling among neighboring transistors and the presence of BEOL metal dummies is evaluated and modeled.

**Keywords:** Hetero-junction bipolar transistors (HBTs), electro-thermal effects, thermal resistance, thermal capacitance, thermal impedance, back end of line (BEOL), emitter-finger layout, SOA specifications, intra device mutual thermal coupling, circuits for model verification, device to circuit interactions, thermal TCAD simulations, doping profile thermal impact, semiconductor device characterization, pulsed measurements, load-pull characterization, HiCuM model, semiconductor device modeling.

### Résumé

Ce travail de thèse présente une étude concernant la caractérisation des effets électrothermiques dans les transistors bipolaires à hétérojonction (HBT) en SiGe. Lors de ces travaux, deux procédés technologiques BiCMOS à l'état de l'art ont été analysés: le B11HFC de Infineon Technologies (130nm) et le B55 de STMicroelectronics (55nm).

Des structures de test dédiées ont étés conçues, pour évaluer l'impact électrothermique du back end of line (BEOL) de composants ayant une architecture à un ou plusieurs doigts d'émetteur. Une caractérisation complète a été effectuée en régime continu et en mode alternatif en petit et en grand signal. De plus, une extraction des paramètres thermiques statiques et dynamiques a été réalisée et présentée pour les structures de test proposées. Il est démontré que les figures de mérite DC et RF s'améliorent sensiblement en positionnant des couches de métal sur le transistor, dessinées de manière innovante et ayant pour fonction de guider le flux thermique vers l'extérieur. L'impact thermique du BEOL a été modélisé et vérifié expérimentalement dans le domaine temporel et fréquentiel et aussi grâce à des simulations 3D par éléments finis. Il est à noter que l'effet du profil de dopage sur la conductivité thermique est analysé et pris en compte.

Des topologies de transistor innovantes ont étés conçues, permettant une amélioration des spécifications de l'aire de sécurité de fonctionnement, grâce à un dessin innovant de la surface d'émetteur et du deep trench (DTI).

Un modèle compact est proposé pour simuler les effets de couplage thermique en dynamique entre les émetteurs des HBT multi-doigts; ensuite le modèle est validé avec de mesures dédiées et des simulations TCAD.

Des circuits de test ont étés conçus et mesurés, pour vérifier la précision des modèles compacts utilisés dans les simulateurs de circuits; de plus, l'impact du couplage thermique entre les transistors sur les performances des circuits a été évalué et modélisé. Finalement, l'impact du dissipateur thermique positionné sur le transistor a été étudié au niveau circuit, montrant un réel intérêt de cette approche.

**Mots-clés:** Transistors bipolaires à hétérojonction (HBTs), effets électrothermiques, résistance thermique, capacitance thermique, impédance thermique, back end of line (BEOL), layout des doigts d'émetteur, spécifications SOA, couplage thermique intra-device, circuits pour l'évaluation de modèles, interactions du composant au circuit, simulations thermiques TCAD, impact thermique du profile de dopage, caractérisation de composants à semi-conducteur, mesures pulsées, caractérisation load-pull, modèle HiCuM, modélisation de composants semi-conducteur.

## Acknowledgments

This thesis work is the result of my three years' experience as a PhD student at the IMS laboratory of Bordeaux. I would like to express my gratitude to all the people that gave me help and support in the realization of this work.

I want to thank all the members of the committee for their time and for very interesting discussions and remarks during the thesis defense. I want to thank the reviewers, Gilles Dambrine and Raymond Quéré for their valuable comments and suggestions to improve this thesis work.

I want to express my deepest gratitude to my thesis supervisor Thomas Zimmer. He has always believed in me, leaving me all the freedom I needed to manage this research project, always trusting that I would have performed well.

I would like to underline his great wisdom and experience in the field of research as well as his human qualities. Thank you very much for everything you have done for me!

I am very grateful to my supervisor Sébastien Frégonèse for his guidance and for always being available whenever I needed help or support. His deep knowledge and assistance have been essential to help me achieving the best results. It has been a real pleasure to work with you!

I would like to thank as well XMOD Technologies for providing the model cards needed in this work; thanks to Bertrand Ardouin and Christian Raya for interesting conversations about the art of compact modelling and about other pleasing topics.

Next, I want to thank STMicroelectronics and Infineon Technologies for providing the different wafers that have been measured and for their assistance in specific moments during this work.

A special thank goes to Magali De Matos and Cyril Hainaut for their precious support during all the measurement sessions.

I want to say thanks as well to Anjan Chakravorty and Suresh Balanethiram from IIT Madras for very fruitful collaborations and discussions.

At the IMS laboratory I have had the opportunity to meet many colleagues from all over the world. It was really enriching for me to work with you and learn from your experiences. Thank you for all your support, it was also cool to share with you many funny moments, I really enjoyed the time we spent together, merci!

During my stay in Bordeaux I had the chance to live in and be part of a small family, where I met lots of amazing people. Coming back from work you have helped me finding a convivial atmosphere, where I have spent many nice moments. Thank you la coloc' in rue Pierre Duhem!

A very special thank goes to the école de Karate-Do of Gradignan. It has been a real honor for me to train under the guidance of Noël Carrere, a charismatic Sensei and a man of virtue, who has taught me the technical basis and the philosophy of traditional Karate. Thanks to all the people I met at the Dojo, training with you was an amazing experience and the best way to empty my mind after hard days of work.

I have to thank as well all my friends, both here and far away, who never stopped to believe in what I was doing, always being available with their advices every time that I needed them. Thank you guys!

My family has helped me all along the way and has been the best source of inspiration and values. I am particularly grateful to my parents, who have always supported me, providing me everything that I needed. With your love and support you have made my success possible.

Finally I want to thank Sara for her immense patience and her continuous encouragement. You have helped me thinking positive, understanding my moments of craziness, despite all the difficulties due to our long distance relationship. Your caring for me has provided me the energy needed in the hardest moments.

## **Chapter 1 General introduction**

#### 1.1 THz waves and applications

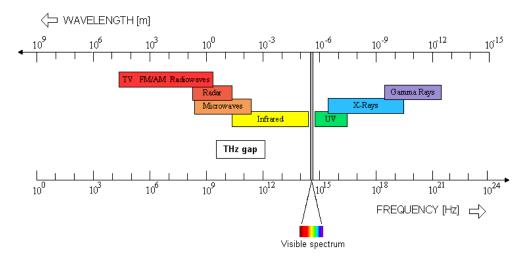

Figure 1.1: Overview of the electro-magnetic spectrum and related applications.

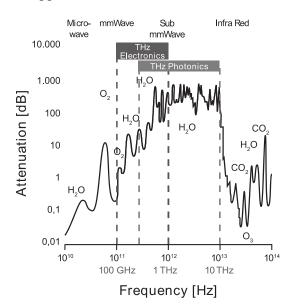

The terahertz (THz) region is a part of the electromagnetic spectrum lying between microwaves and infrared light, and is typically referred to frequencies from 300GHz up to 3THz [1], although there is no stated convention. Terahertz waves can penetrate various materials (clothing, plastic, ceramics, etc.) as well as tissues with low water content (millimeter wave dosimeters of human skin). Unlike X-rays, THz radiation is not ionizing, and, therefore, should cause no damage to live biological tissues. These characteristics allow a large number of new innovative applications [2] in the field of THz imaging and sensing for biology and medical sciences [3]–[5], non-destructive evaluation [6], [7], homeland security [8], [9]. Moreover, ultra-high-speed communication systems at THz frequencies [10], [11] can be attractive for the professional as well as the consumer market. However, with currently available and practical THz detectors and sources, measurements over distances larger than 20m are very difficult [12], besides, the attenuation level in the earth atmosphere for THz waves is higher than for the neighboring bands (see Figure 1.2). Obtaining THz signals with sufficient output power is exceptionally challenging and the lack of suitable devices to generate, detect, or properly process THz signals is the so called THz-gap. In fact, electronic sources, like transistors or multipliers, can go up to 1THz at room temperature [13], [14]; conventional laser diodes can easily generate signals at very high frequencies [15], but their use in the THz-gap region still appears impractical. For instance, free-electron lasers can generate electromagnetic radiation over a very wide range: from microwaves, through THz radiation to X-ray. However, apart from being extremely expensive, they are bulky and not suitable for consumer applications.

Figure 1.2: The atmospheric attenuation at terahertz frequencies shows the challenges of signal generation and detection for THz electronics and photonics [18].

#### 1.2 SiGe BiCMOS technology

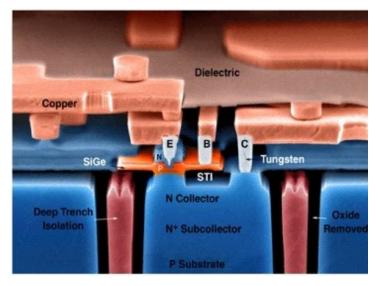

In millimeter wave applications, the III-V technologies have dominated the silicon technologies for many years. Performances of silicon technologies are still lower than GaAs, PHEMT and InP HBT HEMT. Devices fabricated in III-V technologies tend to have a superior performance compared to Si devices, due to higher carrier mobility. However, the high fabrication costs, due to expensive and small wafers and the poor reliability are not attractive for high volume applications. Moreover, due to their high thermal resistance, the integration level is much lower than for silicon. The power handling capability on Si is respectively 3.5 and 2.7 times as large as that on GaAs and InP substrates [16]. These arguments make silicon, even with lower performances, the favorable technology for large scale applications. High performance SiGe HBTs integrated in a BiCMOS technology seem to be a promising solution.

The acronym HBT stands for Heterostructure Bipolar Transistor, since in these devices one or both junctions are formed between dissimilar semiconductor materials, differently than the classical silicon based bipolar transistor, in which we talk about homojunctions (e.g. the junctions are formed by similar semiconductor materials). In fact, the silicon (Si) and the germanium (Ge) have different energy band-gaps (Eg) between the conduction and the valence band (Eg,Si=1.12eV and Eg,Ge=0.66eV at 300K). For this reason, the Si<sub>x</sub>Ge<sub>1-x</sub> alloy has a smaller Eg than pure Si, which can be adjusted by tuning the percentage of Ge. The effect of this band-gap engineering is to ensure a high current gain ( $\beta$ ), while at the same time maintaining a high base doping [17], which in turn yields a reduced base resistance and therefore improved high-frequency characteristics, needed to design performing RF circuits.

Thanks to these technological innovations, SiGe HBTs provide a higher current and voltage driving capability, higher linearity, larger transconductance  $(g_m)$ , lower 1/f noise property, excellent reliability, better device matching and superior performance in comparison to standard silicon metal oxide semiconductor field effect transistors (MOSFETs). This makes them ideal devices for microwave power applications [18], [19]. Therefore, several companies have chosen to integrate their high performance SiGe HBTs in a lower cost CMOS process (BiCMOS) which allows an improved functionality, but at the same time increases process complexity, due to the HBT integration.

Figure 1.3: SEM cross sectional view of a SiGe HBT. (http://users.ece.gatech.edu/cressler/)

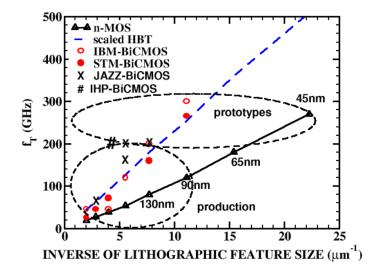

Moreover, SiGe HBT technology continues to gain momentum over CMOS process nodes, as shown in Figure 1.4; although the evolution of SiGe has been rather irregular, with missed technology nodes, a clear scaling law exists (as indicated by the trend in blue dashed line), which allows SiGe BiCMOS to retain an advantage of around 2 generations over CMOS in terms of  $f_T$  and  $f_{max}$ .

Optimized device structure along with aggressive scaling lead to comparable performance as III-V devices ( $f_T$ =300GHz,  $f_{max}$ =500GHz [20]). The Seventh Framework Programme project DOTSEVEN has reached the development of SiGe:C HBTs technologies with cut off frequencies  $f_{max}$  of around 700GHz. This continuous improvement of the device performances allows the design of circuits for RF applications having outstanding performances. A power density of 18.5mW/µm<sup>2</sup> at 1dB compression was obtained at 94GHz in [21], which can be attractive for designing power amplifiers in W-band. In [22] a record gate delay of 1.65ps is demonstrated, which represents a record for a bipolar transistor based technologies. In [23] an 820GHz transceiver chipset for terahertz active imaging applications was fabricated using IHP technology. This scenario opens the doors for terahertz (THz) applications [24] that can be mass-produced in a cost-effective way.

Figure 1.4: SiGe BiCMOS technology evolution over the inverse of the technology feature size. Comparison with CMOS technology trend [24]

#### 1.3 Thermal issues in SiGe technologies

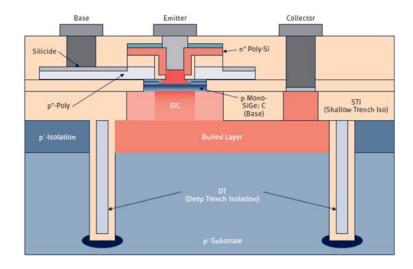

In advanced SiGe technologies, higher device performances are mainly achieved with downscaling of device dimensions and by improving the device architecture [25]-[27]. The higher is the speed of advanced HBTs, the higher are their current densities and internal electric fields, which lead to a continuous increase of the power dissipation per unit area [28]. In these technologies, structural innovation has contributed to reduce the parasitic elements and to decrease the transit time by introducing shallow trench, deep trench, and other technological process steps [29]. The key improvements, (which can have a strong impact on the electro-thermal behavior of the HBTs) are: (i) the introduction of the deep-trench isolation (DTI), which surrounds the whole device, thus helping to reduce the parasitic capacitances (see Figure 1.5); the drawback is that the DTI is mainly made of silicon dioxide (SiO<sub>2</sub>) having a very poor thermal conductivity and so its presence restricts the heat flow, resulting in larger thermal impedances  $Z_{\text{th}}$  [30]–[32]. (ii) In order to boost the transit frequency  $f_{\rm T}$ , a lot of attention is paid to carefully design the base-collector (BC) junction and the epitaxial collector. This permits to push the Kirk effect to higher current densities, leading to higher  $f_{\rm T}$  on the one hand, but on the other hand, it shifts the operating point to higher current densities [33] and thus to higher values of power dissipation. Both (i) and (ii) aspects result in a more pronounced self-heating effect, leading to higher device operating temperatures, which affect the circuit performances, the reliability and the packaging costs.

Figure 1.5: cross section of a SiGe HBT realized in the B7HF200 technology

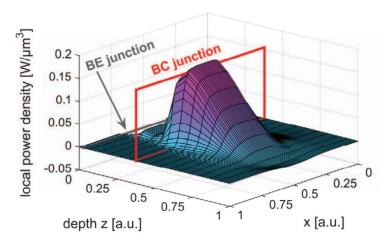

In conventional approaches for the study of thermal phenomena arising in state of the art SiGe HBTs, it is assumed that the main part of the power dissipation occurs at the base-collector space charge region, due to the intense electric fields and the high current densities which are present in this region of the device [34]. In Figure 1.6 it is depicted the distributed power density obtained from simulation using a 2-D hydrodynamic model [34].

Figure 1.6: local power density dissipated in correspondence of the BC space charge region for a HBT in Infineon Technology (effective emitter area  $0.13 \times 2.73 \mu m^2$ ). The results are obtained from 2-D hydrodynamic model simulation [27].

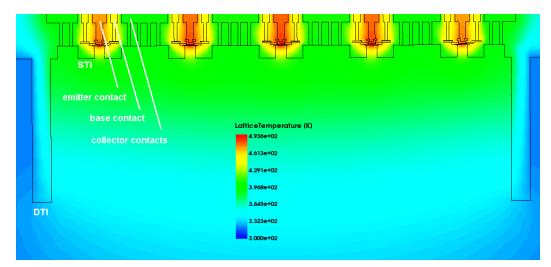

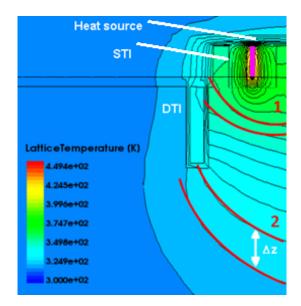

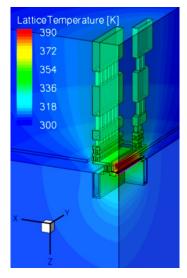

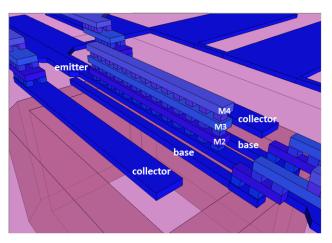

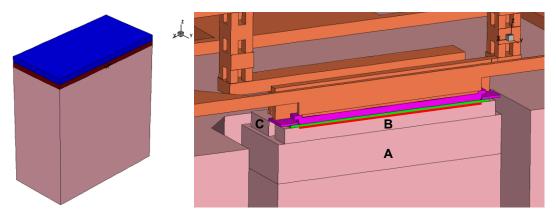

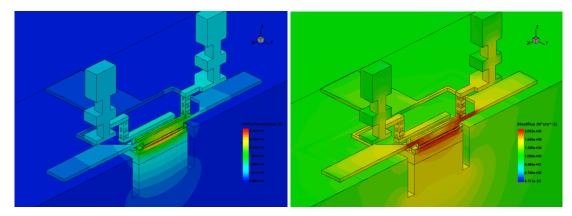

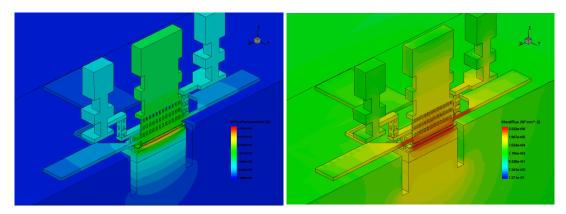

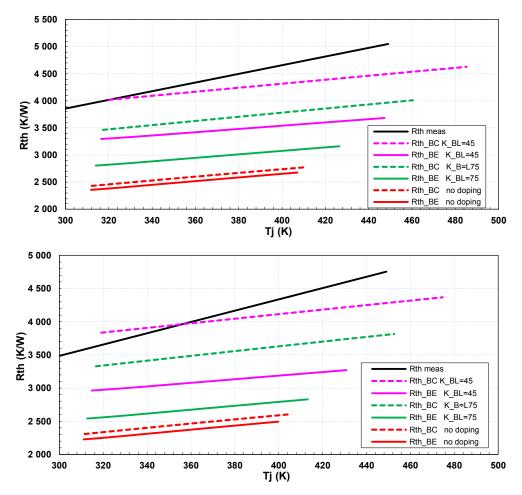

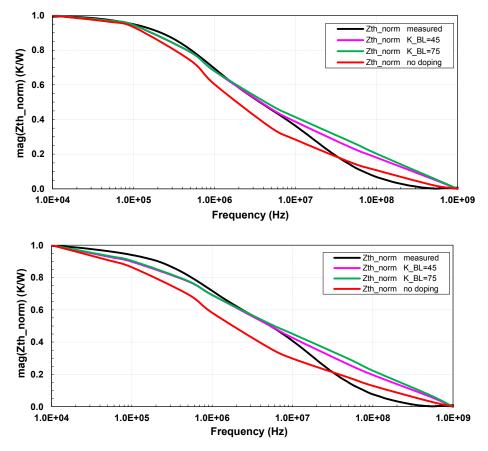

Due to the complex architecture of state of the art components, which make use of doped materials, passivation layers and metallization, having very different thermal properties, the study and modelling of the thermal diffusion mechanism within the transistor is a challenging topic of increasing interest. In Figure 1.7 is shown the temperature profile simulated in Sentaurus TCAD for a five fingers transistor in ST B55 technology, when planar heat sources are considered at the BC junctions: it is clear how the presence of

different materials within the HBT yields thermal gradients; these temperature profiles propagate in different ways, according to the thermal conductivity of the different materials and thus an estimation of the temperature reached by the transistor requires a deep insight into the physics and the geometry of the component.

Figure 1.7: temperature profile simulated in Sentaurus TCAD for a five fingers SiGe HBT realized in ST B55 technology. The five heat sources are placed at the BC junction and the 3D transistor structure contains the different layers till the contacts at metal-1 level.

The determination of the temperature reached by the transistor is mandatory from a modelling point of view, since it impacts in a considerable way its electric behavior. When an HBT handles high levels of power dissipation, thermal instabilities can occur due to the positive feedback between the collector current and the device temperature [35], [36]. In fact, HBTs can be considered unconditionally stable when driven by a constant base current, but when biased with a constant base emitter voltage, the device shows a positive electro-thermal feedback; in this situation, in fact, the self-heating causes an increase of the collector current, which will determine an increase of the power dissipation, thus creating a positive feedback loop. This situation can cause the onset of the flyback behavior in the output characteristics, thus limiting the safe operating area (SOA) of the transistor in the region at high currents [37].

To mitigate the negative effects of self-heating, multifinger architectures can be used, which can have an increased power handling capability. These devices consist of multiple transistors in parallel, placed within the same DTI (as visible in Figure 1.7). Due to the close proximity of the different fingers, thermal coupling can cause the central emitter to reach the highest temperature and thus drive more current than the other emitters, starting the thermal instability mechanisms. This situation can lead to an uneven distribution of the currents among the different emitters, till reaching the situation where one finger tends to conduct the whole current (current hogging effect) [38], [39]. This unwanted focalization of the current in a single finger can lead to the generation of hot spots within the transistor and may eventually cause the device failure.

To overcome these thermal instabilities, properly designed ballasting resistors can be added at the emitter nodes and can limit the rapid current increase and the current hogging phenomenon [40], [41].

#### 1.4 This work

#### 1.4.1 Motivation

As underlined in the previous section, the thermal issue is one of the key factors limiting the performance and reliability of the devices and integrated circuits realized in SiGe technology.

For instance, it has been discussed how SiGe HBTs realized in multifinger architecture can suffer from thermal instabilities due to current hogging effect, which can eventually lead to device failure; one of the possible approaches to improve the thermal stability in these components, is to use ballasting resistors [41], [42], but this solution leads to degradation of the output power and of the power-added efficiency (PAE) of the transistor, so alternative transistor topologies can be helpful to extend the safe operating limits of the transistor without any loss in performance.

In general, due to the strong relationship between electrical and thermal effects in SiGe HBTs, an efficient characterization of the device is essential, in order to generate trustable compact models and thus allow precise electrical simulations for circuit designers. Consequently, a realistic modeling must provide an electrical representation, but also a precise and physics based reproduction of the thermal characteristics of the HBTs, which can be also helpful for thermal stability and reliability analysis. Besides, due to the intrinsic nonlinearity of the transistor, third-order intermodulation products, generated near its thermal time constant, can trigger low frequency variations of the junction temperature, which can affect the electrical behavior of the component [43], so a precise characterization of the thermal impedance is necessary and can help in the design of predistortion linearizers [44]. It must be taken into account, though, that external parasitic elements, like the metallization in the BEOL, can impact to a considerable extent the thermal impedance of the transistor [45] and so its impact should be analyzed and modeled.

Thermal interactions can take place not only at device level; in fact, transistors that are placed in close proximity can experience mutual thermal coupling [46], [47]. These effects have to be characterized to provide more accurate electrical simulations during the circuit design phase.

#### 1.4.2 Organization

This thesis work is organized as follows:

#### Chapter 2

This chapter will be focused on the description of the measurement techniques adopted for the characterization of self-heating related effects in state of the art SiGe HBT technologies. The methodologies to extract the  $R_{th}$  and  $C_{th}$  are presented and the impact of thermal memory effect is discussed, with large signal two tones simulations, showing also the limitations in the use of a single pole thermal network.

#### Chapter 3

In this chapter it is presented an analysis of the impact of the BEOL on the electrical and thermal properties of a state-of the-art SiGe HBT technology from Infineon (B11HFC); dedicated transistor structures are designed and the results of a complete DC and RF electrical characterization at small and large signal, as well as a thermal characterization are reported. A compact model is also proposed, to take into account the impact of the BEOL metallization on the thermal impedance and is validated with dedicated measurements in the time and frequency domain. Finally the variation of the thermal behavior with the doping concentration is analyzed by means of TCAD simulations and is compared to the experimental data obtained from measurements.

#### Chapter 4

In this chapter a set of alternative transistor topologies is presented, which can ensure an improved electro-thermal behavior and better SOA specifications; the test structures contain a multifinger HBT from the ST Microelectronics B55 process. The different methodologies proposed to yield better performances are: (i) exploiting the metal dummies in the BEOL, (ii) modifying the layout of the drawn emitter window, (iii) increasing the DTI enclosed area. For all the proposed test structures a complete DC and AC characterization, as well as an extraction of the  $R_{th}$  and  $Z_{th}$  is proposed.

#### Chapter 5

This chapter will focus on the mutual thermal coupling in multi-finger transistors in dynamic operation. A physics based approach is proposed to study and model the thermal coupling effect between the different emitter fingers and is validated upon TCAD simulations and dedicated on-wafer pulsed measurements. Then, with the help of TCAD simulations, the impact of the BEOL on the thermal dynamics has been analyzed, and a new method to evaluate the thermal coupling coefficients under the real operating conditions of the transistor is proposed.

#### Chapter 6

This chapter is dedicated to the study of thermal interactions at circuit level in different circuit topologies. The impact of thermal coupling is modeled for a differential pair and two versions of a cascode amplifier, in which different distances among the transistors are used. The calibrated thermal coupling model is used to simulate the impact of distance in a two stages Darlington amplifier. Moreover the R<sub>th</sub> variation caused by the BEOL is modeled and its impact at circuit level is estimated for the VM multifinger transistors presented in Chapter 4.

## **Chapter 2 Device characterization in SiGe HBT technologies**

#### 2.1 Introduction

As already presented in Chapter 1, state of the art SiGe technologies are affected by serious thermal issues that can degrade the performances of the active components and eventually lead to their failure. A deep insight into the mechanisms of heat generation and diffusion at device level, as well as an accurate characterization and modelling of these phenomena is mandatory in order to allow a realistic circuit simulation during the design phase, but also to improve the performances and push the limits of a given technology.

This chapter will be focused on the description of the measurement techniques adopted for the characterization of self-heating related effects in state of the art SiGe HBT technologies. First the effect of self-heating on the electrical behavior of the transistor is shown by means of simulations for state of the art technology, secondly an overview of the methodologies to extract the static and dynamic thermal properties of the transistors is presented and finally the impact of thermal memory effect is discussed, with large signal two tones simulations, showing also the limitations in the use of a single pole thermal network.

#### 2.2 Compact modeling: the HiCuM model

The main goal of compact modeling is to enable circuit design. A compact model should be a physics-based mathematical description of the electrical behavior of a device for use in a circuit simulator. There is a large demand for fast and reliable compact models that are accurate for a great variety of technologies. A trustable compact model provides high accuracy over a wide electrical (and temperature) range, geometrically scalable parameter calculation, numerical stability and fast execution time.

A compact model determines the specific electrical behavior of the component, while meeting the criteria of robustness, convergence of the simulator and simulation time. It is the key element on which the circuit designer can relay and, therefore, the model should provide an accurate picture of physical phenomenon that may affect the behavior of a circuit in the useful operating area of the transistor. Nowadays the main models for silicon-based bipolar transistors are: Gummel-Poon (SGP), VBIC, MEXTRAM, and HiCuM, which are physics based models.

In this work the HiCuM/L2 model is considered for all the electrical device simulations, which represents the most widespread model for the design of circuits using SiGe HBTs.

The HiCuM (High-Current Model) [48] is a scalable physics-based compact model for bipolar transistors, taking into account the high current effects which are significant for

certain high speed transistor applications. The first version was introduced in 1986 by H.M. Rein and M. Schröter and it is now a Compact Model Council (CMC) standard model [49] and integrated in a wide range of simulators like ADS, ELDO, SPECTRE, HSPICE, GoldenGate, etc. HiCuM is based on an extended and generalized integral charge-control relation (GICCR). However, in contrast to the (original) Gummel-Poon model, in HiCuM the GICCR concept is applied without simplifications and additional fitting parameters (such as the Early voltages). Therefore it allows a reliable design and circuit optimization.

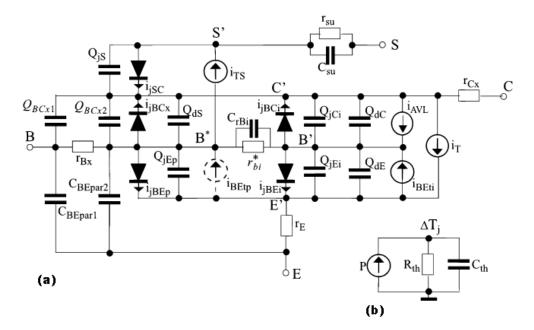

The HiCuM large signal equivalent circuit is shown in Figure 2.1. The internal transistor has the four nodes E', B', B\* and C'. The internal circuit consists of the diode current  $i_{JBEi}$  and the depletion charge  $Q_{JEi}$  of the base-emitter (BE) junction, the diode current  $i_{JBCi}$ and the depletion charge  $Q_{JCi}$  of the base-collector (BC) junction, and the voltage controlled transfer current source  $i_T$ . Furthermore, the minority charge is represented by its forward and reverse component,  $Q_f$  and  $Q_r$ . In addition, breakdown in the BC space charge region is taken into account by the avalanche current source,  $i_{AVL}$ , and possible tunneling through the BE space charge region is represented by  $i_{BEti}$ . By comparing with the equivalent circuit of SGP, there are two additional nodes named B\* and S' in HiCuM. The node B\* has been added to separate the internal base resistance  $r_{Bi}$  (bias dependent) from the external component  $r_{Bx}$ . The internal substrate node S' is connected to the substrate network with the capacitance  $C_{Su}$  and the resistance  $r_{Su}$ . Moreover, an emitter-base isolation capacitance  $C_{BEpar}$  as well as a base-collector oxide capacitance  $C_{BCpar}$  is taken into account. More information about this compact model can be found in [48].

Figure 2.1: (a) Large-signal HICUM/L2 equivalent circuit. (b) Thermal network used for self-heating calculation (figure taken from [44]).

Device characterization in SiGe HBT technologies

#### 2.3 Modeling of device self-heating in compact simulators

Heat is generated in all active areas of a device which results in an increase of the device temperature. Self-heating leads to a shift in device characteristics and can be described with an equivalent electrical circuit. In fact, as shown in Figure 2.1, in the HiCuM/L2 compact model, a dedicated sub-circuit allows the calculation of the increase of the junction temperature ( $\Delta T_j$ ); it consists of one thermal resistance  $R_{th}$  and one thermal capacitance  $C_{th}$  in parallel, forming a single-pole circuit, which represents the simplest form of model for calculating the junction temperature evolution. The units for  $R_{th}$  and  $C_{th}$  are K/W and Ws/K, respectively. The voltage node in the thermal equivalent network corresponds to the temperature rise  $\Delta T$  experienced by the transistor:

$$\Delta T = T_j - T_{amb} = P_{diss} R_{th}$$

Eq. 2.1

where  $T_j$  and  $T_{amb}$  are the junction and ambient temperatures respectively. The current source corresponds to the dissipated power  $P_{diss}$  and represents the amount of heat that is generated by the device. In HiCuM/L2 the flag FLSH allows three different approximations for the calculation of  $P_{diss}$  [48]:

- If FLSH=0 the self-heating effect is not taken into account and the device temperature is constantly equal to the ambient temperature  $T_{amb}$

- If FLSH=1, only the most relevant dissipative elements are considered for the calculation of *P*<sub>diss</sub>, as follows:

$$P_{diss} = |I_T V_{C'E'}| + |I_{AVL} V_{B'C'}|$$

Eq. 2.2

• If FLSH=2, *P*<sub>diss</sub> is calculated from all relevant dissipative elements in the equivalent circuit:

$$P_{diss} = \left| I_T V_{C'E'} \right| + \left| I_{AVL} V_{B'C'} \right| + \sum \frac{\left| \Delta V_n^2 \right|}{R_n} + \left| I_{TS} V_{B^*S} \right|$$

Eq. 2.3

with  $R_n = \{r_{Bi}, r_{Bx}, r_E, r_{Cx}\}$  as non-zero series resistances and  $\Delta V_n$  as the corresponding voltage drop across those resistances.

The thermal network and the electrical part of the transistor model are solved together for each DC and transient operation. The temperature dependent model parameters are calculated using the voltage at the temperature node. Furthermore (if the internal  $R_{th}$  and  $C_{th}$  are deactivated), the thermal node can be connected to more complex external thermal networks, in order to allow a more accurate simulations of specific thermal phenomena. For instance this option is later used in this work to consider the heat flow in the metallization upon the transistor or to account for intra-device thermal coupling within multifinger HBTs or to simulate inter-device thermal interactions at circuit level.

#### 2.4 Self-heating effect on the device DC and AC characteristics

A detailed description of the different regions of operation of SiGe HBTs can be widely find in literature [17], [48], [50] and is not reported here. The attention will be focused on how the self-heating affects the electrical behavior.

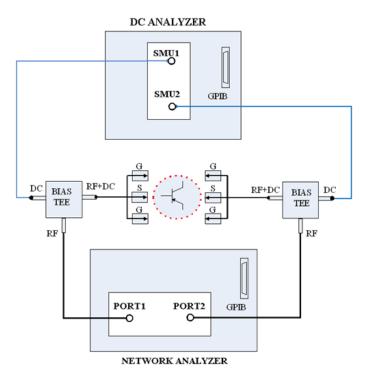

Measurements for device characterization are normally conducted on-wafer, thanks to the use of automatic or manual probe stations; the transistor test structures are normally realized in common emitter configuration (a GSG arrangement for the pads is preferred to avoid possible oscillations and allow RF measurements): the base and the collector are connected to the source and monitor units (SMU) of a semiconductor parameter analyzer, which applies and measures voltages and currents directly on the transistor (see Figure 2.2). The parameter analyzer is connected via GPIB to a PC, and the desired voltage or current sweeps are controlled from a user interface allowing to collect and handle the measured data.

Figure 2.2: block diagram showing a typical measurement setup for the DC and AC characterization of active components on-wafer

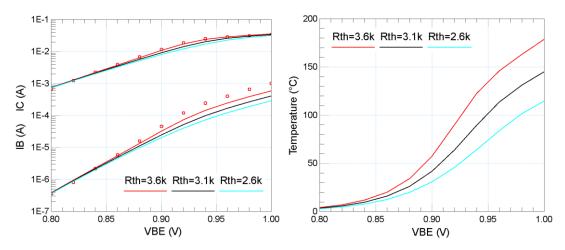

The measurement of the I(V) current-voltage relationships is the most basic form for a DC characterization of the transistors: in Figure 2.3 (on the right) is reported the Gummel plot measured on a HBT realized in the Infineon B11HFC process ( $W_{ExLE}=0.22x5\mu m^2$ ) for  $V_{CE}=1.5V$  when the transistor is driven by a constant  $V_{BE}$ . In this biasing condition the collector current I<sub>C</sub> increases with increasing temperature [36]; since the temperature reached by the component T<sub>j</sub> is directly proportional to the power dissipated P<sub>diss</sub> (according to Eq. 2.1) and the P<sub>diss</sub> is proportional to current flowing into the device

#### *Chapter 2* Device characterization in SiGe HBT technologies

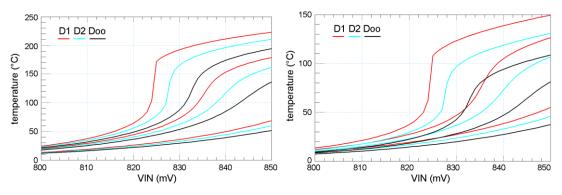

(following Eq. 2.2 or Eq. 2.3), it results that for this biasing condition, the  $I_C$  will experience an uncontrolled increase, as the P<sub>diss</sub> increases (thermal runaway) [38], which can eventually lead to instability and device failure. In Figure 2.3 the measurements are also compared to the results from simulation using the HiCuM/L2 compact model, using a model card that has an Rth value of 3600K/W (red line). Two additional simulation results are added, using two lower values of the thermal resistance Rth: 3100K/W and 2600K/W, in order to evaluate the differences that can be expected in the electrical characteristics when the effects of self-heating are lower. It can be seen that, from around 850mV on and as the Rth is set to a smaller value, the simulated IB decreases, whereas for what concerns the simulated I<sub>C</sub>, the region where the maximum deviation is obtained is for  $V_{BE}$ =925mV. This can appear strange, since observing the temperature increase predicted by the compact model, (on the right in Figure 2.3) it is clear that the temperature difference among the 3 different model cards continues to increase for V<sub>BE</sub>>925mV. It must be taken into account, in fact, that for higher values of  $V_{BE}$ , the increase of  $I_C$  is caused by a combination of other effects (mainly impact ionization and avalanche multiplication, and in particular the feedback role played by the emitter resistance) rather than solely by self-heating and thus the difference among the I<sub>C</sub> obtained for the three R<sub>th</sub> considered starts to decrease.

Figure 2.3: (left) forward Gummel plot at constant  $V_{CE}$ =1.5V for an Infineon B11HFC CBEBC HBT with  $A_E$ =0.22x5 $\mu$ m<sup>2</sup>: comparison between measurements (symbols) and compact model simulations (solid lines) for different values of the R<sub>th</sub>. (right) corresponding temperature increase simulated in HiCuM

Figure 2.4: simulated output curves for an Infineon B11HFC CBEBC HBT with  $A_E=0.22x5\mu m^2$ : (left) the forced  $V_{BE}$  ranges from 0.9V to 1V; (right) the forced  $I_B$  ranges from 60 $\mu$ A to 600 $\mu$ A. Different values of the  $R_{th}$  are used in compact model simulations.

The effect of the positive electro-thermal feedback when forcing the device at constant  $V_{BE}$  is also visible on the output curves in Figure 2.4 (left), and the same considerations made for the Gummel plot still hold: among the different R<sub>th</sub> considered, the bias condition at which the highest variation of I<sub>C</sub> is observed is for V<sub>BE</sub>=900mV; in fact for V<sub>BE</sub>=850mV the self-heating effects are less evident, since the temperature reached by the component is lower, whereas for V<sub>BE</sub>=950mV the increase of I<sub>C</sub> is caused by a combination of other effects, as previously discussed and thus the difference among the results obtained for the three R<sub>th</sub> considered is lower.

On the right in Figure 2.4 another situation is presented, corresponding to the case where the transistor is driven by a current injected in the base terminal; in this scenario, instead, the self-heating causes the  $I_C$  current to drop when the high power dissipation region is reached and so the device is intrinsically stable.

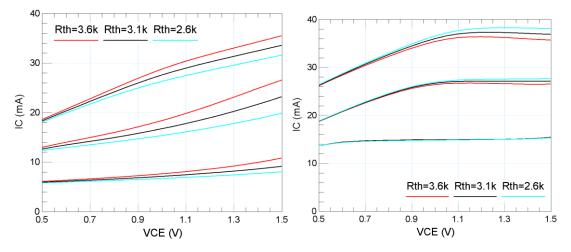

For what concerns the AC characterization, one of the main figures of merit that is used for comparing the performances of a given transistor is the unity gain cut-off frequency (*f<sub>T</sub>*), which is defined as the frequency where the extrapolated small-signal current gain  $\beta_F$  equals one (Figure 2.5):

$$|\beta_{F}(f = f_{T})| = \left|\frac{dI_{C}(f_{T})}{dI_{B}(f_{T})}\right|_{V_{CE}} = |H_{21}(f_{T})| = 1$$

Eq. 2.4

$$f_{T} = f_{meas} |H_{21}(f_{meas})| = \frac{f_{meas}}{\Im(Y_{11}/Y_{21})}$$

Eq. 2.5

where  $f_{meas}$  has to be chosen as a frequency at which  $\beta_F$  is rolling-off at a slope of -20dB/dec, whereas in Eq. 2.5 are reported two possible expressions to extract  $f_T$ . Another commonly used figure of merit is the  $f_{max}$ , defined as the frequency at which the unilateral power gain U (or Mason's invariant gain) becomes unity (Figure 2.5).

#### *Chapter 2* Device characterization in SiGe HBT technologies

$$|U(f = f_{\max})| = \frac{|Y_{21} - Y_{12}|}{4(\Re(Y_{11})\Re(Y_{22}) - \Re(Y_{12})\Re(Y_{21}))} = 1$$

Eq. 2.6

$$f_{\max} = f_{meas}\sqrt{|U(f_{meas})|}$$

Eq. 2.7

Eq. 2.7 is a commonly used expression to extract  $f_{max}$  based on the definition of U.

Figure 2.5: illustration of the small-signal current gain  $\beta_F$  (left) and Mason's gain (right) vs. frequency; the  $f_T$  and  $f_{max}$  are extrapolated as the frequencies at which  $\beta_F$  and U respectively reach 0dB.

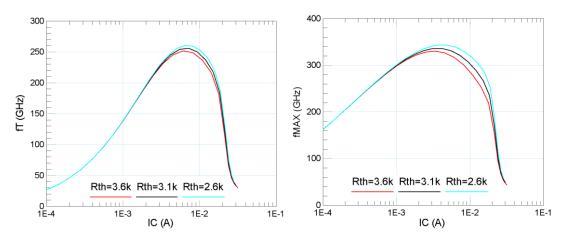

Figure 2.6: simulated  $f_T$  (left) and  $f_{max}$  (right) plotted versus  $I_C$  for a constant  $V_{CE}$  of 1.5V; different values of  $R_{th}$  are used in compact model simulations.

In Figure 2.6 are shown the simulated  $f_T$  and  $f_{max}$  as function of the I<sub>C</sub> for the same transistor and the same values of R<sub>th</sub> discussed above; it can be noticed that varying the R<sub>th</sub> (and thus changing the amount of self-heating effect within the transistor) impacts the  $f_T$  and  $f_{max}$  in the region around the peak and after (more precisely, in the I<sub>C</sub> range that has been observed to vary with the R<sub>th</sub> in Figure 2.3).

#### 2.5 Extraction of the R<sub>th</sub>

The extraction of the  $R_{th}$  is one of the long lasting challenges encountered for device characterization and several different methodologies have been proposed in literature in the last years [51]–[55]. In general, these methods consist in performing measurements at different chuck temperatures, in order to determine the thermal dependence of the electrical parameter which will be used as thermometer.

The  $R_{th}$  extraction procedure used in this work is based on the theory given in [52] and the necessary steps are reported for the case of a five fingers transistor realized in ST Microelectronics B55 process (0.18x5µm<sup>2</sup>).

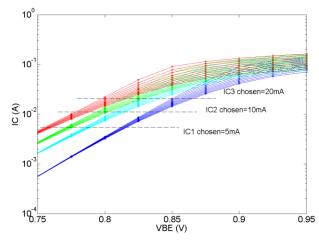

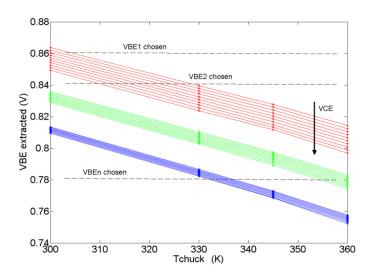

This procedure uses the base-emitter voltage as the temperature sensitive parameter and consists in measuring the  $V_{BE}$  as function of the ambient temperature  $T_{amb}$  for constant collector currents  $I_C$  and different  $V_{CE}$ ; the approach used here is to measure  $I_C$  for swept  $V_{BE}$ , as done for Gummel plots and to determine  $V_{BE}$  as function of  $I_C$  by interpolation. In Figure 2.7 are shown the Gummel plots for different values of  $V_{CE}$  from 1V to 1.24V and for 4 values of the chuck temperature  $T_{chuck}$ , ranging from 300K to 380K. Three different values of  $I_C$  (5mA, 10mA and 20mA) are chosen for the extrapolation, and the related  $V_{BE}$  extracted are then plotted as function of the chuck temperature, as reported in Figure 2.8; this calibration curve shows a very linear relationship between  $V_{BE}$  and  $T_{chuck}$ .

Figure 2.7: Gummel plot measured on a five fingers HBT in ST B55 technology; the  $V_{CE}$  ranges from 1V to 1.24V. The measurements are performed at different chuck temperature ranging from 300K (blue) to 380K (red). The values of I<sub>C</sub> chosen for the R<sub>th</sub> extraction are also shown.

Figure 2.8:  $V_{BE}$  values extracted from the Gummel plot for the 3 values of  $I_C$  fixed (blue=5mA, green=10mA, red=20mA). The  $V_{BE}$  are plotted versus  $T_{chuck}$  for the different values of  $V_{CE}$  considered. The values of  $V_{BE}$  fixed to extract the corresponding  $T_{chuck}$  are also shown in the plot

#### *Chapter 2* Device characterization in SiGe HBT technologies

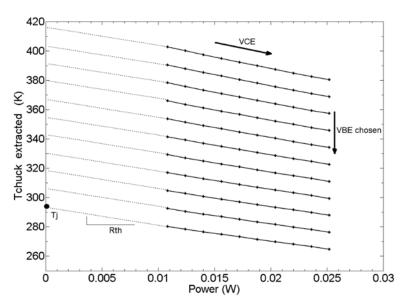

As can be seen in Figure 2.8, for small values of  $I_C$  (e.g. at  $I_C$  chosen=5mA colored in blue), where the power dissipation and the thus self-heating is negligible, the extracted  $V_{BE}$  does not vary too much for the different  $V_{CE}$  values considered. However, if  $I_C$  is increased to 20mA (red curves), we observe that the  $V_{BE}$  values extracted start to vary if  $V_{CE}$  is swept; for this value of current,  $P_{diss}$  is significantly higher, and thus self-heating can be considered responsible for the change of  $V_{BE}$  with  $V_{CE}$  varying. Next, different values of  $V_{BE}$  (from  $V_{BE1}$  to  $V_{BEn}$ ) are chosen and the corresponding  $T_{chuck}$  are extracted by interpolation. These points correspond to the determination of the ambient temperature for which the transistor exhibits a certain  $V_{BE}$  (which has been chosen) at an  $I_C$  of 20mA. These chuck temperatures are now plotted versus their corresponding dissipated power dissipation (which is approximated here as  $P_{diss}=I_C V_{CE}$ ).

Figure 2.9: chuck temperatures extracted for the values of  $V_{BE}$  which have been fixed, plotted as function of the corresponding  $P_{diss}$ . This plot allows to extract, for each  $V_{BE}$  fixed, the corresponding values of the  $T_j$  and  $R_{th}$

Since the junction temperature  $T_j$  can be expressed as the sum of the ambient temperature and the temperature increase in the device caused by self-heating:

$$T_j = R_{th} P_{diss} + T_{chuck}$$

Eq. 2.8

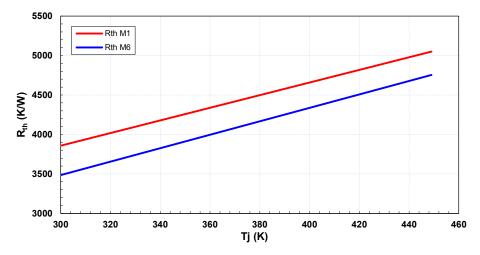

it follows that  $T_j$  can be determined by extrapolation of the  $T_{chuck}$  at  $P_{diss}=0$ , as marked in Figure 2.9; moreover the  $R_{th}$  can be estimated as the slope of the  $T_{chuck}(P_{diss})$  curve. Repeating this procedure for all the values of  $V_{BE}$  which have been fixed leads to the results in Figure 2.10 (left), which represent the extracted  $R_{th}$  as function of the junction temperature  $T_j$ .

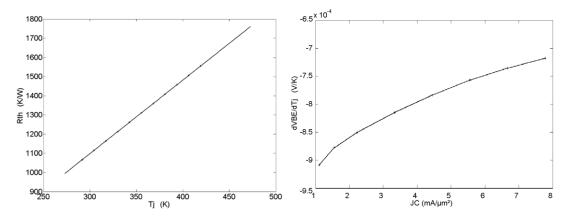

Since the  $T_j$  is extracted at fixed I<sub>C</sub>, for every values of  $V_{BE}$ , the  $dV_{BE}/dT_j$  can be also determined using this technique (Figure 2.10 (left); this parameter characterizes the technology and does not depend on the transistor layout.

Figure 2.10: (left)  $R_{th}$  extracted as function of the  $T_j$  using the method described. (right)  $dV_{BE}/dT_j$  measured for the ST B55 technology.

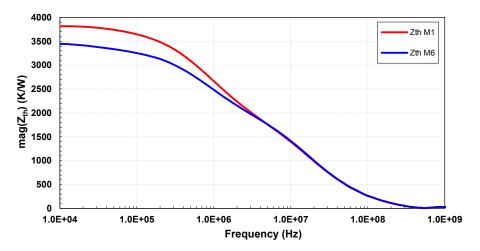

#### 2.6 Extraction of the Z<sub>th</sub>

The characterization of dynamic electro-thermal self-heating inside SiGe HBTs remains an essential task for model developers in order to determine the device operating temperature in practical applications where a signal having a certain frequency bandwidth is fed at the input of the transistor. The dynamic behavior can be described by the thermal impedance  $Z_{th}$  which can be seen as the parallel of R<sub>th</sub> and C<sub>th</sub> in the thermal subcircuit in Figure 2.1b.

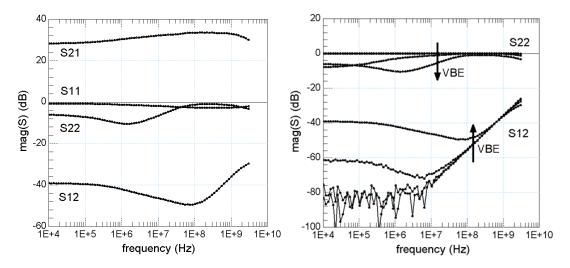

The device thermal response ranges from about few kilohertz to about 200MHz in SiGe HBTs [56], hence,  $Z_{th}$  is limited to low frequencies where it can be extracted. Low frequency S-parameter measurements are suitable since it is a relatively simple and precise measurement procedure. Several approaches have been presented in literature to provide an expression to determine the Z<sub>th</sub> from dedicated measurements at low frequency. For example, generalized formulations for thermal impedance from y-parameters are proposed by Rinaldi [57] through a rigorous mathematical treatment. Also dynamic characterization of thermal effect, based on h-parameters has been proposed in [58], [59]. The dispersive phenomenon presented by the device at low frequencies is caused by dynamic self-heating effects: performing S-parameter measurements it is possible to observe a certain deviation of the  $S_{12}$  and  $S_{22}$  in the low frequency range; in Figure 2.11 (left) are reported the magnitude of the S-parameters measured in the frequency range 10kHz-3GHz for the bias point V<sub>BE</sub>=0.9V and V<sub>CE</sub>=1.25V at which a significant amount of self-heating can be expected. The measurements are performed on the low-frequency vector network analyzer (VNA) Agilent E5061B (5Hz-3GHz), making use of bias tees particularly developed to cover this specific frequency range. The VNA was calibrated on-wafer using SOLT method. The measured results were de-embedded using Open and Short test structures.

#### *Chapter 2* Device characterization in SiGe HBT technologies

The measurements refer to a five fingers HBT fabricated in ST Microelectronics B55 technology ( $0.18x5\mu$ m<sup>2</sup>): it is possible to notice that the S<sub>12</sub> and S<sub>22</sub> exhibit the largest variation among the four S-parameters. If we analyze these parameters for different bias conditions, it is possible to identify the frequency range where dynamic self-heating affects is predominant; in Figure 2.11 (right) are plotted the S<sub>12</sub> and S<sub>22</sub> for different V<sub>BE</sub> ranging from 0.75V to 0.9V: it is shown that as V<sub>BE</sub> increases (and thus self-heating becomes more pronounced) it is possible to identify the frequency range till around 200MHz as the region where the S-parameters start to deviate. At these low frequencies, in fact, the junction temperature is able to follow the variations of power dissipation, thus affecting the S-parameters, whereas at higher frequencies, the junction temperature is not able to follow the evolution of power dissipation and thus just DC self-heating occurs, as will be also detailed in the next paragraph. The frequency that marks this difference in the thermal behavior will be referred to as thermal cutoff frequency. For the extraction of the Z<sub>th</sub> the S-parameters are converted to Y-parameters, as will be described below.

Figure 2.11: (left) measured low frequency S-parameters at  $V_{BE}$ =0.9V and  $V_{CE}$ =1.25V for the five fingers HBT from ST B55 technology. (right) S<sub>12</sub> and S<sub>22</sub> for  $V_{CE}$ =1.25V and  $V_{BE}$  ranging from 0.75V to 0.9V

#### 2.6.1 Theoretical formulation

Collector current  $I_C$  and base current  $I_B$  are functions of the three independent variables: (i) the base-emitter voltage  $V_{BE}$  (ii) the collector-emitter voltage  $V_{CE}$  and (iii) the junction temperature T. To generalize the following equations  $V_{BE}$ ,  $V_{CE}$ ,  $I_B$  and  $I_C$  are replaced by  $V_1$ ,  $V_2$ ,  $I_1$  and  $I_2$ , respectively:

$$I_{1} = f_{1}(V_{1}, V_{2}, T)$$

$$I_{2} = f_{2}(V_{1}, V_{2}, T)$$

Eq. 2.9

A linearization valid for small signal excitations at a constant bias condition leads to:

$$i_1 = y_{11}v_1 + y_{12}v_2$$

$i_2 = y_{21}v_1 + y_{22}v_2$

Eq. 2.10

where each y-parameter is defined as:

$$y_{mn} = \frac{\partial f_m}{\partial V_n} \qquad m = 1; 2 \quad n = 1; 2. \qquad \text{Eq. 2.11}$$

Here, index 1 and 2 indicate the base and collector ports, respectively.

The following expression can be written for the Y parameters [60] (the bar indicates that the parameter is temperature dependent)

$$\overline{y}_{mn} = \frac{dI_m}{dV_n}\Big|_{V_m = const.} = \frac{\partial f_m}{\partial V_n}\Big|_{V_m, T = const.} + \frac{\partial f_m}{\partial T} \cdot \frac{dT}{dV_n}\Big|_{V_m = const.} = y_{mn\_iso} + \frac{\partial f_m}{\partial T} \cdot \frac{dT}{dV_n}\Big|_{V_m = const.}$$

Eq. 2.12

where  $y_{mn_iso}$  is temperature independent. The temperature dependence is approximated for small signal excitations with:

$$\alpha_m = \frac{\partial f_m}{\partial T} \bigg|_{V_m = const.}$$

Eq. 2.13

where  $\alpha_m$  is the relative change of  $I_m$  per degree temperature change at a constant voltage  $V_m$ . The junction temperature T is defined as:

$$T = T_{amb} + Z_{th} \cdot P_{diss}$$

Eq. 2.14

where  $T_{amb}$  is the ambient temperature (chuck temperature) and  $P_{diss}$  is the dissipated power in the device that results from

$$P_{diss} = V_1 I_1 + V_2 I_2$$

Eq. 2.15

The change in dissipated power dP<sub>diss</sub> with small signal excitation can be written as:

$$dP_{diss} = dV_1I_1 + V_1dI_1 + dV_2I_2 + V_2dI_2.$$

Eq. 2.16

From equation Eq. 2.14 and Eq. 2.15 it follows that:

$$\frac{dT}{dV_n}\Big|_{V_m = const.} = Z_{th} \left( I_n + V_n \frac{\partial I_n}{\partial V_n} \Big|_{V_m = const.} + V_k \frac{\partial I_k}{\partial V_n} \Big|_{V_m = const.} \right) \qquad k = 3 - n \qquad \text{Eq. 2.17}$$

which can be transformed to:

$$\frac{dT}{dV_n}\Big|_{\Delta V_m} = Z_{th} \left( I_n + V_n \overline{y}_{nn} + V_k \overline{y}_{kn} \right).$$

Eq. 2.18

Using the equations Eq. 2.12 and Eq. 2.18, the following expression for Z<sub>th</sub> is obtained:

$$Z_{th} = \frac{\overline{y}_{mn} - y_{mn\_iso}}{\left(\frac{\partial f_m}{\partial T_j}\right) \left[I_n + V_n \overline{y}_{nn} + V_k \overline{y}_{kn}\right]}$$

Eq. 2.19

#### *Chapter 2* Device characterization in SiGe HBT technologies

Since in equation Eq. 2.12 the term  $dT/dV_n$  is greater for  $V_2$  ( $V_{CE}$ ) than for  $V_1$  ( $V_{BE}$ ),  $y_{12}$  and  $y_{22}$  are the most affected by self-heating, and therefore, should be the most suitable for the extraction of  $Z_{th}$ . In case of  $y_{22}$ ,  $Z_{th}$  would be:

$$Z_{ih} = \frac{\overline{y}_{22} - y_{22\_iso}}{\alpha_2 \left[ I_2 + V_2 \overline{y}_{22} + V_1 \overline{y}_{12} \right]} = \frac{\overline{y}_{22} - y_{22\_iso}}{\alpha_{IC} \left[ I_C + V_{CE} \overline{y}_{22} + V_{BE} \overline{y}_{12} \right]}.$$

Eq. 2.20

As expressed in Eq. 2.20 it is assumed that the measured Y-parameters contain two parts: one is an isothermal part where only DC self-heating effects are visible and which has been measured at high frequency (above thermal cut-off frequency) and the other is the thermal part (below thermal cut-off frequency) where both dynamic and DC self-heating effects are equally visible.

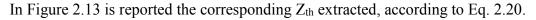

In Figure 2.12 (left) are plotted the measured  $Y_{22}$  parameters for different values of  $V_{BE}$  ranging from 0.75V to 0.95V and  $V_{CE}$ =1.25V. It can be seen that, as  $V_{BE}$  (and consequently the amount of self-heating) increases, the variation of  $Y_{22}$  at low frequency becomes always higher; in particular the highest deviation is observed at  $V_{BE}$ =0.9V. From Figure 2.12 (left) it looks evident the presence of two regions in the  $Y_{22}$  parameters: (i) the isothermal region (above 200 MHz) and (ii) the dynamic self-heating affected region or non-isothermal region (below 200 MHz). Once the cutoff frequency is determined, the  $Y_{22_iso}$  necessary for the extraction of  $Z_{th}$  is calculated as an extrapolation of  $Y_{22}$ , starting from the highest frequency measured down till the cutoff frequency, as shown Figure 2.12 (right) for the bias point  $V_{BE}$ =0.9V.

Figure 2.12: (left) variation of the low frequency  $Y_{22}$  parameter for  $V_{CE}$ =1.25V and  $V_{BE}$  ranging from 0.75V to 0.95V. (right)  $Y_{22}$  for  $V_{CE}$ =1.25 and  $V_{BE}$ =0.9V: the calculated  $Y_{22\_iso}$  is shown.

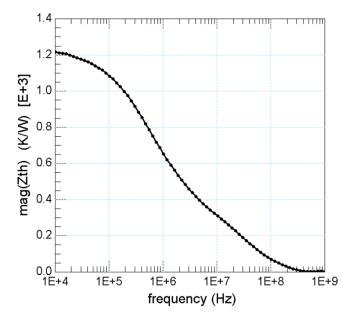

Figure 2.13: extracted  $Z_{th}$  versus frequency in the 10kHz-1GHz range, using the extraction methodology described

#### 2.7 Recursive thermal network model

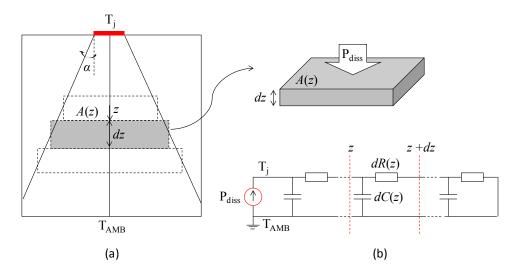

As already detailed in section 2.3, state of the art compact models (in this case HiCuM/L2) normally adopt a single pole network for the simulation of the junction temperature of the transistor  $T_j$ . This assumption represents the easiest model possible to reproduce the evolution of  $T_j$  when a dynamic power dissipation is present within the transistor, but it can show its limitations in specific conditions of operation of the component. In fact, the heat diffusion phenomena from the heat source to the heat sink show a distributed nature, and thus multiple time constant can be needed to approximate this thermal behavior. In literature different modeling approaches have been proposed to threat this problem, and mostly rely on the use of transmission line equivalent circuits, where a distributed RC network is used to model the diffusion of heat; more precisely a Cauer type network is normally chosen for this purpose, since it is more suitable as a thermal analogy from the physical point of view [61], [62]. Using these distributed approaches, the transistor structure can be divided in multiple volume elements [63] and each segment can be associated to its corresponding lumped R<sub>th</sub> and C<sub>th</sub>, as shown in Figure 2.14, making the following assumptions [63]:

- The graduation of layer thickness should be chosen so that progressively larger thermal time constants ( $\tau_{th} = R_{th i} C_{th i}$ ) are produced in the direction of the heat propagation.

- If the dimensions of the heat source are smaller than the cross section of the heat conducting material, the heat spreading region can be assumed to be confined within a spreading angle α. For heat propagation in homogeneous media, a spreading angle α of about 40° can be considered.

*Chapter 2* Device characterization in SiGe HBT technologies

Figure 2.14: (a) Heat diffusion within spreading angle  $\alpha$  in a simple structure (b) electrical transmission line equivalent circuit diagram [10].

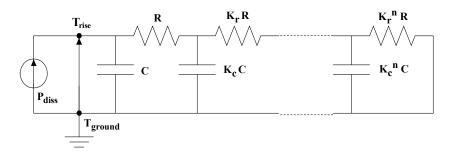

Figure 2.15: A Cauer type recursive network for the  $Z_{th}$  representation (the different elements of the network are in recursive order).

In this work a recursive thermal network will be mainly used, in which the lumped elements are scaled using two different recursive multiplication factors:  $K_r(<1)$  and  $K_c(>1)$  respectively for the  $R_{th i}$  and  $C_{th i}$  as shown in Figure 2.15. The elements of this network can be related to the different volumes in which the transistor structure is ideally subdivided according to the model in Figure 2.14.

Thermal TCAD simulations can help to identify the different volumes delimited by the isothermal contours created when a power source is applied to the transistor structure; in Figure 2.16 is reported the thermal profile simulated in TCAD Sentaurus for the five fingers HBT realized in ST Microelectronics B55 technology for which the  $Z_{th}$  extraction has been previously demonstrated ( $A_E=0.18x5\mu m^2$ ), in the case where a power dissipation of 30mW per finger is applied. The simulated structure does not include the BEOL and a zoom on just one finger is shown.

Figure 2.16: thermal TCAD simulations for a five fingers HBT in ST B55 technology. The image is zoomed on one finger, to show the isothermal contours that identify the different volumes in which the structure can be subdivided.

It can be observed in Figure 2.16 that the isothermal contours identify multiple regions in the simulated structure and that the distance between the isothermal contours (and thus the volume) increases as the distance from the heat source increases. The  $R_{th}$  and  $C_{th}$  related to these volumes can be expressed as:

$$\Delta R_{th} = \frac{\Delta z}{kA(z)}$$

Eq. 2.21

$$\Delta C_{th} = \frac{k A(z) \Delta z}{\alpha}$$

Eq. 2.22

where  $\Delta z$  represents the distance between two isothermal contours, A(z) the related local cross section area and k and  $\alpha$  are respectively the thermal conductivity and the heat diffusion coefficient of the material. If we compare the  $\Delta R_{th}$  related to the volume number 1 to the number 2 in Figure 2.16, it will result  $\Delta R_{th1} > \Delta R_{th2}$  (this assumption can be considered valid within the DTI enclosed area, where A(z) is kept constant by the adiabatic wall created by the DTI), while the opposite will hold for the  $\Delta C_{th}$ , being  $\Delta C_{th1} < \Delta C_{th2}$ . So, as the distance from the heat source increases, the R<sub>th</sub> of the discrete volumes decreases, while the related C<sub>th</sub> increases; the same trend is obtained in the recursive thermal network in Figure 2.15, moving from the current source till the pole with index *n*.

This network architecture in Figure 2.15 ensures a particular behavior as the frequency of the heat source is swept: at low frequency the  $C_{th}$  can be seen as open circuits and thus the  $Z_{th}$  can be approximated as the series of all the  $R_{th}$ ; as the frequency increases, the high valued capacitances located far from the current source start to shunt to ground, thus short-circuiting the related  $R_{th}$ . As the frequency further increases, the smaller

### *Chapter 2* Device characterization in SiGe HBT technologies

capacitances located closer to the current source will start to shunt as well, thus yielding an equivalent  $Z_{th}$  which tends to 0 (compare to the  $Z_{th}$  versus frequency extracted in Figure 2.13).

In other words at low frequency the whole volume of silicon below the heat source participates to the  $Z_{th}$  and big valued  $C_{th}$  are thermally charged and discharged; as the frequency increases this big volume cannot participate to the thermal sinusoidal variations due to its inertia and so the AC dynamic phenomena can be approximated to happen in a smaller volume, located close to the heat source. It is then evident that the  $Z_{th}$  has a physically distributed nature.

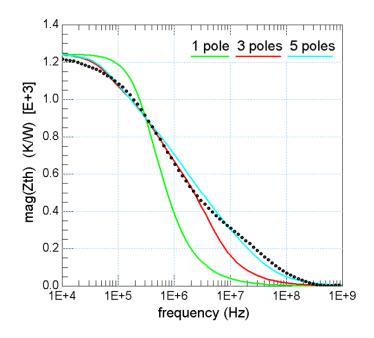

To check the inaccuracies that are introduced in compact models considering a simple single pole thermal network, in Figure 2.17 it is shown the measured  $Z_{th}$  on the five fingers transistor under study and the results of simulation using a thermal network having respectively 1, 3 and 5 poles. The values of  $R_{th}$  and  $C_{th}$  are tuned to obtain the best fit and it is shown that using 3 poles can already lead to an acceptable accuracy in the frequency range measured.

Figure 2.17: comparison of the measured and simulated  $Z_{th}$  using a thermal network having 1, 3 and 5 poles

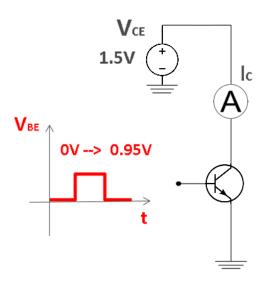

An alternative way to characterize the distributed nature of the thermal impedance of state of the art transistors, is to perform pulsed measurements; in fact, when operated in pulsed conditions, SiGe HBTs show a transient variation of the junction temperature  $T_j$ , which can lead to a slow response in the I<sub>C</sub> evolution; in fact, if a pulsed V<sub>BE</sub> is applied to the transistor (see Figure 2.18), after a quick electrical response, the I<sub>C</sub> will slowly reach its steady state value, over a time proportional to the thermal time constant of the component [64]–[66].

Figure 2.18: measurement setup to characterize the thermal response of the transistor under pulsed operation

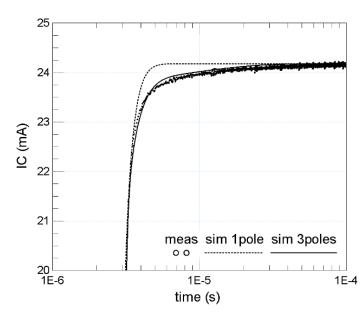

In Figure 2.19 it is shown the I<sub>C</sub> measured on a HBT realized in the B11HFC technology from Infineon ( $A_E=0.22x5\mu m^2$ ) for  $V_{CE}=1.5V$ , when a pulse of  $V_{BE}$  is applied, having an amplitude of 0.95V. It can be seen that the I<sub>C</sub> reaches a stable value in around 27µs; this thermal evolution is not representable with a good accuracy with a single pole thermal network (represented in the plot by a dotted line), whereas a 3 poles recursive network can provide a more realistic simulation of the pulsed I<sub>C</sub>. The simulations using a single pole network can significantly deviate from the measurements in correspondence of the instant where the V<sub>BE</sub> pulse is applied, especially in the case of large emitter area transistors, where the I<sub>C</sub> can reach higher values [64].

Figure 2.19: measured and simulated IC in pulsed conditions using a thermal network having 1 and 3 poles on a HBT in B11HFC technology.

# 2.8 Behavior of the transistor under two tones excitation

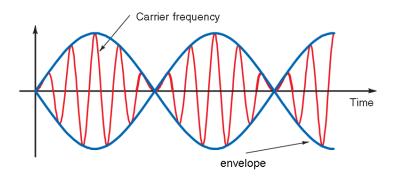

As shown in section 2.6, the thermal impedance of state of the art SiGe HBTs has a cutoff frequency in the order of few hundreds of MHz; in other words, if a sinusoid at a given frequency  $f_{IN}$  is fed at the input of the transistor (and thus a sinusoidal power is dissipated within the component), the junction temperature  $T_j$  will experience a sinusoidal variation, synchronized with the time evolution of the power dissipation. This will happen till  $f_{IN}$  is lower than the thermal cutoff frequency of the transistor, whereas for higher frequencies the  $T_j$  will remain stable, due to the thermal inertia of the component [67].

Even if the thermal impedance of these components is mainly located in the low frequency range, it can affect the transistor behavior also when it is operated at much higher frequencies; in fact when a large-amplitude signal or a modulated input signal is put at the input of the transistor, due to its intrinsic non-linearities, inter modulation products are generated [68].

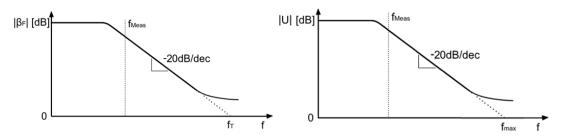

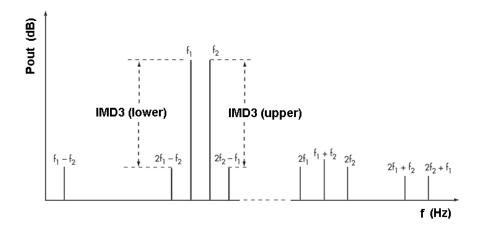

In power amplifier design, an important figure of merit used to characterize linearity is the intermodulation distortion (IMD), caused when multiple frequencies are mixed to form sum and difference products of the original signals; these signals occur as integer multiples of the input frequencies. It is possible to identify IMD of different orders, according to the frequencies which are mixed, however the intermodulation distortion from the third order (IMD3) is of particular importance in narrow band signals because its distortion is often in the signal band. In Figure 2.20 is represented the output spectrum of a transistor affected by intermodulation distortion products, when two frequency tones ( $f_1$  and  $f_2$ ) are put at its input.

Figure 2.20: schematic representation of the different intermodulation products that can be generated when nonlinearities arise in a transistor.

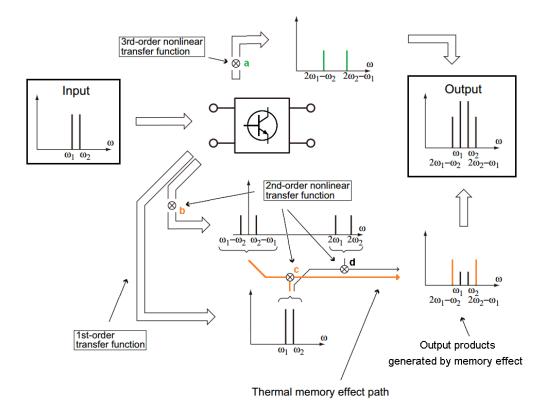

In general these nonlinear phenomena can be caused by electrical effects, but can also come from thermal self-heating. The mechanism of IMD3 generation for a two-tone input signal is shown in Figure 2.21: there are two processes which lead to the generation of

IMD3 at the output: the first is related to the third-order nonlinear transfer function that directly generates IMD3 (the products depicted in green in Figure 2.21). The second is related to the nonlinear transfer functions of second-order named *b* and *c* in Figure 2.21: it has to be considered, in fact, that a nonlinear component, such as a transistor, generally has more than one nonlinear transfer functions; the IMD3 can thus be generated when a signal passes the second-order nonlinear transfer function twice. This second process is called the memory effect [69]. In the memory effect, the base-band signal ( $\omega_1-\omega_2$  and  $\omega_2-\omega_1$ ), and the second-order higher harmonic signals ( $2\omega_1$  and  $2\omega_2$ ) interact with the fundamental frequency tones ( $\omega_1$  and  $\omega_2$ ), as shown in Figure 2.21. Since the spectra of the thermal transient phenomena due to self-heating can be very close to the baseband components  $\omega_1-\omega_2$  and  $\omega_2-\omega_1$ , the thermal transient phenomenon modulates the electrical memory effect. This is the origin of the thermal memory effect [43], [67], [69], [70] (the frequency interactions leading to output intermodulation products affected by thermal memory effect are highlighted in orange in Figure 2.21).

Due to the complex nature of these phenomena, in order to test the linearity of power amplifiers, it is useful to drive them with a two-tone test signal with varying tone spacing and amplitudes, to check how intermodulation distortion mechanisms affect the transistor behavior. If the amplifier behaves properly for a wide range of tone spacings, it can be expected to behave correctly also in the case of wide-band signals.

Figure 2.21: Mechanisms of third-order intermodulation distortion (IMD3) generation for a two-tone input signal [28]. The frequency interactions which lead to output intermodulation products affected by thermal memory effect are highlighted in orange.

#### *Chapter 2* Device characterization in SiGe HBT technologies

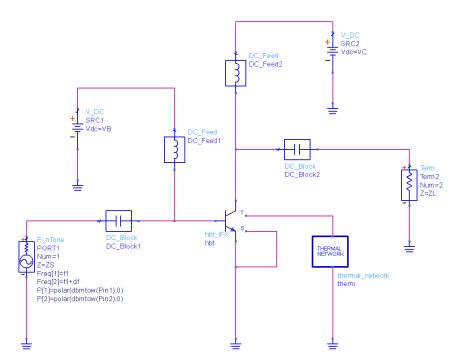

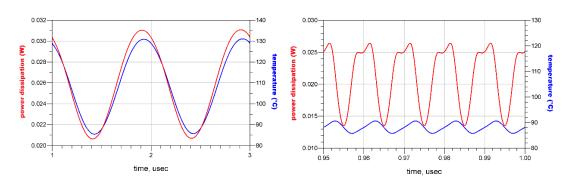

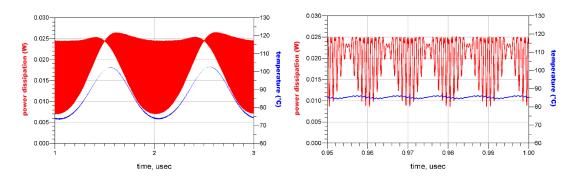

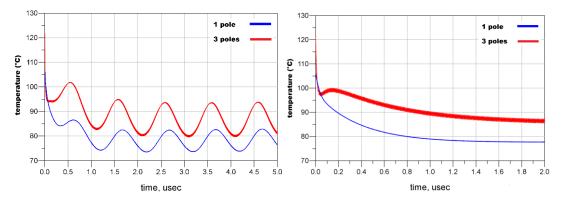

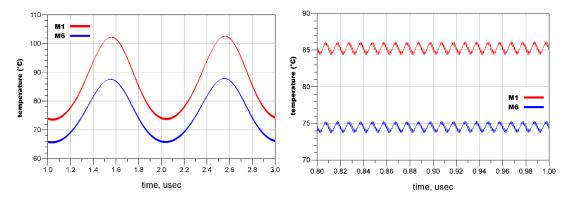

In Figure 2.22 it is shown an ADS setup to simulate the effect of tone spacing on the time evolution of  $T_j$  predicted by the compact model. The transistor is biased at a  $V_{BE}$ =0.925V and  $V_{CE}$ =1.5V, at the input two sinusoidal tones are applied ( $f_1$  and  $f_2$ ), both having an amplitude of -20dBm. A three poles network is used for these simulations, which has been validated upon low frequency measurements (Figure 2.19 (right) shows the measured and simulated  $Z_{th}$  using the three poles network and a single pole network for the transistor under study).

Figure 2.22: ADS schematic used to simulate the behavior of the transistor under a two tones large signal excitation

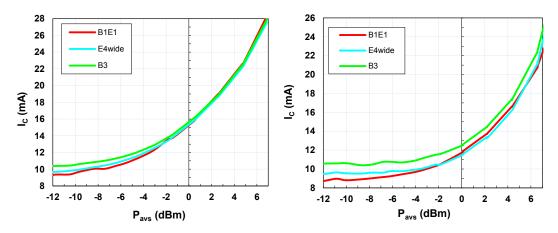

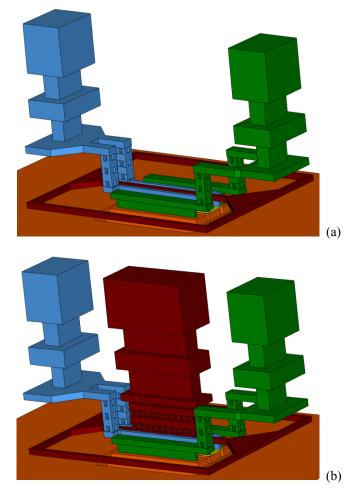

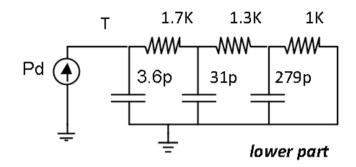

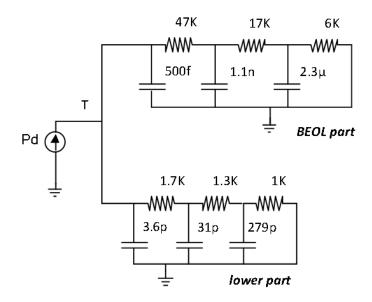

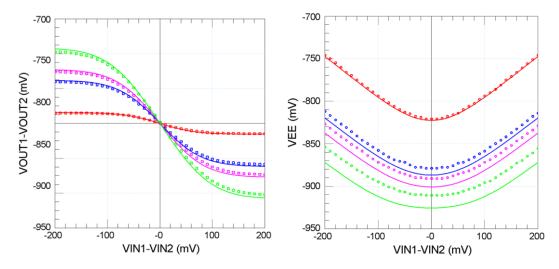

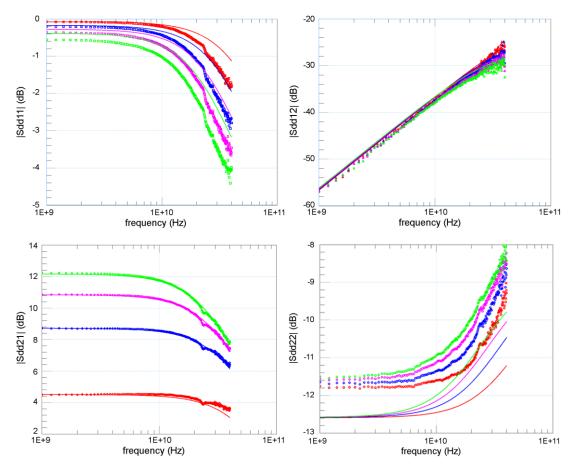

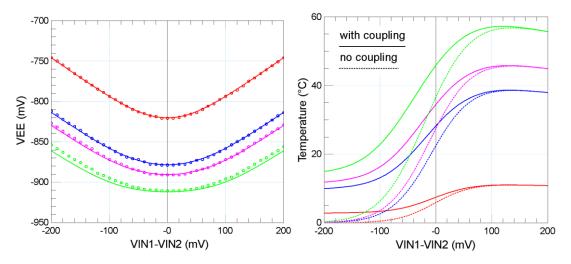

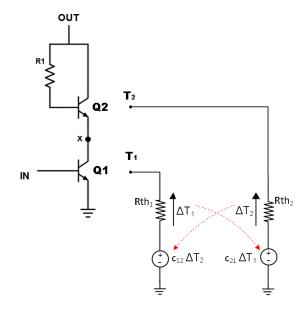

First of all it is shown in Figure 2.24 the evolution of temperature for a single frequency of operation: the  $f_2$  tone is switched off, while the frequency of  $f_1$  is set equal to 1MHz (left) and 10MHz (right); it is evident that, at low frequency, the  $T_j$  (in blue) is synchronized to the power dissipated in the transistor (in red) and a considerable temperature variation of around 45°C is predicted. If the frequency of the input signal is set to 10MHz instead, due to the reduced  $Z_{th}$ , the  $T_j$  responds to a lower extent to the power dissipated in the transistor appears distorted due to a phase shift between the I<sub>C</sub> and V<sub>CE</sub> waveforms.