# Research on virtualisation technlogy for real-time reconfigurable systems

Tian Xia

## ▶ To cite this version:

Tian Xia. Research on virtualisation technology for real-time reconfigurable systems. Electronics. INSA de Rennes, 2016. English. NNT: 2016ISAR0009. tel-01418453v2

## HAL Id: tel-01418453 https://theses.hal.science/tel-01418453v2

Submitted on 16 Dec 2016

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THESE INSA Rennes**

sous le sceau de l'Université Bretagne Loire pour obtenir le titre de

DOCTEUR DE L'INSA RENNES

Spécialité : Electronique et Télécommunications

présentée par

# Tian Xia

**ECOLE DOCTORALE**: MATISSE

**LABORATOIRE: IETR**

Research on Virtualization Technology for Real-time Reconfigurable Systems

## Thèse soutenue le 05.07.2016

devant le jury composé de :

## François Verdier

Professeur, Université de Nice, Nice / Président

### **Emmanuel Grolleau**

Professeur, ISAE-ENSMA, Chasseneuil-Futuroscope / Rapporteur

#### **Guy Gogniat**

Professeur, Université de Bretagne-Sud, Lorient / Rapporteur

#### Jean-Luc Bechennec

Chargé de Recherche, Ecole Centrale de Nantes, Nantes / Examinateur

## Jean-Christophe Prévotet

Maître de Conférence, INSA, Rennes / Co-encadrant de thèse

#### **Fabienne Nouvel**

Maître de Conférence HDR, INSA, Rennes / Directrice de thèse

# Research on Virtualization Technology for Real-time Reconfigurable Systems

Tian Xia

# Résumé de la Thèse

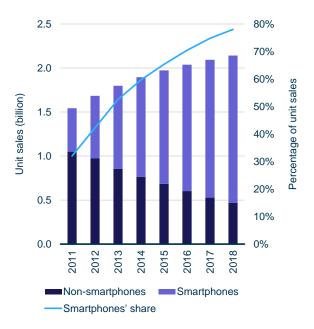

Aujourd'hui, les systèmes embarqués jouent un rôle prépondérant dans la vie quotidienne des utilisateurs. Ces systèmes sont très hétérogènes et regroupent une énorme diversité de produits tels que les smartphones, les dispositifs de contrôle, les systèmes communicants, etc. Couvrant une large gamme d'applications, ces systèmes ont évolué en différentes catégories. Il existe des systèmes avec une grande puissance de calcul pouvant mettre en œuvre des logiciels complexes et permettre la gestion de ressources complexes. D'autres systèmes embarqués à faible coût, avec des ressources limitées, sont destinés à l'implantation de dispositifs simples, tel que ceux mis en œuvre dans l'Internet des Objets (IdO). Fondamentalement, la plupart de ces appareils partagent des caractéristiques communes telles que la taille, le poids et la faible consommation d'énergie.

Tandis que la complexité des systèmes embarqués augmente, il devient de plus en plus coûteux d'améliorer les performances des processeurs par des approches technologiques classiques comme la diminution de la taille des transistors, par exemple. Dans ce contexte, l'idée d'une architecture hétérogène CPU-FPGA est devenue une solution prometteuse pour les concepteurs de systèmes sur puce. D'autre part, la forte capacité d'adaptation et son faible coût en font une solution très prisée. Cette solution permet de faire bénéficier aux architectures matérielles classiques des avantages et de la flexibilité d'un processeur. Elle permet également d'étendre les concepts logiciels classiques, tels que la virtualisation, aux circuits matériels.

Dans cette thèse, notre recherche apporte une contribution dans ce domaine, en étudiant la virtualisation en temps réel des systèmes embarqués mettant en œuvre la reconfiguration partielle (DPR) de circuits, et ce, dynamiquement. Les objets cibles de la thèse sont les systèmes embarqués hétérogènes comportant au moins un processeur et une architecture reconfigurable de type FPGA.

Dans ce type d'architectures, les principales limitations sont les ressources de calculs restreintes, la faible quantité de mémoire, et des contraintes d'exécution temps réel. Nos travaux se concentrent sur deux aspects en : 1) proposant un micro-noyau léger, personnalisé, hautement adaptable, nommé Ker-ONE, qui prend en charge la virtualisation en temps réel, et 2) en proposant un mécanisme de coordination innovant des accélérateurs reconfigurables entre plusieurs machines virtuelles.

ii Résumé de la Thèse

## 1. Concepts et état de l'art

## 1.1 Virtualization des systèmes embarqués

La virtualisation sur les systèmes embarqués nécessite de répondre à plusieurs contraintes spécifiques. Tout d'abord, la sécurité doit être garantie puisque les appareils embarqués peuvent contenir des informations personnelles sensibles telles que les numéros de téléphone, des informations bancaires, des clés privées, etc. Un machine virtuelle doit être protégée et ne plus dépendre d'autres machines. Au cas où une machine virtuelle viendrait à être défaillante, elle ne doit en aucun cas corrompre le système dans sa globalité. Deuxièmement, les processus temps réel sont indispensables afin d'effectuer des tâches critiques (comme la mise en oeuvre des systèmes d'airbags, la gestion des systèmes d'assistance au freinage des véhicules, ou le traitement des appels d'urgence dans les téléphones mobiles). Troisièmement, en raison de la limitation des ressources des systèmes embarqués, des systèmes virtuels doivent être conçus avec peu de complexité, ce qui peut être obtenu en utilisant un hyperviseur léger.

Dans les dispositifs embarqués qui sont dédiés à l'Internet des objets, les contraintes de conception sont encore plus grands. Ces contraintes portent principalement sur le manque de ressources de calculs et sur la consommation d'énergie : les appareils sont généralement très simples, basés sur un seul micro-contrôleur ou un petit processeur intégré dans un FPGA avec une quantité limitée de mémoire et d'E/S. Ces derniers sont généralement alimentés par des batteries, ce qui impose une très faible consommation d'énergie associée à une gestion efficace de cette même énergie. Dans un tel scénario, une faible complexité du logiciel devient incontournable, de manière à implanter efficacement les machines virtuelles.

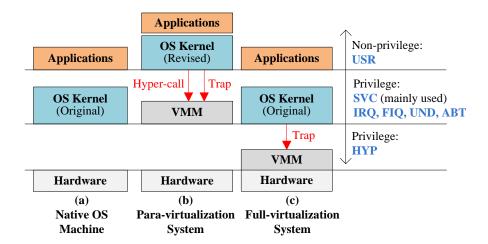

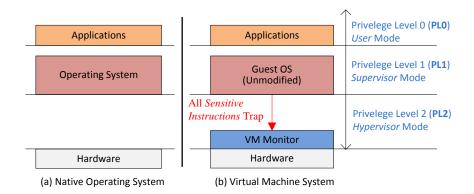

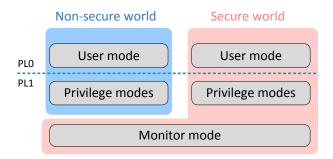

Certaines architectures x86 traditionnelles (par exemple Intel VT, AMD-V, etc.) comportent des extensions de virtualisation matérielle, permettant de "piéger" et "émuler" toutes les instructions sensibles. Les OS invités peuvent ainsi être hébergés sans modification. Toutefois, la couche ISA d'un processeur ARM traditionnel ne convient pas à la virtualisation. L'architecture ARMv7 offre deux niveaux de privilège : PL0 et PL1. Si l'on peut considérer que PL0 peut accéder librement à des ressources globales du processeur, les ressources vitales ne sont accessibles que dans les modes de PL1, ce qui garantit la sécurité du code privilégié.

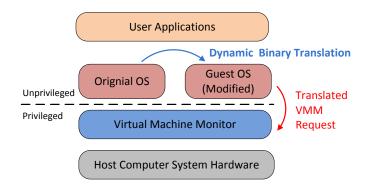

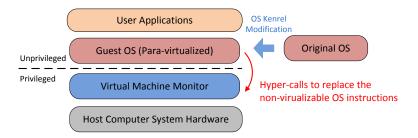

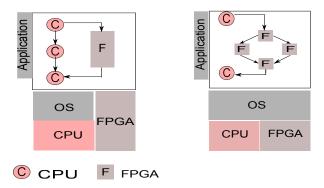

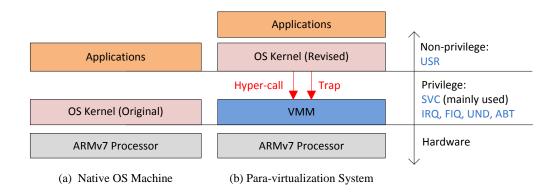

En général, un noyau d'OS fonctionne dans les modes de PL1, et gère toutes les ressources et les tâches. Les applications utilisateur s'exécutent dans le mode PL0, comme le montre la figure FIGURE 1(a). Cependant, en para-virtualisation, les systèmes d'exploitation invités devraient être portés à un niveau non-privilégié alors que le niveau privilégié est occupé par l'hyperviseur (ou VMM pour Virtual Machine Monitor). Dans ce cas, le code source d'un système d'exploitation client doit être modifié pour fonctionner correctement en mode utilisateur et les instructions sensibles doivent être remplacées par des hyper-calls, comme le montre la figureFIGURE 1(b).

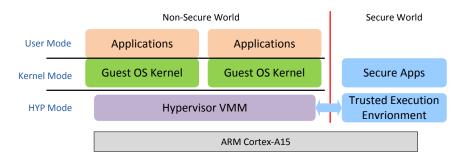

Récemment, ARM a inclus des extensions matérielles pour permettre une virtualisation complète. Ces extensions offrent un mode supplémentaire d'exécution, le mode hyperviseur (HYP), pour les noyaux de virtualisation les plus privilégiés. Cette prise en Résumé de la Thèse iii

FIGURE 1 – Systèmes de virtualisation complète et de para-virtualisation sur une architecture ARM.

charge n'a été introduite que récemment (en 2010) pour le processeur Cortex-A15. Ce mécanisme complet de virtualisation est décrit dans la figure FIGURE 1(c).

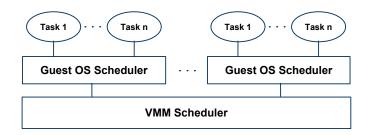

Un autre défi dans la virtualisation intégrée de systèmes est une compatibilité avec les contraintes temps réel, ce qui signifie que le respect des latences des tâches doit être garanti en temps réel. Dans la littérature, l'ordonnançabilité en temps réel a déjà été étudiée et correspond souvent à un ordonnancement hiérarchique. Nous définissons respectivement les concepts d'inter-VM et de programmation intra-VM pour l'ordonnancement des machines virtuelles, et l'ordonnancement des tâches locales au sein d'une même machine virtuelle. Puisque les OSs invités partagent la même ressource processeur, l'ordonnançabilité d'un jeu de tâches est non seulement déterminée par l'algorithme d'ordonnancement deployé au sein d'une machine virtuelle, mais aussi par l'algorithme d'ordonnancement des machines virtuelles. Par conséquent, afin de respecter les contraintes d'un OS temps réel, le respect des échéances des tâches temps réel doit être également garanti dans l'hyperviseur.

### 1.2 État de l'art sur la Virtualisation des architectures ARM

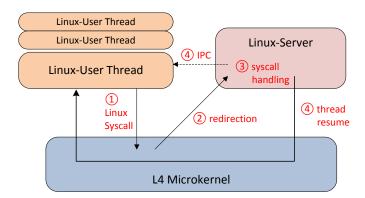

Dans les approches classiques de para-virtualisation, un système d'exploitation invité est normalement fourni avec un patch de virtualisation pour interagir avec l'hyperviseur, ce qui exige que le code source du système d'exploitation soit disponible. En conséquence, la majorité des OS actuellement pris en charge se résume à quelques OS libres ,largement distribués, comme Linux embarqué et  $\mu C/OS$ -II.

Une autre solution envisageable permettant d'implanter la para-virtualisation consiste à utiliser un micro-noyau, qui, comme son nom l'indique est un petit noyau avec des ressources essentielles telles qu'un espace d'adressage, des mécanismes de communications inter-processus, etc. .

Toutes les autres fonctionnalités additionnelles sont normalement mises en œuvre

iv Résumé de la Thèse

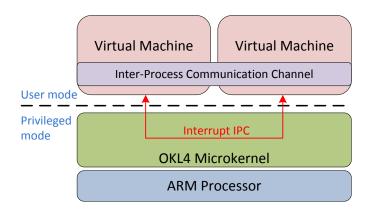

au niveau utilisateur. Les micro-noyaux de type L4 s'articulent généralement autour de Linux pour porter les machines virtuelles. Une solution prometteuse est microvisor de OKL4 d'Open Kernel Labs, qui a amélioré considérablement les noyaux L4 classiques. Cependant, le fait que OKL4 ne soit pas libre rend impossible l'acquisition de détails de mise en œuvre ainsi que de proposer d'autres études sur ce système.

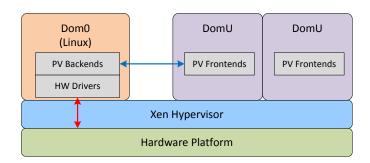

Une autre solution disponible autour de de la para-virtualisation consiste à utiliser de grands hyperviseurs monolithiques, dont la plupart sont d'abord conçus pour la virtualisation des architectures x86, tels que KVM et Xen. Kernel-based Virtual Machine (KVM), par exemple, a été revisité afin de fonctionner dans le ARMv5 et a été proposé en tant que KVM pour ARM (KVM/ARM). Il se compose d'un module de noyau léger qui doit être inclus dans le noyau Linux, et repose sur une version de QEMU modifiée pour mettre en œuvre l'émulation de l'hyperviseur. Les hyperviseurs de type XEN ont également été mis en œuvre sur les architectures ARM, comme Xen-on-ARM.

L'inconvénient des hyperviseurs basés sur KVM ou Xen est leur dépendance vis à vis de Linux en tant que système d'exploitation hôte, ce qui augmente considérablement la taille du code du système global.

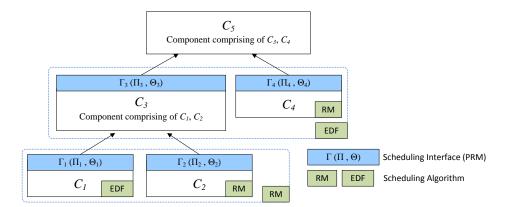

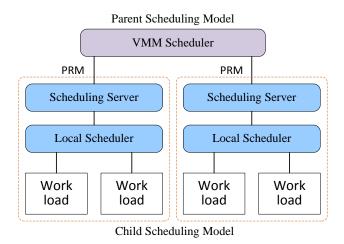

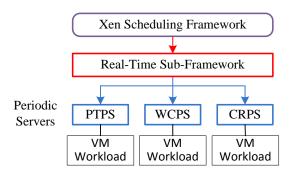

L'ajout d'un support temps-réel pour la virtualisation des systèmes a été l'objet de nombreuses études. Un modèle type de planification en temps réel est le Compositional Real-time Scheduling Framework (CSF) basée sur une planification hiérarchique des tâches. Cet algorithme utilise le modèle de ressource périodique (PRM) afin de faire abstraction d'un groupe d'applications temps réel dans un modèle de charge de travail qui peut être considéré comme une seule tâche périodique. Sur la base de ce modèle de tâches périodiques, l'ordonnancement de machines virtuelles peut être analysé directement en utilisant des algorithmes de programmation classiques. Le micro-noyau L4 Fiasco a revisité le serveur L4Linux pour intégrer ce modèle dans la programmation en temps réel. RT-Xen a également été proposé afin d'étendre l'hyperviseur XEN et profiter ainsi de l'ordonnancement temps réel hiérarchique.

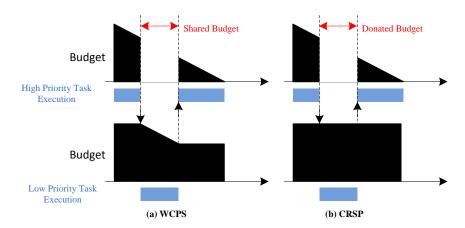

Un autre problème concernant la mise en œuvre de tels systèmes est le surcoût de latence provoqué par les interruptions du service d'horloge. Ce problème a été résolu dans [YY14]. Les auteurs ont proposé un nouvel algorithme d'ordonnancement pour XEN, notée SHQuantization. Ce dernier permet de prendre en compte les surcoûts temporels. Cependant, cette technologie nécessite la modification de l'interface de programmation du système d'exploitation invité. Dans cette approche, l'ordonnanceur de l'OS invité dépend également fortement de l'hyperviseur.

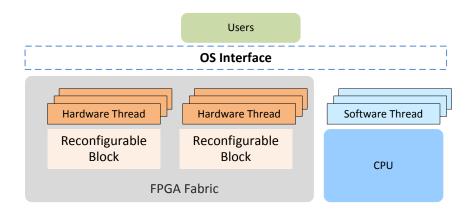

### 1.3 Accélérateur reconfigurable sur plate-forme CPU-FPGA hétérogène

Dans le domaine universitaire, le thème des systèmes hétérogènes basés sur le couple CPU-FPGA a été massivement étudié pour fournir des dispositifs FPGA reconfigurables actuels mettant en œuvre un système d'exploitation. Une approche réussie dans ce domaine est ReconOS, qui est basé sur un RTOS open-source (eCos) prenant en charge les tâches matérielles/logicielles multithread. ReconOS fournit une solution classique pour la gestion des accélérateurs matériels dans un système hybride et dans un modèle de

Résumé de la Thèse v

gestion classique de threads. Cependant, la possibilité de tirer profit de la virtualisation n'a pas été pleinement discutée dans ces travaux.

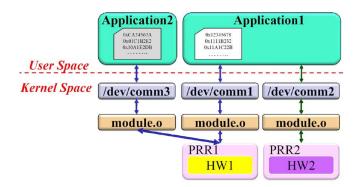

Une attention particulière a également été portée sur des accélérateurs FPGA partagés dans un contexte multi-clients, par exemple des OS complexes, des serveurs cloud ou des systèmes de machines virtuelles. Dans ces recherches, une technologie de virtualisation DPR est proposée. Cette technologie offre des accès efficaces à des accélérateurs virtuels et simplifie considérablement le développement logiciel.

Dans [HH09], ce concept est mis en œuvre à l'aide de OS4RS sous Linux. Le matériel virtuel permet aux périphériques matériels et aux ressources logiques d'être partagés simultanément entre les différentes applications logicielles. Cependant, cette approche est proposée dans le cadre d'un seul système d'exploitation, sans tenir compte des fonctionnalités de virtualisation. Une autre étude est présentée dans [WBP13]. Les auteurs tentent d'étendre l'hyperviseur Xen afin de partager un accélérateur FPGA entre les machines virtuelles. Cependant, cette recherche porte uniquement sur la méthode de transfert de données entre le CPU et le FPGA, et n'inclut pas la technologie de reconfiguration dynamique partielle.

La virtualisation des systèmes reconfigurables est beaucoup plus populaire sur les serveurs cloud et les centres de données, qui ont généralement un besoin plus fort en termes de performance et de flexibilité. Par exemple, dans des travaux tels que [BSB+14] et [KS15], les auteurs utilisent la reconfiguration partielle pour diviser un seul FPGA en plusieurs régions reconfigurables, dont chacune est gérée comme un seul FPGA virtualisé (VFR). Ce type de virtualisation n'est néanmoins pas approprié pour les systèmes embarqués, dont les ressources disponibles sont très limitées, comparées à celles qui sont disponibles dans les serveurs ou les centres de données.

Dans notre travail, la plate-forme cible est le SoC Xilinx Zynq-7000 comprenant un processeur Cortex-A9 dual-core et un FPGA reconfigurable partiellement. Ce dernier est actuellement un des systèmes SoPC (System on Programmable Chip) le plus utilisé. Dans cette plate-forme, nous souhaitons bénéficier d'une solution de virtualisation légère, appropriée pour des systèmes dédiés à l'internet des objets. Dans ce contexte, les technologies de virtualisation existantes ne semblent pas appropriées, car leur complexité étant très élevée, il devient inimaginable de les adapter à notre plate-forme cible. En outre, plusieurs technologies, par exemple OKL4, ne sont pas libres et sont donc in-envisageables pour nos travaux. Nous avons également écarté l'algorithme d'ordonnancement hiérarchique, décrit précédemment, car ce dernier nécessite le calcul d'interfaces PRM ou des ordonnancements de serveurs supplémentaires.

Par conséquent, un objectif de nos travaux a consisté à proposer une approche micronoyau qui prend en charge la virtualisation en temps réel avec un minimum de complexité. Nous avons également proposé une approche originale de virtualisation sur un hyperviseur embarqués que nous avons développé. Des efforts ont été réalisés pour assurer efficacement le partage des ressources reconfigurables entre les machines virtuelles.

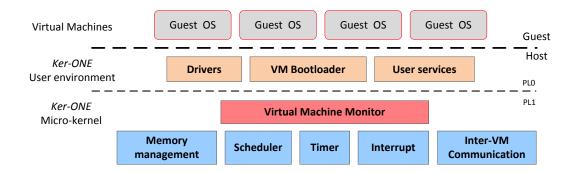

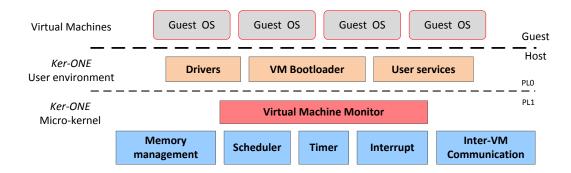

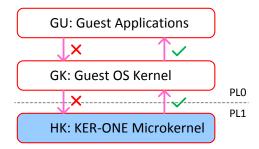

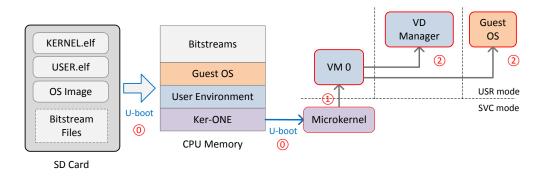

FIGURE 2 – Ker-ONE se compose d'un micro-noyau exécuté en mode privilégié et d'un environnement utilisateur s'exécutant au niveau non-privilégié.

## 2. KER-ONE: un micro-noyau léger et temps réel

La virtualisation sur plate-formes ARM-FPGA a quelques limitations. La virtualisation complète des processeurs ARM est actuellement disponible en utilisant des extensions de virtualisation ARM comme dans le Cortex-A15. En revanche, cette technologie est actuellement indisponible sur les plateformes ARM-FPGA actulles. Par conséquent, Ker-ONE est développé sur la base de l'architecture ARMv7 en utilisant le principe de para-virtualisation. La conception de Ker-ONE est dictée par le principe de faible complexité, qui consiste à se concentrer uniquement sur la fonctionnalité de virtualisation critique et élimine tous les services non primordiaux. Ker-ONE offre une petite taille de TCB, et propose un mécanisme permettant de gérer les contraintes temps réel de la plupart des applications. Actuellement, notre recherche est basée sur les hypothèses suivantes :

- Dans une première étape, nous avons seulement considéré des architectures monocoeur, renvoyant les système multi-cœurs aux futures études.

- Nous nous concentrons sur la virtualisation des systèmes d'exploitation simples, au lieu des gros OSs monolithiques tels que Linux. En effet, para-virtualiser de tels systèmes d'exploitation serait très coûteux et complexe et irait à l'encontre des objectifs de notre travail.

- Afin de réaliser la virtualisation en temps réel avec un ordonnanceur moins complexe, nous supposons que toutes les taches critiques temps réel s'exécutent dans un RTOS invité spécifique, alors que les autres taches, moins critiques, s'exécutent sur un OS généraliste (GPOSs). Aussi, Ker-ONE est conçu pour abriter au moins un client RTOS et plusieurs GPOSs.

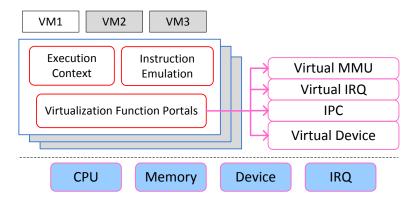

Ker-ONE se compose du micro-noyau à proprement parler et d'un environnement de niveau utilisateur. La FIGURE 2 représente les éléments clés de notre architecture.

Le micro-noyau est le seul composant fonctionnant dans le mode le plus privilégié, principalement en mode superviseur.

Résumé de la Thèse vii

Les caractéristiques de base implantées dans le noyau sont : la gestion de la mémoire, les communications inter-VM, la gestion des exceptions, et l'ordonnanceur. L'hyperviseur tourne au-dessus des fonctions de base du micro-noyau pour permettre l'exécution d'un système d'exploitation invité dans la machine virtuelle associée. Il fournit une couche de matériel virtuel, émule des instructions sensibles et gère les hyper-calls provenant des machines virtuelles. L'environnement utilisateur fonctionne en mode (PL0) et propose des services supplémentaires, tels que les systèmes de fichiers, bootloaders et services spécialisés (comme le gestionnaire de tâches matérielles qui contrôle les accélérateurs matériels dans FPGA Zynq-7000). Une machine virtuelle peut accueillir un système d'exploitation para-virtualisé ou une image logicielle d'une application utilisateur. Chaque machine a un espace d'adressage indépendant, et s'exécute sur le matériel virtuel (CPU virtuel) fourni par l'hyperviseur.

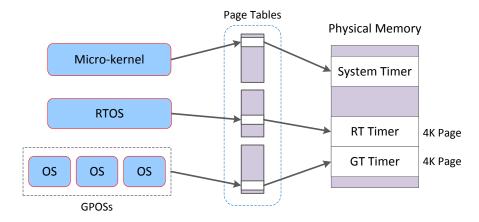

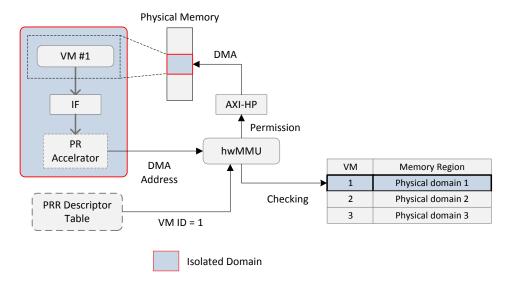

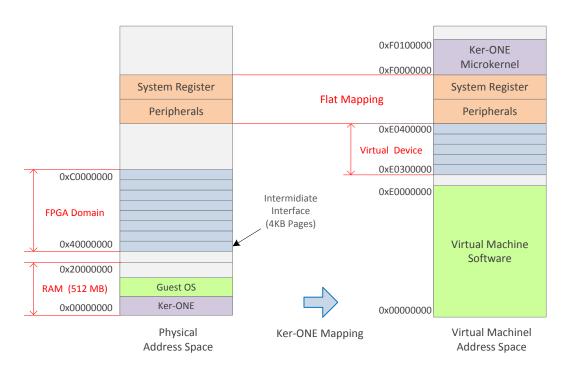

## 2.1 Gestion de la mémoire

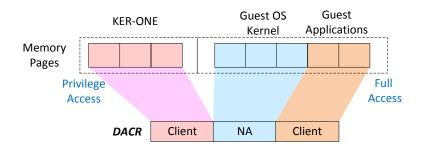

Dans la virtualisation des systèmes, la gestion de la mémoire est essentielle pour fournir des espaces isolés de mémoire pour les machines virtuelles. Ker-ONE offre trois niveaux de privilège de mémoire pour hôte (host) (pour VMM), noyau invité (pour le noyau de l'OS invité) et utilisateur invité (pour les applications de l'OS invité). Chaque niveau est protégé contre les niveaux inférieurs. Par exemple, les pages mémoire dans le hôte ne sont accessibles que par le micro-noyau. De plus, les applications en cours d'exécution dans le domaine utilisateur client ne peuvent accéder au noyau de l'OS.

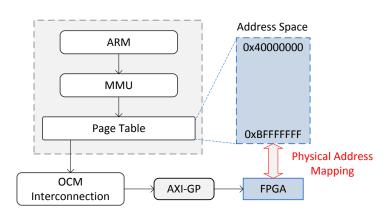

Pour chaque machine virtuelle, une table de page indépendante est créée par l'hyperviseur. Une structure de données de MMU virtuelle est associée à chaque machine virtuelle et contient les informations d'espace d'adressage. Les OSs invités peuvent changer le contenu des tables de pages sous la supervision de l'hyperviseur, à l'aide d'hyper-calls.

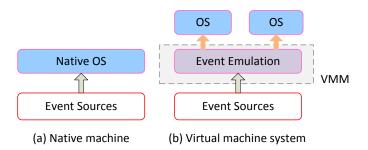

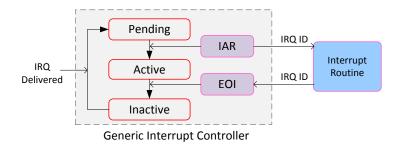

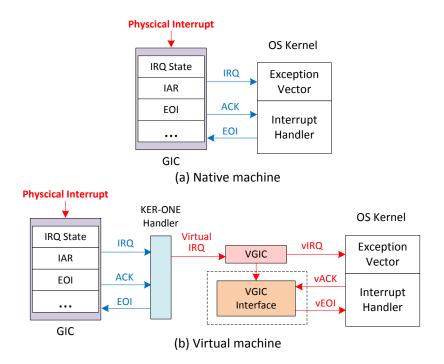

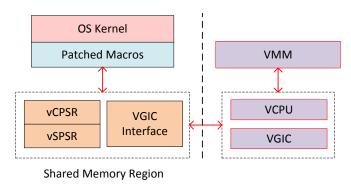

## 2.2 Interruptions

KER-ONE gère toutes les interruptions matérielles. Lors de l'exécution dans une machine virtuelle, toutes les interruptions matérielles sont d'abord prises au piège dans l'hyperviseur. KER-ONE gère les interruptions physiques et envoie ensuite une interruption virtuelle correspondant à la machine virtuelle cible si nécessaire. Dans le domaine de la machine virtuelle, ces interruptions virtuelles sont exactement gérées comme les interruptions physiques grâce à l'hyperviseur. Chaque machine virtuelle est libre de configurer les interruptions virtuelles dans son propre domaine, et est indépendante des autres machines virtuelles.

KER-ONE catégorise et divise les sources d'interruptions en différents groupes. Les interruptions utilisées par les systèmes d'exploitation invités sont divisées en deux niveaux : RTOS et GPOS. Une RTOS se voit attribuer un niveau de priorité supérieur à celui d'un GPOS, de sorte que les interruptions d'un RTOS particulier peuvent être ni désactivées, ni être bloquées par un GPOSs. Ceci garantit que les événements prioritaires peuvent être reçus par le RTOS, même lors de l'exécution de GPOSs. Ceci est très important pour assurer l'ordonnançabilité des tâches en temps réel.

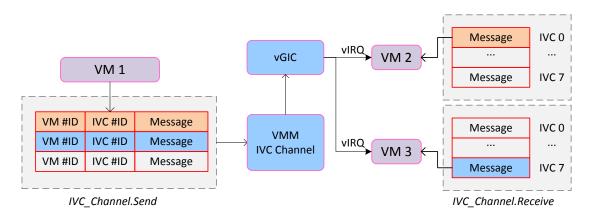

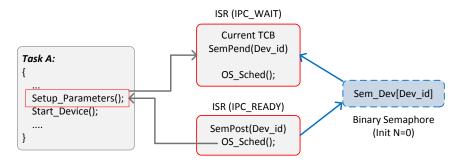

## 2.3 Les communications Inter-Process (IPC)

Un mécanisme de communication inter-processus efficace (IPC) est essentiel dans la plupart des micro-noyaux. KER-ONE utilise de simples approches basées sur la communication asynchrone, à base d'interruptions pour faciliter les IPCs.

Pour effectuer une communication inter-VM, l'hyperviseur lève l'interruption correspondante dans la machine virtuelle cible et délivre un message. Pendant ce temps, dans chaque machine virtuelle, une page de mémoire partagée VMM/VM est créée avec une structure nommée canal IPC (IPC Channel). Les machines virtuelles sont en mesure d'envoyer des messages IPC en programmant le canal IPC dans la région partagée. Ce message sera ensuite traité et livré à la machine virtuelle cible lors du prochain ordonnancement. Il est important de noter que ce mécanisme IPC nécessite seulement quelques cycles d'écriture/lecture mémoire sans utiliser d'hyper-calls, ce qui entraîne peu de surcoût en terme de latence.

## 2.4 Virtualisation des OS temps réel

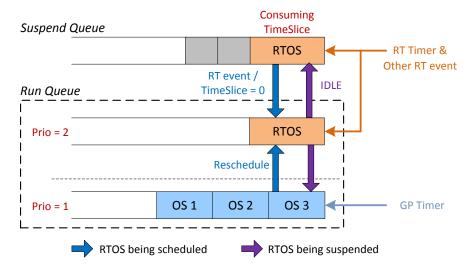

KER-ONE met en œuvre un ordonnanceur round-robin préemptif, basé sur la priorité. Chaque machine virtuelle est créée avec un niveau de priorité fixe. L'ordonnanceur sélectionne toujours la machine virtuelle de plus haute priorité. Une machine avec une faible priorité ne peut fonctionner que lorsque les machines virtuelles plus prioritaires sont suspendues ou arrêtées. Dans le cas où les machines virtuelles sont de même priorité, le CPU est partagé équitablement.

Un RTOS doit fonctionner à un niveau de priorité supérieur à celui d'un GPOS; l'hyperviseur permet aux GPOSs de s'exécuter, uniquement lorsque le RTOS est inactif. Le GPOS poursuivra alors son exécution jusqu'à ce que sa tranche de temps soit écoulée, ou jusqu'à ce qu'un autre événement se produise dans le RTOS. Dans les deux cas, l'hyperviseur ré-exécute le RTOS et préempte les GPOSs.

Pa rapport à une exécution native, la virtualisation dégrade inévitablement les performances. Par conséquent, en ce qui concerne l'ordonnancement des tâches des RTOS, nous proposons un modèle de coût qui formalise les surcoûts liés à la virtualisation. Nous définissons le temps d'exécution réel d'une tâche qui se compose du WCET  $(e_i)$  et de la latence nécessaire à sa libération ou son ordonnancement. Le modèle est le suivant :

$$E_i = e_i + relEv. (1)$$

Et  $e_i$  est le chemin d'exécution de la tâche, et relEv est le temps de libération de cette même tâche.

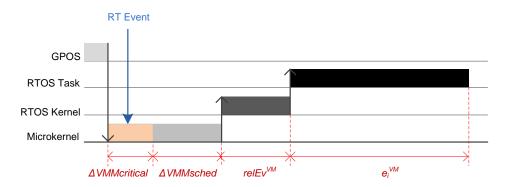

La FIGURE 3 décrit la manière dont la virtualisation affecte le temps d'exécution. Le surcoût engendré par la virtualisation peut être inclus dans le temps d'exécution réel des tâches :  $E_i^{VM}$  :

Résumé de la Thèse ix

FIGURE 3 – Surcoût d'exécution des tâches d'un RTOS lorsqu'exécutée dans une machine virtuelle. Ce dernier est composé de surcoûts critiques liés à l'ordonnancement et les surcoûts intrinsèques liés au RTOS.

$$\begin{split} E_i^{VM} &= e_i^{VM} + relEv^{VM} + \Delta VMMsched + \Delta VMMcritical, \\ and & e_i^{VM} = e_i^{Native} + \Delta_{VM}^{ei}, \\ and & relEv^{VM} = relEv^{Native} + \Delta_{VM}^{relEv}, \end{split} \tag{2}$$

$e_i^{VM}$  et  $relEv^{VM}$  sont respectivement le temps réel d'exécution et le temps de libération de la tâche dans une machine virtuelle. Ces temps sont majorés par  $\Delta_{VM}^{relEv}$  et  $\Delta_{VM}^{ei}$ , qui correspondent respectivement à la latence nécessaire à l'ordonnancement des tâches et au temps d'exécution dans une machine virtuelle.

$\Delta VMMsched$  est la latence supplémentaire requise pour l'ordonnancement du RTOS.  $\Delta VMMcritical$  est le retard causé par l'exécution critique de l'hyperviseur. En résumé, le temps de réponse des machines virtuelles pour prendre en compte un événement temps réel peut être représenté comme suit :

$$Response^{VM} = relEv^{VM} + \Delta VMMsched + \Delta VMMcritical. \tag{3}$$

A partir de  $Response^{VM}$ , le surcoût sur le temps de réponse d'une tâche peut être obtenu par :

$$\Delta_{VM}^{Response} = Response^{Native} - Response^{VM}$$

$$= \Delta_{VM}^{relEv} + \Delta VMMsched + \Delta VMMcritical,$$

(4)

Etant donné que l'ordonnancement d'un RTOS est rythmé par les cycles du timer, tous les paramètres d'ordonnancement sont exprimés en nombre de cycles. Le nombre de cycles  $(\Theta_i)$  représente le temps minimal nécessaire à l'exécution d'une tâche et est exprimé comme suit :

$$\Theta_i = \lceil \frac{E_i^{Native} + \Delta_{VM}^{ei} + \Delta_{VM}^{Response}}{\Delta^{Tick}} \rceil, \tag{5}$$

$\Delta^{Tick}$  représente la durée d'un cycle du timer,  $\Delta^{Rponse}_{VM}$  est le surcoût lié au temps de réponse de la tâche.

x Résumé de la Thèse

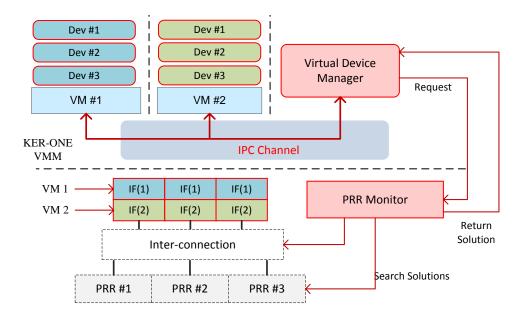

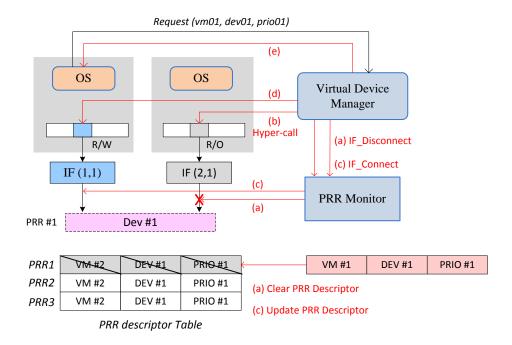

FIGURE 4 – Vue d'ensemble de la gestion de la zone reconfigurable dans KER-ONE.

## 3. Gestion des accélérateurs reconfigurables

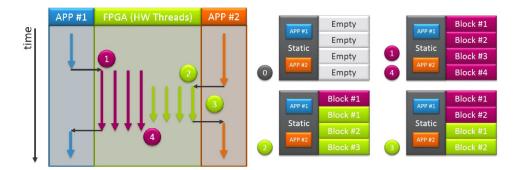

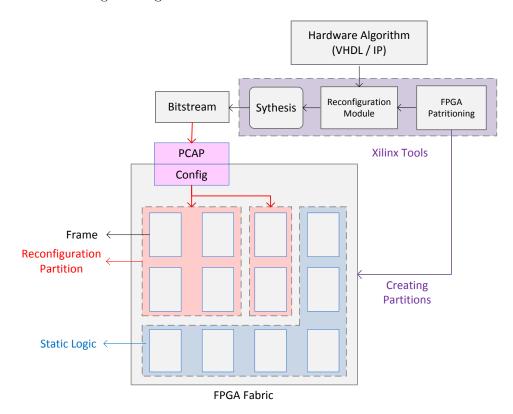

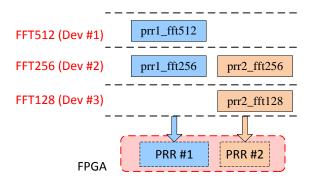

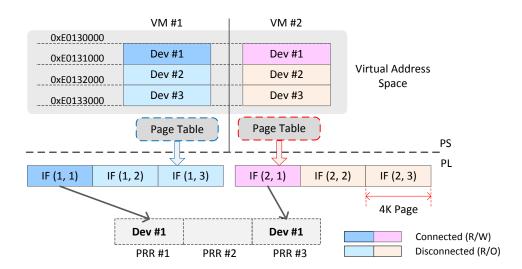

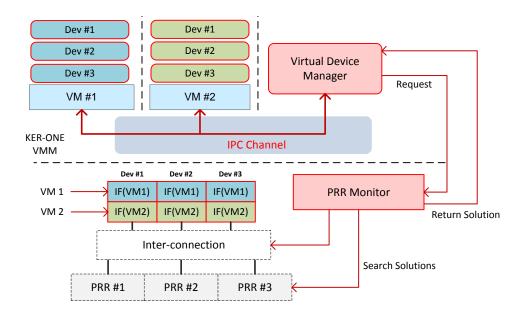

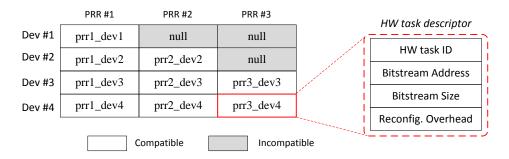

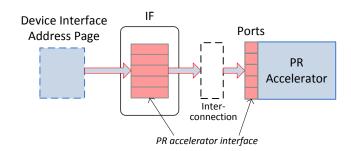

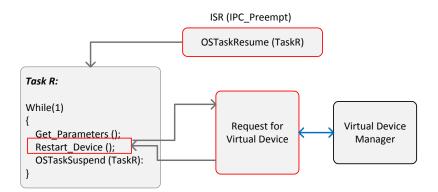

Dans notre système, les accélérateurs reconfigurables sont mis en œuvre dans des régions de reconfiguration partielle prédéterminées (PRR) du FPGA. Nous avons proposé une interface standard pour tous les accélérateurs DPR, de sorte qu'une PRR peut être utilisée par différents accélérateurs. Entre le logiciel et les accélérateurs reconfigurables, une couche intermédiaire composée d'interfaces (IF) a été proposée. Ces IF sont mappées dans l'espace d'adressage des machines virtuelles et sont vues comme étant différents périphériques virtuels. Chaque IF est exclusivement associée à un accélérateur virtuel spécifique dans une machine virtuelle spécifique. Un périphérique virtuel est toujours mappé à la même adresse dans toutes les machines virtuelles, mais est mis en œuvre dans différents IF dans la couche inférieure.

Une interface IF possède deux états, connecté à une certain PRR ou sans lien. Lorsqu'une interface est connectée, elle indique que l'accélérateur virtuel correspondant est mis en œuvre dans la PRR et qu'il est prêt à être utilisé. Etre dans l'état sans lien signifie que l'accélérateur est indisponible et les registres de l'interface IF sont mappés uniquement en lecture seule.

Quand une machine virtuelle tente d'utiliser ce périphérique virtuel en écrivant dans son interface, cette action provoquera un défaut de page et sera détectée par l'hyperviseur. Comme les accélérateurs reconfigurables sont indépendants, notre système introduit des mécanismes de gestion supplémentaires pour gérer dynamiquement les demandes d'utilisation des ressources provenant des machines virtuelles.

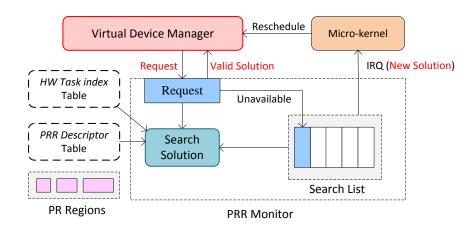

Dans la figure 4, le mécanisme de gestion proposé est décrit. Le Gestionnaire de périphériques virtuel est un service logiciel particulier proposé à une machine virtuelle

Résumé de la Thèse xi

visant à allouer des ressources reconfigurables . Dans la partie statique du FPGA, un *PRR Moniteur* est créé et est en charge des interconnexions entre les IF et les PRR, ainsi que de la surveillance dynamique des accélérateurs reconfigurables. Ce service est également en charge de trouver des solutions disponibles pour l'affectation des ressources aux machines virtuelles.

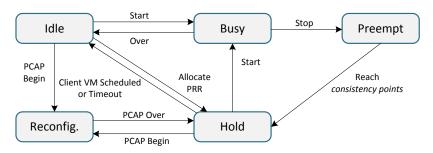

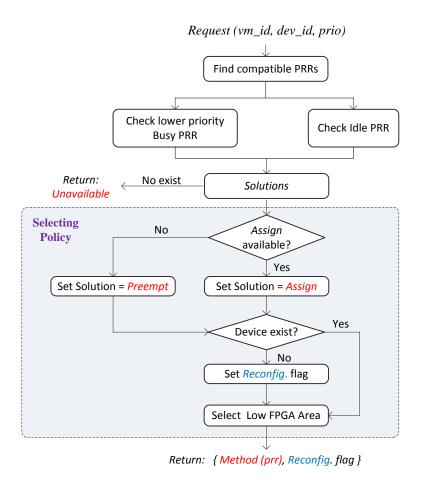

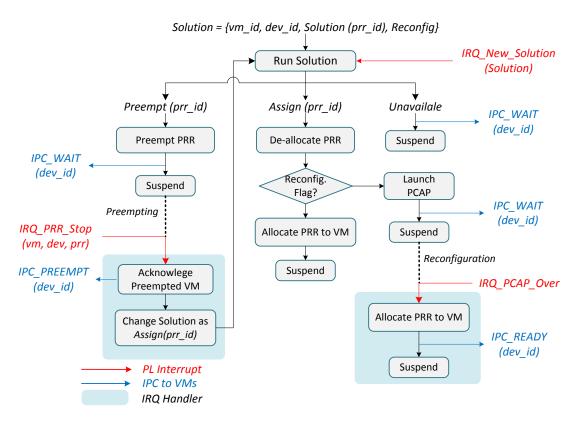

Chaque fois qu'une machine virtuelle accède à une interface IF non connectée, l'hyperviseur exécute immédiatement le *Virtual Device Manager* pour gérer cette demande de ressources. Une requête est de la forme :  $Request(vm_id, dev_id, prio)$ , qui est composée de l'identifiant de machine virtuelle, de l'identifiant du périphérique virtuel ainsi que d'une priorité de demande qui est en réalité la priorité de la machine virtuelle appelante. Cette demande est envoyée au *Moniteur* du côté du FPGA pour rechercher une solution de configuration appropriée. Cette solution comporte différentes méthodes :

- Allocate (prr\_id): alloue directement une zone reconfigurable (prr\_id) à une machine virtuelle. Si le périphérique dev\_id n'est pas déjà implanté dans la zone, un drapeau Reconfig est positionné.

- Preempt (prr\_id): aucune zone ne peut être directement attribuée, mais la zone (prr\_id) peut être préemptée et réaffectée. Si le périphérique dev\_id n'est pas mis en œuvre dans la zone, le drapeau Reconfig sera positionné.

- Unavailable : cet état signifie que la zone reconfigurable n'est pas disponible actuellement. Une demande non aboutie est ensuite ajoutée à la liste des recherches dans le PPR Moniteur qui continue la recherche de solutions. De nouvelles solutions seront envoyées au Gestionnaire de périphériques virtuels immédiatement.

Le Gestionnaire de périphériques virtuels effectue ensuite l'allocation en fonction de la solution retournée. L'allocation peut être effectuée en plusieurs étapes : (1) déconnecter la zone reconfigurable des autres IF, et modifier la page de mémoire en lecture seule dans la machine virtuelle correspondante; (2) la connecter à la machine virtuelle nécessitant la ressource et mettre à jour la page de mémoire en lecture/écriture; (3) continuer l'exécution de la machine virtuelle à l'endroit où elle a été interrompue. Dans les solutions où l'exécution est différée (à savoir Reconfig et Preempt), le processus d'allocation ne peut pas être terminé directement car il doit attendre l'achèvement de la reconfiguration ou la préemption. Dans ce cas, le Gestionnaire de périphériques virtuel prévient la machine virtuelle en envoyant des requêtes IPC, et laisse au PPR Moniteur le suivi de ces solutions côté de FPGA. Ce dernier fournit des interruptions au Gestionnaire de périphériques virtuels lorsque la reconfiguration/preemption est terminée.

## 4. Implémentation

Le micro-noyau Ker-ONE est construit sur l'architecture ARMv7 basée sur une plateforme Zynq-7000. Dans le domaine du logiciel, le système est divisé en trois objets : le micro-noyau Ker-ONE, l'environnement utilisateur, et le client OS/applications. Tant le micro-noyau et de l'environnement de l'utilisateur sont construits de façon indépendante, ils coopèrent pour établir l'environnement de virtualisation. Les clients/applications sont développés et construits par les utilisateurs.

Dans le cadre de cette thèse, nous avons para-virtualisé un RTOS bien connu,  $\mu$ C/OS-II, qui est massivement utilisé dans l'éducation et la recherche. Le système d'exploitation client virtualisé résultant est appelé Mini- $\mu$ C/OS. La quantité de lignes de code (LoC) qui a été nécessaire pour modifier l'OS original  $\mu$ C/OS est très faible. Il faut compter 139 lignes pour le code source modifié et 223 lignes supplémentaires pour le patch.

La conception de Ker-ONE se traduit par une mise en œuvre légère avec une petite taille de TCB. Le micro-noyau KER-ONE est construit avec moins de 3000 lignes de Code. Ce résultat a été obtenu grâce aux efforts fournis pour éliminer toutes les fonctionnalités inutiles du noyau.

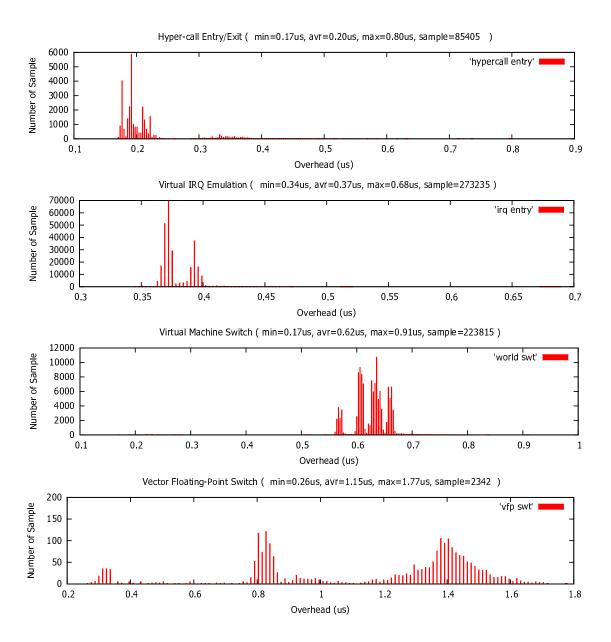

## 5. Evaluations

## 5.1 Impact de la virtualisation

Nous avons mené plusieurs expériences afin d'évaluer les performances de Ker-ONE. Les expériences sont basées à la fois sur des mesures et des critères standards. Dans une première étape, nous avons évalué les fonctions de base de l'hyperviseur afin d'obtenir une évaluation générale. Ces fonctions se traduisent par un faible surcoût en termes de temps d'exécution. Ce surcoût temporel a été estimé à  $1 \mu s$ .

Ensuite, nous nous sommes concentrés sur la performance du client RTOS. Nous avons effectué des tests qualitatifs sur les fonctions du RTOS, et mesuré l'impact des surcoûts réels sur l'ordonnancement. Finalement, nous avons exécuté des applications embarquées pour estimer une vitesse effective. Sur la base des résultats obtenus, nous avons présenté une analyse approfondie de l'ordonnançabilité des clients RTOS. Les résultats montrent que notre approche met en œuvre la virtualisation en temps réel avec de faibles coûts et des performances proches de celles obtenues avec un OS natif.

Sur la base des résultats de l'expérience évaluant l'impact de la virtualisation sur le RTOS original, l'impact global que la virtualisation provoque sur le temps de réponse du RTOS  $\Delta_{VM}^{Response}$  peut être estimée à 3.08  $\mu s$ . L'équation Eq.(5) peut alors être simplifiée comme suit :

$$\Theta_i \approx \lceil \frac{E_i^{Native} + \Delta_{VM}^{ei}}{\Lambda^{Tick}} \rceil, \ if \ \Delta_{VM}^{Response} \ll \Delta^{Tick}.$$

(6)

Par conséquent, l'influence majeure sur la configuration de l'ordonnancement du RTOS est causée par  $\Delta_{VM}^{ei}$ . Pour garantir l'ordonnançabilité du système, le temps d'exécution réel des taches doit être mesuré avec précision. Pour une  $T_k$  qui fonctionne à l'origine sur un RTOS natif, son ordonnançabilité est toujours garantie sur Ker-ONE si :

$$\forall T_i \in T_k, \lceil \frac{E_i^{Native} + \Delta_{VM}^{ei}}{\Delta^{Tick}} \rceil = \lceil \frac{E_i^{Native}}{\Delta^{Tick}} \rceil. \tag{7}$$

Si cette contrainte n'est pas respectée, la configuration des paramètres d'ordonnancement pour  $T_k$  doit être recalculée pour répondre aux contraintes temps réel.

Résumé de la Thèse xiii

## 5.2 Evaluation du coût de la reconfiguration dynamique

Notre évaluation porte sur la latence d'allocation d'une tâche au sein d'une zone reconfigurable. Cette latence provient de plusieurs sources : les défauts de pages,les IPCs, l'ordonnancement des machines virtuelles et l'exécution du Gestionnaire de périphériques virtuels. Les coûts globaux sont résumés dans la TABLE 1.

Table 1 – Les overheads de l'allocation des DPR

| Methods                   | Overheads $(\mu s)$                  |

|---------------------------|--------------------------------------|

| Assign                    | $3.03\mu s$                          |

| $\{Assign,\ Reconfig.\}$  | $6.76\mu s + T_{RFCG}$               |

| $\{Preempt\}$             | $5.10\mu s + T_{preempt}$            |

| $\{Preempt, Reconfig. \}$ | $9.96\mu s + T_{preempt} + T_{RFCG}$ |

D'après le tableau, on peut clairement observer que les allocations directes peuvent être efficacement réalisées avec une latence de 3  $\mu s$ .

## 6. Conclusion et perspectives

Cette thèse décrit un micro-noyau original permettant de gérer la virtualisation des systèmes embarqués et fournissant un environnement pour les machines virtuelles en temps réel. Nous avons simplifié l'architecture du micro-noyau en ne gardant que les caractéristiques essentielles requises pour la virtualisation, et massivement réduit la complexité de la conception du noyau. Sur la base de ce micro-noyau, nous avons mis en place un environnement capable de gérer des ressources reconfigurables dans un système composé de machines virtuelles. Les accélérateurs matériels reconfigurables sont mappés en tant que dispositifs classiques dans chaque machine. Grâce à une gestion efficace de la mémoire dédiée, nous permettons de détecter automatiquement le besoin de ressources et autorisons l'allocation dynamique.

Selon diverses expériences et évaluations, nous avons montré que Ker-ONE ne dégrade que très peu les performances en termes de temps d'exécution. Les surcoûts engendrés peuvent généralement être ignorés dans les applications réelles. Nous avons également étudié l'ordonnançabilité temps réel dans les machines virtuelles. Les résultats montrent que le respect de l'échéance des tâches du RTOS est garanti. Nous avons également démontré que le noyau proposé est capable d'allouer des accélérateurs matériels très rapidement.

Pour les travaux futurs, nous envisageons de proposer une gestion de la mémoire plus sophistiquée afin que de gros OS généralistes comme Linux puissent être pris en charge. Nous souhaiterions aussi porter notre micro-noyau sur une architecture ARM plus avancée afin d'exploiter pleinement l'extension de la virtualisation matérielle. D'autre part, la politique d'allocation des ressources DPR doit être pleinement étudiée. Il serait intéressant de développer l'algorithme de recherche de solutions plus sophistiquées et de

xiv Table of Contents

discuter de l'influence des différents paramètres à prendre en compte pour l'allocation des ressources. Finalement, nous souhaitons considérer la mise en œuvre de scénarios réels afin de pouvoir concrètement évaluer la performance de notre approche par rapport aux solutions existantes dans ce domaine.

# TABLE OF CONTENTS

| Ta           | able o | of Con  | tents                                                                                                                                                              | xiv  |

|--------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| $\mathbf{A}$ | bbre   | viation | ıs                                                                                                                                                                 | xix  |

| In           | trod   | uction  |                                                                                                                                                                    | 1    |

| 1            | Cor    | NCEPTS  | S AND RELATED WORKS                                                                                                                                                | 5    |

|              | 1.1    | Basic   | Virtualization Theories                                                                                                                                            |      |

|              |        | 1.1.1   | Fundamental Theories of Virtualization                                                                                                                             | . 5  |

|              |        |         | 1.1.1.1 Machine Model                                                                                                                                              | . 6  |

|              |        |         | 1.1.1.2 Mapping Mechanism                                                                                                                                          | . 8  |

|              |        |         | 1.1.1.3 Instruction behavior                                                                                                                                       | . 9  |

|              |        | 1.1.2   | Virtualization Approaches                                                                                                                                          | . 10 |

|              |        |         | 1.1.2.1 Hardware Virtualization Extension                                                                                                                          | . 11 |

|              |        |         | 1.1.2.2 Dynamic Binary Translation                                                                                                                                 | . 13 |

|              |        |         | 1.1.2.3 Para-Virtualization                                                                                                                                        | . 14 |

|              | 1.2    | ARM-    | -based Embedded System Virtualization                                                                                                                              | . 16 |

|              |        | 1.2.1   | Micro-kernels                                                                                                                                                      | . 19 |

|              |        |         | 1.2.1.1 L4 Micro-kernels                                                                                                                                           | . 20 |

|              |        |         | 1.2.1.2 OKL4 Microvisor                                                                                                                                            | . 21 |

|              |        | 1.2.2   | Hypervisors                                                                                                                                                        | . 21 |

|              |        |         | 1.2.2.1 KVM                                                                                                                                                        | . 22 |

|              |        |         | 1.2.2.2 Xen                                                                                                                                                        | . 24 |

|              |        | 1.2.3   | ARM-based Full Virtualization                                                                                                                                      | . 25 |

|              | 1.3    | Real-t  | ime Scheduling for Virtual Machines                                                                                                                                | . 26 |

|              |        | 1.3.1   | Compositional Real-time Scheduling                                                                                                                                 | . 27 |

|              |        |         | 1.3.1.1 L4/Fiasco Micro-kernel with Compositional Scheduling                                                                                                       | . 29 |

|              |        |         | 1.3.1.2 RT-Xen                                                                                                                                                     | . 30 |

|              |        | 1.3.2   | Other Real-time Approaches                                                                                                                                         | . 31 |

|              | 1.4    | CPU-I   | FPGA Hybrid Architecture                                                                                                                                           | . 32 |

|              |        | 1.4.1   | Dynamic Partial Reconfiguration                                                                                                                                    | . 34 |

|              |        | 1.4.2   | $\label{eq:cpu} \text{CPU/FPGA Execution Model} \dots \dots$ | . 35 |

|              |        |         | 1.4.2.1 CPU/FPGA offload model                                                                                                                                     | . 36 |

|   |     |            | 1.4.2.2 CPU/FPGA unified model                    | 37        |

|---|-----|------------|---------------------------------------------------|-----------|

|   |     | 1.4.3      | DPR Resource Virtualization                       | 39        |

|   | 1.5 | Summ       | ary                                               | 42        |

| 2 | Kei | R-ONE      | E: LIGHTWEIGHT REAL-TIME VIRTUALIZATION ARCHITEC- |           |

|   | TUE | <b>t</b> E |                                                   | <b>45</b> |

|   | 2.1 | Overv      | iew of the Ker-ONE Microkernel                    | 45        |

|   | 2.2 | Resou      | rce Virtualization                                | 48        |

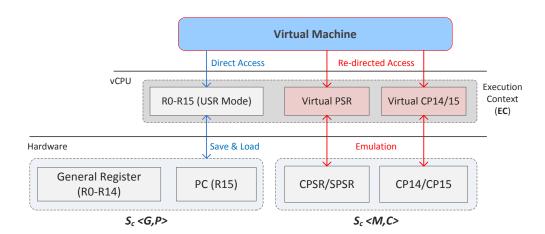

|   |     | 2.2.1      | CPU virtualization                                | 48        |

|   |     |            | 2.2.1.1 CPU Resource Model                        | 50        |

|   |     |            | 2.2.1.2 Instruction Emulation                     | 52        |

|   |     |            | 2.2.1.3 Virtual CPU Model                         | 54        |

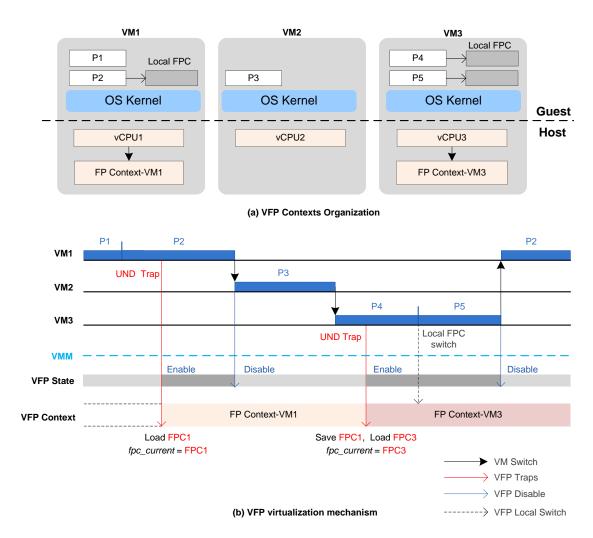

|   |     | 2.2.2      | Vector Floating-Point Coprocessor Virtualization  | 55        |

|   |     | 2.2.3      | Memory Management                                 | 57        |

|   |     |            | 2.2.3.1 Memory Access Control                     | 57        |

|   |     |            | 2.2.3.2 Address Space Virtualization              | 59        |

|   |     |            | 2.2.3.3 Memory Virtualization Context             | 61        |

|   | 2.3 | Event      | Management                                        | 61        |

|   |     | 2.3.1      | Interrupt Virtualization                          | 62        |

|   |     |            | 2.3.1.1 Emulation of Interrupts                   | 63        |

|   |     |            | 2.3.1.2 Virtual Interrupt Management              | 65        |

|   |     | 2.3.2      | Timer Virtualization                              | 66        |

|   |     | 2.3.3      | Inter-VM Communication                            | 67        |

|   | 2.4 | Optim      | nization                                          | 68        |

|   | 2.5 | Real-t     | ime OS Virtualization                             | 70        |

|   |     | 2.5.1      | VMM Scheduler                                     | 71        |

|   |     | 2.5.2      | RTOS Events                                       | 72        |

|   |     | 2.5.3      | RTOS Schedulability Analysis                      | 73        |

|   | 2.6 | Summ       | ary                                               | 75        |

| 3 | Dy  | /NAMI      | C Management of Reconfigurable Accelerators on    |           |

|   | KEI | R-ONE      | E                                                 | 77        |

|   | 3.1 | Introd     | uction to the Zynq-7000 platform                  | 77        |

|   |     | 3.1.1      | PS/PL Communication                               | 78        |

|   |     | 3.1.2      | Partial Reconfiguration                           | 80        |

|   |     | 3.1.3      | Interrupt Sources                                 | 81        |

|   | 3.2 | DPR I      | Management Framework                              | 81        |

|   |     | 3.2.1      | Framework Overview                                | 82        |

|   |     | 3.2.2      | Hardware Task Model                               | 84        |

|   |     | 3.2.3      | PRR State Machine                                 | 86        |

|   |     | 3.2.4      | PR Resource Requests and Solutions                | 88        |

|   |     | 3.2.5      | Virtual Device Manager                            | 90        |

|   |     | 3.2.6      | Security Mechanisms                               | 94        |

| Table of Contents | xvii |

|-------------------|------|

|                   |      |

|               | 3.3            | 3.2.7 Initialization Sequence                  | . 96<br>. 96<br>. 97 |  |

|---------------|----------------|------------------------------------------------|----------------------|--|

| 4             | Імр            | PLEMENTATION AND EVALUATION                    | 101                  |  |

|               | 4.1            | . 101                                          |                      |  |

|               |                | 4.1.1 RTOS Para-virtualization                 | . 102                |  |

|               |                | 4.1.2 Complexity                               | . 103                |  |

|               |                | 4.1.3 System Mapping                           | . 104                |  |

|               |                | 4.1.4 Ker-ONE Initialization Sequence          | . 106                |  |

|               | 4.2            | Ker-ONE Virtualization Performance Evaluations | . 106                |  |

|               |                | 4.2.1 Basic Virtualization Function Overheads  | . 107                |  |

|               |                | 4.2.2 RTOS Virtualization Evaluation           |                      |  |

|               |                | 4.2.2.1 RTOS Benchmarks                        |                      |  |

|               |                | 4.2.2.2 RTOS Virtualization Overheads          |                      |  |

|               |                | 4.2.3 Application Specific Evaluation          |                      |  |

|               |                | 4.2.4 Real-time Schedulability Analysis        |                      |  |

|               | 4.3            | DPR Allocation Performance Evaluation          |                      |  |

|               |                | 4.3.1 Overhead Analysis                        |                      |  |

|               |                | 4.3.2 Experiments and Results                  |                      |  |

|               |                | 4.3.3 Real-time Schedulability Analysis        |                      |  |

|               |                | 4.3.3.1 Response Time                          |                      |  |

|               |                | 4.3.3.2 Execution Time                         |                      |  |

|               | 4.4            | Summary                                        | . 125                |  |

| 5             | Con            | aclusion and Perspectives                      | 127                  |  |

|               | 5.1            | Summary                                        | . 127                |  |

|               | 5.2            | Perspectives and Future Works                  | . 129                |  |

| Li            | st of          | Figures                                        | 131                  |  |

| $\mathbf{Li}$ | List of Tables |                                                |                      |  |

| Bi            | Bibliography   |                                                |                      |  |

# **ABBREVIATIONS**

API: Application Programming Interface

ASIC: Application-Specific Integrated Circuit

$\mathbf{CP}: \mathbf{Control} \ \mathrm{co-Processor}$

CPSR : Current Processor State Register DACR : Domain Access Control Register

DMA: Direct-Memory Access

**DPR**: Dynamically Partial Reconfiguration

EC : Execution Context

$\mathbf{FFT}: \mathbf{Fast} \ \mathbf{Fourier} \ \mathbf{Transform}$

FPGA: Field Programmable Gate Array

GIC : Generic Interrupt Controller

$\mathbf{GPOS}: \mathbf{General\text{-}Purpose}$  Operating System

IP: Intellectual Property

$\begin{array}{l} \mathbf{IPC}: \mathbf{Inter\text{-}Process} \ \mathbf{Communication} \\ \mathbf{IRS}: \mathbf{Interrupt} \ \mathbf{Routine} \ \mathbf{Service} \end{array}$

ISA: Instruction Set Architecture

IVC: Inter-Virtual machine Communication

LoC: Lines of Code

MMU: Memory Management Unit

OFDM: Orthogonal Frequency Division Multiplexing

$\mathbf{OS}: \mathbf{O} \mathbf{perating} \ \mathbf{S} \mathbf{ystem}$

PCAP: Processor Configuration Access Port

$\mathbf{PL}: \mathbf{Programmable} \ \mathbf{Logic}$

PL0/1: Privilege Level 0/1 PRR: Partial Reconfigurable Region

PS: Processing System

PSR: Processor Status Register

**QAM**: Quadrature Amplitude Modulation

$\mathbf{RM}$ : Reconfigurable Module

RP: Reconfigurable Partition RTOS: Real-Time Operating System

SoC: System on Chip

SRAM: Static Random Access Memory

TCB: Trusted Computing Base

TTBR: Translation Table Base Register

xx Abbreviations

$\mathbf{TTC}:\mathbf{Triple}\ \mathbf{Timer}\ \mathbf{Counter}$

$\mathbf{VD}$ : Virtual Device

$\mathbf{VFP}: \mathbf{Vector} \ \mathbf{Floating-Point}$

VHDL : Very high speed integrated circuit Hardware Description Language

$\mathbf{VM}: \mathbf{V}$ irtual  $\mathbf{M}$ achine

$\mathbf{VMM}: \mathbf{V}irtual\ \mathbf{M}achine\ \mathbf{M}onitor$

# INTRODUCTION

## Context

Virtualization has become more and more popular in the embedded computing domain, especially for today's intelligent portable devices such as smart-phones and vehicles. This technology offers the advantage of better energy efficiency, shorter time-to-market cycles and higher reliability. As a result, the exploration of virtualization techniques on embedded systems constitutes a hot topic in the industrial and personal embedded computing domains.

Traditionally, embedded computing systems are used to be relatively simple single-purpose devices, where software is subject to particular constraints, such as power consumption or real-time processing. Only simple operating systems (OS) or bare-metal applications generally run on top of systems. Modern embedded systems, however, are increasingly playing the role of general-purpose systems, due to their growing computing abilities and resources. In this case, software-based systems that were formerly divided to provide different functions are now merging into one platform. As an example, in modern embedded devices, some critical background services may run concurrently with some user-oriented applications, which may be designed for different systems.

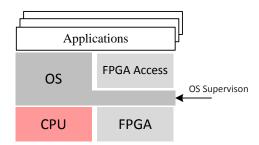

Virtualization technology can help device vendors by enabling concurrent execution of multiple operating systems, so that the legacy software stack can be easily ported to contemporary platforms, saving the expensive development and verification efforts. On the other hand, some conventional constraints still remain for embedded systems: limited resources (compared to PCs), real-time processing, and limited battery capacity, which are critical factors in virtualization. Furthermore, in such a mixed-criticality system, it is essential for a virtualization system to guarantee the correctness of critical task timing constraints, since they may significantly influence the system safety. In this case, the system scheduling mechanism is forced to guarantee the real-time tasks deadlines, so that the system manner can be predictable.

One key characteristic of virtualization technology is security, i.e. the isolation and independence among different system components, so that any malfunction or incorrect behaviors are constrained to their own domains. The virtual and physical computing platforms are decoupled via virtual machine (VM), which provides each hosted guest with a separate and secure execution environment. The guest OS runs on the virtual platform, while the actual physical layer is managed by an underlying hypervisor, the virtual ma-

2 Introduction

chines monitor (VMM). Virtual machines are temporally and logically independent from each other and cannot affect the system outside its domain. Such systems are also called virtual machine systems. In fact, the issue of security has become increasingly important since OS security is more and more threatened by malicious pieces of code. In order to ensure system security, hypervisors must be kept as small as possible and feature a small trust computing size (TCB).

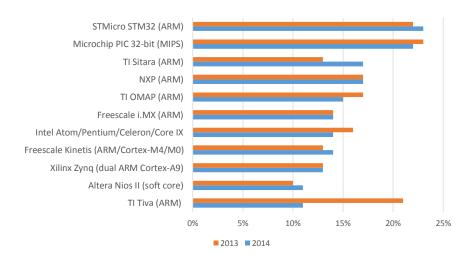

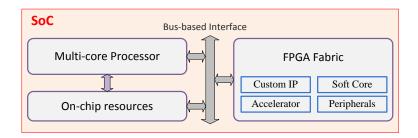

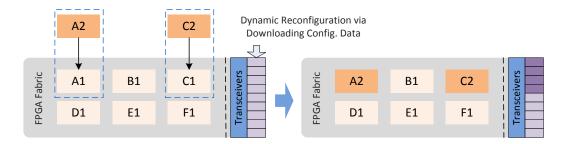

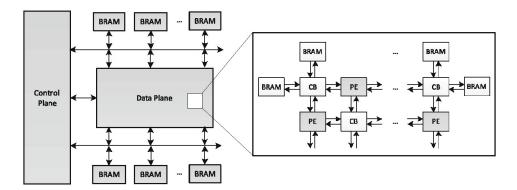

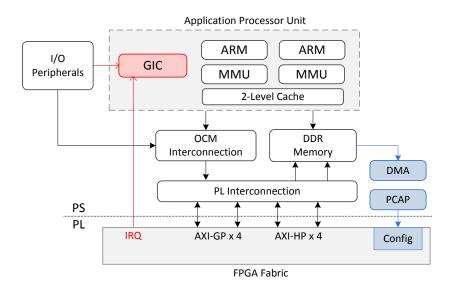

Besides these software aspects, another challenge for embedded device vendors is that the improvement of computing performance has become more and more difficult to manage with traditional approaches such as IC scaling and ASIC. As an alternative, the interest of vendors have progressively move on to the concept of CPU-FPGA hybrid System-on-Chip (SoC). Currently, FPGA devices are already popular in embedded system designs as a result of their outstanding flexibility, low power consumption and speed-up performance. This is especially true with the Dynamic Partial Reconfiguration (DPR) technique, which has revealed considerable potential in hosting hardware accelerators with less resource consumption. Therefore, the idea of enhancing embedded processor with an FPGA fabric has been considered as a promising solution to improve performances. Xilinx and Altera have both released ARM-FPGA hybrid embedded systems, while Intel's Xeon-FPGA devices are also on their way.

Embedded systems that are based on this type of platforms can benefit from the flexibility of processors and from the FPGA performances. This makes it possible to extend the virtualization technology to the reconfigurable computing technology. In this case, virtual machine users can easily and securely access IP accelerators on the FPGA using the DPR technique.

In this context, a new challenge consists in providing an efficient management mechanism while respecting the independence of virtual machines. The reconfigurable resources have to be virtualized so that virtual machines can access them independently. This feature is critical in virtualization to guarantee the system security. However, though reconfigurable accelerators on conventional embedded systems have been studied in numerous researches, they are mostly implemented in simple applications and OSs, while the usage and management of the DPR technique in a virtualized environment remains an open problem.

This thesis is based on the mentioned issues of current embedded systems. In our research, we focus on the small-scaled embedded ARM-FPGA hybrid systems. These systems are designed with limited resources, and may be used for small devices such as Internet-of-Things (IoT). In this context, we propose an innovative lightweight virtualization approach that is capable of hosting real-time virtual machines and efficiently utilizing reconfigurable FPGA devices. Our approach is implemented with low complexity and high adaptivity, and is suitable for embedded devices that try to take advantage of both virtualization and DPR techniques. In this dissertation we have also run extensive experiments on our system to evaluate the overall performance of the proposed approach.

## Manuscript organization

The remainder of this thesis is organized as follows: In Chapter 1, we introduce the general techniques and concepts used throughout this thesis. We first focus on the major theories of virtualization technology in embedded systems, dealing especially with real-time constraints. We then describe the concepts and principles of DPR technology. We will also present the state of the art in related researches, introducing their principles and major features. In Chapter 2, we describe in details the proposed virtualization architecture. Fundamental structures and designs are presented and explained. We also focus on the real-time virtualization mechanism. In Chapter 3, we propose the management of DPR modules in our system, describing both sharing and security mechanisms. In Chapter 4, we demonstrate the evaluations taken from standard open-source benchmarks as well as custom experiments. The performance of our system in terms of real-time scheduling and reconfigurable computing are given and analyzed. We conclude this thesis and give the perspectives of our work in Chapter 5.

4 Introduction

## CHAPTER 1

# CONCEPTS AND RELATED WORKS

## 1.1 Basic Virtualization Theories

In the context of computing systems, the "virtualization" term refers to a system virtualization technology, which permits multiple operating systems to be executed simultaneously on the same physical machine. The concept of virtualization dates back to the 1960s and has been initially implemented in IBM's mainframes [Gol74]. In 1974, Popek and Goldberg defined formal system virtualization criteria for computing architectures, as the essential conditions for a computing machine to be virtualized. These criteria constitute the groundwork of the virtualization technology [PG74]. Starting from this model, virtualization experienced decades of research, and has achieved tremendous success in both academic and commercial domains. In this section, we first introduce the fundamental theories of virtualization technology.

#### 1.1.1 Fundamental Theories of Virtualization

In modern computer architectures, a working space is generally divided into several execution layers called *privilege levels* (or *rings*), in order to protect critical resources. While the highest privilege level is authorized to freely control the whole computing machine resources, the lowest privilege level, or the non-privilege level, is only permitted to limited non-critical parts. Accessing high-privilege resources from low-privilege levels may cause an exception, denoted as a *trap*, which will alert the processor of the forbidden behavior. Thus, the highest privilege level is always used by operating systems to hold the most important codes and data to ensure the security, while user applications and processes are running on the non-privilege levels.

In classic implementations, virtualization is achieved by adding a software abstract layer that interfaces the platform resources and the users, which decouples the underlying hardware from the operating systems [Gol74]. The de-privileged operating systems are executed in a virtual and isolated environment that emulates the hardware resources, and are viewed as guest operating systems. A virtual machine (VM) refers to all software components, e.g. guest operating systems and applications that are running within such

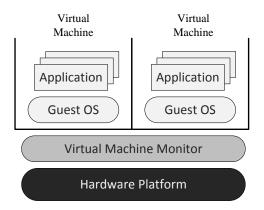

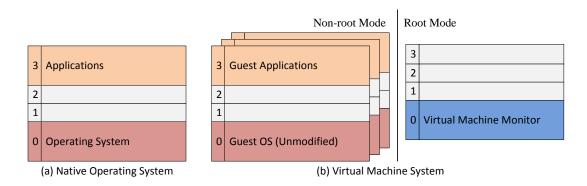

Figure 1.1 – Typical virtual machine system architecture

environments. Virtual machines are under the supervision of a virtual machine monitor (VMM). This architecture is also called the virtual machine system. The typical architecture of virtual machine system is shown in Figure 1.1.

The Virtual machine monitor is the most privileged component of a virtualization system, and runs directly on the hardware. The VMM provides a basic functionality that is similar to an OS kernel: controlling the hardware platform and managing the components on its top. Additionally, VMM ensures the temporal and logical isolation of virtual machines in the less-privilege levels. Any behavior of a virtual machine is constrained to its own domain, which makes it impossible to influence the outside world. In a sense, VMM holds virtual machines as if traditional OS holding processes, except that virtual machines are given the impression that they are granted with the whole hardware platform.

In virtual machine systems, two metrics should be considered: the virtualization efficiency and the trust computing base (TCB) size. Virtualization efficiency evaluates the mechanism of virtualization, indicating the adaptivity of a virtualization approach. In most cases, higher virtualization efficiency means lower performance degradation for OS hosted in virtual machine. On the other hand, the TCB is the part of software that runs with the highest privilege and must be trusted. In the context of virtualization, TCB size generally corresponds to the size of VMM. Lower TCB size implies less threats and smaller attack surface from malicious user applications or guest OS that has been compromised. For the consideration of system security, small-sized TCB is always preferred in virtualization techniques.

#### 1.1.1.1 Machine Model

The criteria of virtual machine systems were formally defined by Popek and Goldberg [PG74], which are well known as the conditions for *classical virtualizability*. Architectures that meet these criteria are considered as capable to host virtual machines. The machine model that Popek and Goldberg used was based on the computers available at that time,

such as DEC PDP-10 and IBM 360/67, and was intentionally simplified as:

$$S \equiv \langle E, M, P, R \rangle \tag{1.1}$$

In this definition, the state of the machine model S is composed of the memory E, the processor mode M, the program counter P and the relocation-bounds register R. This model considers the memory space as linearly addressable and ignores the interactions with I/O devices and interrupts, which were rational simplifications according to the state of micro-processors at that time.

However, due to the advances in computing technologies, the model no longer fits current architectures. Some novel characteristics of modern computers have been greatly developed, and have become too significant to be ignored, which are listed as follows:

- Paged virtual memory system is fully exploited in modern operating systems to provide applications with many key facilities and protections, such as dynamic linking, shared libraries and independent virtual address spaces. The details of mapping and translations must be included in the machine state.

- Modern machines are also significantly sensitive to timing. In some cases, timingdependent behaviors influence not only the user experiences but also the correction of the system.

- Peripherals and integrated controllers also play important roles in contemporary computers, for they help the processor to manage hardware resources. They may include various controllers (e.g. interrupt controller and bus controller), and general I/O devices.

Therefore, some researchers have attempted to extend the model proposed by Popek and Goldberg to adjust it to modern computer architectures. In [VGS08] authors redefined the *classical virtualizability* model by extending it to include system constructs that do not belong to the original model. The research of [DH10] also tried to include interrupts and I/O in their updated model. However, the complete machine model of current computer architecture was given by Penneman in [PKR<sup>+</sup>13]:

$$S \equiv \langle E, M, P, G, C, A, D^M, D^P \rangle$$

. (1.2)

In this model, besides original elements E, M and P, additional objects are included: the general-purpose registers G, the configuration registers C, the address space mapping A, the Memory-Mapped IO (MMIO) device state  $D^M$  and the Port-Mapped IO (PMIO) device state  $D^P$ . Note that, even though I/O devices may be mapped into the physical memory, the device state  $D^M/D^P$  is omitted from E.

When considering timing-dependent systems, this definition of machine model can also be revised to be:

$$S \equiv \langle E, M, P, G, C, A, D^M, D^P, T \rangle,$$

(1.3)

where the additional element T stands for the execution timings of computer.

## 1.1.1.2 Mapping Mechanism

In modern computing machines, paged virtual address translation mechanism has been critical for resource management. Software are compiled and executed according to the virtual address, while the actual physical space is generally hidden from them. Via the translation table, each virtual address page can be assigned with independent physical memory spaces and access permissions. For simplification, we can assume that all memory accesses are performed in the virtual address space.

According to the definition of machine model Eq.(1.2), virtual addresses are accessed by the address mapping A, which can be defined as:

**Definition 1.** Address mapping A(V, P, X) maps the physical address space P to a virtual address space V according to the access control policy X. A consists of a set of 3-tuples (v, p, x) in which  $v \in V$  is a virtual address,  $p \in P$  is the corresponding physical address, and x is the access permission identifier.

We denote the translation function performed according to translation table A as  $Trans_A(v,x)$ . Thus, its virtual address space V is valid when :

$$\forall v \in V, \exists p \in P, p = Trans_A(v, x). \tag{1.4}$$

Upon every memory access, the translation function  $Trans_A(v, x)$  calculates the physical memory space according to the virtual address v and permission check x. If for an address v, the corresponding translation does not exist or is not permitted, a memory trap will be triggered.

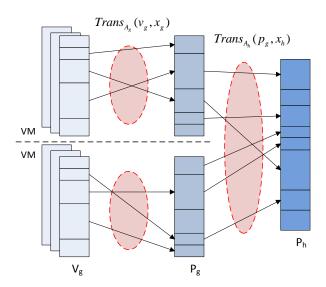

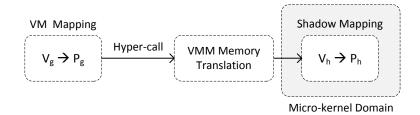

In the context of virtual machine systems, address mapping becomes more complex than traditional physical-to-virtual translation. Operating systems tend to build up its own translation tables to create virtual address space. In virtualization, however, the physical memory space of guest OS needs to be virtualized by the VMM In this case, a two-stage translation is performed. First, the virtual address space  $(V_g)$  of guest OS is translated to the guest OS physical address  $(P_g)$ . Second,  $P_g$  is translated to the actual physical memory  $(P_h)$  in the host machine, as shown in FIGURE 1.2.

Therefore, VMM is responsible to manage both the address mappings of guest OS and host machine, respectively denoted as  $A_g(V_g, P_g, X_g)$  and  $A_h(P_g, P_h, X_h)$ . We assume  $E_N$  is the physical memory space which VMM allocates to virtual machine  $VM_N$  on the host machine, the address space of virtual machine  $VM_N$  is valid when it meets the criterion:

$$\forall v \in V_q, \exists p \in E_N, p = Trans_{A_h}(Trans_{A_g}(v, x_q), x_h). \tag{1.5}$$

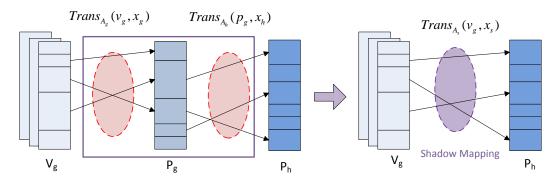

Maintenance of address mappings is one of the most complicated functionality of VMM. A guest OS is generally permitted to freely map the virtual addresses. During the translation, VMM should respect the guest translation table and accordingly allocate memory resources. For typical memory management units (MMU) that only support one-stage translation, one solution is to compose the guest and VMM mappings into a single address mapping, which directly maps the guest virtual address to the host physical memory. This map is called shadow mapping [AA06], which is shown in Figure 1.3. By

FIGURE 1.2 – Two-stage address mapping in virtual machine systems.

FIGURE 1.3 – Using shadow mapping to perform two-stage address mapping.

denoting the shadow mapping as  $A_s(V_g, P_h, X_s)$ , the access permission condition  $X_s$  must meet the following criteria :

$$\forall v \in V_g, Trans_{A_g} \text{ traps when } Trans_{A_g}(v, x_g) \text{ traps } \cup Trans_{A_g}(p_g, x_h) \text{ traps.}$$

(1.6)

As we can notice, the mechanism of shadow mapping requires additional effort from the VMM to monitor and establish protected shadow page table based on the mappings of guest and host machine. Therefore, to accelerate the maintenance of shadow mapping, in some computer architectures (e.g. ARMv7A/v8) MMU is enhanced with dedicated two-stage translation mechanisms, so that the translation from guest virtual address to host physical space is automatically handled by hardware [ARM12].

#### 1.1.1.3 Instruction behavior

In the context of virtualization, instructions are classified in three categories:

- **Privileged instructions** are those that execute correctly only in privilege level, and always trap in non-privilege level.

- Sensitive instructions are the ones that may threat the correction of virtualization. They can be further classified as: (1) *control-sensitive* instructions which manipulate the processor configurations; (2) *behavior-sensitive* instructions whose results depend on the processor execution mode.

- Innocuous instructions those instructions that are not sensitive.

Sensitive instructions must be monitored or prevented in virtual machines, since virtual machines are not allowed to change the configuration of processors, such as the execution mode or physical memory allocations. Furthermore, considering that guest OSs are not running at the privilege levels that they are originally intended for, the results of behavior-sensitive instructions are then incorrect.

Base on the classification of instructions, in [PG74], the theorem that defines the condition of instructions in virtualization was proved:

**Theorem 1.** (Popek and Goldberg [PG74]) For any conventional third generation computer, a virtual machine monitor may be constructed if the set of sensitive instructions for that computer is a subset of the set of privileged instructions.

According to this theorem, in an instruction set architecture (ISA) that meets the criterion, a trap will be triggered whenever sensitive instructions are executed in virtual machines. In this case, these behaviors are automatically detected and monitored, which is ideal for the construction of VMM, since software based on this ISA can be easily monitored in virtual machines. For this reason, such an instruction set is considered as *virtualizable*. A VMM based on a virtualizable ISA is called an *execute-and-trap* VMM.

In a virtual machine, the behaviors of instructions are constrained to the virtual machine domain, and should not influence the outside world. All sensitive instructions have to be interpreted and properly handled by the VMM. The virtualization of instructions follows the principles:

- Efficiency: all innocuous instructions are executed natively without the VMM intervention;

- Resource control: guest software is forbidden access to physical state and resources;

- **Equivalence**: guest software behaves identically as it runs natively on a system.

### 1.1.2 Virtualization Approaches

With decades of research, virtualization has been implemented on various platforms and architectures with different solutions. Considering that virtual machines are built on the simulation of physical platforms, the features of instruction set and processor architecture may significantly influence the approaches. Some processor vendors have

considered the demand of virtualization, and provided virtualizable architectures, including virtualizable ISAs and extensional hardware assistance. Such architecture will be ideal for virtualization since a VMM can be easily established. In other cases, for architectures which are not suitable for virtualization, alternate approaches are proposed to implement virtualization.

Generally, while being hosted in a virtualized environment, the performance of guest software will be inevitably degraded, so we wish to reduce the complexity of virtualization mechanisms to minimize the extra workload on the machine. On the other hand, the VMM must guarantee the isolated and secure virtual machine environment. To give more details, the implementation of virtualization should consider the following principles:

- Low complexity or footprint of VMM, so that the resources required for virtualization may be minimized.

- Low reliance on the guest OS source code. Virtualization should minimize the modification of guest software to maintain adaptability. The ideal solution is to host native OS directly in virtual machines without any modification.

- High virtualization efficiency, which means reducing virtualization cost to host guest software with a level of performance close to the native one.

- Strong isolation of system components, so that virtual machines are temporally and logically separated from each other.

While it is not likely that all principles could be emphasized equally, the solution of virtualization should try to maintain balance. For example, an embedded system which has limited resources may prefer a small-sized VMM. On the other hand, a tight-timing system can afford significant modifications on guest OS to obtain a higher performance.

There are two main virtualization approaches: full virtualization and para-virtualization. The full virtualization technique is also called native virtualization [ISM09]. It requires no modification of the guest software, and relies on the VMM to emulate the low-level features of the hardware platform. This feature allows native OSs like Linux or Android to run directly inside the virtual machines. Since it does not rely on the OS code, even close-source software can be easily hosted. Full virtualization relies on supporting technologies e.g. virtualizable ISA and hardware extensions.

Para-virtualization, on the other hand, refers to communication between the guest software and the VMM to implement virtualization. This mechanism is mostly implemented by modifying the guest software codes. Para-virtualization is especially suitable for architectures without hardware assistance or virtualizable ISA.

In this section we will introduce the existing technologies of full virtualization and para-virtualization. We will also overview the characteristics of different approaches.

### 1.1.2.1 Hardware Virtualization Extension

Considering the potentiality of virtualization, some contemporary computer architectures have introduced hardware support to help building virtual machine systems. This

FIGURE 1.4 – Virtualization extension provided by Intel VT-x/VT-i, where the guest software execute in original privilege levels, but in the non-root mode.

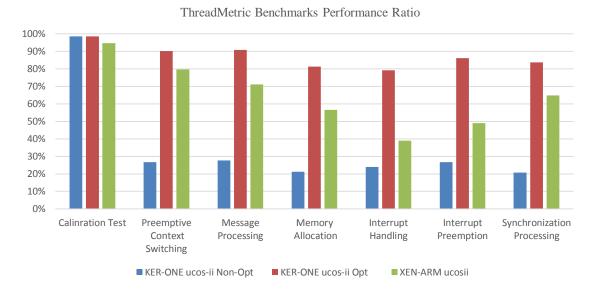

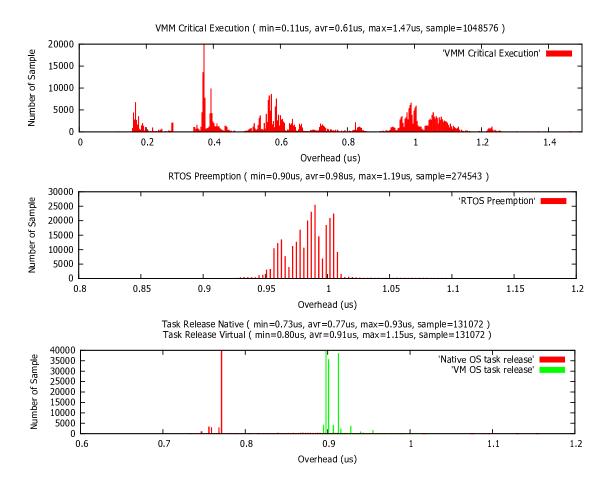

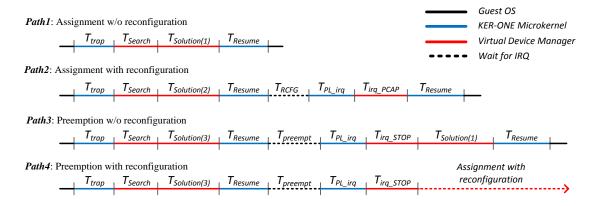

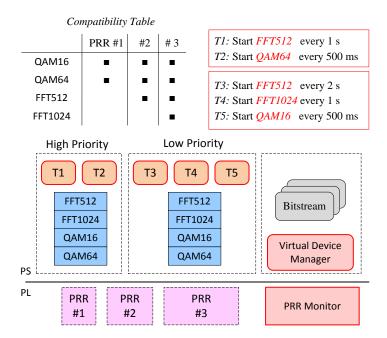

is denoted as hardware virtualization extension. Typical extensions include additional execution mode, virtualizable ISA, multi-stage MMU translation and virtual interfaces of system registers. Such extensions have been introduced to the traditional PC and server world for a decade, and have been used for the new generations of embedded processors recently. Here, we introduce two typical architectures : Intel VT-x/VT-i and ARM Cortex-A15.