# Transforming TLP into DLP with the dynamic inter-thread vectorization architecture

Sajith Kalathingal

## ▶ To cite this version:

Sajith Kalathingal. Transforming TLP into DLP with the dynamic inter-thread vectorization architecture. Hardware Architecture [cs.AR]. Université de Rennes, 2016. English. NNT: 2016 REN1S133 . tel-01426915v3

## HAL Id: tel-01426915 https://theses.hal.science/tel-01426915v3

Submitted on 28 Aug 2017  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

ANNÉE 2016

THÈSE / UNIVERSITÉ DE RENNES 1 sous le sceau de l'Université Bretagne Loire

pour le grade de DOCTEUR DE L'UNIVERSITÉ DE RENNES 1 Mention : Informatique École doctorale Matisse

> présentée par Sajith Kalathingal

préparée à l'unité de recherche INRIA Institut National de Recherche en Informatique et Automatique Université de Rennes 1

Transforming TLP into DLP with the Dynamic Inter-Thread Vectorization Architecture

Thèse soutenue à Rennes le 13 Décembre 2016

devant le jury composé de :

Bernard GOOSSENS Professeur à l'Université de Perpignan Via Domitia / Rapporteur Smail NIAR Professeur à l'Université de Valenciennes / Rapporteur Laure GONNORD Maître de conférences à l'Université Lyon 1 / Examinatrice Cédric TEDESCHI Maître de conférences à l'Université Rennes 1 / Examinateur André SEZNEC Directeur de recherches Inria / Directeur de thése Sylvain COLLANGE Chargé de recherche INRIA / Co-directeur de thése

## Acknowledgement

I would like to express my sincere gratitude to my thesis advisors, André SEZNEC and Sylvain COLLANGE. I would like to thank you for encouraging me and providing guidance during the course of work. Your advice on research have been priceless.

I would like to thank the jury members Bernard GOOSSENS, Smail NIAR, Laure GONNORD and Cédric TEDESCHI for providing the opportunity to defend the thesis.

I would like to thank my parents for supporting me throughout my life. Thank you for all of the sacrifices that you have made for me. Without your support I would not have reached so far.

I would like to thank the members of ALF team for their help and support and also for making my stay at Rennes really enjoyable.

I would like to thank my wonderful wife Amrutha Muralidharan for the moral support she has given me from thousands of kilometers away, in India. Thank you motivating me and for having the patience.

| Ta | ıble o | f Conte  | ents                                                  | 1  |

|----|--------|----------|-------------------------------------------------------|----|

| Ré | ésumé  | é en Fra | nçais                                                 | 5  |

| In | trodu  | ction    |                                                       | 9  |

| 1  | Bac    | kground  | 1                                                     | 15 |

|    | 1.1    | Instru   | ction-level parallelism                               | 18 |

|    |        | 1.1.1    | Instruction pipelining                                | 20 |

|    |        | 1.1.2    | Superscalar execution                                 | 21 |

|    |        | 1.1.3    | Out-of-order execution                                | 22 |

|    |        | 1.1.4    | Clustering for ILP                                    | 23 |

|    | 1.2    | Data-    | level parallelism                                     | 23 |

|    |        | 1.2.1    | Single Instruction Multiple Data                      | 24 |

|    |        | 1.2.2    | Single Instruction Multiple Threads (SIMT) $\ldots$ . | 27 |

|    | 1.3    | Threa    | d-level parallelism                                   | 30 |

|    |        | 1.3.1    | Coarse-grained multi-threading                        | 31 |

|    |        | 1.3.2    | Fine grained multi-threading                          | 31 |

|    |        | 1.3.3    | Simultaneous multi-threading (SMT)                    | 32 |

|    |        | 1.3.4    | Clustered multi-threading (CMT)                       | 33 |

|   | 1.4 | TLP v   | vs DLP                                                                                          | 35 |

|---|-----|---------|-------------------------------------------------------------------------------------------------|----|

|   | 1.5 | Chip i  | multiprocessor                                                                                  | 36 |

|   | 1.6 | Concl   | usion                                                                                           | 36 |

| 2 | Exp | loiting | inter-thread similarity in microprocessors                                                      | 39 |

|   | 2.1 | Inter-  | thread similarities in SPMD applications                                                        | 39 |

|   |     | 2.1.1   | Source of inter-thread similarities                                                             | 40 |

|   |     | 2.1.2   | Vectorization efficiency in an SMT                                                              | 42 |

|   |     | 2.1.3   | Dynamic Vectorization                                                                           | 43 |

|   | 2.2 | Threa   | d reconvergence for SPMD applications                                                           | 44 |

|   |     | 2.2.1   | Stack-based explicit reconvergence                                                              | 45 |

|   |     | 2.2.2   | SIMT extensions for stack-based implicit reconvergence                                          | 45 |

|   |     | 2.2.3   | Stack-less explicit reconvergence                                                               | 46 |

|   |     | 2.2.4   | Stack-less implicit reconvergence                                                               | 47 |

|   | 2.3 | Vector  | rization of instructions across threads                                                         | 49 |

|   | 2.4 | Gener   | al purpose architectures exploiting inter-thread redundancy                                     | 50 |

|   | 2.5 | GPU     | architectures to exploit inter-thread redundancies                                              | 51 |

|   | 2.6 | Concl   | usion $\ldots$ | 52 |

| 3 | Dyn | amic Ir | nter-Thread Vectorization Architecture                                                          | 55 |

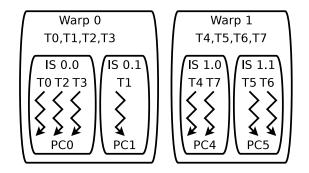

|   | 3.1 | Warps   | s in DITVA                                                                                      | 56 |

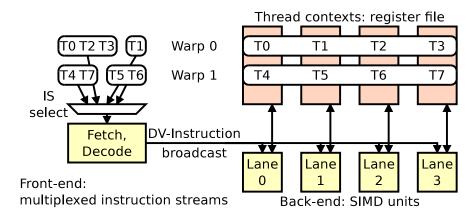

|   | 3.2 | Overv   | iew of the Dynamic Inter-Thread Vectorization Architecture                                      | 58 |

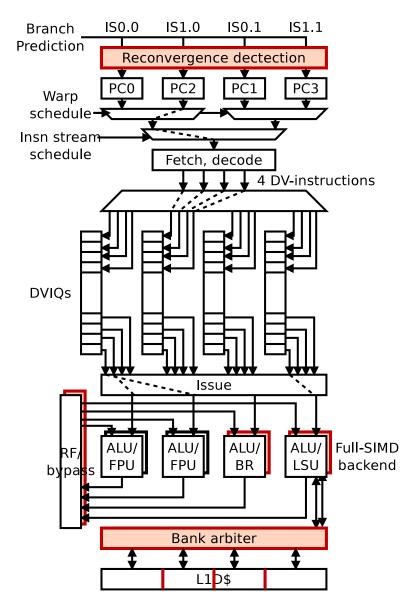

|   | 3.3 | Pipeli  | ne architecture                                                                                 | 60 |

|   |     | 3.3.1   | Front-end                                                                                       | 60 |

|   |     | 3.3.2   | In-order issue enforcement and dependency check $\ . \ . \ .$                                   | 63 |

|   |     | 3.3.3   | Execution: register file and functional units                                                   | 66 |

|   |     | 3.3.4   | Leveraging explicit SIMD instructions                                                           | 68 |

|   |     | 3.3.5   | Handling misprediction, exception or divergence                                                 | 69 |

|   | 3.4  | Data :  | memory accesses                                                                                 | 70 |

|---|------|---------|-------------------------------------------------------------------------------------------------|----|

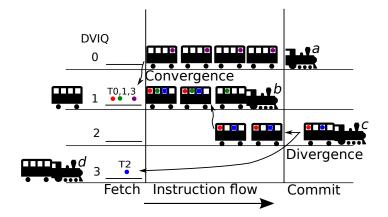

|   | 3.5  | Maint   | aining lockstep execution                                                                       | 71 |

|   | 3.6  | Cluste  | ered Multi-threading in DITVA                                                                   | 72 |

|   | 3.7  | Concl   | usion                                                                                           | 73 |

| 4 | Eval | luation |                                                                                                 | 77 |

|   | 4.1  | Exper   | imental Framework                                                                               | 77 |

|   |      | 4.1.1   | DITVA-SIM                                                                                       | 77 |

|   |      | 4.1.2   | Evaluations using DITVA-SIM                                                                     | 79 |

|   | 4.2  | Perfor  | mance evaluation                                                                                | 81 |

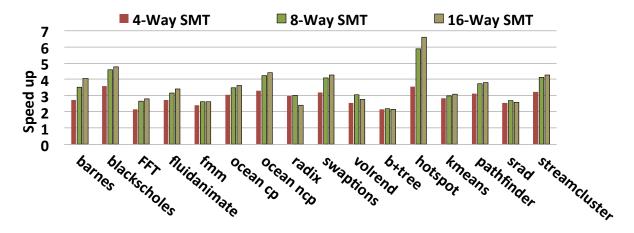

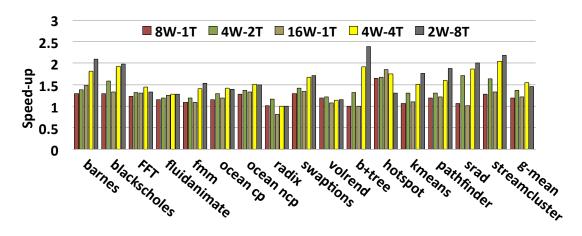

|   |      | 4.2.1   | Throughput                                                                                      | 81 |

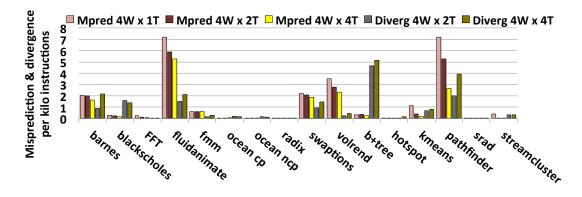

|   |      | 4.2.2   | Divergence and mispredictions                                                                   | 82 |

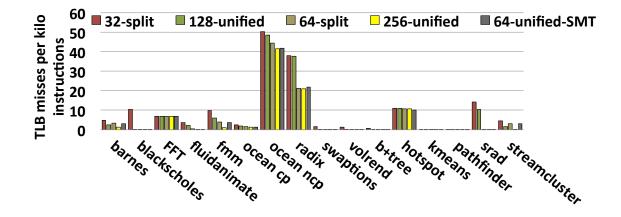

|   |      | 4.2.3   | Impact of split data TLB                                                                        | 83 |

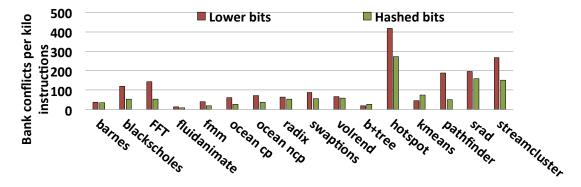

|   |      | 4.2.4   | L1 cache bank conflict reduction                                                                | 83 |

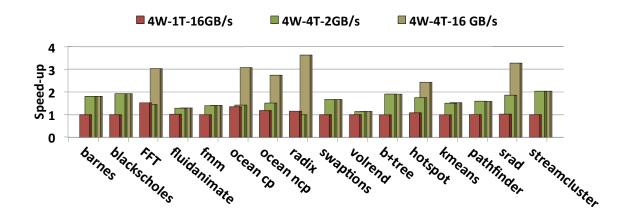

|   |      | 4.2.5   | Impact of memory bandwidth on memory intensive appli-<br>cations                                | 84 |

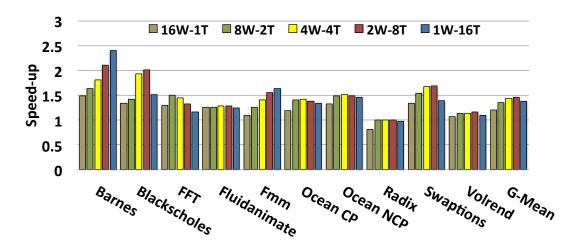

|   |      | 4.2.6   | Impact of Warp size                                                                             | 86 |

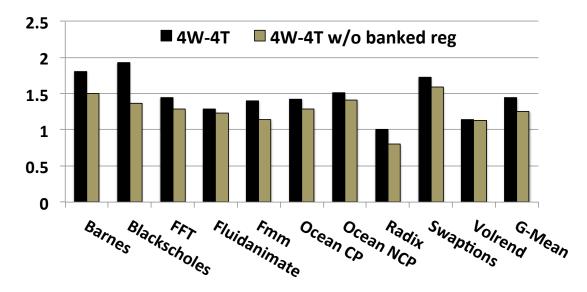

|   |      | 4.2.7   | Impact of banked DV-SIMD register banking                                                       | 86 |

|   | 4.3  | Hardv   | vare Overhead, Power and Energy                                                                 | 87 |

|   |      | 4.3.1   | Qualitative evaluation                                                                          | 87 |

|   |      | 4.3.2   | Quantitative evaluation                                                                         | 89 |

|   | 4.4  | Concl   | usion $\ldots$ | 90 |

| 5 | Futu | ure wor | k                                                                                               | 93 |

|   | 5.1  | Out-o   | f-order execution                                                                               | 93 |

|   |      | 5.1.1   | Register renaming                                                                               | 94 |

|   |      | 5.1.2   | Reservation station / Issue queue                                                               | 95 |

|   |      | 5.1.3   | Reorder buffer                                                                                  | 95 |

3

|           | 5.1.4   | Branch     | misprediction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 95  |

|-----------|---------|------------|------------------------------------------------------------------------------------------------|-----|

| 5.2       | Out-o   | f-order ex | tension for DITVA architecture                                                                 | 96  |

|           | 5.2.1   | Register   | $-management\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$                | 97  |

|           |         | 5.2.1.1    | Register allocation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                         | 98  |

|           |         | 5.2.1.2    | Register deallocation                                                                          | 99  |

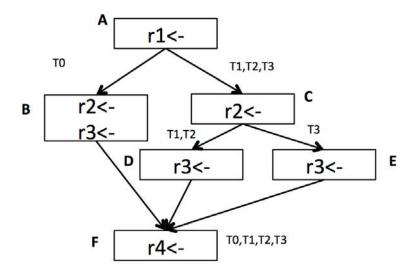

|           |         | 5.2.1.3    | Handling divergence and reconvergence                                                          | 99  |

|           | 5.2.2   | Handlin    | g branch misprediction                                                                         | 100 |

| 5.3       | Concl   | usion      |                                                                                                | 100 |

| Bibliog   | raphy   |            |                                                                                                | 119 |

| List of : | figures |            |                                                                                                | 121 |

## Résumé en Français

Dans cette thèse, nous proposons l'architecture Dynamic Inter-Thread Vectorization (DITVA), une technique pour améliorer les performances des applications multi-thread SPMD dans un microprocesseur généraliste. Les threads d'applications SPMD exécutent souvent les mêmes instructions sur des données différentes. Pour tirer parti de la redondance de contrôle dans les applications SPMD, DITVA assemble dynamiquement des instructions identiques de plusieurs threads en cours d'exécution en une seule instruction vectorielle au moment de l'exécution. La vectorisation réduit le nombre d'opérations dans le pipeline, car l'instruction vectorisée factorise le contrôle entre les threads en travaillant sur des données différentes. DITVA étend un processeur SMT disposant d'instructions SIMD avec un mode d'exécution de vectorisation inter-threads. Dans ce mode, DITVA exploite les unités vectorielles existantes, améliorant ainsi l'utilisation des capacités vectorielles des microprocesseurs existants. DITVA maintient la compatibilité binaire avec les architectures CPU existantes. Grâce à l'utilisation des unités vectorielles et à la réduction des opérations de pipeline, DITVA vise à améliorer le débit d'exécution d'une puce microprocesseur x86 64 tout en réduisant sa consommation globale d'énergie.

Limitations au niveau transistor d'un microprocesseur La technologie des microprocesseurs a beaucoup évolué depuis l'introduction du premier microprocesseur Intel 4004 en 1971 par Intel. L'Intel 4004 était réalisé avec une finesse de gravure de 10  $\mu$ m avec seulement 2300 transistors. Le processeur Intel Skylake, mis sur le marché en 2015, emploie un process de 14nm avec près de 1,9 milliards de transistors. Gordon E. Moore a observé que le nombre de transistors dans un circuit intégré double chaque année. [M<sup>+</sup>98]

Robert H. Dennard a observé qu'avec la réduction de taille des transistors,

la puissance totale requise reste constante [DRBL74]. La loi de Moore associée au passage à l'échelle de Dennard se traduit par une croissance exponentielle de la performance par watt. La loi de Dennard a pris fin avec l'augmentation de la finesse de gravure. Les courants de fuite et la dissipation de chaleur ont commencé à devenir un réel problème pour le passage à l'échelle de la performance au travers le l'augmentation des fréquences d'horloge. Par conséquent, les fréquences d'horloge ont commencé à se stabiliser après le milieu des années 2000, malgré l'adoption de différentes technologies de transistors.

**Techniques micro-architecturales pour améliorer la performance** Alors que l'augmentation des fréquences d'horloge est une façon d'améliorer les performances des microprocesseurs, la micro-architecture elle-même joue un rôle important dans l'optimisation des microprocesseurs pour le débit, la latence et l'efficacité énergétique. Suivant ces exigences, les fabricants de processeurs doivent souvent assurer des compromis lors de la conception d'un processeur à usage généraliste. Par exemple, un processeur mobile, qui utilise des petits cœurs est optimisé pour l'énergie aux dépens du débit, tandis qu'un GPU est optimisé pour le débit au détriment de la latence.

Avec l'évolutivité limitée des fréquences d'horloge, le multiprocesseur sur puce (CMP), c'est-à-dire un multi-cœur [ONH<sup>+</sup>96], a été largement adopté au cours des dix dernières années. Au lieu d'un grand cœur monolithique, un CMP se compose de plusieurs cœurs dans une seule puce qui partagent certaines des ressources matérielles telles que des caches. Une application mono-thread est exécutée dans un cœur unique du CMP tandis qu'une application parallèle peut utiliser plusieurs cœurs grâce à un faible coût de communication entre les processeurs. Les processeurs multi-core hétérogènes [KTJR05] sont également de plus en plus répandus. Pour conserver un meilleur compromis entre consommation d'énergie et performance, une puce peut être constituée de plusieurs cœurs grands et petits pouvant être allumés et éteints, la charge de travail pouvant être migrée en fonction des exigences de l'application [PG13].

Les grands cœurs utilisent des techniques telles que l'exécution spéculative, l'exécution superscalaire, l'exécution dans le désordre, etc., pour améliorer la performance d'un thread unique. La performance mono-thread est limitée par le parallélisme d'instructions (ILP) d'une application. Les caractéristiques microarchitecturales peuvent améliorer l'ILP mais sont encore limitées par les propriétés inhérentes de l'application. Avec un ILP limité, l'utilisation des ressources

#### Résumé en Français

d'un cœur diminue. Le multi-threading a été mis en œuvre pour améliorer l'utilisation des ressources d'un cœur avec un impact minimal sur la latence monothread [TEL95, Upt, SBB+07, BEKK00]. Les petits cœurs évitent la plupart de ces optimisations pour améliorer l'efficacité énergétique.

Microarchitecture pour application extrêmement parallèle Il existe de nombreuses catégories d'applications extrêmement parallèles, orientées sur le débit et tolérantes à la latence. Les GPU, introduits en 1999, sont plus efficaces dans l'exécution de ces applications [NBGS08, KWm12, LNOM08, ND10a]. Avec un grand nombre d'applications de jeu et multimédia, les GPU sont devenus populaires dans les années 2000. L'architecture Tesla de NVIDIA a été introduite en 2006 et permet notamment l'exécution d'applications de calcul parallèle haute performance écrites en langage C à l'aide de l'architecture CUDA pour le calcul généraliste sur GPU. Les GPU ne sont pas des dispositifs de calcul autonomes. Ils sont conçus pour compléter le CPU existant pour améliorer l'efficacité de l'exécution d'application hautement parallèles. Le CPU se décharge de ce travail vers un GPU. D'autre part, un GPU ne peut pas exécuter les processus critiques nécessaires pour exécuter un système d'exploitation. Les CPU et GPU ont différentes philosophies de conception architecturale, le problème qu'ils essaient de résoudre étant différent. Ils mettent en œuvre différents jeux d'instructions (ISA).

**DITVA - une optimisation pour les architectures SMT généralistes** Dans cette thèse, nous proposons l'architecture de vectorisation dynamique interthread (DITVA), un point de conception intermédiaire entre un CPU et un GPU. DITVA est une optimisation pour les applications parallèles s'exécutant sur un CPU tout en maintenant la performance mono-thread. DITVA optimise les threads d'application en vectorisant dynamiquement les instructions entre threads. DITVA est basé sur l'architecture x86\_64 et supporte les applications régulières exécutées dans un CPU. DITVA peut être réalisé comme un cœur spécial dans une puce CMP (multi-core) hybride pour optimiser l'exécution des applications parallèles. DITVA n'a pas besoin de modifications dans l'ISA x86\_64 existante. Les binaires existants peuvent être exécutés dans un cœur DITVA, sans nécessiter pas de recompilation. DITVA améliore le débit des cœurs existants tout en consommant moins d'énergie.

Résumé en Français

## Introduction

In this thesis, we propose Dynamic Inter-Thread Vectorization Architecture (DITVA), a technique to improve the performance of multi-threaded Single-Program Multiple-Data (SPMD) applications in a general purpose microprocessor. Threads of SPMD applications often execute the same instructions on different data. To take advantage of the control redundancy in SPMD applications, DITVA dynamically aggregates identical instructions of several threads running in lockstep into a single *vector instruction* at runtime. Vectorization reduces the number of pipeline operations as a vectorized instruction shares the control across threads while operating on multiple data. DITVA extends a vector enabled inorder SMT processor with an inter-thread vectorization execution mode. In this mode, DITVA leverages existing SIMD units, thus improving the utilization of the *vector* capabilities of the existing microprocessors. DITVA maintains binary compatibility with existing CPU architectures. With the improved utilization of SIMD units and the reduction of pipeline operations, DITVA intends to improve the throughput of an x86 64 microprocessor chip while reducing the overall energy consumption.

Limitations at the transistor-level of a microprocessor Microprocessor technology has evolved a lot since the introduction of the first microprocessor Intel 4004 in 1971 by Intel Corp. Intel 4004 was a 10  $\mu$ m process with just 2,300 transistors. Skylake processors, released by Intel in 2015, has a 14nm process with almost 1.9 billion transistors. Gordon E. Moore observed that the number of transistors in an integrated circuit doubles every year [M<sup>+</sup>98]. The projection of process technology shrinkage remained accurate for several decades, but it is predicted that this will not be true in the near future [Moo].

Robert H. Dennard observed that with the scaling down of transistor size, the

required power stays constant [DRBL74]. Moore's Law coupled with Dennard scaling translates to exponential growth of performance-per-watt. Dennard's law began to fail when the transistors started to become too small. Current leakage and heat dissipation began to become a real issue for performance scaling by increasing clock rates. Hence, the clock rates started to plateau after the mid-2000s even after adopting different transistor designs.

**Microarchitectural techniques to improve performance** While increasing the clock rates is one way to improve the performance of the microprocessor, microarchitecture itself plays a significant role in optimizing microprocessors for throughput, latency and energy efficiency. Depending on the requirements, the processor manufacturers often have to balance the trade-offs when designing a general purpose processor. For example, a mobile processor, which uses *small cores* is optimized for energy at the cost of throughput, while a GPU is optimized for throughput at the expense of latency  $^1$ .

With the limited scalability concerning clock rates, Chip Multi-Processor(CMP), i.e., multi-core processors [ONH+96] are widely adopted in the past decade as an alternative design direction. Instead of a large monolithic core, a CMP consists of multiple cores in a single chip. The cores in a CMP shares some of the hardware resources such as caches. A single threaded application is executed on a single core of the CMP, and a parallel application can utilize multiple cores thanks to low inter-processor communication overhead. Heterogeneous multi-core processors [KTJR05] are also becoming popular. To maintain a better performance-energy profile, a chip may consist of multiple *large* and *small* cores that may be turned on and off or the workload can be migrated depending on the application requirements [PG13].

Large cores use techniques such as instruction pipelining, speculative execution, superscalar execution, out-of-order execution, etc., to improve the single thread performance. Single thread performance is bounded by the Instructionlevel parallelism (ILP) of an application. Microarchitectural features can improve the ILP but are still limited by the inherent properties of the application. With

<sup>&</sup>lt;sup>1</sup>Throughput is the number of instructions completed in a cycle and latency is the number of cycles taken to complete an instruction. In a single threaded microprocessor, latency is inversely proportional to throughput. However, in a multi-threaded processor, even though there are more instructions completed in a cycle, a thread could still slow down since it is sharing the resources with other threads

#### Introduction

limited ILP, the resource utilization of a core goes down. As an afterthought multi-threading [TEL95, Upt, SBB<sup>+</sup>07, BEKK00] was implemented to improve the resource utilization of a core with a slight impact on single thread latency. *Small cores* avoid many of these optimizations to improve energy profile.

Microarchitecture for embarrassingly parallel applications There are broad classes of *embarrassingly parallel*, throughput oriented, latency-tolerant applications. GPUs, introduced in 1999, are more efficient in executing these applications [NBGS08, KWm12, LNOM08, ND10a]. With a large number of gaming and multimedia applications, GPUs became popular in 2000's. NVIDIA's Tesla architecture was introduced in 2006 to extend GPUs to enable the execution of high-performance parallel computing application written in C language using the Compute Unified Device Architecture(CUDA) for general purpose computing on GPUs. GPUs are not stand-alone computational devices. They are designed to compliment the existing CPU to improve the efficiency of executing highperformance, embarrassingly parallel applications. CPU's offload such workload to a GPU. On the other hand, GPUs cannot run critical processes required to run an operating system. CPU and GPU have different architectural design philosophies as the problem they are trying to solve is different. They implement different Instruction Set Architecture(ISA).

#### DITVA - an optimization for general purpose SMT architectures

SMT [TEL95] is a common implementation of multi-threading in modern microprocessors. In SMT, multiple thread context co-exists in a single core of a microprocessor. The threads in an SMT are scheduled simultaneously so that when one of the thread is blocked, some other thread can execute the instructions. SMT processors, unlike GPUs, are designed to execute both single threaded as well as multi-threaded applications. While SMT processors are beneficial for both single and multi-threaded applications, however, they fail to benefit from the unique property of embarrassingly parallel applications i.e., the instructions across the threads are mostly identical although they work with different data. DITVA architecture is designed to exploit this property that exists in parallel applications. By doing so, DITVA improves the throughput of the existing cores while consuming significantly less energy.

In this thesis, we propose Dynamic Inter-Thread Vectorization Architecture (DITVA), an intermediate design point between a CPU and a GPU. DITVA is

a hardware optimization for parallel applications running on a CPU while maintaining the single thread performance. DITVA optimizes the application threads by dynamically vectorizing instructions across threads. We evaluate DITVA on a x86\_64 architecture and show that it supports the regular applications executed in a CPU. DITVA may be implemented as special cores in a hybrid CMP (multi-core) chip to optimize the execution of parallel applications. DITVA does not need any modifications in the existing x86\_64 ISA. Existing binaries can be executed in a DITVA core as it does not require recompilation of the program with compiler hints.

## Contributions

We developed a microarchitectural model, DITVA, to leverage the implicit datalevel parallelism in SPMD applications by assembling dynamic vector instructions at runtime. DITVA extends an SIMD-enabled in-order SMT processor with an inter-thread vectorization execution mode. In this mode, multiple scalar threads running in lockstep share a single instruction stream and their respective instruction instances are aggregated into SIMD instructions. To balance thread and data-level parallelism, threads are statically grouped into fixed-size independently scheduled warps. DITVA leverages existing SIMD units and maintains binary compatibility with existing CPU architectures.

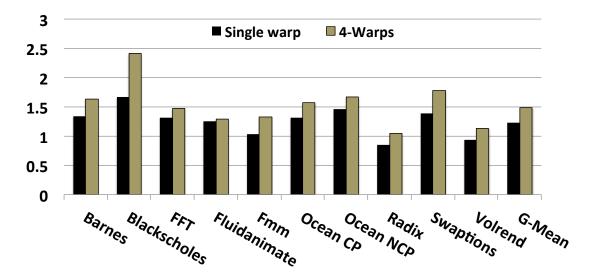

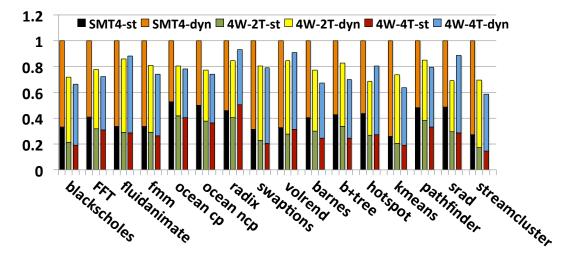

We also developed an in-house, trace based simulator to simulate SMT and DITVA architectures. Our evaluation on the SPMD applications from the PAR-SEC and Rodinia OpenMP benchmarks shows that a 4-warp  $\times$  4-lane 4-issue DITVA architecture with a realistic bank-interleaved cache achieves  $1.55 \times$  higher performance than a 4-thread 4-issue SMT architecture with AVX instructions while fetching and issuing 51% fewer instructions, achieving an overall 24% energy reduction.

## Organization

The thesis is organized as follows: Chapter 1 provides background for microarchitectural techniques used to exploit parallelism in a program. In chapter 2, we discuss inter-thread similarities and the techniques used to exploit them. We

#### Introduction

also discuss various thread reconvergence techniques that enables dynamic vectorization of instruction across threads. In chapter 3, we present the Dynamic Inter-Thread Architecture (DITVA). We discuss the implementation details and the design aspects of DITVA. In chapter 4, we demonstrate the energy/performance benefits of DITVA over an SMT architecture. We show that DITVA is able to achieve this without significant hardware overhead. In chapter 5, we provide some insights for an out-of-order version of DITVA (OOO-DITVA). Materials from chapter 3 and chapter 4 were presented at SBAC-PAD 2016 [KCSS16].

Introduction

## Chapter 1

## Background

| Implementation<br>level | DLP                | TLP                  |  |  |

|-------------------------|--------------------|----------------------|--|--|

| Program                 | Vector             | Threads              |  |  |

| Compiler                | Auto-vectorization | Auto-parallelization |  |  |

| Hardware                | SIMD               | MIMD                 |  |  |

Figure 1.1: Source of parallelism in a program

In this chapter, we will discuss different kinds of parallelism that exist in a program, i.e., Instruction-level parallelism (ILP, section 1.1), Data-level parallelism (DLP, section 1.2) and Thread-level parallelism (TLP, section 1.3) and provides the background for the transformation of TLP to DLP using DITVA. We will also discuss different methods utilized by the current microarchitectures to exploit these parallelisms. Amdahl's law [Amd67] identifies the serial section of a program as the limiting factor in the speedup of a workload. The implicit and explicit parallelism in a program is exposed at the program level, compiler level or microarchitectural level. The source of TLP and DLP in a conventional program execution is shown in figure 1.1. DLP is used to form vector instructions, and TLP is used to create program threads. At the program level, vector instructions and parallel threads expose parallelism using programming intrinsics and algorithms that use programming models based on the data decomposition [Fos95]. At the

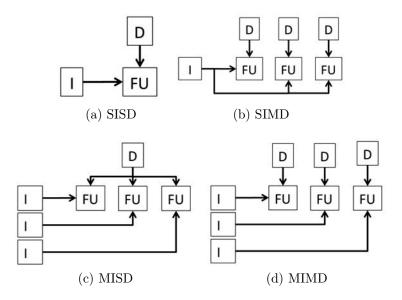

compiler level, automatic vectorization and automatic parallelization expose parallelism of the program. At the microarchitectural level, execution models based on Flynn's taxonomy [Fly66, Fly72] are used to exploit parallelism. Based on the instruction control and the number of data it is working with, Flynn's taxonomy [Fly66, Fly72] classifies the execution model of computer architecture into SISD (Single instruction stream, single data stream), MISD (Multiple instruction stream, single data stream), SIMD (Single instruction stream, multiple data stream) and MIMD (Multiple instruction stream, multiple data stream).

Figure 1.2: Flynn's taxonomy and MISD model

| Flynn's<br>classification | 1 thread            | > 1<br>thread |

|---------------------------|---------------------|---------------|

| SISD                      | Scalar<br>processor | Multi-thread  |

| SIMD                      | Vector<br>Processor | DITVA         |

| MIMD                      | -                   | Multi-core    |

Figure 1.3: Classification of architectures based in thread count

Diagrams representing Flynn's taxonomy is shown in figure 1.2. Multi-

#### Background

threaded architectures add another dimension to Flynn's taxonomy. For the sake of clarity, we can define the stream as a sequence of instructions that is mapped to a thread at the program level.<sup>1</sup> Some example architectures based on the number of streams in shown in figure 1.3. Traditional scalar uniprocessor architectures were SISD. A single threaded superscalar processor 1.1.2 is also classified as an SISD. SISD with more than one thread is a multi-threaded architecture. SIMD machines exploit data parallelism by using a single instruction stream to work on multiple data elements. Vector processors used for high-performance computing are SIMD architectures. Vector architectures are based on explicit vector instructions. MIMD consists of multiple processors that may be executing different instruction streams that are working with different data streams. A multi-core processor is primarily an MIMD architecture but many modern x86 64 architectures is a combination of different models, they support the execution of scalar instructions (SISD) and with SSE and AVX instruction sets they support the execution of vector instructions (SIMD). In addition to threads and vector instructions, microarchitecture techniques also exploit ILP from within the same thread.

SIMD architectures such as vector processors, GPUs, and CPUs with SIMD extensions, use vector instructions generated either by compiler or programmer. A large number of applications that are executed in x86\_64 architectures does not efficiently utilize SIMD extensions even though the programs have data-parallelism (see section 2.5). The inefficiency is due to the existence of dynamic properties such as branches in the instruction flow. Such programs are often written using threads running the same code. Many multi-threaded programs have implicit data-parallelism.

In the following sections, we will discuss implicit and explicit techniques that are used to exploit parallelism in a program. The parallelism in SISD is the instruction-level parallelism, data-level parallelism is exploited by the SIMD model and MIMD is exposed by the thread-level parallelism. In this thesis, we will only consider single process model and hence we will not consider parallel programming with multiple processes.

<sup>&</sup>lt;sup>1</sup>In section 3.2, we will redefine the notion of instruction stream as a sequence of instructions that is mapped to one or more threads at the program level, to adapt it for DITVA.

Listing 1.1: Array addition

## 1.1 Instruction-level parallelism

Compiler techniques and programming constructions are used to exploit implicit parallelism between instructions of a sequential program. Several microarchitectural features efficiently utilize this parallelism and often enhance it at runtime. *Hazards* are factors limiting parallelism. Two of the most common hazards are *Control hazard* and *Data hazard*.

Control hazards occur with branches. A branch is an instruction which alters the sequence of execution based on a condition. Branches are often resolved at runtime and hence the instruction fetch should not be stalled until branch resolution. Modern branch predictors such as TAGE [Sez11] are highly accurate. Microprocessors use branch predictors to continue fetching from one of the predicted branches. In the case of a misprediction, the instructions that are already in the pipeline are flushed.

Data hazards occur when an instruction with data dependency changes the order of read/write operation. Data hazards can be classified as follows

- 1. Read after write (RAW)

- 2. Write after read (WAR)

- 3. Write after write (WAW)

RAW is a true dependency and cannot be circumvented as the instruction which is reading the value should wait until the previous instruction produces the result. WAR and WAW are false dependencies and can be prevented using microarchitectural techniques.

1

Listing 1.2: Array addition (ASM)

| 1  |   | 100000 f15:         | lea                   | 0xe4(%rip),%rax # 100001000 <_N>             |

|----|---|---------------------|-----------------------|----------------------------------------------|

| 2  |   | 100000  f1c:        | $\operatorname{cmpl}$ | 0x0, (% rax)                                 |

| 3  |   | 100000 f1f:         | jle                   |                                              |

| 4  |   | 100000 f21:         | movslq                | (%rax),%rax                                  |

| 5  |   | 100000 f24:         | xor                   | %edx,%edx                                    |

| 6  |   | 100000 f26:         | lea                   | 0xe3(%rip),%r8                               |

|    | # | 100001010 <         | _a_array2             | >                                            |

| 7  |   | 100000  f2d:        | lea                   | 0x10c(%rip),%r9                              |

|    | # | 100001040 <         | _b_array2             | >                                            |

| 8  |   | 100000  f34:        | lea                   | 0x135(%rip),%r10                             |

|    | # | 100001070 <         | _c_array2             | >                                            |

| 9  |   | 100000  f3b:        | lea                   | 0x15e(%rip),%r11                             |

|    | # | $1000010{ m a0}$ <_ | _d_array>             | >                                            |

| 10 |   | 100000  f42:        | lea                   | 0x187(%rip),%rcx                             |

|    | # | $1000010{ m d0}$ <_ | _e_array2             | >                                            |

| 11 |   | 100000  f49:        | lea                   | 0x1b0(%rip),%rsi                             |

|    | # | 100001100 <         | _f_array2             | >                                            |

| 12 |   | 100000  f50:        | mov                   | (%r9,%rdx,4),%edi                            |

| 13 |   | 100000  f54:        | mov                   | (% rcx,% rdx,4),% ebx                        |

| 14 |   | $100000{ m f57}$ :  | add                   | (%r8,%rdx,4),%edi                            |

| 15 |   | 100000  f5b :       | add                   | (%r11,%rdx,4),%ebx                           |

| 16 |   | 100000  f 5  f:     | mov                   | %edi,(%r10,%rdx,4)                           |

| 17 |   | 100000  f63:        | mov                   | %ebx,( $%$ rsi, $%$ rdx,4)                   |

| 18 |   | 100000  f66:        | lea                   | 0x1(%rdx),%rdx                               |

| 19 |   | 100000  f6  a:      | $\operatorname{cmp}$  | %rax, $%$ rdx                                |

| 20 |   | 100000  f6d:        | jl                    | $100000{ m f50}\ <\_{ m add}{+}0{ m x40}{>}$ |

|    |   |                     |                       |                                              |

Consider the pseudocode in list 1.1 for array addition and its corresponding assembly code in list 1.2 produced after compilation. When the compiled code is executed in a scalar microprocessor with a single execution unit, the instructions are sequentially executed as shown in the figure. However, in practice, a program in execution have a large amount of implicit parallelisms called *Instruction-Level Parallelism (ILP)*. In listing 1.1, the statements in line 4 and line 5 are independent. Hence, the instructions corresponding to these statements can be executed in parallel. In listing 1.2, we find that the instructions from line 6 to line 11 are parallel. Similarly, inside the loop statements, instructions in line (12, 14, 16) and (13, 15, 17) can be executed in parallel.

Microarchitectural techniques such as instruction pipelining, speculative execution, superscalar execution, and out-of-order execution are used to exploit the ILP. Our DITVA proposal supports these microarchitectural techniques except out-of-order execution  $^{2}$ .

|    | <b>C1</b> | C2 | C3 | C4  | C5  | C6  | C7 |

|----|-----------|----|----|-----|-----|-----|----|

| 11 | IF        | ID | EX | MEM | со  |     |    |

| 12 |           | IF | ID | EX  | MEM | со  |    |

| 13 |           |    | IF | ID  | EX  | MEM | СО |

Figure 1.4: Instruction pipelining

### 1.1.1 Instruction pipelining

Instruction pipelining is a process an instruction technique in which the instruction processing is done in multiple stages and rather than waiting for the entire instruction processing to complete, subsequent instructions are processed concurrently. Figure 1.4 shows a simple 5 stage pipeline execution of instruction I1, I2, and I3. In the example, each stage has a single cycle latency. Instruction I2 starts fetch at cycle 2 as soon as instruction I1 completes the fetch stage. Similarly, I3 starts fetch at cycle 3. A non-pipelined execution would have taken 15

$<sup>^2\</sup>mathrm{DITVA}$  can be extended to support out-of-order execution. We provide some insights for an out-of-order implementation in Chapter 5

$(3 \times 5)$  cycles to complete the execution of 3 instructions, with pipelining, the total latency reduces to 7 cycles.

|   |    | C1 | C | 22 | C3 | C4  | С  | 5 | ( | 6 |  |

|---|----|----|---|----|----|-----|----|---|---|---|--|

| Ĩ | 11 | IF | I | D  | EX | MEM | C  | 0 |   |   |  |

| 8 | 12 | IF | 1 | D  | EX | MEM | С  | 0 |   |   |  |

|   | 13 |    |   | F  | ID | EX  | M  | M | 0 | 0 |  |

|   | 14 |    |   | F  | ID | EX  | ME | M | 0 | 0 |  |

Figure 1.5: Superscalar execution (degree 2)

#### 1.1.2 Superscalar execution

In superscalar processors, more than one instructions are processed at the same clock cycle. In Flynn's taxonomy, superscalar processors are classified as SISD. A superscalar processor has replicated pipelined resources that allow multiple fetches, decodes, executions and writebacks per cycle. Superscalar execution of degree 2 is shown in figure 1.5. A superscalar processor improves the execution throughput by issuing independent instructions in the replicated functional units. An in-order processor issues the instructions in the order of fetch. Hence, the adjacency of the independent instructions becomes the limiting factor in the scalability of a superscalar processor. To illustrate this limitation, let us consider listing 1.3, which is hypothetical reordered instruction sequence of listing 1.1. In listing 1.2 the instructions corresponding to  $c_{array}[i] = a_{array}[i] + b_{array}[i];$  and  $f_{array}[i] = d_{array}[i] + e_{array}[i];$  are interleaved to increase ILP. In listing 1.3, the interleaving is removed. And consequently, line 14 and 15 are the only instructions inside the loop which can be executed in parallel in an in-order machine. Even though modern compilers are smart enough to reorder the instructions to improve the ILP, the parallelism is limited by the program behavior. The added hardware remains idle when a superscalar machine executes a program with limited ILP. Considering the high cost of replicating the pipeline units, increase in hardware have diminishing returns in terms of performance [PJS97, KHL99].

Listing 1.3: Array addition (ASM) - Reordered

|    | Ensuing 1.0.                  |                                                                         |

|----|-------------------------------|-------------------------------------------------------------------------|

| 1  | $100000{ m f15}:$ lea         |                                                                         |

| 2  | $100000 \mathrm{f1c}:$ cmpl   | 0x0, (% rax)                                                            |

| 3  | 100000f1f: jle                | $100000{ m f6f}\ <\_{ m add}{+}0{ m x5f}{>}$                            |

| 4  | $100000 \mathrm{f21}:$ movsle | $q \ (\% rax),\% rax$                                                   |

| 5  | $100000 { m f24}:$ xor        | %edx, $%$ edx                                                           |

| 6  | $100000 { m f26}:$ lea        | 0xe3(%rip),%r8                                                          |

|    | $\# 100001010 < a_array2$     | >                                                                       |

| 7  | $100000 { m f2d}:$ lea        | 0x10c(%rip),%r9                                                         |

|    | $\# 100001040 < b_array2$     | >                                                                       |

| 8  | 100000  f34: lea              | 0x135(%rip),%r10                                                        |

|    | $\# 100001070 < c_array2$     | >                                                                       |

| 9  | 100000f3b: lea                | 0x15e(%rip),%r11                                                        |

|    | $\#~1000010a0~<\_d\_array2$   | >                                                                       |

| 10 | $100000 { m f42}:$ lea        | 0x187(%rip),%rcx                                                        |

|    | $\# 1000010 d0 < e_array2$    | >                                                                       |

| 11 | $100000 { m f49}:$ lea        | 0x1b0(%rip),%rsi                                                        |

|    | $\# 100001100 < f_array2$     | >                                                                       |

| 12 | 100000  f50: mov              | (%r9,%rdx,4),%edi                                                       |

| 13 | $100000 { m f54}:$ add        | (%r8,%rdx,4),%edi                                                       |

| 14 | 100000  f58: mov              | %edi,(%r10,%rdx,4)                                                      |

| 15 | $100000 \mathrm{f5c}:$ mov    | $(\% \operatorname{rcx},\% \operatorname{rdx},4),\% \operatorname{ebx}$ |

| 16 | $100000 { m f60}:$ add        | $\left(\%\mathrm{r11},\%\mathrm{rdx},4 ight),\%\mathrm{ebx}$            |

| 17 | $100000 \mathrm{f64}:$ mov    | %ebx,(%rsi,%rdx,4)                                                      |

| 18 | $100000  { m f68}:$ lea       | 0x1(%rdx),%rdx                                                          |

| 19 | $100000 \mathrm{f6c}:$ cmp    | %rax,%rdx                                                               |

| 20 | $100000 \mathrm{f70}:$ jl     | $100000{ m f50}\ <\_{ m add}{+}0{ m x40}{>}$                            |

|    |                               |                                                                         |

### 1.1.3 Out-of-order execution

Out-of-order processors improve the execution throughput by not strictly issuing the instructions in the order of fetch. For example, in listing 1.3, instructions in line 13 and line 16 can be issued in parallel as they are no longer required to strictly conform to the order. Out-of-order processors use techniques such as scoreboarding [BRI<sup>+</sup>90] to resolve the dependencies. In out-of-order processors instruction-level parallelism (ILP) is often limited by data hazards. As mentioned earlier, false dependencies can be avoided. False dependencies occur because of the limited number of registers provided by the ISA. This limitation forces the compiler to reuse registers in an instruction sequence that often result in producing false dependencies. Out-of-order processors uses register renaming [Tom67, Kes99, MPV93] to prevent false dependencies.

### 1.1.4 Clustering for ILP

Clustering allows the implementation of wide superscalar processors without compromising much on the clock rate. Essentially, clustering partitions a wide superscalar processor into multiple windows of smaller width. This reduces the delays in the critical path at various stages of the pipeline. Clustering can be done at different stages of the pipeline. [PJS97] study the complexity and delay characteristics of increasing the width of the superscalar processor. [CPG00, BM00, AF01, BDA03] discuss various techniques for clustering in superscalar processors. [Kes99] is one of the earliest implementation of a single threaded clustered micro-architecture that clusters the functional units.

## 1.2 Data-level parallelism

When a task operates on different pieces of data Data-level parallelism (DLP) arises. Data parallel algorithms perform independent operations on a large set of data and share the control flow. Many scientific applications, as well as multimedia applications, have DLP. DLP is exploited with the SIMD model of Flynn's taxonomy. Vectorization exposes DLP and SIMD/vector architectures are used to exploit them. Auto-vectorization [Nai04, NZ06, gcc, icc, MLN07] is done by many modern compilers for high-level programming languages such as C, C++, Fortran etc. Auto-vectorization compilers try to identify the Data parallel regions in the program code and vectorize them. Alternatively, the programmer rely on *intrinsics* [int] for vectorization efficiency. *Intrinsics* are often difficult to write and affects the portability. A relatively easier approach is SPMD-based programming environments such as CUDA, OpenCL, and OpenMP [KDT<sup>+</sup>12, DM98]. ISPC [PM12] is a compiler specifically aiming to exploit data parallelism in CPU.

### 1.2.1 Single Instruction Multiple Data

Microarchitectures such as vector processors and Graphics Processor Units (GPUs) exploit vectorization by using vector instructions. SIMD architectures optimize microprocessors for power efficiency by reducing the number of instruction operations at the front-end of the pipeline. x86 architectures implement SIMD exposed through MMX, SSE, and AVX [FBJ<sup>+</sup>08] instruction sets. In the Intel's implementation of SIMD, in addition to the supported instructions, MMX, SSE and AVX support varying data paths. MMX implementation reused the existing floating point registers for the 64-bit SIMD instructions. SSE implementation uses xmm registers with 128-bit wide data path [SKR00]. AVX instructions further widened the data path from 128-bit to 256-bit ymm registers (AVX-512 [R13], with zmm registers, supports 512-bit datapath) <sup>3</sup>. SIMD instructions may support different data types. For instance, SSE2 supports two 64-bit double-precision floating point numbers or two 64-bit integers or four 32-bit integers or eight 16-bit short integers or sixteen 8-bit characters.

Listing 1.4: Array addition (ASM) - SIMD

| 1  | 100000  db4:            | lea     | 0x245(%rip),%rax                             |

|----|-------------------------|---------|----------------------------------------------|

|    | # 100001000 < 1         | N>      |                                              |

| 2  | 100000dbb:              | movslq  | (%rax),%r9                                   |

| 3  | 100000  dbe:            | test    | %r9, $%$ r9                                  |

| 4  | 100000 dc1:             | jle     | $100000{ m e9a}~<\_{ m add}{+}0{ m xea}{>}$  |

| 5  | 100000  dc7:            | xor     | %eax,%eax                                    |

| 6  | 100000 dc9:             | test    | %r9d,%r9d                                    |

| 7  | 100000  dcc:            | је      | $100000{ m e50}\ <\_{ m add}{+}0{ m xa0}{>}$ |

| 8  | 100000 dd2:             | xor     | % eax, % eax                                 |

| 9  | $100000 \mathrm{dd4}:$  | mov     | %r 9, $%$ r 8                                |

| 10 | $100000 \mathrm{dd7}$ : | and     | \$0xfffffffffffff ,%r8                       |

| 11 | 100000  ddb:            | је      | $100000{ m e4a}~<\_{ m add}{+}0{ m x9a}{>}$  |

| 12 | 100000 ddd:             | mov     | %r 9, $%$ r 10                               |

| 13 | $100000 \mathrm{de0}:$  | and     | \$0xfffffffffffff ,%r10                      |

| 14 | $100000 \mathrm{de4}$ : | lea     | 0x225(%rip),%r11                             |

|    | $\# 100001010 < \_$     | a_array | 7>                                           |

<sup>&</sup>lt;sup>3</sup>Note that scalar double precision instructions in  $x86_64$  architecture use half of the register width of xmm registers and 1/4 width of ymm registers [R14]. Similarly, SSE instructions are implemented using half of the register width of ymm registers.

#### Data-level parallelism

100000deb: lea 0x26e(%rip),%rdi 15 $100001060 < b_array>$ # 100000df2: lea 0x2b7(%rip),%rcx 16  $\# 1000010 \, {

m b0} < {

m c} {

m array} >$ 100000df9: lea 0x300(%rip),%rax 17  $100001100 < d_array>$ # 100000e00: lea 0x349(%rip),%rdx 18 # 100001150 < e array>100000e07: lea 0x392(%rip),%rsi 19 # 1000011a0 < f array>100000e0e: xchg %ax,%ax 20 100000e10: vmovdqa (%rdi),%xmm0 21100000e14: vpaddq (%r11),%xmm0,%xmm0 22 100000e19: vmovdqa %xmm0,(%rcx) 23 100000e1d: vmovdqa (%rdx),%xmm0 24 100000e21: vpaddq (%rax),%xmm0,%xmm0 25100000e25: vmovdqa %xmm0,(% rsi) 26 100000e29: add \$0x10,%r11 27\$0x10.%rdi  $100000 \,\mathrm{e2d}:$ add 28 \$0x10,%rcx  $100000 \,\mathrm{e}31:$ add 29 100000e35: add \$0x10,%rax 30 \$0x10,%rdx 100000e39: add 31 \$0x10,%rsi 100000e3d: add 32 \$0xfffffffffffff ,%r10  $100000 \,\mathrm{e}41:$ add 33  $100000\,e10\ <\ add{+}0x60{>}$ 100000e45: jne 34%r8.%rax  $100000 \,\mathrm{e}47: \,\mathrm{mov}$ 35 %rax,%r9 100000e4a: cmp 36 100000e4d: je 100000e9a < add+0xea>37 100000e4f: nop 38 100000e50: lea 0x1b9(%rip),%rcx 39 100001010 < a array># 100000e57: lea 0x202(%rip),%rdx 40100001060 < b array># (%rdx,%rax,8),%rdx 100000e5e: mov41 100000e62: add (%rcx,%rax,8),%rdx 420x243(%rip),%rcx 100000e66: lea 43 $1000010\,{

m b0}$  < c array> #

```

100000e6d: mov

% rdx, (% rcx, % rax, 8)

44

0x288(%rip),%rcx

100000e71: lea

45

100001100 < d array>

#

100000e78: lea

0x2d1(%rip),%rdx

46

100001150 < e_array>

#

100000 \, e7f: mov

(%rdx,%rax,8),%rdx

47

100000e83: add

(%rcx,%rax,8),%rdx

48

100000e87: lea

0x312(%rip),%rcx

49

1000011a0 < f array>

100000e8e: mov

% rdx, (% rcx, % rax, 8)

50

100000e92: inc

%rax

51

%r9,%rax

100000e95: cmp

52

100000e98: jl

100000\,{\rm e50}\ <\_{\rm add}{\rm +}0{\rm xa0}{\rm >}

53

```

Listing 1.4 is the assembly for the array addition when compiled for SSE architecture. In comparison to listing 1.2, the difference here is that the integer array elements (each element is 4-bytes) are grouped into 4 and are executed as SIMD instructions using 128-bit xmm registers. In listing 1.4, the block of instructions between line 21 and line 37 are the SIMD implementation of the array addition. However, as the array elements are grouped into 4, some of the last elements might not be vectorizable, these array elements are executed by the non-SIMD code block between line 39 and line 53.

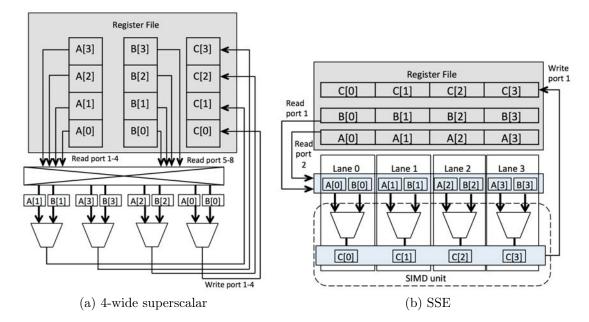

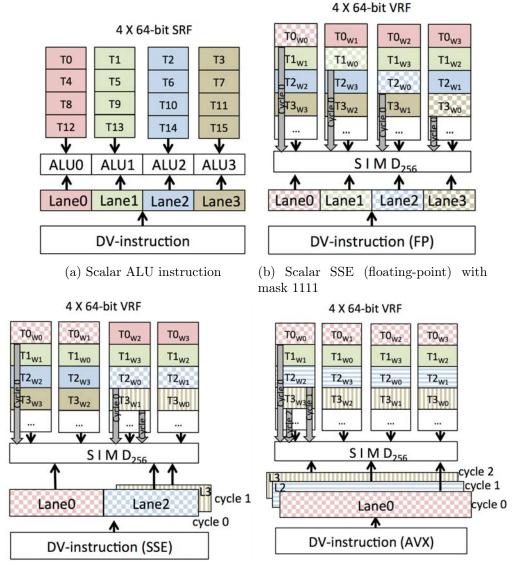

SIMD instructions reduce pressure in the front end of a pipeline as there are fewer instructions to be fetched (and consequently fewer instructions in other frontend pipeline stages). For example, the number of loop iterations (and hence the number of fetched instructions) in listing 1.4 is approximately reduced by 4 times. At the backend, for performance reasons, a common implementation of SIMD functional units is by banked register file/wide registers [RDK<sup>+</sup>00]. However, SIMD is not equivalent to a wide superscalar processor. Figure 1.6 shows the execution of 32-bit integer array of size 4 in a 4-wide superscalar and a SSE unit. SIMD implementation partitions the register and data-path resources into multiple lanes. The reduced design complexity of the pipeline backend improves the scalability. The cost of implementation of SIMD architecture is much lower than a wide superscalar processor [PJS97].

26

Figure 1.6: 32-bit integer execution in 4-wide superscalar processor and a SSE unit

### 1.2.2 Single Instruction Multiple Threads (SIMT)

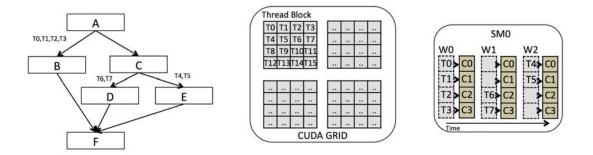

Single Instruction Multiple Threads (SIMT) [LNOM08] is a parallel execution model that is used to capture implicit DLP from SPMD code. NVIDIA introduced SIMT in their Tesla GPU architecture. SIMT eased programmability of NVIDIA GPU's with the use of Compute Unified Device Architecture (CUDA) [Nvi07] programming libraries. NVIDIA later continued to use SIMT in their Fermi, Kepler, and Maxwell architectures. SIMT is generally combined with multithreading and multi-core. SIMT relies on a large number of threads to keep the execution resources busy. SIMT works well for throughput oriented applications with large amount of implicit DLP. Hence, the program in execution may consist of a large number of threads. A simplified overview of array execution is shown in figure 1.7. Streaming Multiprocessors(SM) consists of many CUDA cores. An SM executes the SIMD instructions. Threads in CUDA is grouped into thread blocks. Using CUDA, the programmer specifies the number of threads per block and the number of thread blocks. CUDA maps multiple thread blocks to an SM. Hence, many warps are always active in an SM. A thread block is sub-divided

Lane 0 Lane 1 Lane 2 Lane 3 Thread I+1 Thread I Thread I+2 Thread I+3 Thread 11 Thread 10 Thread 8 Thread 9 Thread block Thread 4 Thread 5 Thread 6 Thread 7 Thread 0 Thread 1 Thread 2 Thread 3 A[15] A[11] B[11] B[15] A[3] B[3] A[7] B[7] A[10] B[10] A[14] B[14] A[2] B[2] A[6] B[6] A[13] A[13] A[1] || B[1] A[5] B[5] A[9] B[9] A[12] SIMD Instruction A[12] A[0] || B[0] A[4] B[4] A[8] || B[8] **SIMD** Pipeline

into groups of 32 threads (in our example this number is 4) called warps<sup>4</sup>. In SIMT, the threads in the warp form the lanes of the vectorized instructions.

Figure 1.7: SIMT

Figure 1.8: SIMT

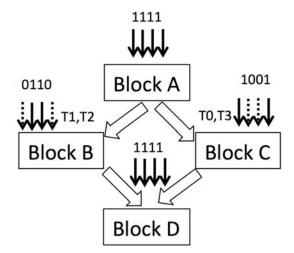

Figure 1.8 shows a simplified overview of subdivision of a program with divergence into multiple thread blocks, their assignment to an SM and the execution of warps. A *thread* in SIMT is bound to a *lane* in SIMD. Threads in a warp

$<sup>^4\</sup>mathrm{Thread}$  block is sub-divided into groups of 32 threads because there are 32 lanes (CUDA cores).

#### Data-level parallelism

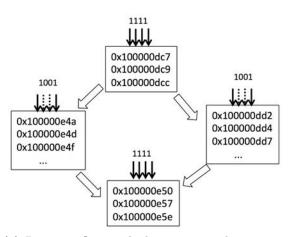

that are executing the same instructions form an SIMD instruction. When the threads are not executing the same PC, they are on a divergent path. SIMT uses an active bit mask to identify the participant threads in a vectorized instruction. Figure 1.9 illustrates the masks in SIMT, corresponding to the active threads, when there is a divergence. There is 1 bit corresponding to each thread in an SIMT. A set bit (i.e., 1) indicates that the thread is active and an unset bit (i.e., 0) corresponds to an inactive thread. SIMT can be considered as SIMD instructions with hardware assisted divergence management. Branches in a data-parallel application cause the execution to follow divergent paths. Divergence adversely affects the efficiency of SIMD execution. The divergent paths merge at the reconvergence point. In figure 1.9, block D is a reconvergence point. SIMT requires compiler hints to identify the reconvergence points after the divergence. NVIDIA GPUs uses a stack-based divergence management. Stack-based reconvergence is discussed in section 2.2.1.

Figure 1.9: SIMT divergence

As we have seen in figure 1.8, a thread block consists of multiple warps. SIMT hides the execution latency by switching between warps.

## 1.3 Thread-level parallelism

Thread-level parallelism (TLP) arises when independent threads work on different data. Even though the thread/process works with own data, some of the data might be shared. Synchronization techniques such as locks, mutex, semaphores, etc., are used to prevent race conditions in those cases. TLP is exploited by using threads. Single Program Multiple Data (SPMD) is a sub-class of MIMD that consist of multiple threads and processes that execute nearly the same instruction but with its own data. In comparison with DLP, a program written to exploit TLP tends to work better when there is a possibility of multiple divergent paths of execution. DLP and TLP are often interchangeable, especially in a SPMD application in which the threads are on a convergent path. However, when there is a divergence, the execution path can only be determined at the runtime. Hence, SPMD applications often have implicit DLP that are often unexploited. Hardware optimizations to exploit MIMD is explained in section 1.3.

High-level programming languages such as C/C++, Java, Python, etc. provide abstractions to implement multi-threading with the support of operating system. Programmers use the libraries offered by the high-level languages to implement multi-threading in programs. POSIX threads [C+95], often referred to as PThreads, is an application programming interface for C and C++ languages.

| TO <sub>I1</sub> TO <sub>I3</sub> | T0 <sub>14</sub> | т0 <sub>15</sub> | TO <sub>I7</sub> | т0 <sub>18</sub> |

|-----------------------------------|------------------|------------------|------------------|------------------|

| TO <sub>I2</sub>                  |                  | TO <sub>I6</sub> |                  | т0 <sub>19</sub> |

| T1 <sub>11</sub> | T1 <sub>I3</sub> | T1 <sub>15</sub> | T1 <sub>18</sub> |

|------------------|------------------|------------------|------------------|

| T1 <sub>12</sub> | T1 <sub>14</sub> | T1 <sub>I6</sub> | T1 <sub>19</sub> |

Figure 1.10: Thread execution without multi-threading

**Explicit TLP** Hardware multi-threading supports multiple thread contexts at the same time on the same processor core. Processes or threads are mapped to

each of the hardware threads. In general, software threads and process scheduling is done by the operating system. However, at a much finer granularity, the microprocessor schedules the hardware threads to maximize the resource utilization. Figure 1.10 shows the execution of two threads without hardware multi-threading. Hardware multi-thread allows both the context to execute at the same time. Depending on the scheduling technique, hardware multi-threading can be classified into

- Coarse grained multi-threading

- Fine grained multi-threading

- Simultaneous multi-threading

| T0 <sub>I1</sub> | T1 <sub>11</sub> | T1 <sub>I3</sub> | T1 <sub>15</sub> | T0 <sub>13</sub> | T0 <sub>14</sub> | TO <sub>I5</sub> | T0 <sub>17</sub> | T0 <sub>18</sub> | T1 <sub>17</sub> | T1 <sub>18</sub> |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| T0 <sub>12</sub> | T1 <sub>12</sub> | T1 <sub>I4</sub> | T1 <sub>16</sub> |                  |                  | T0 <sub>16</sub> |                  | TO <sub>I9</sub> |                  | T1 <sub>19</sub> |

Figure 1.11: Coarse grained multi-threading (After cycle 1 T1 is scheduled as there is a long latency operation, T0 is rescheduled only when there is a long latency operation for T1)

## 1.3.1 Coarse-grained multi-threading

In coarse-grained multi-threading [ALKK90, SBCVE90, TE94] the processor switches the context when there is a very high latency operation such as a cache miss. Figure 1.11 illustrates how threads context switch when there is a long latency operation. Context switching could cost a few cycles to flush the pipeline. For coarse-grained muti-threading to be effective, the pipeline refill time should be much less than the stall time. IBM AS/400 [EJK+96] and Intel Itanium2 Montecito [MB05] cores implement coarse-grained multi-threading.

## 1.3.2 Fine grained multi-threading

In fine-grained multi-threading [Smi82] the thread interleaved execution between pipeline stages. However, only one thread is scheduled at a time in a given pipeline

| T0 <sub>I1</sub> | T1 <sub>I1</sub> | T1 <sub>13</sub> | т0 <sub>із</sub> | T1 <sub>15</sub> | T0 <sub>14</sub> | T0 <sub>15</sub> | T0 <sub>17</sub> | T0 <sub>18</sub> | T1 <sub>17</sub> | T1 <sub>18</sub> |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| TO <sub>I2</sub> | T1 <sub>12</sub> | T1 <sub>14</sub> |                  | T1 <sub>16</sub> |                  | T0 <sub>16</sub> |                  | т0 <sub>19</sub> |                  | T1 <sub>19</sub> |

Figure 1.12: Fine grained multi-threading (Rescheduling T0 do not wait until there is a very long latency operation for T1)

stage. The context switch happens without any cost. Figure 1.12 illustrates finegrained multi-threading. In comparison with coarse-grained multi-threading, finegrained multi-threading improves the throughput by hiding both short and long stalls. The disadvantage of fine-grained multi-threading is that it slows down the individual threads when there are no stalls [PH13]. Fine-grained multi-threading works well for the in-order processors with narrow issue width. Sun Microsystems Niagara [KAO05] uses fine-grained multi-threading.

| TO               | T1 <sub>I1</sub> | T1 <sub>I3</sub> | T0 <sub>13</sub> |                  | T0 <sub>14</sub> | T0 <sub>16</sub> | TO <sub>I8</sub> | т0 <sub>19</sub> | T1 <sub>18</sub> |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| T0 <sub>I2</sub> | T1 <sub>12</sub> | T1 <sub>14</sub> | T1 <sub>15</sub> | T1 <sub>16</sub> | T0 <sub>15</sub> | T0 <sub>17</sub> |                  | T1 <sub>17</sub> | T1 <sub>19</sub> |

Figure 1.13: Simultaneous multi-threading

#### 1.3.3 Simultaneous multi-threading (SMT)

SMT improves the throughput of a superscalar core by enabling independent threads to share CPU resources dynamically. Resource sharing policies have [TEE<sup>+</sup>96a, CRVF04, LFMS01, EA03, EE07] huge impact on execution throughput. Many studies have focused on optimizing the instruction fetch policy and leaving the instruction core unchanged while other studies have pointed out the ability to benefit from memory level parallelism through resource sharing policies. Fairness among threads has been recognized as an important property that should be also tackled by resource sharing policies [LGF01]. However, these resource sharing heuristics essentially address multi-program workloads.

SMT architectures [TEL95] were introduced to exploit thread-level and/or multi-program level parallelism to optimize the throughput of a superscalar core.

Typically, on an SMT processor, instructions from the different hardware threads progress concurrently in all stages of the pipeline. Depending on the precise implementation, some pipeline stages only treat instructions from a single thread at a given cycle. For instance, the instruction fetch pipeline stage [SFKS02], while some other pipeline stages like the execution stage, mix instructions from all threads.

SMT architectures aim at delivering throughput for any mix of threads without differentiating threads of a single parallel application from threads of a multiprogram workload. Therefore, when threads from an SPMD application exhibit very similar control flows, SMT architectures only benefit from these similarities by side-effects of sharing structures such as caches or branch predictors [HS96].

SMT architectures have often been targeting both high single-thread performance and high parallel or multi-program performance. As a consequence, most commercial designs have been implemented with out-of-order execution. However, in the context of parallel applications, out-of-order execution may not be cost effective. An in-order 4-thread SMT 4-issue processor has been shown to reach 85 % of the performance of an out-of-order 4-thread SMT 4-issue processor [HS99]. Therefore, in-order SMT appears as a good architecture tradeoff for implementing the cores of an SPMD oriented throughput processor.

In a conventional single-threaded processor low ILP phases leave unused resources. SMT processors can leverage higher issue width with the use of multiple threads. [PJS97] identifies the various source of complexity for implementing a wider superscalar microprocessor. With higher complexity, various delays at different pipeline stages increase, forcing the architecture to scale down the clock cycle rates at which the processor runs. Intel's implementation of SMT is called Hyperthreading [Upt], which appeared in 2002 and is still in use. [TT03, ECX<sup>+</sup>11] reports the performance improvement over a non-SMT architecture as around 20% in the older processors and 30% in the modern Intel processors.

### 1.3.4 Clustered multi-threading (CMT)

Clustering is also implemented in multi-threaded architectures. [KT98] proposed a clustered SMT architecture, which partitioned an aggressive, dynamic superscalar core into several independent clusters that do not share the resources. This architecture is analogous to a multi-core SMT. [CT04, DS02] proposed combining SMT architectures with clustering to have higher IPC while maintaining higher clock rates. CASH [DS02] proposed a hybrid of SMT and CMP architectures, in which certain hardware is shared between the threads and use split resources for hardware whose implementation complexity is high. [CT04] explored the impact of clustering on instruction window wakeup and functional unit bypass logic, register renaming logic, fetch unit and integer register file on an SMT. AMD's Bulldozer [BBSG11] implements clustering in the multi-threaded processor.

SIMT is intended to run applications that are throughput oriented. SIMT does not support interrupts. Hence, it does not support operating system process. SIMT amortizes the control overhead. Unlike CMT, the pipeline operations are greatly reduced by sharing of instruction fetch and memory accesses. SIMT also needs specialized ISA for thread divergence management.

To improve the single thread performance CMT uses techniques such as superscalar execution, branch prediction, cache hierarchy, out-of-order execution, register renaming, speculative execution, etc. SIMT, on the other hand, is used in architectures aggressively optimized for throughput. SIMT supports a large number of cores. However, they are simple. They do not implement microarchitectural techniques to improve the single thread performance. Instead, it tries to improve the resource utilization with a large number of threads. More threads hide high latency operations. SIMT architectures have the benefits of clustering because of the independence of its participant threads. However, this can have adverse effects when there is less instruction occupancy or lots of thread divergence <sup>5</sup>.

**Multi-threading in DITVA** DITVA is implemented over an SMT architecture. Whenever possible the instructions across SMT threads are vectorized. When vectorization is not feasible, the threads in DITVA executes as regular SMT. Like SIMT, DITVA groups the SMT threads into warps. Each thread in the warp occupies a lane. Consequently, DITVA also benefits from clustering, as the threads within the warp utilize independent resources.

<sup>&</sup>lt;sup>5</sup>There are techniques such as Dynamic warp formation [FSYA07] and Dynamic warp subdivision [MTS10a] to have a higher tolerance for branch divergence

1

## 1.4 TLP vs DLP

As mentioned in section 1.3, TLP arises when independent task works on different data. In the code segment given in listing 1.1, exploiting TLP is straightforward.

Listing 1.5: Array addition with multi-threading

```

void add(int threadid, int num_threads) {

int N_per_thread = N/num_threads;

for(int i=threadid*N_per_thread; i<N_per_thread; i++){

c_array[i] = a_array[i] + b_array[i];

f_array[i] = d_array[i] + e_array[i];

}

</pre>

```

A simple multi-threaded implementation of the code segment is shown in listing 1.5. All the threads execute the add function. In the given example, each thread adds a slice of the array. Parallel execution of the slices hides the long latency operations. Transformation of an algorithm with DLP to TLP is simple. However, vice versa is not straightforward. To illustrate this, consider listing 1.6, with 'condition' variable which is known at the run-time. Even though there is data independence, the control flow of the program becomes dependent on the outcome of the conditional variable that is independent between iterations. The code segment in listing 1.6 still has inherent TLP. To exploit DLP in this example, the programmer has to rely on software based SPMD vectorization languages such as OpenCL [Mun09, SGS10] and ISPC [PM12], or hardware based SPMD techniques such as Single Instruction Multiple threads (SIMT).

Listing 1.6: Array addition with branch

```

1

void add() {

2

for (int i = 0 ; i < N; i++) {

3

if (condition [i]) {

4

c_array[i] = a_array[i] + b_array[i];

\mathbf{5}

f array[i] = d array[i] + e array[i];

6

}

7

}

}

9

```

Background

## 1.5 Chip multiprocessor

In section 1.1.4 and section 1.3.4 we have seen that clustering reduces the hardware complexity that allows the microprocessors to run at a higher clock rate. SMT architectures are introduced to improve resource sharing, but this increases the complexity. On the other hand, simultaneous multiprocessors (SMP) are computing elements that share nothing at all. However, on an SMP, the interprocessor communication is expensive. Moreover, the process or the threads running on different processors may share data. Caches, which reduce the latency of expensive memory operations when there is data reuse, are not shared on an SMP.

Chip multiprocessors (CMP) consist of multiple computing elements (cores) on a single chip. The cores may have a separate L1 cache but may share caches at other levels. It has to be noted that the each core in a CMP may still support SMT. CMP aims to improve the scalability by clustering less critical hardware resources. A typical desktop computer may consist of a microprocessor having up to 8 cores (Intel Core i7 Extreme Edition 5960X [ci7]) and microprocessors designed for high performance may have even more cores.

An alternative CMP design consists of clustering resource by type. A CMP with different types of cores is called heterogeneous CMP. A heterogeneous CMP may consist of some specialized cores. For instance, Cell processors [PAB+05] consists of 1 Power Processing Element (PPE) for general purpose computing and 8 Synergistic Processor Elements(SPE) optimized for SIMD execution. AMD Fusion architecture [BFS12] consists of CPU and GPU in a single chip, big.LITTLE [Gre11] from ARM reduce energy consumption by coupling powerful

large cores(e.g. Cortex-A15) with smaller cores (e.g. Cortex-A7) for energy savings.

## 1.6 Conclusion

In this chapter, we saw different techniques to exploit parallelism in a program. These techniques are not mutually exclusive. Depending on the program behavior (e.g., threadable vs non-threadable) and user requirement (e.g., latency vs throughput) an application can be programmed. Many general purpose microprocessors incorporate all these techniques to exploit parallelism. Scalability

#### Conclusion

and effective resource utilization still remain an issue in these microprocessors. For example, SMT processors do not scale well beyond eight threads. Also, a program compiled with inefficient static vectorization does not use the SIMD execution units very well. There are inter-thread similarities (chapter 2) that allows threads to share the control flow. DITVA removes these inefficiencies of modern general purpose microprocessors. DITVA improves the throughput and overall energy consumption of the cores while maintaining the latency of the threads. DITVA is designed keeping in mind a heterogeneous CMP that may consist of regular cores coupled with DITVA cores optimized for SPMD applications.

DITVA does mask based vectorization of instruction like SIMT. Unlike SIMT, which uses a stack based divergence management, DITVA is heuristic based and hence it does not require the support of any specific ISA for divergence management. Moreover, the use of intrinsics and compiler hints for reconvergence makes SIMT comparable to a predicate based static vectorization. DITVA, on the other hand, is entirely dynamic and even support speculative execution of branches with the help of a branch predictor. SIMT relies on fine-grained multi-threading (section 1.3.2) to maximize resource utilization while DITVA relies on simultaneous multi-threading technique (section 1.3.3).

Inter-thread similarity forms the basis of dynamic vectorization in DITVA. dynamic vectorization enables sharing of control flow when the threads are doing similar instruction operations. Dynamic vectorization results in reduction in pipeline operations in the microprocessor, thus reducing energy consumption and improving the utilization of existing SIMD units. In chapter 2, we discuss inter-thread similarities and the ways to exploit it to dynamically vectorize instructions.

Background

38

# Chapter 2

# Exploiting inter-thread similarity in microprocessors

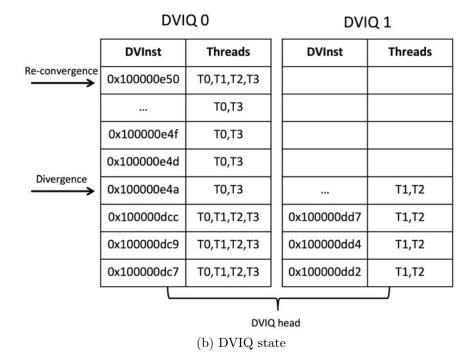

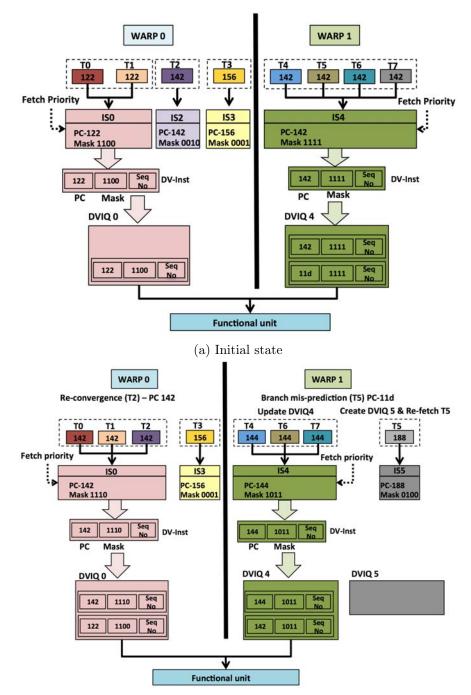

In this chapter, we will discuss the presence of inter-thread instruction similarities that cause redundancy while running SPMD application in an in-order SMT [TEE<sup>+</sup>96a] architecture. Dynamic Inter-Thread Vectorization Architecture (DITVA) avoids this redundancy by dynamically vectorizing the instructions across threads. The efficiency of DITVA relies on convergent execution for dynamic vectorization. Hence, early reconvergence of threads after following divergent paths is of utmost importance. In this chapter, we discuss various reconvergence techniques and our preferred reconvergence heuristics for DITVA. We will also discuss related microarchitectural techniques that exploit inter-thread redundancies.

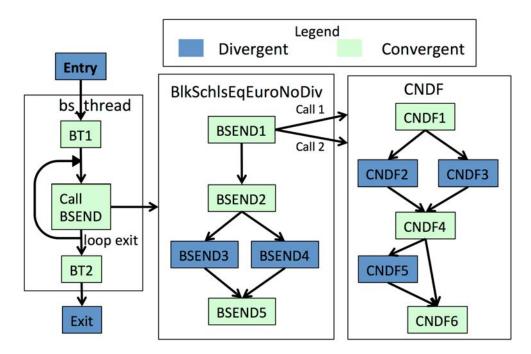

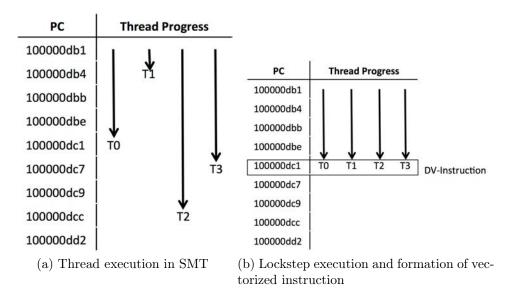

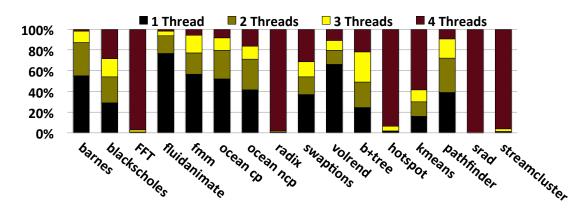

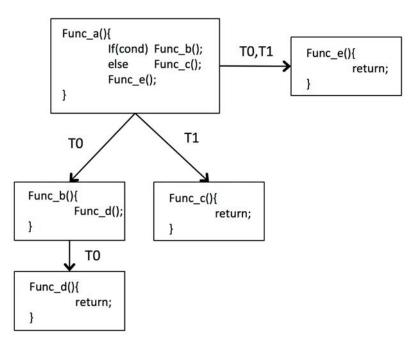

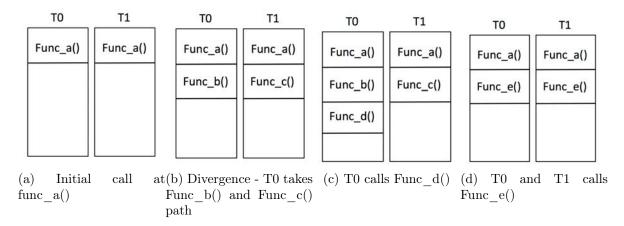

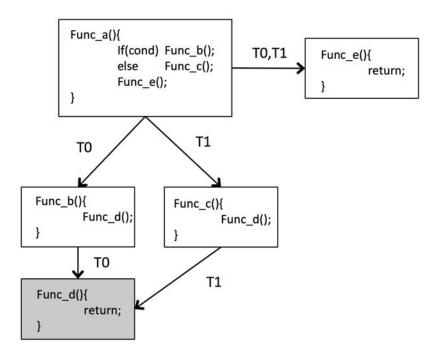

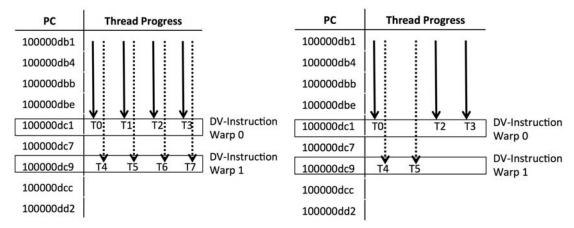

## 2.1 Inter-thread similarities in SPMD applications