## Calcul numérique sur données de grande taille Eddy Caron

#### ▶ To cite this version:

Eddy Caron. Calcul numérique sur données de grande taille. Calcul parallèle, distribué et partagé [cs.DC]. Université de Picardie Jules Verne, 2000. Français. NNT: . tel-01444591

### HAL Id: tel-01444591 https://theses.hal.science/tel-01444591

Submitted on 24 Jan 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

présentée par

#### Eddy CARON

pour obtenir le titre de

#### **DOCTEUR**

de l'Université de Picardie - Jules Verne

spécialité: Informatique

# Calcul numérique sur données de grande taille

Date de soutenance: 14 Décembre 2000

Composition du Jury : Président : Jean-Frédéric Myoupo

Directeurs : Dominique LAZURE

: Gil UTARD

Rapporteurs: Pierre Manneback

: Jean-François МÉНАUT

Examinateurs: Frédéric Desprez

: Vincent VILLAIN

Thèse préparée au sein du Laboratoire de Recherche en Informatique d'Amiens (LaRIA)

À mon père.

#### Remerciements

En premier lieu, je tiens à remercier chaleureusement les membres du jury, Jean-Frédéric Myoupo, Frédéric Desprez et Vincent VILLAIN; ainsi que Pierre Manneback et Jean-François Méhaut pour avoir accepté la lourde charge de rapporteur. Leurs avis et conseils éclairés me furent précieux.

Je profite également, de cette traditionnelle page de remerciement pour témoigner de ma gratitude et de mon profond respect pour mes deux directeurs de thèse. Dominique LAZURE et Gil UTARD ont su au long de ces années me guider et m'accompagner en m'offrant un aperçu de leurs nombreuses connaissances. Le support scientifique fut de grande qualité à l'image des rapports humains que nous avons pu entretenir.

Je tiens également à remercier les membres permanents du LaRIA et plus particulièrement tous ceux qui ont dû, de par leur fonction ou de par leur gentillesse, me consacrer un peu de leur temps.

Dans le même esprit, je tenais à adresser mes remerciements à toutes ces personnes rencontrées en groupe de travail, collaborations ou conférences. Au travers de ces contacts vous m'avez permis de m'intégrer dans la communauté du parallélisme. Je vous en remercie.

Le plus amical des remerciements pour les thésards du LaRIA. L'ambiance particulièrement enrichissante, à bien des égards, dans laquelle s'est déroulée cette thèse est votre œuvre. "Merci. Et puis bonne chance surtout." [7]

Je tiens également à citer les organismes qui ont fourni l'indispensable support financier: le ministère (Bourse MENRT) et le Pôle Modélisation de la région Picarde.

Tous ces remerciements ne se trouveraient pas en préambule de ce manuscrit sans trouver en amont le soutien infaillible de ma famille. Puisse cet aboutissement être aussi le vôtre.

Un remerciement tout particulier à mon père. Outre le fait que cette thèse lui est dédicacée, je tiens à souligner son aide concernant les nombreuses relectures et corrections orthographiques indispensables pour permettre la lecture de ce manuscrit.

Il me reste une personne à remercier. Une personne vraiment particulière à mes yeux. Elle a su durant toutes ces années (et cela n'est pas le moindre des travaux effectués durant cette thèse) être présente à mes côtés. Je lui dois tant. Isabelle, merci.

# Table des matières

| In | trod                   | uction                                                               | 5  |

|----|------------------------|----------------------------------------------------------------------|----|

| Ι  | $\mathbf{A}\mathbf{p}$ | proche système                                                       | 9  |

| 1  | Ges                    | tion de la mémoire virtuelle pour le calcul <i>out-of-core</i>       | 11 |

|    | 1.1                    | Mémoire virtuelle et calcul <i>out-of-core</i>                       | 12 |

|    | 1.2                    | Les mécanismes de gestion de la mémoire virtuelle                    | 12 |

|    |                        | 1.2.1 La pagination                                                  | 13 |

|    |                        | 1.2.2 Politiques de gestion de pagination                            | 14 |

|    | 1.3                    | Influence de l'ordonnancement sur la gestion de la mémoire virtuelle | 15 |

|    |                        | 1.3.1 Ordonnancement vertical                                        | 15 |

|    |                        | 1.3.2 Ordonnancement horizontal                                      | 15 |

|    |                        | 1.3.3 Analyse des résultats                                          | 16 |

|    | 1.4                    | Les failles de la politique LRU                                      | 16 |

|    |                        | 1.4.1 L'effet trou                                                   | 17 |

|    |                        | 1.4.2 Politique LRU et factorisation LU                              | 18 |

|    | 1.5                    | Gestion de la mémoire virtuelle au niveau utilisateur                | 19 |

|    |                        | 1.5.1 La librairie MMUM et le module MMUSSEL                         | 20 |

|    |                        | 1.5.2 Un exemple d'application: la factorisation LU                  | 21 |

|    | 1.6                    | Coordonnancement pagination et multi-threading                       | 24 |

|    | 1.7                    | Mémoire virtuelle et parallélisme                                    | 26 |

|    |                        | 1.7.1 La pagination distribuée                                       | 26 |

|    |                        | 1.7.2 Techniques de réordonnancement pour la pagination distribuée   | 27 |

|    |                        | 1.7.3 Communications et l'algorithme de convolution                  | 27 |

|    | 1.8                    | Autres approches                                                     | 29 |

|    | 1.9                    | Conclusion                                                           | 30 |

| II | Λ-                     | annogha algorithmicus                                                | 31 |

| 11 | Aj                     | pproche algorithmique                                                | ЭТ |

| 2  |                        | e bibliothèque de calcul <i>out-of-core</i> : ScaLAPACK              | 33 |

|    | 2.1                    | Architecture de ScaLAPACK                                            | 34 |

|    |                        | 2.1.1 Les BLAS                                                       |    |

|    |                        | 2.1.2 LAPACK                                                         |    |

|    |                        | 2.1.3 Les BLACS                                                      | 36 |

|    |                        | 0.1.4. L DDT AC                                                      | 90 |

|    | 2.2<br>2.3<br>2.4         | Scalapack et le prototype out-of-core                                                  |                      |

|----|---------------------------|----------------------------------------------------------------------------------------|----------------------|

| 3  | La f<br>3.1<br>3.2<br>3.3 | factorisation LU out-of-core  La factorisation LU                                      | 41<br>41<br>43<br>44 |

|    | 3.4                       | Prédiction des performances                                                            | 45<br>45<br>45<br>49 |

|    | 3.5                       | Analyse des surcoûts out-of-core                                                       | 49<br>49<br>52       |

|    | 3.6                       | Conclusion                                                                             | 54                   |

| 4  | Inve                      | ersion matricielle $out	ext{-}of	ext{-}core$                                           | 57                   |

|    | 4.1                       | Inversion matricielle par factorisation LU                                             | 57                   |

|    | 4.2                       | Parallélisation de l'inversion                                                         | 59                   |

|    | 4.3                       | Inversion matricielle out-of-core                                                      | 62                   |

|    |                           | 4.3.1 Principe général                                                                 | 62<br>62             |

|    | 4.4                       | 4.3.2 Résolution triangulaire <i>out-of-core</i>                                       | 63                   |

|    | 4.4                       | 4.4.1 Modélisation de l'inversion matricielle                                          | 63                   |

|    |                           | 4.4.2 Validation expérimentale                                                         | 65                   |

|    | 4.5                       | Analyse des surcoûts out-of-core                                                       | 65                   |

|    | 1.0                       | 4.5.1 Réduction du surcoût des communications                                          | 65                   |

|    |                           | 4.5.2 Réduction du surcoût des Entrées/Sorties                                         | 65                   |

|    | 4.6                       | Optimisation par variation de la taille des super-blocs                                | 69                   |

|    | 4.7                       | Conclusion                                                                             | 69                   |

| 5  | Rec                       | ouvrement des accès disques sur grappes                                                | 71                   |

|    |                           | Un mécanisme de recouvrement des E/S                                                   |                      |

|    | 5.2                       | Factorisation LU parallèle <i>out-of-core</i> avec recouvrement des accès disques      | 72                   |

|    |                           | 5.2.1 Principe algorithmique                                                           | 72                   |

|    |                           | 5.2.2 Expérimentation et résultats                                                     | 72                   |

|    | 5.3                       | Inversion matricielle parallèle <i>out-of-core</i> avec recouvrement des accès disques | 76                   |

|    | 5.4                       | Conclusion                                                                             | 76                   |

| II | I A                       | application                                                                            | 79                   |

| 6  | Scil                      | $Lab^{ooc}_{//}$                                                                       | 81                   |

|    | 6.1                       | Scilab                                                                                 | 82                   |

|    |                           | 6.1.1 L'interfaçage dans Scilab                                                        | 82                   |

|    | 6.2                       | $Scilab_{//} \dots \dots \dots \dots$                                                  | 84                   |

|    | 6.3                       | Interfaçage des PBLAS dans Scilab: niveau applicatif                                   | 85                   |

|                 | 6.3.1 Nouveaux types $Scilab_{//}$                                    | 86  |

|-----------------|-----------------------------------------------------------------------|-----|

| 6               |                                                                       | 87  |

|                 | 6.4.1 Nouveaux types de Scilab $^{ooc}_{//}$                          | 87  |

| 6               | .5 Optimisations pour les traitements out-of-core                     | 88  |

|                 | 6.5.1 Opérateurs et fonctions purs                                    |     |

|                 | 6.5.2 Persistance des matrices out-of-core                            | 88  |

|                 | 6.5.3 Promotions, contagions et dégradations des matrices distribuées |     |

| 6               | 6 Conclusions et travaux futurs                                       | 91  |

| Con             | clusion                                                               | 93  |

| IV              | Annexe                                                                | 95  |

| ۸ (             | Commandes Scalapack                                                   | 97  |

|                 | .1 Commandes BLACS                                                    |     |

|                 | .2 Commandes PBLAS                                                    |     |

|                 | .3 Commandes du prototype out-of-core                                 |     |

|                 | .4 Contribution au prototype out-of-core                              |     |

| вР              | Prototypage de Scilab                                                 | 105 |

| — -<br>В        | 3.1 Prototypage de Scilab <sub>//</sub>                               |     |

|                 | B.1.1 Type contexte                                                   | 105 |

|                 | B.1.2 Type distribution                                               |     |

|                 | B.1.3 Type sous-matrice                                               |     |

|                 | B.1.4 Type matrice distribuée                                         |     |

| В               | 8.2 Prototypage de Scilab $^{ooc}_{//}$                               | 107 |

|                 | B.2.1 Type distribution out-of-core                                   | 107 |

|                 | B.2.2 Type matrice distribuée <i>out-of-core</i>                      | 108 |

| Liste           | e des figures                                                         | 109 |

| $\mathbf{Bibl}$ | iographie                                                             | 111 |

# Introduction

D ans de nombreux domaines, tels que l'astronomie [80], les simulations de crash test automobiles [26], l'électromagnétisme [2] ou encore les modèles climatiques, et, plus généralement dans le calcul numérique hautes performances [74], le Méga-octets vaut de l'or. Dans la pratique, il est le facteur fixant la taille maximale du problème que l'utilisateur pourra traiter. L'utilisateur considérera qu'il est inconcevable de recourir au système de pagination ou aux disques du fait de l'importante chute des performances. Et pourtant, le paradoxe est là d'un côté des capacités mémoire rapide mais de petite taille et coûteuses, de l'autre des capacités mémoire à bon marché et de grande taille, plusieurs Téra-octets, mais très lente d'accès. Malgré cet handicap, on retrouve dans le calcul scientifique trois champs d'application qui sollicitent de manière importante les entrées/sorties:

- Le checkpointing ou reprise sur erreur: la reprise de longs calculs à partir d'un résultat intermédiaire peut éviter parfois de grandes pertes de temps; exemple, reprise d'un calcul débuté il y a plusieurs jours et interrompu par un crash. Cependant pour être efficace cette méthode nécessite une sauvegarde régulière de résultats intermédiaires sur disques ce qui peut s'avérer très coûteux pour le temps de calcul.

- Les entrées/sorties en temps réel: dans certains domaines comme par exemple dans le cadre de l'imagerie médicale, il est parfois très utile de pouvoir réaliser un affichage en temps réel; exemple, l'affichage des données obtenues à partir d'une spectroscopie par résonance magnétique nucléaire [58]).

- Le calcul *out-of-core*: nombreuses sont les applications qui nécessitent le traitement de données importantes, bien souvent au delà des capacités mémoire des machines. L'axe de recherche s'orientant vers un calcul en dehors de la mémoire est appelé calcul *out-of-core*.

#### Le calcul out-of-core

La problématique du calcul *out-of-core* n'est pas nouvelle. Les machines vectorielles avaient par le passé introduit cette notion. Les récentes avancées scientifiques dans le domaine des réseaux hauts débits et l'accroissement de la puissance des processeurs définissent ou redéfinissent, à juste titre, les accès disques comme le facteur le plus pénalisant dans le cadre d'applications parallèles de très grande taille. Le concept du calcul *out-of-core* est d'utiliser au mieux les ressources des mémoires externes. Deux approches différentes mais complémentaires existent:

- soit on utilise une technique de swap mémoire distribuée [10] qui est viable grâce aux nouvelles technologies réseaux sur des architectures type grappe. Cependant cette approche reste très coûteuse et même si elle étend les capacités mémoire globale de l'architecture cela peut s'avérer encore insuffisant. - soit on utilise les disques des différents nœuds comme un swap disque distribué. Cette solution s'avère d'un faible coût mais encore une fois est fortement pénalisée par des accès disques très lents. Cependant, il est possible de trouver des solutions permettant de réduire les accès disques et par conséquent de limiter la chute des performances. C'est sur cet objectif que nous nous focaliserons.

#### Situation par rapport à l'existant

Dans le cadre du traitement de problèmes parallèles *out-of-core*, nous pouvons dissocier deux approches. La première plus générique via la compilation *out-of-core* et l'autre approche plus spécifique via l'algorithmique *out-of-core*.

- La compilation *out-of-core*, propose des solutions sans avoir à réécrire le code. Cependant comme tout outil de compilation, les performances restent loin d'un traitement spécifique. Bordawekar, Choudhary, Kennedy, Koelbel et Paleczny proposent un modèle et des stratégies pour le calcul *out-of-core* dans le cadre d'applications data-parallèles [8]. L'analyse de code est basée sur les méthodes utilisées dans le cadre de la compilation type HPF. On peut distinguer trois phases distinctes lors de la compilation:

- (a) La phase data-parallèle

- Analyse du parallélisme et modèle de distribution des entrées/sorties de chaque tableau.

- Distribution du calcul en fonction de la distribution des données.

- Déterminer les communications nécessaires.

- Déterminer les limites locales.

- (b) La phase out-of-core

- Distribution du calcul en fonction de la distribution des E/S.

- Déterminer les entrées/sorties nécessaires pour l'accès aux tableaux.

- Déterminer les limites mémoire.

- (c) La phase de génération de code

- Séquentialisation du code local.

- Insérer les communications et les entrées/sorties.

- Optimiser les communications et les entrées/sorties.

Notons également que Peter Brezany, Thomas A. Mueck, et, Erich Schikuta, proposent dans le même esprit un langage et un compilateur permettant la gestion des accès disques dans les applications hautes performances [9].

L'algorithmique out-of-core est la seconde approche de résolution out-of-core. Elle implique du programmeur, contrairement à la compilation out-of-core, la réécriture de son code. Cet inconvénient est compensé par des solutions dont la granularité est plus fine et qui permettent donc de proposer des résolutions spécifiquement adaptées aux traitements à effectuer. C'est le cas de la résolution de la transformée rapide de Fourier out-of-core [29] sur le système de disques parallèles de Vitter et Shriver [84]. La résolution de la factorisation LU et de l'inversion matricielle seront basées sur une approche algorithmique.

#### Cadre de travail

Un nouveau type de calculateurs parallèles est né. Les évolutions techniques des processeurs alliés aux progrès réalisés dans le domaine des réseaux à haut débit ont permis l'émergence et le succès des grappes de station ou *cluster*. Il est désormais possible de réaliser une machine parallèle pour un coût nettement inférieur à une architecture parallèle dédiée et offrant de bonnes performances.

Le concept de la grappe est basé sur une architecture SIMD à mémoire distribuée; Cela consiste à relier via un réseau rapide un ensemble de stations de travail. L'ensemble des ressources est distribué: mémoire locale, disques locaux, unités de traitement local.

Les premières grappes ont été mises au point et commercialisées par *DIGITAL Equipment* à la fin des années 80 sous le nom de VAXCluster [55]. Une des premières réalisations concrètes de grappe date de 1995. Afin de simuler des phénomènes physiques et de réaliser l'acquisition de données, la NASA a mis au point une grappe basée sur 16 PCs de type 486DX4 à 100MHz avec chacun deux interfaces Ethernet à 10Mbps et des disques durs de 250Mo.

Aujourd'hui, les grappes apparaissent dans le TOP-500 des super-calculateurs les plus puissants au monde, et peuvent aller jusqu'à plusieurs dizaines de stations chacune multiprocesseurs et totalisant des Téra-octets de capacité de disque et plusieurs dizaines de Giga-octets de mémoire RAM. Les grappes se présentent donc comme une solution économique et efficace pour le traitement de problèmes *out-of-core*.

#### Approche Système

La première approche étudiée sera liée aux mécanismes de pagination et à son comportement face aux problèmes parallèles *out-of-core*. Nous montrerons que les programmes de pagination proposés par le système ne sont pas adaptés au calcul numérique et nous illustrerons par diverses expérimentations les facteurs responsables de cette inadéquation. Nous évoquerons l'importance des réordonnancements dans le calcul *out-of-core*. Enfin, nous présenterons une nouvelle librairie de gestion de la mémoire virtuelle au niveau utilisateur. À l'aide de cet outil, nous proposerons une optimisation de la factorisation LU *out-of-core* par gestion des mécanismes de pagination.

#### Approche Algorithmique

L'approche algorithmique est basée sur la librairie de calcul d'algèbre linéaire Scalapack présentée au chapitre 2. À partir de cette librairie nous avons mené une étude des performances de la factorisation LU *out-of-core* et proposé une modélisation de cette dernière (chapitre 3). Un travail similaire a été mené sur l'inversion matricielle (chapitre 4). Nous avons montré qu'il est théoriquement possible d'effectuer une factorisation LU *out-of-core* ou une inversion matricielle *out-of-core* avec des performances proches du traitement en mémoire. Afin d'expérimenter ce résultat nous avons réalisé pour ces deux problèmes une version effectuant le recouvrement des accès disques (chapitre 5).

#### Intégration dans un outil de calcul numérique

Une dernière partie présentera l'intégration de ces travaux dans Scilab<sub>//</sub> un outil de calcul numérique. La participation à ce projet de l'INRIA, permet d'offrir à la librairie *out-of-core* une interface plus conviviale et accroît ainsi le champ d'application de Scilab<sub>//</sub>.

# Première partie Approche système

# Chapitre 1

# Gestion de la mémoire virtuelle pour le calcul *out-of-core*

#### Sommaire

| 1.1 Mémoire virtuelle et calcul out-of-core       12         1.2 Les mécanismes de gestion de la mémoire virtuelle       12         1.2.1 La pagination       13         1.2.2 Politiques de gestion de pagination       14 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2.2 Politiques de gestion de pagination                                                                                                                                                                                   |

| 1.2.2 Politiques de gestion de pagination                                                                                                                                                                                   |

|                                                                                                                                                                                                                             |

| 1.3 Influence de l'ordonnancement sur la gestion de la mémoire virtuelle . 15                                                                                                                                               |

| 1.3.1 Ordonnancement vertical                                                                                                                                                                                               |

| 1.3.2 Ordonnancement horizontal                                                                                                                                                                                             |

| 1.3.3 Analyse des résultats                                                                                                                                                                                                 |

| 1.4 Les failles de la politique LRU 16                                                                                                                                                                                      |

| 1.4.1 L'effet trou                                                                                                                                                                                                          |

| 1.4.2 Politique LRU et factorisation LU                                                                                                                                                                                     |

| 1.5 Gestion de la mémoire virtuelle au niveau utilisateur 19                                                                                                                                                                |

| 1.5.1 La librairie MMUM et le module MMUSSEL 20                                                                                                                                                                             |

| 1.5.2 Un exemple d'application: la factorisation LU                                                                                                                                                                         |

| 1.6 Coordonnancement pagination et multi-threading 24                                                                                                                                                                       |

| 1.7 Mémoire virtuelle et parallélisme                                                                                                                                                                                       |

| 1.7.1 La pagination distribuée                                                                                                                                                                                              |

| 1.7.2 Techniques de réordonnancement pour la pagination distribuée 27                                                                                                                                                       |

| 1.7.3 Communications et l'algorithme de convolution                                                                                                                                                                         |

| 1.8 Autres approches                                                                                                                                                                                                        |

| 1.9 Conclusion                                                                                                                                                                                                              |

P our combler les manques de mémoire vive face aux applications scientifiques, le calcul out-of-core offre une solution économique utilisant les ressources disponibles. En effet, le calcul out-of-core se propose d'exploiter les grandes capacités de la mémoire secondaire: les disques. Cependant, le temps d'accès aux informations est l'inconvénient majeur de ce type de calcul. Deux approches ont émergé dans ce cadre de travail. La première développée section 1.1 consiste à proposer des solutions de gestion de mémoire virtuelle, adaptées aux calculs out-of-core; nous parlerons de mémoire virtuelle out-of-core. La seconde approche consiste à proposer des solutions

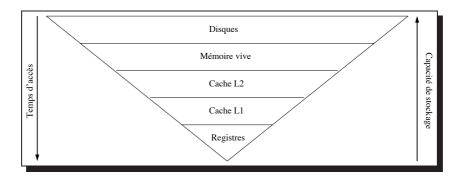

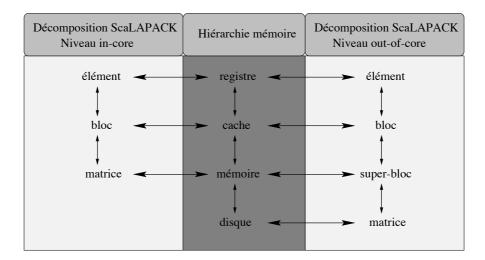

Fig. 1.1 – Représentation de la hiérarchie mémoire.

algorithmiques réduisant les accès disques en proposant une réorganisation des calculs ou une distribution des données adaptées (section 1.4).

#### 1.1 Mémoire virtuelle et calcul *out-of-core*

Dans cette section nous montrerons que des techniques de réordonnancement permettent de diminuer le nombre d'accès disques dans le cas d'un traitement sur machine à mémoire partagée, puis nous proposerons une approche globale de la gestion d'une mémoire virtuelle parallèle distribuée.

L'architecture des stations de travail actuelle renferme plusieurs niveaux mémoire, dont l'ordre est déterminé par le temps d'accès moyen. On observe généralement un volume de stockage inversement proportionnel au temps d'accès: registres, cache de premier niveau, de second niveau, mémoire vive.... Les techniques de génération de code ou les bibliothèques (cf chapitre 2) permettent aujourd'hui, dans le meilleur des cas, d'exploiter au mieux un niveau avant d'accéder au niveau inférieur.

Dans le cadre de la gestion mémoire pour le calcul intensif sur grappe de stations, les performances du disque (dernier étage de la hiérarchie mémoire (cf figure 1.1)) constituent un obstacle fortement contraignant. L'utilisateur doit alors limiter la taille de ses données à la mémoire physique disponible; la mémoire virtuelle est de facto bannie de l'univers du calcul scientifique, alors que les volumes de données à traiter sont toujours plus importants. Pour franchir cette frontière matérielle, il convient d'ordonnancer le calcul de façon à réduire au maximum le nombre des accès disques et/ou de recouvrir les temps d'accès disques et de calcul [54].

#### 1.2 Les mécanismes de gestion de la mémoire virtuelle

Lorsque les ressources mémoire nécessaires à un calcul dépassent la capacité disponible, un mécanisme de gestion de la mémoire virtuelle (également appelé mécanisme de pagination disque) permet de poursuivre le traitement. Dès lors, on se retrouve dépendant du système de gestion de la mémoire virtuelle du système d'exploitation. Il est donc intéressant de rappeler les mécanismes de fonctionnement de la pagination et plus particulièrement de la pagination sous Linux sur lequel nous avons effectué nos expérimentations.

#### 1.2.1 La pagination

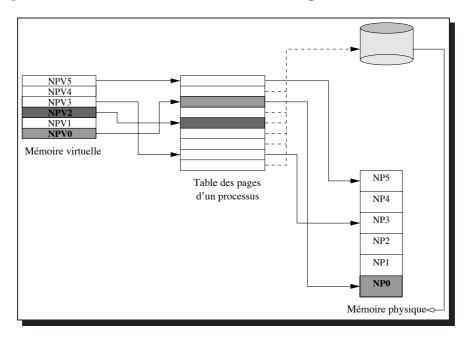

L'organisation de la mémoire sous Linux est réalisée par l'intermédiaire d'un système de pagination. Le système a pour charge de maintenir une table des pages contenant diverses informations [11] comme le bit validité, l'adresse physique de la page et les informations de contrôles d'accès . À partir de cette table le système effectue la correspondance entre l'adresse virtuelle et l'adresse physique mémoire. Lorsque le processus requiert l'accès à une donnée, trois cas de figure peuvent alors survenir:

- L'adresse est transmise au système, ce dernier dispose pour celle-ci d'une adresse physique valide en mémoire. La donnée est alors transmise au processus. L'accès à la page NPVO figure 1.2 illustre l'accès mémoire classique.

- Dans un autre cas, cette adresse est référencée dans la table des pages du processus mais l'adresse physique associée est invalide. La donnée n'est donc plus disponible en mémoire. Le système informe le processeur que l'adresse virtuelle est invalide suite à un défaut de page. La figure 1.2 visualise la requête au disque par une flèche en pointillé. L'accès à la page NPV2 illustre le **défaut de page**.

- L'adresse virtuelle transmise au système n'est pas présente dans la table des pages du processus. Le système informe ce dernier qu'un adressage invalide vient d'être provoqué. L'accès à la page NPV9 provoque pour le processus un adressage invalide.

Fig. 1.2 – Modèle de gestion mémoire avec pagination, NPV correspond au Numéro de la Page Virtuelle (adresse virtuelle) et NP au Numéro de la Page (adresse physique).

Le coût prohibitif engendré par le mécanisme de défaut de page découle implicitement des accès disques. Pour obtenir de bonnes performances de calcul, il est indispensable de minimiser les accès disques et de minimiser ainsi les défauts de pages. L'exécution est optimale lorsque l'ensemble de travail (working set) est disponible en mémoire. L'ensemble de travail correspond aux pages couramment utilisées [75]. Cependant, dans le cas de traitement de grandes données, l'exécution

nécessite de parcourir un grand nombre de pages et l'utilisation du système de pagination est inévitable. On cherche alors à minimiser le nombre d'accès aux pages et de favoriser au maximum les accès à une même page. La gestion des défauts de pages est déterminée par la politique de pagination.

#### 1.2.2 Politiques de gestion de pagination

Lorsque le système génère un défaut de page, la page doit être transférée du disque vers la mémoire. Lorsqu'il n'y a plus de page mémoire disponible, le système doit libérer l'espace mémoire nécessaire en déchargeant certaines pages mémoire. L'état de la page est pris en compte lors de cette opération. En effet, si la page a été modifiée, il est indispensable d'inscrire son contenu dans la zone de pagination avant de libérer son espace, il s'agit des dirty pages. Dans le cas contraire la page peut être simplement évincée de la mémoire.

Cependant, le choix de la page qui va être déchargée de la mémoire influence considérablement les performances. Comme nous le montrent les expérimentations menées en section 1.3 si l'on se retrouve à évincer la page mémoire qui va être accédée lors de l'opération suivante, les performances s'écroulent. Afin d'éviter ce genre de situation, différentes politiques de pagination existent :

- la politique optimale: elle consiste à décharger la page qui sera réutilisée le plus tard. Cette stratégie est optimale mais impossible à mettre en place dans le cas général puisqu'il ne nous est pas possible de prévoir les références aux futures pages.

- une politique basée sur l'algorithme FIFO¹: les pages sont déchargées selon leur ordre d'arrivée. L'inconvénient majeur de cette stratégie réside dans le fait que l'on ne tient aucun compte de l'utilisation de chaque page. De plus, cette stratégie présente l'anomalie de Belady [6] c'est-à-dire que le nombre de défauts de pages peut augmenter avec la taille du cache mémoire.

- la politique de la seconde chance: lorsqu'une page est chargée ou utilisée on positionne son bit de la seconde chance à 1. Lorsqu'une page est candidate (selon l'ordre FIFO) au déchargement de la mémoire, on vérifie la valeur de son bit de la seconde chance. Si son bit est à 1 alors on met le bit à 0 et on n'évince pas la page; dans le cas contraire la page est déchargée. Cette méthode peut être considérée comme une extension de la politique FIFO. Elle diminue les défauts de cette méthode sans les supprimer.

- une politique de pagination basée sur la fréquence appelée également LFU<sup>2</sup>: dans ce cas le système mémorise la quantité de fois où une page est accédée. Lorsque l'on doit décharger de la mémoire une page, ce sont les pages les moins fréquemment utilisées qui sont évincées en premier lieu. L'inconvénient de cette méthode est que lorsqu'une page a été fortement Utilisée, elle va s'attarder en mémoire alors que sa période d'utilisation est terminée.

- Une politique de pagination basée sur le temps appelée également algorithme de la LRU<sup>3</sup>: le système associe à chaque page un âge en fonction du dernier accès à celle-ci. Les premières pages à être évincées de la mémoire sont les plus anciennes. Reconnu comme un bon algorithme, il ne présente pas l'anomalie de Belady, mais cependant cette politique nécessite une implémentation plus complexe puisqu'elle doit connaître la date de la dernière utilisation de chaque page et gérer une pile dont le sommet contient le numéro de la page la plus récemment utilisée. Cette stratégie est celle adoptée par Linux.

<sup>1.</sup> First In First Out

<sup>2.</sup> Least Frequently Used

<sup>3.</sup> Least Recently Used.

# 1.3 Influence de l'ordonnancement sur la gestion de la mémoire virtuelle

Dans le cadre de la programmation (ou de la génération de code) multi-threadée ou SMP, la multiplicité des flux d'exécution et leurs mauvais ordonnancement peut induire la multiplicité des défauts de pages. Afin d'illustrer ces propos nous avons étudié le comportement d'une convolution simple *out-of-core* (moyenne des quatre voisins). La méthode classique de calcul consiste à découper la matrice en blocs, pour améliorer la localité des accès aux données.

Pour maîtriser l'ordonnancement des flux d'exécution, nous simulons une exécution sur architecture SMP dans laquelle chaque processeur est en charge du traitement d'une tranche de la matrice commune. Les processeurs sont considérés comme uniformément performants (i.e. ils restent synchronisés).

Nous avons considéré deux types de découpage de la matrice en tranches: un découpage vertical (dans le sens de la mémoire), l'autre horizontal. Pour observer le comportement du système de pagination dans ces deux cas nous avons mesuré le nombre de défauts de pages provoquant un accès disque, en fonction du nombre de flux d'exécution parallèle.

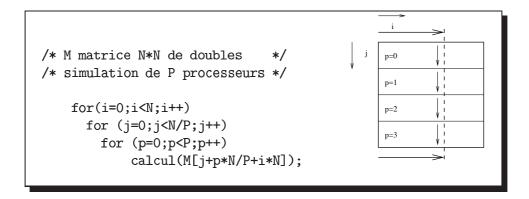

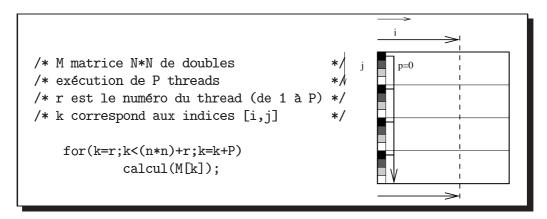

#### 1.3.1 Ordonnancement vertical

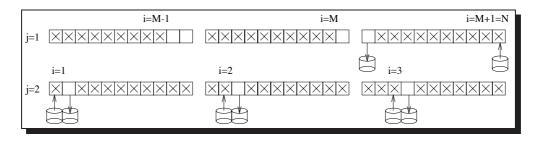

Chaque processeur accède linéairement à la mémoire, pour la tranche verticale qui lui a été attribuée (cf. figure 1.3). L'expérience a été réalisée sur une matrice double précision de taille 4096x4096, i.e. 128 Mo sur un Celeron disposant de 32 Mo de mémoire réelle et 700 Mo de mémoire paginée. On mesure le nombre d'accès disques effectué par le système de pagination. Lorsque le nombre de flux d'exécution est trop important (de l'ordre de 256 et plus, cf. figure 1.5) le nombre d'accès disque augmente brutalement.

```

/* M matrice N*N de doubles */

/* simulation de P processeurs */

for(i=0;i<N/P;i++)

for (j=0;j<N;j++)

for (p=0;p<P;p++)

calcul(M[j+(i+p*N/P)*N]);

```

Fig. 1.3 – Découpage vertical, le front d'accès parallèle à la mémoire est représenté en pointillé. Le sens du parcours du front mémoire est parallèle au sens du parcours de la matrice par les flux d'exécution.

#### 1.3.2 Ordonnancement horizontal

Dans le second cas, la matrice est découpée par bandes horizontales. Chaque processeur simulé accède colonne par colonne aux éléments de sa bande (cf. figure 1.4).

Fig. 1.4 – Découpage horizontal, le front d'accès parallèle à la mémoire est représenté en pointillé. Le sens du parcours du front mémoire est perpendiculaire au sens du parcours de la matrice par les flux d'exécution.

La deuxième courbe de la figure 1.5 montre l'indépendance du nombre de pages paginées par rapport au nombre de flux d'exécution. Le nombre de pagination est ici constant et correspond à la première expérimentation sans le phénomène d'augmentation.

Le temps d'exécution de la convolution pour 4096 flux d'exécution est alors 6,66 fois inférieur que pour l'ordonnancement vertical.

#### 1.3.3 Analyse des résultats

Ces résultats s'expliquent en considérant le *front* d'accès parallèle à la mémoire. Dans le cas du découpage vertical, on constate un accès parallèle à un nombre de zones mémoire discontiguës correspondant au nombre de flux d'exécution. Dans le cas du découpage horizontal, l'accès parallèle s'effectue dans une zone contiguë de la mémoire (la colonne), et ce quel que soit le nombre de flux d'exécution. On obtient donc de meilleures performances dans cette dernière situation.

Dans le cas du traitement des données de grande taille, la génération de code pour machine à mémoire partagée ne doit pas être considérée de la même façon que la génération de code pour machine à mémoire distribuée, sous peine de mauvaise gestion mémoire. En effet, l'expérience a montré que le cache processeur est plus efficace pour des accès contigus en mémoire. Dans le cadre des calculs *out-of-core*, la problématique diffère: le coût d'un défaut de page prédomine largement celui d'un défaut de cache.

#### 1.4 Les failles de la politique LRU

Dans cette section nous allons montrer que la gestion de la mémoire virtuelle proposée par les systèmes d'exploitation n'est pas adaptée au calcul *out-of-core*.

La section 1.2.2 décrit les principes des politiques de gestion de mémoire virtuelle. L'objectif d'une politique de pagination est de favoriser la localité temporelle, c'est-à-dire de préserver en mémoire les pages qui ont été récemment utilisées. La politique utilisée (LRU) considère que les pages qui ont le plus de chance d'être accédées par la suite sont celles qui viennent d'être récemment utilisées.

Nous allons illustrer par un exemple les répercutions de cette politique dans le cadre du calcul out-of-core. L'exemple présenté dans cette section met en évidence les limites de la politique LRU

Fig. 1.5 – Nombre de pagination en fonction du nombre de flux d'exécution : découpage par colonne et découpage par ligne.

lors de calcul séquentiel.

#### 1.4.1 L'effet trou

La politique LRU n'est pas adaptée aux accès linéaires en mémoire qui apparaissent souvent dans les calculs générés par des applications data-parallèles. Lorsque la taille des données est plus grande que la mémoire physique, le système de pagination est pris à défaut et l'on voit apparaître un effet trou. Dans cette partie nous allons définir cet effet trou sur un exemple simple puis nous verrons ces répercutions dans le cas d'une factorisation LU sur une matrice de grande taille.

```

real V[N];

for j = 1 to P

for i = 1 to N

V[i] = f(i,j);

```

Fig. 1.6 - Accès linéaire en mémoire.

Considérons le programme figure 1.6. Il y a P accès linéaires à un vecteur V de N éléments. Soit M le nombre de pages mémoire physique disponible en mémoire, et B la taille de la page. Considérons le cas où  $\lceil N/B \rceil > M$ , par exemple  $N = M \times B + 1$ , et V[1..N-1] est initialement dans la mémoire physique. Les accès à V[N] provoquent un défaut de page. Afin de répondre à la requête, le système de gestion de mémoire virtuelle va donc ôter de la mémoire physique la page qui contenait V[1]. Cependant, le programme va effectuer un nouveau parcours du vecteur V et par conséquent accéder à V[1]. Ce qui va provoquer un défaut de page. Ce défaut de page va alors évincer de la mémoire les pages qui contiennent V[B+1], c'est-à-dire les pages qui seront nécessaires à la poursuite de l'algorithme. Ce phénomène se répercute à chaque page accédée. On parle alors d'effet trou (figure 1.7).

Le nombre d'accès disques est égal à  $2 \times \lceil N/B \rceil \times (P-1) + 1$ , et est dépendant de la taille de la mémoire physique M (lorsque  $N > M \times B$ ).

L'exemple présenté pour illustrer l'effet trou est trivial. Cependant, on retrouve ce phénomène dans de nombreuses applications de calcul numérique nécessitant un accès linéaire en mémoire,

Fig. 1.7 – Principe de l'effet trou.

comme par exemple dans le cas de factorisation LU.

#### 1.4.2 Politique LRU et factorisation LU

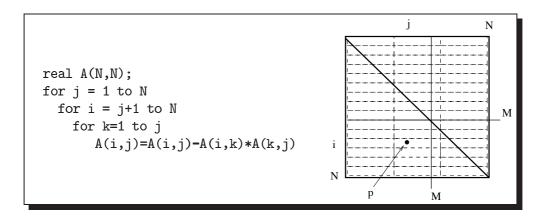

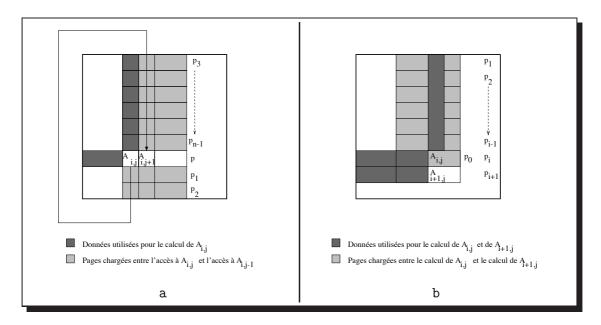

FIG. 1.8 – Factorisation LU. La matrice est stockée par ligne en mémoire. La page p possède les éléments A(i,j). La matrice d'ordre N est plus grande que M le nombre de pages disponibles en mémoire physique.

Considérons le cas d'une factorisation LU sur une matrice d'ordre N. L'algorithme est présenté figure 1.8. Dans ce programme, chaque élément  $A(i,j)_{i>j}$  est le résultat du vecteur A(i,1:j) par le vecteur A(1:j,j). Nous estimons le nombre de défauts de pages lorsque N est supérieur au nombre de pages physiques en mémoire M. Considérons pour cela l'itération  $(i,j)_{i>j}$  et p la page qui contient A(i,j). Par dépendance des données, nous montrons que la prochaine utilisation de la page p s'effectuera à l'itération (i,j+1), comme le montre la figure 1.9a. Le nombre de pages accédées avant le prochain accès à la page p, est supérieur ou égal à  $N-1 \ge M$ . En appliquant la politique LRU, la page p n'est pas disponible suffisamment longtemps en mémoire. Cela se vérifie pour toutes les itérations où  $(i,j)_{i>j}$ . En fait dans ce cas, on produit un effet trou lors de l'accès à deux éléments contiguës sur la même ligne. On a donc au moins  $(\frac{N}{2}-1)N$  défauts de pages.

À présent considérons les itérations  $(i,j)_{i>j}$  dans le cas où j>M. On effectue alors (N-j) accès linéaires aux pages j, associés au vecteur A(1:j,j) dans la boucle interne. Le calcul de  $A_{(i,j)}$  effectue trop de chargement de pages pour conserver en mémoire les premières pages utilisées pour le calcul de  $A_{(i+1,j)}$  (cf figure 1.9b). On se retrouve alors dans l'effet trou qui va provoquer j défauts de pages. Globalement les deux effets trou impliquent un nombre de défauts de pages p(N,M) qui

Fig. 1.9 – L'effet trou dans la factorisation LU. Entre deux éléments de deux colonnes consécutives (a) et entre deux éléments consécutifs (b).

est supérieur à

$$(\frac{N}{2}-1)N+\sum_{j=M+1}^{j=N}j(N-j).$$

Lorsque M est constant, p(N,M) est en  $O(N^3)$ . Dans la section suivante nous présentons une nouvelle stratégie de pagination qui permet d'éviter l'écroulement provoqué par l'effet trou.

#### 1.5 Gestion de la mémoire virtuelle au niveau utilisateur

Nous avons montré que les politiques de gestion de mémoire virtuelle, mises en œuvre dans les systèmes d'exploitation, ne sont pas adaptées au schéma d'exécution des applications data-parallèle. Deux approches sont alors envisageables:

- soit on s'oriente vers une solution algorithmique. Dans ce cas, l'utilisateur doit réécrire son code. Les performances d'un code *out-of-core* pourront être améliorées si le programmeur peut mettre à profit ses connaissances sur le système de pagination. En effet, le programmeur connaissant la politique de pagination peut, si cela lui est possible, réordonnancer l'accès aux données afin de diminuer les défauts de pages. C'est ce type de solution qui est développé dans la partie II.

- ☐ soit on s'oriente vers une solution système en modifiant la politique de gestion de la mémoire virtuelle. Malheureusement, il n'est pas aisé de modifier cette politique. Une des rares approches consiste en général à réécrire des parties du noyau du système d'exploitation qui gère la stratégie de gestion mémoire. Dans la suite de ce chapitre, nous présentons un nouvel outil qui permet l'implémentation de gestion de la mémoire virtuelle au niveau utilisateur. À l'aide de cet outil nous pourrons proposer une nouvelle stratégie de gestion de la mémoire virtuelle pour la factorisation LU.

#### 1.5.1 La librairie MMUM et le module MMUSSEL

Comme nous venons de le démontrer les politiques de gestion de mémoire virtuelle ne sont pas adaptées aux applications numériques de grande taille. Nous avons également énoncé (section 1.2.2) la stratégie de pagination optimale. Son implémentation est, dans la réalité, irréalisable mais en offrant la possibilité à l'utilisateur de pouvoir modifier la méthode de pagination en fonction de son application ou même de redéfinir sa propre stratégie de pagination en fonction de son application, on tend à se rapprocher de la solution optimale puisque spécifique à une application donnée. C'est à partir de ce constat qu'un nouvel outil de gestion de la mémoire virtuelle au niveau utilisateur a vu le jour.

#### Description

L'outil de gestion de la mémoire virtuelle est composé d'une librairie appelée MMUM<sup>4</sup>, et d'un module noyau appelé MMUSSEL<sup>5</sup> [13]. Le module noyau est écrit pour LINUX, mais pourrait être écrit pour n'importe quel Unix utilisant une organisation de la mémoire virtuelle de type MACH [1] (BSD, OSF/1, Hurd, ...). MMUM est une librairie consacrée aux mécanismes d'écriture en gestion de mémoire virtuelle au niveau applicatif. La librairie peut être combinée avec le module MMUSSEL. Ce module interagi avec le système d'exploitation pour effectuer la gestion des pages en mémoire physique. Une description plus approfondie du module MMUSSEL est disponible dans [32]

Cette librairie permet au programmeur de définir une nouvelle région mémoire à laquelle on peut associer une politique de pagination particulière. Une nouvelle zone mémoire est créée par l'appel à la fonction mmum\_create(size,init,nopage).

Le paramètre size est la taille en bytes de la nouvelle région. La fonction init est appelée lorsqu'une référence est réalisée sur une nouvelle région. La fonction nopage est appelée à chaque fois qu'un défaut de page est provoqué dans cette zone mémoire.

Afin de définir une nouvelle stratégie de gestion de la mémoire virtuelle, il faut dans un premier temps écrire les deux procédures init et nopage. Plusieurs fonctions de MMUM sont conçues pour permettre la gestion de la mémoire physique avec la nouvelle région créée.

- mmum\_newpage(void \*a): associe une nouvelle page de la mémoire physique à la page référencée par l'adresse (virtuelle) a. Le bit lecture/écriture de la nouvelle page est positionné à 0.

- mmum\_releasepage(void \*a): libère la page physique associée à l'adresse (virtuelle) a.

- mmum\_xchg(void \*a,void \*b): échange les deux pages physiques associées respectivement aux adresses (virtuelles) a et b. Il n'est pas nécessaire d'associer une page physique à l'adresse virtuelle. Pour le moment, si l'adresse a est associée avec la page physique et qu'il n'y a pas de page associée à l'adresse b, après l'appel à mmum\_xchg(a,b), l'adresse b est associée avec la page précédemment pointée par l'adresse a, et aucune page n'est associée à l'adresse a.

- mmum\_use\_rw(void \*a): retourne la valeur du bit de lecture/écriture de la page associée à l'adresse (virtuelle) a et la remet à zéro.

<sup>4.</sup> Memory Management in User Mode.

<sup>5.</sup> Memory Management at USer SpacE Level.

```

void main() {

double *v;

int i;

...

/* Le fichier A est projeté sur le vecteur v */

v = mmum_create(N,fm_init,fm_nopage);

for (i=0;i<N;i++) v[i]=f(v,i);

...

}</pre>

```

FIG. 1.10 - Application nécessitant l'accès à un fichier projeté dans une région mémoire.

#### Projeter un fichier dans la mémoire virtuelle

Pour illustrer MMUM/MUSSEL, nous présentons une gestion de la mémoire virtuelle qui permet de projeter un fichier à une nouvelle zone mémoire <sup>6</sup>.

Le système de gestion de mémoire virtuelle est utilisé par une application qui effectue quelques calculs sur un vecteur de taille N, comme le décrit le programme en figure 1.10. Le contenu du vecteur est en fait le contenu du fichier placé dans une nouvelle zone mémoire. La variable V est un pointeur sur le début de cette nouvelle zone. Les itérations du programme modifient les valeurs du vecteur par la fonction f. Les accès au fichier sont transparents et sont effectués par le système de gestion de la mémoire virtuelle, c'est-à-dire par la fonction fm\_init et fm\_nopage.

Figure 1.11 on peut voir le code source des fonctions fm\_init et fm\_nopage qui implémente les mécanismes pour projeter le fichier.

Dans cette implémentation, il n'y a qu'une seule page présente à la fois. Par initialisation, cette page est la première page du fichier (fonction fm\_init). Quand un défaut de page survient, c'est-à-dire qu'une autre page de la zone mémoire est accédée, la page courante est écrite sur le disque si elle a été modifiée, et la nouvelle page est chargée en mémoire (fonction fm\_nopage).

#### 1.5.2 Un exemple d'application: la factorisation LU

Nous allons définir une nouvelle stratégie de pagination pour la factorisation LU précédemment introduite dans la section 1.4.2. Nous proposons de modifier dynamiquement la politique de pagination en cours d'exécution. Nous définissons pour cela différentes phases de calcul.

La matrice est stockée en ligne, les colonnes sont regroupées par blocs de taille B. Durant le calcul de tous les éléments d'une colonne de bloc, N pages de la mémoire sont accédées plusieurs fois. Au lieu d'utiliser un algorithme LRU comme politique de gestion de la mémoire virtuelle, nous pouvons utiliser un algorithme LIFO (Last In First Out), avec la page M-1 comme première page en mémoire. Ainsi un défaut de page est provoqué pour chaque accès à un élément de A(i,j) lorsque i >= M, cette stratégie permet d'éviter l'effet trou et de réduire le nombre de défauts de pages.

À chaque itération i, du fait de la localité spatiale, on a une utilisation étendue des pages associées au vecteur A(i, 1:j). Lorsque ces pages sont présentes en mémoire physique, c'est-à-dire

<sup>6.</sup> Notons que dans les systèmes d'exploitation actuels la fonction mmap permet d'effectuer cette opération.

```

/* Adresse de la nouvelle région mémoire

void *fm_start;

void *fm_current;

/* Adresse virtuelle de la page courante

*/

/* Chargement dans la région

*/

int fm_size;

/* Taille de la nouvelle région mémoire

*/

int fm_fd;

/* Descripteur de fichier

*/

void fm_init(void *v,int size) /* La nouvelle zone mémoire est initialisée */

/* Enregistre l'adresse de la nouvelle zone */

fm_start=v;

/* Enregistre la taille de la nouvelle zone */

fm_size=size;

fm_fd=fopen(FILENAME,"rw"); /* Ouvre le fichier à projeter dans la zone */

/* mémoire

/* Association d'une nouvelle page physique */

new_page(fm_start);

/* avec le début de la zone

/* Lit la première page de la région

*/

fread(fm_start,PAGE_SIZE,1,fm_fd);

fm_current=fm_start;

/* Enregistre l'adresse virtuelle courante

*/

/* de la page physique

*/

void fm_nopage(void *a)

/* La page adressée n'est pas présente en

*/

/* mémoire physique

*/

{

/* Vérifie si la page a été modifiée

*/

/* Si oui, elle est inscrite sur le disque

if (WRITTEN(mmum_use_rw(fm_current)))

fseek(fm_fd,(fm_current-fm_start)/PAGE_SIZE);

fwrite(fm_start,PAGE_SIZE,1,fm_fd);

/* La page physique associée à l'adresse

*/

/* virtuelle fm_current est à présent

*/

/* associée à l'adresse virtuelle a

*/

/* Lit la page correspondant à l'adresse

*/

/* virtuelle a

*/

fseek(fm_fd,(a-fm_start)/PAGE_SIZE);

fread(a,PAGE_SIZE,1,fm_fd);

/* Enregistre l'adresse virtuelle courante

fm_current=a;

/* de la page physique

*/

```

FIG. 1.11 – Fonctions associées à la nouvelle zone mémoire pour l'implémentation de la projection de fichier.

| Ordre de la mémoire | LRU        | Optimisée     | Efficacité |

|---------------------|------------|---------------|------------|

| 512                 | 41 194 616 | 22 761 454    | 55%        |

| 768                 | 7 477 734  | $3\ 024\ 878$ | 40%        |

| 921                 | 1 651 317  | $281\ 996$    | 17%        |

TAB. 1.1 – Comparaison entre la factorisation LU version LRU et la version optimisée. Expérimentation sur une matrice d'ordre 1024.

suite à un défaut de page, le système de gestion de mémoire virtuelle ne les remplace pas.

Lorsqu'un bloc de colonnes est atteint, on doit remplacer le bloc de colonnes précédent, et plus précisément ses pages physiques par de nouvelles. Pour cela, le mécanisme de remplacement des pages est changé pour une stratégie LRU. Cela permet d'accéder aux M premiers éléments de la première colonne du nouveau bloc. Une fois ces accès effectués, on reprendra la stratégie LIFO.

Pour implémenter dynamiquement ce changement de stratégie, on réalise un programme de factorisation LU avec plusieurs directives de gestion de la mémoire virtuelle comme le montre la figure 1.12.

- LIFO(A): quand un défaut de page est provoqué sur la matrice A, on utilise la stratégie de remplacement des pages LIFO.

- Spatial(A(i,1:j)): les pages qui contiennent le vecteur A(i,1:j) ne sont pas remplacées par le système de gestion de la mémoire virtuelle.

- $\square$  NoSpatial(A(i,1:j)): les pages qui contiennent le vecteur A(i,1:j) peuvent être remplacées par le système de gestion de la mémoire virtuelle.

Fig. 1.12 – Factorisation LU avec les directives de pagination.

Toutes les données dans la sous matrice A(M:N,1:N) sont gérées par une stratégie de remplacement de type LIFO, excepté pour la zone définie pour bénéficier de la localité spatiale que nous appellerons zone spatiale. Toutes les autres données sont accédées suivant la stratégie LRU. L'intérêt de cette solution est de supprimer les défauts de pages dans la sous matrice A(1:M,1:N).

Lorsque l'on expérimente cette stratégie sur un PC sous Linux pour une matrice d'ordre N=1024, les résultats avec différentes valeurs pour M sont présentés dans le tableau 1.1. Plus le rapport M/N est grand, plus l'optimisation proposée est efficace.

#### 1.6 Coordonnancement pagination et multi-threading

Les expérimentations et les conclusions obtenues précédemment sont basées sur le postulat que les processeurs sont considérés comme uniformément performants. L'exécution sur architecture SMP est totalement asynchrone ce qui implique des conséquences néfastes sur la pagination. Nous proposons alors une approche multithreadée. Le parcours selon un découpage vertical est alors soumis à des perturbations significatives comme le montre la figure 1.13.

Fig. 1.13 - Nombre de pagination en fonction du nombre de threads : découpage vertical.

Ces phénomènes de perturbations s'expliquent par la désynchronisation des threads. Lorsqu'un défaut de page est provoqué, le thread est mis en attente et le système effectue un changement de contexte afin de permettre à un autre processus de s'exécuter. Prenons, par exemple, deux threads qui désirent accéder à une même page. Le temps de latence entre ces deux accès est dépendant de la charge mémoire occasionnée par l'exécution des autres threads qui se réalisera entre ces deux accès. Si cette charge mémoire est supérieure à la mémoire disponible la page aura été évincée de la mémoire. La désynchronisation des threads conduit à la propagation de ce phénomène et entraîne l'écroulement des performances. En fait, les accès multiples à la mémoire par les différents flux, reproduisent le phénomène de l'effet trou. Le facteur déclencheur est différent mais le résultat est similaire.

Pour améliorer les performances nous avons dans un second temps proposé une solution axée sur le data-driving. Dans ce cas, le flux d'exécution n'est plus déterminé par le flux de contrôle mais par le flux de données. Tant qu'une page est disponible en mémoire, on exploite ses données. On effectue en fait une distribution cyclique du flux d'exécution sur les données comme le montre la figure 1.14. Nous avons constaté que la désynchronisation qui nous pénalisait dans l'exécution précédente, n'apparaît plus. En effet, lorsqu'un défaut de page est occasionné par un thread celui-ci est mis en attente jusqu'à ce que la page soit chargée en mémoire physique. Ce laps de temps

associé à la priorité de traitement des threads est suffisant pour absorber une désynchronisation significative.

Fig. 1.14 — Découpage data-driven, les threads sont distribués de manière cyclique sur les données. Le front d'accès parallèle à la mémoire est représenté par les pointillés. Le sens du parcours du front mémoire est cyclique mais reste globalement perpendiculaire au sens du parcours de la matrice pour les flux d'exécution.

En adoptant cette méthode, les résultats obtenus ne subissent plus de perturbations pour un faible nombre de threads. Mais on continue à constater un écroulement des performances lorsque le nombre de threads augmente. Ce phénomène semble en contradiction avec la solution algorithmique adoptée. En effet, chaque page mémoire peut contenir jusqu'à 512 éléments de type double, soit 512 threads dans notre cas. Les threads posix [85] de Linux sont des threads système, mais la gestion de leur contexte d'exécution ne peut justifier une telle consommation de pagination. Afin de comprendre les causes d'un tel écroulement, nous avons mené diverses expérimentations qui ont mis en exergue un problème système.

Lorsqu'un processus déclenche un défaut de page le système prend en compte sa demande et place le processus en attente. Dans le même temps où la page est extraite du disque et chargée en mémoire physique, un ou plusieurs autres threads peuvent provoquer le même défaut de page. Si l'on analyse de près le comportement du noyau système on constate qu'une file d'attente des pages à charger est créée. Une entrée dans cette file ne tient pas compte du fait qu'une demande similaire est déjà présente. Lorsque le chargement d'une page donnée a été effectué et que le processus demandeur reprend son exécution, il met à jour la table des pages. L'information est alors disponible pour les autres processus. Cependant, les processus ayant effectué la requête sur cette page vont occasionner exactement le même accès disque. Deux pages ne peuvent être stockées dans la mémoire physique à des adresses différentes. Par conséquent, ce traitement est inutile et catastrophique pour les performances.

Ce problème système n'est pas une erreur conceptuelle puisqu'une telle optimisation ne se justifiait pas avant l'avènement des threads. En effet, chaque processus dispose de sa table de pages et par conséquent le cas évoqué précédemment correspondait à un cas pathologique très spécifique. L'émergence des threads associée à l'évolution du calcul *out-of-core* nous incite à concevoir une politique de coordonnancement pagination-threads. Les résultats obtenus en sont l'illustration directe.

#### 1.7 Mémoire virtuelle et parallélisme

La résolution de problèmes de grande taille est souvent liée au parallélisme. L'approche parallèle permet d'introduire une nouvelle technique de gestion de la mémoire virtuelle: la pagination distribuée, mémoire distante.

#### 1.7.1 La pagination distribuée

La pagination distribuée est également appelée pagination en mémoire distante. Le principe est d'utiliser, pour un nœud surchargé, la mémoire d'un nœud voisin afin de stocker les pages paginées [10]. Les technologies haut-débit permettent ainsi de diminuer le temps de chargement d'une page, mais ce mécanisme ne résout qu'une situation localement dégradée : le volume total des données est toujours limité à la mémoire physique répartie. Cette technique équivaut à traiter la surcharge mémoire locale par un rééquilibrage de charge.

La gestion de la pagination distribuée ainsi définie implique la prise en considération ou la reconsidération de critères comme la cohérence de cache ou encore l'importance de la localité des données. Dans le cadre d'une pagination distribuée, deux stratégies de contrôle peuvent être mises en place [30]: le contrôle centralisé ou le contrôle distribué.

#### Contrôle centralisé

Dans cette configuration, une unité est désignée comme serveur entre les nœuds et le (ou les) disque(s). La distribution des données est alors réalisée par le serveur selon une fonction de hachage prédéfini. Aucune cohérence de cache n'est à envisager car aucune recopie des données n'est autorisée par le serveur. Cette solution est efficace pour un nombre de nœuds peu élevé. La localité des données n'est pas un argument primordial si l'on considère un réseau à large bande passante. On peut envisager un recouvrement communication/calcul pour combler un manque de localité des données.

#### Contrôle distribué

Un exemple de ce type de pagination est fourni au travers de la politique de pagination développée pour une architecture PAFS (Parallel/distributed File System) [30]. Dans cette configuration, on dispose d'un ou plusieurs serveurs de traitement dont la fonction est d'interfacer les nœuds de calcul avec les serveurs de disques. Les serveurs de disques sont quant à eux la passerelle entre les nœuds de calcul et les unités disques. Dans ces conditions, deux types de distribution des données entrent en jeu, dans un premier temps la distribution des données sur les disques et dans un second temps leur distribution sur les nœuds de calcul. Afin de limiter les communications, on envisage d'attribuer à un nœud les blocs qui sont référencés par son serveur. La politique de pagination associée à ce type d'architecture est l'algorithme LRU-Interleaved.

#### Une politique de gestion de pagination distribuée: LRU-Interleaved

la pagination LRU-Interleaved appelée également PG-LRU est une extension de la politique LRU, pour les systèmes de fichiers distribués [31]. Cette stratégie intègre une structure de données capable de gérer la distribution des blocs. Cette structure donne une vision partielle des pages les moins récemment utilisées pour l'ensemble du système. Le premier critère pour décharger une page de la mémoire consiste pour un nœud demandeur à vérifier si un bloc de ce nœud est présent dans

cette liste. Si c'est le cas, la pagination restera locale à ce nœud. Dans le cas contraire, on utilise l'algorithme LRU sans se préoccuper du nœud destinataire.

#### 1.7.2 Techniques de réordonnancement pour la pagination distribuée

#### L'ordonnancement des flux d'exécution sur mémoire partagée

Avec l'utilisation d'une machine à mémoire commune, l'accès à une page se trouvant sur un disque est toujours très pénalisant. Tout comme dans le cas séquentiel, pour obtenir de meilleurs performances le code devra tenir compte de ce facteur. Comme nous l'avons vu dans le cas séquentiel, la solution consistant à réordonnancer le flux d'instruction (cf section 1.1) reste applicable dans le cadre d'une mémoire distribuée.

#### L'ordonnancement de la pagination distribuée

Lorsque l'utilisation mémoire est très supérieure à la mémoire physique totale, chaque nœud du réseau est contraint d'utiliser la pagination sur disque. Cette charge ne peut être laissée au système : pour minimiser le nombre de pages accédées sur disque, il faut ordonnancer les calculs de façon à utiliser les données distantes dès que celles-ci sont chargées en mémoire. La synchronisation des diverses paginations doit permettre d'utiliser efficacement une mémoire virtuelle distribuée dont la taille dépasse celle de la mémoire physique. Le code exécutable doit alors prendre en charge explicitement la pagination afin d'éviter les accès disques inutiles.

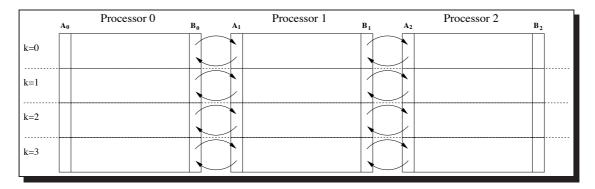

#### 1.7.3 Communications et l'algorithme de convolution

Le traitement parallèle, ne résout en rien les problèmes liés à l'effet trou. De plus, d'autres facteurs peuvent s'ajouter à son déclenchement, comme par exemple les communications. Cette partie illustre les interférences entre les communications et le système de pagination. Pour cela, nous basons notre approche sur l'algorithme de convolution. Le cœur de cet algorithme consiste à déterminer chaque élément en effectuant la moyenne de ses voisins. Le programme HPF et le code généré correspondant sont fournis figure 1.15.

```

Send(A(1:n,1),left)

REAL A(N,N)

Send(A(1:n,n),right)

!HPF DISTRIBUTE A(BLOCK,*)

Recv(A(1:n,0),left)

Recv(A(1:n,n+1),right)

FORALL (I=2:N-1, J=2:N-1)

A(I,J) = (A(I,J+1)

FORALL (i=1:n, j=1:n)

+ A(I+1,J)

A(i,j)=(A(i,j+1)

+ A(I,J+1)

+A(i,j-1)

+ A(I-1,J))/4

+A(i+1,j)

+A(i-1,j))/4

```

FIG. 1.15 – À gauche, un programme HPF classique d'un calcul d'une convolution à deux dimensions. Le tableau A est distribué par blocs de colonnes. À droite, le code généré à partir du programme HPF sur une architecture à p processeurs. Les communications entre les sections du tableau sont introduites par le compilateur. La constante n = N/p est l'ordre de la matrice A sur chaque processeur.

Le tableau est distribué par blocs de colonnes sur les processeurs. Les données nécessaires pour les processeurs voisins sont envoyées ou reçues dans la première et la dernière colonne (appelée généralement zone fantôme).

Nous avons exécuté le code généré sur un réseau de PC avec  $8192 \times 4 \text{KB}$  par page. L'ordre de la matrice sur chaque processeur est égal à 4096. La partie gauche du tableau 1.2 donne le nombre de défauts de pages obtenu dans les différentes étapes de l'algorithme. Toute la mémoire physique est utilisée dans les étapes de communication. Lors du calcul la plupart des pages envoyées et reçues sont écrites sur le disque. Ces pages sont alors chargées à nouveau lorsqu'elles sont utilisées par la phase de calcul.

|                               | Sans tiling |          |          | Avec tiling |          |          |

|-------------------------------|-------------|----------|----------|-------------|----------|----------|

|                               | Proc. 0     | Proc. 1  | Proc. 2  | Proc. 0     | Proc. 1  | Proc. 2  |

| Send(A[],left)                |             | 9024     | 9106     |             | 10237    | 10220    |

| Send(A[],right)               | 9218        | 9547     |          | 10085       | 10155    |          |

| Recv(A[],left)                |             | 3        | 9291     | 27          | 53       |          |

| Recv(A[],right)               | 9576        | 5715     |          |             | 0        | 31       |

| FORALL                        | 79713       | 78513    | 79272    | 72288       | 64925    | 72111    |

| Total                         | 98595       | 102858   | 97734    | 82400       | 85370    | 82362    |

| Temps écoulé pour l'exécution | 720,80 s    | 771,84 s | 777,54 s | 571,55 s    | 536,44 s | 576,98 s |

Tab. 1.2 – Nombre de défauts de pages dans le cas du programme de convolution.

Une solution pour éviter les effets de pagination inutile consiste à coupler le calcul et les communications. L'idée est de communiquer uniquement les données qui se trouvent en mémoire pour les besoins du calcul. On peut obtenir ce résultat en effectuant un découpage (tiling) sur la matrice (cf figure 1.16).

Fig. 1.16 – Produit de convolution avec une décomposition du calcul.

L'espace mémoire nécessaire à la phase de calcul est décomposé en tuiles. Les tuiles sont déterminées de manière à ce que le nombre de pages accédées, lors des communications et lors du calcul, soit égal au nombre de pages mémoire physique disponible. Le pseudo-code de la version de la convolution en tiling est présenté figure 1.17.

Le tableau 1.2 donne le nombre de défauts de pages pour chaque étape de l'algorithme. Il n'y a pas de défaut de page redondant ce qui permet d'obtenir un gain de 30% pour le temps d'exécution.

```

p=n/t;

FOR k=1,t

Send(A((k-1)*p:k*p,1),left);

Send(A((k-1)*p:k*p,n),right)

Recv(A((k-1)*p:k*p,0),left);

Recv(A((k-1)*p:k*p,n+1),right);

FORALL(i=(k-1)*p:k*p,j=1:n)

A[i][j]= (A[i][j+1]

+A[i][j-1]

+A[i+1][j]

+A[i-1][j])/4;

```

Fig. 1.17 – Convolution version décomposée.

#### 1.8 Autres approches

Bordawekar and Choudhary proposent différentes stratégies de communication pour les programmes *out-of-core* parallèles dans [8]. La première appelée méthode de communication *out-of-core*, où les communications et les calculs sont séparés. La seconde méthode qui a servi d'inspiration à notre solution, est appelée méthode de communication *in-core*. Dans ce cas, les communications sont associées avec le calcul de la même tuile.

Une analyse plus étendue de l'activité du système de pagination dans les programmes parallèles out-of-core est proposée par Marinescu et Wang dans [60, 61]. Dans ces travaux, ils ont effectué une analyse statistique de l'activité de pagination de plusieurs applications sur machines parallèles. Ils observent la non-corrélation entre la pagination des différents nœuds dans les programmes SPMD. Aucune explication n'est fournie à ce sujet. Cependant, cette non-corrélation introduit une nouvelle difficulté dans la dérivation des algorithmes de gang scheduling [62] (technique d'ordonnancement de différents calculs parallèles indépendants, avec de meilleures performances [69]).

La seconde partie de ce chapitre présente une nouvelle librairie qui permet de définir des algorithmes de gestion de la mémoire virtuelle au niveau de l'application. Cet outil a été utilisé pour proposer une nouvelle stratégie de gestion de la mémoire virtuelle dans le cadre de la factorisation LU. Nous obtenons des améliorations significatives en nombre de défauts de pages.

Il existe deux autres approches qui permettent de redéfinir les stratégies de gestion de la mémoire virtuelle pour les applications scientifiques de grande taille. La première, ce sont les travaux de Park, Scott and Sechrest sur une architecture Cenju-3 de NEC [71]. Sur cette architecture, le système d'exploitation dispose d'une interface utilisateur pour définir la gestion du système de pagination. Ils ont écrit des gestionnaires de mémoire virtuelle pour deux applications et obtiennent de bons résultats. La seconde approche, ce sont les travaux de Krueger, Loftesness, Vahdat and Anderson [56] qui présentent une interface orientée objet pour la gestion de la mémoire virtuelle et un outil pour étudier les accès à la mémoire virtuelle. L'idée maîtresse est de posséder assez d'informations de la part de l'outil d'étude de la mémoire virtuelle pour définir une stratégie de pagination générale pour des applications spécifiques.

Dans ces deux approches, l'utilisateur doit écrire un système de gestion de la mémoire virtuelle comme nous l'avons fait pour la factorisation LU. Ce n'est pas une tâche aisée et ne doit pas être laissé à la charge de l'utilisateur final.

Dans le cas de programmes data-parallèles *out-of-core*, il est intéressant de réutiliser les informations extraites lors de la compilation. Dans les travaux de Mowry, Demke et Krieger, à partir d'une analyse statique du code séquentiel, le compilateur peut extraire des informations concernant la localité spatiale et temporelle des données. Ces informations sont utilisées pour insérer des préchargements et des directives durant le calcul [65]. Dans les travaux de Collard et Utard [27] le compilateur détermine le découpage du calcul en accord avec la mémoire physique et l'agencement des données. L'espace de travail de chaque partie est de taille égale ou inférieure à la mémoire physique disponible; le compilateur essaie de réutiliser les données entre les parties successives.

#### 1.9 Conclusion

Dans ce chapitre nous observons le comportement du système de gestion de la mémoire virtuelle standard du système d'exploitation lors d'une exécution type *out-of-core*, comme une factorisation LU. La première conclusion est que la politique LRU du système de gestion de la mémoire virtuelle n'est pas adaptée aux calculs numériques sur des données de grande taille. Le chapitre illustre ensuite l'importance du réordonnancement des données. À partir de ces résultats, nous proposons une optimisation, sur notre exemple de factorisation LU, avec un outil de gestion de la mémoire virtuelle au niveau utilisateur.

Nous avons ensuite étudié les solutions de pagination dans le cadre d'exécutions parallèles et souligné les nouvelles contraintes introduites. Ce qui nous a permis de constater que les communications dans les programmes data-parallèles introduisent de nouveaux threads d'accès mémoire. Ces nouveaux threads peuvent être incompatibles avec les threads d'accès mémoire utilisés pour la phase de calcul. Une solution consiste à "tiller" le calcul et les communications.

# Deuxième partie Approche algorithmique

# Chapitre 2

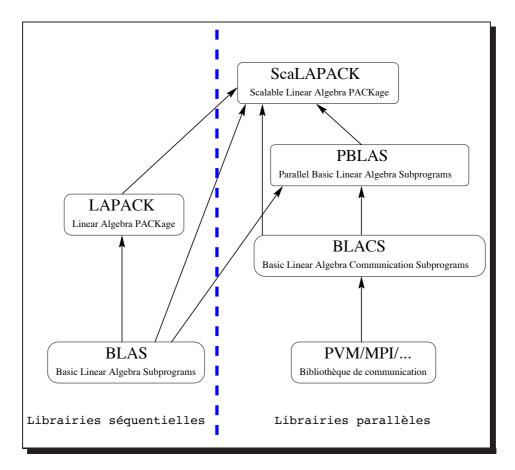

# Une bibliothèque de calcul out-of-core: Scalapack

#### Sommaire

| 2.1 | Arch                    | itectur | e de S  | caL  | APAC | K    |         |        |     |    |    |    |     |     |     |   |  |  |  |  |

|-----|-------------------------|---------|---------|------|------|------|---------|--------|-----|----|----|----|-----|-----|-----|---|--|--|--|--|

|     | 2.1.1                   | Les BL  | AS      |      |      |      |         |        |     |    |    |    |     |     |     |   |  |  |  |  |

|     | 2.1.2                   | LAPACK  |         |      |      |      |         |        |     |    |    |    |     |     |     |   |  |  |  |  |

|     | 2.1.3                   | Les BL  | ACS .   |      |      |      |         |        |     |    |    |    |     |     |     |   |  |  |  |  |

|     | 2.1.4                   | Les PBI | LAS     |      |      |      |         |        |     |    |    |    |     |     |     |   |  |  |  |  |

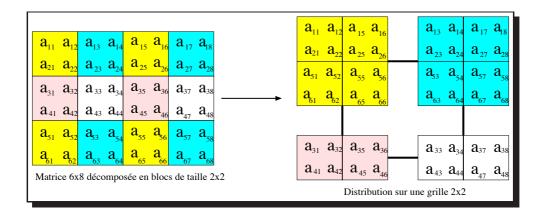

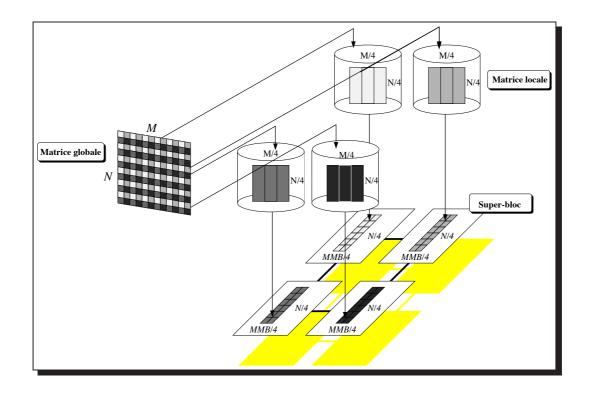

| 2.2 | $\operatorname{ScaL} A$ | APACK e | t le pi | oto  | type | e or | ut- $o$ | f- $c$ | ore |    |    |    |     |     |     |   |  |  |  |  |

| 2.3 | Cont                    | ributio | n au    | prot | oty  | ре   | out     | of     | -co | re | de | Sc | aL. | AP/ | ACK | 7 |  |  |  |  |

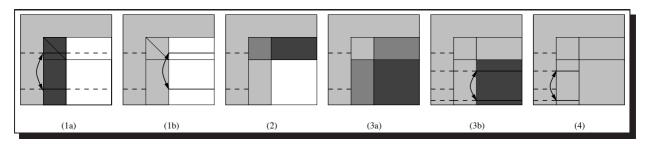

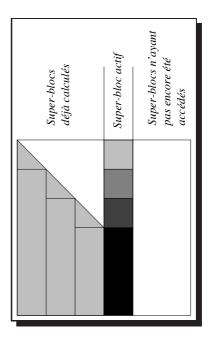

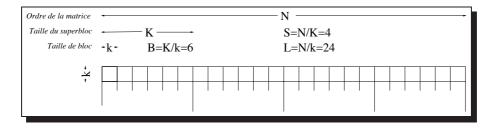

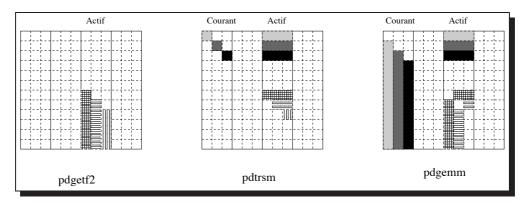

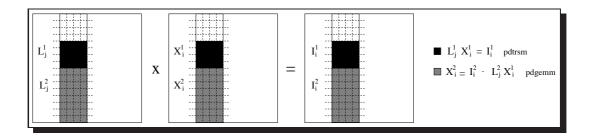

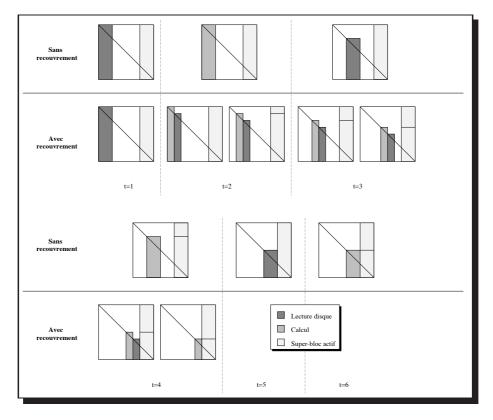

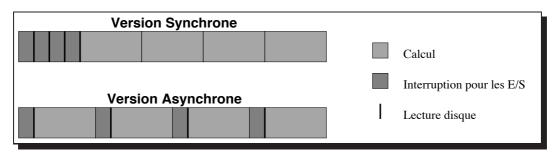

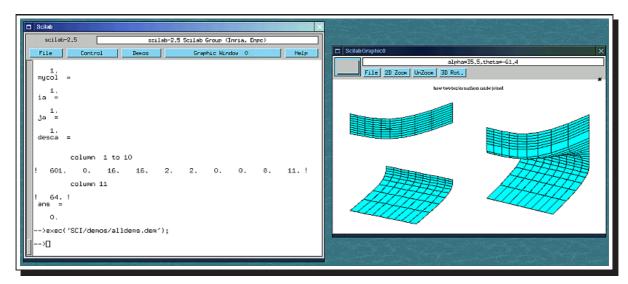

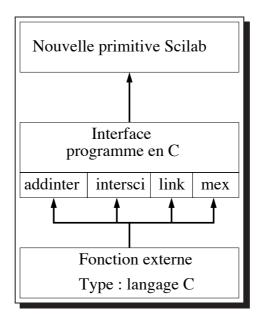

| 2.4 | Conc                    | lusion  |         |      |      |      |         |        |     |    |    |    |     |     |     |   |  |  |  |  |