# Technologies for integrated power converters Chenjiang Yu

#### ▶ To cite this version:

Chenjiang Yu. Technologies for integrated power converters. Electric power. Université Paris Saclay (COmUE), 2016. English. NNT: 2016SACLS485. tel-01445404

## HAL Id: tel-01445404 https://theses.hal.science/tel-01445404

Submitted on 24 Jan 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Comprendre le monde, construire l'avenir

NNT: 2016SACLS485

## THESE DE DOCTORAT DE L'Université Paris-Saclay PRÉPARÉE À "L'Université Paris-Sud"

ECOLE DOCTORALE N° (575) Electrical, optical, bio-physics and engineering (EOBE) Spécialité de doctorat (Génie Electrique)

Par

## Mr Chenjiang YU

## Technologies de fabrication pour les convertisseurs de puissance intégrés

(Technologies for integrated power converters)

Thèse présentée et soutenue à GeePs, 11 rue Joliot Curie, Gif sur Yvette, le 13/12/2016 :

#### Composition du Jury:

Pr, FOREST, François Professeur des universités – Université de Montpellier Président Dr, AVENAS, Yvan Maître de conférence HDR - Grenoble INP Rapporteur Pr, IDIR, Nadir Professeur des universités - Université Lille 1 Rapporteur Dr, LABROUSSE, Denis Maître de conférence - CNAM Paris Examinateur Pr, LABOURE, Eric Professeur des universités - Université Paris-Sud Directeur de thèse Chargé de recherche HDR – INSA Lyon Co-encadrant de thèse Dr, BUTTAY, Cyril Dr, BLEY, Vincent Maître de conférence - Université Paul Sabatier Invité Mr, ASFAUX, Pascal Ingénieur de recherche – Airbus Operations S.A.S Invité

Titre: Technologies de fabrication pour les convertisseurs de puissance intégrés

Mots clés : Convertisseur de puissance, gestion thermique, technologie de packaging

**Résumé:** Les convertisseurs électroniques de puissance sont aujourd'hui très largement utilisés dans tous les domaines de la conversion d'énergie. Ils sont des outils désormais incontournables de tout processus de gestion des transferts de l'énergie électriques depuis les puissances les plus faibles (quelques mW) jusqu'à plusieurs dizaines voire centaines de MW. Le domaine de l'électronique de puissance subit actuellement une double mutation liée aux possibilités offertes par les technologies d'intégration d'une part et l'arrivée de nouveaux composants à semi-conducteur de puissance de type grand-Gap d'autre part.

Dans cette thèse supportée par l'ANR, nous avons étudié et évalué les potentialités associées à l'intégration de composants de puissance traditionnels (Silicium) et à base de matériaux grands Gap (GaN). Nous avons, pour cela, développé des procédés de fabrication destinés à l'intégration de composants GaN à structure latérale et de composants Silicium à structure verticale. Le contexte applicatif de cette thèse est celui de l'accroissement du niveau d'électrification dans les avions de nouvelle génération.

Pour les composants grand Gap de type GaN à structure latérale (basse tension), nous avons proposé un nouveau procédé de report sur substrat céramique (DBC) et nous avons démontré que cette solution permettait d'améliorer considérablement la gestion thermique de ces composants.

Sur la base de ces structures, nous avons également présenté et évalué des méthodes de modélisation permettant la conception de ces dispositifs. Cette modélisation, utilisant des méthodes numériques type éléments finis ou des méthodes analytiques, traite de deux aspects de la conception : la prédétermination du comportement thermique et la prédétermination du comportement électrique et CEM (en ce qui concerne les aspects conduits). Pour les composants à structures verticales (haute tension), nous avons démontré la faisabilité technologique d'une solution alternative aux packagings traditionnels (assemblage sur DBC et connexion par fils de Bonding). Le process proposé permet, par enterrement des puces dans le PCB, de réaliser une interconnexion permettant de réduire les inductances parasites de boucle très largement dues aux inductances parasites des fils de Bonding. Ceci a pu être démontré sur un prototype de convertisseur complet. Ce procédé d'enterrement des puces s'avère donc particulièrement adapté dans le cas de composants à commutation très rapide.

**Title:** Technologies for integrated power converters

**Keywords:** Power converter, thermal management, packaging technology

**Abstract:** Power Electronic converters are now widely used in all areas of energy conversion. They are tools that cannot be ignored in any process of managing electrical energy transfers from the lowest powers levels (a few mW) to several tens or even hundreds of MW. Power electronics technologies are currently undergoing a double mutation linked to the possibilities offered by integration technologies on the one hand and the arrival of new Wide-Band-Gap power semiconductor components on the other hand.

In this thesis supported by the French ANR, we studied and evaluated the potentialities associated with the integration of traditional power components (Silicon) as well as those based on Wide-Band-Gap materials (GaN). We have developed new technological processes for the integration of GaN components with a lateral structure and silicon components with a vertical structure. The application context of this thesis is linked to the problematic of increasing the level of electrification in new generation of aircrafts.

For Wide-Band Gap GaN type power devices with a lateral structure (low voltage), we proposed a new method of device-attachment to a metalized ceramic substrate (DBC) and we demonstrated that this solution made it possible to considerably improve the thermal management of these components.

On the basis of these structures, we also presented and evaluated modeling methods allowing the design of the whole packaging. This modeling, using numerical tools based on finite element method or analytical equations, deals with two aspects of the design: the predetermination of the thermal behavior and the predetermination of the electrical and electromagnetic behavior (with regard to the conducted aspects).

For components with vertical structures (high voltage), we have demonstrated the technological feasibility of an alternative solution to traditional packaging (assembly on a DBC substrate and electrical connection by wire bonding process). The proposed process allows, by embedding the power dies in the PCB, to carry out a 3D interconnection making it possible to reduce the parasitic loop inductances mainly linked to the parasitic inductances of the bondwires. This has been demonstrated on a converter prototype. Embedding power devices is thus particularly suitable in the case of components with very fast switching capabilities.

## Remerciements

Sur cette page dédiée aux remerciements je souhaite m'adresser à toutes les personnes qui m'ont aidé à grandir dans l'univers des sciences et des technologies durant ces trois années de thèse.

Je tiens tout d'abord à remercier l'ensemble des membres de mon jury de thèse; M. François Forest pour m'avoir fait l'honneur de présider ma soutenance; M. Yvan Avenas et M. Nadir Idir d'avoir accepté d'être rapporteurs de mon travail de thèse et de me donner les conseils sur mes travaux; M. Denis Labrousse d'avoir accepté de faire partie de ce jury en tant qu'examinateur; M. Vincent Bley de sa présence à ma soutenance et son soutien quand j'étais à Toulouse; M. Pascal Asfaux d'avoir accepté d'évaluer ma soutenance et de me donner une vue industrielle de mes travaux.

J'adresse ma profonde reconnaissance et mes sincères remerciements à mes deux directeurs de thèse : M. Eric Labouré et M. Cyril Buttay, d'une part pour leurs compétences scientifiques et d'autre part pour l'aide qu'ils m'ont apporté durant mes travaux de recherche et dans ma vie personnelle. Je n'oublierai jamais nos réunions au cours desquelles des propositions, des solutions et des idées ruisselaient telle une source inépuisable née par leur passion pour la recherche. C'est vraiment une grande joie de travailler avec eux. Merci !

Un grand merci à Mme **Céline Combettes**, ingénieur de la plateforme 3DPHI, pour ses conseils, son aide, et son expérience sur les matériels technologiques qu'elle a bien voulu me faire partager.

Je remercie également M. **Gilles Brillat**, M. **Guillaume Maffre** et M. **Olivier Dagut**, techniciens du service commun d'électronique de l'Université Paul Sabatier, pour toutes les aides techniques qu'ils ont pu m'apporter.

Je voudrais adresser mes remerciements à tout le personnel du laboratoire GeePs – avec une mention spéciale pour mes amis : Qi, Chao, Shuangfeng, Man, Xiaotao, Zuqi, Mingyong, Xiang, Ming, pour nos longues discussions, les pauses café, les repas au CESFO et les bons moments que nous avons passé ensemble.

Je souhaite aussi remercier toutes les personnes du laboratoire LAPLACE qui m'ont apporté des conseils ou de l'aide au cours de ma thèse – permanents, doctorants. Merci à mes collègues de bureau : **Trung**, **Simon**, **François** pour les petits cadeaux, les discussions, pour leurs savoirs, conseils et aides qui m'ont fait également progresser. Merci à mes amis : **Xiaolin**, **Xi**, **Bo**, **Feng**, **Yuan**, **Song**, pour leur accompagnement pendant mes séjours à Toulouse.

Je voudrais remercier tous mes amis en France, qui m'ont accompagné pendant ces 9 ans de vie à l'étranger. Malgré mon éloignement de mon pays natal, grâce à vous je me suis senti à la maison.

Enfin, un très grand merci à toute ma famille qui m'a toujours encouragé et sans qui je ne serais pas arrivé à ce stade.

## Résumé en français

#### Contexte de l'étude

Au cours des dernières années, l'électricité est devenue de plus en plus importante dans le domaine aéronautique. En fait, le concept de l'avion «plus électrique» induit une forte amélioration potentielle par rapport aux systèmes hydrauliques et pneumatiques classiques, principalement par la simplification de la maintenance, l'amélioration de l'efficacité et de la réduction de l'effort de développement et du coût d'exploitation [1].

Au-delà des applications ciblées qui en ont bénéficié, comme par exemple les avions suivants : A380, B787, A400M et A350 (contrôle de vol électrique, distribution alternatif à fréquence variable, etc.), les programmes correspondants ont permis d'identifier les évolutions architecturales pour améliorer les performances des avions civils futurs. Cela concerne en particulier l'utilisation d'une distribution électrique à courant continu haute tension appelée "HVDC".

Ce mode de distribution, rendue possible par l'évolution de l'électronique de puissance, a offert des perspectives multiples, comme un gain de poids de la distribution (câbles et protections), l'interopérabilité du réseau HVDC avec plusieurs sources, en particulier avec le réseau basse tension LVDC 28V. C'est cette liaison HVDC-LVDC qui est au cœur du projet ETHAER présenté dans ce mémoire. Cependant, l'introduction massive de l'électronique de puissance dans un contexte très restrictif, qui impose des contraintes importantes en matière de compétitivité, de performance et de fiabilité des équipements, s'accompagne de nombreuses difficulté.

La résolution de cette équation compliquée impose, d'une part, la définition d'une approche multi-domaine basée sur une approche de conception 3D incluant les problématiques technologiques et normatives (thermique, CEM) mais également fonctionnelle (contraintes associées à l'intégration au système), d'autre part, l'utilisation de nouvelles solutions (topologies de conversion, lois de contrôle spécifiques associées) et de technologies émergentes (intégration hybride, composants grand Gap SiC, GaN, ...).

La perspective globale offerte par cette démarche est principalement la diminution du coût de développement, de production et d'exploitation ainsi que l'optimisation de la maintenance et l'amélioration de la sécurité.

## Description du projet et travaux réalisés

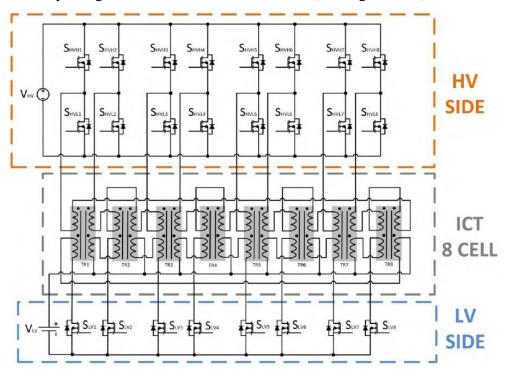

Le projet "ANR ETHAER" est à la frontière entre la recherche fondamentale et industrielle. Le domaine étudié est celui de l'électronique de puissance dans le contexte de l'avion plus électrique, domaine ayant concentré beaucoup d'activités de recherche ces 5 dernières années. Il vise à contribuer à la définition de convertisseurs électroniques de puissance pour les avions de la prochaine génération (2015-2025). Pour atteindre cet objectif, ETHAER se concentre sur une fonction électrique spécifique très limitée :

l'interconnexion entre les réseaux électriques de bord, à savoir le réseau 28V et le réseau haute tension +/- 270V DC.

Ce projet comporte une forte composante expérimentale et technologique, ce qui s'est traduit par la réalisation de nombreux démonstrateurs. Dans ce projet, le choix a été fait de proposer et d'évaluer de nouvelles architectures de convertisseurs basés sur des topologies dites multicellulaires.

La réalisation pratique d'un convertisseur multicellulaire est basée sur un certain nombre de défis technologiques. La recherche de la fiabilité et l'augmentation de la densité de puissance impose de proposer et développer de nouvelles technologies d'intégration et de packaging. Les niveaux de puissance visés nous conduisent tout naturellement à envisager des technologies d'intégration hybride plutôt que monolithique, ces dernières n'étant envisageables que pour de très faibles puissances. Comme l'association série / parallèle de composants ou de convertisseurs élémentaires dans les nouvelles topologies que nous proposons implique une augmentation considérable du nombre d'interconnexions, nous nous sommes tournés vers des solutions compatibles avec des méthodes de fabrication appelés «collectives», par opposition aux méthodes classiques « individuelles » utilisées pour l'assemblage de convertisseurs. Le coût et le temps de réalisation de ces procédés classiques (par ex. le Wire Bonding) sont proportionnels au nombre d'interconnexions étant donné qu'ils sont réalisés de manière séquentielle. Pour les méthodes dites "collectives", la durée de réalisation change peu, et le coût est plutôt lié à la surface / volume du système.

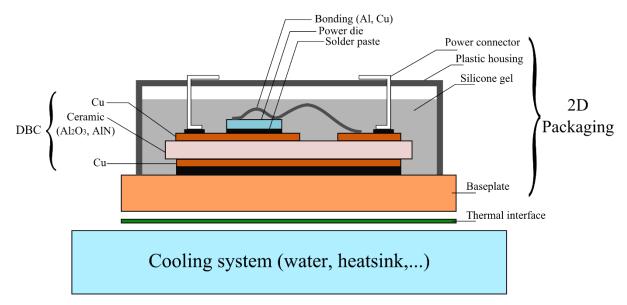

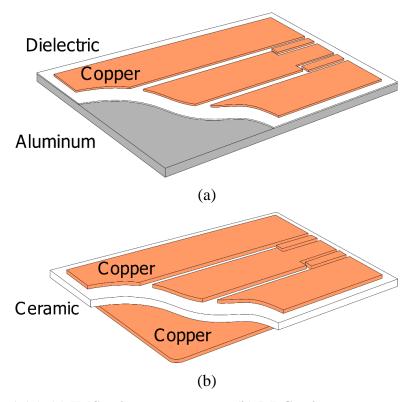

Parmi les technologies matures utilisées dans le domaine de l'électronique de puissance, le PCB (Printed Circuit Board) répond aux contraintes techniques pour les petite et moyenne puissances (quelques centaines de Watts jusqu'à quelques kW), le DBC (Bonded Copper Direct) est pour sa part utilisé aux puissances élevées. Dans le projet ETHAER, une intégration originale en deux étapes est proposée. La première est basée sur la technologie DBC et la seconde est la composition des deux technologies PCB, DBC.

La partie la plus importante du développement réalisé sur la technologie DBC est liée à l'interconnexion des puces sur le substrat (DBC). L'objectif ici est d'éviter l'utilisation des fils de liaison (fils de Bonding) puisque ces liaisons sont une cause importante de défaillance dans les modules de puissance. Dans le cas des composants verticaux, nous sommes à la recherche d'une solution alternative à cette liaison par fils de bonding. Dans la solution proposée, l'interconnexion peut être établie par l'intermédiaire d'un substrat flexible ou bien par métallisation selon un procédé d'électrodéposition.

Le mémoire de thèse est divisé en trois parties, hors conclusion et perspectives, présentant successivement :

- un état de l'art des techniques de packagings actuels utilisés en électronique de puissance. Ce chapitre permet de mettre en évidence les limites d'utilisation associées à chacune de ces technologies et de présenter certains procédés utilisés dans les process de fabrication des assemblages de puissance

- de nouveaux packaging basse tension et les procédés de fabrication associés. Ceuxci sont basés sur des composants à semi-conducteur GaN à structure latérale. Dans cette partie, sont également présentées et évaluées, les méthodes de modélisation utilisées en vue de la conception de ces dispositifs. Cette modélisation, utilisant des méthodes numériques de type éléments finis ou des méthodes analytiques, traite de

- deux aspects de la conception : la prédétermination du comportement thermique et la prédétermination du comportement électrique et CEM (en ce qui concerne les aspects conduits)

- un niveau type de packaging destiné aux composants à semi-conducteur à structure verticale et donc utilisable dans des applications de conversion en haute tension. Sont présentés dans cette partie : le procédé de fabrication original proposé ; l'évaluation des performances de ce packaging en terme de performances électriques ; la réalisation d'un convertisseur dc dc complet à partir de ce procédé et l'analyse de son fonctionnement

## Les principaux résultats

## Packaging basse tension pour composant latéraux de type GaN

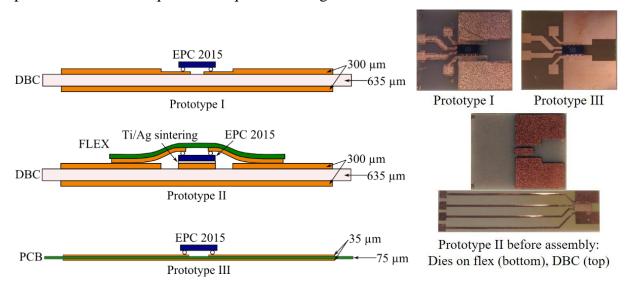

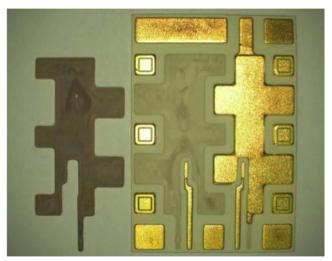

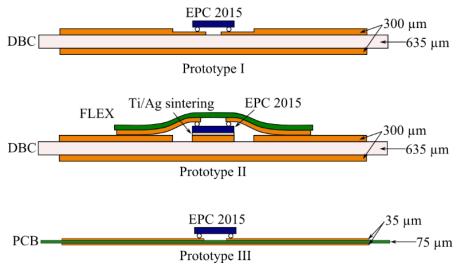

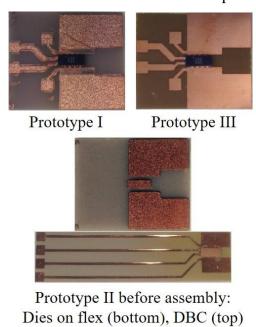

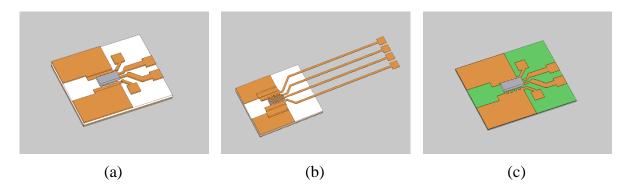

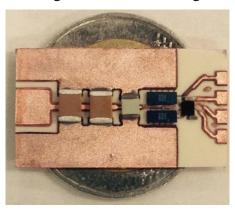

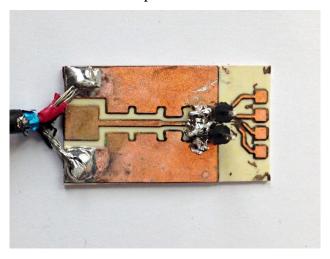

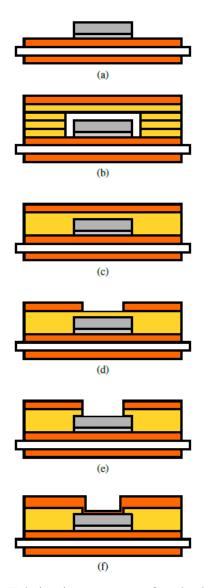

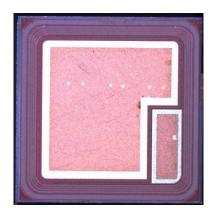

Trois prototypes basse tension ont été réalisés (voit fig. 1). Ces prototypes ont permis de mettre au point les procédés de fabrication. Ils sont réalisés autour d'un seul composant actif de type GaN à structure latérale et permettent de réaliser une comparaison des performances thermiques de chaque assemblage.

Figure 1 : Vue en coupe et photographie des 3 prototypes

#### Ces prototypes ont permis :

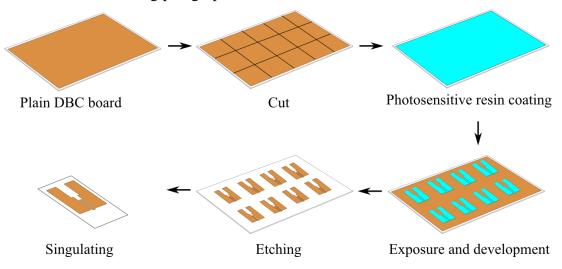

• De développer une technique de double gravure permettant la mise en œuvre sur DBC (substrats céramiques) de composants possédant des distances entre électrodes théoriquement incompatibles avec ce type de technologie

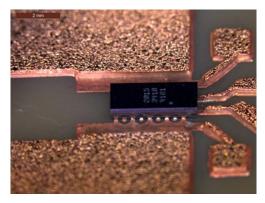

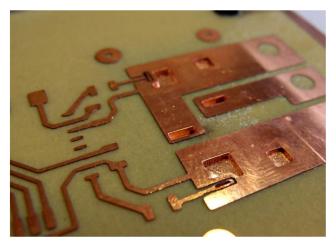

Figure 2 : Substrat céramique gravé par la technique de double gravure et exemple d'utilisation avec un componsant GaN EPC

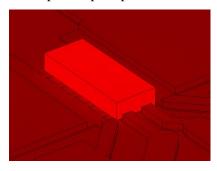

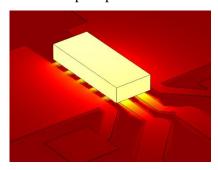

• De démontrer l'intérêt de ce report sur substrat céramique en matière de performances thermiques. Il est ainsi démontré l'intérêt du packaging proposé visà-vis de l'état de l'art actuel basé sur des technologies PCB

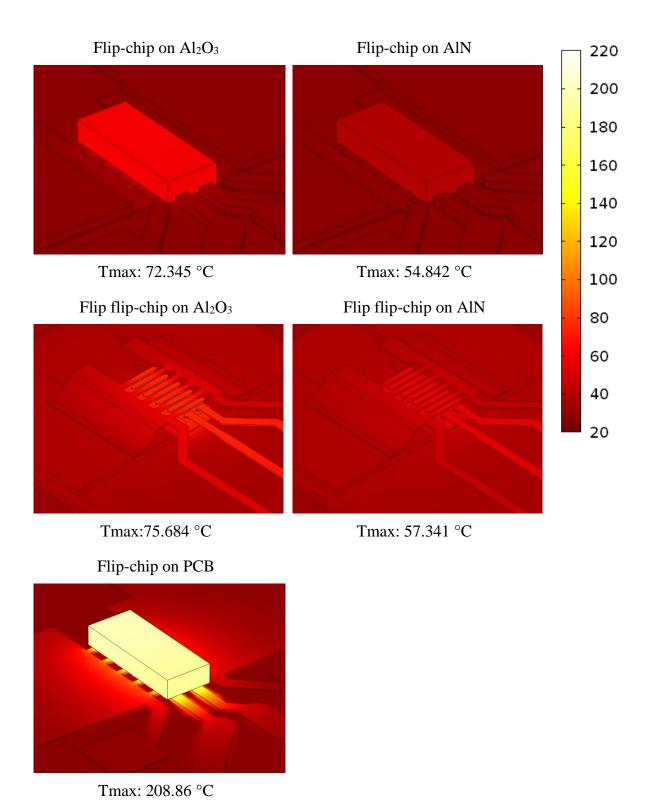

Report Flip-chip sur Al<sub>2</sub>O<sub>3</sub>

Tmax: 72.345 °C

Flip-chip on PCB

Tmax: 208.86 °C

Figure 3 : Comportement thermique de l'assemblage sur substrat céramique mis en forme par la technique de double gravure et comparaison avec la technologie traditionnelle sur PCB

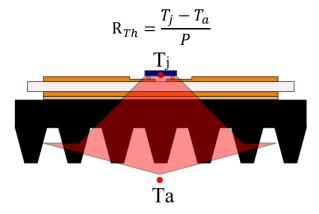

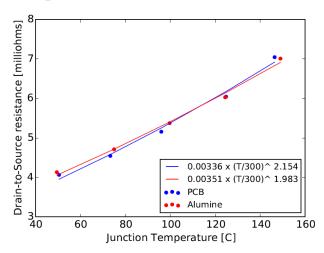

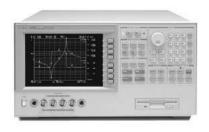

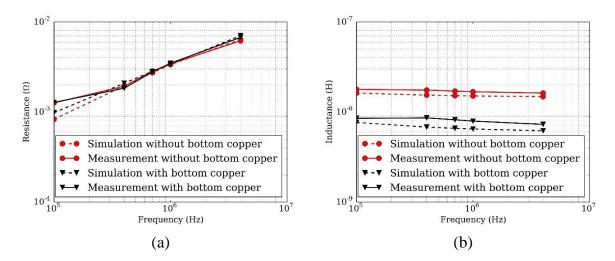

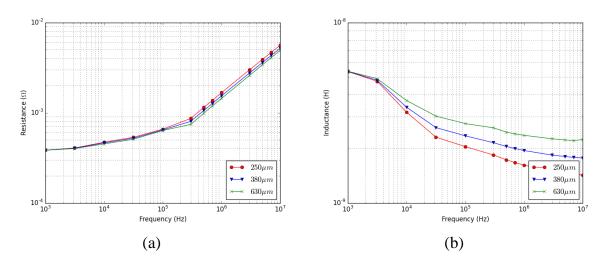

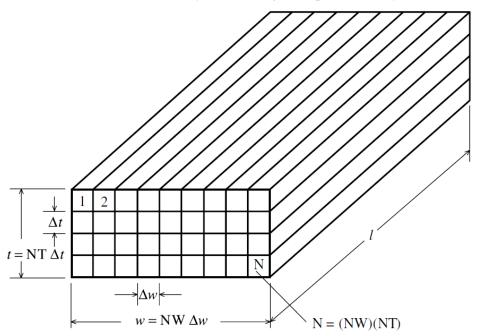

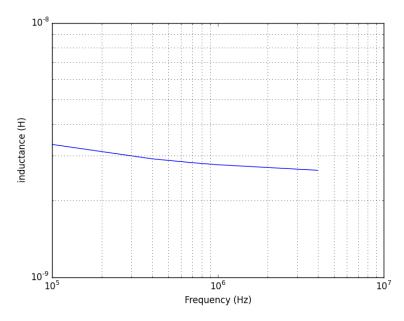

• De mettre en place les outils de modélisation thermique et électrique et de réaliser des comparaisons expérimentales permettant une validation des outils

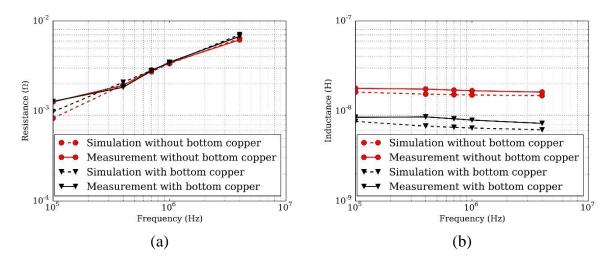

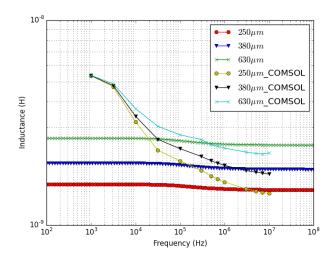

Figure 4 : Comparaison entre simulation et mesure de la valeur de la résistance et de l'inductance de boucle d'une cellule de commutation

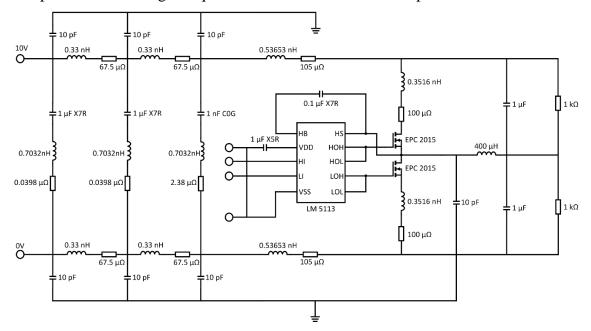

Sur ce principe une cellule de commutation complète a pu être réalisée. Cette cellule comprend deux transistors GaN, le Driver permettant de piloter les deux composants en mode demi-pont et les capacités de découplage.

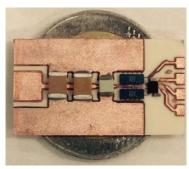

Figure 5 : Convertisseur élémentaire de type demi-pont construit sur substrat DBC en utilisant la technique de double gravure

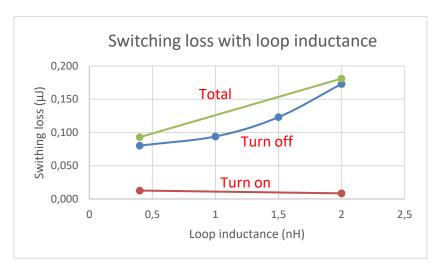

Ce convertisseur élémentaire a permis d'analyser les performances électriques et électromagnétiques des packagings céramiques proposés. Il a ainsi été démontré que l'accroissement de la valeur de l'inductance de câblage associé aux contraintes technologiques du packaging céramique, accroissement occasionnant une augmentation des pertes par commutation, a un effet moins important qu'attendu. Ceci est analysé comme étant lié à l'effet d'écrantage apporté par la métallisation inférieure du substrat DBC et que l'accroissement des pertes de commutation est largement compensé par l'amélioration importante des performances thermiques du module utilisant la technologie proposée.

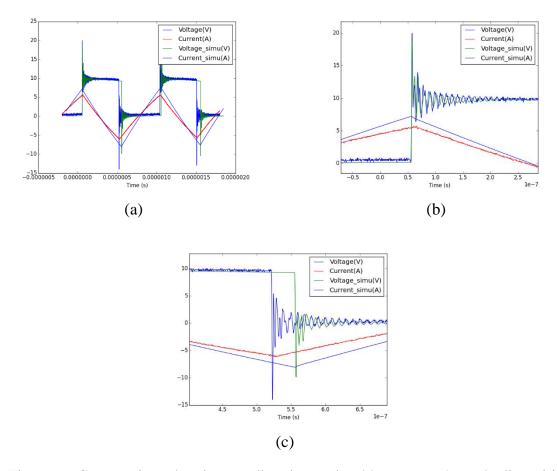

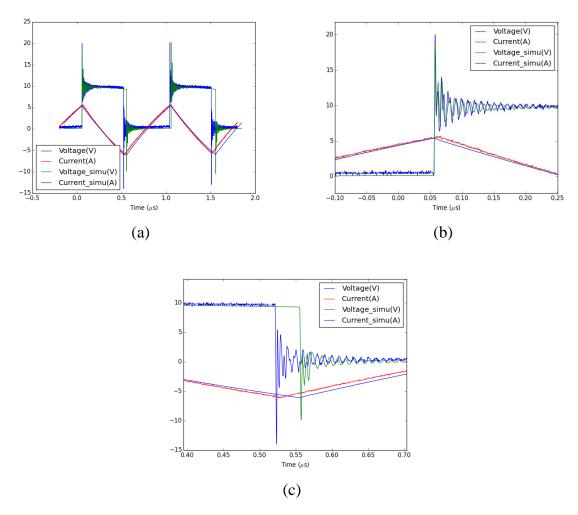

Figure 6 : Comparaison des signaux électriques simulés et mesurés sur le dispositif expérimental

# Packaging haute tension adapté aux composants de puissance à structure verticale

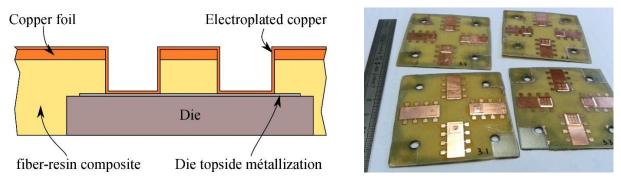

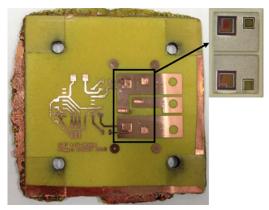

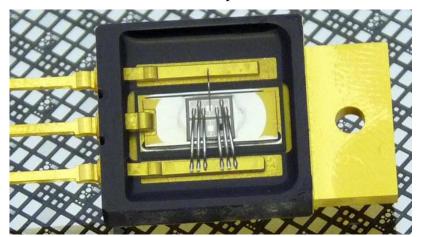

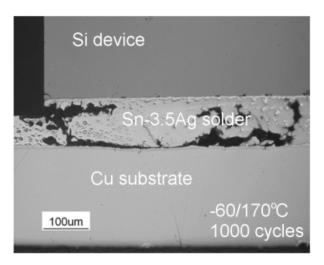

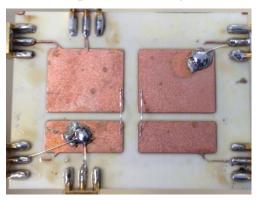

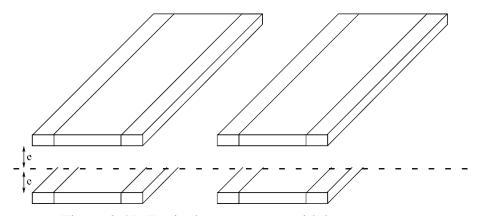

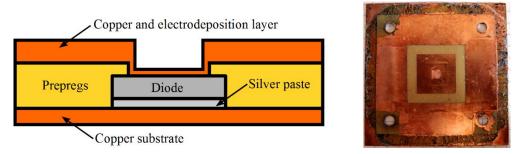

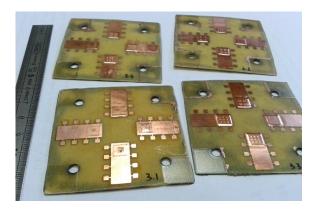

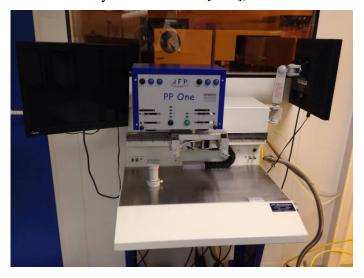

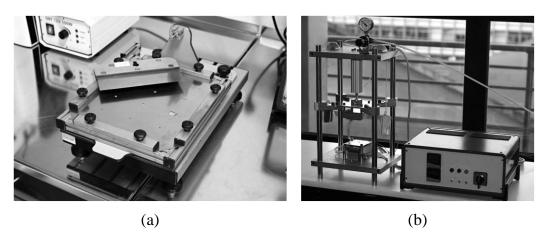

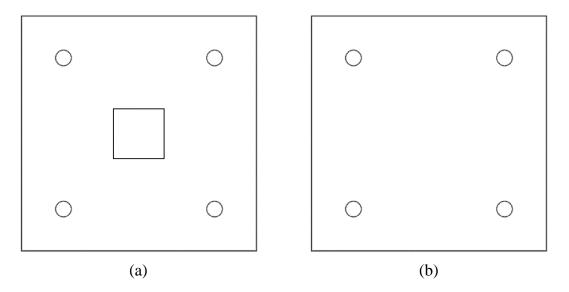

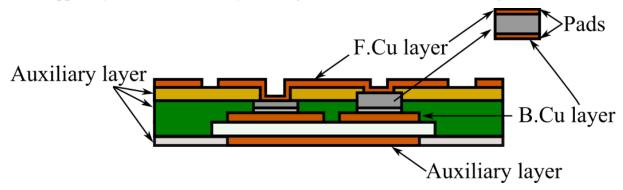

Deux prototypes ont été réalisés (voit fig. 7). Ces prototypes ont permis de mettre au point les procédés de fabrication. Ils sont réalisés autour d'un seul composant actif (une diode 600V) à structure verticale et permettent de tester les différentes options du process de fabrication et d'évaluer l'évolution des performances électriques en fonction du mode de prise de contact électrique sur la partie supérieure du composant.

Figure 7 : Vue en coupe et photographie des 2 prototypes

Ces prototypes ont permis:

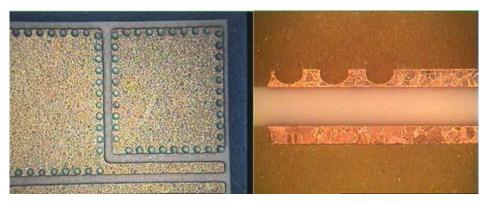

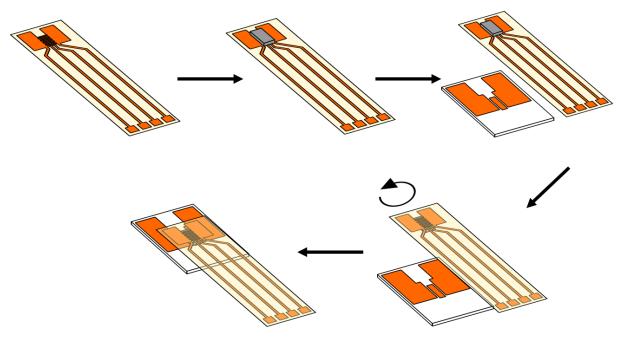

• De développer le procédé d'enterrement de puce de puissance

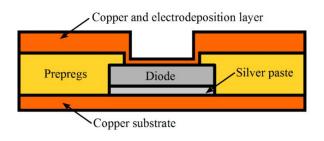

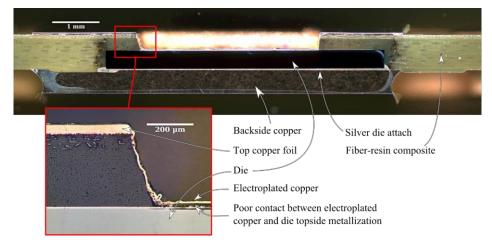

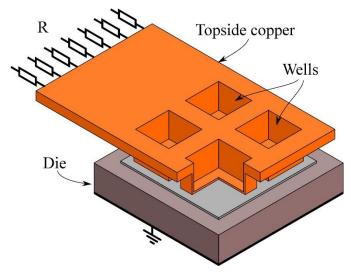

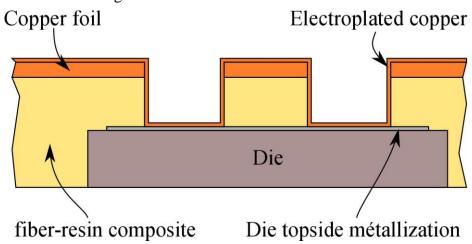

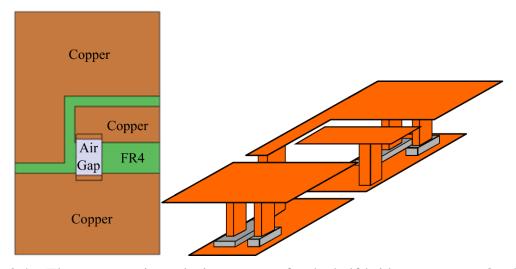

Figure 8 : Vue en coupe d'un prototype : diode à structure verticale enterrée dans le PCB avec prise de contact sur la partie supérieure du composant

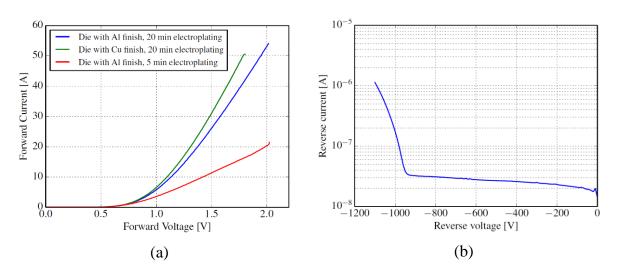

D'évaluer l'évolution des performances électriques du composant après enterrement dans le PCB

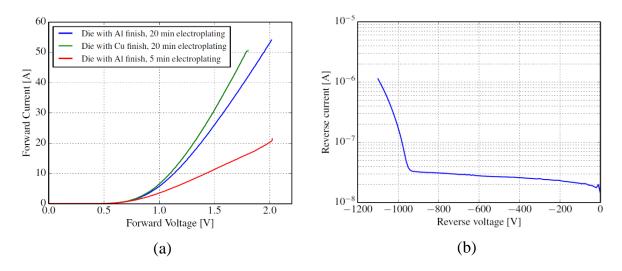

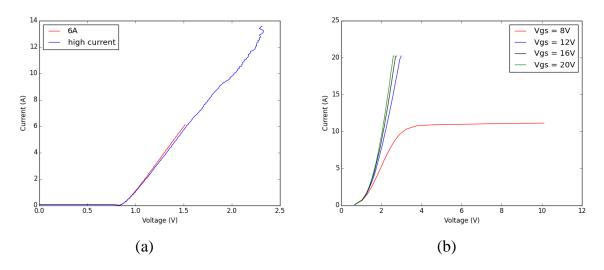

Figure 9 : Comportement électrique de la diode à l'état passant (a) et à l'état bloqué (b)

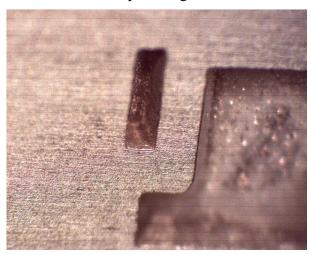

• D'évaluer et analyser plusieurs modes de prise de contact électrique en partie haute

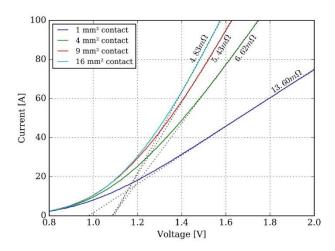

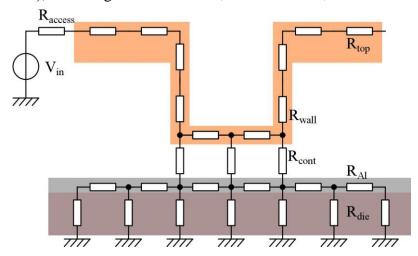

Figure 10 : Caractéristiques à l'état passant d'une diode enterrée en fonction du mode de prise de contact

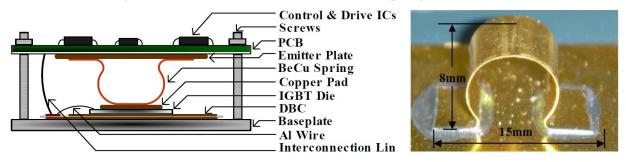

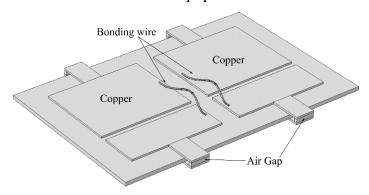

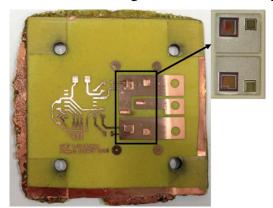

Sur ce principe une cellule de commutation complète a pu être réalisée. Cette cellule comprend deux transistors IGBT et deux diodes.

Figure 11 : Convertisseur élémentaire de type demi-pont construit par procédé d'enterrement de puces à structures verticales (IGBTs + diodes)

Le travail réalisé dans cette partie a permis de démontrer la faisabilité technologique d'une solution alternative aux packagings traditionnels des composants verticaux (assemblage sur DBC et connexion par fils de Bonding). Le process proposé permet, par enterrement des puces dans le PCB, de réaliser une interconnexion 3D permettant de réduire les inductances parasites de boucle très largement dues aux inductances parasites des fils de Bonding. Ceci a pu être démontré par simulation sur le prototype de convertisseur complet de la fig. 11. Ce procédé d'enterrement des puces s'avère donc particulièrement adapté dans le cas de composants à commutation très rapide.

## TABLE OF CONTENTS

| TABLE                                                                                                                              | E OF CONTENTS                                                                                                                                                                                                                                                                                                       | 1                    |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| LIST O                                                                                                                             | F FIGURES                                                                                                                                                                                                                                                                                                           | 5                    |

| LIST O                                                                                                                             | OF TABLES                                                                                                                                                                                                                                                                                                           | 11                   |

| GENEI                                                                                                                              | RAL INTRODUCTION                                                                                                                                                                                                                                                                                                    | 12                   |

| CHAP                                                                                                                               | FER 1. STATE-OF-THE-ART                                                                                                                                                                                                                                                                                             | 14                   |

| 1.1 Intro                                                                                                                          | oduction                                                                                                                                                                                                                                                                                                            | 14                   |

| 1.2.1 A<br>1.2.1.1<br>1.2.1.2<br>1.2.2 Sv<br>1.2.2.1                                                                               | ctive Components  GaN power devices  SiC power devices  witching cell  Parasitic elements and their issues  fulticell power converter                                                                                                                                                                               | 14<br>15<br>17<br>18 |

|                                                                                                                                    | er Packaging                                                                                                                                                                                                                                                                                                        |                      |

| 1.3.1 2I<br>1.3.1.1<br>1.3.1.2<br>1.3.2 3I<br>1.3.2.1<br>1.3.2.2<br>1.3.2.3<br>1.3.2.4<br>1.3.2.5<br>1.3.2.6<br>1.3.2.7<br>1.3.2.8 | D Packaging Structure Limiting points  D Packaging Metal post interconnection technology Solder bump interconnection technology Dimple array interconnection technology Direct solder interconnection technology Embedded power technology Press Pack technology Spring contact technology PCB technology Onclusion |                      |

|                                                                                                                                    | rication Process                                                                                                                                                                                                                                                                                                    |                      |

| 1.4.1.50                                                                                                                           | older                                                                                                                                                                                                                                                                                                               |                      |

| 1.4.2 Sintering                                                                                                                                                                                                                           |                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.5 Conclusion                                                                                                                                                                                                                            |                            |

| CHAPTER 2. LOW VOLTAGE PACKAGING WITH GAN FETS                                                                                                                                                                                            |                            |

| 2.1 Introduction                                                                                                                                                                                                                          | 44                         |

| 2.2 Proposed structures                                                                                                                                                                                                                   | 44                         |

| 2.3 Fabrication process                                                                                                                                                                                                                   | 48                         |

| 2.3.1 DBC preparation 2.3.1.1 Substrate cleaning 2.3.1.2 Photolithography 2.3.2 Reflow Soldering 2.3.3 Prototype I: Flip-chip with DBC 2.3.4 Prototype II: "Flip flip" chip on DBC 2.3.5 Prototype III: Flip-chip on PCB 2.3.6 Conclusion | 48<br>50<br>52<br>53<br>55 |

|                                                                                                                                                                                                                                           |                            |

| 2.4 Thermal analysis                                                                                                                                                                                                                      |                            |

| 2.4.2 Thermal convection                                                                                                                                                                                                                  |                            |

| 2.4.3 Thermal Radiation                                                                                                                                                                                                                   |                            |

| 2.4.4 FEM analysis                                                                                                                                                                                                                        | 59                         |

| 2.4.5 Thermal simulation of GaN prototypes                                                                                                                                                                                                | 59                         |

| 2.4.6 Experimental characterizations                                                                                                                                                                                                      |                            |

| 2.4.7 Conclusion                                                                                                                                                                                                                          | 65                         |

| 2.5 Electromagnetic and electric study                                                                                                                                                                                                    |                            |

| 2.5.1 Half-bridge demonstrator                                                                                                                                                                                                            |                            |

| 2.5.2 Electromagnetic analysis                                                                                                                                                                                                            |                            |

| 2.5.2.1 Wire bonding prototype                                                                                                                                                                                                            |                            |

| 2.5.2.3 Analytical approach for partial inductance                                                                                                                                                                                        | 73                         |

| 2.5.3 Electric analysis                                                                                                                                                                                                                   | 78                         |

| 2.5.3.1<br>2.5.3.2  | Electrical Simulation Experimental characteristics  |       |

|---------------------|-----------------------------------------------------|-------|

| 2.6 Conc            | lusion                                              | 84    |

| СНАРТ               | TER 3. HIGH VOLTAGE PACKAGIN<br>VERTICAL COMPONENTS | IG    |

| 3.1 Intro           | duction                                             | 86    |

| 3.2 Prop            | osed structures for the analysis of the contac      | et 86 |

| 3.3 Fabri           | ication process                                     | 87    |

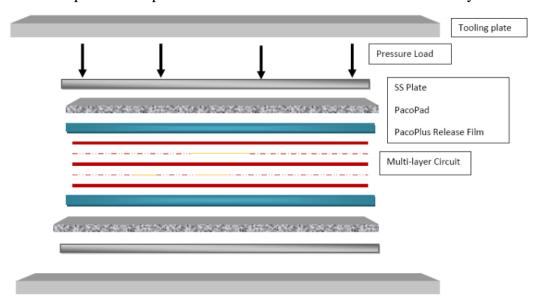

|                     | CB materials used in fabrication                    |       |

|                     | Isola PCL370HR and Arlon 55NT                       |       |

|                     | Release film and press-pads                         |       |

|                     | nemical Ag deposition                               |       |

|                     | nip preparation                                     |       |

| -                   | Sintering                                           |       |

|                     | etailed description of the process  PCB embedding   |       |

|                     | Etching                                             |       |

| 3.3.6 La            | ser ablation                                        | 97    |

| 3.3.7 M             | etallization                                        | 99    |

| 3.4 Statio          | c characterization of the embedded diode            | 103   |

| 3.5 Analy           | ysis of electric contact                            | 104   |

| •                   | odelling                                            |       |

|                     | perimental measurement                              |       |

|                     | onclusion                                           |       |

| <b>3.6 Half</b>     | bridge prototype                                    | 111   |

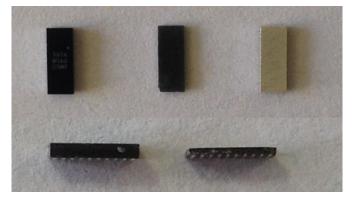

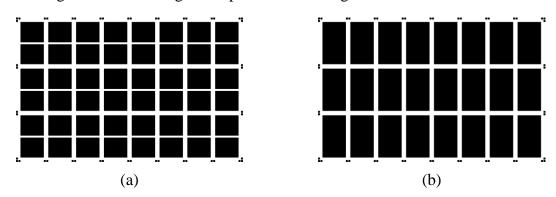

| 3.6.1 La            | yout adaption for component surface                 | 112   |

| 3.6.1.1             | IGBT                                                |       |

| 3.6.1.2<br>3.6.2 Pr | Diodeocess flow                                     |       |

|                     |                                                     |       |

|                     | anufacturing data generationesign Tolerance         |       |

|                     | EM simulation                                       |       |

|                     | sperimental characterization                        |       |

| 3.6.7 Improvement           | 121 |

|-----------------------------|-----|

| <b>3.7 Conclusion</b>       | 121 |

| CONCLUSION AND PERSPECTIVES | 123 |

| BIBLIOGRAPHY                | 126 |

| ANNEX A                     | 133 |

| ANNEX B                     | 137 |

## LIST OF FIGURES

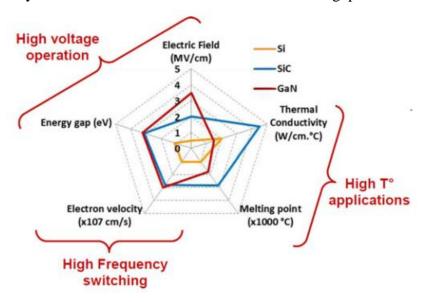

| Figure 1.1: Summary of Si, SiC and GaN relevant material properties [4]                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

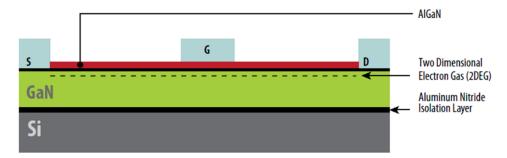

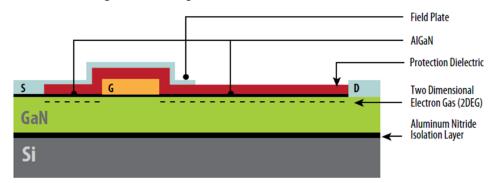

| Figure 1.2: Depletion mode GaN transistor [12]                                                                                                                                       |

| Figure 1.3: Enhancement mode GaN transistor [12]                                                                                                                                     |

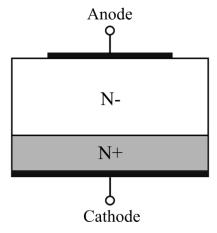

| Figure 1.4: Structure of a Schottky diode [18]                                                                                                                                       |

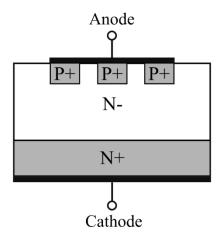

| Figure 1.5: Structure of a Merged PiN Schottky (MPS) diode [18]                                                                                                                      |

| Figure 1.6: An example of SiC power MOSFET [21]                                                                                                                                      |

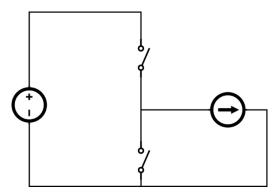

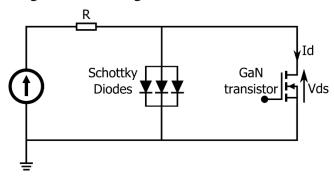

| Figure 1.7: A switching cell diagram                                                                                                                                                 |

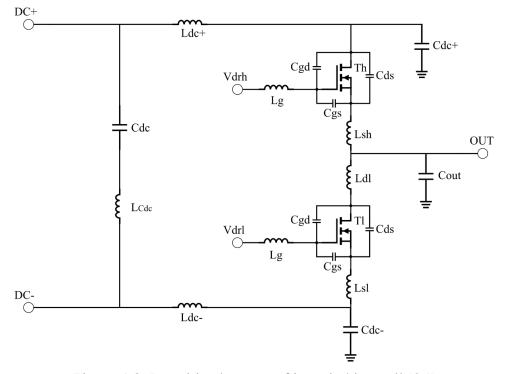

| Figure 1.8: Parasitic elements of in switching cell [25]                                                                                                                             |

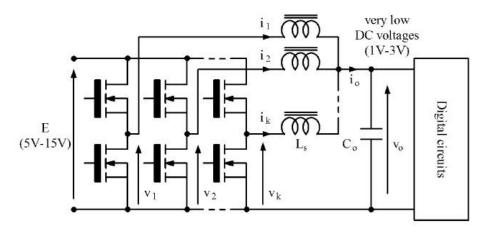

| Figure 1.9: Example of an interleaved VRM converter with uncoupled inductors [32] $\dots$ 22                                                                                         |

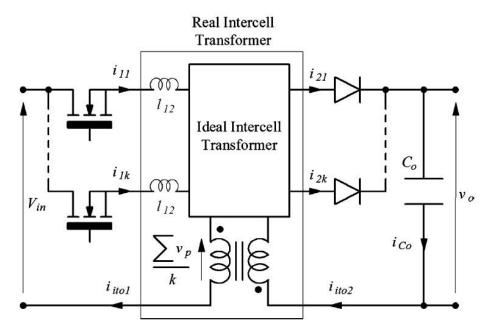

| Figure 1.10: Output and winding currents for (a) uncoupled inductors and (b) InterCell transformer [35].                                                                             |

| Figure 1.11: Interleaved flyback using IT [36]                                                                                                                                       |

| Figure 1.12: Buck or Boost (BoB) topology [39]                                                                                                                                       |

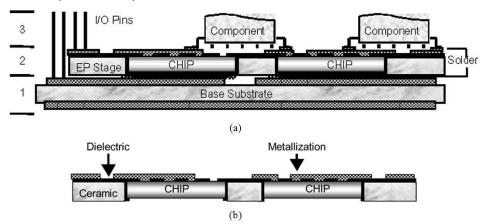

| Figure 1.13: Cross-section of a 2D module                                                                                                                                            |

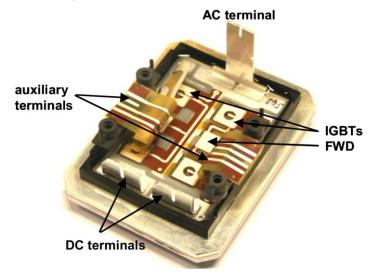

| Figure 1.14: example of 2D package inverter arm (Doc. University of Nottingham) 26                                                                                                   |

| Figure 1.15: (a) IMS substrate structure, (b) DBC substrate structure [40]                                                                                                           |

| Figure 1.16: fatigue cracks in soldering between the Si die and the metallic part of a DBC substrate [44]                                                                            |

| Figure 1.17: Delamination of metal layer of a metallized ceramic substrate (Doc. University of Nottingham)                                                                           |

| Figure 1.18: photograph of "dimples", etched pattern for increasing the thermal cycle [50]                                                                                           |

| Figure 1.19: MPIPPS module [51]                                                                                                                                                      |

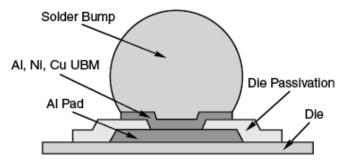

| Figure 1.20: Solder bump interconnection [21]                                                                                                                                        |

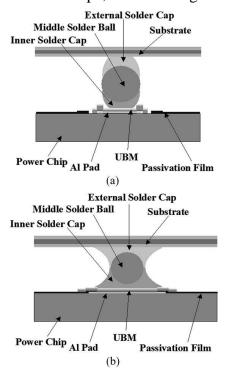

| Figure 1.21: Stacked solder joint configurations. (a) Triple-stack barrel shape. (b) Triple-stack hourglass shape [51]                                                               |

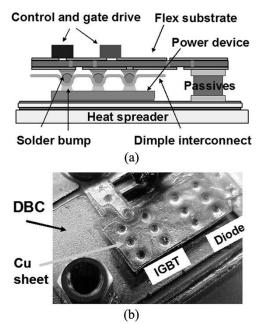

| Figure 1.22: (a) Implementation of the DAI in an integrated 3-D power module. (b) Section of a DAI half-bridge power module showing the dimpled copper sheet over the IGBT and diode |

| Figure 1.23: DS interconnected device attached to DBC substrates [61]                                                                                                                |

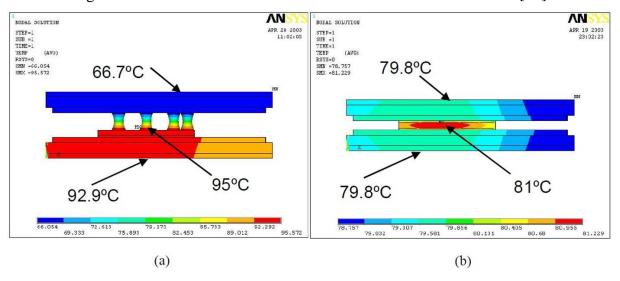

| Figure 1.24: Temperature distribution of (a) the Direct Solder and (b) Solder Bump packages during the same operation and (double-sided) cooling conditions [61]                     |

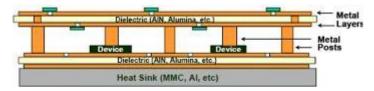

| Figure 1.25: Structural schematic of (a) an embedded power module and (b) an integrated power chips stage [62]                                                                       |

| Figure 1.26: Photography of a Press-pack module (Dynex Semiconductor)                                                                                                                |

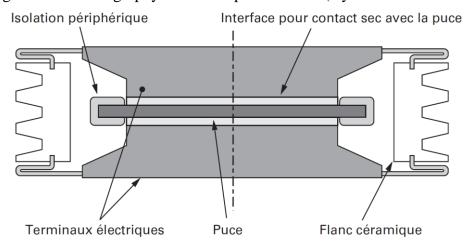

| Figure 1.27: Cross section of Press-pack module [40]                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

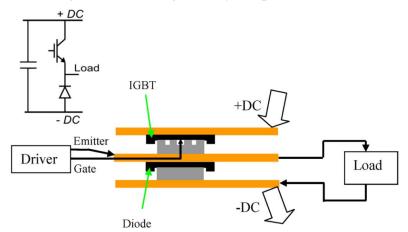

| Figure 1.28: Switching cell by using the Press-Pack technology [66]                                                                                                                                                                                           |

| Figure 1.29: The <i>MiniSKiip</i> module with spring contacts [70]                                                                                                                                                                                            |

| Figure 1.30: Spring pressure contact technology [69]                                                                                                                                                                                                          |

| Figure 1.31: Photo of a 400A, 600V dual IGBT SKiN device [75]                                                                                                                                                                                                 |

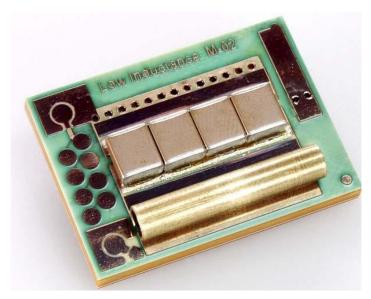

| Figure 1.32: Thin 60-W offline converter with PCB integrated transformer and capacitors [76]                                                                                                                                                                  |

| Figure 1.33: Manufactured module with DC-link capacitors and current measurement [82]                                                                                                                                                                         |

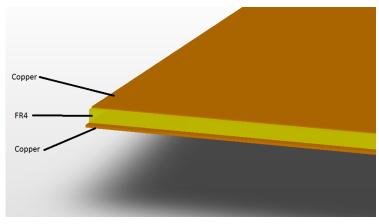

| Figure 1.34: Double-sided copper clad FR4 substrate [90]                                                                                                                                                                                                      |

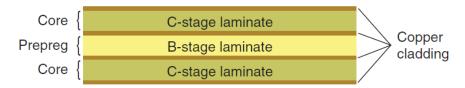

| Figure 1.35: Cores and prepreg [91]                                                                                                                                                                                                                           |

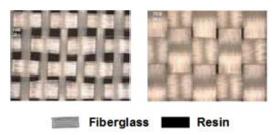

| Figure 1.36: Glass fabric composition [95]                                                                                                                                                                                                                    |

| Figure 1.37: Non-woven aramid (photo Courtesy of Dupont)                                                                                                                                                                                                      |

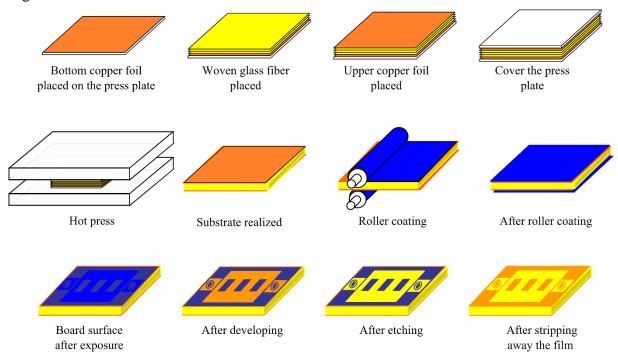

| Figure 1.38: Fabrication process of PCB [96]                                                                                                                                                                                                                  |

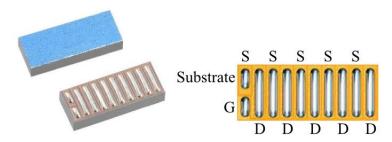

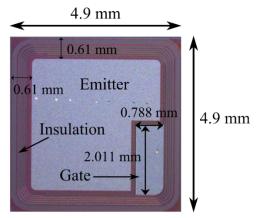

| Figure 2.1: EPC GaN transistor [97]                                                                                                                                                                                                                           |

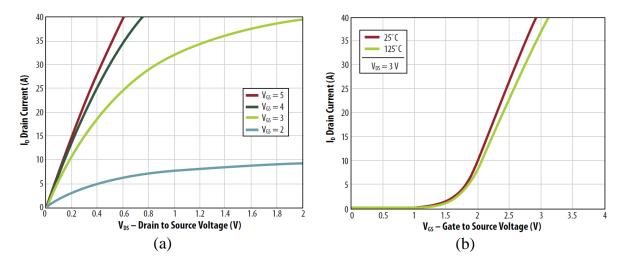

| Figure 2.2: (a) $I_D(V_{DS})$ , (b) $I_D(V_{GS})$ [98]                                                                                                                                                                                                        |

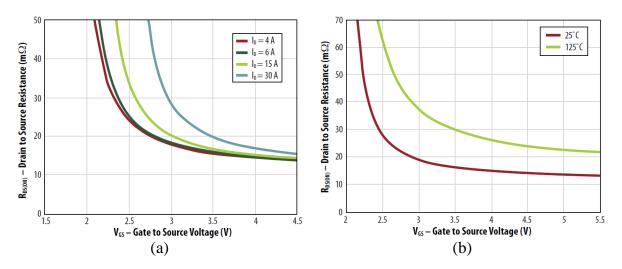

| Figure 2.3: (a) $R_{DS(on)}(V_{GS})$ with different $I_D$ , (b) $R_{DS(on)}(V_{GS})$ with different temperature [98]                                                                                                                                          |

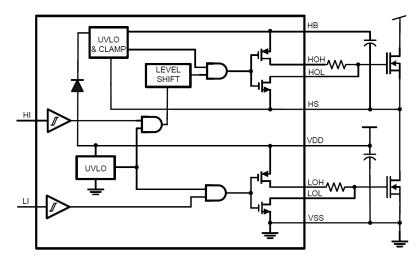

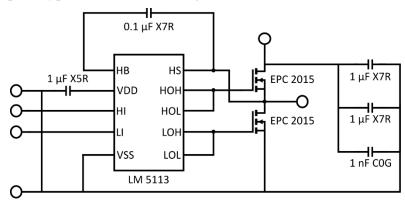

| Figure 2.4: LM5113 control circuit [99]                                                                                                                                                                                                                       |

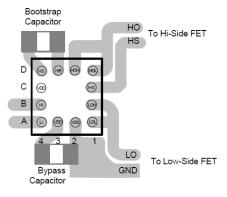

| Figure 2.5: Proposed layout for LM5113 [99]                                                                                                                                                                                                                   |

| Figure 2.6: Cross-section of the three prototypes                                                                                                                                                                                                             |

| Figure 2.7: Photographs of the three prototypes                                                                                                                                                                                                               |

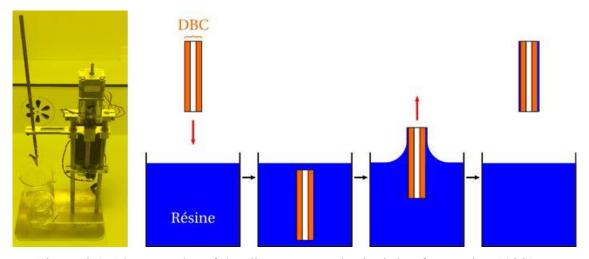

| Figure 2.8: Fabrication process of DBC                                                                                                                                                                                                                        |

| Figure 2.9: Photography of the dip coater, and principle of operation [100] 50                                                                                                                                                                                |

| Figure 2.10 : UNB 100 Universal Oven used for "dip coating" [101]                                                                                                                                                                                             |

| Figure 2.11 : Mask aligner Q-2001 CT                                                                                                                                                                                                                          |

| Figure 2.12: ZEVAC ONYX 21 Flip-chip bonder [102]                                                                                                                                                                                                             |

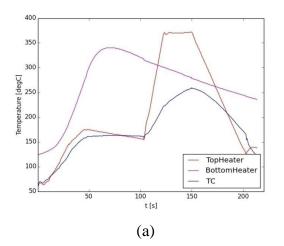

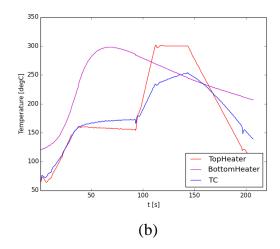

| Figure 2.13: Reflow soldering process for DBC (a) and PCB (b). The substrate temperature (TC) is first brought between 160 and 170°C (pre-heating) and then above the liquidus of the solder bumps (217°C) for a short time (1 min), for the actual soldering |

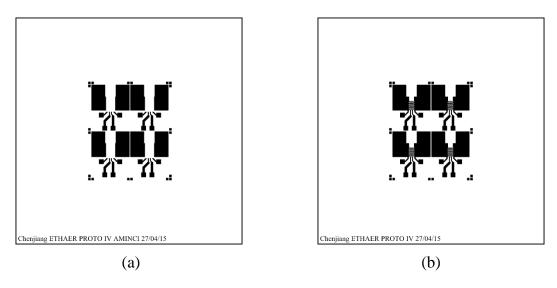

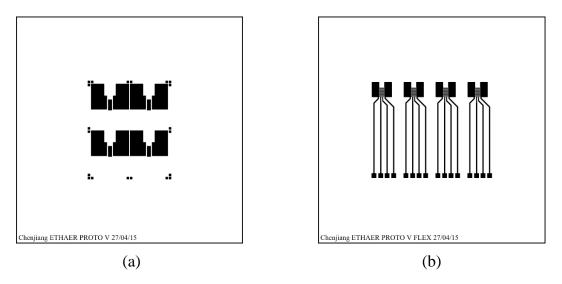

| Figure 2.14: (a) First mask for dual-step etching, (b) Second mask                                                                                                                                                                                            |

| Figure 2.15: Fabrication process for dual-step etching                                                                                                                                                                                                        |

| Figure 2.16: Dual-step etching result                                                                                                                                                                                                                         |

| Figure 2.17: (a) Mask for DBC etching, (b) Mask for flex substrate etching 56                                                                                                                                                                                 |

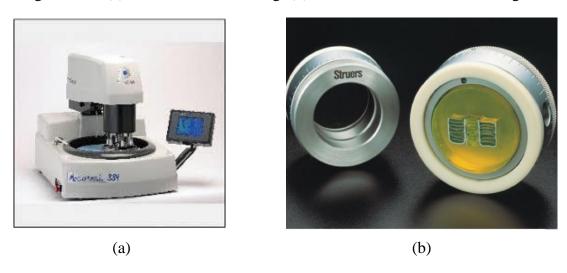

| Figure 2.18: (a) MECATECH 334 polishing machine [103], (b) Struers' AccuStop sample holder [104]                                                                                                                                                              |

| Figure 2.19: Polished GaN transistors. Top line: top view of the devices before grinding, after grinding, and after Ti/Ag PVD plating. Bottom line: side view of the devices before and after grinding. Original device size is $4075 \times 1602 \times 685 \mu \text{m}$                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.20: Fabrication process for flip flip-chip prototype                                                                                                                                                                                                                                                                                                                            |

| Figure 2.21: COMSOL geometry of the three prototypes: flip chip on DBC, "flip-flip"-chip on DBC, and flip chip on PCB. All three prototypes are attached to a large heatsink (grey) using a layer of thermal interface material                                                                                                                                                          |

| Figure 2.22: Thermal simulation results for GaN prototypes                                                                                                                                                                                                                                                                                                                               |

| Figure 2.23: Heat flow from junction to ambient                                                                                                                                                                                                                                                                                                                                          |

| Figure 2.24: Calibration Curve (Rdson as a function of T)                                                                                                                                                                                                                                                                                                                                |

| Figure 2.25: Circuit diagram used for the transient thermal characterization                                                                                                                                                                                                                                                                                                             |

| Figure 2.26: Test bench for thermal characterization                                                                                                                                                                                                                                                                                                                                     |

| Figure 2.27: Parasitic elements of a switching cell                                                                                                                                                                                                                                                                                                                                      |

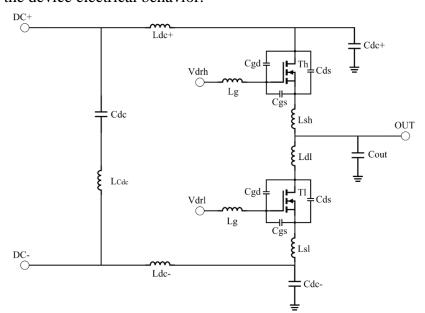

| Figure 2.28: Circuit diagram of the half-bridge demonstrator                                                                                                                                                                                                                                                                                                                             |

| Figure 2.29: Photograph of the half-bridge demonstrator. The TI5113 gate driver is the black square on the right of the substrate (with 4 connecting pads for power supply and driving signals of each transistor)                                                                                                                                                                       |

| Figure 2.30: Photograph of the prototype used to validate the simulation method. It consists in 4 copper tracks, connected using two bond wires (center of the picture). High frequency SMA connectors are soldered on the edge of the substrate for connection with the test equipment.                                                                                                 |

| Figure 2.31: COMSOL structure of wire-bonding prototype                                                                                                                                                                                                                                                                                                                                  |

| Figure 2.32: Keysight 4294A                                                                                                                                                                                                                                                                                                                                                              |

| Figure 2.33: Impedance measurement configuration for the wire-bonded DBC prototype                                                                                                                                                                                                                                                                                                       |

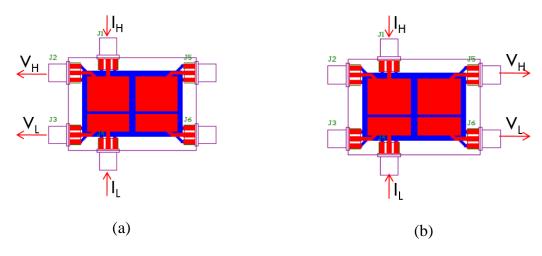

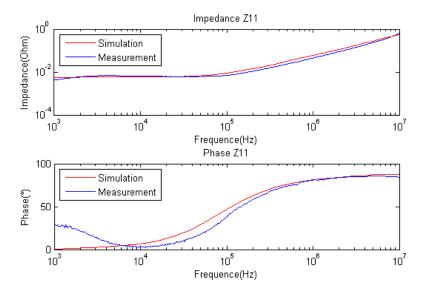

| Figure 2.34: FEM simulation and measurement results for Z11 impedance (module and phase)                                                                                                                                                                                                                                                                                                 |

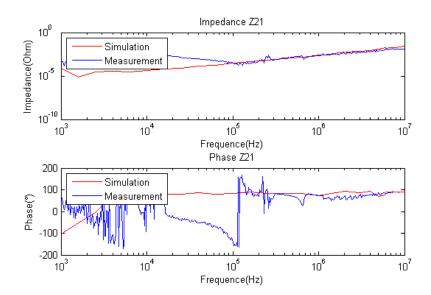

| Figure 2.35: FEM simulation and measurement results for Z21 impedance (module and phase)                                                                                                                                                                                                                                                                                                 |

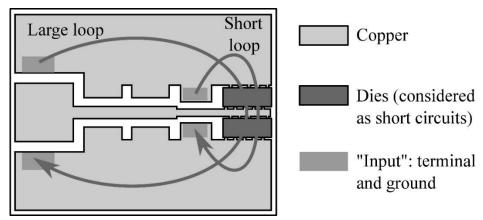

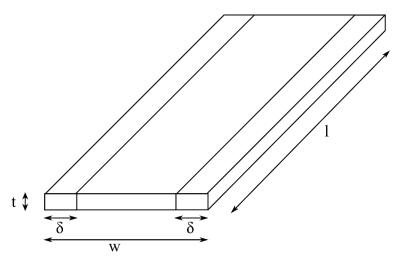

| Figure 2.36: Layout of the prototype used for electromagnetic characterization, with the location of the terminal considered for inductance estimation. The upper and lower copper tracks are the $+$ and $-$ DC links, while the middle track is the output of the half-bridge. The three tooth-like patterns on the left of the dies are the locations of the DC decoupling capacitors |

| Figure 2.37: Test vehicle for inductance measurement                                                                                                                                                                                                                                                                                                                                     |

| Figure 2.38: Resistance and inductance along the "large loop", obtained by simulation and measurement, for DBCs with and without backside copper                                                                                                                                                                                                                                         |

| Figure 2.39: Simulation of different ceramic thickness                                                                                                                                                                                                                                                                                                                                   |

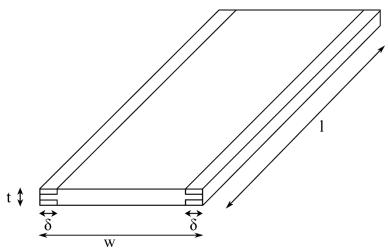

| Figure 2.40: "subbars" decomposition for a rectangular cross section conductor                                                                                                                                                                                                                                                                                                           |

| Figure 2.41: Proposed simplified "subbars" cross section                                                                                                                                                                                                                                                                                                                                | . 74                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Figure 2.42: Mutual partial inductance between two conductors                                                                                                                                                                                                                                                                                                                           | . 75                        |

| Figure 2.43: Equivalent geometry without bottom copper                                                                                                                                                                                                                                                                                                                                  | . 75                        |

| Figure 2.44: Resistance and inductance values without bottom copper for anal calculation and COMSOL simulation                                                                                                                                                                                                                                                                          |                             |

| Figure 2.45: Current distribution at high frequencies ( $\delta$ <t)< td=""><td>. 76</td></t)<>                                                                                                                                                                                                                                                                                         | . 76                        |

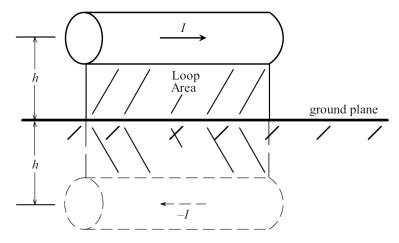

| Figure 2.46: Transmission line with ground plane                                                                                                                                                                                                                                                                                                                                        | . 77                        |

| Figure 2.47: Equivalent geometry with bottom copper                                                                                                                                                                                                                                                                                                                                     | . 77                        |

| Figure 2.48: Inductance values with bottom copper layer; Analytic calculation COMSOL simulation                                                                                                                                                                                                                                                                                         | . 78                        |

| Figure 2.49: Electrical circuit for Pspice simulation                                                                                                                                                                                                                                                                                                                                   | . 78                        |

| Figure 2.50: Switching loss of the circuit in Figure 2.49 with the variation of leaductance (simulation)                                                                                                                                                                                                                                                                                | _                           |

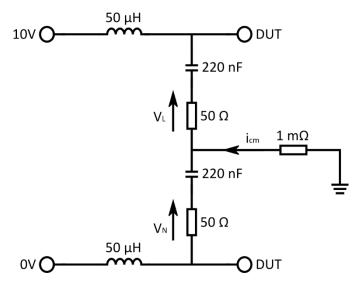

| Figure 2.51: Line Impedance Stabilization Network                                                                                                                                                                                                                                                                                                                                       | . 81                        |

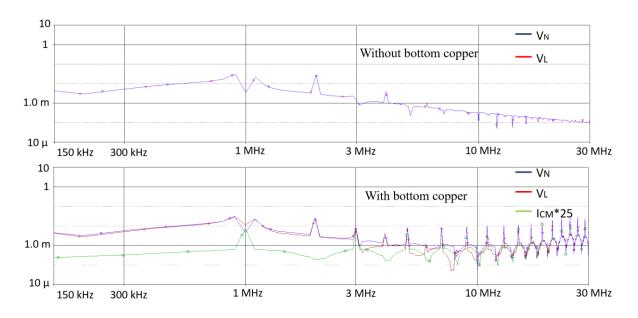

| Figure 2.52: Common mode disturbance simulation results                                                                                                                                                                                                                                                                                                                                 | . 81                        |

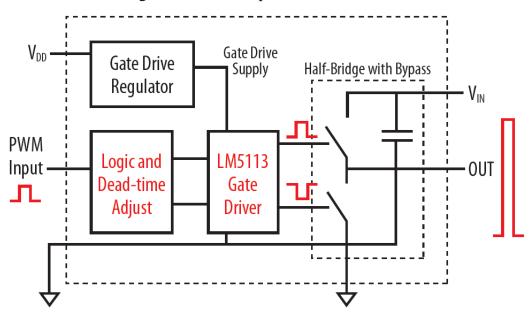

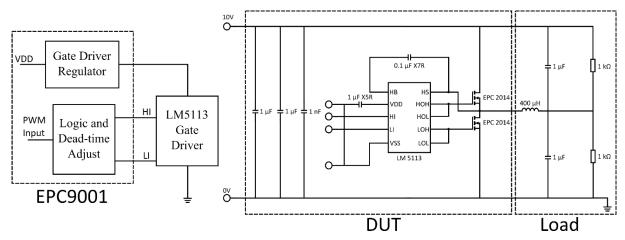

| Figure 2.53: Development board EPC9001                                                                                                                                                                                                                                                                                                                                                  | . 82                        |

| Figure 2.54: Block Diagram of EPC9001 Development Board                                                                                                                                                                                                                                                                                                                                 | . 82                        |

| Figure 2.55: Circuit diagram used for electric characterization                                                                                                                                                                                                                                                                                                                         | . 83                        |

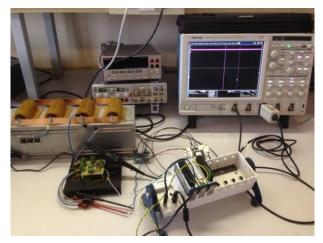

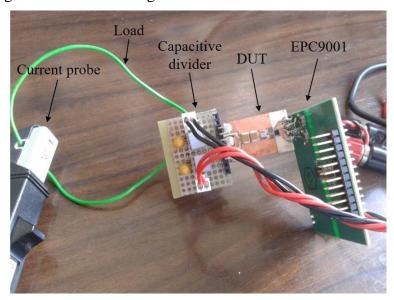

| Figure 2.56: Test bench for DBC half-bridge prototype                                                                                                                                                                                                                                                                                                                                   | . 83                        |

| Figure 2.57: Experimental and simulation results for this DBC half-bridge prototype. Switching waveform for 2 periods, (b) Zoom for turn-off part of low side transistor, Zoom for turn-on part of low side transistor                                                                                                                                                                  | (c)                         |

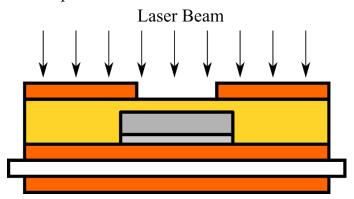

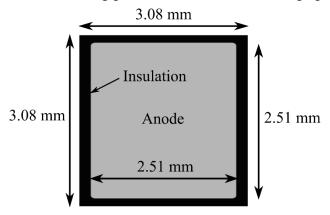

| Figure 3.1: Cross-section and realization of a diode embedded in PCB                                                                                                                                                                                                                                                                                                                    | . 86                        |

| Figure 3.2: Left: some of the test vehicles, with 4 embedded diodes each                                                                                                                                                                                                                                                                                                                | . 87                        |

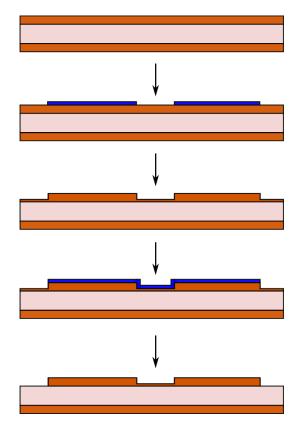

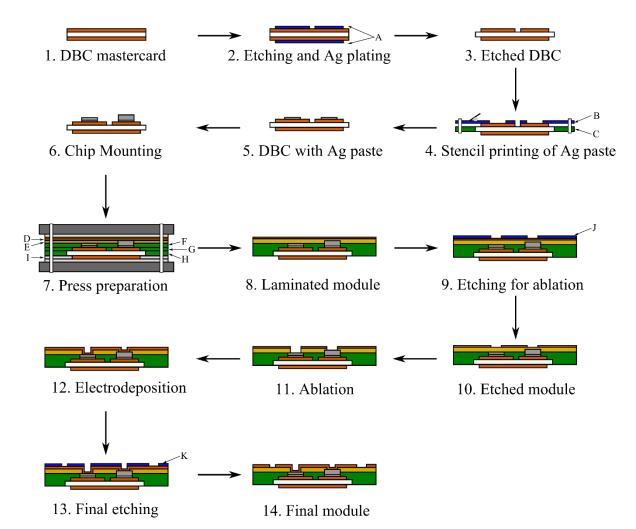

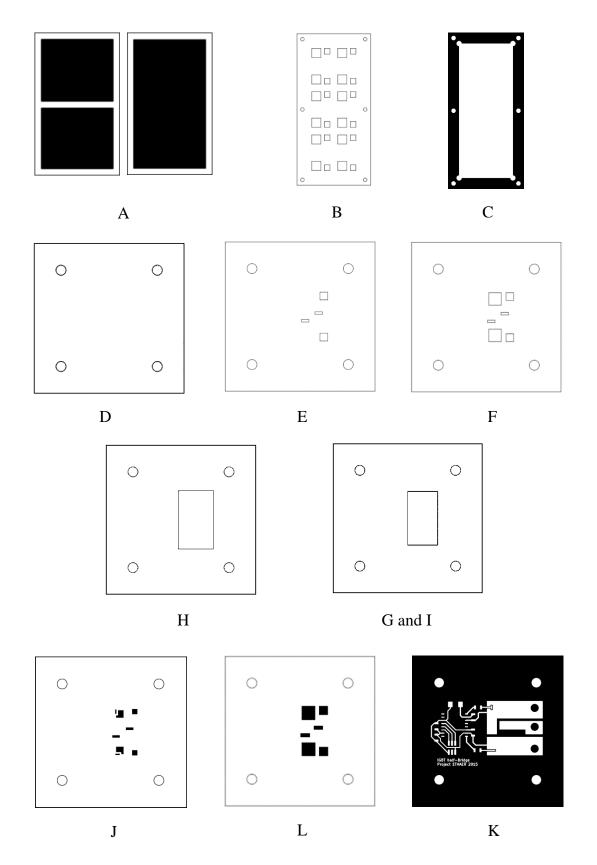

| Figure 3.3: Fabrication process of embedding technique                                                                                                                                                                                                                                                                                                                                  | . 88                        |

| Figure 3.4: Recommended lamination lay-up [120]                                                                                                                                                                                                                                                                                                                                         | . 89                        |

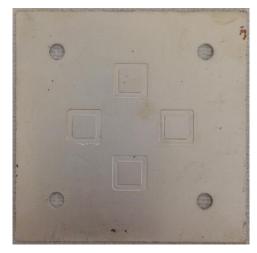

| Figure 3.5: An example of silver deposition on a copper plate. The 4 holes register with alignment pins of the press platen for lamination. The 4 engraved squares are used position the dies in the sintering step.                                                                                                                                                                    | d to                        |

| Figure 3.6: Shadow mask: front (a), showing the openings where the Ti/Cu layers will applied. Back, showing the dies in their locating pockets, kept in place using polyim tape. The mask attached to the PVD system support, ready for deposition (c). The mas made out of two stainless steel plate (laser cut and bonded together by DB Products), measures $100x100 \text{ mm}^2$ . | nide<br>k is<br>and<br>. 91 |

| Figure 3.7: An IGBT with Ti/Cu finish                                                                                                                                                                                                                                                                                                                                                   |                             |

| Figure 3.8: Photography of "pick and place" machine                                                                                                                                                                                                                                                                                                                                     | . 92                        |

| Figure 3.9: Photography of screen printing machine and heated press used for sintering                                                                                                                                                                                                                                                                                                  | 92                          |

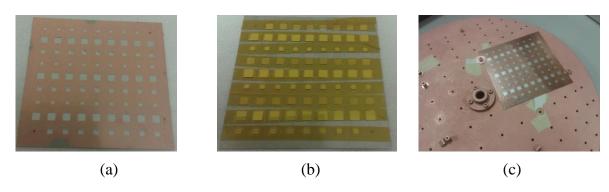

| Figure 3.10: (a) Cutout of PCL370HR, (b) Cutout of 55NT and pacothane plus                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

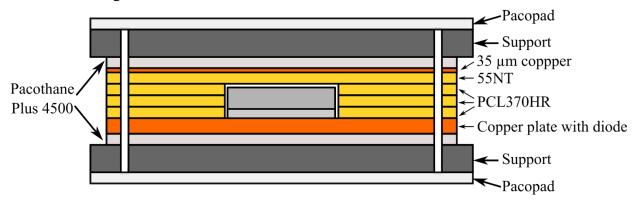

| Figure 3.11: stack-up for the lamination of the PCB, corresponding to step (b) in Figure 3.3.                                                                                                                                                                                                   |

| Figure 3.12: (a) Inox support for press, with 4 registration pins for the alignement of the various layers from Figure 3.10, (b) the heating press used for PCB embedding94                                                                                                                     |

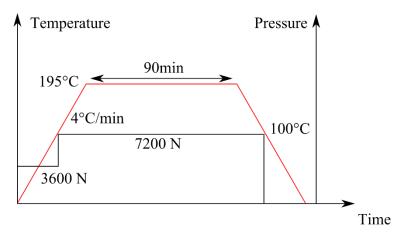

| Figure 3.13: Temperature profile for PCB embedding. The PCB measures 60x60 mm², a force of 3600 newtons corresponds to a pressure of 1 Mpa (approximately 10 bars). 7200 N corresponds to 2 Mpa (20 bars)                                                                                       |

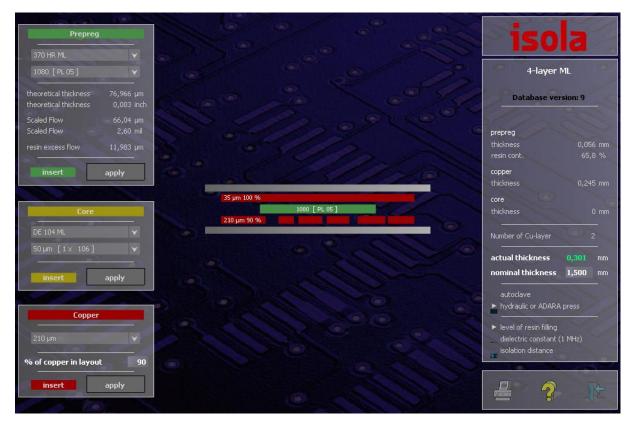

| Figure 3.14: An example of the digital tool Multical by isola                                                                                                                                                                                                                                   |

| Figure 3.15: Photography of a film laminator and its principle function [96]                                                                                                                                                                                                                    |

| Figure 3.16: Photography of exposure machine [21] and a mask example                                                                                                                                                                                                                            |

| Figure 3.17: Copper layer as alignment mask                                                                                                                                                                                                                                                     |

| Figure 3.18: Gravograph LS100EX laser                                                                                                                                                                                                                                                           |

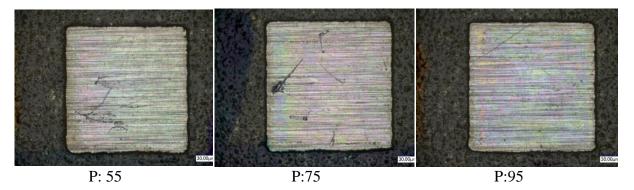

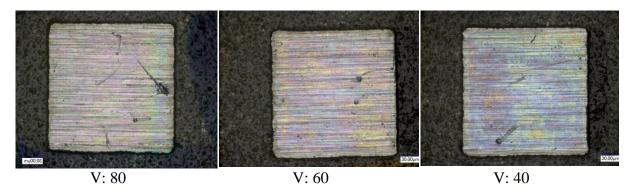

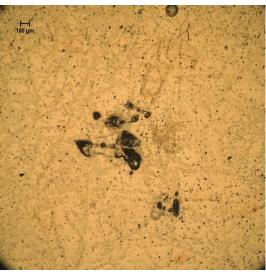

| Figure 3.19: photos of aluminum surface after laser ablation with different power values, for a sweep speed of 80% No difference in appearance of the aluminum surface is noted.                                                                                                                |

| Figure 3.20: photos of aluminum surface after laser ablation with different speed values, for a power of 75%. No difference in appearance of the aluminum surface is noted 99                                                                                                                   |

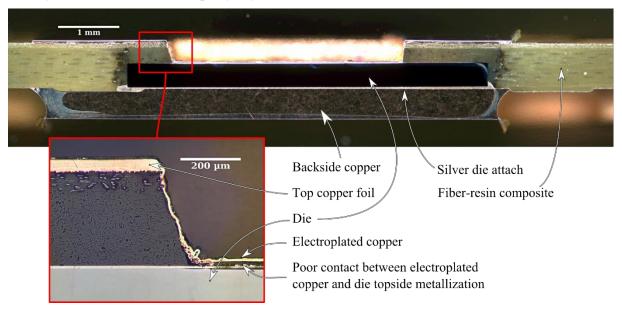

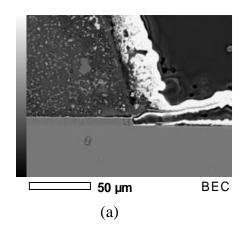

| Figure 3.21: Cross-section of a sample after metallization, taken at the edge of the exposed pad. The wall of the copper electroplated on the die is clearly visible                                                                                                                            |

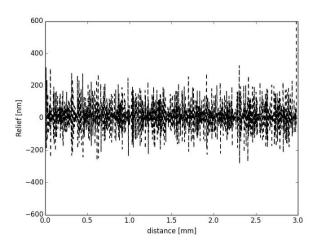

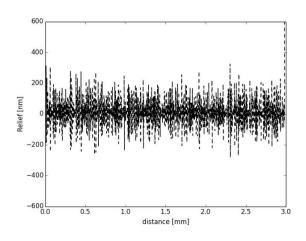

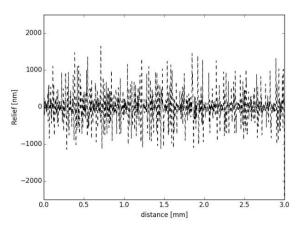

| Figure 3.22: Roughness measurement for aluminum topside finish of the die before metallization                                                                                                                                                                                                  |

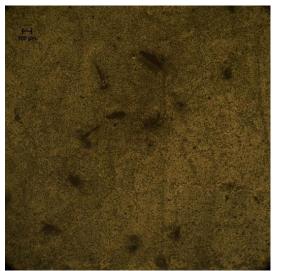

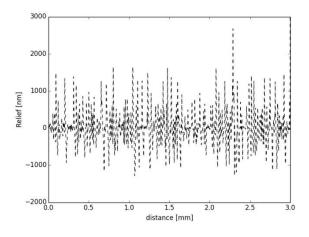

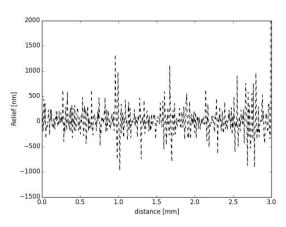

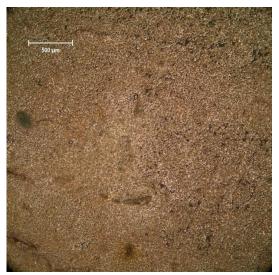

| Figure 3.23: Photo of the metallization surface on aluminum with different copper plating times                                                                                                                                                                                                 |

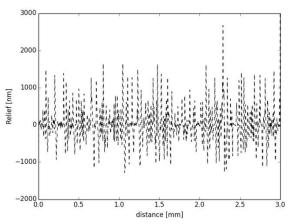

| Figure 3.24: Roughness measurements of the copper surface on aluminum with different plating times                                                                                                                                                                                              |

| Figure 3.25: Photo of the metallization surface for dies with aluminum and copper finish with 20 minutes metallization                                                                                                                                                                          |

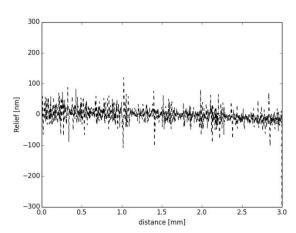

| Figure 3.26: Roughness measurement on metallization surface for aluminum and copper finish with 20 minutes metallization                                                                                                                                                                        |

| Figure 3.27: Sample used for electrical characterization (60×60 mm <sup>2</sup> ) 103                                                                                                                                                                                                           |

| Figure 3.28: Electrical test of an embedded diode                                                                                                                                                                                                                                               |

| Figure 3.29: 3D view of the test vehicles                                                                                                                                                                                                                                                       |

| Figure 3.30: Cross-section of the second test vehicle                                                                                                                                                                                                                                           |

| Figure 3.31 : 2-D view of the resistance network used to represent the test vehicles 106                                                                                                                                                                                                        |

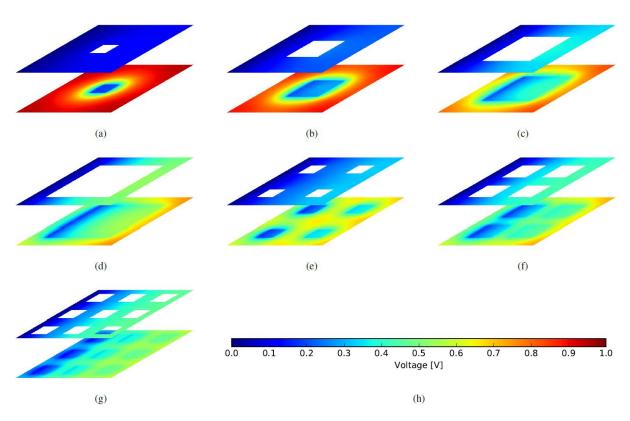

| Figure 3.32: Simulation of the voltage distribution on the PCB top copper layer and on the topside metallization of the die, for various contact layout configurations (the walls are not shown). Current is injected on the left side on the top metallization, and on the backside of the die |

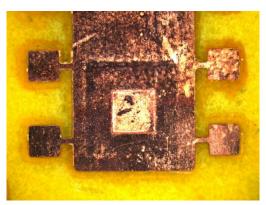

| Figure 3.33: Close-up of one of the embedded dies, with a contact window of $3\times3$ mm <sup>2</sup>                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

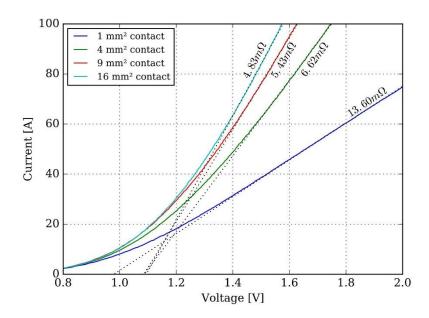

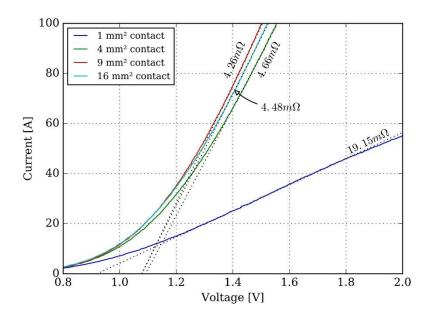

| Figure 3.34: Forward characteristic measured on test vehicle which comprises single well layouts with a surface ranging from 1 to 16 mm <sup>2</sup>                                                                                     |

| Figure 3.35: Forward characteristic measured on test vehicle with the same layout as the test vehicle shown in Figure 3.34. Here, the 9 mm <sup>2</sup> contact is found to offer a lower resistance than the 16 mm <sup>2</sup> contact |

| Figure 3.36: SEM analysis for the half-bridge prototype, (a) the microscopic photo, (b) Cu element in the photo, (c) Al element in the photo                                                                                             |

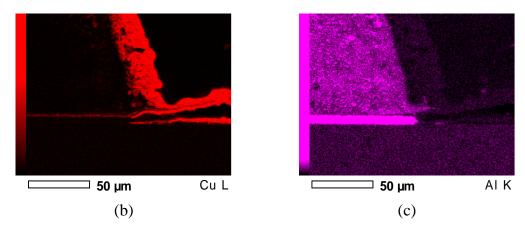

| Figure 3.37: Electric circuit diagram of the half-bridge prototype                                                                                                                                                                       |

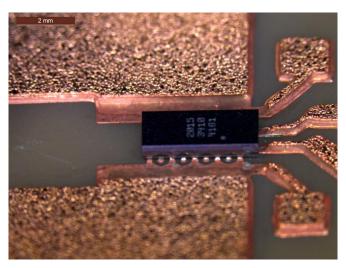

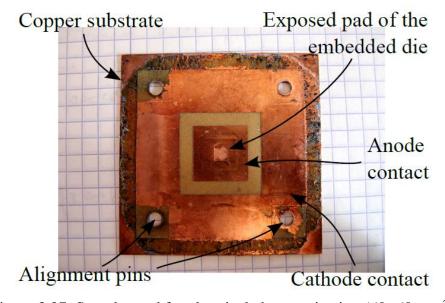

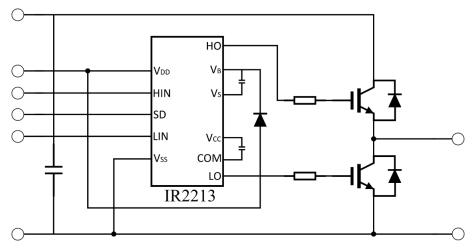

| Figure 3.38: Photograph of a half-bridge module. The DBC (with 2 IGBTs and 2 SiC diodes) is shown in the upper right corner prior to embedding                                                                                           |

| Figure 3.39: 1200V/15A Si IGBT                                                                                                                                                                                                           |