# PLL Phase Noise & Jitter Modeling, for High Speed Serial Links

Klodjan Bidaj

#### ▶ To cite this version:

Klodjan Bidaj. PLL Phase Noise & Jitter Modeling, for High Speed Serial Links. Other. Université de Bordeaux, 2016. English. NNT: 2016BORD0355. tel-01452514

## HAL Id: tel-01452514 https://theses.hal.science/tel-01452514v1

Submitted on 2 Feb 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE PRÉSENTÉE

POUR OBTENIR LE GRADE DE

# DOCTEUR DE

# L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE

## SPÉCIALITÉ ELECTRONIQUE

Par Klodjan BIDAJ

# Modélisation du bruit de phase et de la gigue d'une PLL, pour les liens séries haut débit.

Sous la direction de : Jean-Baptiste BEGUERET, Laboratoire IMS, Bordeaux Co-directeur : Jerome DEROO, STMicroelectronics, Grenoble

Soutenue le 30/11/2016

#### Membres du jury :

| DALLET, Dominique | Professeur                                                                            |

|-------------------|---------------------------------------------------------------------------------------|

| MIR, Salvador     | Directeur de recherche CNRS                                                           |

| MAZZANTI, Andrea  | Professeur                                                                            |

| AZAIS, Florence   | Chargé de recherche CNRS                                                              |

| BEGUERET, JB      | Professeur                                                                            |

| DEROO, Jerome     | Ingénieur                                                                             |

| THIES, William    | Ingénieur                                                                             |

|                   | MIR, Salvador<br>MAZZANTI, Andrea<br>AZAIS, Florence<br>BEGUERET, JB<br>DEROO, Jerome |

IPB TIMA Univ. de Pavia LIRMM Univ. de Bordeaux STMicroelectronics STMicroelectronics Examinateur Rapporteur Rapporteur Examinateur Directeur de Thèse Encadrant industriel Invité

# Titre : Modélisation du bruit de phase et de la gigue d'une PLL, pour les liens séries haut débit.

## Résumé :

La vitesse des liens séries haut débit (USB, SATA, PCI-express, etc.) a atteint les multi-gigabits par seconde, et continue à augmenter. Deux des principaux paramètres électriques utilisés pour caractériser les performances des SerDes sont la gigue transmis à un niveau de taux d'erreur donné et la capacité du récepteur à suivre la gigue à un taux d'erreur donné.

Modéliser le bruit de phase des différents components du SerDes, et extraire la gigue temporelle pour la décomposer, aideraient les ingénieurs en conception de circuits à atteindre les meilleurs résultats pour les futures versions des SerDes. Générer des patterns de gigue synthétiques de bruits blancs ou colorés permettrait de mieux analyser les effets de la gigue dans le système pendant la phase de vérification.

La boucle d'asservissement de phase est un des contributeurs de la gigue d'horloge aléatoire et déterministe à l'intérieur du système. Cette thèse présente une méthode pour modéliser la boucle d'asservissement de phase avec injection du bruit de phase et estimation de la gigue temporelle. Un modèle dans le domaine temporel en incluant les effets de non-linéarité de la boucle a été créé pour estimer cette gigue. Une nouvelle méthode pour générer des patterns synthétiques de gigue avec une distribution Gaussienne à partir de profils de bruit de phase coloré a été proposée.

Les standards spécifient des budgets séparés de gigue aléatoire et déterministe. Pour décomposer la gigue de la sortie de la boucle d'asservissement de phase (ou la gigue généré par la méthode présentée), une nouvelle technique pour analyser et décomposer la gigue a été proposée. Les résultats de modélisation corrèlent bien avec les mesures et cette technique aidera les ingénieurs de conception à identifier et quantifier proprement les sources de la gigue ainsi que leurs impacts dans les systèmes SerDes.

Nous avons développé une méthode, pour spécifier la boucle d'asservissement de phase en termes de bruit de phase. Cette méthode est applicable à tout standard (USB, SATA, PCIe, ...) et définit les profils de bruits de

phases pour les différentes parties de la boucle d'asservissement de phase, pour s'assurer que les requis des standards sont satisfaits en termes de gigue. Ces modèles nous ont également permis de générer les spécifications de la PLL, pour des standards différents.

**Mots clés :** bruit de phase, gigue, taux d'erreur, décomposition de la gigue, liens séries haut débit, SerDes, analyse temps-fréquence, boucle d'asservissement de phase, gigue aléatoire, gigue déterministe, génération de bruit coloré, génération de bruit blanc

# Title : PLL Phase Noise & Jitter Modeling, for High Speed Serial Links

## Abstract :

Bit rates of high speed serial links (USB, SATA, PCI-express, etc.) have reached the multi-gigabits per second, and continue to increase. Two of the major electrical parameters used to characterize SerDes Integrated Circuit performance are the transmitted jitter at a given bit error rate (BER) and the receiver capacity to track jitter at a given BER.

Modeling the phase noise of the different SerDes components, extracting the time jitter and decomposing it, would help designers to achieve desired Figure of Merit (FoM) for future SerDes versions. Generating white and colored noise synthetic jitter patterns would allow to better analyze the effect of jitter in a system for design verification.

The phase locked loop (PLL) is one of the contributors of clock random and periodic jitter inside the system. This thesis presents a method for modeling the PLL with phase noise injection and estimating the time domain jitter. A time domain model including PLL loop nonlinearities is created in order to estimate jitter. A novel method for generating Gaussian distribution synthetic jitter patterns from colored noise profiles is also proposed.

The Standard Organizations specify random and deterministic jitter budgets. In order to decompose the PLL output jitter (or the generated jitter from the proposed method), a new technique for jitter analysis and decomposition is proposed. Modeling simulation results correlate well with measurements and this technique will help designers to properly identify and quantify the sources of deterministic jitter and their impact on the SerDes system.

We have developed a method, for specifying PLLs in terms of Phase Noise. This method works for any standard (USB, SATA, PCIe, ...), and defines Phase noise profiles of the different parts of the PLL, in order to be sure that the standard requirements are satisfied in terms of Jitter.

**Keywords :** Phase Noise, Jitter, BER, jitter decomposition, high speed serial links, SerDes, time-frequency analysis, PLL, RJ, DJ, colored noise generation, white noise generation

## **Table of Contents**

| Chapter | 1: High Speed Serial Links                                                | 9    |

|---------|---------------------------------------------------------------------------|------|

| 1.1     | Introduction                                                              | . 10 |

| 1.2     | Applications of High Speed Serial Links                                   | .11  |

| 1.3     | Challenges of High Speed Serial Links                                     | .11  |

| 1.4     | Jitter Role in High Speed Serial Links                                    | . 13 |

| 1.5     | High Speed Serial Links System Study                                      | . 15 |

| 1.6     | Motivation of this thesis                                                 | . 16 |

| 1.7     | Thesis Organization                                                       | .17  |

| Chapter | 2: Jitter and Phase Noise Theoretical Study                               | . 19 |

| 2.1     | Introduction to Jitter                                                    | . 20 |

| 2.2     | Jitter Calculation                                                        | . 23 |

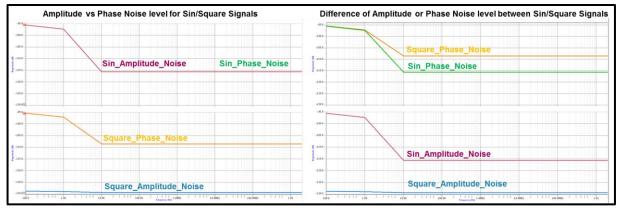

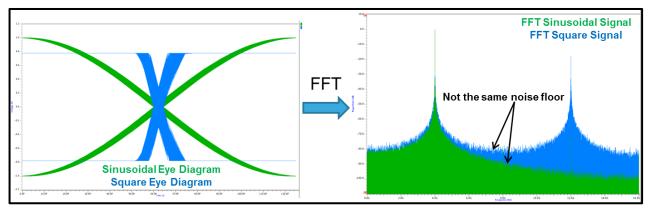

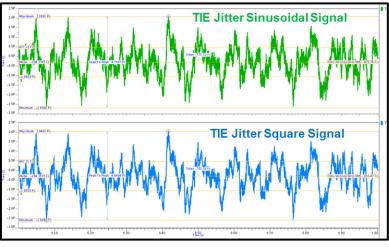

| 2.3     | Phase and Amplitude Noise Study                                           | . 28 |

| 2.4     | Phase & Amplitude Noise Impact onto TIE jitter                            | . 31 |

| 2.5     | RJ/DJ Jitter Correlation Algorithm                                        | . 33 |

| 2.6     | Chapter Conclusion                                                        | . 35 |

| Chapter | 3: PLL Modeling                                                           | . 37 |

| 3.1     | Introduction                                                              | . 38 |

| 3.2     | PLL Architecture                                                          | . 38 |

| 3.3     | Frequency Domain PLL modeling with phase noise injection                  | .43  |

| 3.4     | Time domain PLL modeling with jitter injection                            | .46  |

| 3.5     | Frequency-Time domain comparison                                          | . 50 |

| Chapter | 4: Generation of colored noise patterns with Gaussian Jitter distribution | . 53 |

| 4.1     | Introduction                                                              | . 54 |

| 4.2     | Definition of criteria for colored noise with Gaussian distribution       | . 55 |

| 4.3     | White noise generation with Gaussian distribution                         | . 60 |

| 4.4     | Methods from literature for generating colored noise patterns             | . 62 |

| 4.5     | New method for generating colored noise with Gaussian distribution        | . 67 |

| 4.6     | Results - generating colored noise patterns with Gaussian distribution    | .72  |

| 4.7     | Chapter's conclusion                                                      | .72  |

| Chapter | 5: RJ/DJ Jitter Decomposition Technique                                   | .73  |

| 5.1     | Introduction                                                              | .74  |

| 5.2     | Various existing RJ/DJ decomposition techniques                           | .75  |

| 5.3     | Extended Jitter Decomposition Technique                                   | .77  |

| 5.4     | Results of the generated noise patterns                                   | . 82 |

| 5.5     | Results of the Laboratory Measurements                                    | . 84 |

| 5.6     | Conclusion                                                                | . 86 |

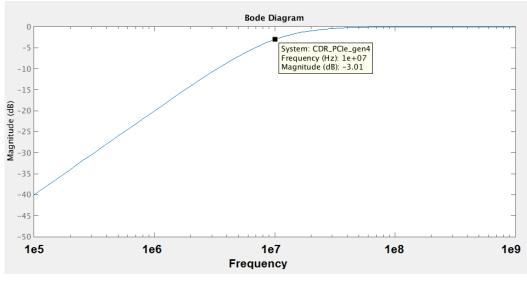

| Chapter   | 6: PCI-Express PLL Specifications               | 87 |

|-----------|-------------------------------------------------|----|

| 6.1       | Introduction                                    | 88 |

| 6.2       | PCIe Standard Specifications                    | 89 |

| 6.3       | PLL Loop Filter Calculations                    | 90 |

| 6.4       | CDR equivalent Transfer Function                | 92 |

| 6.5       | RMS Jitter Calculation                          | 93 |

| 6.6       | Resuming Results                                | 99 |

| Chapter   | 7: Conclusions and Perspectives                 | 01 |

| Chapter   | 8: Annexes                                      | 05 |

| 8.1       | Sinusoidal Signal, Phase & Amplitude Noise      | 07 |

| 8.2       | Square Signal, Phase & Amplitude Noise 1        | 10 |

| 8.3       | Measuring Transition Position at a given Offset | 21 |

| 8.4       | Integration Band for Sin and Square Signal 1    | 22 |

| 8.5       | Convolution of different Diracs:                | 42 |

| List of a | cronyms1                                        | 47 |

| Bibliogr  | aphy1                                           | 49 |

| Publicat  | ions related to this work                       | 55 |

| Confe     | rences                                          | 55 |

| Journ     | als1                                            | 55 |

| Résumé    | de la thèse1                                    | 56 |

# Chapter 1: High Speed Serial Links

| 1.1 | Introduction                            | . 10 |

|-----|-----------------------------------------|------|

| 1.2 | Applications of High Speed Serial Links | . 11 |

| 1.3 | Challenges of High Speed Serial Links   | . 11 |

| 1.4 | Jitter Role in High Speed Serial Links  | . 13 |

| 1.5 | High Speed Serial Links System Study    | . 15 |

| 1.6 | Motivation of this thesis               | . 16 |

| 1.7 | Thesis Organization                     | . 17 |

# Table of Figures

| Figure 1-1: Why High Speed Serial Links?                                        | 10 |

|---------------------------------------------------------------------------------|----|

| Figure 1-2: Worldwide Data Transferring Traffic - Cisco Visual Networking Index | 12 |

| Figure 1-3: HSSLs Speed Evolution over years                                    | 12 |

| Figure 1-4: Power consumption evolution of STM HSSL circuits                    |    |

| Figure 1-5: Jitter Definition                                                   | 13 |

| Figure 1-6: Transmission Error due to Jitter                                    | 14 |

| Figure 1-7: High Speed Serial Links System                                      |    |

|                                                                                 |    |

#### **1.1 Introduction**

Integrated Circuits have become essential part of our lives in the last decades. They are found in our daily life applications. Their range of applications is very large (such as smartphones, tablets, computers, cars, TVs, screens, cameras, connected objects, electronic gadgets, etc.) and is growing daily. This increasing number of applications and the all-time increasing quality of service requested by users, results in more components complexity and much more data transferred between them.

In order to make the connection between different devices easier by replacing a multitude of connectors, and simplify software configuration of all devices, the Universal Serial Bus (USB) was developed in the early 1990's. The USB [USB] was designed to standardize the connection of computer peripherals to computers. Since then, it has been used in a lot of other devices (such as smartphones, tablets, video game consoles, etc.).

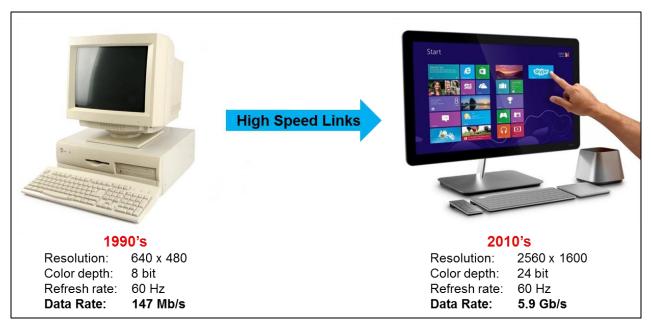

The reason for creating high speed serial links is to be able to transfer much more data within the same timeframe, and get better quality. For example, as shown in Fig 1-1, the transfer rate necessary in 1990's of 147 Mbps has been increased by 40 times within 20 years, reaching 5.9 Gbps in 2010's, in order to obtain todays FULL HD quality on our PC screens. [Yonsei]

Figure 1-1: Why High Speed Serial Links?

Therefore, the serial communication techniques transferring data within devices (or interconnecting several devices together) have been revolutionized in the last decades to respond the continuously increasing market demand [Hong] - [Kuo].

High Speed Serial Links (HSSLs) are today the "dominant" [Stauffer] communication links of Input/Output for many chips, and reach currently speeds up to tens of Gbps [Hanumolu] – [Ong].

#### **1.2 Applications of High Speed Serial Links**

HSSLs are used in most mobile devices (such as smartphones or tablets) to interconnect different components inside them. For example they connect the processor to the camera, to the storage device, to the modem, to another chip, etc... This kind of communications uses channels' length of up to 10 cm.

HSSLs are also used inside laptops, computers, TVs, screens, etc. They connect board-to-board chips, such as processor-to-memory, or processor-to-processor communications. This kind of communications uses channels up to 50 cm long.

Another utility of HSSLs is to connect different devices together, for example processor-to-peripheral or processor-to-storage devices. Some of the most known HSSLs for these kinds of connections are PCIe, USB, SATA, etc. This kind of communications uses channels up to 3 m long.

In addition to these applications, HSSLs are also used in network communications (such as LAN: Ethernet), which might use channels up to 100 meters long.

As each of the above applications has different requirements, a variety of HSSLs with different protocols are designed to fulfill their needs.

#### **1.3 Challenges of High Speed Serial Links**

Two of the main challenges of HSSLs are increasing the data rates and reducing the power consumption.

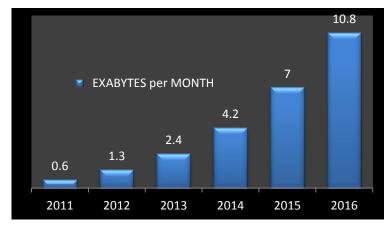

As shown in Fig 1-2, the data centers have a real challenge looking for about 80% of transfer rate growth each year.

Figure 1-2: Worldwide Data Transferring Traffic - Cisco Visual Networking Index

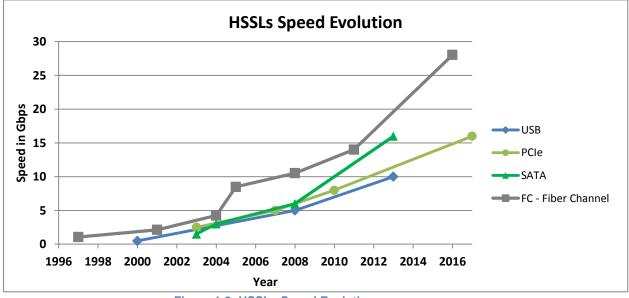

To answer to the permanent increasing request of bandwidth, Fig 1-3 shows the different standards that double their bandwidths every 4 years. Furthermore, we remark an average period of 4 years between technologies used in industrial market (FC - Fiber Channel), and the standards developed for consumer market (PCI-Express, USB, DP).

Consequently, the expertise capitalized during the design of High Speed serial links might be reused for the design of HSSLs dedicated for consumer market.

As shown in Fig 1-3, the data rates have increased from 480 Mbps to 16 Gbps within the last 15 years.

Figure 1-3: HSSLs Speed Evolution over years

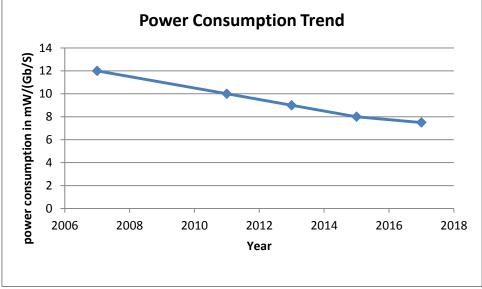

Decreasing power consumption has been staying a priority for decades on all integrated circuits. Fig 1-4 shows STMicroelectronics HSSLs circuits IP performances in terms of power consumption in the last 10 years:

Figure 1-4: Power consumption evolution of STM HSSL circuits.

It is a big challenge to find out the compromise of how much we can decrease the power consumption of each block of the IP without degrading global performances of the system.

### 1.4 Jitter Role in High Speed Serial Links

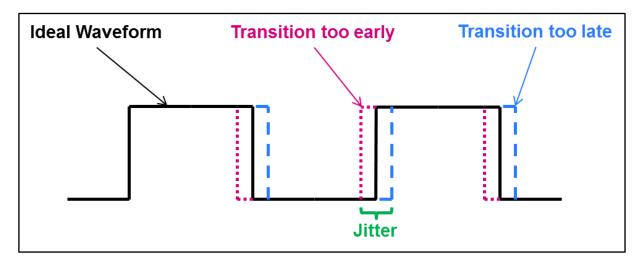

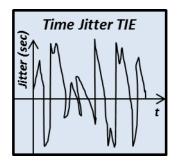

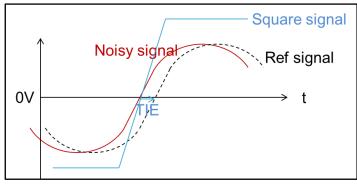

Jitter is defined as the phase variation of a timing signal from its ideal positions in time, which corresponds to an early or late transition, as shown in Fig 1-5 [Dou\_1] - [HFE] - [Kuo] - [LeCroy] - [Sui] - [Wisetphanichkij].

Figure 1-5: Jitter Definition

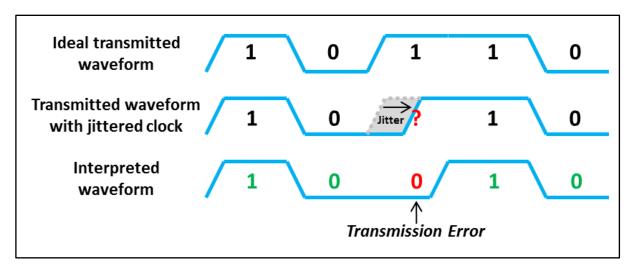

The amount of jitter on a transmission is related to the BER (Bit Error Rate). If jitter is too high, it can cause transmission errors [Zhang]. The receiving circuit will interpret the bit differently from the transmitted one, as shown in Fig 1-6 [HFE]. Hence, the global transmission performance is degraded.

#### Figure 1-6: Transmission Error due to Jitter

With the growing speeds of HSSLs, it becomes very difficult to maintain high signal quality. The absolute tolerated jitter quantity gets smaller [Tripathi], and the noise level becomes much more sensitive. High Speed Serial Links standards require an expected error rate (BER) of 10<sup>-12</sup> [LeCroy]. While this represents only 1 bit error every 167 minutes at 100 Mbps, it translates to 1 bit error every ~3 minutes at 5 Gbps and to 1 bit error every 1 minute at 16 Gbps. This is why the capacity to determine and limit jitter is one of the most important elements in maintaining high signal quality in HSSL transmissions [Sharma].

#### 1.5 High Speed Serial Links System Study

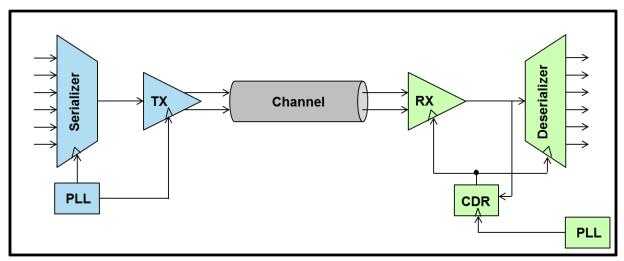

In Fig 1-7 we find the principal components of a High Speed Serial Links System. [Hanumolu] - [Palermo] - [Yonsei]

Figure 1-7: High Speed Serial Links System

On the left side of the picture, the "**Serializer**" converts the incoming parallel data into series ones. It serializes data from 10 or 20 bits into 1 bit.

The "PLL" generates the different clocks needed for the Transmission and the Reception. *It is one of the main contributors for clock Random and Periodic jitter*. [Hansel] - [Telba]

The "**TX**" enables the transmission. It takes the digital stream and transforms it to electrical signal (First stage of Signal Amplitude Pre-Equalization is done here). This block *contributes to clock jitter*. It is *the first contributor of ISI jitter* (circuit non linearity).

On the right side of the figure, the receiver block "**RX**" decodes the received signal, and transforms electrical signal into digital stream. This block *contributes to clock jitter* (clock recovery algorithm + analog sampling clock source). Second stage of Signal Post-Equalization is done here: CTLE + DFE (circuit non linearity).

The "**CDR**" (Clock and Data Recovery) is responsible for locking the receiver clock to the transmitter clock by correcting the phase and frequency offsets, and recovering the transmitted data.

The "**Deserializer**" converts the data from series to parallel. It de-serializes data from 1 bit to 10 or 20 bits.

Between the "TX" and the "RX" the "**channel**" has different properties, depending on the transmission medium (Backpannel, Ports, Cables ...).

#### **1.6 Motivation of this thesis**

Two of the major electrical parameters used to characterize SerDes Integrated Circuit performances are the Transmitter & Receiver clocks jitter at a given BER and the Insertion Loss capabilities.

Modeling the phase noise of the different SerDes components, extracting the time jitter and decomposing it, would help designers to achieve desired FoM for future SerDes versions.

As mentioned in 1.5, the PLL is the main contributor of clock random and periodic jitter inside the HSSLs system. This is the reason why we decided to create a PLL Model with phase noise injection in order to estimate the time domain jitter. To better estimate the time jitter by including the PLL loop nonlinearities, a time domain model is also created.

The Standard Organizations (such as USB or PCIe) specify random and deterministic jitter budgets. In order to decompose the PLL output estimated TIE jitter into random and deterministic jitter, a new technique for jitter analysis and decomposition is proposed.

Modeling simulation results correlate well with measurements and this technique will help designers to properly identify and quantify the sources of deterministic jitter and their impact on the SerDes system.

Furthermore, these models permit us to determine System Specifications for a new IP development, by determining maximum phase noise profile to be respected by designers for each sub-block, in order to satisfy standards in term of Random and Deterministic Jitter.

#### **1.7 Thesis Organization**

This thesis is organized as follows:

Chapter 2, "*Jitter and Phase Noise Theoretical Study*" presents the general theoretical study of jitter. The complete study for calculating Jitter in the Time and Frequency domain is detailed here.

Chapter 3, "*PLL Modeling*" is divided into two main sections; the first one presents complete PLL Modeling in the Frequency Domain. The second section presents the chart flow, and the Time Domain PLL Modeling including nonlinearities. Result comparison is done between both models in order to validate the Time Domain Model.

Chapter 4, "Generation of colored noise patterns with Gaussian Jitter distribution" describes a novel method for generating colored noise patterns with Gaussian distributions. PLL has Colored Noise profile properties. In order to analyze SerDes system characteristics, it is important to generate synthetic colored noise patterns with a Gaussian distribution. The patterns will be used to predict impact of jitter on the system performance with time domain simulation during the design verification phase.

Chapter 5, "*RJ/DJ Jitter Decomposition Technique*", presents a new technique for decomposing Random from Deterministic Jitter. Results of Simulations and Measurements are given to verify that this technique works properly.

Chapter 6, "PLL *Specifications*", gives detailed example of specifications in term of Phase Noise and Jitter for PLL. The specifications are given as example based on PCI-Express Standard requirements, using our developed models.

Chapter 7, "*Conclusions and Perspectives*", summarizes the work presented in this thesis and gives future perspectives on algorithm improvements.

# Chapter 2: Jitter and Phase Noise Theoretical Study

| 2.1 | Intr  | oduction to Jitter                          | . 20 |

|-----|-------|---------------------------------------------|------|

| 2.2 | Jitte | er Calculation                              | . 23 |

| 2.2 | .1    | Jitter Calculation in Time Domain           | . 23 |

| 2.2 | .2    | Jitter Calculation in Frequency Domain      | . 24 |

| 2.3 | Pha   | se and Amplitude Noise Study                | . 28 |

| 2.3 | .1    | Noise Spur Modulation                       | . 28 |

| 2.3 | .2    | Phase Noise & Amplitude Noise Modulation    | . 29 |

| 2.4 | Pha   | se & Amplitude Noise Impact onto TIE jitter | . 31 |

| 2.4 | .1    | Translate phase noise into TIE Jitter       | . 31 |

| 2.4 | .2    | Translate amplitude noise into TIE Jitter   | . 31 |

| 2.5 | RJ/   | DJ Jitter Correlation Algorithm             | . 33 |

| 2.5 | .1    | Introduction                                | . 33 |

| 2.5 | .2    | Proposed Method Principle                   | . 33 |

| 2.6 | Cha   | apter Conclusion                            | . 35 |

# **Table of Figures**

| Figure 2-1: Time Jitter                                                    |    |

|----------------------------------------------------------------------------|----|

| Figure 2-2: Cumulative Jitter                                              |    |

| Figure 2-3: Periodic Jitter                                                | 21 |

| Figure 2-4: Cycle to Cycle Jitter                                          |    |

| Figure 2-5: BER Graph                                                      |    |

| Figure 2-6: Time Domain Phase Modulation                                   |    |

| Figure 2-7: Frequency Representation of the modulated signal               |    |

| Figure 2-8: Spectral Analysis of multi-spur phase noise modulated signal   |    |

| Figure 2-9: Spectral Analysis of Area Profile Phase Noise Modulated Signal |    |

| Figure 2-10: Carrier Frequency with given Noise                            |    |

| Figure 2-11: Noise decomposition into Amplitude and Phase Noise            |    |

| Figure 2-12: Amplitude & Phase Noise Modulation for Sinusoidal Signal      |    |

| Figure 2-13: Total Jitter Estimation                                       |    |

| C                                                                          |    |

## **Table of Tables**

| Table 2-1: Multiplying coefficients depending of | n BER |

|--------------------------------------------------|-------|

|--------------------------------------------------|-------|

### 2.1 Introduction to Jitter

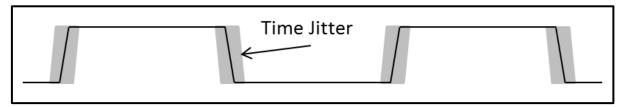

Jitter is defined as the phase variation of a timing signal from its ideal positions in time, as shown in Fig 2-1 [Dou\_1] - [HFE] - [Kuo] - [LeCroy] - [Sui] - [Zamek] -[Wisetphanichkij].

Figure 2-1: Time Jitter

It can be viewed as different forms:

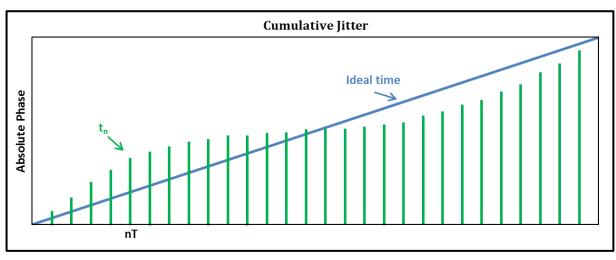

**The cumulative jitter** corresponds to the difference between the n<sup>th</sup> measured edge instant ' $t_n$ ' and the ideal 'nT' where T corresponds to the ideal signal period [HFE] - [Kuo]. This is the time interval error (TIE), shown in Fig 2-2 and expressed as (2.1):

$\Phi n = t_n - nT$

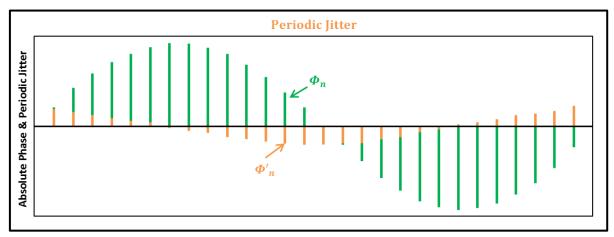

**The periodic jitter** corresponds to the difference between the measured period and the ideal period. It is shown in Fig 2-3 and expressed as (2.2) [Kuo].

$$\Phi_n' = \Phi_n - \Phi_{n-1}$$

(2.2)

(2.1)

Figure 2-3: Periodic Jitter

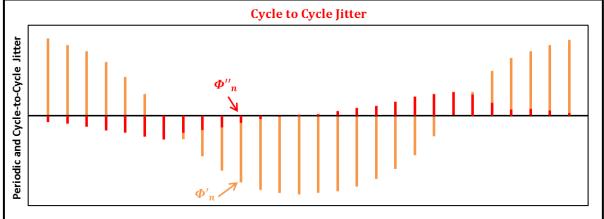

**The cycle to cycle jitter** corresponds to the difference between consecutive bit periods. It is shown in Fig 2-4 and expressed as (2.3) [Kuo].

$\Phi_{n}{}^{\prime\prime} = \Phi_{n}{}^{\prime} - \Phi_{n-1}{}^{\prime}$ (2.3)

In this thesis we will study the cumulative TIE jitter. It consists of Random Jitter (RJ), which is unpredictable, unbounded timing noise, and Deterministic Jitter (DJ), which is uncorrelated to data and bounded [Dou\_1] - [Hansel] - [Kim] - [Kuo] - [Li] - [Sharma] - [Sui] - [Wisetphanichkij]. The PCI-express standard [PCIe] gives the decomposition of jitter as follow:

- Data Uncorrelated Jitter

- o Unbounded Jitter

- Random Jitter (*T<sub>TX-RJ</sub>*)

- Total Jitter  $(T_{TX-UTJ})$

- o Bounded

- Deterministic Jitter (*T<sub>TX-UDJDD</sub>*)

Equation (2.4) describes the total jitter as a function of BER and is related to the RJ and DJ components of jitter. [LeCroy] - [Tektronix]

$$TJ = N(BER) * RJ + DJ \tag{2.4}$$

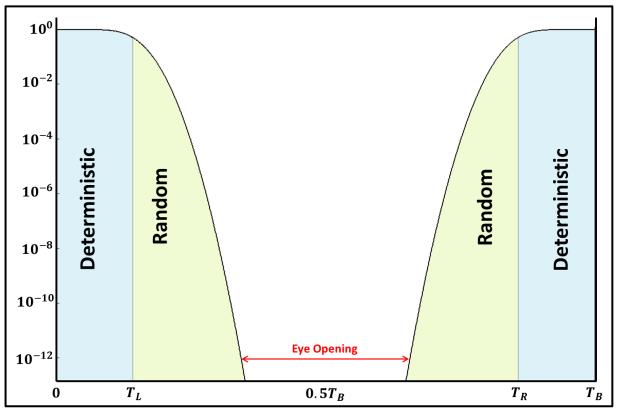

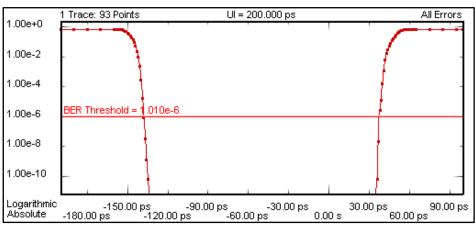

The Bit Error Rate is the measurement of data reliability; it corresponds to the probability of doing an error while determining a bit level. Another view of jitter is provided by the bathtub plot. It is a graph of BER in log scale versus jitter as shown in Fig 2-5 [HFE] - [Zhang].

Figure 2-5: BER Graph

In the above bathtub plot, for a given BER, we have an eye-opening which corresponds to the distance between the two curves of the bathtub curve.

The purpose of this chapter is to present the general theoretical study of jitter. The complete study for calculating Jitter in the Time and Frequency domain is given here. This chapter is composed as follows:

In Section 2.2 we provide Jitter fundamentals and equations to calculate it in Time & Frequency domain.

Section 2.3 presents a complete study about Phase & Amplitude noise. In this section we will show that a noise is composed of a Phase and an Amplitude Noise. Study will be done for noisy sinusoidal signals.

Section 2.4 proves that the Amplitude noise has no impact on jitter (under a given Noise Profile Power limit).

Chapter's conclusions are given in Section 2.5.

#### 2.2 Jitter Calculation

In this section, we provide principal equations, for calculating Jitter, in the Time Domain, and in the Frequency Domain.

#### 2.2.1 Jitter Calculation in Time Domain

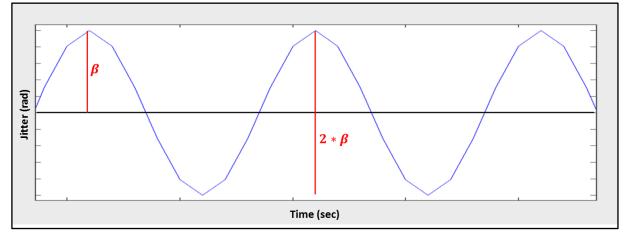

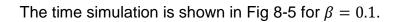

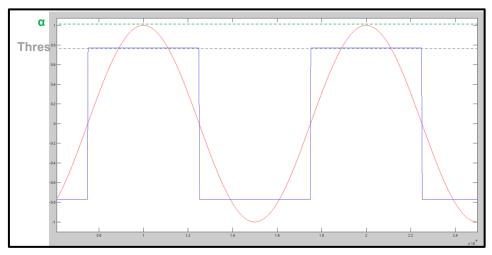

In the Time Domain, the phase noise modulated signal is expressed as in (2.6) and is shown in Fig 2-6:

| Original Signal:        | sig                  | $= \alpha \sin(\omega_c t)$                          | (2.5) |

|-------------------------|----------------------|------------------------------------------------------|-------|

| Phase Modulated Signal: | sig <sub>noisy</sub> | $= \alpha \sin(\omega_c t + \beta \sin(\omega_m t))$ | (2.6) |

where:

$\beta$  is the Amplitude of the jitter,  $2 * \beta$  is the Jitter peak to peak, and  $\omega_m = 2 * \pi * F_m$  the jitter modulation (with  $F_m$  the modulating Frequency).

$\alpha$  is the Amplitude of the signal, and  $\omega_c = 2 * \pi * F_c$  the carrier modulation (with  $F_m$  the carrier Frequency).

Figure 2-6: Time Domain Phase Modulation

The Jitter peak-to-peak can be expressed in radians (2.7), and in seconds (2.8).

$$Jitter_{pp_{radians}} = 2 * \beta \tag{2.7}$$

$$Jitter_{pp_{seconds}} = \frac{Jitter_{pp_{radians}}}{2*\pi*F_c} = \frac{2*\beta}{2*\pi*F_c} \quad \text{with} \quad F_c = Carrier_{Frequency}$$

(2.8)

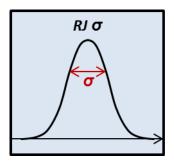

Let's consider we have a TIE Jitter with **N** random  $x_i$  values. The Jitter RMS is expressed as in (2.9). It corresponds to the Standard Deviation of the TIE Jitter.

*Jitter*<sub>RMS</sub> =

$$\sigma(TIE) = \sqrt{\frac{1}{N} \sum_{i=1}^{N} (x_i - \mu)^2}$$

where  $\mu = \frac{1}{N} \sum_{i=1}^{N} x_i$  (2.9)

#### 2.2.2 Jitter Calculation in Frequency Domain

#### 2.2.2.1 1 Spur Noise

From time domain jitter calculation above, we show how to perform this computation in frequency domain. As previously computed in the time domain (2.8), the equation for the Jitter peak-to-peak is given in (2.10):

$$Jitter_{spur}{}_{pp} = \frac{2*\beta}{2*\pi*F_c}$$

(2.10)

As  $\beta$  is not directly available, we need to express this equation with information available from a spectrum analyzer, or a phase noise analyzer.

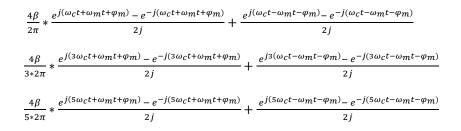

From Annexe 8.1, we can decompose (2.6) equation into the following expression (2.11), with the condition that jitter rms is well below  $2\pi$ :

$$f(t) \simeq \alpha \sin(\omega_c t) + \frac{\alpha \beta}{2} (-\sin(\omega_c t - \omega_m t - \varphi_m) + \sin(\omega_c t + \omega_m t + \varphi_m))$$

(2.11)

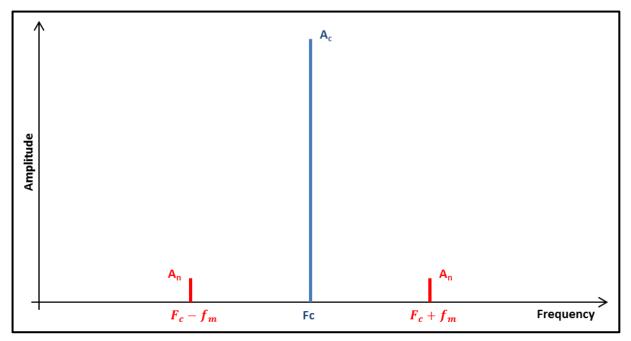

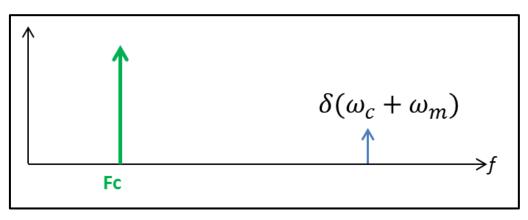

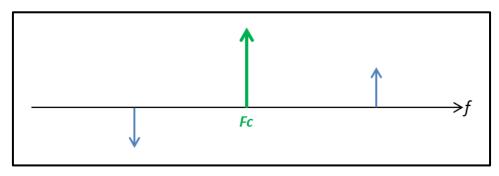

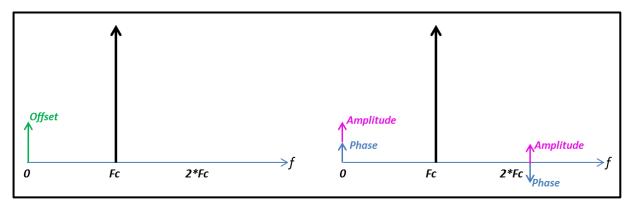

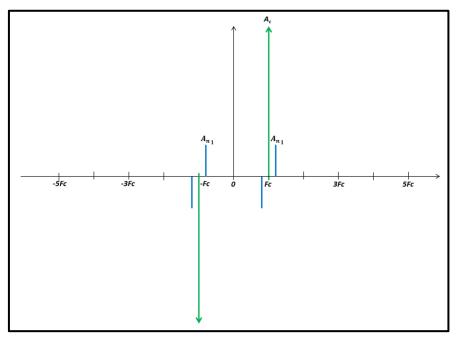

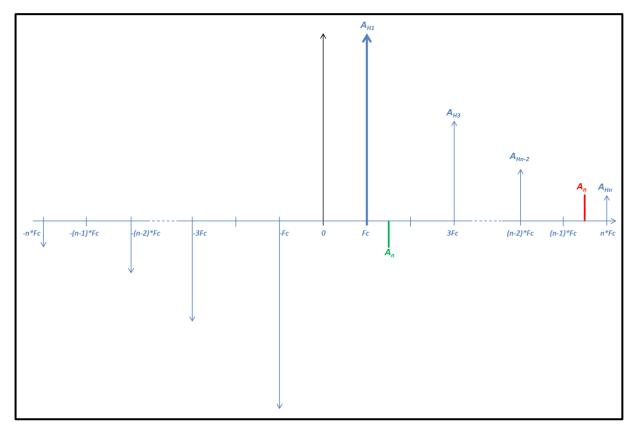

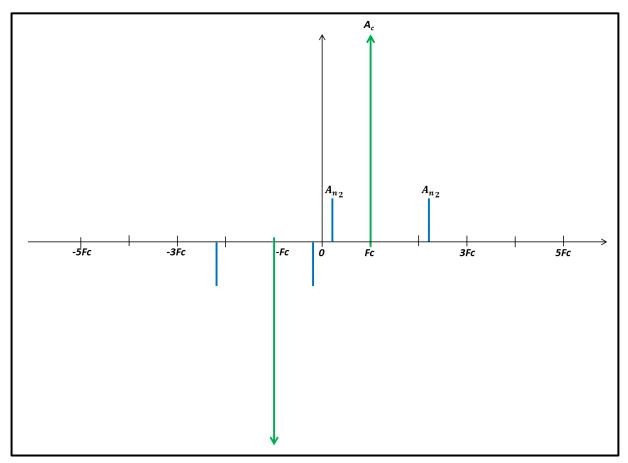

The frequency (in absolute value) representation of this modulated signal (2.11) is given in Fig 2-7.

With:  $A_n = \frac{\alpha * \beta}{2}$  and  $A_c = \alpha$ . From which we extract  $\beta$ :  $\beta = 2 * \frac{A_n}{A_c}$

So the Jitter Peak-To-Peak equation (2.10) can be expressed as (2.12):

$$Jitter_{spur}_{pp} = \frac{4*\frac{A_n}{A_c}}{2*\pi*F_c}$$

(2.12)

Figure 2-7: Frequency Representation of the modulated signal

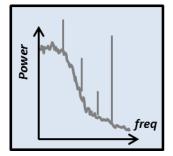

The spectrum analyzer provides the Power information, in *dB*. In order to use information provided by spectrum analyzer, or phase noise analyzer, we need to express  $A_n$  and  $A_c$  into *dBc*. The Phase Noise Profile is then expressed as in (2.13)

$$L_{spur_{dBc}} = P_{n_{dB}} - P_{c_{dB}} = 10 * \log\left(\frac{P_n}{P_c}\right) = 10 * \log\left(\frac{A_n^2}{A_c^2}\right) = 20 * \log(\frac{A_n}{A_c})$$

(2.13)

From the equation (2.13), we can extract:

$$\frac{A_n}{A_c} = 10^{\frac{L_{spur_{dBc}}}{20}} = \sqrt{10^{\frac{L_{spur_{dBc}}}{10}}} \quad (2.14) \quad \text{and} \quad Jitter_{spur_{pp}} = \frac{4*\sqrt{10^{\frac{L_{spur_{dBc}}}{10}}}}{2*\pi*F_c} \quad (2.15)$$

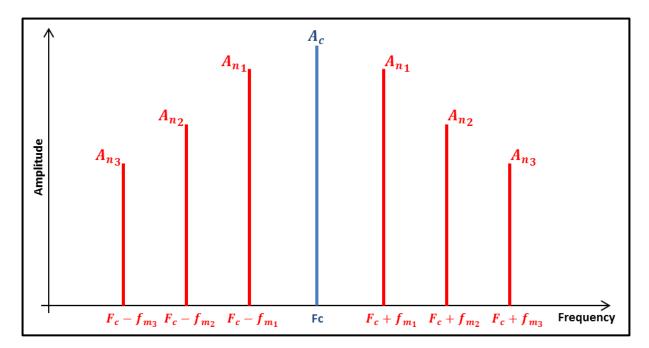

#### 2.2.2.2 Multi Spurs Noise Profile

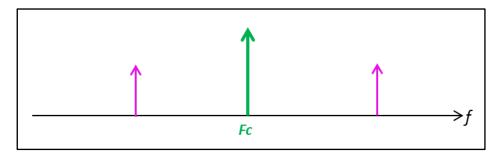

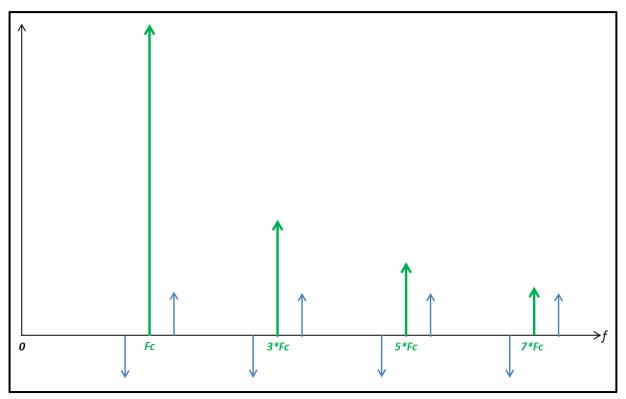

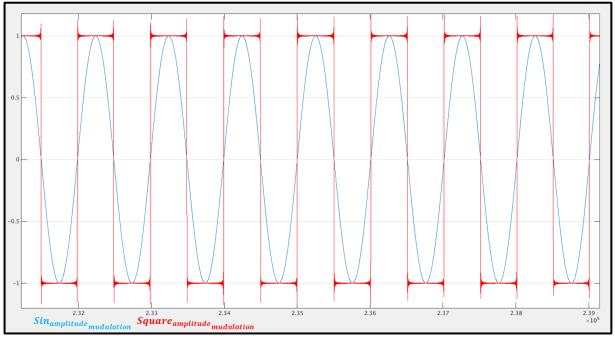

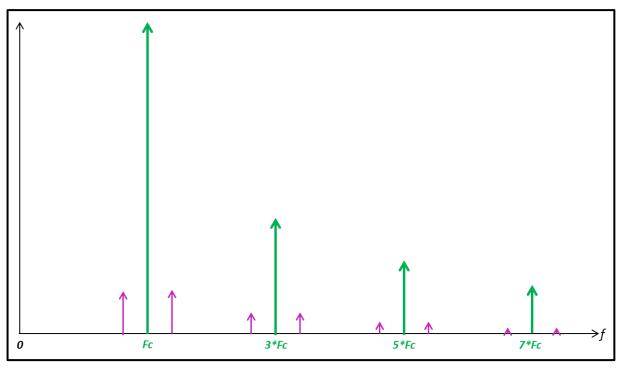

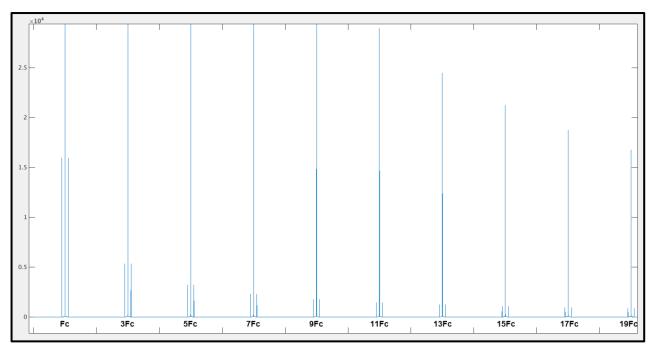

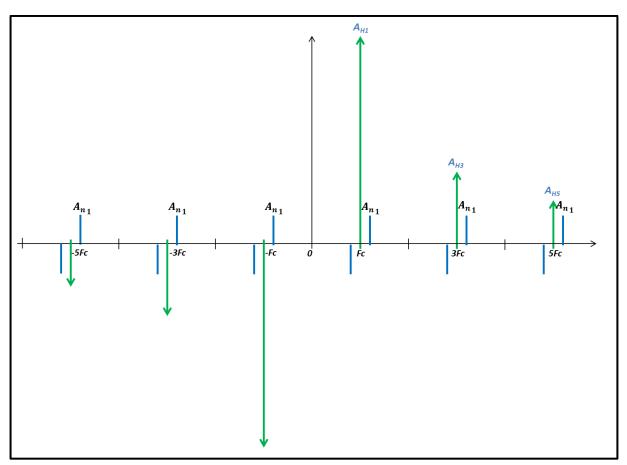

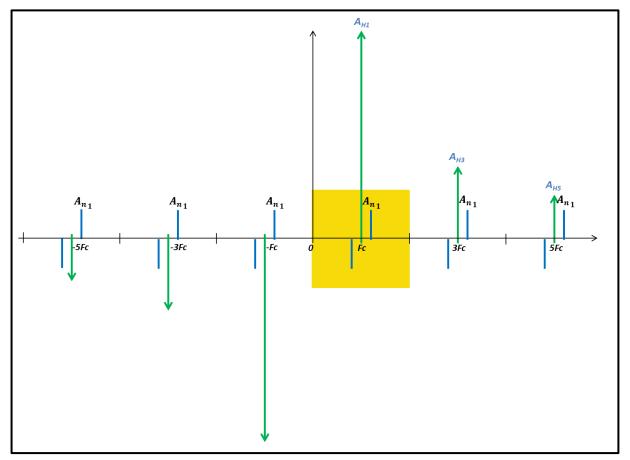

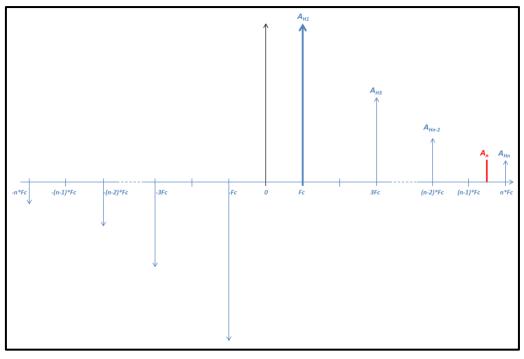

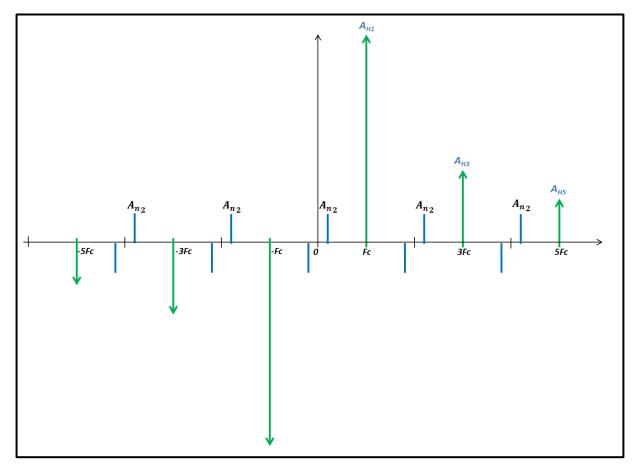

Before calculating RMS Jitter of an area, we consider a carrier frequency Fc with multiple phase modulation sinuses. We have presented in Fig 2-8 the FFT with **|absolute|** values:

Any periodic signal, with the Fourier Series, can be written as (2.16):

$$f(t) = \alpha \sin(\omega_c t + \beta_1 \sin(\omega_{m_1} t) + \beta_2 \sin(\omega_{m_2} t) + \dots + \beta_k \sin(\omega_{m_k} t))$$

(2.16)

With Jitter:

$$F_{Jitter}(t) = \beta_1 \sin(\omega_{m_1} t) + \beta_2 \sin(\omega_{m_2} t) + \dots + \beta_k \sin(\omega_{m_k} t)$$

(2.17)

The average value of  $F_{Jitter} = 0$ .

Figure 2-8: Spectral Analysis of multi-spur phase noise modulated signal

From the Parseval Theorem, with conservation of energy, we can express the RMS value of  $F_{Jitter}$  (2.18):

$$(F_{jitter}_{rms})^2 = \frac{1}{T} \int_0^T F_{jitter}(t)^2 dt = \sum_0^\infty \frac{1}{2} \beta_1^2 + \frac{1}{2} \beta_2^2 + \dots + \frac{1}{2} \beta_k^2$$

(2.18)

So the Jitter RMS will be calculated as following:

$$RMS_{Jitter_{multispurs}} = \frac{\sqrt{(\frac{1}{2}(\beta_1)^2 + \frac{1}{2}(\beta_2)^2 + \dots + \frac{1}{2}(\beta_k)^2)}}{2\pi F_c} = \frac{\sqrt{(\frac{1}{2}(2\frac{A_{n_1}}{A_c})^2 + \frac{1}{2}(2\frac{A_{n_2}}{A_c})^2 + \dots + \frac{1}{2}(2\frac{A_{n_k}}{A_c})^2)}}{2\pi F_c}$$

(2.19)

$$RMS_{Jitter_{multispurs}} = \frac{\sqrt{4*\frac{1}{2}*\sum_{k=1}^{m} (\frac{A_{n_k}}{A_c})^2}}{2\pi F_c} = \frac{\sqrt{4*\frac{1}{2}*\sum_{k=1}^{m} \sqrt{10^{\frac{L_{spur_{k_{dBc}}}}{10}}}}{2\pi F_c}} = \frac{\sqrt{2*\sum_{k=1}^{m} 10^{\frac{L_{spur_{k_{dBc}}}}{10}}}}{2\pi F_c}$$

(2.20)

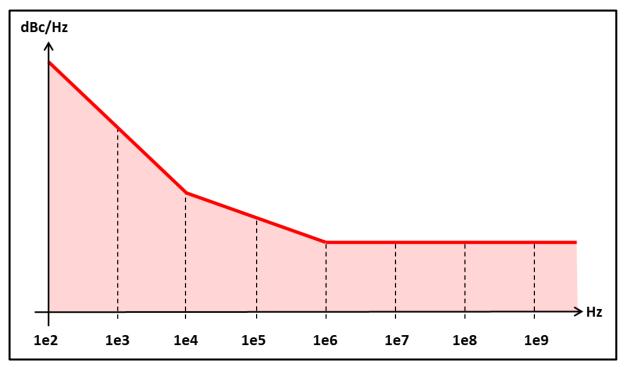

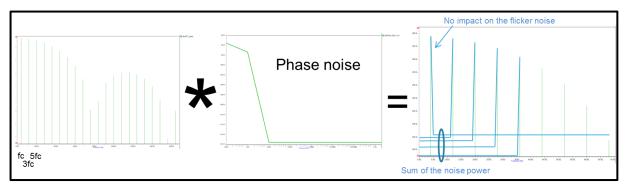

#### 2.2.2.3 Area Noise Profile

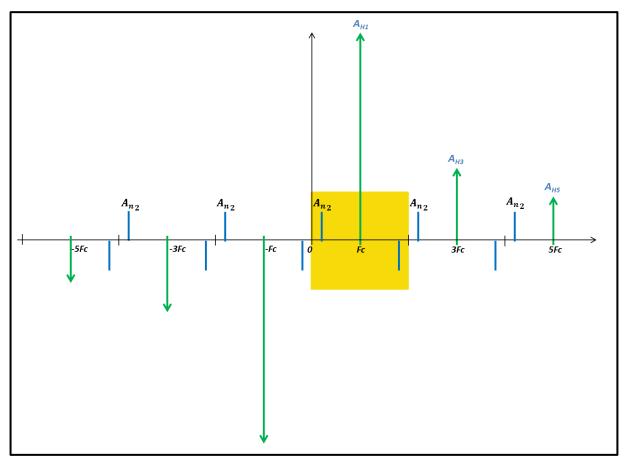

The RMS Jitter, when a given L(f) noise profile is continuous (Fig 2-9), and not discrete as given before (Fig 2-8), is calculated with the following formula (2.21) [Analog] - [Feng] - [Maxim] - [Zamek], which is the integration of the whole band of frequencies:

$$RMS_{Jitter_{area}} = \frac{1}{2*\pi*F_c} \sqrt{2*\int_0^\infty 10^{\frac{L(f)}{10}} df}$$

(2.21)

Figure 2-9: Spectral Analysis of Area Profile Phase Noise Modulated Signal

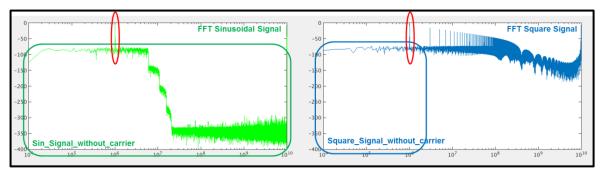

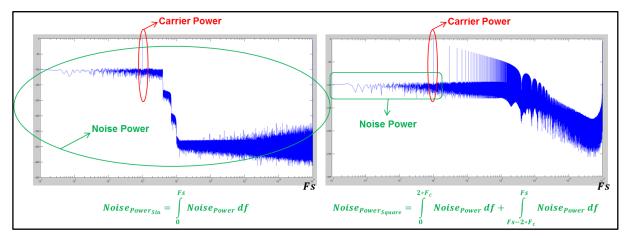

In order to calculate the  $RMS_{Jitter_{area}}$ , we must integrate the following frequency bandwidths:

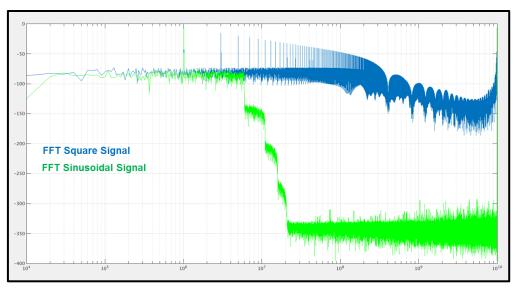

- Up to infinite for Sinusoidal Signal

- Up to  $2 * F_c$  for Square Signal

The demonstrations of Integrating Bandwidth are given in Annex 8.4.

#### 2.3 Phase and Amplitude Noise Study

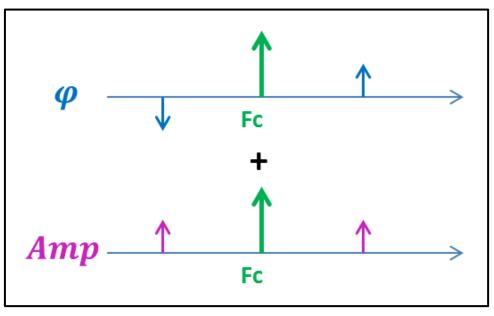

The objective of this section is to show that a given Noise profile can be expressed as a sum of a phase and amplitude noise.

#### 2.3.1 Noise Spur Modulation

Let's consider we have following Carrier Frequency with given Noise. The noise can be described as a phase modulation, with one spur Dirac, as shown in Fig 2-10:

Figure 2-10: Carrier Frequency with given Noise

The phase modulation of Fig 2-10 can be written as (2.22):

$\delta(\omega_c + \omega_m) = \frac{1}{2}\delta(\omega_c - \omega_m) + \frac{1}{2}\delta(\omega_c + \omega_m) - \frac{1}{2}\delta(\omega_c - \omega_m) + \frac{1}{2}\delta(\omega_c + \omega_m) \quad (2.22)$

Our hypothesis is that this is expressed with an Amplitude Noise (2.23) and Phase noise (2.24). We will prove these equations in (2.29):

Amplitude<sub>Noise</sub> =

$$\frac{1}{2}\delta(\omega_c - \omega_m) + \frac{1}{2}\delta(\omega_c + \omega_m)$$

(2.23)

**Phase**<sub>Noise</sub> =

$$-\frac{1}{2}\delta(\omega_c - \omega_m) + \frac{1}{2}\delta(\omega_c + \omega_m)$$

(2.24)

For equation development details, check Annex 8.1.

Equation (2.22) is Equivalent to Fig 2-11:

Figure 2-11: Noise decomposition into Amplitude and Phase Noise

So, a given Noise (Fig 2-10) can be expressed as sum of a Phase and an Amplitude Noise (Fig 2-11).

#### 2.3.2 Phase Noise & Amplitude Noise Modulation

Let's consider that we have a phase and amplitude noise Modulation (2.25):

$$V(t) = V_0 sin[(\omega_c t) + \beta sin(\omega_m t + \varphi_m)] [1 + \alpha cos(\omega_m t + \varphi_m)]$$

(2.25)

Equation (2.25) can be expressed as (2.26):

$$V(t) = \left[ V_0 si n(\omega_c t) + \frac{V_0 \beta}{2} \left( -si n(\omega_c t - \omega_m t - \varphi_m) + sin(\omega_c t + \omega_m t + \varphi_m) \right) \right] * \quad (2.26)$$

$$[1 + \alpha cos(\omega_m t + \varphi_m)]$$

If we develop equation (2.26), we obtain (2.27):

$$V(t) = \left[ V_0 si n(\omega_c t) + \frac{V_0 \beta}{2} (-si n(\omega_c t - \omega_m t - \varphi_m) + sin(\omega_c t + \omega_m t + \varphi_m)) \right] + (2.27)$$

$$\left[ V_0 si n(\omega_c t) + \frac{V_0 \beta}{2} (-si n(\omega_c t - \omega_m t - \varphi_m) + sin(\omega_c t + \omega_m t + \varphi_m)) \right] * \alpha cos(\omega_m t + \varphi_m)$$

As  $\alpha^*\beta << 1$ , (2.27) becomes (2.28):

$$V(t) = \left[ V_0 \sin(\omega_c t) + \frac{V_0 \beta}{2} \left( -\sin(\omega_c t - \omega_m t - \varphi_m) + \sin(\omega_c t + \omega_m t + \varphi_m) \right) \right] + \quad (2.28)$$

$$V_0 \sin(\omega_c t) \alpha \cos(\omega_m t + \varphi_m)$$

Equation (2.28) is also expressed with Phase Noise and Amplitude Noise:

$$V(t) = V_0 \sin(\omega_c t) + \frac{\beta V_0}{2} \left[ -\sin(\omega_c t - \omega_m t - \varphi_m) + \sin(\omega_c t + \omega_m t + \varphi_m) \right]$$

(2.29)

$$+ \frac{V_0 \alpha}{2} \left[ \sin(\omega_c t - \omega_m t - \varphi_m) + \sin(\omega_c t + \omega_m t + \varphi_m) \right]$$

Equation (2.29) is represented in Fig 2-12.

Figure 2-12: Amplitude & Phase Noise Modulation for Sinusoidal Signal

In conclusion, any noise added to the signal, can be represented as a sum of a Phase and an Amplitude noise.

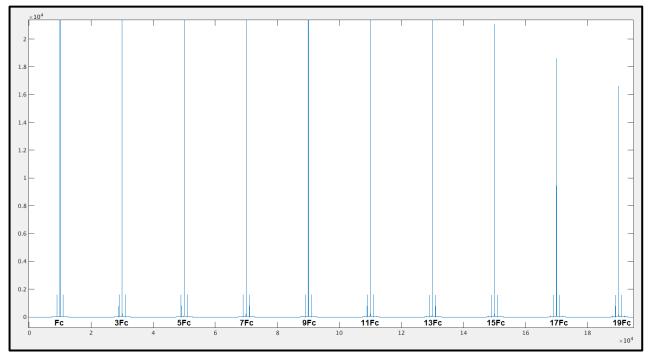

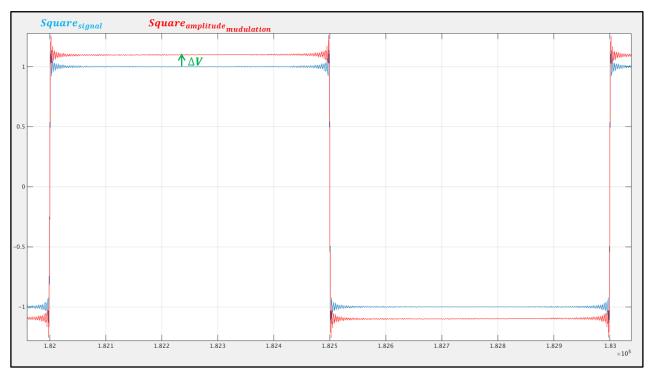

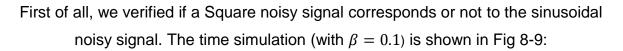

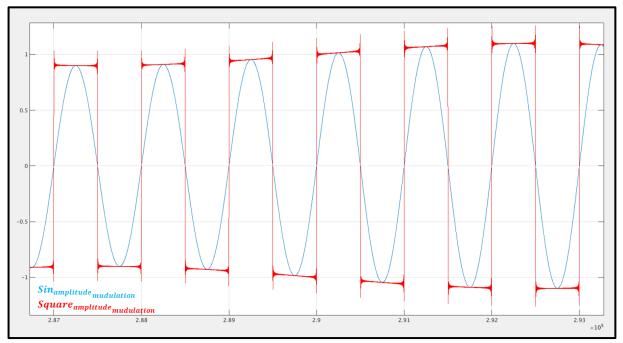

This is also demonstrated for Square Signals. For equations and demonstration of noise added to square signals, check Annex 8.2.

The particular case of measuring transition positions at a given offset is given in **Annex 8.3**.

#### 2.4 Phase & Amplitude Noise Impact onto TIE jitter

In this chapter, we will show the impact of Phase and Amplitude noise on TIE jitter:

#### 2.4.1 Translate phase noise into TIE Jitter

As shown in Section 2.2, the TIE Jitter is calculated as follows:

• In Time Domain:

$$Jitter_{spur}{}_{pp} = \frac{2*\beta}{2*\pi*F_c}$$

(2.30)

#### • In Frequency Domain:

• 1 Spur Noise:

$$Jitter_{spur_{pp}} = \frac{4*\sqrt{10^{\frac{L_{spur_{dBc}}}{10}}}}{2*\pi*F_{c}}$$

(2.31)

• Multi Spur Noise:

$$RMS_{Jitter_{multispurs}} = \frac{\sqrt{2*\sum_{k=1}^{m} 10^{\frac{L_{spur_{kdBc}}}{10}}}}{2\pi F_c}$$

(2.32)

#### • Area Noise:

$$RMS_{Jitter_{area}} = \frac{1}{2*\pi*F_c} \sqrt{2*\int_0^\infty 10^{\frac{L(f)}{10}} df}$$

(2.33)

We integrate:

- Up to infinite for Sinusoidal Signal

- Up to  $2 * F_c$  for Square Signal

#### 2.4.2 Translate amplitude noise into TIE Jitter

#### 2.4.2.1 One spur Amplitude Noise Modulation

The Amplitude Noise Modulation is expressed as follows (2.34):

$$V(t) = V_0 \sin(\omega_c t) \left[1 + \alpha \cos(\omega_m t)\right]$$

(2.34)

We will have a transition due to amplitude jitter, each time  $|\alpha \cos(\omega_m t)| > 1$ . This might come at any time, and would deteriorate our TIE Jitter. In order to prevent this effect,  $\alpha$  should be <<1.

If

$$\alpha \ll 1$$

, then  $-1 \ll \alpha \cos(\omega_m t) \ll 1$  (2.35)

Or,

$$1 + \alpha \cos(\omega_m t) \gg 0$$

(2.36)

So if  $\alpha \ll 1$ , the sign on V(t) will not change and **the amplitude noise will not impact the TIE Jitter**.

#### 2.4.2.2 Spectrally flat profile Amplitude Noise modulation

In this section, we will define the profile limit, below which the amplitude noise has No impact on the Jitter. This is done following several steps:

First of all, depending on the samples number (N<sub>samples</sub>), we find how many sigma σ we have:

For example, if we have  $N_{samples} = 1e6$  samples, then, we find the corresponding number of sigma  $\sigma$  ( $N_{sigma}$ ):

$$N_{sigma} = 2 * \sqrt{2} * erfcinv\left(\frac{1}{N_{samples}} * 2\right) = 2 * \sqrt{2} * erfcinv\left(\frac{1}{10^6} * 2\right) = 9.5068\sigma \quad (2.37)$$

In order to have half of the jitter Peak-to-Peak being below -1 (so we have a transition due to Amplitude Noise), we create a random amplitude noise with twice the  $\sigma$  value:

The value of 2 times the

$$\sigma$$

is:  $\frac{2}{N_{sigma}} = 0.2104.$  (2.38)

$$Amplitude_{noise_{modulation}} = rand(1, N_{samples}) * \frac{2}{N_{sigma}}$$

(2.39)

After multiple simulation results on Matlab, we verify that this is the limit, below which amplitude noise will have no impact on TIE Jitter.

The 2<sup>nd</sup> step is to find the Profile Limit, below which the Amplitude Noise has no Impact.

As in (2.39), in order to have a transition due to Amplitude Noise, we search the limit for twice the value of  $\sigma$ .

We have found it theoretically, and confirmed it through Matlab Simulations.

In conclusion, under a defined profile, the amplitude noise will have no impact on TIE Jitter. This is why we will take only the Phase Noise into account.

#### 2.5 RJ/DJ Jitter Correlation Algorithm

#### **2.5.1 Introduction**

The total Random (2.40) and total Deterministic (2.41) jitters are defined as following in the literature [Agilent] - [Kim] - [Tektronix]:

$$RJ_{Total} = \sqrt{RJ_1^2 + RJ_2^2 + RJ_3^2 + \dots}$$

(2.40)

$$DJ_{Total} = DJ_1 + DJ_2 + DJ_3 + \dots (2.41)$$

The Total Jitter is given as in (2.42):

$$TJ = N(BER). RJ_{Total} + DJ_{Total}$$

(2.42)

with N(BER), a multiplicative coefficient depending on the BER value, as given in Table 2-1:

#### Table 2-1: Multiplying coefficients depending on BER.

| BER    | 10 <sup>-7</sup> | 10 <sup>-8</sup> | 10 <sup>-9</sup> | 10 <sup>-10</sup> | 10 <sup>-11</sup> | 10 <sup>-12</sup> | 10 <sup>-13</sup> | 10 <sup>-14</sup> | 10 <sup>-15</sup> |

|--------|------------------|------------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| N(BER) | 10.399           | 11.224           | 11.996           | 12.723            | 13.412            | 14.069            | 14.698            | 15.301            | 15.883            |

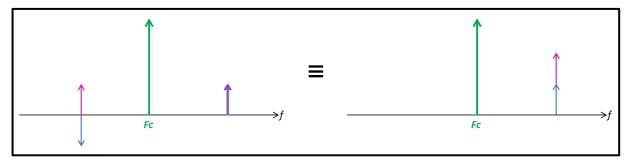

This value is given as a Worst Case value in the standards [PCIe]. For the Total Deterministic Jitter, all DJ variables are independent from each other, so they can be considered as Random variables. Therefore, the total DJ is a convolution between all DJ [Papoulis] - [Tektronix]. The real Total Jitter (TJ) is then smaller than the calculation equation given in (2.42). This is why we are proposing to better estimate the Total Jitter. This would help designers to better constraint design and achieve desired FoM.

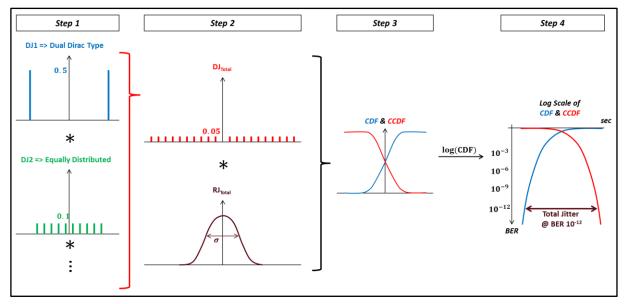

#### 2.5.2 Proposed Method Principle

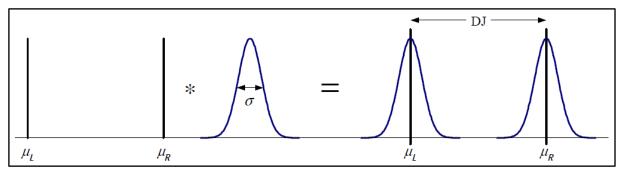

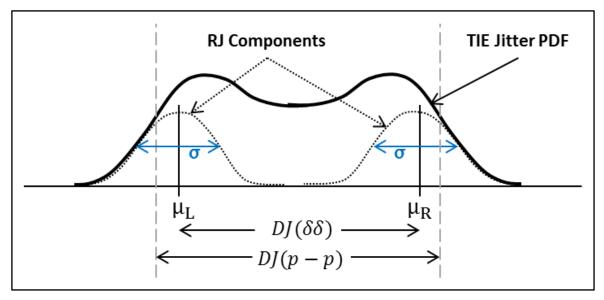

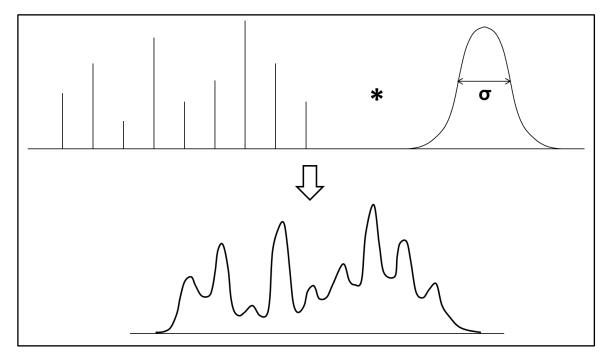

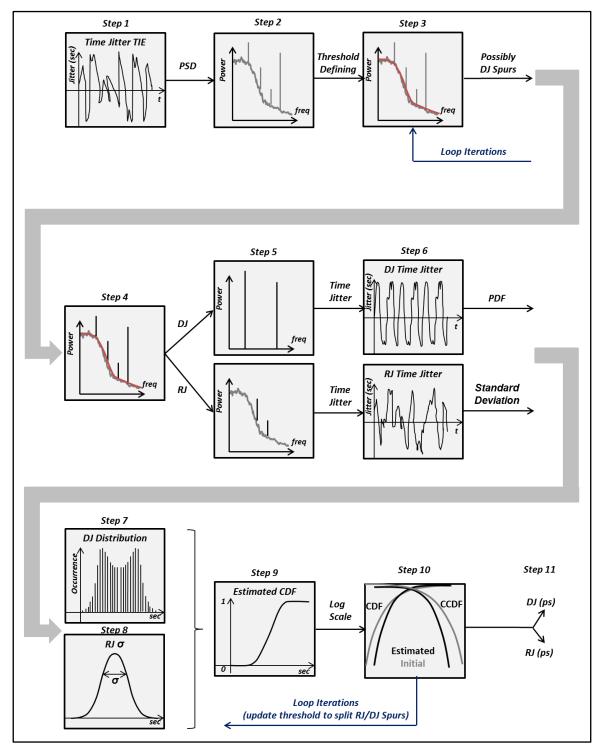

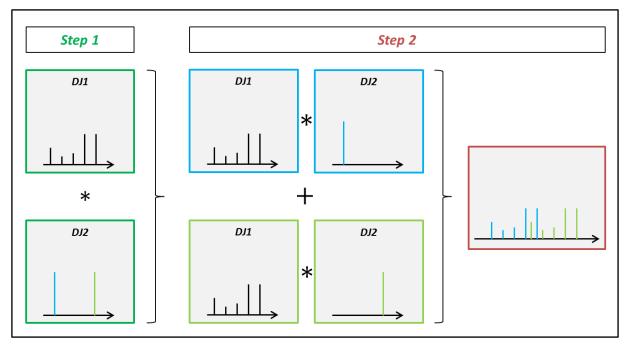

The idea of the new calculation method, with all steps is given in Fig 2-13. Its principle is the following:

#### <u>Step 1:</u>

As explained above, the total Deterministic Jitter is defined as the convolution of all Deterministic Jitters found in the system, as given in (2.43).

$$DJ_{Total} = DJ_1 * DJ_2 * DJ_3 * \dots$$

(2.43)

The total Random Jitter is defined same as before (2.40).

#### <u>Step 2:</u>

The Total Jitter corresponds then to the convolution of the total DJ spurs (2.43) to the RJ standard deviation (2.40), and is expressed as in (2.44):

$$TJ = DJ_{Total} * RJ_{Total}$$

(2.44)

#### <u>Step 3:</u>

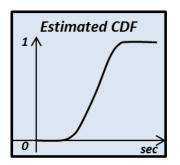

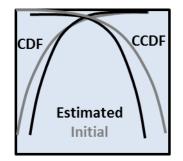

Equation (2.44) will give the CDF and CCDF of the total Jitter, in a linear scale.

#### <u>Step 4:</u>

The calculated CDF & CCDF are transposed to a logarithmic scale, and extrapolated to have curve estimation at different BER. The difference between the CDF and CCDF curves at any given BER will give the Total Jitter estimation at this BER.

Figure 2-13: Total Jitter Estimation

Some examples of different convolutions are given in Annex 8.5. They prove that the developed algorithm which performs the convolutions between all DJ jitters works as expected.

### 2.6 Chapter Conclusion

In this section we have given all necessary equations to calculate jitter in the time and frequency domain.

We have shown that any given noise can be expressed as sum of a Phase and an Amplitude Noise.

We have demonstrated that the Amplitude Noise has no impact on Jitter under a given profile. Therefore, in this thesis, we will only work on Phase Noise Profiles for the jitter.

## Chapter 3: PLL Modeling

| 3.1 In | troduction                                              |  |

|--------|---------------------------------------------------------|--|

| 3.2 PI | LL Architecture                                         |  |

| 3.2.1  | Phase Detector                                          |  |

| 3.2.2  | Charge Pump (CP)                                        |  |

| 3.2.3  | Loop Filter                                             |  |

| 3.2.4  | VCO                                                     |  |

| 3.2.5  | Divider                                                 |  |

| 3.2.6  | Sigma-Delta Modulator:                                  |  |

| 3.3 Fr | requency Domain PLL modeling with phase noise injection |  |

| 3.3.1  | Fractional PLL modeling for a small signal analysis     |  |

| 3.3.2  | Open Loop Phase Noise Profiles                          |  |

| 3.3.3  | PLL Simulation in the Frequency Domain                  |  |

| 3.4 Ti | me domain PLL modeling with jitter injection            |  |

| 3.4.1  | Time jitter generation                                  |  |

| 3.4.2  | PLL Simulation in the Time Domain                       |  |

| 3.5 Fr | requency-Time domain comparison                         |  |

## **Table of Figures**

| Figure 3-1: PLL Architecture                                                      | 38 |

|-----------------------------------------------------------------------------------|----|

| Figure 3-2: Phase-Frequency Detector Output                                       | 39 |

| Figure 3-3: Charge Pump schematic                                                 | 39 |

| Figure 3-4: Loop Filter Schematic                                                 | 40 |

| Figure 3-5: VCO                                                                   | 41 |

| Figure 3-6: Divider                                                               | 41 |

| Figure 3-7: PLL schematic with Sigma Delta Modulator                              | 42 |

| Figure 3-8: Sigma Delta Modulator                                                 | 42 |

| Figure 3-9: PLL Schematic with Phase Noise Injection                              | 43 |

| Figure 3-10: Noise Transfer Function for each sub-block of the PLL                | 44 |

| Figure 3-11: Open-loop phase noise profiles                                       | 44 |

| Figure 3-12: Closed-loop phase noise profiles                                     |    |

| Figure 3-13: Time Jitter Generation Technique                                     | 46 |

| Figure 3-14: Chronogram                                                           | 47 |

| Figure 3-15: Flow Chart                                                           | 48 |

| Figure 3-16: Flow Chart with Jitter injection                                     | 49 |

| Figure 3-17: VCO Phase Noise at the PLL Output for Frequency & Time Domain Models | 50 |

## Table of Tables

| Table 3-1: Correlations between Frequency | z Time Domain Simulations51 |

|-------------------------------------------|-----------------------------|

|-------------------------------------------|-----------------------------|

#### 3.1 Introduction

Modeling the phase noise of the different SerDes components and extracting the time jitter would help designers to achieve desired Figure of Merit for future SerDes versions [Bidaj]. The phase locked loop (PLL) is one of the main contributors of clock random and periodic jitter inside the system [Hansel] - [Telba]. This chapter presents a method for modeling the PLL with phase noise injection and estimating the time domain jitter. A time domain model including PLL loop nonlinearities is created in order to estimate jitter. We present in this chapter a particular PLL architecture, which is also implemented in STMicroelectronics SerDes circuits.

#### 3.2 PLL Architecture

A phase-locked loop is a feedback system where an oscillator-generated signal is phase locked to a reference clock [Soyuer]. Phase-locked loops can be used, for example, to generate stable output high frequency clock from a fixed lower-frequency one.

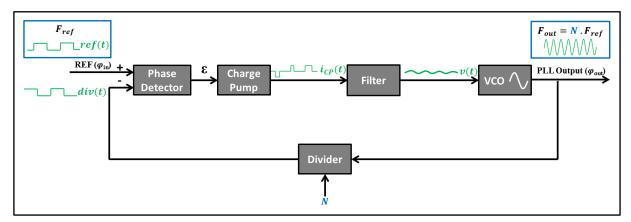

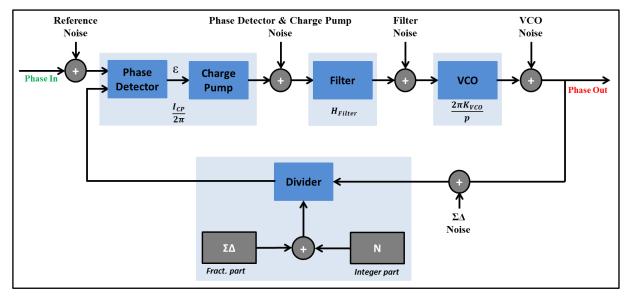

A PLL is composed of the following building blocks: Phase Detector, Charge Pump, Low-Pass Filter, Voltage Controlled Oscillator (VCO) and Feedback Divider, as shown in Fig 3-1. [Analog] - [Arakali] - [Chu] - [Herzel] - [Nonis] - [Pu] - [Schober] - [Ting] - [Wu] - [Yuan].

#### Figure 3-1: PLL Architecture

At the input of the PLL, we have the **Reference Clock (Oscillator)**, which is a periodic signal. For SerDes applications, it is generally a Clock signal, between 20MHz and 100MHz.

#### 3.2.1 Phase Detector

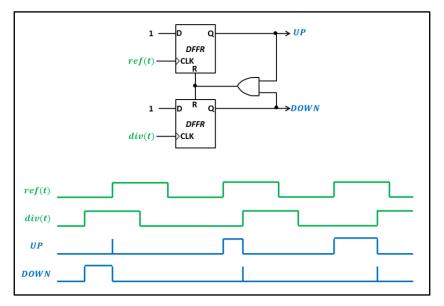

The **Phase-Frequency Detector** (PFD) compares the phase and frequency of the feedback clock generated by the VCO to the ones of the REF clock, and generates an error to adjust the oscillator and keep the phases and frequencies matched. It produces an UP and DOWN output signal [Chu] - [Kennedy] - [Pu] - [Schober] - [Young] - [Yuan], proportional to the phase error when the PLL reaches the locked state (as shown in Fig 3-2).

Figure 3-2: Phase-Frequency Detector Output

#### 3.2.2 Charge Pump (CP)

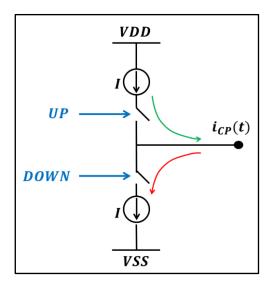

The above UP and DOWN output phase error signals enter the **Charge Pump** as shown in Fig 3-3 [Schober].

Figure 3-3: Charge Pump schematic

The charge pump generates a current related to the input phase errors, which is proportional to the PFD pulse widths [Chu]. (3.1)

$$CP_{Gain} = \frac{1}{2\pi} * I_{CF}$$

#### 3.2.3 Loop Filter

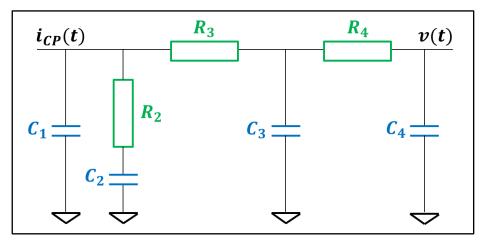

The Loop **Filter** is an integrator. It generates a voltage to control the VCO from phase detector pulses [Young], and make it go faster/slower depending on the phase error sign. In Fig 3-4 we show a 4<sup>th</sup> order filter, very common in the PLL for RF applications.

Figure 3-4: Loop Filter Schematic

The  $C_1$  capacitance is used to integrate the current coming from the Charge Pump. The resistance  $R_2$  and the capacitance  $C_2$  add one zero to the Transfer Function to ensure the loop stability. The two first order low-pass filters added afterwards serve to better filter the high frequency noises and the reference frequency spurs.

#### 3.2.4 VCO

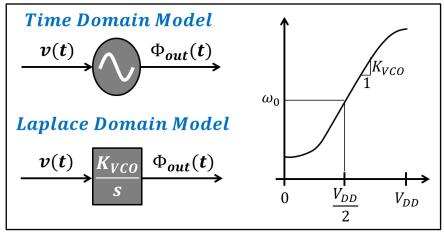

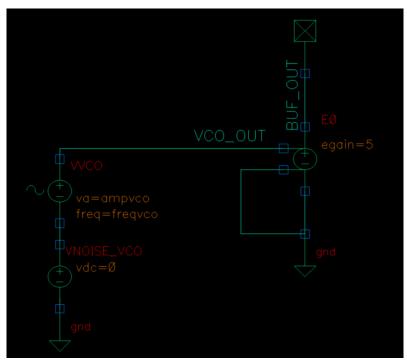

A Voltage-Controlled oscillator is an oscillator whose output oscillation frequency is controlled by the filter's output voltage v(t), as shown in Fig 3-5.

Figure 3-5: VCO

The time-domain phase relationship is given in (3.1).

$$\Phi_{out}(t) = \int \Delta \omega_{out}(t) dt = K_{VCO} \int v(t) dt$$

with  $\omega_{out}(t) = \omega_0 + \Delta \omega_{out}(t) = \omega_0 + K_{VCO} v(t)$

3.2

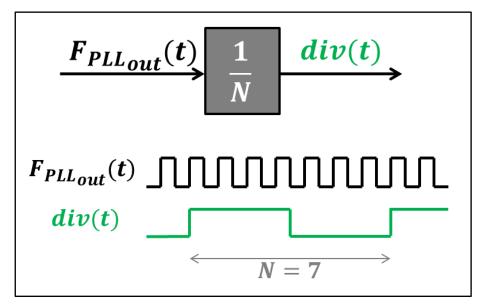

#### 3.2.5 Divider

The **Divider** will serve as a frequency divider as shown in Fig 3-6. The loop feedback frequency will be a division of the PLL output frequency.

Figure 3-6: Divider

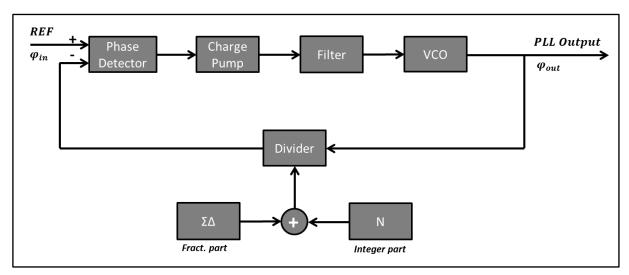

#### 3.2.6 Sigma-Delta Modulator:

A Sigma Delta (SD) modulator is implemented for the Fractional PLL [Kennedy] - [Sadeghi] - [Ye]. The schematic of the PLL with the SD modulator added is given in Fig 3-7.

Figure 3-7: PLL schematic with Sigma Delta Modulator

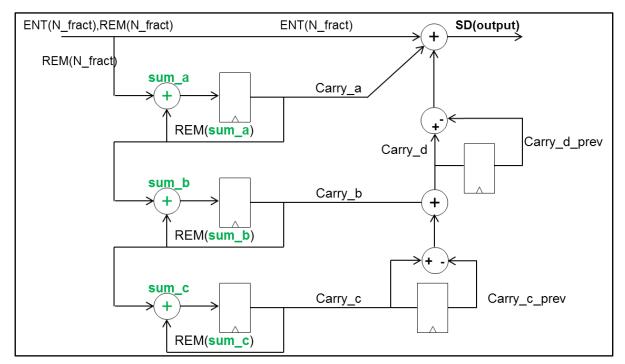

The schematic of the SD modulator (3-TAP Sigma Delta Modulator) is given in Fig 3-8:

Figure 3-8: Sigma Delta Modulator

A 3-TAP Sigma Delta Modulator is chosen in order to send the noise due to the division in the High Frequencies. This noise will then be filtered by the PLL Low Pass Filter equivalent transfer function.

#### 3.3 Frequency Domain PLL modeling with phase noise injection

#### **3.3.1 Fractional PLL modeling for a small signal analysis**

The first step is to model each sub-block of the PLL in MATLAB, with its proper transfer function. A phase noise profile is then injected for each sub-block. The PLL schematic with phase noise injection for each sub-block is given in Fig 3-9.

Figure 3-9: PLL Schematic with Phase Noise Injection

The small-signal closed-loop transfer function of the PLL is described in (3.3):

$$TF(s) = \frac{\frac{I_{CP}}{2\pi} H_{Filter}(s) 2\pi \frac{K_{VCO}}{s}}{1 + \frac{1}{N} \frac{I_{CP}}{2\pi} H_{Filter}(s) 2\pi \frac{K_{VCO}}{s}}$$

(3.3)

With:  $I_{CP}$ : Charge pump current.

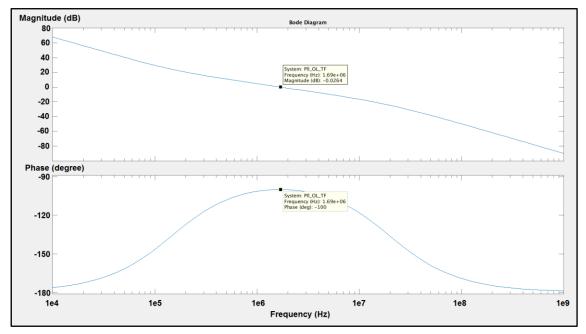

$H_{Filter}(s)$ : Filter transfer function to ensure loop stability with a cutoff frequency at 150 kHz, and a phase margin of 60°.

K<sub>VCO</sub>: Gain of the VCO in Hz/V, N: Frequency Division ratio

We give in Fig 3-10 an example of the Noise Transfer Function of each subblock of the PLL.

Figure 3-10: Noise Transfer Function for each sub-block of the PLL

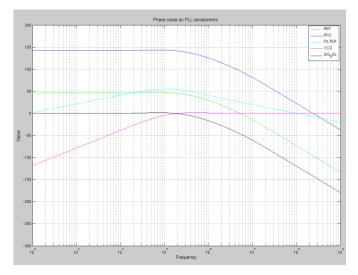

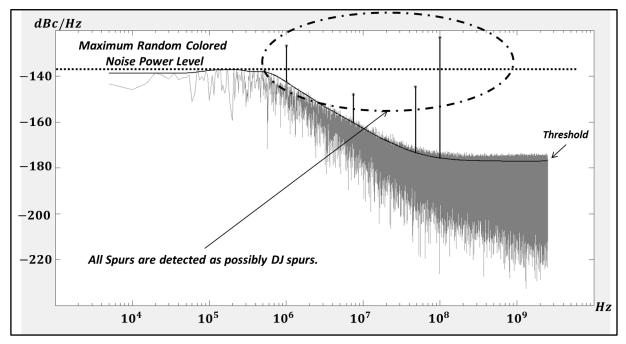

#### 3.3.2 Open Loop Phase Noise Profiles

Phase noise profiles for each sub-block of the PLL (except the  $\Sigma\Delta$  profile which is a mathematical equation of order 3  $\Sigma\Delta$ ) are simulated with ELDO RF. Their open-loop phase noise profiles (in dBc/Hz) are shown in Fig 3-11 (Charge pump noise profile is in  $\frac{dBA}{\sqrt{Hz}}$  and Filter loop noise profile is in  $\frac{dBV}{\sqrt{Hz}}$ ).

Simulation conditions might change the different phase noise profiles. We have a realistic distribution of the noise. All profiles are given in single-sideband (SSB) power [Howe]. The VCO and the  $\Sigma\Delta$  noise profiles are around the 1st harmonic (H1) of the VCO frequency. The reference profile is around H1 of the reference frequency. The filter and phase detector/charge-pump profiles are around DC.

Figure 3-11: Open-loop phase noise profiles

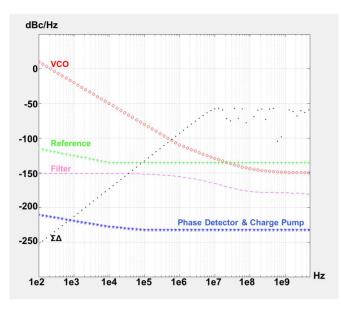

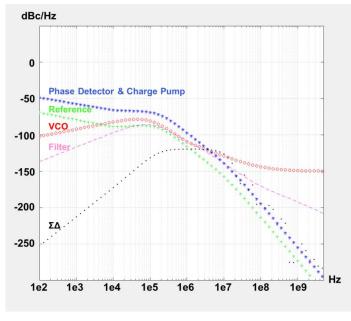

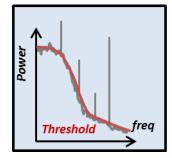

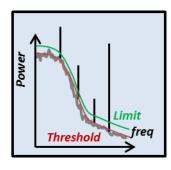

These open-loop phase noise profiles (Fig 3-11) are passed through the closed-loop system response (Fig 3-10) and the output closed-loop noise profiles are given in Fig 3-12:

Figure 3-12: Closed-loop phase noise profiles

#### 3.3.3 PLL Simulation in the Frequency Domain

It is important to estimate the jitter present at the output of the PLL (in closedloop) as the PLL is one of the main contributors of jitter. To do this, the RMS jitter is computed in the frequency domain using the closed-loop **phase noise profiles** L(f)presented in Fig 3-12. This is done using the mathematical formula (3.4) with  $F_c$ (Carrier Frequency) [Feng] - [Maxim] - [Zamek]. The integration is multiplied by 2 (to include the total power, as the noise profiles are given in SSB).

$$RMS_{Jitter} = \frac{1}{2\pi F_C} \sqrt{2 \int_0^{\frac{F_C}{2}} 10^{\frac{L(f)}{10}} df}$$

(3.4)

The frequency domain model gives a global estimation of the RMS jitter. It does not give visibility of the DJ linked to imperfections of the PLL loop, which is possible with time domain model.

In order to characterize SerDes performance in terms of BER including nonlinearities, we need to model and measure the jitter in the time domain.

#### 3.4 Time domain PLL modeling with jitter injection

The time domain PLL simulation was done using the generated open-loop phase noise profiles.

#### 3.4.1 Time jitter generation

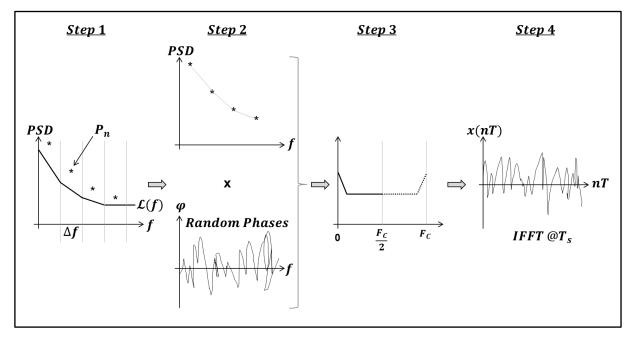

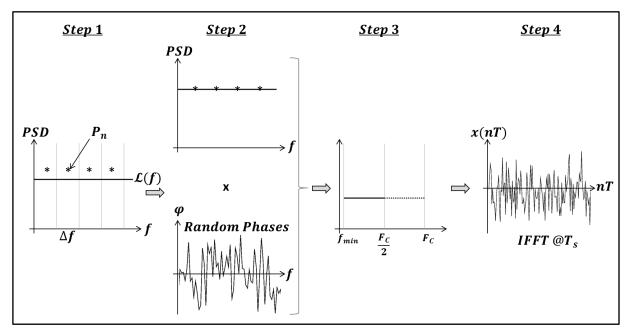

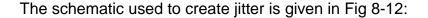

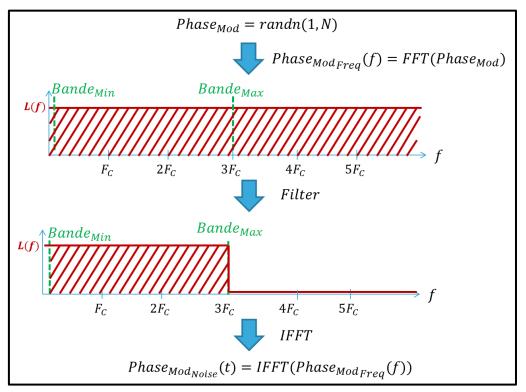

The steps to generate the time noise jitter are given below, and are shown in Fig 3-13. This method allows the time jitter to be obtained from the phase noise profile.

Figure 3-13: Time Jitter Generation Technique

**Step 1**: First open-loop phase noise profile  $\mathcal{L}(f)$  is recovered from the ELDO RF simulation, calculated as in (3.4).

$$\mathcal{L}(f) = 10 \log_{10}(\frac{A_N(f)^2}{A_C^2})$$

(3.4)

where  $A_N$  is the phase noise and  $A_C$  the carrier amplitude at a given frequency.

The power *P* of a spur *n*, corresponding to  $\Delta f$  frequency step, around 'f<sub>n</sub>' offset frequency, is calculated in (3.5):

$$P_n = \int_{f_n - \frac{1}{2}\Delta f}^{f_n + \frac{1}{2}\Delta f} \mathcal{L}(f) df \qquad \text{(in dBc/}\Delta f\text{)}$$

(3.5)

**Step 2**: For each value of the power profile  $P_n$ , we associate a random phases with equal probability to be from 0 to  $2\pi$  defined by the formula (3.6).

$$\varphi_n = e^{j \, 2\pi \, rand[0:1]} \tag{3.6}$$

By multiplying the power profile defined in (3.5) by the associated random phases as in (3.6), we obtain the phase noise  $PN_n$  which is the noise corresponding to frequency offsets from 0 to  $F_c/2$ , by step of  $\Delta f$ , with  $F_c$  carrier frequency (3.7).

$PN_n = P_n \varphi_n \tag{3.7}$

**Step 3**: To generate the time noise jitter from the frequency noise, the inverse FFT is used. To do this, we complete the vector of the FFT corresponding to frequencies  $F_c/2 \rightarrow F_c$ , with the conjugate and symmetric of the phase noise profile. In this way, performing the IFFT of the frequency vector provides a time vector with real values only.

**Step 4**: The IFFT is calculated, and the time jitter noise is added to the transition position of the perfect clock signal, on the different sub-blocks of the PLL. This will be shown in next paragraph.

#### 3.4.2 PLL Simulation in the Time Domain

We present here a time domain model (sampled model) which permits to take into account the non-linearity effect of the PLL. Furthermore, this permits to study precisely the time and frequency behavior of the PLL, and predict the different spurs in the frequency spectrum.

The model proposed in this section is a sampled model, which means that only some events inside the PLL are taken into account. This increases the efficiency of the model, because it can reduce the number of points of the simulation, and keep a good precision.

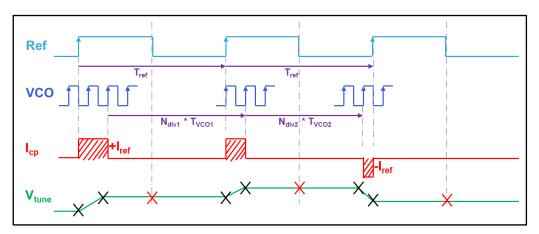

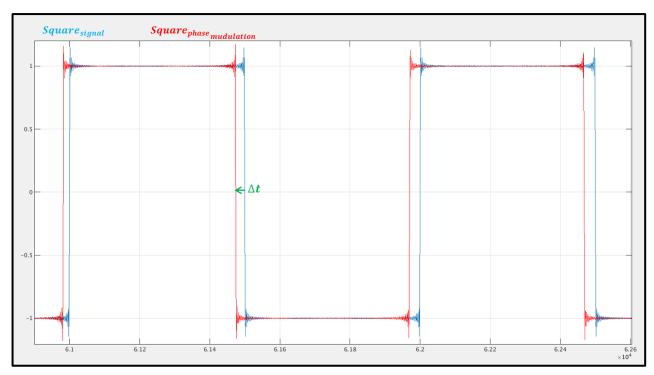

The samples for calculations are taken only on useful edges, as shown in the chronogram of Fig 3-14.

Figure 3-14: Chronogram

The minimum calculation points for the model are represented with a cross on the voltage control  $V_{tune}$  in Fig 3-14. They correspond to modifications of state of the system, as for example the change of the charge pump  $I_{cp}$  value. This chronogram (Fig 3-14) represents the behavior of the PLL as introduced in previous section 3.3.

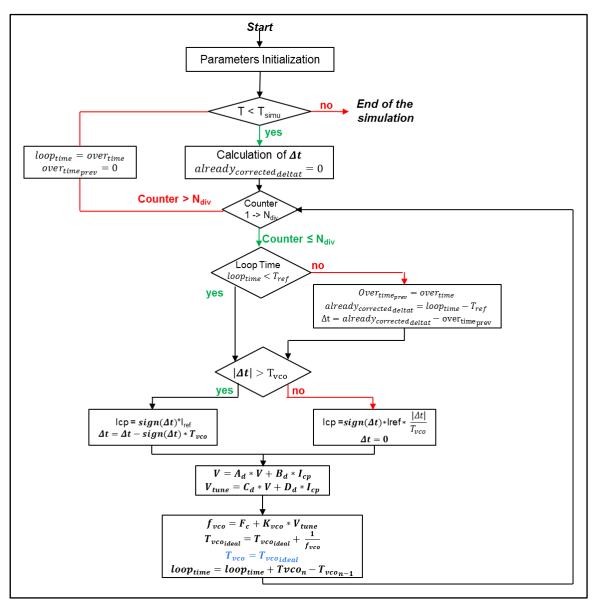

Based on Fig 3-14, we can develop the model sampled at  $T_{ref}$  and based on the complete flow chart shown in Fig 3-15.

#### Figure 3-15: Flow Chart

First of all it is important to initialize the simulation parameters (simulation duration, sampling frequency, ...), and the different PLL parameters (reference frequency, division ratio, VCO gain, ...).

Then the phase difference (or delay)  $\Delta t$  between the reference edges and the division feedback are calculated. This corresponds to the modeling of the Phase Detector. A counter up to  $N_{div}$  is used, in order to simulate the VCO,  $N_{div}$  times faster than the reference. The Loop time is calculated, in order to update  $\Delta t$  value.

Then depending the  $\Delta t$  sign and value, the  $I_{cp}$  is calculated. This corresponds to the Charge Pump generated current. The loop filter converts the generated  $I_{cp}$  into the  $V_{tune}$  voltage. At the end, the VCO generates the  $f_{vco}$  frequency output depending on the  $V_{tune}$  voltage input.

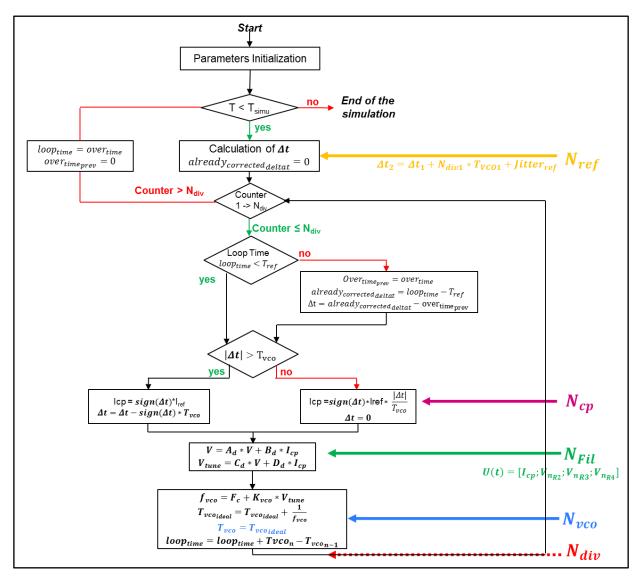

The next step is to inject the jitter corresponding to each block, into the Time Domain PLL Model. This is done as shown in the Flow Chart in Fig 3-16. We add the jitter corresponding to the different blocks of the PLL, in specific places at the flow chart.

Figure 3-16: Flow Chart with Jitter injection

At the end of the time simulation of the PLL in closed-loop we measure the standard deviation,  $\sigma$ , of the TIE which corresponds to the closed-loop RMS jitter and the jitter due to circuit model nonlinearities.

#### 3.5 Frequency-Time domain comparison

We simulated Phase Noise of each sub-block of the PLL in both models and compared them to see if they correlate in terms of Phase Noise and RMS Jitter.

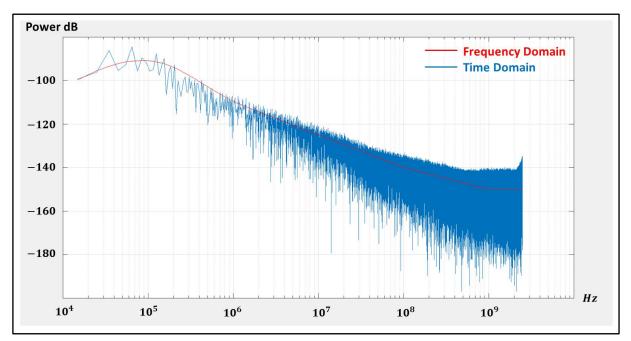

We show in Fig 3-17 one example of simulation results comparing VCO Phase Noise at the Output of the PLL, for both models. In red color, we have the Frequency Domain, and in blue color, the Time Domain simulation results. We remark that both models correlate very well.

Furthermore, Table 3-1 shows one example of jitter results in terms of RMS jitter for each sub-block of the PLL, and the comparison between frequency domain simulations as defined in 3.3 and time domain simulations as defined in 3.4. For the comparison, in the time domain simulation, we have not introduced nonlinearity defaults, but have taken into account only the jitter due to Phase Noise profiles.

| PLL Sub-Blocks  | Frequency Domain<br>RMS Jitter | Time Domain<br>RMS Jitter | Correlation %<br>Error |

|-----------------|--------------------------------|---------------------------|------------------------|

| VCO             | 4.57 ps                        | 4.52 ps                   | 1.1 %                  |

| REF             | 0.82 ps                        | 0.81 ps                   | 1.2 %                  |

| СР              | 0.62 ps                        | 0.63 ps                   | 1.6 %                  |

| FILTER          | 1.06 ps                        | 1.07 ps                   | 0.9 %                  |

| $\Sigma \Delta$ | 1.23 ps                        | 1.21 ps                   | 1.6 %                  |

Table 3-1: Correlations between Frequency & Time Domain Simulations

Table 3-1 shows accurate correlation between both simulation methods, allowing RMS jitter to be modelled within 2% of error between the time and the frequency domain analysis.

In the time domain we have loop imperfections (mainly due to phase error discretization) which lead to additional jitter at TIE output [Kieffer]. The time model was created in order to estimate the time jitter of the system.

# Chapter 4: Generation of colored noise patterns with Gaussian Jitter distribution

| 4.1 | Introduction                                                                                | 54 |

|-----|---------------------------------------------------------------------------------------------|----|

| 4.2 | Definition of criteria for colored noise with Gaussian distribution                         | 55 |

| 4.3 | White noise generation with Gaussian distribution                                           | 50 |

| 4.3 | .1 White noise patterns generation                                                          | 50 |

|     | 2.2 Verifying if generated white noise pattern has Gaussian distribution based of criteria. |    |

| 4.4 | Methods from literature for generating colored noise patterns                               | 52 |

| 4.4 | .1 Filtering generated white noise pattern                                                  | 52 |

| 4.4 | .2 IIR filtering method                                                                     | 54 |

| 4.4 | .3 Colored noise generation with IFFT                                                       | 56 |

| 4.5 | New method for generating colored noise with Gaussian distribution                          | 57 |

| 4.6 | Results - generating colored noise patterns with Gaussian distribution                      | 72 |

| 4.7 | Chapter's conclusion                                                                        | 72 |

## **Table of Figures**

| Figure 4-1: Phase Noise Analyzer Measurement                                              |

|-------------------------------------------------------------------------------------------|

| Figure 4-2: J-BERT Measurement                                                            |

| Figure 4-3: Example of a white and colored noise profile                                  |

| Figure 4-4: Histogram of PDF of the TIE Jitter                                            |

| Figure 4-5: CDF Calculation from PDF                                                      |

| Figure 4-6: Log. scale CDF & CCDF example of a Gaussian and not Gaussian distribution. 58 |

| Figure 4-7: CDF Templates to ensure Gaussian distribution for the generated pattern       |

| Figure 4-8: Time jitter generation from phase noise profiles                              |

| Figure 4-9: White noise profile generated Power                                           |

| Figure 4-10: CDF & CCDF curves of the generated white noise pattern                       |

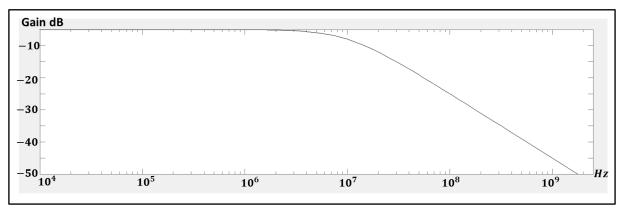

| Figure 4-11: Filter Response for filtering white noise                                    |

| Figure 4-12: Filtered noise power profile                                                 |

| Figure 4-13: CDF & CCDF of Colored Noise generated by Filtering                           |

| Figure 4-14: DJ Spurs added to random colored noise                                       |

| Figure 4-15: Colored noise generated with IIR filtering                                   |

| Figure 4-16: PSD of a -20dB/dec generated noise profile                                   |

| Figure 4-17: Colored noise generated with IFFT                                            |

| Figure 4-18: Generated types of colored noise profiles                                    |

| Figure 4-19: RMS power of low and high frequencies                                        |

| Figure 4-20: Step 1 - Generating white and colored noise profiles                         |

| Figure 4-21: Step 2 - Generating colored noise profiles with Gaussian distribution71      |

| Figure 4-22: Generated colored noise profiles with Gaussian distribution72                |

### **Table of Tables**

| Table 4-1: Maximum error in fs to have Gaussian distribution    59 |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

#### 4.1 Introduction

In this chapter we will concentrate our study only on unbounded & uncorrelated jitter, also called Gaussian random noise or Random Jitter (RJ).

RJ can have different noise properties. It can have a white (spectrally flat) or colored (spectrally curved) noise profile. Many approaches have been developed based on white noise generation [Endo] - [Kafadar]. Nevertheless theoretical studies on colored noise generation are less common as it depends on dedicated requirements for a specific application [Chow] - [İspir] - [Murch] - [Kasdin].

From laboratory measurements of a transmitter output (TX of a SerDes) we may observe two characteristics:

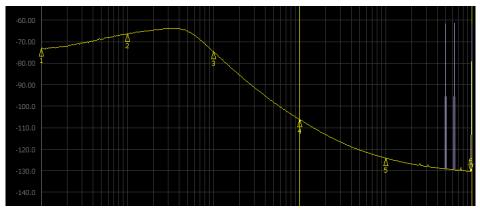

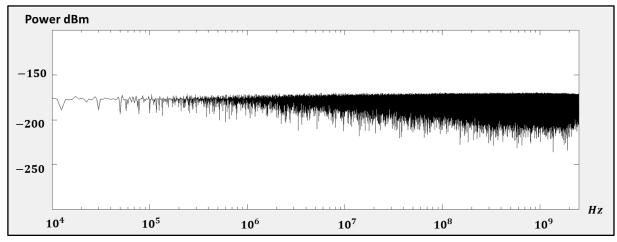

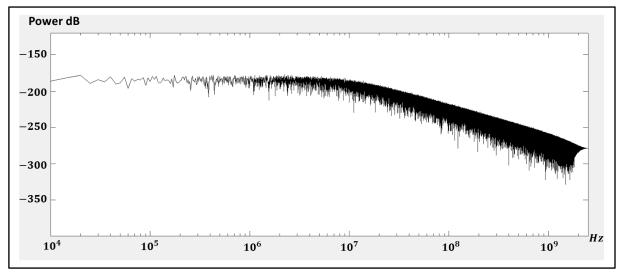

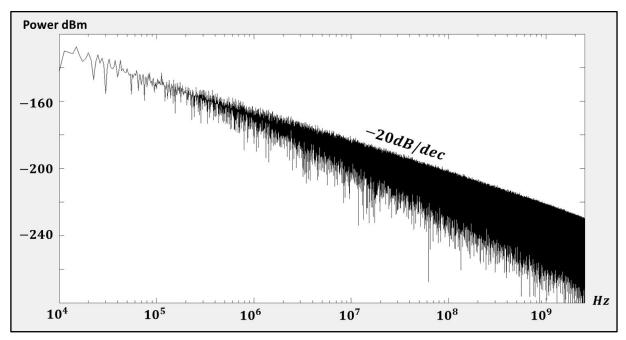

From Phase Noise Analyzer measurement (Agilent (Keysight) E5052B) in Fig

4-1 we observe that the jitter has a profile that is spectrally colored.

Figure 4-1: Phase Noise Analyzer Measurement

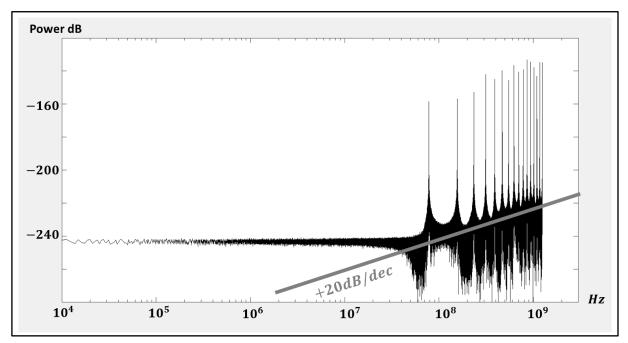

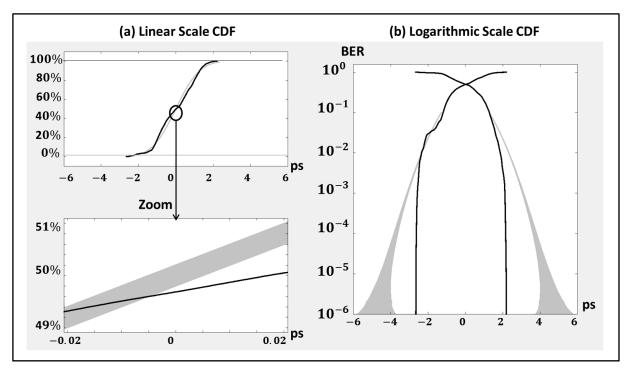

From J-BERT measurement (N4903B 12.5Gbps Agilent (Keysight) Serial Bert) in Fig 4-2 we observe the unbounded tails of timing jitter which show its Gaussian distribution properties.

Figure 4-2: J-BERT Measurement

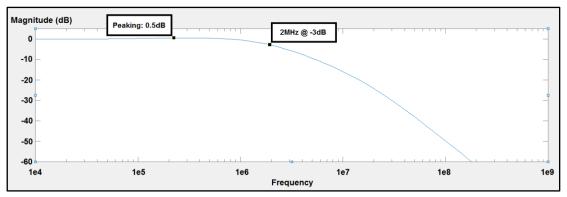

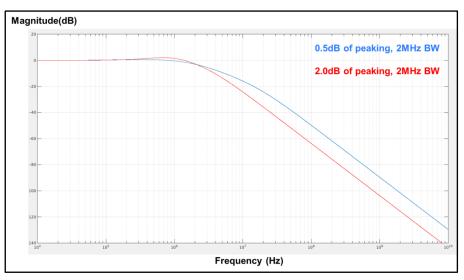

In order to analyze SerDes system characteristics, it is important to generate synthetic colored noise patterns with a Gaussian distribution. The patterns will be used to predict impact of jitter on the system performances with time domain simulation during the design verification phase.

In this chapter we present a different method for generating synthetic patterns with Gaussian distribution from colored noise PSD profiles.

In section 4.2 of this chapter we describe our criteria to decide whether or not a generated white or colored noise pattern has a Gaussian distribution.

In section 4.3, we generate white noise patterns with a Gaussian distribution, with the method explained in 3.4.1. We will also validate our criteria used to decide whether or not the generated noise patterns have Gaussian distribution properties.

In section 4.4 we describe several methods from the literature for generating colored noise patterns. We will determine, based on our criteria, if these methods match our expectations in term of noise power profile and Gaussian jitter distribution.

Section 4.5 describes our novel method for generating colored noise patterns with Gaussian distributions.

Results and conclusions are given in section 4.6.

#### 4.2 Definition of criteria for colored noise with Gaussian distribution

In this section we describe different criteria for determining whether or not the generated noise patterns have Gaussian distribution properties. This will be done in two steps:

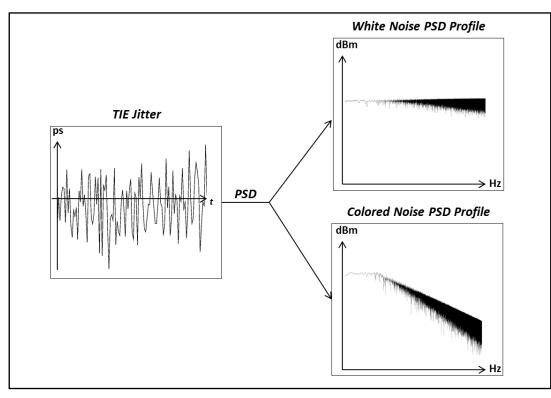

The first step is to process the Power Spectral Density (PSD) of the TIE jitter in order to define the type of noise profile (white or colored).

The second step evaluates the maximum acceptable error between a Cumulated Density Function (CDF) from a synthetic pattern with Gaussian jitter distribution (obtained from a signal with white noise PSD) and the CDF from the ideal Gaussian error function (4.1). This maximum error will then be used to define the template to determine whether or not a synthetic pattern has Gaussian distribution properties.

$$Error_{fct} = \frac{1}{2} + \frac{1}{2} \operatorname{erf}(\frac{x}{\sigma\sqrt{2}})$$

(4.1)

With

$$erf(x) = \frac{2}{\sqrt{\pi}} \int_0^x e^{-t^2} dt$$

(4.2)

<u>Step 1:</u>

Once a TIE jitter pattern is generated, the first step is to calculate its PSD using (4.3).

$$\Phi_{lin}(\omega) = \int_{-\infty}^{+\infty} \varphi(\tau) e^{-j\omega t} dt$$

(4.3)

The Power Spectral Density  $\Phi(\omega)$  of the signal x(t), is the Fourier Transform of the autocorrelation function  $\varphi(\tau)$ .

The power of the PSD is converted to dB using (4.4).

$$\Phi_{dB}(\omega) = 10 * \log_{10}(\frac{|\Phi_{lin}(\omega)|}{\Phi_{1ps}})$$

(4.4)

with

$$\sqrt{\int_0^{+\infty} (\Phi_{1ps})^2 d\omega} = 1ps$$

(4.5)

This allows the noise profile to be better visualized and to determine whether it is white or colored noise. An example of a white and colored noise profile is shown in Fig 4-3.

Figure 4-3: Example of a white and colored noise profile

<u>Step 2:</u>

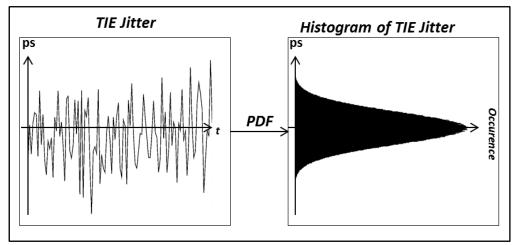

The next step is to calculate the CDF & the Complementary Cumulated Density Function (CCDF) of the TIE jitter. In order to calculate the CDF & the CCDF of the TIE, we need to plot its Probability Density Function (PDF), as shown in Fig 4-4.

Figure 4-4: Histogram of PDF of the TIE Jitter

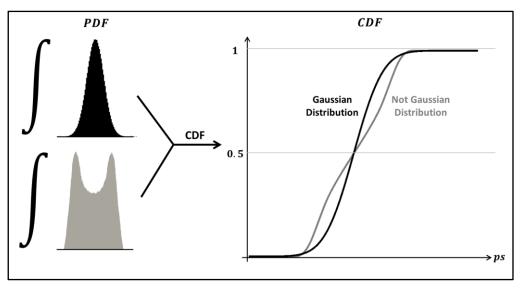

From the PDF we can calculate the CDF & CCDF of the Jitter. The CDF is calculated by integrating the PDF curve, as shown in Fig 4-5.

Figure 4-5: CDF Calculation from PDF

The CCDF is calculated using (4.6).

CCDF = 1 - CDF

(4.6)

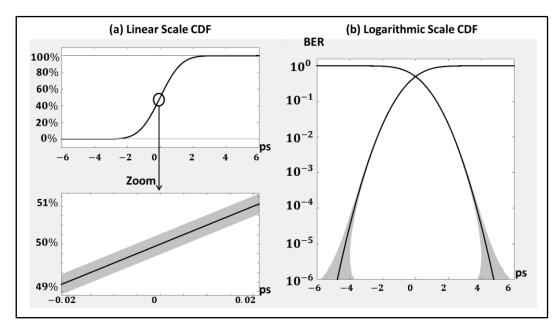

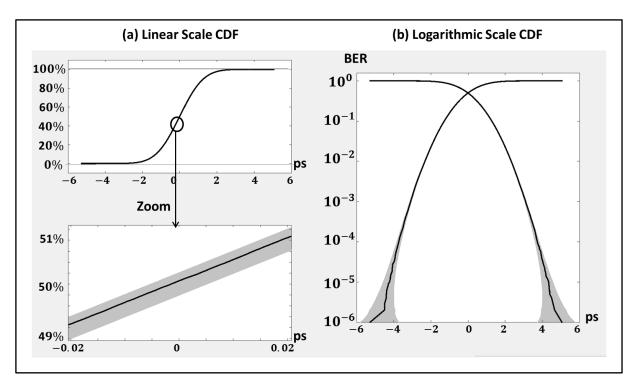

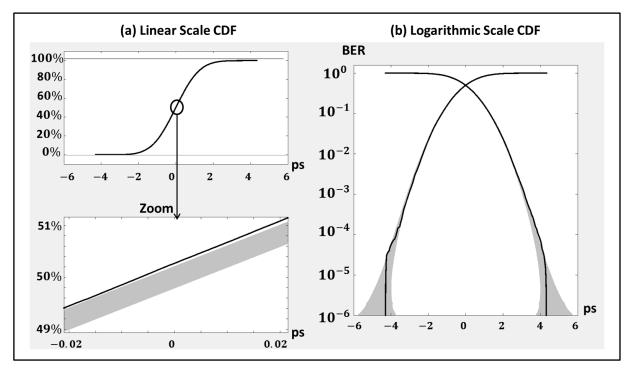

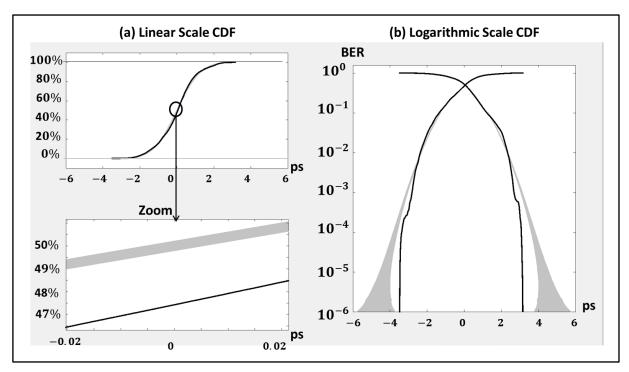

The linear scale allows the global distribution to be properly represented. Nevertheless, it is there difficult to compare the tails of the distribution on a linear scale. This is why the calculated CDF and CCDF are transposed to a logarithmic scale, as shown in Fig 4-6. The logarithmic scale allows the tails of the distribution to be properly compared.

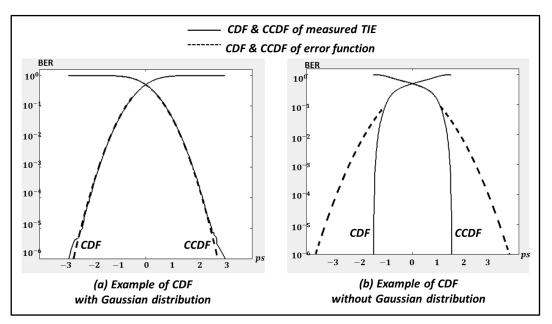

The CDF curve (plotted using both linear and logarithmic scales) and the CCDF curve (plotted using the logarithmic scale only) of the TIE jitter are compared to the template based on the Gauss error function (4.1) in order to determine whether or not it has Gaussian distribution properties.

If the CDF and the CCDF of the TIE jitter from the generated synthetic pattern lies within the template (Fig 4-6.a) then we determine that the synthetic pattern has Gaussian distribution properties. Otherwise, the synthetic pattern is set as non-Gaussian distribution, as shown in Fig 4-6.b.

To define the template used to determine whether or not a CDF has Gaussian distribution properties, we generated synthetic pattern with 10<sup>6</sup> values using pseudo random pattern generation techniques. From [Kang] - [Lee], we may claim that the pseudo random sequence generation we use for simulation has Gaussian distribution properties and white PSD profile.

For the CDF on a linear scale, we define the maximum error used for the template between 1% and 99% of the CDF.

For the CDF on a logarithmic scale we define the maximum error used for the template between BER from  $10^{-2}$  to  $10^{-6}$ .

The standard deviation of the error  $\sigma_{error}$  (in fs) is calculated for a total random jitter with a standard deviation of 1ps. This level is chosen arbitrarily, then as the error  $\sigma_{error}$  is calculated from this value, it can be scaled to any other RMS jitter values.

In order to estimate properly  $\sigma_{error}$  between a simulated CDF and its ideal Gaussian error function (4.1), we perform 1000 simulations. A template of  $\pm 4\sigma_{error}$  is then defined around the Gauss error function. Consequently, 99.99% of synthetic patterns with Gaussian distribution properties will be detected positively by our criteria. For the sake of clarity, we provide the template range of  $\pm 4\sigma_{error}$  for a limited set of values in Table 4-1.

| Linear Scale CDF (Fig 4-6.a) |                        | Logarithmic Scale CDF (Fig 4-6.b) |                         |

|------------------------------|------------------------|-----------------------------------|-------------------------|

| Percentage                   | $\pm 4 \sigma_{error}$ | BER                               | $\pm 4  \sigma_{error}$ |

| 20 %                         | ± 5.40 fs              | 10-2                              | ± 14.04 fs              |

| 40 %                         | ± 5.04 fs              | 10-3                              | ± 35.64 fs              |

| 50 %                         | ± 4.96 fs              | 10-4                              | ± 104.80 fs             |

| 60 %                         | ± 5.08 fs              | 10-5                              | ± 288.80 fs             |

| 80 %                         | ± 5.36 fs              | 10-6                              | ± 996.00 fs             |

Table 4-1: Maximum error in fs to have Gaussian distribution

These templates are illustrated with grey regions in the following CDF plots for a linear (Fig 4-7.a) and a logarithmic scale (Fig 4-7.b). We have a Gaussian distribution only if the CDF and CCDF curves of the TIE jitter lie within limits shown in grey.

Figure 4-7: CDF Templates to ensure Gaussian distribution for the generated pattern

#### 4.3 White noise generation with Gaussian distribution

#### 4.3.1 White noise patterns generation

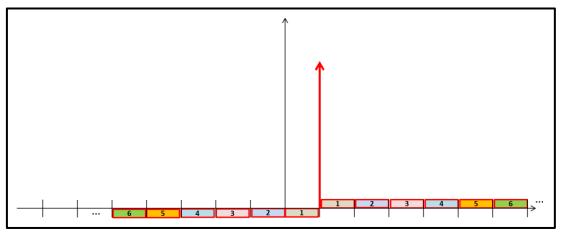

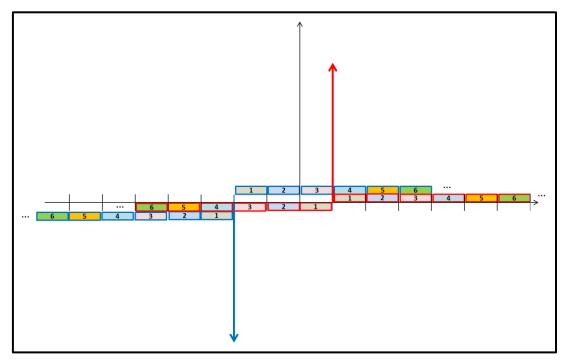

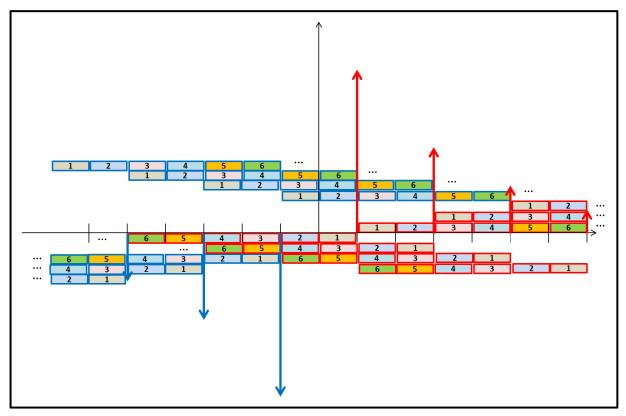

In this section we will generate white noise patterns of Gaussian distribution. The steps to generate the time noise jitter (based on 3.4.1) are given below, and are shown in Fig 4-8. This method allows the time jitter to be obtained from the phase noise profile.

**Step 1:** We first define a white noise profile,  $\mathcal{L}(f)$ , calculated using (4.7).

$$\mathcal{L}(f) = 10 \log_{10}(\frac{A_N^2}{A_C^2}) \tag{4.7}$$

where  $A_N$  is the phase noise and  $A_C$  the carrier amplitude at a given frequency.

The power *P* of a spur *n*, corresponding to a  $\Delta f$  frequency step, around 'f<sub>n</sub>' offset frequency, is calculated using (4.8):

$$P_n = \int_{f_n - \frac{1}{2}\Delta f}^{f_n + \frac{1}{2}\Delta f} \mathcal{L}(f) df \qquad \text{(in dBc/}\Delta f\text{)}$$

(4.8)

Figure 4-8: Time jitter generation from phase noise profiles.

**Step 2:** For each value of the power profile,  $P_n$ , we associate a random phase with equal probability of lying between 0 and  $2\pi$ , defined by the formula (4.9).

$$\varphi_n = e^{j \, 2\pi \, rand[0:1]} \tag{4.9}$$

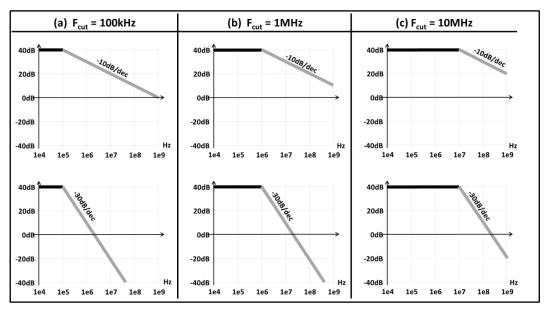

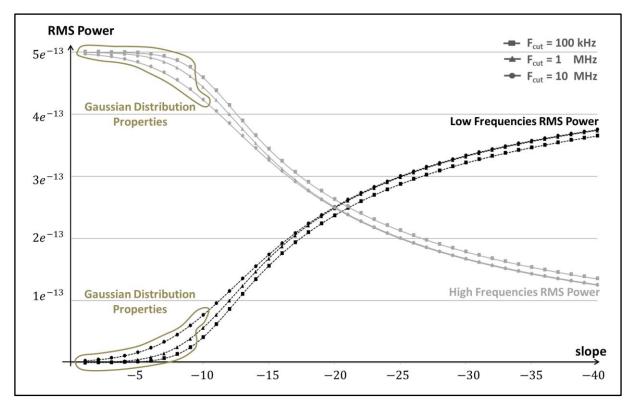

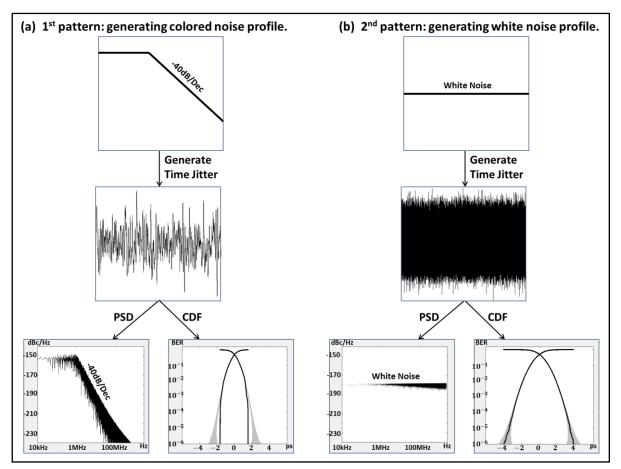

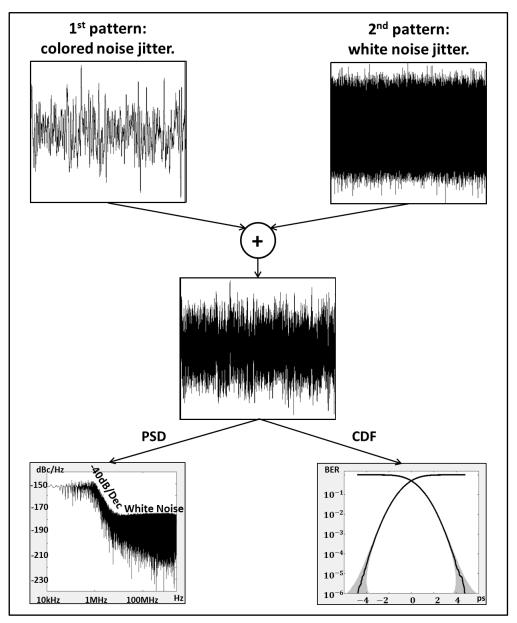

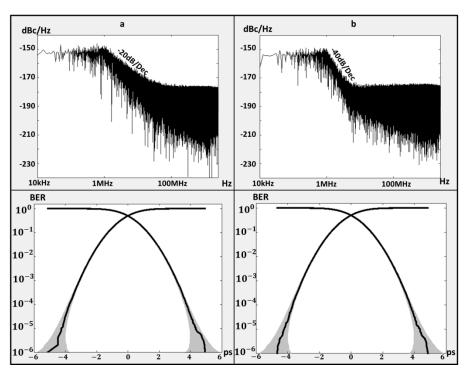

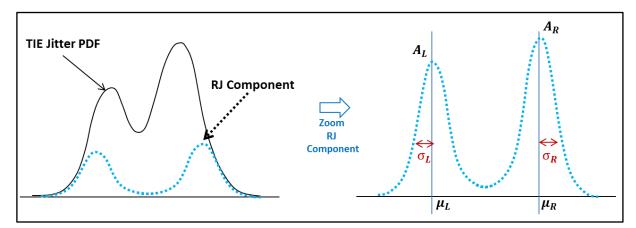

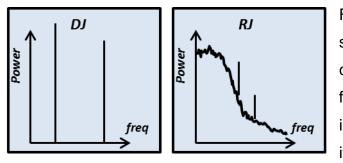

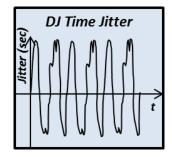

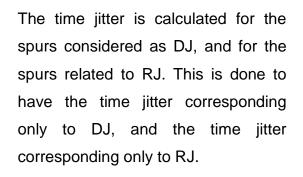

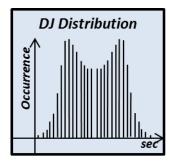

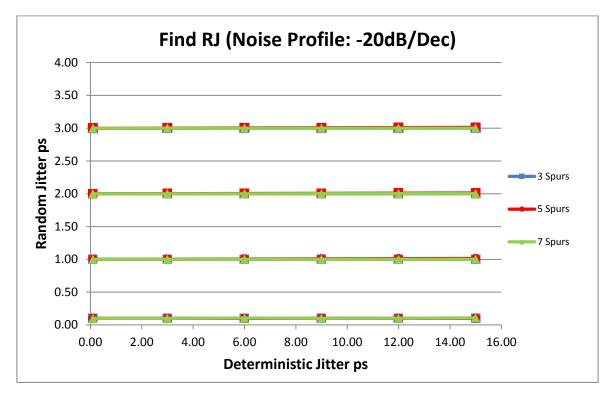

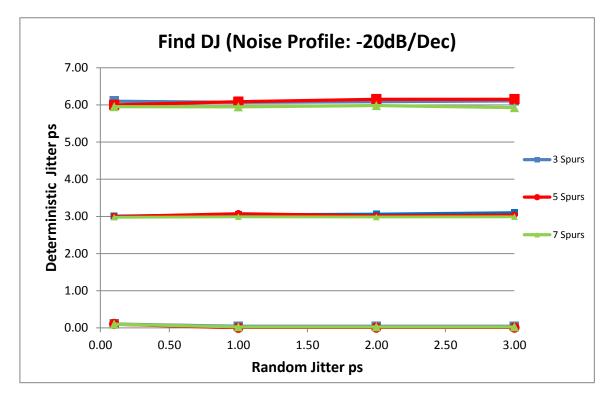

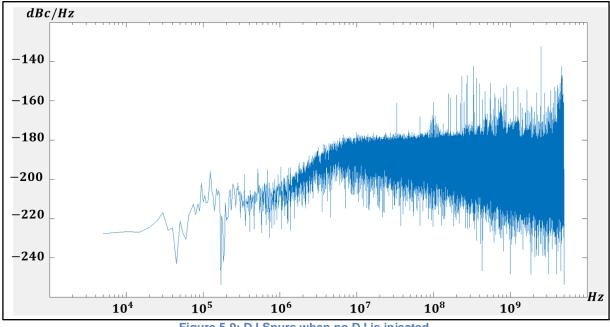

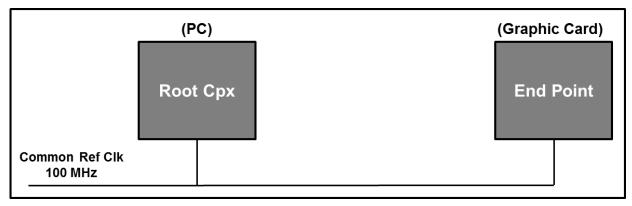

By multiplying the power profile defined in (4.8) with the associated random phases in (4.9), we obtain the phase noise,  $PN_n$  using (4.10), which is the noise