#### Pipeline ADC Built-In Self Test

Guillaume Renaud

#### ▶ To cite this version:

Guillaume Renaud. Pipeline ADC Built-In Self Test. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2016. English. NNT: 2016GREAT064. tel-01468218

#### HAL Id: tel-01468218 https://theses.hal.science/tel-01468218

Submitted on 15 Feb 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE la Communauté UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano-électronique et Nano-technologies

Arrêté ministériel: 7 Août 2006

Présentée par

#### **Guillaume Renaud**

Thèse dirigée par Salvador Mir et co-encadrée par Manuel J. Barragán

préparée au sein TIMA et de l'École Doctorale Électronique, Électrotechnique, Automatique et Traitement du Signal (E.E.A.T.S)

## **Auto Test de Convertisseurs de Signal de Type Pipeline**

Thèse soutenue publiquement le **29 Novembre 2016**, devant le jury composé de :

#### M. Dominique Dallet

Professeur, IMS/Bordeaux INP, Président

#### Mme. Adoración Rueda

Professeur, IMSE-CNM/Institut de Séville, Rapporteur

#### M. Serge Bernard

HDR, LIRMM/Université de Montpellier, Rapporteur

#### M. Hervé Naudet

Ingénieur senior, STMicroelectronics Grenoble, Examinateur

#### M. Salvador Mir

Directeur de recherche CNRS, TIMA/Université Grenoble-Alpes, Directeur de thèse

#### M. Manuel J. Barragán

Chargé de recherche CNRS, TIMA/Université Grenoble-Alpes, Co-Encadrant

## Acknowledgments

I would like to first and foremost thank my advisors Salvador Mir and Manuel Barragán for their guidance and support. I learned a lot during my PhD thesis, and it is definitely thanks to them. I would also like to thank Salvador and Emmanuel Simeu for hosting me in the RMS team.

Many thanks also go to the people who helped me during these years. I would like to acknowledge the staff of TIMA Laboratory for their efficient help (Anne-Laure Fourneret Itié, Laurence Bentito, Youness Rajab, Frédéric Chevrot, Ahmed Khalid and Nicolas Garnier). Thanks to Mamadou Diallo for the design of the test chip and the evaluation boards, and thanks to Alexandre Chagaloya for the support during the test chip design phase. Morevover, thanks to Skandar Basrour for letting me access and use the equipment of the test room facilities at CIME. Thanks to Slim Bellil and Robin Rolland for their support on the testing platform, and thanks to the MNS/Hap2U squad (Mickaël, Emilie, François, Adrian, Achraf) for kind of accepting me in the team while I was performing the measurements. Thanks to Hervé Le Gall, Hervé Naudet, and Alexandre Proust for the technical support at STMicroelectronics.

Sincere thanks to the members of the jury for accepting and finding the time in their respective agendas, especially Adoración Rueda, Dominique Dallet, and Serge Bernard for travelling long distances in order to attend my PhD defense.

I would like to thank my (former) colleagues and close friends from the RMS team (Martin, Thanasis, Asma, Rshdee, Hani, Laurent, Brice, Diane) and from other teams (Simon, Alban) for the technical help and the good times we spent together in (and outside) the lab.

Many (if not all) of those who are PhD now know that the PhD thesis is not an easy path to walk, so I would like to specially thank my friends, my family, and my fiancée for their caring love and support during rough times.

## **Contents**

| Ac  | cknowledgments                                             | 1  |

|-----|------------------------------------------------------------|----|

| Lis | ist of Figures                                             | vi |

| Lis | ist of Tables                                              | X  |

| 1.  | Introduction                                               | 1  |

|     | 1.1. Context                                               | 1  |

|     | 1.2. Industrial production testing                         | 3  |

|     | 1.3. Motivation                                            | 4  |

|     | 1.4. Outline of this thesis                                | 7  |

| 2.  | State of the art of ADC testing                            | 9  |

|     | 2.1. ADC performance testing                               | 9  |

|     | 2.1.1. Basic concepts                                      | 9  |

|     | 2.1.2. Differential Non Linearity                          | 11 |

|     | 2.1.3. Integral Non Linearity                              | 12 |

|     | 2.1.4. Gain error                                          | 13 |

|     | 2.1.5. Input offset error                                  | 14 |

|     | 2.1.6. Correction of gain and offset                       | 15 |

|     | 2.2. ADC testing techniques                                | 16 |

|     | 2.2.1. Standard static linearity test techniques           | 16 |

|     | 2.2.2. State-of-the-art static linearity test techniques   | 20 |

|     | 2.3. On-chip stimulus generation                           | 40 |

|     | 2.3.1. Integration-based stimulus generator                | 40 |

|     | 2.3.2. DAC-based stimulus generator                        | 44 |

|     | 2.3.3. Discussion                                          | 47 |

| 3.  | Servo-loop algorithm                                       | 49 |

|     | 3.1. Description                                           | 49 |

|     | 3.1.1. Classical servo-loop technique                      | 49 |

|     | 3.1.2. Proposed servo-loop technique for BIST application  | 51 |

|     | 3.2. Characterization and comparison of the two techniques | 56 |

|     | 3.2.1. Number of averaged samples                          | 56 |

|     | 3.2.2. Generator step size                                 | 59 |

#### Contents

|    |      | 3.2.3. Accuracy-test time trade-off                                      | 63  |

|----|------|--------------------------------------------------------------------------|-----|

|    |      | 3.2.4. INL estimation                                                    | 68  |

|    | 3.3. | Reduced-code testing techniques for pipeline ADCs                        | 70  |

|    |      | 3.3.1. Pipeline ADC overview                                             | 70  |

|    |      | 3.3.2. Application of the RCLT to pipeline ADCs                          | 78  |

|    | 3.4. | Proposed servo-loop algorithm with RCLT for pipeline ADC BIST $$         | 87  |

|    |      | 3.4.1. Description                                                       | 87  |

|    |      | 3.4.2. Comparison of the proposed servo-loop algorithm with and without  |     |

|    |      | RCLT                                                                     | 88  |

|    | 3.5. | Discussion                                                               | 89  |

| 4. |      | ign of a ramp generator for ADC testing                                  | 91  |

|    |      | Proposed signal generation technique                                     | 91  |

|    | 4.2. | Design considerations for a practical implementation of the proposed on- |     |

|    |      | chip stimulus generator                                                  |     |

|    |      | 4.2.1. Operational amplifier design                                      |     |

|    |      | 4.2.2. Finite gain and integrator leakage                                |     |

|    |      | 4.2.3. Gain bandwidth and slew rate                                      |     |

|    |      | 4.2.4. Input-referred noise                                              |     |

|    |      | 4.2.5. Operational amplifier input offset                                |     |

|    |      | 4.2.6. Charge injection and clock feedthrough                            |     |

|    |      | 4.2.7. Clock generation                                                  |     |

|    | 4.3. | Practical implementation                                                 |     |

|    |      | 4.3.1. Fully-differential ramp generator for static linearity ADC test   |     |

|    |      | 4.3.2. Layout of the generator                                           | 116 |

| 5. |      | ulation and experimental results                                         | 119 |

|    | 5.1. | Simulation results                                                       |     |

|    |      | 5.1.1. Ramp generator simulation results                                 |     |

|    |      | 5.1.2. Servo-loop simulation results                                     |     |

|    | 5.2. | Experimental results                                                     |     |

|    |      | 5.2.1. Test setups                                                       |     |

|    |      | 5.2.2. Ramp generator experimental results                               |     |

|    |      | 5.2.3. ADC test experimental results                                     | 136 |

| 6. | Con  | nclusion                                                                 | 141 |

|    | 6.1. | Summary of the contributions                                             | 141 |

|    | 6.2  | Further work                                                             | 143 |

|                       | Contents |

|-----------------------|----------|

| Bibliography          | 145      |

| Publications          | 153      |

| A. Résumé en français | 154      |

| Abstract              | 187      |

## **List of Figures**

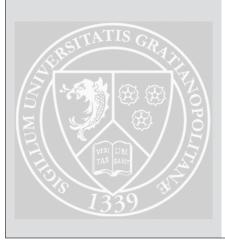

| 1.1.  | Cost of silicon manufacturing and test                                             | 1  |

|-------|------------------------------------------------------------------------------------|----|

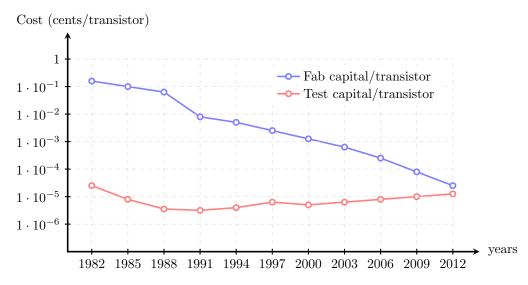

| 1.2.  | Pie chart of the test times per circuitry of a mobile phone SoC                    | 2  |

| 1.3.  | Simplified scheme of an industrial testbench                                       | 4  |

| 1.4.  | Verigy V93000 mixed-signal automated test equipment                                | 5  |

| 2.1.  | Transfer function of an ideal N-bit ADC                                            | 10 |

| 2.2.  | Representation of the DNL of an N-bit ADC                                          | 12 |

| 2.3.  | Representation of missing codes for an N-bit ADC                                   | 13 |

| 2.4.  | Representation of the INL of an N-bit ADC                                          | 14 |

| 2.5.  | Representation of the gain and offset errors of an N-bit ADC                       | 15 |

| 2.6.  | Histograms of input stimuli at ideal ADC output                                    | 17 |

| 2.7.  | Errors due to occurence probability of histogram-based test                        | 18 |

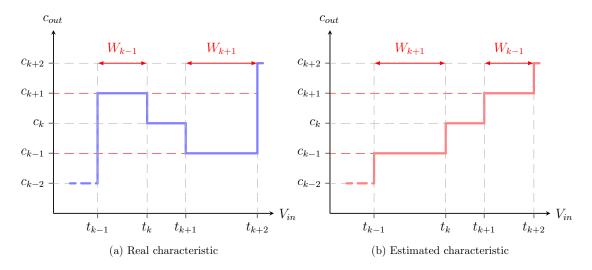

| 2.8.  | Two implementations of the servo-loop test                                         | 20 |

| 2.9.  | Experimental setup for testing an ADC with code density test or FFT test           | 21 |

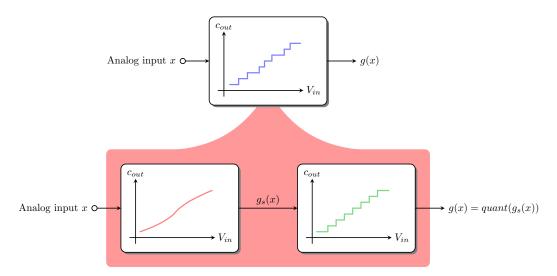

| 2.10. | Decomposition of the static ADC transfer function $g(x)$ in the cascade of         |    |

|       | a smooth nonlinear function $g_s(x)$ and an ideal quantizer $quant(x)$             | 23 |

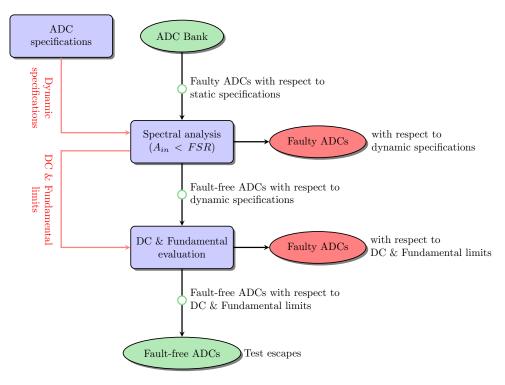

| 2.11. | (FFT + DC + Fundamental) test procedure                                            | 24 |

| 2.12. | Small triangle-wave test procedure                                                 | 25 |

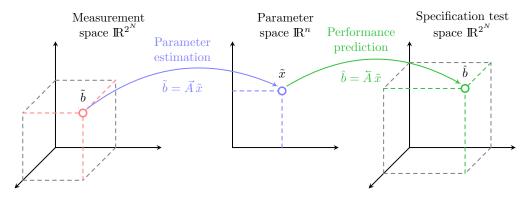

| 2.13. | Linear model-based testing of an N-bit converter: from a measurement $\tilde{b}$ , |    |

|       | to the least-squares estimate $\tilde{x}$ of the model parameter vector, and to an |    |

|       | approximation $\hat{b}$ of the unknown noise-free device characteristic            | 25 |

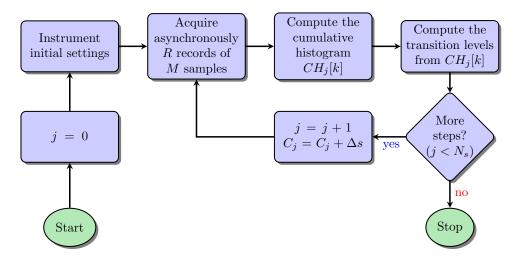

| 2.14. | Block diagram of the algorithm for dramatically more efficient ADC li-             |    |

|       | nearity test                                                                       | 26 |

| 2.15. | ADC test method using SEIR algorithm                                               | 28 |

| 2.16. | SEIR method with signal conditioning and resistive adder for the $V_{\alpha}$ off- |    |

|       | set generation                                                                     | 29 |

| 2.17. | Test setup for loop-back DAC/ADC SEIR method and $V_{\alpha}$ offset generation    | 30 |

| 2.18. | Blind-adaptive INL estimation method                                               | 32 |

| 2.19. | Example of code selection for a 4-bit SAR ADC reduced code linearity               |    |

|       | test (only one transition per bit to select for complete ADC test)                 | 33 |

| 2.20. | Oscillation-based ADC test method                                                  | 35 |

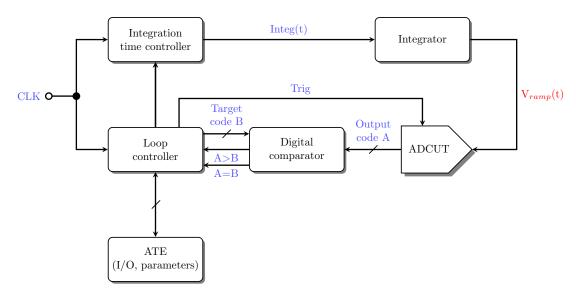

| 2.21. | Embedded servo-loop ADC test method                                                | 36 |

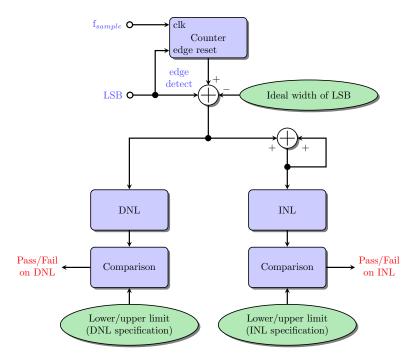

| 2.22. | Digital counter-based ADC BIST method                                              | 37 |

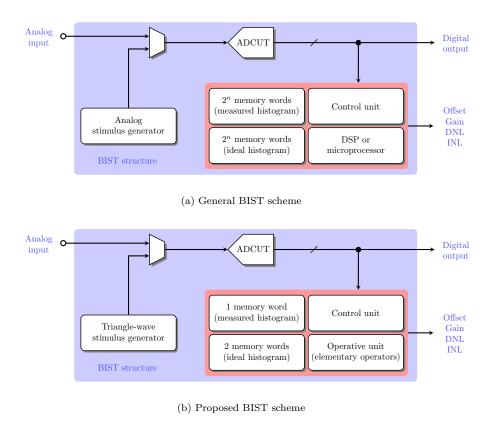

| 2.23. | ADC BIST resource minimization                                                     | 38 |

| 2.24. | Phase-controlled-stimulus ADC BIST technique                                       | 40 |

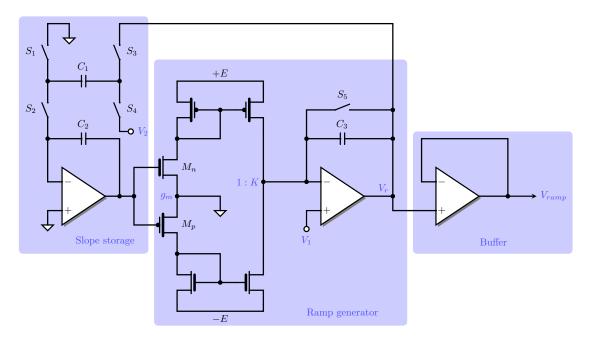

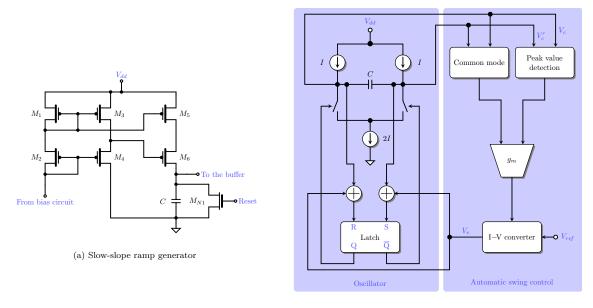

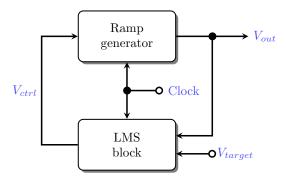

| 2.25. | Linear ramp generator with automatic slope adjustment                         | 41 |

|-------|-------------------------------------------------------------------------------|----|

| 2.26. | Two types of linear generators                                                | 42 |

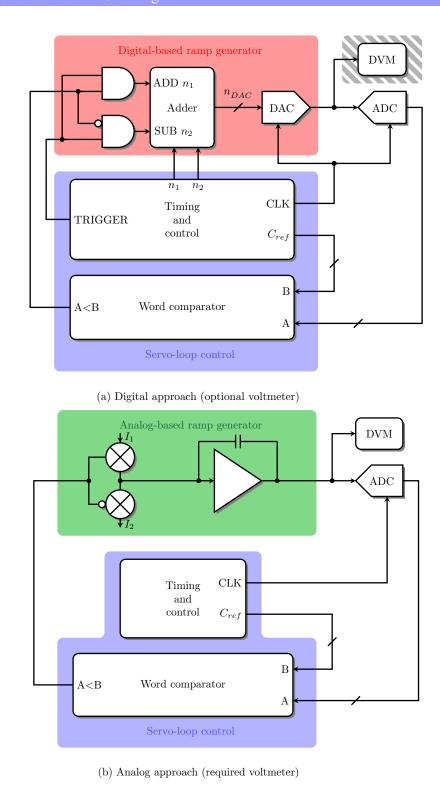

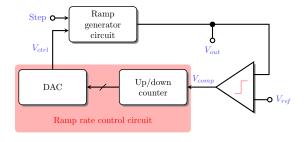

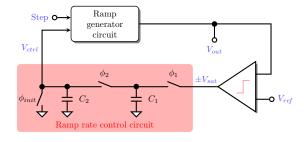

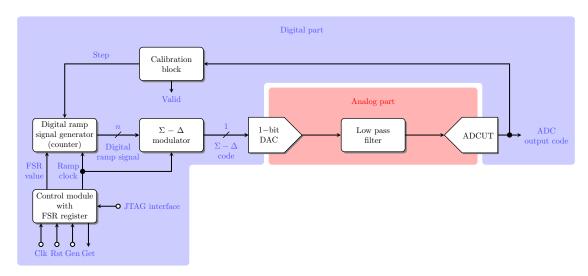

| 2.27. | Digital and analog adaptive ramp generators                                   | 43 |

| 2.28. | Block diagram of the adaptive LMS ramp generator                              | 44 |

| 2.29. | Structure of the $\Sigma\Delta$ -based on-chip analog ramp generator          | 45 |

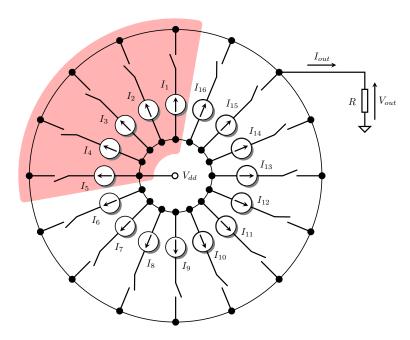

| 2.30. | Four-bit DDEM DAC with $P = 4$ and $k = 5$ , where sources $I_1$ to $I_5$ are |    |

|       | active (red section)                                                          | 46 |

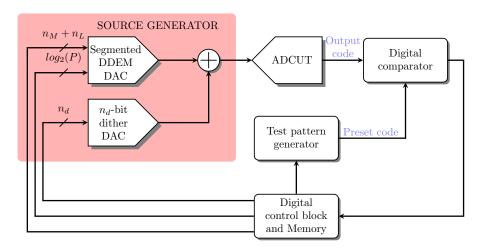

| 2.31. | Segmented DDEM DAC with $n_d$ -bit dither DAC BIST structure                  | 47 |

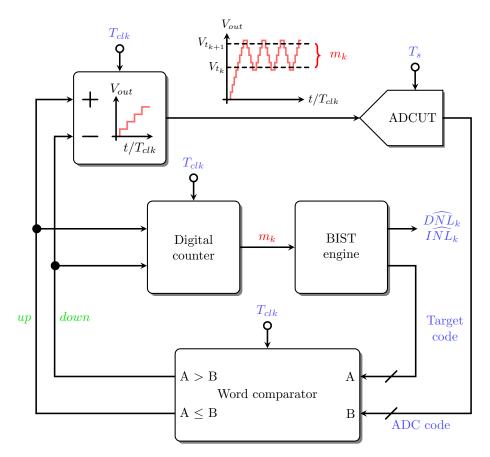

| 3.1.  | Schematic of the modified servo-loop circuit                                  | 52 |

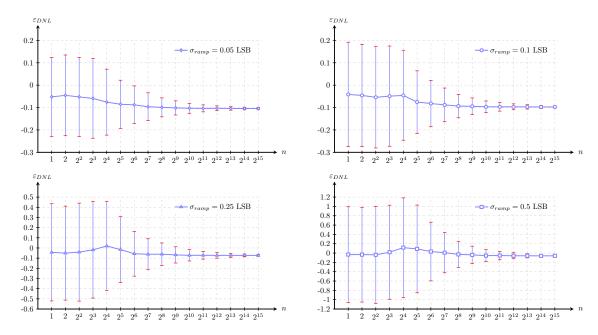

| 3.2.  | Mean and standard deviation of DNL estimation error with respect to the       |    |

|       | number of samples to average using the proposed servo-loop technique .        | 59 |

| 3.3.  | Mean and standard deviation of DNL estimation error with respect to the       |    |

|       | ratio of generator step size over the ADC input-referred noise magnitude      |    |

|       | using the classical servo-loop technique                                      | 61 |

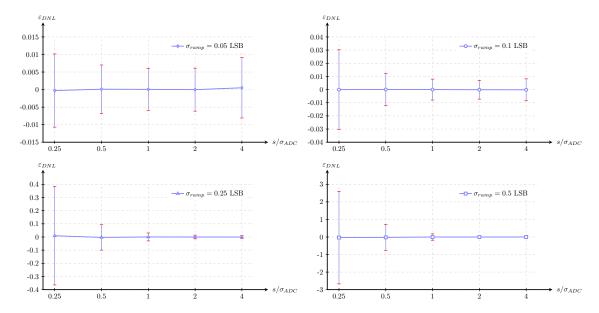

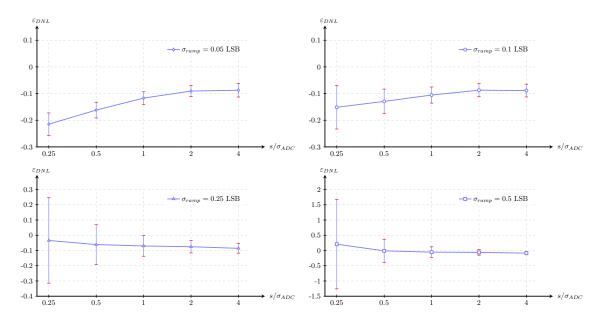

| 3.4.  | Mean and standard deviation of DNL estimation error with respect to the       |    |

|       | ratio of the generator step size over the LSB of the ADCUT using the          |    |

|       | classical servo-loop technique                                                | 62 |

| 3.5.  | Mean and standard deviation of DNL estimation error with respect to the       |    |

|       | ratio of generator step size over the ADC input-referred noise magnitude      |    |

|       | using the proposed servo-loop technique                                       | 63 |

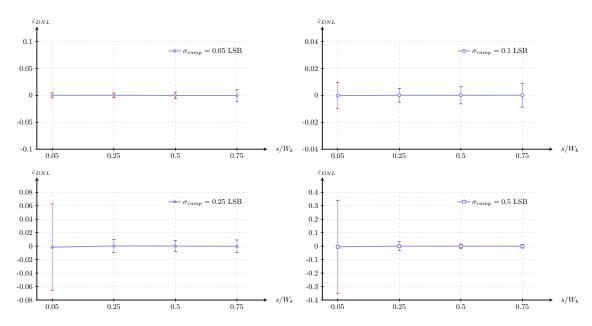

| 3.6.  | Mean and standard deviation of DNL estimation error with respect to the       |    |

|       | ratio of the generator step size over the LSB of the ADCUT using the          |    |

|       | proposed servo-loop technique                                                 | 64 |

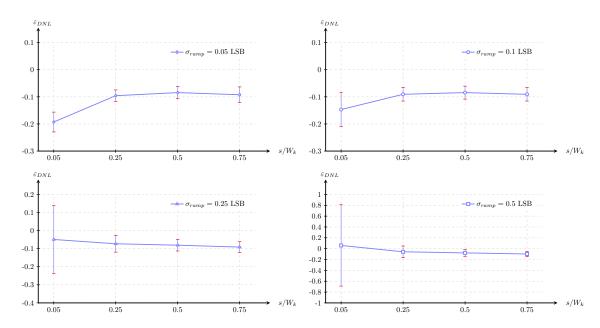

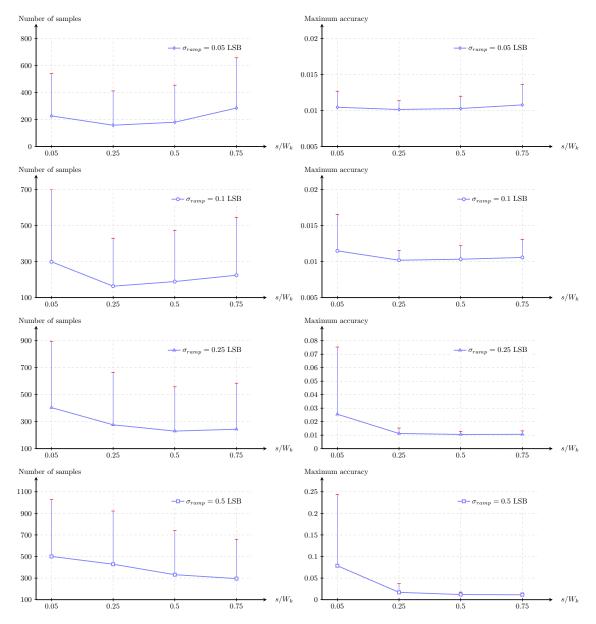

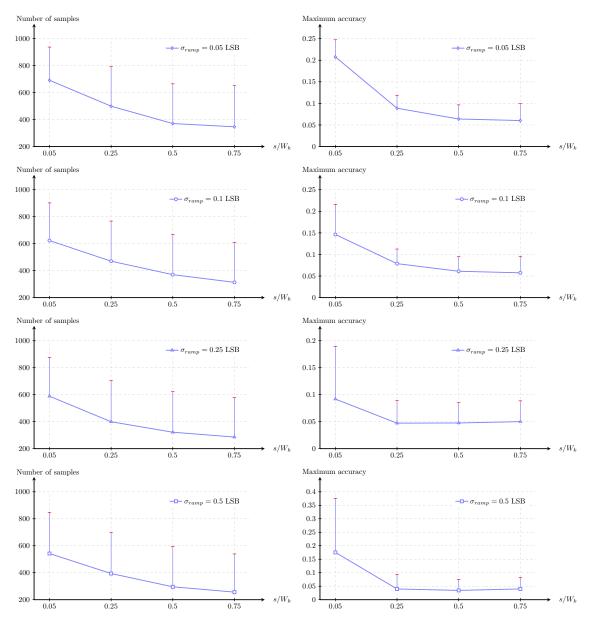

| 3.7.  | Mean value and standard deviation of the number of samples with respect       |    |

|       | to the ratio of the generator step size over the LSB of the ADCUT using       |    |

|       | the classical servo-loop technique                                            | 65 |

| 3.8.  | Mean value and standard deviation of the number of samples with respect       |    |

|       | to the ratio of the generator step size over the LSB of the ADCUT using       |    |

|       | the proposed servo-loop technique                                             | 67 |

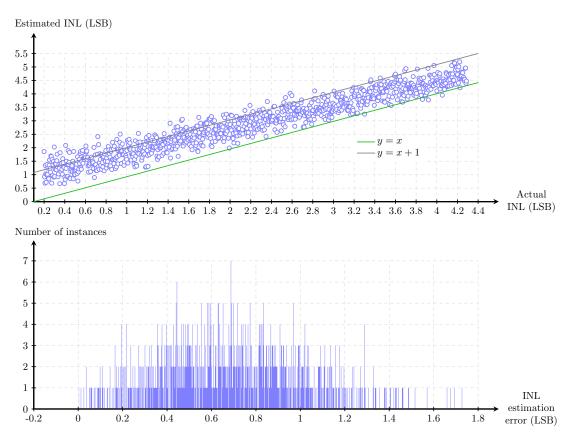

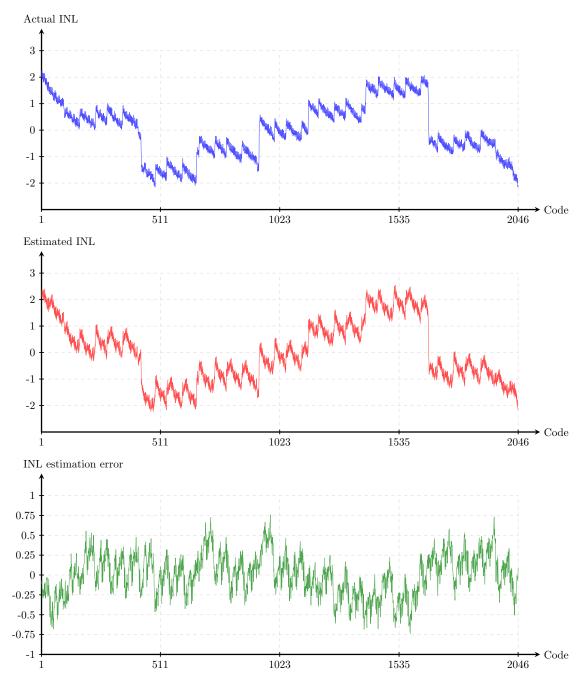

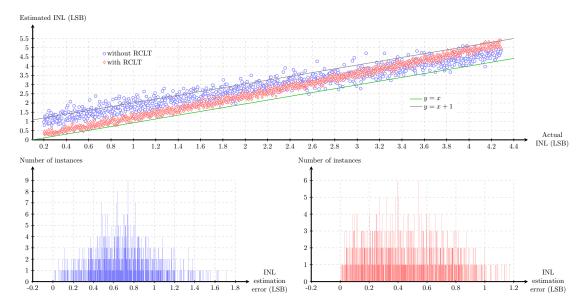

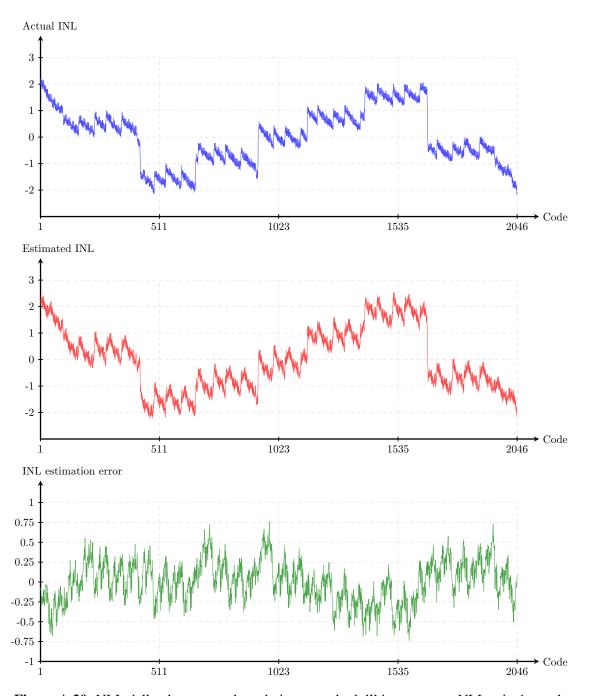

| 3.9.  | Estimated INL versus actual INL and respective histograms of the INL          |    |

|       | estimation error for 1000 ADC/ramp generator pairs using the proposed         |    |

|       | servo-loop technique without RCLT                                             | 69 |

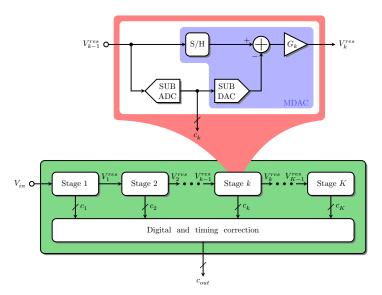

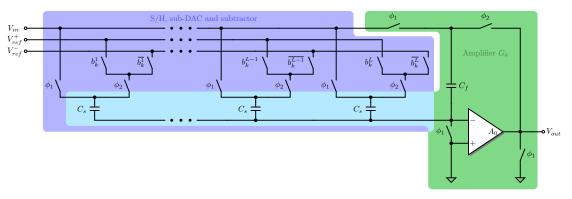

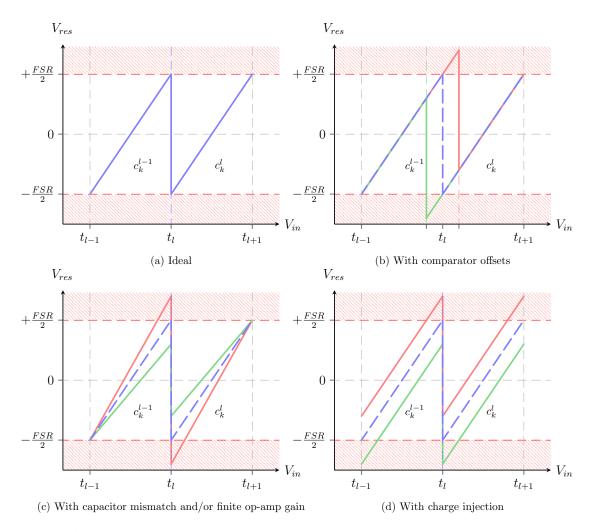

| 3.10. | Architecture of an N-bit, K-stages pipeline ADC                               | 71 |

| 3.11. | Transfer function of a pipeline stage when looking at transition $t_l$        | 74 |

|       | Ideal pipeline stage input-output transfer function                           | 75 |

| 3.13. | Digital correction logic scheme using redundancy                              | 77 |

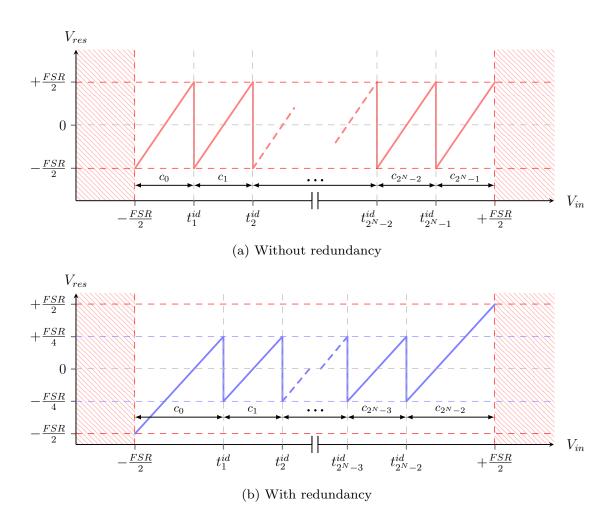

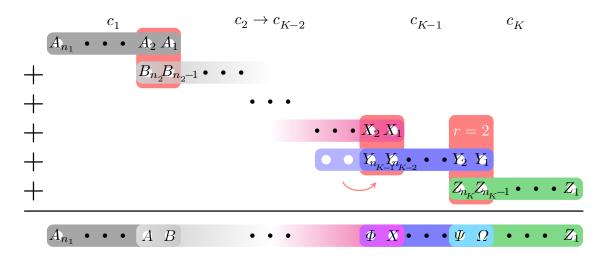

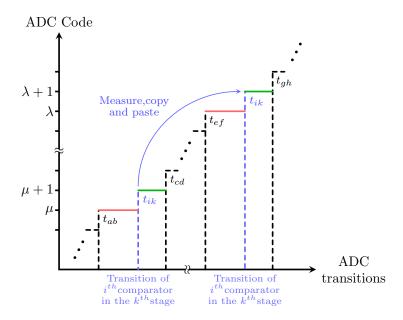

| 3.14. | Reduced-code testing technique principle                                      | 79 |

#### List of Figures

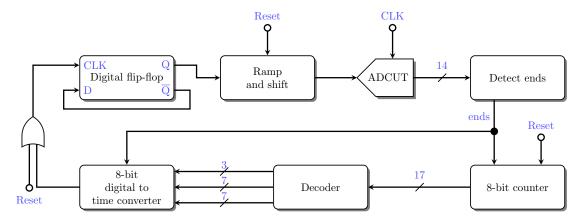

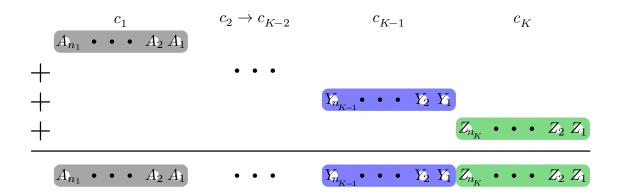

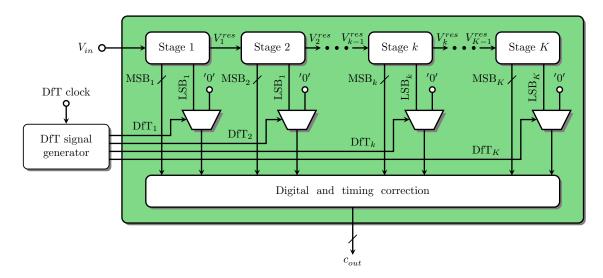

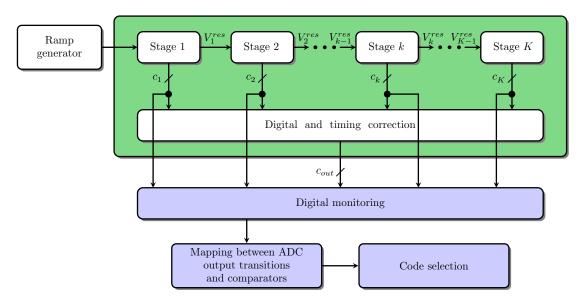

| 3.15. | Transition-code based BIST method for pipeline ADCs 80                          |

|-------|---------------------------------------------------------------------------------|

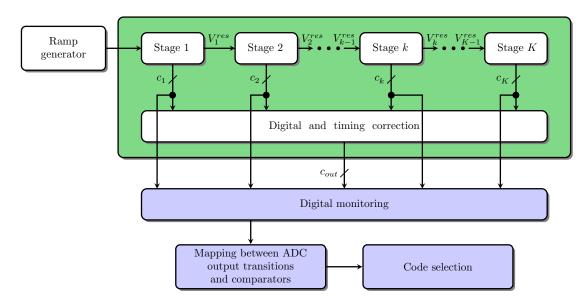

| 3.16. | Digital monitoring of the digital outputs of the pipeline stages 82             |

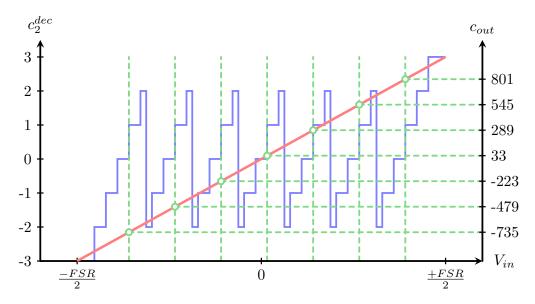

| 3.17. | Second stage digital decimal output $c_2^{dec}$ and corresponding digital deci- |

|       | mal output $c_{out}$ of a 2.5-bit/stage pipeline ADC model 85                   |

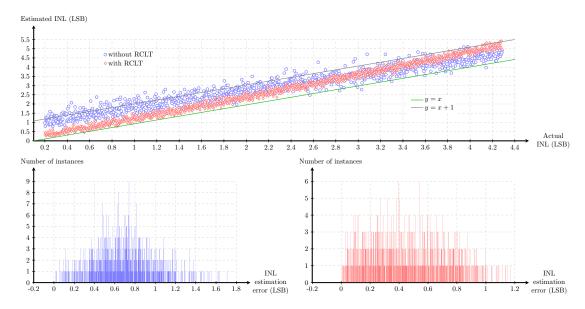

| 3.18. | Estimated INL versus actual INL and respective histograms of the INL            |

|       | estimation error for 1000 ADC/ramp generator pairs using the proposed           |

|       | servo-loop technique without RCLT, then with RCLT                               |

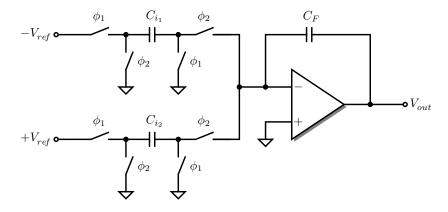

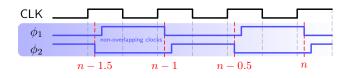

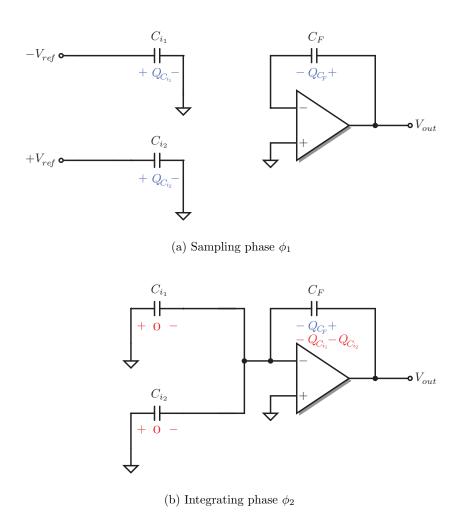

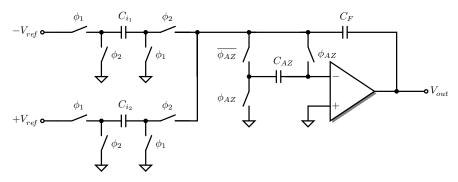

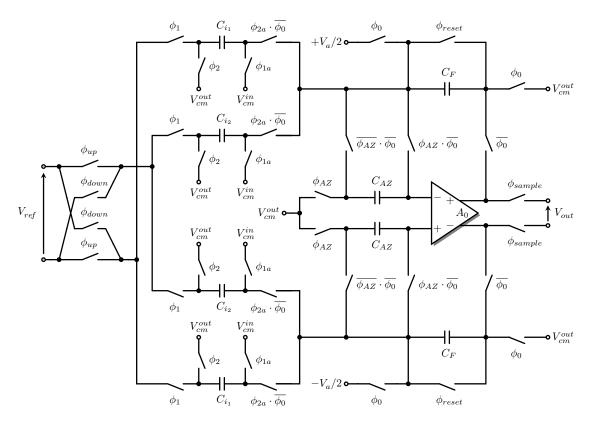

| 4.1.  | Proposed switched-capacitor ramp generator                                      |

| 4.2.  | Charges at phases $\phi_1$ and $\phi_2$                                         |

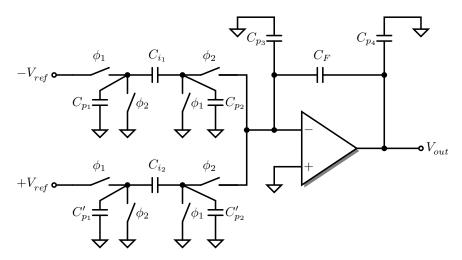

| 4.3.  | Proposed switched-capacitor ramp generator with parasitic capacitances          |

|       | shown                                                                           |

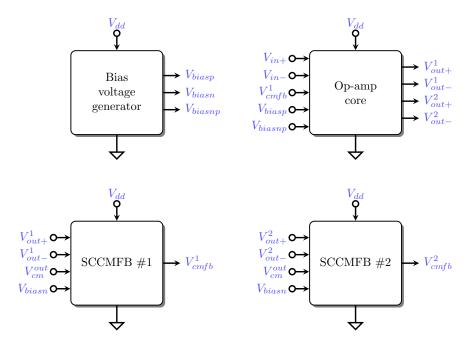

| 4.4.  | Architecture of the op-amp                                                      |

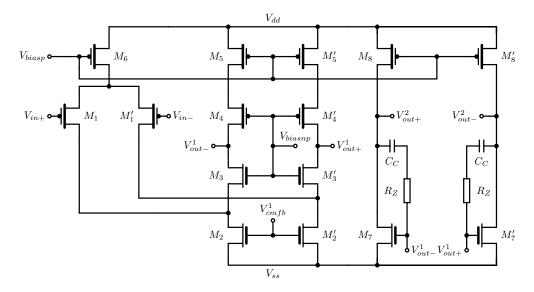

| 4.5.  | Fully differential two-stage folded cascode operational amplifier 97            |

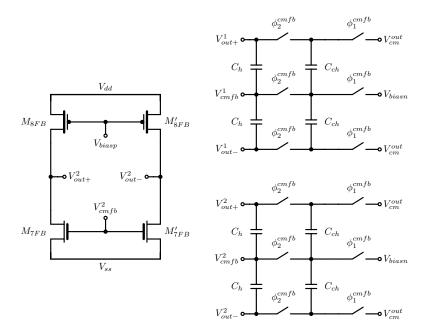

| 4.6.  | First-stage and second-stage SCCMFBs networks                                   |

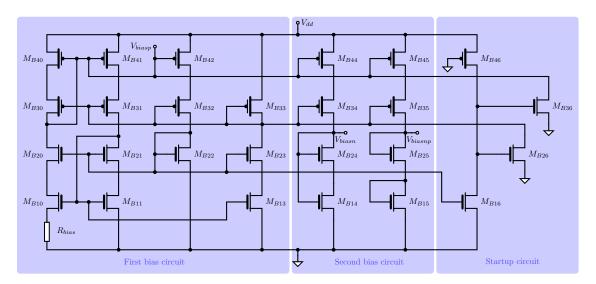

| 4.7.  | Self-biased bias generator with startup circuit                                 |

| 4.8.  | Auto zero implementation                                                        |

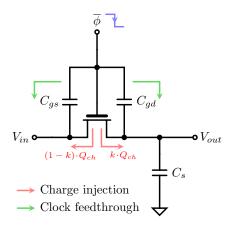

| 4.9.  | Sources of voltage errors on switches                                           |

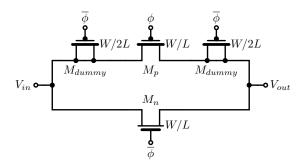

| 4.10. | Implementation of CMOS switches with dummy transistors 107                      |

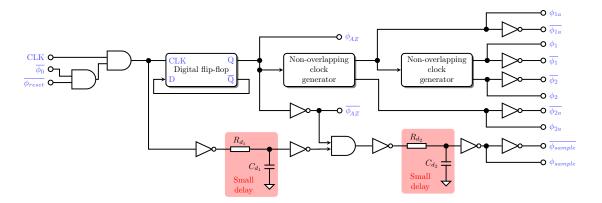

| 4.11. | Clock generation circuit                                                        |

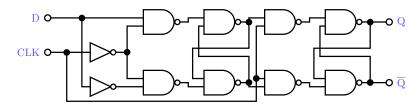

| 4.12. | Digital flip-flop circuit                                                       |

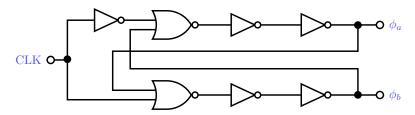

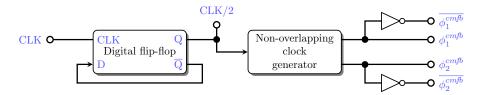

| 4.13. | Non-overlapping clock generation circuit                                        |

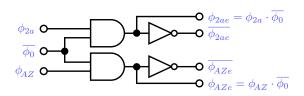

| 4.14. | Generation of the phases for the SCCMFB circuits                                |

| 4.15. | Circuit for integrator disabling during phase $\phi_0$                          |

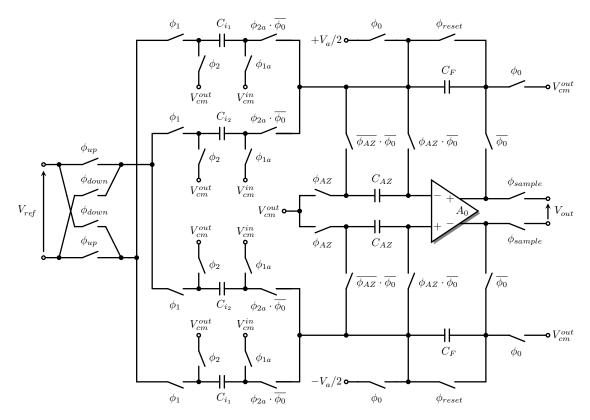

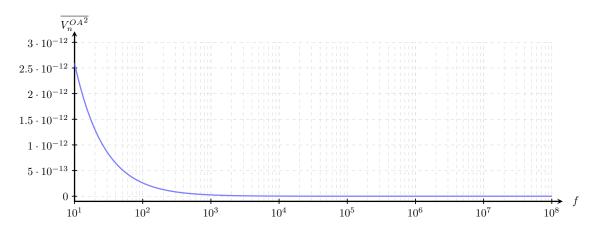

| 4.16. | Proposed fully-differential switched-capacitor ramp generator 112               |

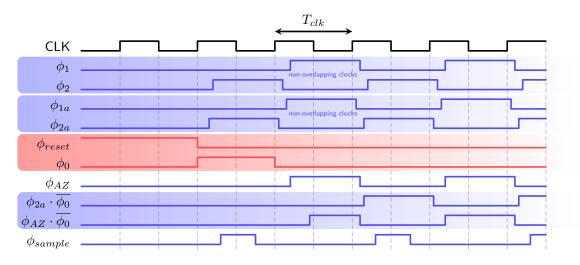

| 4.17. | Timing for the SC integrator                                                    |

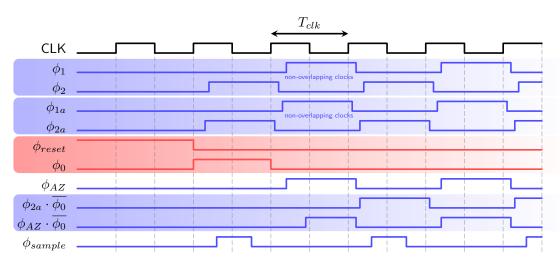

| 4.18. | Bode plot of the op-amp in open-loop operation                                  |

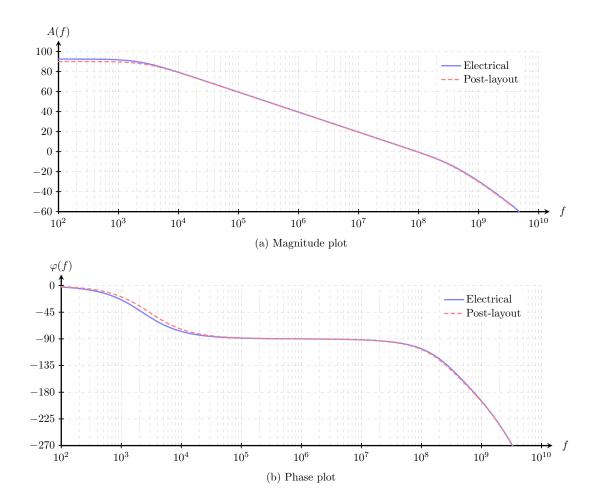

| 4.19. | Input-referred noise of the op-amp                                              |

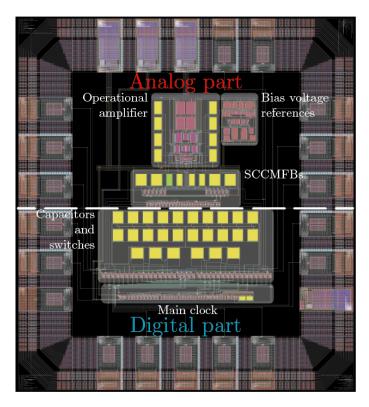

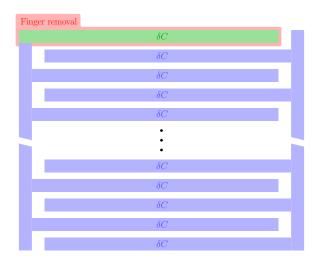

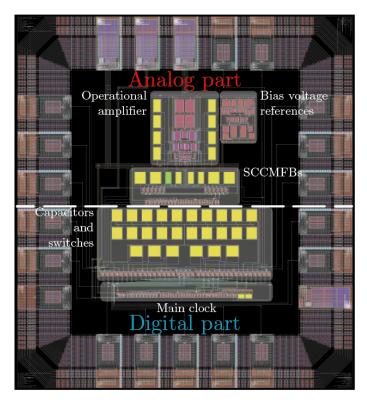

| 4.20. | Layout of the proposed generator                                                |

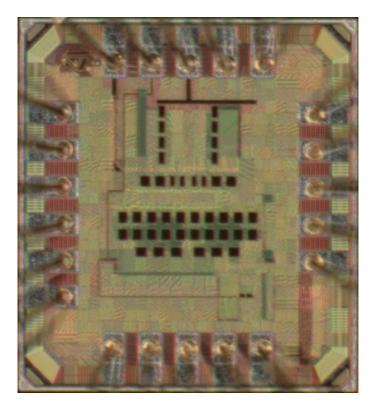

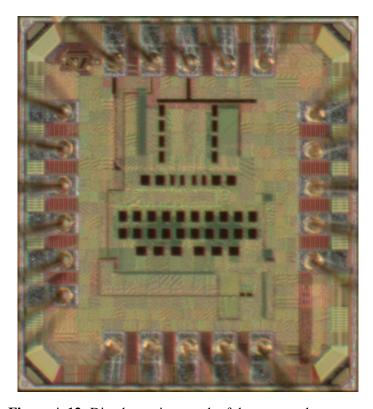

| 4.21. | Die photomicrograph of the proposed generator                                   |

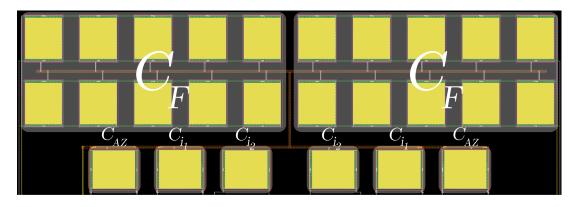

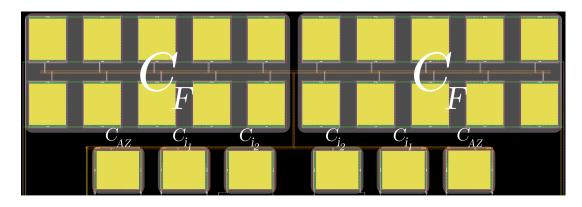

| 4.22. | Top view of the capacitor layout                                                |

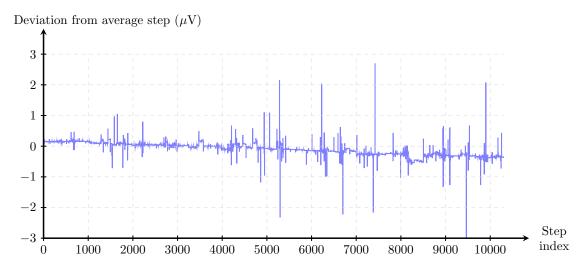

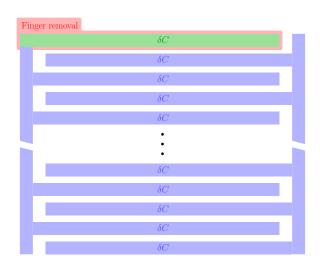

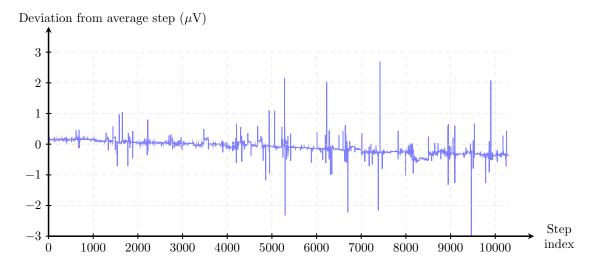

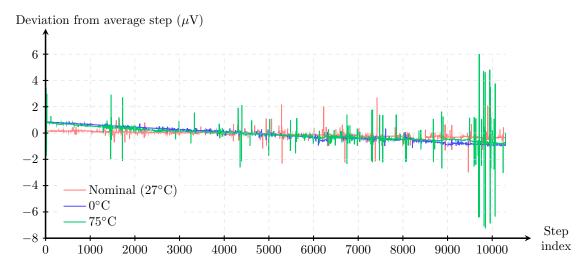

| 5.1.  | Deviation of the magnitude of the steps with respect to the average ramp        |

|       | step                                                                            |

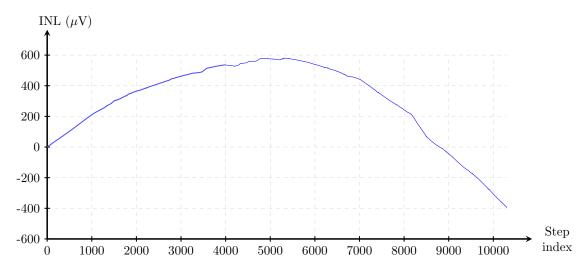

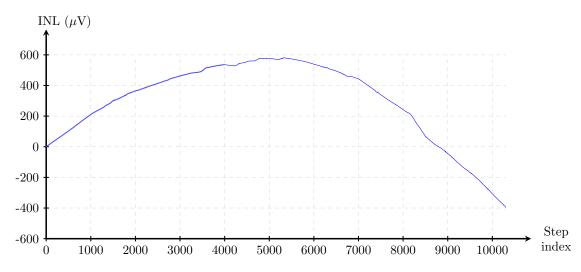

| 5.2.  | INL of the generated ramp                                                       |

| 5.3.  | Deviation of the magnitude of the ramp steps with respect to the average        |

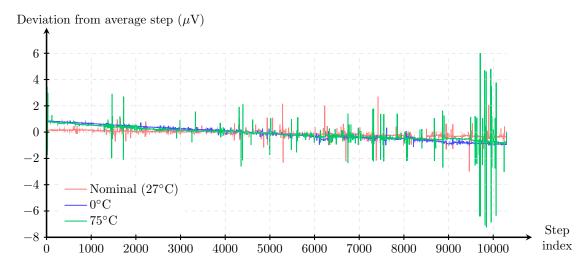

|       | ramp step at different operation temperatures                                   |

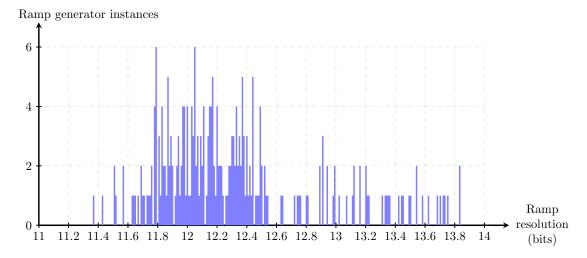

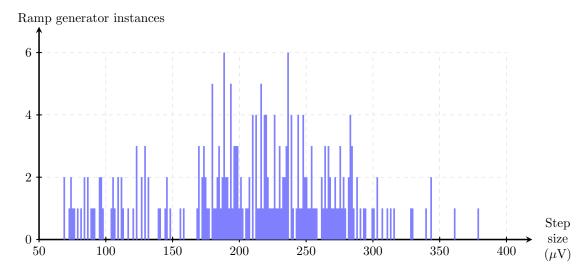

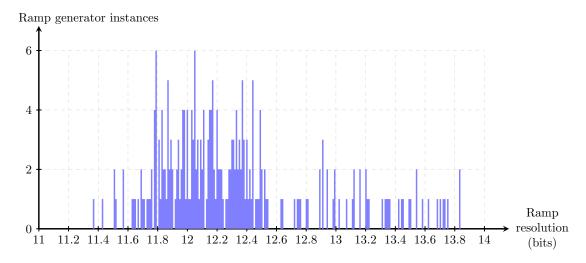

| 5.4.  | Histogram of the resolution of the generated ramp obtained by Monte                                        |     |

|-------|------------------------------------------------------------------------------------------------------------|-----|

|       | Carlo process and mismatch simulations                                                                     | 122 |

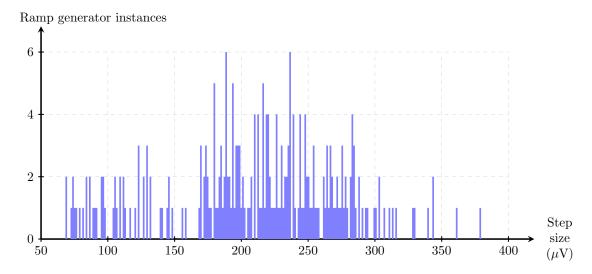

| 5.5.  | Histogram of the step size of the generated ramp obtained by Monte Carlo                                   |     |

|       | process and mismatch simulations                                                                           | 122 |

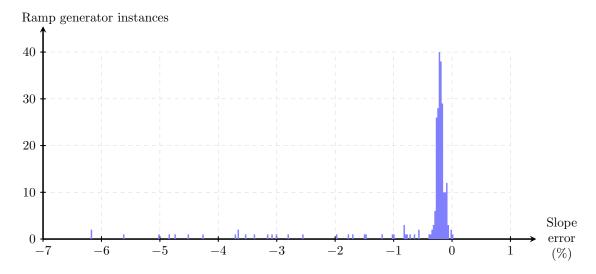

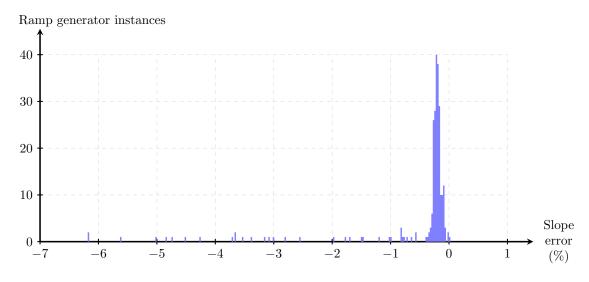

| 5.6.  | Histogram of the average slope error of the generated ramp obtained by                                     |     |

|       | Monte Carlo process and mismatch simulation                                                                | 123 |

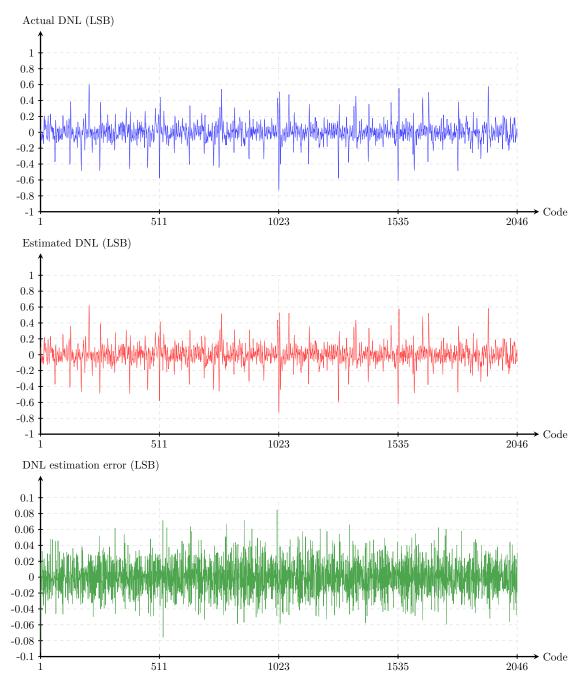

| 5.7.  | Actual INL obtained by standard histogram test, estimated INL obtained                                     |     |

|       | by BIST, and INL estimation error                                                                          | 124 |

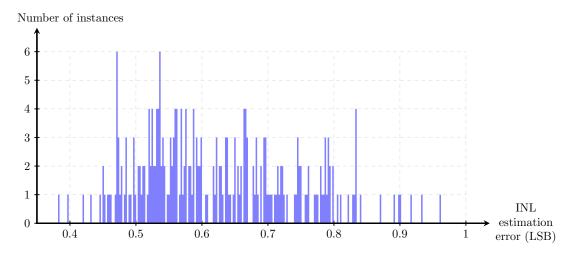

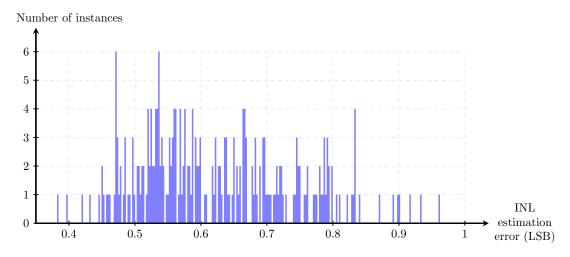

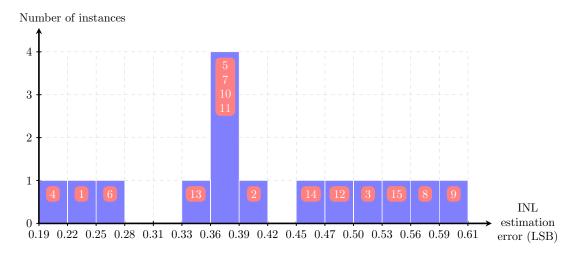

| 5.8.  | Histogram of the maximum absolute INL estimation error obtained by the                                     |     |

|       | BIST by assuming different Monte Carlo instances of the ramp generator                                     | 125 |

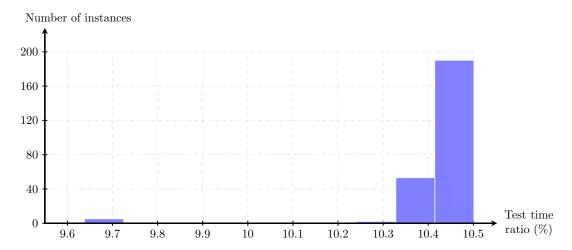

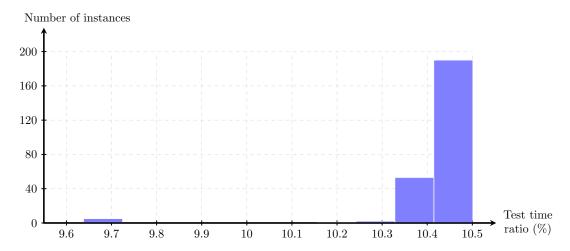

| 5.9.  | Histogram of the ratio of test times of the BIST with RCLT/without RCLT                                    | 126 |

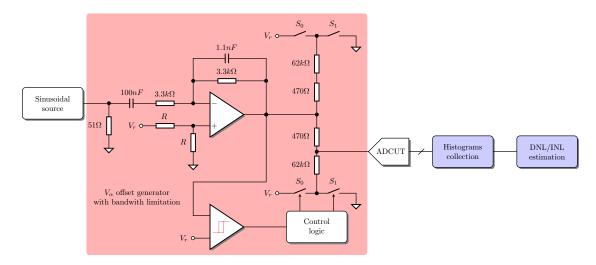

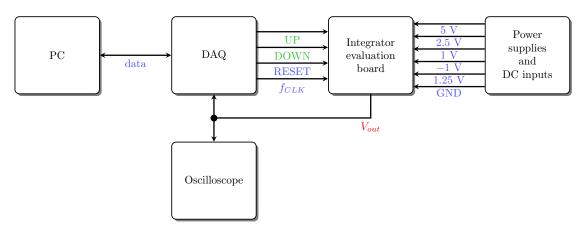

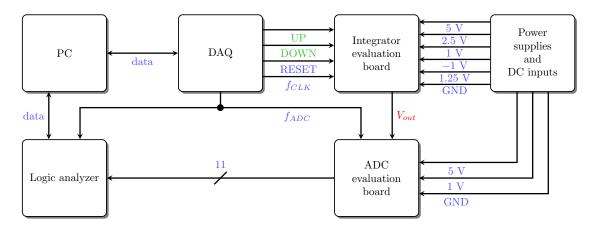

| 5.10. | Schematic of the test setup for the characterization of the ramp generator                                 | 127 |

| 5.11. | Schematic of the test setup for the ADC test                                                               | 127 |

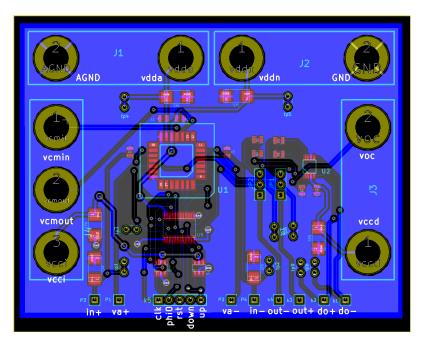

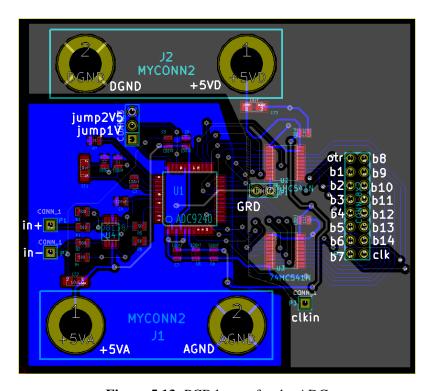

| 5.12. | PCB layout for the ramp generator                                                                          | 129 |

| 5.13. | PCB layout for the ADC                                                                                     | 129 |

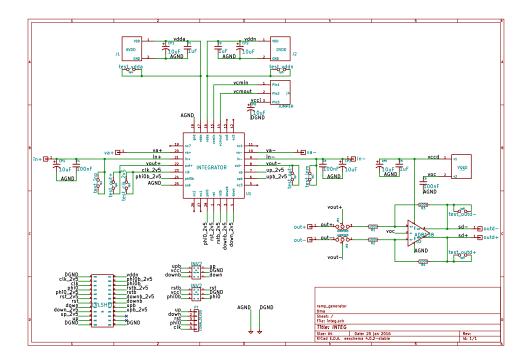

| 5.14. | PCB schematic for the ramp generator                                                                       | 130 |

| 5.15. | PCB schematic for the ADC                                                                                  | 130 |

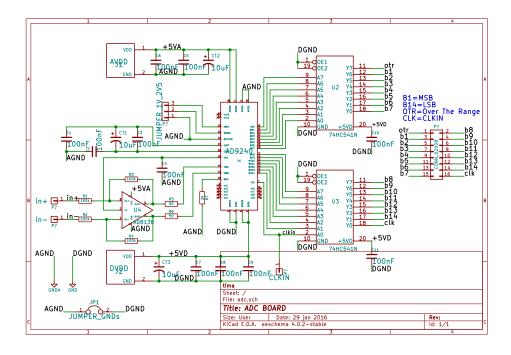

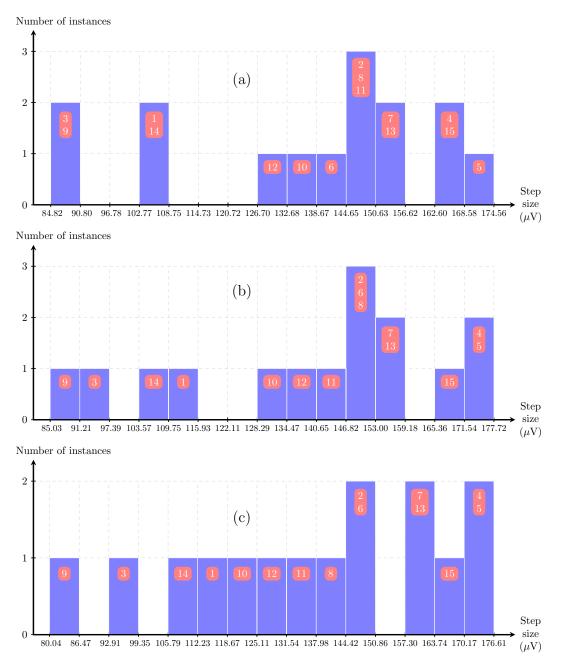

| 5.16. | Histogram of the measured step size for the 15 samples: (a) full output                                    |     |

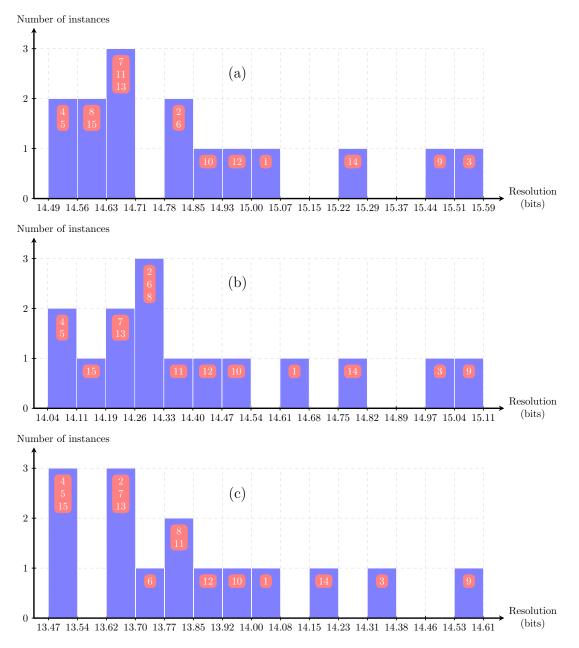

|       | range, (b) $-1.5 \text{ V/}+1.5 \text{ V}$ , (c) $-1 \text{ V/}+1 \text{ V} \dots \dots \dots \dots \dots$ | 132 |

| 5.17. | Histogram of the measured resolution for the 15 samples: (a) full output                                   |     |

|       | range, (b) $-1.5 \text{ V/}+1.5 \text{ V}$ , (c) $-1 \text{ V/}+1 \text{ V} \dots \dots \dots \dots \dots$ | 133 |

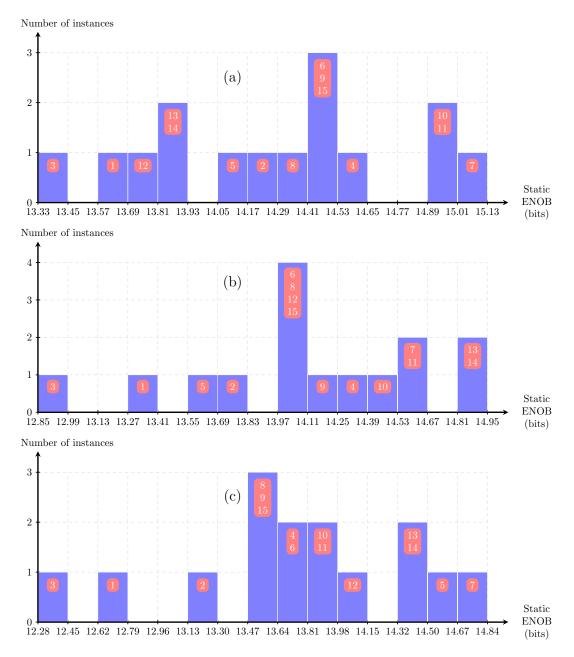

| 5.18. | Histogram of the measured static effective number of bits for the 15 sam-                                  |     |

|       | ples: (a) full output range, (b) $-1.5$ V/ $+1.5$ V, (c) $-1$ V/ $+1$ V                                    | 134 |

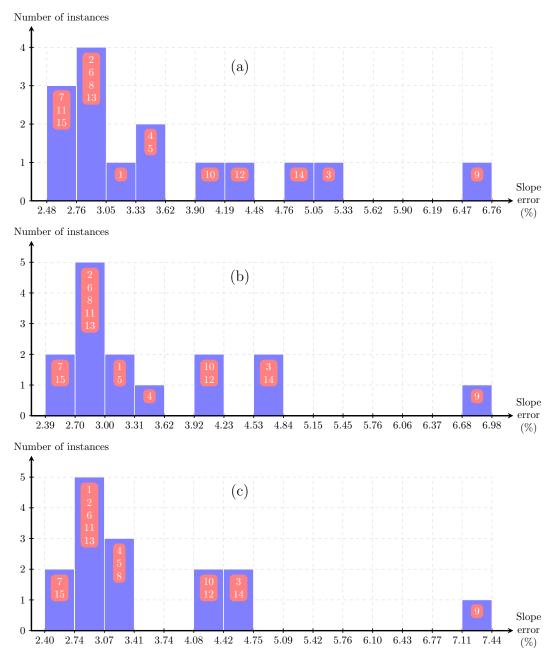

| 5.19. | Histogram of the measured slope error for the 15 samples: (a) full output                                  |     |

|       | range, (b) $-1.5 \text{ V/}+1.5 \text{ V}$ , (c) $-1 \text{ V/}+1 \text{ V} \dots \dots \dots \dots \dots$ | 135 |

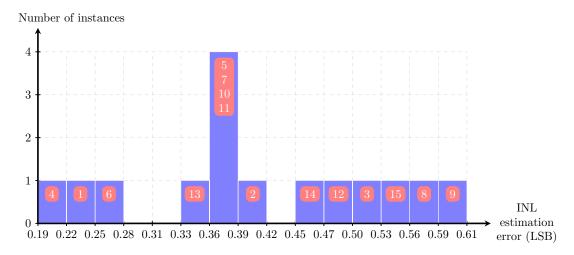

| 5.20. | Histogram of the measured INL estimation error of the ADCUT using                                          |     |

|       | the 15 samples (histogram test technique)                                                                  | 137 |

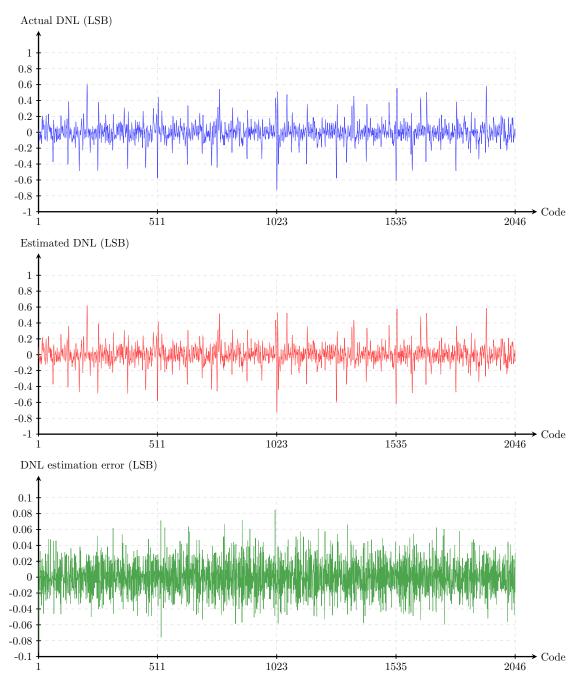

| 5.21. | Actual DNL obtained by standard histogram test and high-linearity sti-                                     |     |

|       | mulus, estimated DNL obtained by standard histogram test with sample                                       |     |

|       | #5, and DNL estimation error                                                                               | 138 |

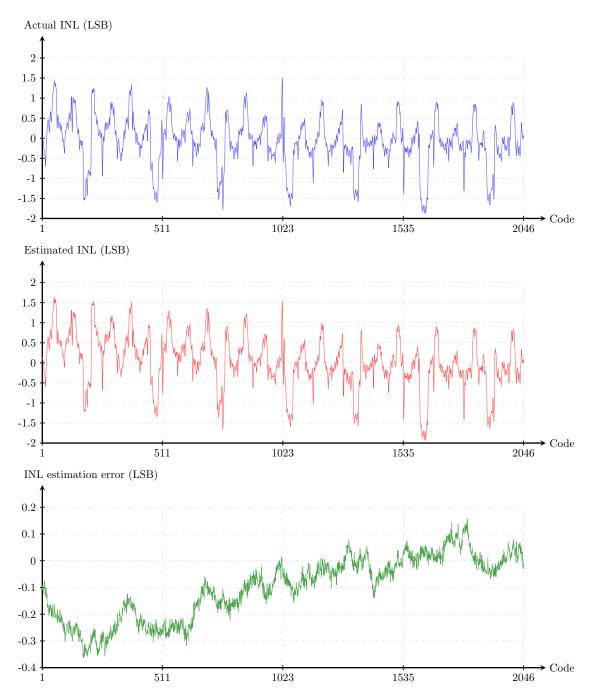

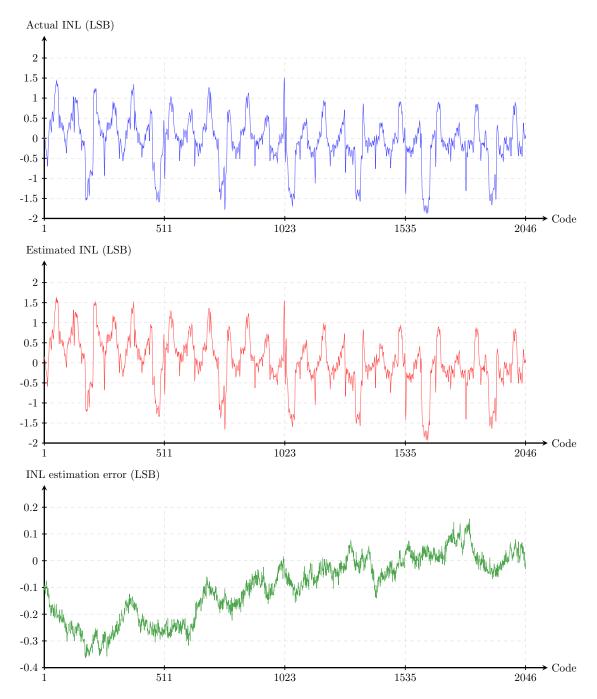

| 5.22. | Actual INL obtained by standard histogram test and high-linearity stimu-                                   |     |

|       | lus, estimated INL obtained by standard histogram test with sample #5,                                     |     |

|       | and INL estimation error                                                                                   | 139 |

## **List of Tables**

| 1.1. | Comparison of ATE analog and digital options cost                                                                                                                                    | 6   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1. | Comparison of ramp generation techniques                                                                                                                                             | 48  |

| 3.1. | Mean value and standard deviation in LSB of the estimation error for                                                                                                                 |     |

|      | the measurement of a transition voltage $V_{t_k}$ using the classical servo-loop technique ( $V_{t_k} = 1$ LSB, $s = 0.2$ LSB step, $\sigma_{ramp} = 0.5$ LSB, $\sigma_{ADC} = 0.15$ |     |

|      | LSB)                                                                                                                                                                                 | 57  |

| 3.2. | Mean value and standard deviation in LSB of the DNL estimation error                                                                                                                 |     |

|      | of code width $W_k$ using the classical servo-loop technique ( $W_k = 1$ LSB,                                                                                                        |     |

|      | $s = 0.2$ LSB step, $\sigma_{ramp} = 0.5$ LSB, $\sigma_{ADC} = 0.15$ LSB)                                                                                                            | 58  |

| 3.3. | Mean value and standard deviation in LSB for the measurement of a code                                                                                                               |     |

|      | width $W_k$ using the proposed servo-loop technique ( $W_k = 1$ LSB, $s = 0.2$                                                                                                       |     |

|      | LSB step, $\sigma_{ramp} = 0.5$ LSB, $\sigma_{ADC} = 0.15$ LSB)                                                                                                                      | 58  |

| 3.4. | Possible transitions in a 2.5-bit pipeline stage                                                                                                                                     | 83  |

| 4.1. | Goal specifications for the integrator                                                                                                                                               | 111 |

| 4.2. | Sizing of the op-amp and SCCMFBs                                                                                                                                                     | 113 |

| 4.3. | Sizing of the bias voltage generator                                                                                                                                                 | 114 |

| 4.4. | Sizing of the CMOS switches                                                                                                                                                          | 115 |

| 4.5. | Ramp generator parameters                                                                                                                                                            | 116 |

| 5.1. | Comparison of previous work on ramp generation with proposed solution .                                                                                                              | 136 |

### Introduction

#### 1.1. Context

In today's modern society, electronics are taking a prominent position as they are more and more associated to our daily life. Within the last 50 years, the semiconductor industry have shown a dramatic, exponential growth under the lead of Moore's law [?]. Integrated circuits (IC) are now widely used and serve multiple purposes for a large number of applications: consumer goods, avionics, automotive, medical applications, telecommunications, computing, etc.

Figure 1.1: Cost of silicon manufacturing and test [?]

While the manufacturing cost is steadily dropping (more than 30% cost reduction per year over the last 50 years), test cost tends to rise, or at least remains constant, as seen in Figure 1.1, extracted from the International Technology Roadmap for Semiconductors [?]. Indeed, the increasing complexity on a single die makes the test more and more difficult to perform, especially for analog and mixed-signal ICs. The primary role of production testing is to ensure that no defective devices are mistakenly sent to the market.

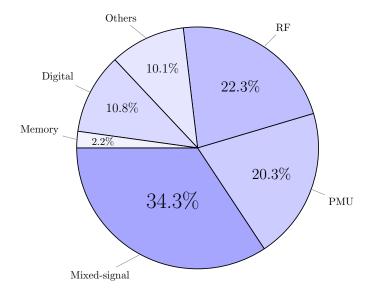

Figure 1.2: Pie chart of the test times per circuitry of a mobile phone SoC [?]

As a consequence, more than 50% of the overall production cost can be dedicated to IC testing during this crucial phase [?]. We can take the example of system-on-chips (SoC), containing analog, mixed-signal, digital, RF circuitry, even MEMS and optical devices on a single die. They have been developed since a few decades in an effort to reduce fabrication cost by embedding a complex system with a large set of functionalities on a single ship, with a higher level of integration, using new advanced deep submicron technologies. Testing such highly-integrated devices is a challenging task that has a direct impact on the yield and the throughput of the fabrication process. As an example, Figure 1.2 depicts the test time distribution of a mobile phone SoC. It takes into account the test, at wafer and package level, for the different subsections of the SoC (i.e. analog, digital, RF, power, etc.). It can be seen that the test time of the mixed-signal blocks is taking more than one third of the total test time (34.3%). RF and power management unit (PMU) blocks are also taking a significant amount of time compared to digital and memory devices in contrast with the total area occupation, that is dominated by digital circuitry ( $\geq$  90 % of the area of state-of-the-art SoCs).

A lenient test would indeed reduce test time and hence improve the yield and throughput of the fabrication process. However, we cannot forget that the cost of shipping defective parts, what is usually denoted as test escape (TE), is higher (approximately  $\times 10$ ) than the cost associated to yield loss (YL). Even more, it can damage a company public image.

#### 1.2. Industrial production testing

Current industrial test procedures for embedded analog and mixed-signal devices are becoming a major bottleneck in the production of these systems. Manufacturers must check the functionality stated in the data sheet of every IC before shipping them. Actually, the only selling point of a given IC is the set of performance figures listed in its data sheet, hence the importance of guaranteeing these figures to the customer with a proper and comprehensive test program.

Cost effective methods for testing the digital circuitry, based on standardized fault models, are already available. Digital circuits handle a discrete number of signal states, usually at discrete time intervals, and can then be studied from a high level of abstraction. This allows to define efficient structural test techniques aimed at detecting fabrication defects in the circuitry. Digital test is nowadays a (mostly) automated process in which an Automated Test Pattern Generator (ATPG) is used to generate an optimized test sequence that maximizes the defect detection rate for a given circuit based on a standardized set of fault models. Moreover, the silicon implementation of the test is also semi-automatic due to the adoption of standardized test access and BIST circuitry based on scan-chain shift-registers.

On the other hand, testing analog, mixed-signal, and RF circuits still relies on costly functional characterization. In contrasts to their digital counterparts, these circuits handle continuous signals and states affected by many sources of variability, and correct functionality can only be defined in terms of intervals or acceptance regions. Moreover, the relation between signals, states and variation sources is often non-linear and multidimensional. In this scenario, any standardization of a fault model is a challenging task (in spite of interesting recent advances in this line [?],[?],[?]), and the default test strategy relies on the complete functional characterization of the set of circuit performances. Similarly, standardized BIST techniques are also lacking.

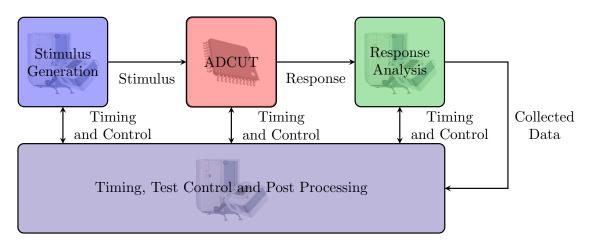

In current industrial AMS production test, an ATE generates a very well-controlled test stimulus at the DUT input, and acquires its output for further post-processing and performance assessment [2]. The simplified test bench is illustrated in Figure 1.3, and an example of widely-used ATE is shown in Figure 1.4. This is a time-consuming procedure, that is sensitive to environmental noise, loading conditions, etc. Furthermore, the test equipment, which consists of the ATE itself, the device interface board (DIB) and other daughter boards, is expensive because of the accuracy requirements for testing high-performance mixed-signal devices.

Figure 1.3: Simplified scheme of an industrial testbench

Nowadays, ATE suppliers are proposing a modular tester approach. The tester is equipped with different type of options depending on the DUT requirements: digital options, analog options, RF options, power options, etc. The DUT content (i.e. analog, digital, RF, power, etc.) will then define the tester configuration (tester options) and obviously the tester cost. Test cost can be split into two main components. To a first order, the capital expenditure (CapEx) is defined as the cost of ATE hardware, and the operational expenditure (OpEx) is defined as the labor cost ensuring the ATE is up and running. Other expenses (recurrent or not) are summing to the total cost as test boards, test sockets, or maintenance. However, these can be considered as second order costs. On an industrial point of view, labor cost can be reduced, so the main cost differentiator is the CapEx component. Moreover, when an ATE investment is amortized, the CapEx component disappears from the test cost structure, and the OpEx component is becoming dominant. Nevertheless, due to aging of the test equipment, the maintenance requirement is increasing over time, the CapEx component is still present because of the new spare parts cost.

Furthermore, the analog content of DUT directly have an impact on the CapEx component. The impact of an analog option onto the tester configuration cost is depending on the number of analog channels to address. Using 20% of the total number of analog channels yields about 75% of the tester configuration cost.

#### 1.3. Motivation

Focusing on AMS testing, the ATE must be equipped with analog and digital options. Table 1.1 shows the evolution of the CapEx component for both analog and digital options recorded for three consecutive generations of instruments (roughly equivalent to a

Figure 1.4: Verigy V93000 mixed-signal automated test equipment

15-year period) [?]. Over this time, the digital option integration factor has been more effective than the analog one. This could be explained by the fact that digital options take benefit of semiconductor Moore's law (reduced size, increased speed), while analog options performance is not linked to unitary transistor size. In average, the option cost has been decreased by 25% from one generation to another, regardless of the type of option (analog or digital). The cost ratio between a digital tester channel and an analog tester channel is constant along the three generations: an analog tester channel costs about ten times more than a digital tester channel.

In an effort to reduce the test cost, the BIST approach is a promising solution. Built-In-Self-Test consists in integrating some of the ATE functionality on the DUT itself, namely test stimulus generation, test response evaluation and test protocol control. This approach provides several advantages such as wafer-to-system testability, good test quality, at-speed testing, reduced need for ATE, reduced development time, more economical testing, reduced production test time and cost, and reduced time-to-market. Moreover, BIST advantages are not limited to production test. BIST enables in-the-field test during the complete lifetime of the DUT, it may be used for self-repair and adaptive operation, aging monitoring, self-test in inaccessible or rough environment, etc. However, it also comes at the expense of area overhead, risk of performance degradation, and additional design time. Moreover, a lot of challenges, especially for AMS testing, such as area overhead, test quality requirements in state-of-the-art applications, and test time reduction, are still challenging.

In this thesis, we will focus on ADC testing, and particularly on static linearity testing

|                                                  |      | Analog option<br>CapEx |        | Digital option<br>CapEx |        |        | Digital/Analog channel cost ratio |       |      |

|--------------------------------------------------|------|------------------------|--------|-------------------------|--------|--------|-----------------------------------|-------|------|

| Generation                                       | 1    | 2                      | 3      | 1                       | 2      | 3      | 1                                 | 2     | 3    |

| # of channels per option<br>(integration factor) | Ref. | ×2                     | ×4     | Ref.                    | ×1.25  | ×1.25  |                                   |       |      |

| Cost per channel evolution                       | Ref. | -11.3%                 | -39.8% | Ref.                    | -31.5% | -16.0% | 9.9%                              | 12.8% | 9.2% |

| Cost per channel evolution (average)             |      | -25.5%                 |        |                         | -23.7% |        | -                                 |       |      |

**Table 1.1:** Comparison of ATE analog and digital options cost

of pipeline ADCs. In this framework, ADCs are key components amongst mixed-signal devices because they can be found in every mixed-signal system along with digital-to-analog converters (DAC). They are the front-end between analog and digital sections in a mixed-signal system. Two types of test are usually performed: a static test targeted at static specifications such as differential and integral nonlinearities, gain and offset, and a dynamic test targeted at dynamic specifications such as equivalent number of bits, signal-to-noise ratio, signal-to-noise and distortion ratio, total harmonic distortion, spurious-free dynamic range, two-tone intermodulation distortion. During production testing of ADCs, Differential Non-Linearity (DNL) and Integral Non-Linearity (INL) are the two main metrics that are estimated for the static test.

In order to evaluate the static parameters of ADCs such as DNL and INL, standard testing techniques employ statistical methods. The main drawbacks appear when dealing with high resolution ADCs. The two main problems are the cost of the test equipment and the test time. Indeed, the input stimulus provided by the ATE has to be very linear, consequently tightening its specifications and increasing its cost. Moreover, the decreasing trend of the LSB amplitude makes the measurements more sensitive to noise. While the DNL (histogram technique) estimation is inherently robust versus Gaussian noise (stochastic behavior), INL estimation is not. A way to reach good INL measurements is to perform noise averaging. This implies a large amount of data to be collected and analyzed. Such a huge amount of data collection makes test time prohibitive.

A solution to the presented issues is to integrate the analog test stimulus generator inside the ADC under test (ADCUT). For example, the test of a 12-bit ADC should require one (single-ended or differential) analog channel for the ADC input, twelve digital channels for the ADC outputs and one more for the ADC clock input. In an embedded configuration, it can be computed that 43% of the CapEx cost is skipped because the analog channel is no longer needed. Another benefit of integrated signal generator is the

noise sensitivity. An internally generated signal routed outside the chip and looped back into the internal ADC might provide ten times more noise to the ADC input, which is problematic. The development of a static BIST method for high-resolution ADCs is then a promising solution for alleviating the cost of static test. Signal generation and manipulations remain internal to the system. The problem of accessing an embedded device is eliminated, and the requirements on the ATE, and hence its cost, are greatly reduced.

#### 1.4. Outline of this thesis

This thesis aims at the exploration of a novel technique for BIST ADC testing. The goal consists of developing a low-cost stimulus generator along with efficient measurement techniques for the evaluation of the static performance of high resolution ADCs, with a focus on pipeline ADCs. A feedback loop solution is implemented using a modified servo-loop technique in order to measure the ADC static metrics. The manuscript contains six chapters organized as follows.

Chapter 2 details the techniques employed for the static test of ADCs during a typical production testing flow. A review of the state-of-the-art techniques in the field of ADC testing and BIST is shown. Several works are detailed on the generation of a high-linearity test stimulus for ADC testing and BIST purposes.

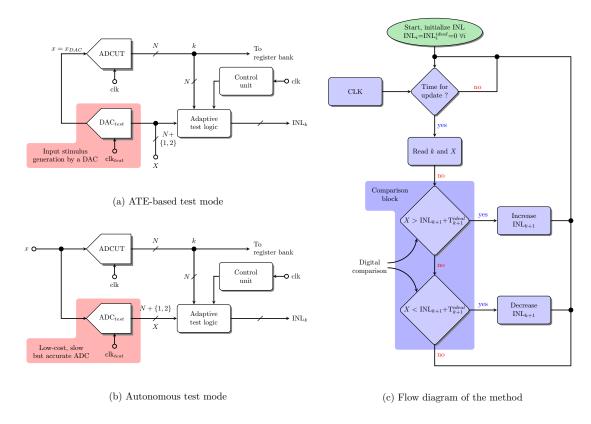

The proposed technique for ADC testing is explained in chapter 3. First, the concept of the technique is analyzed and studies are conducted to prove its efficiency for a BIST approach and show the trade-offs to consider. A comparison is made between the classical approach and our approach in terms of test time and accuracy. Then, a description of the pipeline ADC architecture and operation is provided. Finally, simulation results are presented on the modified technique in combination with a reduced-code linearity test algorithm.

In chapter 4, a high-linearity test stimulus generator designed for the BIST approach is described at system and transistor levels along with design techniques to reduce the inherent design nonidealities.

Chapter 5 details the simulation and experimental results of the proposed generator and BIST technique. First, the generator is characterized at transistor level using electrical simulations, and Monte-Carlo simulations are provided to verify the performance of the proposed generator. Then, the BIST strategy is evaluated using the data collected from the generator model using behavioral simulations. On the second part of the chapter, the results of the physical characterization of the fabricated ICs are presented along with

#### 1. Introduction

the test setup. Furthermore, the test chips are used to estimate the static linearity of a commercial ADC on its evaluation PCB, and validate the functionality of the intended stimulus generation.

Finally, chapter 6 concludes this thesis and discusses the directions for our future research on this topic.

# Chapter 2

## State of the art of ADC testing

#### 2.1. ADC performance testing

The performance of an ADC is usually expressed in terms of two sets of specifications, namely static and dynamic specifications. In the scope of this thesis, we will focus on the description of the static specifications, namely the DNL, INL, gain error and input offset error.

#### 2.1.1. Basic concepts

An analog-to-digital converter is a system that transforms samples of an analog signal  $x_k$  into a digital representation of these samples. Each analog sample is codified into a n-bit digital word  $c_k$ , where n is the ADC resolution and  $c_k \in [0; 2^N - 1]$ .

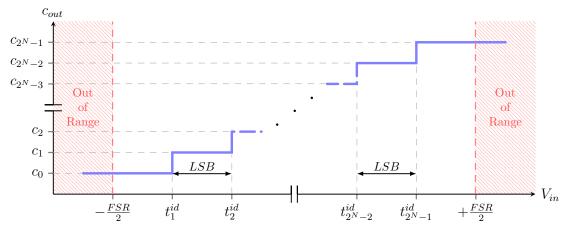

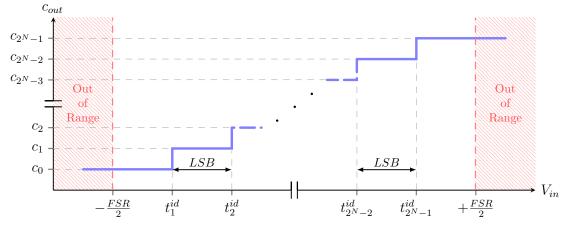

In general, an ideal ADC, as depicted in Figure 2.1, associates a different digital code to each of the  $2^N$  intervals in the input analog Full-Scale Range (FSR), [-FSR/2;FSR/2] (if bipolar, [0;FSR] if unipolar), in such a way that, provided an analog input x, the output c of the ADC can be expressed as

$$c = c_k \iff t_k \leqslant x < t_{k+1} \tag{2.1}$$

where  $t_k$  is the code transition threshold that defines the value at which the output of the converter switches from code  $c_{k-1}$  to code  $c_k$ . In an ideal converter, the distance between two consecutive thresholds is a constant, usually called Least Significant Bit (LSB), or converter quantum q. It can be expressed as

$$LSB = t_{k+1}^{id} - t_k^{id} \tag{2.2}$$

(a) Ideal characteristic (bipolar range with 2's complementary binary output)

Figure 2.1: Transfer function of an ideal N-bit ADC

where  $t_k^{id}$  and  $t_{k+1}^{id}$  are the ideal transition voltages for codes  $c_k$  and  $c_{k+1}$ . Equivalently,

$$LSB = \frac{V_{ref}^{+} - V_{ref}^{-}}{2^{N}} = \frac{FSR}{2^{N}}$$

(2.3)

where  $V_{ref}^+$  and  $V_{ref}^-$  represent the maximum and minimum input voltage values, and define the ADC full-scale range FSR. They also correspond to the virtual transitions  $t_{2^N}^{id}$  and  $t_0^{id}$ , respectively. For a bipolar ADC,  $V_{ref}^+ = FSR/2$  and  $V_{ref}^- = -FSR/2$ . If the ADC is unipolar,  $V_{ref}^+ = FSR$  and  $V_{ref}^- = 0V$ .

Moreover, the ADC can output different data representations. Amongst the most used are the Unipolar Straight Binary representation (USB) and the Binary Two's Complement representation (BTC). The USB representation is the most natural. It can be used for unipolar or bipolar input ranges, and sets  $c_0 = 0$  and  $c_{2^N-1} = 2^N - 1$ . The BTC representation, usually associated to a bipolar analog input range, sets  $c_0 = 2^{N-1}$  and  $c_{2^N-1} = 2^{N-1} - 1$ . The N-bit digital output is given a sign which depends on the value of its MSB.

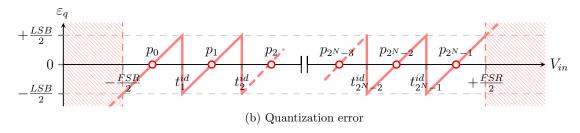

If the ideal ADC transfer function depicted in Figure 2.1 (a) is subtracted to a straight line between -FSR/2 and +FSR/2, the residue is called the quantization error  $\varepsilon_q$ . Points

where  $\varepsilon_q$  is null are called potencies  $p_k$  which ideal expression is

$$p_k = t_k^{id} + 0.5LSB, \quad k = 0, 1, ... 2^N - 1.$$

(2.4)

As seen in Figure 2.1 (b), finite amplitude resolution introduces a quantization error between the analog input voltage and the reconstructed output voltage. If it is assumed that the quantization error is a white noise having an uniform probability density function (PDF) over the code width from -LSB/2 to +LSB/2 defined as

$$PDF_{\varepsilon_q} = \left\{ \begin{array}{ll} 1/LSB & if \ |\varepsilon_q| < LSB/2 \\ 1 & otherwise \end{array} \right\}, \tag{2.5}$$

then the expected value of the quantization error power can be expressed as

$$P_{\varepsilon_q} = E[\varepsilon_q^2] = \frac{1}{LSB} \int_{-\frac{LSB}{2}}^{+\frac{LSB}{2}} \varepsilon_q^2 \cdot PDF_{\varepsilon_q} \ d\varepsilon_q = \frac{LSB^2}{12}. \tag{2.6}$$

This means that any input signal with a lower power than this power value is smeared into the ADC quantization noise.

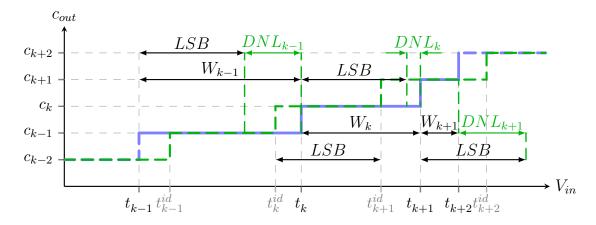

#### 2.1.2. Differential Non Linearity

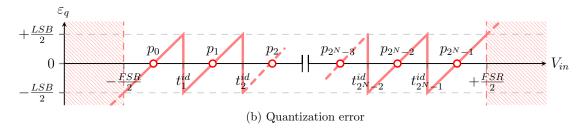

The Differential Non Linearity of an ADC is defined as difference between a specified code width and the ideal code width being the LSB of the ADC, divided by the LSB. It is a consequence of static errors in the components of the ADC under test. For example, the offsets in each comparator of a flash ADC are responsible for this local nonlinearities. Using equation (2.2), the DNL for code  $c_i$ , before gain and offset compensation, can be analytically expressed as

$$DNL_k = \frac{W_k - LSB}{LSB}, \quad k = 1, 2, \dots 2^N - 2$$

(2.7)

where  $W_k = t_{k+1} - t_k$  is the width of code  $c_k$ . With equation (2.7), it can be noted that neither  $DNL_0$  nor  $DNL_{2^N-1}$  are computed because the code widths  $W_0$  and  $W_{2^N-1}$  are not clearly defined.

In Figure 2.2, the DNL values of codes  $c_{k-1}$ ,  $c_k$ , and  $c_{k+1}$  are represented. For the given transitions,  $DNL_{k-1}$  and  $DNL_k$  have a positive value because  $W_{k-1}$  and  $W_k$  are above the LSB, whereas  $DNL_{k+1}$  has a negative value because  $W_{k+1}$  is below the LSB.

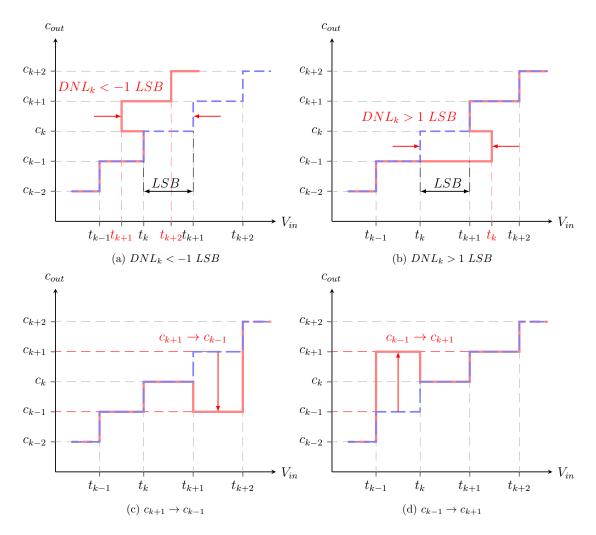

Figure 2.2: Representation of the DNL of an N-bit ADC

If the DNL of a code k is inferior to -1 LSB or superior to 1 LSB, then this code is a missing code. Those cases are shown in Figure 2.3. In Figure 2.3 (a), code  $c_k$  is missing because transition  $t_{k+1}$  is inferior to transition  $t_k$ , causing its DNL to be inferior to -1 LSB. Conversely, in Figure 2.3 (b), code  $c_k$  is missing because transition  $t_k$  is superior to transition  $t_{k+1}$ , causing its DNL to be superior to 1 LSB. In any case, if the DNL of each code is contained between -1 LSB and 1 LSB, the characteristic is assured to be monotonic.

Generally, the DNL of an ADC is expressed as the maximum of  $|DNL_k|$  for all k.

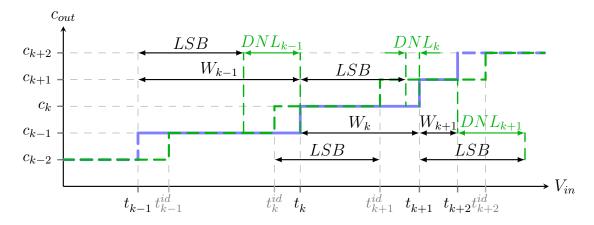

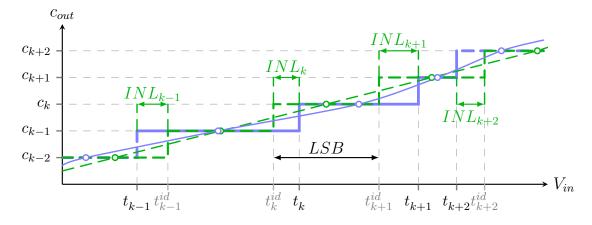

#### 2.1.3. Integral Non Linearity

The Integral Non Linearity of an ADC is defined as the difference of its transfer function with respect to the ideal transfer function line. It is seen as the cumulative sum of the DNL, so it can also take positive and negative values. The INL can be expressed before gain and offset compensation as

$$INL_k = \frac{t_k - t_k^{id}}{LSB}, \quad k = 1, 2, ... 2^N - 2.$$

(2.8)

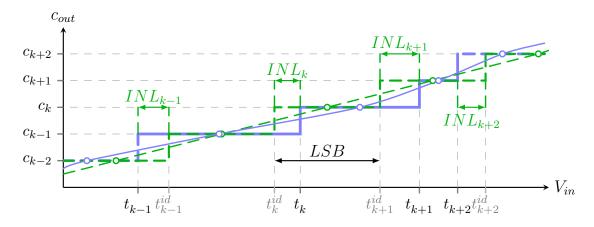

As an example, in Figure 2.4 are represented the INL values of codes  $c_{k-1}$ ,  $c_k$ ,  $c_{k+1}$  and  $c_{k+2}$ .

Generally, the INL of an ADC is expressed as the maximum of  $|INL_k|$  for all k.

The INL can be computed from the DNL as

$$INL_k = \sum_{l=0}^{k} DNL_l, \quad k = 0, 1, ... 2^N - 1$$

(2.9)

Figure 2.3: Representation of missing codes for an N-bit ADC

or vice versa as

$$DNL_k = INL_k - INL_{k-1}, \quad k = 0, 1, ... 2^N - 1.$$

(2.10)

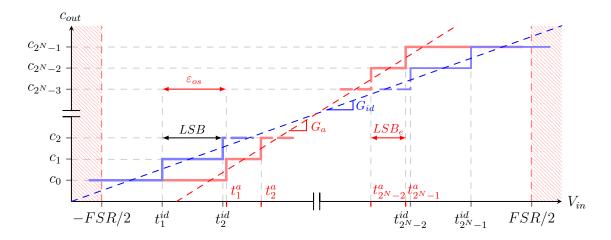

#### 2.1.4. Gain error

The gain error of an ADC is defined as the difference of the slope of the actual output values and the ideal output values. The actual gain of the ADC can differ from the ideal best-fit straight line and modify its real LSB value. In that case, with only the gain error taken into account, the transfer function for a given analog input x can be modeled as

$$c_k = \frac{x}{LSB_e} - \varepsilon_{q_e}, \quad t_k \leqslant x < t_{k+1}$$

(2.11)

with  $LSB_e = LSB/G_a$  the effective LSB value being the real value divided by the actual gain  $G_a$  of the ADC and  $\varepsilon_{q_e} = \varepsilon_q/G_a$  the effective quantization error of the ADC. After

#### 2. State of the art of ADC testing

Figure 2.4: Representation of the INL of an N-bit ADC

performing offset calibration, one can then define the resulting gain error as the ratio between the actual slope and the ideal one, giving the expression

$$\varepsilon_G = \frac{G_a - G_{id}}{G_a} \times 100\% \tag{2.12}$$

where  $G_{id}$  is the ideal value of the ADC gain and  $G_a$  is expressed as

$$G_{a} = \frac{dc_{out}}{dV_{in}}$$

$$= \frac{c_{2^{N}-1} - c_{1}}{t_{2^{N}-1}^{a} - t_{1}^{a}}$$

$$= \frac{2^{N} - 2}{t_{2^{N}-1}^{a} - t_{1}^{a}}$$

(2.13)

with  $t_{2^{N}-1}^{a}$  and  $t_{1}^{a}$  being the actual transition voltages induced by the gain error.

#### 2.1.5. Input offset error

The input offset error of an ADC is defined as a constant difference, over its FSR, between the actual output value and its ideal output value. It can be found when no input signal is fed to the ADC as the difference between the first actual transition and the first ideal transition of the ADC, namely

$$\varepsilon_{os} = V_{os_a} - V_{os_{id}}. (2.14)$$

Figure 2.5: Representation of the gain and offset errors of an N-bit ADC

#### 2.1.6. Correction of gain and offset

The gain error and the offset voltage can be corrected with a simple best-fit algorithm [1], which is used in this thesis work to also correct accumulated errors that leads in bad INL estimation.

First, four intermediate variables are computed from the estimated ADC nonlinearity as

$$\begin{cases}

k_1^0 = 0, k_2^0 = 0, k_3^0 = 0, k_4^0 = 0 \\

k_1 = k_1 + i \\

k_2 = k_2 + \widehat{INL}(i) \\

k_3 = k_3 + i^2 \\

k_4 = k_4 + i \cdot \widehat{INL}(i)

\end{cases}, \quad i = 1, 2, ..., 2^N - 1. \tag{2.15}$$

Then, the gain error and offset error can be estimated from equation (2.15) as

$$\left\{ \begin{array}{l}

\varepsilon_{G} = ((2^{N} - 1) \cdot k_{4} - k_{1} \cdot k_{2}) / ((2^{N} - 1) \cdot k_{3} - k_{1}^{2}) \\

V_{os} = k_{2} / (2^{N} - 1) - \varepsilon_{G} \cdot k_{1} / (2^{N} - 1)

\end{array} \right\}, \quad i = 1, 2, ..., 2^{N} - 1. \quad (2.16)$$

Finally, the best-fit line BF is computed from equation (2.16) and the corrected INL estimation  $\widehat{INL_{BF}}$  is evaluated as

$$\left\{ \begin{array}{l}

BF(i) = \varepsilon_G \cdot i + V_{os} \\

\widehat{INL_{BF}}(i) = \widehat{INL}(i) - BF(i)

\end{array} \right\}, \quad i = 1, 2, ..., 2^N - 1.$$

(2.17)

#### 2.2. ADC testing techniques

#### 2.2.1. Standard static linearity test techniques

This subsection first deals with the classical standardized testing techniques widely used in the industry. The two mainly employed techniques are the histogram-based linearity test and the servo-loop-based test. The histogram-based test is an open-loop technique, while the servo-loop-based test is a closed-loop one.

#### 2.2.1.1. Histogram-based testing

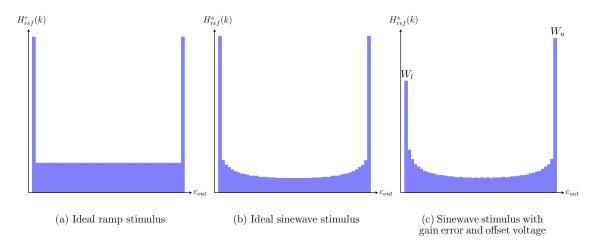

In the case of the histogram-based test technique, the ADC is excited by a very linear, quasi-static stimulus at its input. It can either be a ramp stimulus or a sinewave one.

The input is slow enough compared to the ADCUT sampling rate, so a very high amount of samples is collected for each code. Those samples are processed into a histogram where the number of occurrences for each code (hits per code) is represented. If the ADC is ideal, and an ideal ramp stimulus is applied to its input, the same amount of occurrences is expected to appear for each code, except for the first and last code because of the need to overdrive the ADC input. For an actual ADC, the nonlinear behavior is translated to variations of these occurrences. For a given code, the higher the number of hits per code, the higher is the width of the code and its associated DNL.

These differences are revealed by subtracting the actual ADC histogram to the ideal ADC histogram. The DNL is then computed for the whole transfer function of the ADC. Note however that in a practical implementation, the input stimulus might not be perfectly linear and might degrade the DNL estimation as the histogram now contains the nonlinearities of both the ADC and the stimulus. As a standard practice in the industry, the stimulus is chosen with a linearity 2 to 3 bits higher than the ADCUT in order to provide a significant measurement.

For a ramp stimulus, if  $H_k^r$  is the number of hits per code for code  $c_k$ , the ideal number of hits per code  $H_{ref}^r$  can be expressed as

$$H_{ref}^{r}(k) = n_T \cdot \frac{FSR}{2^N \cdot A_r}, \quad k = 1, 2, ... 2^N - 2$$

(2.18)

where  $n_T$  is the total number of samples collected on the ADC FSR and  $A_r$  the overdriving amplitude of the ideal ramp. From equation (2.18), the width of code  $c_k$  can be computed

Figure 2.6: Histograms of input stimuli at ideal ADC output

as

$$W_k = \frac{H_k^r}{H_{ref}^r}, \quad k = 1, 2, \dots 2^N - 2.$$

(2.19)

The DNL and INL of code  $c_k$  are then calculated as

$$DNL_k = W_k - 1 LSB, \quad k = 1, 2, ... 2^N - 2$$

(2.20)

and

$$INL_k = \sum_{k=1}^k DNL_k, \quad k = 1, 2, \dots 2^N - 2.$$

(2.21)

Histogram-based testing can be also performed using a sinewave stimulus. However, the distribution of the sinewave stimulus voltages is not uniform. Assuming they are acquired at a constant sampling rate, it implies gathering more samples at the extremes of the sinewave because of the higher sample density at its peaks. Then data collection has to be extended in order to have a sufficient number of hits at the center of the sinewave. Knowing the sinusoidal distribution, a compensation is carried out involving trigonometric calculations in order to compute DNL and INL.

The corrected reference histogram  $H_{ref}^s$  is computed as

$$H_{ref}^{s}(k) = \frac{n_{T}}{\pi} \cdot \left(\arcsin\left[\frac{k - (2^{N-1} - 1) - V_{os}^{s}}{A_{s}}\right] - \arcsin\left[\frac{k - 2^{N-1} - V_{os}^{s}}{A_{s}}\right]\right), \quad k = 1, 2, ... 2^{N} - 2$$

(2.22)

where  $V_{os}^s$  and  $A_s$  are respectively the offset and the gain of the sinusoidal stimulus. Considering  $W_l$  and  $W_u$  being respectively the occurrences of the first and last ADC codes

#### 2. State of the art of ADC testing

Figure 2.7: Errors due to occurence probability of histogram-based test

which are correlated to the lowest and highest peaks of the sinewave stimulus, we can calculate the offset  $V_{os}^s$  and the amplitude  $A_s$  of the sinusoidal stimulus as

$$V_{os}^{s} = (2^{N-1} - 1) \cdot \left( \frac{\cos(\pi \cdot W_{l}/n_{T}) - \cos(\pi \cdot W_{u}/n_{T})}{\cos(\pi \cdot W_{l}/n_{T}) + \cos(\pi \cdot W_{u}/n_{T})} \right)$$

(2.23)

and

$$A_s = \frac{(2^{N-1} - 1) - V_{os}^s}{\cos(\pi \cdot W_u/n_T)}.$$

(2.24)

The same reasoning as in the ramp stimulus case is applied for the DNL and INL calculation using equations (2.19), (2.20) and (2.21).

Notice however that this testing method has a major flaw. If the ADC has missing codes, its non-monotonic behavior might not be accurately measured. As an example, in Figure 2.7 (b), due to the accumulative function of the histogram-based method, the occurrences of missing codes  $c_{k-1}$  are incorrectly attributed to the occurrences of code  $c_{k+1}$  and vice-versa. This leads to two problems: first, codes  $c_{k-1}$  and  $c_{k+1}$  are not detected as missing, but are given an incorrect amount of occurrences, and secondly, the following transitions ( $t_k$  and  $t_{k+1}$  in the example) are estimated with offset errors.

#### 2.2.1.2. Servo-loop-based testing

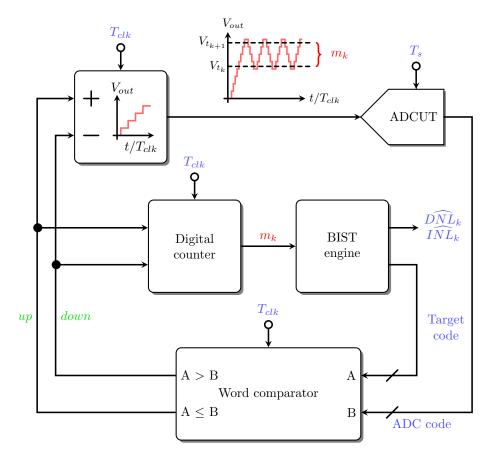

The servo-loop-based techniques are closed-loop approaches. The principle is shown in Figure 2.8. An input is applied to the ADC under test and the ADC outputs are compared to a reference code  $C_{ref}(k)$ , which specifies the code transition level  $t_k$  that needs to be determined.

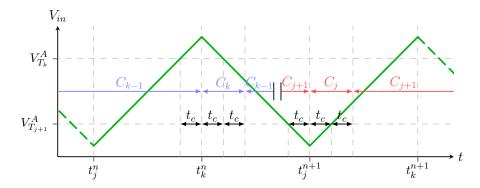

By setting a given target code transition  $t_k$ , if the ADC output code is below the targeted reference code  $C_{ref}(k)$ , the ADC input is raised until the corresponding transition  $t_k$  is met. If the output code is above or equal to the reference code, the ADC input is lowered until the target transition is crossed. Once the code transition level  $t_k$  has been reached, the input signal is forced to oscillate across this transition. The measurement of the transition voltage is now a triangle-wave signal oscillating around the real transition value. The signal is filtered in order to eliminate the oscillations and obtain a fixed estimated value, which can be compared later to the ideal voltage value in order to estimate the INL of the measured code C(k).

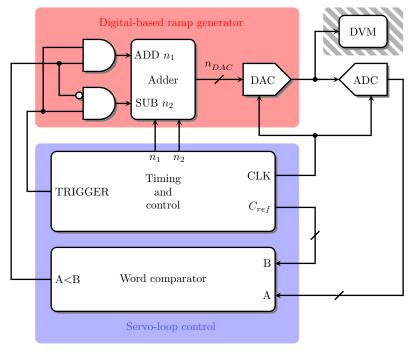

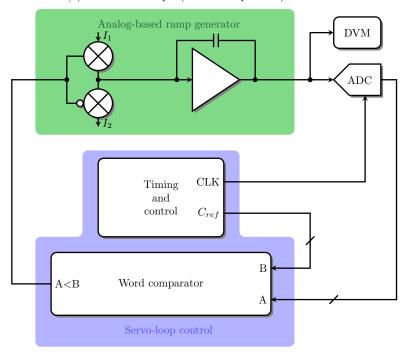

A schematic of the digital-based approach is given in Figure 2.8 (a) where an  $n_{DAC}$ -bit DAC generates the input stimulus. In this test,  $n_1$  and  $n_2$  are initially equal and given the value  $n_0$ . The DAC input value is set by adding or subtracting  $n_0$  after each conversion cycle according to the result of the comparison between the ADC output code and the targeted reference code  $C_{ref}(k)$ . This means that transition level  $t_k$  is known only to an accuracy of  $n_0$ . However, the DAC output step size can be as small as desired down to the DAC resolution ( $n_0$  equal to one DAC input code), so that iterating the test with smaller values of  $n_0$  enhances the measurement accuracy of this transition voltage. The ADC input level is calculated from the known transfer function of the DAC, or is measured by an optional high-precision voltmeter.

A schematic of the analog-based approach is given in Figure 2.8 (b). In this case, the input stimulus is generated by a current-driven integrator, delivering a continuous ramp stimulus. In the same manner, the charge pump composed of current sources  $I_1$  and  $I_2$  delivers a current into the capacitor which integrates it into a voltage ramp. If the ADC output code is below the targeted reference code  $C_{ref}(k)$ , the current source  $I_1$  injects current into the integrating capacitor, raising the integrator output with a positive slope ramp. If the ADC output code is above or equal to the reference code, the current source  $I_2$  pumps out current from the integrating capacitor and the integrator output is lowered with a negative slope ramp. With a fixed capacitor size, the positive and the negative slopes are determined by the magnitude of the currents sources  $I_1$  and  $I_2$ .

In any case, the resolution of the generator, analog or digitally driven, should be higher than the resolution of the ADC under test in order to obtain a desired precision for the measurements. Moreover, due to noise, averaging is necessary and the magnitude of the voltage increment should be chosen accordingly. The interested reader can find more information in [3], [4], [5] and [6] and this topic is further discussed in chapter 3.

**Figure 2.8:** Two implementations of the servo-loop test [2]

#### 2.2.2. State-of-the-art static linearity test techniques

As the complexity and resolution of the ADCUT rise, more effort must be put into producing a test stimulus with greater quality. Conventional testing techniques will eventually

Figure 2.9: Experimental setup for testing an ADC with code density test or FFT test [7]

comply with the requirements, but at a very high expense in terms of test equipment and ever-increasing test time, as stated in section 1.1. To that purpose, alternative test techniques have been investigated over the last years, dampening the need for costly ATE while keeping a relatively high level of accuracy. In the first part of this subsection, we will talk about present advanced DfT strategies for ADC testing while in the second part we will focus on BIST solutions.

#### 2.2.2.1. DfT techniques

DfT is defined as any technique implemented at design level in order to facilitate the test of a particular DUT. In this subsection, we present relevant DfT techniques for ADC static test.

The work in [7] proposes an open-loop computer-aided ADC characterization technique which relies on the code density test and spectral analysis using the Fast Fourier transform (FFT). The code density test produces a histogram of the ADCUT output which samples a known input sinewave stimulus. The DNL and INL can be extracted from the code density as well as gain error, offset error, and internal noise. Three different successive approximation (SAR) ADCS are tested: an 8-bit resistor-string ADC, a 12-bit R-2R ladder ADC, and a 15-bit self-calibrating ADC. For the first ADC, a precision of 0.1 LSB on the INL estimation error is met with 268000 samples. The paper compares the proposed method to the classical servo-loop test method, showing an improvement in the test time by a factor 10, but still very slow. FFT tests are also performed on the 12-bit ADC to measure its INL, distortion, and signal-to-noise ratio. The maximum INL is directly estimated by measuring the spurious free dynamic range (SFDR) out of the FFT curve. The experimental test setup is shown in Figure 2.9. The technique is effective but involves several minutes of test time and complex computations for FFT operation.

### 2. State of the art of ADC testing

The works in [8], [9], and [10] propose to use a noisy signal as input for ADC linearity test. The method in [8] presents a statistical method for characterizing ADCs using Gaussian noise as the test stimulus for the histogram test. Nonetheless, the measurement of maximum INL is prone to large errors and a high number of samples is needed for the test procedure to work. Furthermore, a high-speed DAC is required in order to characterize the ADC.

The work in [9] employs the classical histogram method to evaluate the ADC nonlinearity with  $2^{22}$  collected samples. The noise-based approach is compared to the standard sinewave-based approach. Results show that the two INL curves have the same trend, but the INL estimation error is about 4 LSB at 12 bits. Although the methodology allows an automated and extensive characterization of the ADCUT static parameters, it still requires a high-linearity DAC and the computations are very complex, thus not suited for a BIST implementation.

The work in [10] is based on the use of a simple set of DC voltages on which a white Gaussian noise signal is applied. The test method relies on a set of repeated measurements. Although they are not needed to be equally spaced, the set of DC input signals must be known and are dithered by a small amount of additive white Gaussian noise. The superimposed noise is composed of the input noise of the ADCUT but also of a noise signal generated from a dedicated noise generator. The transition levels of the ADC are then estimated from a statistical analysis. Simulation and experimental results demonstrate the robustness of the theoretical approach. The test time is a few minutes long. For comparison, the classical histogram test is performed with the acquisition of 800000 points of a sinusoidal waveform. The difference between the two resulting INL curves is small and shows the effectiveness of the method. However, this method is applied on a slow, low-resolution oscilloscope. The authors do not discuss whether this method can be applied to high-speed, high-resolution integrated ADCs.

The techniques proposed in [11], [12] and [13] explore the use of a sinewave input stimulus for ADC linearity test. Results concerning the extraction of the ADCUT DNL and INL using a sinewave histogram-based technique are proposed in [11]. Intensive calculations are performed as functions of the noise level, the desired test accuracy and desired confidence level in order to determine the required amount of samples as well as the required stimulus magnitude to overdrive the ADC. An analysis of the error induced by the stimulus harmonic distortion on the results accuracy is carried out as well as simulations on a 6-bit ADC model. It is shown that the number of samples required to obtain any desired tolerance and confidence level using a combination of coherent and random sampling is smaller than that required with pure random sampling.

**Figure 2.10:** Decomposition of the static ADC transfer function g(x) in the cascade of a smooth nonlinear function  $g_s(x)$  and an ideal quantizer quant(x) [12]

The authors in [12] proposed a novel test technique consisting in an approximation of the ADC transfer function by a linear combination of Chebyshev polynomials, its coefficients being the spurious harmonics of the ADC output spectrum in response to as sinewave input stimulus. The concept of the technique is depicted in Figure 2.10. The method reduces the test time significantly and works for any ADC resolution, which appears to be very interesting for the test of high-resolution ADCs. It is sufficient and useful for many practical applications, such as the evaluation of harmonic distortion effects on multi-tone input signals. However it is inaccurate for the measurement of the maximum and minimum INL as it only yields an indirect information being the harmonic distortion generated by the nonlinearity.

On a similar approach, the methodology in [13] is based on spectral analysis. The proposed test flow, based on a statistical analysis, allows evaluating the static linearity parameters of an ADCUT based on dynamic measurements. Complementary spectral tests (such as stimulus magnitude modulation, DC and fundamental components evaluation) are performed after the classical FFT analysis, as shown in Figure 2.11. The first test separates the fault-free ADCs from the faulty ones based only on dynamic measurements, then the second test distinguishes fault-free and faulty devices with respect to static specifications. The test flow is first applied to a population of computer-generated ADCs and then to on-the-shelf ADCs with real specifications. Despite of the method being highly specific to the performances of a given type of ADC, results show a very high test efficiency for both generated and real data. Moreover, the absence of static test and dynamic test analysis greatly reduce the test time. Intensive calculations are still required for the

Figure 2.11: (FFT + DC + Fundamental) test procedure [13]

spectral analysis and parameters extraction, which limit the interest of the technique as a BIST solution.

The works in [14] and [15] present a histogram-based technique using small-amplitude triangular waves. A small offset-stepping ramp is added to the original triangle-wave pattern. The difference between two offsets is small enough in order to be assured that the amplitude ranges of adjacent triangular waves are crossed and the whole ADC transfer function is covered. Linearity constraints on the triangular generator are relaxed by using a signal of amplitude much lower than the ADC FSR. The diagram flow of the procedure appears in Figure 2.12. At the same sampling frequency and input stimulus frequency as it would be in the standard histogram procedure, each generated triangular signal is sampled with the same amount of samples and stored in a cumulative histogram. Then calculations are performed in order to gather the data and estimate the ADC static parameters. Closed-form expressions for designing the test as well as for its characterization in terms of efficiency and uncertainty are provided. However, this approach is more complex than a simple classical histogram code hit counting as more calculations are involved. Furthermore, the offset ramping must be accurate and no solutions are reported in the paper regarding the design of a generator for this operation.

The works in [16], [17], [18], and [19] propose a model-based approach for ADC linearity test. The work in [16] introduces a model-based testing technique in order to

**Figure 2.12:** Small triangle-wave test procedure [15]

**Figure 2.13:** Linear model-based testing of an N-bit converter: from a measurement  $\tilde{b}$ , to the least-squares estimate  $\tilde{x}$  of the model parameter vector, and to an approximation  $\hat{b}$  of the unknown noise-free device characteristic [16]

estimate the ADC INL with a reduced set of samples and the linear modeling that predicts the performances of the ADCUT, as seen in Figure 2.13. The test uncertainty and the noise contribution in each measured sample are reduced by the means of the ADC linear model, leading to a reduction of the required number of samples. However, the computational aspect of this method (46 parameters for the ADC model) makes it a bad candidate for a BIST implementation.

The work in [17] proposes another model-based test technique. Here, the INL is modeled as a superposition of a low-frequency INL and a high-frequency INL. On one side, the low-frequency INL is evaluated by the means of a spectral analysis, revealing the smooth, global variations of total INL curve. On the other side, the high-frequency INL is identified by measuring the DNL of a set of specific codes with the histogram algorithm using a input triangular stimulus. Those codes are chosen as the ones with dominant DNL error, and selected not only according to the multi-periodicity model in the middle, quarters, and 1/8 of the transfer function, but also from the data of the low-frequency

**Figure 2.14:** Block diagram of the algorithm for dramatically more efficient ADC linearity test [19]

INL estimation. The requirement on the distortion of the triangular voltage is reduced as only small portions of the ADCUT transfer function are measured and implies that the variations with respect to a linear ramp stimulus are very small. Results show that the approximative estimated INL curve match closely with the real measured INL trend, even with a small number of collected samples. However, the calculations for both INL components are very complex to handle, and a significant error in the INL estimation remains.

A model-based technique for pipeline ADCs testing is detailed in [18]. The expression of the input voltage of each pipeline stage is modeled by a Taylor series expression and is represented as a combination of the input voltages of the further stages, weighted by the inverse of their respective interstage gains. The expression includes nonlinear errors such as gain errors and offset voltages of each stage, which are the parameters to be identified by the method. For the identification of the parameters, a collection of *M* data samples is performed. On a nonlinear statistical approach, starting from initial parameters values, the *M* error terms are evaluated using an iterative optimization algorithm and the optimal parameters are solved with the Newton-Ralphson method, minimizing the errors in the estimated values. Finally, the computed ADC model is used to compute the transition voltages and estimate the static parameters of the device.

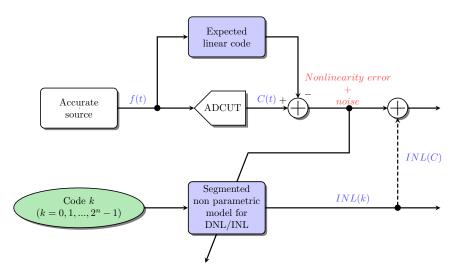

The authors in [19] propose another model-based technique for ADC linearity test which relies on the modeling of the ADC INL with a segmented, non-parametric model, as depicted in Figure 2.14. This model cuts the INL in several segments of constant value being an average value of the real INL: the MSB segments where the MSB code do not change, the ISB segments where the code of intermediate bits do not change, and

finally the remaining LSB segments. The ADCUT must be sufficiently linear in order to begin the test. This is verified by performing a FFT of the ADC response to a very linear sinewave stimulus and checking the total power of the error signal after subtracting the expected linear code from the actual ADC output code. If the error power is reasonably low, then the test can continue with the INL estimation. However, no theoretical demonstration on the validity of the algorithm has been carried out. Moreover, the purity of the input sinewave signal must be very high and the algorithm requires complex calculations to obtain the estimated INL and DNL, which bounds this method to ATE-based test.

The authors in [20], [21], [22], [23], [24], [25], [26], [27], [28], [29], [30], and [31] propose different techniques for relaxing the linearity requirements on the test stimulus for ADC linearity test.

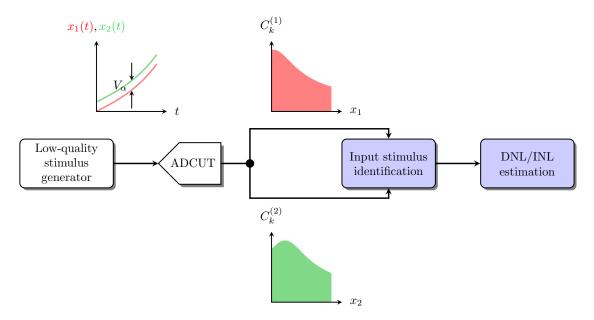

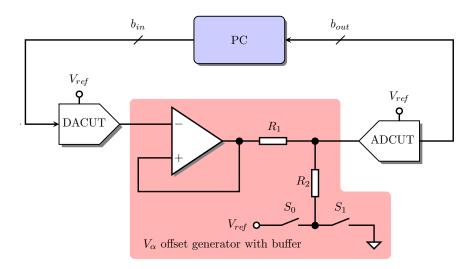

The work in [20], [21], and [22] introduce the so-called Stimulus Identification and Error Removal technique (SEIR). As the ADC resolution goes higher it becomes more and more difficult to generate an input stimulus that complies with the required resolution (2 to 3 bits more than the ADCUT resolution). The SEIR method allows the use of input stimulus that are much less linear than the ADCUT. The proposed test method is shown in Figure 2.15. First, a low resolution stimulus is applied to the ADCUT. Then, the histogram  $C_k^{(1)}$  collects the ADC output data. A second low-resolution stimulus is applied to the ADCUT, identical to the first one, but adding an offset voltage  $V_{\alpha}$ . The ADC output data is stored in a second histogram  $C_k^{(2)}$ . The SEIR algorithm then uses the redundant information from  $C_k^{(1)}$  and  $C_k^{(2)}$  in order to identify the nonlinearity of the original input stimulus. Finally, the identified errors from the stimulus are removed from the ADC output data, allowing to precisely compute the ADC DNL and INL. The approach was experimentally validated in production test on an industrial 16-bit SAR ADC by using 7-bit linear input signals. Nevertheless, the test time attributed to SEIR algorithm can be insignificant only if the resolution of the ADCUT is sufficiently high. Furthermore, the required offset accuracy is very demanding, as the voltage drift must not be larger than 0.1 LSB in order to obtain a good accuracy in the results. Additionally, from the point of view of an on-chip implementation of the technique, the fact that it relies on least-square error estimations may lead to complex implementations.