# Reliability of SiGe, C HBTs operating at 500 GHz: characterization and modeling

Thomas Jacquet

#### ▶ To cite this version:

Thomas Jacquet. Reliability of SiGe, C HBTs operating at 500 GHz: characterization and modeling. Other. Université de Bordeaux; Università degli studi di Napoli Federico II. Di.Pi.S.T., 2016. English. NNT: 2016BORD0354. tel-01476084

### HAL Id: tel-01476084 https://theses.hal.science/tel-01476084v1

Submitted on 24 Feb 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE EN COTUTELLE PRÉSENTÉE POUR OBTENIR LE GRADE DE

#### **DOCTEUR DE**

### LÆUNIVERSITÉ DE BORDEAUX

### ET DE LEUNIVERSITÉ DE NAPLES FEDERICO II

ECOLE DOCTORALE DE SCIENCE PHYSIQUES ET DE L**q**NGENIEUR SPÉCIALITÉ ELECTRONIQUE

Par Thomas JACQUET

# Reliability of SiGe :C HBTs operating at 500 GHz: characterization and modeling

Sous la direction de Cristell MANEUX et de Niccolò RINALDI

Soutenue le 7 décembre 2016 Membres du jury :

Mme ANGHEL, Lorena, Professeur Grenoble INP, France

M. ANIEL, Frederic, Professeur University Paris Sud, France

M. PASCAL, Fabien, Professeur University of Montpellier, France

Mme. SANSEVERINO, Annunziata, Associated Professor University of Cassino, Italy

Mme. MANEUX Cristell, Professeur university of Bordeaux, France

M. RINALDI Niccolò, Professeur University of Napoli, Italy

Président

Rapporteur

Rapporteur

Examinateur

Co-superviseur

Co-superviseur

## Titre: Mécanismes de défaillance des transistors bipolaires SiGe fonctionnant jusqua 500 GHz: Caractérisation et modélisation

#### Résumé :

Le sujet de cette thèse est l'analyse de la fiabilité des transistors bipolaires à hétérojonction SiGe:C et des circuits intégrés associés. Dans ce but, un modèle compact prenant en compte l'évolution des caractéristiques des transistors SiGe:C a été développé. Ce modèle intègre les lois de vieillissement des mécanismes de défaillance des transistors identifiés lors des tests de vieillissement. Grâce aux simulations physiques TCAD complétées par une analyse du bruit basses fréquences, deux mécanismes de dégradations ont été localisés. En effet, selon les conditions de polarisation, des porteurs chauds se retrouvent injectés aux interfaces du transistor. Ces porteurs chauds ont suffisamment d'énergie pour dégrader l'interface en augmentant progressivement leurs densités de pièges. L'une des deux interfaces dégradées se situe au niveau de l'"espaceur" émetteur-base dont l'augmentation de la densité de piège dépend des porteurs chauds créés par ionisation par impact. L'autre interface dégradée se situe entre le silicium et le STI dont l'augmentation de densité de pièges dépend des porteurs chauds générés par ionisation par impact et/ou par génération Auger. En se basant sur ces résultats, une loi de vieillissement a été incorporée dans le modèle compact HICUM. En utilisant ce modèle, l'étude de l'impact des mécanismes de défaillance sur un circuit amplificateur faible bruit a été menée. Cette étude a montré que le modèle compact intégrant les lois de vieillissement offre la possibilité d'étudier la fiabilité d'un circuit complexe en utilisant les outils de conception standard permettant ainsi de diminuer le temps de conception global.

**Mots clés :** HBT SiGe:C, Fiabilité à long-terme, Dégradation par porteur chaud, Modélisation compact

# Title: Reliability of SiGe: CHBTs operating at 500 GHz: characterization and modeling

#### Abstract:

The SiGe:C HBT reliability is an important issue in present and future practical applications. To reduce the design time and increase the robustness of circuit applications, a compact model taking into account aging mechanism activation has been developed in this thesis. After an aging test campaign and physical TCAD simulations, one main damage mechanism has been identified. Depending on the bias conditions, hot carriers can be generated by impact ionization in the base-collector junction and injected into the interfaces of the device where trap density can be created, leading to device degradation. This degradation mechanism impacting the EB/spacer interface has been implemented in the HICUM compact model. This compact model has been used to perform reliability studies of a LNA circuit. The CPU simulation time is not impacted by the activation of the degradation compact model with an increase in computation time lower than 1%. This compact model allows performing a reliability analysis with conventional circuit simulators and can be used to assist the design of more robust circuits, which could help in reducing the design time cycle.

**Keywords:** SiGe: C HBT, long-term reliability, hot carriers degradation, compact modeling

# Title : Affidabilità di transistori bipolari a etero giunzione SiGe:C operanti a 500 GHz: caratterizzazione e modelli

#### Abstract:

L'affidabilità dei transistori a eterogiunzione SiGe:C è un aspetto molto importante nella progettazione circuitale, sia per le tecnologie attuali che per quelle in fase di sviluppo. In questo lavoro di tesi è stato sviluppato un modello compatto in grado di descrivere i principali meccanismi di degrado, in modo da contribuire alla progettazione di circuiti relativamente più robusti rispetto a tali fenomeni, ciò che potrebbe favorire una riduzione dei tempi di progetto. A seguito di una campagna sperimentale e di un'analisi con tecniche TCAD, è stato identificato un meccanismo principale di degrado. In particolari condizioni di polarizzazione, i portatori ad elevata energia generati per ionizzazione a impatto nella regione di carica spaziale, possono raggiungere alcune interfacce del dispositivo e ivi provocare la formazione di trappole. Solo la generazione di trappole relativa allo spacer emettitore-base è stata considerata nella formulazione del modello, essendo il fenomeno più rilevante. Il modello è stato utilizzato per effettuare alcuni studi di affidabilità di un amplificatore a basso rumore. Il tempo computazionale non è significativamente influenzato dall'attivazione del modello di degrado, aumentando solo dell'1%. Il modello sviluppato è compatibile con i comuni programmi di simulazione circuitale, e può essere impiegato nella progettazione di circuiti con una migliore immunità rispetto ai fenomeni di degrado, contribuendo così a un riduzione dei tempi di progetto.

**Keywords:** transistori a eterogiunzione SiGe:C, portatori ad elevata energia, modello compatto

#### Unité de recherche

Laboratoire IMS (Integration du materiau au système), UMR 5218, 351 cours de la libération, 33405 Talence cedex, France.

Department of Electrical Engineering and Information Technology, University of Naples Federico II, Via Claudio, 21, 80125 Naples, Italy

#### Résumé Substantiel :

La fiabilité des transistors SiGe:C modernes est un critère important pour le développement de futures applications, en particulier dans le domaine millimétrique. La fiabilité des transistors est étudiée à travers des tests de vieillissement. Ces tests donnent une estimation de la fiabilité caractérisant une technologie de transistor SiGe:C. Cependant, ces résultats de test sont difficilement utilisables pour prédire l'évolution des caractéristiques des transistors sous des conditions de polarisations dynamiques impactant les performances des circuits. C'est donc pour prédire l'évolution des caractéristiques des transistors dans une application que nous avons développé un modèle compact prenant en compte l'activation de mécanismes de vieillissement.

Afin de caractériser l'évolution des caractéristiques électriques des composants, deux campagnes de vieillissement ont été réalisées sur les transistors SiGe :C fabriqués par Infineon Technology AG. Les tests de vieillissement ont été réalisés sur des structures en émetteur commun à des points de polarisations dans et au-delà de l'aire de sécurité de fonctionnement. La première campagne de vieillissement a été réalisée au point de polarisation P1, P2 et P3 sur un banc de test dédié. Les tracés de Gummel en direct et en inverse ont été mesurés durant ces tests de vieillissement à intervalles de temps prédéfinis. Les tests de vieillissement et les mesures DC ont été réalisés directement sur le banc dédié, sans action supplémentaire sur les composants afin de garantir l'intégrité des tests.

La seconde campagne de mesures a été réalisée avec un testeur sous pointe. C'est pourquoi, contrairement à la première campagne, un seul composant a été vieilli à la fois. Cette campagne de vieillissement a été menée pour deux points de polarisation, P23 et P2. Les mêmes caractéristiques électriques DC ont été mesurées que lors de la première campagne.

Le courant de base du tracé de Gummel en direct augmente avec le temps de vieillissement pour les points de polarisation P2P3 durant la première campagne et pour le point de polarisation P23 durant la seconde campagne. Pour ces points de polarisation, la tension collecteur-émetteur est supérieure à BV<sub>ceo</sub>. De plus, aux faibles niveaux d'injection, le courant de base des composants vieillis aux points de polarisations P2 and P23 (Vce=2V) présentent la même évolution avec la même dynamique temporelle. Le courant de base augmente durant les premières heures de vieillissement avant d'atteindre une valeur constante. La dynamique de cette évolution et la valeur finale dépendent des conditions de polarisation, plus précisément de la valeur de la tension collecteur-émetteur.

Pour les composants vieillis aux points de polarisations P12 et P23, une augmentation du courant de base du tracé de Gummel en inverse est observée. Le courant de base augmente pour le composant vieilli en P12 et

atteint une valeur constante après 1h. Pour le composant vieilli sous P23, nous observons une évolution du courant de base similaire à celui observé pour le tracé de Gummel en direct. Cette augmentation du courant de base du tracé de Gummel en inverse semble activée pour un fort courant de collecteur.

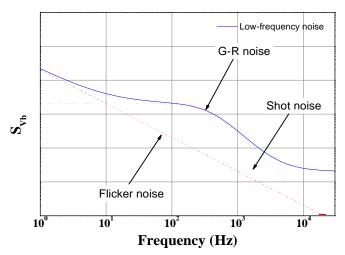

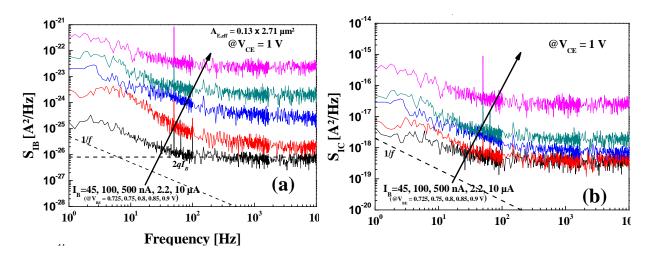

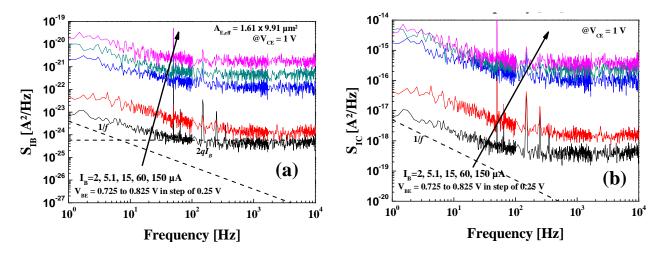

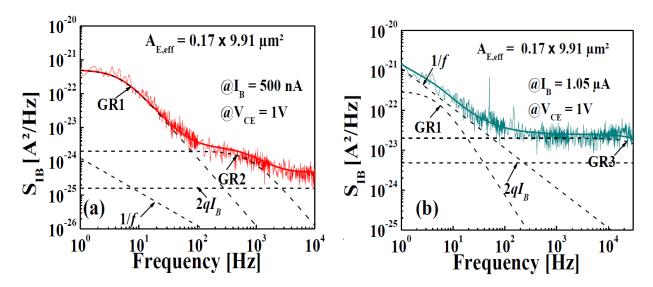

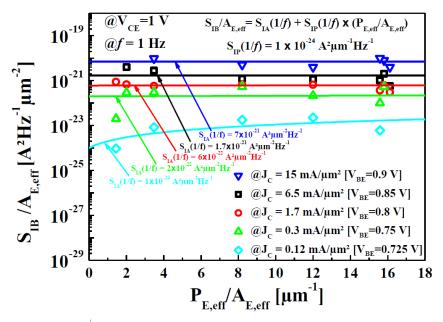

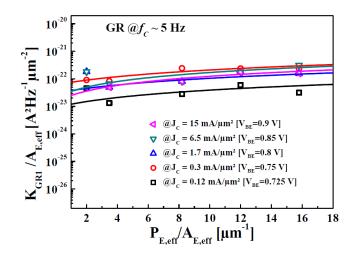

Le bruit basse-fréquence des transistors SiGe :C a été analysé. Les origines physiques et la localisation des sources de bruit ont pu être identifiées. Nous avons démontré que l'évolution de la densité de bruit basse-fréquence peut aussi être utilisé comme indicateur de défaillance.

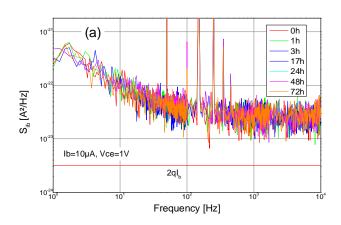

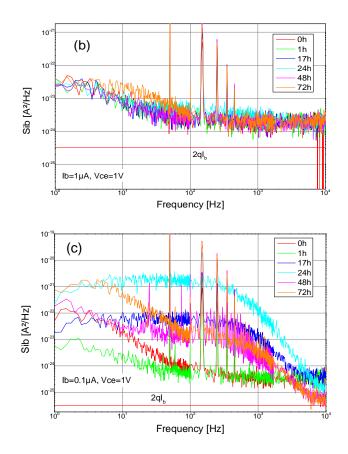

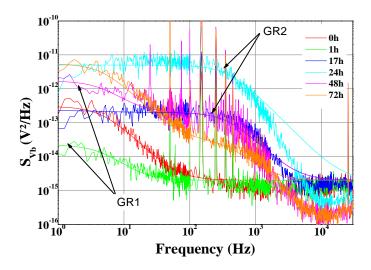

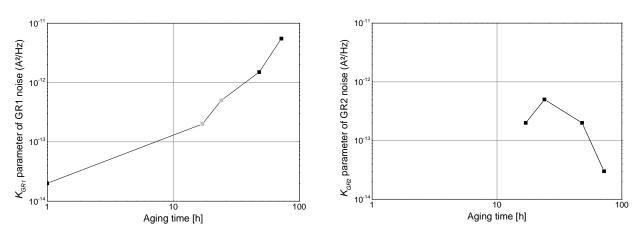

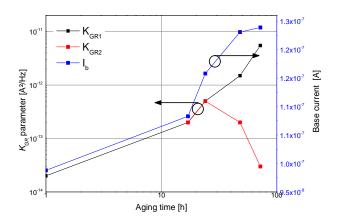

En effet, le bruit basse-fréquence a été évalué pour les composants vieillis sous deux points de polarisation différents jusqu'à 72h pour un courant de base  $I_b$  égale à  $0.1\mu A$ ,  $1\mu A$  et  $10\mu A$ . Le bruit basse fréquence pour le composant vieilli sous P12 ne montre aucune variation significative durant le temps de vieillissement, ce qui est en accord avec les mesures DC. Pour le composant vieilli en P23, le bruit basse-fréquence pour lb égal à  $1\mu A$  et  $10\mu A$  ne présente aucune variation significative alors que, pour  $1b=0.1\mu A$ , le bruit basse-fréquence présente une variation. Nous avons montré que les variations de la partie Génération-recombinaison (G-R) du bruit BF à la même source que l'évolution du courant de base du tracé de Gummel en direct.

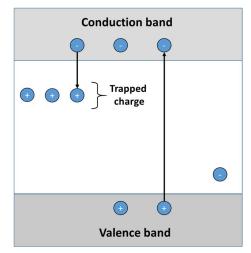

Cette corrélation entre bruit basse-fréquence et tracé de Gummel en direct peut être expliquée par la création de pièges dans le composant. L'augmentation de la densité de pièges a un impact sur la partie G-R du bruit BF et sur le courant de base à faible injection observé sur le tracé de Gummel. La localisation et l'origine des pièges sont difficiles à extraire de ces résultats.

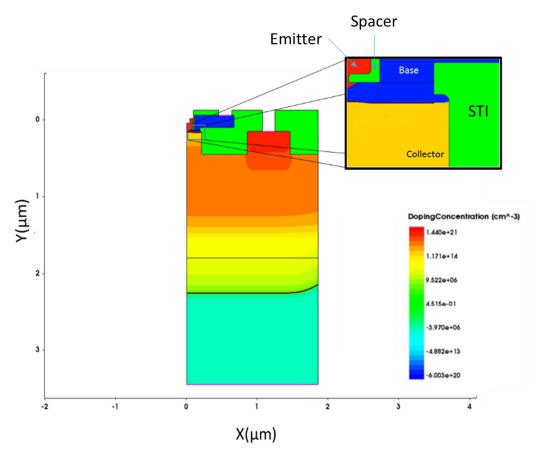

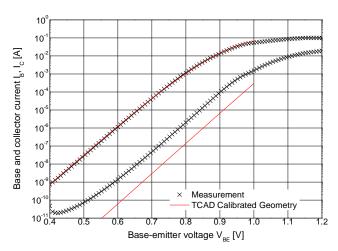

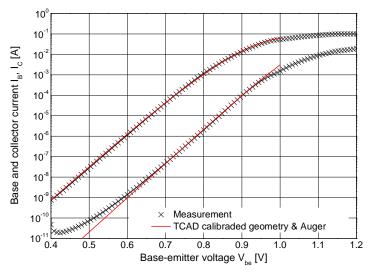

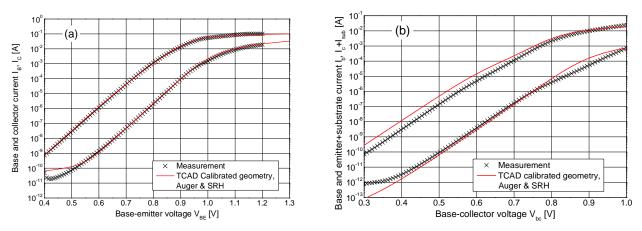

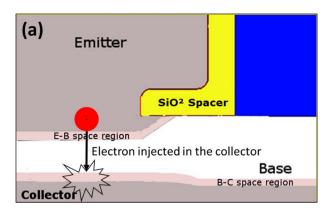

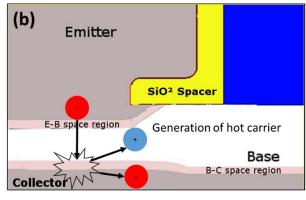

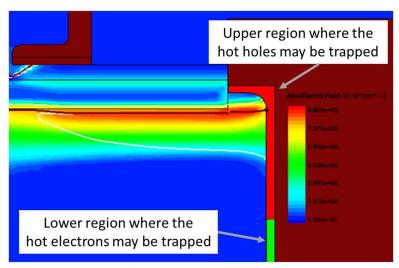

Afin de déterminer les origines physiques des mécanismes de défaillance, des simulations 2D TCAD ont été menées. Un modèle hydrodynamique avec des paramètres de transport optimisés pour Sentaurus TCAD a été utilisé. Après une calibration des profils de dopage et des paramètres du modèle, des simulations ont été menées pour confirmer les hypothèses des mécanismes de dégradations activés pendant les tests de vieillissement sous différentes conditions de polarisation.

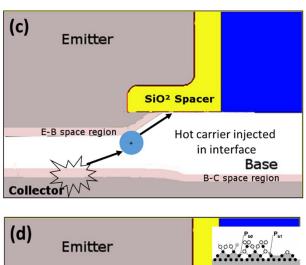

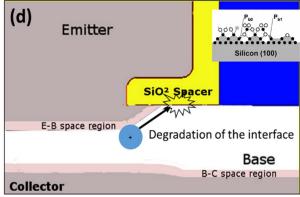

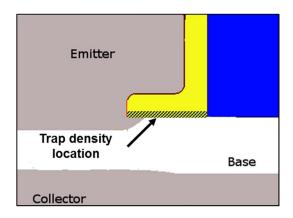

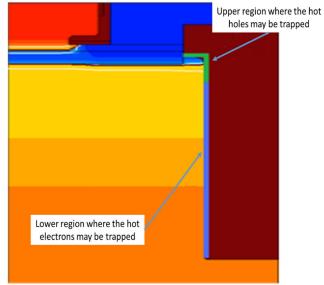

Pour les composants soumis à une tension Vce supérieure à BVceo, P2, P2 et P23, une variation du courant de base pour le tracé de Gummel en direct a été observée. Du fait de la valeur importante de Vce, des porteurs chauds sont générés par ionisation par impact. Ces porteurs chauds sont injectés à l'interface entre l'émetteurbase et le Spacer avec suffisamment d'énergie pour rompre les liaisons covalentes à l'interface, augmentant la densité de pièges. Cette augmentation de la densité de pièges à l'interface EB-Spacer provoque une augmentation du courant de base du tracé de Gummel en direct aux faibles niveaux d'injection.

Pour les composants vieillis au point de polarisation P23 et P12, une variation du courant de base pour le tracé de Gummel en inverse a été observée. Cette augmentation du courant de base est attribuée à l'activité de pièges à l'interface entre le Silicium et le STI. Les pièges de l'interface STI/Si sont attribués à deux mécanismes de défaillance différents :

- Pour les conditions de polarisation associé à des tensions V<sub>ce</sub> supérieures à BV<sub>ceo</sub>, l'ionisation par impact peut être le mécanisme dominant,

- Pour les conditions de polarisation associée à des tensions V<sub>ce</sub> inférieures à BV<sub>ceo</sub>, et à fort courant, les recombinaisons Auger peuvent être le mécanisme dominant.

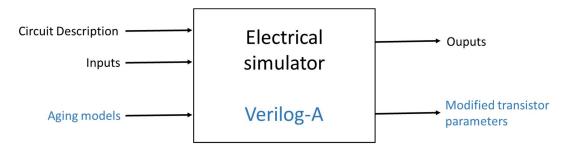

En se basant sur ces mécanismes de dégradations, une loi de vieillissement a été proposée prenant en compte les conditions de polarisation. Cette loi de vieillissement décrit l'évolution des dégradations de l'interface EB-Spacer, en fonction des conditions de polarisations et du temps de vieillissement. Pour intégrer cette loi de vieillissement dans le code Verilog-A du modèle compact, la dérivée de cette loi de vieillissement est calculée.

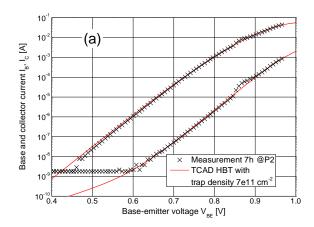

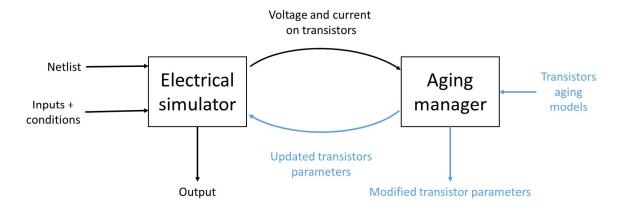

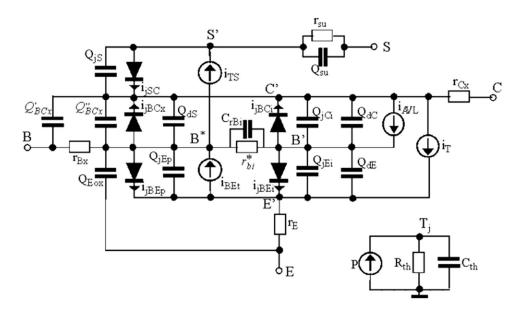

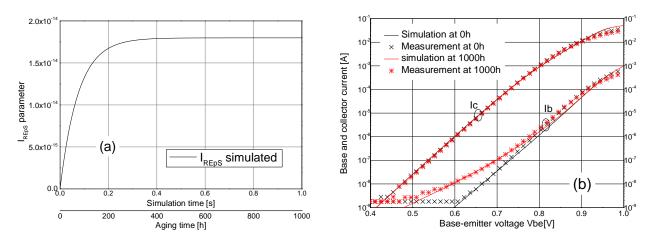

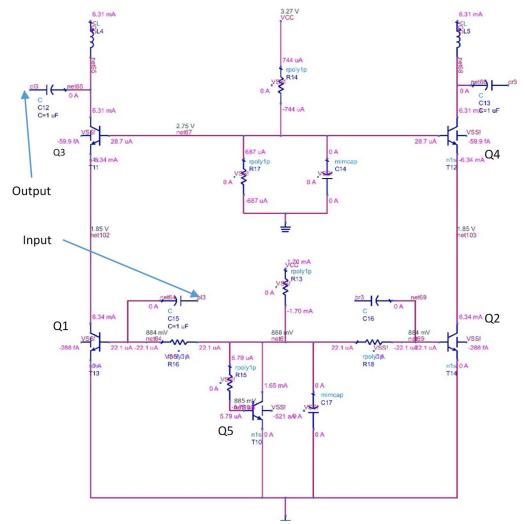

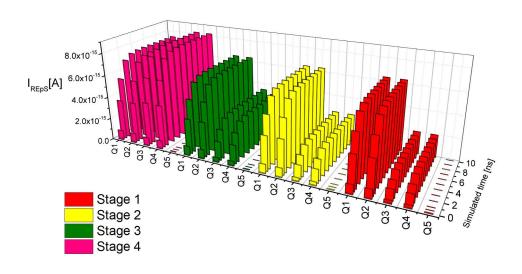

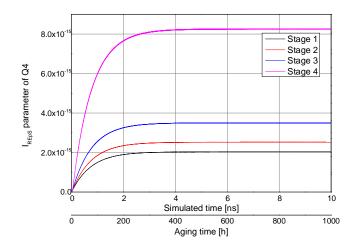

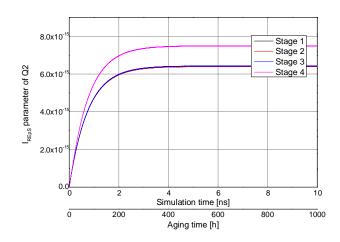

Pour implémenter la loi de vieillissement dans un modèle compact, le modèle HICUM a été choisi. Ce modèle a été choisi par le projet DOTSEVEN pour simuler les transistors SiGe:C. Le modèle compact HICUM a l'avantage de décrire de nombreux phénomènes physiques régissant les transistors SiGe:C. Pour implémenter la loi de vieillissement, le paramètre I<sub>REpS</sub> a été utilisé. Ce courant correspond à la partie du courant de base correspondant à de l'interface EB-Spacer. I<sub>REpS</sub> a été convertie en variable selon la loi de vieillissement.

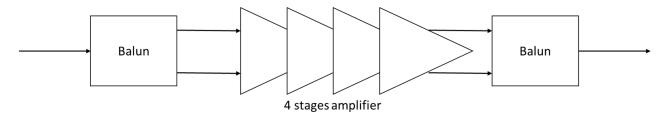

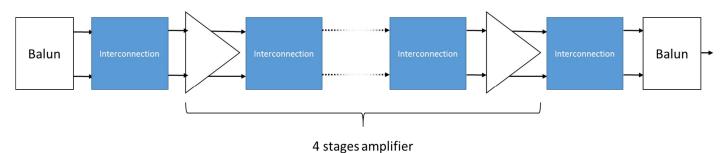

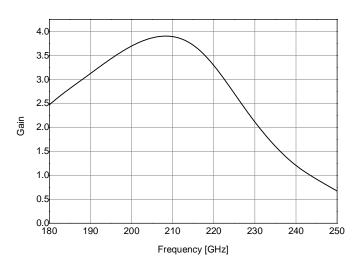

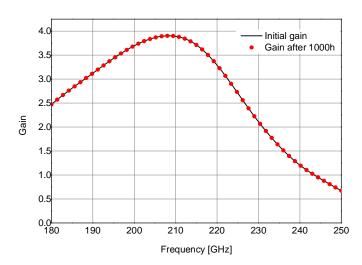

En utilisant ce modèle compact, une simulation de fiabilité d'un amplificateur faible bruit à 4 étages a été réalisée. L'activation de la loi de vieillissement n'a pas d'impact significatif sur le temps de simulation , soit une augmentation du temps de simulation inférieure à 1%. En prenant en compte les dégradations de l'interface EB-Spacer en fonction des conditions de polarisation de chacun des transistors, le signal de sortie du circuit ne présente pas de variation significative avec le temps en dépit de l'augmentation du courant de base de certains transistors du dernier étage . Ces résultats montrent la robustesse du circuit face aux dégradations de l'interface EB-Spacer. D'un point de vue de la méthodologie d'analyse de la fiabilité, la possibilité d'évaluer l'évolution de chaque transistor a été démontrée avec un faible impact sur le temps de simulation. De ce fait, cette méthodologie apporte un outil d'évaluation de la fiabilité supplémentaire.

### **Tables of contents**

| Chapter 1 State of the art of SiGe:C HBT reliability      |    |

|-----------------------------------------------------------|----|

| 1.1. General introduction                                 | 1  |

| 1.2. Terahertz semiconductor technologies                 | 2  |

| 1.3. Bipolar safe operating area                          | 4  |

| 1.4. Reliability of modern SiGe:C HBT                     | 6  |

| 1.5. This thesis                                          | 11 |

| Chapter 2 Aging tests                                     |    |

| 2.1. Introduction                                         |    |

| 2.2. SiGe:C technology                                    | 13 |

| 2.3. Long-term aging stress procedure                     | 17 |

| 2.4. The aging test results                               | 23 |

| 2.5. Conclusion                                           | 30 |

| Chapter 3 Low-frequency noise                             |    |

| 3.1. Introduction                                         |    |

| 3.2. Low-frequency noise of SiGe:C HBT                    | 34 |

| 3.3. Evolution of low-frequency noise during aging tests  |    |

| 3.4. Conclusion                                           | 49 |

| Chapter 4 Physical simulation damage mechanism origins    |    |

| 4.1. Introduction                                         |    |

| 4.2. Calibration of TCAD simulation                       |    |

| 4.3. Investigation of physical origin of the degradation  |    |

| 4.4. Conclusion                                           | 68 |

| Chapter 5 Compact model                                   |    |

| 5.1. Introduction                                         |    |

| 5.2. Aging laws implementation within HICUM compact model |    |

| 5.3. Reliability assessment of a complex circuit          |    |

| 5.4. Conclusion                                           | 88 |

| Chapter 6 Conclusion                                      | 89 |

| References                                                | 93 |

# Chapter 1 State of the art of SiGe:C HBT reliability

#### 1.1. General introduction

The first bipolar transistor has been developed in 1947 by J. Bardeen, W. Shockley et W. Brattain. Since this invention, semiconductor industry has witnessed exceptional growth and achievements in integrated circuit (IC) manufacturing. The evolution of the bipolar technology, following Moore laws [Moor\_1975], has been driven by the device downscaling until now.

The development of the Silicon Germanium based Heterojunction Bipolar Transistor starts in 1987 [Lyer\_1987]. Based on band-gap engineering, modern Silicon (Si) Germanium (Ge) HBT have been developed to extend the performance of standard silicon based transistors. The Heterojunction Bipolar Transistor is a solution to develop ultra-speed applications. Compared to III-V HBTs, SiGe HBTs allow for a higher level of integration and a lower cost. More specifically, SiGe HBTs allow a really good integration level in BiCMOS technology where analog and digital signals can be processed on the same System-on-Chip (SoC). These advantages of SiGe HBTs compared to other technologies, make the SiGe HBT technology the perfect candidate to develop low-cost and highly integrated terahertz applications.

In Europe, several projects have been launched to develop SiGe:C HBT technology. During the DOTFIVE project [Dotfive\_online], the operating frequency of SiGe:C HBT has been pushed toward 0.5 THz. This project has been followed by the DOTSEVEN project [Dotseven\_online] to further improve the operating frequency up to 0.7 THz and envisage future terahertz applications in the 0.1 to 1 THz frequency range. To give an example, a terahertz receiver front-end based on SiGe:C HBT technology [Ojef\_2010], opens new opportunities like THz imaging. These applications cover a wide range of domains, like security, high speed wireless communication or medical imaging. The reliability of these applications appear also as a challenge which has been considered in the DOTSEVEN project.

Indeed, SiGe:C technology improvements are performed by shrinking the structure dimensions to reduce the parasitic elements and by improving the doping profile. Among several consequences, these improvements lead to the increase of hot carrier generation. This increase of hot carriers can worsen device reliability through the degradation of the device interfaces [Sass1 2014] leading to the onset of failure mechanisms.

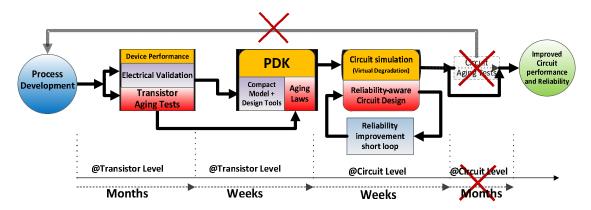

In this context, a new tool for designers has been proposed in this Thesis: The compact model takes into account the relevant failure mechanisms. This new tool, already used for III-V devices [Ardo\_2012], could help designers to enhance performance of future applications with a limited impact on reliability.

#### 1.2. Terahertz semiconductor technologies

#### 1.2.1. Terahertz application

The SiGe:C technology has been developed for millimeter wave (mm-wave) or terahertz applications which lie in the frequency range between microwaves and infrared light, corresponding to the 0.3 THz and 3 THz frequency range. Terahertz signals can penetrate many materials. This ability of terahertz signals therefore can be used for medical imaging with a limited damage to organic tissues as compared to X-ray.

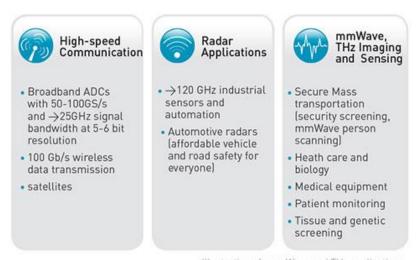

Illustration of mm-Wave and THz applications

Figure 1 mm-Wave applications proposed by DOTSEVEN project

A large number of mm-wave applications (Figure 1) are possible, including THz imaging and sensing for biology and medical sciences [Taba\_2015], non-destructive evaluation [Fuka\_2015], homeland security [Fede\_2005]. Ultra-high-speed communications appears to be a major application market [Akyi\_2014].

#### 1.2.2. Terahertz semiconductor technologies

#### 1.2.2.1. General overview

Diodes and transistors are the two semiconductor electronic devices used to implement terahertz systems. Diodes have already been widely employed for various terahertz systems. Impact avalanche transit time (IMPATT) diodes, Gunn diodes, and resonant tunneling diodes (RTDs) are widely employed as sources [Mile\_2007]. Whereas Schottky barrier diodes are a popular choice to detect terahertz signals [Sank\_2005].

However, as an active device, transistors can be better integrated in multistage systems than diodes. Therefore, the main focus lies on the development of high speed transistors integrated in complementary metal oxide semiconductor (CMOS) or in III-V technologies.

To characterize the RF performance of a transistor technology, two figures of merits are commonly used, the transit frequency ( $F_t$ ) and the maximum oscillation frequency ( $F_{max}$ ). The transit frequency ( $F_t$ ) corresponds to the unity gain cut-off frequency in the common emitter configuration which is the frequency where the small-signal current gain  $\beta_F$  equals unity [Gumm\_1969]. The maximum oscillation frequency ( $F_{max}$ ) corresponds to the frequency at which the unilateral power gain becomes unity.

For RF circuit design, the  $F_{max}$  FoM, corresponding to operating frequency limit of the device, is the most used to characterize the device ability to develop terahertz applications. However, the maximum oscillation frequency is sensitive to device layout and more difficult to extract than the transit frequency. Therefore,  $F_t$  is the most frequently used to characterize and compare device technologies [Rieh\_2009].

#### 1.2.2.2. III-V technology

Widely used transistor technologies for terahertz applications are the HBT (Heterojunction Bipolar Transistor) and the HEMT (High Electron Mobility Transistor) III-V device technology. The record of RF performance has been reached for the III-V InP HEMT technology with an  $F_{max}$  at 1.2THz [Lai\_2007]. For the 0.25 $\mu$ m InP HBT technology [Urte\_2010], the published RF characteristics  $F_t/F_{max}$  are equal to 392GHz and 859GHz, respectively, at  $I_c$ =13mA. Therefore, this technology is a good candidate to develop terahertz application. Moreover, the high speed of III-V transistors comes along with an excellent noise figure (NF).

However, the hole mobility of III-V devices is low in comparison with the silicon value. Hence, complementary logic blocks as in CMOS technology are rather hard to design. Moreover, the expensive and small wafers and the low reliability of these devices, increase the fabrication costs reducing the attractiveness of this technology for high volume applications. These arguments make silicon the favorable technology for large scale applications despite the lower performances. Therefore, high performance SiGe HBTs integrated in a BiCMOS technology appears as a promising solution.

#### 1.2.3. SiGe:C Technology

SiGe HBTs provide a higher current driving capability, higher linearity, larger transconductance g<sub>m</sub>, lower 1/f noise property, excellent reliability, better device matching and superior performance in comparison with the standard silicon metal oxide semiconductor field effect transistors (MOSFETs) [Rieh\_2009]. This makes them ideal devices for microwave power applications [Ruck\_2012], [Chev\_2012]. Therefore, several companies have chosen to integrate their high performance SiGe HBTs in a lower cost CMOS process (BiCMOS) which allows an improved functionality but at the same time increases process complexity due to HBT integration.

In contrast with high speed III-V technologies, the intrinsic material properties of Si limits the device operation speed. Nevertheless, SiGe HBT technology continues to gain momentum. Optimized device structure along with aggressive scaling lead to reduce the gap of RF performances with III-V devices ( $F_t$ =300GHz,  $F_{max}$ =500GHz [Hein\_2010]) as reported within project DOTFIVE [Dotfive\_online]. In the follow up project DOTSEVEN [Dotseven\_online], the performance of SiGe has been pushed to a higher frequency ( $F_{max}$ =570GHz

[Bock\_2015]). Moreover, SiGe:C HBT has been integrated in a new BiCMOS technology to replace expensive III-V components in radar production [Knap\_2012].

#### 1.3. Bipolar safe operating area

#### 1.3.1. Physical limits

Bipolar transistor technologies have been developed to achieve new applications in the terahertz range, like terahertz communications [Song\_2011]. However, all bipolar devices, like SiGe:C HBT, suffer from various feedback mechanisms, which may cause instability and device failure. To avoid the activation of these mechanisms, a Safe Operating Area (SOA) has been defined. As explain in [Rina\_2005] [Rina\_2006], self-heating and impact ionization are two main mechanisms limiting the operation of bipolar transistors. A clear understanding of these mechanisms is thus an obvious prerequisite for the designers and technologists, in order to exploit the maximum circuit performances achievable with a given technology.

#### 1.3.2. Thermal runaway

One of the well-known damaging mechanisms is the thermal runaway activated by the self-heating of the device [Rina\_2005] [Liou\_1994]. When bipolar transistors operate at high power, the increase of junction temperature causes the intrinsic carrier concentration to increase. As a result, the collector current increases. At high power operations, the  $I_c$ - $V_{be}$  curve can bend backwards at high currents. Once the device hits the bend-over point, two possible operating points appear in its current-voltage characteristics, leading to the device instability.

To estimate the junction temperature of the device, and therefore the thermal runaway activation, the thermal resistance,  $R_{th}$ , of the device is used. A simple equation (equation 1.1) is used to estimate the junction temperature:

To avoid the destruction of the device, bias conditions must be defined within the safe operating area to avoid this thermal runaway.

#### 1.3.3. Avalanche effect

A second limit of the safe operating area is the avalanche effect, [Rina\_2006]. Under large reverse bias conditions, a large electric field takes place in the base-collector junction. This high electric field accelerates electrons from the emitter to the collector. When carriers are injected in the base-collector space charge region, they can gain enough energy to create free electron-hole pairs via collision with bound electrons (impact ionization) [Lu\_1989]. These carriers can subsequently generate new electron-hole pairs. This creation of electron-hole pairs results in a hole current which is back injected in the base yielding a negative base current. In a similar way as the thermal runaway, an instability condition occurs in the device, and possibly cause the destruction of the device.

One parameter used to characterize the activation of the impact ionization effect is the open-base breakdown voltage ( $BV_{ceo}$ ).  $BV_{ceo}$  corresponds to the collector-emitter voltage when the base current equal to 0A and therefore represents the upper limit of the collector-emitter voltage under forced base current conditions.

#### 1.3.4. Safe operating area

The limits of the SOA are mainly defined by two mechanisms, self-heating, leading to thermal runaway and impact ionization, leading to avalanche effect. The safe operating area is thus limited by these two mechanisms. As explained in [Rina\_2006][Lee\_2006], the combined effect of impact ionization and self-heating is complex. Different experimental methodologies have been developed to define the SOA limits, like the one presented in [Cism\_2010]. This methodology consists in measuring the  $J_{c}$ - $V_{ce}$  curves in specific bias configurations to avoid the destruction of the device.

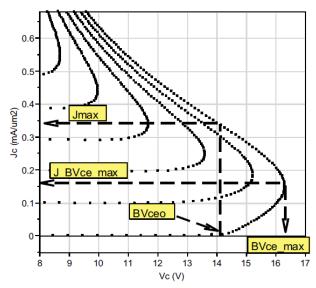

Figure 2 HBT  $J_c$  - $V_{ce}$  curve. Breakdown parameters of the device are reported in the figure. Picture from [Cism 2010]

A typical  $J_{c^-}V_{ce}$  curve measured using this methodology is presented Figure 2. On this  $J_{c^-}V_{ce}$  curse, the snapback behavior of the device, an instability effect, can be observed. Using this curve, the breakdown parameters of the HBT can be extracted, like  $BV_{ceo}$  corresponding to maximum collector voltage while the collector current is substantially low.  $J_{max}$  corresponds to the maximum current achievable in the snap-back branch at  $BV_{ceo}$ . Another breakdown parameter, the maximum collector voltage  $BV_{ce_{max}}$ , can also be extracted using the same curve with the associated current density  $J_{max}$ .

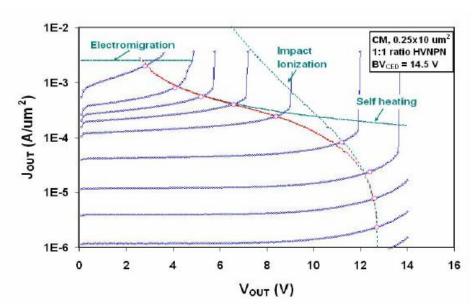

Based on the extraction of breakdown voltage and taking into account self-heating and impact ionization, a safe operating area can be defined. Figure 3 shows the limits of the safe operating area of a NPN device on thick film SOI with effective area equal to  $0.25 \times 10 \mu m^2$ . The safe operating area is limited by three physical mechanisms. The first one is electromigration at low  $V_{ce}$  and extremely high  $J_c$ . Electromigration impacts the back end of line, by degrading metal interconnections. For medium  $V_{ce}$  and high  $J_c$ , the SOA is limited by the self-heating of the device. At higher  $V_{ce}$  and lower  $J_c$ , impact ionization limits the SOA.

Figure 3 Safe Operating Area of bipolar transistor showing different physical limits.

Picture from [Kim\_2007], SOA of a SiGe HBT on SOI.

#### 1.4. Reliability of modern SiGe:C HBT

#### 1.4.1. SiGe:C HBT SOA

#### 1.4.1.1. Improvements of SiGe:C HBT and impact on SOA

To improve the figures of merit  $F_t$  and  $F_{max}$ , the device structure has to be downscaled [Schr1\_2011] [Schr2\_2011]. In this publication, the "ultimate" limit of SiGe HBT has been studied by simulation, based on physical and application oriented considerations. The resulting SiGe HBT has a  $F_t/F_{max}$  at 1.98THz@J<sub>c</sub>=139mA/ $\mu$ m² and 0.98THz @J<sub>c</sub>=168mA/ $\mu$ m², respectively.

As mentioned in the previous section, the SOA is limited by self-heating and avalanche effect. These two effects are characterized by the thermal resistance for self-heating and by  $BV_{ceo}$  for avalanche effect. The  $BV_{ceo}$  is estimated between 1V and 1.2V, and the thermal resistance around 76000K/W. These values could considerably reduce the SOA of future SiGe devices.

For present SiGe:C devices, the thermal resistance is not yet too high to limit practical applications, around 2000K/W for STMicroelectronics SiGe:C HBT [Ales\_2010]. However, BV<sub>ceo</sub> has decreased for advanced SiGe:C HBT. Indeed, the BV<sub>ceo</sub> is measured at 1.5V for Infineon technology SiGe:C HBT exhibit  $F_t/F_{max}$ = 240GHz/380GHz at  $J_c$ =10mA/ $\mu$ m² [Chev\_2011].

Hence, the downscaling of SiGe:C HBT reduces  $BV_{ceo}$ , limiting the SOA. This limit of  $V_{ce}$ , lower than  $BV_{ceo}$ , has a huge impact on future application performances, like the power amplifier with a lower output voltage swing and therefore a lower output power.

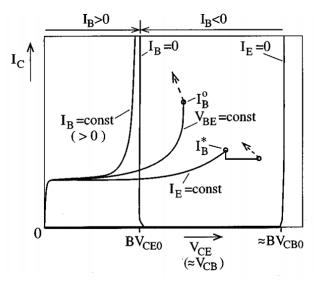

#### 1.4.1.2. Extending SOA

The  $BV_{ceo}$  is measured in an "extreme" condition, the open base configuration, which is rarely the case in real applications. As proposed by [Rick\_2001] and [Kraf\_2005], the SOA can be extended above this value if some bias conditions are respected. Figure 4 from [Rick\_2001] illustrates the evolution of the output characteristics as a function of the driving conditions. When the device is controlled by the base current, the instability occurs at  $V_{ce}$  =B $V_{ceo}$ , confirming the previously mentioned limit of the SOA. For base voltage controlled device, the instability occurs at a collector-emitter voltage higher than  $BV_{ceo}$  and lower than  $BV_{cbo}$  and for an even higher  $V_{ce}$  for an emitter current controlled device.

Figure 4 Influence of the impact ionization on the output characteristics for constant  $I_b$ ,  $V_{be}$  and  $I_e$ . Picture from [Rick\_2001].

To reach a voltage higher than  $BV_{ceo}$ , the device has to be controlled by the base voltage or the emitter current with a low external base resistance to allow excess carriers, generated by impact ionization, to flow out. According to these observations, [Kraf\_2005] proposed to extend the safe operating area above  $BV_{ceo}$  taking into account the external base resistance and the temperature of the device.

#### 1.4.2. Aging tests of SiGe:C HBT in the SOA

The safe operating area corresponds to the limits of bias conditions of SiGe:C HBT. The SOA is defined to avoid the destruction of the device due to instability effects leading to catastrophic destruction. However, this not warrants the device from degradations occurring while it is biased within the SOA. Indeed, the device also suffers from wear-out mechanisms that generally decrease the current gain, and ultimately limit the device lifetime.

#### 1.4.2.1. Reverse stress test

The studies of bipolar transistor aging begun at the end of the eighties [Josh\_1987]. The main issue at that time was to assess degradation for a strongly reverse biased emitter-base junction, since the reverse BE breakdown voltage (at the BE perimeter) had declined to below 1V and a reverse-biased EB junction may occur in circuit operation. When the EB junction is subject to a sufficiently high reverse voltage, the current flowing

through the BE perimeter junction is mainly due to band-to-band tunneling. In these conditions it was suggested that the main degradation mechanism was related to hot holes, [Gogi\_2000]. This kind of aging tests is still performed on modern bipolar transistors.

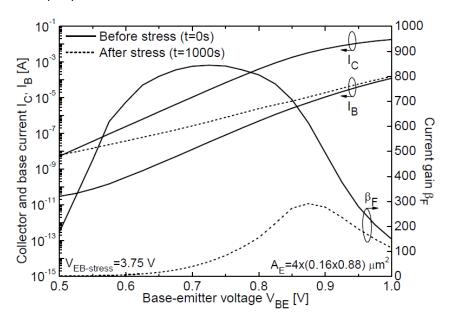

A reverse stress test has been performed by [Sass2\_2014] on IHP 0.13 $\mu$ m SiGe BiCMOS technology exhibiting a peak cut-off frequency F<sub>t</sub> of 240 GHz and a F<sub>max</sub> of 300 GHz [Ruck\_2010]. The samples have been stressed at V<sub>eb</sub> equal to 3.75, 4.00, 4.25 and 4.50V hence always above the reverse open-collector breakdown voltage BV<sub>ebo</sub> estimated at 1.7V for this process. The applied stress conditions, rather extreme and very far from the usual device bias conditions, caused the acceleration of the degradation and, thereby, allow an estimation of the transistor time-to-failure (TTF).

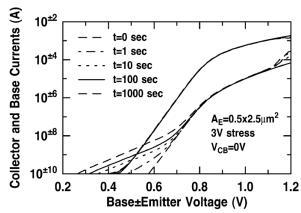

Figure 5: Current (left) and current gain (right) measured at Vcb=0V of one SiGe:C device before and after reverse stress test at V<sub>eb-stress</sub>= 4.0V for 1000s. Picture from [Sass2\_2014]

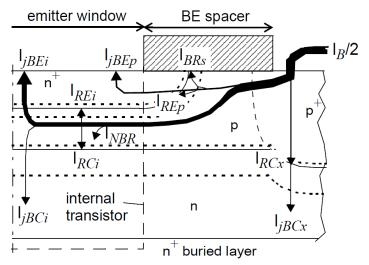

A typical result of reverse stress test is represented Figure 5. After 1000s at  $V_{eb}$ =3.75V, the collector current remains almost constant while the base current increases, consequently, the current gain  $\beta_F$ =I<sub>c</sub>/I<sub>b</sub> decreases. This evolution of DC characteristics has been explained by the large reverse current during the stress test. This reverse current, which is primarily confined to the emitter perimeter region, under the influence of localized electrical fields can generate hot carriers. These hot carriers can damage the Si-SiO<sub>2</sub> interface by increasing the interface trap density at this interface.

#### 1.4.2.2. Mixed-mode degradation

During the 2000 decade, a new degradation mode of SiGe:C HBT has been reported which is more appropriate to device operation in mixed-signal circuit applications, [Zhan\_2002]. Mixed-mode degradation occurs when a high collector current density and a high collector-base voltage are imposed simultaneously to the device. In this case, hot carriers are generated by impact ionization in the base-collector space charge region. Some of the carriers may be redirected towards oxide-silicon interfaces, either at the emitter-base sidewall or at the shallow trench. Then, if carriers have enough energy when they reach the interface, they may create defects.

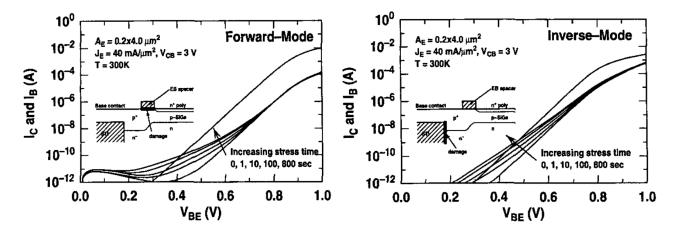

Results of mixed-mode stress test has been reported in [Zhu\_2005] for SiGe HBT exhibiting a transit frequency of 120GHz [Jose\_2001]. For mixed-mode stress, the device is biased in a common-base mode under variable forced emitter current and collector-base conditions. The stress tests usually range from 1msec to 1000 sec.

Figure 6 Forward-mode and inverse-mode Gummel plot evolution during mixed-mode stress test of a device aged at V<sub>cb</sub>=3V and J<sub>E</sub>=40mA/µm<sup>2</sup>. Pictures from [Zhu\_2005].

A typical forward-mode Gummel plot and an inverse-mode Gummel plot are shown in Figure 6 from [Zhu\_2005] for a device aged at  $V_{cb}$ =3V and  $J_e$ =40mA/ $\mu$ m². For both Gummel plots, the base current increases with the stress time. The increase of the base current in the forward-mode Gummel plot is attributed to the degradation of the EB-spacer interface damage, while the base current increase in the inverse-mode Gummel plot corresponds to STI/Si interface damage.

#### 1.4.3. Long-term reliability

Reverse stress tests and mixed-mode stress tests have been performed to estimate the robustness of device. The main goal of these stress tests is the evaluation of the time-to-failure of the device by extrapolation of the degradation at circuit bias conditions. One limit of these stress tests is the estimation of device characteristics evolution as a function of bias conditions during the circuit operating time.

Based on the same conclusion, [Fisc\_2014] has proposed to study the long-term reliability of SiGe:C HBT. This methodology is based on the observed base current evolution and can be described as follows:

- traps created at the EB spacer oxide interface cause an increase in the non-ideal forward-mode base current due to additional Shockley-Read-Hall (SRH) recombination current.

- traps annihilated by thermal recovery (self-annealing). This reaction is thermally activated and when hot carrier injection is switched off annealing can occur through thermal recovery.

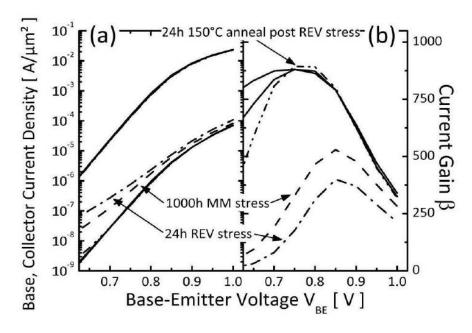

Altogether this leads to complex dynamics of trap generation and annealing. The characterization of trap generation as a function of bias conditions has been reported in [Fisc\_2015] for mixed-mode and reverse stress tests for SiGe:C HBT from IHP's  $0.13\mu m$  BiCMOS technology exhibiting a  $F_t/F_{max}$  equal to 250/300 GHz,

respectively. The increase of the base current and the reduction of the device current gain has been reported in Figure 7 for both long-term stress tests.

Figure 7 forward Gummel chracteristics (a) and current gain (b) before and after Mixed-mode and reverse long-term stress tests and a 24h post stress aneal. Picture from [Fisc\_2014].

To characterize the annealing of trap density by thermal recovery, the 100h reverse stress test was followed by a high temperature anneal at 150°C. An almost full recovery of the base current is then observed after 24h.

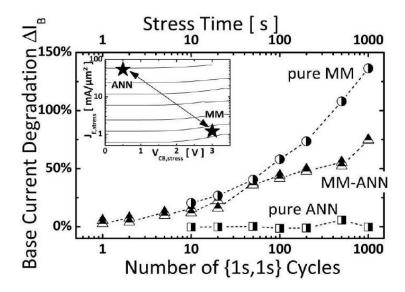

Ultimately, HBT degradation is the result of the interplay between trap creation (aging) and annihilation (recovery). This is already obvious for DC stress but the consequence for the HBT during its duty cycle in a given circuit is more complex. In power amplifiers for example, the HBT operating bias point quickly switches between two extremes: the state of low  $V_{cb}$  and high  $J_c$  (annealing region) and the state of high  $V_{ce} > BV_{ceo}$  and low  $J_c$  (aging region) as indicated in the inset of Figure 8. In Figure 8, 1000 switching cycles are then compared with 1000s of pure DC stress.

Figure 8 HBT degradation during pure MM and high-current (ANN) stress and 1s cycles between both states (MM-ANN). Inset shows the stress load conditions. Picture from [Fisc\_2014].

After 100 cycles, the resulting base current increase stays well below that of pure mixed-mode stress. Aging of the device in the mixed-mode state occurs but meanwhile, the high-T<sub>i</sub> state yields a significant annealing.

This experimental long-term analysis of mixed-mode and reverse SiGe HBT base current degradation shows that aging is a complex function of the electrical load, local temperature, and particularly of stress-time. Device degradation in circuit applications is the result of the interplay between trap creation (aging) and annihilation (recovery), depending of the bias conditions.

#### 1.5. This thesis

#### 1.5.1. Long-term reliability modeling

The modern SiGe:C HBT reliability is mainly affected by hot carrier degradation, increasing with device downscaling and more severe operating conditions. The reliability of SiGe:C HBTs is historically studied through stress tests. These stress tests have been realized to estimate the time-to-failure of the device by applying extreme bias conditions and tracking the evolution of device characteristics. The advantage of these techniques is the estimation of the device life time on the basis of short-term results with stress-times up to few hours. However, as described in section 1.4.3 of this chapter, the device bias conditions in circuit operation switching between extreme conditions leads to over-estimate the degradation of the device.

This difference between stress tests and real circuit operating conditions is also studied in the MOS technology which is also affected by hot carrier degradation. In MOS devices, hot carrier injection affects the gate interface. For this device, a long-term circuit aging models have been proposed, e.g. [Zhen\_2009]. The model proposed by [Zhen\_2009] takes into account the specificity of the application, active and sleep modes, to estimate the reliability of circuit. However, this model is used for digital applications with only two device states, ON or OFF, while bipolar technology is used for analog applications with a wide range of bias conditions.

To estimate the SiGe:C HBT reliability for these applications, the bias conditions in the circuit have to be taken into account. In [Ardo\_2012] it has been proposed to estimate hot carrier degradation in practical circuit applications by implementing the aging laws in the transistor compact model. This methodology provides an accurate description of device reliability by computing degradation laws directly in the compact model. Due to its straightforward implementation into commercial computer-aided design (CAD) flows, this method allows circuit-designers to realize a reliability-aware circuit architecture at the early stage of the design procedure, well before circuit fabrication.

#### 1.5.2. Organization of this thesis

This thesis is organized as follows:

**Chapter 2 Aging tests** This chapter presents the aging tests used to characterize the damage mechanisms of the SiGe:C HBT fabricated by Infineon technology AG. After a description of the samples used during this work, aging stress tests are presented. Results of the aging tests performed at different bias conditions are then presented.

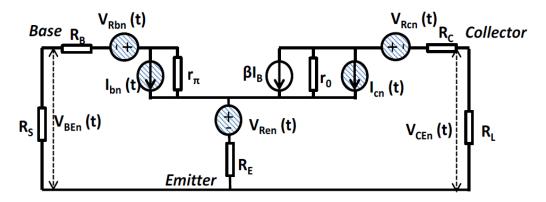

Chapter 3 Low-frequency noise The low-frequency noise is studied before aging tests with a description of its different components. The low-frequency noise is then used as an additional parameter to analyze degradation effects. Actually, low-frequency noise is sensitive to evolution of trapped carrier in the device. The evolution of LF-noise can help to characterize and locate trapped charge in the structure. Therefore, LF-noise has been measured during aging tests.

**Chapter 4 Physical simulation with TCAD** This chapter describes the physical simulation performed to identify the physical origin of damage mechanisms. The SiGe:C structure has been drawn using Sentaurus TCAD software. The physical origin of the damage mechanisms and their impact on the DC characteristics of the device is described. An equation describing the evolution of damage mechanisms is then proposed.

**Chapter 5 Compact model** This chapter describes the implementation of the aging laws in the HBT compact model. The aging laws have been integrated into the compact model. To test the aging compact model, a reliability analysis has been performed on a LNA circuit.

Chapter 6 Conclusion Majors results of this work are summarized.

### Chapter 2 Aging tests

### Description and results

#### 2.1. Introduction

The first step to develop a compact model including the aging laws is a proper characterization of the damage mechanisms occurring in the SiGe:C HBT detail in section 2.2. In literature, to characterize damage mechanisms, conventional stress tests are performed. These conventional stress tests are performed in specific bias configurations such as the reverse stress test [Gogi 2000].

These stress tests are performed at aggressive bias conditions to accelerate device damage mechanisms. The advantage of this bias conditions, very far from the safe operating area borders, is the shorter stress time required to produce significant degradation. Based on accelerated test results, the time-to-failure of the device technology can be estimate. Results of stress test performed on the SiGe:C HBTs studied during this thesis, have been performed and published in [Sass1\_2014]. In this study, relatively short stress times and aggressive bias conditions are considered.

In order to study long-term reliability in circuit operating conditions it is necessary to develop a compact model including the aging laws. Therefore, a long-term stress tests has been proposed and detailed in the section 2.3 of this chapter. Bias conditions are adapted to applications targeted by DOTSEVEN project [Dotseven\_online] and a large stress test time is reached, up to 1000h. In section 2.4, the long-term aging test results are reported and analyzed according to the bias conditions.

#### 2.2. SiGe:C technology

#### 2.2.1. Infineon SiGe:C technology

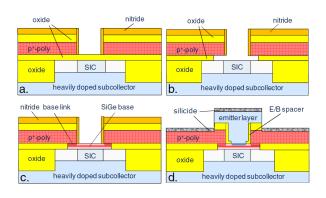

During the DOTFIVE project [Dotfive\_online], AC characteristics of Infineon SiGe:C HBT technology fabricated in the 200nm node have been pushed up to the terahertz range. To obtain such AC performances, a conventional

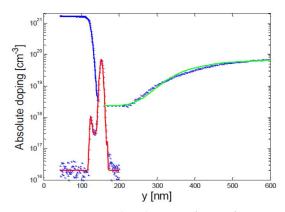

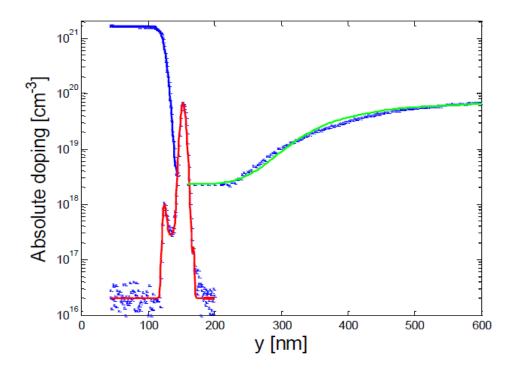

architecture with vertical base link is used. The architecture specification is described in [Chev\_2011], which summarizes the remarkable optimization of the architecture from Infineon technology AG. The fabrication of this device is based on a conventional double-polysilicon self-aligned architecture with epitaxial growth of the base (DPSA-SEG), detailed in Figure 9. To improve the transit frequency and the maximum oscillation frequency, the germanium profile of the base and the doping of the emitter and collector, Figure 10, are optimized to decrease transit times. Additionally, the size of the base-emitter spacer has been shrunk to reduce the base access resistance.

Figure 9: Conventional DPSA-SEG HBT process. Pictures from [Chev\_2011]

Figure 10: Germanium profile of the base (red line) and doping profile of the emitter (blue line) and collector (green line).

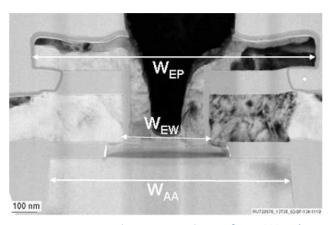

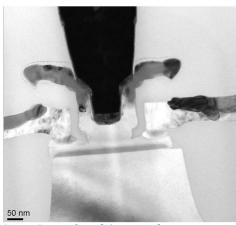

Based on this optimized architecture, a scaled HBT has been integrated in a 130nm technology node (B7HF500), which is the device considered in this thesis work. This transistor exhibits a  $W_{ew}$  equal to 230nm and a  $W_{e}$  of 130nm (Figure 11). HBTs feature a collector-emitter breakdown voltage of 1.5V and a collector-base breakdown voltage of 5.5V. The pinched base resistance is 2.6 kW/sq and the maximum  $\beta$  is 1300 at  $V_{be}$ =0.6 V.

Figure 11 TEM picture of B7HF200 and B7HF500 transistor. Pictures from [Chev\_2011].

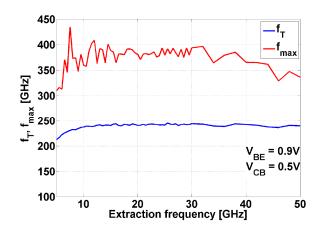

They provide a  $f_T$  of 240 GHz, a  $f_{max}$  of 380 GHz at  $J_C$  = 10 mA/ $\mu$ m<sup>2</sup> (Figure 12) and a ring-oscillator gate delay time  $t_D$  of 2.38 ps measured on 53-stage CML ring-oscillators operating at a collector current density of 14mA/ $\mu$ m<sup>2</sup> [Knap\_2010].

Figure 12: Ft and Fmax of studied HBT for different extraction frequency. Pictures from [Chev\_2011].

#### 2.2.2. Thermal resistance extraction

One limit of SiGe:C HBTs is the thermal runaway due to the self-heating (see Chapter 1 section 1.3.2). Thermal runaway is characterized by a critical junction temperature of the component. Besides, associated with long-term reliability, thermal recovery could occur in the device, limiting the impact of damage mechanism on DC electrical characteristics as described in [Fisc\_2014]. To characterize the junction temperature of the device, and therefore possible recovery or thermal runaway, the device thermal resistance  $R_{th}$  has to be determined.

To extract the  $R_{th}$  parameter, different methodologies can be used [Meno\_2005], [Mane\_2004], [Hout\_2004], [Suli\_2005], [Gran\_2007], [Nodj\_2009]. The selected methodology to extract the thermal resistance is detailed in [Gran\_2007]. This methodology developed in IMS lab can be explained in two steps.

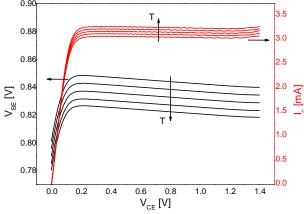

Figure 13 Base emitter voltage and collector current function of the collector emitter voltage at constant base current of SiGe:C HBT under test for different ambient temperatures

The first step consists in measuring the collector current  $I_c$  and the base emitter voltage  $V_{be}$  as a function of the collector-emitter voltage  $V_{ce}$ . This measurement is performed at different controlled ambient temperatures  $T_i$  between 300K and 370K at a constant base current  $I_b$ . The base current value is sufficiently high to activate the self-heating and low to avoid a significant ohmic drop across the access base resistance. Results of these

measurements performed on the SiGe:C HBT under investigation in this thesis have been reported in Figure 13. These results show an increase of the collector current  $I_c$  with the temperature when  $V_{be}$  decreases.

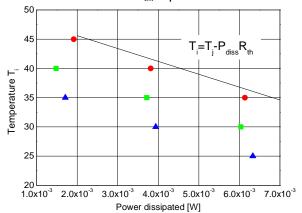

The second step consist in plotting the dependence of the ambient temperature  $T_i$  as a function of the dissipated power. Using equation 2.1,  $T_i$  as a function of the dissipated power is represented Figure 14. The slope of these curves correspond to the thermal resistance  $R_{th}$ , equation 2.1.

Figure 14 Junction temperature as a function of dissipated power for different values of V<sub>be</sub>

Figure 14 shows the results for SiGe:C device under investigation in this thesis. The evaluated  $R_{th}$  is 2200K/W for CBEBC samples. This value is consistent with the thermal resistance extracted in [Ales\_2010], ranging between 1691 and 2306K/W, as a function of the deep trench depth, for SiGe:C HBT manufactured by STMicroelectronics with almost same size (Ae=0.13x9.88 $\mu$ m<sup>2</sup>).

#### 2.2.3. Samples

Samples manufactured by Infineon technology AG, presented in Table 1, have been used to perform the reliability investigations. Every sample has a double collector and double emitter configuration (CBEBC). This CBEBC configuration is chosen to limit the self-heating effect and to optimize the homogenous distribution of the electric field in the structure. The test structures used to perform the stress tests are designed for RF measurement with a ground-signal-ground pad (GSG pad). Furthermore, samples have an emitter-common configuration with the emitter and the substrate connected to the ground pad.

| Name   | Draw di | mension | Effective ( | dimension | Number of device in | Reference in module |  |  |

|--------|---------|---------|-------------|-----------|---------------------|---------------------|--|--|

| Name   | We      | Le      | We          | Le        | parallel            | AC_NPNHS11<br>(TD4) |  |  |

| Size 1 | 0.2μm   | 1μm     | 0.13μm      | 0.93µm    | 9                   | TAS010C20           |  |  |

| Size 2 | 0.2μm   | 2.8µm   | 0.13μm      | 2.73µm    | 3                   | TAS028C20           |  |  |

| Size 3 | 0.2μm   | 10μm    | 0.13μm      | 9.93µm    | 1                   | TAS100C20           |  |  |

Table 1: HBT size under stress test

Size 1 and size 2 samples are composed of 9 HBTs and 3 HBTs in parallel, respectively, whereas the size 3 device is a single device. To perform stress tests, only size 3 devices have been used. Indeed, the analysis of stress test results is much more complex for multiple devices of size 1 and size 2.

#### 2.3. Long-term aging stress procedure

Modern SiGe:C HBTs suffer from degradation mechanisms while the device is biased in the safe operating area [Zhan\_2002], [Fisc\_2015]. Degradation mechanisms are responsible of the wear-out of device performance with time. To characterize device degradation, a long-term stress test procedure has been defined below.

#### 2.3.1. Methodology

To perform the aging tests, stress is applied to the common-emitter test structures. Bias conditions have been chosen at the limit of the SOA. Compared to conventional stress tests, the aging time is considerably increased, several minutes in conventional stress test compared to 1000h for this aging stress test. For the chosen stress conditions, a large aging time is necessary to observe an impact on device electrical characteristics; not accelerated by drastic stress conditions like in conventional stress tests.

To characterize the evolution of the electrical characteristics, measurements have been performed at defined stress times during the aging tests. Due to the long aging time, a logarithm scale is used to define the stress time between each measurement. The aging times are reported in Table 2. The stress time corresponds to the time between each DC characterization and the cumulative aging time to the total time. The aging time is up to 1000h, depending on the evolution of DC characteristics.

| Stress time [h]        | 0 | 1 | 2 | 4 | 10 | 7  | 12 | 12 | 24 | 48  | 130 | 250 | 250 | 250  |

|------------------------|---|---|---|---|----|----|----|----|----|-----|-----|-----|-----|------|

| Cumulative<br>time [h] | 0 | 1 | 3 | 7 | 17 | 24 | 36 | 48 | 72 | 120 | 250 | 500 | 750 | 1000 |

Table 2: Stress time and cumulative time used for the first aging campaign

#### 2.3.2. Electrical characterization during aging test

During the stress test, device electrical characteristics evolve according to the stress conditions. To characterize this evolution, different DC measurements are performed. Depending on their physical locations, the damage mechanism can affect one or several electrical characteristics between each stress time. In the following we detail the electrical characteristics measured between each stress time.

#### 2.3.2.1. Forward Gummel plot

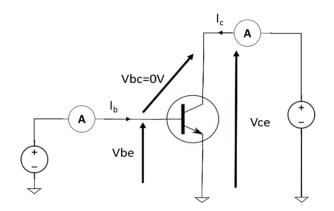

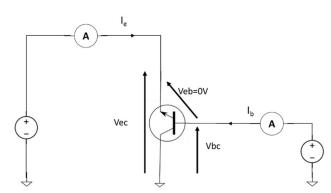

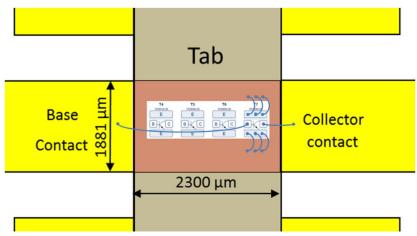

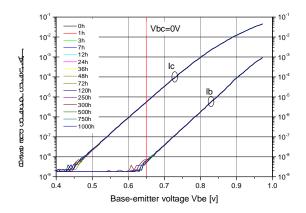

Forward Gummel plots are performed by keeping the base and the collector contacts at the same voltage, so as to keep the base-collector voltage at 0V ( $V_{bc}$ = 0V), see Figure 15. The base current and the collector current are measured for several values of the base-emitter voltage,  $V_{be}$ .

Figure 15: Forward Gummel plot configuration

Figure 16: Example of forward Gummel evolution during time of first generation of SiGe:C device aged in reverse stress test.

Picture from [Cress 2004].

As reported in literature, i.e. [Cress\_2004] (see Figure 16), the forward Gummel plot is affected by the aging test, a reverse stress test in this example. Variations of the forward Gummel plot can be the result of different damage mechanisms, like contact degradation and degradation of the Silicon/Polysilicon interface. The damage can be inferred from the observed modification in the forward Gummel plot. In Figure 16, for example, the increase of the base current at low-injection levels indicates a degradation of the emitter-base spacer interface.

In the forward Gummel measurements in this work, the base-emitter voltage and the collector-emitter voltage are biased at the same bias to keep  $V_{bc}$ =0V ( $V_b$ = $V_c$ ).  $V_{be}$  and  $V_{ce}$  range between 0.4V to 1V with a step of 7mV while the collector current ( $I_c$ ) and the base current ( $I_b$ ) are measured for each step.

#### 2.3.2.2. Reverse Gummel plot

The second electrical characteristics measured at different stress times is the reverse Gummel plot. To measure the reverse Gummel plot, the emitter-base voltage is maintained at 0V,  $V_{eb}$ =0V. To obtain this condition, the emitter-collector voltage and the base-collector voltage are kept at the same value, see Figure 17. The emitter current and the base current are measured for different values of the base-collector voltage ( $V_{bc}$ ). As for the forward Gummel plot, depending on the injection level, the evolution of the reverse Gummel plot during aging tests can provide an indication of the activated ohmic drop damage mechanism. As an example, Figure 18 represents the evolution of the reverse Gummel plot of InP HBTs after a storage test.

Since the SiGe:C HBTs have the emitter and the substrate connected to the ground pad, it's impossible to realize the configuration describe earlier to perform reverse Gummel plots. To obtain  $V_{be}$ =0V, the base voltage is fixed to 0V. A negative collector voltage is applied between 0V and -1V to obtain a positive base-collector voltage. Since the substrate is connected to the ground pad as well as the emitter, this configuration causes a forward biasing of the substrate collector junction. Thus, a substrate current is added to the collector current. However, since during the aging test, the substrate collector junction is reverse biased, the substrate current can be considered constant and thus the emitter-substrate current evolution attributed to base-collector junction.

Figure 17: Reverse Gummel plot configuration

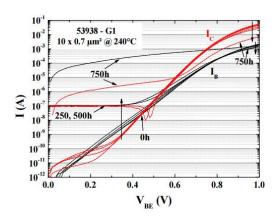

Figure 18: Example of evolution of reverse Gummel plot of InP transistor after storage test @ 240°C. Picture from [Kone 2011]

#### 2.3.2.3. Low-frequency noise measurement

The low-frequency noise measurement at constant  $V_{ce}$  and constant base current ( $I_b$ ) can be also used as a means to characterize the damage mechanisms in the device. As described in [laba\_2004], the LF-noise measurement evolution depends on the damage mechanism occurring at the device interfaces. Therefore, the generation-recombination component of low-frequency noise evolution during time indicates a variation of the trapped charge in the device.

Low-frequency noise evolution during the aging time is an additional means to confirm the nature of the damage mechanisms. This behavior is more detailed in the Chapter 3 of this thesis.

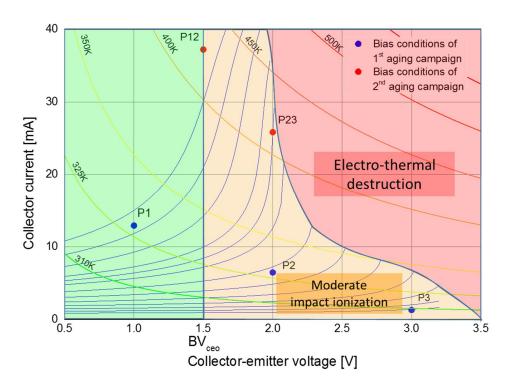

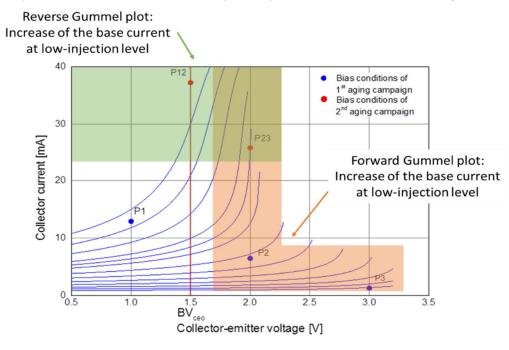

#### 2.3.3. Bias conditions

For the first aging campaign, three bias conditions have been chosen. Blue dots in Figure 19 show bias conditions along the limit of the SOA. Since these conditions are close to the SOA edges, the simulated output characteristics with calibrated HICUM model are shown in Figure 19. The first bias conditions P1 has been defined at  $V_{ce}$ =1V below the BV<sub>ceo</sub> (measured at 1.5V) but with a high collector current density  $J_c$ =10mA/ $\mu$ m<sup>2</sup> ( $I_c$ = 12.91 mA for size 3 HBT). The second bias conditions P3 has been defined for a large collector-emitter voltage  $V_{ce}$ =3V, twice the BV<sub>ceo</sub>. To keep this bias point in the safe operating area, the collector current density is fixed at  $J_c$ =1mA/ $\mu$ m<sup>2</sup> ( $I_c$ = 1.29mA for size 3 HBT). An intermediate bias conditions P2 is defined between these bias points,  $V_{ce}$ =2V and  $J_c$ =5mA/ $\mu$ m<sup>2</sup> ( $I_c$ = 6.45mA for size 3 HBT).

Figure 19: Output characteristics simulated using HICUM level 2 at  $V_{be}$  constant between 0.82V and 0.91V (Step of 0.01V) and junction temperature contours for an ambient temperature of 300K. Bias conditions of first (P1, P2 and P3) and second (P12 and P23) aging campaign are reported in the figure with the estimate SOA.

For the first aging campaign, the reliability investigation is focused on the impact of the collector-emitter voltage. Therefore, a second aging campaign has been performed with new bias conditions. The bias conditions of the second aging campaign, red dot in Figure 19, have been chosen to characterize the impact of higher values of collector current density on HBT reliability. The collector-emitter voltage of bias condition P23 is fixed at 2V, as for the P2 bias condition. A higher collector current density is chosen at  $J_c=20mA/\mu m^2$  ( $I_c=25.82mA$  for size 3 HBT). The second bias condition P12 is fixed at  $V_{ce}=1.5V$ , between P1 and P2 bias conditions, at the limit of the BV<sub>ceo</sub>. The collector current density of P12 is fixed at  $30mA/\mu m^2$  ( $I_c=37.2mA$  for size 3 HBT), at the limit of the electro-thermal destruction.

| Bias conditions | $V_{ce}$ | Ic      | T <sub>j</sub> |

|-----------------|----------|---------|----------------|

| P1              | 1V       | 12.91mA | 328,4K         |

| P2              | 2V       | 6.45mA  | 328,4K         |

| Р3              | 3V       | 1.29mA  | 308,5K         |

| P23             | 2V       | 25.82mA | 413,6K         |

| P12             | 1.5V     | 37.2mA  | 422,7K         |

Table 3: Bias conditions and junction temperature

#### 2.3.4. Aging test campaign configuration

#### 2.3.4.1. First Aging test campaign

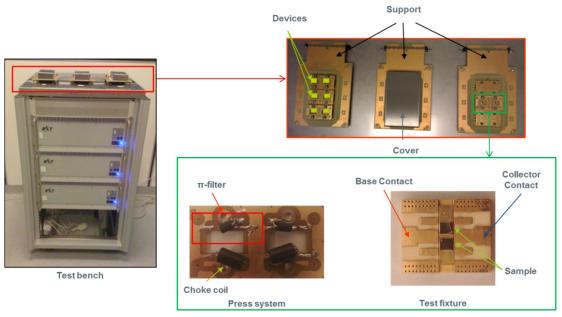

The first aging test campaign has been performed on a dedicated test bench. This test bench is composed of 3 identical test supports. Each support hosts 6 devices in the same slot, for a maximum of 18 HBTs on the test bench. Each device can be biased independently in a common-emitter configuration. A photo of the test bench is presented Figure 20.

Figure 20: Photography of the dedicated test bench

To apply bias conditions, samples are reported on a specific test fixture. Two samples are reported on one test fixture to optimize the space. The base contact of one device is bonded to one contact of the test fixture, Figure 21. The same process is repeated on the collector side with the other contact of the test fixture.

Figure 21 Illustration of test fixture with bounded samples

The emitter has to be grounded. Therefore, the emitter is connected with multiple ball bonding to the test fixture to reduce associated bonding resistance. The report and bonding of die on test fixture have been realized at the IMS lab. During aging test, only one sample is bonded to the test fixture to perform the aging test.

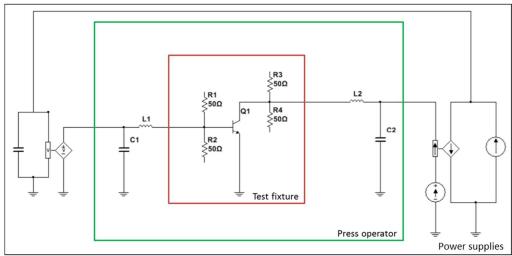

The first measurement performed before the aging test shows parasitic oscillations observed on the forward Gummel plot and the reverse Gummel plot. To avoid these parasitic oscillations, a  $\pi$ -type low-pass filter to the base and a choke coil to the collector have been added in the press system.

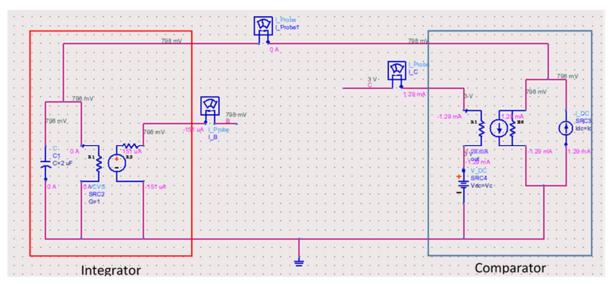

A system to perform the aging test at constant collector current and constant collector-emitter voltage is included in the test bench. The collector-emitter voltage is directly applied to the device. The collector current is controlled by adjusting the base current or voltage. Indeed, the test bench includes a feedback loop to control the collector current by adjusting the base current or voltage. The schematic of the whole system is represented Figure 22. This feedback loop is used to the keep the collector current constant during the aging test. It is possible to define a compliance of the base and the collector currents or voltage to avoid the destruction of the device. All these parameters and the aging time are controlled using a computer connected by USB link on the Easy stress software. For the measurement during aging tests a dedicated software, Easy report, is used.

Figure 22: Electrical equivalent circuit of the stress test bench

#### 2.3.4.2. Second aging test campaign

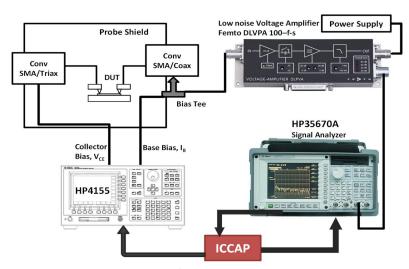

The second aging test campaign has been performed with another measurement setup. For this campaign, the device under test have been aged and measured using a probe station. With this test setup, low-frequency noise measurement could be performed at each step. The measurement setup is used to perform aging test and measurements between each stress time. All the setup is controlled using the IC-CAP software.

To avoid any problem with contacts between each stress test, the aging of the device and measurements have been performed on the same setup without removing the probes. A routine on IC-CAP software has been developed to maintain the collector current constant during the aging test. Every minutes, the collector current has been measured and the base-emitter voltage adapted to keep I<sub>c</sub> according to the aging bias conditions.

To characterize the degradation mechanisms, three different measurements have been performed during the aging test. The forward Gummel plot and the reverse Gummel plot have been measured between each stress steps with the methodology described in section 2.3.2.

Thanks to the new measurement setup, the low-frequency noise measurement has been added (which is not possible with the first test setup). Low-frequency noise measurements have been performed at a collector-emitter voltage ( $V_{ce}$ ) equal to 1V for different base current ( $I_b$ ) values equal to 0.1 $\mu$ A, 1 $\mu$ A and 10 $\mu$ A.

#### 2.4. The aging test results

In this part, the evolution of the DC electrical characteristics of the device under test at different aging conditions are reported. Only the forward Gummel plot and reverse Gummel plot results for the first and the second aging campaign are reported. The low-frequency noise evolution during aging test is reported in the chapter 3.

#### 2.4.1. First aging campaign results

For each bias conditions (P1, P2 and P3), 6 devices have been aged at the same time at a controlled ambient temperature equal to 300K. The forward Gummel plot and the reverse Gummel plot are measured at each aging time for each bias conditions.

#### 2.4.1.1. Measurement results under P1 bias conditions

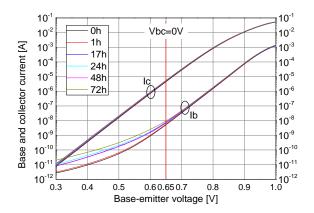

The forward Gummel plot of one device aged under P1 bias conditions is represented Figure 23. For a base-emitter voltage higher than 0.7V, no significant variation of the base current has been reported during the aging stress test. The slight variation of the base current at  $V_{be}$ <0.7V has the same order of magnitude as the resolution of the test bench. Therefore, the base current for the forward Gummel plot is almost constant during the aging test. The collector current is also almost constant during the aging test. Also, the base current and the emitter-substrate current of the reverse Gummel plot, Figure 24, are almost constant during the aging test.

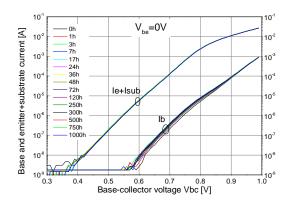

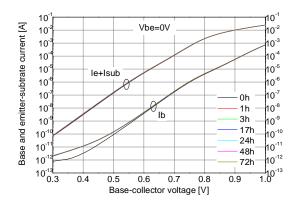

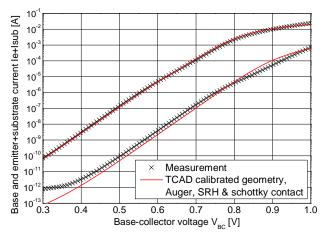

V<sub>be</sub>=0V Base and emitter+substrate current [A] 10 10 10 0 10 le+Isub 10 10 10 10⁴ 10 10 10-10 <sup>⊥</sup>10<sup>-9</sup> 1.0 0.3 0.4 0.5 0.6 0.7 0.8 Base-collector voltage Vbc [V]

Figure 23: Forward Gummel plot at V<sub>bc</sub>=0V at different aging times for one device aged under P1 bias conditions

Figure 24: Reverse Gummel plot at V<sub>be</sub>=0V at different aging times for one device aged under P1 bias conditions

The SiGe:C HBTs aged under P1 bias conditions do not depict any significant variation of their DC electrical characteristics during the aging test. The SiGe:C structure seems not being affected by P1 stress bias conditions.

#### 2.4.1.2. Measurement results under P2 bias conditions

For devices aged under the P2 bias conditions the forward and reverse Gummel plot at different aging times are reported in Figure 25 and Figure 26, respectively. The emitter+substrate current of the reverse Gummel plot, Figure 26, remains almost constant during the aging time. Likewise, the base current is constant or the variation of the base current has the same order of magnitude as the resolution of the test bench.

Figure 25: Forward Gummel plot at V<sub>bc</sub>=0V for different aging times of one device aged under P2 bias conditions

Figure 26: Reverse Gummel plot at V<sub>be</sub>=0V for different aging times of one device aged under P2 bias conditions

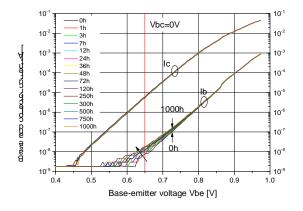

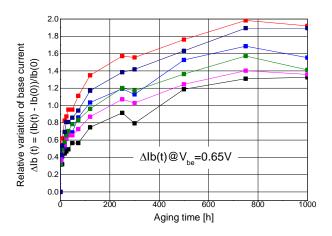

The collector current of the forward Gummel plot, Figure 25, is almost constant during the aging time. Likewise, the base current at  $V_{be}$  higher than 0.75V is constant during the aging test. On the contrary, the base current for  $V_{be}$  lower than 0.75V tends to increase with the stress time. To characterize the evolution of base current of the forward Gummel plot, the relative variation of the base current  $\Delta I_b(t)$ , as defined in equation 2.3, is extracted at  $V_{be}$ =0.65V.

$$\Delta \quad (\ ) = \frac{-\quad (0)}{(0)}$$

2.3

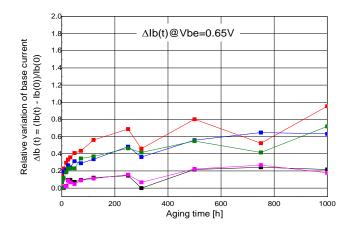

The evolution of the base current as a function of the stress test, for all devices aged under P2 bias conditions, is shown in Figure 27. The  $\Delta l_b$  of each device aged under P2 present the same evolution as a function of the aging time. The base current increase during the first hours of the stress test seems to reach a saturation value. However, we can note a relative variation of the final constant value of the base current for each device.

Figure 27: Relative variation of the base current during aging test for device aged under P2 bias conditions at  $V_{be}$ =0.65V.

For each device, a systematic decrease of the base current at 300h is observed, Figure 27. For this stress test cycle a delay of 50h has occurred between the end of the stress application and the measurement time. Therefore, the decrease of the base current can be ascribed to natural recovery phenomena. Natural recovery has also been observed for a comparable technology [Sass2 2014] aged under very high-reverse EB stress.

#### 2.4.1.3. Measurement results under P3 bias conditions

Figure 28 represents the forward Gummel plot at  $V_{bc}$ =0V for the device aged under P3 bias conditions. The collector current is almost constant or its variation is below the resolution of the test bench during the aging test. For  $V_{be}$  higher than 0.7V, the base current does not significantly change. On the contrary, for  $V_{be}$  lower than 0.7V, the base current tends to increase with the aging time.

Figure 28: Forward Gummel plot at V<sub>bc</sub>=0V for one device aged under P3 bias conditions for different aging times

Figure 29: Reverse Gummel plot at V<sub>be</sub>=0V for one device aged under P3 bias conditions for different aging times

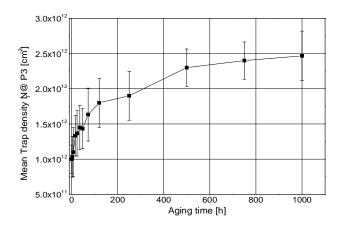

The relative evolution of the base current at  $V_{be}$ =0.65V has been reported in Figure 30. The evolution of the base current increase under P3 bias conditions has the same evolution as the base current increase under P2 bias conditions: the base current increases during the first hours of the stress and reaches a saturation value after 700h.

Figure 30: Relative Increased of the base current for devices aged under P3 bias conditions under  $V_{be}$ =0.65V as a function of the aging time

The relative variation of the base current at 300h due to natural recovery occurring for the device under P2 bias conditions also occurs for the device aged under P3 bias conditions. For the reverse Gummel plot, Figure 29, the base current and the emitter+substrate current is almost constant during the aging test.

#### 2.4.1.4. Conclusion of the first aging test campaign

During the first aging campaign, 6 devices size 3 per bias conditions have been aged during 1000h. For each device, the forward Gummel plot and the reverse Gummel plot have been measured during the aging test.

The base current and collector currents of the reverse Gummel plot are almost constant for P1, P2 and P3 bias conditions during the aging test. At P1 bias conditions, the electrical characteristics of the device are almost constant during the aging test. Therefore, the reliability of the devices is not impacted by a low collector-emitter voltage and moderate collector current density.

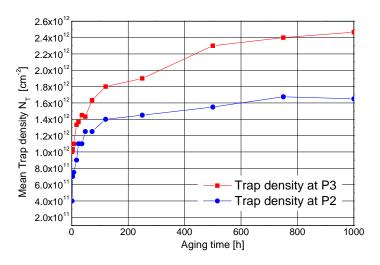

The base current of forward Gummel plot of device aged under P2 and P3 bias conditions tends to increase with the stress time for  $V_{be}$  lower than 0.75V. For both bias conditions, the increase of the base current  $\Delta I_b$  has the same evolution as a function of the aging time. The  $\Delta I_b$  increases rapidly during the first hours of the aging test eventually reaching a constant value. However, the increase of the base current  $\Delta I_b$  presents a rate different between device aged under P2 and device aged under P3 bias conditions. Also, the final constant value of the base current relative increase is higher for P3 compared to P2. This difference is probably the result of the higher  $V_{ce}$  of P3 bias conditions,  $V_{ce}$ =3V compared to  $V_{ce}$  of P2 bias conditions,  $V_{ce}$ =2V. To conclude, the higher the collector-emitter voltage is, the more rapid is the increase of the base current. The constant value reached by the variation of the base current also increases for higher  $V_{ce}$ .

#### 2.4.2. Second aging test campaign

The second aging test campaign has been performed on a different measurement setup. However, the DC characteristics measured during the aging test is the same as the first aging test campaign, forward and reverse Gummel plot.

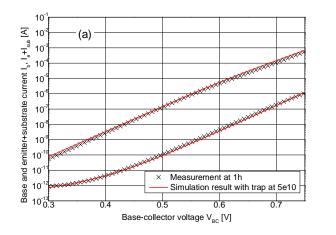

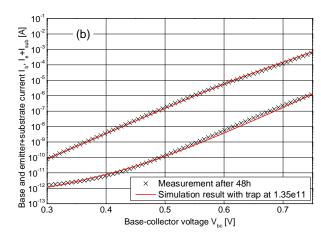

#### 2.4.2.1. Measurement results under P23 bias conditions

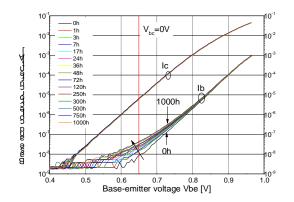

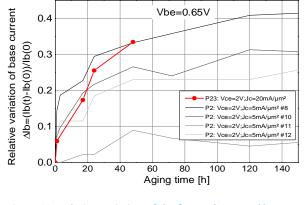

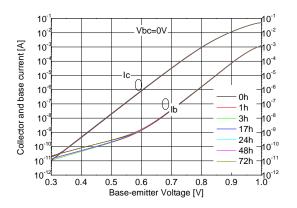

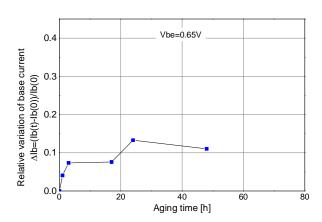

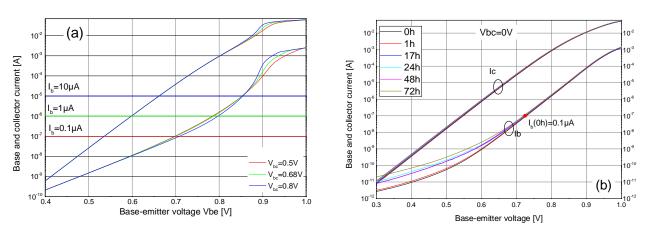

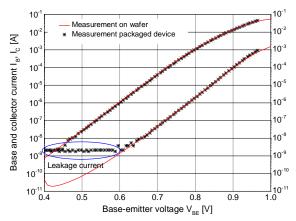

The evolution of the forward Gummel plot of the device aged under P23 bias conditions is depicted in Figure 31. The collector current remains almost constant during the aging test. For  $V_{be}$  higher than 0.7V, the base current is constant while the base current tends to increase for  $V_{be}$  lower than 0.7V. The variation of the base current at  $V_{be}$ =0.65V is compared to the variation of the base current under P2 bias conditions, Figure 32. Since P2 and P23 bias conditions have the same collector-emitter voltage ( $V_{ce}$ = 2V) but with a collector current density 4 times higher under P23 compared to P2 bias conditions. The variation of the base current of the forward Gummel plot under P23 bias conditions has the same evolution as the base current under P2 bias conditions. This behavior confirms the impact on reliability of the collector-emitter voltage: a larger  $V_{ce}$  yields higher base current evolution.

Figure 31: Forward Gummel plot at V<sub>bc</sub>=0V for a device aging under P23 bias conditions for different aging times

Figure 32: Relative variation of the forward Gummel base current of devices aging under P23 and P2 bias conditions

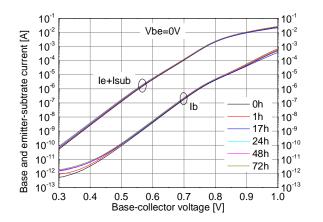

Figure 33: Reverse Gummel plot for a device aging under P23 bias conditions for different aging times

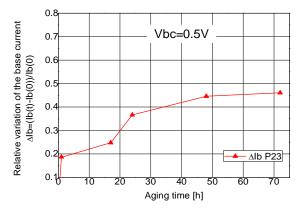

Figure 34: Relative variation of the base current for a device aging under P23 bias conditions for different aging times

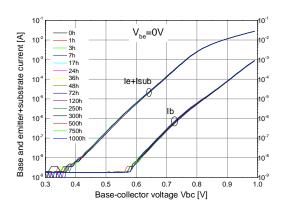

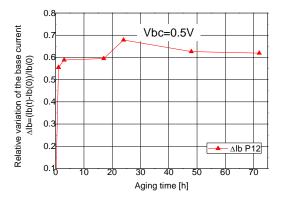

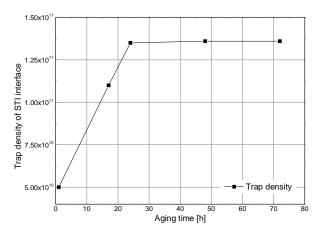

The reverse Gummel plot of the device aged under P23 at different aging times is represented in Figure 33. The emitter-substrate current is almost constant during the aging test. The base current at  $V_{bc}$  higher than 0.7V is almost constant during the aging test. For  $V_{bc}$  lower than 0.7V, the base current tends to increase during the aging test. To analyze this behavior, the relative variation of the base current at  $V_{bc}$ =0.5V has been reported in Figure 34. The base current increases during the first 48h of aging to reach a constant value. We can note that the evolution of the reverse Gummel base current is similar to the evolution of forward Gummel plot.

#### 2.4.2.2. Measurement results under P12 bias conditions

One device has been aged under P12 bias conditions,  $V_{ce}$ =1.5V and  $J_c$ =30mA/ $\mu$ m². During this aging test, the forward Gummel plot and the reverse Gummel plot have been measured and presented in Figure 35 and Figure 37, respectively.

Figure 35: Forward Gummel plot at V<sub>bc</sub>=0V for a device aged under P12 bias conditions

Figure 36 Relative variation of the base current of forward Gummel plot of a device aged under P12 bias conditions

Figure 37: Reverse Gummel plot at V<sub>be</sub>=0V for a device aged under P12 bias conditions

Figure 38: Relative variation of the base current of reverse Gummel plot of a device aged under P12 bias conditions

The collector current and the base current of the forward Gummel plot at  $V_{bc}$ =0V are almost constant during the aging test under P12 bias conditions. This slight variation of the base current, Figure 36, could be explained by the low  $V_{ce}$  of P12 bias conditions (lower than  $BV_{ceo}$ ).

The reverse Gummel plot in Figure 37, shows that the emitter+substrate current is almost constant during the aging test. The base current at  $V_{bc}$  higher than 0.7V is almost the same during the aging test. Moreover, for  $V_{bc}$  lower than 0.7V, the base current increases rapidly after 1h, Figure 38. Subsequently, after 3h, the base current reaches a constant value.

## 2.4.2.3. Conclusion of the second aging test campaign

An aging test campaign has been performed under P23 and P12 bias conditions during 72h. For the device aged under P23 bias conditions, the base current of the forward Gummel plot increases during the aging test. The variation of the base current has the same evolution as the variation of the one under P2 bias conditions, subject to the same collector-emitter voltage equal to 2V. Indeed, the variation of the base current of the forward Gummel plot is mainly affected by  $V_{ce}$  rather than the collector current density.

The base current of the reverse Gummel plot increases during the aging time for both aging tests performed under P23 and P12 bias conditions. The evolution of the base current at low injection seems to be more activated by a high collector current density rather than a high emitter-collector voltage.

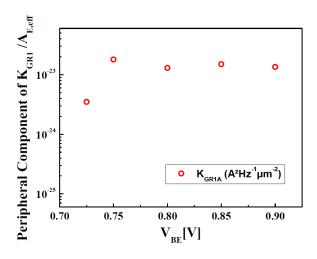

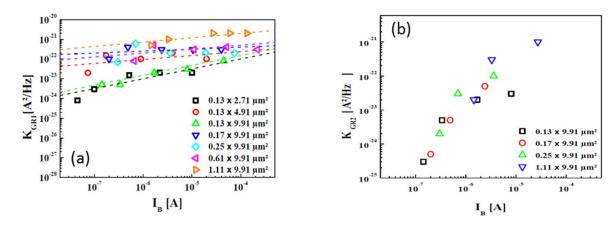

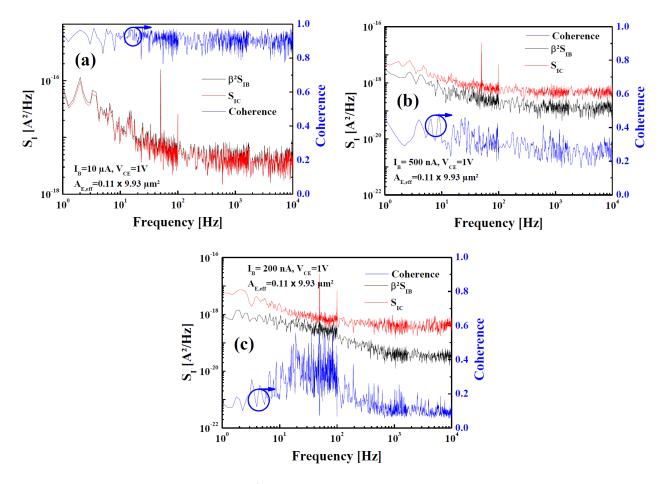

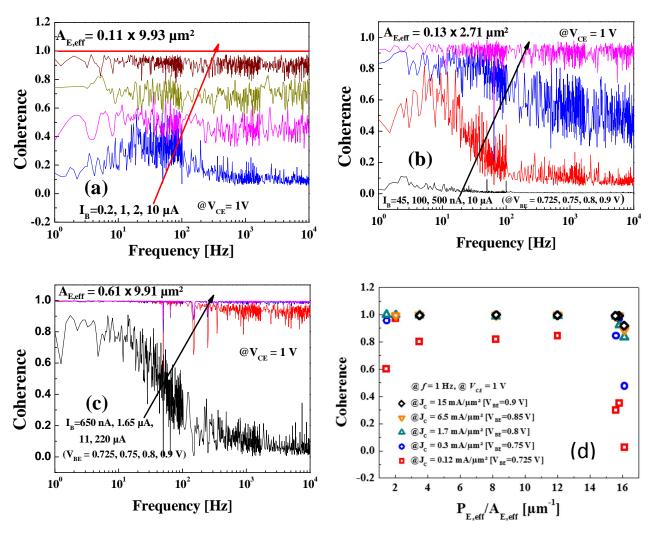

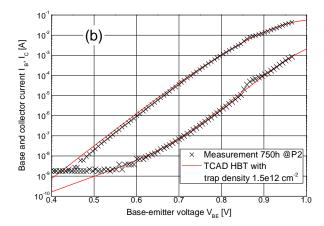

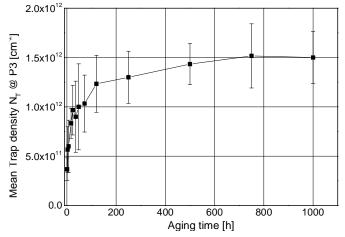

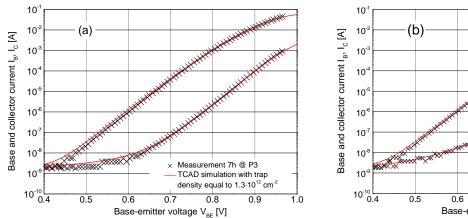

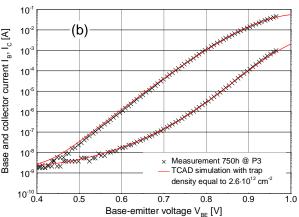

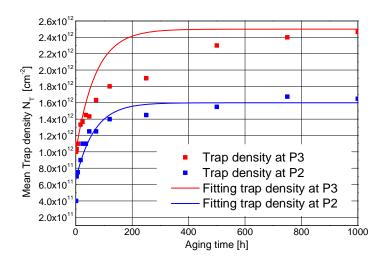

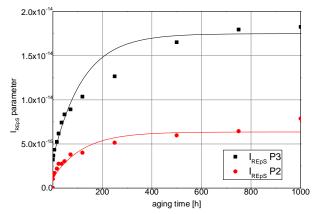

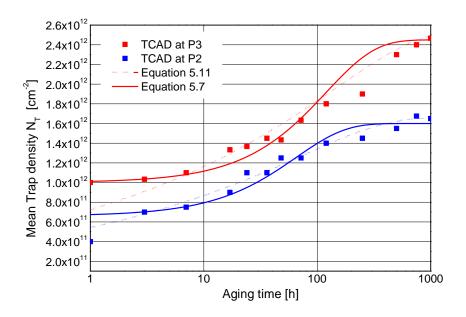

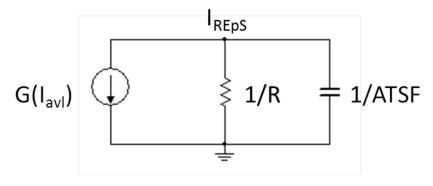

#### 2.5. Conclusion