## Co-design of architectures and algorithms for mobile robot localization and model-based detection of obstacles

Daniel Tortei

#### ▶ To cite this version:

Daniel Tortei. Co-design of architectures and algorithms for mobile robot localization and model-based detection of obstacles. Embedded Systems. Université Paul Sabatier - Toulouse III, 2016. English. NNT: 2016 TOU 30294. tel-01477662 v 2

### HAL Id: tel-01477662 https://theses.hal.science/tel-01477662v2

Submitted on 16 Feb 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

En vue de l'obtention du

### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par : l'Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier) Cotutelle internationale Université de Novi Sad

### Présentée et soutenue le 02.12.2016 par :

### Dániel TÖRTEI

#### CO-DESIGN OF ARCHITECTURES AND ALGORITHMS FOR MOBILE ROBOT LOCALIZATION AND MODEL-BASED DETECTION OF OBSTACLES

#### **JURY**

BRANISLAV BOROVAC MOHAMED AKIL JONATHAN PIAT ĐORDE OBRADOVIĆ Professeur d'Université Professeur d'Université Maître de Conférences Maître de Conférences Président Rapporteur Examinateur Examinateur

#### École doctorale et spécialité :

EDSYS: Systèmes embarqués 4200046

Unité de Recherche:

LAAS-CNRS (UMR 8001)

Directeur(s) de Thèse:

Michel DEVY et Mirko RAKOVIĆ

Rapporteurs:

Mohamed AKIL et Branislav BOROVAC

# УНИВЕРЗИТЕТ У НОВОМ САДУ ФАКУЛТЕТ ТЕХНИЧКИХ НАУКА У НОВОМ САДУ

Даниел Тертеи

### КОДИЗАЈН АРХИТЕКТУРЕ И АЛГОРИТАМА ЗА ЛОКАЛИЗАЦИЈУ МОБИЛНИХ РОБОТА И ДЕТЕКЦИЈУ ПРЕПРЕКА БАЗИРАНИХ НА МОДЕЛУ

ДОКТОРСКА ДИСЕРТАЦИЈА

#### Abstract

An autonomous mobile platform is endowed with a navigational system English. which must contain multiple functional bricks: perception, localization, path planning and motion control. As soon as such a robot or vehicle moves in a crowded environment, it continuously loops several tasks in real time: sending reference values to motors' actuators, calculating its position in respect to a known reference frame and detection of potential obstacles on its path. Thanks to semantic richness provided by images and to low cost of visual sensors, these tasks often exploit visual cues. Other embedded systems running on these mobile platforms thus demand for an additional integration of high-speed embeddable processing systems capable of treating abundant visual sensorial input in real-time. Moreover, constraints influencing the autonomy of the mobile platform impose low power consumption. This thesis proposes SOPC (System on a Programmable Chip) architectures for efficient embedding of vison-based localization and obstacle detection tasks in a navigational pipeline by making use of the software/hardware co-design methodology. The obtained results are equivalent or better in comparison to state-of-the-art for both EKF-SLAM based visual odometry: regarding the local map size management containing seven-dimensional landmarks and model-based detection-by-identification obstacle detection: algorithmic precision over execution speed metric.

Keywords: Robot navigation, visual SLAM, visual obstacle detection, hw/sw co-design, SoPC, heterogeneous embedded boards

Un véhicule autonome ou un robot mobile est équipé d'un système de Français. navigation qui doit comporter plusieurs briques fonctionnelles pour traiter de perception, localisation, planification de trajectoires et locomotion. Dès que ce robot ou ce véhicule se déplace dans un environnement humain dense, il exécute en boucle et en temps réel plusieurs fonctions pour envoyer des consignes aux moteurs, pour calculer sa position vis-à-vis d'un repère de référence connu, et pour détecter de potentiels obstacles sur sa trajectoire; du fait de la richesse sémantique des images et du faible coût des caméras, ces fonctions exploitent souvent la vision. Les systèmes embarqués sur ces machines doivent alors intégrer des cartes assez puissantes pour traiter des données visuelles en temps réel. Par ailleurs, les contraintes d'autonomie de ces plateformes imposent de très faibles consommations énergétiques. Cette thèse proposent des architectures de type SOPC (System on Programmable Chip) conçues par une méthodologie de co-design matériel/logiciel pour exécuter de manière efficace les fonctions de localisation et de détection des obstacles à partir de la vision. Les résultats obtenus sont équivalents ou meilleurs que l'état de l'art, concernant la gestion de la carte locale d'amers pour l'odométrie-visuelle par une approche EKF-SLAM, et le rapport vitesse d'exécution sur précision pour ce qui est de la détection d'obstacles par identification dans les images d'objets (piétons, voitures...) sur la base de modèles appris au préalable.

Mots clés: Navigation du robot, SLAM visuel, detection visuelle d'obstacles, adéquation algorithme architecture, SoPC, cartes embarquées hétérogenes

Autonomna mobilna platforma opremljena sistemom za navigaciju podrazumeva više funkcionalnih blokova: percepciju, lokalizaciju, planiranje putanje i upravljački podsistem. U slučaju kada se robot kreće u sredini sa mnoštvom prepreka na putu, on kontinualno izvršava nekolicinu zadataka u realnom vremenu: šalje referentnu vrednost fizičkih veličina za upravljanje aktuatorima, računa svoju poziciju u odnosu na poznati referentni koordinatni sistem u prostoru i detektuje potencijalne prepreke na svom putu. Zahvaljujući kamerama koje pružaju bogatu semantičku informaciju u vidu slika u boji i njihovoj niskoj ceni, ovi zadaci se često baziraju na viziji. Prema tome, standardni namenski sistemi implementirani na ovim mobilnim platformama zahtevaju dodatno integrisanje brzih procesnih sistema sa kapacitetom obrade velike količine vizuelnih podataka u realnom vremenu. Štaviše, zarad što veće autonomije mobilne platforme potrebno je osigurati njenu minimalnu energetsku potrošnju. Ova teza bavi se dizajnom SoPC (engl. System on a Programmable Chip) arhitektura i algoritama za efikasnu implementaciju zadataka lokalizacije i detekcije prepreka baziranih na viziji u kontekstu autonomne navigacije koristeći metodologiju hardver/softver kodizajna. Ostvareni rezultati su ekvivalentni ili bolji od aktualnog stanja u oblasti pri lokalizaciji pomoću vizuelne odometrije bazirane na EKF-SLAM algoritmu i pri detekciju prepreka putem algoritama identifikacije bazirane na modelu. Za lokalizaciju, razvijena je efikasna računarska arhitektura za EKF algoritam, koja podržava skladištenje i obradu sedmodimenzionalnih orijentira u lokalnoj mapi. Za detekciju prepreka je predložena nova metoda prepoznavanja objekata u slici putem prozora detekcije fiksne dimenzije, koja omogućava veću brzinu izvršavanja algoritma detekcije.

Ključne reči: Robotska navgacija, vizuelni SLAM, detekcija prepreka u slici, kodizajn hardver-softver, SoPC, heterogene namenske kartice

### Acknowledgements

This doctoral dissertation is the result of a rich past experience that spans far over last four years. It would have been an impossible feat, if not for my childhood education, early manufacturing-related working experience and most importantly the values taught at me at home: discipline, passion to quality work and the need for critical and focused thinking in this world characterized by evermore complex dynamics. I cannot express enough my gratitude to my grandparents: Nagytata (András), Nagymama (Mária), Baka (Ruža) and Deda (Josip), who, with their comprehension, patience and care, nurtured an early flourishment of my creative skills and enabled their very first embodiments. I am eternaly thankful to my parents, Mama (Erika) i Tata (Branislav), who aided me in my endeavors and pushed me into the unknown, while always finding a way to be by my side even when physically apart for several thousand kilometers. Not less worthy was my partner's support, which is proven to be inevitable for sharpening my communicational and social skills. Thank you Brigitta for your daily efforts and sacrifices.

This PhD thesis was conducted under joint supervision of Michel Devy at LAAS-CNRS, Toulouse, France and Mirko Raković at Faculty of Technical Sciences, University of Novi Sad, Serbia. Funds allocated in the 2012-2016 period are:

- French Government Scholarship for joint-PhD students,

- FUI-AAP14 project *AIR-COBOT*, co-funded by BPI France, FEDER and the Midi-Pyrénées region and

- Project Robot Viticole funded by the Midi-Pyrénées region.

In France, I was integrated in the Robotics, Action, Perception (RAP) group in LAAS-CNRS laboratory and affiliated to University Paul Sabatier (Toulouse III). In Serbia, I was registered at Computation and Control Engineering Department at Faculty of Technical Sciences (University of Novi Sad). During the joint thesis preparation I have had an opportunity to immerse myself largely into French and Serbian customs in terms of private and professionnal life, leaving my zone of comfort well behind me. That resulted in an exciting, multicultural and challenging adventure that improved greately my perception of both Academia and Industry, given these aforementioned research projects I was entrusted with. I would like to express my gratitude to Michel Devy who equivocally believed in my capacities and under whose supervision I was able to fully experience driving on the bulky road of a researcher's work constrained by industrial applications. Thanks to financial support from his behalf, I was able to attend and present my work at the International conference on reconfigurable computing and FPGAs, which had a huge impact on my understanding of the field of SoPC architectures design. I tend to thank Dorđe Obradović for his initial instructions, help and advices. Thanks to the genuine help of Mirko Raković, under whose supervision the dissertation came to its final shape, focus of the research content has been firmly formulated. Special thanks to Jonathan Piat and Bertrand Vandeportaele, for all the advices for both sw/hw conceptual and technical issues. I would like to thank Patrick Danès for his unreserved trust and support and foremost for his time devoted to me during hard times when the joint cooperation seemed almost unsustainable. Thank you Mohamed Akil and Branislav Borovac, and to other members of the jury of the defence of my thesis, for your invested time for reading, evaluating and synthesizing the dissertation. Your comments and critics are unambiguously assertaining the value of this joint work and, to my great delight, give motivation for consequent research.

As part of RAP group, I had the opportunity to interchange ethical views and conceptions first hand with people originating from Middle East, India, Americas, Ethiopia, Germany and Far East. It left me with tremendeous appreciation towards muslim, latin and hindu traditions and cultural values and a much better understanding of the human being and its potential. Thank you for all cooperation, funny conversations and great babyfoot and table tennis games we had Ariel, Diego, Xavier, Alhayat, Ali, Mustaffa, Wassim, Nemanja, Igor, Dušan, Marko, Borislav, Mukunda, Nirmal, Ganesh, Harmish, Renliw, François, Phillippe-Antoine, Jean-Thomas, Justin, Marcus, Pierrick, Alexandre, Stanislas and Guido.

The technical, scientific and social skills needed to surmount such a joint PhD program are very well summarized in an old Hungarian proverb:

"Szemesnek áll a világ"

"World is upon those who see" (eng. trans.)

because, at the same time, it expresses the need of a physical ability of seeing the world as is with **eyes**, the hypothesis of perceiving the world in a right way by means of **vision**, and the skills requirement of one's **adaptability** and **cunning** to process the acquired knowledge and make something valuable out of it.

### Contents

| L |      | oducu    |                                                 |

|---|------|----------|-------------------------------------------------|

|   | 1.1  |          | al Introduction                                 |

|   | 1.2  |          | aneous Localization and Mapping                 |

|   | 1.3  |          | ele Detection and Tracking                      |

|   | 1.4  | Organi   | zation of the manuscript                        |

| 2 | Arc  | hitectu  | res and Algorithms for Robot Navigation 21      |

|   | 2.1  | Robot    | Navigation                                      |

|   |      | 2.1.1    | The navigation system for the AIR-COBOT robot   |

|   |      | 2.1.2    | Specifications of an embedded navigation system |

|   | 2.2  | HW/S     | W co-design methodology                         |

|   | 2.3  | Conclu   | sion                                            |

| 3 | Stat | te-of-th | ne-art 31                                       |

|   | 3.1  | Compu    | nter vision for object classification           |

|   |      | 3.1.1    | Interest Point Detectors and Descriptors        |

|   |      |          | 3.1.1.1 Raw pixel patches                       |

|   |      |          | 3.1.1.2 Scale-invariant feature transform       |

|   |      |          | 3.1.1.3 Speeded-up robust features              |

|   |      |          | 3.1.1.4 Histogram of Gradients                  |

|   |      |          | 3.1.1.5 Other Descriptors                       |

|   |      | 3.1.2    | Explicit Shape                                  |

|   |      |          | 3.1.2.1 K-fans                                  |

|   |      |          | 3.1.2.2 Implicit-shape model (ISM)              |

|   |      |          | 3.1.2.3 Alphabets of visual words               |

|   |      | 3.1.3    | Without explicit shape                          |

|   |      |          | 3.1.3.1 Hierarchical object recognition         |

|   |      | 3.1.4    | Machine learning for classification             |

|   |      |          | 3.1.4.1 Boosting                                |

|   |      |          | 3.1.4.2 Support vector machines                 |

|   |      |          | 3.1.4.3 Application in computer vision 41       |

|   | 3.2  | Compl    | ete real-time video analytics systems           |

|   |      | 3.2.1    | Non-embedded solutions                          |

|   |      | 3.2.2    | Embedded solutions                              |

|   | 3.3  | Visual   | EKF-SLAM                                        |

|   |      | 3.3.1    | Monocular SLAM implementations                  |

|   |      | 3.3.2    | FPGA-based SLAM implementations                 |

|   |      |          |                                                 |

| 4 | $\mathbf{E}\mathbf{K}$ | F-SLA    | M HW/SW co-design: part I                        | <b>47</b> |

|---|------------------------|----------|--------------------------------------------------|-----------|

|   | 4.1                    |          | ling                                             | . 48      |

|   | 4.2                    |          | vare specification before partitioning           |           |

|   |                        | 4.2.1    | System Cost Measure Definition                   |           |

|   |                        | 4.2.2    | Update Specifications                            |           |

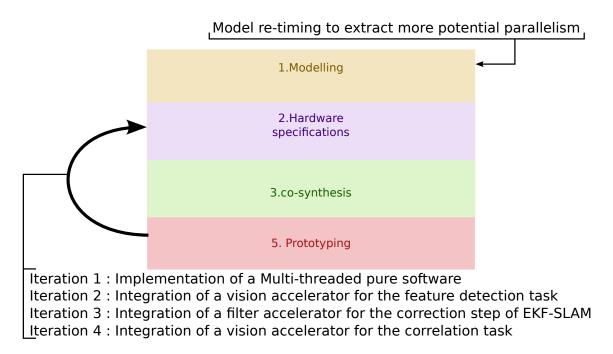

|   | 4.3                    | Iterati  | ive prototyping                                  |           |

|   |                        | 4.3.1    | First iteration: software-only prototype         |           |

|   |                        | 4.3.2    | Second iteration: Front-end hardware accelerator |           |

|   |                        |          | 4.3.2.1 Corner detector FAST                     |           |

|   |                        |          | 4.3.2.2 Tesselation                              |           |

|   |                        | 4.3.3    | Third iteration: Back-end hardware accelerator   |           |

|   |                        | 4.3.4    | Fourth iteration: Front-end hardware accelerator |           |

|   |                        | 1.0.1    | 4.3.4.1 Correlation accelerator co-design        |           |

|   | 4.4                    | Final    | hardware prototype                               |           |

|   | 1. 1                   | 4.4.1    | Experimental results and discussion              |           |

|   |                        | 4.4.2    | Comparison with state of the art                 |           |

|   | 4.5                    |          |                                                  |           |

|   | 4.0                    | 4.5.1    | Towards EKF-SLAM at 100Hz                        |           |

|   |                        | 4.0.1    | Towards Litt-GLITIN at 100Hz                     | . 00      |

| 5 | $\mathbf{E}\mathbf{K}$ | F-SLA    | M HW/SW co-design: part II                       | 69        |

|   | 5.1                    | Algori   | thmic overview                                   | . 70      |

|   |                        | 5.1.1    | Computational bottleneck identification          | . 71      |

|   | 5.2                    | Design   | n considerations                                 | . 72      |

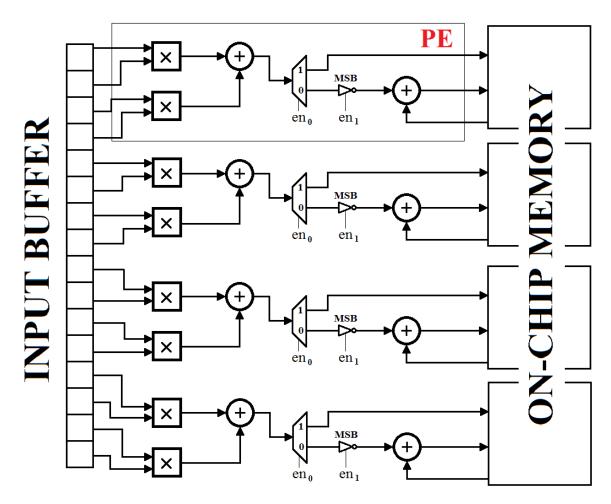

|   |                        | 5.2.1    | Matrix multiplication tradeoffs on FPGAs         |           |

|   |                        | 5.2.2    | Notion of systolic arrays on an FPGA             | . 73      |

|   |                        | 5.2.3    | Computational model mapping                      | . 73      |

|   | 5.3                    | Cross-   | covariance matrix block accelerator              | . 76      |

|   |                        | 5.3.1    | HW/SW Integration                                | . 79      |

|   | 5.4                    | Design   | n evaluation                                     | . 81      |

|   |                        | 5.4.1    | Multiplier Latency                               | . 81      |

|   |                        | 5.4.2    | Resource usage                                   | . 81      |

|   |                        | 5.4.3    | Power consumption                                | . 82      |

|   | 5.5                    | Exper    | imental results                                  | . 83      |

|   |                        | 5.5.1    | Measured multiplication latencies                | . 83      |

|   |                        | 5.5.2    | Design scalability                               | . 84      |

|   |                        | 5.5.3    | Power per feature                                | . 84      |

|   |                        | 5.5.4    | Future work                                      |           |

|   | 5.6                    | Conclu   | usion                                            | . 86      |

| c | ID                     | L . J J! | an Almanithus for Visual Obstacle Detection      | 0.7       |

| 6 |                        |          | ag Algorithms for Visual Obstacle Detection      | 87        |

|   | 6.1                    |          | ed work and motivation                           |           |

|   | 6.2                    | -        | sed framework                                    |           |

|   |                        | 6.2.1    | Appearance kernel                                |           |

|   |                        | 6.2.2    | Shape kernel                                     |           |

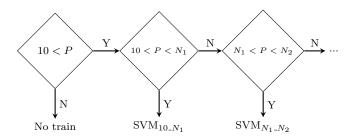

|   |                        | 6.2.3    | Classifiers co-design                            |           |

|   |                        | 6.2.4    | Classifiers training                             |           |

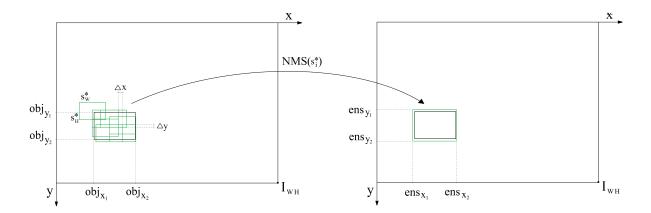

|   |                        | 6.2.5    | Single scale decision making                     | . 99      |

|   | 6.3 | Conclusion                                                     | . 103 |

|---|-----|----------------------------------------------------------------|-------|

| 7 | Tow | vards Real-Time Visual Vehicle Detection                       | 105   |

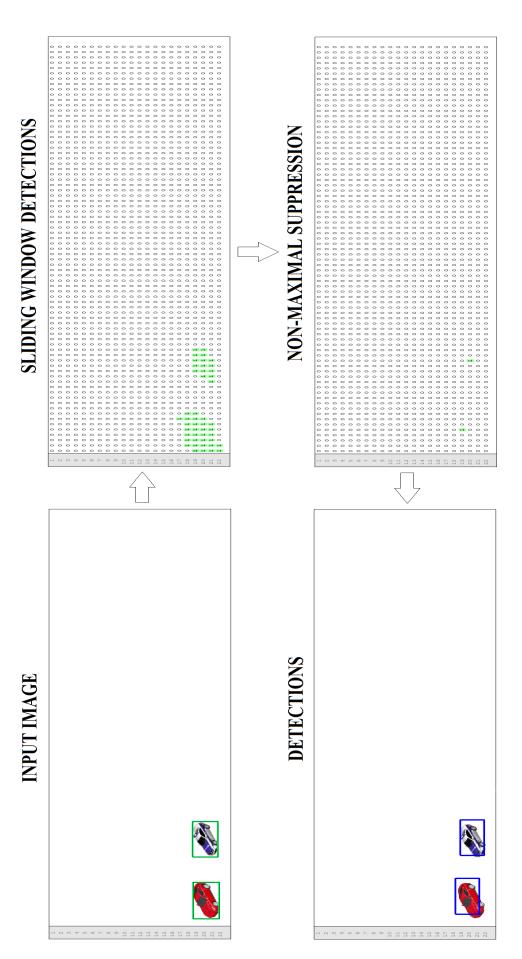

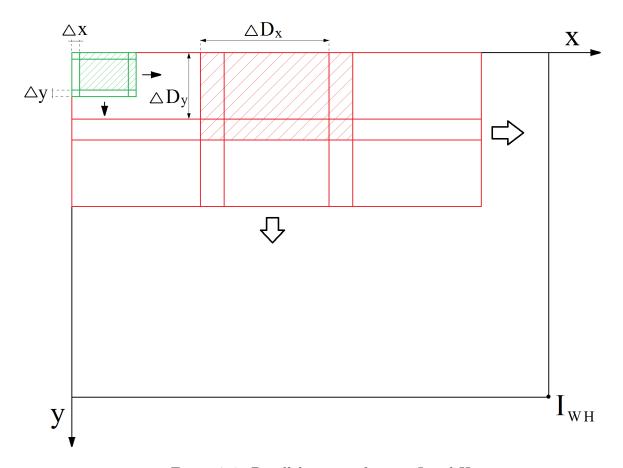

|   | 7.1 | Software architecture                                          | . 106 |

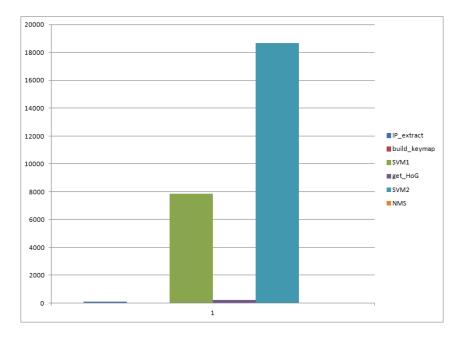

|   |     | 7.1.1 Concurrence                                              | . 108 |

|   | 7.2 | Algorithmic Evaluation                                         | . 109 |

|   |     | 7.2.1 Estimation of vehicles detection on an embedded platform | . 112 |

|   | 7.3 | Conclusion                                                     | . 114 |

| 8 | Con | nclusion                                                       | 115   |

### List of Figures

| 1.1                      | 2D SLAM with an obstacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2.1<br>2.2<br>2.3<br>2.4 | Robot OZ from Naio Technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22<br>23<br>24<br>29 |

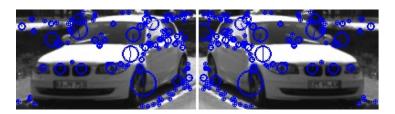

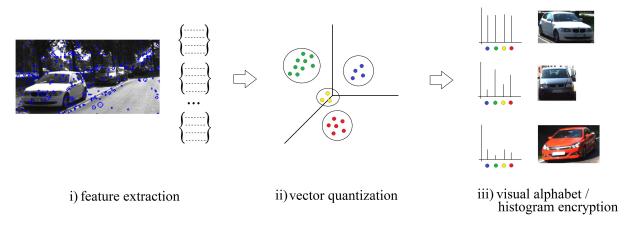

| 3.1                      | SIFT keypoints: left image is mirrored and SIFT is applied on both images. The extracted keypoints's locations are invariant to image rotations An example of alphabet encoding with 4 cluster centers for intra-class classification: i) interest points are extracted and described with a decriptor in form of encoded feature vectors; ii) each of the feature vectors is assigned to closest visual word from codebook based on a distance measure; iii) histogram containing this combination of visual words is passed to a classifier which determines object instance | 33                   |

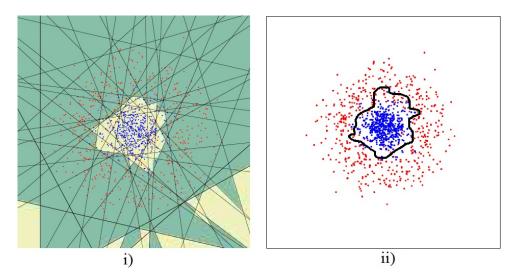

| 3.3                      | i) AdaBoost's linear kernel vs ii) SVM's Gaussian kernel: an example over a complex, linearly non-separable dataset.                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42                   |

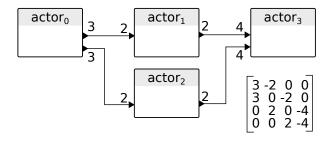

| 4.1                      | Example dataflow graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48                   |

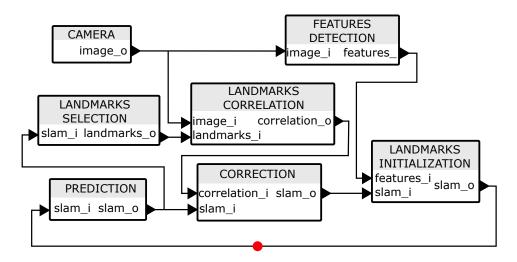

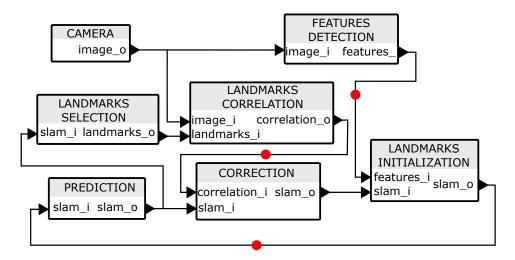

| 4.2                      | The vision-based EKF-SLAM SDF model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                   |

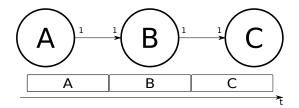

| 4.3                      | A simple dataflow graph and its one processor schedule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                   |

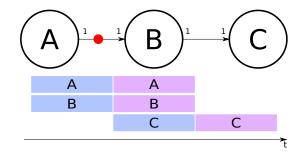

| 4.4                      | The simple dataflow graph with re-timing (delay token denoted by a red dot) and its multi processor schedule                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51                   |

| 4.5                      | Re-timed application SDF model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $5^{1}$              |

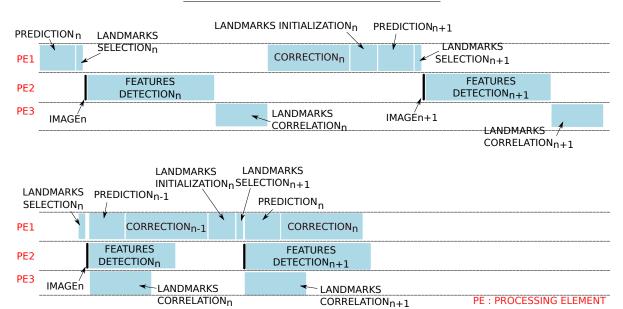

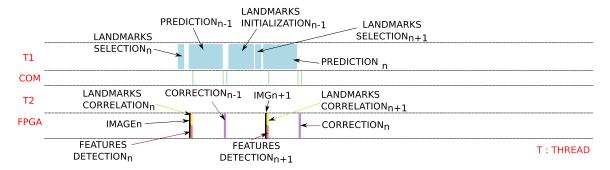

| 4.6                      | Theoretical schedule of the SLAM aplication before and after re-timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53                   |

| 4.7                      | Schedule of the SLAM aplication after first iteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54                   |

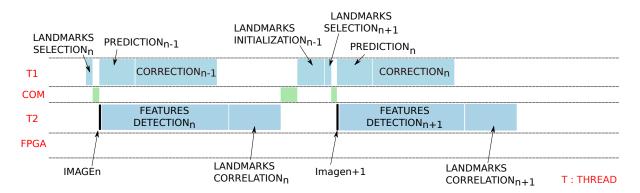

| 4.8                      | FAST corner detection result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56                   |

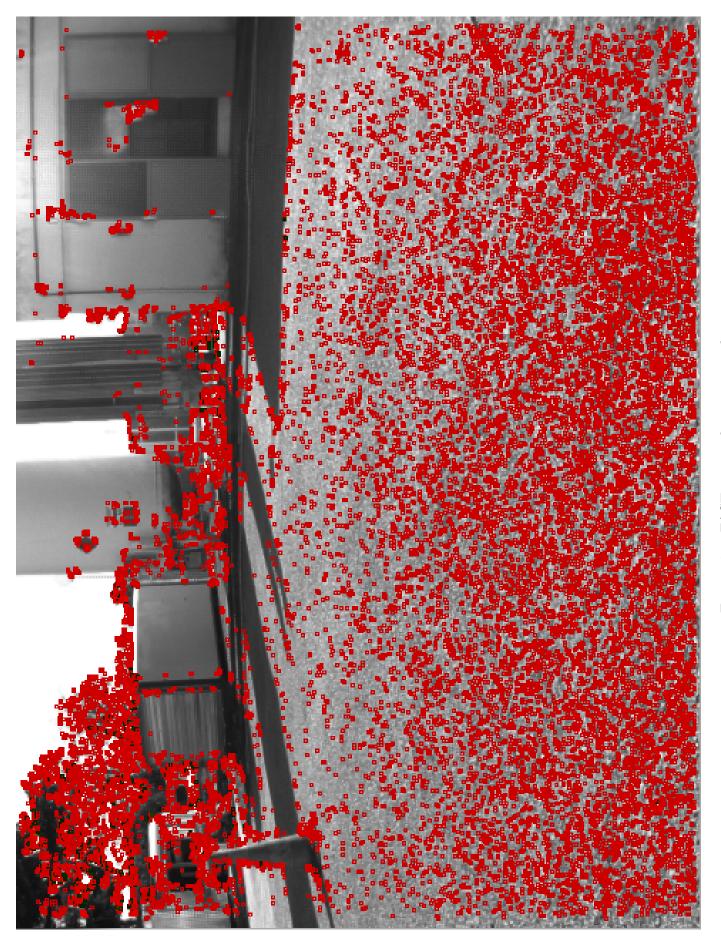

| 4.9                      | Image acquisition as a 1-D pixel stream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57                   |

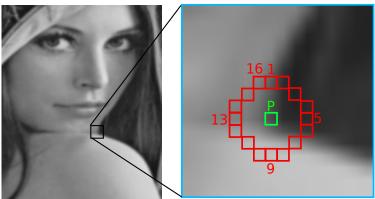

| 4.10                     | Fast segment test. Pixels from 1 to 16 form the Bresenham circle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57                   |

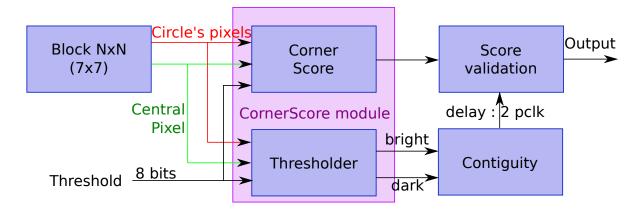

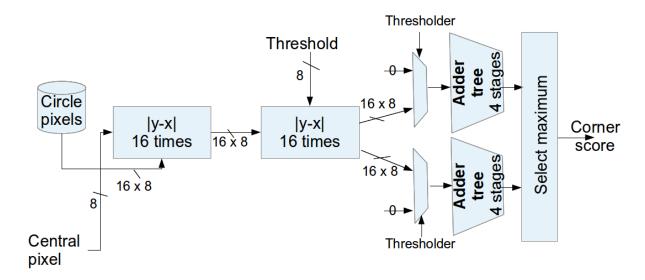

| 4.11                     | FAST hardware architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58                   |

| 4.12                     | Corner score module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58                   |

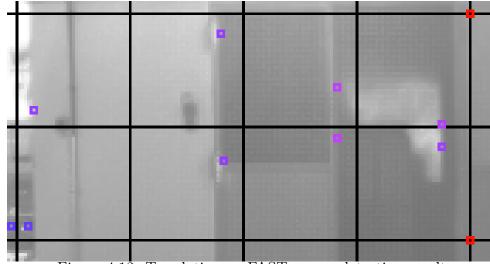

| 4.13                     | Tesselation on FAST corner detection result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59                   |

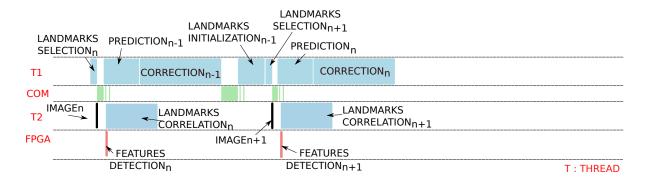

| 4.14                     | Schedule of the SLAM application after second iteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60                   |

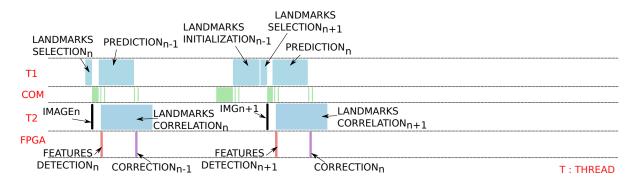

| 4.15                     | Schedule of the SLAM application after third partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61                   |

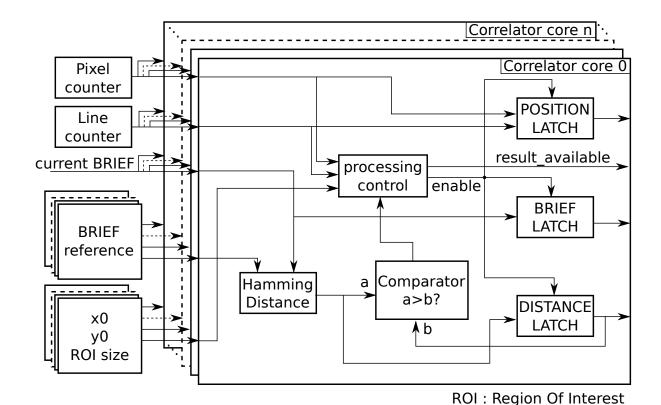

|                          | Instantiation of a multicore correlator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63                   |

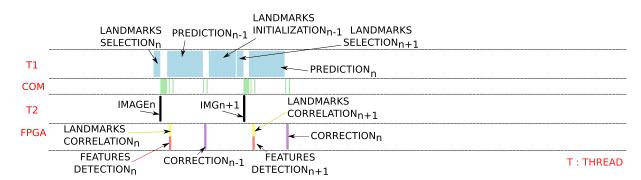

|                          | Schedule of the SLAM application after fourth partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63                   |

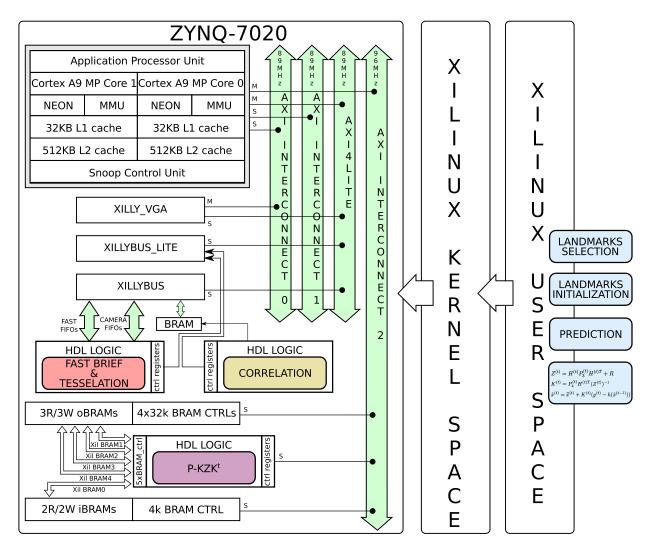

| 4.18                     | Embedded SLAM's SoC architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64                   |

| 4.19 | Summary over the iterative prototyping 67                                 |

|------|---------------------------------------------------------------------------|

| 4.20 | Expected schedule of the SLAM application after fifth partitioning $68$   |

| 5.1  | Our tiling of the 1-D systolic array for visual EKF-SLAM matrix multipli- |

|      | cations                                                                   |

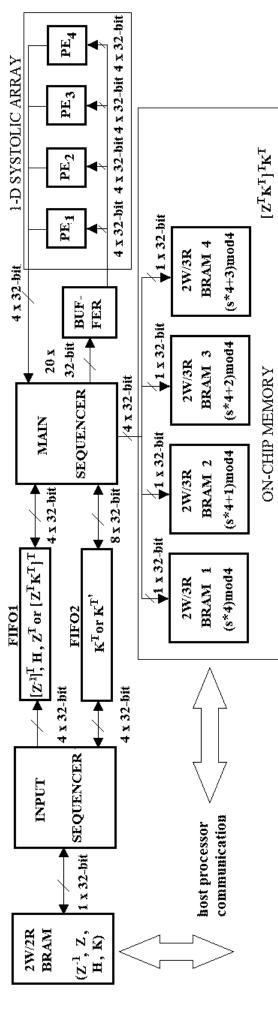

| 5.2  | Tri-matrix multiplication architecture                                    |

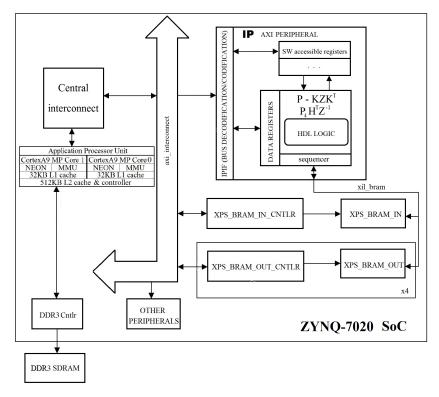

| 5.3  | Our SoC implementation of the 3D EKF-SLAM application                     |

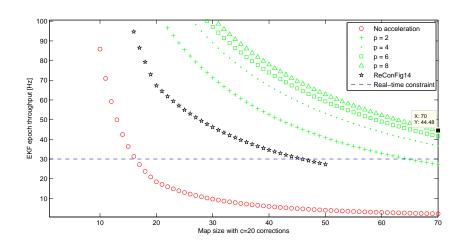

| 5.4  | EKF block throughput comparison #1                                        |

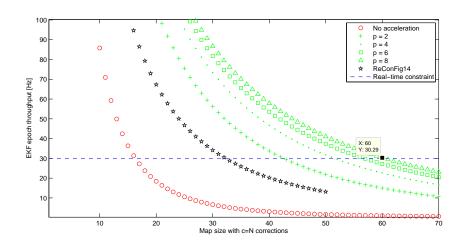

| 5.5  | EKF block throughput comparison $\#2$                                     |

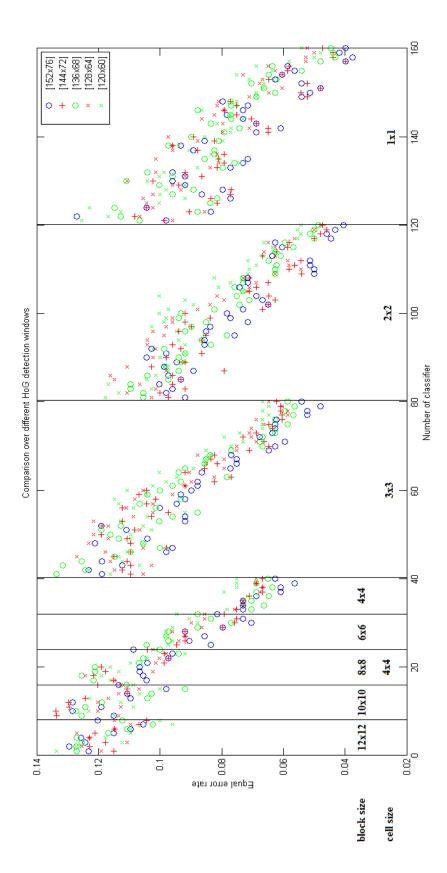

| 6.1  | Equal error rate of a set of classifiers for $N\_SET = 300 \dots 93$      |

| 6.2  | Rule-based BoW classification                                             |

| 6.3  | Learning curves for $SVM(K_{raw})$ and $SVM(K_{HoG})$                     |

| 6.4  | Single scale detection window non-maximal suppression scheme 99           |

| 6.5  | Subtractive clustering in a template-based NMS inferring                  |

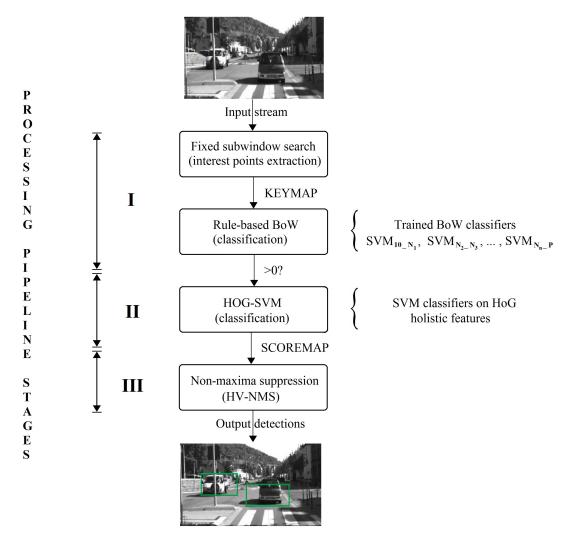

| 6.6  | Block diagram of the proposed framework                                   |

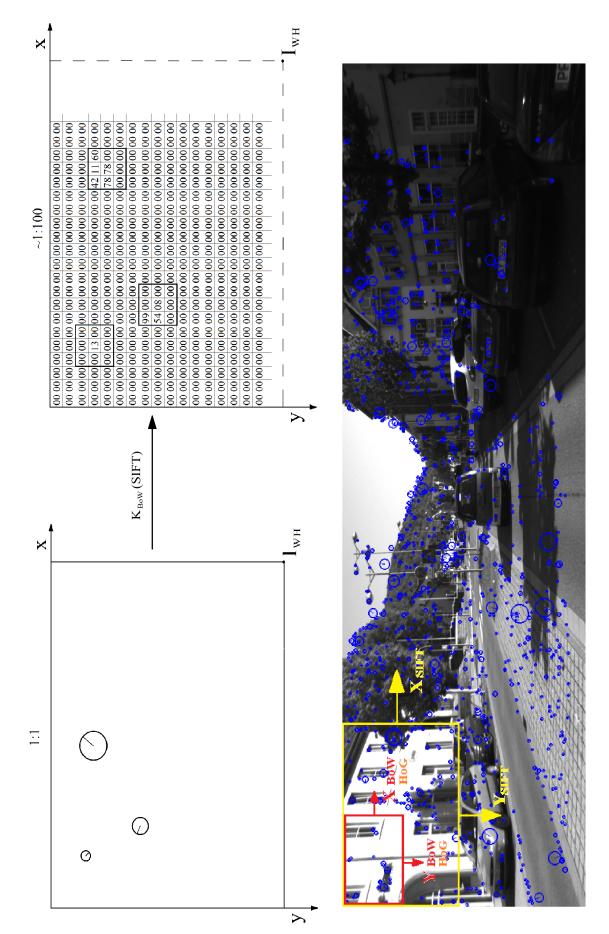

| 7.1  | Partial SIFT KEYMAP, after having applied $K_{BoW}$ on extracted SIFT     |

|      | keypoints                                                                 |

| 7.2  | Parallelization of stages I and II                                        |

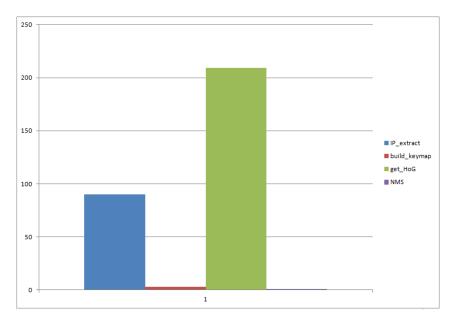

| 7.3  | Tasks timing in hierarchical detection pipeline                           |

| 7.4  | Tasks timing without linear SVMs computation                              |

### List of Tables

| 1.1        | Visual SLAM implementations - an overview                                                                                                                                                     | 18       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1        | Comparison of generative and discriminative classfiers                                                                                                                                        | 39       |

| 4.1<br>4.2 | vSLAM tasks execution before iterative prototyping                                                                                                                                            | 53<br>65 |

| 4.3        | Execution time of SLAM functional blocks in [ms] on ZedBoard                                                                                                                                  | 66       |

| 5.1        | Description and matrices dimensions according to our implementation of the EKF algorithm                                                                                                      | 71       |

| 5.2        | Number of floating-point operations in an EKF loop taking into consideration symmetry of the cross-covariance matrix. Equations $5.4 - 5.7$ are executed $c = 20$ times, for each observation | 71       |

| 5.3        | Transfer analysis regarding P matrix in EKF equations                                                                                                                                         | 72       |

| 5.4        | Control of en signals                                                                                                                                                                         | 76       |

| 5.5        | 1-D systolic array resource usage                                                                                                                                                             | 81       |

| 5.6        | Accelerator resource usage with on-chip memory                                                                                                                                                | 82       |

| 5.7        | Visual EKF-SLAM accelerator's power distribution: comparison with the                                                                                                                         |          |

|            | previous version                                                                                                                                                                              | 83       |

| 5.8        | EKF equations cycles measured with 125 MHz counter                                                                                                                                            | 83       |

| 5.9        | Device resources usage with $N_{max} = 70 \dots \dots \dots \dots$                                                                                                                            | 84       |

| 5.10       | Power per feature metric for visual EKF-SLAM with AHP points                                                                                                                                  | 85       |

| 6.1        | Histogram of Gradients: an empirical study                                                                                                                                                    | 92       |

| 6.2        | SVM kernels: an empirical study                                                                                                                                                               |          |

| 7.1        | Stage II training                                                                                                                                                                             | 110      |

| 7.2        | Stage I training                                                                                                                                                                              |          |

| 7.3        | Stage I implementation                                                                                                                                                                        |          |

| 7.4        | Stage II implementation                                                                                                                                                                       |          |

| 7.5        | Stage III implementation                                                                                                                                                                      |          |

### Chapter 1

### Introduction

| Contents |                                       |    |

|----------|---------------------------------------|----|

| 1.1      | General Introduction                  | 9  |

| 1.2      | Simultaneous Localization and Mapping | 11 |

| 1.3      | Obstacle Detection and Tracking       | 14 |

| 1.4      | Organization of the manuscript        | 17 |

#### 1.1 General Introduction

Increasingly applications rely on mobility whatever the system - be it a robot, a vehicle, a drone or an operator with a tablet or a smartphone, equipped with several sensors. As soon as such a system moves in an environment, it must be endowed with several functions able to provide its position with respect to a known reference frame. It also needs to detect obstacles in order to avoid collisions (for robot navigation) or to recognize some known objects (for augmented reality). Main subject studied in this thesis concerns the localization and obstacle detection functionalities in the context of navigation of a mobile platform.

Many solutions exist in the literature, depending on the available sensory modalities, on the locomotion system, on the a priori knowledge learnt on the environment, and overall, on the available resources (energy, memory, computing power). Many robots (e.g. Automated Guided Vehicles (AGV) for industrial environments) and vehicles (e.g. the Google car) are equipped with laser range finders in order to perceive the environment; in this thesis it is proposed to use only vision, i.e. a low-cost sensor that could be embedded both on autonomous robots and on smart devices moved by humans.

A standard Visual Odometry (VO) algorithm is exploited for the localization of our system moving in an initially unknown environment. Such a function builds up a local map that corresponds to its environment in the form of positions of *landmarks* observed in images, estimates the local motion made by the system, and then, cumulating these motions, estimates the system position with respect to a specific reference frame, generally the initial position when the VO algorithm has been started. Landmarks are presumed to be static. Our mobile system must be equipped with a camera and besides it may also have proprioceptive sensors in order to give other measurements on the motions: wheel odometry for a robot, Inertia Measurement Unit (IMU) for a device worn by an operator or for a drone.

A VO algorithm is very similar to a Visual Simultaneous Localization and Mapping approach (VSLAM), but the localization in VO is only estimated from a local map. Such a map is built over a given horizon time, defined e.g. by the M last acquired images or by the N last detected landmarks. As the localization is computed from local information, it will be impacted by a drift growing over time. With a Visual SLAM algorithm, it is possible to build a global map, even on large environments: if the mobile system returns in a known area and succeeds in matching observed features with mapped landmarks, cumulative errors may be corrected using a loop closure function. VO and VSLAM could be based either on Filtering, e.g. EKF and Rao-Blackwellized Particle Filter, or on Optimization (global or incremental, iterative or direct). It is known [Strasdat et al., 2010] that the localization given by Optimization methods is more accurate than for Filtering ones, but it requires more computing power, and moreover, for large environments, the map size could be huge, so that some map management strategy has to be applied.

It is the reason why, for systems of limited size, an EKF-based VO algorithm is most often applied for position estimation; moreover it is easier to take into account measurements acquired from asynchronous multiple modalities (several cameras, gyros and accelerometers). Drifts could be corrected from time to time either fusing with a priori knowledge given to the system (e.g. Open Street Map in urban scenes, or a building map for indoor scenes) or with a global position provided by a GPS receiver in outdoor environments.

In spite of the increasing computing power on compact embedded system, EKF-based VO's computational complexity still may be too important with only a software implementation. It is so mainly due to image processing in order to extract features from images and due to large scale matrix-matrix multiplications when applying the filter on large state vectors. The real-time constraint for typical applications of drones, robots or augmented reality on smart devices, involves to update the system position at least at 30Hz(33.33ms). Moreover improving the frequency allows to enter a virtuous cycle: faster is the VO process, easier and more robust is the feature-landmark matching. Another issue is that of autonomy for a mobile system: standard processors, such as Intel's quad core i7, consume a lot of power, thereby limiting the level of autonomy.

The SLAM and obstacle detection functionalities are interconnected. First as the SLAM paradigm itself is used for both self-localization of the mobile platform and cartography of the static world around the moving platform, obstacle detection plays an important role in providing reliant visual cues only on static entities. Moreover estimating the speed of the mobile platform helps to characterize other mobile objects sharing the same world. In mobile robotics (including drones, micro-aerial vehicles (MAVs), terrestrial rovers, autonomous driving vehicles), the navigation performance in crowded environments depends heavily on efficient obstacle detection. In Advanced Driver Assistance Systems (ADAS) and Intelligent Transportation Systems (ITS) early collision avoidance systems play a crucial part in safe navigation. As vehicle speeds in urban areas may reach 50km/h, real-time execution of obstacle detection task at 10Hz implies that a single image is to be fully treated at each 1.39m of path traveled.

Cutting edge computer vision algorithms, benchmarked on public data-sets such as KITTI [Geiger et al., 2013] require huge amounts of processing power to deal with this issue: they most often rely on Graphical Processing Units (GPUs) to compute intensive image-related operations or multi-core personal computers with tens of gigabytes of RAM. Well-performing image indexation algorithms such as [Harzallah et al., 2009] cope with multiclass object detection by creating large computational kernels for non-linear Support Vector Machines (SVMs). In the literature this is known as "the curse of dimensionality". Calculating dense optical flow or depth map from stereo camera setup in real-time is unimaginable without a GPU or a dedicated hardware platform. Other known techniques for foreground/background segmentation are mainly used for visual monitoring of environments from static cameras, such as Gaussian Mixture Models (GMMs) which come with heavy computational load.

To overcome these difficulties, an embedded system ensuring high computational efficiency at low power consumption must be designed. Modern reconfigurable devices such as Field-Programmable Gate Arrays (FPGAs) may meet this requirement. Their reconfigurable fabric consists of a large number of configurable slices, and embedded Digital Signal Processing (DSP) blocks that can be used for floating-point applications. Compared to a standard processor, computationally extensive algorithms may be parallelized and thus executed several times faster on FPGAs in floating-point precision [Underwood and Hemmert, 2004]. While Graphical Processing Units (GPUs) also make use of the parallelization techniques, the main advantage of FPGAs over both GPUs and general purpose central processing units (GPCPUs) remains in significantly lower power consumption. Embedded GPUs have as well emerged on the market today with similar power consumption to an FPGA [NVIDIA, 2015b]. However, they are designed as to improve computational performances on highly demanding image processing applications.

Thus FPGAs with their algorithm-specific memory management capabilities owing to reconfigurability still remain a better choice over embedded GPUs in terms of computational efficiency of a custom application.

Hence, migrating SLAM and obstacle detection algorithms on systems of limited size, such as MAVs and intelligent vehicles, is most often done by developing dedicated hardware accelerator architectures on Field Programmable Gate Arrays (FPGAs) [Advani et al., 2015], [Chang et al., 2013], [Wilson et al., 2014], [Hahnle et al., 2013]. Their convenient size, powerful parallel processing capabilities and low power drain (~5W vs ~300W for an average GPU) make them an optimal tool for embedded systems development. Nowadays, the embedded industry is shifting towards issuing heterogeneous hardware architectures which port besides an FPGA (which already comes with a multicore hard processor such as ARMv7) also an embedded GPU [Xilinx, 2015].

Contribution of this thesis concerns the localization and obstacle detection functionalities by identifying the underlying particularities within visual SLAM and computer vision algorithms: their complexity, inherent parallelisms and memory management specificities. It describes and evaluates an efficient FPGA-based hardware accelerator for solving the localization task and proposes a model-based obstacle detection framework to be executed on multi-core heterogeneous hardware platforms.

### 1.2 Simultaneous Localization and Mapping

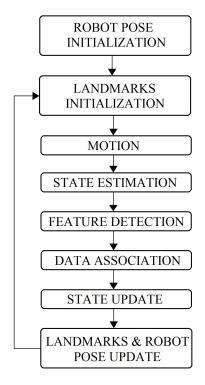

Simultaneous Localization and Mapping (SLAM) is a paradigm that intends to infer structure of an initially unknown environment from sensors moved by a mobile platform or by a person while performing self-localization of this platform or person by matching observations with the incrementally built map. In literature, this localization-mapping iterative process is known as "chicken or egg" problem, while in practice the answer to "where am I" question is given after an initial observation of the environment. To date, several thousand scientific and engineering papers have contributed to solving this intriguing puzzle, with the cornerstone being laid by [Cheeseman et al., 1987] who used landmarks in the environment in order to construct its map. SLAM may be divided into six separate tasks, as can be seen on Figure 1.1:

Initialization is the first step in establishing a priori information about the unknown world by identifying first landmarks in the vicinity of the robot via exteroceptive sensors. After having performed a motion, it calculates its new position based on proprioceptive sensors (odometers, accelerometers, gyros, magnetometers) and/or dynamic displacement model- it estimates its new position. Because of incertitude on data readings which eventually leads to a faulty pose estimation, it has to compare features observed from the current position with potential observations of known landmarks so it can estimate its pose relative to the point of departure (origin). For that it does feature detection anew, following by a posteriori data association with cues collected in initialization step. Upon successful data matching, the robot may update its state (localization) and update landmarks' positions in the map (mapping). As the process is iterative, a new loop initializes new landmarks and the SLAM goes on in same fashion.

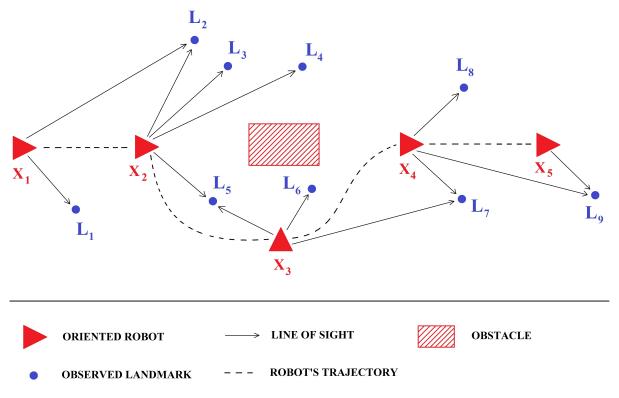

A hypothetical two-dimensional SLAM process is depicted on Figure 1.2. Here, a holonomous robot is passing from state  $x_1$  to  $x_5$  while avoiding an obstacle. Initially, at

$<sup>^{1}</sup>$ multi-core CPU + FPGA

Figure 1.1: Tasks in a SLAM process

state  $x_1$ , it observes two landmarks  $L_1$  and  $L_2$ . After having moved, it reobserves  $L_2$  and updates its position along with the positions of both first two landmarks in its map. At  $x_2$  three new landmarks are initialized:  $L_3$ ,  $L_4$ ,  $L_5$  and at  $x_3$  the fifth is reobserved, upon which it is able to adjust all the five landmarks in the map. At the final state  $x_5$  robot's map contains nine landmarks.

All tasks involved in feature acquisition, data association and map management belong to so-called *front-end* part of SLAM while the tasks related to the state estimation and update both of the robot's state vector and of the map are alltogether known as *back-end* SLAM. Along past decades, the community has proposed different algorithmic solutions to these two distinct parts of the paradigm, treating several major problems arising from data uncertainty that eventually lead to loss of localization and mapping accuracy. Data uncertainty may be caused by unpredictive physical phenomena, environment conditions, material properties of objects and quality of the sensors.

A state-space based estimator, the Kalman filter [Kalman, 1960] - KF for short, was first used to model the dynamic system behavior, from imprecise sensory data. It functions well under two assumptions: the system is modelled as a linear system and transitional processes are affected by Gaussian-characterizable noise. For nonlinear system model, an Extended KF [Maybeck, 1979] - or simply EKF is used. The important particularity of an EKF-SLAM is the ability of updating the whole state-space vector based on a measure of its single element (observation) by means of convolving innovation with cross-correlation matrix. EKF-SLAM's algorithmic drawback comes after unsuccessful data association, due to linearization errors in state estimation and update phases, known as filter inconsistency. A study was conducted by [Castellanos et al., 1997] on impact of correlating mapping with state-space vector, where it is shown that tightly coupled systems contribute to more accurate mapping (consistent maps) than loosely coupled

Figure 1.2: 2D SLAM with an obstacle

ones. In addition, the theoretical work of [Dissanayake et al., 2001] showed the need of having all the information regrouped in a single cross-covariance matrix for the sake of filter's good convergence.

First exteroceptive to be used were laser rangefinders sensors [Betge-Brezetz et al., 1996] [Csorba, 1998] - fast and providing confident 3D observations, but being too costly for larger-scale SLAM use. It is the reason why the robotics community has studied visual SLAM for almost fifteen years, taking profit of the existing "Structure from Motion" contributions of the Machine vision community. Use of a multi-camera setup with odometry for localization was proposed first by [Harris and Pike, 1987]. Three-dimensional point representation used in this work raised new questions about point parametrization during initialization phase due to perspective 3D (real-world) to 2D (camera plane) projection, as they didn't make use of stereo setup in their multi-camera configuration in order to acquire depth. There, several landmark observations are required to build landmark's 3D representation. Their work is equally valuable in presenting active search strategy, a technique used for limiting the search space in image plane during feature tracking phase, which greatly increases processing speeds in comparison to brute-force matching over the entire image.

The first ground-breaking work on monocular real-time SLAM was done by [Davison, 2003a]. From sensors, he used only a low-cost webcam which was connected to a those-days standard personal computer (PC). Mapping was done in three dimensions with a tightly-coupled back-end, using a delayed initialization of landmarks, based on a particle filter (PF). The depth uncertainty of each landmark is reduced over time while reobserving it during displacement. Once the uncertainty passes under a certain threshold, the point is added to the map. In order to keep real-time performance, a limited

amount of landmarks is held within the map.

In literature, based on environment representation (front-end) we may distinguish between different types of SLAM: semantic SLAM, topological SLAM, and geometric SLAM. Semantic SLAM, also known as *object-based* SLAM, uses object detection for self-localization. Here, the most common representative is grid-based SLAM (i.e. FastSLAM2.0 [Magnenat et al., 2010]) which uses laser telemetry to construct a map which is a discrete occupancy grid of robot's vicinity. Topological SLAM (i.e. TSLAM [Choset and Nagatani, 2001]) uses known topological maps (forms of structured graphs) of the environment for localization. Geometric SLAM uses low-dimensional spatial priors as landmarks: points, line segments, circular arcs.

On the other hand, based on back-end methods, the SLAM corpus may be divided into following categories: probabilistic, graph (optimization-based), and interval propagation SLAM. Probabilistic SLAM uses filtering techniques such as EKF and PF (i.e. Fast-SLAM [Montemerlo et al., 2002]) for state-space vector transformations. Graph SLAM [Kaess et al., 2011] [Kümmerle et al., 2011] makes use of energy optimization in a generalized graph whose vertices are ensembles of landmarks and robot poses through all past frames. The interval propagation SLAM methods transform the SLAM problem into a hybrid constraint satisfaction problem (CSP), which estimates a set-valued representation of the state [Jaulin, 2011].

This thesis deals with a monocular EKF SLAM that builds 3D maps of robot's environment for localization. An overview over existing monocular SLAM implementations may be seen on Table 1.1. Relevant methods will be cited and briefly described in Chapter 3. The more recent methods are based on optimization, but considering constraints related to embedded systems, filtering-based approaches remain interesting.

### 1.3 Obstacle Detection and Tracking

Obstacle detection, and overall Mobile Object Tracking (MOT), are critical functionalities in robotics or intelligent transportation systems, so many works have been devoted to this topics. As mentionned, SLAM and MOT are interconnected, mainly because features created by mobile objects in sensory data, could be considered as perturbations for the SLAM methods, as it was analyzed in [Márquez-Gámez, 2012]. Obstacles could be detected from many sensors, depending on the constraints upon minimal and maximal distances between the robot/vehicle and the obstacle to be detected. The more classical sensor used for this function on a terrestrial robot or for a vehicle, is a 2D laser range finder (LRF), scanning the environment on a plane parallel to the ground: it is known that it is very efficient, but it cannot detect obstacles under the laser plane (short objects on the ground) and the laser data are too poor in order to recognize the obstacle class (car, pedestrian, bicycle, etc.) with a good success rate. It is the reason why vision has been also used for obstacle detection for many years, either alone or tightly coupled with the 2D LRF. Here only obstacle detection and MOT are considered from vision.

In general, image indexation (content retrieval) is a two-stage hierarchical process which consists of

- I. Hypothesis generation on object location within an image

- II. Hypothesis verification

Table 1.1: Visual SLAM implementations - an overview

| $_{ m SLAM}$                               | Features         |        |       | Mapping | Pose estimation | nation    |

|--------------------------------------------|------------------|--------|-------|---------|-----------------|-----------|

| implementations                            | Descriptor-based | Direct | Dense | Sparse  | Optimization    | Filtering |

| PTAM [Klein and Murray, 2007]              | yes              |        |       | yes     | yes             |           |

| DTAM [Newcombe et al., 2011]               |                  | yes    | yes   |         | yes             |           |

| LSDSLAM [Engel et al., 2014]               | At loop closure  | yes    | yes   |         | yes             |           |

| ORBSLAM [Mur-Artal et al., 2015b]          | yes              |        |       | yes     | yes             |           |

| SVO [Forster et al., 2014]                 | At keyframes     | yes    |       | yes     | yes             |           |

| RTSLAM [Roussillon et al., 2011]           | yes              |        |       | yes     |                 | yes       |

| CSLAM [Gonzalez et al., 2011]              | yes              |        |       | yes     |                 | yes       |

| 2D EKF-SLAM [Bonato et al., 2008]          | yes              |        |       | yes     |                 | yes       |

| 3D EKF-SLAM [Vincke et al., 2012b]         | yes              |        |       | yes     |                 | yes       |

| 3D EKF-SLAM w/ submaps [Lee and Lee, 2013] | yes              |        |       | yes     | yes             | yes       |

In the first stage and based on sensor setup, obstacle detection methods in computer vision and image processing follow two main directions: monocular and stereo (binocular) camera detection. The latter takes advantage of the Inverse Perspective Mapping (IPM) [Mallot et al., 1991] to estimate the locations of obstacles. In case of vehicles, [Bertozzi and Broggi, 1998] IPM was computed from the left and right images and based on the comparison objects not belonging to ground plane (road presumed to be flat) were identified as vehicles. Another classical approach for obstacle detection from stereovision is based on the v-disparity [Labayrade, 2004], which requires also a flat ground. Dedicated architectures have been proposed both for IPM or v-disparity approaches [Botero-Galeano, 2012] [Irki et al., 2013]. Main problem with obstacles detection by stereo-vision is that it is very sensitive to the camera calibration parameters (extrinsics) and range of the detection is limited to about 10m upfront the sensor rig (depending on the stereo baseline - wider the baseline, higher the range).

Hypothesis generation in monocular setup may be further divided into three categories: (1) constrained IPM (2) motion-based and (3) knowledge-based. An IPM-based on-road obstacles detection system in urban areas is presented in [Itu and Danescu, 2014]. Executing on a smart-phone and making use of its main camera and accelerometer, the algorithm makes assumptions of an upfront flat road free from obstacles. age transformation, color-based segmentation is used for obstacle areas identification. Motion-based approaches calculate optical flow, generating a displacement vector for each pixel - [Bruhn et al., 2005] [Stein, 2004]. High computational complexity of optical flow based approaches still remains a challenge for a straightforward implementation on an embedded platform. Knowledge-based methods employ various abstractions on object representation i.e. about shape, color, texture as well as contextual information about its environment: streets for pedestrians and vehicles, freeways for trucks .... Object location is searched for via sliding-windows (brute force) approach [Harzallah et al., 2009] or after some scene geometry-related assumption - i.e. vanishing point calculation [Hartley and Zisserman, 2004] or edge detection [Sun et al., 2002] for image search-space reduction.

In the second stage, methods that corroborate hypotheses on object location can be classified into two categories: (1) template-based and (2) appearance-based. Template-based approach defines an object class pattern. Each input sample (sub)image is correlated upon the class representative. Authors in [Betke et al., 1996] proposed a multiple-vehicle detection approach using deformable gray-scale template matching. Appearance-based methods detect the presence of an object in the scene based upon characteristics of the object class from a set of training image patches which capture the variability in object appearance. Local and/or global characteristics called features are extracted and most often learned by a binary classifier (e.g. convolutional neural network [Krizhevsky et al., 2012] or support vector machine (SVM)). These knowledge-based methods tend to be used alone, both for hypothesis generation and verification. They are now very popular, thanks to the massive distribution of low cost cameras on the market, to the success of the Viola&Jones's approach to detect faces on images using an AdaBoost classifier, and also, to the emerging use of Deep Learning for this topic.

In order to ease object redetection in successive frames, detected obstacles may be tracked. In this scenario a tracklet is initialized for each detected obstacle. Then, interframe object's position estimation is most often performed by a Kalman filter, following data association via a graph-search based algorithm (i.e. the Hungarian method). Only

tracklets that are at least three frames long are taken into further consideration.

### 1.4 Organization of the manuscript

The main body of this thesis is divided as follows.

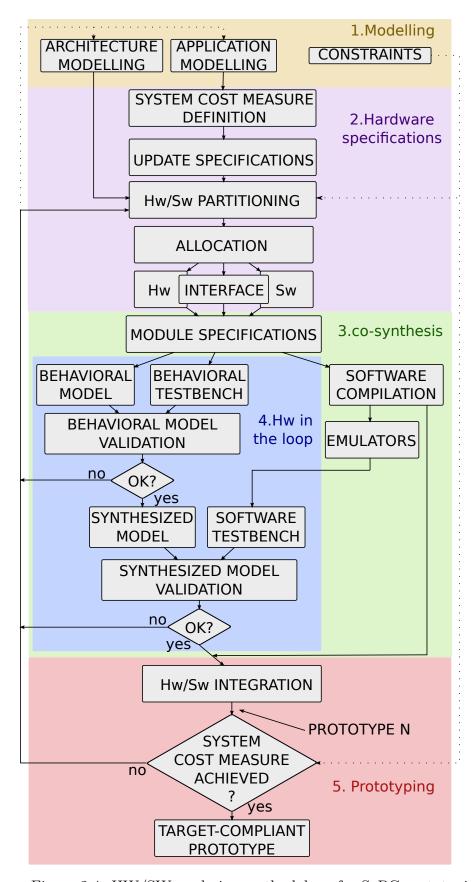

Chapter 2 describes applicative domain, raises designing constraints and precises evaluation metrics of the research. Consequently it introduces and explains the methodology used for conception, emulation, design and validation steps of software and hardware components developed during my thesis.

Chapter 3 references state-of-the-art and relevant visual EKF SLAM applications and computer vision techniques used for model-based object recognition.

Chapter 4 describes iterative prototyping on the given visual EKF SLAM application ending with a functional SoPC model capable of executing at 100Hz.

Chapter 5 puts forward the co-design with evaluation metrics of FPGA based EKF co-processor's architecture.

Chapter 6 introduces a framework for model-based obstacle detection with focus on embedded target devices. A theoretical basis with relevant statistical studies has been profoundly explained.

Chapter 7 begins with a software implementation of previously described framework. Afterwards it presents results after a case-study evaluation on the exemple of *vehicles* type of obstacles.

Chapter 8 summarizes the thesis, exposes the remaining questions to be asked, and gives an outline of the subsequent work enabled by my research.

### Chapter 2

# Architectures and Algorithms for Robot Navigation

| Contents |                        |                                                                   |           |

|----------|------------------------|-------------------------------------------------------------------|-----------|

| 2.1      | Robot Navigation       |                                                                   | 19        |

|          | 2.1.1                  | The navigation system for the AIR-COBOT robot $\ \ldots \ \ldots$ | 20        |

|          | 2.1.2                  | Specifications of an embedded navigation system                   | 23        |

| 2.2      | $\mathbf{H}\mathbf{W}$ | /SW co-design methodology                                         | <b>24</b> |

| 2.3      | Con                    | clusion                                                           | 27        |

### 2.1 Robot Navigation

In the context of this thesis the applicative domain of autonomous navigation includes following environment types:

- Indoor structured: popular off-the-shelf solution for these kinds of constrained environments is Robotics Operating System's ROS-nav-stack. It usually uses grid-based SLAM methods for localization.

- Outdoor structured (urban robotics) or large indoor, assuming robot motions on a flat terrain with possibly cluttered environment: service robots in factories, airports (i.e. in the context of AirCobot project<sup>1</sup>). Obstacles may be also dynamic (people, bikes, vehicles, other mobile robots) and this problem is too large for classical SLAM methods.

- Outdoor natural (typically agricultural robotics Figure 2.1<sup>2</sup>): uneven and 3D terrain, with few dynamic obstacles, but many static obstacles on the terrain (ditches, puddles, tools on the ground).

Figure 2.1: Robot OZ from Naio Technologies

and different navigation methods:

- Reactive navigation: complementary to planned motions and used for obstacle avoidance i.e. the robot leaves the nominal trajectory if an obstacle is found on the path (i.e. in the context of AirCobot project).

- Sensor-based navigation: motions are defined as a sequence of sensor-based commands. Typically it is used when navigating in a field following successive raws, or navigating around an aircraft based on different targets.

- Trajectory-based navigation: robot learns the map of an obstacle-free environment and the motion planner finds a trajectory consistent with the robot's characteristics.

<sup>&</sup>lt;sup>1</sup>image courtesy of Airbus Group

<sup>&</sup>lt;sup>2</sup>image courtesy of Naio Technologies

Figure 2.2: Robot for pre-flight inspection used in AirCobot project

It then executes this trajectory, based on a localization method (along with obstacle avoidance) in order to generate a control law.

Before giving some conceptual constraints for embedded navigational systems, in next subsection the system developed for the AirCobot robot by AKKA and LAAS will be presented. Here, the central role of the localization function on such a system will be accentuated.

#### 2.1.1 The navigation system for the AIR-COBOT robot

During the preparation of this thesis, PhD candidate participated on the two projects illustrated on figures 2.1 (on agricultural robotics with the start-up NAIO Technologies) and 2.2 (on service robotics in airports with a consortium lead by AKKA Research and AIRBUS). Contribution on these projects was devoted to the evaluation of several visual SLAM methods for Visual Odometry (VO): the VO results are typically fused with motion estimates provided by wheel odometry and by inertial measurements, to improve the localization obtained from the integration of these motion estimates. It is well known that the odometry based localization drifts. So dead-reckoning navigation, based on these position estimates, can only work locally: this strategy is used only when other localization methods integrated on the robot fail.

By now, the VO function is executed in software, consuming important computational resources on the embedded system. A long term objective for these two projects is to integrate the VO method on a dedicated hardware platform, i.e. to generate a smart camera or stereo sensor specialized for visual odometry.

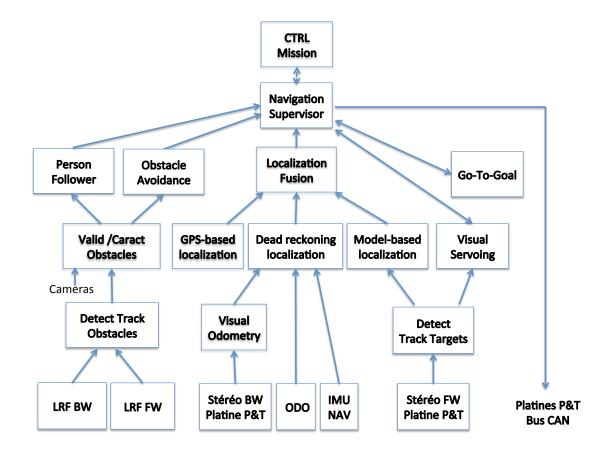

A simplified navigational schematic with its functional architecture, executed on the AIRCOBOT demonstrator (Figure 2.2 on the left) in a complex operational environment, is presented on Figure 2.3. This robot assists a pilot for the pre-flight inspection task, performed on the parking area before every departure. It must navigate autonomously around an airplane, going successively to every check point (from 1 to 21, presented on Figure 2.2 on the right). These motions must be executed on the taxiway, avoiding vehicles, trucks or operators executing other tasks (refueling, baggage loading, etc.), knowing that close to the airport buildings or to the airplane, GPS-based localization is not reliable. Moreover, airlines or AIRBUS prevent the robot navigating in some areas around the airplane, typically under the wings to avoid collisions with reactors. Before any mission, during an interactive initialization step, the robot learns several representations:

Figure 2.3: Functional architecture of navigational module in AIRCOBOT project

- first the airplane model (here an A320) expressed in the aircraft reference frame and the visual targets it could detect, track and use to control motions around the airplane,

- then the airport model expressed in the airport reference frame, mainly along the trajectories that the robot will have to execute between its docking station and the different parking areas where the pre-flight inspection must be performed,

- and finally the transform between the GPS geo-centered frame (WGS84 or ECEF) and the airport reference frame through a local orthographic projection.

Many modules have been integrated to deal with obstacle detection using laser and visual data (Figure 2.3 on the right), robot localization fusing dead-reckoning, model-based and GPS-based methods (Figure 2.3 in the middle) and motion control based on four modes:

- Visual Servoing activated typically to reach precisely a check point based on imagebased control from visual targets detected and tracked on the airplane surface.

- Go-to-Goal used to execute trajectories defined as a sequence of way points expressed either in the airport or in the aircraft reference frame.

- Obstacle Avoidance in order to locally avoid an obstacle, maintaining the camera pointed towards the visual targets if required.

• Person follower: the AIR-COBOT robot may also be used as a cobot, i.e. executing collaborative tasks with an operator, especially following him until a given point where it could execute an inspection task, or following him in order to avoid an obstacle when the autonomous avoidance strategy fails.

Motions are planned by the navigation supervisor knowing the mission to be executed (typically, the next check point to be visited): it activates a navigation mode based on different events (obstacle detected close to the trajectory, detection of visual targets, failure of the tracking, failure of the obstacle avoidance, etc.); it combines low-level orders generated by these modes before sending them to the micro-controllers through the CAN bus. This architecture shows the central role of the localization functions. Whatever the navigation mode, the robot position with respect to the airport and the airplane reference frames are updated using available observations. This knowledge allows the navigation supervisor to plan trajectories, to select a better mode and to switch smoothly between modes. The dead-reckoning localization is only taken into account when GPS-based or model-based methods fail (either due to occlusions for GPS, or to failures of the feature detection or matching functions for vision); when a GPS or a model-based localization is available, it allows to correct the drifts and to maintain the localization error below a maximal value (typically 1.5m for GPS, 1m for vision), consistent with the other modules.

This navigation system is implemented on an embedded PC (2,3GHz quad core i7): it has been integrated using the middleware ROS and some ROS standard modules:

- the drivers used to acquire sensory data: LRF modules linked to the 2D laser range finders at 40Hz and image acquisition at 15Hz

- and the module Robot-Pose-EKF integrated to perform the dead reckoning localization from a loose fusion of three methods executed in order to estimate the robot motions (Visual odometry, Wheel odometry and Inertial measurements).

In this context we evaluated several VO methods: first CSLAM from LAAS, then ORB-SLAM proposed recently by authors from the University of Zaragoza:

- CSLAM will be described in detail in chapter 4; it performs a tight fusion between wheel odometry, inertial measurements and visual observations in order to update both the robot state (position and speed) and landmarks positions. It could replace the Robot-Pose-EKF module. In the AIR-COBOT context, it gave poor results, mainly because we could not guarantee a good synchronization between all sensory data.

- ORB-SLAM exploits only visual data in order to estimate the camera trajectory by an optimization method. It provides better position estimates as it makes use of a large number of landmarks (approx. 2000) and performs loop closure technique when revisiting known locations in order to correct for drifts. The cost of using it involves higher computational latencies and active memory requirements (its visual vocabulary takes only approx. 1GB of RAM while maximum operating frequency does not exceed 10Hz).

#### 2.1.2 Specifications of an embedded navigation system

In the AirCobot project, all functionalities were implemented in software as ROS nodes. If an embedded device supporting these functionalities on a mobile operating platform is to achieve satisfactory behavior, some constraints must be taken into consideration:

- portability: one of the paramount conditions of an embedded device is that it should be small in dimensions and thus easily integrable into different systems,

- processing power: it should dispose of high processing power capabilities, as the problem we are treating is deeply rooted in computer vision and localization domains,