## Optimization and implementation of bio-inspired feature extraction frameworks for visual object recognition

Olivier Boisard

#### ▶ To cite this version:

Olivier Boisard. Optimization and implementation of bio-inspired feature extraction frameworks for visual object recognition. Computer Vision and Pattern Recognition [cs.CV]. Université de Bourgogne - Franche Compté, 2016. English. NNT: . tel-01483419v1

#### HAL Id: tel-01483419 https://theses.hal.science/tel-01483419v1

Submitted on 5 Mar 2017 (v1), last revised 9 Mar 2017 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Copyright

#### UNIVERSITE DE BOURGOGNE

**UFR Sciences Humaines**

THÈSE

Pour obtenir le grade de

Docteur de l'Université de Bourgogne

Discipline : Informatique

par Olivier Boisard

le 25 octobre 2016

# Optimization and implementation of bio-inspired feature extraction frameworks for visual object recognition

#### Directeur de thèse Michel Paindavoine

Jury

Philippe Coussy, Professeur des universités, Rapporteur Christophe Garcia, Professeur des universités, Rapporteur Andres Perez-Uribe, Professeur des universités, Examinateur Robert M. French, Directeur de recherches au CNRS, Examinateur Michel Doussot, Maître de conférences, Examinateur Olivier Brousse, Ingénieur de Recherche, Examinateur "Airplanes don't flap their wings and don't have feathers."

Yann LeCun

#### Abstract

Industry has growing needs for so-called "intelligent systems", capable of not only acquire data, but also to analyse it and to make decisions accordingly. Such systems are particularly useful for video-surveillance, in which case alarms must be raised in case of an intrusion. For cost saving and power consumption reasons, it is better to perform that process as close to the sensor as possible. To address that issue, a promising approach is to use bio-inspired frameworks, which consist in applying computational biology models to industrial applications. The work carried out during that thesis consisted in selecting bio-inspired feature extraction frameworks, and to optimize them with the aim to implement them on a dedicated hardware platform, for computer vision applications. First, we propose a generic algorithm, which may be used in several use case scenarios, having an acceptable complexity and a low memory print. Then, we proposed optimizations for a more global framework, based on precision degradation in computations, hence easing up its implementation on embedded systems. Results suggest that while the framework we developed may not be as accurate as the state of the art, it is more generic. Furthermore, the optimizations we proposed for the more complex framework are fully compatible with other optimizations from the literature, and provide encouraging perspective for future developments. Finally, both contributions have a scope that goes beyond the sole frameworks that we studied, and may be used in other, more widely used frameworks as well.

#### Résumé

L'industrie a des besoins croissants en systmes dits intelligents, capable d'analyser les signaux acquis par des capteurs et prendre une dcision en consquence. Ces systmes sont particulirement utiles pour des applications de vido-surveillance ou de contrle de qualit. Pour des questions de cot et de consommation d'nergie, il est souhaitable que la prise de dcision ait lieu au plus prs du capteur. Pour rpondre cette problematique, une approche prometteuse est d'utiliser des mthodes dites bio-inspires, qui consistent en l'application de modles computationels issus de la biologie ou des sciences cognitives des problmes industriels. Les travaux mens au cours de ce doctorat ont consist choisir des mthodes d'extraction de caractristiques bio-inspires, et les optimiser dans le but de les implanter sur des plateformes matrielles ddies pour des applications en vision par ordinateur. Tout d'abord, nous proposons un algorithme gnrique pouvant tre utiliss dans diffrents cas d'utilisation, ayant une complexit acceptable et une faible empreinte mmoire. Ensuite, nous proposons des optimisations pour une mthode plus gnrale, bases essentiellement sur une simplification du codage des donnes, ainsi qu'une implantation matrielle bases sur ces optimisations. Ces deux contributions peuvent par ailleurs s'appliquer bien d'autres mthodes que celles tudies dans ce document.

## Acknowledgements

So here I am, after three years spent playing around with artificial neurons. That went fast, and I guess I would have needed twice as long to get everything done. That was a great experience, which allowed me to meet extraordinary people without whom those years wouldn't have been the same.

First of all, I wish to thank my mentor Michel Paindavoine for letting me be his student, along with my co-mentors Olivier Brousse and Michel Doussot. All three showed real implication in my work, and your advices and the long discussions we had was of great help. I would also like to thank Xavier Bruneau, for allowing me to realize that thesis in his company – too often we hear about PhD students in companies who had no time for academic works, and I'm glad I wasn't one of them. I also wish to thank Bob French and Lionel Lacassagne for accepting to be part of the follow-up committee, as well as Thomas Serre and all the staff at Serre Lab for welcoming me. Then I would like to thank Philippe Coussy and Christophe Garcia, for being the first readers of this document and accepting to review it. Finally, I would like to thank the ANRT, i.e the French National Research and Technology Agency, for giving me the opportunity to realize that PhD with the CIFRE program.

But all of those years wouldn't have been the same without my colleagues and fellow PhD students, at GlobalSensing Technologies and at the LEAD. So I thank you all, whether you were there for a few months only or several years, for your support, advices, and the laughs that we shared: Mathieu, Lolita, Laura, Luc, Jonathan, Sabrina, Vivien, Rémi (he ain't here!), Pierre, Julie, Margaux, Stéphane, Alessandro, Danilo, Philippe, Corinne, Sandrine, Léa, Lydia, Christophe, Radka, Yannick, Alex, Axel, Guillaume, Guillaume, Éric, David, Christophe... And I sure hope I haven't forgotten anybody!

Finally, although working was my primary hobby during those years, I wouldn't have gone through that adventure without my relatives, friends and family. So I would like to thank my family, and particularly my parents Jean-Louis and Françoise, my adoptive parents Phi and Sun, my brother and sister Vincent and Marianne and their respective wife and husband Anastasia and Matthieu, and my adoptive brother Jérémy for their outstanding support despite the distance. I also want to thank my friends – some of them shared a bit of my life, in their own ways. So thank you to Benoît, Kiki, Drak, Émilie, Rémi "Goodfinger", Manjo, Élisa, Clémence, Romain, Roswitha, Hélène, Margot, Alena, Chloé, Jimmy, Mélissa, Valentin, David, Claire, Jordan, Alexis, Franck, Thomas "Vougny-Pensez-Pas", Manon, Jack, Annabelle, Matthieu, Yankel, Paméla, Céline, and Antoine.

Thank you all!

## Contents

| A            | bstra        | ct                |                         |         |        |       |        |    |      |      |   |  |       |      |   |   | iii           |

|--------------|--------------|-------------------|-------------------------|---------|--------|-------|--------|----|------|------|---|--|-------|------|---|---|---------------|

| $\mathbf{R}$ | ésum         | ıé                |                         |         |        |       |        |    |      |      |   |  |       |      |   |   | iv            |

| A            | ckno         | $\mathbf{wledge}$ | ments                   |         |        |       |        |    |      |      |   |  |       |      |   |   | $\mathbf{v}$  |

| Li           | st of        | Figure            | es                      |         |        |       |        |    |      |      |   |  |       |      |   |   | xii           |

| Li           | st of        | Tables            | 5                       |         |        |       |        |    |      |      |   |  |       |      |   | - | xiv           |

| 1            | Ger          | neral ir          | ıtroduct                | ion     |        |       |        |    |      |      |   |  |       |      |   |   | 1             |

|              | 1.1          | The ne            | eed for in              | tellige | ent sy | stem  | s      |    | <br> | <br> |   |  |       |      |   |   | 1             |

|              | 1.2          |                   | ne Learni               | _       |        |       |        |    |      |      |   |  |       |      |   |   | 2             |

|              | 1.3          |                   | dded syste              |         |        |       |        |    |      |      |   |  |       |      |   |   | 3             |

|              | $1.4 \\ 1.5$ |                   | DSP: a no<br>nent over  |         |        |       | _      |    |      |      |   |  |       |      |   |   | $\frac{4}{5}$ |

|              |              |                   |                         |         |        |       |        |    |      |      |   |  |       |      |   |   |               |

| 2            |              |                   | orks and                | -       |        |       |        |    |      |      |   |  |       |      |   |   | 7             |

|              | 2.1          | 2.1.1             | etical bac<br>Classific |         |        |       |        |    |      |      |   |  |       |      |   |   | 7<br>7        |

|              |              | 2.1.1             | 2.1.1.1                 |         |        |       | rks .  |    |      |      |   |  |       |      |   |   | 8             |

|              |              |                   |                         | Percept |        |       |        |    |      |      |   |  |       |      |   |   | 9             |

|              |              |                   |                         | Aultila |        |       |        |    |      |      |   |  |       |      |   |   | 10            |

|              |              |                   |                         | RBF .   | •      |       | -      |    |      |      |   |  |       |      |   |   | 11            |

|              |              |                   | $\mathbf{S}$            | piking  | g Neu  | ral N | letwo: | rk | <br> | <br> |   |  |       | <br> |   |   | 12            |

|              |              |                   | 2.1.1.2                 | SVN     | 1      |       |        |    | <br> | <br> |   |  |       |      |   |   | 13            |

|              |              |                   | 2.1.1.3                 | Ense    | emble  | learı | ning   |    | <br> | <br> |   |  |       |      |   |   | 13            |

|              |              | 2.1.2             | Feature                 | extrac  | ction  | fram  | eworl  | ζS | <br> | <br> |   |  | <br>• |      |   |   | 14            |

|              |              |                   | 2.1.2.1                 | _       | _      |       |        | _  |      |      |   |  |       |      |   |   | 14            |

|              |              |                   |                         | Classic |        | -     |        |    |      |      |   |  |       |      |   |   | 14            |

|              |              |                   |                         | Vavele  |        |       |        |    |      |      |   |  |       |      |   |   | 16            |

|              |              |                   | 2.1.2.2                 |         |        |       | pproa  |    |      |      |   |  |       |      |   |   | 17            |

|              | 2.2          | Enom.             | 2.1.2.3                 |         |        |       |        |    |      |      |   |  |       |      |   |   | 19<br>20      |

|              | 4.4          | rrame             | works im                | риение  | maur   | JHS   |        |    | <br> | <br> | • |  | <br>• |      | • | • | 2U            |

Contents viii

|   |      | 2.2.1   | Software implementations                          | 20 |

|---|------|---------|---------------------------------------------------|----|

|   |      |         | 2.2.1.1 Workstations                              | 21 |

|   |      |         | 2.2.1.2 Embedded systems                          | 21 |

|   |      | 2.2.2   | Hardware implementations                          | 21 |

|   |      |         | 2.2.2.1 Neural networks                           | 22 |

|   |      |         | HMAX                                              | 22 |

|   |      |         | ConvNet                                           | 24 |

|   |      |         | Spiking Neural Networks                           | 26 |

|   |      |         | 2.2.2.2 Other frameworks implementations          | 27 |

|   | 2.3  | Discus  | ssion                                             | 29 |

|   |      | 2.3.1   | Descriptors and classifiers comparison            | 29 |

|   |      |         | 2.3.1.1 Descriptors                               |    |

|   |      |         | 2.3.1.2 Classifiers                               |    |

|   |      | 2.3.2   | Implementations comparison                        |    |

|   |      | 2.3.3   | Problem statement                                 |    |

|   | 2.4  | Conclu  | usion                                             | 33 |

| 3 | Foot | tuno de | election                                          | 35 |

| 3 | 3.1  |         | re selection for face detection                   | 35 |

|   | 5.1  | 3.1.1   | Detecting faces                                   |    |

|   |      | 5.1.1   | 3.1.1.1 Cascade of Haar-like features             | 36 |

|   |      |         | Framework description                             |    |

|   |      |         | Complexity analysis                               |    |

|   |      |         | Memory print                                      | 40 |

|   |      |         | 3.1.1.2 CFF                                       | 41 |

|   |      |         | Framework description                             | 41 |

|   |      |         | Complexity analysis                               |    |

|   |      |         | Memory print                                      |    |

|   |      |         | 3.1.1.3 HMIN                                      |    |

|   |      |         | Framework description                             |    |

|   |      |         | Complexity analysis                               |    |

|   |      |         | Memory print                                      | 46 |

|   |      | 3.1.2   | HMIN optimizations for face detection             | 46 |

|   |      |         | 3.1.2.1 C1 output                                 | 46 |

|   |      |         | 3.1.2.2 Proposed optimizations                    | 47 |

|   |      |         | $\mathrm{HMIN}_{	heta=\pi/2}$                     | 47 |

|   |      |         | $\operatorname{HMIN}_{	heta=\pi/2}^{	heta=\pi/2}$ | 48 |

|   |      | 3.1.3   | Experiments                                       | 49 |

|   |      |         | 3.1.3.1 Test on LFWCrop_grey                      | 49 |

|   |      |         | 3.1.3.2 Test on CMU                               | 50 |

|   |      |         | 3.1.3.3 Test on Olivier dataset                   | 54 |

|   | 3.2  | Featur  | re selection for pedestrian detection             | 55 |

|   |      | 3.2.1   | Detecting pedestrians                             | 55 |

|   |      |         | 3.2.1.1 HOG                                       | 56 |

|   |      |         | Gradients computation                             | 56 |

|   |      |         | Binning                                           | 57 |

|   |      |         | Local normalization                               |    |

|   |      |         |                                                   |    |

Contents

|   |                |         | Complexity analysis                                                                                                                                            | 59         |

|---|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |                |         | Memory print                                                                                                                                                   | 60         |

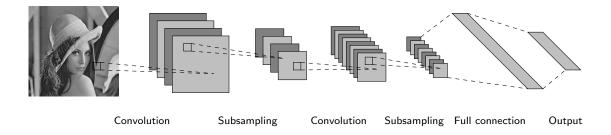

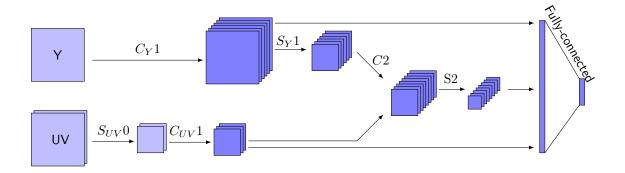

|   |                |         | 3.2.1.2 ConvNet                                                                                                                                                | 61         |

|   |                |         | Presentation                                                                                                                                                   | 61         |

|   |                |         | Complexity analysis                                                                                                                                            | 62         |

|   |                |         | Memory print                                                                                                                                                   | 65         |

|   |                | 3.2.2   | HMAX optimizations for pedestrian detection                                                                                                                    | 66         |

|   |                | 3.2.3   | Experiments                                                                                                                                                    | 66         |

|   | 3.3            | Discuss | $\operatorname{sion}$                                                                                                                                          | 66         |

|   | 3.4            | Conclu  | sion                                                                                                                                                           | 69         |

| 4 | TT             | 1       | *1                                                                                                                                                             | <b>7</b> 1 |

| 4 | <b>Har</b> 4.1 |         | $egin{array}{lll} \mathbf{implementation} \\ \mathbf{for} \ \mathbf{HMAX} & \ldots & $ | 71         |

|   | 4.1            | 4.1.1   |                                                                                                                                                                |            |

|   |                | 4.1.1   | Description                                                                                                                                                    |            |

|   |                |         |                                                                                                                                                                | 73         |

|   |                |         | 4.1.1.2 C1                                                                                                                                                     |            |

|   |                |         | 4.1.1.4 C2                                                                                                                                                     |            |

|   |                | 4.1.2   |                                                                                                                                                                |            |

|   | 4.2            |         |                                                                                                                                                                |            |

|   | 4.2            | 4.2.1   | sed simplification                                                                                                                                             |            |

|   |                | 4.2.1   | Input data                                                                                                                                                     |            |

|   |                | 4.2.2   | S1 output encoding                                                                                                                                             |            |

|   |                | 4.2.4   | Filter reduction in S2                                                                                                                                         |            |

|   |                | 4.2.4   | Manhattan distance in S2                                                                                                                                       |            |

|   | 4.3            |         | implementation                                                                                                                                                 |            |

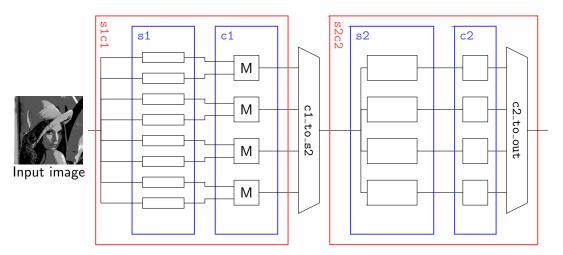

|   | 4.0            | 4.3.1   | Overview                                                                                                                                                       |            |

|   |                | 4.3.1   | s1c1                                                                                                                                                           |            |

|   |                | 4.3.4   | 4.3.2.1 <b>s1</b>                                                                                                                                              |            |

|   |                |         | pixel_manager                                                                                                                                                  |            |

|   |                |         | pix_to_stripe                                                                                                                                                  |            |

|   |                |         | pixmat                                                                                                                                                         |            |

|   |                |         | coeffs_manager                                                                                                                                                 |            |

|   |                |         | conv_filter_bank                                                                                                                                               |            |

|   |                |         | conv_crop                                                                                                                                                      |            |

|   |                |         | 4.3.2.2 conv                                                                                                                                                   |            |

|   |                |         | convrow                                                                                                                                                        | 0.0        |

|   |                |         | sum acc                                                                                                                                                        |            |

|   |                |         | s1degrader                                                                                                                                                     |            |

|   |                |         | 4.3.2.3 shift_registers                                                                                                                                        |            |

|   |                |         | 4.3.2.4 c1                                                                                                                                                     |            |

|   |                |         | c1_max_2by2                                                                                                                                                    |            |

|   |                |         | c1_pix_to_stripe                                                                                                                                               |            |

|   |                |         | c1_reorg_stripes                                                                                                                                               |            |

|   |                |         | c1_orientations_demux                                                                                                                                          |            |

|   |                |         | c1_orientation                                                                                                                                                 |            |

|   |                |         | clunit                                                                                                                                                         |            |

|   |                |         |                                                                                                                                                                |            |

*Contents* x

|              |      |         | maxfilt                                           | 93 |

|--------------|------|---------|---------------------------------------------------|----|

|              |      |         | c1unit_ctrl 9                                     |    |

|              |      |         |                                                   | 94 |

|              |      |         |                                                   | 95 |

|              |      | 4.3.3   |                                                   | 97 |

|              |      | 1.0.0   | -                                                 | 97 |

|              |      |         |                                                   | 98 |

|              |      |         | s2_input_handler                                  |    |

|              |      |         | s2_pix_to_stripe                                  |    |

|              |      |         | 4.3.3.3 s2_coeffs_manager                         |    |

|              |      |         | 4.3.3.4 s2processors                              |    |

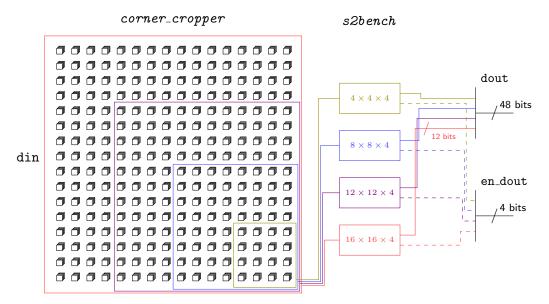

|              |      |         | 4.3.3.5 corner_cropper                            |    |

|              |      |         | 4.3.3.6 s2bank                                    |    |

|              |      |         |                                                   |    |

|              |      |         | 4.3.3.7 <b>s2unit</b>                             |    |

|              |      | 4.0.4   | cum_diff                                          |    |

|              |      | 4.3.4   | <b>c2</b>                                         |    |

|              |      |         | 4.3.4.1 c2_to_out                                 |    |

|              | 4.4  | -       | nentation results                                 |    |

|              |      | 4.4.1   | Resource utilization                              |    |

|              |      | 4.4.2   | Timing                                            |    |

|              | 4.5  |         | sion                                              |    |

|              | 4.6  | Conclu  | ision                                             | )9 |

| 5            | Con  | clusio  | n 11                                              | .1 |

| A            | RBI  | F netw  | orks training 11                                  | 6  |

|              |      |         | iew                                               | 16 |

|              | A.2  |         | ring                                              |    |

|              | A.3  |         | t layer training                                  |    |

|              | 11.0 | Опгра   | viagor training                                   |    |

| $\mathbf{B}$ | Rés  | umé e   | n français 11                                     | 9  |

|              | B.1  | Introd  | uction générale                                   | 19 |

|              | B.2  | État d  | e l'art                                           | 21 |

|              |      | B.2.1   | Fondements théoriques                             | 21 |

|              |      |         | B.2.1.1 Méthodes de classification                | 21 |

|              |      |         | B.2.1.2 Méthodes d'extraction de caractéristiques | 22 |

|              |      | B.2.2   | Implantations matérielles                         | 25 |

|              |      | B.2.3   | Discussion                                        | 26 |

|              | B.3  | Sélecti | on de caractéristiques                            | 27 |

|              |      | B.3.1   | Détection de visages                              | 27 |

|              |      |         | B.3.1.1 Viola-Jones                               |    |

|              |      |         | B.3.1.2 CFF                                       |    |

|              |      |         |                                                   |    |

|              |      |         | B.3.1.3 HMIN et optimisations                     | 29 |

|              |      |         | •                                                 |    |

|              |      | B.3.2   |                                                   | 29 |

*Contents* xi

|         |        | B.3.2.2    | ConvNet     |           |       | <br> | <br> | <br> | <br> | <br>. 132 |

|---------|--------|------------|-------------|-----------|-------|------|------|------|------|-----------|

|         |        |            | Expérime    |           |       |      |      |      |      |           |

|         | B.3.3  | Conclusi   | on          |           |       | <br> | <br> | <br> | <br> | <br>. 133 |

| B.4     | Implar | ntation ma | atérielle . |           |       | <br> | <br> | <br> | <br> | <br>. 134 |

|         | B.4.1  | Optimisa   | ations      |           |       | <br> | <br> | <br> | <br> | <br>. 135 |

|         |        | B.4.1.1    | Données e   | en entrée |       | <br> | <br> | <br> | <br> | <br>. 135 |

|         |        | B.4.1.2    | Filtres de  | Gabor .   |       | <br> | <br> | <br> | <br> | <br>. 135 |

|         |        | B.4.1.3    | Autres op   | timisatio | ons . | <br> | <br> | <br> | <br> | <br>. 136 |

|         | B.4.2  | Résultat   | s d'implant | tation    |       | <br> | <br> | <br> | <br> | <br>. 137 |

|         | B.4.3  | Conclusi   | on          |           |       | <br> | <br> | <br> | <br> | <br>. 138 |

| B.5     | Conclu | usion      |             |           |       | <br> | <br> | <br> | <br> | <br>. 139 |

|         |        |            |             |           |       |      |      |      |      |           |

| Public  | ations |            |             |           |       |      |      |      |      | 140       |

| Bibliog | graphy |            |             |           |       |      |      |      |      | 141       |

## List of Figures

| 1.1  | Application examples                                                           | 2  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | Perceptron applied to PR                                                       | 3  |

| 1.3  | NeuroDSP architecture                                                          | 5  |

| 2.1  | A feedforward architecture                                                     | 9  |

| 2.2  | Perceptron                                                                     | 11 |

| 2.3  | Multi-layer perceptron                                                         | 11 |

| 2.4  | MLP activation functions                                                       | 12 |

| 2.5  | RBF neural network                                                             | 13 |

| 2.6  | Support vectors determination                                                  | 14 |

| 2.7  | Invariant scattering convolution network                                       | 16 |

| 2.8  | HMAX                                                                           | 20 |

| 2.9  | Convolutional neural network                                                   |    |

| 3.1  | Example of Haar-like features used in Viola-Jones                              | 37 |

| 3.2  | Integral image representation                                                  | 38 |

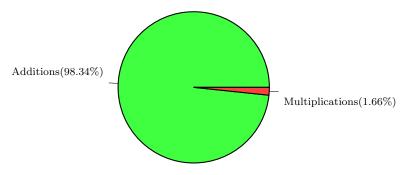

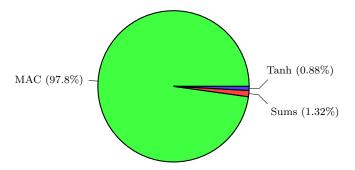

| 3.3  | Complexity repartition of Viola and Jones' algorithm                           | 40 |

| 3.4  | CFF                                                                            | 42 |

| 3.5  | Complexity repartition of the CFF algorithms                                   | 44 |

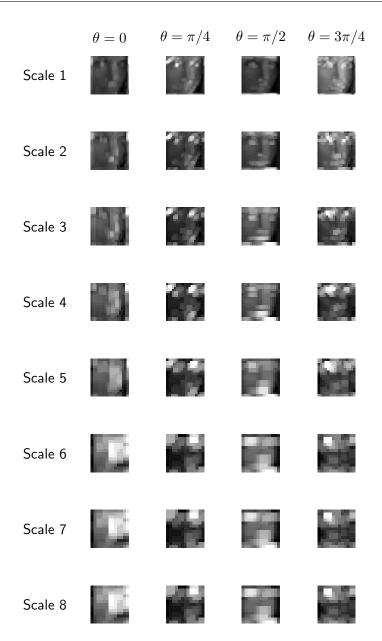

| 3.6  | C1 feature maps for a face                                                     | 47 |

| 3.7  | S1 convolution kernel sum                                                      | 48 |

| 3.8  | Feature map obtained with the unique kernel in S1                              | 48 |

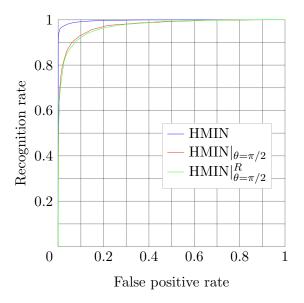

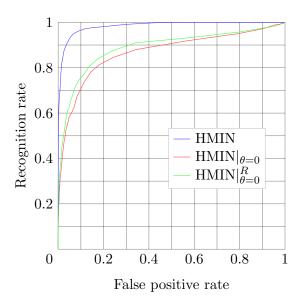

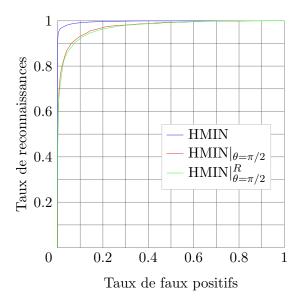

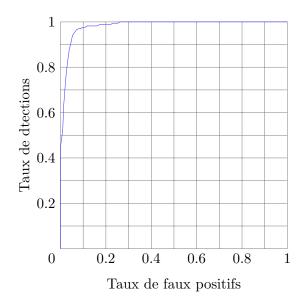

| 3.9  | ROC curves of the HMIN classifiers                                             | 51 |

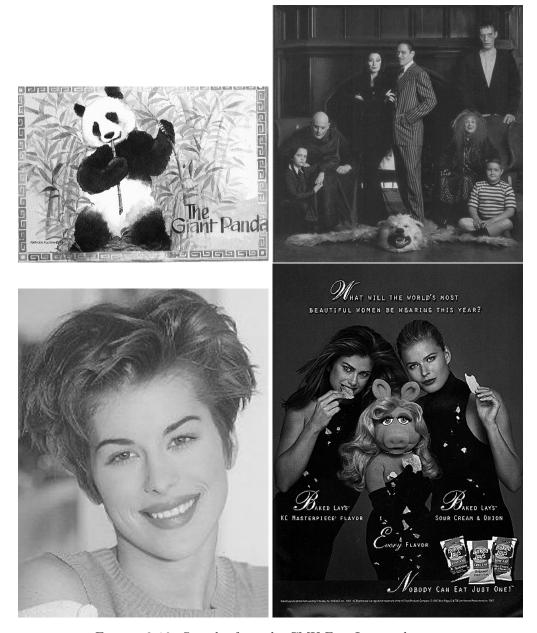

| 3.10 | Samples from the CMU Face Images dataset                                       | 52 |

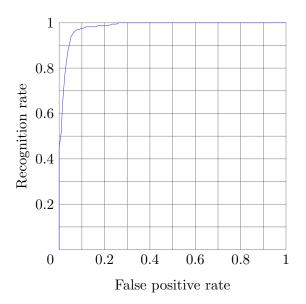

| 3.11 | ROC curve obtained with $HMIN_{\theta=\pi/2}^{R}$ on CMU dataset               | 53 |

| 3.12 | Example of frame from the "Olivier" dataset                                    | 54 |

|      | ROC curves obtained with $\mathrm{HMIN}_{\theta=\pi/2}^R$ on "Olivier" dataset |    |

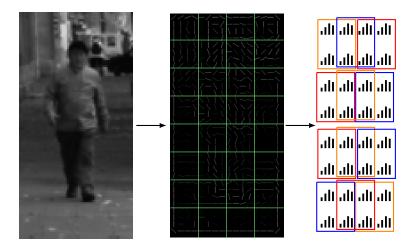

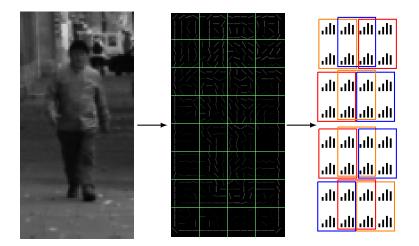

| 3.14 | HOG descriptor computation                                                     | 57 |

|      | Binning of the half-circle of unsigned angles                                  |    |

|      | Complexity repartition of HOG features extraction                              |    |

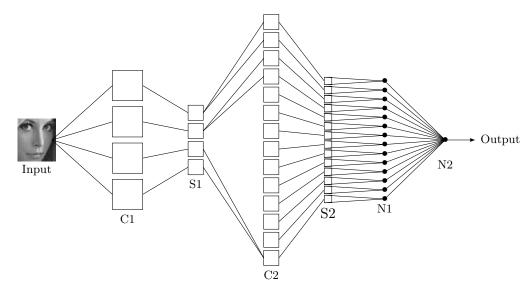

|      | ConvNet for pedestrian detection                                               |    |

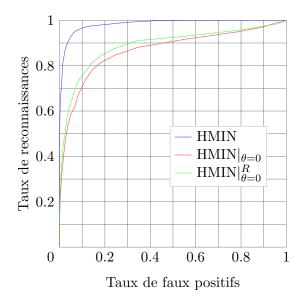

| 3.18 | ROC curves of the HMIN classifiers on the INRIA pedestrian dataset $$          | 67 |

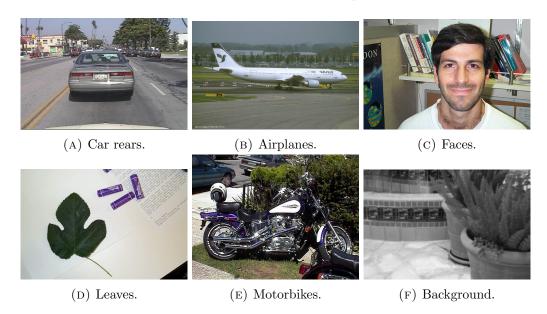

| 4.1  | Caltech101 samples                                                             | 75 |

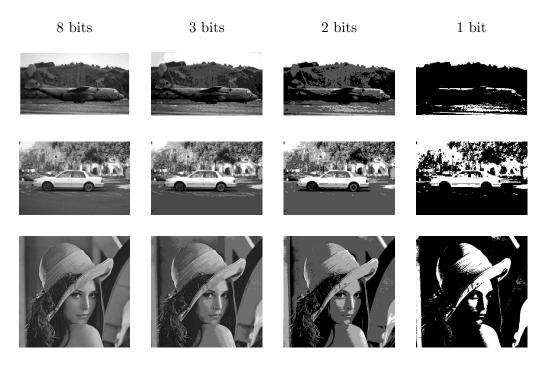

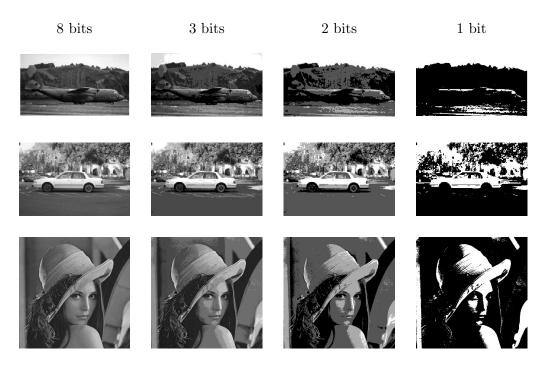

| 4.2  | Precision degradation in input image                                           |    |

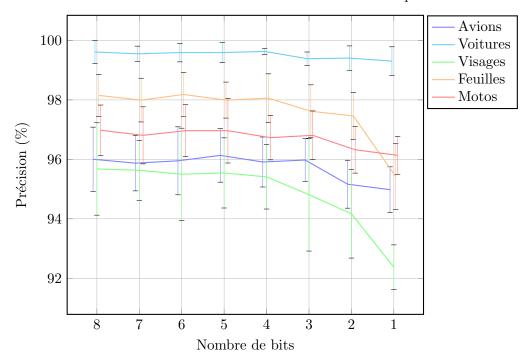

| 4.3  | Recognition rates of HMAX w.r.t input image bit width                          |    |

| 4.4  | Recognition rates w.r.t S1 filters precision                                   | 79 |

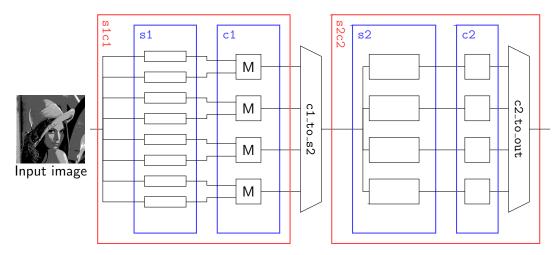

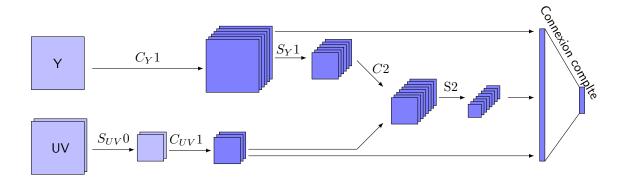

| 4 5  | HMAX VHDL module                                                               | 84 |

List of Figures xiii

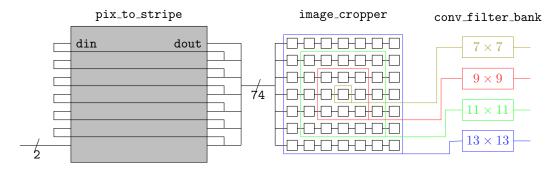

| 4.6  | Dataflow in <b>s1</b>                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------|

| 4.7  | coeffs_manager module                                                                                                   |

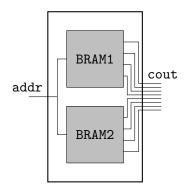

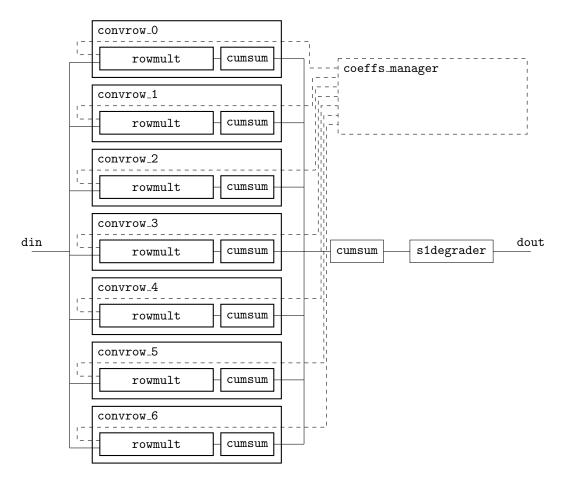

| 4.8  | $7 \times 7$ convolution module                                                                                         |

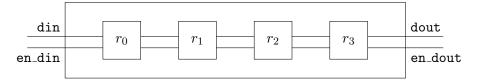

| 4.9  | shift_registers                                                                                                         |

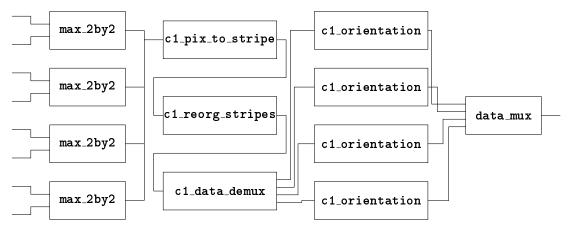

| 4.10 | <b>c1</b> module                                                                                                        |

| 4.11 | clunit                                                                                                                  |

| 4.12 | c1_to_s2 module                                                                                                         |

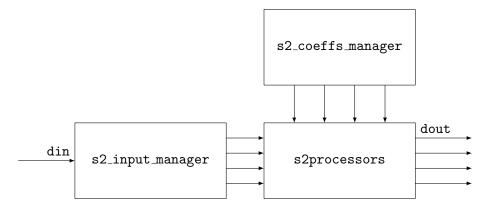

| 4.13 | Dataflow in s2c2. The data arriving to the module is handled by s2_input_manager,                                       |

|      | which make it manageable for the s2processors. The latter also gets                                                     |

|      | the pre-learnt filter needed for the pattern-matching operations from                                                   |

|      | s2_coeffs_manager in parallel, and perform the computations. Once it                                                    |

|      | is over, the data is sent in parallel to the dout output port, which feed                                               |

|      | the next processing module                                                                                              |

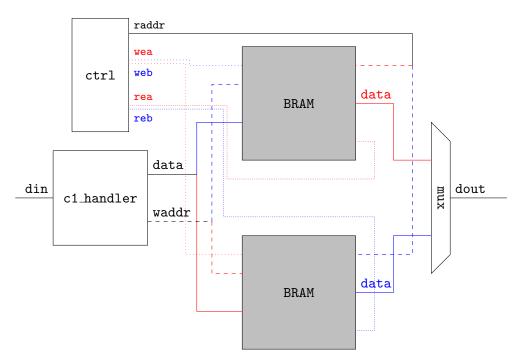

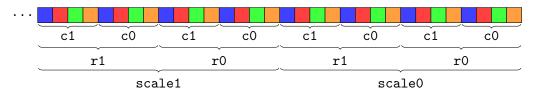

|      | Data management in s2_handler                                                                                           |

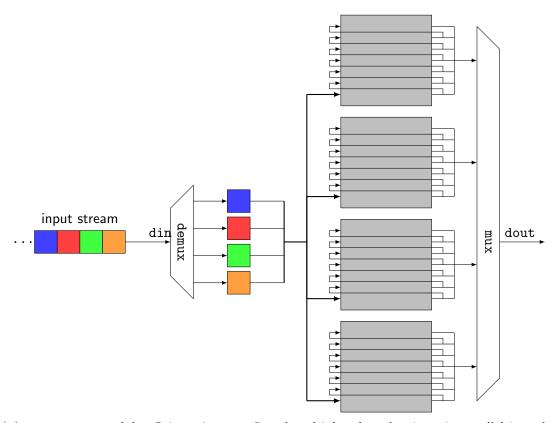

| 4.15 | Data flow in s2processors                                                                                               |

| B.1  | Exemples d'applications                                                                                                 |

| B.2  | NeuroDSP architecture                                                                                                   |

| B.3  | Architecture feedforward                                                                                                |

| B.4  | Invariant scattering convolution network                                                                                |

| B.5  | HMAX                                                                                                                    |

| B.6  | Réseaux de neurones à convolutions                                                                                      |

| B.7  | Examples de caractéristiques utilisés dans Viola-Jones                                                                  |

| B.8  | Représentation en image intégrale                                                                                       |

| B.9  | CFF                                                                                                                     |

| B.10 | Sorties des C1 pour un visage                                                                                           |

|      | Somme des noyaux de convolutions dans S1                                                                                |

|      | Réponse du filtre unique dans S1 sur un visage                                                                          |

|      | Courbes ROC obtenues avec différentes versions de HMIN sur LFW_Crop. 131                                                |

|      | Courbe ROC obtenue avec $\mathrm{HMIN}_{\theta=\pi/2}^R$ sur la base CMU                                                |

|      | $HOG \dots \dots$ |

| B.16 | ConvNet pour la détection de piétons                                                                                    |

|      | Courbes ROC obtenues avec les descripteurs HMIN sur la base INRIA 133                                                   |

|      | Effet de la dégradation de précision sur l'image d'entrée                                                               |

|      | Taux de reconnaissances avec HMAX en fonction de la précision des pixels                                                |

|      | en entrée                                                                                                               |

| B.20 | Précisions en fonction du nombres de bits dans les filtres de Gabor de S1,                                              |

|      | avec 2 bits pour l'image d'entrée                                                                                       |

| B.21 | Aperçu du module VHDL HMAX                                                                                              |

| 2.1 | Paramaters for HMAX S1 and C1 layers                                            |

|-----|---------------------------------------------------------------------------------|

| 2.2 | Comparison of descriptors                                                       |

| 3.1 | Accuracies of the different version of HMIN on the LFW_crop dataset 50          |

| 3.2 | Complexity and accuracy of face detection frameworks                            |

| 3.3 | Complexity and accuracy of human detection frameworks 67                        |

| 4.1 | Hardware resources utilized by Orchard's implementation                         |

| 4.2 | Accuracies of Orchard's implementations on Caltech101                           |

| 4.3 | Code books and partitions for C1                                                |

| 4.4 | Accuracies of HMAX with several optimizations                                   |

| 4.5 | Address offsets in c1_to_s2                                                     |

| 4.6 | Mapping between $N$ and dout_scale                                              |

| 4.7 | Resource utilization of HMAX implementation on XC7A200TFBG484-1 106             |

| 4.8 | Hardware resources comparison between the Virtex-6 FPGA used in [99],           |

|     | and the Artix-7 200T we chose                                                   |

| B.1 | Paramètres des couches S1 et C1 de HMAX                                         |

| B.2 | Comparaison des principaux extracteurs de caractéristiques                      |

| B.3 | Précision des différentes versions de HMIN sur la base de données LFW_crop. 129 |

| B.4 | Complexité et précision de différentes méthodes de détections de visages . 132  |

| B.5 | Complexité et précisions de différentes méthode de détections de personnes.134  |

| B.6 | Précision de HMAX en utilisant différentes optimisations                        |

| B.7 | Utilisation des ressources matérielles de HMAX sur un Artix7-200T 138           |

To Ryan and Théo.

### Chapter 1

## General introduction

#### 1.1 The need for intelligent systems

Automating tedious or dangerous tasks has been an ongoing challenge for centuries. Many tools have been designed to that end. Among them lies computing machines, allowing to assist human beings in calculations or even performing them. Such machines are everywhere nowadays, in devices that fit into our pockets. However, despite the fact that they are very efficient for mathematical operations that are complicated for our brains, they usually perform poorly at tasks that are easy for us, such as recognizing a landmark on a picture or analysing and understanding a scene.

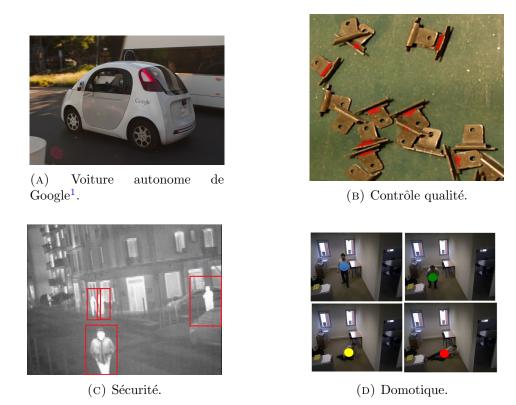

There are many applications for systems that are able to analyze their environments and to make a decision accordingly. In fact, Alan Turing, one of the founder of modern computing, estimated one of the ultimate goal of computing is to build machines that could be said *intelligent* [1]. Perhaps one of the most well known applications of such technology would be for autonomous vehicules, e.g cars that would be able to drive themselves, with little to no help from humans. In order to drive safely, those machines obviously need to retrieve information from different channels, e.g audio of video. Such systems may also be useful for access control for areas that need to be secured, or for quality control on production chains, e.g as was proposed for textile products in [2].

One could think of two ways to achieve a machine of that kind: either engineer how it should process the information, or use methods allowing it to learn it and determine it automatically. Those techniques form a research fields that have been active for decades called *Machine Learning*, which is part of the broader science of *Artificial Intelligence* (AI).

<sup>&</sup>lt;sup>1</sup>By Michael Shick - Own work, CC BY-SA 4.0, https://commons.wikimedia.org/w/index.php?curid=44405988.

(A) Google's self driving car<sup>1</sup>.

(B) Production control.

(c) Security.

(D) Home automation.

Figure 1.1: Application examples.

#### 1.2 Machine Learning

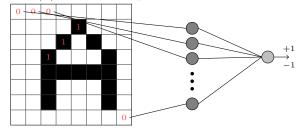

In 1957, the psychologist Frank Rosenblatt proposed the *Perceptron*, one of the first system capable of learning automatically without being explicitly programmed. He proposed a mathematical model, and also built a machine implementing that learning behavior; he tested it with success on a simple letter recognition application. Its principle is very simple: the input image is captured by a retina, producing a small black and white image of the letter – black corresponds to 1, and white to 0. A weighted sum of those pixels is performed, and the *sign* function is applied to the result – for instance, one could state that the system must return 1 when the letter to recognize is an A, and -1 if its a B. If the system returns the wrong value, then the weights are corrected so that the output is correct. A more formal, mathematical description of the Perceptron is provided latter, in Section 2.1.1.1 on page 9. The system is also illustrated in Figure 1.2. Since the Perceptron, many trainable frameworks have been proposed, most of them following a *neuro-inspired* approached like the Perceptron or a statistical approach. They are described in Section 2.1.

Recently, Machine Learning – and AI in general – gained renown from the spectacular research breakthrough and applications initiated by companies such as Facebook, Google, Microsoft, Twitter, etc. For instance, Google DeepMind recently developed AlphaGo,

(A) Mark I Perceptron<sup>2</sup>.

(B) Principle.

FIGURE 1.2: Perceptron applied to pattern recognition. Figure 1.2a shows an hardware implementation, and Figure 1.2b presents the principle: each cell of the retina captures a binary pixel and returns 0 when white, 1 when black. Those pixels are connected to so called input units, and are used to compute a weighted sum. If that sum is positive, then the net returns 1, otherwise it returns -1. Training a Perceptron consists in adjusting its weights. For a more formal and rigorous presentation, see page 9.

a software capable of beating the world champion of Go [3]. Facebook is also using AI to automatically detect, localize and identify faces in pictures [4]. However those applications are meant to be performed on machines with high computational power, and it is beyond question to run such programs on constraint architectures, like those one expect to find on autonomous systems. Indeed, such devices fall into the field of *Embedded Systems* which shall be presented now.

#### 1.3 Embedded systems

Some devices are part of larger systems, in which they perform one task in particular – e.g control the amount of gas that should be injected in the motor of a vehicle. Those so-called *embedded systems* must usually meet high constraints in terms of volume, power consumption, cost, timing and robustness. Indeed, they are often used in autonoumous systems carrying batteries with limited power. In the case of mass produced devices such as phones or cars, it is crucial that their cost is as low as possible. Furthermore, they

<sup>&</sup>lt;sup>2</sup>By Arvin Calspan Advanced Technology Center; Hecht-Nielsen, R. Neurocomputing (Reading, Mass.: Addison-Wesley, 1990).

are often used in critical systems, where they must process information and deliver the result on time without error – any malfunction of those systems may lead to disastrous consequences, especially in the case of autonomous vehicles or military equipments. All those constraints also mean that embedded systems have very limited computational power.

Many research teams have proposed implementations of embedded intelligent systems, as shown in Section 2.2.2. The work proposed in this thesis falls into that research field. However, as we shall see many of those implementations require high-end hardware, thus leading to potentially high cost devices. The NeuroDSP project<sup>3</sup>, in the frame of which this PhD thesis was carried out, aims to provide a device at a lower cost with a low power consumption.

#### 1.4 NeuroDSP: a neuro-inspired integrated circuit

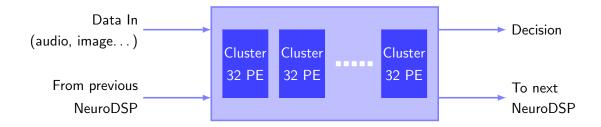

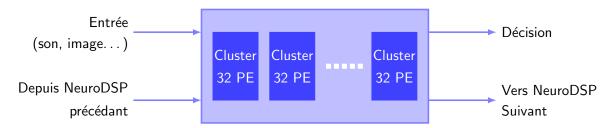

The goal of the research project of which this PhD is part of is to design a chip capable of performing the computation required by the "intelligent" algorithms presented earlier. As suggested in its name, NeuroDSP primarily focuses on the execution of algorithms based on the neural networks theory, among which lie the earlier mentioned Perceptron. As shown in Section 2.1, the main operators needed to support such computations are linear signal processing operators such as convolution, pooling operators and non-linear functions. Most Digital Signal Processing (DSP) operators, such as convolution, actually need similar features – hence that device shall also be able to perform DSP operation, for signal preprocessing for instance. As we shall see, all those operations may be, most of the time, performed in parallel, thus leading to a single-instruction-multiple-data (SIMD) architecture, in which the same operations is applied in parallel to a large amount of data. The main advantage of this paradigm is obviously to carry those operations faster, potentially at a lower clock frequency. As the power consumption of a device is largely related to its clock frequency, SIMD may also allow a lower power consumption.

NeuroDSP is composed of 32 so called P-Neuro blocks, each basically consisting of a cluster of 32 *Processing Elements* (PE), thus totalling 1024 PE. A PE may be seen as an *artificial neuron* performing a simple operation on some data. All PEs in a single P-Neuro perform the same operation, along the lines of the aforementioned SIMD paradigm. A NeuroDSP device may then carry out signal processing and decision making operations. Since 1024 neurons may not be enough, they may be multiplexed to emulate larger systems – of course at a cost in terms of computation time. When timing is so

<sup>3</sup>http://goo.gl/Ax6CoF

FIGURE 1.3: NeuroDSP architecture [5]. A NeuroDSP device is composed of 32 clusters, called *P-Neuro*, each constituted of 32 artificial neurons called PE, thus representing a total of 1024 neurons. The PEs may be multiplexed, so that they can perform several instruction sequentially and thus emulate bigger neural networks. When timing is critical, one may instead cascade several NeuroDSP processors and use them as if it was a single device.

critical that multiplexing is not a satisfying option, it is possible to use several NeuroDSP devices in cascade. The device's architecture is illustrated in Figure 1.3.

#### 1.5 Document overview

While NeuroDSP was designed specifically to run signal processing and decision making routines, such algorithms are most of the time too resource consuming to be performed efficiently on that type of device. It is therefore mandatory to optimize them, which is the main goal of the research work presented here.

In Chapter 2, a comprehensive tour of the works related to our research is proposed. After presenting machine learning theoretical background and also algorithms inspired by biological data, the main contribution concerning their implementations are shown. A discussion shall also be proposed, from which arises the problematic that is aimed to be addressed in this document, namely: how may a preprocessing algorithm be optimized given particular face and pedestrian detection applications, and how the data may be efficiently encoded so that few hardware resources may be used?

The first part of that problem is addressed in Chapter 3. While focusing on a preprocessing algorithm called HMAX, the main works in the literature concerning feature selection are recalled. Our contribution to that question is then proposed.

Chapter 4 presents our contribution of the second part of the raised problems, concerning data encoding. After reminding the main research addressing that issue, we show how a preprocessing algorithm may be optimized so that it may process data coded on a few bits only, with few to none performance drop. An implementation on a reconfigurable hardware shall then be proposed.

Finally, Chapter 5 draws final thoughts and conclusions about the work proposed here. The main problems and results are reminded, as well as the limitations. Considered future research are also proposed.

## Chapter 2

## Related works and problem statement

This chapter proposes an overview of the frameworks used in the pattern recognition field. Both its theoretical backbone and the main implementation techniques shall be presented. It is shown here that one of the key problems of many PR frameworks is their computational cost. Those approaches mainly consists in either using machines with high parallel processing capabilities and high computational power, or on the contrary in optimizing the algorithms so they can be run with less resources. The problematics underlying the work proposed in this thesis, which follows the second paradigm, shall also be stated.

#### 2.1 Theoretical background

In this section, the major theoretical contributions to PR are presented. The principle classification frameworks are first presented to the reader. Then, a description of several descriptors which aim to capture the useful information from the processed images and to get rid of the noise, is proposed.

#### 2.1.1 Classification frameworks

The classification of an unknown data, also called *vector* or *feature vector*, consists in predicting the category it belongs to. Perhaps the simplest classification framework there is is Nearest Neighbor. It consists in storing examples of feature vectors in memory, each associated with the category it belongs to. To classify a unknown feature vector, one

simply uses a distance (e.g Euclidean or Manhattan) to determine the closest example. The classifier then returns the category associated to that selected vector. While really simple, that framework however has many issues. The most obvious is its memory print and its computational cost: the more examples we have, the more expansive that framework is. From a theoretical point of view, that framework is also very sensitive to outliers; any peculiar feature vector, for instance in the case of labelling error, may lead to disastrous classification performance. A way to improve this framework is to take not only the closest feature vector, but the K closest, and to make them vote for the category. The retained category is then the one having the most votes [6]. That framework is called K-Nearest Neighbour (KNN). While this technique may provide better generalization and reduce the effects due to outliers, it still requires lots of computational resources.

There exist many more other pattern classification frameworks. The most used of those frameworks shall now be described. Neural networks are presented first. A presentation of the Support Vector Machines framework shall follow. Finally, Ensemble Learning methods are presented. This document focuses on feedforward architecture only – non-feedforward architectures, such as Boltzmann Machines [7, 8], Restricted Boltzmann Machines [9, 10] and Hopfield networks [11] shall not be described here. We also focus on supervised learning frameworks, as opposed to unsupervised learning, such as self-organizing maps [12]. In suppervised learning, each example is manually associated to a category, while in unsupervised learning the model "decides" by itself which vector goes to which category.

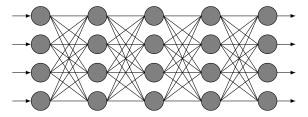

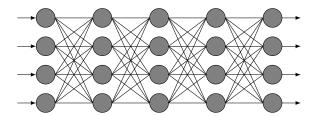

#### 2.1.1.1 Neural Networks

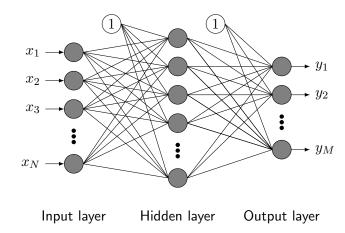

Artifical Neural Networks (NN) are machine learning frameworks inspired by biolocical neural systems, used both for classification and regression tasks. Neural networks are formed of units called neurons, interconnected to each others by synapses. Each synapse has a synaptic weight, which represents a parameter of the model that shall be tuned during training. During prediction, each neuron performs a sum of its inputs, weighted by the synaptic weights. A non linear function called activation function is then applied to the result, thus giving the neuron's activation which feeds the neurons connected to the outputs of the considered one. In this thesis, only feedforward network shall be considered. In those systems, neurons are organized in successive layers, where each unit in a layer gets inputs from units in the previous layer and feeds its activation to units in the next layer. The layer getting the input data is called input layer, while the layer from which the network's prediction is read is the output layer. Such a framework is represented in Figure 2.1. For a complete overview of the existing neural networks, a good review is given in [13].

FIGURE 2.1: A feedforward architecture. In each layer, units get their inputs from neurons in the previous layer and feed their outputs to units in the next layer.

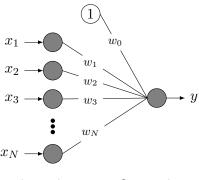

**Perceptron** The perceptron is one of the most fundamental contribution to the Neural Network field, and was introduced by Rosenblatt in 1962 in [14]. It is represented in Figure 2.2. It has only two layers: the input layer and the output layer. A "dummy" unit is added to the input layer, the activation of which is always 1 – the weight  $w_0$  associated to that unit is called *bias*. Those layers are fully connected, meaning each output unit is connected to all input units. Thus, the total input value z of a neuron with N inputs and a bias  $w_0$  is given by:

$$z = w_0 + \sum_{i=1}^{N} w_i x_i \tag{2.1}$$

Or, in an equivalent, more compact matrix notation:

$$z = W^{\mathrm{T}}\mathbf{x} \tag{2.2}$$

with  $\mathbf{x} = (1, x_1, x_2, \dots, x_n)^{\mathrm{T}}$  and  $W = (w_0, w_1, w_2, \dots, w_N)^{\mathrm{T}}$ . W is called weight vector. In the case where there is more than one output unit, then W becomes a matrix where the i-th column is the weight vector for the i-th output unit. By denoting M the number of output units,  $z_i$  the input value of the i-th output unit and  $\mathbf{z} = (z_1, z_2, \dots, z_M)$ , one may write:

$$\mathbf{z} = W^{\mathrm{T}}\mathbf{x} \tag{2.3}$$

The output unit's activation function f is as follows:

$$\forall x \in \mathbf{R}, \quad f(x) = \begin{cases} +1 & x > \theta \\ 0 & x \in [-\theta, \theta] \\ -1 & x < \theta \end{cases}$$

(2.4)

Where  $\theta$  represents a threshold  $(\theta \ge 0)^1$ .

To train a Perceptron, it is fed with each feature vector  $\mathbf{x}$  in the training set along with the corresponding target category t. Let's consider for now that we only have two different categories: +1 and -1. The idea is that, if the network predicts the wrong

<sup>&</sup>lt;sup>1</sup>In the literature the definition of the activation function may be slightly different, with " $\geq$ " signs instead of ">" in Equation 2.4 and with  $\theta > 0$ .

Input layer Output layer

FIGURE 2.2: Perceptron.

category, the difference between the target and the prediction, weighted by a *learning* rate and the input value, is added to the weights and bias. If the prediction is correct, then no modifications is made. The training algorithm is shown in more details for a Perceptron having a single output unit in Algorithm 1. It is easily extensible to systems with several output units; the only major difference is that t is replaced by a target vector  $\mathbf{t}$ , the components of which may be +1 or -1.

```

n \leftarrow number of input units;

\eta \leftarrow learning rate;

Initialize all weights and bias to 0;

while Stopping condition is false do

forall (\boldsymbol{x} = (x_1, x_2, \dots, x_n), t) in training set do

y \leftarrow f(w_0 + w_1x_1 + w_2x_2 + \dots + w_nx_n);

for i \leftarrow 1 to n do

w_i \leftarrow w_i + \eta x_i (t - y);

end

w_0 \leftarrow w_0 + \eta (t - y);

end

end

```

**Algorithm 1:** Learning rule for a perceptron with one output unit.

If there exists a hyperplan separating the two categories, then the problem is said *linearly separable*. In that case, the perceptron convergence theorem [13, 15–17] states that such a hyperplan shall be found in a finite number of iterations – even if one cannot now that number a priori. However, that condition is required, meaning the perceptron is not able to solve non-linearly separable problems. Therefore, it is not possible to train a perceptron to perform the XOR operation. This is often referred to as the "XOR problem" in the literature, and was one of the main reasons why neural network had not known great popularity in industrial applications in the past. A way to address this class of problems is to use several layers instead of a single one.

FIGURE 2.3: Multi-layer perceptron with one hidden layer.

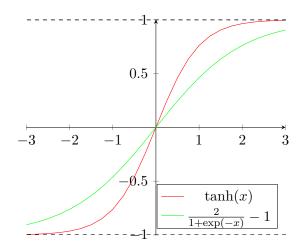

Multilayer Perceptron In terms of architecture, the Multilayer Perceptron (MLP) is very similar to the single-layer perceptron, except that it has one or several *hidden layers* between its input and output layers, as shown in Figure 2.3. That architecture allows it to address non linearly separable problems, contrary to the single-layer Perceptron. As required by its training algorithm, its neurons' activation function must be defined and derivable on  $\mathbf{R}$ , and staked in [-1, +1]. Therefore, f may be the hyperbolic tangent:

$$\forall x \in \mathbf{R} \quad f(x) = \tanh(x) \tag{2.5}$$

or the very similar bipolar sigmoid:

$$\forall x \in \mathbf{R} \quad f(x) = \frac{2}{1 + e^{-x}} - 1$$

(2.6)

Those functions' curves are represented in Figure 2.4. Its training algorithm is somewhat more complicated, and follows the *Stochastic Gradient Descent* approach. Let E be the *cost function* measuring the error between the expected result and the network's prediction. The goal is to minimize E, the shape of which is unknown. The principle of the algorithm achieving that is called *back-propagation of error* [18, 19].

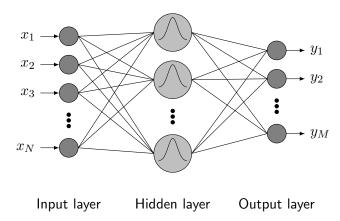

**RBF** Radial Basis Function networks were proposed initially by Broomhead and Lowe [20, 21] and fall in the *kernel methods* family. They consist in three layers: an input layer similar to the Perceptron's, a hidden layer containing kernels and an output layer. Here, a kernel i is a radial basis function  $f_i$  (hence the name of the network) that measures the proximity of the input pattern  $\mathbf{x}$  with a learnt pattern  $\mathbf{p}_i$  called *center*, according to a radius  $\beta_i$ . It typically has the following form:

$$f_i(x) = \exp\left(-\frac{||\mathbf{x} - \mathbf{p}_i||}{\beta_i}\right)$$

(2.7)

FIGURE 2.4: MLP activation functions.

FIGURE 2.5: RBF neural network.

The output layer is similar to a Perceptron: the hidden and output units are fully connected by synapses having synaptic weights, which are determine during the training stage. The network is illustrated in Figure 2.5.

To determine the kernels parameters, one may adopt different strategies. Centers may be directly drawn from the training set, and radius may be arbitrarily chosen – however such empirical solution leads to poor results. A more efficient way is to use a clustering algorithm that gathers the centers into clusters, the center of which shall represent an example center while the corresponding radius is evaluated w.r.t the proximity with other kernels. Such an algorithm is presented in Appendix A. The computational power and the memory required by this network grows linearly with the number of kernels. While the training method presented in Appendix A tend to reduce the number of kernels, it still may be quite important. There exists sparse kernel machines, that work in a similar way than RBF networks but are designed to use as few kernels as possible, like the Support Vector Machines described in Section 2.1.1.2.

Spiking Neural Network All the models presented above treat the information at the level of the neurons activation. Spiking neural networks intend to describe the behaviour of the neurons at a lower level. That model was first introduced by Hodgkin et al [22], who proposed a description of the propagation of the action potentials between biological neurons. There exists different variations of the spiking models, but the most used nowadays is probably the "integrate and fire", where the neurons' inputs are accumulated over time. When the total reaches a threshold, the neuron is committed. Thus, the information sent by a neuron is not carried by a numerical value, but rather by the spikes order and the duration between two spikes. It is still an active research subject, with many applications in computer vision – Masquelier and Thorpe proposed the "spike timing dependent plasticity" (STDP) algorithm, which allows unsupervised learning of visual features [23].

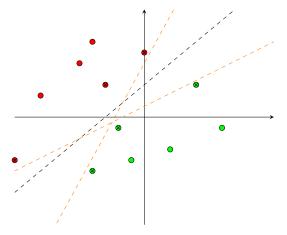

#### 2.1.1.2 Support Vector Machine

Support Vector Machines (SVM) are linear classifiers. Much like any other such model, they aim to find the parameters of the hyperplan separating best a category with the others. It may be used in conjunction with kernel functions, in the same way as presented in the description of RBF neural networks in Section 2.1.1.1, page 11. SVM training's algorithm aims to determine the vectors that are the nearest to those of the other categories [24]. The selected vectors are called *support vectors*. After selecting them, the decision boundary's parameters are optimized so that it is as far as possible to all support vectors. Typically, a quasi-Newton optimization process could be choosen to that end; however its description lies beyond the scope of this document. Figure 2.6 shows an example of their determination as well as the resulting decision boundary.

#### 2.1.1.3 Ensemble learning

The rational behind Ensemble Learning frameworks is that instead of having one classifier, it may be more efficient to use several ones [25–28]. Those classifiers are called weak classifiers, and the final decision results from their predictions. Their exists several paradigms, among which Boosting [29] in particular.

Boosting algorithm are known for their computational efficiency during prediction. A good example is their use in Viola and Jone's famous face detection algorithm [30]. The speed of the algorithm comes partly from the fact that the classifier is composed of a cascade of weak classifiers, in which all regions of the image that are clearly not faces are discarded by the top-level classifier. If the data goes through it, then it is "probably a face", and is processed by the second classifier, which either discard of accept it, and

FIGURE 2.6: Support vectors determination. Green dots belong to a class, and red ones to the others. Dots marked with a  $\times$  sign represent the selected support vectors. The unmarked dots have no influence over the determination of the decision boundary's parameters. The black dashed line represents the determined decision boundary, and the orange lines possible decision boundaries that would not be optimal.

so on. This allows to rapidly eliminate irrelevant data and the noise. Boosting is also known to be slightly more efficient than SVM for multiclass classification tasks with HMAX [31], which is described in Section 2.1.2.2.

#### 2.1.2 Feature extraction frameworks

#### 2.1.2.1 Signal processing approach

Classical approaches More than ten years ago, Lowe proposed a major contribution in computer vision with his Scale Invariant Feature Transform (SIFT) descriptor [32], which became quickly very popular due to its efficiency. Its primary aim was to provide, as suggested by its name, features that are invariant to the scale and to some extent to the orientation and small changes in viewpoint. It consists in matching features from the unknown image to a set of learnt features at different locations and scales, followed by a Hough transform that gathers the matched points in the image into clusters, which represent detected objects. The matching is operated by a fast nearest-neighbour algorithm, that indicates for a given feature the closest learnt feature. However, doing so at every locations and scale would be very inefficient, as most of the image probably does not contain much information. In order to find locations which are the most likely to hold information, a Difference of Gaussian (DoG) filter bank is applied to the image. Each DoG filter behaves as a band-pass filter, selecting edges at a specific spatial frequency and allowing to find features at a specific scale. Extrema are then evaluated across all those scales in the whole image, and constitute a set of keypoints at which the aforementioned matching operations are performed. As for rotation invariance, it

is brought by the computation of gradients that are local to each keypoint. Before performing the actual matching, the data at a given keypoint is transformed according to those gradients so that any variability caused by the orientation is removed.

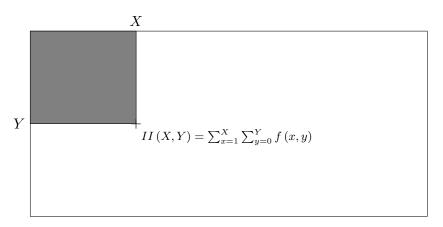

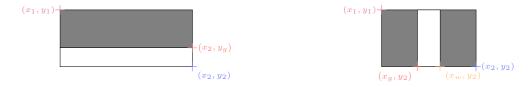

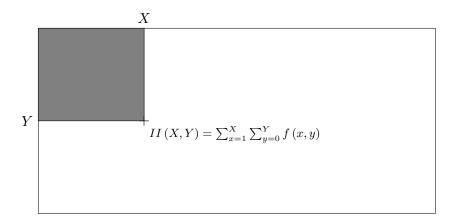

Bay et al. proposed in [33] a descriptor aiming to reproduce the result of the state of the art algorithm, but much faster to compute. They called their contribution SURF, for Speeded-Up Robust Features. It provides properties similar to SIFT (scale and rotation invariance), with a speed-up of 2.93X on a feature extraction task, where both frameworks were tuned to extract the same number of keypoints. Like SIFT, SURF consists in a detector that takes care of finding keypoints in the image, cascaded with a descriptor that computes features at those keypoints. The keypoints are evaluated using a simple approximation of the Hessian matrix, which can be efficiently computed thanks to the integral image representation, i.e an image where each pixels contains the sum of all the original image's pixels located left and up to it [30]. Descriptors are then computed locally using Haar wavelet, which can also be computed with the integral image [30]. [34, 35]

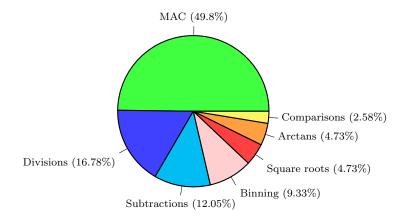

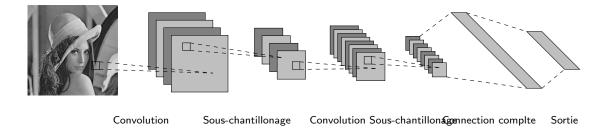

Another popular framework for feature extraction is Histograms of Oriented Gradients (HOG) [36]. It may be used in many object detection applications, though it was primarly designed for the detection of human beings. It consists in computing the gradients at each pixel, and make each of those gradients vote for a particular bin of a local orientation histogram. The weight with which each gradient votes is a linear function of its norm and of the difference between its orientation and the orientation of the closest bins' centers. Those gradients are then normalized over overlapping spatial blocks, and the result forms the feature vector. The classifier used here is typically a linear SVM, presented in Section 2.1.1.

Like many feature extraction frameworks, there exists some variations of the HOG feature descriptor. Dalal and Triggs present two of them in [36]: R-HOG and C-HOG, respectively standing for "Rectangular HOG" and "Circular HOG". The difference with the HOG lies in the shape of the overlapping spatial blocks used for the gradient normalization. R-HOG is somewhat close to presented earlier SIFT, except that computations are performed at all locations, thus providing a dense feature vector. C-HOG is somewhat trickier to implement due to the particular shape it induces, and shall not be presented here. All three frameworks provide similar recognition performances, which were the state of the art at that time.

There are many other descriptors for images, like FAST [34, 35], and we shall not describe them in detail here as it lies beyond the scope of this document. However it is worth detailing another type of frameworks based on so-called *wavelets*, which allow to retreive

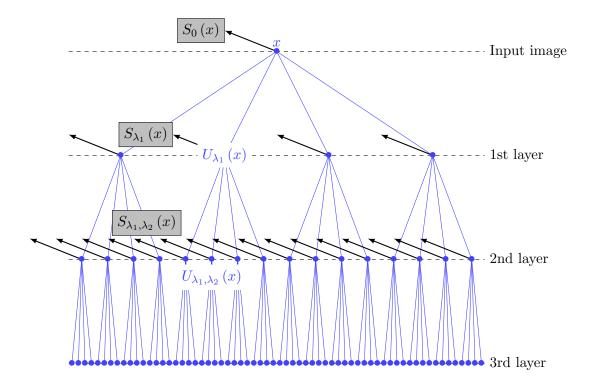

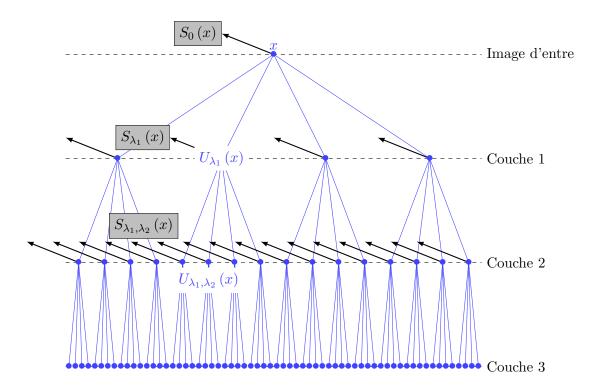

FIGURE 2.7: Invariant scattering convolution network [38]. Each layer applies a wavelet decomposition  $U_{\lambda}$  to its inputs, and feed the next layer with the filtered images  $U_{\lambda}(x)$ . At each layer, a low-pass filter is applied to the filtered images and the results are sub-sampled. The resulting so-called "scattering coefficients"  $S_{\lambda}(x)$  are kept to form the feature vector.

frequency information while keeping local information – which is not possible with the classical Fourier transform.

Wavelets Wavelets have known a great success in many signal processing applications, such as signal compression or pattern recognition, including for images. They are linear operators decomposing locally a signal on a frequency basis. A wavelet decomposition consists in applying a "basis" linear filter, called *mother wavelet*, on the signal. It is then dilated in order to extract features of different sizes and, in the case of images, rotated so that it responds to different orientations. An excellent and comprehensive guide to the theory and practice of wavelets is given in [37].

Wavelets are used as the core operators of the Scattering Transform frameworks. Among them lie the Invariant Scattering Convolution Networks (ISCN), introduced by Bruna and Mallat [38]. They follow a feedforward, multistage structure, along the lines of ConvNet described in Section 2.1.2.3, though contrary to ConvNet its parameters are fixed, not learnt. They alternate wavelet decompositions with low-pass filters and subsampling – the function of which is to provide invariance in order to raise classification performances. Each stage computes a wavelet decomposition of the images produced

at the previous stage, and feed the resulting filtered images to the next stage. At each stage the network also outputs a low-pass filtered and sub-sampled version of those decompositions – the final feature vector is the concatenation of those output features. Figure 2.7 sums up the data flow of this framework. It should be noted that in practice, not all wavelet are applied at each stage to all images: indeed it is shown in [38] that some of those wavelet cascades do not carry information, and thus their computation may be avoided, which allows to reduce the algorithmic complexity. Variations of the ISCN with invariance to rotation are also presented in [39, 40], which may be used for texture [39] or objects [40] classification.

#### 2.1.2.2 A biological approach: HMAX

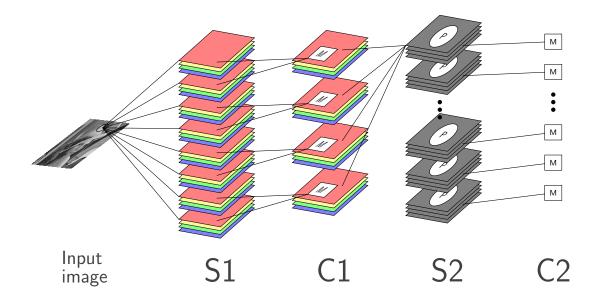

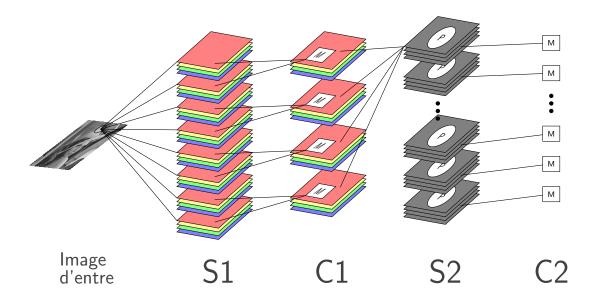

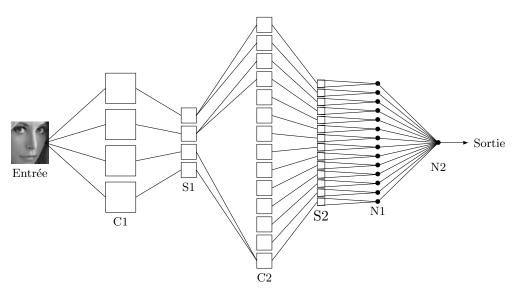

Some frameworks are said to be biologically plausible. In such case, their main aim is not so much to provide a framework as efficient as possible in terms of recognition rates or computation speed, but rather to propose a model of a biological system. One of the most famous of such frameworks is HMAX, which also happens to provide decent recognition performances. The biological background was proposed by Riesenhuber and Poggio in [41], on the base of the groundbreaking work of Hubel and Wiesel [42]. Its usability for actual object recognition scenarios was stated by Serre et al. 8 years later in [31]. It is a model of the ventral visual system in the cortex of the primates, accounting for the first 100 to 200 ms of processing of visual stimuli. As its name suggests – HMAX stands for "Hierarchical Max" – that model is built in a hierarchical manner. Four successive stages, namely S1, C1, S2 and C2 process the visual data in a feedforward way. The S1 and S2 layers are constituted of simple cells, performing linear operations or proximity evaluations, while the C1 and C2 contain complex cells that provide some degrees of invariance. Figure 2.8 sums up the structure of this processing chain. Let's now describe each stage in detail.

The S1 stage consists in a Gabor filter bank. Gabor filters – which are here two dimensional, as we process images – are linear filters responding to patterns of a given spatial frequency and orientation. They are a particular form of the wavelets described in Section 2.1.2.1. A Gabor filter is described as follows:

$$G(x,y) = \exp\left(-\frac{x_0^2 + \gamma^2 y_0^2}{2\sigma^2}\right) \times \cos\left(\frac{2\pi}{\lambda}x_0\right)$$

(2.8)

$$x_0 = x \cos \theta + y \sin \theta$$

and  $y_0 = -x \sin \theta + y \cos \theta$  (2.9)

where  $\gamma$  is the filter's aspect ratio,  $\theta$  its orientation,  $\sigma$  the Gaussian effective width and  $\lambda$  the cosine wavelength. The filter bank has several filters, each having a specific wavelength, effective width, size and orientation. The wavelength, effective width and

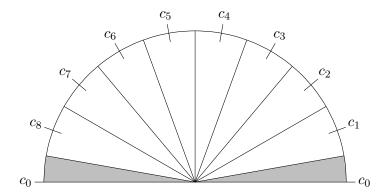

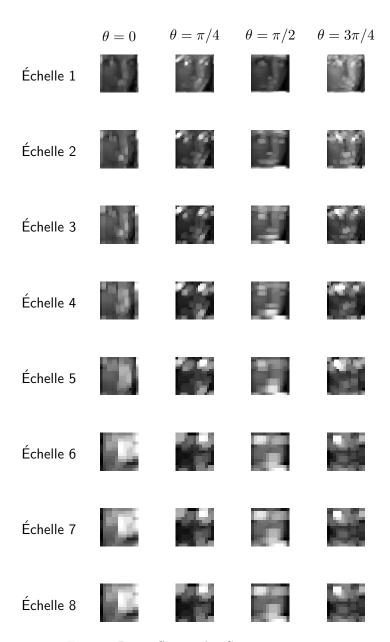

size define the filter's *scale*. There are 16 different scales and four different orientations, thus totaling 64 filters. During the S1 stage, each filter is applied independently on the input image and the filtered images are fed to the next layer.

The C1 stage gives a first level of location invariance of the features extracted in S1. It does so with maximum pooling operators: each C1 unit pools over several neighboring S1 units with a 50% overlap and feed the S2 layer with the maximum value. The number of S1 units a C1 unit pools over depends on the scale of the considered S1 units. Furthermore, each C1 unit pools across two consecutive scales, with no overlap. This leads to a number of images divided by two, thus only 32 images are fed to the following layer. The parameters of the S1 and C1 layers are presented in Table 2.8.