# Burst CMOS image sensor with on-chip analog to digital conversion

Rémi Bonnard

### ► To cite this version:

Rémi Bonnard. Burst CMOS image sensor with on-chip analog to digital conversion. Micro and nanotechnologies/Microelectronics. Université de Strasbourg, 2016. English. NNT: 2016STRAD006. tel-01484398

# HAL Id: tel-01484398 https://theses.hal.science/tel-01484398v1

Submitted on 7 Mar 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

**UNIVERSITÉ DE STRASBOURG**

# ÉCOLE DOCTORALE MSII Laboratoire ICube UMR 7375

soutenue le : 10 Février 2015

# pour obtenir le grade de : **Docteur de l'université de Strasbourg** Discipline/Spécialité : Mathématiques, Sciences de l'Information et de l'Ingénieur / Optoélectronique

# Burst CMOS Image Sensor with on-chip Analog to Digital Conversion

| THÈSE dirigée par :      |                                                                                            |

|--------------------------|--------------------------------------------------------------------------------------------|

| Prof. UHRING Wilfried    | Professeur, Université de Strasbourg / CNRS                                                |

|                          |                                                                                            |

| RAPPORTEURS :            |                                                                                            |

| Prof. MAGNAN Pierre      | Chef du Département Electronique, Optronique et Signal, ISAE                               |

| Prof. DrIng. FEY Dietmar | Chef de l'Equipe Computer Science 3, Friedrich-Alexander-<br>Universität Erlangen-Nürnberg |

### AUTRES MEMBRES DU JURY :

| Dr. KOCH Andreas   | Scientifique, European XFEL GmbH            |

|--------------------|---------------------------------------------|

| Dr. DUPRET Antoine | HDR, CEA/Leti                               |

| Prof. HEBRARD Luc  | Professeur, Université de Strasbourg / CNRS |

# Rémi BONNARD Burst CMOS Image Sensor with on-chip A/D Conversion

# Résumé

Ce travail vise à étudier l'apport des technologies d'intégration 3D à l'imagerie CMOS ultrarapide. La gamme de vitesse d'acquisition considérée ici est du million au milliard d'images par seconde. Cependant au-delà d'une dizaine de milliers d'images par seconde, les architectures classiques de capteur d'images sont limitées par la bande passante des buffers de sortie. Pour atteindre des fréquences supérieures, une architecture d'imageur burst est utilisée où une séquence d'une centaine d'images est acquise et stockée dans le capteur.

Les technologies d'intégration 3D ont connu un engouement depuis une dizaine d'années et sont considérées comme une solution complémentaire aux travaux menés sur les dispositifs (transistors, composants passifs) pour améliorer les performances des circuits intégrés. Notre choix s'est porté sur une technologie où les circuits intégrés sont directement empilés avant la mise en boitier (3D-SIC). La densité d'interconnections entre les différents circuits est suffisante pour permettre l'implémentation d'interconnections au niveau du pixel. L'intégration 3D offre d'intéressants avantages à l'imagerie intégrée car elle permet de déporter l'électronique de lecture sous le pixel. Elle permet ainsi de maximiser le facteur de remplissage du pixel tout en offrant une large place aux circuits de conditionnement du signal. Dans le cas de l'imagerie burst, cette technologie permet de consacrer une plus grande surface aux mémoires dédiées au stockage de la séquence d'image et ce au plus proche des pixels. Elle permet aussi de réaliser sur la puce la conversion analogique numérique des images acquises.

Dans un premier temps, nous avons conçu un modèle pour évaluer les performances de deux architectures d'imageurs. La première stocke les images sous forme analogique puis réalise la conversion durant la lecture de la mémoire. Cette solution offre de très hautes vitesses d'acquisition allant jusqu'au milliard d'images par seconde. Cependant, ce mode de stockage présente les inconvénients des mémoires analogiques comme le bruit d'échantillonnage et un temps de rétention limité des données. L'architecture à mémoire analogique est capable d'acquérir et de stocker des centaines d'images en mémoire selon la dynamique désirée. La seconde architecture convertit l'image en données numériques avant le stockage en mémoire. La vitesse d'acquisition est alors limitée par la fréquence des convertisseurs analogiques numériques à des dizaines de millions d'images par seconde selon la résolution de la conversion. L'utilisation de mémoires numériques permet de stocker des milliers d'images à chaque acquisition. Cette dernière architecture offre une amélioration de la profondeur mémoire d'un facteur dix par rapport à l'architecture à stockage analogique. Une telle architecture est rendue possible grâce à l'intégration 3D alors

que les imageurs à stockages analogiques sont concevables sans cette technologie. La suite de notre étude s'est donc portée sur les imageurs burst à mémoires numériques.

Lors de la modélisation des performances du l'imageur burst à stockage numérique, il est apparu que la consommation du système était très élevée. Pour évaluer les risques de surchauffe, un modèle thermique de l'imageur a été réalisé. Il confirme la faisabilité d'une telle structure pour l'acquisition d'une simple séquence d'images et définit des limites de fonctionnement pour un mode d'acquisition répété.

Une attention particulière a été portée à la réalisation d'un circuit de lecture adapté à notre architecture d'imageur. Un circuit de lecture inspiré des « active pixel sensors » permettant une acquisition « global shutter » a été réalisé. De plus différentes solutions ont été envisagées pour augmenter la sensibilité du circuit. Un pixel basé sur une structure à injection directe a été implémenté sur le test chip. Enfin un pixel sans source de courant a été étudié et conçu pour réduire la consommation du capteur.

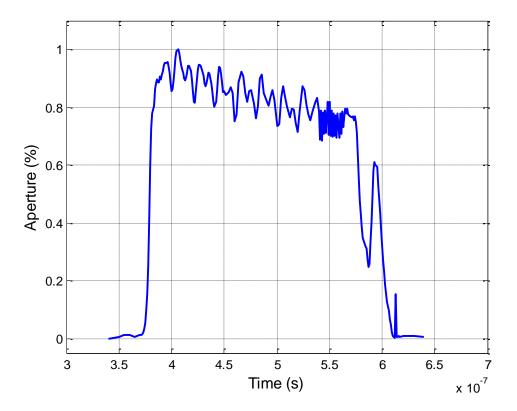

Suite à la fabrication du test-chip, des tests électriques et optiques ont été menés. La photosensibilité de la photodiode et les caractéristiques du pixel inspiré de « l'active pixel sensor» et du pixel à injection direct ont été mesurées. La vitesse de ces deux pixels a aussi été caractérisée grâce à la mesure de leur ouverture électronique. Ces structures ont été validées respectivement pour des vitesses de 1,6 et 5 millions d'images par seconde. Enfin, la fin de ce manuscrit présente la réalisation d'un prototype d'imageur burst à stockage numérique. Cet imageur est composé d'un empilement de deux matrices de pixels. Le circuit pixel supérieur contient les photodiodes, le circuit de lecture global shutter et le comparateur d'un convertisseur simple rampe. Le circuit pixel inférieur est composé du compteur 8 bits du convertisseur et d'une mémoire numérique.

Mots-clés : Capteur d'Image, Imageur CMOS, Imageur Ultra Rapide, Circuit Intégré en Trois Dimensions, Imagerie Burst, Conversion Analogique Numérique

### Summary

This work aims to study the inflows of the 3D integration technology to ultra-high speed CMOS imaging. The acquisition speed range considered here is between one million to one billion images per second. However above ten thousand images per second, classical image sensor architectures are limited by the data bandwidth of the output buffers. To reach higher acquisition frequencies, a burst architecture is used where a set of about one hundred images are acquired and stored on-chip.

3D integration technologies become popular more than ten years ago and are considered as a complementary solution to the technological improvements of the devices. We have chosen a technology where integrated circuits are stacked on the top of each other (3D-SIC). The interconnection density between the circuits is high enough to enable interconnections at the pixel level. The 3D integration offers some significant advantages because it allows deporting the readout electronic below the pixel. It thus increases the fill factor of the pixel while offering a wide area to the signal processing circuit. For burst imaging, this technology provides more room to the memory dedicated to the image storage while staying close to the pixel. It also allows implementing analog to digital converter on-chip.

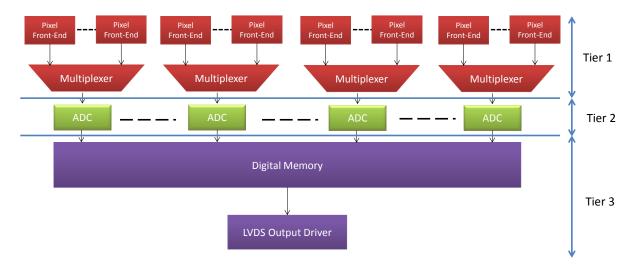

First, we have proposed a model to assess the performances of two image sensor architectures. The first one stores the images into analog memory and then performs the conversion during the memory reading. This architecture enables very high frame rates up to billion images per second. However, the analog storage has some drawbacks as the sampling noise and the limited retention time. The analog storage architecture is able to store hundreds of images depending on the targeted dynamic range. The second architecture converts images into digital data before their storage. The frame rate is then limited by the analog to digital conversion to tens millions images per second depending on the conversion resolution. Using digital memories allows storing thousands of images at each acquisition. This architecture provides an improvement of the memory depth of a factor ten compared to the analog storage architecture. Such architecture is possible thanks to 3D integration while the analog storage architecture can be implemented without this technology. The continuation of this PhD work has then focused on the burst image sensor with digital storage.

During the performance study of the burst image sensor with digital storage, it has appeared that the power consumption of this sensor is very high. To assess the risk of overheating, a thermal model of the sensor has been made. It has confirmed the feasibility of this structure for the acquisition of a single burst of images and has defined some operating limits to the multi burst acquisition mode.

A specific attention has been paid to the design of a readout circuit suited to our architecture. A circuit which enables global shutter acquisition inspired from the "active pixel sensor" (APS) pixel has been designed. Moreover different solutions have been considered to increase the pixel sensitivity. A pixel with a direct injection circuit has been implemented on a test-chip. Finally a pixel without current source has been studied and designed to reduce the power consumption of the sensor.

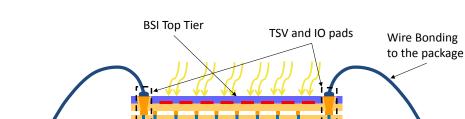

After the manufacturing of the test-chip, electrical and optical tests have been carried out. The photo-responsivity of the photodiode and the characteristics of the APS based pixel and the direct injection pixel have been measured. The speed both of these pixels has been evaluated thanks to electronic aperture measurements. These structures have respectively been validated for a frame rate of 1.6 and 5 million images per second. Finally, the end of the report describes the design of a digital storage burst image sensor prototype. This image sensor is made of a stack of two pixel arrays. The top tier pixel contains the photodiode, the global shutter circuit and the comparator of a single slope ADC. On the bottom tier pixel, the 8 bit counter of the converter and the digital memory are implemented.

Keywords: Image Sensor, CMOS Imaging, Ultra High Speed Imaging, Three-Dimensional Integrated Circuit, Burst Imaging, Analog to Digital Conversion

#### International Conference Communications:

R. Bonnard, F. Guellec, J. Segura, A. Dupret, W. Uhring; "*New 3D-integrated burst image sensor architectures with in-situ A/D conversion*", DASIP 2013, Cagliari, Italy, pages 215-222, ECSI (Eds.), IEEE, October 2013

R. Bonnard, J. Segura Puchades, F. Guellec, W. Uhring; *"Signal conditioning circuits for 3D-integrated burst image sensors with on-chip A/D conversion"*, Electronic Imaging 2015, San Francisco, United States of America

R. Bonnard, M. Garci, J. Kammerer, W. Uhring; "*Electrothermal Analysis of 3D Integrated Ultra-fast Image Sensor With Digital Frame Storage*", Therminic 2015, Paris, France

## Résumé de la thèse : Capteur d'Image Burst CMOS avec Conversion Analogique-Numérique sur Puce

### 1. Introduction

L'imagerie rapide est un vaste domaine qui propose des caméras enregistrant à des cadences allant du millier à des milliards d'images par seconde. Ces caméras sont destinées à des applications industrielles ou scientifiques pour enregistrer des évènements rapides. Selon la vitesse d'acquisition envisagée, l'architecture du capteur d'image diffère. Pour des vitesses d'acquisition allant jusqu'à la dizaine de milliers d'images par seconde pour une résolution d'un million de pixels, l'architecture des capteurs d'image CMOS classique est utilisée. Cependant pour éviter des distorsions spatiotemporelles de l'image, une acquisition d'obturation globale « global shutter » est implémentée. Lors de l'enregistrement de chaque image de la vidéo, les pixels de toute la matrice sont acquis au même instant contrairement à l'acquisition « rolling shutter ». Ce type de caméra est utilisé surtout pour enregistrer des ralentis sportifs ou animaliers, pour enregistrer des séquences de crash test automobile ou faire du contrôle sur les chaines de production. La vitesse d'acquisition est en pratique limitée par l'opération de lecture de la matrice et le débit de l'électronique de sortie de l'imageur. L'état de l'art actuel de la caméra rapide continue offre un débit d'environ 25 milliards de pixels par seconde en sortie de l'imageur. Pour une conversion analogiquenumérique réalisée sur 8 bits, cela correspond à un débit de 25 Go/s. Pour contourner cette limitation, une architecture d'imageur par rafale dite burst est employée. Avec cette structure, une vidéo est acquise à très haute vitesse et stockée dans l'imageur. La vidéo stockée est ensuite envoyée à vitesse conventionnelle hors de l'imageur se libérant ainsi de la contrainte de débit de l'électronique de sortie. Cependant comme la vidéo est stockée au cœur de la puce, la longueur de la vidéo est limitée et va d'une dizaine à quelques centaines d'images. Ce type d'imageur est principalement utilisé dans le domaine scientifique pour l'étude de phénomènes rapides comme les tests de ruptures mécaniques, la formation de plasma et l'étude de certaines combustions. Ce type de caméra enregistre à des cadences pouvant dépasser le million d'images par seconde. Pour atteindre des vitesses supérieures jusqu'à des milliards d'images par seconde, des architectures « streak » sont employées. Ces caméras permettent d'atteindre des résolutions temporelles de quelques centaines de picosecondes. Cependant ces caméras produisent une vidéo d'images constituées d'une seule colonne de pixels. Une image en deux dimensions peut être reconstituée selon la répétabilité de l'évènement enregistré. Ce type de caméra est utilisé pour enregistrer des phénomènes d'optiques (ablation laser), de photochimie (mesure de constantes de temps de fluorescence) ou de physique de la matière condensée.

L'objectif de ce travail est d'étudier les apports des technologies d'intégration en trois dimensions (3D) à l'imagerie rapide. Cette étude s'est portée plus spécifiquement sur les architectures d'imageur *burst* en technologie CMOS. Suite à une étude de l'état de l'art des

imageurs *burst*, deux architectures d'imageur intégré en 3 dimensions ont été évaluées et comparées. Cette étude nous a permis de sélectionner l'architecture burst à stockage numérique pour maximiser le nombre d'images par *burst*. Cette architecture a été modélisée pour évaluer les élévations de températures dans différents modes de fonctionnement. Suite à cette approche haut niveau, des pixels ont été conçus pour réduire la consommation et augmenter la sensibilité du capteur. Un microcircuit de test a été réalisé et a permis de valider les différents pixels. Enfin un prototype d'imageur *burst* à stockage numérique intégré en 3 dimensions a été fabriqué grâce à un empilement de deux circuits.

### 2. Etat de l'art

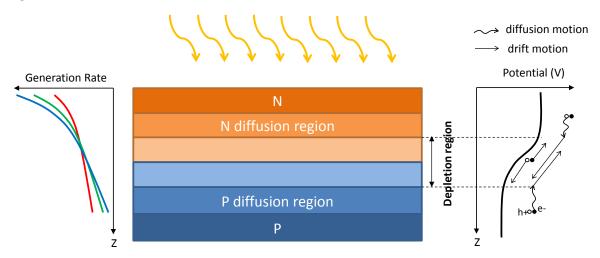

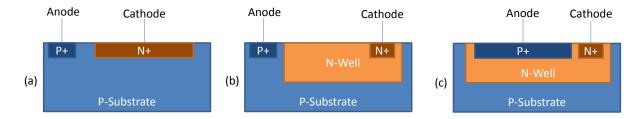

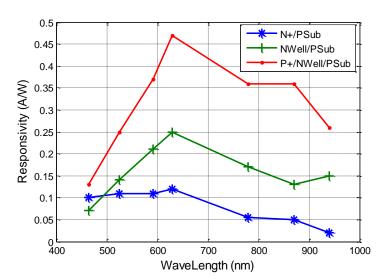

Avant de présenter les différentes implémentations d'imageur burst, nous allons brièvement présenter les photodétecteurs classiques. Les pixels des imageurs burst sont de grandes tailles (>  $30x30 \mu m^2$ ). Par conséquence, les différents photodétecteurs comparés ici font une taille de 40x40 µm<sup>2</sup>. Le photodétecteur le plus connu est la photodiode qui est composée d'une ou plusieurs jonctions PN polarisées en inverse. Les photons reçus génèrent dans le silicium des paires électron/trou. Les électrons se déplacent vers les zones dopées N et les trous vers les zones dopées P. Les charges générées dans la zone de charge d'espace se déplacent sous l'effet du champ électrique de la jonction (haute vitesse). Les charges générées hors de la zone de charge d'espace doivent d'abord l'atteindre sous les effets de la diffusion (faible vitesse). Les performances de la photodiode dépendent ainsi fortement du type de jonctions utilisées (profondeur et dopage). Pour augmenter la zone de collection (zone de charge d'espace et zone de diffusion), des jonctions faiblement dopées doivent être préférées. La capacité équivalente de la jonction joue un rôle important dans la sensibilité de l'imageur, car elle définit le gain de conversion d'une structure de pixel classique (pixel 3T). De plus cette capacité peut limiter la bande passante de structures de pixel plus évoluées (ex : pixel à injection directe). Les caractéristiques de différentes photodiodes sont résumées dans le tableau ci-dessous :

| Structure         | Réponse Maximale | Bande Passante | Capacité de<br>Jonctions |

|-------------------|------------------|----------------|--------------------------|

| N+/PSub           | 0.1 A/W          | 70 MHz         | 1 pF                     |

| NWell/PSub        | 0.25 A/W         | 70 MHz         | 100 fF                   |

| P+/NWell/PSu<br>b | 0.45 A/W         | 100 MHz        | 1.3 pF                   |

| P+/NWell          | Mauvais (~0.1)   | 2 GHz          | 1 pF                     |

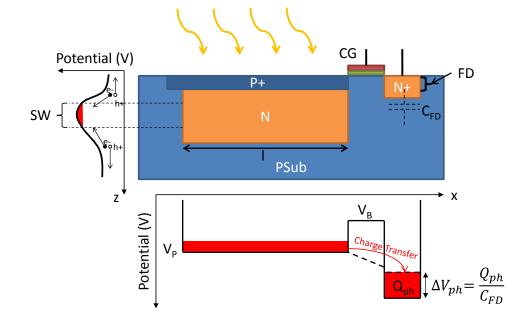

La seconde structure classique de photodétecteur utilisée en imagerie est la *pinned* photodiode. Ce photodétecteur a une structure en sandwich P+/N/Substrat P. Les électrons photogénérés sont collectés dans la zone N aussi appelée puits de stockage. A la fin de l'exposition les électrons ainsi collectés sont déplacés vers une zone N fortement dopée (diffusion flottante) grâce à une grille de transfert. Ce photodetecteur offre une collection efficace des électrons photogénérés caractérisée par une efficacité quantique pouvant atteindre 80 %. Cette valeur correspond à une réponse d'environ 0,3 A/W. De plus, la conversion charge-tension est réalisée par la zone de diffusion flottante qui possède une très faible capacité (~3 fF). Le gain de conversion est donc très élevé (>70  $\mu$ V/e-). Cette structure est optimisée pour offrir une bonne sensibilité. En terme de vitesse, cette structure est limitée par le processus de transfert des charges vers la diffusion flottante. Bien que les

charges se déplacent sous la grille de transfert sous l'effet du champ électrique, la vitesse de déplacement des charges au sein du puits de stockage est limitée par des phénomènes de diffusion. Ce phénomène empire pour les larges photodiodes et limite le *frame rate* des imageurs utilisant une *pinned* photodiode à 20 Mfps. Les photodiodes seront donc privilégiées pour les imageurs *burst* ayant un frame rate de plus de 20 Mfps alors que les *pinned* photodiodes sont plus adaptées aux imageurs *burst* nécessitant une forte sensibilité.

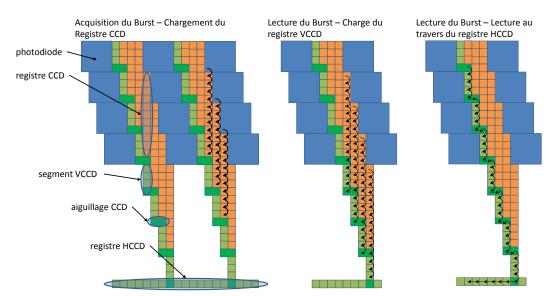

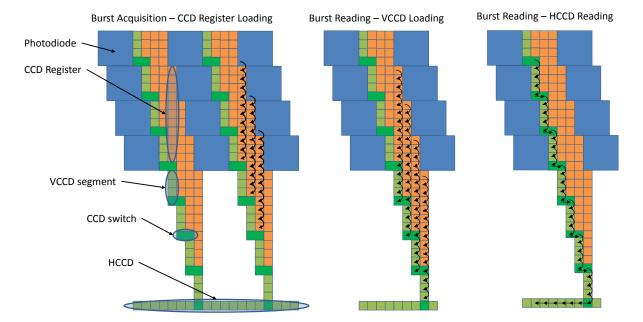

Les capteurs d'images *burst* peuvent être implémentés en technologies CCD et CMOS. Lorsque la technologie CCD est utilisée, l'imageur est composé d'une matrice de photodiode avec à l'aplomb de chaque photodiode un registre à décalage CCD comme illustré en Fig. 1. Ce registre stocke environ une centaine d'images par *burst*. La lecture de la mémoire s'effectue grâce à des registres CCD verticaux (VCCD) et des registres CCD horizontaux (HCCD). La vitesse d'acquisition maximale des imageurs *burst* de type CCD est de 16 Mfps et est limitée par l'opération de transfert de charge entre la photodiode et le registre de stockage CCD. Des solutions ont été proposées pour augmenter la vitesse d'acquisition jusqu'à 100 Mfps à l'aide de plusieurs grilles de collection.

Fig. 1 Architecture d'Imageur *Burst* en Technologie CCD

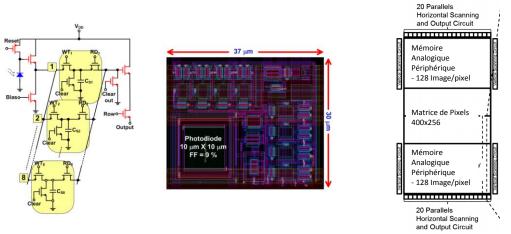

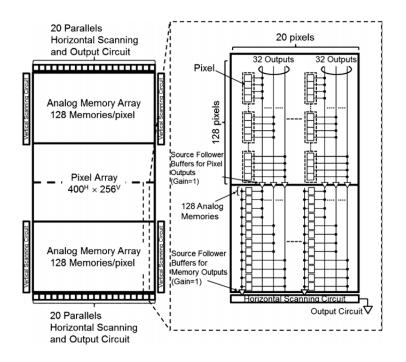

En technologie CMOS, les imageurs *burst* stockent les images dans le pixel ou hors de la matrice (Fig. 2). Le stockage est réalisé par une mémoire analogique à base de capacité. Si le stockage est réalisé dans le pixel, la profondeur mémoire est limitée à une dizaine d'images par *burst*. De plus la sensibilité est réduite à cause du faible facteur de remplissage du pixel qui contient les mémoires et la photodiode. Cependant comme la mémoire est au plus proche du pixel, l'accès à la mémoire est très rapide et la vitesse d'acquisition peut atteindre jusqu'à 1 Gfps. La seconde solution est de réaliser le stockage des images hors de la matrice dans des bancs de capacités. Cette architecture offre une profondeur mémoire de plus de 256 images. La sensibilité d'une telle architecture est élevée grâce au bon facteur de forme et à l'utilisation d'une photodiode *pinned* qui fournit un bon gain de conversion (74  $\mu$ V/e-). La vitesse d'acquisition est de 20 Mfps et est limitée par l'accès aux bancs de mémoire

analogique en périphérie de la matrice et par l'opération de transfert de charge de la photodiode *pinned*.

#### Fig. 2 Architectures d'Imageur Burst en Technologie CMOS

Imageur à Stockage dans le Pixel

En technologie CMOS, une architecture à stockage dans le pixel sera privilégiée pour offrir un frame rate élevé alors qu'une architecture à stockage hors du pixel sera choisie pour augmenter le nombre d'images stockées par *burst*. La technologie CCD, quant à elle, offre un bon compromis entre profondeur mémoire du *burst* et la vitesse d'acquisition.

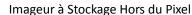

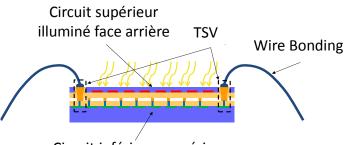

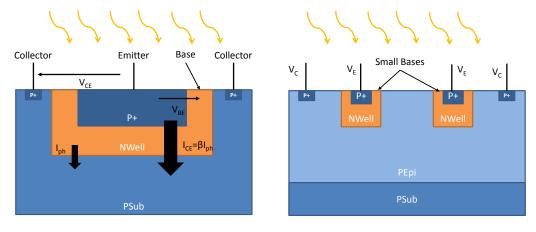

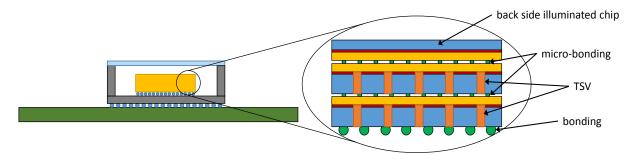

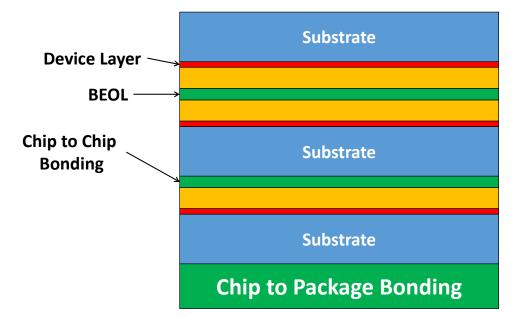

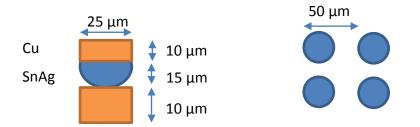

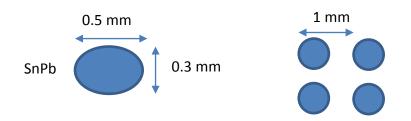

Les dix dernières années ont vu l'apparition de l'intégration en trois dimensions (3D) qui propose d'augmenter la densité d'intégration par empilement de circuits. Différentes technologies existent pour réaliser l'empilement et les interconnexions verticales. Selon les technologies, la densité des interconnexions est plus ou moins élevée. Pour réaliser des imageurs intégrés en 3D ayant une interconnexion ou plus par pixel, la technologie considérée est l'empilement de circuits intégrés au sein d'un même boitier. Les circuits sont empilés comme illustré en Fig. 3. Dans cet exemple l'empilement est constitué de trois circuits. Le circuit supérieur et le circuit central sont connectés face à face (F2F) et leurs niveaux de métallisation supérieure sont connectés par des *bondings*. Le circuit central et le circuit inférieur sont connectés face à dos (F2B) par des *bondings* et le signal est routé d'une face à l'autre du circuit central à l'aide de via traversant le substrat (*through silicon via* appelé TSV).

Fig. 3 Circuits Intégrés en 3 Dimensions

### 3. Proposition d'architecture

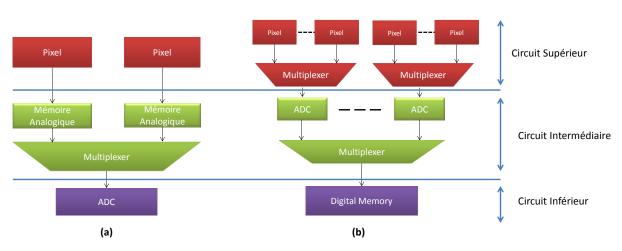

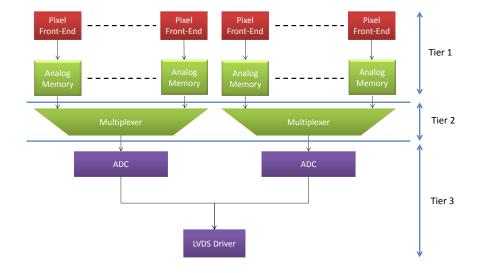

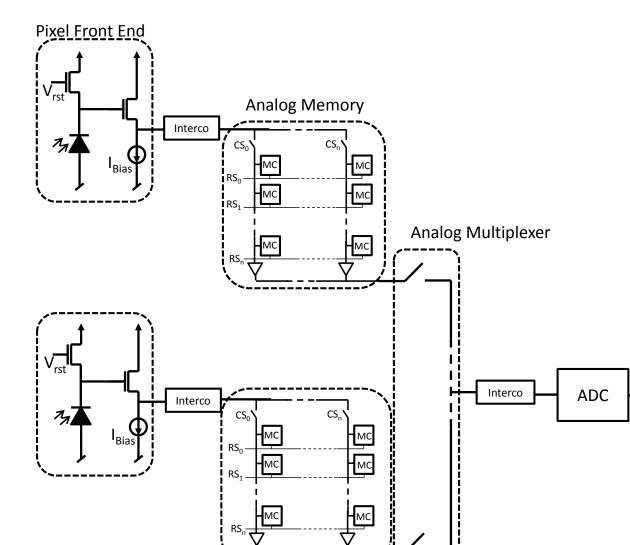

Deux architectures d'imageurs *burst* ont été proposées et analysées. Ces architectures réalisent la conversion analogique/numérique des données avant leur transfert hors de la puce. La conversion peut être effectuée avant ou après le stockage du *burst* d'images en mémoire comme illustré en Fig. 4. Dans le premier cas, la conversion est effectuée à haute vitesse durant l'acquisition du *burst* d'images qui est stocké dans des mémoires numériques. Dans le second cas, le *burst* d'images est stocké dans des mémoires analogiques et la conversion est effectuée durant la lecture de ces mémoires.

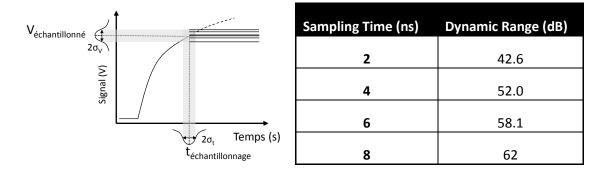

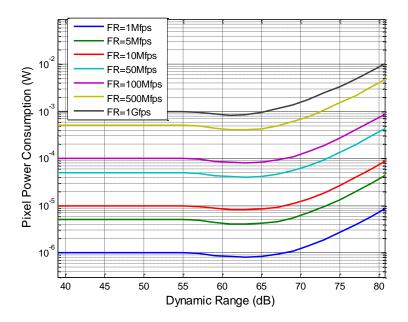

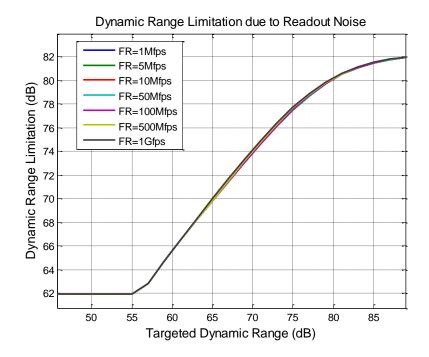

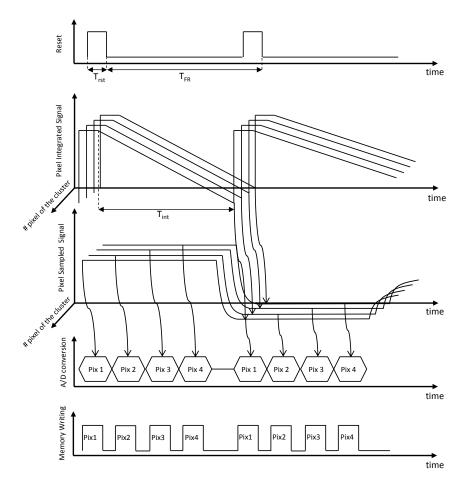

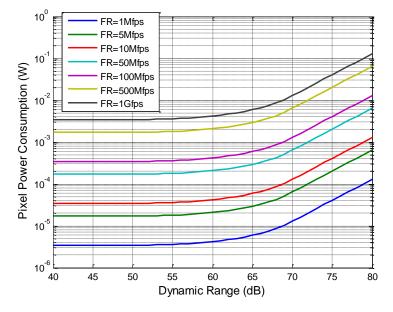

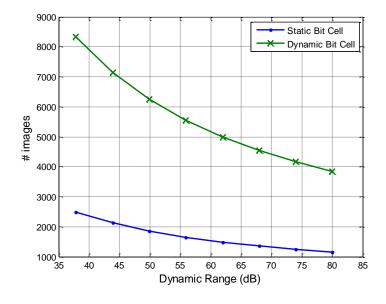

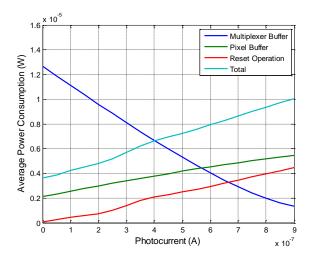

Les performances de ces différents modèles ont été évaluées en terme de vitesse d'acquisition, de dynamique, de profondeur mémoire et de consommation. La taille de la mémoire analogique est contrainte par le bruit d'échantillonnage du signal dans la capacité de stockage. La principale source de consommation de l'architecture à stockage analogique est la source de courant du buffer du pixel qui doit charger la mémoire analogique. La vitesse d'acquisition de l'architecture à stockage analogique fait l'objet d'un compromis avec la consommation et la dynamique du capteur. En terme de vitesse d'acquisition et de dynamique, l'architecture à stockage numérique est fortement contrainte par le choix du convertisseur analogique numérique qui doit avoir une grande fréquence de conversion pour une taille minimale. La principale source de consommation de l'architecture à stockage numérique qui contribue à 50 % de la consommation totale devant la mémoire numérique (~20 %) et le multiplexeur pixels vers convertisseur (~20 %).

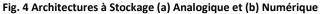

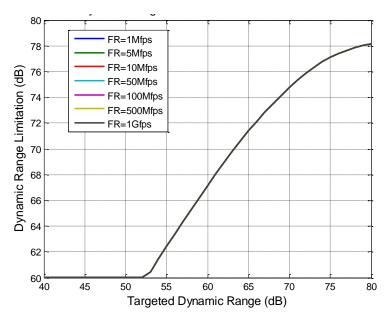

Les évaluations des performances de ces deux architectures montrent que pour une vitesse d'acquisition et une dynamique identiques, l'architecture à stockage analogique est plus économe en énergie comme illustré en Fig. 5. Ce graphique montre aussi que pour les deux architectures, la consommation croît avec la dynamique. Cette augmentation est respectivement due à l'augmentation de la capacité de stockage des mémoires de l'architecture à stockage analogique et de la capacité de l'étage *global shutter* de

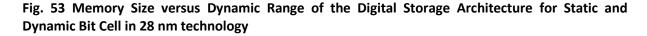

l'architecture à stockage numérique. En terme de profondeur mémoire, l'architecture à stockage numérique offre une capacité largement supérieure à celle à stockage analogique sur toute la gamme de dynamique. De plus, l'utilisation d'une mémoire numérique dynamique permet de multiplier par quatre le nombre d'images stockées comparé à une mémoire numérique statique. Cependant les mémoires dynamiques nécessitent la mise en place d'un système de rafraichissement régulier des cellules mémoires.

Fig. 5 Consommation et Profondeur Mémoire pour Différentes Dynamiques

L'intégration 3D permet la réalisation d'architecture permettant l'augmentation de la profondeur mémoire de l'imageur *burst*. L'architecture à stockage numérique offre une profondeur 10 à 40 fois supérieure selon le type de mémoire utilisé (statique ou dynamique) comparé à l'état de l'art. Notre choix s'est donc porté vers ce type d'architecture. La vitesse d'acquisition ciblée est de 5 Mfps pour une dynamique de 54 dB soit une conversion analogique numérique de 9 bits.

### 4. Etude thermique

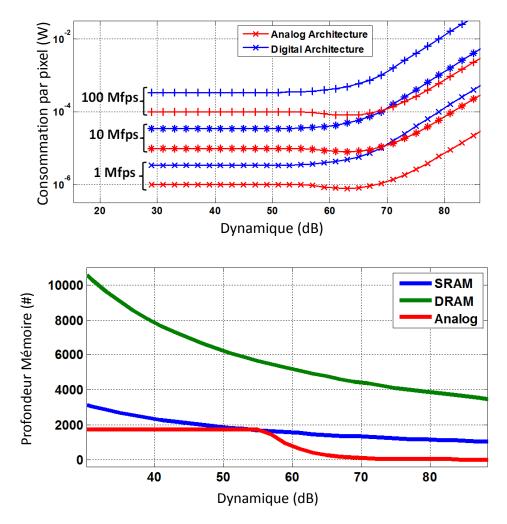

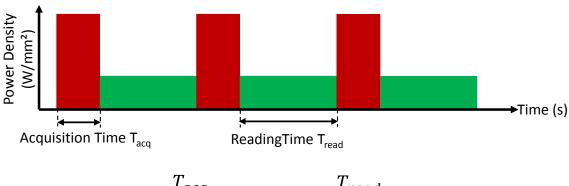

L'intégration des circuits en 3 dimensions soulève souvent des questions de gestion de la température. En effet la consommation du système croît du fait de l'augmentation de la densité d'intégration, mais les surfaces d'échange avec l'extérieur restent constantes. Comme l'étude précédente l'a démontré, la consommation est très importante pour l'architecture à stockage numérique, une évaluation des températures de jonction du capteur d'image est présentée ici. La température du circuit dépend du mode de fonctionnement de l'imageur. En effet le capteur d'images *burst* peut acquérir un seul *burst* ou enchaîner l'acquisition et la lecture de plusieurs *bursts* comme illustré en Fig. 6. De plus il est important de synchroniser la caméra *burst* et l'évènement enregistré. Si l'occurrence de l'évènement (déclenchement pré-évènement). Si l'occurrence de l'évènement est mal contrôlée ou aléatoire, l'enregistrement doit être démarré avant l'évènement et stoppé après l'occurrence de l'évènement (arrêt post-évènement). Ce dernier mode de déclenchement nécessite l'enregistrement des images dans une mémoire cyclique.

Fig. 6 Etats de Consommations pour une Acquisition Multi-Burst

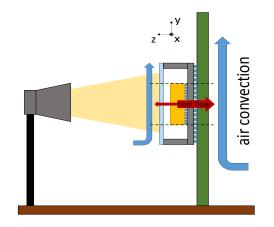

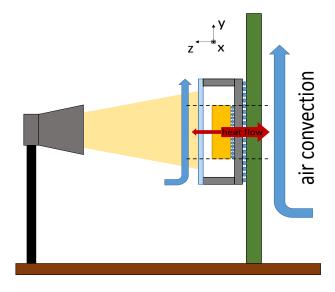

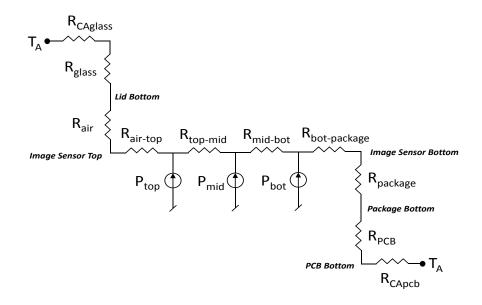

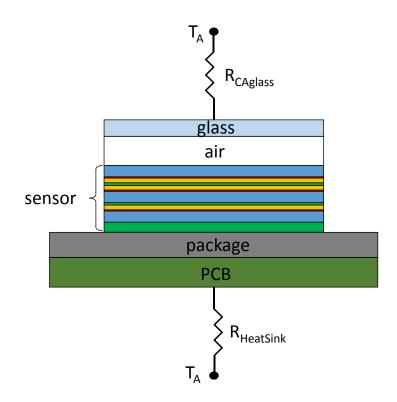

Le modèle considère que l'imageur intégré en 3D est placé dans un boitier disposant d'un capot transparent. Le boitier est connecté à l'aide d'un BGA à un PCB comme illustré en Fig. 7. Le système est refroidi grâce aux échanges convectifs avec l'air ambiant. On considère que les échanges thermiques s'effectuent selon l'axe z.

#### Fig. 7 Circuit et PCB pour le Modèle Thermique

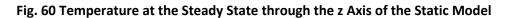

Un premier modèle statique a été réalisé pour évaluer la température en enregistrement multi-*burst*. La consommation moyenne de chaque couche de l'empilement 3D est évaluée grâce à la formule présentée en Fig. 6. Les simulations statiques démontrent la nécessité de couper les sources de courant des pixels et d'éteindre le convertisseur analogique numérique durant la lecture des mémoires. De plus l'échange thermique est limité par l'échange convectif entre le circuit imprimé et l'air. Pour augmenter cet échange et réduire la température de jonction, un radiateur est placé sur la surface du circuit imprimé. Ce faisant la consommation moyenne est réduite et la température de jonction est de 40 °C pour un mode de déclenchement pré-évènement.

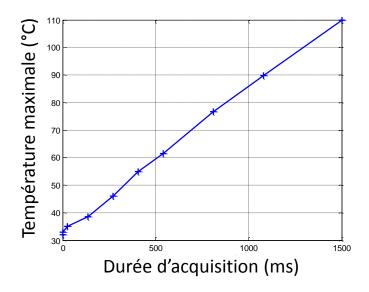

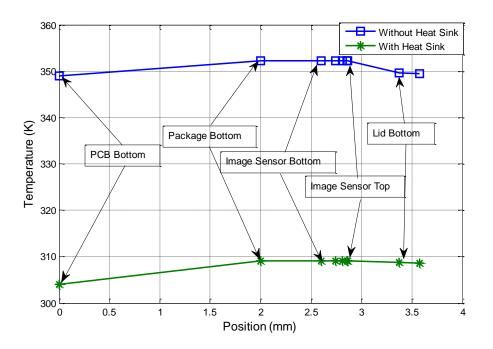

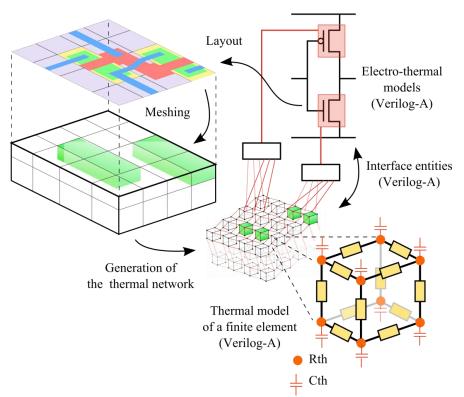

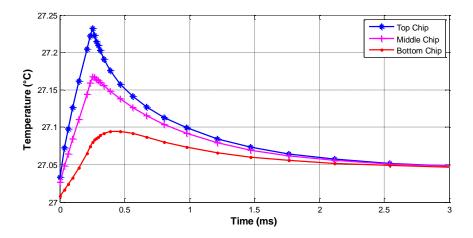

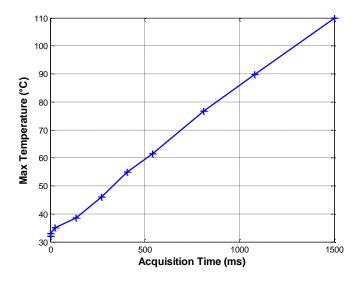

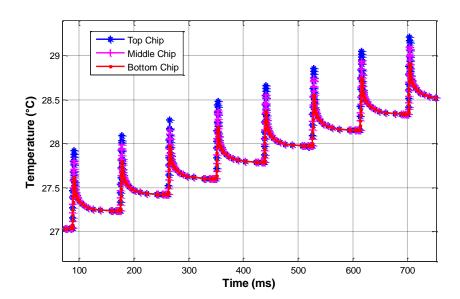

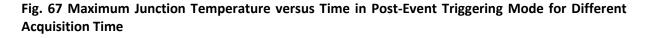

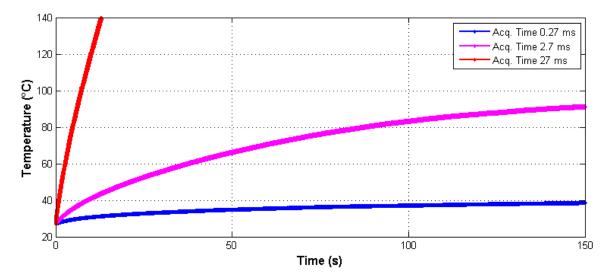

Pour évaluer la température de jonction lors de l'enregistrement d'un unique *burst* d'images, un simulateur électrothermique à éléments finis a été utilisé. Différentes simulations ont été réalisées pour un déclenchement pré évènement et des arrêts post évènement. La température maximale atteinte par la jonction est tracée pour différentes durées d'acquisition en Fig. 8. Ces simulations démontrent que l'imageur *burst* à stockage numérique peut enregistrer un simple *burst* d'images en arrêt post évènement jusqu'à une durée de 1,7 s avant que la température de jonction dépasse les 125 °C. Des simulations pour le mode d'enregistrement multi-*burst* ont été réalisées. Elles confirment les résultats de l'étude statique et évaluent la durée limite d'acquisition en arrêt post-évènement à 3 ms.

Fig. 8 Températures de Jonction Maximale pour Différentes Durées d'Acquisition

### 5. Circuits Pixel

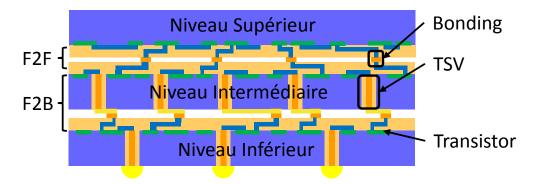

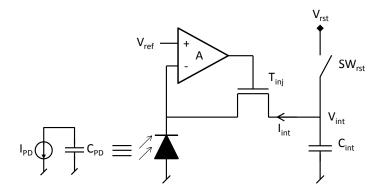

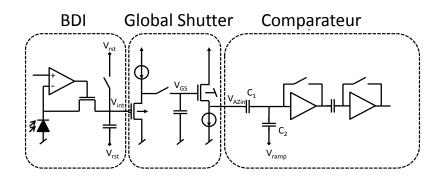

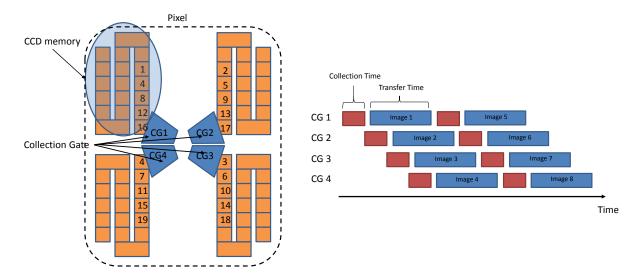

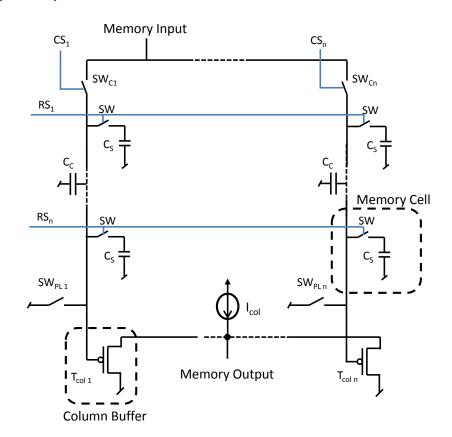

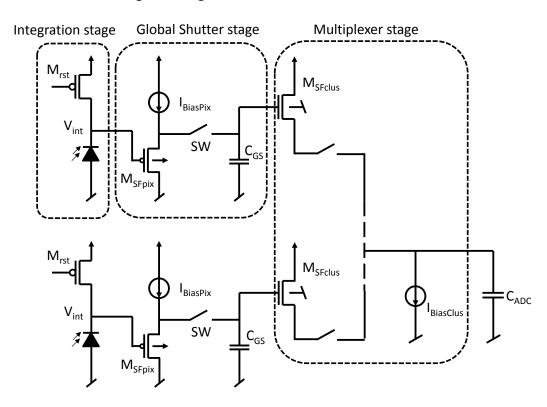

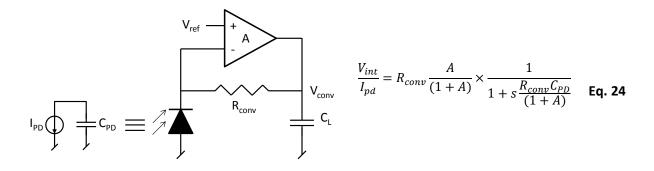

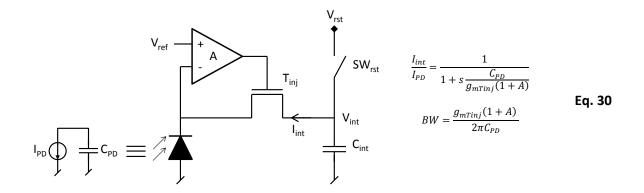

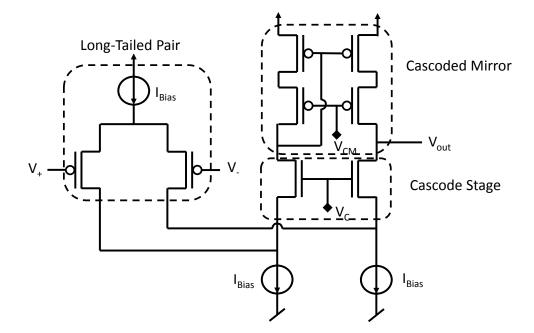

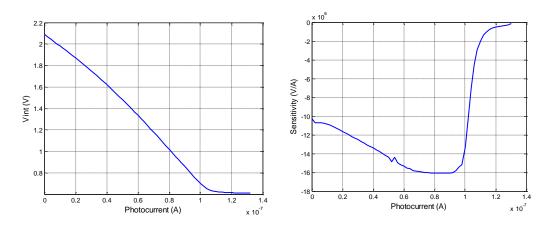

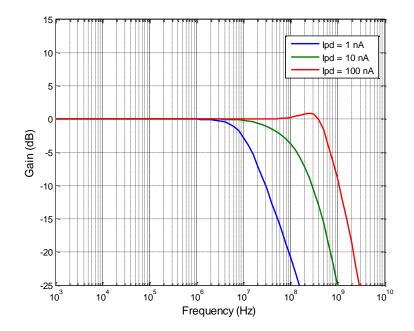

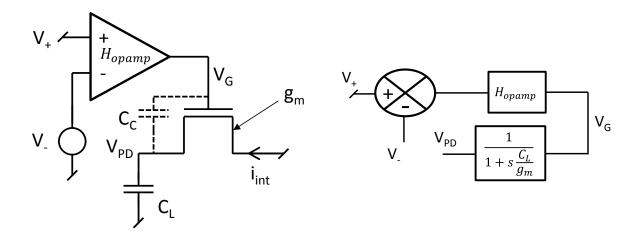

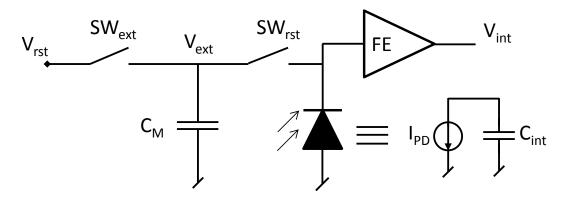

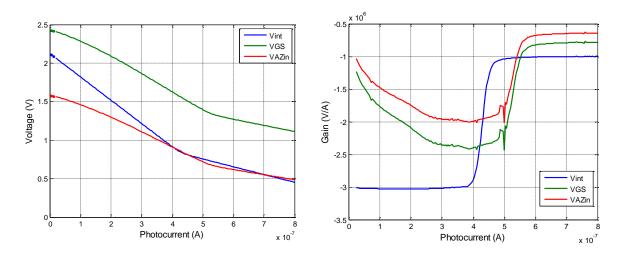

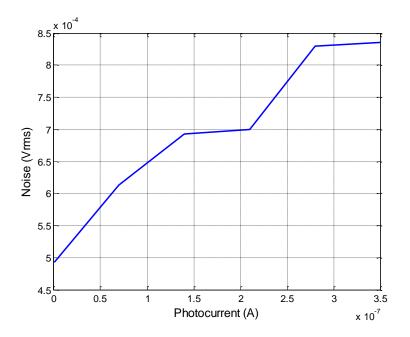

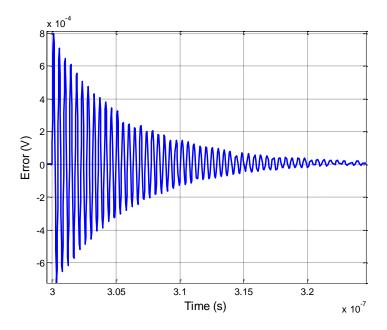

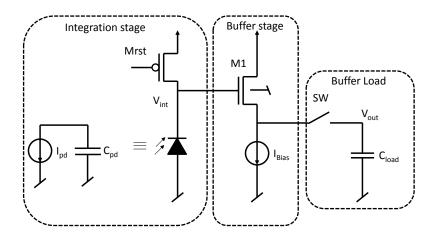

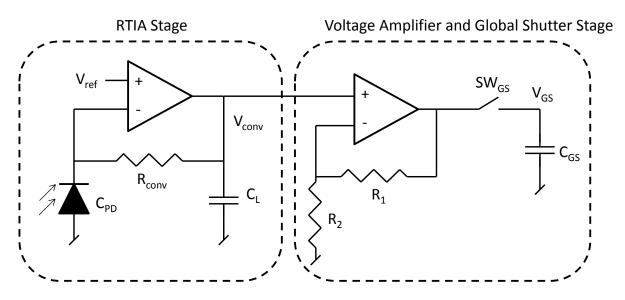

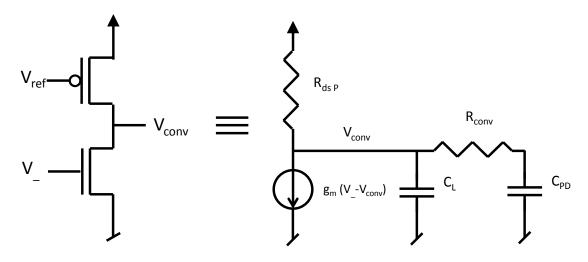

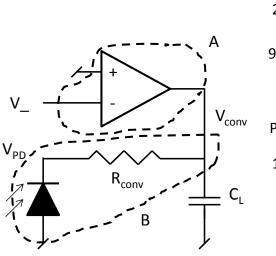

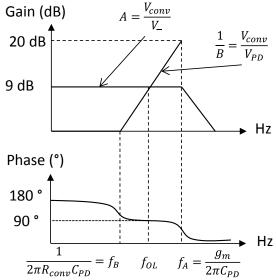

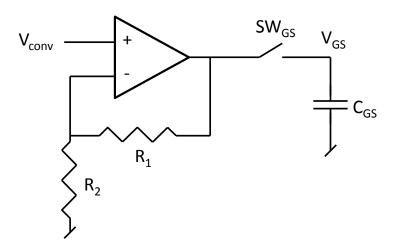

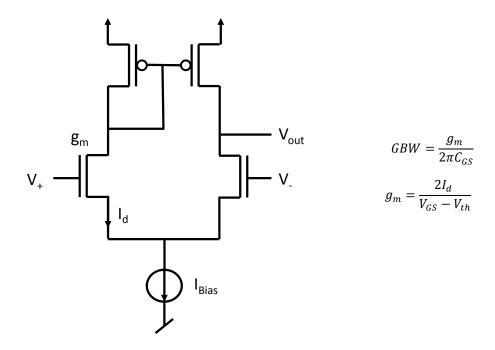

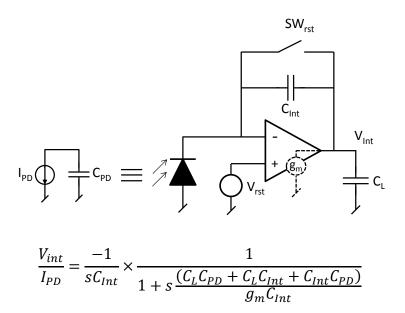

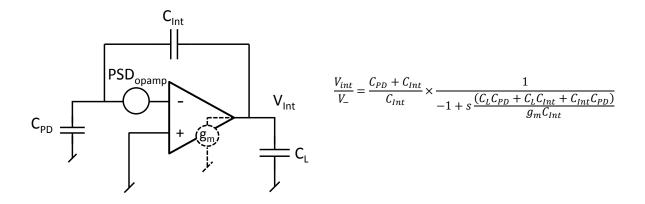

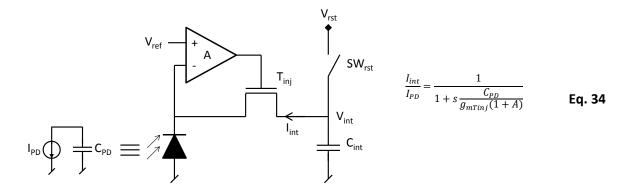

Différents circuits pixels ont été réalisés pour l'imageur burst à stockage numérique. Le premier circuit est simplement constitué d'une photodiode NWell/Psub, d'un étage de global shutter et d'un multiplexer 9 pixels vers 1 ADC. L'intégration du photo-courant est réalisée sur la capacité de jonction de la photodiode. Ce circuit pixel a été simulé à 5 Mfps et offre une sensibilité de 2.1 V/lux/s ainsi qu'une dynamique de 70 dB. La consommation par pixel est de 226 µW. Deux circuits pixel ont ensuite été proposés, l'un pour augmenter la sensibilité du circuit et l'autre pour réduire la consommation. Pour augmenter la sensibilité la solution retenue a été de réaliser la conversion courant tension sur une faible capacité (20 fF). Pour copier le courant sur cette capacité un circuit d'injection direct bufférisé a été utilisé. Ce circuit est constitué d'un transistor d'injection en saturation qui connecte la photodiode à la capacité de 20 fF. Un amplificateur opérationnel est placé entre la photodiode et la grille du transistor d'injection comme illustré en Fig. 9. Sans amplificateur la bande passante de la copie de courant est définie par le ratio de la transconductance du transistor d'injection  $g_{mTini}$  et la capacité de la photodiode  $C_{PD}$ . La transconductance dépend du photocourant qui polarise le transistor d'injection. Pour les faibles photocourants, la bande passante n'est pas suffisante pour notre vitesse d'acquisition de 5 Mfps. L'amplificateur augmente la bande passante de la copie de courant par son gain A. Pour atteindre nos spécifications, le gain de l'ampli doit être d'environ 60 dB. Des mesures ont été réalisées et ce circuit offre une sensibilité de 21 V/lux/s ce qui est une augmentation d'un facteur 10 par rapport à la solution précédente. Le bruit de lecture dépend du signal d'entrée, car le photo-courant polarise le transistor d'injection. La dynamique du circuit est de 55 dB. L'inconvénient de ce circuit est l'implémentation d'un amplificateur opérationnel par pixel ce qui augmente la consommation à 450  $\mu$ W par pixel.

Fig. 9 Pixel à Injection Direct Bufférisée

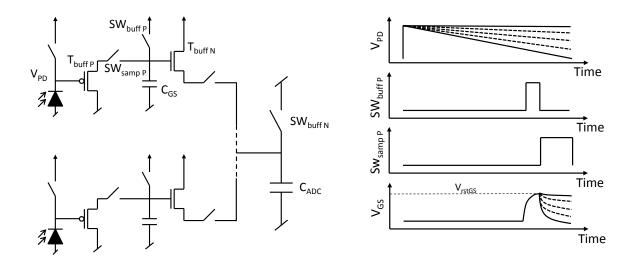

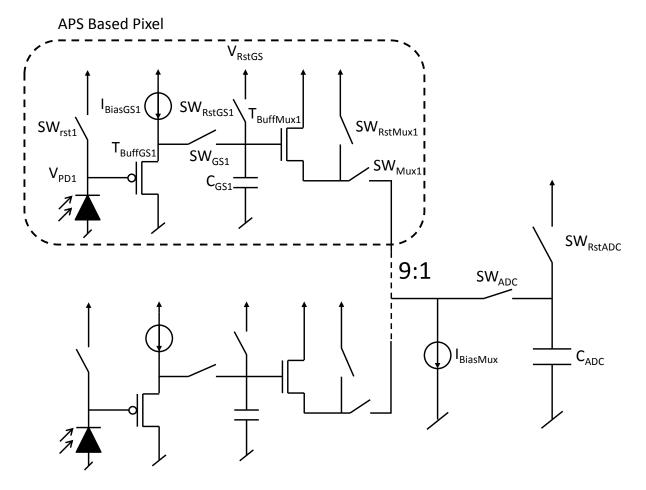

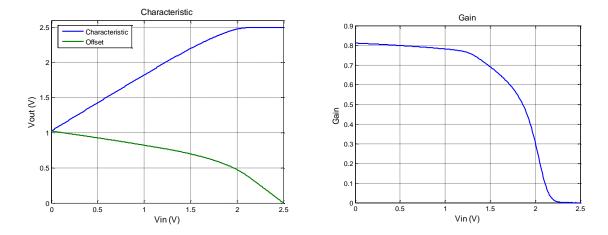

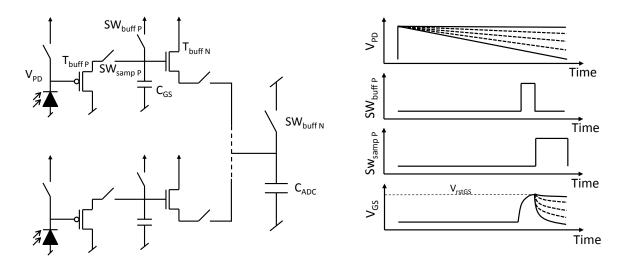

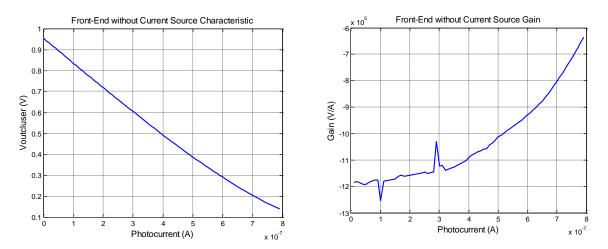

Le troisième circuit réalisé est conçu pour réduire la consommation du circuit pixel. L'idée est d'enlever les sources de courants des différents buffers du pixel comme illustré en Fig. 10. Ce circuit nécessite cependant une opération de pré-charge réalisée par les interrupteurs SW<sub>buffP</sub> et SW<sub>buffN</sub>. Les simulations réalisées montrent que la consommation est réduite d'un facteur 20 par rapport au premier circuit.

Fig. 10 Pixel Sans Source de Courant

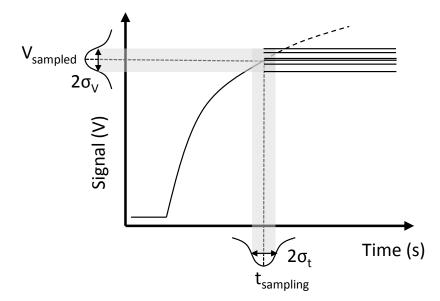

Cependant comme les buffers ne sont plus polarisés, l'état d'équilibre n'est pas atteint avant l'opération d'échantillonnage de l'étage de *global shutter* ou du multiplexeur. Comme le signal est échantillonné dans son régime transitoire, une variation temporelle du signal de contrôle génère une variation de tension du signal échantillonné. L'effet du *jitter* (i.e. bruit temporel) du signal de contrôle a donc été évalué. Pour un *jitter* de 50 ps rms, les dynamiques limitées par ce bruit sont résumées dans le tableau suivant pour différentes durées d'échantillonnage.

Fig. 11 Variation de Tension et Limite de Dynamique Causée par le Jitter sur le Signal d'Echantillonnage

### 6. Prototype intégré en 3 dimensions

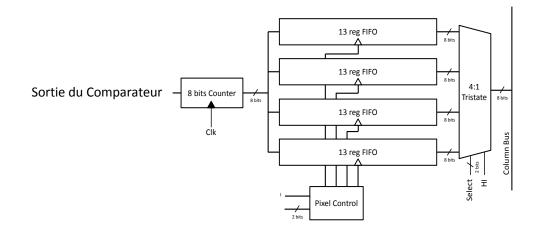

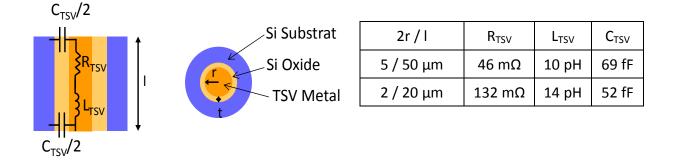

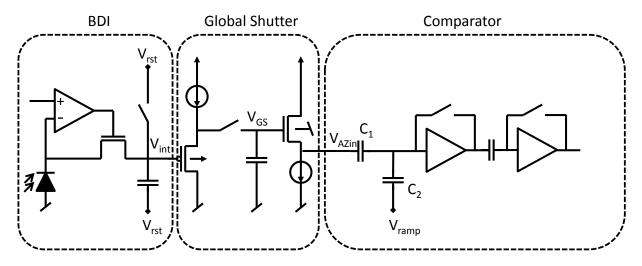

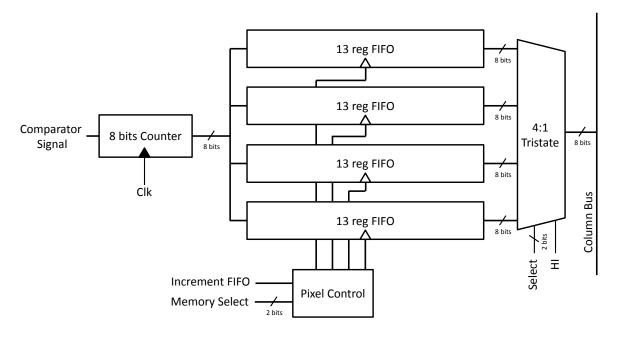

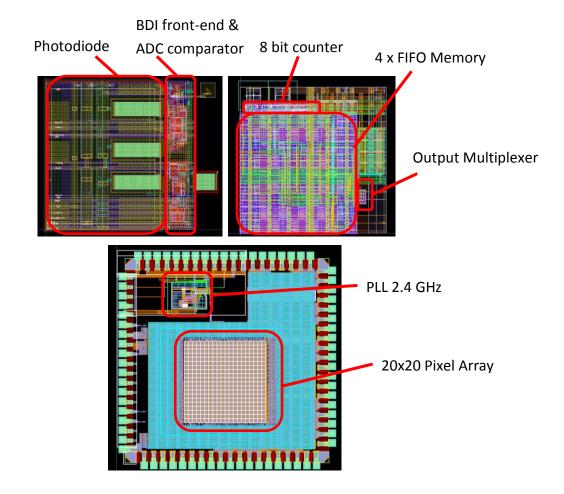

Un prototype d'imageur *burst* intégré en 3D et fonctionnant à 5 Mfps a été réalisé. Comme le fabricant proposait un empilement de deux circuits (Fig. 12), le convertisseur analogique numérique a été partagé entre le circuit supérieur (i.e. matrice de pixels) et le circuit inférieur (i.e. mémoire numérique). De plus la chaine d'acquisition de l'image n'est pas multiplexée, un pixel est associé à un convertisseur et une mémoire numérique.

Fig. 12 Prototype d'Imageur Burst à Stockage Numérique pour un Empilement Deux Circuits

Circuit inférieur numérique

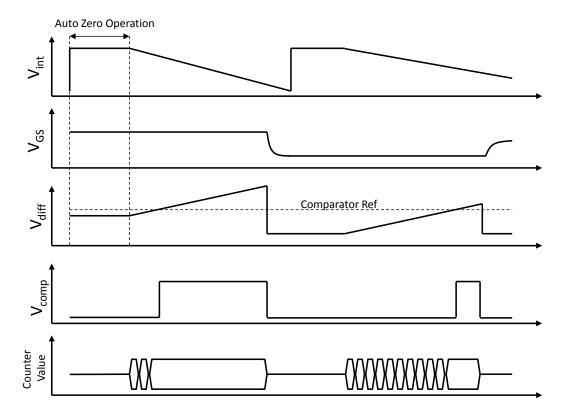

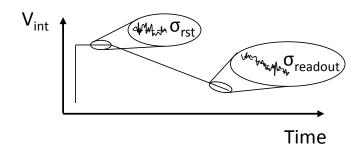

Le pixel est formé d'une photodiode en îlots et d'un circuit à injection direct bufférisé pour réaliser la conversion courant-tension. Une cellule de *global shutter* est aussi implémentée dans le pixel. La conversion analogique numérique est réalisée à l'aide d'un convertisseur simple rampe 8 bits fournissant 5 MC/s. Le comparateur est implémenté sur le circuit supérieur et effectue une opération d'auto-zéro (Fig. 13). Le compteur est implémenté sur le circuit inférieur. La rampe analogique est générée en externe et l'horloge du compteur est fournie par une PLL. La mémoire digitale est réalisée grâce à 4 registres à décalage. La profondeur mémoire de l'imageur est de 52 images et la résolution spatiale de 20x20 pixels pour un pitch de 50 µm par 50 µm. L'utilisation de SRAM au lieu de registre pour réaliser la mémoire numérique aurait permis de stocker un millier d'images par *burst*. Le temps de développement ne nous a pas de permis de réaliser une telle mémoire. Le circuit a été validé en simulation et envoyé en fabrication. Les tests optiques seront effectués au retour du circuit.

Fig. 13 Circuit Supérieur et Inférieur pour le Prototype d'Imageur Burst Intégré en 3D

### 7. Conclusion

Cette étude a permis d'identifier les apports des technologies d'intégration 3D à l'imagerie burst. Suite à une étude de l'état de l'art, deux architectures d'imageur burst intégrées en 3D ont été proposées. La première architecture effectue la conversion analogique numérique de la vidéo après le stockage en mémoire du burst d'images. La seconde architecture effectue la conversion analogique numérique durant l'acquisition de la vidéo et avant le stockage en mémoire. Une étude a été menée pour évaluer les performances de ces deux architectures et a démontré que l'intégration 3D permettait l'augmentation du nombre d'images stockées par burst d'un ordre de grandeur par rapport à l'état de l'art. De plus l'architecture à stockage numérique est apparue comme la plus efficace pour maximiser la profondeur mémoire qui peut alors atteindre jusqu'à 8000 images. Comme cette dernière architecture a une consommation élevée, une étude thermique a été menée pour évaluer la faisabilité. Elle révèle la nécessité de couper les sources de courant du pixel et d'éteindre les ADCs durant la phase de lecture de la mémoire ainsi que de placer un radiateur sur le circuit imprimé support. Ce faisant, les acquisitions d'un simple burst et d'une succession de burst sont possibles d'un point de vue thermique pour un déclenchement pré évènement ou un arrêt post évènement. Différents circuits pixels ont ensuite été proposés pour l'architecture à stockage numérique fonctionnant à 5 millions d'images par seconde. Une première structure de pixel à *global shutter* a été proposée et testée sur silicium. Deux autres pixels ont ensuite été conçus, l'un pour augmenter la sensibilité d'un facteur 10 grâce à l'utilisation d'une structure à injection directe bufférisée et l'autre pour réduire la consommation d'un facteur 20 en supprimant les sources de courant. La structure à injection directe a été testée et validée sur silicium alors que la seconde n'a pour l'instant été validée qu'en simulation. Enfin un prototype d'imageur burst intégré en 3D a été réalisé. Ce prototype est constitué d'un empilement de deux circuits. Le pixel est implémenté avec un circuit à injection directe bufférisée. Le convertisseur est un ADC simple rampe 8 bits qui permet une vitesse d'acquisition à 5 millions d'images par seconde. La mémoire numérique est réalisée avec des bancs de registres à décalage.

Différentes compléments pourraient être apportés à cette étude des imageurs *burst* intégrés en technologie 3D. Tout d'abord des tests du pixel sans source de courant et des mesures de bruit (*phototransfer curve*) seraient à effectuer. D'autre part et d'un point de vue système, l'étude du risque d'emballement thermique pourrait être menée. En effet les courants de fuite des mémoires numériques qui augmentent avec la température génèrent une surconsommation. Cette surconsommation entraine elle-même une augmentation de la température. D'autre part l'étude de l'évolution de la température sur la qualité de l'image pourrait être faite. D'un point de vue circuit, la conception d'un pixel à base de photodiode *pinned* ou de phototransistor semble une piste intéressante pour augmenter la sensibilité sans ajouter de circuiterie additionnelle à la fréquence d'acquisition considérée. Enfin l'étude et la conception d'un ADC adapté à notre capteur semblent importantes, car l'ADC est l'élément déterminant du capteur en termesde fréquence d'acquisition et de dynamique.

### **Remerciements :**

Je souhaite tout d'abord remercier les rapporteurs Prof. Pierre MAGNAN et Prof. Dr.-Ing. Dietmar FEY pour leur relecture et leurs remarques constructives sur mon manuscrit de thèse. Je remercie aussi les membres du jury Dr. Andreas KOCH, Dr. Antoine DUPRET et Prof. Luc HEBRARD ainsi que M. Fabrice GUELLEC pour leurs remarques sur mes travaux et leur disponibilité.

Je remercie grandement mon directeur de thèse Prof. Wilfried UHRING pour m'avoir fait partager sa grande expérience de l'imagerie rapide et sa passion communicative pour la recherche. Je suis très heureux d'avoir pu réaliser ma thèse sous son encadrement. Cette thèse a été réalisée en partie grâce aux moyens du laboratoire ICUbe. Je tiens en particulier à remercier Prof. Luc HEBRARD, Dr. Jean-Baptiste KAMMERER et Maroua GARCI pour leurs aides sur les simulations électro-thermiques. J'ai aussi pu tester mon circuit grâce à l'aide de Pascal LEINDECKER et Jérémy BARTRINGER. Enfin je remercie les doctorants du laboratoire Imane, Octavian, Laurent, Vincent, Fitsum, Abdelatif et Thomas pour l'accueil qu'ils ont fait à un grenoblois.

D'autre part, cette thèse a été menée à bien grâce aux moyens du L3I qui ont été mis à ma disposition par M. Michael TCHAGASPANIAN et M. Fabrice GUELLEC. Je remercie aussi M. Josep SEGURA pour avoir participé à la proposition de ce sujet de thèse et m'avoir encadré au quotidien. J'ai aussi eu la chance de pouvoir discuter avec tous les permanents du L3I qui ont partagé leurs expériences sur de nombreux sujets. Ces trois ans ont aussi été un moment agréable grâce à tous les doctorants, stagiaires et permanents que j'ai croisé au sein de l'équipe Timothé, William, Amr, Assim, Simon, Nicolas, Camille, Victor, Bertrand et Margaux. Je remercie aussi Michele pour ses feedbacks sur l'expérience de thèse qui m'ont permis de relativiser dans les moments durs. J'ai pu aussi décrocher de mon travail pour profiter de Grenoble et ses environs avec Cédric, Amélie, Sabine, Jean Michel, Raphaëlle, Davide, Cornelia, Agustin, Andres, Pierre L et Pierre L. Ces trois ans ont été l'occasion de reprendre la rivière avec les kayakistes du GACK, Thomas, Téo, Julian, GuiGui, Denis, Jérémy, Mark, CriCri et tous les autres...

Enfin je souhaite remercier toute ma famille qui m'a soutenu et aidé à prendre du recul durant ces années de thèse.

# **Table of Contents**

| Ta | able of Co | ontents                                             | I   |

|----|------------|-----------------------------------------------------|-----|

| Ta | able of Fi | gures                                               | . V |

| Ta | able of Al | obreviations                                        | . X |

| 1. | Intro      | duction                                             | . 1 |

| 2. | Back       | ground & Bibliographical Review                     | . 4 |

|    | 2.1.       | Classical Image Sensor Architecture                 | . 4 |

|    | 2.2.       | High Speed Image Sensor                             | . 6 |

|    | 2.3.       | Burst Image Sensor                                  | . 8 |

|    | 2.3.1.     | Architectures                                       | . 9 |

|    | 2.3.1.1.   | CCD Image Sensor                                    | . 9 |

|    | 2.3.1.2.   | CMOS Image Sensor                                   | 12  |

|    | 2.3.1.3.   | Synthesis                                           | 15  |

|    | 2.4.       | Photodetectors                                      | 16  |

|    | 2.4.1.     | Photodiodes                                         | 16  |

|    | 2.4.2.     | Pinned Photodiode                                   | 21  |

|    | 2.4.3.     | Phototransistor                                     | 22  |

|    | 2.4.4.     | Photodetector Synthesis                             | 23  |

|    | 2.5.       | Three-Dimensional (3D) Interconnection Technologies | 24  |

|    | 2.5.1.     | Technology Offers                                   | 24  |

|    | 2.5.2.     | 3D Stacked Integrated Circuit                       | 25  |

|    | 2.5.3.     | 3D Integration and High Speed Image Sensor          | 27  |

|    | 2.6.       | Conclusion                                          | 27  |

| 3. | 3D In      | tegrated Burst Image Sensor                         | 28  |

|    | 3.1.       | Motivations                                         | 28  |

|    | 3.2.       | Architectural General Considerations                | 28  |

|    | 3.2.1.     | Recording and Triggering Modes                      | 29  |

|    | 3.3.       | Burst Image Sensor with Analog Storage              | 30  |

|    | 3.3.1.   | Architecture Overview                                   | . 30 |

|----|----------|---------------------------------------------------------|------|

|    | 3.3.1.1. | 3D Integration                                          | . 31 |

|    | 3.3.1.2. | Circuit Implementation                                  | . 31 |

|    | 3.3.2.   | Performance Evaluation                                  | . 33 |

|    | 3.3.2.1. | Analog Memory                                           | . 33 |

|    | 3.3.2.2. | Pixel Front-End                                         | . 36 |

|    | 3.3.2.3. | Model Results                                           | . 39 |

|    | 3.3.3.   | Performance Synthesis                                   | . 42 |

|    | 3.4.     | Burst Image Sensor with Digital Storage                 | . 43 |

|    | 3.4.1.   | Architecture Overview                                   | . 43 |

|    | 3.4.2.   | Performance Evaluation                                  | . 45 |

|    | 3.4.2.1. | Pixel Front End and Multiplexer                         | . 45 |

|    | 3.4.2.2. | Analog to Digital Conversion                            | . 48 |

|    | 3.4.2.3. | Digital Memory                                          | . 50 |

|    | 3.4.3.   | Performance Synthesis                                   | . 53 |

|    | 3.5.     | Conclusions and Perspectives                            | . 54 |

| 4. | Therr    | nal Study of a 3D Integrated Digital Burst Image Sensor | . 56 |

|    | 4.1.     | Introduction                                            | . 56 |

|    | 4.2.     | Thermal System                                          | . 56 |

|    | 4.2.1.   | Package Description and Model Assumptions               | . 56 |

|    | 4.2.2.   | Power Consumption                                       | . 59 |

|    | 4.3.     | Static Simulation                                       | . 61 |

|    | 4.3.1.   | Static Model                                            | . 61 |

|    | 4.3.2.   | Simulations                                             | . 63 |

|    | 4.4.     | Finite Element Simulations                              | . 64 |

|    | 4.4.1.   | Finite Element Model                                    | . 64 |

|    | 4.4.2.   | Transient Simulations                                   | . 66 |

|    | 4.4.2.1. | Single Burst Recording                                  | . 66 |

|    | 4.4.2.2. | Multi-Burst Recording                                   | . 68 |

|    | 4.5.     | Thermal Runaway                               | 69    |

|----|----------|-----------------------------------------------|-------|

|    | 4.6.     | Conclusion                                    | 69    |

| 5. | Anal     | og Front-End Circuits                         | 71    |

|    | 5.1.     | APS Based Pixel Front-End Circuit             | 71    |

|    | 5.1.1.   | Description                                   | 71    |

|    | 5.1.2.   | Current to Voltage Conversion                 | 72    |

|    | 5.1.3.   | Global Shutter Stage                          | 74    |

|    | 5.1.4.   | Multiplexer Stage                             | 76    |

|    | 5.1.5.   | Full Front-End Performances                   | 78    |

|    | 5.1.6.   | Conclusion                                    | 79    |

|    | 5.2.     | Design Strategies to Increase Sensitivity     | 80    |

|    | 5.2.1.   | Introduction                                  | 80    |

|    | 5.2.2.   | Resistive Trans-Impedance Amplifier Circuit   | 80    |

|    | 5.2.3.   | Capacitive Trans-Impedance Amplifier Circuit  | 83    |

|    | 5.2.4.   | Buffered Direct Injection Circuit             | 85    |

|    | 5.2.5.   | Implementation and Simulation                 | 87    |

|    | 5.2.6.   | Conclusion                                    | 92    |

|    | 5.3.     | Design Strategies to Reduce Power Consumption | 93    |

|    | 5.3.1.   | Conclusion                                    | 98    |

| 6. | Circu    | it Implementations and Tests                  | . 100 |

|    | 6.1.     | Test-Chip for Pixel Front-End Evaluation      | . 100 |

|    | 6.1.1.   | Test-Chip and Test Board                      | . 100 |

|    | 6.1.2.   | Test Results                                  | . 104 |

|    | 6.1.2.1. | Photodiode Characterization                   | . 104 |

|    | 6.1.2.2. | APS Front-End Circuit                         | . 107 |

|    | 6.1.2.3. | Pixel with BDI Stage                          | . 110 |

|    | 6.1.3.   | Front-End Without Current Source              | . 113 |

|    | 6.2.     | 3D Integrated Circuit                         | . 113 |

|    | 6.2.1.   | Circuit Implementation                        | . 113 |

| 6.2.    | 2. Simulation Results      |

|---------|----------------------------|

| 6.3.    | Conclusion                 |

| 7. C    | onclusion and Perspectives |

|         | Section 1                  |

|         | ex A 1                     |

|         | ex B                       |

|         | ex C 8                     |

|         | ex D13                     |

|         | ex E                       |

| Bibliog | raphy19                    |

# Table of Figures

| Fig. 1 Digital Camera Diagram                                                                                    | 4    |

|------------------------------------------------------------------------------------------------------------------|------|

| Fig. 2 CMOS Image Sensor Architecture                                                                            | 5    |

| Fig. 3 Rolling Shutter and Global Shutter Acquisitions                                                           | 6    |

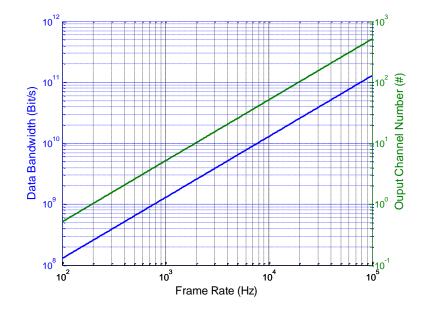

| Fig. 4 CIS Output Bandwidth and Number of Output Channels versus the CIS Frame Rate                              | 7    |

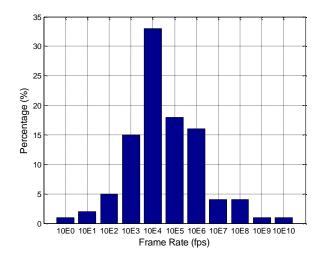

| Fig. 5 Frame Rate Requirement for High Speed Image Sensor                                                        | 9    |

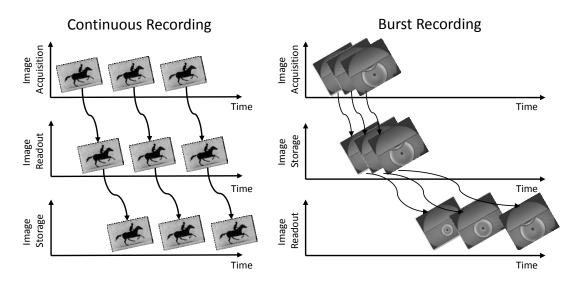

| Fig. 6 Timing Diagram of Burst and Continuous Recording                                                          | 9    |

| Fig. 7 Simplified CCD Burst Image Sensor Architecture                                                            | 10   |

| Fig. 8 Back-Side-Illuminated Burst CCD Image Sensor                                                              | 11   |

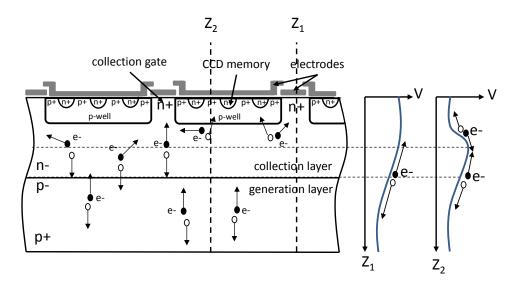

| Fig. 9 Multi-Collection Gate Pixel Architecture and its Timing Diagram                                           | 12   |

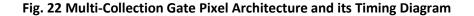

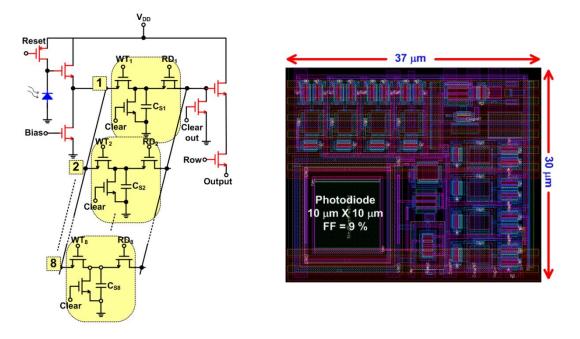

| Fig. 10 Burst CIS Pixel with 8 In-Pixel Memories                                                                 | 13   |

| Fig. 11 Burst CIS with Out-Of-Pixel Storage                                                                      | 14   |

| Fig. 12 Reverse Biased PN Junction                                                                               | 17   |

| Fig. 13 Cross-Sectional Views of (a) N+/PSub, (b) NWell/PSub and (c) P+/NWell/PSub Photodiodes                   | 18   |

| Fig. 14 Photodiodes Responsivity versus the Incident Light Wavelength for 40x40 $\mu$ m <sup>2</sup> Photodiodes | 18   |

| Fig. 15 Pinned Photodiode Cross Section and its Potential Diagrams                                               | 22   |

| Fig. 16 PNP Phototransistor and Quad Small Base PNP Phototransistor Cross Sections                               | 23   |

| Fig. 17 3D Stacked Integrated Circuit                                                                            | 25   |

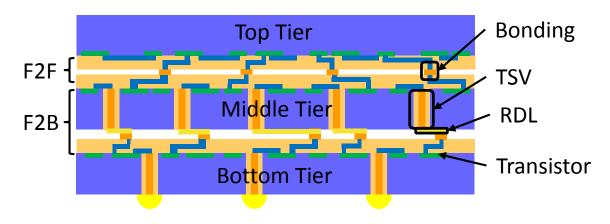

| Fig. 18 Through Silicon Via RLC Model                                                                            | 26   |

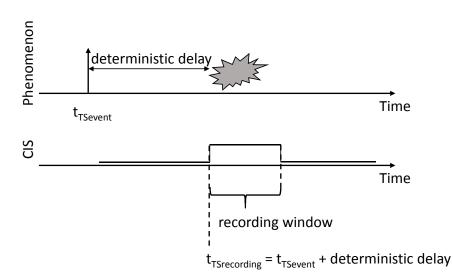

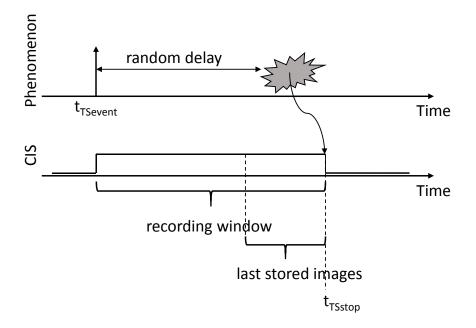

| Fig. 19 Pre-Event Triggering Mode Timing Diagram                                                                 | 29   |

| Fig. 20 Post-Event Triggering Mode Timing Diagram                                                                | 30   |

| Fig. 21 Analog Storage Burst Image Sensor Architecture                                                           | 31   |

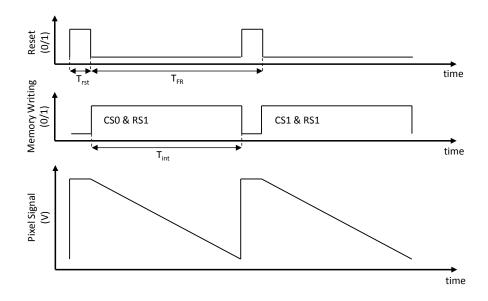

| Fig. 22 Cluster of Pixels of the Analog Storage Architecture                                                     | 32   |

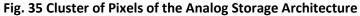

| Fig. 23 Timing Diagram of Analog Storage Architecture                                                            | 33   |

| Fig. 24 Analog Memory Architecture                                                                               | 34   |

| Fig. 25 Analog Front-End Circuit                                                                                 | 37   |

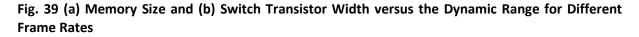

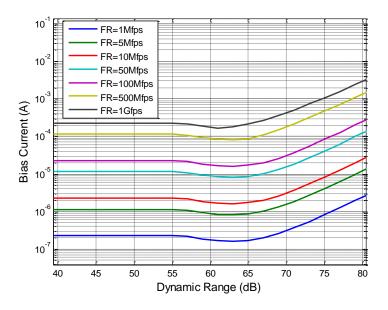

| Fig. 26 (a) Memory Size and (b) Switch Transistor Width versus the Dynamic Range for Different Frame Rate        | s 39 |

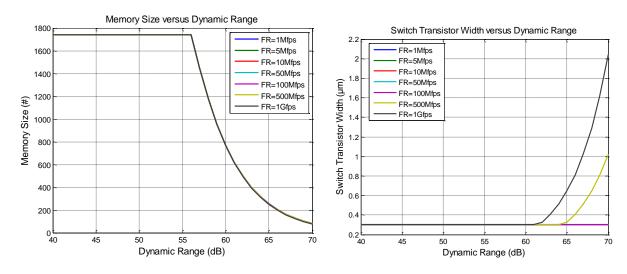

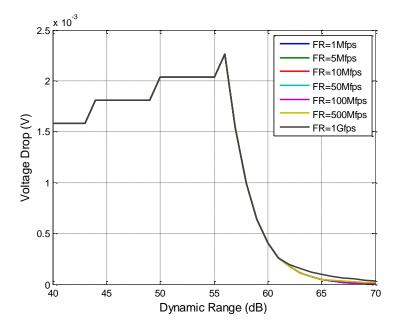

| Fig. 27 Voltage Drop versus the Dynamic Range for Different Frame Rates                                          | 40   |

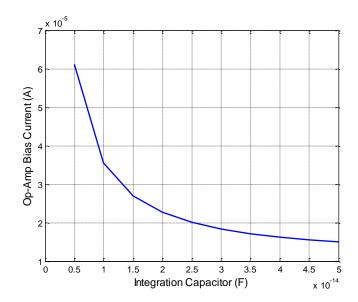

| Fig. 28 Bias Current of the SF Buffer versus the Dynamic Range                                                                               | 41   |

|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 29 Pixel Power Consumption versus the Dynamic Range for Different Frame Rates                                                           | 41   |

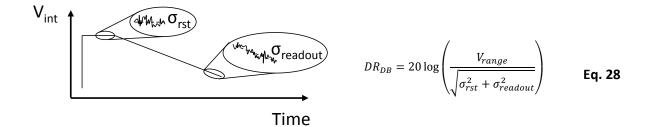

| Fig. 30 Dynamic Range Limitation due to Readout Noise                                                                                        | 42   |

| Fig. 31 Digital Storage Burst Image Sensor Architecture                                                                                      | 44   |

| Fig. 32 Timing Diagram of a Cluster of 4 Pixels for the Digital Storage Architecture                                                         | 45   |

| Fig. 33 Pixel Front-End of Digital Storage Architecture                                                                                      | 46   |

| Fig. 34 Pixel Power Consumption versus the Dynamic Range of Different Frame Rates                                                            | 47   |

| Fig. 35 Dynamic Range Limitation due to the Readout Noise                                                                                    | 48   |

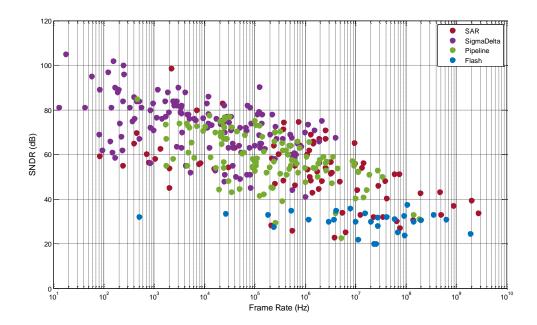

| Fig. 36 SNDR versus the Frame Rate                                                                                                           | 49   |

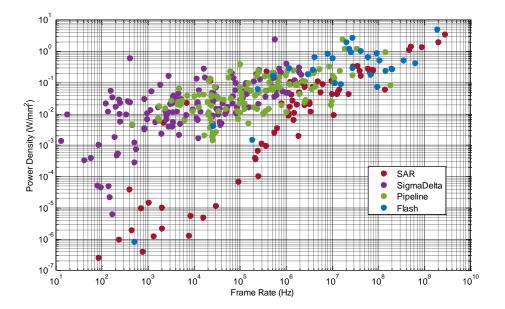

| Fig. 37 Power Consumption Density versus the Frame Rate                                                                                      | 50   |

| Fig. 38 Random Access Memory Architecture                                                                                                    | 51   |

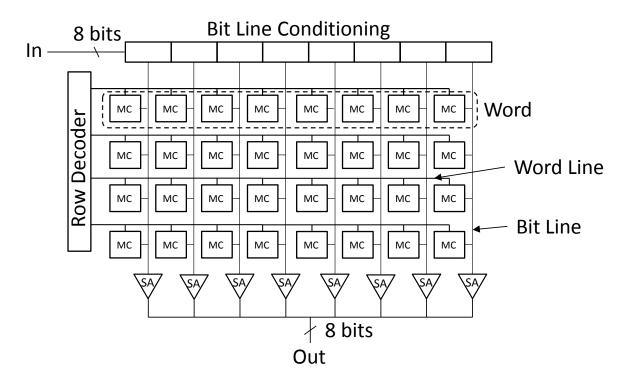

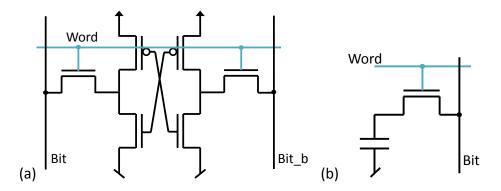

| Fig. 39 (a) 6T SRAM Bit Cell and (b) 1T1C DRAM Bit Cell                                                                                      | 52   |

| Fig. 40 Memory Size versus Dynamic Range of the Digital Storage Architecture for Static and Dynamic Bit Ce<br>28 nm technology               |      |

| Fig. 41 Pixel Power Consumption for Different Pairs of Dynamic Range and Frame Rate                                                          | 54   |

| Fig. 42 Image Sensor Package and Printed Circuit Board                                                                                       | 57   |

| Fig. 43 Cross Section View of Thermal Model of the 3D Burst Image Sensor                                                                     | 58   |

| Fig. 44 3D Integrated Image Sensor in a BGA Package Cooled by Free Air Convection                                                            | 59   |

| Fig. 45 Static Model                                                                                                                         | 62   |

| Fig. 46 Power Consumption States and Weighted Average Power Consumption for Multi-burst Recording                                            | 62   |

| Fig. 47 Temperature at the Steady State through the z Axis of the Static Model                                                               | 63   |

| Fig. 48 Steady State Temperature in Multi-Burst Recording for Different Acquisition Times with an Heat Sink                                  | . 64 |

| Fig. 49 Electro-Thermal Simulator                                                                                                            | 65   |

| Fig. 50 Thermal Model for Finite Element Simulation                                                                                          | 66   |

| Fig. 51 Thermal Transient Simulation for a Single Burst Acquisition with the average temperature on the (x), second (+) and third (•) layers |      |

| Fig. 52 Maximum Junction Temperature versus the Acquisition for Single Burst Recording in Post Ex<br>Triggering Mode                         |      |

| Fig. 53 Junction Temperature of Multi-Burst Recording in Pre-Event Triggering Mode                                                           | 68   |

| Fig. 54 Maximum Junction Temperature versus Time in Post-Event Triggering Mode for Different Act                               | -  |

|--------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 55 Cluster of APS Based Pixel Front-End                                                                                   | 72 |

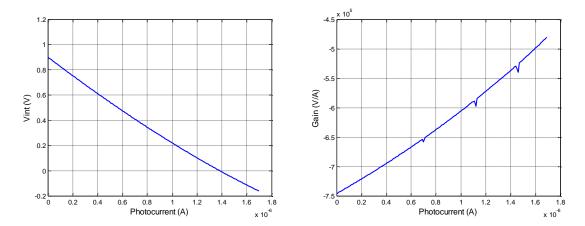

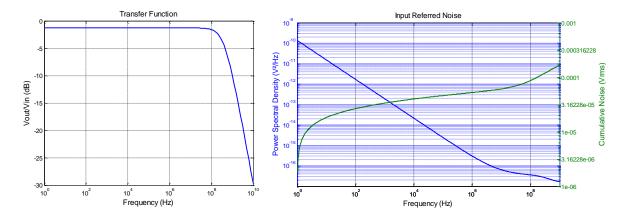

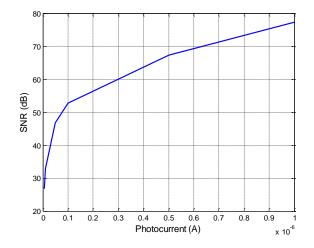

| Fig. 56 (a) Photo-current to voltage characterisctic and (b) photo-current to voltage gain of a 41x4 NWell/PSub photodiode     |    |

| Fig. 57 Integrated Shot Noise and SNR of the Photocurrent to Voltage Conversion of a 41x48.8 μm <sup>2</sup> NW Photodiode     |    |

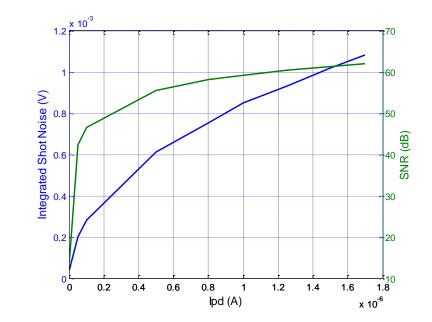

| Fig. 58 (a) Schematic and (b) Timing Diagram of the Global Shutter Stage                                                       | 74 |

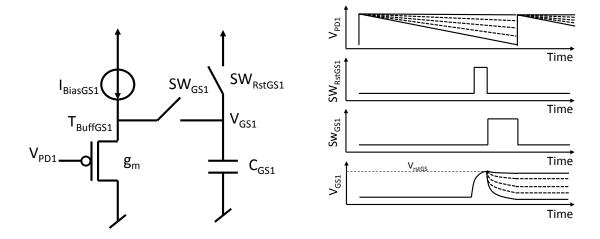

| Fig. 59 DC Characteristic and Gain of the Global Shutter Stage                                                                 | 75 |

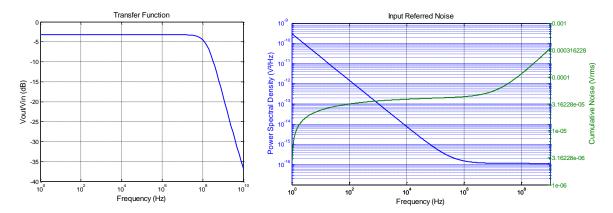

| Fig. 60 Transfer Function and Noise Figure of the Global Shutter SF Buffer                                                     | 75 |

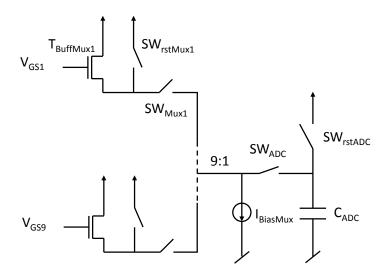

| Fig. 61 Schematic of the Multiplexer Stage                                                                                     | 77 |

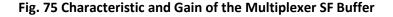

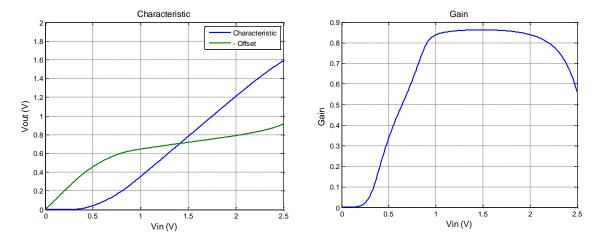

| Fig. 62 Characteristic and Gain of the Multiplexer SF Buffer                                                                   | 77 |

| Fig. 63 Transfer Function and Noise Figure of the Multiplexer SF Buffer                                                        | 78 |

| Fig. 64 Characteristic and Gain of the APS Pixel Front-End for an Integration Time of 180 ns                                   | 78 |

| Fig. 65 Signal to Noise Ratio of the APS Pixel Front-End Readout Chain                                                         | 79 |

| Fig. 66 RTIA Stage and its Transfer Function                                                                                   | 81 |

| Fig. 67 RTIA Stage and Voltage Amplifier Solution                                                                              | 81 |

| Fig. 68 Timing diagram of the RTIA and amplifier stage                                                                         | 82 |

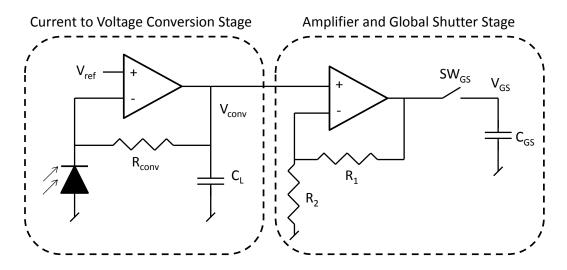

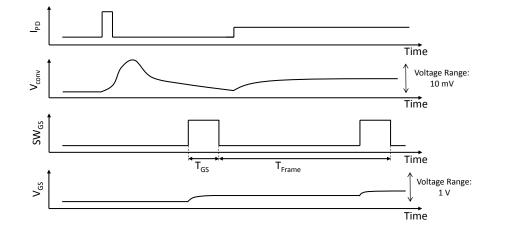

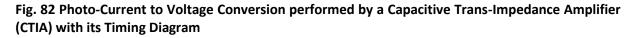

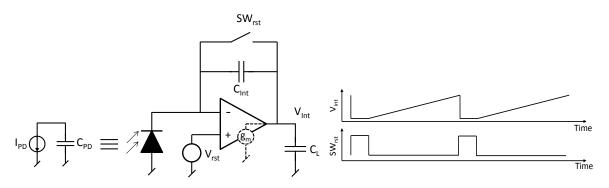

| Fig. 69 Photo-Current to Voltage Conversion performed by a Capacitive Trans-Impedance Amplifier (CT its Timing Diagram         | -  |

| Fig. 70 Bias Current of the Op-Amp versus the Integration Capacitor for a 34 MHz Bandwidth                                     | 84 |

| Fig. 71 Direct Injection Stage and its Transfer Function                                                                       | 86 |

| Fig. 72 Buffered Direct Injection Stage and its Transfer Function                                                              | 86 |

| Fig. 73 Folded Cascode Amplifier                                                                                               | 88 |

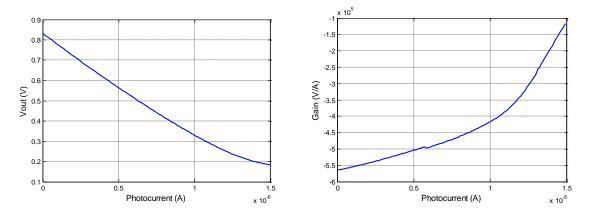

| Fig. 74 Integration Voltage versus Photocurrent Characteristic and Sensitivity of the BDI stage                                | 89 |

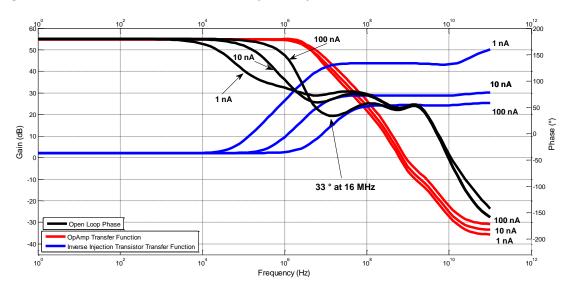

| Fig. 75 I <sub>int</sub> versus I <sub>pd</sub> Transfer Function of the BDI Stage                                             | 89 |

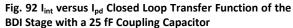

| Fig. 76 Stability Analysis of the BDI stage                                                                                    | 90 |

| Fig. 77 Direct and Feedback Gains of the Open Loop Circuit                                                                     | 90 |

| Fig. 78 Direct and Feedback Gains of the Open Loop Circuit with a 25 fF Coupling Capacitor                                     | 91 |

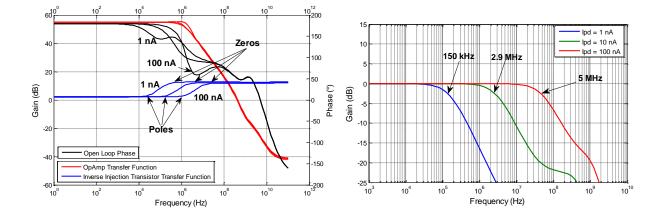

| Fig. 79 I <sub>int</sub> versus I <sub>pd</sub> Closed Loop Transfer Function of the BDI Stage with a 25 fF Coupling Capacitor | 91 |

| Fig. 80 Noise on the Integration Node of the BDI Stage Without and With Coupling Capacitor                                      | 92  |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 81 Pixel Front-End Without Current Source and its Timing Diagram                                                           | 93  |

| Fig. 82 Power Consumption versus the Photocurrent of the Pixel Front-End Without Current Source                                 |     |

| Fig. 83 Characteristic and Gain of the Front-End Circuit without Current Source                                                 | 94  |

| Fig. 84 Effect of a Variation of the Sampling Time on the Sampled Value                                                         | 95  |

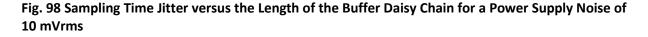

| Fig. 85 Sampling Time Jitter versus the Length of the Buffer Daisy Chain for a Power Supply Noise                               |     |

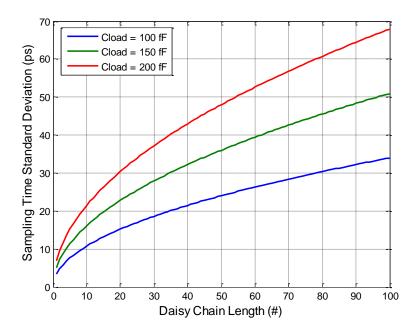

| Fig. 86 Histogram of the Sampled Signal Values for 2 ns and 18 ns Sampling Times with a Standard 48 ps                          |     |

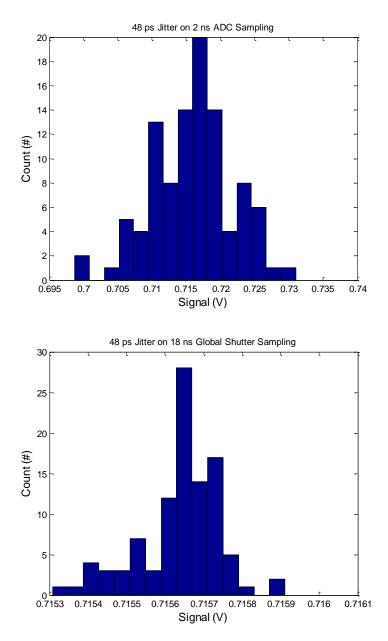

| Fig. 87 (a) Voltage Noise versus the Input Signal for a 48 ps Jitter Noise (b) Voltage Noise and Dy for Different Sampling Time | -   |

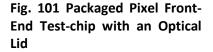

| Fig. 88 Packaged Pixel Front-End Test-chip with an Optical Lid                                                                  | 100 |

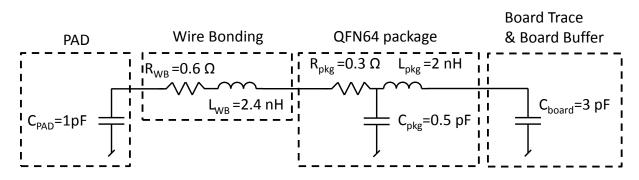

| Fig. 89 Equivalent Electrical Model of the Signal Path from the Chip to the Board                                               | 101 |

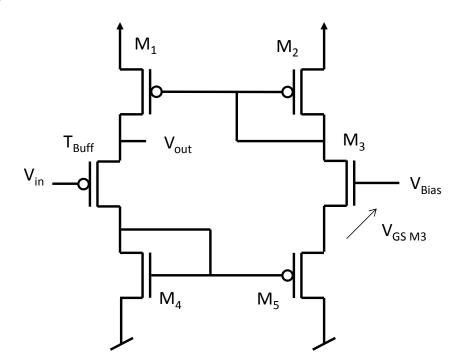

| Fig. 90 Chip Buffer Schematic                                                                                                   | 102 |

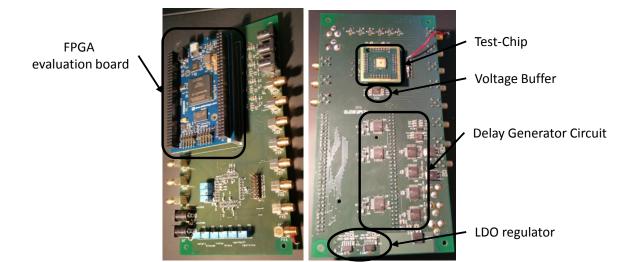

| Fig. 91 Test Board                                                                                                              | 102 |

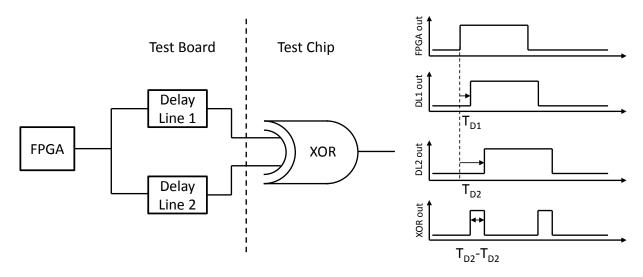

| Fig. 92 Control Signal Generation Circuit based on Delay Lines                                                                  | 103 |

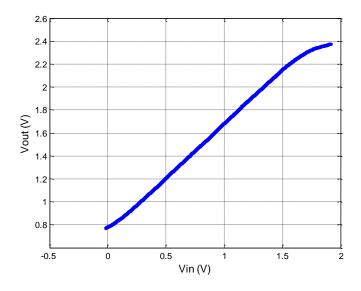

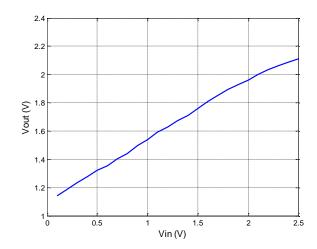

| Fig. 93 DC Characteristics of the Chip and Board Buffers                                                                        | 104 |

| Fig. 94 Measured Characteristic of the APS Front-End without Photodiode                                                         | 105 |

| Fig. 95 Measurement Circuit for Integration Capacitor Extraction                                                                | 106 |

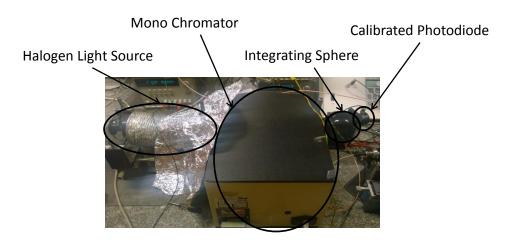

| Fig. 96 Test Bench for Responsivity Measurement                                                                                 | 106 |

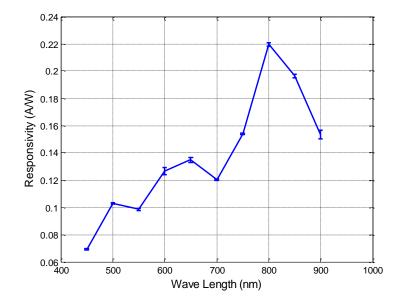

| Fig. 97 Responsivity of the NWell/PSub Photodiode                                                                               | 107 |

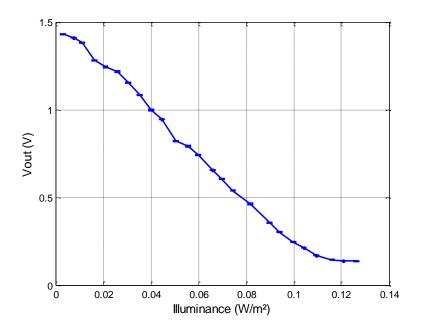

| Fig. 98 Characteristic of the APS front-end circuit                                                                             | 108 |

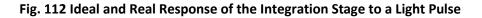

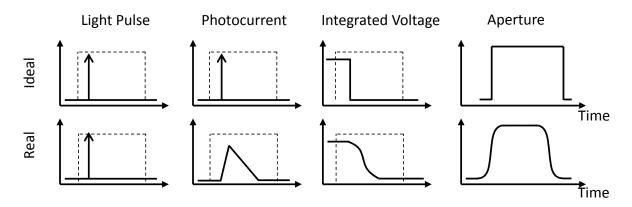

| Fig. 99 Ideal and Real Response of the Integration Stage to a Light Pulse                                                       | 109 |

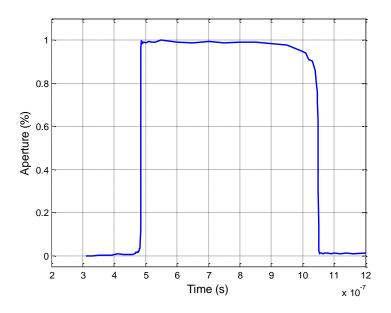

| Fig. 100 Electronic Aperture of the APS Front-End for an Integration Time of 600 ns                                             | 110 |

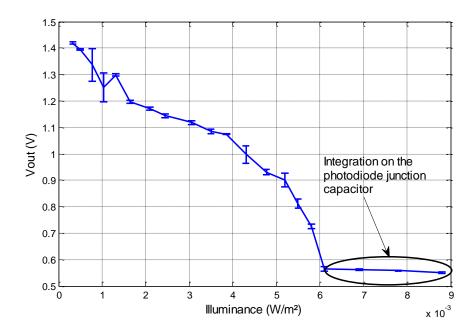

| Fig. 101 Characteristic of the Pixel Front-End with BDI Stage                                                                   | 111 |

| Fig. 102 Electronic Aperture of the BDI Front-End Circuit for an Integration Time of 600 ns                                     | 111 |

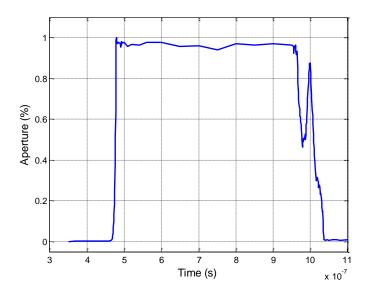

| Fig. 103 Electronic Aperture of the BDI Front-End Circuit for an integration time of 200 ns                                     | 112 |

| Fig. 104 3D Integrated Burst Image Sensor with Two Tiers                                                                        | 113 |

| Fig. 105 Timing Diagram of the 3D Integrated Burst Image Sensor                                                                 | 114 |

| Fig. 106 Pixel Front-End and ADC of the Top Tier                                                                                | 115 |

| Fig. 107 ADC and Memory of the Bottom Tier                                                           | 116 |

|------------------------------------------------------------------------------------------------------|-----|

| Fig. 108 Characteristics and Gain of the BDI Pixel Front-End of the 3D Integrated Burst Image Sensor | 117 |

| Fig. 109 Voltage Noise on the Pixel Font-End Output of the 3D Integrated Burst Image Sensor          | 117 |

| Fig. 110 Voltage Error on the Ramp Signal due to the Wire Bonding                                    | 118 |

| Fig. 111 Top and Bottom Tier Pixel Layout and Full Chip Bottom Layout                                | 119 |

### **Table of Abbreviations**

3D: Three spatial Dimension 3D-IC: 3D Integrated Circuit 3D-P: 3D Packaging 3D-SIC: 3D Stacked Integrated Circuit 3D-WLP: 3D Wafer Level Packaging 3T pixel: Three Transistor pixel 5T: Five Transistor op-amp **CIS: CMOS Image Sensor** ADC: Analog to Digital Converter **APS: Active Pixel Sensor BDI: Buffered Direct Injection BEOL: Back-End-Of-Line BSI: Back Side Illuminated** CCD: Coupled Charge Device CG: Collection Gate **CIS: CMOS Image Sensor** CMOS: Complementary Metal Oxide Semiconductor **CTIA:** Capacitive Trans-Impedance Amplifier DAC: Digital to Analog Converter **DSP: Digital Signal Processor** F2B: Face To Back stacking F2F: Face To Face stacking FD: Floating Diffusion FIFO: First In First Out memory FPA: Focal Plan Array **FPN: Fixed Pattern Noise** FWHM: Full Width at Half Maximum fps: Frame Per Second GBW: Gain BandWidth product **HCCD:** Horizontal CCD segment h/e pair: Hole Electron pair **IC:** Integrated Circuit **IO: Input Output IP: Intellectual Property IS: Image Sensor** ITRS: International Technology Roadmap for Semiconductor KOZ: Keep-Out-Zone LDO: Low Dropout Voltage MCG: Multi Collection Gate MOS: Metal Oxide Semiconductor MOSFET: MOS Field Effect Transistor N+: heavily N-type doped region NWell: N-type doped well P+: heavily P-type doped region PN junction: P-type N-type junction **PSD:** Power Spectral Density

PSub: P-type doped substrate PWell: P-type doped well rms: Root Mean Square RTIA: Resistive Trans-Impedance Amplifier SNDR: Signal to Noise and Distortion Ratio SNR: Signal to Noise Ratio TSV: Through Silicon Via VCCD: Vertical CCD segment

### 1. Introduction

The high speed imaging is a wide domain that covers frame rates from thousands to billions frames per second (fps). Integrated high speed image sensors are used in industrial cameras as well as in research laboratories to observe fast phenomena. The high speed cameras are sorted in three categories depending on their architecture. The continuous video cameras record video up to 25 kfps. The recording length is not limited by the camera but by the mass storage devices (i.e. hard disks). Such cameras are used to perform industrial production line control, automotive crash test, sport and wildlife slow motion recording... [1] The second type of camera are the burst video cameras which record a video of one hundred images at a frame rate up to 100 Mfps. They are mainly used for R&D applications to observe phenomena such as crack propagation (1 Mfps), mechanical stress test (2 Mfps), inkjet droplet formation (5 Mfps), plasma formation (4 Mfps) and combustion [2]. The last type of fast camera is the streak camera which records at frame rates above 1 Gfps. These cameras shoot a video of a hundred images and produce images of one spatial dimension. They are used to record ultra-high speed phenomena in different scientific fields such as condensed matter physics, plasma physics, photochemistry, biology and optical communication [3]. Depending on the recorded phenomenon, a two spatial dimension image can be reconstructed [4].

As for other fields of the visible imaging, coupled charge device (CCD) and complementary metal oxide semiconductor (CMOS) technologies are both competing to implement the image sensors of high speed video cameras. For this PhD research work, only solutions based on CMOS technology are considered. This choice first relies on the industrial environment of my laboratory which is more focused on CMOS technology rather than CCD. Moreover, this choice has also been done for a practical reason. The company where our test-chip was made only provides CMOS technologies for its multi project wafers. However, high speed CCD image sensors will still be presented and compared with CMOS image sensor solutions.

During 40 years, the technological choices of the microelectronic industry have been driven by the transistor shrinking. However, the transistor shrinking seems to reach its limits as the transistor dimensions are now about few hundreds atoms and the devices are prone to quantic effects that degrade their performances. The last decade has seen the emergence of disruptive technologies to bypass this issue and keep improving the performances of the integrated circuits. Therefore, many alternatives have been proposed and developed. At the devices level, new structures of transistors have been presented to improve the carrier mobility and reduce the current leakages such as germanium based transistor, trigate transistor or carbon nanotube transistor [5]. The memory technologies have seen the same development of alternative solutions. These solutions are based on different physic phenomena such as magnetic effects, spin orientation, phase change or resistive materials [6]. These technologies combine fast access times and high density storages. At the integration level, a promising technology is the three dimension (3D) integration technology which offers the possibility to implement transistors in three spatial dimensions instead of two. This technology has been developed at different levels and it is now possible to stack the packages, the integrated circuits or the transistors. This technology is especially interesting for system in package as it allows the nearby implementation of circuits made with different technologies and also enables high bandwidths between the different circuits. 3D integration technology has already proved its efficiency for digital applications with the stacking of memories on a processor [7]. In imaging, the 3D integration has been used to implement image sensor with embedded digital processing, large spatial resolution image sensors or hybrid pixel detectors for particle physics [8] [9] [10]. However, only few works have been done for high speed imaging and have been implemented with a non-standard 3D integration technology [11].

The objective of this PhD work is first to identify the inflows of the 3D integration technology to the development of high speed image sensors. Then, the aim is to propose and study some architectures of high speed burst image sensors based on the 3D integration technology. In this thesis dissertation, we first present a review of the high speed images sensors for both CCD and CMOS image sensors. The emphasis is put on the burst high speed image sensor architectures. We also describe the different characteristics of the photodetectors and the 3D integration technologies with respect to our high speed imaging concern. Based on this background description, we then propose architectures of burst CMOS image sensor using 3D integration technologies. This chapter highlights two 3D integrated burst image sensors. Both these architectures perform an on-chip analog to digital conversion of images but the first one stores the burst of images before the conversion (i.e. analog storage) while the second one memorizes the images after the conversion (i.e. digital storage). The performances of both architectures are assessed and compared in term of frame rate, memory depth and power consumption. Thanks to the information obtained from this analysis, we chose to focus our work on the burst image sensor with digital storage. The analysis also reveals a high power consumption of the burst image sensor with digital storage during the image acquisition. To estimate the risk of overheating, we then conduct a thermal study of the sensor. This thermal analysis is carried out for the different recording and triggering modes of the camera and demonstrates the feasibility of such architecture. At this point, we chose to focus our work more on the circuit than the system and we presents the design of different pixel front-end circuits for 3D integrated burst image sensor with digital storage. A basic front-end circuit inspired from active pixel sensor (APS) structure is first designed. This pixel performs the current to voltage conversion, the global shutter acquisition and a multiplexing operation. Two front-end circuits are then presented and designed. One increases the pixel sensitivity while the other reduces the power consumption. Finally, we present the measurement results of a test-chip where those pixel front-end circuits have been implemented. These measurements include the photodiode responsivity, the pixel front-end characteristic and its electric aperture. This last chapter also presents a proof of concept of a 3D integrated image sensor. This sensor is made of a stack of two circuits with on the top the pixel front-end and on the bottom the A/D converter and the burst digital memory. This image sensor has 20x20 pixels and acquires a video at 5 Mfps.

# 2. Background & Bibliographical Review

## 2.1. Classical Image Sensor Architecture

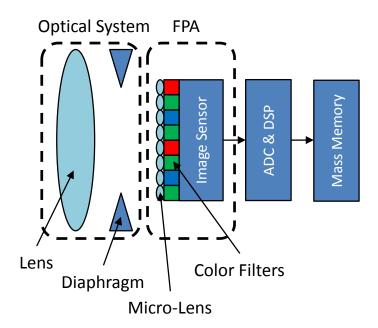

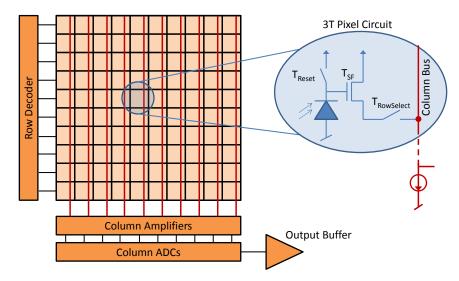

This section gives a brief description of a digital camera and presents the basic architecture of a CMOS image sensor (CIS). A digital camera is composed of an optical system, an image sensor, and some electronic systems [12] [13]. The optical system is made of a set of lens and a diaphragm. This system focuses the light emitted by the scene to provide a clear and sharp image on the focal plane and also performs optical zooms. At this point, the camera performs a spatial discretization of the image thanks to an array of pixels, commonly known as focal plan array (FPA). The FPA is composed of a micro-lens array to focalize the light on the photosensitive area of each pixel. A color filter array (red, green, blue) is used to produce a color image. The image sensor converts the optical signal into an electrical signal thanks to photodiodes. Several analog to digital converters (ADC) convert the signal into digital data that can be processed by a digital signal processor (DSP). The digital image is then stored into a mass memory. The image sensor can be implemented in two technologies. The first technology is based on coupled charge devices (CCD) [14], the second is based on the classic CMOS technology. The first CMOS image sensors (CIS) were designed in the 60's [15]. However, CIS technology was abandoned in the 70's because of the small pixel pitch offered by CCD. Since the 1990s, CIS takes over the market due to the continuous shrinking of CMOS technology that enables small pixels for the mainstream market [16]. Contrary to CCD, CIS embeds the ADCs on the image sensor chip.

### Fig. 14 Digital Camera Diagram

A CIS is composed of an array of pixels, a row decoder on the side of the array and a readout circuit at the bottom of it, Fig. 15. To acquire an image, each pixel of the CIS is exposed to the light and collects an amount of photons. The pixel then performs the photoelectric conversion and produces an electrical signal proportional to the number of collected photons. The signal is conditioned inside the pixel. On Fig. 15, this operation is performed by a three transistors (3T) pixel circuit. The row decoder acts as an addressing circuit which connects through the column bus a row of the pixel array to the column amplifiers. The amplified signal is then converted into digital data thanks to a column ADC. Finally, the outputs of the column ADCs are multiplexed to be connected to an output buffer.

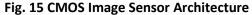

Throughout the rest of the CIS description, a pixel with charge integration is considered [13]. An image acquisition is thus composed of three steps. First each pixel is reset to a common voltage value. Then, the electrical charges received during the exposition time are integrated on a capacitor into a voltage. Finally, the pixel voltage values are transferred to the column ADCs by the read-out circuit. The method to readout the pixel array plays a significant role in the image acquisition. There are two modes of acquisition known as rolling shutter and global shutter acquisition [17]. In rolling shutter mode, an acquisition signal is propagated successively from the first row to the last row of the image sensor. This signal is then followed by a reading signal that connects the pixel row to the read-out circuit. This reading signal corresponds to the end of the integration. The timing diagram of the rolling shutter mode is illustrated in Fig. 16. For the pixels of two different rows, the charges collected during the integration process do not correspond to the same time. Some artifacts, also known as skew effect, can thus appear on the image if an object of the scene is moving. To tackle this issue, it is necessary to perform the charge integration in the same time for each pixel of the array. This acquisition method known as global shutter is the natural read-out method for CCD [18]. The image sensor control unit sends the reset and the integration stop signal at the same time to every pixel of the CIS. The signal is stored inside the pixel in an analog memory which is then read through the column bus. Depending on the pixel circuit, another image can be acquired during the reading of the current image. This feature is

implemented to remove dead time between two images of a video and is known as acquirewhile-read.

Fig. 16 Rolling Shutter and Global Shutter Acquisitions

### 2.2. High Speed Image Sensor